Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

672results about How to "Reduce electric field strength" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

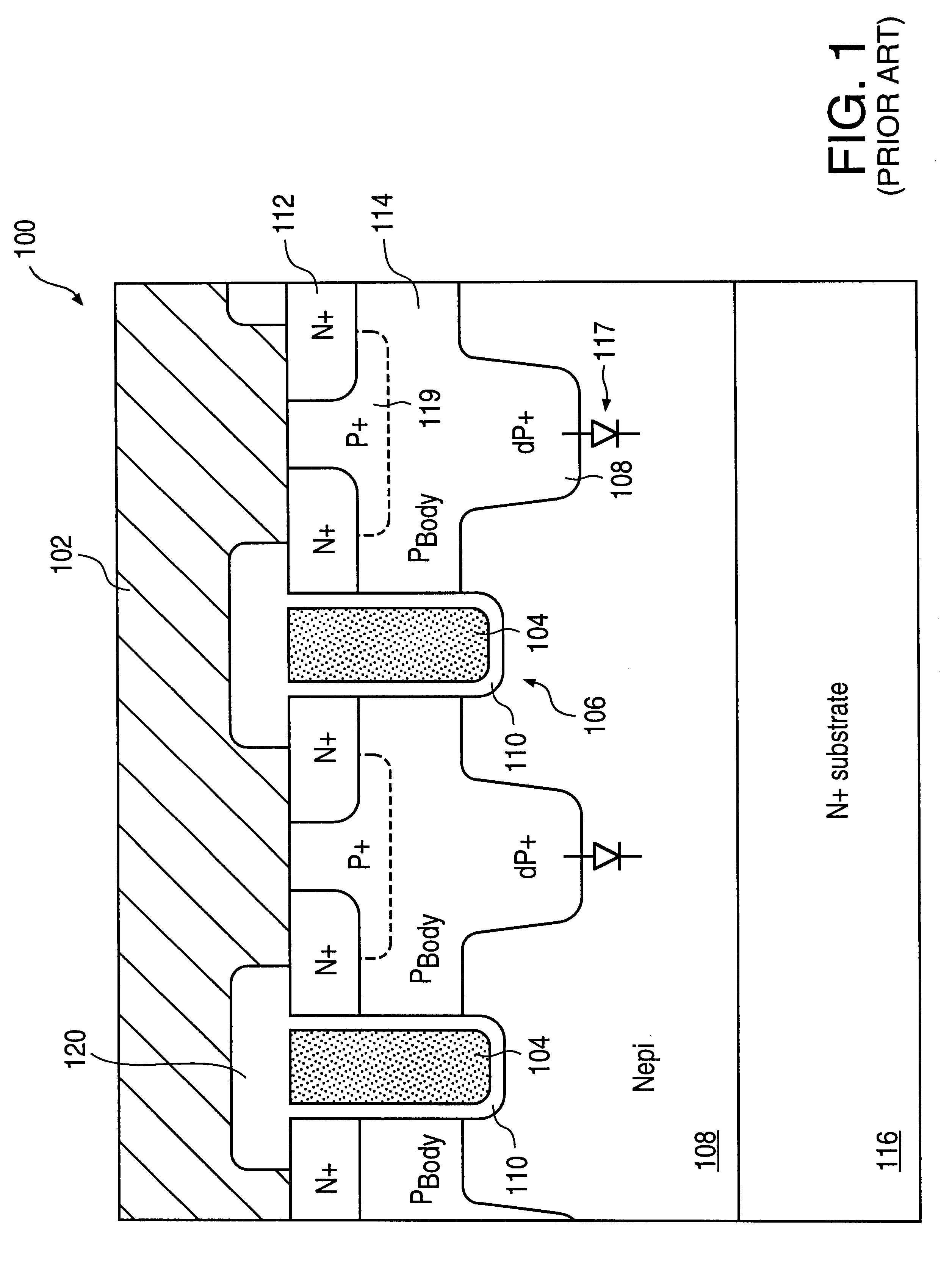

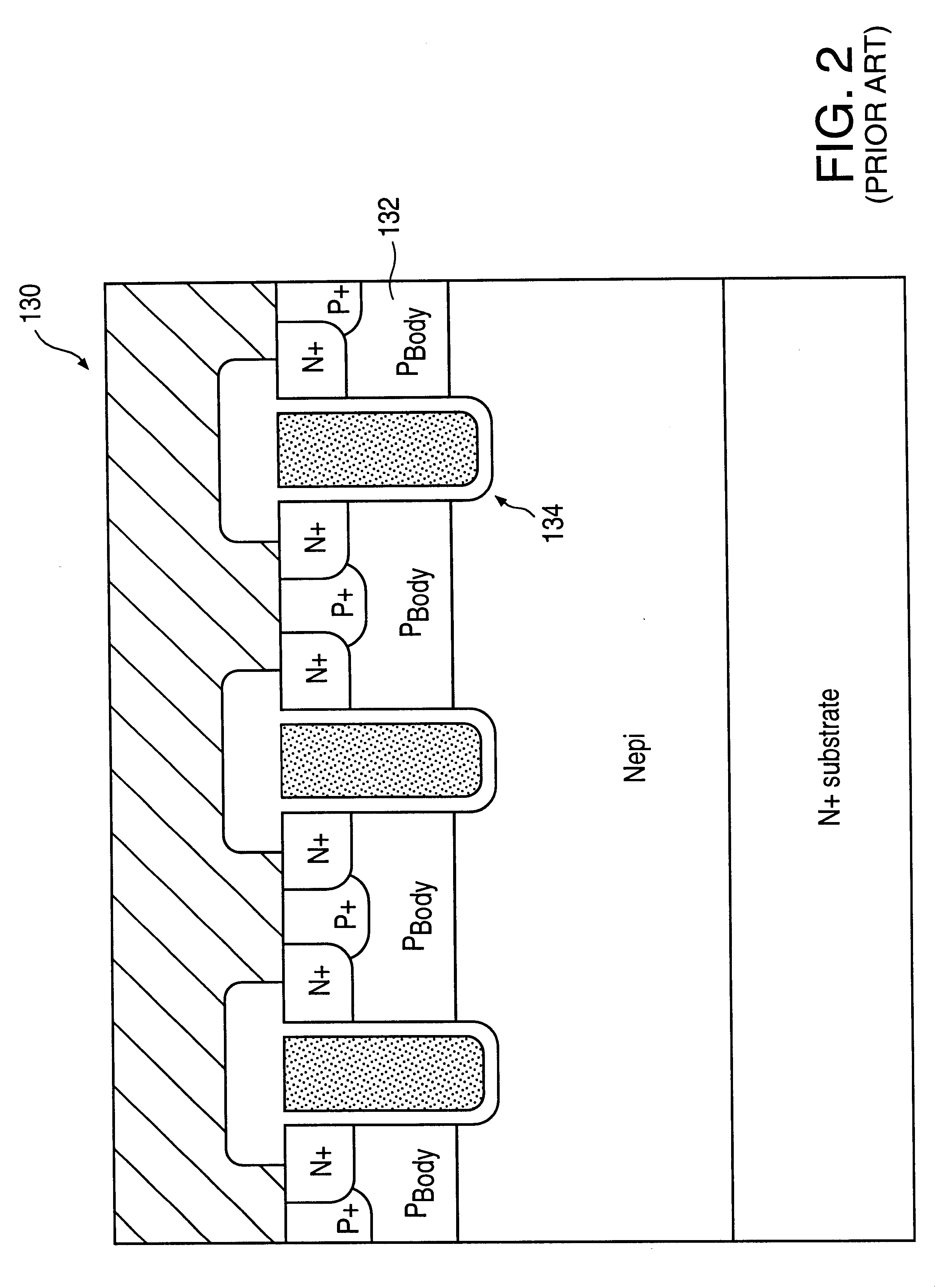

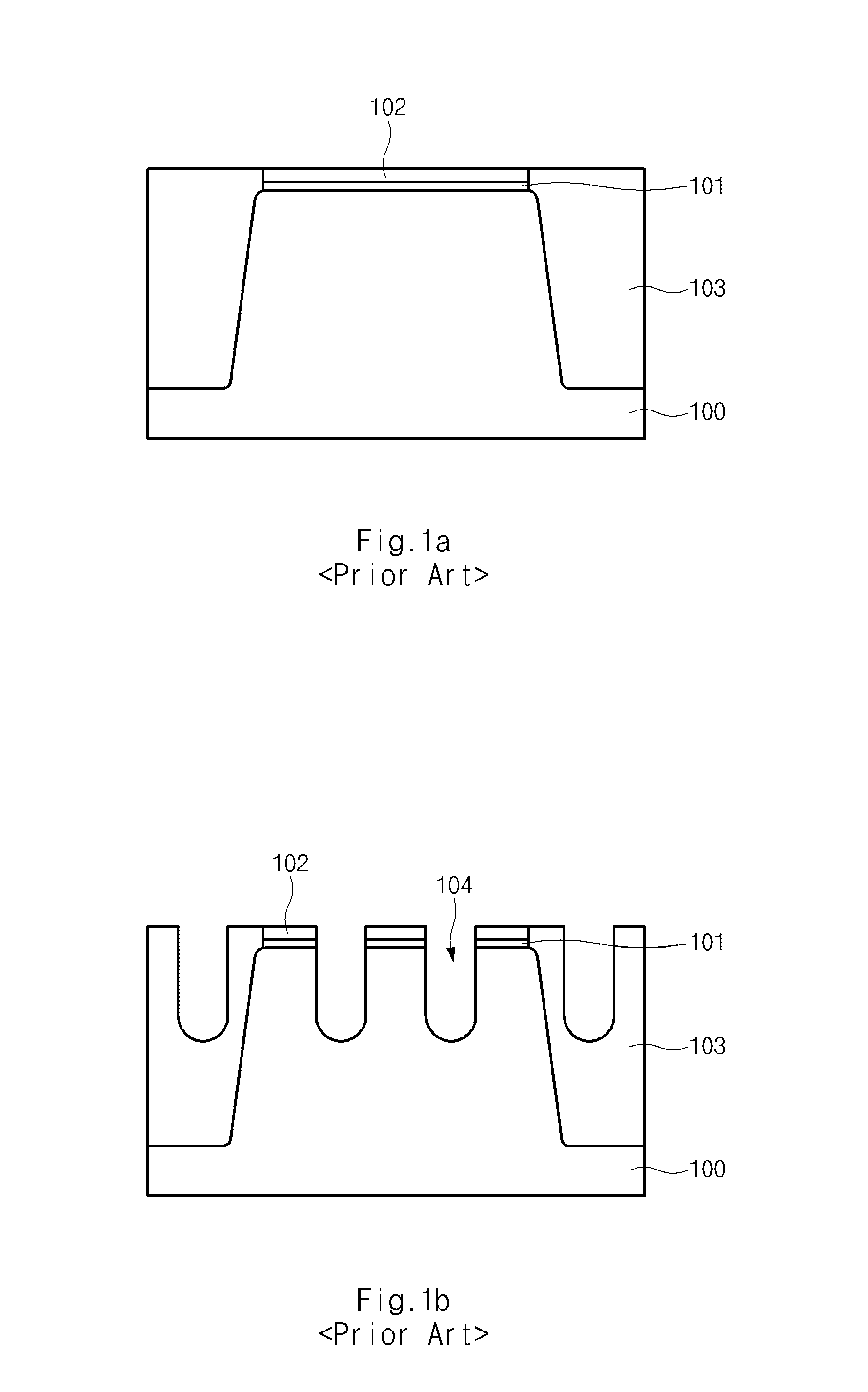

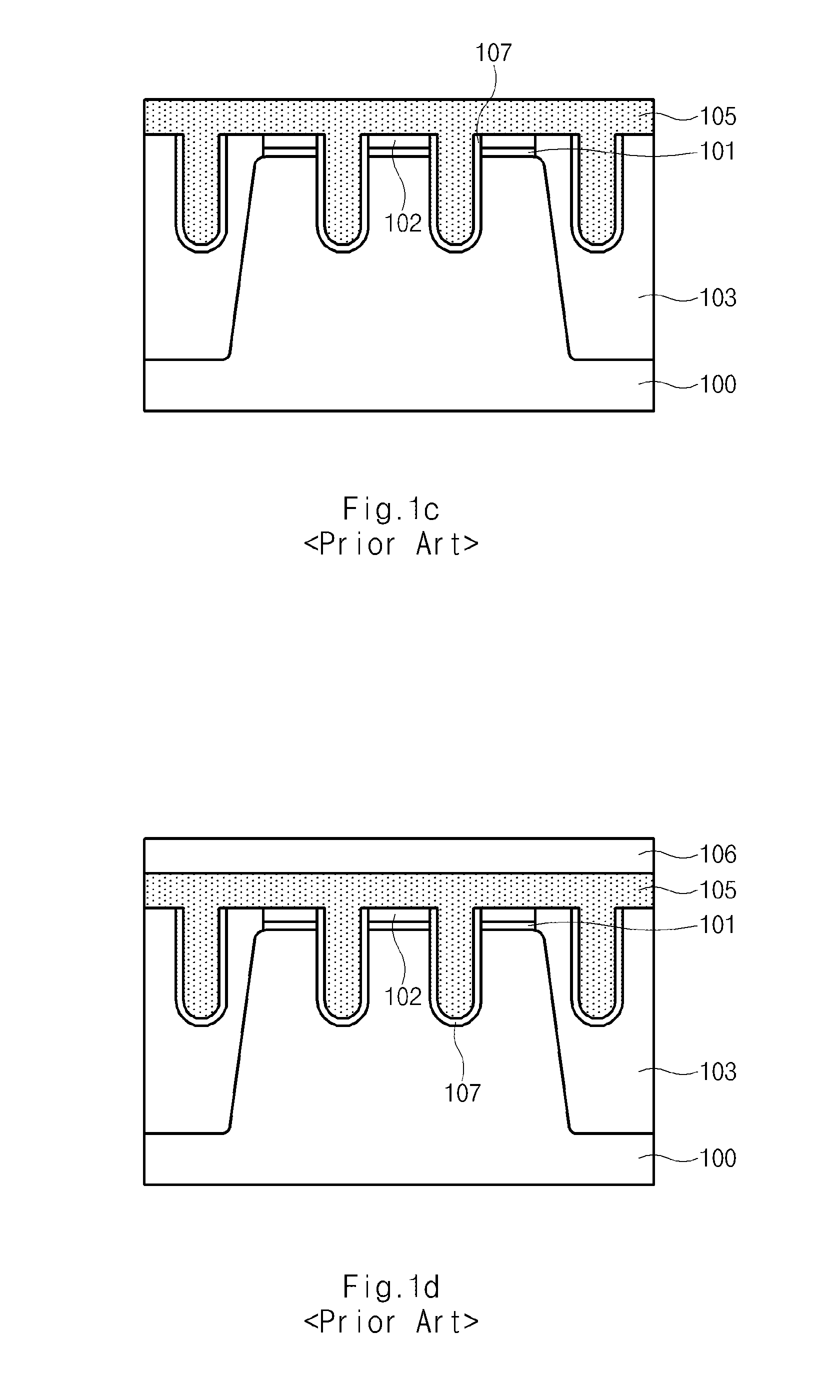

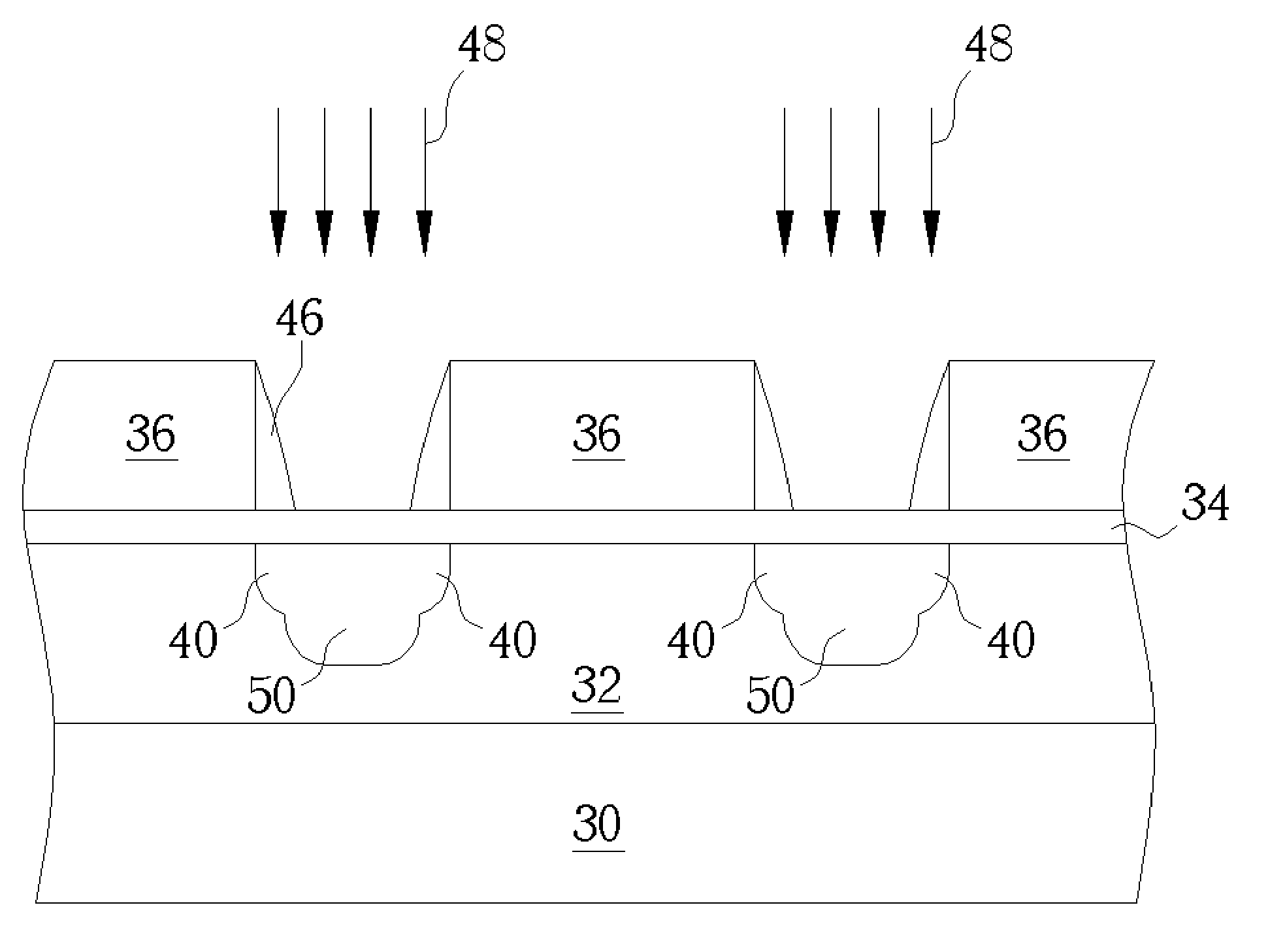

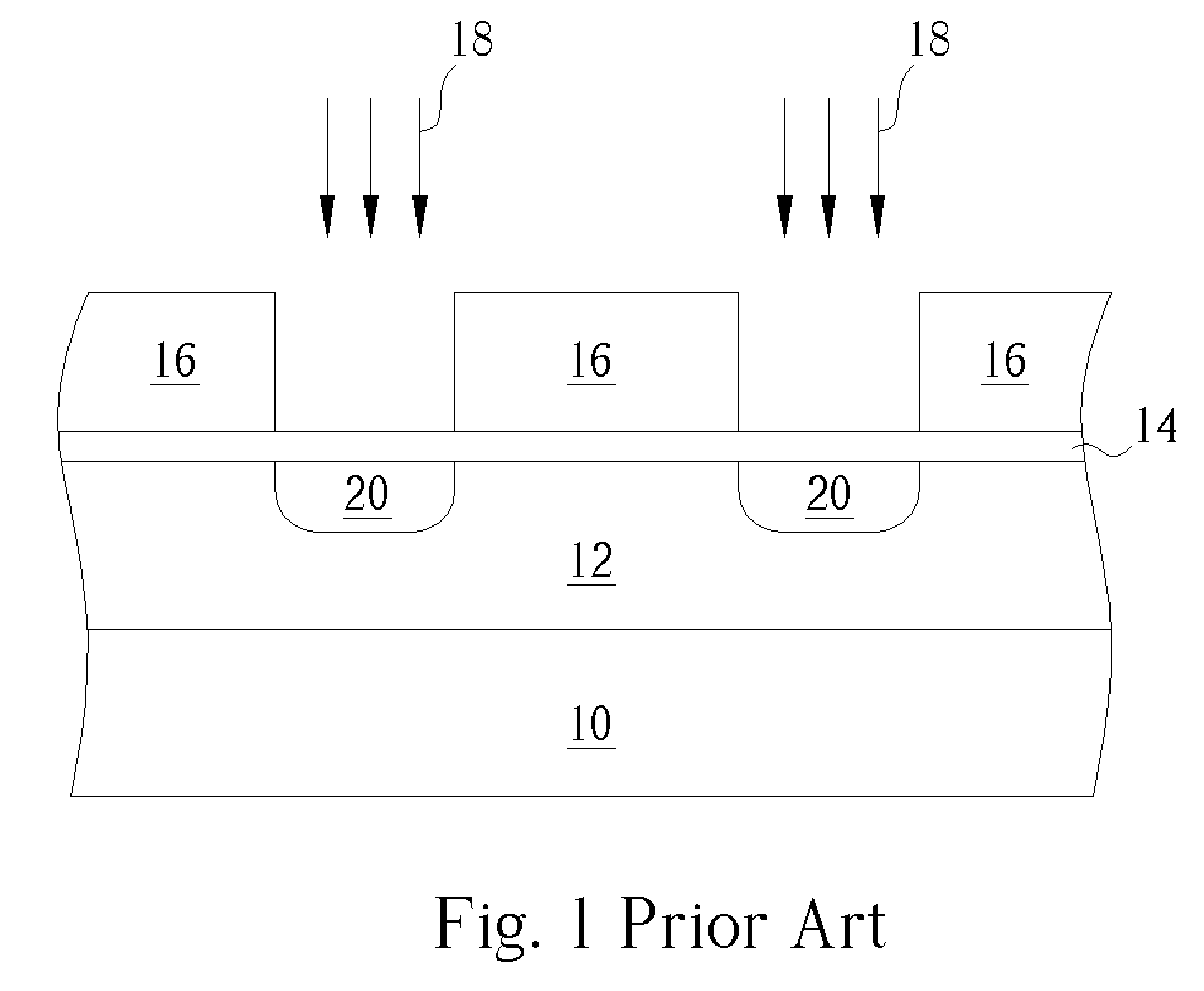

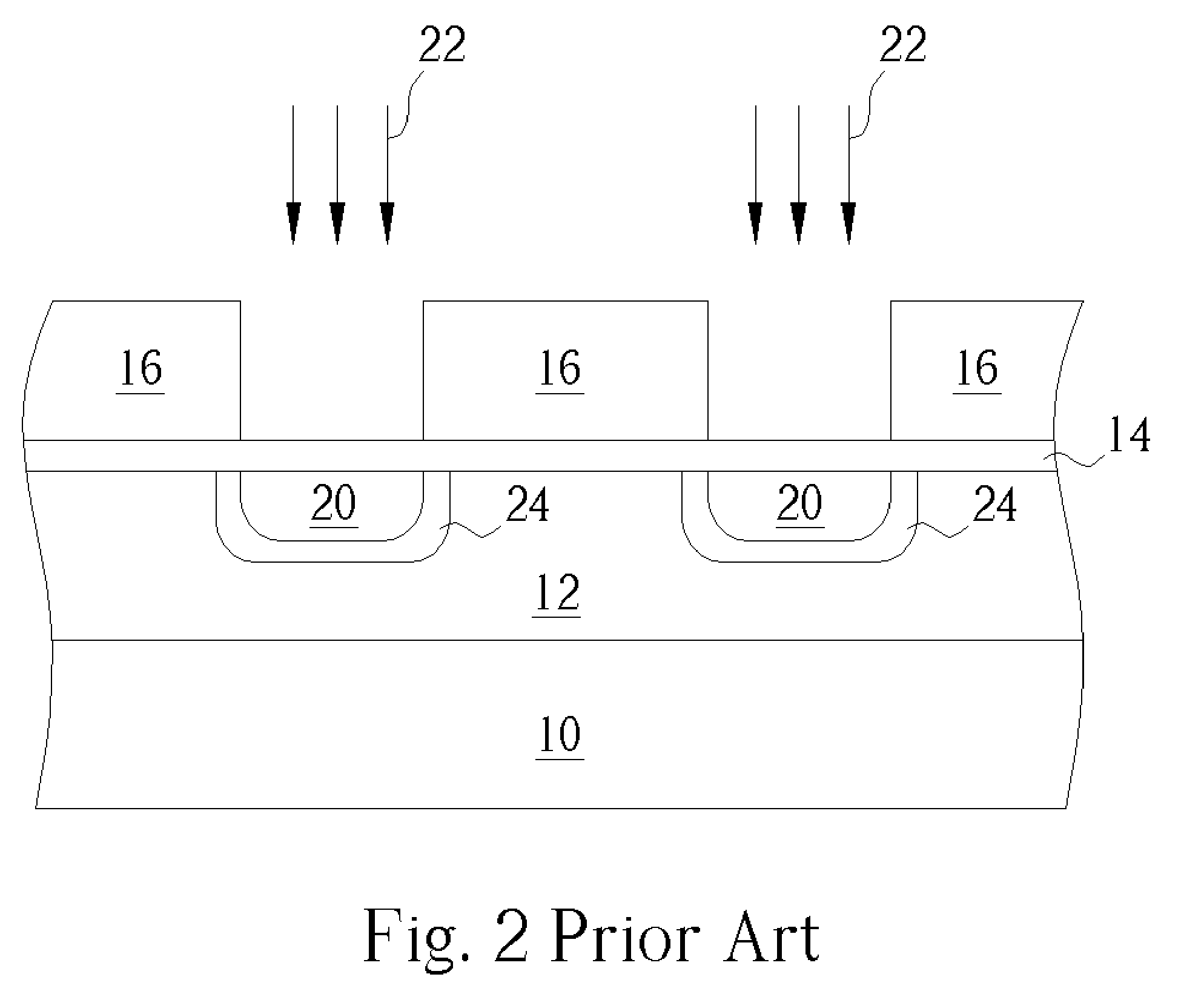

Process of manufacturing Trench gate semiconductor device having gate oxide layer with multiple thicknesses

InactiveUS6291298B1Reduced strengthReduce capacitanceSemiconductor/solid-state device manufacturingDiodePhysicsPhotoresist

The a trench semiconductor device such as a power MOSFET the high electric field at the corner of the trench is diminished by increasing the thickness of the gate oxide layer at the bottom of the trench. Several processes for manufacturing such devices are described. In one group of processes a directional deposition of silicon oxide is performed after the trench has been etched, yielding a thick oxide layer at the bottom of the trench. Any oxide which deposits on the walls of the trench is removed before a thin gate oxide layer is grown on the walls. The trench is then filled with polysilicon in or more stages. In a variation of the process a small amount of photoresist is deposited on the oxide at the bottom of the trench before the walls of the trench are etched. Alternatively, polysilicon can be deposited in the trench and etched back until only a portion remains at the bottom of the trench. The polysilicon is then oxidized and the trench is refilled with polysilicon. The processes can be combined, with a directional deposition of oxide being followed by a filling and oxidation of polysilicon. A process of forming a "keyhole" shaped gate electrode includes depositing polysilicon at the bottom of the trench, oxidizing the top surface of the polysilicon, etching the oxidized polysilicon, and filling the trench with polysilicon.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

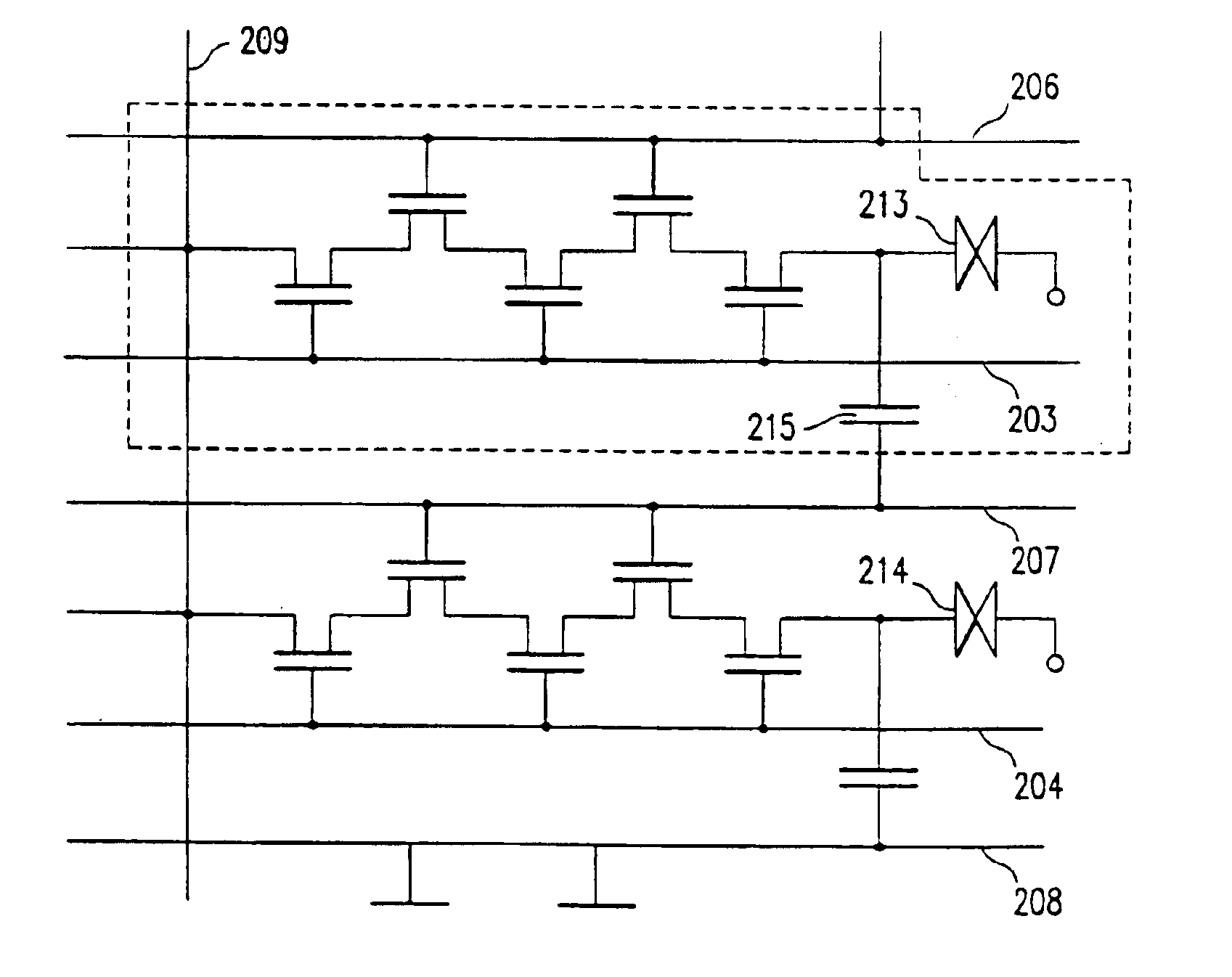

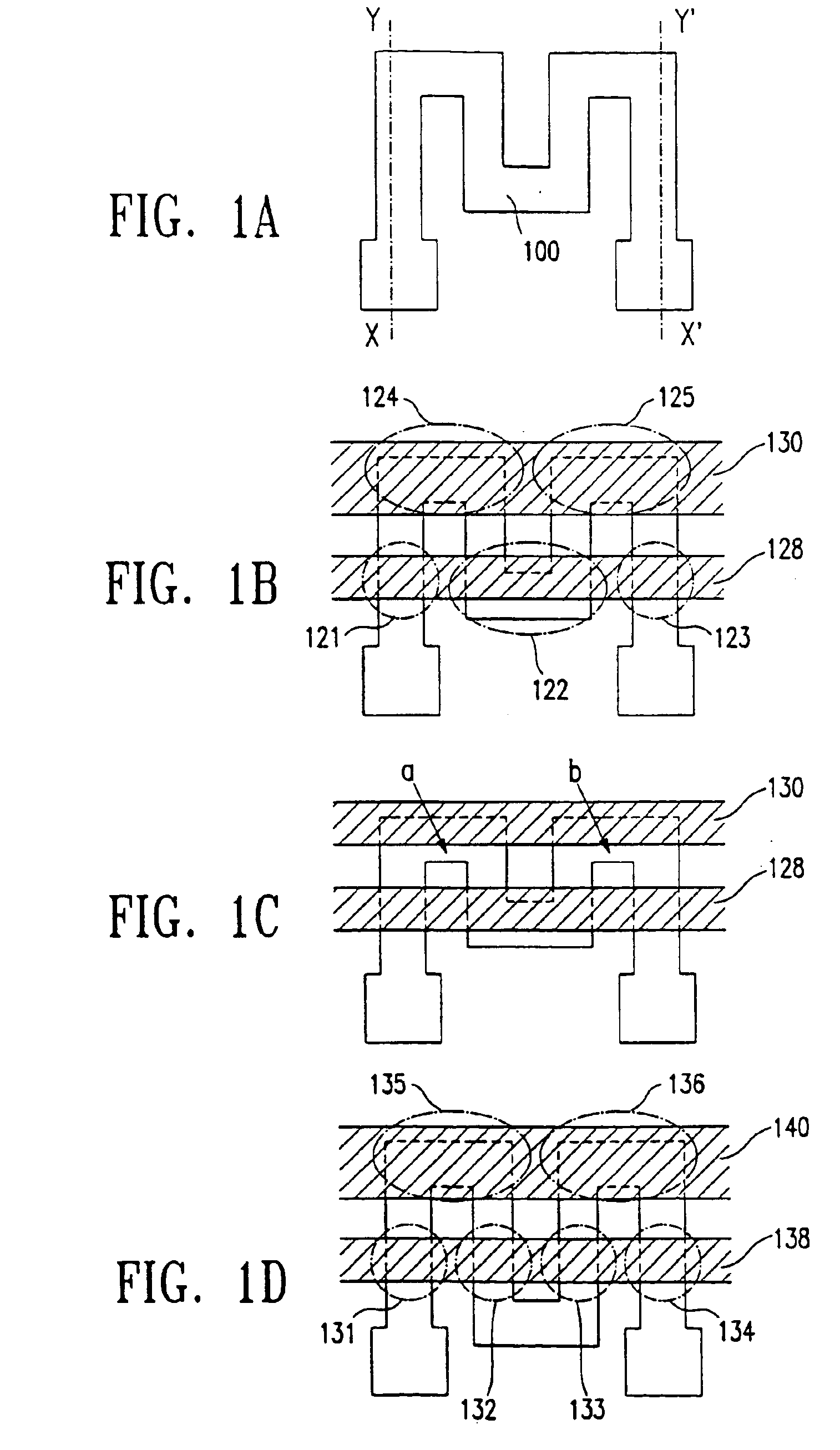

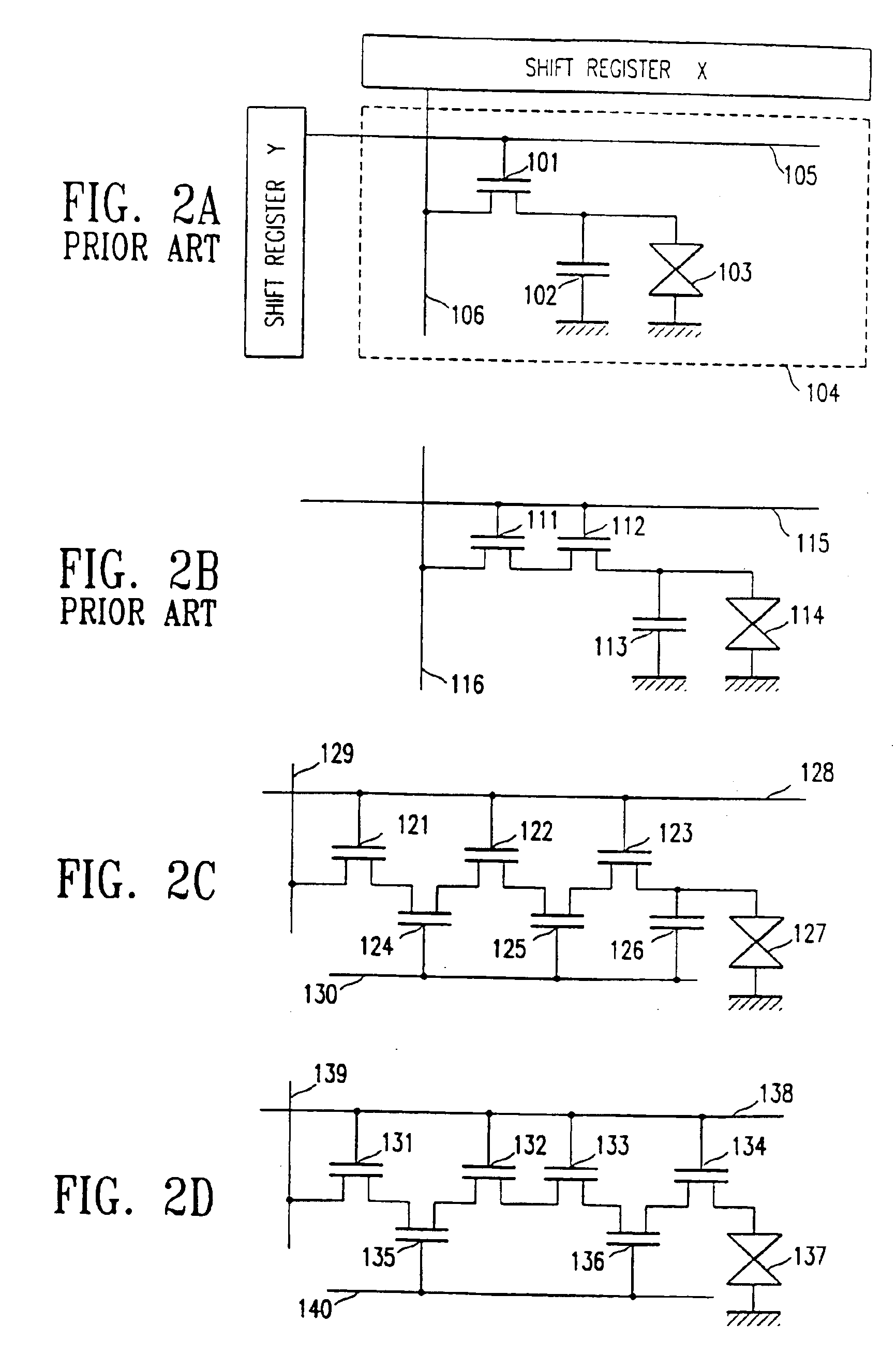

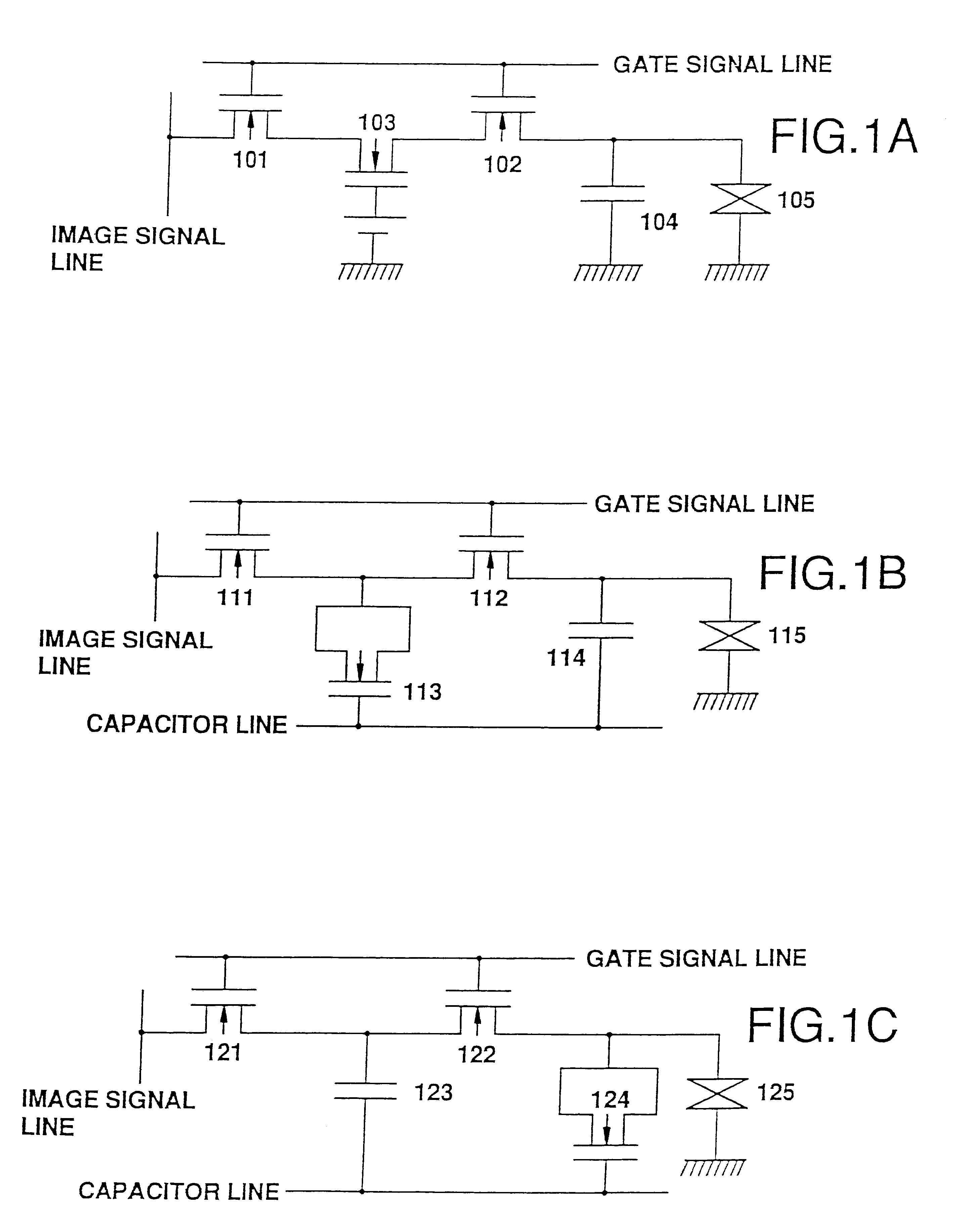

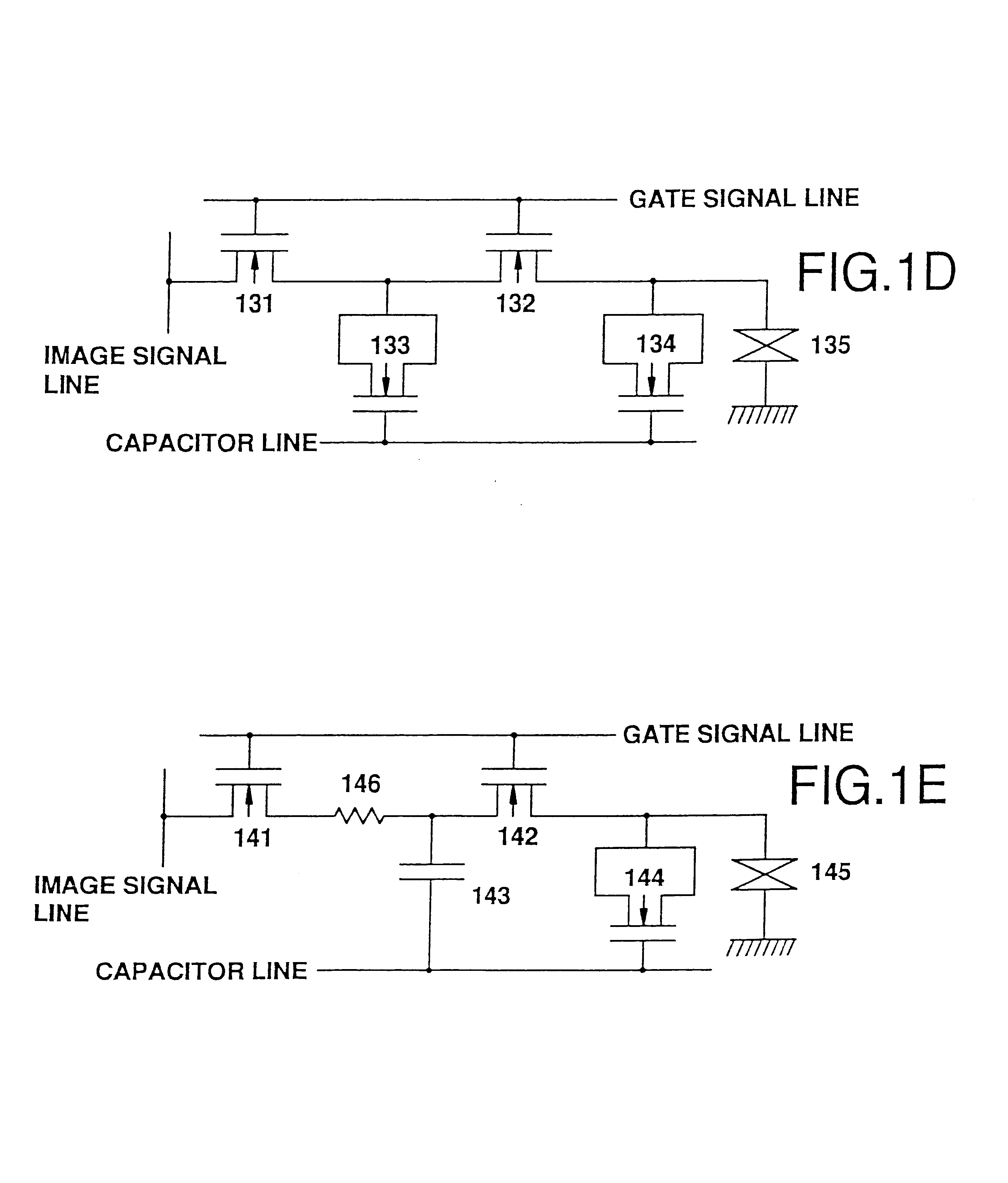

Active matrix display device

InactiveUS6914642B2Off-current can be reducedReduce electric field strengthTransistorStatic indicating devicesCapacitanceSemiconductor

In an active matrix display device, a circuit including at least five thin film transistors (TFTs) which are provided with an approximately M-shaped semiconductor region for a single pixel electrode and gate lines and a capacitances line which cross the M-shaped semiconductor region, is used as a switching element. Each of the TFT have offset regions and lightly doped drain (LDD) regions. Then, by supplying a selection signal to the gate lines, the TFTs are operated, thereby writing data to the pixel, while a suitable voltage is supplied to the capacitance line, a channel is formed thereunder and it becomes a capacitor. Thus the amount of discharge from the pixel electrode is reduced by the capacitor.

Owner:SEMICON ENERGY LAB CO LTD

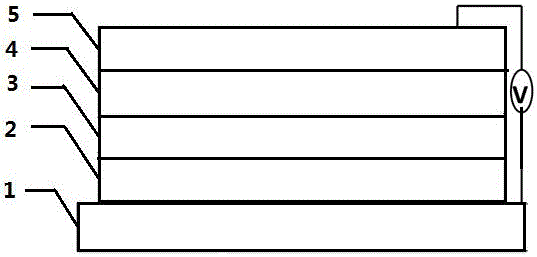

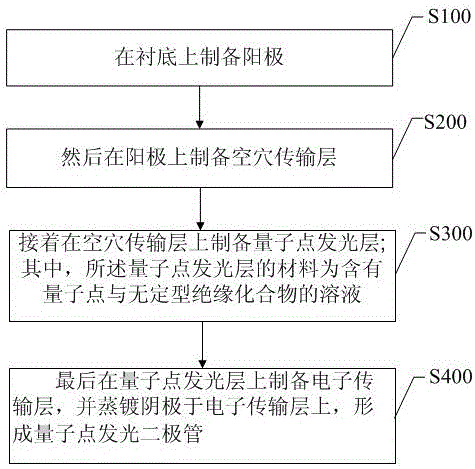

Quantum dot light emitting diode and preparation method thereof

ActiveCN106384765AReduce electric field strengthIncrease chance of compoundingSolid-state devicesSemiconductor/solid-state device manufacturingQuantum dotHole transport layer

The invention discloses a quantum dot light emitting diode and a preparation method thereof. The quantum dot light emitting diode comprises a substrate, an anode, a hole transport layer, a quantum dot light emitting layer, an electron transport layer and a cathode in sequence from bottom to top, wherein the materials of the quantum dot light emitting layer include quantum dots and an amorphous insulating compound. The quantum dot light emitting layer is prepared by forming a film through spin coating of solution of the amorphous insulating compound containing the quantum dots, in order to weaken the electric field intensity at the quantum dot light emitting layer. Therefore, the possibility of electron recombination is improved while the electron and hole injection barriers are reduced, and thus, the efficiency and service life of QLED devices are increased effectively.

Owner:TCL CORPORATION

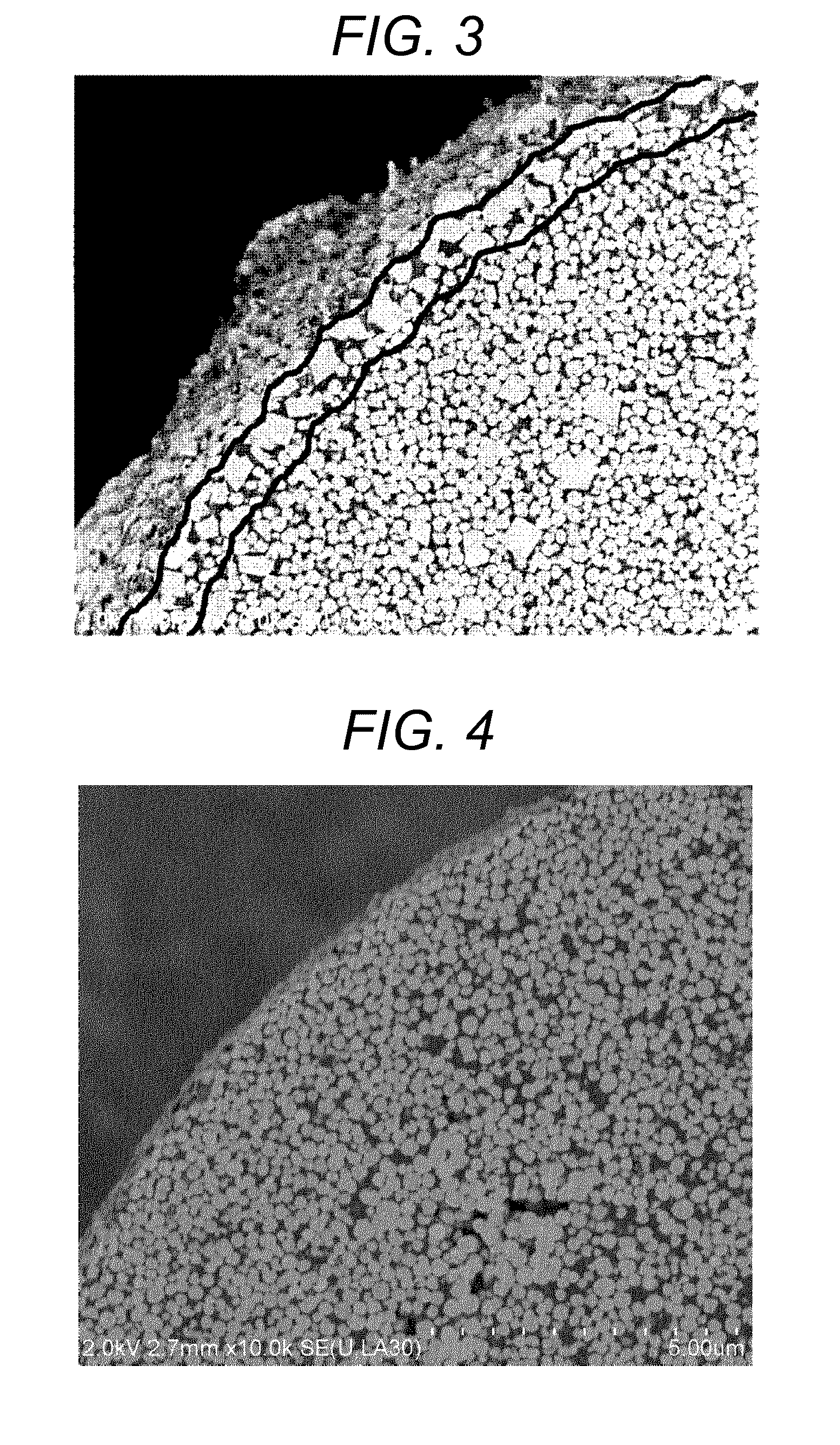

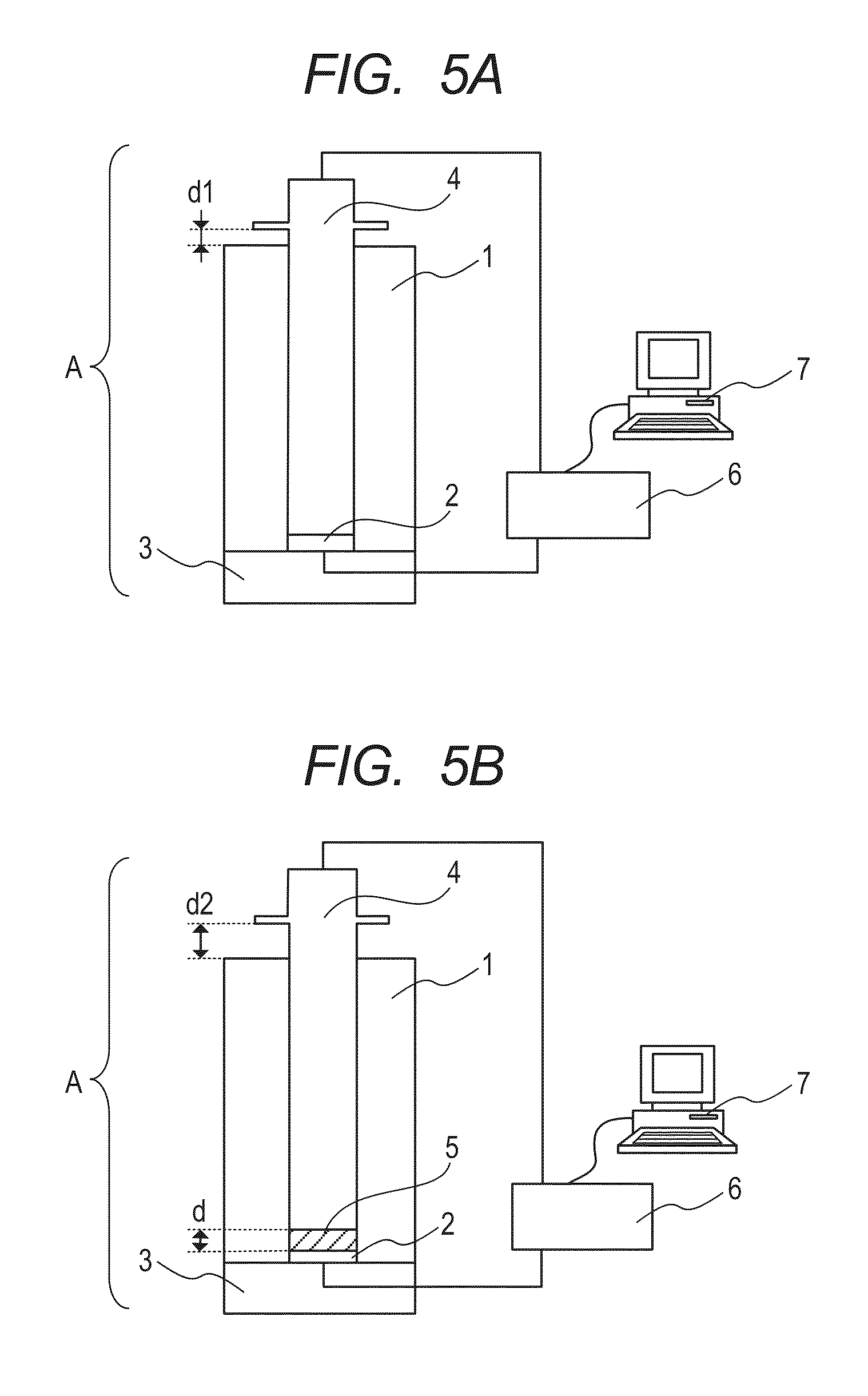

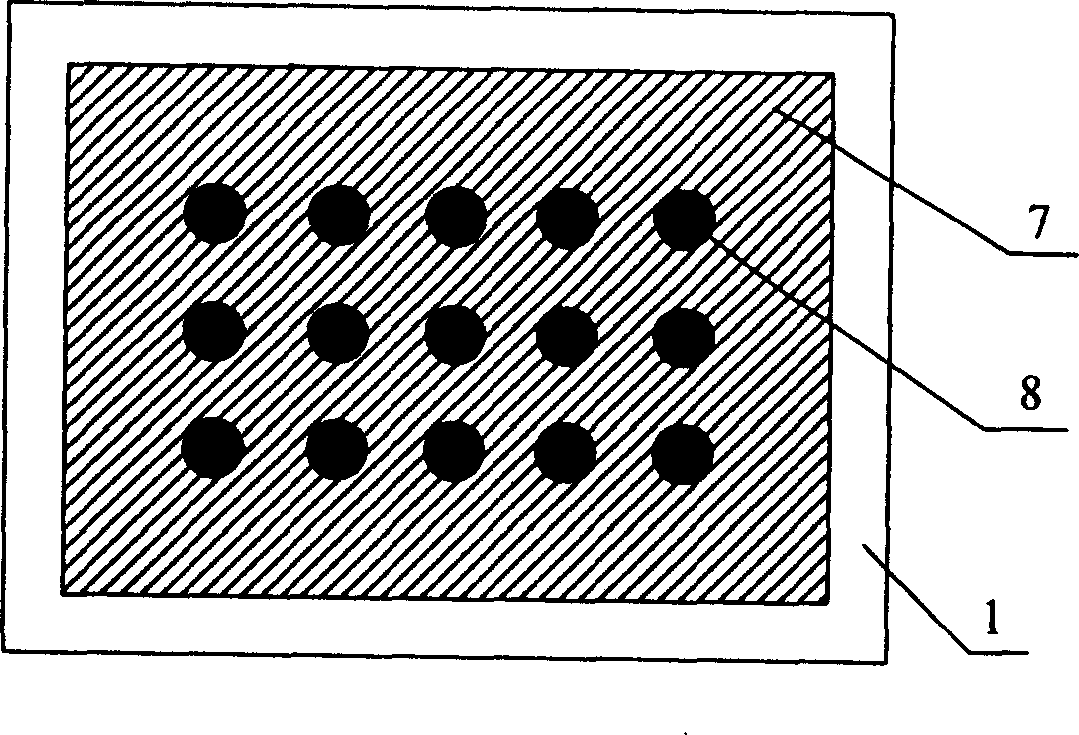

Magnetic carrier and two-component developer

InactiveUS20140134535A1Suppressing white spotsSatisfactory imageDevelopersScanning electron microscopeEngineering

Provided is a magnetic carrier satisfying leakage, white spots, charging property and high developing performance in a low electric field and having excellent durability. The magnetic carrier is a magnetic carrier comprising a magnetic substance-dispersed resin carrier core containing a magnetic substance and a binder resin, and a coating resin on a surface thereof, wherein the magnetic substance comprises a magnetic substance A having a shape without vertexes and a magnetic substance B having a shape with vertexes, the magnetic substance B has a number average particle diameter of 0.40-2.00 μm, and in a reflection electron image of a section of the magnetic substance-dispersed resin carrier core taken by a scanning electron microscope, an area proportion of the magnetic substance B is larger than an area proportion of the magnetic substance A within a region from the surface of the magnetic substance-dispersed resin carrier core to a depth of 1.0 μm.

Owner:CANON KK

System and method for tissue treatment using non-symmetric radio-frequency energy waveform

ActiveUS9168096B2Minimize shocking effectReducing the IEP thresholdSurgical instruments for heatingNon symmetricTissue heating

A method for soft tissue destruction comprises applying high voltage pulses causing irreversible electroporation alternating with low amplitude pulses of opposite polarity balanced to provide negligible average current and minimize risk of electrical shock. The method may be accompanied by tissue heating to reduce the electroporation threshold and negative pressure for skin shaping and optimal voltage distribution.

Owner:INVASIX

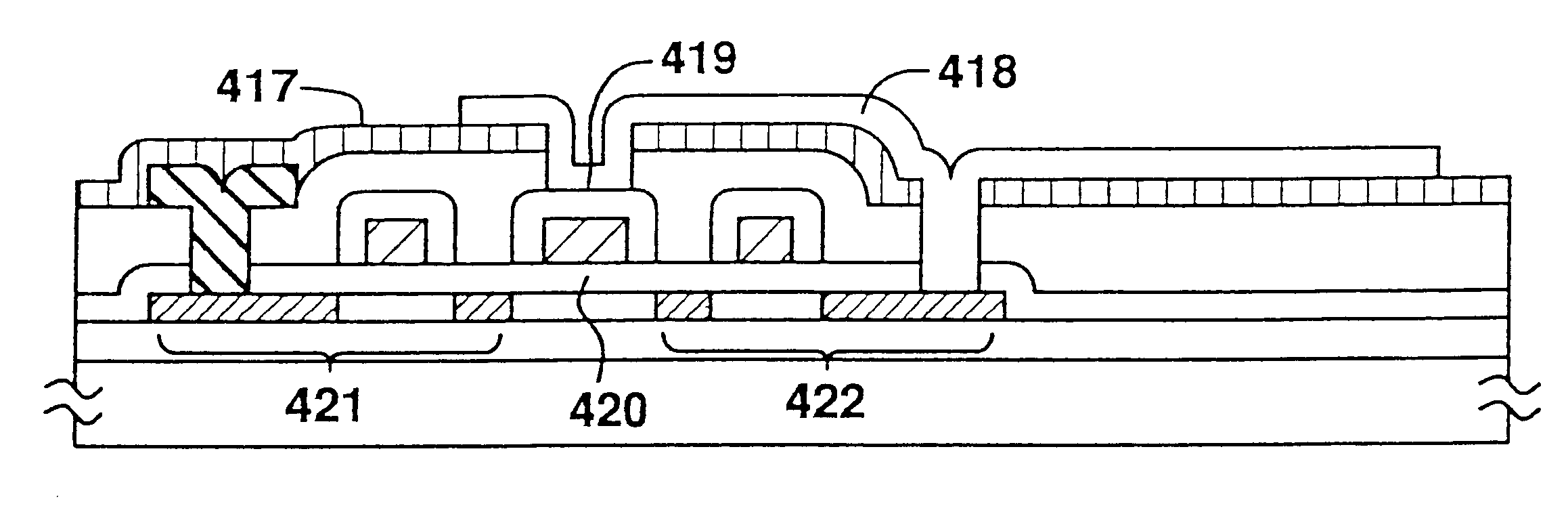

Active matrix display and electrooptical device

InactiveUS6885027B2Reduce electric field strengthTotal current dropTransistorStatic indicating devicesActive matrixDisplay device

A structure for reducing the OFF current of an active matrix display. In the active matrix display, plural TFTs are connected in series with each one pixel electrode. Of these TFTs connected in series, at least one TFT excluding the TFTs located at opposite ends is maintained in conduction. Alternatively, at least one capacitor is connected between the junction of the drain and source of each TFT connected in series and an AC grounded point. Thus, the amount of electric charge released from auxiliary capacitors during cutoff of the TFTs is reduced.

Owner:SEMICON ENERGY LAB CO LTD

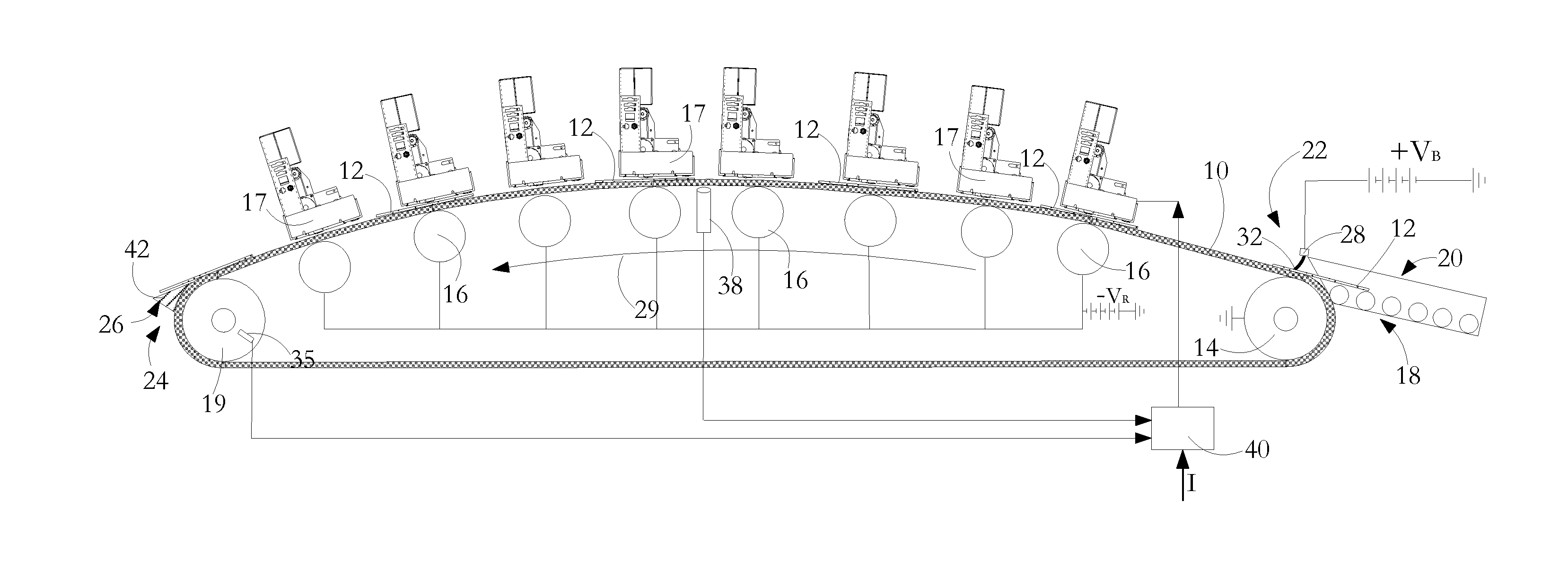

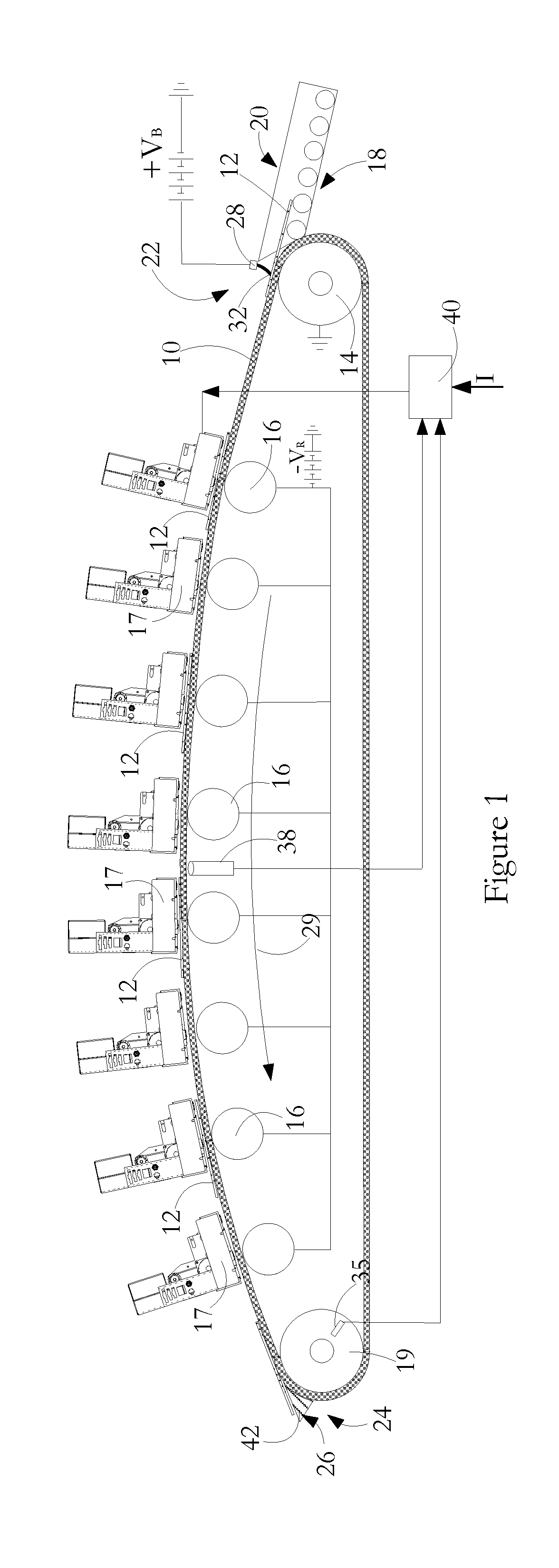

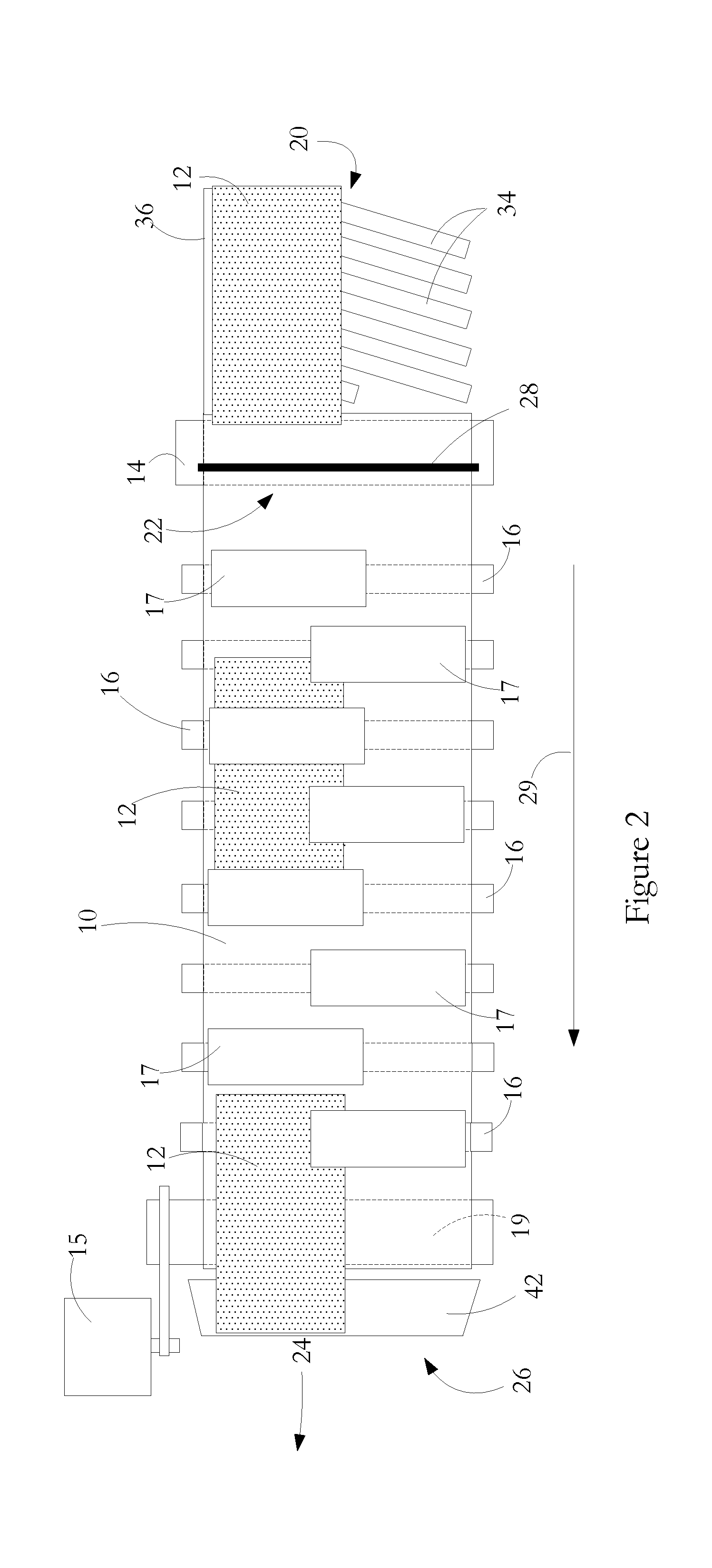

Multiple print head printing apparatus and method of operation

ActiveUS20130201237A1Precise positioningSmall toleranceTypewritersOther printing apparatusEngineeringMotor coordination

A printing apparatus has a series of inkjet print heads spaced from one another in a transport direction. A continuous belt driven around a roller system is used to feed sheet media successively to the print heads so that a partial image printed by one print head is overprinted at a subsequent print head with registration of the partial images. A sheet medium is caused to become electrostatically tacked to the belt by passing the sheet past a charging device. Movement of the belt is tracked by a tracking sub-system and operation of the print heads is coordinated with the tracked belt movement to achieve precise registration of the partial images.

Owner:DELPHAX TECH

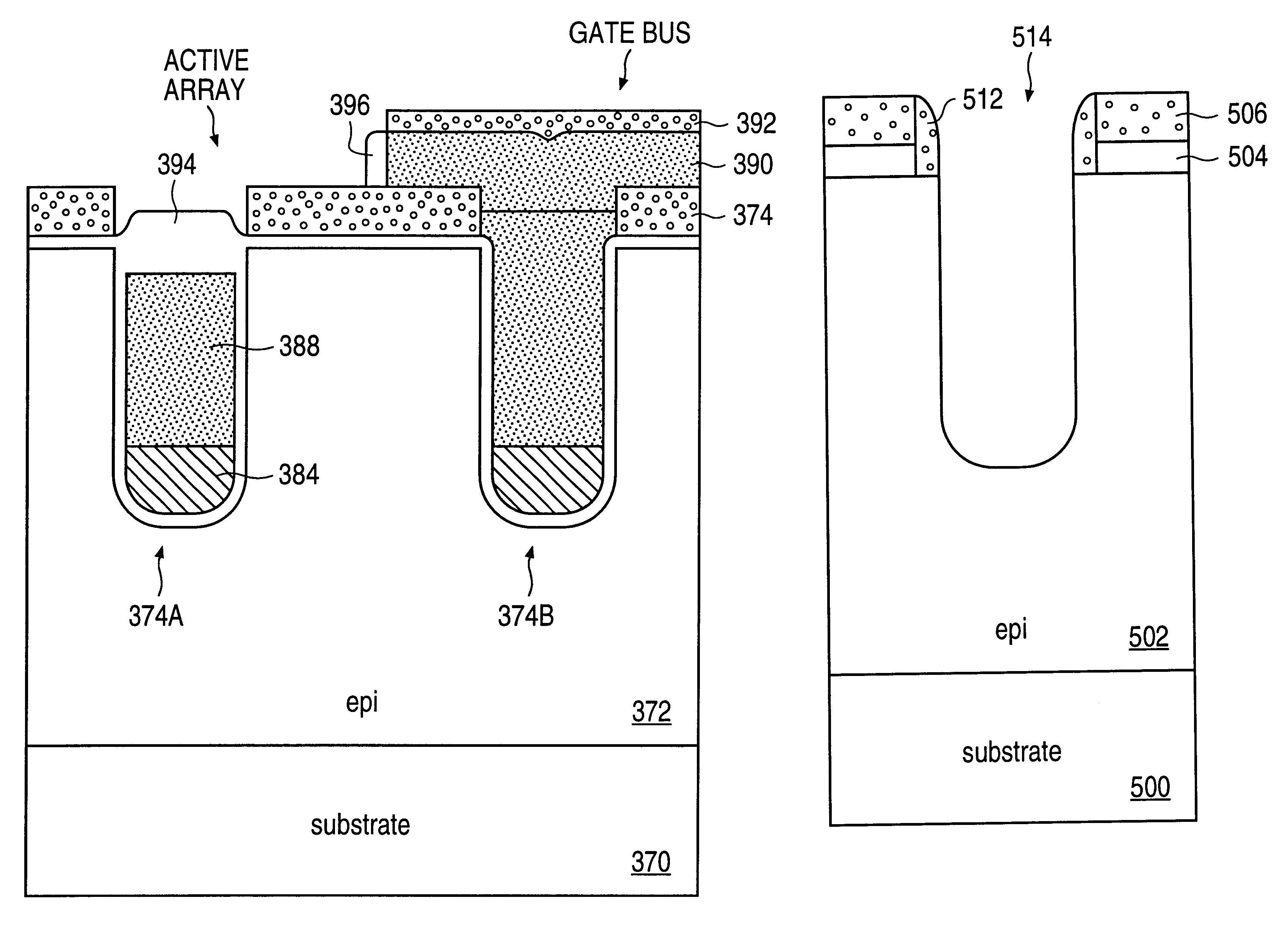

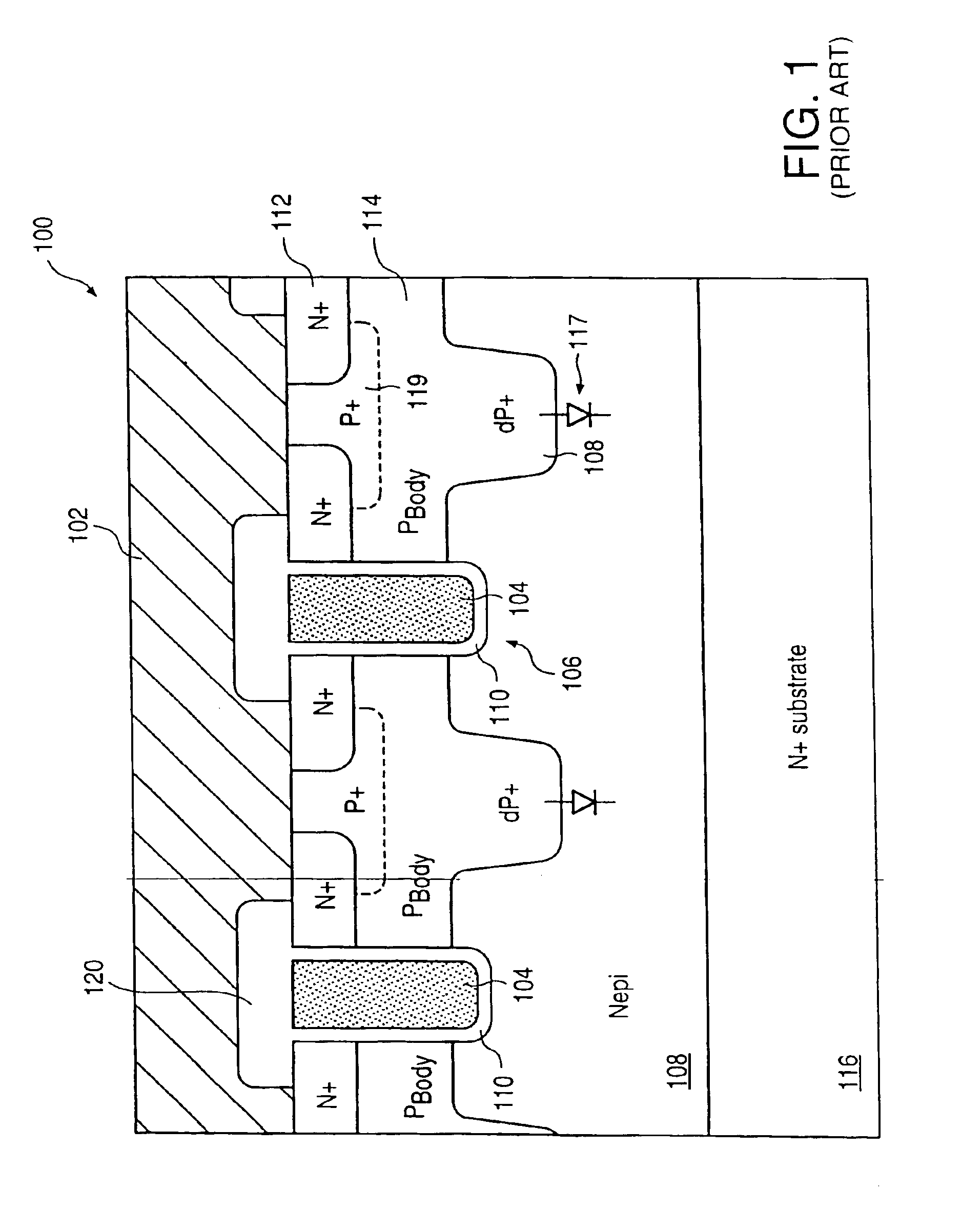

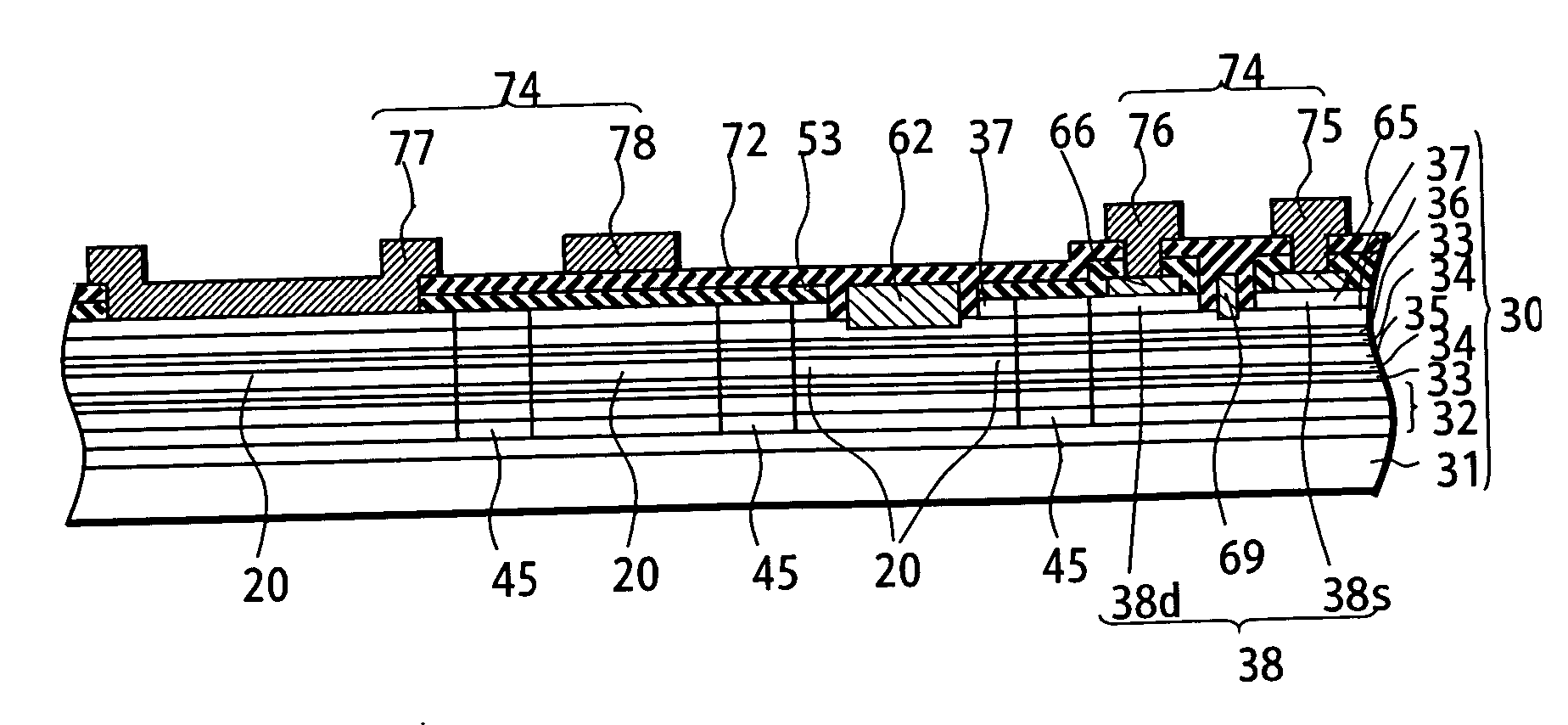

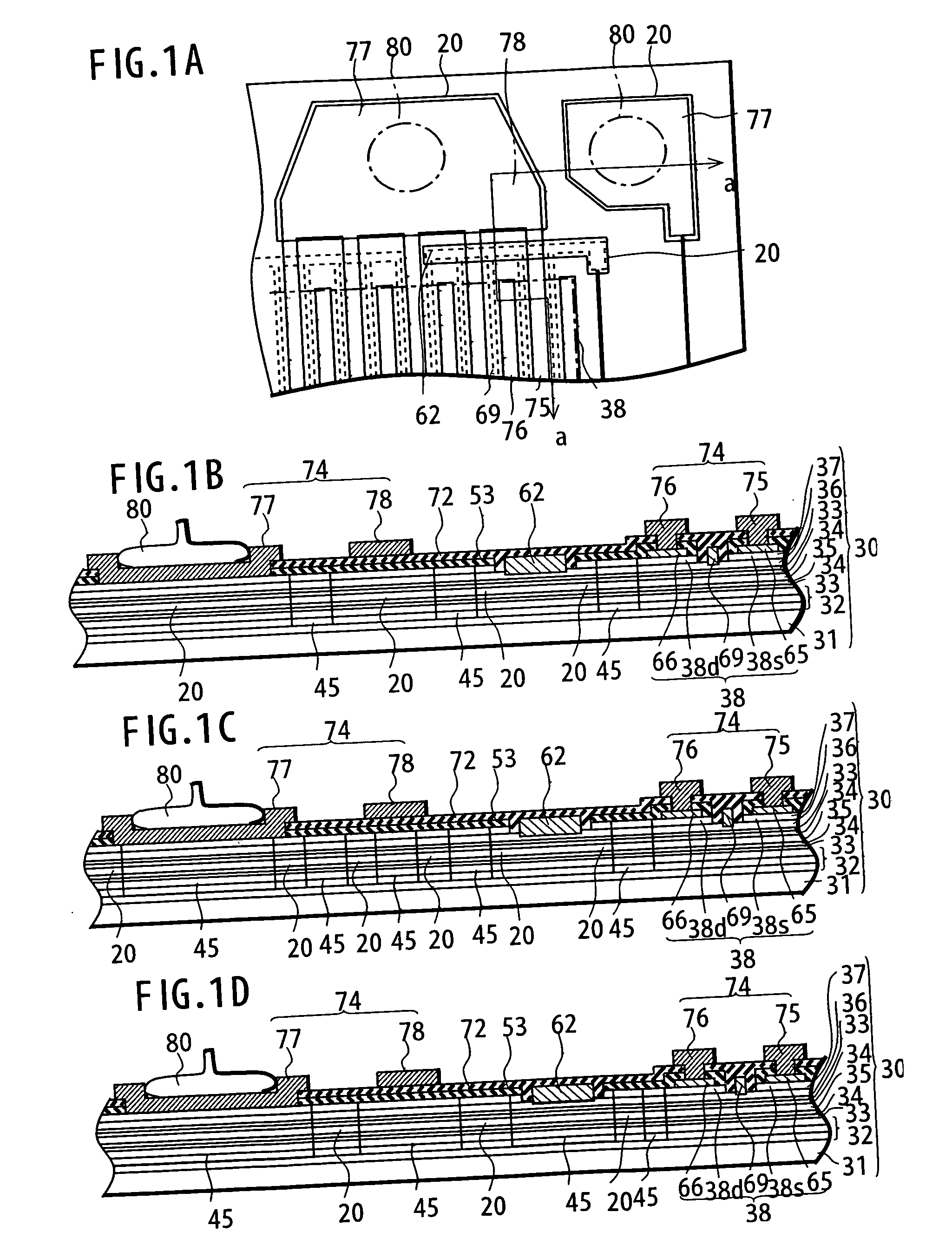

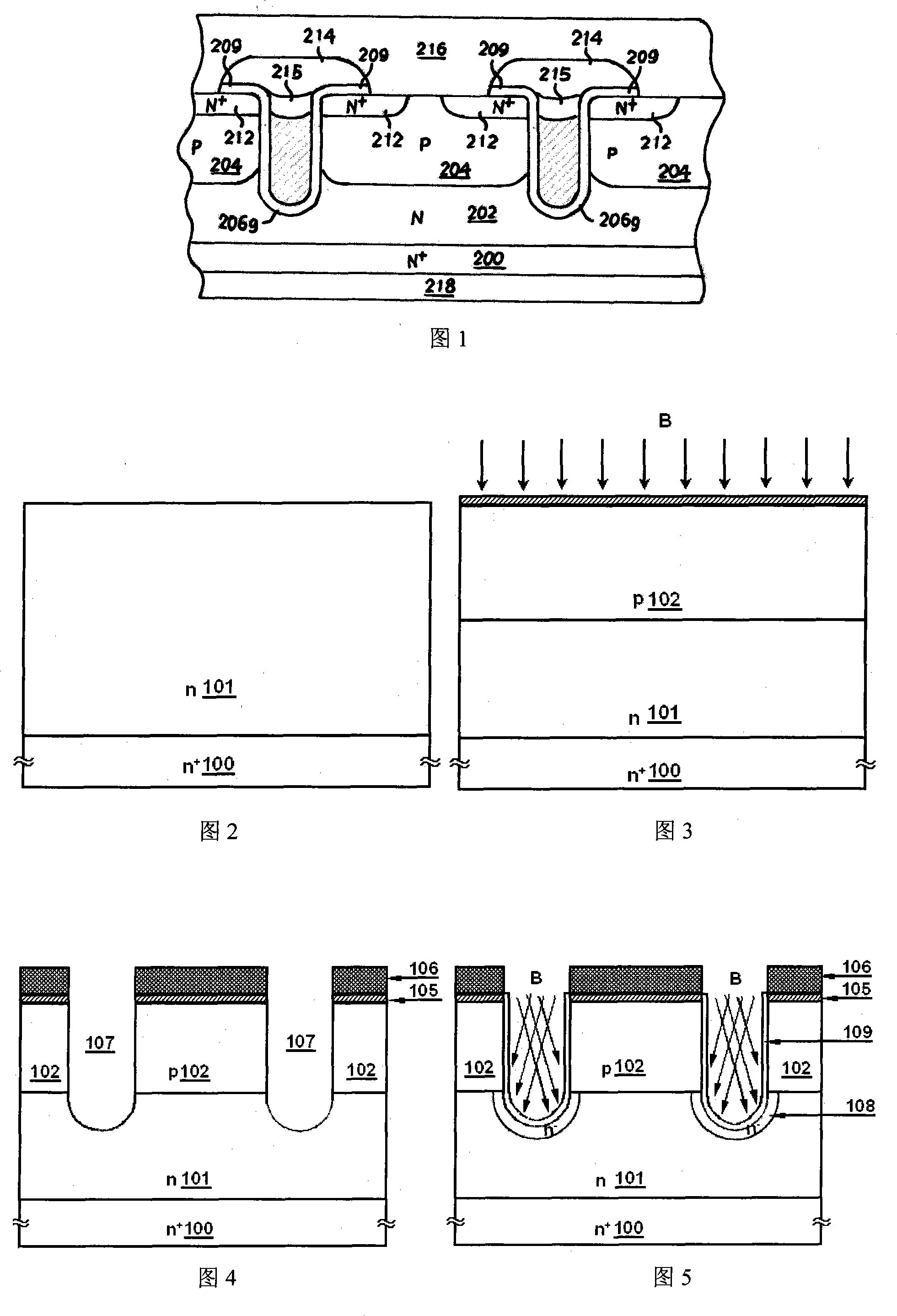

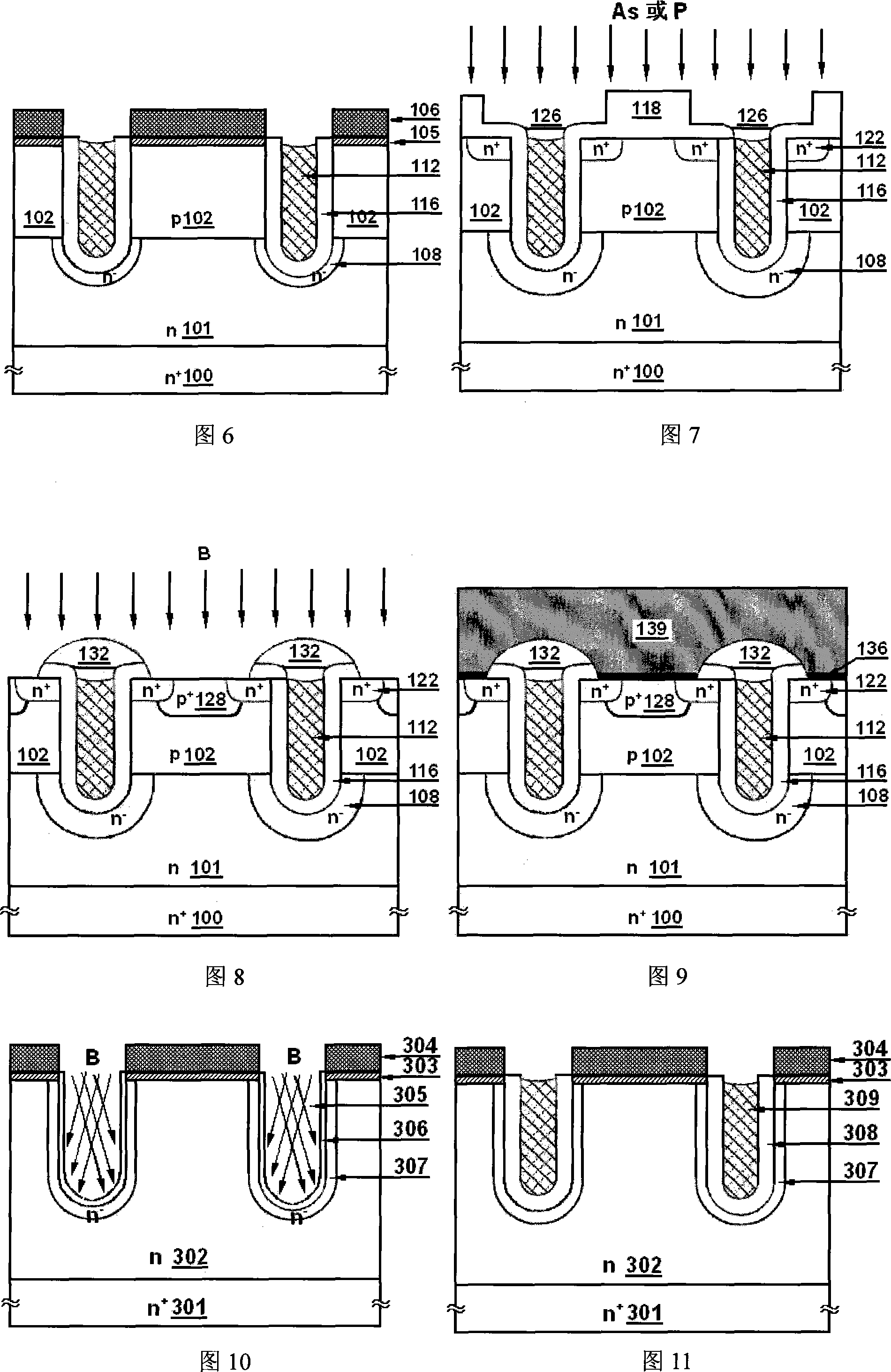

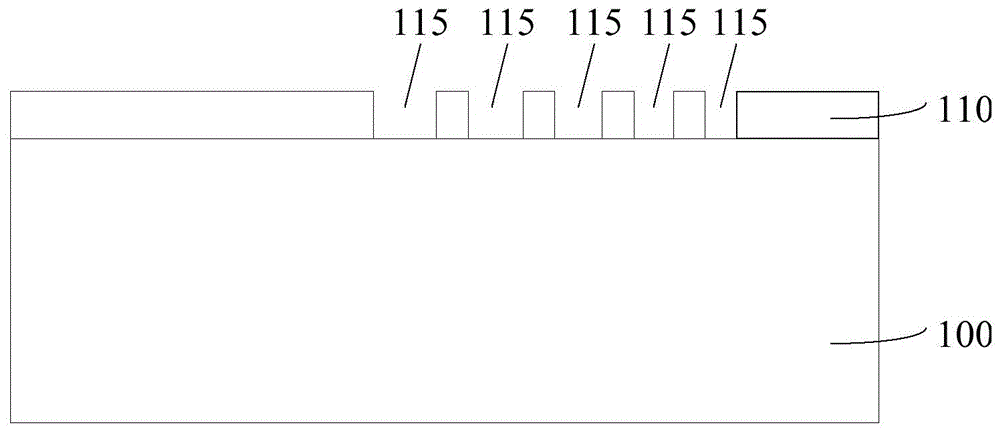

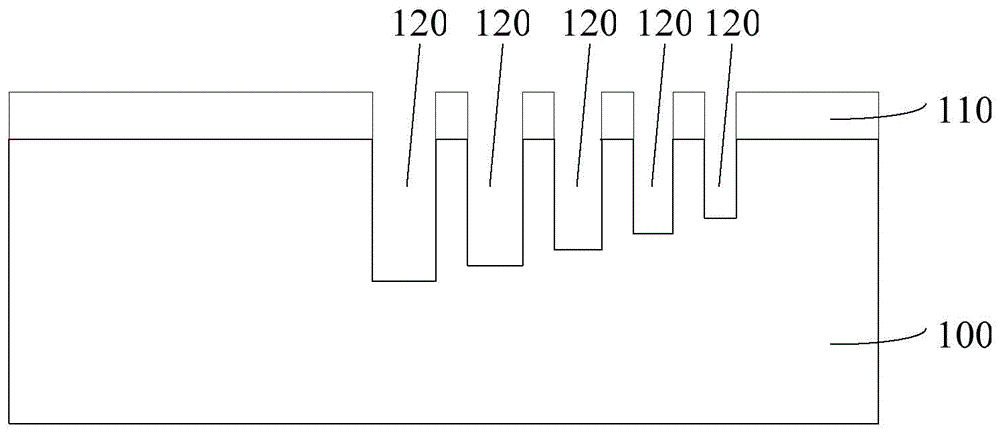

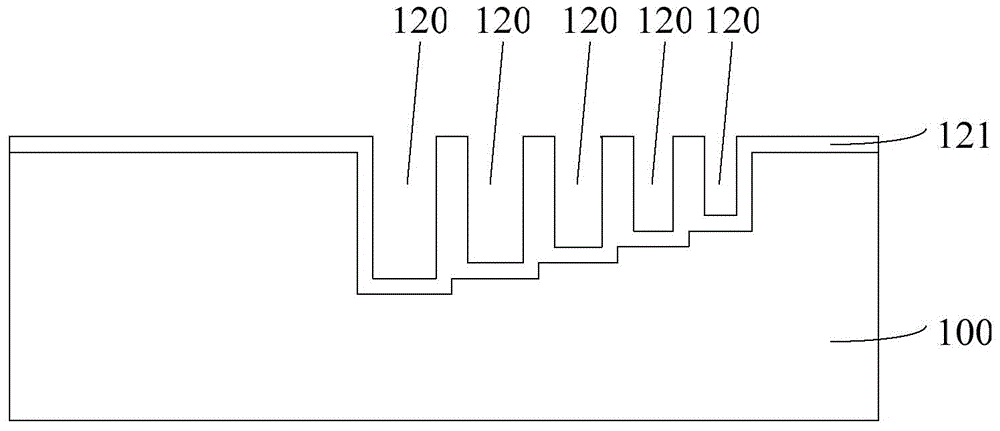

Trench semiconductor device having gate oxide layer with multiple thicknesses and processes of fabricating the same

InactiveUS6900100B2Reduce electric field strengthReduce capacitanceSemiconductor/solid-state device manufacturingDiodeSilicon oxidePower MOSFET

The a trench semiconductor device such as a power MOSFET the high electric field at the corner of the trench is diminished by increasing the thickness of the gate oxide layer at the bottom of the trench. Several processes for manufacturing such devices are described. In one group of processes a directional deposition of silicon oxide is performed after the trench has been etched, yielding a thick oxide layer at the bottom of the trench. Any oxide which deposits on the walls of the trench is removed before a thin gate oxide layer is grown on the walls. The trench is then filled with polysilicon in or more stages. In a variation of the process a small amount of photoresist is deposited on the oxide at the bottom of the trench before the walls of the trench are etched. Alternatively, polysilicon can be deposited in the trench and etched back until only a portion remains at the bottom of the trench. The polysilicon is then oxidized and the trench is refilled with polysilicon. The processes can be combined, with a directional deposition of oxide being followed by a filling and oxidation of polysilicon. A process of forming a “keyhole” shaped gate electrode includes depositing polysilicon at the bottom of the trench, oxidizing the top surface of the polysilicon, etching the oxidized polysilicon, and filling the trench with polysilicon.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

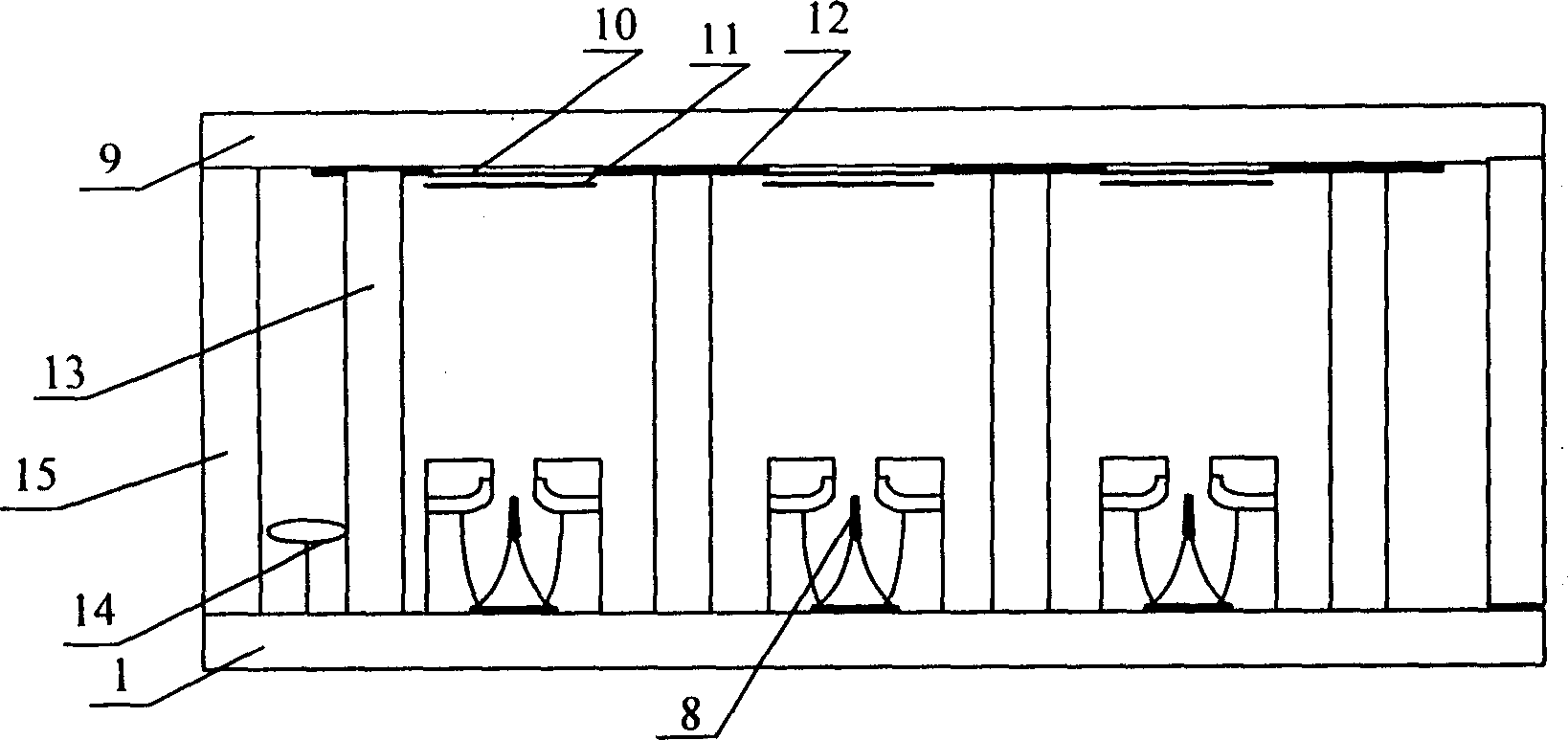

Panel display having adulterated polycrystal silicon field emission cathode array structure and its manufacturing technology

InactiveCN1794408AHighly integratedSimple preparation processImage/pattern display tubesDischarge tube/lamp detailsManufacturing technologyGrating

This invention relates to a panel display with doped-polysilicon field emission cathode array structure and its process technology, in which, the display includes a sealed vacuum cavity composed of a cathode panel, an anode panel and surrounding glasses, anode conduction strips etched on the anode panel and fluorescence powder layer on the conduction strips, a supporting wall and getter attached elements, in which, a doped polysilicon field emission cathode array structure is prepared on the cathode panel to reduce the distance between the cathode and the grating, control the working voltage of the grating and reduce the current of the control grating.

Owner:ZHONGYUAN ENGINEERING COLLEGE

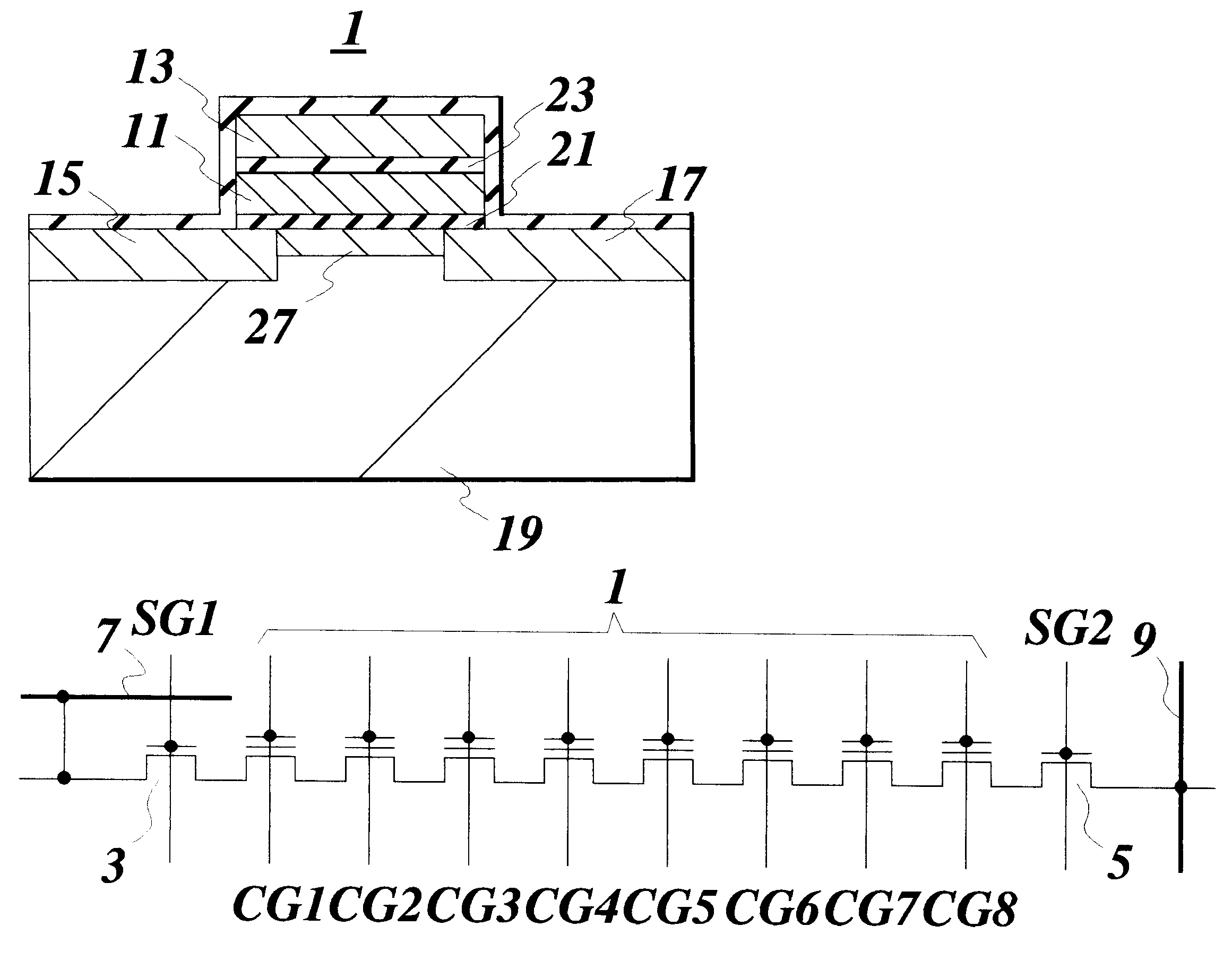

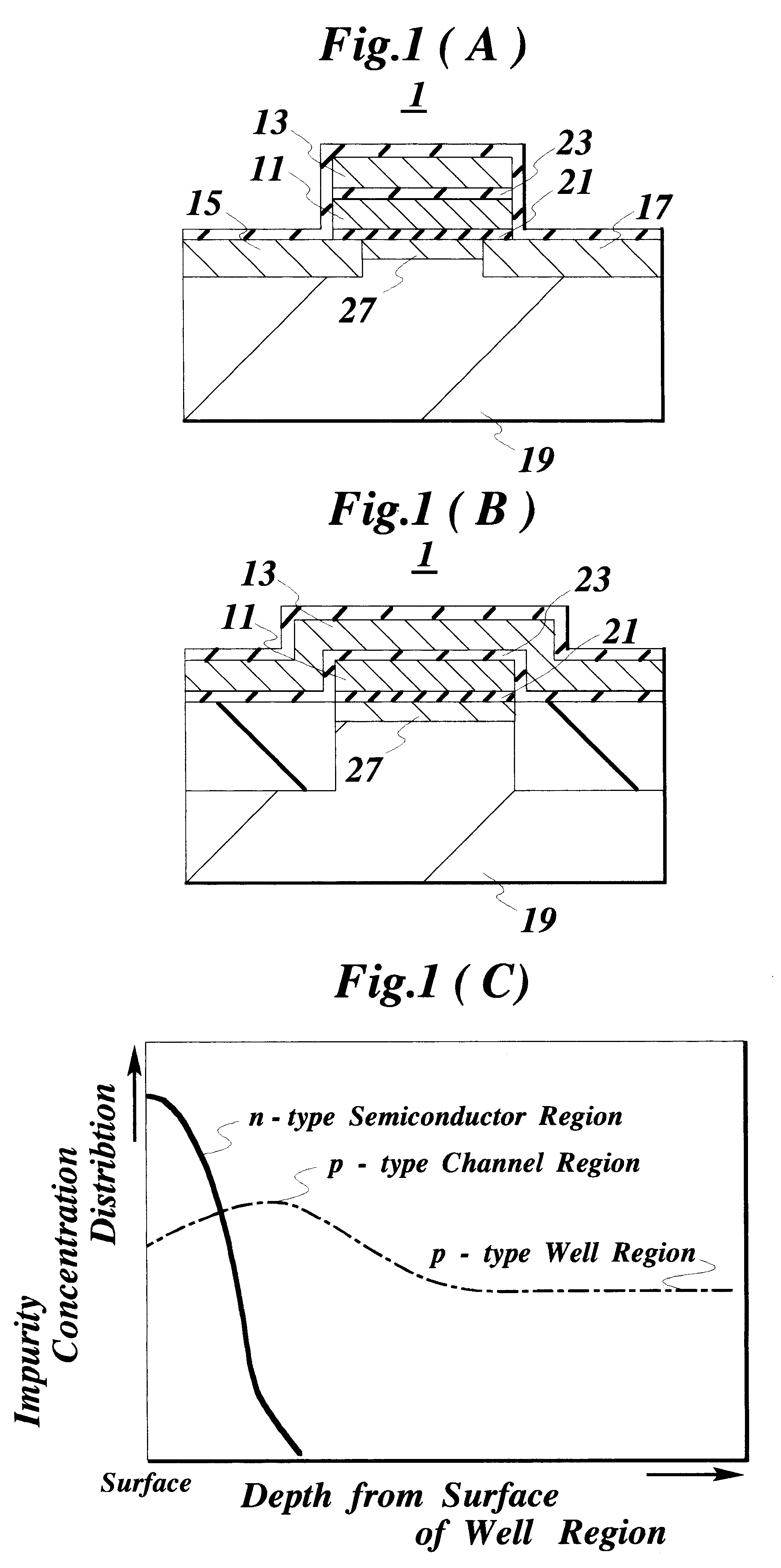

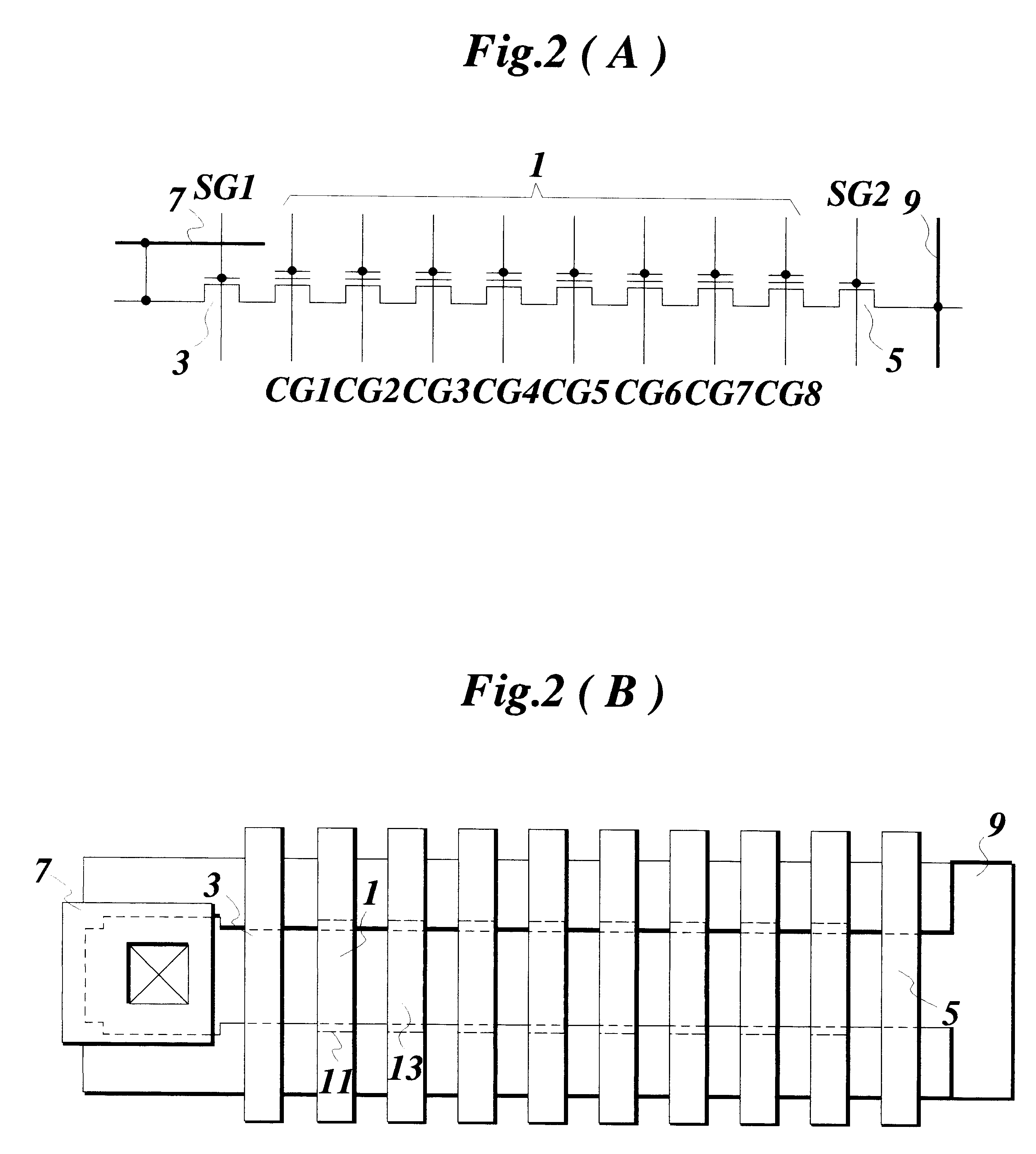

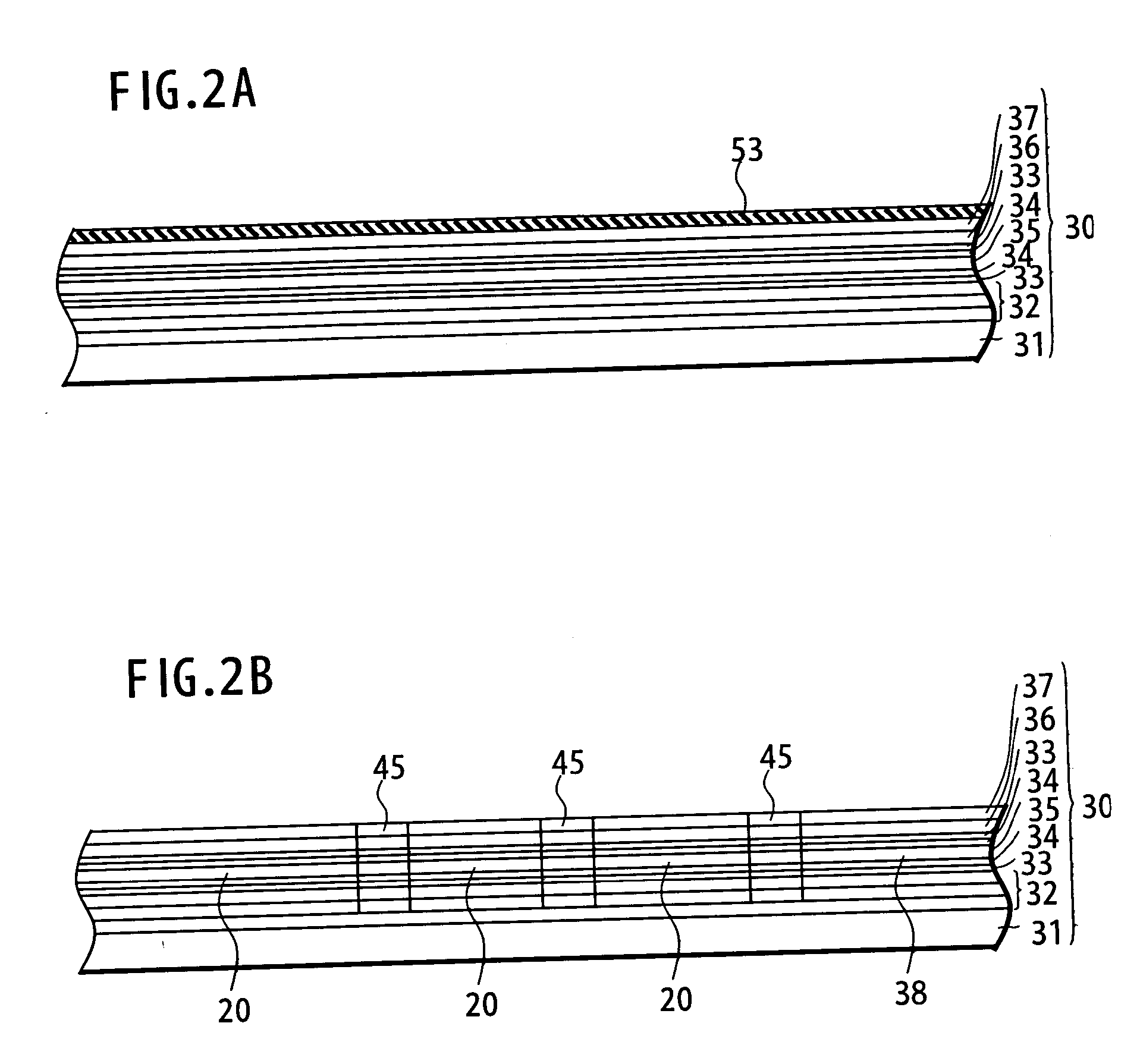

Erasable and programmable nonvolatile semiconductor memory, semiconductor integrated circuit device having the semiconductor memory and method of manufacturing the semiconductor memory

InactiveUS6222224B1Improve reliabilityReduced strengthTransistorSolid-state devicesChannel conductivitySemiconductor

A nonvolatile semiconductor memory has memory cells (1) each having an insulated-gate FET that has an information storage part. A semiconductor region (27) is formed at the surface of a channel region of each memory cell. The semiconductor region has the same conductivity type as a channel conductivity type and functions to decrease the strength of an electric field at the surface of the channel region. If the insulated-gate FET is of an n-channel type, the semiconductor region is of an n-type. The semiconductor region suppresses threshold voltage variations among the insulated-gate FETs of the memory cells and prevents soft-writing in the memory cells.

Owner:KK TOSHIBA

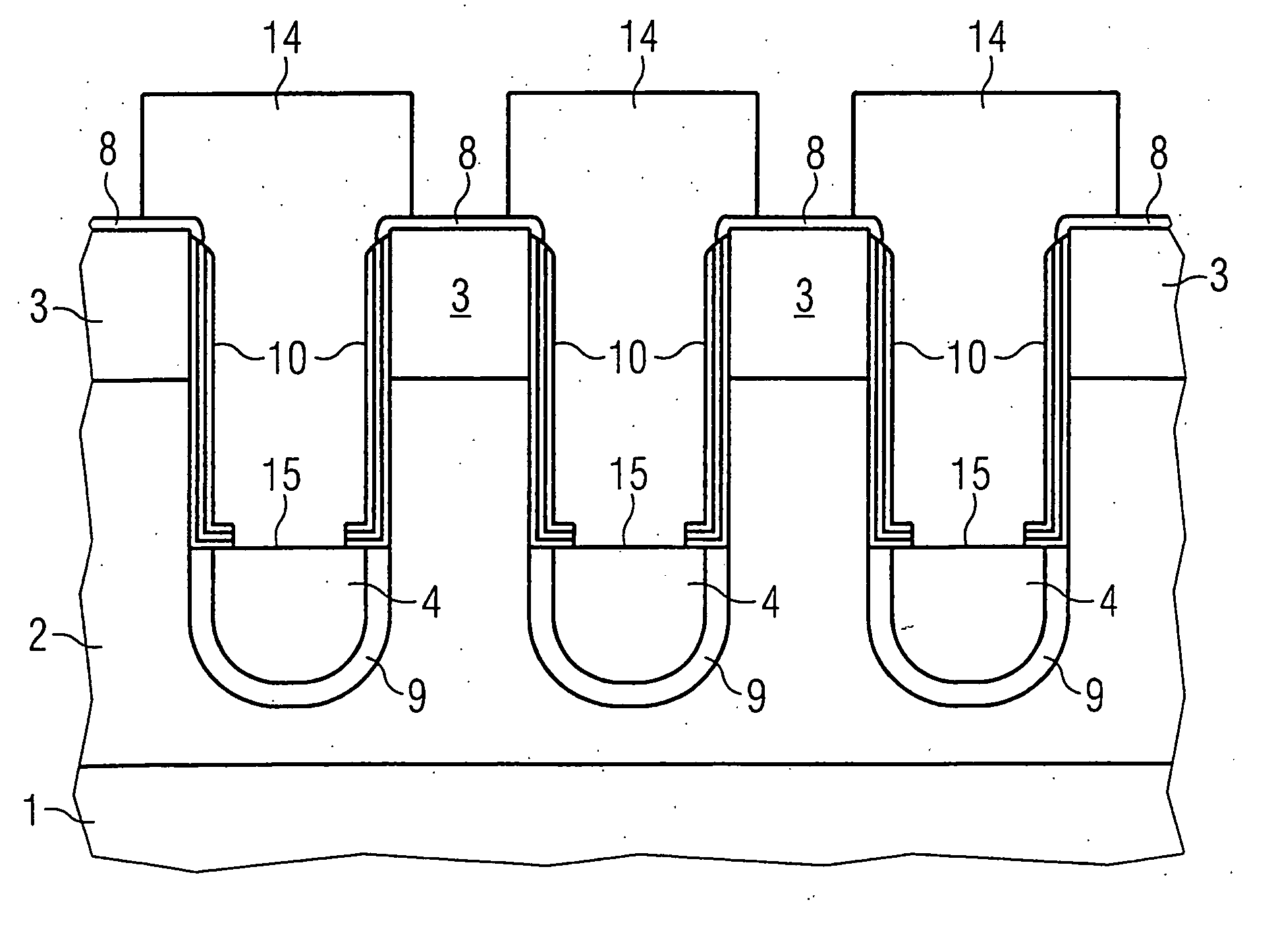

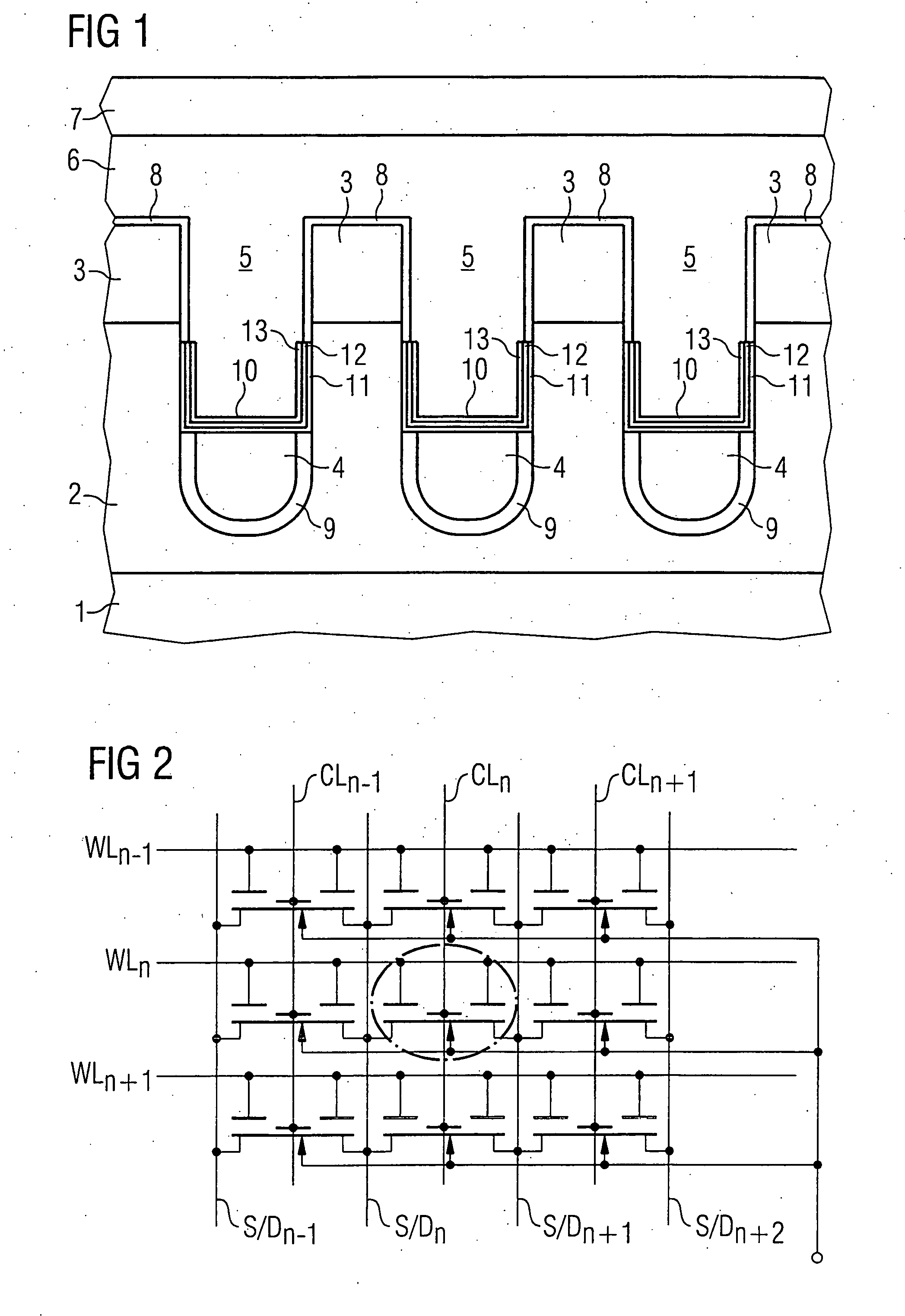

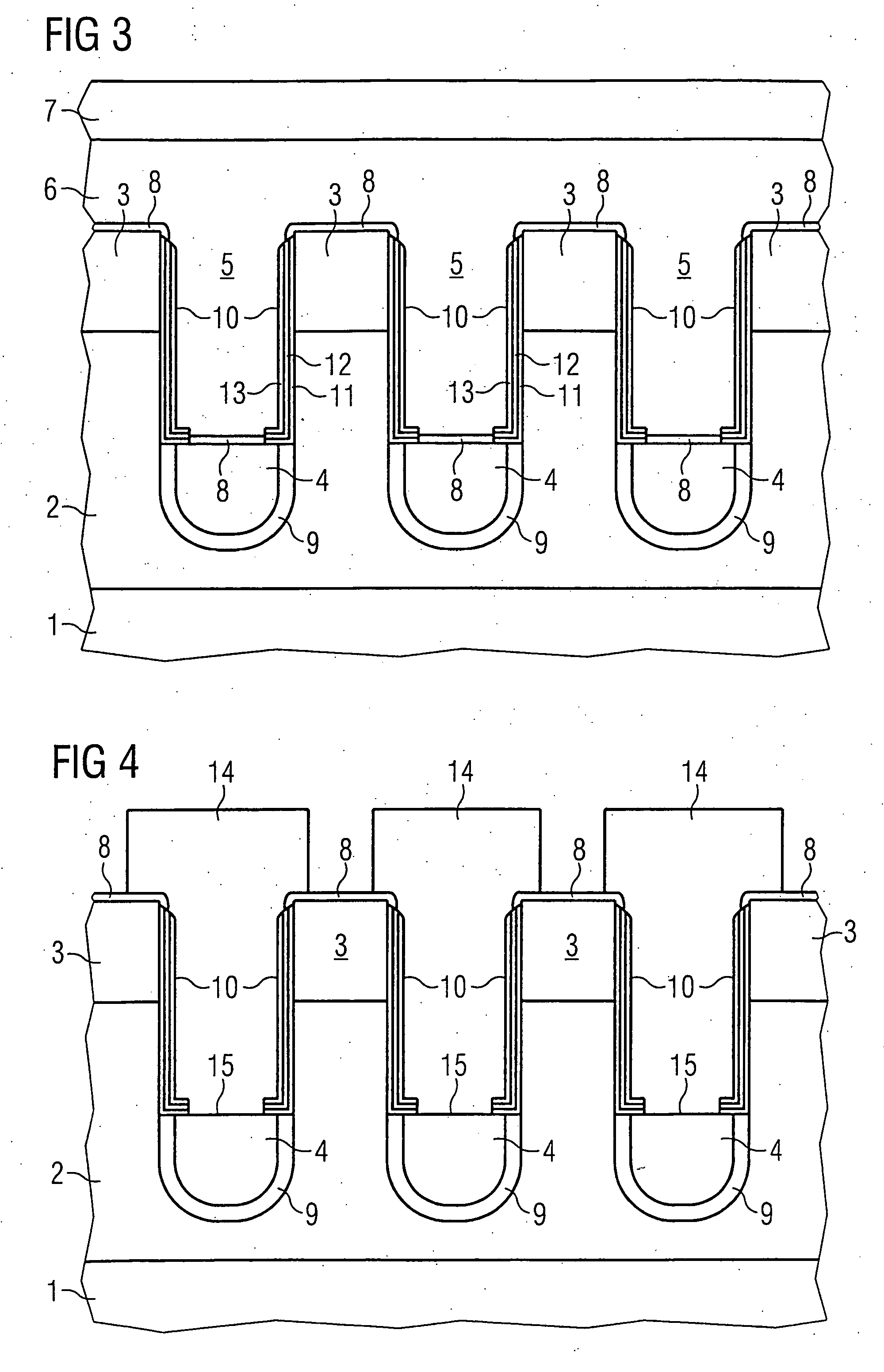

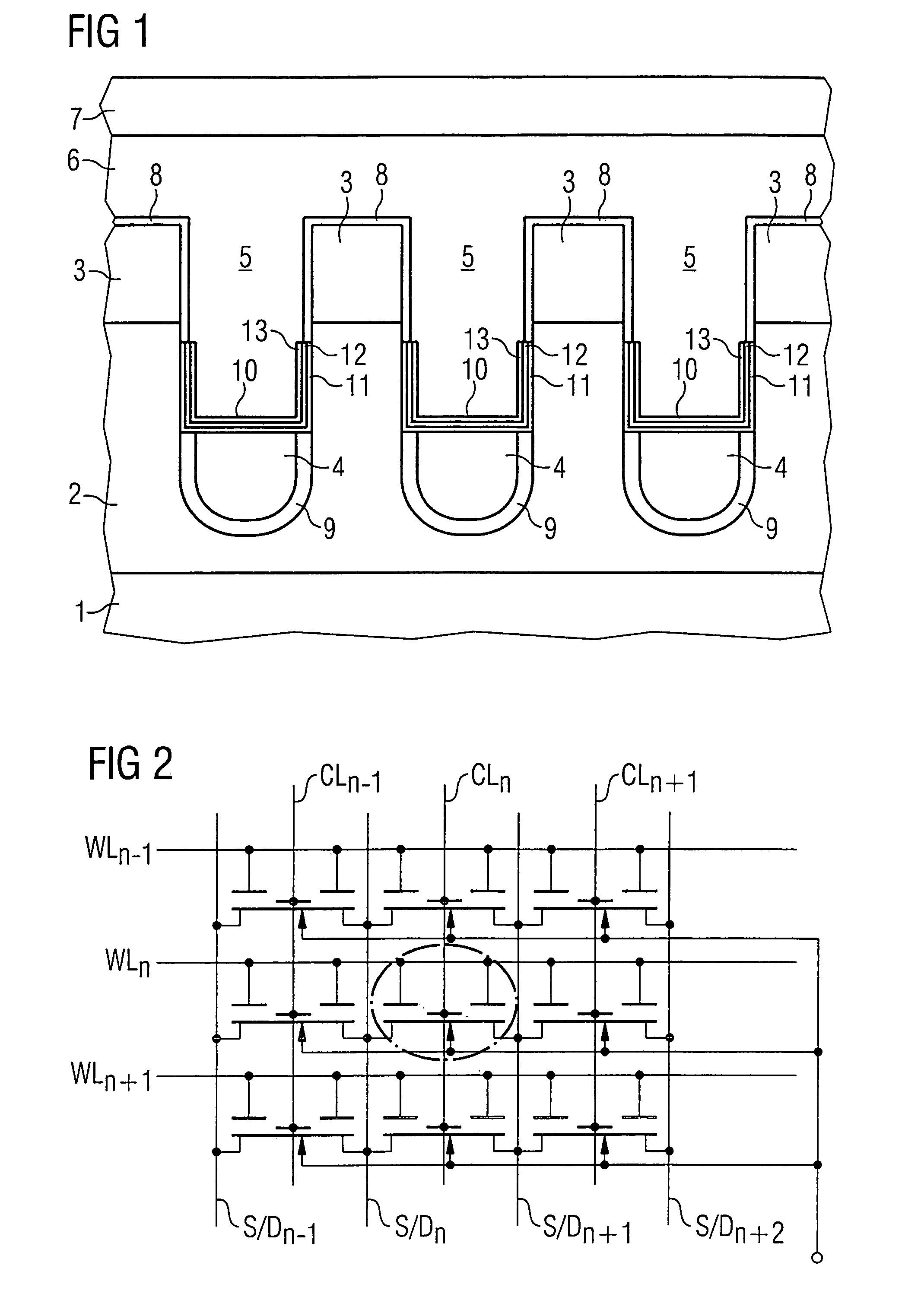

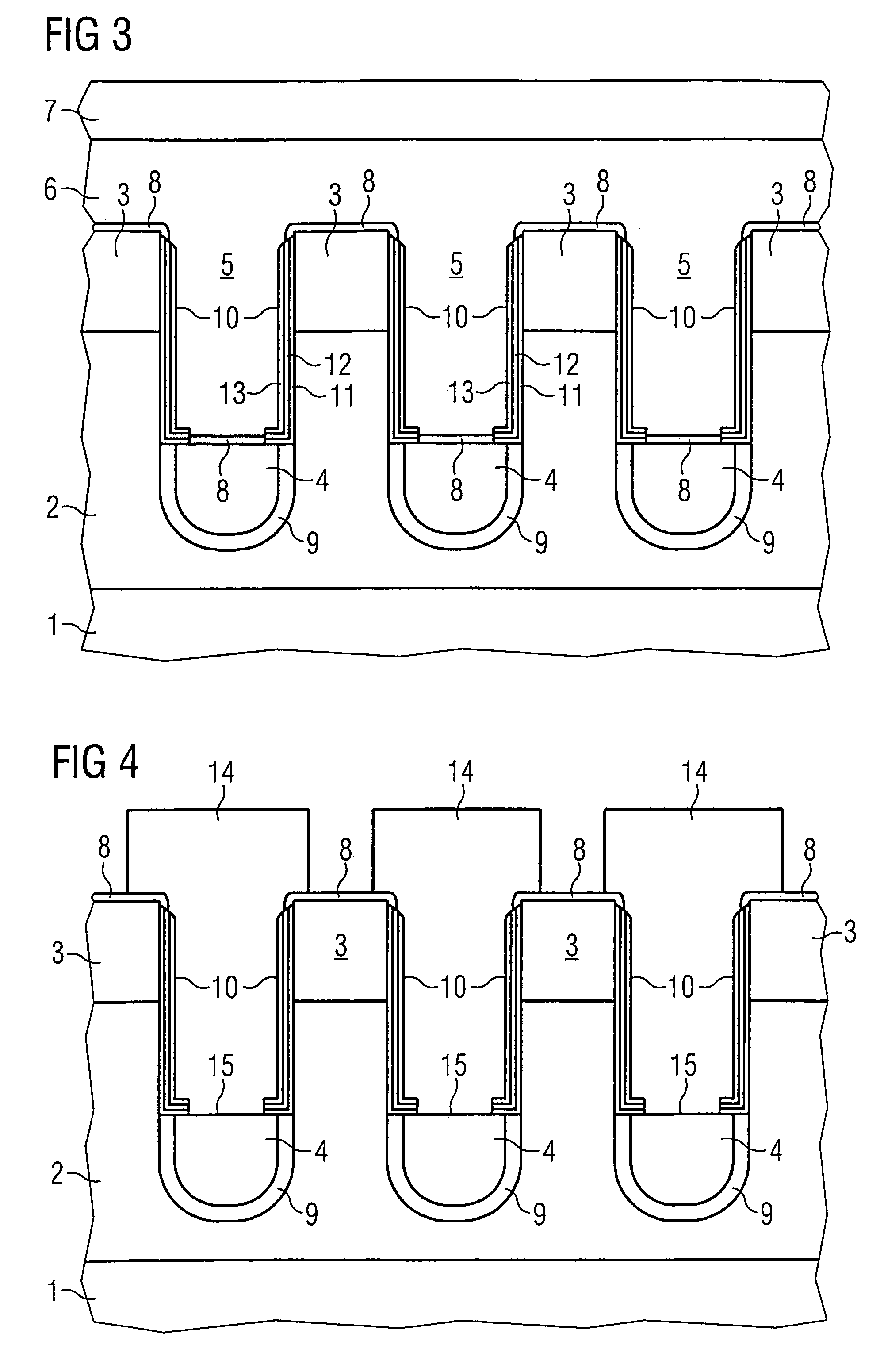

Charge trapping memory cell and fabrication method

InactiveUS20050189582A1Accelerated programImproved erasing propertySolid-state devicesSemiconductor/solid-state device manufacturingStorage cellTransistor

A memory cell patterned as a trench transistor is provided with a first gate electrode (4) as auxiliary gate for source-side injection and a second gate electrode (5) electrically insulated therefrom, which are arranged in the trench, and has, at the trench walls, a storage layer sequence (10) provided for charge trapping and comprising a storage layer (12) between boundary layers (11, 13). The first gate electrode (4) and the second gate electrode (5) are electrically insulated from one another, which can be effected by means of a portion of the storage layer sequence (10). Source / drain regions (3) are arranged on the top side laterally with respect to the trenches. Word lines (6), source / drain lines and control gate lines are present for the electrical driving.

Owner:POLARIS INNOVATIONS

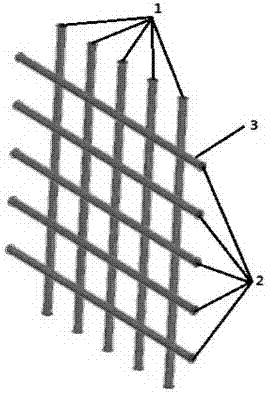

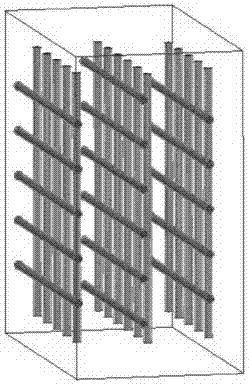

Method and device for integrally desulfurizing, denitrating and dust-removing by plasma

ActiveCN103566722AIncrease the number ofReduce electric field strengthDispersed particle separationElectrode constructionsChemical reactionAdditive ingredient

The invention discloses an integrated treatment method capable of desulfurizing, denitrating and dust-removing at the same time, and provides a device which adopts the treatment method. Smoke formed after the combustion in a boiler contains the main ingredients of SO2, NOX and dust, and passes through a plasma generation electrode; generated plasmas contain a large amount of high-energy electronics and act on O2 and H2O to generate a large quantity of active particles, such as H, O, OH and O3. The SO2 and the NOX can perform chemical reaction to generate high-valence state sulfur oxides and nitrogen oxides under the effect of the active particles, and then the sulfur oxides and the nitrogen oxides are combined with introduced ammonia gas to generate ammonium salts; the ammonium salts are recovered and serve as secondary products; and therefore, the desulfurizing and the denitrating are realized. In the process, charged particles in the plasmas can electrify dust particles, so that the charged particles can move directionally under the effect of an additional direct-current bias electric field; and therefore, the function of removing the dust is realized. According to the method and the device, the static electricity dust removal and the plasma desulfurizing and denitrating are integrated, so that the number of power supplies is reduced, the efficiency of a discharge power supply is improved, the energy consumption can be reduced, the investment is saved, the occupied area is reduced, and the cost is reduced.

Owner:BEIJING RUIYUDA TECH

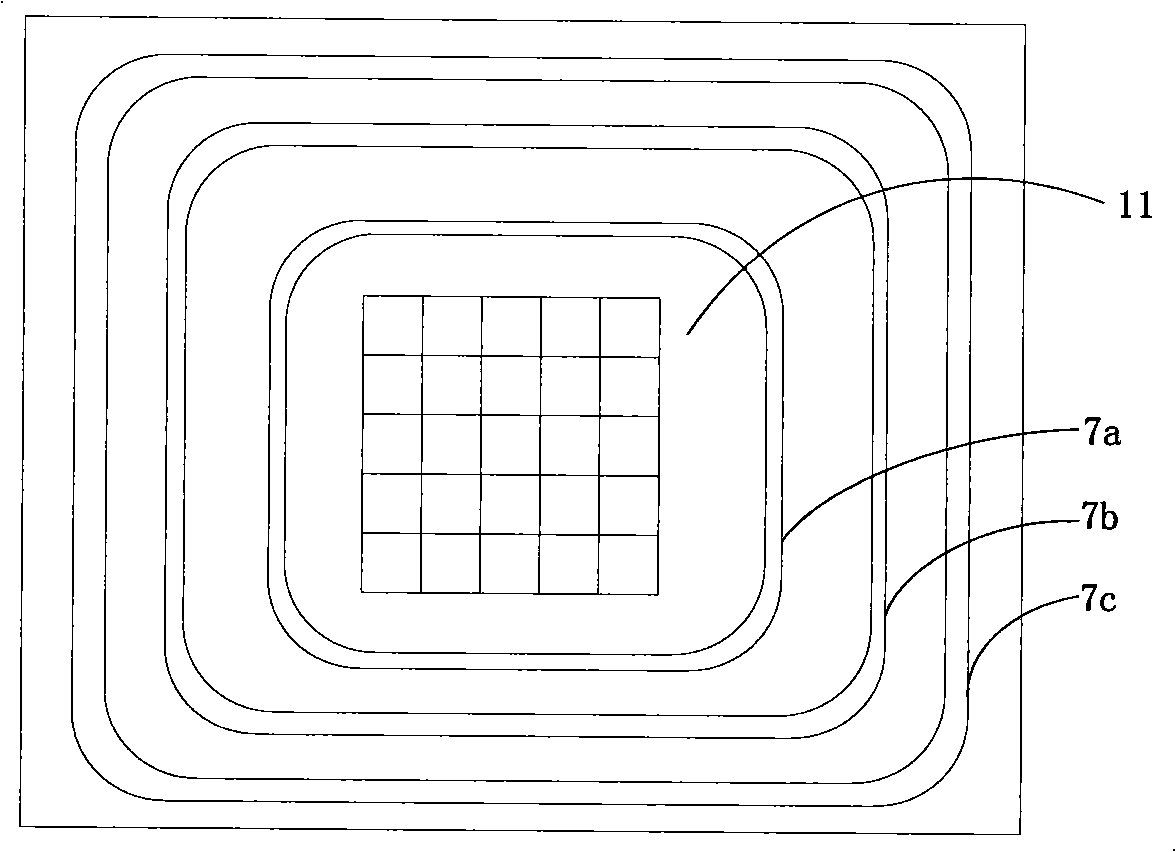

Edge terminal structure of high-voltage power semiconductor device

InactiveCN101969068AReduce electric field strengthReduce concentrationSolid-state devicesSemiconductor devicesPower semiconductor deviceElectrical field strength

The invention discloses an edge terminal structure of a high-voltage power semiconductor device. The edge terminal structure comprises a plurality of field limiting rings which wind the power semiconductor device and have a conduction type opposite to that of a substrate; one or two side of each field limiting ring is provided with a doped region which has a conduction type the same as that of the field limiting ring and the doping concentration smaller than that of the field limiting ring; the field limiting rings are coated with field plates; and the field limiting rings and the field plates are separated by silicon dioxide layers. The material of the field plate can be selected from copper, aluminum, polysilicon, oxygen-doped polysilicon and the like. The doped regions with lower concentration are added around the conventional field limiting rings, so the intensity of electric field lines of an edge cellular can be effectively reduced, the electric field strength borne by the edge cellular is reduced, the breakdown voltage is improved, the area efficiency of the edge terminal structure is effectively improved, the chip area is saved, and the chip cost is reduced.

Owner:ZHEJIANG UNIV +1

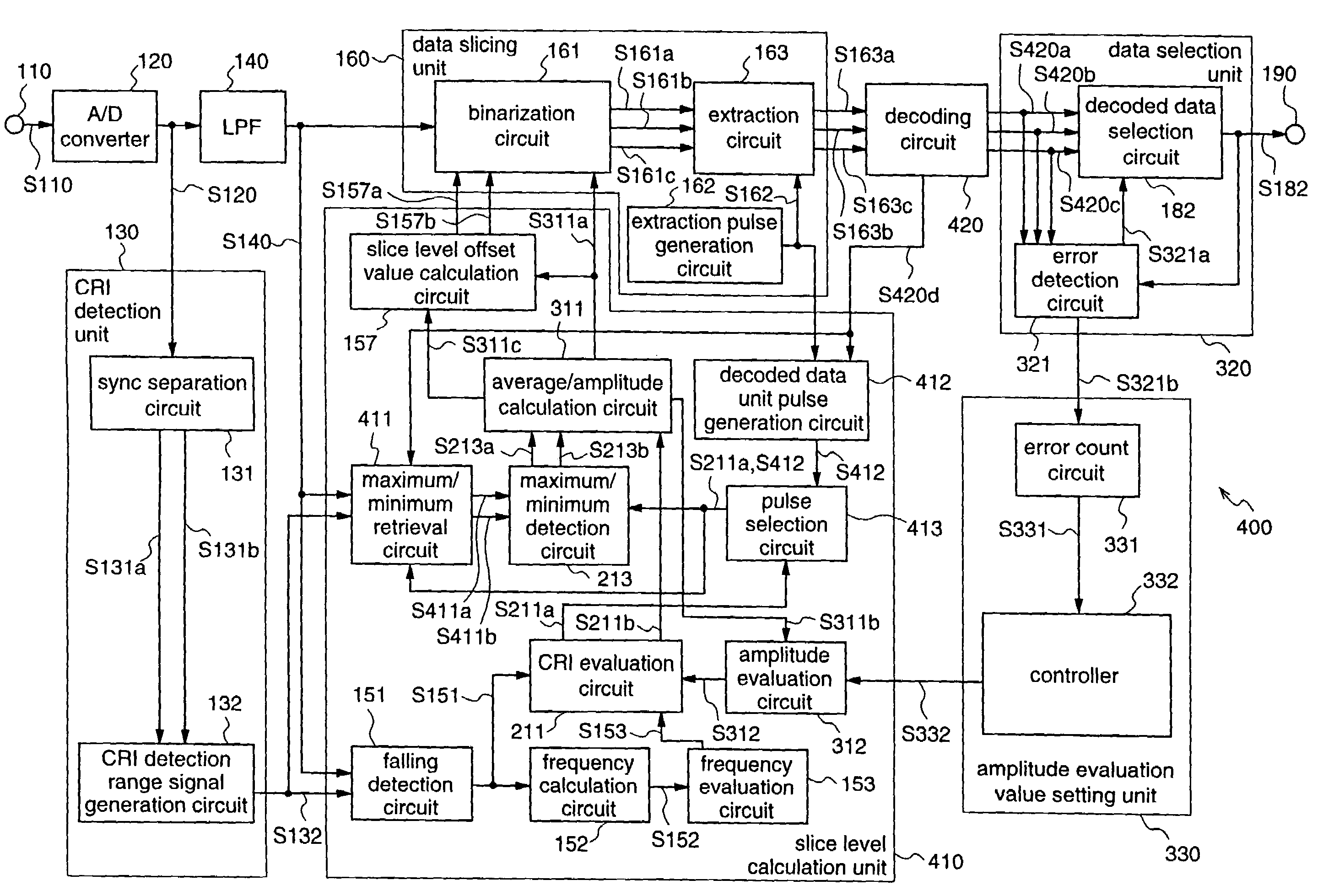

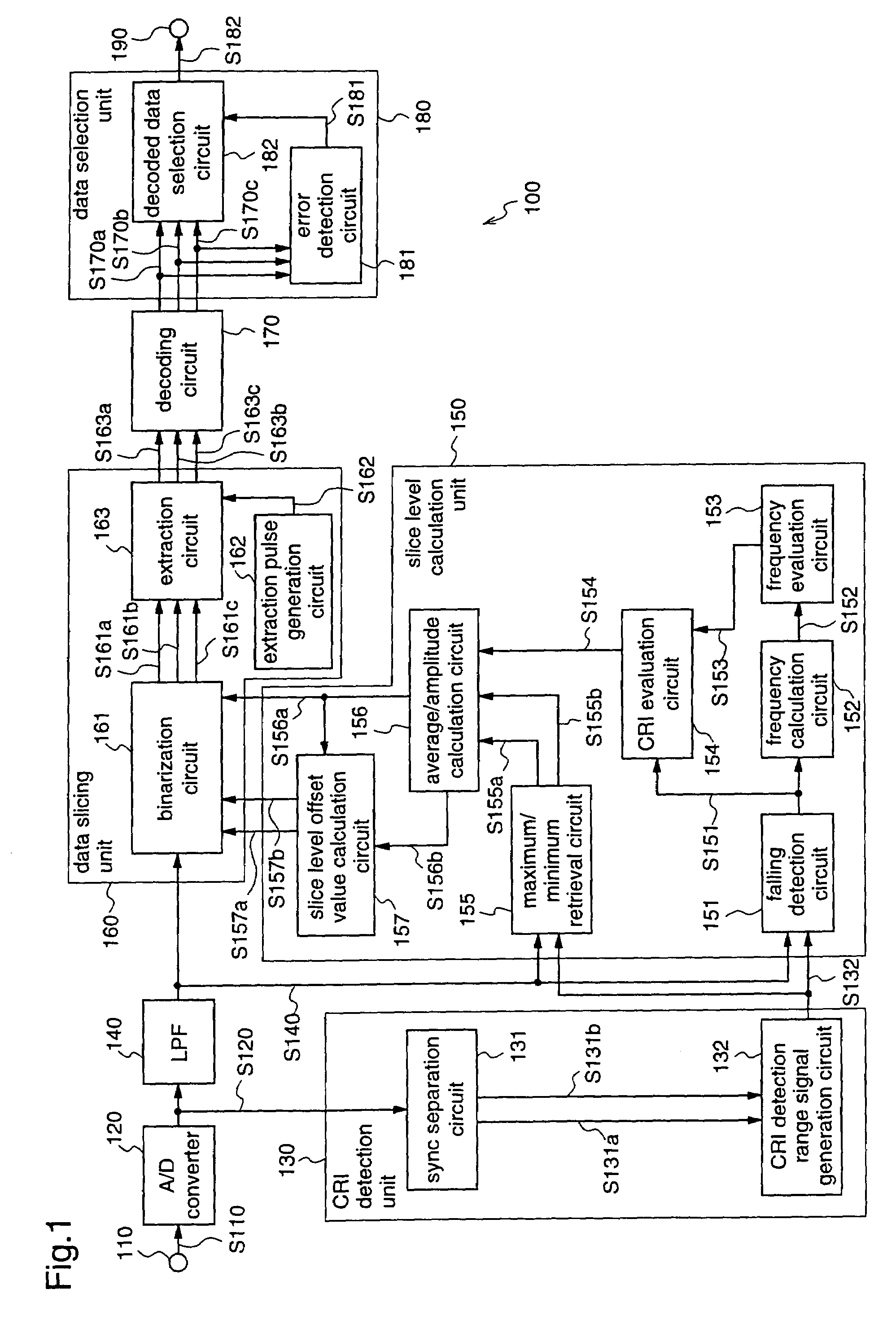

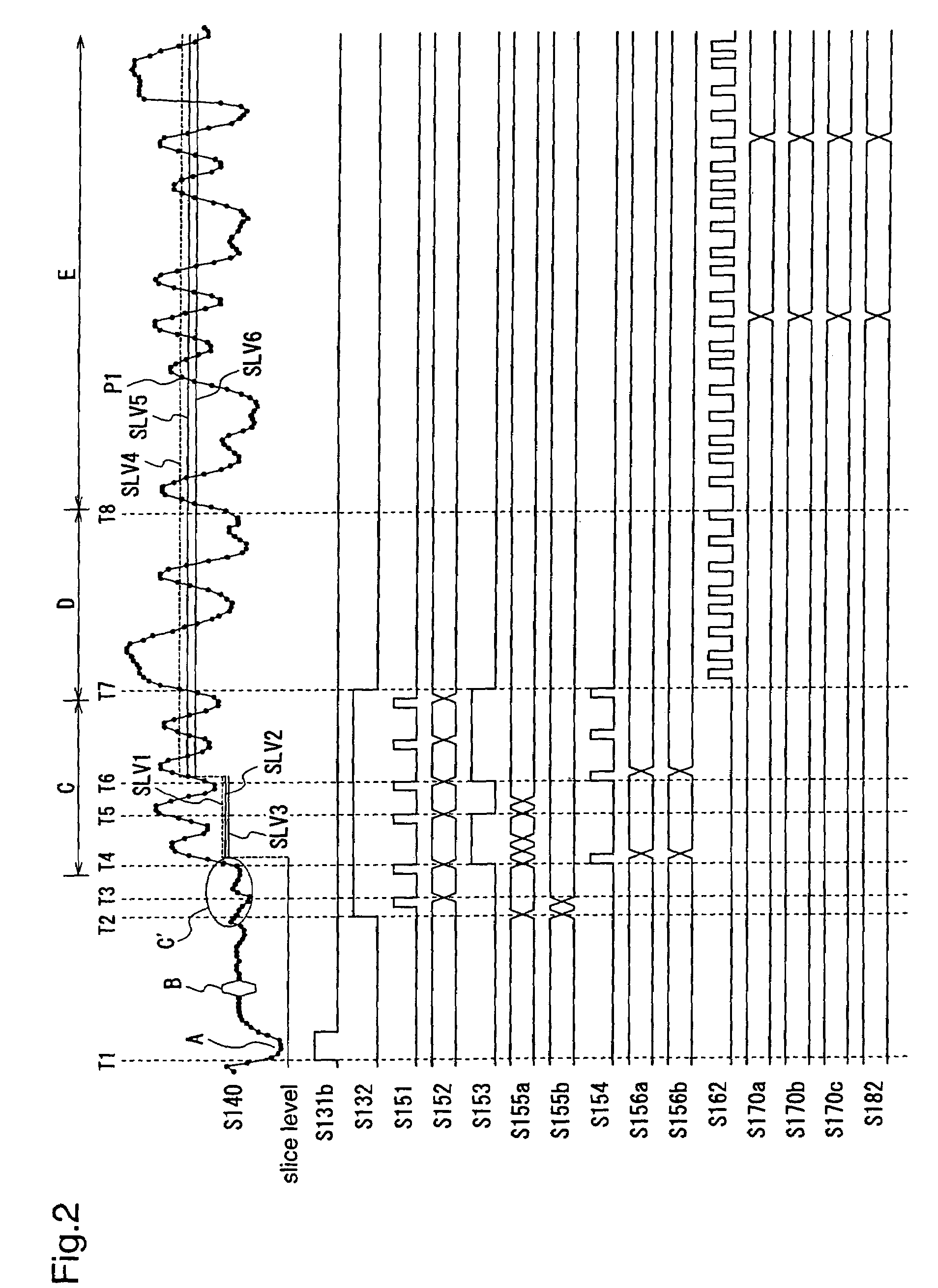

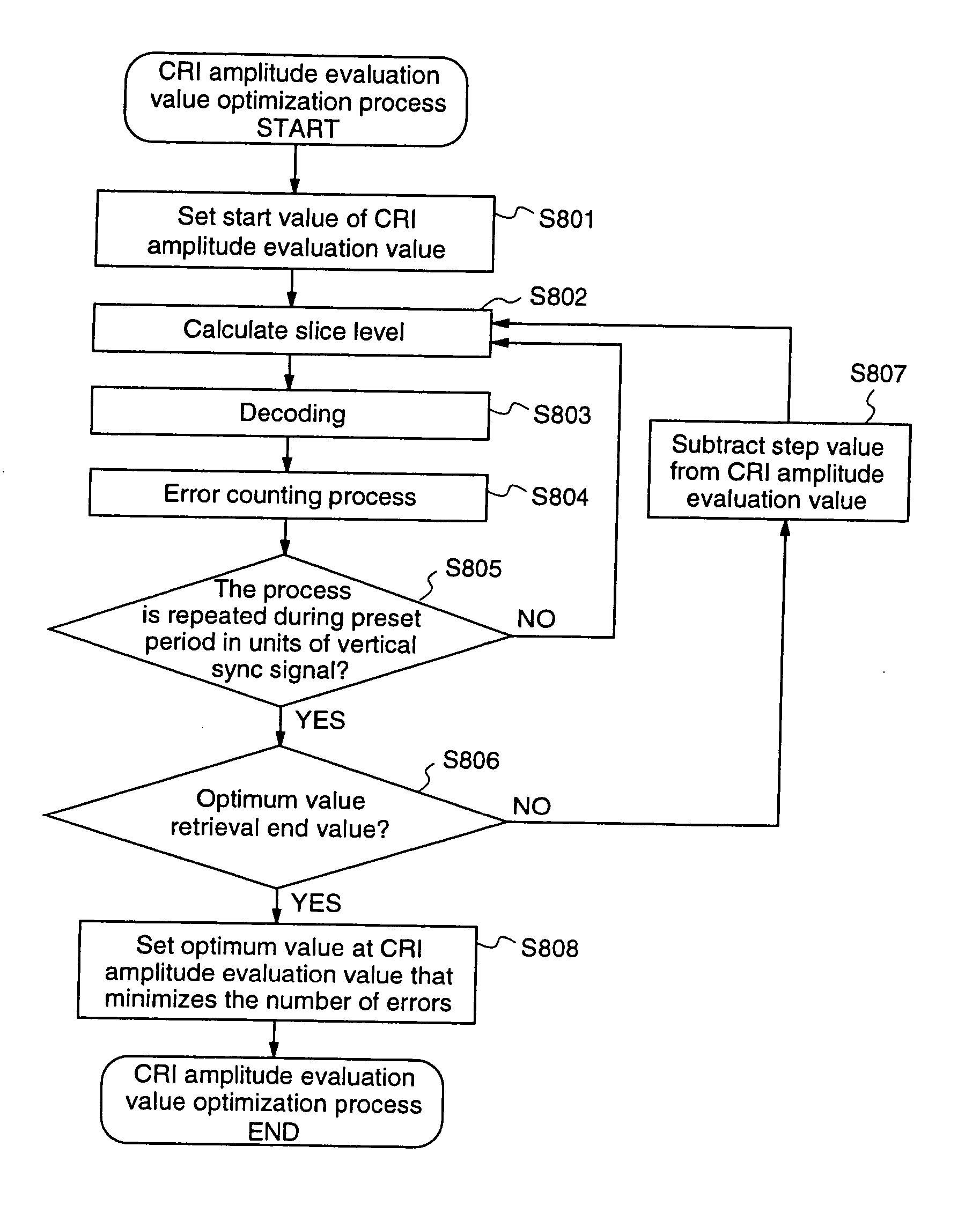

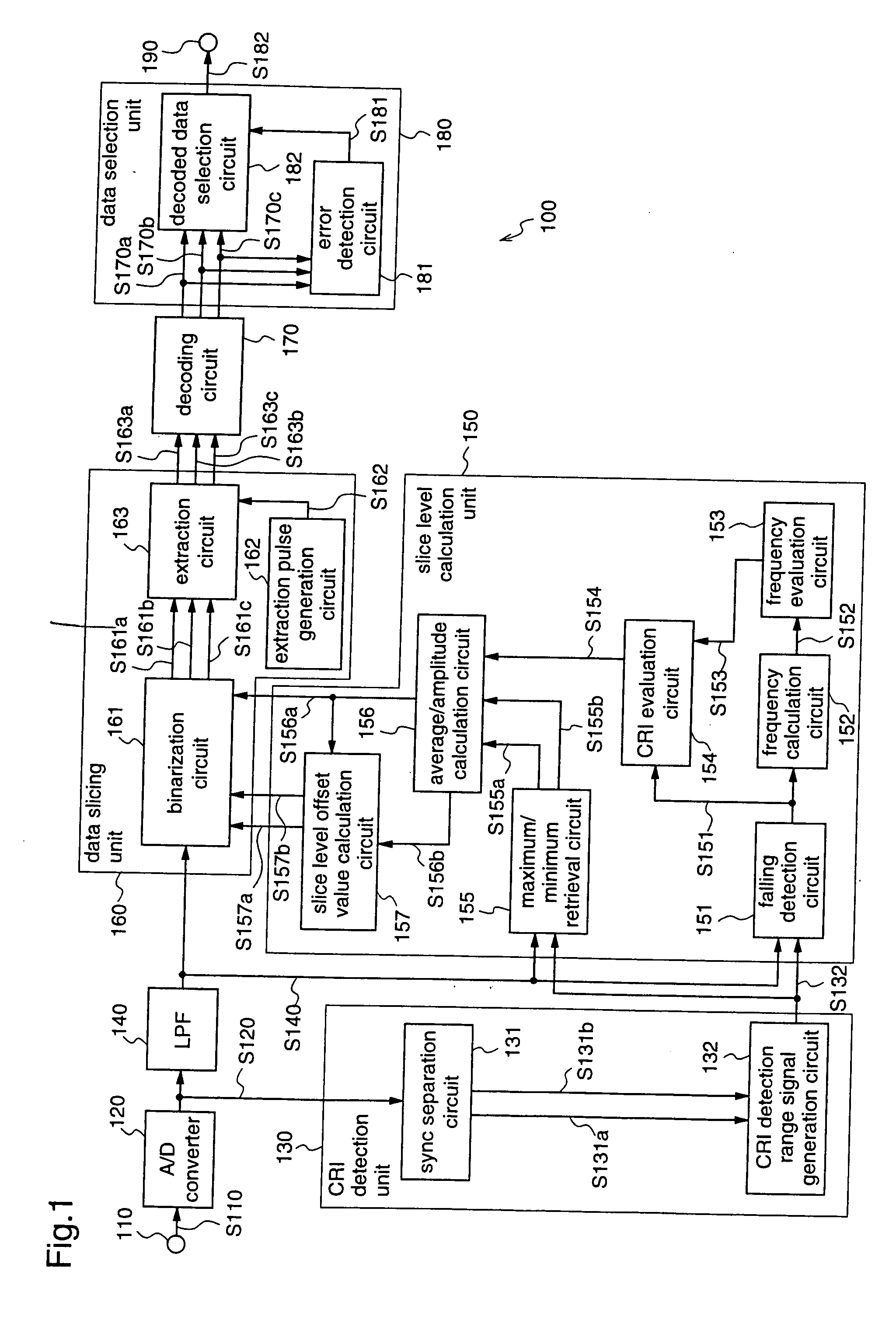

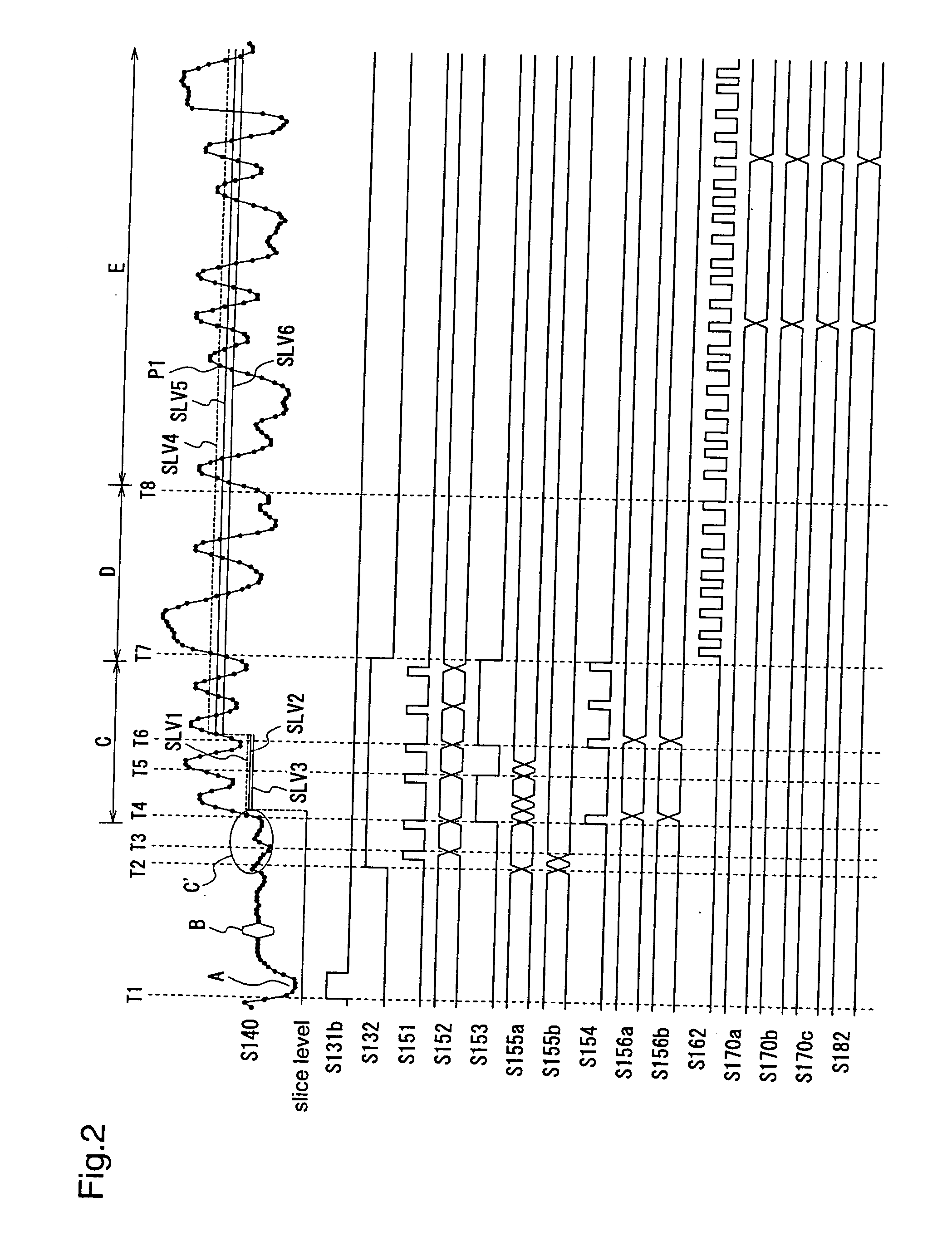

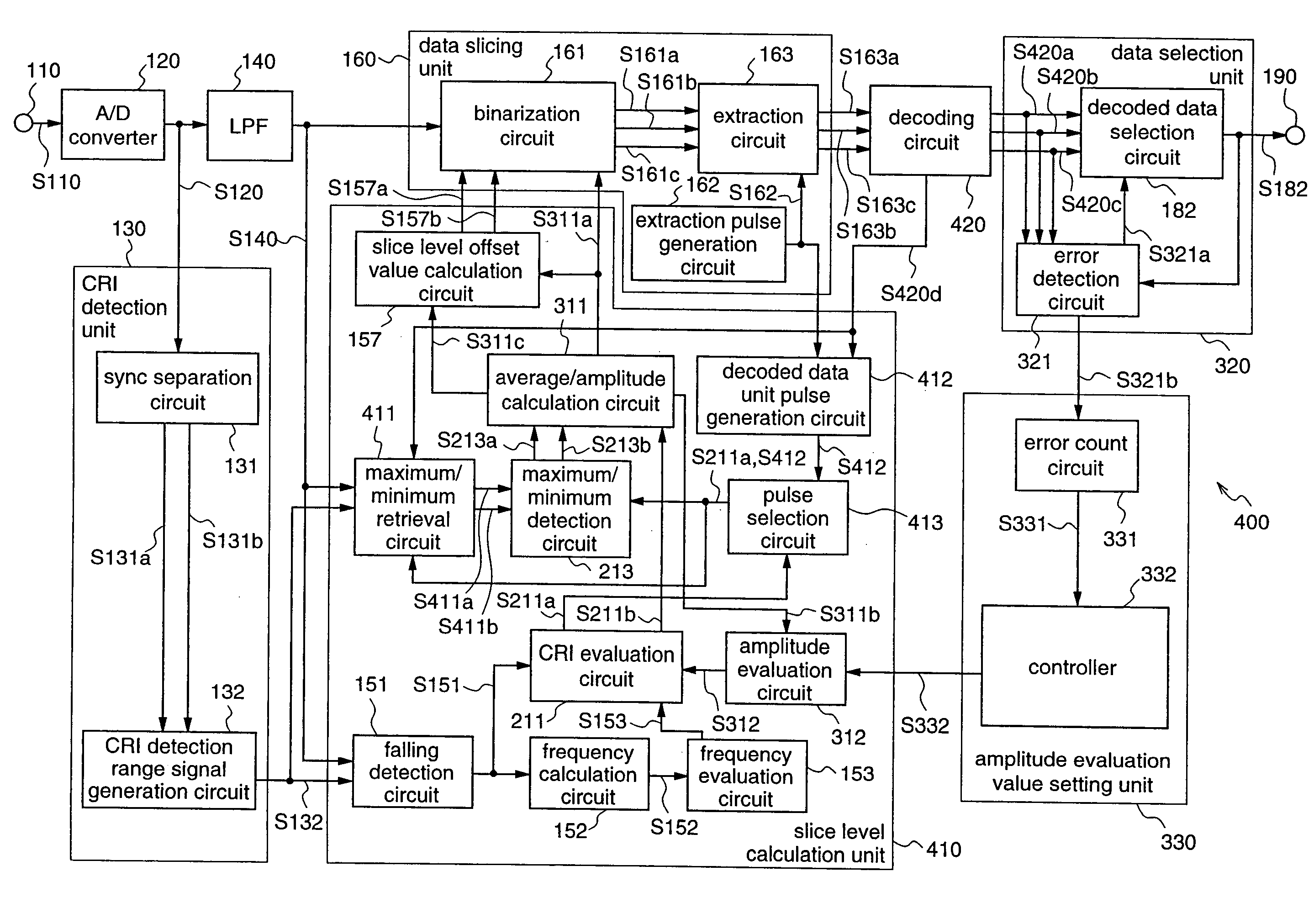

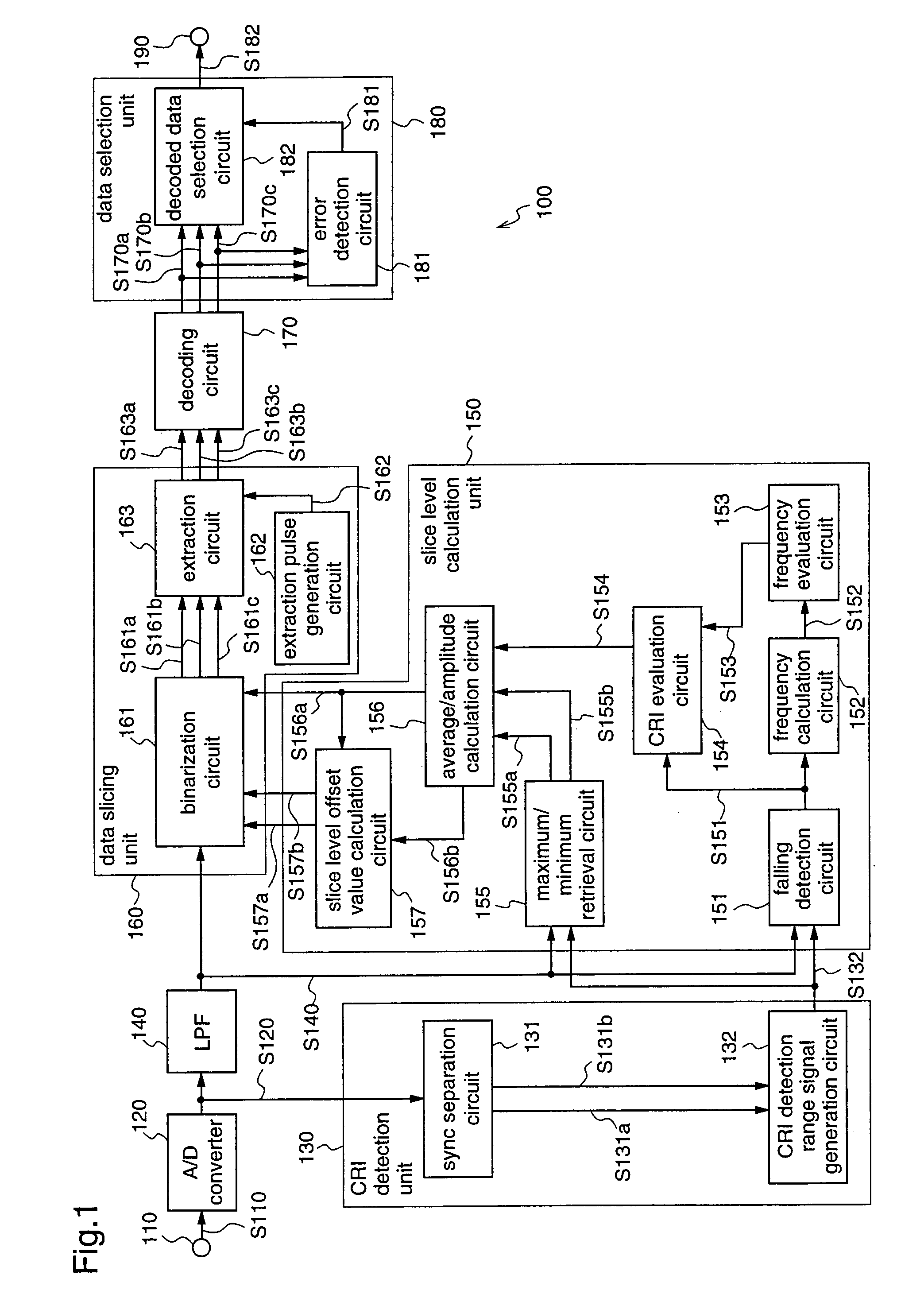

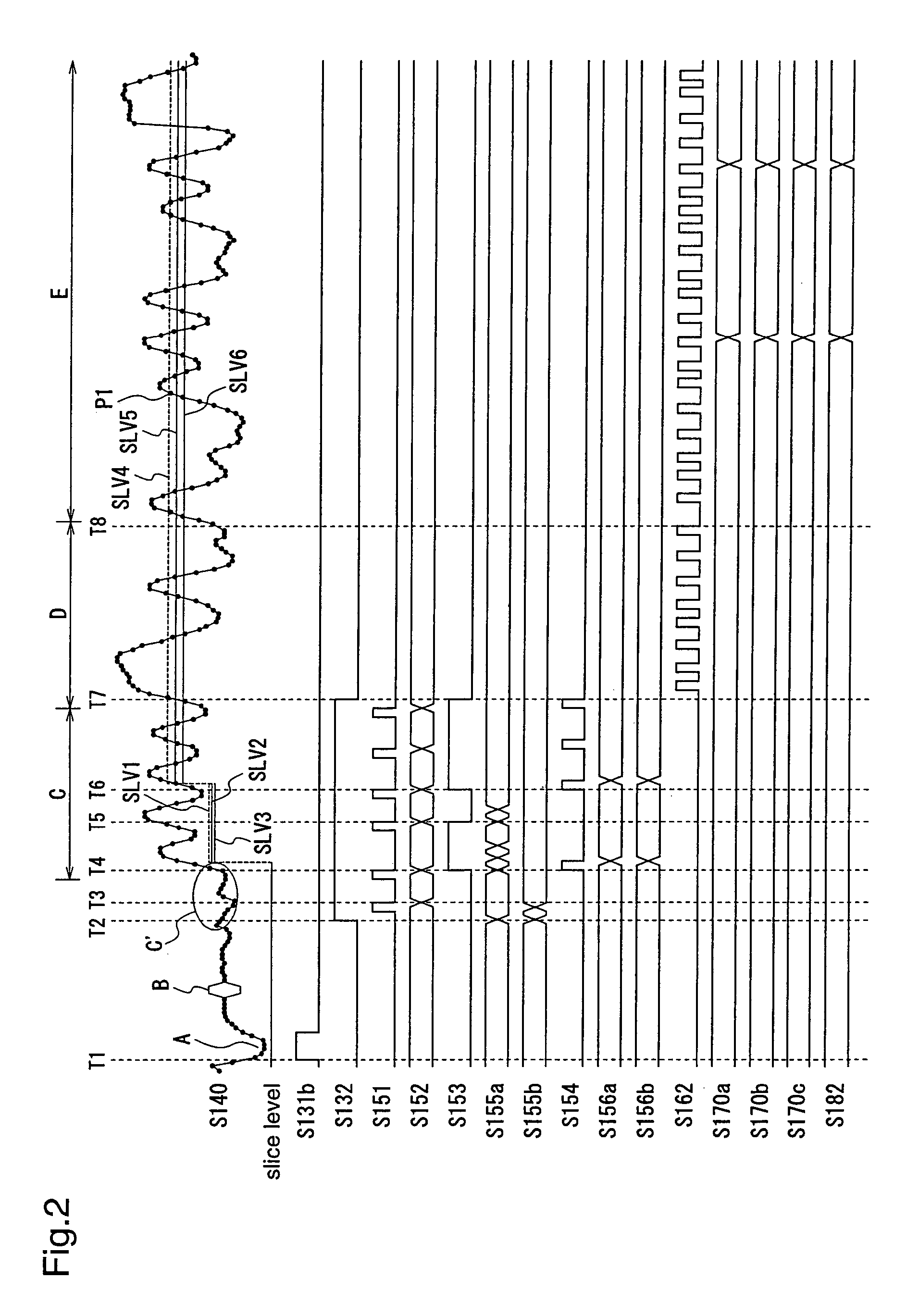

Data slicer, data slicing method, and amplitude evaluation value setting method

ActiveUS7599003B2Reduce electric field strengthPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningDigital videoData transformation

A data slicer 300 includes a slice level calculation unit 310 that determines whether a detected digital video signal is a CRI signal on the basis of the amplitude of the signal, and sets a reference slice level and upper and lower slice levels which are obtained by providing offset in the reference slice level, by using only the CRI signal; a data slicing unit 160 that binarizes a digital video signal S140 using the slice levels; a decoding circuit 170 that converts binarized serial data into parallel data; and a data selection unit 320 that selects data including no error from the decoded data, and outputs the selected data through a video signal output terminal 190. Therefore, even when the video signal is distorted, this data slicer can set appropriate slice level data to binarize the video signal, thereby suppressing the occurrence rate of decoding errors.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Compound semiconductor device and manufacturing method thereof

InactiveUS20050277255A1Avoid defectsImprove reliabilityTransistorSemiconductor/solid-state device detailsHigh concentrationNitride

A pad electrode of a high electron mobility transistor is formed solely of a pad metal layer without providing a gate metal layer. A high concentration impurity region is provided below the pad electrode, and the pad electrode is directly contacted to a substrate. Predetermined isolation is ensured by the high concentration impurity region. Accordingly, in a structure not requiring a nitride film as similar to the conventional art, it is possible to avoid defects upon wire boding attributing to hardening of the gate metal layer. Therefore, even in the case of a buried gate electrode structure for enhancing characteristics of the high electron mobility transistor, it is possible to enhance reliability and yields.

Owner:SANYO ELECTRIC CO LTD

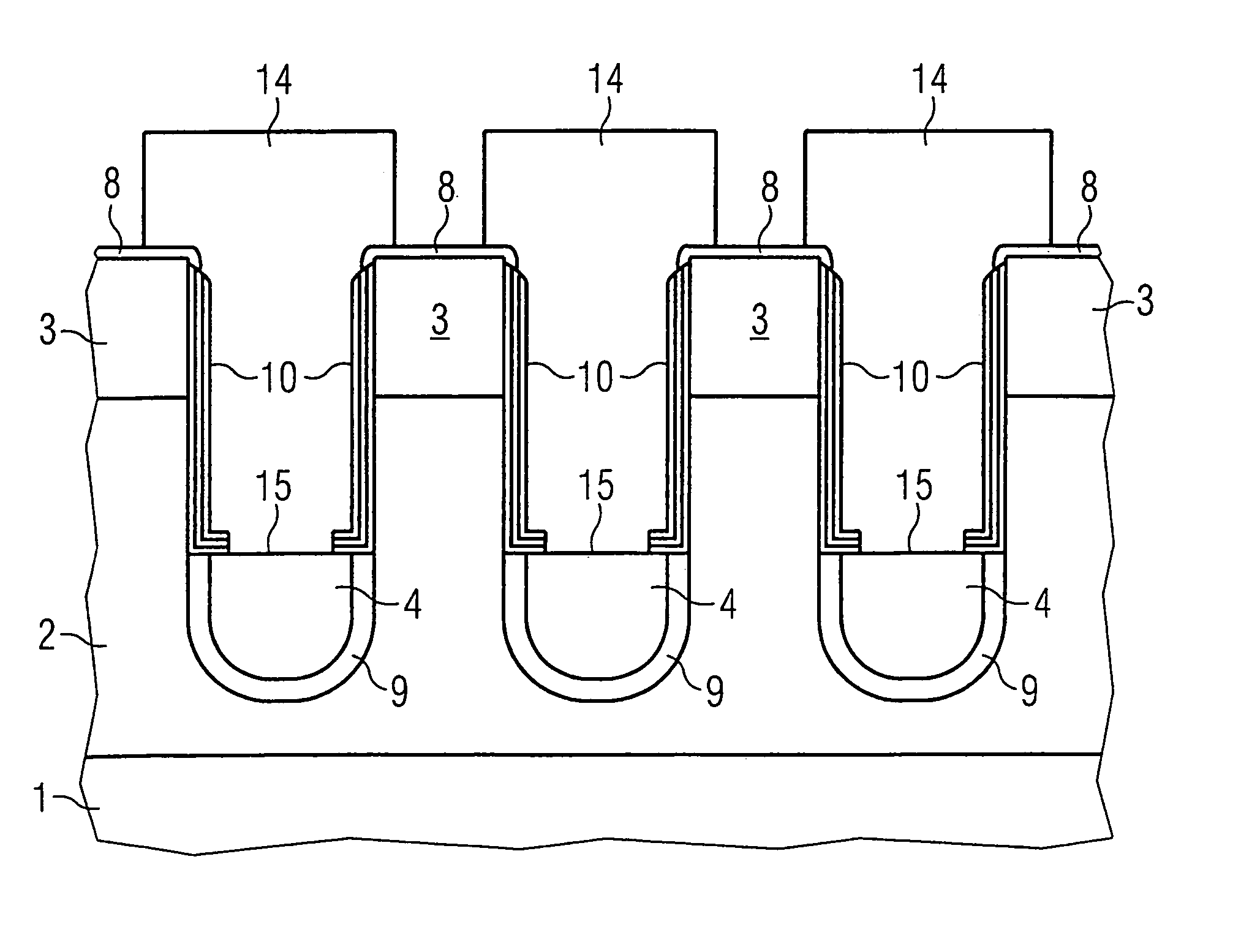

Charge trapping memory cell and fabrication method

InactiveUS7227219B2Improved programming and erasing propertyWeaker electric fieldsTransistorSolid-state devicesTransistorElectrical and Electronics engineering

A memory cell patterned as a trench transistor is provided with a first gate electrode (4) as auxiliary gate for source-side injection and a second gate electrode (5) electrically insulated therefrom, which are arranged in the trench, and has, at the trench walls, a storage layer sequence (10) provided for charge trapping and comprising a storage layer (12) between boundary layers (11, 13). The first gate electrode (4) and the second gate electrode (5) are electrically insulated from one another, which can be effected by means of a portion of the storage layer sequence (10). Source / drain regions (3) are arranged on the top side laterally with respect to the trenches. Word lines (6), source / drain lines and control gate lines are present for the electrical driving.

Owner:POLARIS INNOVATIONS LTD

Data slicer, data slicing method, and amplitude evaluation value setting method

ActiveUS20060268170A1Reduce electric field strengthElectric signal transmission systemsPicture reproducers using cathode ray tubesDigital videoData selection

A data slicer 300 includes a slice level calculation unit 310 that determines whether a detected digital video signal is a CRI signal on the basis of the amplitude of the signal, and sets a reference slice level and upper and lower slice levels which are obtained by providing offset in the reference slice level, by using only the CRI signal; a data slicing unit 160 that binarizes a digital video signal S140 using the slice levels; a decoding circuit 170 that converts binarized serial data into parallel data; and a data selection unit 320 that selects data including no error from the decoded data, and outputs the selected data through a video signal output terminal 190. Therefore, even when the video signal is distorted, this data slicer can set appropriate slice level data to binarize the video signal, thereby suppressing the occurrence rate of decoding errors.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

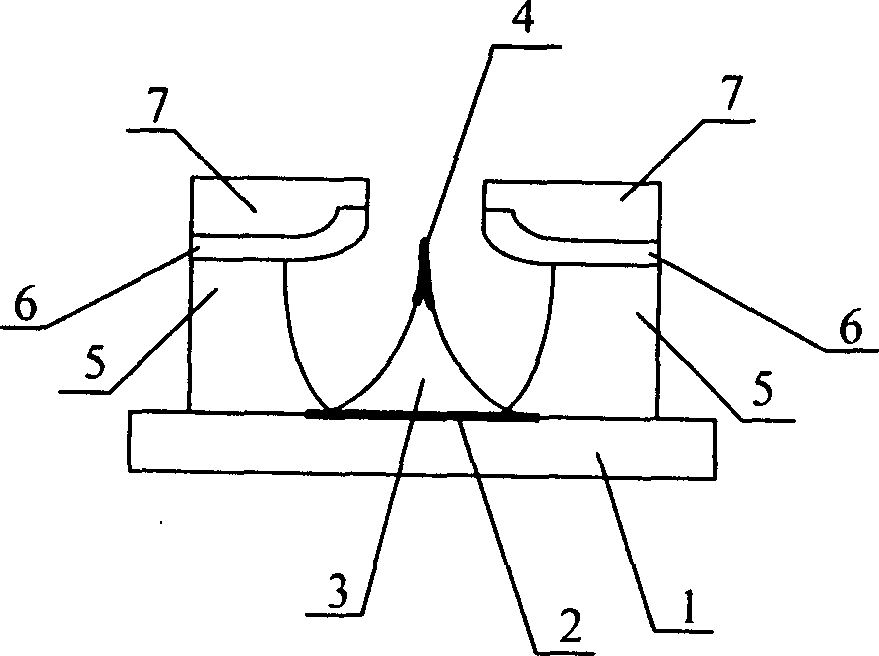

Method for making groove power semiconductor device

InactiveCN101101877AInhibition of channel punch throughReduce electric field strengthSemiconductor/solid-state device manufacturingSemiconductor devicesBreakdown strengthEngineering

The invention is concerned with the manufacture method of the ditch groove power semiconductor device. It is: provides the materials of the basal; forms the first electric transmit epitaxy layer on the basal; forms the second electric transmit zone and the ditch groove inside the epitaxy layer; forms the ebb first electric transmit area and the medium layer with the ditch groove; and then, forms the electric transmit area within the medium layer; forms the first electric transmit source area on the surface of the second electric transmit area; forms the second electric transmit contact area with higher doping PH indicator on the second electric transmit zone surface; forms the passivation layer cap on the top of the ditch groove which must with the medium layer and the electric transmit area; forms the diffusion protecting layer on the surface of the source area and the contact area; finally, forms the structure surface with good electric connection. The invention can control the threshold voltage of the device and improves the breakdown strength of the oxide layer of the device bottom area, and improves its electric connection reliability with no extra cover film printing plate and complex method request.

Owner:HARBIN ENG UNIV

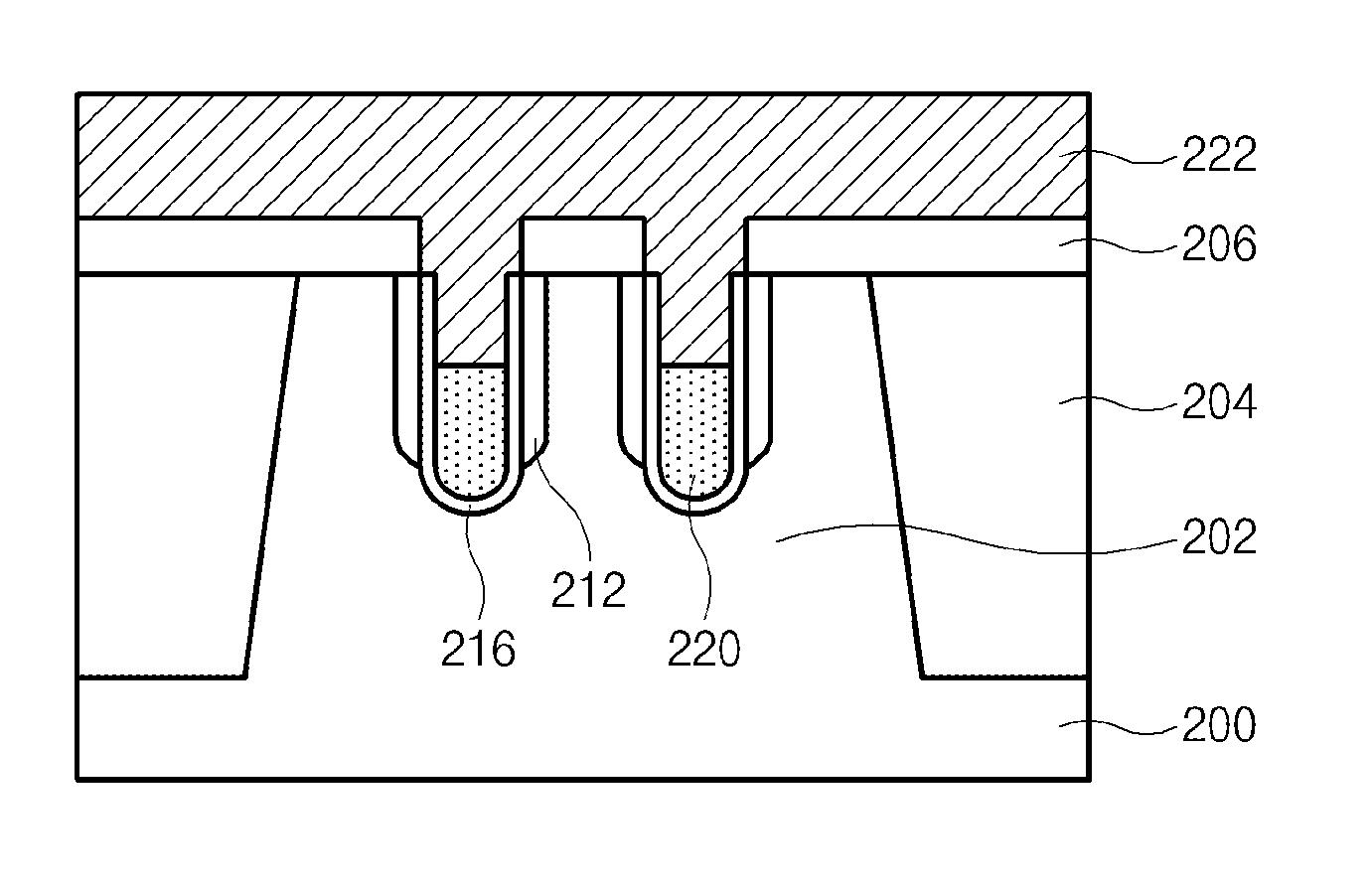

Semiconductor memory device and method for fabricating the same

InactiveUS20110018057A1Reducing GIDL occurrenceSuppress parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A manufacturing method of a semiconductor device comprises forming a semiconductor substrate including an active region and an element isolation film, forming a first recess on the semiconductor substrate, forming an oxide film on a sidewall of the first recess, forming a second recess by etching a lower part of the first recess, and forming a gate in a lower part of the second recess.

Owner:SK HYNIX INC

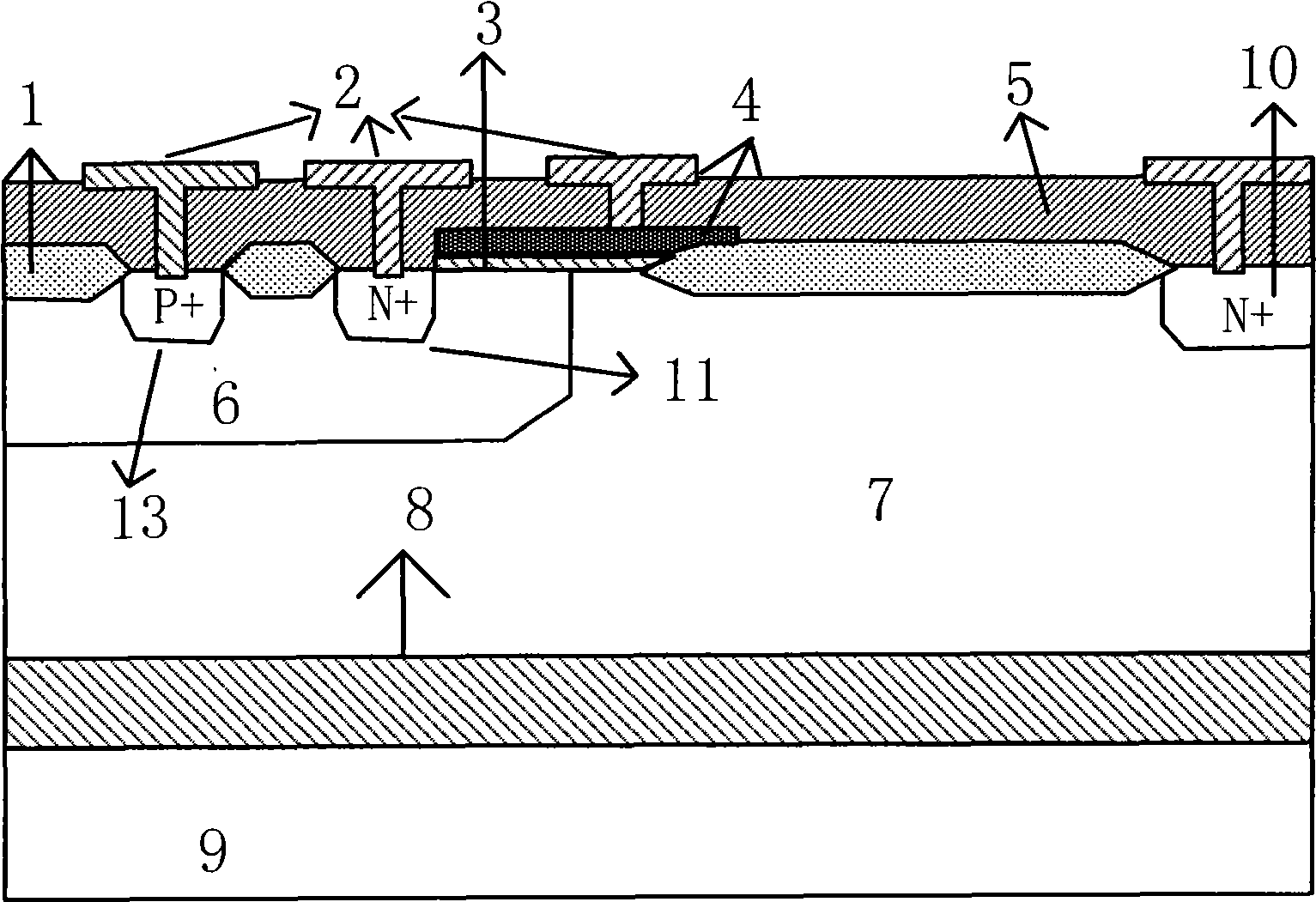

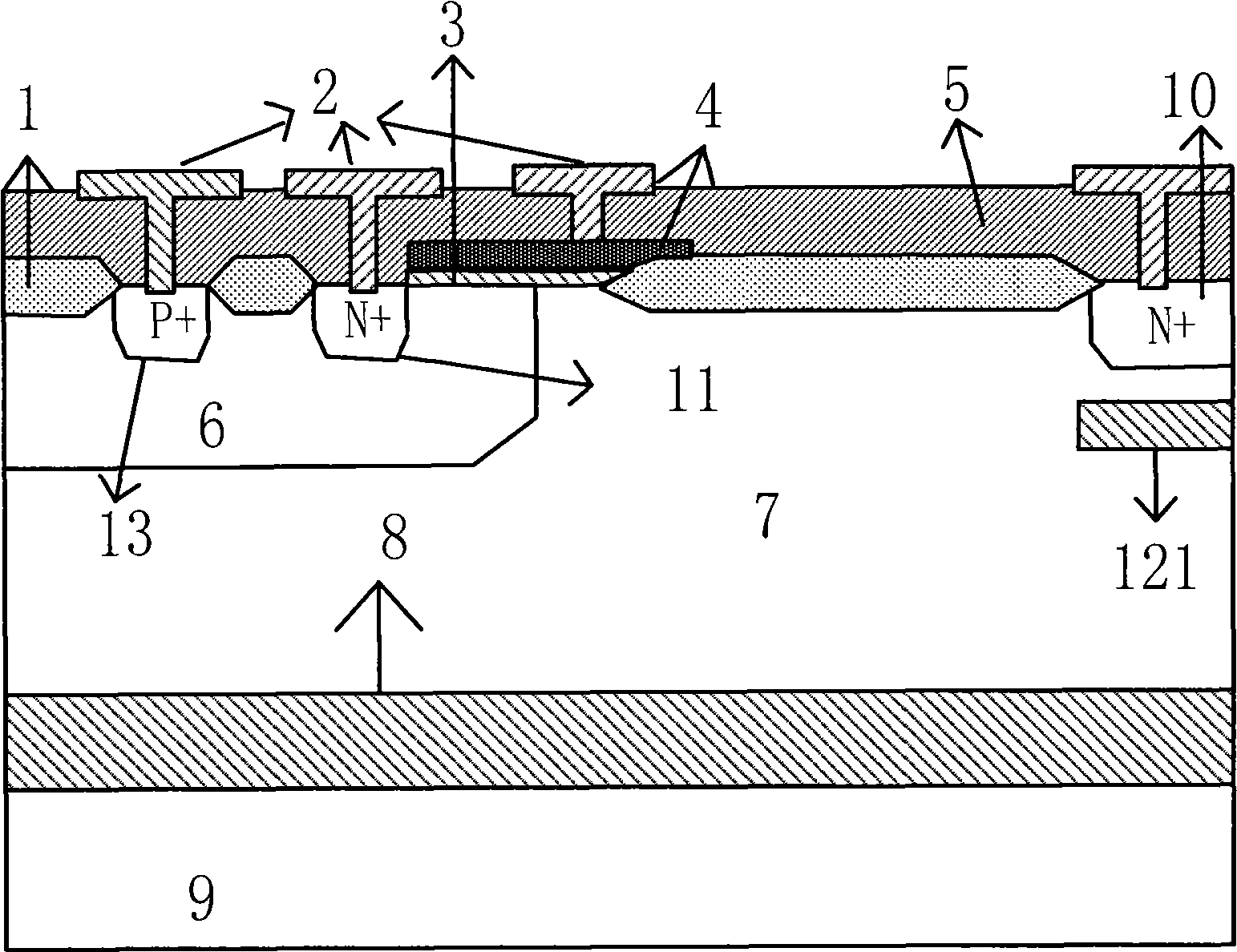

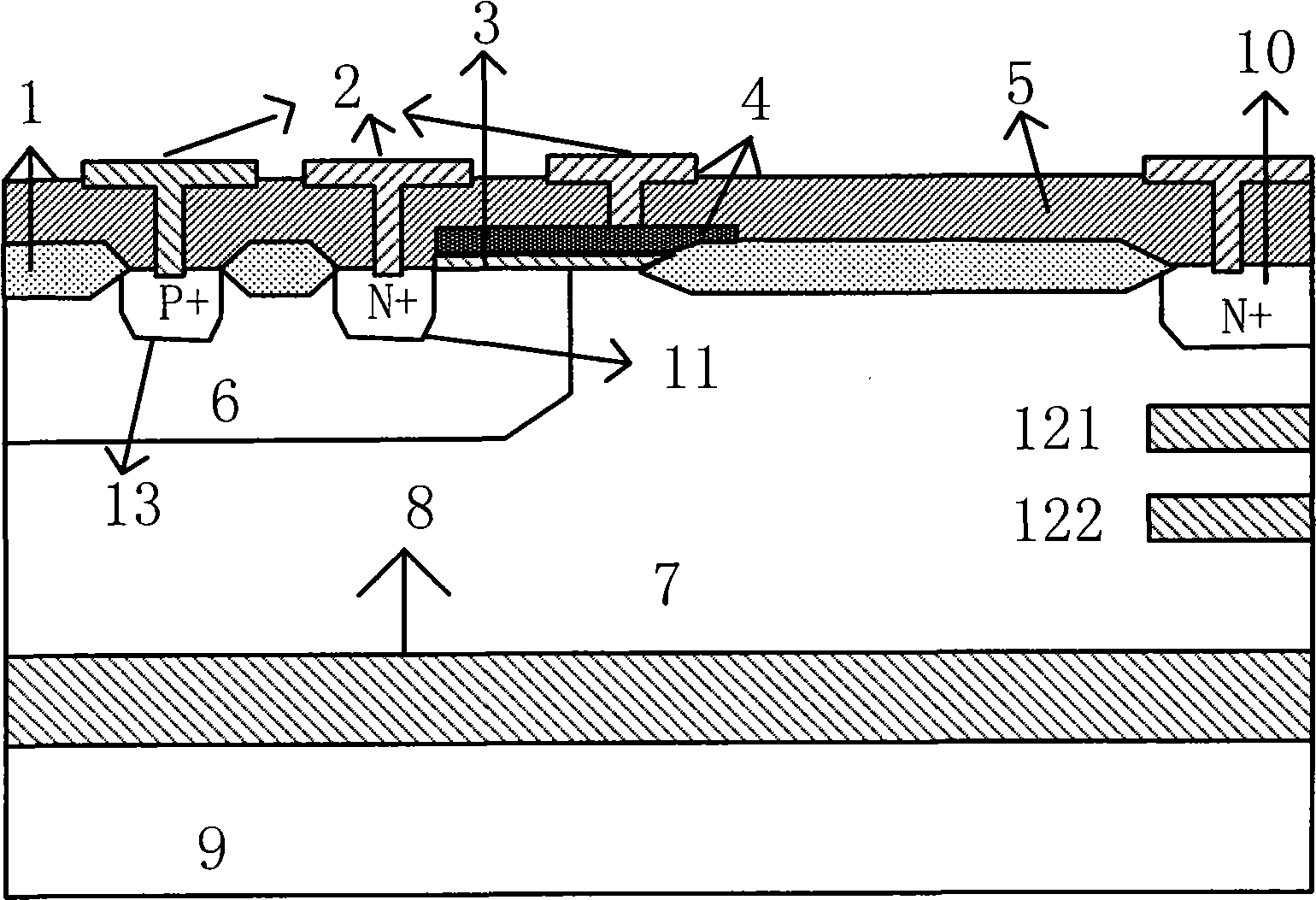

N type SOI lateral double-diffused metal-oxide semiconductor transistor

InactiveCN101488526AImprove the overall withstand voltageImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorBuried oxide

A laterally double diffused metal oxide semiconductor transistor of an N-shaped silicon-on-insulator (SOI) comprises a semiconductor substrate. A buried oxide is arranged on the semiconductor substrate, an N-shaped doped semiconductor drift region is arranged on the buried oxide and a P-shaped well region is arranged above the N-shaped doped semiconductor drift region, and a field oxide, a metal layer, a gate oxide, a polysilicon gate and an oxide layer are arranged on the surface of the transistor. An N-shaped source region and a P-shaped contact region are arranged in a P-shaped well. The transistor is characterized in that the transistor also comprises at least a layer of floating oxide structure which is positioned in the N-shaped doped semiconductor drift region between a drain region and the buried oxide; moreover, a plurality of layers of floating oxide structure are allowed to further optimize the distribution of longitudinal electric fields in the drain region, thereby increasing the entire breakdown voltage of the transistor.

Owner:SOUTHEAST UNIV

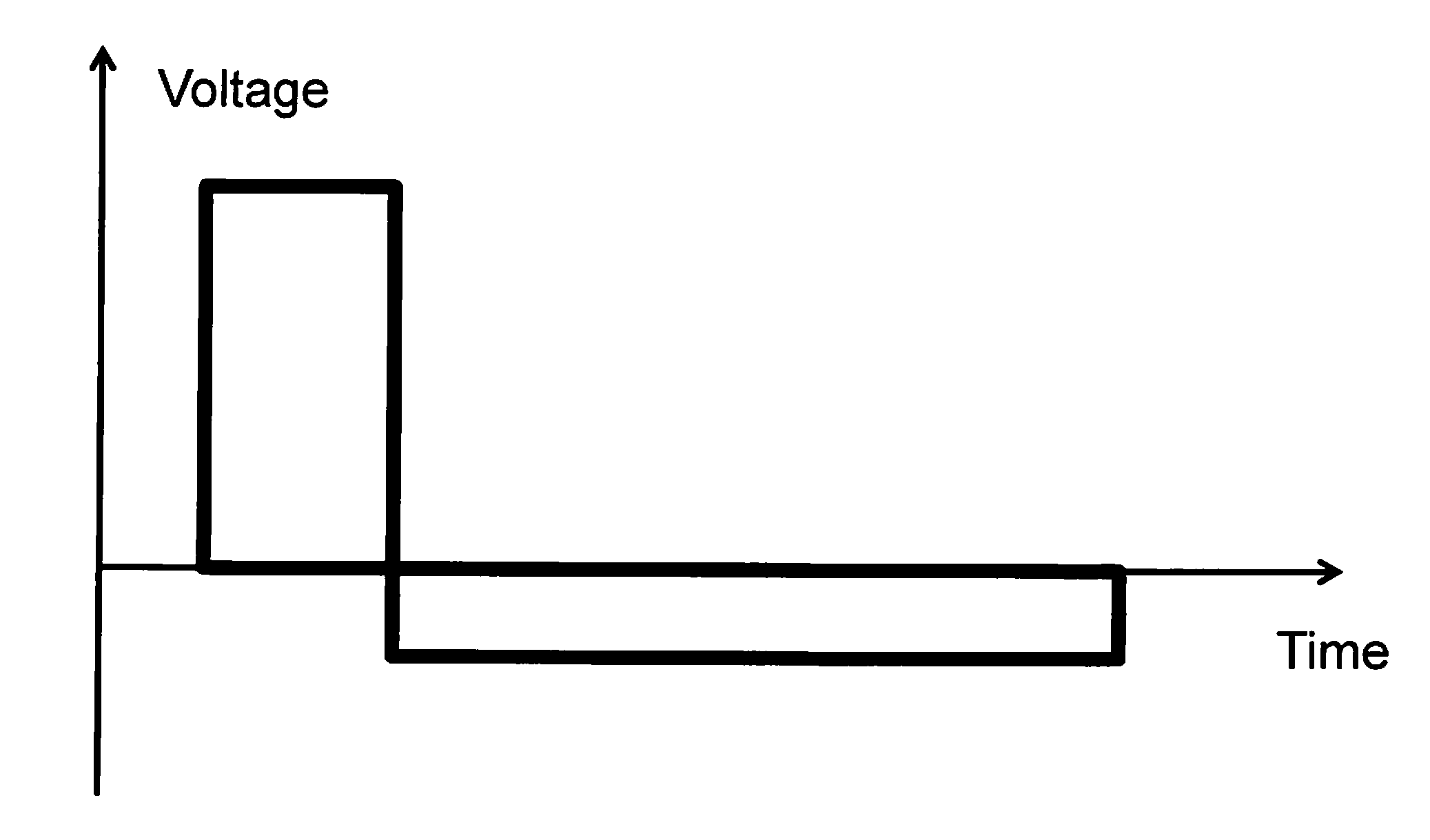

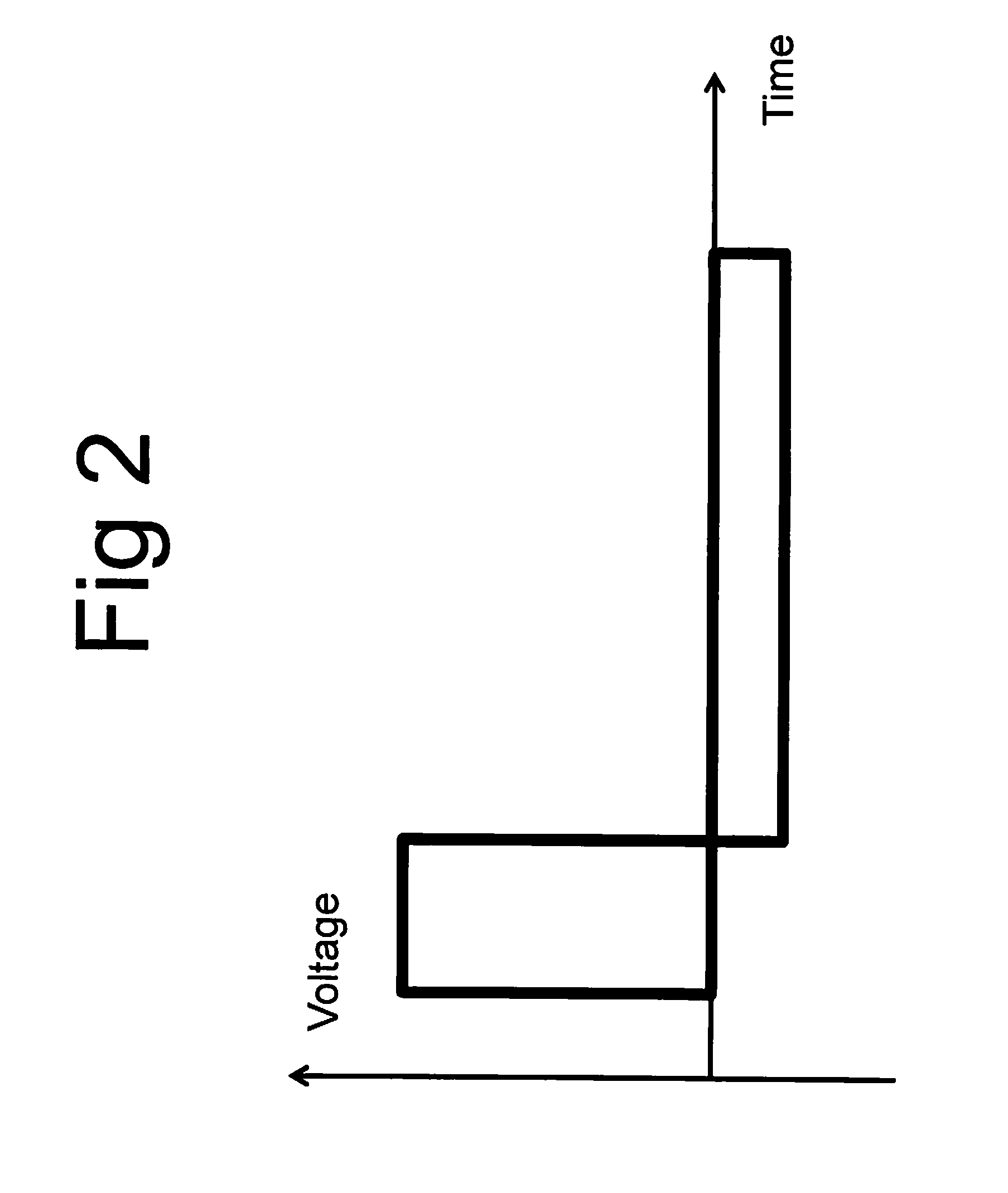

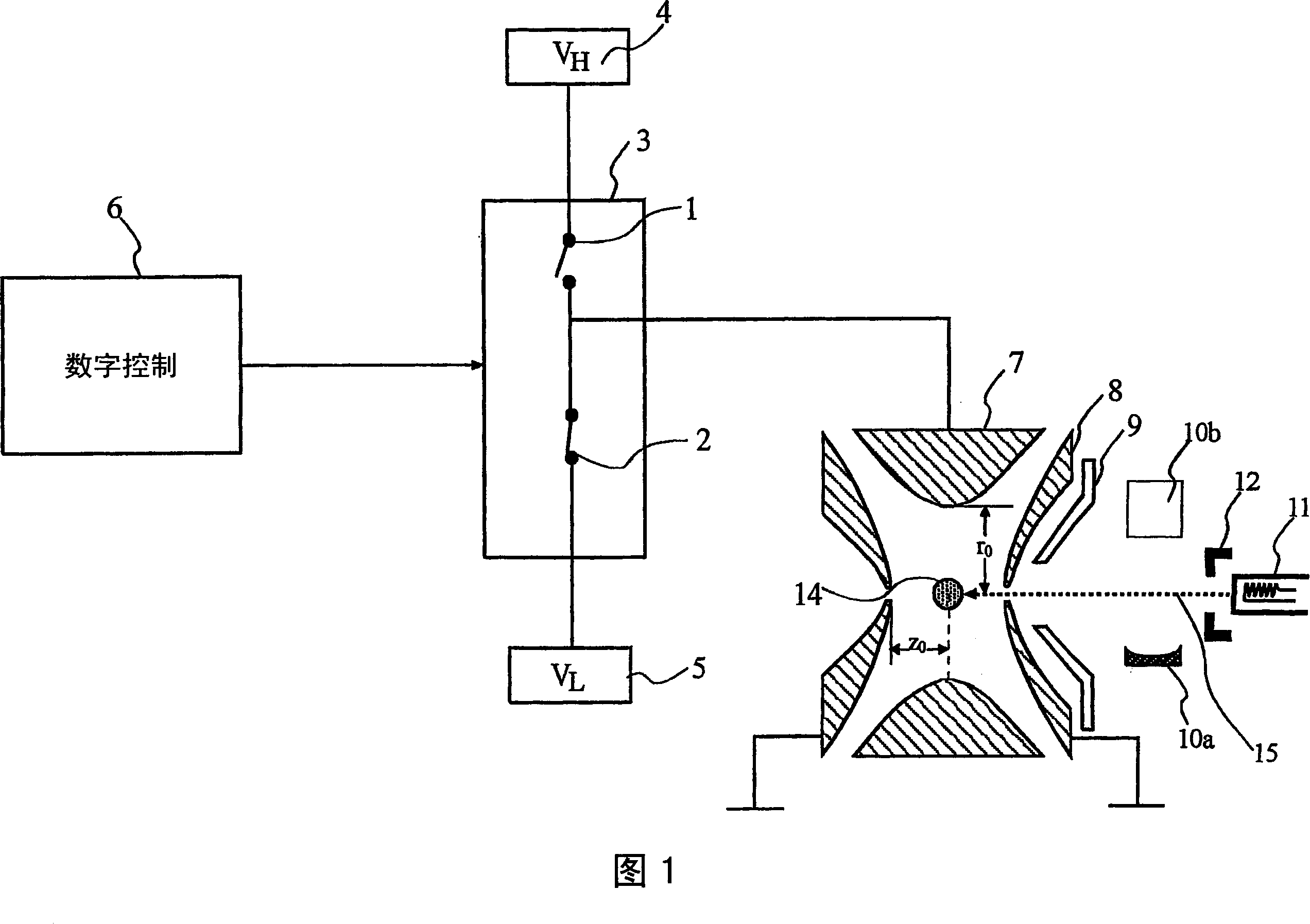

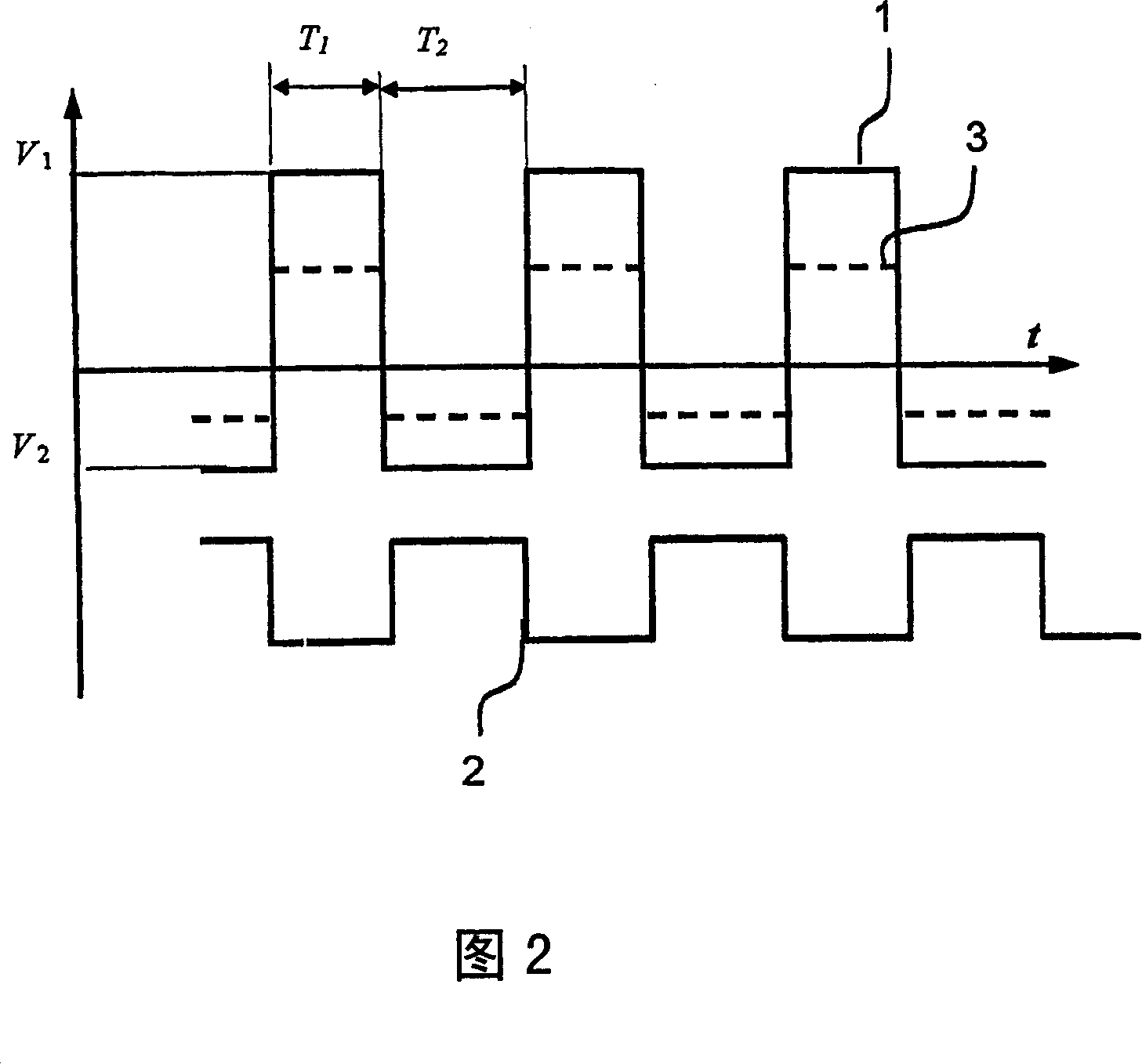

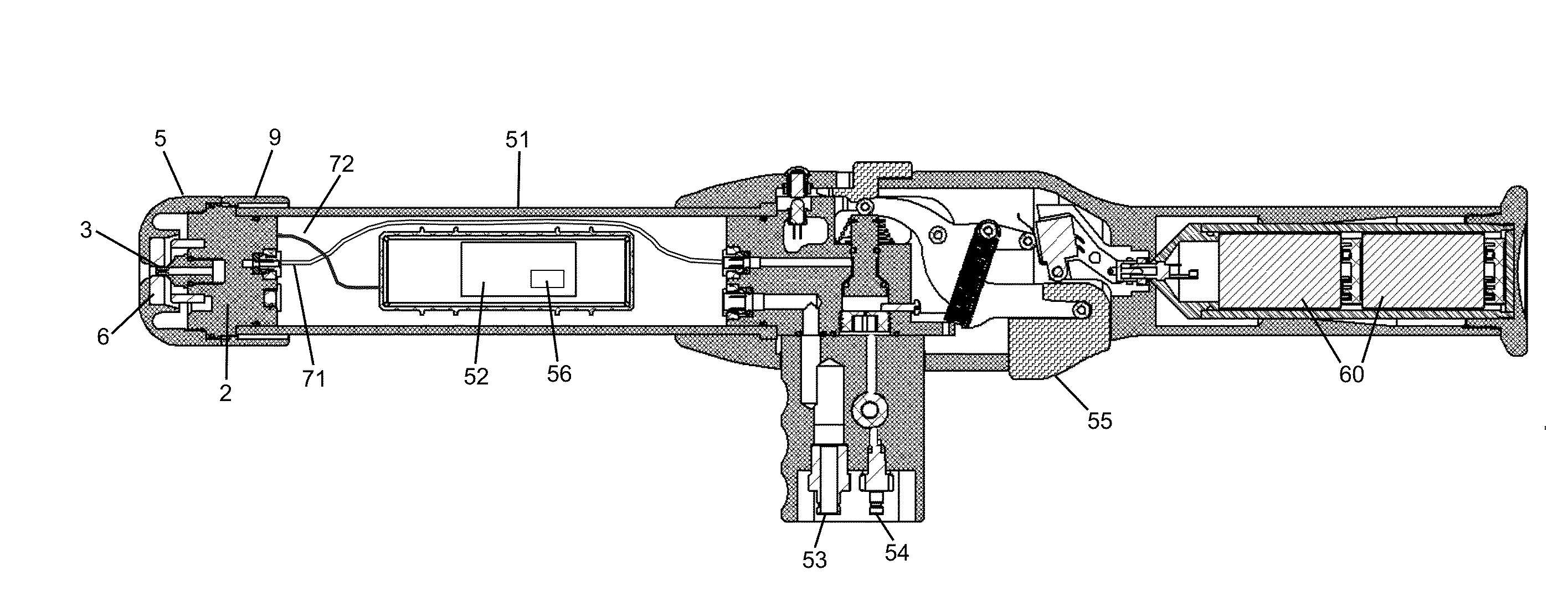

An ion trap and a method for dissociating ions in an ion trap

ActiveCN1922711AReduce electric field strengthRelieve pressureStability-of-path spectrometersTime-of-flight spectrometersIon trap mass spectrometryElectron injection

A quadrupole ion trap includes a switch (3) for switching a trapping voltage between discrete voltage levels VH, VL. This creates a digital trapping field for trapping precursor ions and product ions in a trapping region of the ion trap. A gating voltage is applied to a gate electrode (12) to control injection of source electrons into the ion trap. Application of the gating voltage is synchronised with the switching so that electrons are injected into the trapping region while the trapping voltage is at a selected one of the voltage levels and can reach the trapping region with a kinetic energy suitable for electron capture dissociation to take place.

Owner:岛津欧州研究所

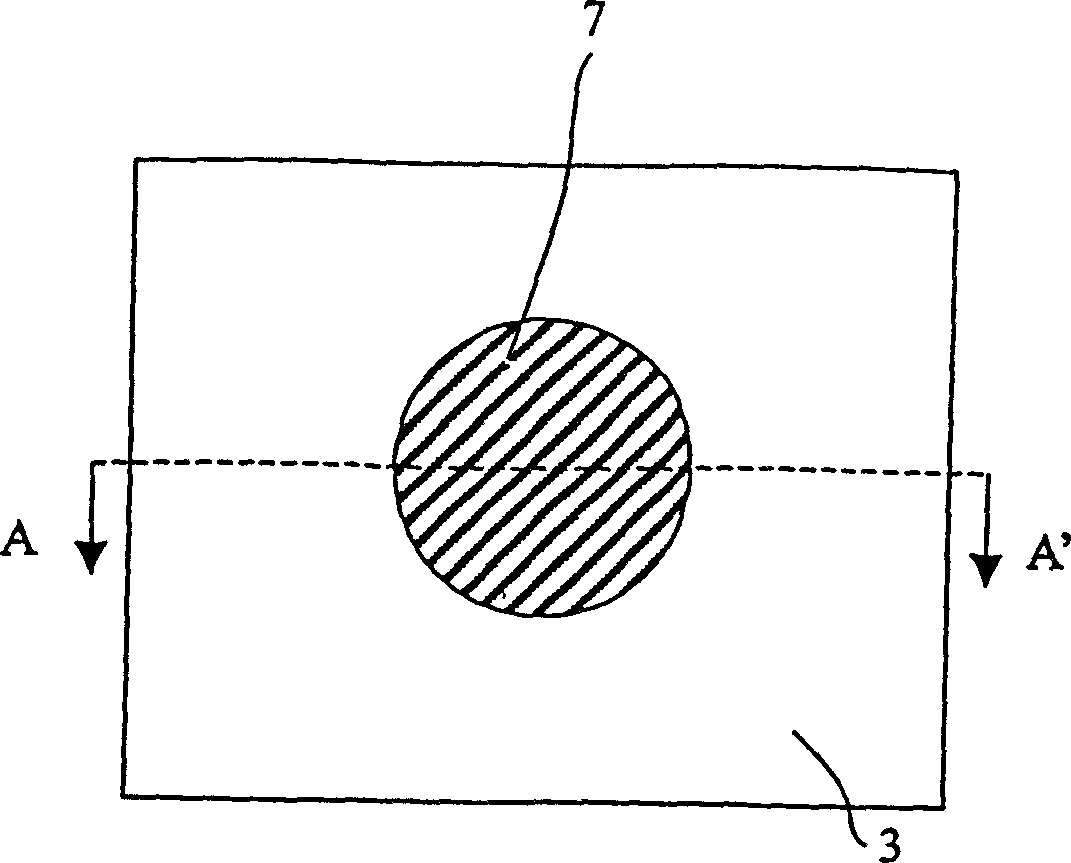

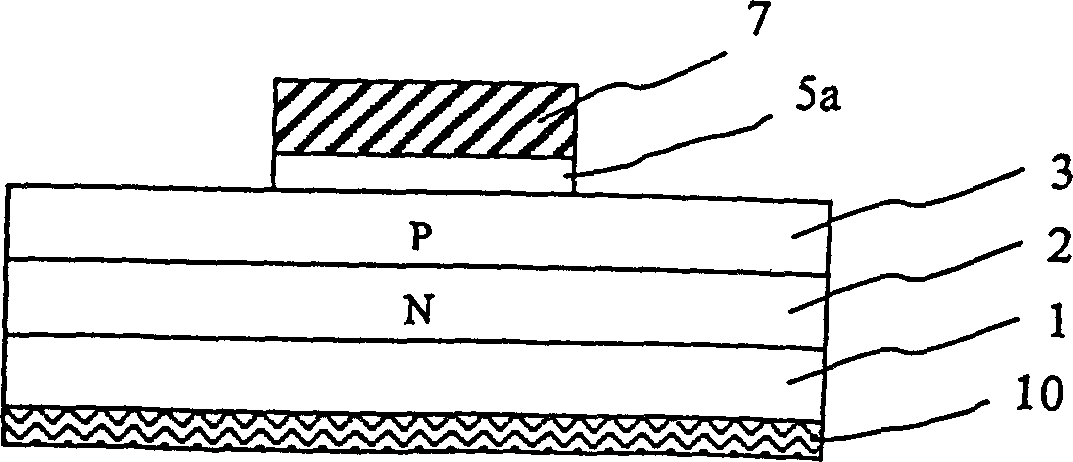

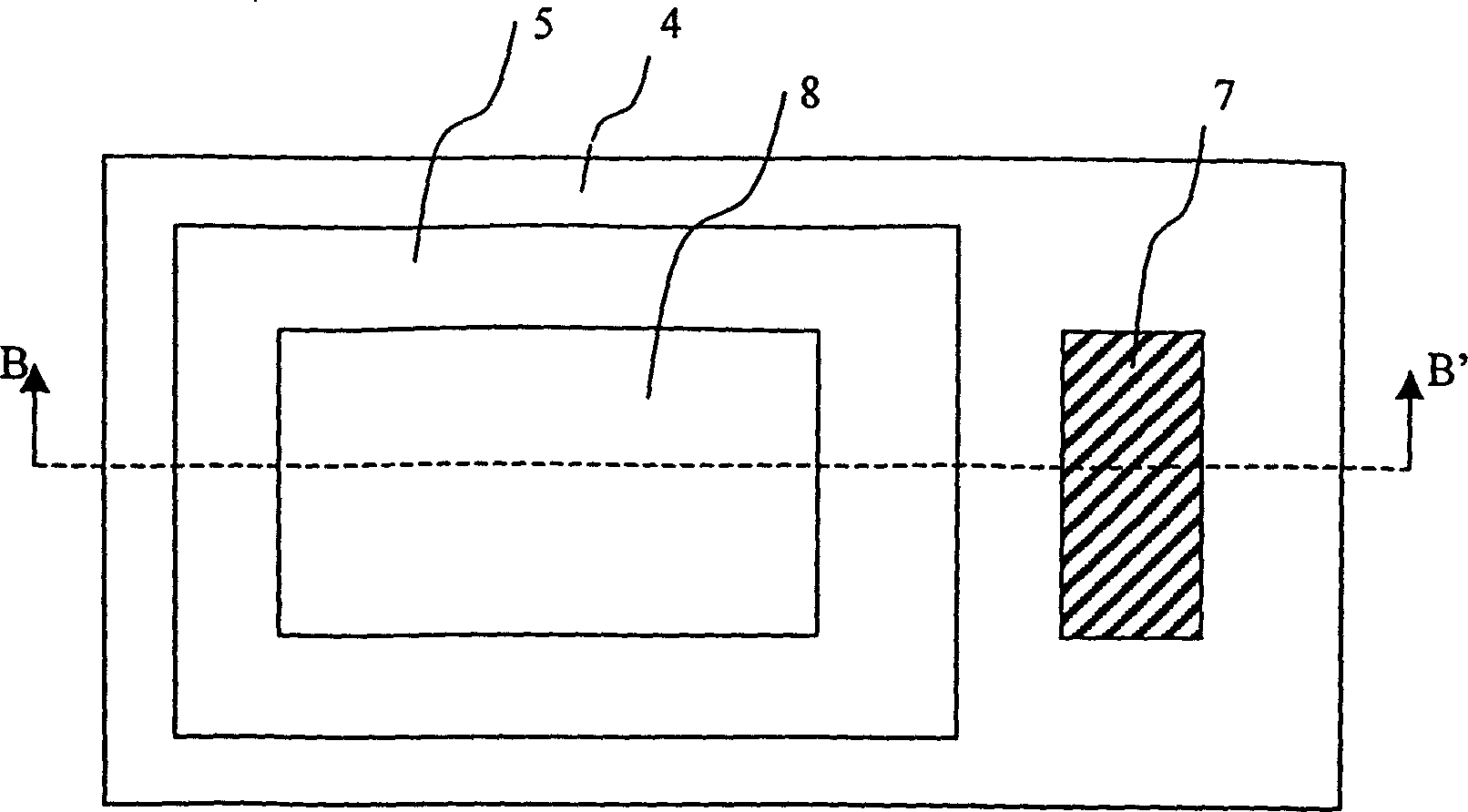

Structure of LED electrode and producing method

InactiveCN1458701AReduce electric field strengthSemiconductor devicesSilicon oxideLight-emitting diode

This invention discloses a structure of LED electrode and its manufacturing method. After forming a pn contact surface LED on the baseplate, a layer of silicon oxide is formed around the grain and onthe cut-path part, and deposited by a transparent conductive layer and a layer of Au or AuGe on it, or and opening an open-end at the center; after contacting with heated and alloy formed ohm, a longstrip of Al, Al alloy or Au connecting wire pad is formed at a side of the grain for writing and used as the LED positive electrode, and the negative electrode is formed on the substrate by metal contact. The other structure is that both positive and negative electrodes are on the front with etched pn interface p-type layer, and negative electrode is formed with n-type material and positive electrode with p-type material.

Owner:张修恒

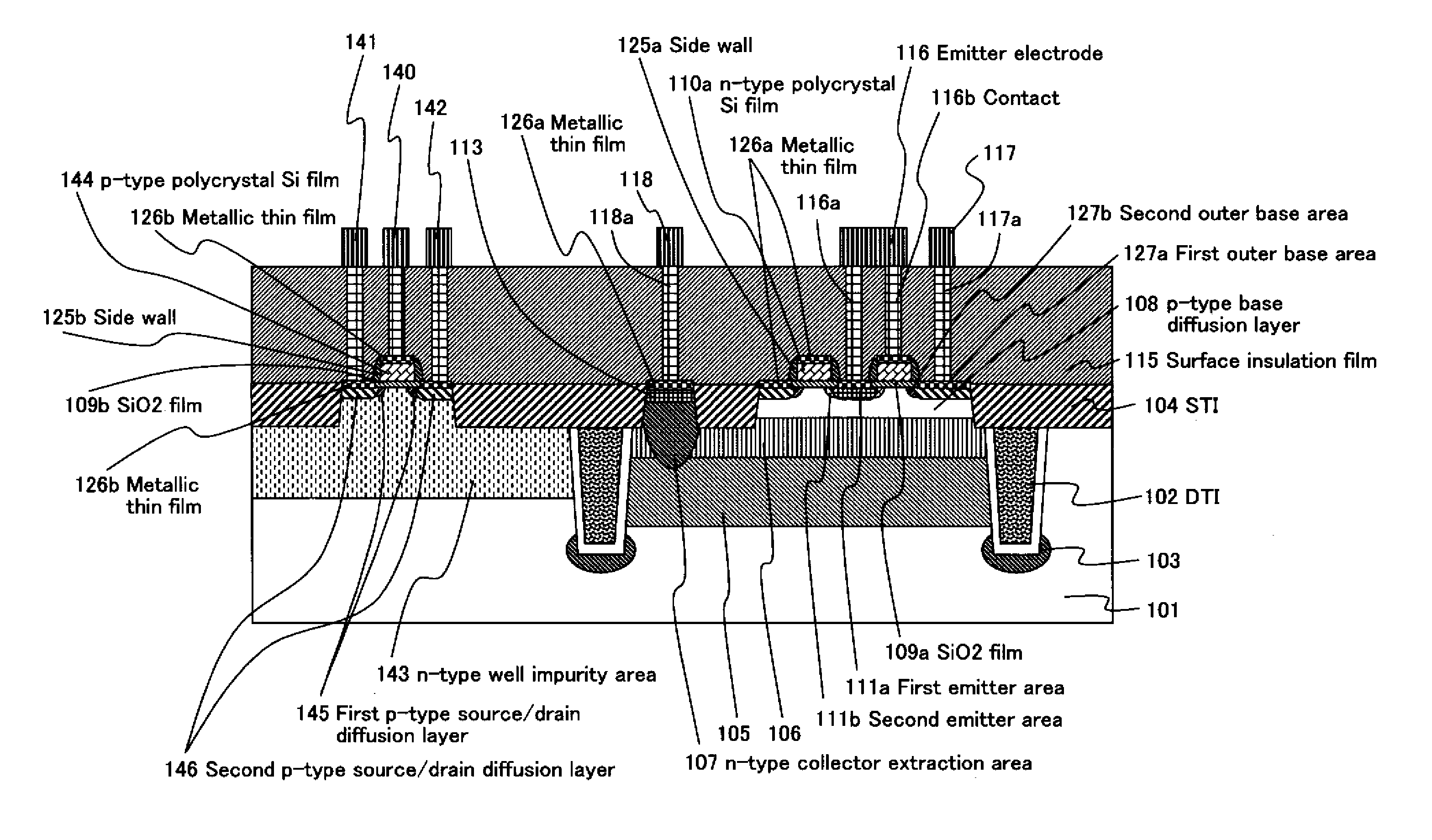

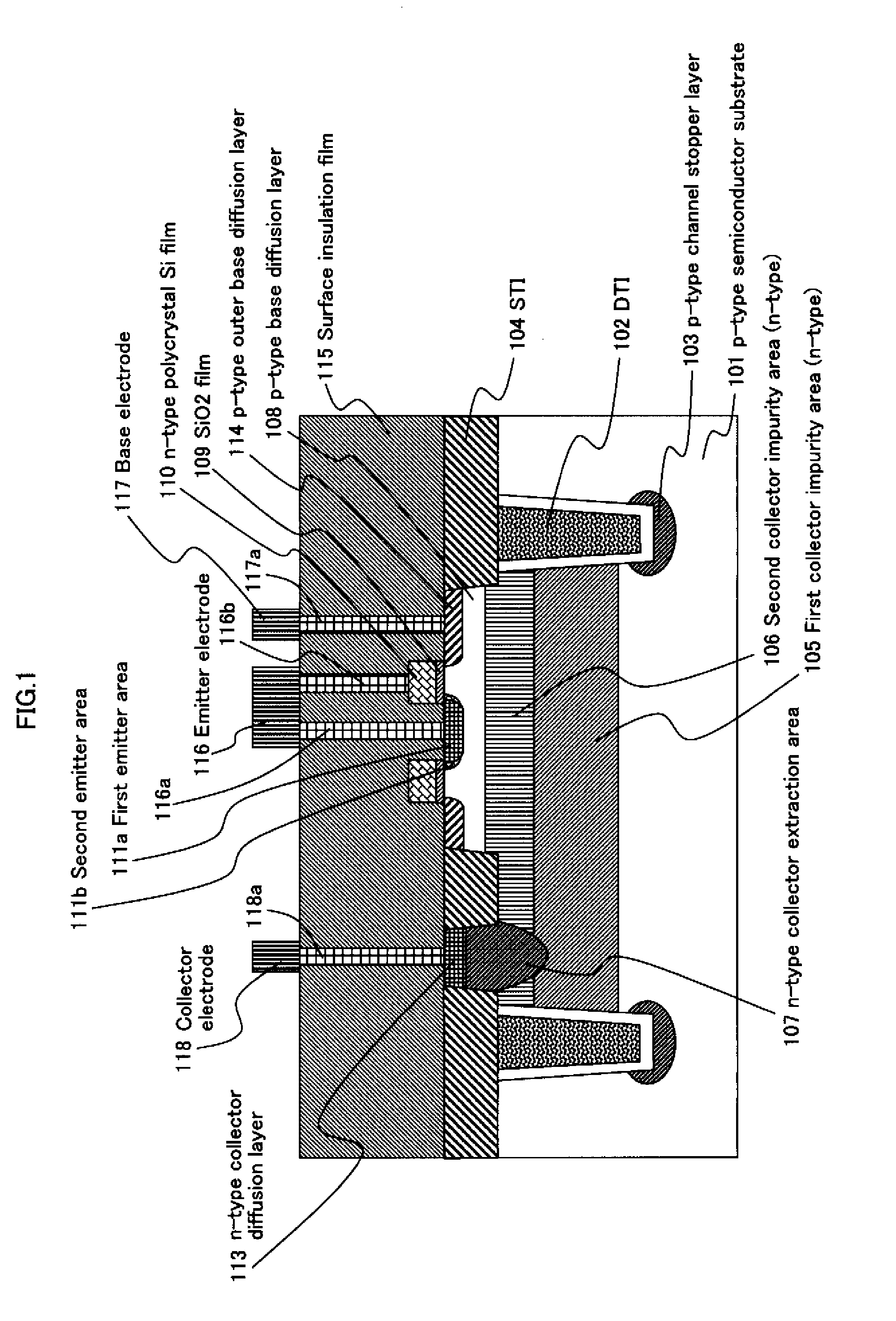

Semiconductor apparatus and manufacturing method thereof

InactiveUS20110127615A1Reduce leakage currentReduce electric field strengthTransistorSolid-state devicesElectrical field strengthImpurity ions

A high-performance semiconductor apparatus which can be easily introduced into the MOS process, reduces the leakage current (electric field strength) between the emitter and the base, and is insusceptible to noise or surge voltage, and a manufacturing method of the semiconductor apparatus. The emitter 111 is formed by performing the ion implantation twice by using the conductive film (109) as a mask. The second emitter area (111b) is formed by ion implantation of a low impurity density impurity ion, and the first emitter area (111a) is formed by ion implantation of a high impurity density impurity ion. As a result, the low impurity density second emitter area is formed in the circumference of the emitter 111, which lowers the electric field strength, and reduces the leakage current. Also the conductive film is connected with the emitter electrode (116), which makes the apparatus insusceptible to noise.

Owner:PANASONIC CORP

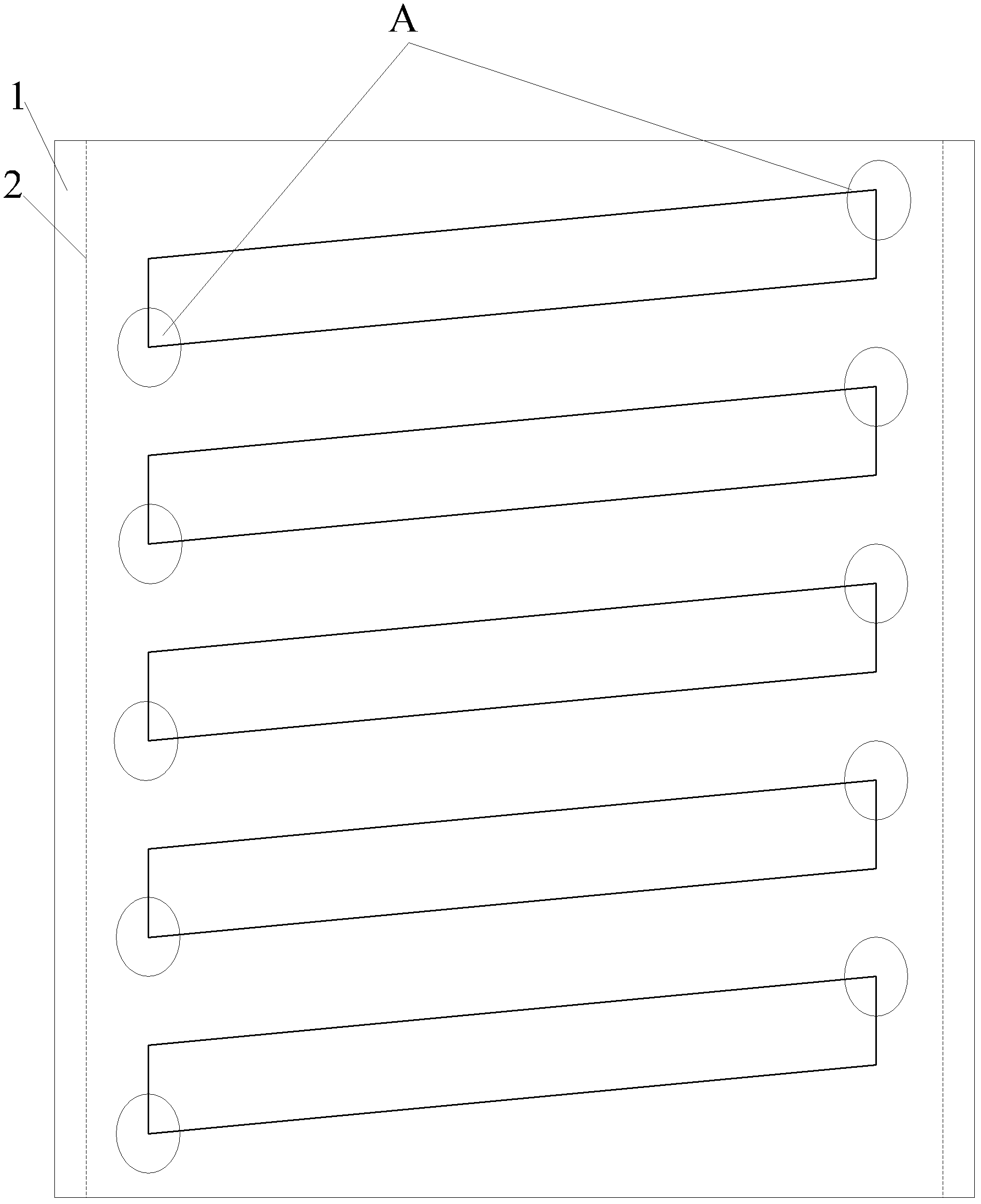

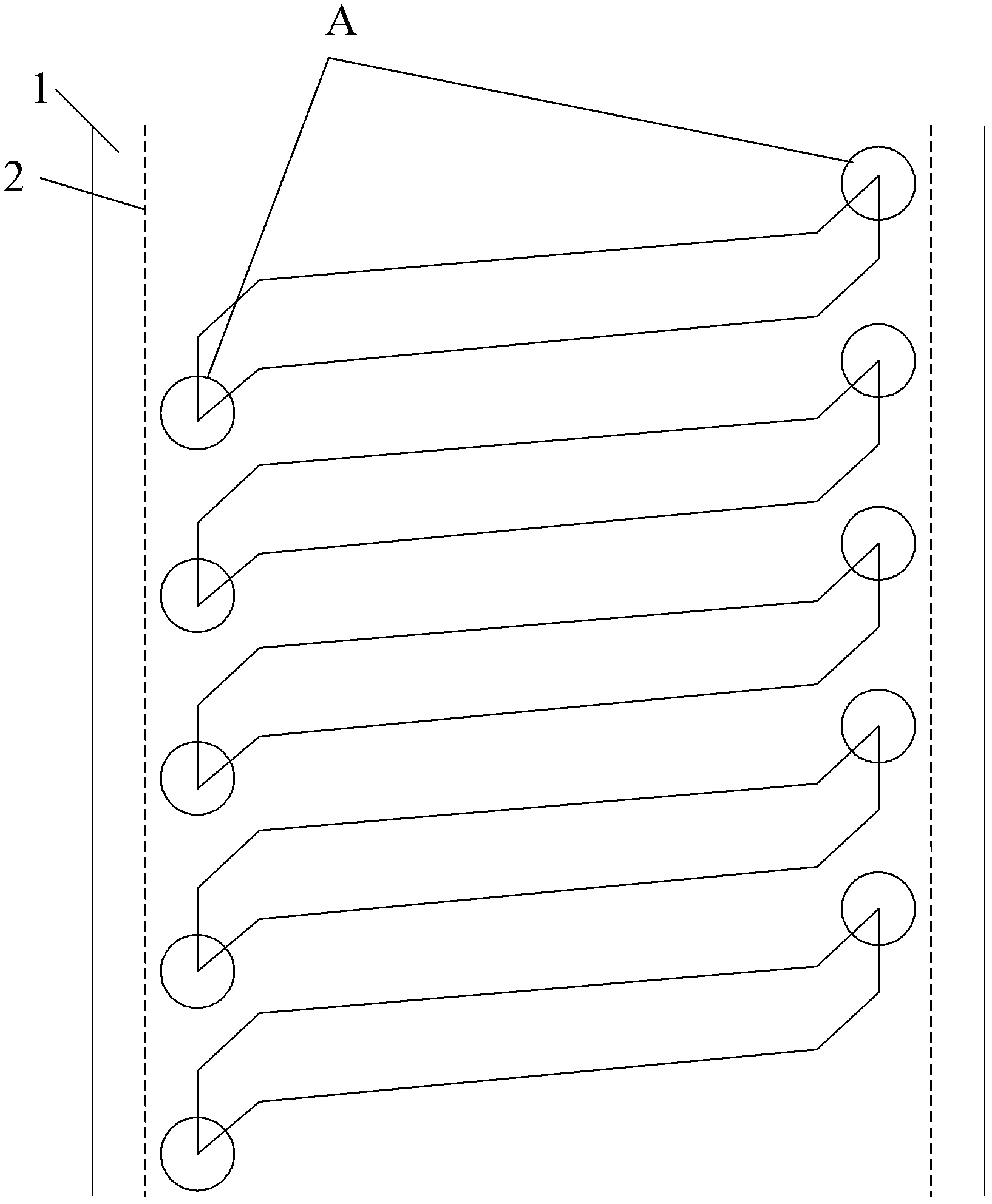

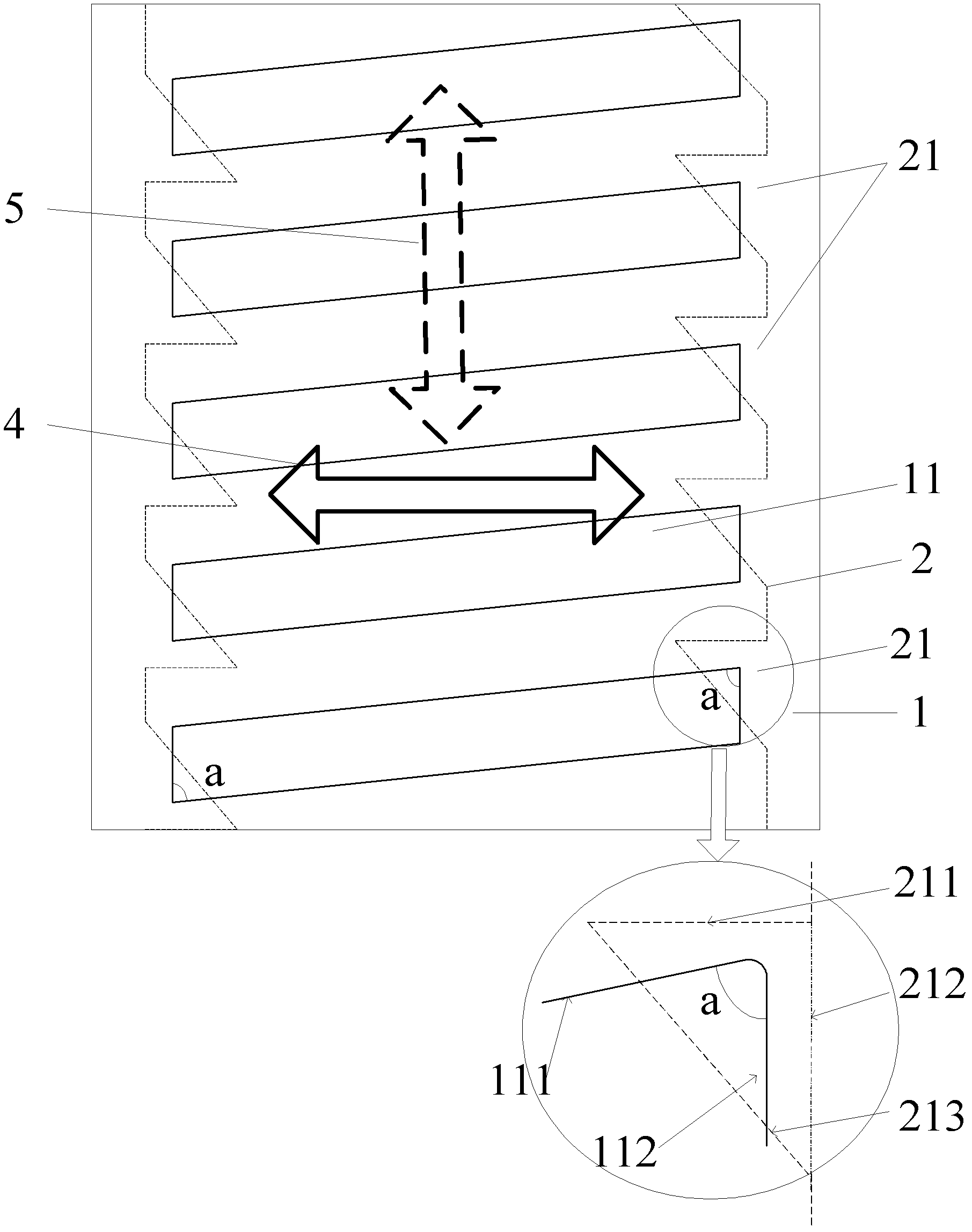

Thin film transistor (TFT) array substrate, manufacture method thereof and display device

ActiveCN102629038AThe case of less counter-rotating domainsThe case of one less pair of small counter-rotating domainsSolid-state devicesSemiconductor/solid-state device manufacturingElectrical field strengthDisplay device

The invention provides a thin film transistor (TFT) array substrate, a manufacture method thereof and a display device, which relate to the field of display device manufacture and prevent an electrode slit corner from generating a liquid crystal contrarotation domain and a disclination line so as improve light transmitting rate of the area. The method includes that by changing the shape of a lower-layer electrode, and the slit corner of an upper-layer electrode and the lower-layer electrode do not have corresponding overlapping in the vertical direction so that electric field strength of the area is weakened. An embodiment of the TFT array substrate, the manufacture method and the display device is applied to manufacture of the TFT array substrate.

Owner:BOE TECH GRP CO LTD

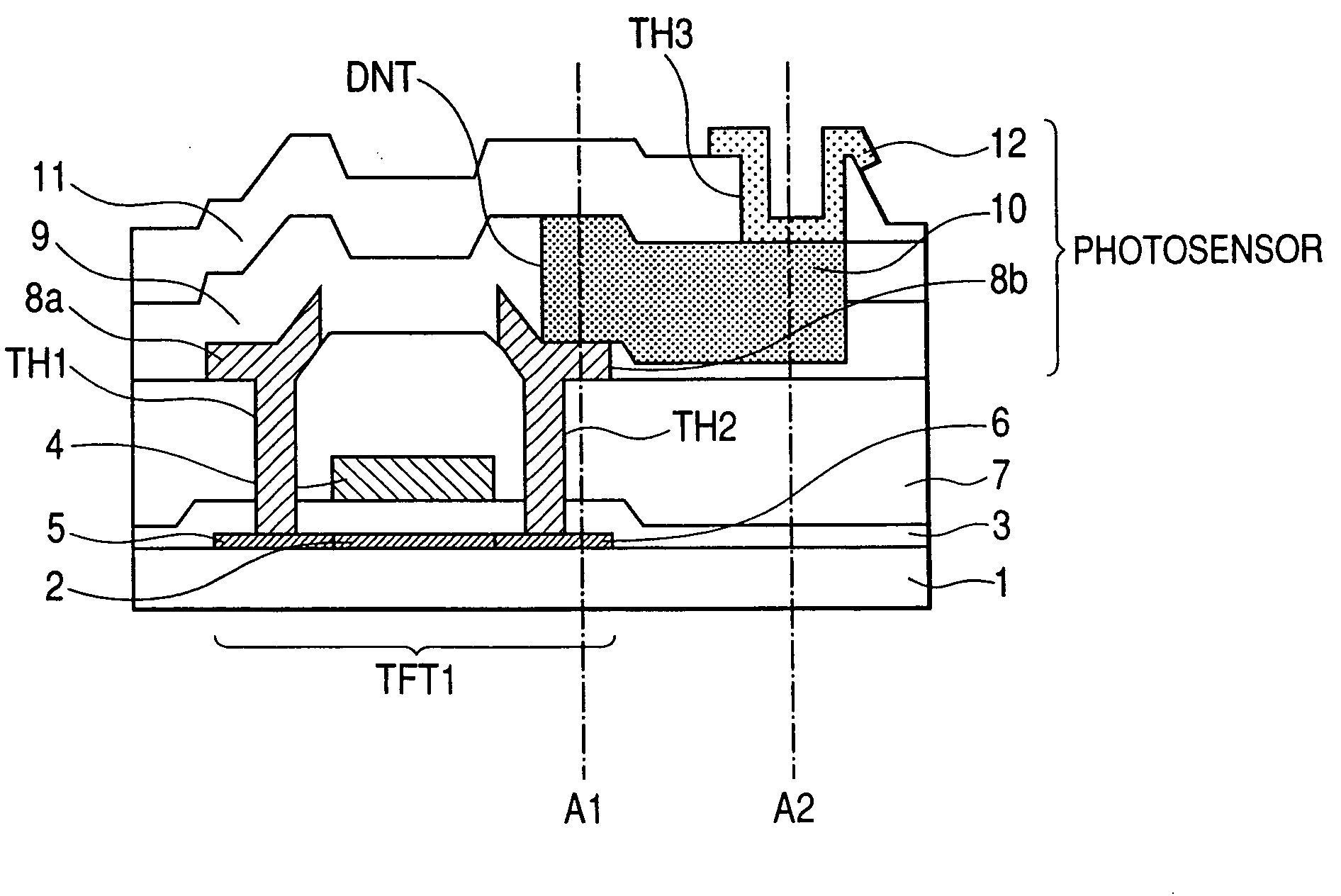

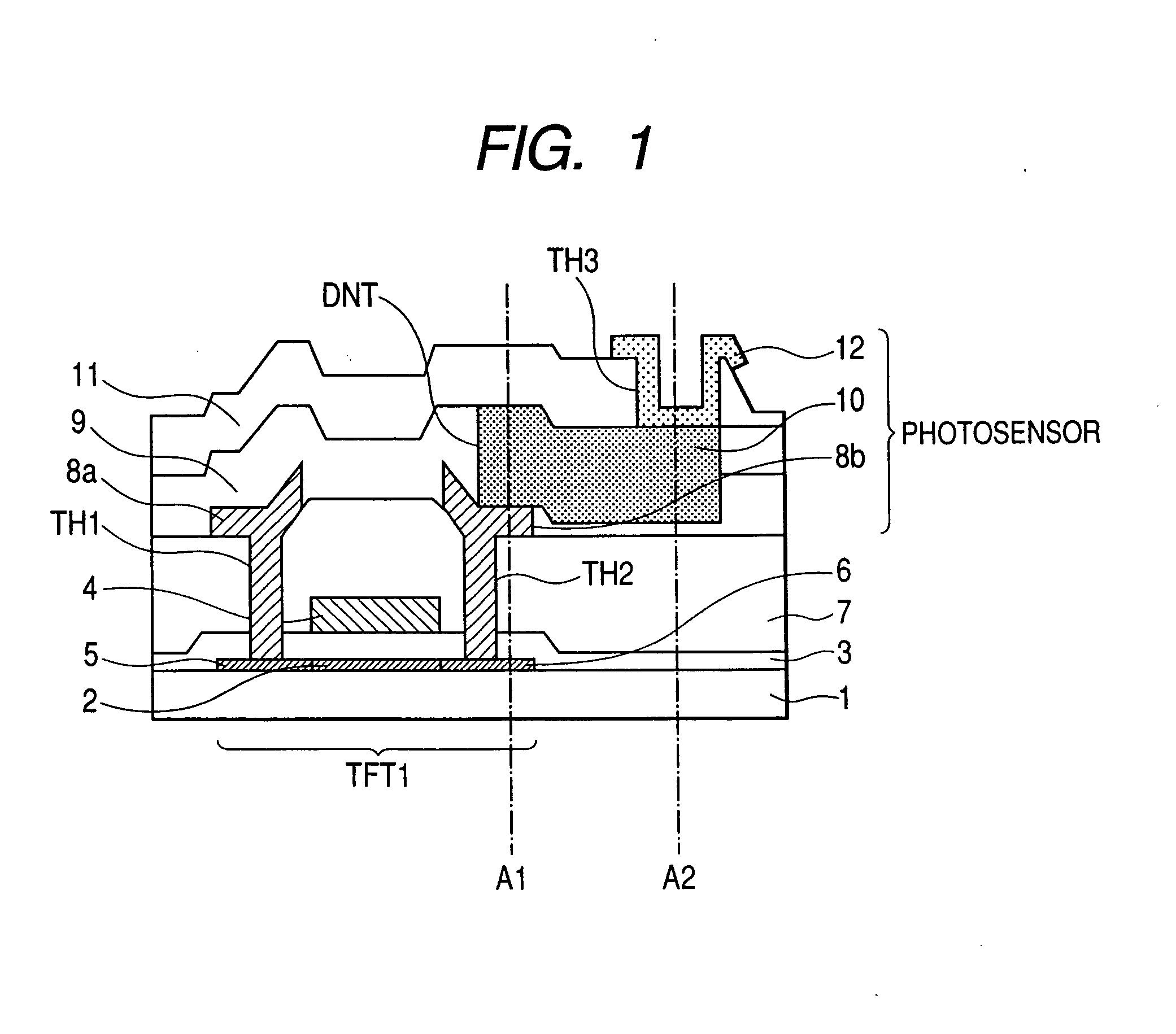

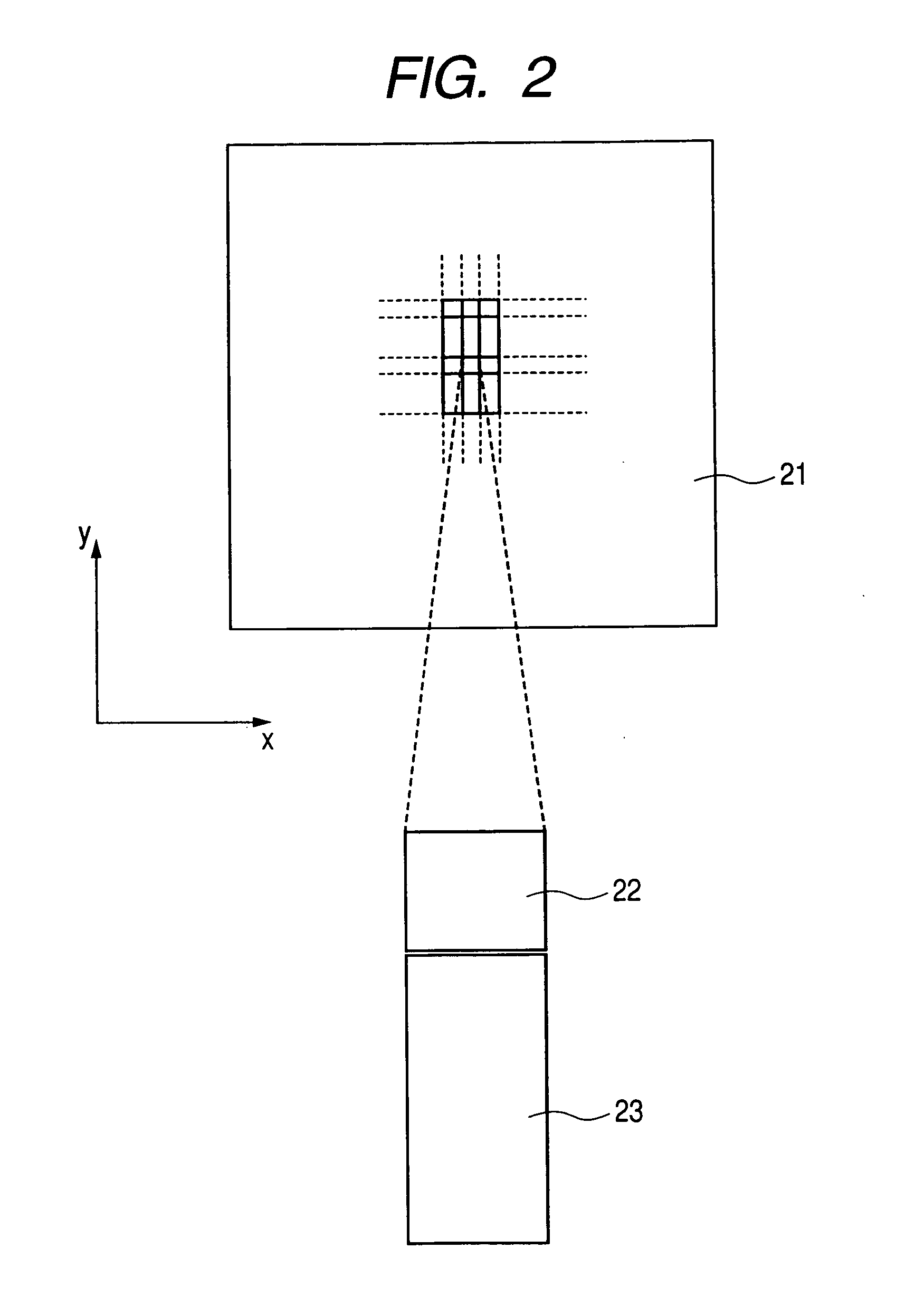

Image displaying device

InactiveUS20090032824A1Suppress leakage currentReduce dark currentStatic indicating devicesSolid-state devicesEngineeringMatrix pattern

An image displaying device having multiple photosensing devices have successfully suppressed a leakage current from each photosensing device and improved the S / N ratio. In the image displaying device, pixels and photosensing devices are disposed as pairs in a matrix pattern on a substrate. Each of the pixels and each of the photosensing devices are driven independently. Each photosensing device includes a semiconductor layer that is a photoelectric conversion layer connected to at least a first electrode and a second electrode. The contact surfaces of the first and second electrodes with respect to the semiconductor layer are disposed so that their center axes are separated from each other.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Semiconductor device and forming method thereof

ActiveCN104465379AIncrease the on-currentReduce electric field strengthSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSemiconductor

A semiconductor device and a forming method thereof are provided. The semiconductor device comprises a semiconductor substrate, a body region and a drift region disposed in the semiconductor substrate, a body connecting region and a source region disposed in the body region, a drain region and a first shallow trench isolation structure disposed in the drift region, and a gate structure disposed on the surface of the semiconductor substrate and across the edges of the body region and the drift region, wherein the first shallow trench isolation structure is disposed between the drain region and the body region, the bottom of the first shallow trench isolation structure is step-shaped, the adjacent steps are not the same in depth, and the gate structure covers part of the surface of the first shallow trench isolation structure. The on resistance of the drift region can be reduced and the on current of the drift region can be increased without lowering the voltage endurance capability.

Owner:SEMICON MFG INT (SHANGHAI) CORP

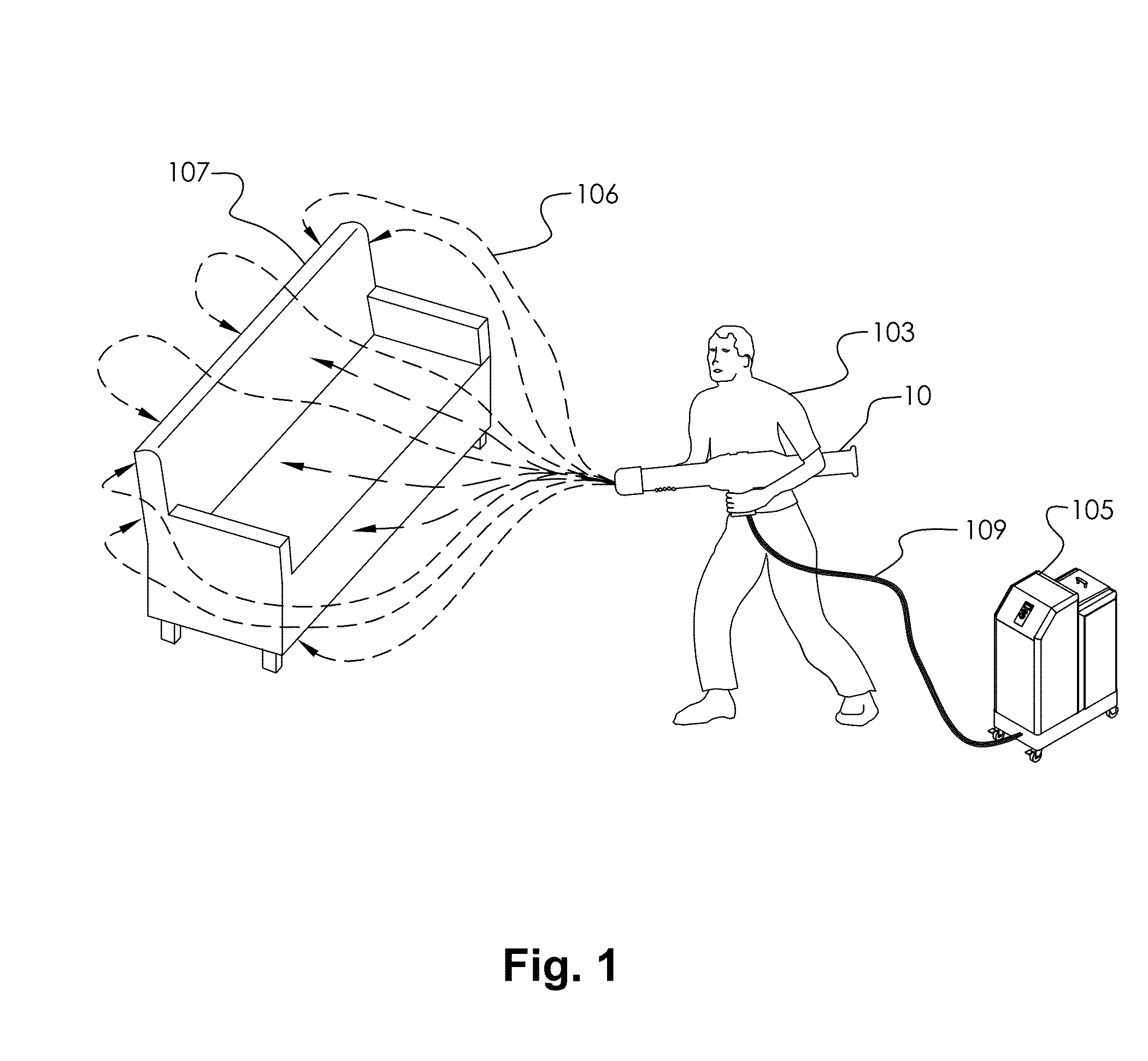

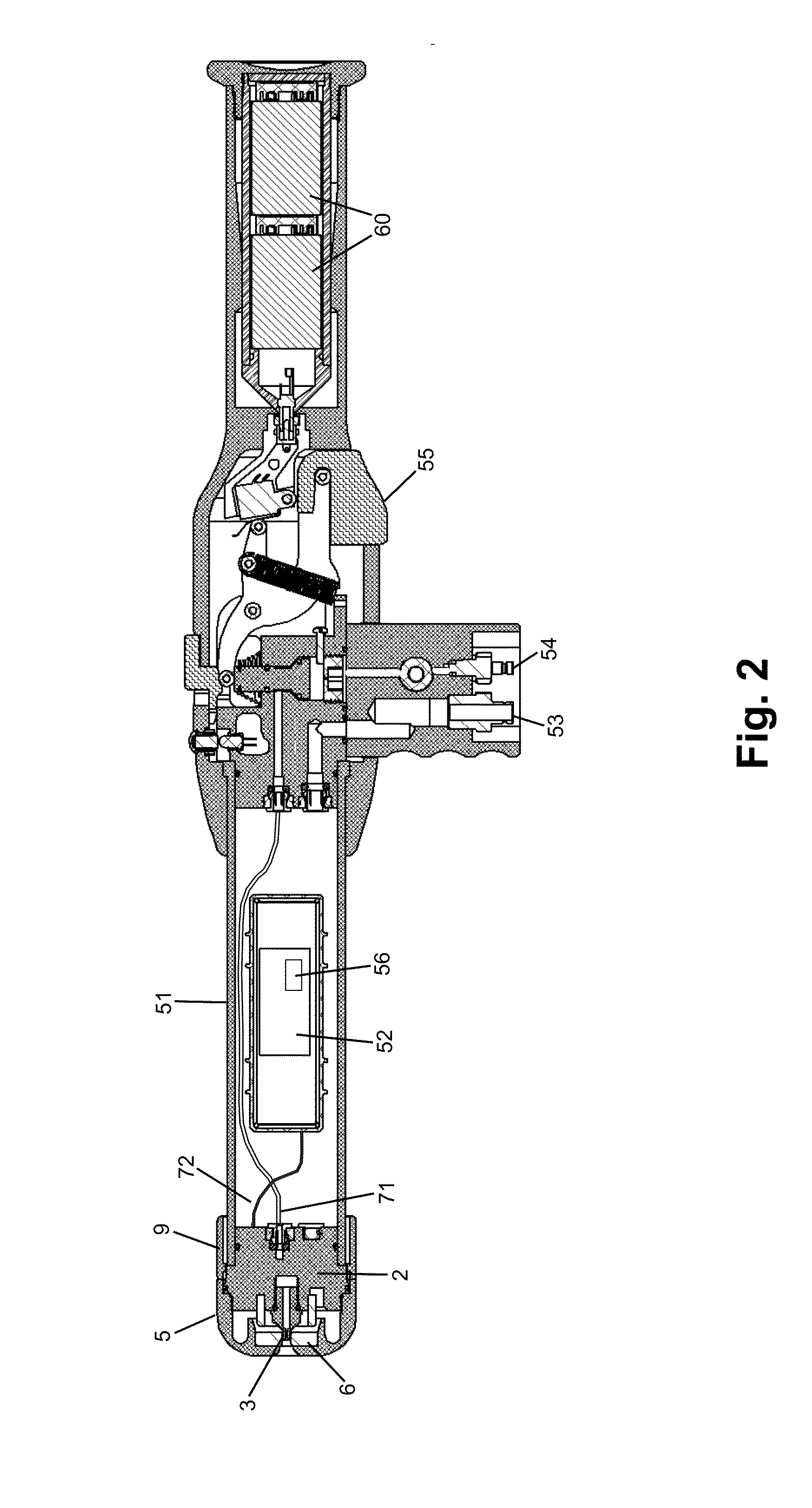

Electrostatic liquid spray nozzle having an internal dielectric shroud

ActiveUS20140110492A1Reduce electric field strengthAvoid leakage currentBurnersLiquid spraying apparatusElectricityElectrical conductor

An electrostatic sprayer for spraying a liquid includes a nozzle formed from a a nozzle body that has an inlet for receiving a liquid and a liquid tip having an outlet for ejection of the liquid to form a liquid spray. The nozzle also includes an electrode disposed around the outlet of the liquid tip for charging the liquid and a dielectric shroud disposed around at least a portion of the liquid tip to prevent leakage currents from reducing a potential of the electric field between the liquid and the electrode, which would otherwise reduce the effectiveness of the sprayer. A conductor that couples the electrode to a power supply may pass through a hole extending through the shroud. The shroud may include one or more vents to permit air and liquid to pass through the dielectric shroud to reduce accumulation of liquid.

Owner:E S PROD DEV

Data slicer, data slicing method, and amplitude evaluation value setting method

InactiveUS7098960B2Reduce electric field strengthPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningDigital videoData selection

A data slicer 300 includes a slice level calculation unit 310 that determines whether a detected digital video signal is a CRI signal on the basis of the amplitude of the signal, and sets a reference slice level and upper and lower slice levels which are obtained by providing offset in the reference slice level, by using only the CRI signal; a data slicing unit 160 that binarizes a digital video signal S140 using the slice levels; a decoding circuit 170 that converts binarized serial data into parallel data; and a data selection unit 320 that selects data including no error from the decoded data, and outputs the selected data through a video signal output terminal 190. Therefore, even when the video signal is distorted, this data slicer can set appropriate slice level data to binarize the video signal, thereby suppressing the occurrence rate of decoding errors.

Owner:SOCIONEXT INC

Method for fabricating a mask ROM

ActiveUS20060014348A1Critical dimension be reduceEasily removeSolid-state devicesSemiconductor/solid-state device manufacturingPhotoresistSemiconductor

The present invention discloses a method for fabricating a buried bit line of a mask ROM. The method includes providing a semiconductor substrate with a photoresist layer, and patterning the photoresist layer to form a photoresist pattern. A first ion implantation process is performed to form a first doped region in the semiconductor substrate not covered by the photoresist pattern. Then, an organic layer is coated on the photoresist pattern and the semiconductor substrate and an etching process is performed to form an organic spacer at two sides of the photoresist pattern. Finally, a second ion implantation process forms a second doped region in the semiconductor substrate not covered by the photoresist pattern and the organic spacer. Finally, the photoresist pattern and the organic spacer are removed.

Owner:UNITED MICROELECTRONICS CORP

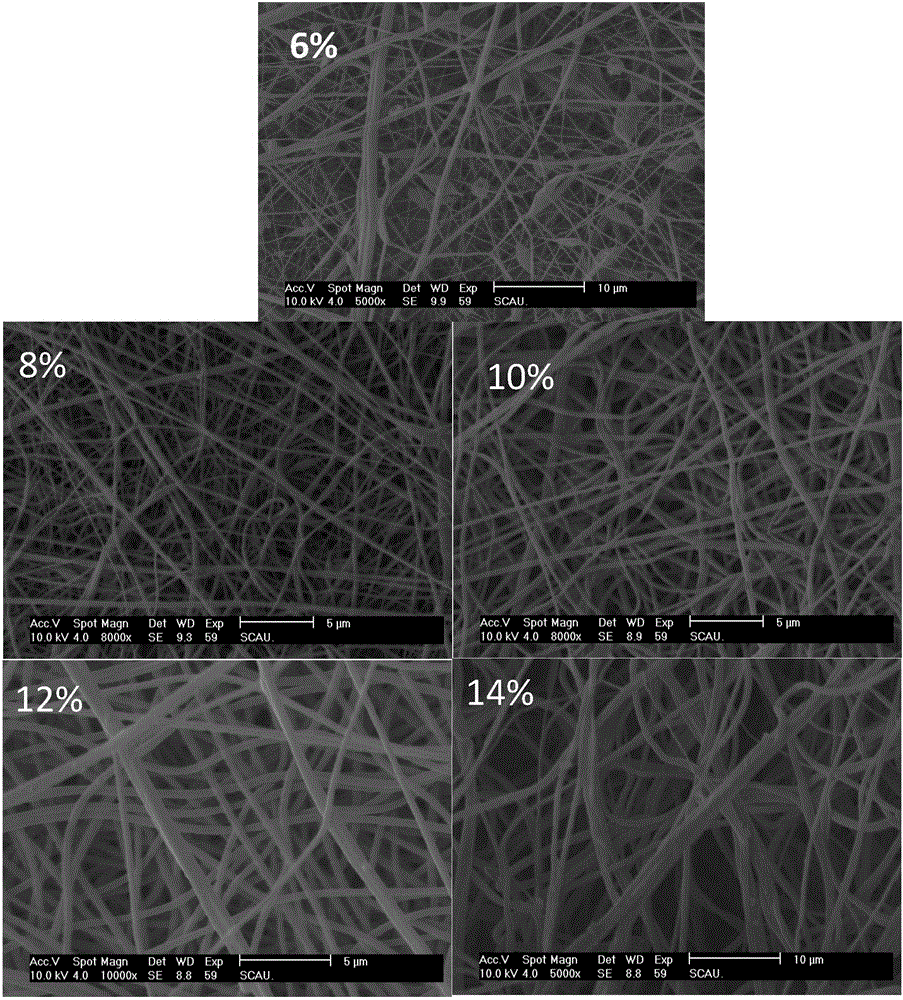

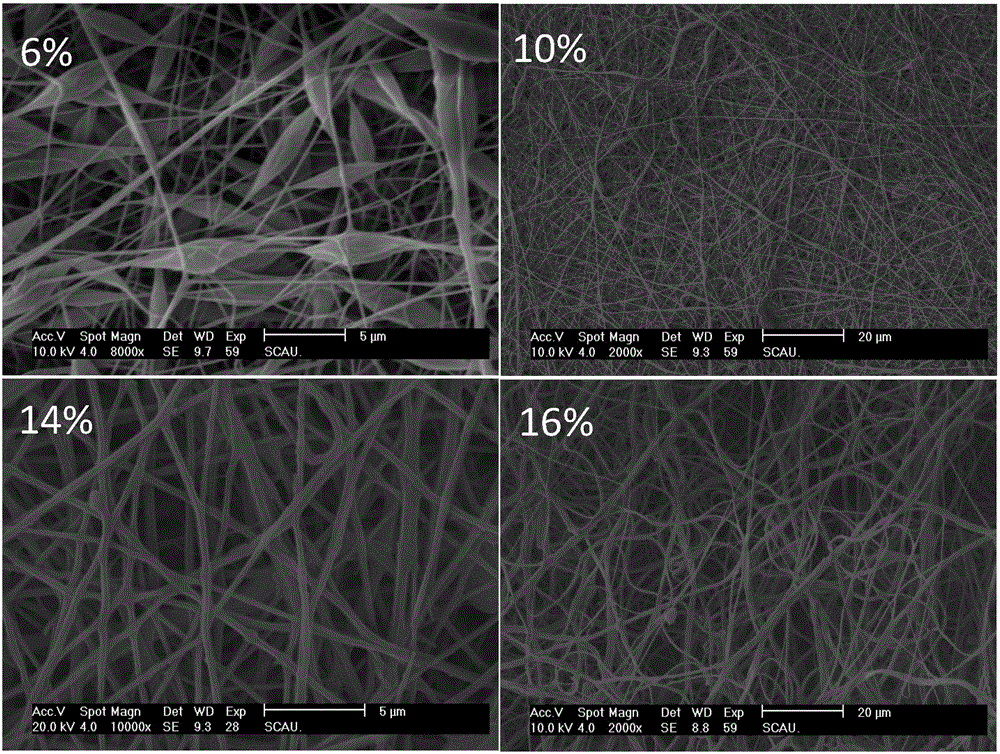

Static spraying composite film and preparation method and application thereof

ActiveCN105908363AAvoid breedingAchieve bi-directional performanceElectro-spinningAbsorbent padsFiberComposite film

The invention discloses a static spraying composite film and a preparation method and application thereof. A PVDF nanofiber thin film is spun on a roller receiver through electrostatic spinning to serve as a supporting material, then a layer of Cur-PLA microspheres is sprayed through an electrostatic spraying method, and a double-layer film is obtained; an Enro-PLA nanofiber film is spun on the double-layer film through an electrostatic spinning method, drying is carried out, and the electrostatic spraying composite film is obtained. Medicine is carried on polylactic acid fibers and the microspheres, so that the biological activity and antibacterial property of the electrospinning film are achieved; compared with like products, a hydrophilic face formed by the PLA microspheres and the PLA fibers is not single in medicine release capacity, wider in antibacterial performance and larger in contact area with the skin surface. PVDF is adopted as an outer layer for isolating invasion of water vapor and bacteria. The preparation method is simple, the production cost is low, large-scale production can be achieved, application and popularization are convenient, and the final product can completely meet various clinical needs.

Owner:SOUTH CHINA AGRI UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com