Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

47results about How to "Good gating ability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

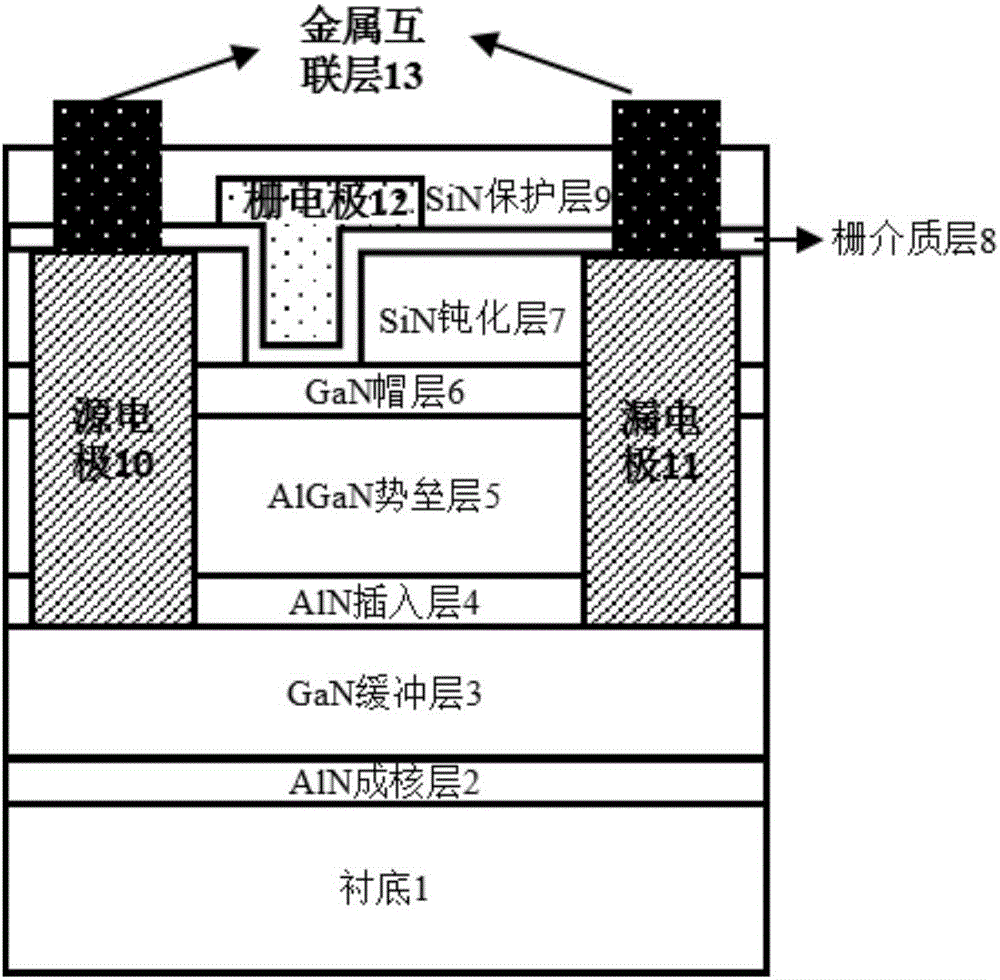

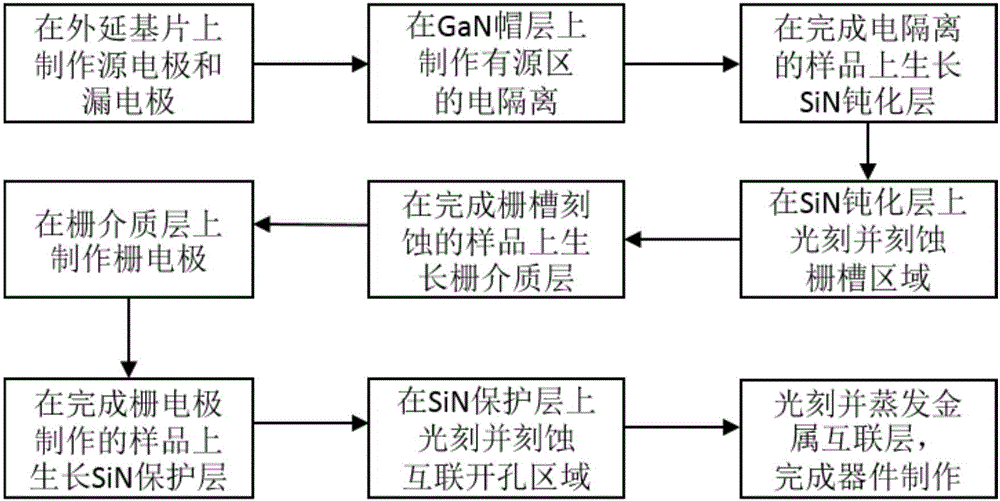

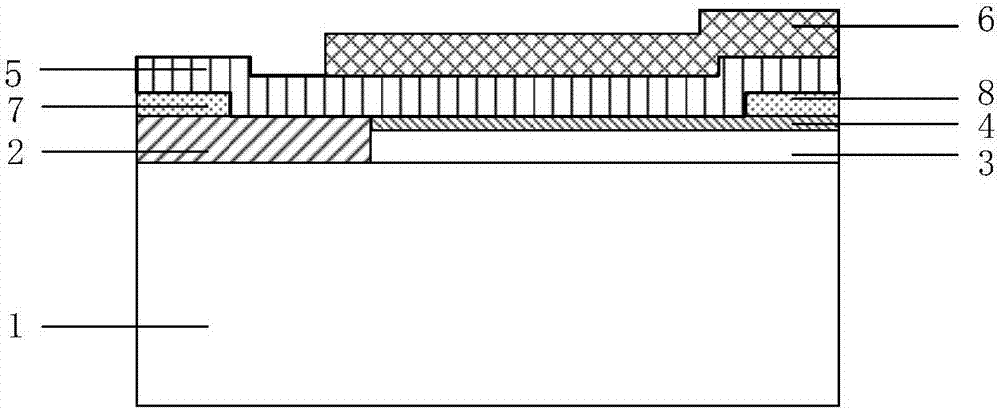

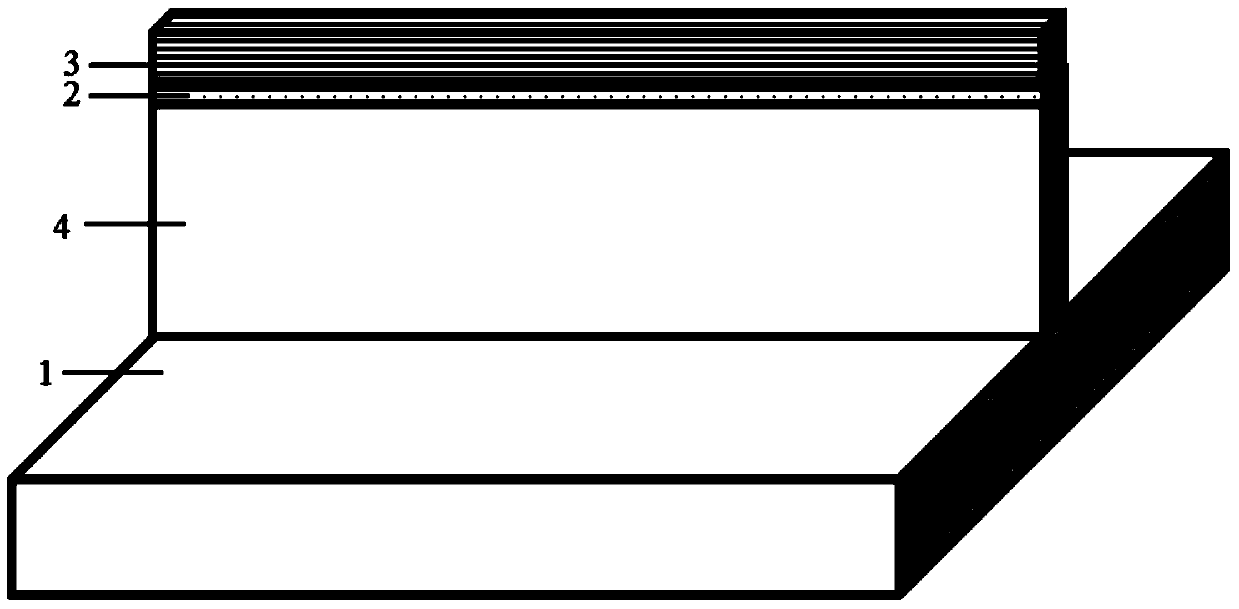

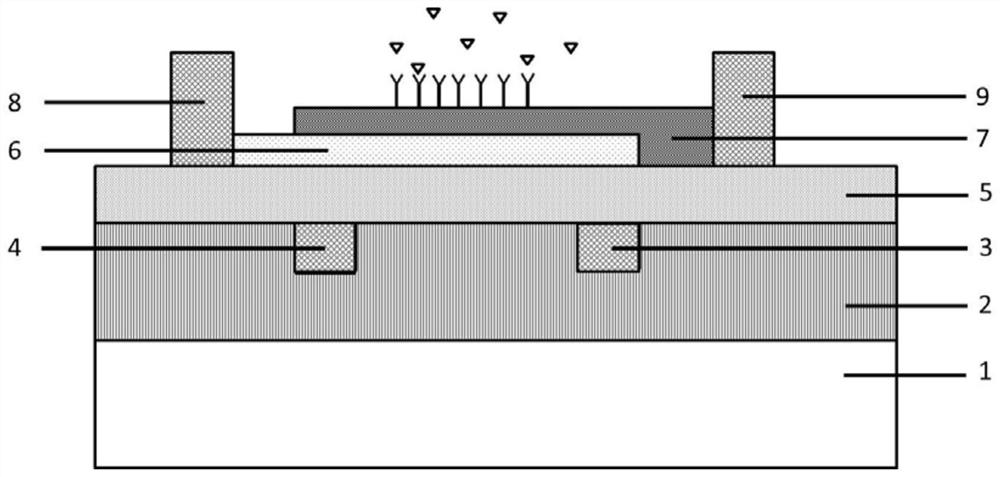

Stacked gate dielectric GaN-based insulated gate high-electron mobility transistor and manufacturing method

InactiveCN106229345AImproved interface quality and gating capabilitiesHigh activitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsHigh-electron-mobility transistor

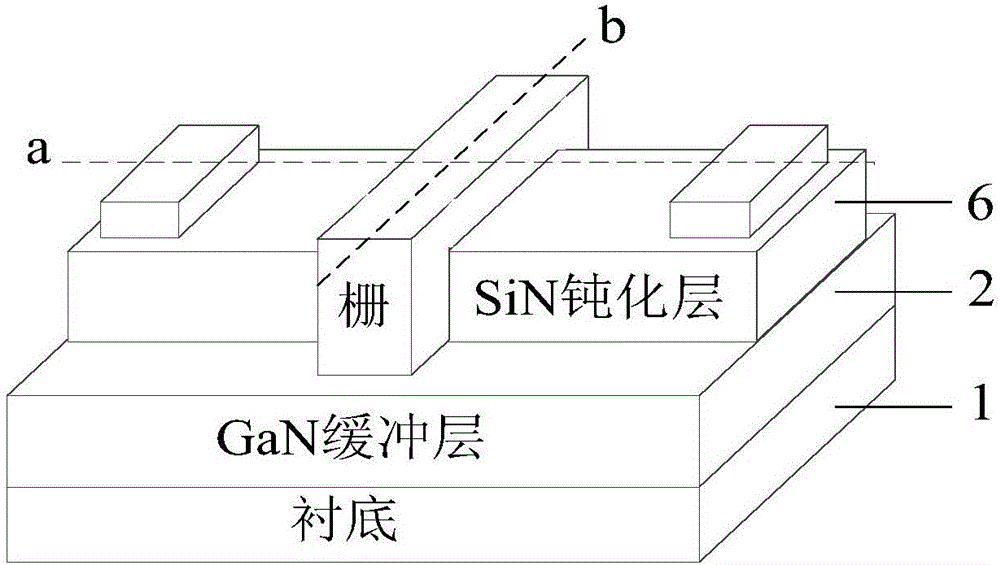

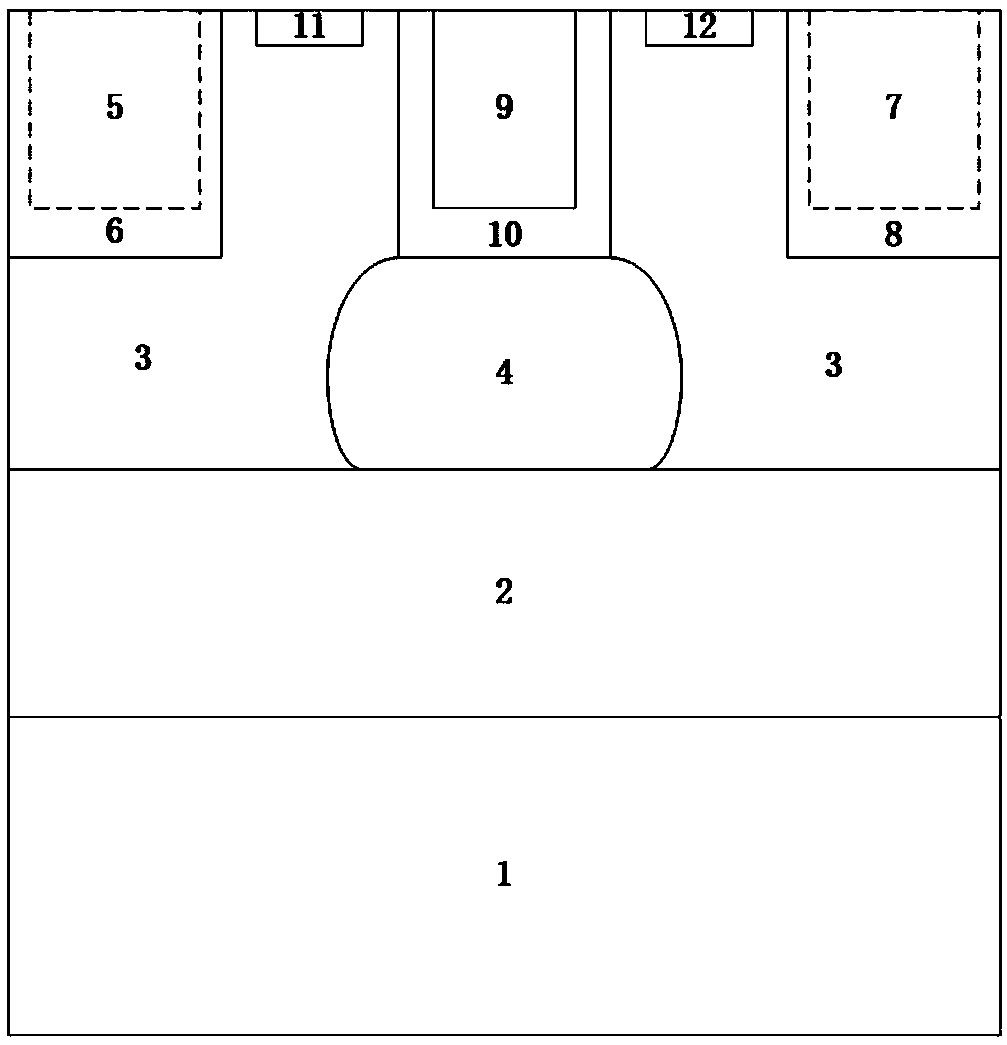

The invention discloses a stacked gate dielectric GaN-based insulated gate high-electron mobility transistor, mainly to solve the problem that existing similar devices are low in reliability. The device comprises a substrate (1), an AlN nucleation layer (2), a GaN buffer layer (3), an AlN insertion layer (4), an AlGaN barrier layer (5), a GaN cap layer (6), a SiN passivation layer (7), a gate dielectric layer (8) and a SiN protection layer (9) from bottom to top, wherein two ends of the GaN buffer layer (3) are provided with a source electrode (10) and a drain electrode (11); the middle of the gate dielectric layer (8) is provided with a gate electrode (12); a metal interconnection layer (13) is arranged on the source electrode (10) and the drain electrode (11); and the gate dielectric layer (8) adopts a stacked structure formed by an AlN dielectric insertion layer (81) and a high k dielectric layer (82). The interface characteristics and the gate control capability of the device are improved, the reliability is improved, and the stacked gate dielectric GaN-based insulated gate high-electron mobility transistor can serve as a high-efficiency microwave power device.

Owner:XIDIAN UNIV

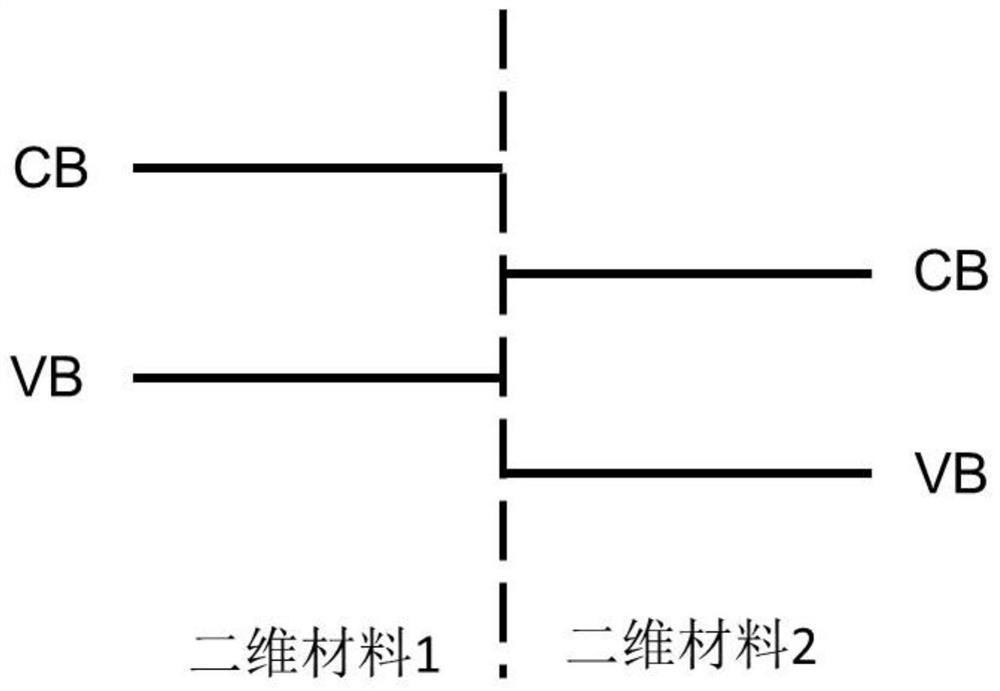

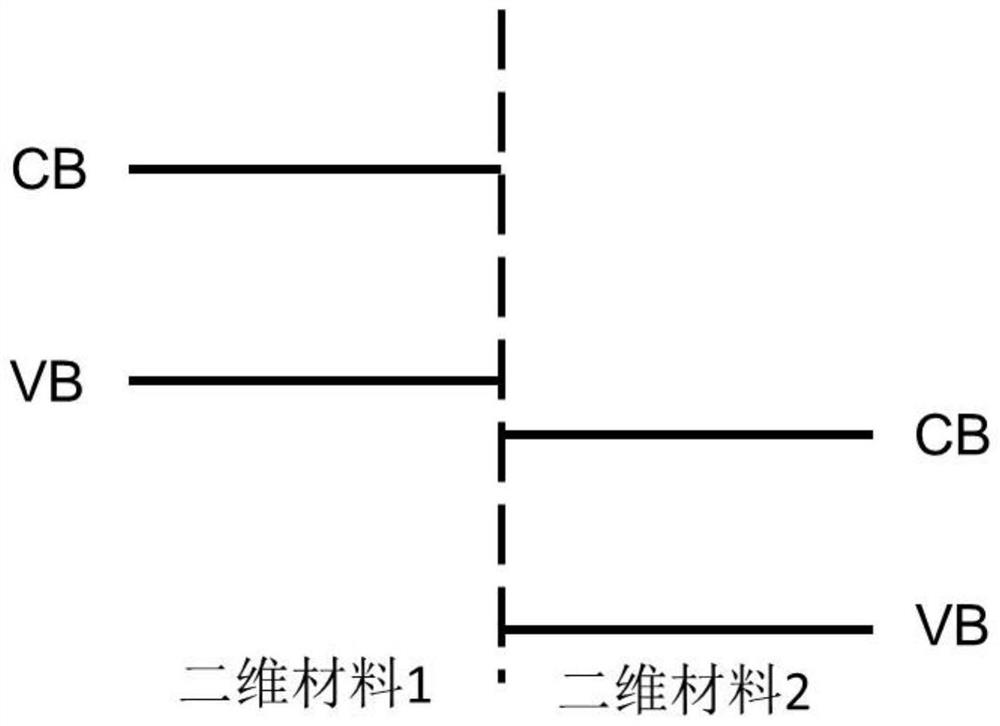

Two-dimensional material/semiconductor hetero-junction tunneling transistor and preparation method thereof

ActiveCN107104140AEffective tunnelingDirect tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsPower flow

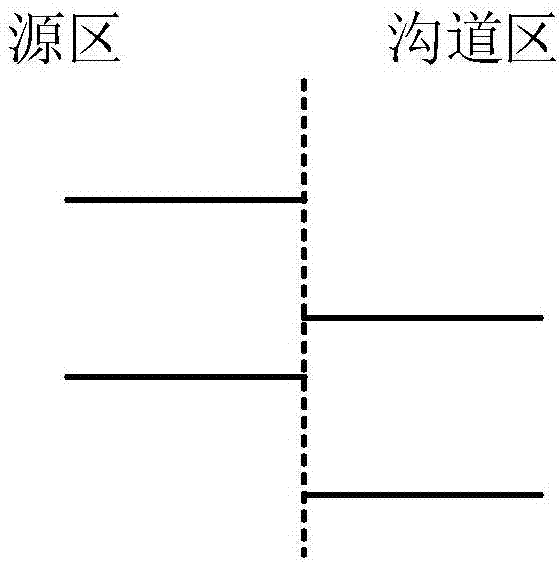

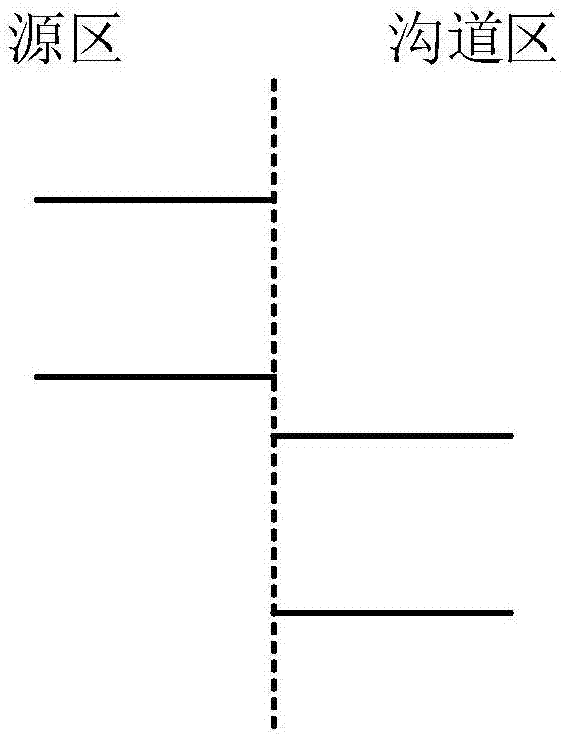

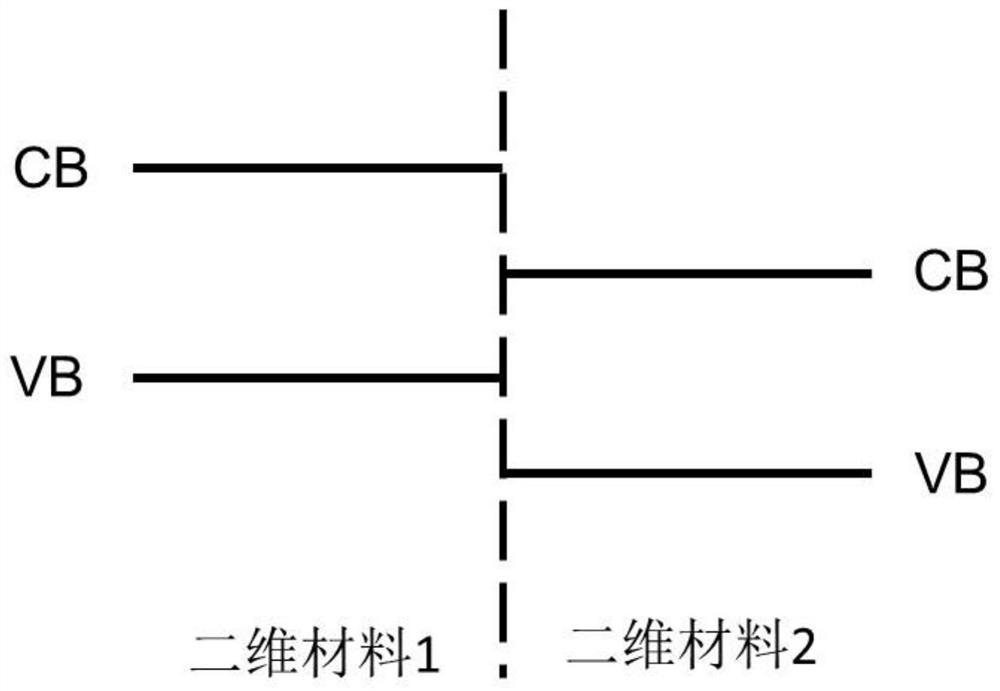

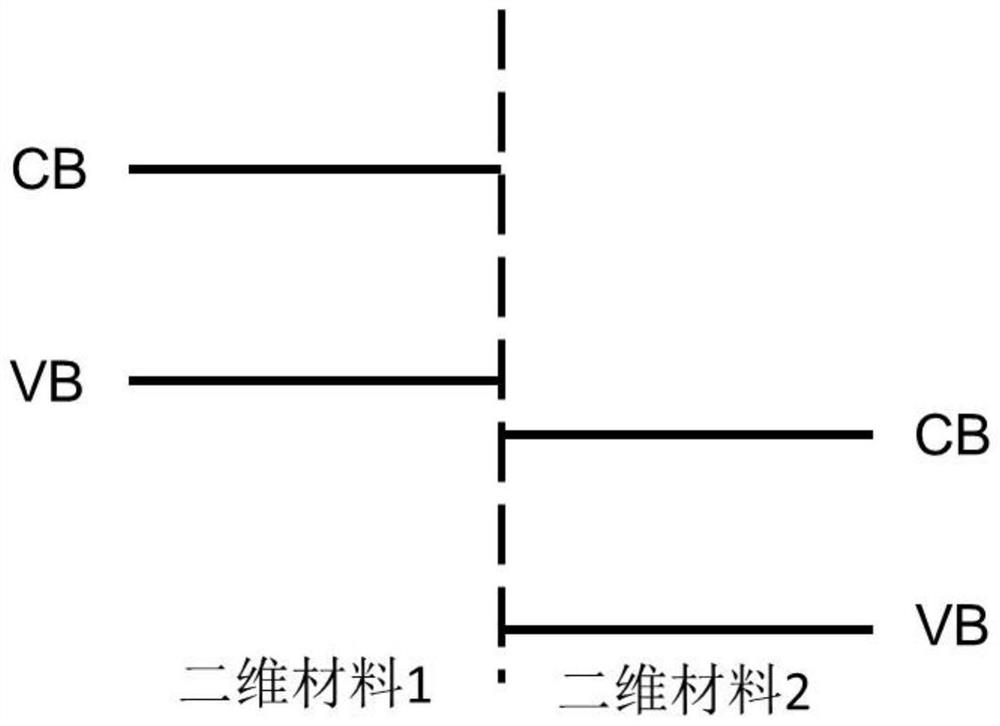

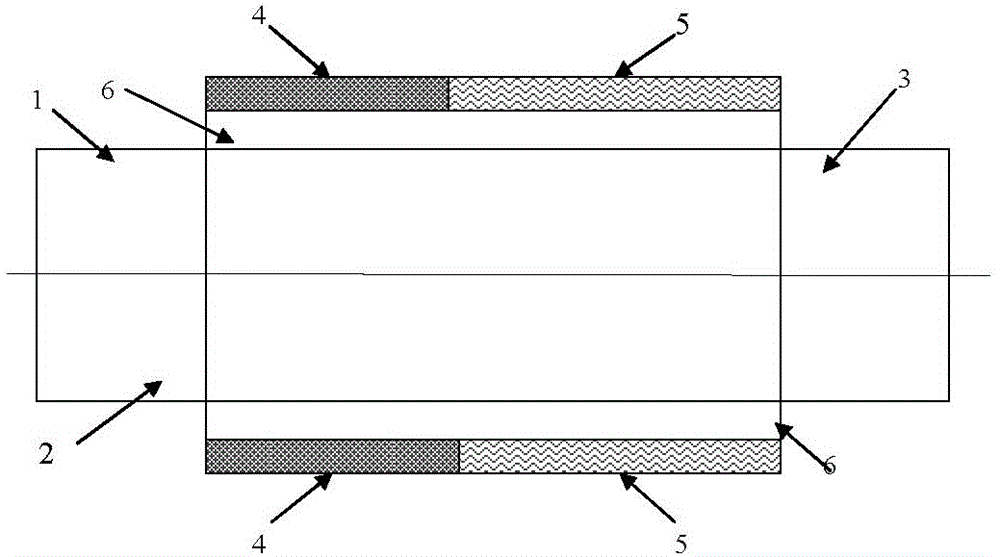

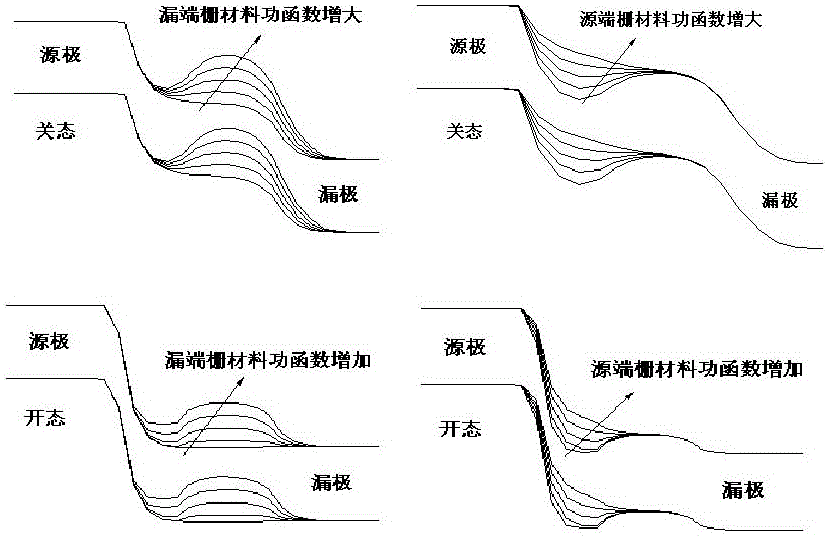

The invention discloses a tunneling field effect transistor based on a two-dimensional material / semiconductor hetero-junction and a preparation method thereof. A device forms an interleaved energy band structure in the off state through the energy band design, namely, a tunneling window is inexistent between the two-dimensional material and the semiconductor material, and the ultra-low off-state current can be acquired; the grid voltage can be applied to regulate an energy band alignment way at the two-dimensional material / semiconductor hetero-junction so that the device can form the staggered energy band structure in the on-state, and the effective tunneling barrier height is a negative value; and meanwhile, the current carrier tunnels to a channel region from a source region to realize the direct tunneling, thereby acquiring large on-state current. The device adopts the highly-doped three-dimensional semiconductor material as the source region material, and the three-dimensional semiconductor material and the metal source electrode are unipotential; since the thickness of the two-dimensional material is ultra-thin, the grid voltage can regulate the two-dimensional material and the energy band at the two-dimensional material / semiconductor hetero-junction interface, thereby acquiring an ideal grid control capacity. The tunneling field effect transistor disclosed by the invention is simple in process, and large in compatibility with the traditional semiconductor process.

Owner:PEKING UNIV

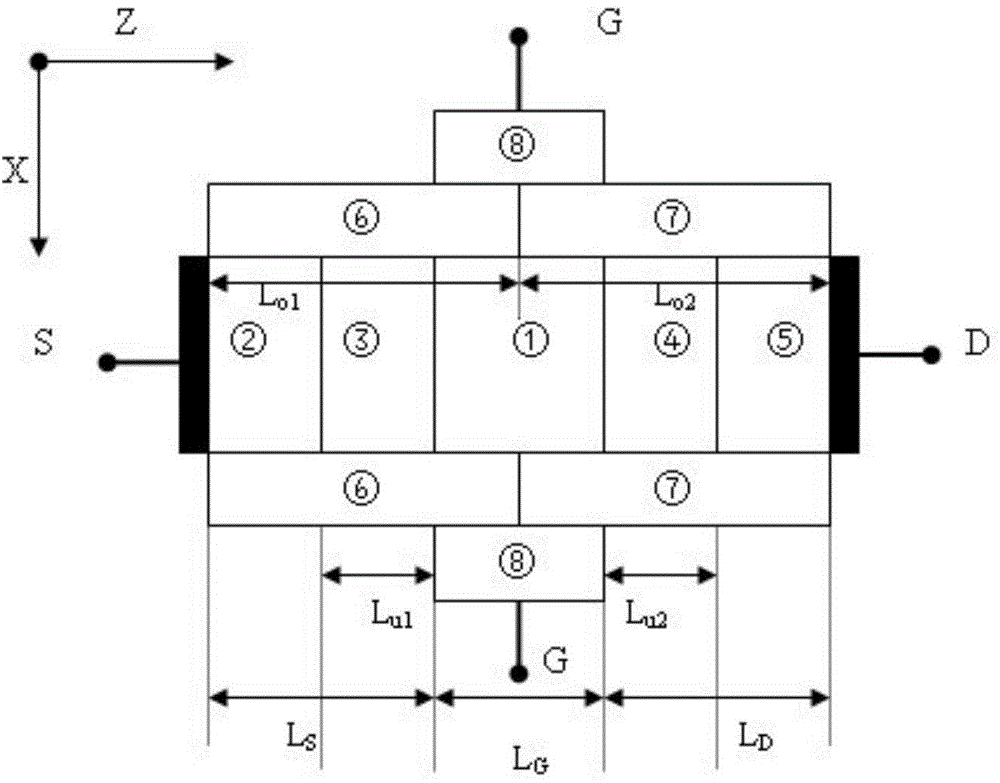

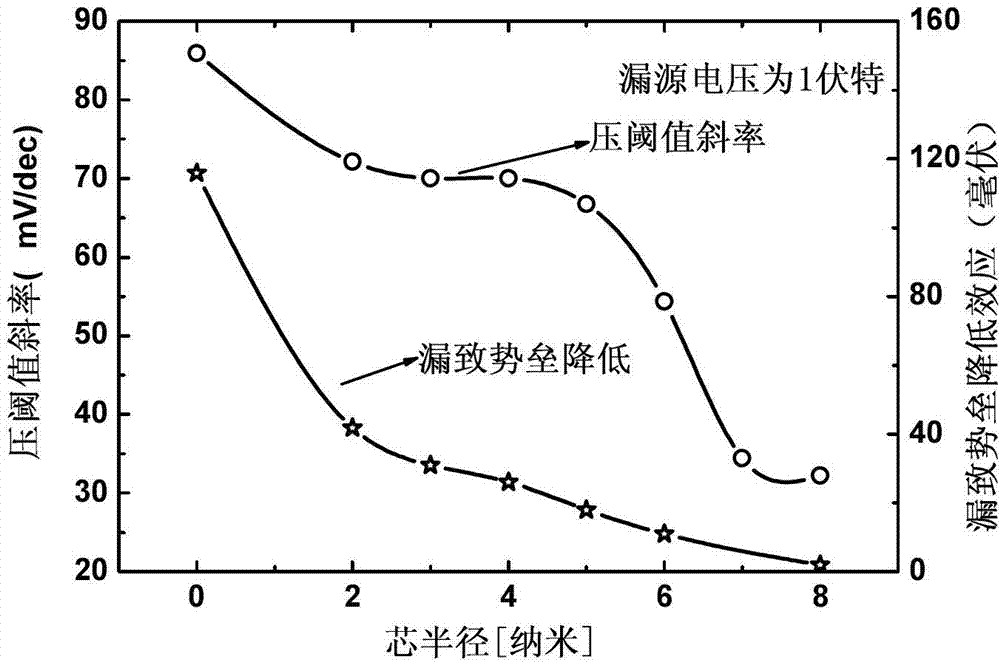

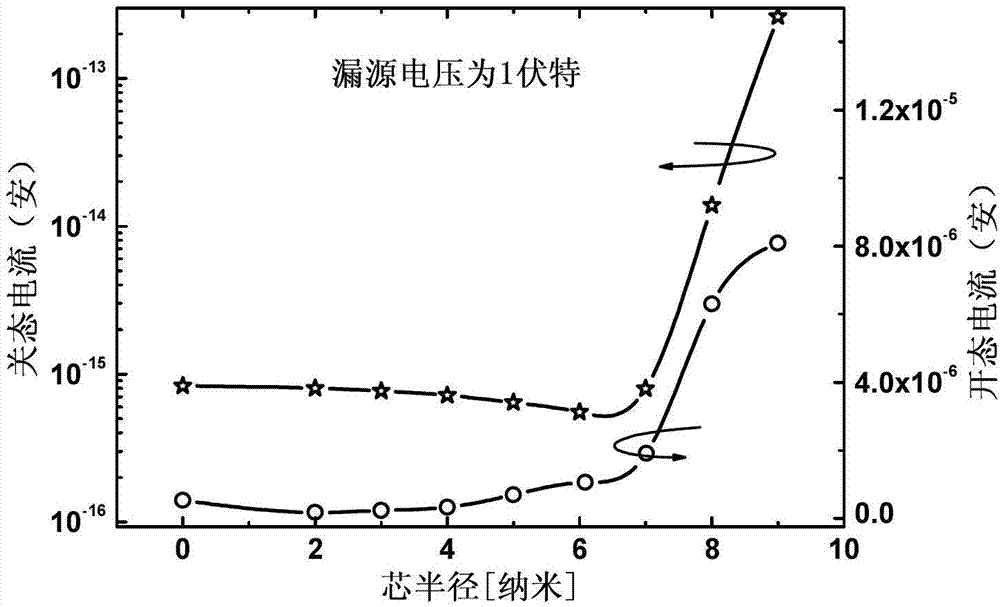

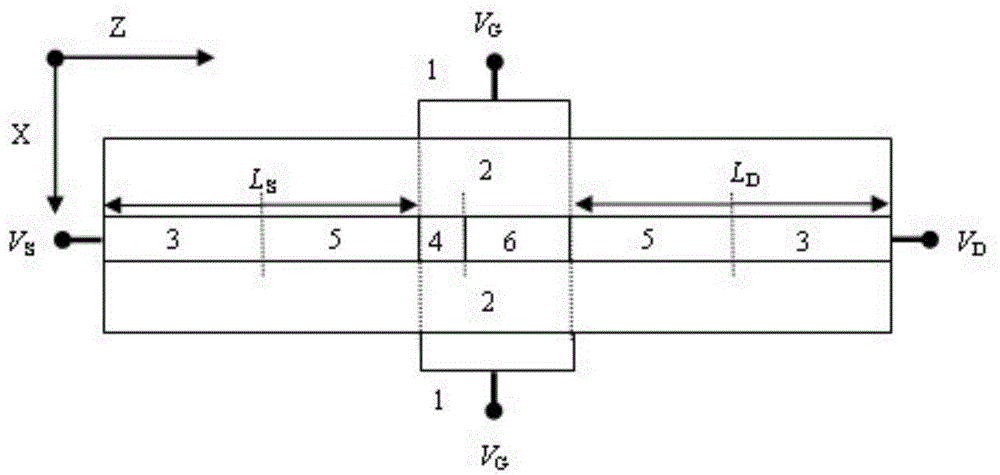

Graphene nanoribbon field-effect tube (GNRFET) with asymmetric HALO-lightly-doped drain (HALO-LDD) structure

InactiveCN103077968AReduce off-state currentGood gating abilitySemiconductor devicesPower flowSwitched current

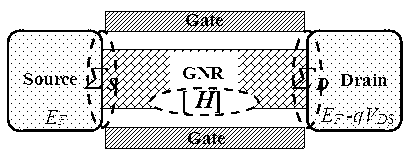

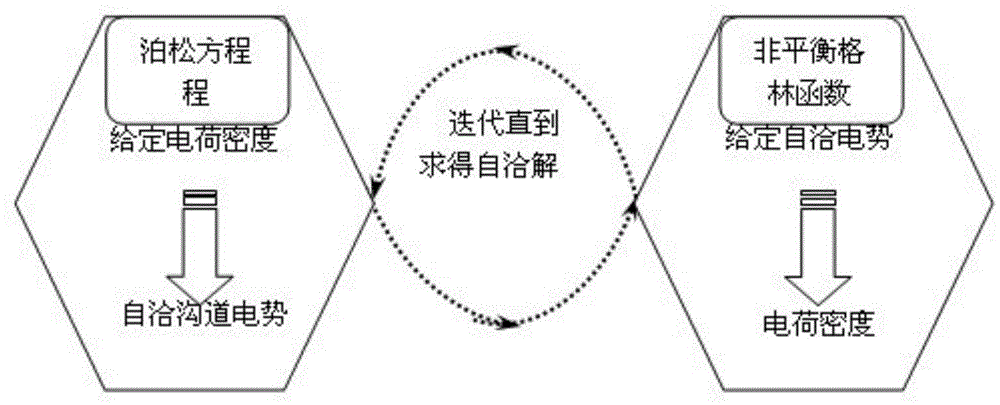

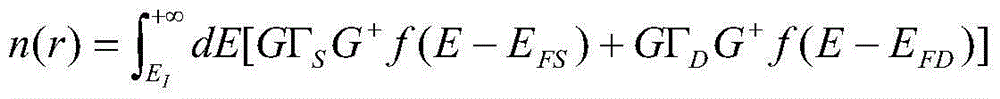

The invention discloses a graphene nanoribbon field-effect tube (GNRFET) with an asymmetric HALO-lightly-doped drain (HALO-LDD) structure. A transport model which is suitable for a non-uniformly-doped GNRFET is constructed on the basis of a quantum mechanics non-balance Green function theoretical frame under an open boundary condition through self-consistent solution of 3D-Poisson and Schr.dinger equations, and the influence of an asymmetric HALO-LDD doping strategy on the electrical properties of the GNRFET is analyzed and calculated by using the model. As proved by comparison and analysis of the electric properties such as the output properties, transfer properties, switch current ratios, sub-threshold amplitudes and threshold voltage drifts of GNRFETs for which other doping strategies are adopted, the GNRFET with the doping structure has a higher switch current ratio, lower drain current, a smaller sub-threshold amplitude and a smaller threshold voltage drift, i.e., the GNRFET for which the asymmetric HALO-LDD doping strategy is adopted has a better grid control capability, and a short-groove effect and a hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

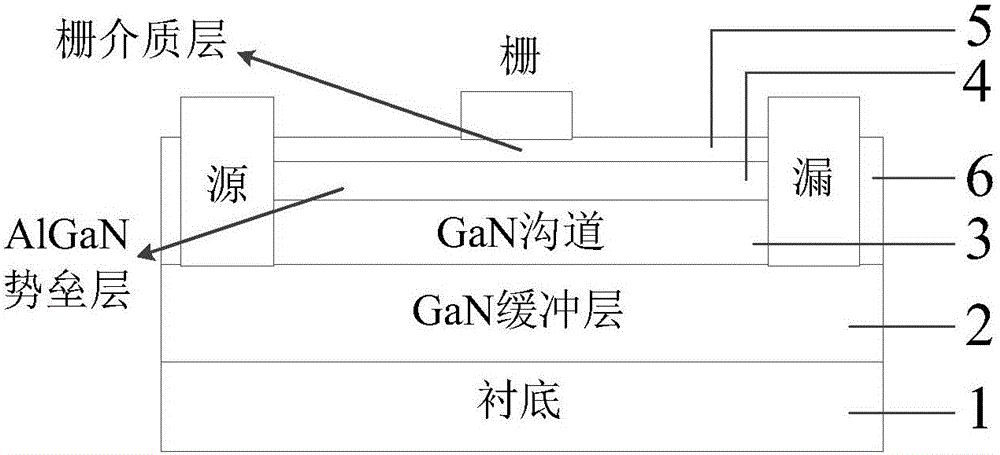

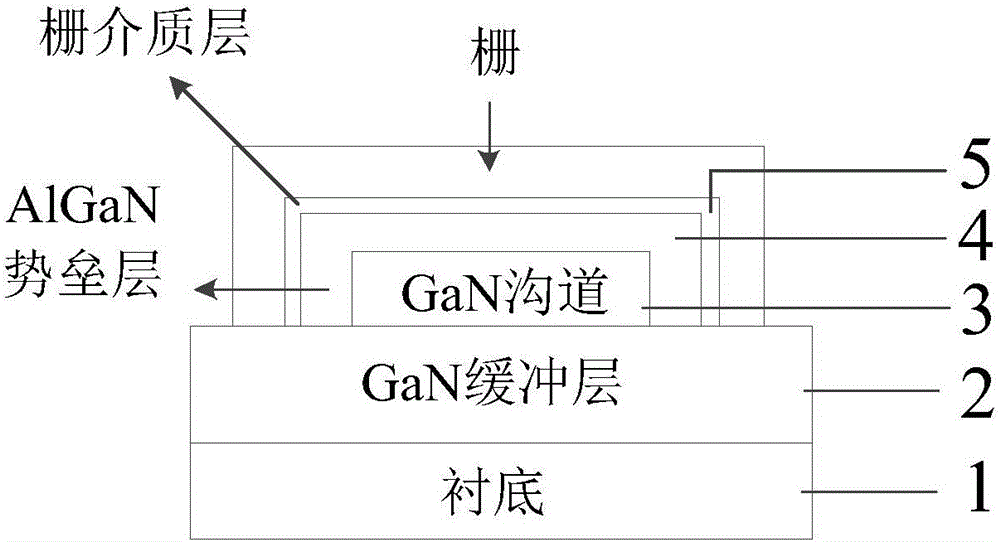

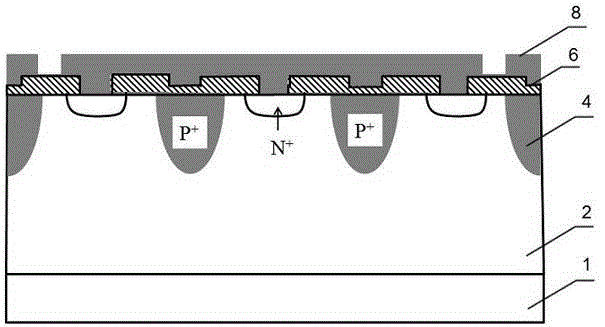

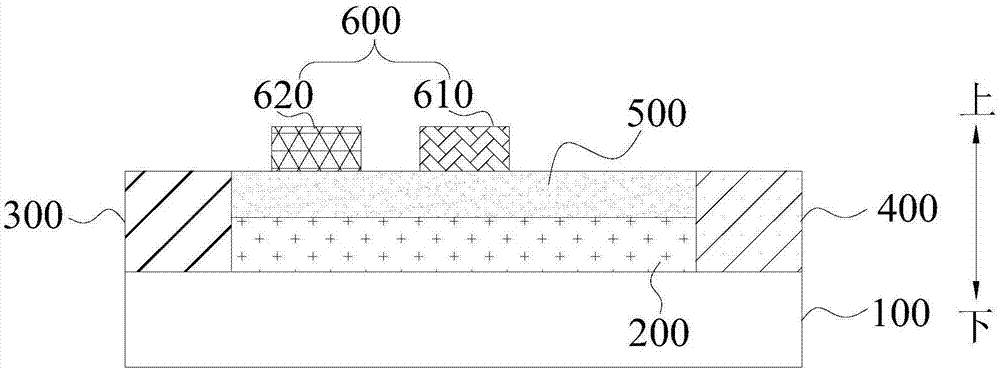

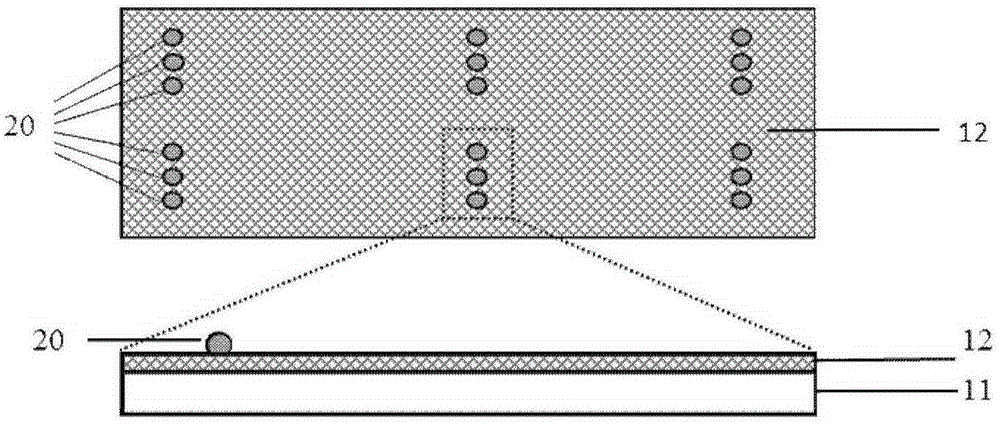

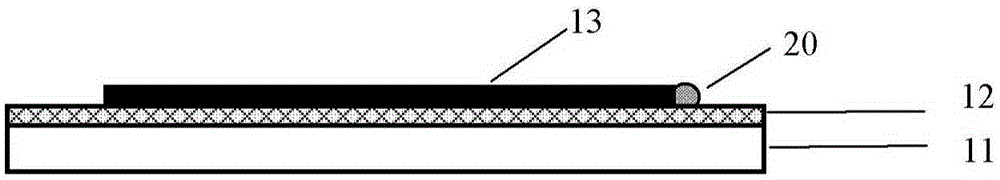

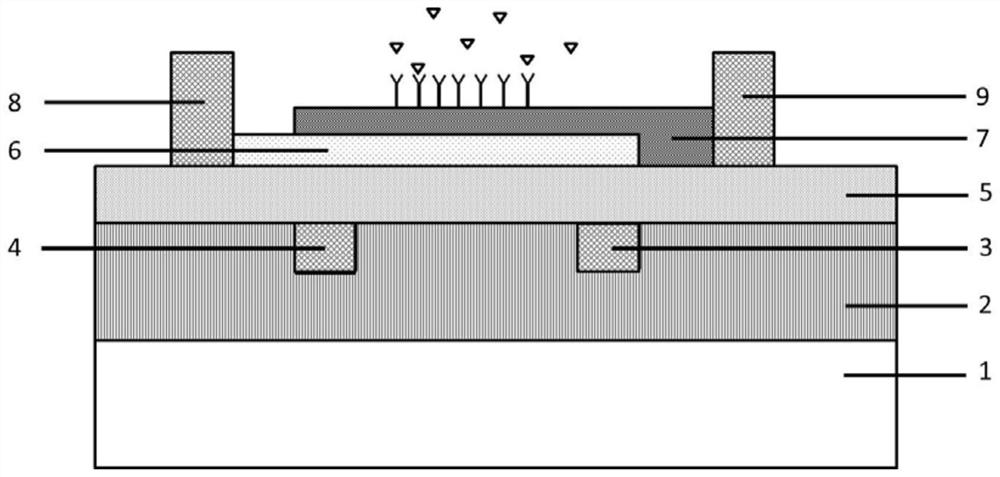

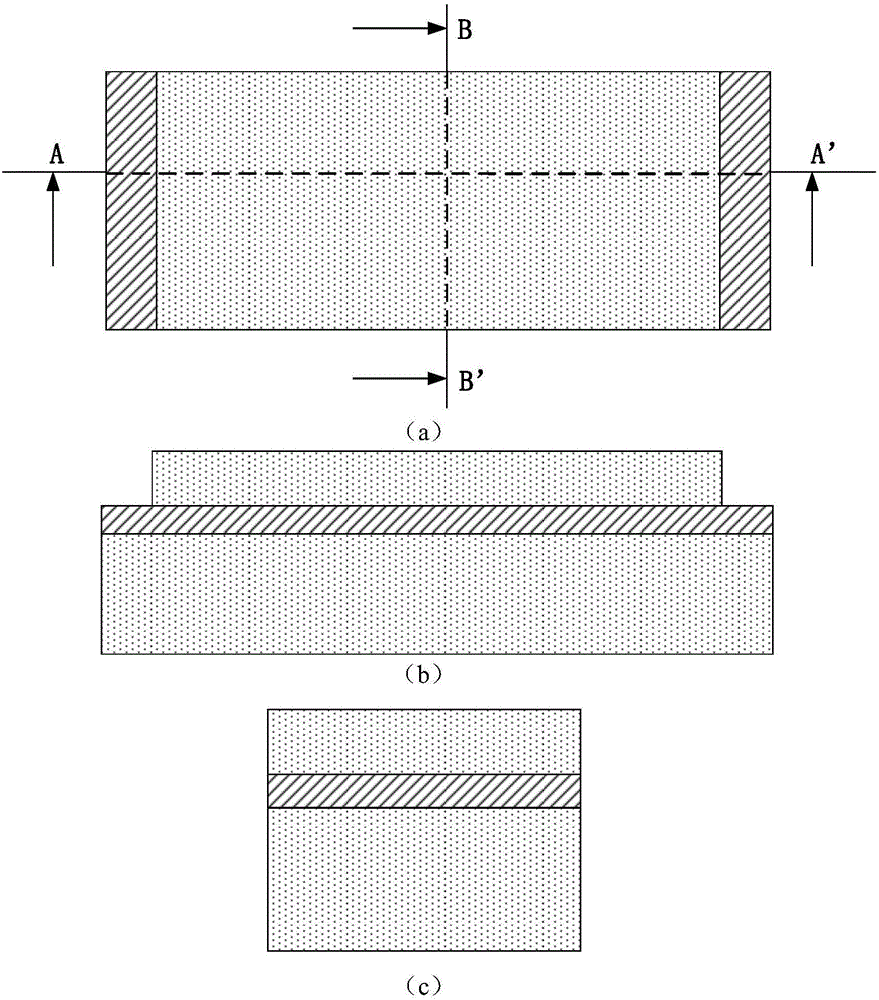

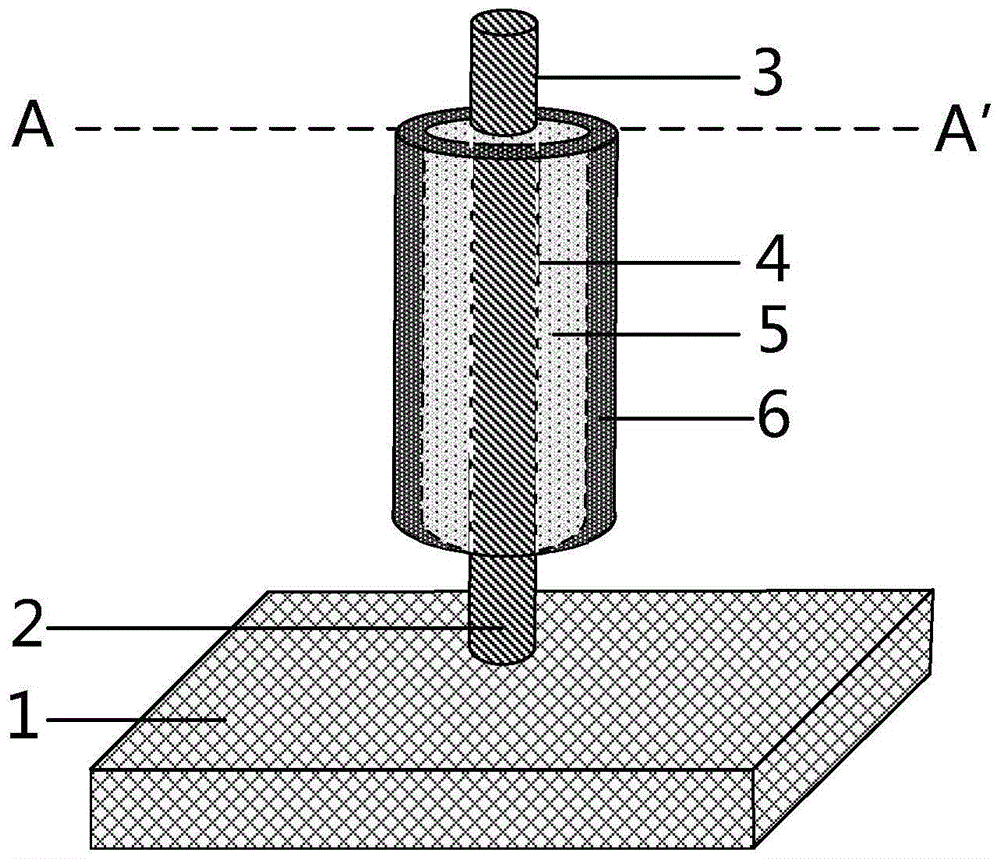

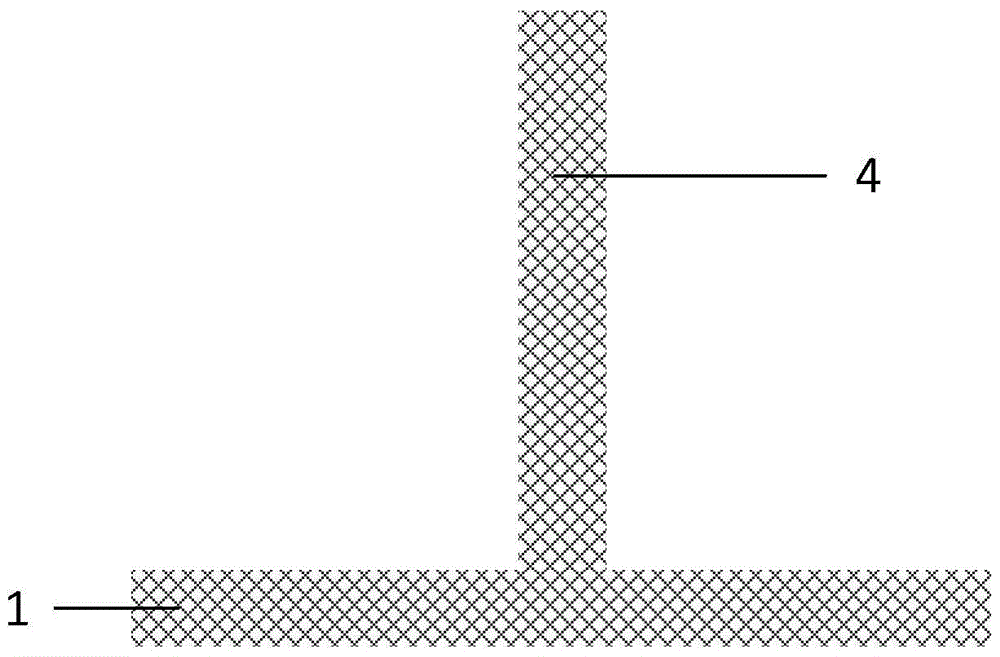

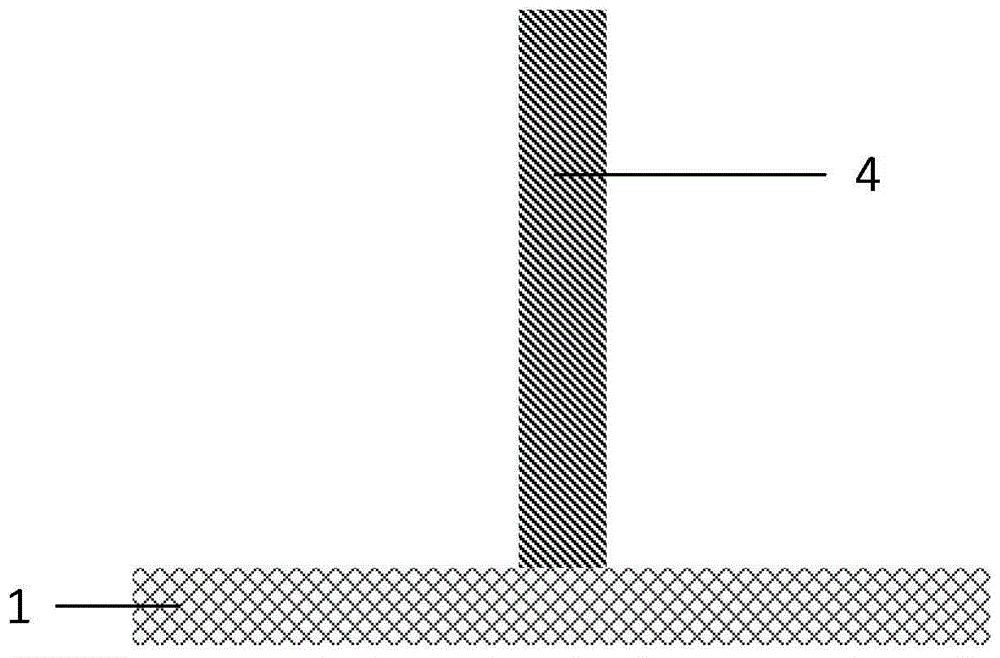

GaN-based nanometer channel transistor with high electron mobility and manufacture method

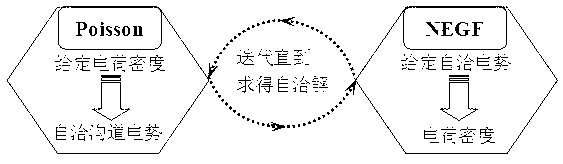

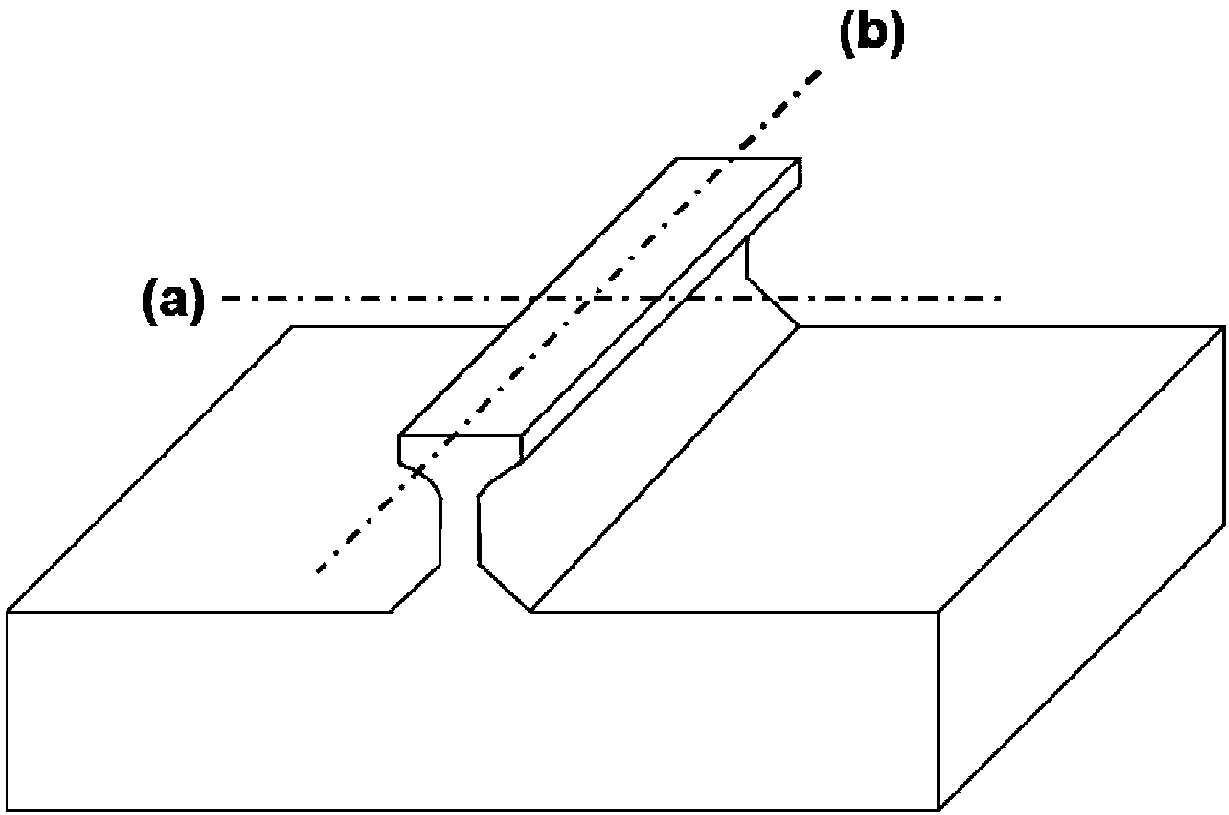

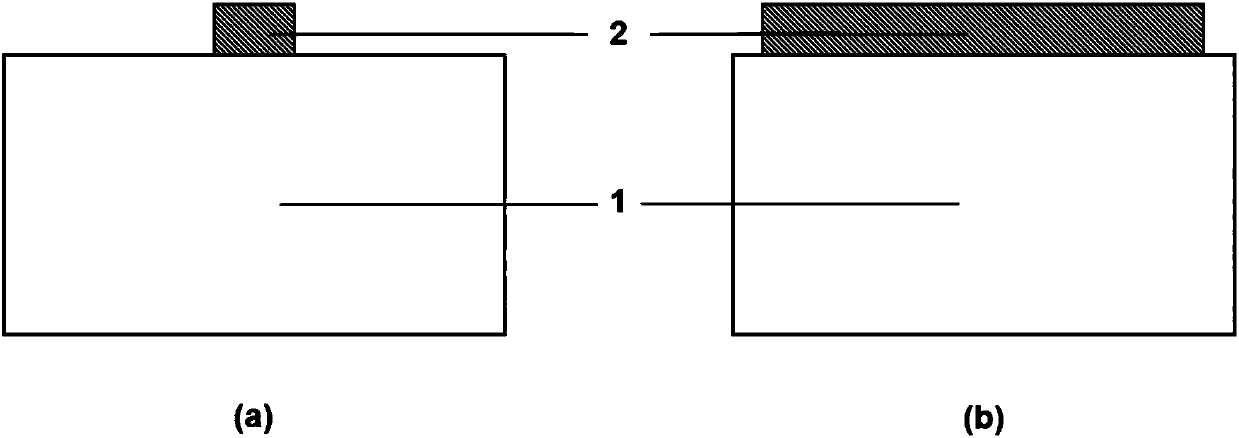

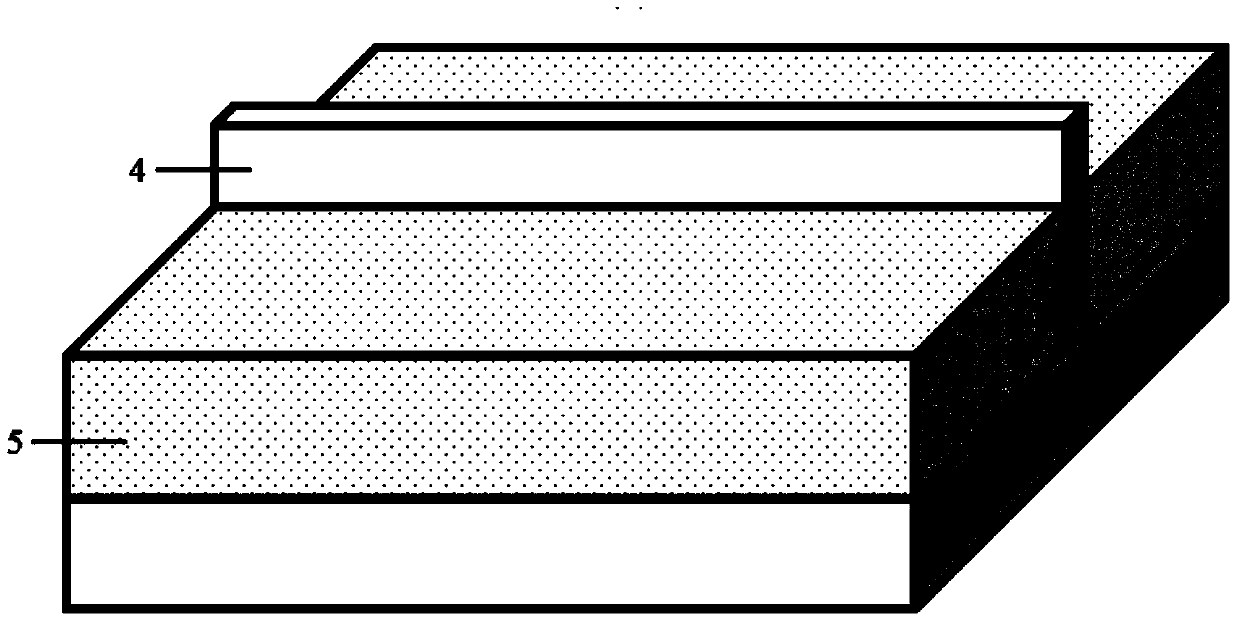

ActiveCN105762078ASuppression of short channel effectsGood gating abilityMaterial nanotechnologySemiconductor/solid-state device manufacturingPhysicsTransconductance

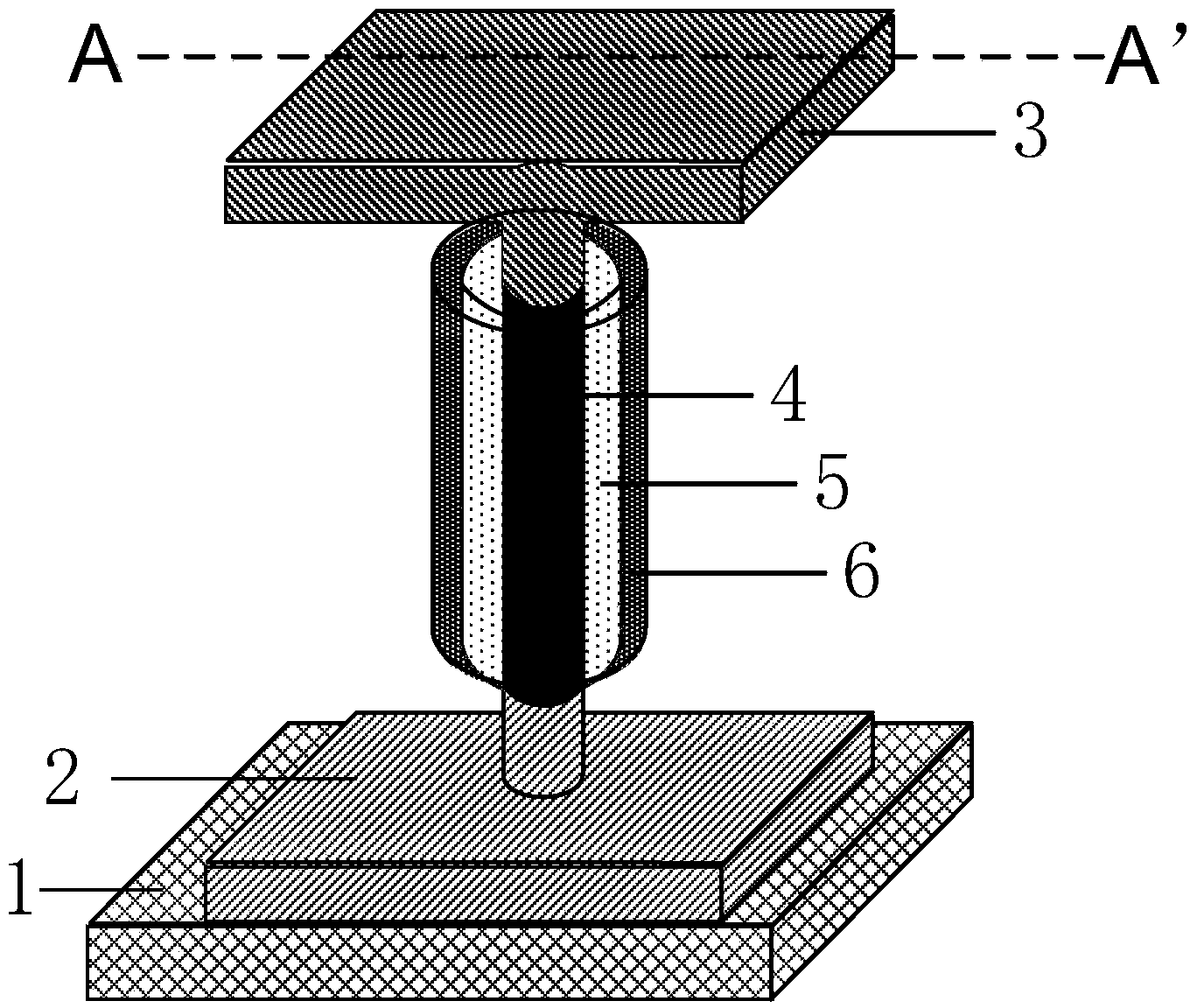

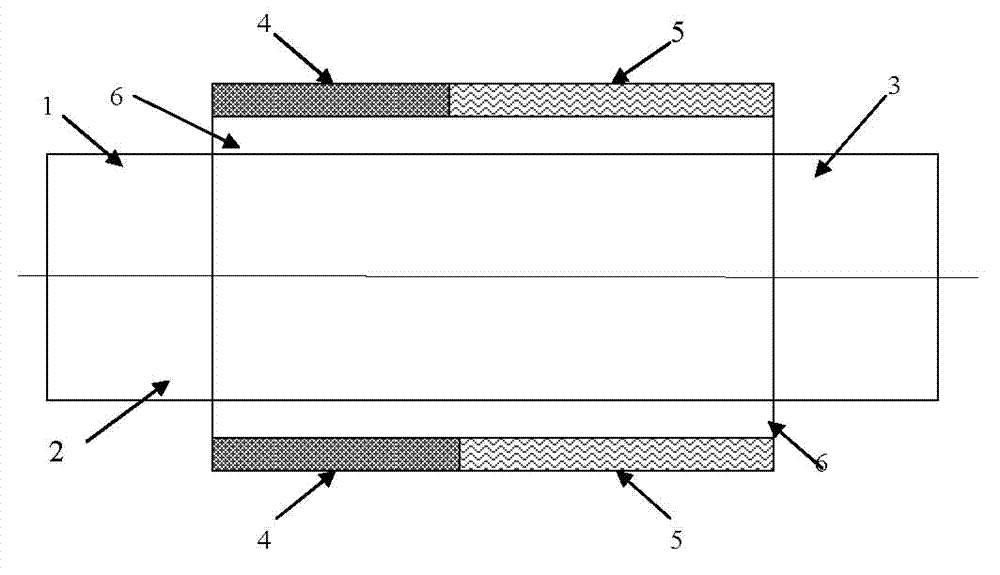

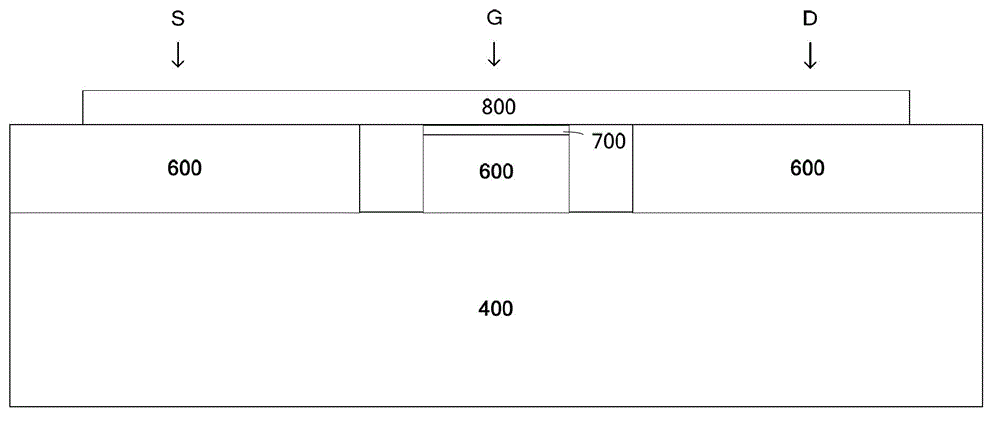

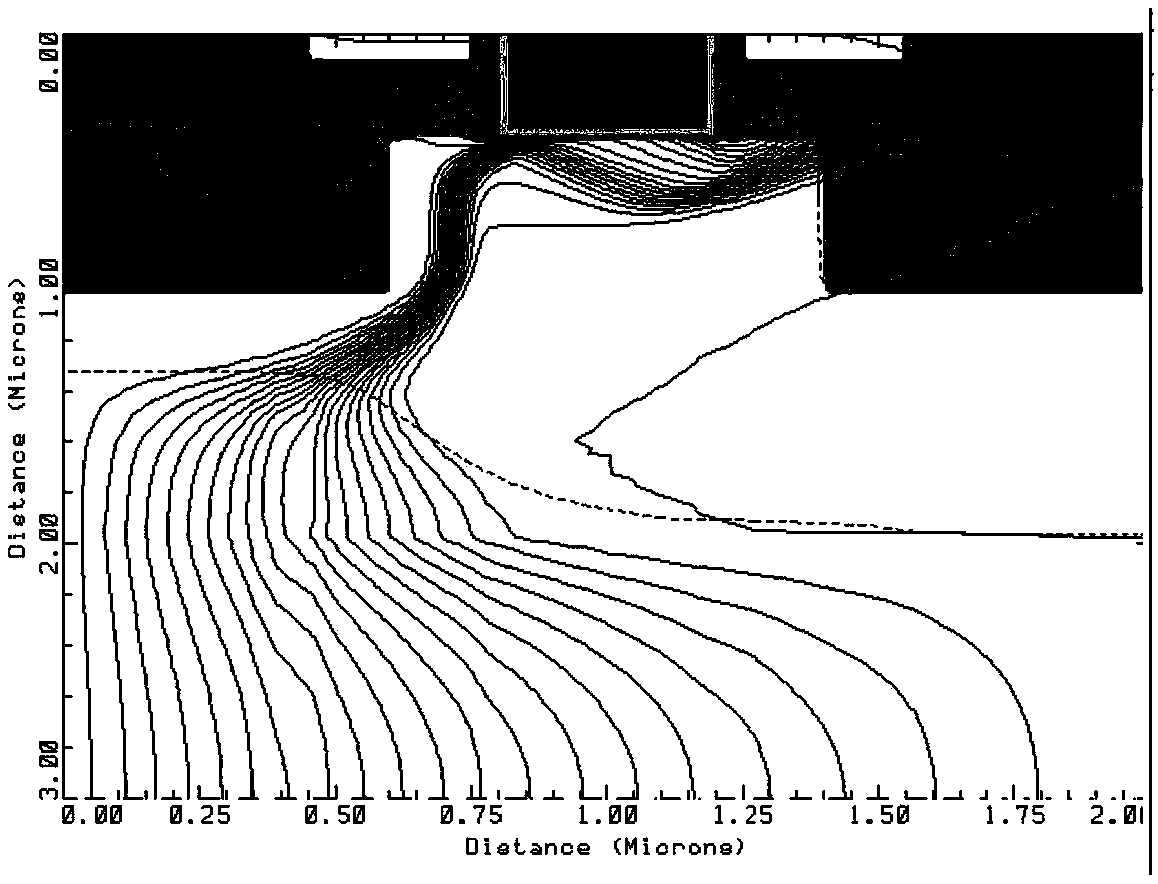

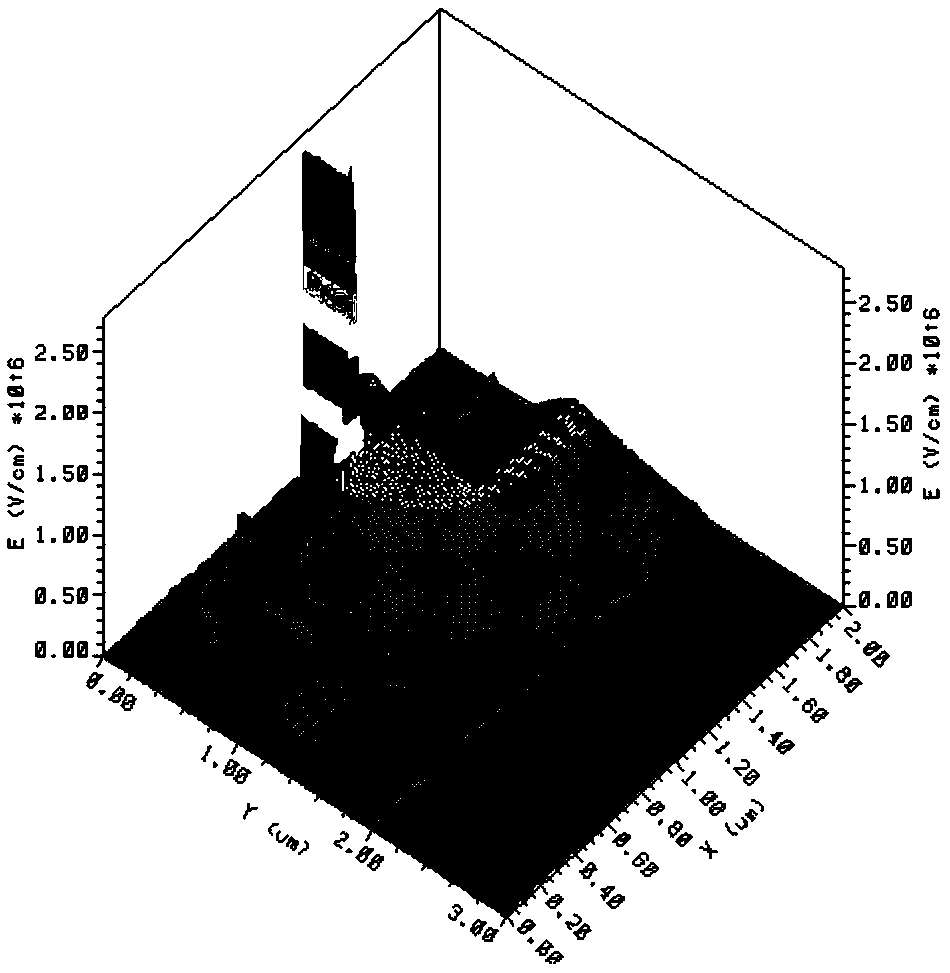

The invention discloses a GaN-based nanometer channel transistor with high electron mobility and mainly aims at solving the problems that in the prior art, the short channel effect is serious, the grid control ability is poor, and the leak current and transconductance are low.The transistor comprises a substrate (1), a GaN buffer layer (2), a GaN channel (3), AlGaN barrier layers (4), a grid dielectric layer (5), a passivation layer (6), a source electrode, grid electrodes and a drain electrode from bottom to top.The AlGaN barrier layers are additionally arranged on the two sides of the GaN nanometer channel, the GaN nanometer channel is wrapped by the AlGaN barrier layers, and AlGaN / GaN heterojunctions are formed on the top and the two sides of the GaN nanometer channel; the grid electrodes are located on the two sides and the top of each AlGaN / GaN heterojunction.The transistor has the advantages of being good in grid control ability, large in saturation current and small in leak resistance, and can be used as a small-size high-speed high-frequency device.

Owner:XIDIAN UNIV

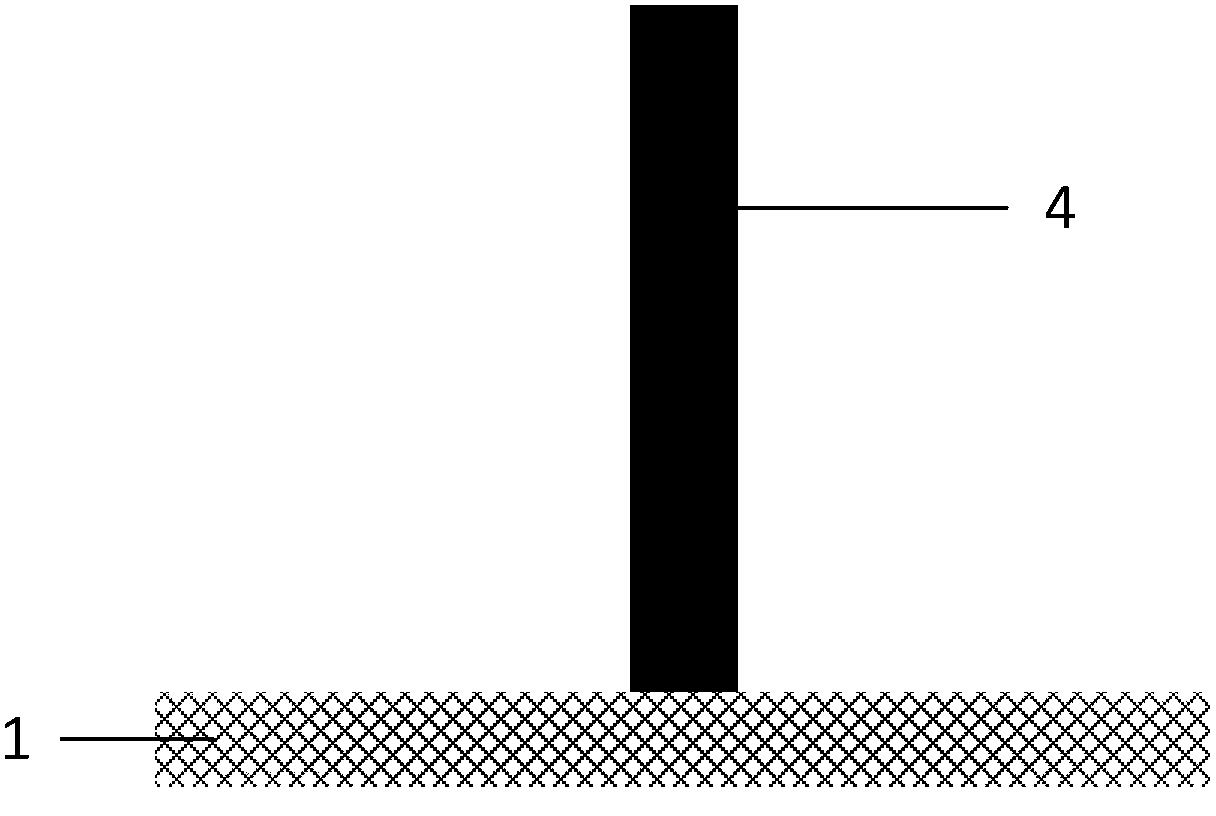

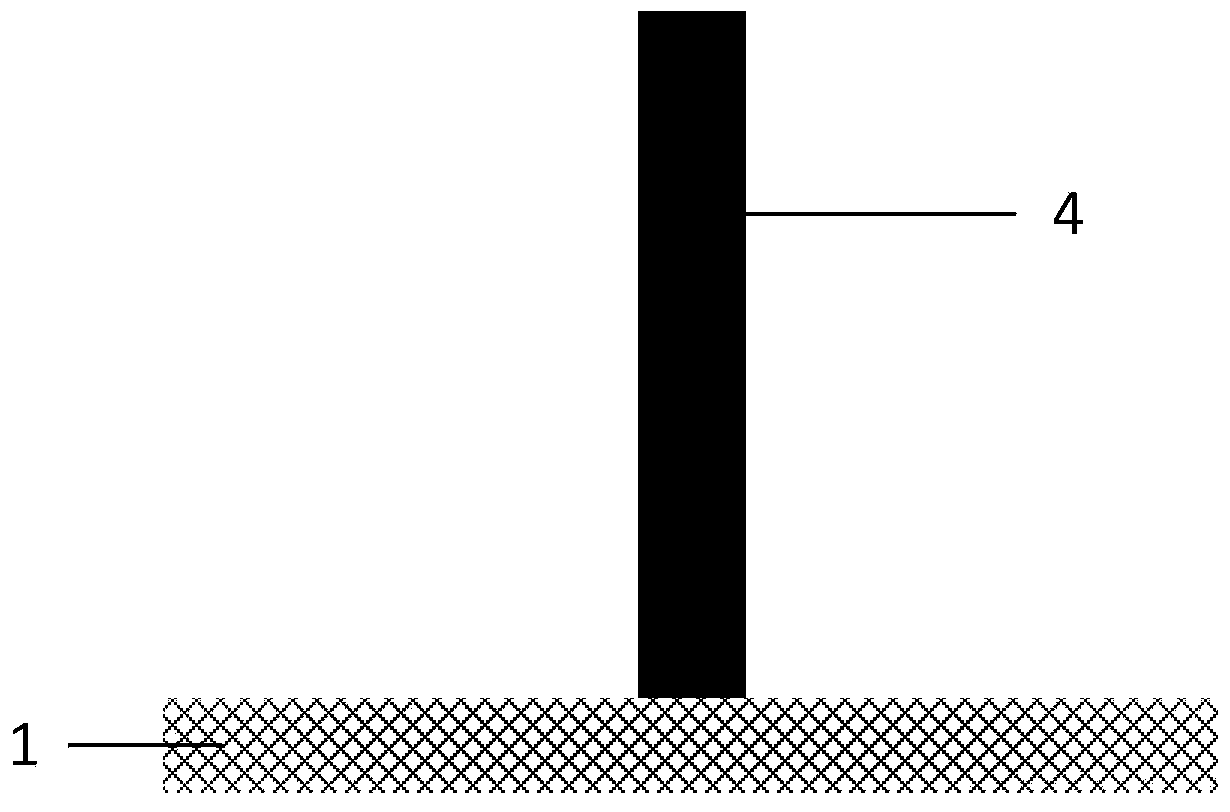

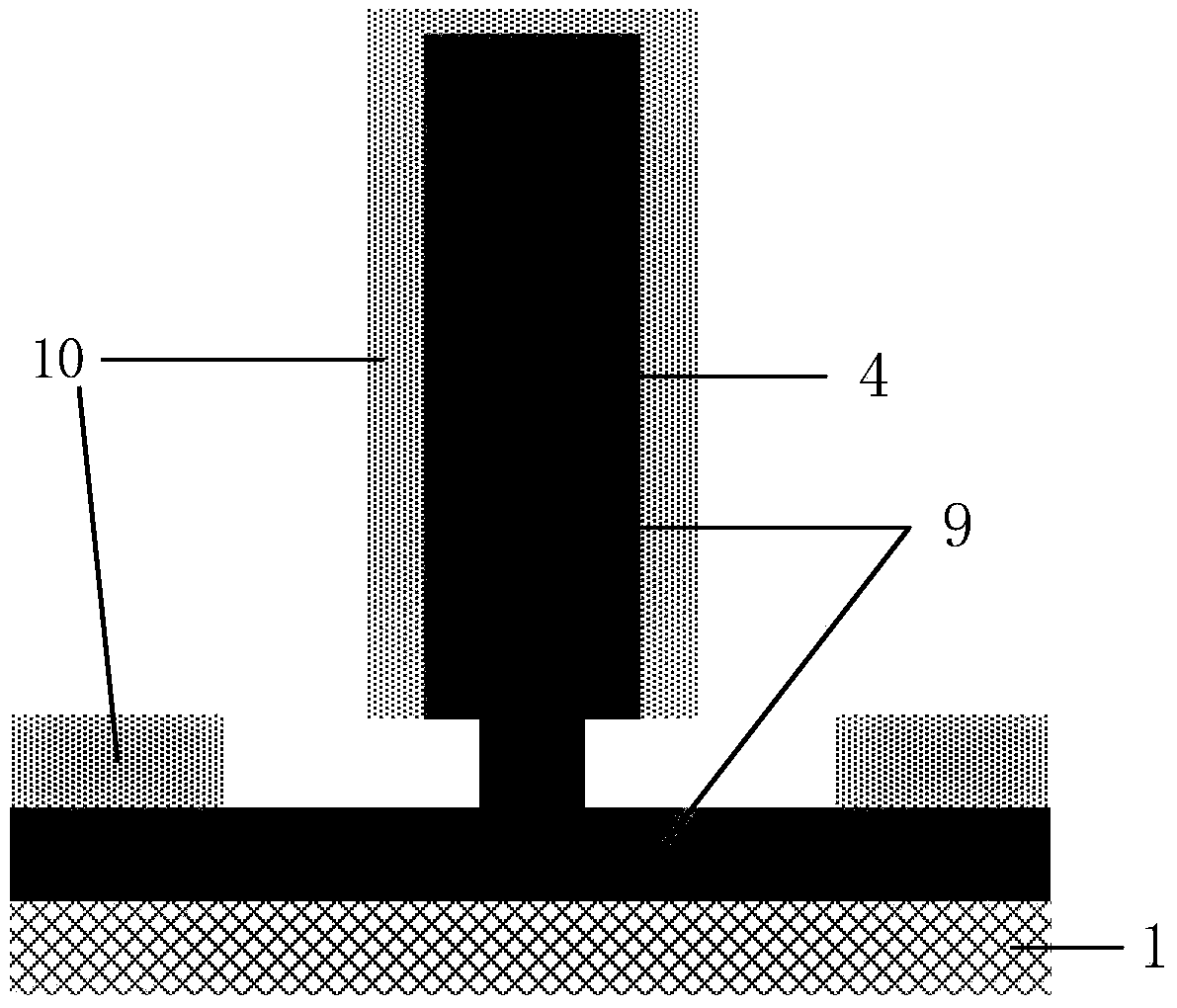

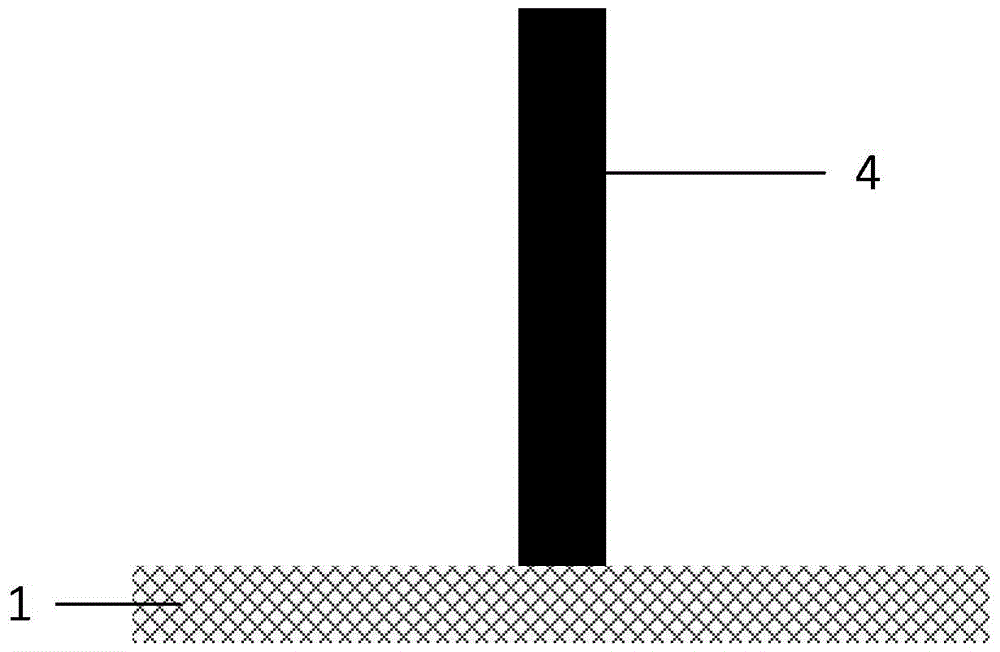

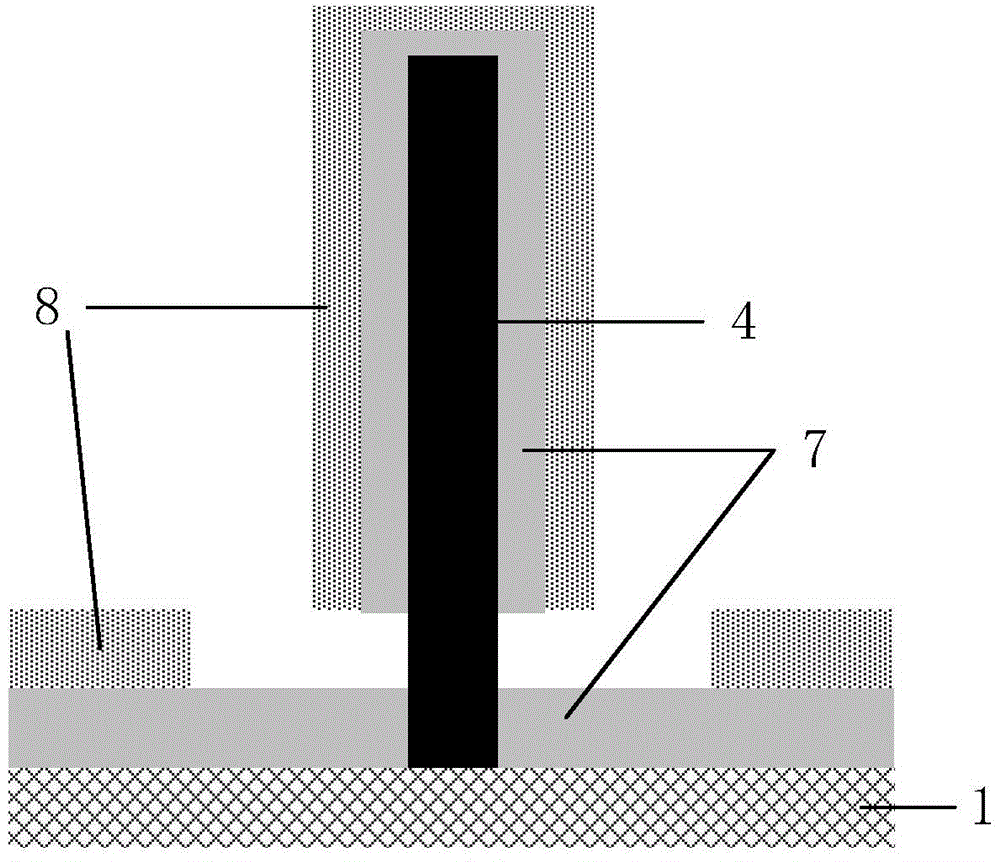

Preparation method of vertical silicon nanowire field effect transistor

ActiveCN102315129AReduce areaIncrease the areaNanoinformaticsSemiconductor/solid-state device manufacturingIntegrated circuit manufacturingManufacturing technology

The invention, which belongs to the super-large-scale integrated circuit manufacturing technology field, provides a preparation method of a vertical silicon nanowire field effect transistor with a small parasitic resistance. Compared to a traditional plane field effect transistor, by using the vertical silicon nanowire field effect transistor prepared in the invention, on one hand, a good abilityof restraining a short channel effect can be provided and leakage current and drain induced barrier lowering (DIBL) can be reduced because of a good gate control ability caused by a one-dimensional geometric structure of the vertical silicon nanowire field effect transistor; on the other hand, a device area can be further reduced and an integration level of an IC system can be raised.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

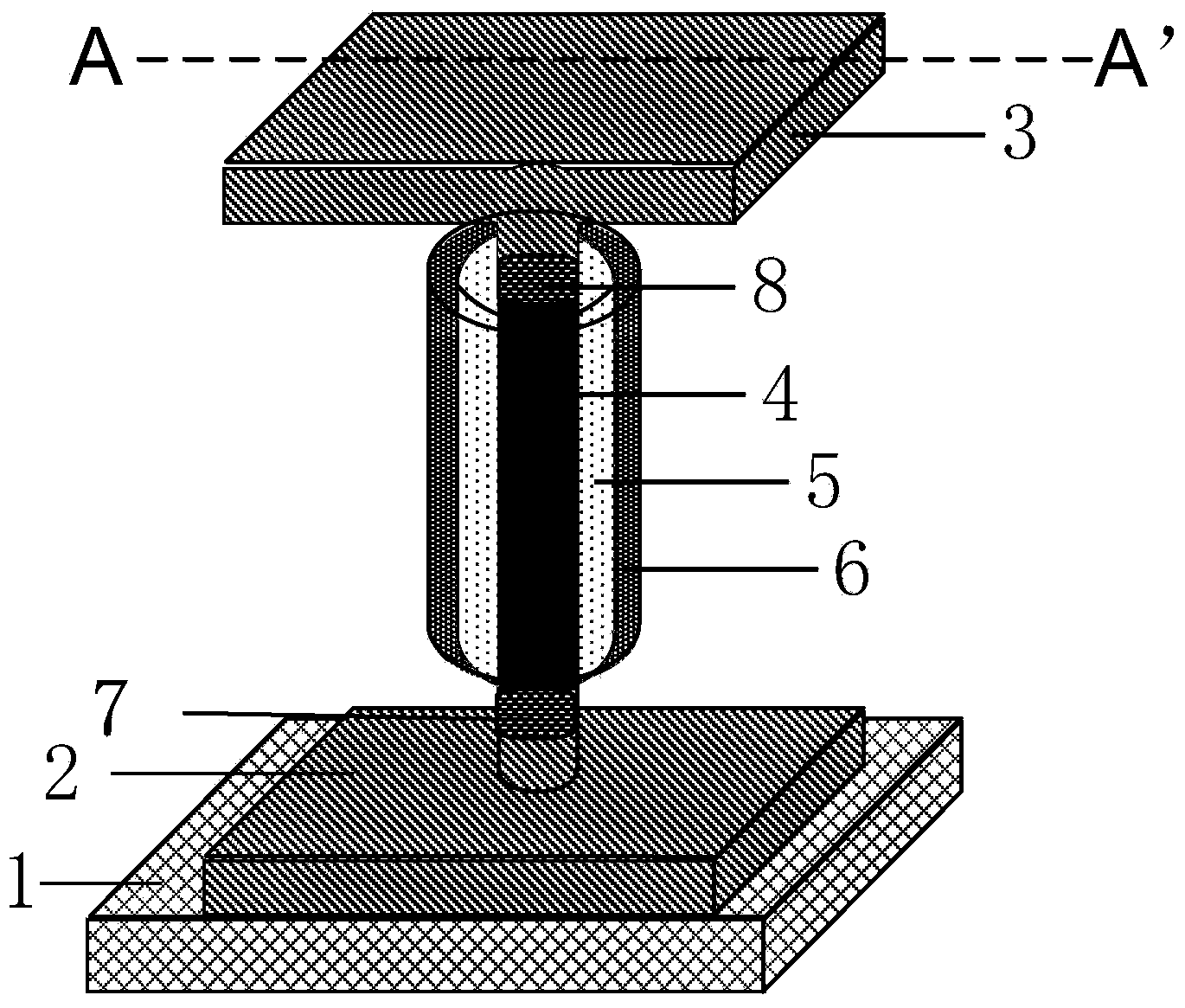

Asymmetric Schottky source drain transistor and preparing method thereof

ActiveCN104134697AHighly integratedGood gating abilityTransistorSemiconductor/solid-state device manufacturingCMOSNon symmetric

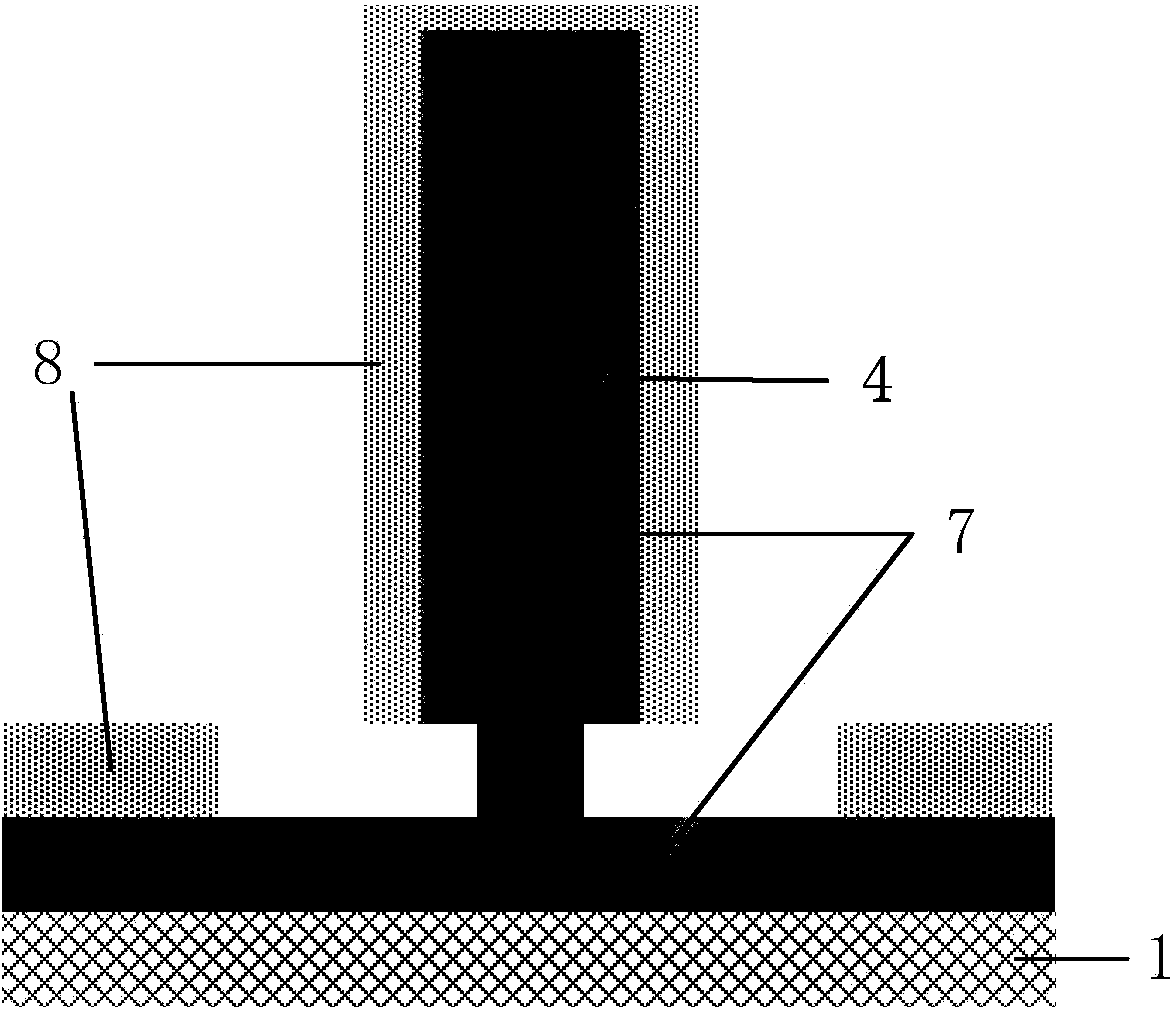

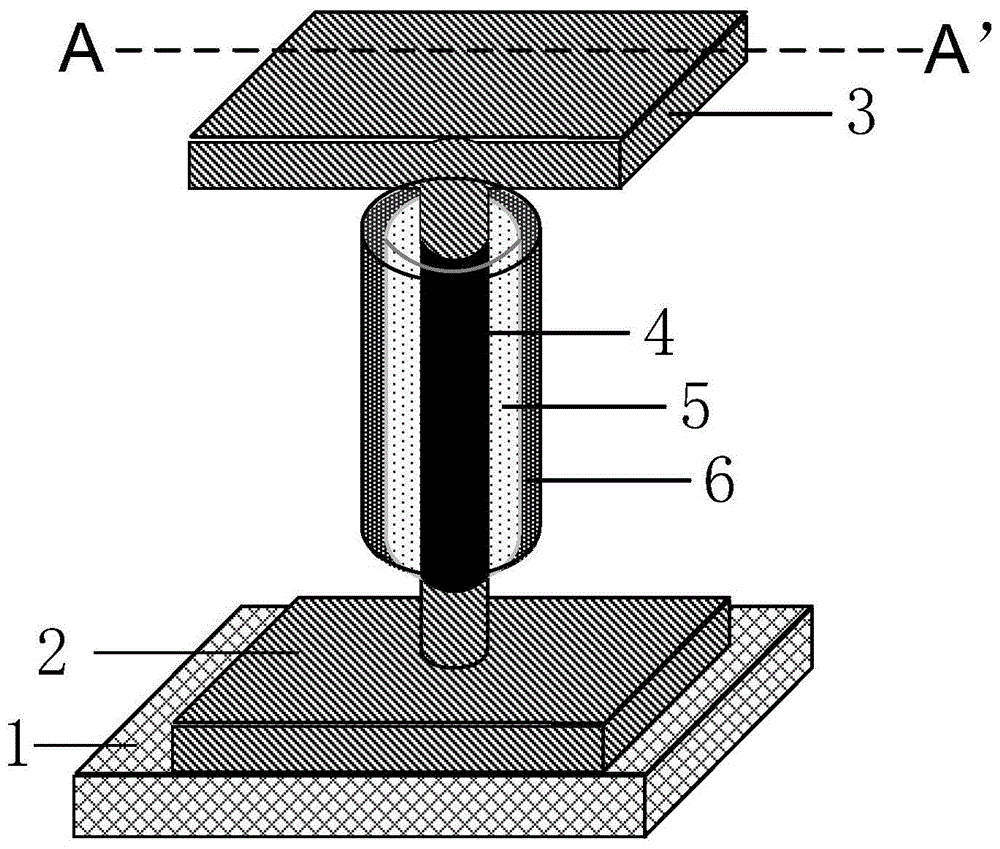

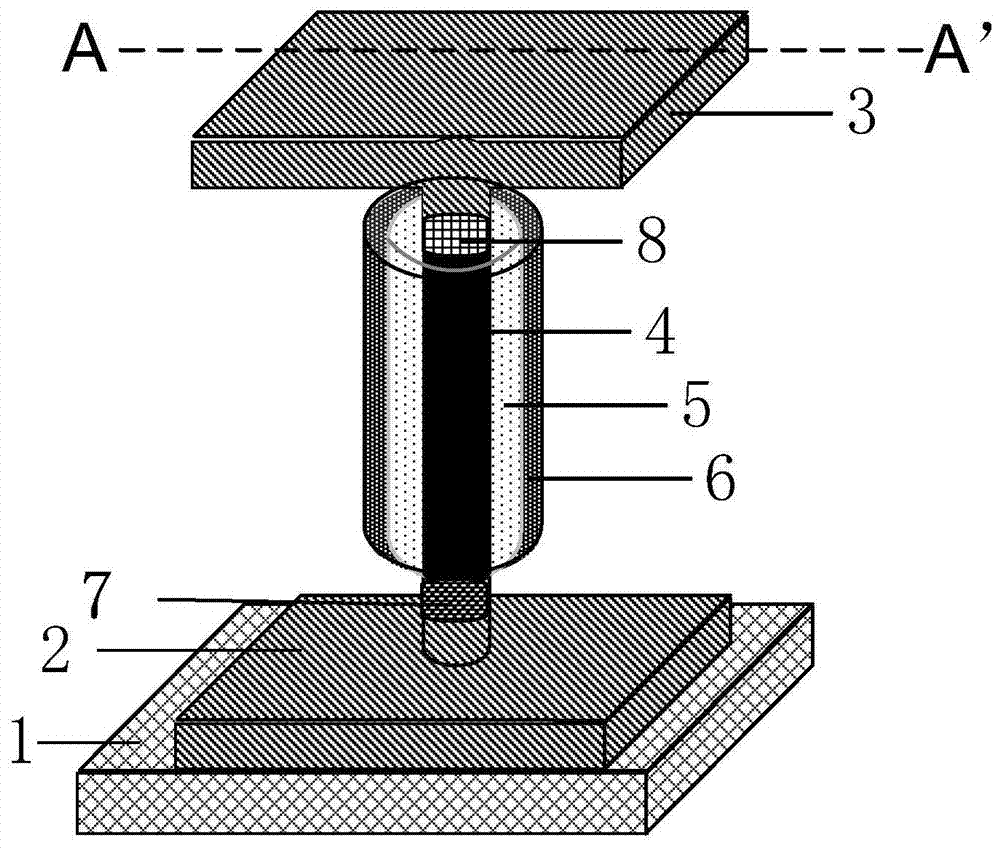

The invention discloses a ring gate MOS transistor combining a vertical channel and an asymmetric Schottky barrier source / drain structure. The ring gate MOS transistor comprises the ring semiconductor channel (4) in the vertical direction, a ring gate electrode (6), a ring gate dielectric layer (5), a source region (2), a drain region (3) and a semiconductor substrate (1), wherein the source region is located at the bottom of the vertical channel (4) and connected with a substrate, the drain region is located on the top of the vertical channel, the gate dielectric layer and the gate electrode annularly surround the vertical channel, Schottky contacts with different barrier heights can be formed by the source region and the channel and the drain region and the channel respectively, and the source region and the drain region are made of different metal materials. The ring gate MOS transistor is compatible with an existing CMOS technology, various advantages of the traditional GAA are reserved, the leakage current is reduced through the asymmetric Schottky barrier source / drain structure, the technology requirement is lowered, the limitation of processing photoetching extremity is broken through via the vertical channel and the ring gate structure, and the integrity is improved.

Owner:PEKING UNIV

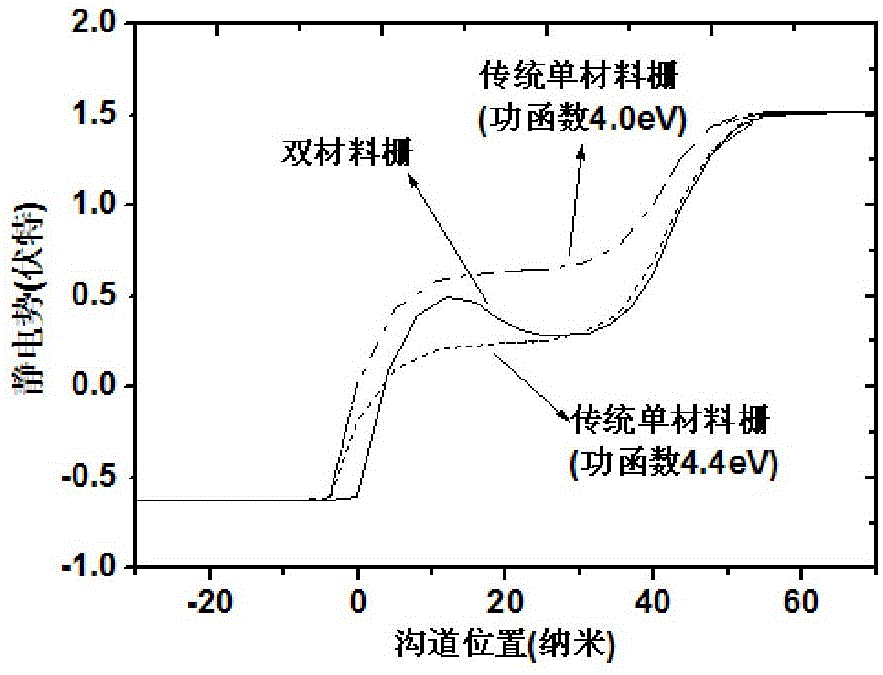

Bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor

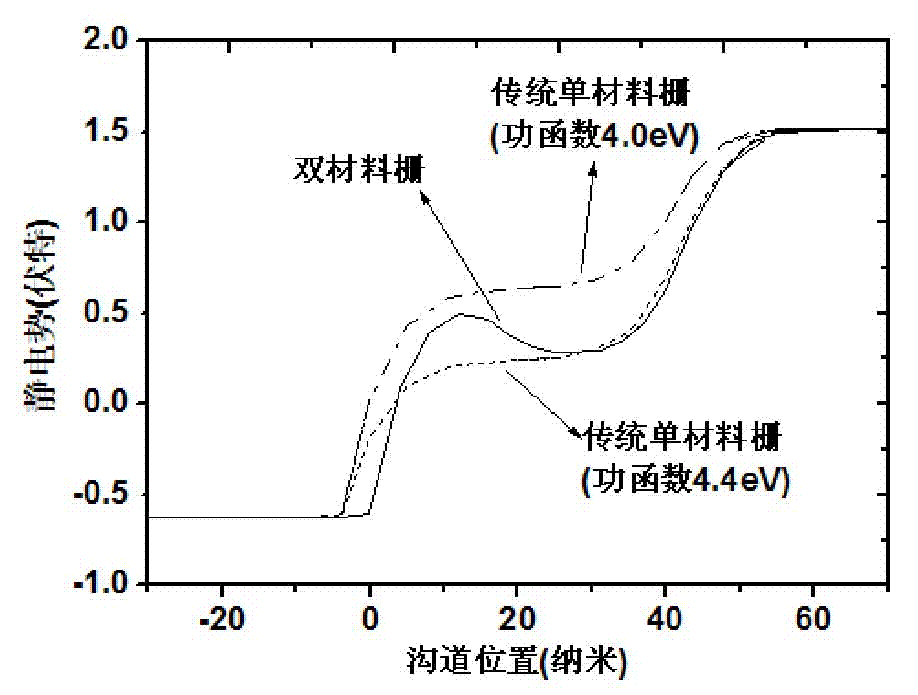

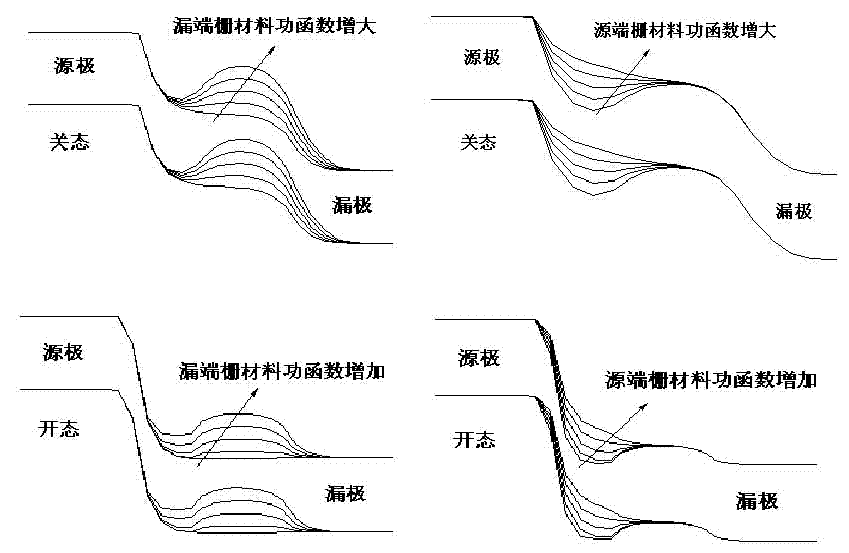

InactiveCN104091829AGood gating abilityImprove gate control abilitySemiconductor devicesDelayed timeLow leakage

The invention discloses a bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor (DL-HTFETs). The field-effect transistor undergoes P / N type heavy doping at a source region and a drain region, linear doping is carried out on regions, close to a channel, of the source end and the drain end, an oxidation layer close to a source electrode is formed by low-K oxide (SiO2), the oxidation layer close to a drain layer is formed by high-K oxide (HfO2), a conveying model of the novel bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor is built by means of a quantum mechanics model, and electrical properties of a high-K tunneling field-effect transistor (HK-TFETs), a common gate oxide tunneling field-effect transistor (LK-TFETs), a heterogeneous oxide tunneling field-effect transistor (HTFETs), a common filed-effect transistor and the DL-HTFETs are compared and analyzed by means of the model. As is shown by a research result, the DL-HTFETs have the advantages of low leakage currents, a high current switch ratio, low power consumption and short delay time and the like.

Owner:NANJING UNIV OF POSTS & TELECOMM

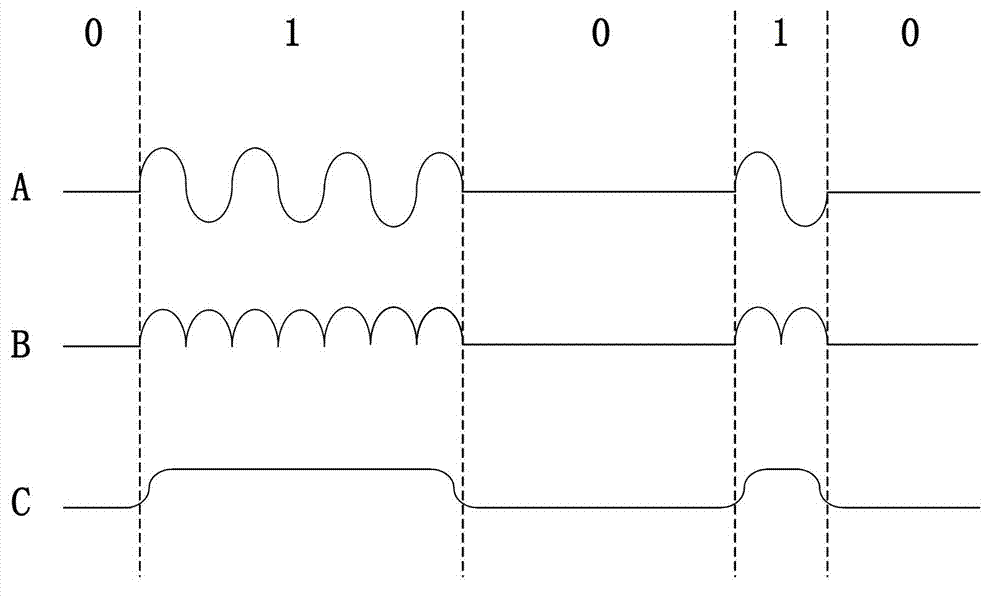

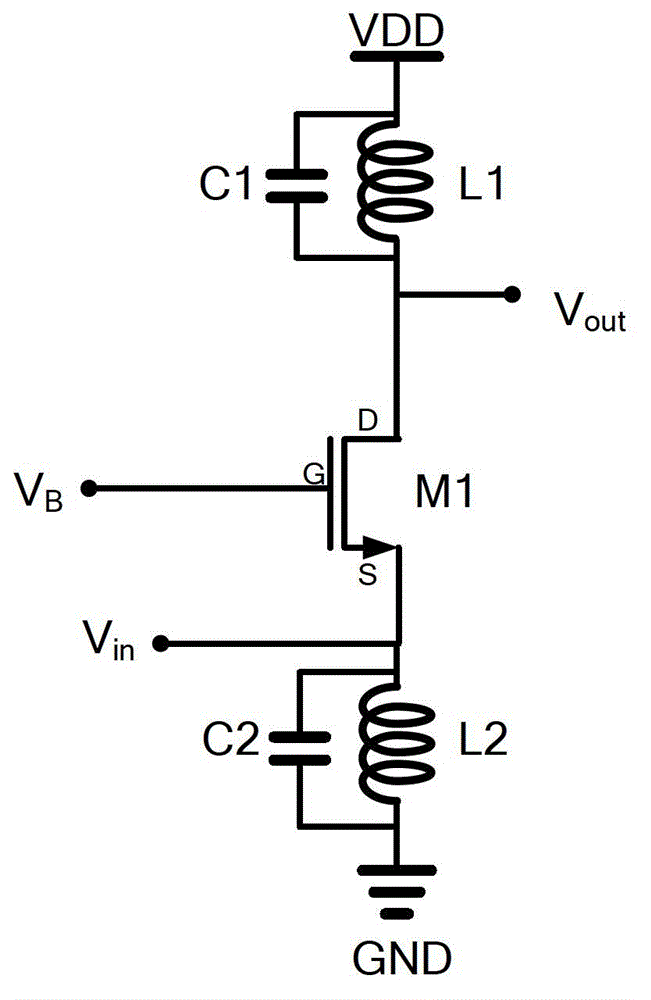

Envelope detector with graphene transistor

The invention discloses an envelope detector with a graphene transistor, comprising the graphene transistor, a first inductor, a first capacitor, a second inductor, a second capacitor, an input end and an output end, wherein the graphene transistor further comprises a substrate, a transition layer, a metal wiring layer, an interlayer medium layer, connecting lines, a source electrode, a drain electrode, a grid electrode and the channel layer of a graphene membrane, the source electrode is connected with ground, the grid electrode is connected with a bias voltage, and the drain electrode is connected with a working voltage. The envelope utilizes dual polarities of the graphene membrane, and has the advantages that the structure of a circuit is simple and gain can be provided simultaneously.

Owner:TSINGHUA UNIV

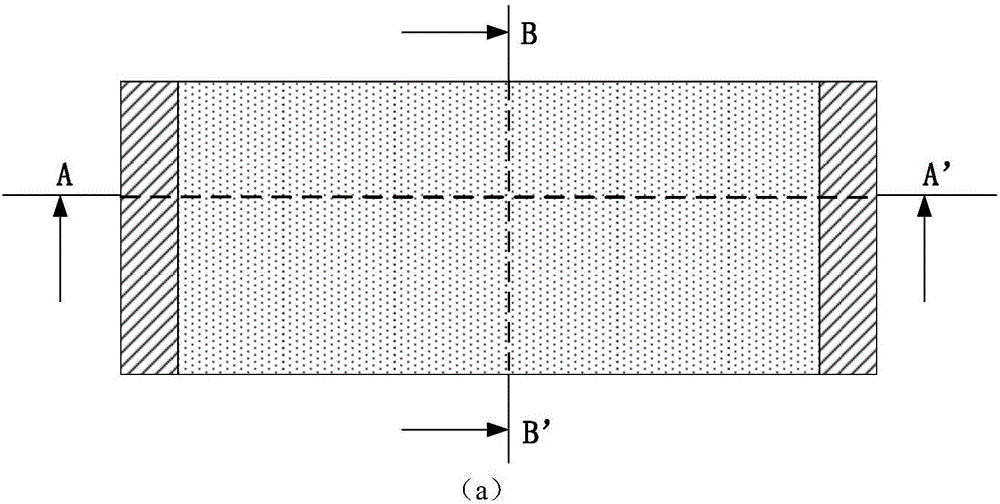

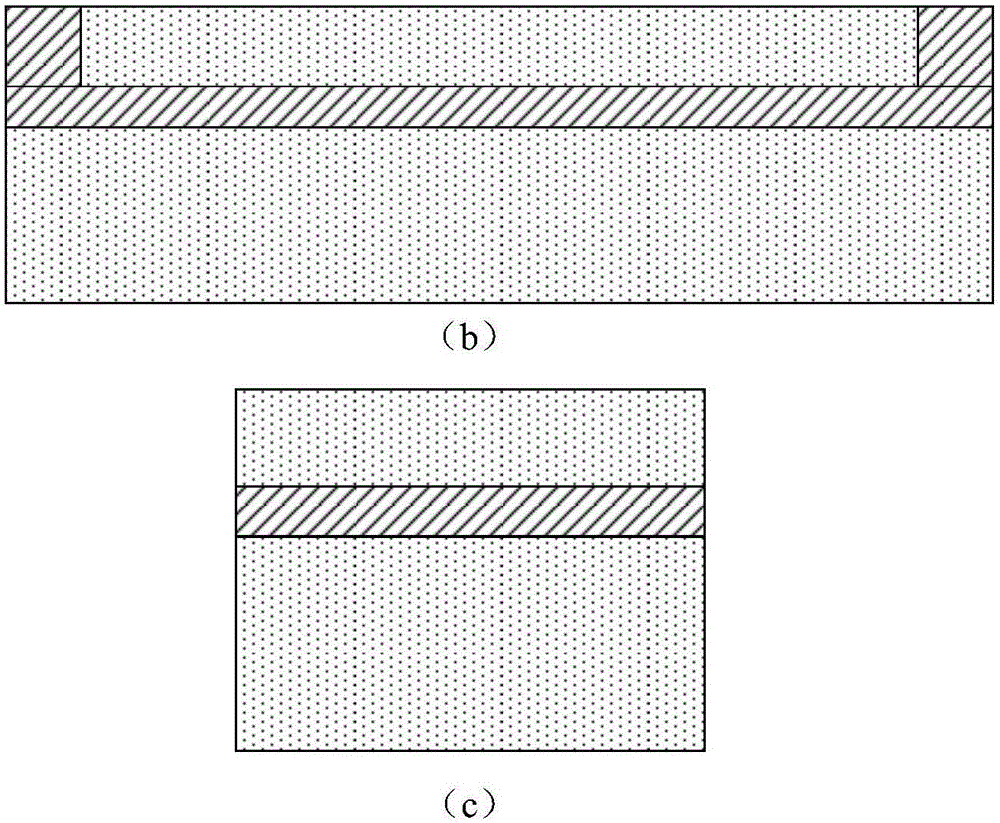

FinFET structure and manufacture method thereof

ActiveCN105470301AImprove short channel effectIncrease working currentSemiconductor/solid-state device manufacturingSemiconductor devicesNew deviceShort-channel effect

The invention provides a FinFET structure and a manufacture method thereof. The FinFET structure comprises a substrate, a first fin, a second fin, a grid lamination layer and isolation regions, wherein the first fin comprises a first channel region and a source region placed on the first channel region and wider than the first channel region; the second fin is parallel with the first pin, and comprises a second channel region and a drain region placed on the second channel region and wider than the second channel region; the grid lamination layer covers the substrate and sidewalls of the first and second channel regions; and the isolation regions are respectively placed at the two sides of the source region and the two sides of the drain region and on the grid lamination layer to isolate the source region, the drain region and the grid lamination layer from one another. According to the invention, the new device structure is provided on the basis of a present FinFET technology, and the grid length of the device is not limited by the footprint size, and the problem caused by the short channel effects is effectively solved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

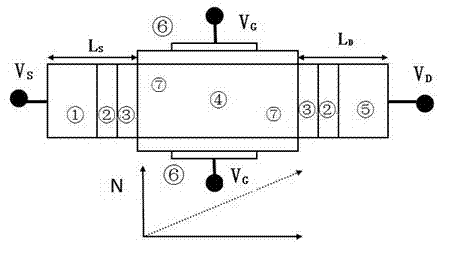

Bi-material railing nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709AReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention relates to a bi-material railing nanowire tunneling field effect device and a manufacturing method thereof. According to the bi-material railing nanowire tunneling field effect device, a channel is arranged at the center, and a source region and a drain region are respectively arranged at two ends, and an oxide and a gate electrode are covered at the periphery of the channel in sequence. The manufacturing method comprises the steps: SF6 etching a silicon column on a silicon wafer by using a round silicon nitride hard mask; conducting high-temperature oxidation, corroding and reducing the size of the silicon column to be a set diameter value of 6nm-30nm with HF aqueous solution, and conducting high-temperature oxidation to form a silicon column coated by an oxidation layer with set thickness; completing the preparation of a bi-material railing structure by adopting deposition and photoetching technology; and injecting boron and phosphorus of 1*10<20>cm<-2> / 10keV and 5*10<18>cm<-2> / 10keV at 120-150 DEG C respectively, and annealing at 900 DEG C / 10s-1100 DEG C / 10s to prepare the source region and the drain region; completing preparation of a metal electrode by CMOS (Complementary Metal-Oxide-Semiconductor) process; and manufacturing the bi-material railing nanowire tunneling field effect device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

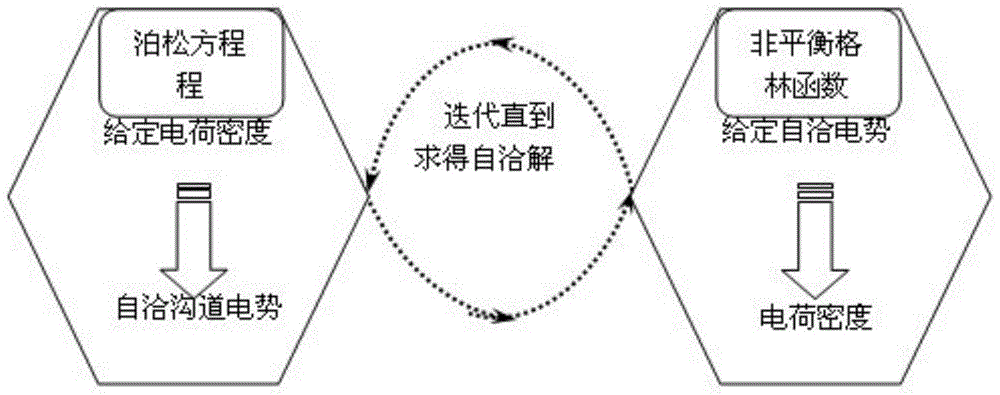

Linear doped spin field-effect tube (Spin-FET)

InactiveCN103094327AReduce off-state currentRaise the threshold voltageSemiconductor devicesSwitched currentSchrödinger equation

The invention discloses a spin field-effect tube (Spin-FET) with a linear light dope structure. A transport model which is suitable for the linear doped Spin-FET is constructed based on the quantum mechanics nonequilibrium green function theoretical framework and through the self-consistent solving Poisson and the Schrodinger equation, and the influence of a linear doping strategy and a common doping strategy on the electrical properties of the Spin-FET is calculated by using the model. Compared with the electrical properties of other doping strategies such as output characteristics, transfer characteristics, switch current ratio and magnetism current rate, the linear doped Spin-FET has larger switch current ratio, higher magnetism current rate, and smaller sub-threshold swing and threshold voltage drift. Not only can show that linear doping has better grid control capability, but also short-channel effect and hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

Surface grid-type static induction transistor

InactiveCN104810395AImprove transconductanceReduce parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceVoltage drop

The invention relates to a normally closed surface grid-type static induction transistor (SIT) of low power and a manufacturing method. The transistor is formed by parallelly connecting a drain electrode, a substrate of N+ low resistance monocrystal located on the drain electrode, an N- high resistance epitaxial layer located on the substrate of N+ low resistance monocrystal and multiple mutually parallelly-connected SIT units located in the N- high resistance epitaxial layer, wherein the active region uses the short channel design. The transistor is capable of enabling the impurity concentration of the device grid body to be high and enabling the impurity distribution to be more uniform under the corresponding technology support, reducing the own voltage drop of the grid body, increasing the sensitivity of the grid control, improving the device transconductance, reducing the grid source area, reducing the stray capacitance of the grid source, and increasing the SIT working frequency. Compared with the prior art, the short channel design is completely improved revolutionarily.

Owner:LANZHOU UNIVERSITY

Impurity segregation and Schottky source drain component and manufacturing method thereof

ActiveCN104134701AHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentSchottky barrier

An impurity segregation and Schottky source drain component comprises an annular semiconductor channel in the perpendicular direction, an annular gate electrode, an annular gate medium layer, a source area, an impurity segregation area, a drain area, an impurity segregation area and a semiconductor substrate. The source area is located at the bottom of the channel in the perpendicular direction and connected with the substrate. The impurity segregation area is located between the source area and the channel in the perpendicular direction. The drain area is located at the top of the channel in the perpendicular direction. The impurity segregation area is located between the drain area and the channel in the perpendicular direction. The gate medium layer and the gate electrode surround the channel in the perpendicular direction in an annular mode. The source area and the drain area respectively make contact with Schottky which are the same as the channel in barrier height. The source end and drain end impurity segregation areas are highly doped areas with the same kind of impurities. According to the structure, the Schottky barrier source drain structure is used for lowering the thermal budget, decreasing leak currents and simplifying technology requirements, impurity segregation is used for thinning barriers and increasing driving currents, and the channel in the perpendicular direction and the annular gate structure are used for breaking through the photo-etching limitation in the integration machining process and increasing the integration level.

Owner:PEKING UNIV

Non-junction tunneling field effect transistor and manufacturing method thereof

ActiveCN107342320AAvoid Auxiliary TunnelingGood gating abilitySemiconductor/solid-state device manufacturingDiodeInsulation layerEngineering

The invention provides a non-junction tunneling field effect transistor and a manufacturing method thereof. The non-junction tunneling field effect transistor comprises an insulation layer, a channel region arranged on the insulation layer, and a source electrode and a drain electrode which are arranged at two sides of the channel region, a gate medium layer arranged on the channel region, and a grid electrode which is arranged on the gate medium layer and comprises a top grid and a static modulation grid electrode. The non-junction tunneling field effect transistor has at least one of advantages as follows, simple structure, easy realization through utilizing the relatively simple process, flexible and adjustable doping concentration and relatively low power consumption.

Owner:TSINGHUA UNIV

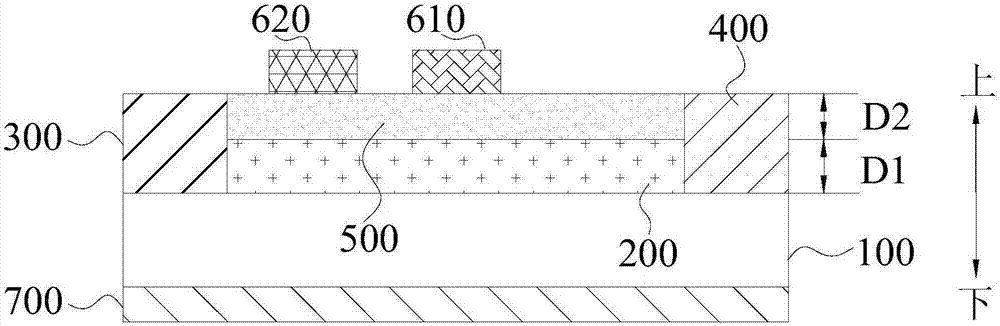

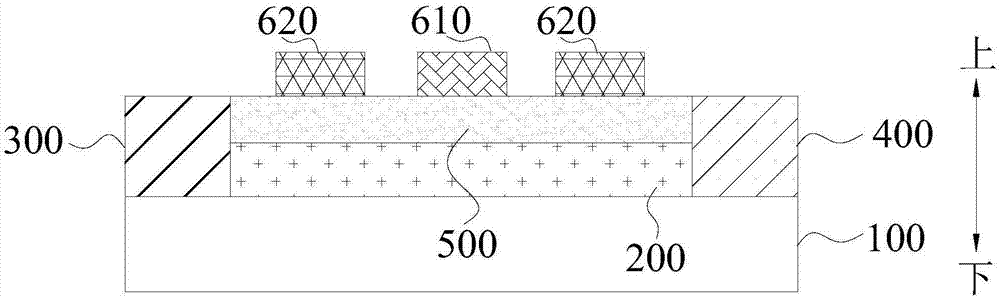

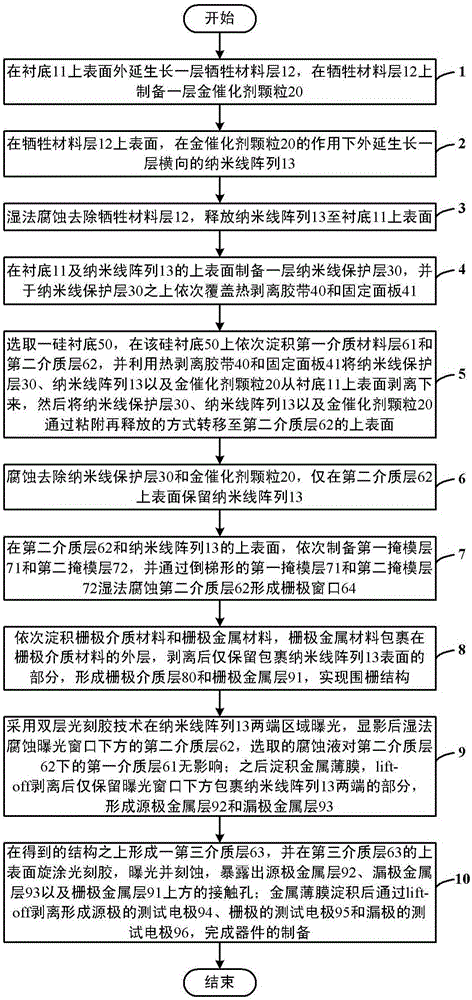

Manufacturing method of ring-fence non-junction nanowire transistor

InactiveCN105185823AImprove current drive capabilityGood gating abilityTransistorSolid-state devicesNanowire arrayNanometre

The invention relates to a manufacturing method of a transistor and especially relates to a manufacturing method of a ring-fence non-junction nanowire transistor. MOCVD is used to epitaxially grow a doped nanowire array on an III-V family material. Through a thermal peeling adhesive tape and a fixing panel, the nanowire is transferred. A non-junction nanowire transistor with a ring-fence structure is manufactured on a silicon-based substrate. By using the manufacturing method of the ring-fence non-junction nanowire transistor provided in the invention, compatibility of an III-V family material nanowire and a plane silicon technology can be realized; simultaneously, mobility degeneration is effectively restrained and a current driving capability of the transistor is increased.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

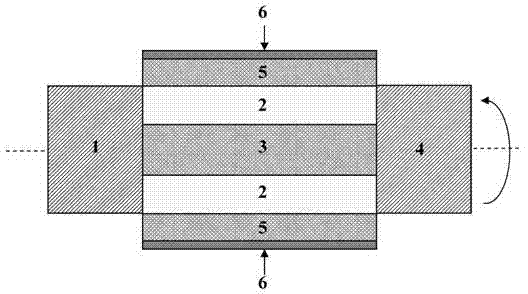

Core shell structure nanowire tunneling field effect device

InactiveCN102969365AReduce off-state currentHigh Switching Current RatioTransistorNanoinformaticsLow leakageShort-channel effect

The invention relates to a core shell structure nanowire tunneling field effect device which comprises a gate electrode (6), a source region (1), a drain region (4), a central region and a gate dielectric layer (5), wherein the central region is in a coaxially symmetrical core shell structure; the core in the core shell structure is made of an insulator material; the shell in the core shell structure is made of a semiconductor material; the gate dielectric layer is completely sleeved into the central region and is used for electrically isolating the central region and the gate electrode; the gate electrode is completely sleeved into the dielectric layer; the grate electrode (6), the gate dielectric layer (5) and the central region are equal in length; and the source region and the drain region are respectively arranged at two sides of the central region. A field effect transistor has low leakage current, high grid-control capability and low subthreshold slope, and the drain induced barrier lowing and the short-channel effect are effectively suppressed, so that various nonideal effects of a ring gate nanowire tunneling field effect device in the size reducing process are reduced, and the comprehensive performance of the device is improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

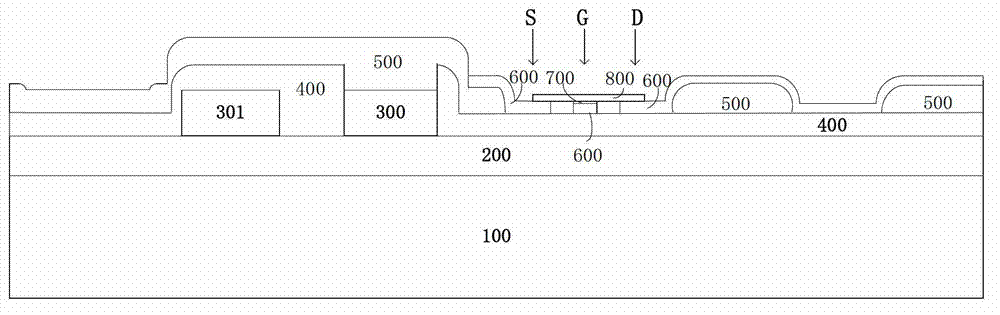

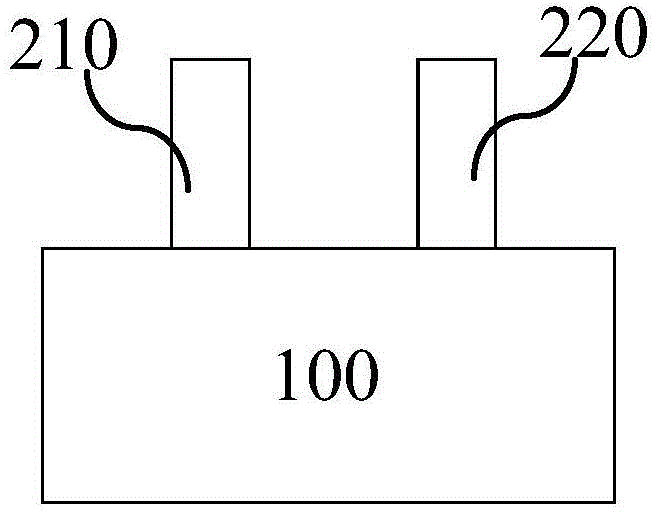

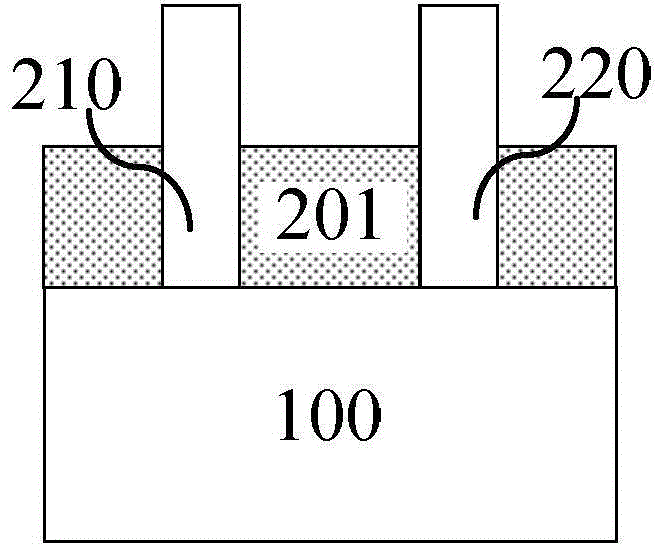

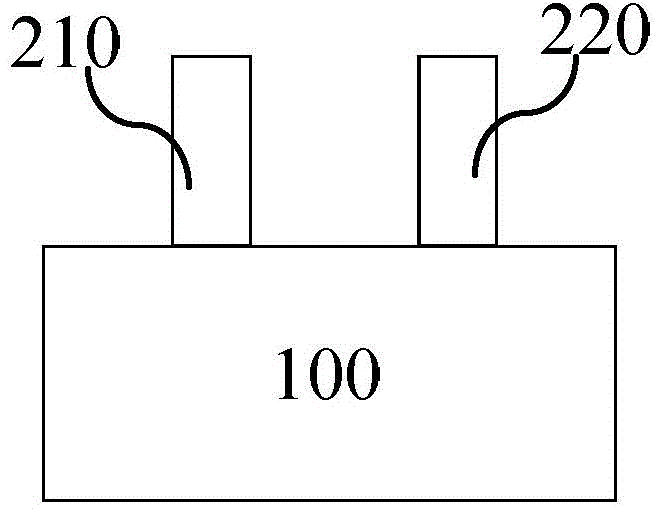

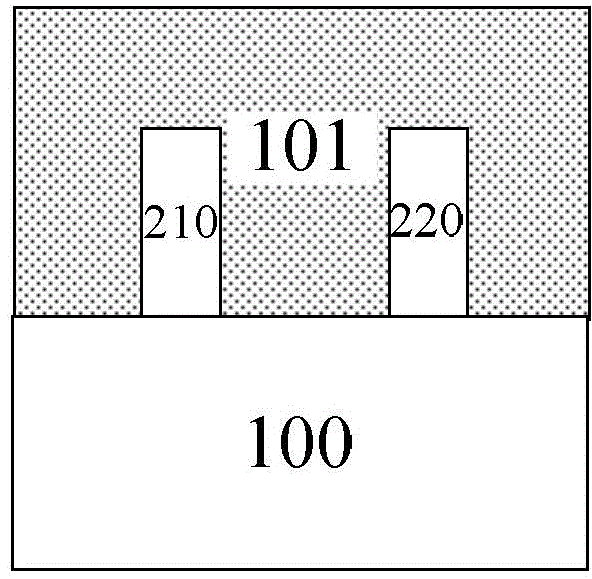

FinFET structure and manufacture method thereof

ActiveCN105470300AImprove short channel effectIncrease working currentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNew device

The invention provides a FinFET structure and a manufacture method thereof. The FinFET structure comprises a substrate (100), a first fin, a second fin, a grid lamination layer (300) and isolation regions (230), wherein the first fin comprises a first channel region (210) and a source region (211) placed on the first channel region and wider than the first channel region; the second fin is parallel with the first pin, and comprises a second channel region (220) and a drain region (221) placed on the second channel region and wider than the second channel region; the grid lamination layer (300) covers the substrate and sidewalls of the first and second channel regions (210, 220); and the isolation regions (230) are respectively placed at the two sides of the source region (211) and the two sides of the drain region (221) and on the grid lamination layer (300) to isolate the source region, the drain region and the grid lamination layer from one another. According to the invention, the new device structure is provided on the basis of a present FinFET technology, and the grid length of the device is not limited by the footprint size, and the problem caused by the short channel effects is effectively solved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Two-dimensional heterojunction tunneling field effect transistor immunosensor and preparation method thereof

ActiveCN112186036AEasy to detectEasy to controlTransistorSemiconductor/solid-state device manufacturingHeterojunctionDielectric

The invention discloses a two-dimensional heterojunction tunneling field effect transistor immunosensor and a preparation method thereof. A two-dimensional material with a specific band gap is selected and stacked into a vertical heterojunction as a channel layer, and the energy band structures of the device in an on state and an off state are respectively in staggered arrangement and staggered arrangement through gate voltage control, low current in the off state is realized, and in an on state, large current is obtained due to inter-band tunneling. A buried gate structure is used, and specific antibody protein molecules are used for surface modification on the surface of the heterojunction modulated by gate voltage. A heterojunction is used as an effective detection area and has ideal grid control capability. The dielectric regulation and control of a detection area is detected along with a detection sample by utilizing a plurality of electrical parameters. The sensor provided by theinvention has a steeper subthreshold slope, can realize ultra-high sensitivity detection of biomolecules and save precious clinical specimens, and meanwhile, because the thickness of a two-dimensional material is ultra-thin, the sensor has great advantages in size reduction and is convenient for energy band regulation and control.

Owner:XI AN JIAOTONG UNIV

Carbon nanotube field effect transistor (CNTFET) with peak-symmetric linearity doped structure

InactiveCN104103692AReduce off-state currentHigh switching current ratioNanoinformaticsSemiconductor devicesSwitched currentDelayed time

The invention discloses a carbon nanotube field effect transistor (CNTFET) with a peak-symmetric linearity doped structure. A transportation model applicable to the CNTFET with the peak-symmetric linearity doped structure is constructed, and by means of the model, the influence of a HALO-Linear doping strategy on electrical properties of the CNTFET is analyzed and calculated. Through contrastive analysis of electrical properties of CNTFETs using other doping strategies, the CNTFET with the peak-symmetric linearity doped structure has a higher switched current ratio, lower leakage current, a smaller subthreshold amplitude, higher cut-off frequency and shorter delay time, that is, the CNTFET using the HALO-Linear doping strategy has better grid-control capacity and better switching characteristics and is capable of effectively inhibiting a short-channel effect and a hot carrier effect.

Owner:NANJING UNIV OF POSTS & TELECOMM

Total dosage radiation-resistant FinFET device and fabrication method thereof

PendingCN107910362AEnhanced off-state leakage currentEnhanced Potential Control AbilitySemiconductor/solid-state device manufacturingSemiconductor devicesRadiation resistantEngineering

The invention discloses a total dosage radiation-resistant FinFET device and a fabrication method thereof. In the device, a dumbbell-shaped Fin strip structure is formed on a semiconductor substrate by etching, on one hand, the potential control capability of a grid on a relatively thin middle part of the dumbbell-shaped Fin strip is improved, and the influence of trap charge caused by radiation in a shallow trench isolation (STI) region on the potential of the Fin strip can be effectively reduced; and on the other hand, the distance between the STI regions at two sides of the Fin is expanded,and an off-state leakage current of the device caused by radiation is reduced. And compared with conventional body silicon FinEFT, the dumbbell-shaped Fin strip structure has the advantages that thenormal-state grid control capability of the device is also improved, and the dumbbell-shaped Fin strip structure has larger on-state current.

Owner:PEKING UNIV

Nanotube device and manufacturing method thereof

ActiveCN110729360AAchieve mass productionStrong drive currentTransistorMaterial nanotechnologyDriving currentGate dielectric

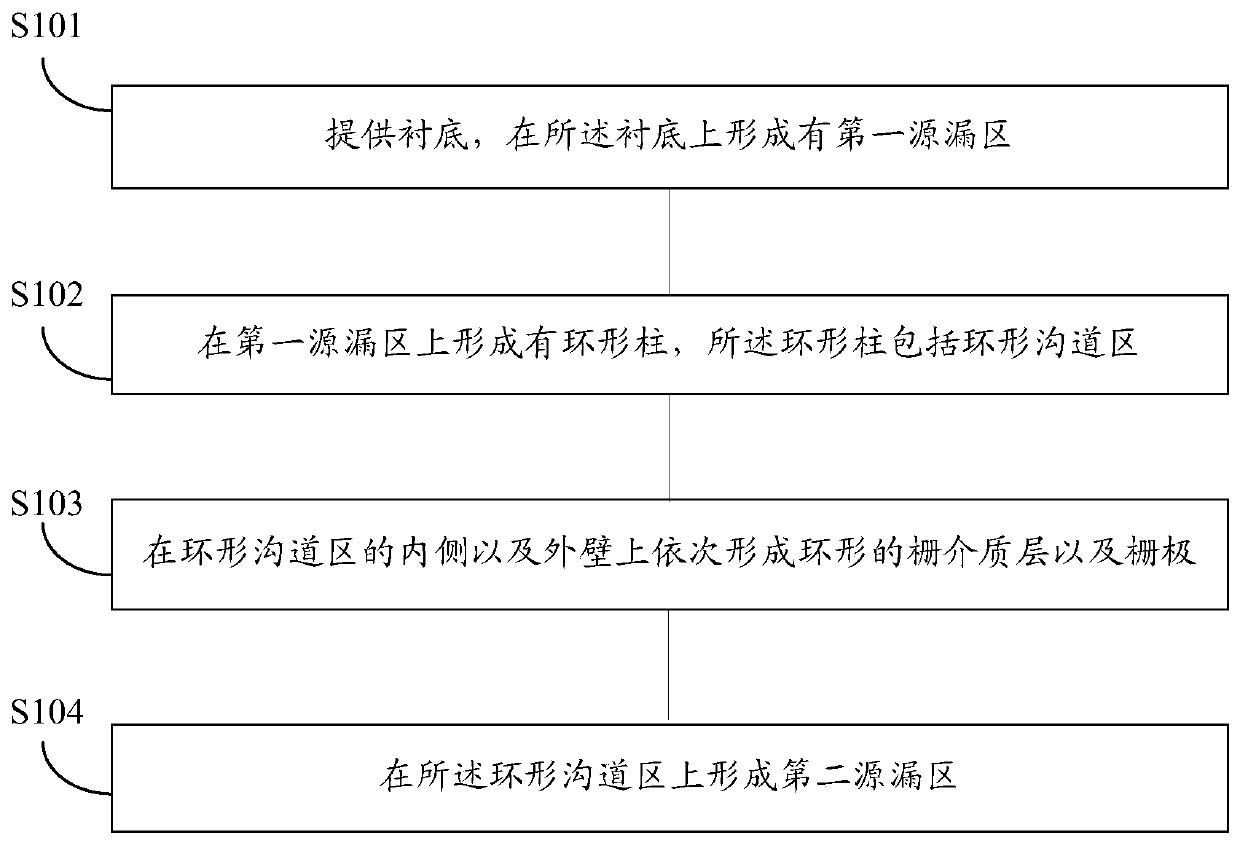

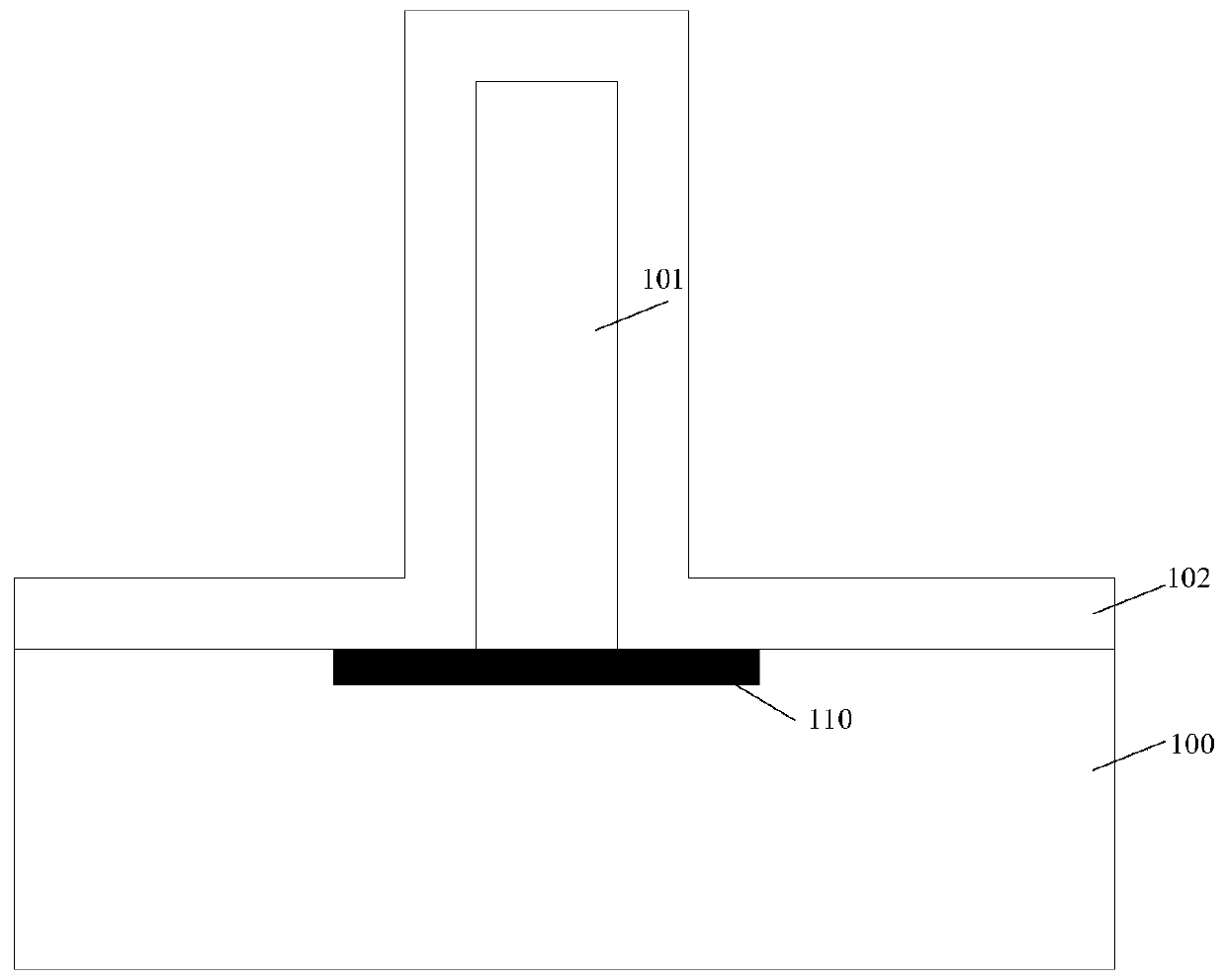

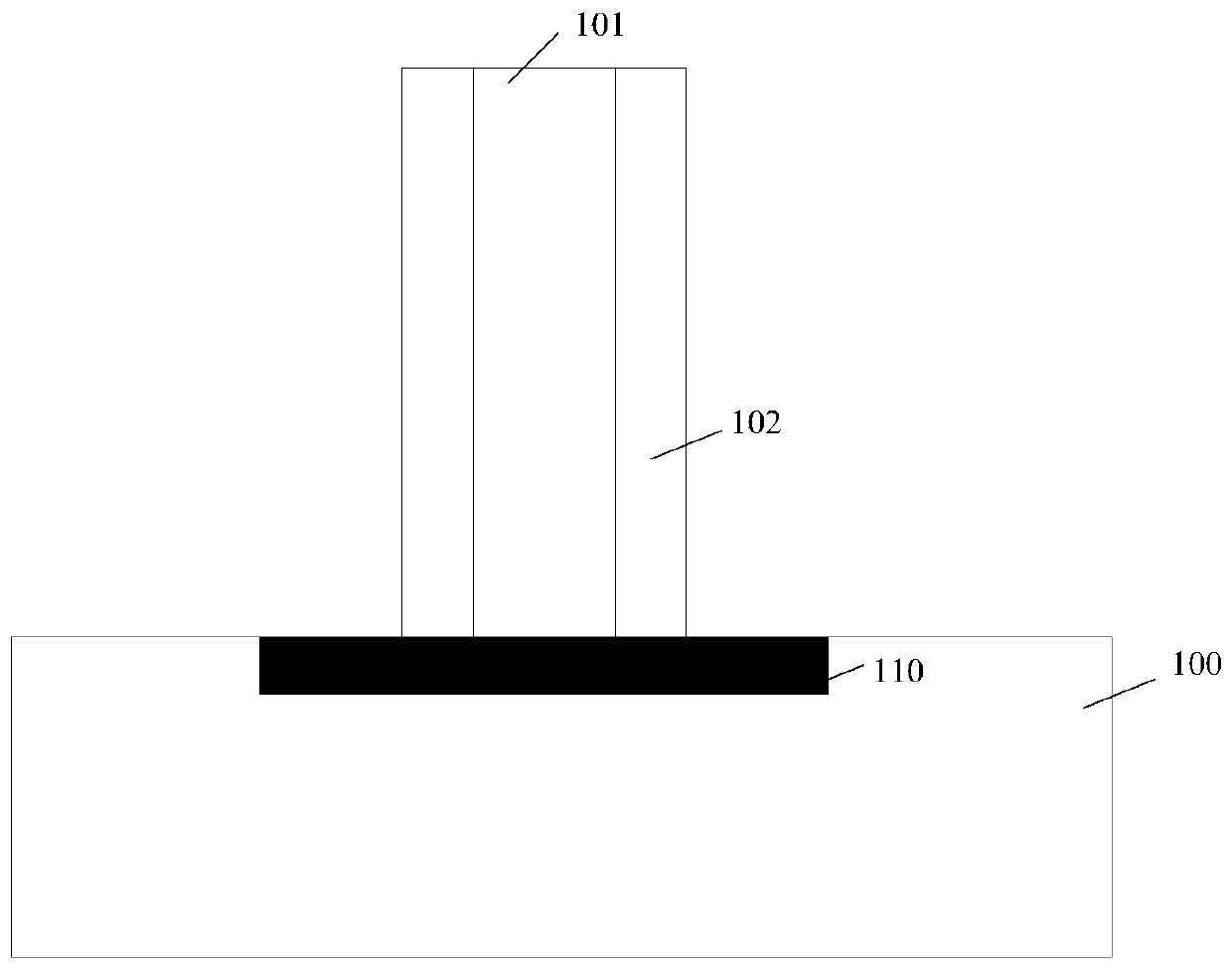

The invention provides a nanotube device and a manufacturing method thereof. The manufacturing method comprises the following steps: providing a substrate in which a first source-drain region is formed; forming an annular column on the first source-drain region, the annular column comprising an annular channel region; sequentially forming annular gate dielectric layers and gates on the inner walland the outer wall of the annular channel region; and forming a second source-drain region on the annular channel region. In the method, gates are formed on the inner side wall and the outer side wallof a nanotube, so that a source region-gate-drain region nanotube device structure is formed on the inner and outer sides of the nanotube in the longitudinal direction, the gate area is increased, the gate control capability is improved, and the device has higher driving current. Moreover, the manufacturing difficulty is low, the compatibility with the existing process is good, and mass production of the nanotube device is facilitated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Low-power fin type field effect transistor and manufacturing method thereof

ActiveCN106098783AAchieve separationTo achieve the effect of isolationSemiconductor/solid-state device manufacturingSemiconductor devicesVery large scale integrated circuitsBody area

The invention provides a low-power fin type field effect transistor and a manufacturing method thereof, and belongs to the technical field of super-large integrated circuit manufacture. The thickness of a sidewall channel layer and the thickness of a top channel layer of the field effect transistor are no greater than 10nm, and a fin-type isolation bar is formed on a deep body area far away from top gate control. Further shortening of a device trench length is facilitated, short channel effect control ability of the device is improved, and static power consumption is minimized. The source-drain area of the device is a monocrystalline active island, and has maller source-drain series resistance. Compared with a fin type field effect transistor employing lifting source-drain structure, the low-power fin type field effect transistor requires no epitaxial lifting source-drain to obtain rapidly high open-state current. The low-power fin type field effect transistor is compatible with conventional IC-manufacture technology and has the advantages of simple process and low manufacture cost.

Owner:PEKING UNIV +1

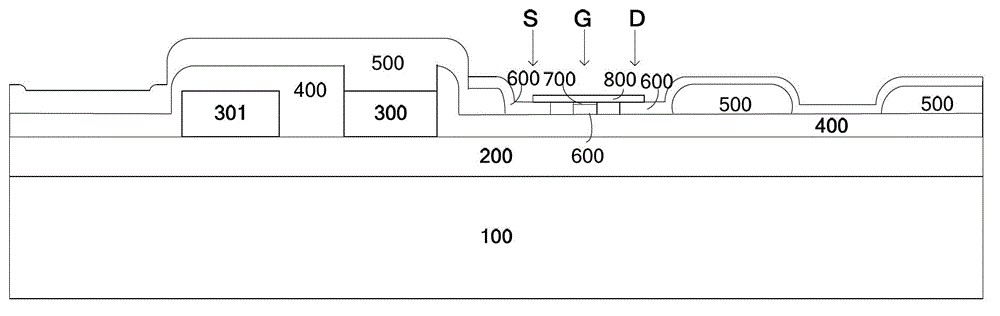

Method for preparing quasi-SOI (silicon on insulator) source drain multi-gate device

ActiveCN103700593AThe multi-gate structure has good gate control performanceGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesIntegrated circuit manufacturingSemiconductor materials

The invention discloses a method for preparing a quasi-SOI (silicon on insulator) source drain multi-gate device, and belongs to the technical field of super-large-scale integrated circuit manufacturing. The method sequentially comprises the following steps that a Fin strip-shaped active region is formed on a first semiconductor substrate; an STI (shallow trench isolation) isolation layer is formed; a grate dielectric layer and a grate material layer are deposited, and a grate lamination structure is formed; a doping structure of a source drain extending region is formed; a recessed source drain structure is formed; a quasi-SOI source drain isolation layer is formed; the in-situ doping epitaxial second semiconductor material source drain is carried out, and in addition, the annealing activation is carried out; false grates are removed, and high-k metal grate deposition is carried out again; the contact and metal interaction is formed. The method has the advantages that the leakage current can be effectively reduced, the power consumption of devices can be reduced, the thermal budgeting is lower, in addition, the process is simple and can be compatible with the traditional CMOS (complementary metal oxide semiconductor) process, the method can also be applied to semiconductor materials except silicon, and the method can be favorably applied to the super-large-scale integrated circuit manufacturing.

Owner:PEKING UNIV

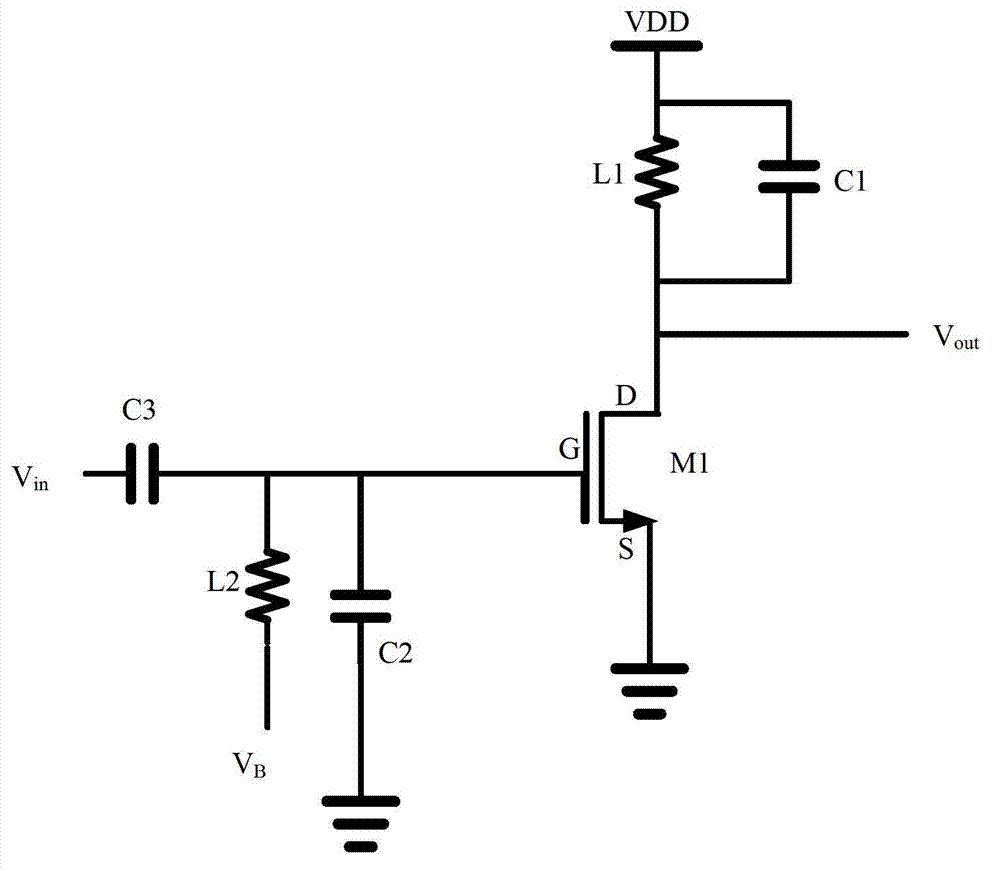

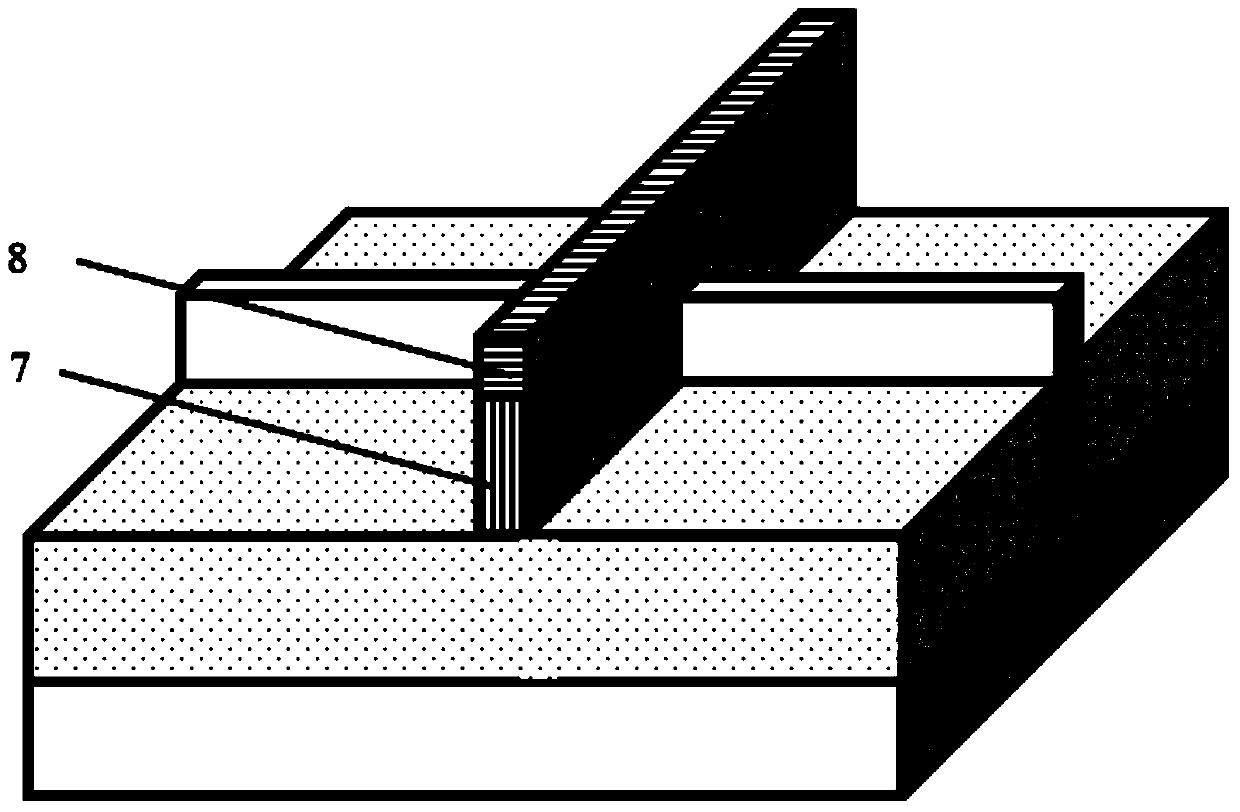

Low Noise Amplifier with Graphene Transistors

ActiveCN102868370BGuaranteed accuracyClose contactAmplifier modifications to reduce noise influenceSemiconductor devicesLow noiseCapacitance

The invention discloses a low-noise amplifier with a grapheme transistor. The low-noise amplifier comprises the grapheme transistor, a first inductor and a first capacitor, a second inductor and a second capacitor, an output end and an input end, a grid medium layer formed on the grid electrode and a channel layer formed on the source electrode, the drain electrode and the grid electrode, wherein the source electrode of the grapheme transistor is connected with the ground, the grid electrode is connected with bias voltage, and the source electrode is connected with working voltage; the first inductor and the first capacitor are connected between the drain electrode and the working voltage; the second inductor and the second capacitor are connected with the source electrode and the ground end; the grapheme transistor further comprises a substrate, a transition layer, a metal routing layer, an interlayer medium layer, a connection wire, the source electrode, the drain electrode and the grid electrode; the source electrode, the drain electrode and the grid electrode are formed above the interlayer medium layer; the source electrode, the drain electrode and the grid electrode comprise metal contact layers above the interlayer medium layer; the source electrode and the drain electrode are respectively connected with the connection wire through the metal contact layers; and the channel layer is a grapheme thin film. The low-noise amplifier provided by the invention has the advantages of low noise, high stability and high reliability.

Owner:TSINGHUA UNIV

A MOSFET device having a recessed drain structure with bidirectional level transfer

ActiveCN109216440AShorten the transmission distanceLower on-resistanceSemiconductor devicesMOSFETSurface breakdown

The present invention provides a MOSFET device having a recessed drain structure with bidirectional level transfer, comprises a p-type substrate, a p-type epitaxial layer, an n-type drift layer, a p-type body region, a groove first drain, a first drain N + implantation region, a groove second drain, a second drain N + implantation region, a groove gate, a gate oxide dielectric layer, a p-type lightly doped first RESURF region and a p-type lightly doped second RESURF region; The invention realizes the complete symmetrical structure of the MOSFET. On the premise of guaranteeing a certain depth of the gate electrode and the drain trench, the device can realize the bidirectional level transmission and reduce the unavoidable loss when the circuit is used for the bidirectional level transmission. By using groove technology, the gate control ability of the device is improved, the transmission distance of the carrier is reduced, the on-resistance is reduced, and the reliability of the device is improved. By using RESURF technology, the electric field of surface breakdown is ensured to be increased, and the on-resistance of the device is also reduced, which further improves the reliabilityof the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A kind of junctionless field effect transistor and preparation method thereof

ActiveCN104201195BHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricImpurity diffusion

A surrounding gate field-effect transistor combined with a vertical channel (4) and a junction-free structure comprises a surrounding semiconductor channel in the vertical direction, a surrounding gate electrode (6), a surrounding gate dielectric layer (5), a source region (2), a drain region (3) and a semiconductor substrate (1), wherein the source region (2) is located at the bottom of the vertical channel (4) and connected with the substrate (1), the drain region (3) is located at the top of the vertical channel (4), and the gate dielectric layer (5) and the gate electrode (6) surround the vertical channel (4) circularly. The impurities of the same type and concentration are doped into the source region (2), the drain region (3) and the vertical channel (4). The same impurities are doped into source and drain channels of the transistor, so that heat budget is greatly reduced, the impurity diffusion and abrupt junction forming problems are eliminated, process requirements are simplified, integration machining photo-etching ultimate limit is broken through by utilizing the vertical channel and a surrounding gate structure, and the integration degree is improved.

Owner:PEKING UNIV

A two-dimensional heterojunction tunneling field effect transistor immunosensor and its preparation method

ActiveCN112186036BEasy to detectEasy to controlTransistorSemiconductor/solid-state device manufacturingHeterojunctionBio molecules

The invention discloses a two-dimensional heterojunction tunneling field effect transistor immunosensor and a preparation method thereof. A two-dimensional material with a specific band gap is selected to be stacked into a vertical heterojunction as a channel layer. The energy band structures in the on-state and off-state are staggered arrangement and staggered arrangement respectively, achieving low current in the off-state and high current due to inter-band tunneling in the on-state. Using buried gate structure, surface modification with specific antibody protein molecules on the heterojunction surface modulated by gate voltage. As an effective detection area, the heterojunction has the ability to obtain ideal gate control. The detection is realized by using multiple electrical parameters to control the dielectric of the detection area along with the detection sample. The sensor of the present invention has a steeper sub-threshold slope, which can realize ultra-high sensitivity detection of biomolecules and save precious clinical specimens. At the same time, due to the ultra-thin thickness of the two-dimensional material, the device has a great advantage in size reduction, which is convenient for energy saving. With regulation.

Owner:XI AN JIAOTONG UNIV

Double material gate nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709BReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSNanowire

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

A gate-all-around field-effect transistor and its manufacturing method

ActiveCN104157686BHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSchottky barrier

Owner:PEKING UNIV

A vertical gate-around tunneling transistor and its manufacturing method

ActiveCN104157687BHighly integratedGood gating abilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierGate dielectric

The invention provides an around-gate field effect transistor which combines a vertical channel, heterogeneous impurity segregation and a schottky barrier source / drain structure. The around-gate field effect transistor comprises an annular semiconductor channel in the vertical direction, an annular gate electrode, an annular gate dielectric layer, a source region, an impurity segregation region (7), a drain region, an impurity segregation region (8), and a semiconductor substrate, wherein the source region is located at the bottom part of the vertical channel and connected with the substrate, and the impurity segregation region (7) is located between eth source region and the vertical channel; the drain region is located at the top part of the vertical channel, and the impurity segregation region (8) is located between the drain region and the vertical channel; the gate dielectric layer and the gate electrode surround the vertical channel; schottky contact is formed respectively between the source region and the drain region and the channel; and impurities of the impurity segregation region (7) and the impurity segregation region (8) choose heterogeneous impurities, that is, impurities of the impurity segregation region (7) choose p-type material, and impurities of the impurity segregation region (8) choose n-type material; and impurities of the impurity segregation region (7) choose n-type material, and impurities of the impurity segregation region (8) choose p-type material.

Owner:PEKING UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com