Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

264results about How to "Improve gate control ability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

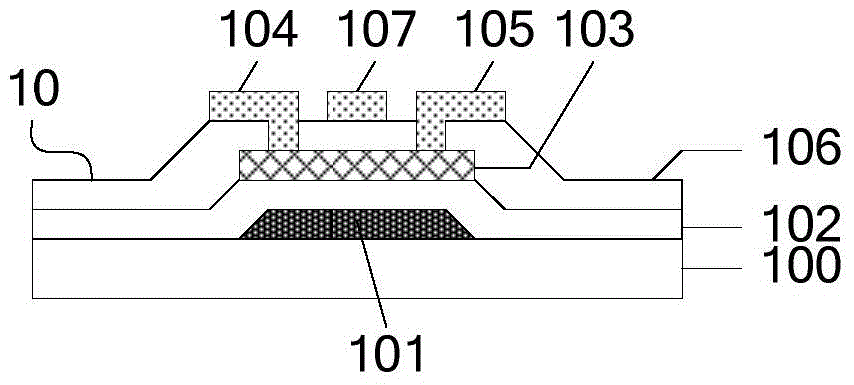

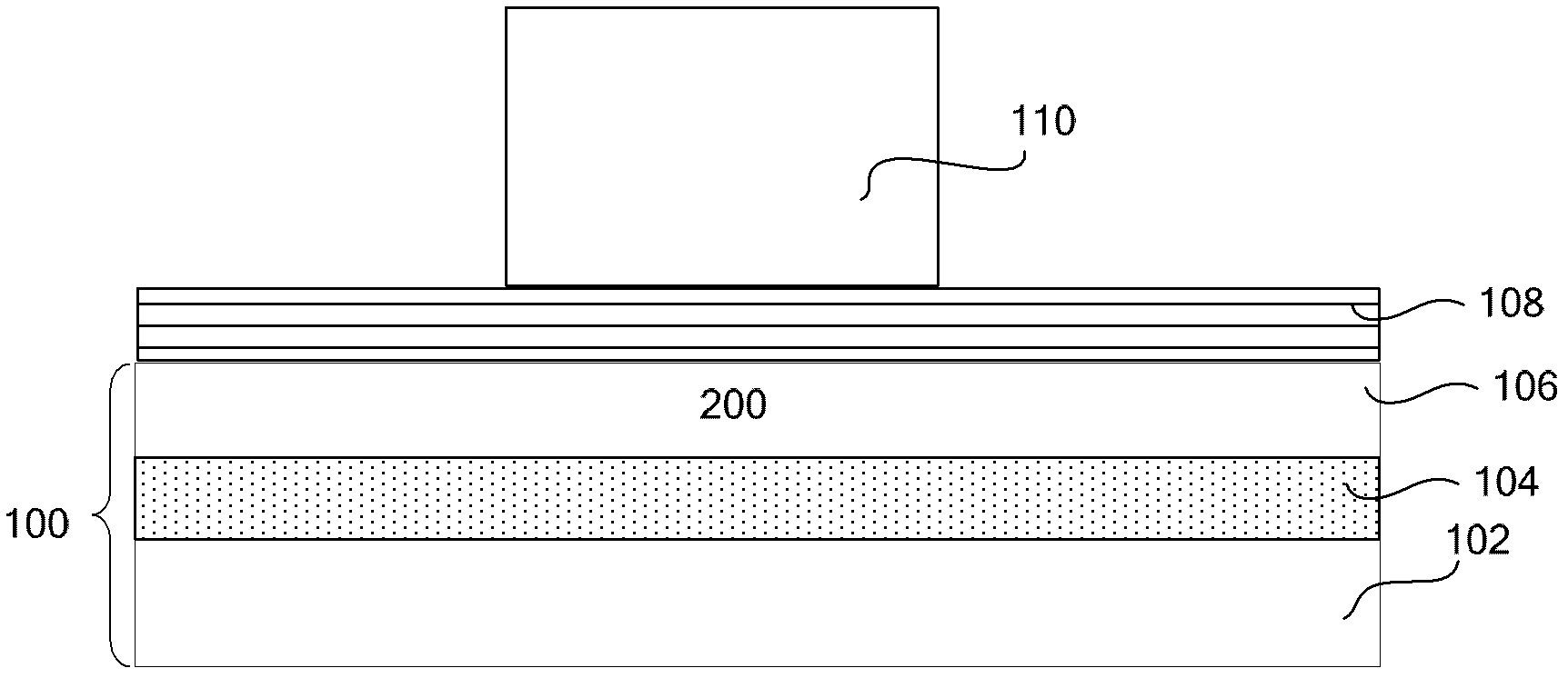

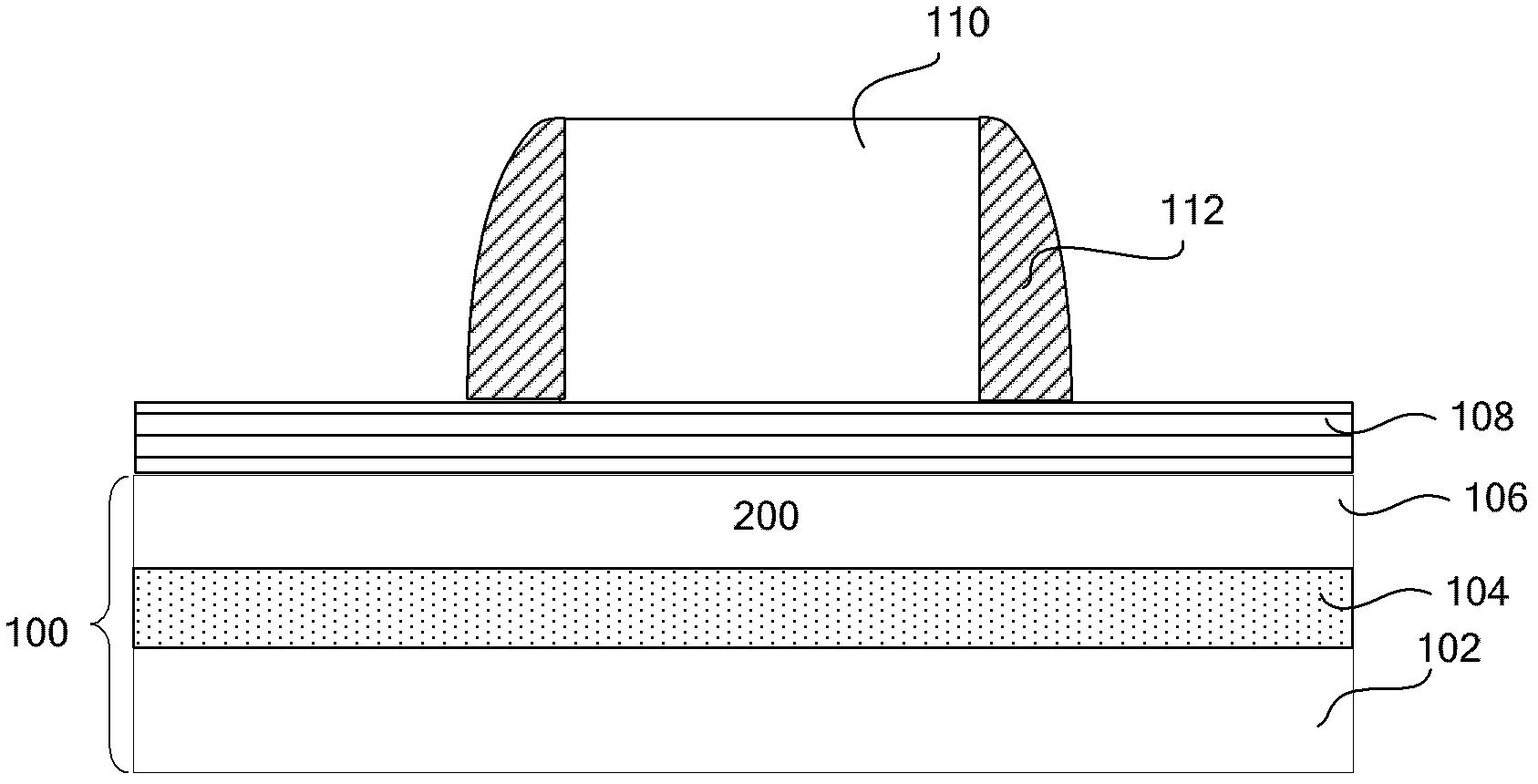

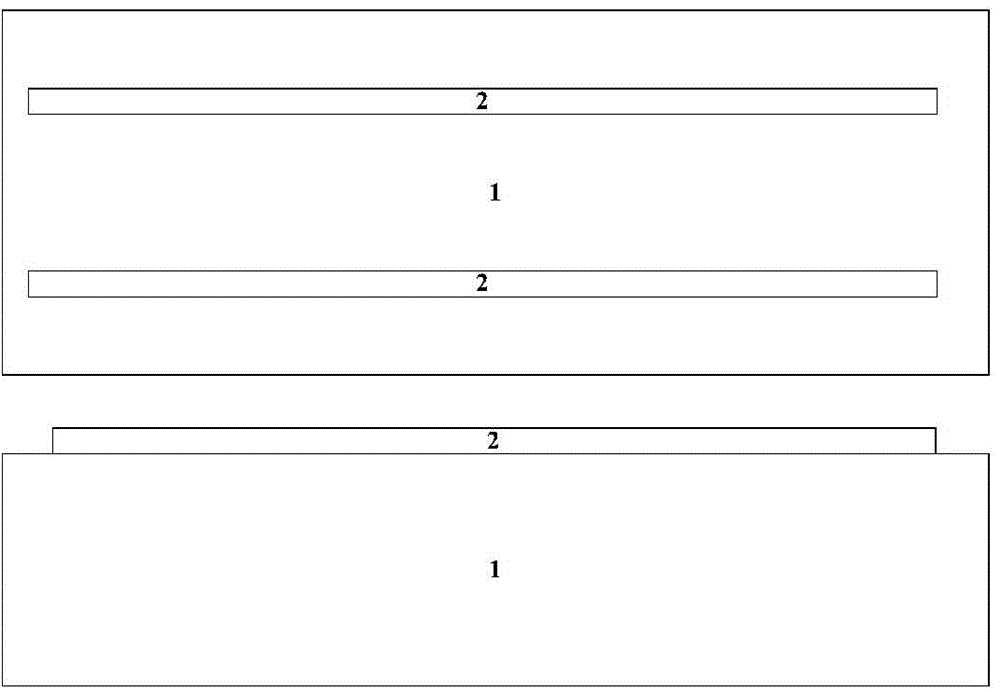

Thin film transistor, preparing method of thin film transistor, array substrate, preparing method of array substrate and display device

InactiveCN104465788AImprove performanceImprove gate control abilityTransistorSolid-state devicesDisplay deviceEngineering

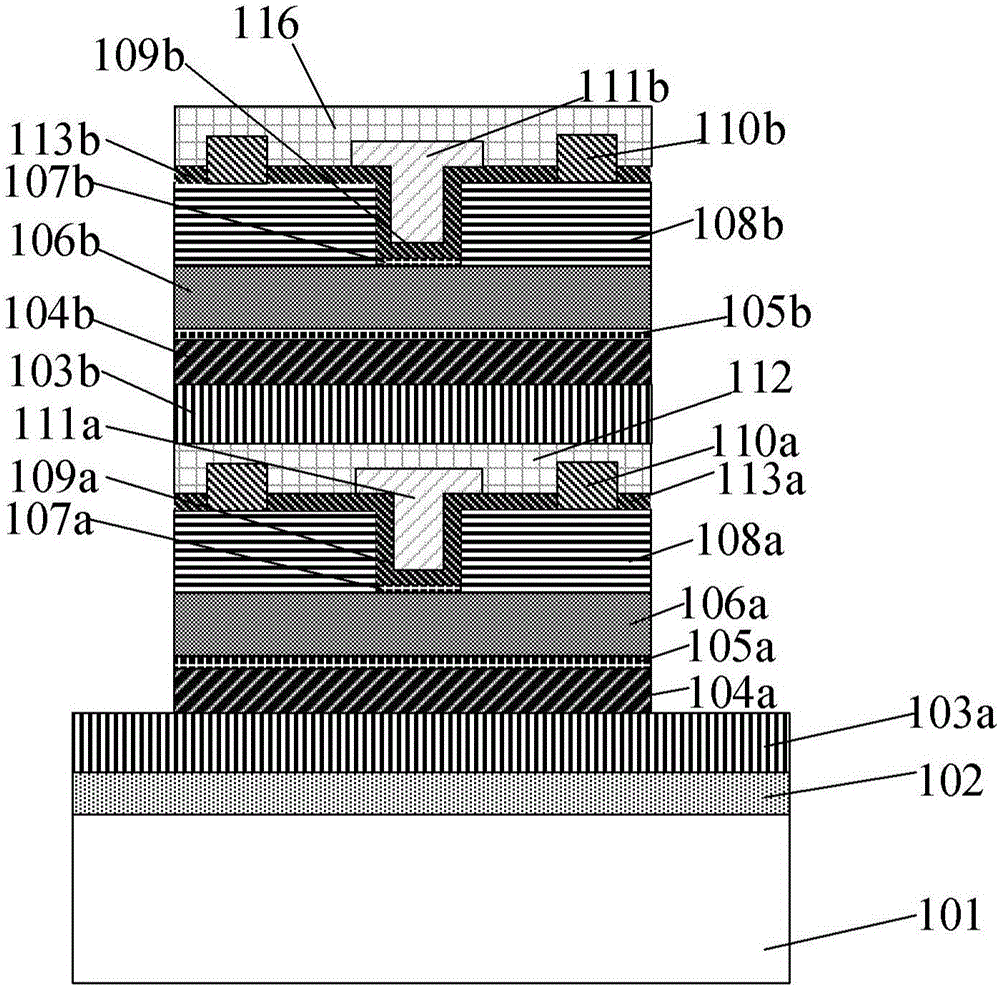

The embodiment of the invention provides a thin film transistor, a preparing method of the thin film transistor, an array substrate, a preparing method of the array substrate and a display device, and relates to the technical field of displaying. The grid control capability of the thin film transistor can be enhanced, the performance of the thin film transistor can be kept stable for a long time, and the service life of the thin film transistor can be further prolonged. The thin film transistor comprises a first grid electrode, a grid insulating layer located on the first grid electrode, a semiconductor active layer located on the grid insulating layer, a source electrode and a drain electrode, wherein the source electrode and the drain electrode are in contact with the semiconductor active layer. The thin film transistor further comprises an interlayer insulating layer and a second grid layer, wherein the interlayer insulating layer is arranged between the second grid electrode and the semiconductor active layer. The thin film transistor can be used for manufacturing a display component.

Owner:BOE TECH GRP CO LTD

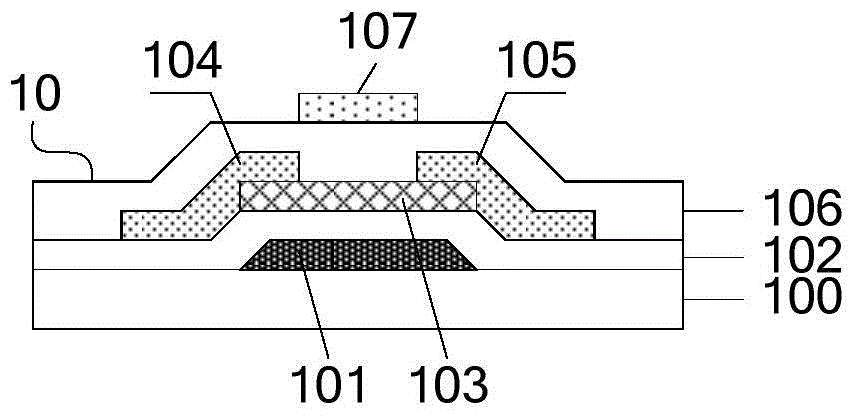

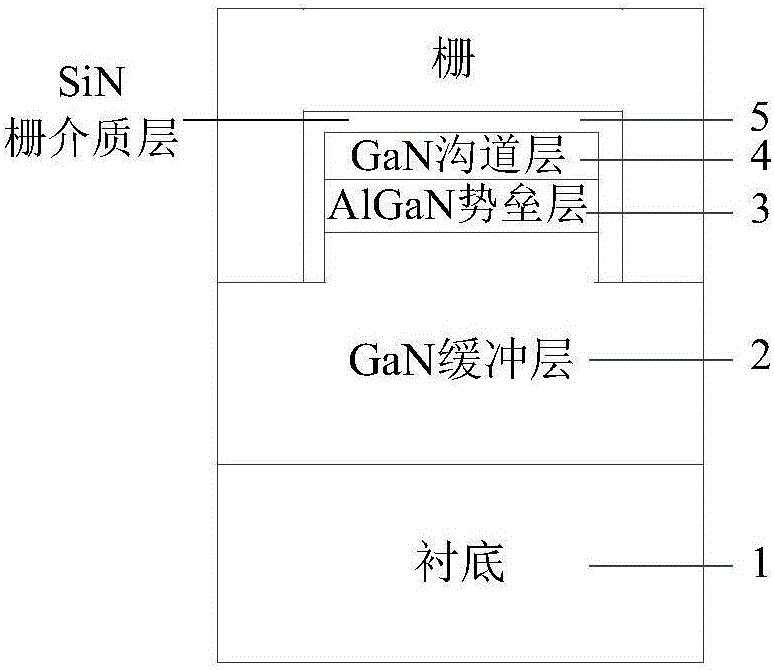

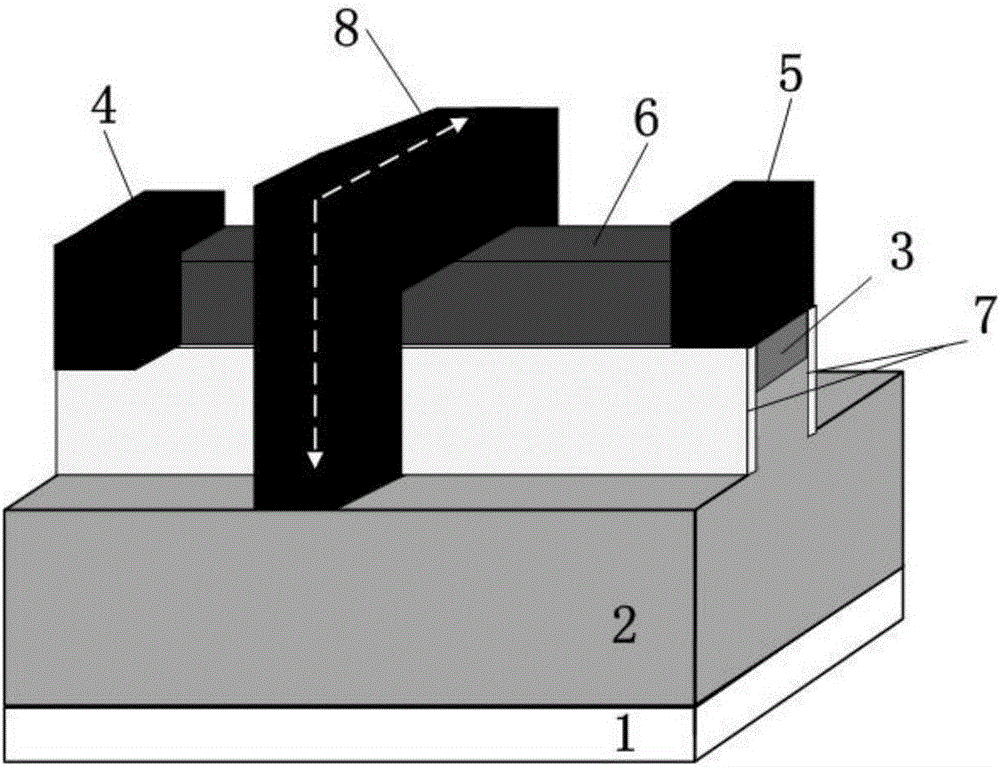

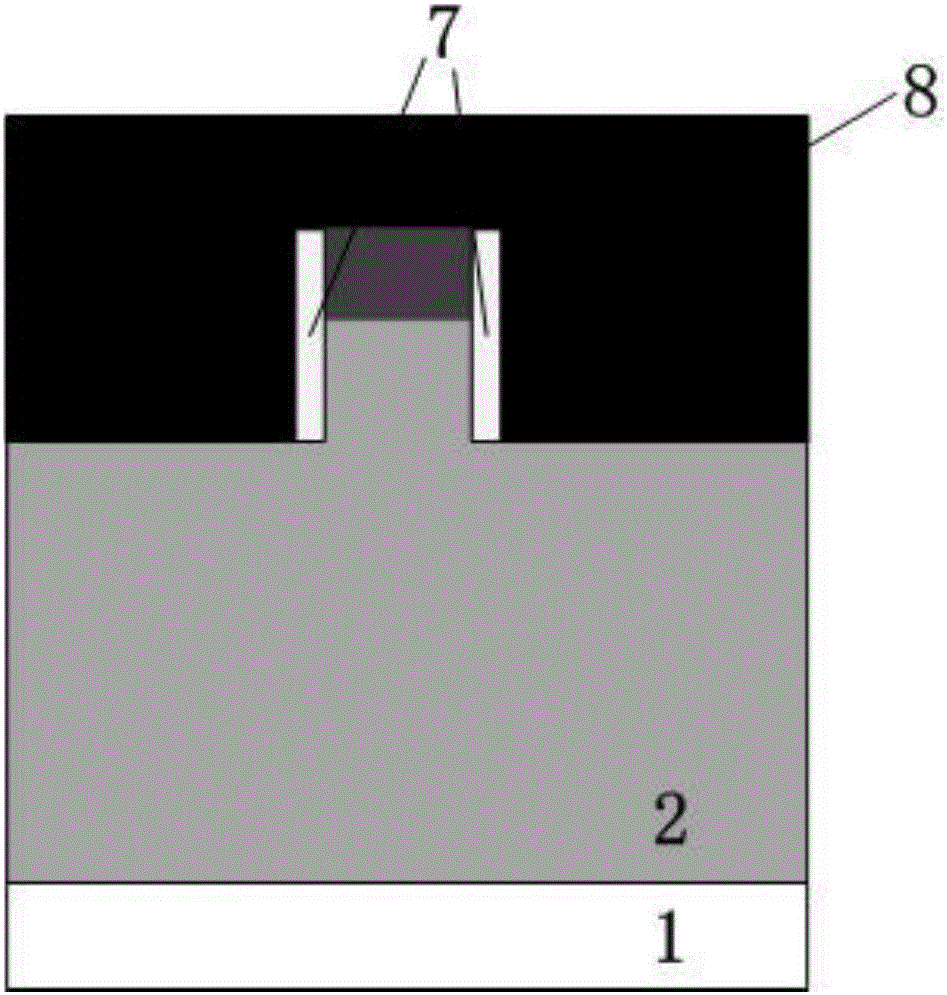

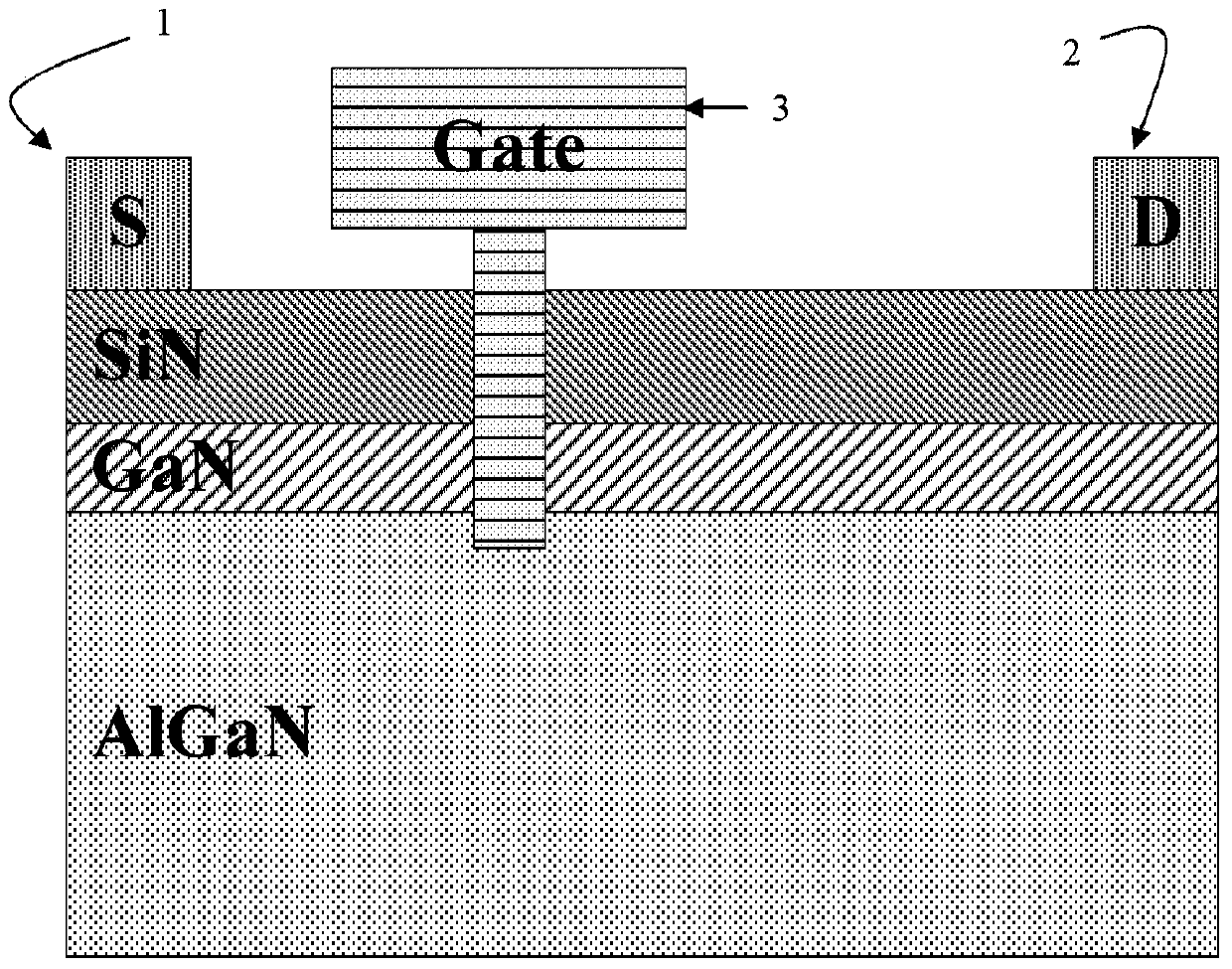

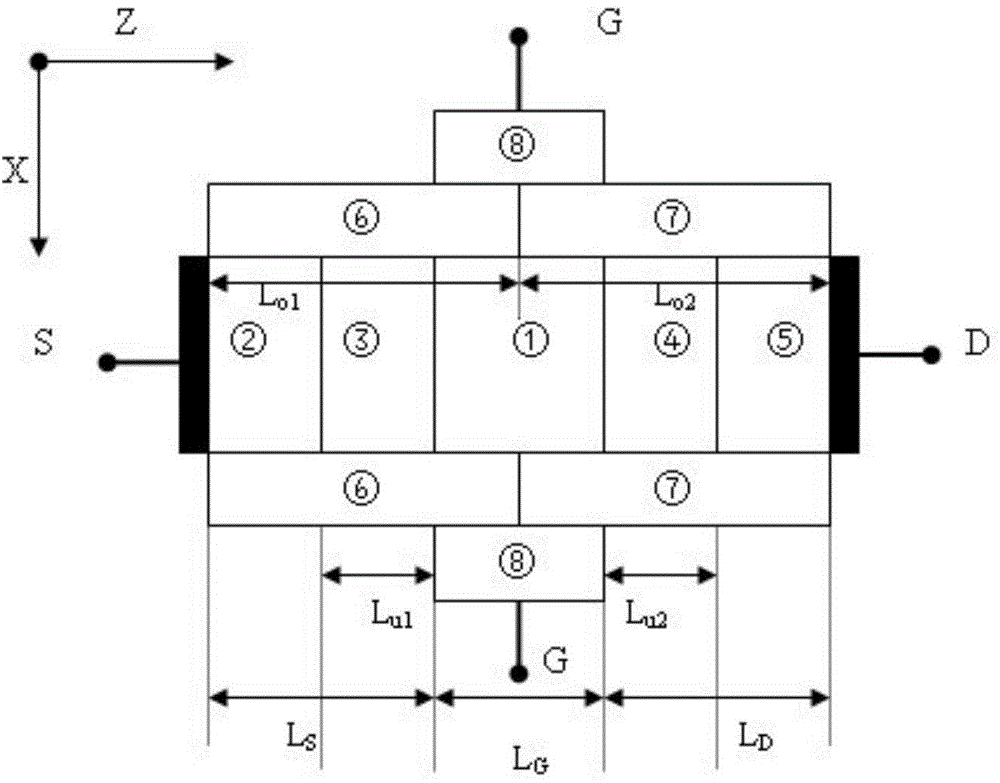

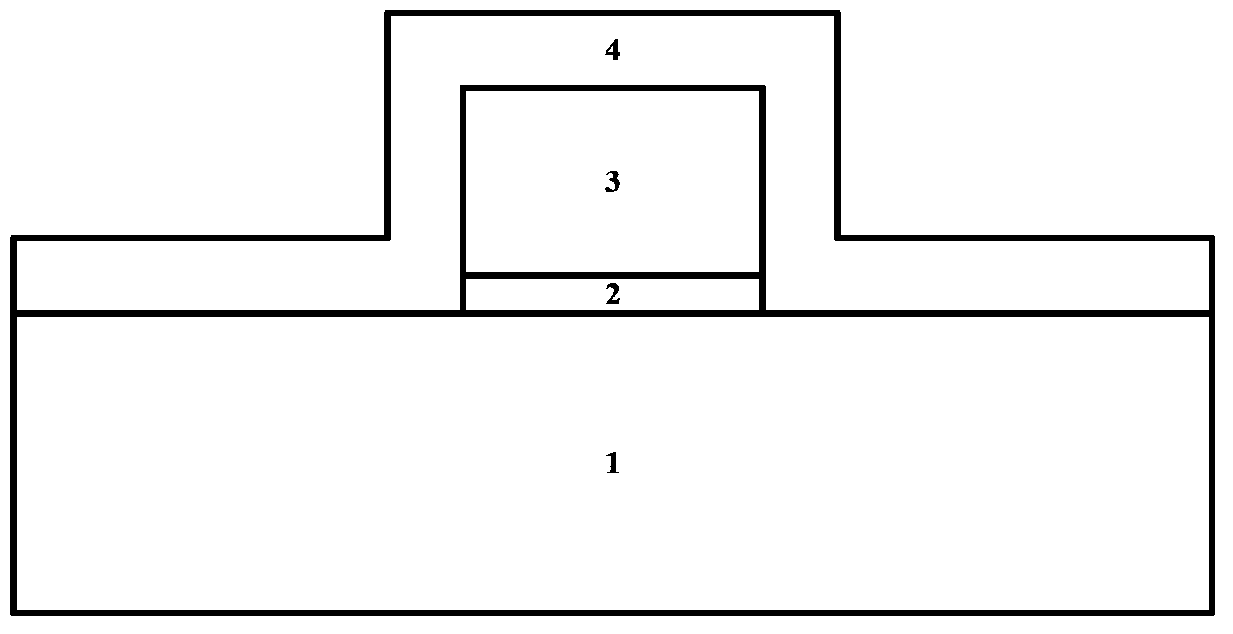

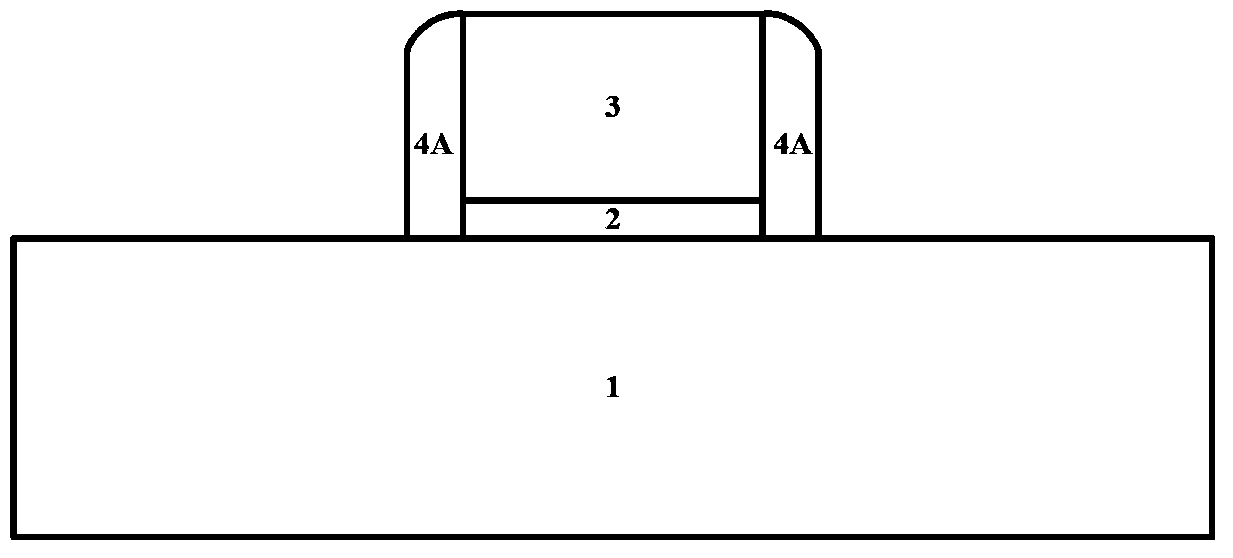

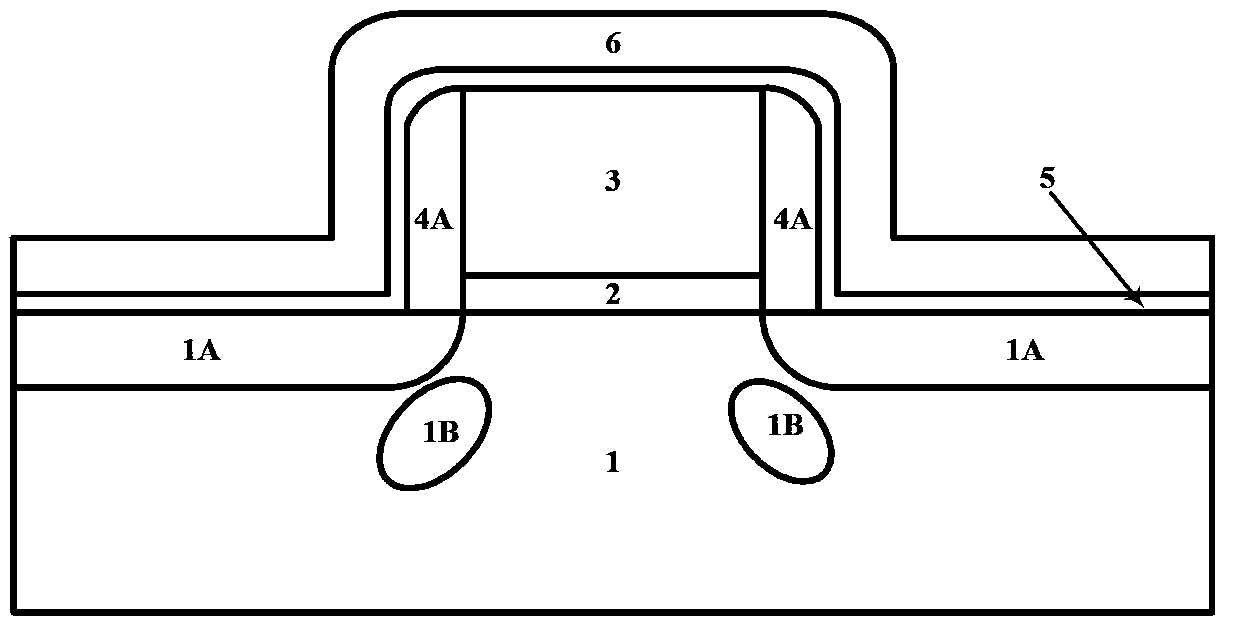

T-gate and N-surface GaN/AlGaN fin-type high electron mobility transistor

ActiveCN105914232AReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionOhmic contact

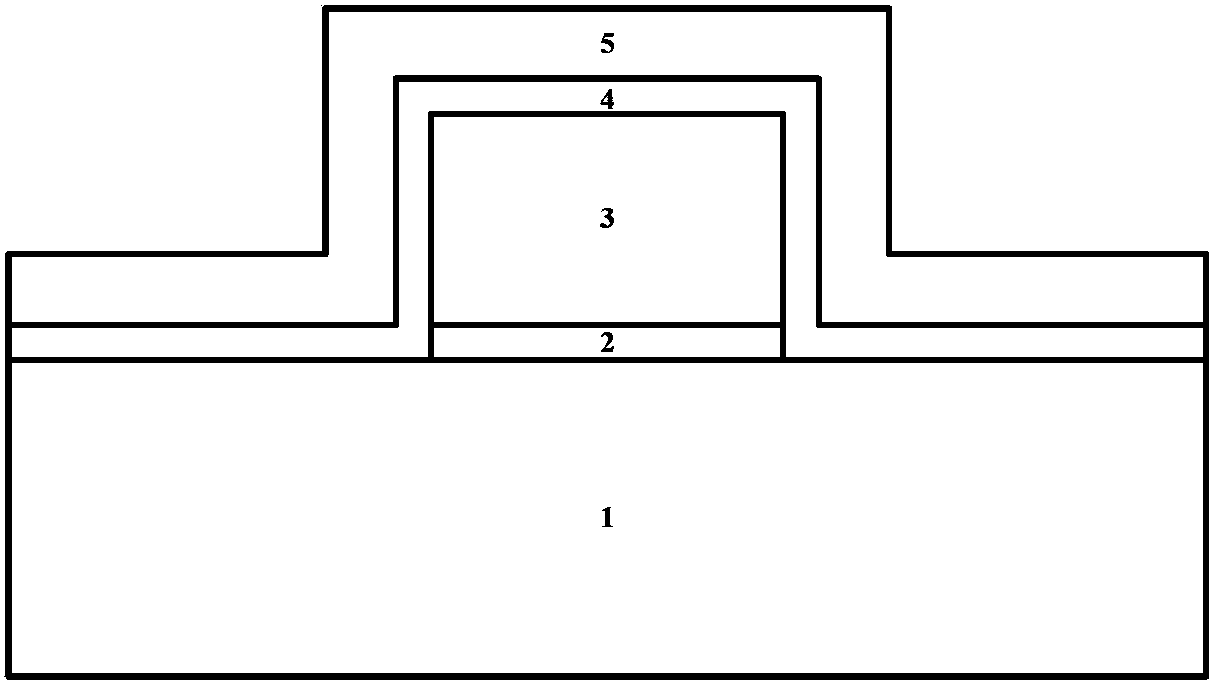

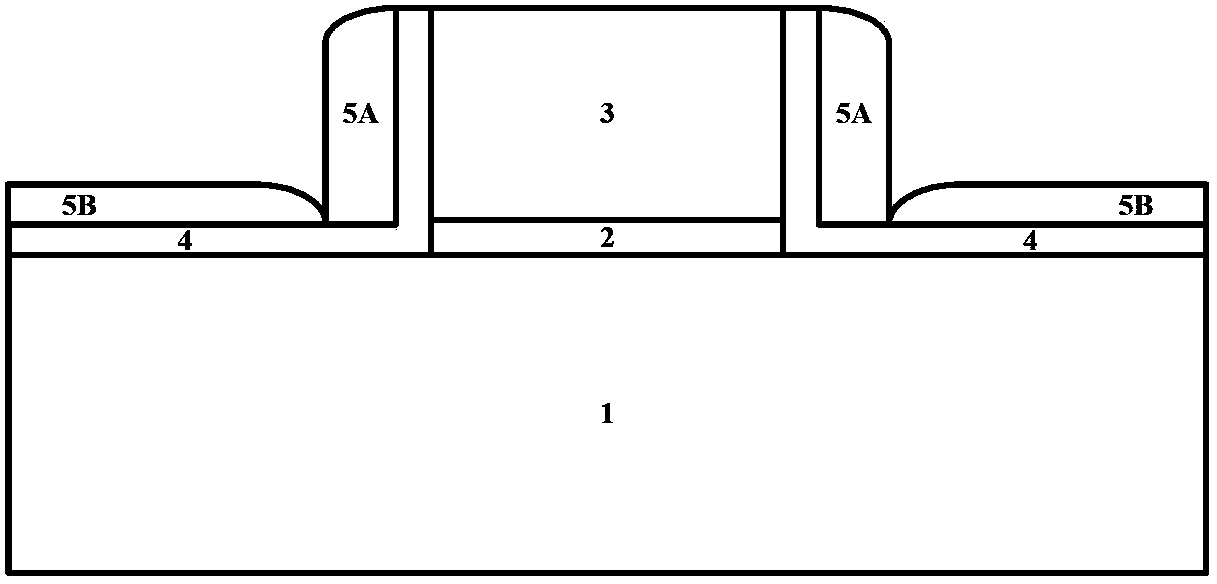

The present invention discloses a T-gate and N-surface GaN / AlGaN fin-type high electron mobility transistor. The problems are mainly solved that the maximum oscillating frequency of a current microwave power device is small, the ohmic contact resistor is large and the short channel effect is severe. The transistor comprises from down to up: a substrate (1), a GaN buffer layer (2), a ALGaN barrier layer (3), a GaN channel layer (4), a gate medium layer (5), a passivation layer (6), a source gate electrode and a drain gate electrode. The buffer layer and the channel layer employ N-surface GaN materials; the GaN channel layer and the ALGaN barrier layer form GaN / AlGaN heterojunction; the gate electrode employs T-type gate and is wrapped at two sides and the upper portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate and N-surface GaN / AlGaN fin-type high electron mobility transistor has good gate-control capability, small resistor and the maximum oscillating frequency, and is able to be a microwave power device with the small size.

Owner:XIDIAN UNIV

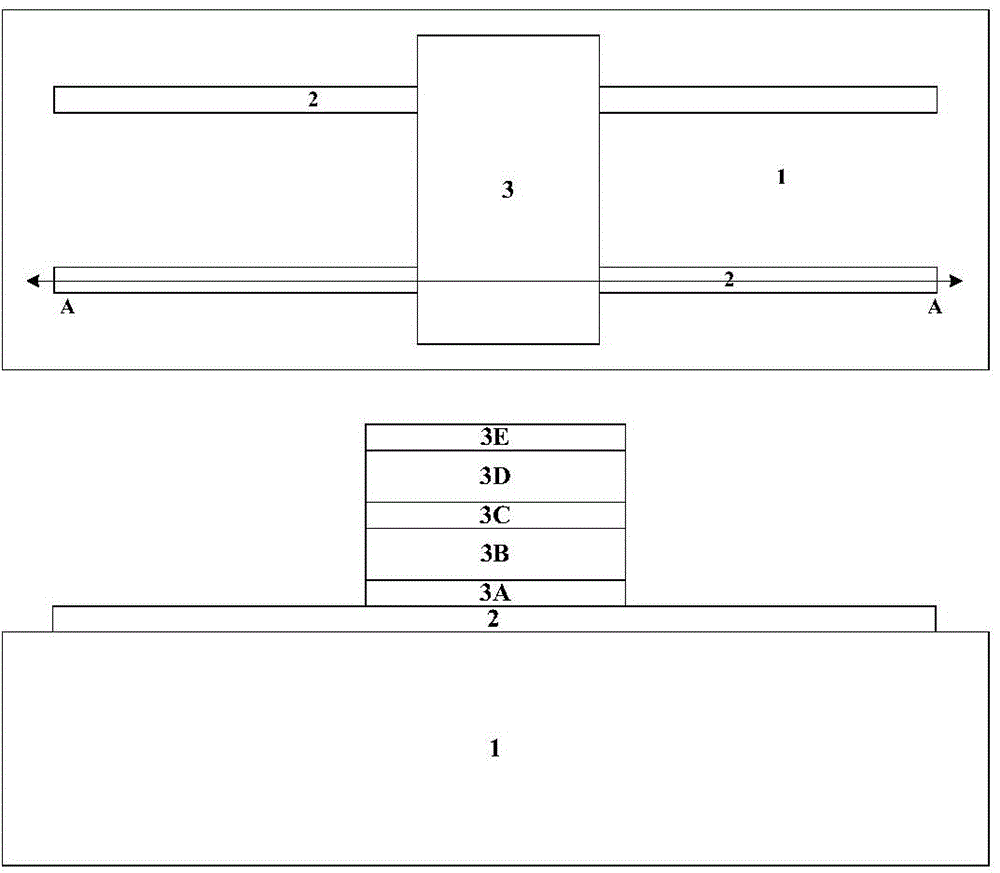

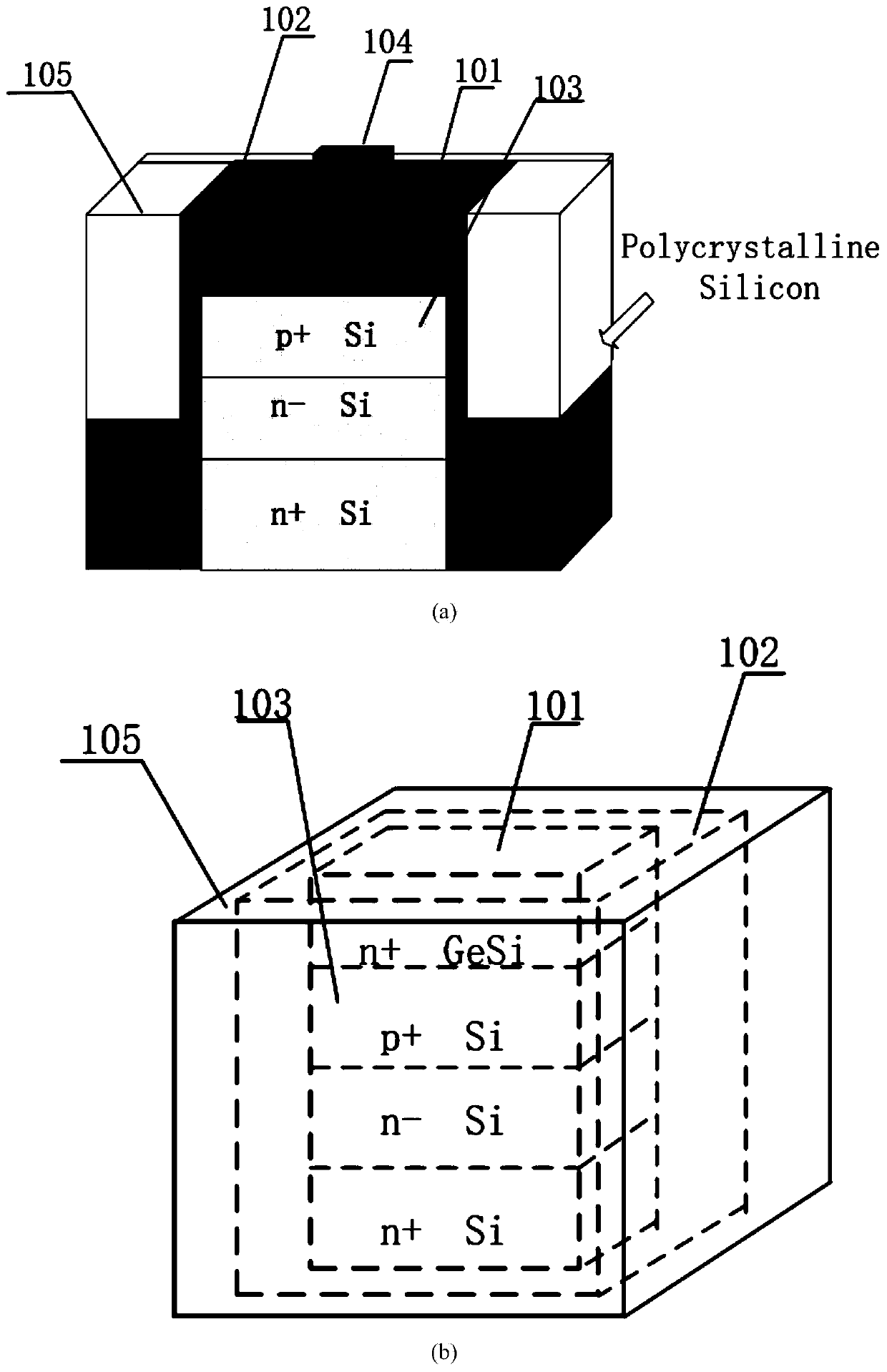

Short-Gate Tunneling Field Effect Transistor Having Non-Uniformly Doped Vertical Channel and Fabrication Method Thereof

InactiveUS20160020306A1Steep sub-threshold slopeImprove gate control abilityNanoinformaticsSemiconductor/solid-state device manufacturingSub thresholdEngineering

The present invention discloses a short-gate tunneling field effect transistor having a non-uniformly doped vertical channel and a fabrication method thereof. The short-gate tunneling field effect transistor has a vertical channel and the channel region is doped in such a slowly-varied and non-uniform manner that a doping concentration in the channel region appears a Gaussian distribution along a vertical direction and the doping concentration in the channel near the drain region is higher while the doping concentration in the channel near the source region is lower; and double control gates are formed at both sides of the vertical channel and the control gates form an L-shaped short-gate structure, so that a gate underlapped region is formed in the channel near the drain region, and a gate overlapped region is formed at the source region. As compared with a conventional TFET, the short-gate tunneling field effect transistor according to the present invention can effectively suppress the impact of the electrical field at the drain region on the tunneling width of the tunneling junction at the source region; the super exponential relationship between the output tunneling current and the drain voltage is weakened; and the output characteristic of the transistor is significantly improved. Meanwhile, the tunneling field effect transistor is beneficial to increase the on-current of the transistor and to gain a steeper sub-threshold slope.

Owner:PEKING UNIV

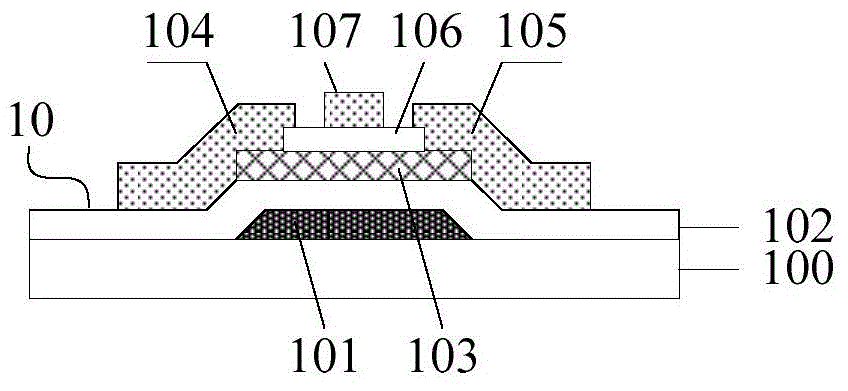

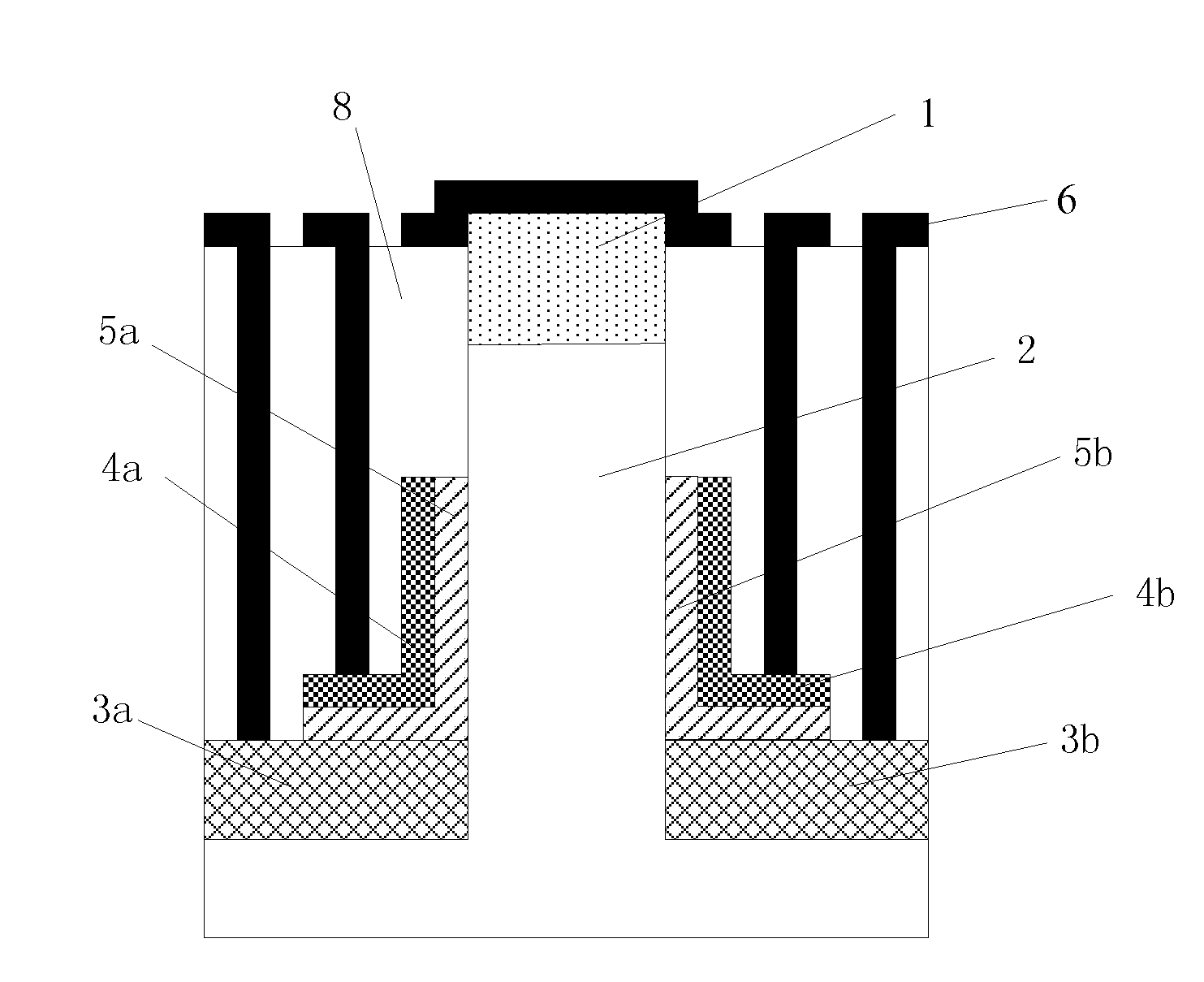

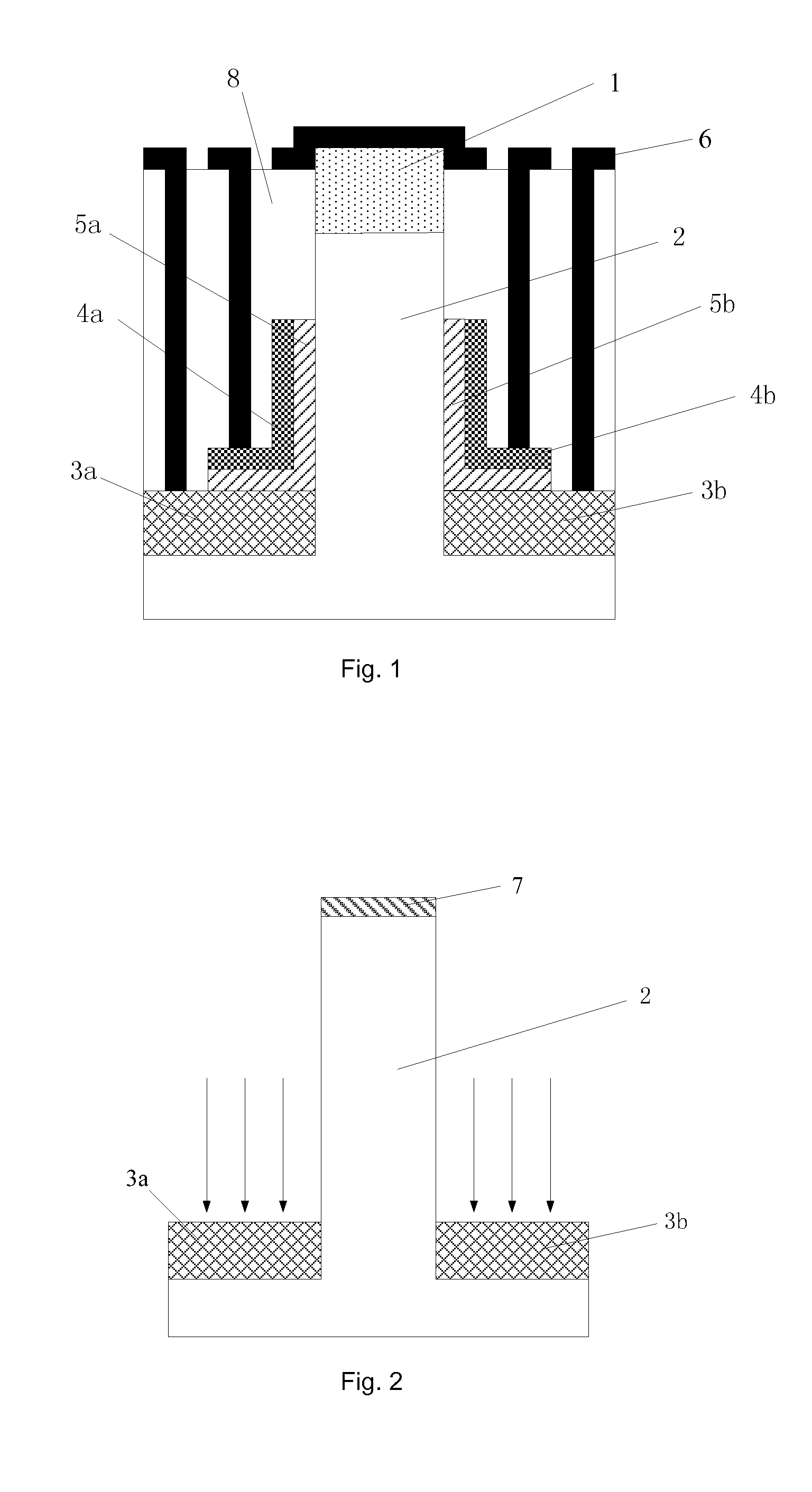

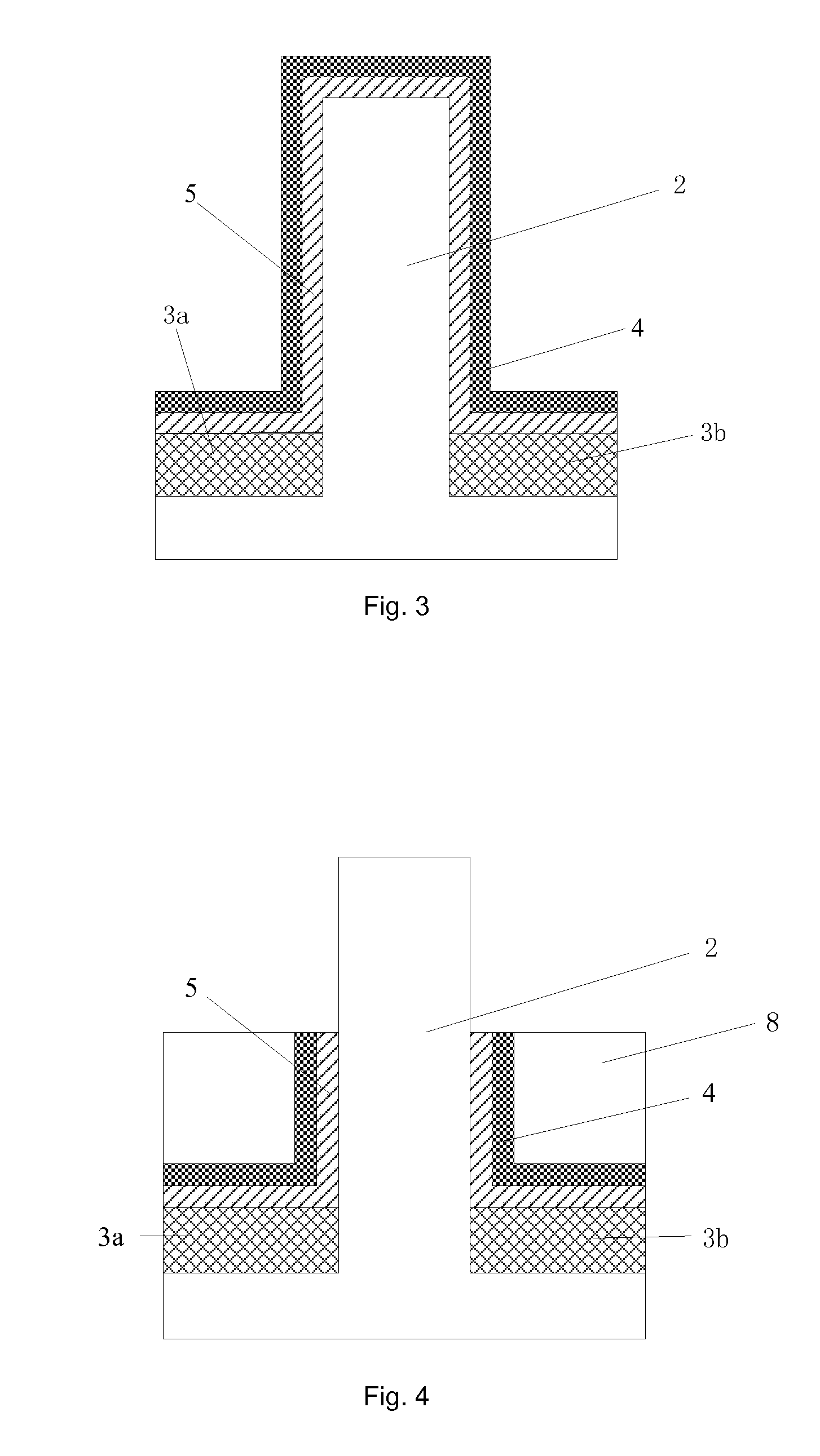

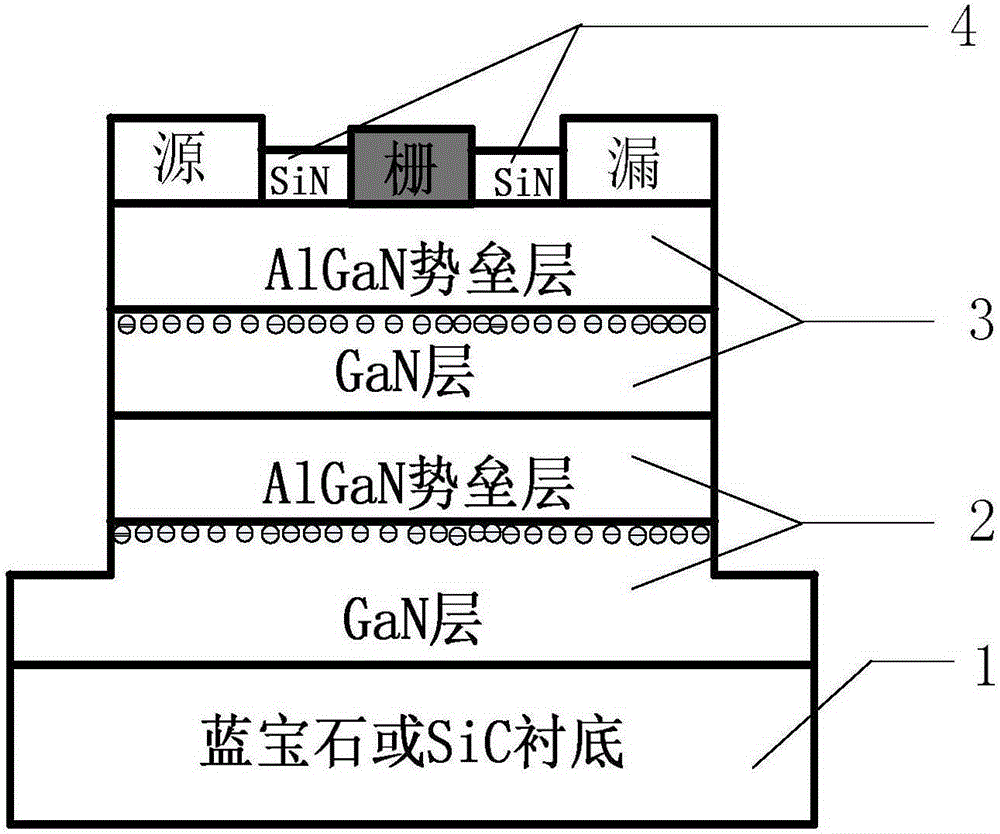

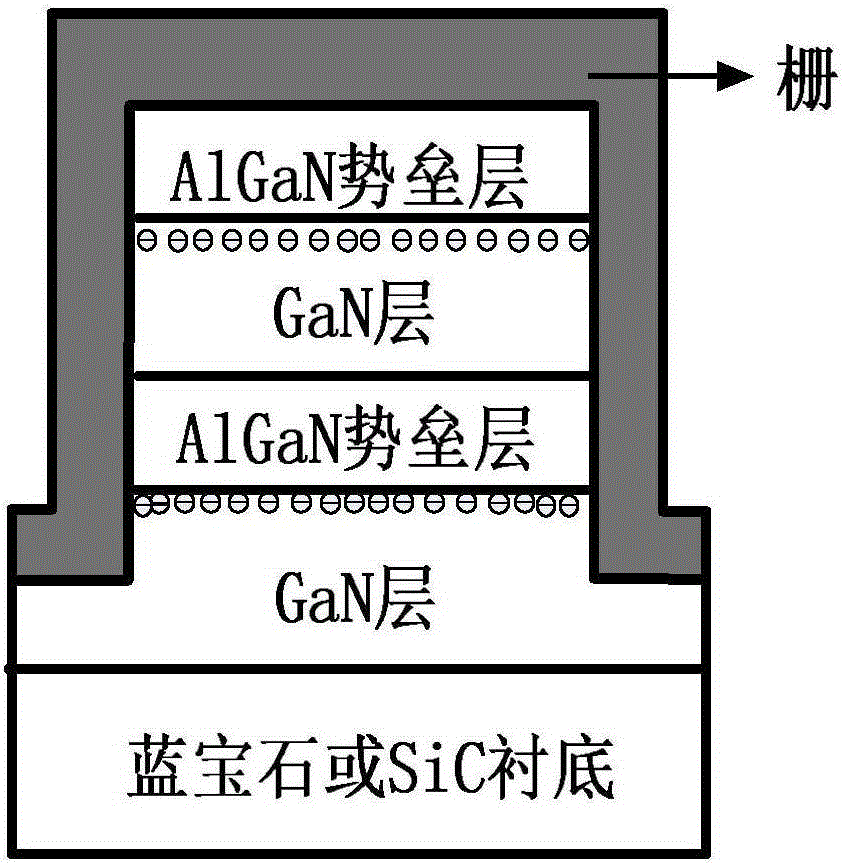

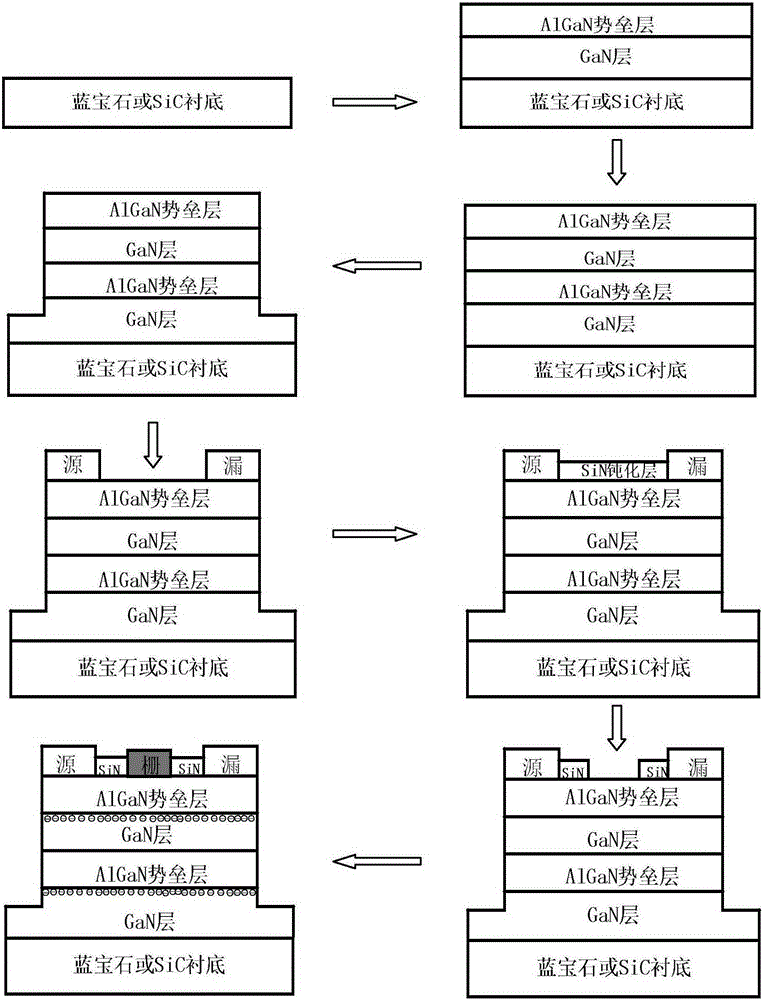

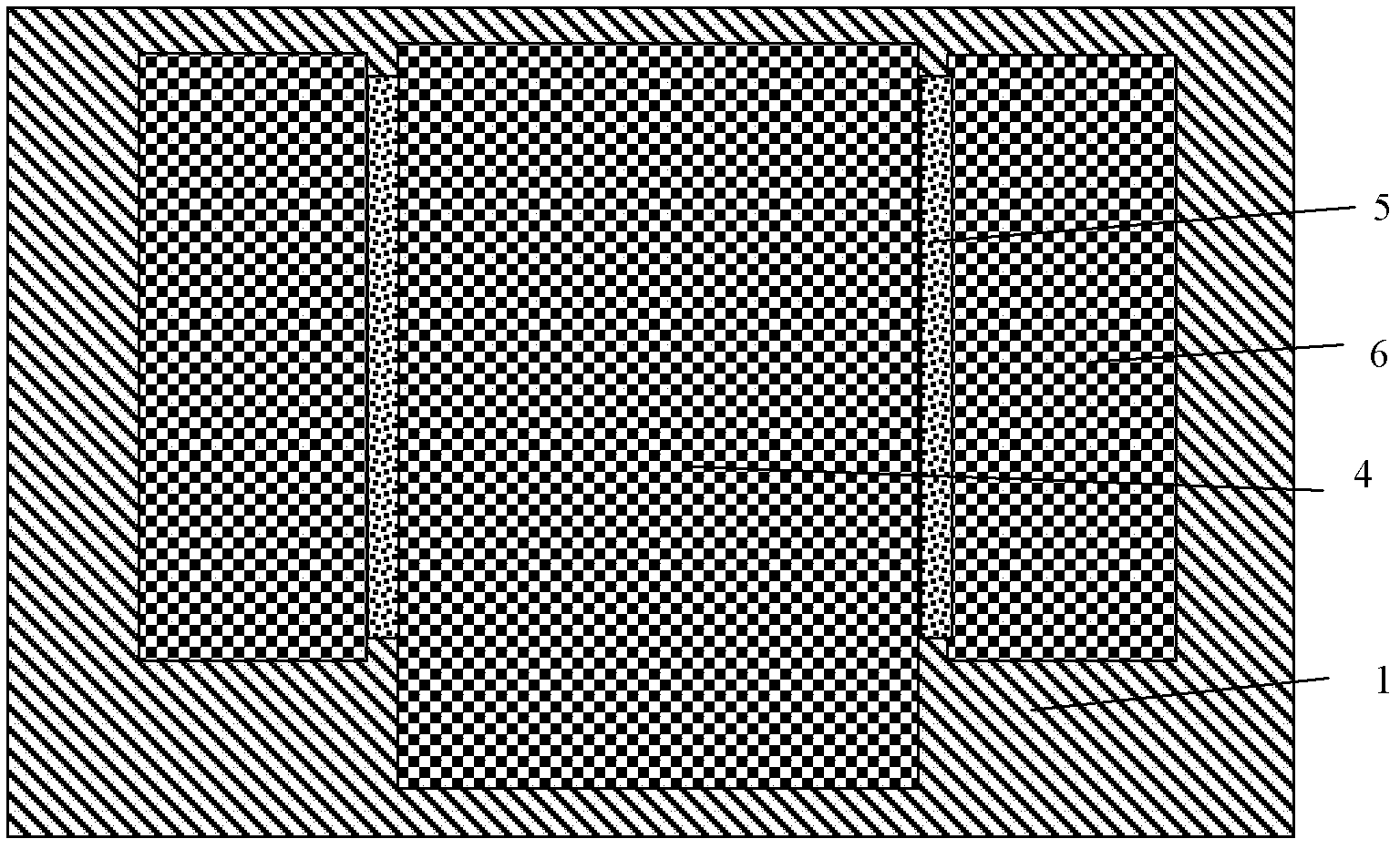

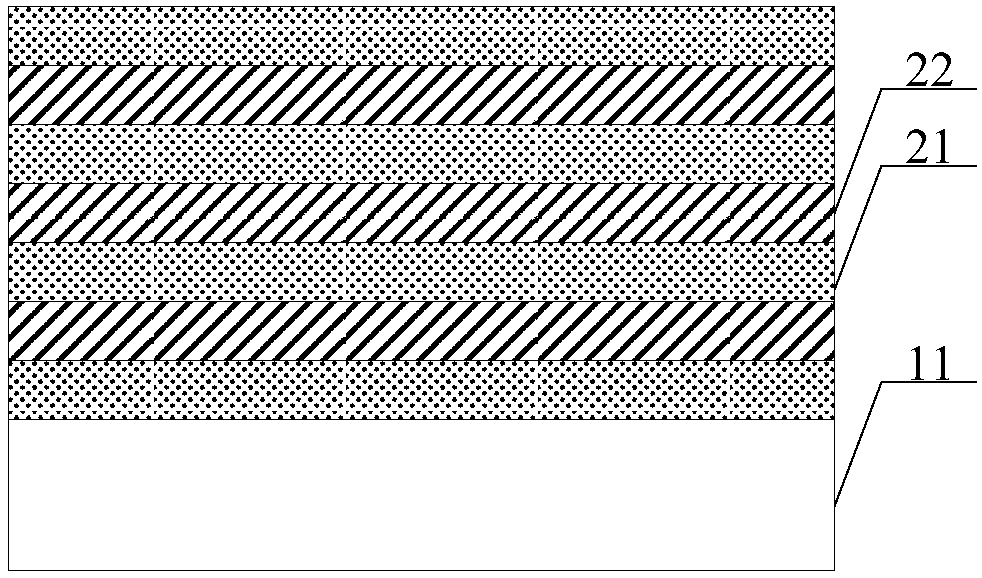

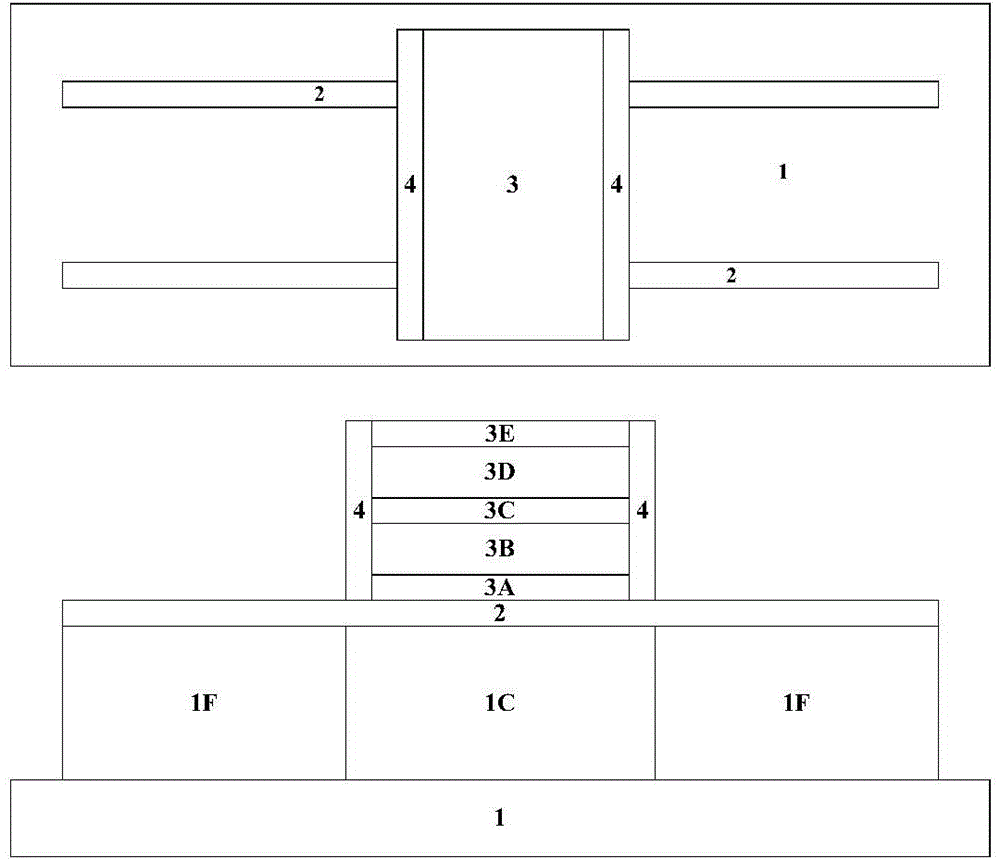

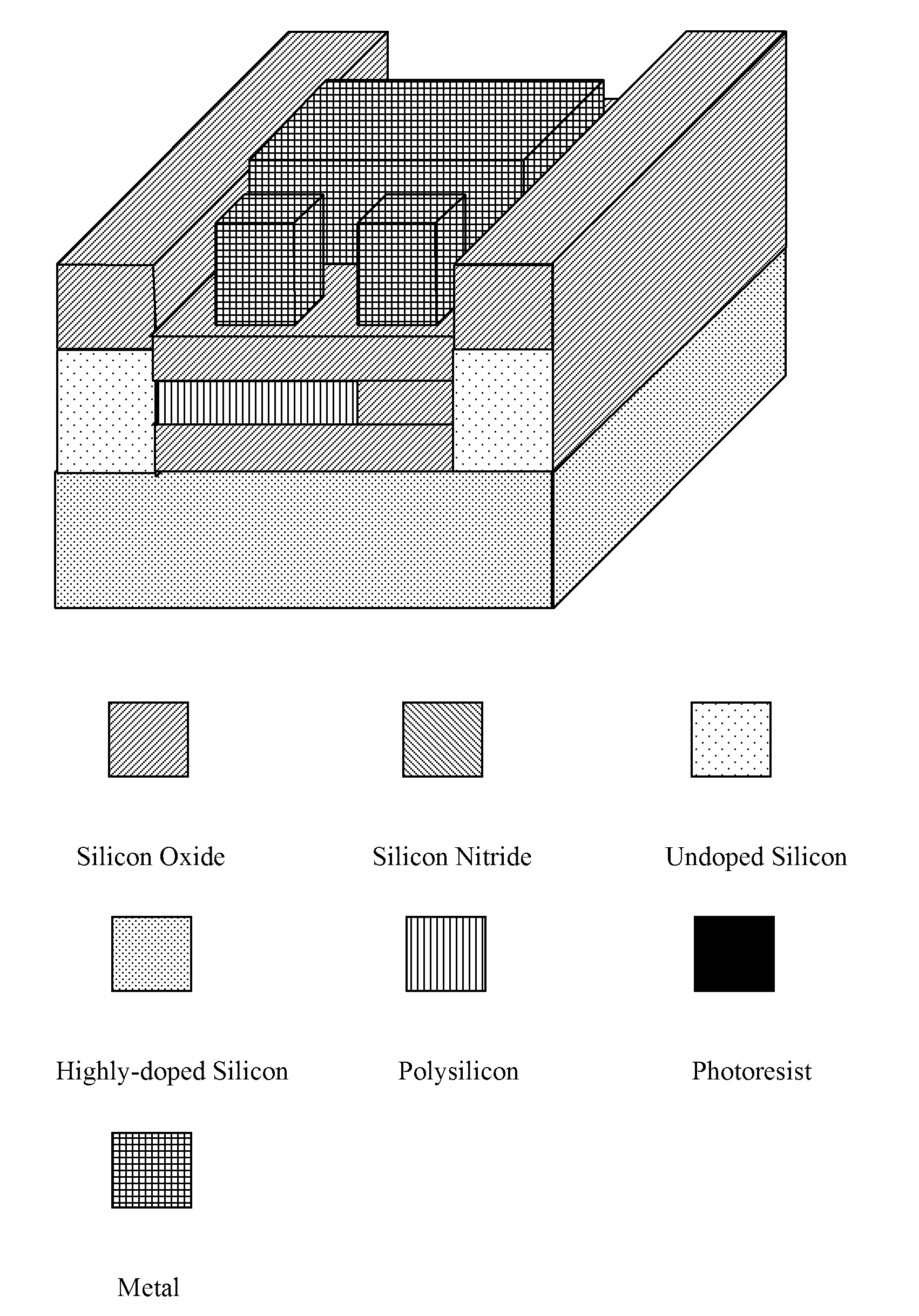

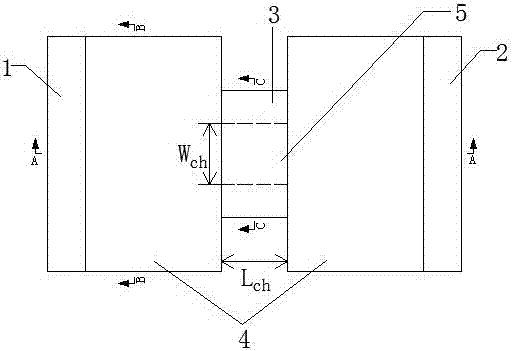

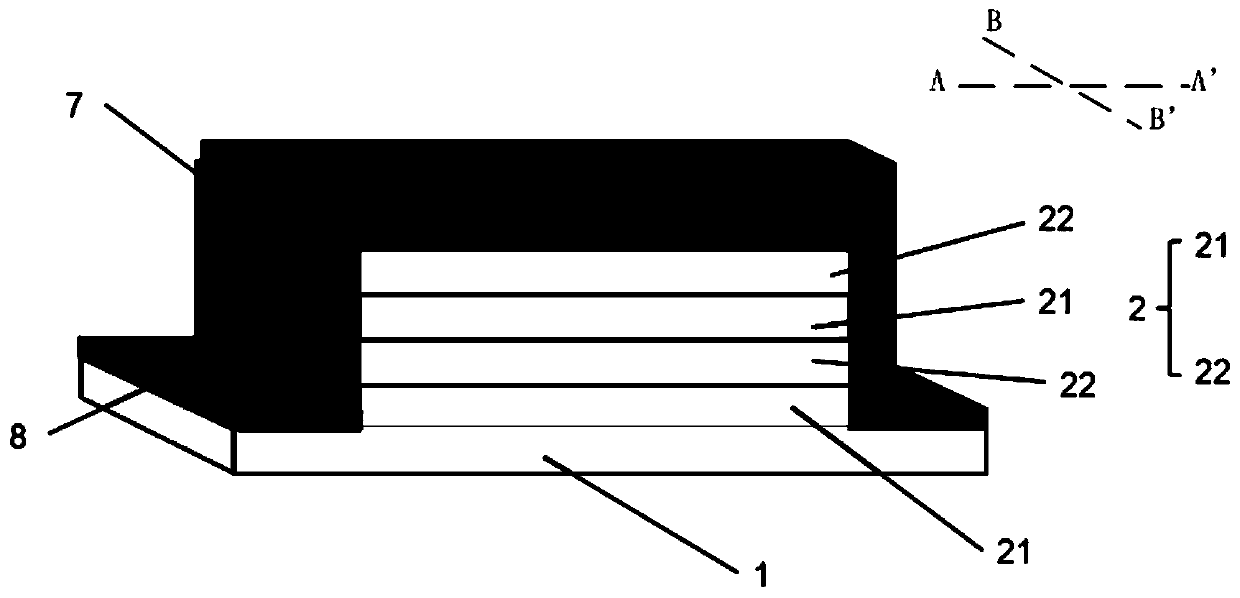

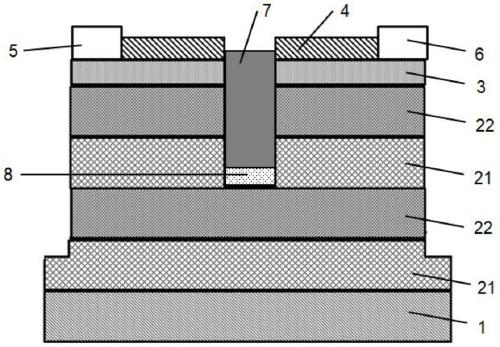

AlGaN/GaN high electron mobility transistor with multi-channel fin-type structure

InactiveCN105280696AReduce widthLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLow noise

The invention discloses a AlGaN / GaN high electron mobility transistor structure with a multi-channel fin-type structure and a manufacturing method, wherein the AlGaN / GaN high electron mobility transistor is designed mainly to solve the problems of the poor gate control ability of a multi-channel apparatus and low electric current of a FinFET apparatus; the AlGaN / GaN high electron mobility transistor comprises a substrate (1), a first layer AlGaN / GaN heterojunction (2), a SiN passivation layer (4) and a source electrode, a drain electroce, and a gate electrode successively from bottom to top; the source electrode and the drain electrode are located on AlGaN potential barrier layers on top layers at two sides of the SiN passivation layer respectively; the AlGaN / GaN high electron mobility transistor is characterized in that a GaN layer and the AlGaN potential barrier layer are set between the first layer AlGaN / GaN heterojunction and the SiN passivation layer so as to form a second layer AlGaN / GaN heterojuntion (3); and the gate electrode covers the top portion of a second layer heterojuntion and the two side walls of the first and the second heterojunctions. According to the invention, the gate control ability is strong; the saturation current is large; the subthreshold property is good; and the AlGaN / GaN high electron mobility transistor can be used for microwave power apparatus with a shrot gate length, low power consumption and low noise.

Owner:XIDIAN UNIV

Preparation method for top-gate self-aligned zinc oxide thin film transistor

ActiveCN102437059AImprove your own performanceReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor package

The invention discloses a preparation method for a top-gate self-aligned zinc oxide thin film transistor. According to the preparation method, only three masks are needed, and a zinc oxide thin film transistor is prepared through three times of photoetching; two layers of photoresist of a gate dielectric layer and a gate electrode outside a channel region are stripped together by adopting a self alignment process; and exposed semiconductor layers at two ends of the channel region are treated to reduce the resistance of the exposed semiconductor layers so as to form a low-resistance source region and a low-resistance drain region. Due to the implementation of self alignment of the gate dielectric layer and the gate electrode, parasitic capacitance and parasitic resistance are effectively reduced, and the grid-control capacity is improved; and therefore the preparation method has positive effects of improving the performance of a thin film transistor device, realizing a high-speed thin film transistor circuit and the like. Simultaneously, the process difficulty is greatly reduced, the manufacturing cost is saved, and the rate of finished products is improved.

Owner:BOE TECH GRP CO LTD

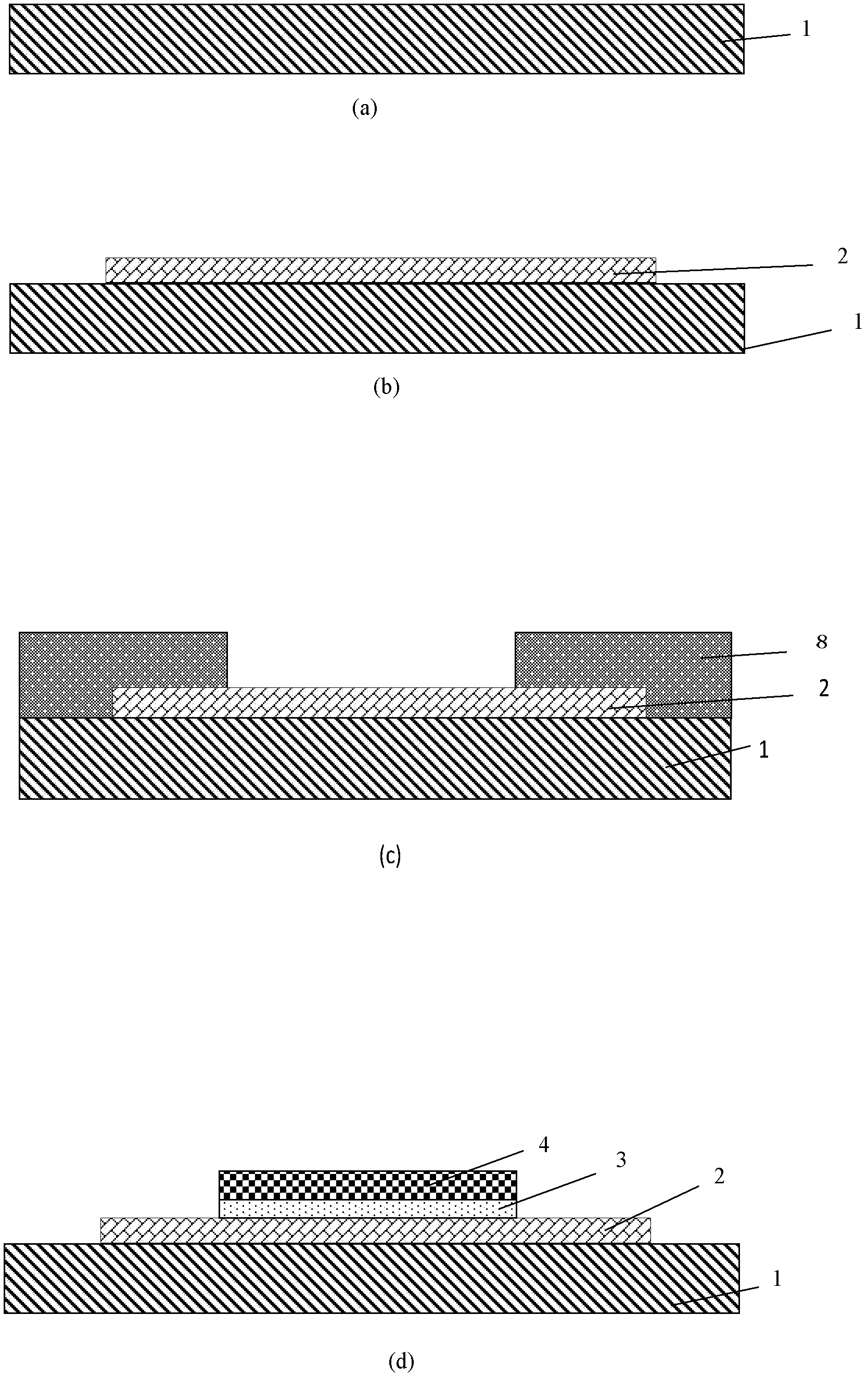

Field-effect transistor structure and fabrication method thereof

InactiveCN107871780AImprove performanceImprove stabilityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireEngineering

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

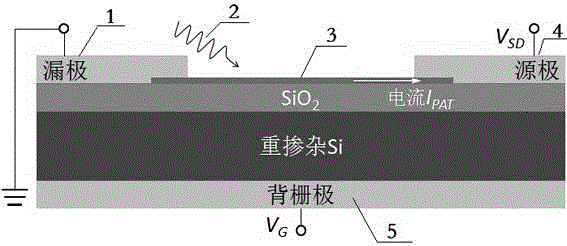

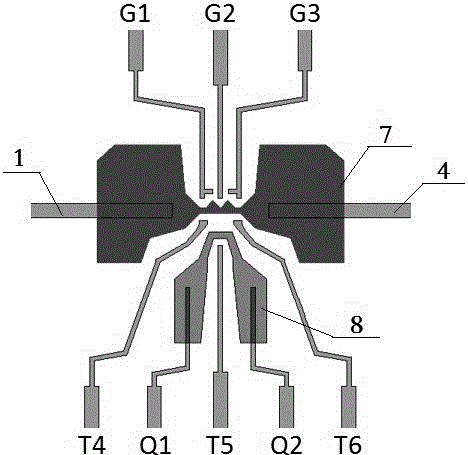

THz single photon detector based on graphene quantum dots and preparation method thereof

InactiveCN106384756AChange the amount of detuningAchieve ultra-high sensitivity measurementFinal product manufactureInstrumentsCapacitanceElectrometer

The invention provides a THz single photon detector based on graphene quantum dots and a preparation method thereof. A basic structure with graphene single-quantum dots or the mutual coupling of graphene dual-quantum dots in a series connection and a nanoribbon graphene electrometer is employed, with a silicon substrate, a source electrode, a drain electrode, a side gate, a back gate, a Coulomb island, an electrometer and a protective layer as basic composition units, the source electrode, the drain electrode, the side gate, the Coulomb island and the electrometer are arranged in an integrated way on a silicon dioxide base formed at the surface of the silicon substrate, and the back gate is arranged on the silicon base of the silicon substrate, wherein the graphene single-quantum dots or graphene dual-quantum dots in a series connection are taken as the Coulomb island of the THz single photon detector, the Coulomb island is between the source and drain electrodes and the side gate, and a graphene nanoribbon is integrated near the Coulomb island as the graphene electrometer. The Coulomb island and the source and drain electrodes are coupled in the form of a tunnel junction, and the Coulomb island, the side gate, the back gate and the graphene electrometer are coupled in the form of capacitance. According to the THz single photon detector and the preparation method, the problems of large technical difficulty and low sensitivity in a present preparation method are overcome.

Owner:NAT UNIV OF DEFENSE TECH

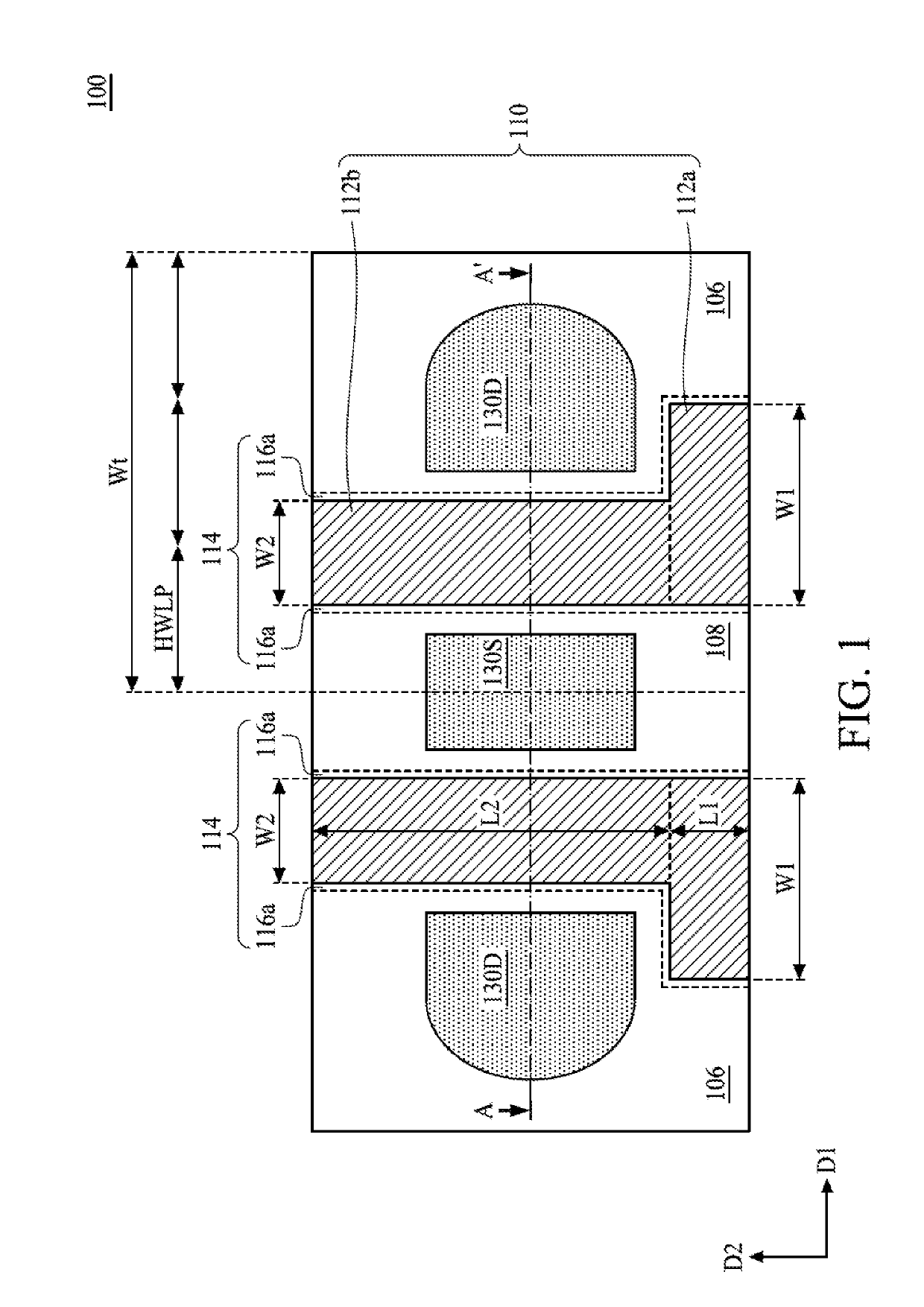

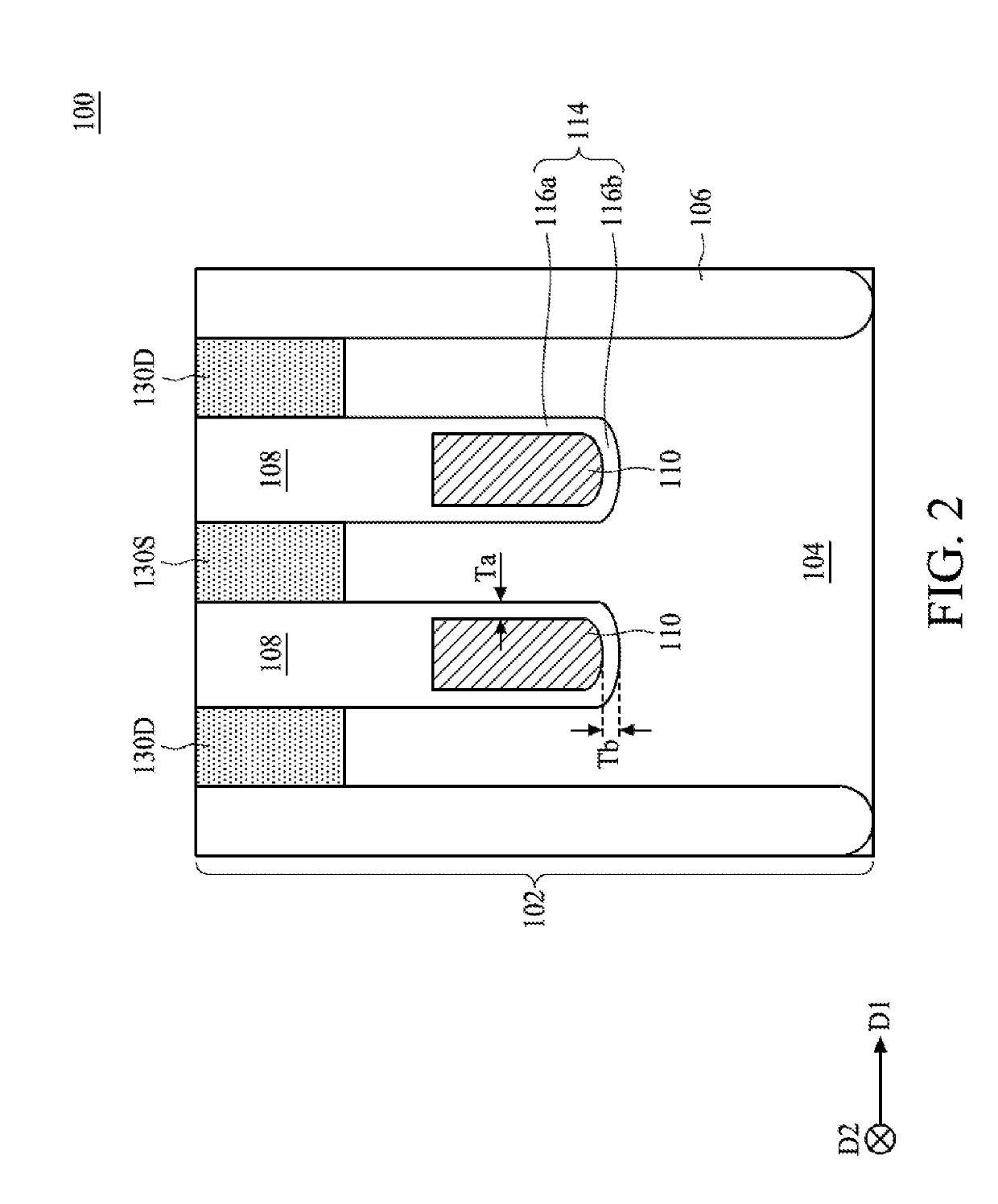

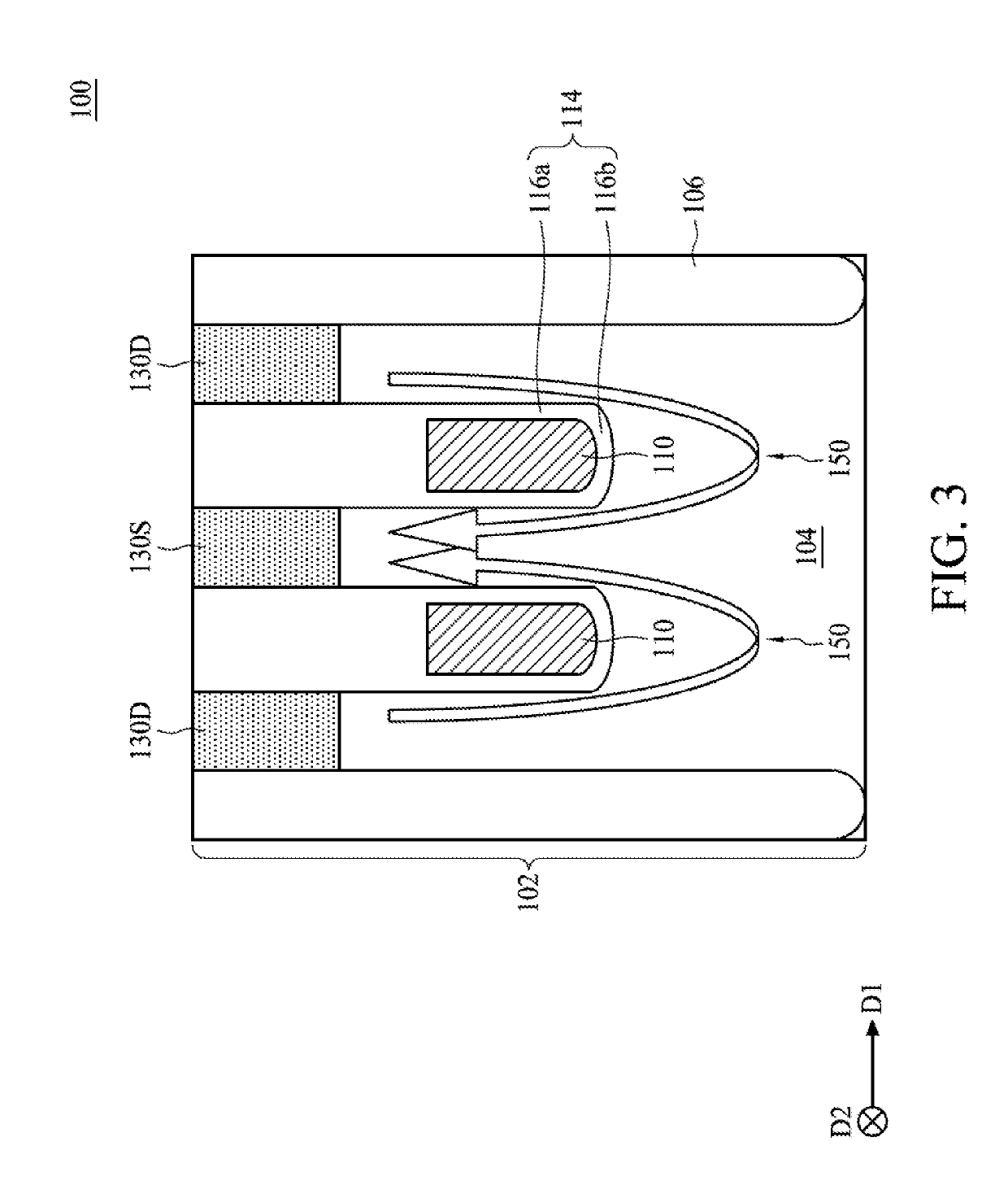

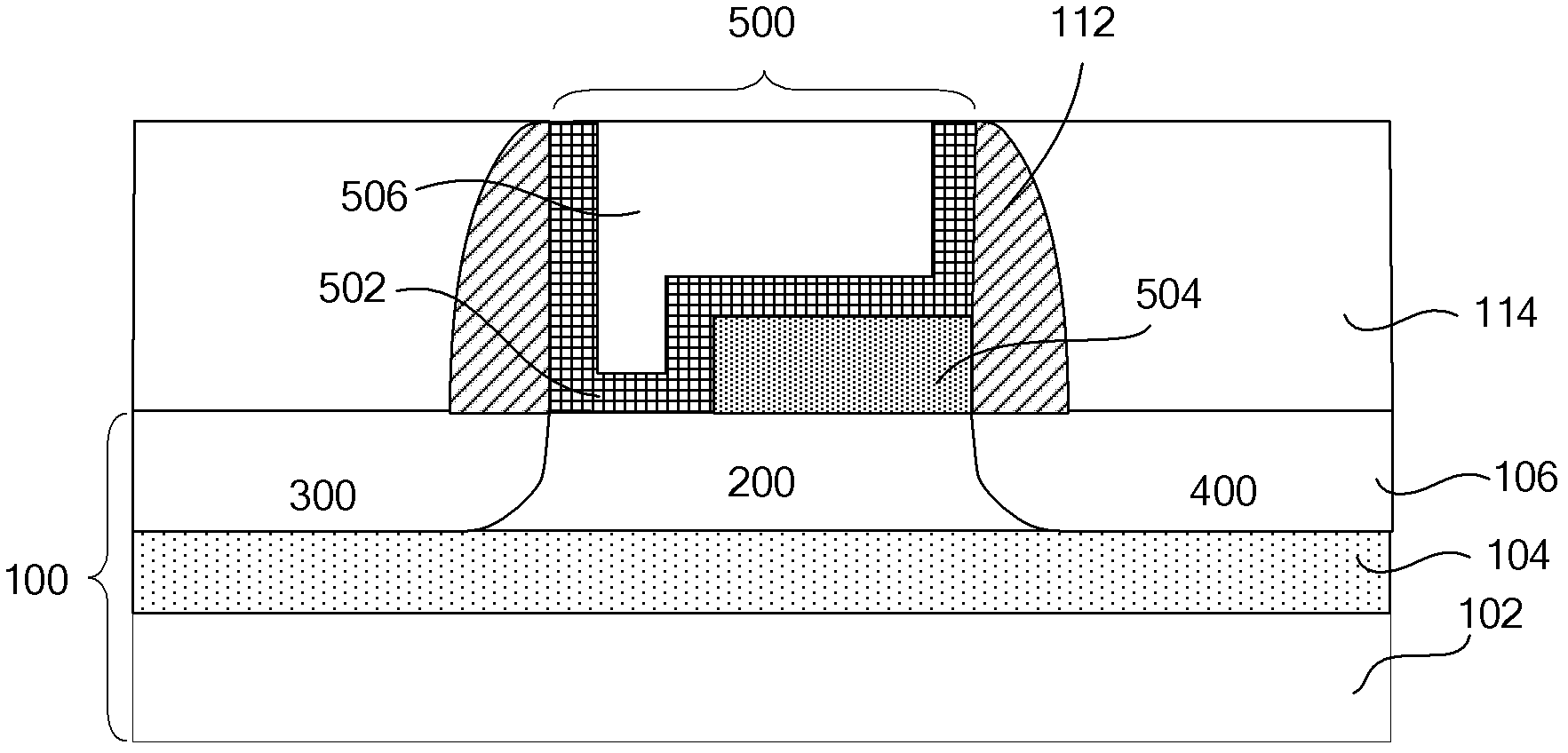

Transistor structure and semiconductor layout structure

ActiveUS20190198502A1Increase currentImprove gate control abilityTransistorSolid-state devicesEngineeringDielectric layer

The present disclosure provides a transistor structure and a semiconductor layout structure. The transistor structure includes an active region, a buried gate structure disposed in the active region, a plurality of first dielectric layers disposed over sidewalls of the buried gate structure, and a source / drain region disposed in the active region at two opposite sides of the buried gate structure. In some embodiments, the buried gate structure includes a first portion and a second portion perpendicular to the first portion. In some embodiments, the buried gate structure is separated from the source / drain region by the first dielectric layers as viewed in a top view.

Owner:NAN YA TECH

Tunneling transistor with hetero-material grid dielectrics and forming method of tunneling transistor

ActiveCN102610647AImprove driving abilityImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowEngineering

The invention provides a tunneling transistor with hetero-material grid dielectrics and a forming method of the tunneling transistor. The tunneling transistor comprises a substrate, a channel region, a source region, a drain region and a grid stack, wherein the channel region is formed in the substrate; the source region and the drain region are formed in the substrate and respectively at both sides of the channel region; the source region belongs to first type of heavy doping; the drain region belongs to second type of heavy doping; the grid stack is formed on the substrate; the grid stack comprises a grid dielectric layer and a grid electrode, wherein the grid dielectric layer is located on the channel region, and the grid electrode is located on the grid dielectric layer; the grid dielectric layer comprises a first section of grid dielectric near the source region and a second section of grid dielectric near the drain region; and the first section of grid dielectric and the second section of grid dielectric are different in material. Through introducing local stress into the channel region by the first section of grid dielectric near the source region, the tunneling effective mass is changed, and the tunneling current is increased, and through introducing the local stress into the channel region by the second section of grid dielectric near the drain region, the electronic mobility is increased.

Owner:TSINGHUA UNIV

GaN side wall insulated gate fin-type high-electron mobility transistor and manufacturing method thereof

InactiveCN106684151ASuppress leakageReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesMicrowave powerEngineering

The invention relates to a GaN side wall insulated gate fin-type high-electron mobility transistor and manufacturing method thereof. A transistor structure of the invention orderly comprises a substrate, a buffer layer, a barrier layer and a passivation layer from bottom to top; a source electrode is arranged at one end above the barrier layer, and a drain electrode is arranged at another end above the barrier layer; the passivation layer is arranged above the barrier layer between the source electrode and the drain electrode; and a groove is formed in the passivation layer; the high-electron mobility transistor is characterized by further comprising a GaN based three-dimensional fin and a gate electrode, and an insulating medium is arranged on a side wall of the GaN based three-dimensional fin; a part of the gate electrode is covered on the barrier layer in the groove to form the Schottky contact; another part of the gate electrode is covered on the insulating medium on the side wall of the GaN based three-dimensional fin to form an insulated gate structure. The GaN based three-dimensional fin type device has the advantages of being small in gate electric leakage, high in output current, good in gate-control capacity and high in frequency characteristics, and can be used for a large-power microwave power device.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Ring gate field effect transistor and preparation method thereof

ActiveCN106711194AReduce scatterImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricElectrical conductor

The invention relates to a ring gate field effect transistor and a preparation method thereof. The preparation method includes the following steps that: a first gate dielectric layer, a channel layer, a second interface control layer, a source-drain layer and a semiconductor material layer are formed on a substrate; the semiconductor material layer is removed through etching, a structure shaped like a Chinese character ''tu' is formed in a channel region along a longitudinal direction through etching, the etching of the protruding part of the structure shaped like a Chinese character ''tu' is performed until arriving at the second interface control layer, and the etching of two sides of the structure shaped like a Chinese character ''tu' is performed until arriving at the first gate dielectric layer; third interface control layers grow on two side walls of the protruding part of the channel region, and a second gate dielectric layer and a second gate metal layer are formed on the upper surface of the protruding part from bottom to top, wherein the upper surface of the protruding part is separated from a source region and a drain region by a certain distance, and the second gate dielectric layer and the second gate metal layer extend to the side walls of the third interface control layers and the upper surfaces of flat stages at two sides of the protruding part; and a source-drain metal layer is formed at a portion at the upper surface of the source-drain layer in the source region and the drain region, wherein the portion is adjacent to the outer side of the upper surface of the source-drain layer. According to the transistor provided by the invention, channel scattering can be decreased, channel carrier mobility, gate control ability and current driving ability can be improved, and a short channel effect and a DIBL effect can be effectively suppressed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

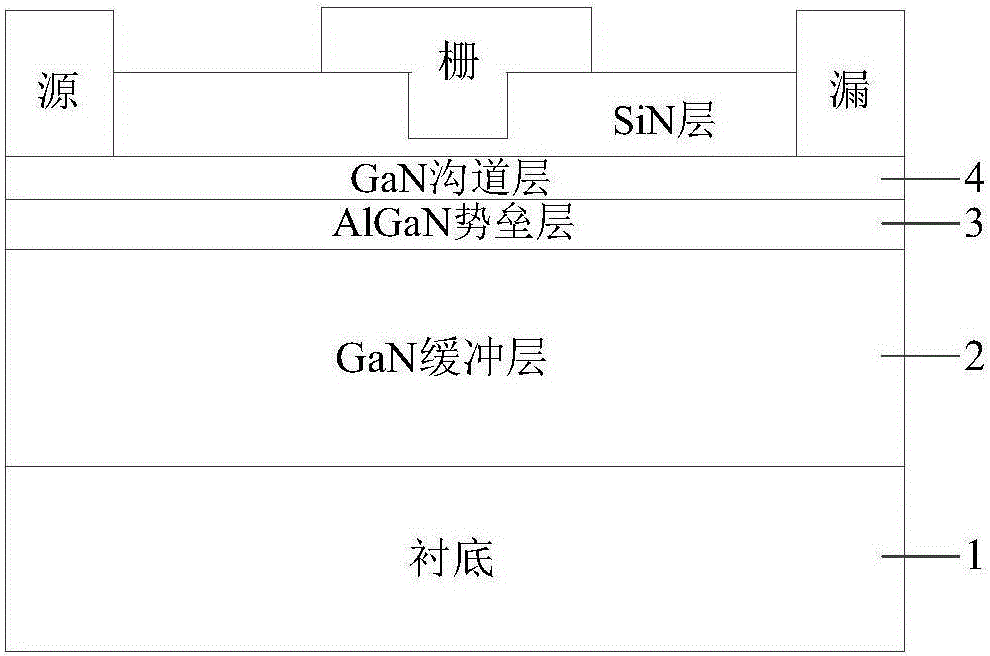

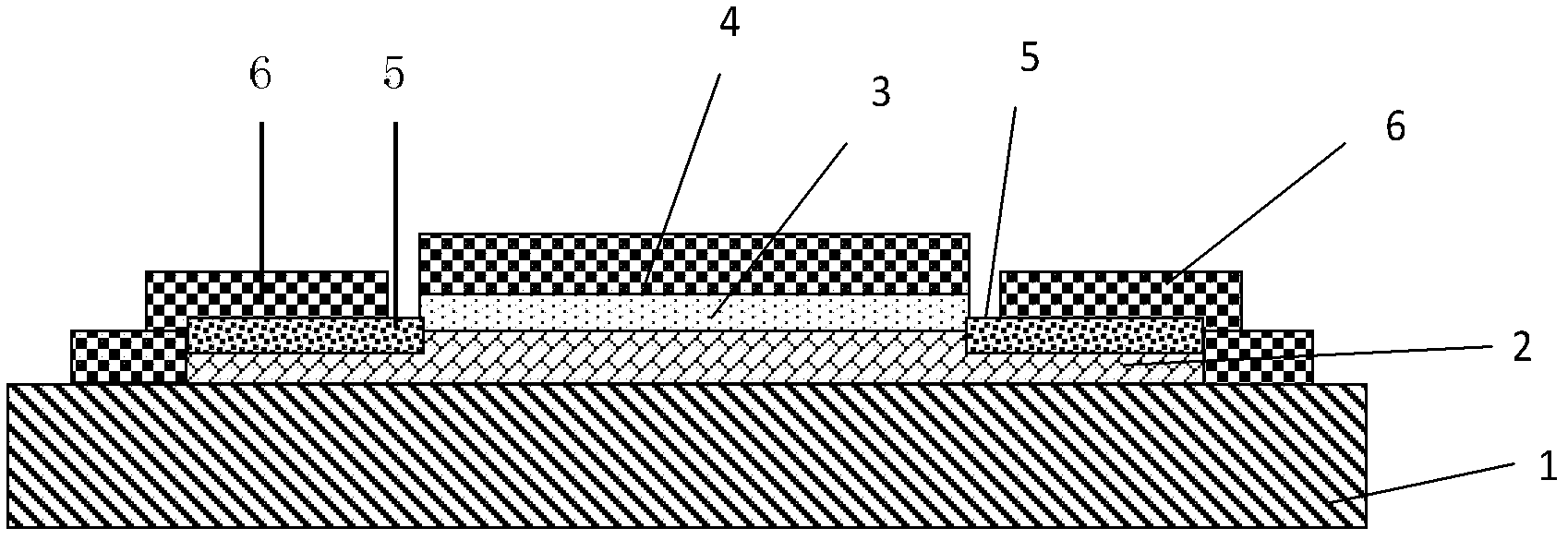

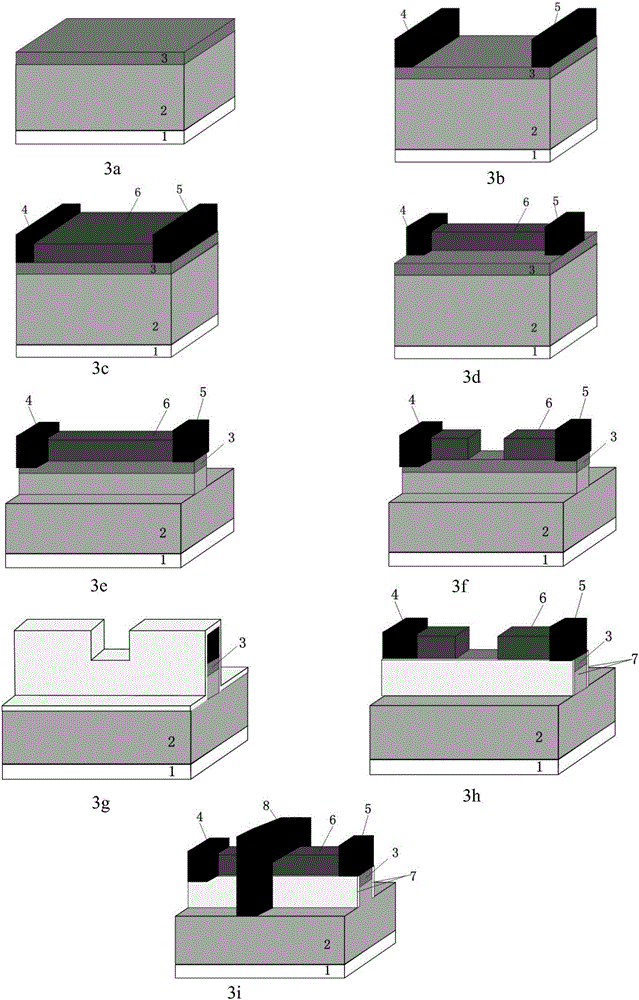

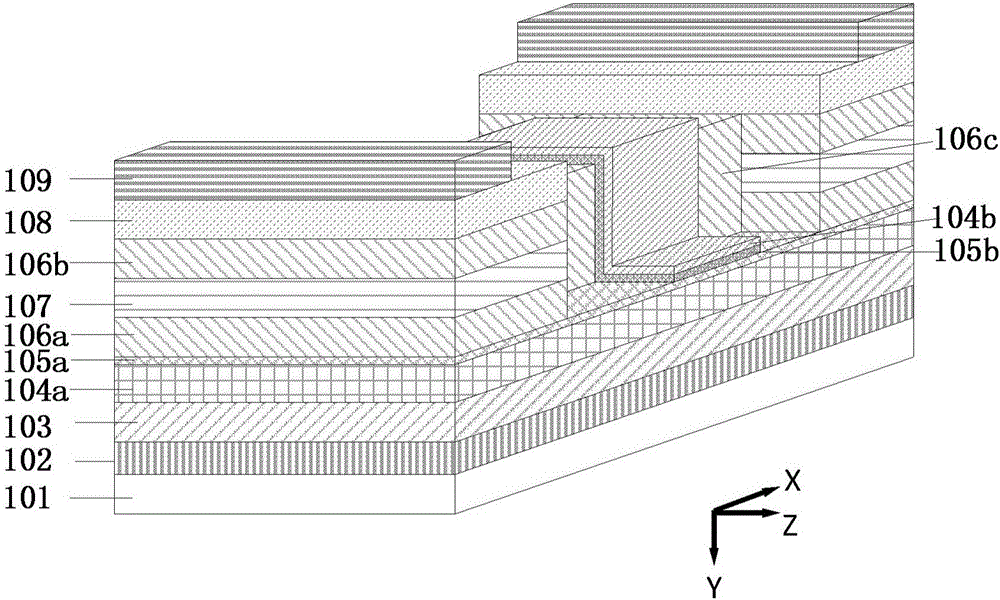

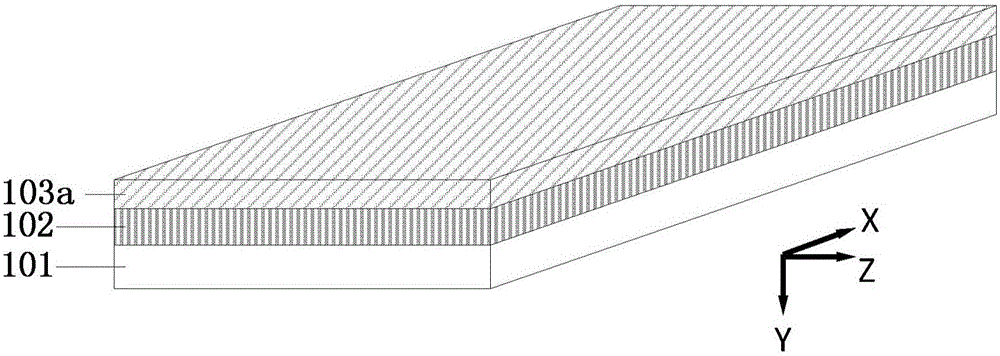

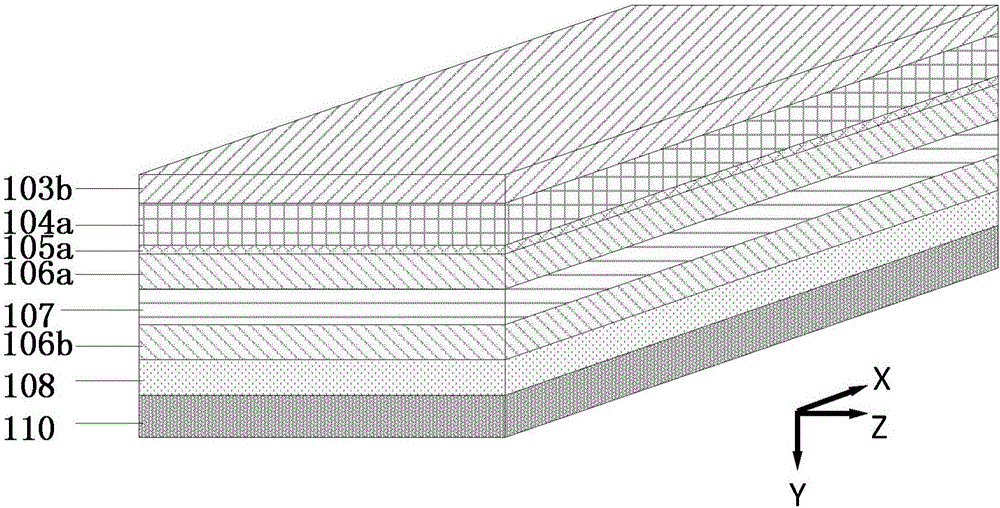

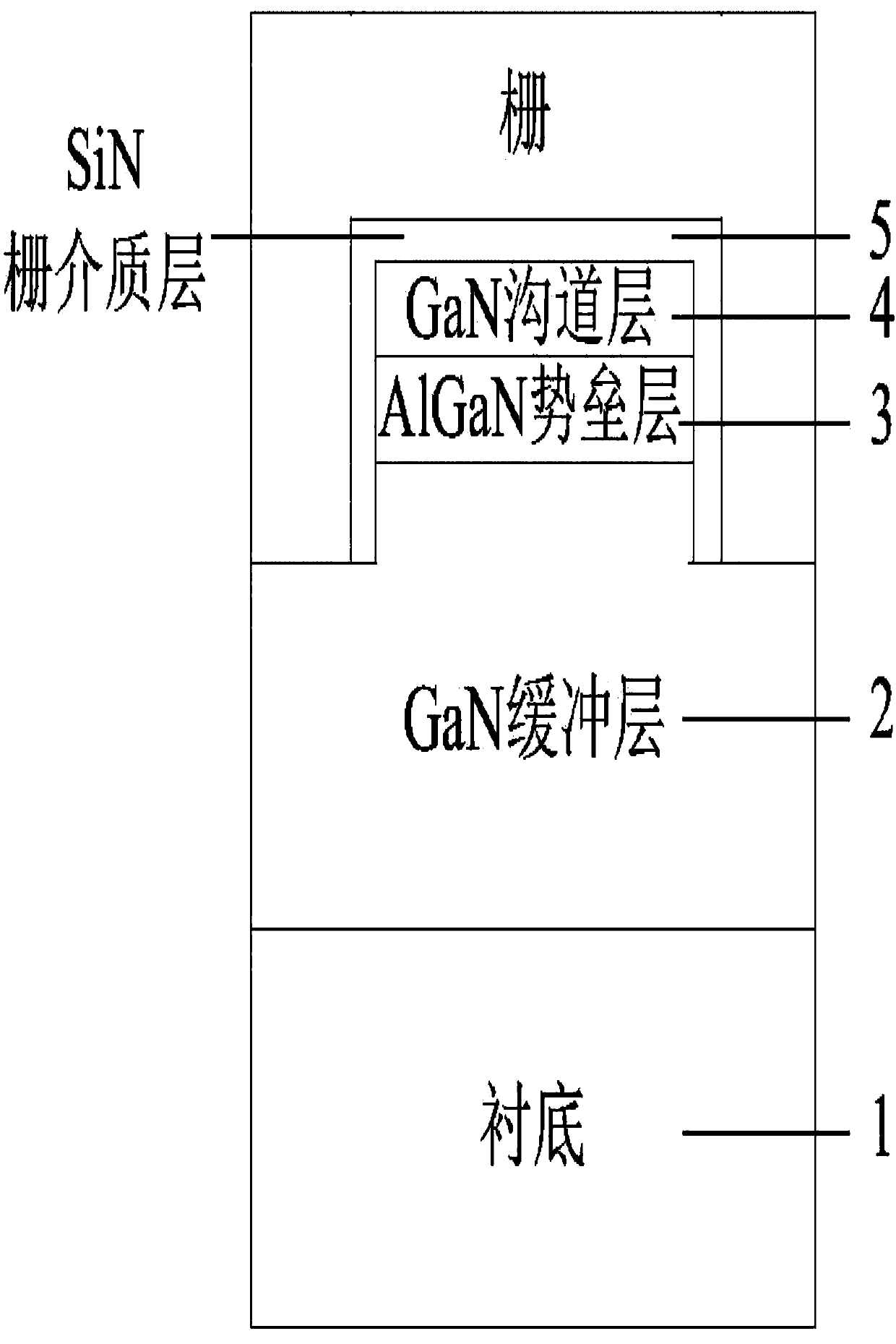

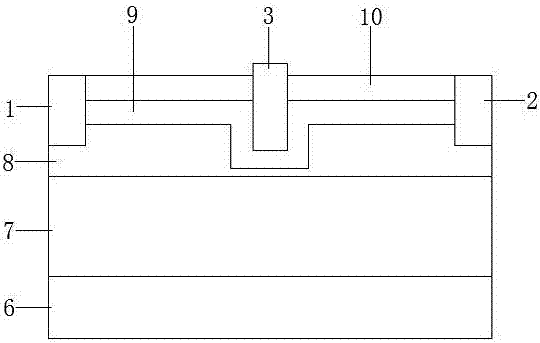

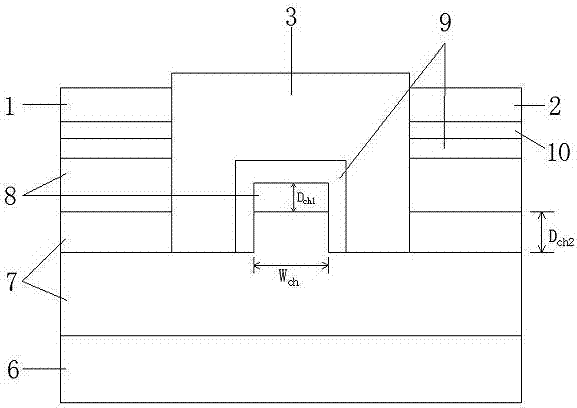

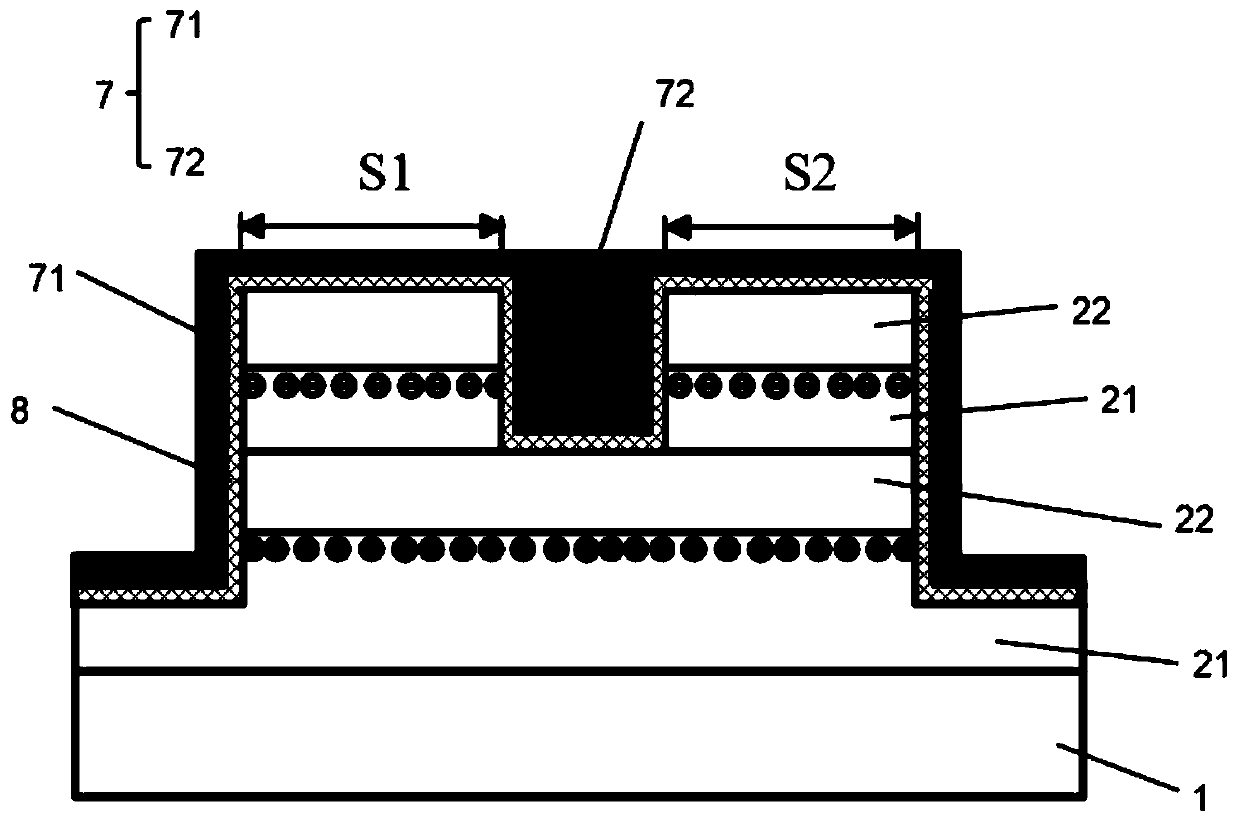

T-gate N-surface GaN/AlGaN fin-type high electron mobility transistor

InactiveCN109285883AReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionOhmic contact

The invention discloses a T-gate N-surface GaN / AlGaN fin-type high electron mobility transistor, which mainly solves the problems of small maximum oscillating frequency, large ohmic contact resistanceand severe short channel effect of the existing microwave power devices. The transistor comprises a substrate (1), a GaN buffer layer (2), an AlGaN barrier layer (3), a GaN channel layer (4), a gatedielectric layer (5), a passivation layer (6), a source electrode, a drain electrode and a gate electrode from the bottom up, wherein the buffer layer and the channel layer adopt N-surface GaN materials; the GaN channel layer and the AlGaN barrier layer form a GaN / AlGaN heterojunction; and the gate electrode adopts a T-type gate and is wrapped at two sides and the upper portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate N-surface GaN / AlGaN fin-type high electron mobility transistor has the advantages of good gate control capability, small ohmic contact resistance and high maximum oscillating frequency, and can be used as a small-size microwave power device.

Owner:吴绍飞

Semiconductor device and manufacture method thereof

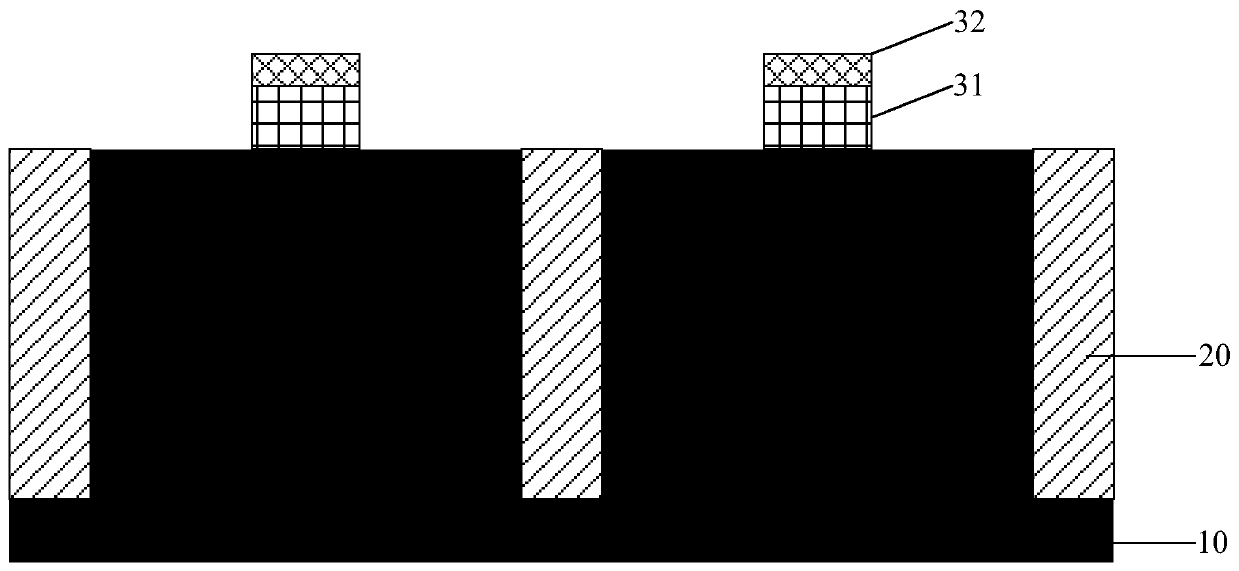

ActiveCN105762190AHigh densityReduce processing costsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceNanowire

The invention relates to a semiconductor device. The semiconductor device includes a plurality of fin structures which vertically protrude out from a substrate and extend along a first direction, source and drain regions which are formed at two ends of each fin structure along the first direction, channel regions which contain a plurality of nanowires and are connected between the source and drain regions along the first direction, and a gate stack structure which extends along a second direction and surrounds each nanowire. According to the semiconductor device and the manufacture method thereof, the channels of nanowires are formed between the fin-shaped source and drain regions, and therefore, process cost can be decreased, process complexity can be reduced, and grid control ability and device density can be effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Structure of novel digital gate integrated circuit

The invention discloses a structure of a novel digital gate integrated circuit, and relates to the technical field of semiconductor devices and integrated circuits. The structure of the novel digitalgate integrated circuit is a longitudinal N-type or P-type TMOS, and a source region, a semiconductor channel region and a drain region are respectively arranged in the longitudinal direction; a gateregion surrounds the periphery in the horizontal direction, a gate dielectric layer is arranged between a gate and a channel semiconductor region, and a bottom drain region can be led out from the outer side through a lead hole. The basic unit can be used for forming an AND gate, an NAND gate or a NOR gate. The key technical problem to be solved by the invention is to provide the structure of thenovel digital gate integrated circuit. The gate of the structure surrounds the device body region, and when proper bias is applied to the gate, four channels are formed so that the gate control capability is improved, and the current density during conduction is improved. The channel region of the novel structure is not completed by a photoetching process, and the length of the channel is not limited by photoetching precision any more. Meanwhile, a narrow bandgap material is adopted as the source region, and an N-drift region structure is added to the front end of the drain region so that small area, large current and low on resistance of the device are realized, and the integration level of the integrated circuit is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

T-gate N-plane GaN/AlGaN fin high electron mobility transistor

InactiveCN109560118AReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionGate dielectric

The invention discloses a T-gate N-plane GaN / AlGaN fin high electron mobility transistor. The objective of the invention is to mainly solve the problems that a current microwave power device is smallin the maximum oscillation frequency, large in ohmic contact resistance and serious in the short channel effect. The T-gate N-plane GaN / AlGaN fin high electron mobility transistor comprises from bottom to top: a substrate (1), a GaN buffer layer (2), an AlGaN barrier layer (3), a GaN channel layer (4), a gate dielectric layer (5), a passivation layer (6), a source, a drain, and a gate. The bufferlayer and the channel layer are made of N-plane GaN materials; the GaN channel layer and the AlGaN barrier layer form a GaN / AlGaN heterojunction; the gate employs a T-shaped gate and coats the two sides and the top portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate N-plane GaN / AlGaN fin high electron mobility transistor is good in gate control capacity,small in the ohmic contact resistance and high in maximum oscillation frequency, and can be used as a mini-type microwave power device.

Owner:南京誉凯电子科技有限公司

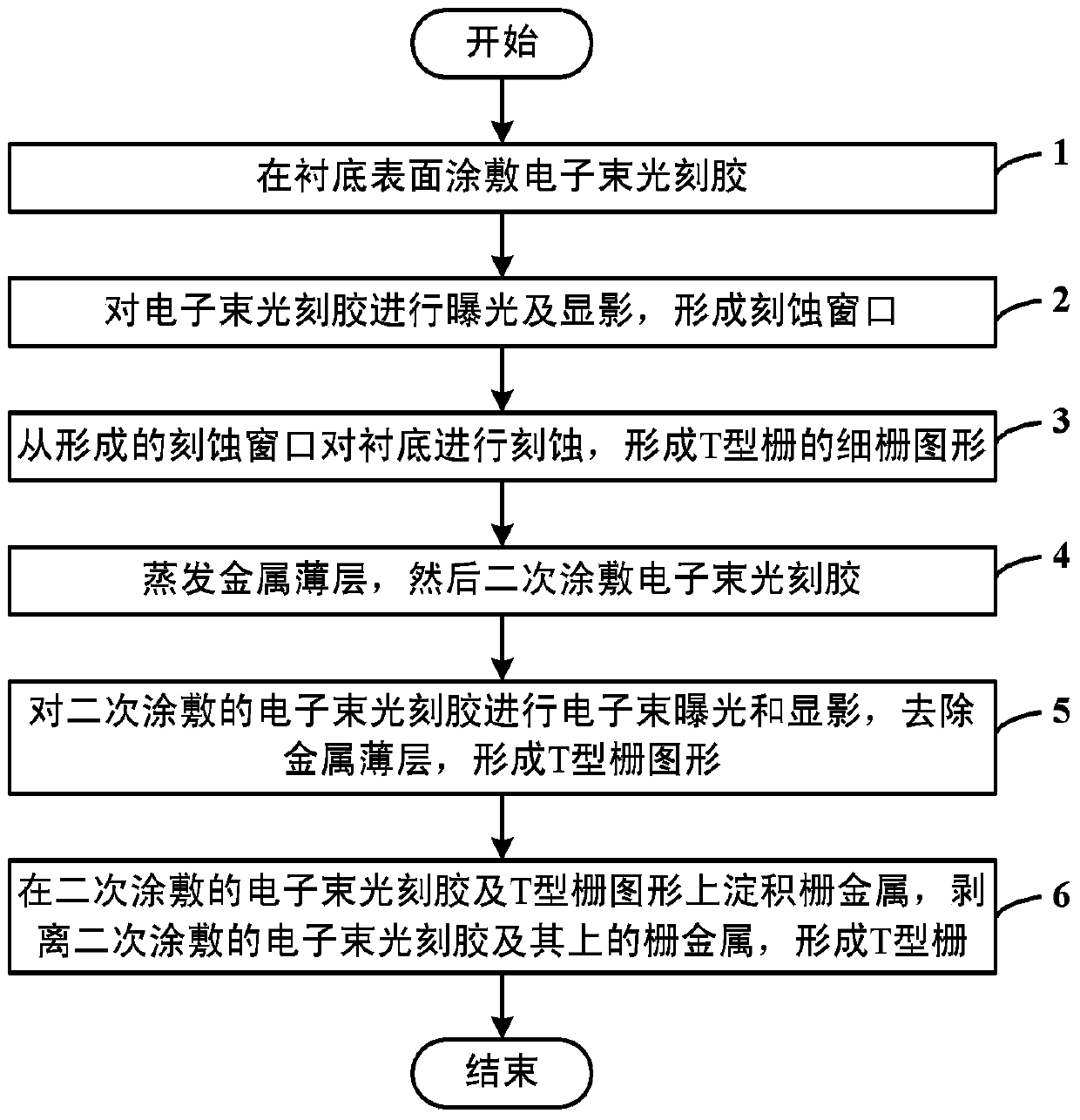

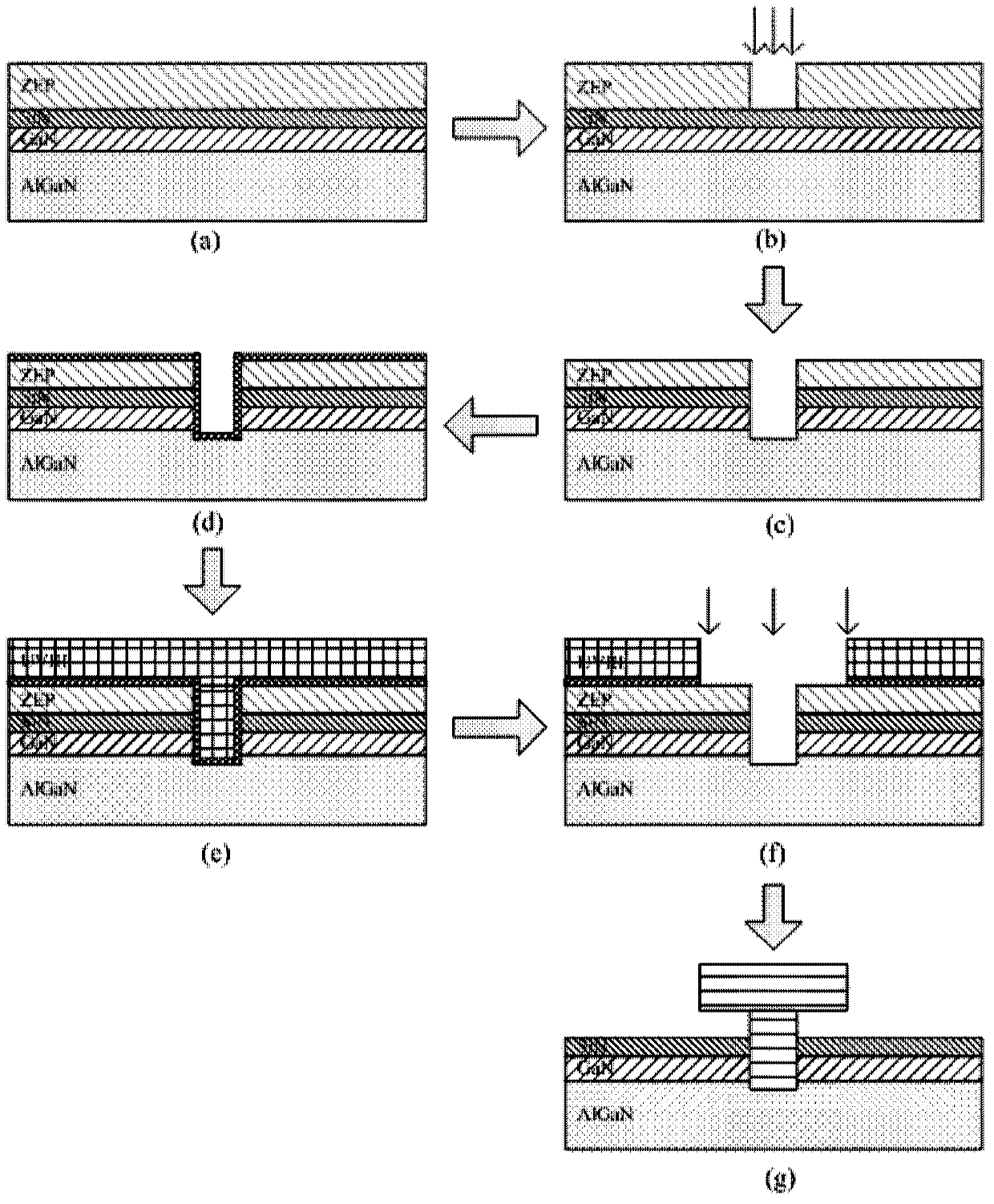

Manufacturing method of T-shaped gate of GaN-based FET (Field Effect Transistor)

InactiveCN103700583AReduce parasitic capacitanceImprove frequency characteristicsSemiconductor devicesParasitic capacitanceThin layer

The invention discloses a manufacturing method of a T-shaped gate of a GaN-based FET (Field Effect Transistor). The manufacturing method comprises the steps of coating an electron beam photoresist on the surface of a substrate; carrying out exposure and development on the electron beam photoresist, and forming an etching window; etching the substrate from the formed etching window, and forming a fine gate graph of the T-shaped gate; evaporating a metal thin layer, and then secondly coating the electron beam photoresist; carrying out electron beam exposure and development on the electron beam photoresist which is secondly coated, removing the metal thin layer, and forming a T-shaped gate graph; evaporating deposited gate metal on the electron beam photoresist which is secondly coated and the T-shaped gate graph, stripping the electron beam photoresist which is secondly coated and the gate metal on the electron beam photoresist which is secondly coated, and forming the T-shaped gate. By utilizing the manufacturing method disclosed by the invention, the current collapse is effectively restrained, the stray capacitances of a gate source and a gate drain are reduced, the gate resistance of a device is reduced, the cut-off frequency (ft) and the maximum oscillation frequency (fmax) of the device are increased, and thus the device can work in an MMW (Millimeter Wave) frequency band.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Fabrication method of vertical silicon nanowire field effect transistor

ActiveUS20130011980A1Reduce leakage currentImprove gate control abilityNanoinformaticsSemiconductor/solid-state device manufacturingElectrical resistance and conductanceSilicon nanowires

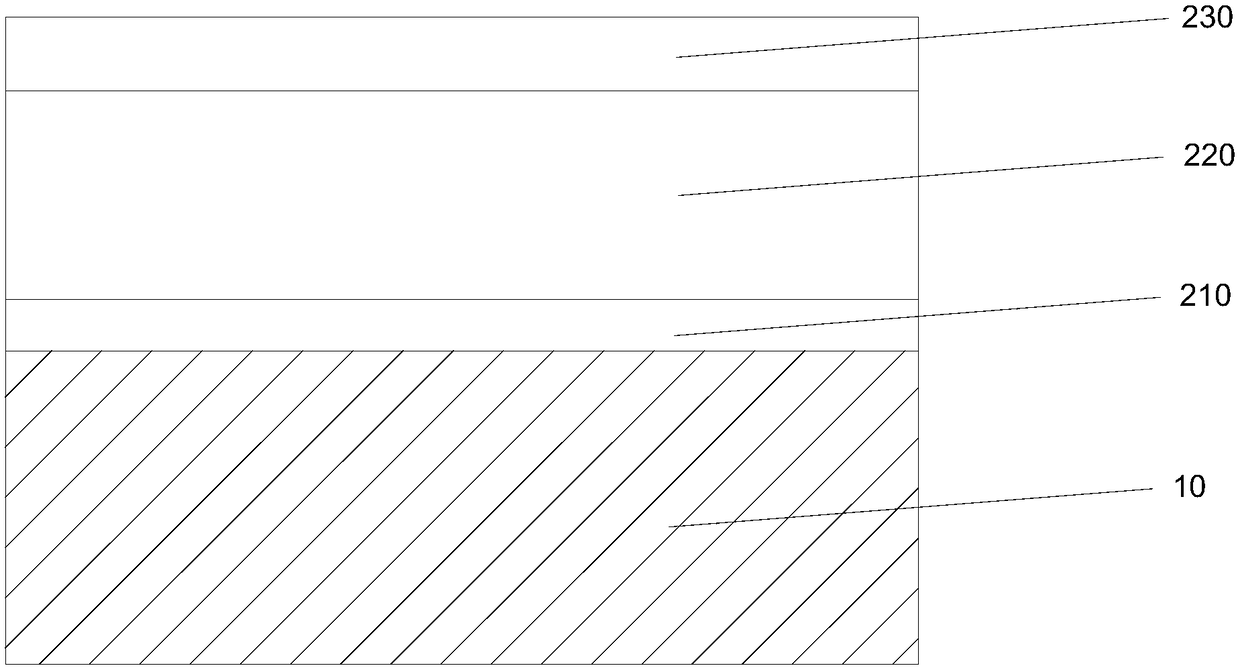

The present invention discloses a fabrication method of a vertical silicon nanowire field effect transistor having a low parasitic resistance, which relates to a field of an ultra-large-integrated-circuit fabrication technology. As compared with a conventional planar field effect transistor, on one hand the vertical silicon nanowire field effect transistor fabricated by the present invention can provide a good ability for suppressing a short channel effect due to the excellent gate control ability caused by the one-dimensional structure, and reduce a leakage current and a drain-induced barrier lowering (DIBL). On the other hand, an area of the transistor is further reduced and an integration degree of an IC system is increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor

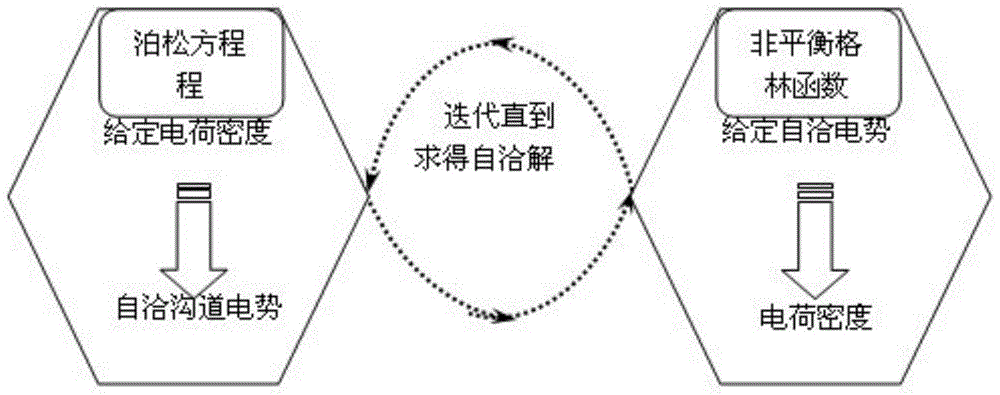

InactiveCN104091829AGood gating abilityImprove gate control abilitySemiconductor devicesDelayed timeLow leakage

The invention discloses a bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor (DL-HTFETs). The field-effect transistor undergoes P / N type heavy doping at a source region and a drain region, linear doping is carried out on regions, close to a channel, of the source end and the drain end, an oxidation layer close to a source electrode is formed by low-K oxide (SiO2), the oxidation layer close to a drain layer is formed by high-K oxide (HfO2), a conveying model of the novel bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor is built by means of a quantum mechanics model, and electrical properties of a high-K tunneling field-effect transistor (HK-TFETs), a common gate oxide tunneling field-effect transistor (LK-TFETs), a heterogeneous oxide tunneling field-effect transistor (HTFETs), a common filed-effect transistor and the DL-HTFETs are compared and analyzed by means of the model. As is shown by a research result, the DL-HTFETs have the advantages of low leakage currents, a high current switch ratio, low power consumption and short delay time and the like.

Owner:NANJING UNIV OF POSTS & TELECOMM

Grooved gate enhanced GaN transistor device based on nano channel

ActiveCN106981514AIncrease widthHigh frequencyEfficient power electronics conversionSemiconductor devicesHeterojunctionGate dielectric

The invention discloses a grooved gate enhanced GaN transistor device based on a nano channel and relates to the technical field of microelectronic devices. The grooved gate enhanced GaN transistor device comprises, from bottom to top, a substrate layer, a GaN buffer layer, an AlGaN barrier layer, a gate dielectric layer, a passivation layer, a source, a drain and a gate. The heterojunction under the gate of an AlGaN / GaN high-electron-mobility transistor device is etched to form the nano channel such that no two-dimensional electron gas exists in the regions on both sides of the nano channel. The gate wraps the top and two sidewalls of the nano channel. The gate modulates the electrons in the nano channel from three directions so as to have good control ability and well suppress a short channel effect. When the nano channel has a small width, the two-dimensional electron gas in the channel is exhausted and the device is enhanced. The combined effect of the nano channel and grooved gate can ensure that the device has a large nano-channel width while enhanced, and reduces the on-resistance.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Manufacturing method of semiconductor device

InactiveCN103632943AAvoid damageNON reductionSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentEtching

Disclosed in the invention is a manufacturing method of a semiconductor device. The manufacturing method comprises the following steps: forming a grid stacking structure at a substrate; depositing a first dielectric material layer at the substrate and the grid stacking structure; etching the first dielectric material layer to form a first side wall; executing LDD and Halo doping injection; successively depositing a second dielectric material layer and a third dielectric material layer at the substrate and the first side wall; and successively etching the third dielectric material layer and the second dielectric material layer so as to form a third side wall and a second side wall respectively. According to the side wall etching method, the NON three-layer composite side wall is used and two-step etching is carries out, thereby reducing the damage on the substrate as well as the process complexity. Besides, the threshold voltage can be optimized; the EoT can be effectively reduced; and the grid-control capability and the drive current can also be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

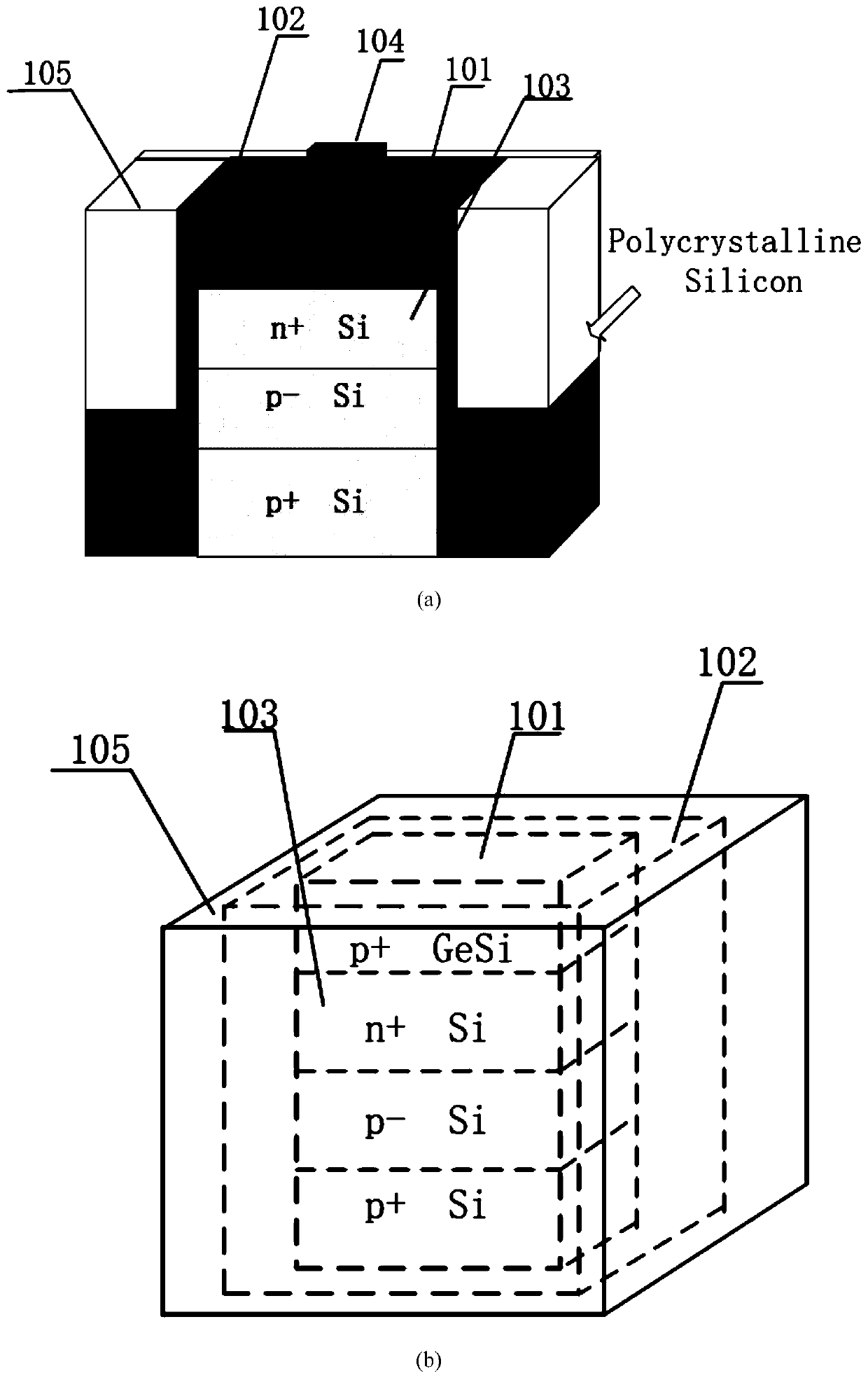

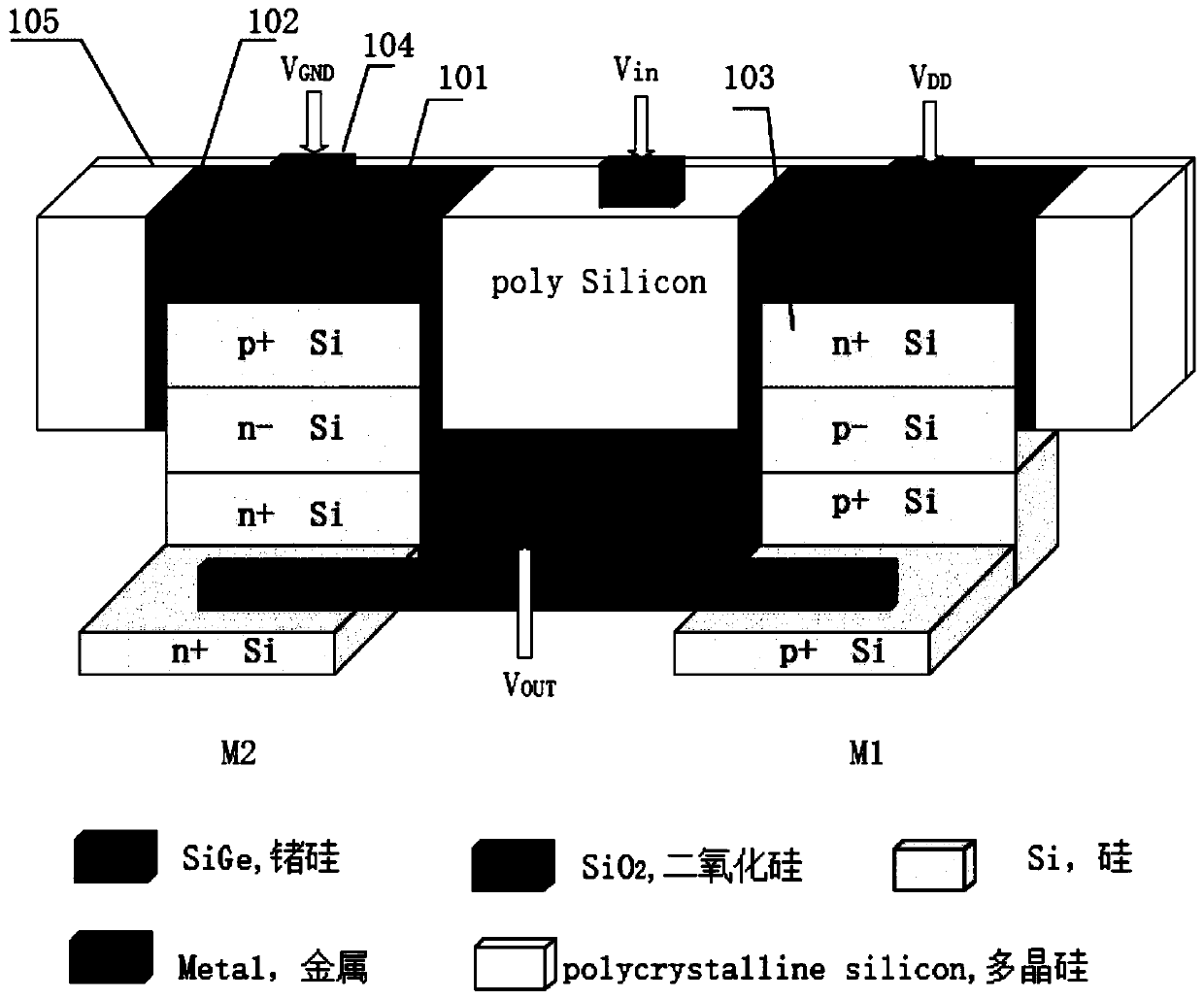

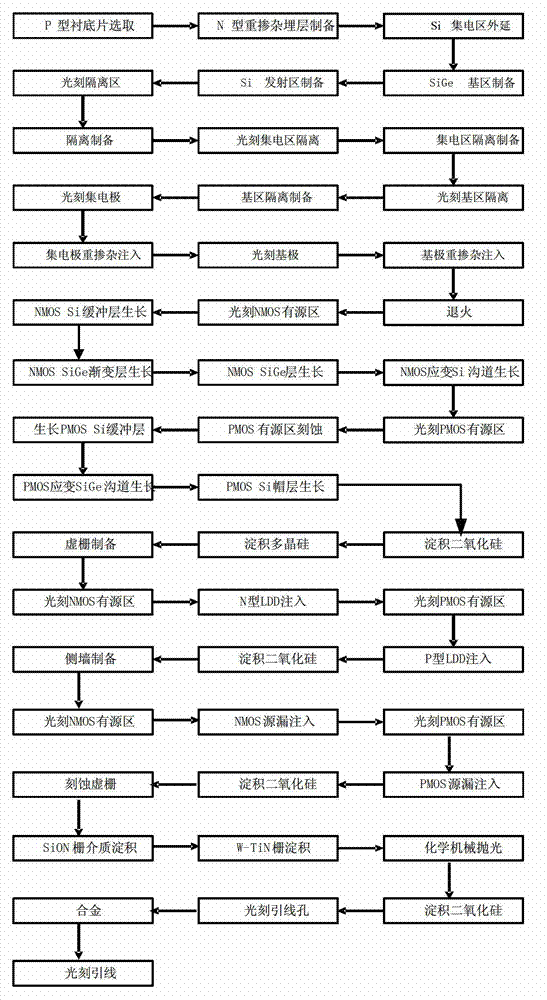

Tri-strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SiGe HBT (Heterojunction Bipolar Transistor) and preparation method

InactiveCN102790052AImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorHeterojunction bipolar transistor

The invention discloses a tri-strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SiGe HBT (Heterojunction Bipolar Transistor) and a preparation method. A buried layer is prepared on a substrate, an N-Si layer, a P-SiGe layer and an N-Si layer are continuously grown, a dielectric layer is deposited, deep-groove isolation is prepared, a collector region, a base region and an emitter region are prepared, a collector electrode, base electrode and emitter electrode contact region is formed, and a SiGe HBT device is formed; active region deep grooves of an NMOS (N-channel Metal Oxide Semiconductor) device and a PMOS (P-channel Metal Oxide Semiconductor) device are etched, a P-type Si layer / a P-type SiGe gradient layer / a P-type SiGe layer / a P-type strain Si layer serving as the active region of the NMOS device and an N-type Si layer / an N-type strain SiGe layer / an N-type Si cap layer serving as the active region of the PMOS device are respectively and selectively grown in the deep grooves in an extending manner; a virtual grid electrode and a side wall are prepared, and source and drain electrodes of the NMOS and the PMOS device are formed through self-alignment; and the virtual grid is etched, a SiON grid dielectric layer and a W-TiN composite grid are deposited to form a CMOS structure, and finally the tri-stain BiCMOS integrated device and a circuit are constructed. Tensile strain Si with high electronic mobility and compressive strain SiGe with high hole mobility are sufficiently utilized as conducting channels for the NMOS device and the PMOS device, and the performance of the BiCMOS integrated circuit is effectively improved.

Owner:XIDIAN UNIV

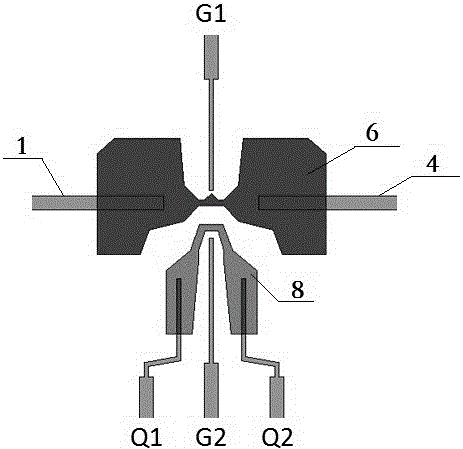

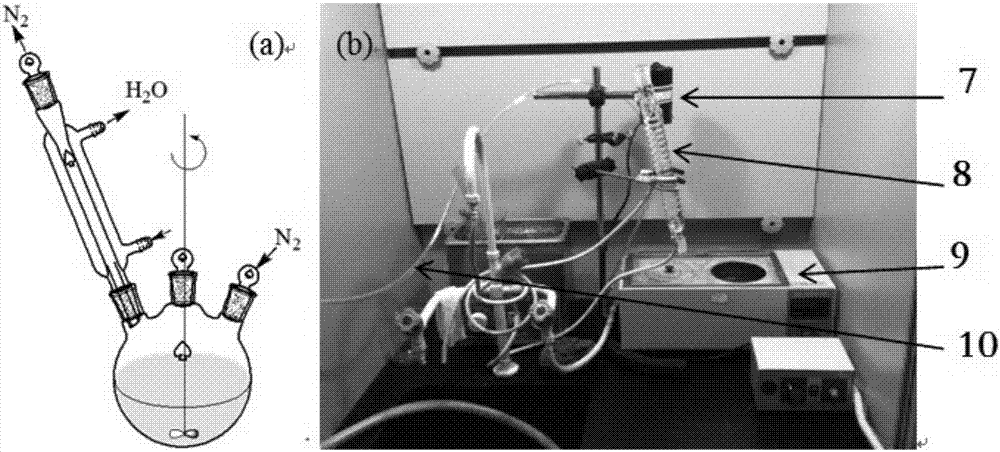

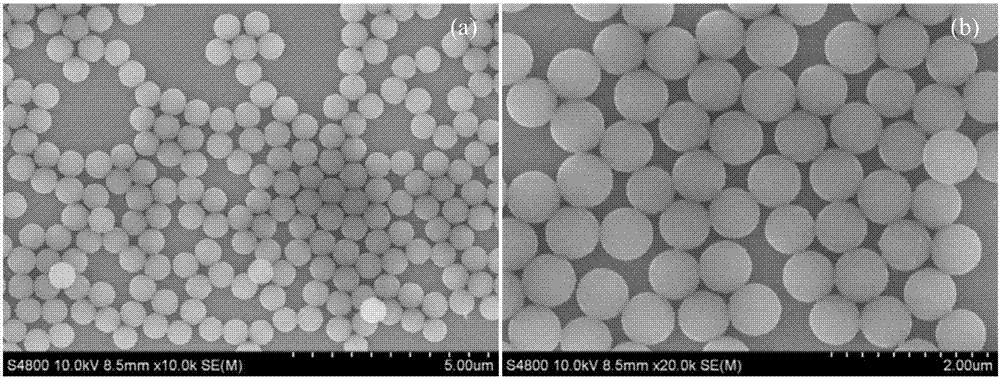

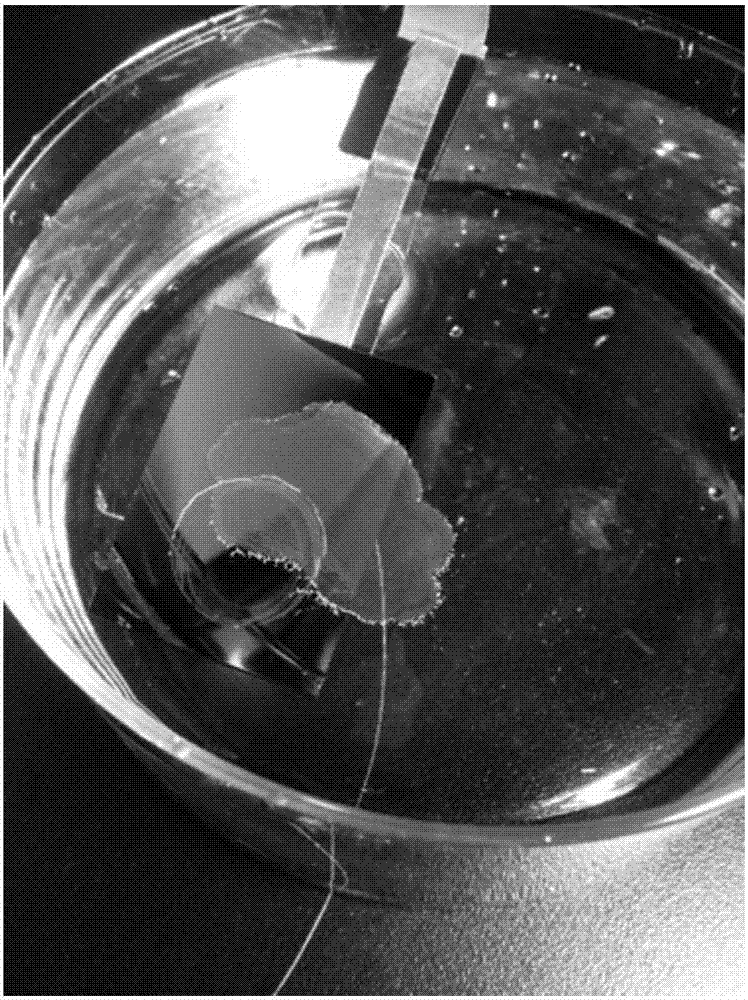

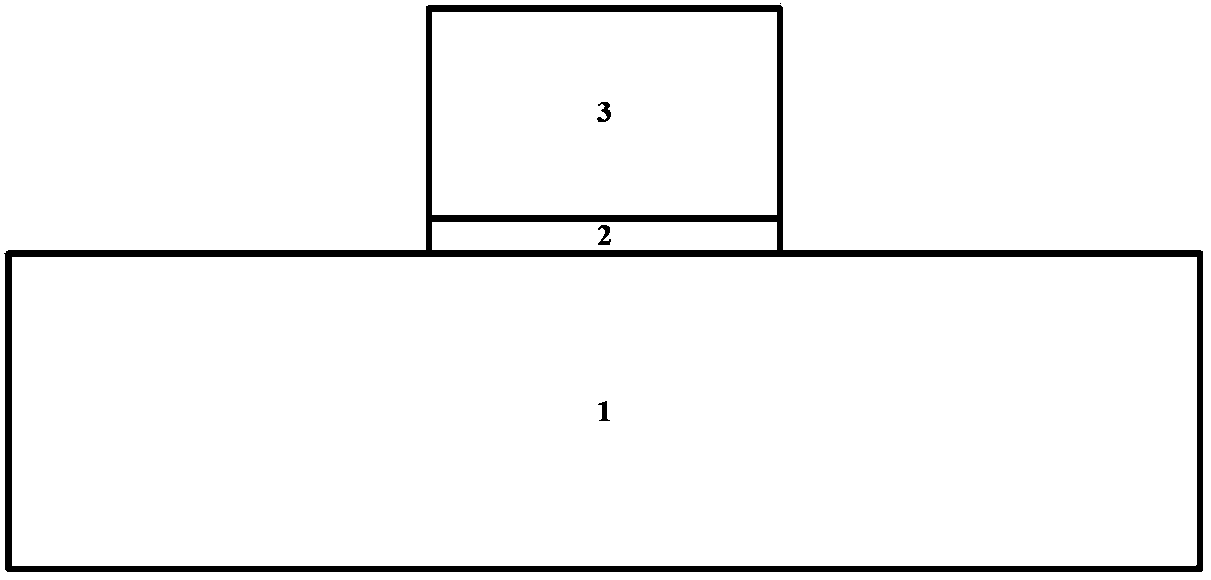

Method for preparing single-electron transistor by assembling gold particles on PS microsphere template

PendingCN106935501AEasy integration of batch preparationImprove gate control abilityNanostructure manufactureSemiconductor/solid-state device manufacturingGold filmAluminium oxide

The invention relates to a method for preparing a single-electron transistor by assembling gold particles on a PS microsphere template. According to the method, a silicon dioxide substrate is formed on the surface of a silicon base sheet; a coulomb island and an electrode are arranged on the silicon dioxide substrate in an integrated manner; an evenly and compactly-arranged PS microsphere single-layer film template is prepared on the silicon dioxide substrate; an electric beam evaporation coating method is utilized to plate a gold film on the surface of the PS microsphere single-layer film template; a chemical etching method and post-treatment are adopted, so that a gold nanoparticle array is obtained; an aluminum oxide barrier layer is formed on the gold nanoparticle array by using atomic layer deposition; the electrode is prepared by using electron beam exposure, electron beam evaporation coating and / or peeling methods; and an aluminum oxide protective layer is prepared on the electrode and the aluminum oxide barrier layer through using atomic layer deposition. The coulomb island is a size-controllable array, and therefore, positioning and batch preparation can be facilitated; and the size of the barrier between the coulomb island and the electrode can be precisely controlled. The method can be widely applied to fields such as photon, electronics, environment and security fields.

Owner:NAT UNIV OF DEFENSE TECH

Method for manufacturing semiconductor device

ActiveCN103531454AAvoid damageReduce process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentPower semiconductor device

Provided in the present invention is a method for manufacturing a semiconductor device. The method comprises: forming a stacked gate structure on a substrate; depositing in succession a first dielectric material layer and a second dielectric material layer on the substrate and the stacked gate structure; and etching in succession the second dielectric material layer and the first dielectric material layer by using an etching gas containing helium so as to form a second side wall and a first side wall respectively. According to the method for manufacturing the semiconductor device, a composite side wall with double layers and a two-step etching by use of the etching gas containing the helium are adopted so that while the damage to the substrate is reduced, the process complexity is also reduced, and besides, the threshold voltage can be optimized, the EoT can be effectively reduced, and the gate-control capability and the drive current can be increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Field-effect transistor manufacturing method and field-effect transistor

PendingCN109904219AEliminate damageImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceGate dielectric

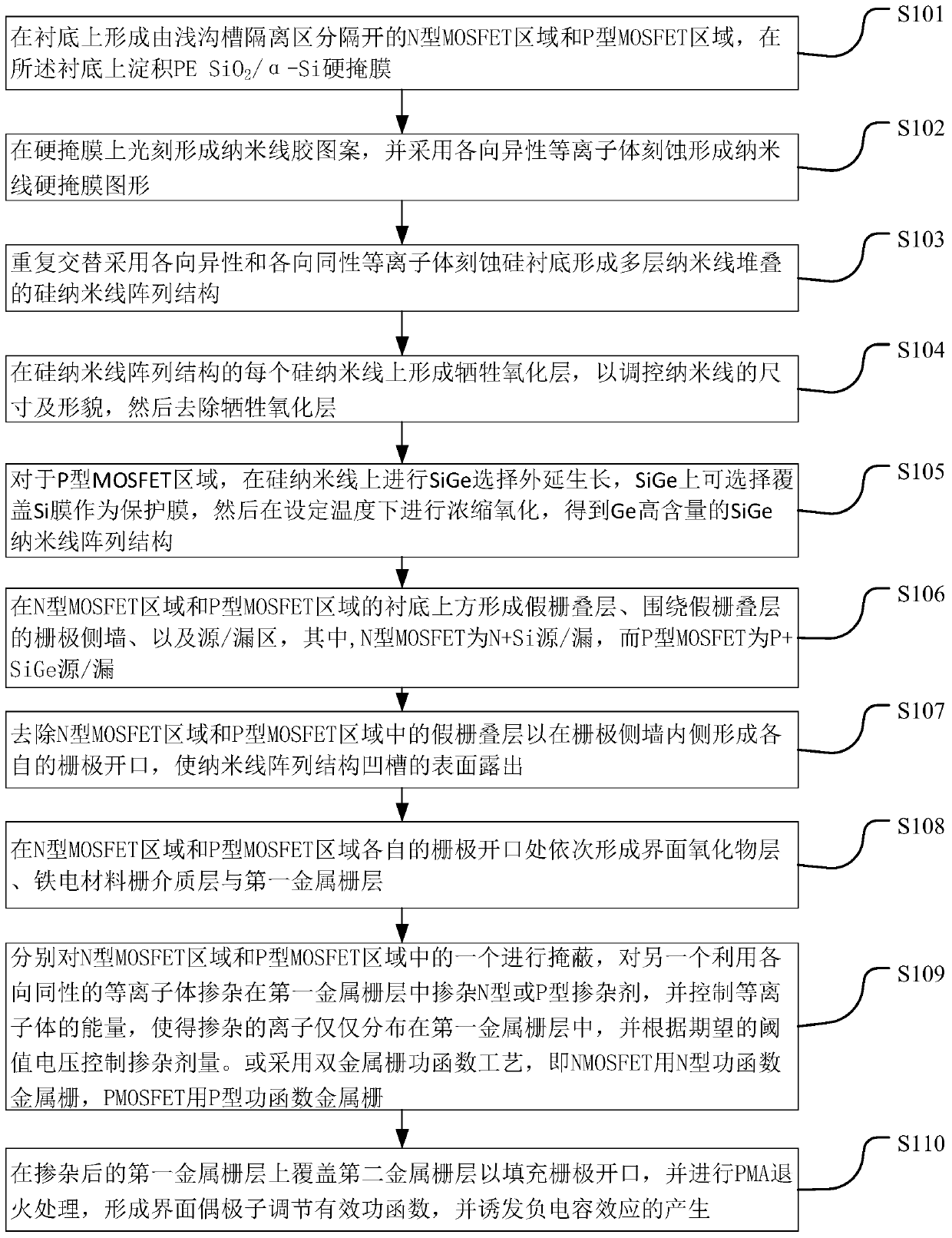

The invention discloses a field-effect transistor manufacturing method and a field-effect transistor. The method comprises the following steps of forming an N-type MOSFET region and a P-type MOSFET region on a substrate; forming a hard mask pattern on the MOSFET region; forming a silicon nanowire array structure; forming a sacrificial oxidization layer on the multi-layer stacked silicon nanowires,and then removing the sacrificial oxidization layer; carrying out selective SiGe epitaxy and concentration oxidation on the multi-layer stacked silicon nanowires of the P-type MOSFET region, and removing the oxidization layer; and sequentially forming an interface oxide layer, a ferroelectric material gate dielectric laminated layer and a metal gate laminated layer on the nanowire array structure. According to the field-effect transistor, the gate-control capability is greatly enhanced due to the ring gate structure; due to the PMOSFET SiGe nanowires and the SiGe source / drain, the hole mobility is greatly improved; and especially due to the fact that the ferroelectric negative capacitance effect is integrated, the potential on the surface of a channel of the device is amplified, so that the nanowire device has a super-steep sub-threshold slope and an improved on / off current ratio.

Owner:SHANGHAI IND U TECH RES INST

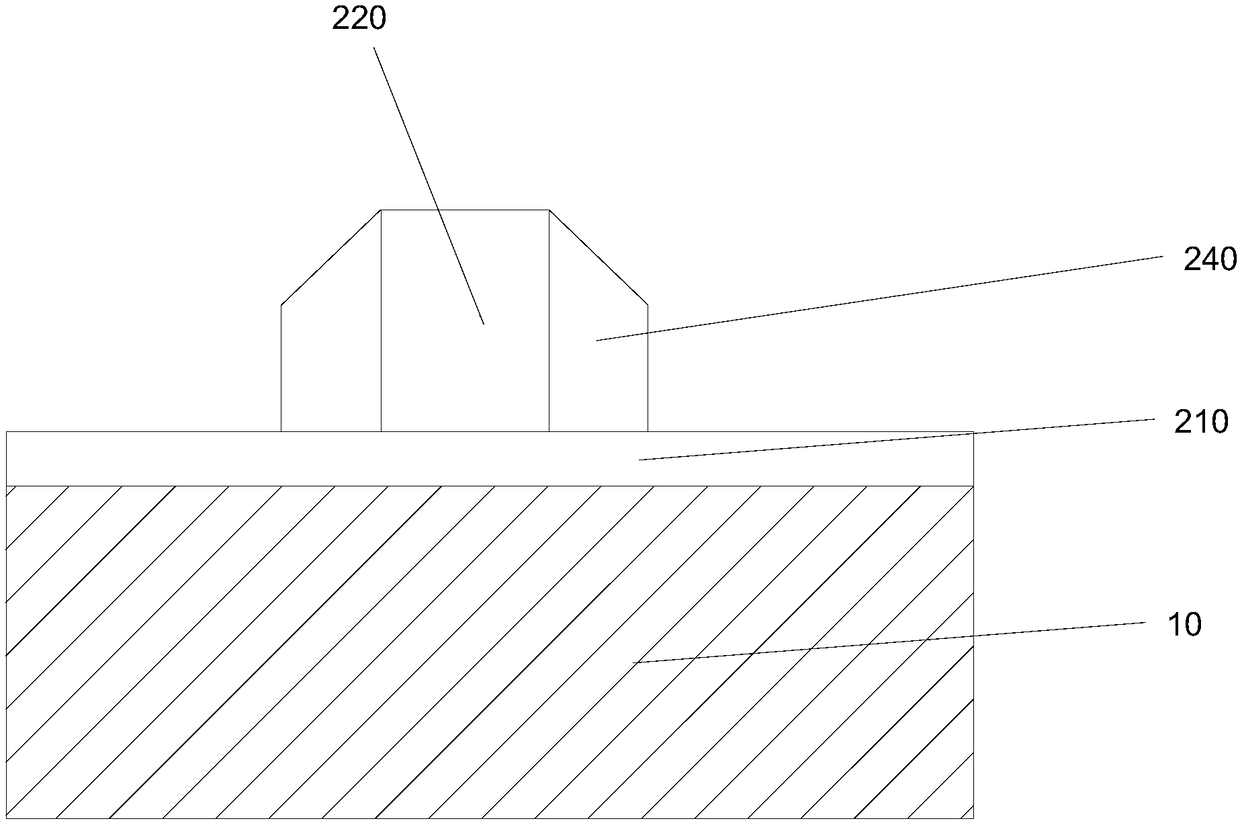

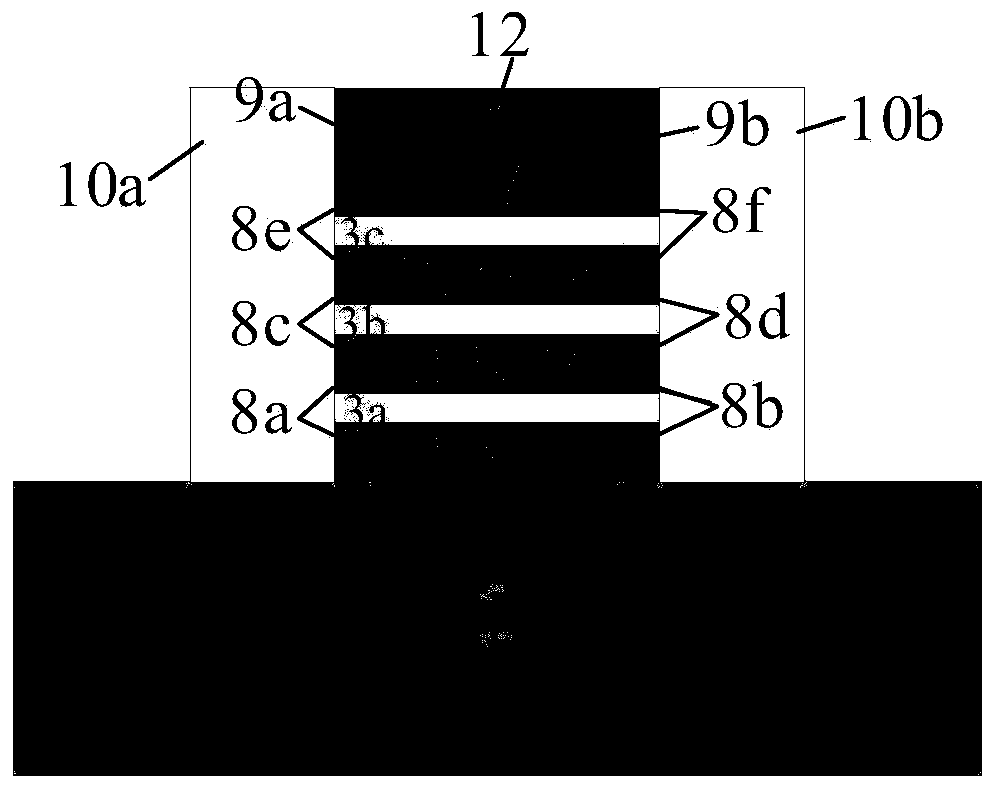

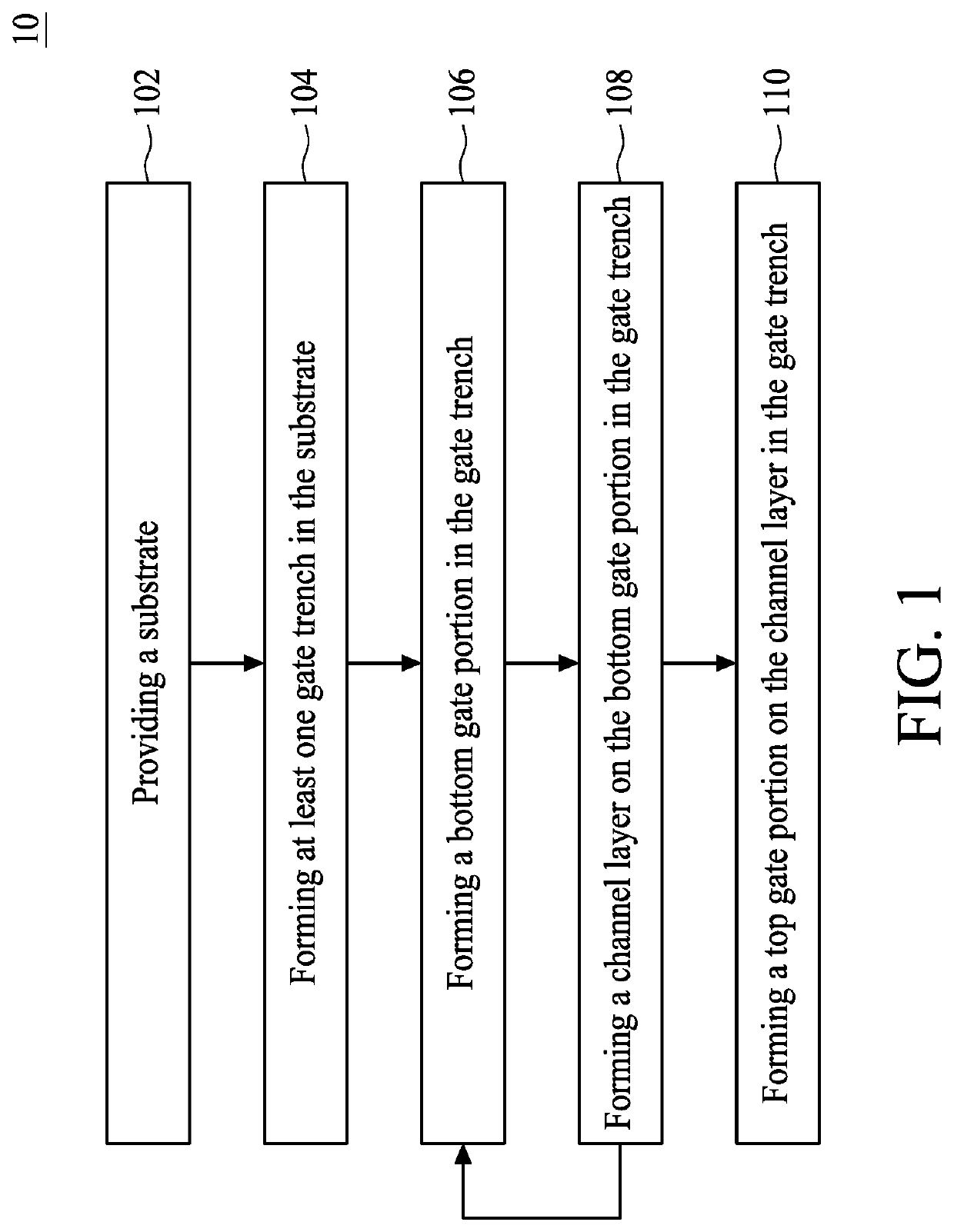

Semiconductor structure and method for preparing the same

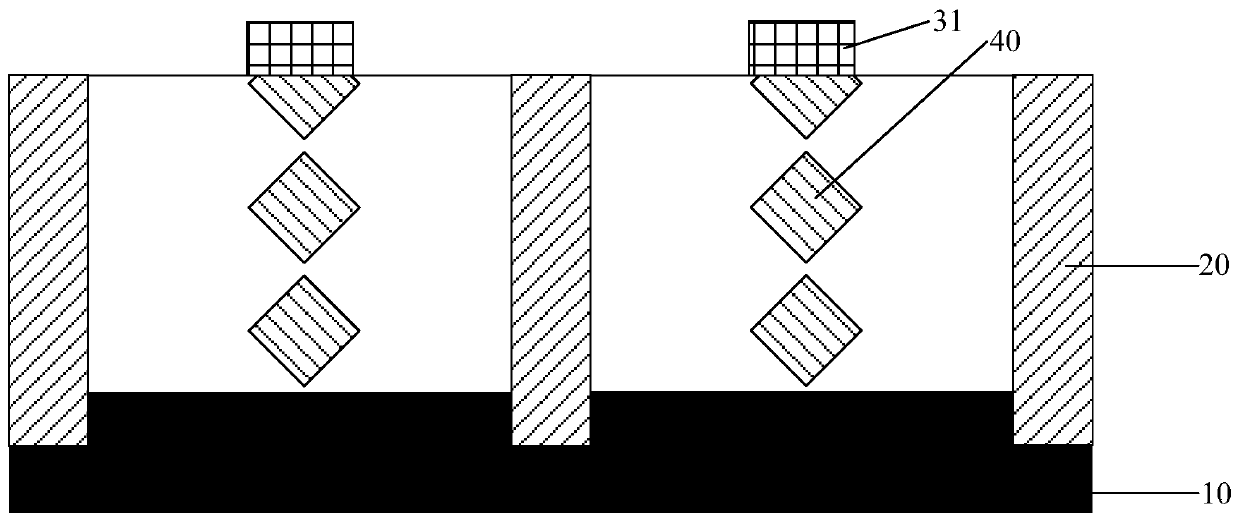

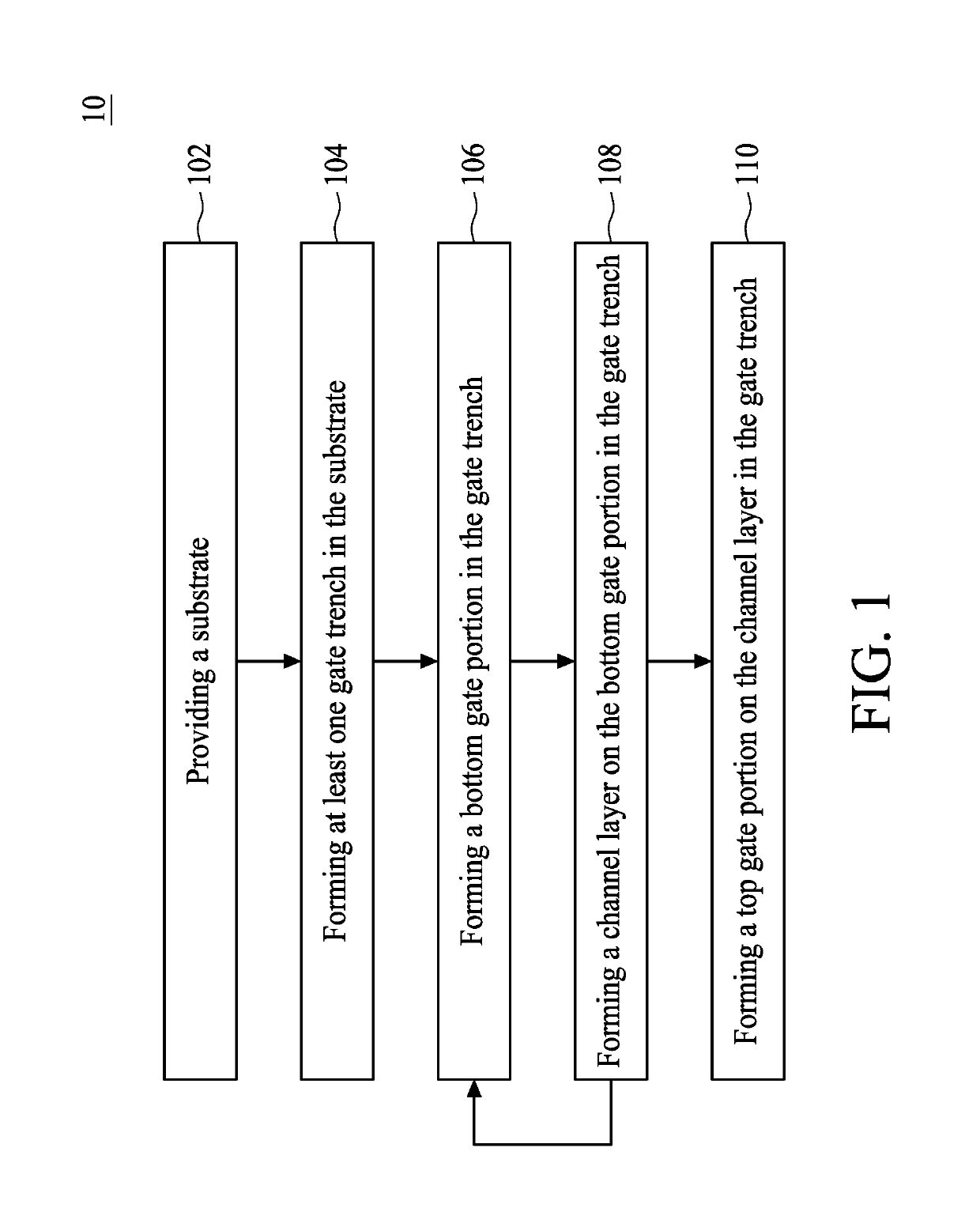

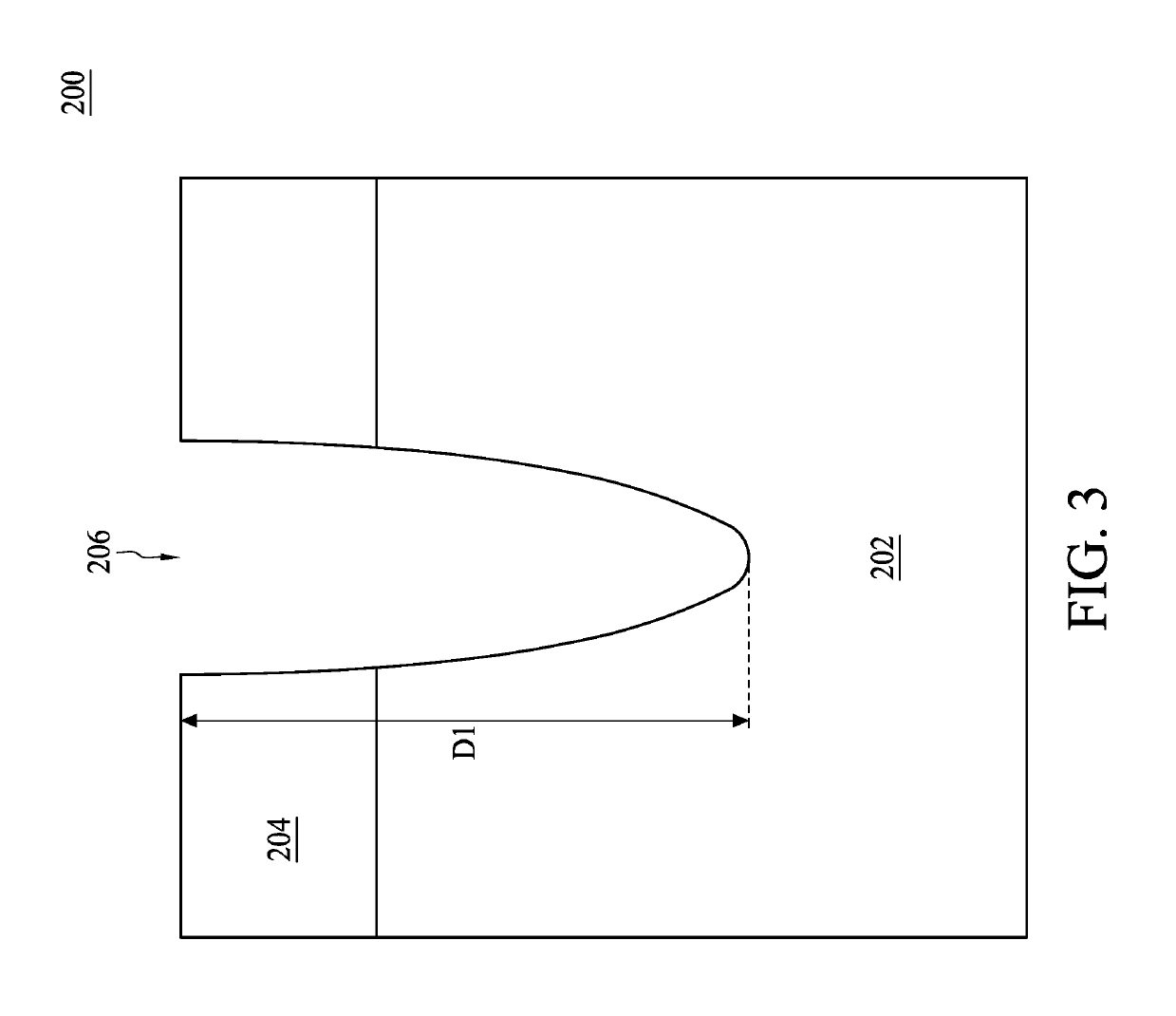

ActiveUS20190198676A1Gate control ability be improveIdsat be increaseTransistorNanotechnologyEngineeringElectrical and Electronics engineering

The present disclosure provides a semiconductor structure including a substrate, a bottom gate portion disposed in the substrate, a top gate portion stacked over the bottom gate portion, a first channel layer sandwiched between the top gate portion and the bottom gate portion, and a source / drain region disposed in the substrate at two opposite sides of the top gate portion.

Owner:NAN YA TECH

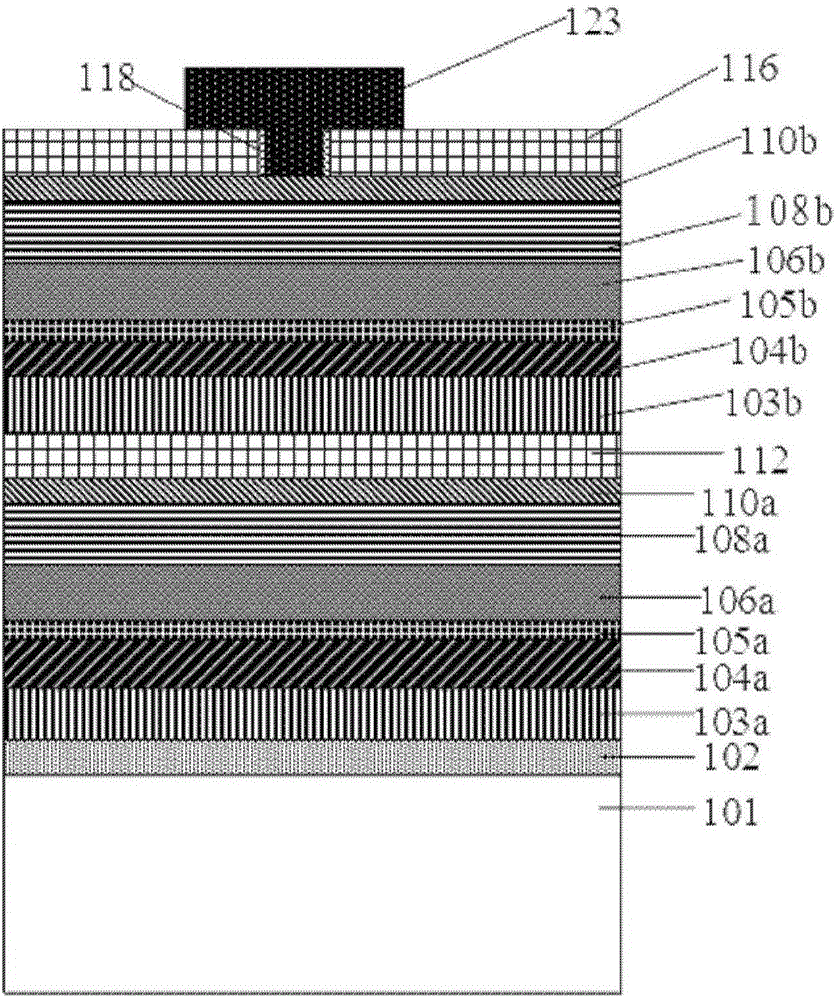

AlGaAs/GaAs high-electron-mobility transistor of multi-channel insulated fin-type gate composite trench gate and preparation method thereof

ActiveCN111430458AImprove transconductanceHigh gain abilityFinal product manufactureSemiconductor/solid-state device manufacturingHeterojunctionEtching

The invention discloses an AlGaAs / GaAs high-electron-mobility transistor of a multi-channel insulated fin-type gate composite trench gate. The AlGaAs / GaAs high-electron-mobility transistor sequentially comprises a GaAs or germanium substrate, a plurality of layers of AlGaAs / GaAs heterojunctions, a GaAs cap layer, a SiN passivation layer, a source electrode, a drain electrode and a gate electrode from bottom to top, wherein the gate electrode comprises a fin gate and a trench gate, and the distance between the boundary of an etching region of the trench gate and the boundary of a top gate region of the corresponding fin gate is less than 100nm; and insulating dielectric layers are further arranged between the gate electrode and the tops and the two side walls of the multiple layers of AlGaAs / GaAs heterojunctions. A three-dimensional fin gate and a concave trench gate structure are adopted at the same time, so that the gate controls a channel from the upper end; a three-dimensional fin gate electrode can control channel electrons from the side surface due to the gate width within 100nm, so that the gate control capability is obviously enhanced, and the transconductance and gain capability of a device are improved; and meanwhile, the insulating dielectric layers are introduced, so that the leakage current introduced by fin structure etching and trench gate etching can be effectively reduced, the static power consumption of the device is reduced, and the breakdown voltage of the device is improved.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

Vertically-integrated double-gate MOSFET structure and preparation method therefor

ActiveCN106298886AImprove mobilityImprove gate control abilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

The invention discloses a vertically-integrated double-gate MOSFET structure and a preparation method therefor. Compared with a conventional planar MOSFET structure, the vertically-integrated double-gate MOSFET structure adopts an III-V group semiconductor material with high electron mobility / hole mobility as a channel material; due to the adopted double-gate structure, the gate control capability of an MOSFET device is effectively improved, and influence from a short channel effect and the like is reduced; an NMOS and a PMOS are integrated in a vertical direction, so that the integration degree of devices on a unit wafer area is improved; and vertical through holes are adopted to realize interconnection of the devices in the vertical direction, so that the length of an interconnecting lead is effectively shortened while the operation speed of the devices is improved. The vertically-integrated double-gate MOSFET structure provided by the invention has an important application value in a post-Moore era CMOS integration technology and a high-performance III-V group semiconductor device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

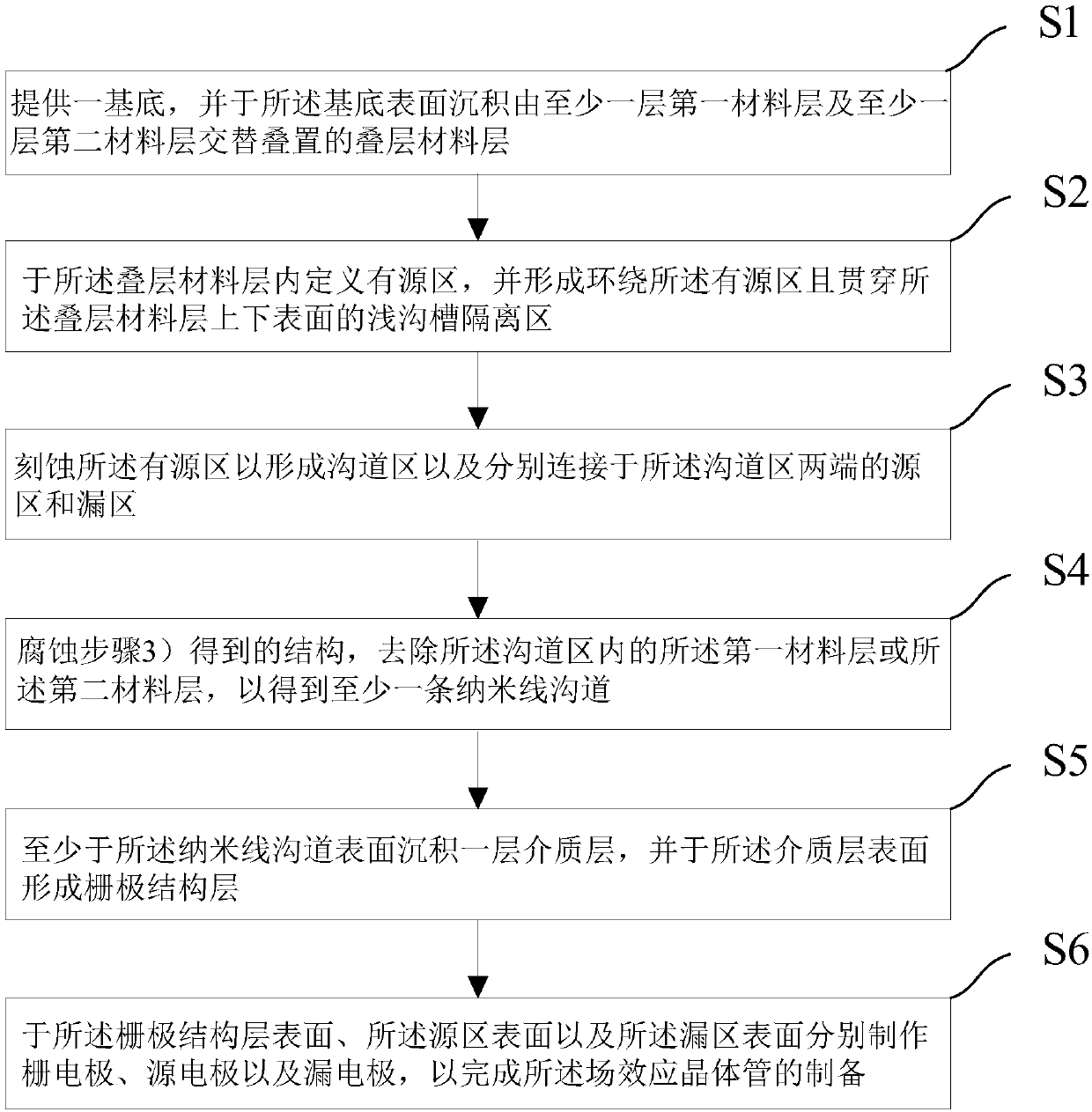

Surrounding gate nanowire field effect transistor and preparation method thereof

InactiveCN108288647AImprove gate control abilityReduce parasitic resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdNanowire

The invention provides a surrounding gate nanowire field effect transistor and a preparation method thereof. The preparation method comprises the following steps of S1, forming a first fin body isolated from a substrate on the substrate, wherein the first fin body consists of a first region, a second region and a third region which are connected in sequence in the length direction; S2, forming a nanowire structure in the second region of the first fin body; and S3, forming an interface oxide layer, a ferroelectric layer and a gate which are laminated around the exposed surface of the nanowirestructure in sequence, wherein the preparation method also comprises the following steps of forming a source / drain in the first region and the third region, wherein the source / drain is connected withthe two ends of the nanowire structure. By virtue of the preparation method, the gate control capability of the device is improved, electric leakage of the device is lowered, source / drain parasitic resistance of the device is lowered, and the sub threshold value slope of the device can be greatly lower than 60mV / dec.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Nano-sheet ring-gate field effect transistor with double-layer side wall structure

ActiveCN110246899AImprove the coupling effectImprove gate control abilitySemiconductor/solid-state device manufacturingSemiconductor devicesCouplingEngineering

The invention discloses a nano-sheet ring-gate field effect transistor with a double-layer side wall structure. The device has two layers of side walls, a side wall close to a nano-sheet channel is made of a material with a low dielectric constant (low-k for short) and high thermal conductivity, and a side wall away from the nano-sheet channel is made of a material with a high dielectric constant (high-k for short). The side wall formed by the low-k material facilitates the heat radiation of the device, the side wall formed by the high-k material facilitates the reinforcement of the coupling between a device gate and the channel, and therefore, the device still has good heat dissipation effect under a large on-state current condition. In addition, the heat dissipation capability and DC performance of the device can be flexibly regulated by changing the thickness ratio of the low-k material to the high-k material.

Owner:EAST CHINA NORMAL UNIV +1

Semiconductor structure and method for preparing the same

ActiveUS10818800B2Increase the lengthImprove gate control abilityTransistorNanotechnologySemiconductor structureBottom gate

The present disclosure provides a semiconductor structure including a substrate, a bottom gate portion disposed in the substrate, a top gate portion stacked over the bottom gate portion, a first channel layer sandwiched between the top gate portion and the bottom gate portion, and a source / drain region disposed in the substrate at two opposite sides of the top gate portion.

Owner:NAN YA TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com