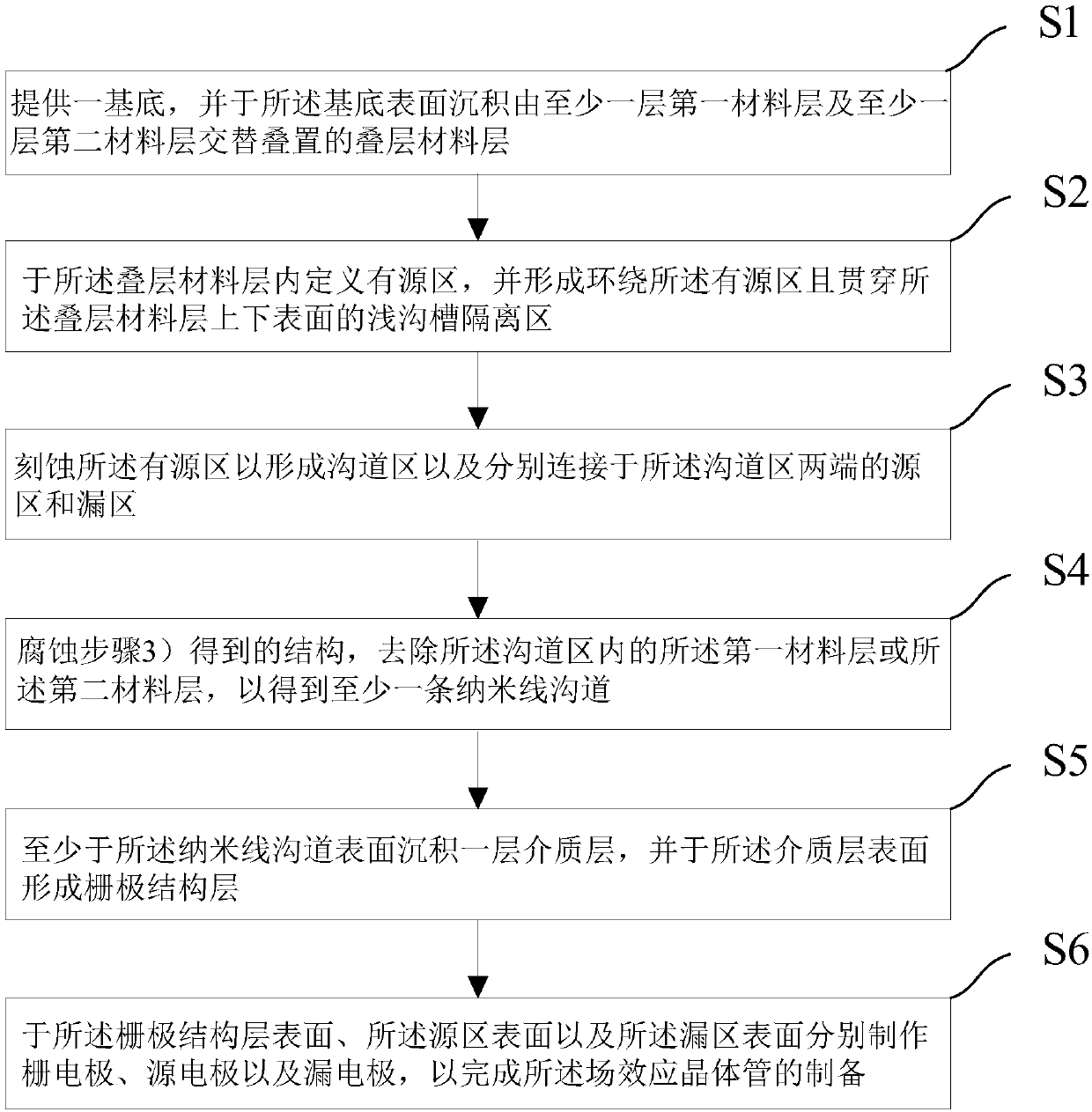

Field-effect transistor structure and fabrication method thereof

A field effect transistor and gate structure technology, which is applied to the field effect transistor structure and its preparation field, can solve the problems of difficult source-drain ion implantation, restricted transport capability, etc., and achieves increasing channel cross-sectional area, reducing device size, enhancing performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0072] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

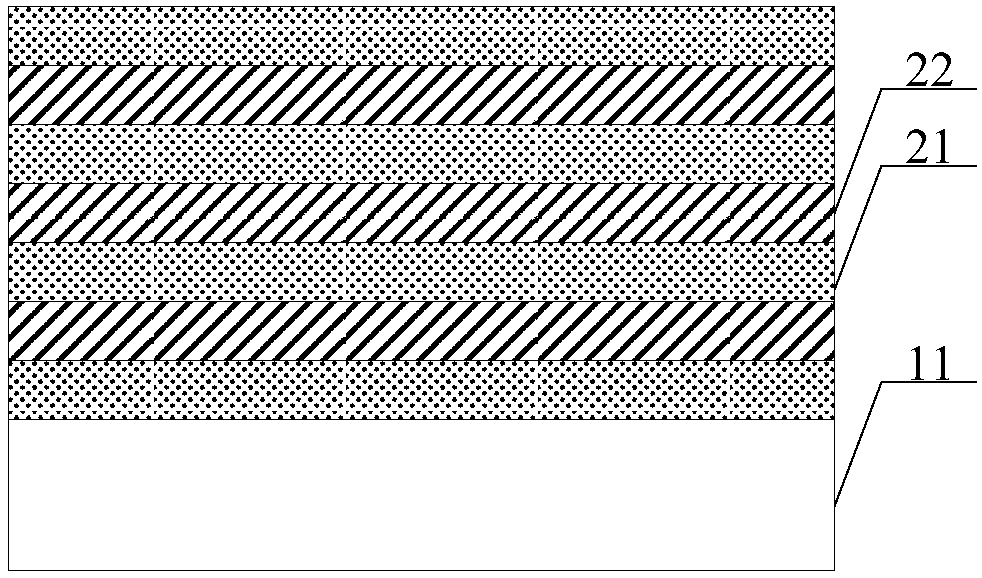

[0073] see Figure 1 to Figure 16 . It should be noted that the diagrams provided in this embodiment are only schematically illustrating the basic concept of the present invention, although only the components related to the present invention are shown in the diagrams rather than the number, shape and Dimensional drawing, the shape, quantity and proportion of each component can be changed arbitrarily during actual implementation, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com