Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

35results about How to "Increase the maximum oscillation frequency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for growth and optimization of heterojunction bipolar transistor film stacks by remote injection

InactiveUS20060292809A1Avoid spreadingEliminates and minimizes deleterious effectSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceDopant

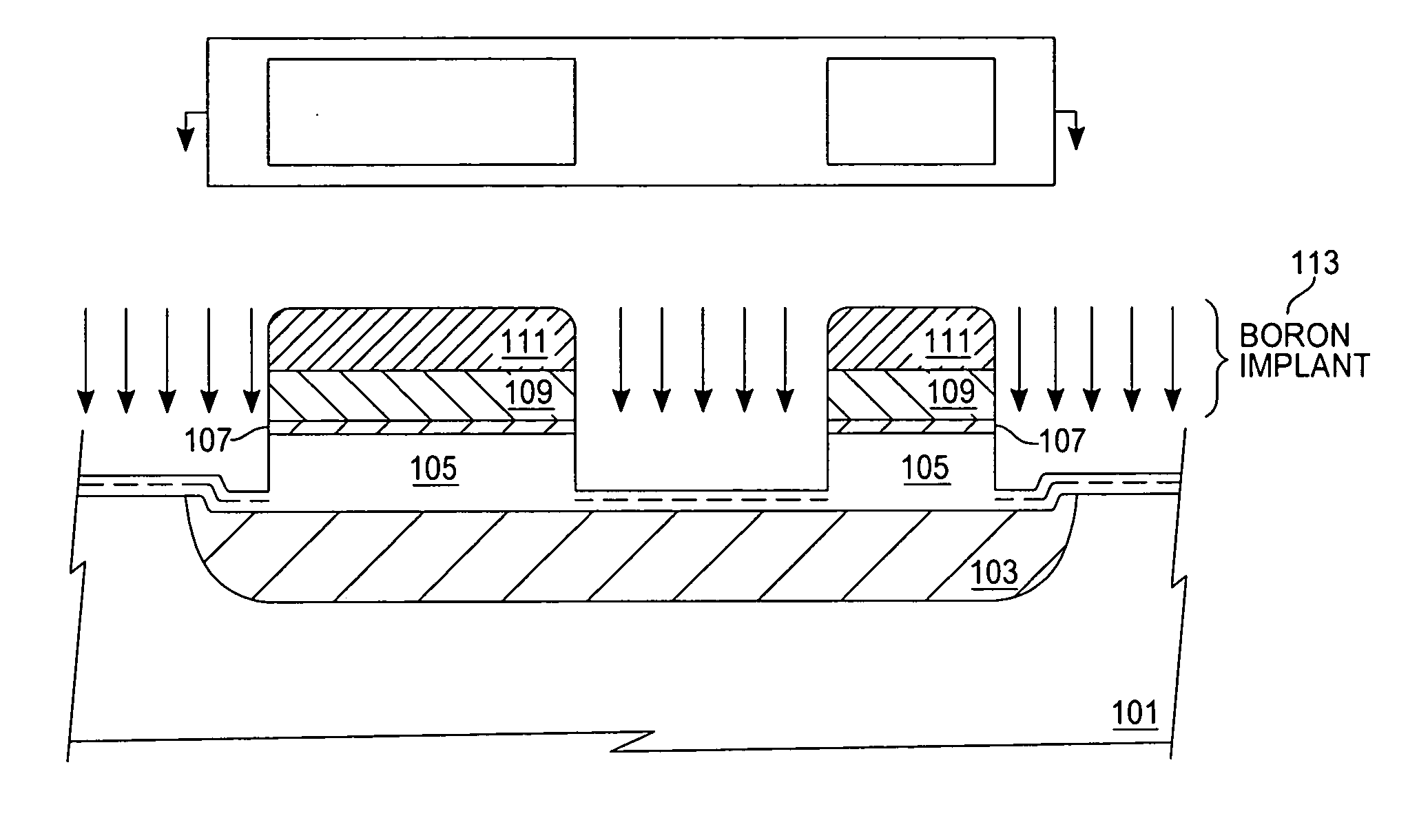

A method, and a resulting device, for fabricating a heterojunction bipolar transistor (HBT). HBT devices have a high transconductance typical of bipolar devices and are additionally capable of high-power operation. To achieve the aforementioned characteristics, HBT devices are generally of the npn type, preferably with a thin, heavily doped base. The thin, heavily doped base maintains a low base-spreading resistance, leading to a high maximum oscillation frequency. In order to maintain a high doping concentration while minimizing outdiffusion of the dopant material, carbon is remotely doped into the base region. Details of the carbon dopant techniques and procedures are described with respect to fabrication of an exemplary HBT device.

Owner:ATMEL CORP

Voltage controlled oscillator

InactiveCN101212198ALarge tuning rangeLow Phase Noise PerformancePulse automatic controlOscillations generatorsCapacitancePhase noise

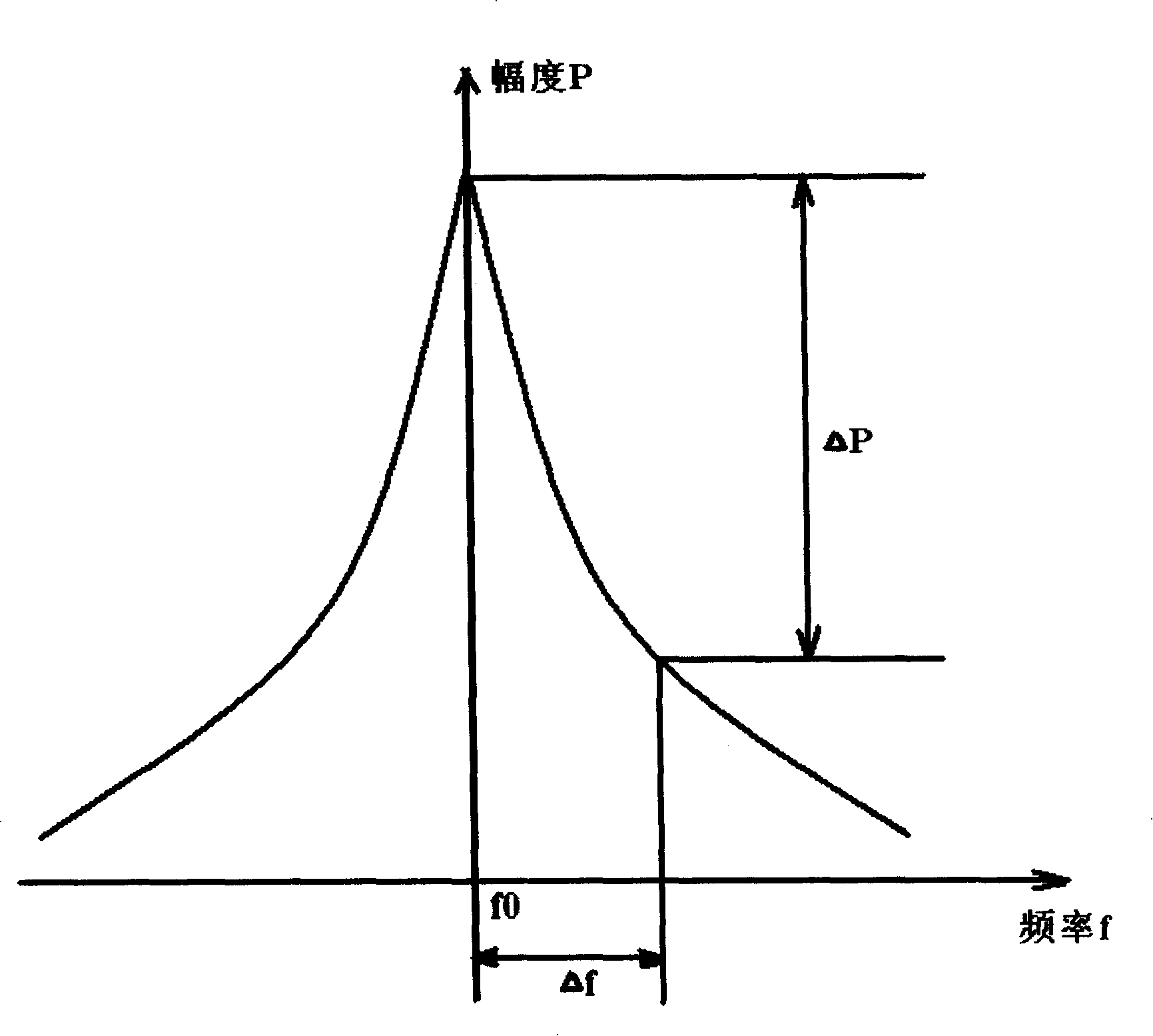

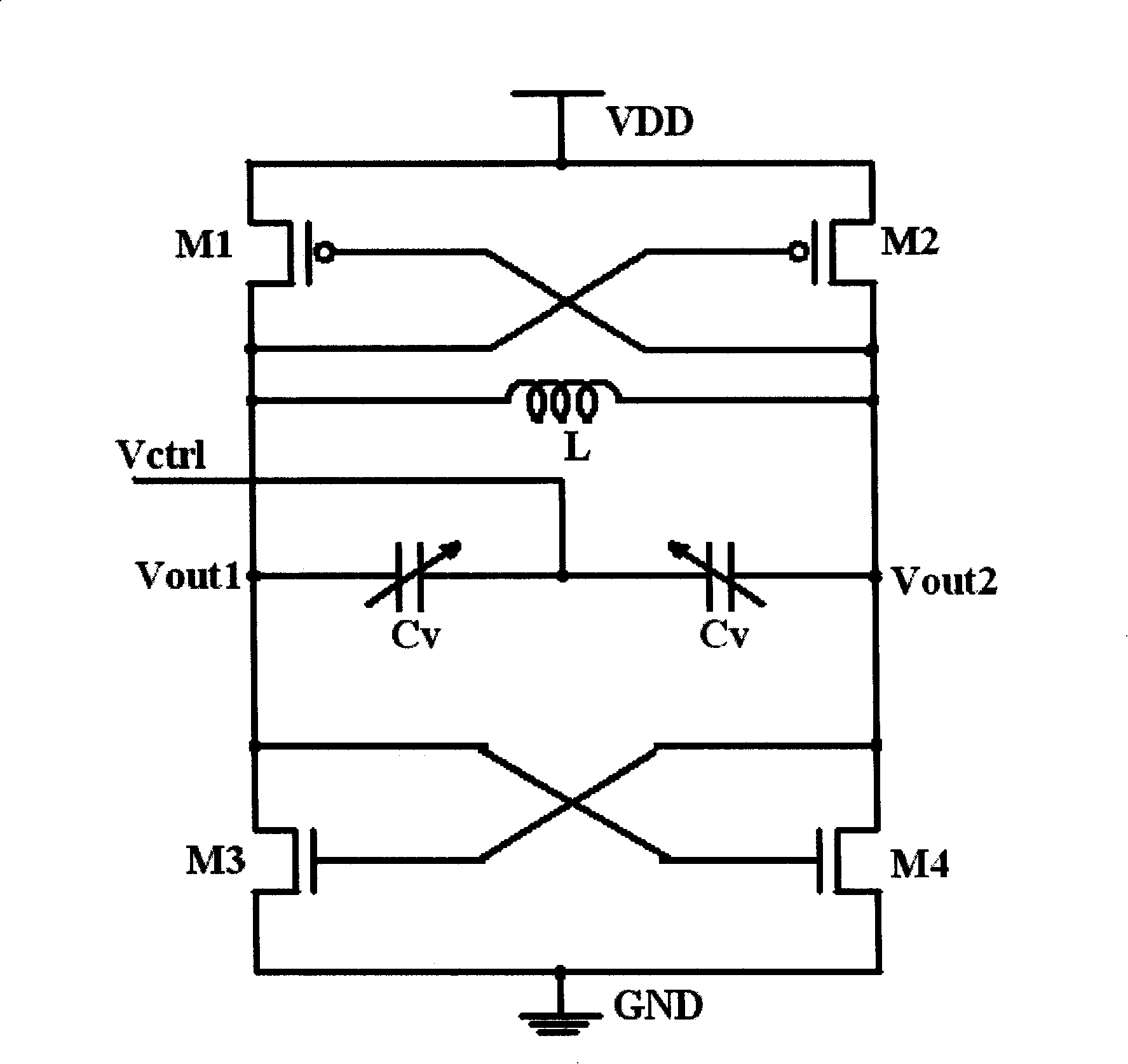

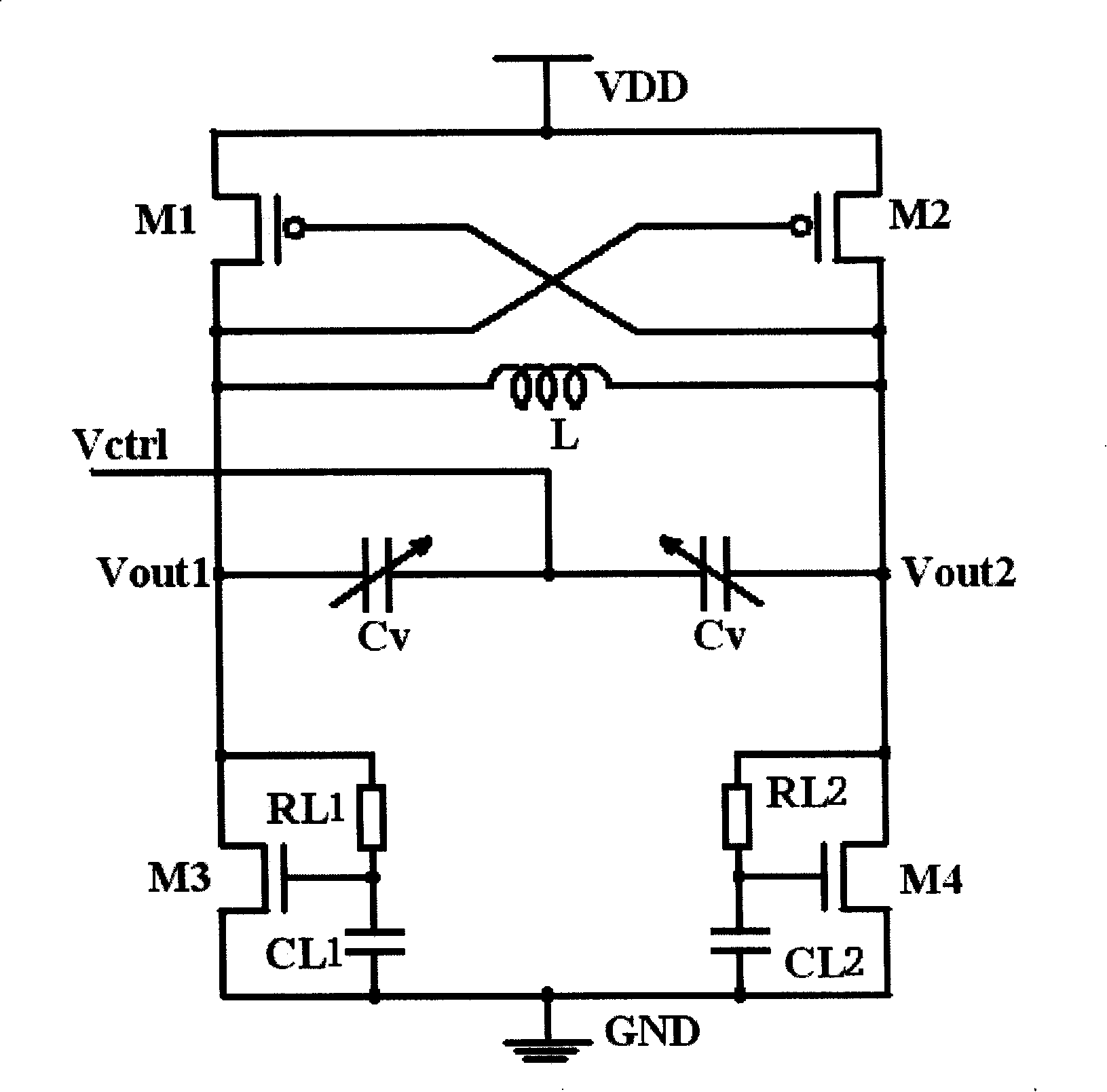

The invention relates to a voltage controlled oscillator, which comprises four transistors, an integrated on-chip inductor and two symmetric variable capacitors, wherein, two transistors realize negative resistance through cross coupling, thereby providing energy to oscillate an LC circuit comprising the inductor and the variable capacitors; by changing the capacitance of the variable capacitors, different output frequencies of the oscillator are obtained. The invention also comprises two resistors with the same value and two capacitors with the same value; a grid terminal of one of the rest transistors is connected with a terminal of a resistor and a terminal of a capacitor at the same time, which jointly form an active inductor; a grid terminal of the last transistor is connected with a terminal of a resistor and a terminal of a capacitor at the same time, thus jointly forming another active inductor; the two active inductors provide bias current for the voltage controlled oscillator. The invention enlarges the tuning range of the voltage controlled oscillator and reduces the phase noise.

Owner:BEIJING LHWT MICROELECTRONICS

Methods to improve the SiGe heterojunction bipolar device performance

ActiveUS7144787B2Improve performanceIncrease the maximum oscillation frequencySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDopant

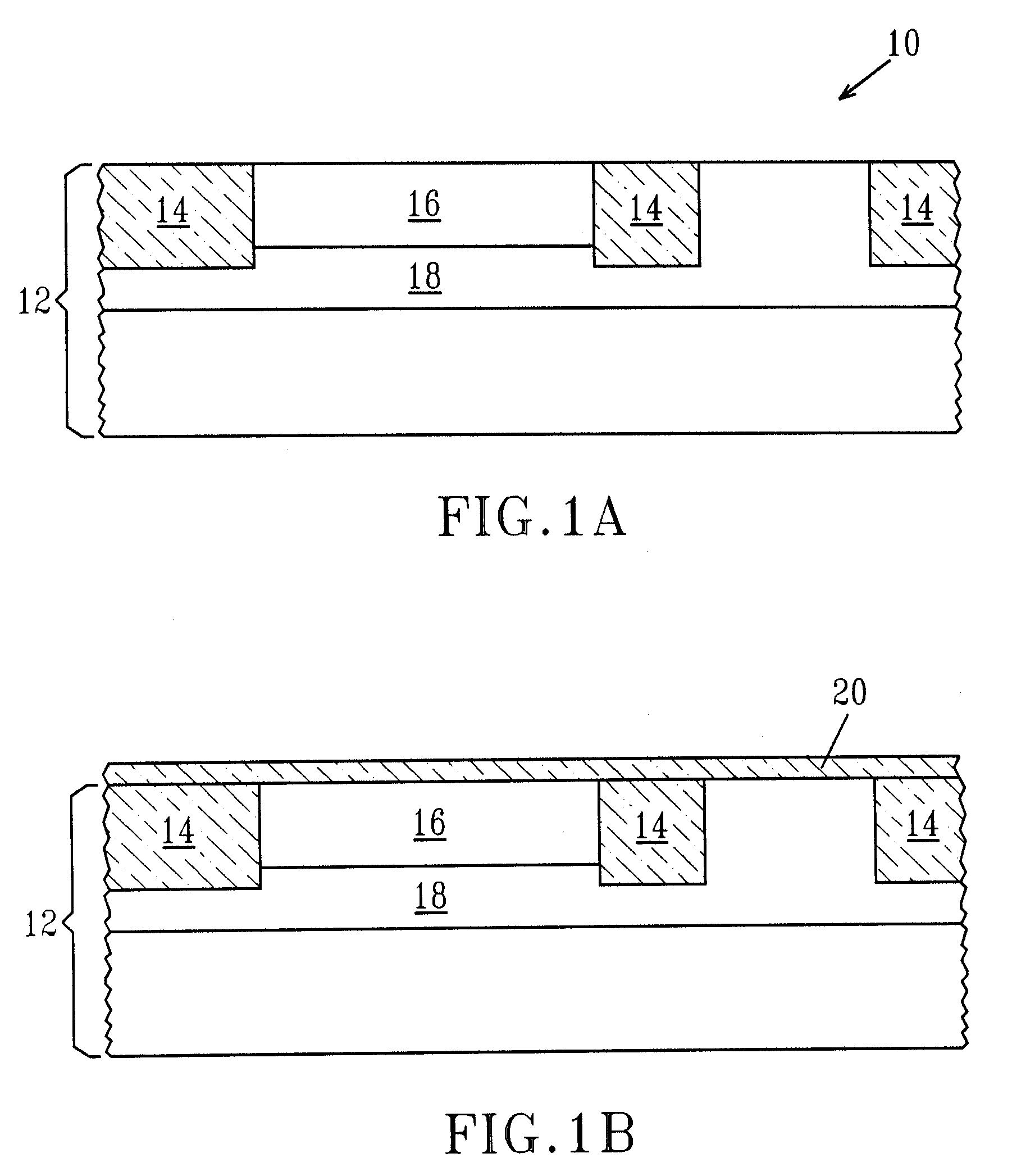

Methods of boosting the performance of bipolar transistor, especially SiGe heterojunction bipolar transistors, is provided together with the structure that is formed by the inventive methods. The methods include providing a species-rich dopant region comprising C, a noble gas, or mixtures thereof into at least a collector. The species-rich dopant region forms a perimeter or donut-shaped dopant region around a center portion of the collector. A first conductivity type dopant is then implanted into the center portion of the collector to form a first conductivity type dopant region that is laterally constrained, i.e., confined, by the outer species-rich dopant region.

Owner:IBM CORP

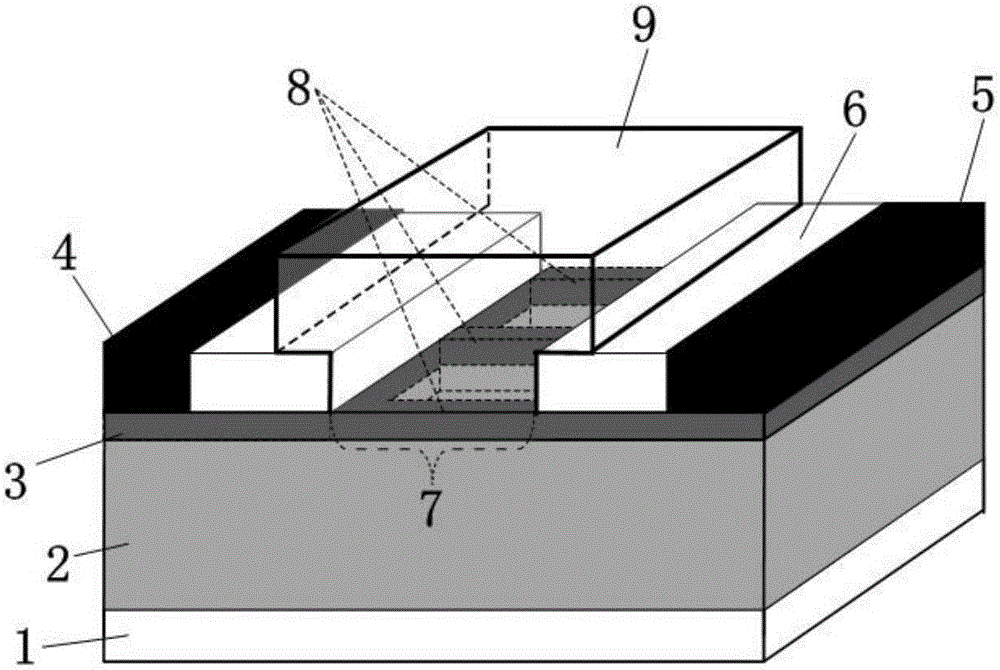

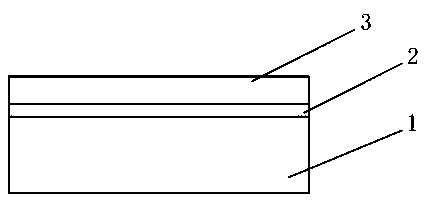

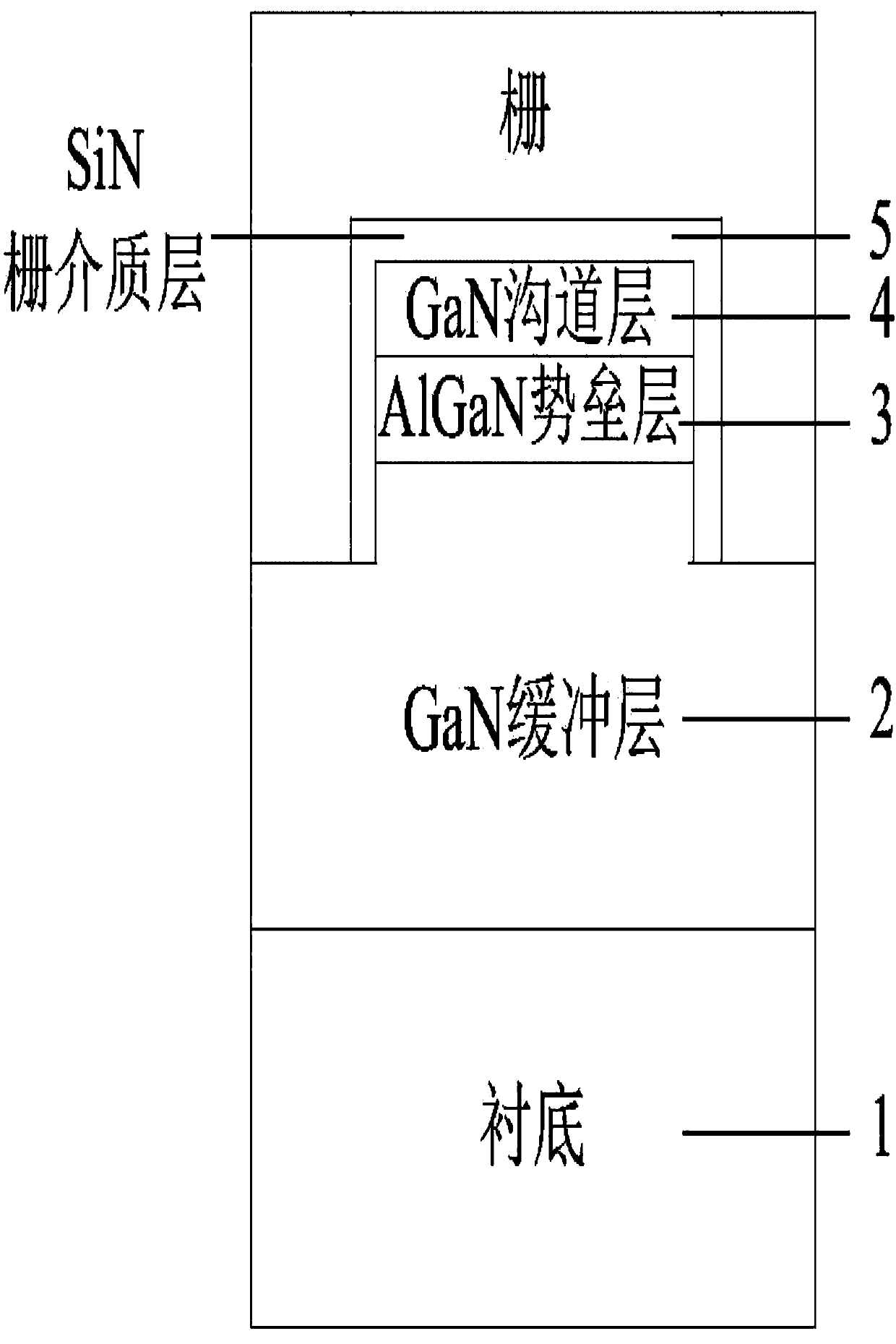

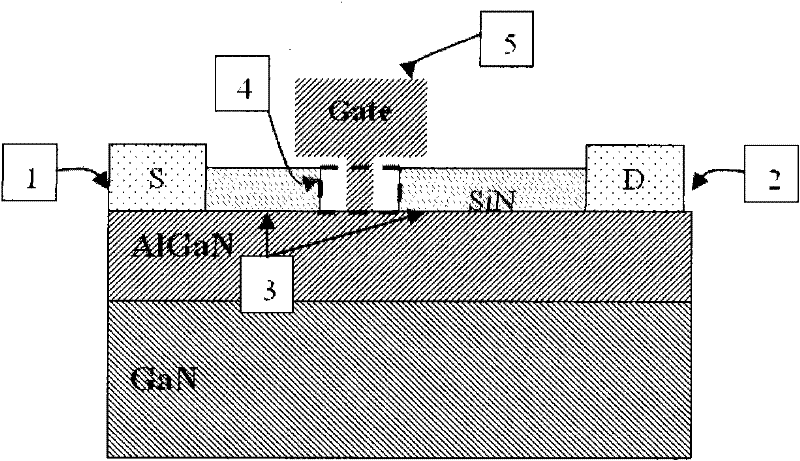

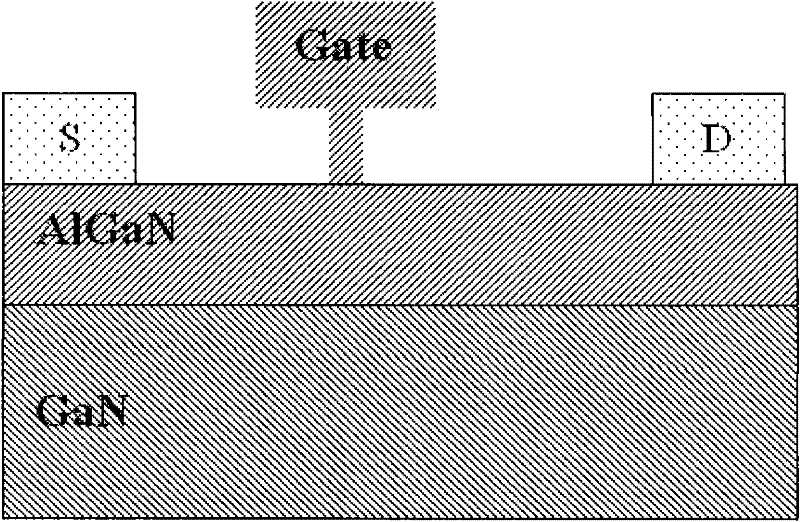

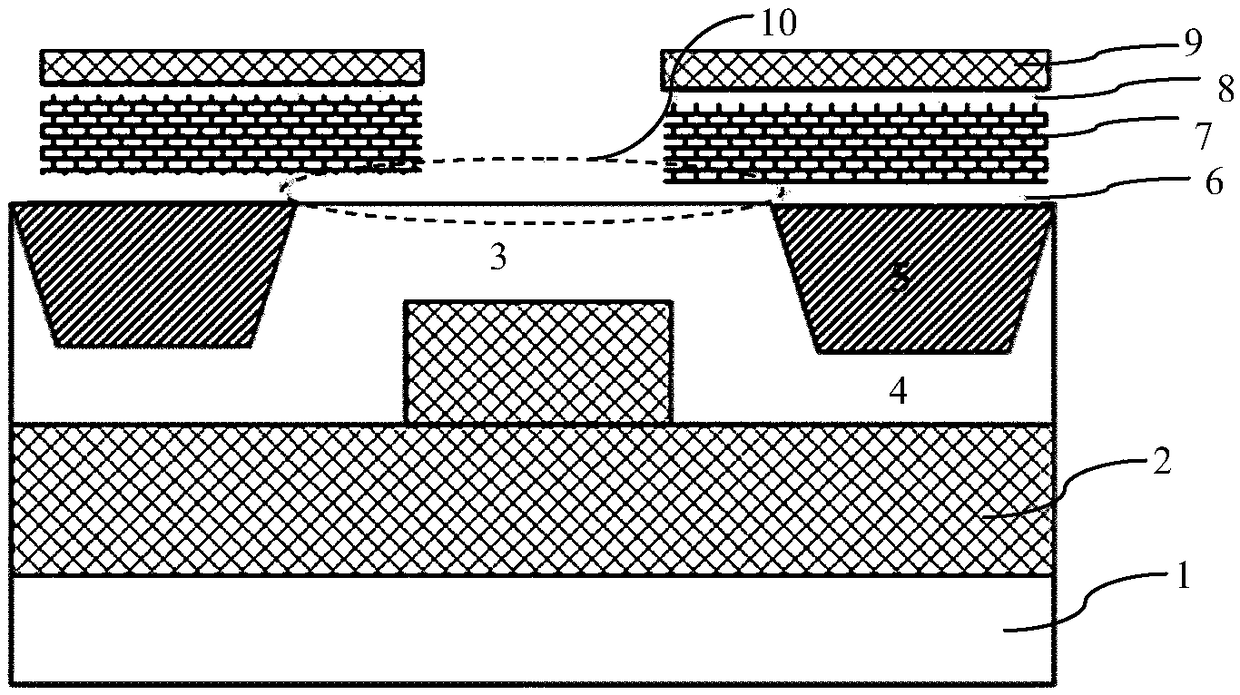

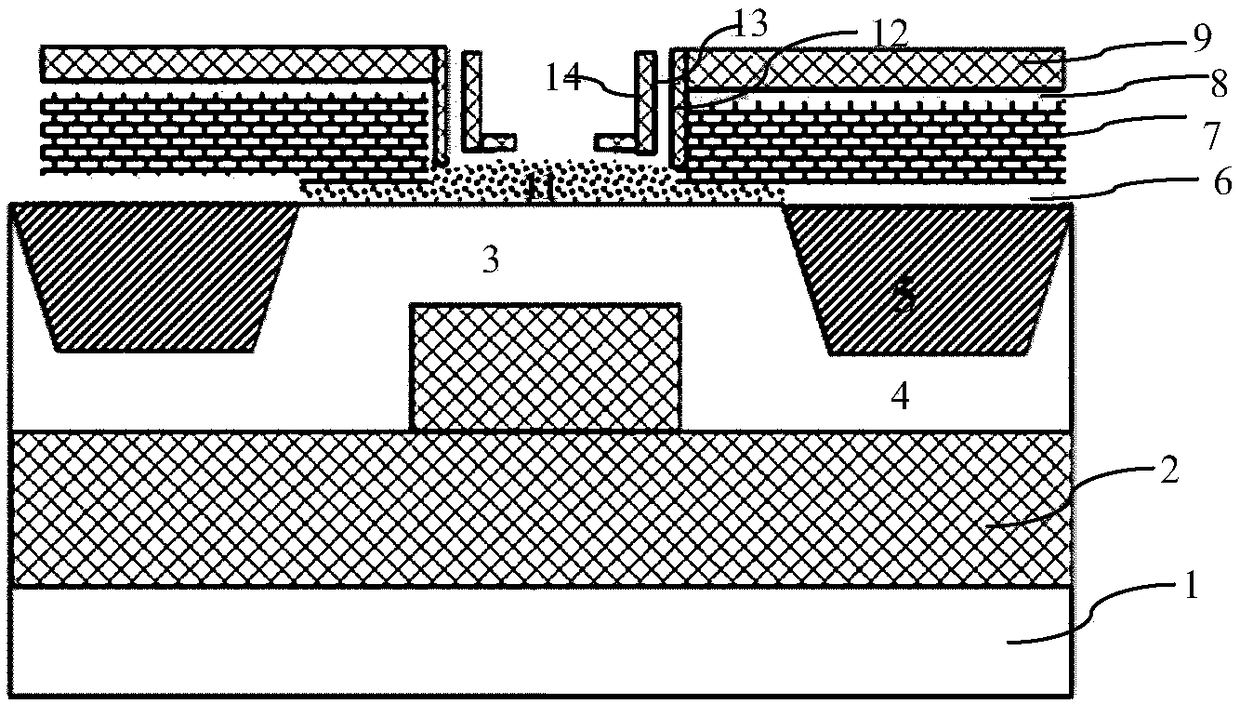

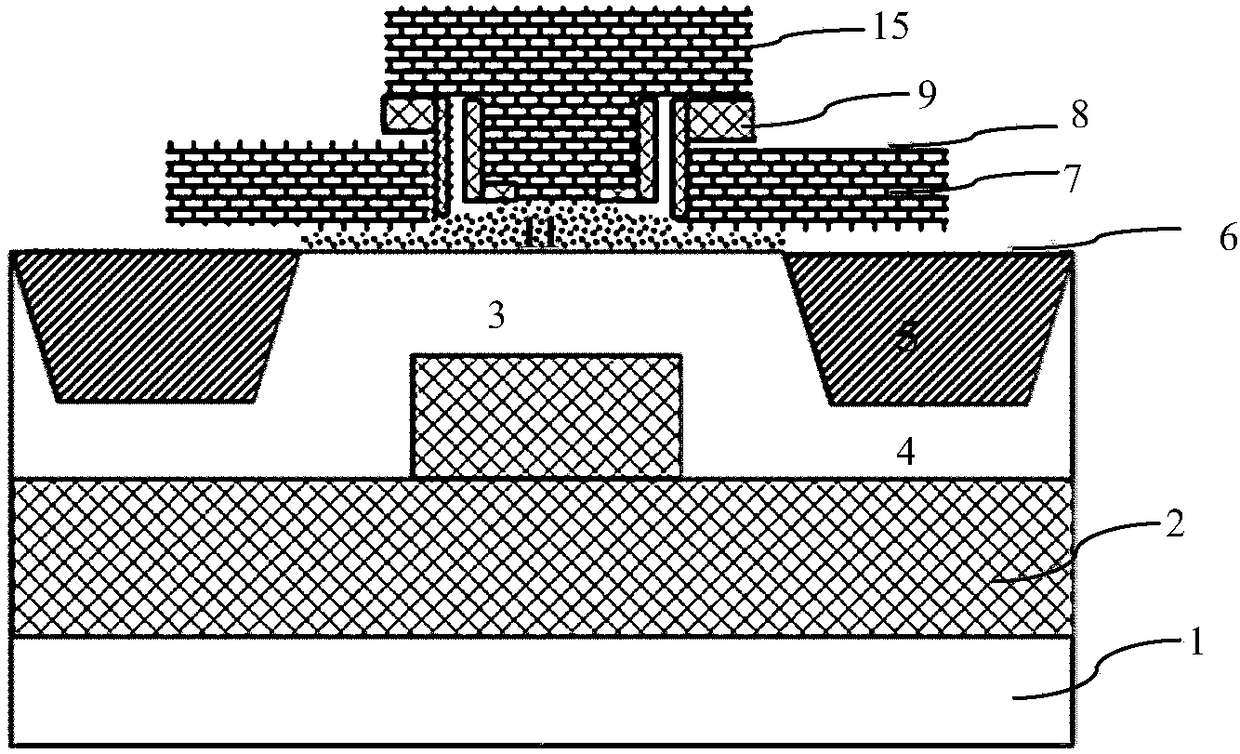

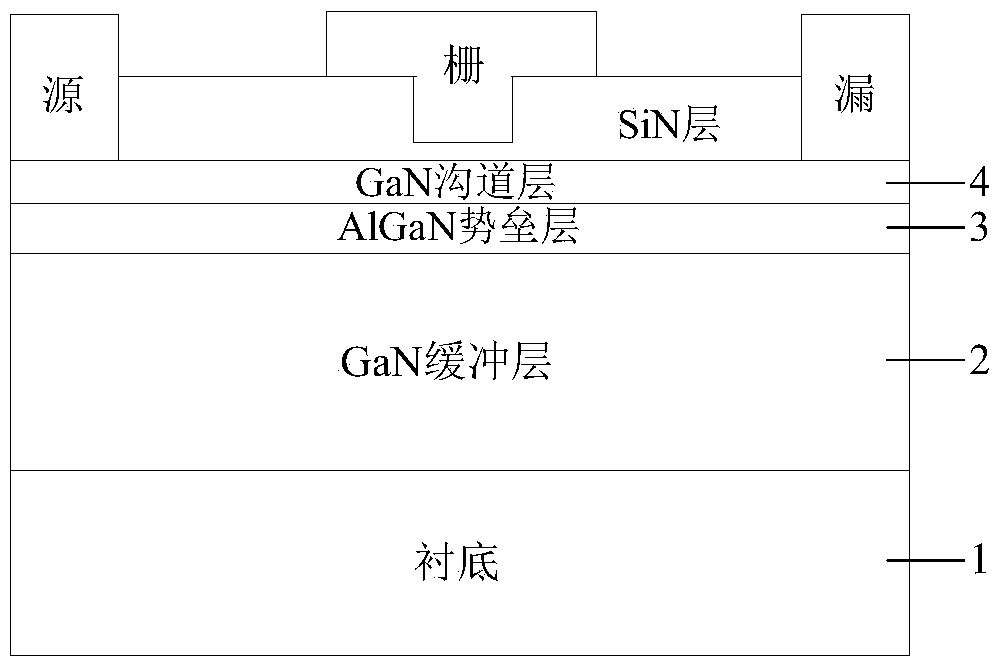

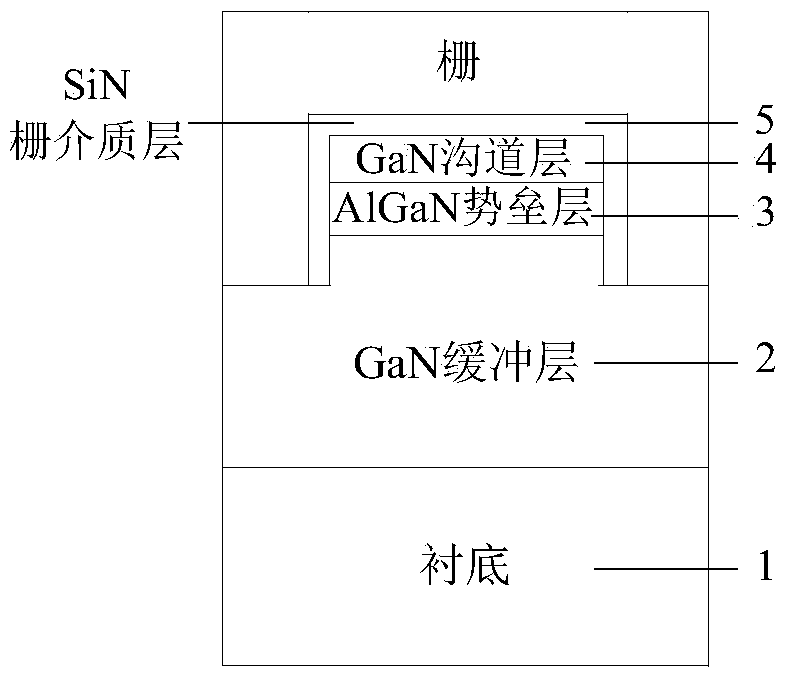

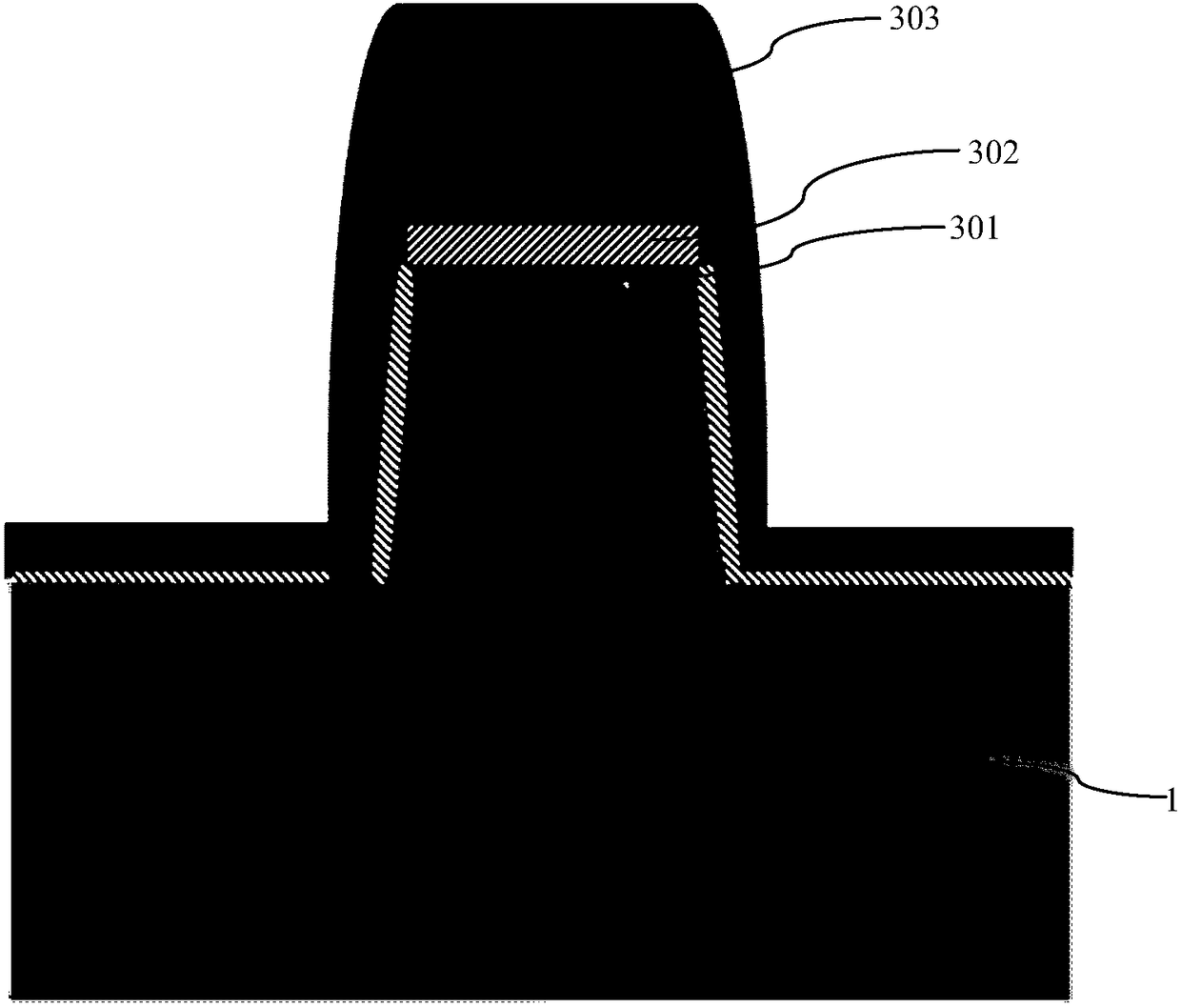

T-gate and N-surface GaN/AlGaN fin-type high electron mobility transistor

ActiveCN105914232AReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionOhmic contact

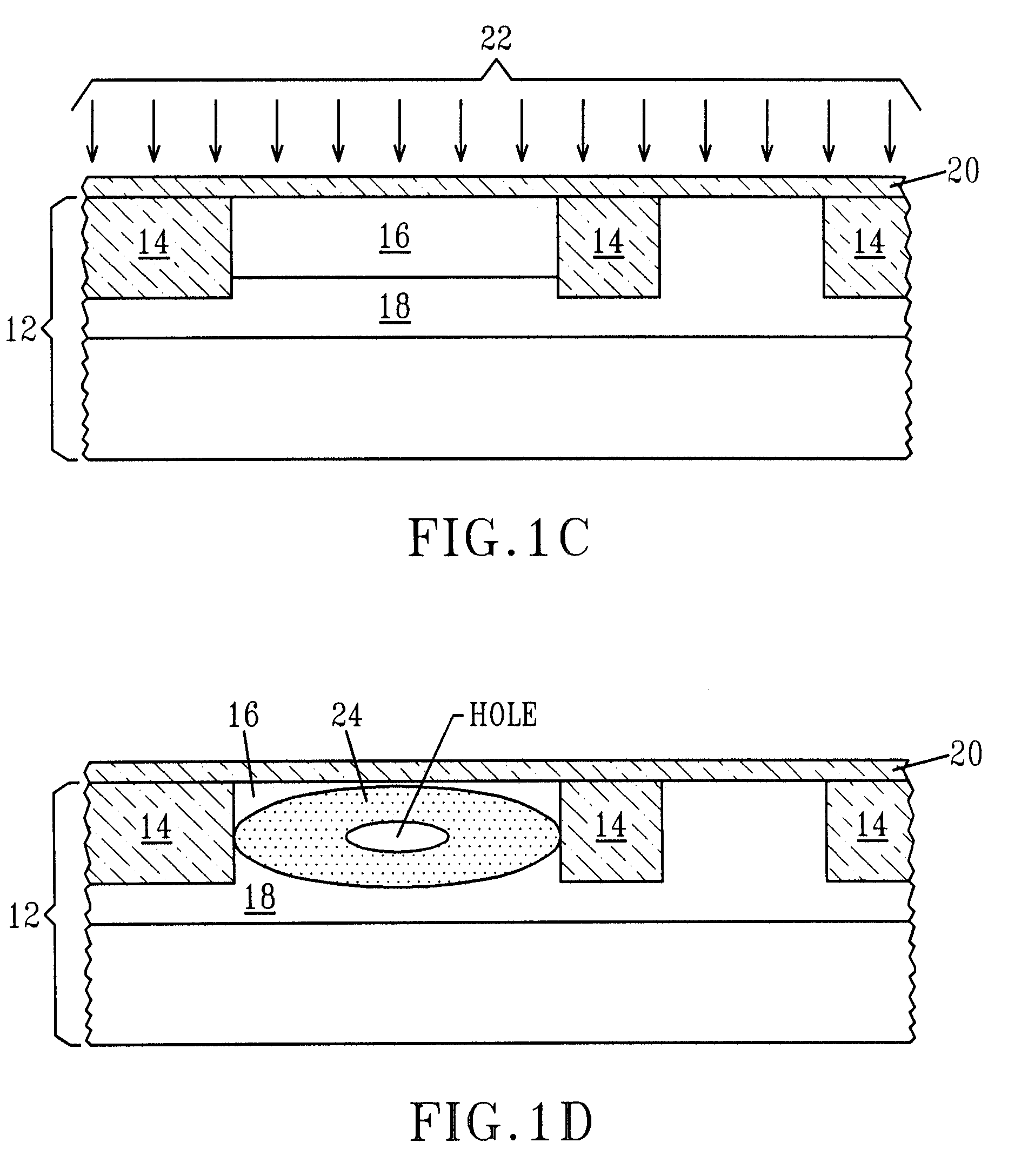

The present invention discloses a T-gate and N-surface GaN / AlGaN fin-type high electron mobility transistor. The problems are mainly solved that the maximum oscillating frequency of a current microwave power device is small, the ohmic contact resistor is large and the short channel effect is severe. The transistor comprises from down to up: a substrate (1), a GaN buffer layer (2), a ALGaN barrier layer (3), a GaN channel layer (4), a gate medium layer (5), a passivation layer (6), a source gate electrode and a drain gate electrode. The buffer layer and the channel layer employ N-surface GaN materials; the GaN channel layer and the ALGaN barrier layer form GaN / AlGaN heterojunction; the gate electrode employs T-type gate and is wrapped at two sides and the upper portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate and N-surface GaN / AlGaN fin-type high electron mobility transistor has good gate-control capability, small resistor and the maximum oscillating frequency, and is able to be a microwave power device with the small size.

Owner:XIDIAN UNIV

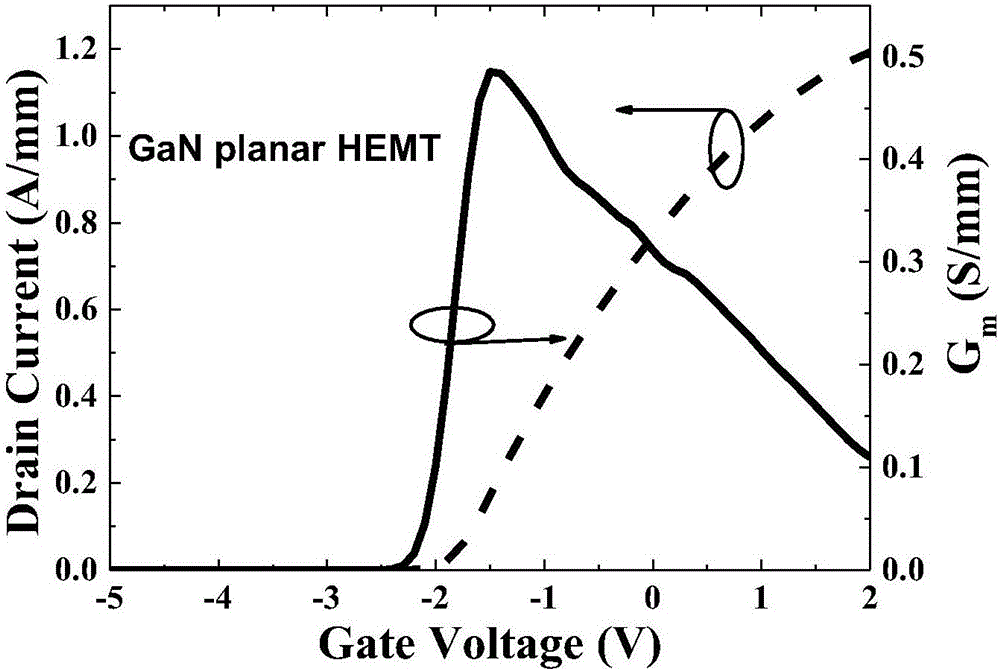

High linearity GaN fin-type high electron mobility transistor and manufacture method thereof

InactiveCN106684141AImprove linearityIncrease the maximum oscillation frequencySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMicrowave power

The present invention relates to a high linearity GaN fin-type high electron mobility transistor and a manufacture method thereof. From bottom to top, the transistor sequentially comprises a substrate, a buffer layer, a barrier layer, and a passivation layer. A source electrode is arranged at one end above the barrier layer and a drain electrode is arranged at the other end. The passivation layer is arranged above the barrier layer between the source electrode and the drain electrode. A groove is arranged in the passivation layer. A T-shaped gate is arranged in the groove. The transistor is characterized in that GaN-based three-dimensional fins in periodical arrangement are etched only on the barrier layer and the buffer layer in an area below the groove, the length of the GaN-based three-dimensional fins is equal to the length of the groove, and an isolation groove that is etched is arranged between adjacent GaN-based three-dimensional fins. The transistor has high linearity and output current, strong gate control capability, good heat dissipation performance, and high frequency characteristic. The manufacture method is simple and reliable, and is applicable to high power, high linearity microwave power devices.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

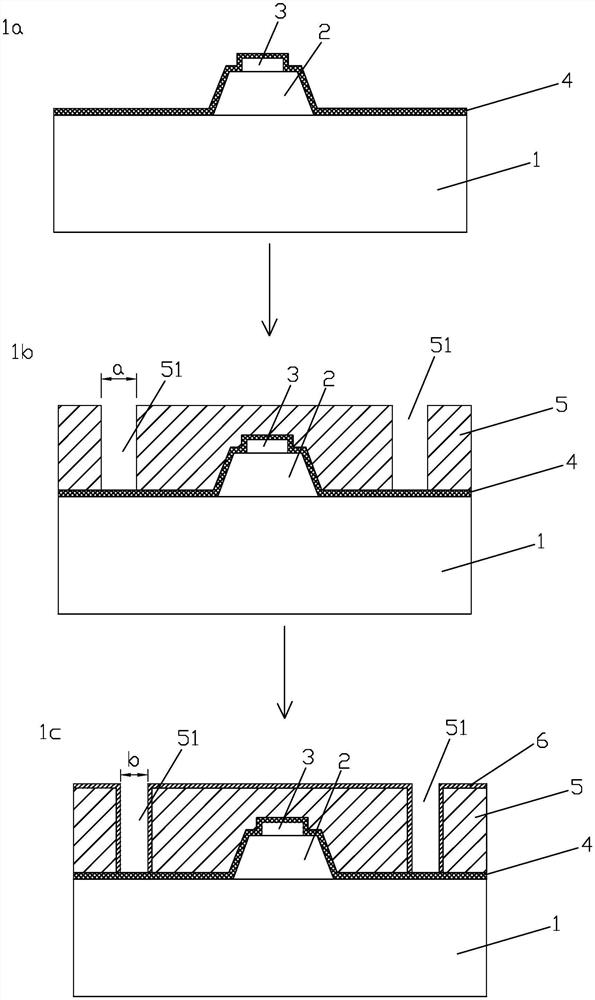

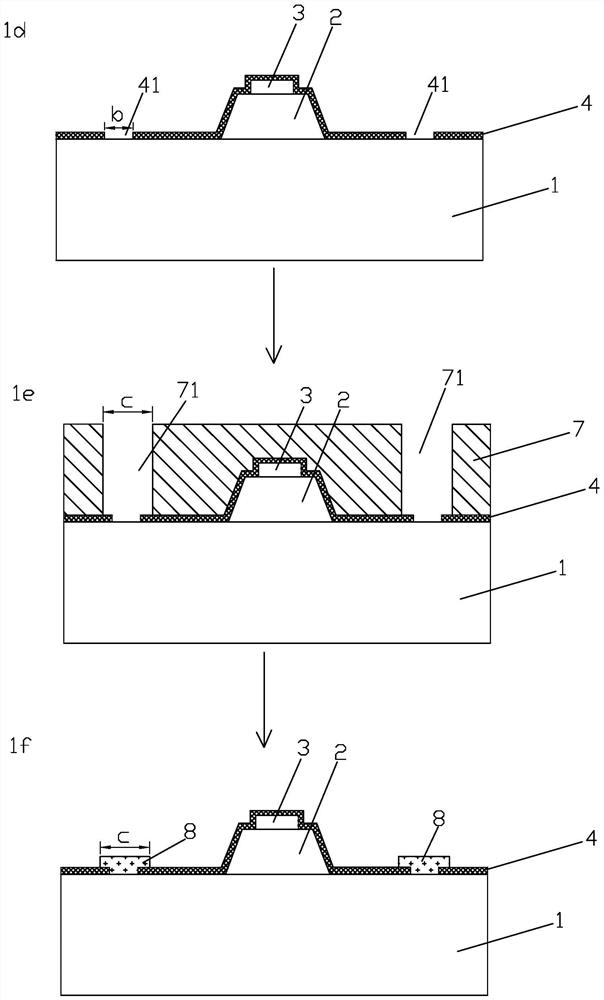

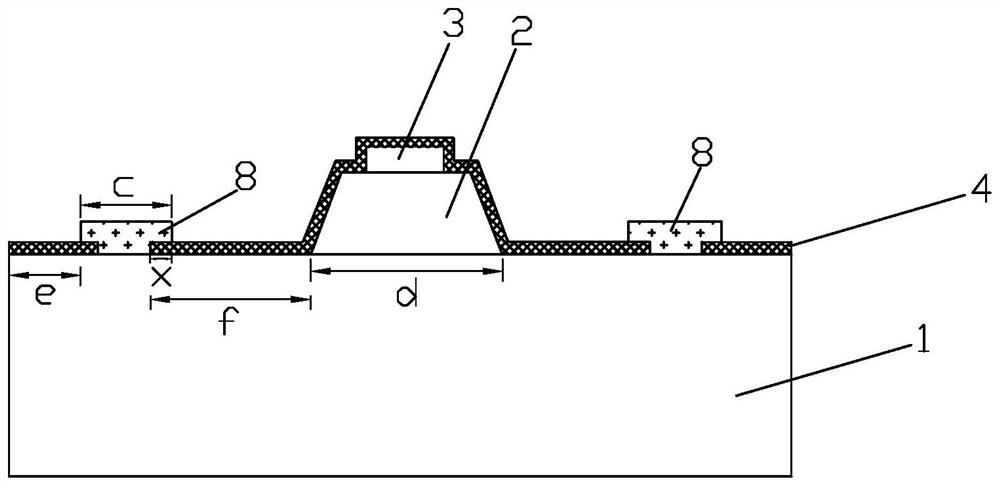

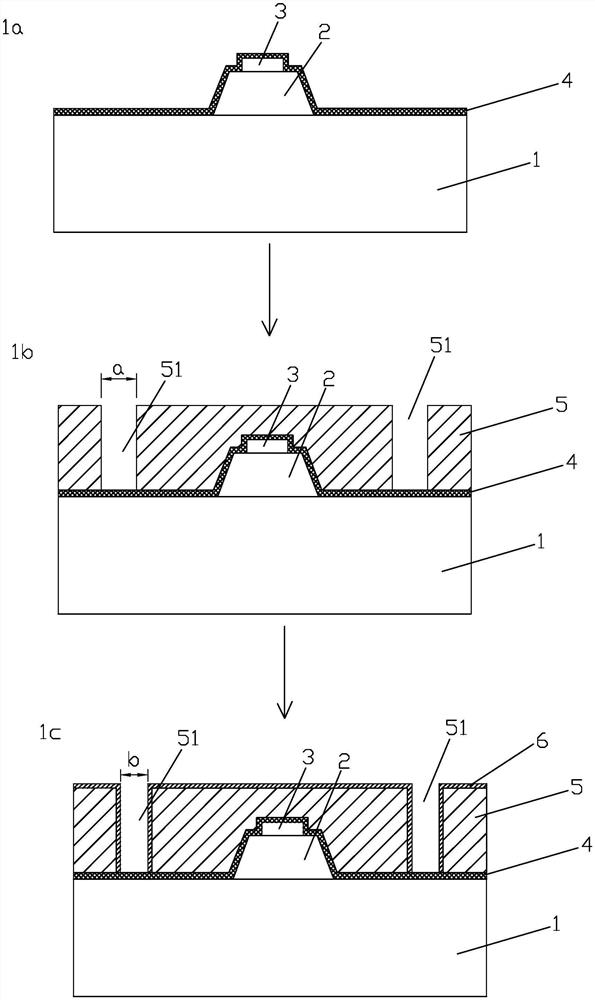

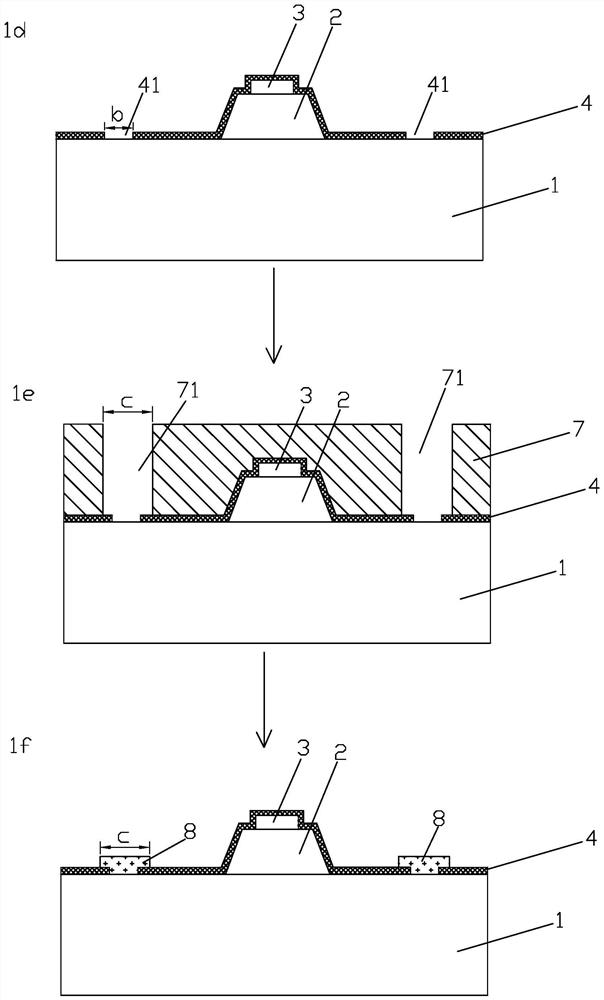

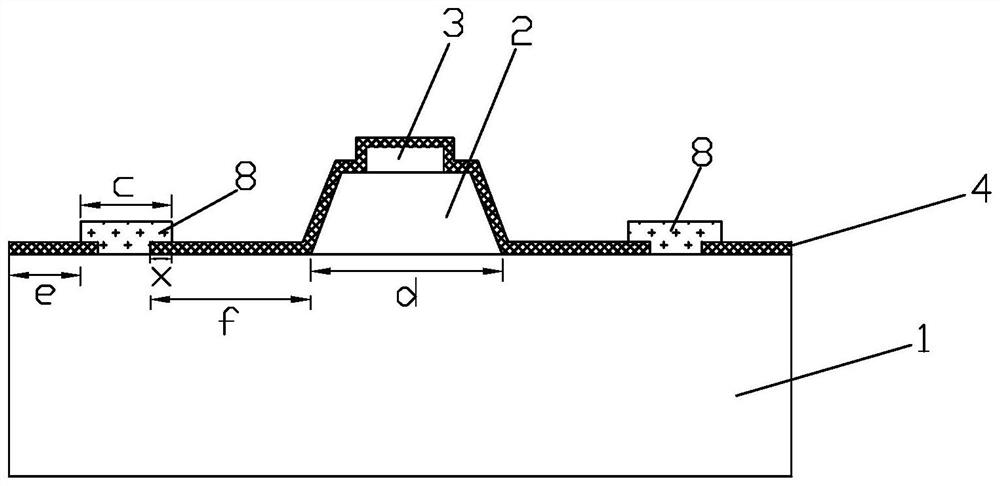

Ultralow ohmic contact resistance graphene transistor and preparation method thereof

ActiveCN103985762AReduce contact resistanceIncrease the maximum oscillation frequencyTransistorSemiconductor/solid-state device manufacturingOhmic contactGraphene

The invention discloses an ultralow ohmic contact resistance graphene transistor comprising a substrate, and a source and a drain which are located on the substrate. A channel region is formed between the source and the drain. The channel region comprises a graphene layer, a dielectric layer and a gate from down to up successively. The preparation method of the ultralow ohmic contact resistance graphene transistor comprises the following steps: (1) the graphene layer is formed; (2) the dielectric layer is deposited; (3) on the dielectric layer, the channel region is covered with a photoresist pattern; (4) the exposed dielectric layer is corroded; (5) the exposed graphene layer is etched; (6) a source-drain ohmic contact metal is evaporated to form an ohmic contact metal layer; (7) the required source and drain regions are covered with the photoresist pattern; (8) the source and the drain are formed; (9) and the gate is formed. According to the method of the invention, the one-dimensional linear contact between the source-drain ohmic contact metal and the graphene can be realized so as to greatly reduce the contact resistance between the graphene and the metal, so that the maximum oscillation frequencycan be increased, and the applications of the graphene field effect transistor can be facilitated.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

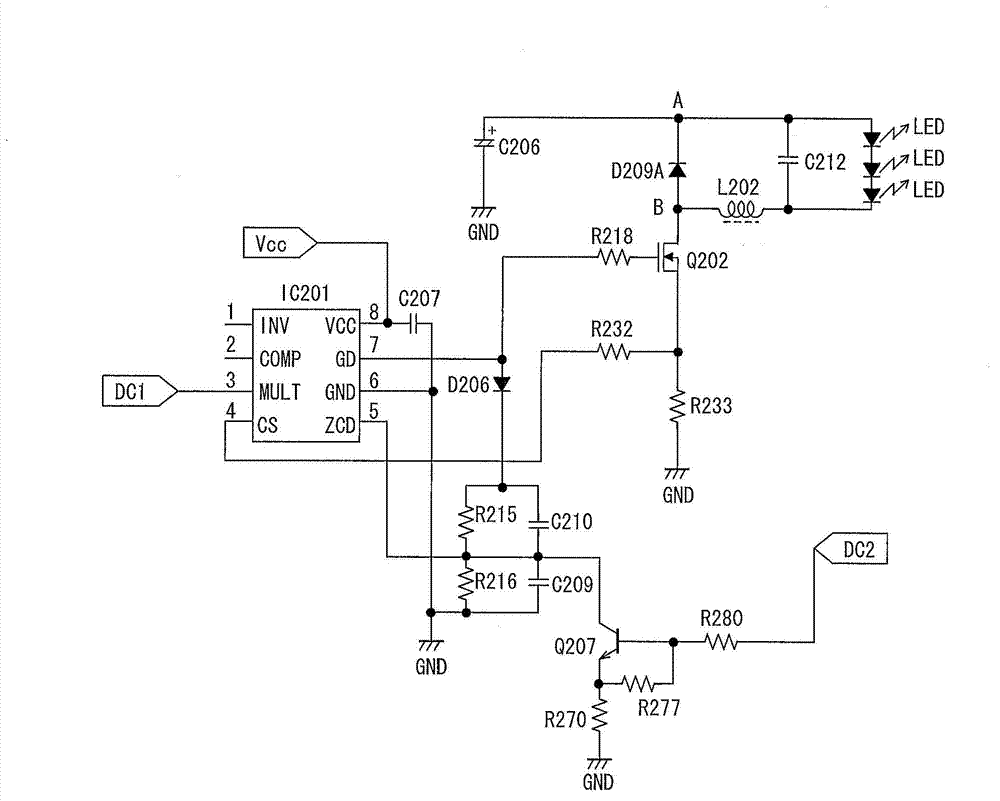

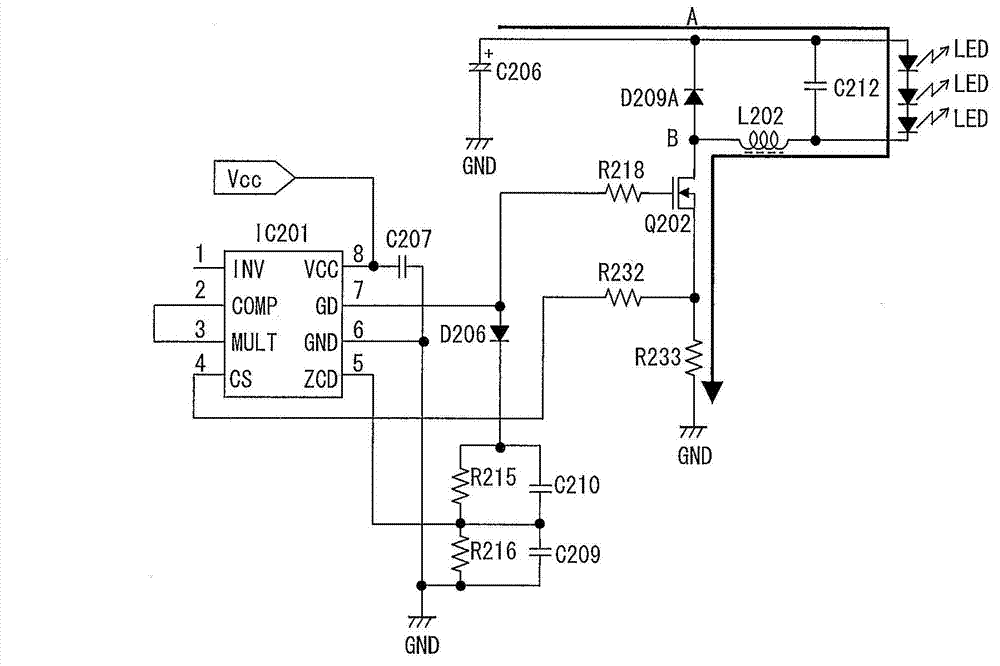

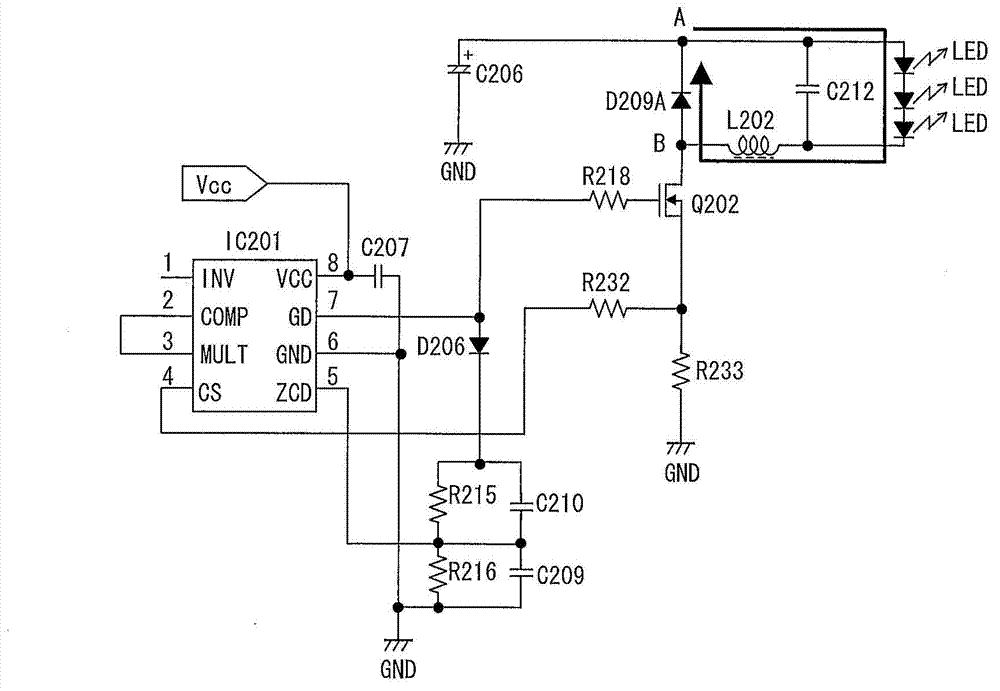

Led drive circuit and led driving method

InactiveCN102958244ANo need to increase oscillation frequencyIncrease the oscillation frequencyElectrical apparatusElectroluminescent light sourcesDriving currentLuminosity

An LED drive circuit of the present invention carries out, by use of a DC-to-DC converter (L202,Q202,D209A,C212), light control of an LED. The light control is carried out, in a region where a light control level is equal to or greater than a certain light control level, by a DC light control method for adjusting a pulse height of an LED drive current. The light control is carried out, in a region where a light control level is equal to or less than the certain light control level, by a PDM light control method for adjusting an off period of oscillation of the DC-to-DC converter.

Owner:SHARP KK

T-gate N-surface GaN/AlGaN fin-type high electron mobility transistor

InactiveCN109285883AReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionOhmic contact

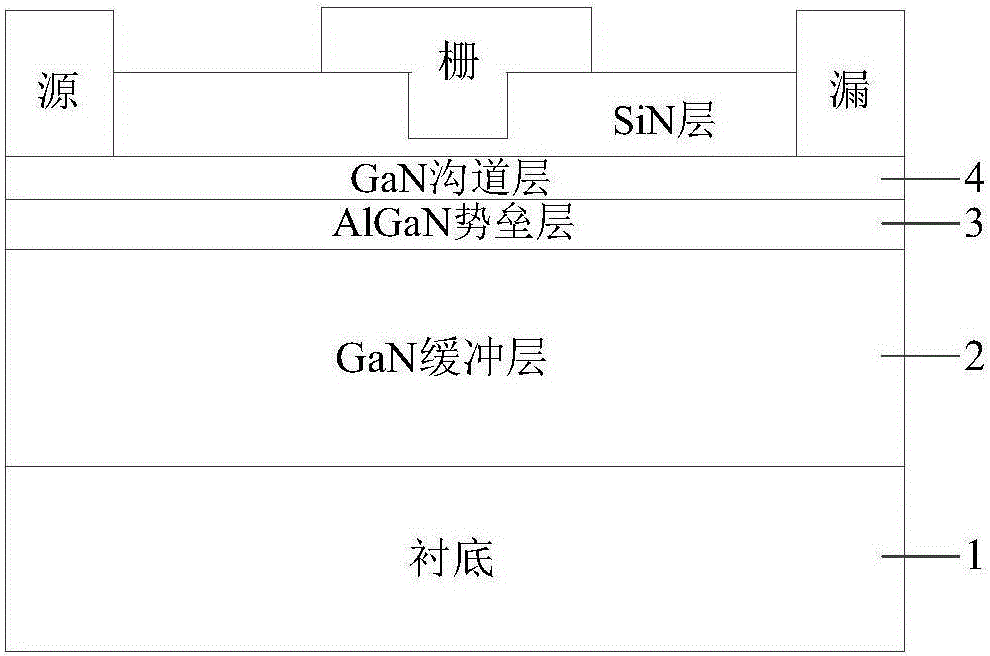

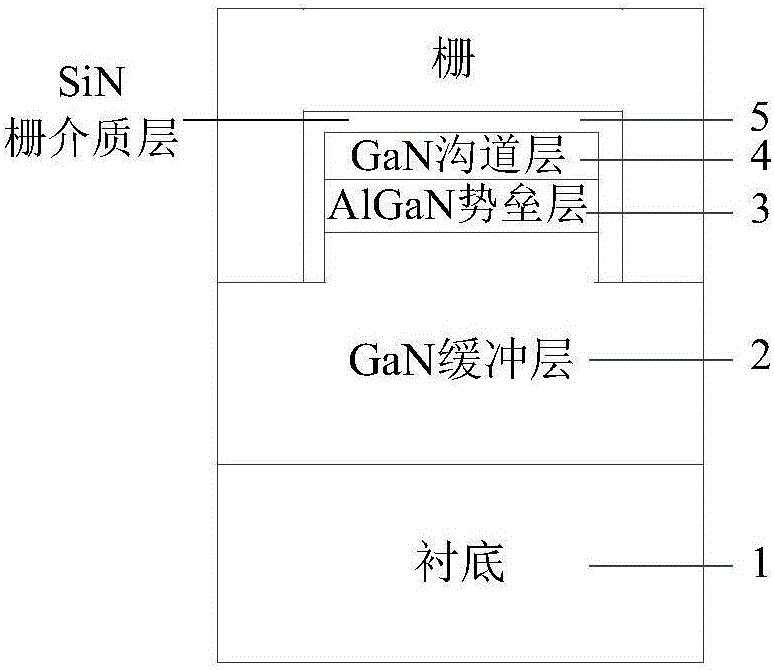

The invention discloses a T-gate N-surface GaN / AlGaN fin-type high electron mobility transistor, which mainly solves the problems of small maximum oscillating frequency, large ohmic contact resistanceand severe short channel effect of the existing microwave power devices. The transistor comprises a substrate (1), a GaN buffer layer (2), an AlGaN barrier layer (3), a GaN channel layer (4), a gatedielectric layer (5), a passivation layer (6), a source electrode, a drain electrode and a gate electrode from the bottom up, wherein the buffer layer and the channel layer adopt N-surface GaN materials; the GaN channel layer and the AlGaN barrier layer form a GaN / AlGaN heterojunction; and the gate electrode adopts a T-type gate and is wrapped at two sides and the upper portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate N-surface GaN / AlGaN fin-type high electron mobility transistor has the advantages of good gate control capability, small ohmic contact resistance and high maximum oscillating frequency, and can be used as a small-size microwave power device.

Owner:吴绍飞

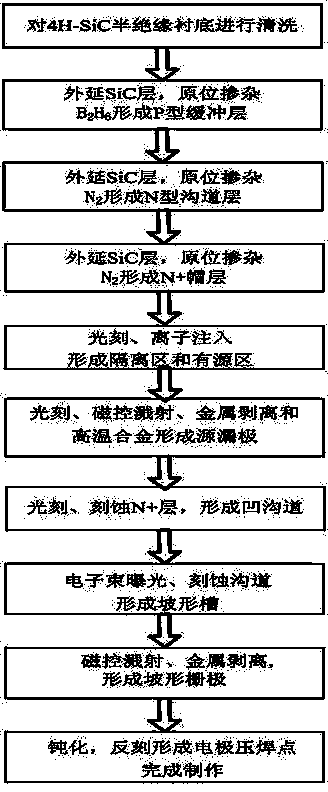

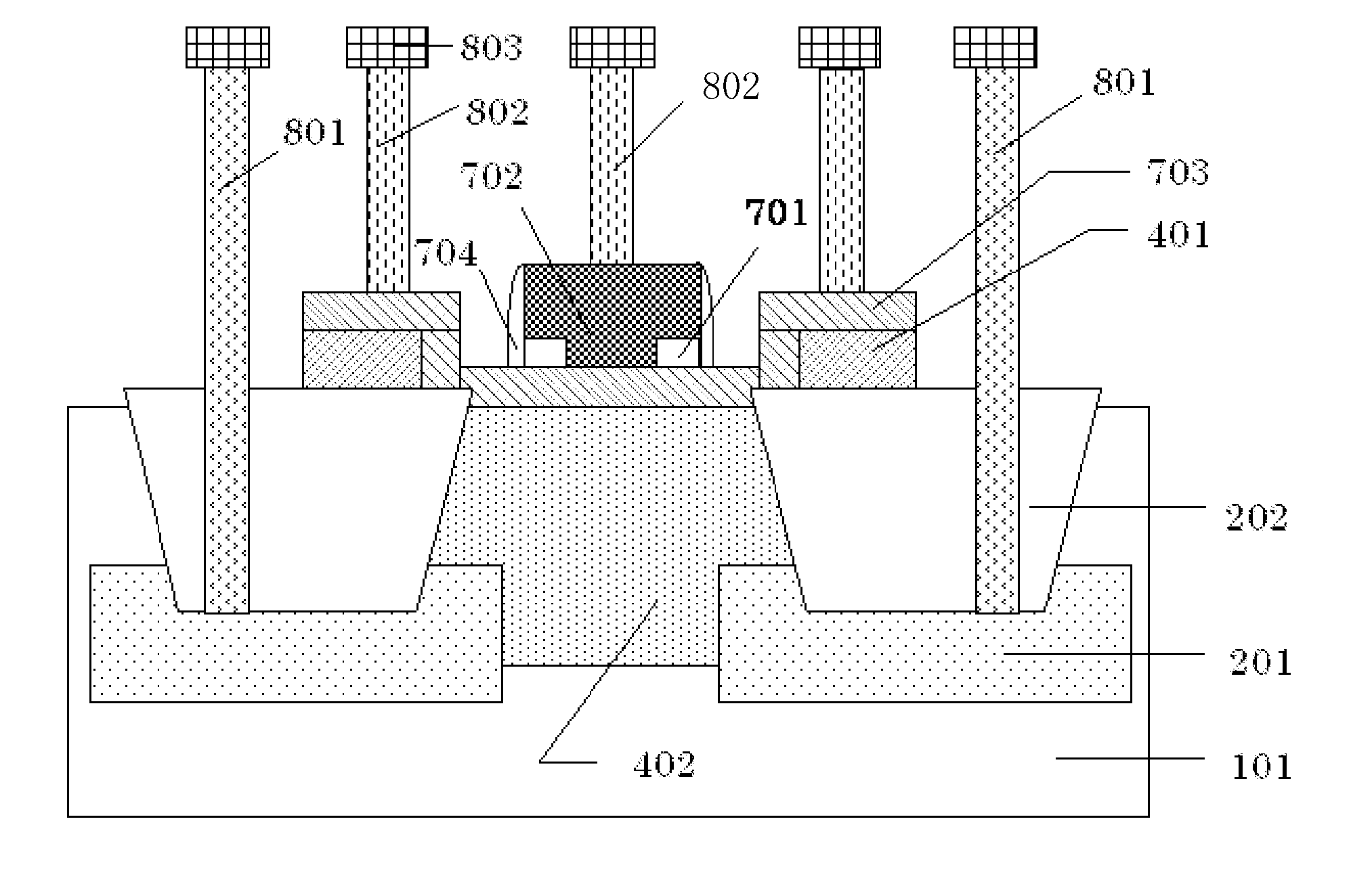

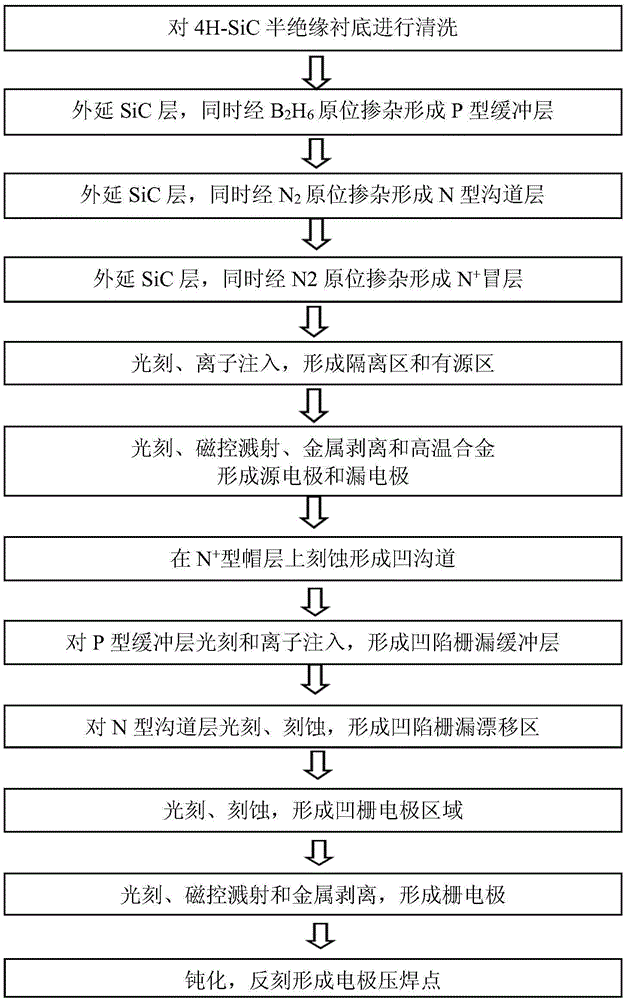

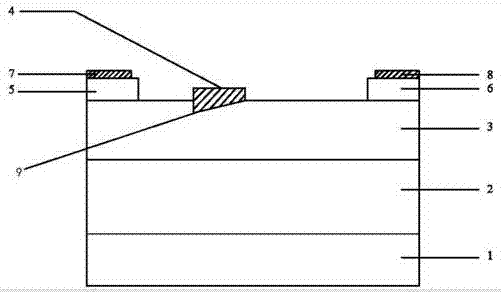

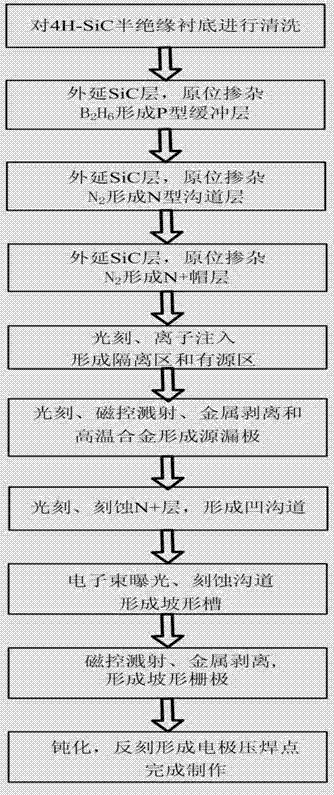

4H-SiC metal semiconductor field effect transistor with slope-shaped grid and manufacturing method

ActiveCN104282764ADrain current increasesLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowMetal

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a slope-shaped grid. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from bottom to top, a source electrode cap layer and a drain electrode cap layer are arranged on the surface of the N-type channel layer, a source electrode and a drain electrode are arranged on the surface of the source electrode cap layer and the surface of the drain electrode cap layer respectively, a slope-shaped groove inclined towards one side of the source electrode cap layer is formed in the upper end face of the N-type channel layer, the slope-shaped grid is arranged is arranged in the slope-shaped groove, the lower end face of the slope-shaped grid is matched with the slope-shaped groove, the upper end face of the slope-shaped grid is parallel to the upper end face of the N-type channel layer, and the distance between the slope-shaped grid and the source electrode cap layer is smaller than that between the slope-shaped grid and the drain electrode cap layer. The field effect transistor has the advantages of being high in drain electrode output current and excellent in frequency property.

Owner:XIDIAN UNIV

T-gate N-plane GaN/AlGaN fin high electron mobility transistor

InactiveCN109560118AReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionGate dielectric

The invention discloses a T-gate N-plane GaN / AlGaN fin high electron mobility transistor. The objective of the invention is to mainly solve the problems that a current microwave power device is smallin the maximum oscillation frequency, large in ohmic contact resistance and serious in the short channel effect. The T-gate N-plane GaN / AlGaN fin high electron mobility transistor comprises from bottom to top: a substrate (1), a GaN buffer layer (2), an AlGaN barrier layer (3), a GaN channel layer (4), a gate dielectric layer (5), a passivation layer (6), a source, a drain, and a gate. The bufferlayer and the channel layer are made of N-plane GaN materials; the GaN channel layer and the AlGaN barrier layer form a GaN / AlGaN heterojunction; the gate employs a T-shaped gate and coats the two sides and the top portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate N-plane GaN / AlGaN fin high electron mobility transistor is good in gate control capacity,small in the ohmic contact resistance and high in maximum oscillation frequency, and can be used as a mini-type microwave power device.

Owner:南京誉凯电子科技有限公司

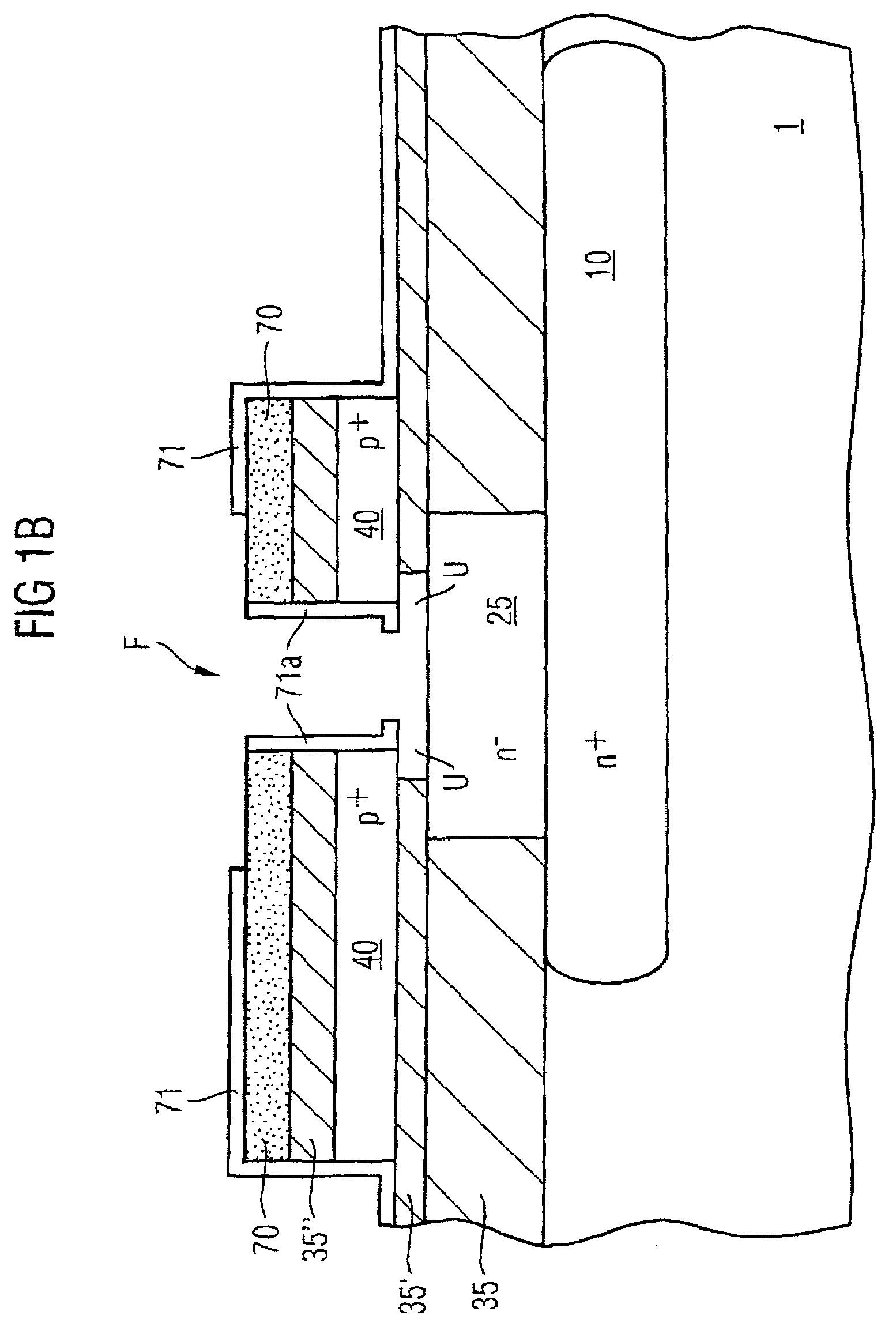

Method for the production of a bipolar semiconductor component, especially a bipolar transistor, and corresponding bipolar semiconductor component

InactiveUS7285470B2High frequency propertyImprove high-frequency propertySemiconductor/solid-state device manufacturingSemiconductor devicesGaseous atmosphereEngineering

The invention relates to a method for producing a bipolar semiconductor element, especially a bipolar transistor, and a corresponding bipolar semiconductor component. The inventive method comprises the following steps: a first semiconductor area (32, 34) of a first conductivity type (p) is provided above a semiconductor substrate (1); a connecting area (40) of the first conductivity type (p<+>) is provided above the semiconductor area (32, 34); a first insulating area (35″) is provided above the connecting area (40); a window (F) is formed within the first insulating area (35″) and the connecting area (40) so as to at least partly expose the semiconductor area (32, 34); a sidewall spacer (80) is provided in the window (F) in order to insulate the connecting area (40); a second semiconductor area (60) of the second conductivity type (n+) is provided so as to cover the sidewall spacer (80) and a portion of the surrounding first insulating area (35″); the surrounding first insulating area (35″) and the sidewall spacer (80) are removed in order to form a gap (LS) between the connecting area (40) and the second semiconductor area (60); and the gap (LS) is sealed by means of a second insulating area (100) while a gaseous atmosphere or a vacuum atmosphere is provided inside the sealed gap (LS).

Owner:INFINEON TECH AG

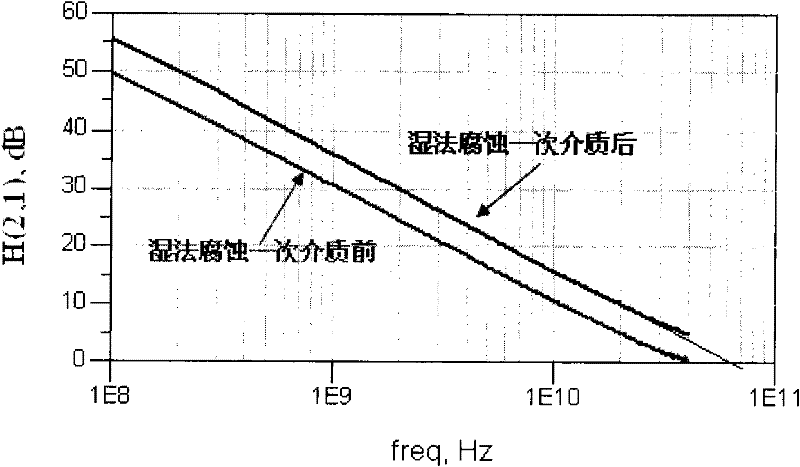

A method for improving frequency characteristics of algan/gan HEMT

InactiveCN102299071ARaise the cutoff frequencyIncrease the maximum oscillation frequencySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringFrequency characteristic

The invention discloses a method for improving the frequency characteristic of AlGaN / GaN HEMT, which comprises: wiring a millimeter-wave GaN HEMT device with a conventional structure, and then forming a metal protection pattern on the surface of the device by optical lithography; The wet etching process performs a medium corrosion on the device; peels and removes the glue on the etched device. The invention reduces parasitic capacitances of the gate source and the gate drain, and improves the cut-off frequency (ft) and the highest oscillation frequency (fmax) of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Ultra-low ohm contact resistance graphene transistor and preparation method thereof

ActiveCN103985762BReduce contact resistanceIncrease the maximum oscillation frequencyTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceOhmic contact

The invention discloses an ultralow ohmic contact resistance graphene transistor comprising a substrate, and a source and a drain which are located on the substrate. A channel region is formed between the source and the drain. The channel region comprises a graphene layer, a dielectric layer and a gate from down to up successively. The preparation method of the ultralow ohmic contact resistance graphene transistor comprises the following steps: (1) the graphene layer is formed; (2) the dielectric layer is deposited; (3) on the dielectric layer, the channel region is covered with a photoresist pattern; (4) the exposed dielectric layer is corroded; (5) the exposed graphene layer is etched; (6) a source-drain ohmic contact metal is evaporated to form an ohmic contact metal layer; (7) the required source and drain regions are covered with the photoresist pattern; (8) the source and the drain are formed; (9) and the gate is formed. According to the method of the invention, the one-dimensional linear contact between the source-drain ohmic contact metal and the graphene can be realized so as to greatly reduce the contact resistance between the graphene and the metal, so that the maximum oscillation frequencycan be increased, and the applications of the graphene field effect transistor can be facilitated.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

GaN heterojunction field effect transistor with high frequency and low junction temperature

InactiveCN110112208ALower peak temperatureInhibit thermogenesisTransistorHeterojunctionJunction temperature

The invention relates to the technical field of power semiconductors, in particular to a GaN heterojunction field effect transistor with a high frequency and a low junction temperature. The GaN heterojunction field effect transistor mainly takes an InAlN as the barrier layer material of a device, the reverse piezoelectric effect is avoided when the InAlN and GaN form a heterojunction so as to overcome the defects that AlGaN is used as the barrier layer material in a traditional structure and facilitate improvement of the working frequency of the device. Besides, the barrier layer employs a biconcave structure, the two sides of a gate are both provided with grooves to improve the electric field distribution condition of a channel, improve the device voltage withstand and reduce the heat generation of the device channel. The channel temperature of the device is reduced, the bad influence of a 'self-heating effect' on the device is weakened, and the working frequency of the device is improved. The GaN heterojunction field effect transistor is especially suitable for the GaN heterojunction field effect transistor with a high frequency and a low channel temperature.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Sige HBT and method of manufacturing the same

ActiveUS20130113020A1Raise the cutoff frequencyBase region is reducedSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPolysilicon gate

A SiGe HBT is disclosed, which includes: a silicon substrate; shallow trench field oxides formed in the silicon substrate; a pseudo buried layer formed at bottom of each shallow trench field oxide; a collector region formed beneath the surface of the silicon substrate, the collector region being sandwiched between the shallow trench field oxides and between the pseudo buried layers; a polysilicon gate formed above each shallow trench field oxide having a thickness of greater than 150 nm; a base region on the polysilicon gates and the collector region; emitter region isolation oxides on the base region; and an emitter region on the emitter region isolation oxides and a part of the base region. The polysilicon gate is formed by gate polysilicon process of a MOSFET in a CMOS process. A method of manufacturing the SiGe HBT is also disclosed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

4H-SiC metal semiconductor field effect transistor having partial sinking channel

ActiveCN105118867AIncrease currentLower impedanceTransistorSemiconductor/solid-state device manufacturingPower flowFrequency characteristic

The invention discloses a 4H-SiC metal semiconductor field effect transistor having a partial sinking channel. The 4H-SiC metal semiconductor field effect transistor having a partial sinking channel, from the bottom to the top, comprises a 4H-SiC half insulation substrate, a P type buffer layer, and an N type channel layer; the N type channel layer surface is provided with a source electrode cap layer and a drain electrode cap layer; the surfaces of the source electrode cap layer and the drain electrode cap layer are provided with a source electrode and a drain electrode; a grating electrode is formed above the N type channel layer and close to one side of the source electrode cap layer; part of the grating electrode close to the source electrode cap layer concaves downwardly to form a concave grating structure; a concave grating drain drifting area is formed between the grating electrode and the drain electrode cap layer; a concave grating drain buffer layer is formed on the upper end surface of a P buffer layer and close to the portion between the drain electrode cap layer and the concave grating drain side; and the concave depth of the concave grating drain drifting area is identical to that of the concave grating drain buffer layer. The 4H-SIC metal semiconductor field effect transistor having a partial sinking channel has advantages that the drain electrode is big in output current, the breakdown voltage is high and frequency characteristic is good.

Owner:XIDIAN UNIV

Method for the production of a bipolar semiconductor component and corresponding bipolar semiconductor component

InactiveCN1771605AImprove deteriorationReduce noiseSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor deviceSemiconductor components

Owner:INFINEON TECH AG

4h-sic metal-semiconductor field-effect transistor with sloped gate and manufacturing method

ActiveCN104282764BDrain current increasesLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSemi insulating

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a slope-shaped grid. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from bottom to top, a source electrode cap layer and a drain electrode cap layer are arranged on the surface of the N-type channel layer, a source electrode and a drain electrode are arranged on the surface of the source electrode cap layer and the surface of the drain electrode cap layer respectively, a slope-shaped groove inclined towards one side of the source electrode cap layer is formed in the upper end face of the N-type channel layer, the slope-shaped grid is arranged is arranged in the slope-shaped groove, the lower end face of the slope-shaped grid is matched with the slope-shaped groove, the upper end face of the slope-shaped grid is parallel to the upper end face of the N-type channel layer, and the distance between the slope-shaped grid and the source electrode cap layer is smaller than that between the slope-shaped grid and the drain electrode cap layer. The field effect transistor has the advantages of being high in drain electrode output current and excellent in frequency property.

Owner:XIDIAN UNIV

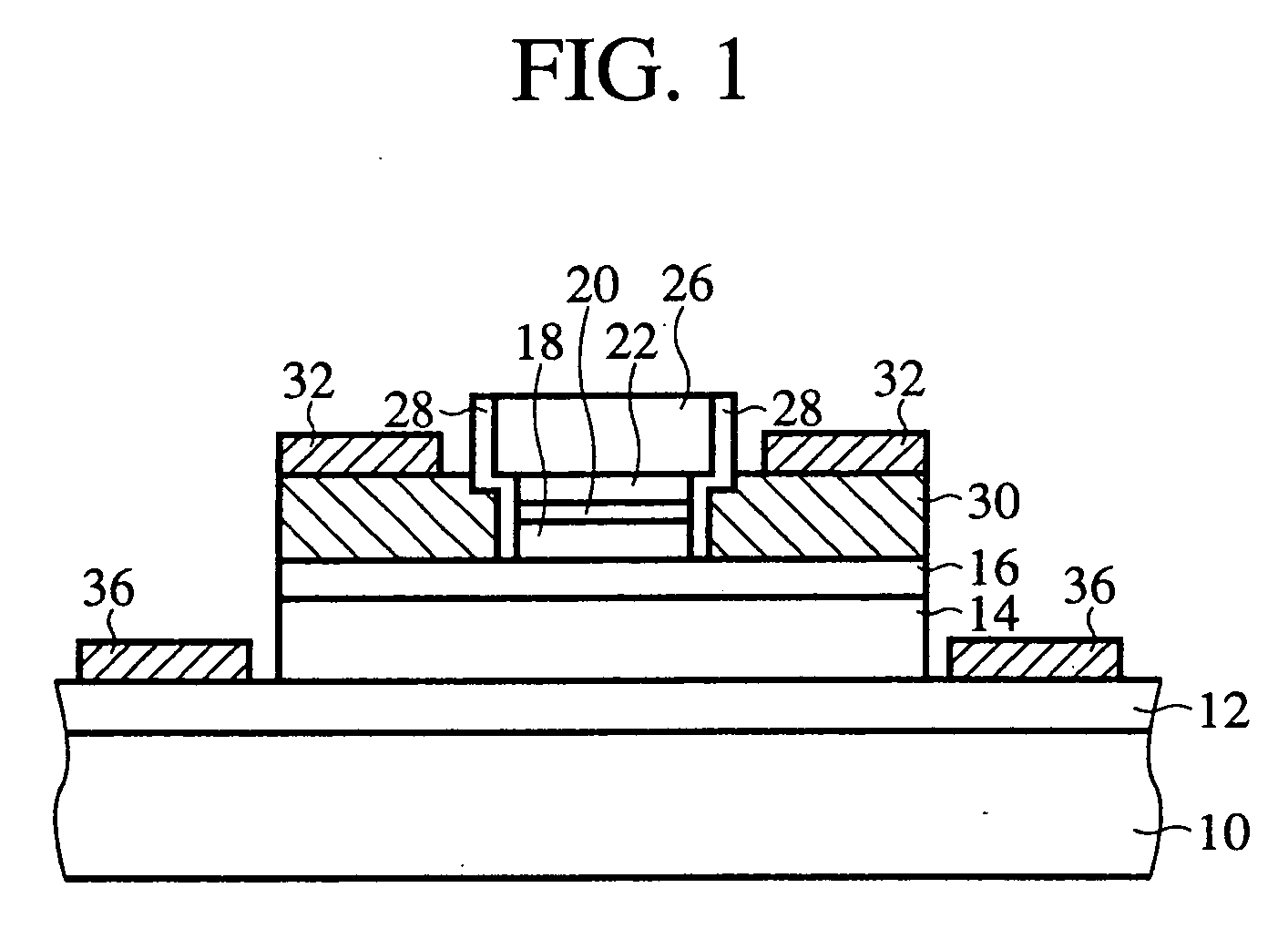

Semiconductor device and method for fabricating the same

InactiveUS20060284213A1Lower base resistanceImprove reliabilityTransistorSemiconductor/solid-state device manufacturingDevice materialContact layer

The semiconductor device comprises a collector layer 14; a base layer 16 of a carbon-doped GaxIn1-xAsySb1-y layer having one surface connected to the collector layer 14; an emitter layer 18 connected the other surface of the base layer 16; a base contact layer 30 of a carbon-doped GaAsSb layer electrically connected to the base layer 16; and a base electrode 32 formed on the base contact layer 30. The semiconductor device of such structure can have a much reduced base resistance RB, whereby InP / GaInAsSb-based HBTs including InP / InGaAs-based HBTs can have higher maximum oscillation frequency fmax. Because of the carbon-doped semiconductor layer the semiconductor device can have higher reliability.

Owner:FUJITSU LTD

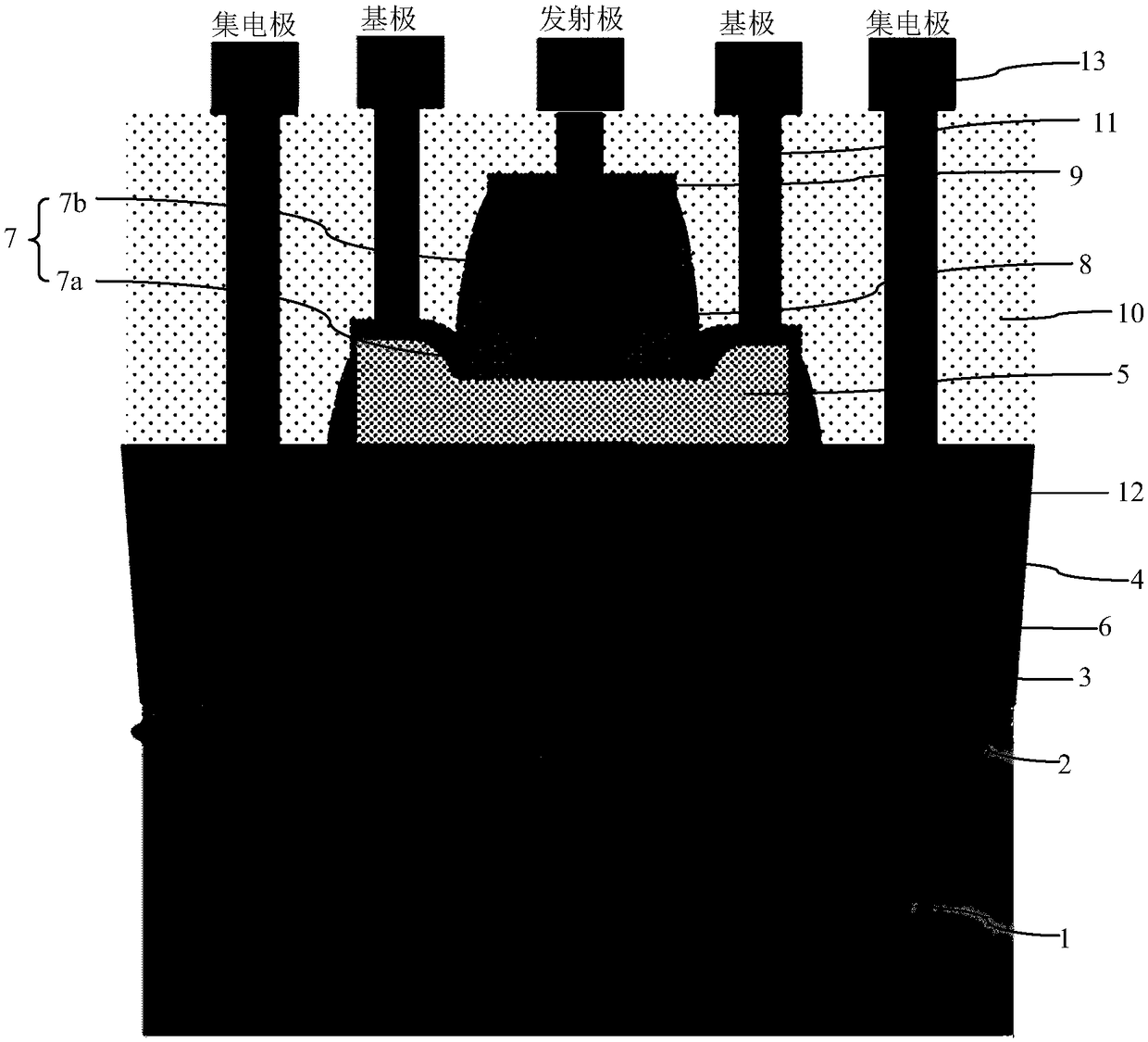

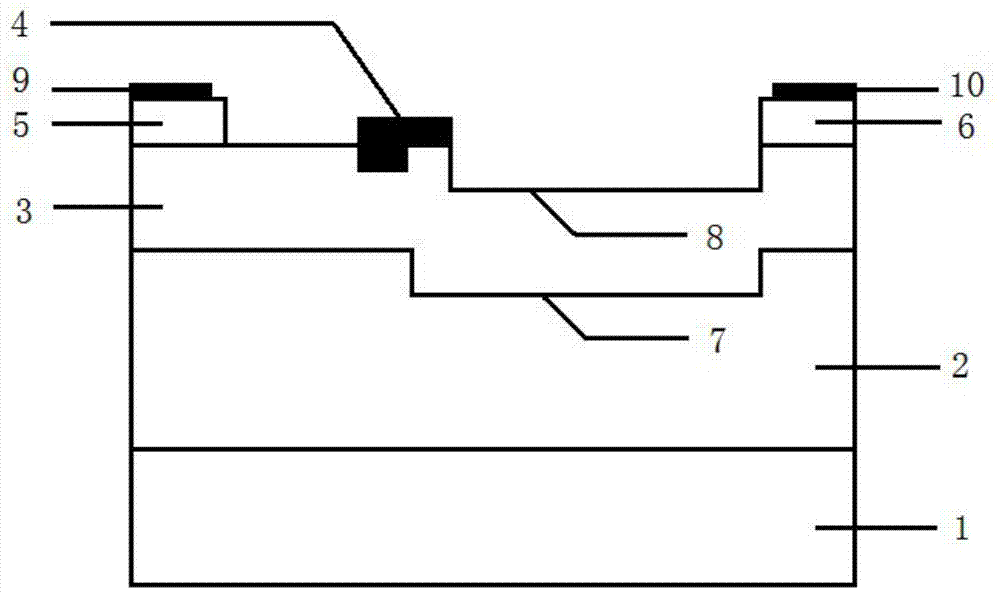

Germanium-silicon heterojunction bipolar transistor and manufacturing method

InactiveCN108110052AReduce processing costsQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSilicon heterojunction

The invention discloses a germanium-silicon heterojunction bipolar transistor. A base region is defined by a base region window formed after photoetching and etching of a base region window substratelayer comprising a first polycrystalline silicon layer, a P-type germanium-silicon epitaxial layer forming the base region is formed by a comprehensive nonselective epitaxial growth technology, and apolycrystalline structure, positioned on the side surface of the base region window, of the P-type germanium-silicon epitaxial layer is in contact with the first polycrystalline silicon layer to formouter base region polycrystalline silicon; an emitter region window is defined in a self-alignment manner through a first side wall formed on the side face of the base region window in the self-alignment manner, and emitter region polycrystalline silicon is formed by filled second polycrystalline silicon and a second substrate layer on the top of the base region window substrate layer as a terminating layer after polycrystalline silicon grinding. The invention also discloses a manufacturing method of the germanium-silicon heterojunction bipolar transistor. The process cost of the P-type germanium-silicon epitaxial layer can be reduced to be lower, the resistance of the base region can be reduced, the transverse dimensions of the whole device are reduced, and the maximum oscillation frequency of the device can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

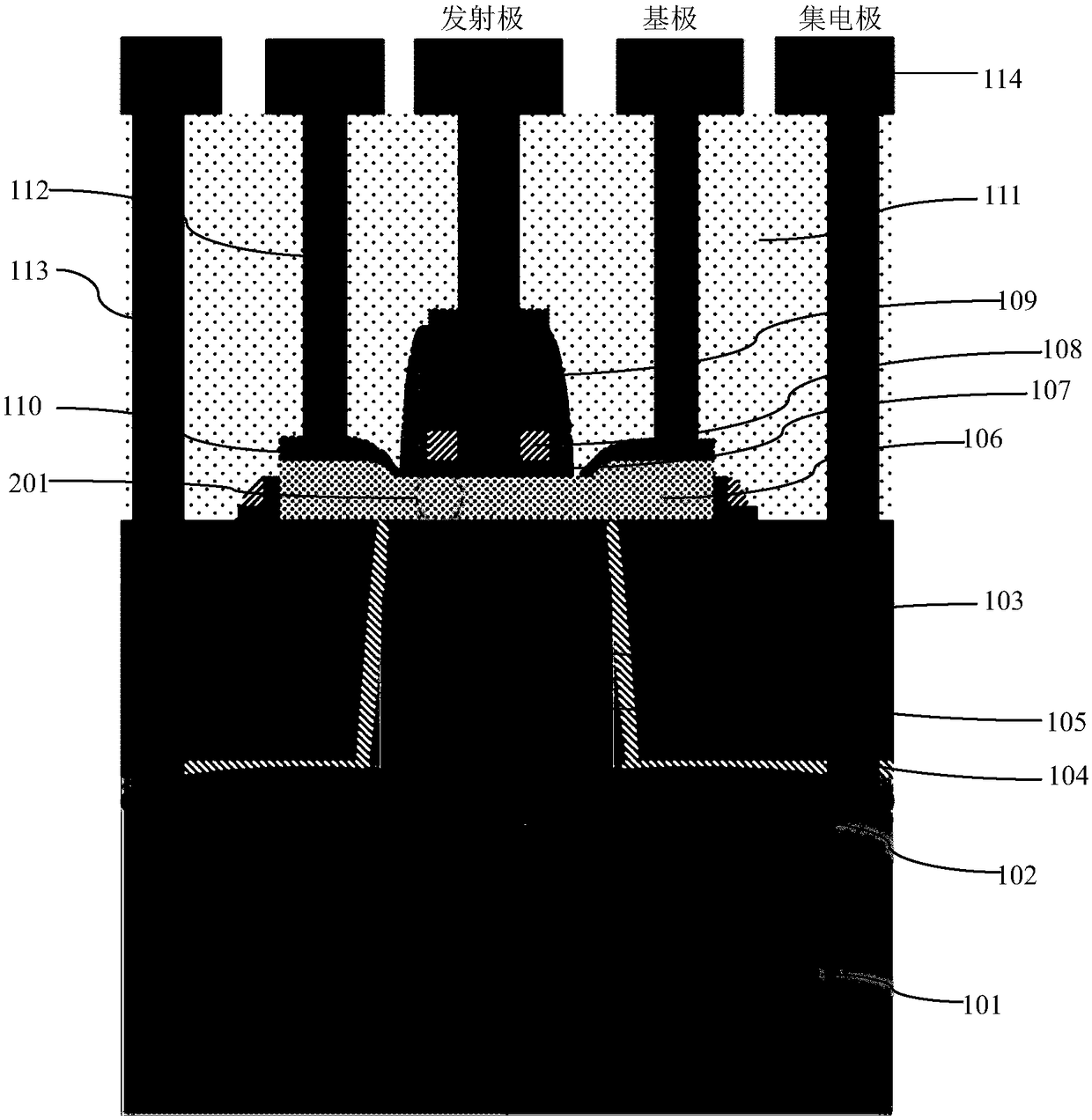

Structure for reducing b-c junction capacitance of heterojunction bipolar transistor and manufacturing method thereof

ActiveCN113078063AReduce junction areaLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention discloses a structure for reducing the b-c junction capacitance of a heterojunction bipolar transistor and a manufacturing method thereof, and the method comprises the steps: firstly coating a chip structure with a first light resistor, exposing and developing the first light resistor to form a first window, then coating a second light resistor, and forming a second window; after the line width of the first window is reduced through a miniature and backflow process, etching the passivation layer in the first window to form a first opening, after the photoresist is removed, coating the passivation layer with a third photoresist, performing exposure and development to form a second window located on the first opening, wherein the line width of the second window is larger than that of the first opening; and depositing metal in the second window and the first opening to form base metal, and removing light resistance. The base metal structure with the bottom line width smaller than the top line width is formed, the b-c junction area is reduced under the condition that the base resistance is not increased, the effect of reducing the b-c junction capacitance is achieved, and therefore the highest oscillation frequency is improved.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

A structure and production method of reducing heterogeneous knot dual-crystal tube B-C knotted capacitance

ActiveCN113078063BReduce junction areaLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

t-gate n-plane gan/algan fin high electron mobility transistor

ActiveCN105914232BReduce contact resistanceFlexibility to reduce the distanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionOhmic contact

The present invention discloses a T-gate and N-surface GaN / AlGaN fin-type high electron mobility transistor. The problems are mainly solved that the maximum oscillating frequency of a current microwave power device is small, the ohmic contact resistor is large and the short channel effect is severe. The transistor comprises from down to up: a substrate (1), a GaN buffer layer (2), a ALGaN barrier layer (3), a GaN channel layer (4), a gate medium layer (5), a passivation layer (6), a source gate electrode and a drain gate electrode. The buffer layer and the channel layer employ N-surface GaN materials; the GaN channel layer and the ALGaN barrier layer form GaN / AlGaN heterojunction; the gate electrode employs T-type gate and is wrapped at two sides and the upper portion of the GaN / AlGaN heterojunction to form a three-dimensional gate structure. The T-gate and N-surface GaN / AlGaN fin-type high electron mobility transistor has good gate-control capability, small resistor and the maximum oscillating frequency, and is able to be a microwave power device with the small size.

Owner:XIDIAN UNIV

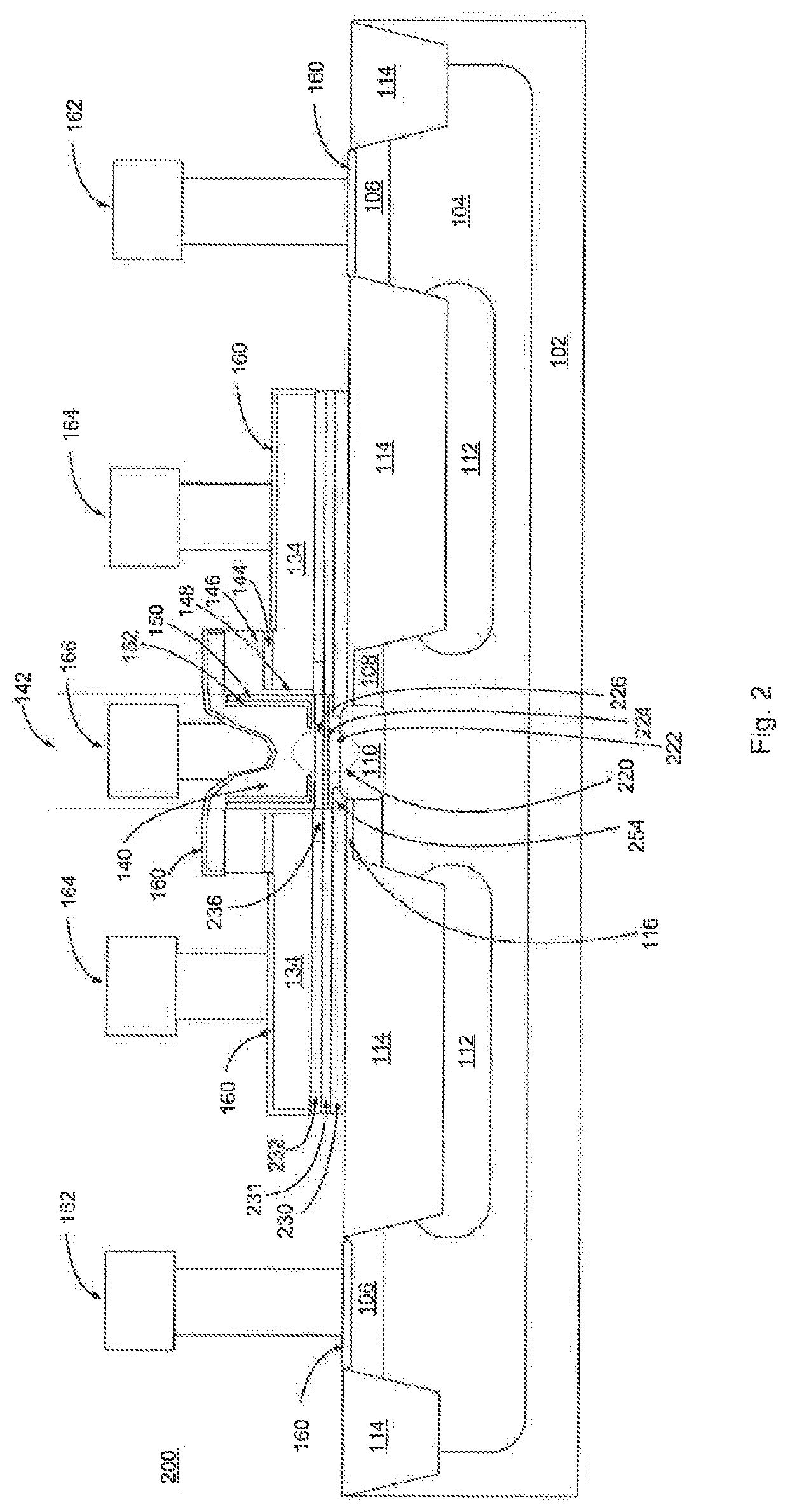

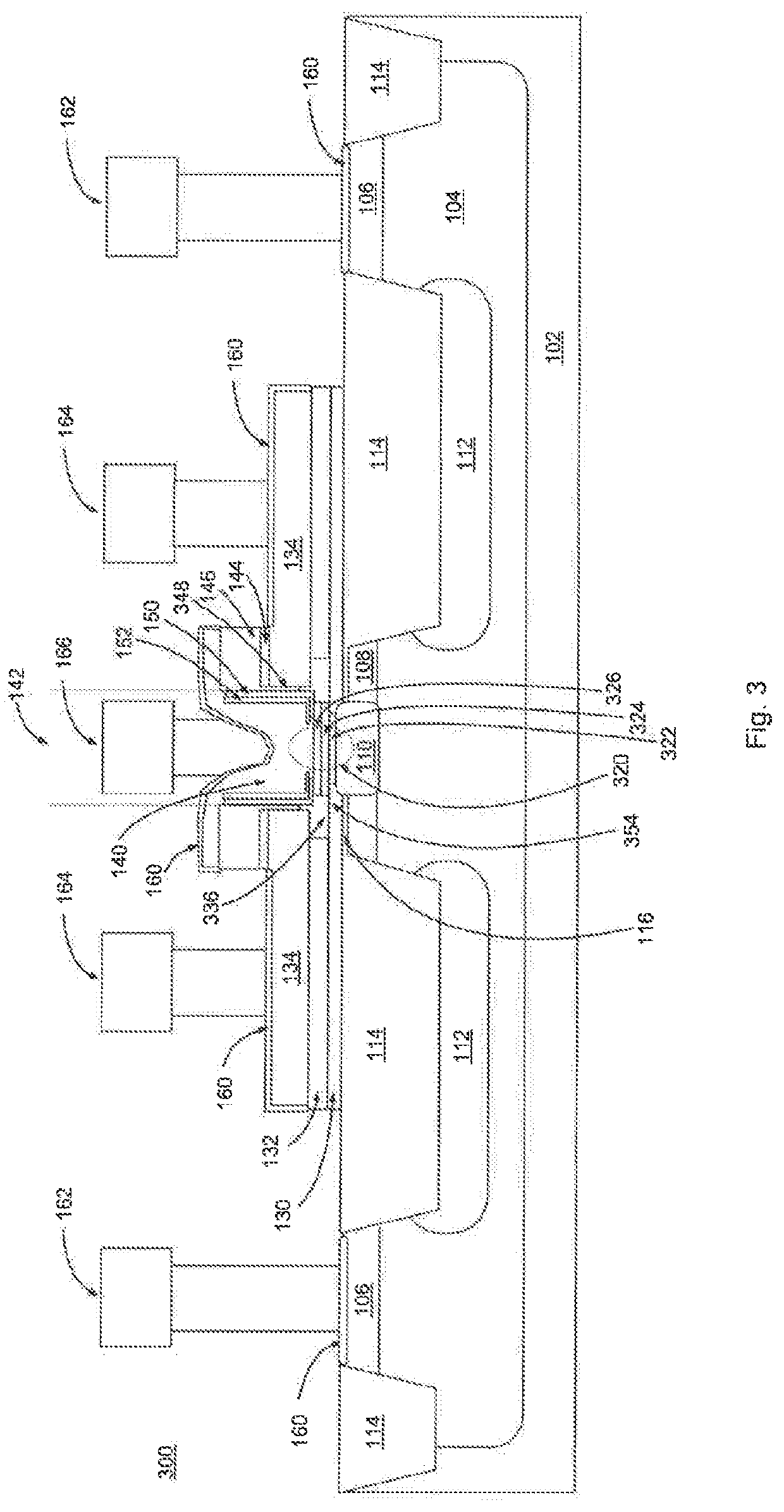

Semiconductor device and method of manufacturing a semiconductor device

ActiveUS10825922B2Increase the maximum oscillation frequencyReduce parasitic junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering physics

Owner:NXP USA INC

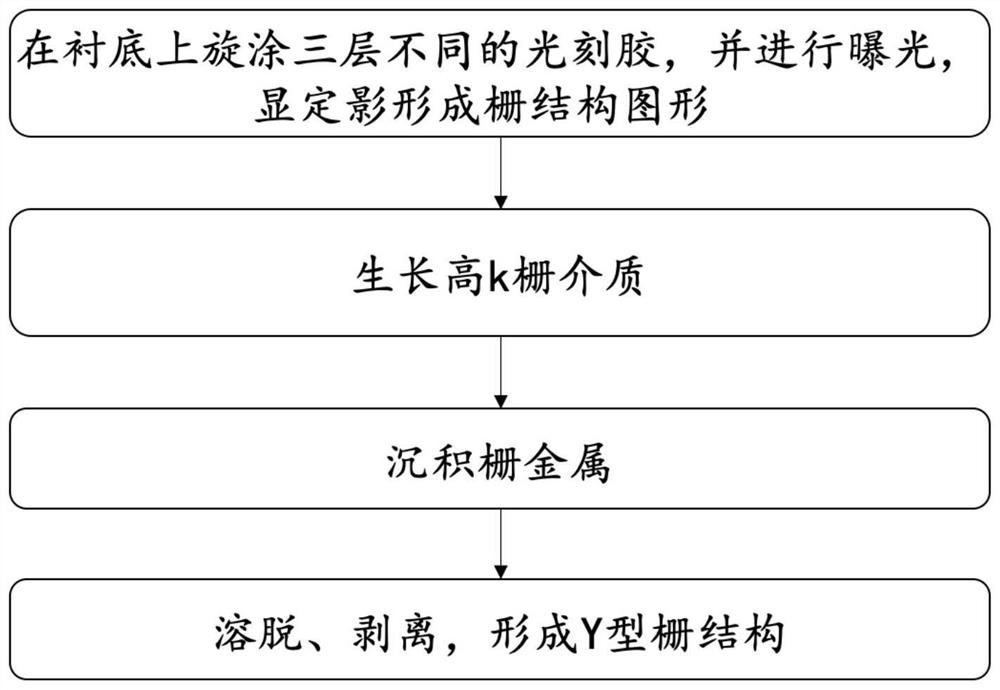

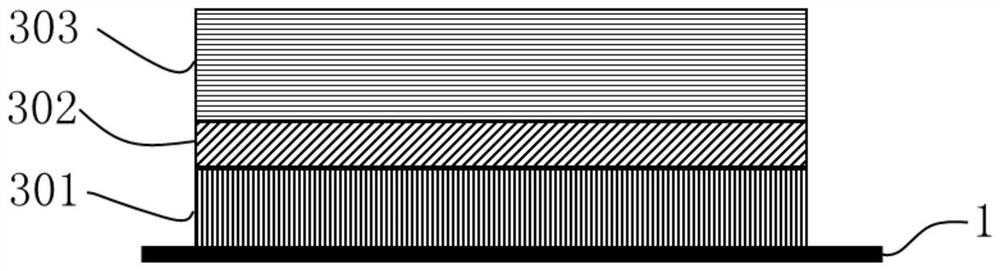

A Y-shaped grid structure based on carbon-based materials and its preparation method

ActiveCN112420821BReduce parasitic effectsIncrease the maximum oscillation frequencySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricPhysical chemistry

Owner:BEIJING INST OF CARBON BASED INTEGRATED CIRCUIT +2

Comb-type gate structure HEMT radio frequency device and preparation method thereof

ActiveCN113257910AImprove linearityImprove Noise PerformanceSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitorNoise

The invention relates to a comb-type gate structure HEMT radio frequency device and a preparation method thereof. The comb-type gate structure HEMT radio frequency device comprises an AlN buffer layer, an AlGaN buffer layer with a gradually-changed Al component, a GaN channel layer, an AlGaN layer, a source electrode, a drain electrode and a comb-type gate located between the source electrode and the drain electrode; the comb-type gate comprises a gate head and a gate foot; the gate foot comprises a first sub-gate foot, a second sub-gate foot and a third sub-gate foot; the first sub-gate foot, the second sub-gate foot and the third sub-gate foot are sequentially arranged on the surface of the AlGaN layer at intervals in the direction from the source electrode to the drain electrode, and an air gap is formed between every two adjacent sub-gate feet. Due to the arrangement of the comb-type gate structure, the gate resistance is reduced, the noise coefficient is reduced, and meanwhile, the gain is improved; a passivation layer medium is not arranged between the gate head and the gate foot, and air is arranged in a gap between the adjacent gate feet, so that the parasitic capacitance of the gate is reduced, and the cut-off frequency is improved; and the three gate feet are arranged at intervals, so that the control of the gate to a channel is enhanced, the transconductance is more stable along with the change of gate-source voltage, and the linearity is obviously improved.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Semiconductor device and method of manufacturing the same

InactiveUS7276744B2Reduce capacitySolve large capacityTransistorSolid-state devicesContact layerEngineering

This invention is intended to provide an HBT capable of achieving, if the HBT is a collector-up HBT, the constriction of the emitter layer disposed directly under an external base layer, and reduction in base-emitter junction capacity, or if the HBT is an emitter-up HBT, reduction in base-collector junction capacity. For the collector-up HBT, window structures around the sidewalls of a collector are used to etch either the emitter layer disposed directly under the external base layer, or an emitter contact layer For the emitter-up HBT, window structures around the sidewalls of an emitter are used to etch either the collector layer disposed directly under the external base layer, or a collector contact layer. In both HBTs, the external base layer is supported by a columnar structure to ensure mechanical strength.

Owner:RENESAS ELECTRONICS CORP

Silicon-germanium heterojunction bipolar transistor and manufacturing method

ActiveCN108258037AReduce processing costsSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesMetallurgyP type silicon

The invention discloses a silicon-germanium heterojunction bipolar transistor. A collector region consists of a global collector region and a local collector region, and is in contact with a pseudo buried layer. A base region is composed of a P-type silicon-germanium epitaxial layer formed on the surface of the collector region. An emitter region is composed of N-type polycrystalline silicon formed on the base region, and the N-type polycrystalline silicon consists of bottom polycrystalline silicon and top polycrystalline silicon. The local collector region and the emitter region window of thebottom polycrystalline silicon adopt the same photolithography definition to realize complete alignment of the local collector region and the bottom polycrystalline silicon. Before ion implantation in an outer base region, an emitter region window dielectric layer is removed. The ion implantation at a dip angle in the outer base region is self-aligned with the side of the bottom polycrystalline silicon, which increases the doping of an overlapping outer base region which is located outside the bottom polycrystalline silicon and covered by the top polycrystalline silicon and reduces the resistance of the base region. The invention further discloses a manufacturing method of the silicon-germanium heterojunction bipolar transistor. The characteristic frequency and the highest oscillation frequency of devices can be simultaneously improved. The silicon-germanium heterojunction bipolar transistor is applicable to the ultrahigh-frequency application requirement of devices, and is of low process cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A kind of fabrication method of 4h-sic metal-semiconductor field-effect transistor with partially sunken channel

ActiveCN105118867BIncrease currentLower impedanceTransistorSemiconductor/solid-state device manufacturingGratingPower flow

Owner:XIDIAN UNIV

Germanium-silicon heterogenous junction bipolar transistor and manufacturing method thereof

ActiveCN103137678AReduce widthReduce lateral spreadSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon impuritiesMaterials science

The invention discloses a germanium-silicon heterogenous junction bipolar transistor. An outer base region comprises germanium impurities or carbon impurities and P-type impurities, wherein the germanium impurities or the carbon impurities are injected in an autoregistration mode by using the outer side periphery of an emission region as an autoregistration boundary. The invention further discloses a manufacturing method of the germanium-silicon heterogenous junction bipolar transistor. According to the germanium-silicon heterogenous junction bipolar transistor and the manufacturing method of the germanium-silicon heterogenous junction bipolar transistor, due to the fact that the germanium impurities or the carbon impurities are injected into the outer base region, transverse diffusion of the P-type impurities can be reduced, the width of the outer base region can be reduced, and a maximum oscillation frequency of a device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com