Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

971 results about "Semi insulating" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

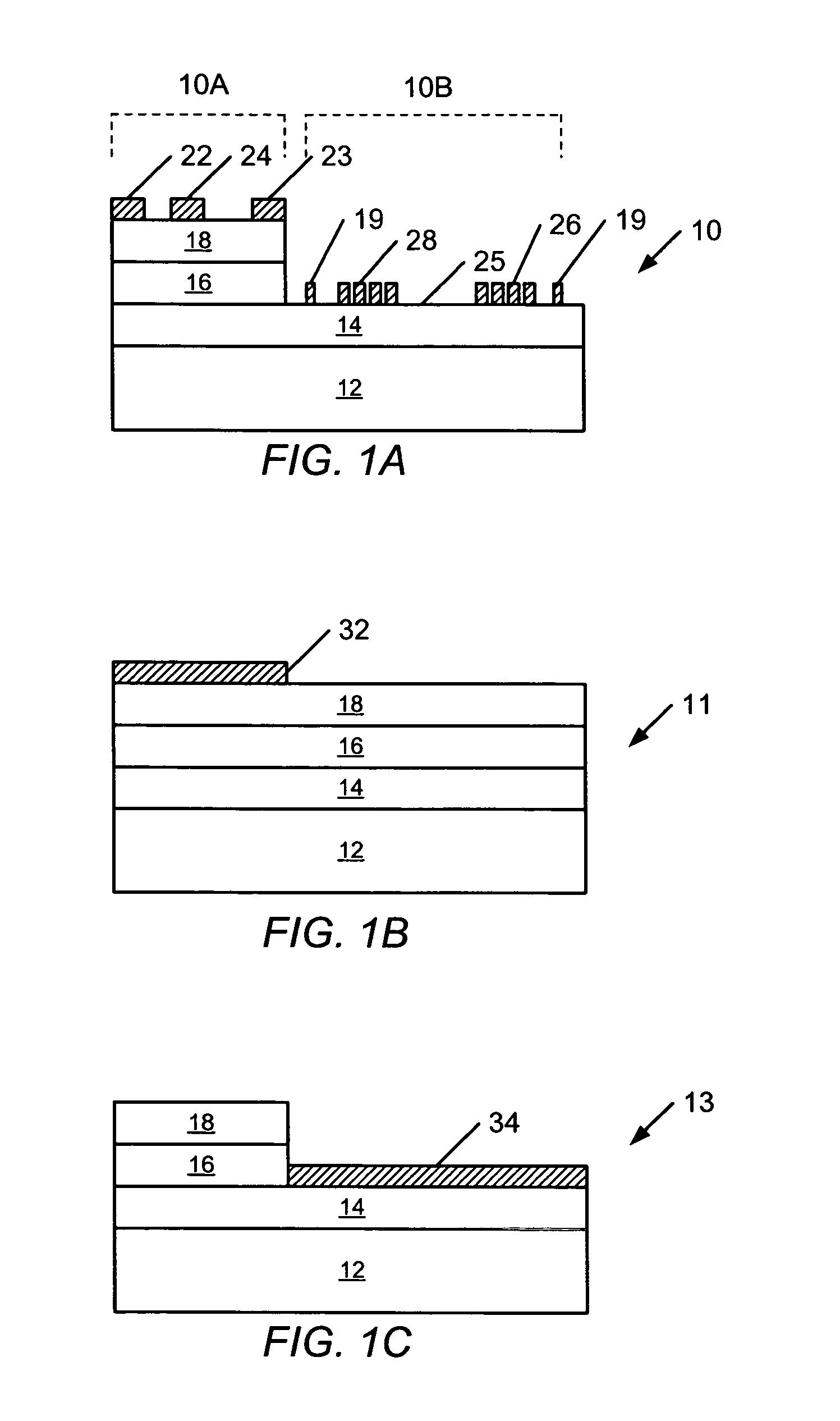

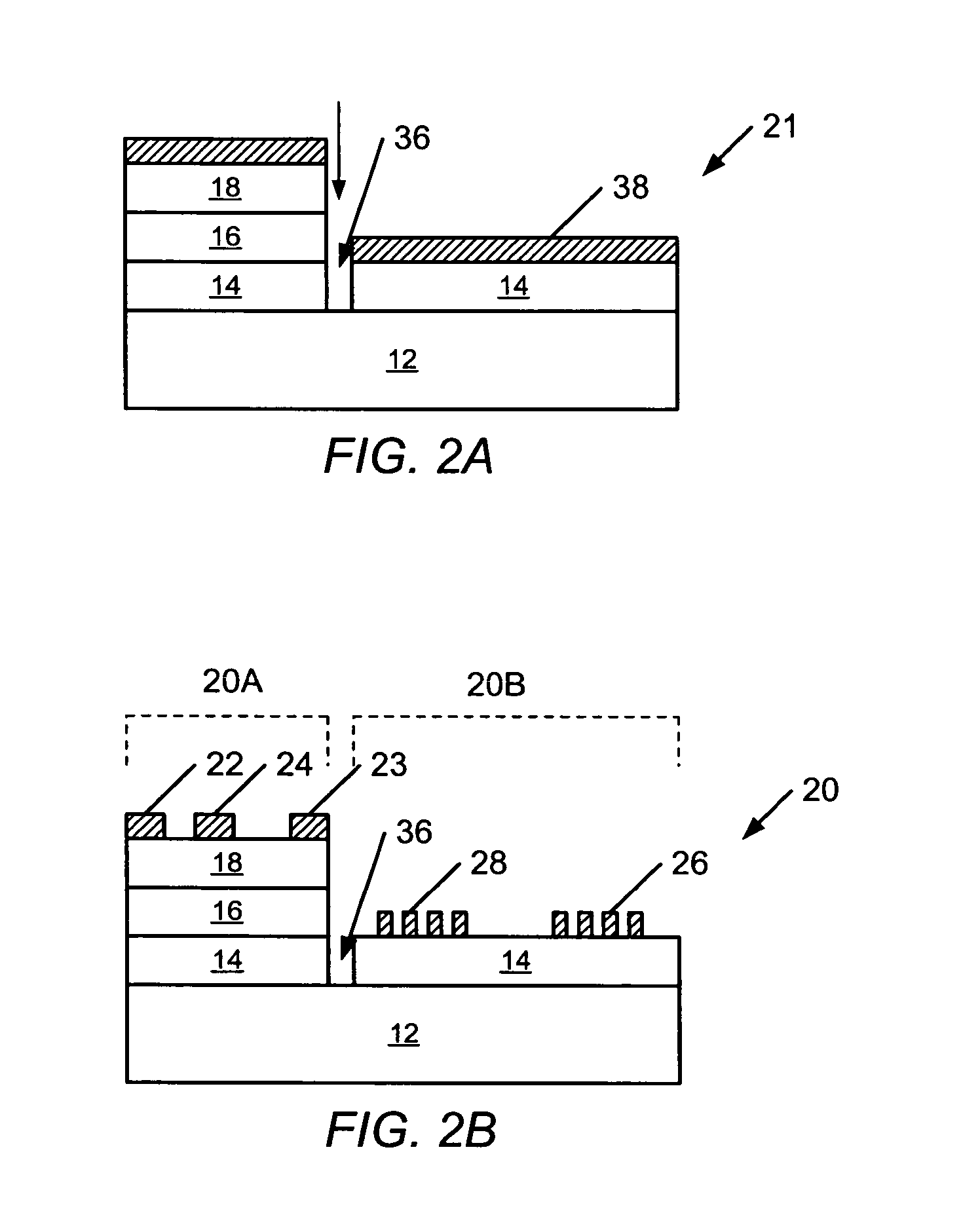

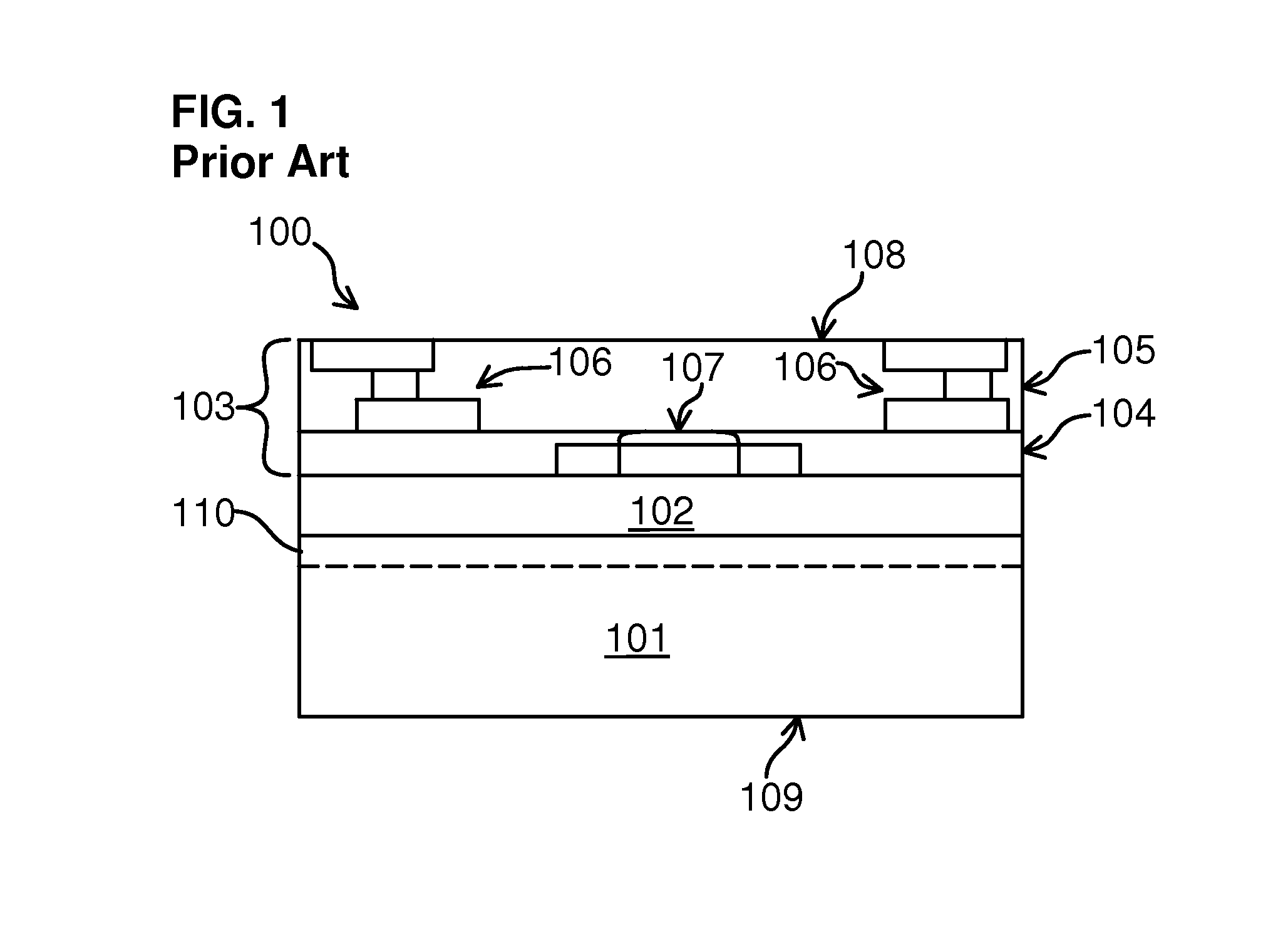

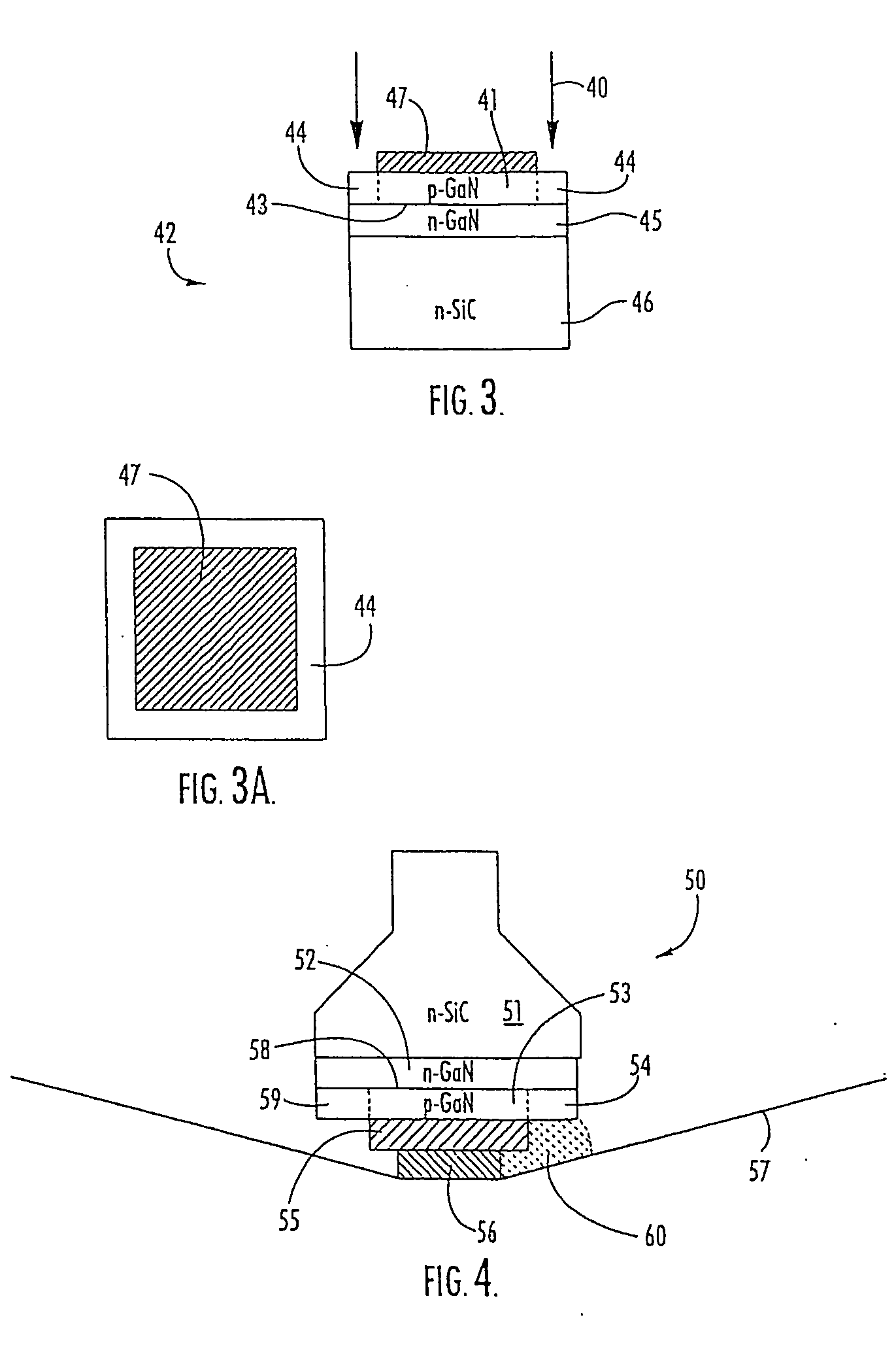

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS6316793B1Quality improvementImprove thermal conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideMaterials science

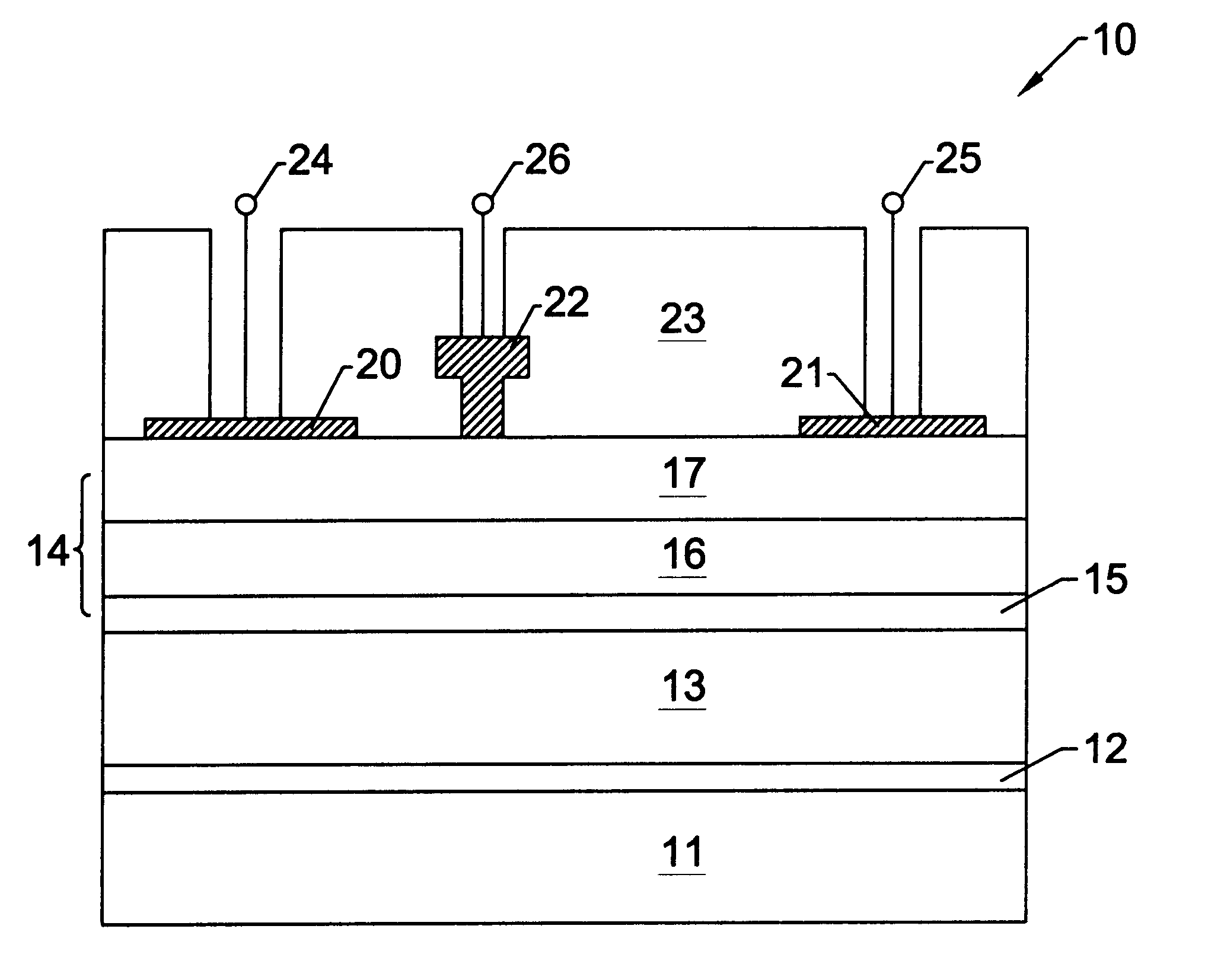

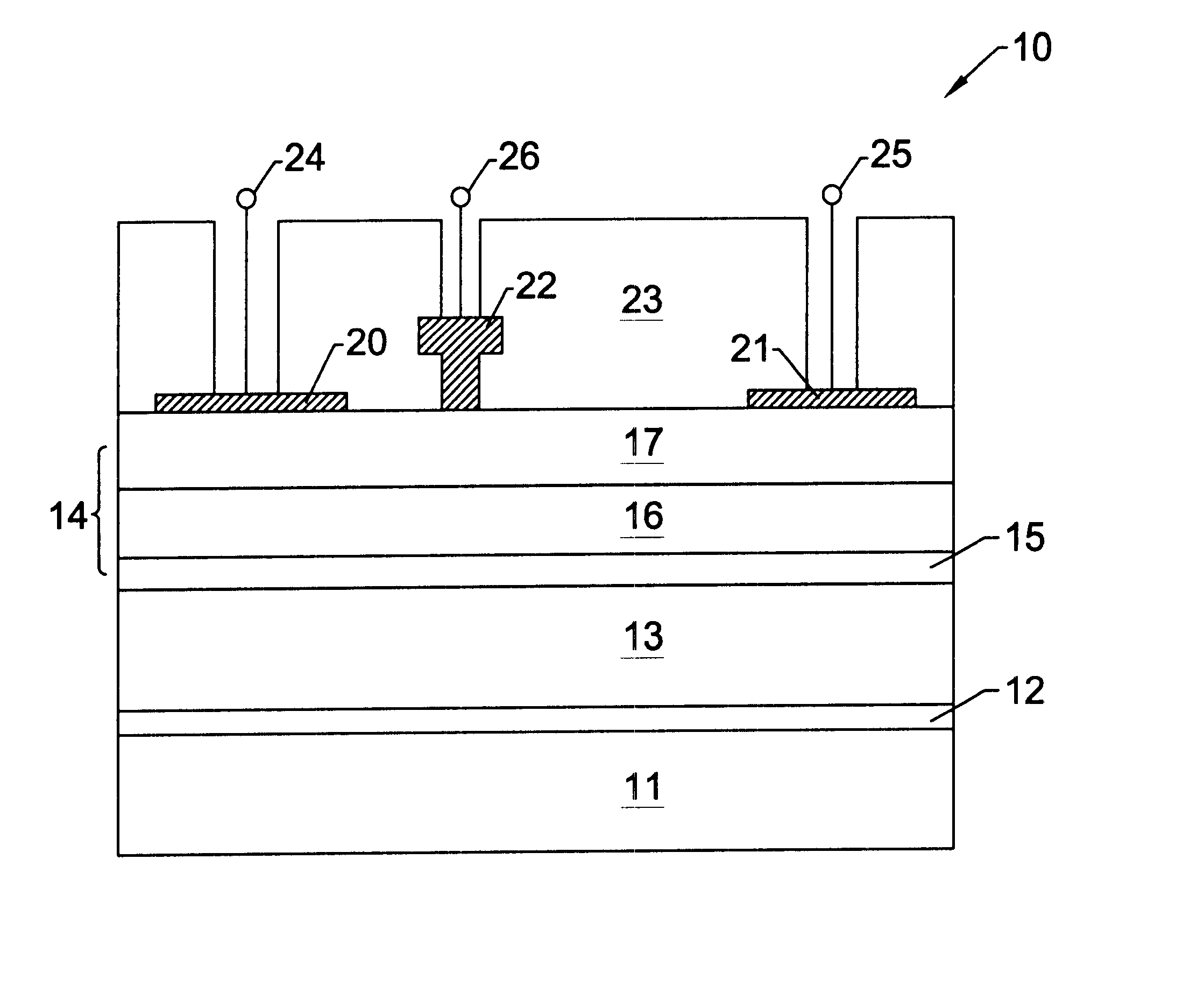

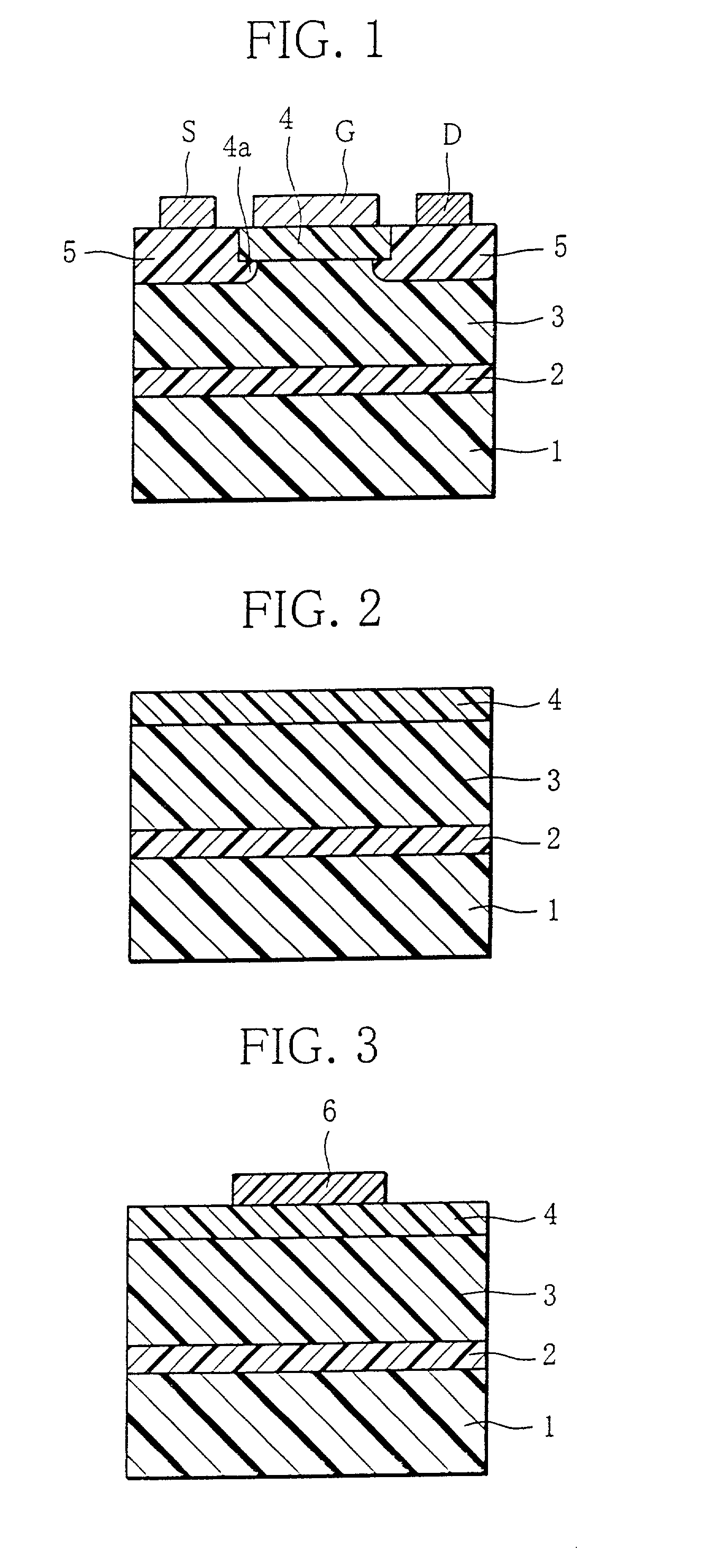

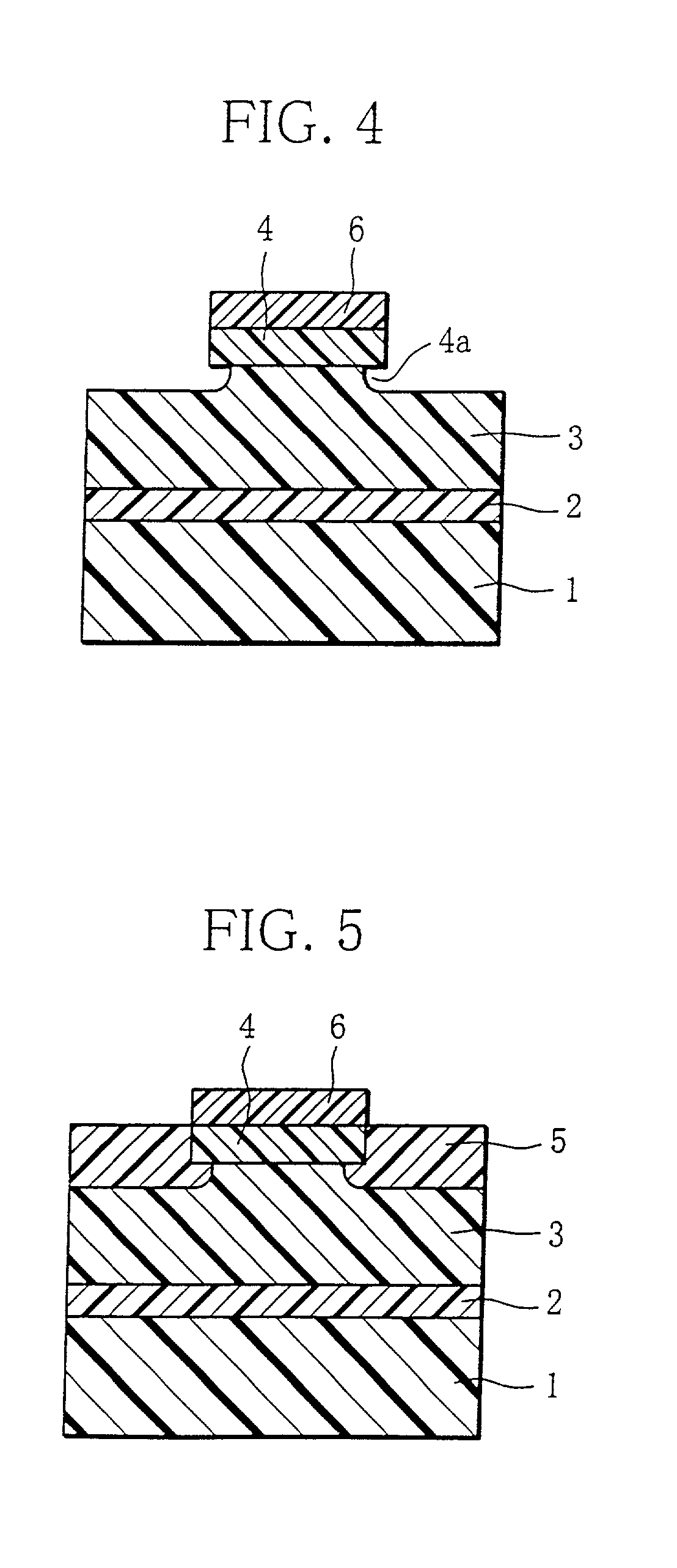

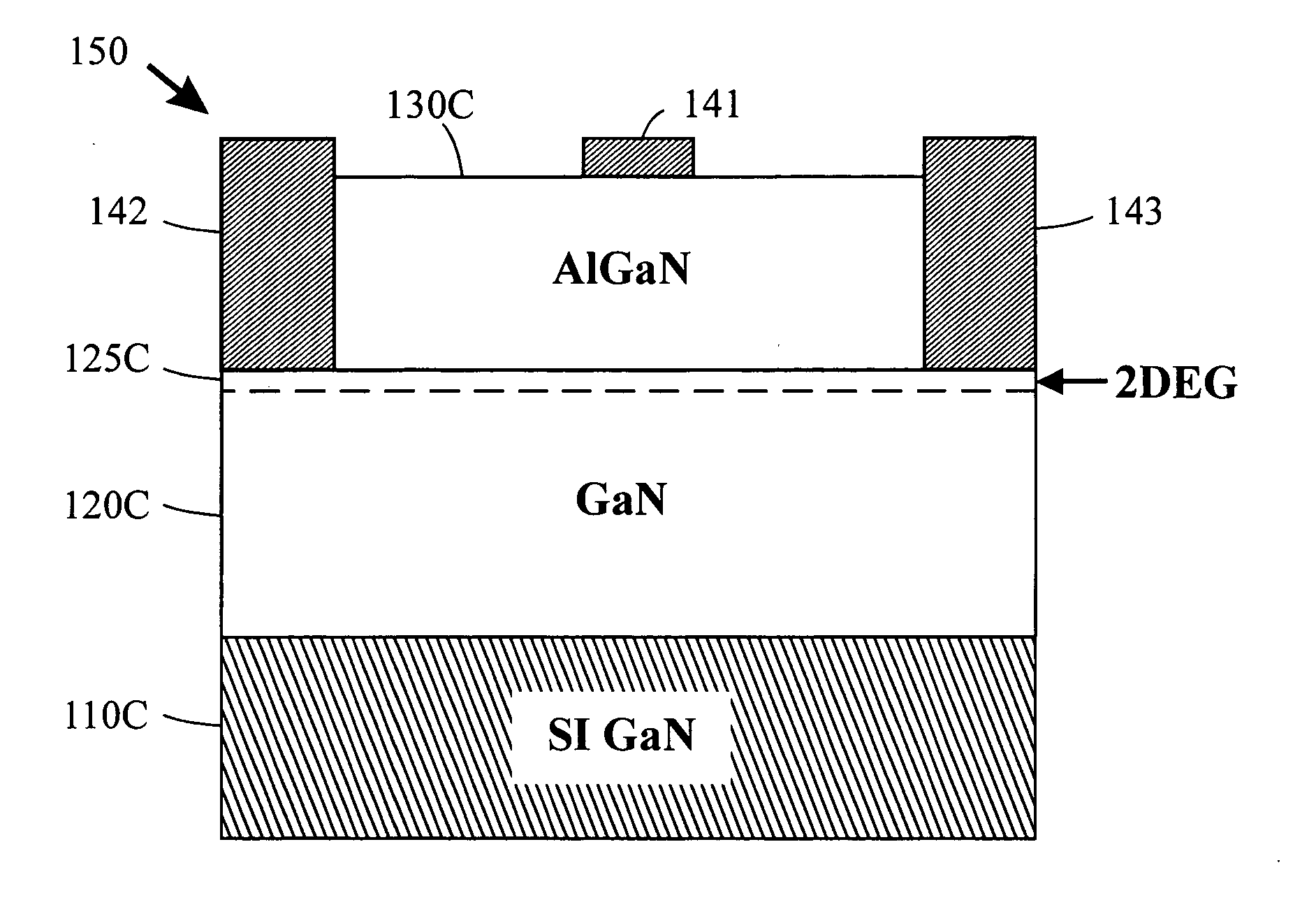

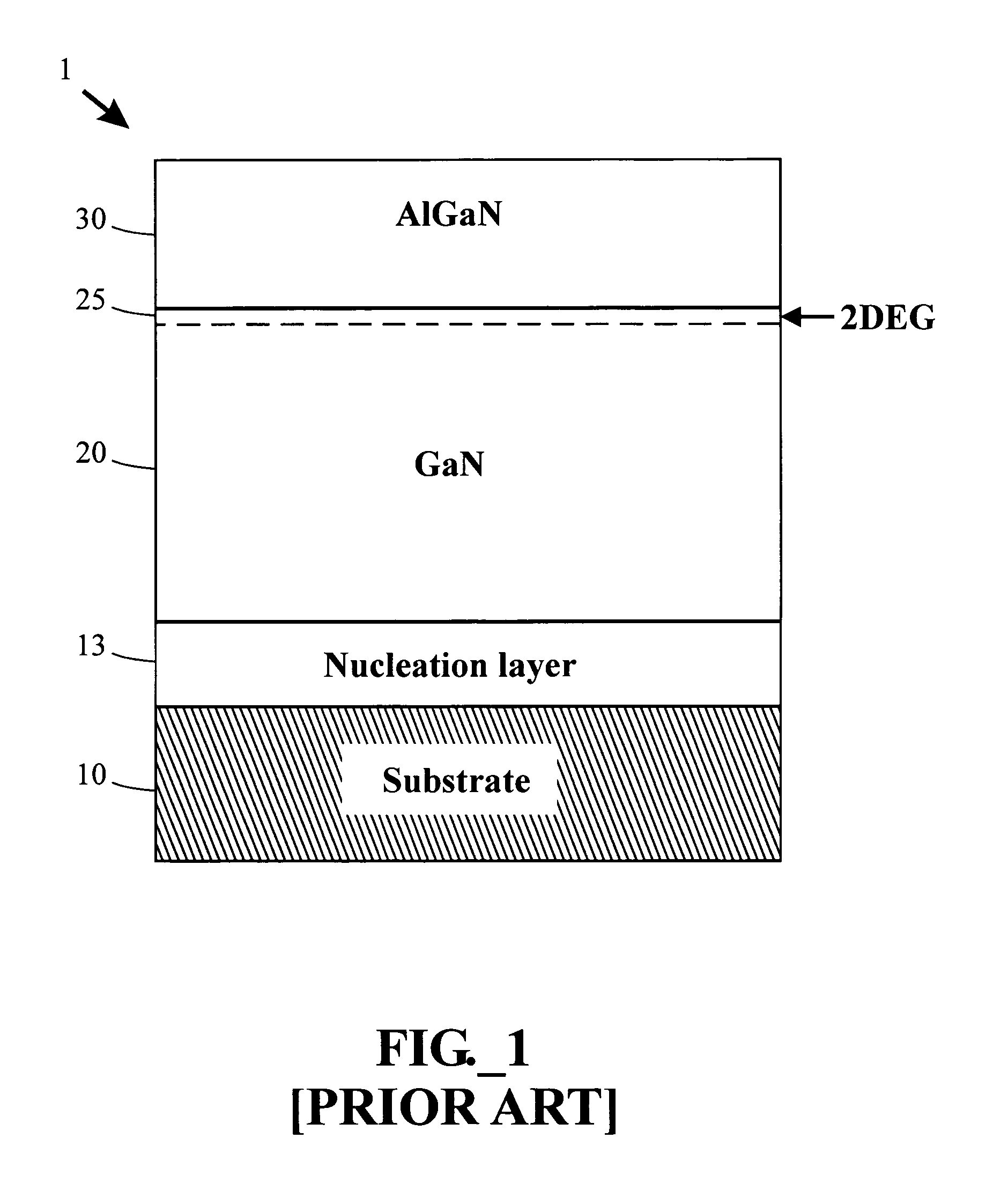

A high electron mobility transistor (HEMT) is disclosed that includes a semi-insulating silicon carbide substrate, an aluminum nitride buffer layer on the substrate, an insulating gallium nitride layer on the buffer layer, an active structure of aluminum gallium nitride on the gallium nitride layer, a passivation layer on the aluminum gallium nitride active structure, and respective source, drain and gate contacts to the aluminum gallium nitride active structure.

Owner:WOLFSPEED INC

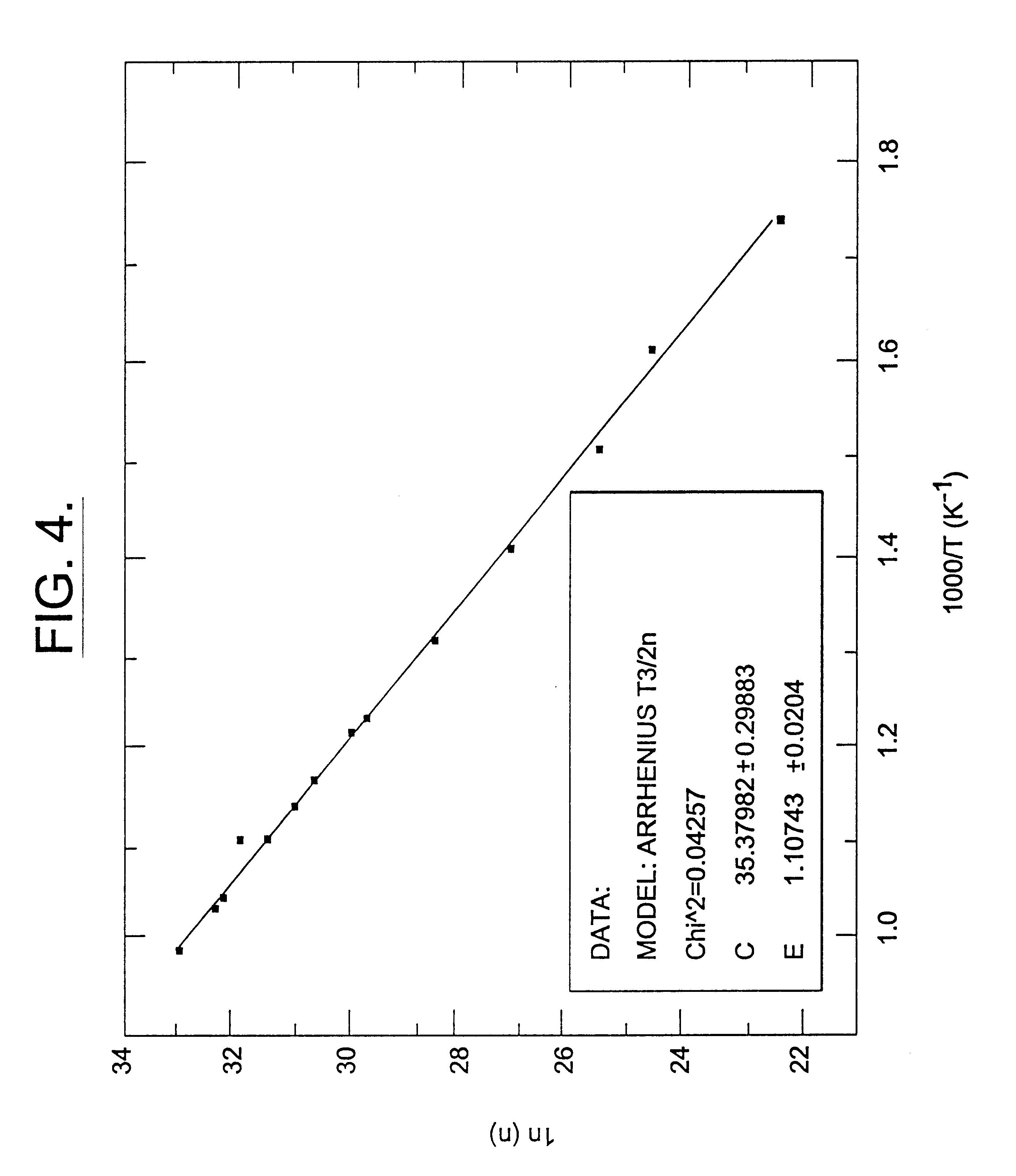

Semi-insulating silicon carbide without vanadium domination

InactiveUS6218680B1Reduce the amount requiredIncrease the number ofPolycrystalline material growthAfter-treatment detailsDevice formTrapping

Owner:CREE INC

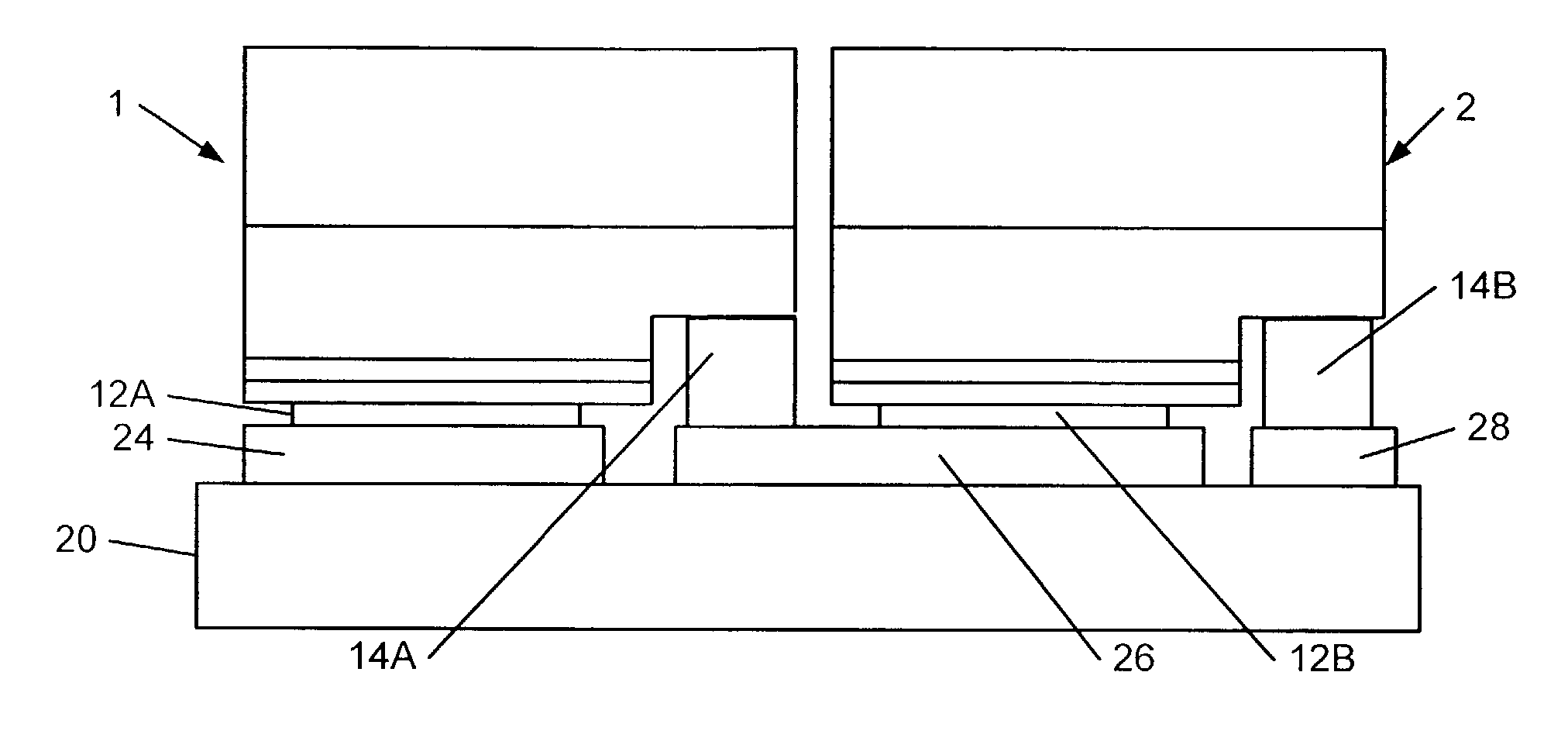

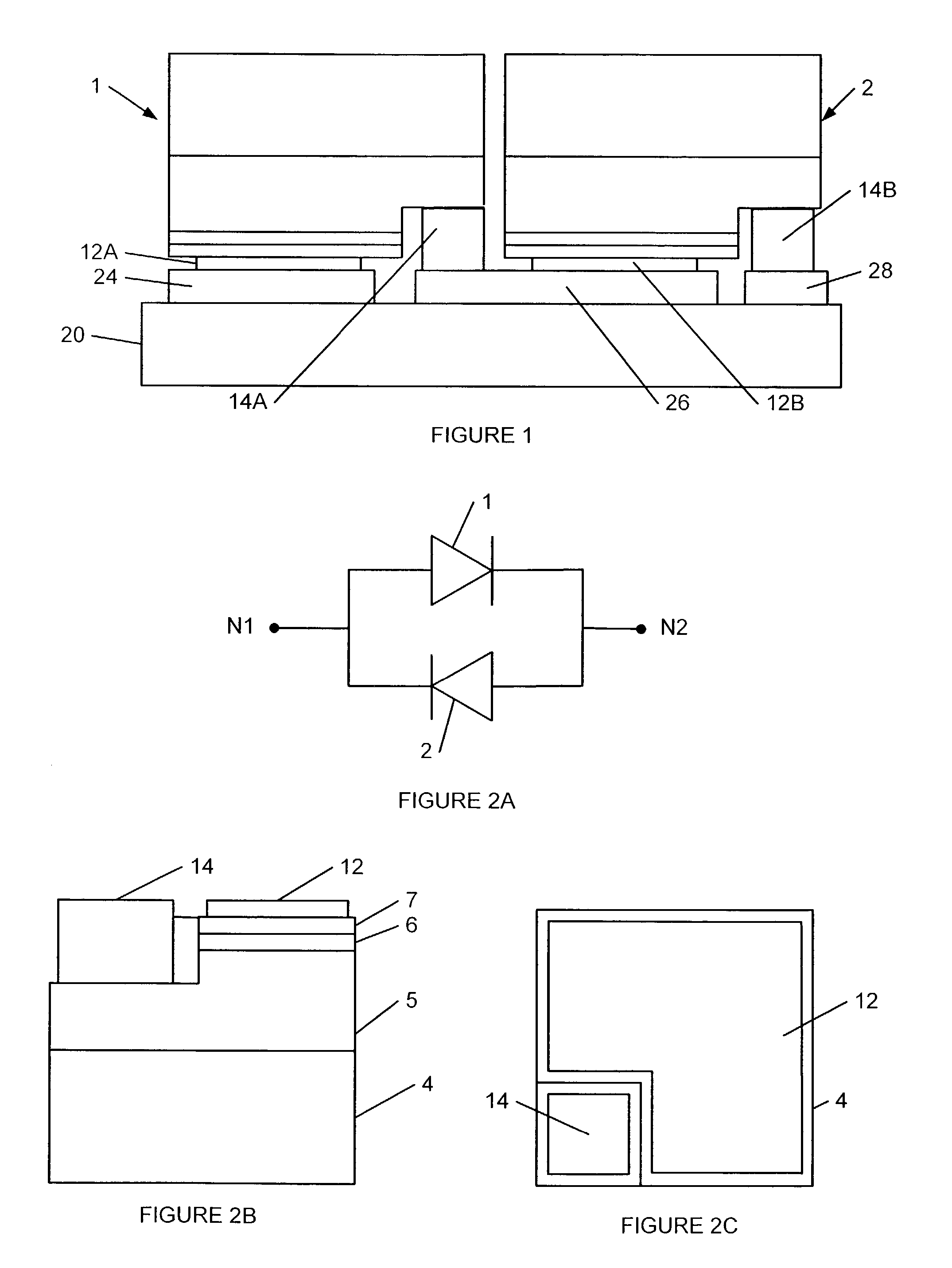

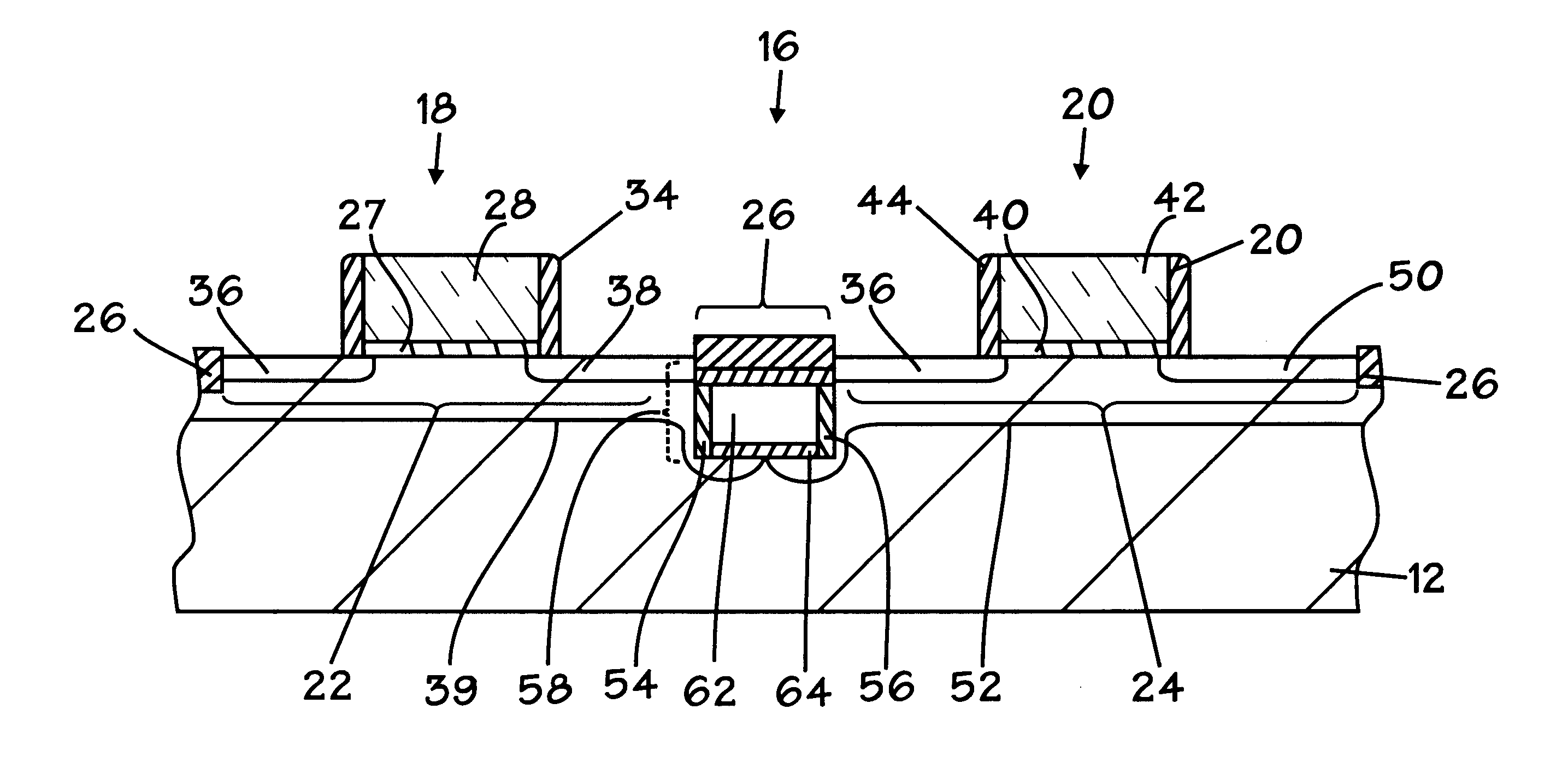

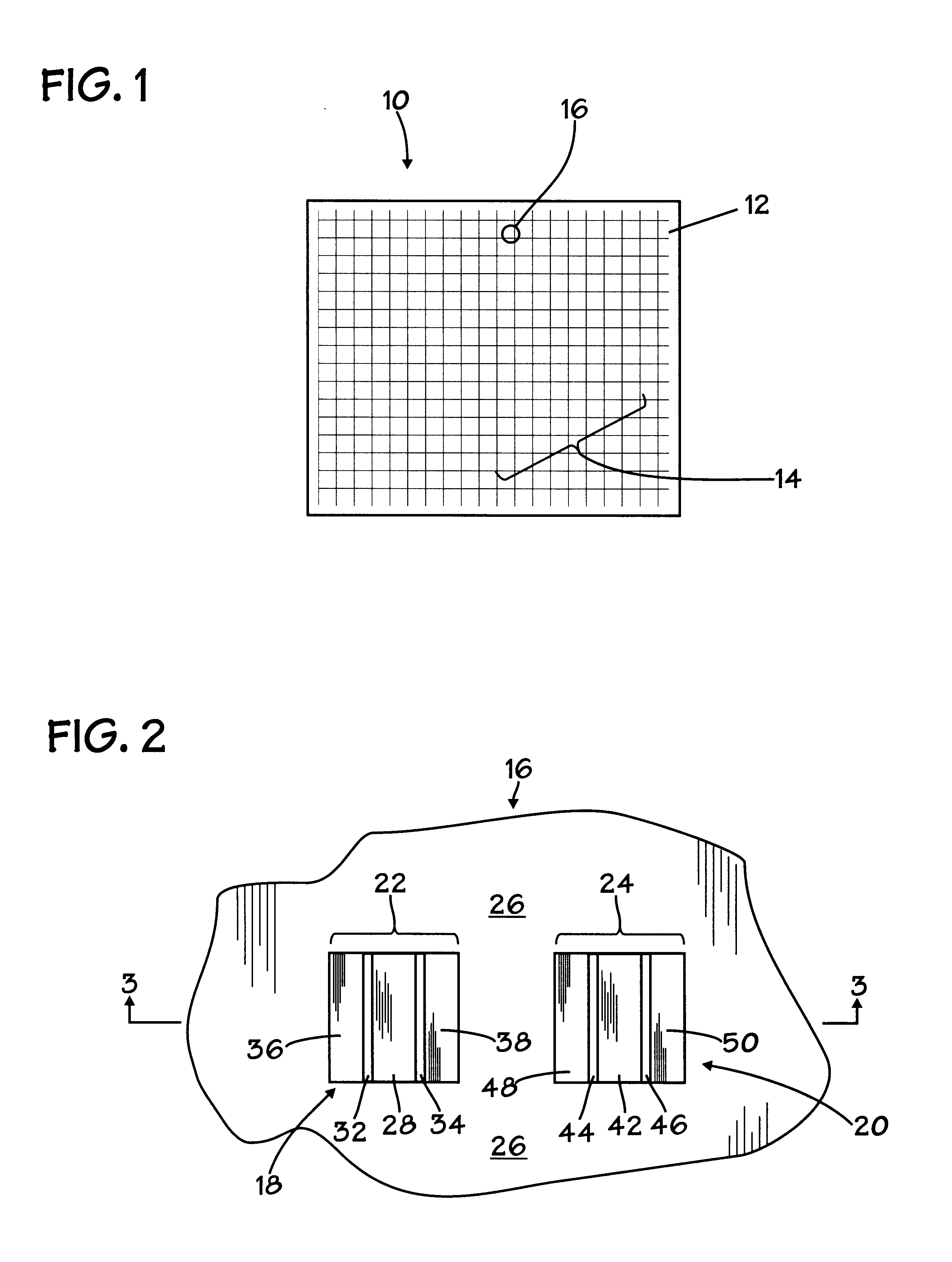

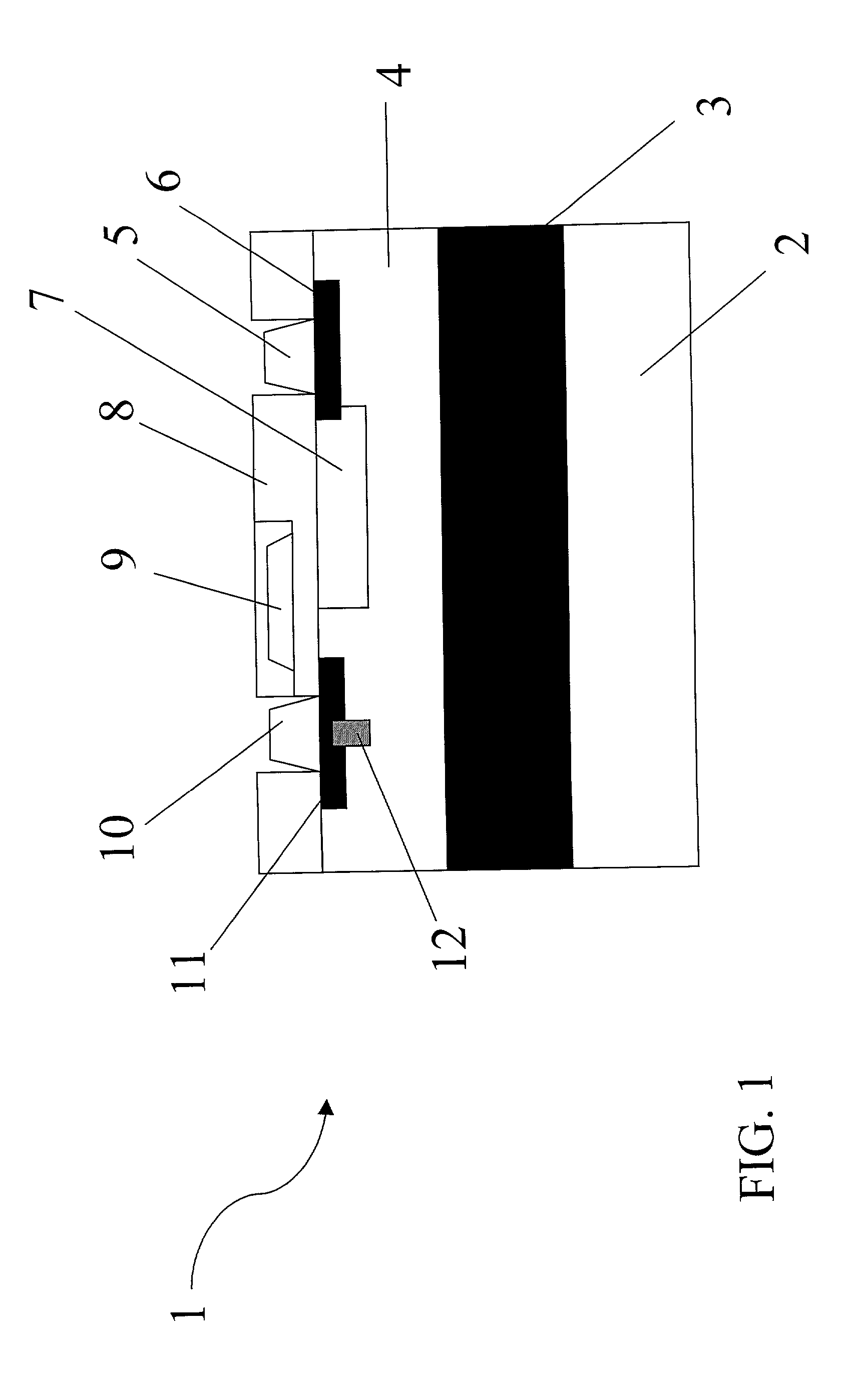

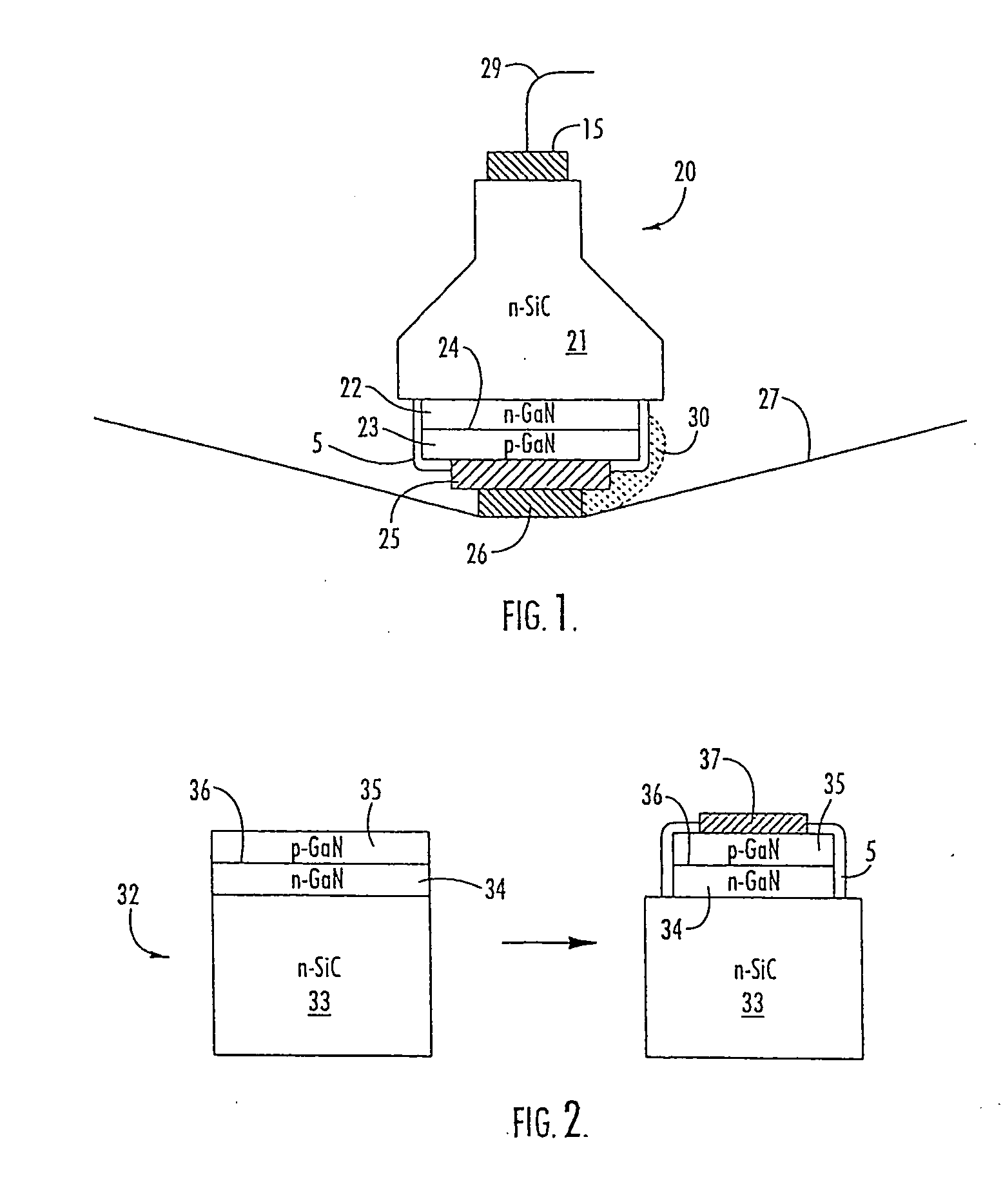

Electronic devices having a header and antiparallel connected light emitting diodes for producing light from AC current

InactiveUS7009199B2Improve light outputEliminate needSolid-state devicesElectric light circuit arrangementEngineeringLight-emitting diode

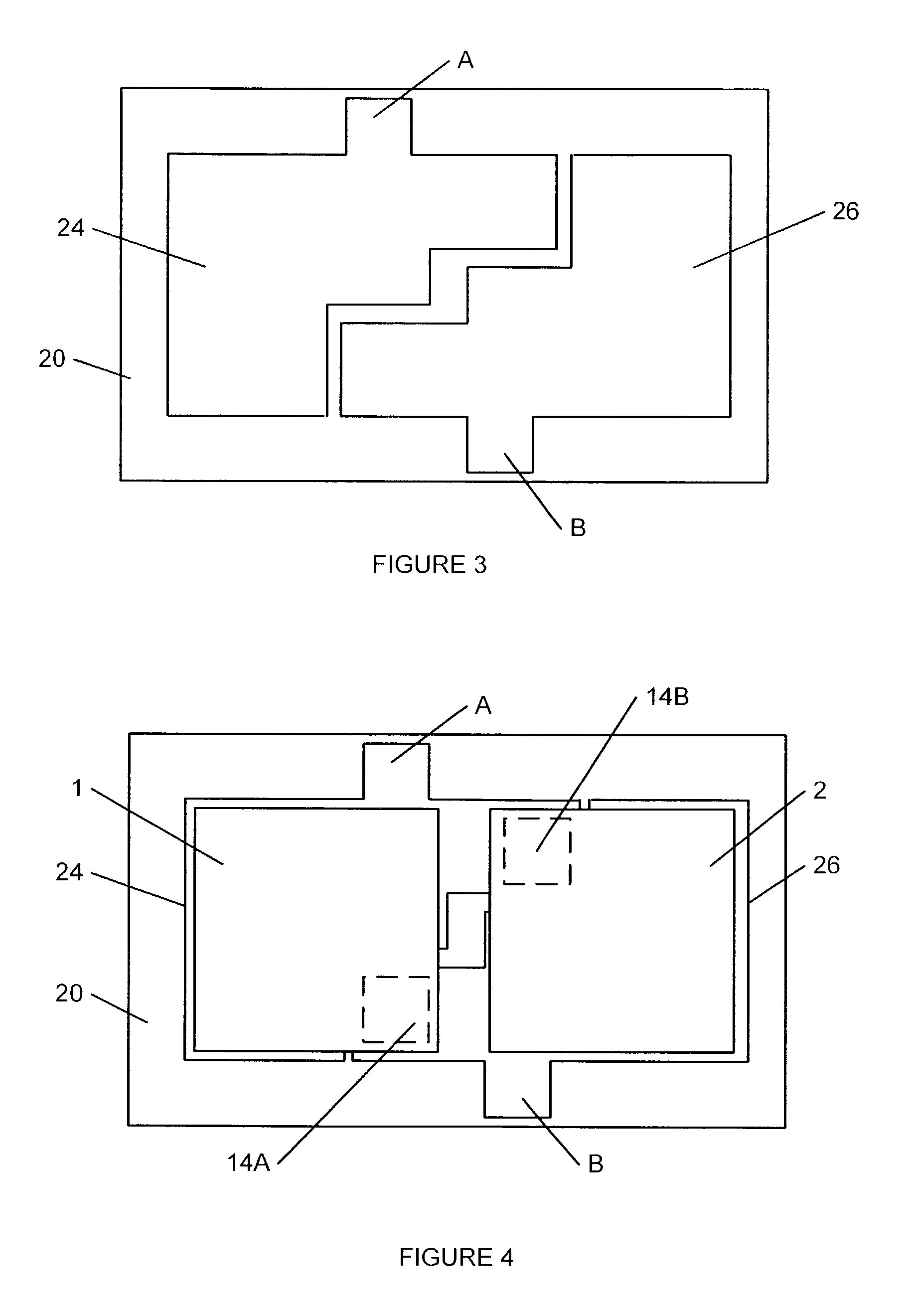

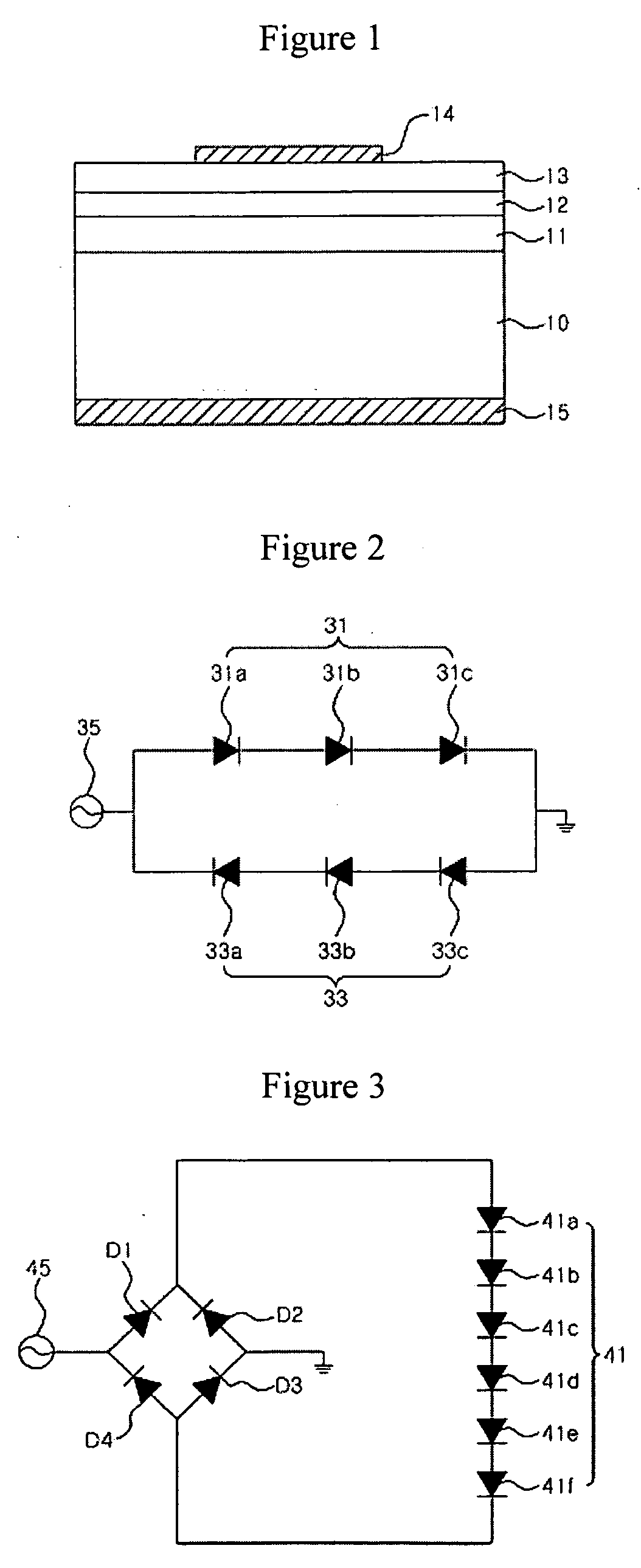

A light engine comprises a pair of LED active elements mounted on a common header having first and second terminals. The first terminal is connected to the cathode of the first LED active element and the anode of the second LED active element, while the second terminal is connected to the anode of the first LED active element and the cathode of the second LED active element, thereby connecting the LEDs in an anti-parallel arrangement. A light engine having a single insulating or semi-insulating substrate having formed thereon plural LED active elements with associated p- and n-type contacts forming cathode and anode contacts, respectively, for each LED active element is also provided. The LED active elements may be mounted in a flip-chip configuration on a header having a plurality of leads. The header may include a pair of leads adapted such that two LEDs may be flip-mounted thereon with the anode of the first LED and the cathode of the second LED contacting one lead, while the cathode of the first LED and the anode of the second LED contact the other lead. In addition, the header may be adapted to permit a substrate having multiple active elements to be mounted thereon.

Owner:IDEAL IND LIGHTING LLC

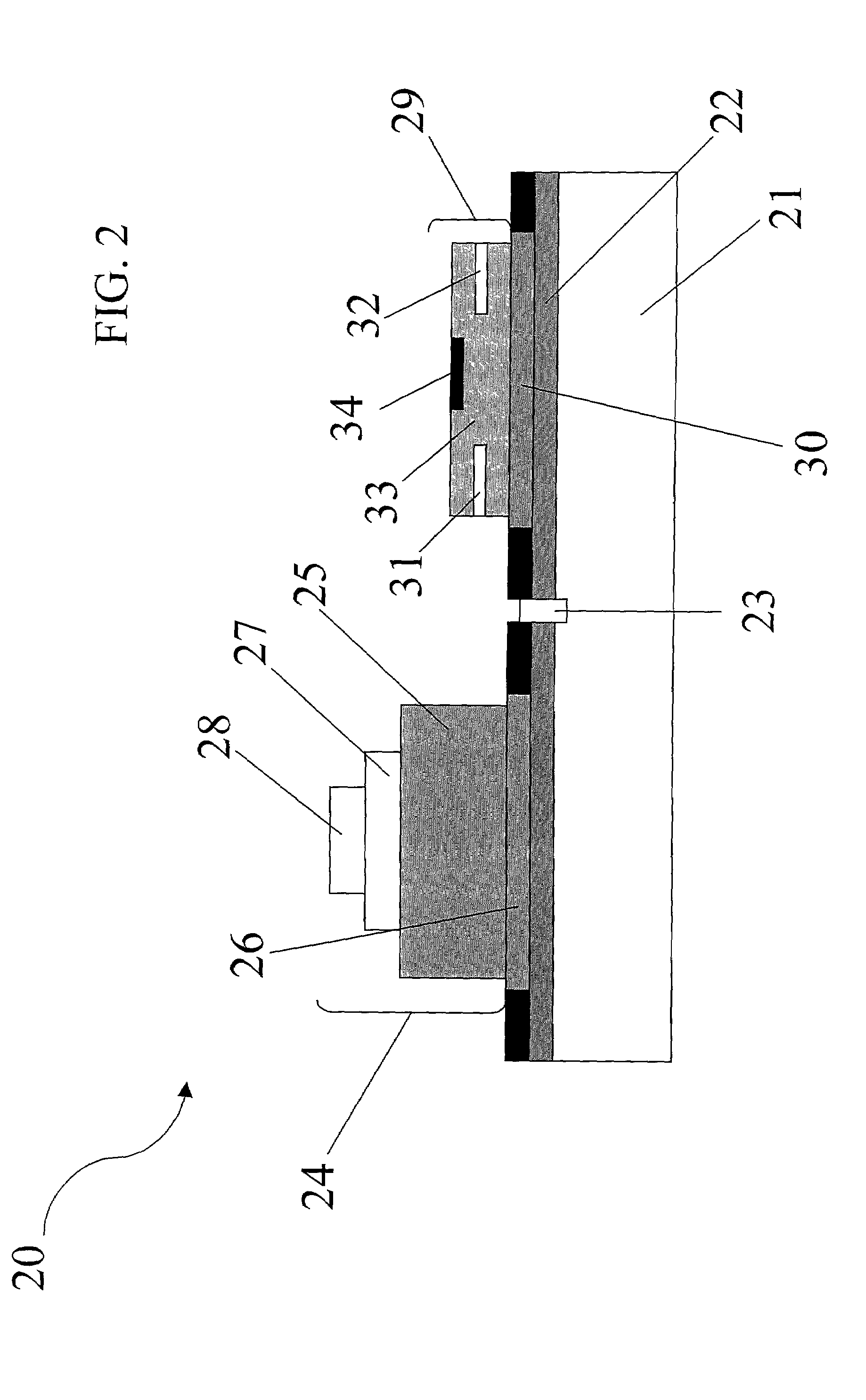

Bidirectional photothyristor chip, optical lighting coupler, and solid state relay

ActiveUS7423298B2Improving luminous sensitivityCoupling device detailsSemiconductor/solid-state device manufacturingOxygenSolid-state relay

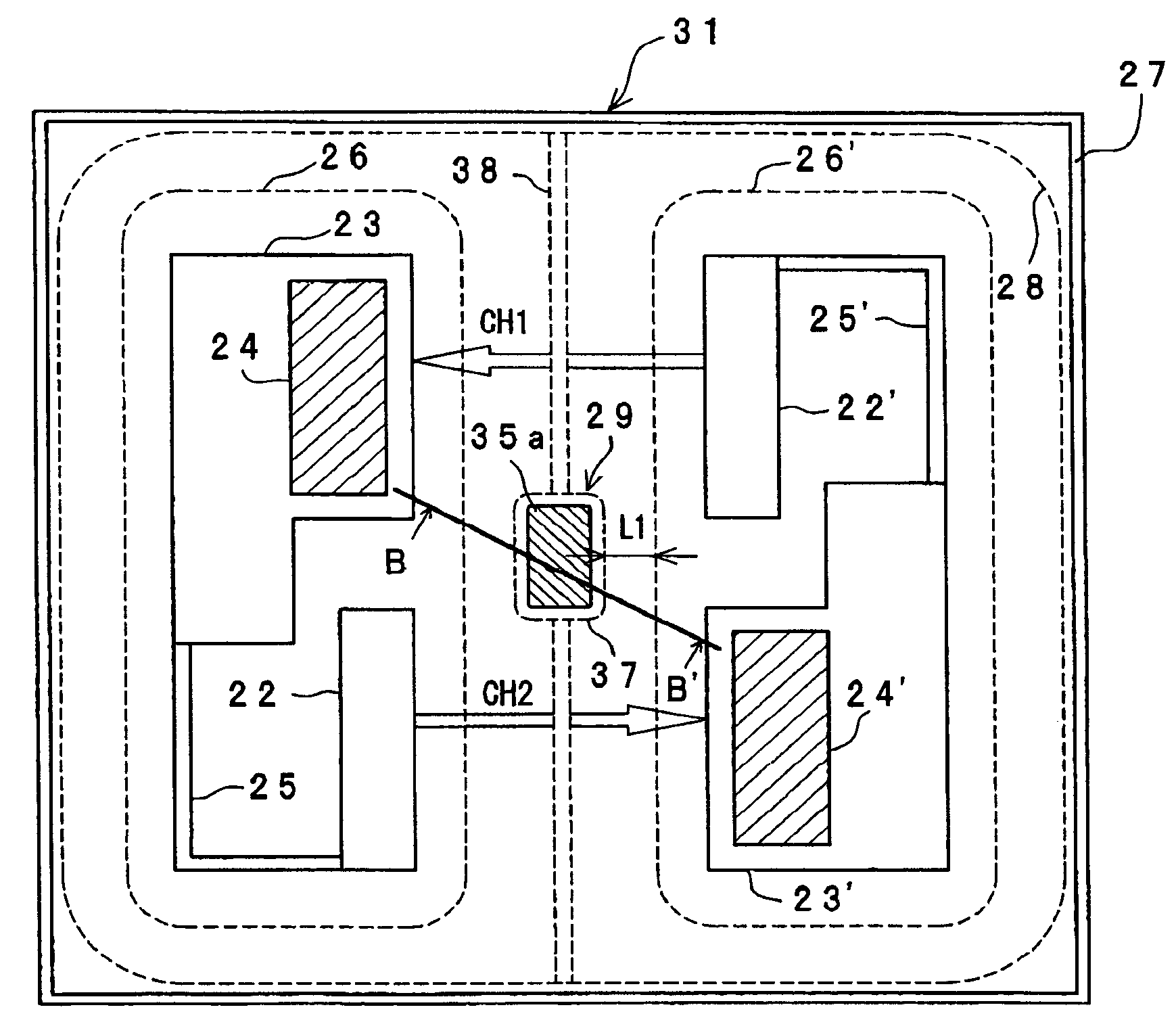

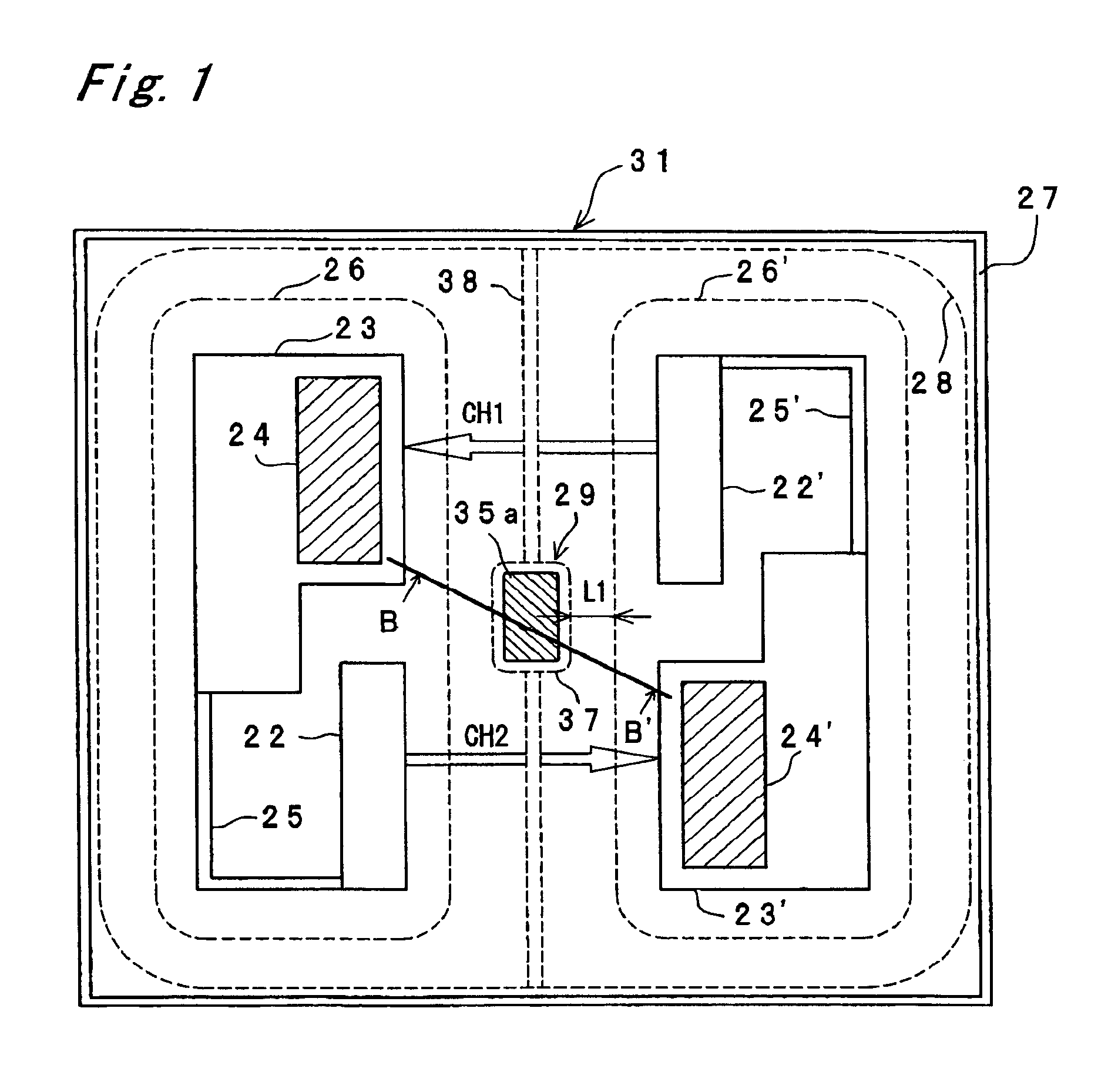

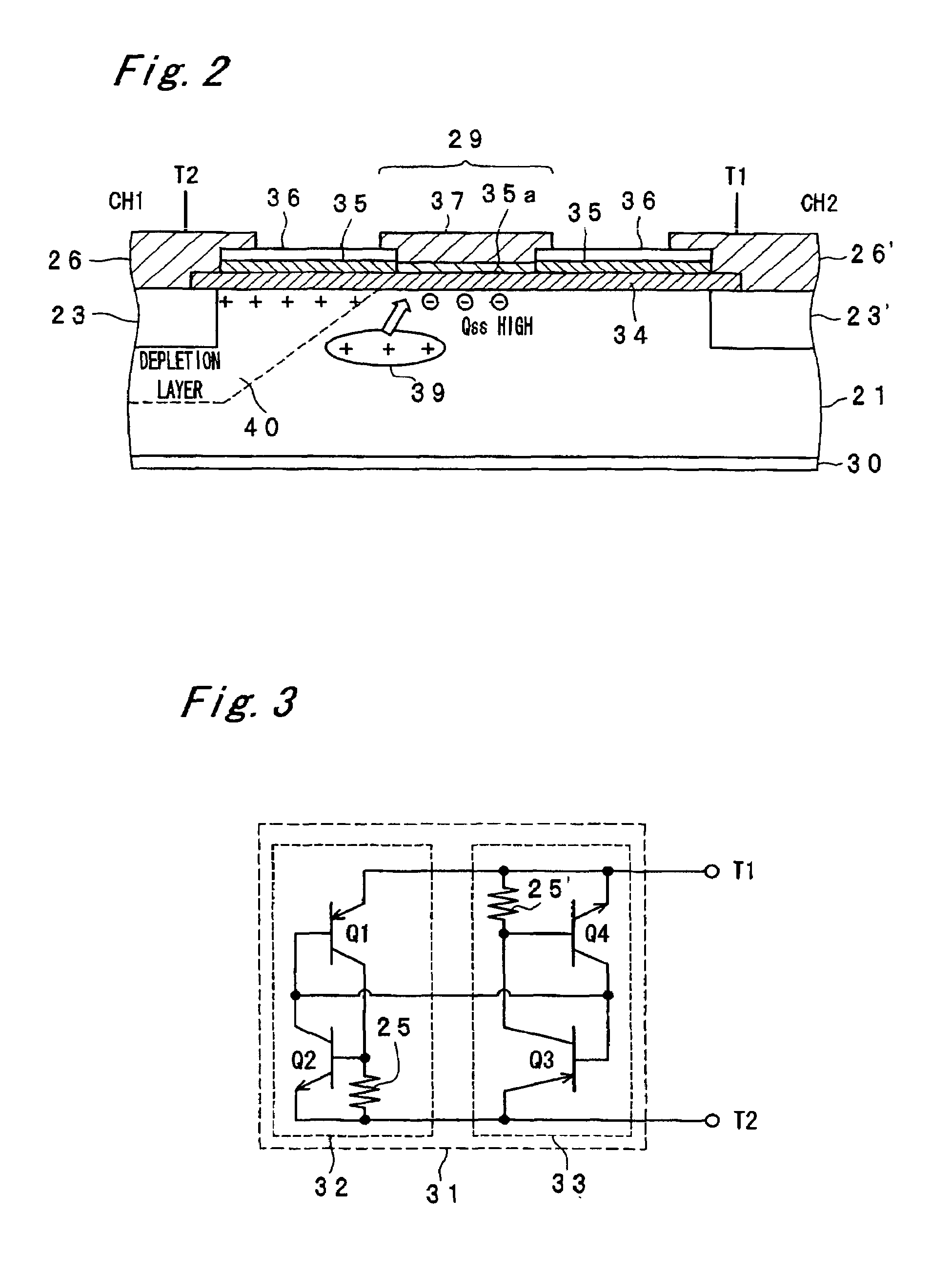

Two operation channels CH1 and CH2 of a bidirectional photothyristor chip 31 are disposed away from each other so as not to intersect with each other. In between a P-gate diffusion region 23 on the left-hand side and a P-gate diffusion region 23′ on the right-hand side on an N-type silicon substrate, and in between the CH1 and the CH2, a channel isolation region 29 comprised of an oxygen doped semi-insulating polycrystalline silicon film 35a doped with phosphorus is formed. Consequently, a silicon interface state (Qss) in the vicinity of the channel isolation region 29 on the surface of the N-type silicon substrate increases, so that holes or minority carriers in the N-type silicon substrate are made to disappear in the region. This makes it possible to prevent such commutation failure that when a voltage of the inverted phase is applied to the CH2 side at the point of time when the CH1 is turned off, the CH2 is turned on without incidence of light, and this allows a commutation characteristic to be enhanced.

Owner:SHARP KK

Nitride based transistors on semi-insulating silicon carbide substrates

InactiveUS6486502B1Quality improvementImprove thermal conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideNitride

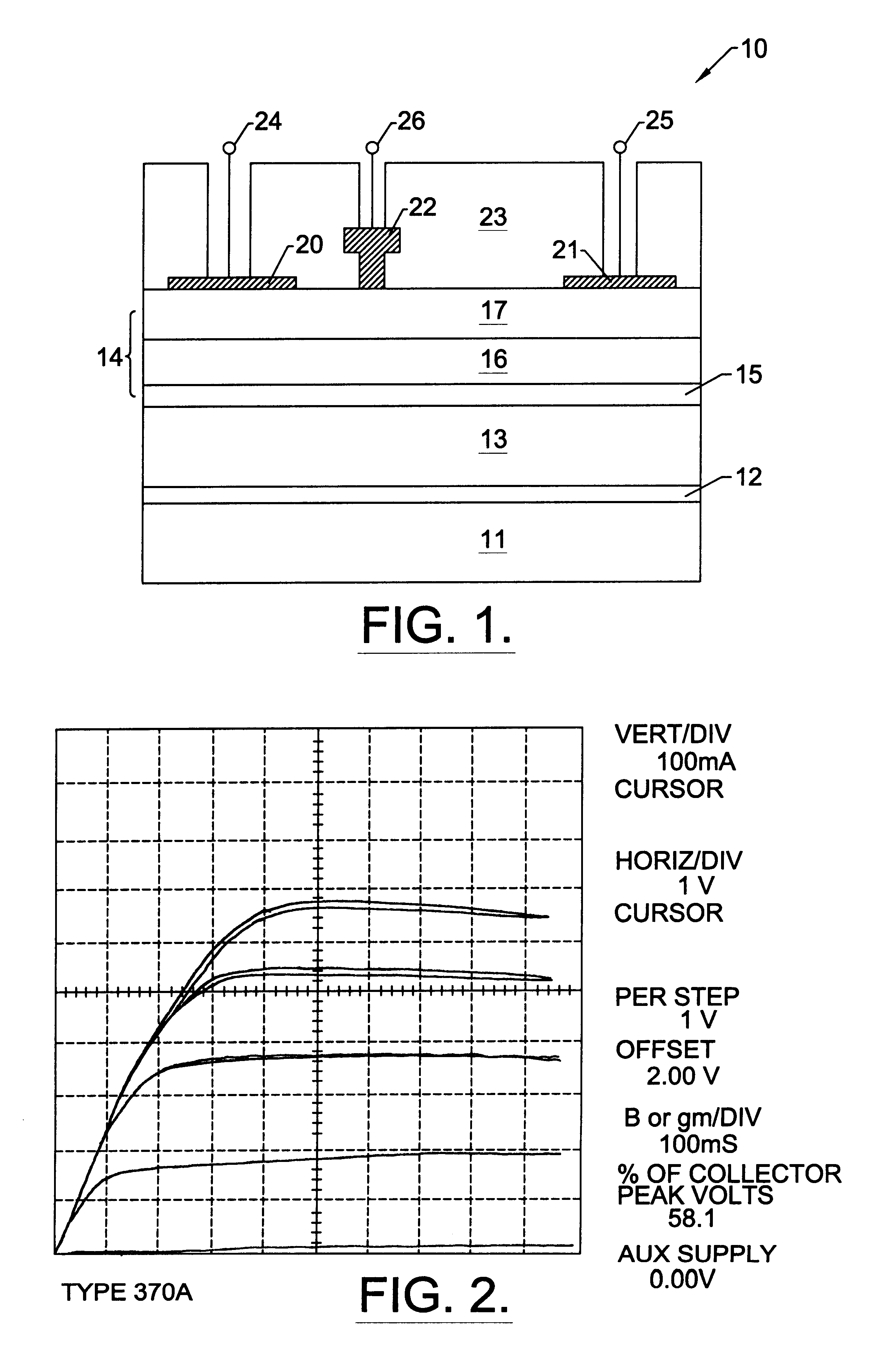

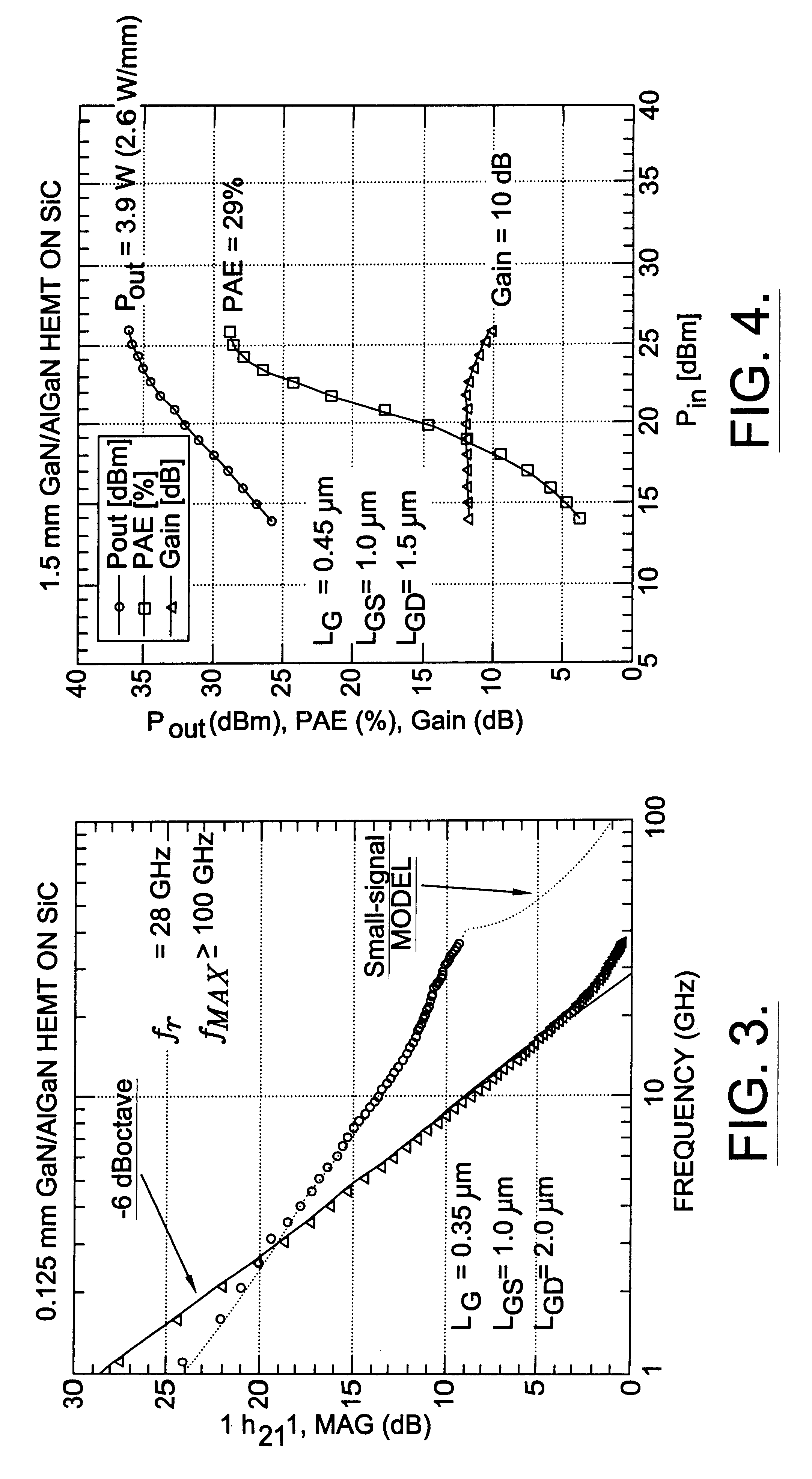

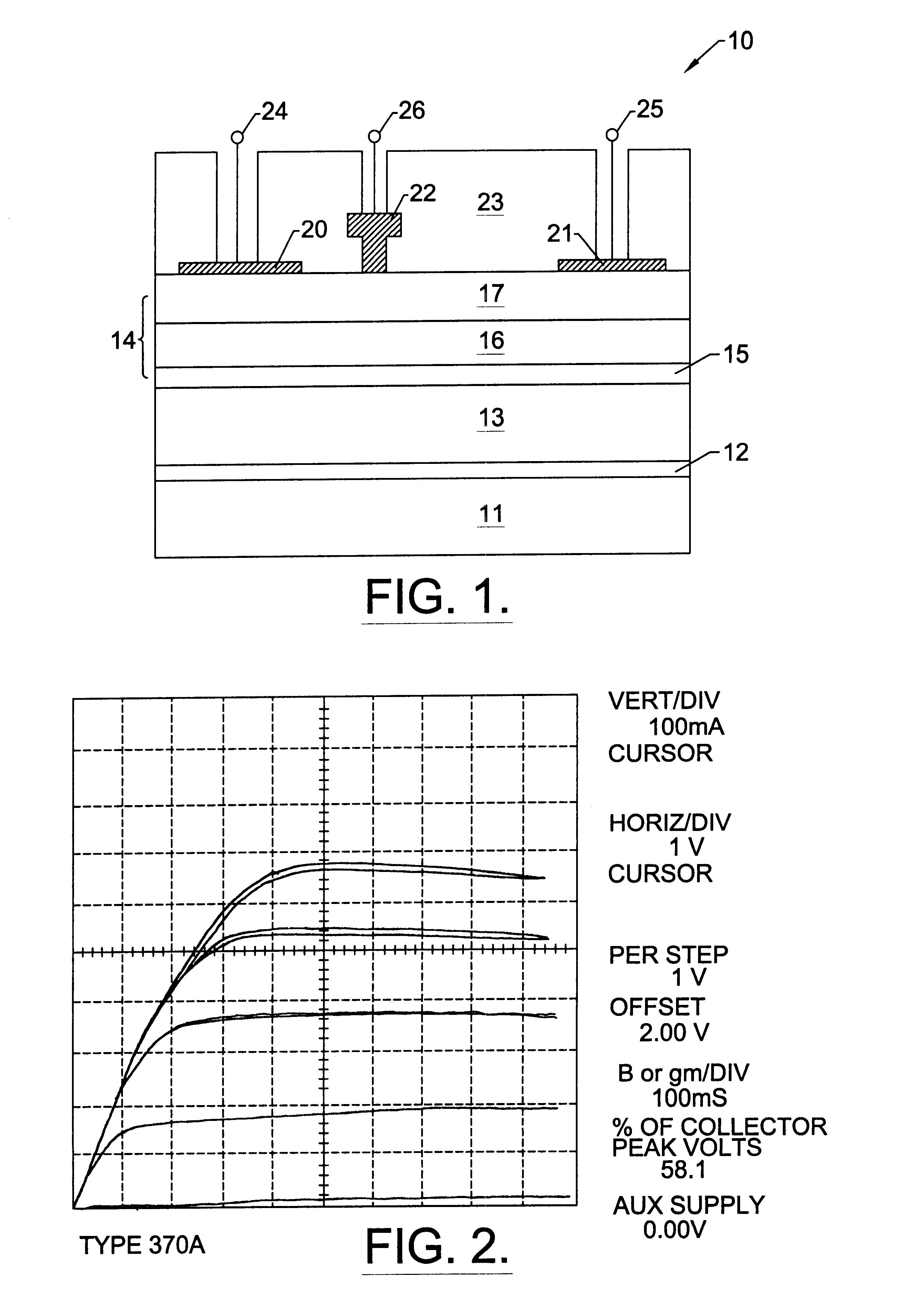

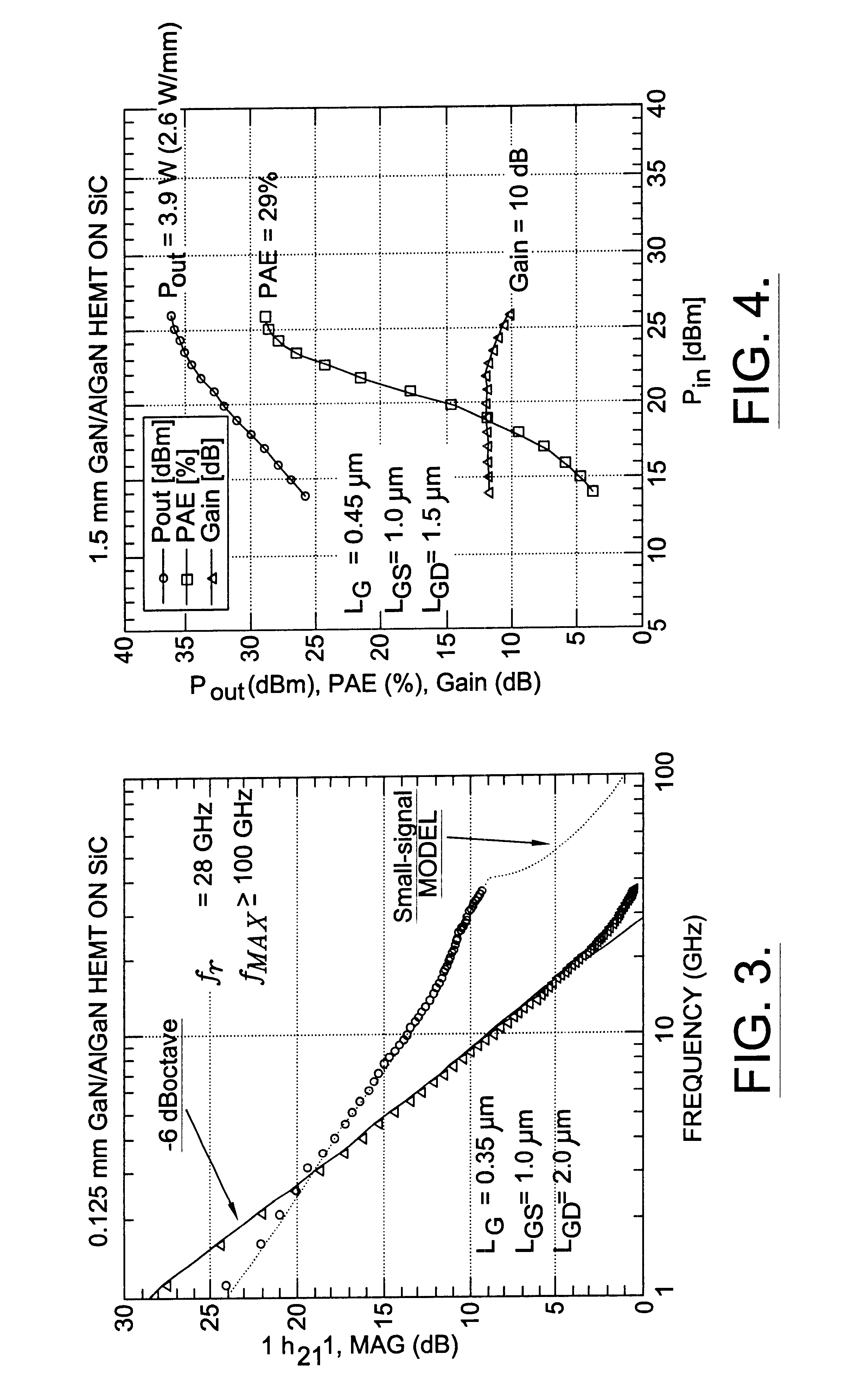

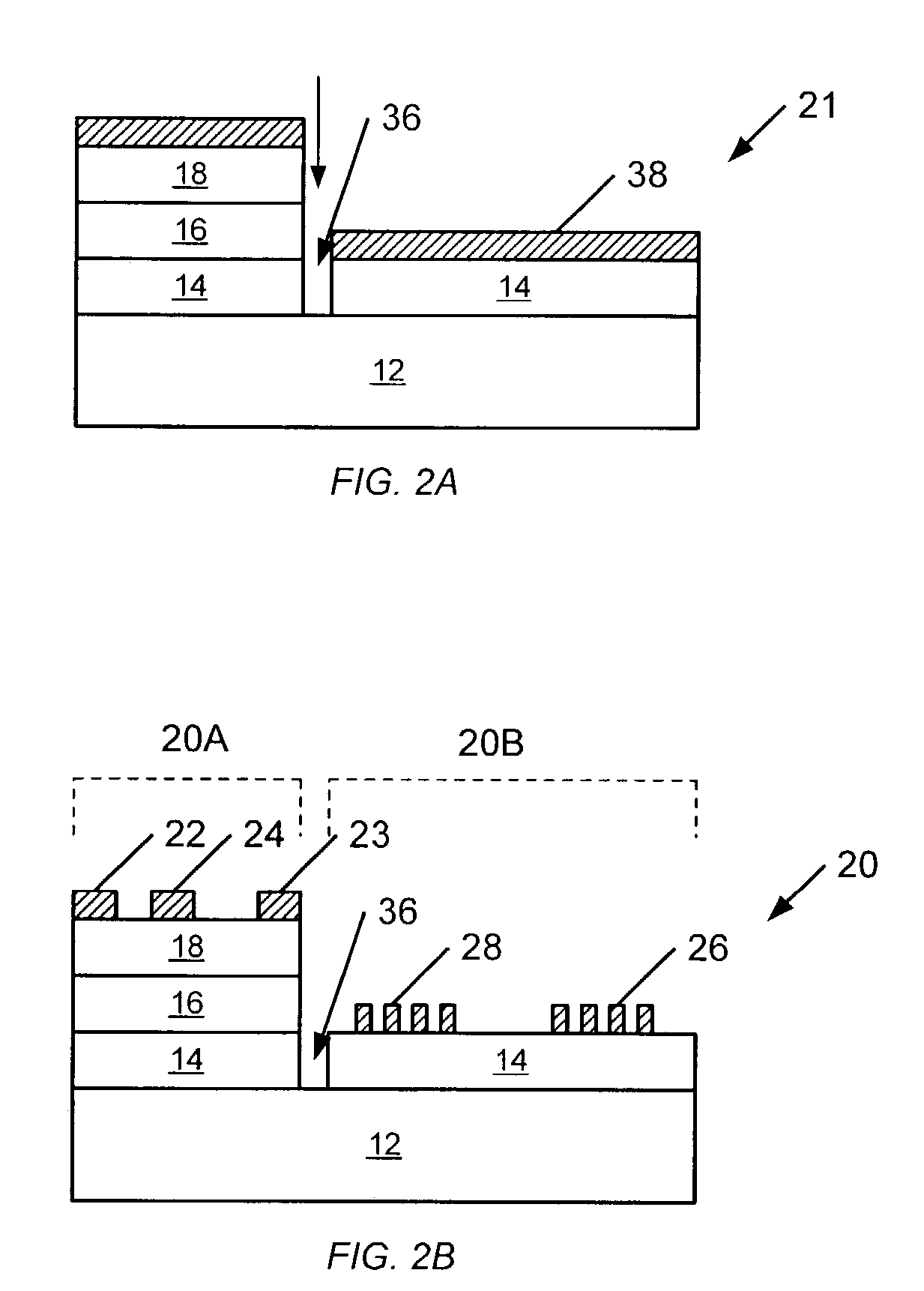

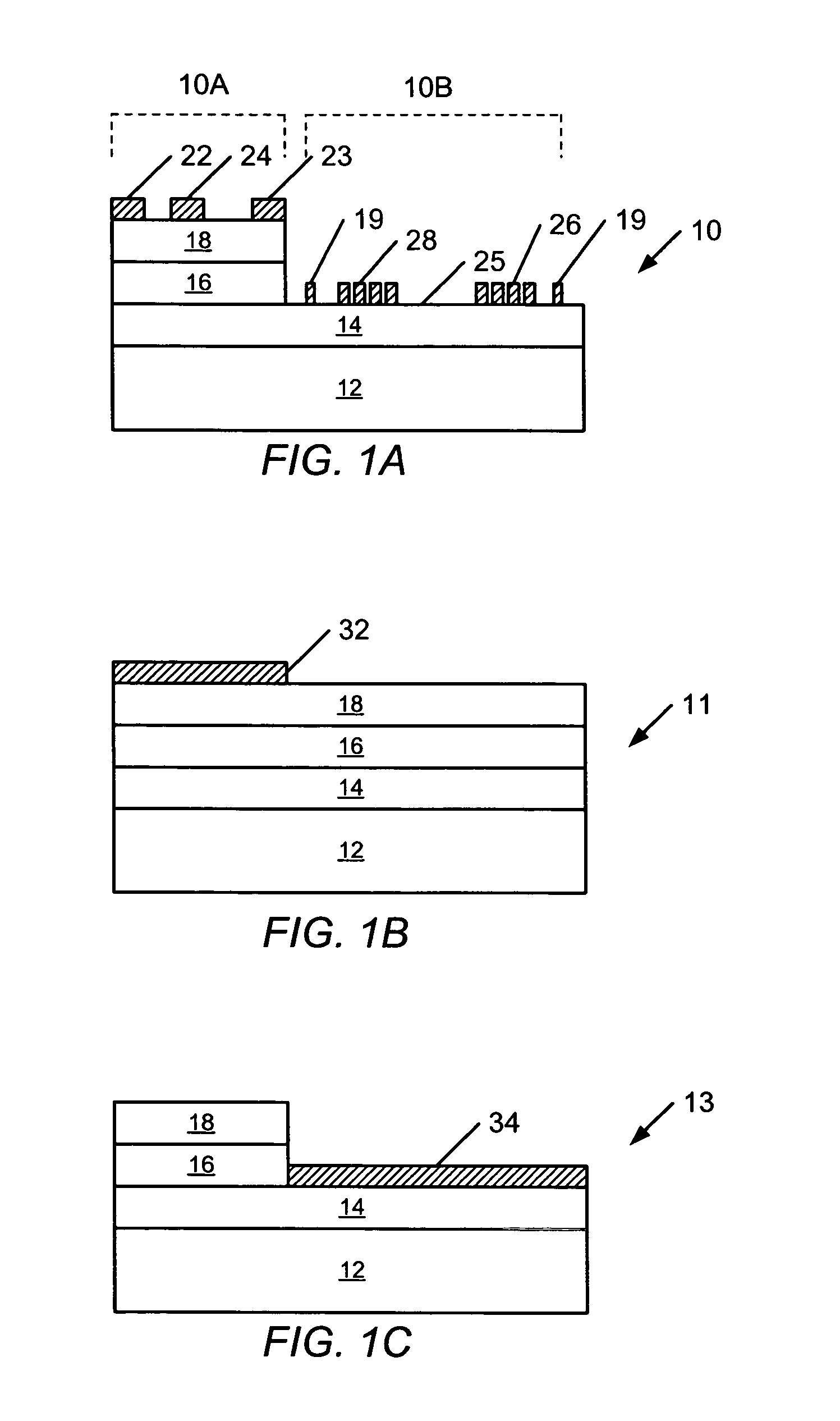

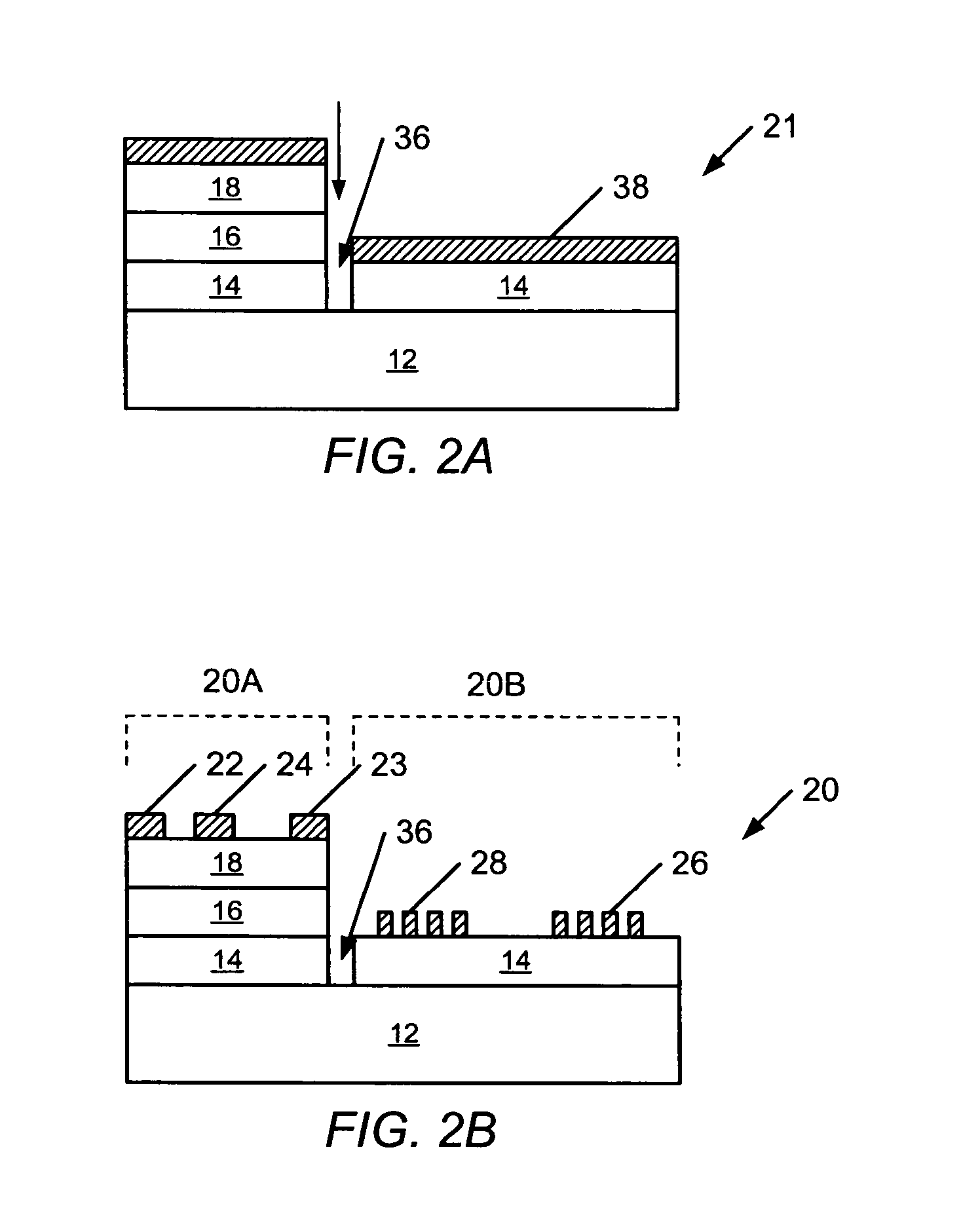

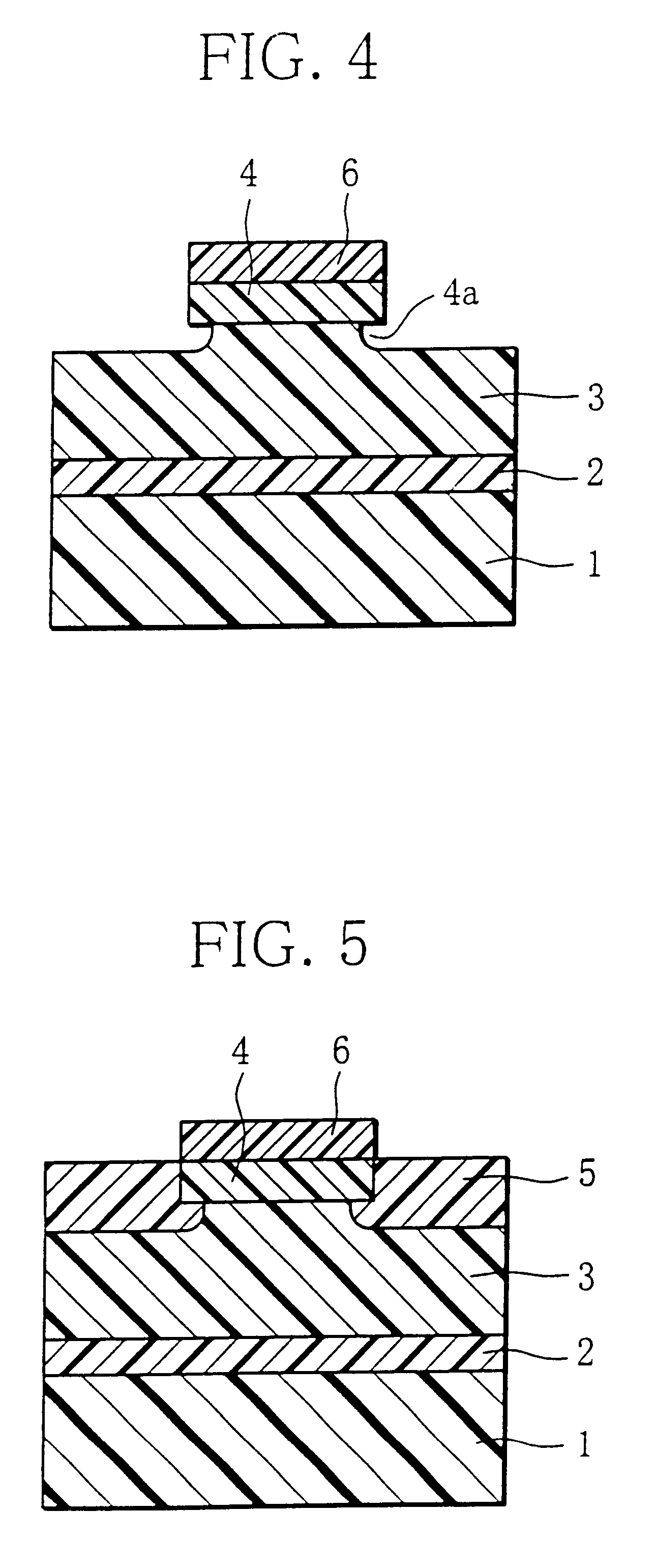

A high electron mobility transistor (HEMT) (10) is disclosed that includes a semi-insulating silicon carbide substrate (11), an aluminum nitride buffer layer (12) on the substrate, an insulating gallium nitride layer (13) on the buffer layer, an active structure of aluminum gallium nitride (14) on the gallium nitride layer, a passivation layer (23) on the aluminum gallium nitride active structure, and respective source, drain and gate contacts (21, 22, 23) to the aluminum gallium nitride active structure.

Owner:WOLFSPEED INC

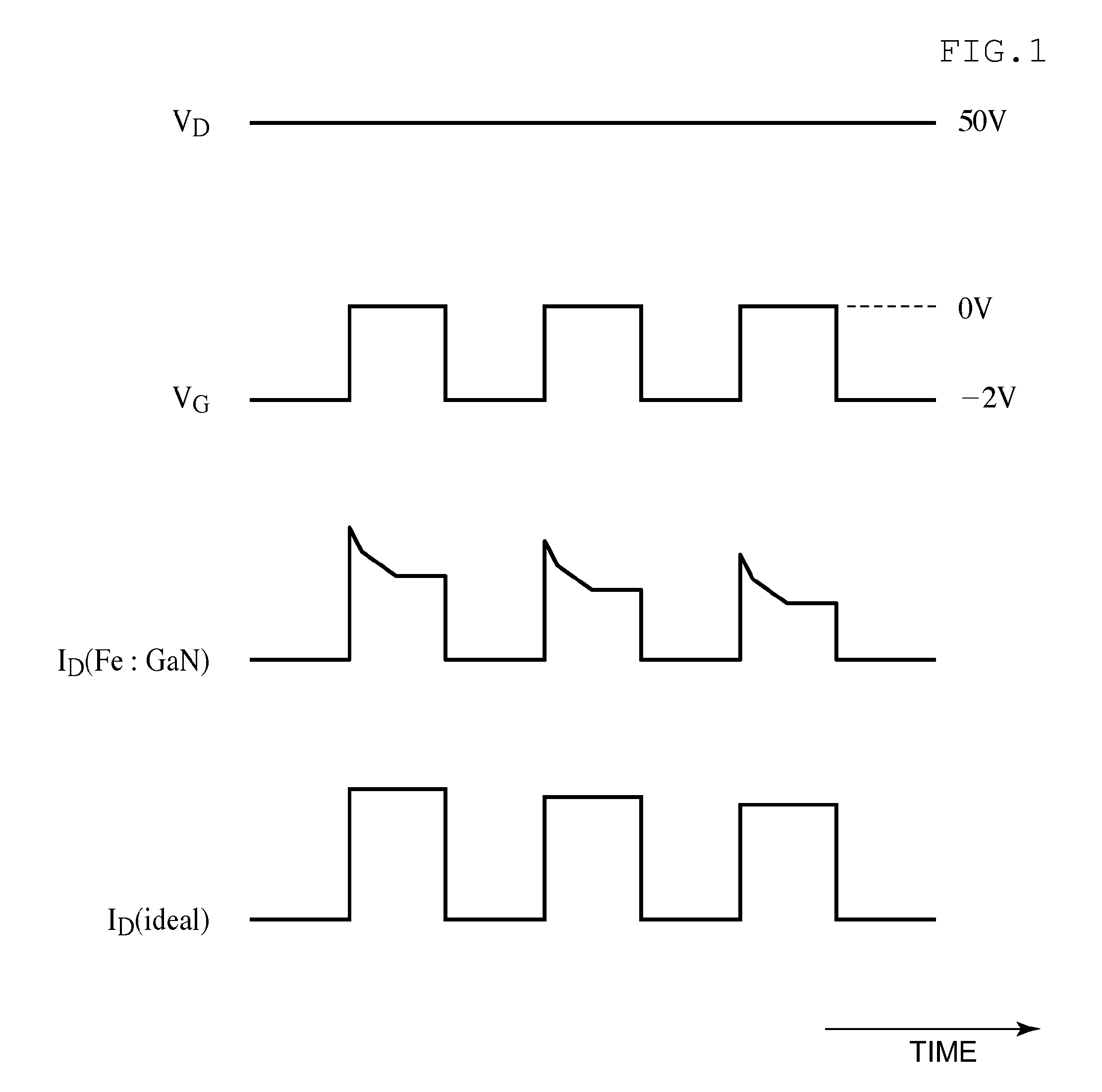

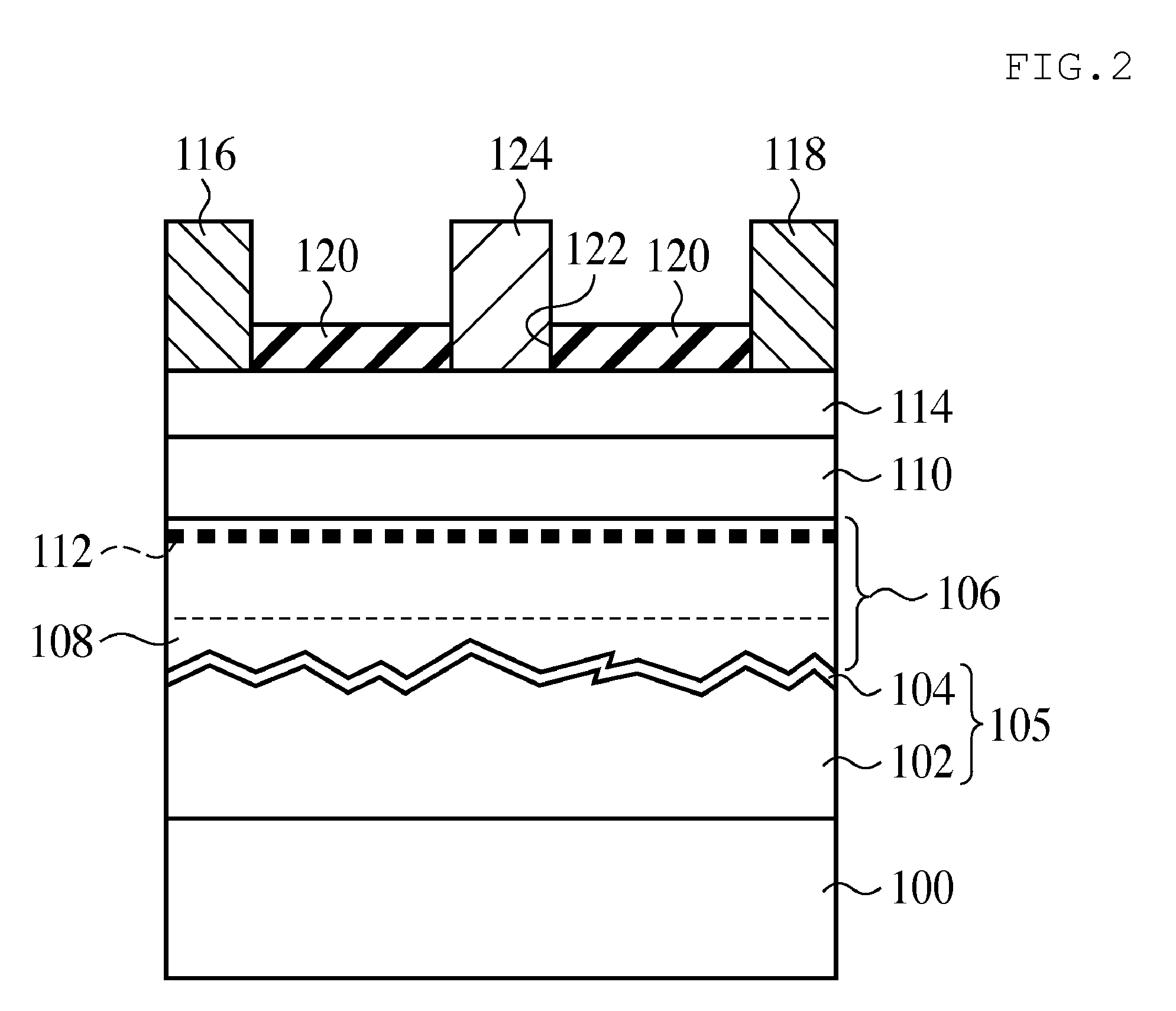

GaN/AIGaN/GaN dispersion-free high electron mobility transistors

InactiveUS20050077541A1High electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh electronGallium nitride

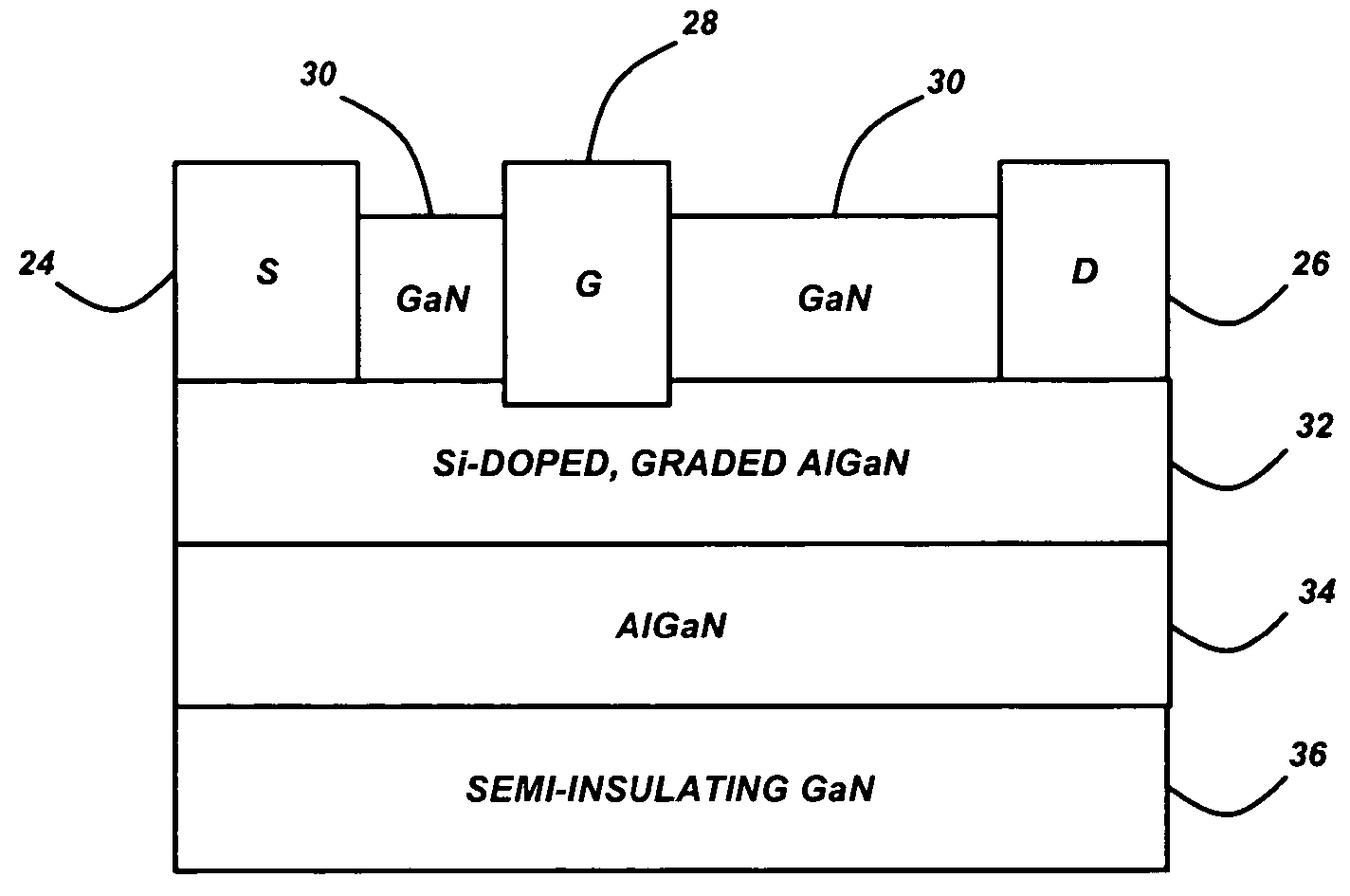

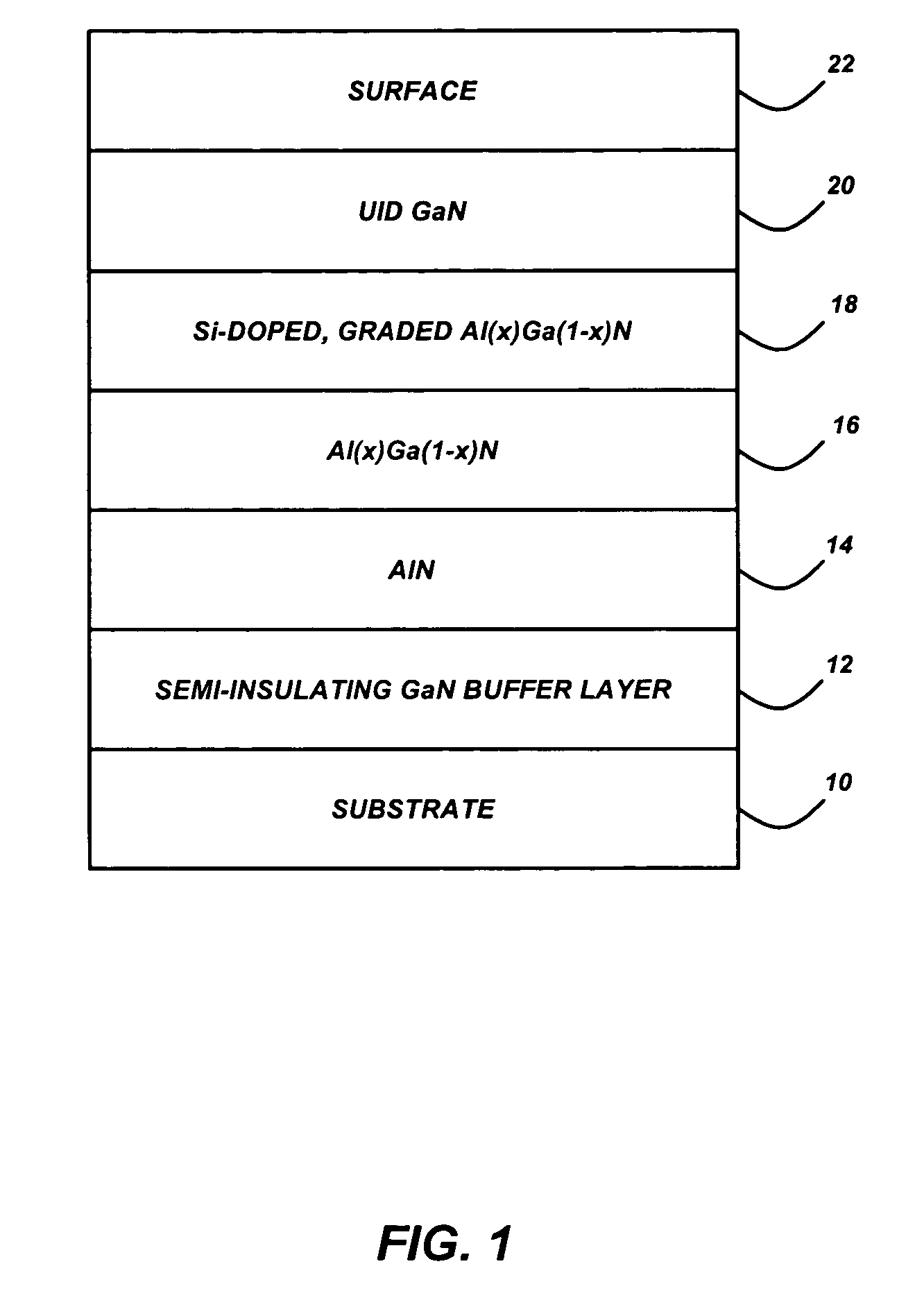

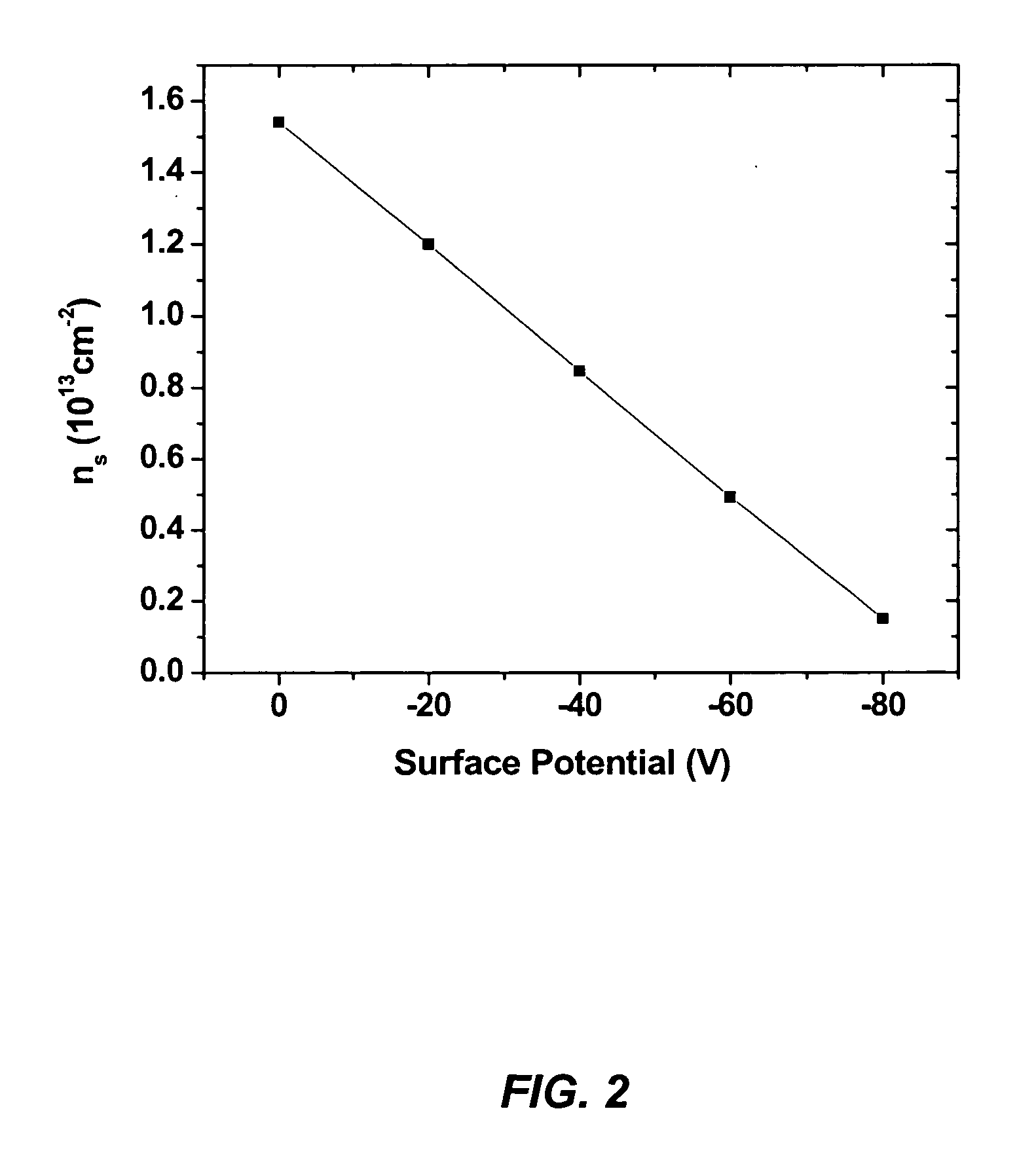

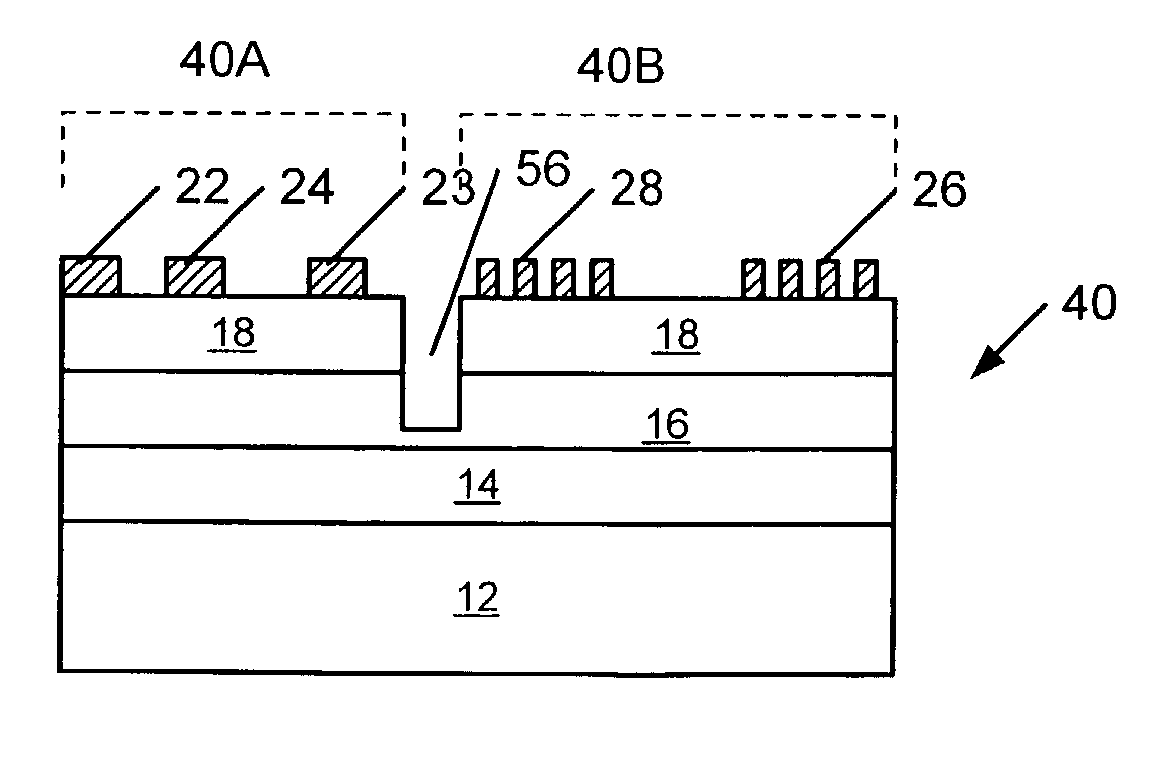

A dispersion-free high electron mobility transistor (HEMT), comprised of a substrate; a semi-insulating buffer layer, comprised of gallium nitride (GaN) or aluminum gallium nitride (AlGaN), deposited on the substrate, an AlGaN barrier layer, with an aluminum (Al) mole fraction larger than that of the semi-insulating buffer layer, deposited on the semi-insulating buffer layer, an n-type doped graded AlGaN layer deposited on the AlGaN barrier layer, wherein an Al mole fraction is decreased from a bottom of the n-type doped graded AlGaN layer to a top of the n-type doped graded AlGaN layer, and a cap layer, comprised of GaN or AlGaN with an Al mole fraction smaller than that of the AlGaN barrier layer, deposited on the n-type doped graded AlGaN layer.

Owner:RGT UNIV OF CALIFORNIA

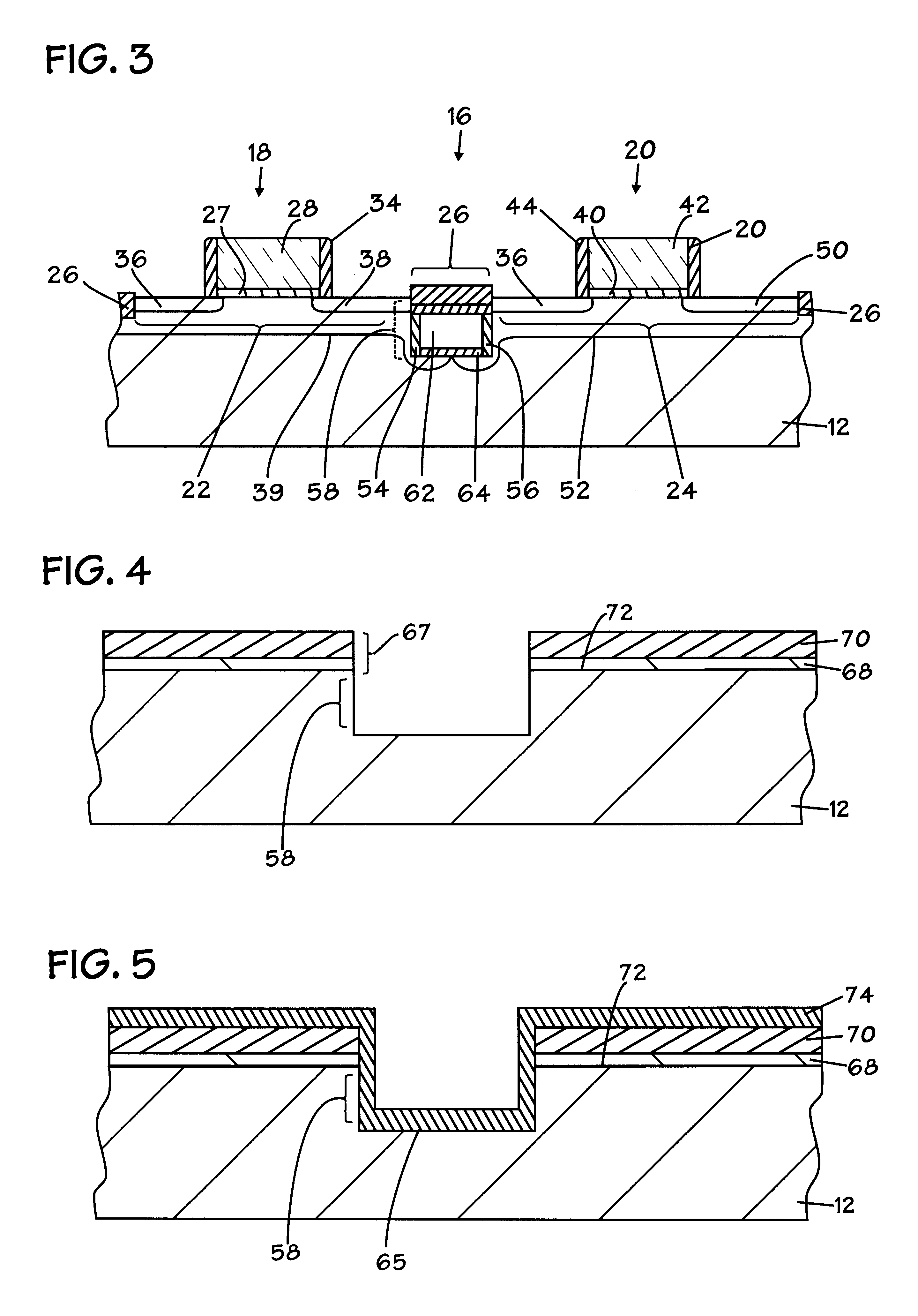

Integrated nitride-based acoustic wave devices and methods of fabricating integrated nitride-based acoustic wave devices

ActiveUS7112860B2Reduce unwanted reflectionReduce reflectionPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesMOSFETMESFET

A monolithic electronic device includes a substrate, a semi-insulating, piezoelectric Group III-nitride epitaxial layer formed on the substrate, a pair of input and output interdigital transducers forming a surface acoustic wave device on the epitaxial layer and at least one electronic device (such as a HEMT, MESFET, JFET, MOSFET, photodiode, LED or the like) formed on the substrate. Isolation means are disclosed to electrically and acoustically isolate the electronic device from the SAW device and vice versa. In some embodiments, a trench is formed between the SAW device and the electronic device. Ion implantation is also disclosed to form a semi-insulating Group III-nitride epitaxial layer on which the SAW device may be fabricated. Absorbing and / or reflecting elements adjacent the interdigital transducers reduce unwanted reflections that may interfere with the operation of the SAW device.

Owner:CREE INC

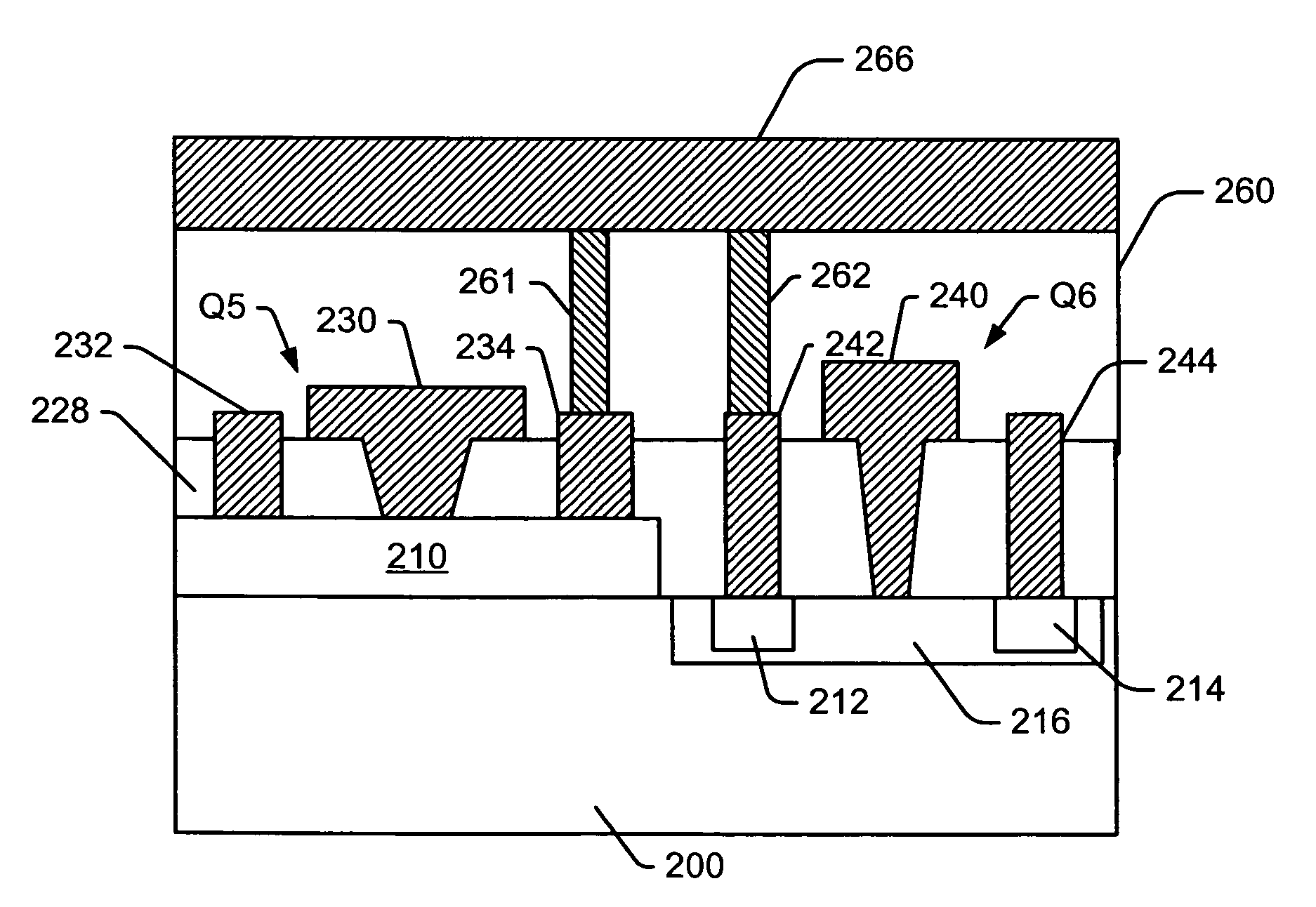

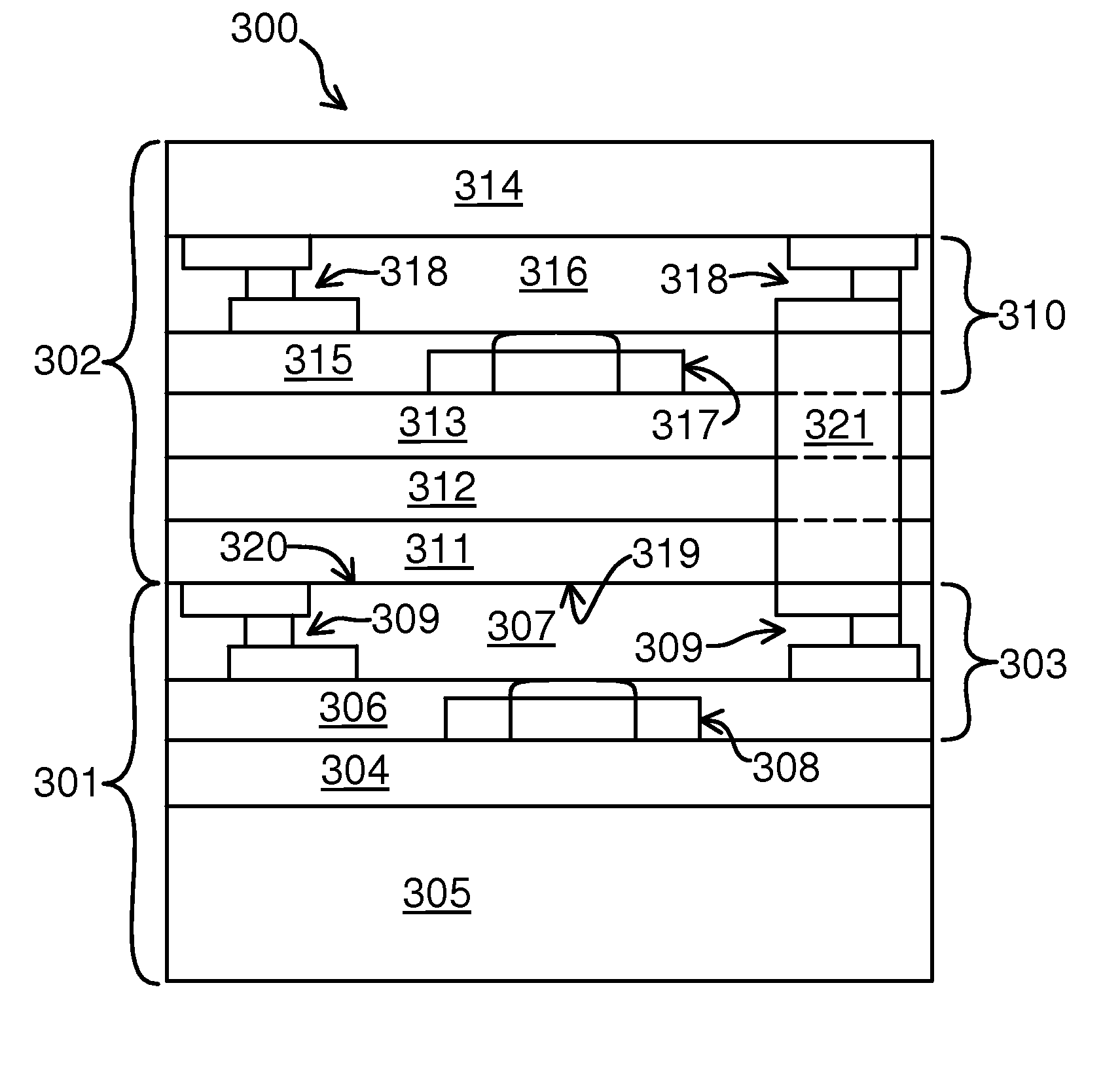

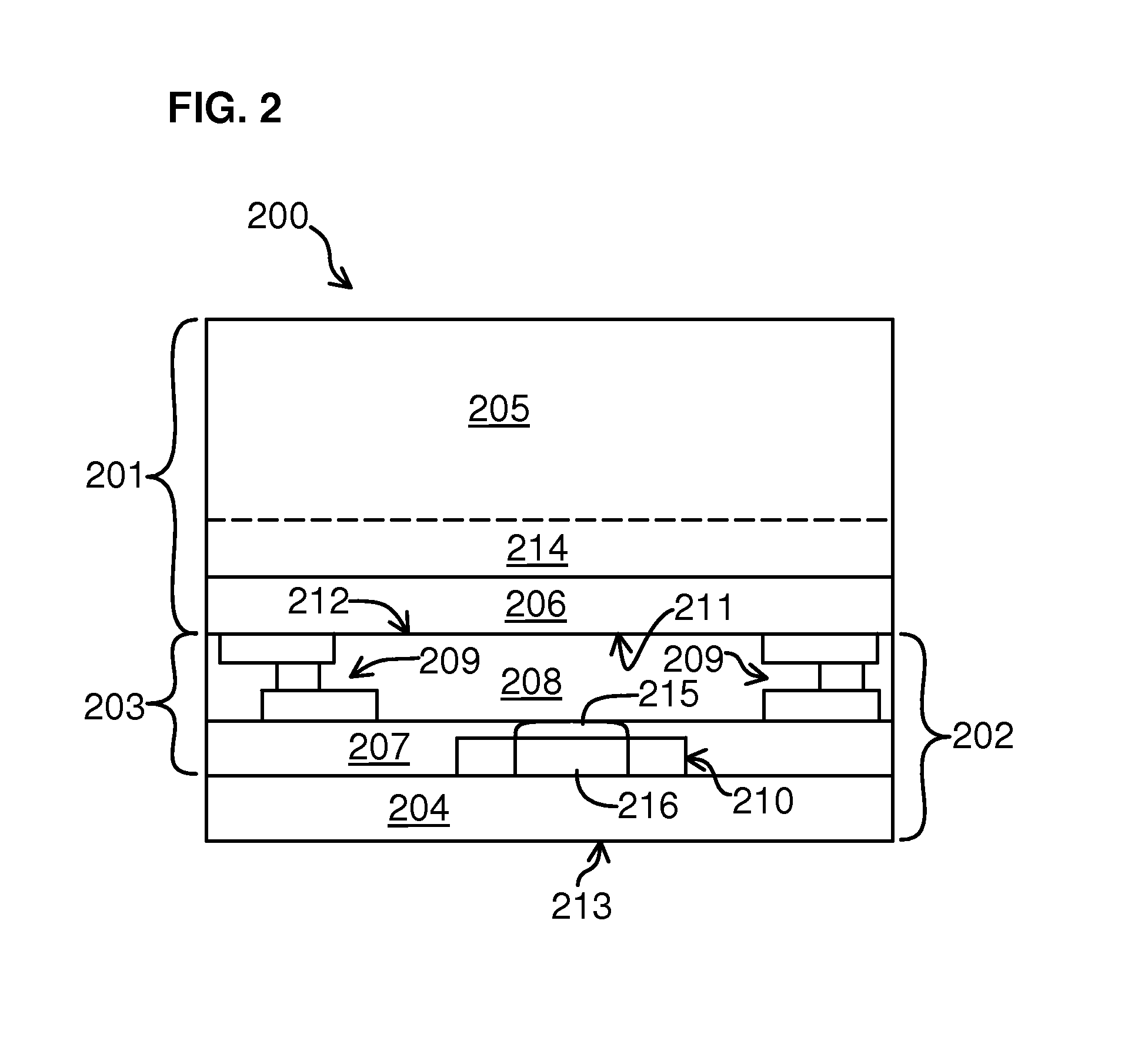

Integrated nitride and silicon carbide-based devices

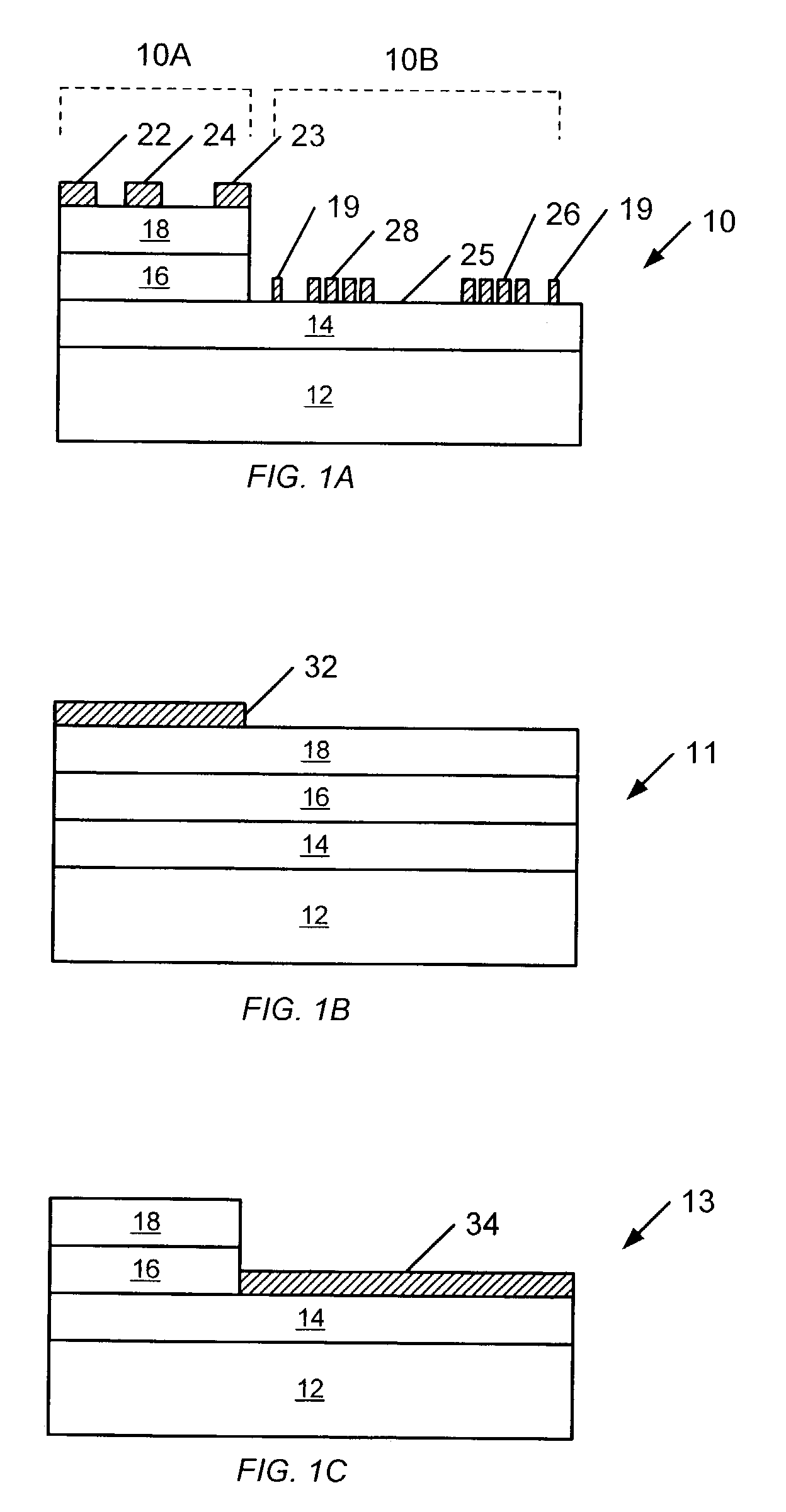

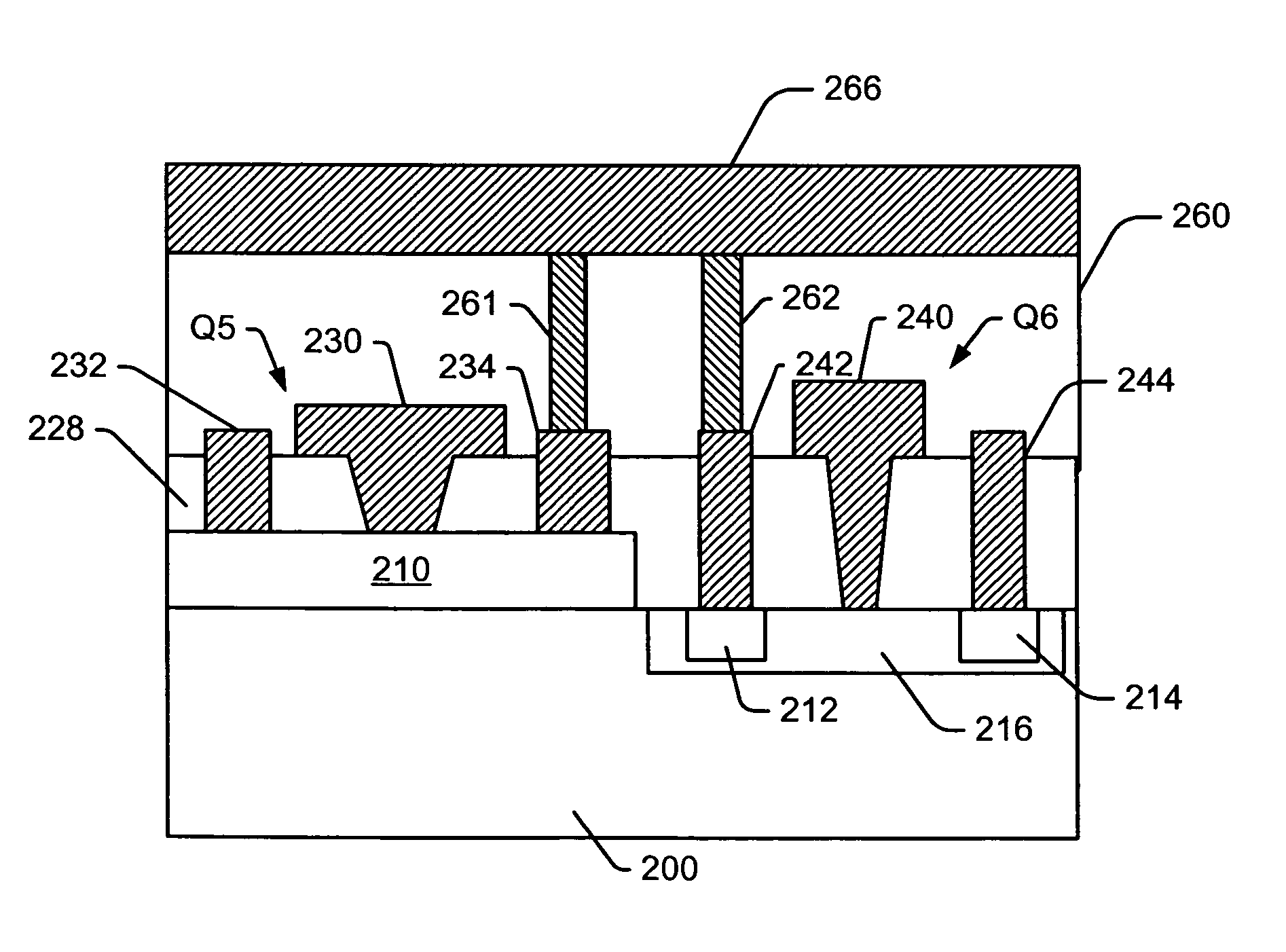

ActiveUS7875910B2TransistorPiezoelectric/electrostrictive device manufacture/assemblyNitrideSemi insulating

A monolithic electronic device includes a first nitride epitaxial structure including a plurality of nitride epitaxial layers. The plurality of nitride epitaxial layers include at least one common nitride epitaxial layer. A second nitride epitaxial structure is on the common nitride epitaxial layer of the first nitride epitaxial structure. A first plurality of electrical contacts is on the first epitaxial nitride structure and defines a first electronic device in the first nitride epitaxial structure. A second plurality of electrical contacts is on the first epitaxial nitride structure and defines a second electronic device in the second nitride epitaxial structure. A monolithic electronic device includes a bulk semi-insulating silicon carbide substrate having implanted source and drain regions and an implanted channel region between the source and drain regions, and a nitride epitaxial structure on the surface of the silicon carbide substrate. Corresponding methods are also disclosed.

Owner:MACOM TECH SOLUTIONS HLDG INC

Semi-insulating GaN and method of making the same

InactiveUS7170095B2Solid-state devicesSemiconductor/solid-state device manufacturingAcceptor dopantSingle crystal

Large-area, single crystal semi-insulating gallium nitride that is usefully employed to form substrates for fabricating GaN devices for electronic and / or optoelectronic applications. The large-area, semi-insulating gallium nitride is readily formed by doping the growing gallium nitride material during growth thereof with a deep acceptor dopant species, e.g., Mn, Fe, Co, Ni, Cu, etc., to compensate donor species in the gallium nitride, and impart semi-insulating character to the gallium nitride.

Owner:WOLFSPEED INC

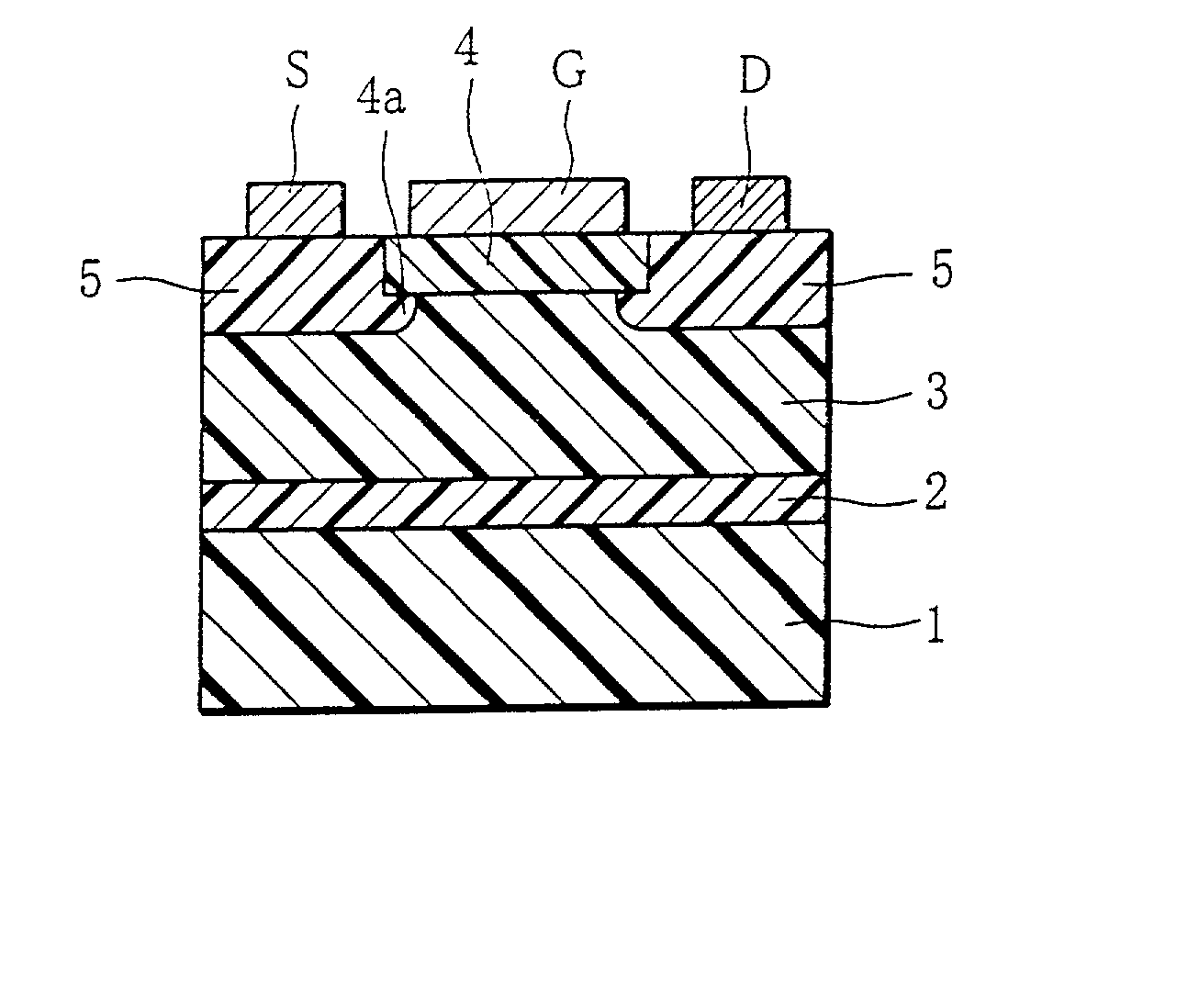

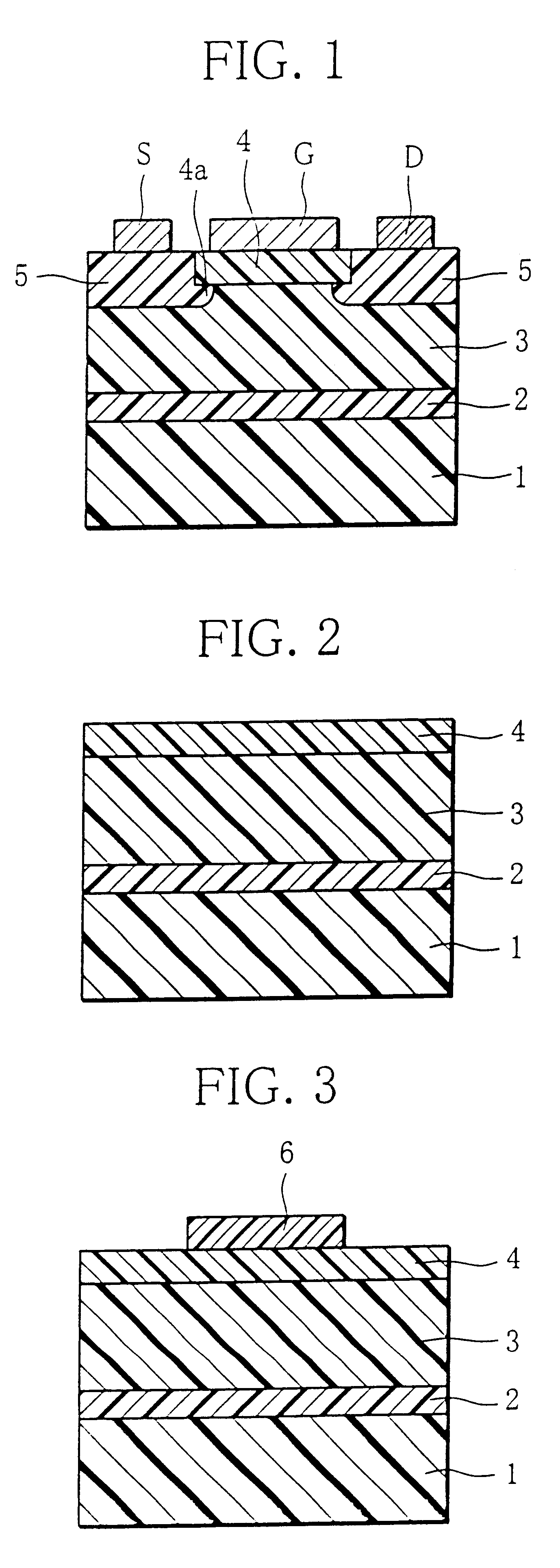

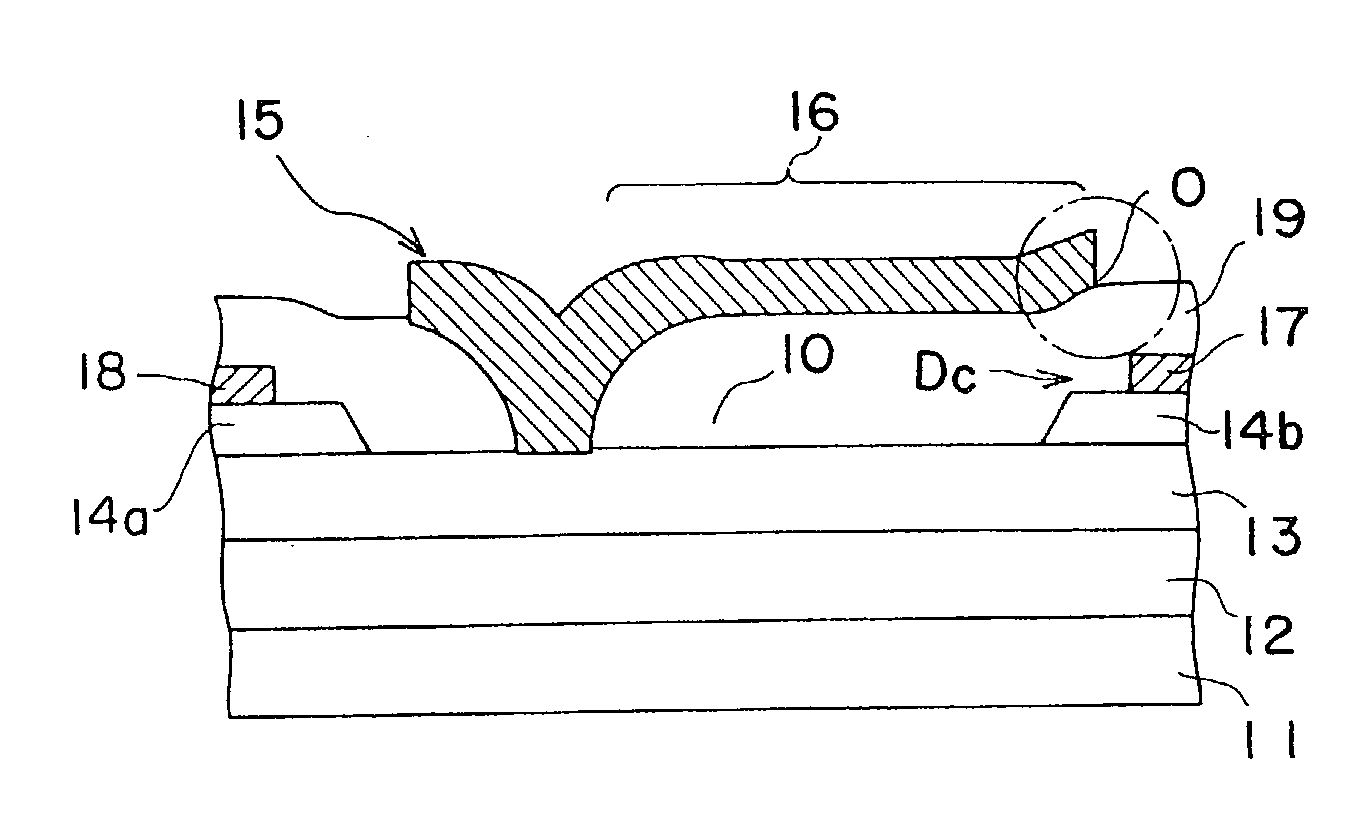

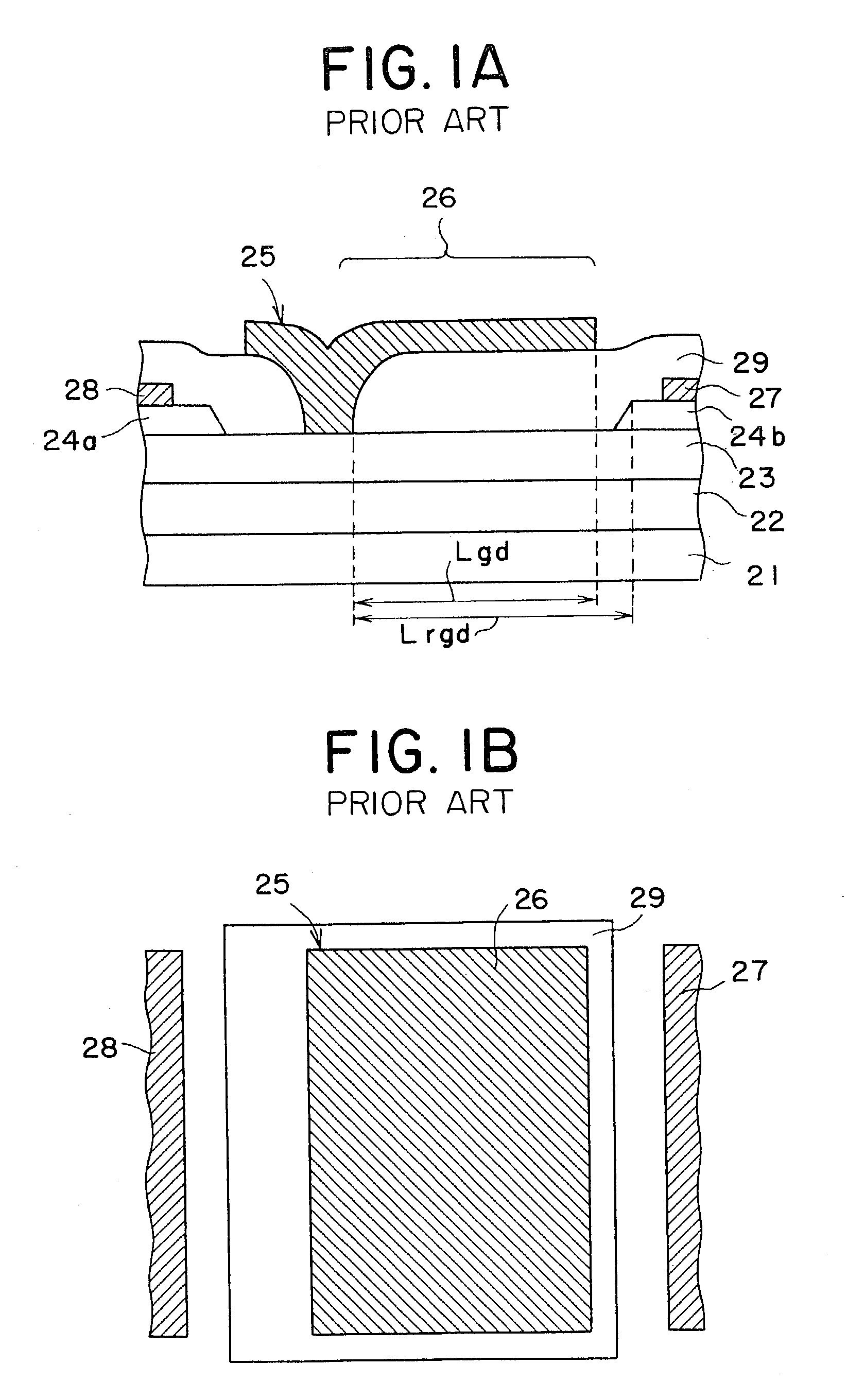

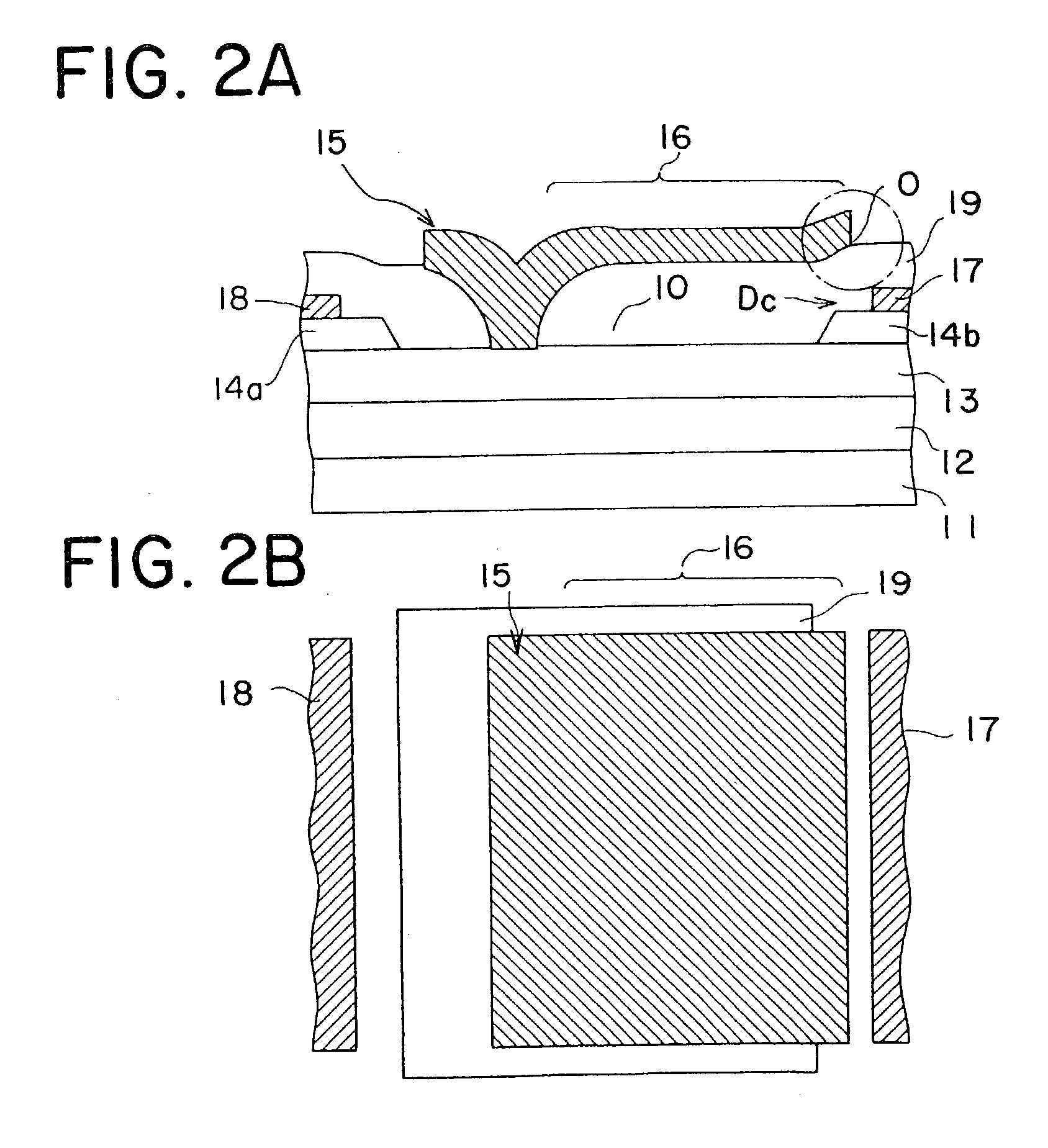

GaN-based high electron mobility transistor

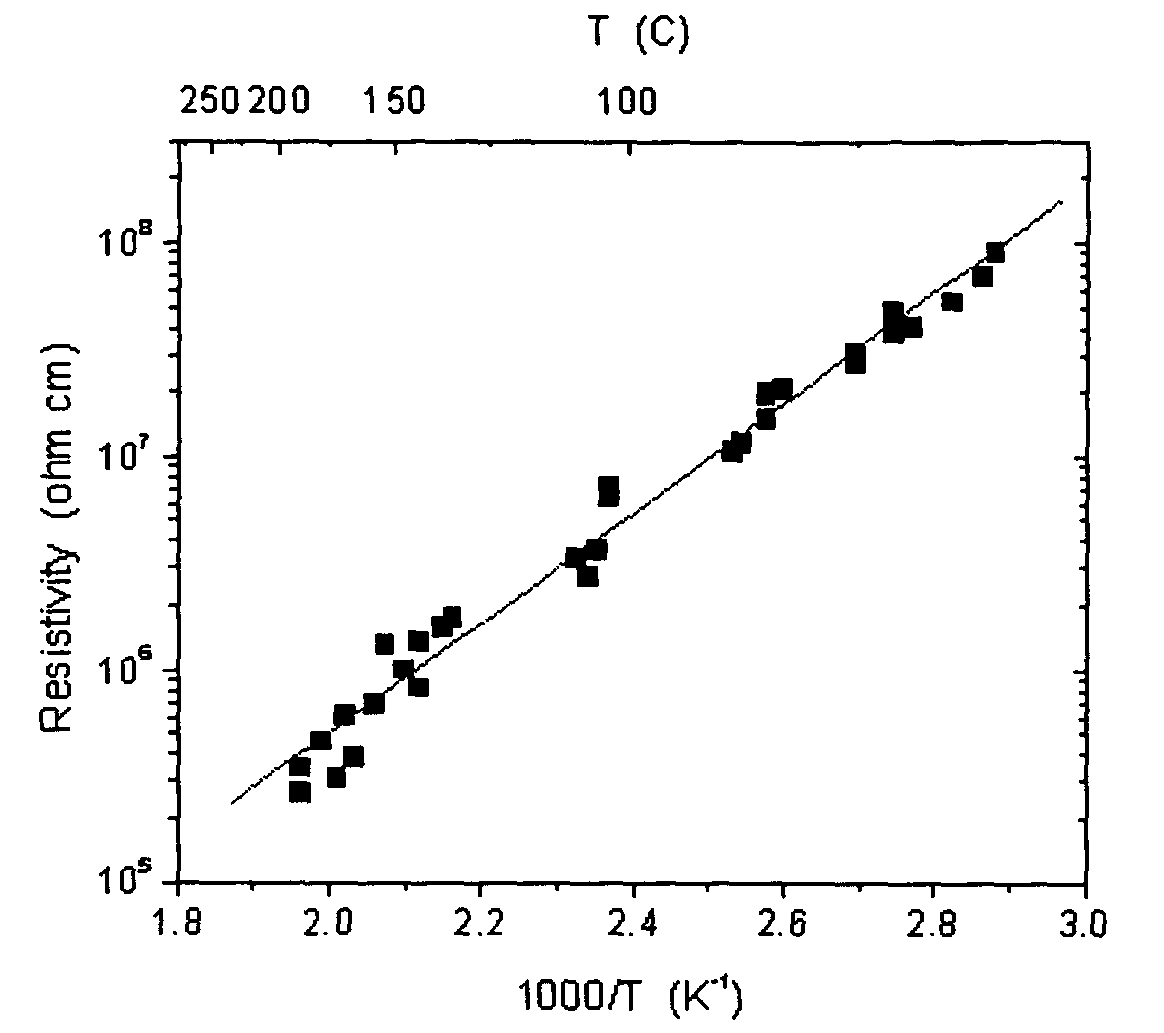

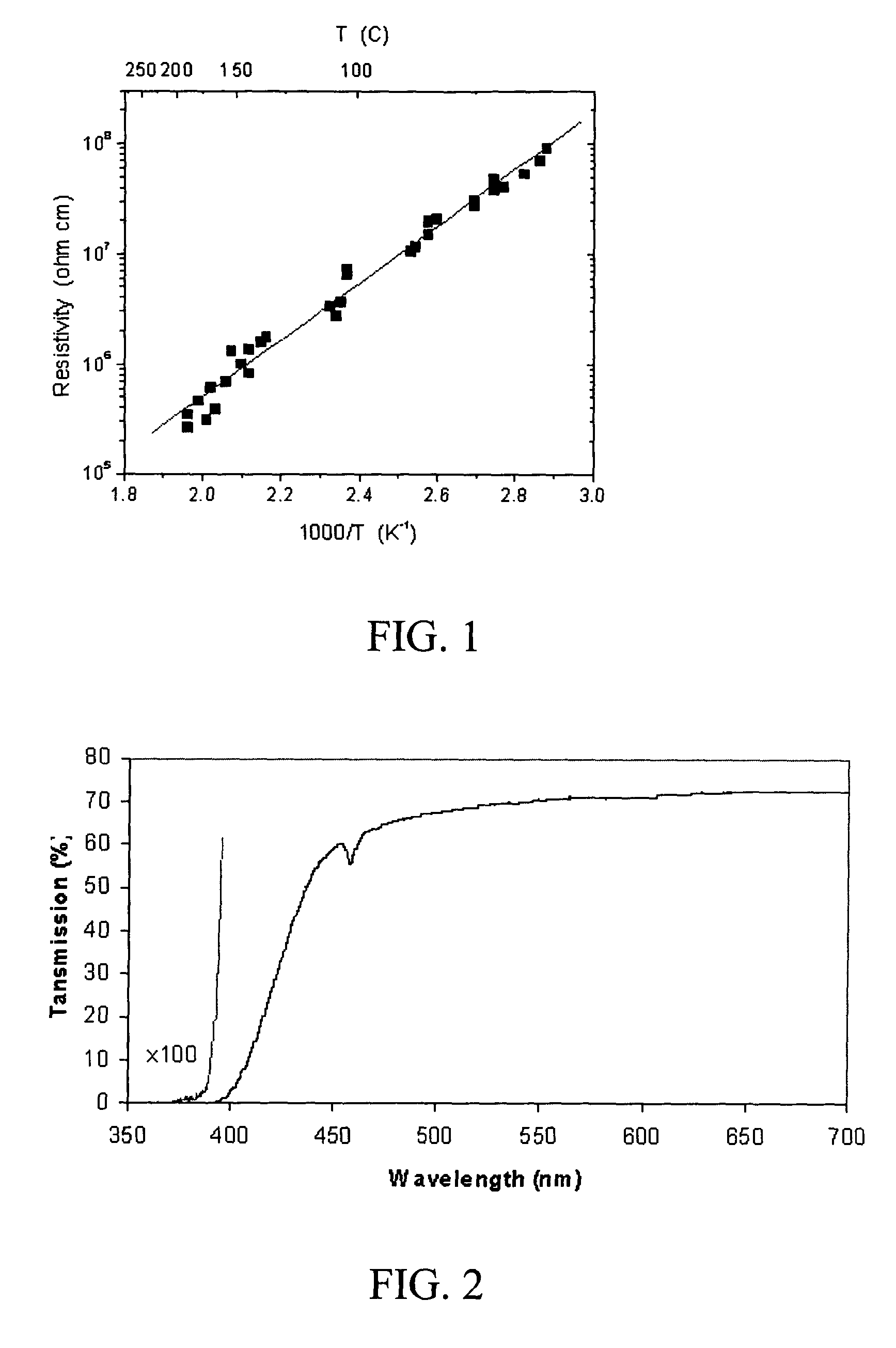

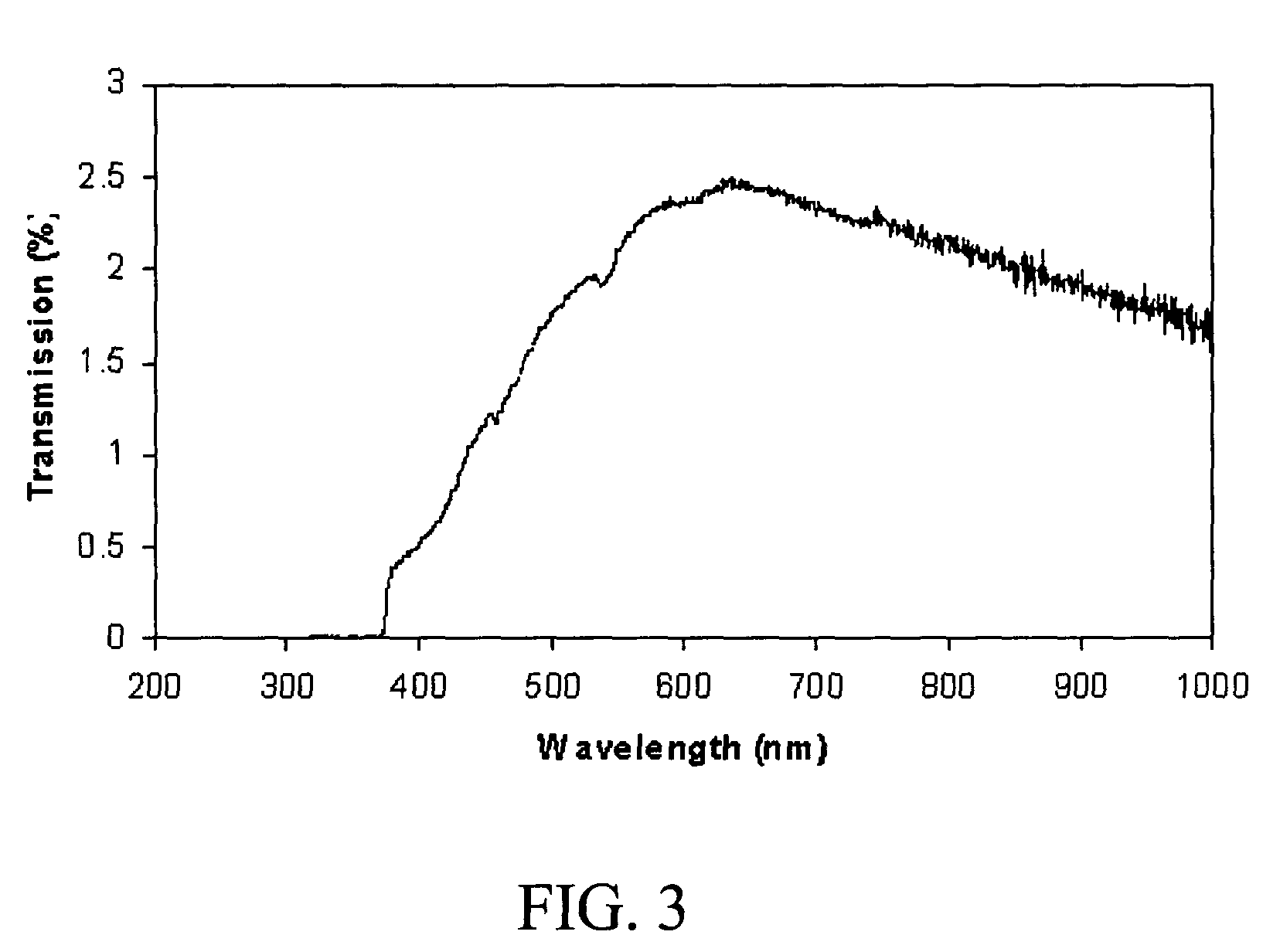

InactiveUS20020079508A1Improve mobilityIncreased electrical resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectric resistivity

A GaN-based high electron mobility transistor (HEMT) has an undoped GaN layer where a two-dimensional electron gas layer is formed, the undoped GaN layer having a high electric resistivity enabling a pinch-off state to be obtained even when the gate bias voltage is 0 V. The GaN-based HEMT comprises a semi-insulating substrate on which a GaN buffer layer is formed. An undoped GaN layer is disposed on the GaN buffer layer and has an electric resistivity of not less than 1x106 OMEGA / cm2. An undoped AlGaN layer is disposed on the undoped GaN layer via a heterojunction such that an undercut portion is formed therebetween. An n-type GaN layer is further disposed in such a manner as to bury side portions of the undoped AlGaN layer and the undercut portion. The individual layers thus Ad form a layered structure. A gate electrode G is formed on the undoped AlGaN layer, and a source electrode S and a drain electrode D are formed on the n-type GaN layer.

Owner:FURUKAWA ELECTRIC CO LTD

Semi-insulating silicon carbide without vanadium domination

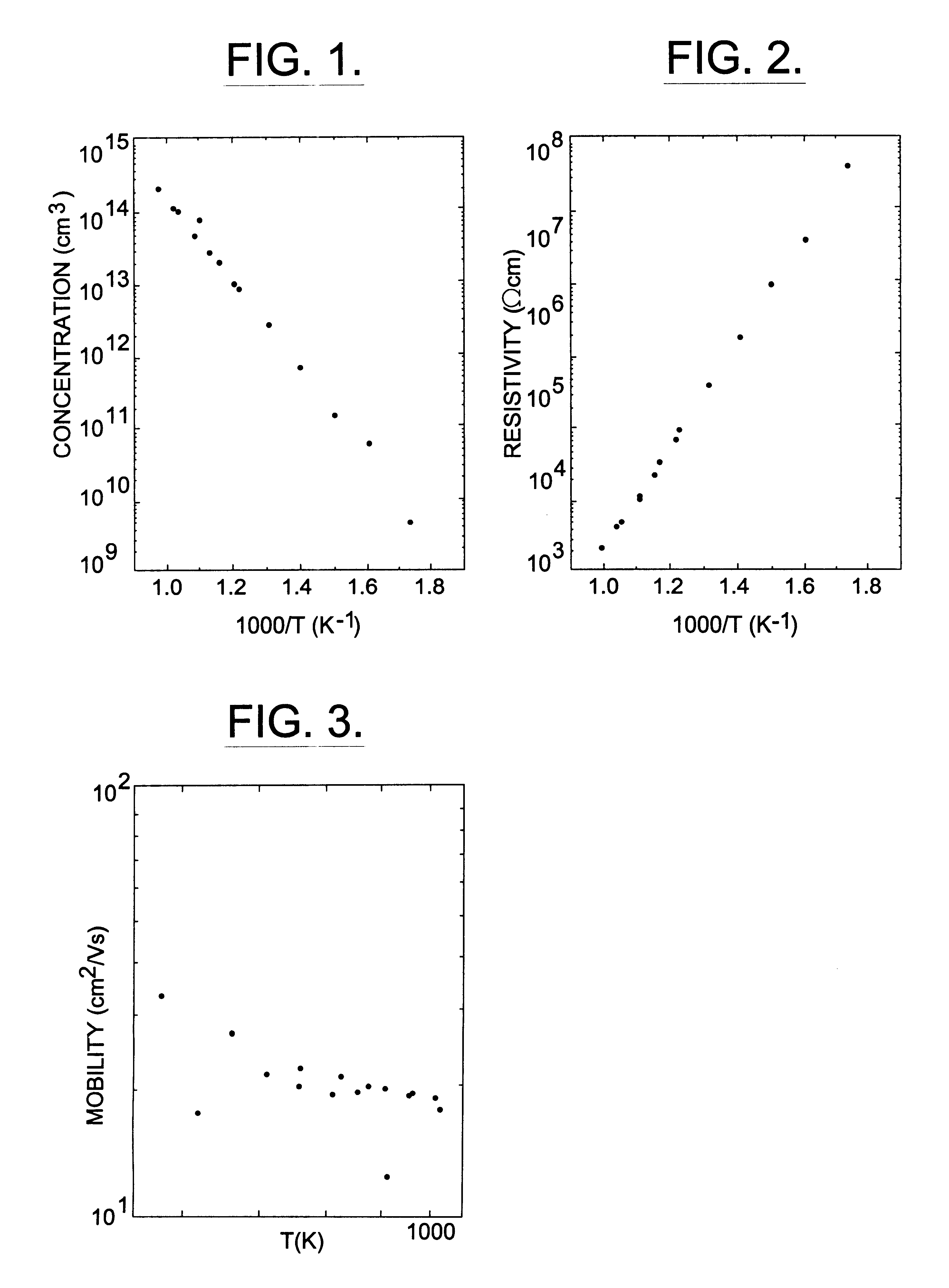

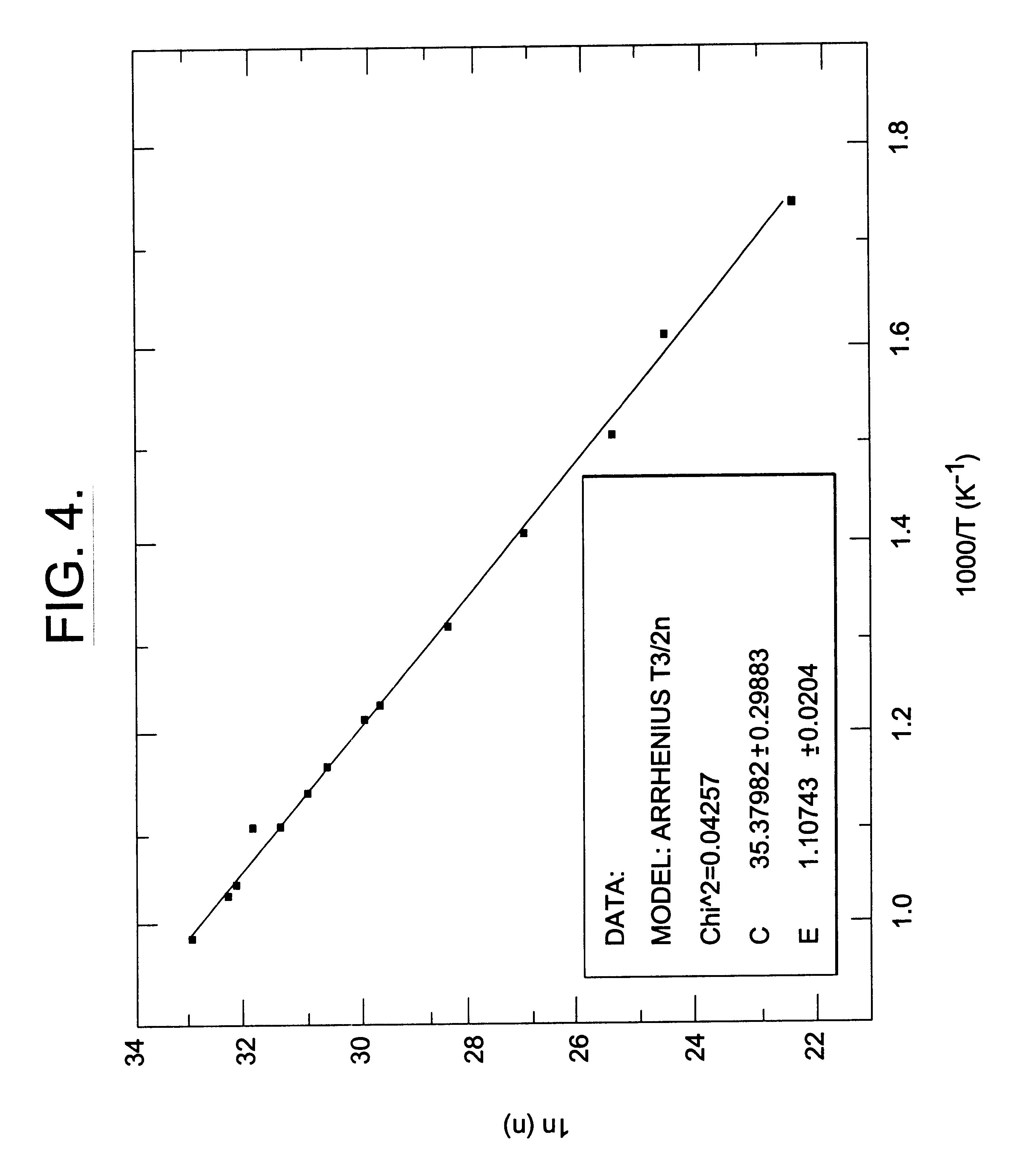

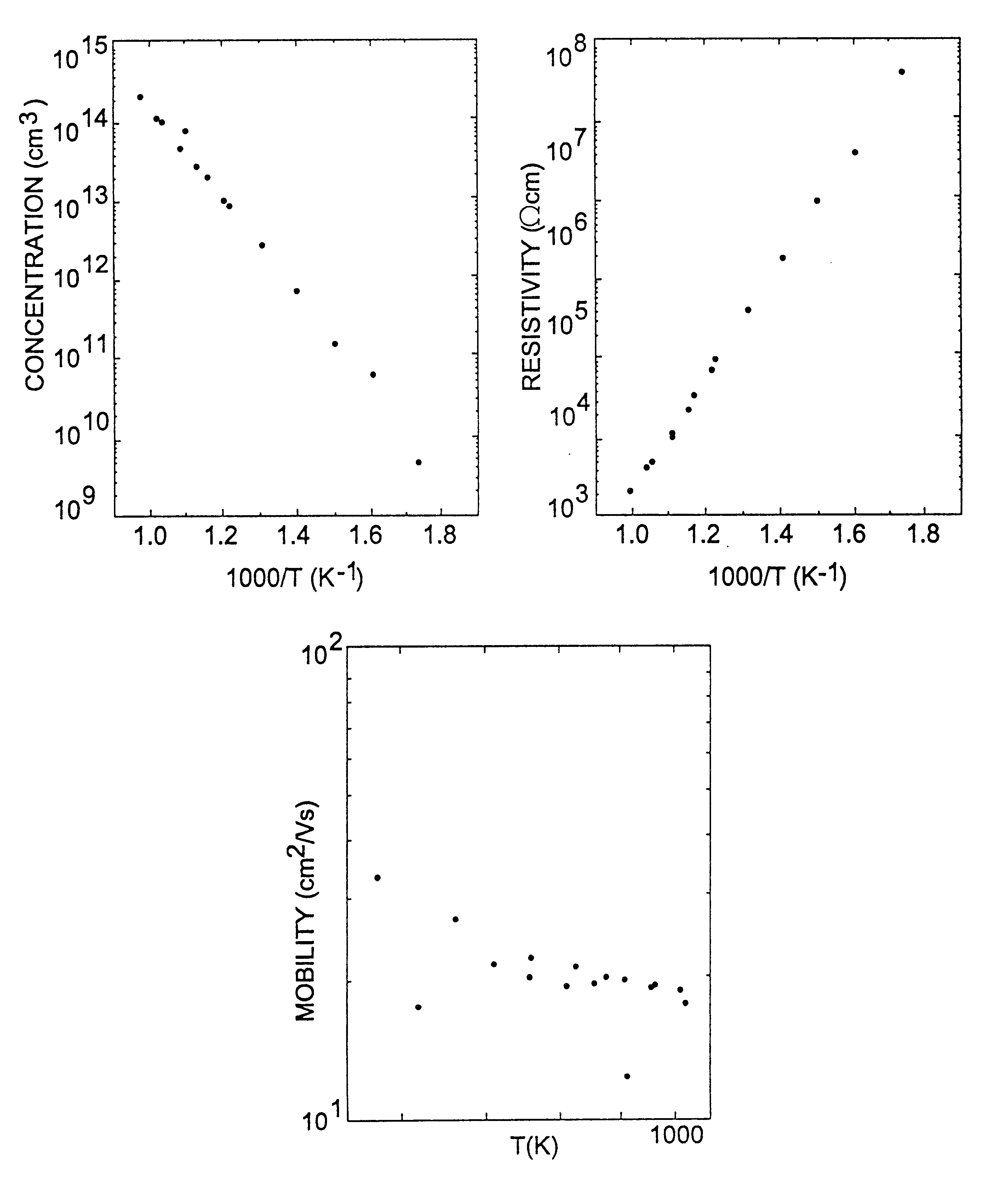

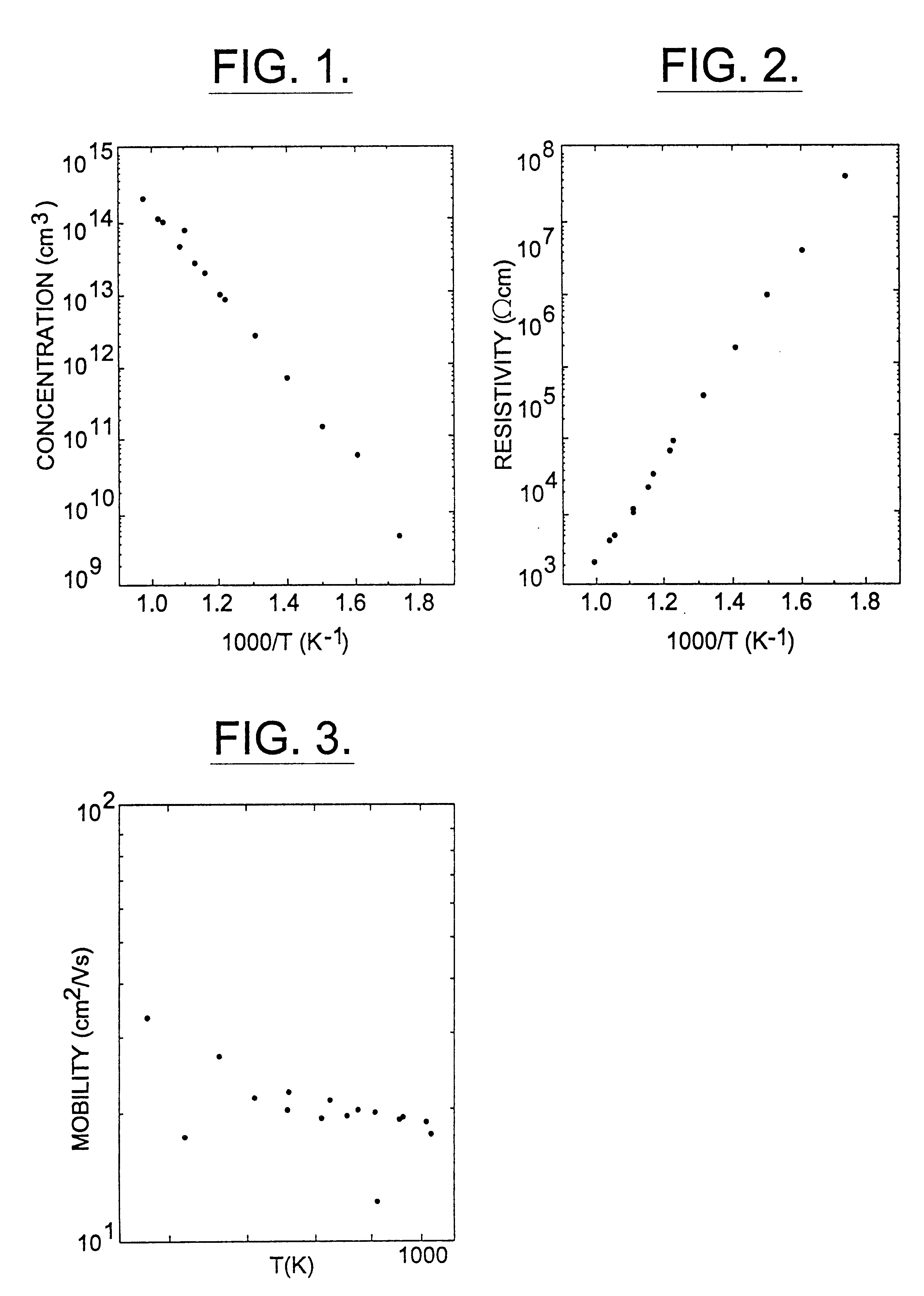

InactiveUS6396080B2High-frequency operationReduce complicationsPolycrystalline material growthAfter-treatment detailsDevice formRoom temperature

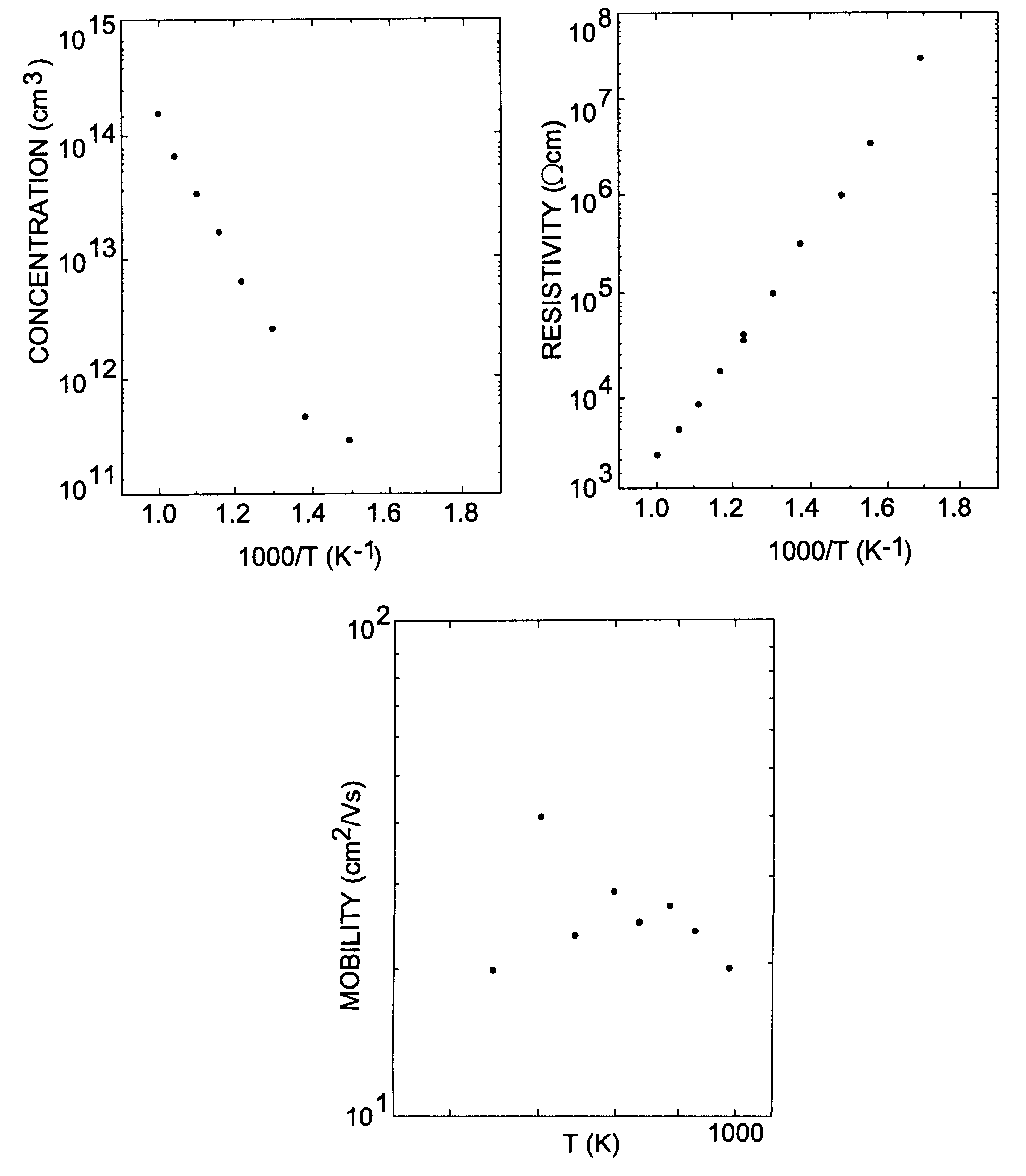

A semi-insulating bulk single crystal of silicon carbide is disclosed that has a resistivity of at least 5000 OMEGA-cm at room temperature and a concentration of trapping elements that create states at least 700 meV from the valence or conduction band that is below the amounts that will affect the resistivity of the crystal, preferably below detectable levels. A method of forming the crystal is also disclosed, along with some resulting devices that take advantage of the microwave frequency capabilities of devices formed using substrates according to the invention.

Owner:CREE INC

Integrated nitride and silicon carbide-based devices and methods of fabricating integrated nitride-based devices

ActiveUS20060289901A1TransistorPiezoelectric/electrostrictive device manufacture/assemblyNitrideSemi insulating

A monolithic electronic device includes a first nitride epitaxial structure including a plurality of nitride epitaxial layers. The plurality of nitride epitaxial layers include at least one common nitride epitaxial layer. A second nitride epitaxial structure is on the common nitride epitaxial layer of the first nitride epitaxial structure. A first plurality of electrical contacts is on the first epitaxial nitride structure and defines a first electronic device in the first nitride epitaxial structure. A second plurality of electrical contacts is on the first epitaxial nitride structure and defines a second electronic device in the second nitride epitaxial structure. A monolithic electronic device includes a bulk semi-insulating silicon carbide substrate having implanted source and drain regions and an implanted channel region between the source and drain regions, and a nitride epitaxial structure on the surface of the silicon carbide substrate. Corresponding methods are also disclosed.

Owner:WOLFSPEED INC

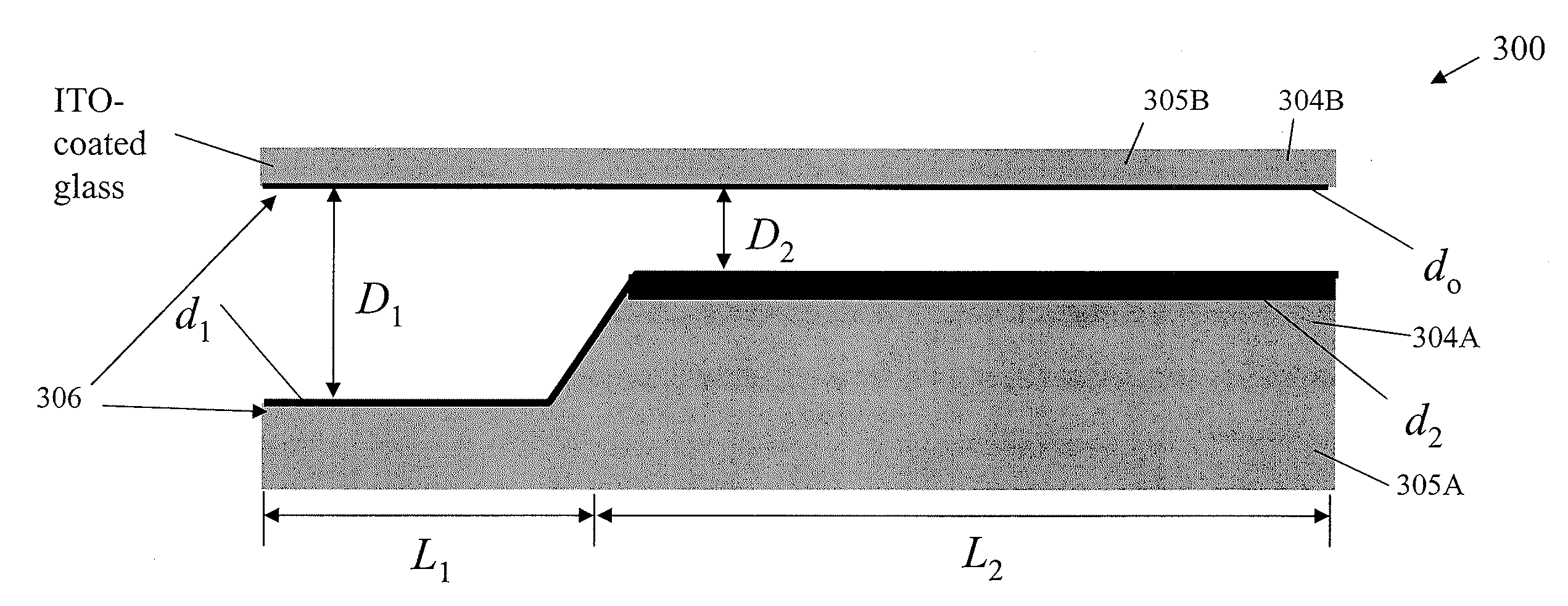

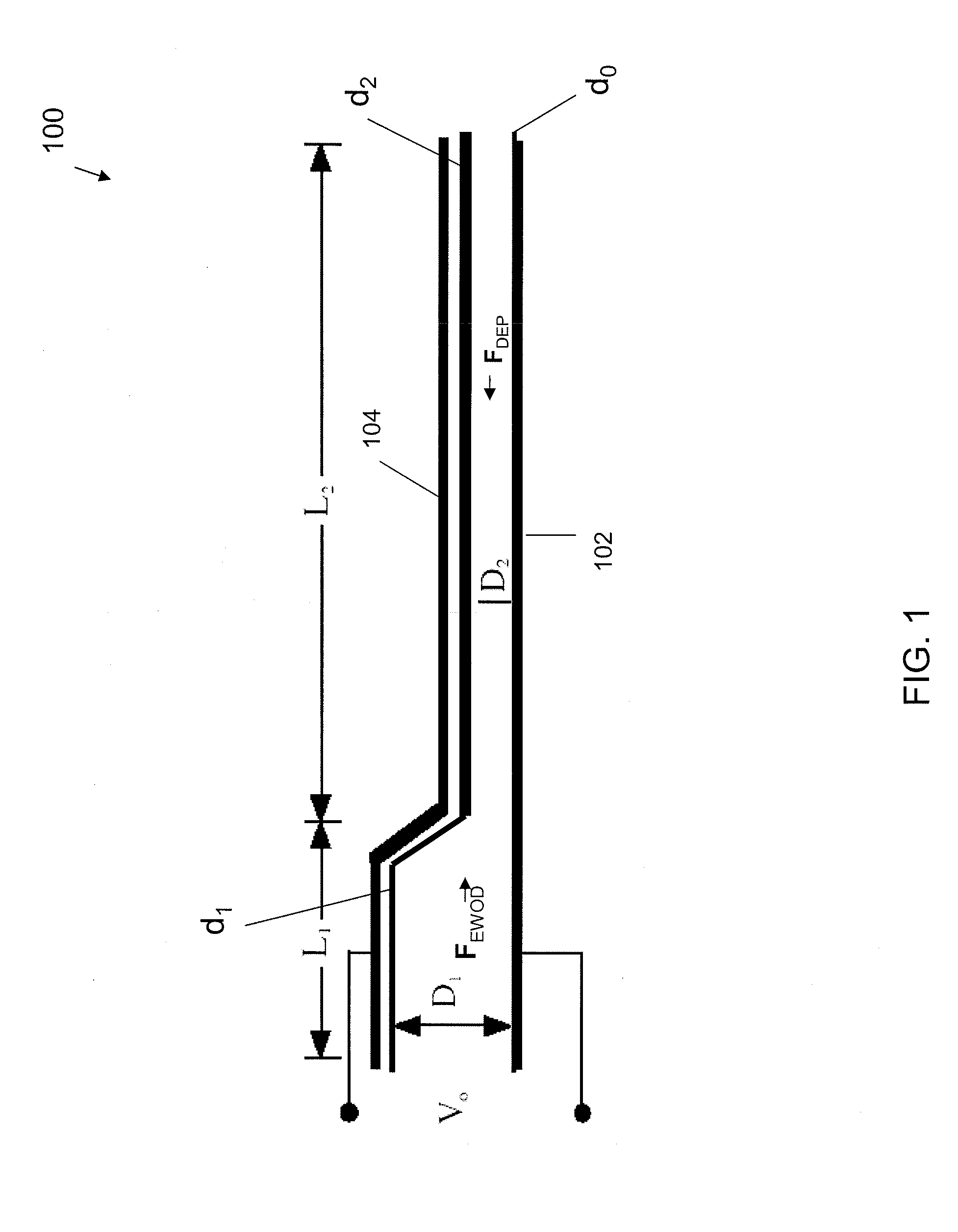

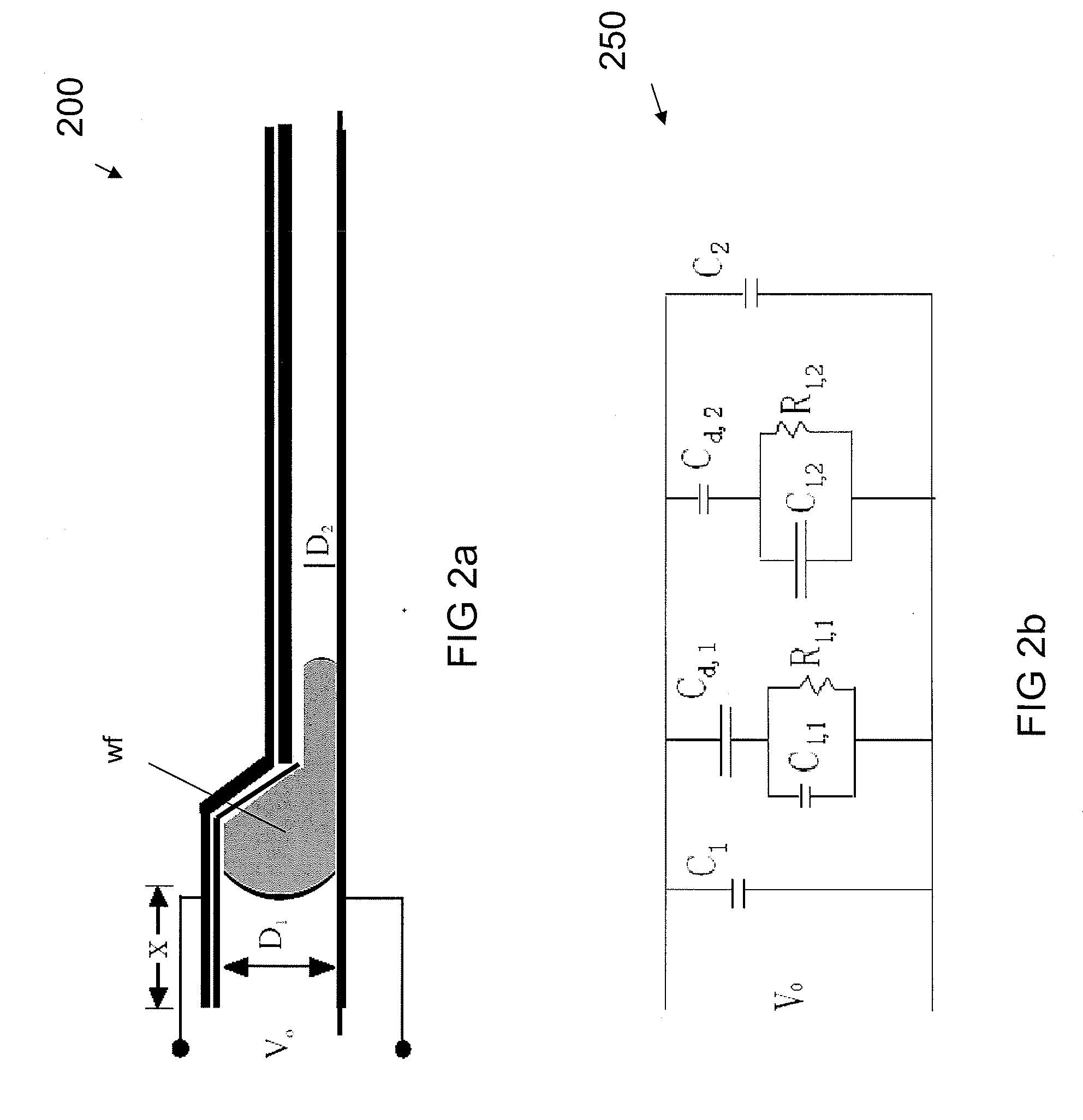

Frequency-addressable Apparatus and Methods for Actuation of Liquids

InactiveUS20080169195A1Uniform thicknessSludge treatmentElectrostatic separatorsDielectricWorking fluid

Embodiments of the invention are directed to apparatus, methods, and applications involving the actuation of a semi-insulative working fluid by electromechanical forces based on electrowetting-on-dielectric (EWOD) and liquid dielectrophoresis (liquid DEP) mechanisms that are controlled by the frequency, but not the magnitude, of an AC voltage (i.e., ‘frequency-addressable). In the various apparatus embodiments of the invention, a single, frequency-addressable electrode pair includes at least one electrode that has a spatially-varying dielectric coating thickness and thus a spatially-varying electrode gap wherein at least a portion of which a volume of a working fluid can stably reside under no influence of an applied voltage. In an exemplary aspect, a frequency-addressable, bistable apparatus includes at least one wider gap and one narrower gap associated, respectively, with a thicker and a thinner dielectric coating thickness of the electrode(s). The working fluid resides in only one of the at least two gap regions only under the influence of capillary force. A brief burst of AC voltage at a selected high frequency or low frequency will move the liquid from one gap region to another (and back) by one of an EWOD-based and a DEP-based force. In an alternative aspect, an analog apparatus has a continuous, spatially-varying electrode gap in which the dielectric coating thickness on the electrodes varies smoothly in an inverse manner. Various applications to a display device, fiber optic coupler and attenuator, controlled liquid volume dispensers, spotting arrays, well plate apparatus, and others are presented, along with control methods.

Owner:UNIVERSITY OF ROCHESTER

High electron mobility electronic device structures comprising native substrates and methods for making the same

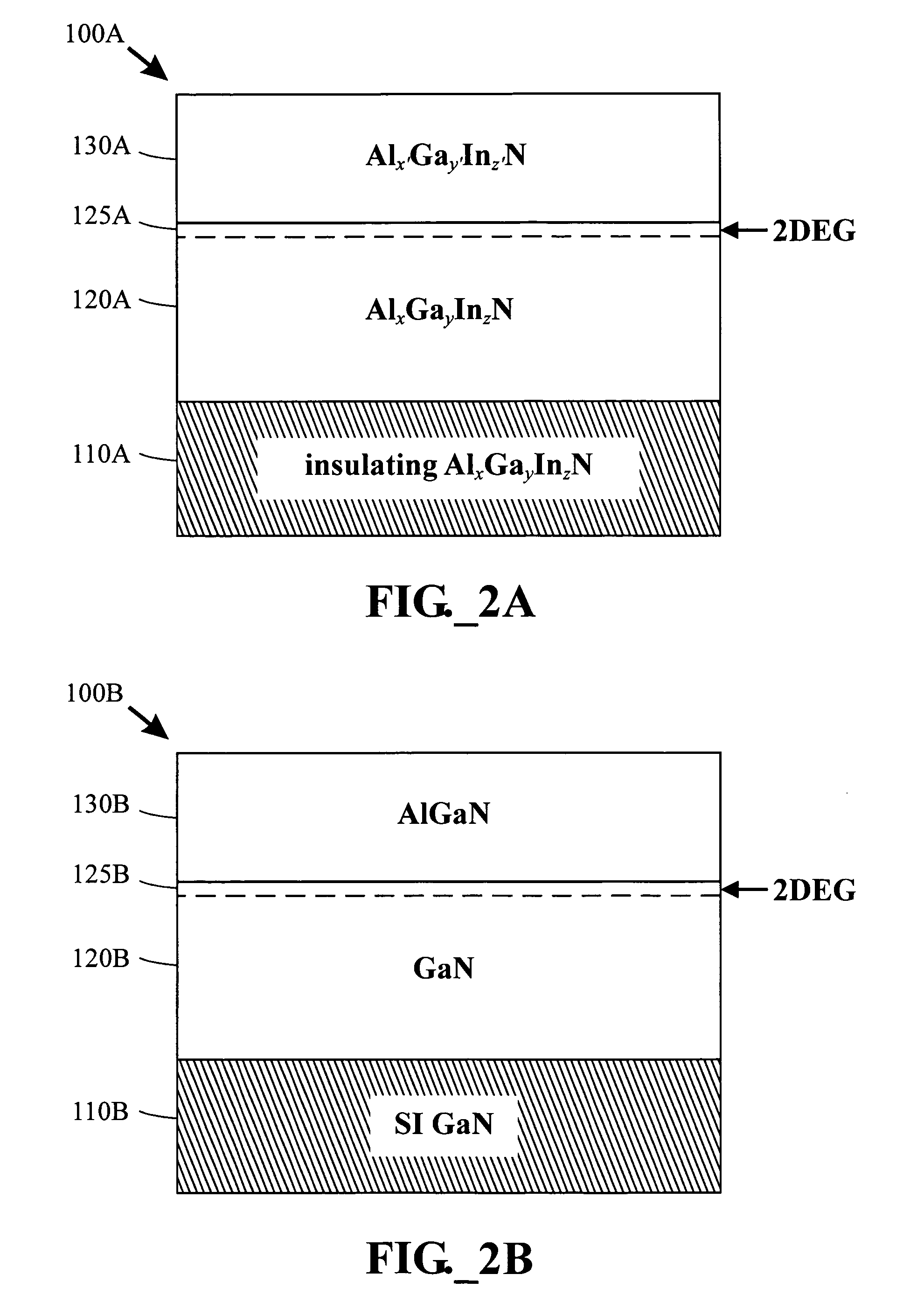

An electronic device structure comprises a substrate layer of semi-insulating AlxGayInzN, a first layer comprising AlxGayInzN, a second layer comprising Alx′Gay′Inz′N, and at least one conductive terminal disposed in or on any of the foregoing layers, with the first and second layers being adapted to form a two dimensional electron gas is provided. A thin (<1000 nm) III-nitride layer is homoepitaxially grown on a native semi-insulating III-V substrate to provide an improved electronic device (e.g., HEMT) structure.

Owner:CREE INC

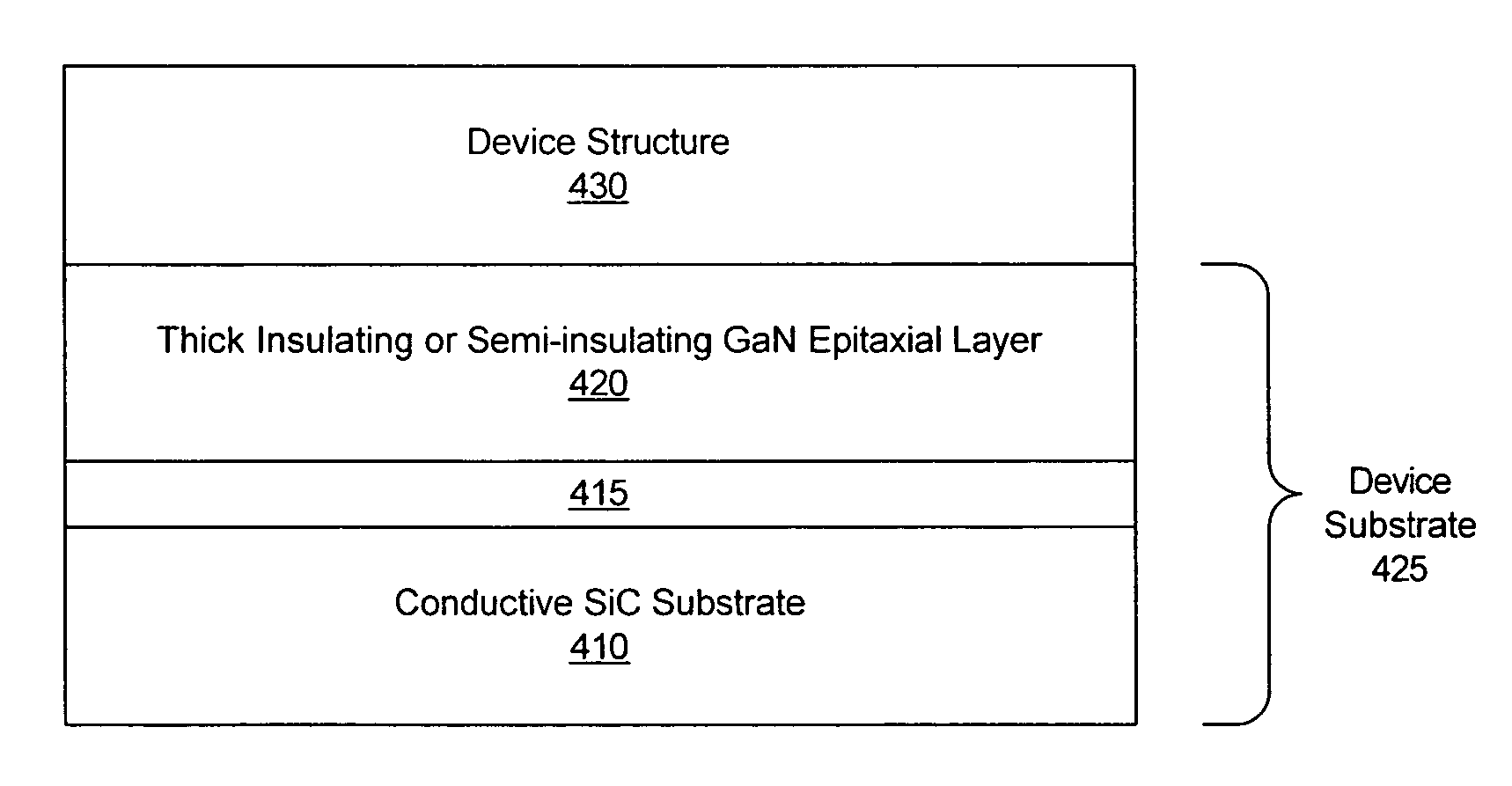

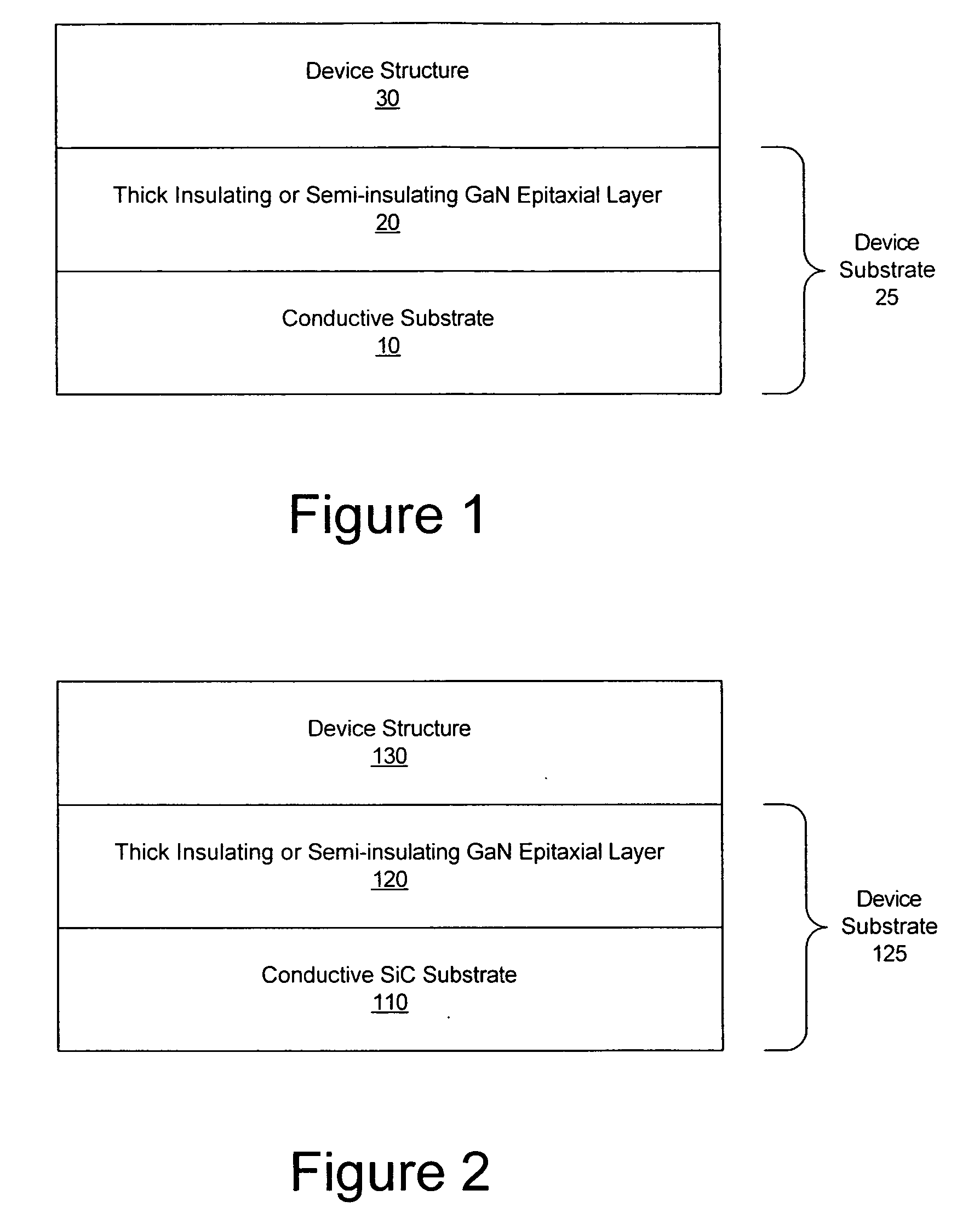

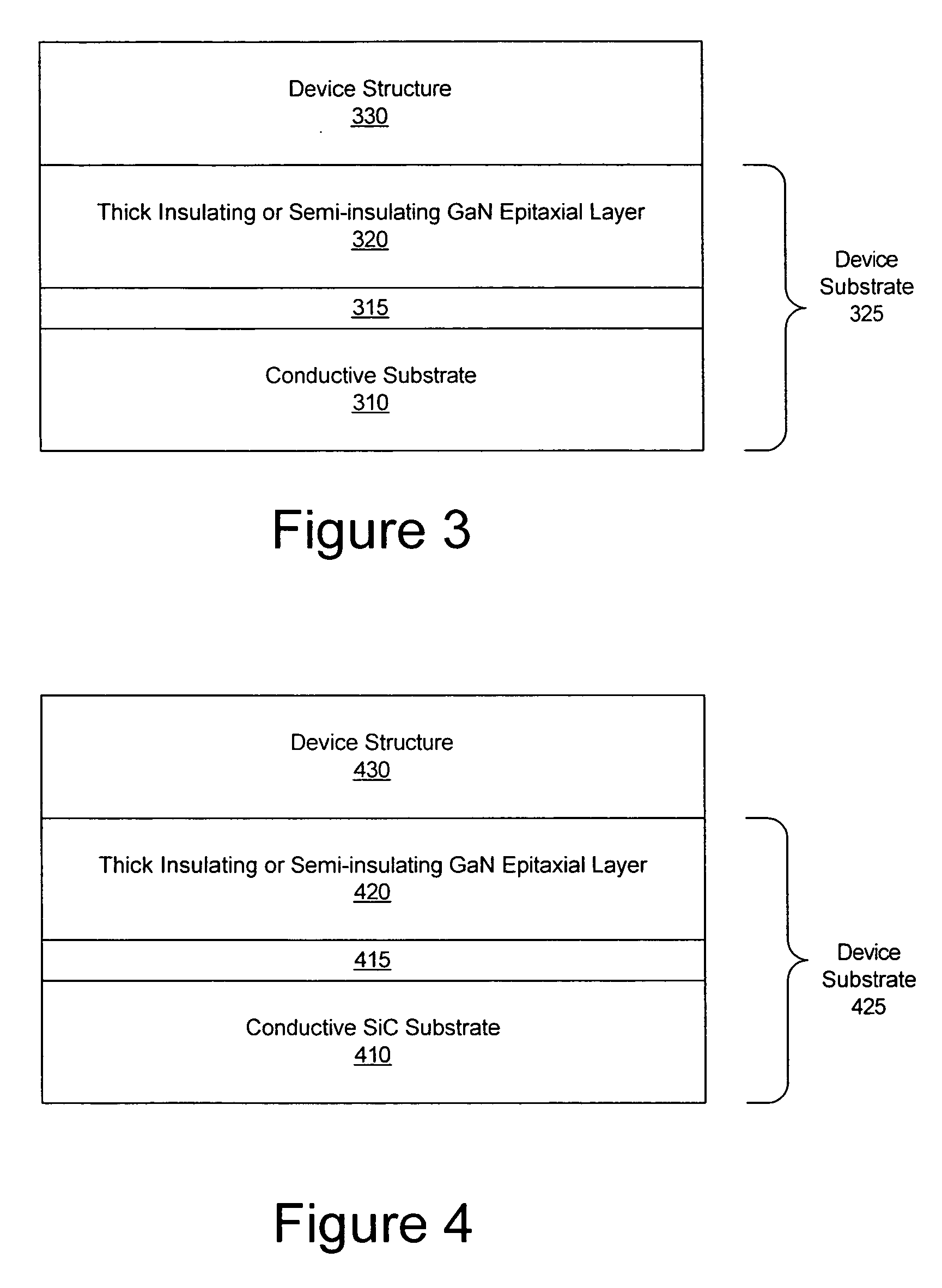

Thick semi-insulating or insulating epitaxial gallium nitride layers and devices incorporating same

ActiveUS20060226412A1High electron mobilityHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialGallium nitride

Semiconductor device structures and methods of fabricating semiconductor devices structures are provided that include a semi-insulating or insulating GaN epitaxial layer on a conductive semiconductor substrate and / or a conductive layer. The semi-insulating or insulating GaN epitaxial layer has a thickness of at least about 4 μm. GaN semiconductor device structures and methods of fabricating GaN semiconductor device structures are also provided that include an electrically conductive SiC substrate and an insulating or semi-insulating GaN epitaxial layer on the conductive SiC substrate. The GaN epitaxial layer has a thickness of at least about 4 μm. GaN semiconductor device structures and methods of fabricating GaN semiconductor device structures are also provided that include an electrically conductive GaN substrate, an insulating or semi-insulating GaN epitaxial layer on the conductive GaN substrate, a GaN based semiconductor device on the GaN epitaxial layer and a via hole and corresponding via metal in the via hole that extends through layers of the GaN based semiconductor device and the GaN epitaxial layer.

Owner:CREE INC

Method of making air gap isolation by making a lateral EPI bridge for low K isolation advanced CMOS fabrication

InactiveUS6268637B1Semiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

An isolation structure and a method of making the same are provided. In one aspect, the method includes the steps of forming a trench in a substrate and forming a first insulating sidewall in the trench and a second insulating in the trench in spaced-apart relation to the first insulating sidewall. A bridge layer is formed between the first and the second sidewalls. The bridge layer, the first and second sidewalls, and the substrate define an air gap in the trench. The isolation structure exhibits a low capacitance in a narrow structure. Scaling is enhanced and the potential for parasitic leakage current due to non-planarity is reduced.

Owner:GLOBALFOUNDRIES INC

Semi-insulating Group III Metal Nitride and Method of Manufacture

ActiveUS20110220912A1Polycrystalline material growthFrom normal temperature solutionsAcceptor dopantSingle crystal

A large-area, high-purity, low-cost single crystal semi-insulating gallium nitride that is useful as substrates for fabricating GaN devices for electronic and / or optoelectronic applications is provided. The gallium nitride is formed by doping gallium nitride material during ammonothermal growth with a deep acceptor dopant species, e.g., Mn, Fe, Co, Ni, Cu, etc., to compensate donor species in the gallium nitride, and impart semi-insulating character to the gallium nitride.

Owner:SLT TECH

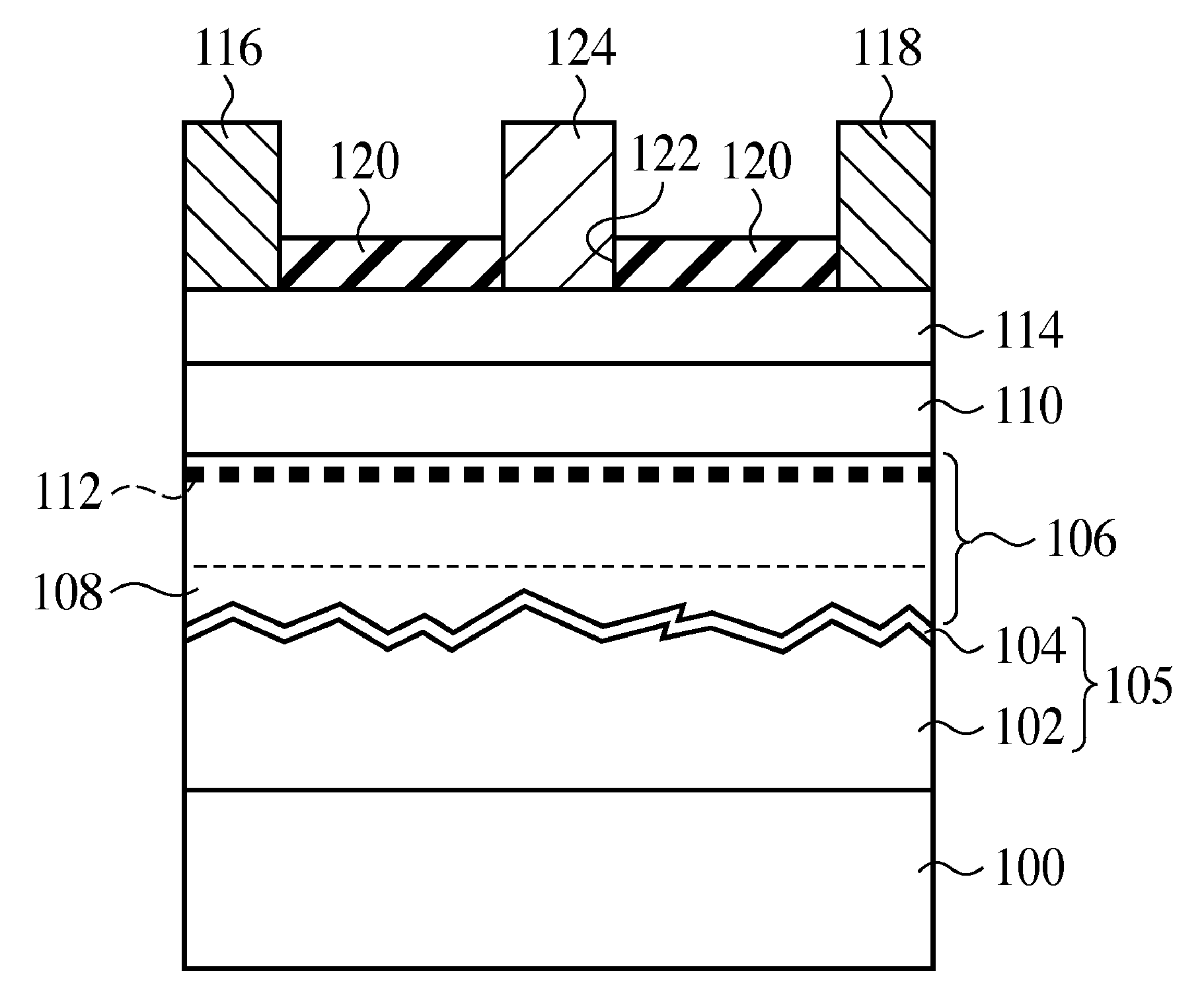

Trap Rich Layer Formation Techniques for Semiconductor Devices

ActiveUS20130084689A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor packageStress relief

A trap rich layer for an integrated circuit chip is formed by chemical etching and / or laser texturing of a surface of a semiconductor layer. In some embodiments, a trap rich layer is formed by a technique selected from the group of techniques consisting of laser texturing, chemical etch, irradiation, nanocavity formation, porous Si-etch, semi-insulating polysilicon, thermal stress relief and mechanical texturing. Additionally, combinations of two or more of these techniques may be used to form a trap rich layer.

Owner:QUALCOMM INC

Compound semiconductor device and method of manufacturing the same

ActiveUS20080197359A1Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCompound (substance)Engineering

A compound semiconductor device has a buffer layer formed on a conductive SiC substrate, an AlxGa1-xN layer formed on the buffer layer in which an impurity for reducing carrier concentration from an unintentionally doped donor impurity is added and in which the Al composition x is 0<x<1, a GaN-based carrier transit layer formed on the AlxGa1-xN layer, a carrier supply layer formed on the carrier transit layer, a source electrode and a drain electrode formed on the carrier supply layer, and a gate electrode formed on the carrier supply layer between the source electrode and the drain electrode. Therefore, a GaN-HEMT that is superior in device characteristics can be realized in the case of using a relatively less expensive conductive SiC substrate compared with a semi-insulating SiC substrate.

Owner:FUJITSU LTD

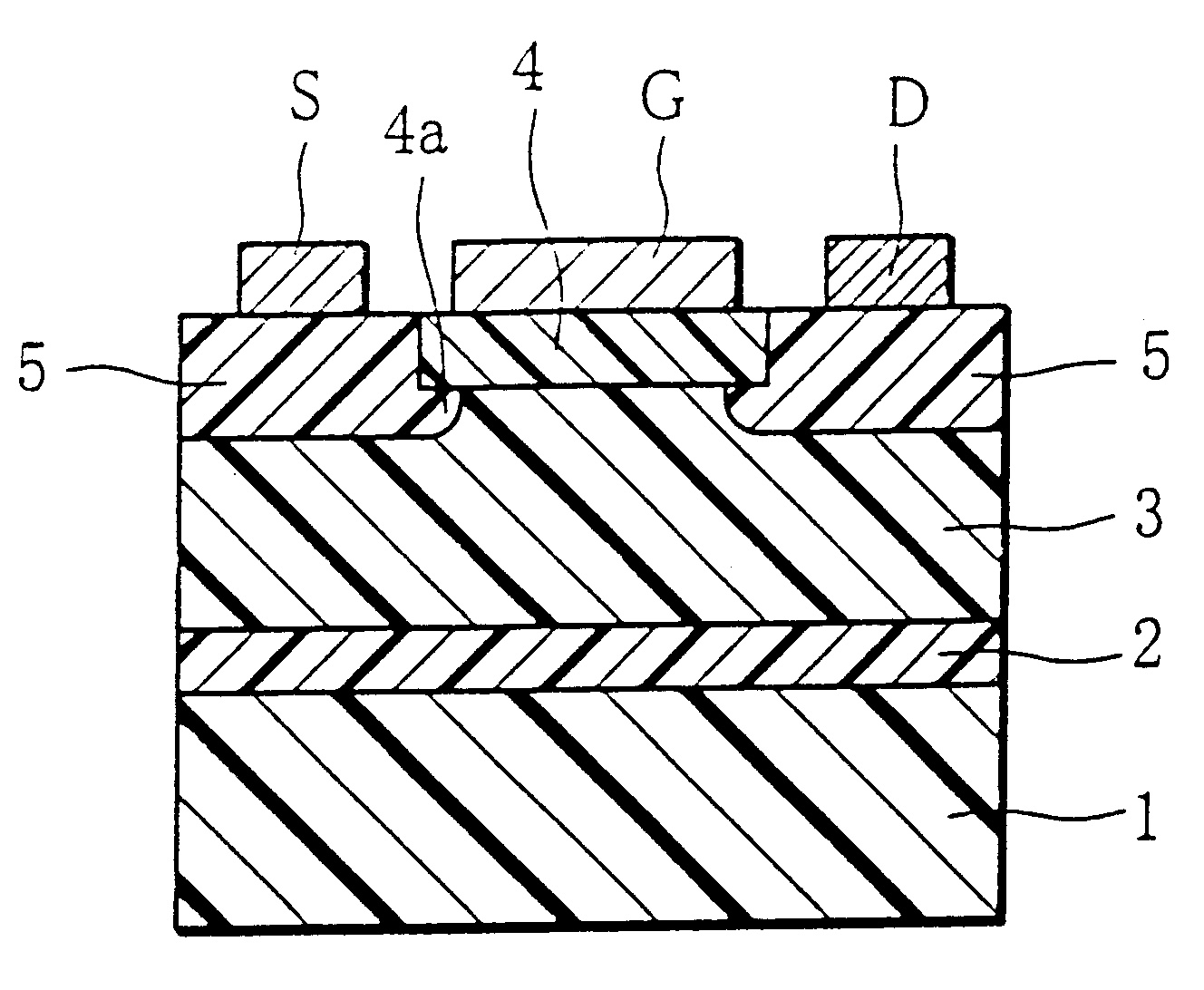

GaN-based high electron mobility transistor

InactiveUS6534801B2Improve mobilityHigh resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectric resistivity

A GaN-based high electron mobility transistor (HEMT) has an undoped GaN layer where a two-dimensional electron gas layer is formed, the undoped GaN layer having a high electric resistivity enabling a pinch-off state to be obtained even when the gate bias voltage is 0 V. The GaN-based HEMT comprises a semi-insulating substrate on which a GaN buffer layer is formed. An undoped GaN layer is disposed on the GaN buffer layer and has an electric resistivity of not less than 1x106 OMEGA / cm2. An undoped AlGaN layer is disposed on the undoped GaN layer via a heterojunction such that an undercut portion is formed therebetween. An n-type GaN layer is further disposed in such a manner as to bury side portions of the undoped AlGaN layer and the undercut portion. The individual layers thus form a layered structure. A gate electrode G is formed on the undoped AlGaN layer, and a source electrode S and a drain electrode D are formed on the n-type GaN layer.

Owner:FURUKAWA ELECTRIC CO LTD

LIGHT EMITTING DIODE HAVING AlInGaP ACTIVE LAYER AND METHOD OF FABRICATING THE SAME

InactiveUS20090272991A1Enhanced current distribution performanceImprove luminous efficiencySolid-state devicesSemiconductor/solid-state device manufacturingAC powerActive layer

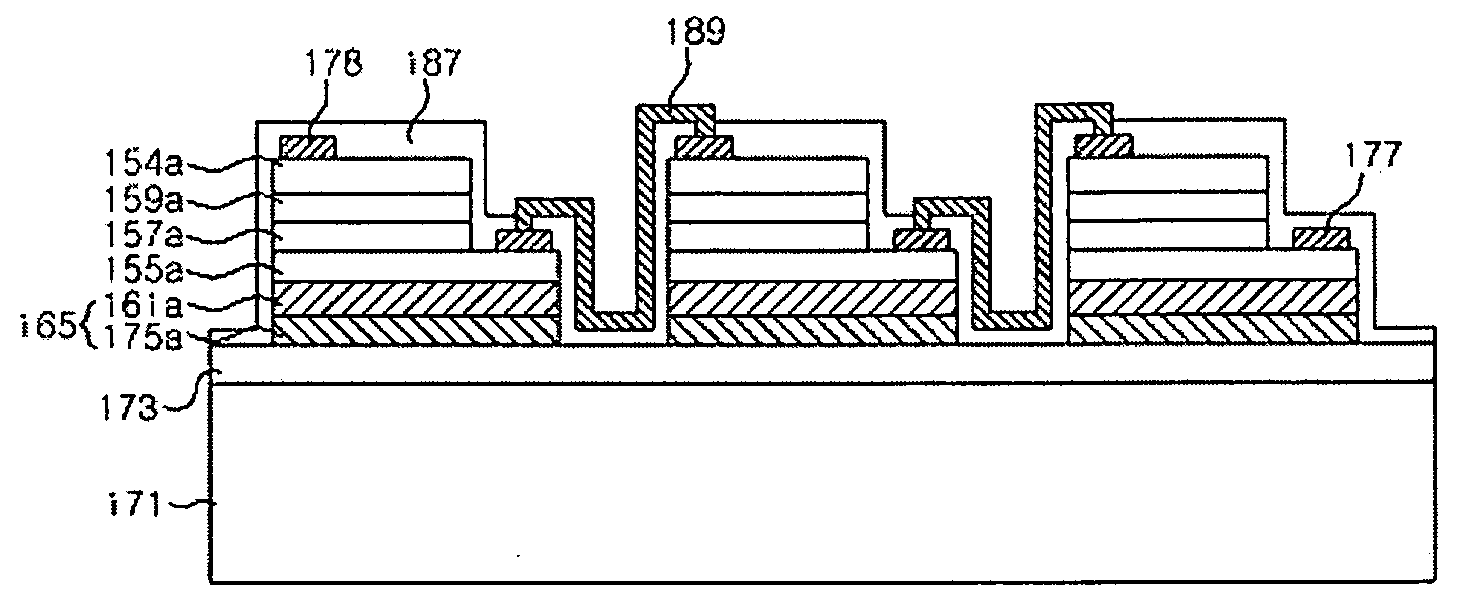

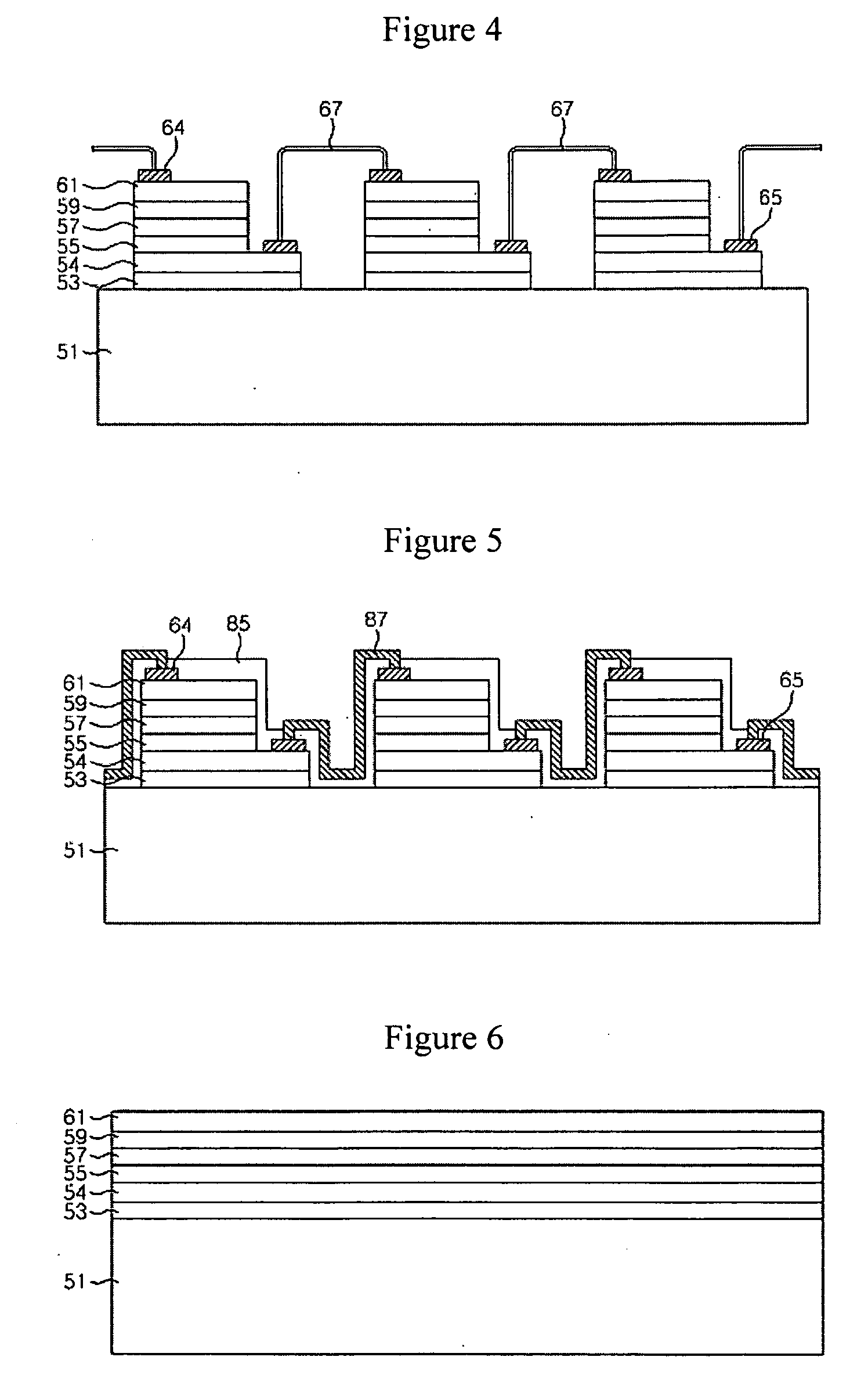

A light emitting diode having an AlInGaP active layer and a method of fabricating the same are disclosed. The light emitting diode includes a substrate. A plurality of light emitting cells are positioned to be spaced apart from one another, wherein each of the light emitting cells has a first conductive-type lower semiconductor layer, an AlInGaP active layer and a second conductive-type upper semiconductor layer. Meanwhile, a semi-insulating layer is interposed between the substrate and the light emitting cells. Further, wires connect the plurality of light emitting cells in series. Accordingly, it is possible to provide a light emitting diode, in which a plurality of light emitting cells are connected in series to one another through wires to be driven by an AC power source.

Owner:SEOUL VIOSYS CO LTD

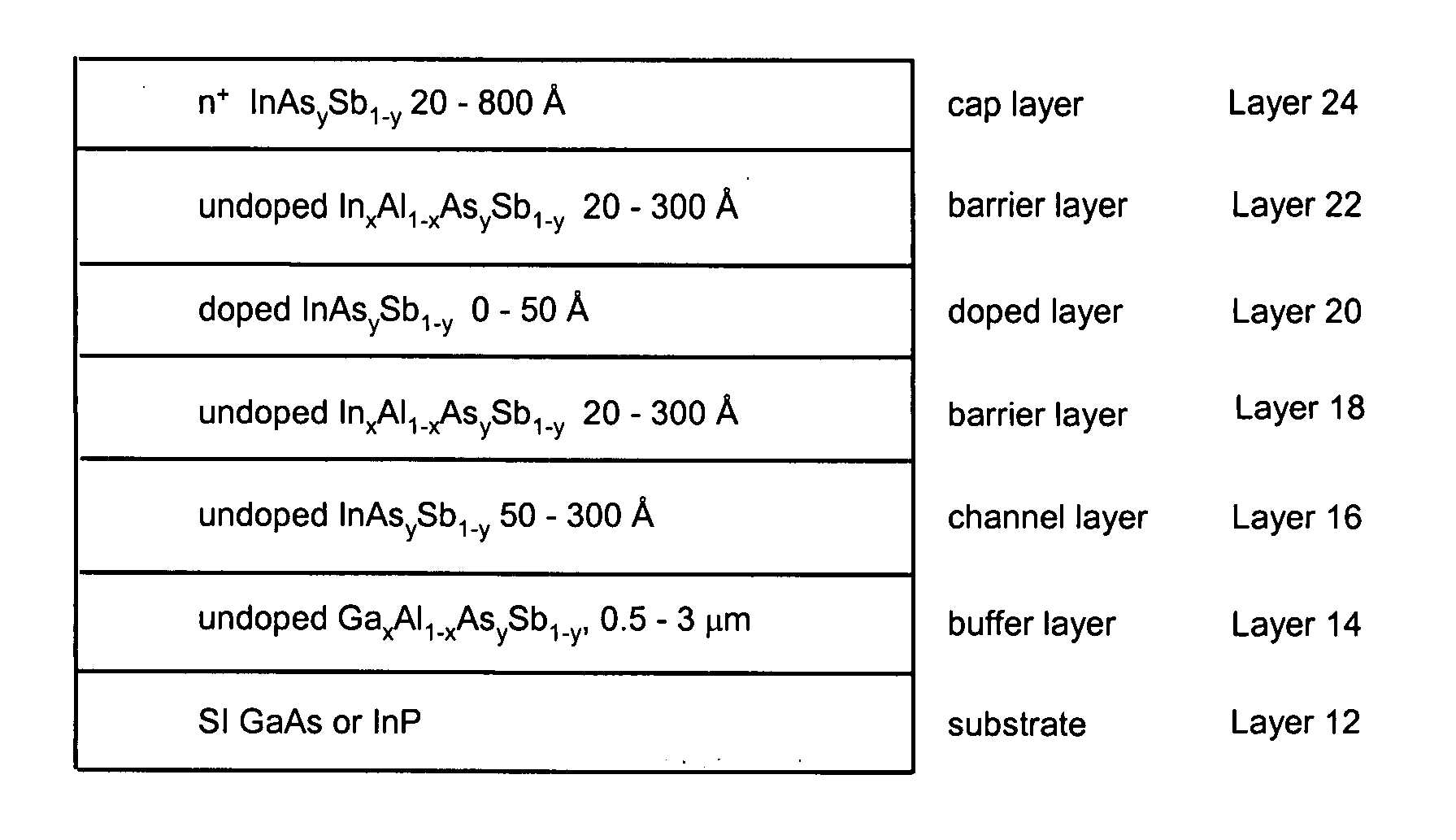

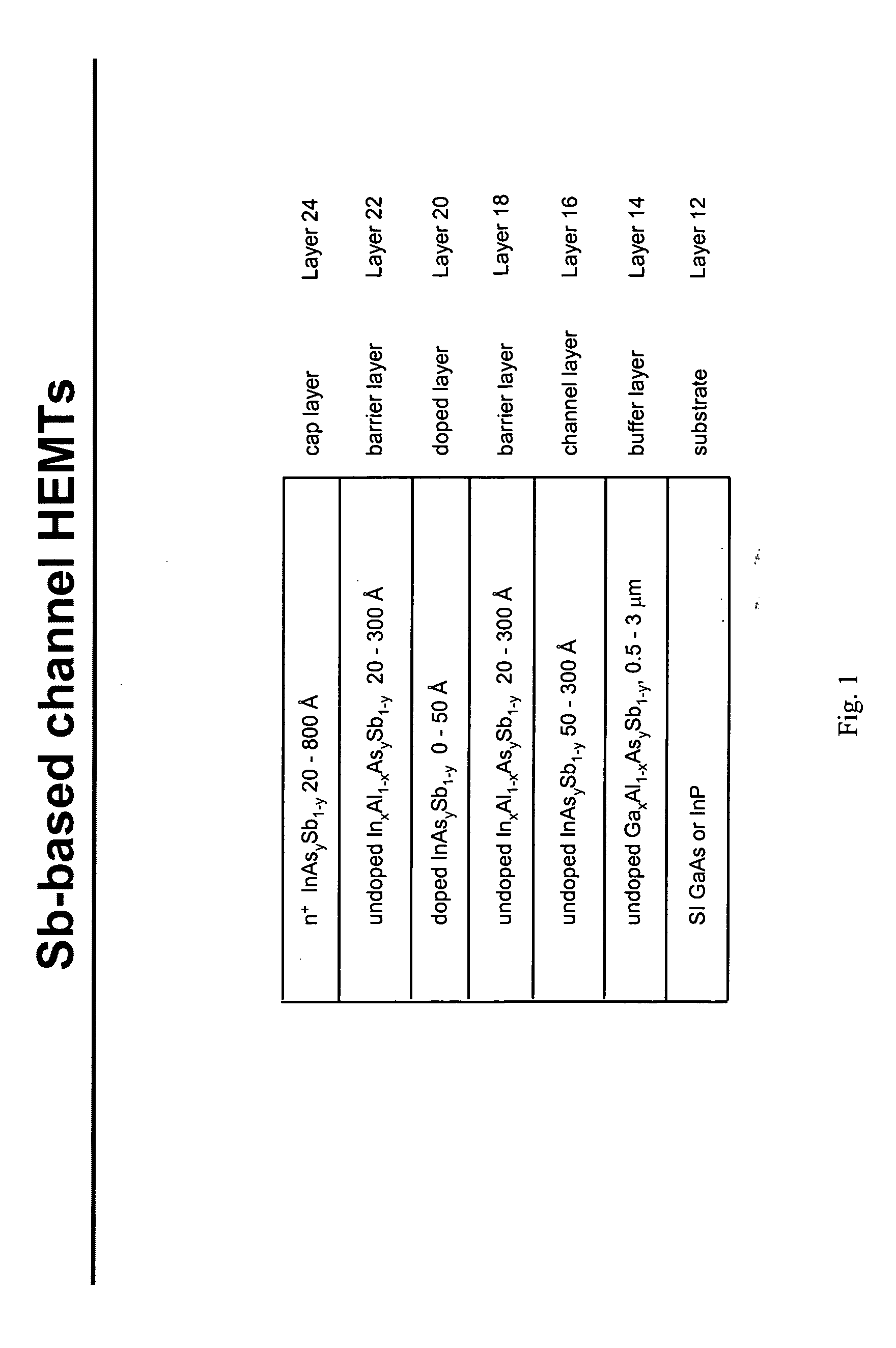

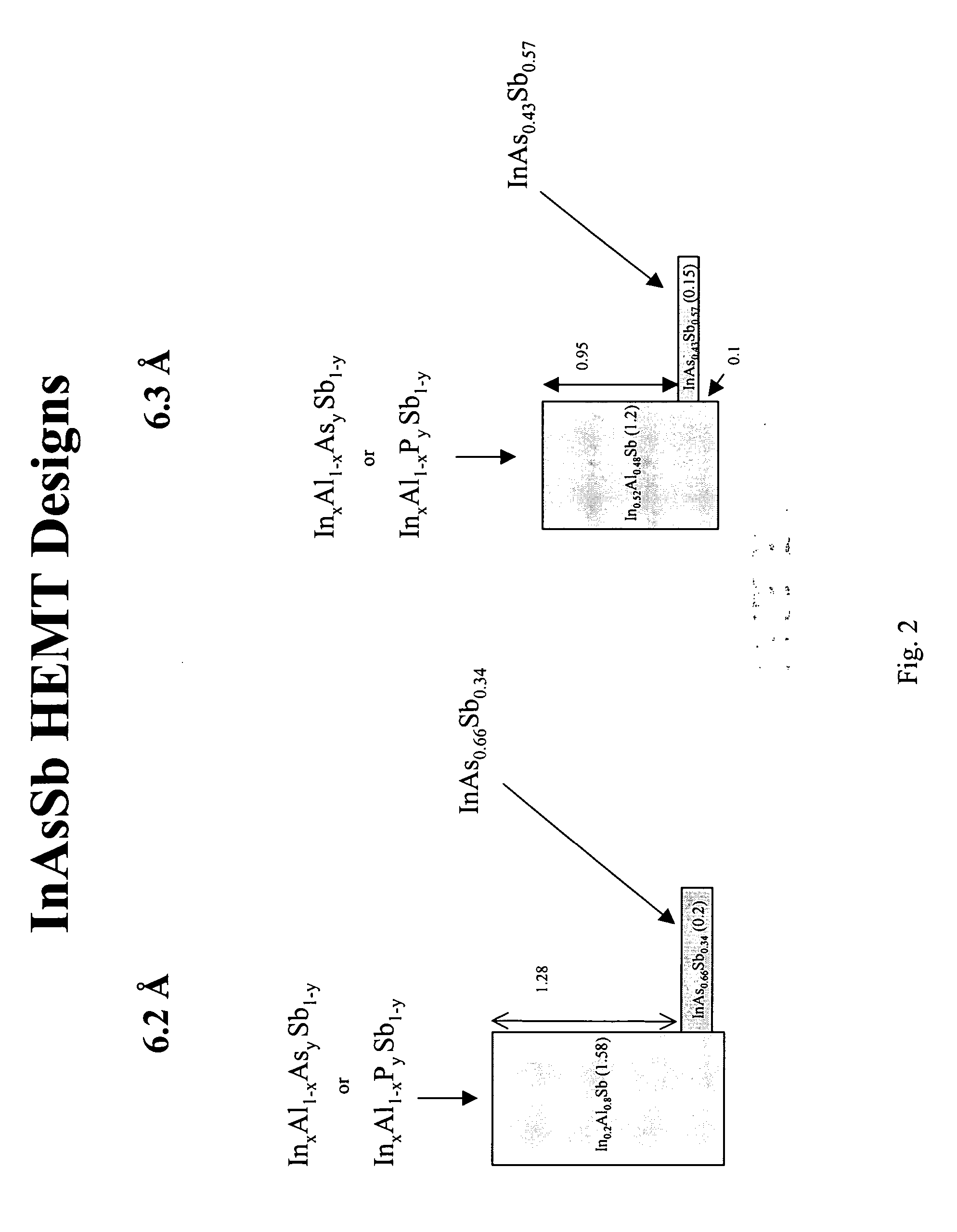

High electron mobility transistors with Sb-based channels

This invention pertains to an electronic device containing a semi-insulating substrate, a buffer layer of an antimony-based material disposed on said substrate, a channel layer of InAsySb1−y material disposed on said buffer layer, a barrier layer of an antimony-based disposed on said channel layer, and a cap layer of InAsySb1−y material disposed on said barrier layer, wherein the device can have frequency of on the order of 500 GHz and a reduced power dissipation.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Silicon carbide and related wide-bandgap transistors on semi-insulating epitaxy for high-speed, high-power applications

A silicon carbide semi-insulating epitaxy layer is used to create power devices and integrated circuits having significant performance advantages over conventional devices. A silicon carbide semi-insulating layer is formed on a substrate, such as a conducting substrate, and one or more semiconducting devices are formed on the silicon carbide semi-insulating layer. The silicon carbide semi-insulating layer, which includes, for example, 4H or 6H silicon carbide, is formed using a compensating material, the compensating material being selected depending on preferred characteristics for the semi-insulating layer. The compensating material includes, for example, boron, vanadium, chromium, or germanium. Use of a silicon carbide semi-insulating layer provides insulating advantages and improved thermal performance for high power and high frequency semiconductor applications.

Owner:MISSISSIPPI STATE UNIVERSITY

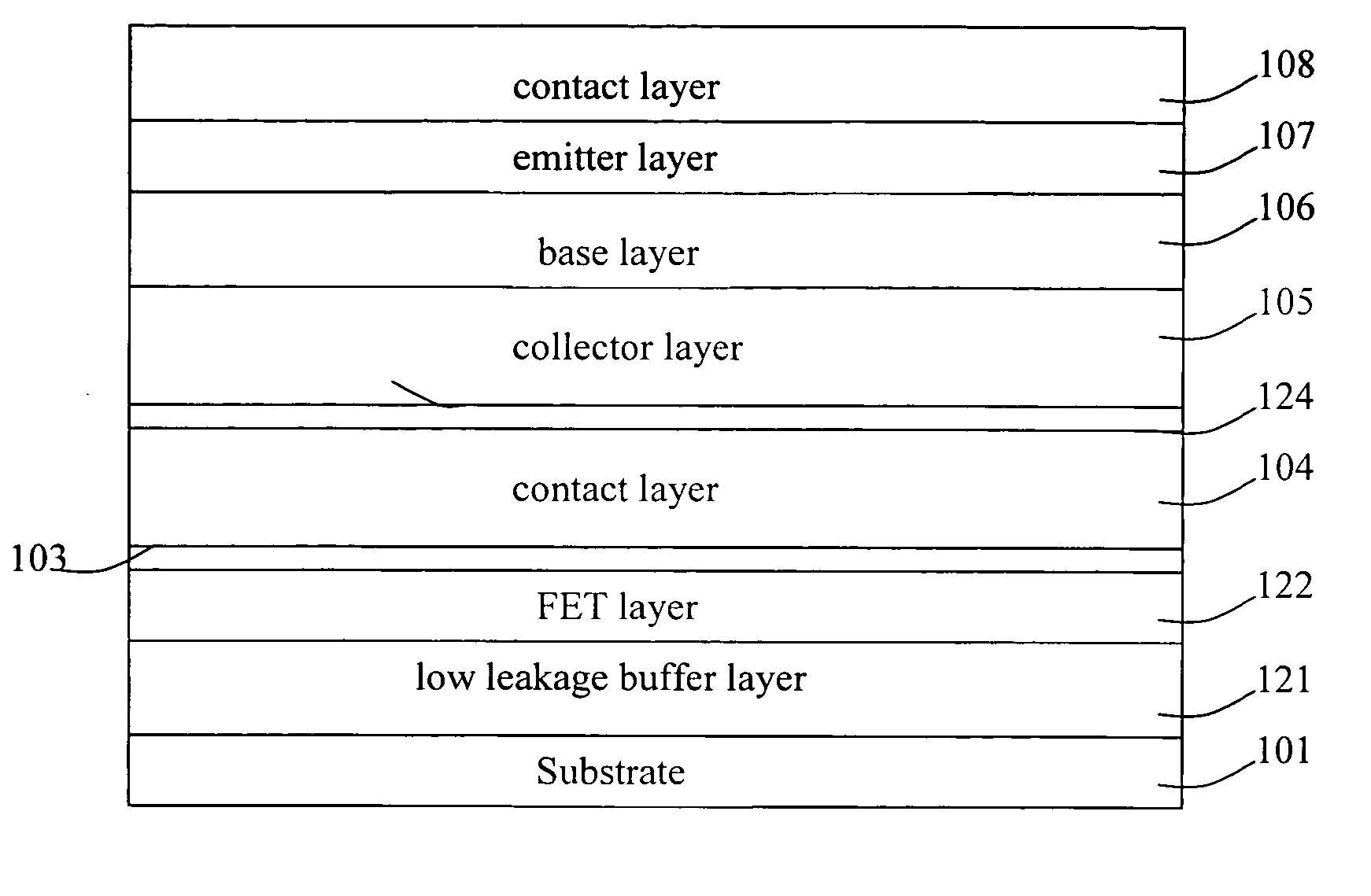

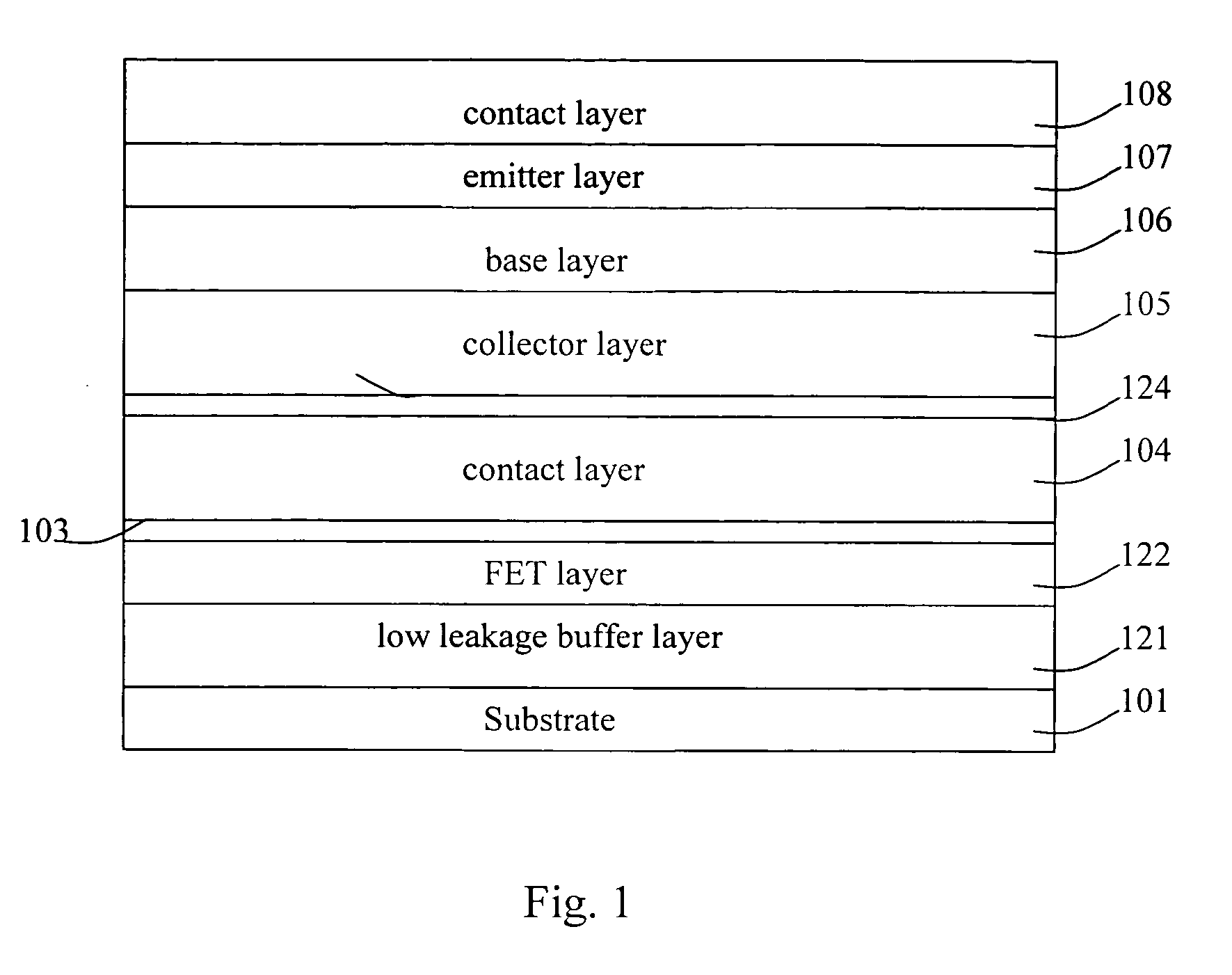

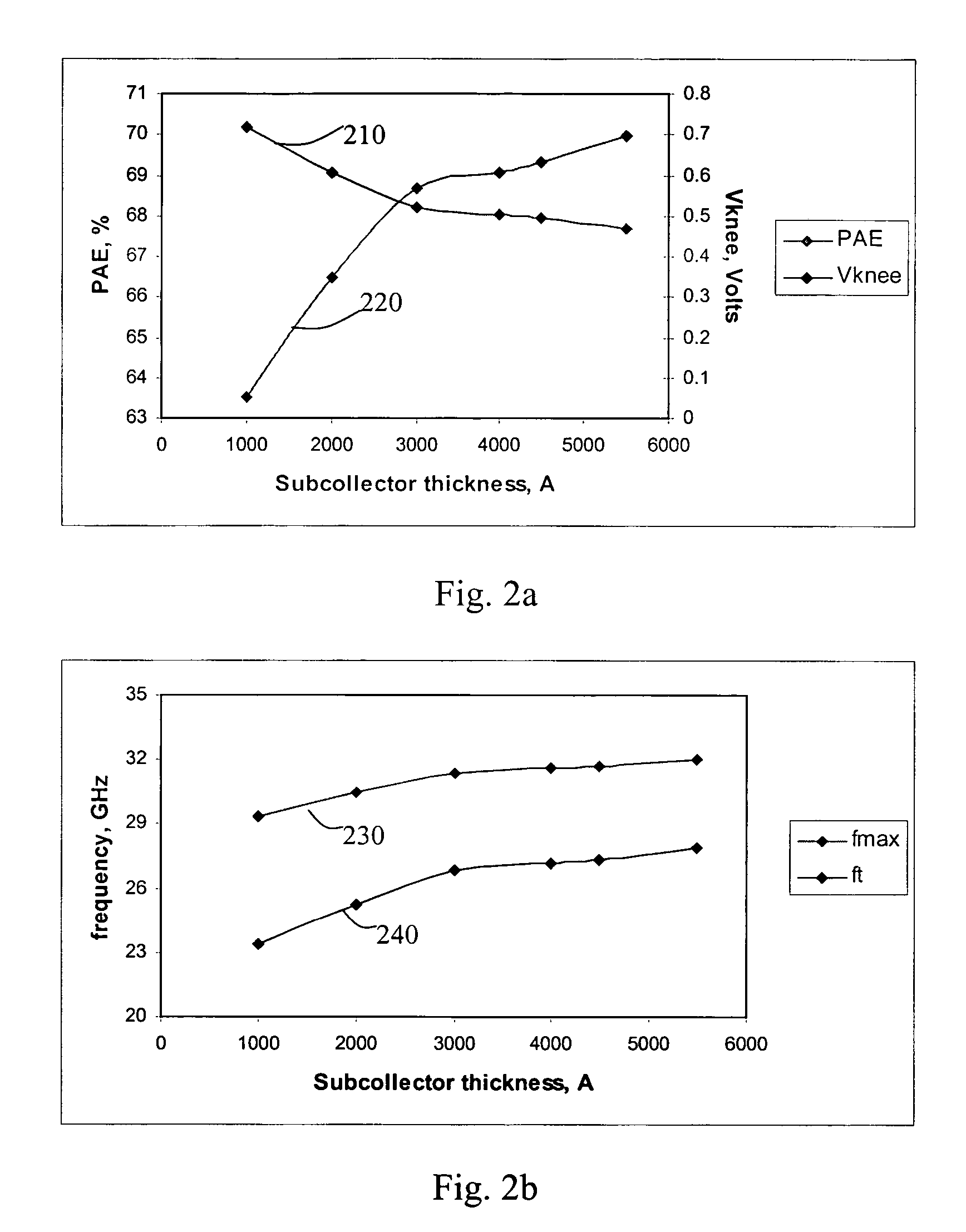

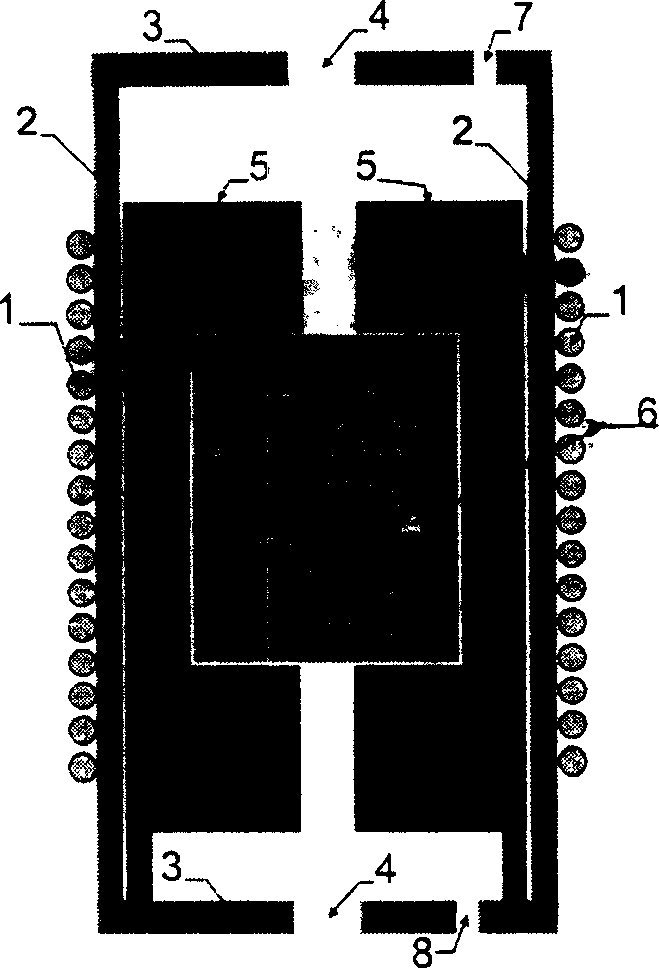

Structures and methods for fabricating integrated HBT/FET's at competitive cost

Methods and systems for fabricating integrated pairs of HBT / FET's are disclosed. One preferred embodiment comprises a method of fabricating an integrated pair of GaAs-based HBT and FET. The method comprises the steps of: growing a first set of epitaxial layers for fabricating the FET on a semi-insulating GaAs substrate; fabricating a highly doped thick GaAs layer serving as the cap layer for the FET and the subcollector layer for the HBT; and producing a second set of epitaxial layers for fabricating the HBT.

Owner:SKYWORKS SOLUTIONS INC

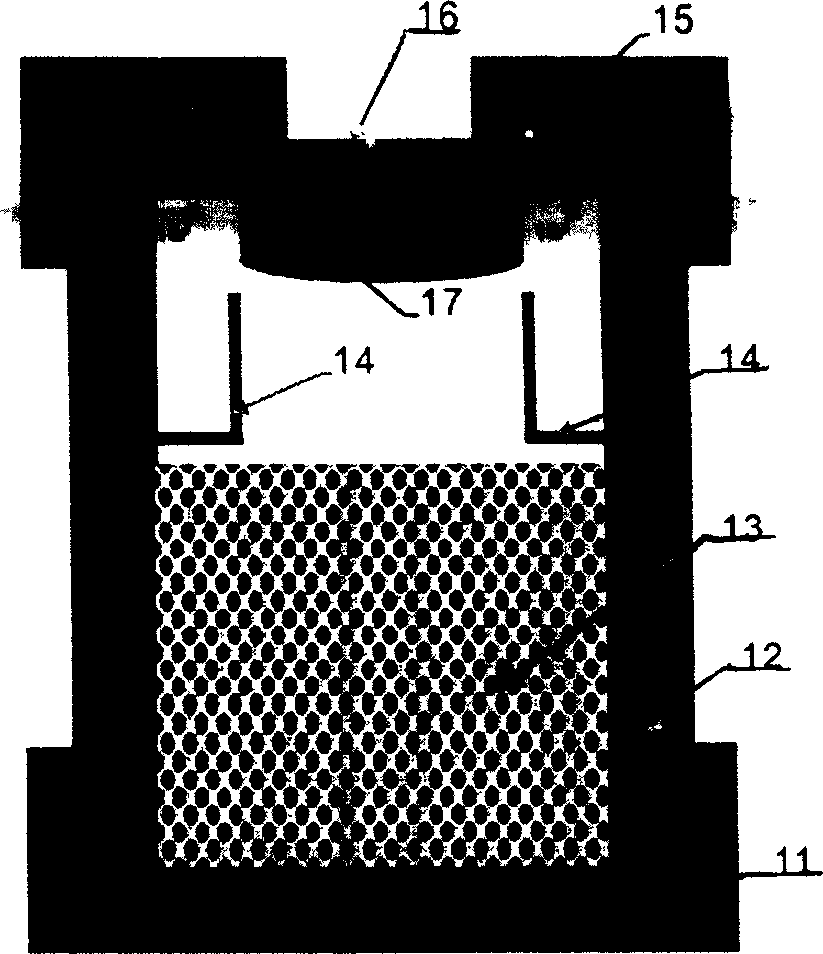

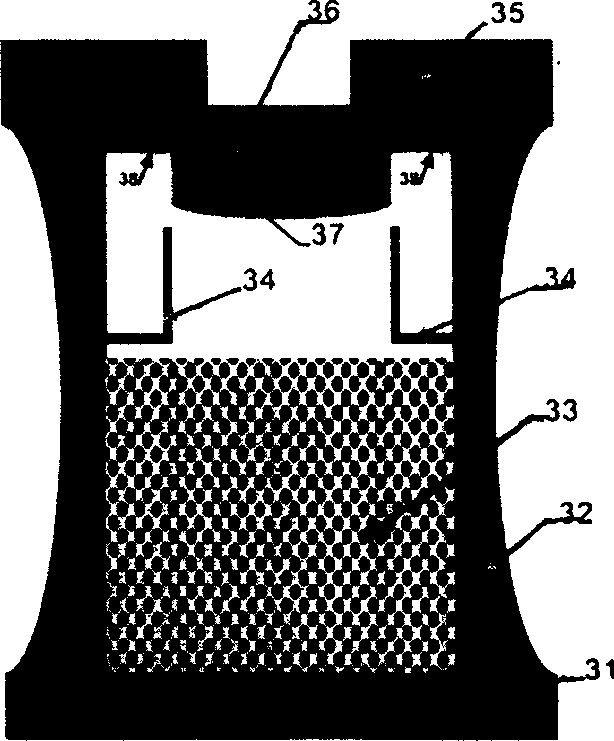

Device and method for growng large diameter 6H-SiC monocrystal with semiconductor property

ActiveCN1554808ALarge crystalsFor the purpose of dopingPolycrystalline material growthFrom condensed vaporsEngineeringSingle crystal

The present invention relates to apparatus and method of growing great diameter 6H-SiC monocrystal with semiconductor characteristic and belongs to the field of crystal growing technology. The apparatus includes growing chamber, water cooler on the side wall of the growing chamber, graphite crucible, heat insulating material, induction heating system, cylindrical vapor guiding plate of Ta inside the crucible, and cylinder. Regulating the position of the crucible relative to the inducing coil can minimize the temperature at the crystal seed inside the crucible and increase the temperature field distribution in the growing direction. Altering the atmosphere composition or material compounding can obtain great diameter SiC monocrystal with n-type, p-type or semi-insulating type semiconductor characteristic. By means of selecting the Si plane of the crystal seed and growing temperature, the crystal form may be controlled and 6H-SiC may be obtained.

Owner:SICC CO LTD

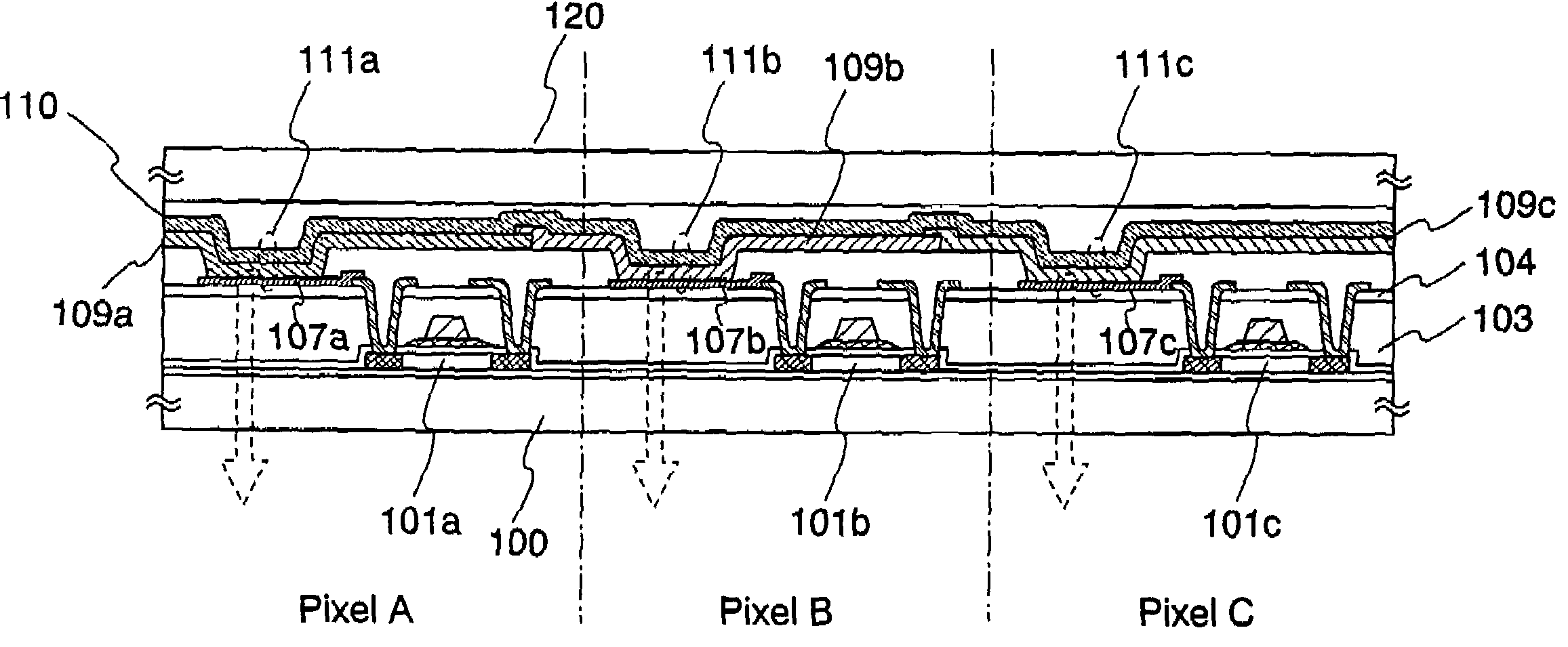

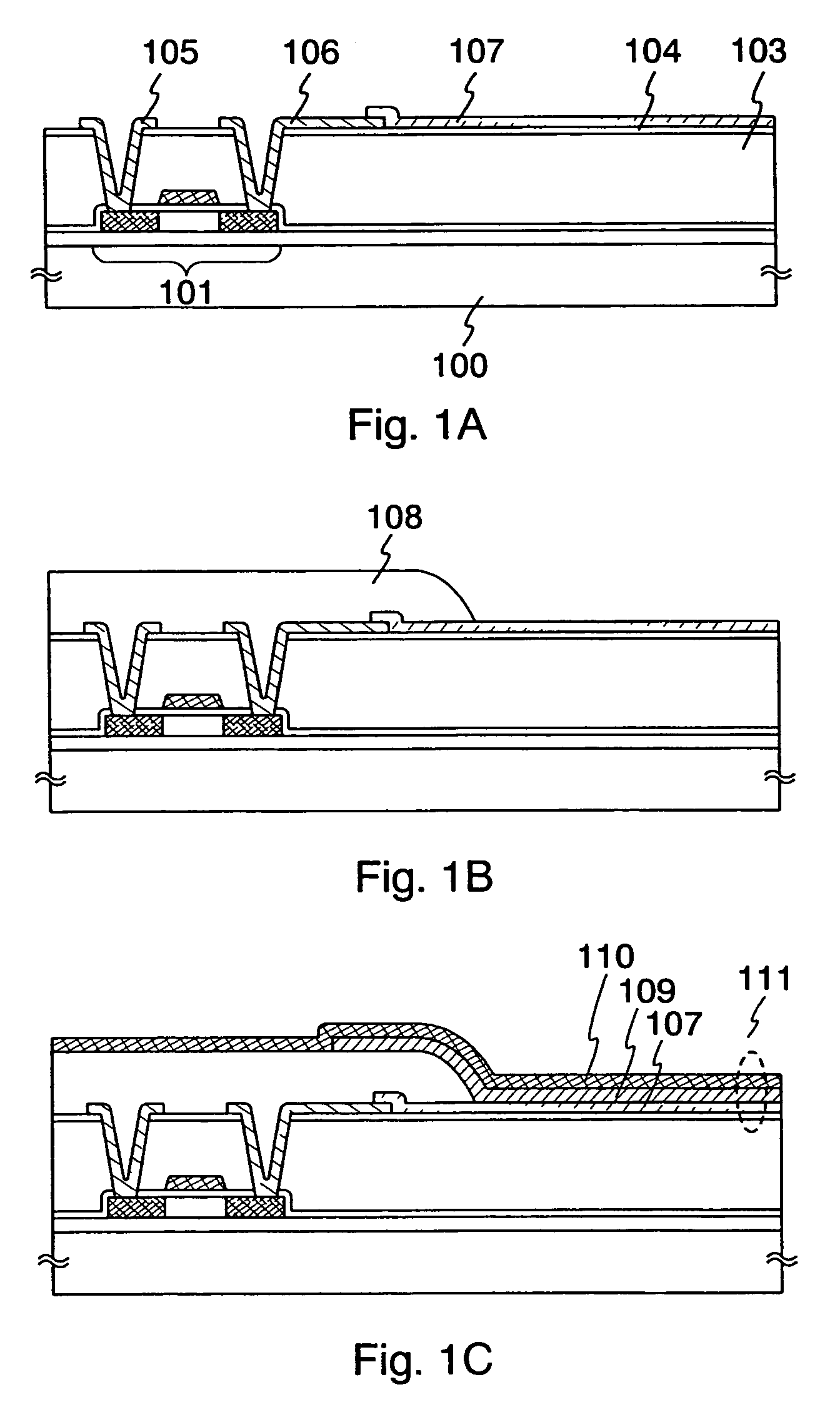

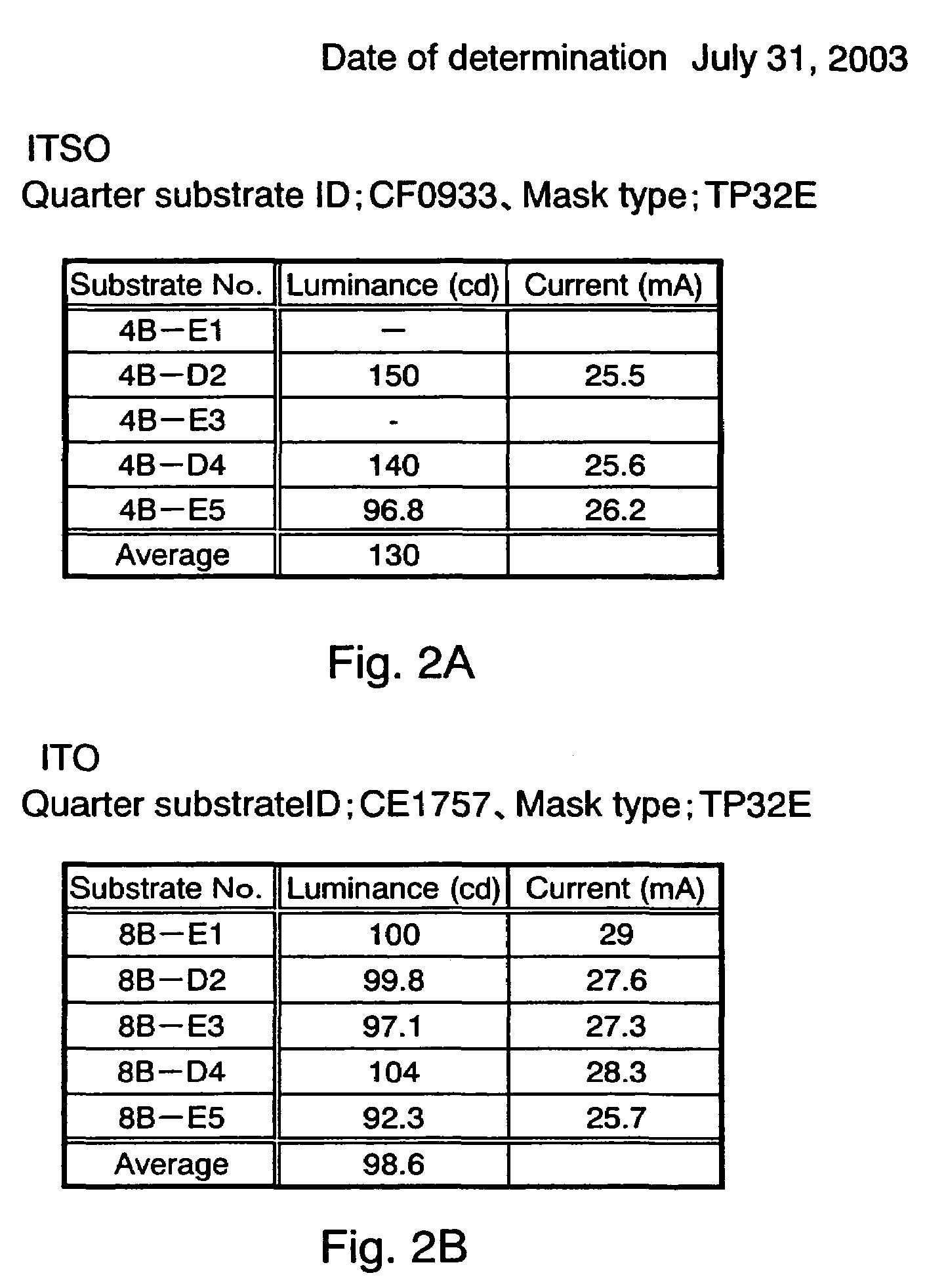

Light emitting element including a barrier layer and a manufacturing method thereof

InactiveUS7291967B2Improve stabilityExcellent luminous propertiesDischarge tube luminescnet screensElectroluminescent light sourcesHole injection layerSilicon oxide

According to the invention, an insulating or semi-insulating barrier layer which has a thickness where a tunnel current can flow through is provided between a hole injection electrode and an organic compound layer with hole transport characteristics (a hole injection layer or a hole transport layer). Specifically, a thin insulating or semi-insulating barrier layer which contains silicon or silicon oxide; silicon or silicon oxide and a light transmitting conductive oxide material; or silicon or silicon oxide, a light transmitting conductive oxide material, and carbon may be provided between a light transmitting conductive oxide film formed of a light transmitting conductive oxide material, such as ITO and a hole injection layer containing an organic compound.

Owner:SEMICON ENERGY LAB CO LTD

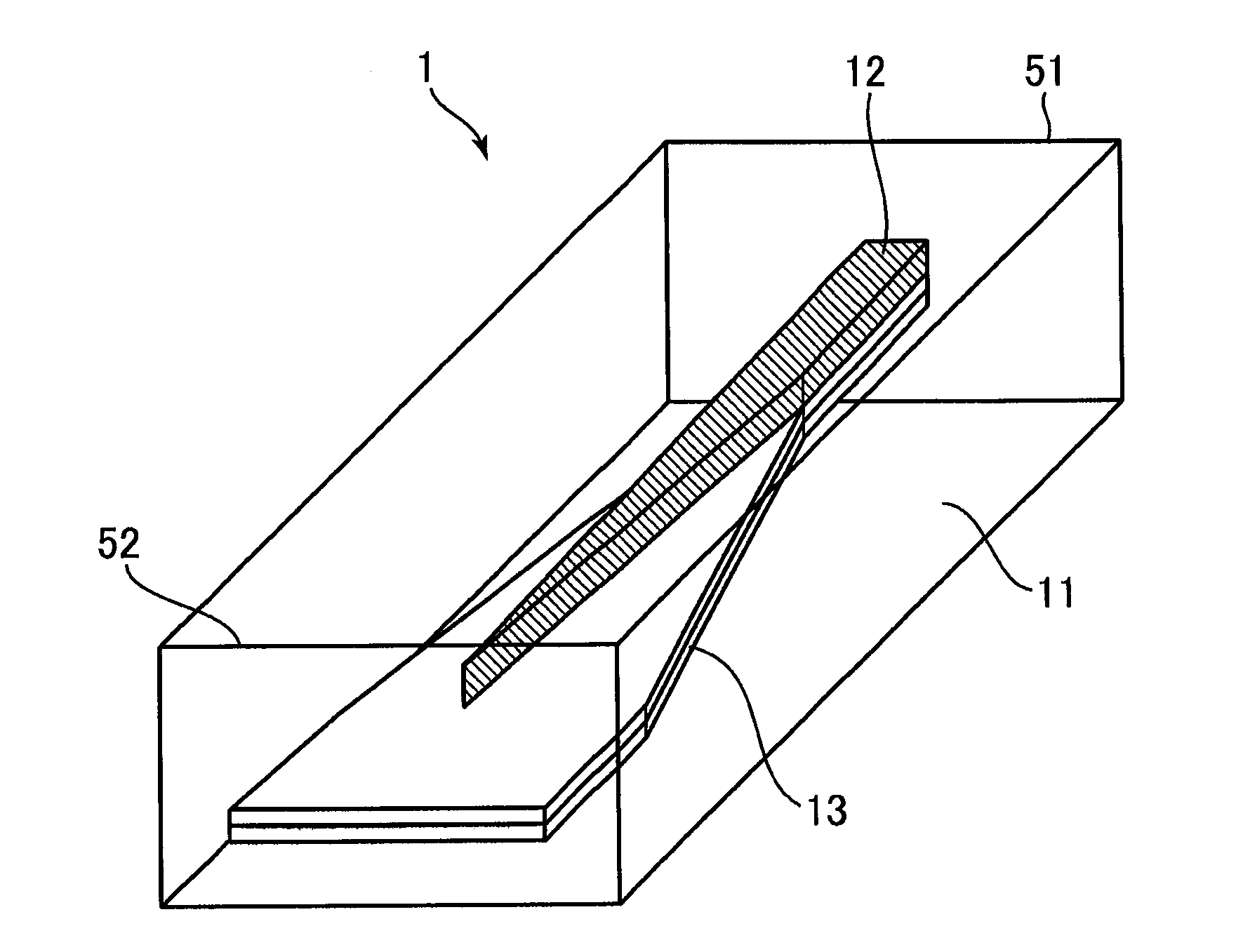

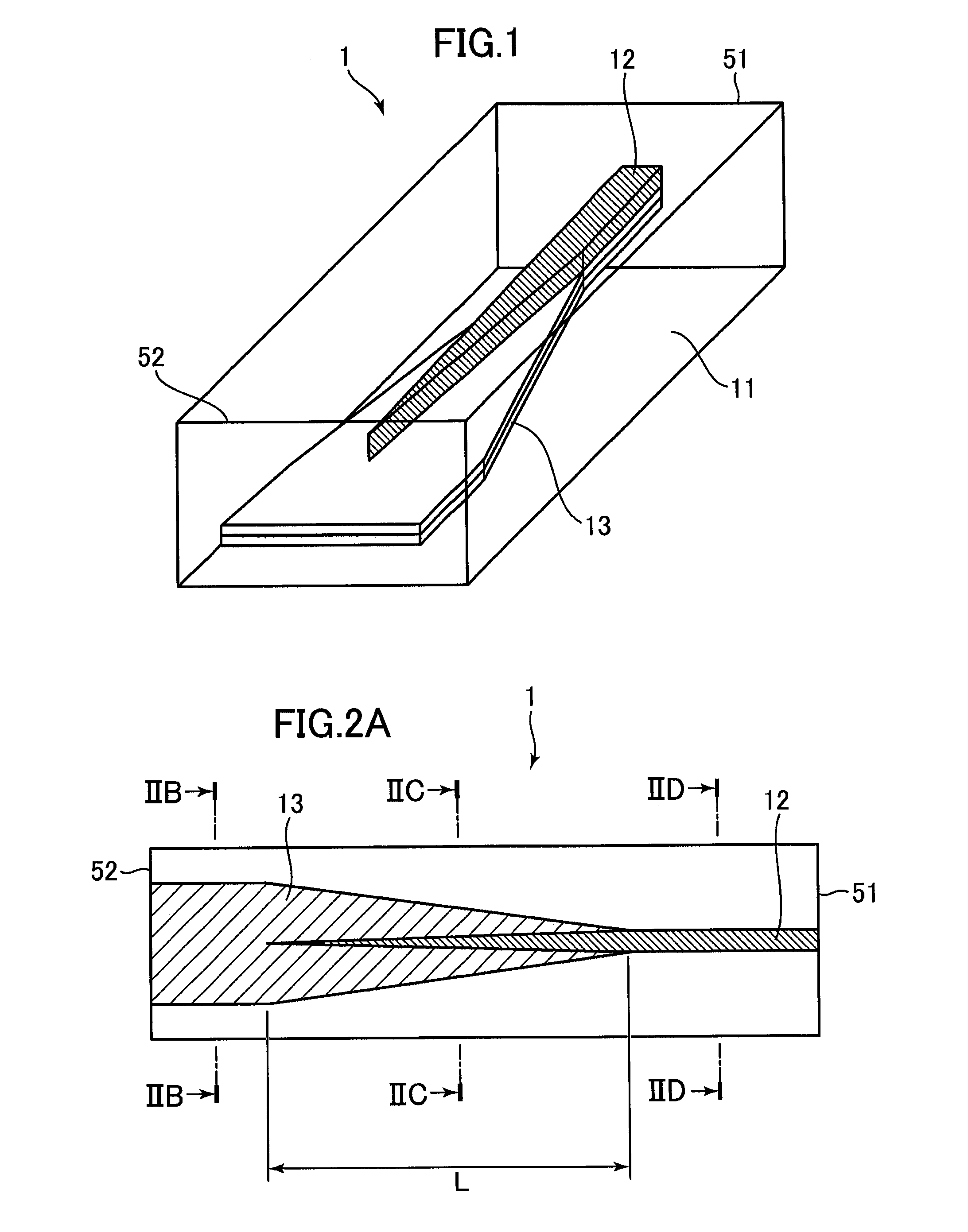

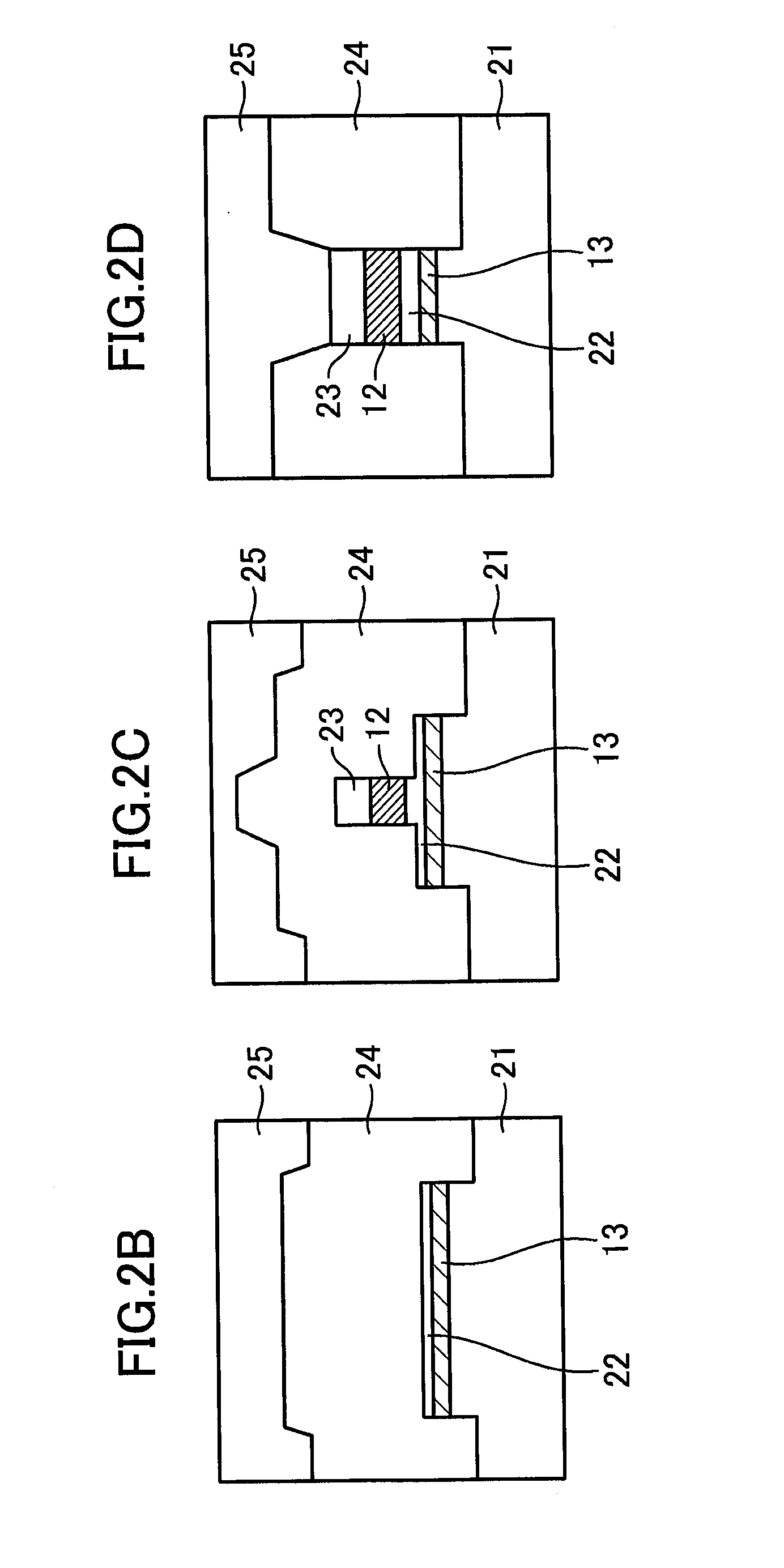

Optical semiconductor device, and manufacturing method thereof

ActiveUS20120321244A1Suppress propagation lossSpeed up the conversion processOptical fibre with multilayer core/claddingSemiconductor/solid-state device manufacturingRefractive indexSemiconductor

The optical semiconductor device includes a spot-size converter formed on a semiconductor substrate. The spot-size converter has a multilayer structure including a light transition region. The multilayer structure includes a lower core layer, and an upper core layer having a refractive index higher than that of the lower core layer. The width of the upper core layer is gradually decreased and the width of the lower core layer is gradually increased in the light transition region. Both sides and an upper side of the multilayer structure are buried by a semi-insulating semiconductor layer in the light transition region. Light incident from one end section of the spot-size converter is propagated to the upper core layer. The light transits from the upper core layer to the lower core layer in the light transition region, is propagated to the lower core layer, and exits from the other end section thereof.

Owner:LUMENTUM JAPAN INC

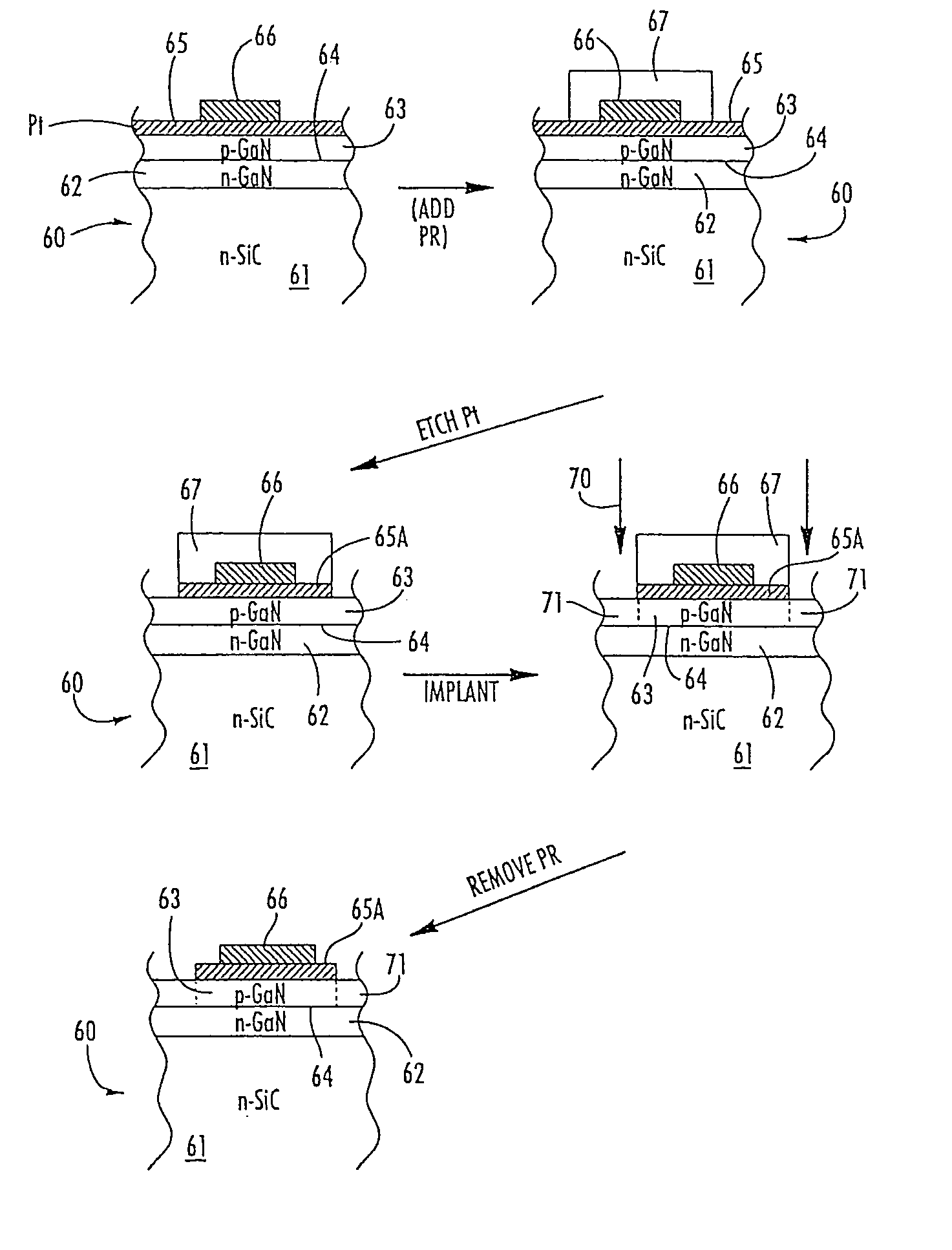

LED fabrication via ion implant isolation

InactiveUS20050194584A1Solid-state devicesSemiconductor/solid-state device manufacturingResistContact layer

A semiconductor light emitting diode includes a semiconductor substrate, an epitaxial layer of n-type Group III nitride on the substrate, a p-type epitaxial layer of Group III nitride on the n-type epitaxial layer and forming a p-n junction with the n-type layer, and a resistive gallium nitride region on the n-type epitaxial layer and adjacent the p-type epitaxial layer for electrically isolating portions of the p-n junction. A metal contact layer is formed on the p-type epitaxial layer. Some embodiments include a semiconductor substrate, an epitaxial layer of n-type Group III nitride on the substrate, a p-type epitaxial layer of Group III nitride on the n-type epitaxial layer and forming a p-n junction with the n-type layer, wherein portions of the epitaxial region are patterned into a mesa and wherein the sidewalls of the mesa comprise a resistive Group III nitride region for electrically isolating portions of the p-n junction. In method embodiments disclosed, the resistive border is formed by forming an implant mask on the p-type epitaxial region and implanting ions into portions of the p-type epitaxial region to render portions of the p-type epitaxial region semi-insulating. A photoresist mask or a sufficiently thick metal layer may be used as the implant mask. In some method embodiments, a mesa is formed in the epitaxial region prior to implantation. During implantation, the epiwafer is mounted at an angle such that ions are implanted directly into the sidewalls of the mesa, thereby rendering portions of the mesa semi-insulating. The epiwafer may be rotated during ion implantation.

Owner:CREE INC

Schottky gate field effect transistor

InactiveUS20030132463A1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringContact layer

A Schottky gate FET including a gate electrode having a gate extension, a drain electrode and a drain contact layer overlying a semi-insulating substrate, wherein the gate extension overlies at least part of the drain electrode and the drain contact layer. The vertical overlapping between the gate extension and the drain contact region prevents the current reduction to make the circuit module mounting the Schottky gate FET non-usable.

Owner:RENESAS ELECTRONICS CORP

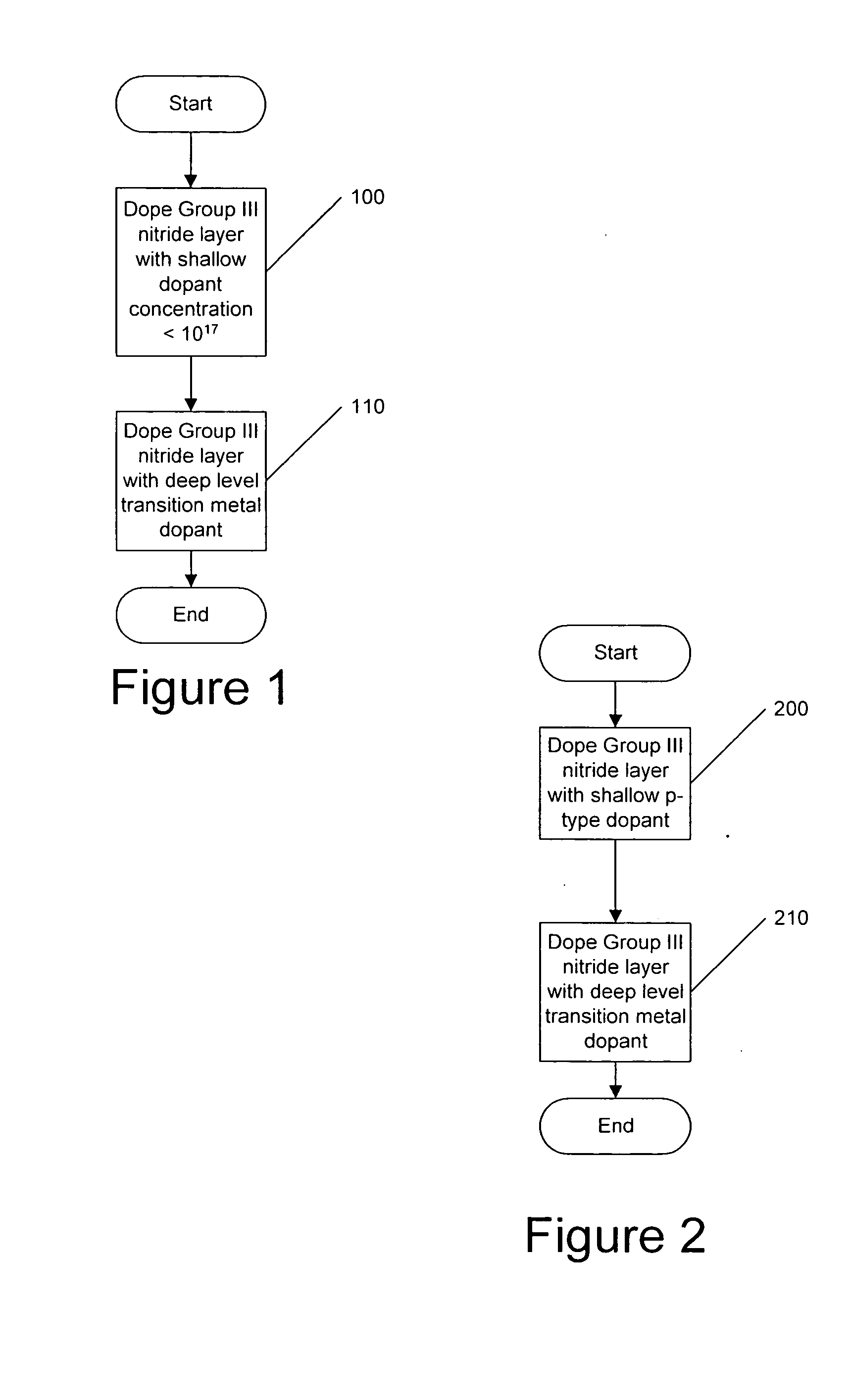

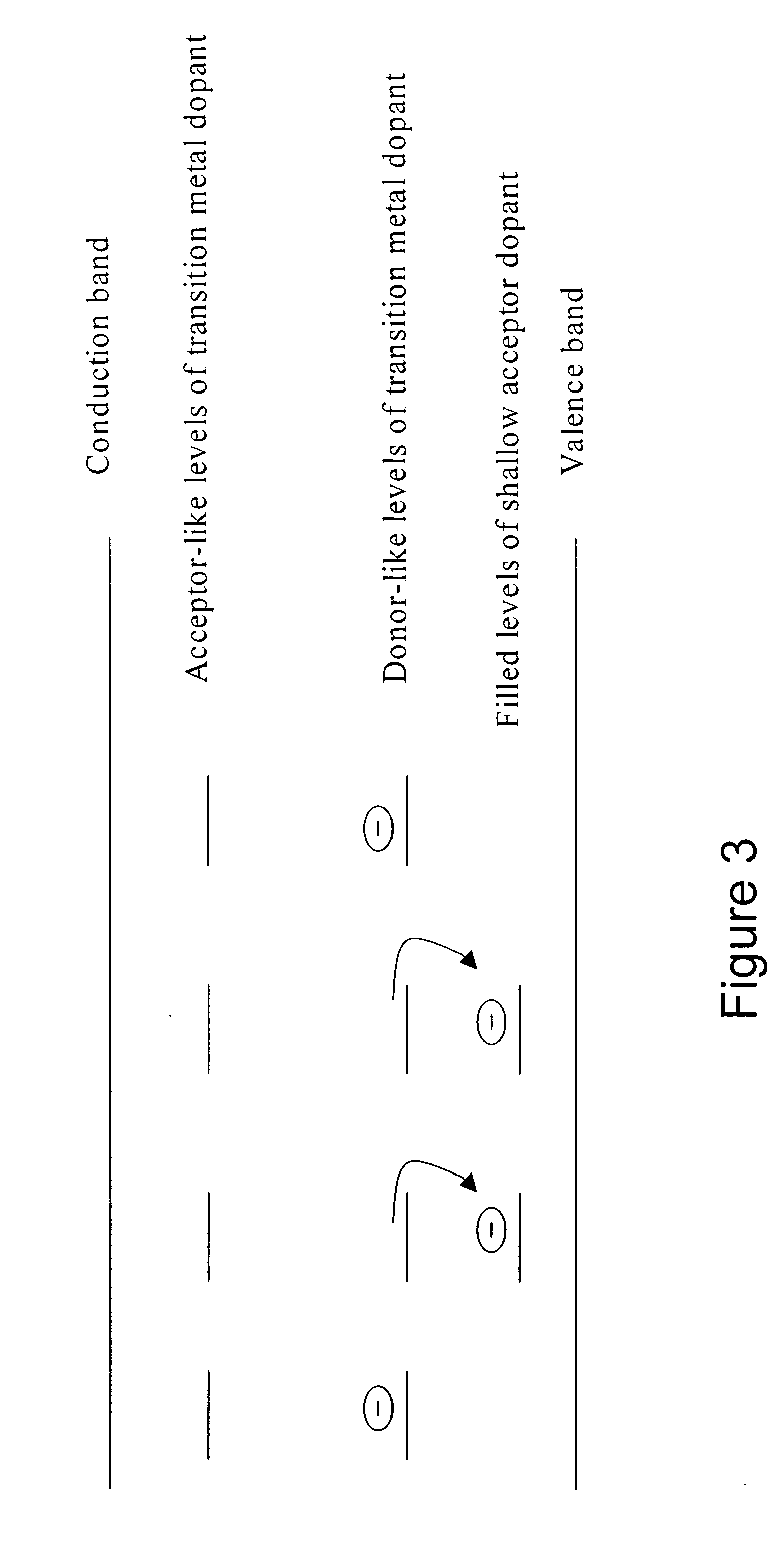

Co-doping for fermi level control in semi-insulating Group III nitrides

ActiveUS20050145874A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantDeep level

Semi-insulating Group III nitride layers and methods of fabricating semi-insulating Group III nitride layers include doping a Group III nitride layer with a shallow level p-type dopant and doping the Group III nitride layer with a deep level dopant, such as a deep level transition metal dopant. Such layers and / or method may also include doping a Group III nitride layer with a shallow level dopant having a concentration of less than about 1×1017 cm−3 and doping the Group III nitride layer with a deep level transition metal dopant. The concentration of the deep level transition metal dopant is greater than a concentration of the shallow level p-type dopant.

Owner:CREE INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com