Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4785results about "From condensed vapors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

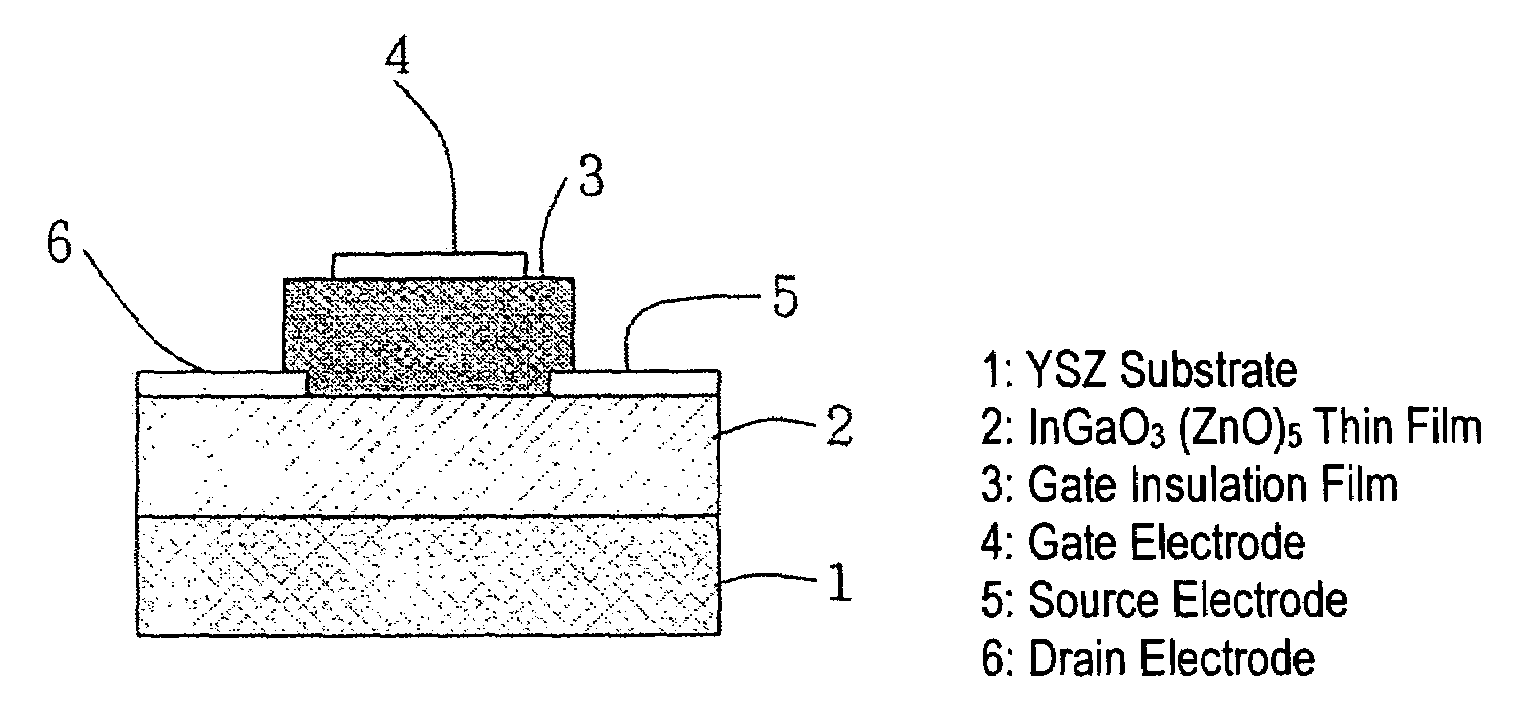

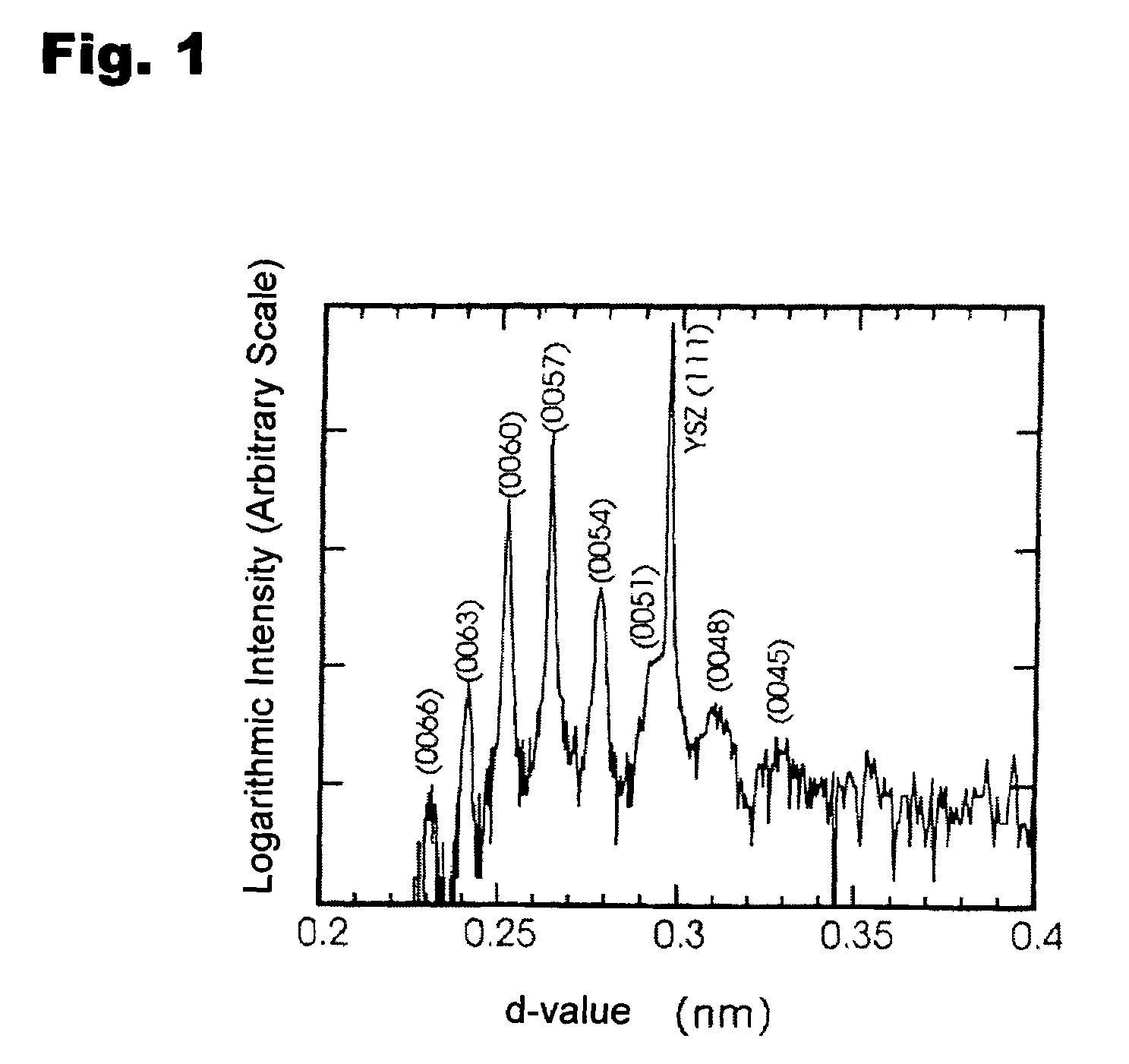

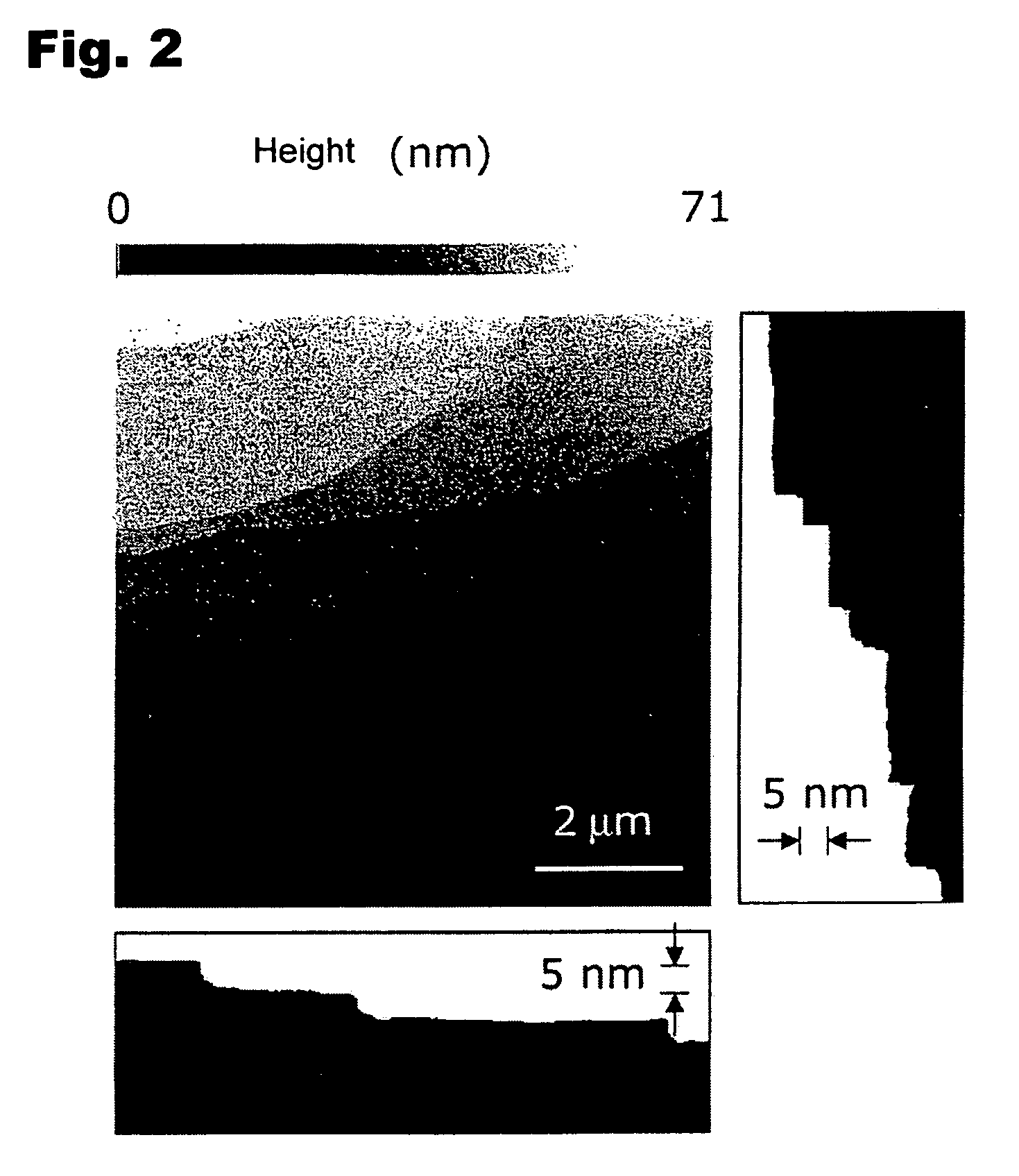

Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film

InactiveUS7061014B2Easy to controlSimple processTransistorPolycrystalline material growthSingle crystal substrateSingle crystal

Disclosed is a natural-superlattice homologous single-crystal thin film, which includes a complex oxide which is epitaxially grown on either one of a ZnO epitaxial thin film formed on a single-crystal substrate, the single-crystal substrate after disappearance of the ZnO epitaxial thin film and a ZnO single crystal. The complex oxide is expressed by the formula: M1M2O3 (ZnO)m, wherein M1 is at least one selected from the group consisting of Ga, Fe, Sc, In, Lu, Yb, Tm, Er, Ho and Y, M2 is at least one selected from the group consisting of Mn, Fe, Ga, In and Al, and m is a natural number of 1 or more. A natural-superlattice homologous single-crystal thin film formed by depositing the complex oxide and subjecting the obtained layered film to a thermal anneal treatment can be used in optimal devices, electronic devices and X-ray optical devices.

Owner:HOYA CORP +1

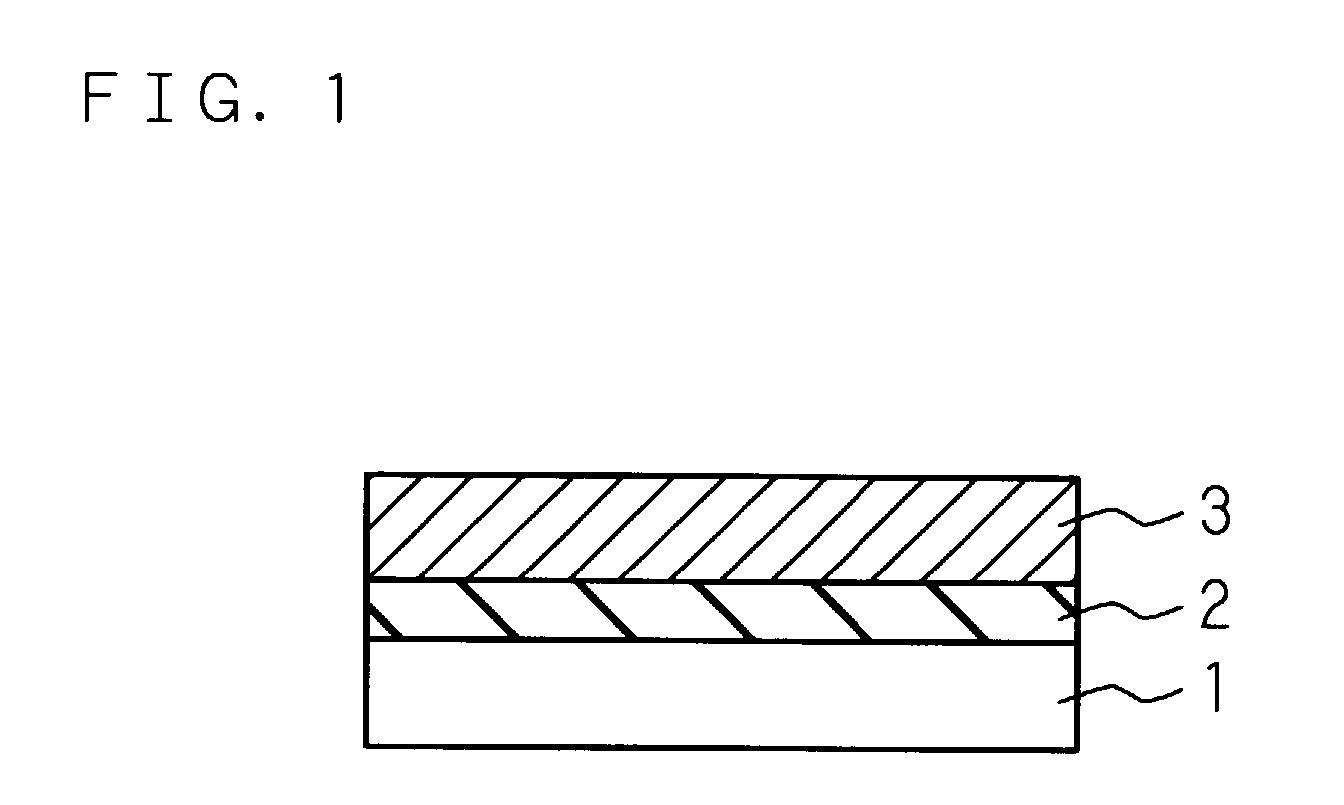

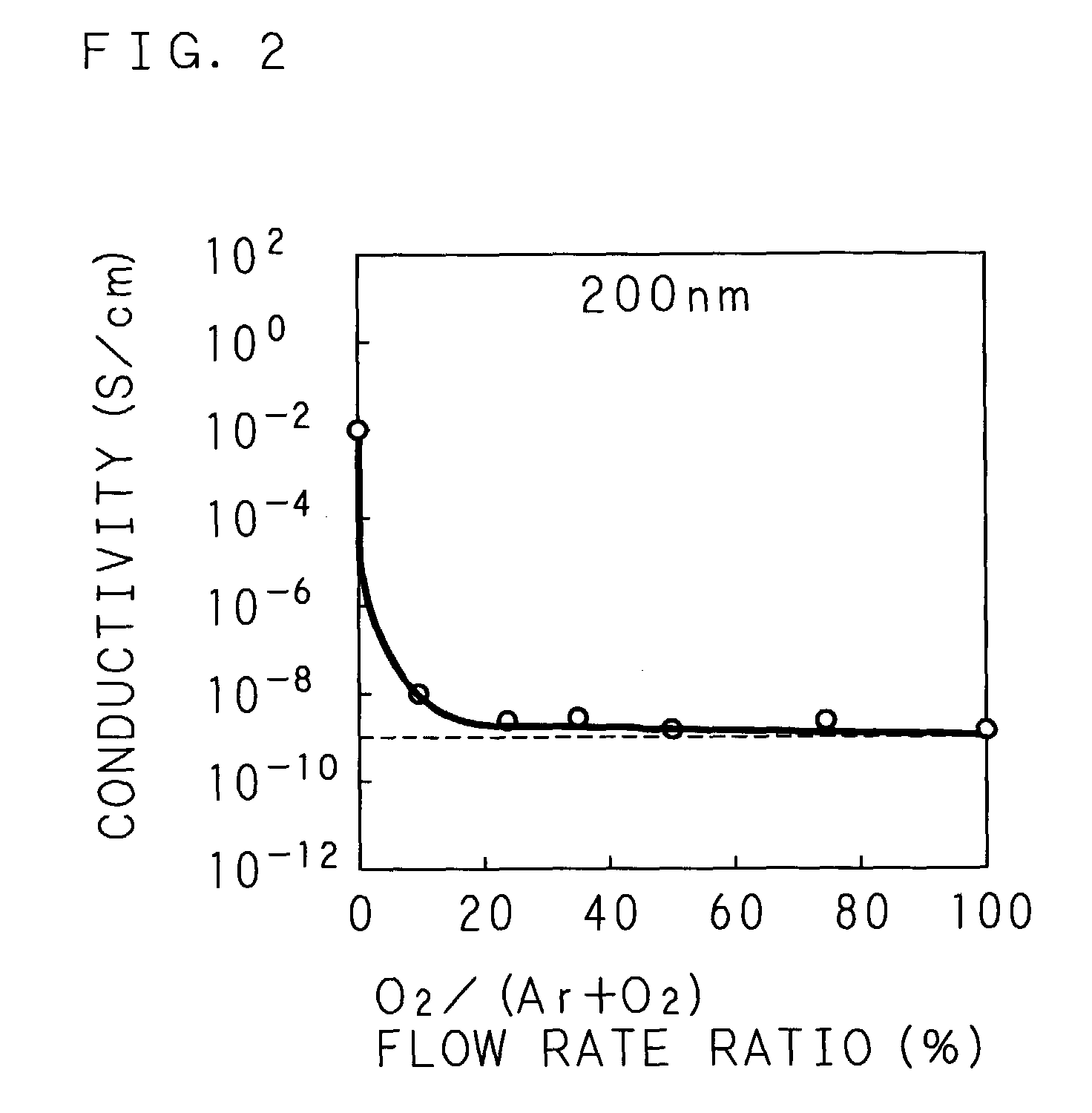

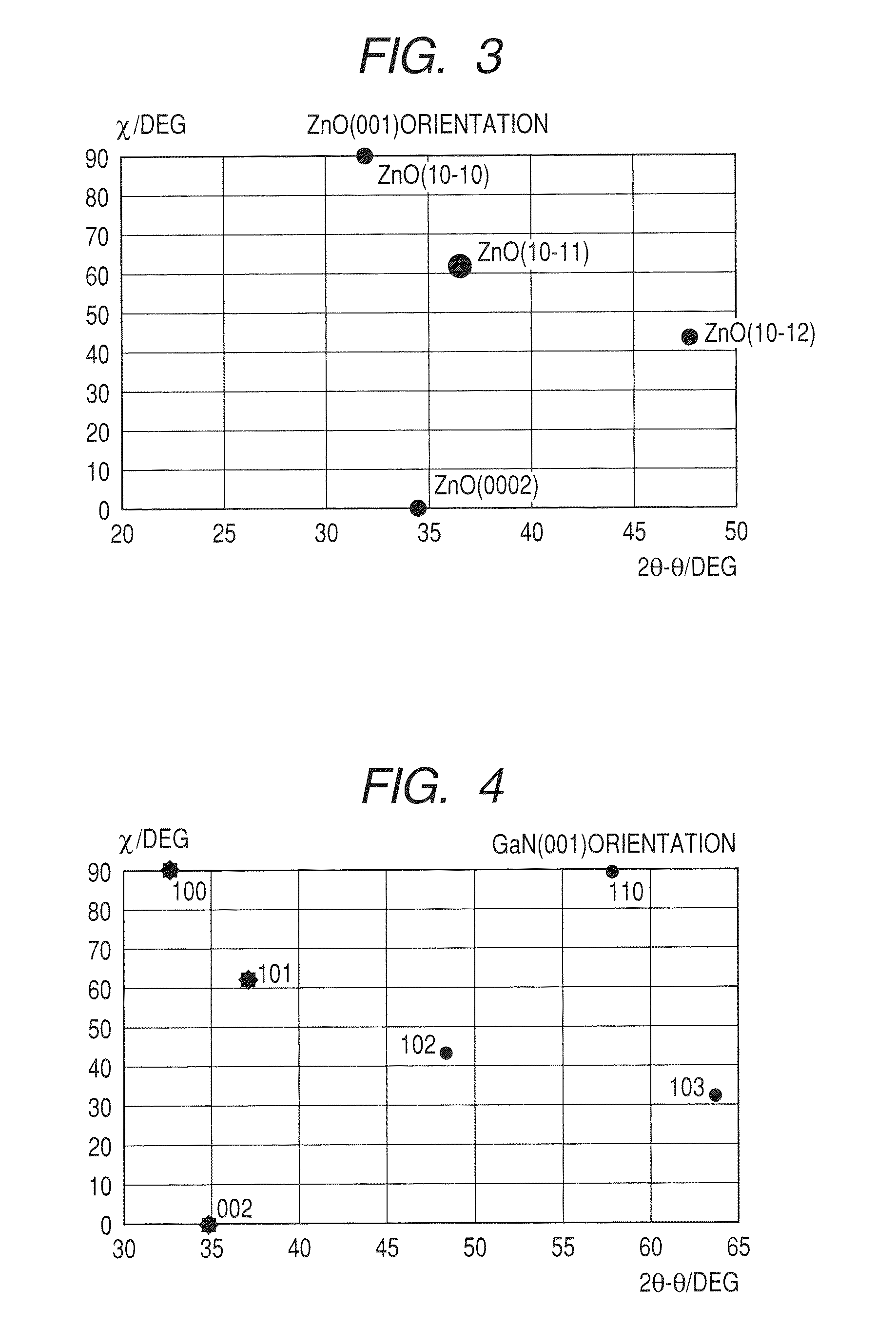

Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device

InactiveUS7049190B2High crystallinityLow costTransistorPolycrystalline material growthX-rayElectrical resistivity and conductivity

A ZnO buffer layer having an electric conductivity of 1×10−9 S / cm or lower or alternatively a ZnO buffer layer having a diffraction peak of a crystal face other than (002) and (004) in X-ray diffraction is formed on a substrate by sputtering. A ZnO semiconductor layer is formed on the ZnO buffer layer. The ZnO semiconductor layer is formed under the condition that the flow rate ratio of an oxygen gas in a sputtering gas is lower than that in the formation of the ZnO buffer layer.

Owner:SANYO ELECTRIC CO LTD

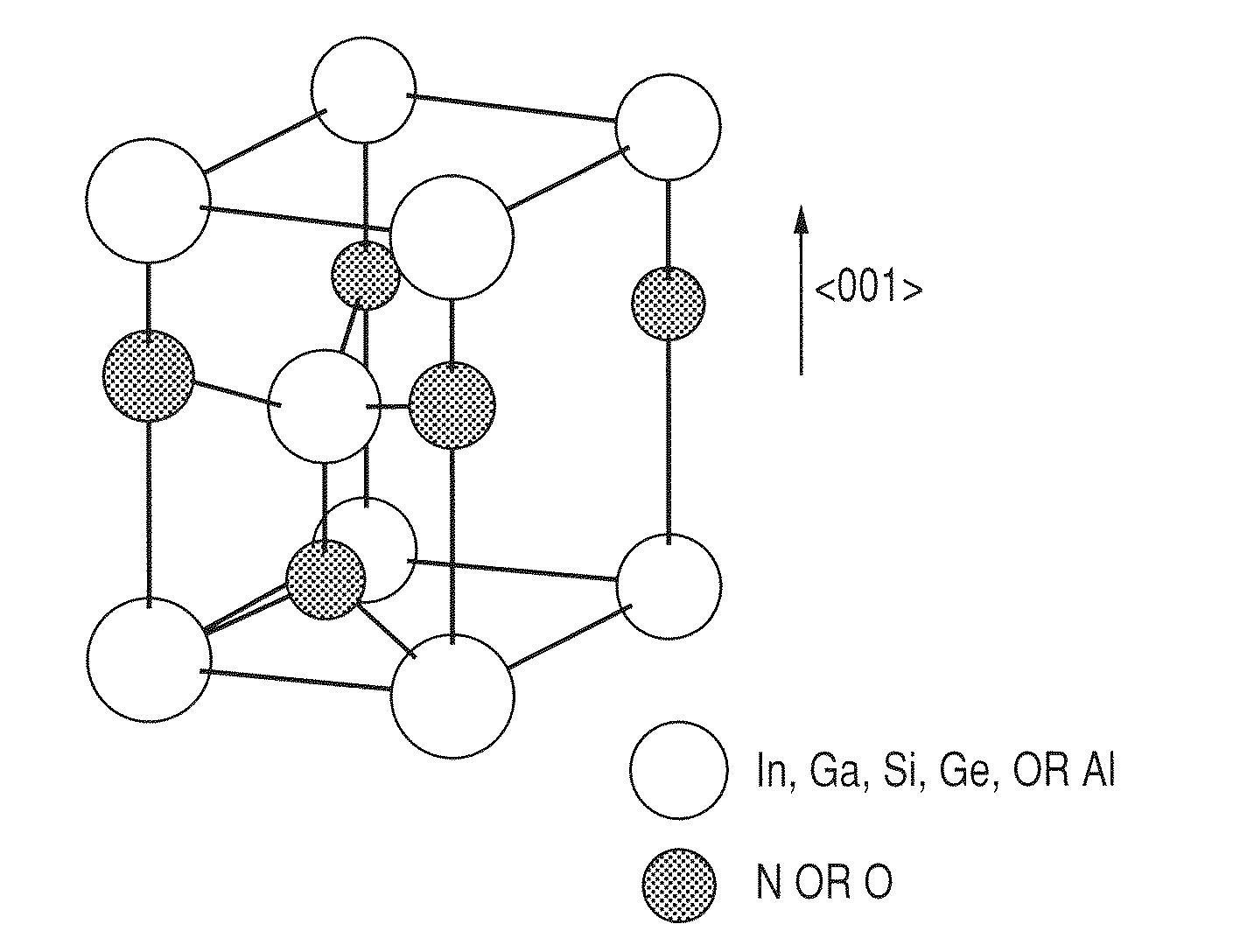

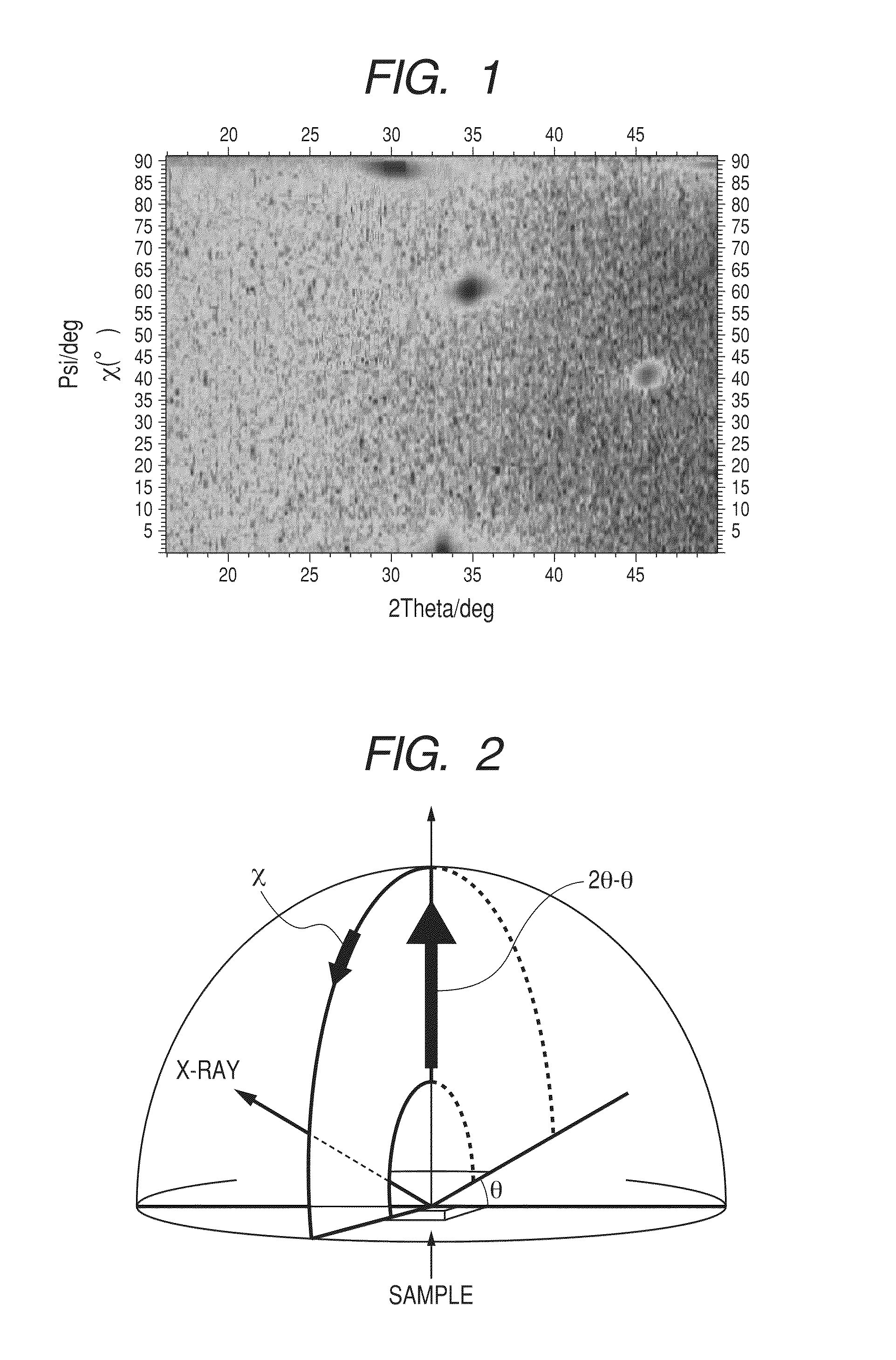

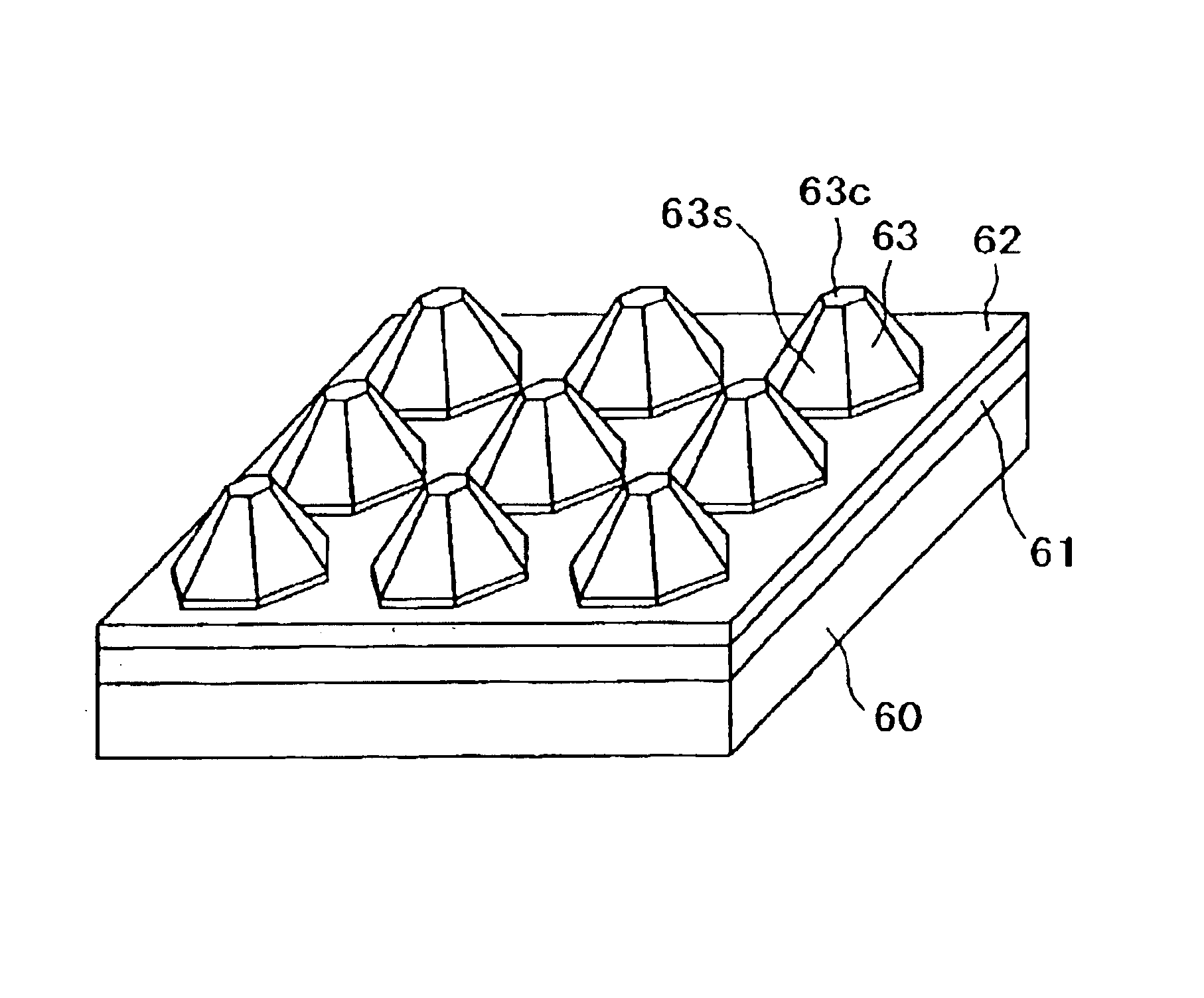

Substrate for growing wurtzite type crystal and method for manufacturing the same and semiconductor device

ActiveUS20100092800A1Low costHigh crystallinityPolycrystalline material growthVacuum evaporation coatingNitrideSemiconductor

A laminated structure comprises a first layer comprising a crystal with six-fold symmetry, and a second layer comprising a metal oxynitride crystal formed on the first layer, wherein the second layer comprises at least one element selected from the group consisting of In, Ga, Si, Ge and Al, N, O and Zn, as main elements, and wherein the second layer has in-plane orientation.

Owner:CANON KK

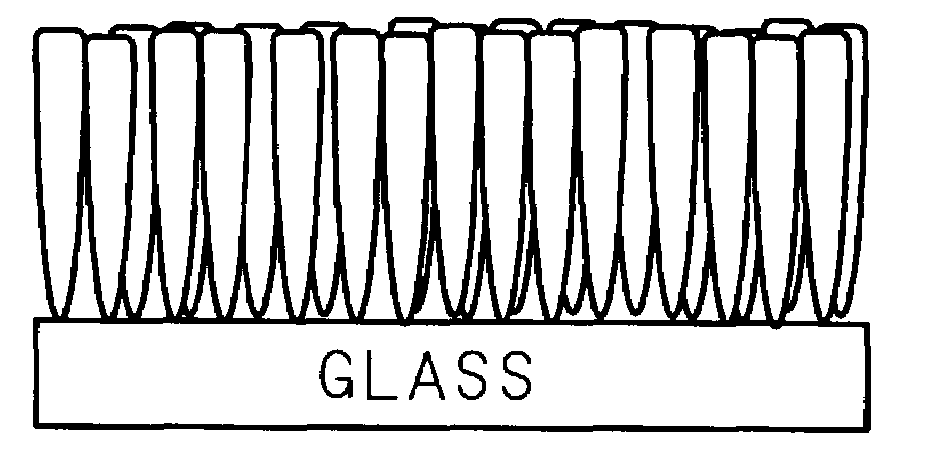

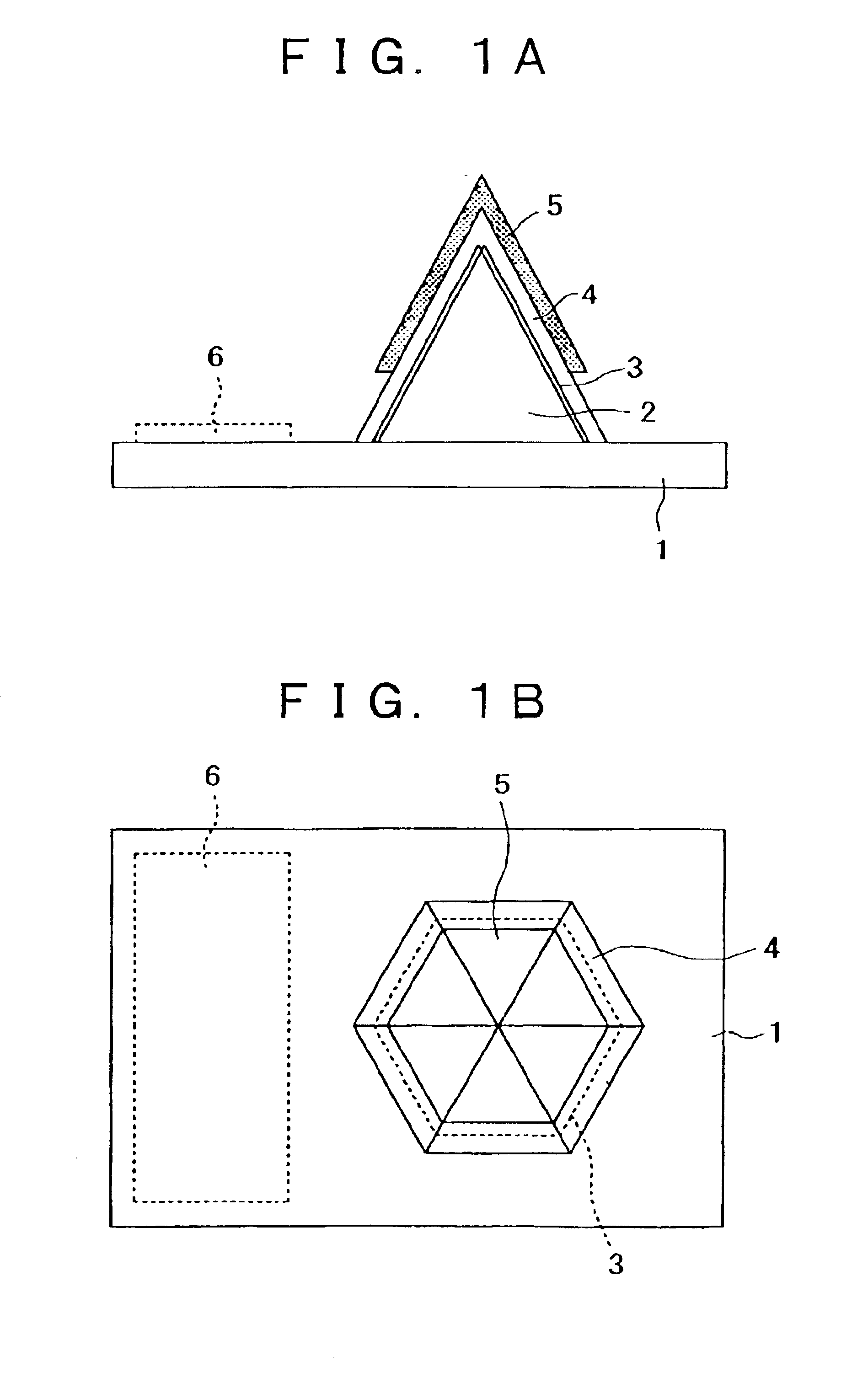

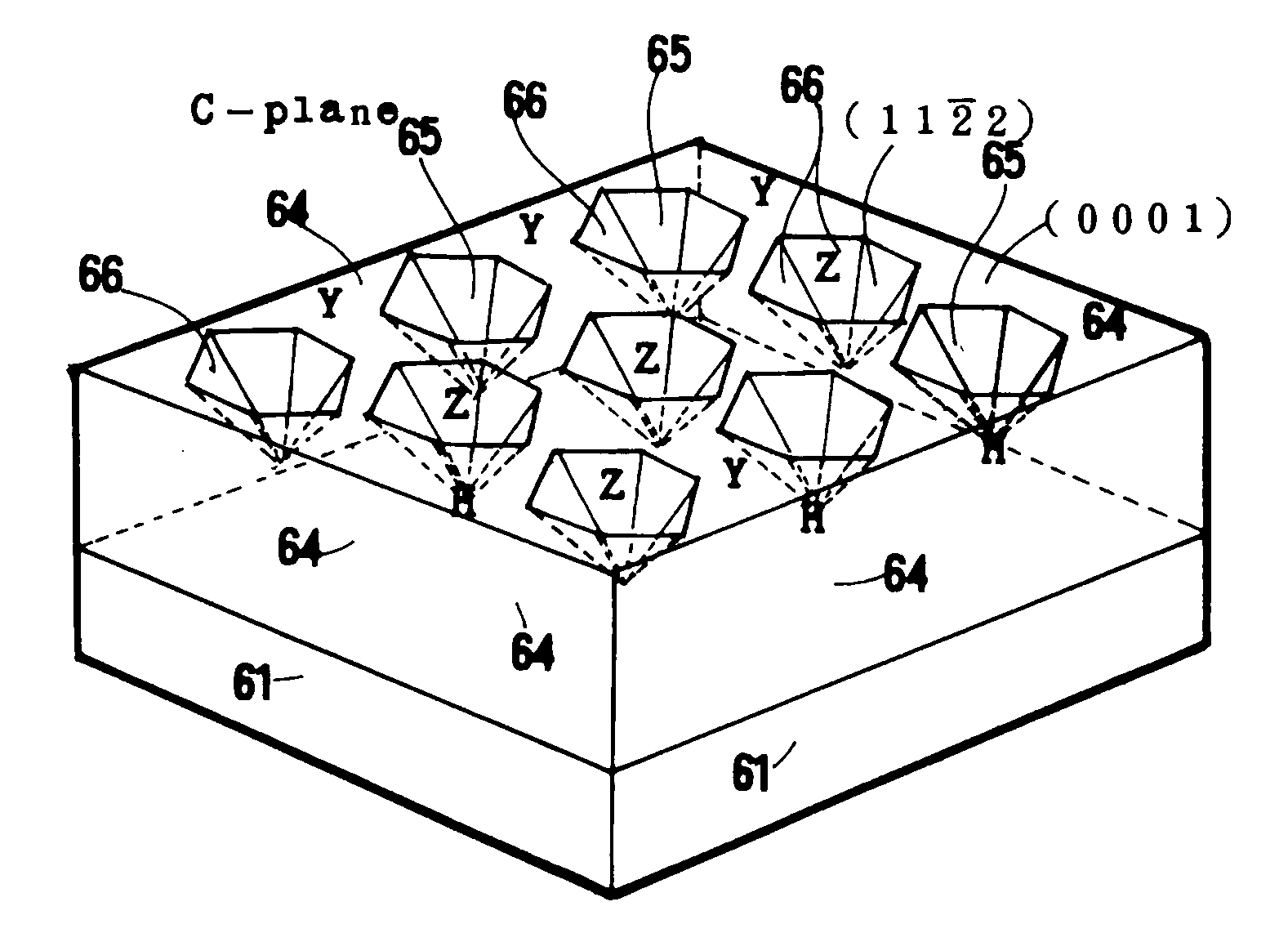

Method of growing nitride semiconductors, nitride semiconductor substrate and nitride semiconductor device

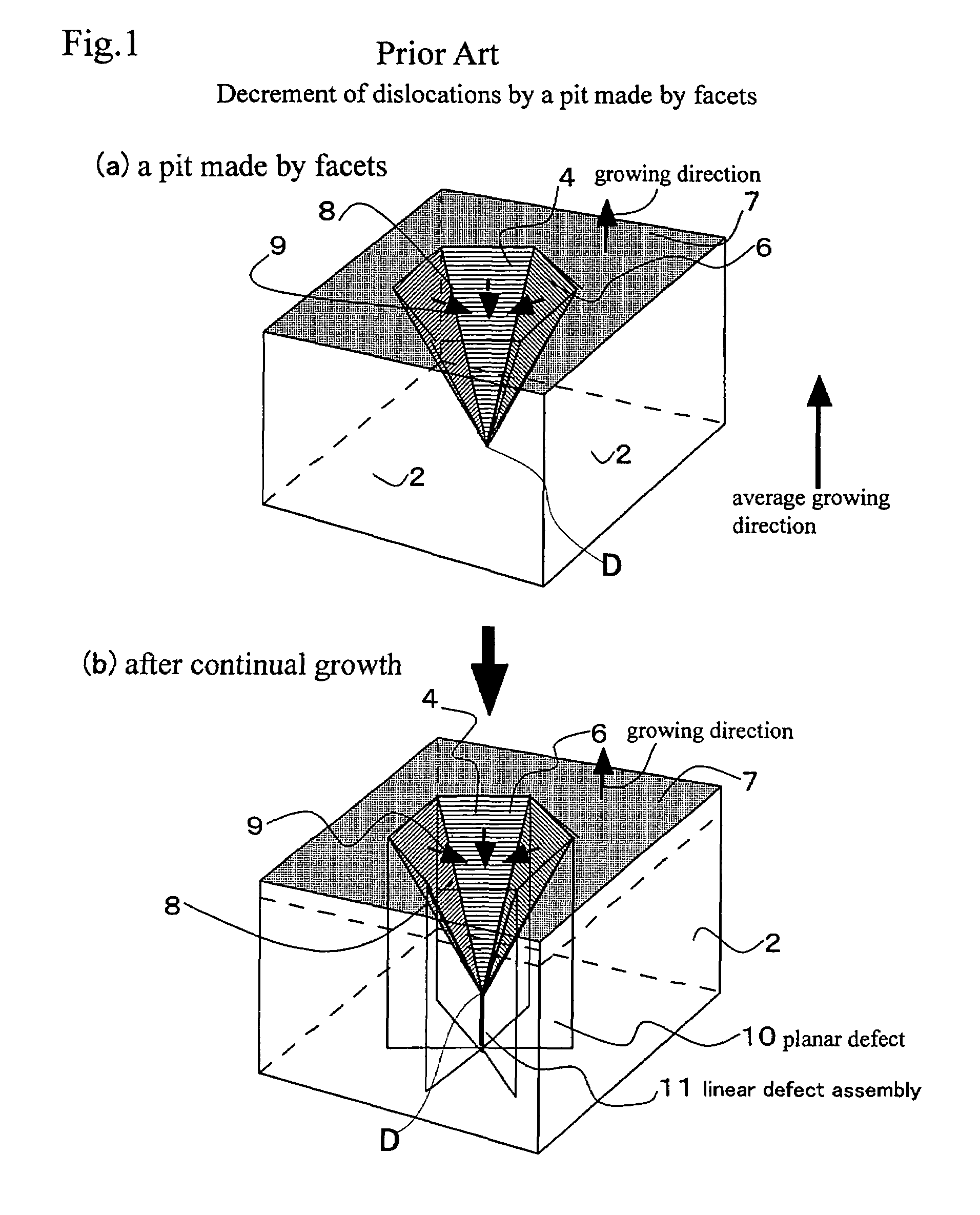

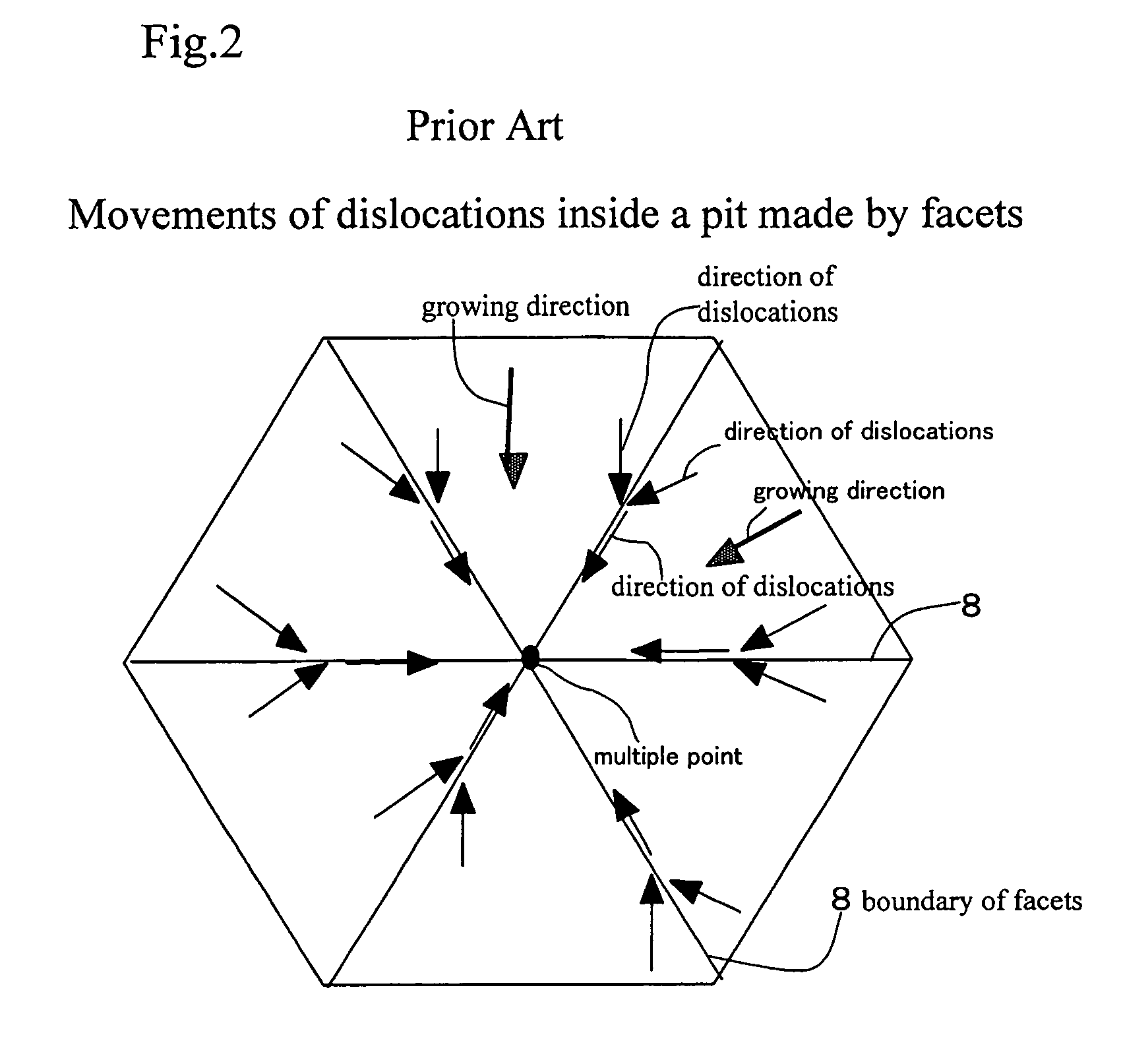

InactiveUS6153010APolycrystalline material growthLaser detailsNitrogen sourceCrystallographic defect

PCT No. PCT / JP98 / 01640 Sec. 371 Date Dec. 9, 1998 Sec. 102(e) Date Dec. 9, 1998 PCT Filed Apr. 9, 1998 PCT Pub. No. WO98 / 47170 PCT Pub. Date Oct. 22, 1998A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

Owner:NICHIA CORP

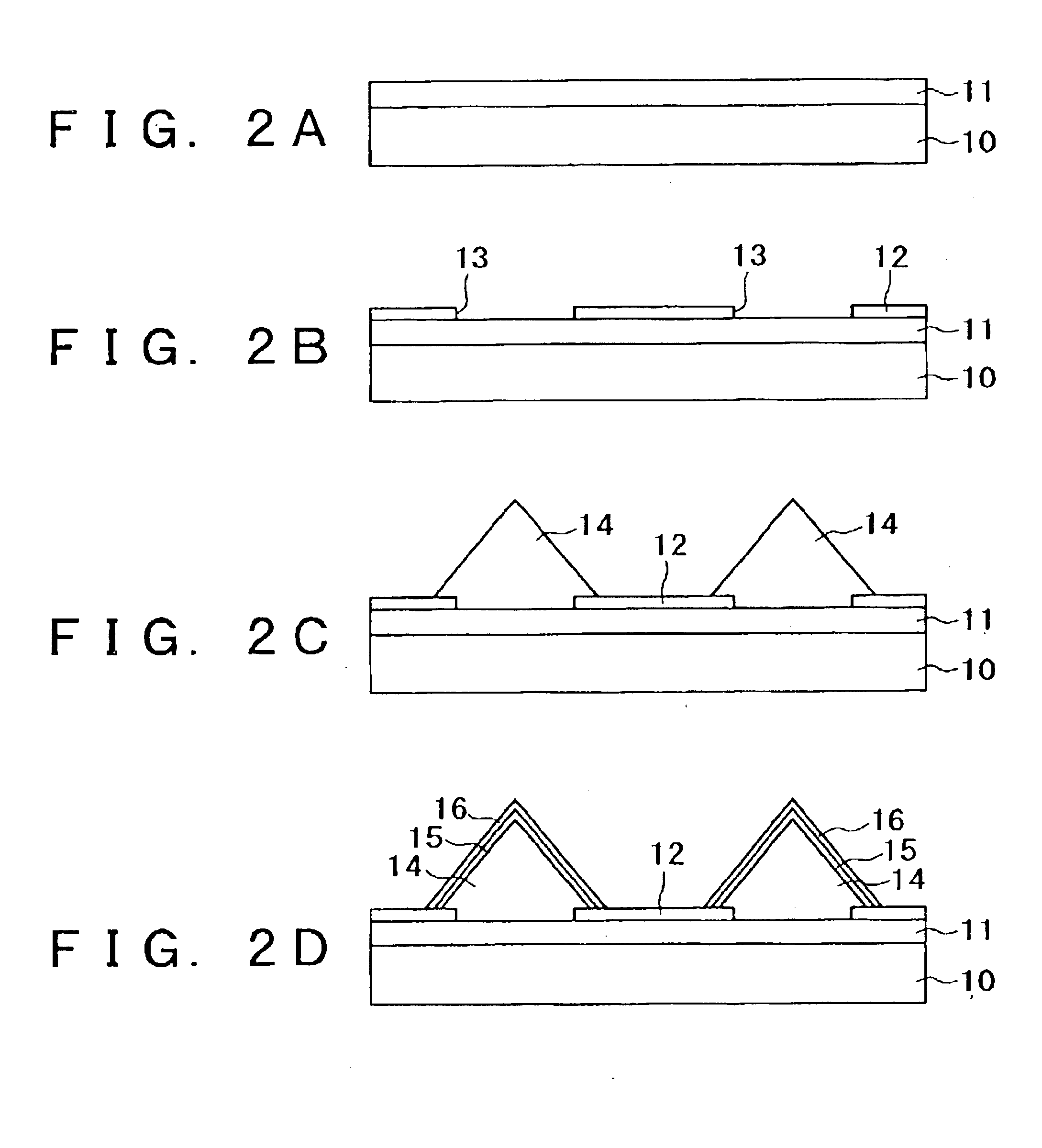

Selective growth method, and semiconductor light emitting device and fabrication method thereof

InactiveUS6858081B2Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

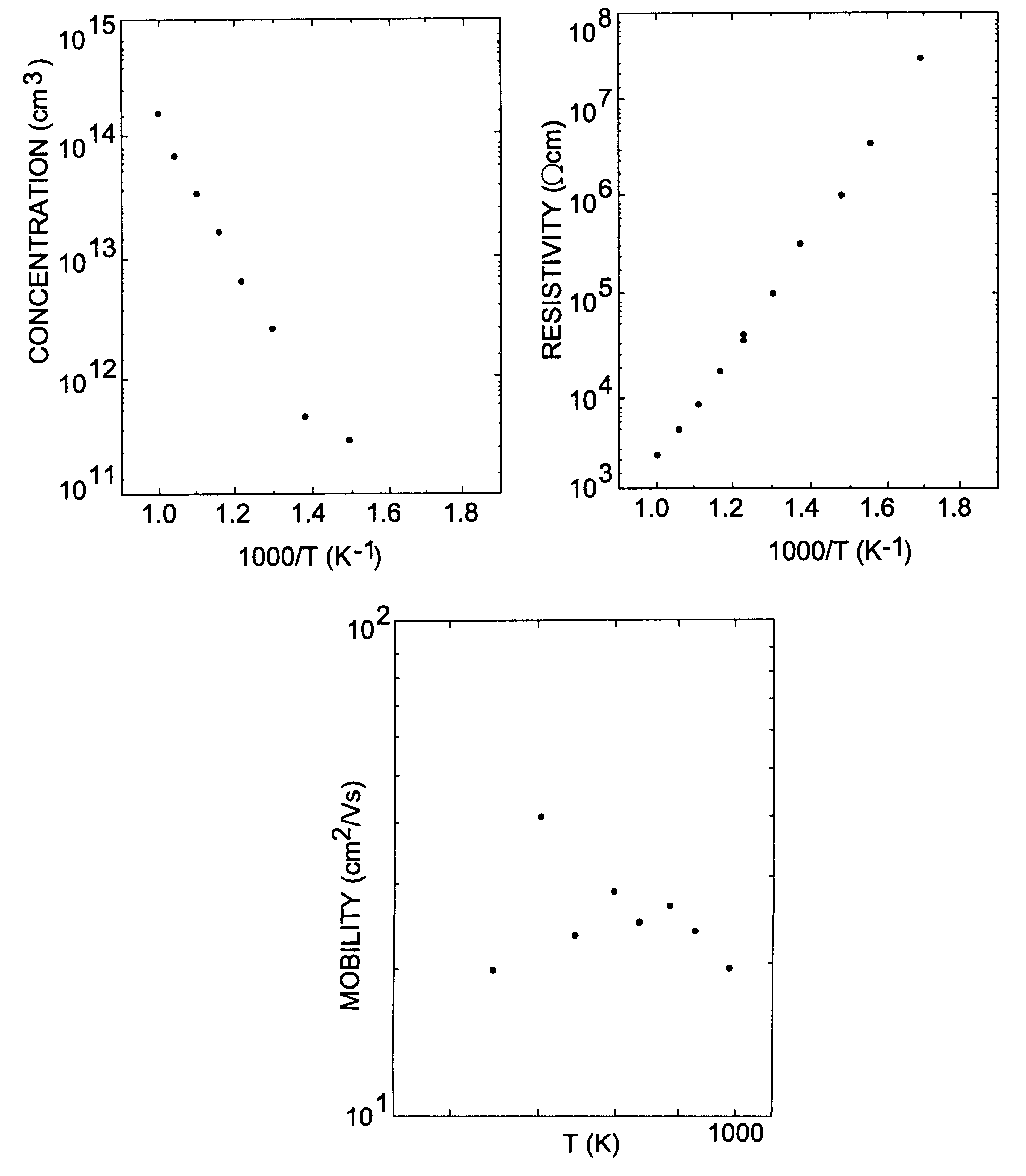

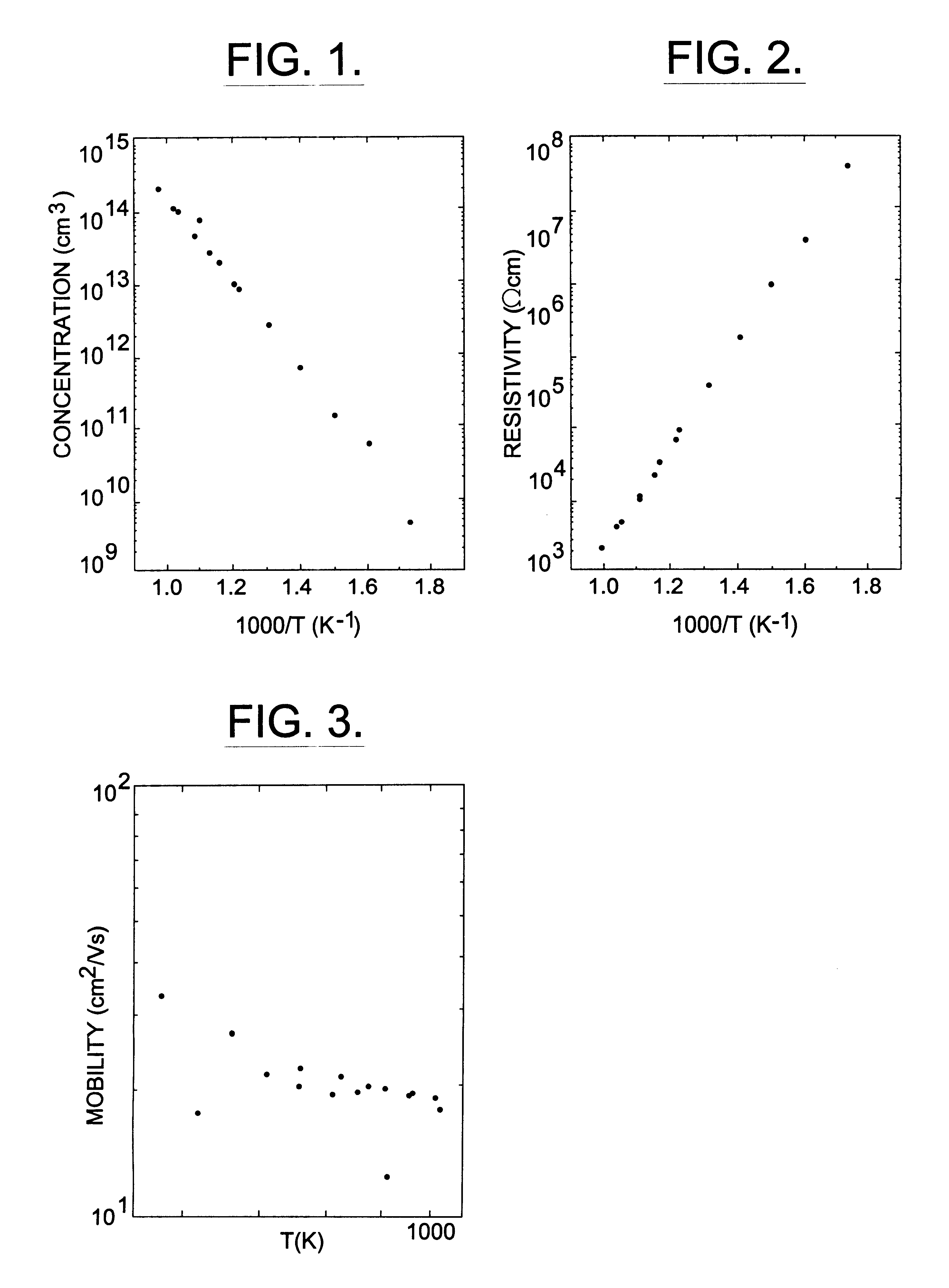

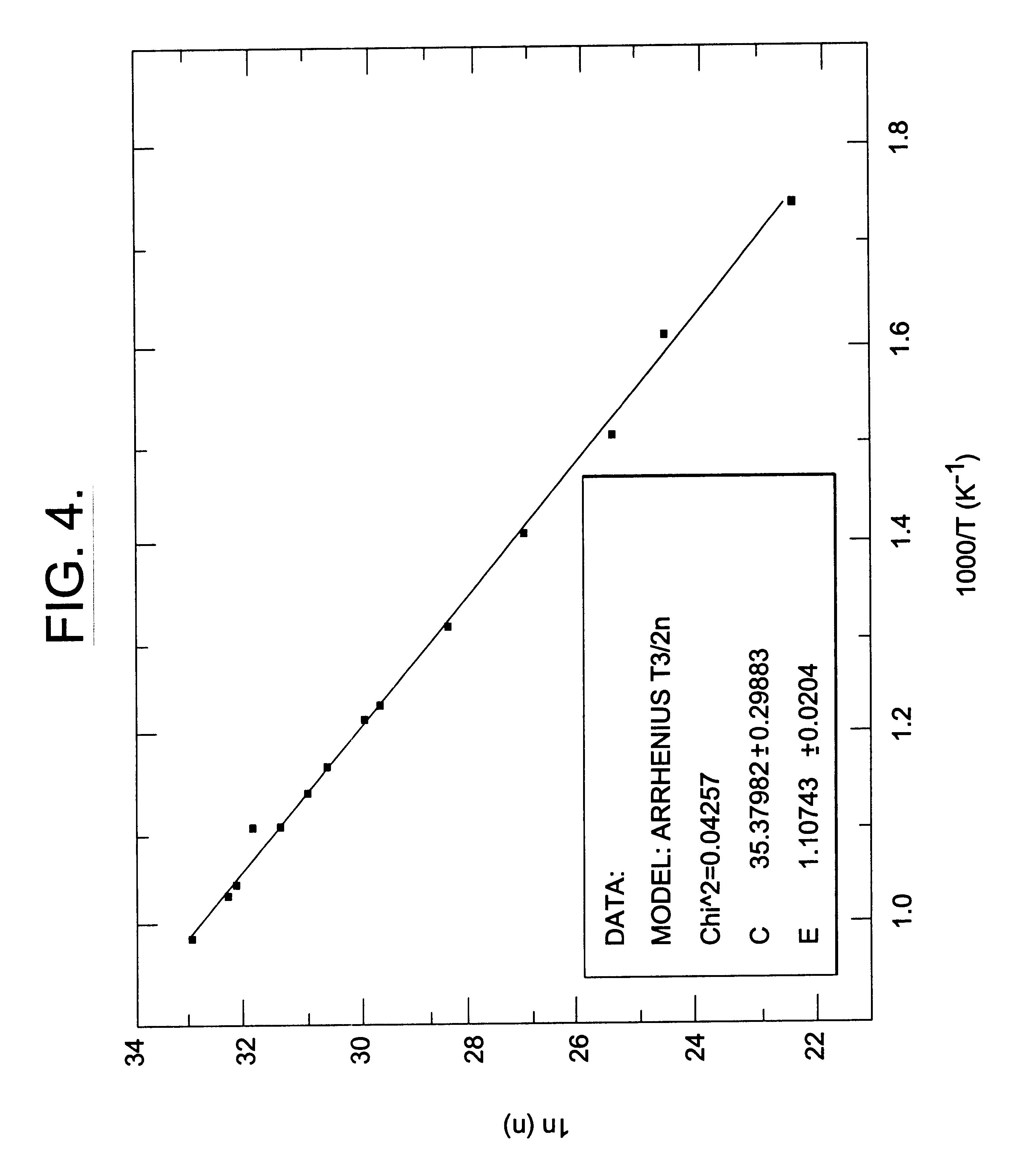

Semi-insulating silicon carbide without vanadium domination

InactiveUS6218680B1Reduce the amount requiredIncrease the number ofPolycrystalline material growthAfter-treatment detailsDevice formTrapping

Owner:CREE INC

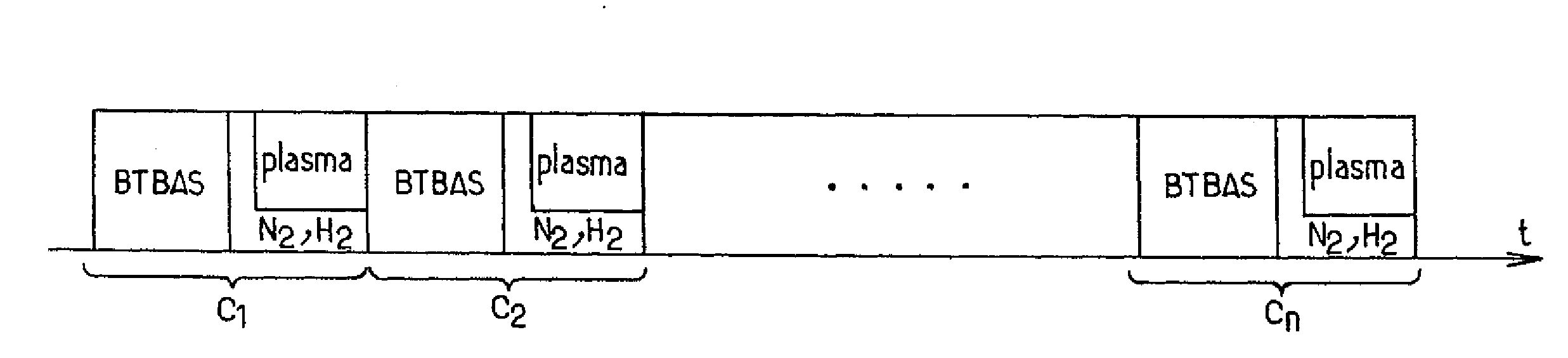

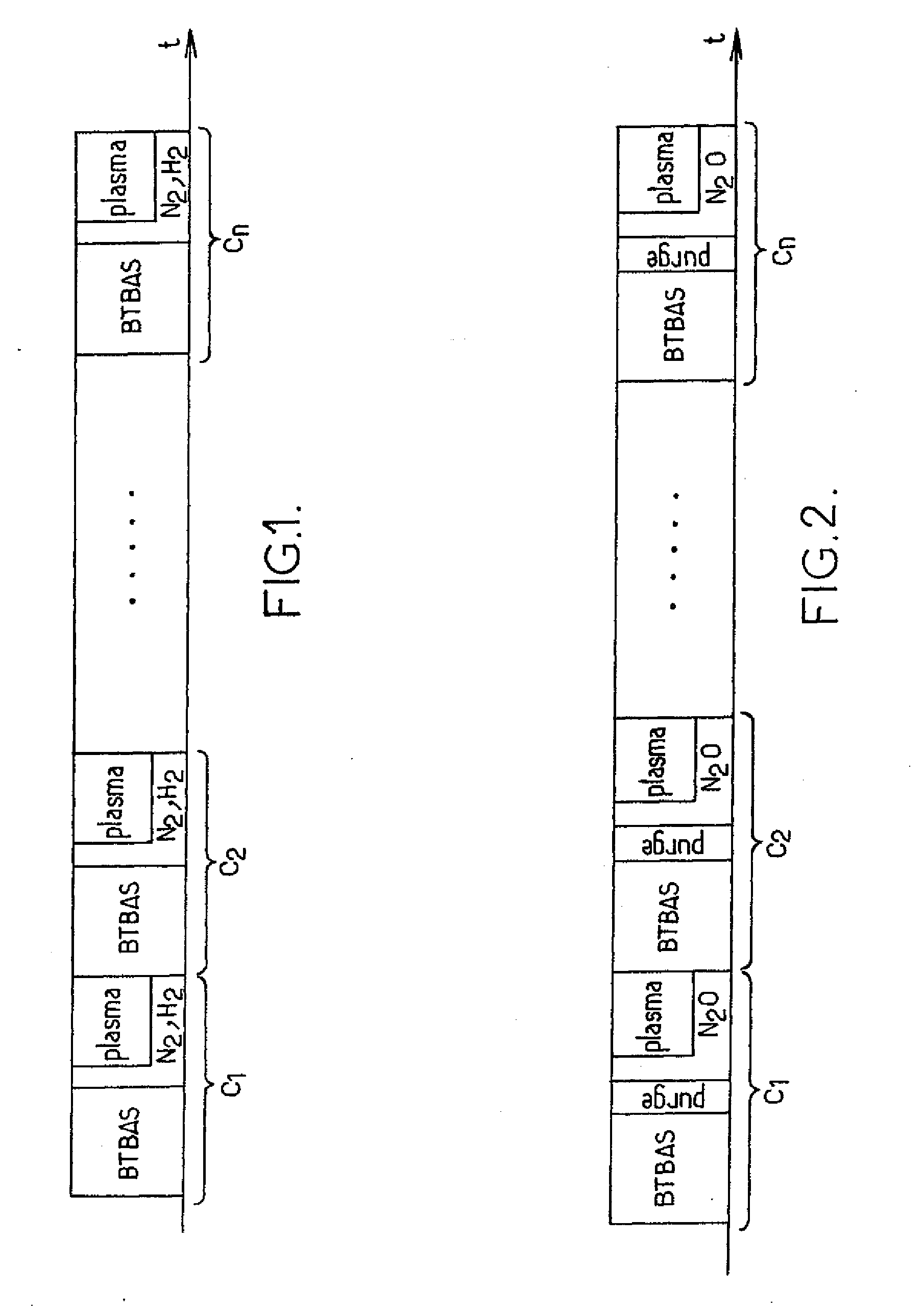

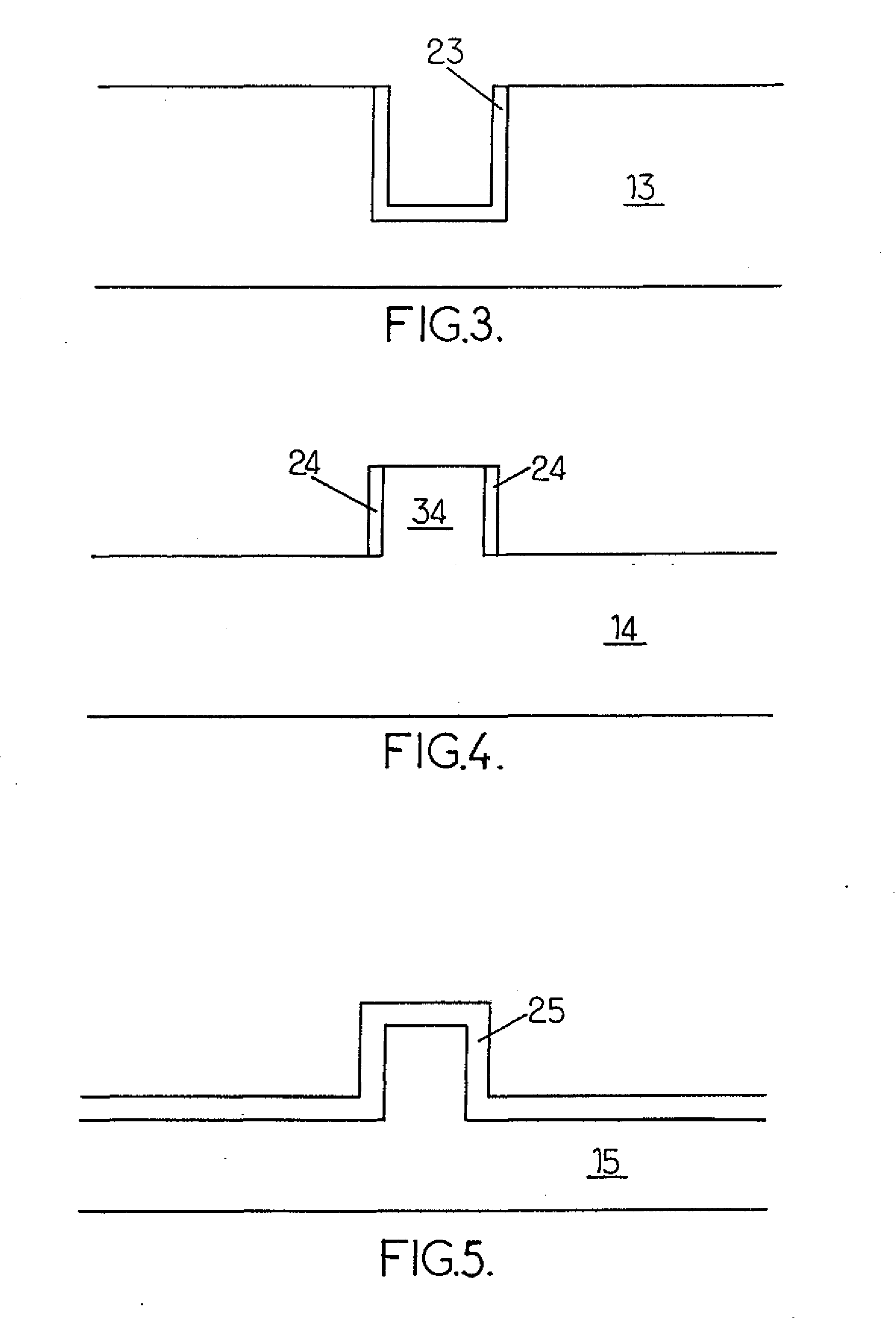

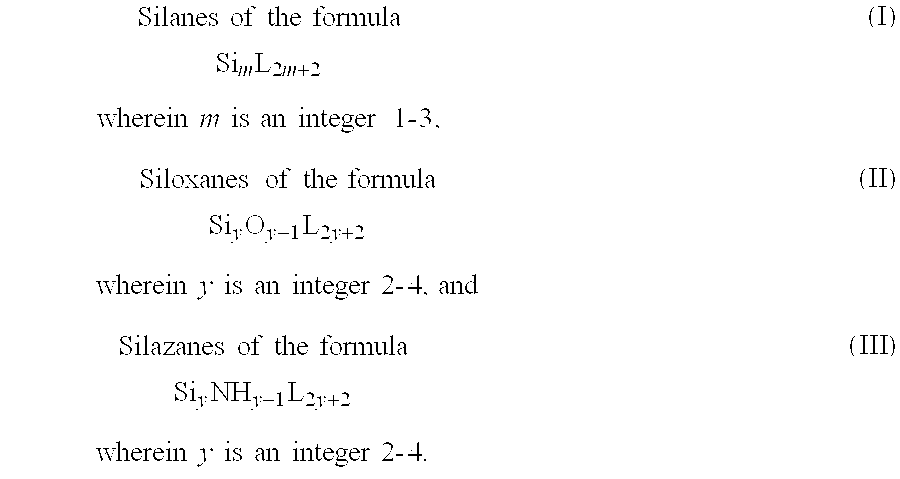

PEALD Deposition of a Silicon-Based Material

InactiveUS20070251444A1Avoiding considerable slow-downInhibition formationPolycrystalline material growthFrom chemically reactive gasesAtomic layer depositionSemiconductor

A process for depositing a silicon-based material on a substrate uses the technology of plasma-enhanced atomic layer deposition. The process is carried out over several cycles, wherein each cycle includes: exposing the substrate to a first precursor, which is an organometallic silicon precursor; and applying a plasma of at least a second precursor, different from the first precursor. Semiconductor products such as 3D capacitors, vertical transistor gate spacers, and conformal transistor stressors are made from the process.

Owner:STMICROELECTRONICS SRL

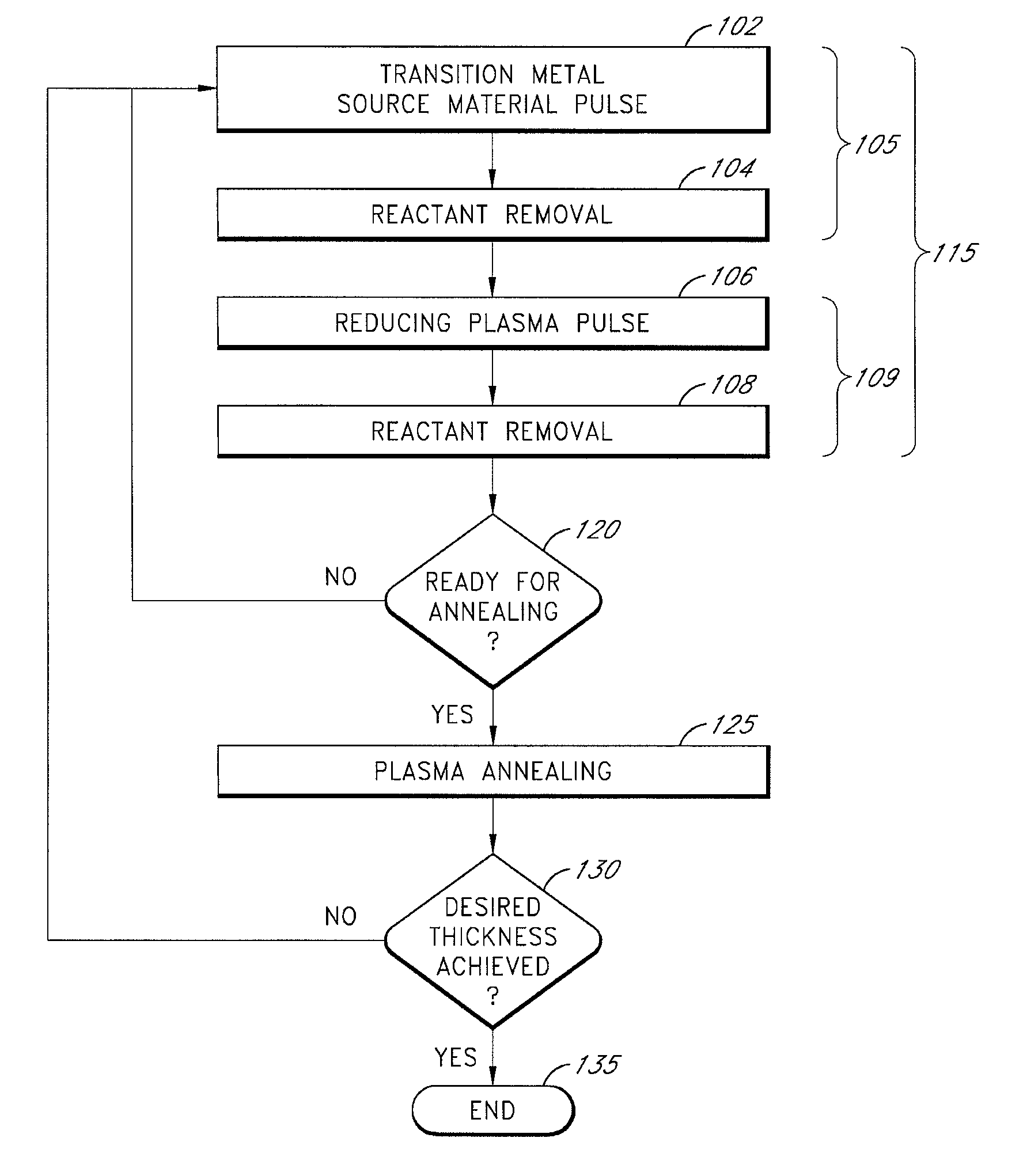

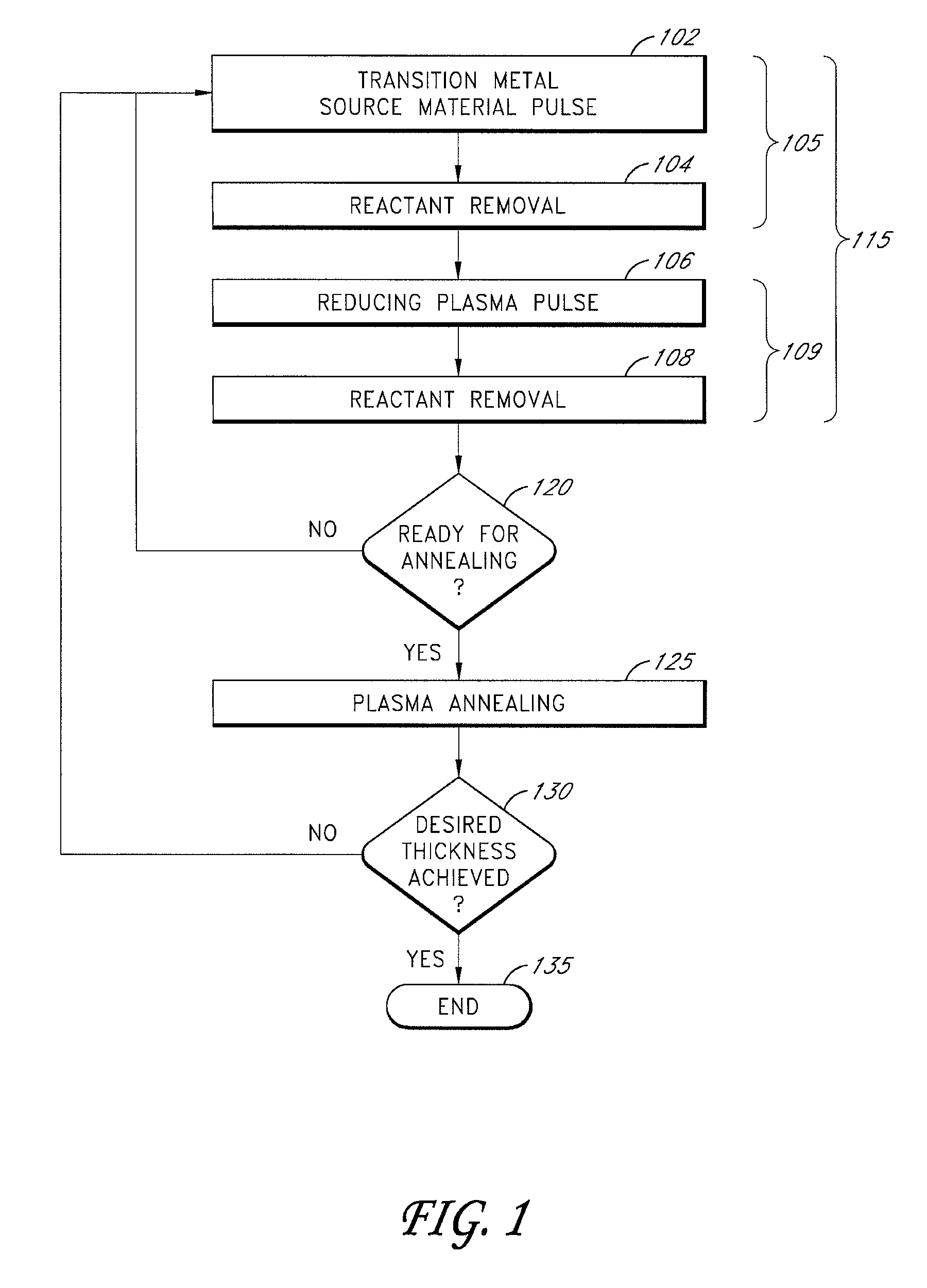

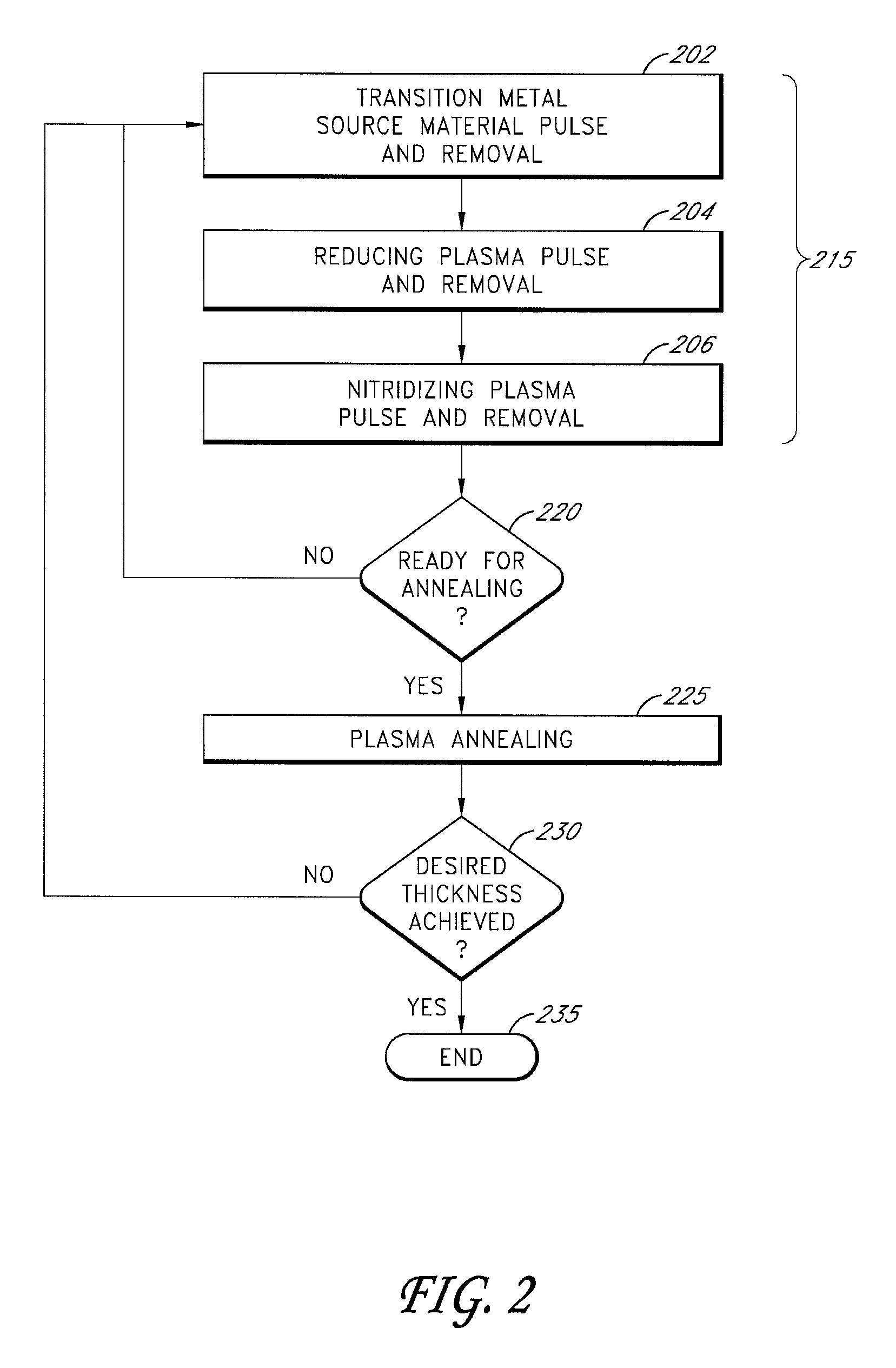

Periodic plasma annealing in an ALD-type process

ActiveUS7713874B2Increase probabilityReduce susceptibility to oxidationPolycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseVapor phase

Methods for performing periodic plasma annealing during atomic layer deposition are provided along with structures produced by such methods. The methods include contacting a substrate with a vapor-phase pulse of a metal source chemical and one or more plasma-excited reducing species for a period of time. Periodically, the substrate is contacted with a vapor phase pulse of one or more plasma-excited reducing species for a longer period of time. The steps are repeated until a metal thin film of a desired thickness is formed over the substrate.

Owner:ASM IP HLDG BV

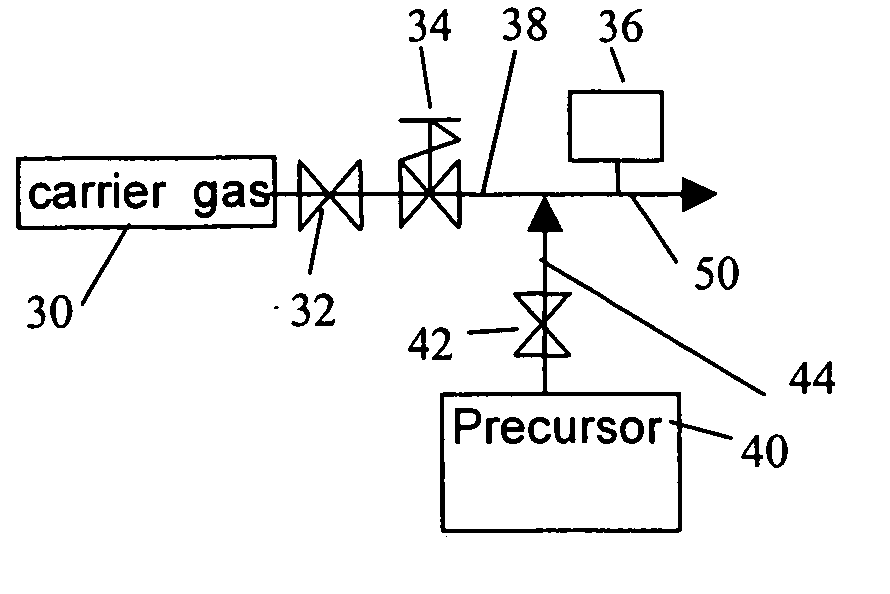

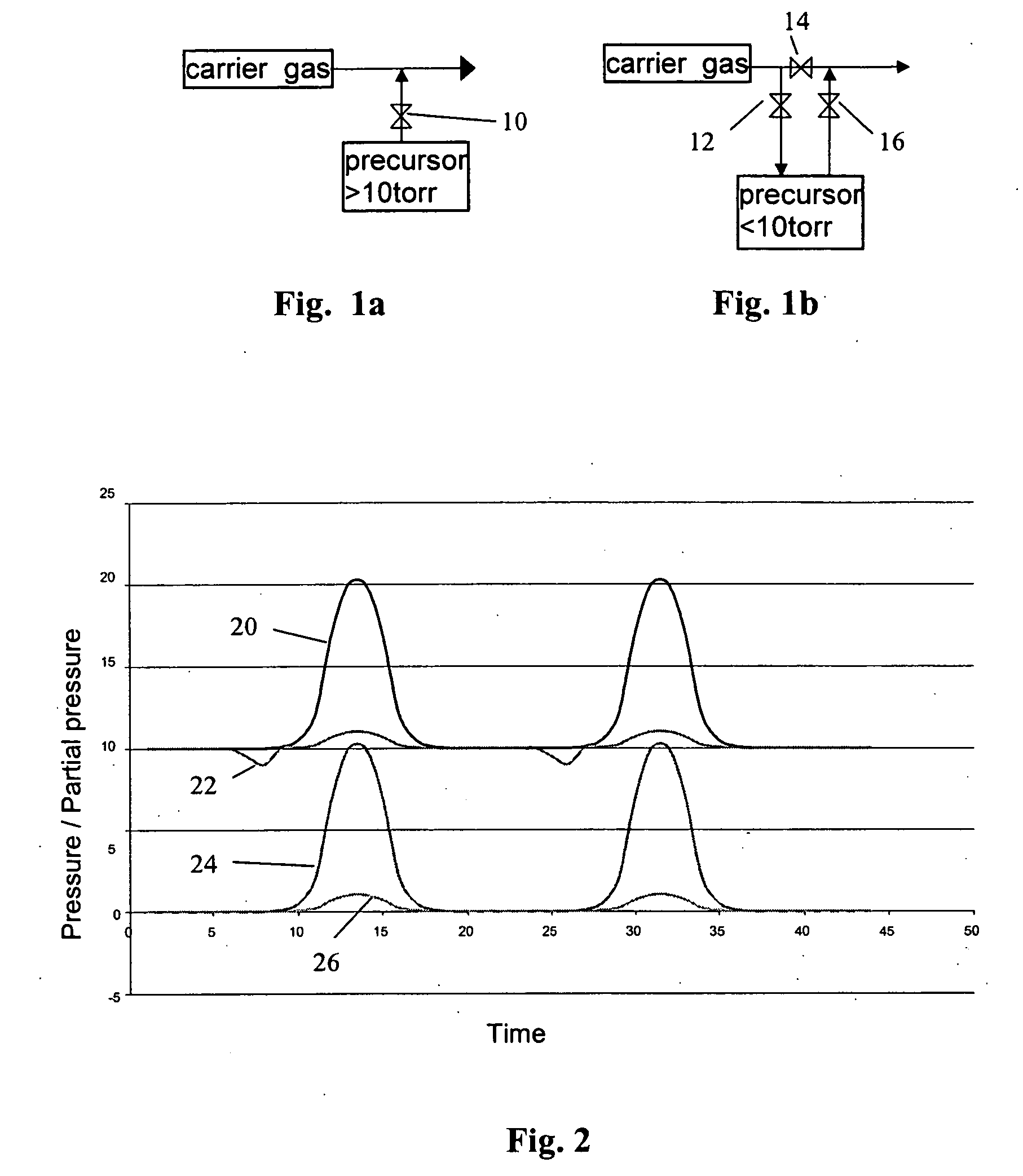

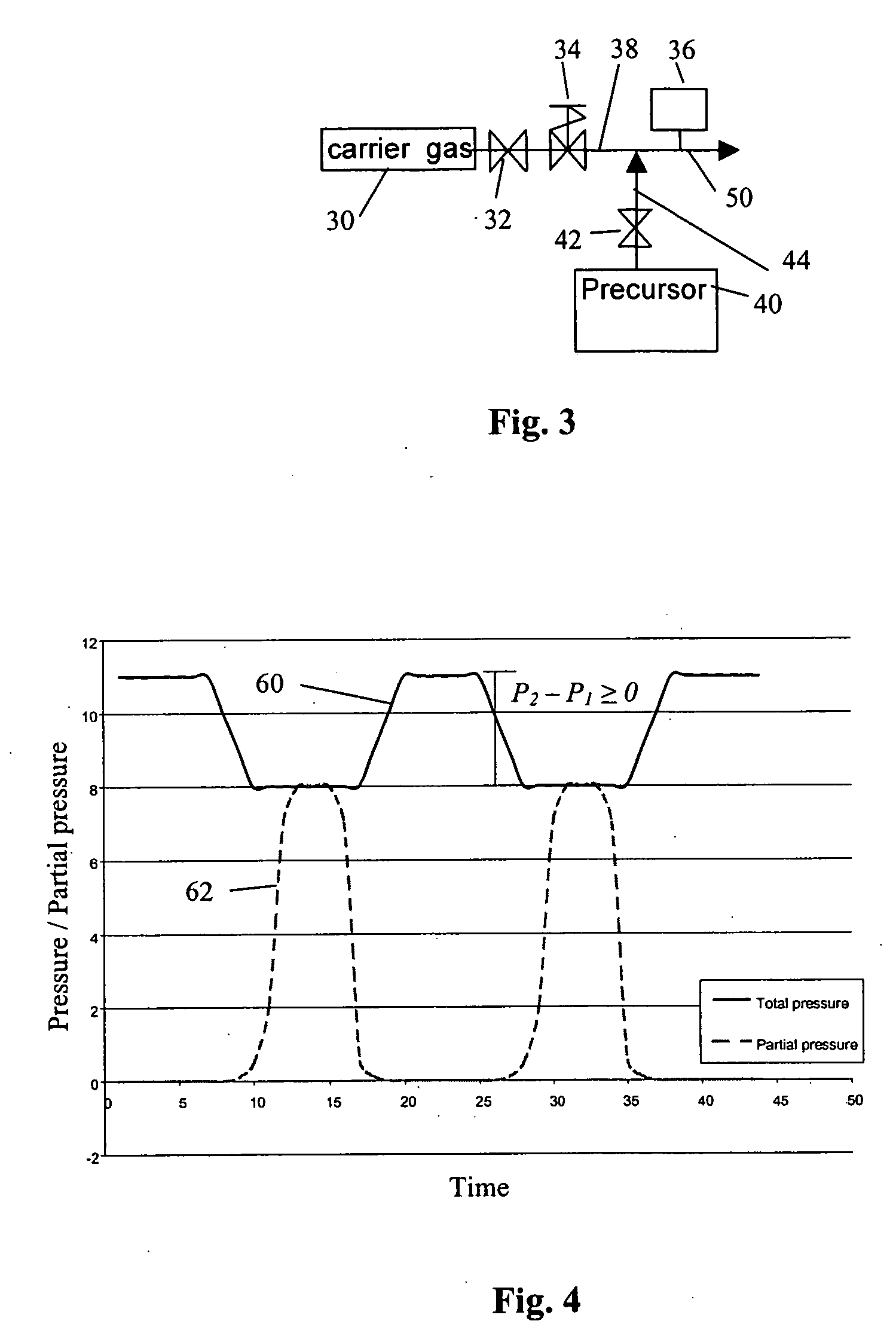

Method of pulsing vapor precursors in an ALD reactor

ActiveUS20060147626A1Faster film growthImproved pulse separationPolycrystalline material growthFrom chemically reactive gasesSource materialGas phase

A method of growing a thin film on a substrate by pulsing vapor-phase precursors material into a reaction chamber according to the ALD method. The method comprises vaporizing at least one precursor from a source material container maintained at a vaporising temperature, repeatedly feeding pulses of the vaporized precursor via a feed line into the reaction chamber at a first pressure, and subsequently purging the reaction chamber with pulses of inactive gas fed via the feed line at a second pressure. The second pressure is maintained at the same as or a higher level than the first pressure for separating successive pulses of said vaporized precursor from each other.

Owner:ASM IP HLDG BV

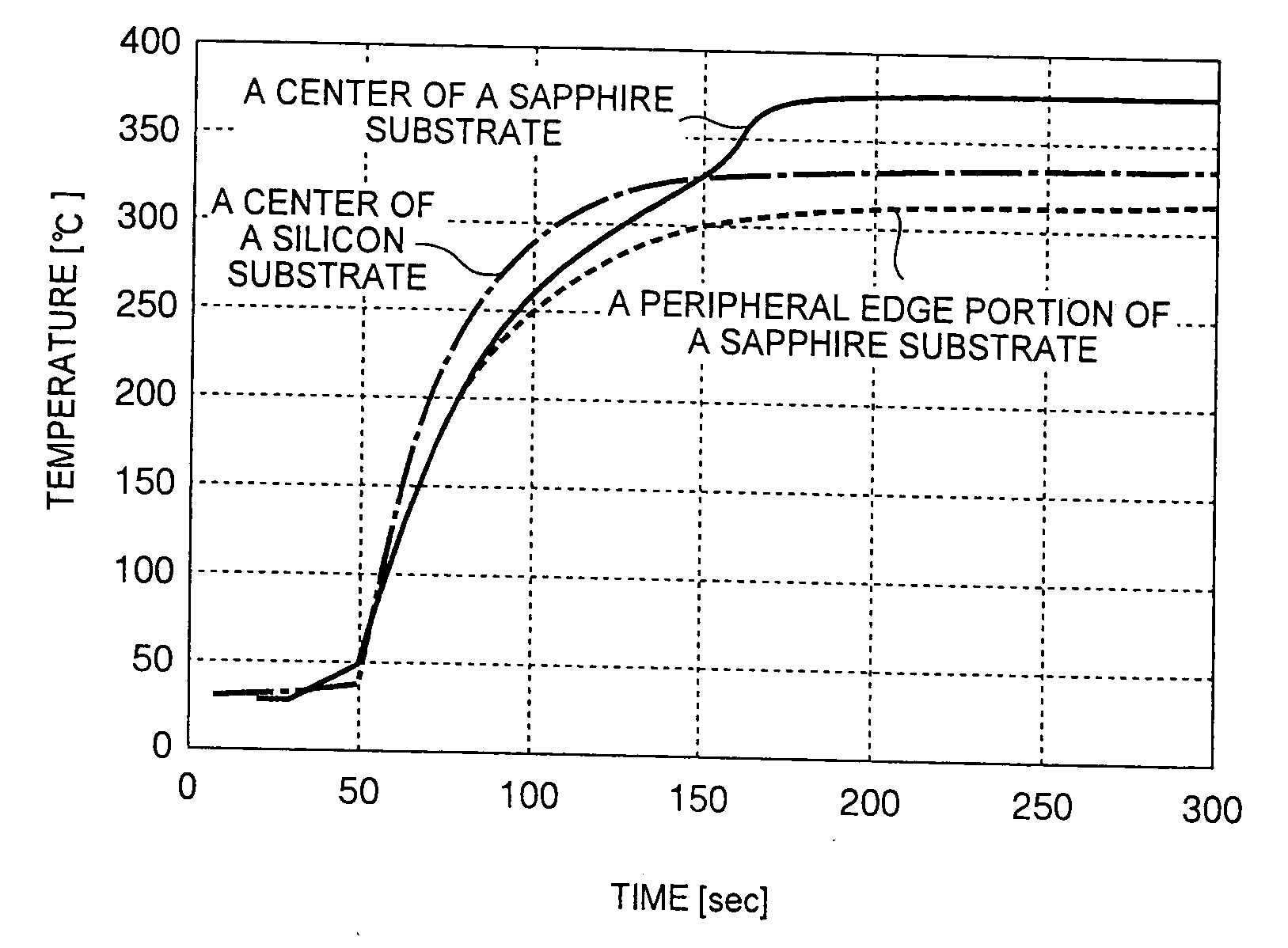

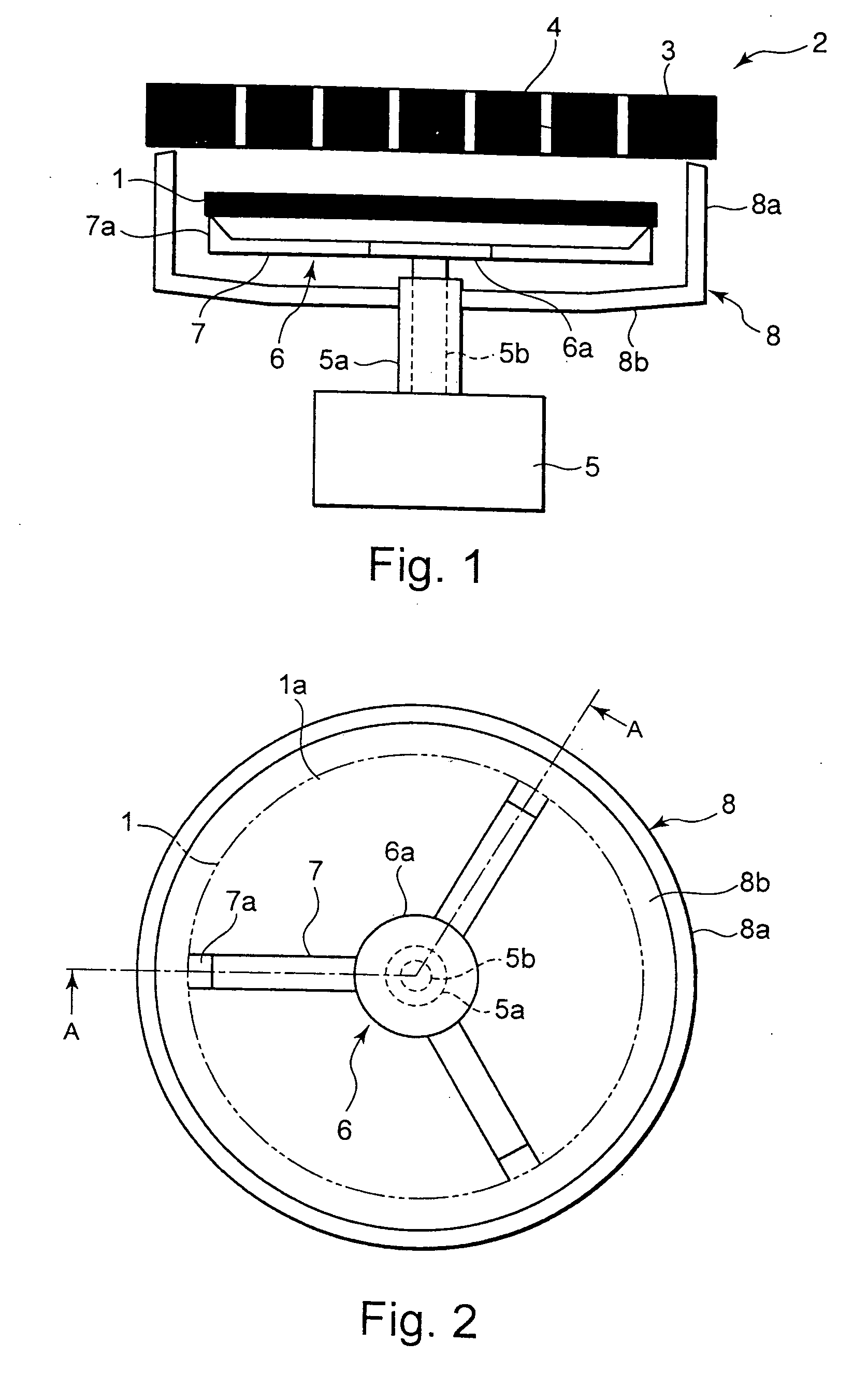

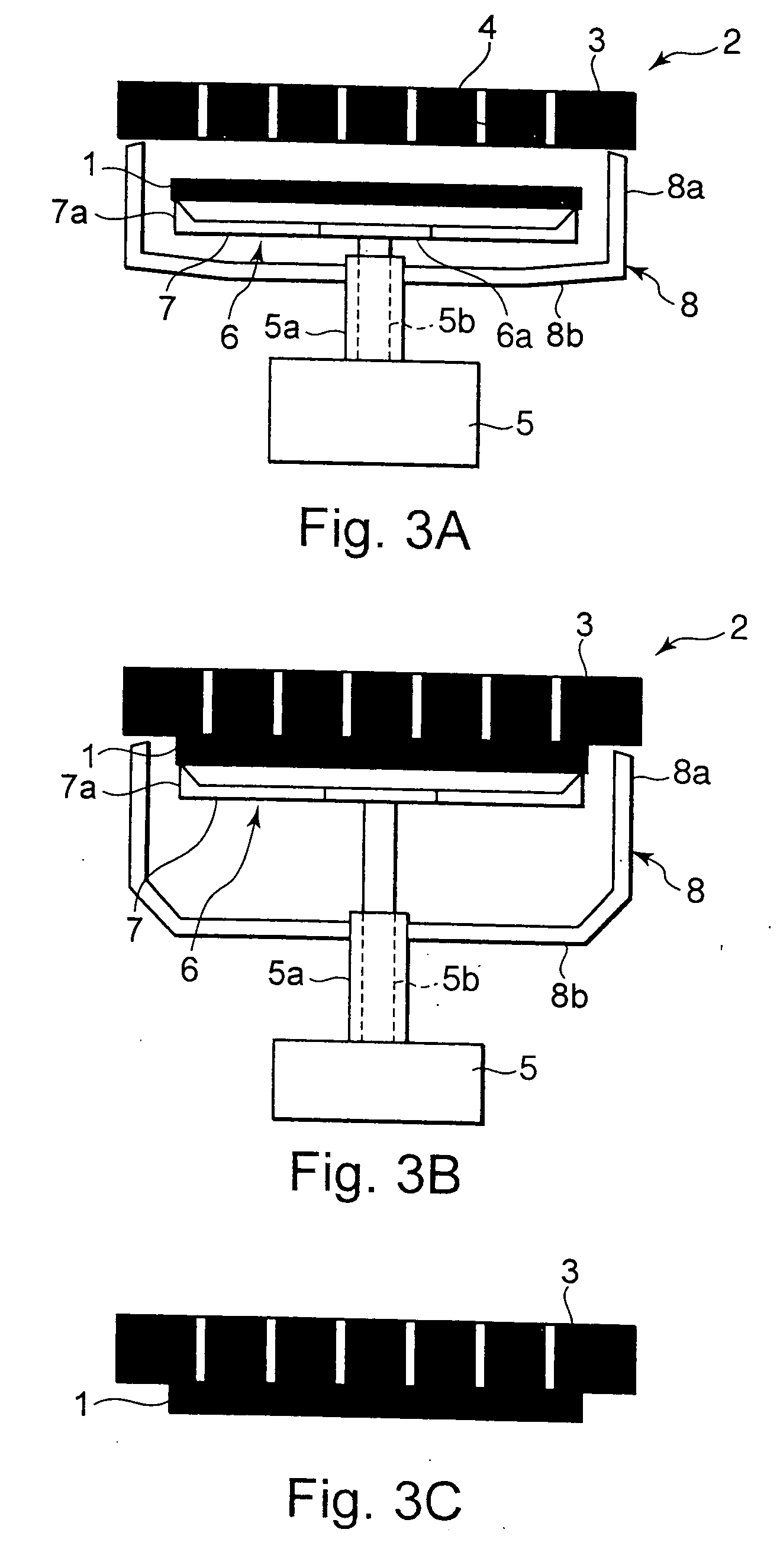

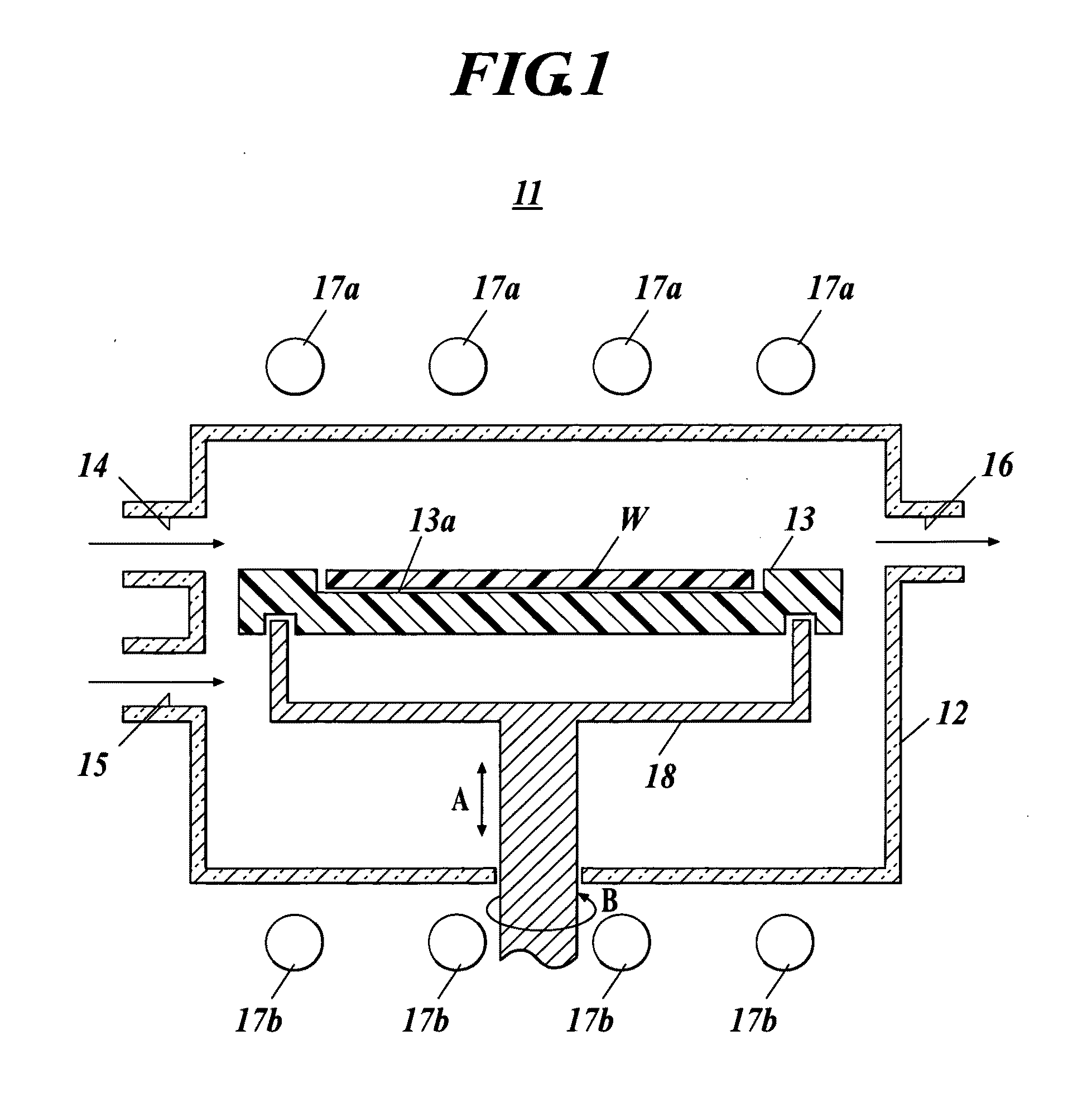

Method for manufacturing semiconductor device

InactiveUS20060240574A1Warpage suppressionPolycrystalline material growthSemiconductor/solid-state device manufacturingDevice materialManufactured apparatus

A semiconductor manufacturing apparatus A semiconductor manufacturing apparatus comprises a hot plate which heats a sapphire substrate; a support table having a support plate disposed with being spaced away from the hot plate by a predetermined interval, and support portions which respectively support the sapphire substrate with being spaced by a predetermined interval between the hot plate and the support plate and support the sapphire substrate in such a manner that back surfaces of the hot plate and the sapphire substrate are opposite to each other; an elevating device which moves the support table up and down; and a shielding cover which externally blocks off spacing defined between the hot plate and the sapphire substrate and spacing defined between the sapphire substrate and the support plate.

Owner:LAPIS SEMICON CO LTD

Process for Polycrystalline film silicon growth

InactiveUS6281098B1Widely distributedQuality improvementPolycrystalline material growthLiquid surface applicatorsVapor barrierProduct gas

A process for depositing polycrystalline silicon on substrates, including foreign substrates, occurs in a chamber at about atmospheric pressure, wherein a temperature gradient is formed, and both the atmospheric pressure and the temperature gradient are maintained throughout the process. Formation of a vapor barrier within the chamber that precludes exit of the constituent chemicals, which include silicon, iodine, silicon diiodide, and silicon tetraiodide. The deposition occurs beneath the vapor barrier. One embodiment of the process also includes the use of a blanketing gas that precludes the entrance of oxygen or other impurities. The process is capable of repetition without the need to reset the deposition zone conditions.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

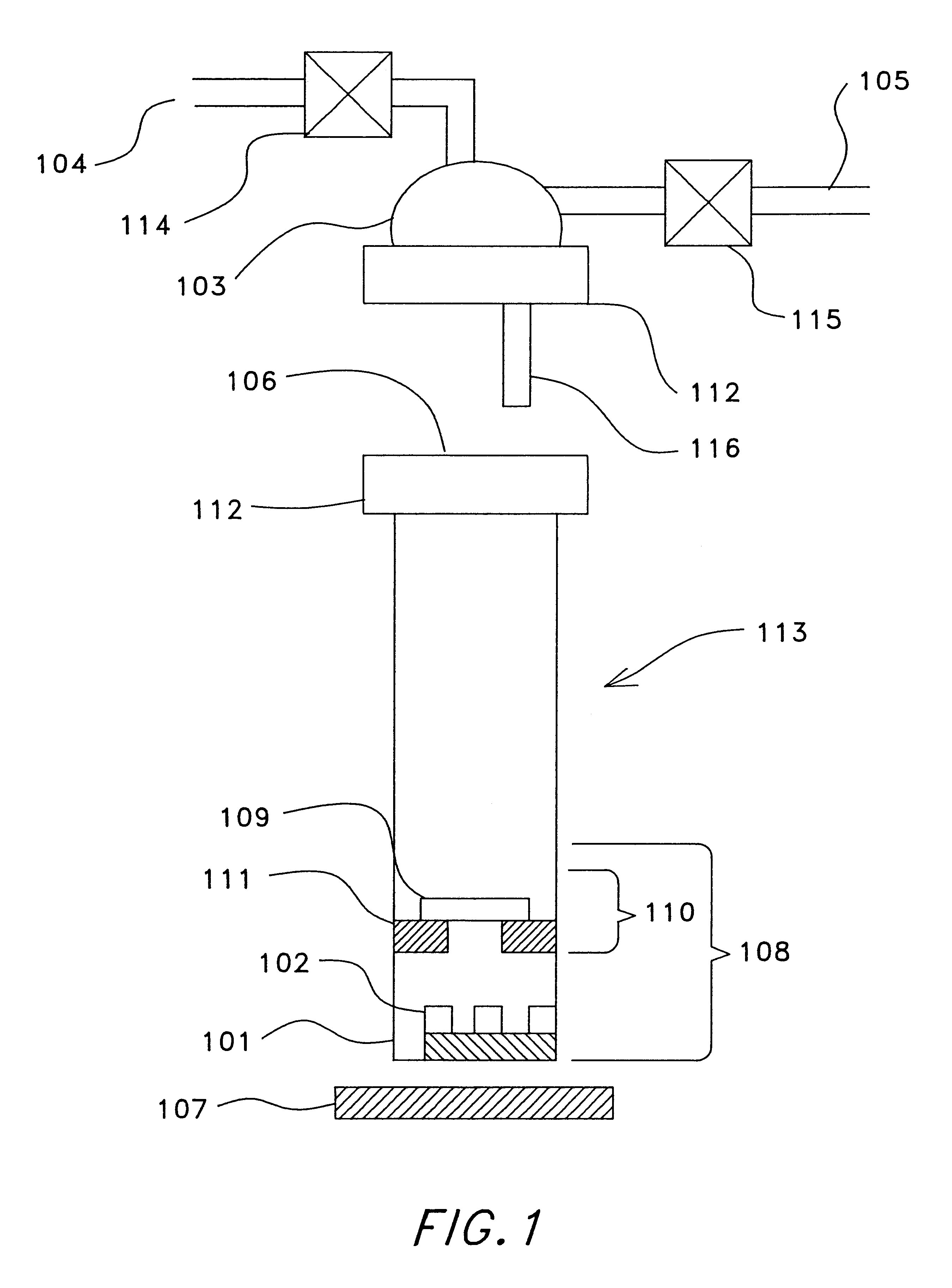

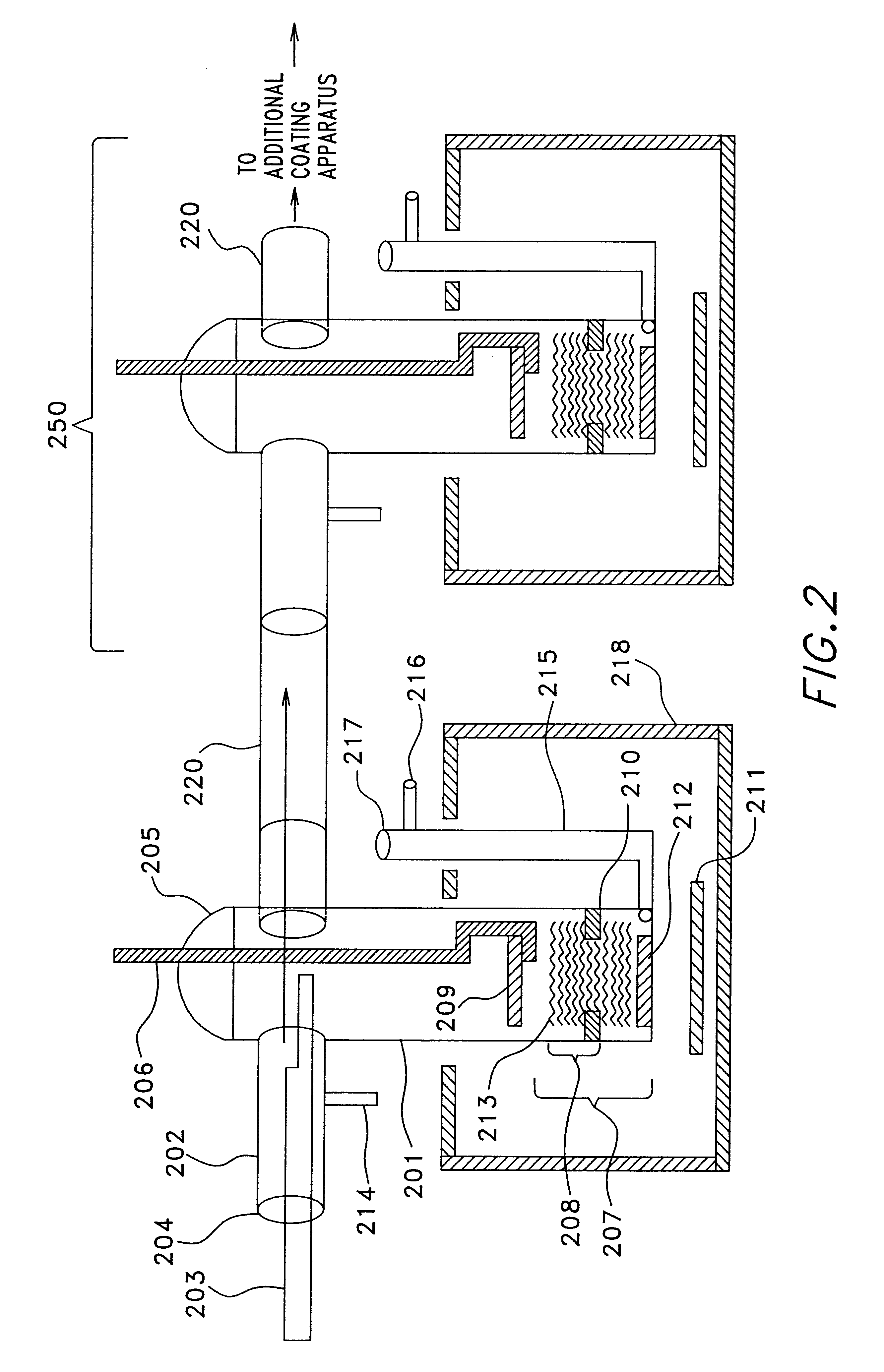

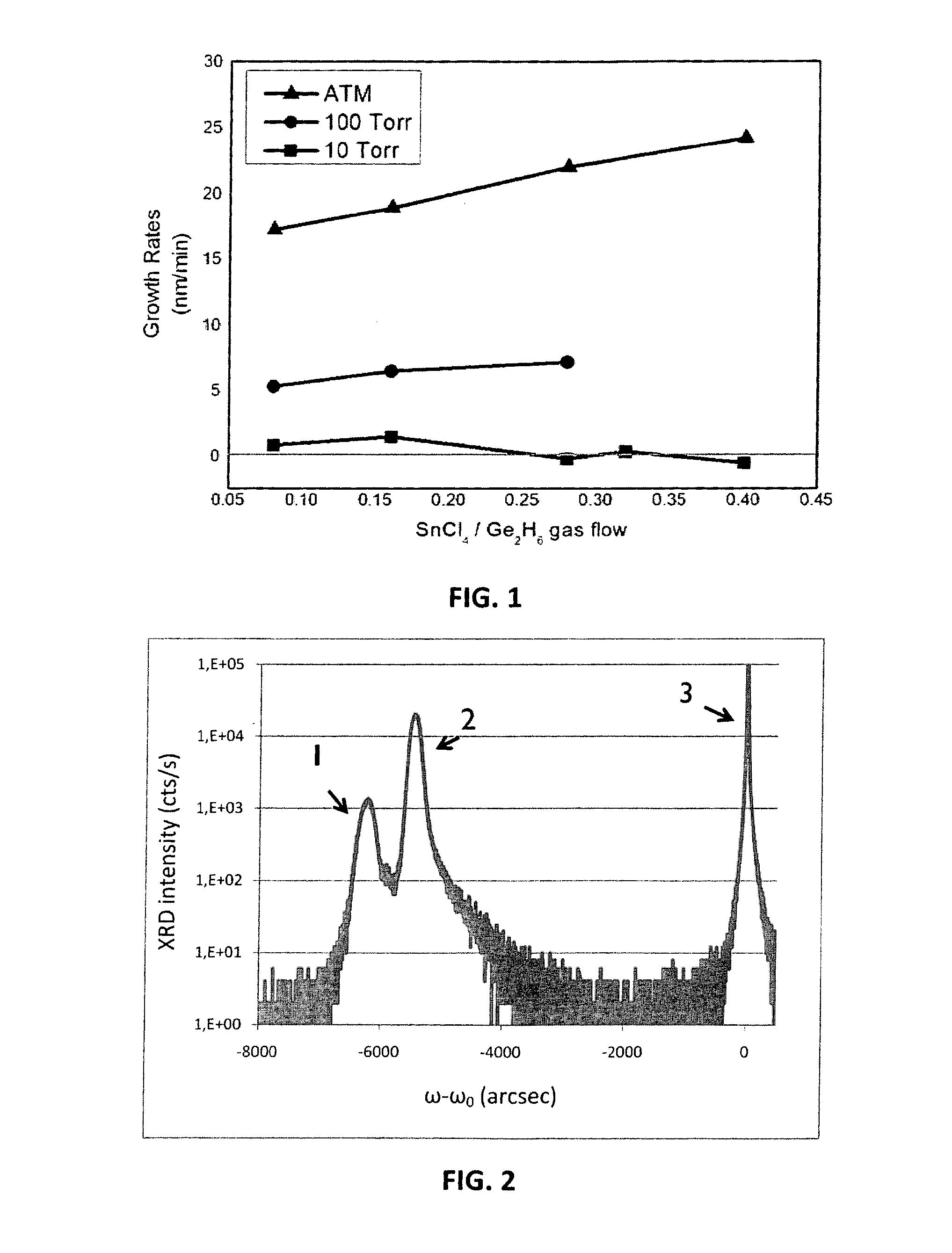

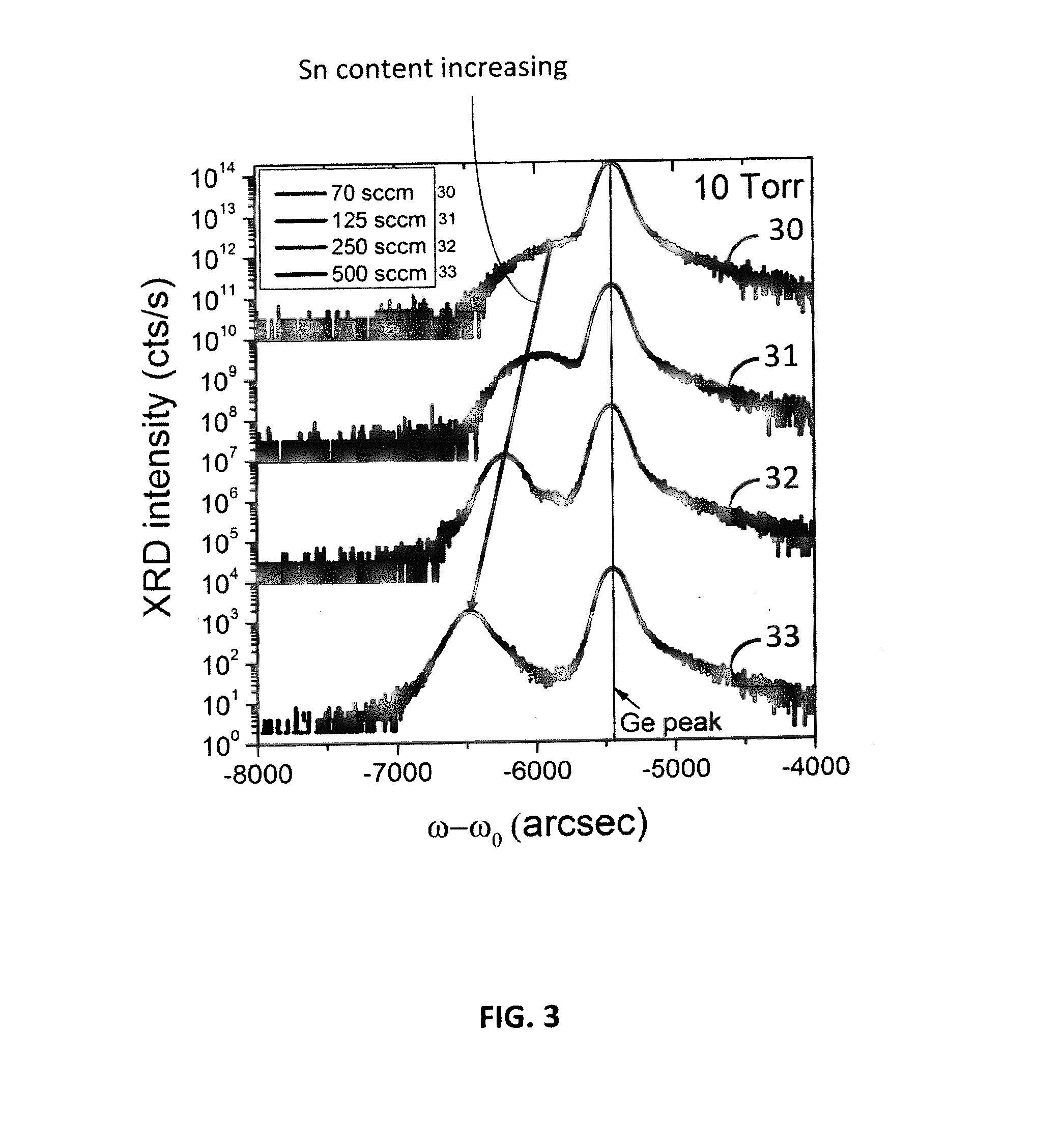

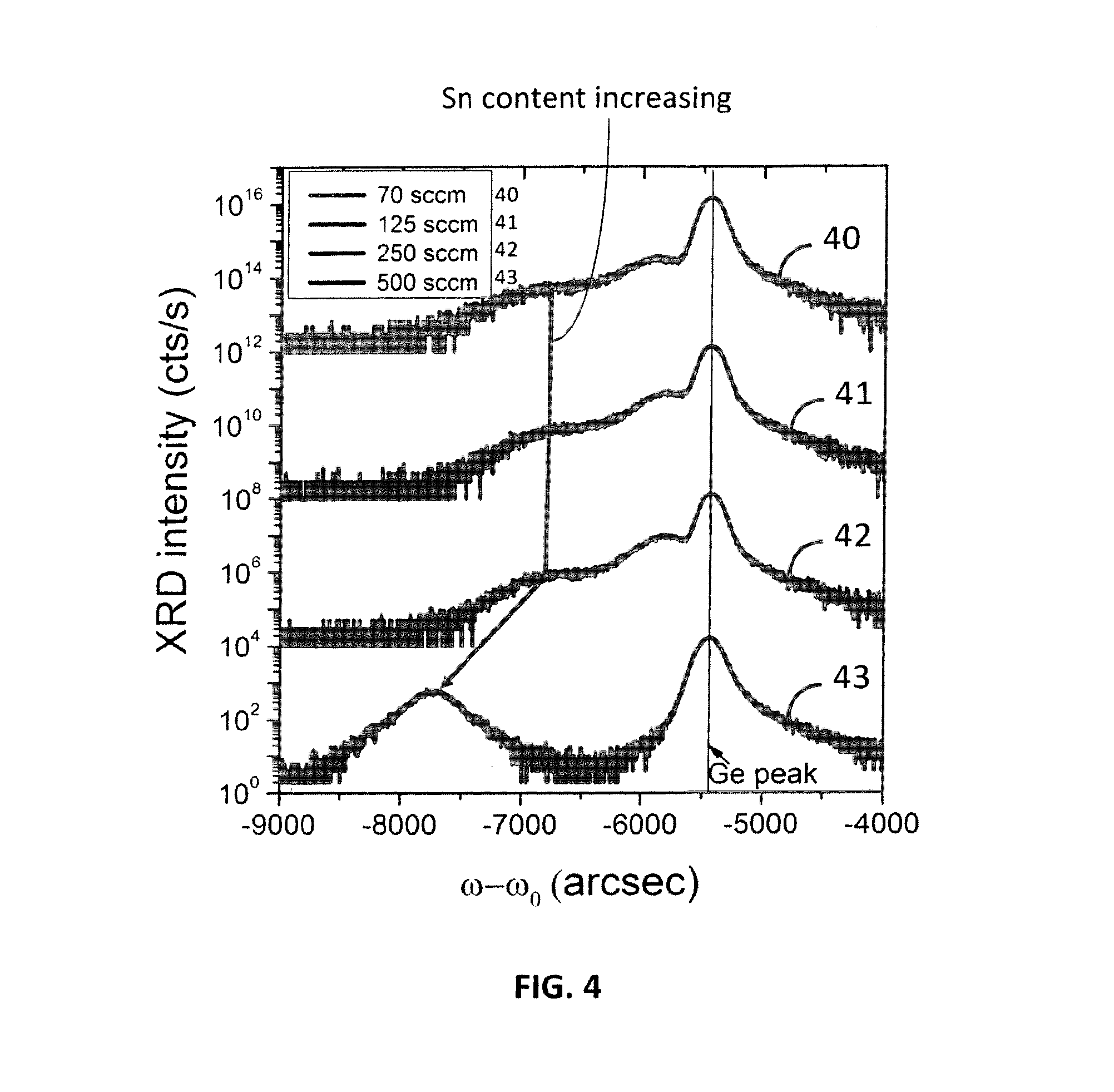

Method for Growing a Monocrystalline Tin-Containing Semiconductor Material

InactiveUS20140020619A1Efficiently provideEfficient methodPolycrystalline material growthAdditive manufacturing apparatusSemiconductor materialsPhysical chemistry

Disclosed are methods for growing Sn-containing semiconductor materials. In some embodiments, an example method includes providing a substrate in a chemical vapor deposition (CVD) reactor, and providing a semiconductor material precursor, a Sn precursor, and a carrier gas in the CVD reactor. The method further includes epitaxially growing a Sn-containing semiconductor material on the substrate, where the Sn precursor comprises tin tetrachloride (SnCl4). The semiconductor material precursor may be, for example, digermane, trigermane, higher-order germanium precursors, or a combination thereof. Alternatively, the semiconductor material precursor may be a silicon precursor.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

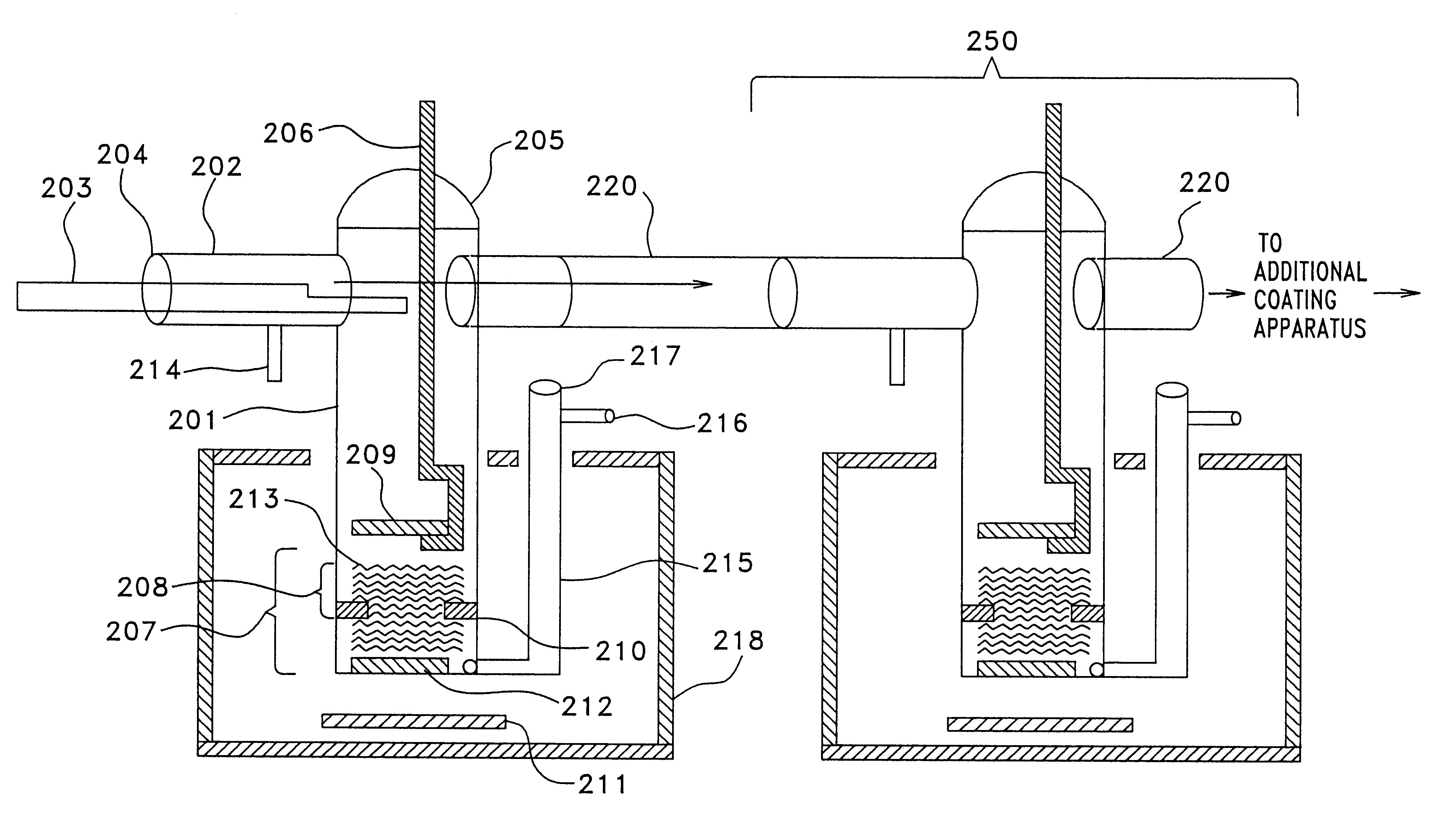

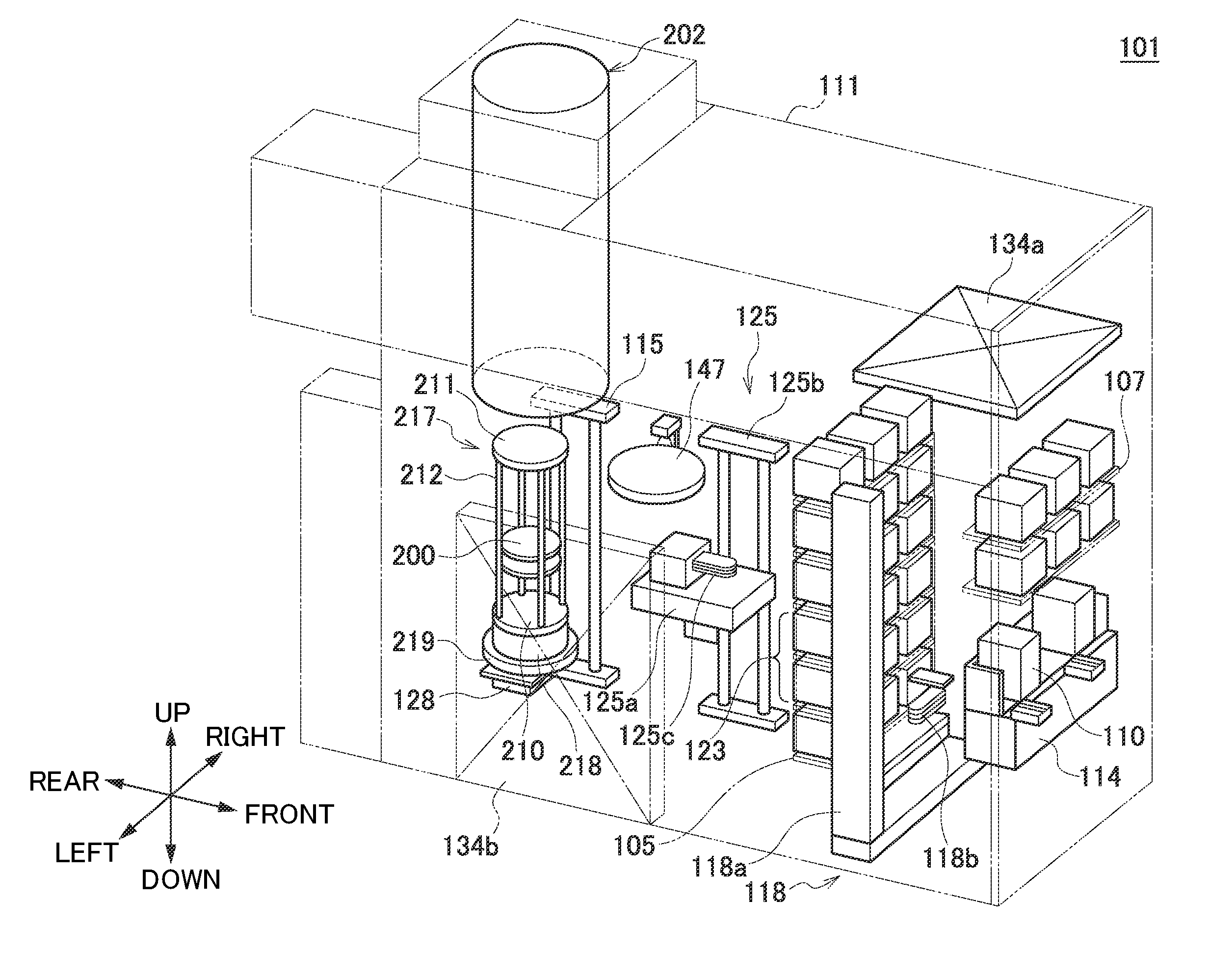

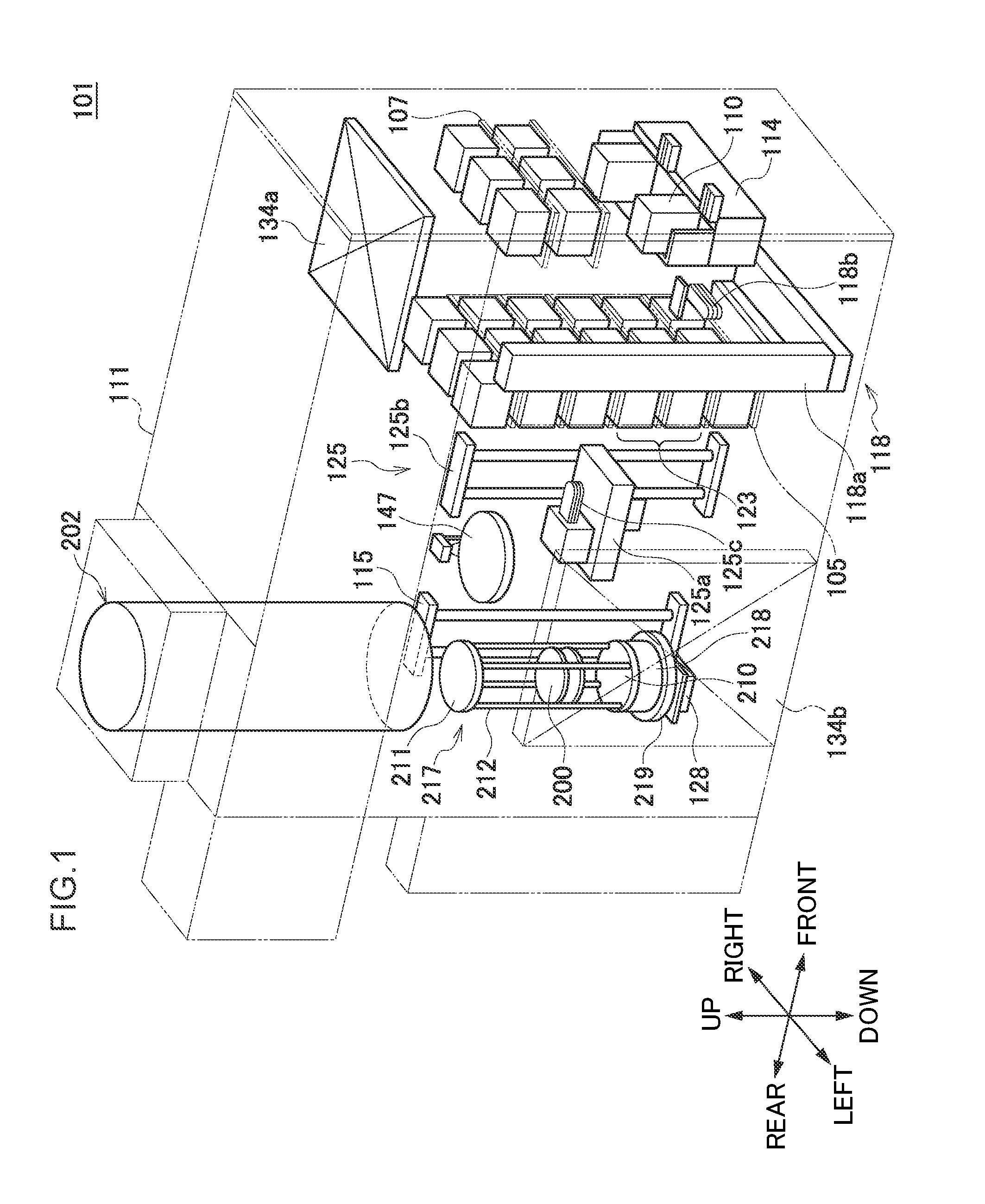

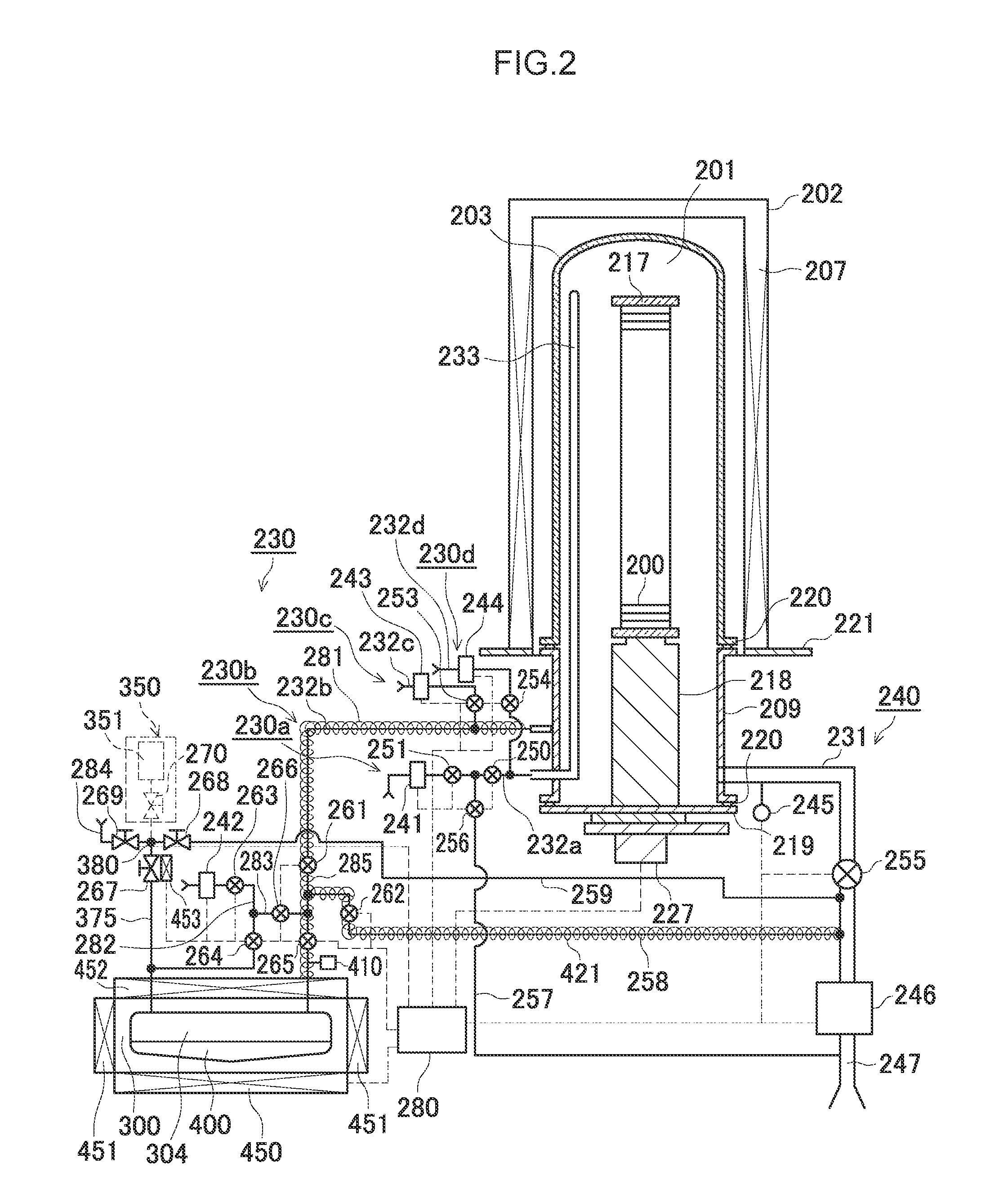

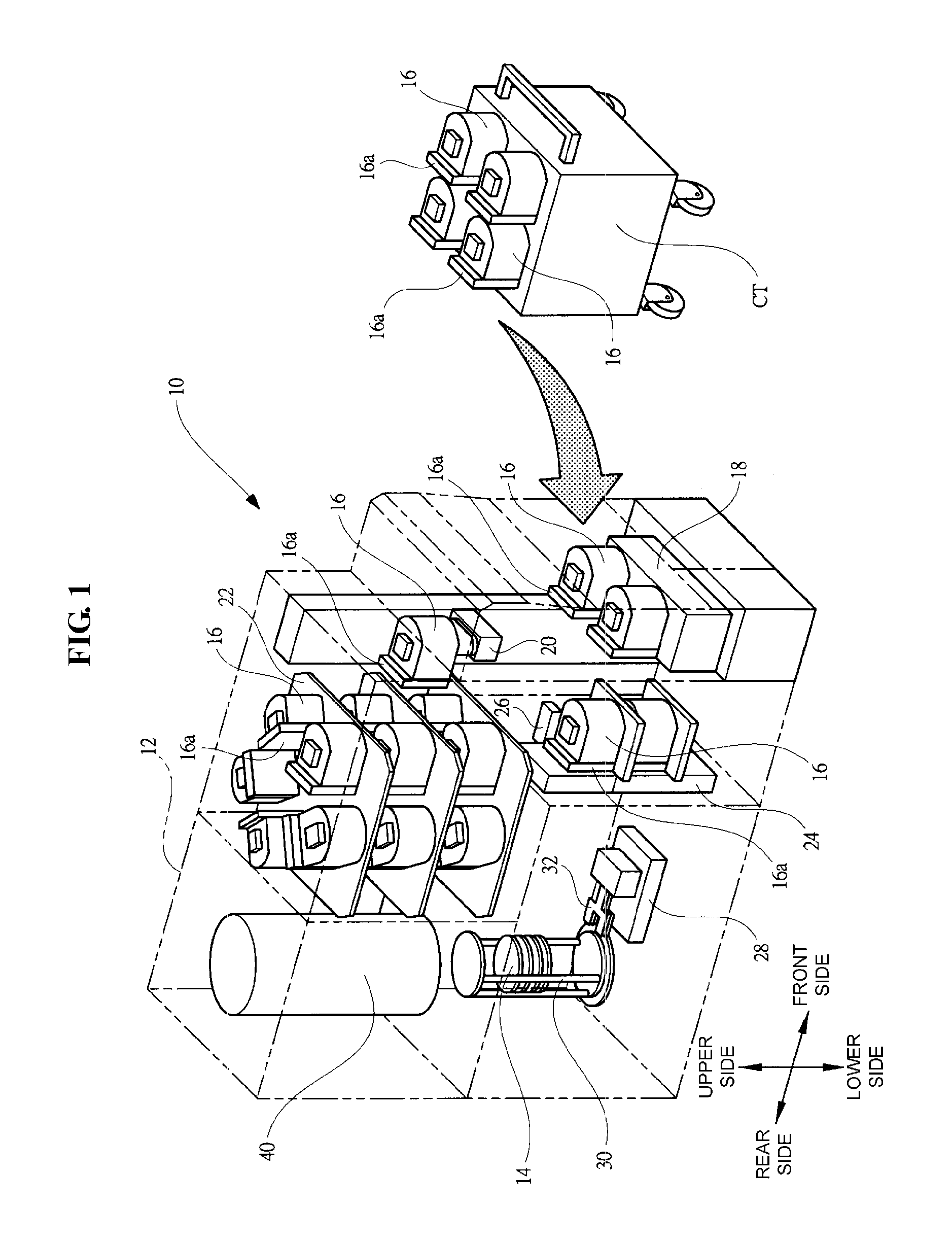

Substrate processing apparatus and solid raw material replenishing method

InactiveUS20120240858A1Simple configurationVacuum evaporation coatingSemiconductor/solid-state device manufacturingProduct gasProcess engineering

Disclosed is a substrate processing apparatus that includes: a processing chamber that accommodates a substrate; and a raw material supply system that sublimates a solid raw material to generate a gas raw material used for processing of the substrate, and supplies the generated gas raw material to the processing chamber. The raw material supply system includes: a solid raw material container that stores the solid raw material; a first piping connected between the solid raw material container and the processing chamber; and a second piping connected with the solid raw material container and equipped with an attachment portion to which a raw material replenishing container that holds the solid raw material for replenishment is attached.

Owner:KOKUSA ELECTRIC CO LTD +1

Method for achieving improved epitaxy quality (surface texture and defect density) on free-standing (aluminum, indium, gallium) nitride ((al,in,ga)n) substrates for opto-electronic and electronic devices

A III-V nitride homoepitaxial microelectronic device structure comprising a III-V nitride homoepitaxial epi layer on a III-V nitride material substrate, e.g., of freestanding character. Various processing techniques are described, including a method of forming a III-V nitride homoepitaxial layer on a corresponding III-V nitride material substrate, by depositing the III-V nitride homoepitaxial layer by a VPE process using Group III source material and nitrogen source material under process conditions including V / III ratio in a range of from about 1 to about 105, nitrogen source material partial pressure in a range of from about 1 to about 103 torr, growth temperature in a range of from about 500 to about 1250 degrees Celsius, and growth rate in a range of from about 0.1 to about 500 microns per hour. The III-V nitride homoepitaxial microelectronic device structures are usefully employed in device applications such as UV LEDs, high electron mobility transistors, and the like.

Owner:WOLFSPEED INC

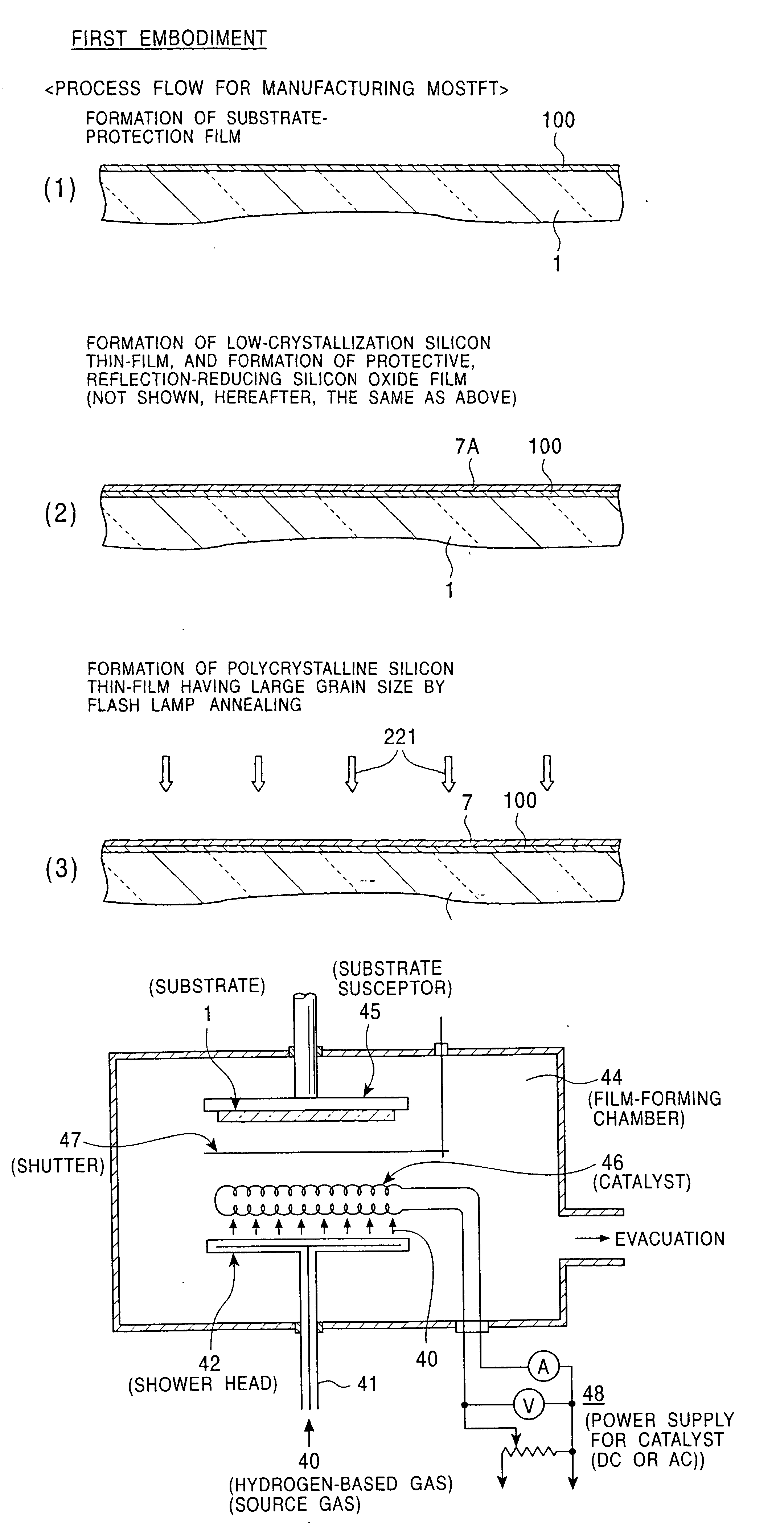

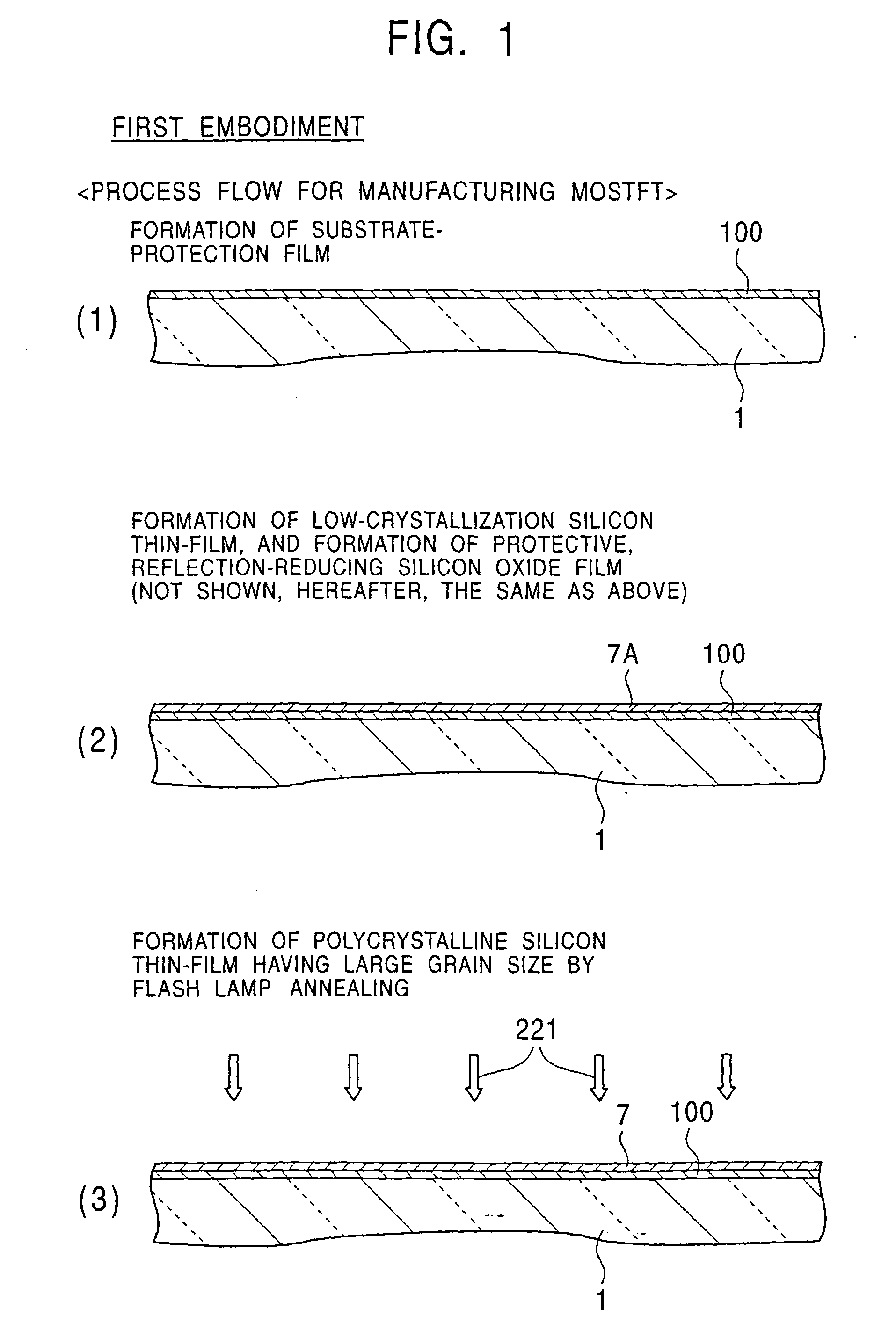

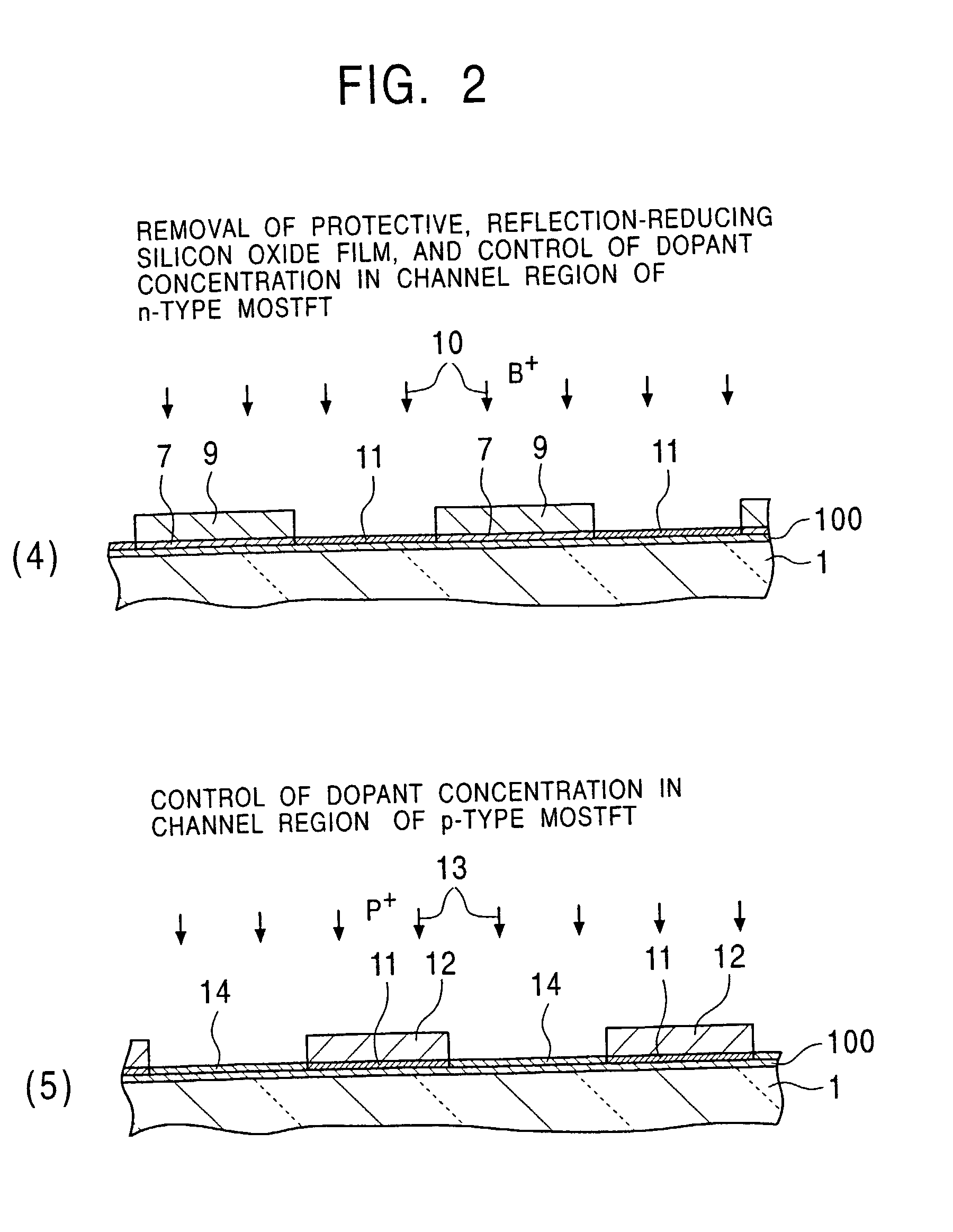

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS20030013280A1Promote crystallizationTransistorPolycrystalline material growthSingle crystalCrystallinity

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

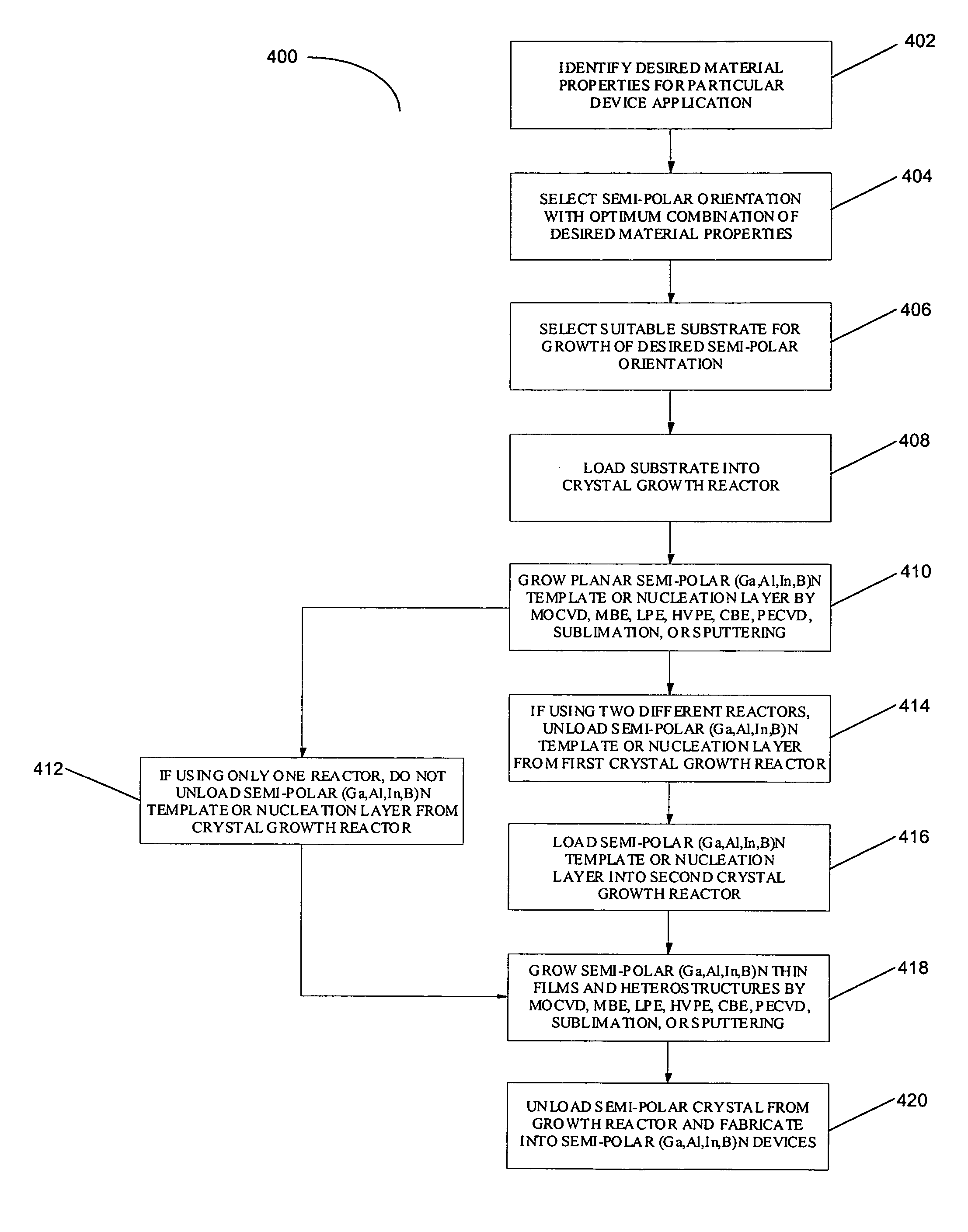

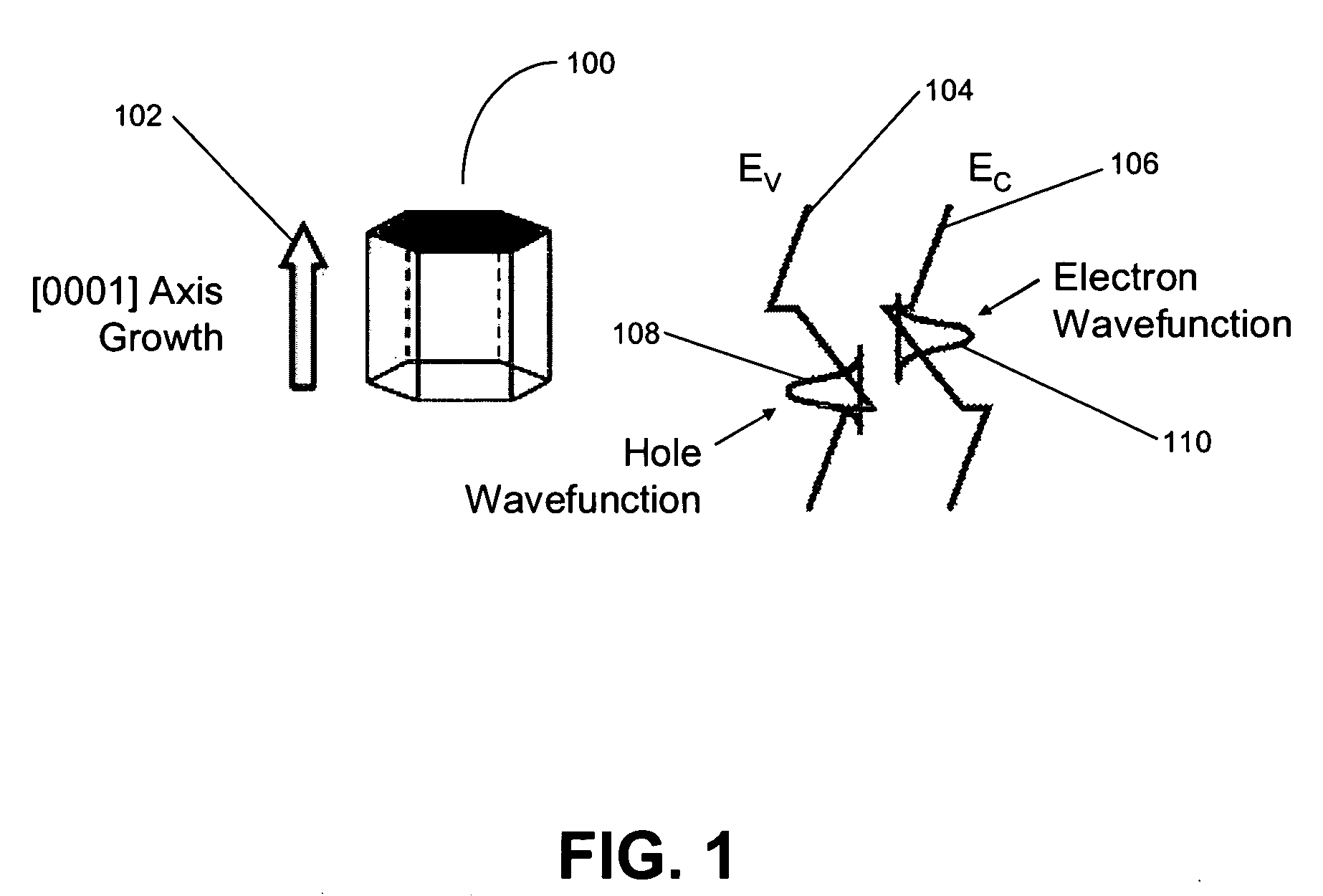

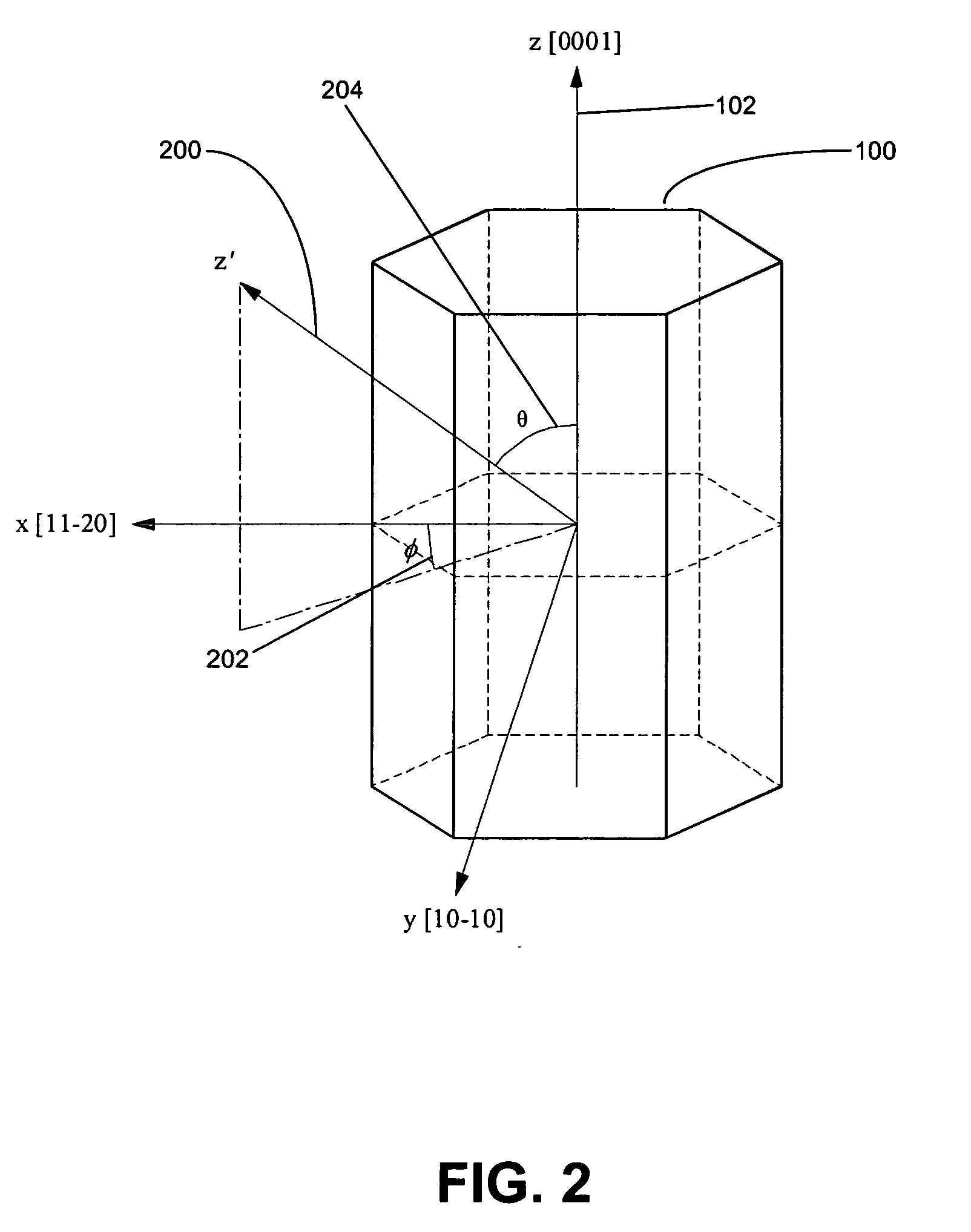

Technique for the growth and fabrication of semipolar (Ga,A1,In,B)N thin films, heterostructures, and devices

ActiveUS20070093073A1Improve device performanceLarge parameter spacePolycrystalline material growthSemiconductor/solid-state device manufacturingNucleationBiology

A method for growth and fabrication of semipolar (Ga, Al, In, B)N thin films, heterostructures, and devices, comprising identifying desired material properties for a particular device application, selecting a semipolar growth orientation based on the desired material properties, selecting a suitable substrate for growth of the selected semipolar growth orientation, growing a planar semipolar (Ga, Al, In, B)N template or nucleation layer on the substrate, and growing the semipolar (Ga, Al, In, B)N thin films, heterostructures or devices on the planar semipolar (Ga, Al, In, B)N template or nucleation layer. The method results in a large area of the semipolar (Ga, Al, In, B)N thin films, heterostructures, and devices being parallel to the substrate surface.

Owner:JAPAN SCI & TECH CORP

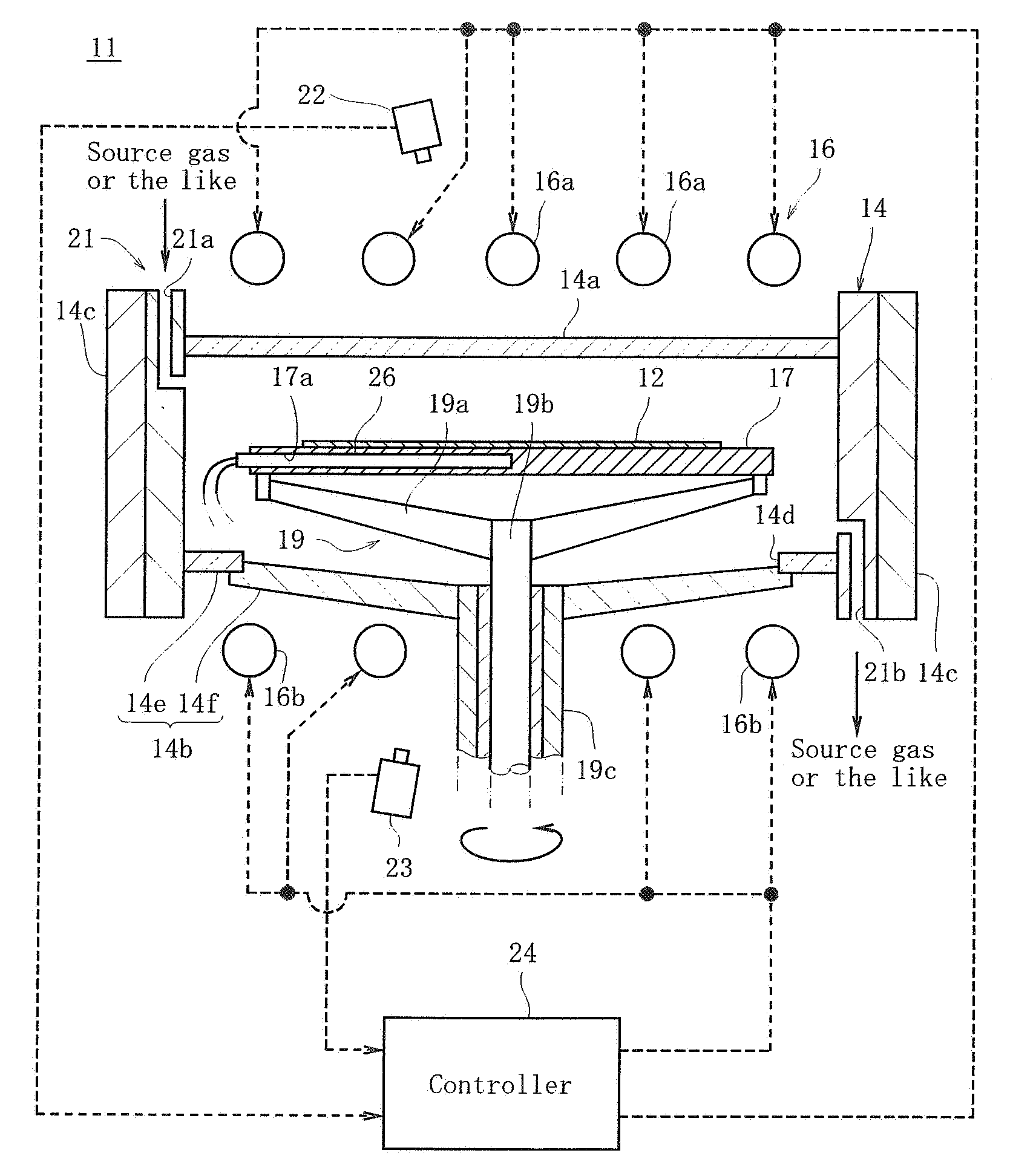

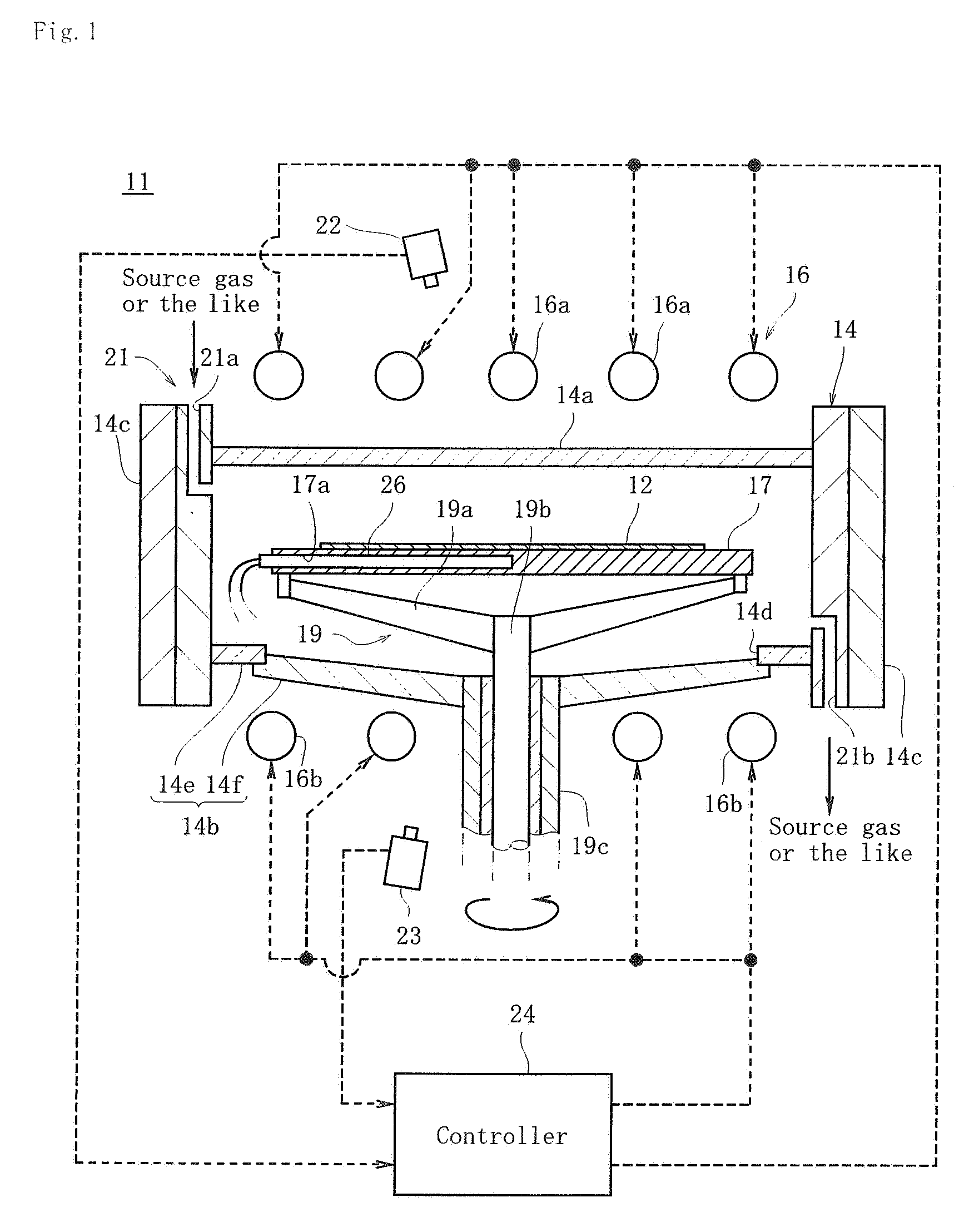

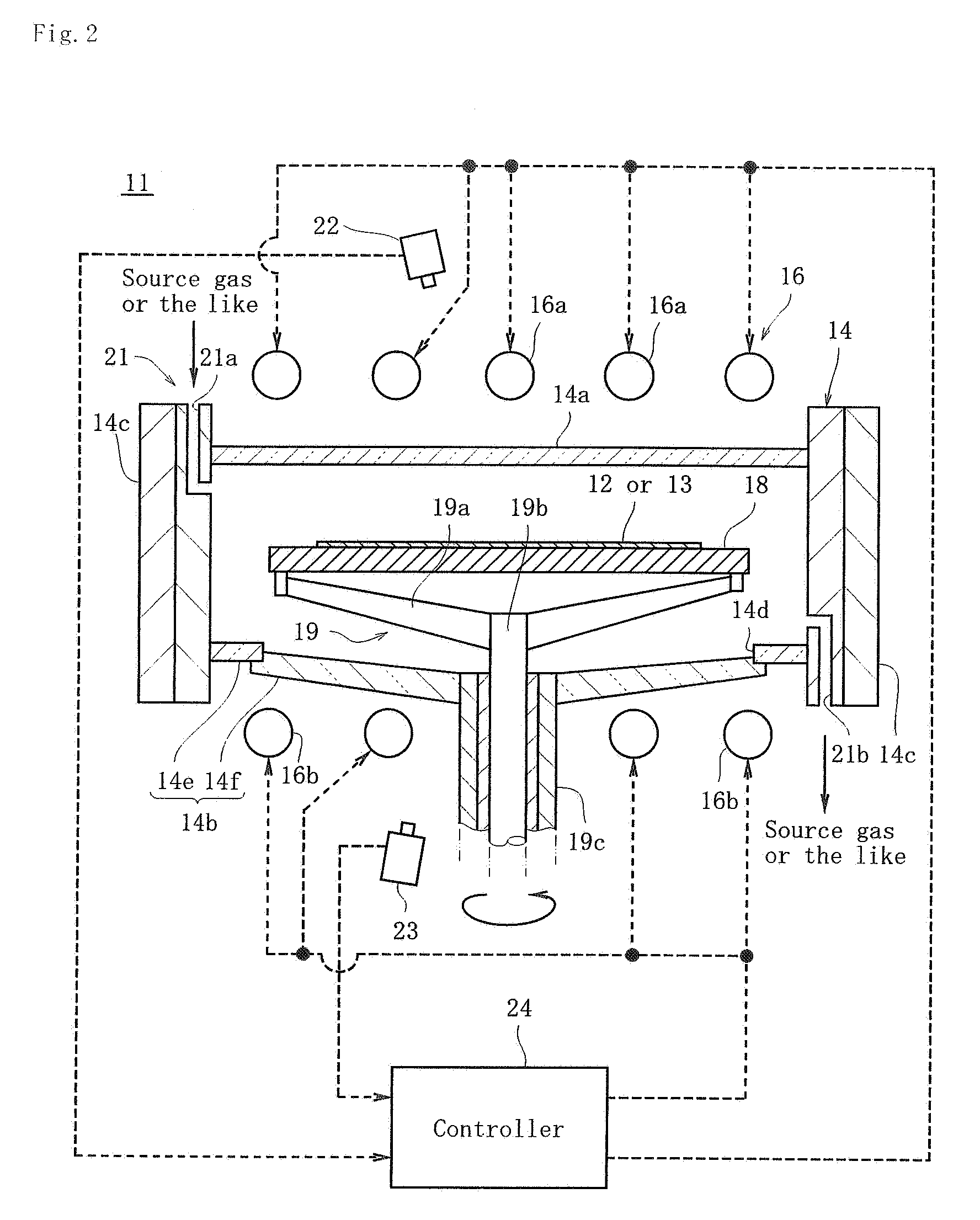

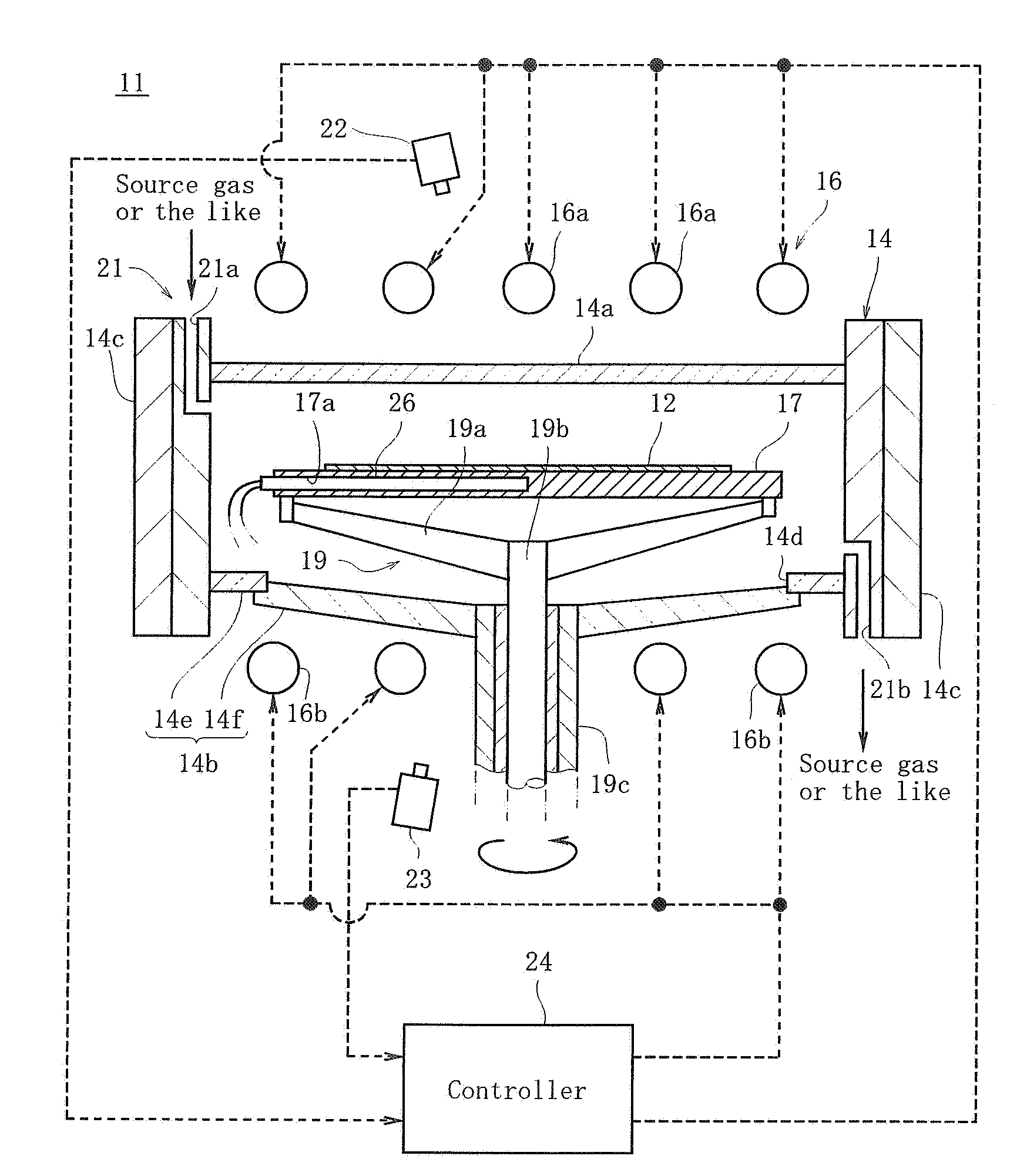

Temperature Control Method of Epitaxial Growth Apparatus

ActiveUS20070062439A1Quality improvementPrevent slippingPolycrystalline material growthThermometer testing/calibrationTemperature controlSusceptor

An object of the invention is to calibrate an upper pyrometer for indirectly measuring a substrate temperature at the time of epitaxial growth in a comparatively short time and with accuracy to thereby improve the quality of an epitaxial substrate. After calibrating an upper pyrometer by a thermocouple mounted to a temperature calibrating susceptor, a measured value of a lower pyrometer is adjusted to a calibrated value of the upper pyrometer. Then, a correlation line between substrate temperature indirectly measured by the upper pyrometer at the time of epitaxial growth onto a sample substrate and haze of a sample substrate measured immediately after epitaxial growth is set to indirectly measure a substrate temperature by the upper pyrometer at the time of epitaxial growth onto a mass-production substrate. Moreover, substrate temperature at the time of epitaxial growth onto the mass-production substrate is estimated by applying the haze of the mass-production substrate measured immediately after epitaxial growth to the correlation line and then a measured temperature of the upper pyrometer is adjusted to the estimated temperature.

Owner:SUMCO CORP

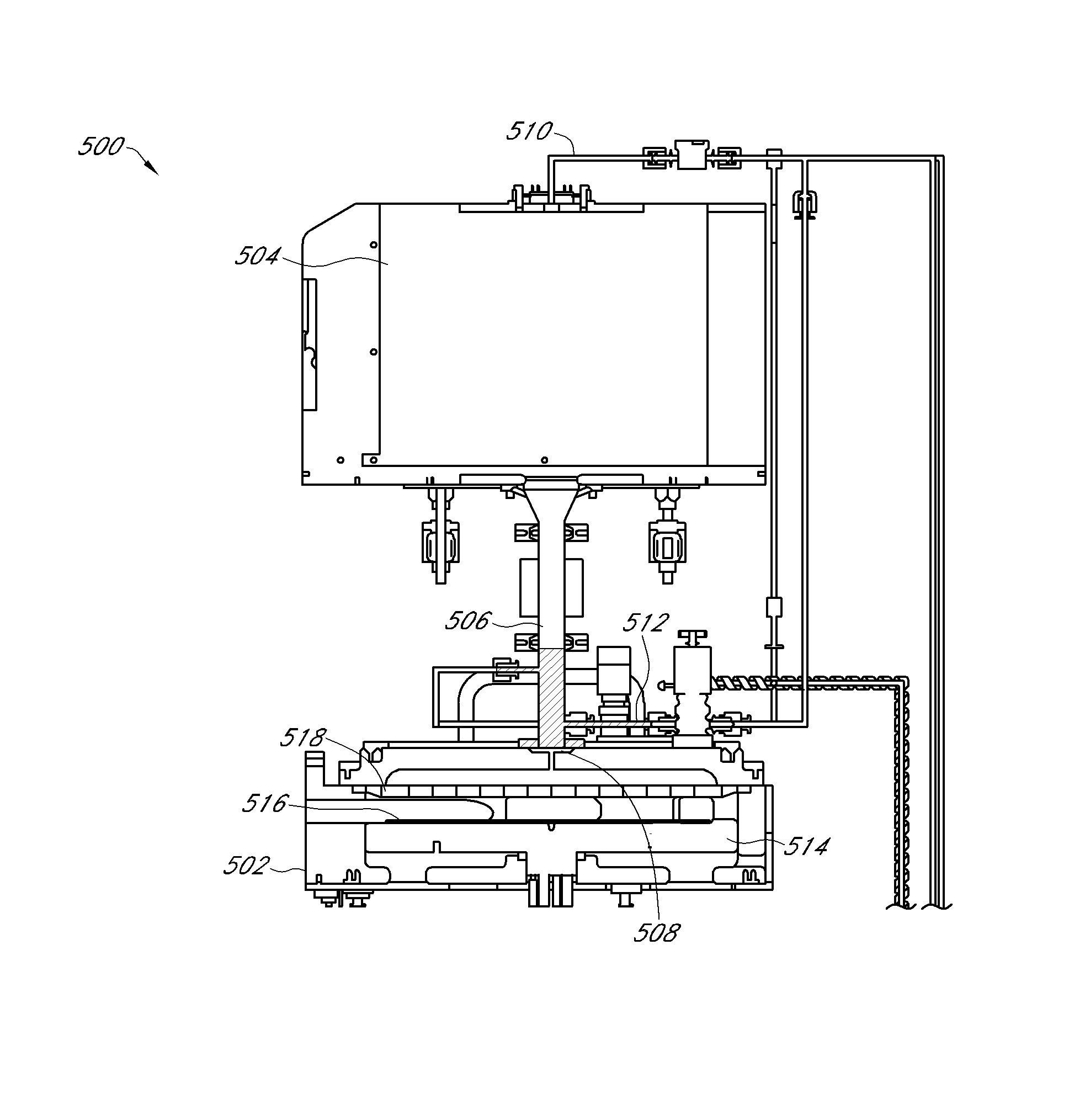

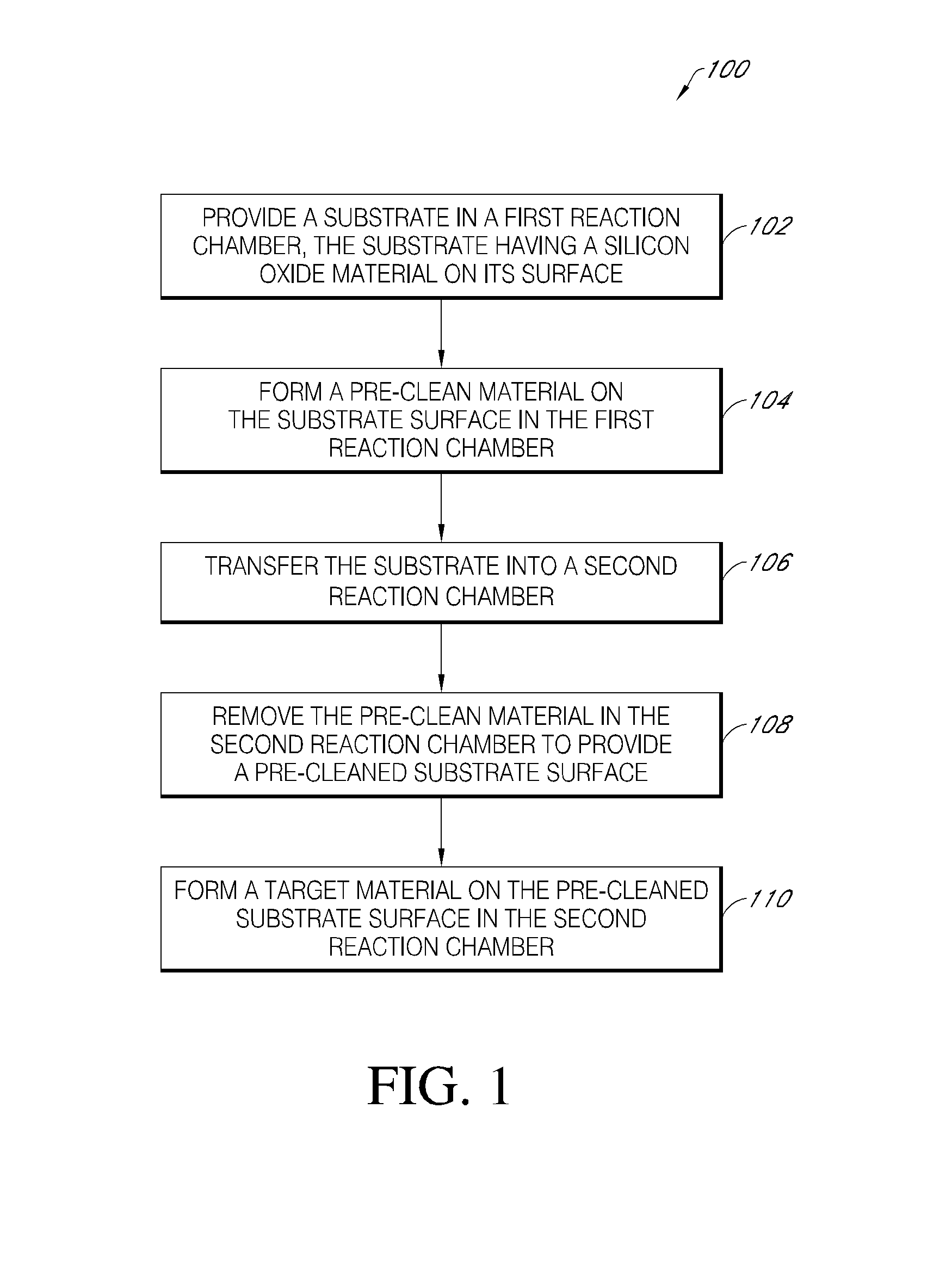

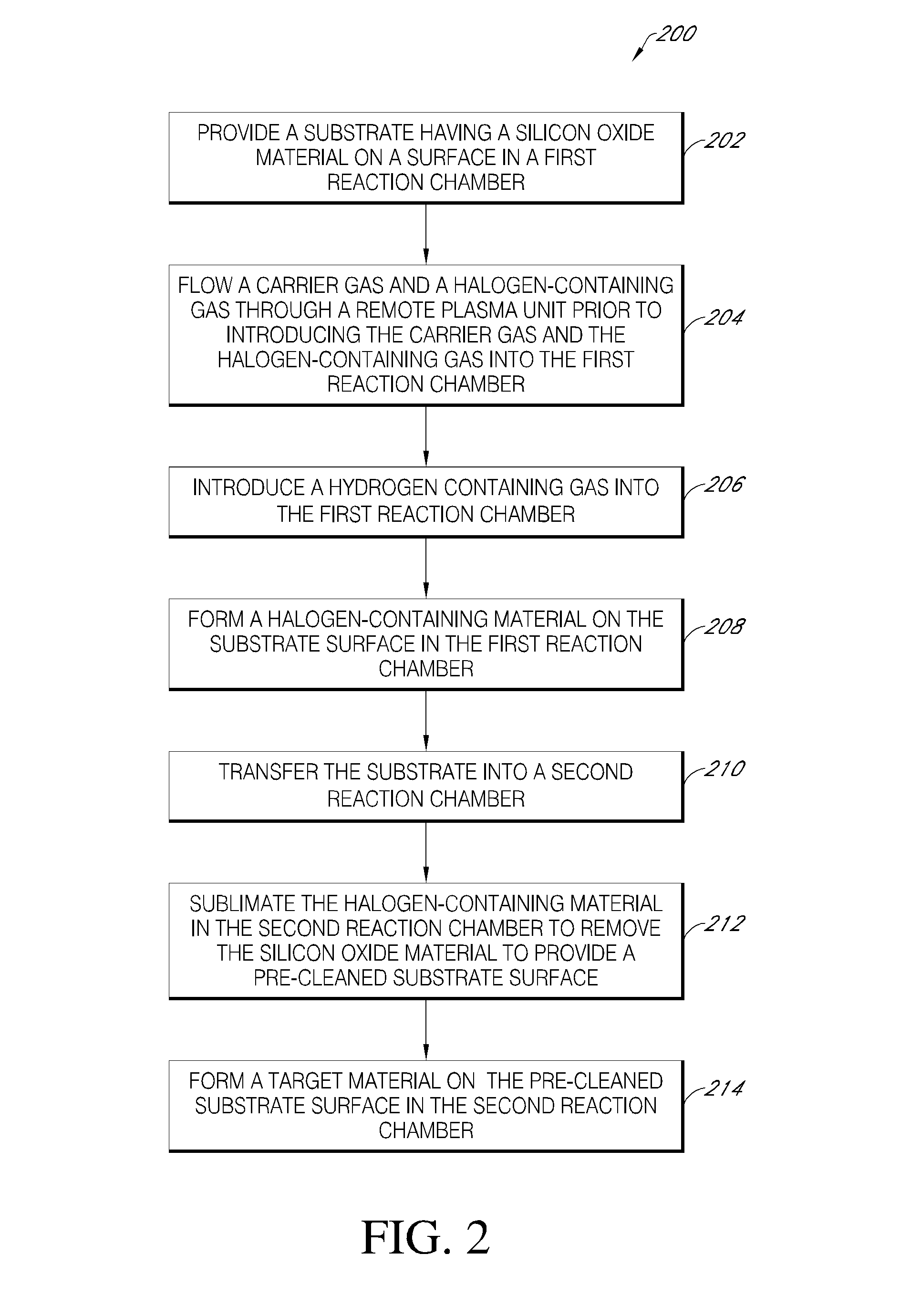

Plasma pre-clean module and process

ActiveUS9299557B2Polycrystalline material growthSemiconductor/solid-state device manufacturingConductive materialsSilicon oxide

A method for integrated circuit fabrication can include removing silicon oxide by a pre-clean process. The pre-clean process can include depositing a halogen-containing material on the surface of a substrate in a first reaction chamber, and transferring the substrate having the halogen-containing material to a second reaction chamber. Silicon oxide material can be removed from a surface of the substrate by sublimating the halogen-containing material in the second reaction chamber. A target material, such as a conductive material, may subsequently be deposited on the substrate surface in the second reaction chamber.

Owner:ASM IP HLDG BV

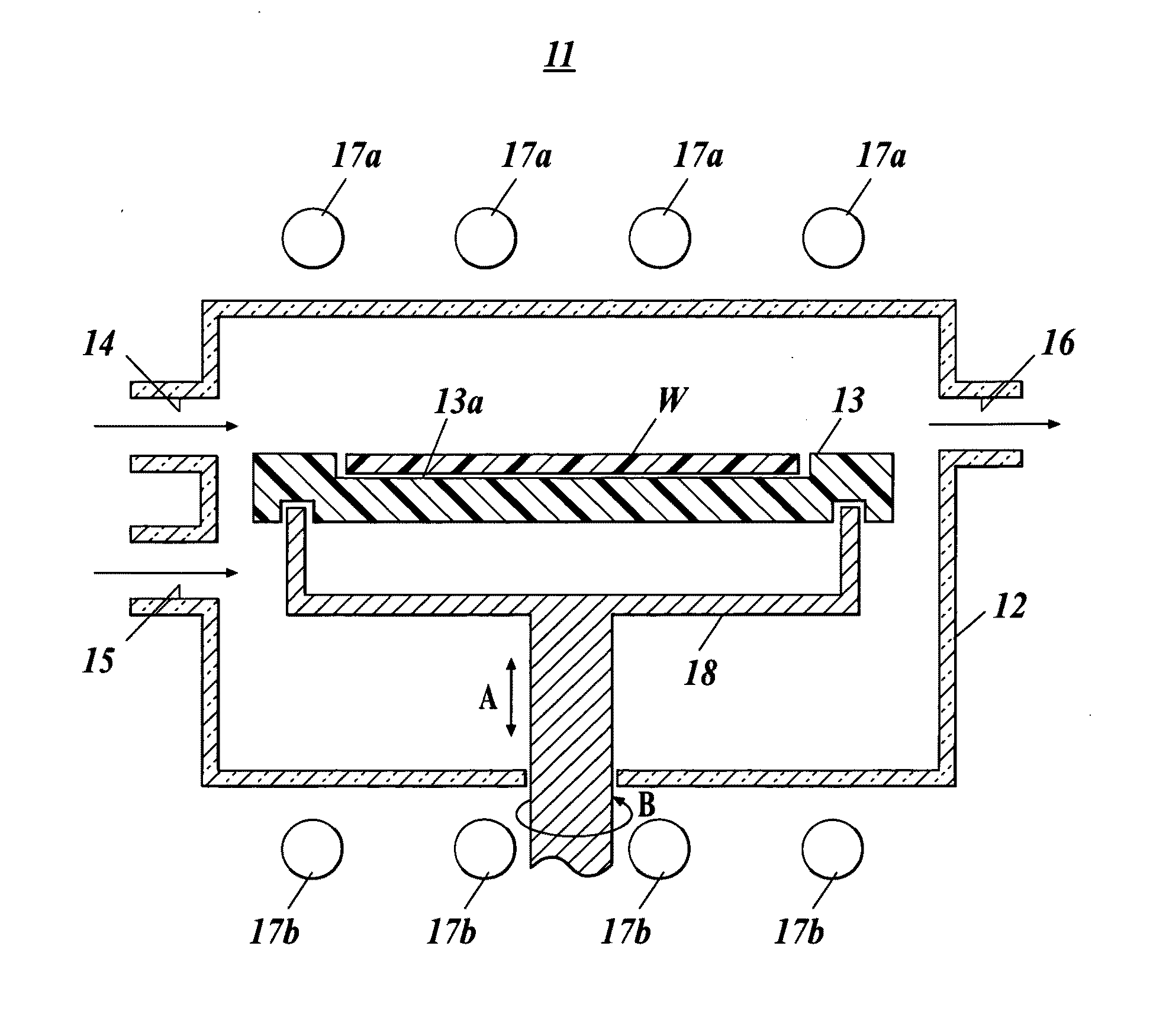

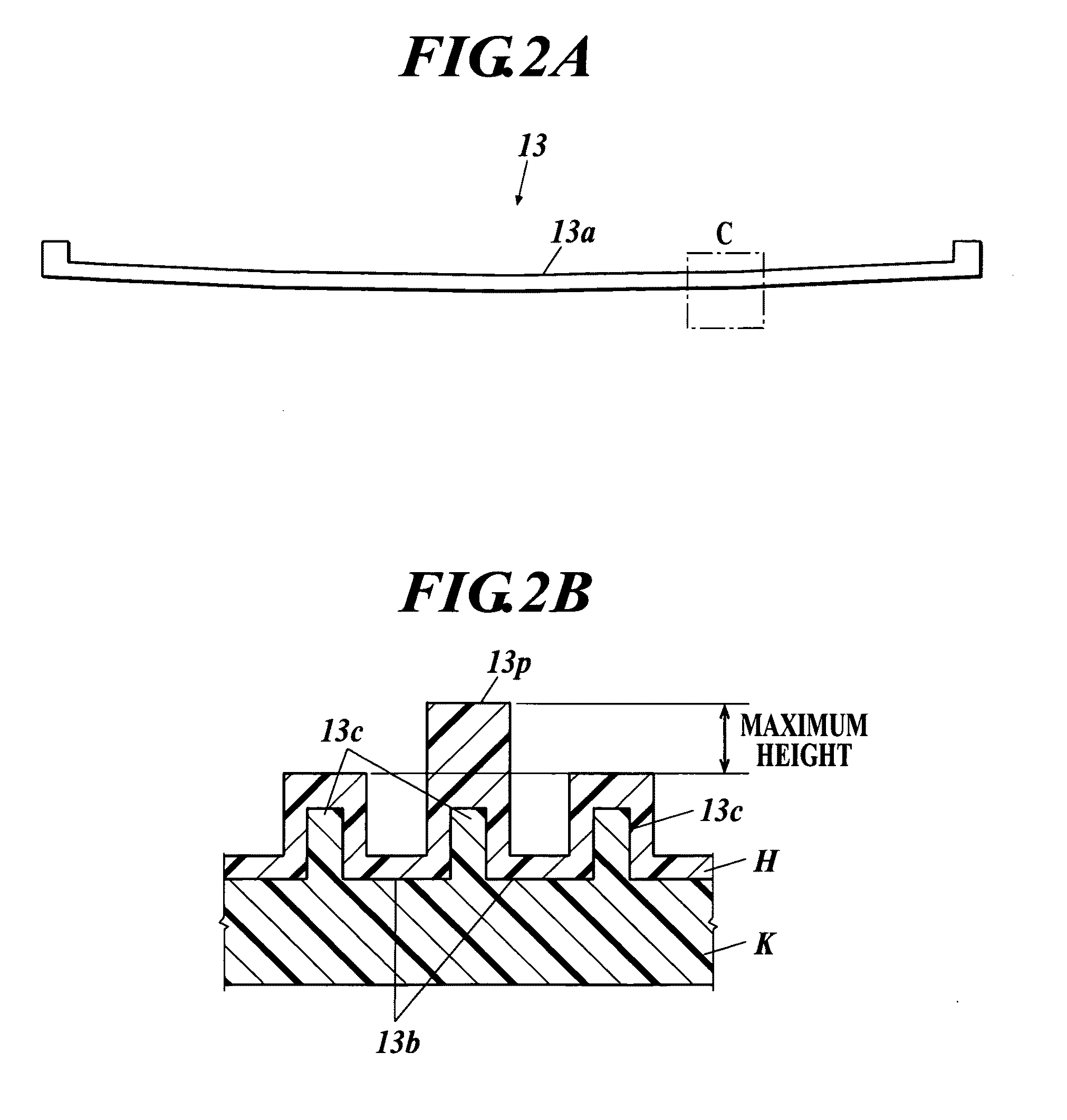

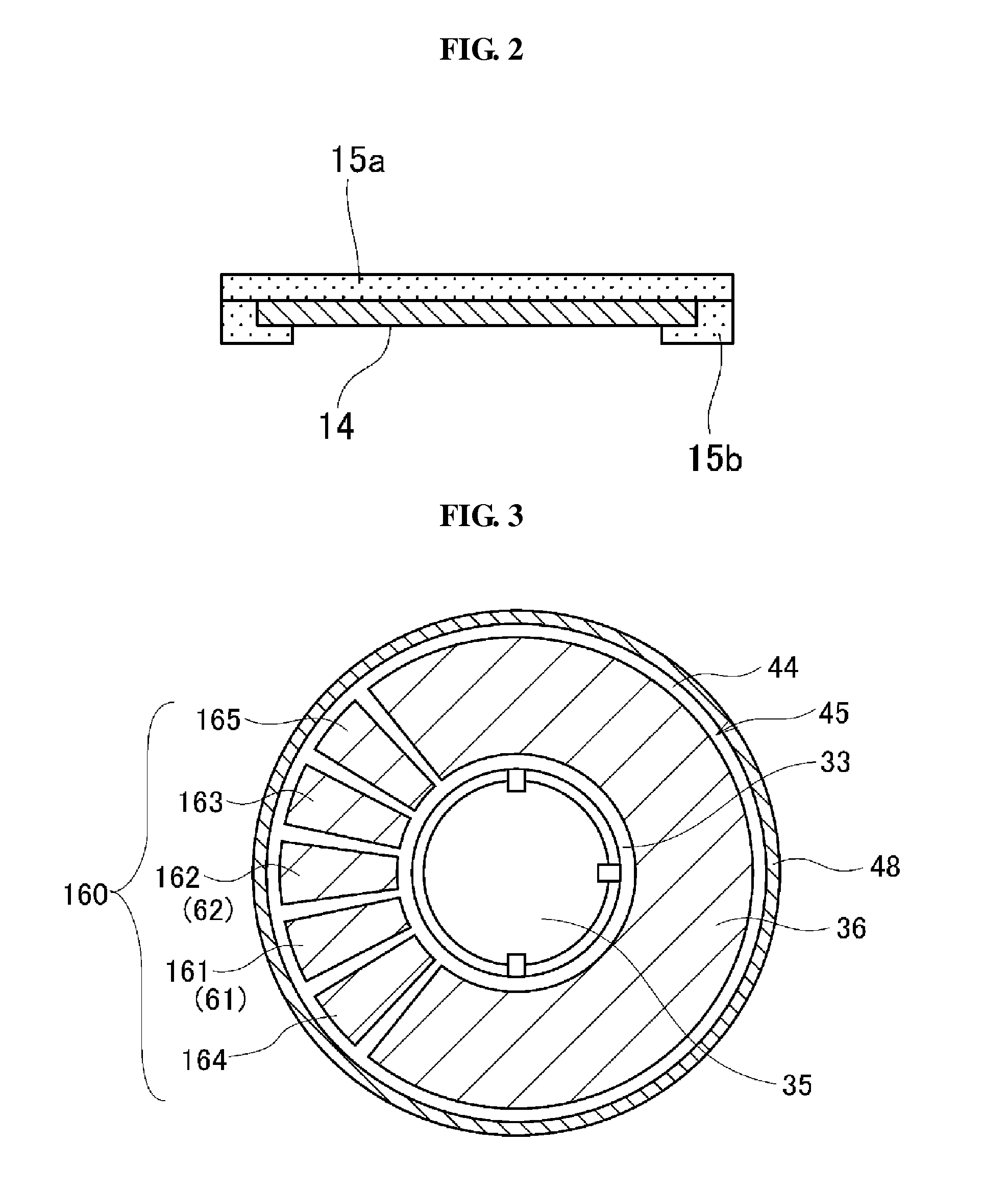

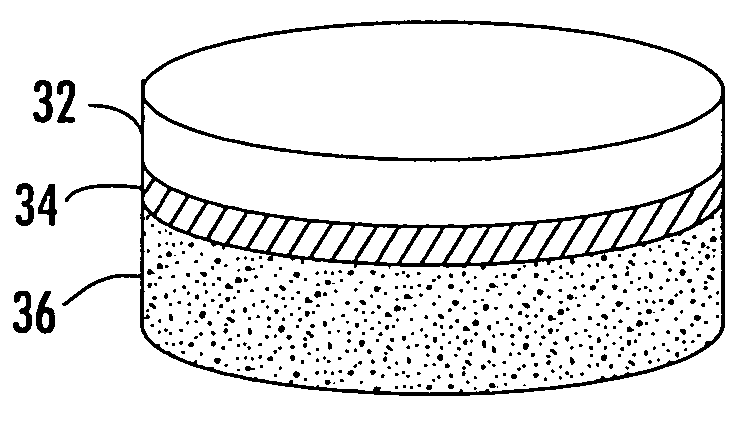

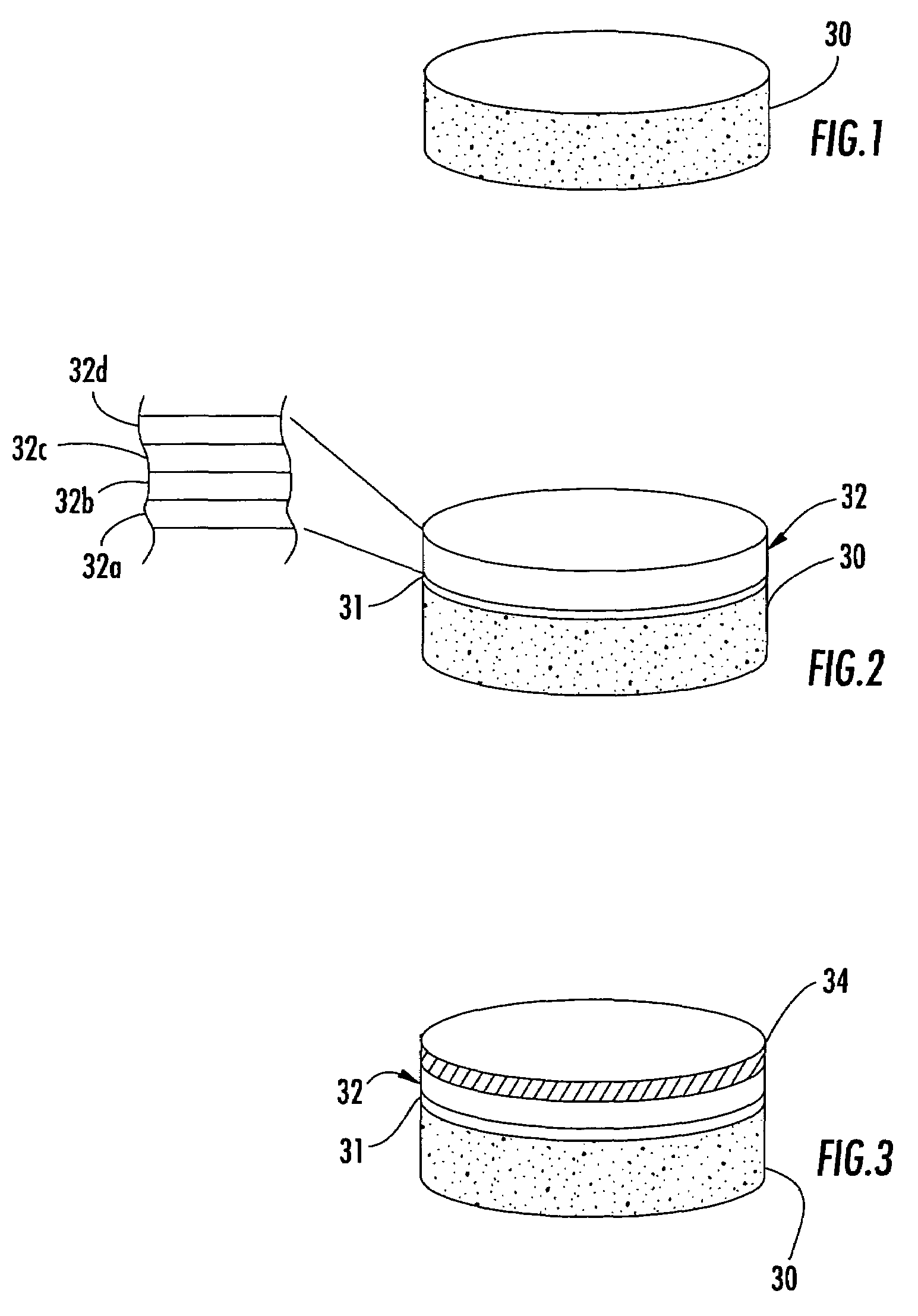

Susceptor and method for manufacturing silicon epitaxial wafer

ActiveUS20100129990A1Avoid stickingPolycrystalline material growthLiquid surface applicatorsSusceptorWafering

Provided is a susceptor 13 for manufacturing an epitaxial wafer, comprising a mesh-like groove 13b on a mount face on which a silicon substrate W is to be mounted, wherein a coating H of silicon carbide is formed on the mount face, and the coating has a surface roughness of 1 μm or more in centerline average roughness Ra and a maximum height of a protrusion 13p generated in forming the coating H of 5 μm or less. Thus, defects such as warping and slip as well as adhesion of the silicon substrate to the susceptor are prevented.

Owner:SHIN-ETSU HANDOTAI CO LTD

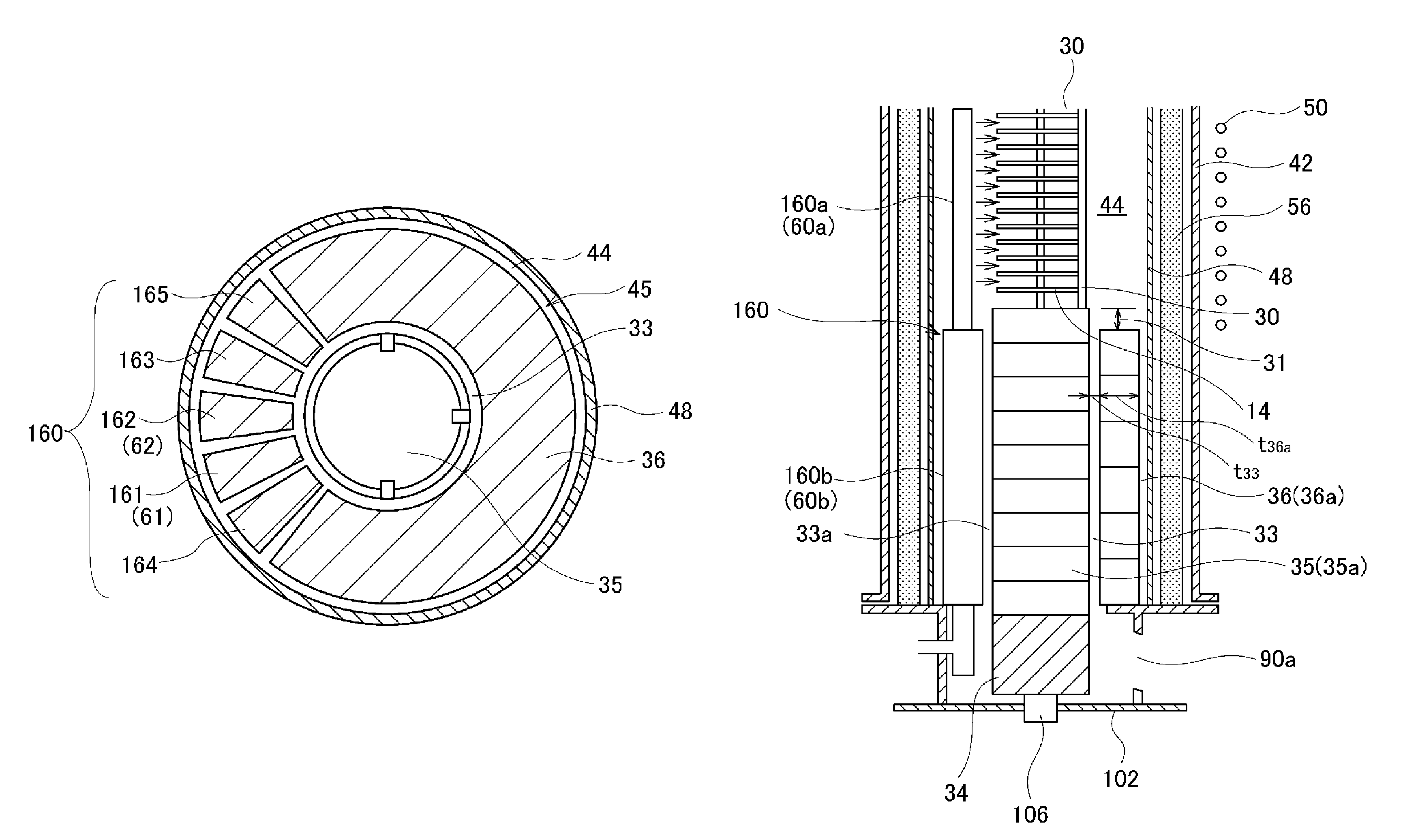

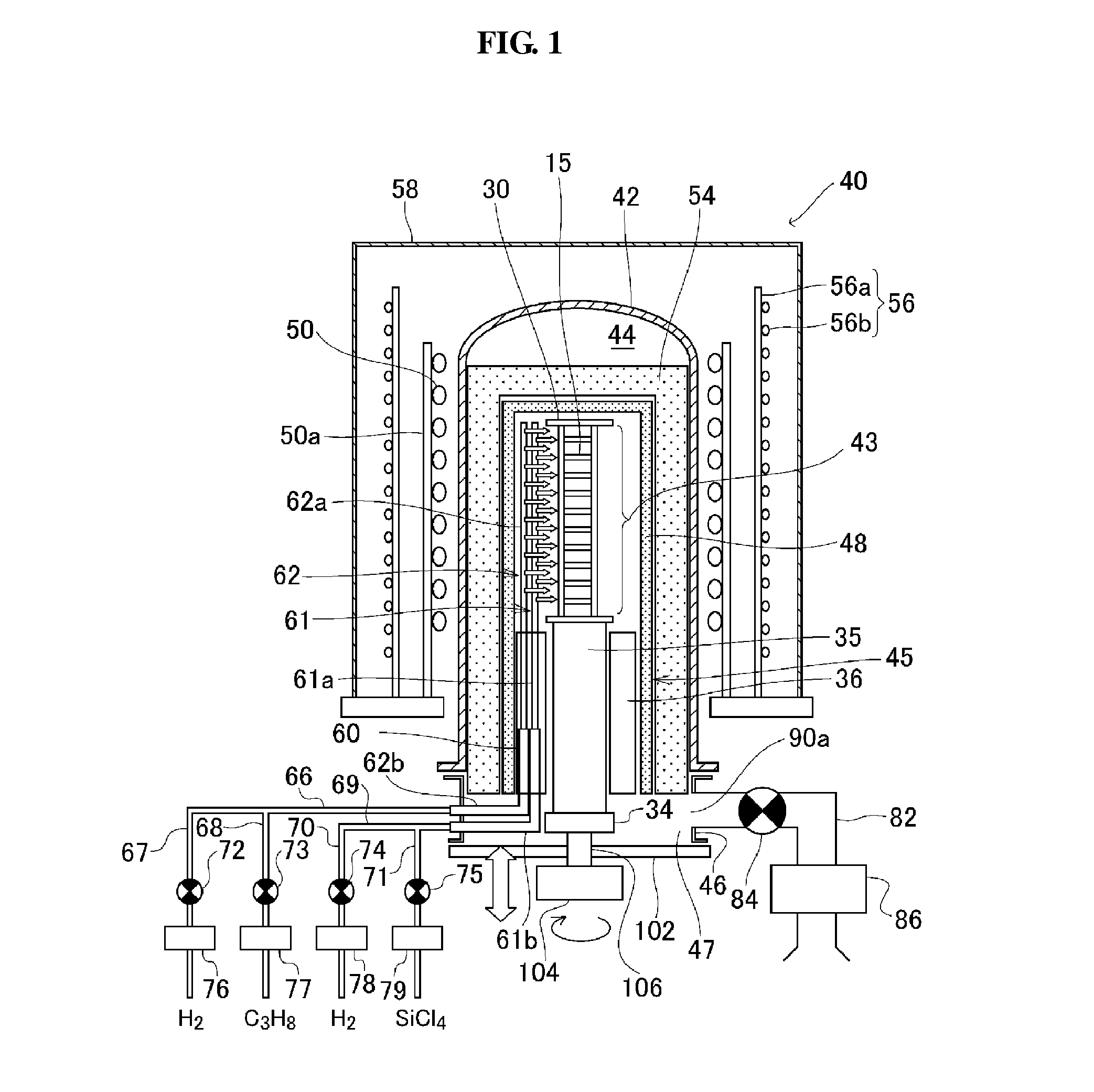

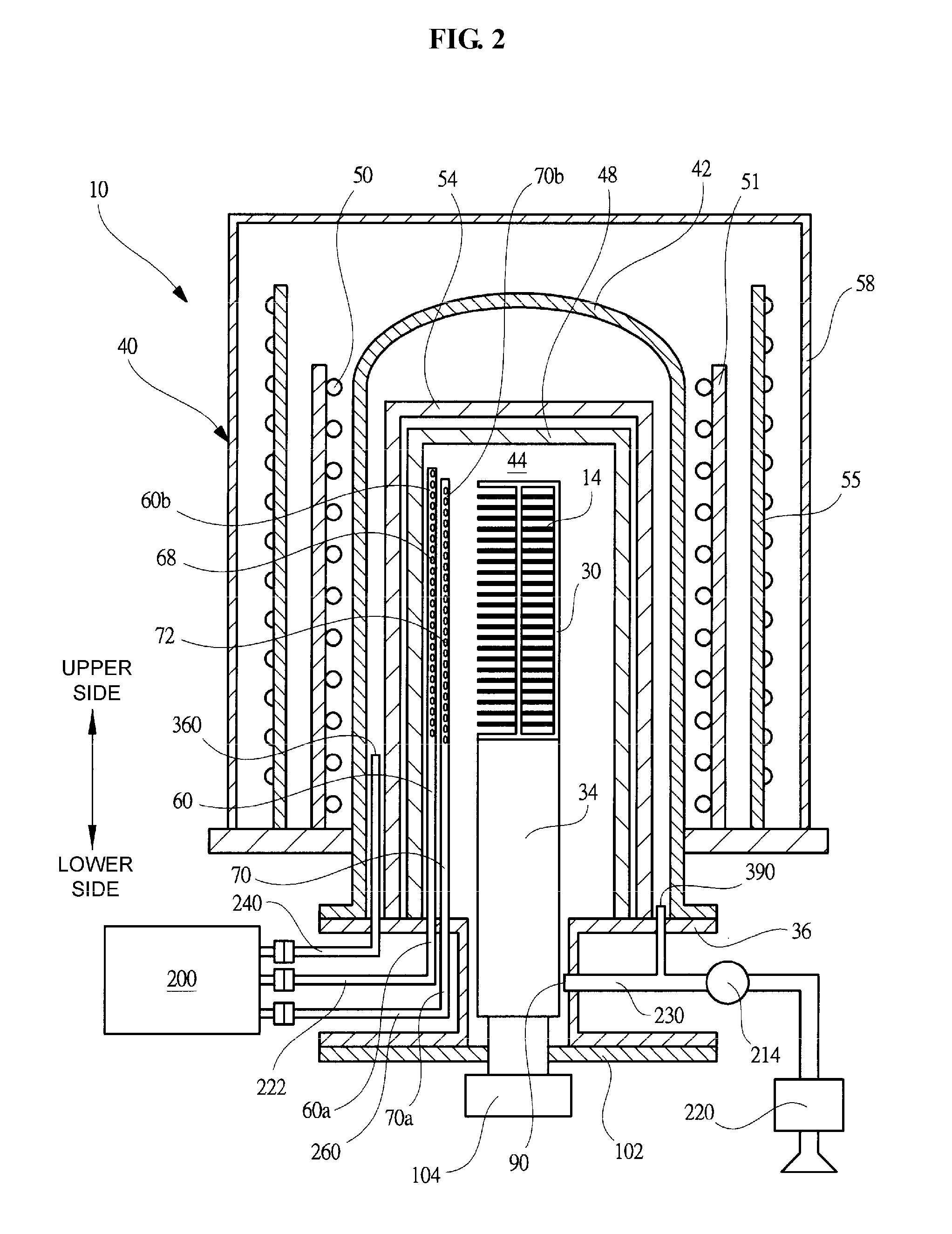

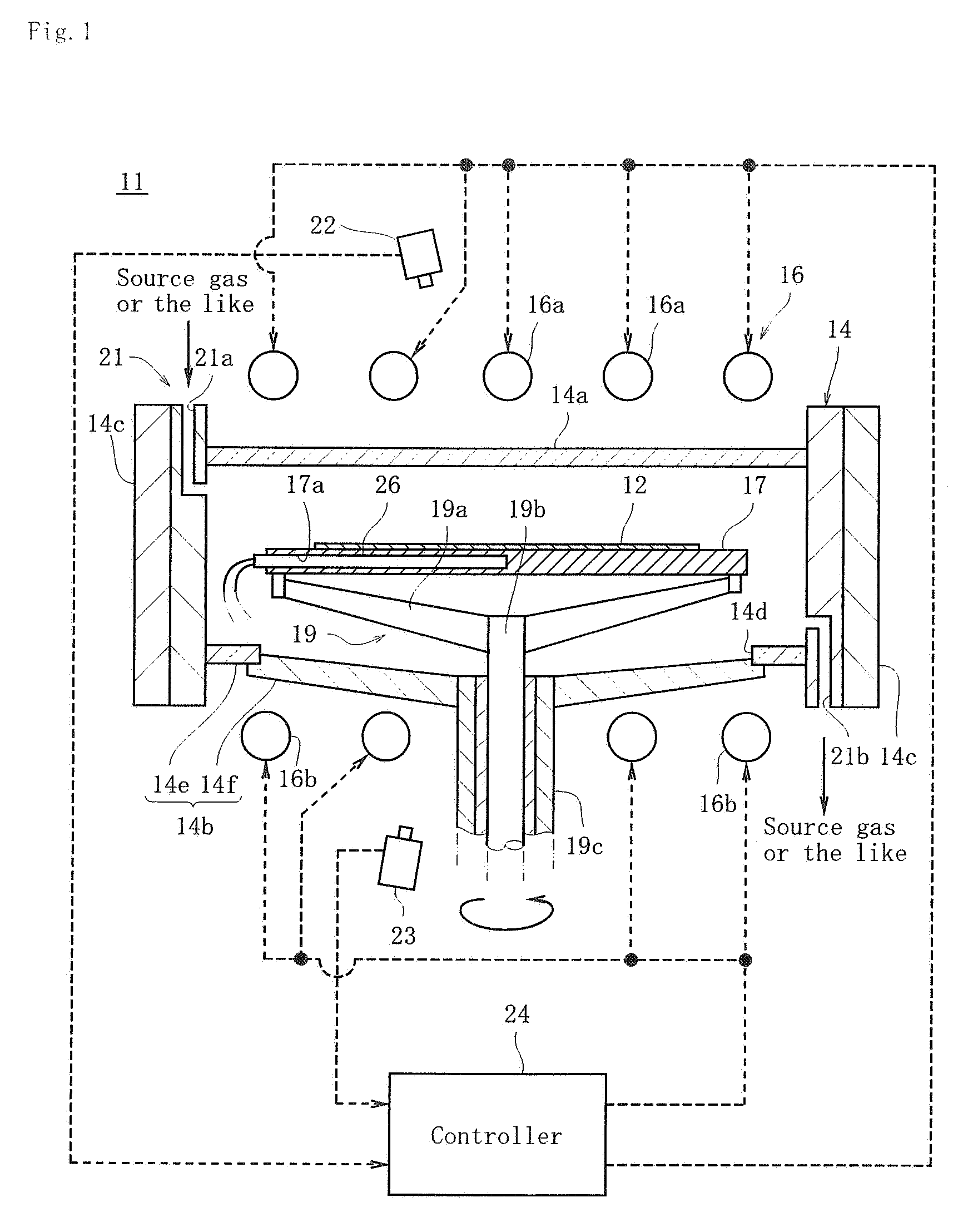

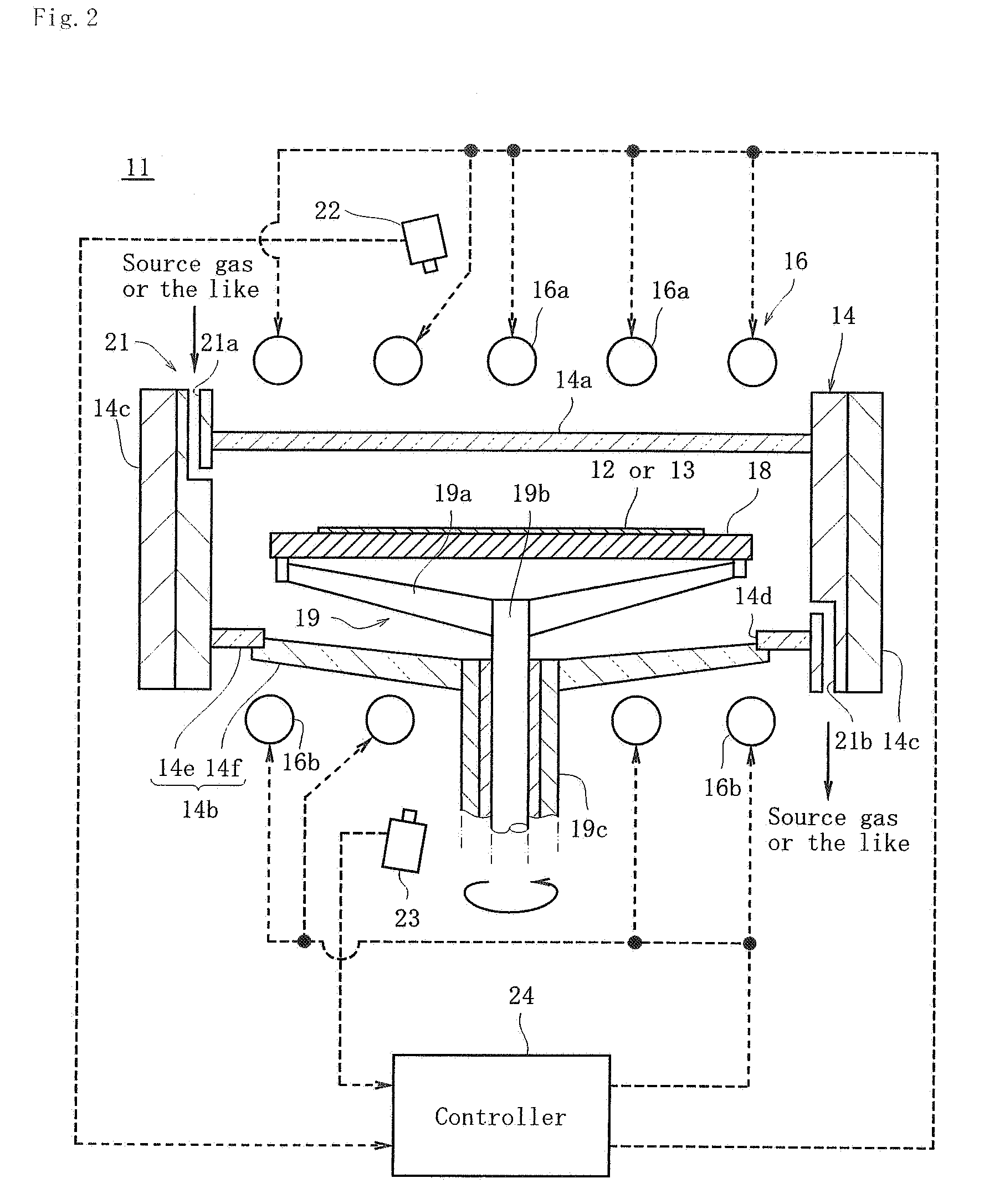

Substrate processing apparatus and method of manufacturing semiconductor device

ActiveUS8882923B2Inhibition of thermal deteriorationHeat deteriorationPolycrystalline material growthSemiconductor/solid-state device manufacturingProcess engineeringSemiconductor

A substrate processing apparatus includes: a process chamber having an object to be heated therein and configured to process a plurality of substrates; a substrate holder configured to hold the substrates with an interval therebetween in a vertical direction in the process chamber; a first heat exchange unit supporting the substrate holder from a lower side thereof in the process chamber and configured to perform a heat exchange with a gas in the process chamber; a second heat exchange unit provided in the process chamber, the second heat exchange unit being horizontally spaced apart from the first heat exchange unit with a gap therebetween and being configured to perform a heat exchange with the gas in the process chamber; and an induction heating unit configured to subject the object to be heated to an induction heating from an outer side of the object to be heated.

Owner:KOKUSA ELECTRIC CO LTD

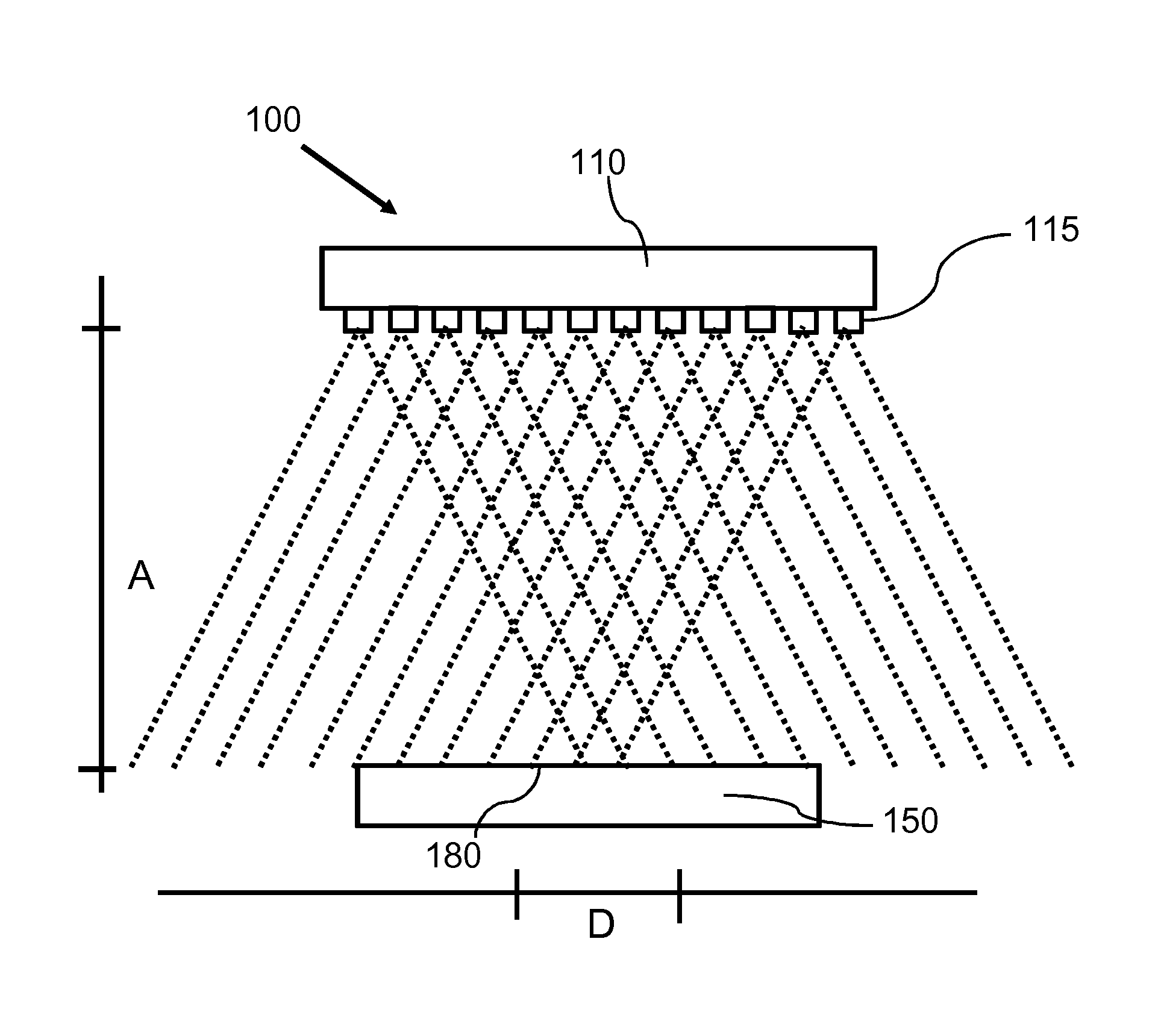

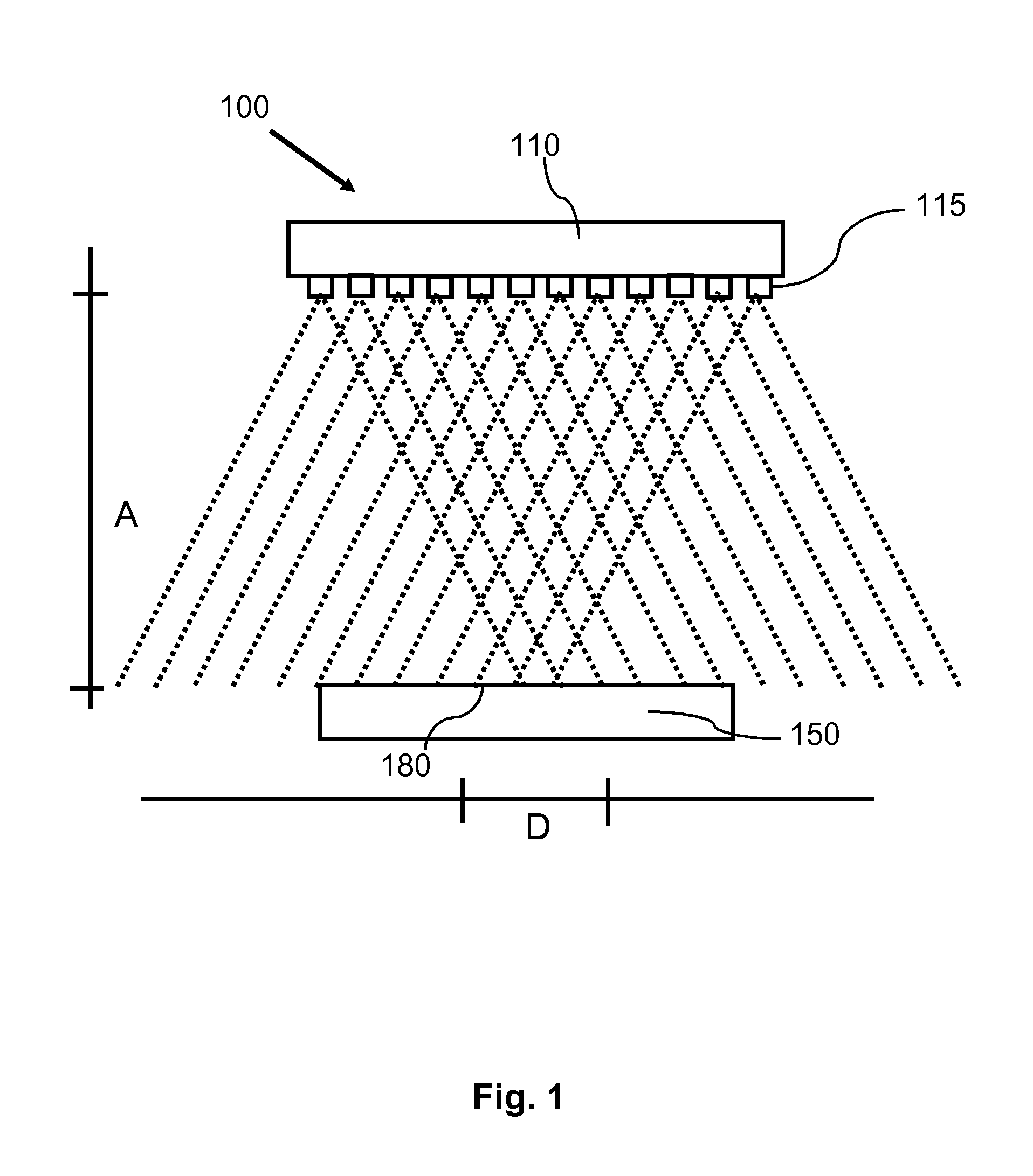

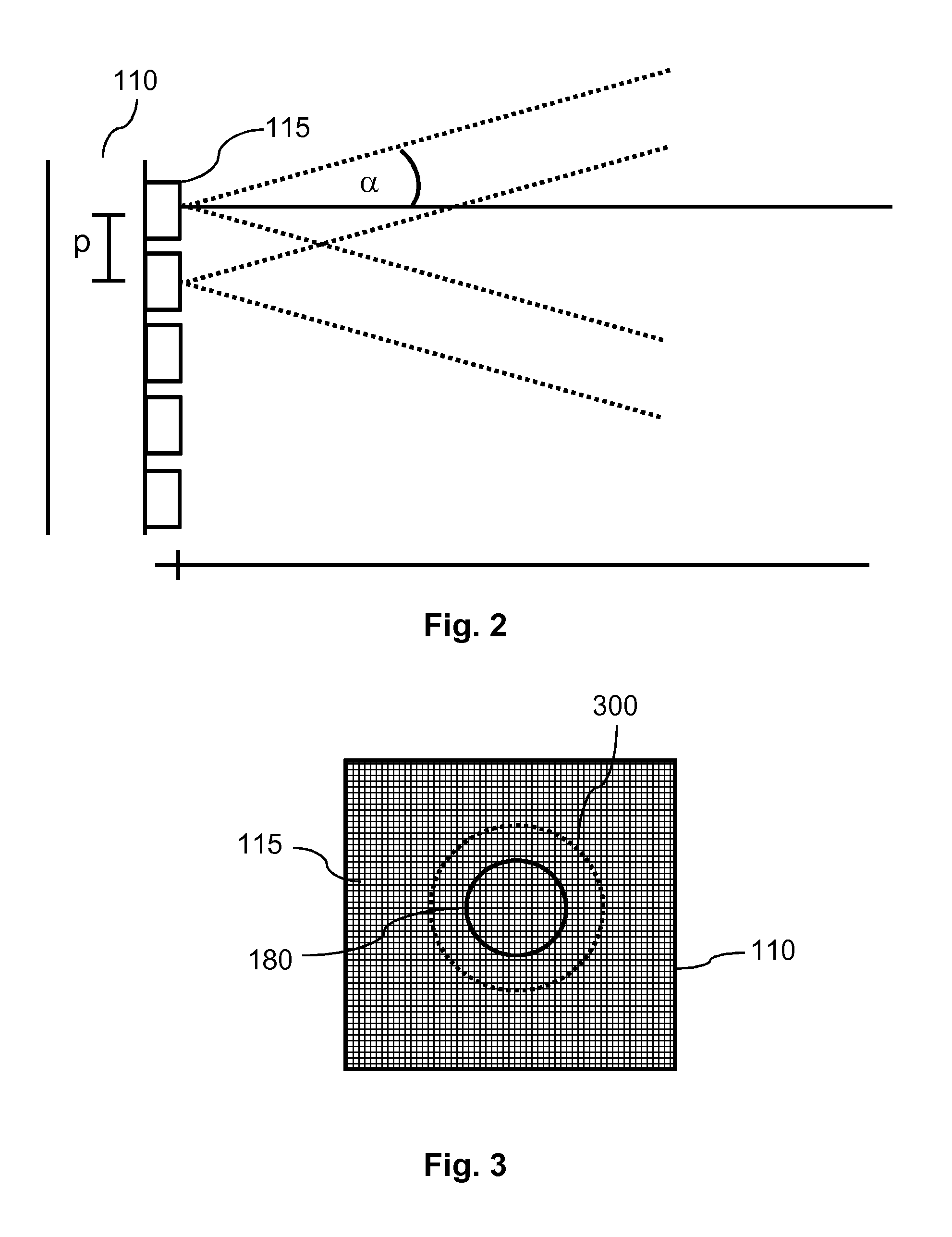

Heating system comprising semiconductor light sources

ActiveUS20160381732A1Improve homogeneityHeating system be improvedSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention describes a heating system (100) and a corresponding method of heating a heating surface (180) of an object (150, 950) to a processing temperature of at least 100° C., wherein the heating system (100) comprises semiconductor light sources (115), and wherein the heating system (100) is adapted to heat an area element of the heating surface (180) with at least 50 semiconductor light sources (115) at the same time. The heating system (100) may be part of a reactor for processing semiconductor structures. The light emitted by means of the semiconductor light sources (115) overlaps at the heating surface (180). Differences of the characteristic of one single semiconductor light source (115) may be blurred at the heating surface (180) such that a homogeneous temperature distribution across a processing surface of a, for example, wafer may be enabled.

Owner:TRUMPF PHOTONIC COMPONENTS GMBH

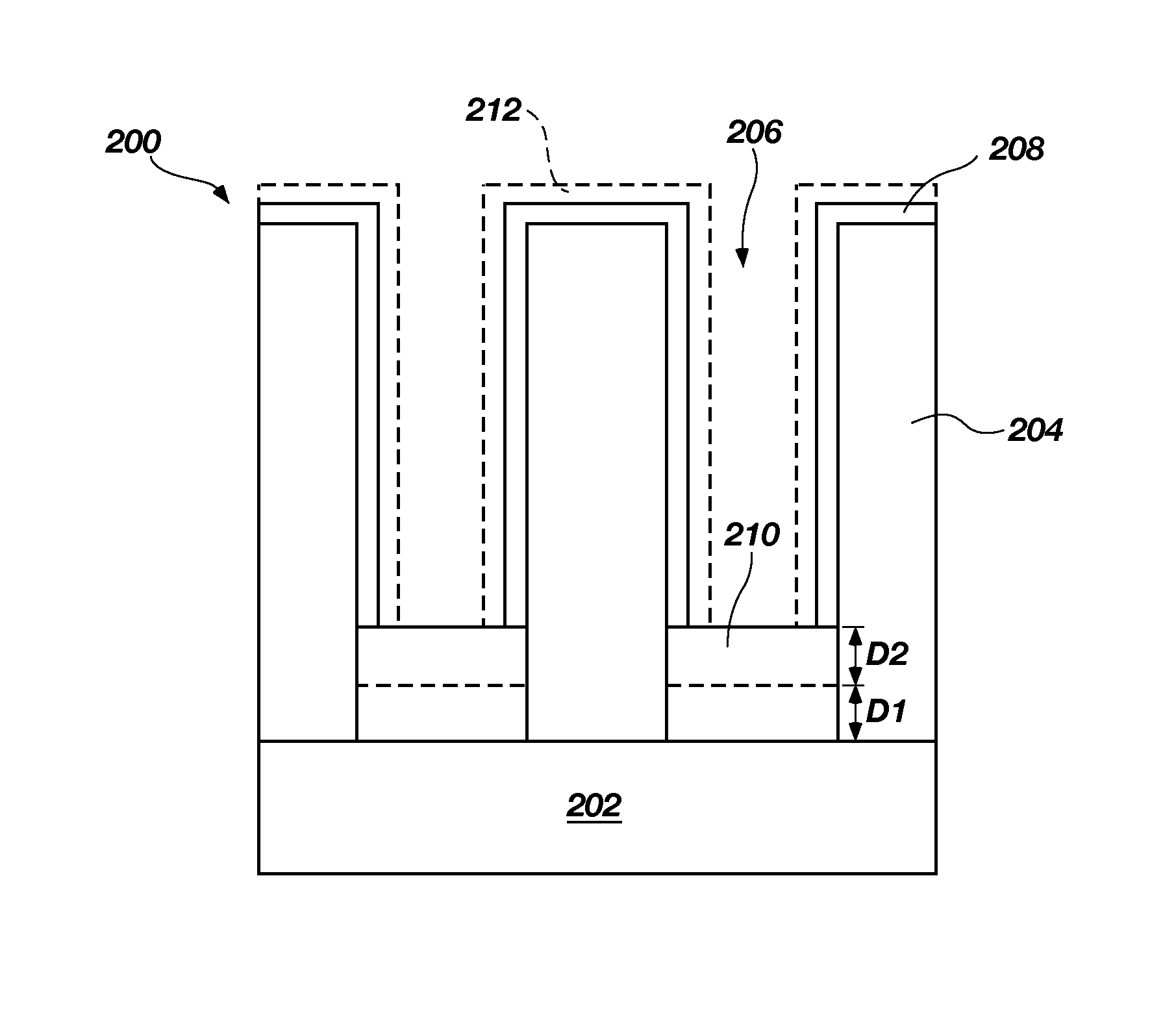

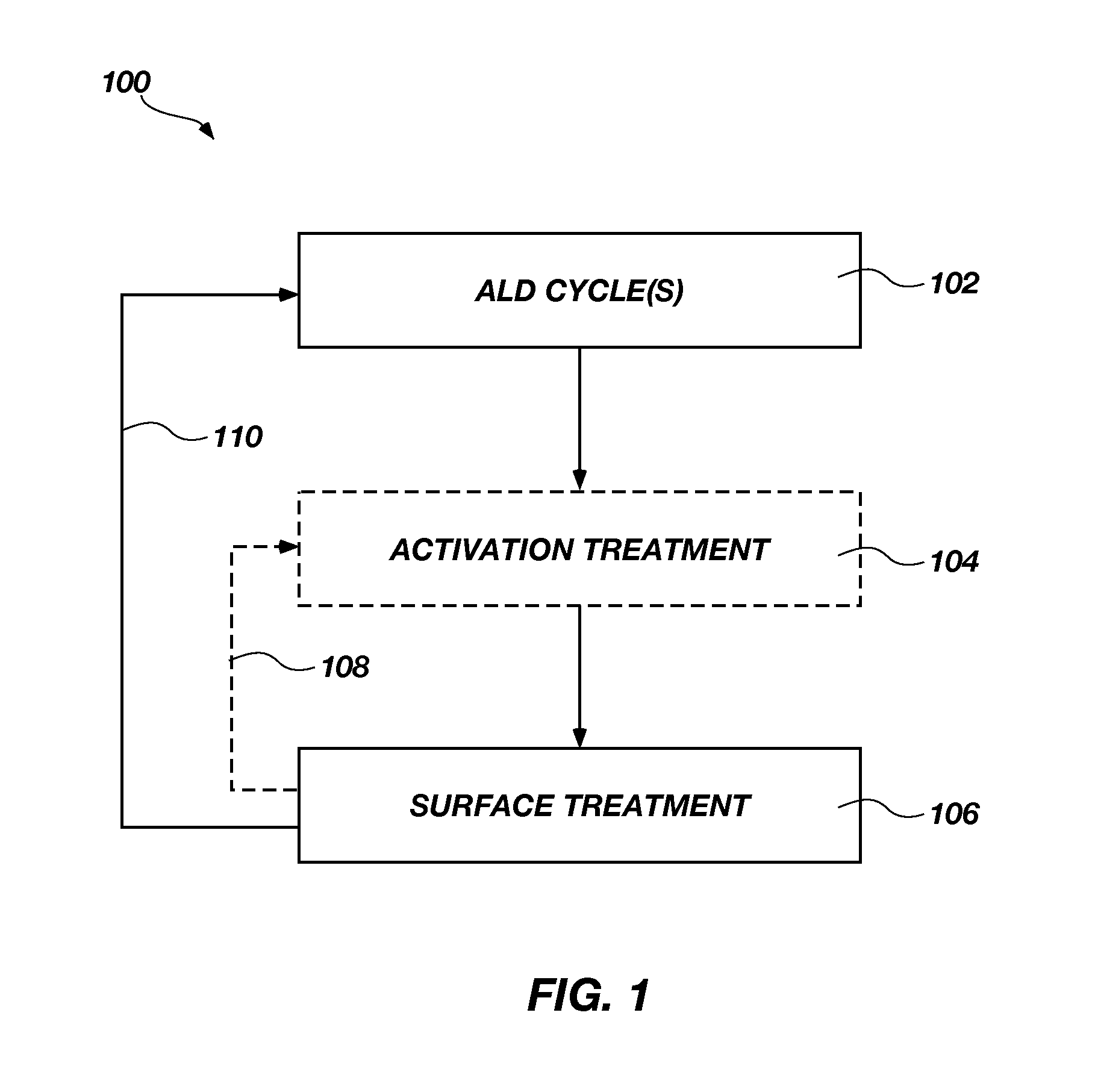

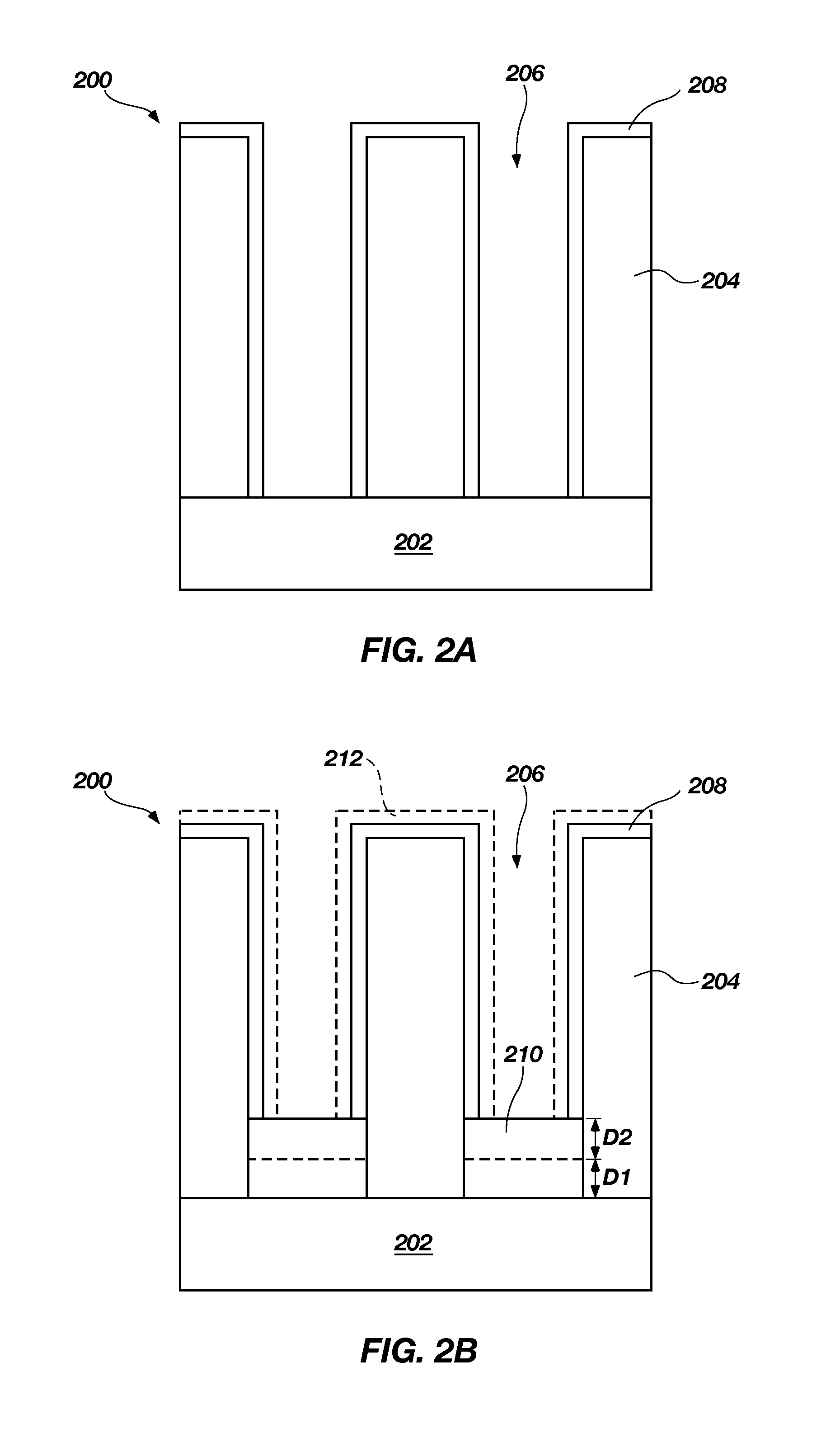

Methods of selectively forming a material using parylene coating

ActiveUS8945305B2Polycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor structureSelective deposition

Methods for depositing a material, such as a metal or a transition metal oxide, using an ALD (atomic layer deposition) process and resulting structures are disclosed. Such methods include treating a surface of a semiconductor structure periodically throughout the ALD process to regenerate a blocking material or to coat a blocking material that enables selective deposition of the material on a surface of a substrate. The surface treatment may reactivate a surface of the substrate toward the blocking material, may restore the blocking material after degradation occurs during the ALD process, and / or may coat the blocking material to prevent further degradation during the ALD process. For example, the surface treatment may be applied after performing one or more ALD cycles. Accordingly, the presently disclosed methods enable in situ restoration of blocking materials in ALD process that are generally incompatible with the blocking material and also enables selective deposition in recessed structures.

Owner:MICRON TECH INC

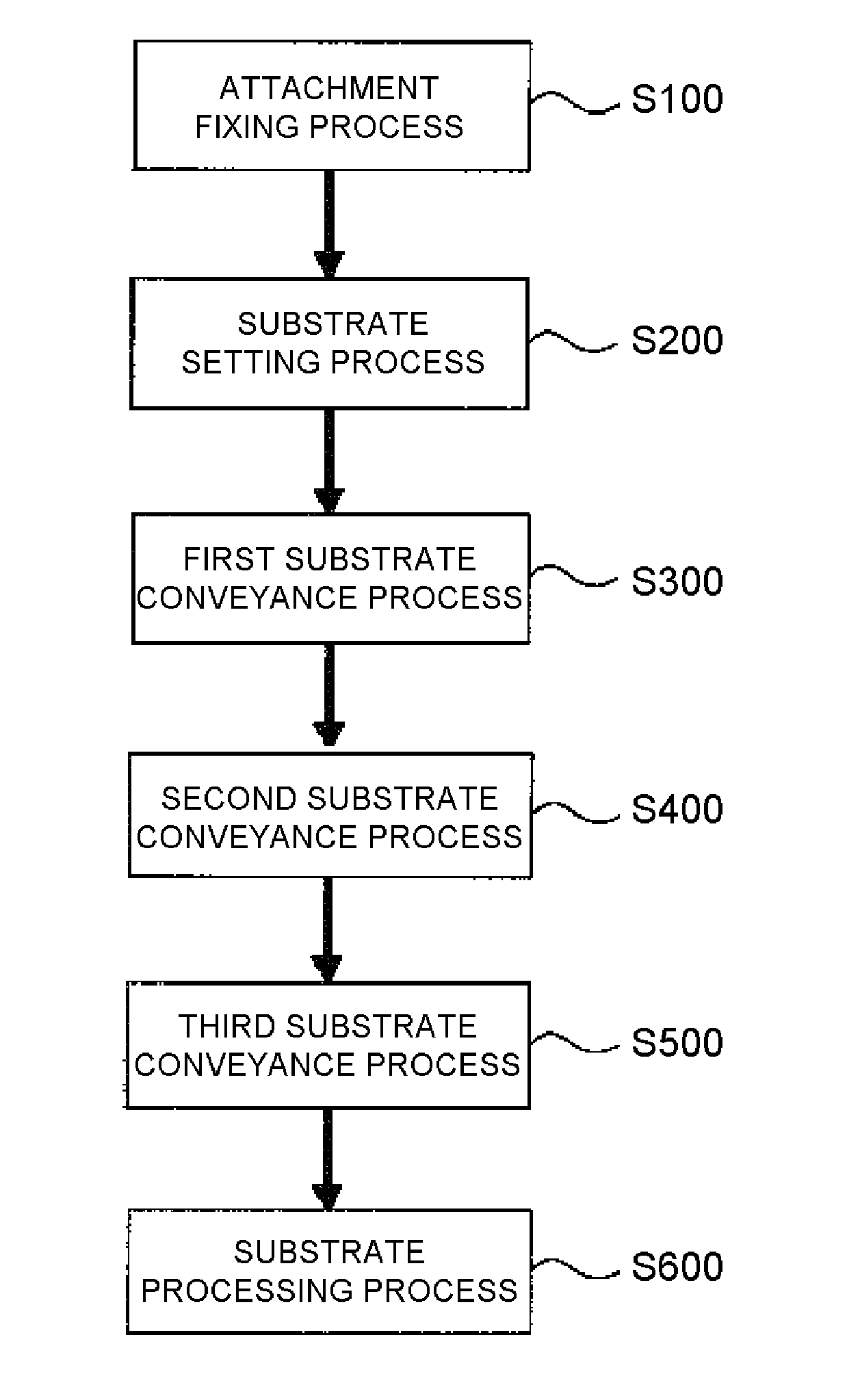

Attachment for substrates having different diameters, substrate processing apparatus, and method of manufacturing substrate or semiconductor device

InactiveUS20120216743A1Low costImprove film-forming precisionPolycrystalline material growthSemiconductor/solid-state device manufacturingReactive gasDevice material

A downsized substrate may be housed in a substrate accommodation vessel (FOUP) constituting a transfer system corresponding to a large diameter substrate. An attachment includes an upper plate and a lower plate supported by a first support groove that can support an 8-inch wafer, and holding columns installed at the upper plate and the lower plate and including a second support groove that can support a 2-inch wafer (if necessary, via a wafer holder and a holder member). Accordingly, the 2-inch wafer can be housed in a pod corresponding to the 8-inch wafer, and the pod, which is a transfer system, can be standardized to reduce cost of a semiconductor manufacturing apparatus. In addition, a distance from each gas supply nozzle to the wafer can be increased to sufficiently mix reactive gases before arrival at the wafer and improve film-forming precision to the wafer.

Owner:KOKUSA ELECTRIC CO LTD

Method of growing oxide films

InactiveUS20030188682A1Easy to prepareExcellent dielectric propertiesPolycrystalline material growthSemiconductor/solid-state device manufacturingSilicon oxideOxygen

Abstract of Disclosure Process for producing silicon oxide containing thin films on a growth substrate by the ALCVD method. In the process, a vaporisable silicon compound is bonded to the growth substrate, and the bonded silicon compound is converted to silicon dioxide. The invention comprises using a silicon compound which contains at least one organic ligand and the bonded silicon compound is converted to silicon dioxide by contacting it with a vaporised, reactive oxygen source, in particular with ozone. The present invention provides a controlled process for growing controlling thin films containing SiO2, with sufficiently short reaction times.

Owner:ASM IP HLDG BV

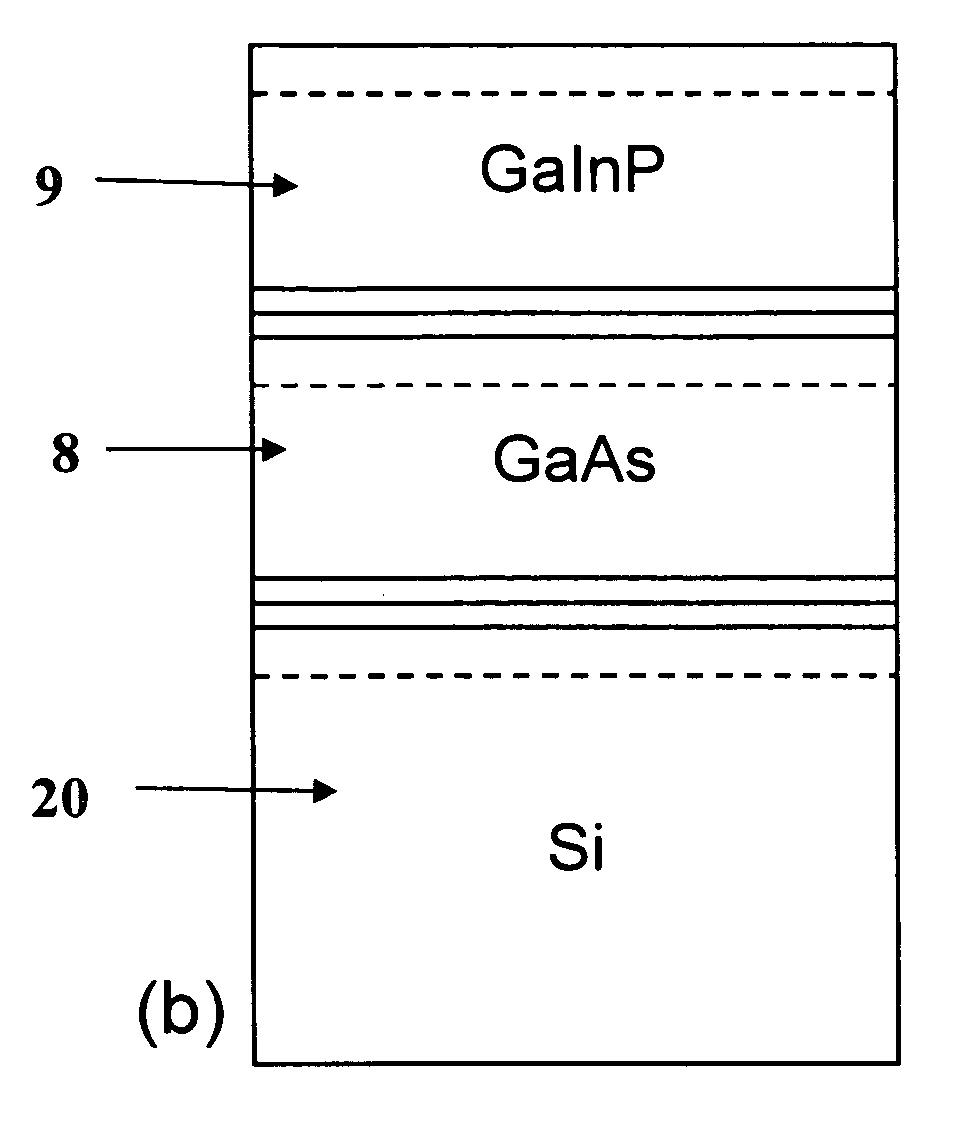

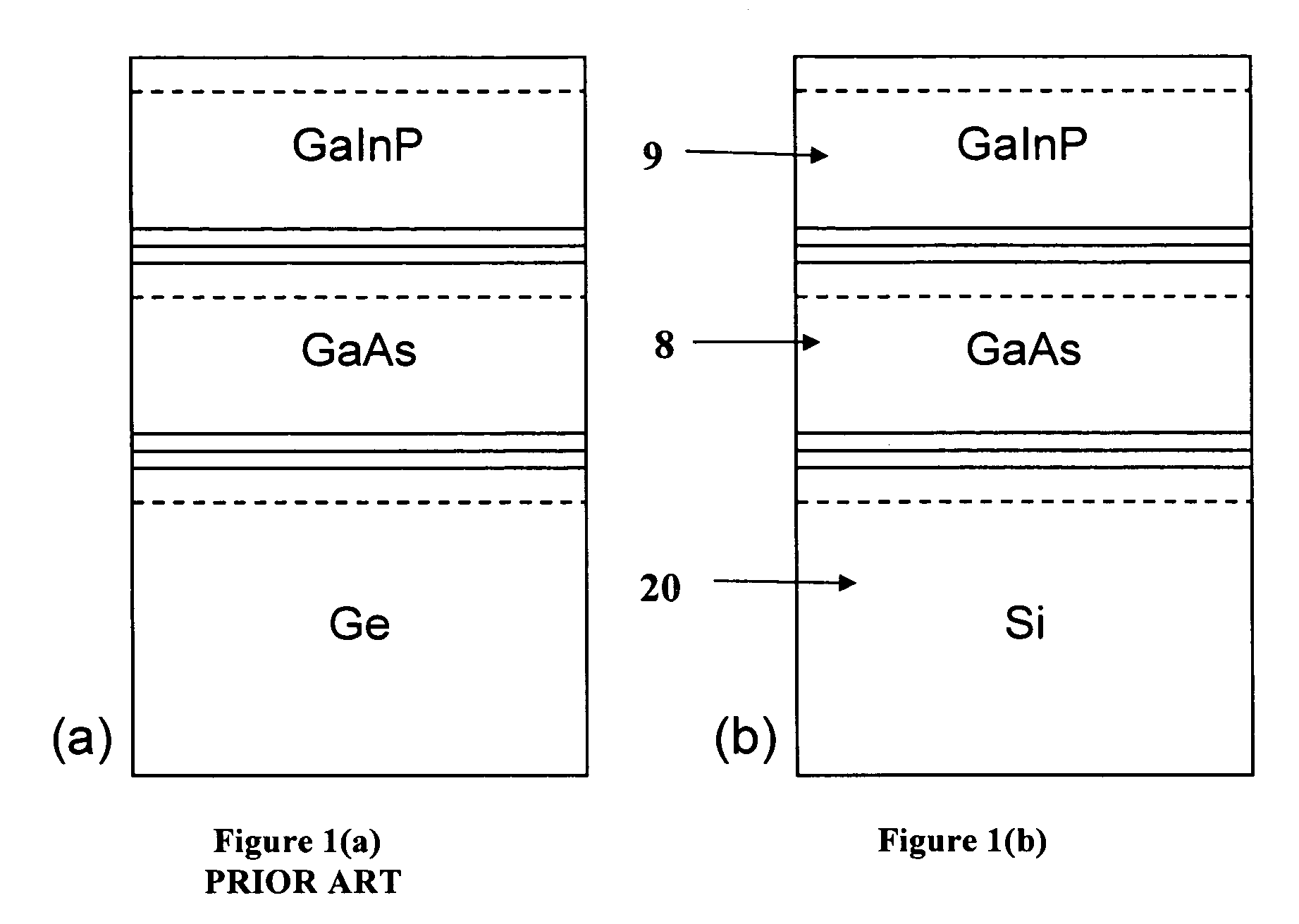

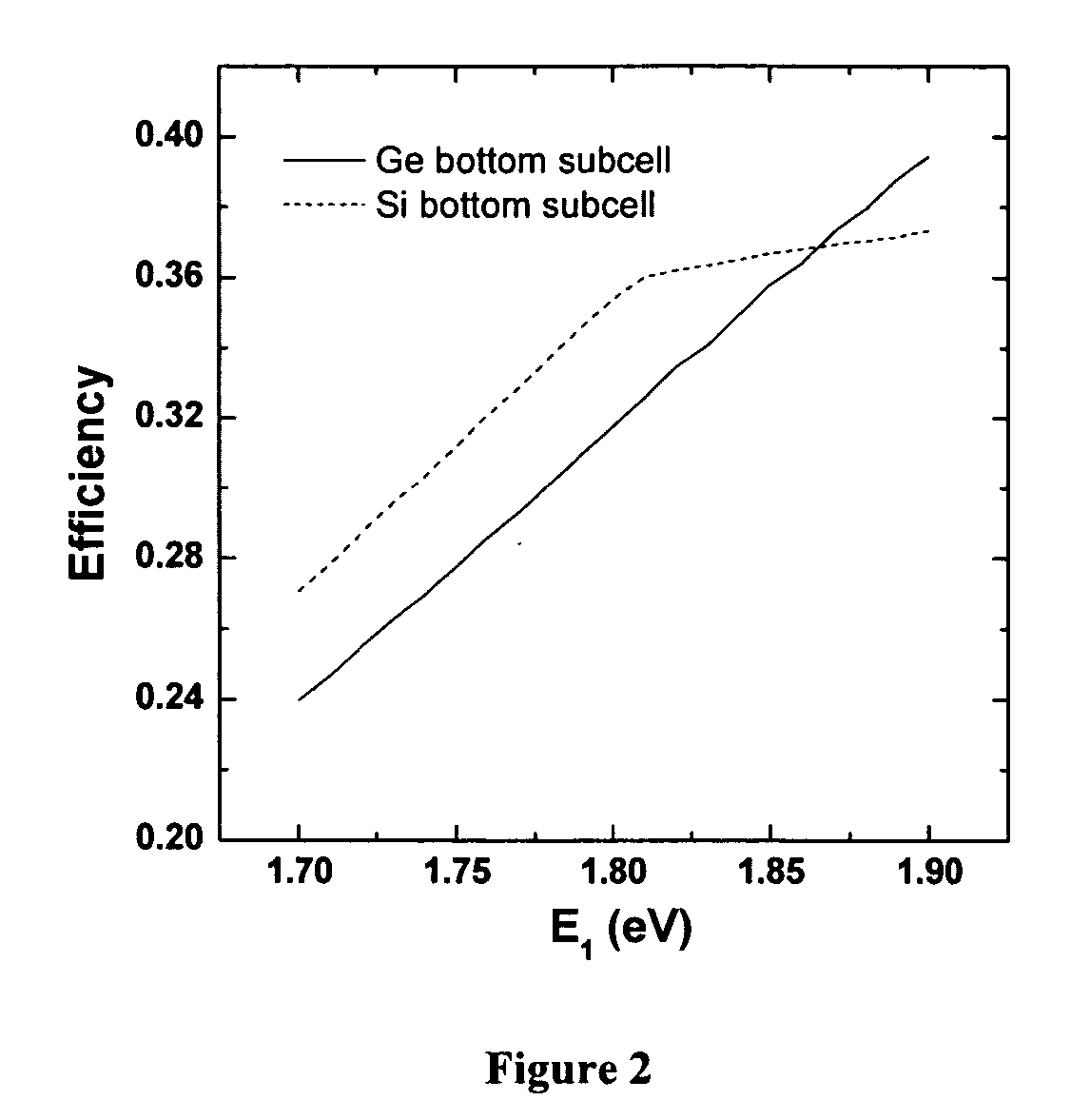

GaInP / GaAs / Si triple junction solar cell enabled by wafer bonding and layer transfer

InactiveUS20060021565A1Polycrystalline material growthFinal product manufactureBond interfaceWafer bonding

A multi-junction solar cell includes a silicon solar subcell, a GaInP solar subcell, and a GaAs solar subcell located between the silicon solar subcell and the GaInP solar subcell. The GaAs solar subcell is bonded to the silicon solar subcell such that a bonded interface exists between these subcells.

Owner:AONEX TECH

Temperature control method of epitaxial growth apparatus

ActiveUS7833348B2Accurate CalibrationQuality improvementPolycrystalline material growthThermometer testing/calibrationTemperature controlSusceptor

An object of the invention is to calibrate an upper pyrometer for indirectly measuring a substrate temperature at the time of epitaxial growth in a comparatively short time and with accuracy to thereby improve the quality of an epitaxial substrate.After calibrating an upper pyrometer by a thermocouple mounted to a temperature calibrating susceptor, a measured value of a lower pyrometer is adjusted to a calibrated value of the upper pyrometer. Then, a correlation line between substrate temperature indirectly measured by the upper pyrometer at the time of epitaxial growth onto a sample substrate and haze of a sample substrate measured immediately after epitaxial growth is set to indirectly measure a substrate temperature by the upper pyrometer at the time of epitaxial growth onto a mass-production substrate. Moreover, substrate temperature at the time of epitaxial growth onto the mass-production substrate is estimated by applying the haze of the mass-production substrate measured immediately after epitaxial growth to the correlation line and then a measured temperature of the upper pyrometer is adjusted to the estimated temperature.

Owner:SUMCO CORP

Method for making Group III nitride devices and devices produced thereby

InactiveUS7033858B2Improve cooling effectThin active areaPolycrystalline material growthSolid-state devicesLithium aluminateNitride

A method is for making at least one semiconductor device including providing a sacrificial growth substrate of Lithium Aluminate (LiAlO2); forming at least one semiconductor layer including a Group III nitride adjacent the sacrificial growth substrate; attaching a mounting substrate adjacent the at least one semiconductor layer opposite the sacrificial growth substrate; and removing the sacrificial growth substrate. The method may further include adding at least one contact onto a surface of the at least one semiconductor layer opposite the mounting substrate, and dividing the mounting substrate and at least one semiconductor layer into a plurality of individual semiconductor devices. To make the final devices, the method may further include bonding the mounting substrate of each individual semiconductor device to a heat sink. The step of removing the sacrificial substrate may include wet etching the sacrificial growth substrate.

Owner:CRYSTAL PHOTONICS

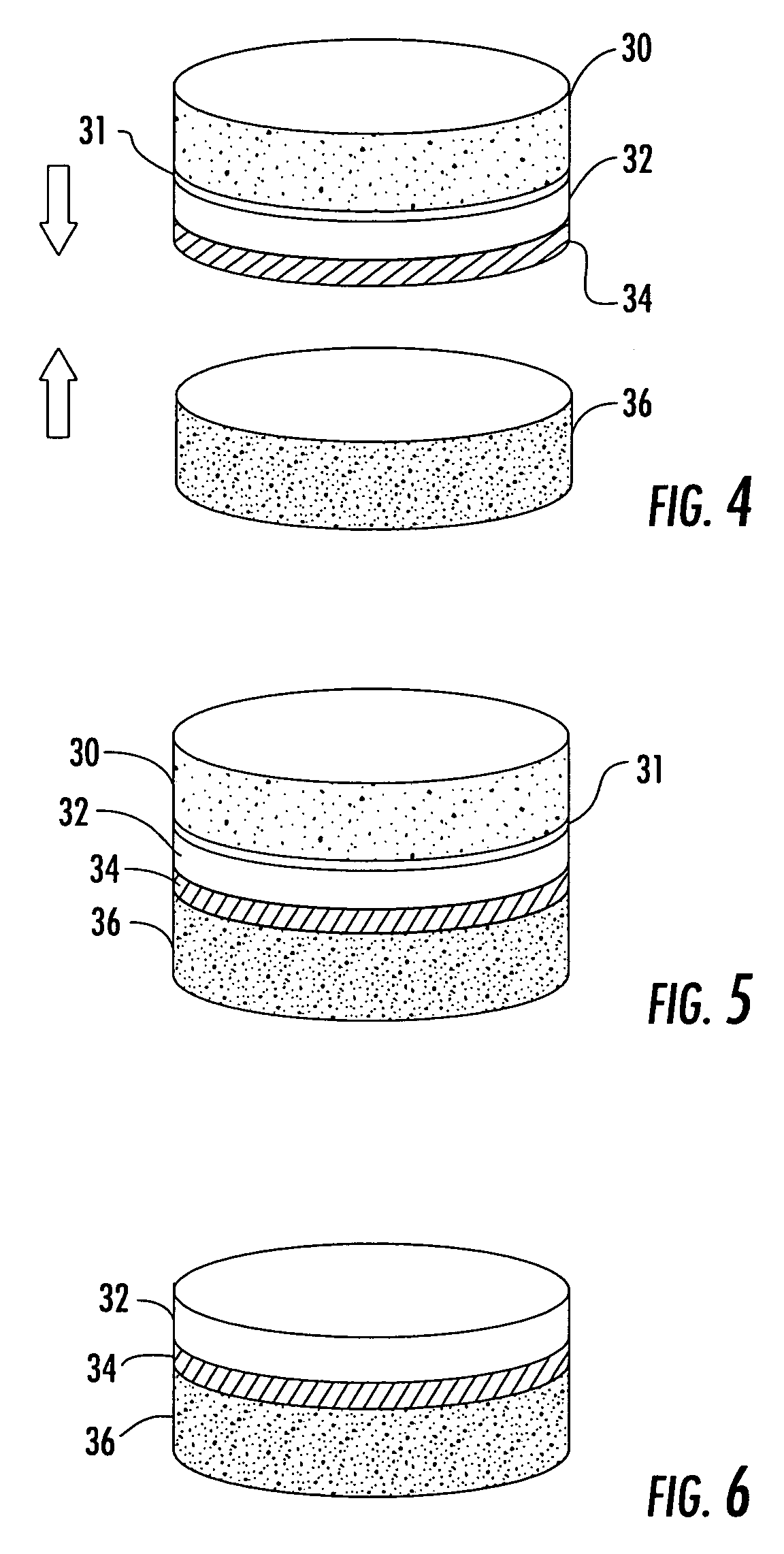

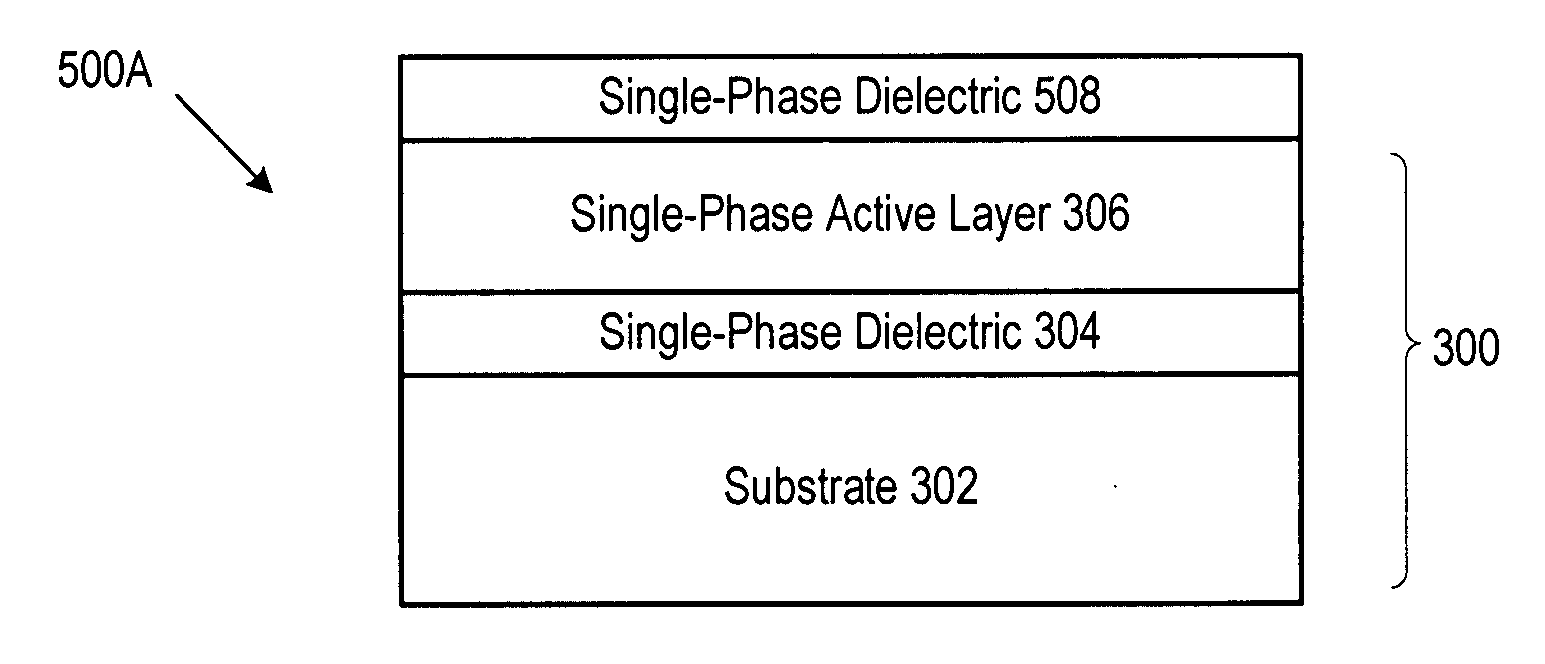

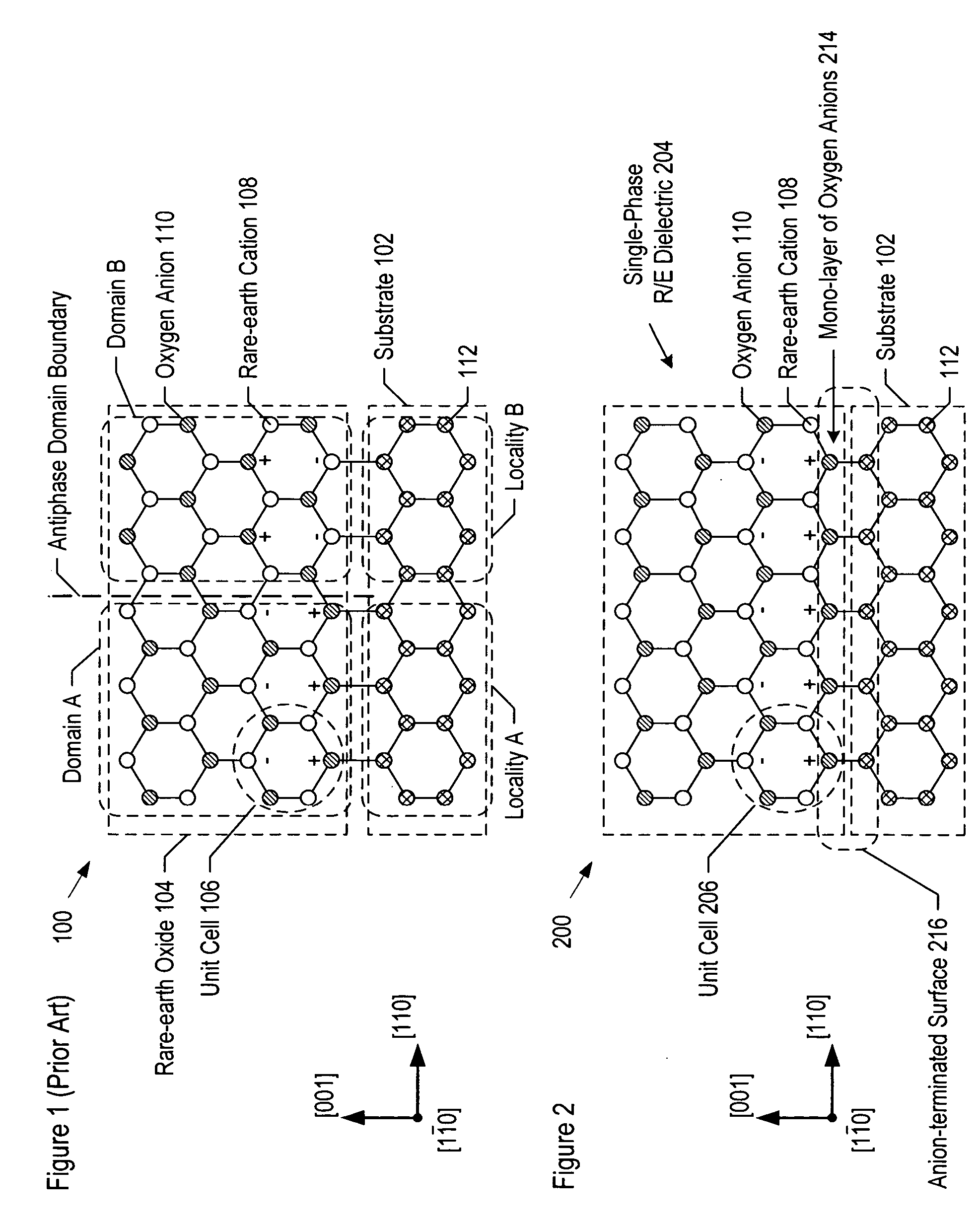

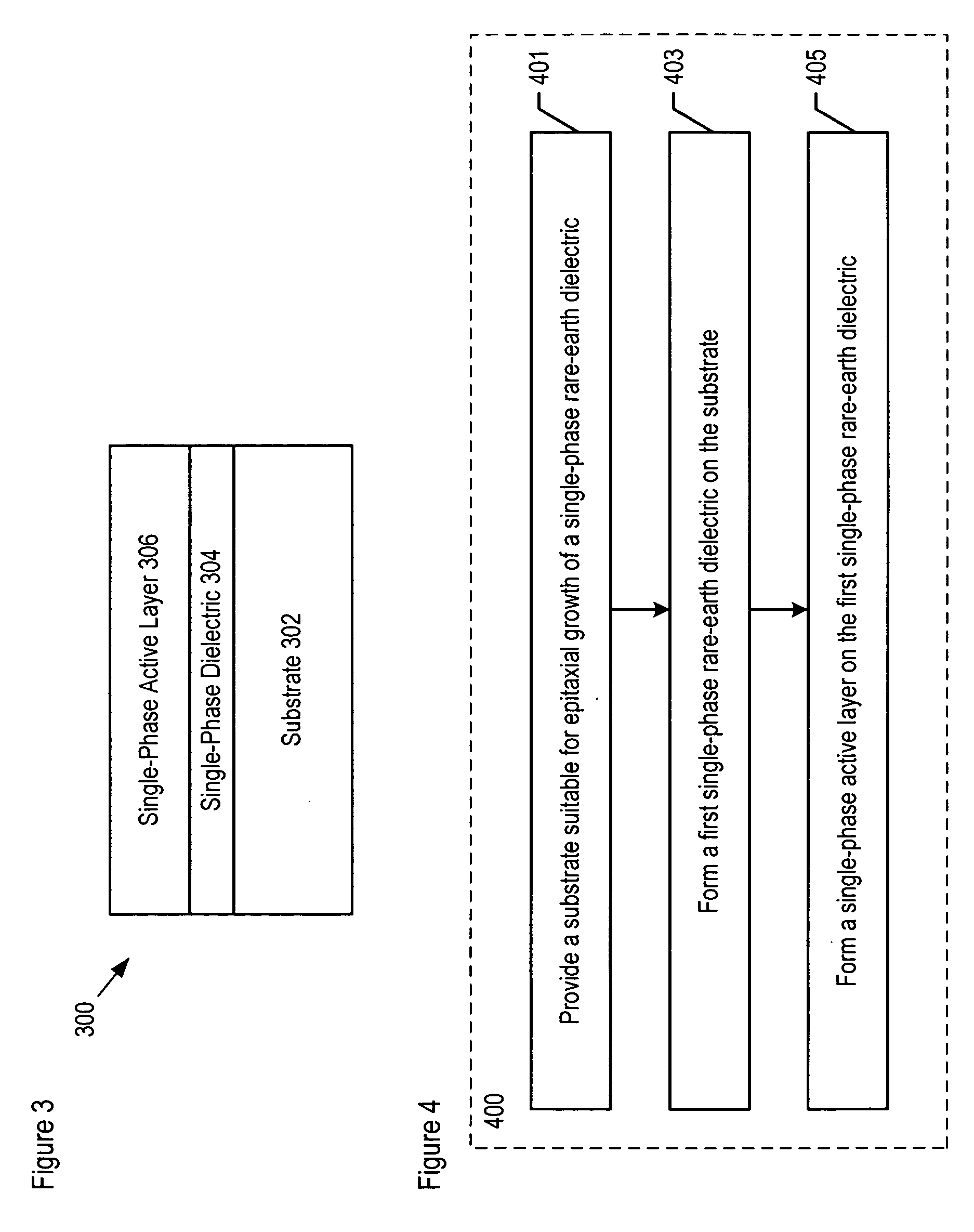

Method of forming a rare-earth dielectric layer

ActiveUS20060060131A1Quality improvementPolycrystalline material growthLaser detailsSemiconductor structureRare earth

Methods for forming compositions comprising a single-phase rare-earth dielectric disposed on a substrate are disclosed. In some embodiments, the method forms a semiconductor-on-insulator structure. Compositions and structures that are formed via the method provide the basis for forming high-performance devices and circuits.

Owner:IQE

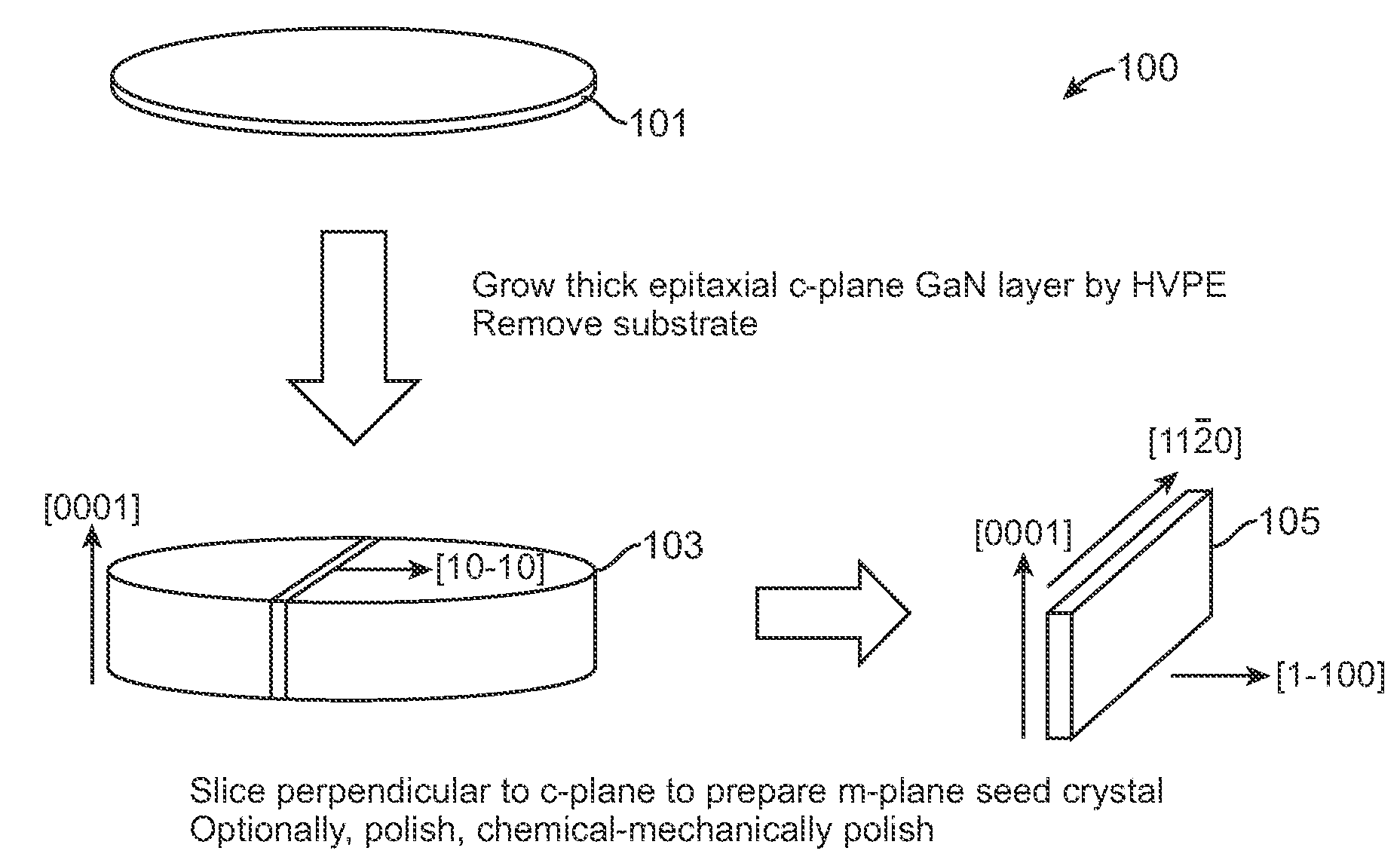

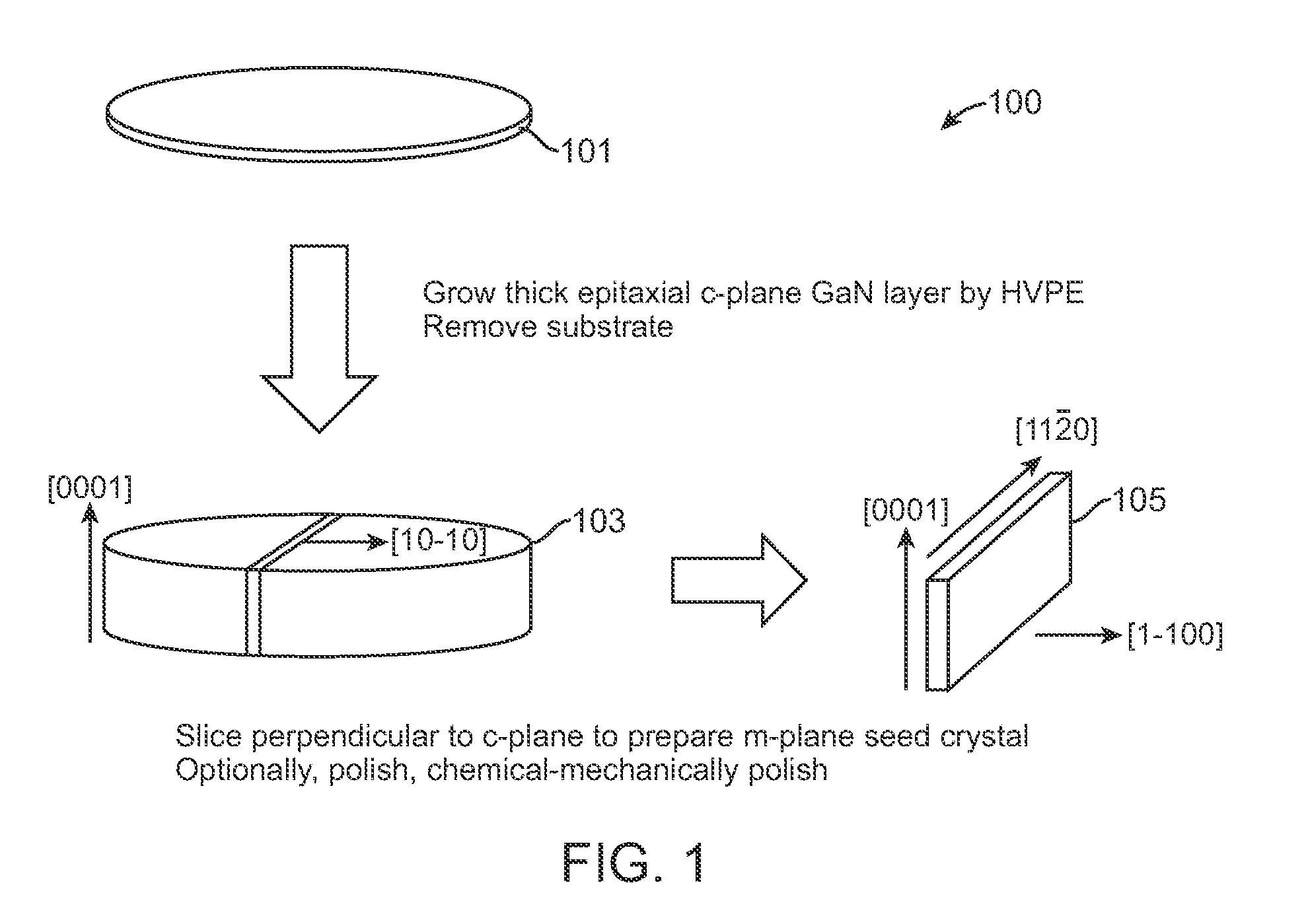

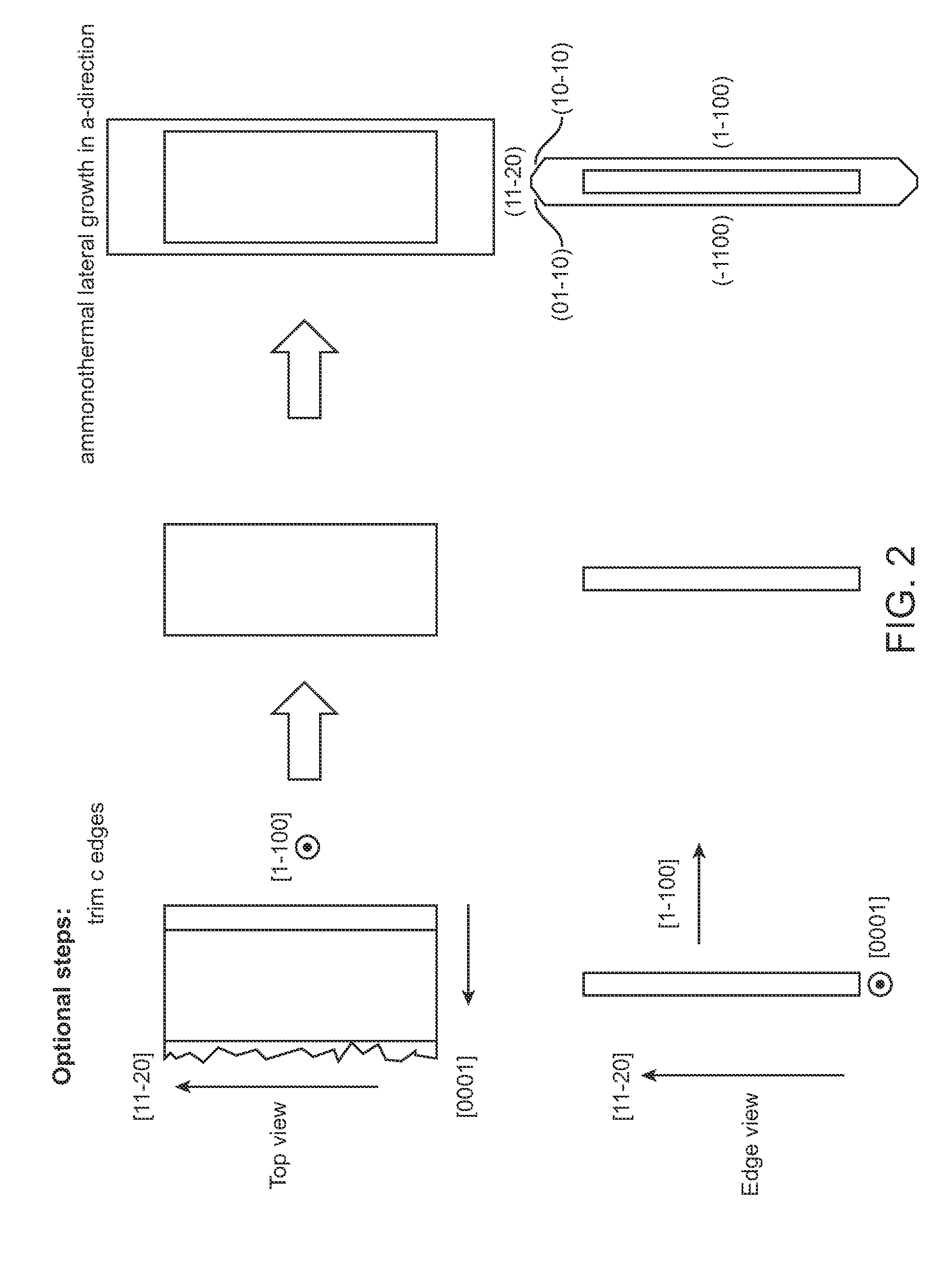

High quality large area bulk non-polar or semipolar gallium based substrates and methods

InactiveUS20100003492A1Great area of substrateCost-effective manufacturingPolycrystalline material growthConductive materialPhotodetectorSolar cell

A large area nitride crystal, comprising gallium and nitrogen, with a non-polar or semi-polar large-area face, is disclosed, along with a method for making. The crystal is useful as a substrate for a light emitting diode, a laser diode, a transistor, a photodetector, a solar cell, or for photoelectrochemical water splitting for hydrogen generation.

Owner:SORAA

Method of growing GaN crystal, method of producing single crystal GaN substrate, and single crystal GaN substrate

InactiveUS7303630B2Resist invasionImprove stabilityPolycrystalline material growthFrom chemically reactive gasesSeed ImplantRegular pattern

Owner:SUMITOMO ELECTRIC IND LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com