Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

124results about How to "Lower channel resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

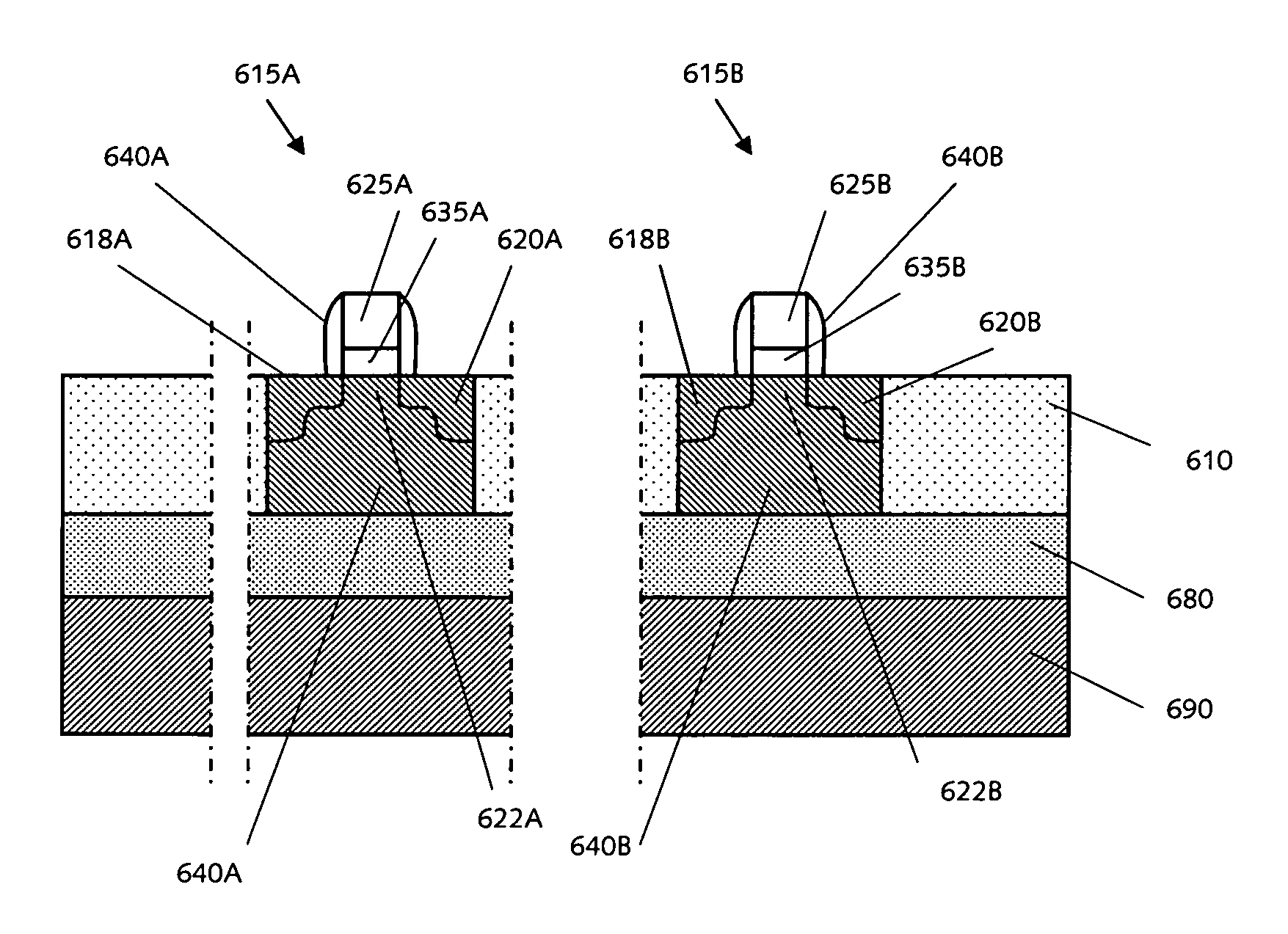

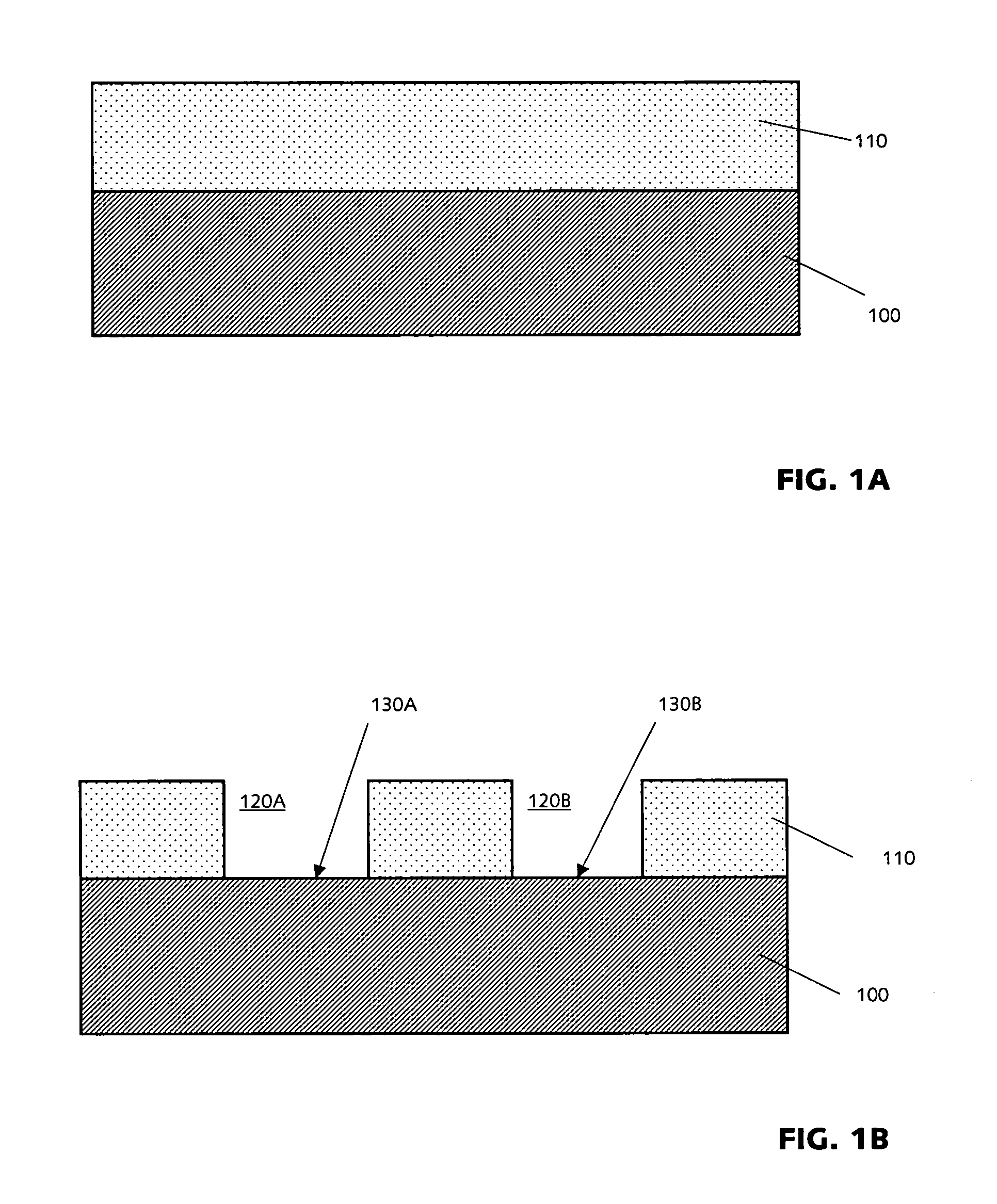

Lattice-mismatched semiconductor structures on insulators

ActiveUS7638842B2Functionality and performance improvementsLower channel resistanceSemiconductor/solid-state device detailsSolid-state devicesThreading dislocationsSemiconductor structure

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

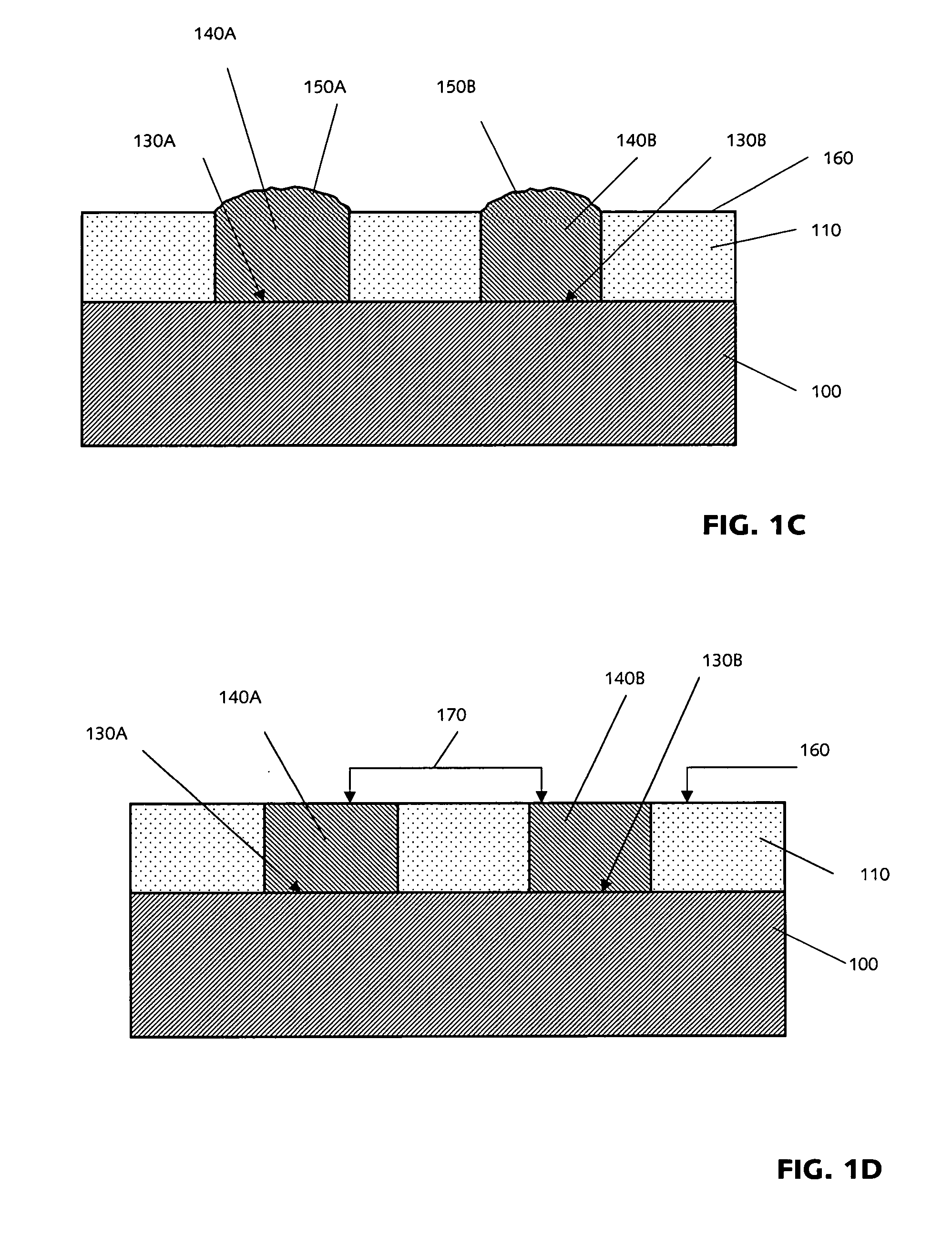

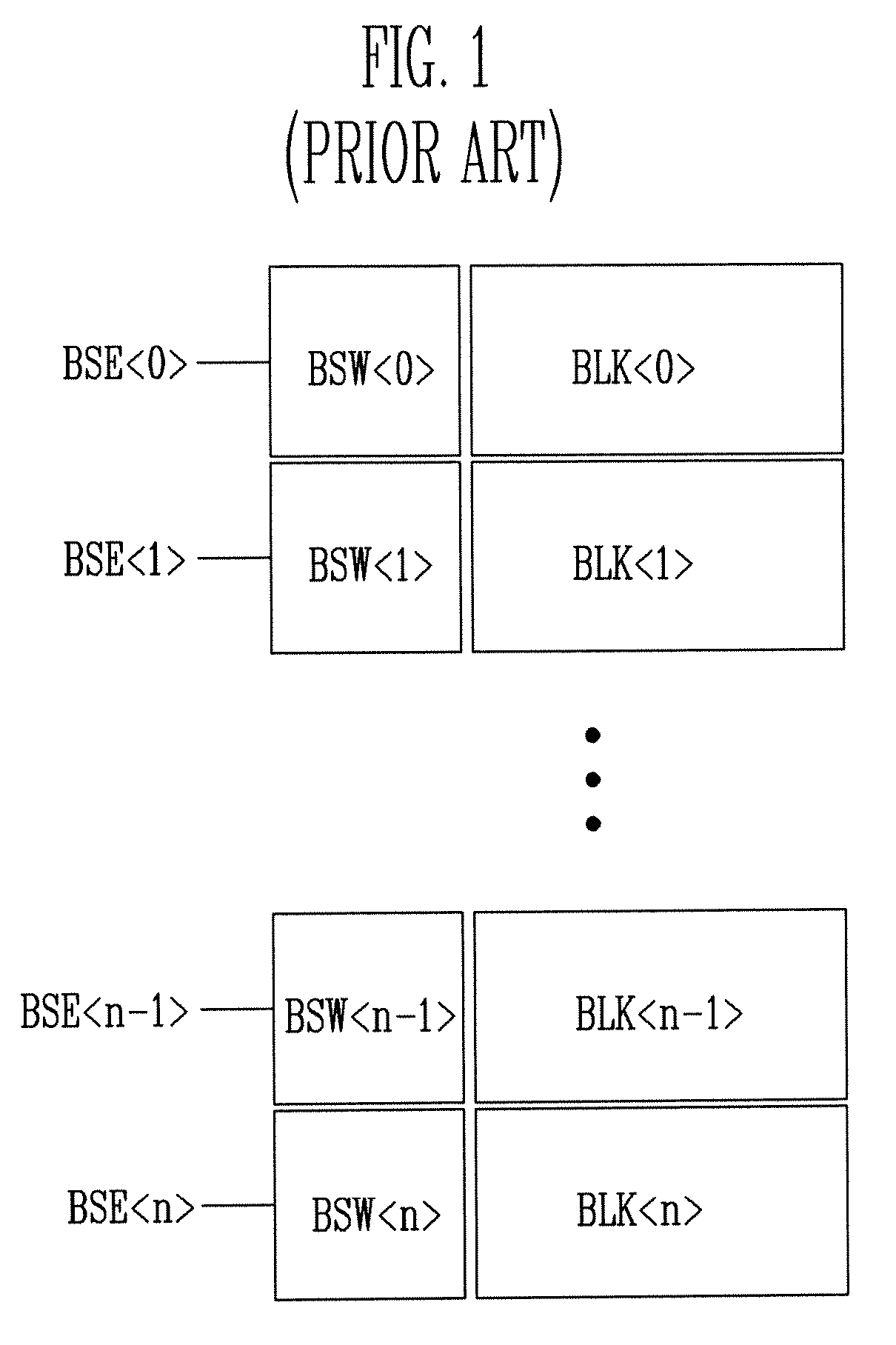

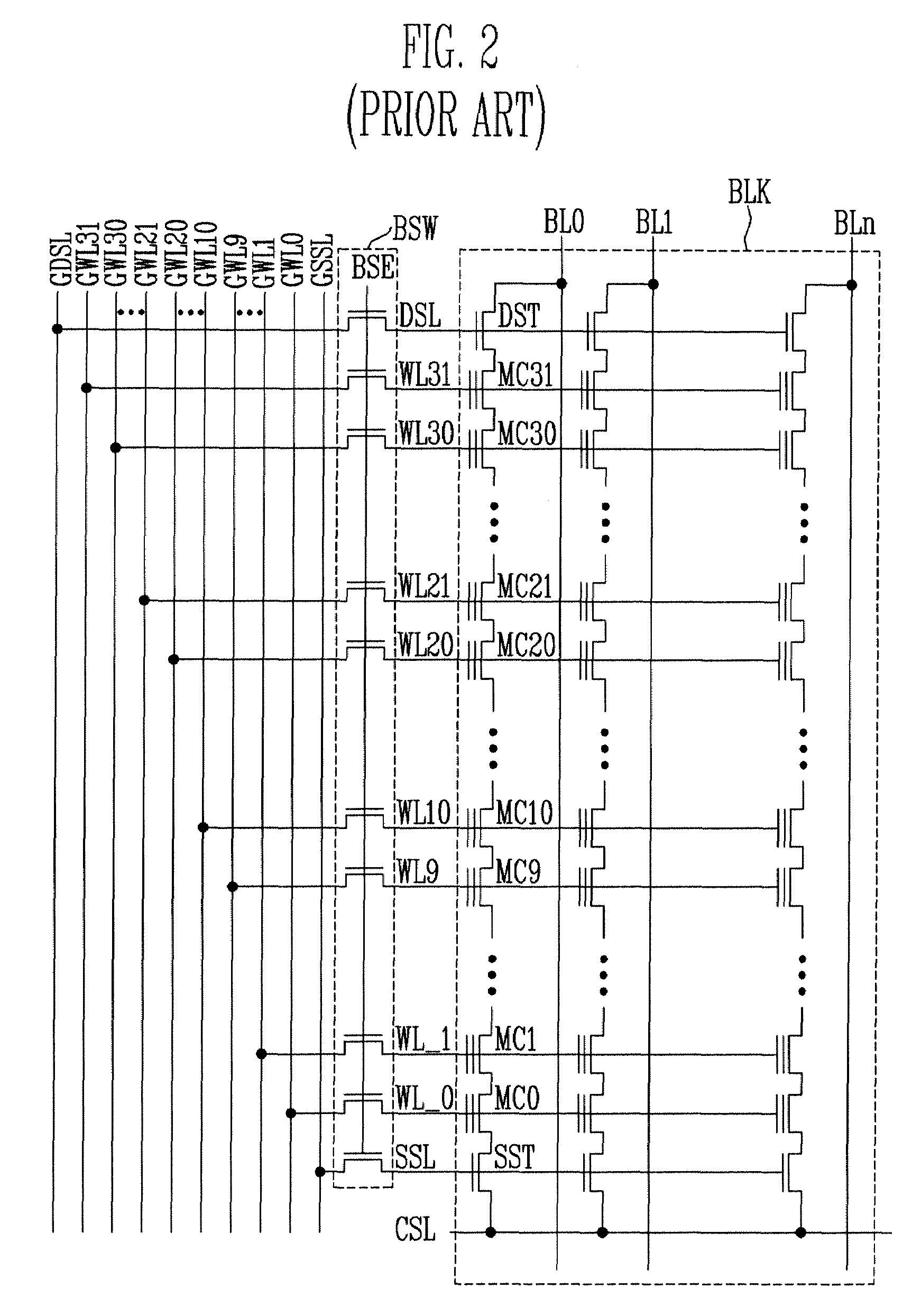

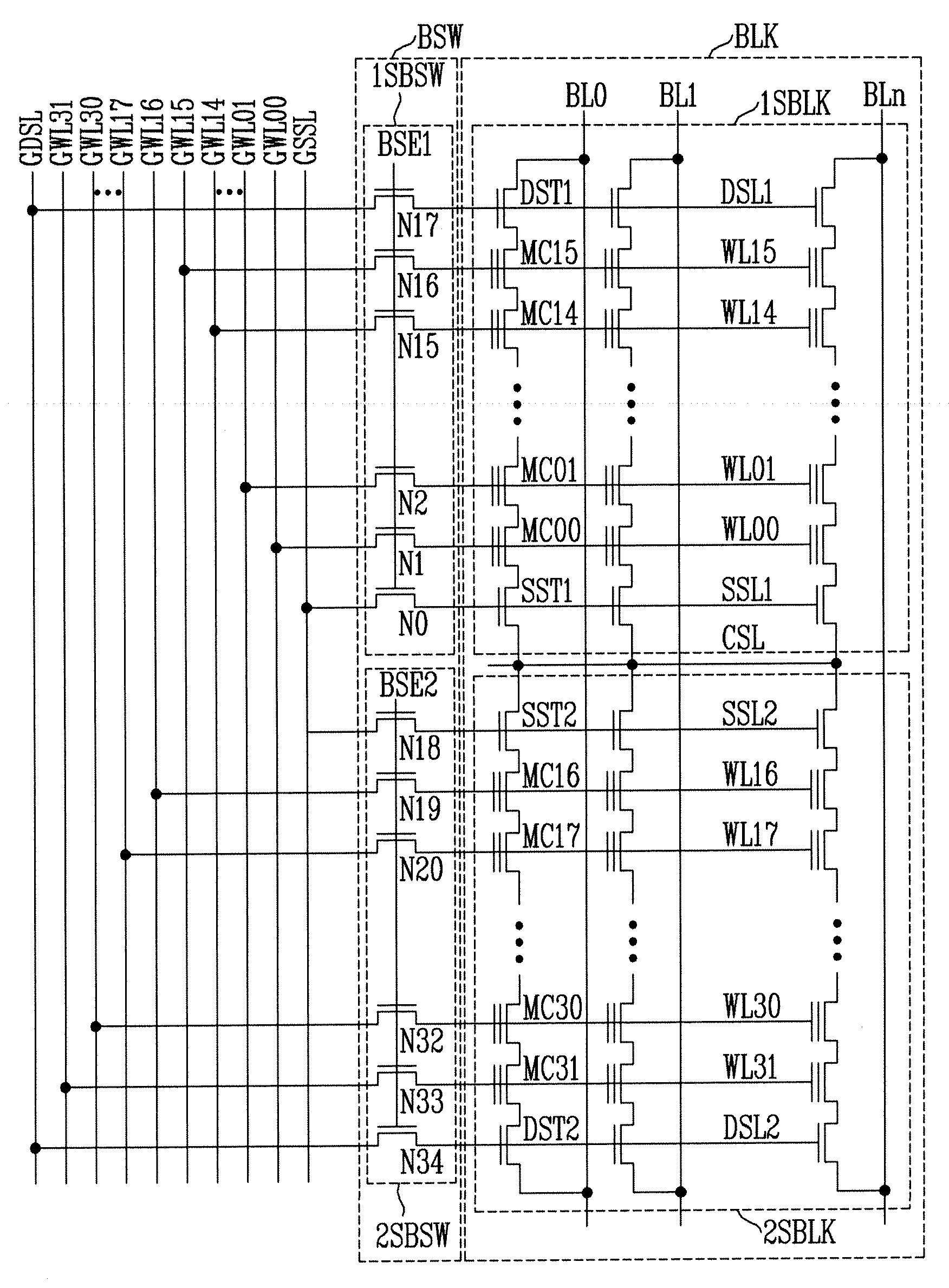

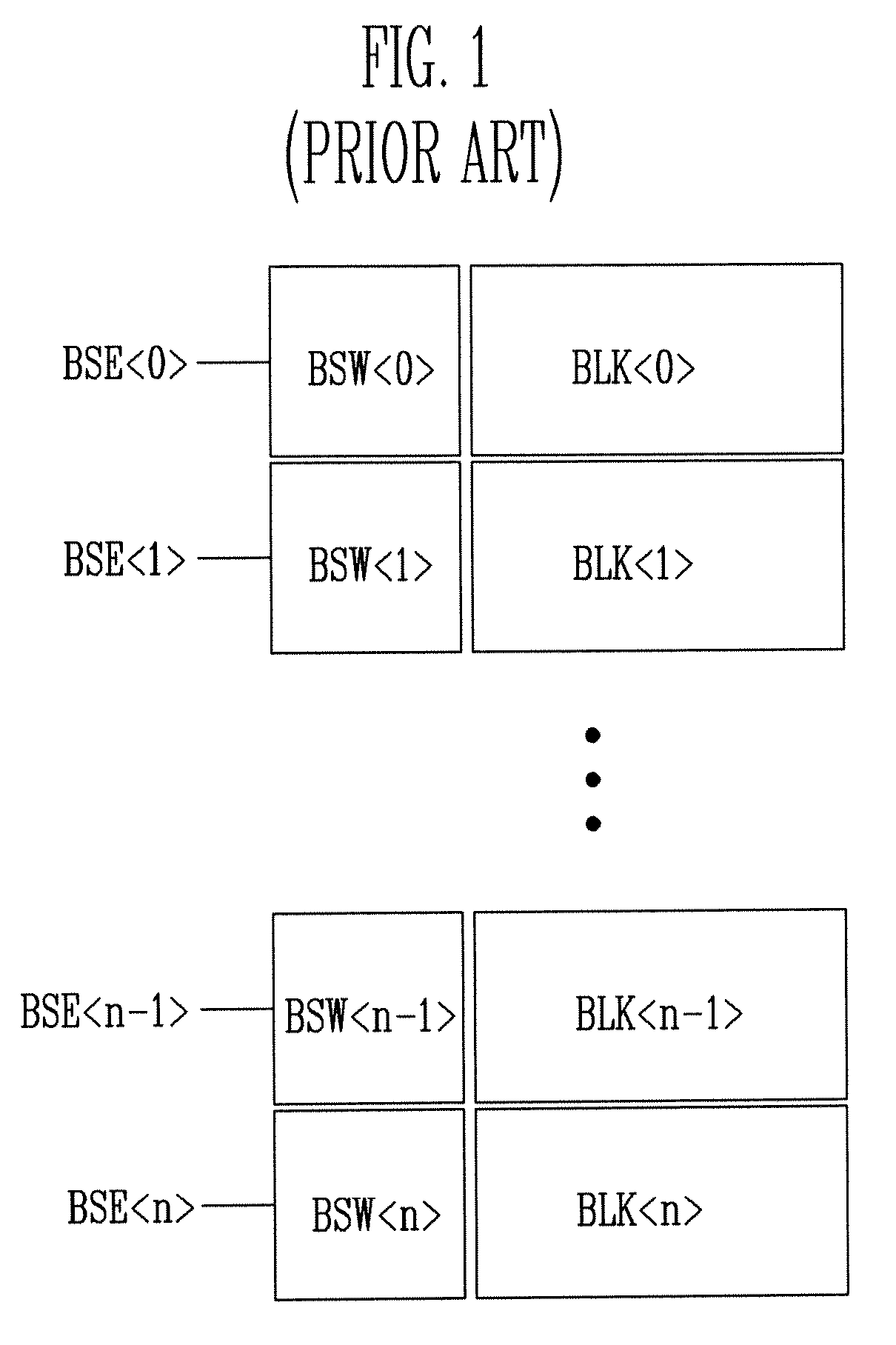

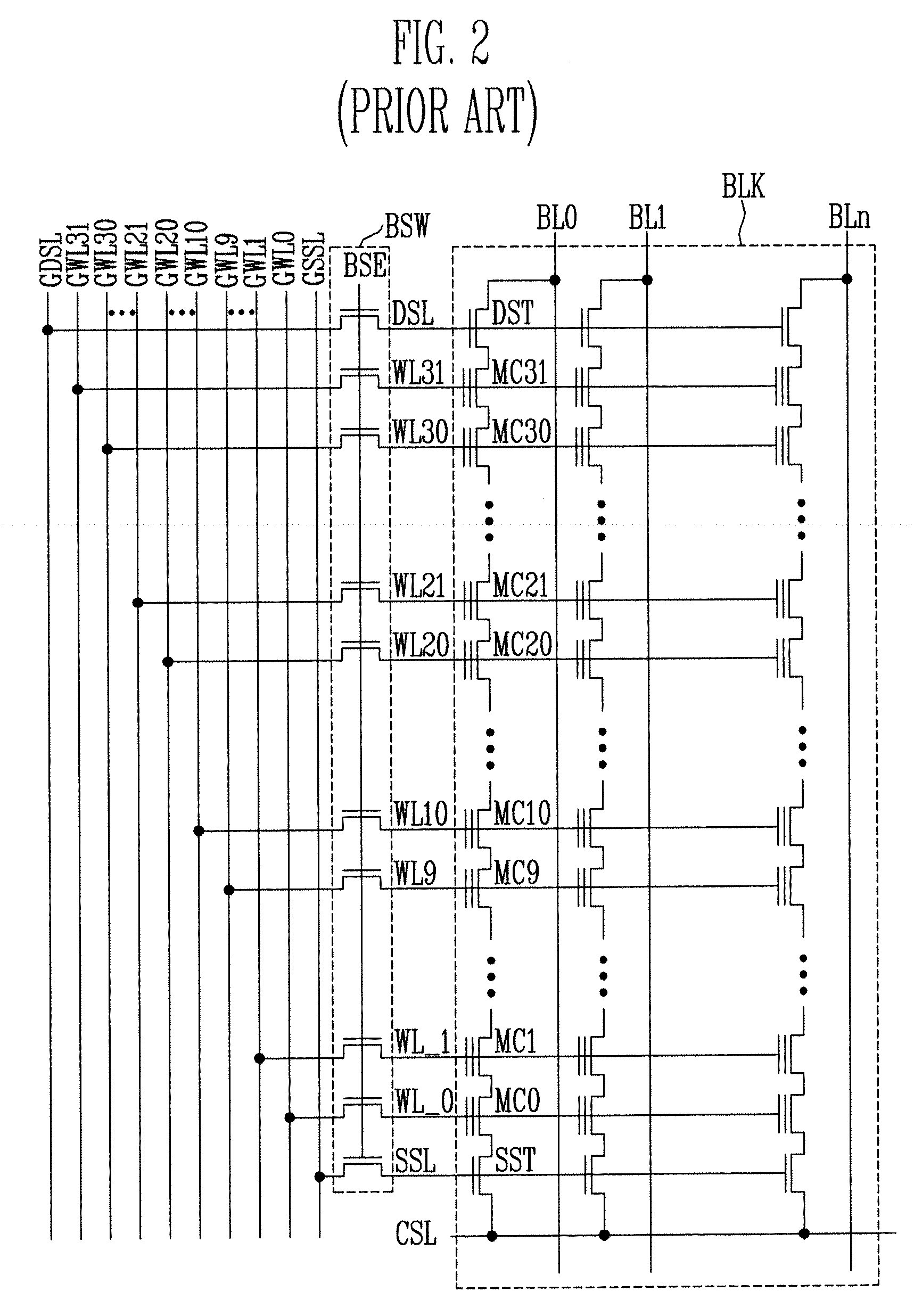

Non-volatile memory device

ActiveUS7315472B2Increase currentLower channel resistanceRead-only memoriesDigital storageOperating systemStorage cell

A non-volatile memory device may include a plurality of memory blocks including memory cells connected in series to bit lines, respectively. Each of the plurality of memory blocks may include a first sub memory block having a first group of memory cells, which are respectively connected in series between first select transistors connected to the bit lines, respectively, and second select transistors connected to a common source line, and a second sub memory block having a second group of memory cells, which are respectively connected in series between third select transistors connected to the bit lines, respectively, and fourth select transistors connected to the common source line.

Owner:SK HYNIX INC

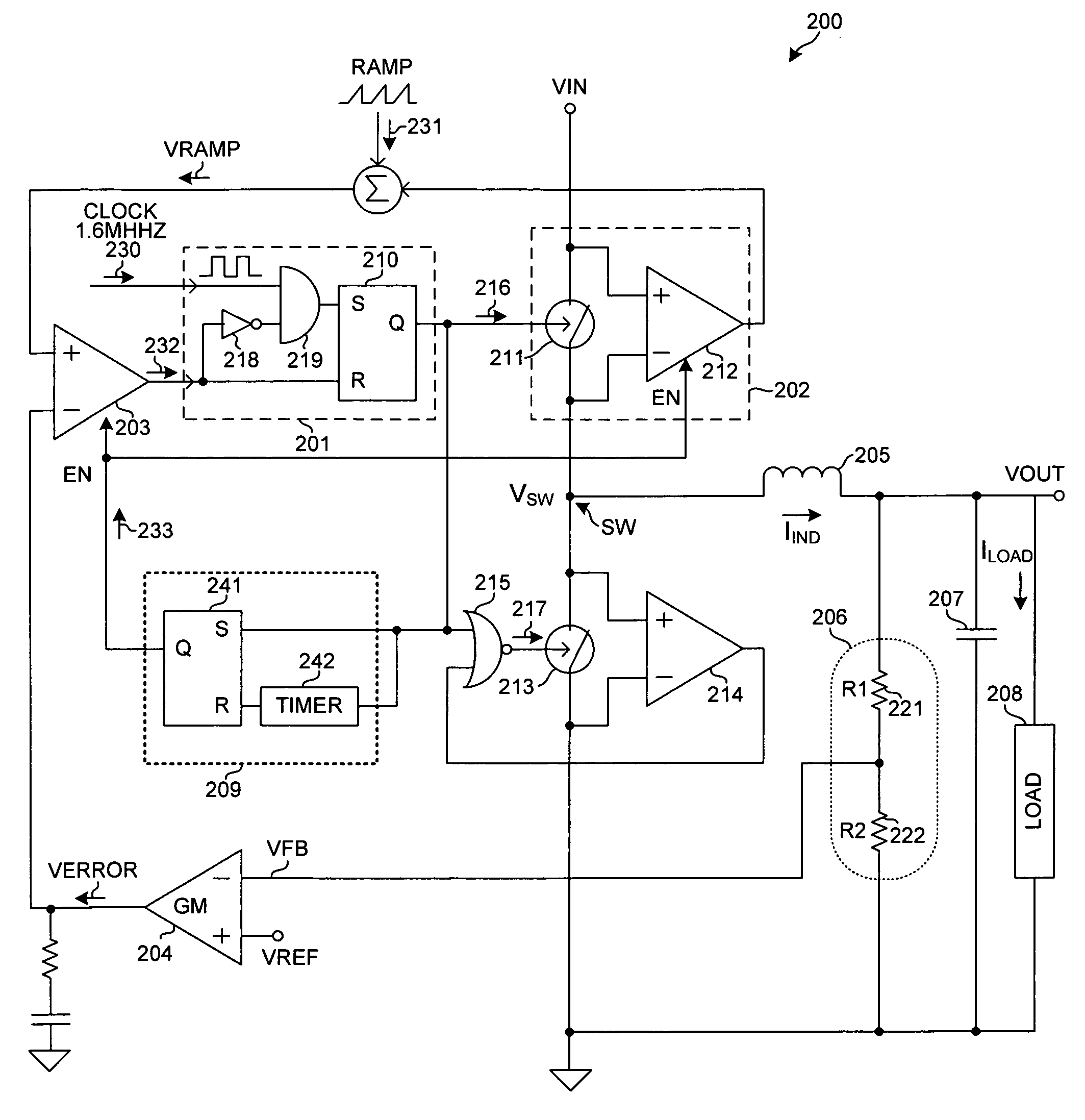

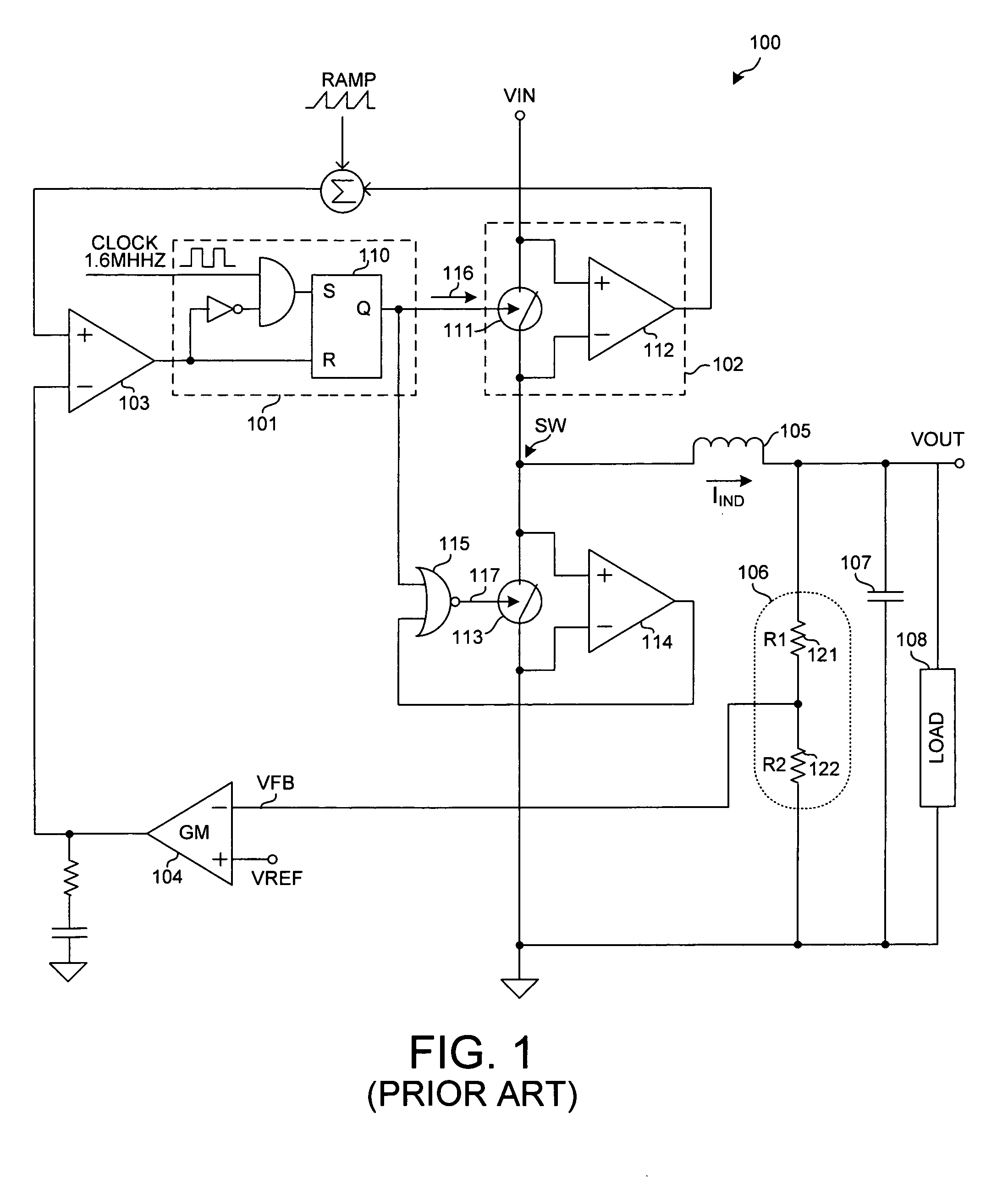

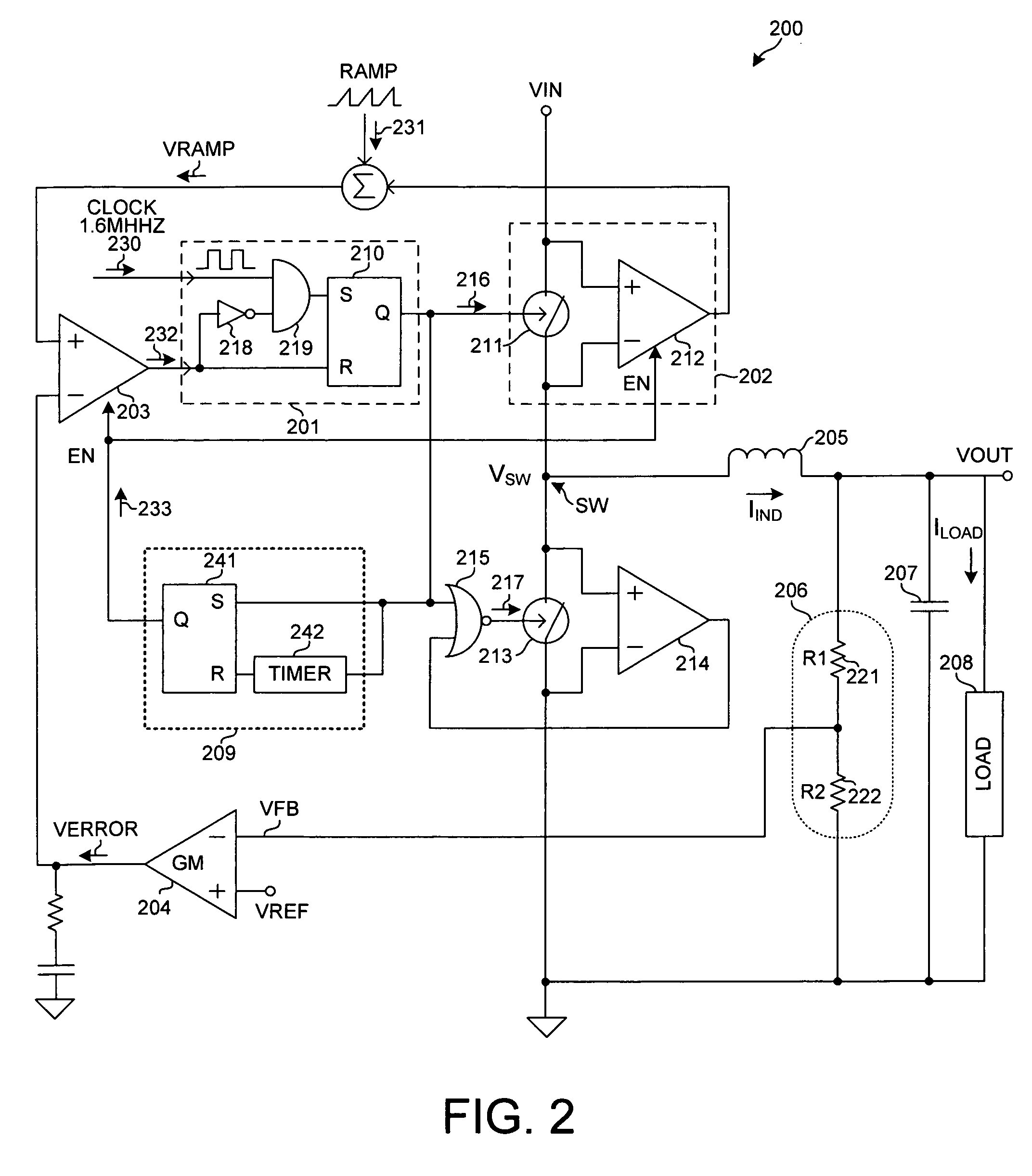

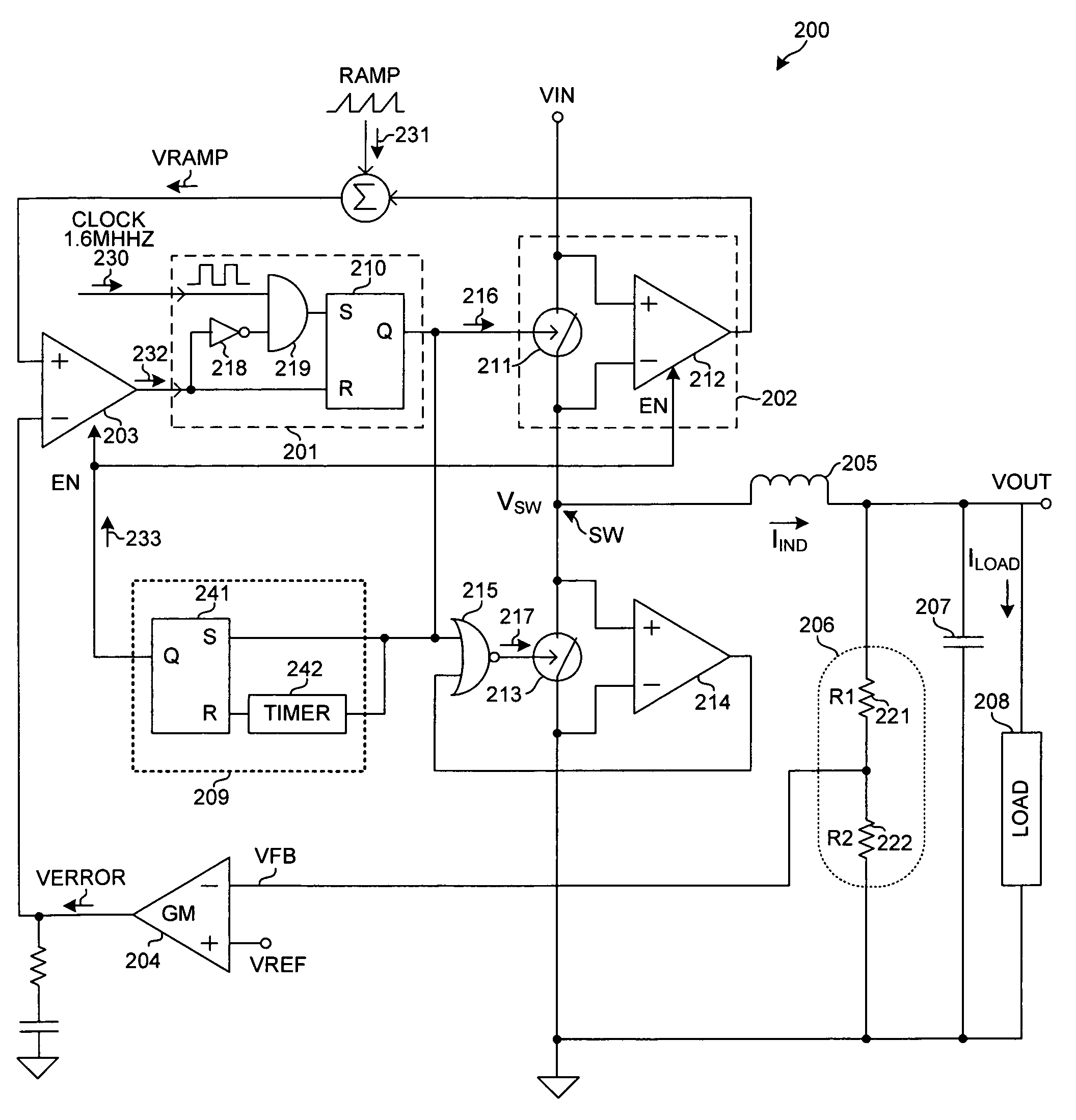

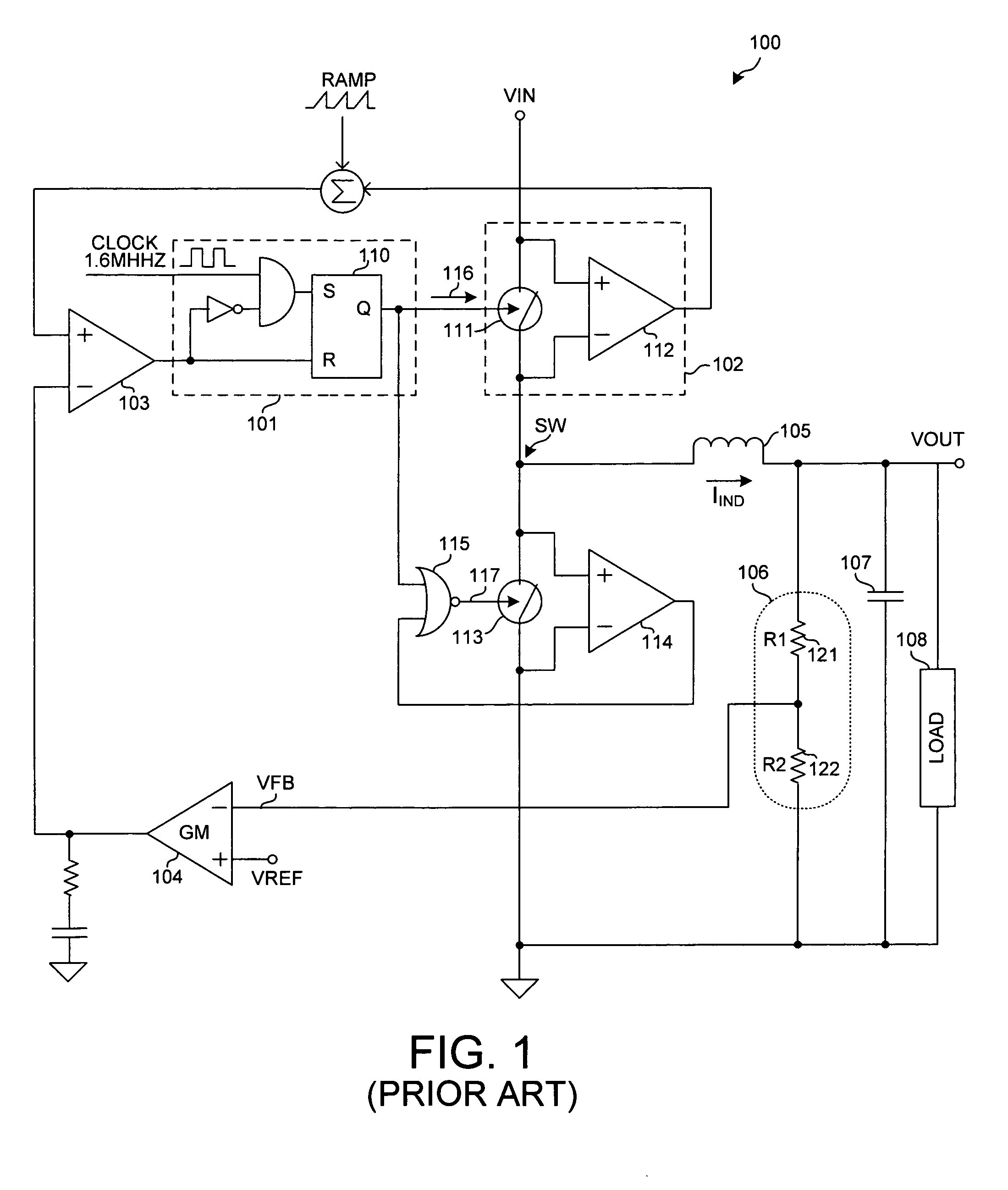

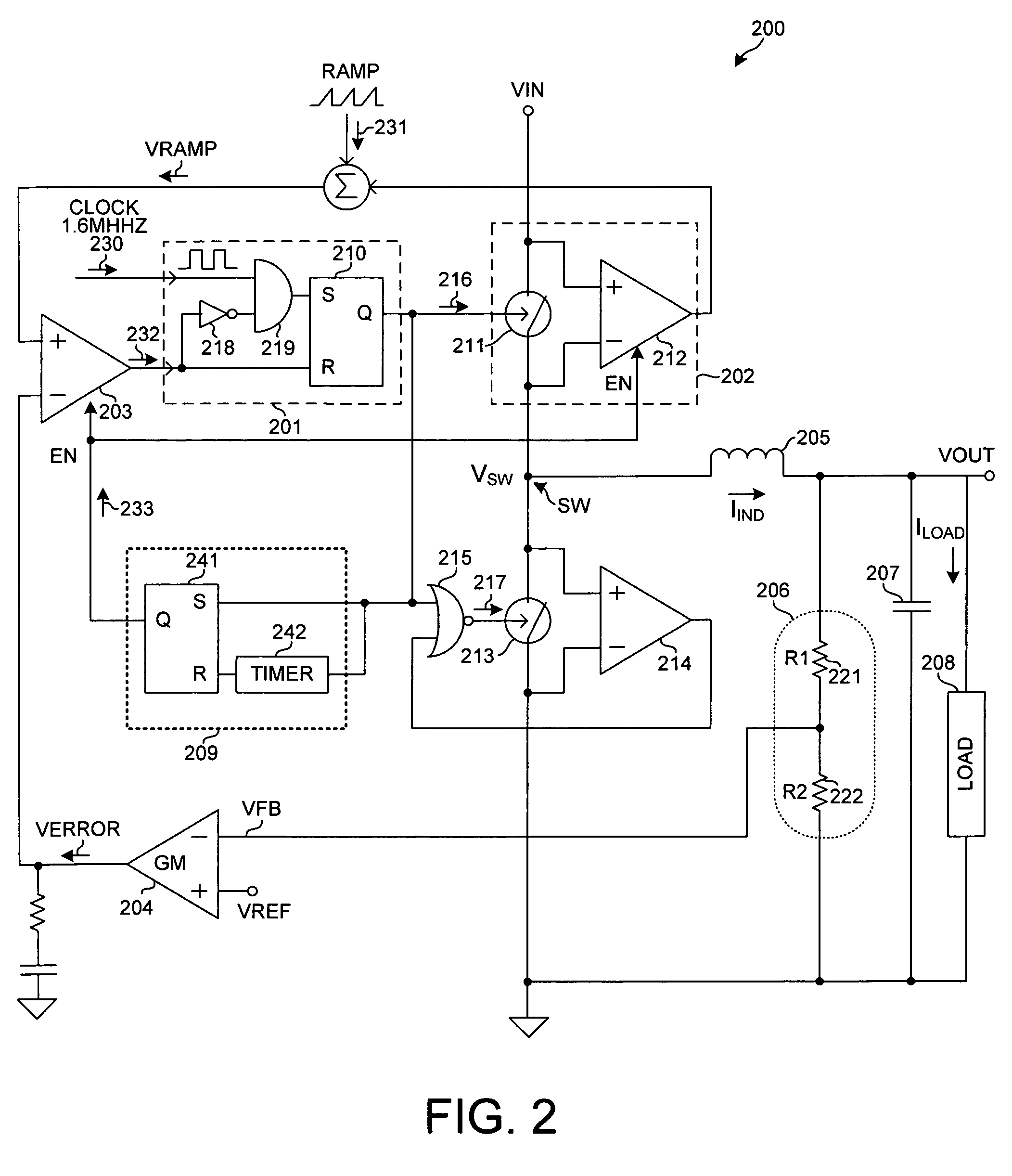

High efficiency voltage regulator with auto power-save mode

ActiveUS20090237053A1Less powerImprove efficiencyAc-dc conversion without reversalEfficient power electronics conversionOperation modeLight load

A DC-to-DC converter comprises an error amplifier, a comparator, a PWM controller, a power switch unit, and a control signal monitoring circuit. The PWM controller receives a comparison signal from the comparator and generates a digital control signal that controls the power switch unit such that the DC-to-DC converter supplies a regulated voltage onto a load. The control signal monitoring circuit monitors the digital control signal and detects either a heavy load or a light load condition based on characteristics of the digital control signal. Under the light load condition, the monitoring circuit generates a first enabling signal such that the DC-to-DC controller operates in a power-save mode. Under the heavy load condition, the monitoring circuit generates a second enabling signal such that the DC-to-DC controller operates in a normal operation mode. The DC-to-DC converter consumes substantially less power in the power-save mode than in the normal operation mode.

Owner:ACTIVE SEMI

High efficiency voltage regulator with auto power-save mode

ActiveUS7800351B2Improve efficiencyLower channel resistanceAc-dc conversion without reversalEfficient power electronics conversionControl signalEngineering

Owner:ACTIVE SEMI

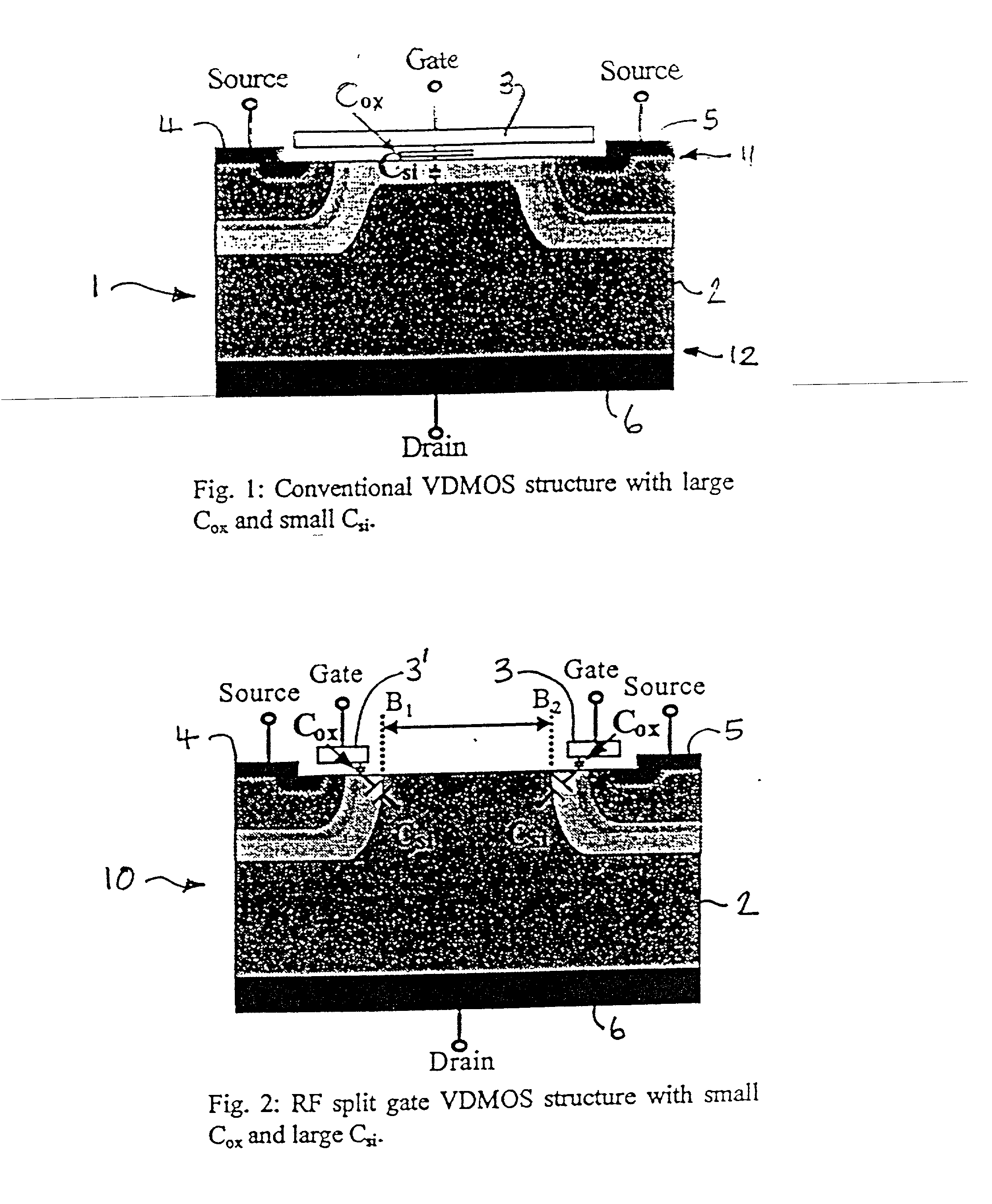

Semiconductor device

InactiveUS20020017682A1Efficient and reliable for applicationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower application

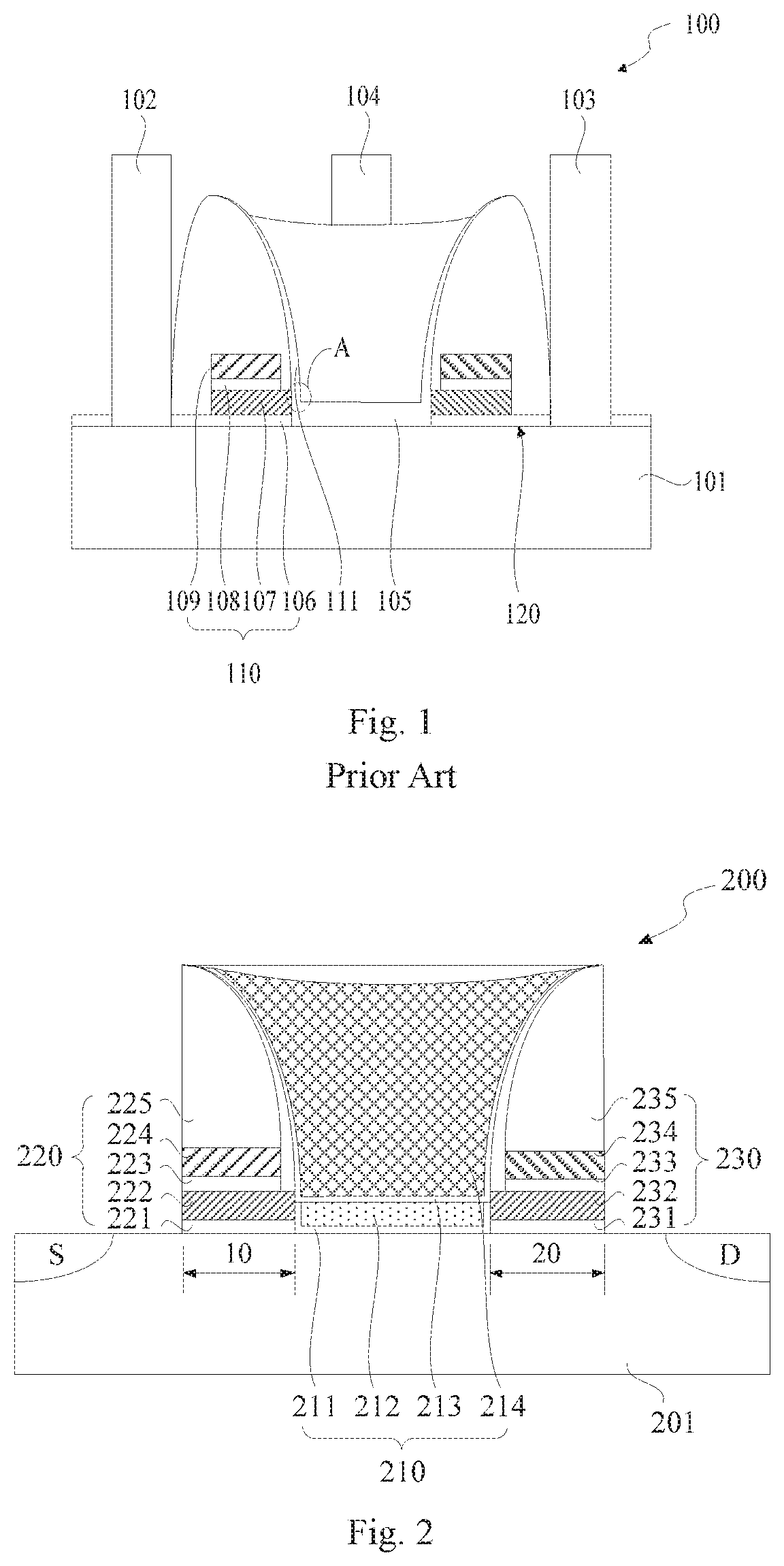

A VD (vertical diffusion) MOSFET device for use in RF power applications has a split gate structure and an additional, dummy gate is provided between the spaced apart gates and, in operation of the device, is electrically coupled to source electrodes provided outside of the gates. The split gate structure reduces gate overlap capacitance and the dummy gate induces depletion in the semiconductor body of the device and reduces the substrate capacitance. The gate overlap capacitance and the substrate capacitance both contribute to the feedback capacitance of the device which has to be as low as possible for high frequency operation. By reducing both of these components, the invention provides advantageous high frequency operation.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

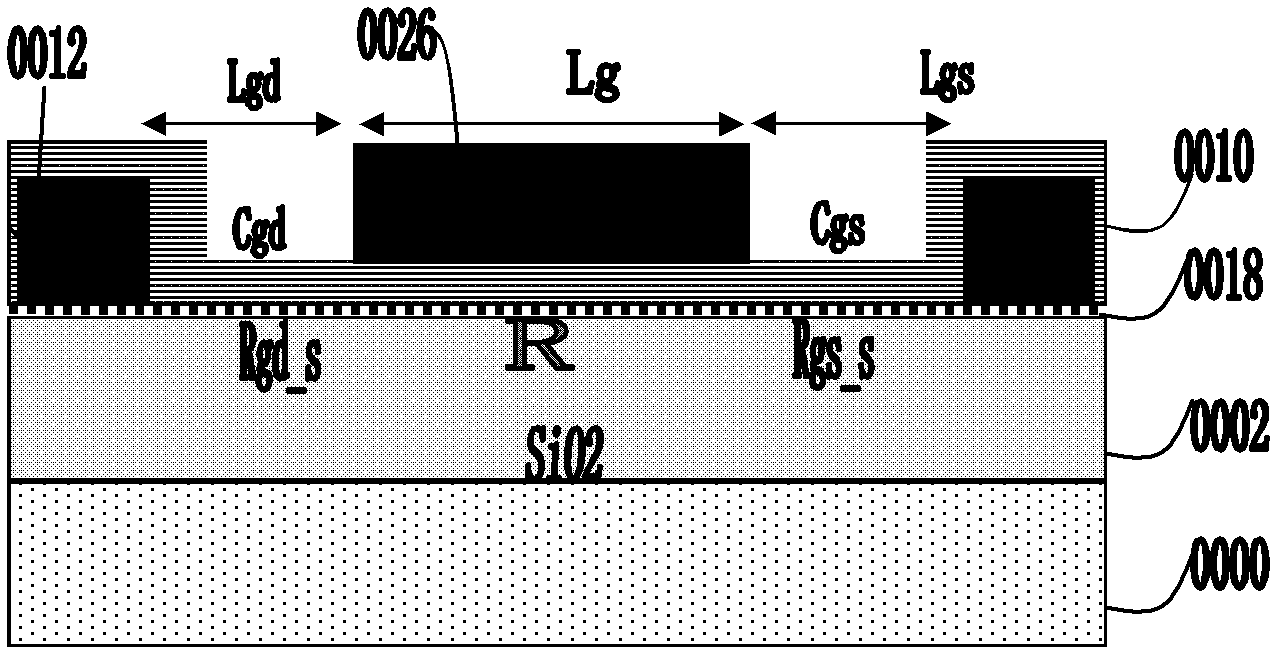

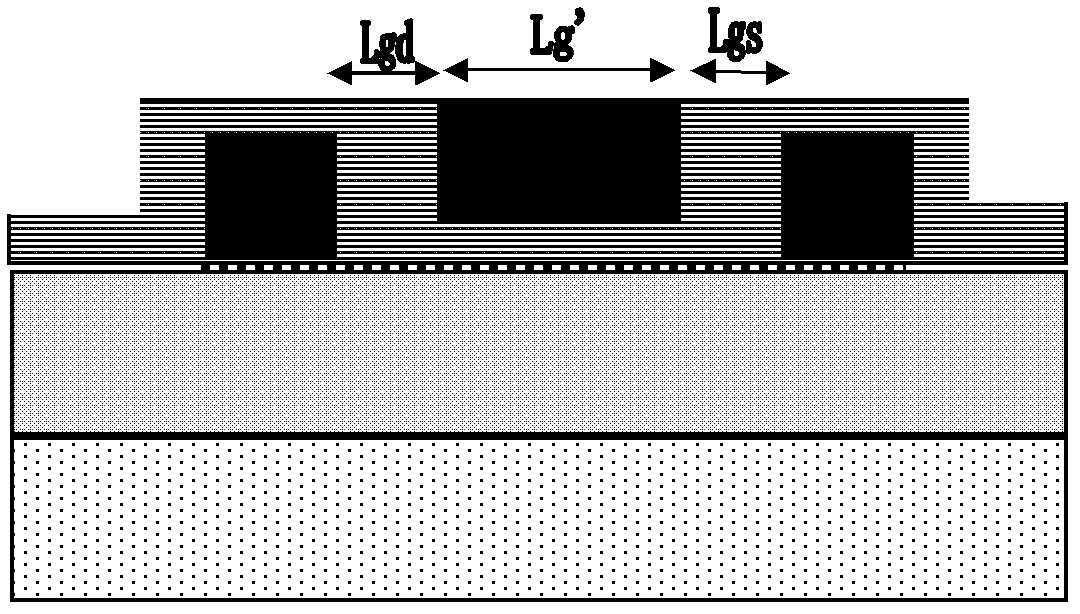

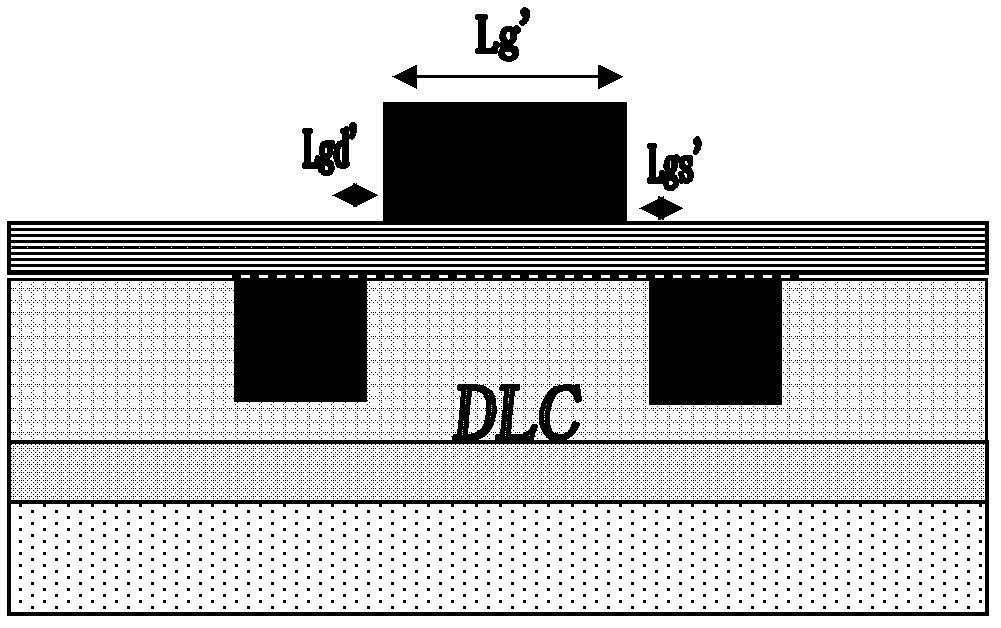

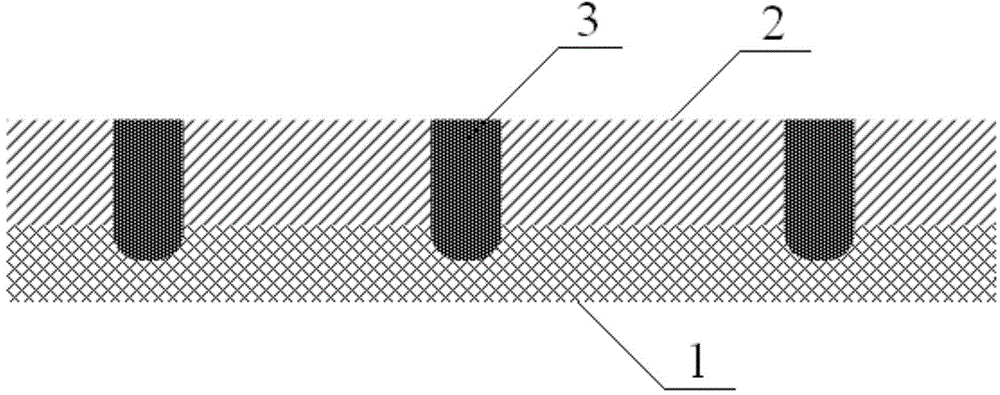

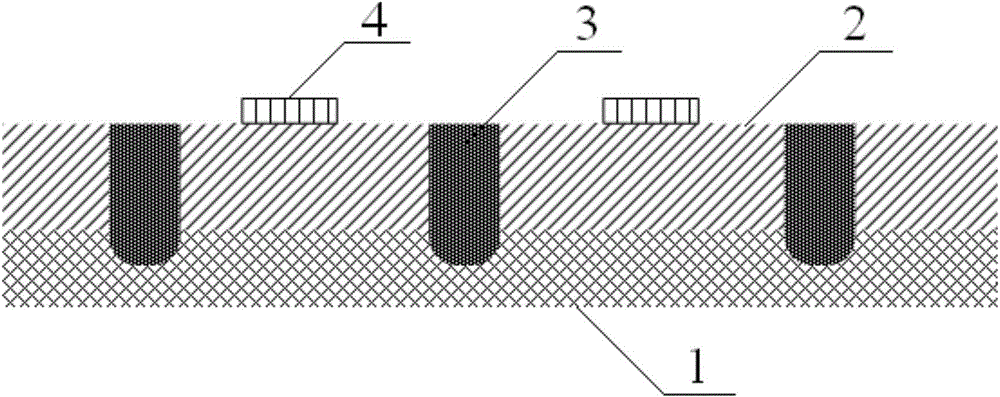

Source-drain buried graphene transistor device on diamond-like carbon substrate and manufacture method

InactiveCN103000669ALower channel resistanceReduce horizontal spacingSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDiamond-like carbon

A source-drain buried graphene transistor device on a diamond-like carbon substrate and a manufacture method are applicable to radio frequency communication. The manufacture method includes: firstly, depositing a layer of diamond-like carbon amorphous carbon smooth in surface and stable in chemical property on the substrate by the aid of a magnetic filtered cathode vacuum arc system; secondly, etching a source trench and a drain trench on the diamond-like carbon amorphous carbon insulating layer and filling electrode metal into the trenches; thirdly, planarizing and cleaning the surface of the substrate prior to transferring graphene grown by a chemical vapor deposition method to the cleaned substrate; fourthly, growing gate insulating dielectric by an atomic layer deposition method and sputtering gate electrode metal; and finally, forming a metal gate by means of reactive ion etching and depositing low-K insulating dielectric to protect the device. Carrier mobility of a graphene transistor is high, and the source-drain buried structure is capable of decreasing the graphene length of a region uncovered by the gate, so that gate-source capacitance, gate-drain capacitance and channel resistance are reduced, and high-frequency performance and efficiency of the graphene transistor are improved. The source-drain buried graphene transistor device can be widely applied to small-sized high-frequency graphene integrated circuits.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

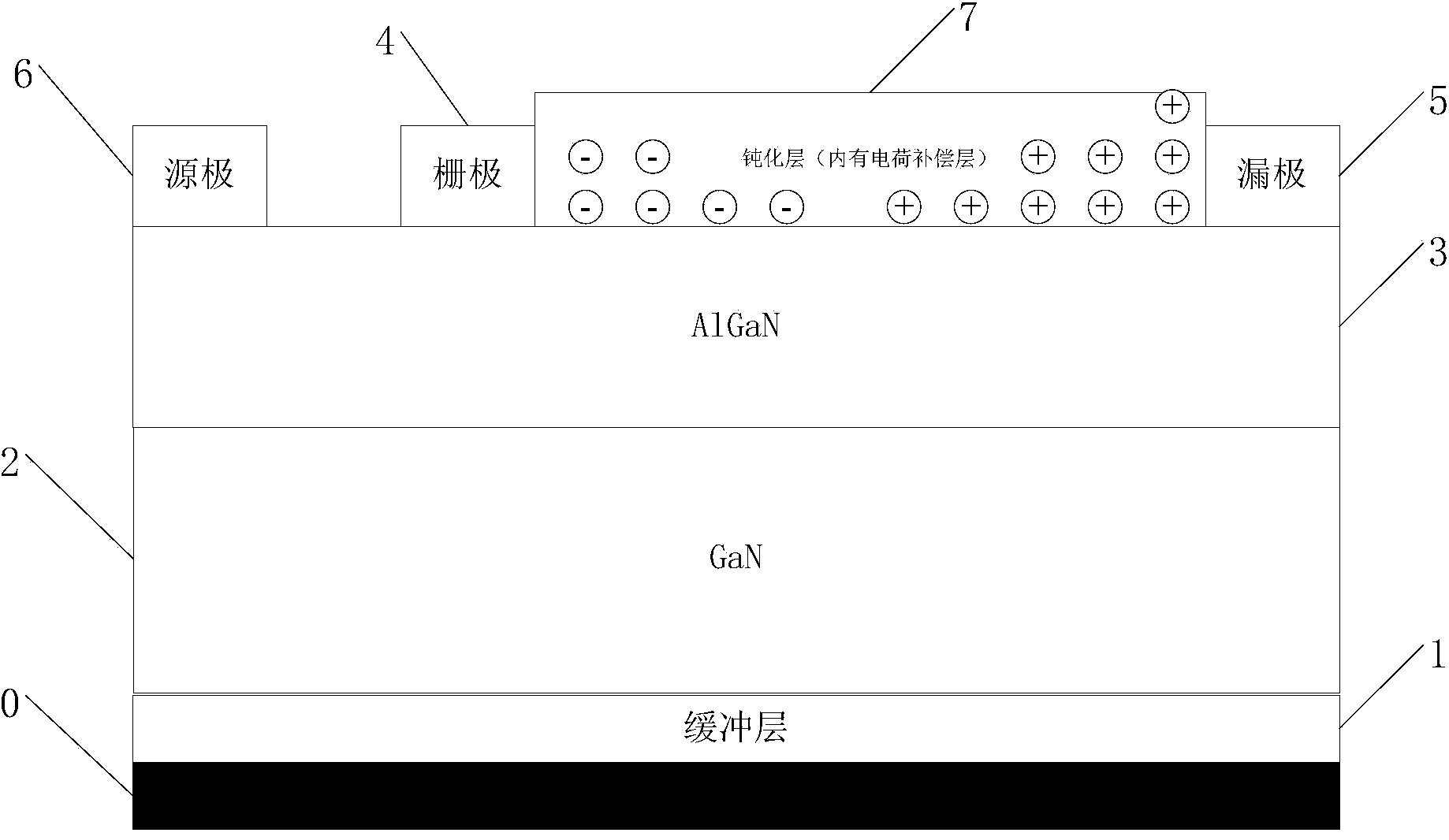

AlGaN/GaN heterojunction field effect transistor

ActiveCN104009076ADoes not affect junction polarization effectsHigh electric field reductionSemiconductor devicesElectric field modulationHeterojunction

The invention discloses a novel AlGaN / GaN high-electronic-mobility transistor with the passivation layer charge compensation function. According to the novel crystal structure, charges are injected into a surface passivation layer between the grid electrode and the drainage electrode of the transistor, so that a charge compensation layer is formed, the charges exist on the surface of the transistor, surface electric fields are re-distributed through the electric field modulation effect on the premise that the AlGaN / GaN heterojunction polarization effect is not affected, a new electric field peak is generated, in this way, high electric fields on the edge of the grid electrode and at the drainage end are lowered, the surface electric fields tend to be even, and compared with a traditional structure, the breakdown voltage and the reliability of devices are improved remarkably; in addition, due to the fact that the charge compensation layer has the charge compensation function, the carrier concentrations of channels are re-distributed, the on resistance of the devices is reduced, and the output current is increased.

Owner:XIDIAN UNIV

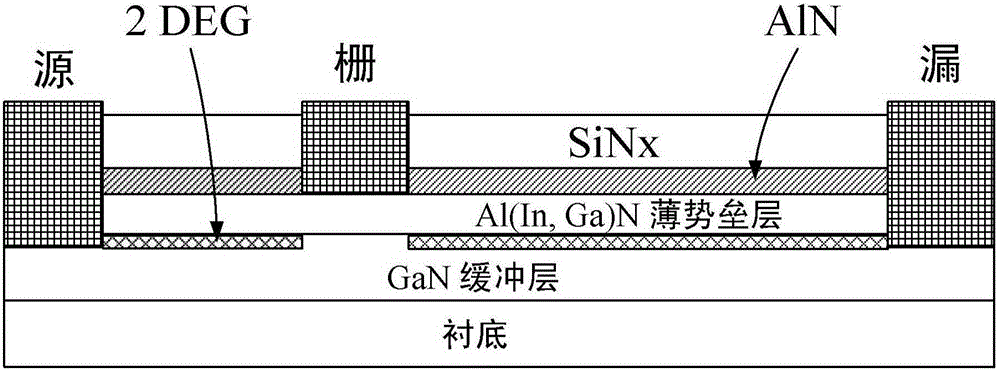

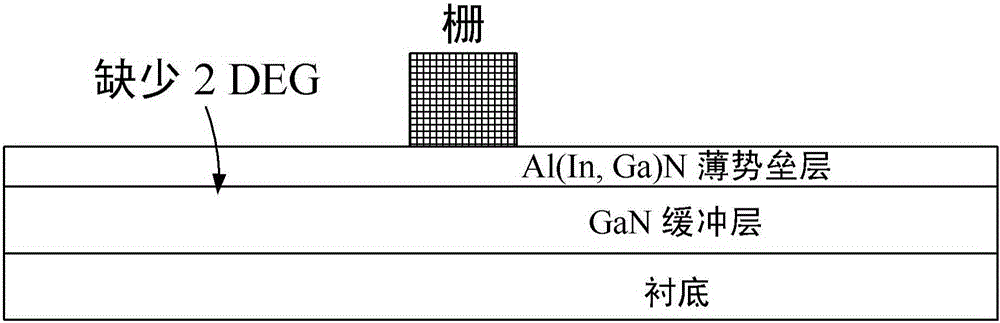

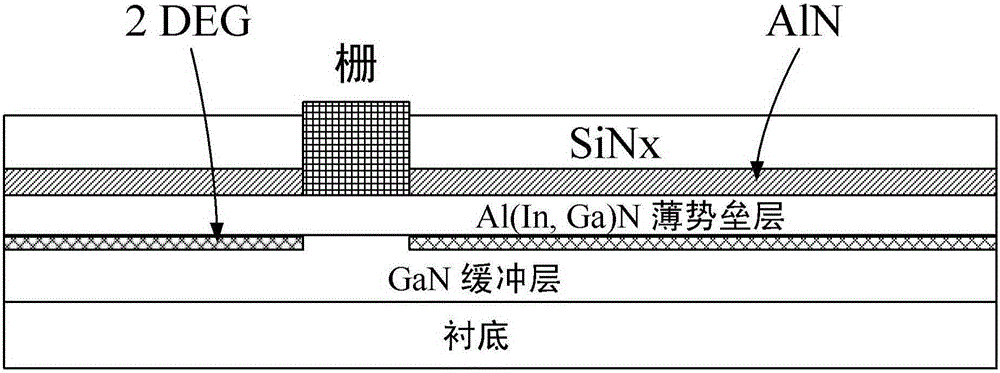

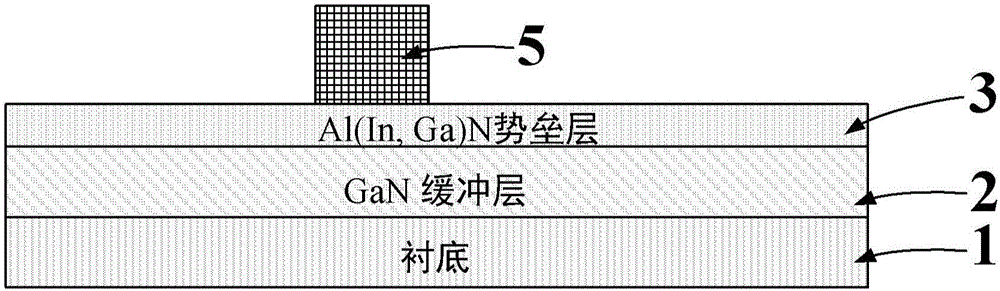

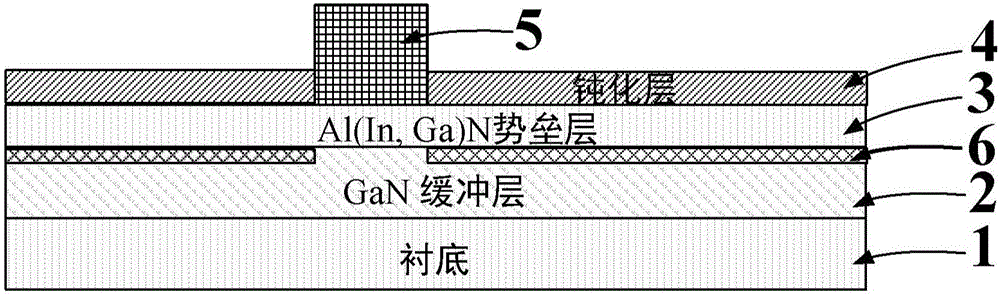

GaN-based enhanced power electronic device and preparation method thereof

InactiveCN105355555ASolve process repeatabilityImprove yieldSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingPower flowOptoelectronics

The invention discloses a GaN-based enhanced power electronic device and a preparation method thereof. The GaN-based enhanced power electronic device comprises a substrate, a thin barrier Al (In, Ga)N / GaN heterostructure formed on the substrate, and a grid electrode, a source electrode and a drain electrode formed on the thin barrier Al (In, Ga)N / GaN heterostructure, wherein AlN passivation layers are formed in access areas between the grid electrode and the source electrode and between the grid electrode and the drain electrode. The AlN passivation layers with a polarization characteristic are utilized to restore two0-dimension electronic gas in channels of the thin barrier Al (In, Ga)N / GaN heterostructure under the AlN passivation layers, so that the conducting resistance of the device is lowered, and high-voltage current collapse of the device is inhibited. According to the invention, the controllability and the consistency of a threshold voltage of the GaN-based enhanced device are improved, the technology repeatability of the GaN-based enhanced device is eliminated, the yield rate of the GaN-based enhanced electronic device is improved, and the industrialization process of the GaN-based enhanced device is promoted.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

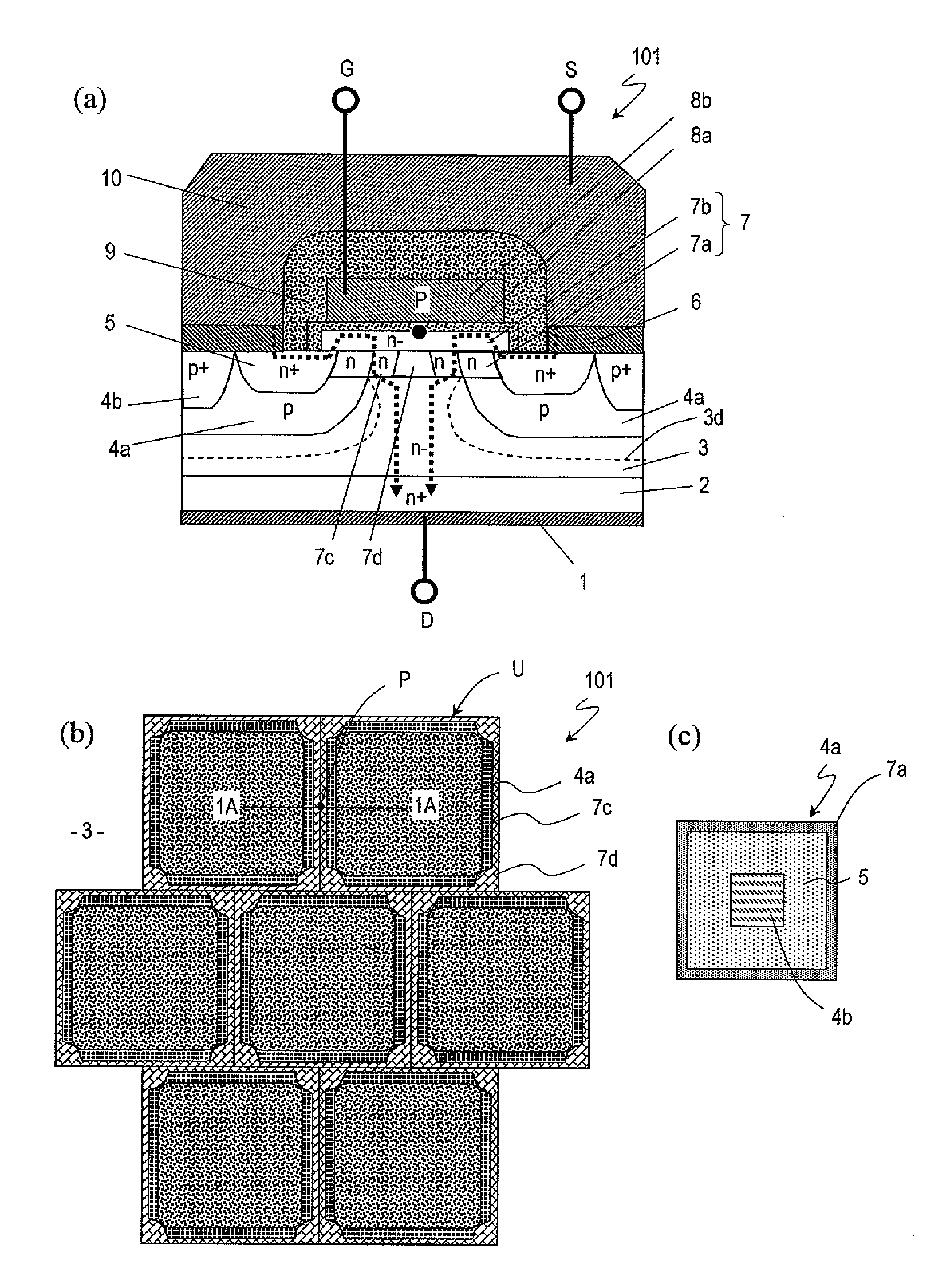

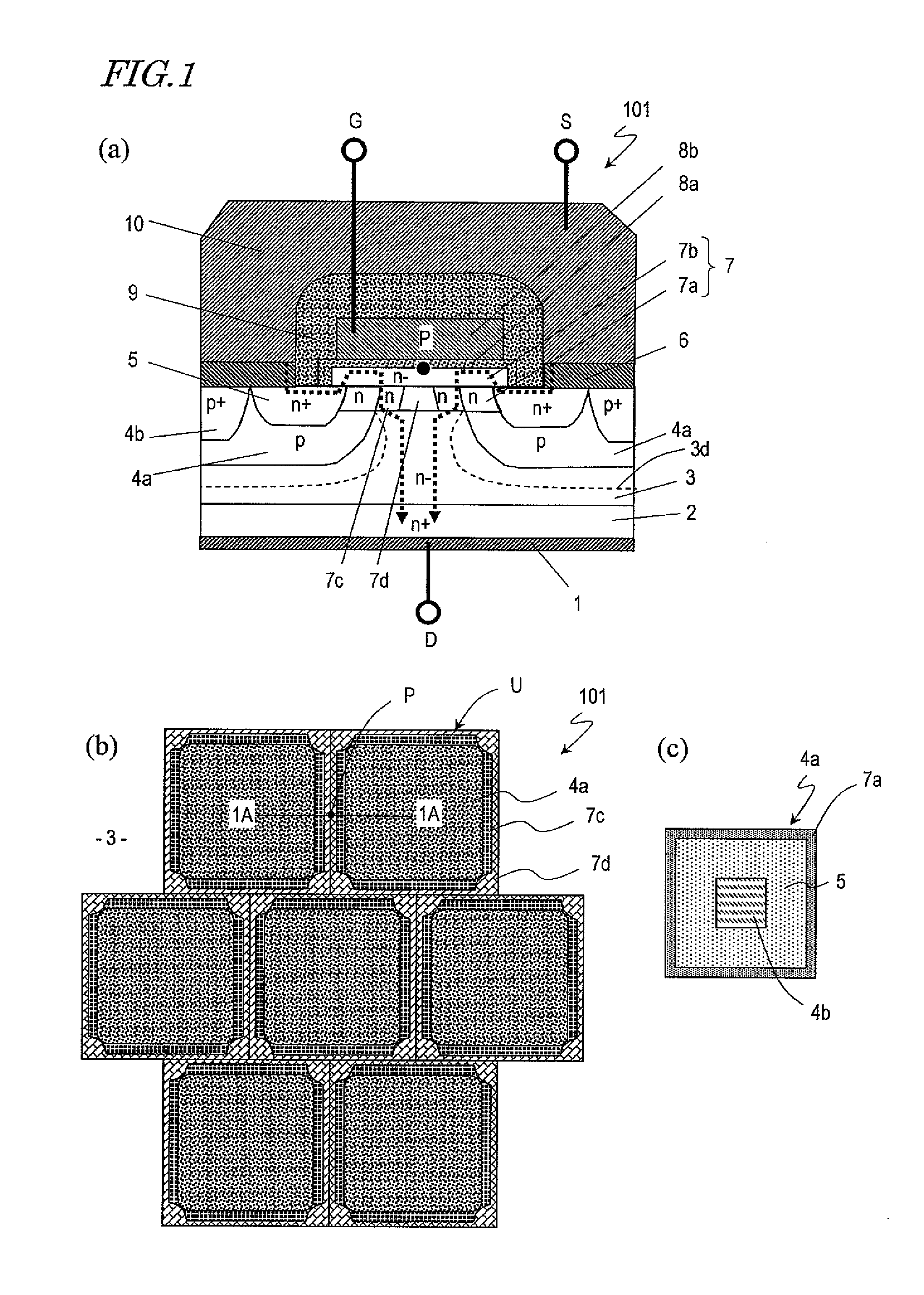

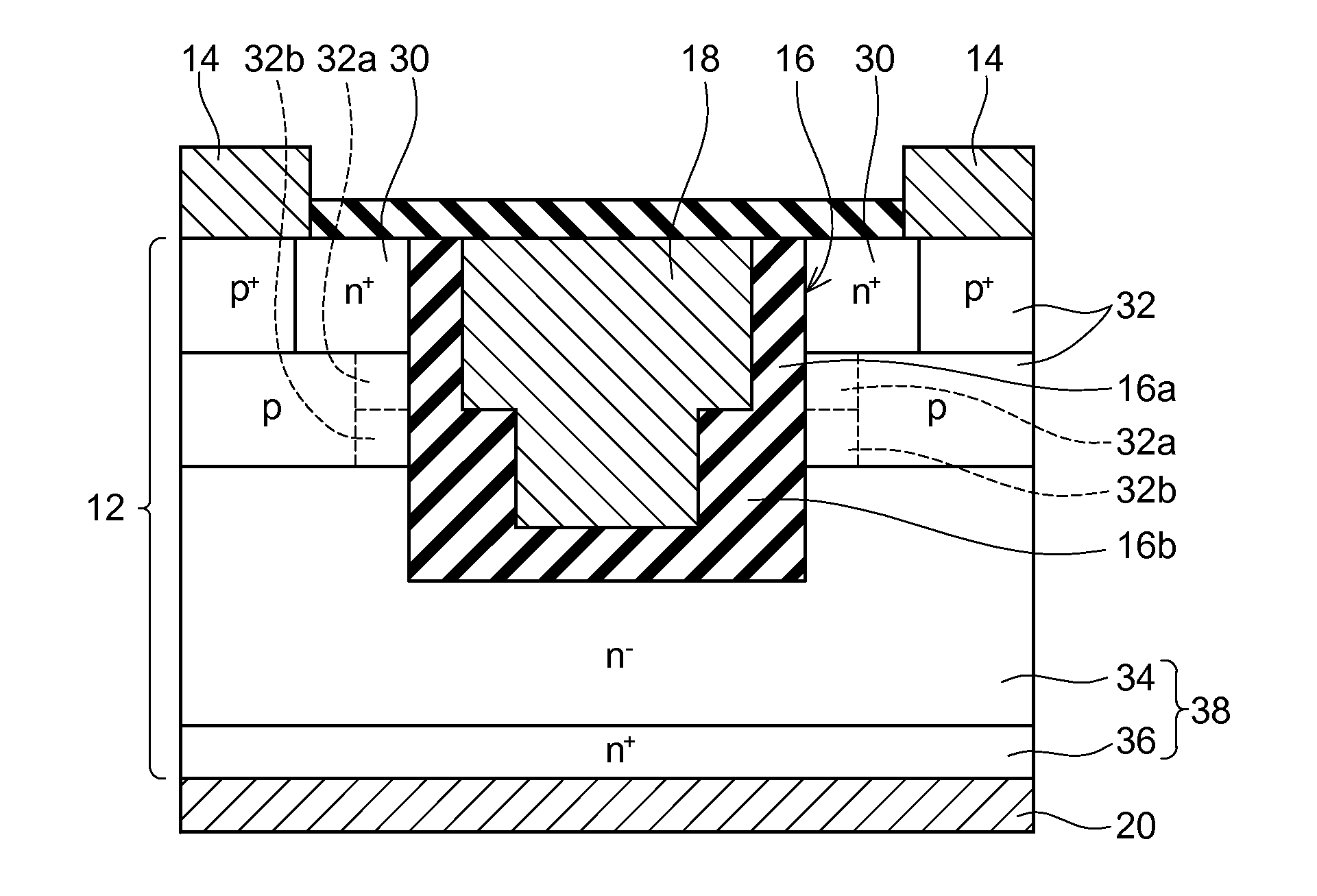

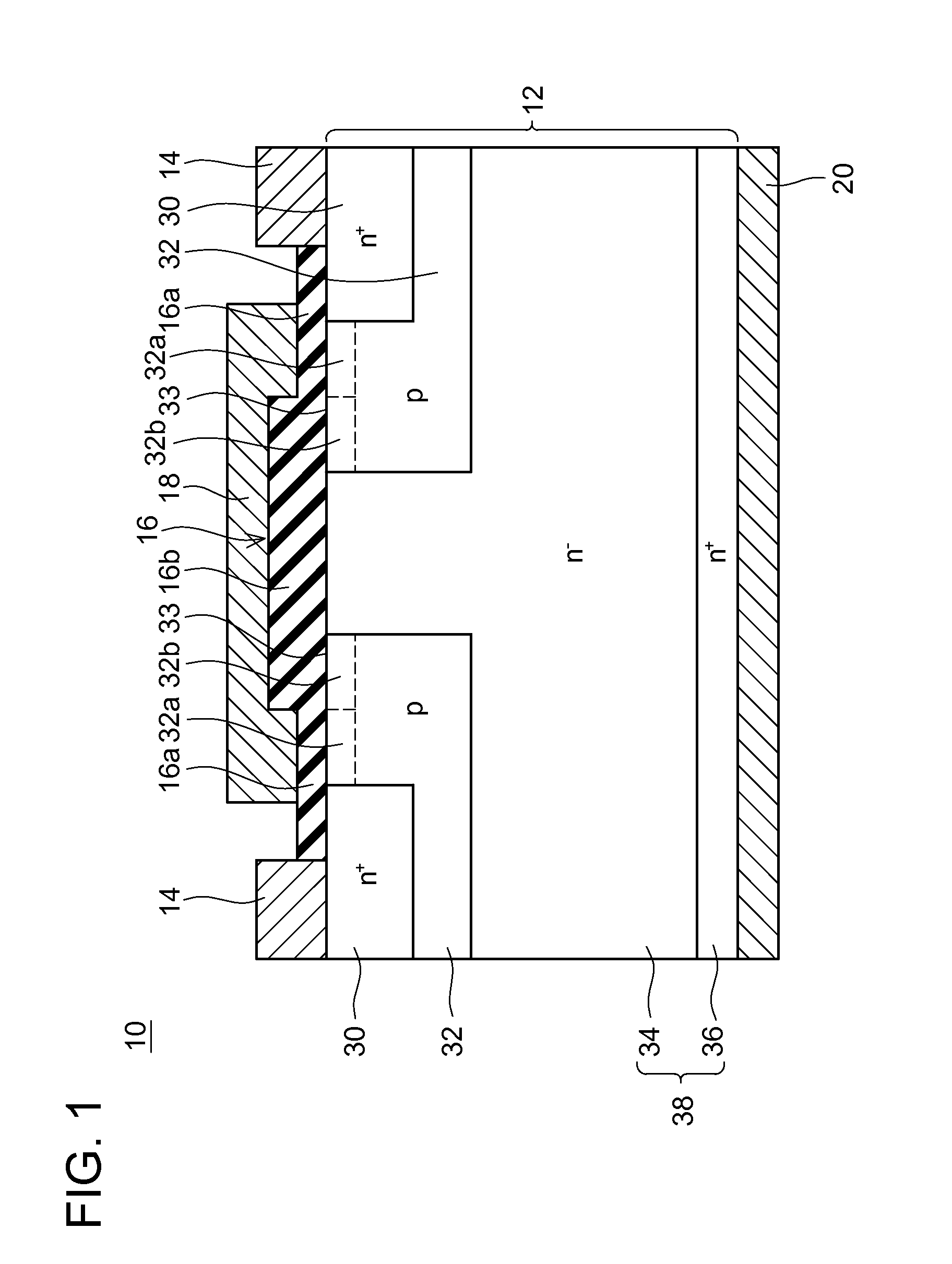

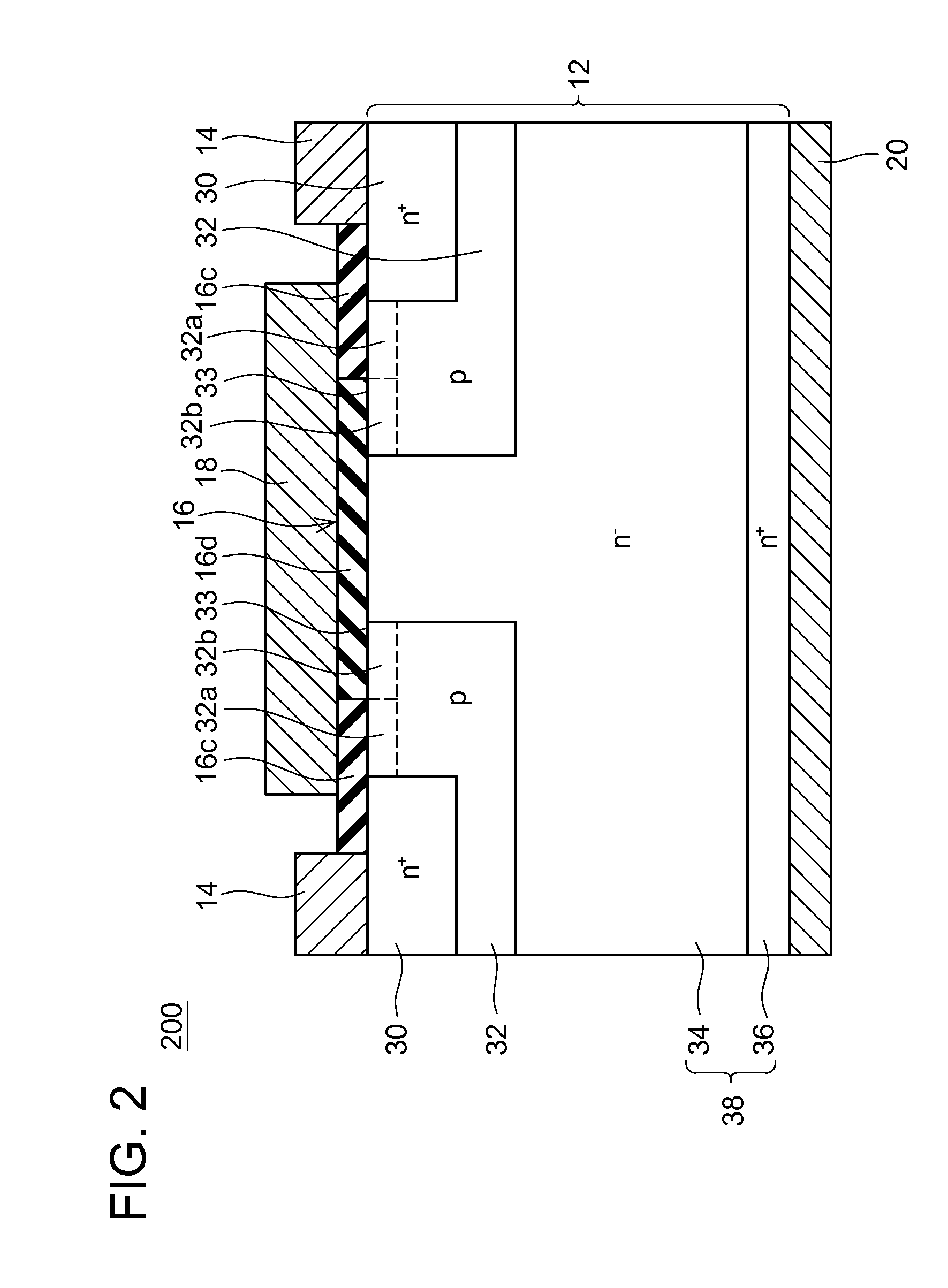

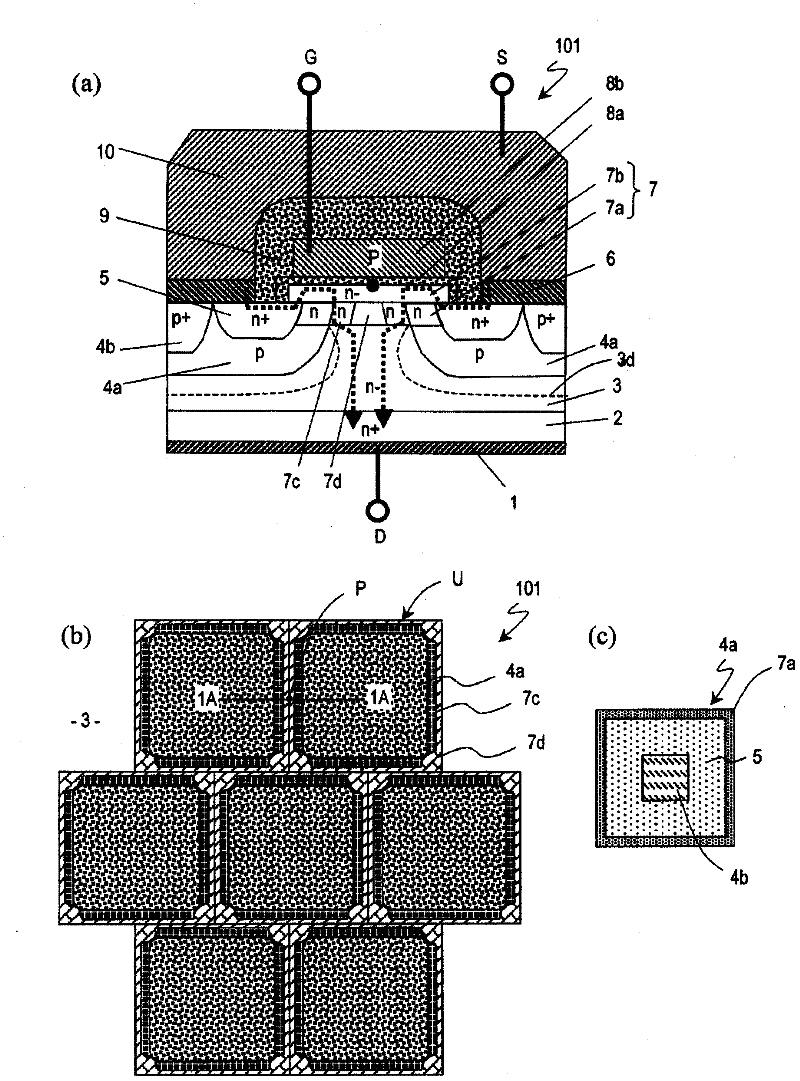

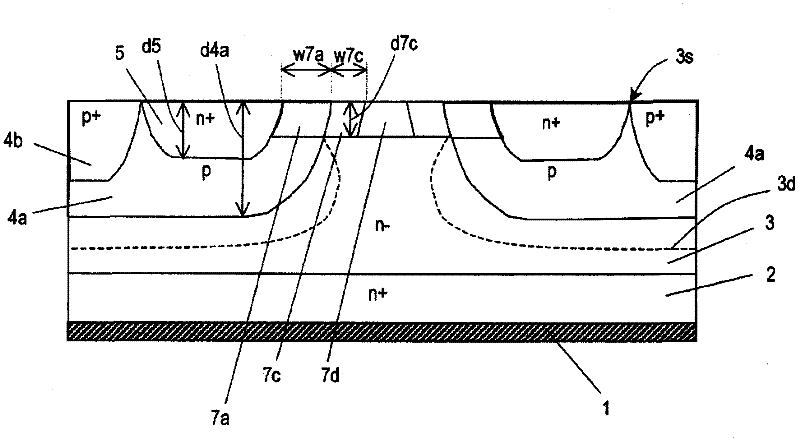

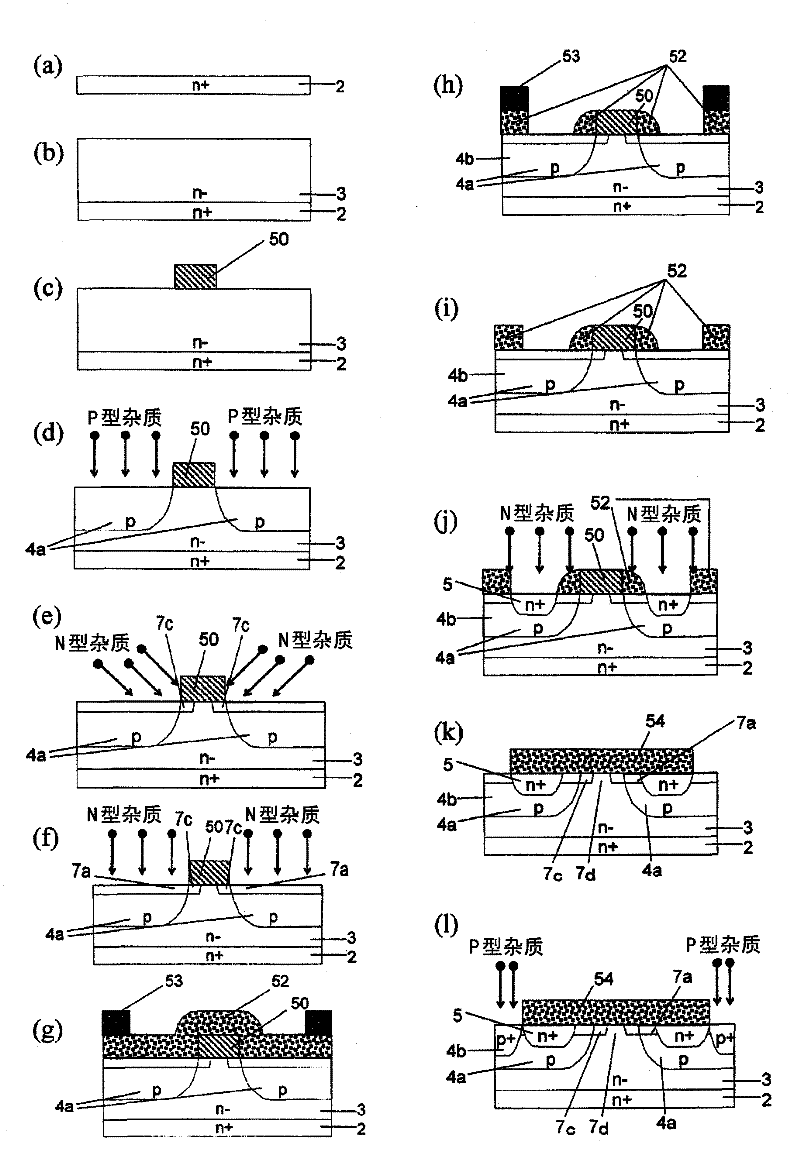

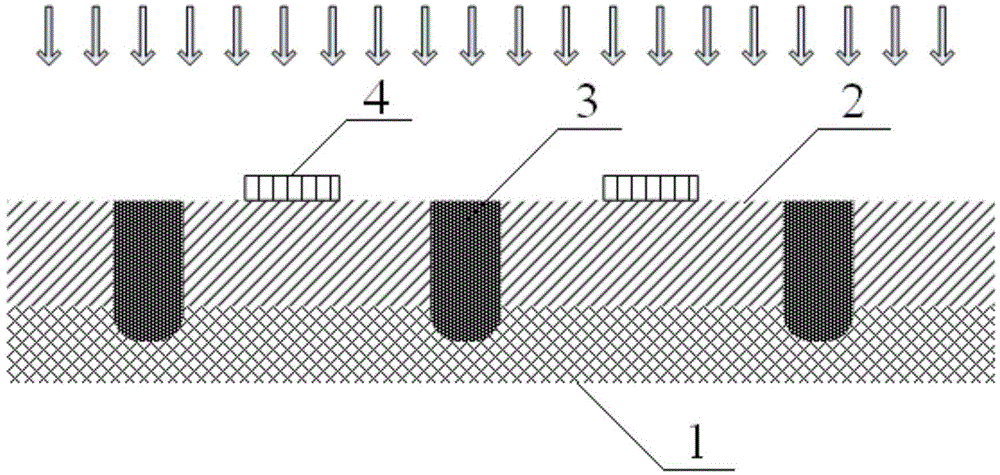

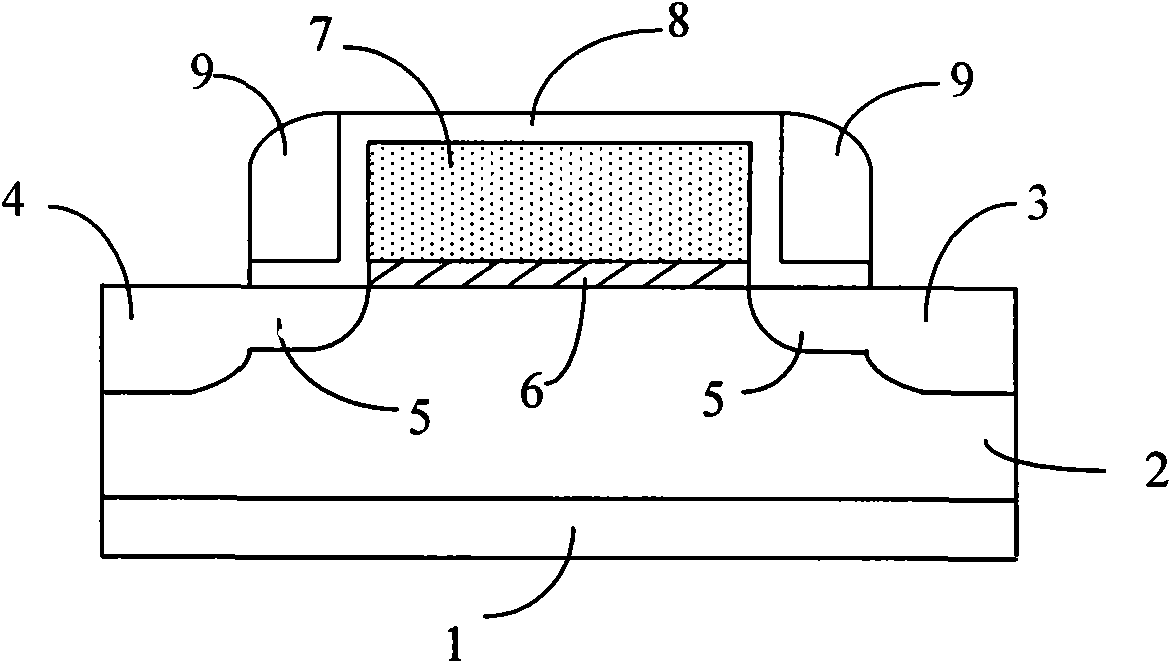

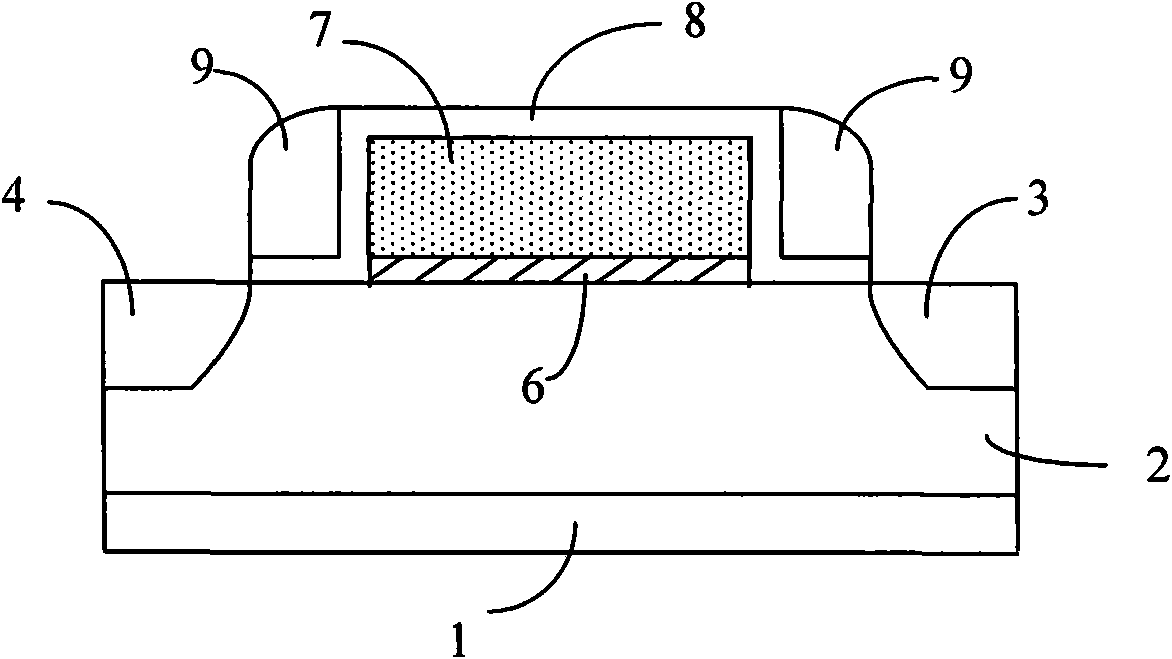

Semiconductor device and method for manufacturing same

InactiveUS20110198616A1Reduce channel resistanceLower channel resistanceTransistorSemiconductor/solid-state device manufacturingImpurityWide-bandgap semiconductor

Each unit cell includes: a drift layer 3 made of an n-type wide bandgap semiconductor formed on a substrate 2 made of an n-type wide bandgap semiconductor; a p-type well 4a provided in the driwhoseft layer 3; a first n-type impurity region 5 provided in the well 4a; a surface channel layer 7b formed at least on a surface of the well so as to connect together the first n-type impurity region 5 and the drift layer 3; a second n-type impurity region 7a provided in a surface region of the well which is under the surface channel layer and which spans the first n-type impurity region 5 and the drift layer 3, the second n-type impurity region 7a having an impurity concentration generally equal to or greater than an impurity concentration of the well 4a; and a third n-type impurity region formed in a surface region of the drift layer 3 adjacent to the second n-type impurity region 7a.

Owner:PANASONIC CORP

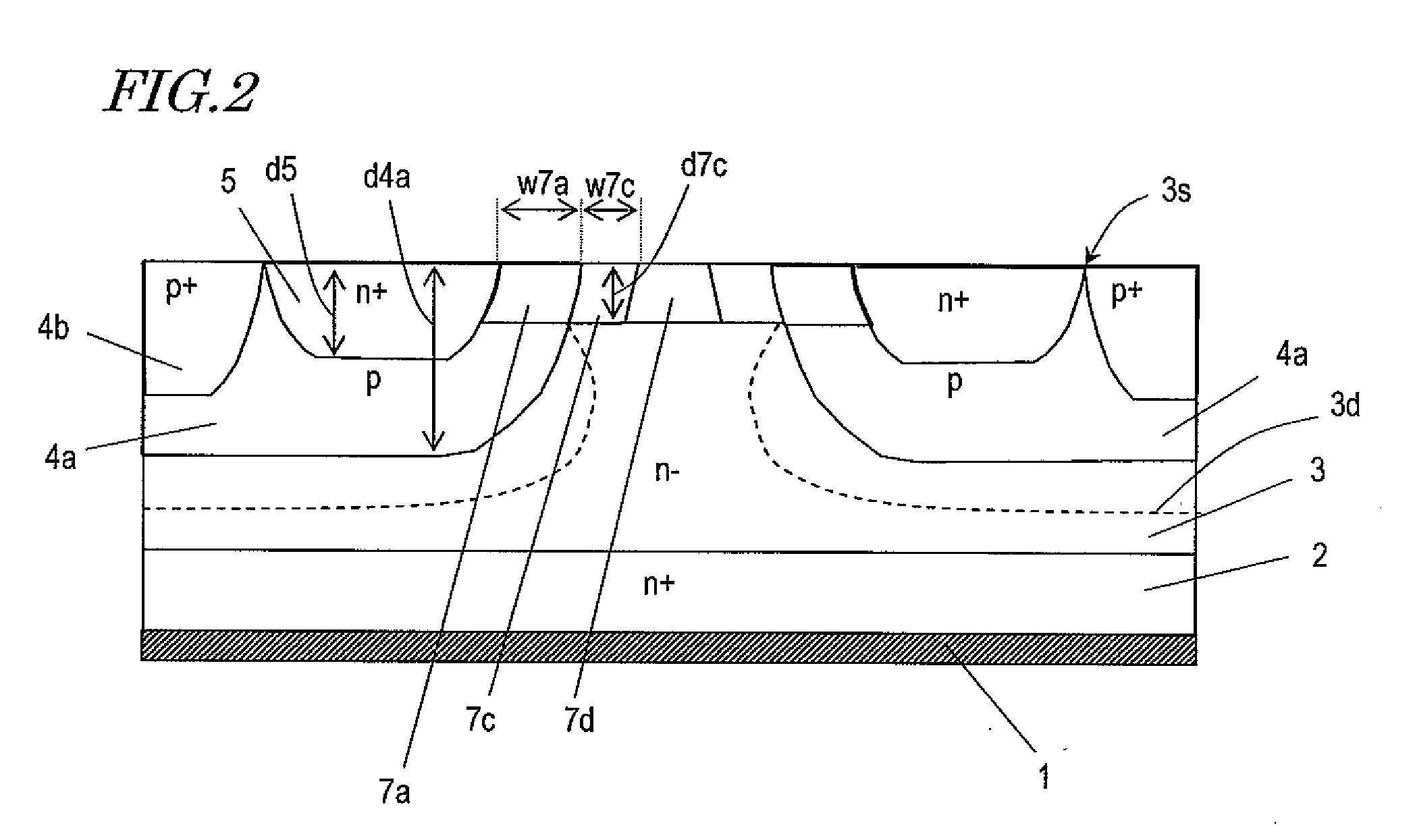

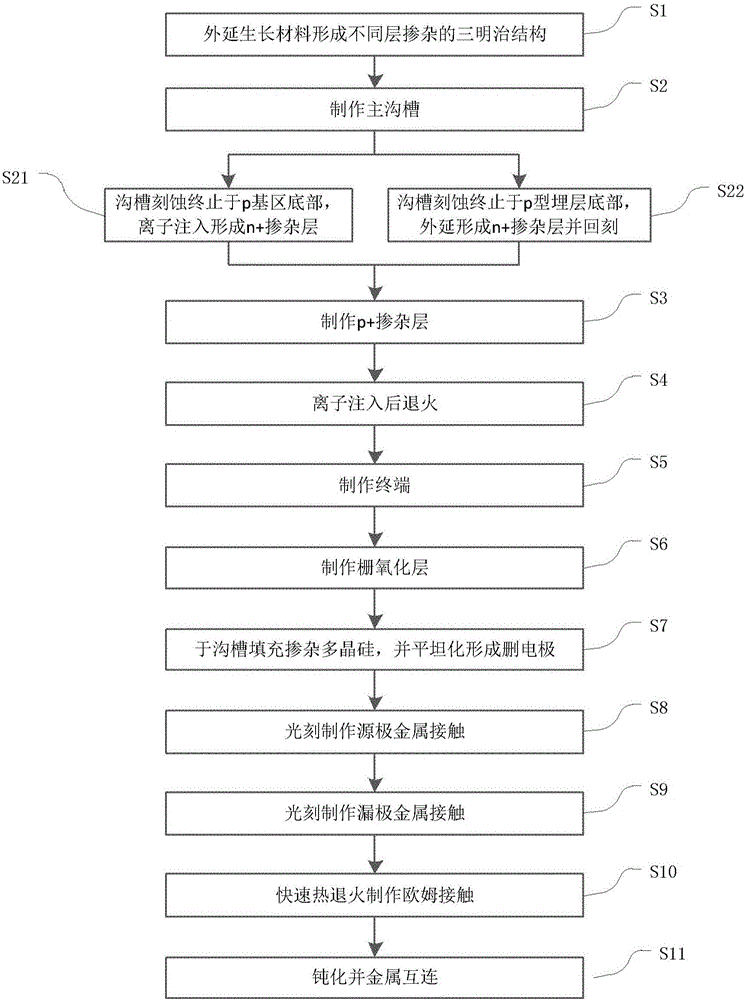

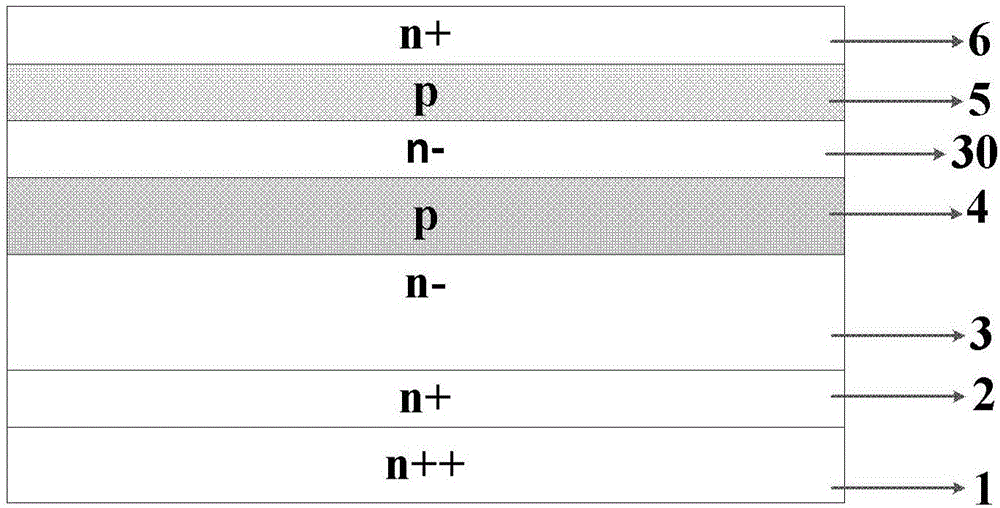

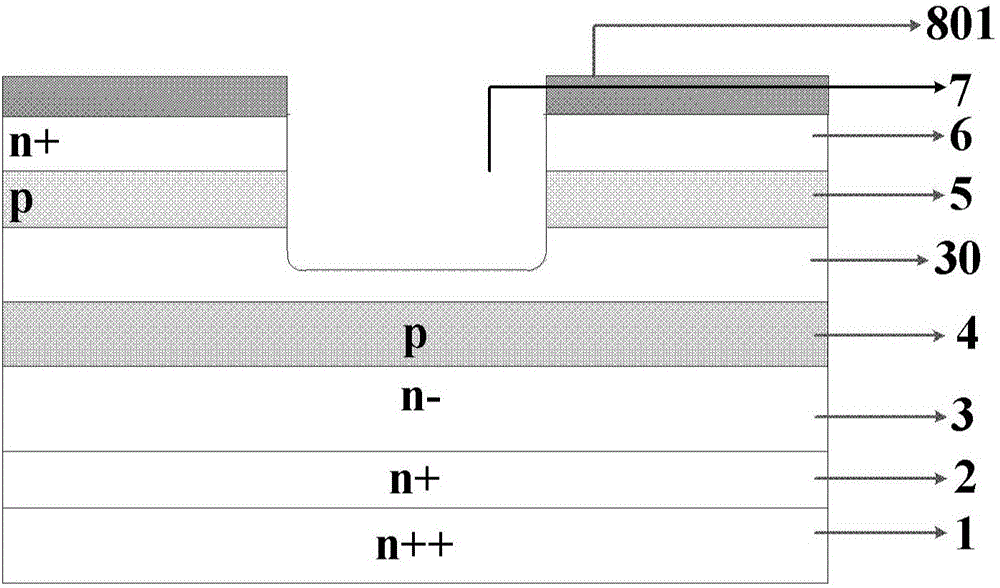

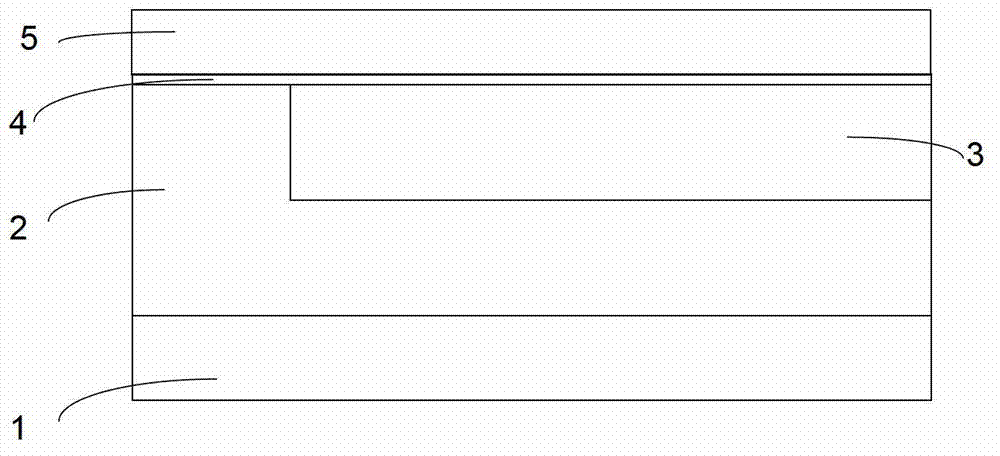

SiC-based groove-type field effect transistor and preparation method thereof

ActiveCN106449757AImprove on-state conductivityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorGate oxide

The invention discloses a preparation method of a bottom n-type doped SiC-based UMOSFET with a p-type buried layer and a groove. The method is characterized in that the p-type buried layer (4) is formed through epitaxial growth on an n- drift layer (3); an n- drift layer (30) is formed through epitaxial growth on the p-type buried layer (4); a p-type base region layer (5) is formed through epitaxial growth on the n- drift layer (30); and an n-type doped layer (900) is formed at the bottom of a main groove (7). The electric field of a gate oxide layer (10) is effectively reduced in a reverse blocking state. Due to the shielding effects of the p-type buried layer (4) and the n-type doped layer (900), the thickness of the p-type base region layer (5) is greatly reduced, the groove is reduced to below 0.5[mu]m and the on-state performance is improved. The SiC-based UMOSFET has a relatively high Baliga optimum value and a relatively low switching loss. The invention further provides a structure of the SiC-based UMOSFET.

Owner:ZHEJIANG XINKE SEMICON CO LTD

Insulated gate type switching device

An insulated gate type switching device includes: a first region being of a first conductivity type; a body region being of a second conductivity type and in contact with the first region; a second region being of the first conductivity type and separated from the first region by the body region; an insulating film being in contact with the first region, the body region and the second region; and a gate electrode facing the body region via the insulating film. The body region includes a first body region and a second body region. The first body region has a theoretical threshold level Vth larger than that of the second body region.

Owner:TOYOTA JIDOSHA KK

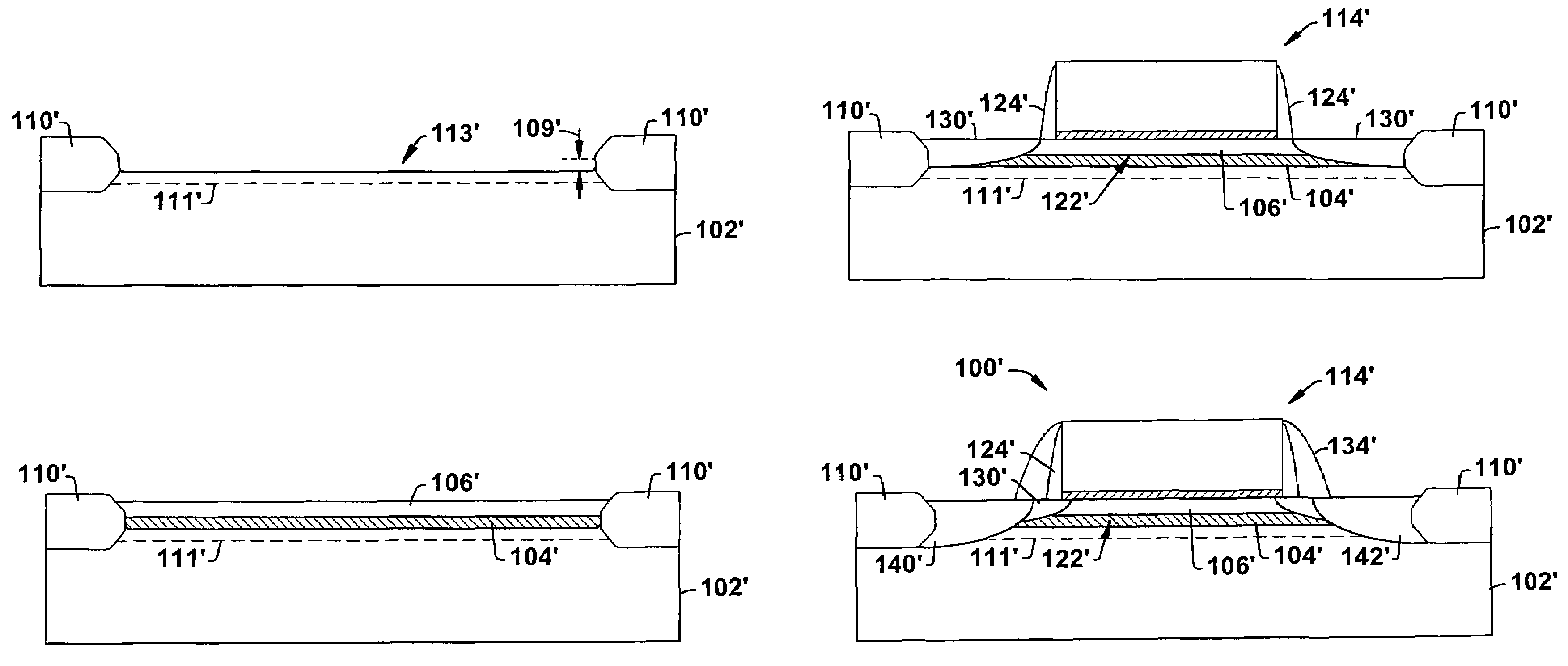

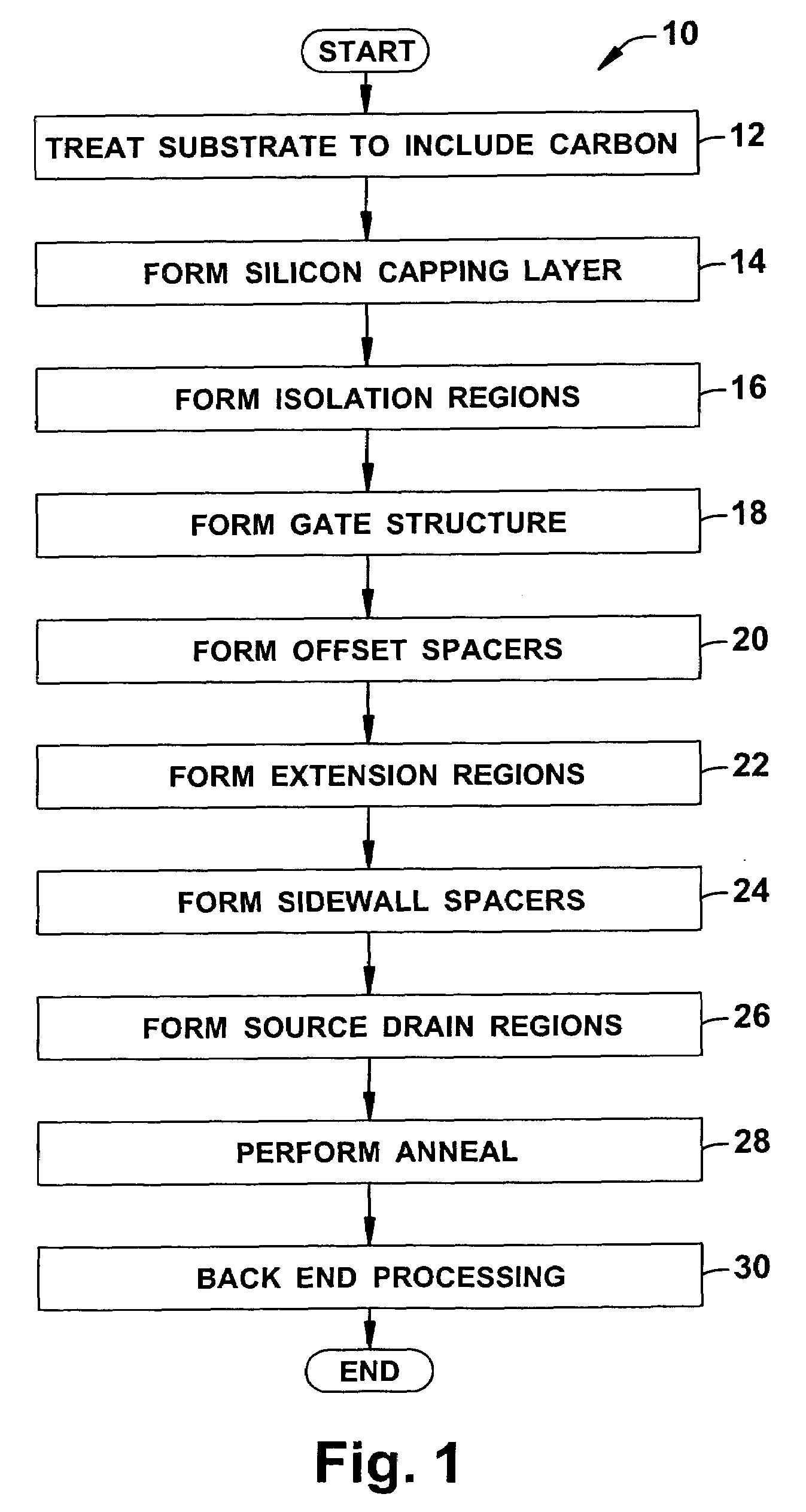

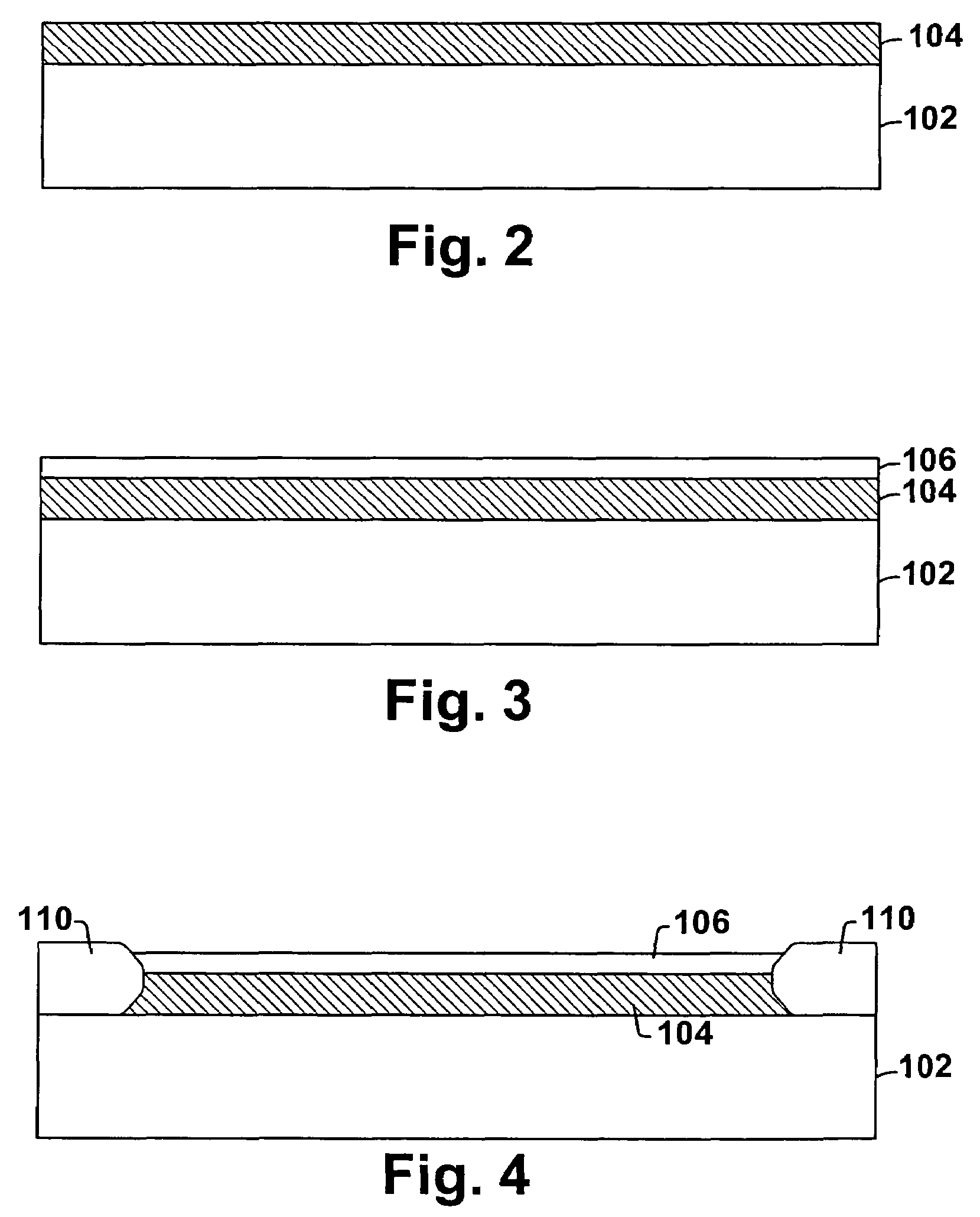

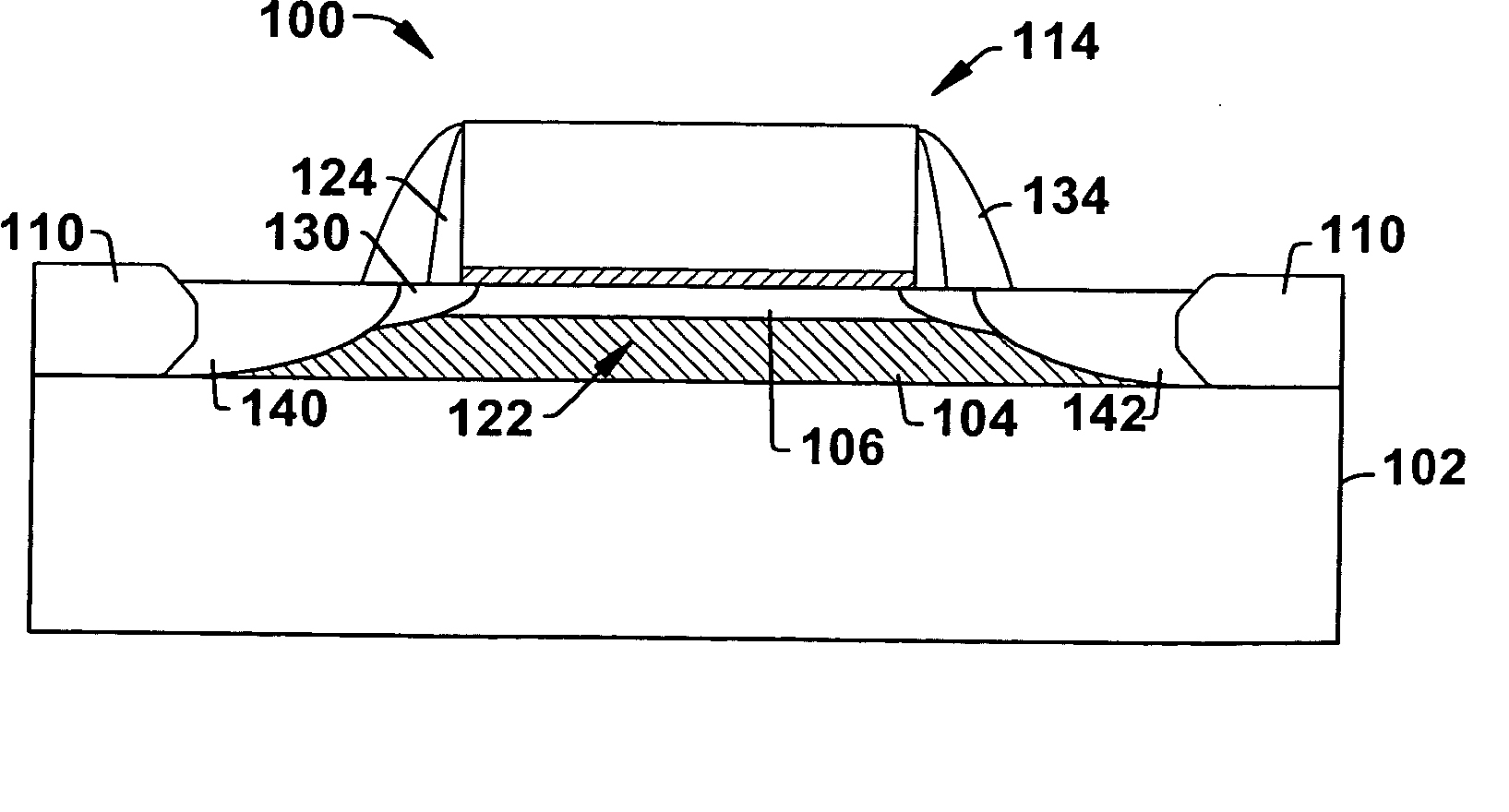

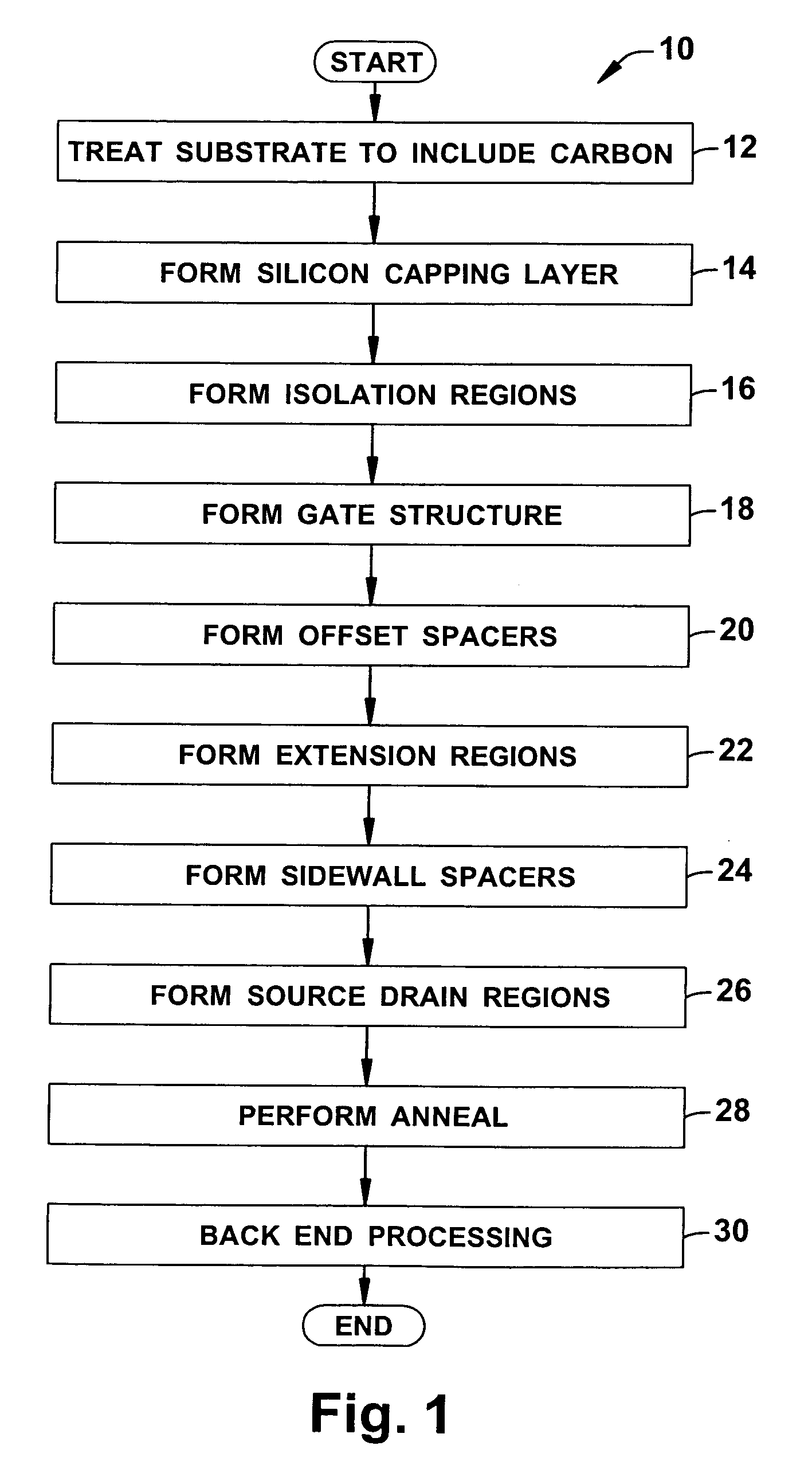

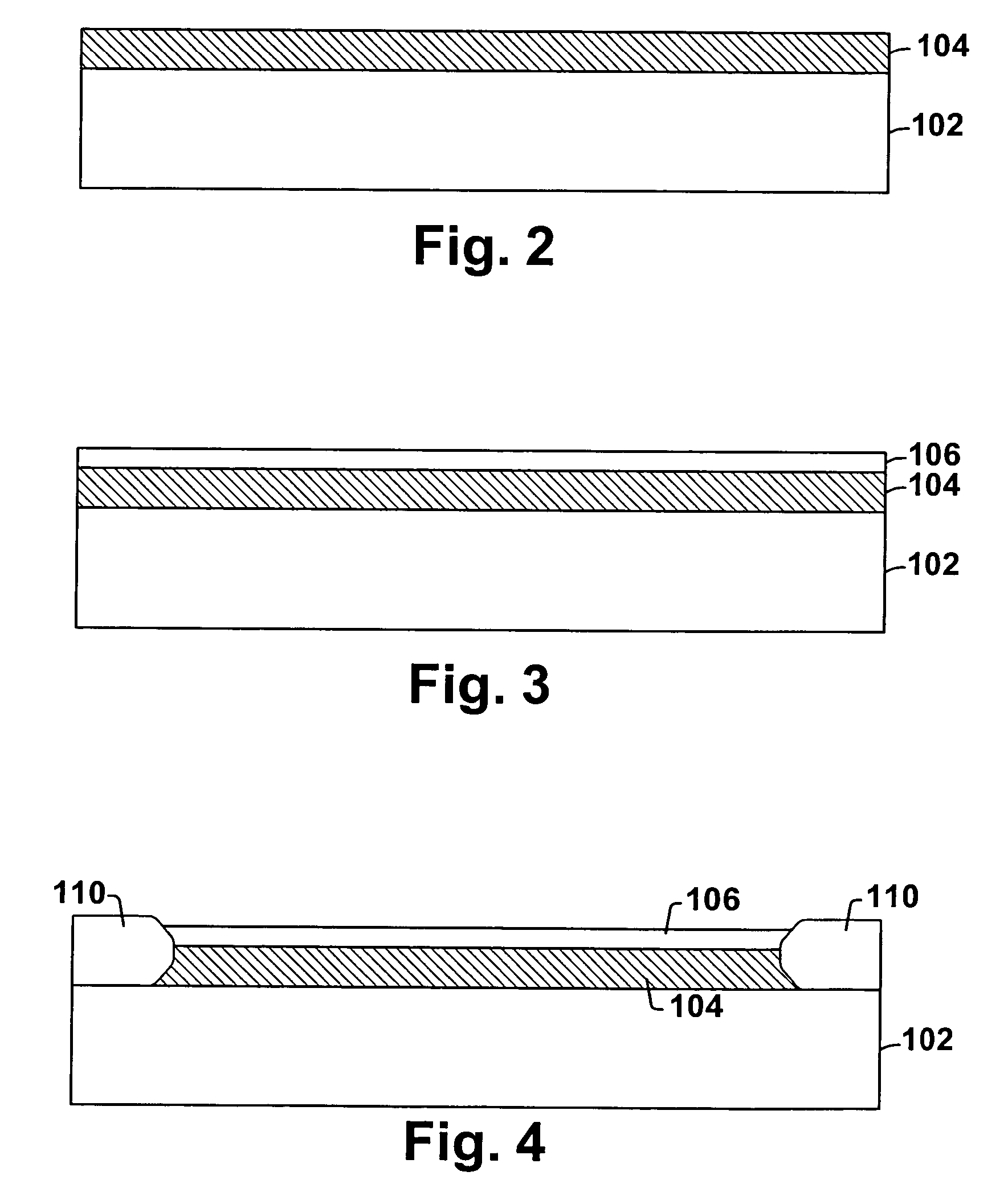

Phosphorus activated NMOS using SiC process

ActiveUS7179696B2High activityReduction tendencyTransistorSemiconductor/solid-state device manufacturingDopantEngineering

A method (10) of forming a transistor (100) includes treating (12) at least some of a semiconductor substrate (102) with carbon and then forming (18) a gate structure (114) over the semiconductor substrate. A channel region (122) is thereby being defined within the semiconductor substrate (102) below the gate structure (114). Source and drain regions (140, 142) are then formed (26) within the semiconductor substrate (102) on opposing sides of the channel (122) with a phosphorus dopant.

Owner:TEXAS INSTR INC

Non-Volatile Memory Device

ActiveUS20070047366A1Increase currentReduce decreaseRead-only memoriesDigital storageOperating systemNon-volatile memory

A non-volatile memory device may include a plurality of memory blocks including memory cells connected in series to bit lines, respectively. Each of the plurality of memory blocks may include a first sub memory block having a first group of memory cells, which are respectively connected in series between first select transistors connected to the bit lines, respectively, and second select transistors connected to a common source line, and a second sub memory block having a second group of memory cells, which are respectively connected in series between third select transistors connected to the bit lines, respectively, and fourth select transistors connected to the common source line.

Owner:SK HYNIX INC

Phosphorus activated NMOS using SiC process

ActiveUS20060060893A1High activityReduction tendencyTransistorSemiconductor/solid-state device manufacturingDopantEngineering

A method (10) of forming a transistor (100) includes treating (12) at least some of a semiconductor substrate (102) with carbon and then forming (18) a gate structure (114) over the semiconductor substrate. A channel region (122) is thereby being defined within the semiconductor substrate (102) below the gate structure (114). Source and drain regions (140, 142) are then formed (26) within the semiconductor substrate (102) on opposing sides of the channel (122) with a phosphorus dopant.

Owner:TEXAS INSTR INC

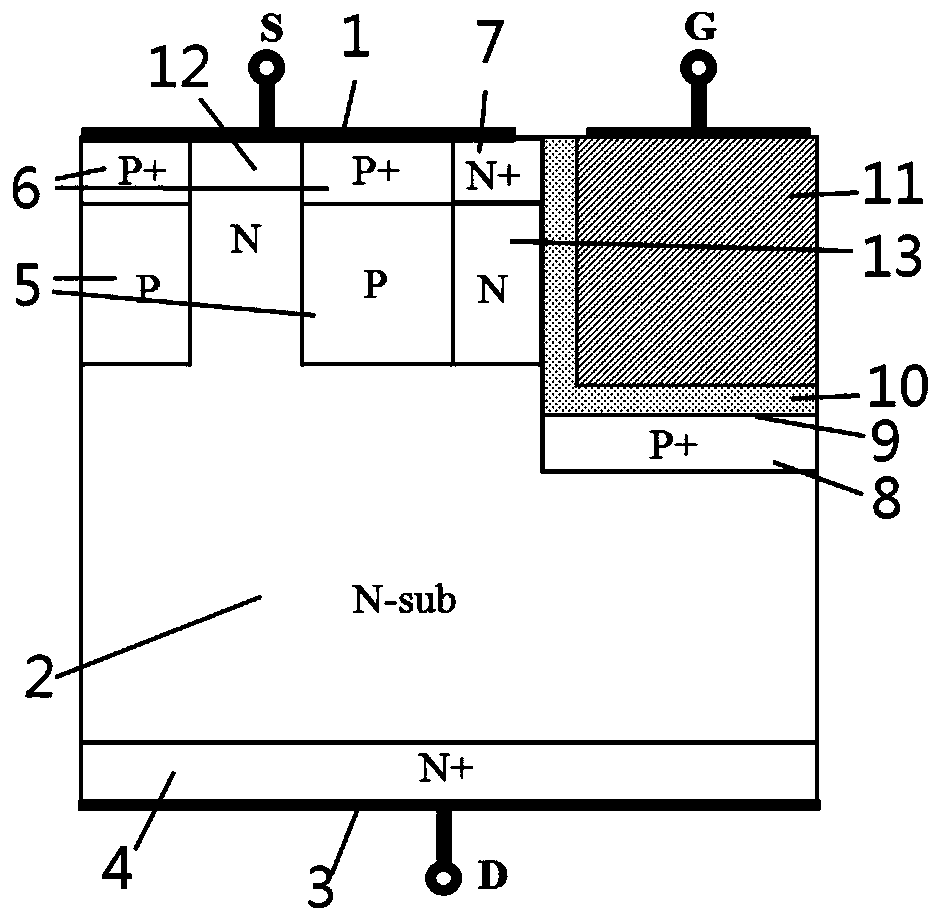

Silicon carbide MOSFET (Metal-Oxide -Semiconductor Field Effect Transistor) device capable of integrating with high-speed reverse free-wheeling diode

ActiveCN109904155ALower channel resistanceLower characteristic resistanceSolid-state devicesSemiconductor devicesMOSFETPower semiconductor device

The invention belongs to the technical field of semiconductor power devices, and relates to a silicon carbide semiconductor device, in particular to a silicon carbide MOSFET (Metal-Oxide-SemiconductorField Effect Transistor) device capable of integrating with a high-speed reverse free-wheeling diode for realizing the integration of the silicon carbide semiconductor device and the reverse free-wheeling diode. Compared with the original body diode of silicon carbide MOSFET, the integrated Schottky barrier FWD (Free-Wheeling Diode) can realize low diode conduction pressure drop and reduce reverse recovery time and loss. By use of the device, the application cost of the silicon carbide power semiconductor device and the number of peripheral devices when the device is applied can be favorablylowered, and therefore, the device has a large application value.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

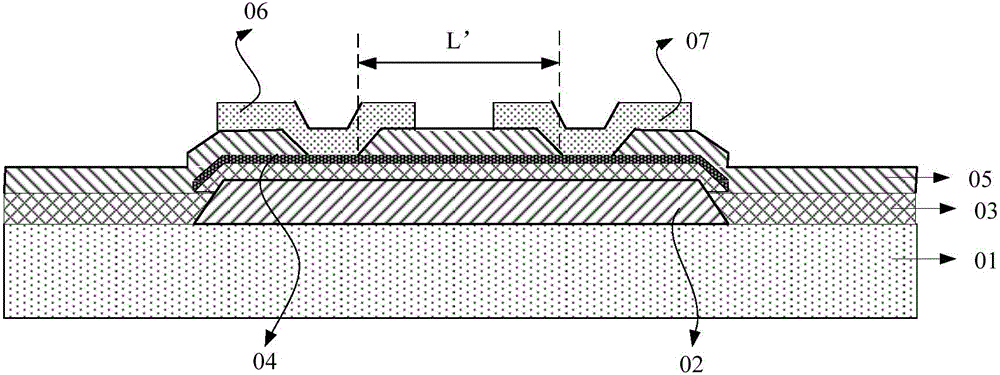

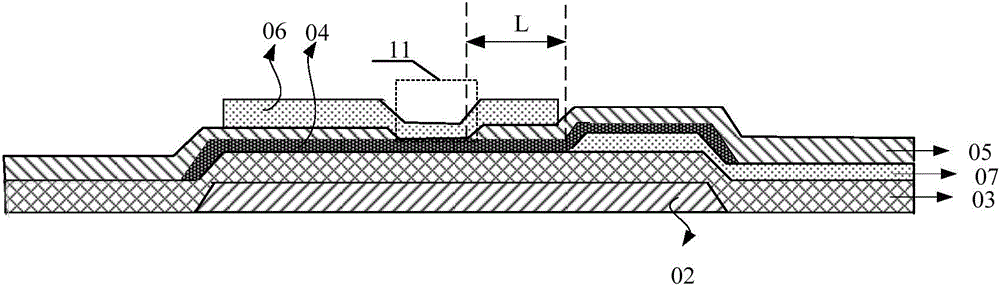

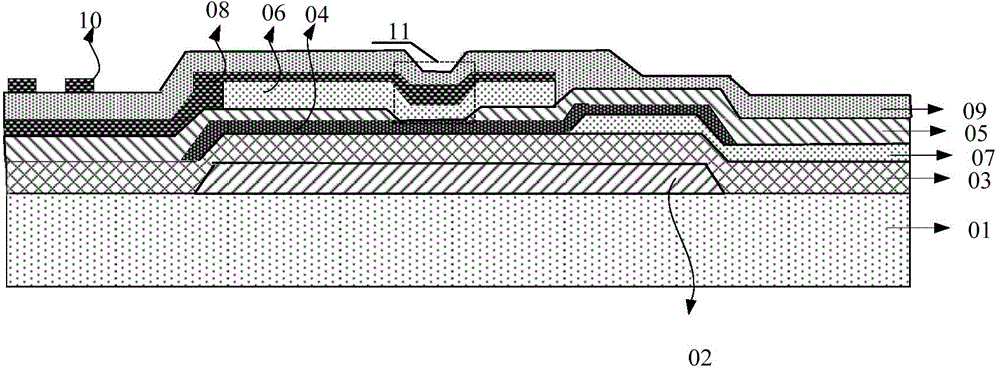

Thin film transistor, array substrate and display device

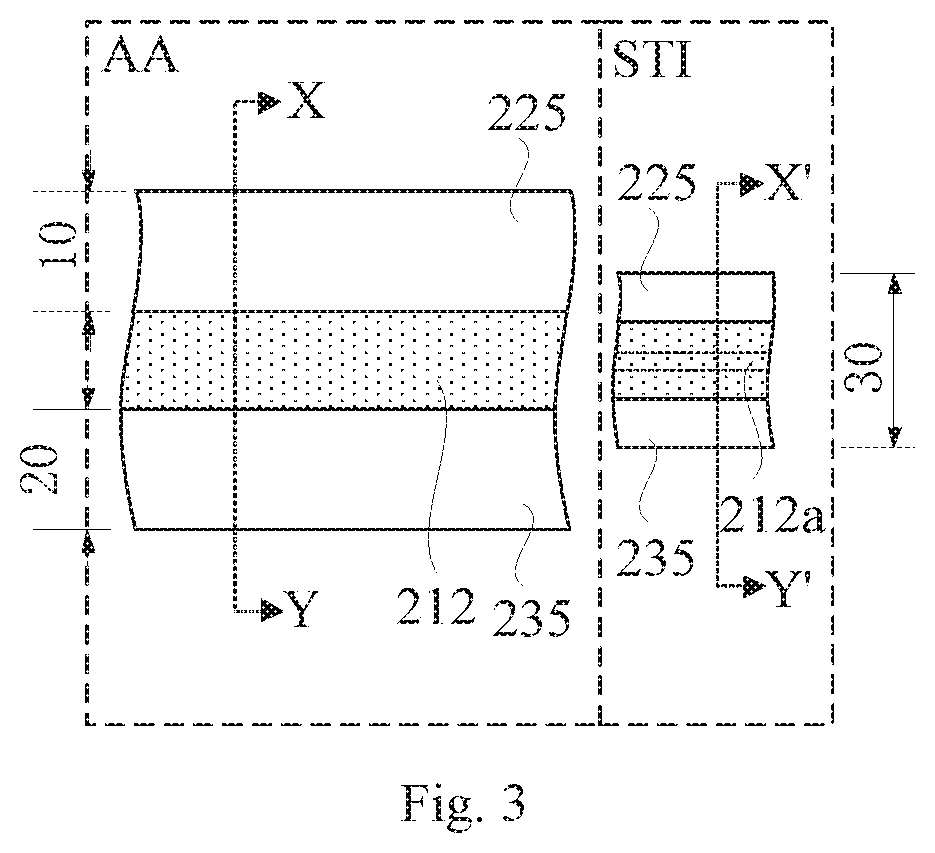

InactiveCN104091831AReduce channel lengthImprove charging efficiencyTransistorSolid-state devicesOxide thin-film transistorDisplay device

The invention discloses a thin film transistor, an array substrate and a display device. The thin film transistor comprises a grid electrode, a source electrode, a drain electrode and a semiconductor layer, wherein the source electrode and the drain electrode are arranged on different layers, the semiconductor layer is electrically connected with the source electrode and the drain electrode, and a channel region is formed on the portion, corresponding to the region between the source electrode and the drain electrode, of the semiconductor layer. The invention further provides the array substrate comprising the thin film transistor and the display device. According to the array substrate comprising the thin film transistor and the display device, the source electrode and the drain electrode are made to be formed on different layers by changing the pattern composition technology, a channel, which is originally 15-micron long, of the thin film transistor is reduced to be smaller than 5 microns at present, the resistance of the channel is greatly reduced, the charging efficiency of the thin film transistor can be greatly improved by reducing the length of the channel, charging time is shortened, and thus the working efficiency of the transistor is improved. Due to the fact that the size of the channel of the transistor is reduced, the area of the transistor can also be reduced, and products which are high in integration level can be obtained easily.

Owner:BOE TECH GRP CO LTD

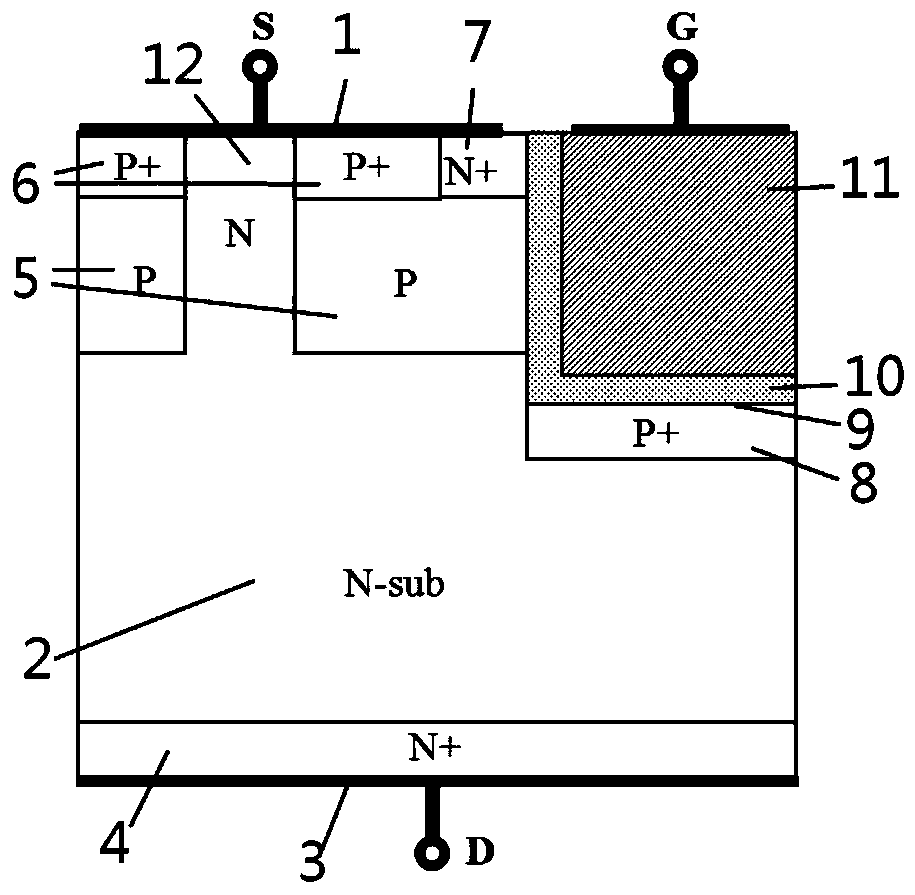

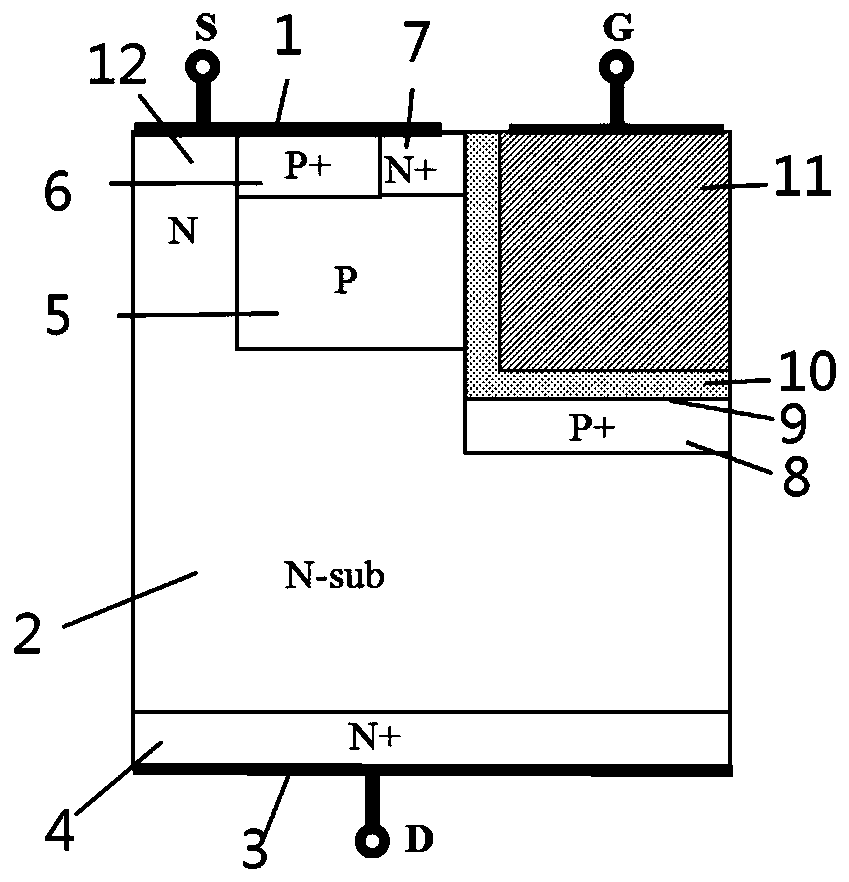

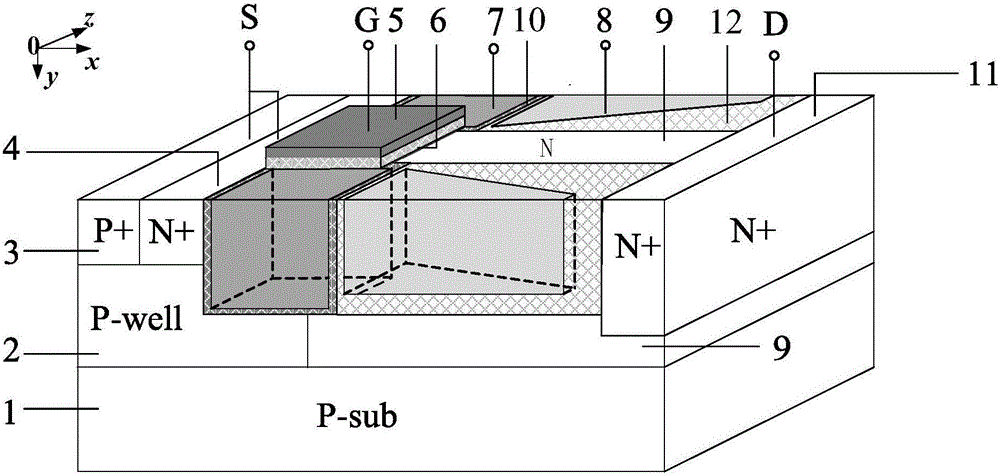

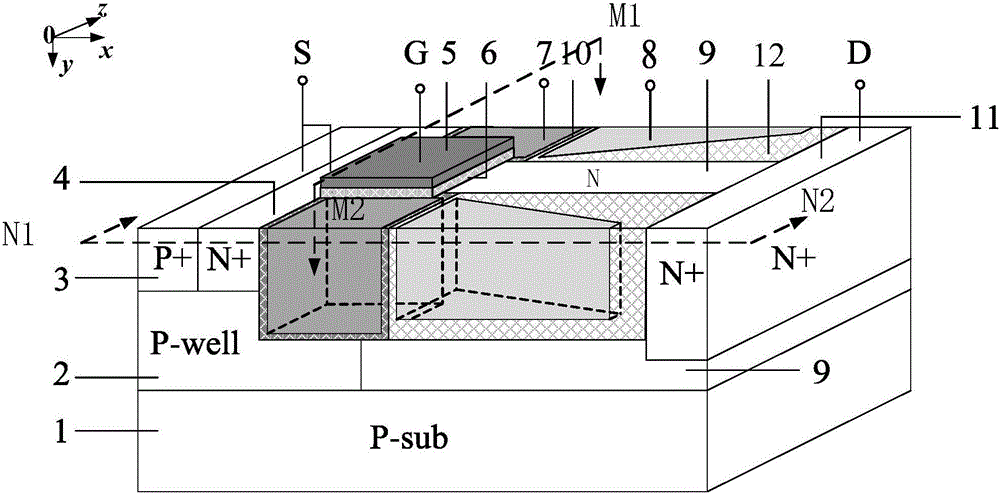

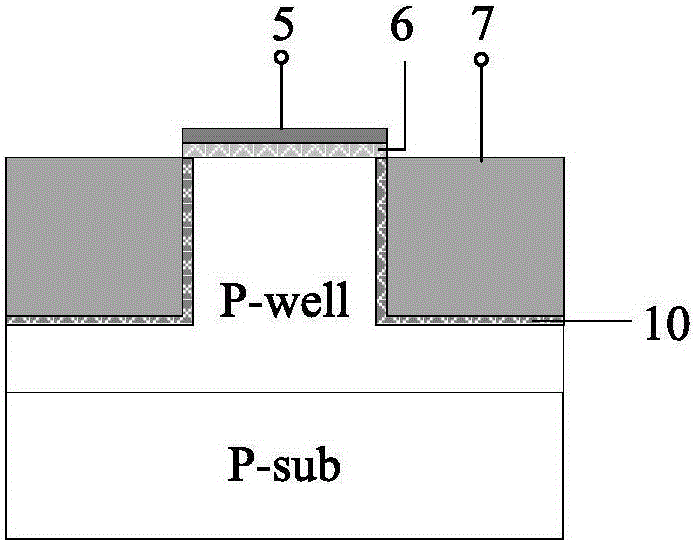

Three-gate power LDMOS

ActiveCN106024897AIncrease the doping concentrationReduce gate-to-drain capacitanceSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the field of power semiconductor devices, and relates to a lateral three-gate power LDMOS based on a bulk silicon technology. The three-gate power LDMOS is mainly characterized by having a three-gate structure and a second conductive material electrically connected with a source or a gate or an external electrode. The three-gate power LDMOS has the main advantages that the three-gate structure increases the channel density and reduces the channel resistance, and thus, the specific on-resistance drops; the second conductive material can freely select the electrode, when the gate electrode is connected, in the positive case, electron accumulation surfaces are formed on the side surface and the bottom surface of a second groove, a multi-dimension low-resistance channel is formed, and the specific on-resistance is greatly reduced, and in the reverse case, assistant depletion of a drift region is carried out, the drift area doping concentration of the device is increased, the specific on-resistance of the device is reduced; when the source electrode is connected, gate-drain overlapping is reduced, the gate-drain capacitance of the device is reduced, and switching loss is reduced; and when the external electrode is electrically connected, multiple effects can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor device and method for manufacturing same

InactiveCN102187463ALower channel resistanceAvoid concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesWide bandWide-bandgap semiconductor

Each unit cell comprises a drift layer (3) composed of an n-type wide band gap semiconductor and formed on a substrate (2) which is composed of an n-type wide band gap semiconductor, a p-type well (4a) formed within the drift layer (3), a first n-type impurity region (5) formed within the well (4a), a surface channel layer (7b) formed at least on the surface of the well so as to connect the first n-type impurity region (5) and the drift layer (3), a second n-type impurity region (7a) which is formed below the surface channel layer within the well in the surface region ranging from the first n-type impurity region (5) to the drift layer (3) and has an impurity concentration almost equal to or higher than the impurity concentration of the well (4a), and a third n-type impurity region formed in the surface region of the drift layer (3) so as to be adjacent to the second n-type impurity region (7a).

Owner:PANASONIC CORP

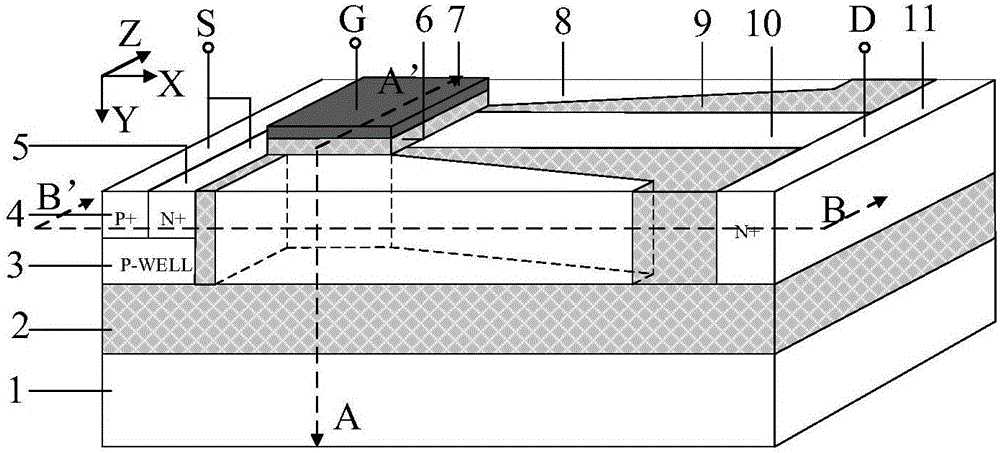

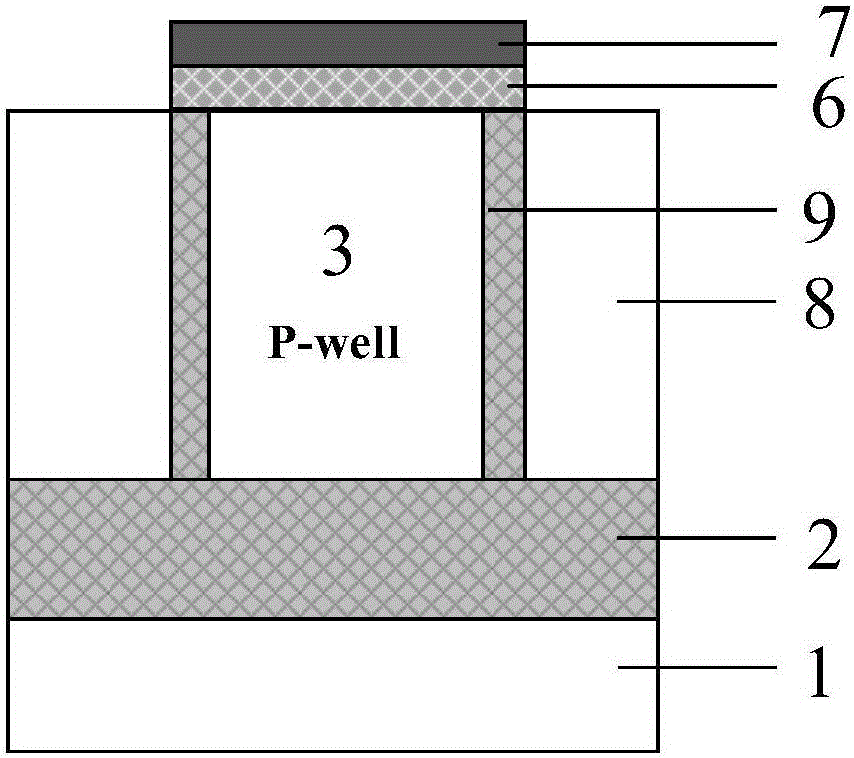

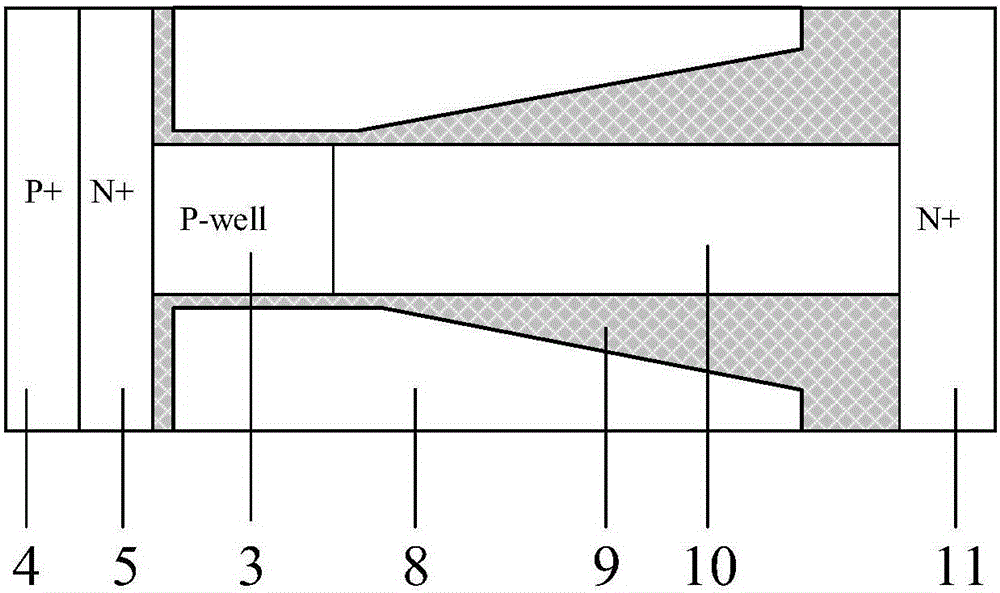

Transverse SOI power LDMOS

InactiveCN105789314AIncrease concentrationLower channel resistanceSemiconductor devicesEngineeringPower flow

The invention belongs to the technical field of semiconductor power devices, and relates to a transverse SOI power LDMOS. Compared with the existing structure, the power LDMOS provided by the invention has a three-dimensional gate structure, and an oxide layer thickness between the part extending to a trench gate field plate of a drift region from a gate and the drift region gradually changes from the gate to a drain end. In a forward conducting state, the trench gate forms a side channel to greatly reduce the channel resistance of the device; an electron accumulation layer is formed in the drift region to constitute a low resistance current channel, so as to greatly reduce the resistance in the drift region of the device; and the conducting resistance of the device is reduced by the two aspects. In a forward blocking state, the trench gate field plate extending to the drift region has a depletion effect on the drift region, thereby improving the concentration in the drift region and reducing the resistance in the drift region. Since most open state current flows by a charge accumulation layer, the specific on-state resistance of the transverse SOI power LDMOS provided by the invention is nearly not affected by the concentration in the drift region, so that the 2.5 power contradictory relationship of the specific on-state resistance Ron, sp of the device and the withstand voltage BV.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

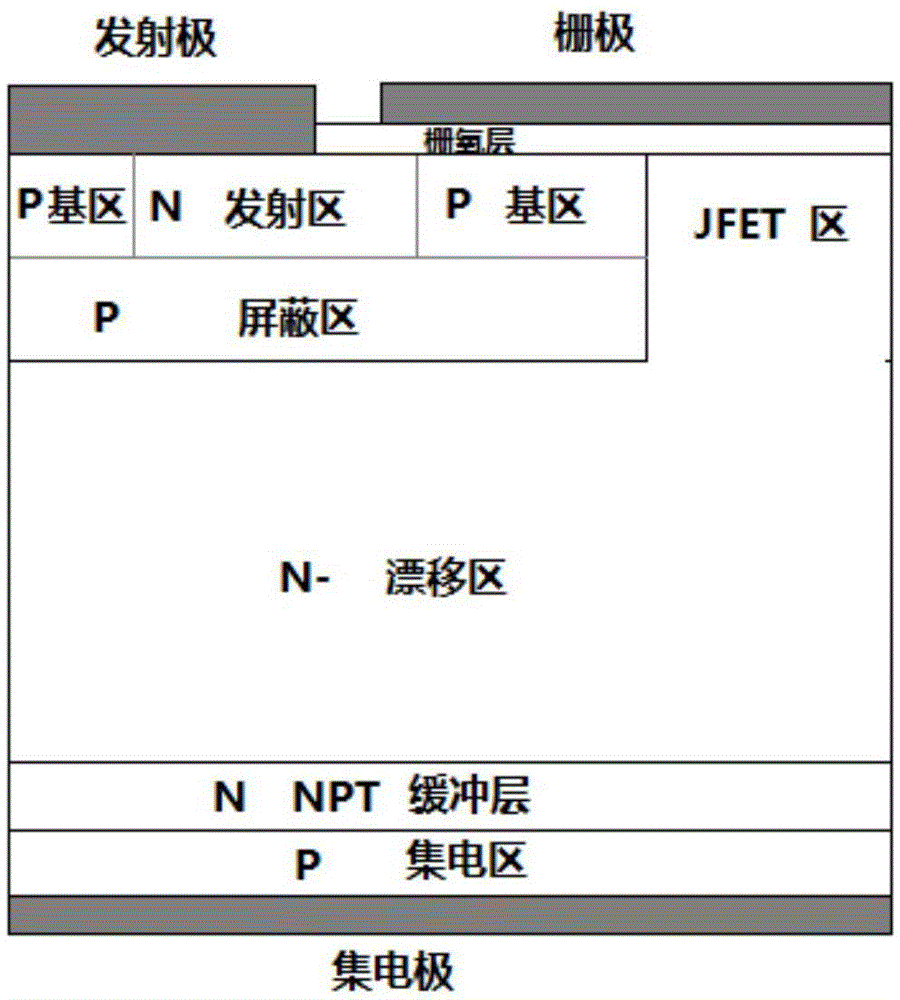

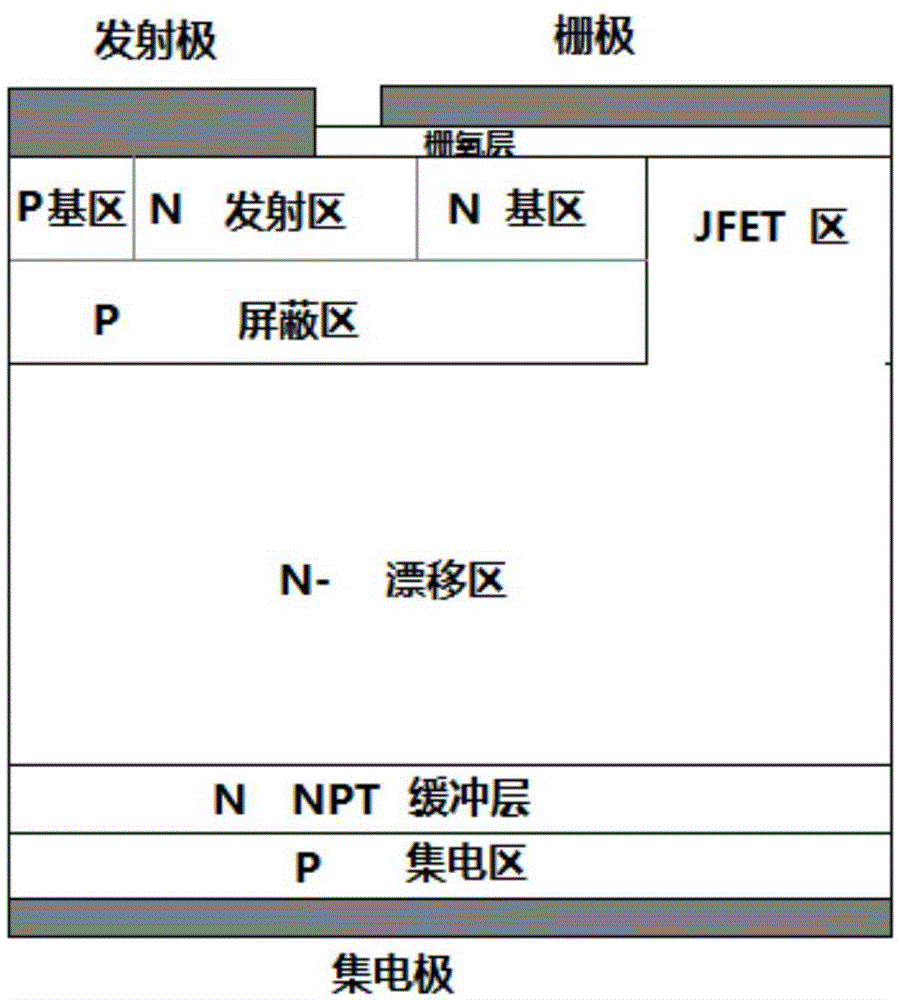

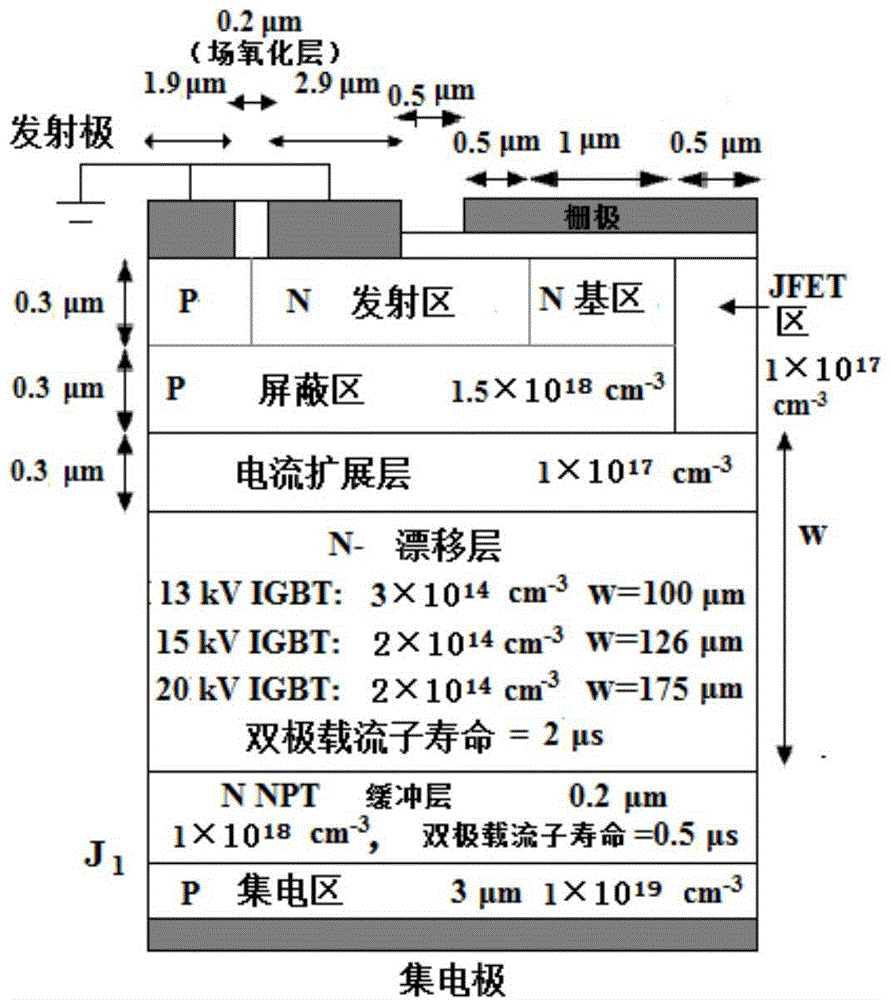

4H-silicon carbide based N-channel accumulating high-voltage insulated gate bipolar transistor

InactiveCN104617136ALower channel resistanceGood on-state characteristicsSemiconductor devicesHigh pressureGate voltage

The invention discloses a 4H-silicon carbide based N-channel accumulating high-voltage insulated gate bipolar transistor. The 4H-silicon carbide based N-channel accumulating high-voltage insulated gate bipolar transistor is characterized in that the traditional inversion channel is replaced by an accumulation channel and an N type base region is adopted between a P type shielding layer and a gate oxide layer. The thickness and the dosage concentration of the N type base region are selected to guarantee that the region is completely deleted when the gate voltage is zero, and therefore, the bipolar transistor is closed in a normal state. When the gate voltage is high enough, the accumulation channel is formed at the interface of SiO2 / SiC so that the bipolar transistor can be switched on. Current carriers in an accumulation layer are distributed farther away from the surface than current carriers in an inversion layer and a higher effective migration rate of the accumulation channel can be expected, and therefore, the differential on resistance of the 4H-SiC based high-voltage N-channel IGBT and the on voltage drop under specific on current density and gate voltage can be effectively reduced by replacing the traditional inversion channel with the accumulation channel, and consequently, the energy loss of the bipolar transistor in the on state can be effectively reduced.

Owner:SHANDONG UNIV

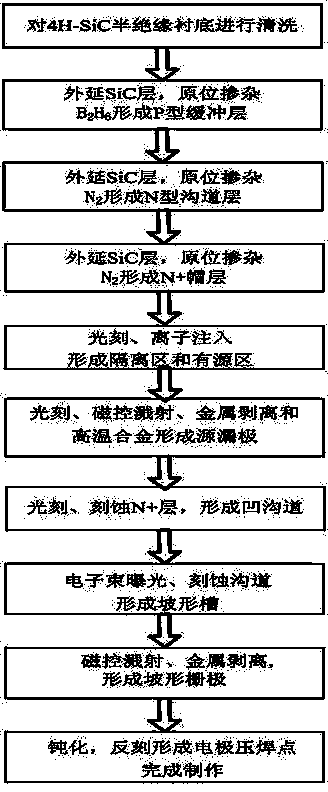

4H-SiC metal semiconductor field effect transistor with slope-shaped grid and manufacturing method

ActiveCN104282764ADrain current increasesLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowMetal

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a slope-shaped grid. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from bottom to top, a source electrode cap layer and a drain electrode cap layer are arranged on the surface of the N-type channel layer, a source electrode and a drain electrode are arranged on the surface of the source electrode cap layer and the surface of the drain electrode cap layer respectively, a slope-shaped groove inclined towards one side of the source electrode cap layer is formed in the upper end face of the N-type channel layer, the slope-shaped grid is arranged is arranged in the slope-shaped groove, the lower end face of the slope-shaped grid is matched with the slope-shaped groove, the upper end face of the slope-shaped grid is parallel to the upper end face of the N-type channel layer, and the distance between the slope-shaped grid and the source electrode cap layer is smaller than that between the slope-shaped grid and the drain electrode cap layer. The field effect transistor has the advantages of being high in drain electrode output current and excellent in frequency property.

Owner:XIDIAN UNIV

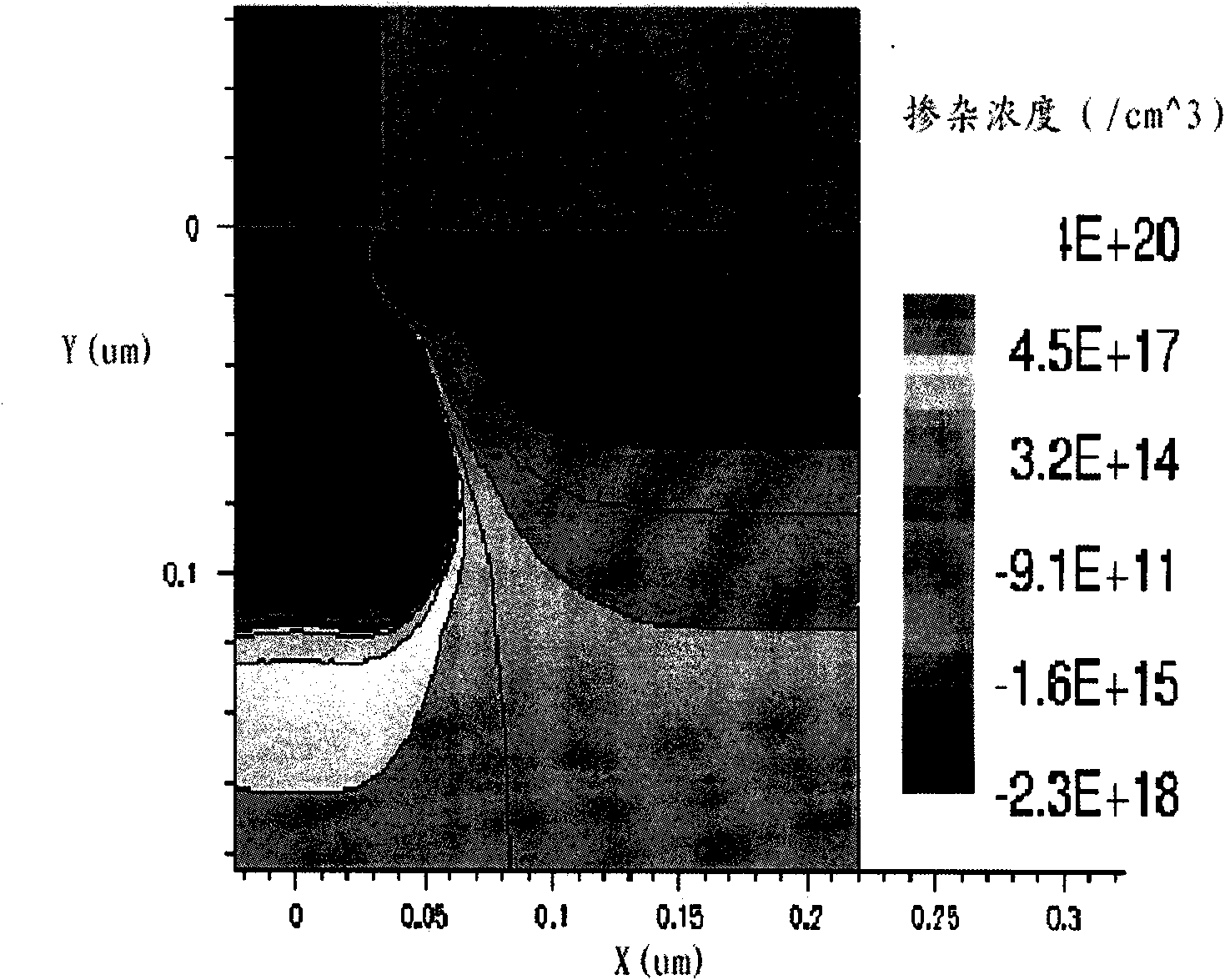

Radio frequency LDMOS (laterally diffused metal oxide semiconductor) device and manufacture method thereof

ActiveCN103050536AReduce doping concentrationDoping concentration unchangedSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate oxide

The invention discloses a radio frequency LDMOS (laterally diffused metal oxide semiconductor) device. The side surface of a channel doping region and the side surface of a drift region of the radio frequency LDMOS device are contacted; a gate oxide and a grid electrode are successively arranged above the channel doping region and the drift region; and the doping density of the part of the drift region, which is below the channel doping region, is smaller than the doping density of rest parts. The invention also discloses a manufacture method for the radio frequency LDMOS device. Because the doping density of the drift region is unevenly distributed, the hot carrier effect can be lowered while the low-conduction resistance is obtained.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

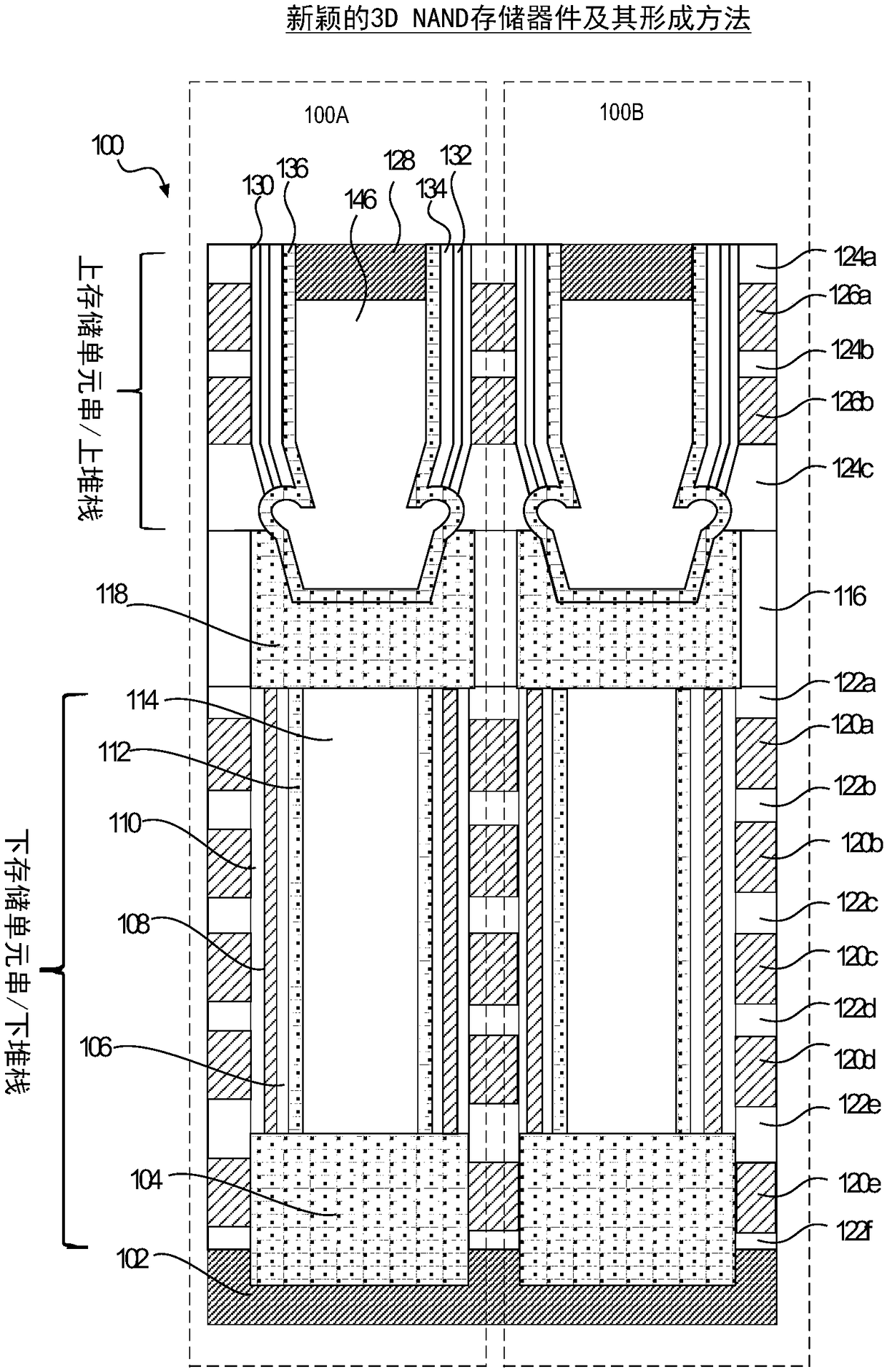

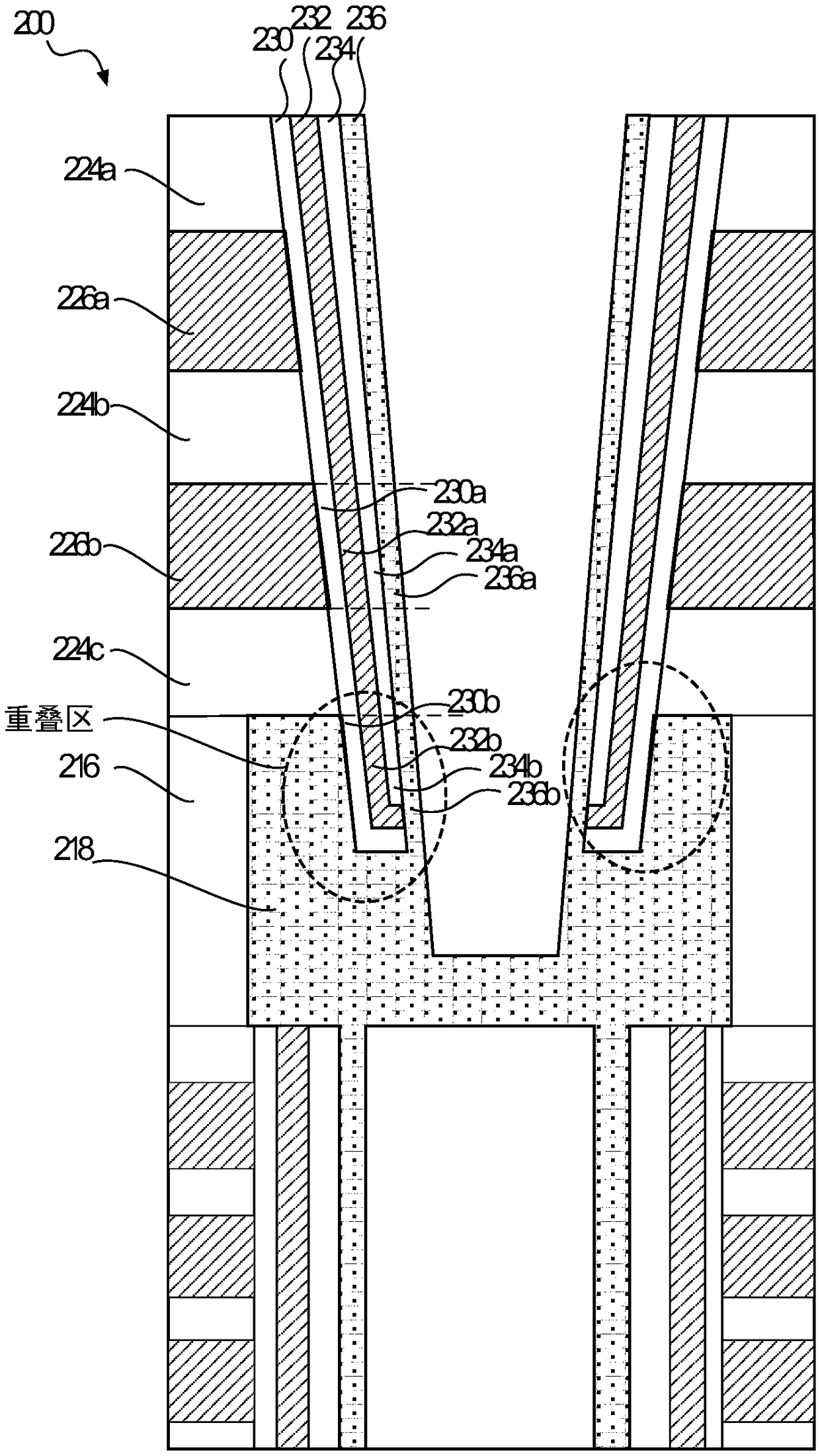

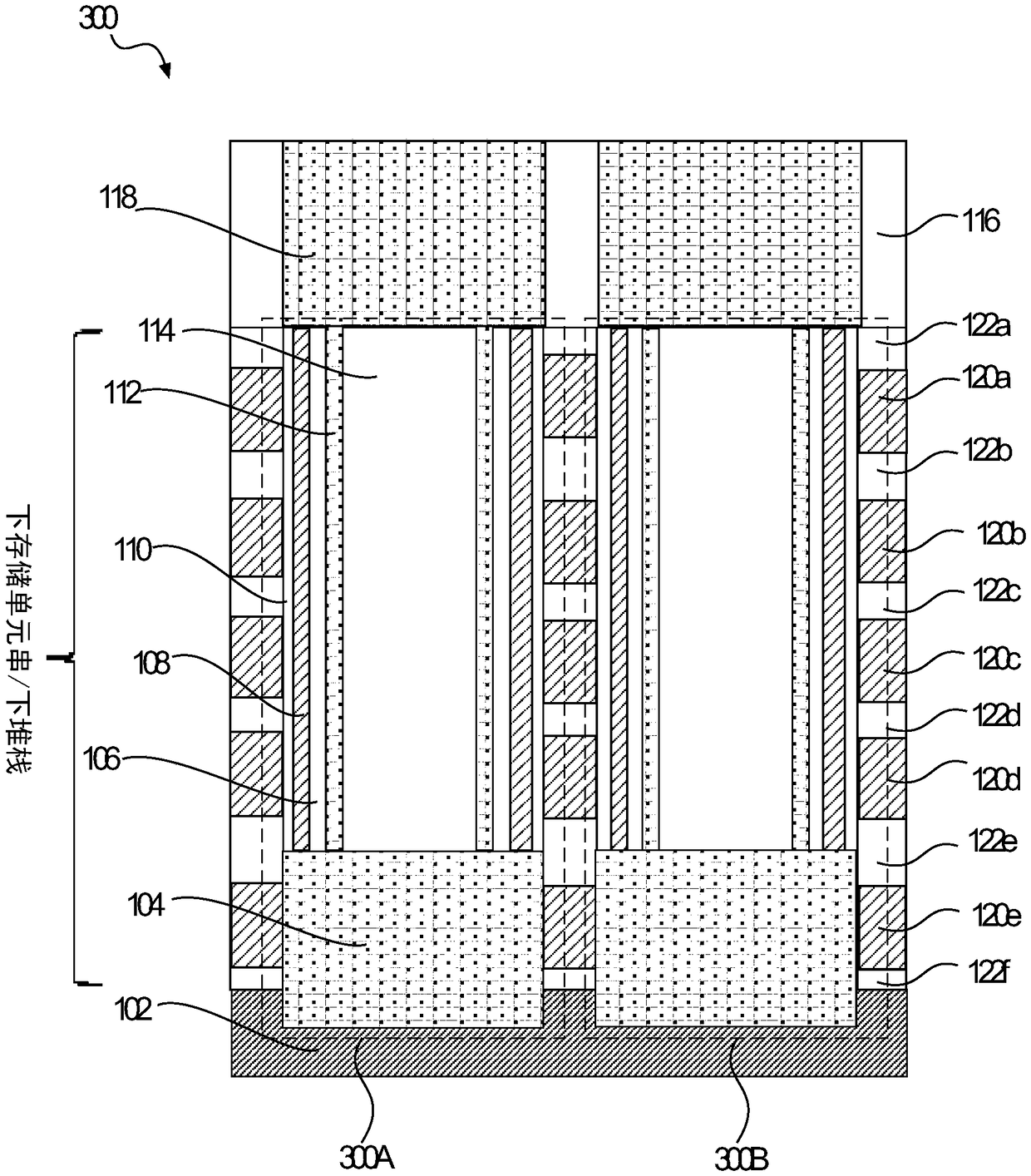

Novel 3D NAND memory device and method of forming same

ActiveCN109417072AAvoid formingLower channel resistanceSolid-state devicesStatic storageDielectricComputer science

In the memory device, a lower memory cell string including a first channel structure, a plurality of first word line layers, and a first insulating layer is formed over a substrate. The first channelstructure extends from the substrate and passes through the first word line layer and the first insulating layer. Inter-stack contacts are formed over the lower memory cell string and coupled to the first channel structure. An upper memory cell string is formed over the inter-stack contacts. The upper memory cell string includes a second channel structure, a plurality of second word lines, and a second insulating layer. The second channel structure passes through the second word line and the second insulating layer and extends into the inter-stack contacts and further laterally into the secondinsulating layer. A channel dielectric region of the second channel structure is above the inter-stack contacts.

Owner:YANGTZE MEMORY TECH CO LTD

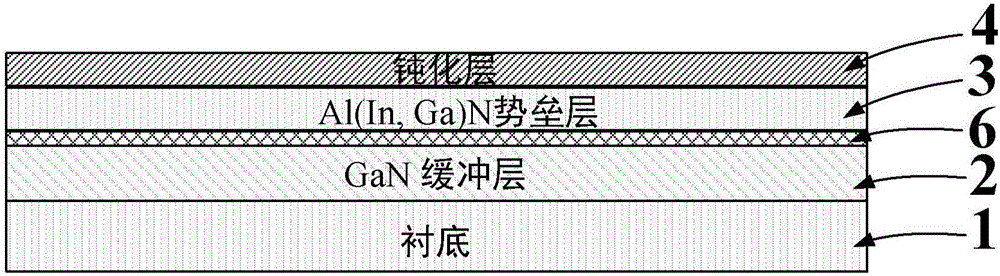

Material structure of GaN-base enhancement-mode electronic device

InactiveCN106783945ASolve process repeatabilityImprove yieldSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectron

The invention discloses a material structure of a GaN-base enhancement-mode electronic device, and relates to the technical field of application of GaN-base power electronics and microwave power amplifiers. The material structure comprises a substrate, a GaN buffer layer and an Al(In,Ga)N barrier layer which are sequentially formed on the substrate, and a passivation layer, wherein the Al(In,Ga)N barrier layer forms a thin barrier Al(In,Ga)N / GaN heterostructure; and the passivation layer is formed on the thin barrier Al(In,Ga)N layer, and prepared from n-GaN, SiO2 or SiNx. Therefore, an enhancement-mode gate structure can be formed without etching the Al(In,Ga)N barrier layer; the density of two-dimensional electron gas in a thin barrier Al(In,Ga)N / GaN heterojunction channel outside a gate is significantly improved by utilizing polarization of the passivation layer or an n-type doping effect; the GaN-base enhancement-mode power electronic device with good threshold uniformity and low dynamic on resistance can be prepared; a yield of the device is increased; and an industrialization progress of the GaN-base power electronic device is pushed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

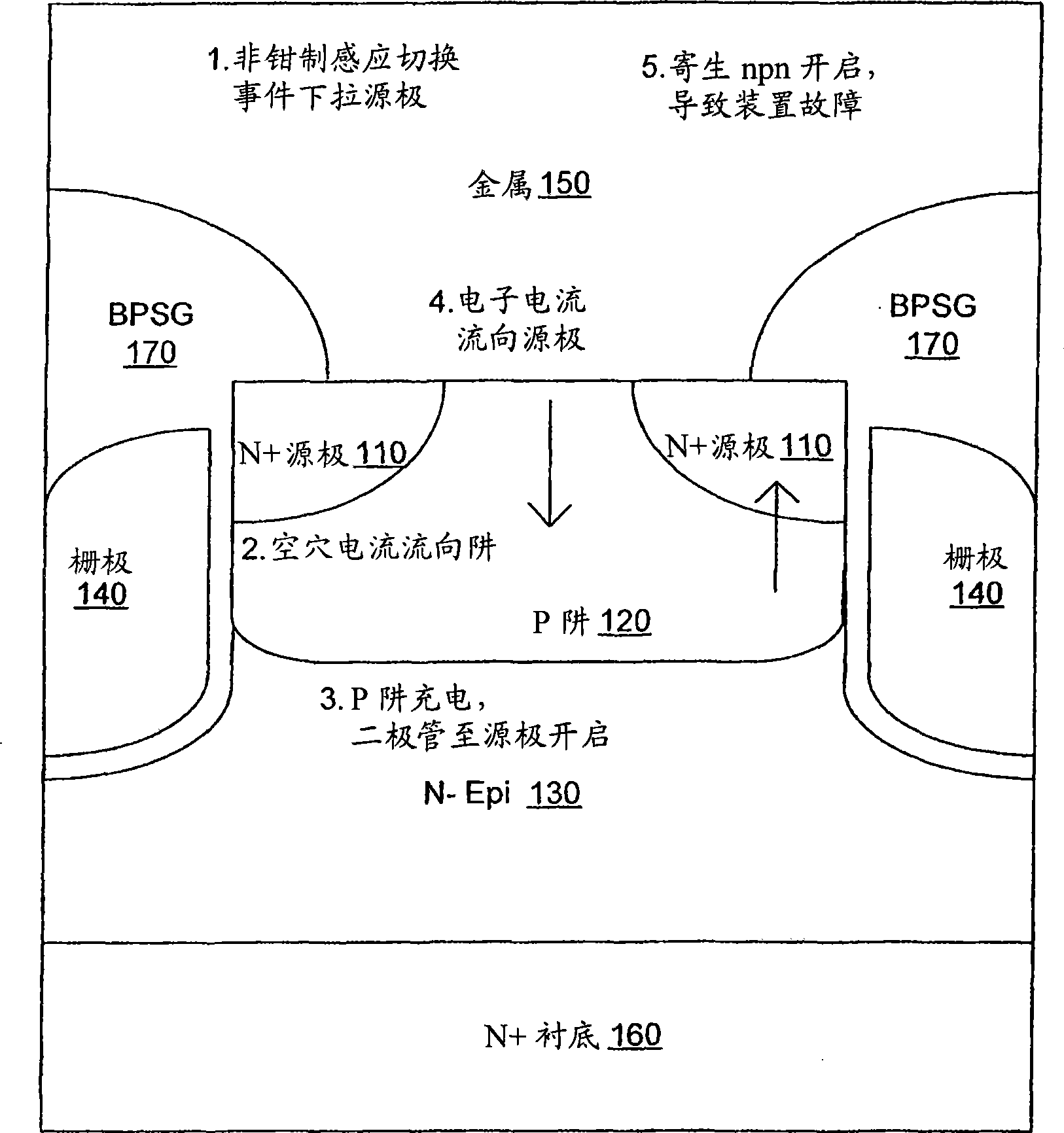

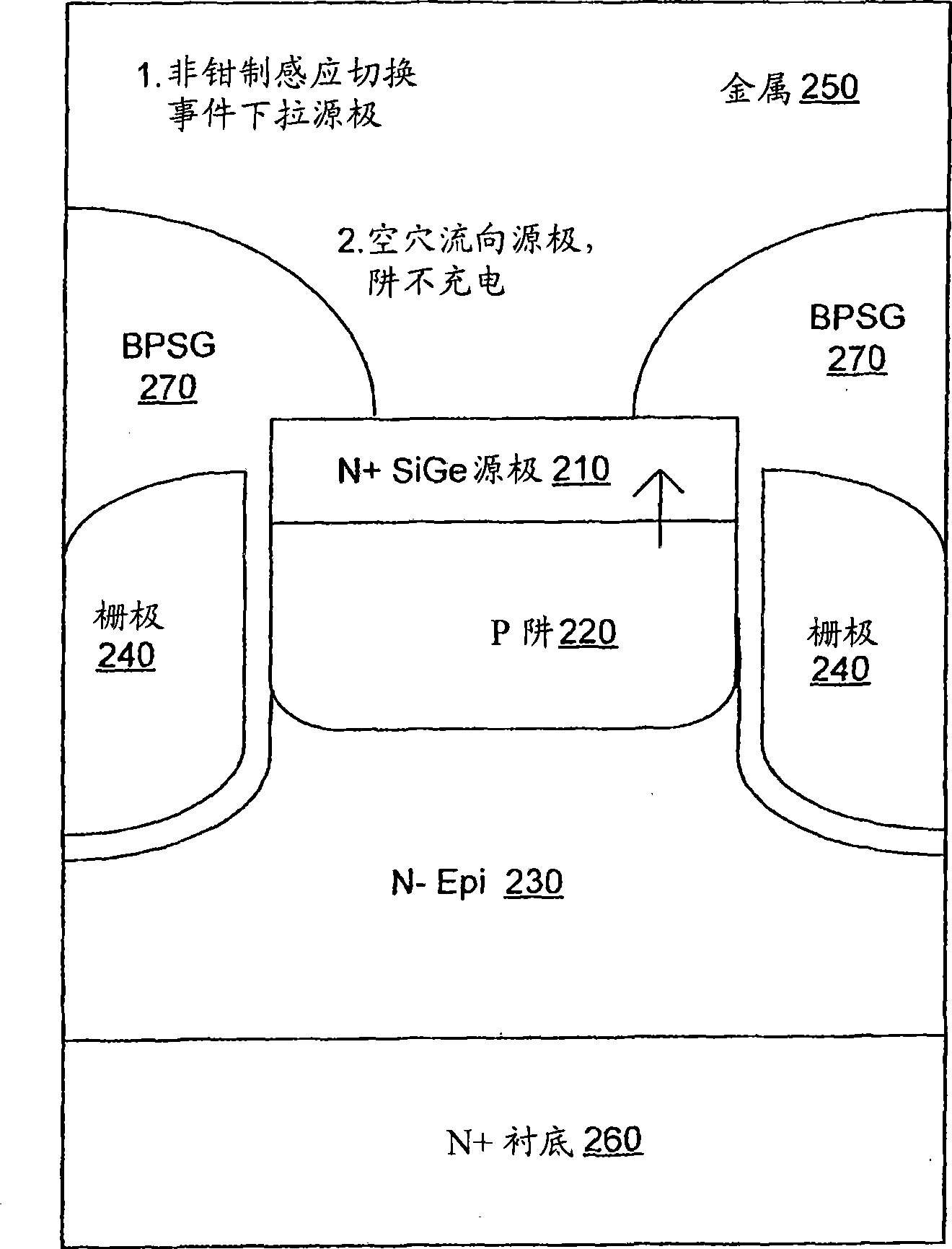

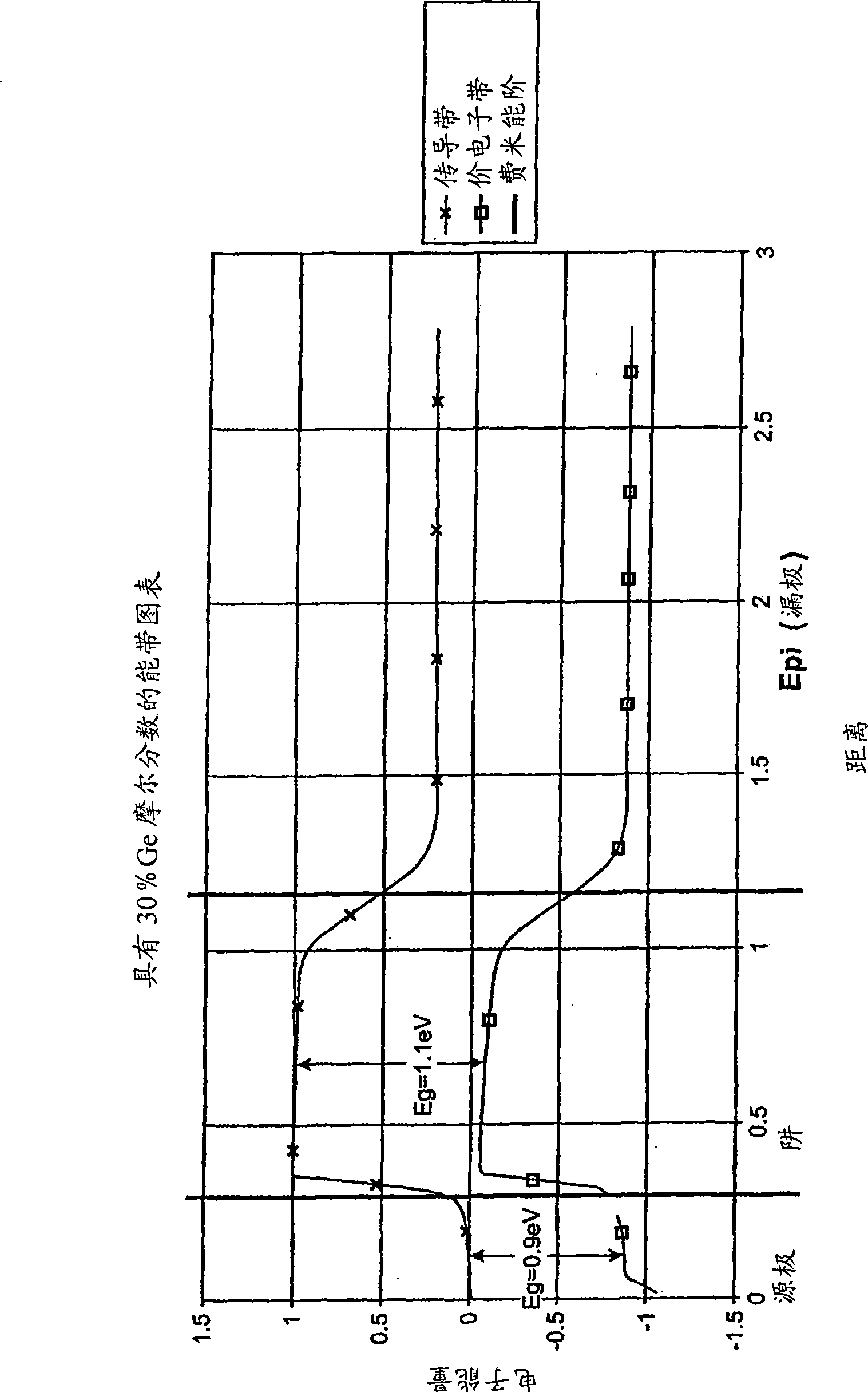

Power trench MOSFET having SiGe/Si channel structure

InactiveCN101512777ALower impedanceImprove featuresTransistorFinal product manufactureCapacitanceTrench mosfet

Devices, methods, and processes that improve immunity to transient voltages and reduce parasitic impedances. Immunity to unclamped inductive switching events is improved. For example, a trench-gated power MOSFET device having a SiGe source is provided, where the SiGe source reduces parasitic npn transistor gain by reducing hole current in the body or well region, thereby decreasing the likelihood of a latch-up condition. A trench-gated power MOSFET device having a SiGe body or well region is also provided. A SiGe body reduces hole current when the body diode is turned on, thereby reducing reverse recovery power losses. Other device characteristics are also improved. For example, parasitic gate impedance can reduced through the use of a poly SiGe gate. Also, channel resistance can be reduced through the use of a SiGe layer near the device's gate and a thick oxide region can be formed under the trench gate to reduce gate-to-drain capacitance.

Owner:FAIRCHILD SEMICON CORP

VDMOS device and manufacturing method thereof

InactiveCN104916686AIncrease contact areaLower threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideBody region

The invention provides a VDMOS device and a manufacturing method thereof. The manufacturing method comprises the following steps that: a gate oxide layer is formed in gate trenches of a silicon substrate, and the gate trenches of the silicon substrate are filled with polycrystalline silicon; a body region is formed; first ions and second ions are sequentially injected into the silicon substrate, and the silicon substrate is subjected to annealing treatment, and therefore, source contact regions can be formed at two sides of each gate trench, and the first ions and the second ions have the same type, and the energy of the first ions is larger than that of the second ions, and the dosage of the first ions is smaller than that of the second ions; a dielectric layer is formed; after a source trench mask is formed on the dielectric layer, and the silicon substrate is etched, and therefore, source trenches can be formed between the source contact regions; and the source trench mask is removed, and a metal layer is formed on the silicon substrate. With the manufacturing method provided by the invention adopted, the contact resistance of the VDMOS device can be decreased without changing the structure of the device, increasing the manufacturing process difficulty of the device and increasing the manufacturing cost of the device, and therefore, the performance of the device can be improved.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

Semiconductor variable capacitor

The invention provides a semiconductor variable capacitor which comprises a semiconductor substrate, an ion trap, a gate dielectric layer, a gate and an insulation layer, wherein the ion trap is arranged on the semiconductor substrate, a plurality of ion doping areas are arranged in the ion trap, and each area is respectively used as a source or a drain; the gate dielectric layer is arranged on the ion trap; the gate is arranged between the source and the drain and is stacked on the gate dielectric layer; the insulation layers are arranged on the upper surface of the ion trap, the side wall stacked by the gate dielectric layer and the gate, and the upper surface of the gate and the sides of the insulation layers are provided with side walls. Compared with the traditional semiconductor variable capacitor, as the semiconductor variable capacitor is arranged on the overlapping part of the gate and the drain, and the overlapping part of the gate and the source, the doping concentration ratio of the invention is lighter than that of the semiconductor variable capacitor containing LDD / Pck, the width of the consumed layer is increased, the capacitor Cf values between the gate and the source and between the gate and the drain are decreased, and thus, the frequency modulating range of the capacitor is enhanced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

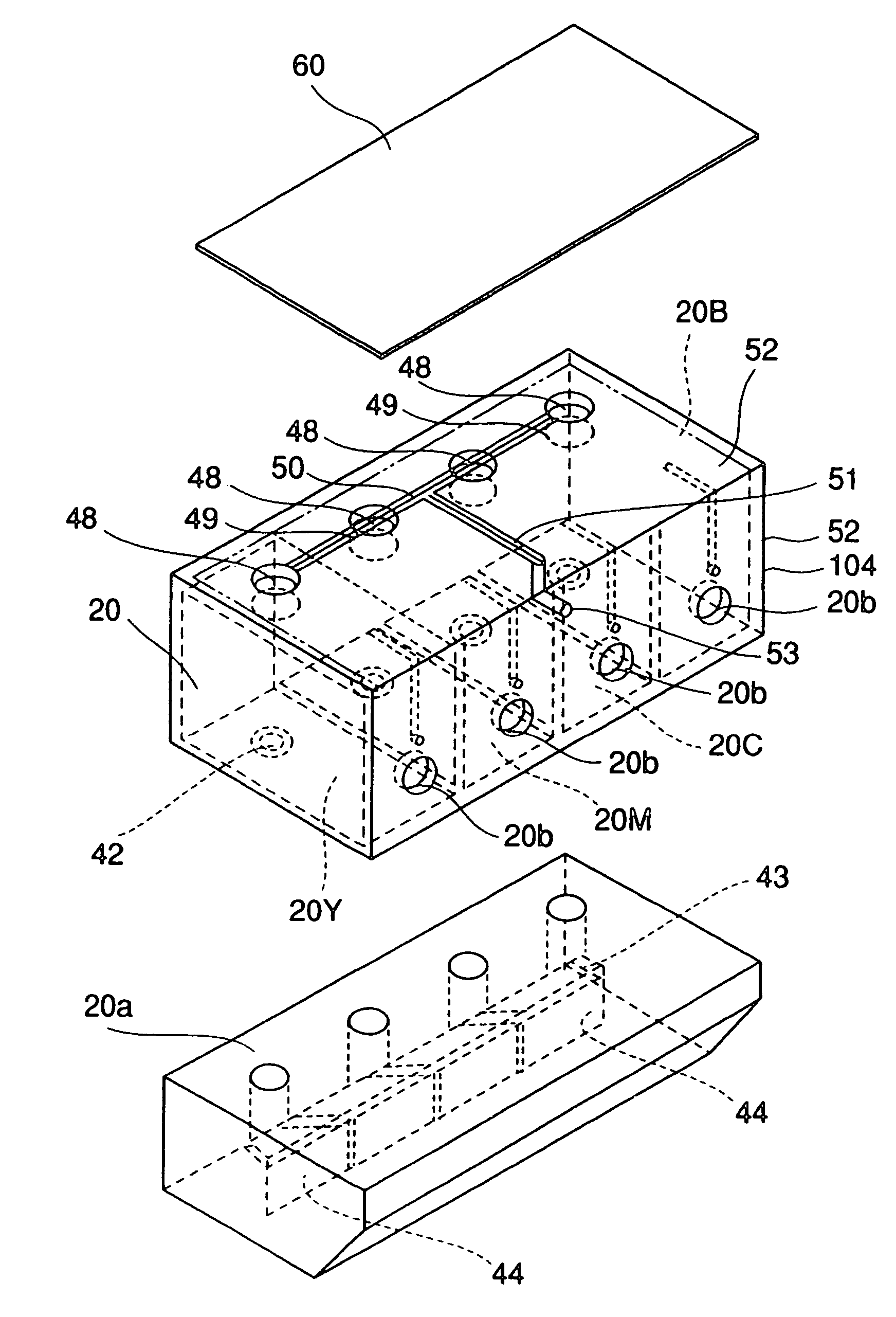

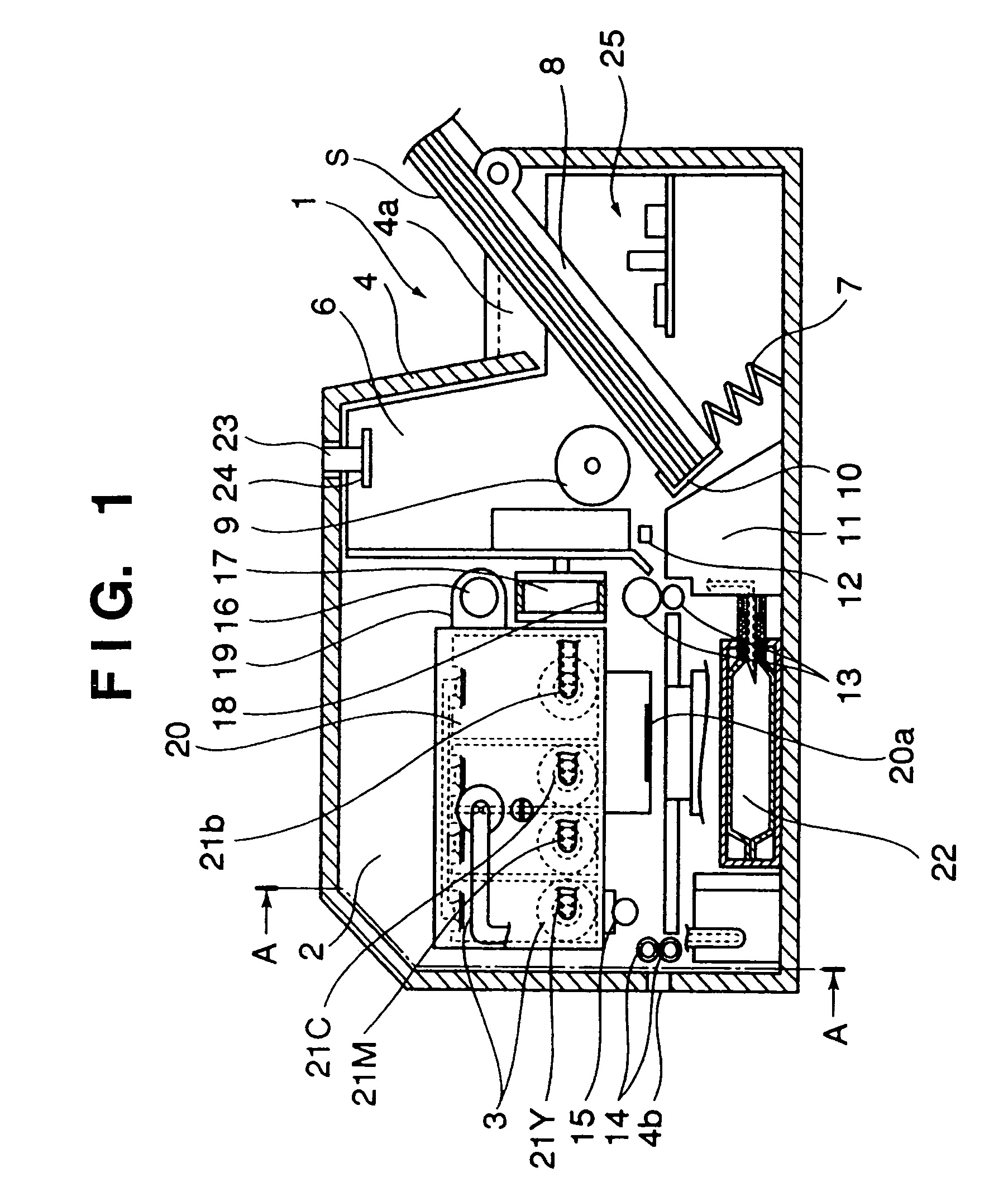

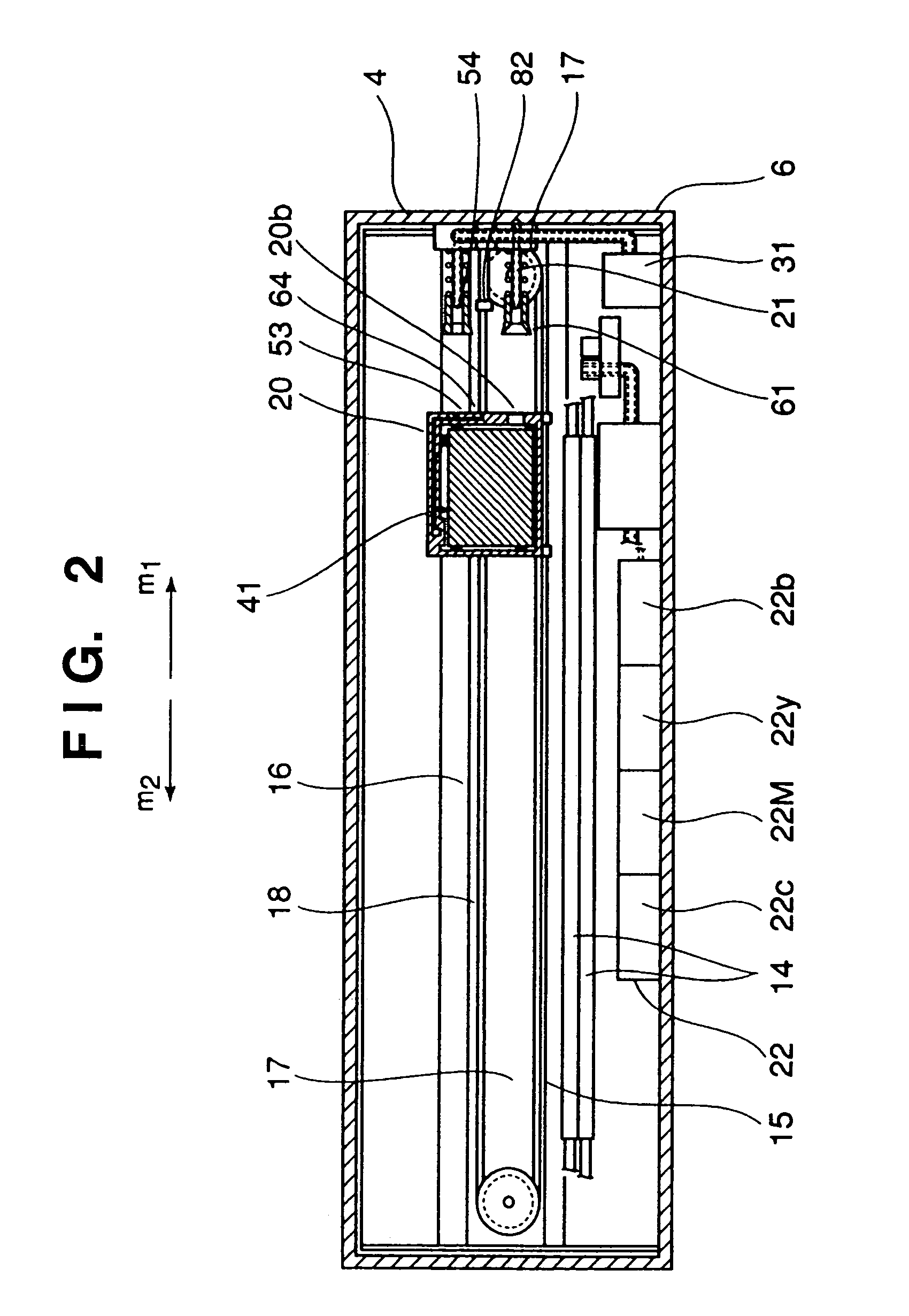

Liquid reservoir apparatus

Owner:CANON KK

Split-gate flash memory, method of fabricating same and method for control thereof

ActiveUS20190355824A1Thin layerLower channel resistanceTransistorSolid-state devicesComputer scienceSemiconductor

A split-gate flash memory, a method of fabricating the split-gate flash memory and a method for control thereof are disclosed. The split-gate flash memory includes: a semiconductor substrate including a first memory region and a second memory region that are separate from each other; and a word-line structure between the first memory region and the second memory region. The word-line structure includes, stacked on the surface of the semiconductor substrate sequentially from bottom to top, a word-line oxide layer, a read gate, a dielectric oxide layer and an erase gate. The read and erase gates can each function as a word line of the split-gate flash memory for enabling a read or erase operation. During the erase operation, a voltage applied on the erase gate has an insignificant impact on the underlying semiconductor substrate, which is helpful in reducing channel leakage in the semiconductor substrate.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

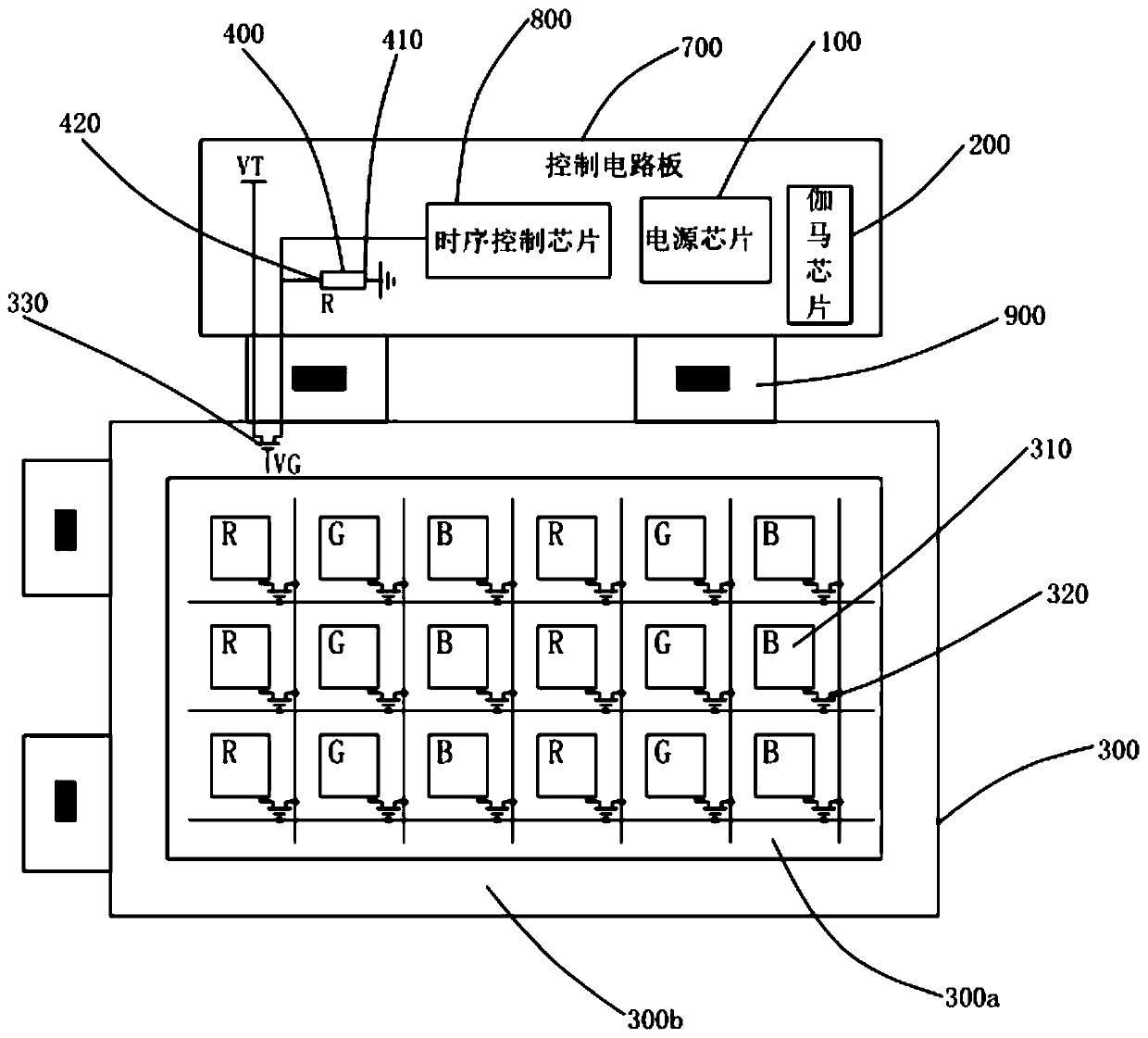

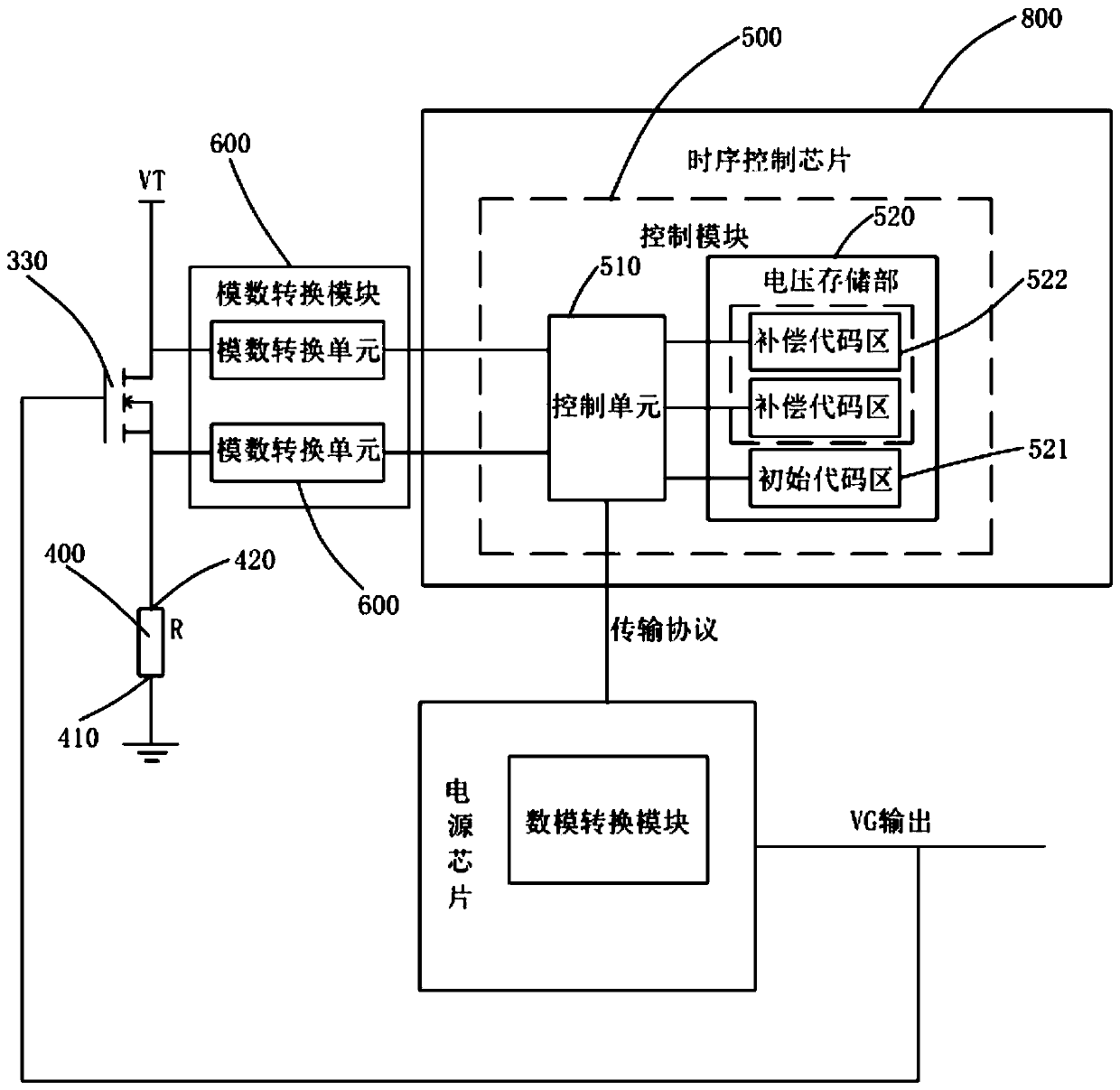

Display device

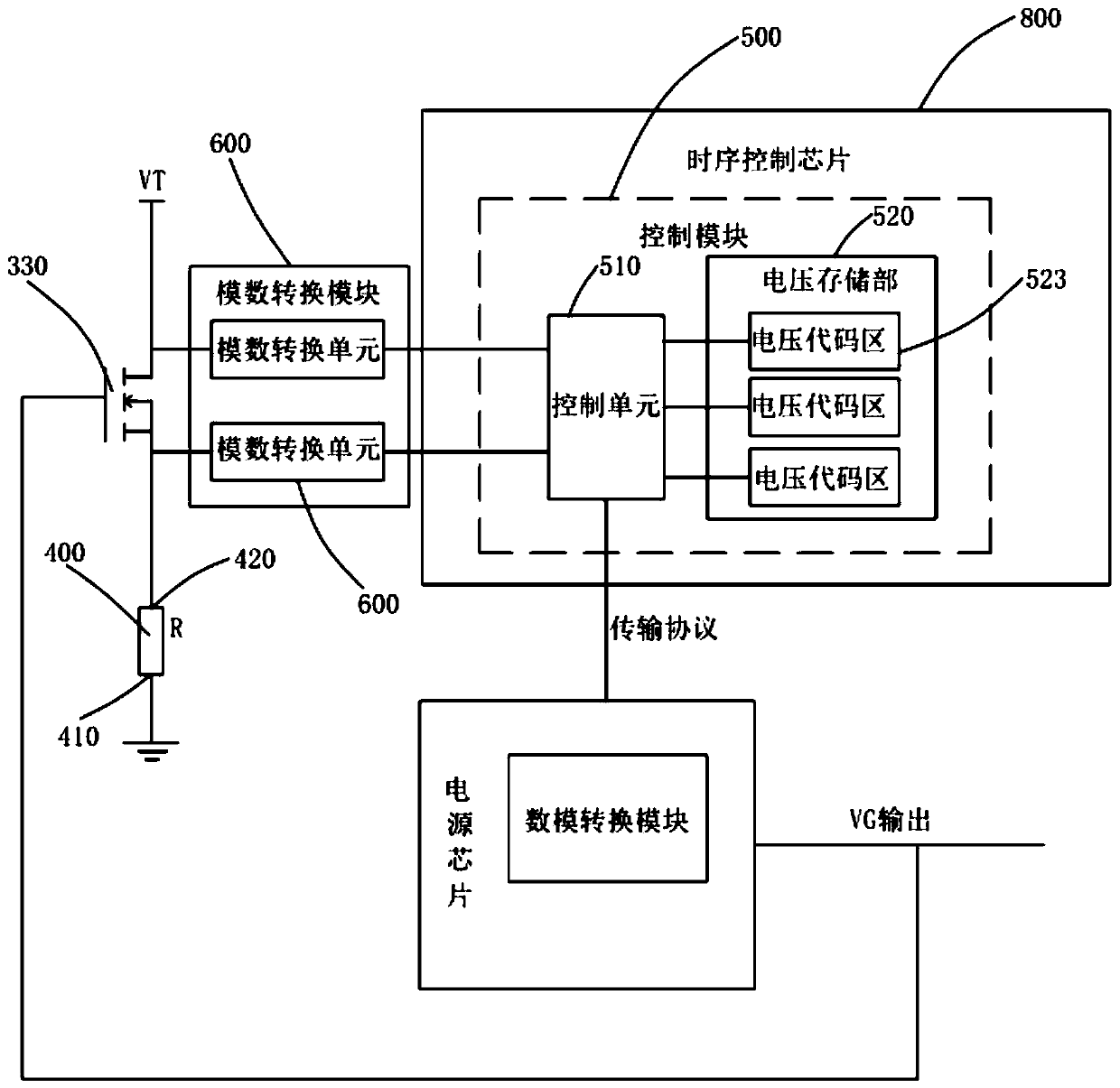

ActiveCN110322850AConsistent brightnessReduce agingStatic indicating devicesElectrical resistance and conductanceElectricity

The present application relates to a display device comprising: a power supply chip for outputting a gate turn-on voltage; a gamma chip which is used for providing gamma voltage; a detection resistorwhich is provided with a first end and a second end which are used for electrical connection, wherein the first end is grounded; a display panel which comprises a plurality of sub-pixels, a pluralityof driving transistors and at least one detection transistor, wherein the grid electrodes of the driving transistors receive a grid electrode turn-on voltage, the first electrodes of the driving transistors receive a gamma voltage, and the second electrodes of the driving transistors are electrically connected with the corresponding sub-pixels, the grid electrode of the detection transistor receives a grid electrode turn-on voltage, the first electrode of the detection transistor receives a test voltage, and the second electrode of the detection transistor is electrically connected with the second end of the detection resistor; and a control module which is electrically connected with the second end of the detection resistor and is used for controlling the power supply chip to increase ordecrease the output of the gate turn-on voltage when the voltage of the detection resistor is decreased. The display device can effectively prevent display darkening after long-term use.

Owner:HKC CORP LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com