Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

52results about How to "Reduce Overlap Capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

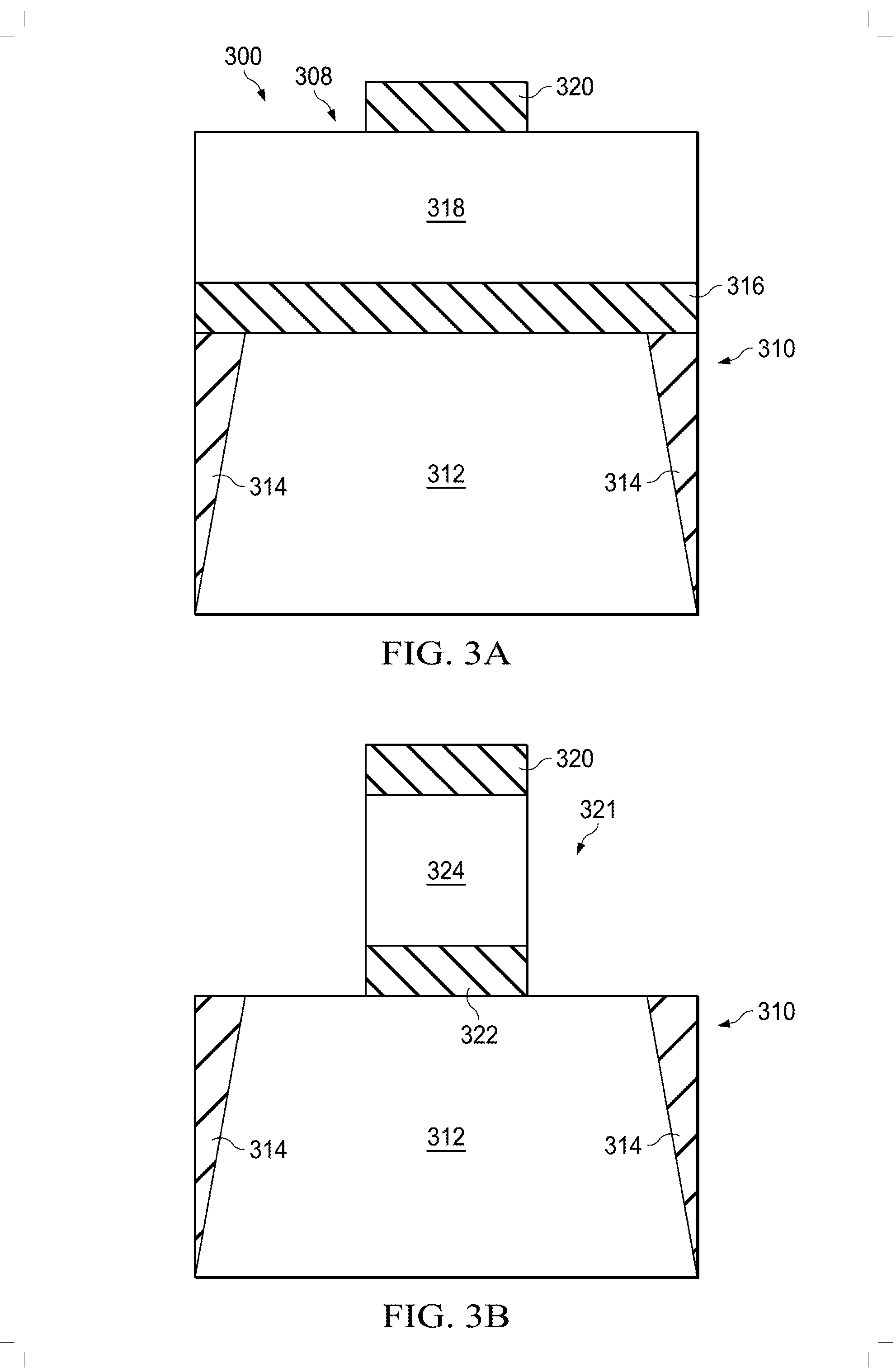

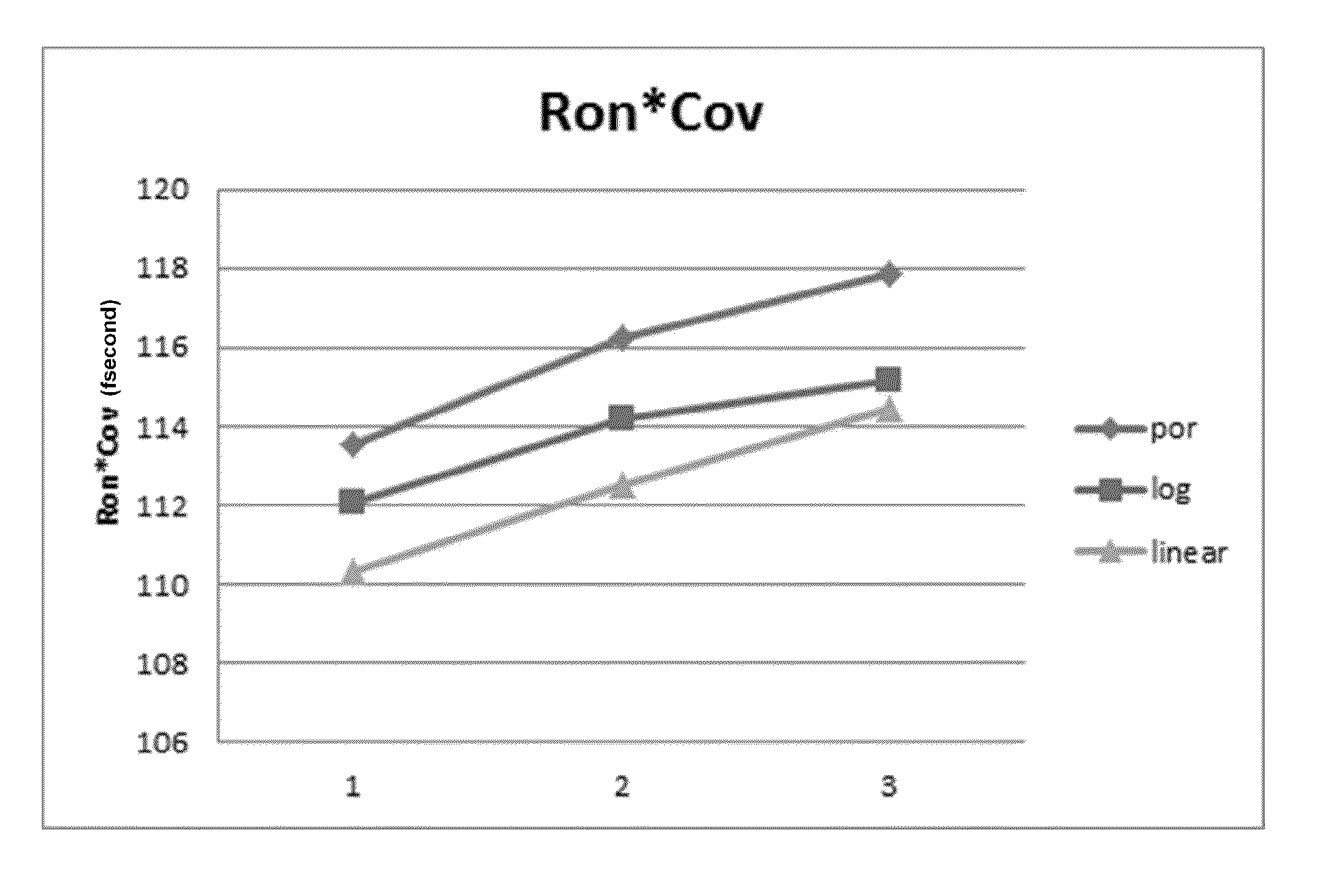

Vertical FET with nanowire channels and a silicided bottom contact

ActiveUS7230286B2Reduce resistanceGood short channel characteristicsTransistorNanoinformaticsCapacitanceNanowire

A vertical FET structure with nanowire forming the FET channels is disclosed. The nanowires are formed over a conductive silicide layer. The nanowires are gated by a surrounding gate. Top and bottom insulator plugs function as gate spacers and reduce the gate-source and gate-drain capacitance.

Owner:GLOBALFOUNDRIES U S INC

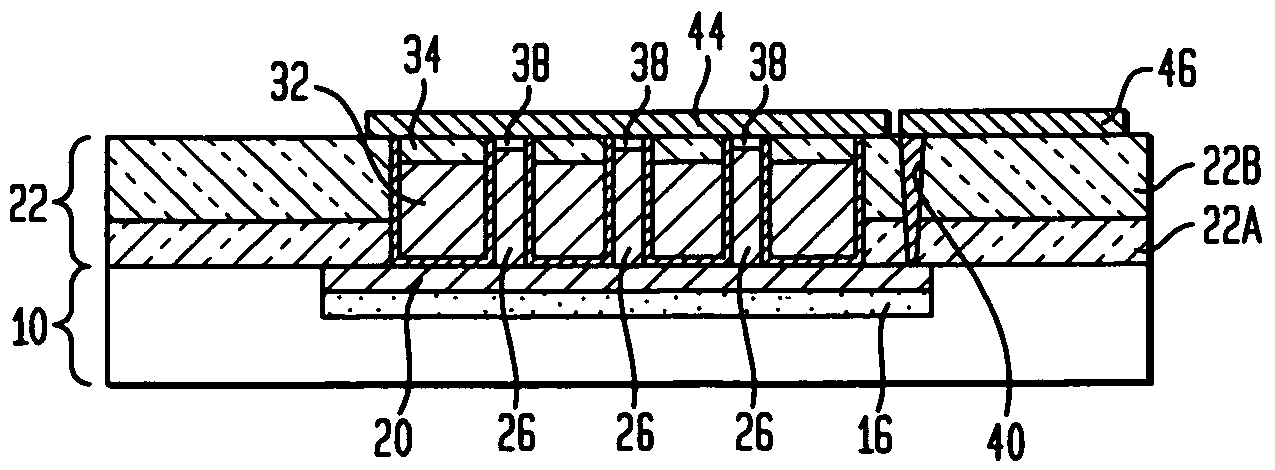

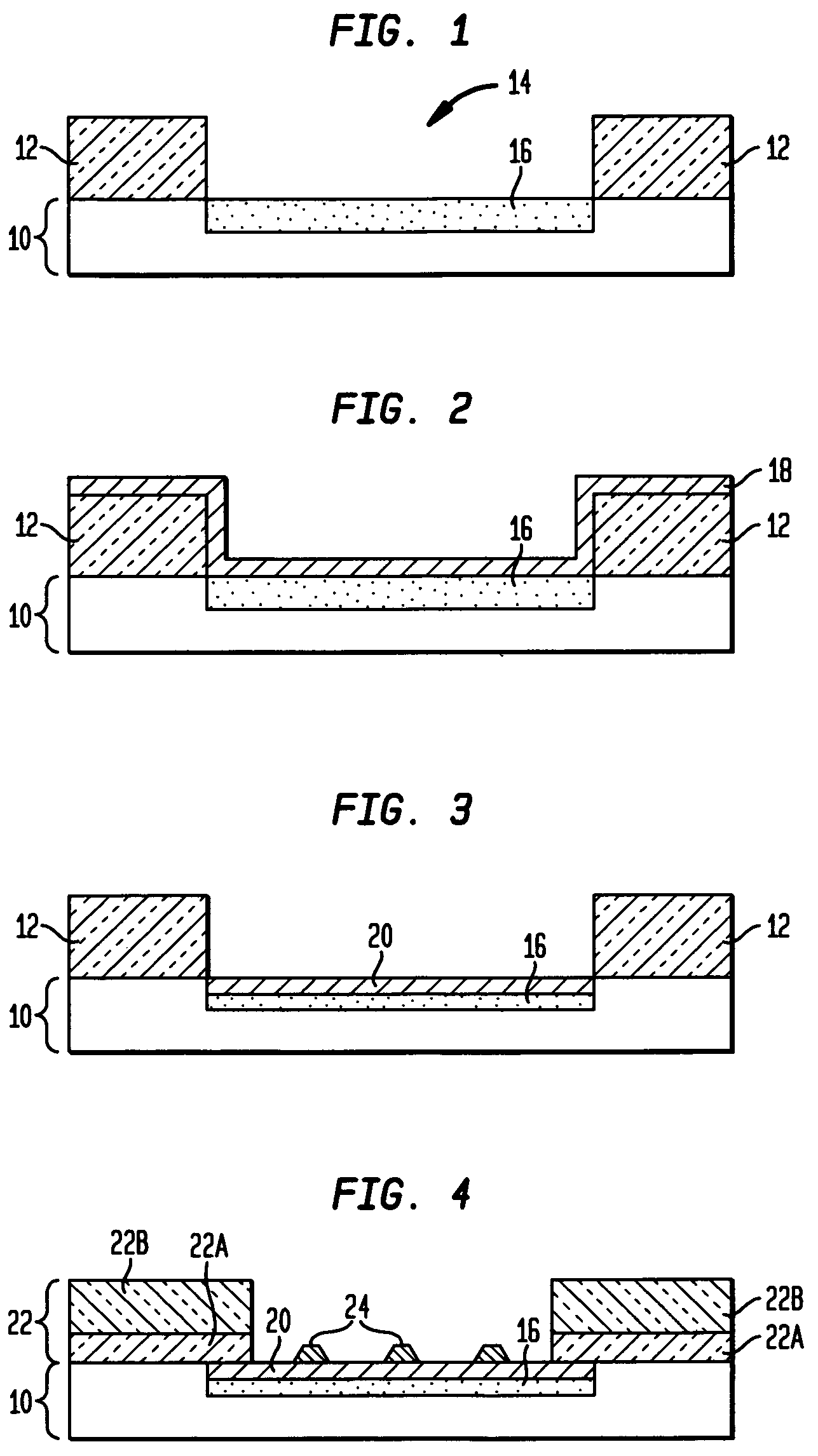

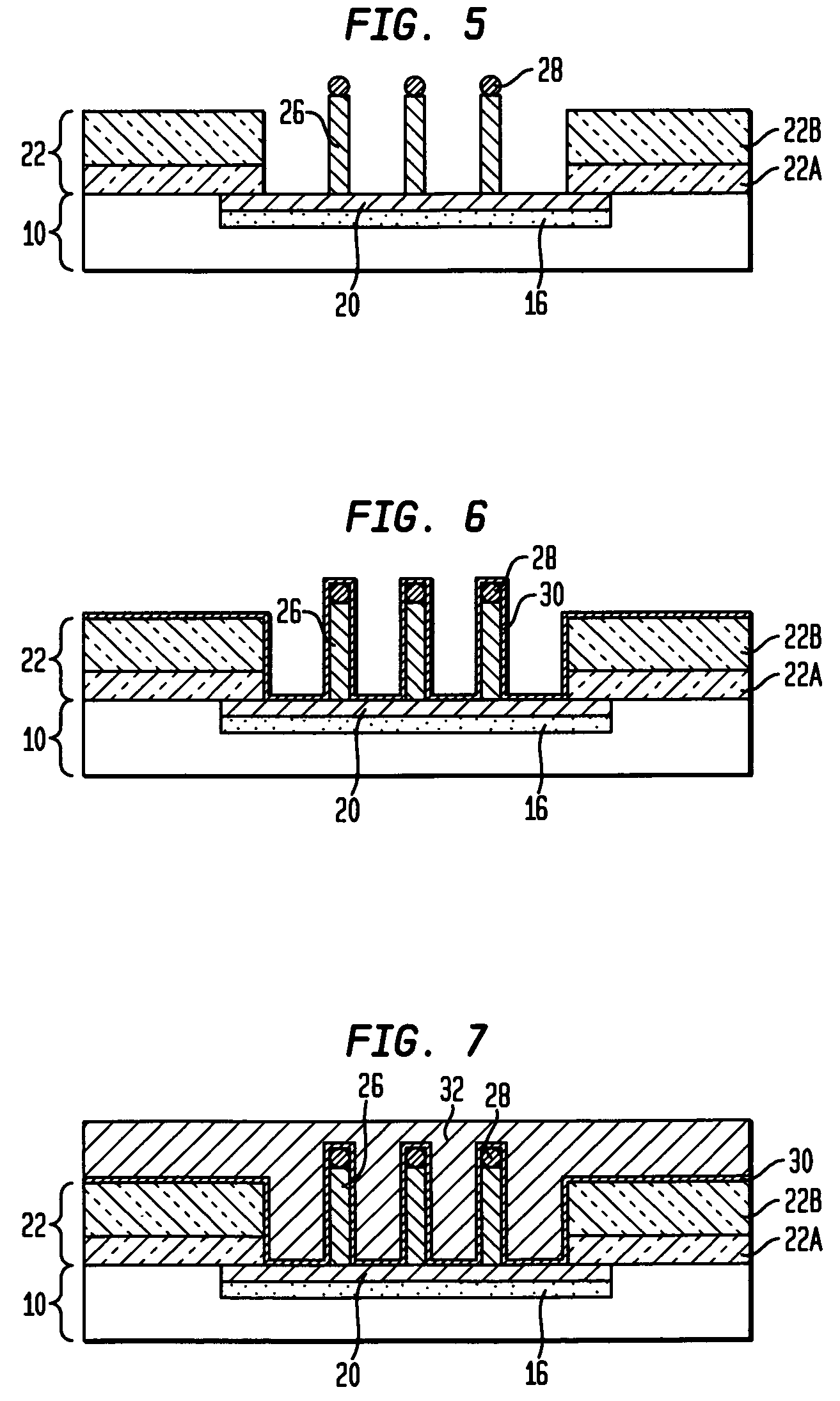

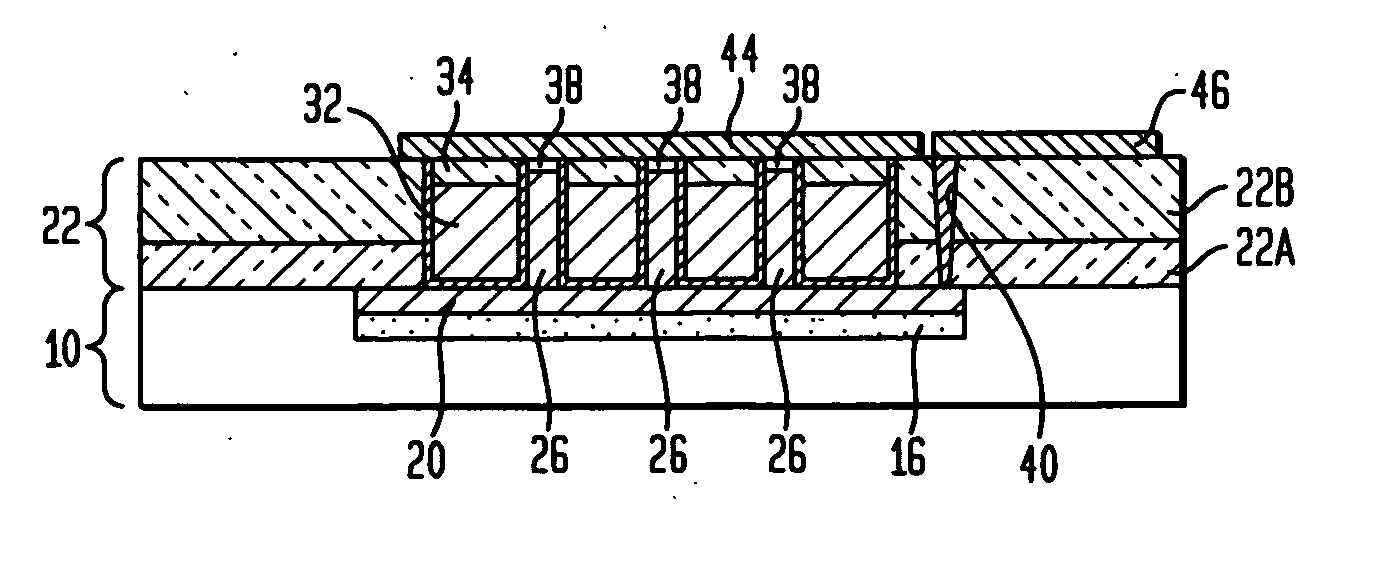

Vertical FET with nanowire channels and a silicided bottom contact

ActiveUS20060273389A1Reduce access series resistanceReduce overlap capacitanceNanoinformaticsSolid-state devicesCapacitanceAND gate

A vertical FET structure with nanowire forming the FET channels is disclosed. The nanowires are formed over a conductive silicide layer. The nanowires are gated by a surrounding gate. Top and bottom insulator plugs function as gate spacers and reduce the gate-source and gate-drain capacitance.

Owner:GLOBALFOUNDRIES US INC

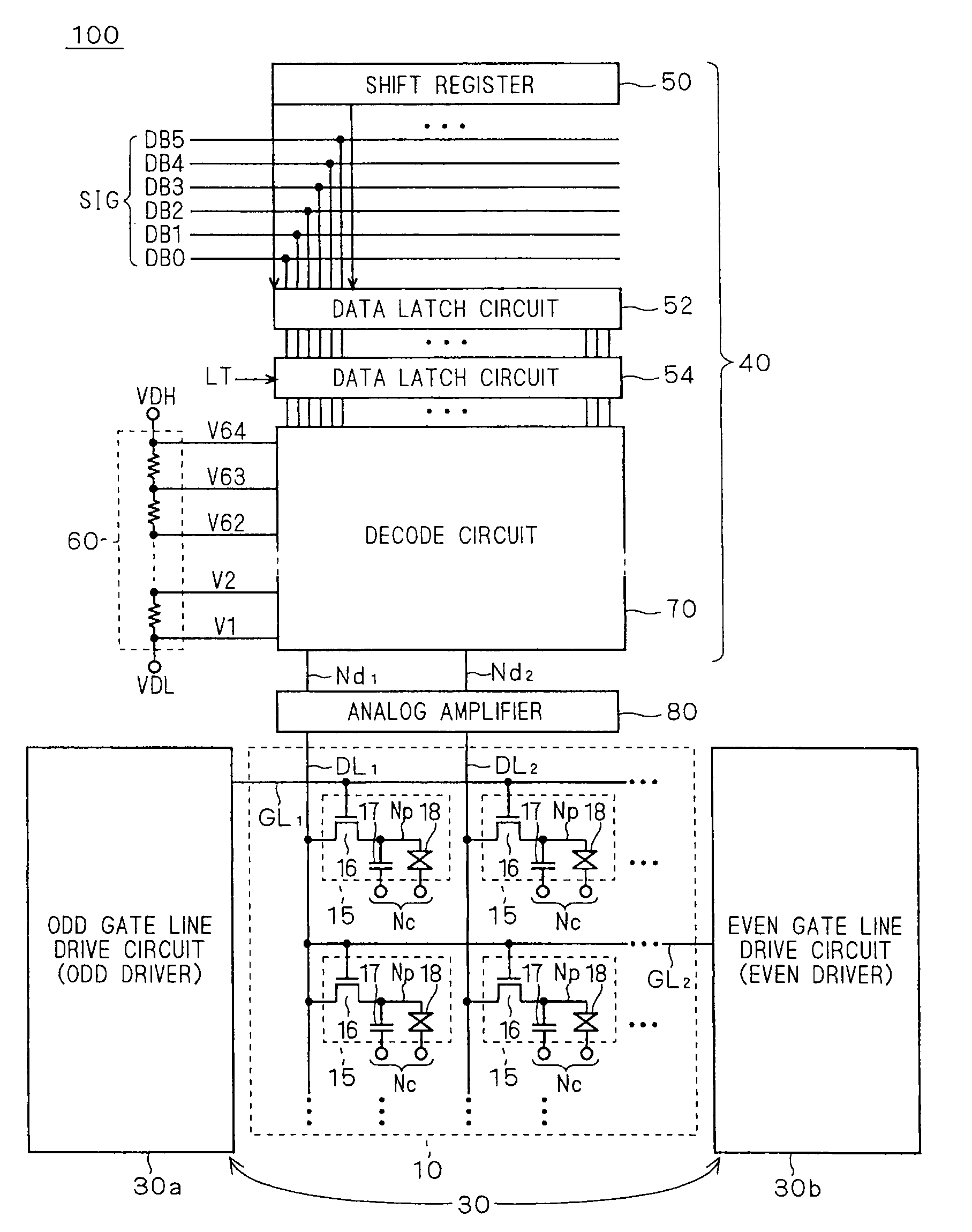

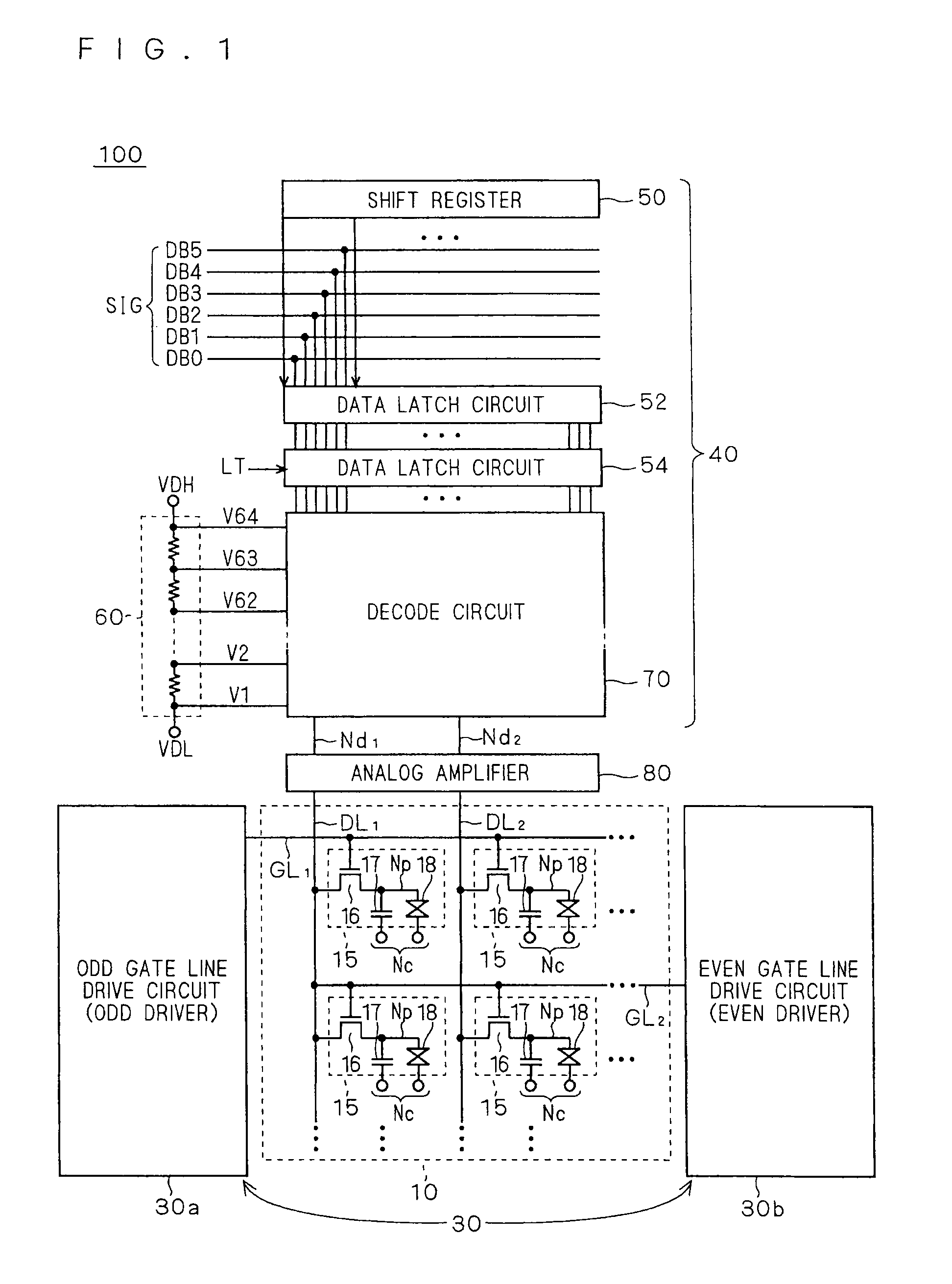

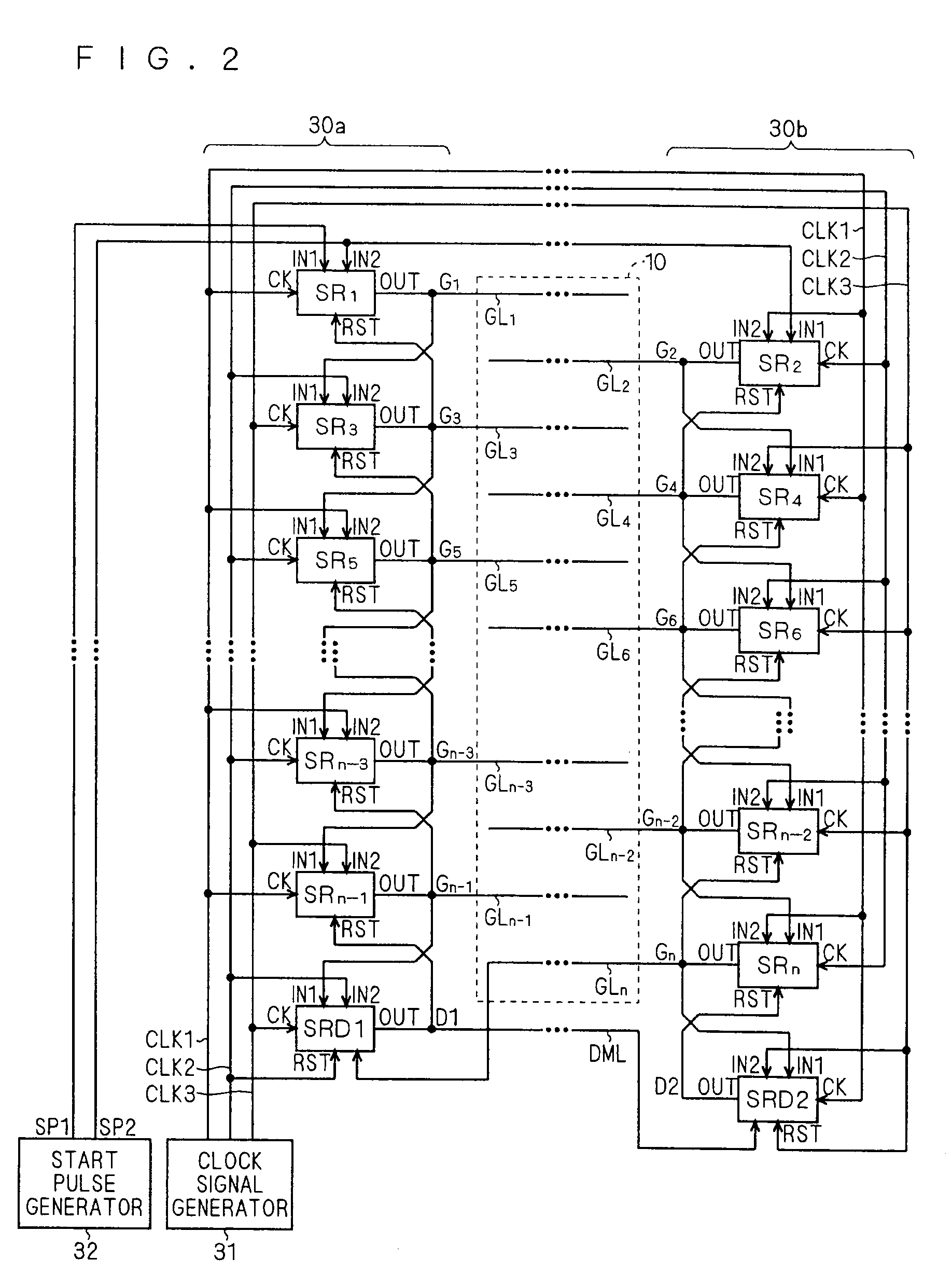

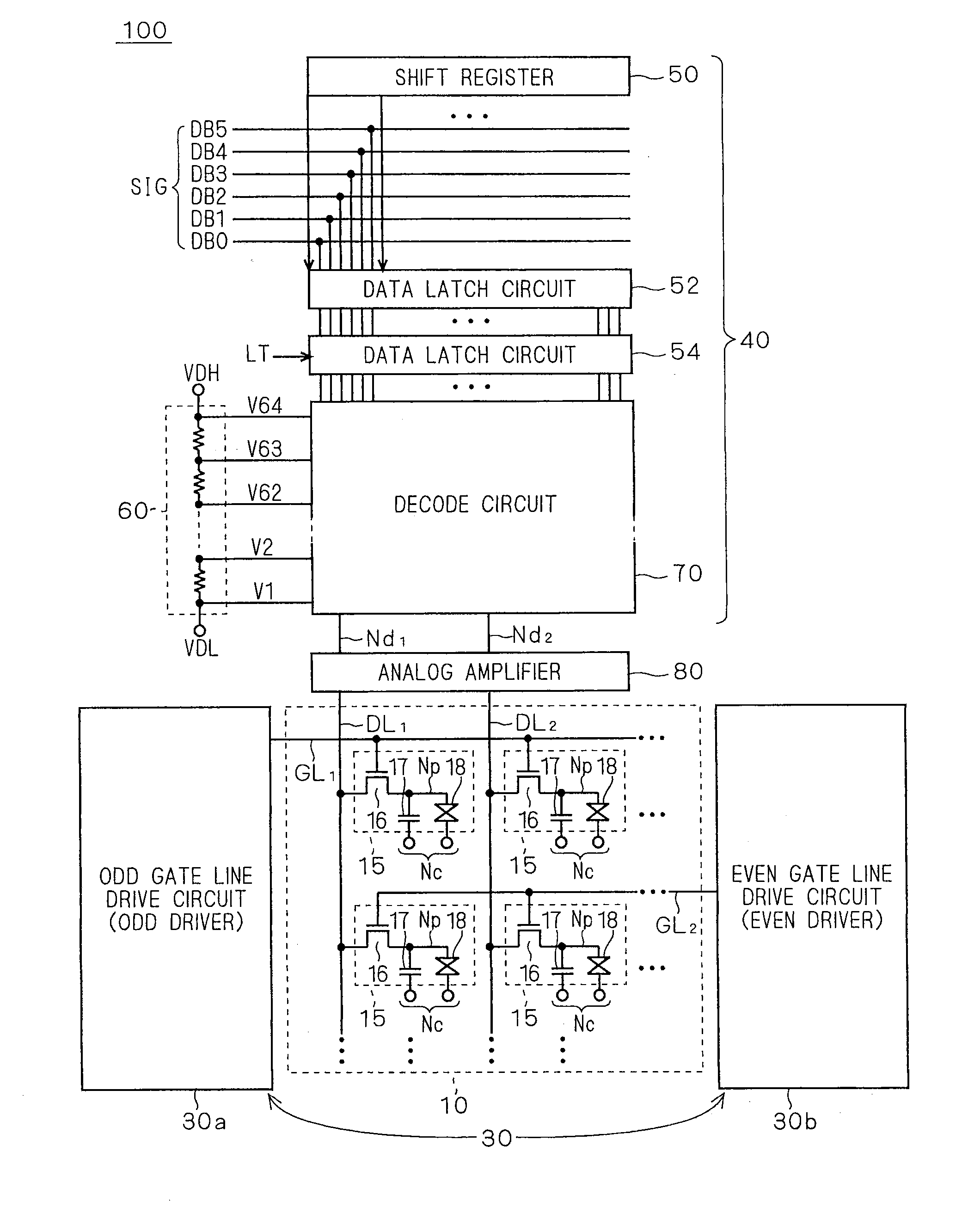

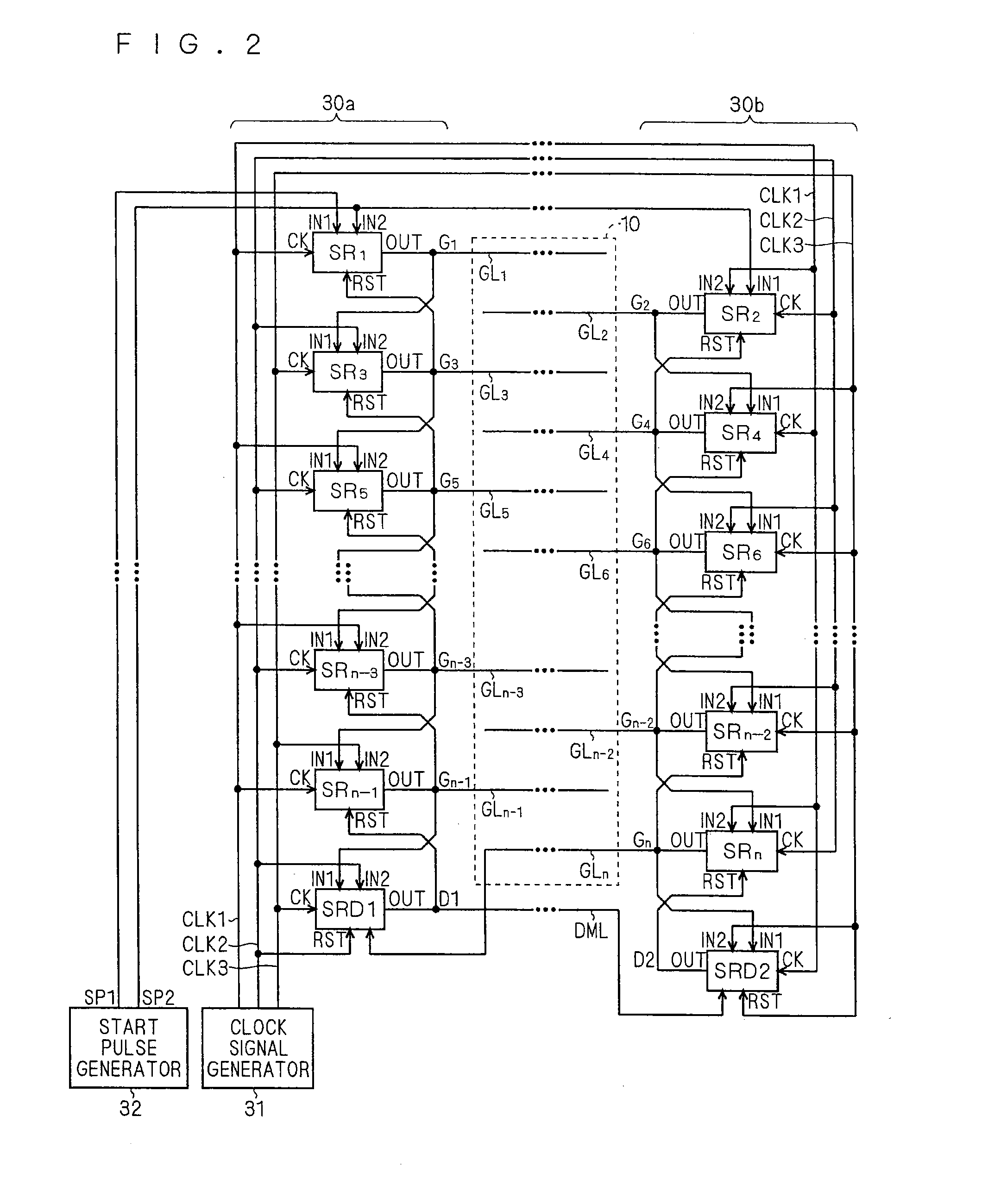

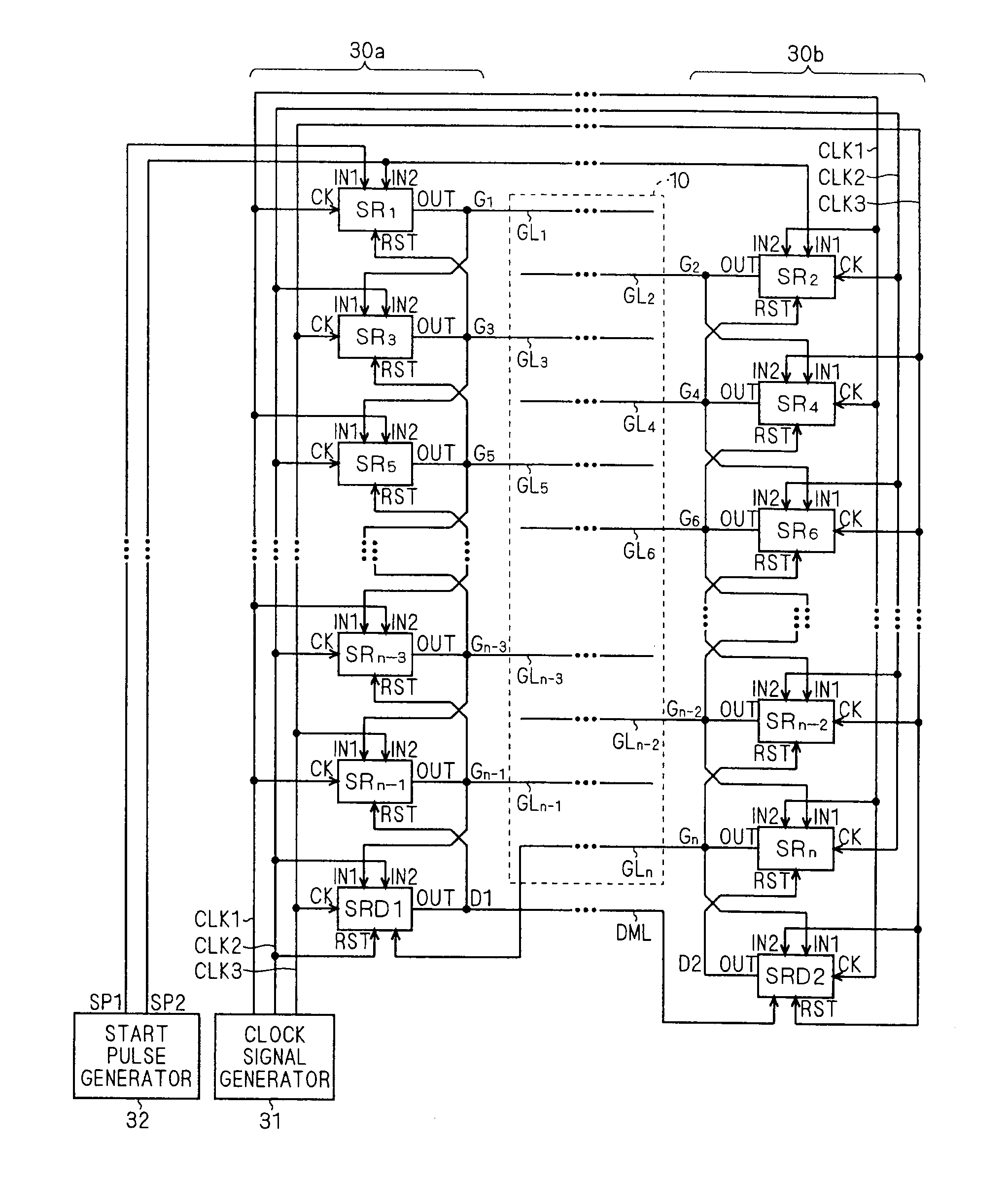

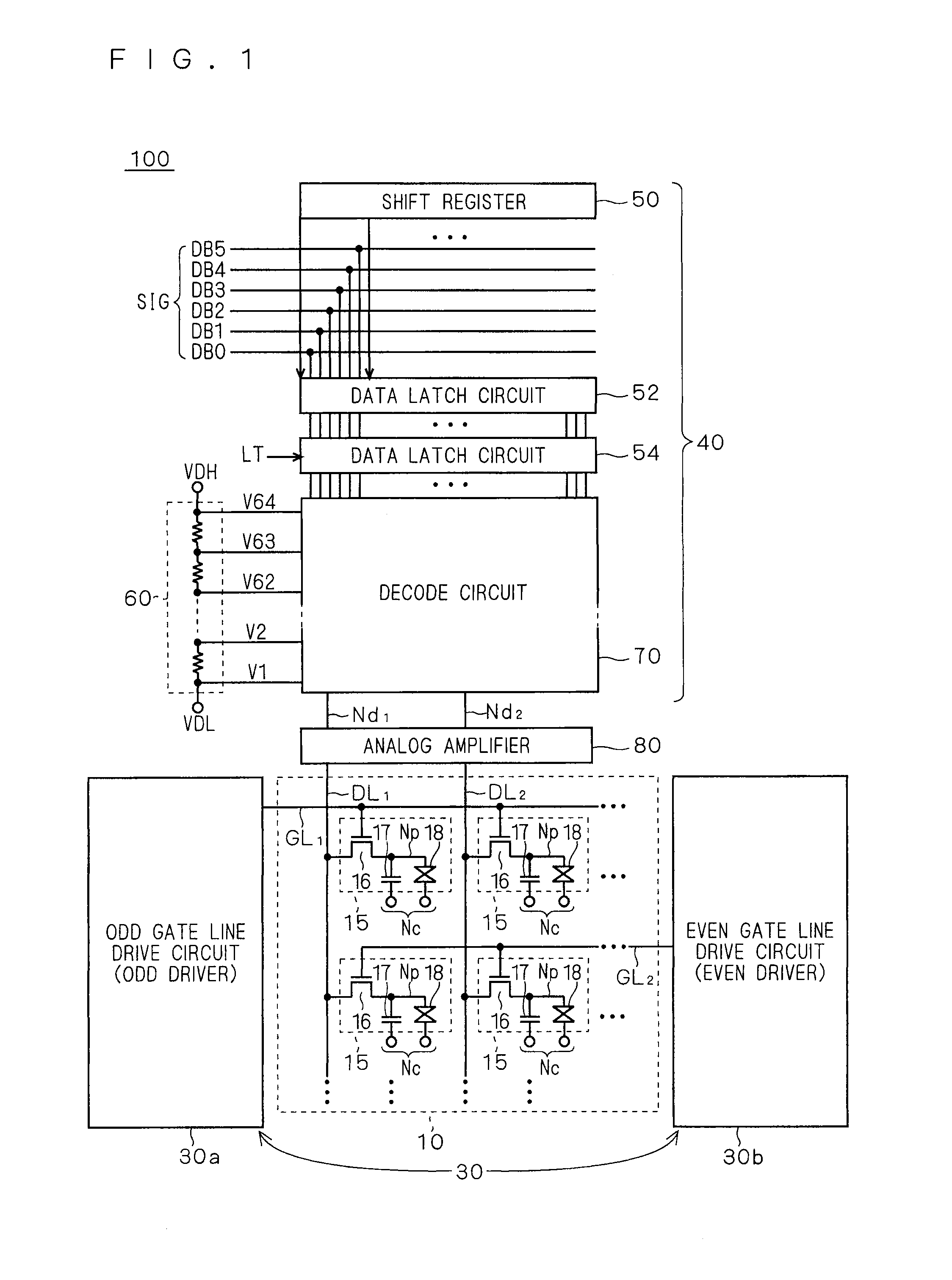

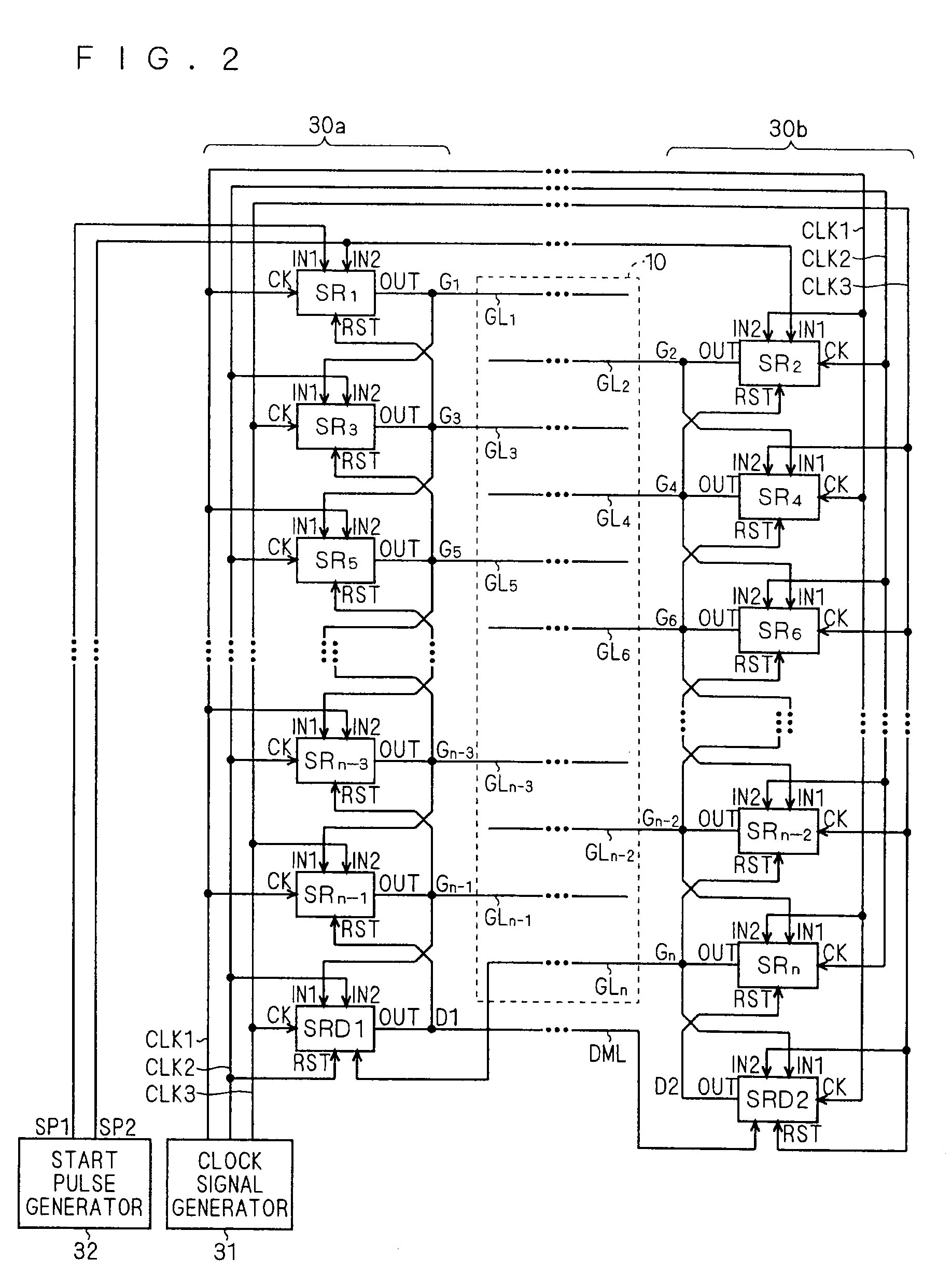

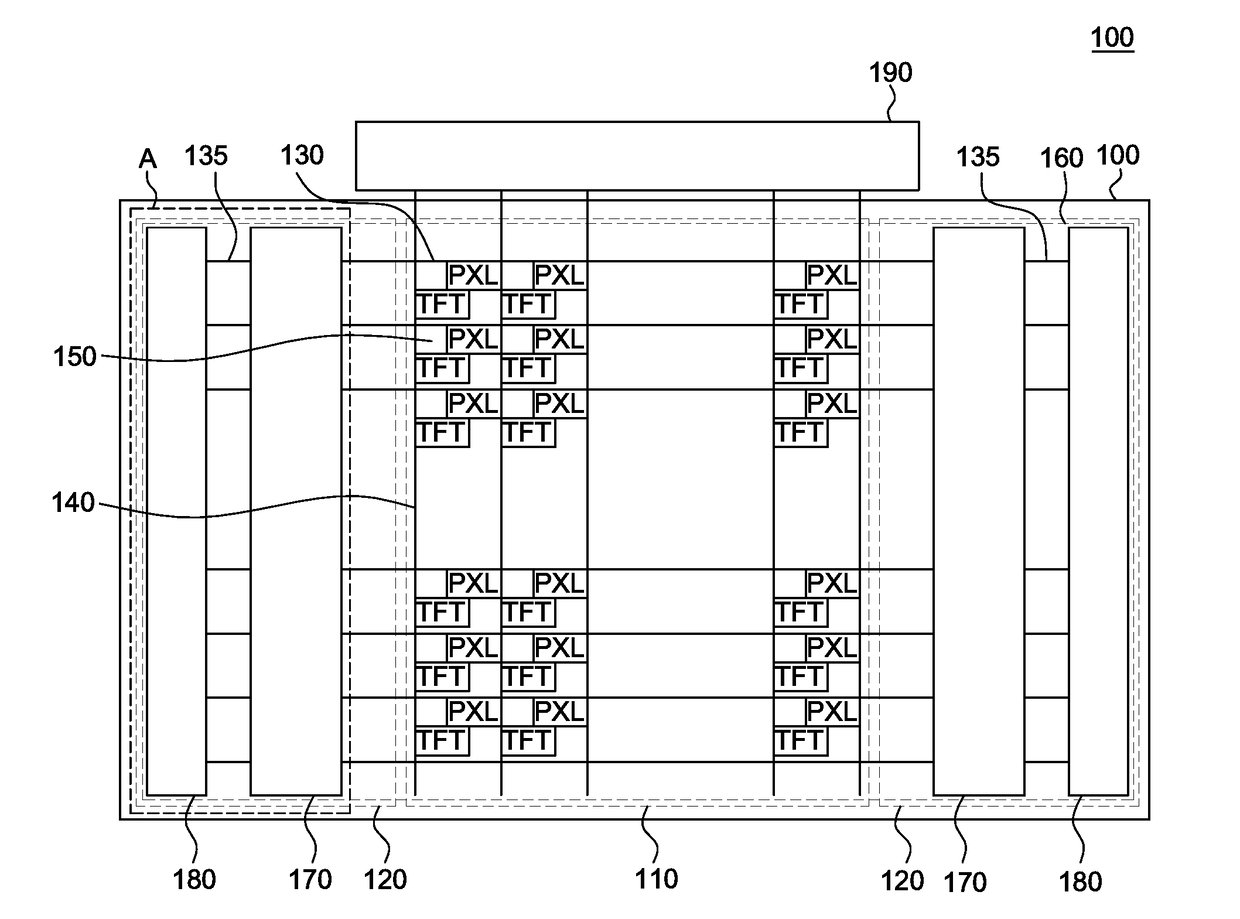

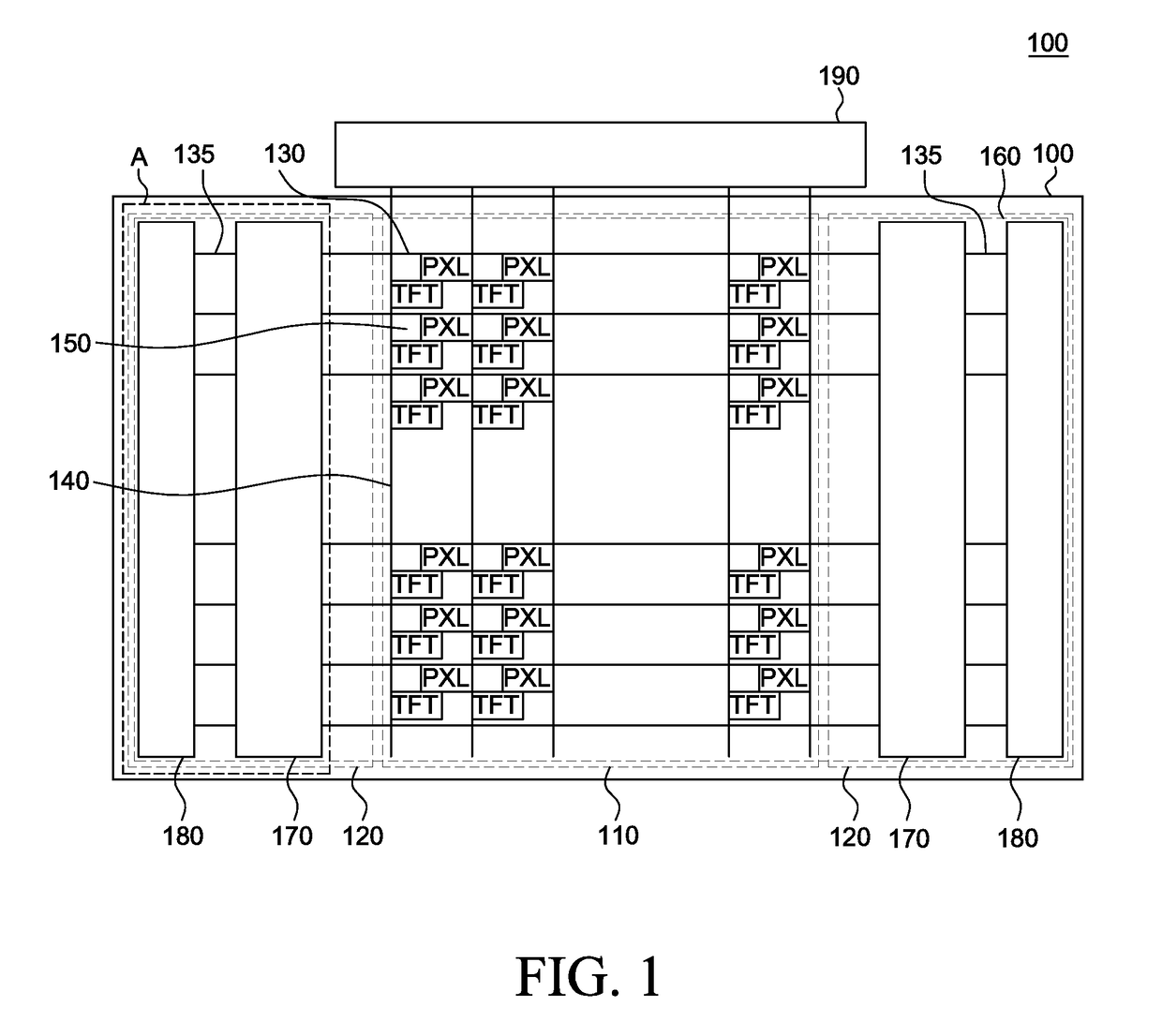

Electro-optical device, shift register circuit, and semiconductor device

ActiveUS20100201666A1Inhibition of rising speedIncrease delayElectric analogue storesCathode-ray tube indicatorsShift registerDevice material

An electro-optical device is configured to be capable of using a region of a gate line drive circuit efficiently and preventing rising speed of a gate line selection signal from decreasing (rising delay), and a shift register circuit is composed of a single conductivity type transistor which is suitable for the device. The gate line drive circuit including an odd driver to drive odd rows of a plurality of gate lines, and an even driver to drive even rows thereof. Each unit shift register in the odd and even drivers receives a selection signal in the second previous row and activates its own selection signal two horizontal periods later. A start pulse of the even driver is delayed in phase by one horizontal period with respect to a start pulse of the odd driver.

Owner:TRIVALE TECH LLC

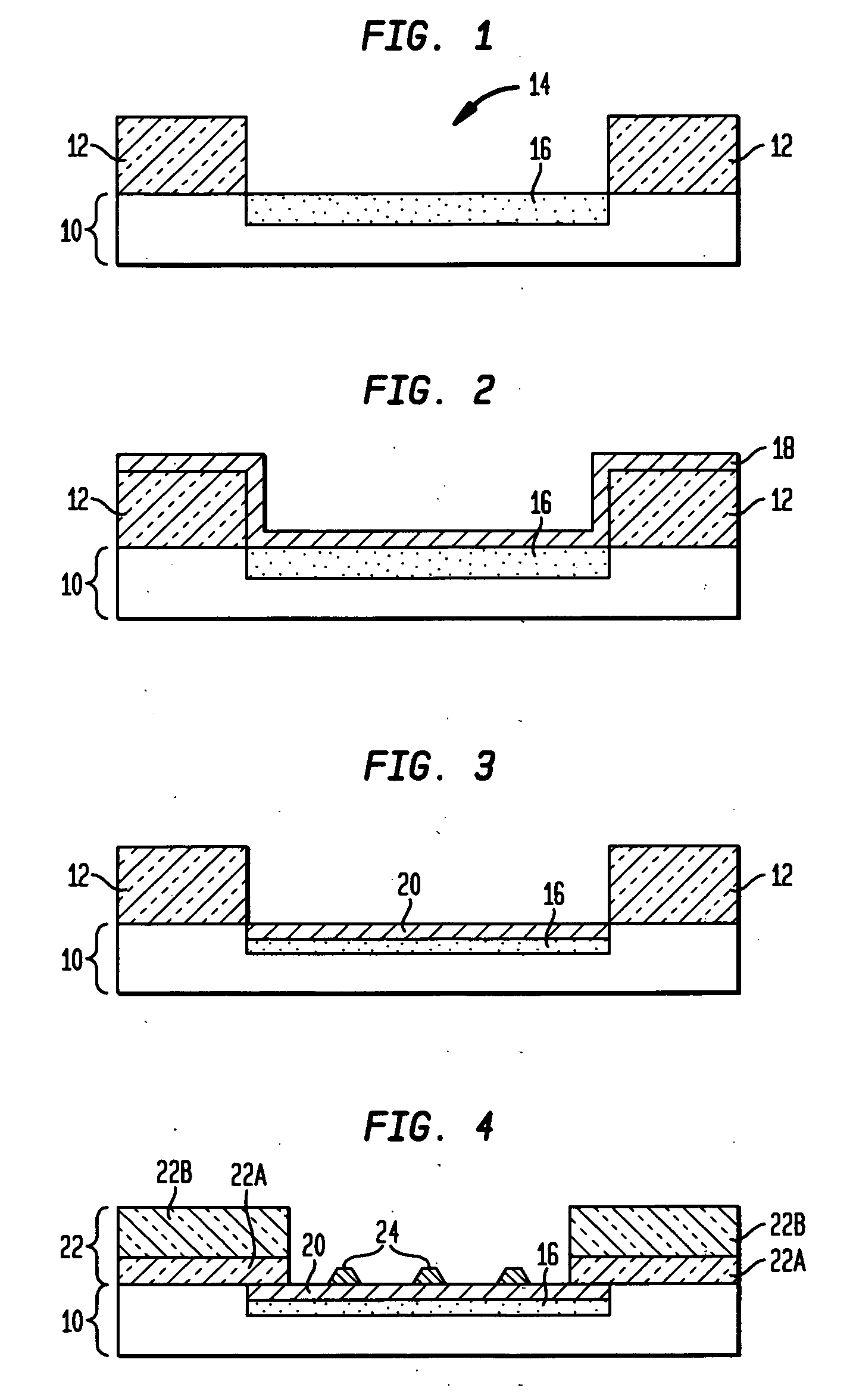

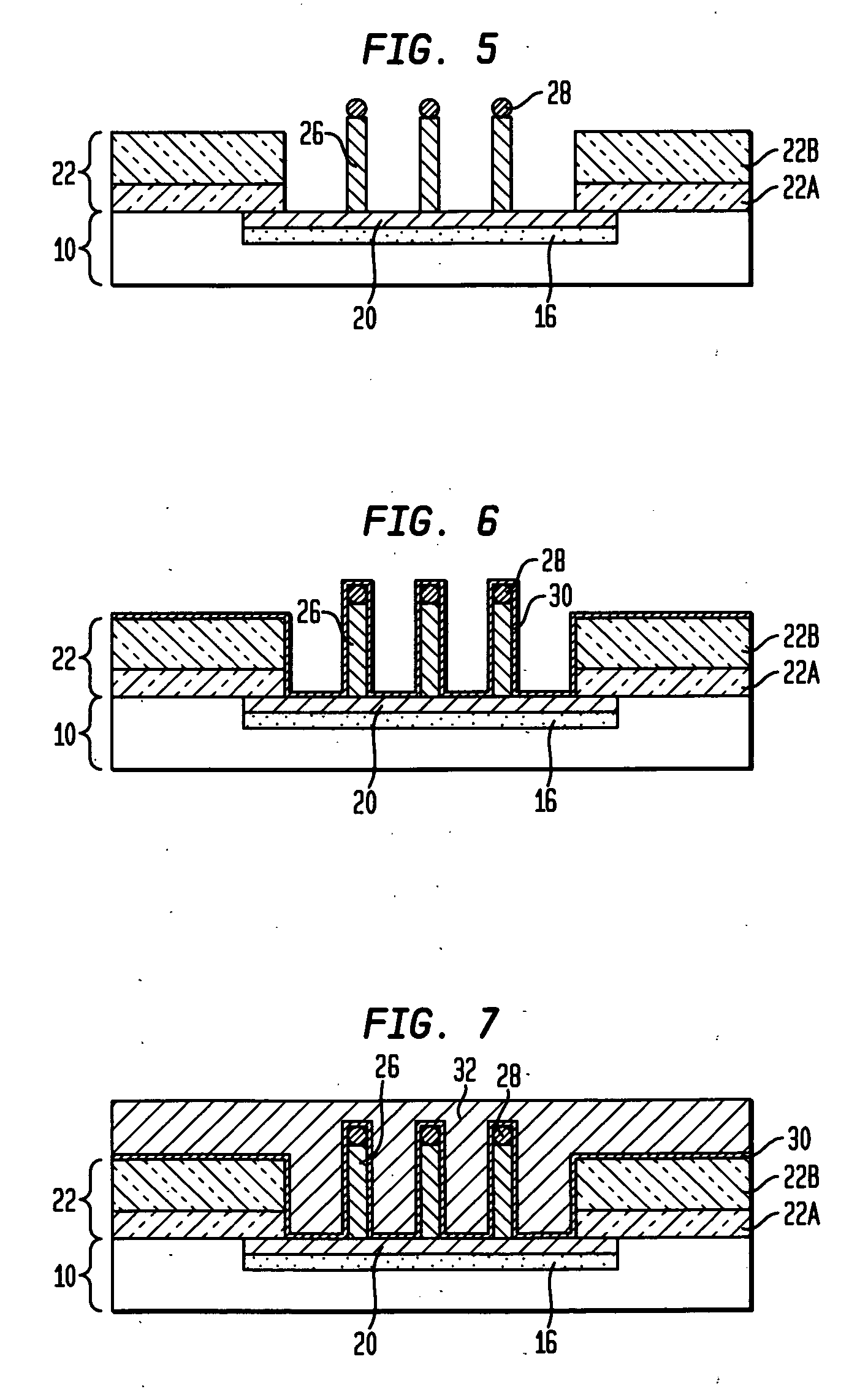

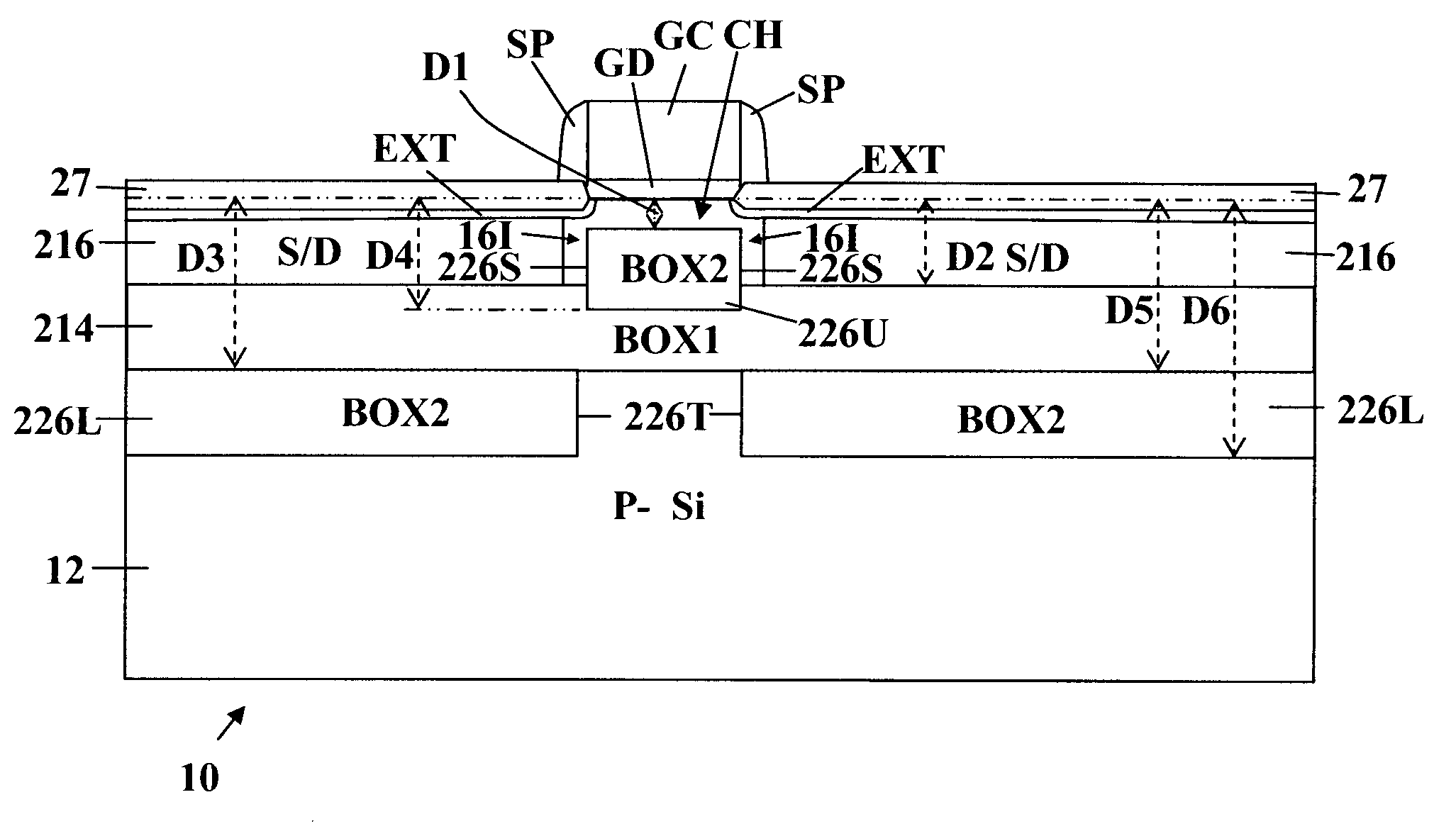

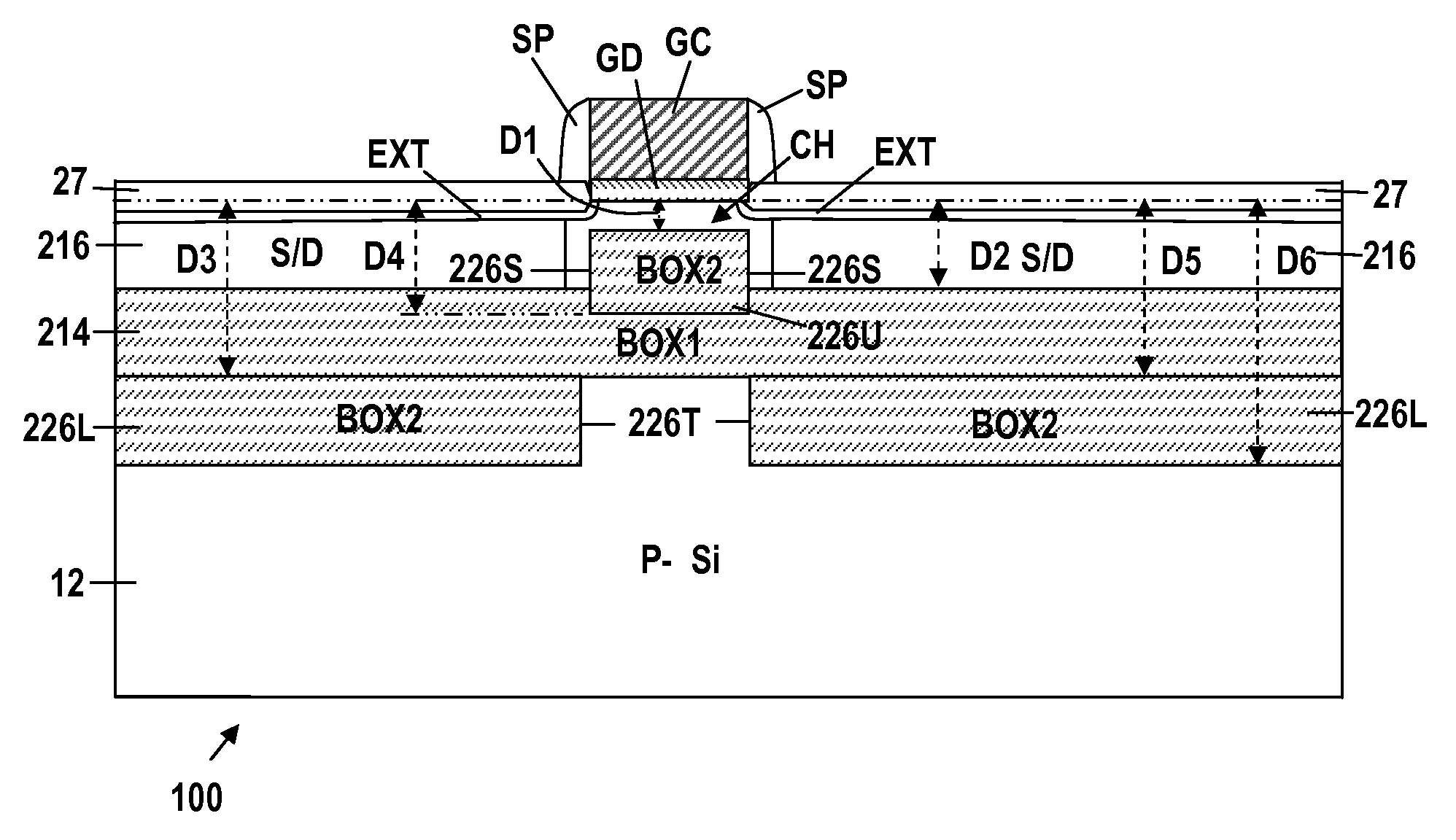

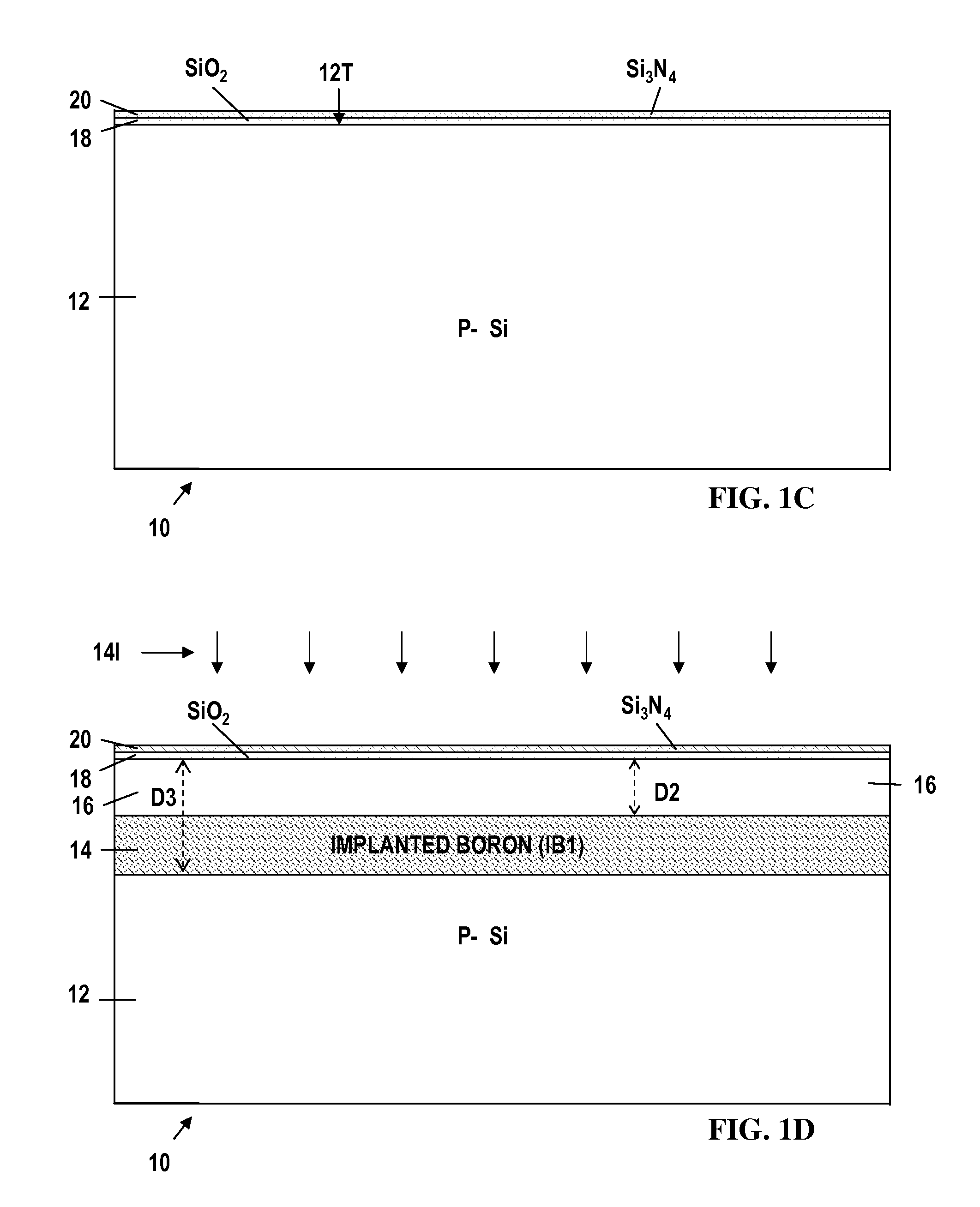

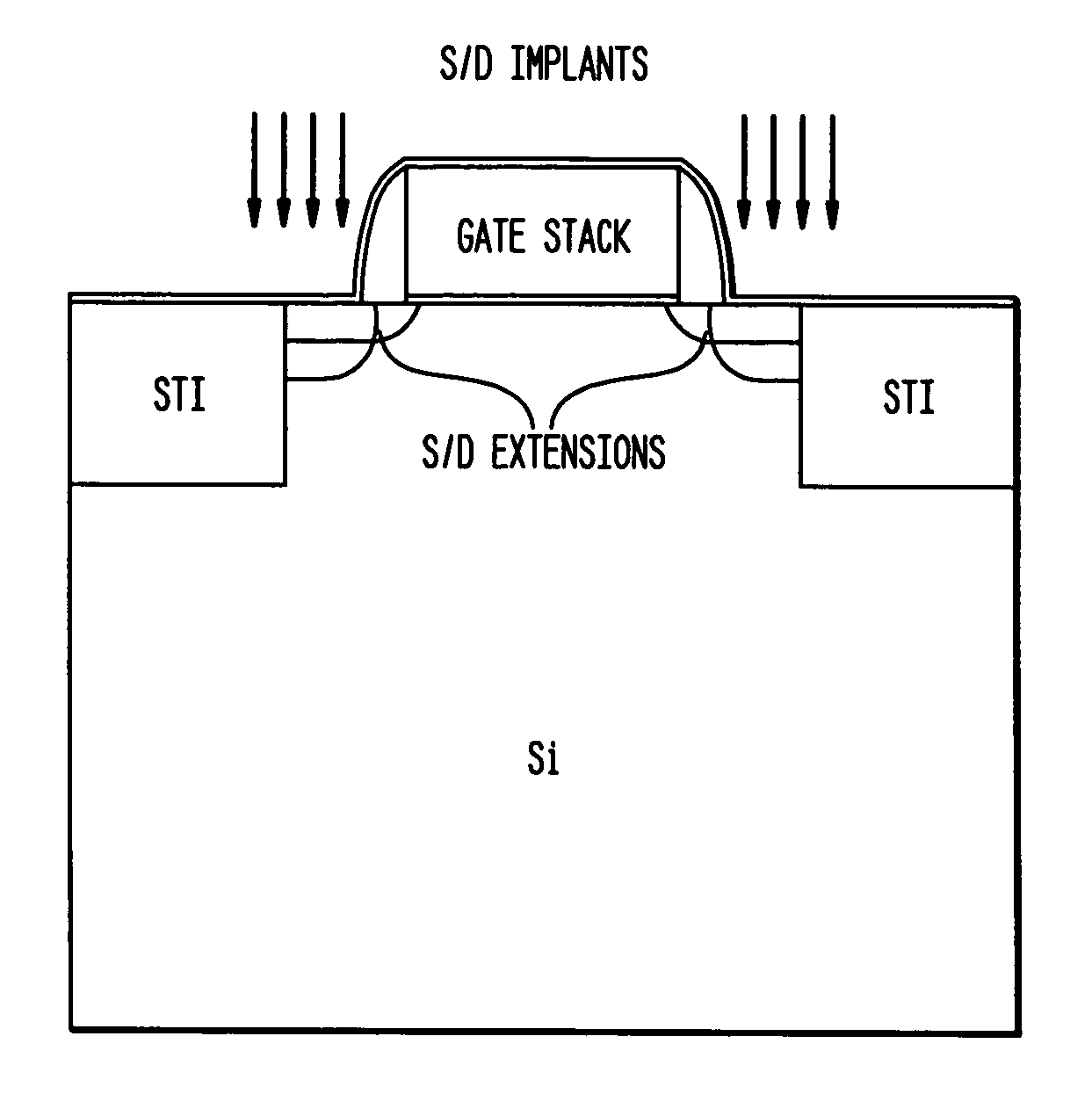

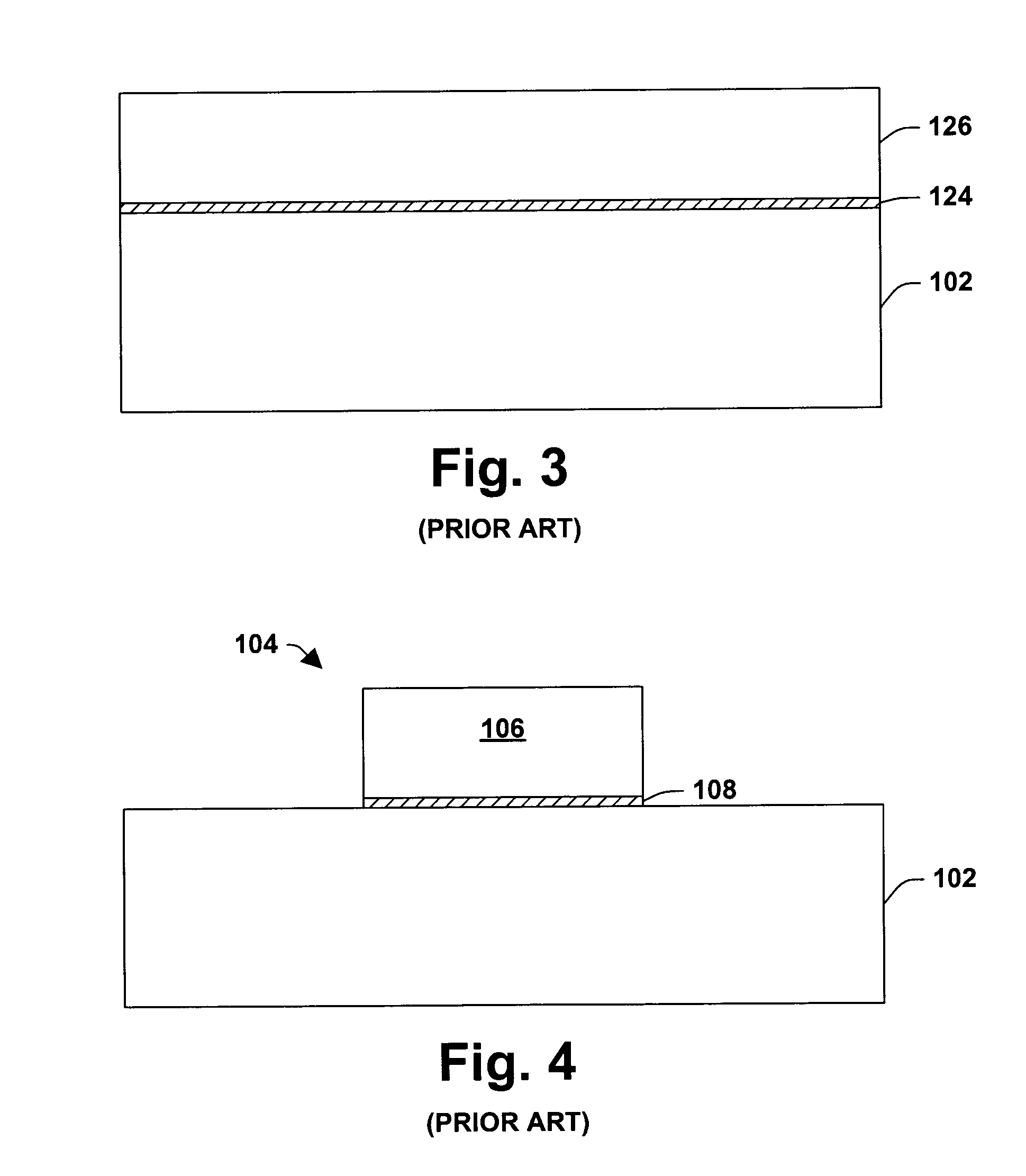

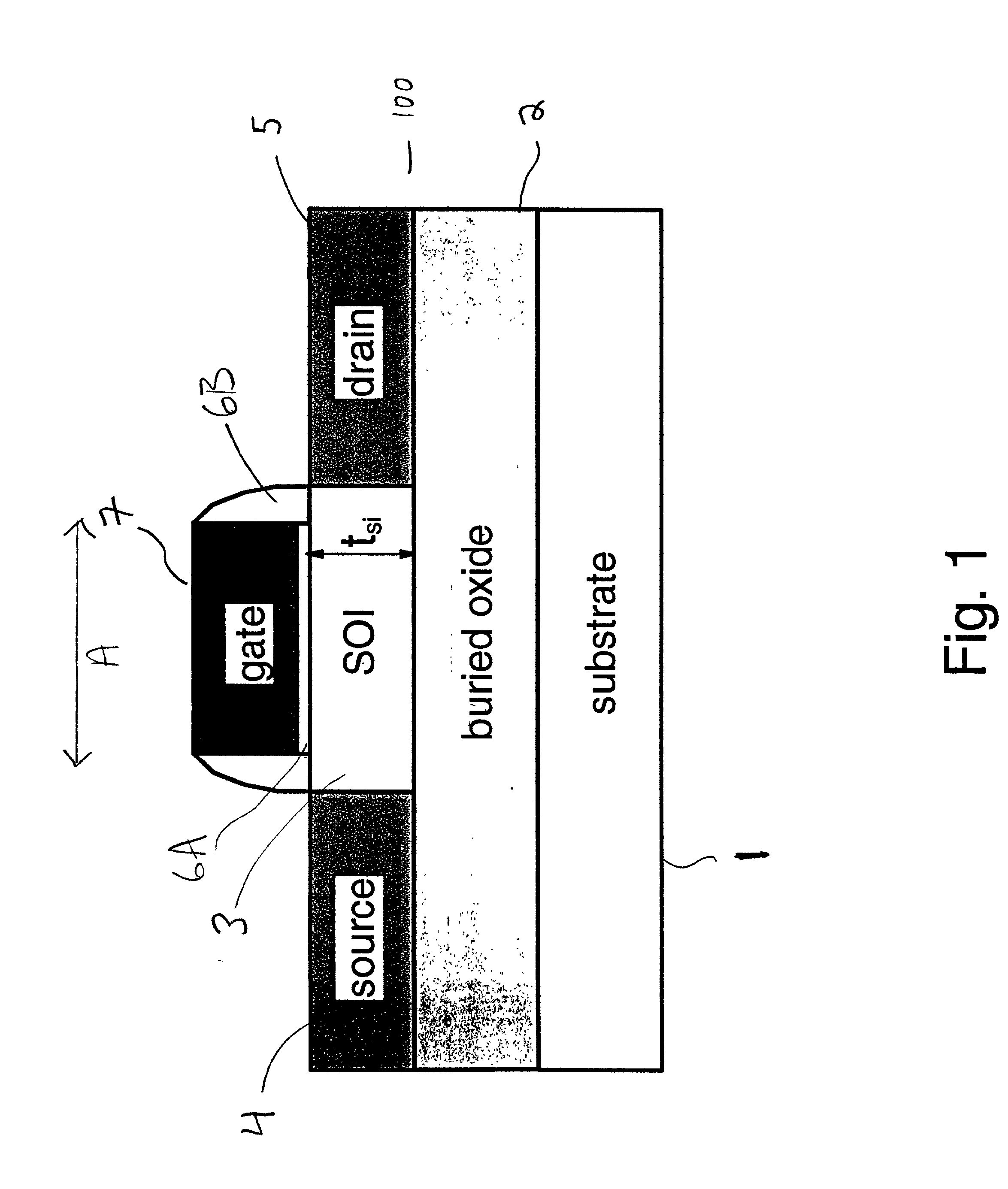

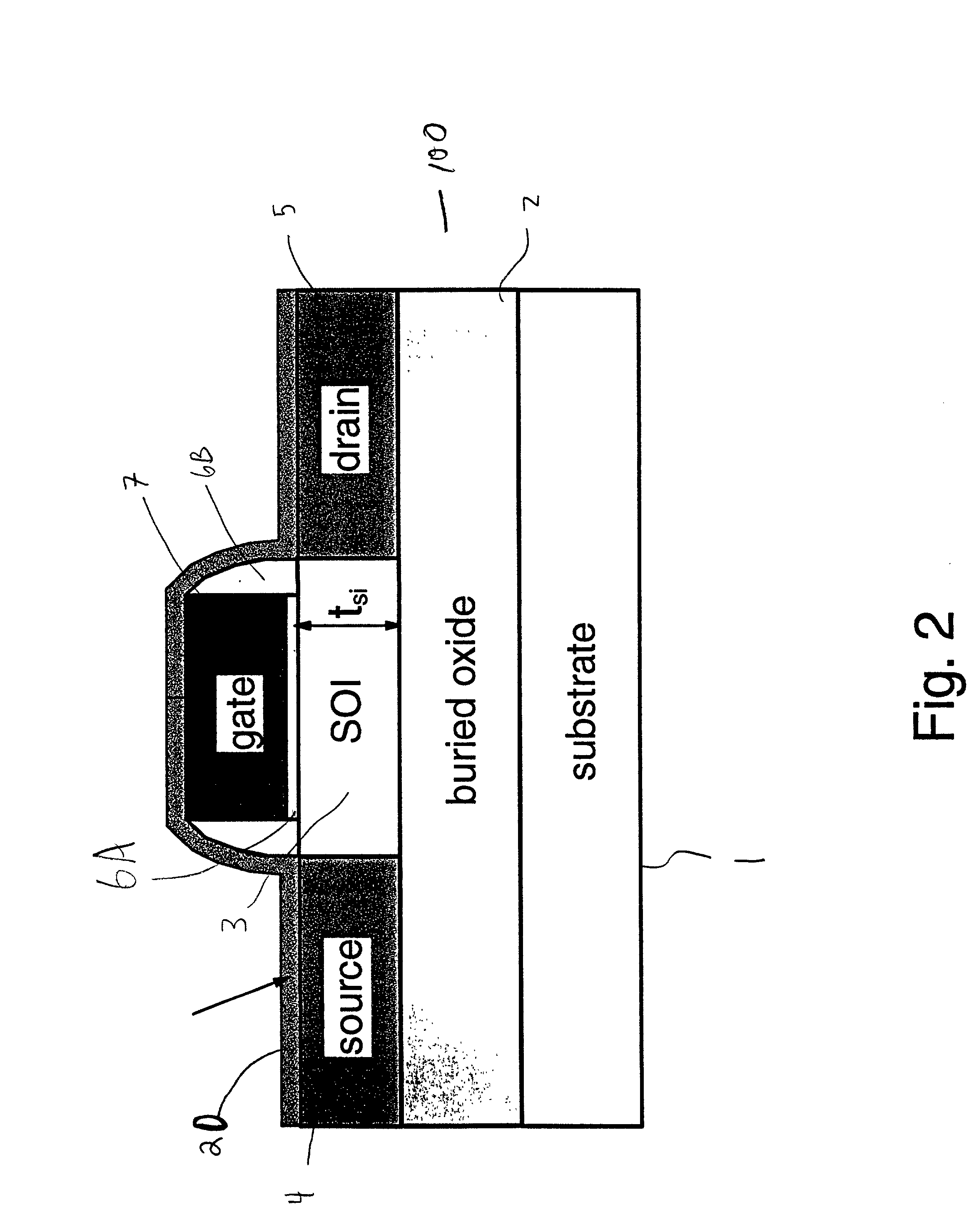

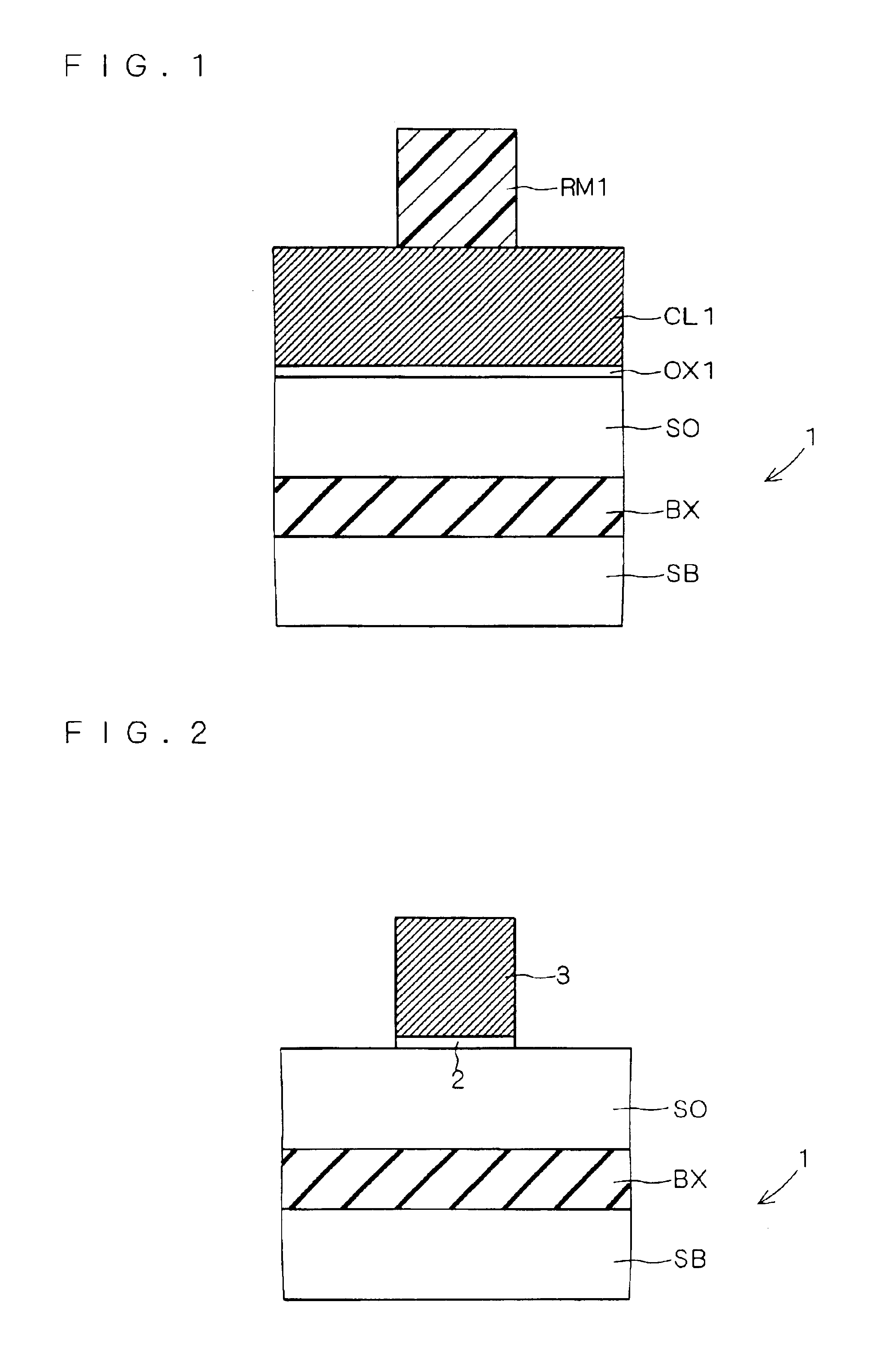

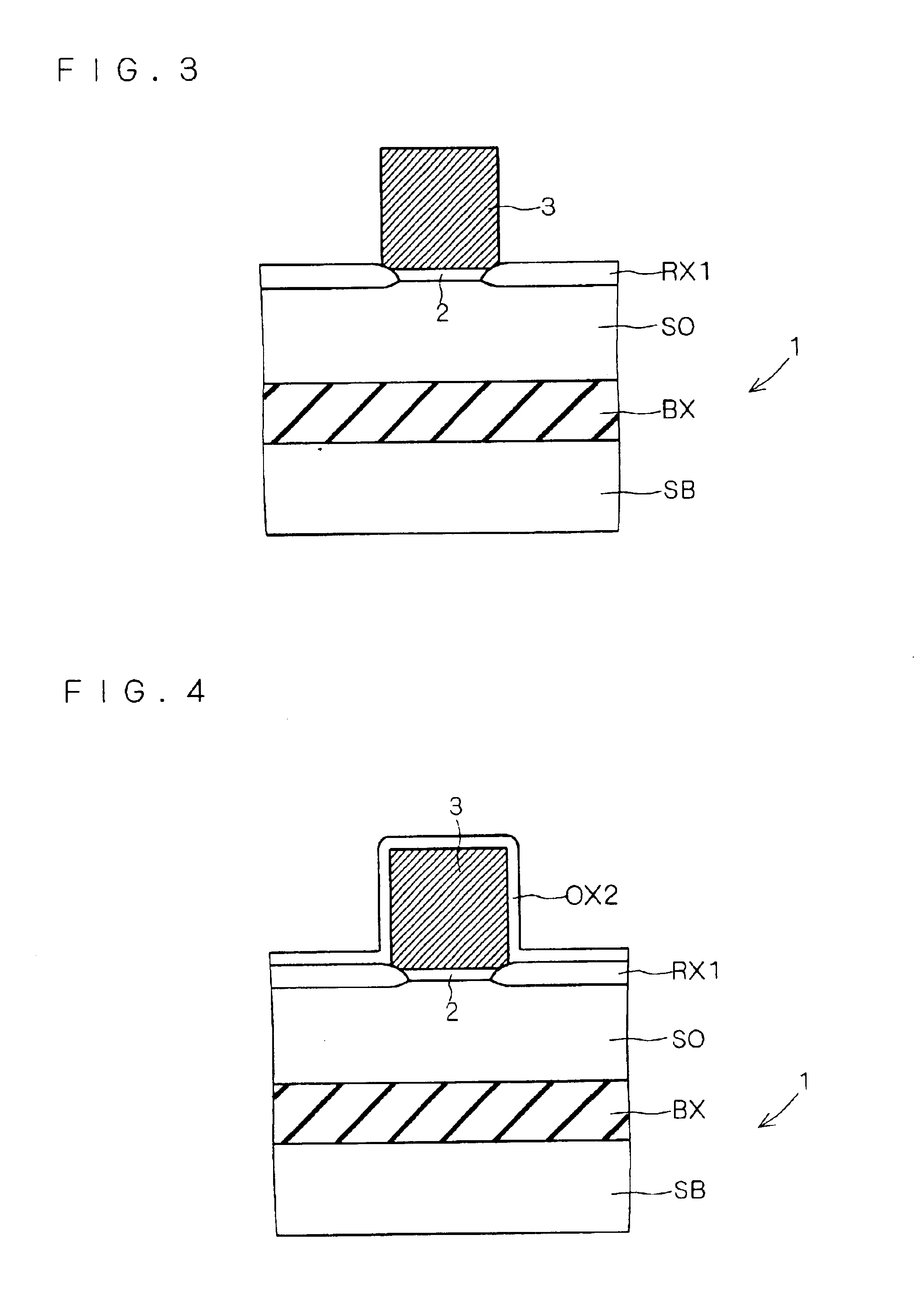

Planar ultra-thin semiconductor-on-insulator channel mosfet with embedded source/drain

InactiveUS20070069300A1Eliminate variationReduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingMOSFETGate dielectric

A MOSFET structure includes a planar semiconductor substrate, a gate dielectric and a gate. An ultra-thin (UT) semiconductor-on-insulator channel extends to a first depth below the top surface of the substrate and is self-aligned to and is laterally coextensive with the gate. Source-drain regions, extend to a second depth greater than the first depth below the top surface, and are self-aligned to the UT channel region. A first BOX region extends across the entire structure, and vertically from the second depth to a third depth below the top surface. An upper portion of a second BOX region under the UT channel region is self-aligned to and is laterally coextensive with the gate, and extends vertically from the first depth to a third depth below the top surface, and where the third depth is greater than the second depth.

Owner:GLOBALFOUNDRIES INC

Electro-optical device, shift register circuit, and semiconductor device

ActiveUS20130222220A1Inhibition of rising speedIncrease delayTransistorStatic indicating devicesShift registerProcessor register

An electro-optical device is configured to be capable of using a region of a gate line drive circuit efficiently and preventing rising speed of a gate line selection signal from decreasing (rising delay), and a shift register circuit is composed of a single conductivity type transistor which is suitable for the device. The gate line drive circuit including an odd driver to drive odd rows of a plurality of gate lines, and an even driver to drive even rows thereof. Each unit shift register in the odd and even drivers receives a selection signal in the second previous row and activates its own selection signal two horizontal periods later. A start pulse of the even driver is delayed in phase by one horizontal period with respect to a start pulse of the odd driver.

Owner:TRIVALE TECH LLC

Electro-optical device, shift register circuit, and semiconductor device

ActiveUS8462098B2Inhibition of rising speedIncrease delayElectric analogue storesCathode-ray tube indicatorsShift registerProcessor register

An electro-optical device is configured to be capable of using a region of a gate line drive circuit efficiently and preventing rising speed of a gate line selection signal from decreasing (rising delay), and a shift register circuit is composed of a single conductivity type transistor which is suitable for the device. The gate line drive circuit including an odd driver to drive odd rows of a plurality of gate lines, and an even driver to drive even rows thereof. Each unit shift register in the odd and even drivers receives a selection signal in the second previous row and activates its own selection signal two horizontal periods later. A start pulse of the even driver is delayed in phase by one horizontal period with respect to a start pulse of the odd driver.

Owner:TRIVALE TECH LLC

Ultra Thin Channel (UTC) MOSFET Structure Formed on BOX Regions Having Different Depths and Different Thicknesses Beneath the UTC and SourceDrain Regions and Method of Manufacture Thereof

ActiveUS20080283918A1Eliminate variationReduce Overlap CapacitanceTransistorSolid-state devicesMOSFETGate dielectric

A MOSFET structure includes a planar semiconductor substrate, a gate dielectric and a gate. A UT SOI channel extends to a first depth below the top surface of the substrate and is self-aligned to and is laterally coextensive with the gate. Source-drain regions, extend to a second depth greater than the first depth below the top surface, and are self-aligned to the UT channel region. A BOX1 region extends across the entire structure, and vertically from the second depth to a third depth below the top surface. An upper portion of a BOX2 region under the UT channel region is self-aligned to and is laterally coextensive with the gate, and extends vertically from the first depth to a third depth below the top surface, and where the third depth is greater than the second depth.

Owner:GLOBALFOUNDRIES US INC

Low-K gate spacers by fluorine implantation

ActiveUS7227230B2Reduce capacitanceReduce overlap capacitanceTransistorSolid-state devicesMOSFETPhysics

A MOSFET device and a method of fabricating a MOSFET device having low-K dielectric oxide gate sidewall spacers produced by fluorine implantation. The present invention implants fluorine into the gate oxide sidewall spacers which is used to alter the properties of advanced composite gate dielectrics e.g. nitridized oxides, NO, and gate sidewall dielectrics, such that the low-K properties of fluorine are used to develop low parasitic capacitance MOSFETs.

Owner:GLOBALFOUNDRIES US INC

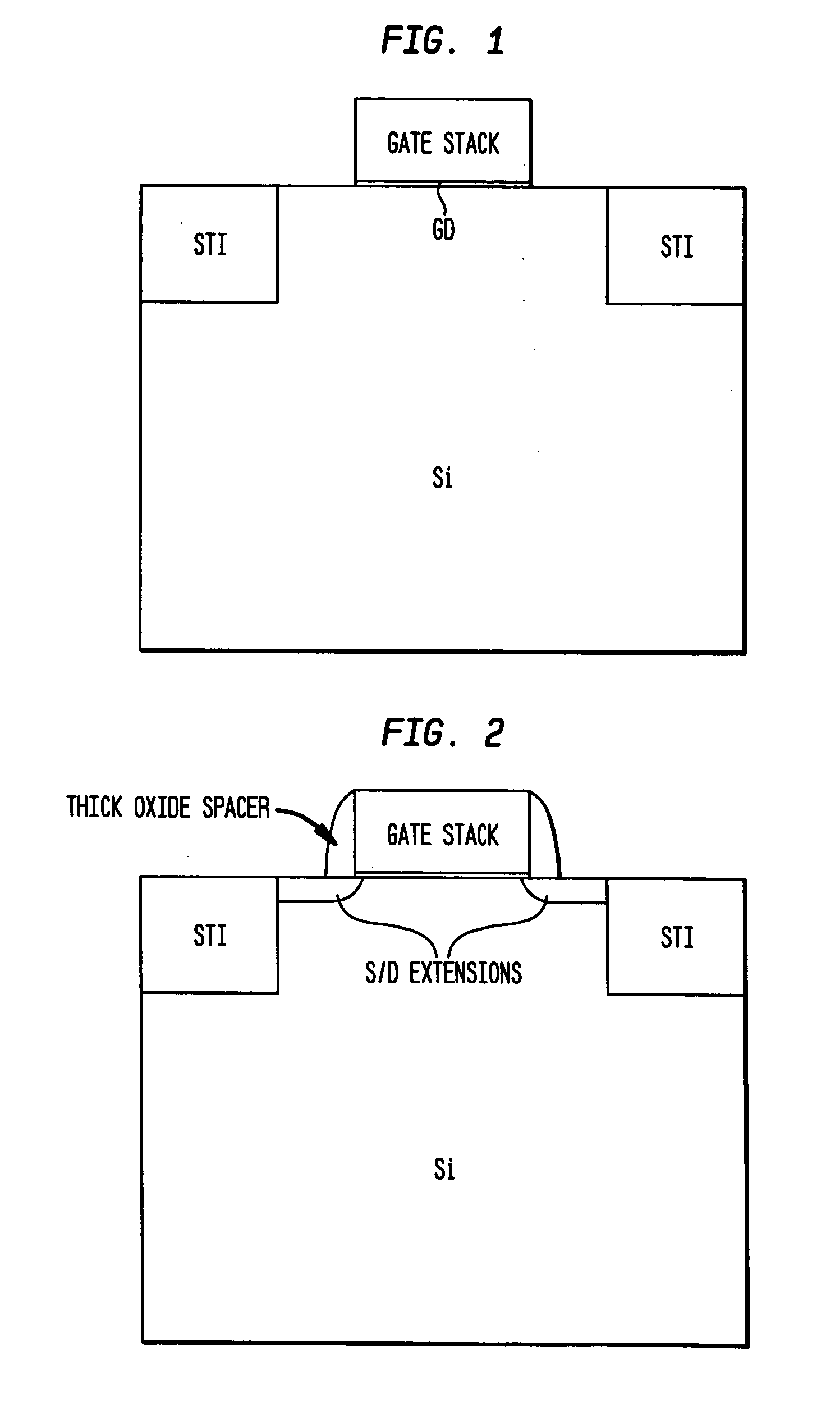

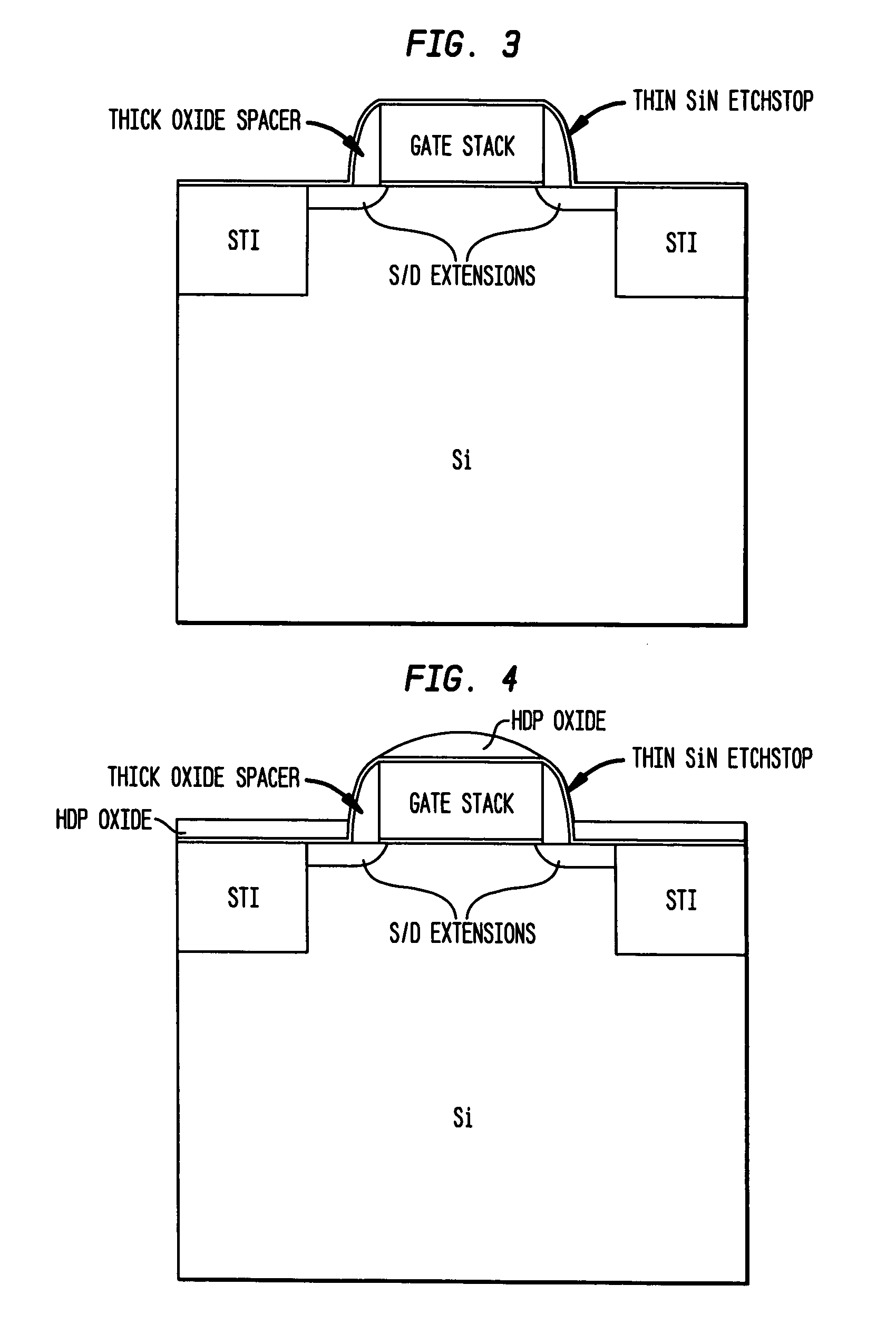

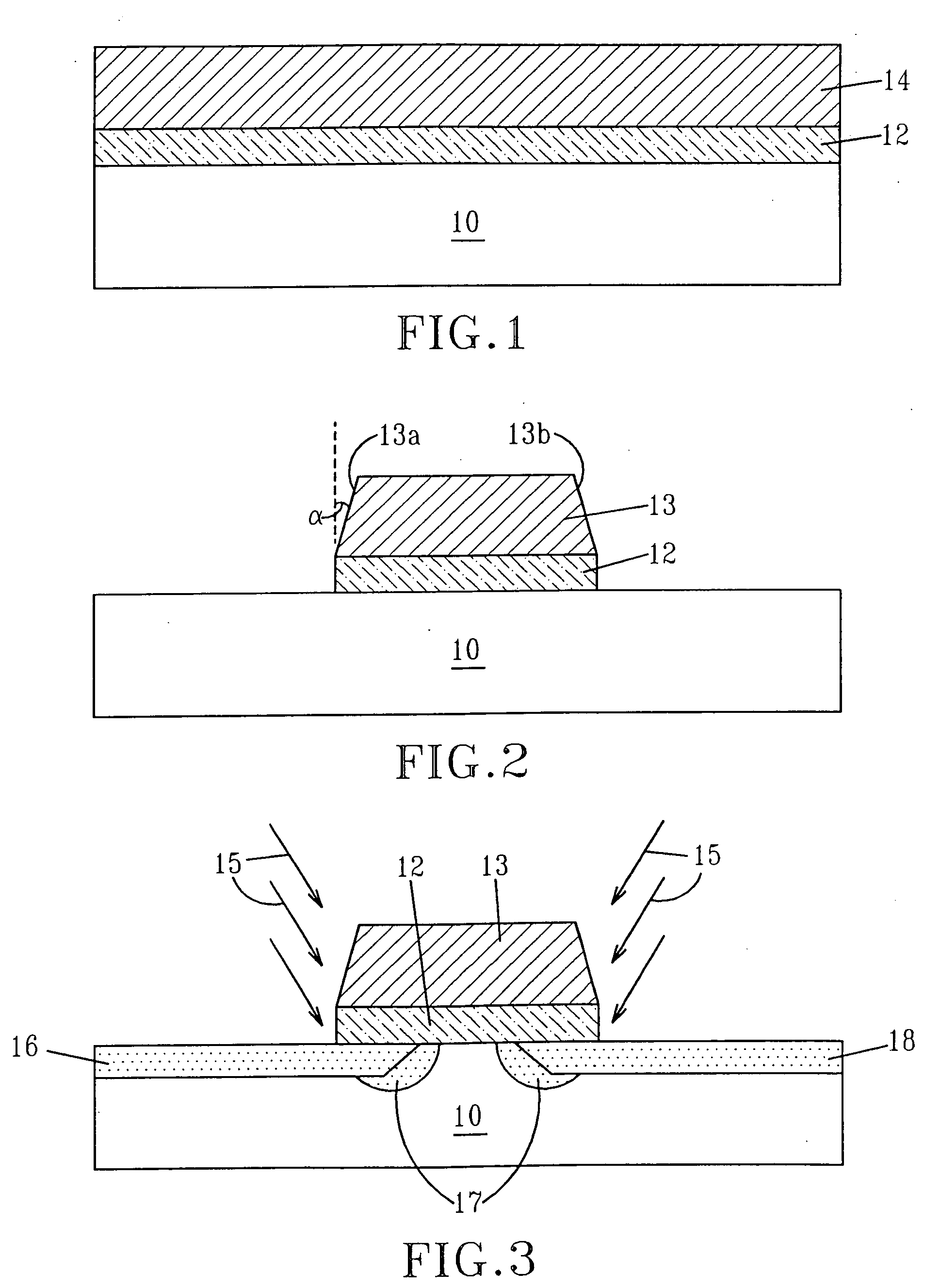

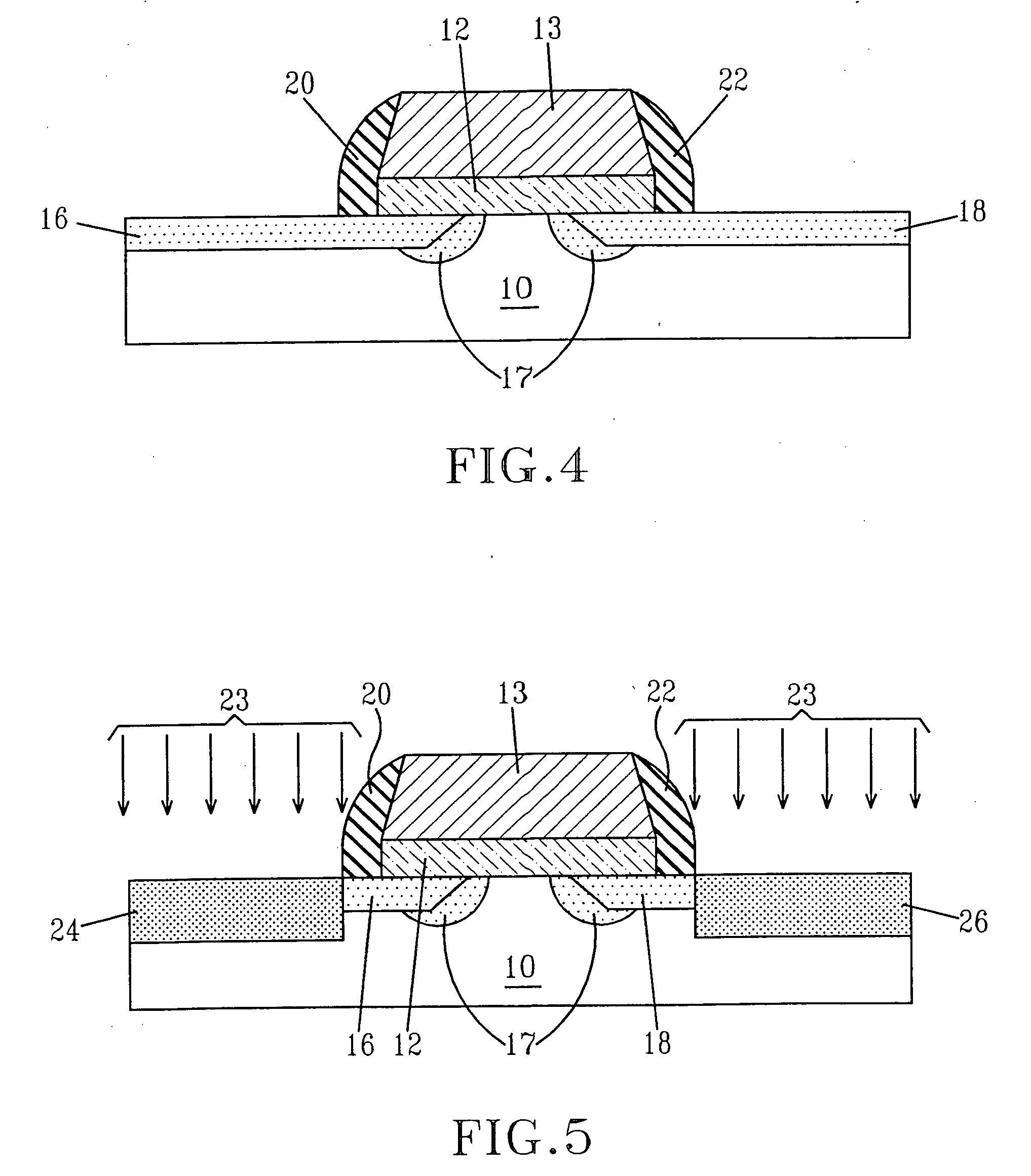

Method to reduce transistor gate to source/drain overlap capacitance by incorporaton of carbon

ActiveUS20050014353A1Reduce Overlap CapacitanceHigh sensitivitySemiconductor/solid-state device manufacturingSemiconductor devicesCarbon dopedEtching rate

The present invention pertains to formation of a transistor in a manner that mitigates overlap capacitances, thereby facilitating, among other things, enhanced switching speeds. More particularly, a gate stack of the transistor is formed to include an optional layer of poly-SiGe and a layer of poly-Si, where at least one or the layers comprises carbon. The stack may also include a polysilicon seed layer that can also comprise carbon. The carbon changes the components of sidewall passivation materials and affects etch rates during an etching process, thereby facilitating isotropic etching. The changed passivation materials coupled with an enhanced sensitivity of the poly-SiGe and carbon-doped poly-SiGe layer to an etchant utilized in the etching process causes the stack to have a notched appearance. The tapered configuration of the gate stack provides little, if any, area for dopants that may migrate under the gate structure to overlap the conductive layers in the stack, and thus mitigates the opportunity for overlap capacitances to arise.

Owner:TEXAS INSTR INC

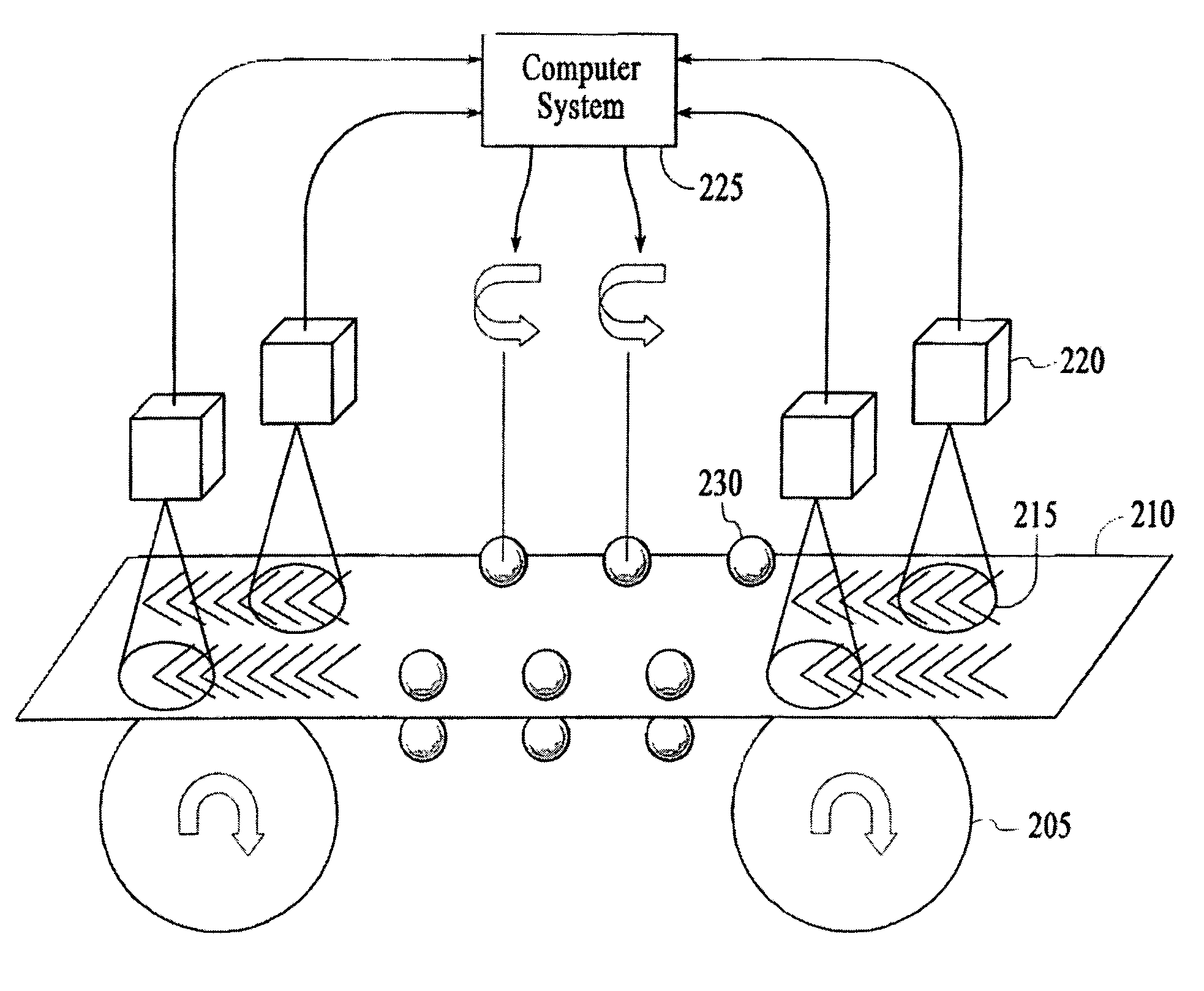

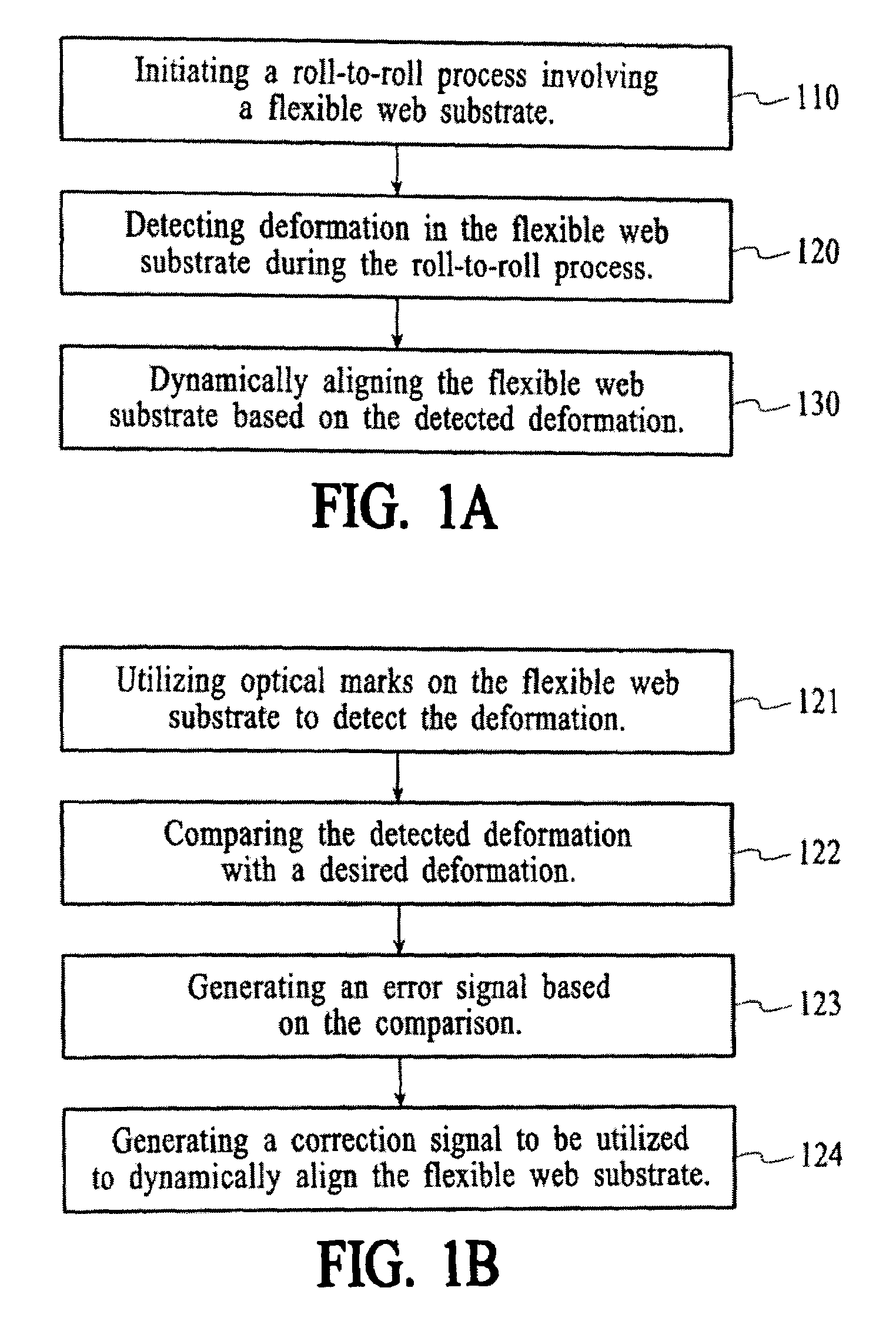

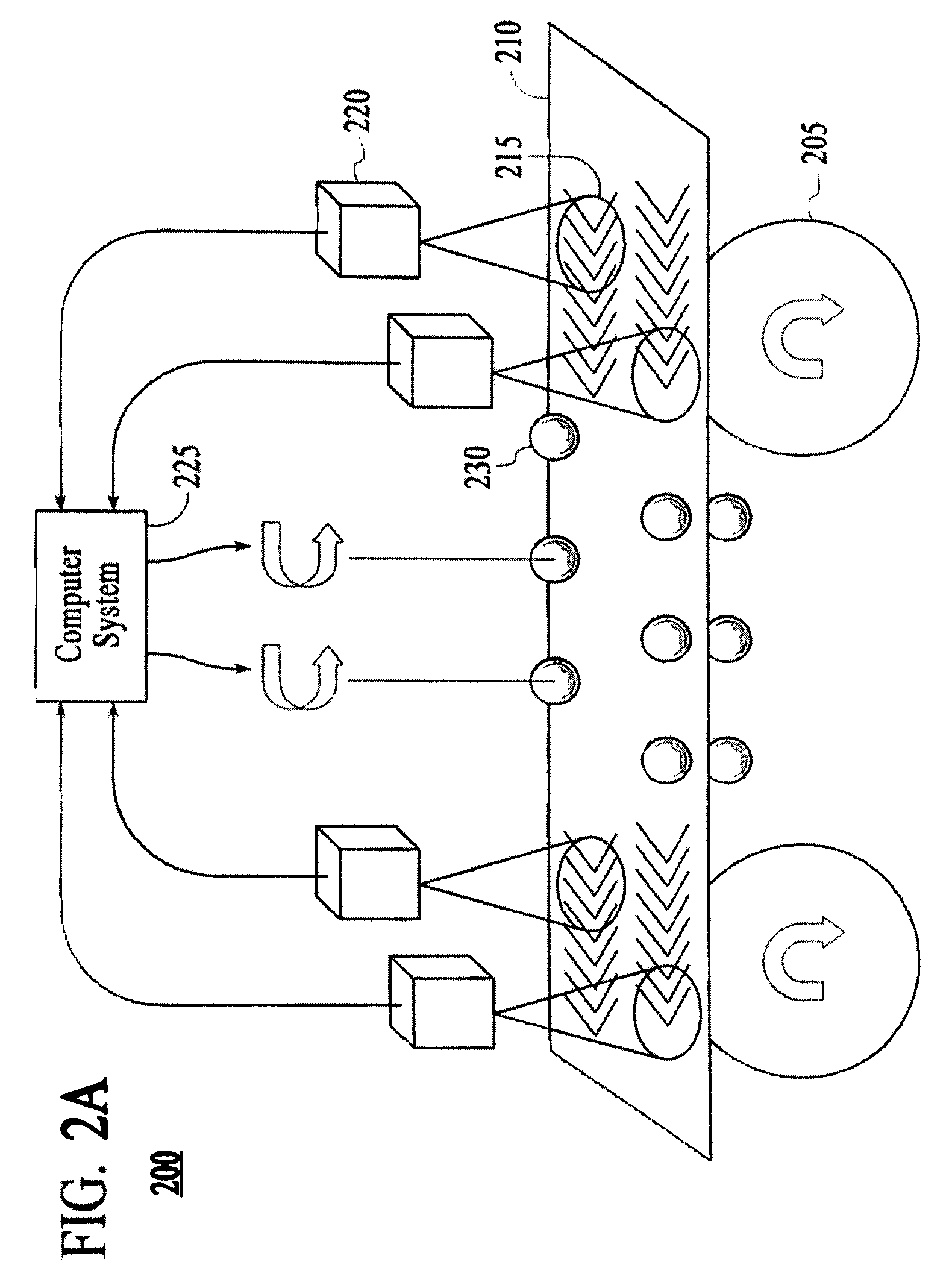

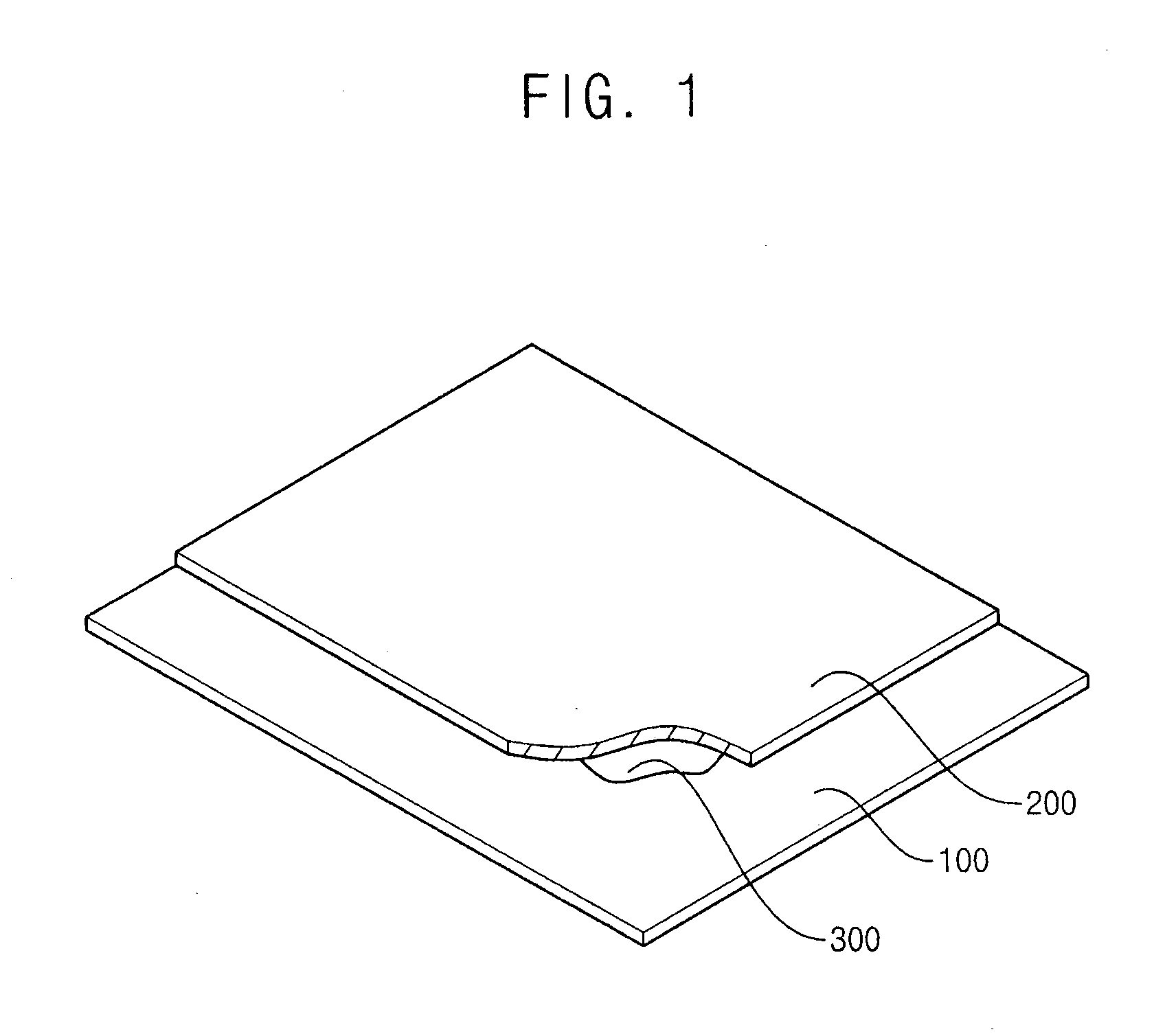

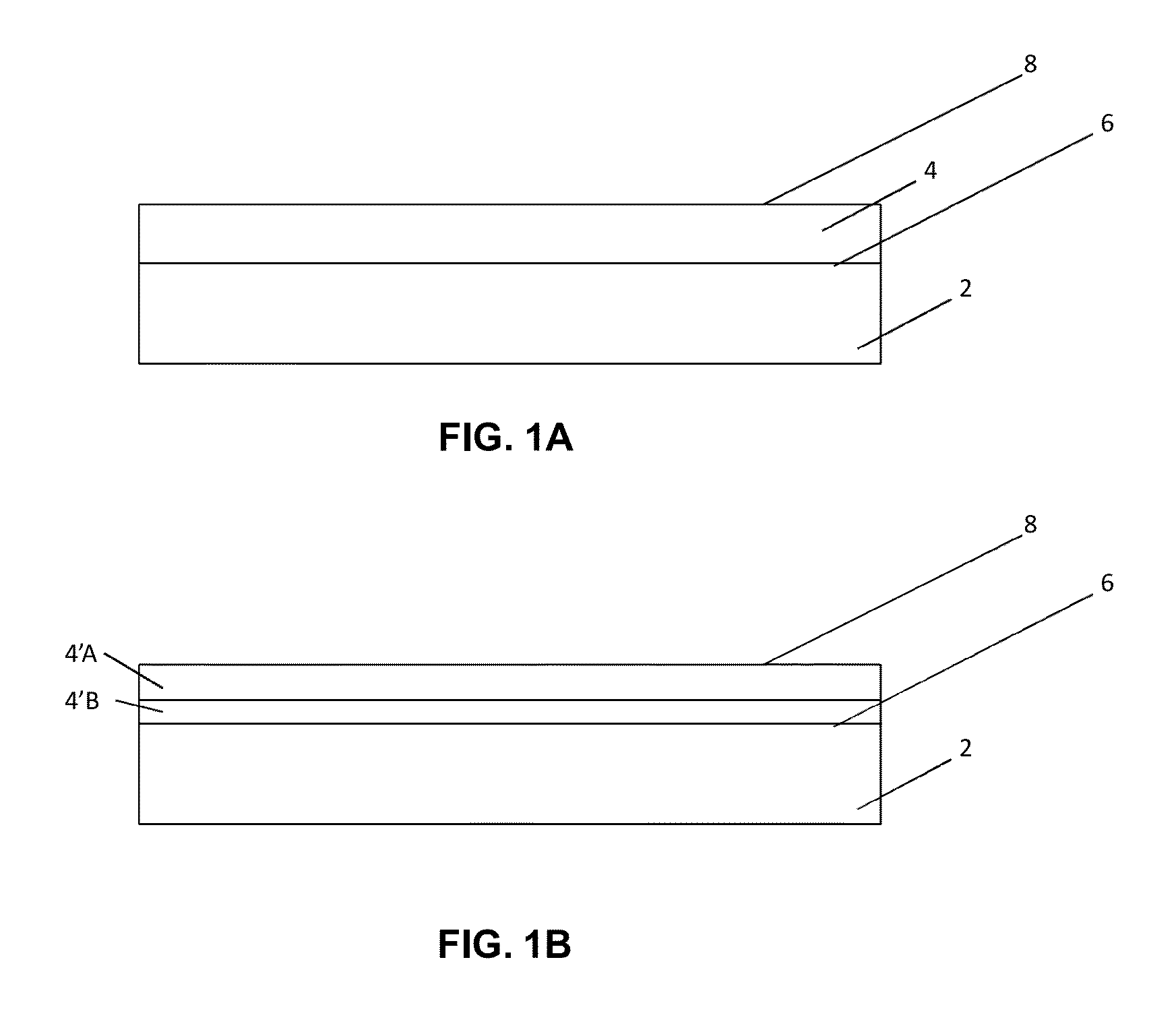

Method and system for correcting web deformation during a roll-to-roll process

InactiveUS7121496B2Improve accuracyReduce Overlap CapacitanceAutomatic control devicesPrecision positioning equipmentCapacitanceElectronic structure

The present invention includes a method and system for correcting web deformation during a roll-to-roll process. The present invention includes controllable mechanical components that are capable of dynamically adjusting the planarity of the web during the roll-to-roll process. By adjusting the web during the roll-to-roll process, the accuracy of the layer-to layer alignment of successive patterning steps is greatly increased thereby enabling the production of electronic structures with lower overlap capacitance and higher resolution. A first aspect of the present invention is a method for correcting web deformation during a roll-to-roll process. The method includes initiating a roll-to-roll process involving a flexible web substrate, detecting deformation in the flexible web substrate during the roll-to-roll process and dynamically aligning the flexible web substrate based on the detected deformation.

Owner:HEWLETT PACKARD DEV CO LP

Self-aligned silicone process for low resistivity contacts to thin film silicon-on-insulator mosfets

InactiveUS20020031909A1Minimize consumptionConsumption of the thin SOI film is additionally reducedTransistorSemiconductor/solid-state device manufacturingSalicideSilicon membrane

A silicide processing method for a thin film SOI device including depositing a metal or an alloy on a gate and a source / drain structure formed in a silicon-on-insulator film, reacting the metal or alloy at a first temperature with the silicon-on-insulator film to form a first alloy, etching the unreacted layer of the metal (or alloy) selectively, depositing a Si film on the first alloy, reacting the Si film at a second temperature to form a second alloy, and etching the unreacted layer of the Si film selectively.

Owner:INT BUSINESS MASCH CORP

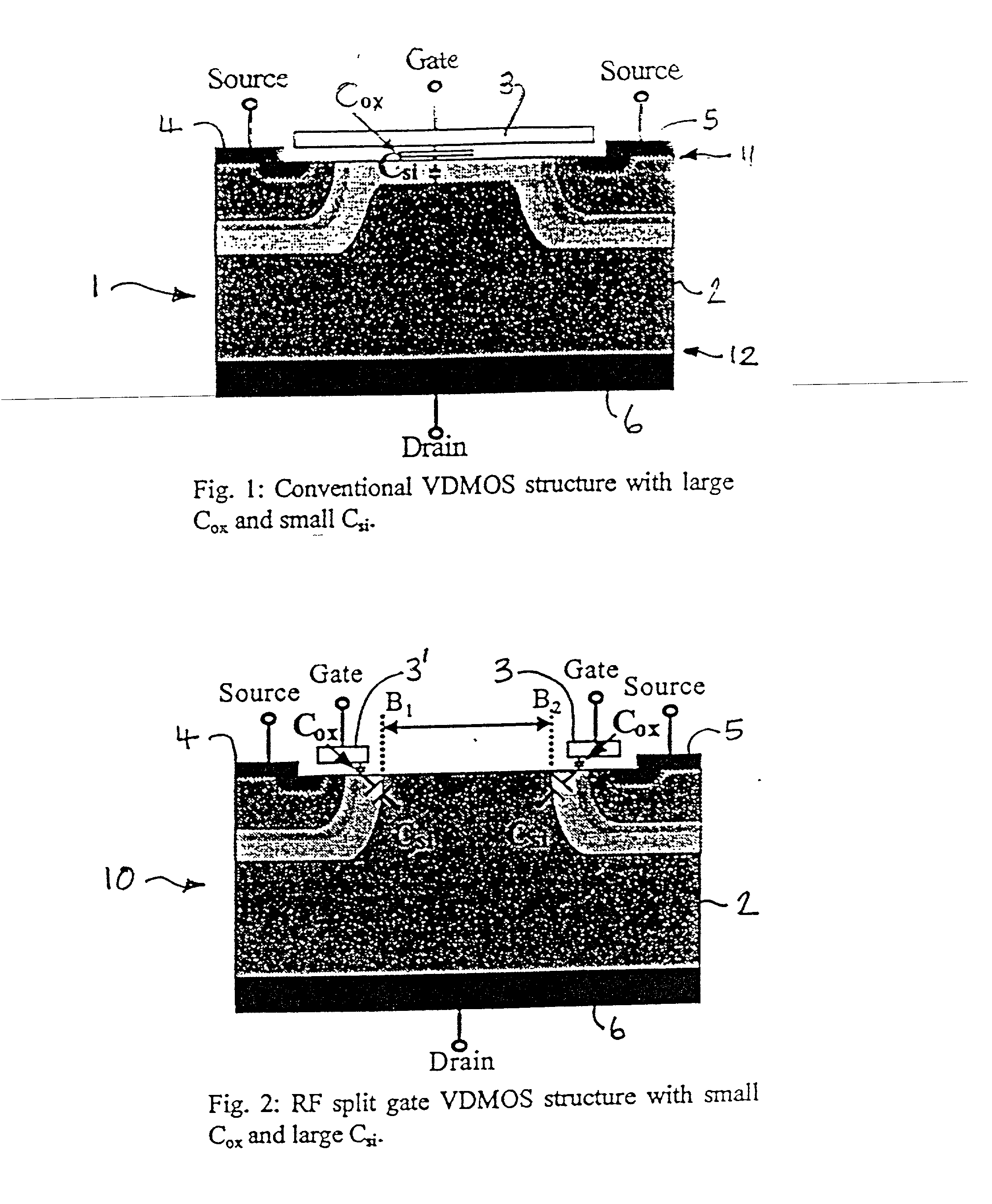

Semiconductor device

InactiveUS20020017682A1Efficient and reliable for applicationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower application

A VD (vertical diffusion) MOSFET device for use in RF power applications has a split gate structure and an additional, dummy gate is provided between the spaced apart gates and, in operation of the device, is electrically coupled to source electrodes provided outside of the gates. The split gate structure reduces gate overlap capacitance and the dummy gate induces depletion in the semiconductor body of the device and reduces the substrate capacitance. The gate overlap capacitance and the substrate capacitance both contribute to the feedback capacitance of the device which has to be as low as possible for high frequency operation. By reducing both of these components, the invention provides advantageous high frequency operation.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

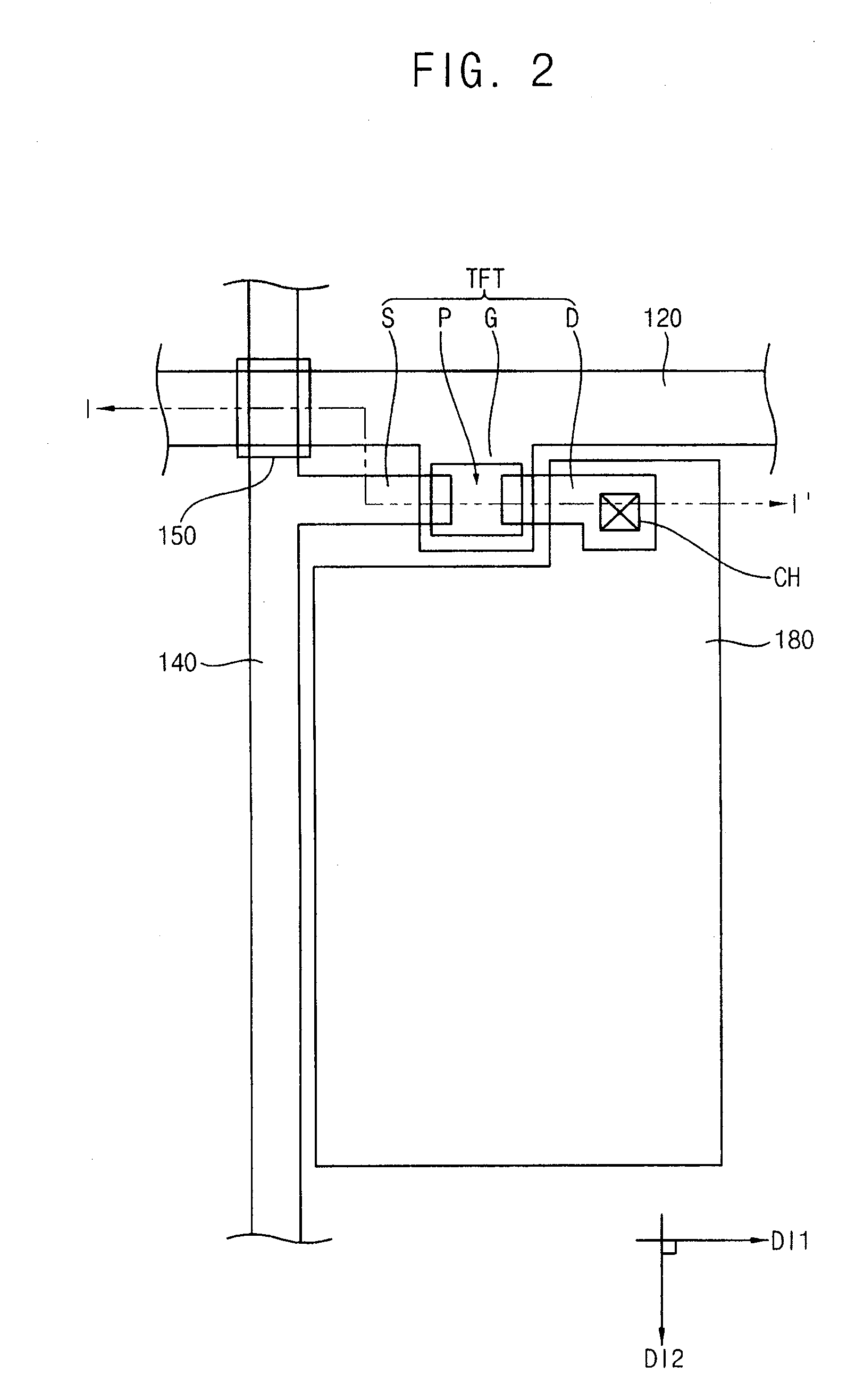

Display substrate, method for manufacturing the display substrate and display apparatus having the display substrate

ActiveUS20090184326A1Overlap capacitance generatedReduce signal delaySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A display substrate includes a base substrate, a gate line, a gate insulation layer, a data line, a thin-film transistor (TFT) and a pixel electrode. The gate line is extended in a first direction on the base substrate. The gate insulation layer is formed on the base substrate to cover the gate line. The data line is extended in a second direction and intersects the gate line at an intersecting portion. At the intersecting portion, the data line is separated from the gate line by an air gap. In another embodiment, the data line also includes at least one etching hole extending to the air gap. The TFT is electrically connected to the data and the gate lines. The pixel electrode is electrically connected to the TFT.

Owner:SAMSUNG DISPLAY CO LTD

Self-aligning metal oxide thin film transistor and manufacturing method thereof

InactiveCN103311128AImprove mobilityLow resistivityTransistorSemiconductor/solid-state device manufacturingDopantGate dielectric

The invention provides a self-aligning metal oxide thin film transistor and a manufacturing method thereof. The method includes depositing a metal oxide semiconductor layer, a gate dielectric layer and a conducting thin film on a substrate and photoetching for imaging, spin-coating a dopant layer on the surface of a device, performing heat treatment to enable doping atoms in the spin-coated dopant layer to be diffused into a lower-layer material. The graphical gate electrode and the graphic gate dielectric exist, so that the doping atoms can only be diffused into metal oxide semiconductor areas on two sides of a channel area, doping of the metal oxide semiconductor on two sides of a channel is realized, resistivity of the metal oxide semiconductor is greatly lowered, and a self-aligned source-drain area is formed. The spin-coated dopant layer can also serve as a passivating layer of the device and is combined with subsequent processes like photoetching of contact holes and leading-out of electrodes and a wiring layer to manufacture a complete TFT (thin film transistor) device. The metal oxide thin film transistor prepared by the method has a self-aligning structure and is simple in process and compatible with large-area substrate process.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Array substrate

ActiveUS20170124972A1Suppress signal delayReduce widthStatic indicating devicesDigital storageEngineeringClock signal

An array substrate includes: a display area; a non-display area outside of the display area; a gate-in-panel (GIP) circuit in the non-display area; a plurality of clock signal lines in the non-display area and configured to transfer signals to the GIP circuit; and connection lines in the non-display area and configured to connect the plurality of clock signal lines to the GIP circuit. Each of the plurality of clock signal lines is a ring shaped line.

Owner:LG DISPLAY CO LTD

Method of Manufacturing Semiconductor Device

ActiveUS20110124173A1Improve electric characteristicExcellent electrical propertiesTransistorSolid-state devicesSemiconductorSemiconductor device

Methods of manufacturing a semiconductor device include forming a gate electrode on a semiconductor substrate, forming spacers on side walls of the gate electrode, and doping impurities into the semiconductor substrate on both sides of the spacers to form highly doped impurity regions. The spacers are selectively etched to expose portions of the semiconductor substrate, and more lightly doped impurity regions are formed in the semiconductor substrate between the highly doped impurity regions and the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

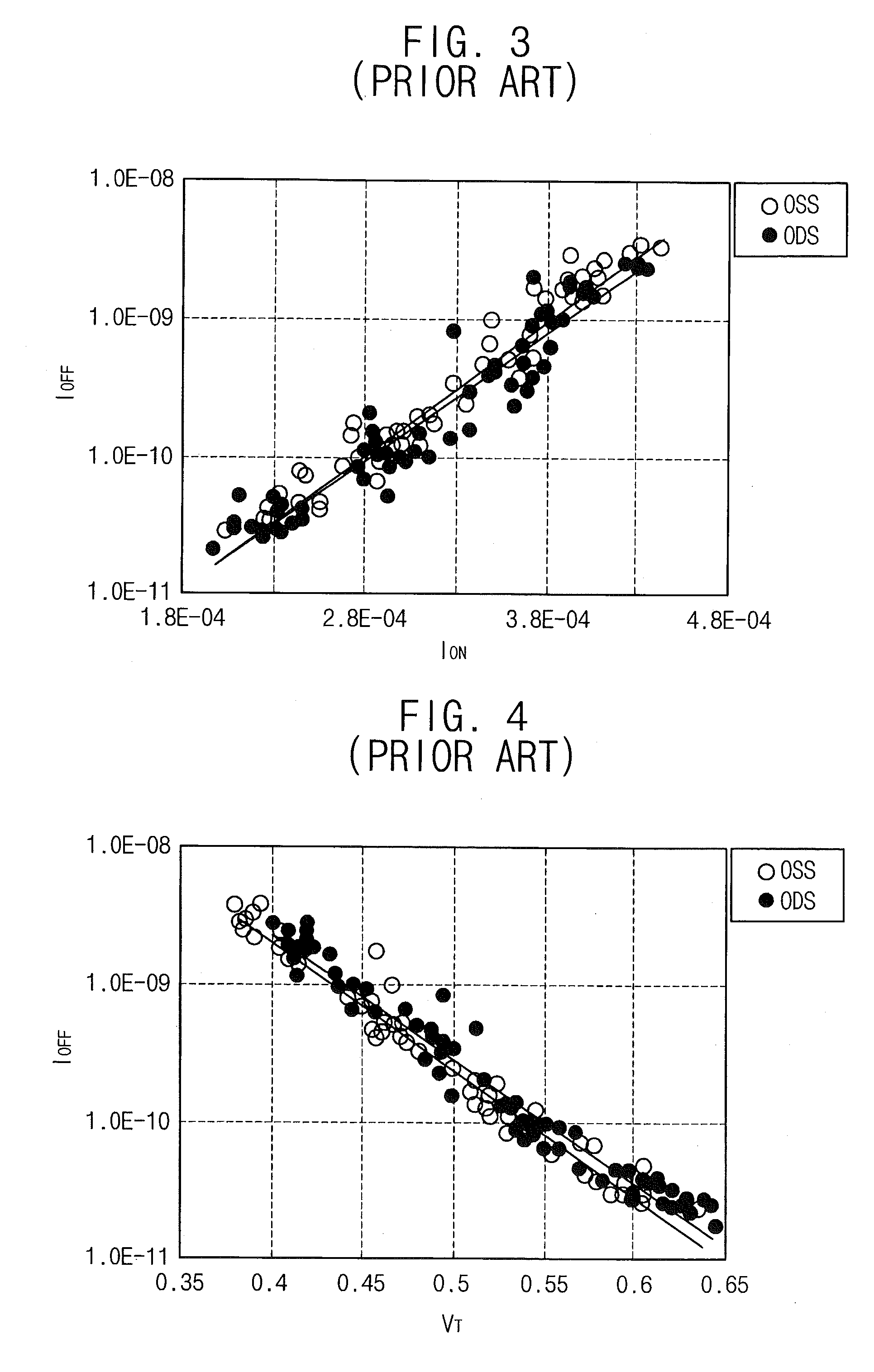

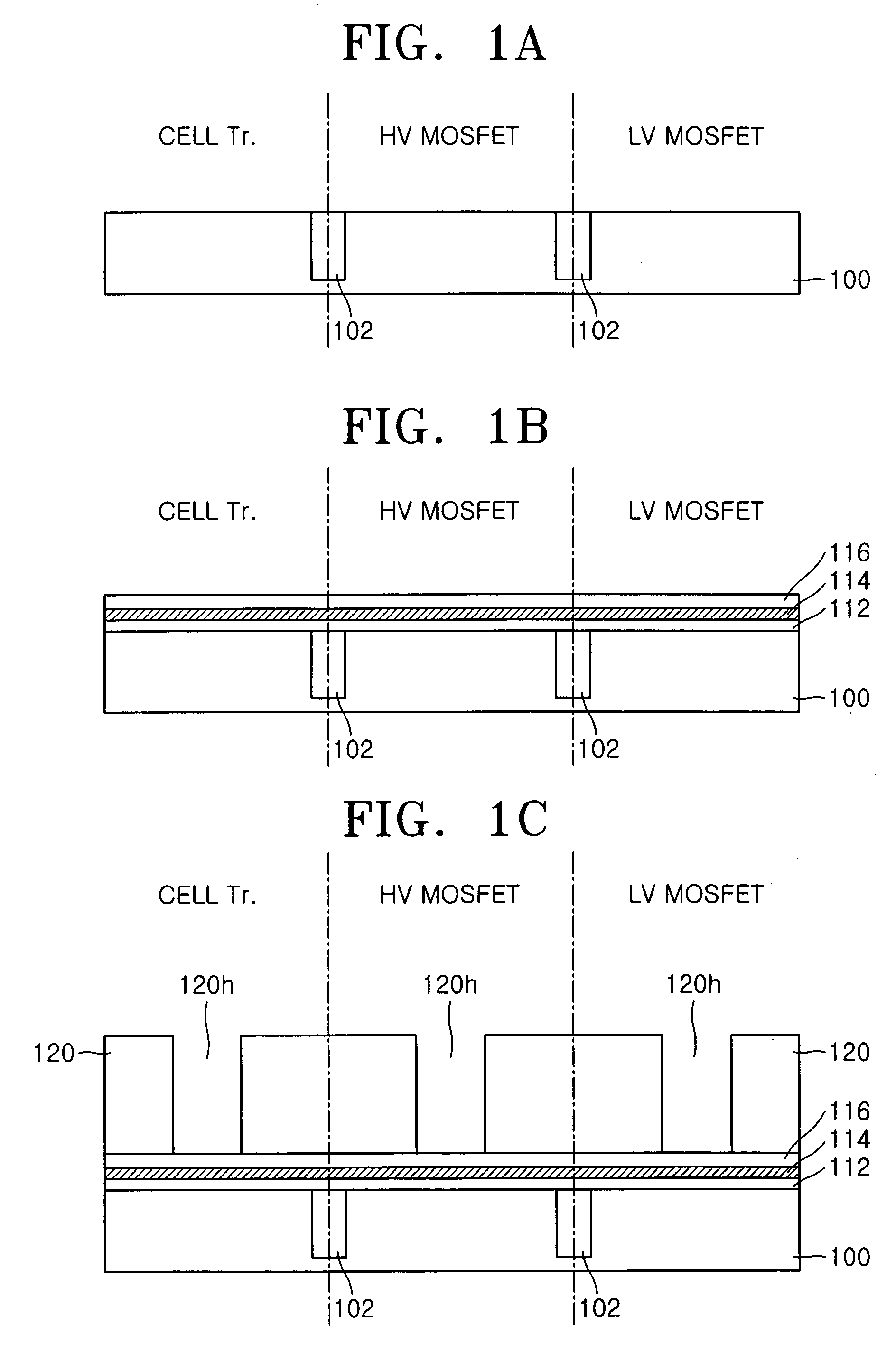

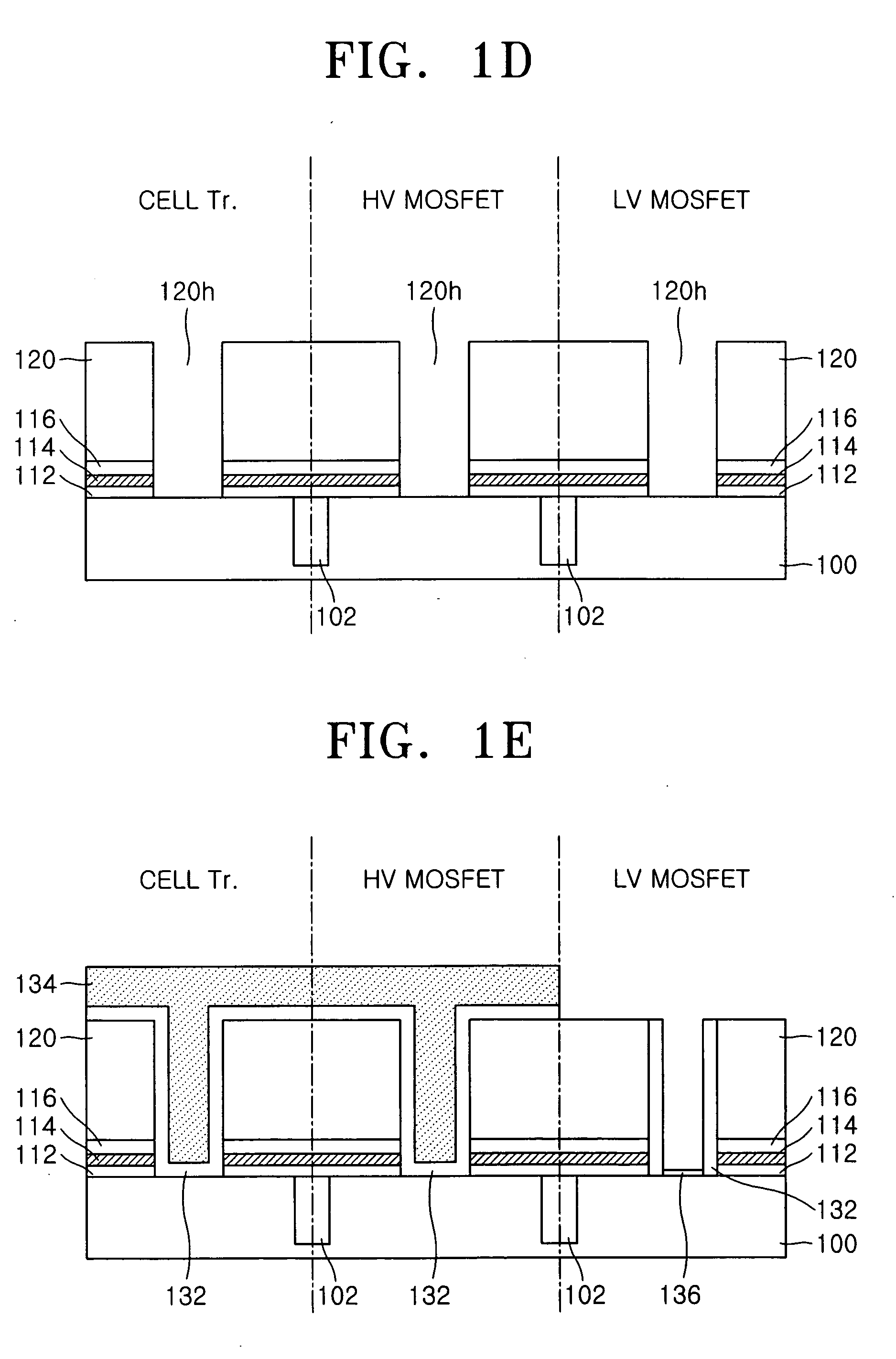

Method of manufacturing semiconductor device having notched gate MOSFET

InactiveUS20060154421A1Easy to integrateSmall sizeTransistorSemiconductor/solid-state device manufacturingMOSFETDevice material

Provided is a method of manufacturing a semiconductor device, by which a cell transistor formed .on a cell array area of a semiconductor substrate employs a structure in which an electrode in the shape of spacers is used to form a gate and a multi-bit operation is possible using localized bits, and transistors having structures optimized to satisfy different requirements depending upon functions of the transistors can be formed on a peripheral circuit area which is the residual area of the semiconductor substrate. In this method, a cell transistor is formed on the cell array area. The cell transistor includes a notch gate structure, a first channel region formed on a semiconductor substrate under the notch gate structure, a source region and a drain region formed on both sides of the first channel region, a first gate insulation film formed between the first channel region and the notch gate structure, and a memory layer locally formed on areas adjacent to the source and drain regions between the first channel region and the notch gate structure. At the same time that the cell transistor is formed, a plurality of peripheral circuit transistors including at least one transistor having a different structure from the cell transistor are formed on the peripheral circuit area.

Owner:SAMSUNG ELECTRONICS CO LTD

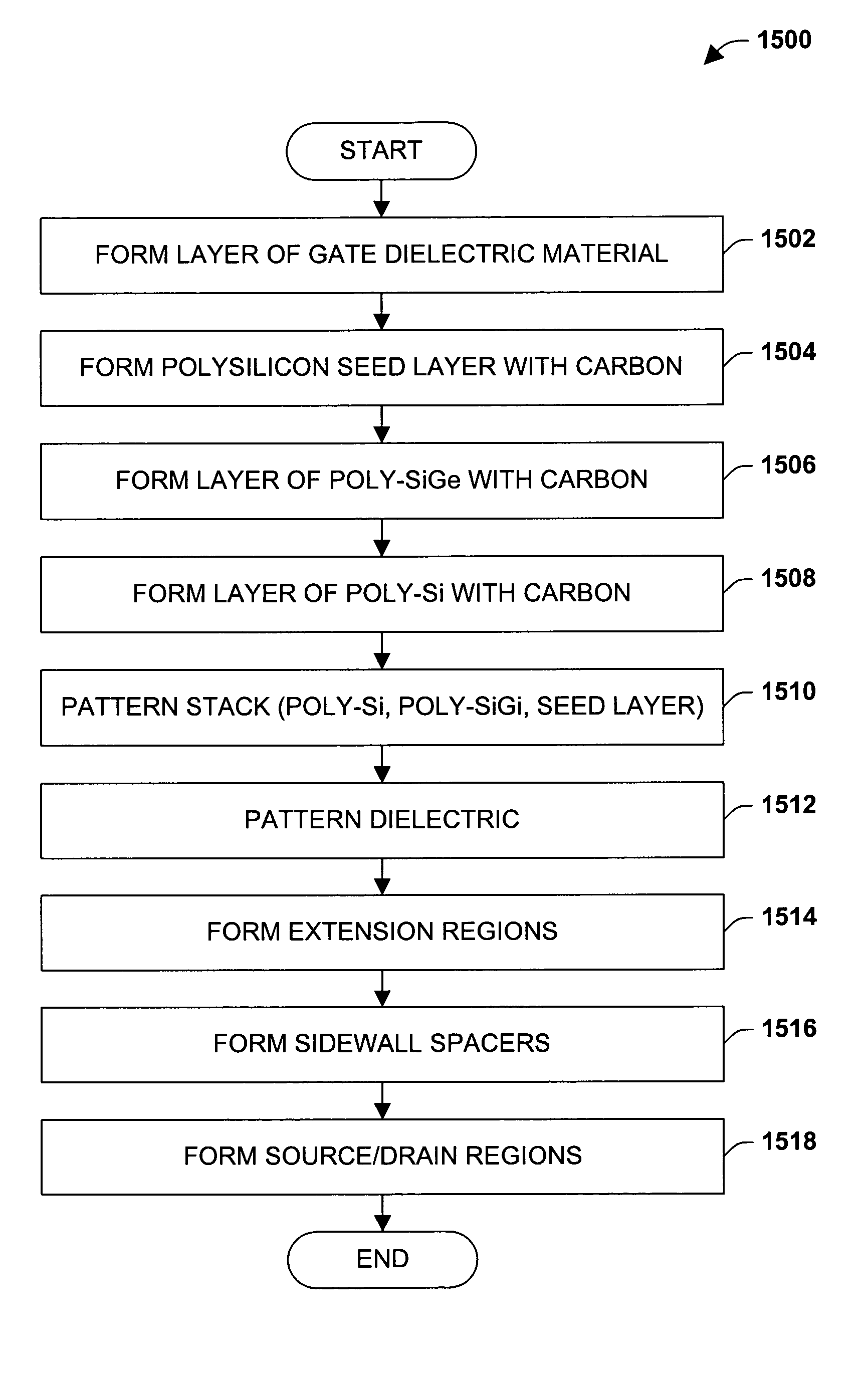

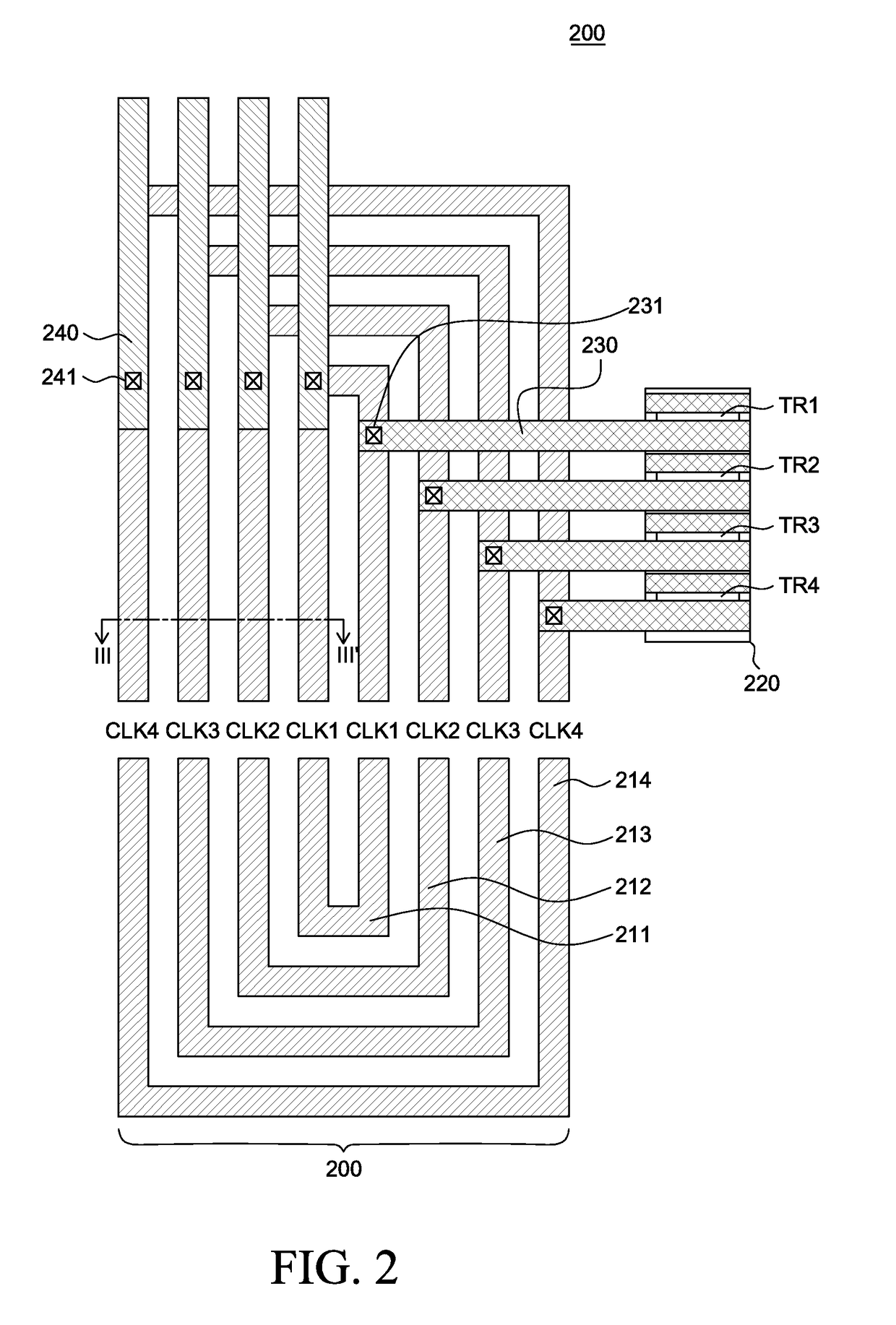

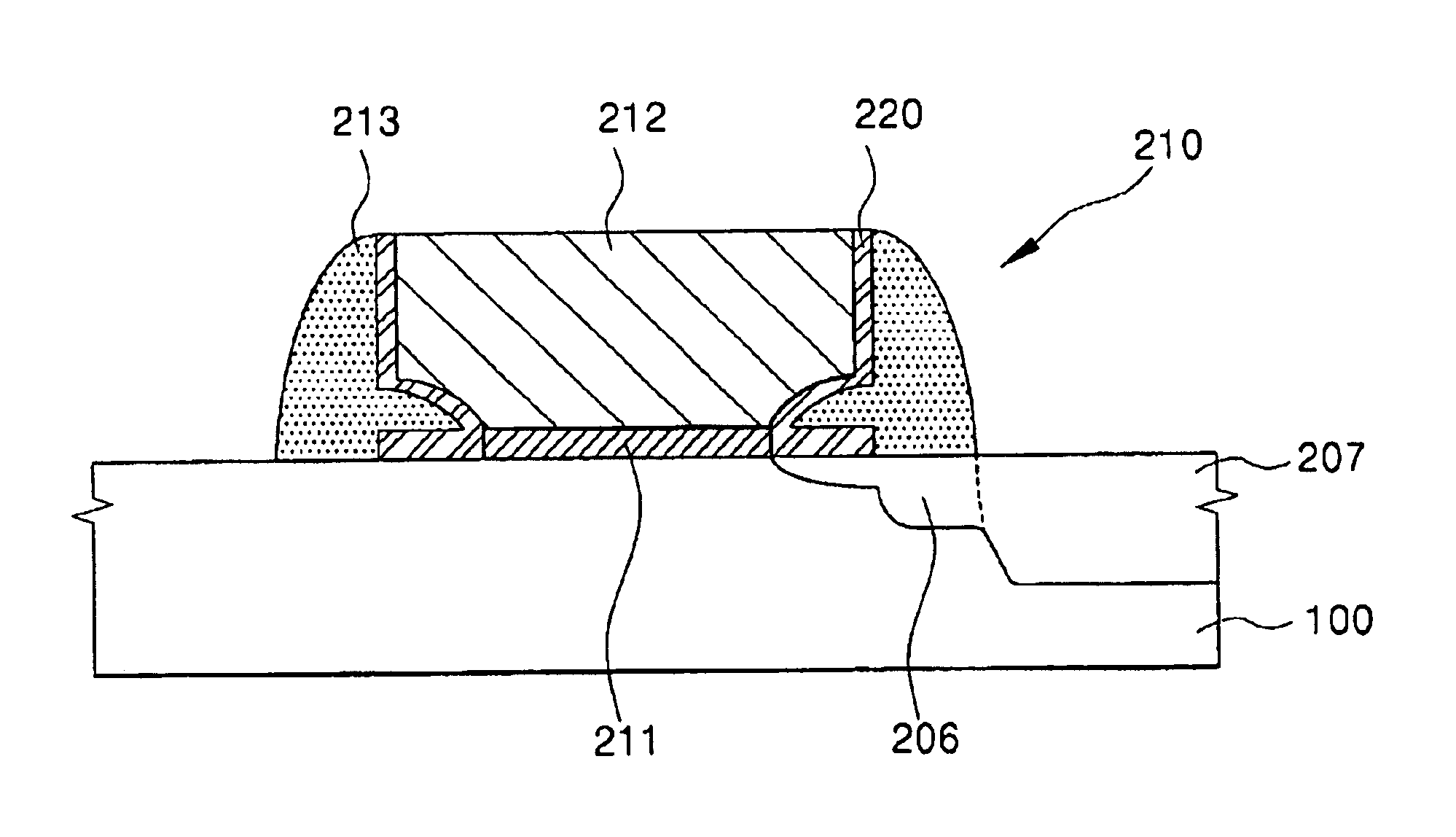

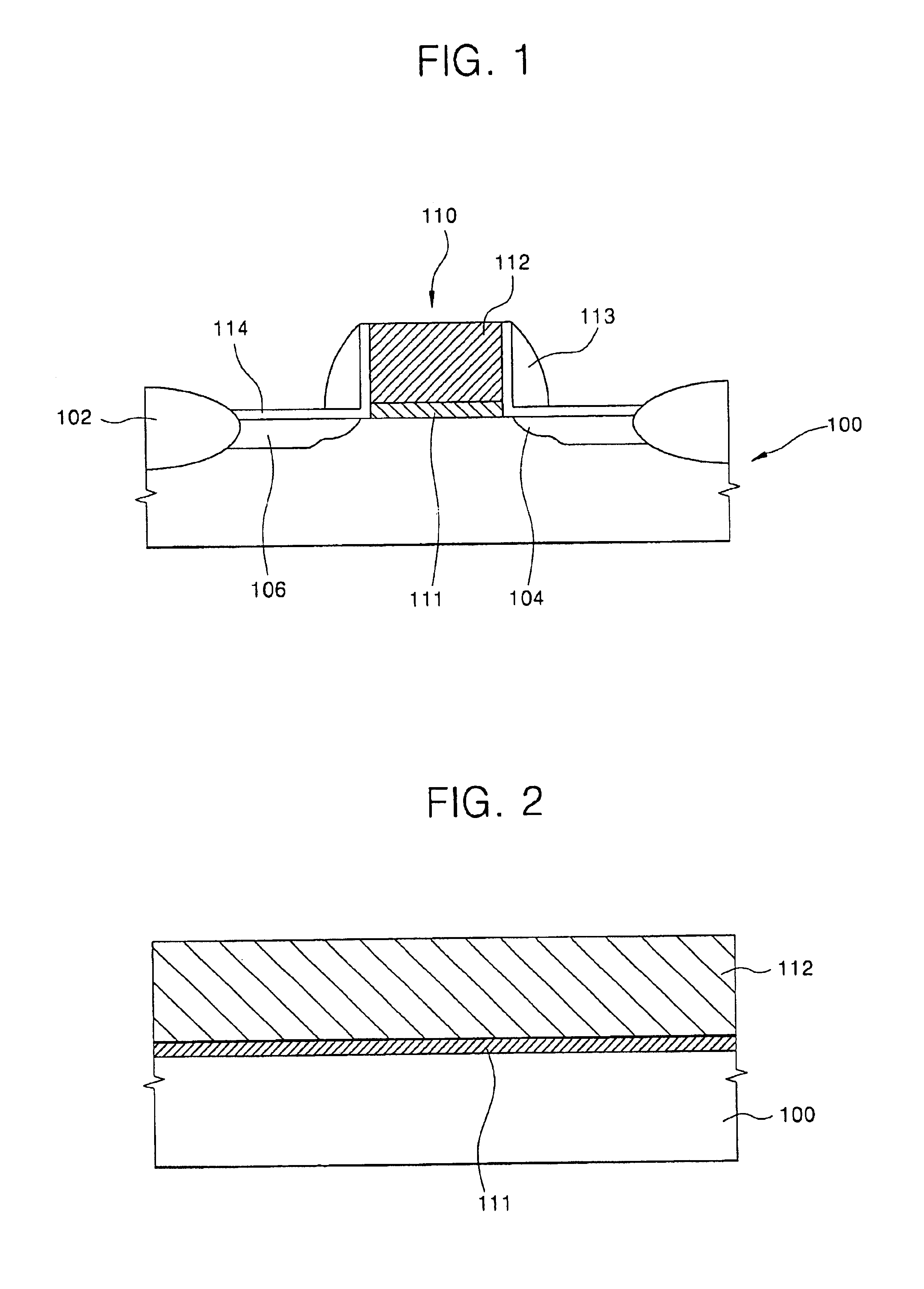

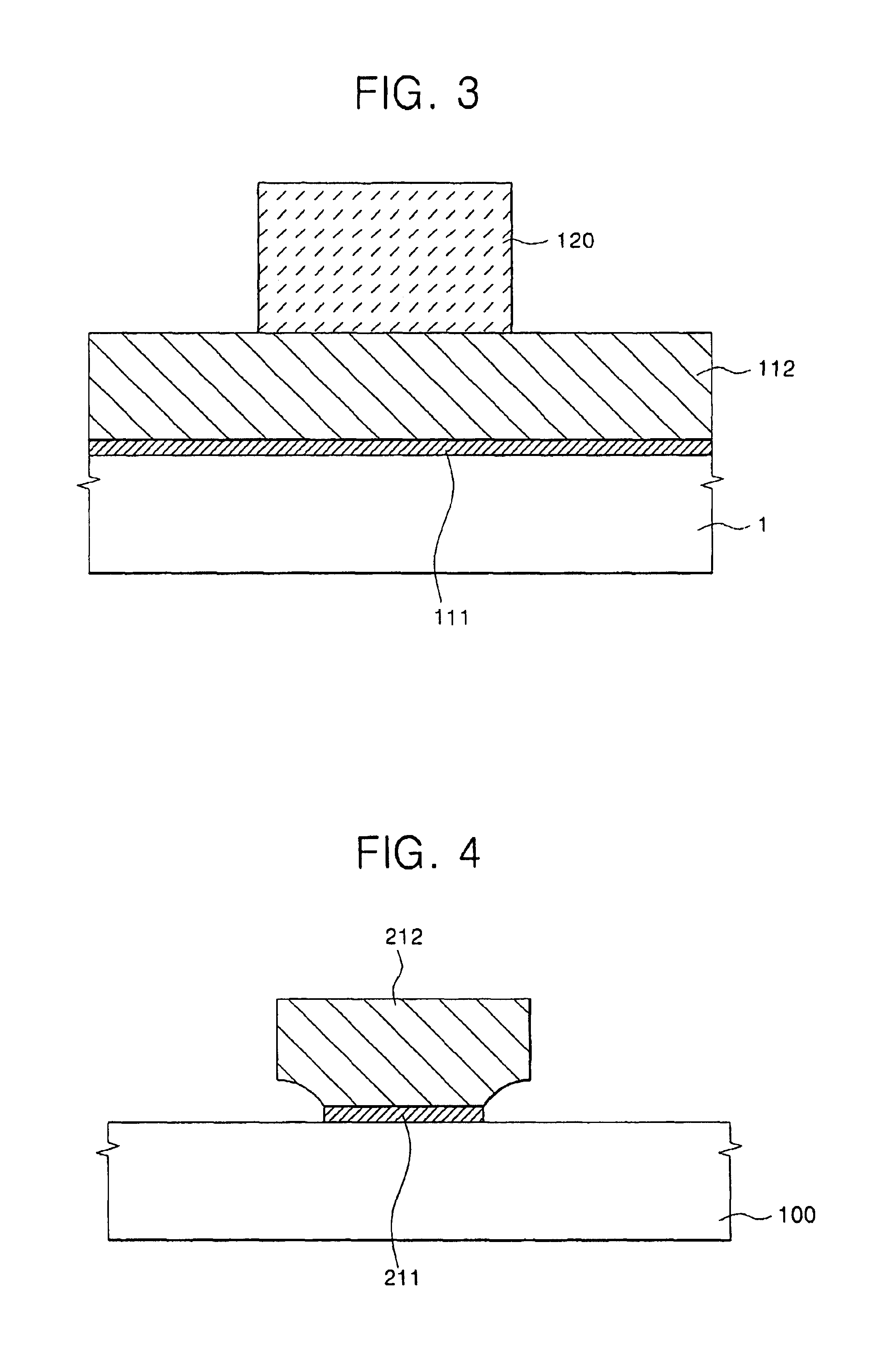

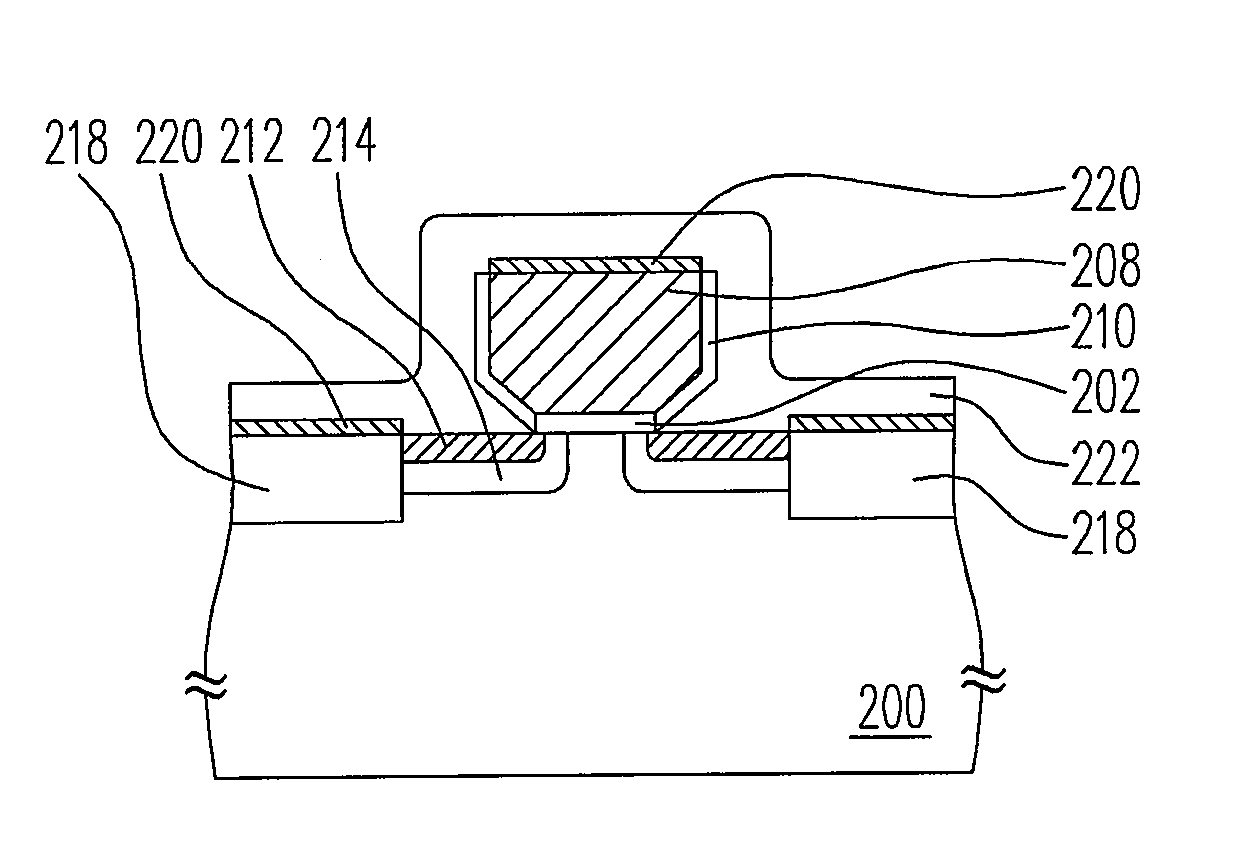

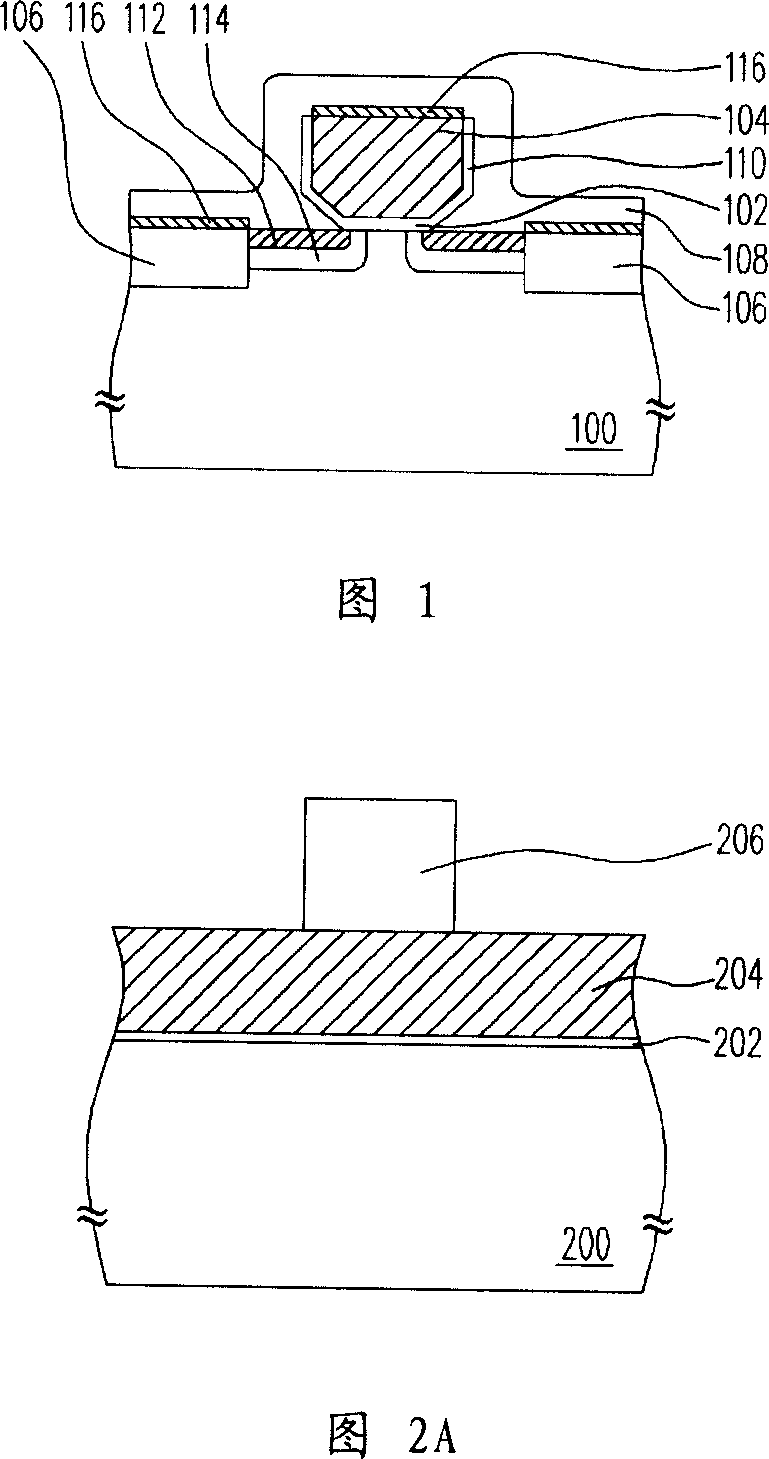

Method of fabricating semiconductor device having notched gate

InactiveUS6858907B2Reduce Overlap CapacitanceReliable maintenanceTransistorSemiconductor/solid-state device manufacturingDevice materialGate oxide

A semiconductor device includes: a silicon substrate; a source / drain region formed in the substrate including a lightly doped region and an adjacent heavily doped region, the depth of the heavily doped region being greater than the depth of the lightly doped region; a gate oxide layer on the silicon substrate; and a notched gate electrode on the substrate, the notched gate electrode including a notch along an outer side surface of a lower portion such that a top portion of the notched gate electrode is wider than the lower portion, the gate oxide layer extending between the interface of the notched gate electrode and the substrate, and a gate poly oxide layer provided along an outer side surface of the notched gate electrode and along an inner wall of the notch, a portion of the lightly doped region being under the notch.

Owner:SAMSUNG ELECTRONICS CO LTD

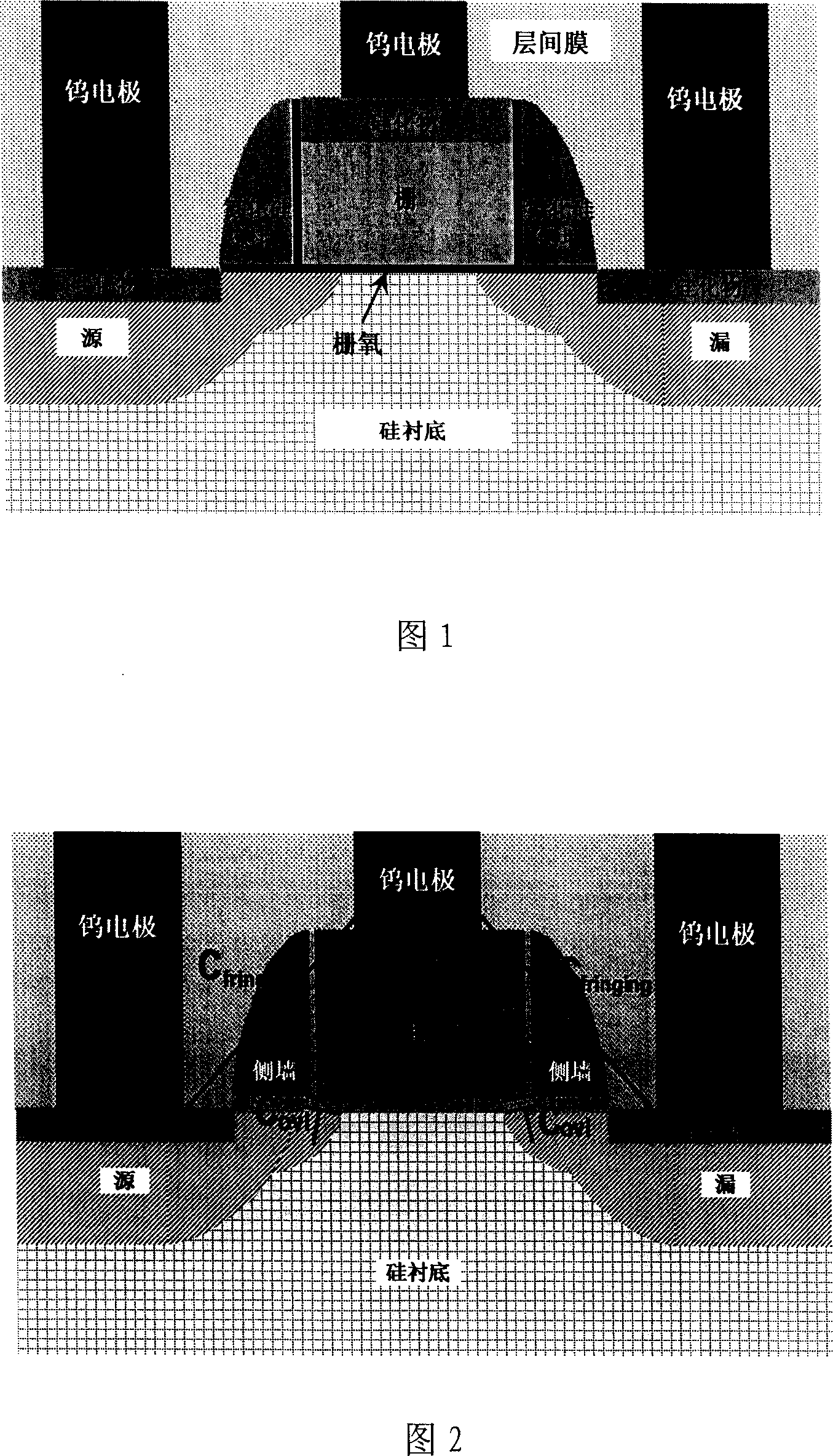

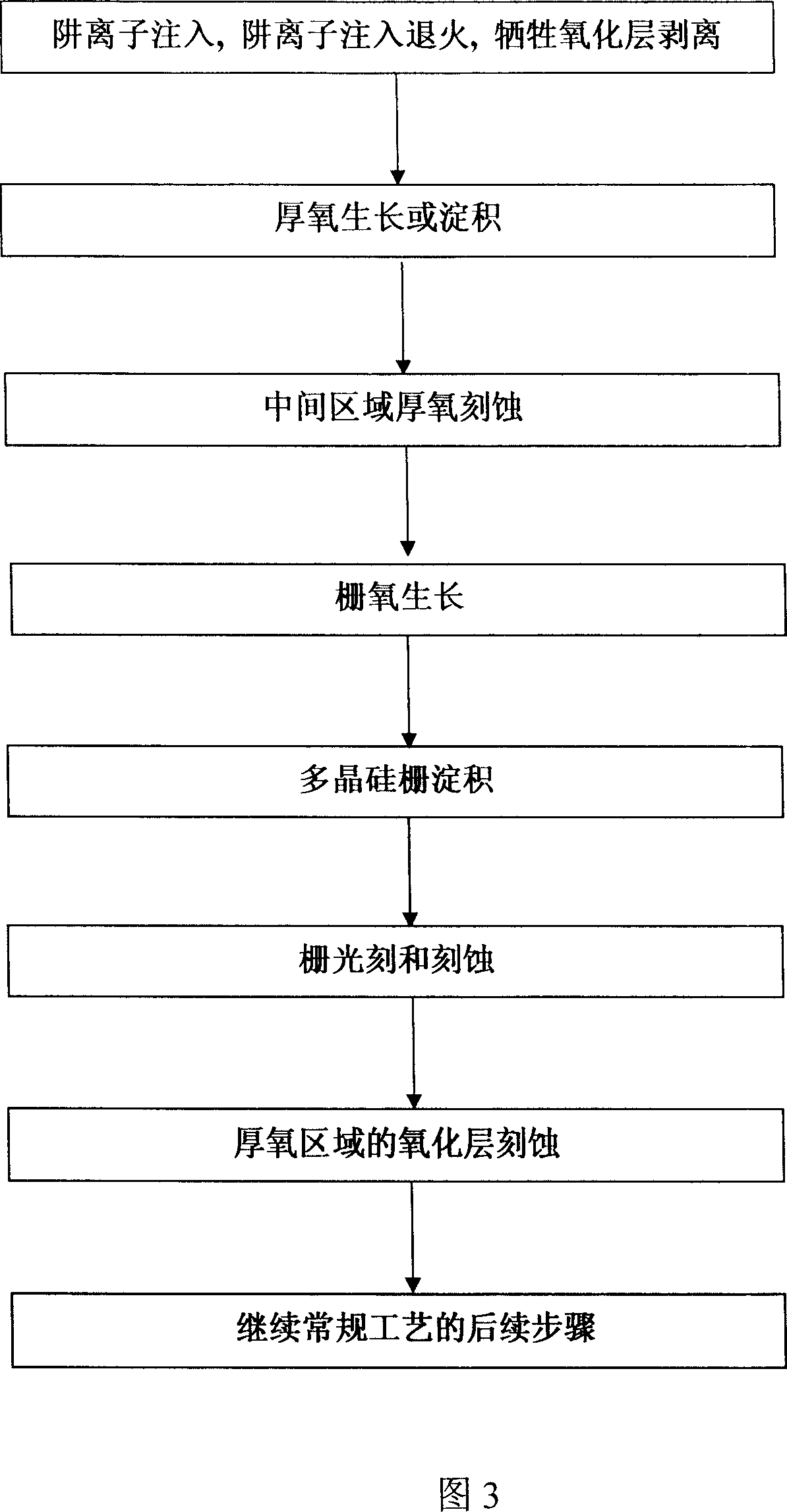

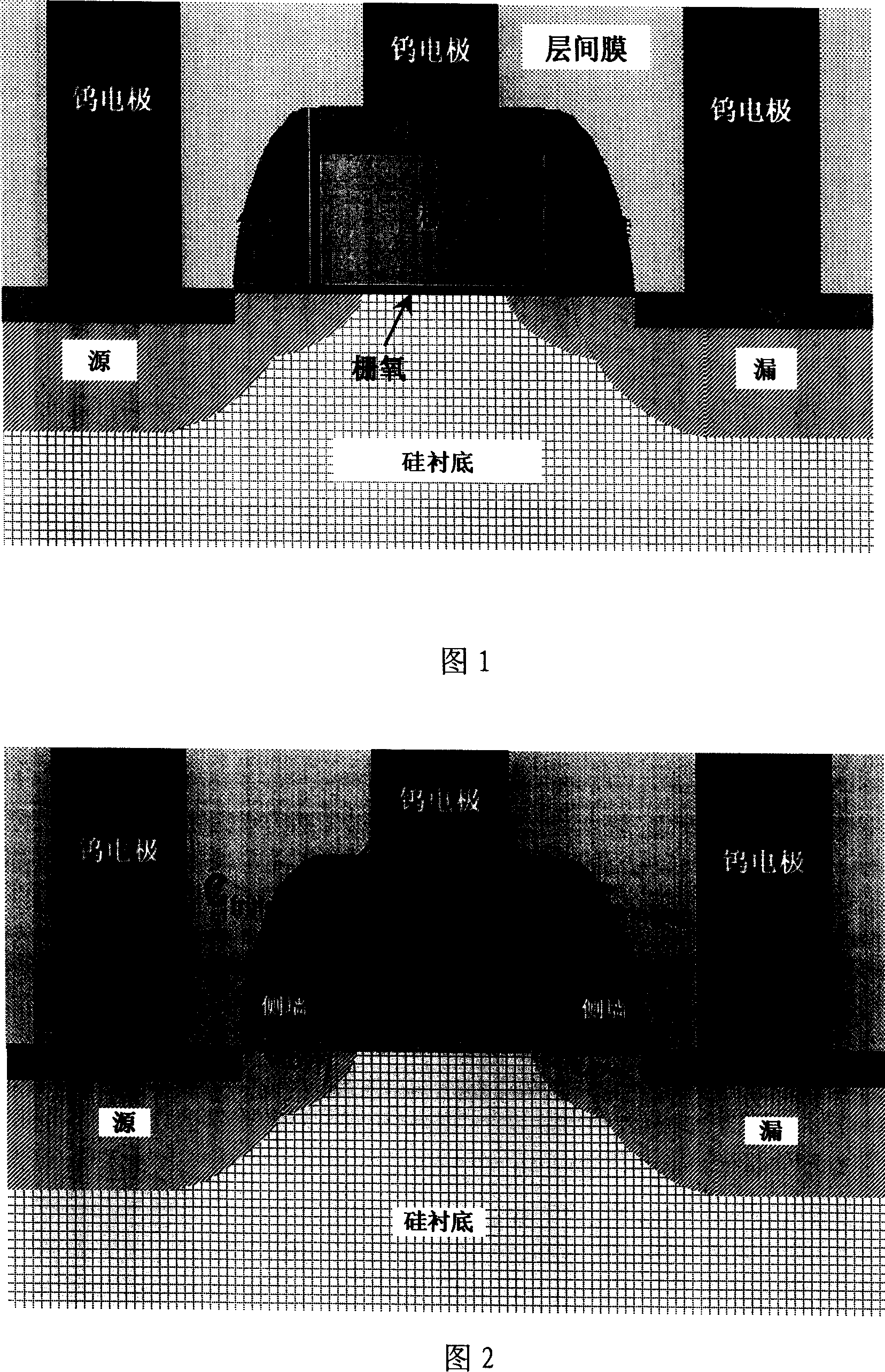

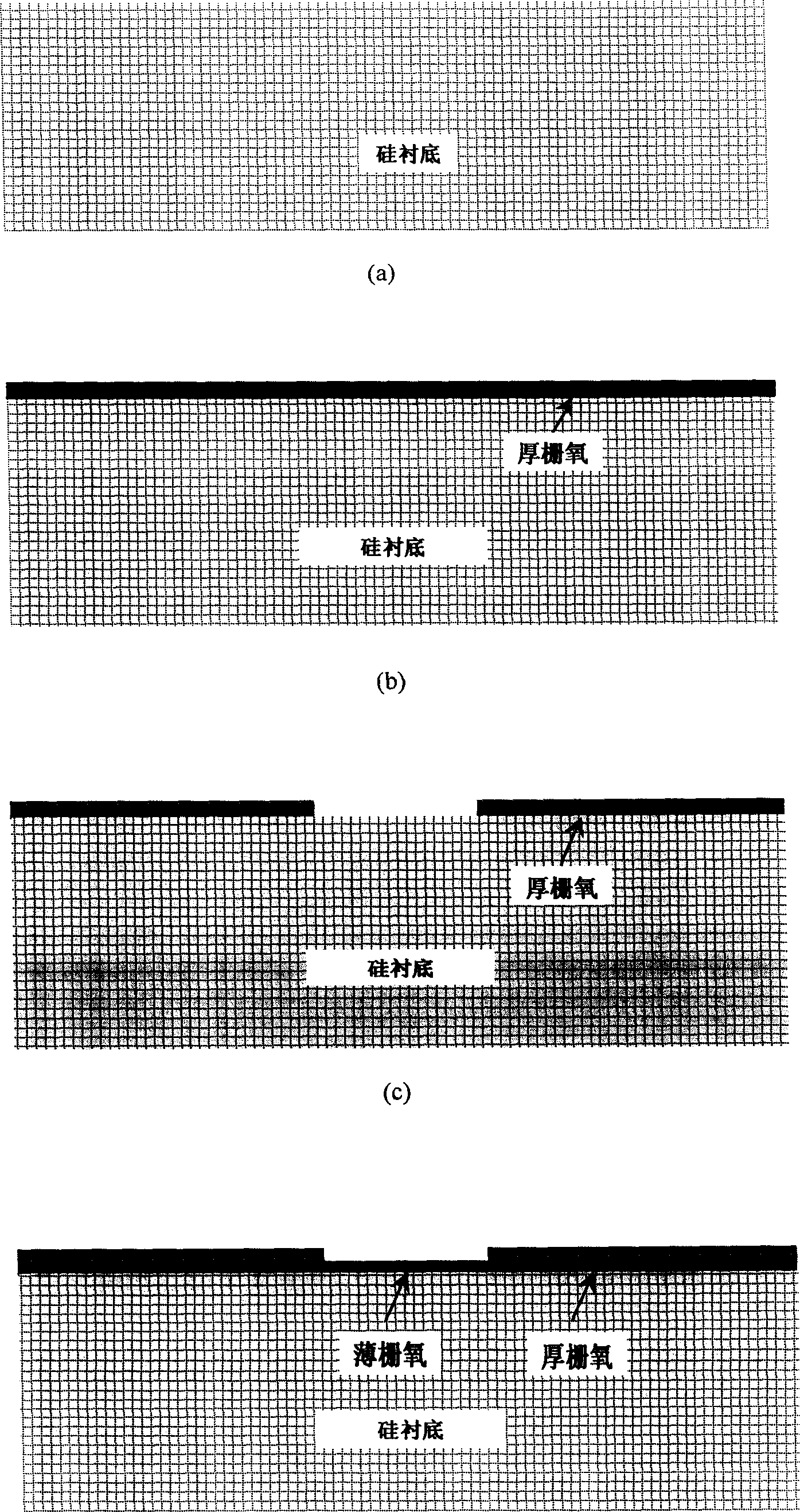

A MOS FET tube and its manufacturing method

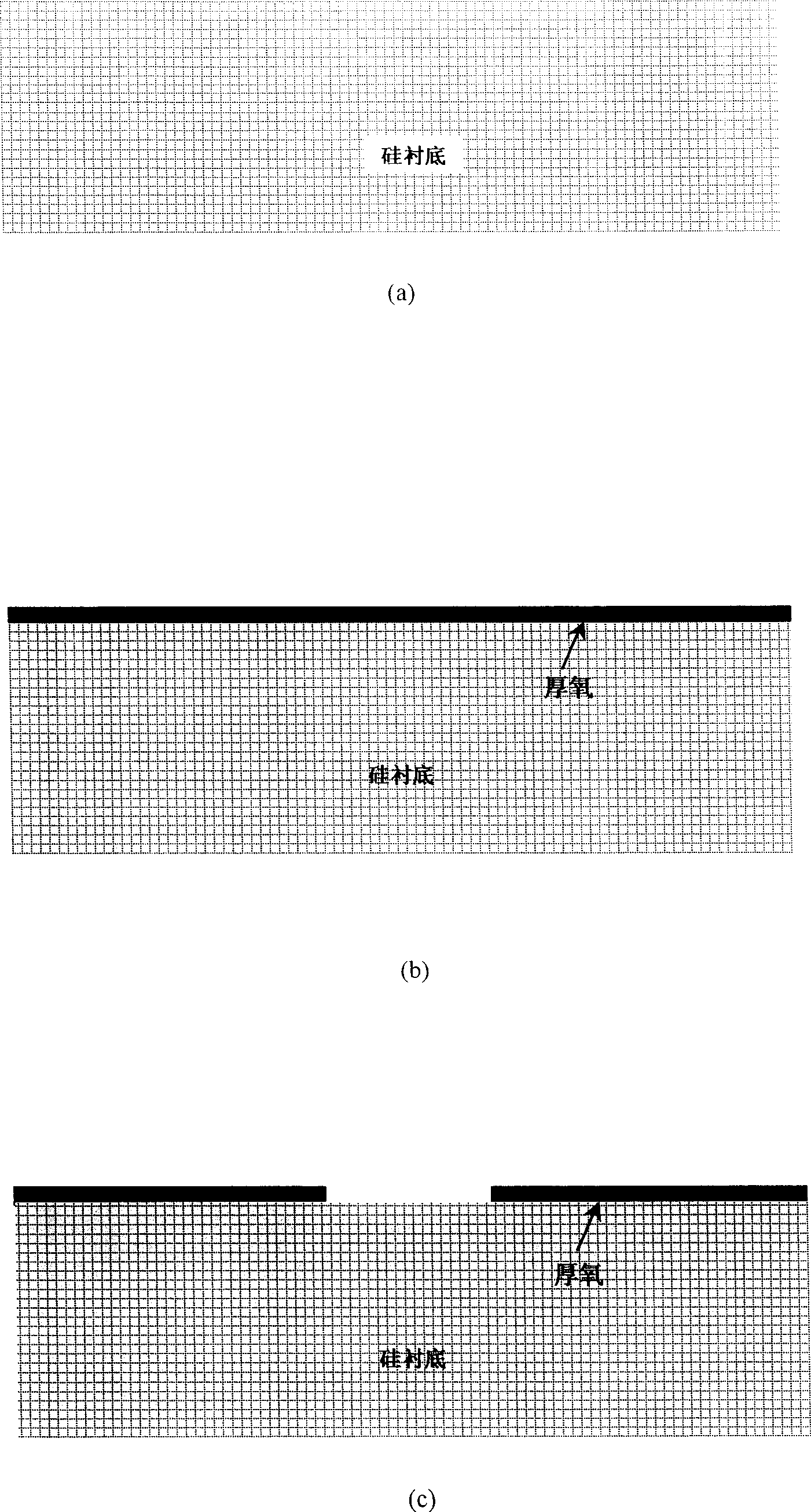

ActiveCN1971941AReduce overlap areaReduce Gate-Drain Overlap CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPolycrystalline silicon

This invention discloses one MOS field effect tube and its process method, which has side wall bottom concaved toward inside. The field effect tube method comprises the following steps: a, injecting well ions for annealing to sacrifice oxidation layer peeling off; b, growing or depositing one layer of thick oxidation layer; c, processing total etching in middle area oxidation; d, growing grating oxidation; e, depositing multiple transistor grating; f, processing light etch on thick oxidation area; g, regular steps after etching.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

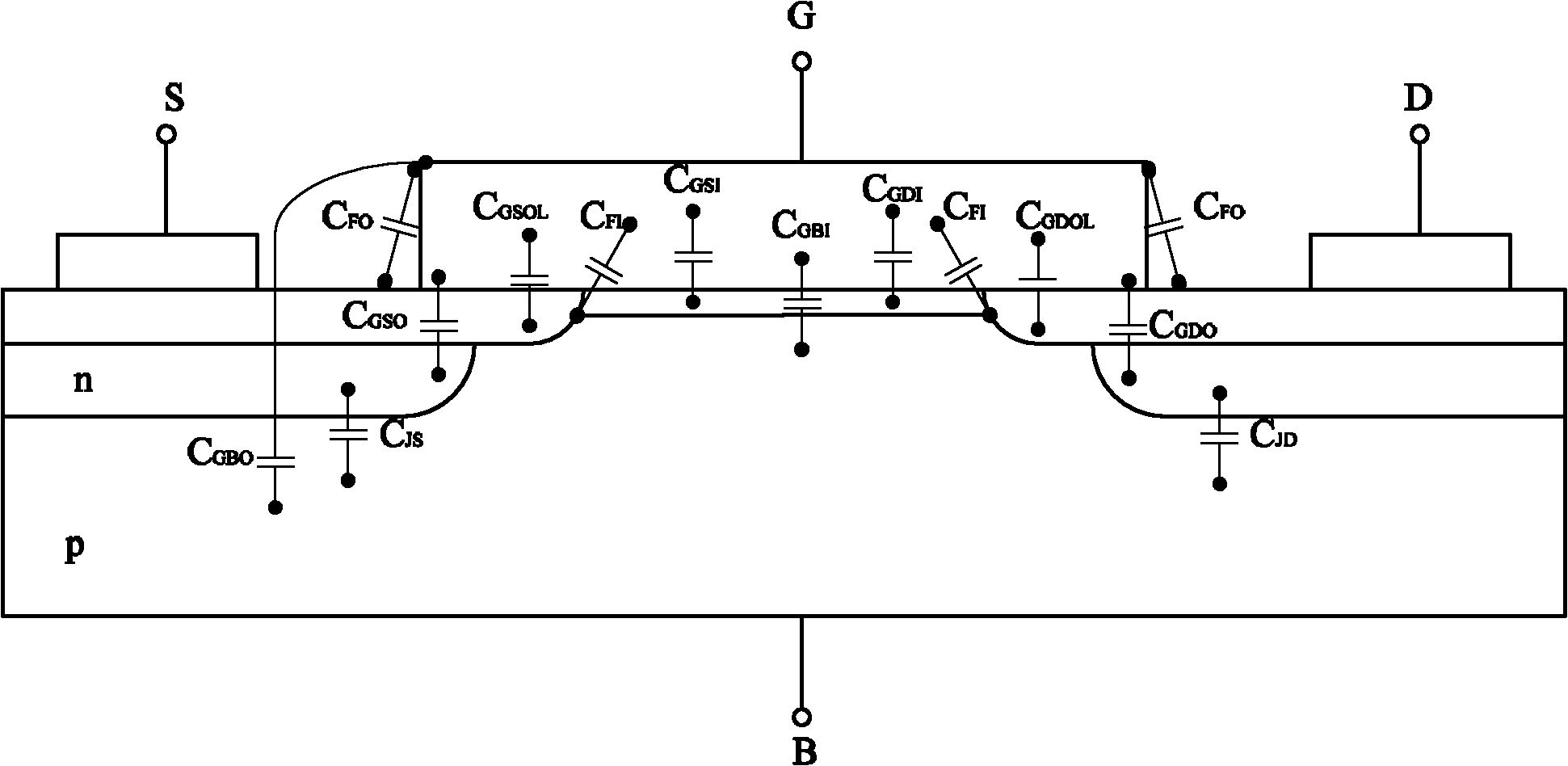

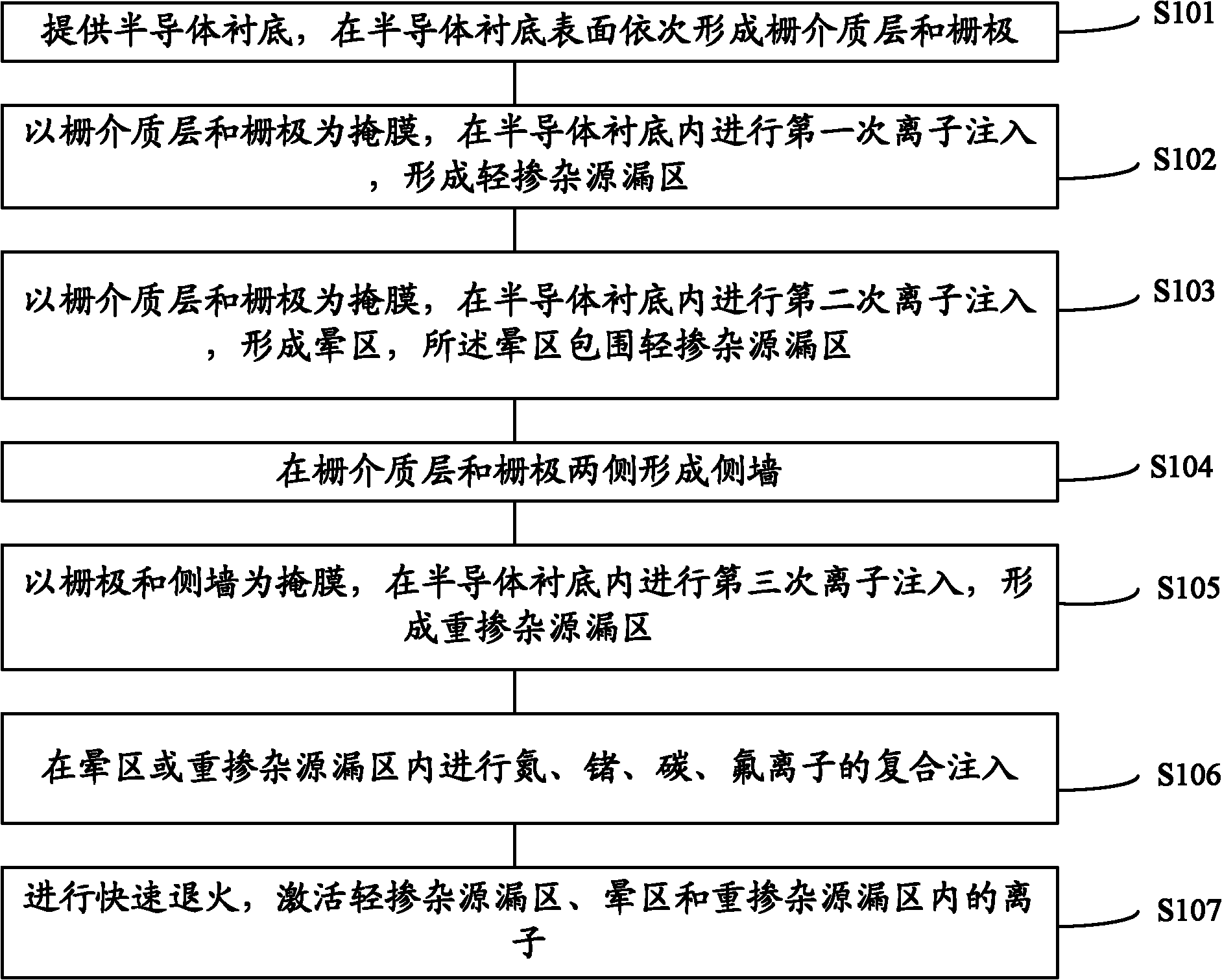

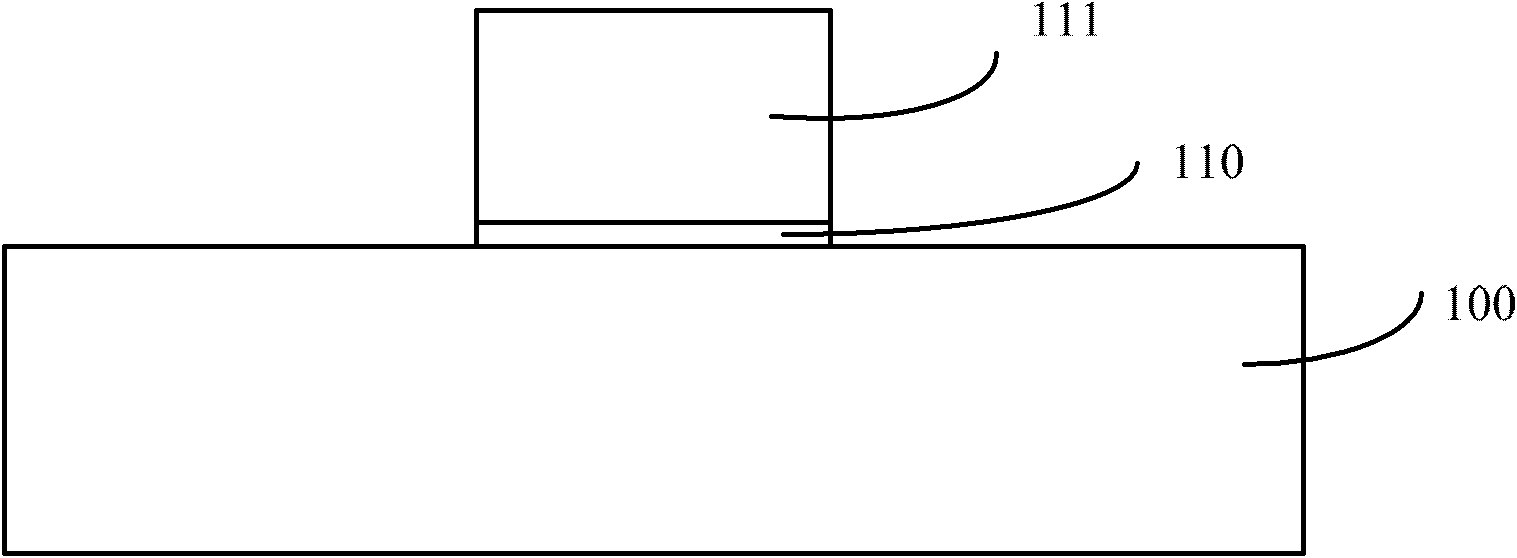

N-type MOS field-effect transistor and formation method thereof, semiconductor device and formation method of semiconductor device

ActiveCN103187276AReduce Overlap CapacitanceReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceDevice material

The invention provides an n-type MOS (metal oxide semiconductor) field-effect transistor and a formation method thereof, a semiconductor device and a formation method of the semiconductor device. The formation method of the n-type MOS field-effect transistor comprises the steps that a semiconductor substrate is provided; a grid medium layer and a grid electrode are formed on the surface of the semiconductor substrate sequentially, and serve as masking films; first ion implantation is conducted in the semiconductor substrate; lightly doped source drain regions are formed; the grid medium layer and the grid electrode serve as the masking films; second ion implantation is conducted in the semiconductor substrate; halo regions are formed, and surround the lightly doped source drain regions; side walls are formed on the two sides of the grid medium layer and the grid electrode; the grid electrode and the side walls serve as masking films; third ion implantation is conducted in the semiconductor substrate; heavily doped source drain regions are formed; composite implantation of nitrogen, germanium, carbon and fluorine ions is conducted in the halo regions or the heavily doped source drain regions; rapid annealing is conducted; and the ions in the lightly doped source drain regions, the halo regions and the heavily doped source drain regions are activated. Overlap capacitance of the formed n-type MOS field-effect transistor is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

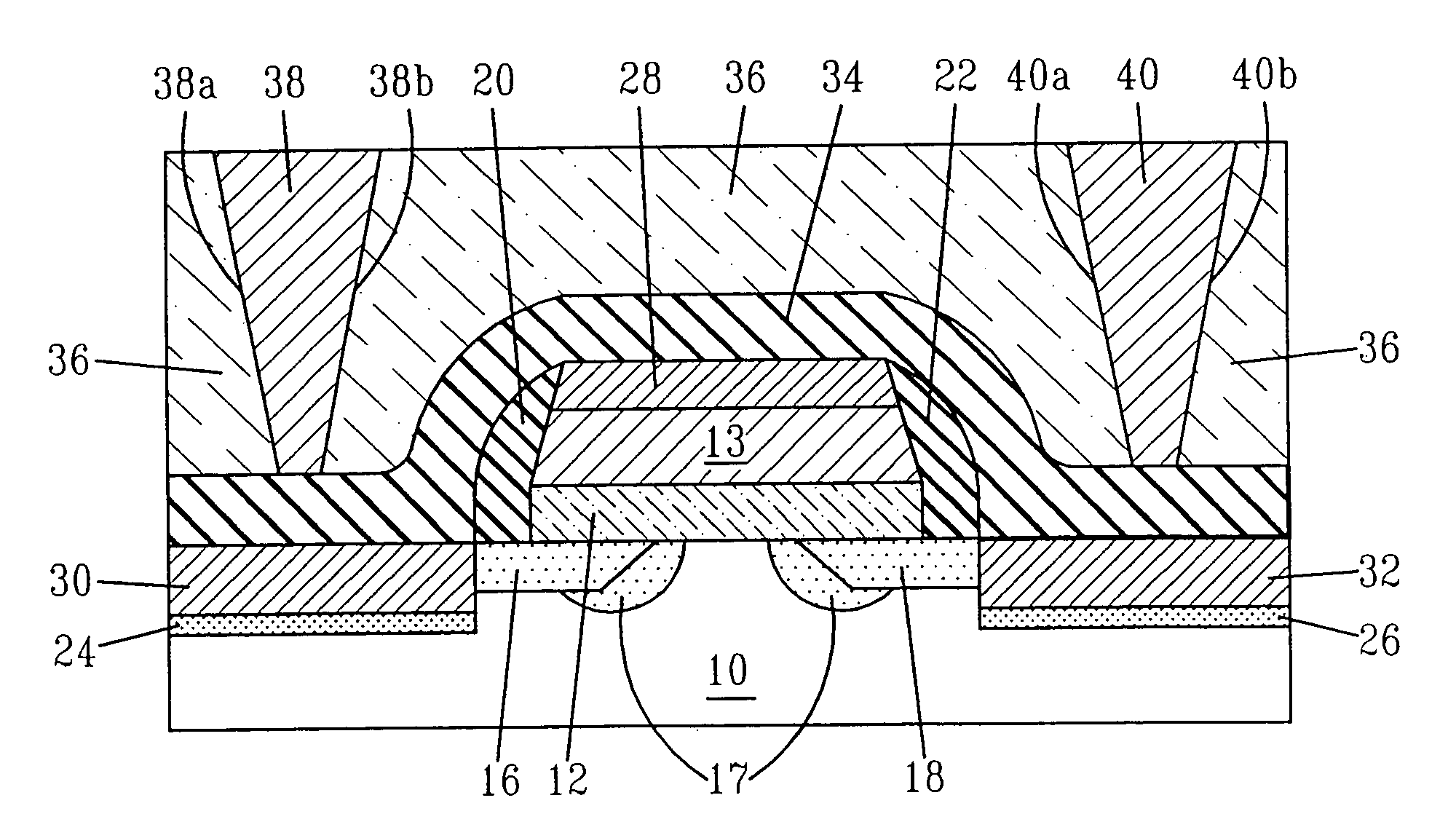

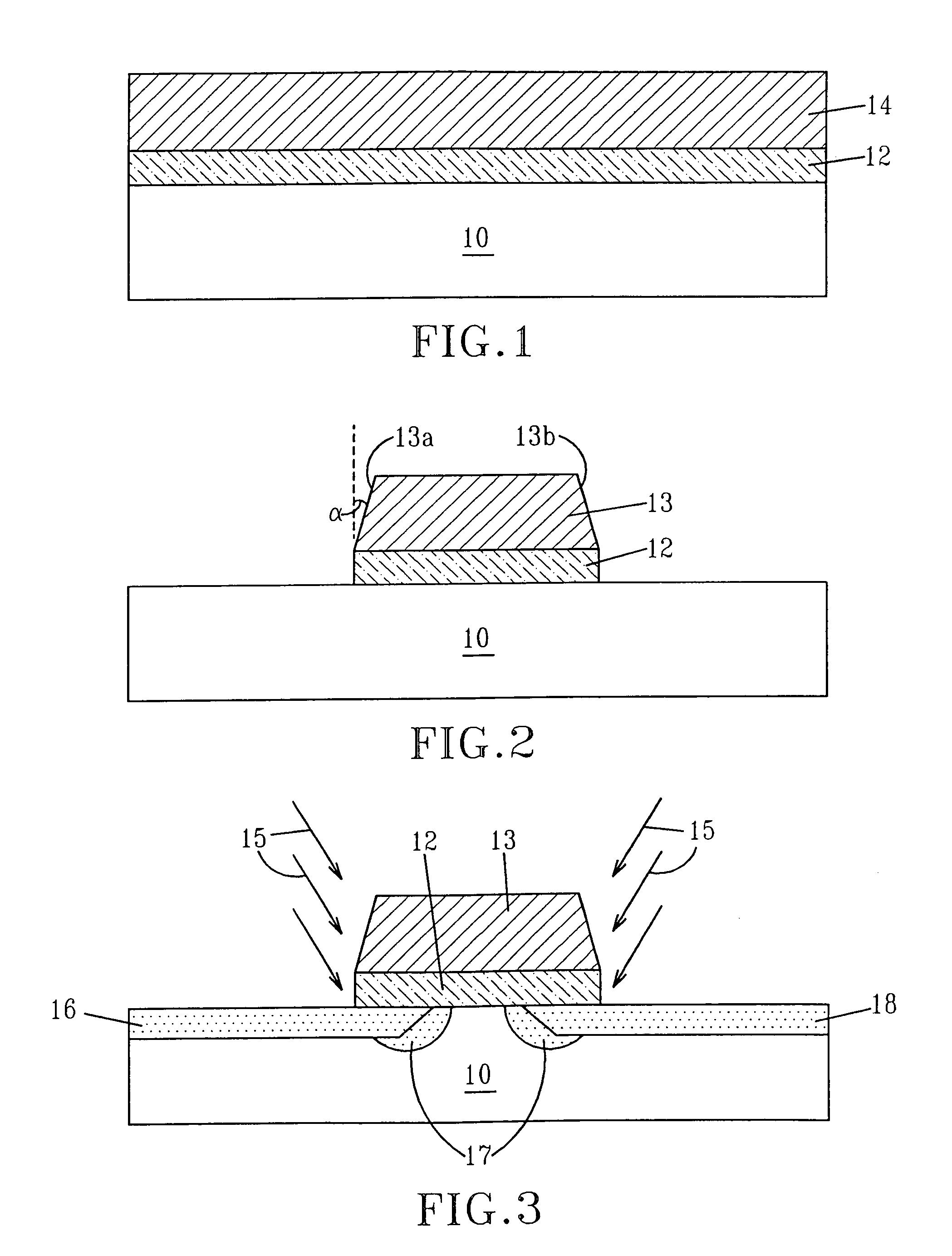

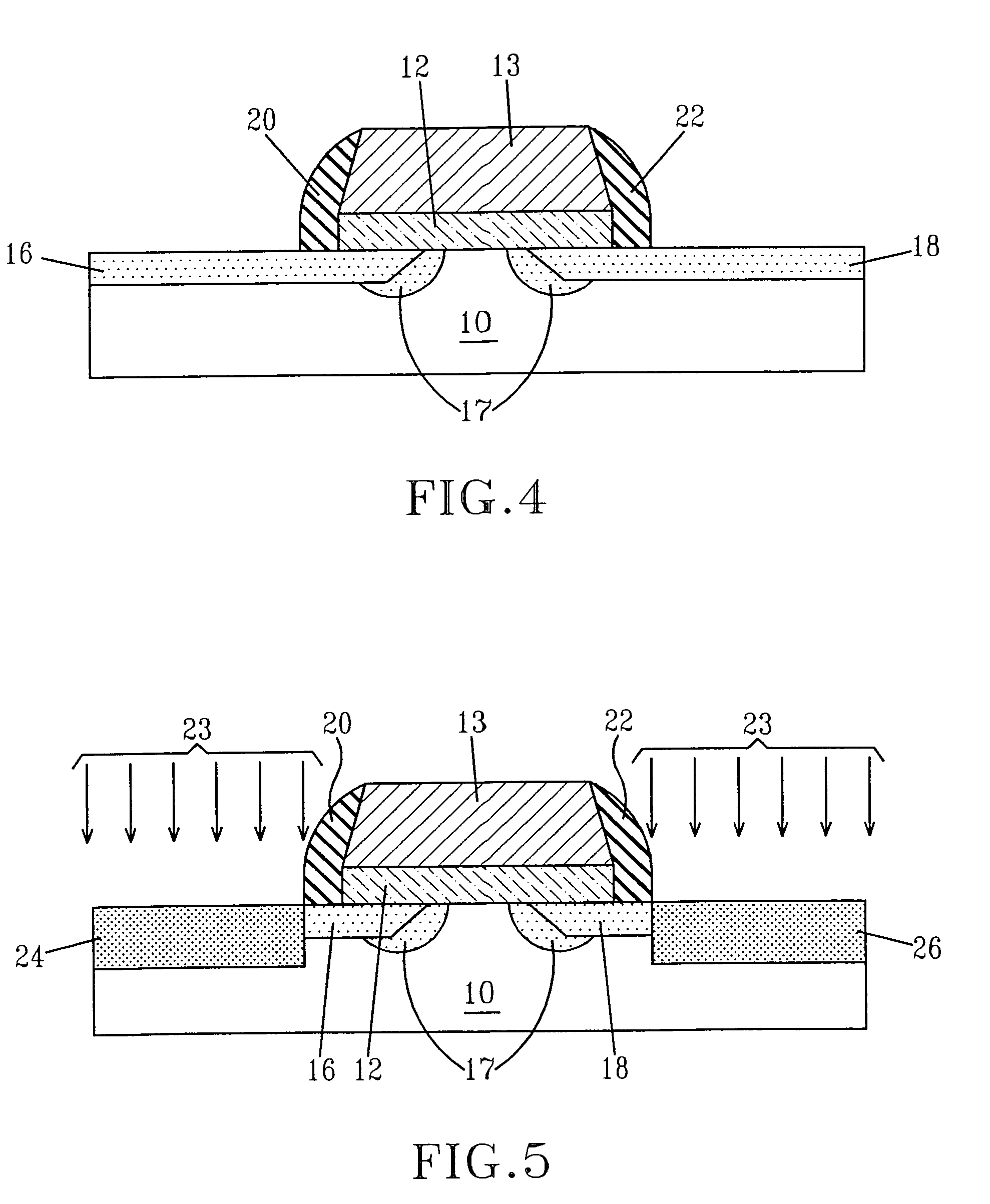

MOSFET with high angle sidewall gate and contacts for reduced miller capacitance

ActiveUS7224021B2Reduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceMOSFET

Owner:ELPIS TECH INC

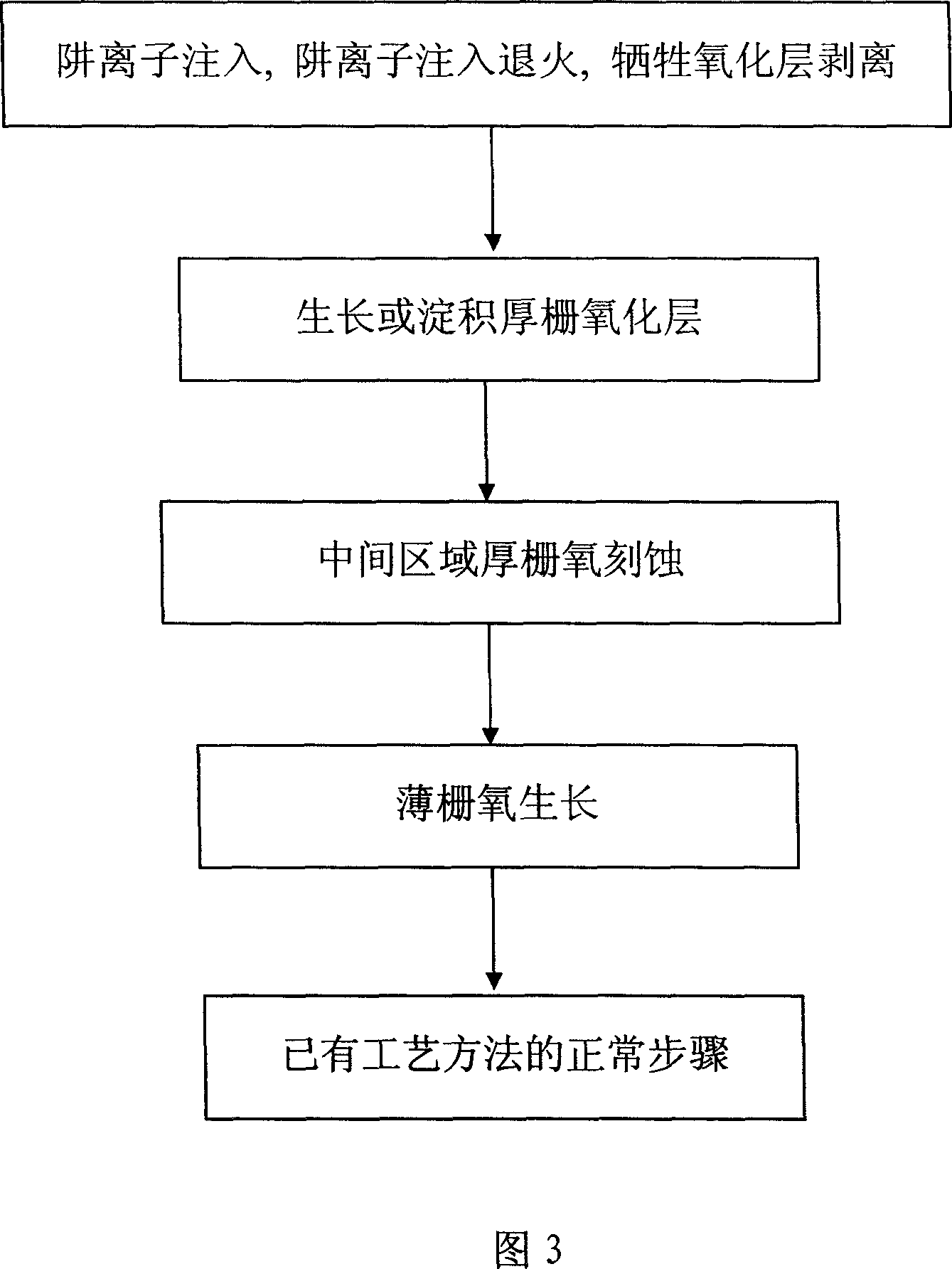

A MOS FET tube and its manufacturing method

InactiveCN1971944AReduce Overlap CapacitanceImprove speed performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGratingGate oxide

This invention discloses one MOS field effect tube and its process method, which has the following steps: a, injecting well ion and annealing and sacrifice oxidation layer for peeling off; b, growing or depositing one layer of grating oxidation layer; c, totally etching middle area grating oxidation; d, growing film grating oxidation; e, the current process method steps are applicable for this invention.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

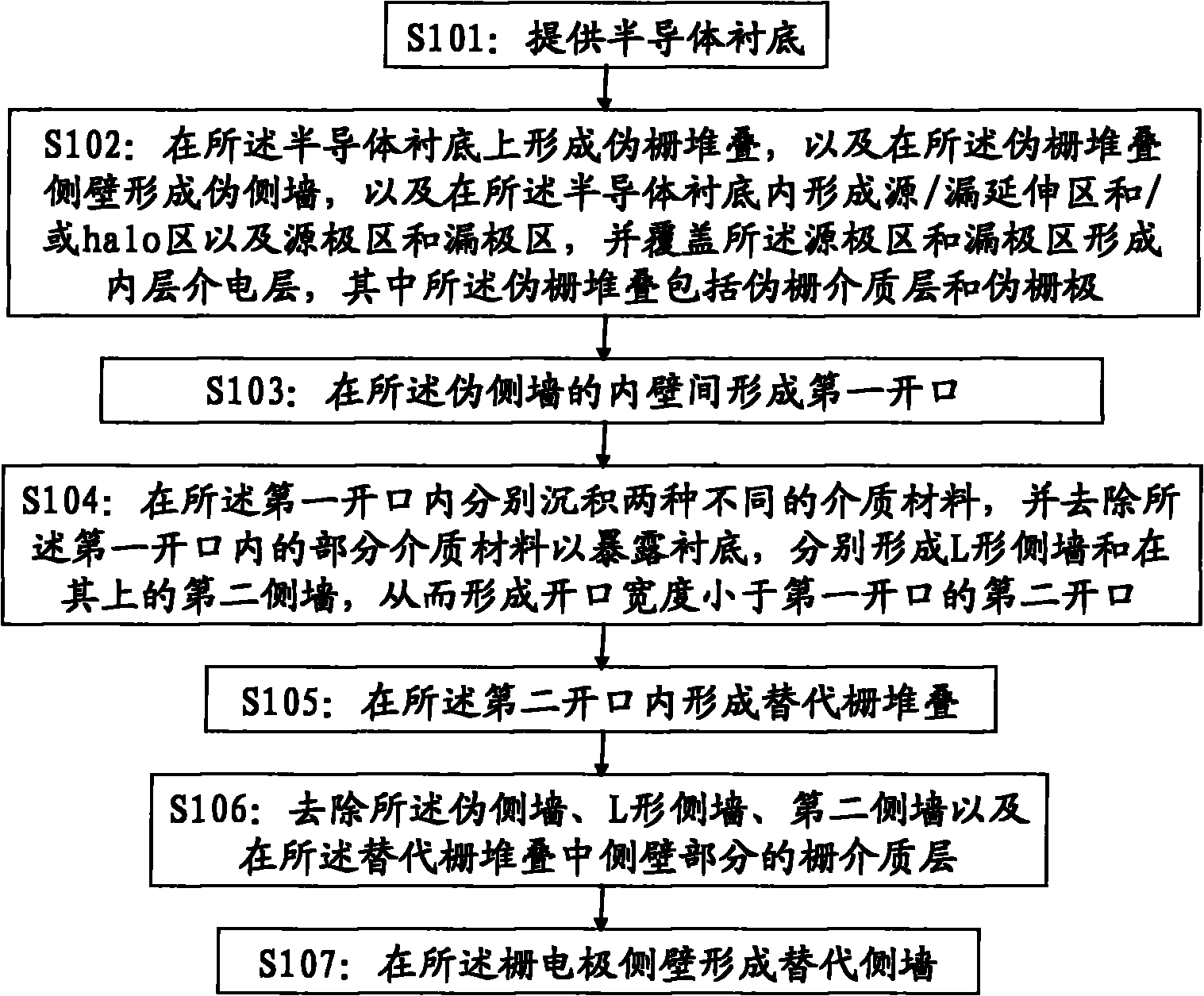

Manufacturing method of semiconductor device

ActiveCN102142373AReduce Overlap CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCMOS

The invention discloses a manufacturing method of a semiconductor device. The method comprises the following steps of: removing a pseudo-gate stack in the process of preparing a complementary metal-oxide-semiconductor (CMOS) transistor by using a replacement gate or gate last process; forming an L-shaped sidewall and a second sidewall on the L-shaped sidewall in a first opening which is formed after the pseudo-gate stack is removed; redefining the size of a replacement gate to play a role in adjusting the overlapped capacitance of a replacement gate stack and a source / drain region and a source / drain extension region; and forming a replacement sidewall by a sidewall of a gate electrode in the replacement gate stack, so that the overlapped capacitance of the sidewall and the source / drain region and the source / drain extension region is further reduced, and the whole overlapped capacitance of the device is further reduced. Furthermore, a device with a smaller size is obtained by a processmethod which is easier to implement.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

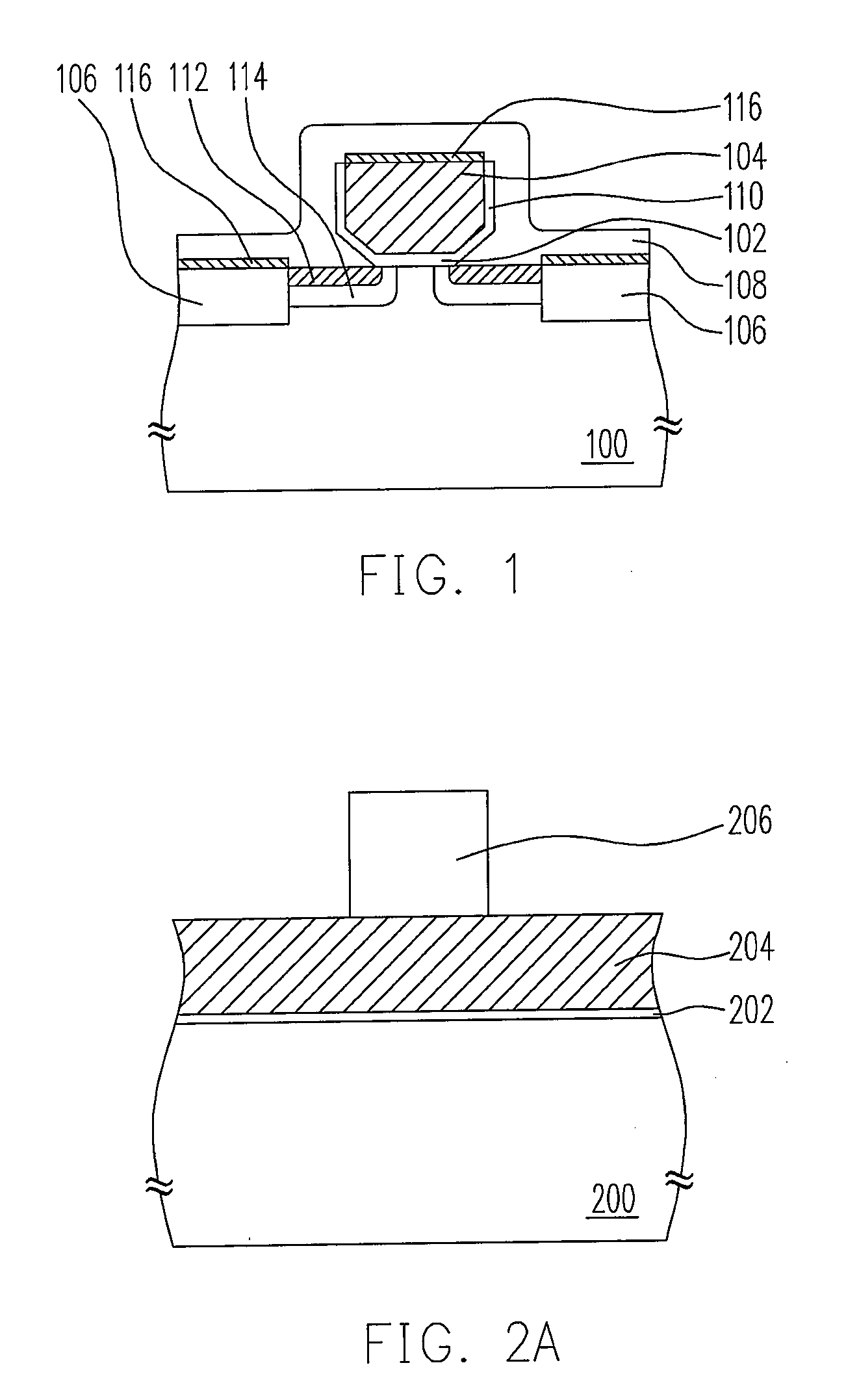

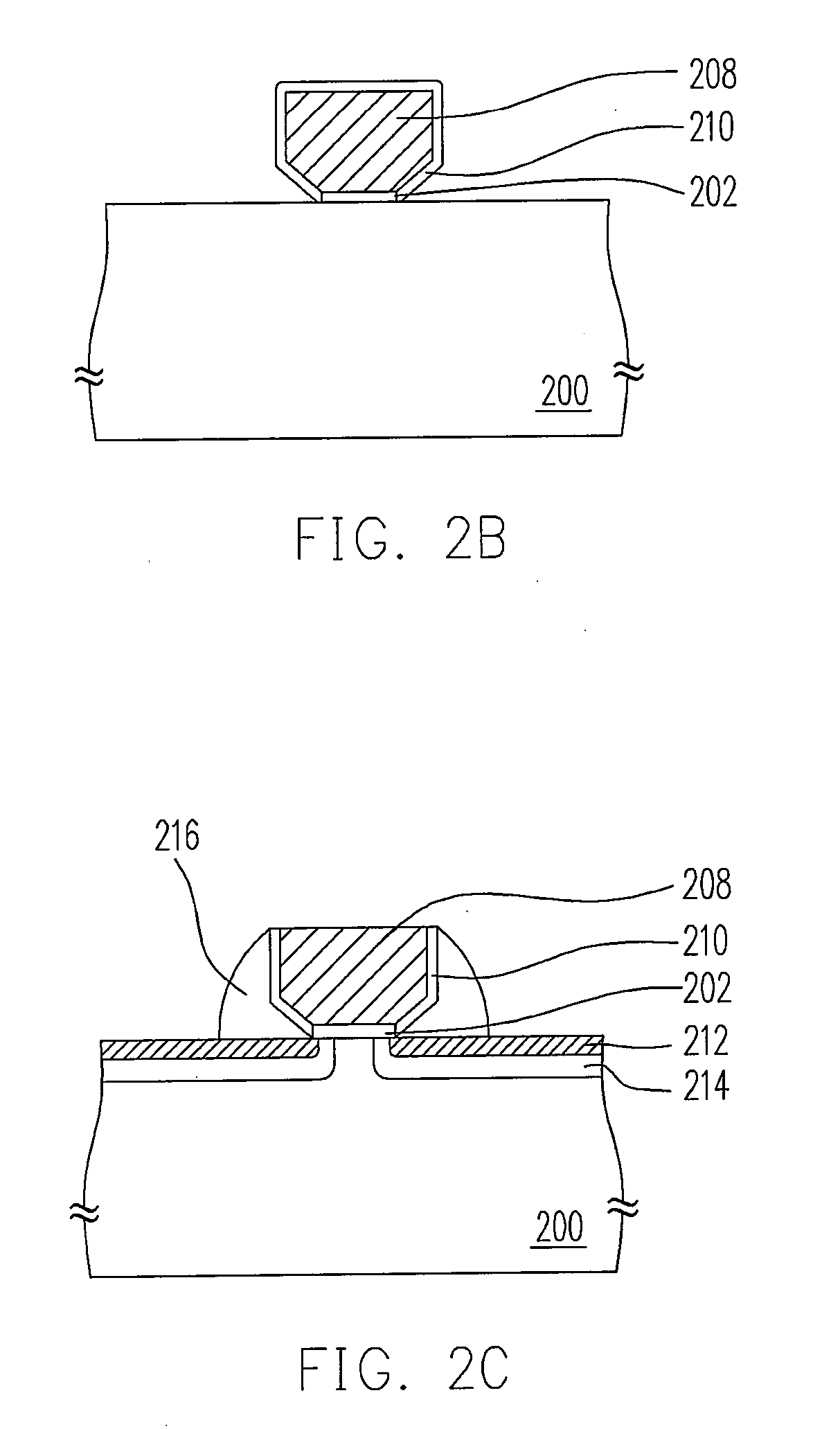

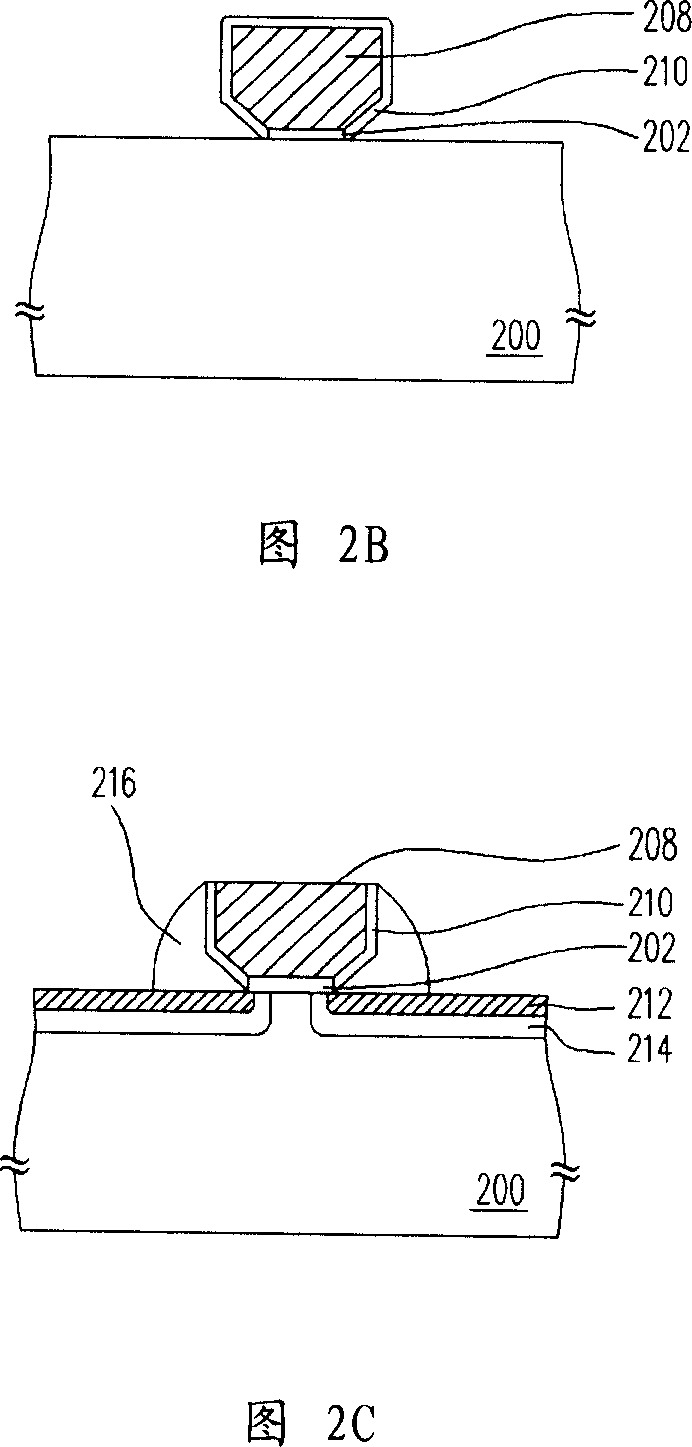

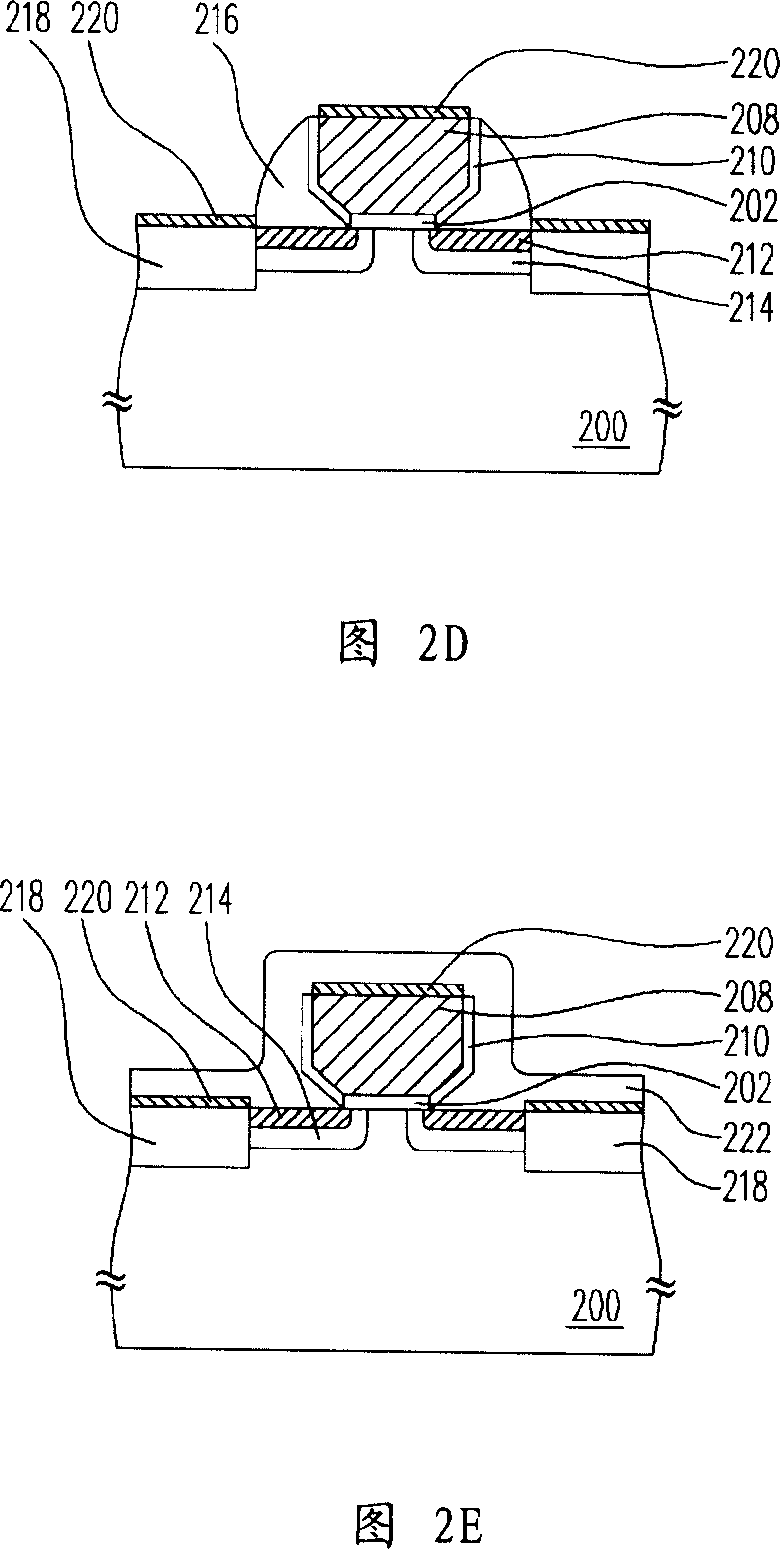

Method of fabricating a semiconductor device

InactiveUS20070259503A1Improve mobilityIncrease computing speedSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor

A method of fabricating a semiconductor device is provided herein. The semiconductor device includes a substrate, a gate dielectric layer, a gate, a pair of source / drain regions and a stressed layer. The gate dielectric layer is disposed on the substrate and the gate whose top area is larger than its bottom area is disposed on the gate dielectric layer. The source / drain regions are disposed in the substrate next to the sidewalls of the gate. The stressed layer is disposed on the substrate to cover the gate and the source / drain regions.

Owner:UNITED MICROELECTRONICS CORP

Mosfet with high angle sidewall gate and contacts for reduced miller capacitance

ActiveUS20070057334A1Reduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingMOSFETCapacitance

The present invention relates to an FET device having a conductive gate electrode with angled sidewalls. Specifically, the sidewalls of the FET device are offset from the vertical direction by an offset angle that is greater than about 0° and not more than about 45°. In such a manner, such conductive gate electrode has a top surface area that is smaller than its base surface area. Preferably, the FET device further comprises source / drain metal contacts that are also characterized by angled sidewalls, except that the offset angle of the source / drain metal contacts are arranged so that the top surface area of each metal contact is larger than its base surface area. The FET device of the present invention has significantly reduced gate to drain metal contact overlap capacitance, e.g., less than about 0.07 femtoFarads per micron of channel width, in comparison with conventional FET devices having straight-wall gate electrodes and metal contacts.

Owner:ELPIS TECH INC

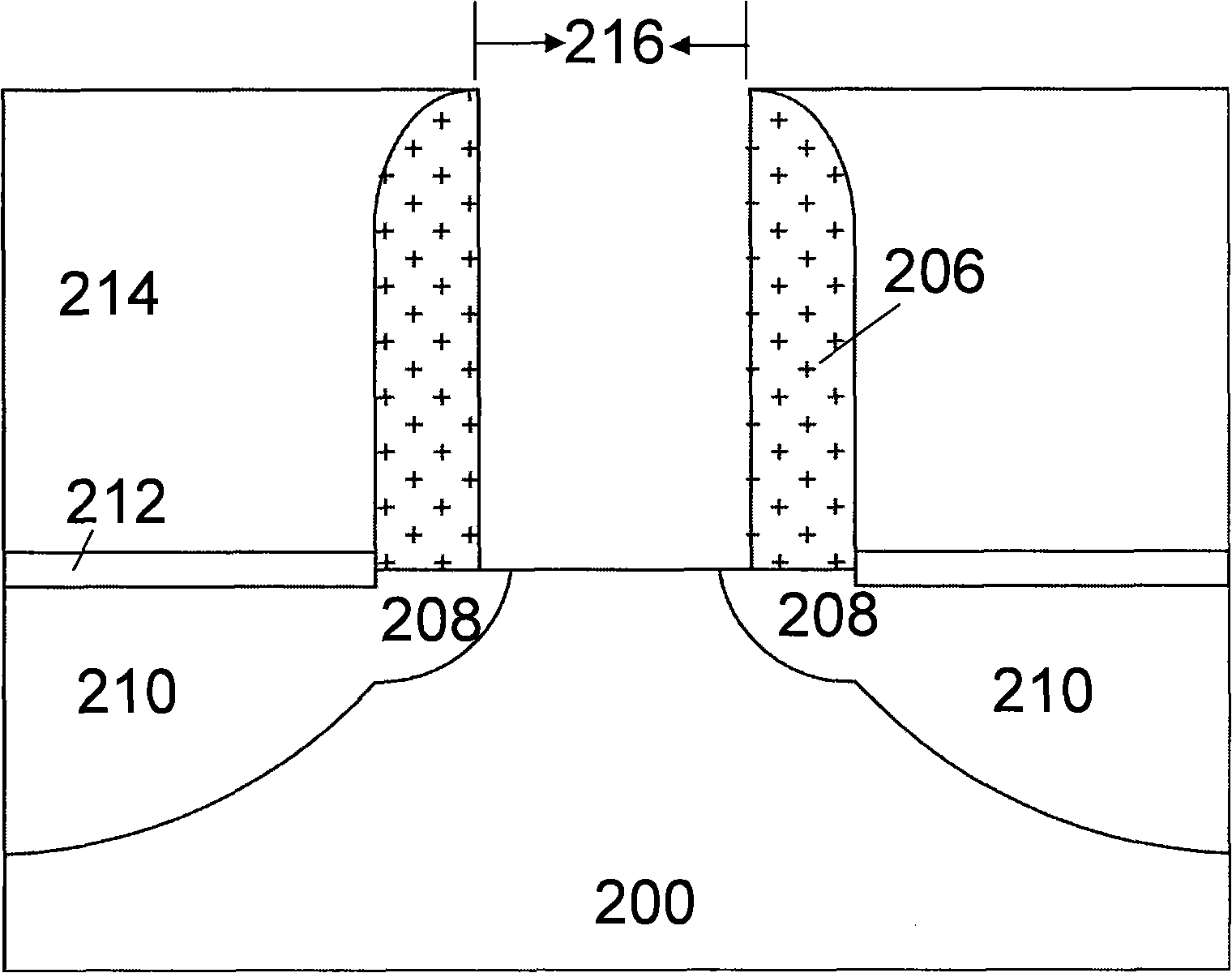

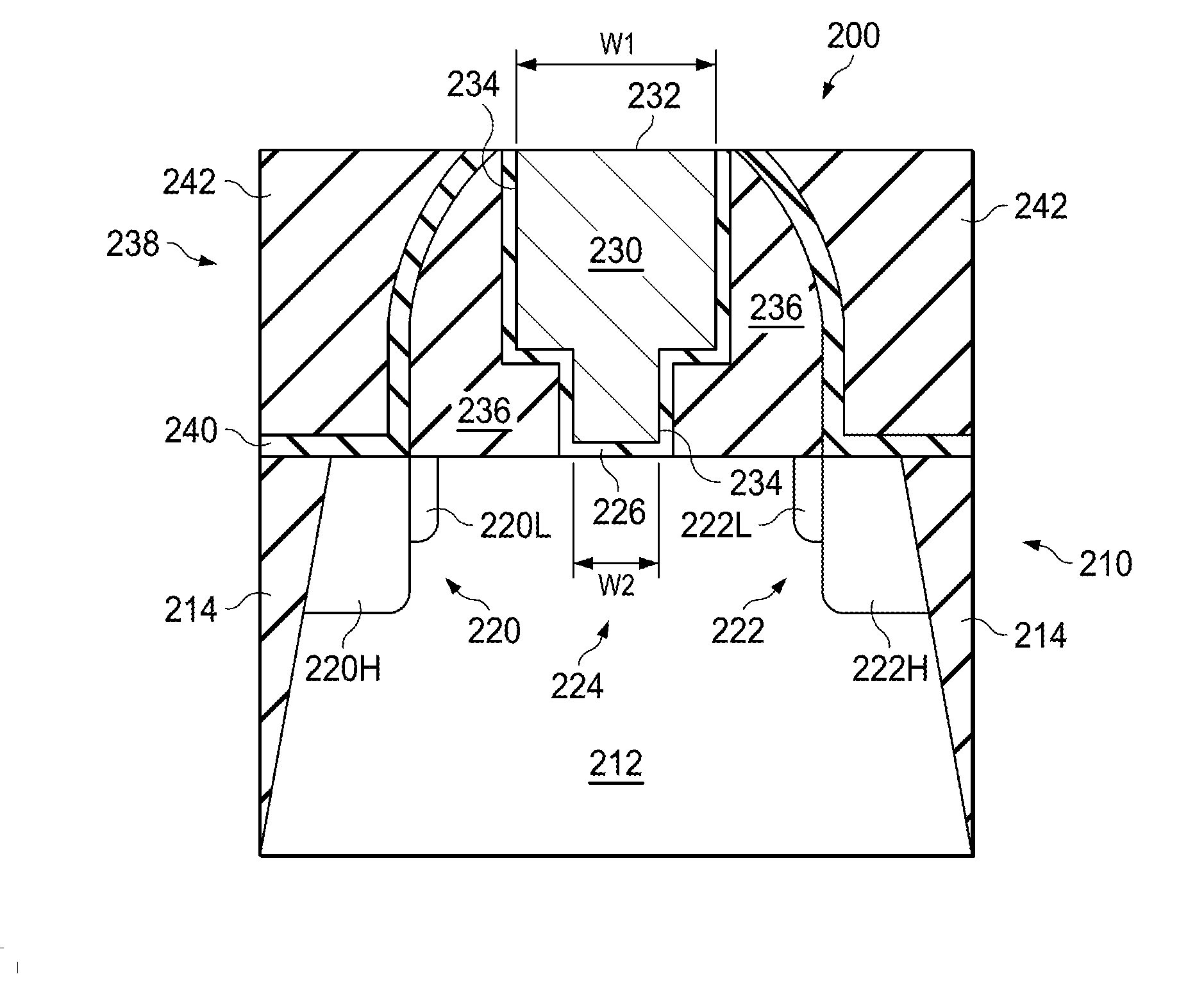

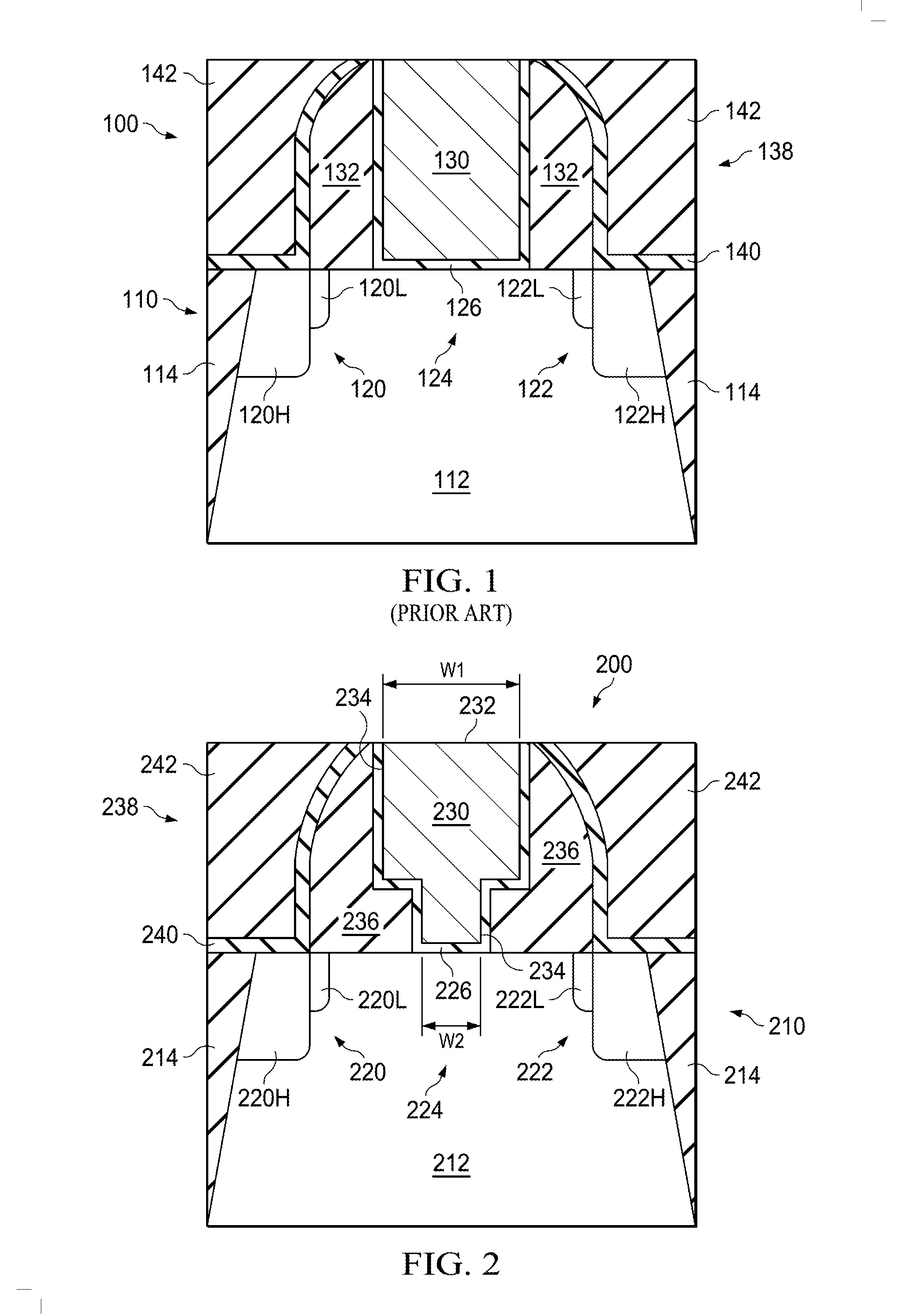

Metal-Gate MOS Transistor and Method of Forming the Transistor with Reduced Gate-to-Source and Gate-to-Drain Overlap Capacitance

ActiveUS20140124874A1Large spacingReduce Overlap CapacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceGate dielectric

The gate-to-source and gate-to-drain overlap capacitance of a MOS transistor with a metal gate and a high-k gate dielectric are reduced by forming the high-k gate dielectric along the inside of a sidewall structure which has been formed to lie further away from the source and the drain.

Owner:TEXAS INSTR INC

Semiconductor element and its manufacturing method

InactiveCN101071823AIncrease stressReduce contact areaSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricPhysics

The invention is a semiconductor component, comprising a substrate, a gate dielectric layer, a gate, a source / drain region, and a stress layer, where the gate dielectric layer is arranged on the substrate, the gate is arranged on the gate dielectric layer and the area of the top of the gate is more than that of the bottom; in addition, the source / drain region is arranged in the substrate on two sides of the gate, and the stress layer is arranged on the substrate and covers the gate and the source / drain region.

Owner:UNITED MICROELECTRONICS CORP

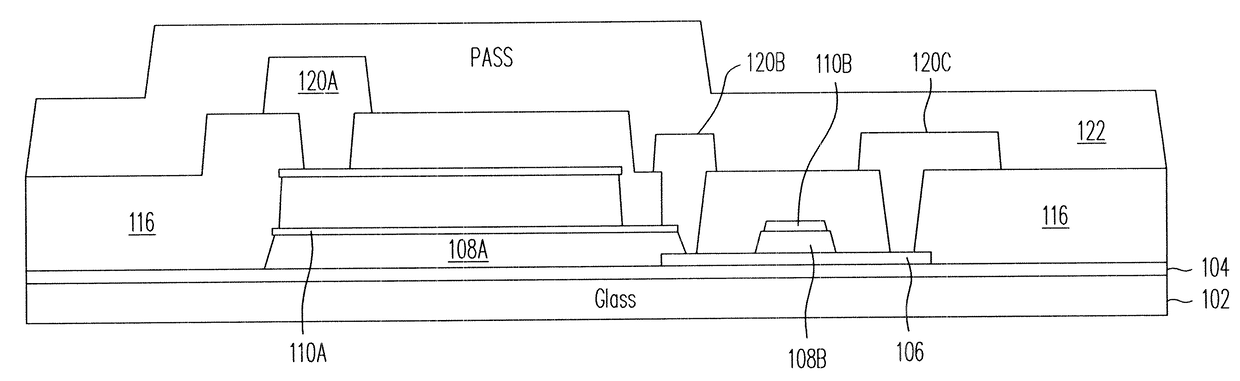

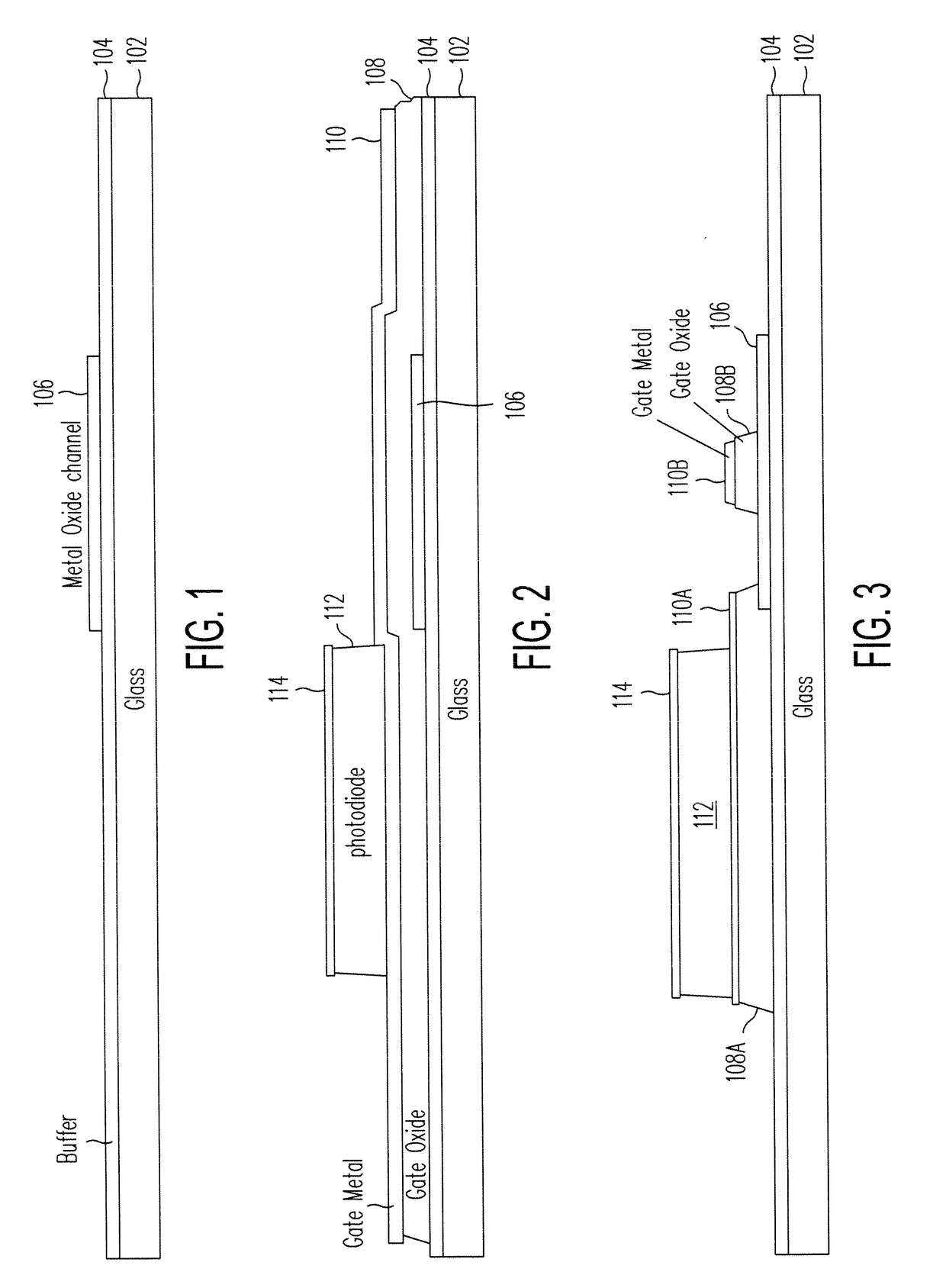

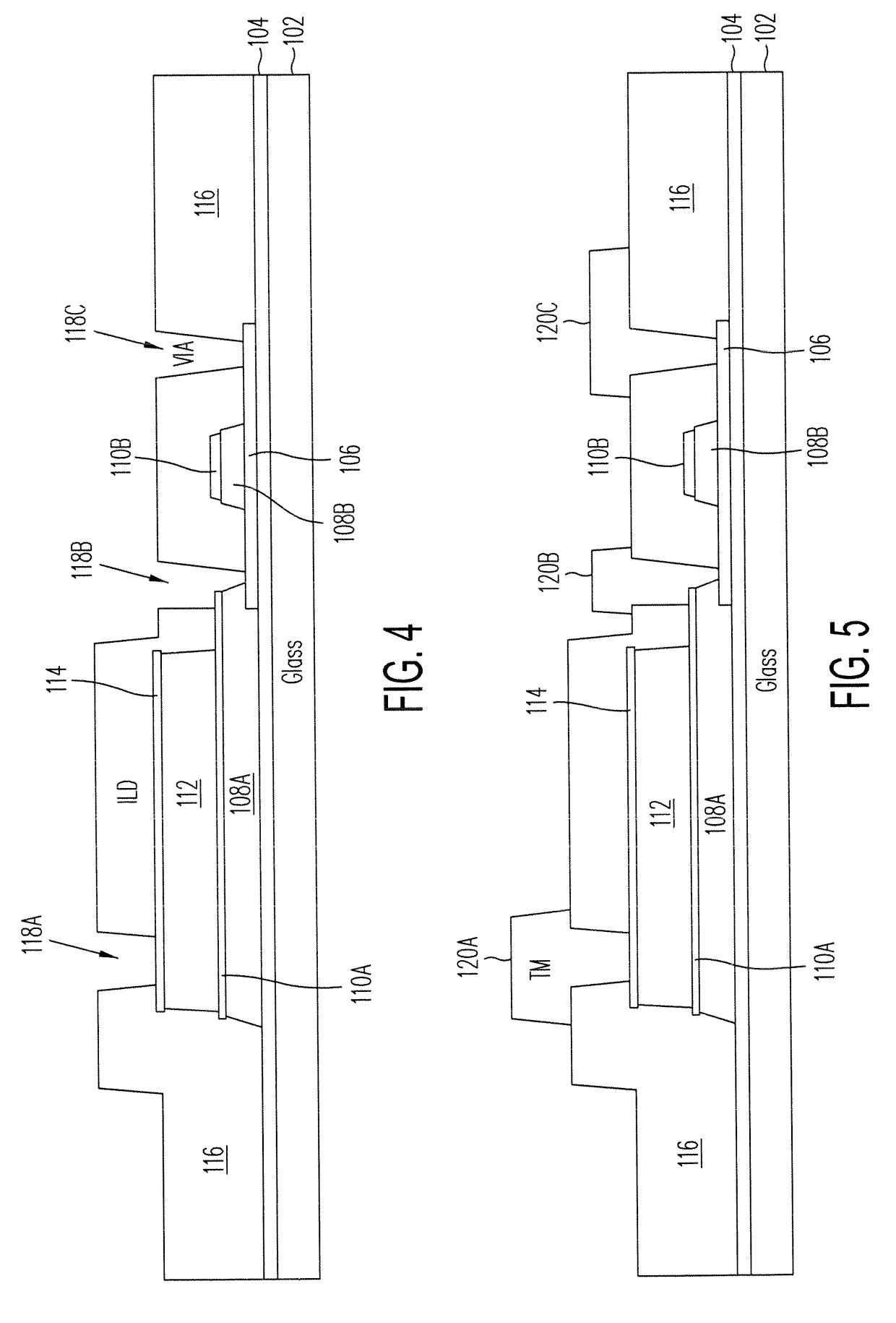

Top gate metal oxide thin film transistor switching device for imaging applications

InactiveUS20170170218A1Fast switching speedImprove electrical performanceTransistorSolid-state devicesGate oxidePhotodiode

A method of manufacturing an image sensor device includes providing a substrate; forming a buffer layer on the substrate; forming a metal oxide channel on the buffer layer; forming a gate oxide layer on the buffer layer and the metal oxide channel; forming a gate metal layer on the gate oxide layer; forming a photodiode stack on the gate metal layer; patterning the gate oxide layer and the gate metal layer to form a first portion under the photodiode stack, and a second portion comprising a transistor; forming an interlayer dielectric layer over at least the photodiode stack and the transistor; forming a plurality of vias in the interlayer dielectric layer; and metalizing the vias to form contacts to the image sensor device.

Owner:DPIX

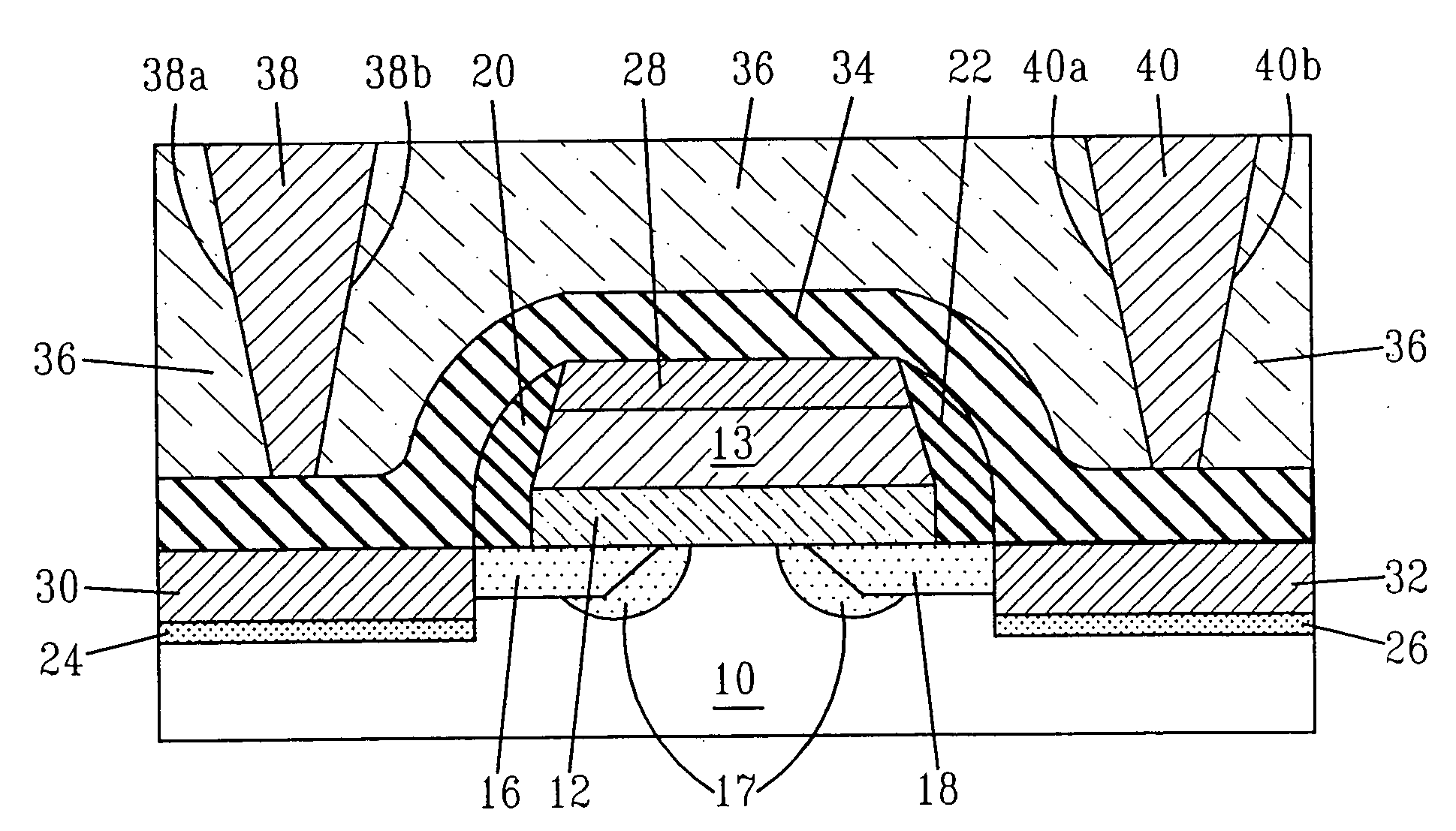

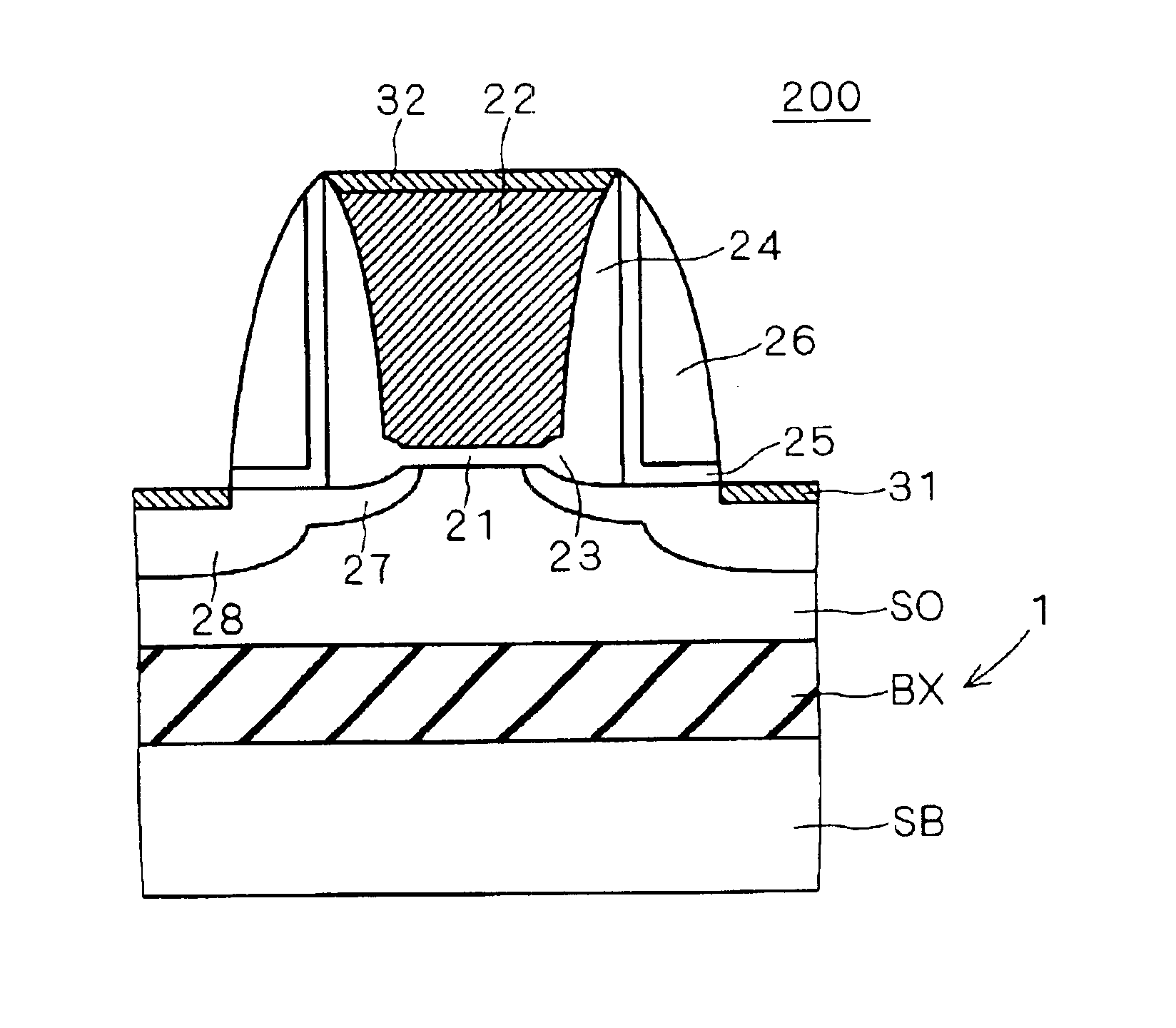

Semiconductor device of reduced gate overlap capacitance and method of manufacturing the semiconductor device

InactiveUS7045867B2Reducing gate overlap capacitanceDecreasing driving currentTransistorSemiconductor/solid-state device manufacturingCapacitanceDriving current

Provided is an MOS transistor capable of reducing gate overlap capacitance without decreasing the driving current of the MOS transistor. Specifically, a double-angle smile oxidation structure is obtainable by curving the side surface of a gate electrode (22) so as to widen upwardly, and thickening the edge portion of a gate oxide film (21) by re-oxidation. The impurity concentration of a source / drain layer under the double-angle smile oxidation structure (a region around point B) is set to the range of 4×1018 cm−3±40%.

Owner:RENESAS ELECTRONICS CORP

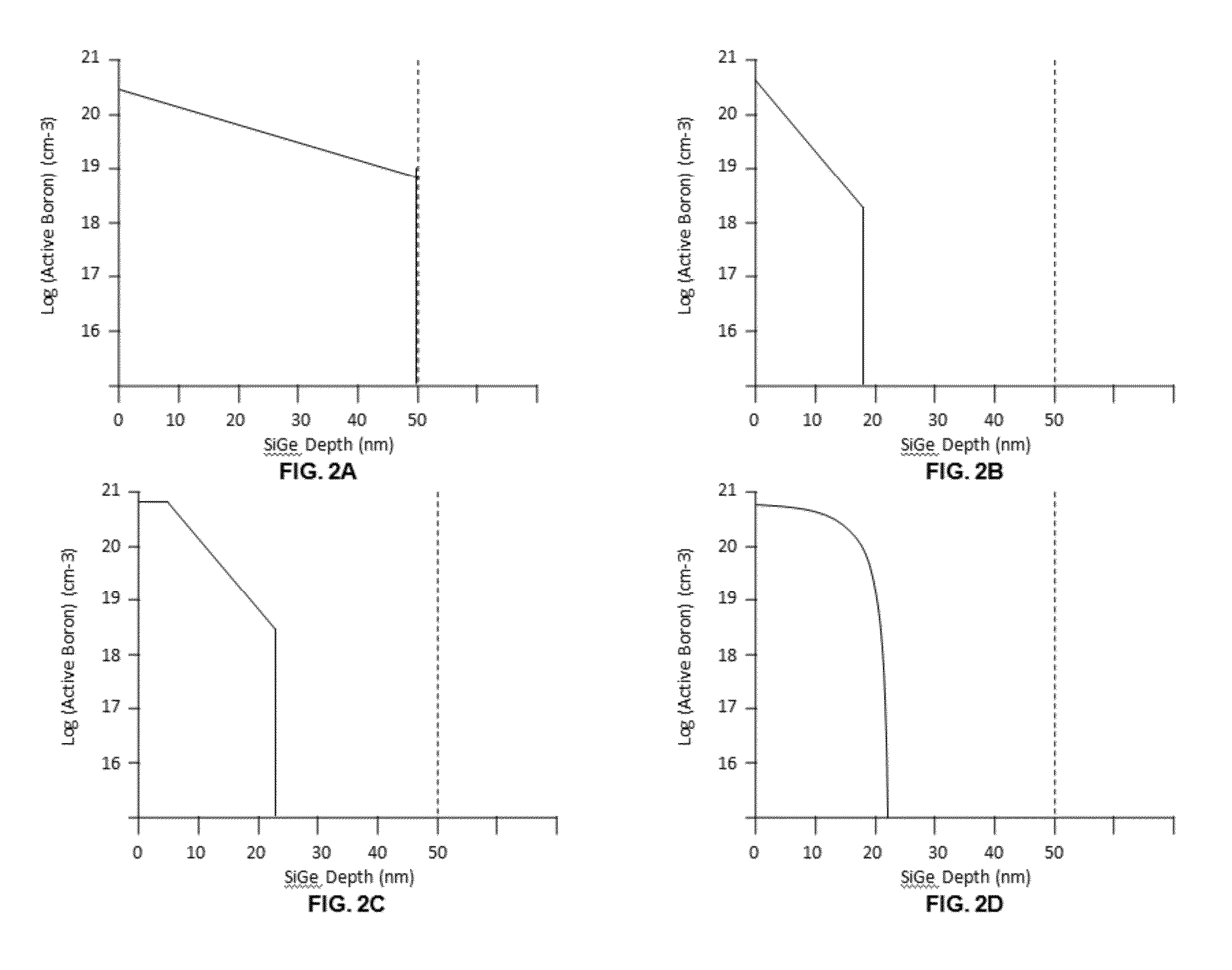

Source/drain profile engineering for enhanced p-MOSFET

ActiveUS9419082B2Reduce Overlap CapacitanceReduce junction leakageTransistorSemiconductor/solid-state device manufacturingOxide semiconductorMOSFET

P-type metal-oxide semiconductor field-effect transistors (pMOSFET's), semiconductor devices comprising the pMOSFET's, and methods of forming pMOSFET's are provided. The pMOSFET's include a silicon-germanium (SiGe) film that has a lower interface in contact with a semiconductor substrate and an upper surface, and the SiGe film has a graded boron doping profile where boron content increases upwardly over a majority of the width of boron-doped SiGe film between the lower interface of the SiGe film and the upper surface of the SiGe film. Methods of forming the pMOSFET's include: providing a semiconductor substrate; depositing a SiGe film on the semiconductor substrate, thereby forming a lower interface of the SiGe film in contact with the semiconductor substrate, and an upper surface of the SiGe film; and doping the SiGe film with boron to form a SiGe film having a graded boron doping profile where boron content increases upwardly over a majority of the width of boron-doped SiGe film between the lower interface of the SiGe film and the upper surface of the SiGe film.

Owner:GLOBALFOUNDRIES US INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com