Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

49results about How to "Increase gate capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

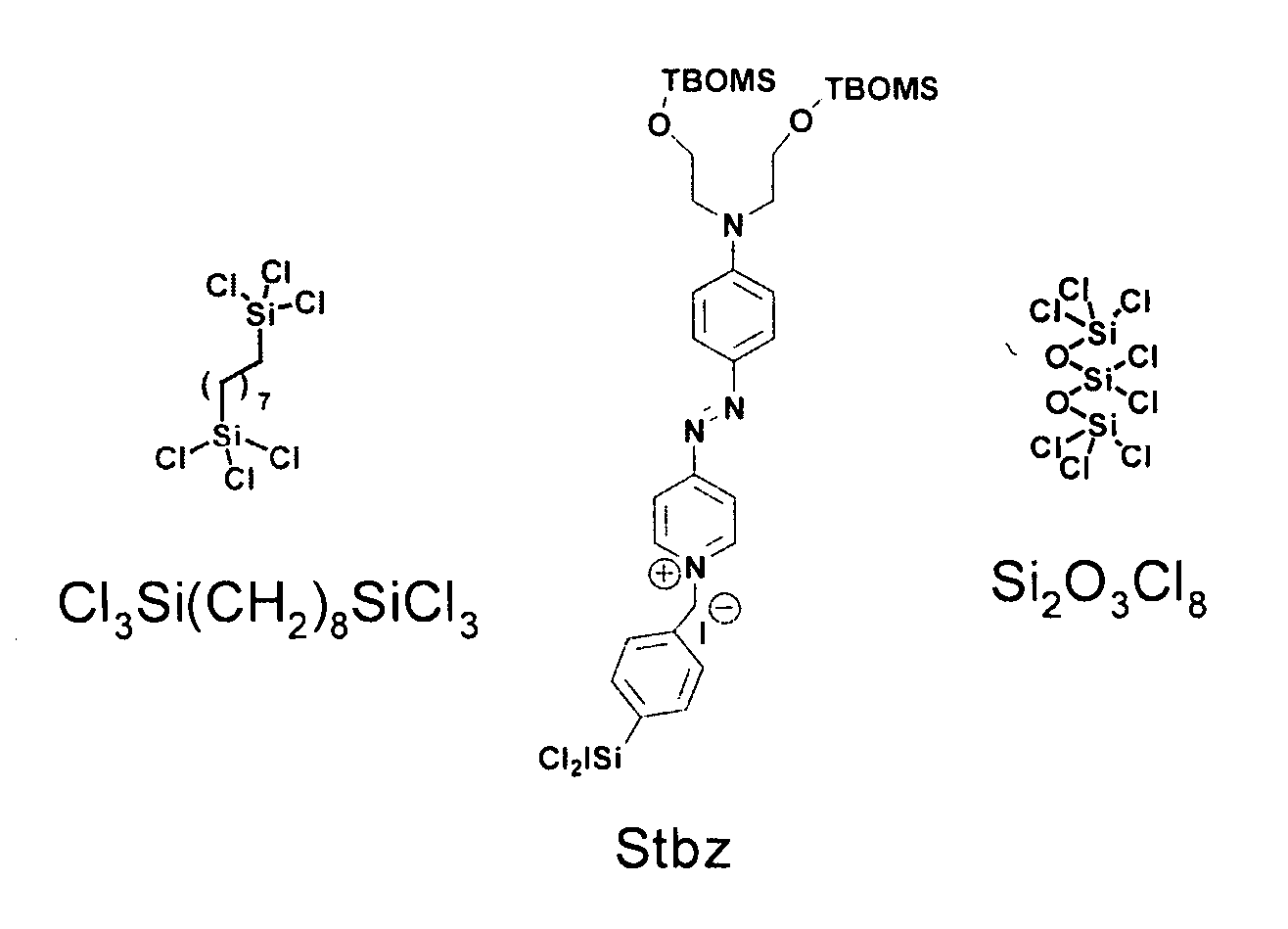

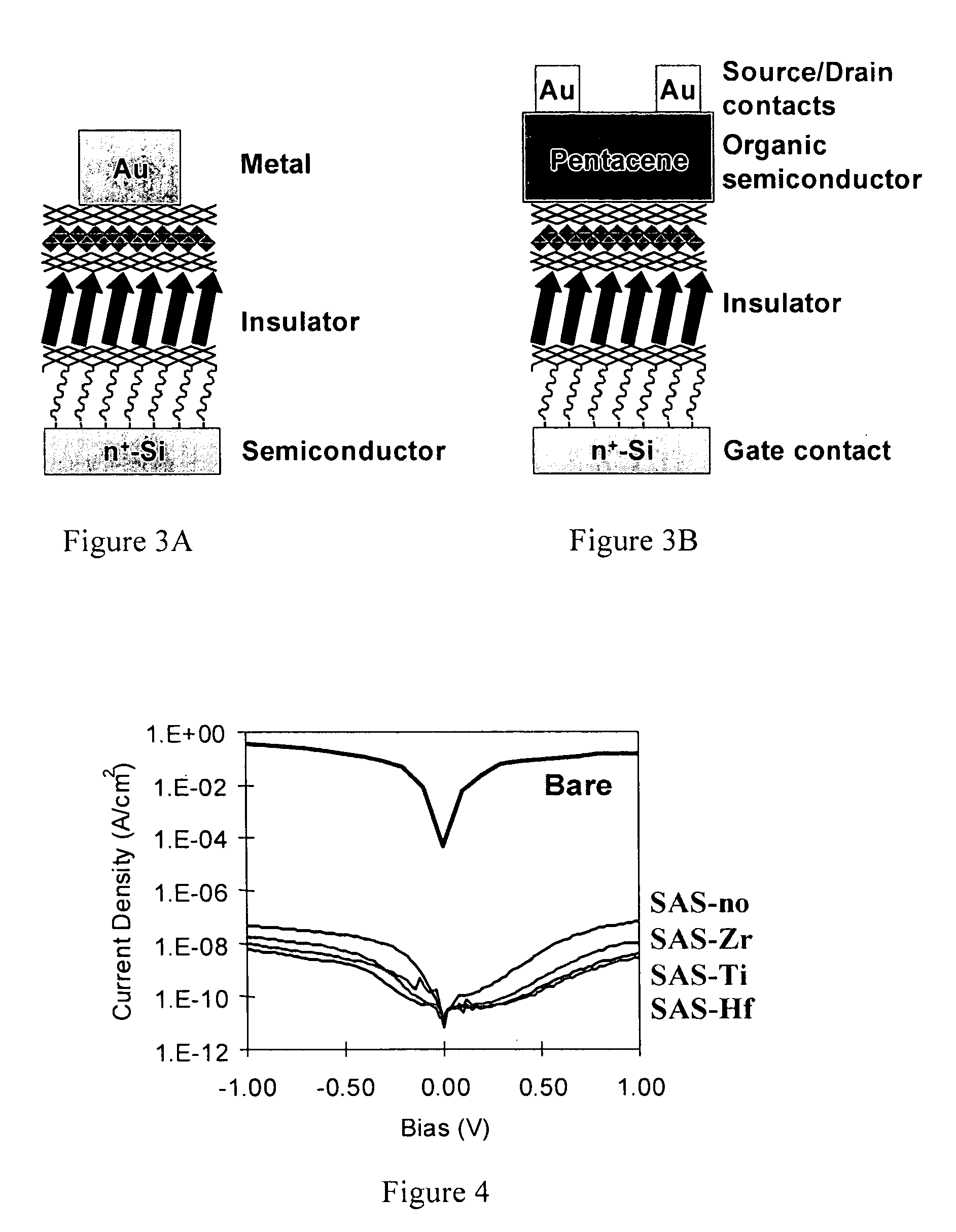

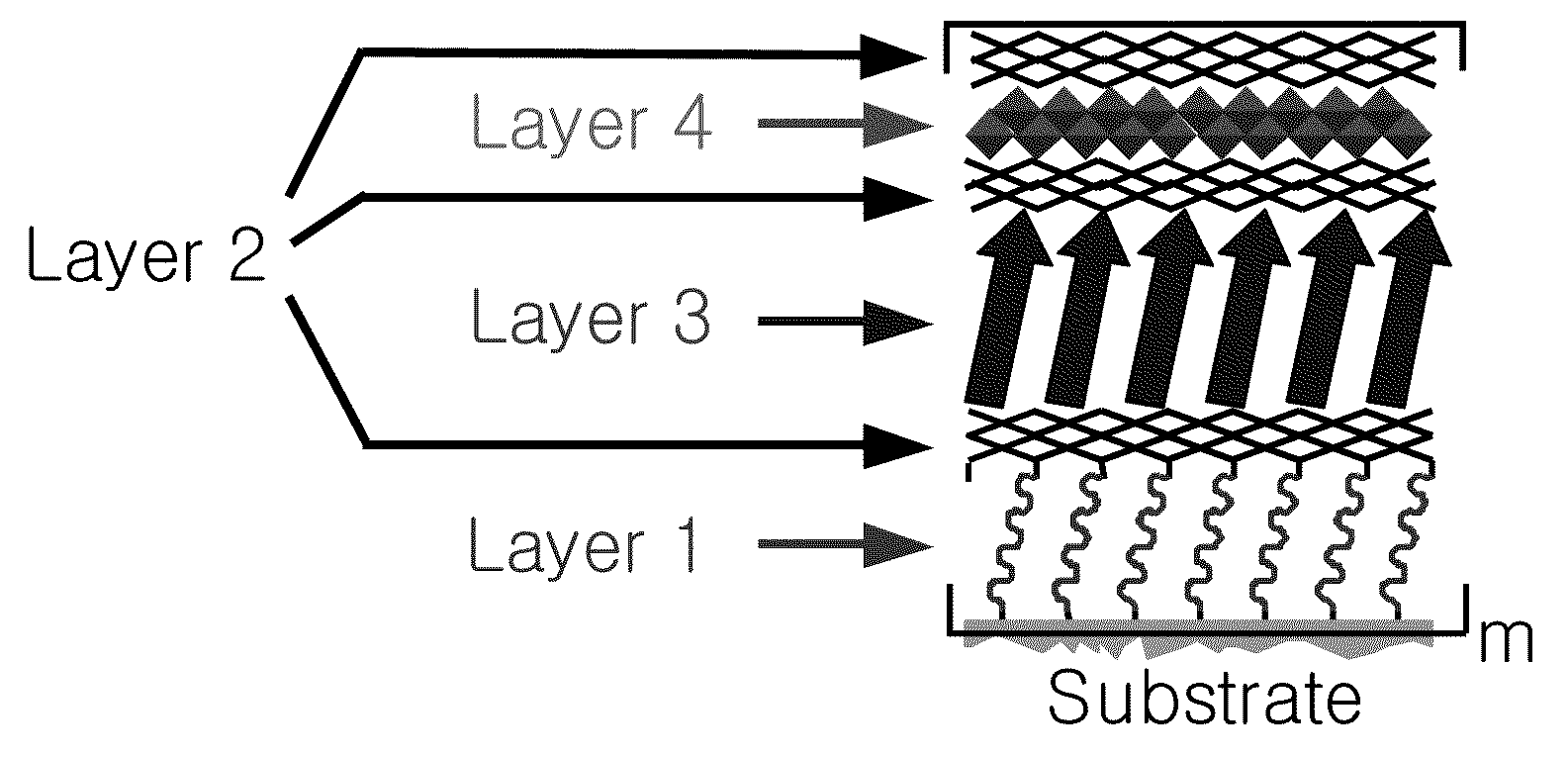

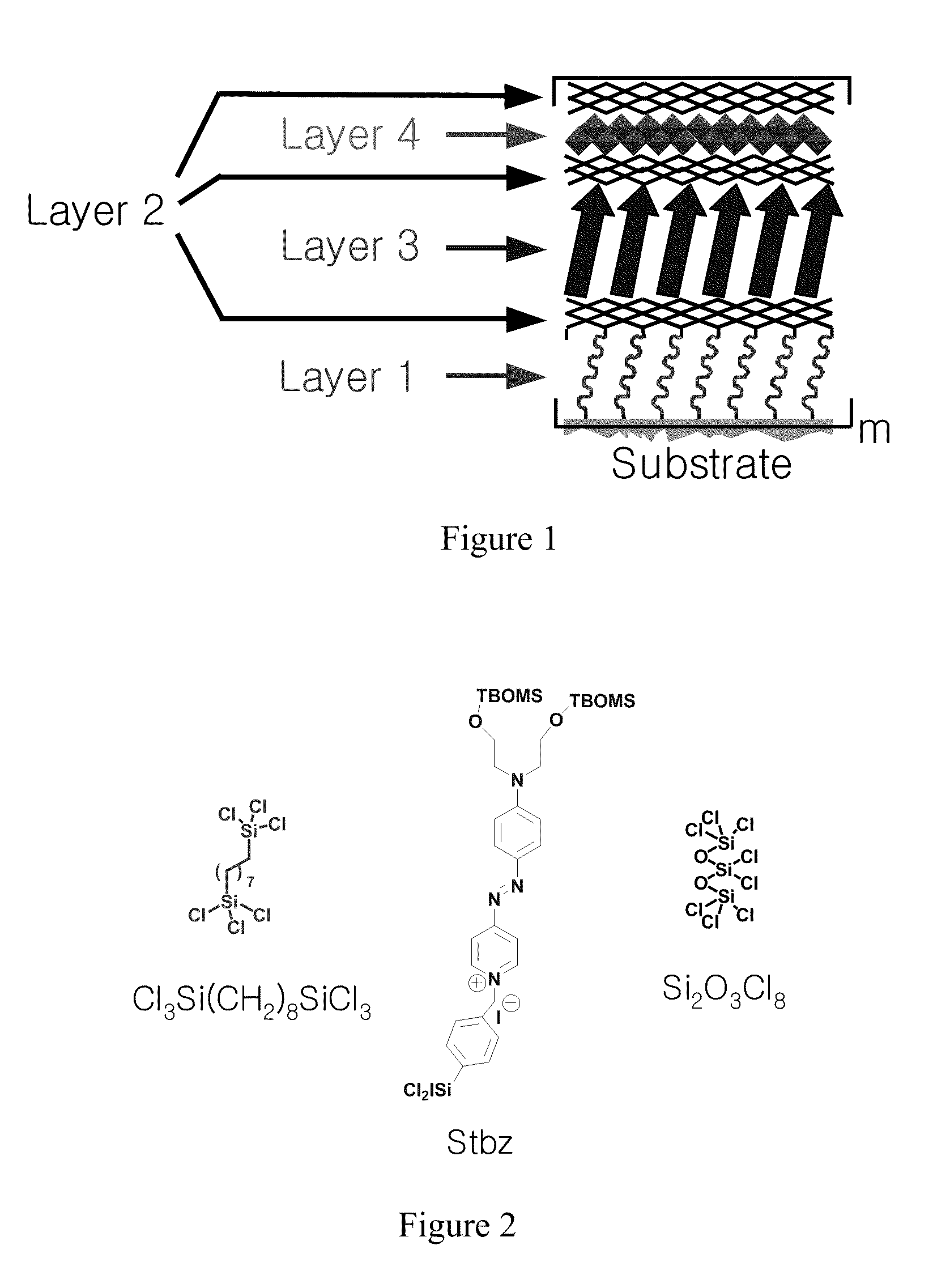

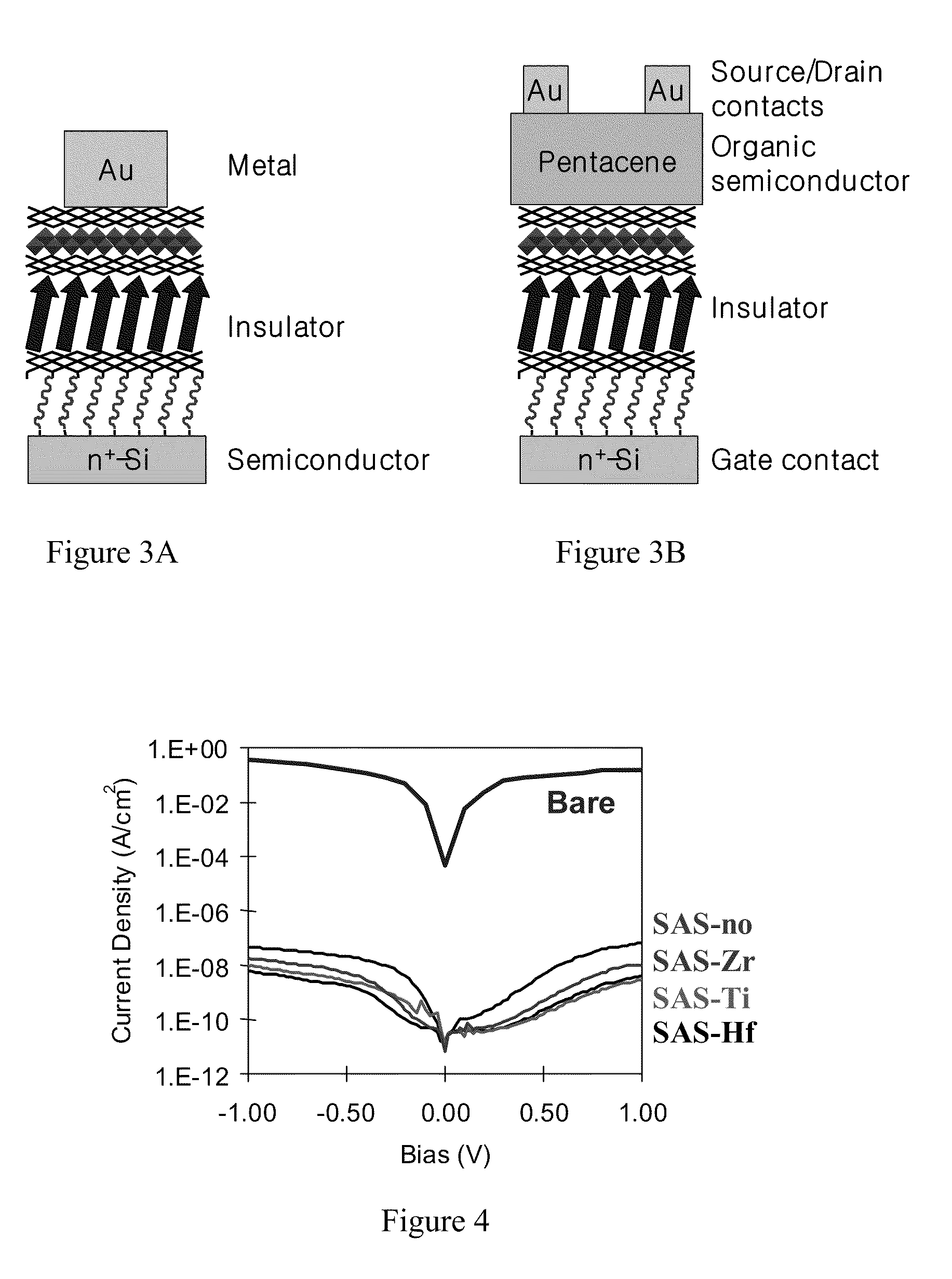

Intercalated superlattice compositions and related methods for modulating dielectric property

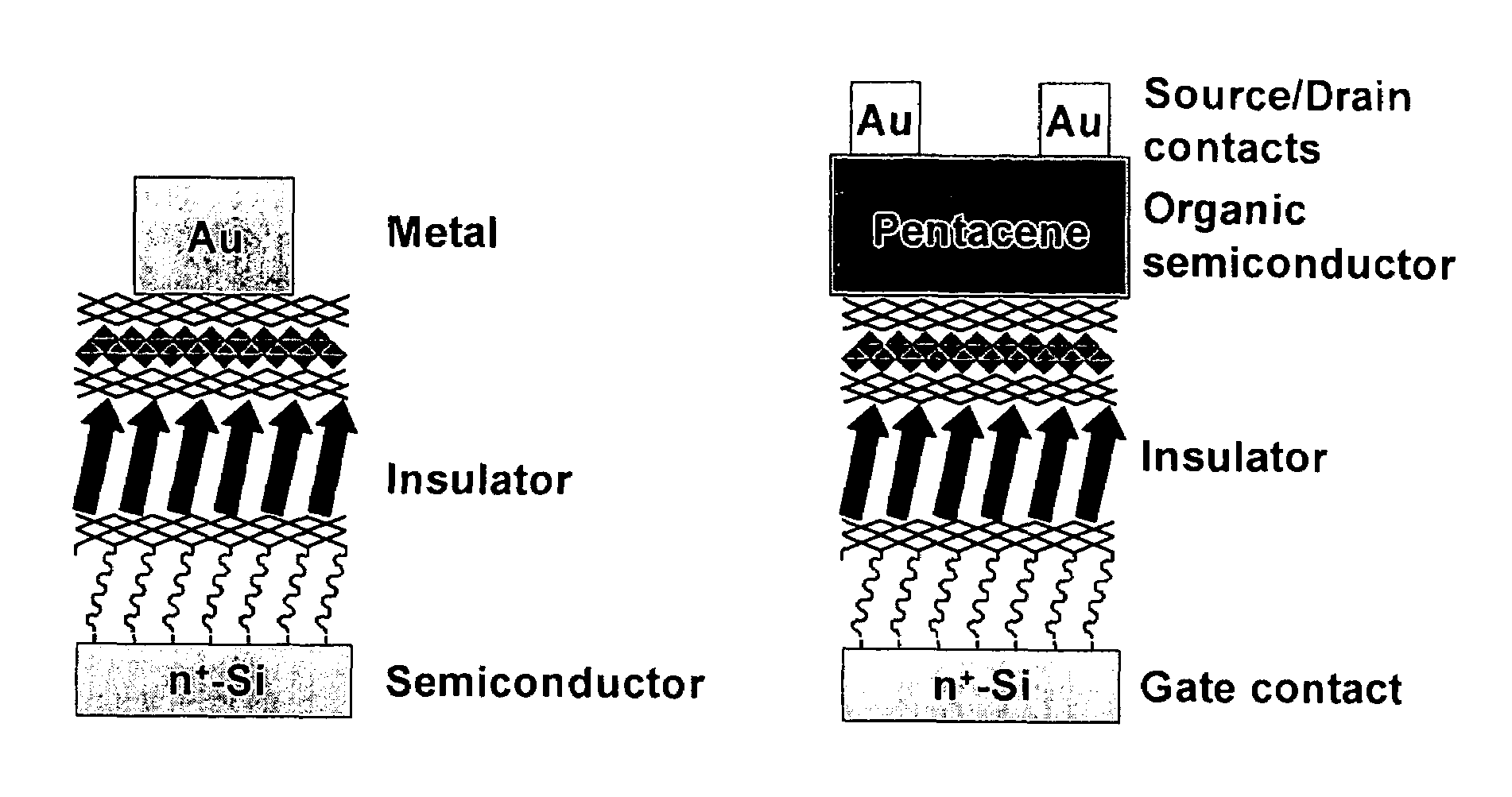

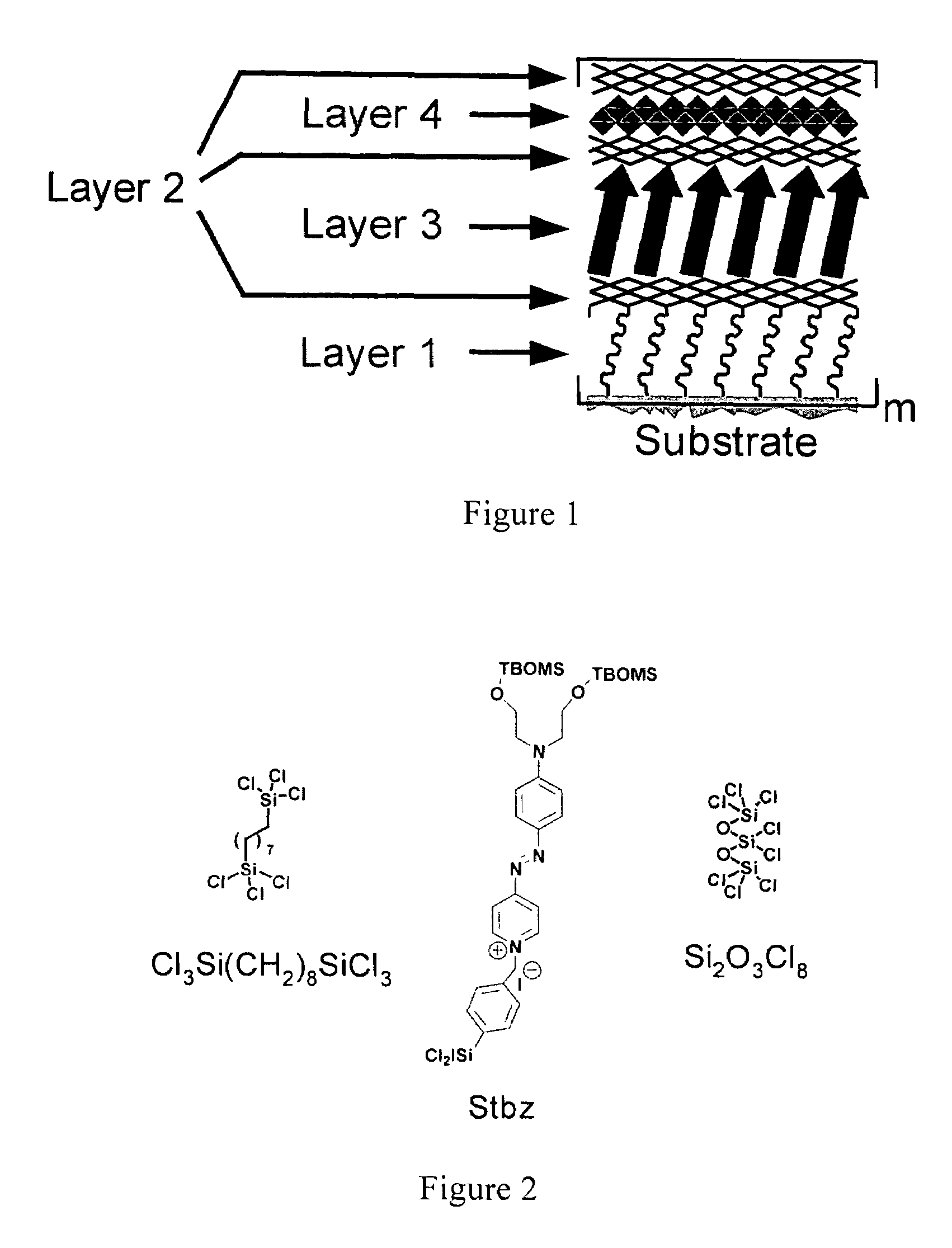

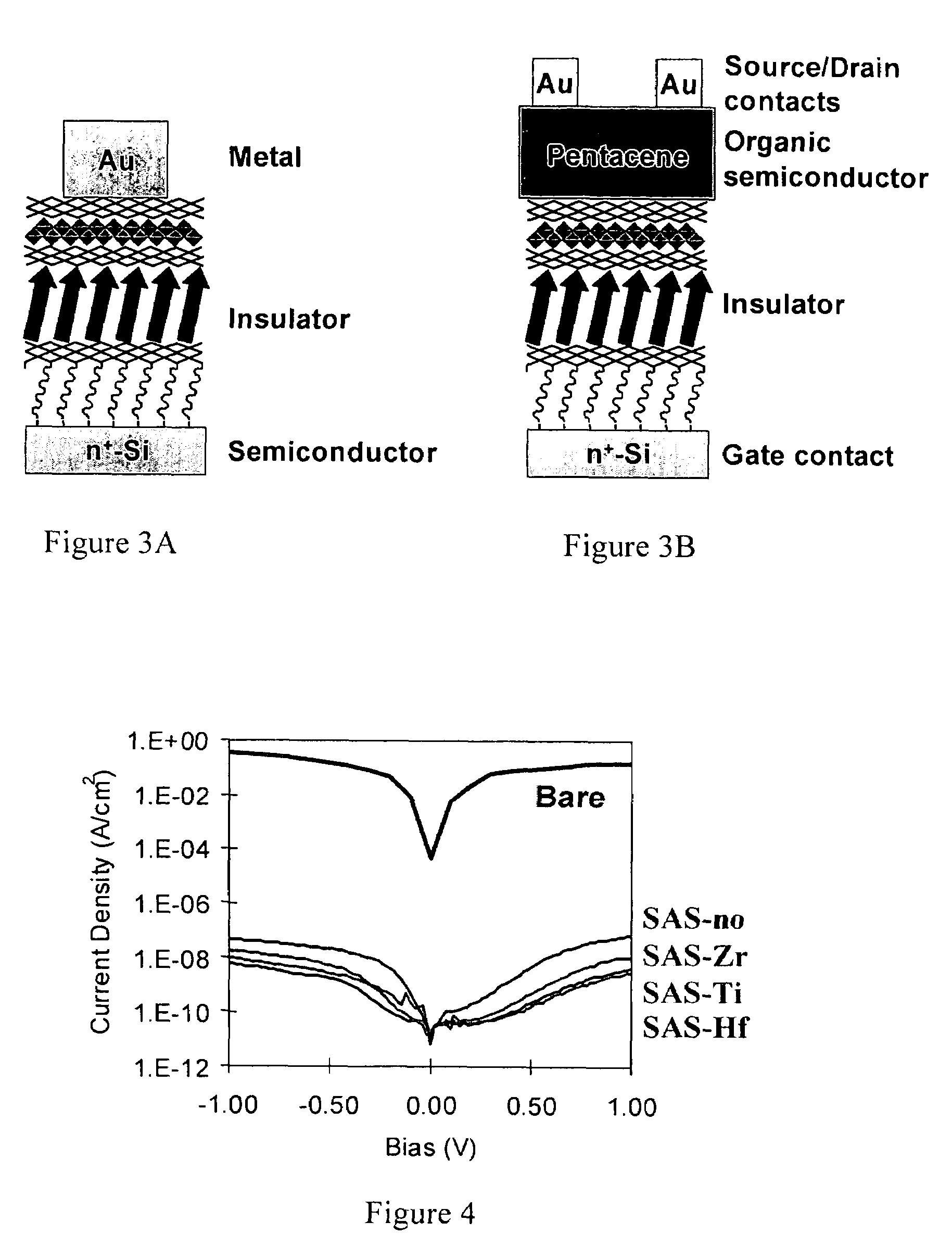

ActiveUS20070181961A1Low working voltageDrain current increasesMaterial nanotechnologyLiquid surface applicatorsDielectricSuperlattice

Compositions, methods of using inorganic moieties for dielectric modulation, and related device structures.

Owner:NORTHWESTERN UNIV

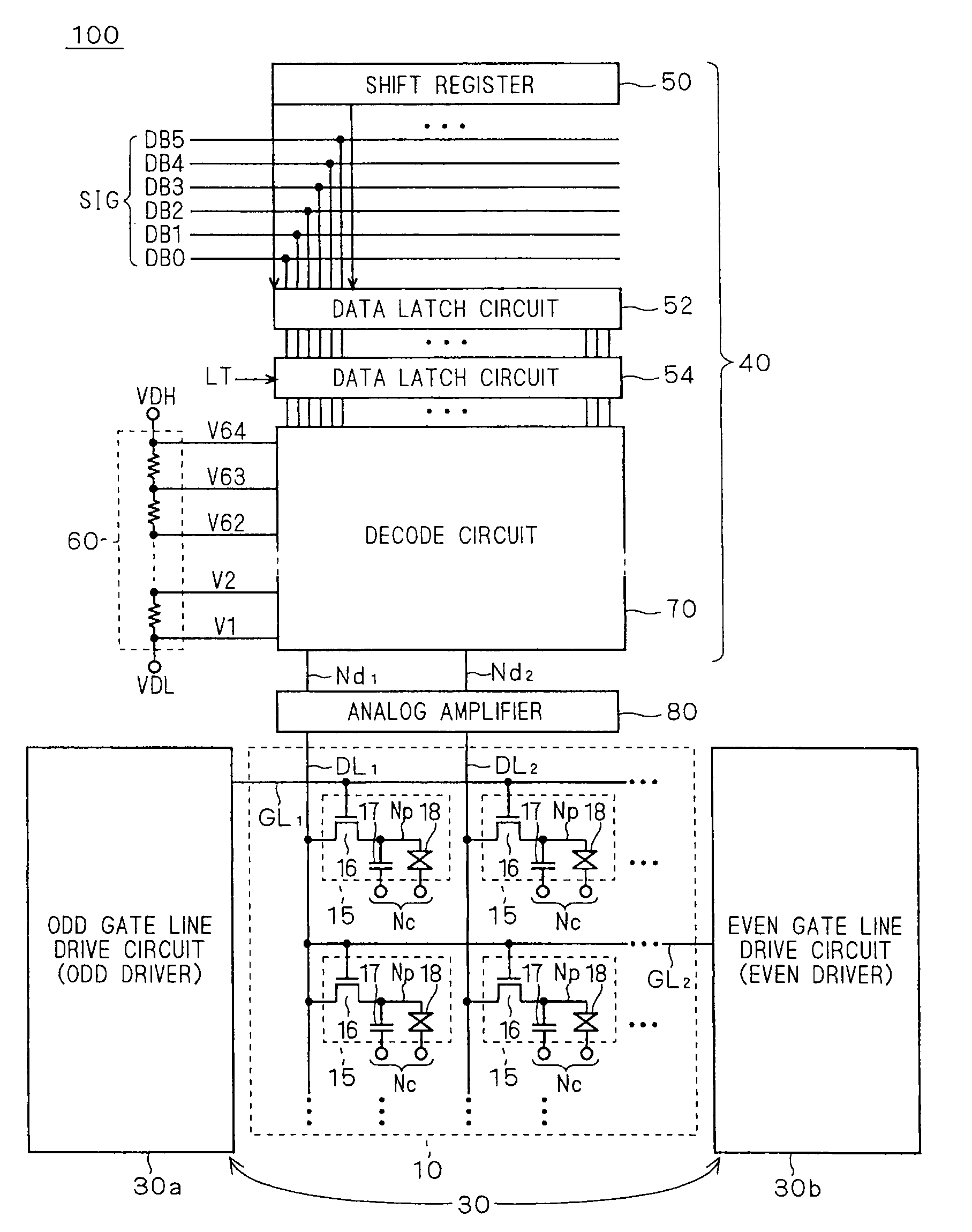

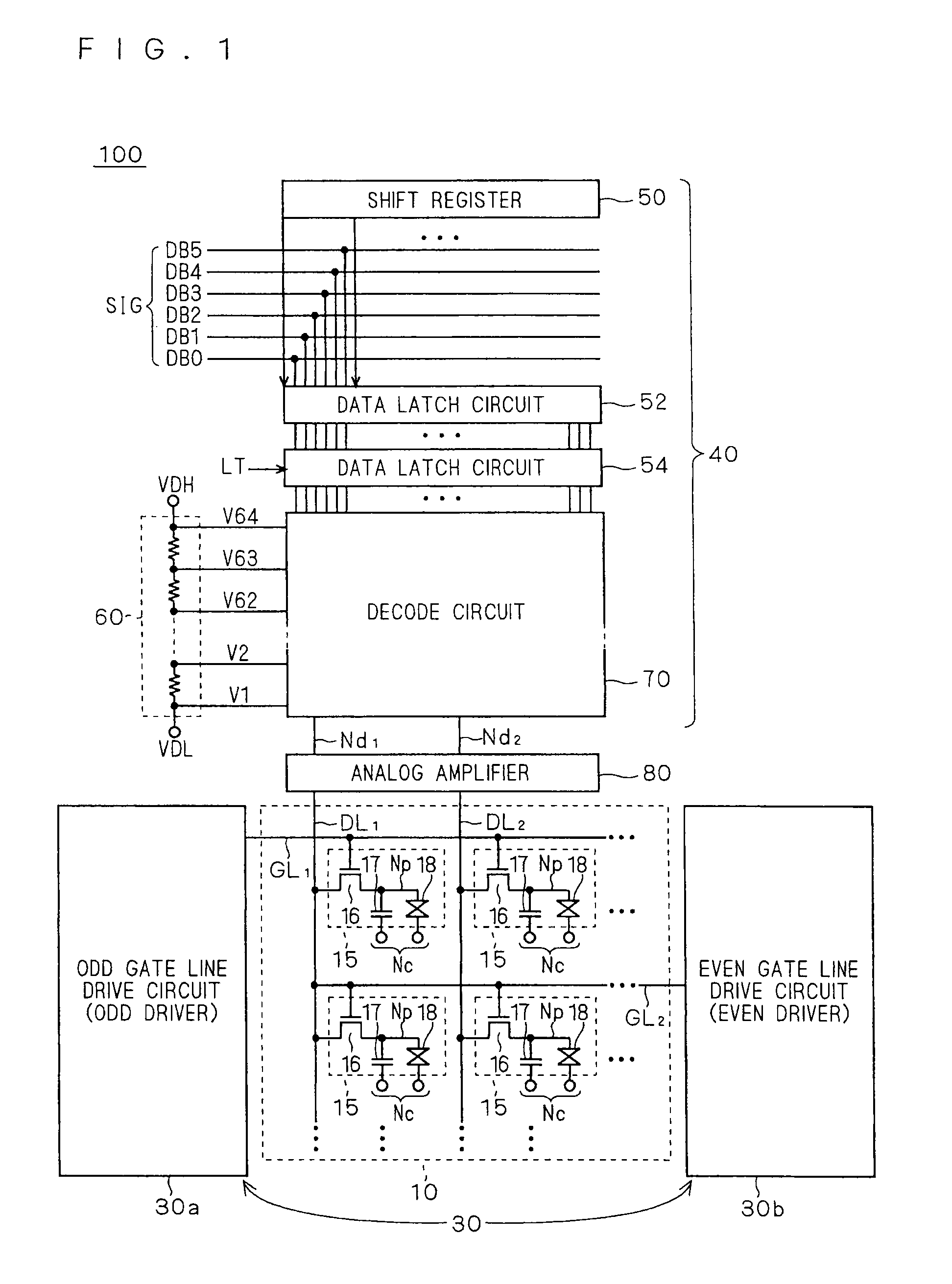

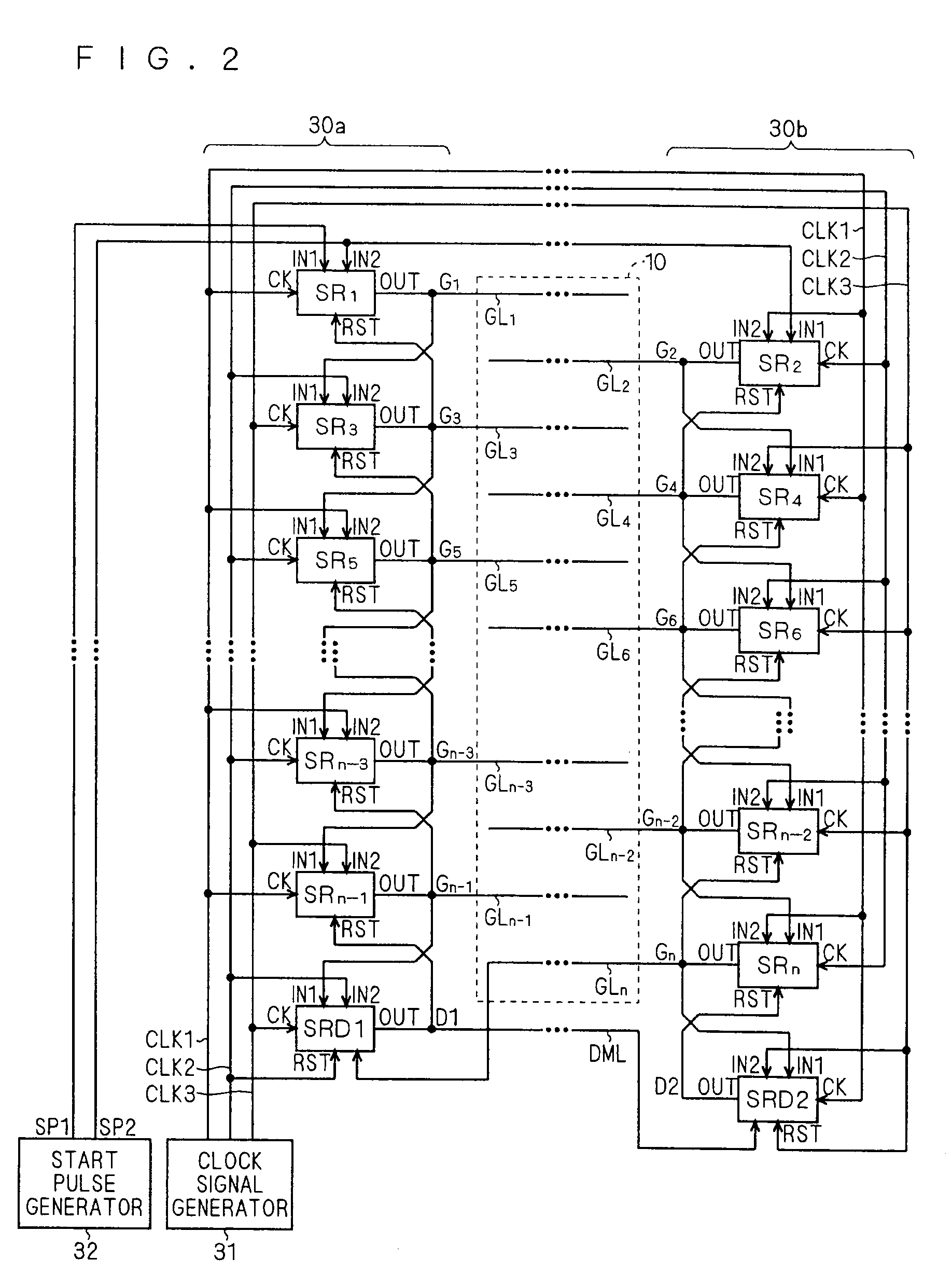

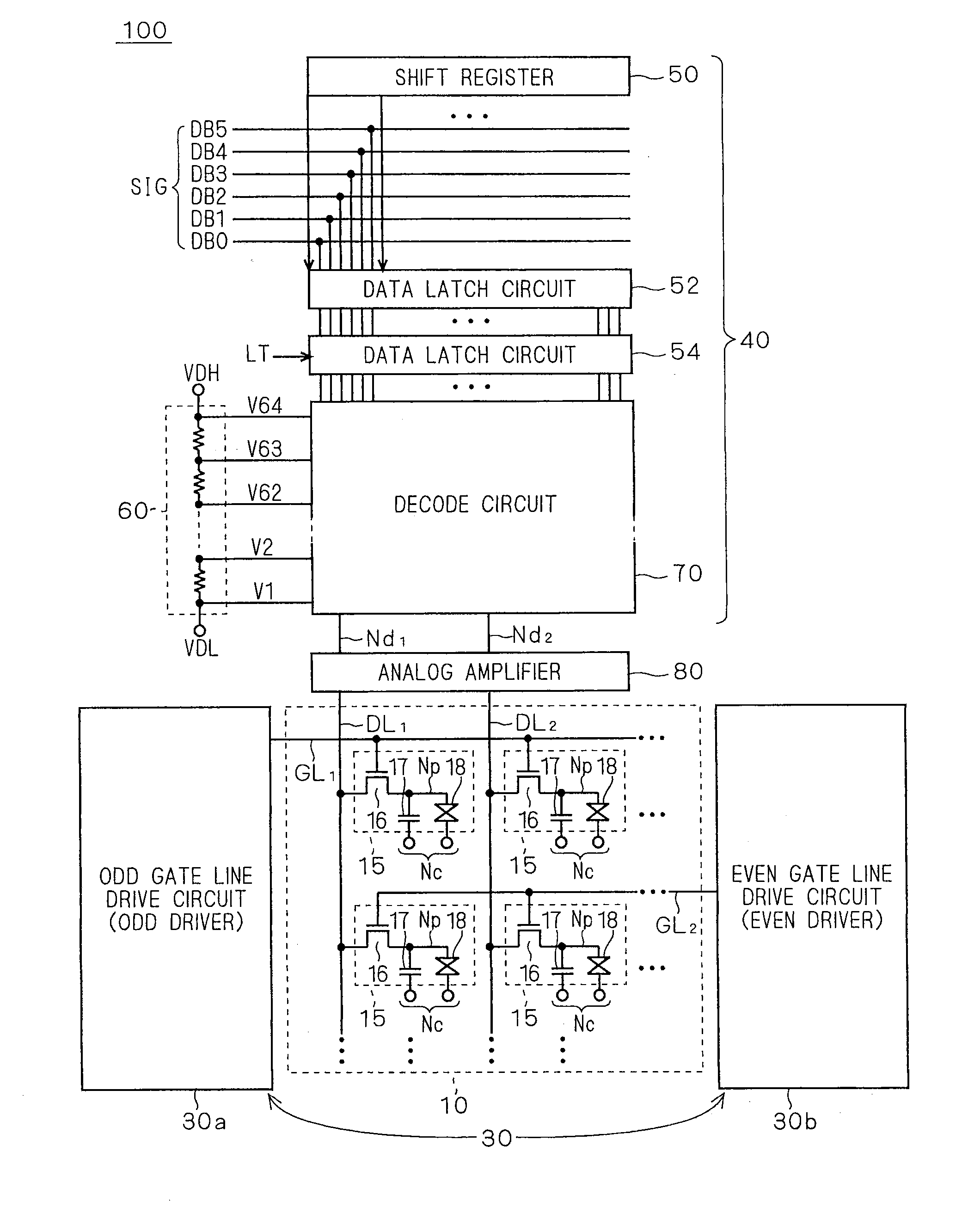

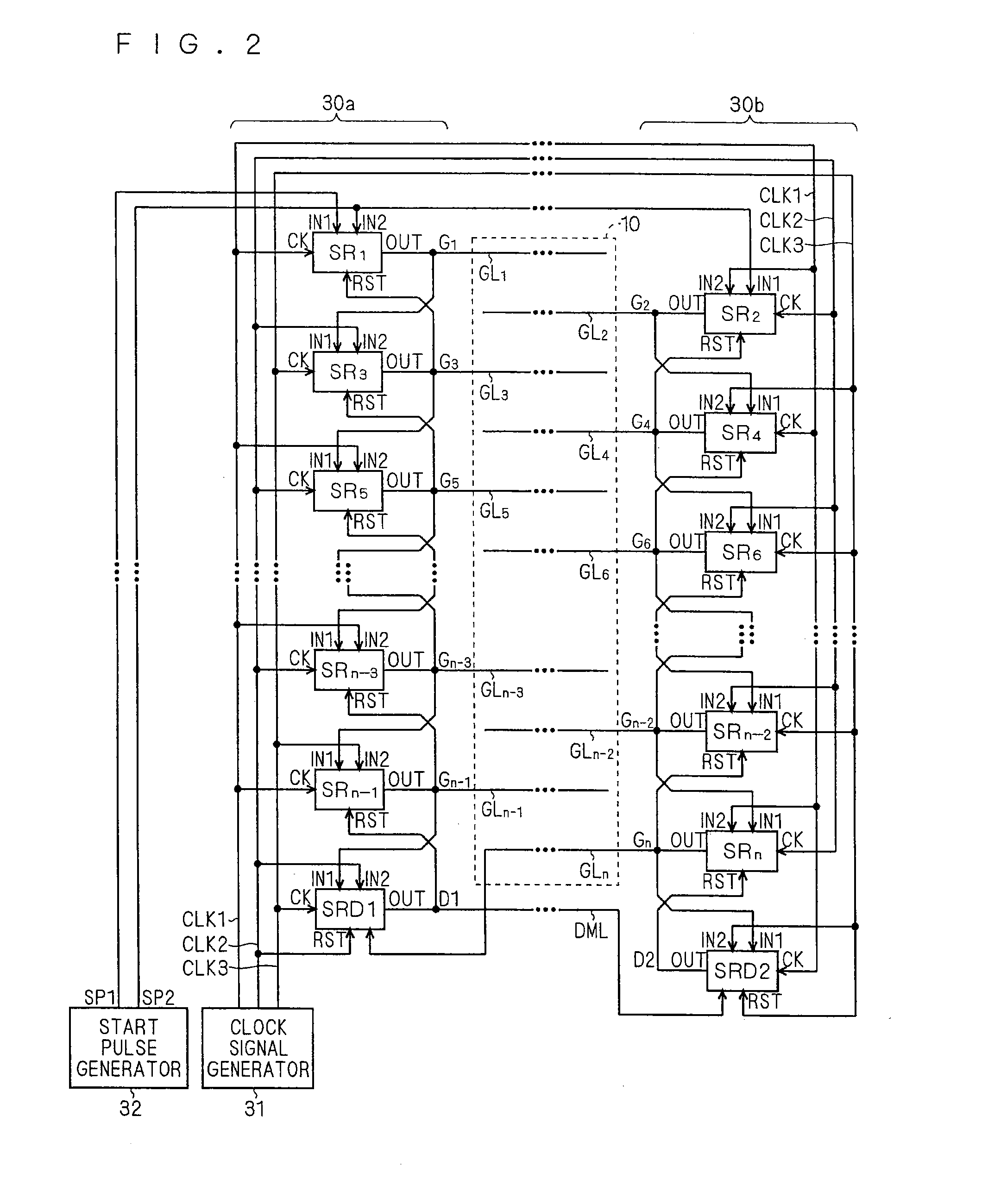

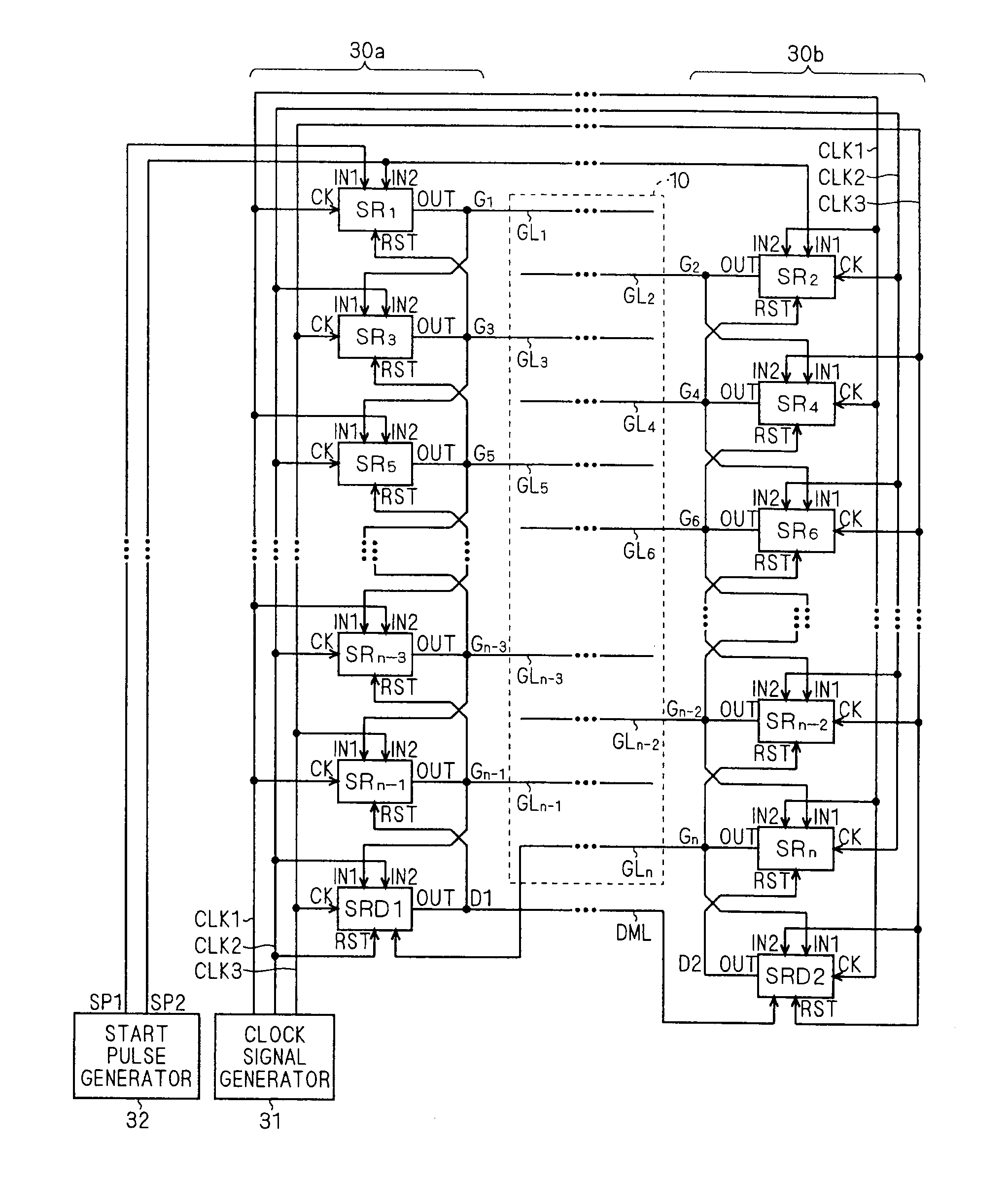

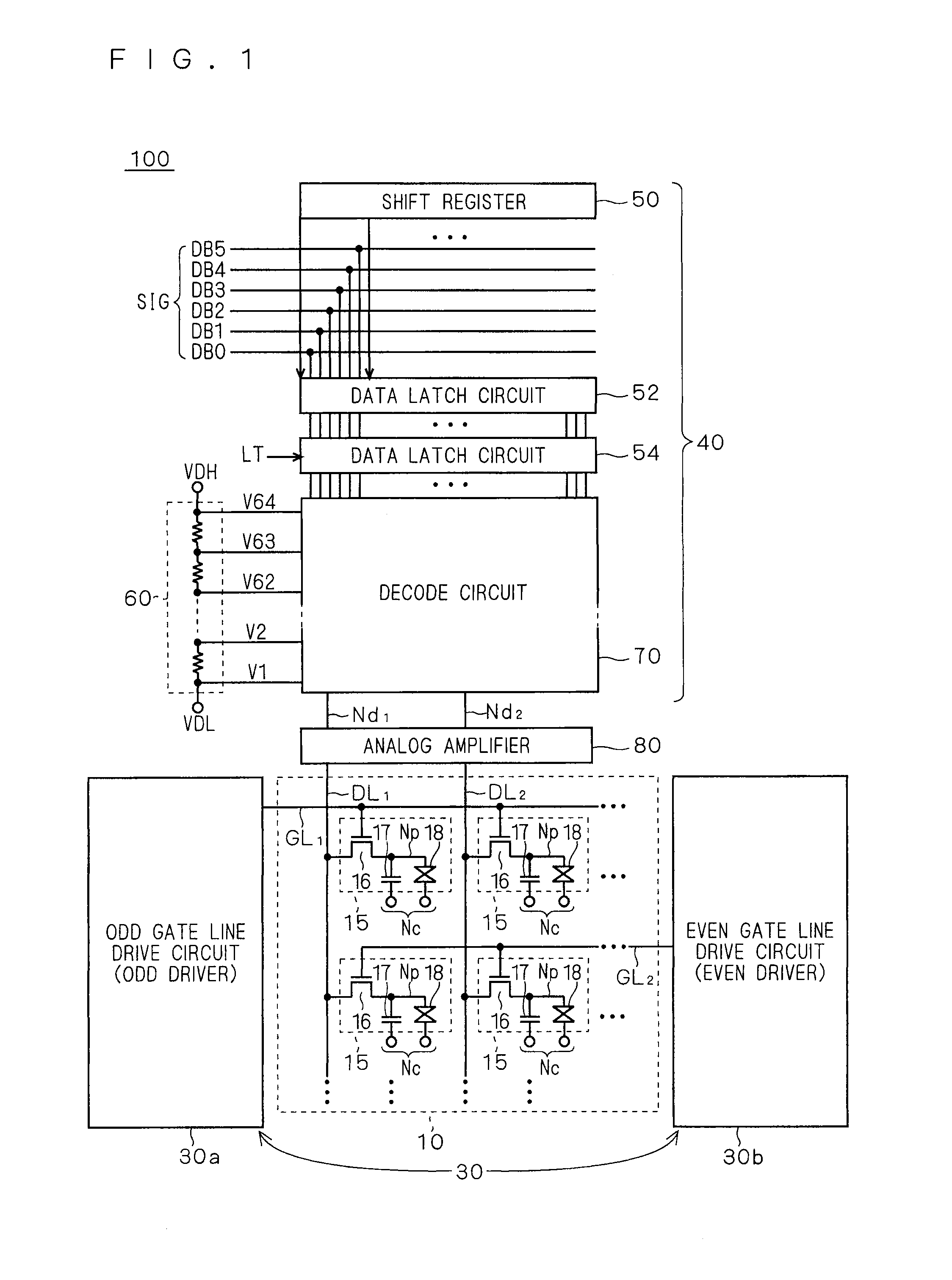

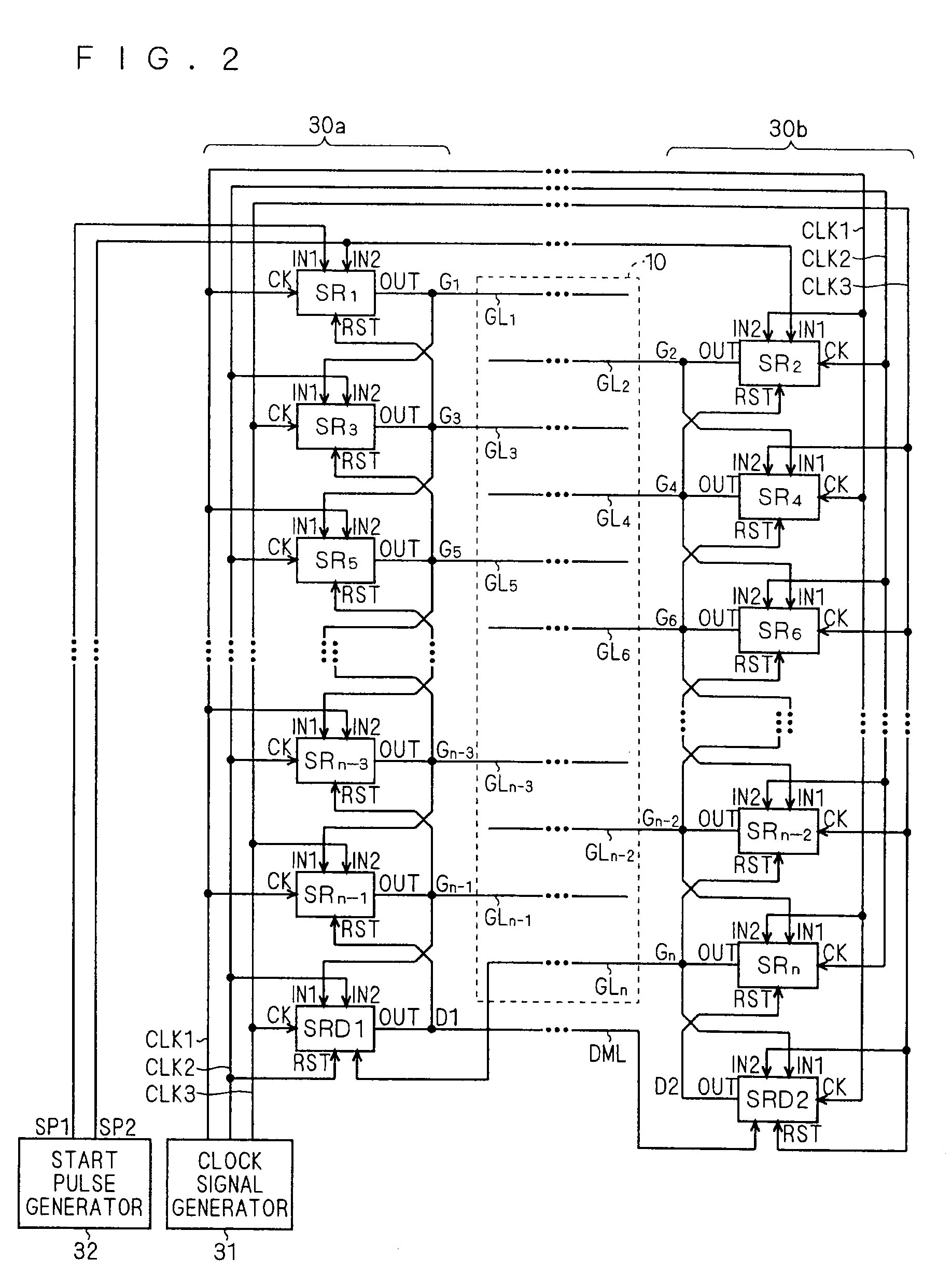

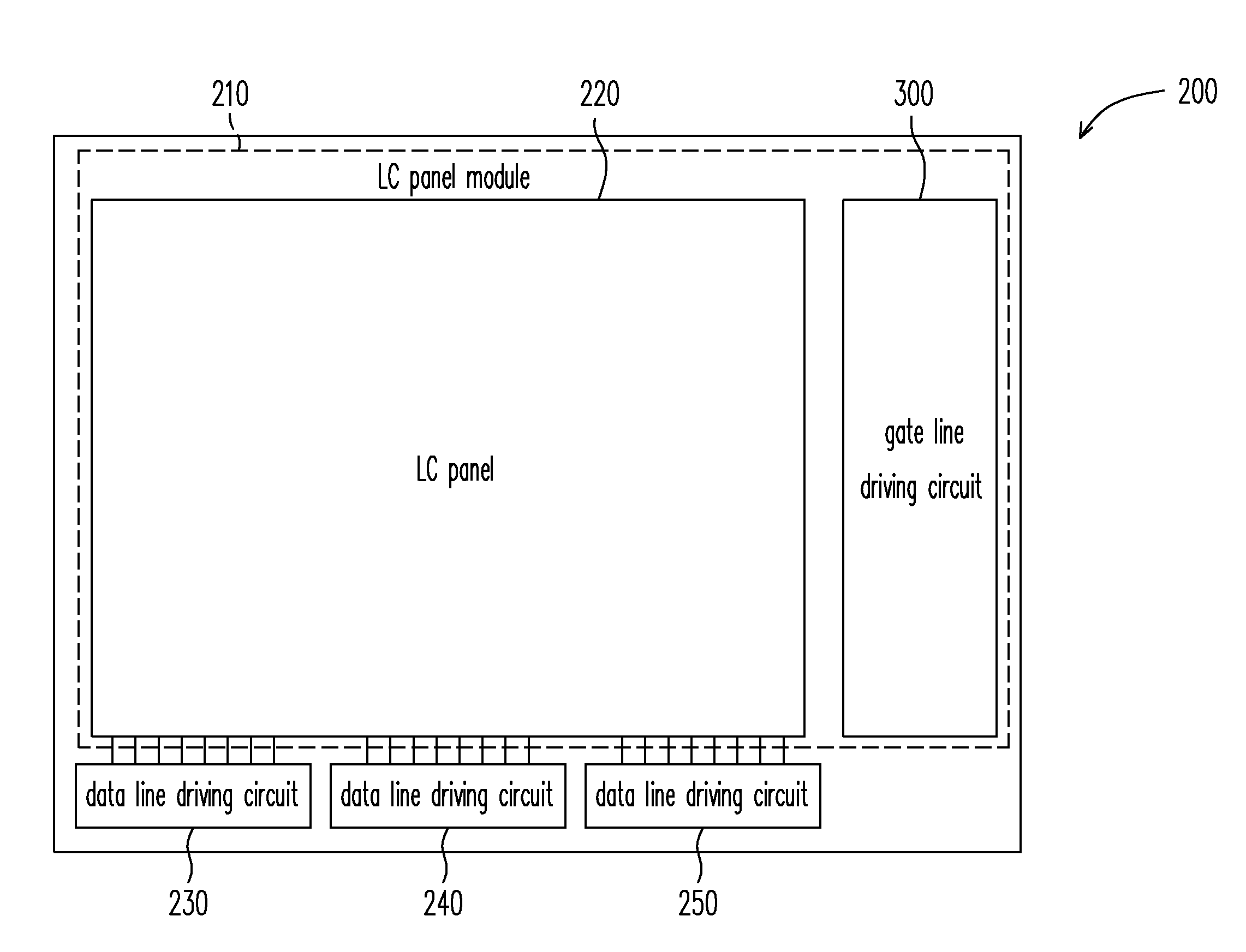

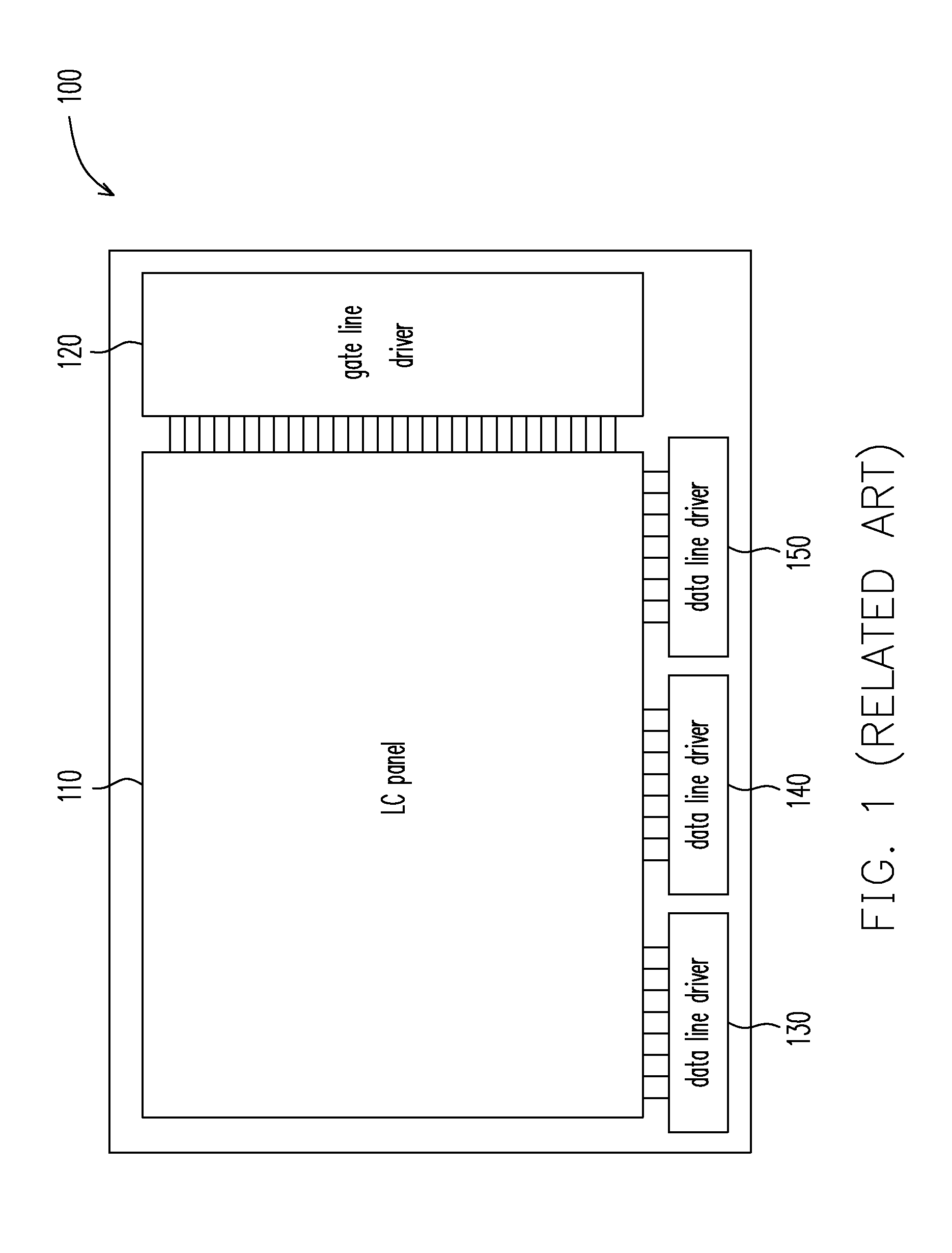

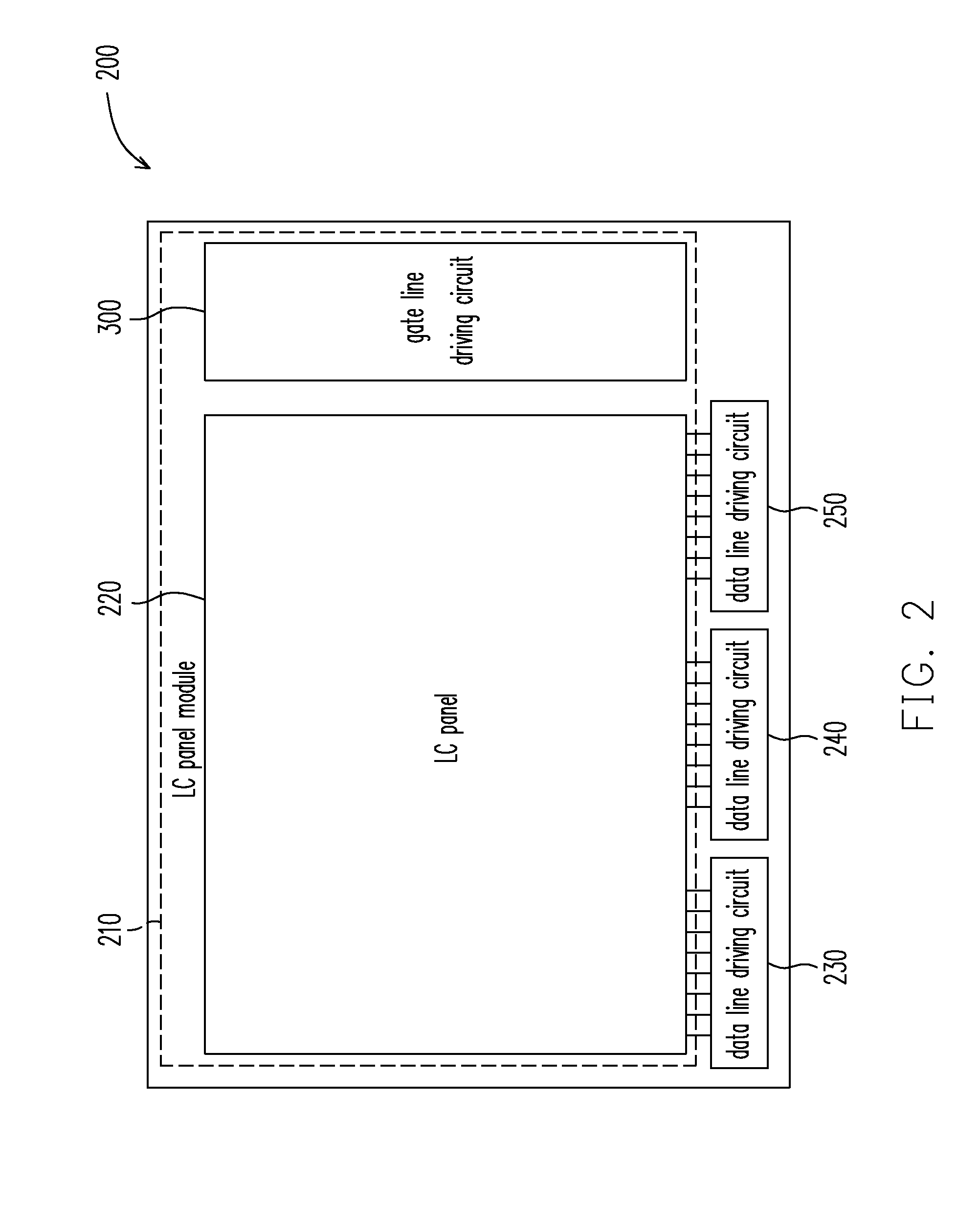

Electro-optical device, shift register circuit, and semiconductor device

ActiveUS20100201666A1Inhibition of rising speedIncrease delayElectric analogue storesCathode-ray tube indicatorsShift registerDevice material

An electro-optical device is configured to be capable of using a region of a gate line drive circuit efficiently and preventing rising speed of a gate line selection signal from decreasing (rising delay), and a shift register circuit is composed of a single conductivity type transistor which is suitable for the device. The gate line drive circuit including an odd driver to drive odd rows of a plurality of gate lines, and an even driver to drive even rows thereof. Each unit shift register in the odd and even drivers receives a selection signal in the second previous row and activates its own selection signal two horizontal periods later. A start pulse of the even driver is delayed in phase by one horizontal period with respect to a start pulse of the odd driver.

Owner:TRIVALE TECH LLC

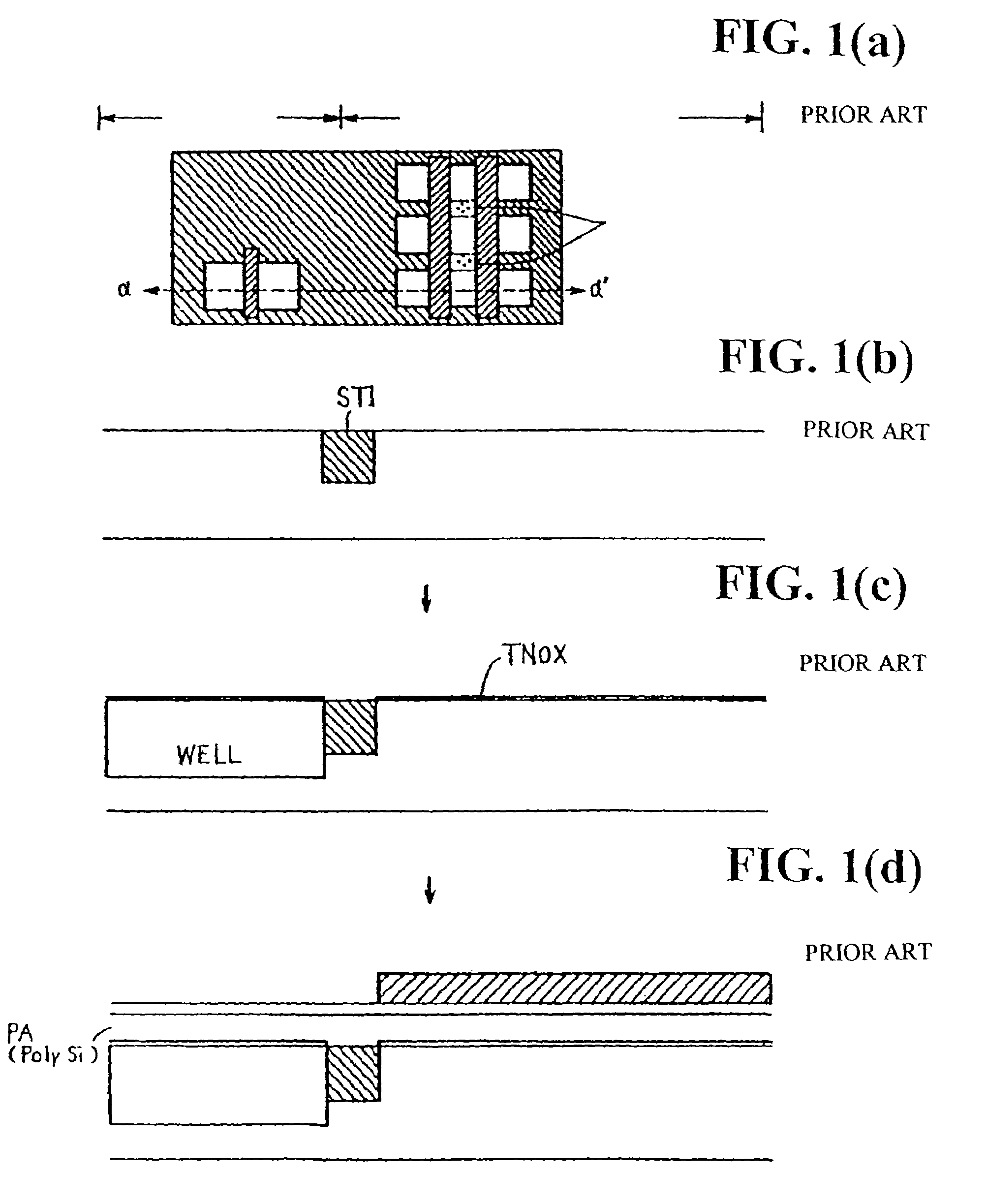

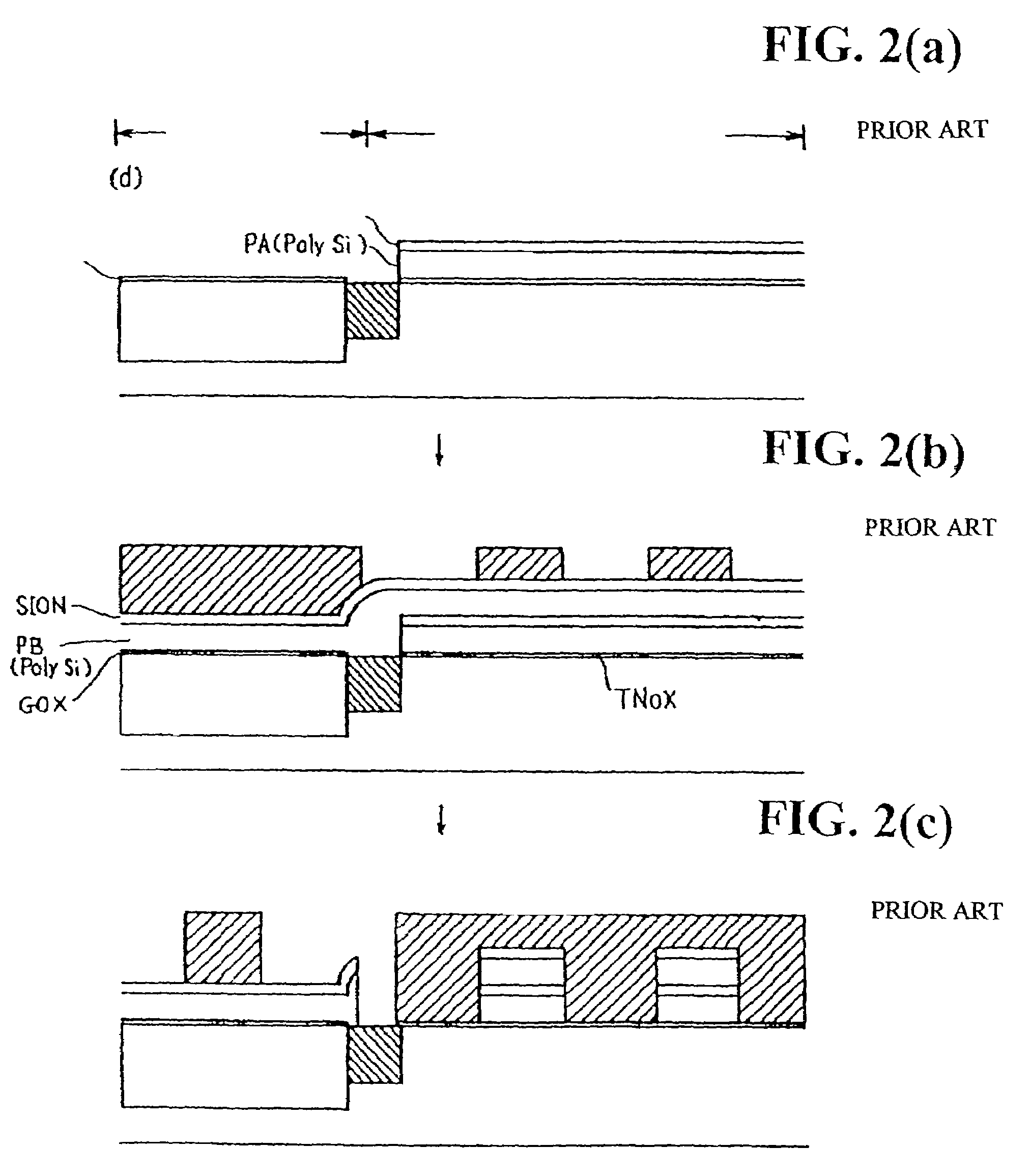

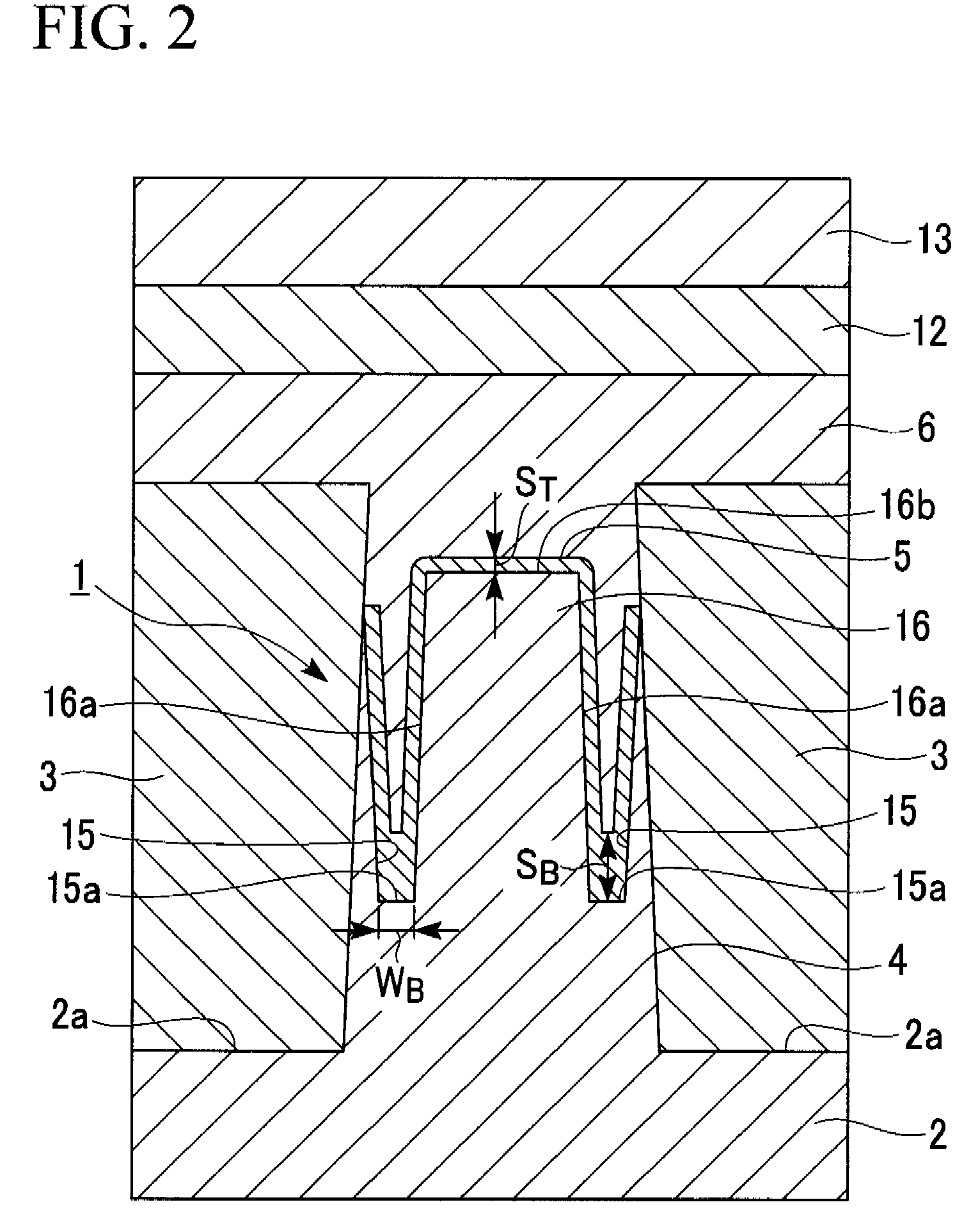

Semiconductor device and its manufacturing method

InactiveUS7476582B2Easy to integrateImprove reliabilityTransistorSolid-state devicesCell regionEngineering

A non-volatile semiconductor memory device which simultaneously possesses a non-volatile memory cell region which possesses an isolating insulation film which has been formed selectively within a semiconductor substrate, which also possesses a first electroconductive film (floating gate electrode) via a first gate insulating film which has been formed on the semiconductor substrate surface, and which also possesses a metal film (control gate electrode) via a second gate insulating film which has been formed above said electroconductive film and a peripheral transistor region which possesses a metal film (gate electrode) via a third gate insulating film which has been formed above the semiconductor substrate surface.

Owner:FUJITSU SEMICON LTD

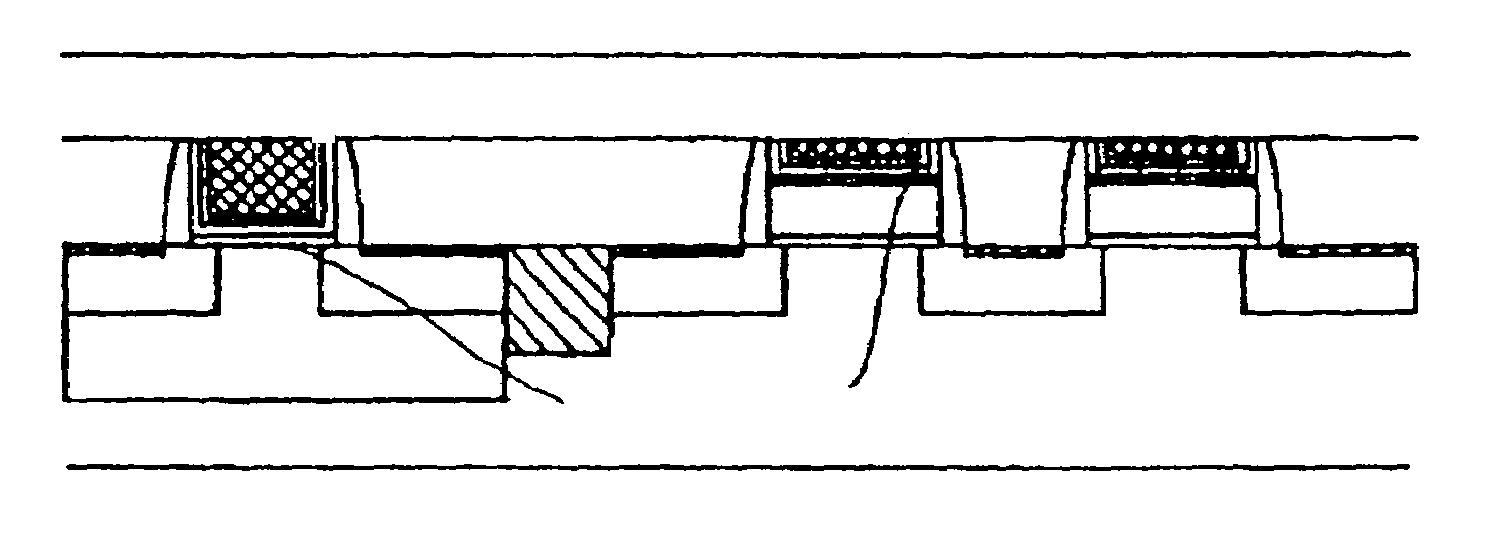

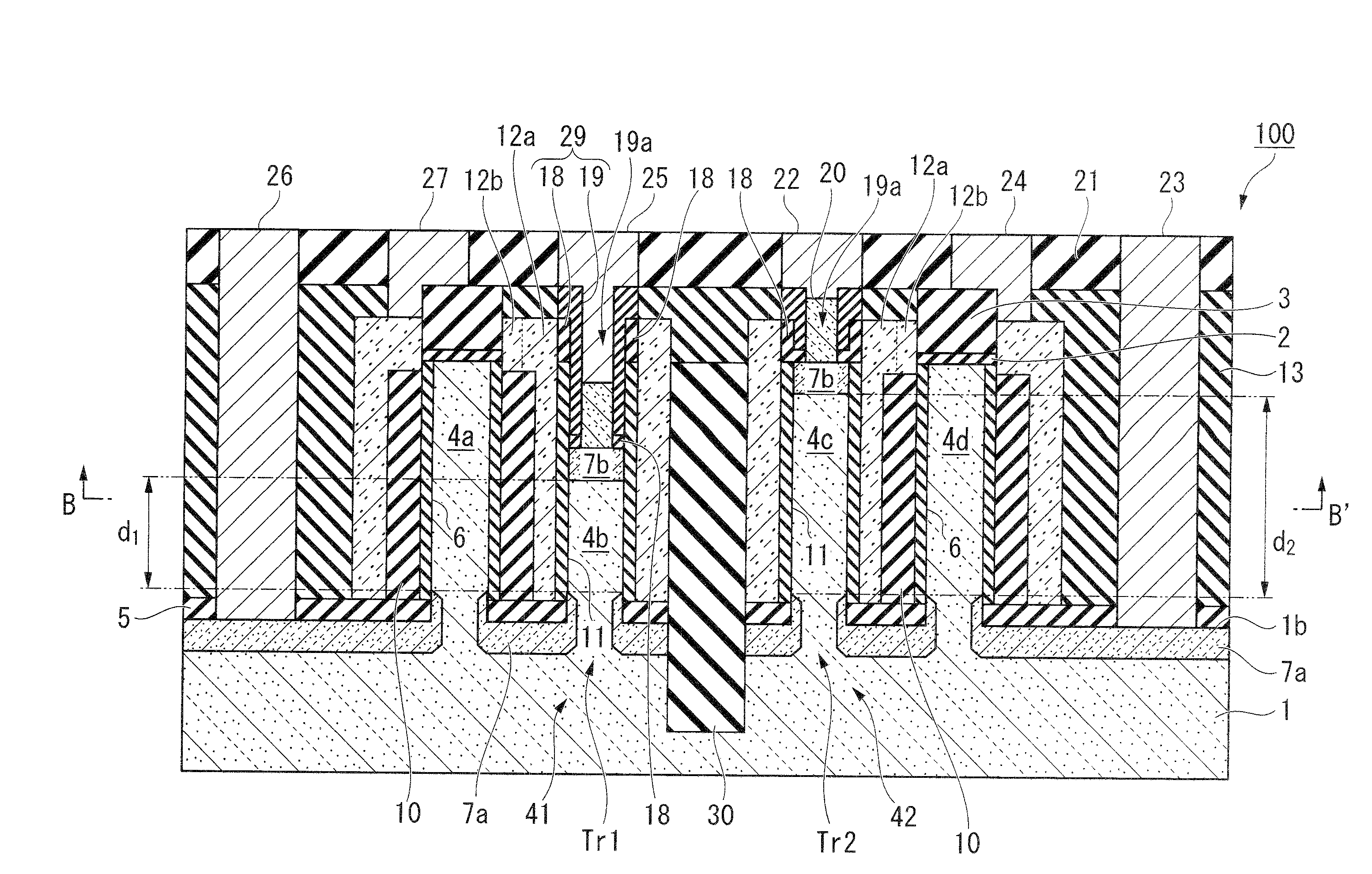

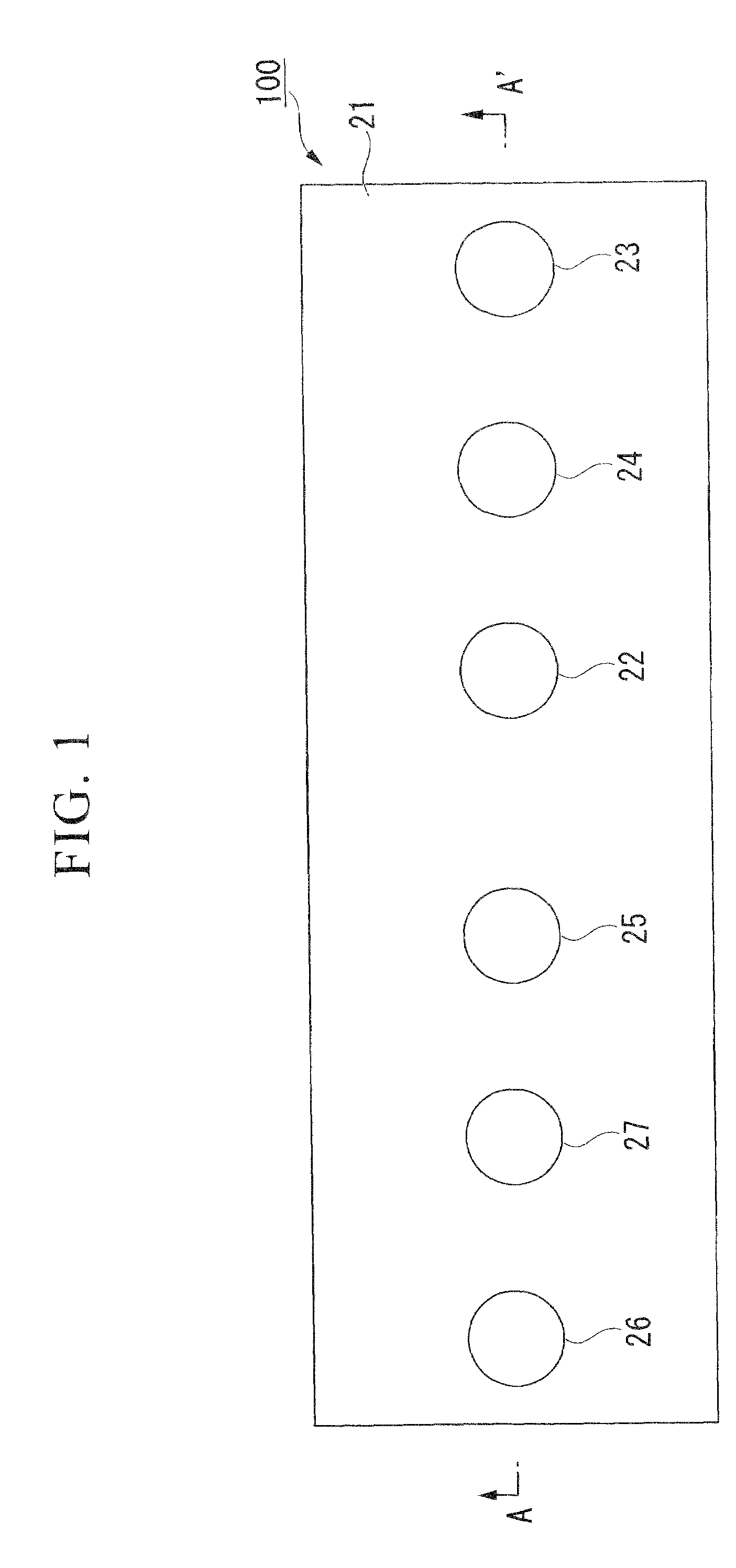

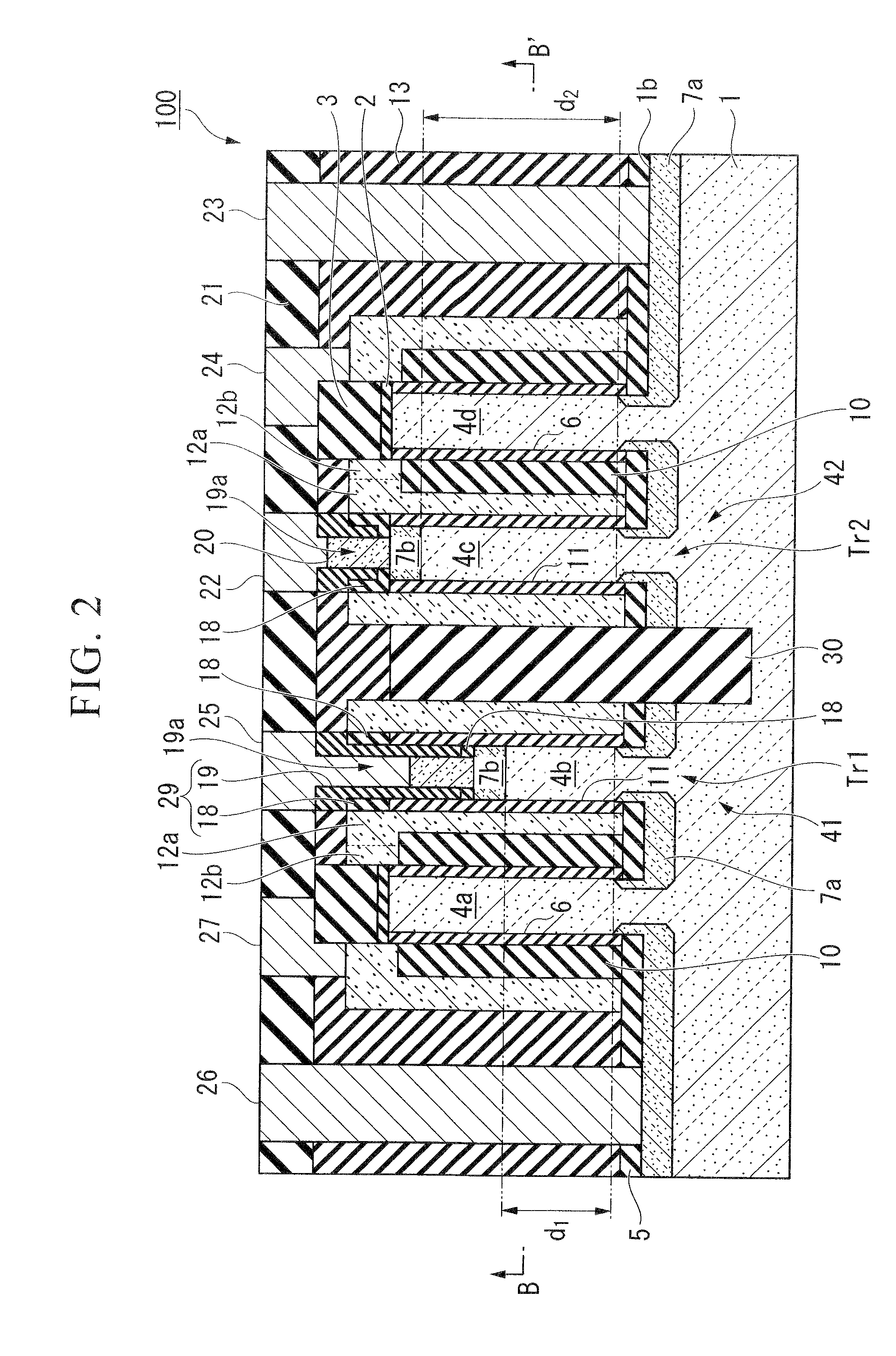

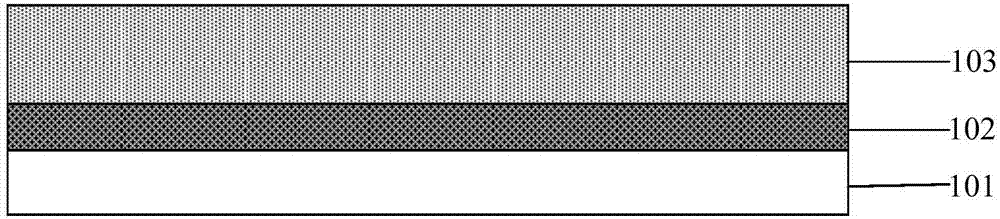

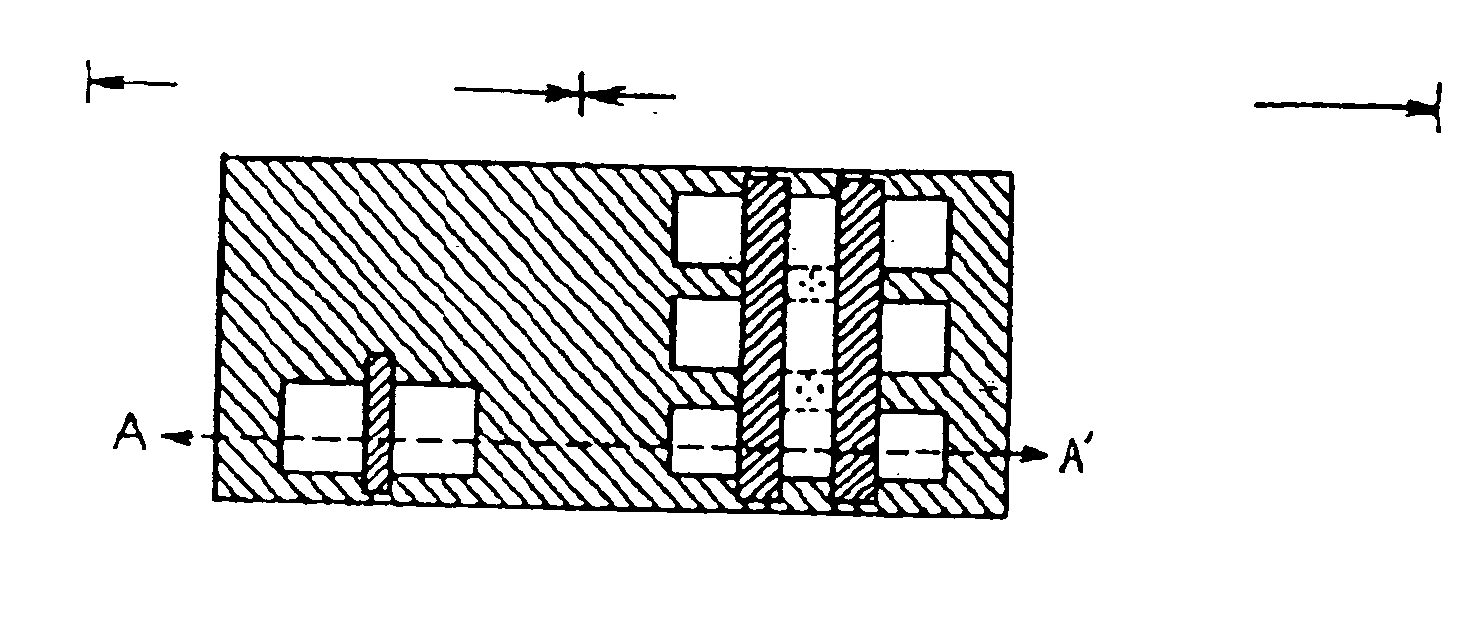

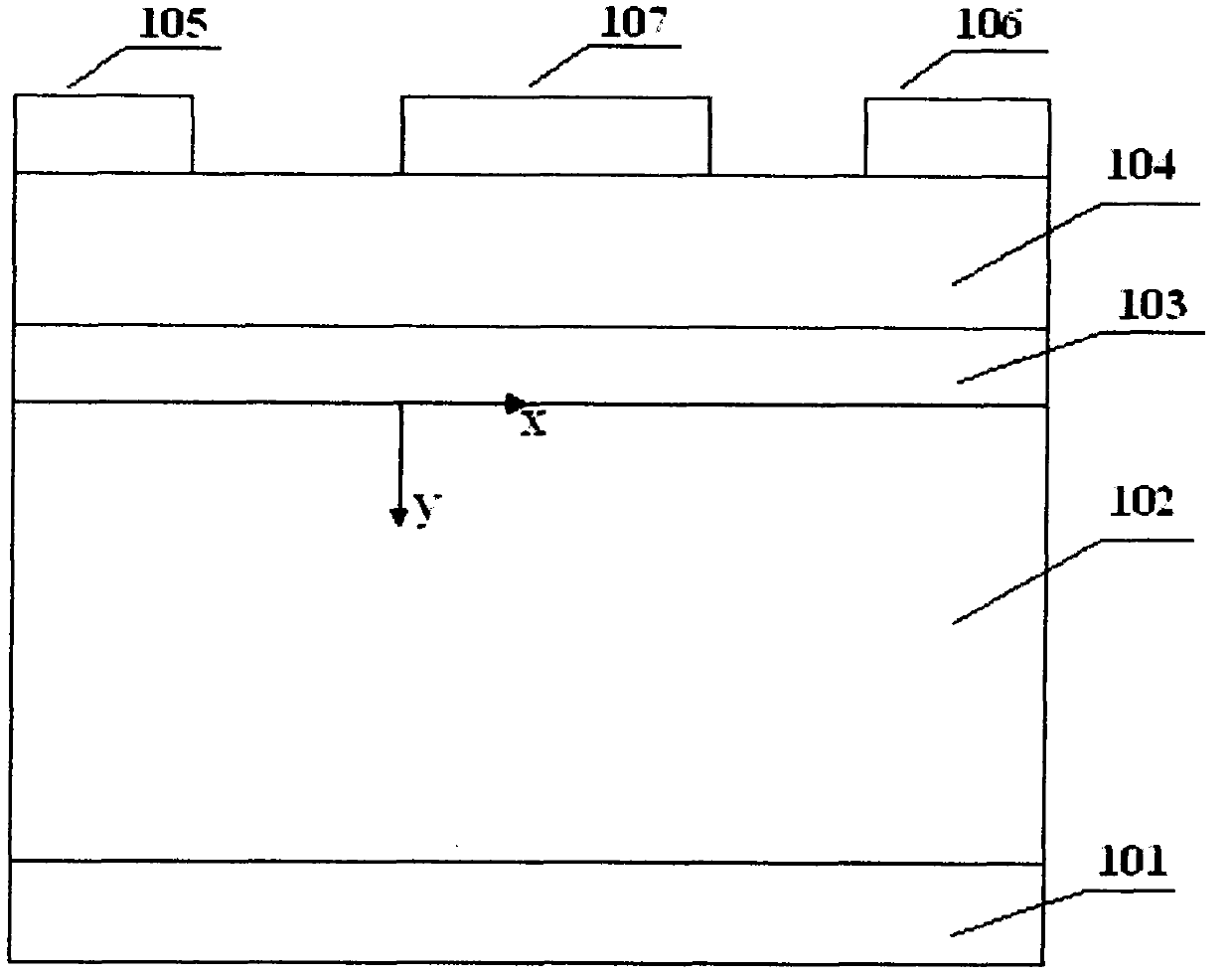

Semiconductor device and method of manufacturing the same

InactiveUS20090148992A1Easy to manufactureIncrease gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A semiconductor device includes: a semiconductor substrate; multiple active regions of a first conductive type isolated from one another by shallow-trench isolation regions provided on one surface of the semiconductor substrate; multiple silicon pillars including channel silicon pillars formed in the active regions; multiple first semiconductor regions of a second conductive type that are respectively formed on bottom ends of the silicon pillars and to be sources or drains; multiple second semiconductor regions of the second conductive type that are formed on top ends of the silicon pillars and to be sources or drains; multiple gate insulating films surrounding the silicon pillars; and multiple gate electrodes surrounding the gate insulating films. At least one of the channel silicon pillars has a height different from that of another one of the channel silicon pillars.

Owner:LONGITUDE SEMICON S A R L

Electro-optical device, shift register circuit, and semiconductor device

ActiveUS20130222220A1Inhibition of rising speedIncrease delayTransistorStatic indicating devicesShift registerProcessor register

An electro-optical device is configured to be capable of using a region of a gate line drive circuit efficiently and preventing rising speed of a gate line selection signal from decreasing (rising delay), and a shift register circuit is composed of a single conductivity type transistor which is suitable for the device. The gate line drive circuit including an odd driver to drive odd rows of a plurality of gate lines, and an even driver to drive even rows thereof. Each unit shift register in the odd and even drivers receives a selection signal in the second previous row and activates its own selection signal two horizontal periods later. A start pulse of the even driver is delayed in phase by one horizontal period with respect to a start pulse of the odd driver.

Owner:TRIVALE TECH LLC

Electro-optical device, shift register circuit, and semiconductor device

ActiveUS8462098B2Inhibition of rising speedIncrease delayElectric analogue storesCathode-ray tube indicatorsShift registerProcessor register

An electro-optical device is configured to be capable of using a region of a gate line drive circuit efficiently and preventing rising speed of a gate line selection signal from decreasing (rising delay), and a shift register circuit is composed of a single conductivity type transistor which is suitable for the device. The gate line drive circuit including an odd driver to drive odd rows of a plurality of gate lines, and an even driver to drive even rows thereof. Each unit shift register in the odd and even drivers receives a selection signal in the second previous row and activates its own selection signal two horizontal periods later. A start pulse of the even driver is delayed in phase by one horizontal period with respect to a start pulse of the odd driver.

Owner:TRIVALE TECH LLC

Intercalated superlattice compositions and related methods for modulating dielectric property

ActiveUS7678463B2Low working voltageDrain current increasesMaterial nanotechnologySolid-state devicesCrystallographyDielectric

Compositions, methods of using inorganic moieties for dielectric modulation, and related device structures.

Owner:NORTHWESTERN UNIV

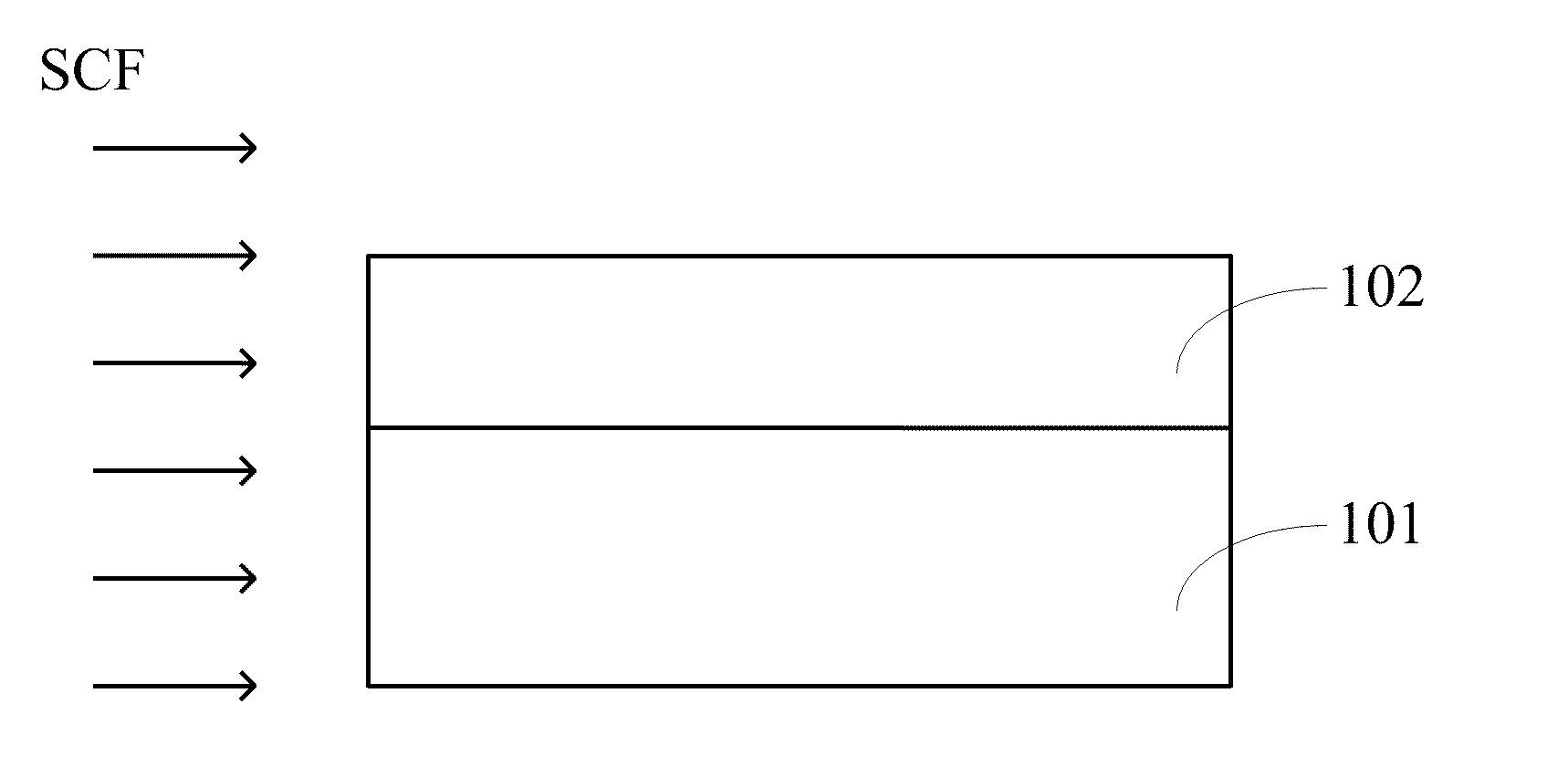

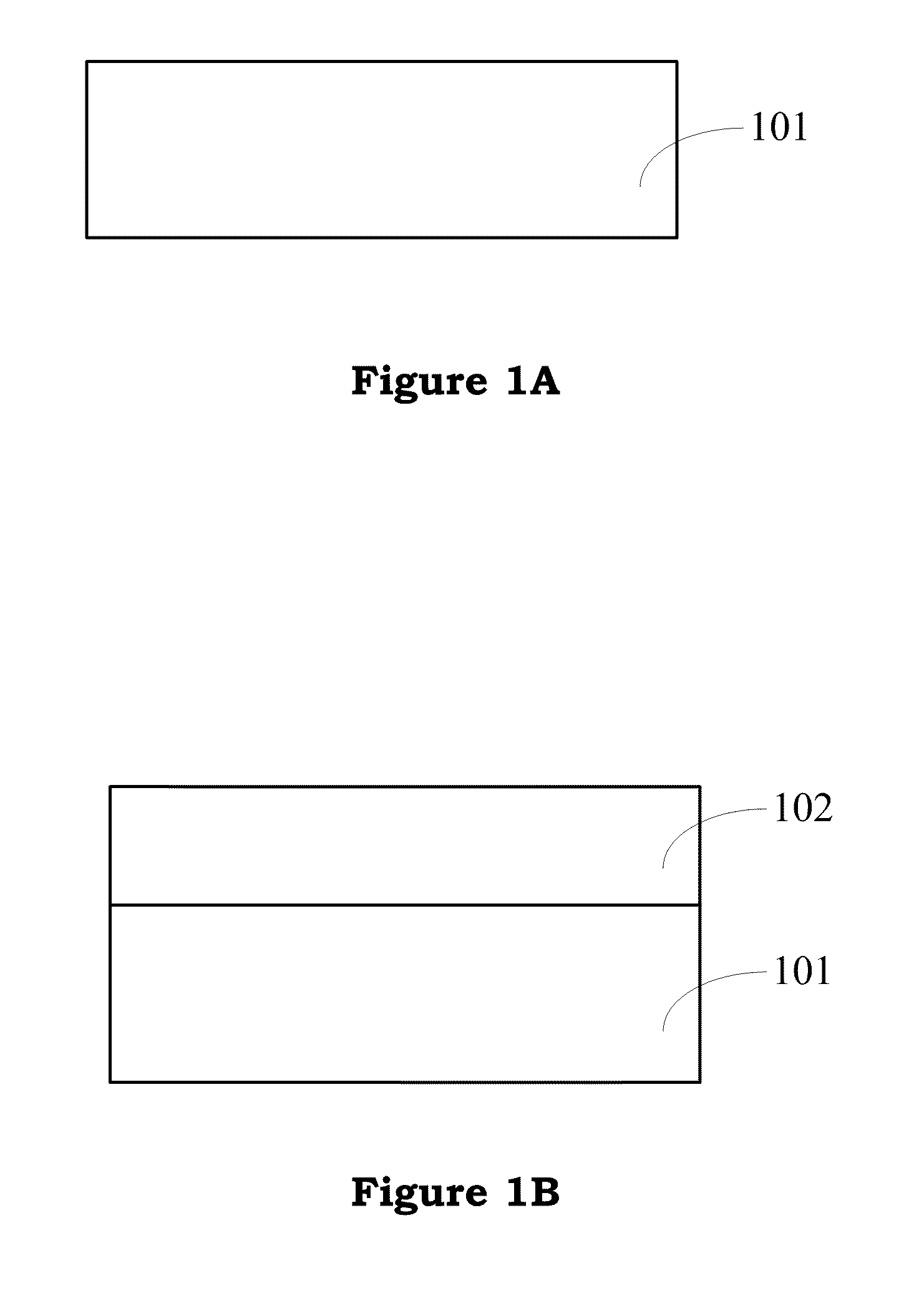

Method for forming an interfacial passivation layer on the Ge semiconductor

ActiveUS8071458B1Quality improvementPromote innovationSemiconductor/solid-state device manufacturingGate insulatorSemiconductor

The invention discloses a method for forming an interfacial passivation layer on the Ge semiconductor. The supercritical CO2 fluids is used to form an interfacial passivation layer between Ge channel and gate insulator layer, and improve the dielectric characteristics of gate insulator after high-temperature thermal annealing process.

Owner:NAT CHIAO TUNG UNIV

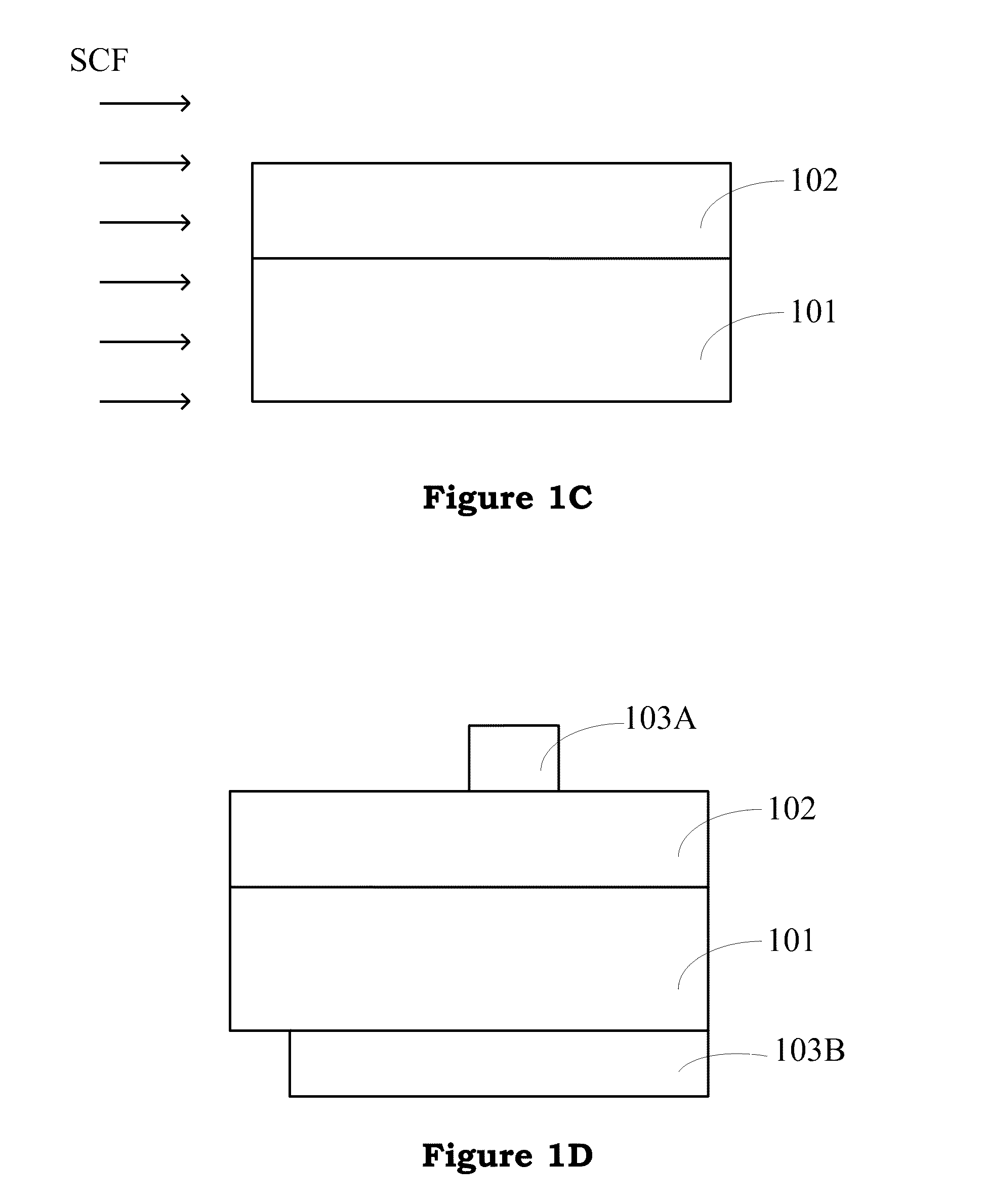

Field-effect transistor and method of manufacturing the same

InactiveUS20100219454A1Increase gate capacitanceImprove moisture resistanceTransistorSemiconductor/solid-state device detailsCapacitanceOrganic film

A field-effect transistor with improved moisture resistance without an increase in gate capacitance, and a method of manufacturing the field-effect transistor are provided. The field-effect transistor includes: a T-shaped gate electrode on a semiconductor layer; and a first highly moisture-resistant protective film including one of an insulating film and an organic film having high etching resistance, the first highly moisture-resistant protective film being located above the T-shaped gate electrodes over all of a region in which the T-shaped gate electrode is located. A cavity is located between the semiconductor layer and the first highly moisture-resistant protective film below a canopy of the T-shaped gate electrode. An end surface of the cavity is closed by a second highly moisture-resistant film.

Owner:MITSUBISHI ELECTRIC CORP

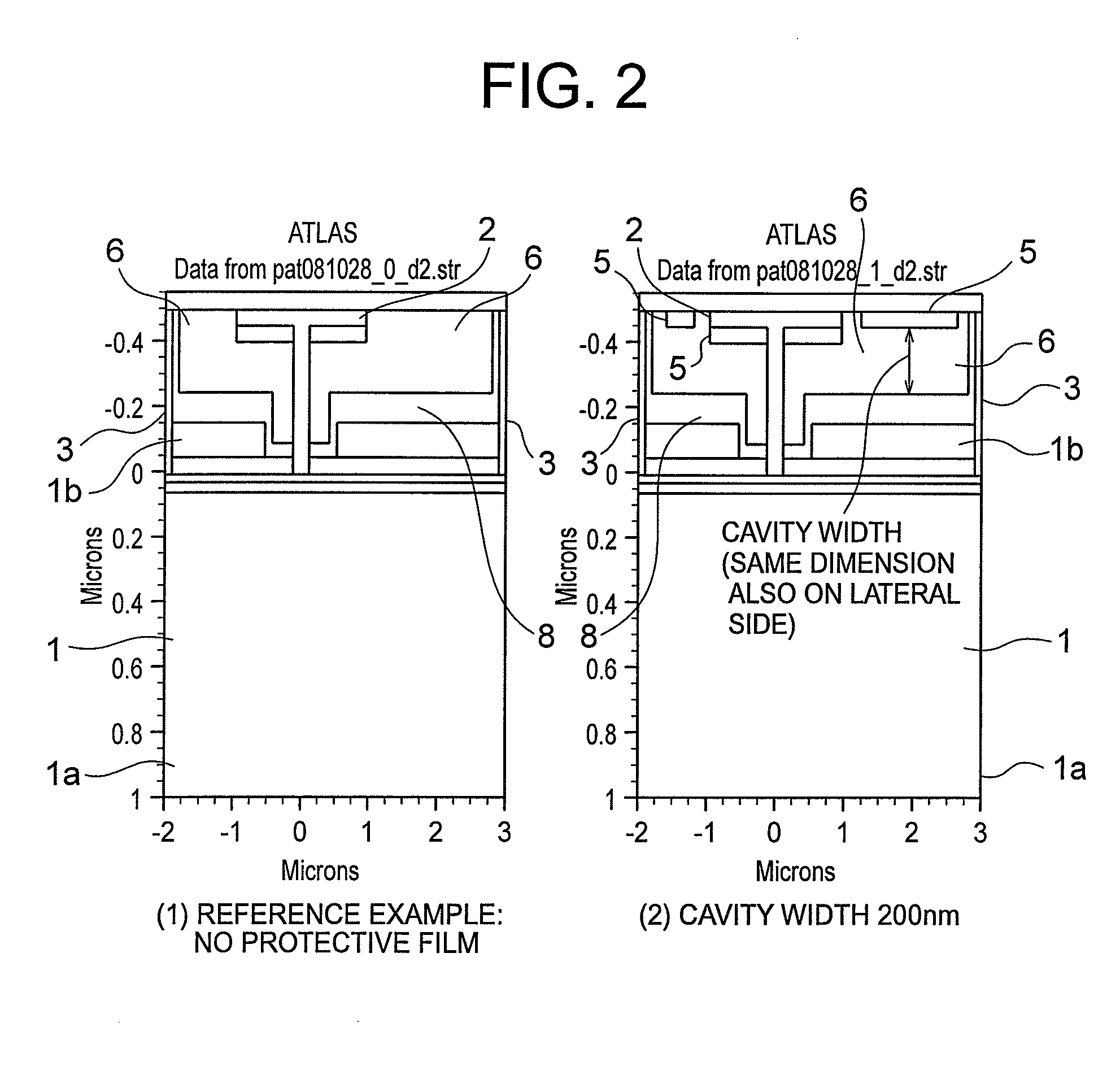

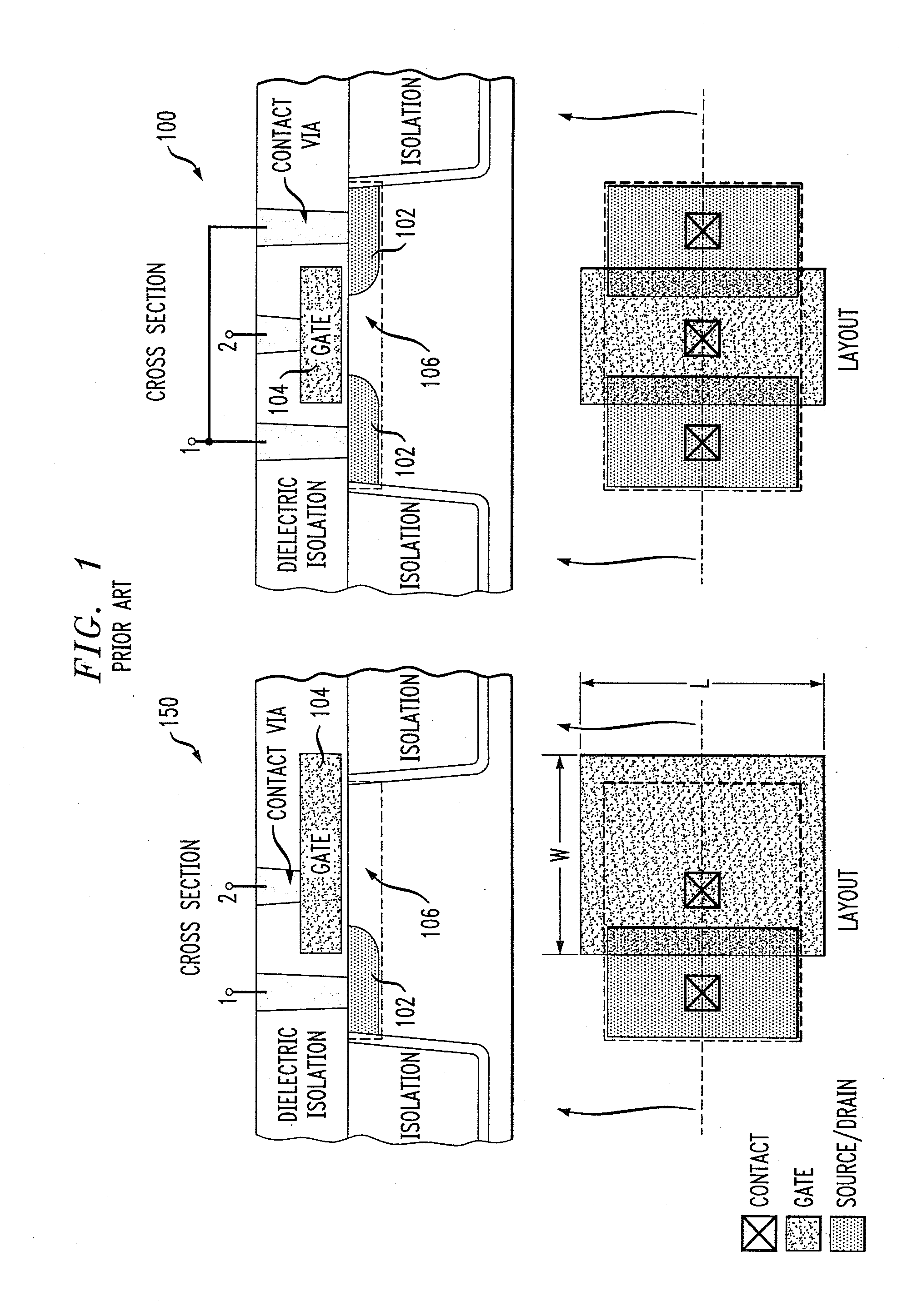

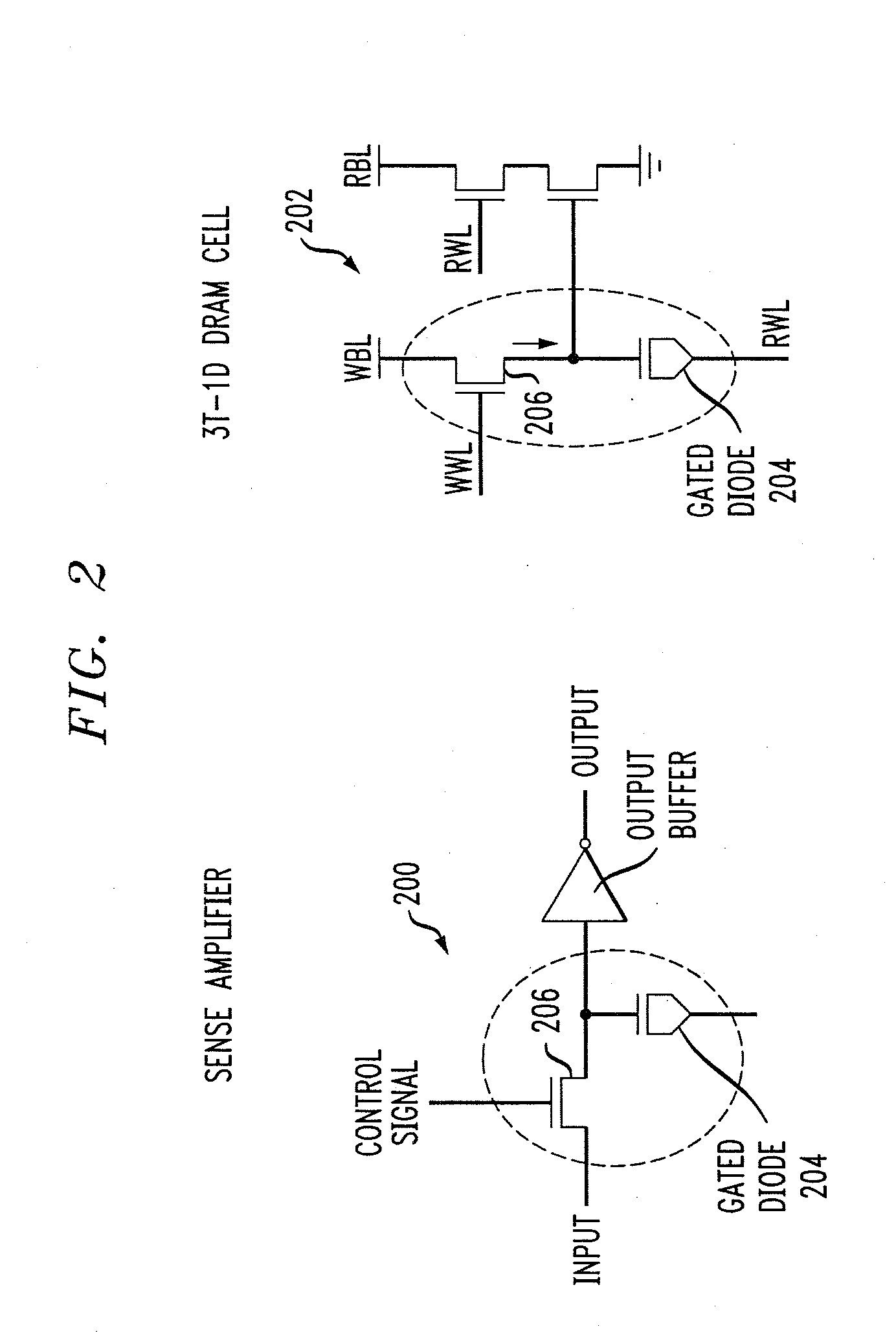

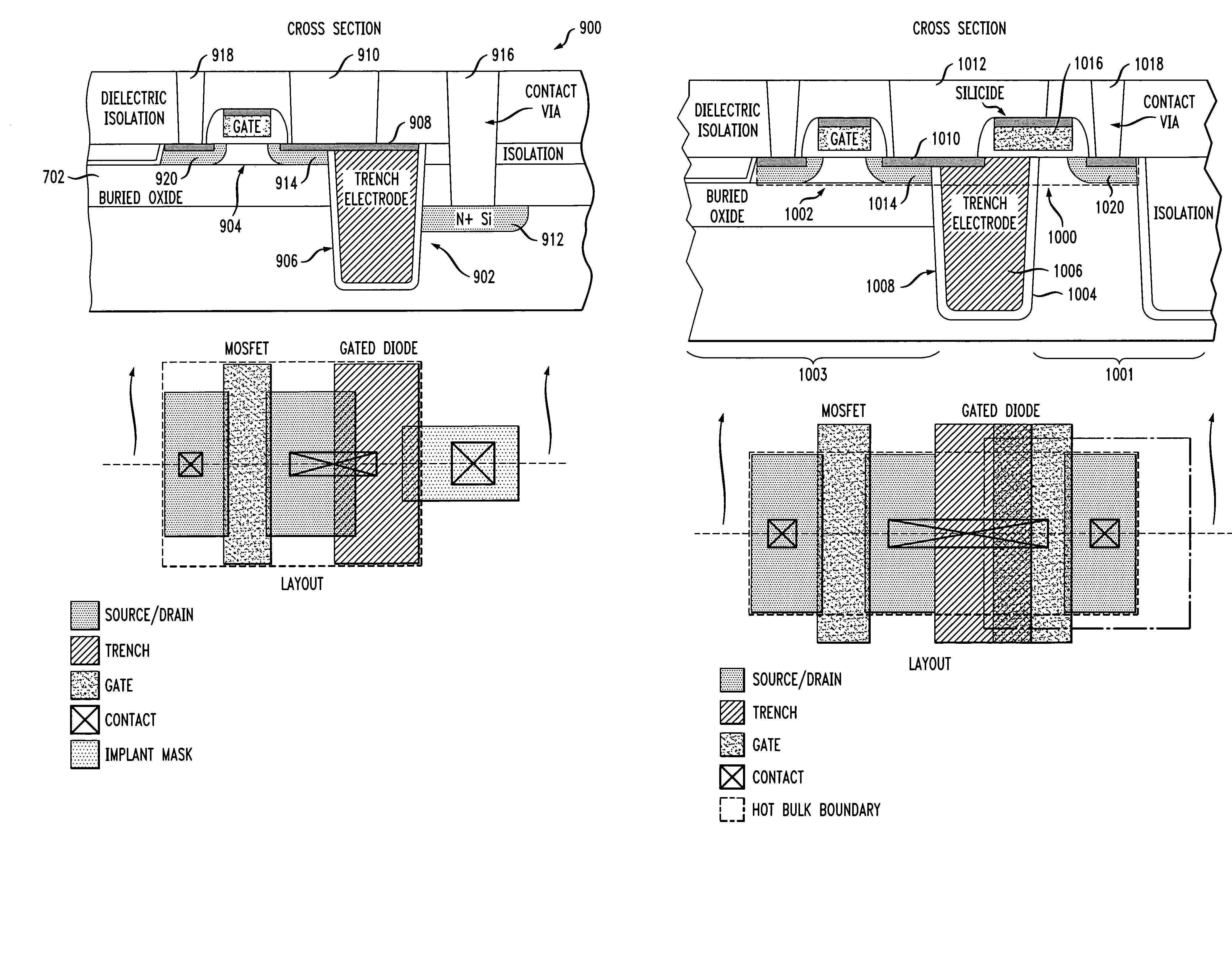

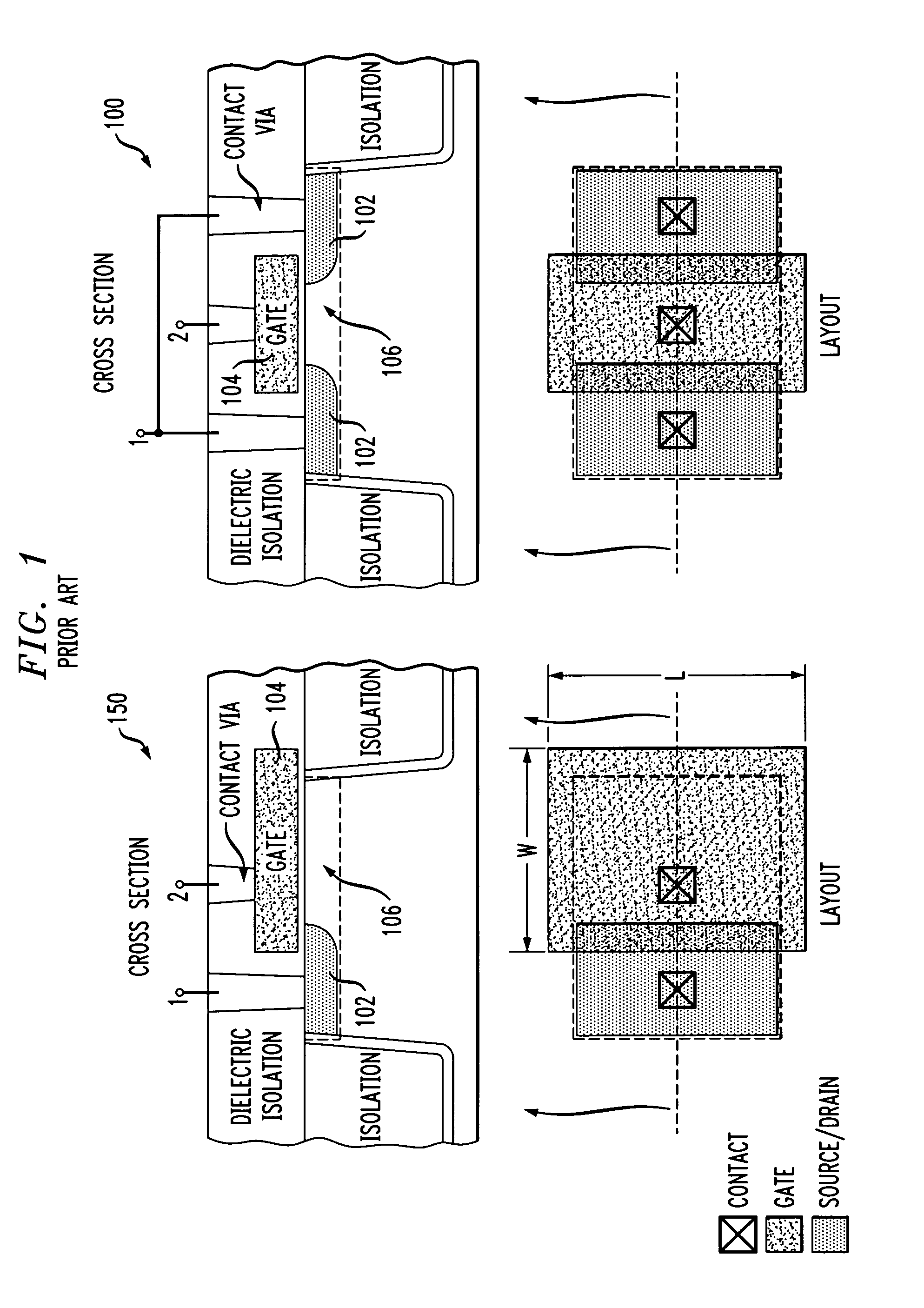

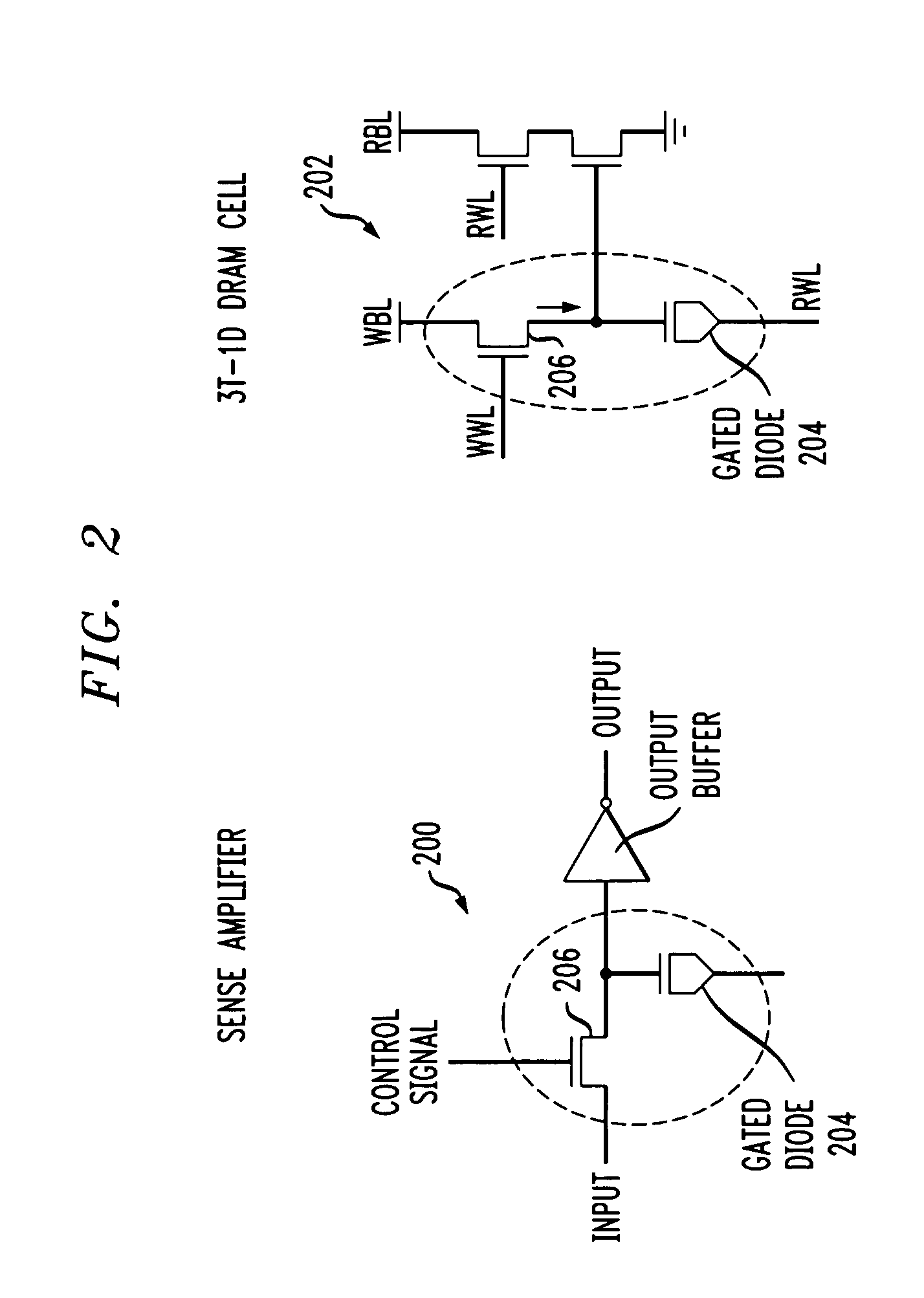

Area-Efficient Gated Diode Structure and Method of Forming Same

InactiveUS20080164507A1Improve area efficiencyIncrease layout areaTransistorSolid-state devicesCapacitanceSemiconductor

An area-efficient gated diode includes a semiconductor layer of a first conductivity type, an active region of a second conductivity type formed in the semiconductor layer proximate an upper surface thereof, and at least one trench electrode extending vertically through the active region and at least partially into the semiconductor layer. A first terminal of the gated diode is connected to the trench electrode, and a second terminal is connected to the active region. The gated diode is operative in one of at least first an second modes as a function of a voltage potential applied between the first and second terminals. The first mode is characterized by the creation of an inversion layer in the semiconductor layer surrounding the trench electrode. The gated diode has a first capacitance in the first mode and a second capacitance in the second mode, the first capacitance being greater than the second capacitance.

Owner:GLOBALFOUNDRIES INC

Array substrate and manufacturing method therefor and display apparatus

ActiveCN107170759AIncrease gate capacitanceIncreased subthreshold swingSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing efficiencyEngineering

The invention provides an array substrate and a manufacturing method therefor and a display apparatus. Each of a switching thin film transistor and a driving thin film transistor in the array substrate comprises an active layer, a planarization gate insulating layer and a gate separately; the active layers are both arranged on a substrate; the thickness of the active layer of the switching thin film transistor is greater than that of the active layer of the driving thin film transistor; the switching thin film transistor and the driving thin film transistor share the planarization gate insulating layer, and are arranged on the active layers and the exposed substrate; and the gate of the switching thin film transistor and the gate of the driving thin film transistor are arranged on the planarization gate insulating layer. The process is simple and the manufacturing efficiency of the array substrate can be improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Semiconductor device and its manufacture method

InactiveUS20070066004A1Easy to integrateImprove reliabilityTransistorSolid-state devicesDevice materialCell region

A non-volatile semiconductor memory device which simultaneously possesses a non-volatile memory cell region which possesses an isolating insulation film which has been formed selectively within a semiconductor substrate, which also possesses a first electroconductive film (floating gate electrode) via a first gate insulating film which has been formed on the semiconductor substrate surface, and which also possesses a metal film (control gate electrode) via a second gate insulating film which has been formed above said electroconductive film and a peripheral transistor region which possesses a metal film (gate electrode) via a third gate insulating film which has been formed above the semiconductor substrate surface.

Owner:FUJITSU SEMICON LTD

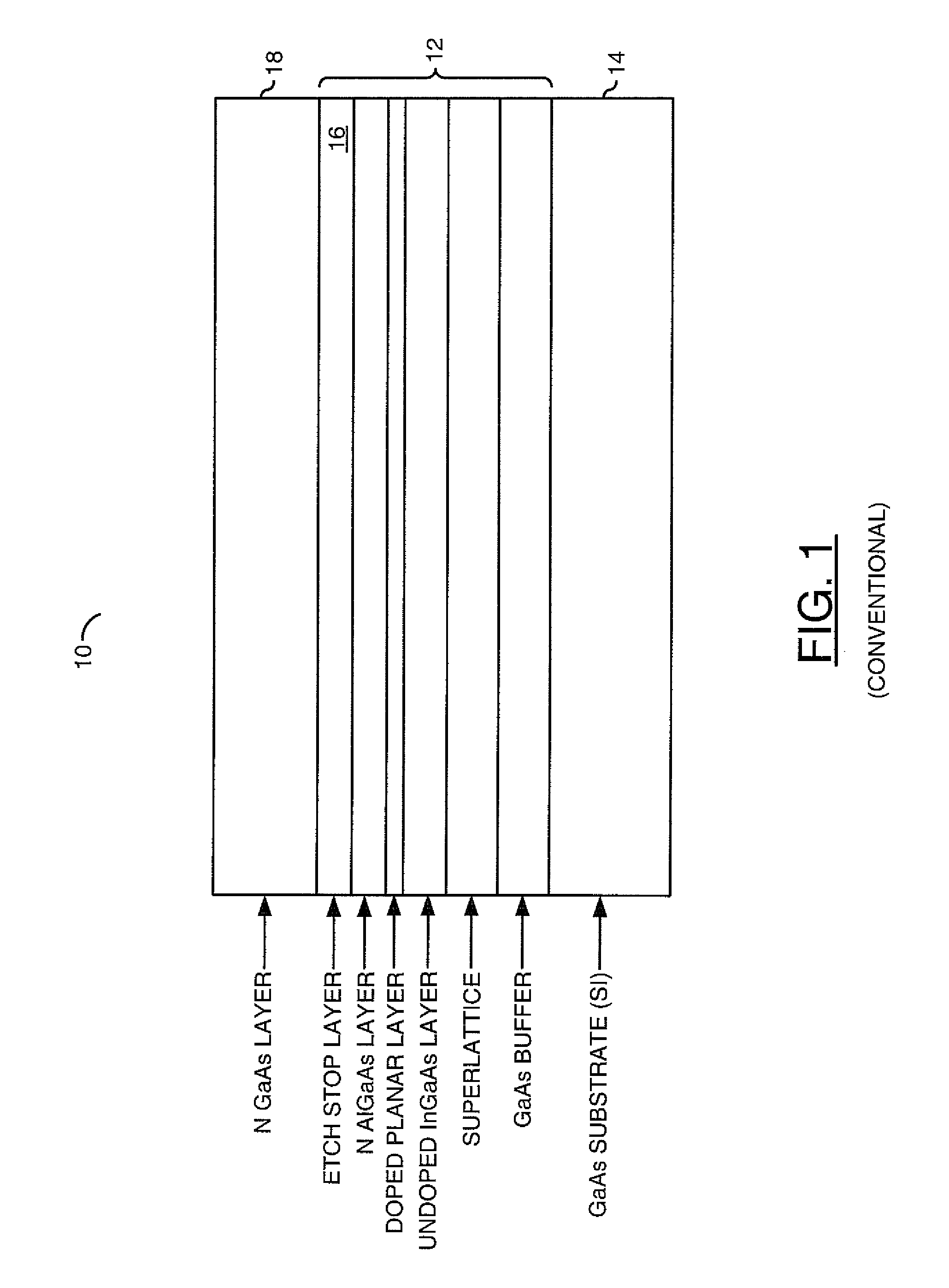

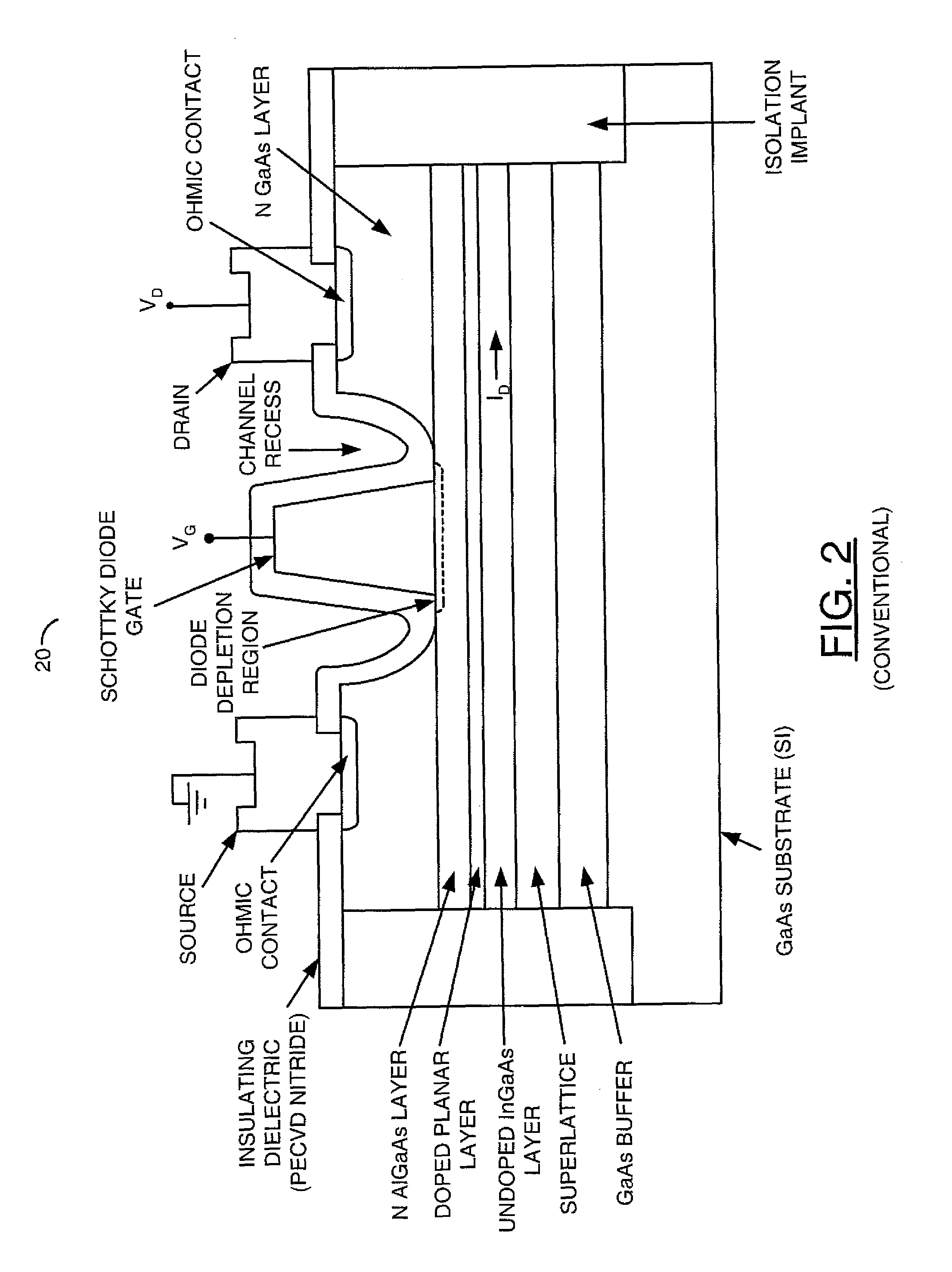

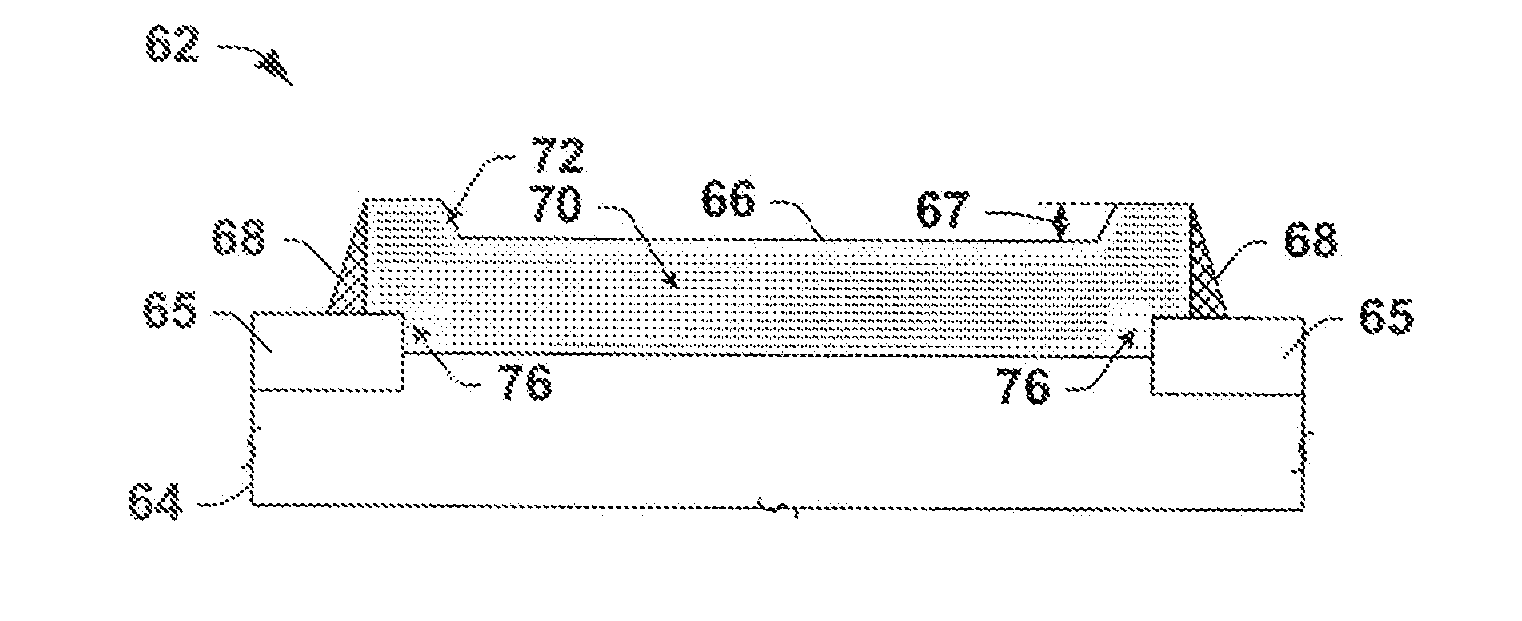

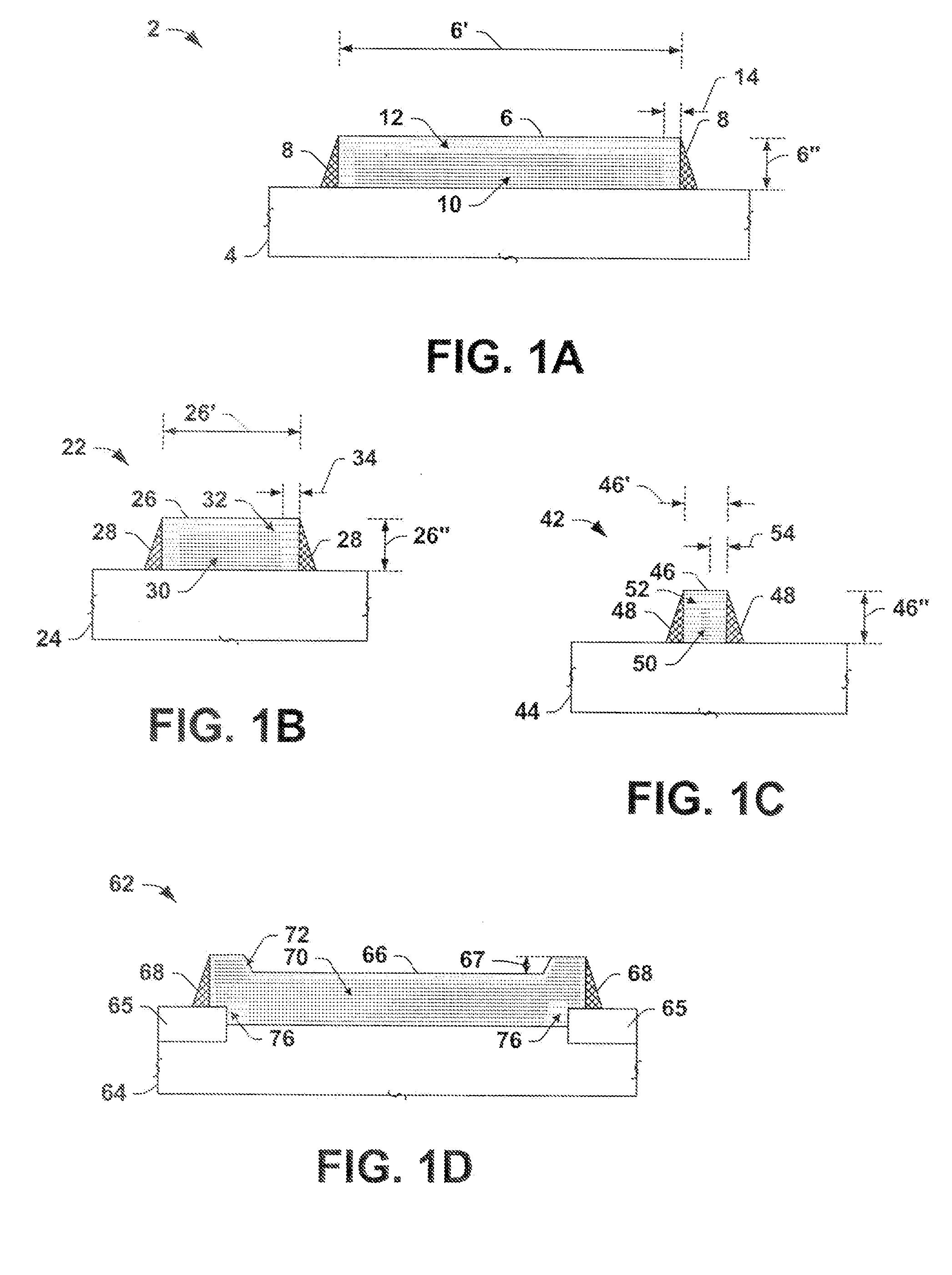

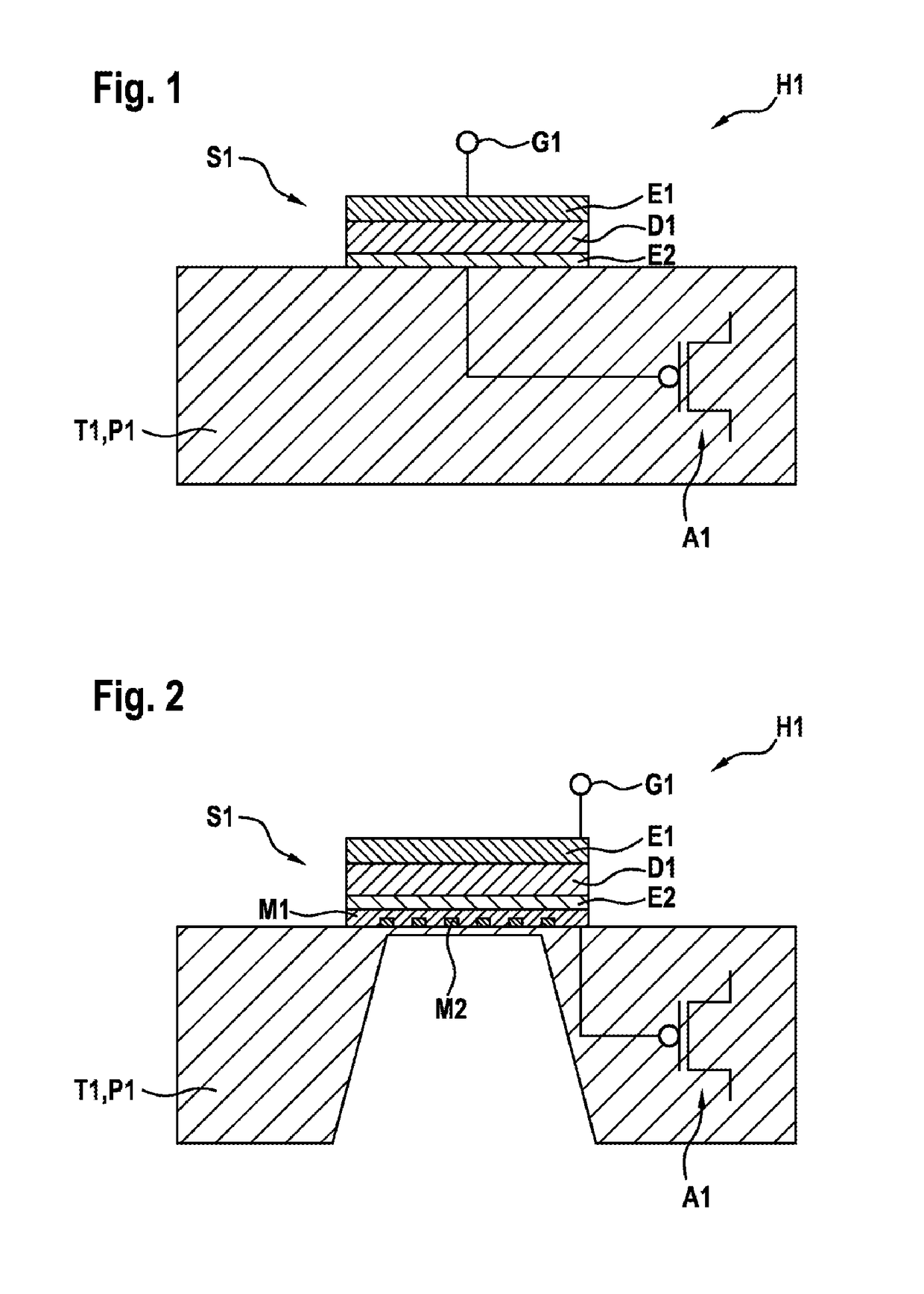

Structure of a pHEMT transistor capable of nanosecond switching

ActiveUS8174050B2Reduce resistanceIncrease gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesNanosecondEngineering

A method for fabricating a transistor and the resulting transistor is disclosed. The method generally includes steps (A) to (E). Step (A) may form a high mobility layer. The high mobility layer is generally configured to carry a two-dimensional electron gas. Step (B) may form a planar layer on the high mobility layer. Step (C) may form a barrier layer on the planar layer. Step (D) may form a doped layer on the barrier layer. The doped layer is generally a low bandgap III-V semiconductor. Step (E) may form a gate in contact with the doped layer. The gate may be separated from both a source and a drain by corresponding ungated recess regions. The high mobility layer, the planar layer, the barrier layer, the doped layer, the source, the gate and the drain are generally configured as a pseudomorphic high electron mobility transistor.

Owner:MACOM TECH SOLUTIONS HLDG INC

Area-efficient gated diode structure and method of forming same

InactiveUS7385251B2Improve area efficiencyIncrease layout areaTransistorSolid-state devicesCapacitanceSemiconductor

An area-efficient gated diode includes a semiconductor layer of a first conductivity type, an active region of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer, and at least one trench electrode extending substantially vertically through the active region and at least partially into the semiconductor layer. A first terminal of the gated diode is electrically connected to the trench electrode, and at least a second terminal is electrically connected to the active region. The gated diode is operative in one of at least a first mode and a second mode as a function of a voltage potential applied between the first and second terminals. The first mode is characterized by the creation of an inversion layer in the semiconductor layer substantially surrounding the trench electrode. The gated diode has a first capacitance in the first mode and a second capacitance in the second mode, the first capacitance being substantially greater than the second capacitance.

Owner:GLOBALFOUNDRIES INC

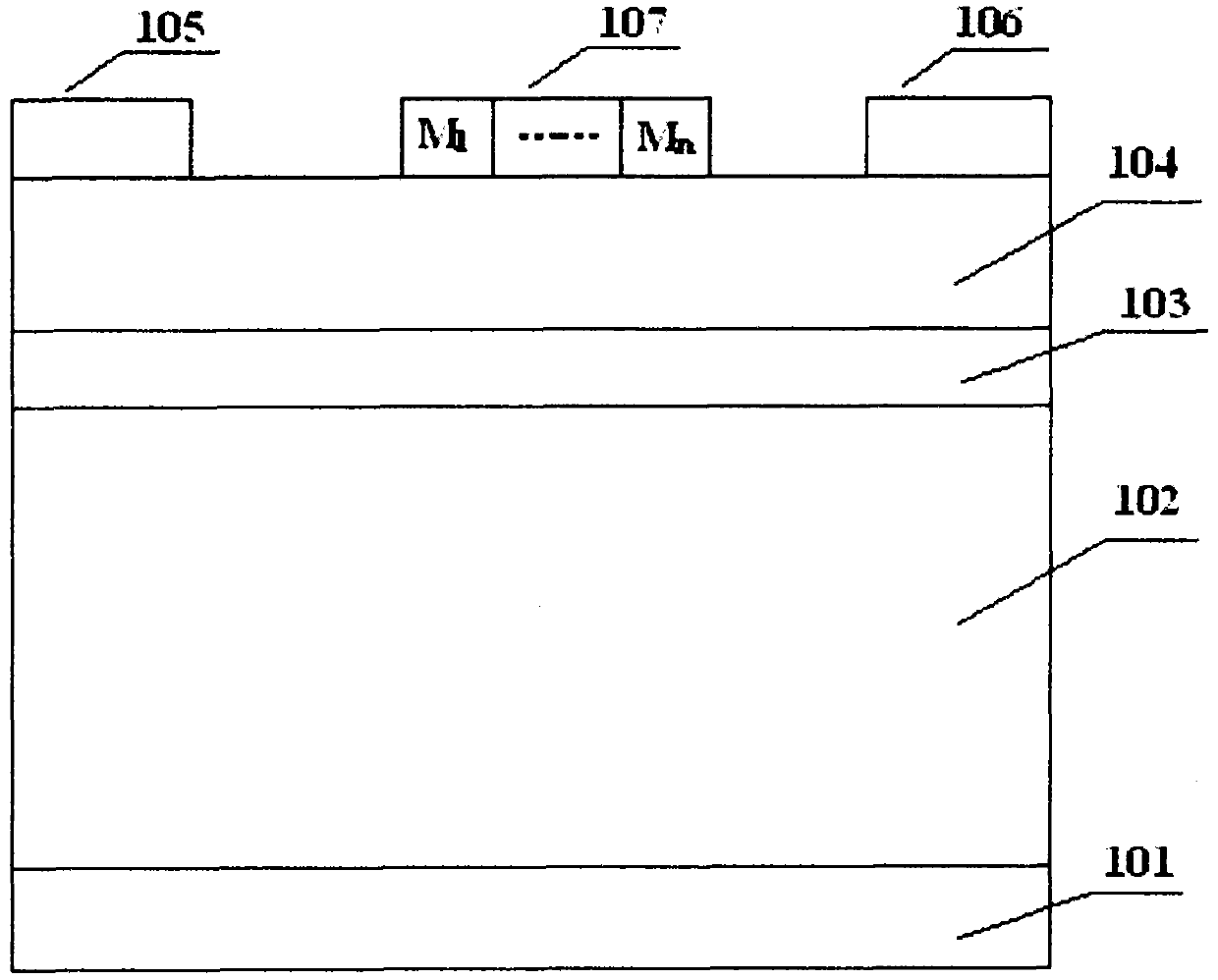

Gallium nitride based high electron mobility transistor with composite metal gate

ActiveCN103474455AInhibition-lowering (DIBL) effectAvoid mechanical propertiesSemiconductor devicesIndiumGallium nitride

The invention relates to a gallium nitride based high electron mobility transistor with a composite metal gate. The gallium nitride based high electron mobility transistor comprises a substrate, a gallium nitride buffer layer, an aluminum nitride inserting layer, an aluminum-indium-gallium-nitrogen barrier layer, and a source electrode, a drain electrode and a grid electrode on the aluminum-indium-gallium-nitrogen barrier layer, wherein the source electrode and the drain electrode form ohmic contact with the aluminum-indium-gallium-nitrogen barrier layer; the grid electrode and the aluminum-indium-gallium-nitrogen barrier layer form Schottky contact; the grid electrode on the aluminum-indium-gallium-nitrogen barrier layer is formed by connecting more than two metals with different work functions. Through the utilization of the influence of a step barrier shielding drain potential formed between the grid metals with different work functions on device channels, the Drain Induced Barrier Lowering (DIBL) effect is inhibited, and the SCEs (Short Channel Effects) of deep submicron gallium nitride based high electron mobility transistor are improved, thus the current gain cut-off frequency fT is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor device and transistor

InactiveUS20090001454A1Increase impurity concentrationReduce gate capacitanceSemiconductor devicesSource areaSemiconductor

A semiconductor device includes active areas which are insulatedly separated from each other by element-separation insulating films; a gate insulating film formed on each active area; a gate electrode which extends across the active area via the gate insulating film; a source area and a drain area formed in the active area so as to interpose the gate electrode; and a fin-channel structure in which at the intersection between the active area and the gate electrode, trenches are provided at both sides of the active area, and part of the gate electrode is embedded in each trench via the gate insulating film, so that the gate electrode extends across a fin which rises between the trenches. In the gate insulating film, the film thickness of a part which contacts the bottom surface of each trench is larger than that of a part which contacts the upper surface of the fin.

Owner:LONGITUDE SEMICON S A R L

Intercalated Superlattice Compositions and Related Methods for Modulating Dielectric Property

InactiveUS20100173165A1Low working voltageDrain current increasesMaterial nanotechnologySemiconductor/solid-state device detailsDielectricElectric properties

Compositions, methods of using inorganic moieties for dielectric modulation, and related device structures.

Owner:MARKS TOBIN J +1

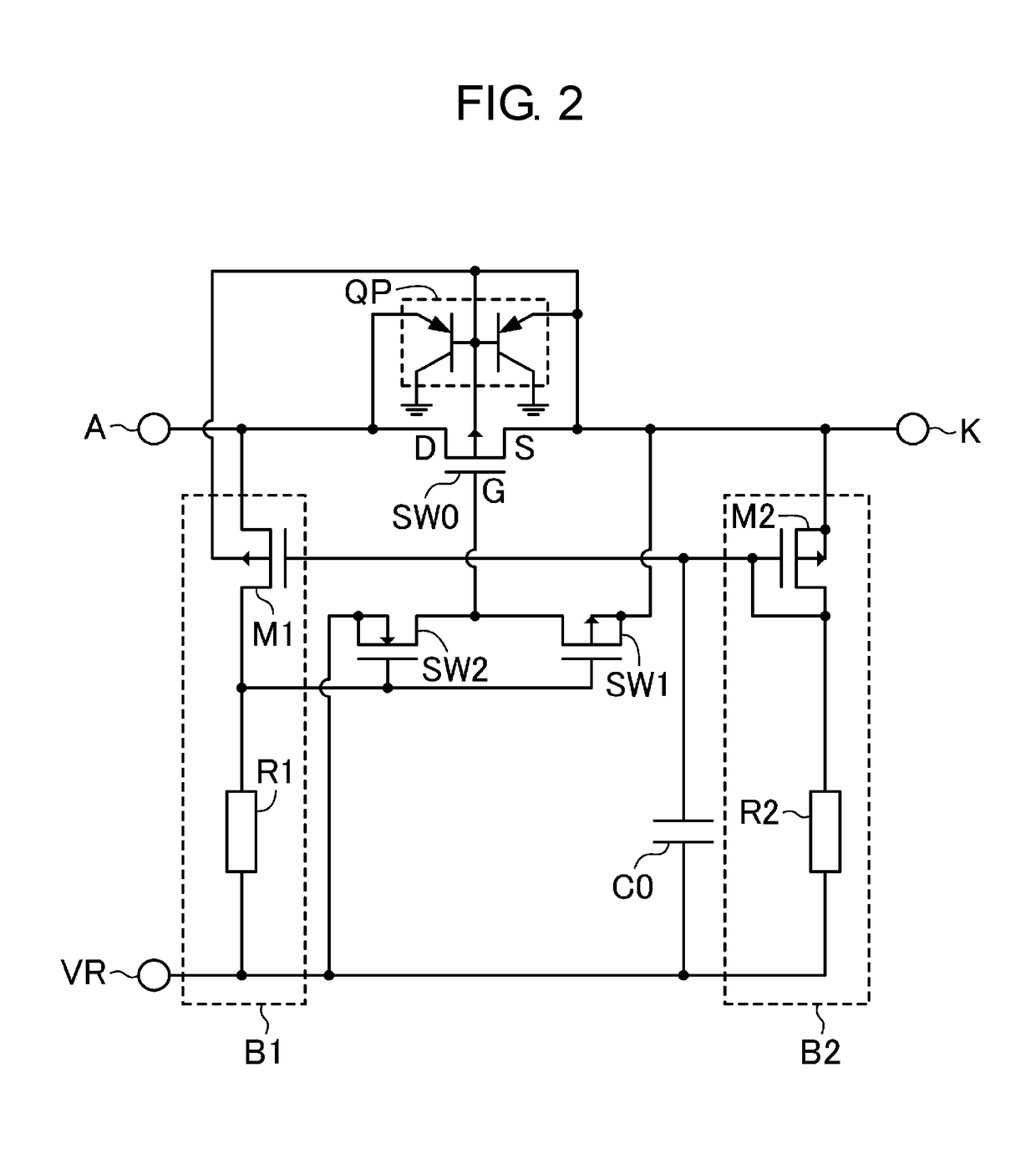

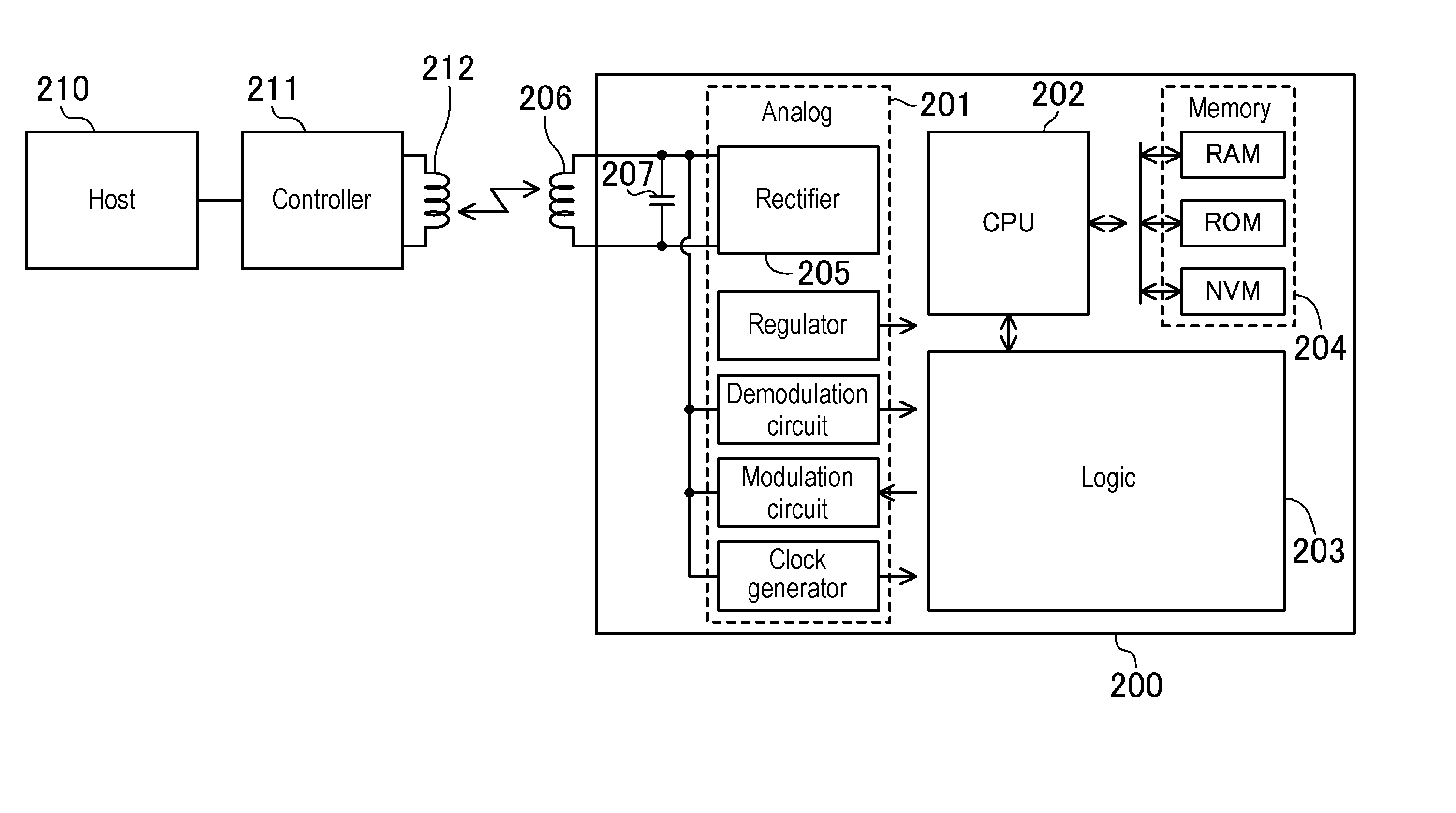

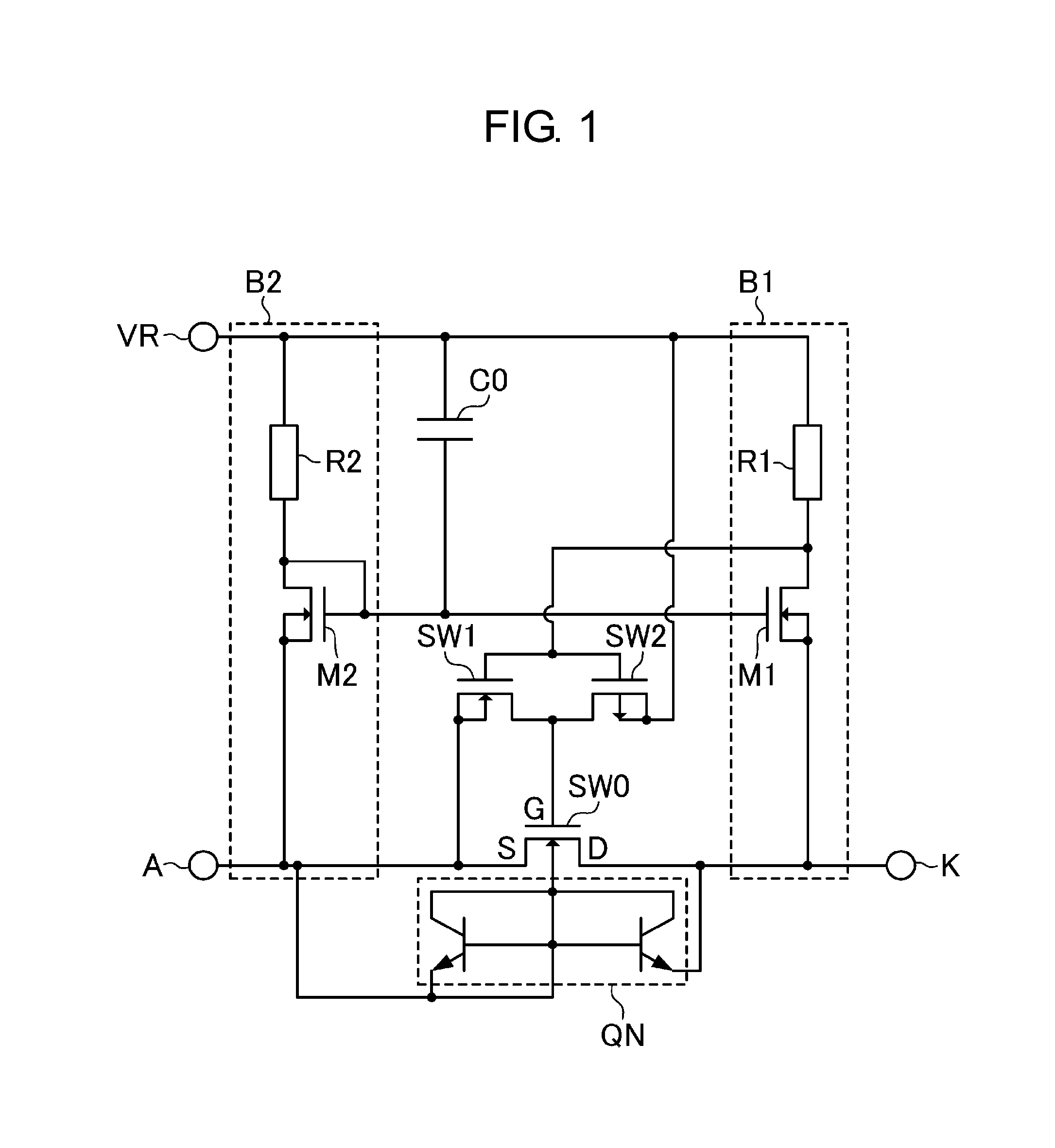

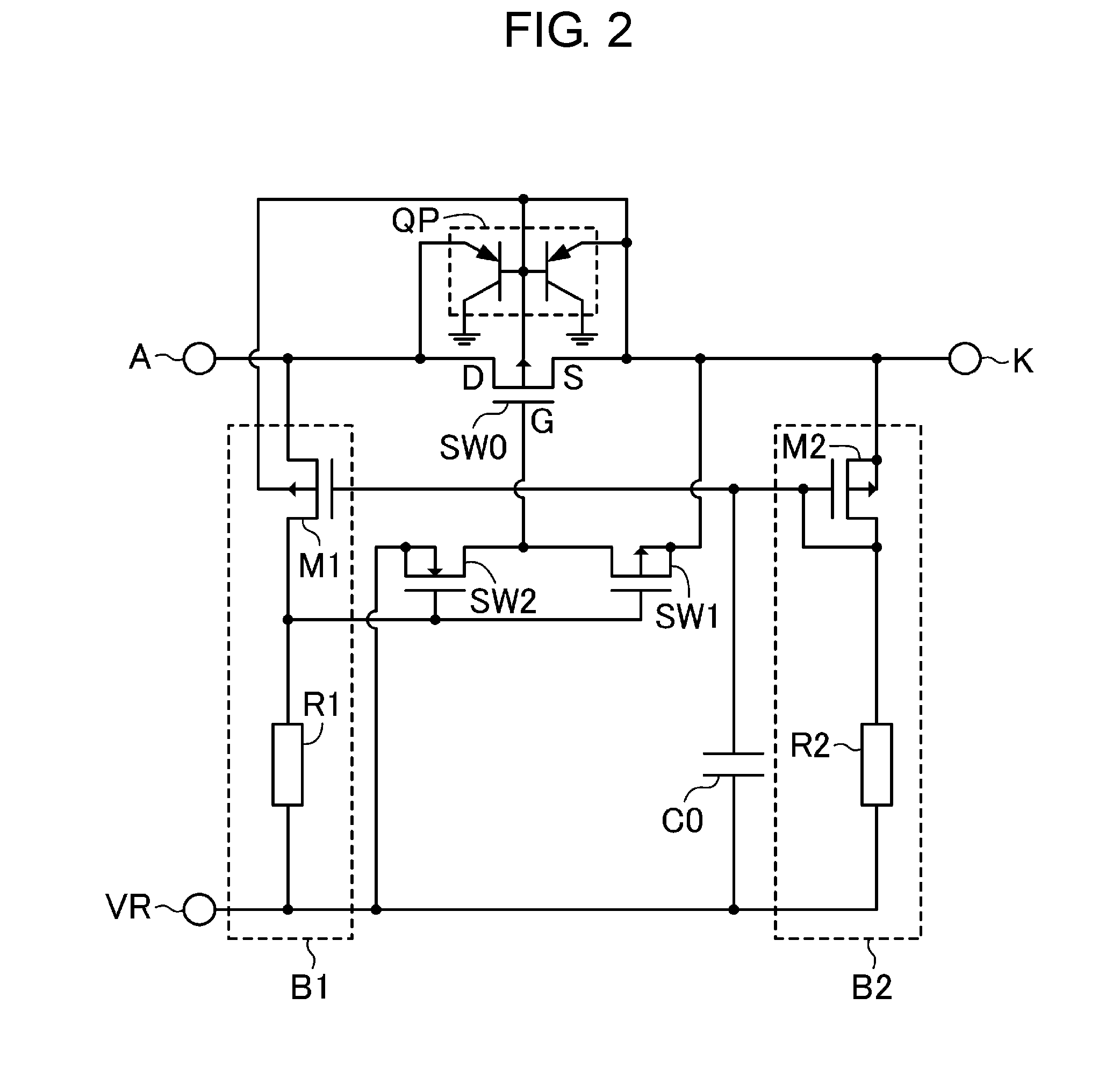

Rectifier circuit, and contactless power supply device

ActiveUS10056787B2Low costReduce variationEfficient power electronics conversionAc-dc conversionVoltage generatorVoltage reference

The rectifier circuit includes: three terminals A, K, VR; voltage comparator including a positive input terminal, a negative input terminal, and a comparative output terminal; current switching unit including source terminal, drain terminal, and control terminal; first switching unit that conducts or cuts off between source terminal and control terminal of the current switching unit; second switching unit that conducts or cuts off between control terminal of the current switching unit and terminal VR; and reference voltage generator that uses terminal A and terminal VR as input terminals, and includes a voltage output terminal. The voltage output terminal of reference voltage generator is connected to the negative input terminal of the voltage comparator, terminal K is connected to the positive input terminal of voltage comparator, and current flow between first switching unit and second switching unit is exclusively allowed or interrupted by a signal output from the comparative output terminal of voltage comparator).

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

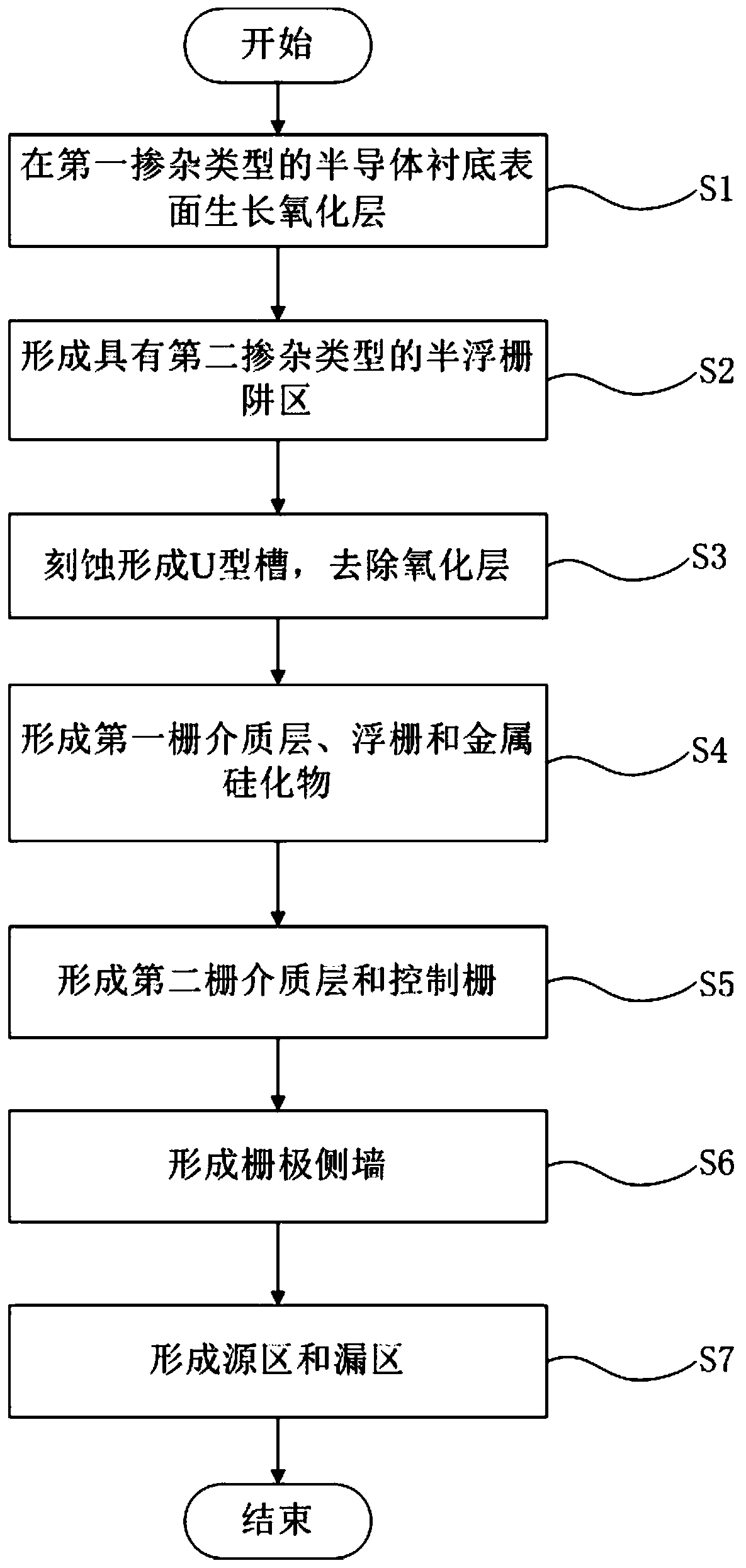

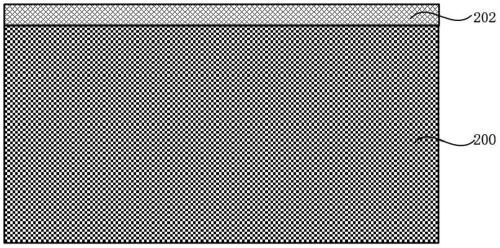

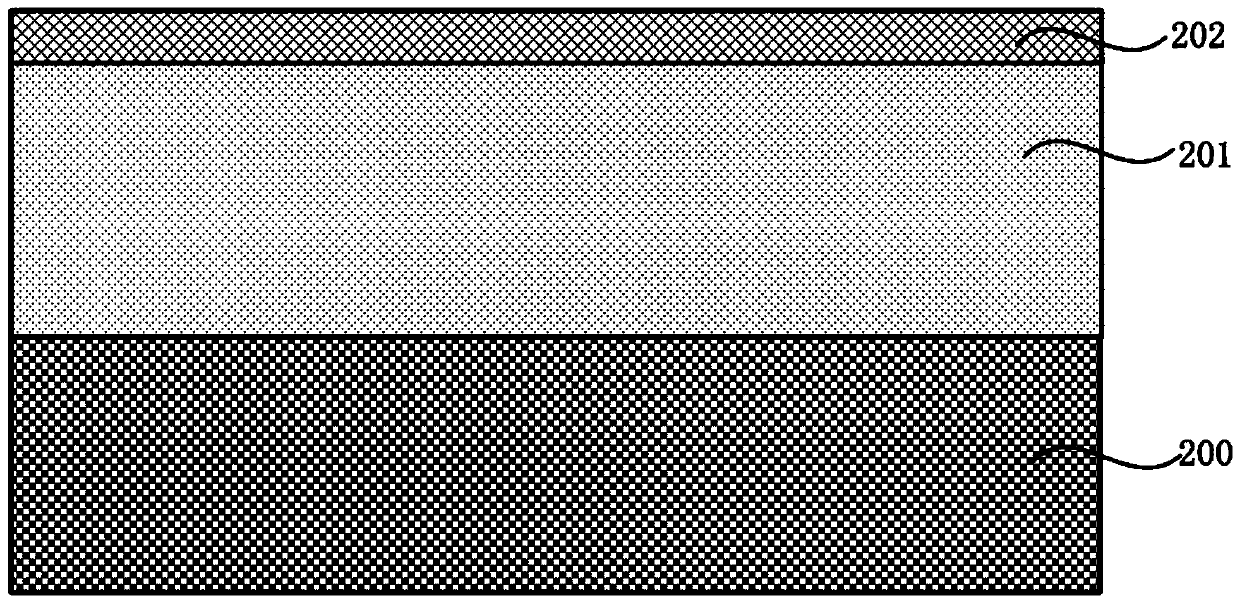

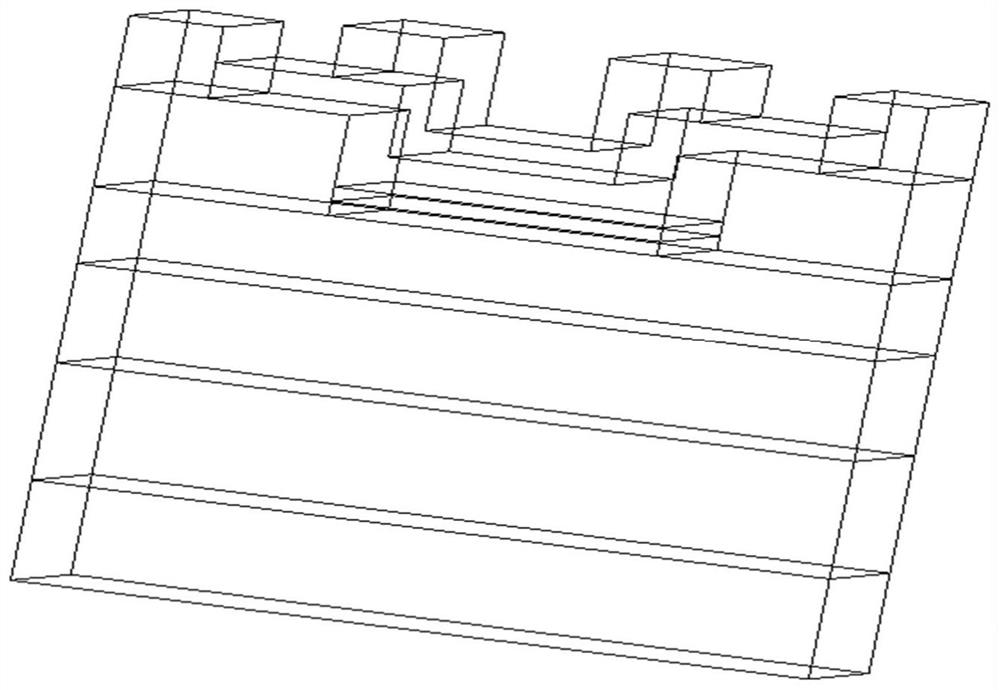

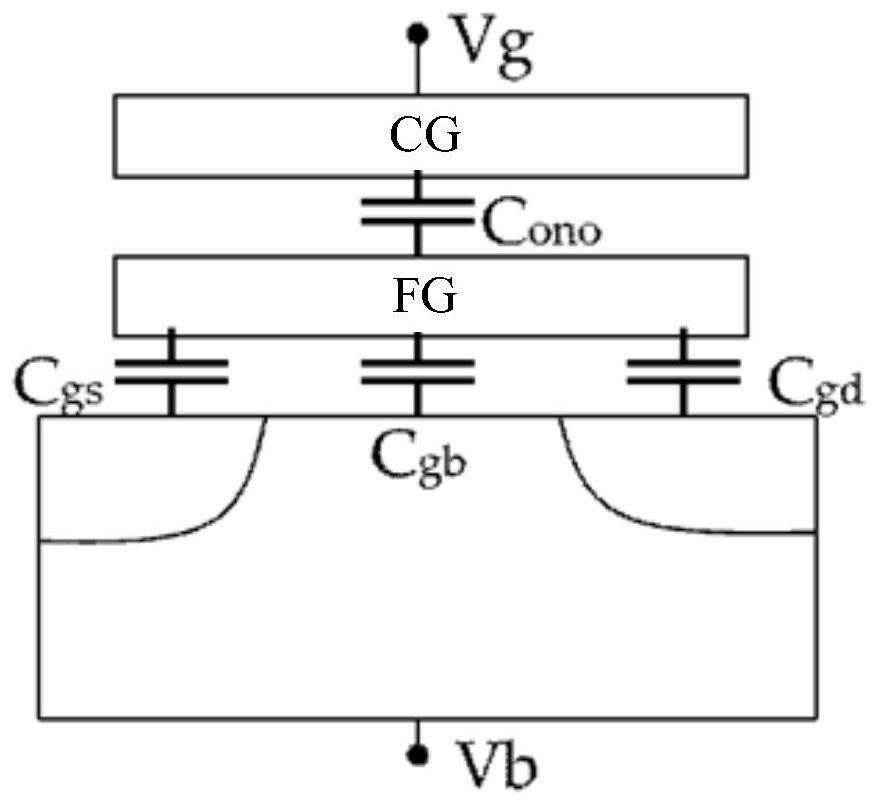

High-erasing-speed semi-floating-gate memory and preparation method thereof

ActiveCN111490046AIncrease write speedIncrease drive currentTransistorSemiconductor/solid-state device manufacturingDriving currentGate dielectric

The invention belongs to the technical field of integrated circuit memories, and particularly relates to a high-erasing-speed semi-floating-gate memory and a preparation method thereof. The semi-floating-gate memory comprises a silicon-containing semiconductor substrate having a first doping type, a semi-floating-gate well region which has a second doping type, and a U-shaped groove which penetrates through the semi-floating-gate well region, wherein the bottom of the U-shaped groove is located at the lower boundary of the semi-floating-gate well region; a first gate dielectric covers the surface of the U-shaped groove, and an opening is formed in the semi-floating-gate well region; a floating gate covers the first gate dielectric, and a metal silicide is formed in the semi-floating-gate well region below the opening; a second gate dielectric layer wraps the floating gate, and a control gate covers the second gate dielectric layer; gate side walls are positioned on the two sides of a first gate stack and a second gate stack; and a source region and a drain region have a second doping type and are positioned on two sides of the first gate stack and the second gate stack. According to the invention, the erasing speed of the memory can be increased, the contact resistance of the source electrode of a tunneling transistor is obviously reduced, the driving current of the tunneling transistor is increased, and the erasing speed of the memory is further increased.

Owner:FUDAN UNIV +1

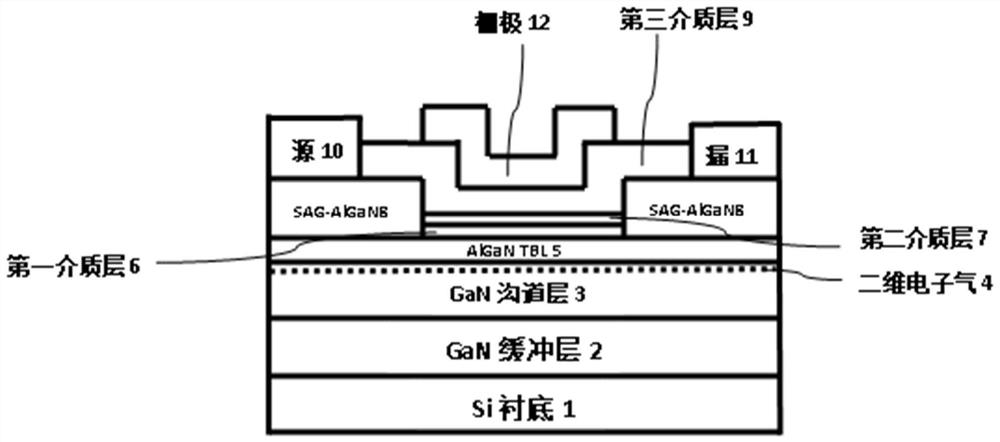

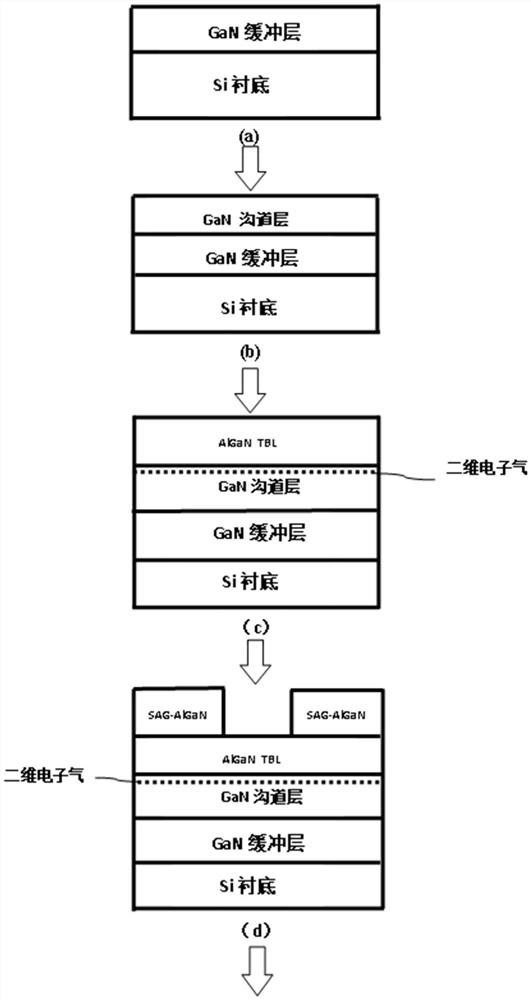

Enhanced GaN-based MIS-HEMT device and preparation method thereof

ActiveCN111613668AEasily damagedEliminate damageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionCapacitance

The invention relates to an enhanced GaN-based MIS-HEMT device and a preparation method thereof. In the MIS-HEMT device, a concave AlGaN barrier layer is arranged on the basis of a thin AlGaN barrierlayer, so that the channel mobility is improved, and the on resistance is improved. On the basis, an electron beam evaporation (EBE) method is adopted to grow a mask layer and is combined with an SAGmethod, compared with a PECVD mask used in a conventional process, the adoption of the EBE for growing the mask completely eliminates plasma damage in the mask technology, and damage-free crystal lattices are reserved for a thin AlGaN / GaN heterojunction. Meanwhile, the Al component of the AlGaN thin barrier layer is different from the Al component of the concave AlGaN barrier layer, and the threshold voltage and the channel electron mobility are further improved. In addition, a gate dielectric layer in the device is formed by stacking three oxide materials with different dielectric constants,the thickness of the dielectric layer is increased to ensure a certain threshold voltage, and the gate capacitance is increased by means of increasing the dielectric constant, so that the transconductance value is prevented from being too low.

Owner:SOUTH CHINA NORMAL UNIVERSITY

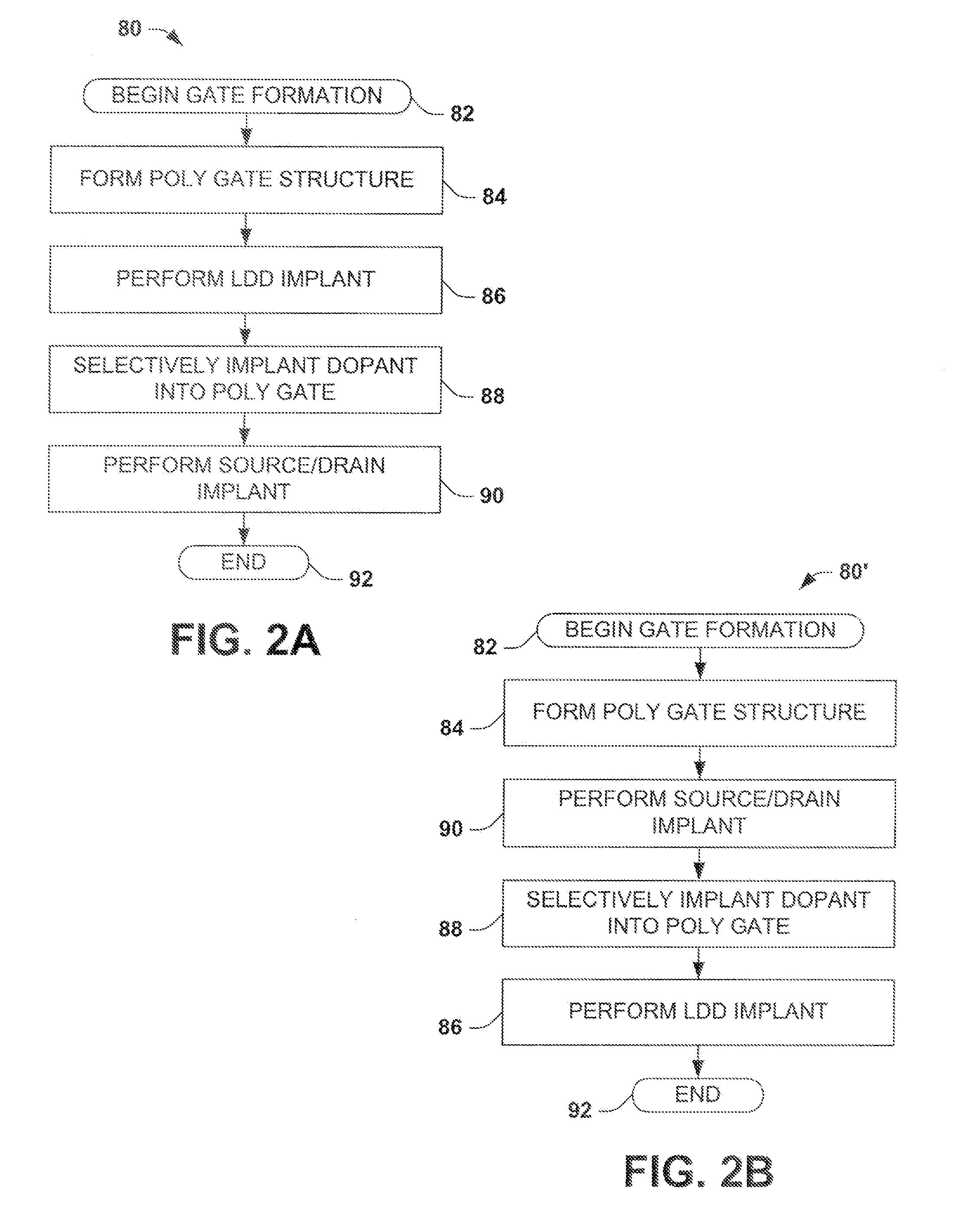

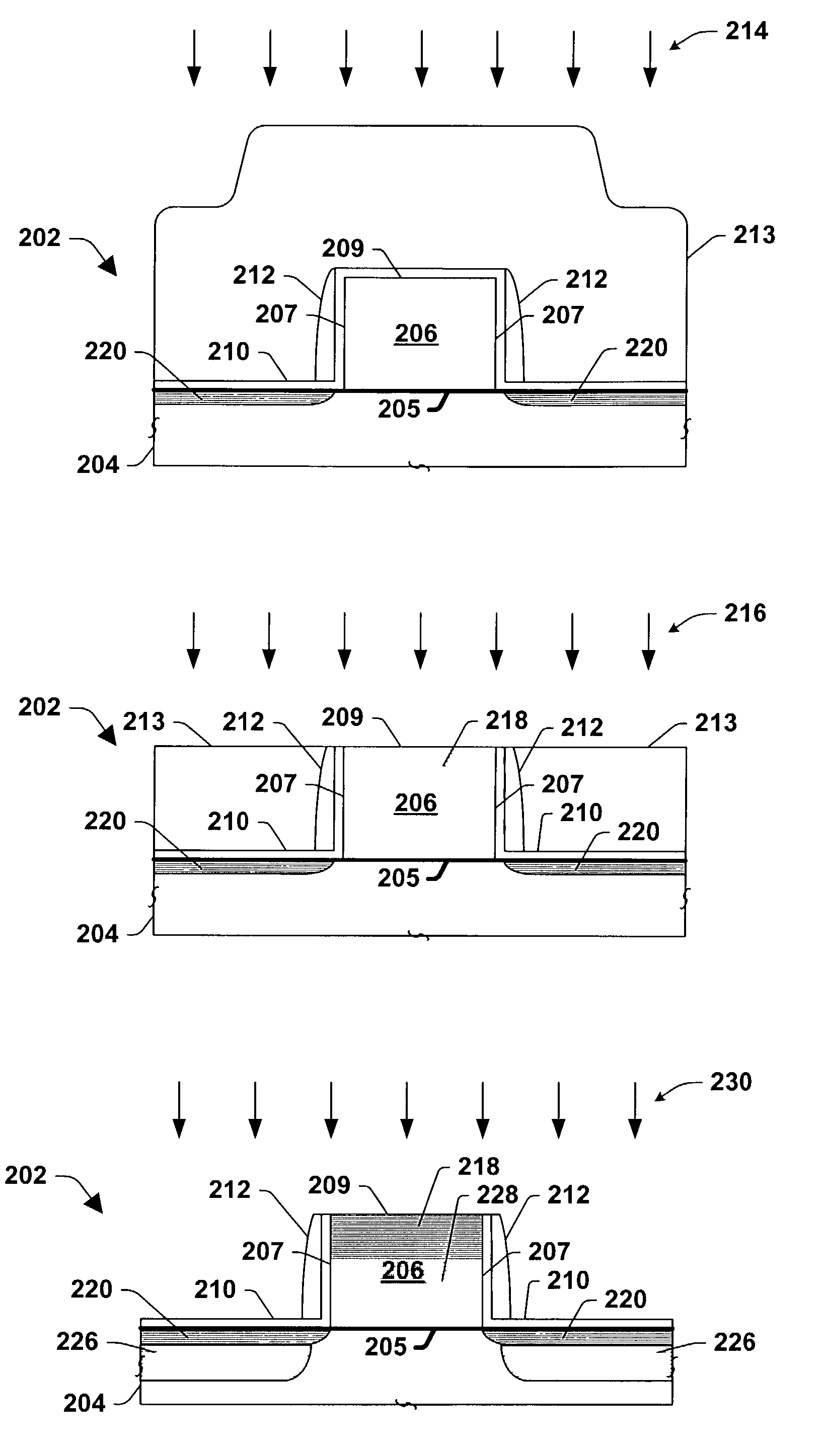

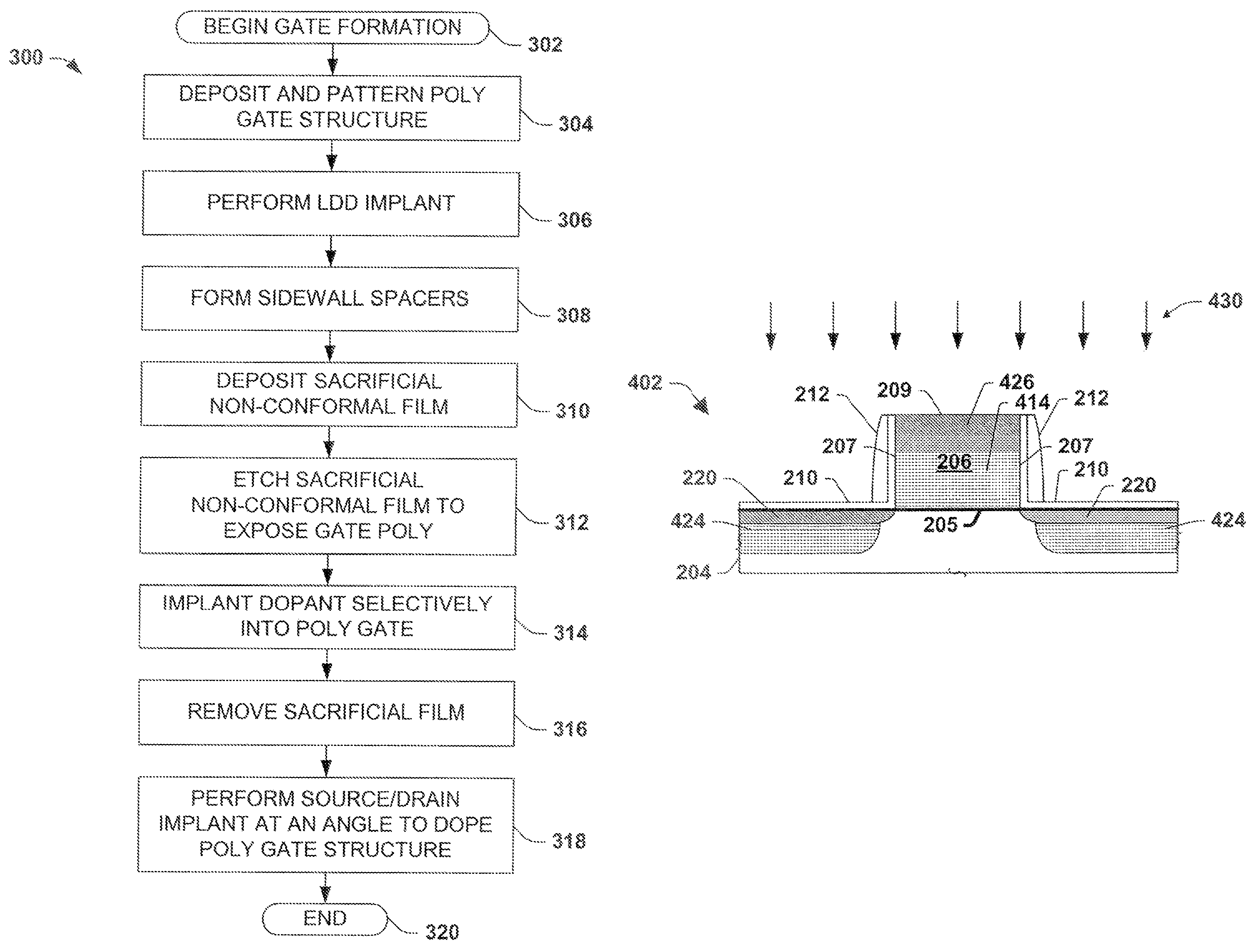

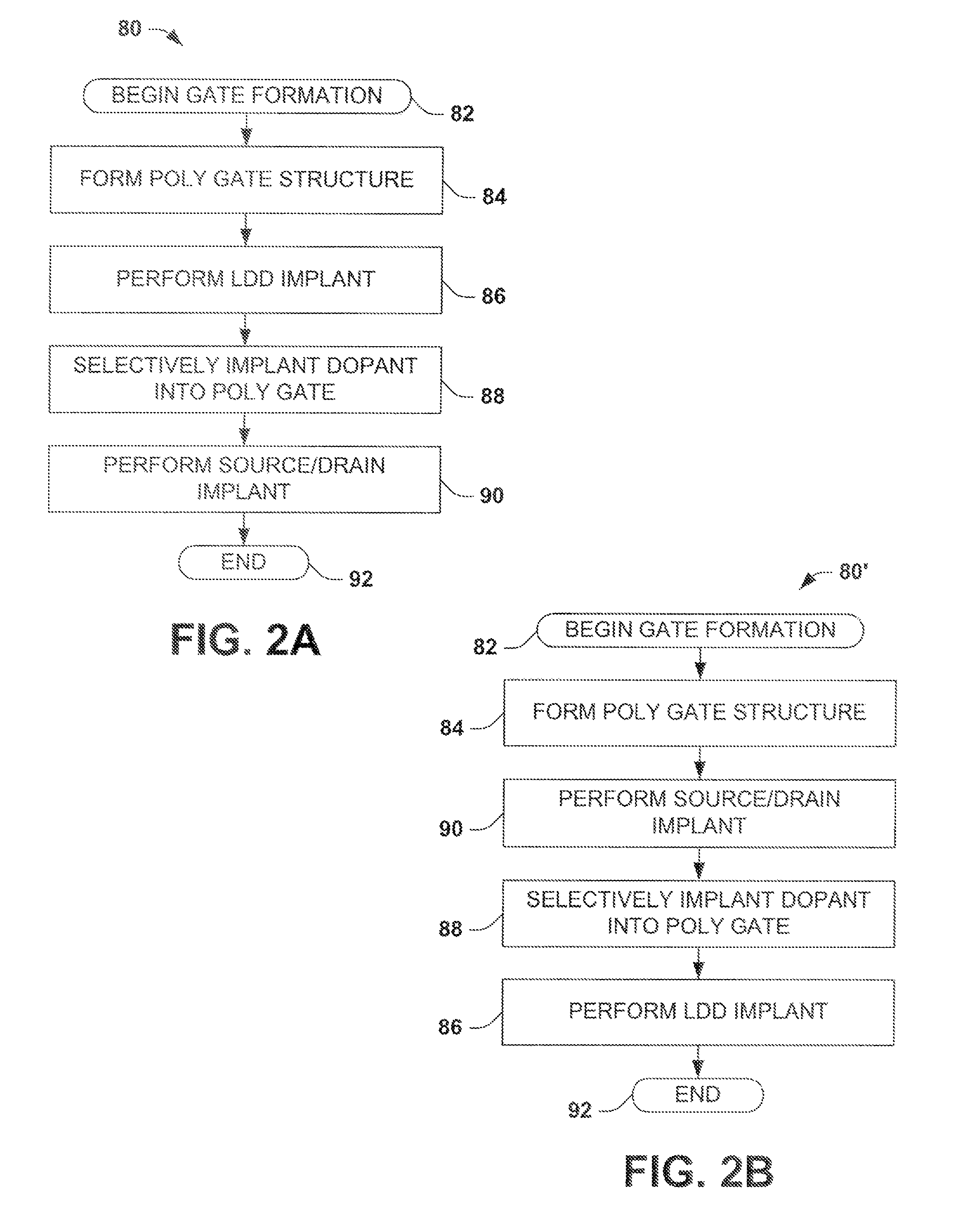

Methods for Transistor Formation Using Selective Gate Implantation

InactiveUS20060270140A1Easy to controlPoly depletion is minimized and mitigatedTransistorSemiconductor/solid-state device manufacturingDopantDevice material

Methods are disclosed for semiconductor device fabrication in which dopants are selectively implanted into transistor gate structures to counteract or compensate for dopant depletion during subsequent fabrication processing. A patterned implant mask is formed over a semiconductor device, which exposes at least a portion of the gate structure and covers the remaining upper surfaces of the device. Thereafter, dopants are selectively implanted in to the exposed gate structure.

Owner:TEXAS INSTR INC

Gate line driving module for liquid crystal display and liquid crystal display using the same

ActiveUS20110007064A1Electron mobilityReduced electron mobilityCathode-ray tube indicatorsNon-linear opticsLiquid-crystal displaySignal source

A gate line driving module used on a liquid crystal display uses clock signal sources in replacement of a high level gate power source, such that the phenomenon of device characteristic drift occurring in the foregoing related art is avoided. The gate line driving module includes a plurality of odd-pixel gate line driving circuits, a plurality of even-pixel gate line driving circuits, and an auxiliary gate line driving circuit. A pair of neighboring odd-pixel gate line driving circuit and even-pixel gate line driving circuit exchange output signals thereof with each other in a forward or feedback manner for ensuring that each the odd-pixel gate line driving circuit and each the even-pixel gate line driving circuit are driven once. The auxiliary gate line driving circuit is used for ensuring that signal iteration of the gate line driving module is under normal operation.

Owner:INNOLUX CORP

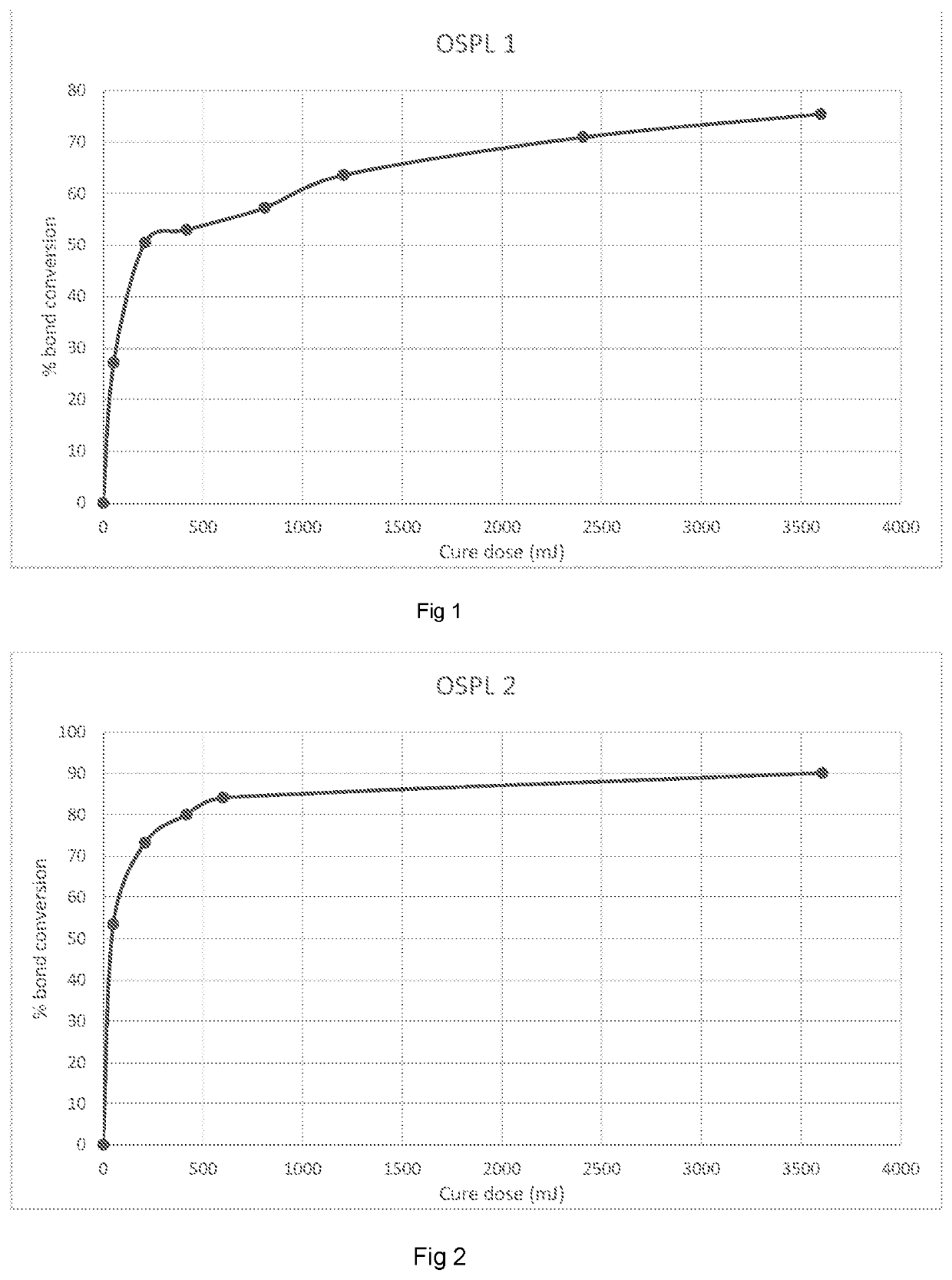

Sputter protective layer for organic electronic devices

PendingUS20210119157A1Low threshold voltage valueHigh currentSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmPhysical chemistry

The present invention provides an organic gate insulator (OGI) layer having a low dielectric constant (k), said organic gate insulator layer being over-coated with a cross-linked organic layer (OSPL) having a relatively high permittivity (k). The present invention also provides an electronic device comprising such an organic thin film transistor. The invention also provides a solution for producing said OSPL, and a process for producing said OSPL.

Owner:SMARTKEM

Methods for transistors formation using selective gate implantation

InactiveUS7098098B2Easy to controlPoly depletion is minimized and mitigatedTransistorSemiconductor/solid-state device manufacturingDopantSemiconductor

Methods are disclosed for semiconductor device fabrication in which dopants are selectively implanted into transistor gate structures to counteract or compensate for dopant depletion during subsequent fabrication processing. A patterned implant mask is formed over a semiconductor device, which exposes at least a portion of the gate structure and covers the remaining upper surfaces of the device. Thereafter, dopants are selectively implanted into the exposed gate structure.

Owner:TEXAS INSTR INC

Rectifier circuit, and contactless power supply device

ActiveUS20170040842A1Reduce power consumptionImprove power supply capacityEfficient power electronics conversionAc-dc conversionVoltage generatorVoltage reference

The rectifier circuit includes: three terminals A, K, VR; voltage comparator including a positive input terminal, a negative input terminal, and a comparative output terminal; current switching unit including source terminal, drain terminal, and control terminal; first switching unit that conducts or cuts off between source terminal and control terminal of the current switching unit; second switching unit that conducts or cuts off between control terminal of the current switching unit and terminal VR; and reference voltage generator that uses terminal A and terminal VR as input terminals, and includes a voltage output terminal. The voltage output terminal of reference voltage generator is connected to the negative input terminal of the voltage comparator, terminal K is connected to the positive input terminal of voltage comparator, and current flow between first switching unit and second switching unit is exclusively allowed or interrupted by a signal output from the comparative output terminal of voltage comparator).

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

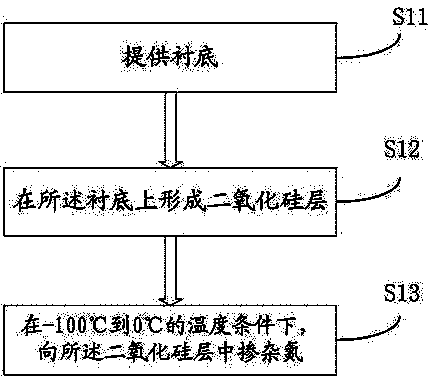

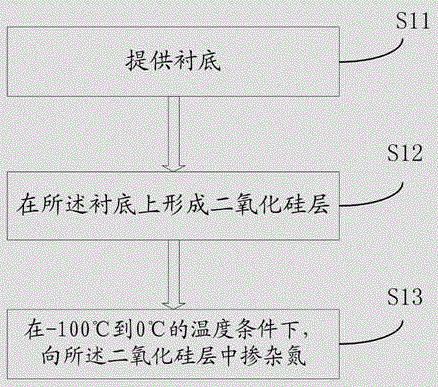

Method for preparing a plasma nitrided gate dielectric layer

ActiveCN104201109AIncrease the nitrogen content of the upper surfaceImprove reliabilitySemiconductor/solid-state device manufacturingCapacitanceGate dielectric

The invention provides a method for preparing a plasma nitrided gate dielectric layer. The method is characterized in that the method includes the steps of providing a substrate, forming a silicon dioxide layer on the substrate and doping nitrogen into a silicon oxide layer under the temperature condition of minus 100 degrees to 0 degree. With the nitrogen doped under the low temperature of minus 100 degrees to 0 degree; diffusion effect of nitrogen ions is reduced; more nitrogen ions gather on the upper surface of the silicon dioxide layer; more bonding between Si-O bond and nitrogen ions is interrupted; nitrogen content on the upper surface of the plasma nitrided gate dielectric layer is increased. Thus, not only is leakage current density reduced but also a high gate capacitance is provided. Furthermore, reliability of the device is improved, and B+ is inhibited from diffusing from gate polysilicon to gate oxide.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Methods for transistor formation using selective gate implantation

InactiveUS7572693B2Poly depletion is minimized and mitigatedIncrease gate capacitanceTransistorSemiconductor/solid-state device manufacturingDopantEngineering

Methods are disclosed for semiconductor device fabrication in which dopants are selectively implanted into transistor gate structures to counteract or compensate for dopant depletion during subsequent fabrication processing. A patterned implant mask is formed over a semiconductor device, which exposes at least a portion of the gate structure and covers the remaining upper surfaces of the device. Thereafter, dopants are selectively implanted in to the exposed gate structure.

Owner:TEXAS INSTR INC

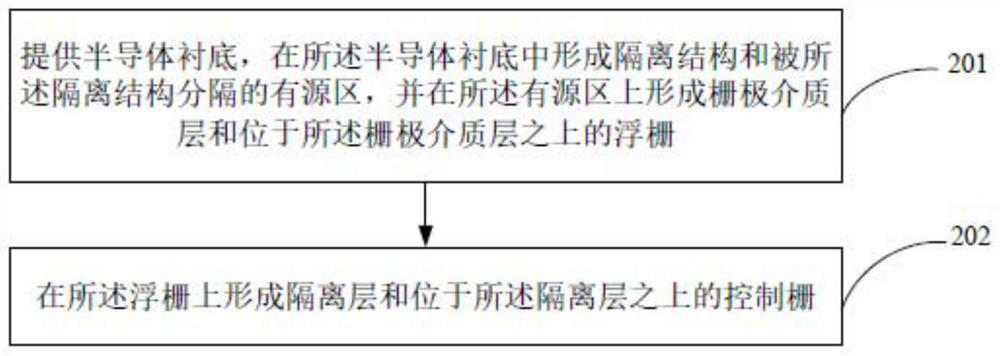

A kind of semiconductor device and its manufacturing method, electronic device

ActiveCN108336086BIncrease power consumptionIncrease gate capacitanceTransistorSolid-state devicesCapacitanceDevice material

The present invention provides a semiconductor device, a manufacturing method thereof, and an electronic device. The manufacturing method includes: providing a semiconductor substrate, forming a floating gate on the semiconductor substrate; forming a control gate on the floating gate, wherein the The floating gate includes a main body over the semiconductor substrate and protrusions located at both ends of the main body and protruding toward the control gate. The manufacturing method can increase the gate capacitance between the control gate and the floating gate interface, improve device power consumption, and reduce leakage current. The semiconductor device and electronic device have similar advantages.

Owner:SEMICON MFG NORTH CHINA (BEIJING) CORP +2

Semiconductor-Based Gas Sensor Assembly for Detecting a Gas and Corresponding Production Method

InactiveUS20180017521A1Increase the number ofHigh sensitivityMaterial analysis by electric/magnetic meansCapacitanceDielectric layer

A semiconductor-based gas sensor assembly for detecting a gas includes a gas-sensitive structure with a gas electrode, an electrode, and a dielectric layer, and also includes a readout transistor and a substrate. The dielectric layer is positioned between the gas electrode and the electrode, and is at least partially polarized. The readout transistor is positioned in or on the substrate, and includes a gate. The gas-sensitive structure is configured to form a capacitance that is coupled to the gate of the readout transistor.

Owner:ROBERT BOSCH GMBH

A method for preparing plasma nitride gate dielectric layer

ActiveCN104201109BIncrease the nitrogen content of the upper surfaceImprove reliabilitySemiconductor/solid-state device manufacturingLeakage current densityGate dielectric

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com