Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

100 results about "Gated diode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

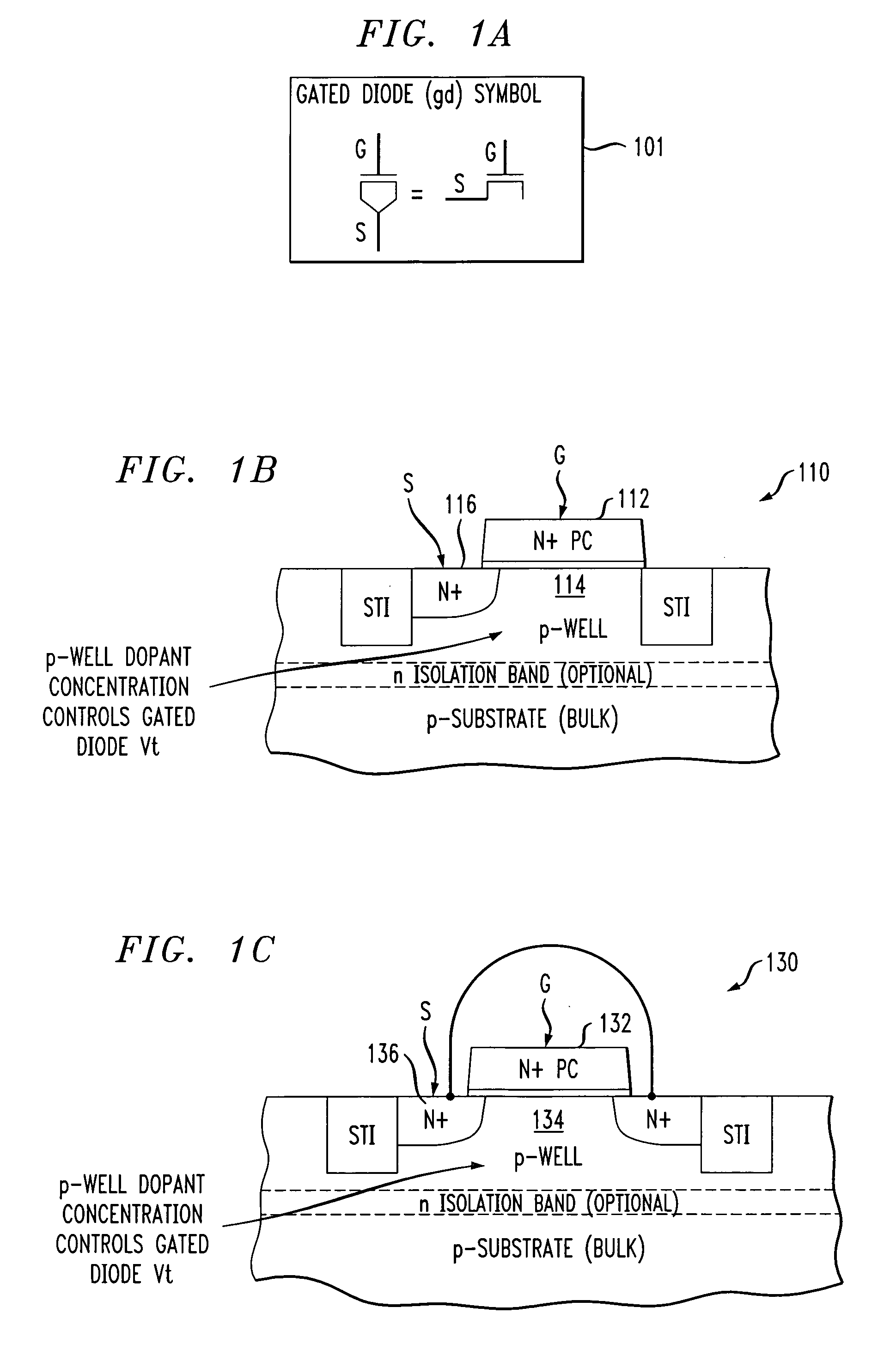

“According to a further embodiment, a gated diode includes a base which is configured to be press-fit into an opening of a diode carrier plate. The gated diode may be press-fitted from both sides of the diode carrier plate. The base includes a pedestal portion with a first flat surface.

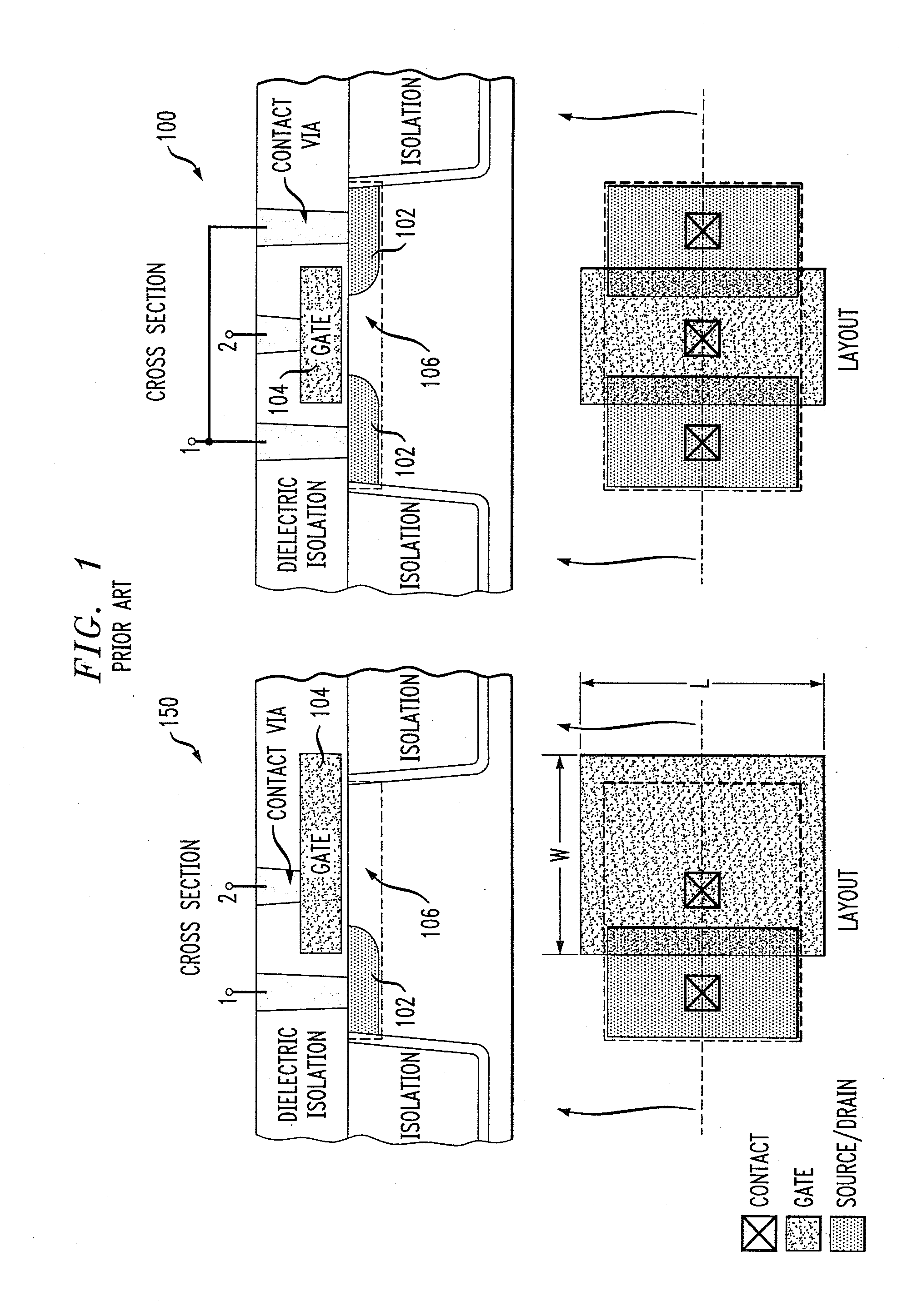

High voltage level shifter for switching high voltage in non-volatile memory integrated circuits

InactiveUS6437627B1High junction breakdownGated diode breakdownPulse automatic controlLogic circuits coupling/interface using field-effect transistorsHigh voltage igbtLow voltage

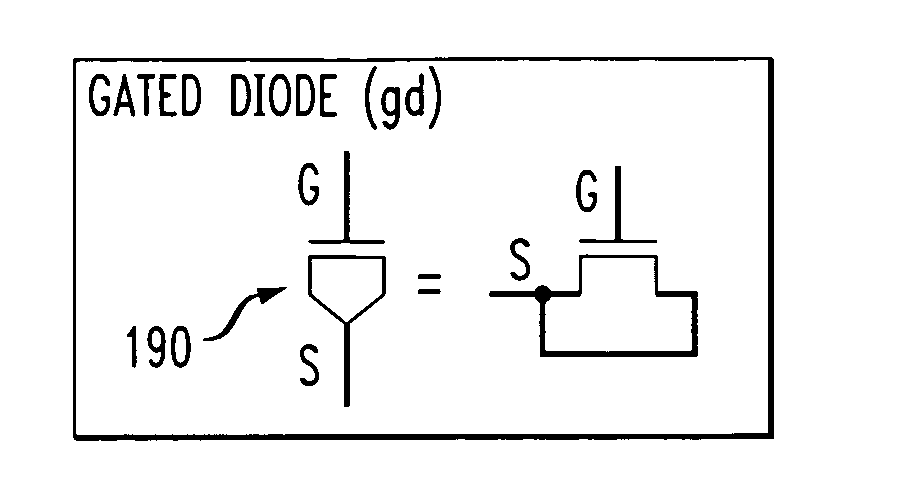

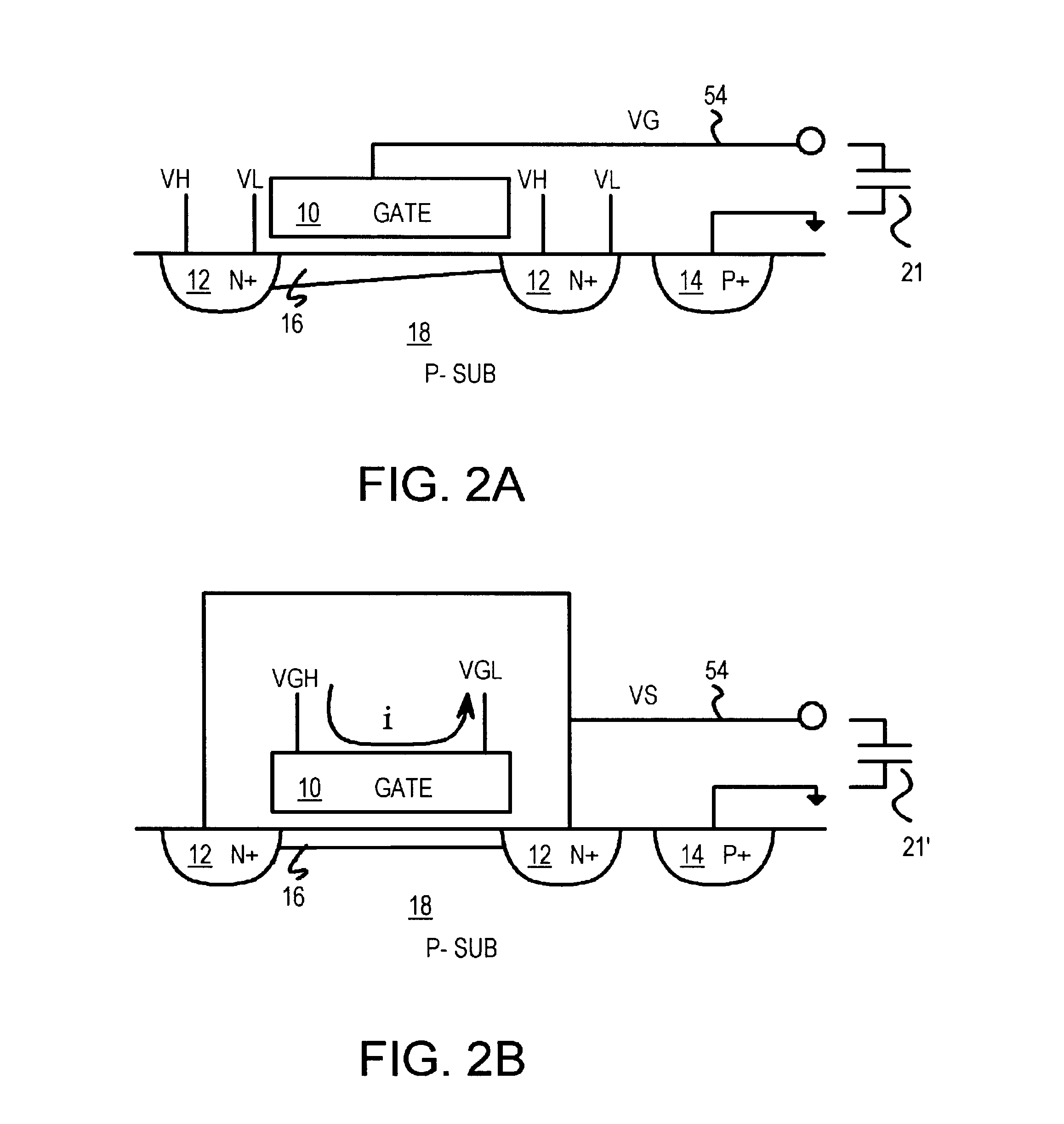

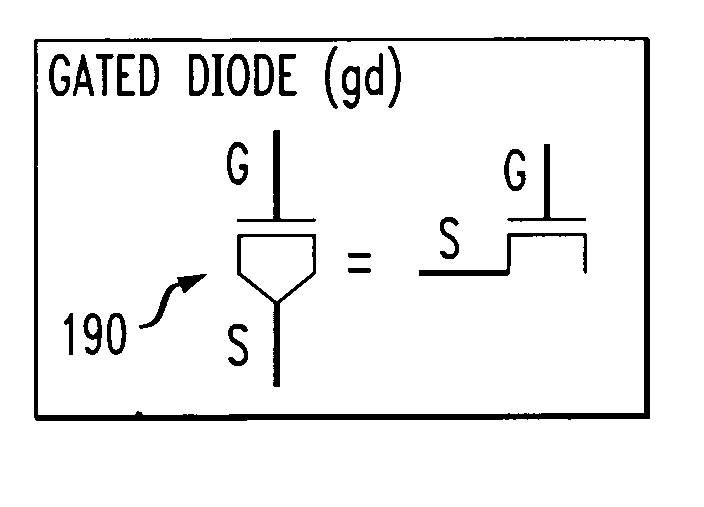

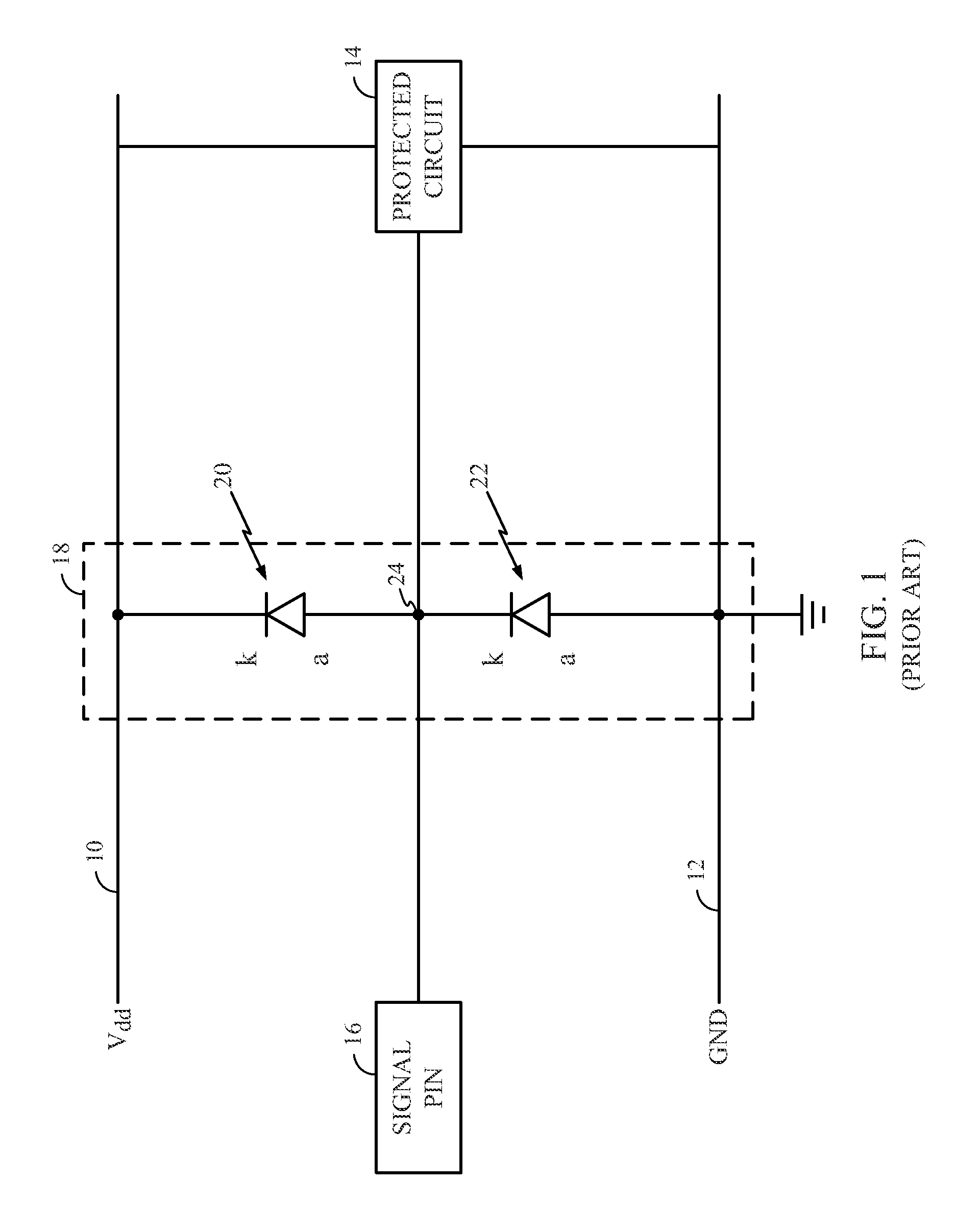

A high voltage level shifter utilizing only low voltage PMOS and low voltage NMOS devices. The high voltage level shifter is used to distribute the high voltage almost equally among the PMOS devices and almost equally among the NMOS devices to meet the device electrical specification of low voltage MOS devices for various breakdown mechanisms. A layout technique is also used to achieve a much higher junction breakdown of N+ drain to P-substrate and a better gated diode breakdown of NMOS devices.

Owner:WINBOND ELECTRONICS CORP

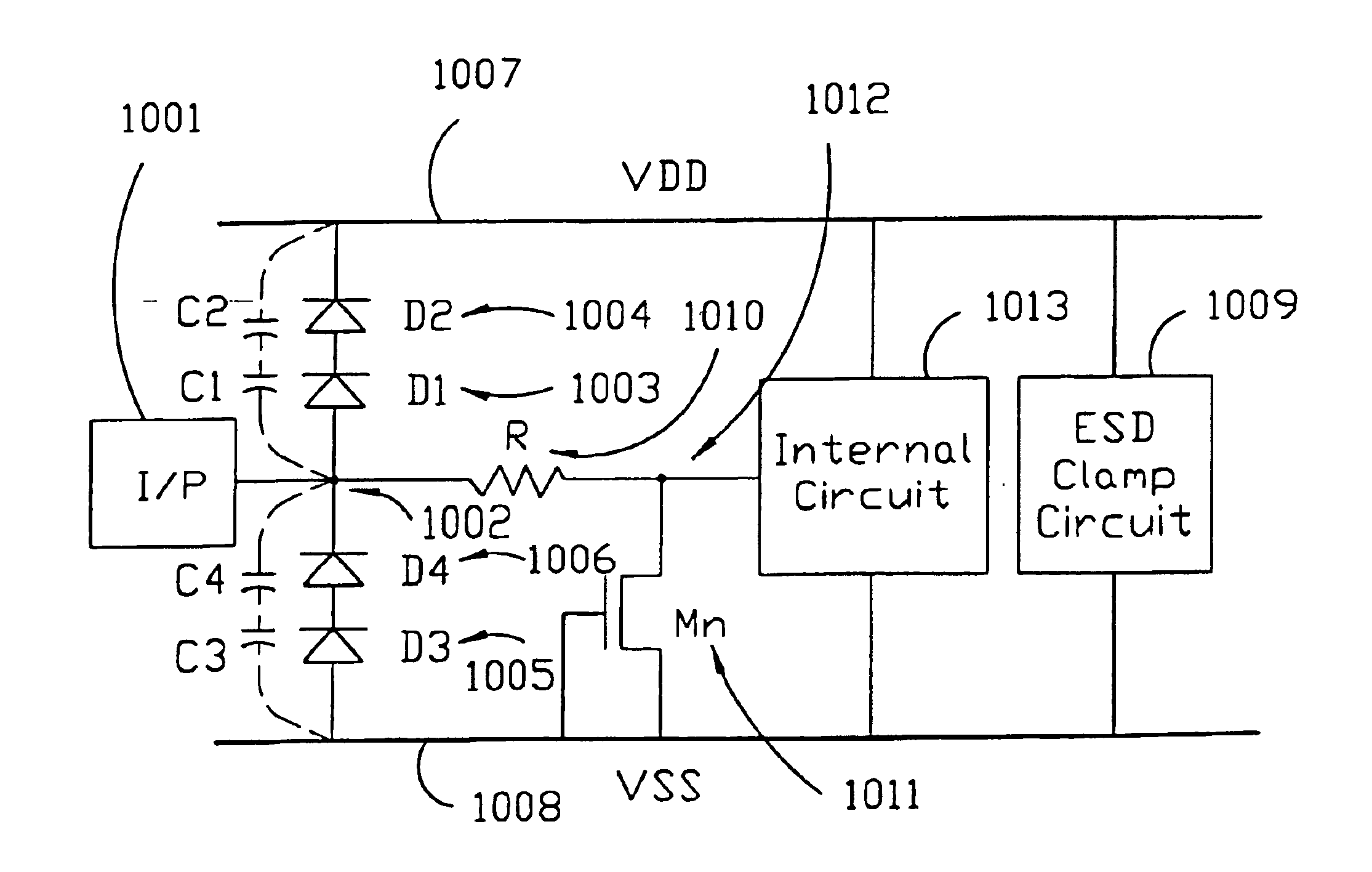

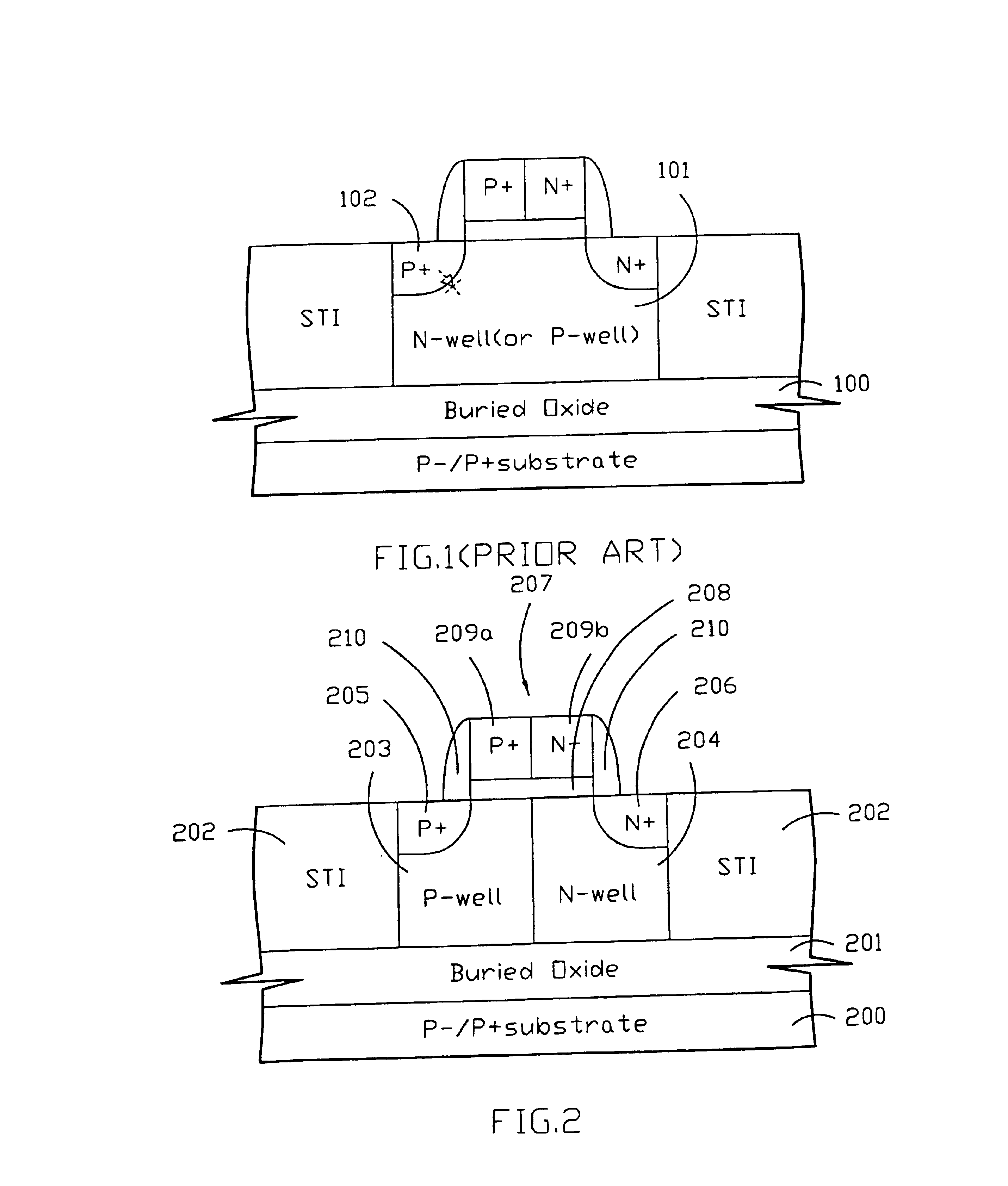

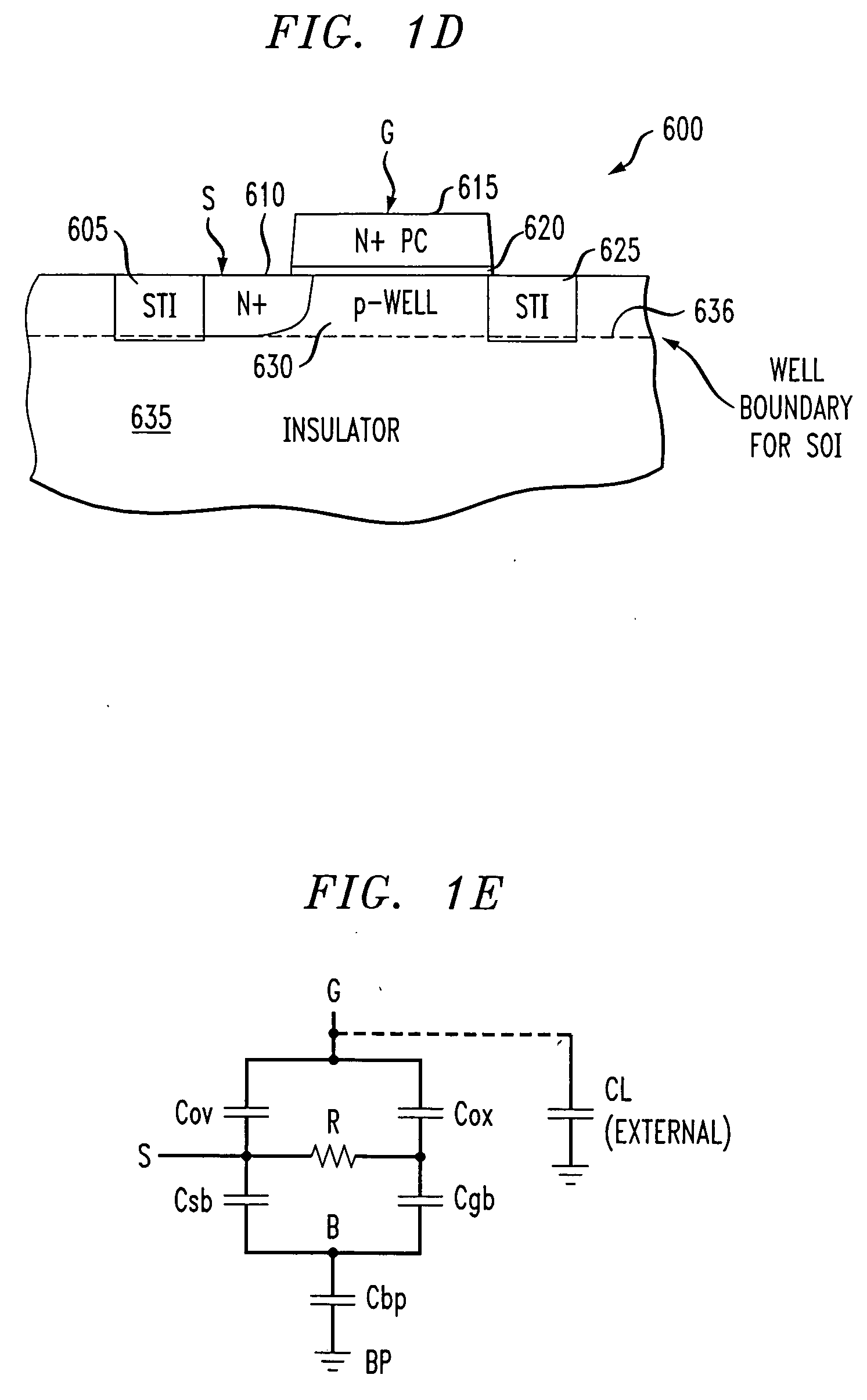

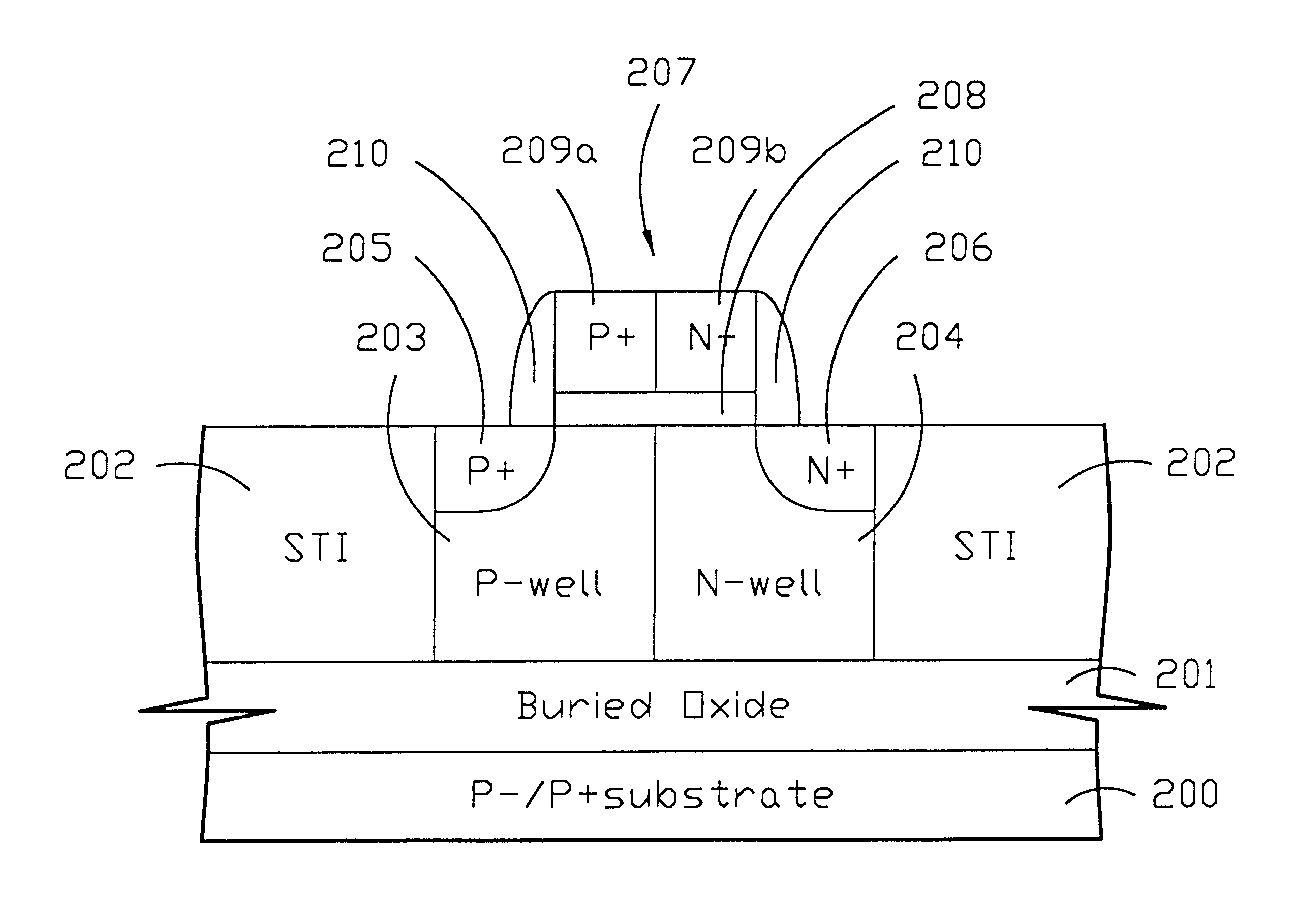

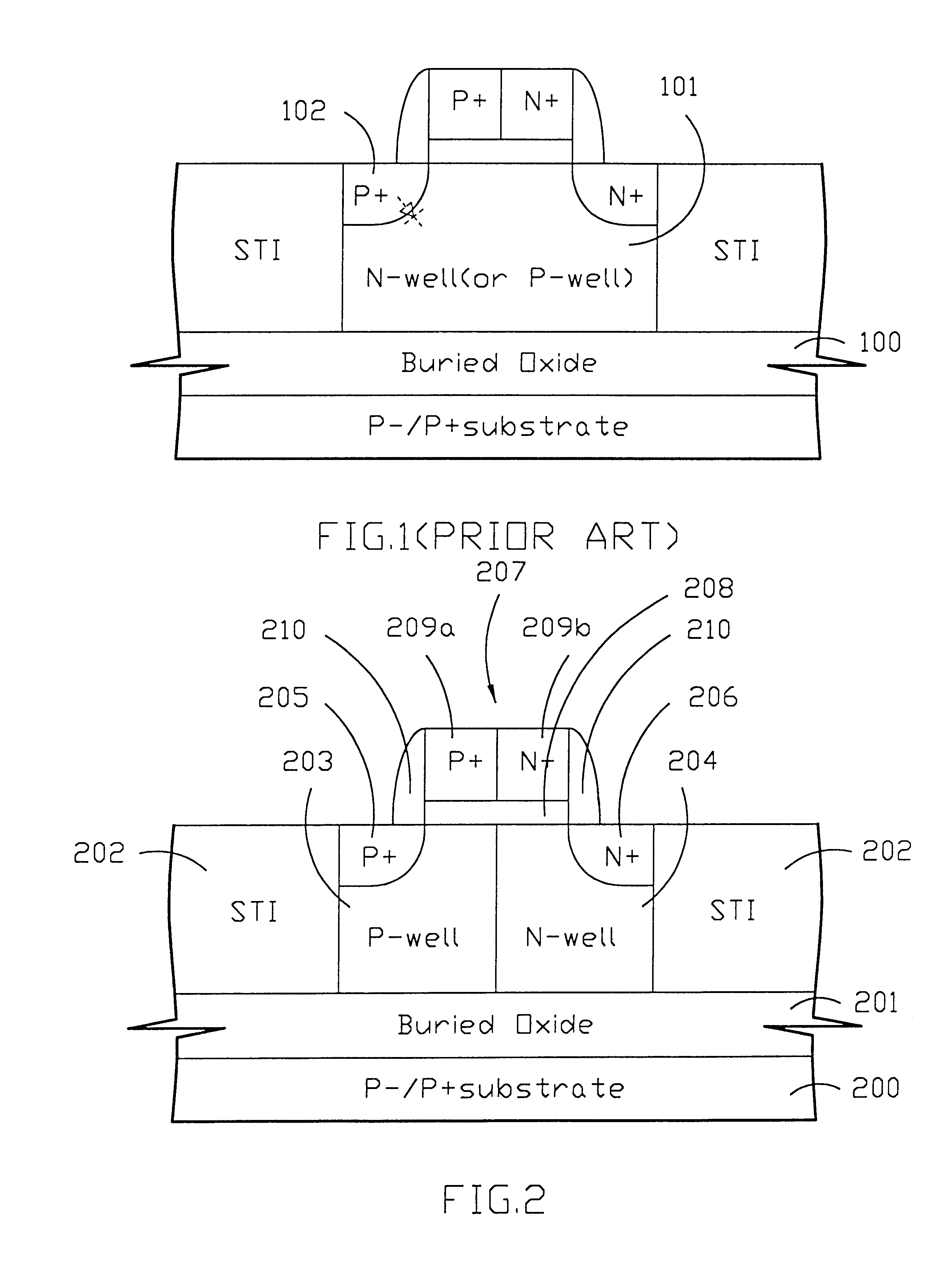

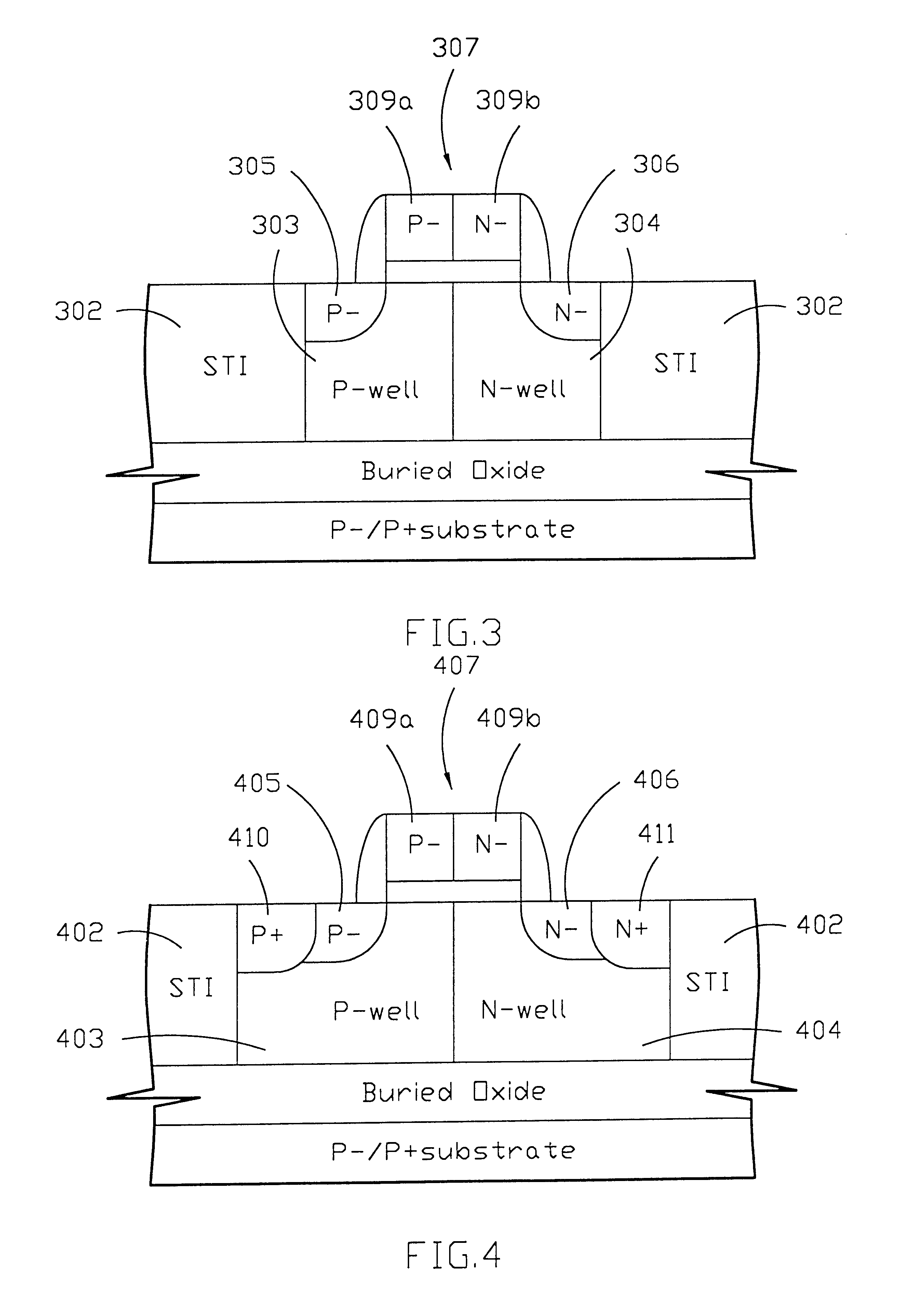

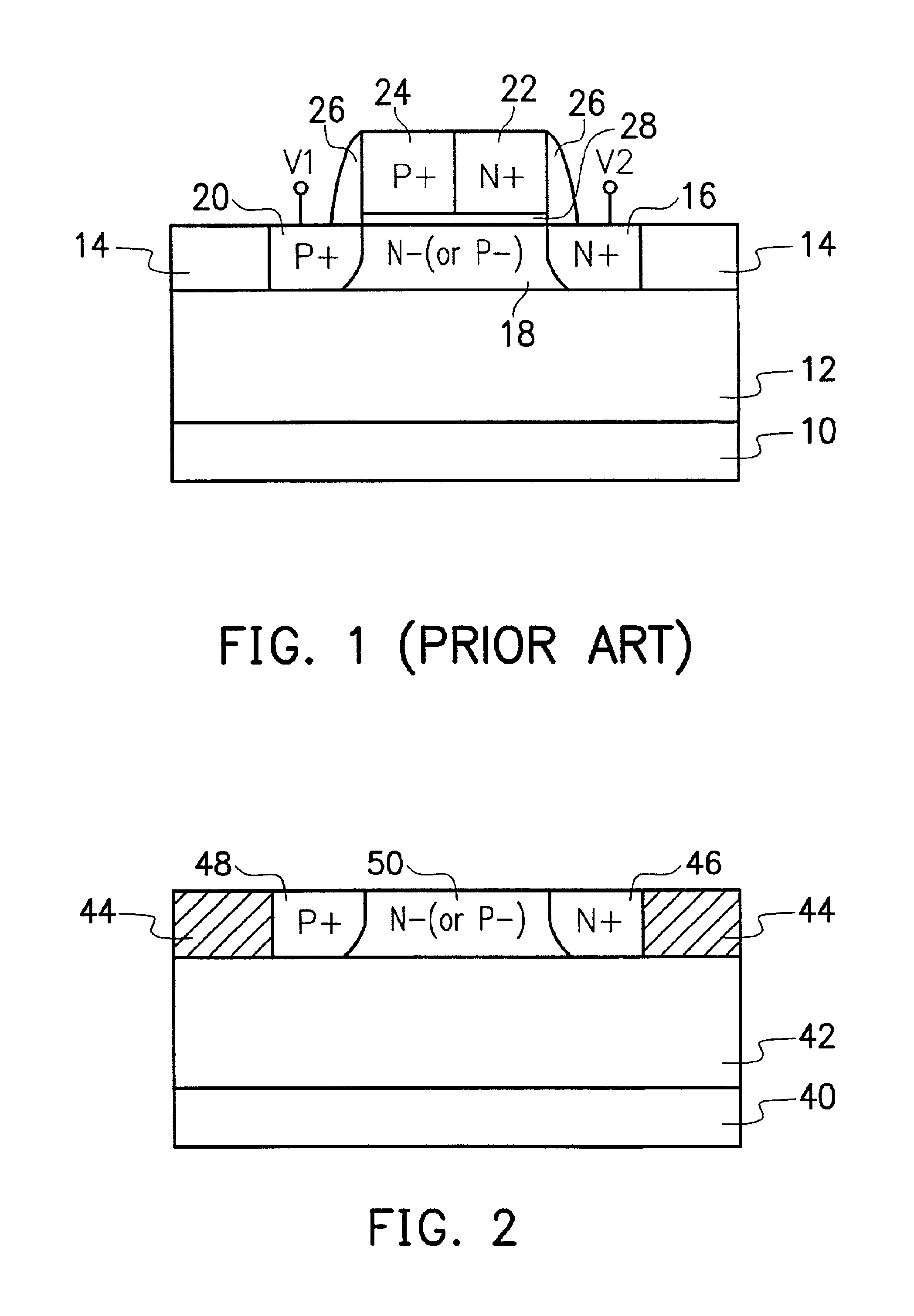

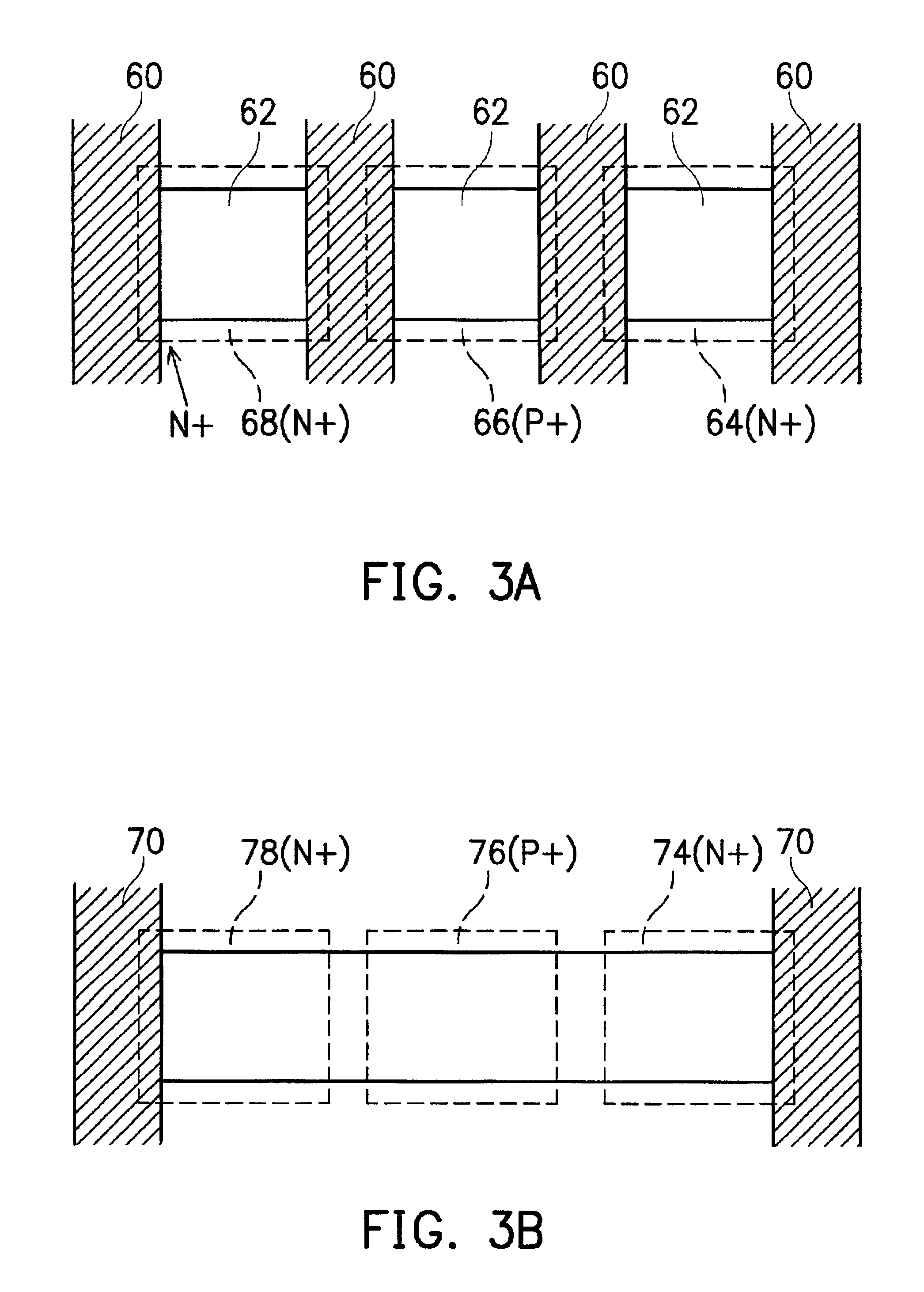

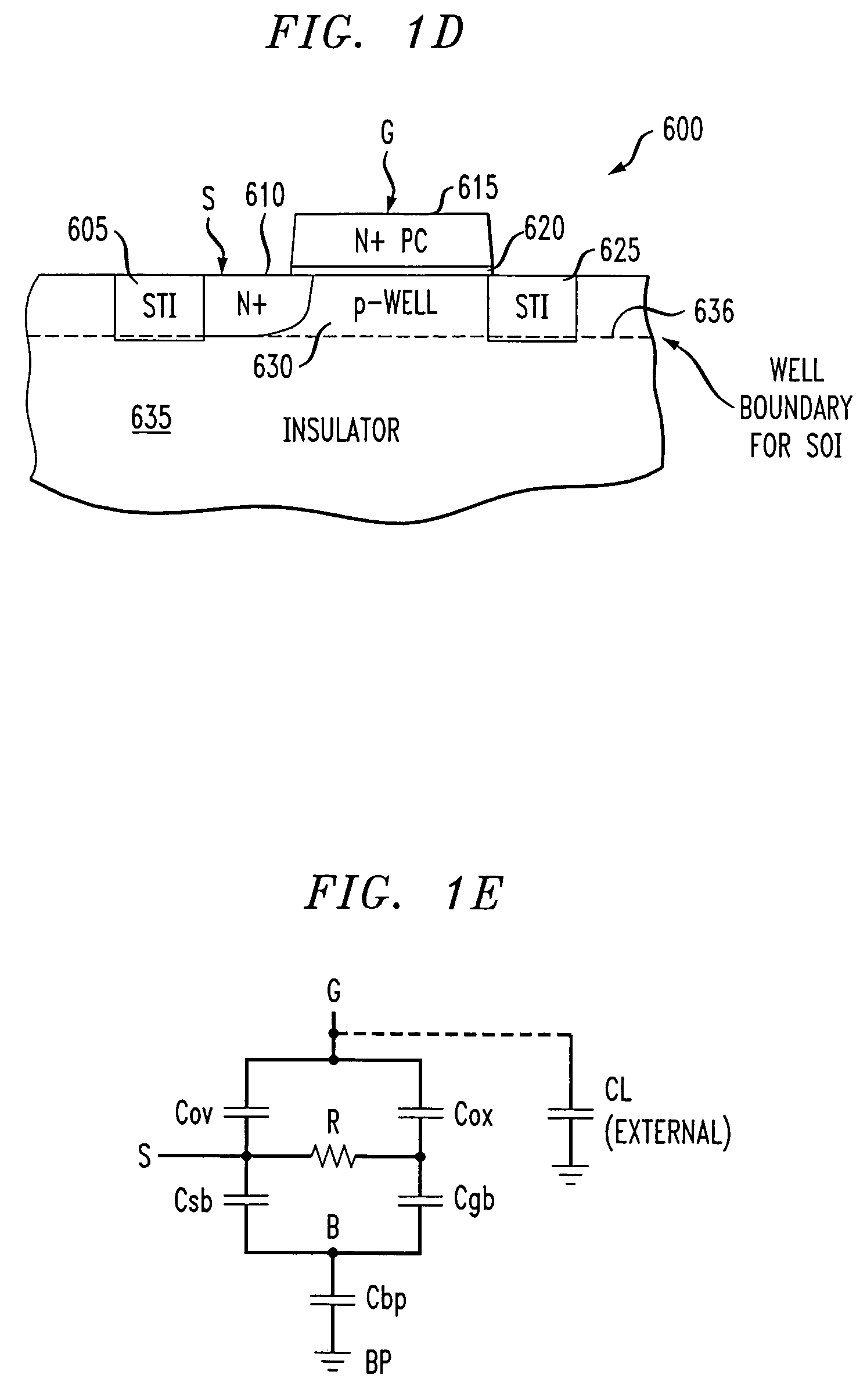

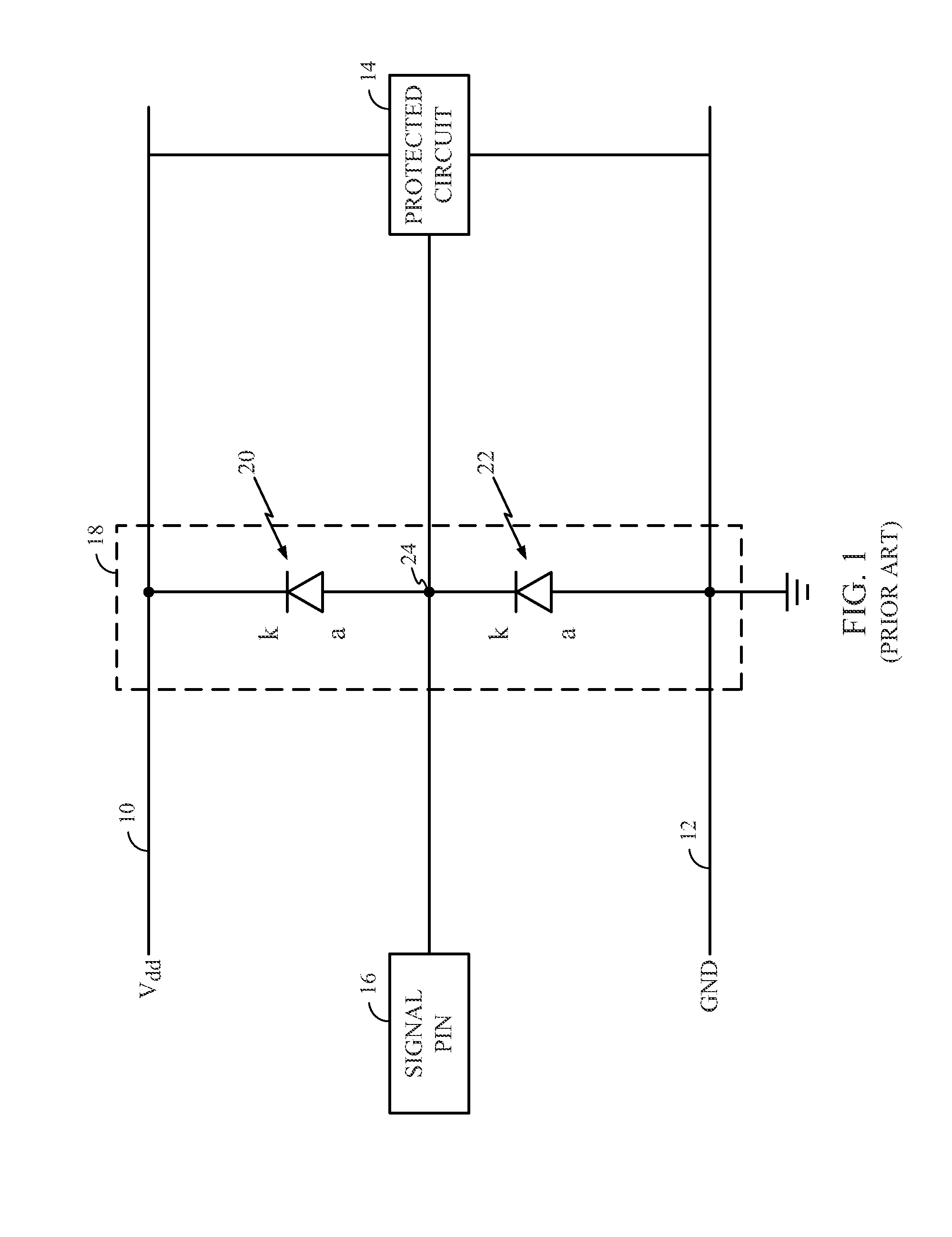

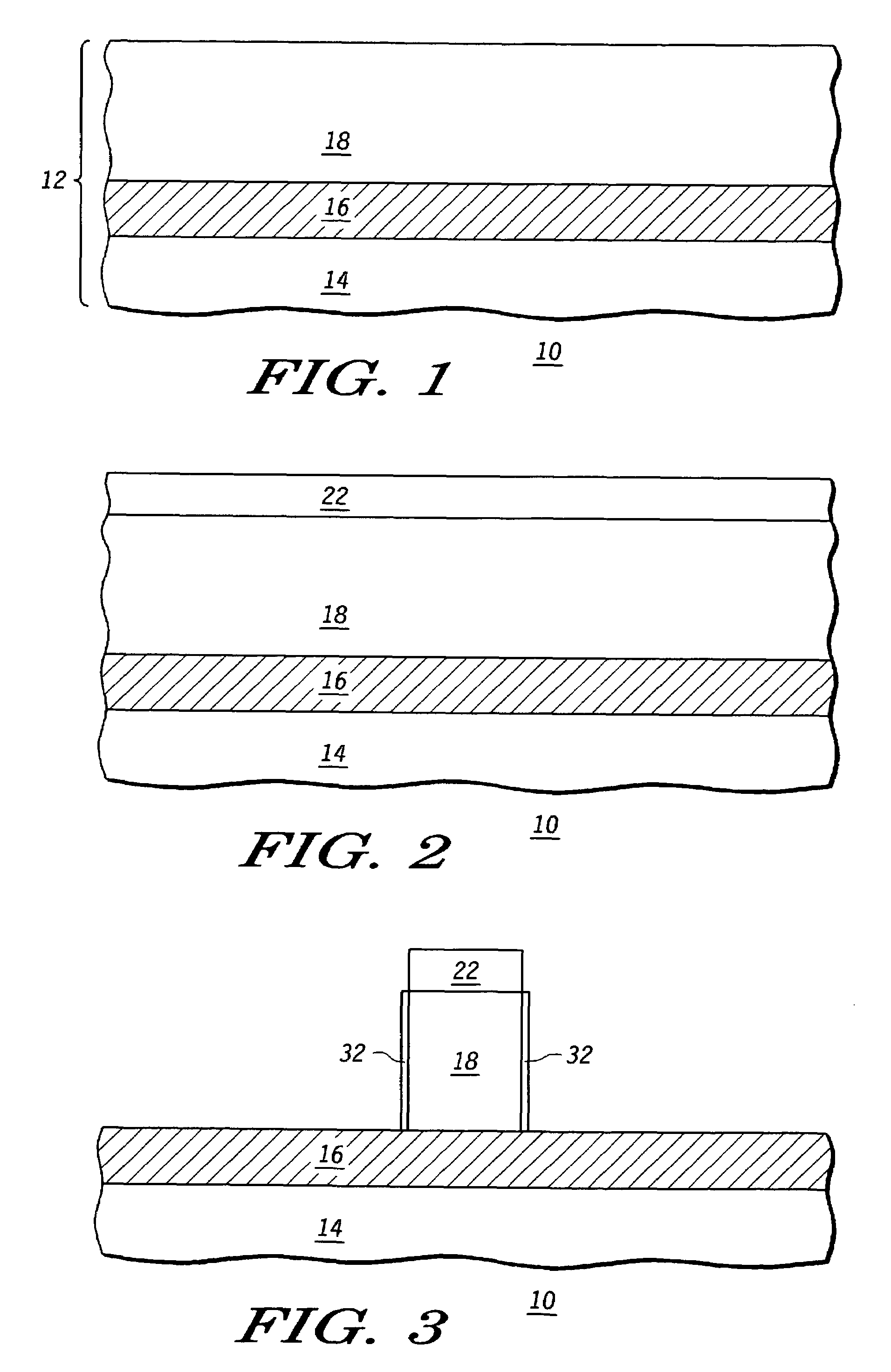

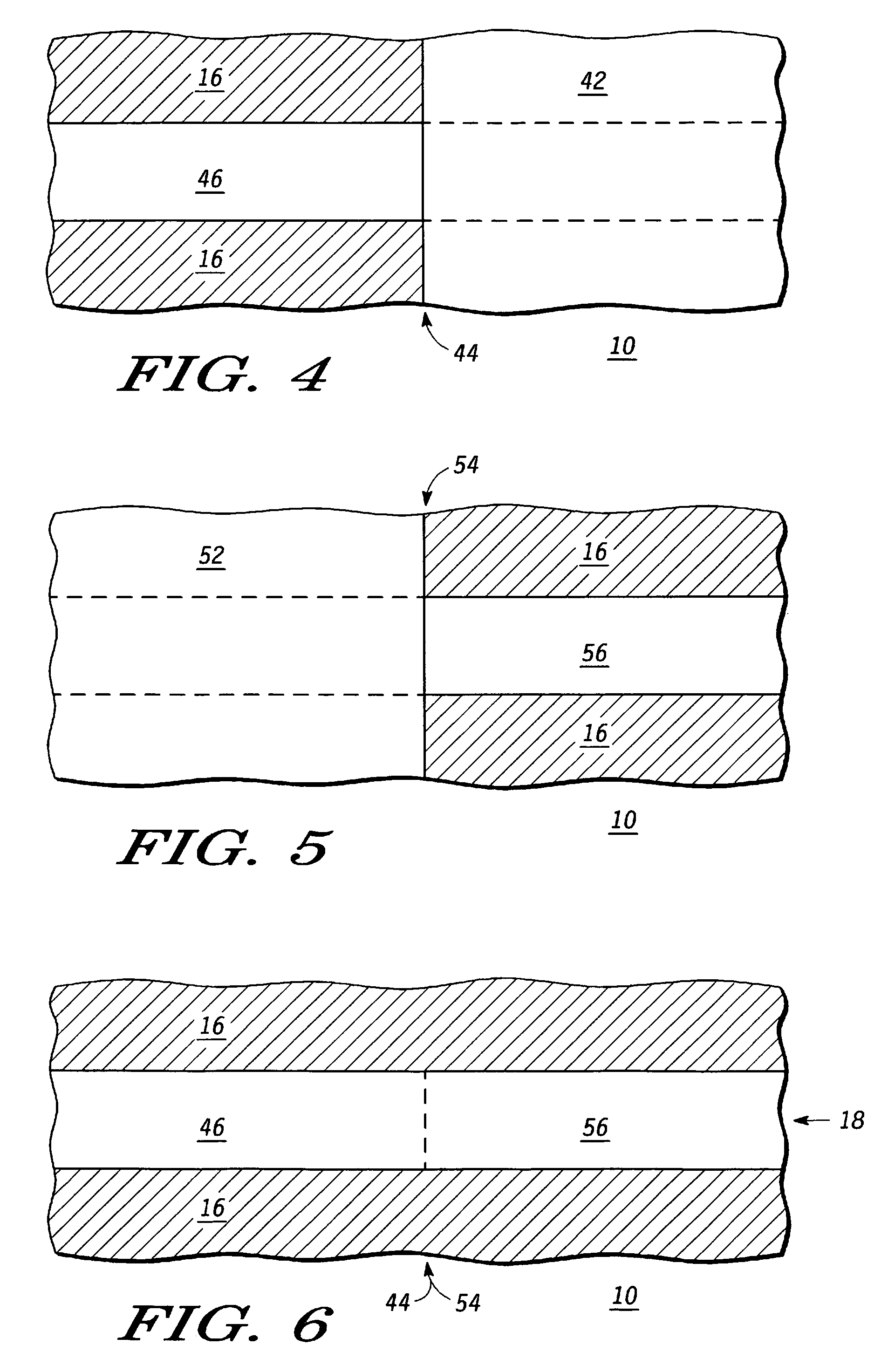

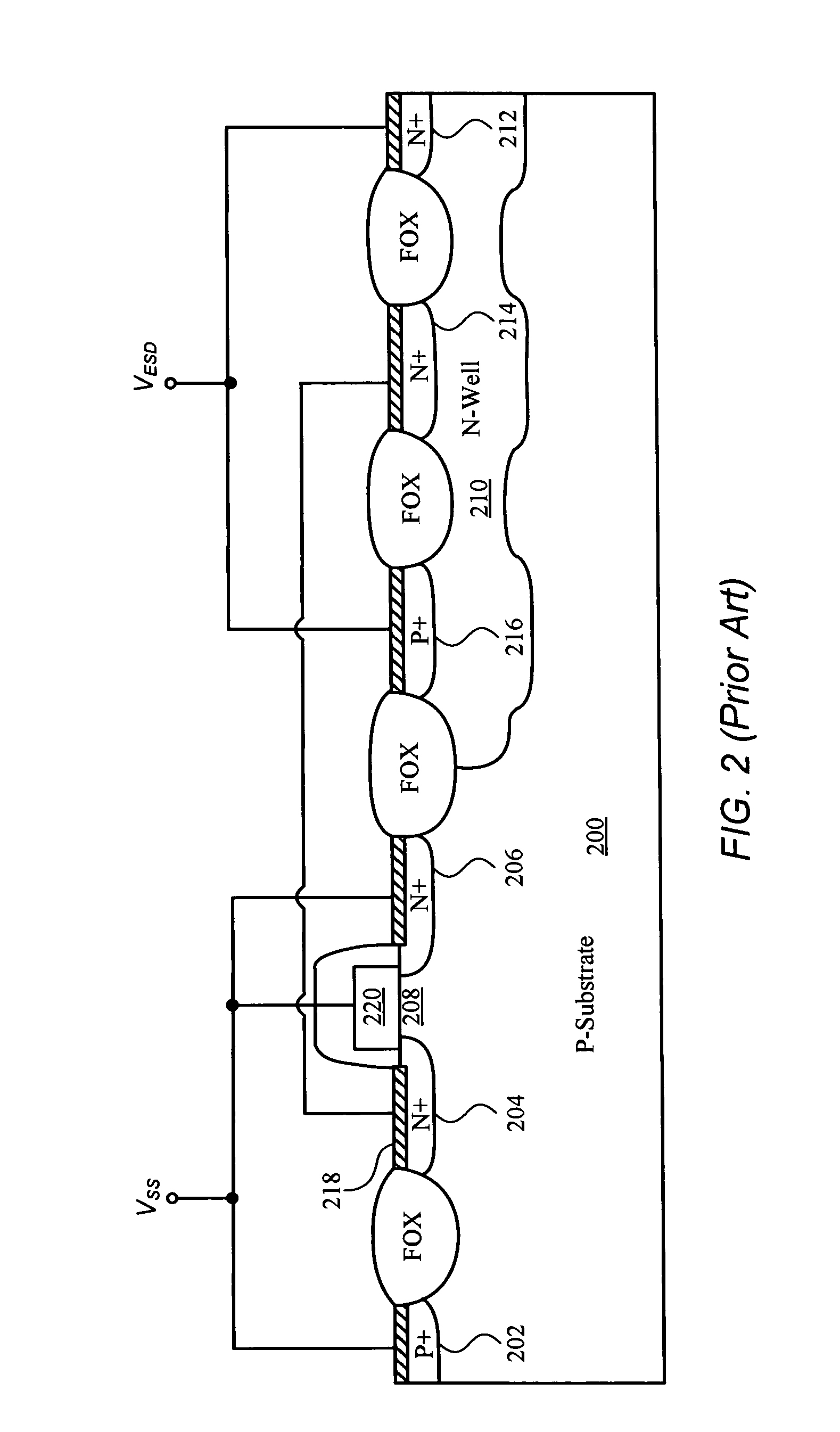

Silicon-on-insulator diodes and ESD protection circuits

InactiveUS6861680B2Reduce power densityHigh protection levelTransistorSolid-state devicesCapacitanceSilicon on insulator

A silicon-on-insulator (SOI) gated diode and non-gated junction diode are provided. The SOI gated diode has a PN junction at the middle region under the gate, which has more junction area than a normal diode. The SOI non-gated junction diode has a PN junction at the middle region thereof, and also has more junction area than a normal diode. The SOI diodes of the present invention improve the protection level offered for electrical overstress (EOS) / electrostatic discharge (ESD) due to the low power density and heating for providing more junction area than normal ones. The I / O ESD protection circuits, which comprise primary diodes, a first plurality of diodes, and a second plurality of diodes, all of which are formed of the present SOI diodes, could effectively discharge the current when there is an ESD event. And the ESD protection circuits, which comprise more primary diodes, could effectively reduce the parasitic input capacitance, so that they can be used in the RF circuits or HF circuits. The proposed gated diode and non-gated diode can be fully process-compatiable to general partially-depleted or fully-depleted silicon-on-insulator CMOS processes.

Owner:UNITED MICROELECTRONICS CORP

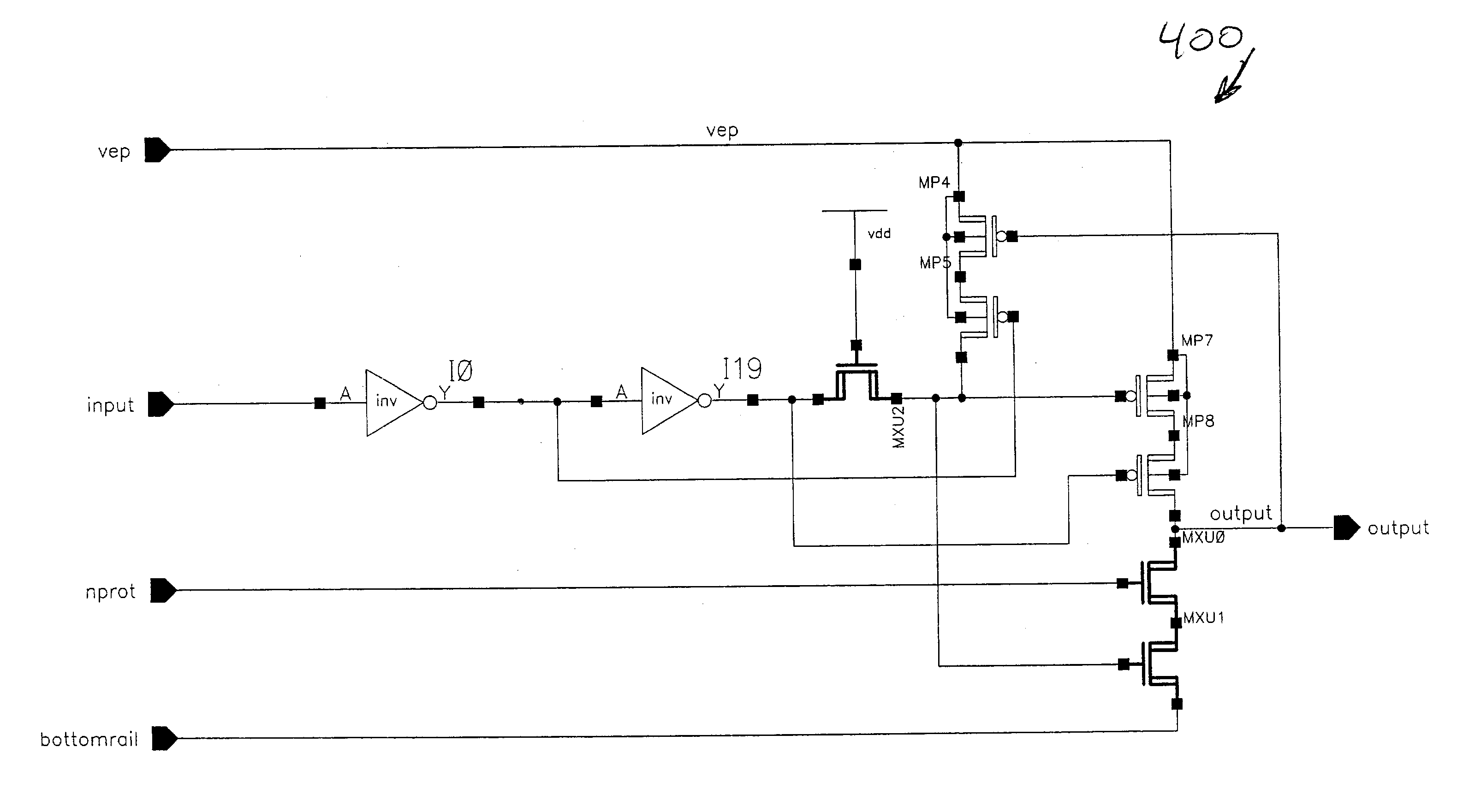

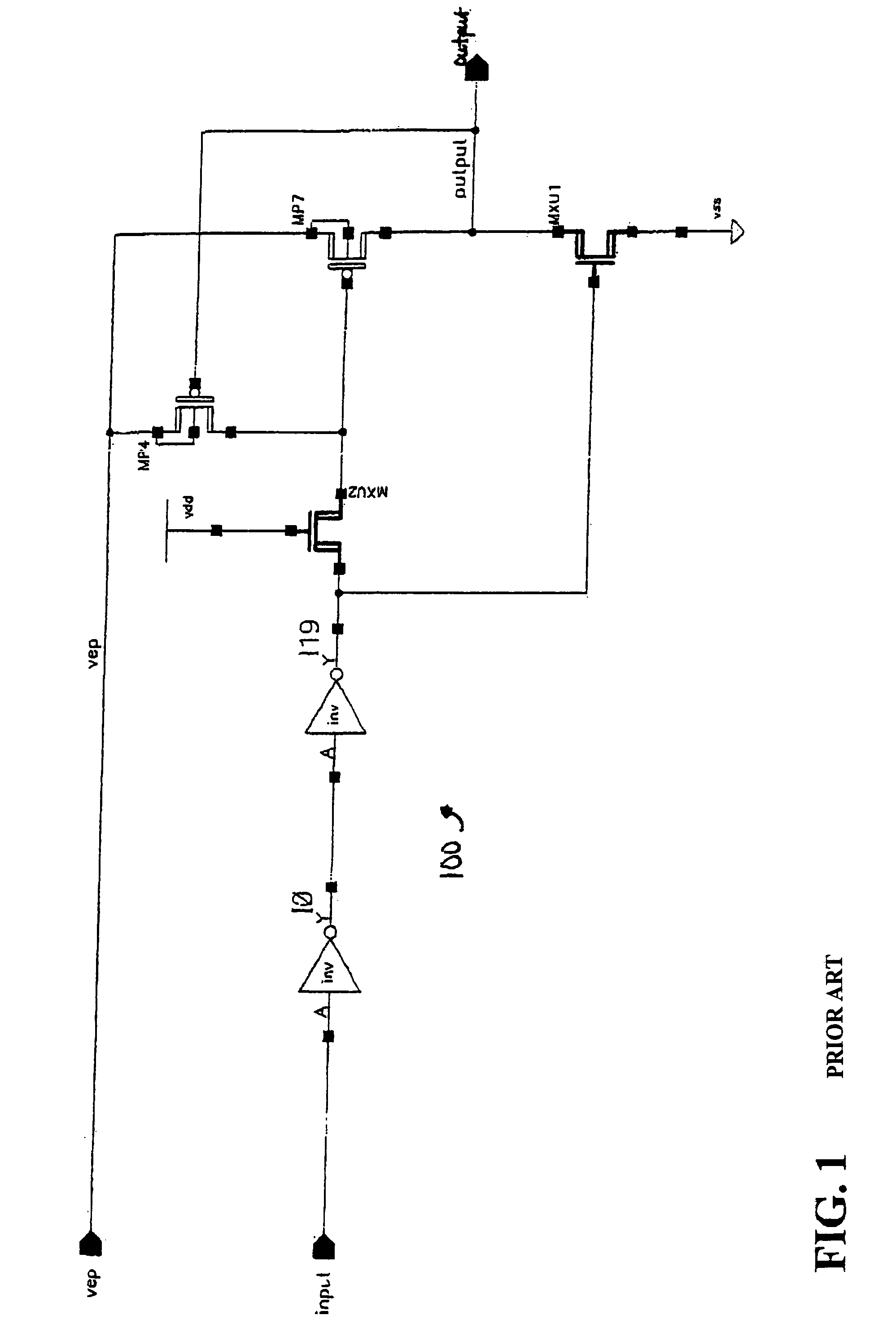

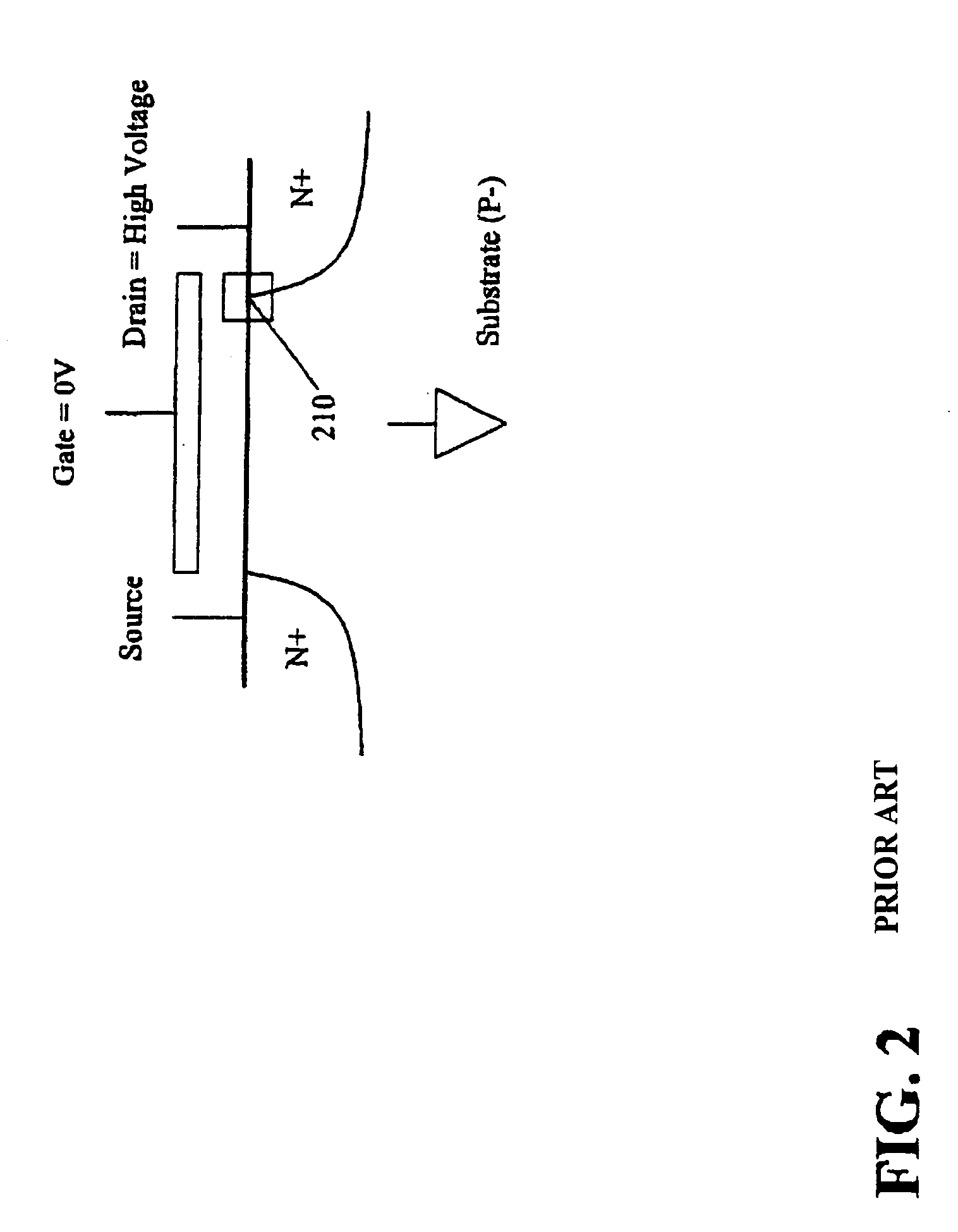

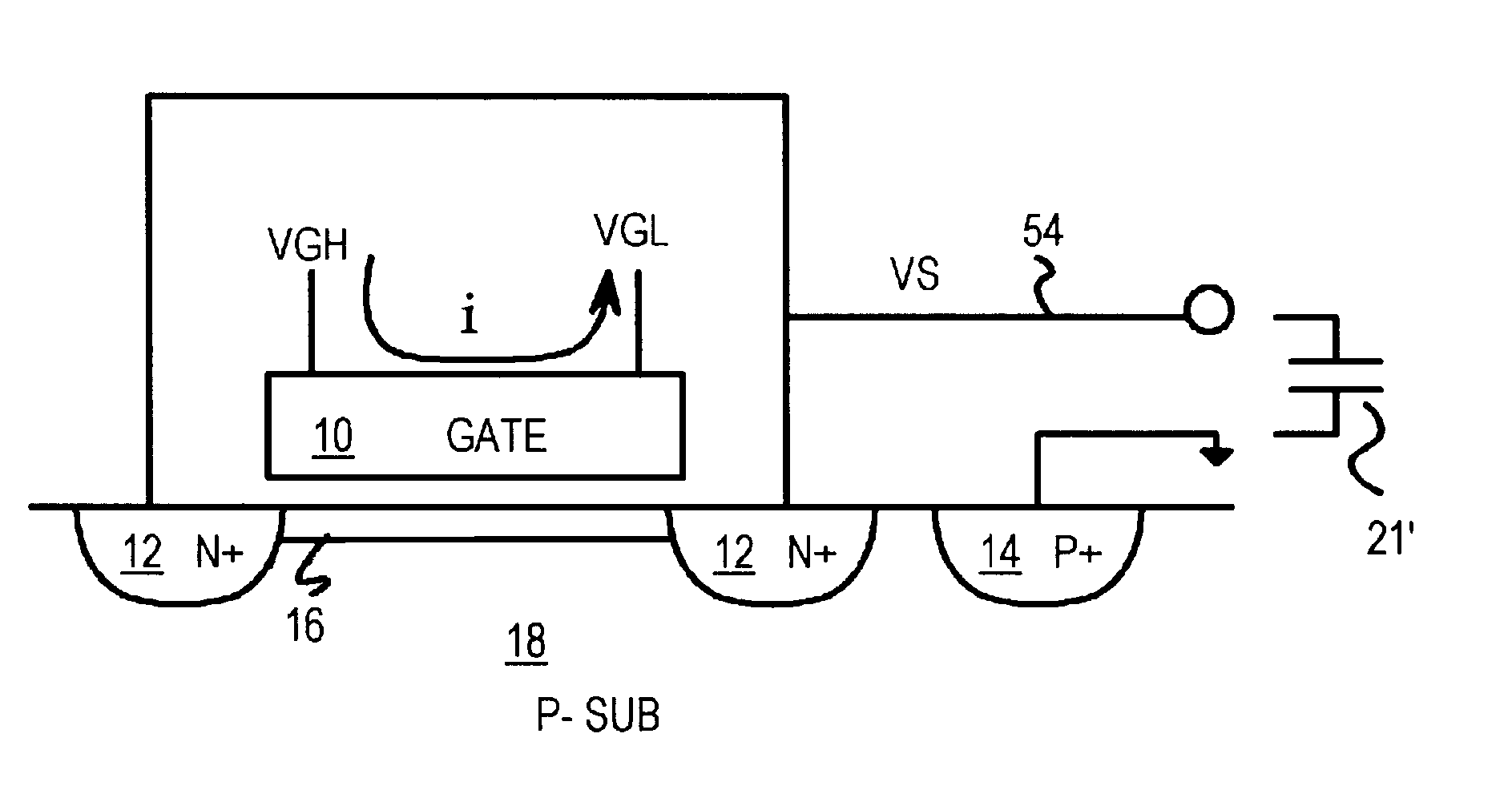

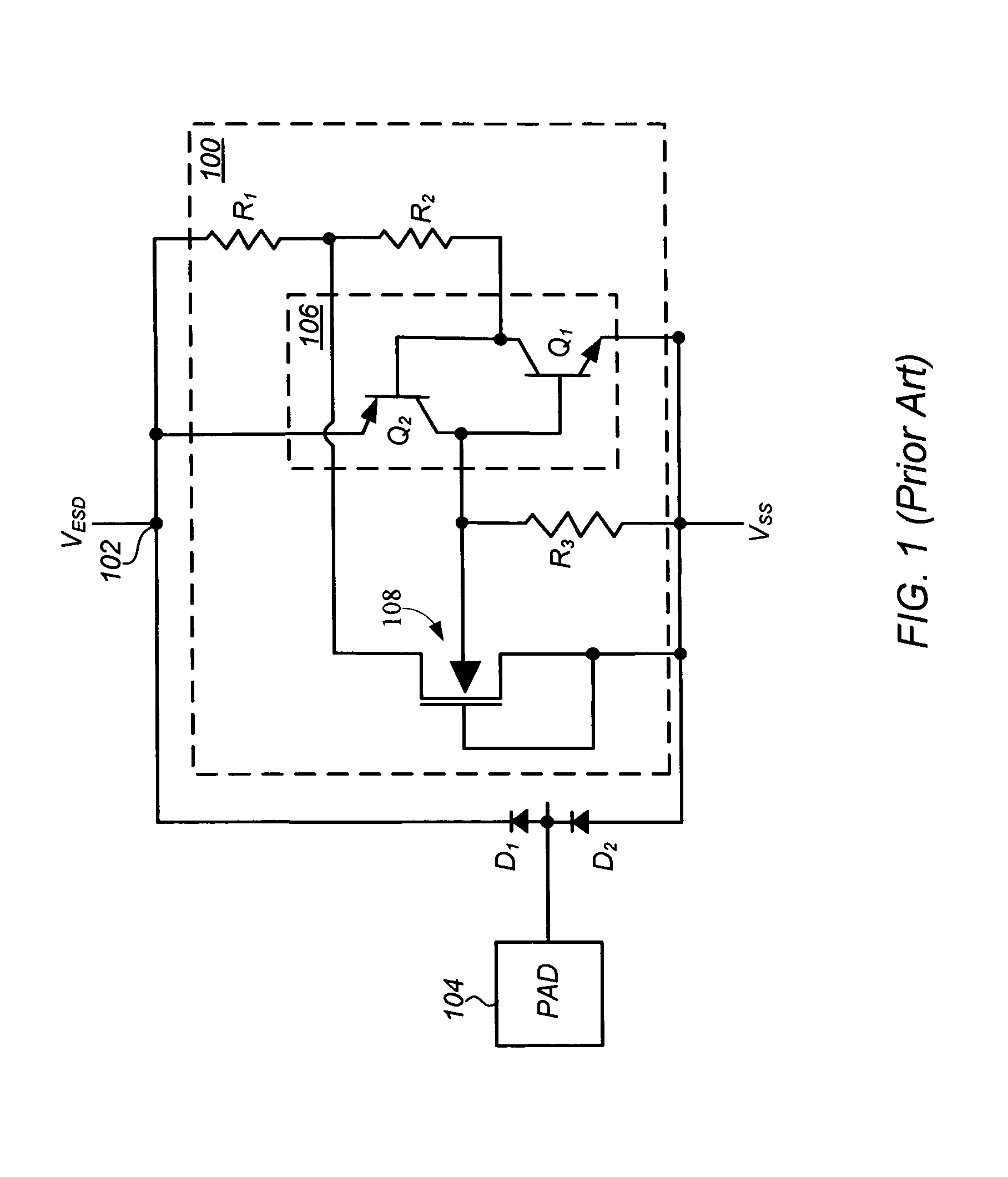

Method and apparatus for avoiding gated diode breakdown in transistor circuits

InactiveUS7132873B2Prevents gated diode breakdownAvoid failureTransistorPulse automatic controlTransistor circuitsHigh pressure

An N-channel transistor protection circuit and method are disclosed that prevent gated diode breakdown in N-channel transistors that have a high voltage on their drain. The disclosed N-channel protection circuit may be switched in a high voltage mode between a high voltage level and a lower rail voltage. A high voltage conversion circuit prevents gated diode breakdown in N-channel transistors by dividing the high voltage across two N-channel transistors, MXU0 and MXU1, such that no transistor exceeds the breakdown voltage, Vbreakdown. An intermediate voltage drives the top N-channel transistor, MXU0. The top N-channel transistor, MXU0, is gated with a voltage level that is at least one N-channel threshold, Vtn, below the high voltage level, Vep, using the intermediate voltage level, nprot. The drain voltage of MXU0 will be at least one N-channel threshold, Vtn, lower than the input voltage level, nprot, and the drain voltage Vd of the bottom N-channel transistor, MXU1, is limited to less than the breakdown voltage, Vbreakdown.

Owner:EMOSYN AMERICA

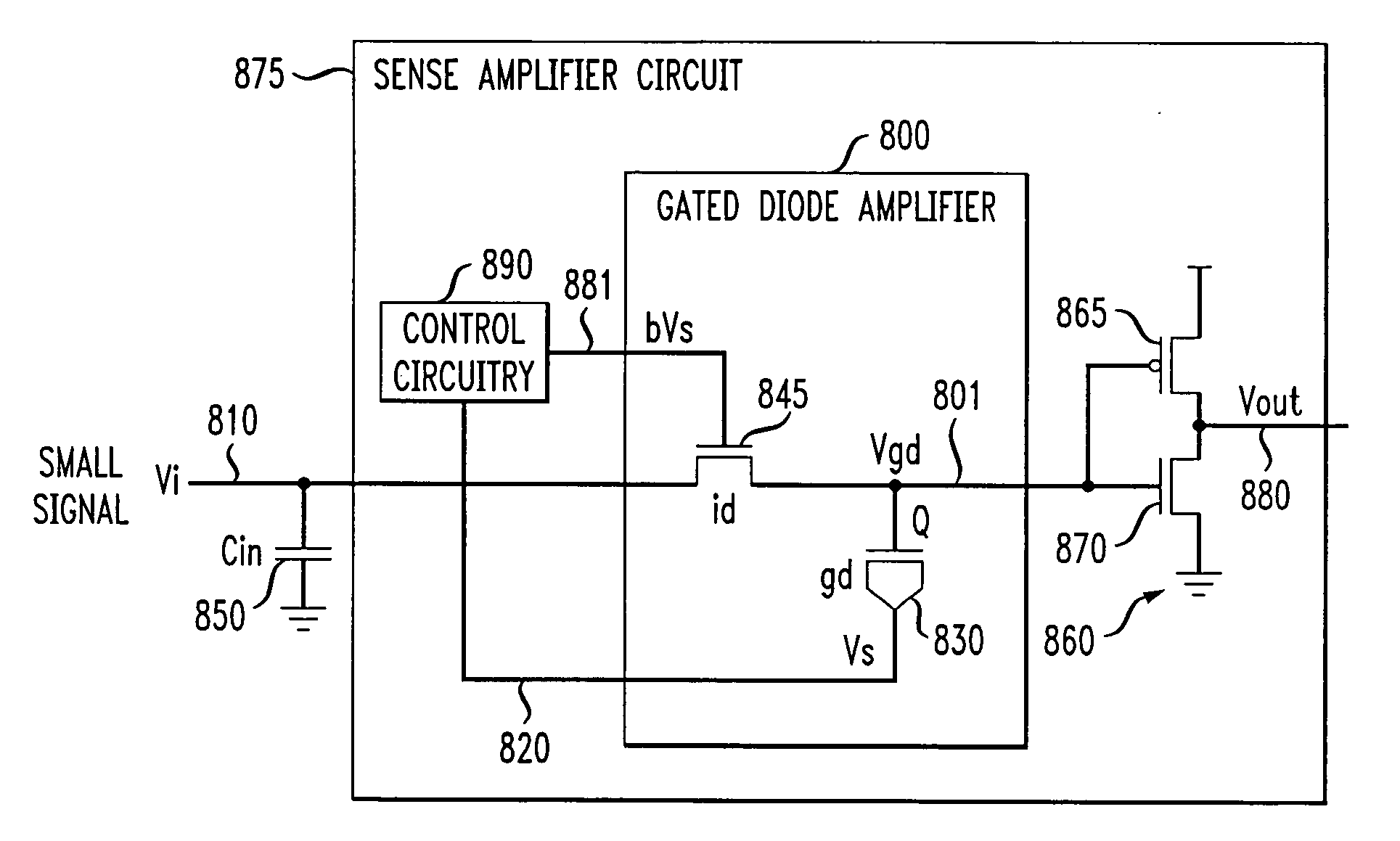

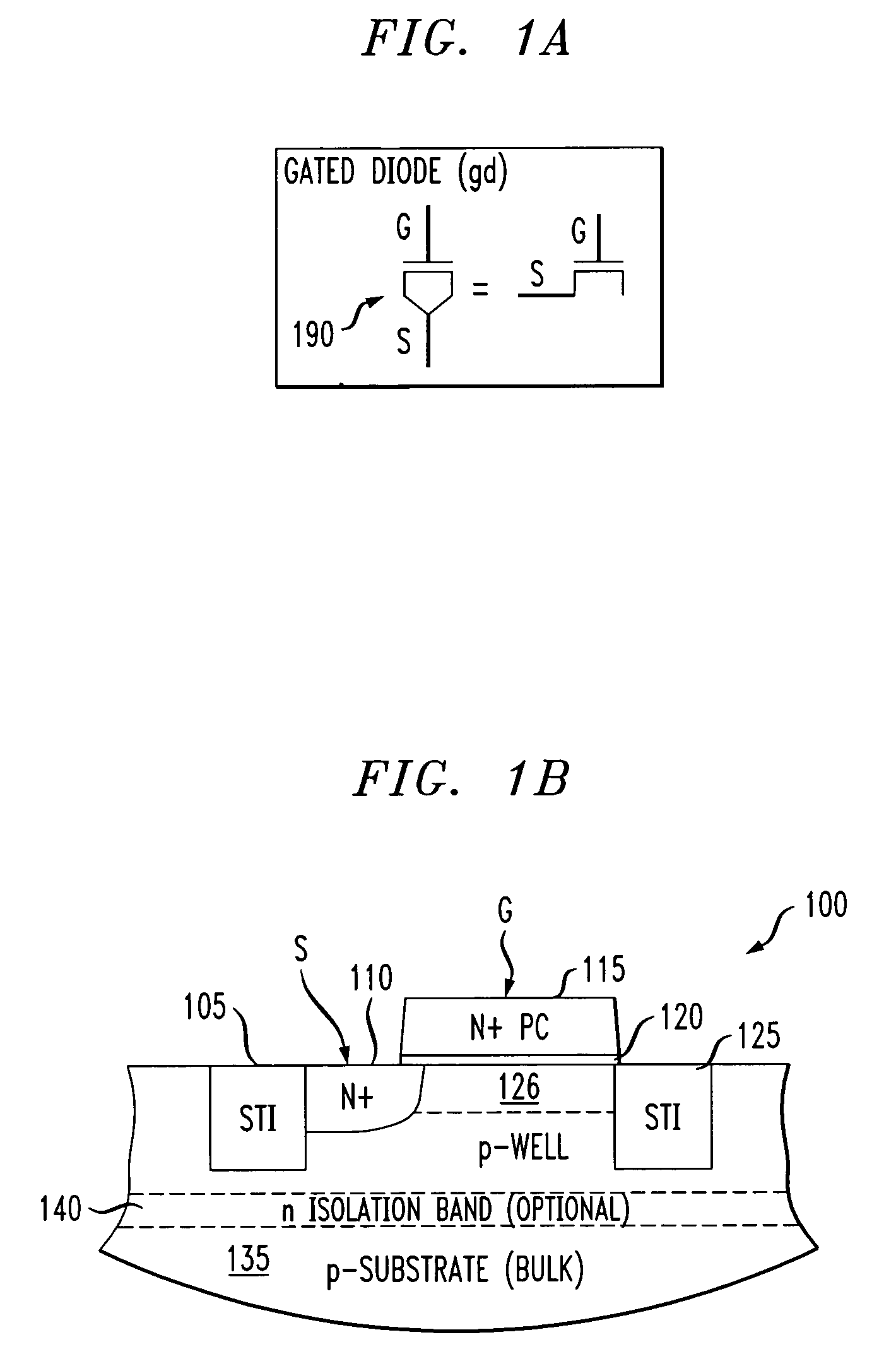

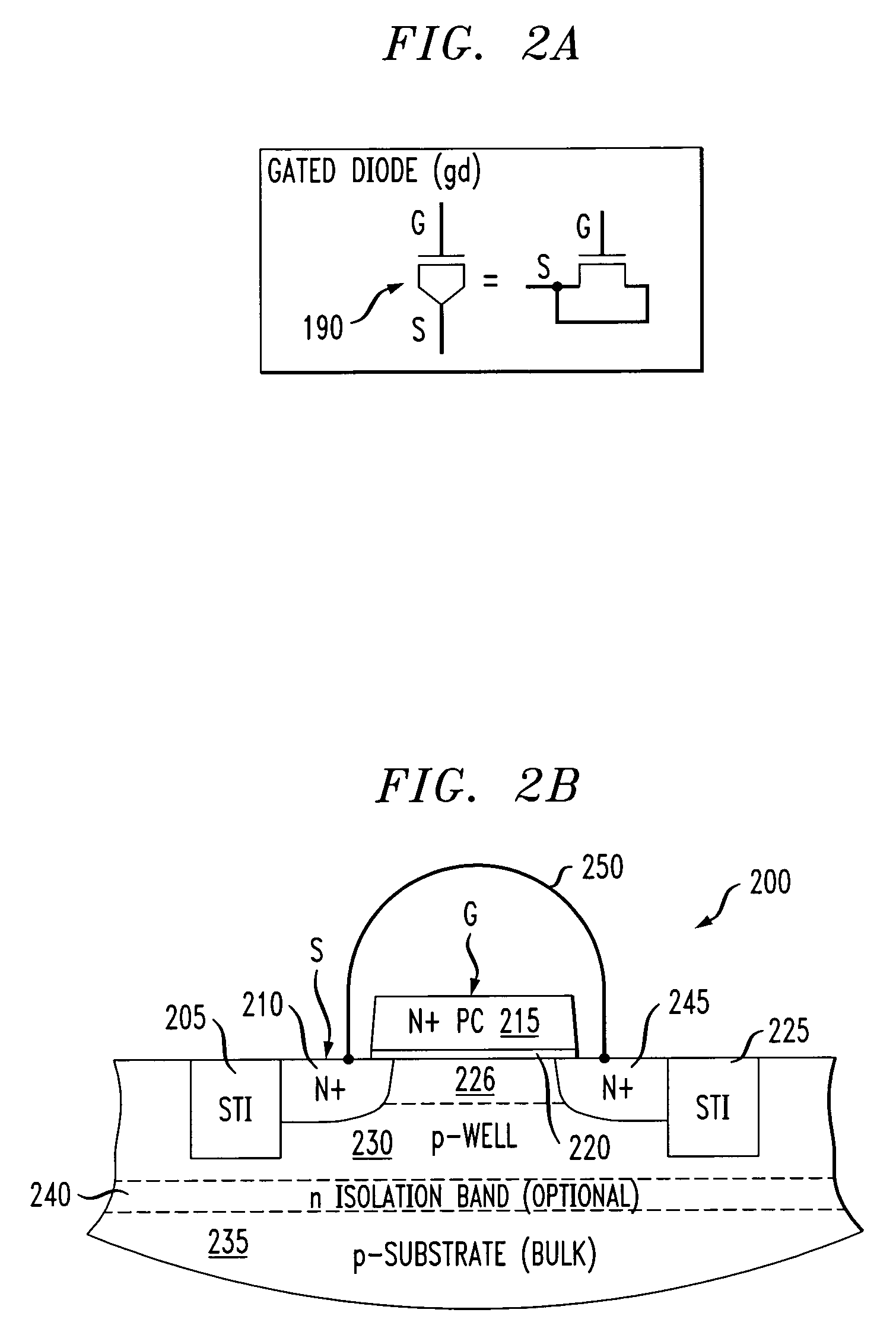

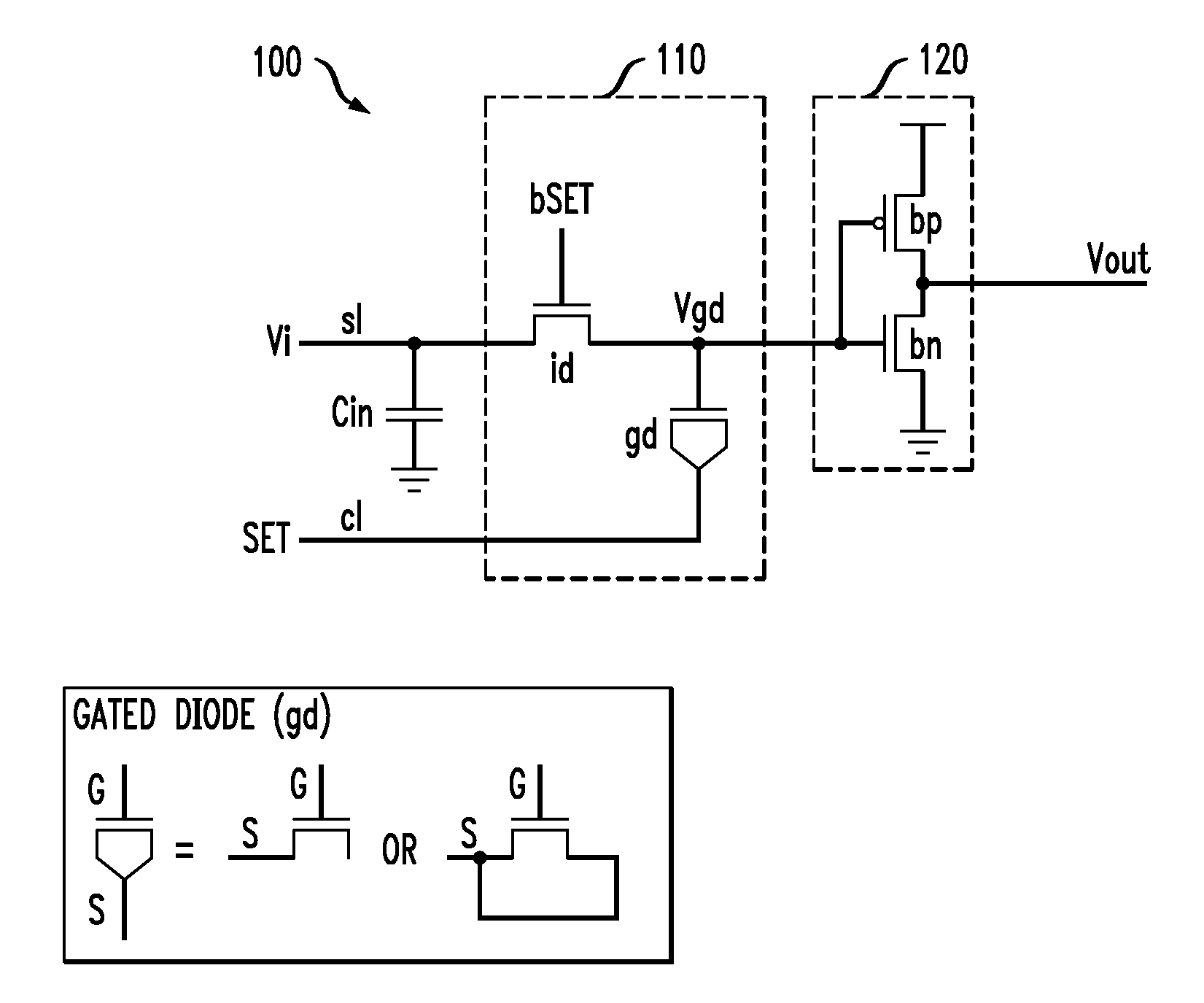

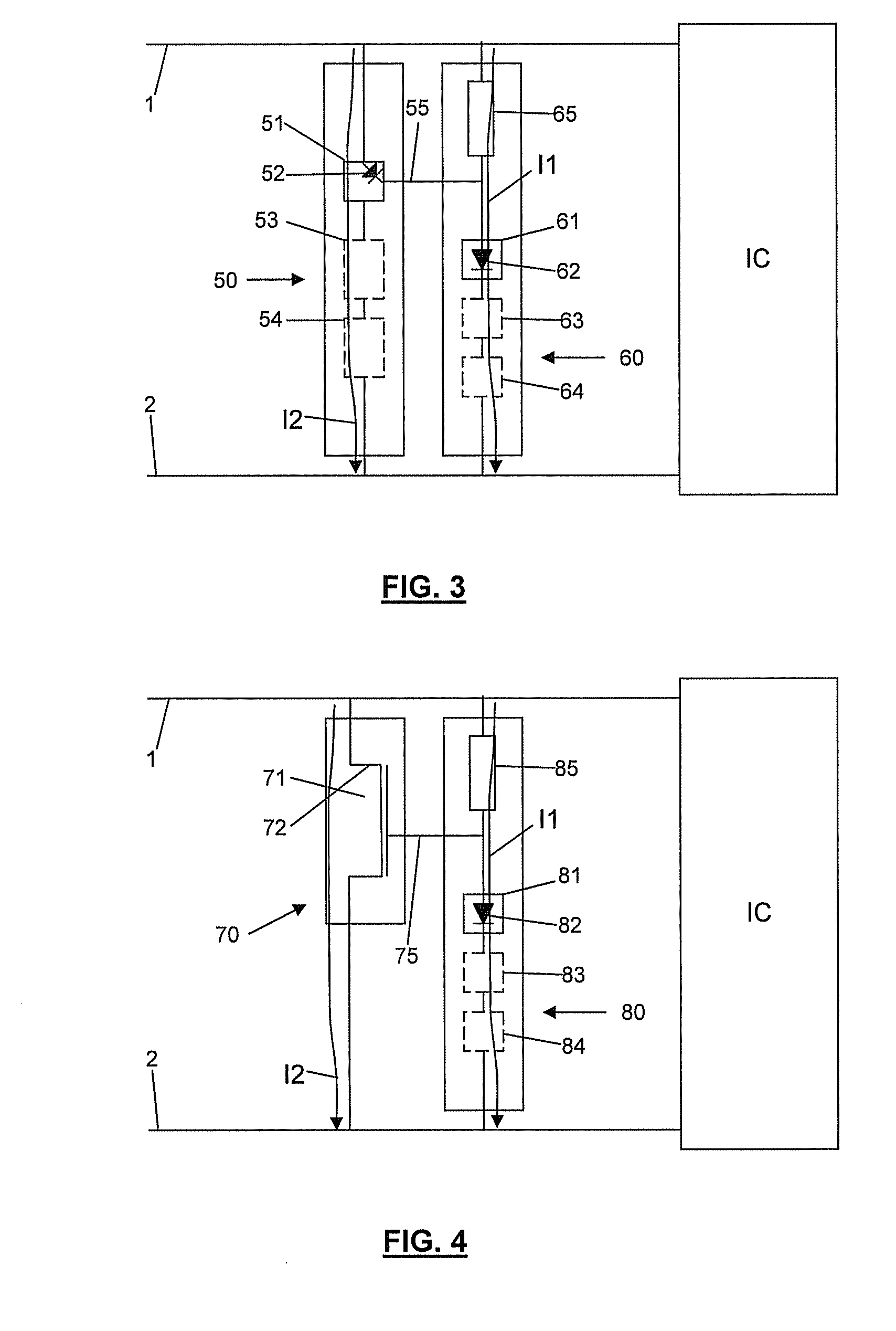

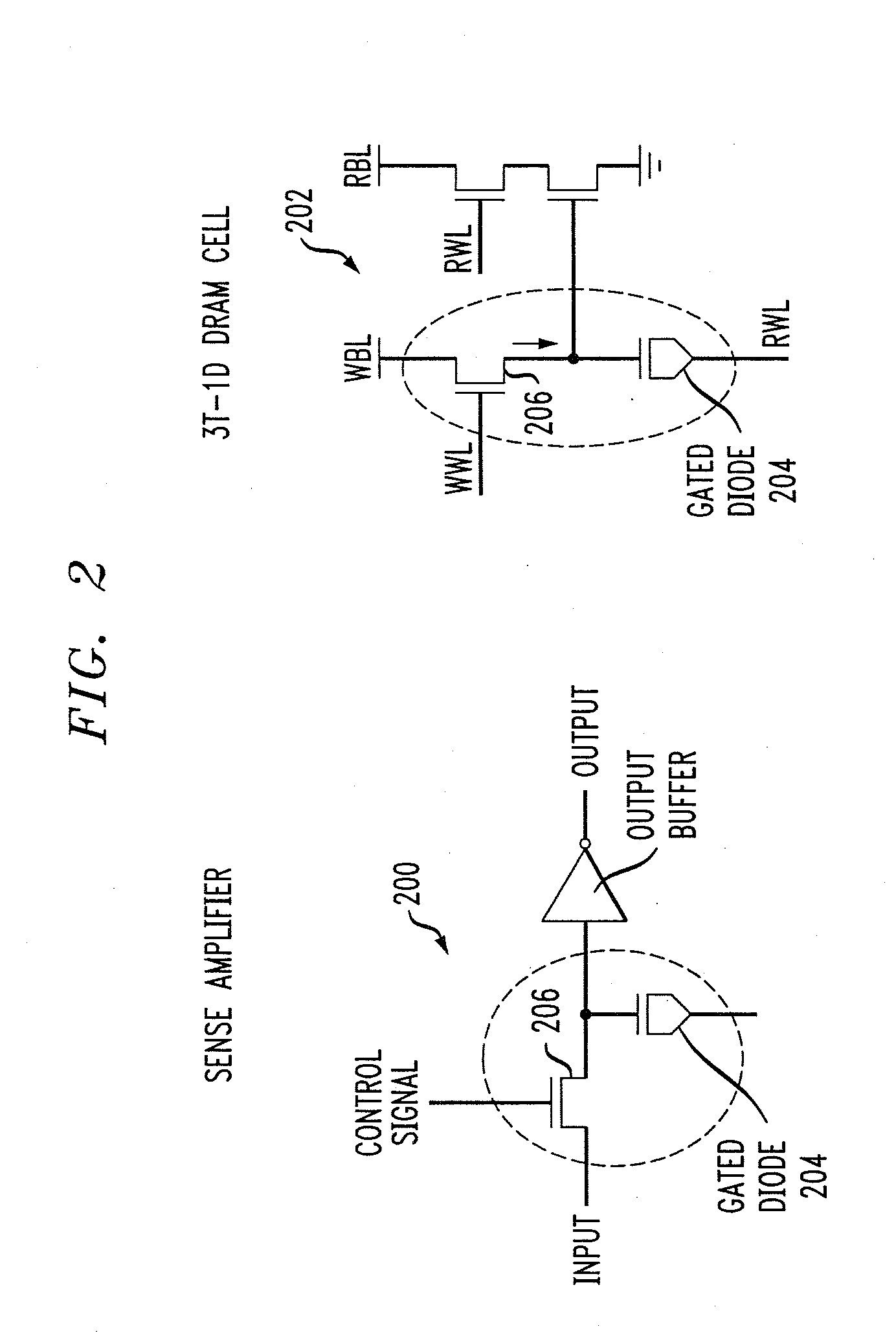

Sense amplifier circuits and high speed latch circuits using gated diodes

InactiveUS20060050581A1Current/voltage measurementInstant pulse delivery arrangementsAudio power amplifierHemt circuits

Owner:GLOBALFOUNDRIES INC

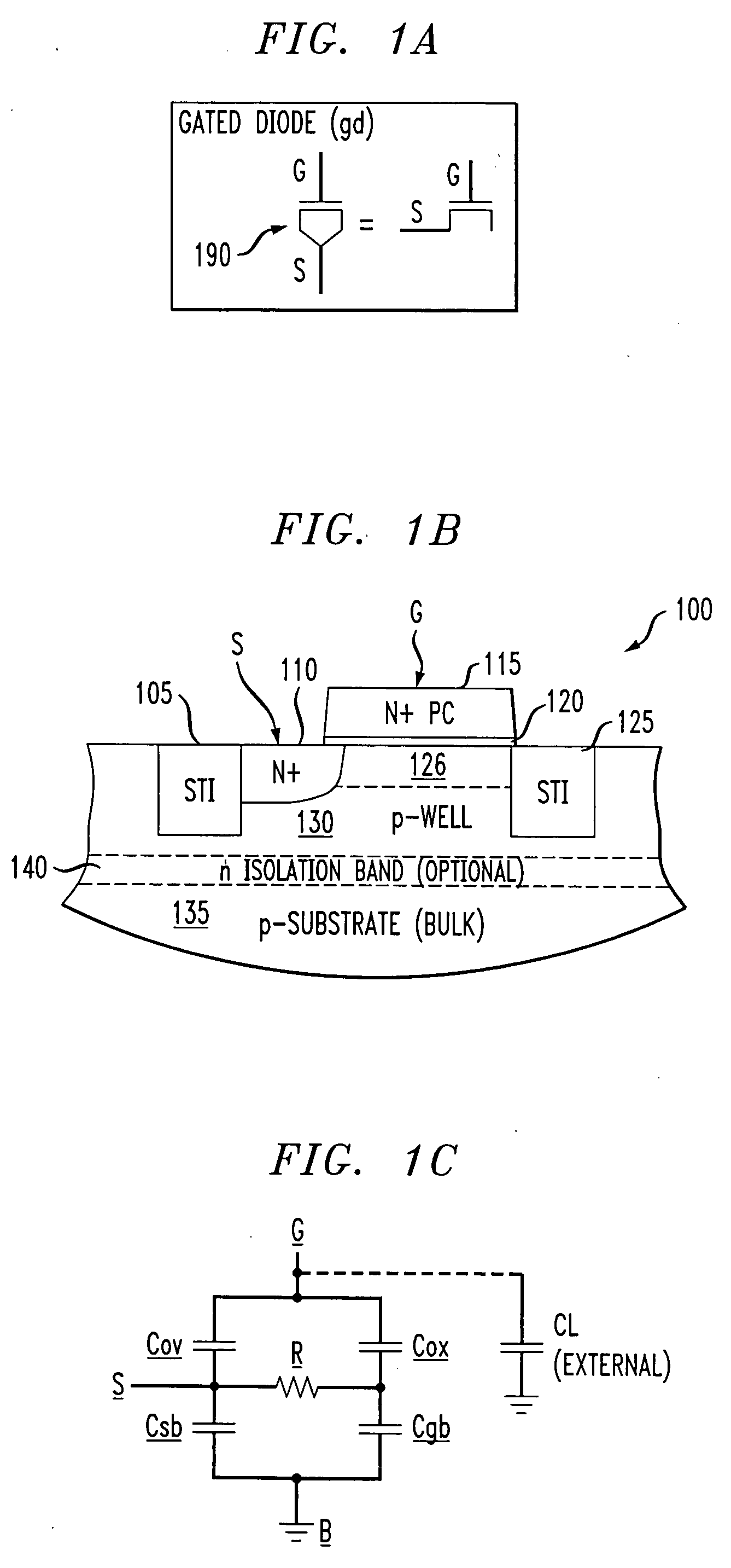

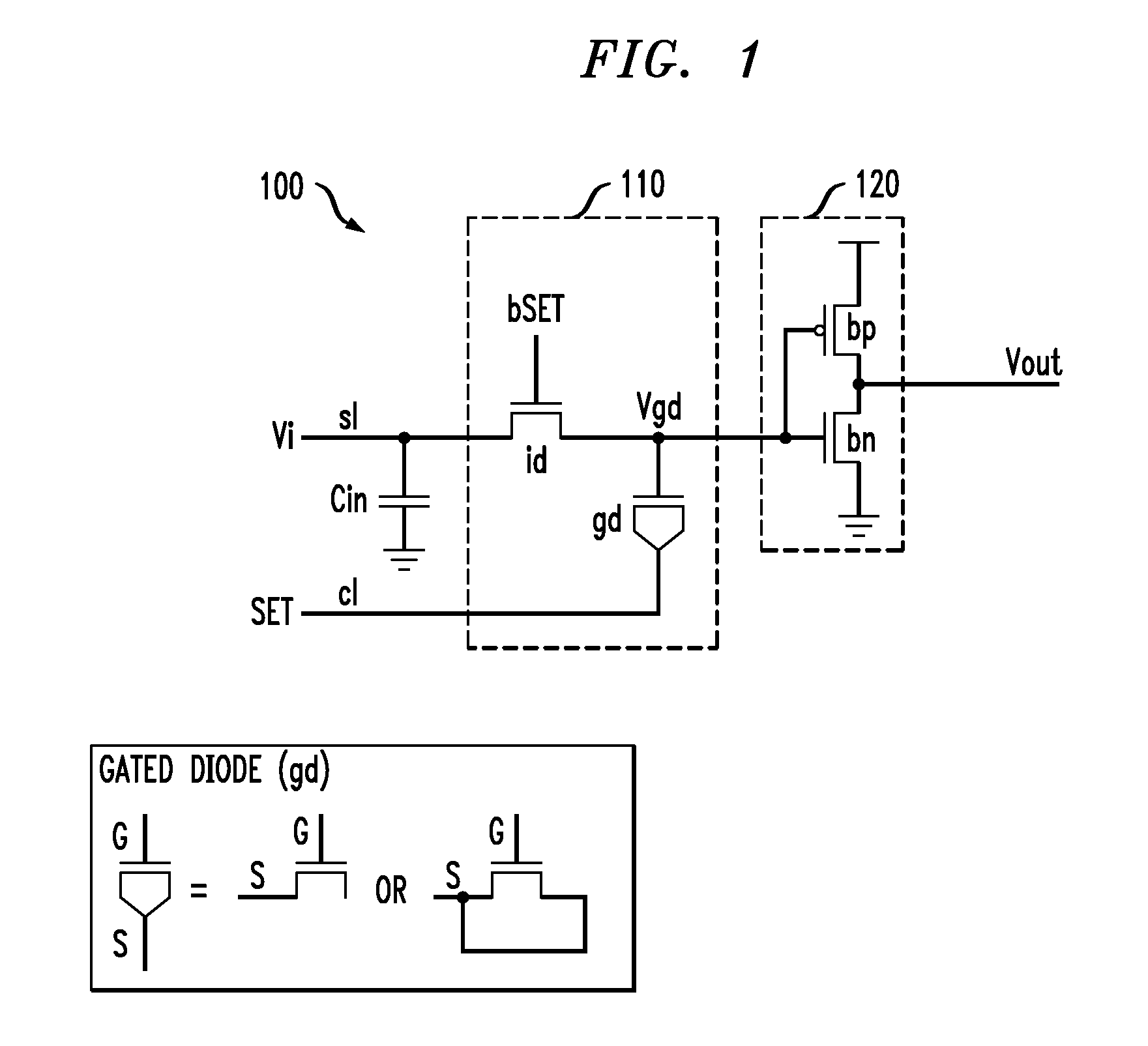

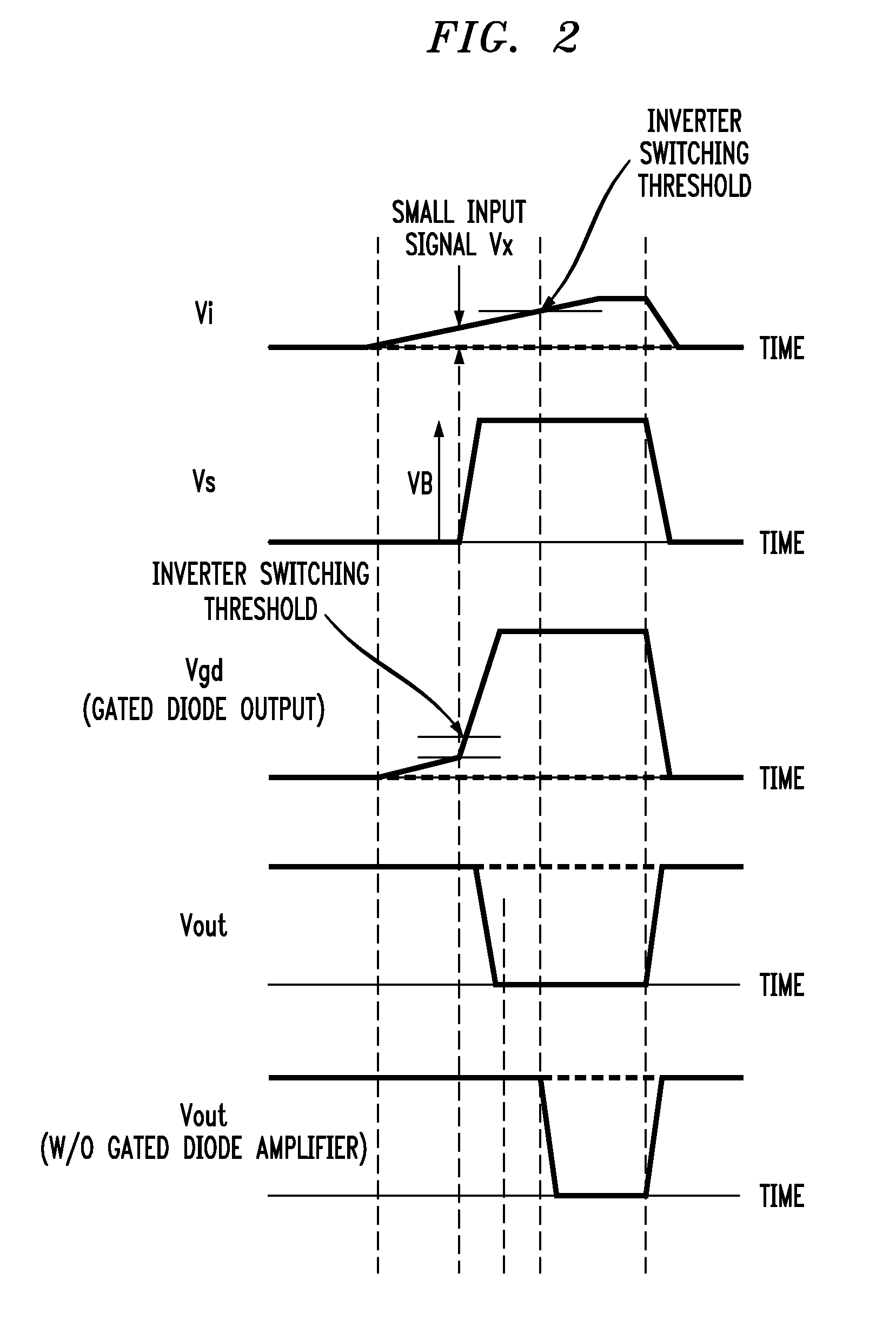

Amplifiers using gated diodes

ActiveUS20050145895A1Avoid voltage riseSolid-state devicesSemiconductor/solid-state device manufacturingControl signalDevice material

A circuit comprises a control line and a two terminal semiconductor device having first and second terminals. The first terminal is coupled to a signal line, and the second terminal is coupled to the control line. The two terminal semiconductor device is adapted to have a capacitance when a voltage on the first terminal relative to the second terminal is above a threshold voltage and to have a smaller capacitance when a voltage on the first terminal relative to the second terminal is below the threshold voltage. The control line is coupled to a control signal and the signal line is coupled to a signal and is output of the circuit. A signal is placed on the signal line and voltage on the control line is modified (e.g., raised in the case of n-type devices, or lowered for a p-type devices). When the signal falls below the threshold voltage, the two terminal semiconductor device acts as a very small capacitor and the output of the circuit will be a small value. When the signal is above the threshold voltage, the two terminal semiconductor device acts as a large capacitor and the output of the circuit will be influenced by both the value of the signal and the value of the modified voltage on the control line and therefore the signal will be amplified.

Owner:GLOBALFOUNDRIES US INC

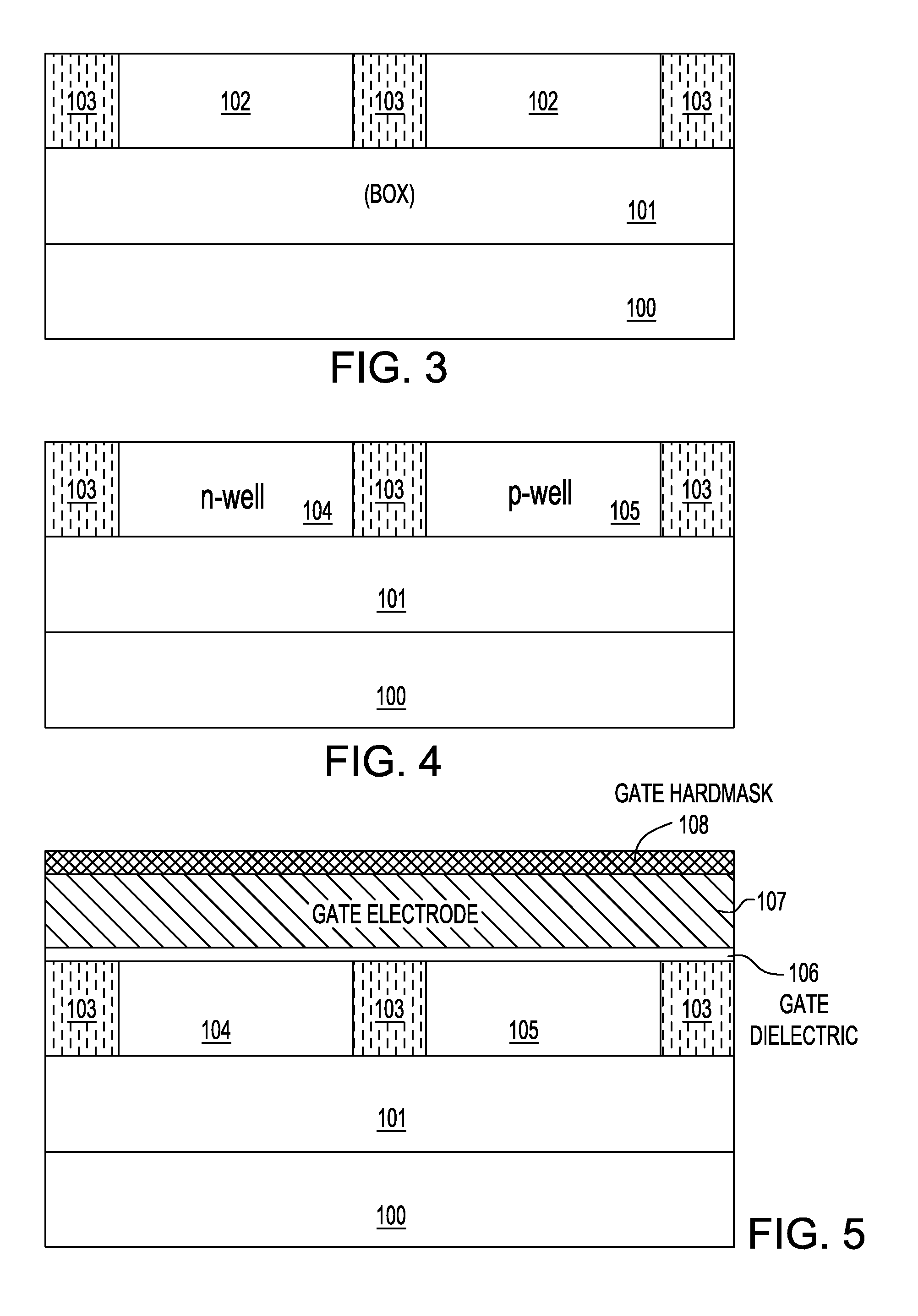

Silicon-on-insulator diodes and ESD protection circuits

InactiveUS6894324B2More junction areaReduce power densityTransistorSemiconductor/solid-state device detailsCapacitanceSilicon on insulator

A silicon-on-insulator (SOI) gated diode and non-gated junction diode are provided. The SOI gated diode has a PN junction at the middle region under the gate, and which has more junction area than a normal diode. The SOI non-gated junction diode has a PN junction at the middle region thereof, and then also has more junction area than a normal diode. The SOI diodes of the present invention improve the protection level offered for electrical overstress (EOS) / electrostatic discharge (ESD) due to the low power density and heating for providing more junction area than normal ones. The I / O ESD protection circuits, which comprise primary diodes, a first plurality of diodes, and a second plurality of diodes, all of which are formed of the present SOI diodes, could effectively discharge the current when there is an ESD event. And, the ESD protection circuits, which comprise more primary diodes, could effectively reduce the parasitic input capacitance, so that they can be used in the RF circuits or HF circuits. The proposed gated diode and non-gated diode can be fully process-compatiable to general partially depleted or fully-depleted silicon-on-insulator CMOS processes.

Owner:UNITED MICROELECTRONICS CORP

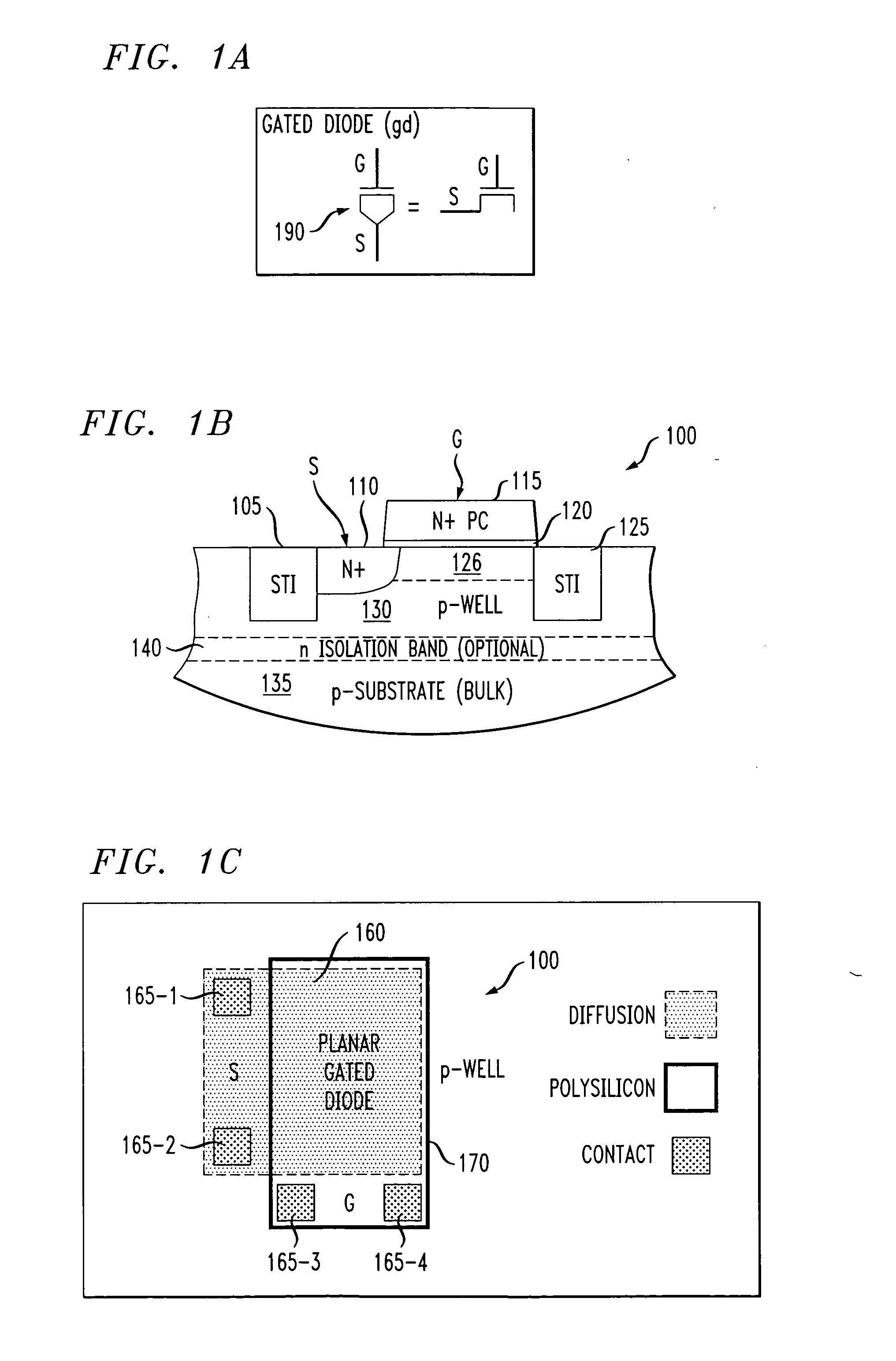

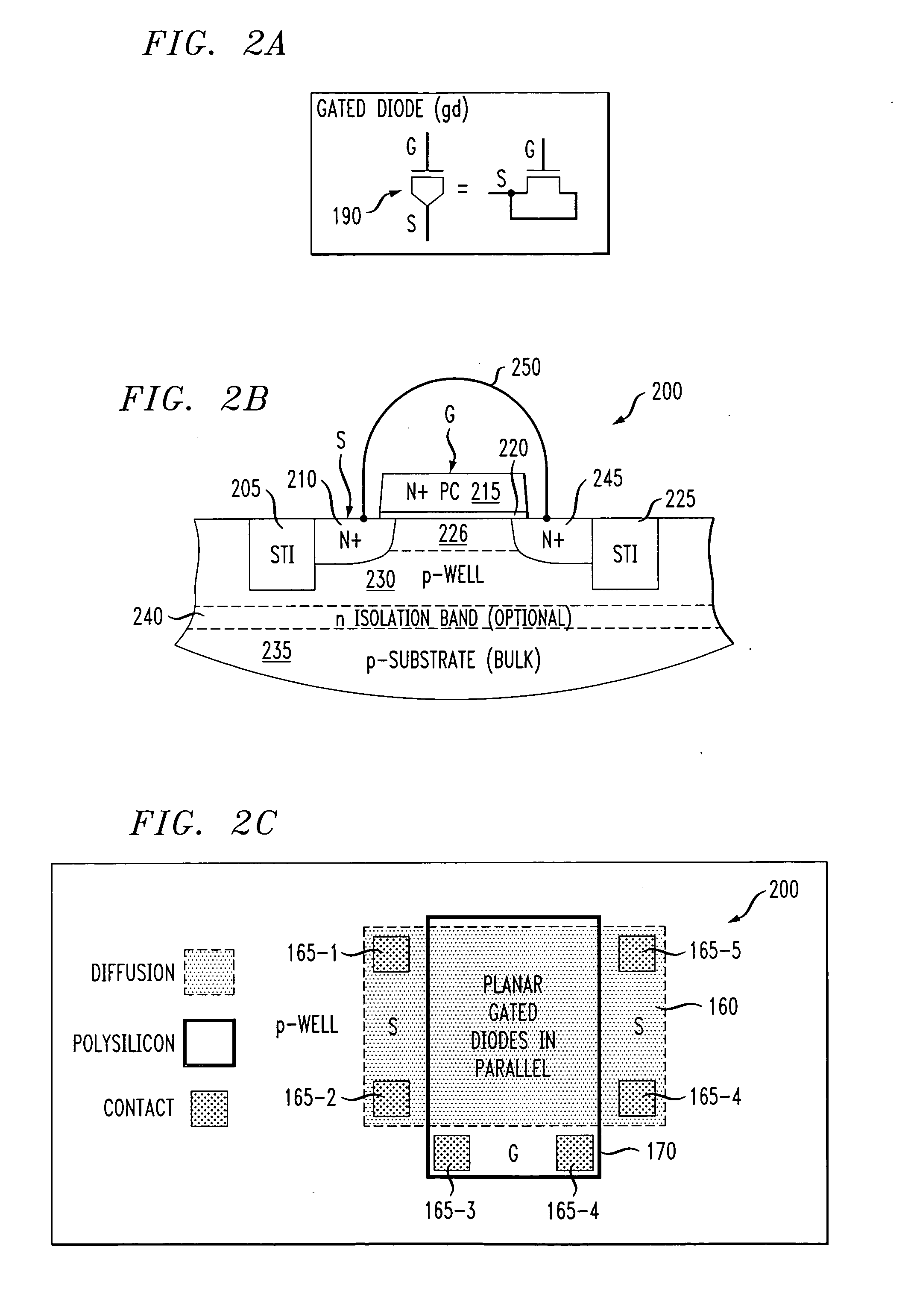

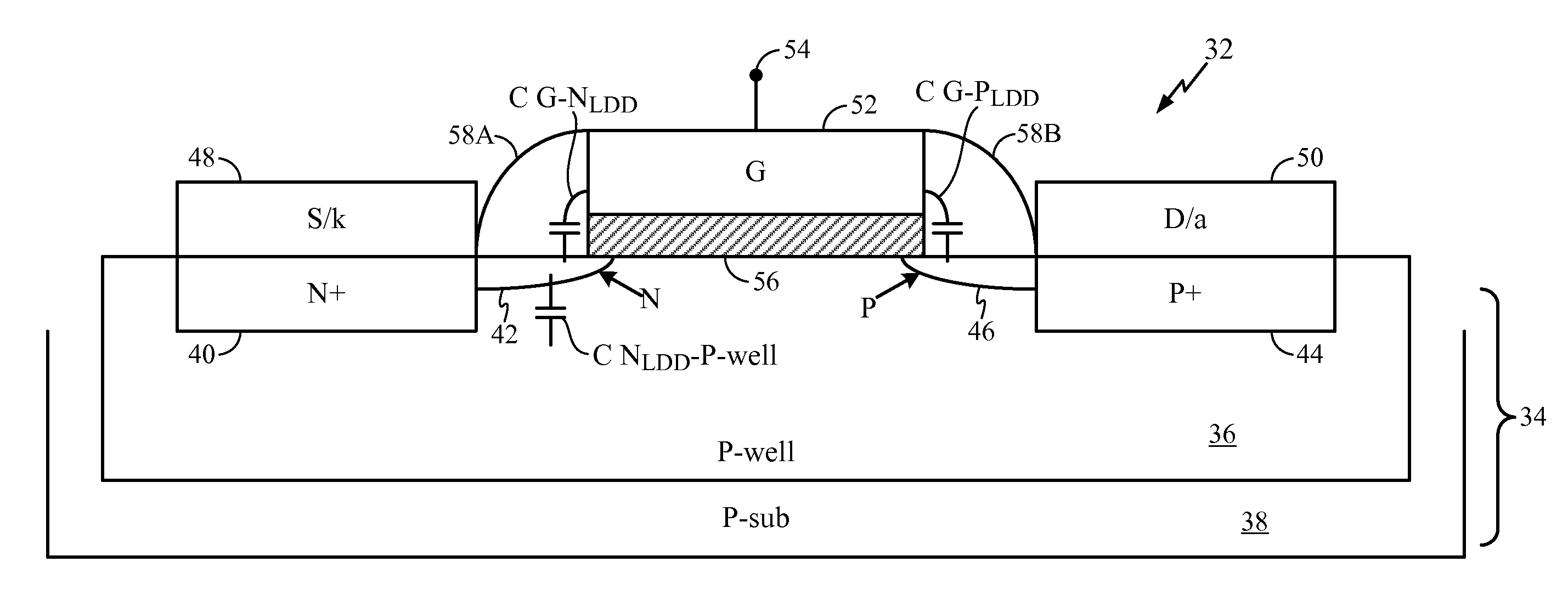

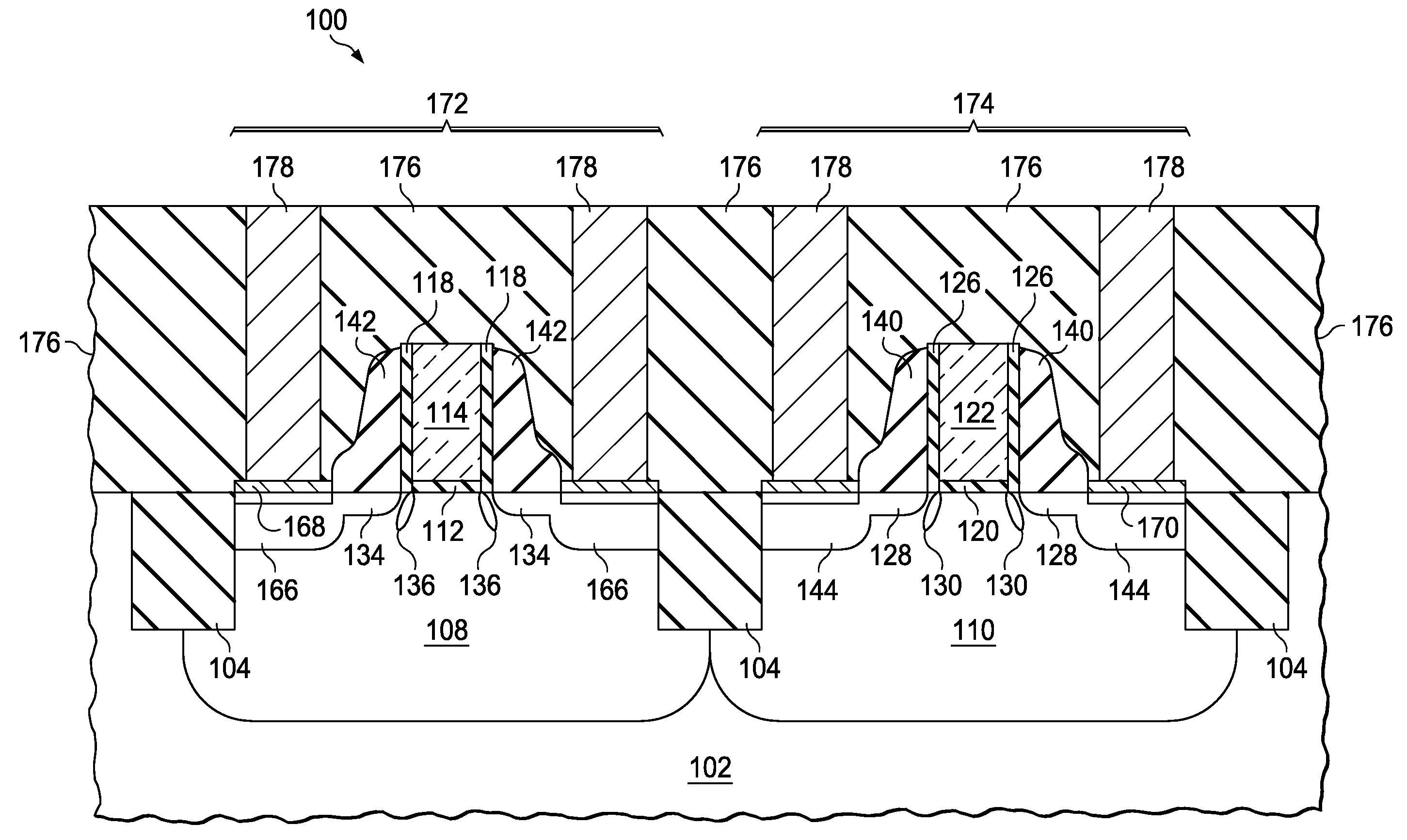

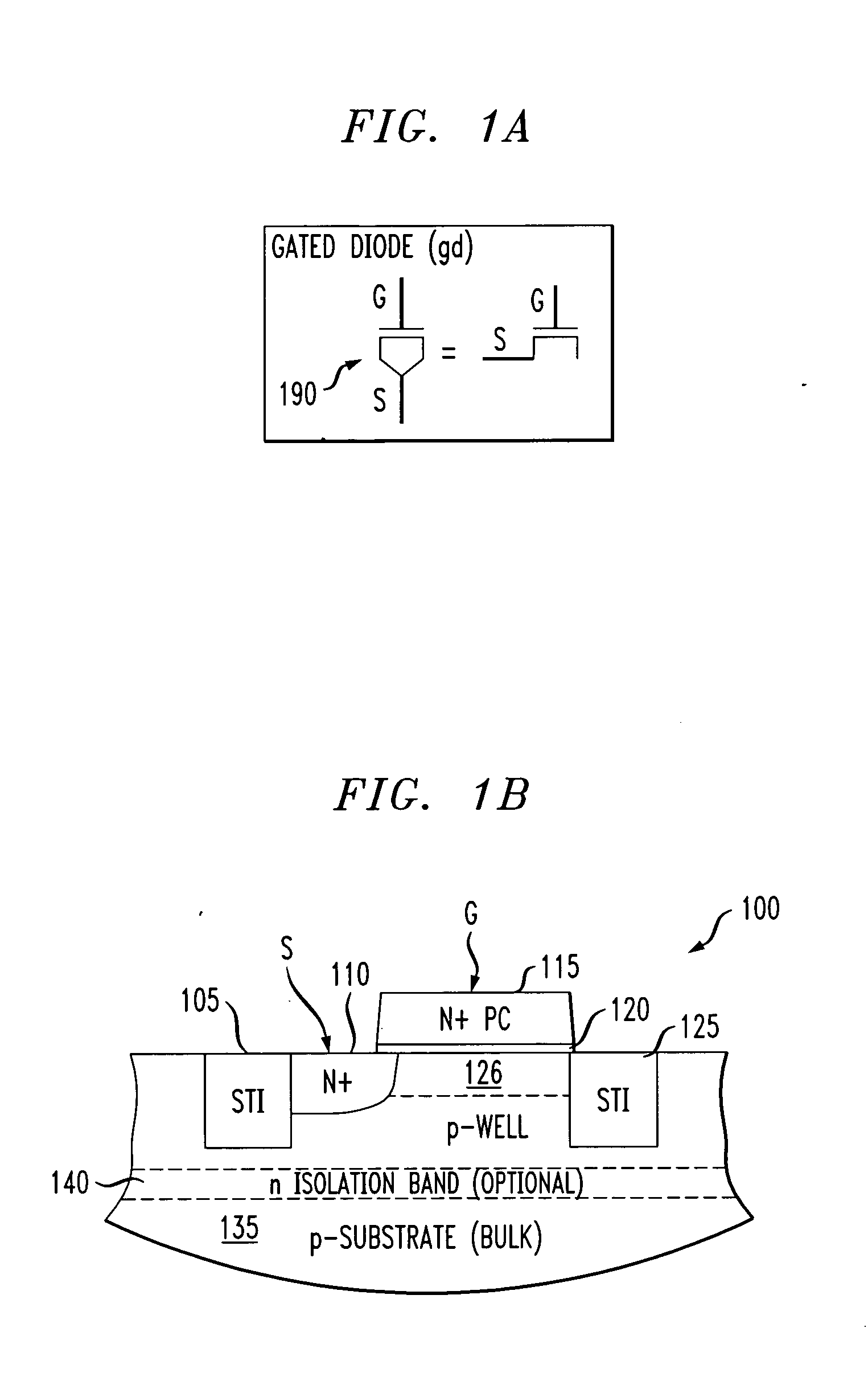

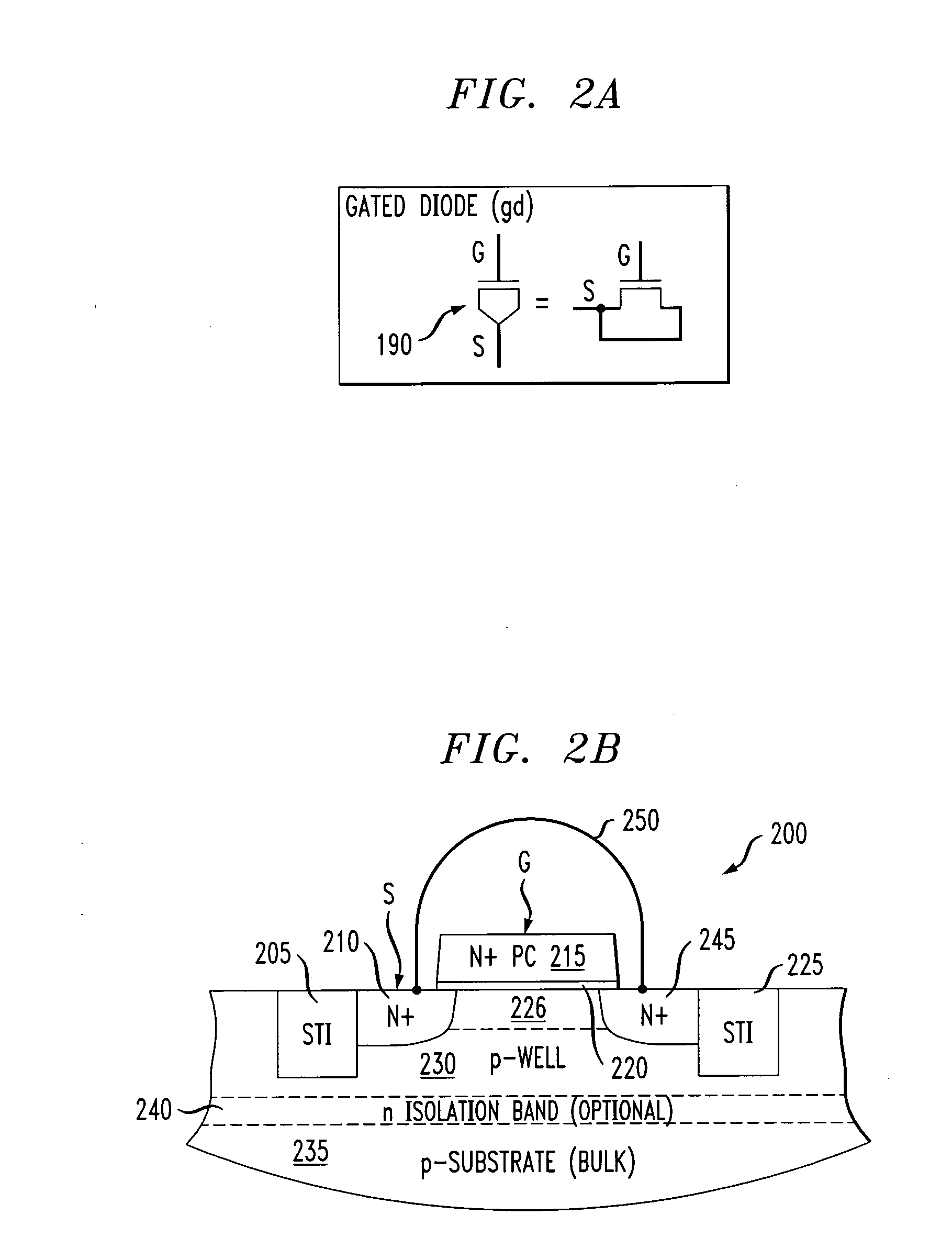

Gated diode having at least one lightly-doped drain (LDD) implant blocked and circuits and methods employing same

InactiveUS20100232077A1Enhanced ESD protectionFast turn-on timeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

Gated diodes, manufacturing methods, and related circuits are provided wherein at least one lightly-doped drain (LDD) implant is blocked in the gated diode to reduce its capacitance. In this manner, the gated diode may be used in circuits and other applications whose performance is sensitive to load capacitance while still obtaining the performance characteristics of a gated diode. These characteristics include fast turn-on times and high conductance, making the gated diodes disclosed herein well-suited for electro-static discharge (ESD) protection circuits as one application example. The examples of the gated diode disclosed herein include a semiconductor substrate having a well region and insulating layer thereupon. A gate electrode is formed over the insulating layer. Anode and cathode regions are provided in the well region, wherein a P-N junction is formed. At least one LDD implant is blocked in the gated diode to reduce capacitance.

Owner:QUALCOMM INC

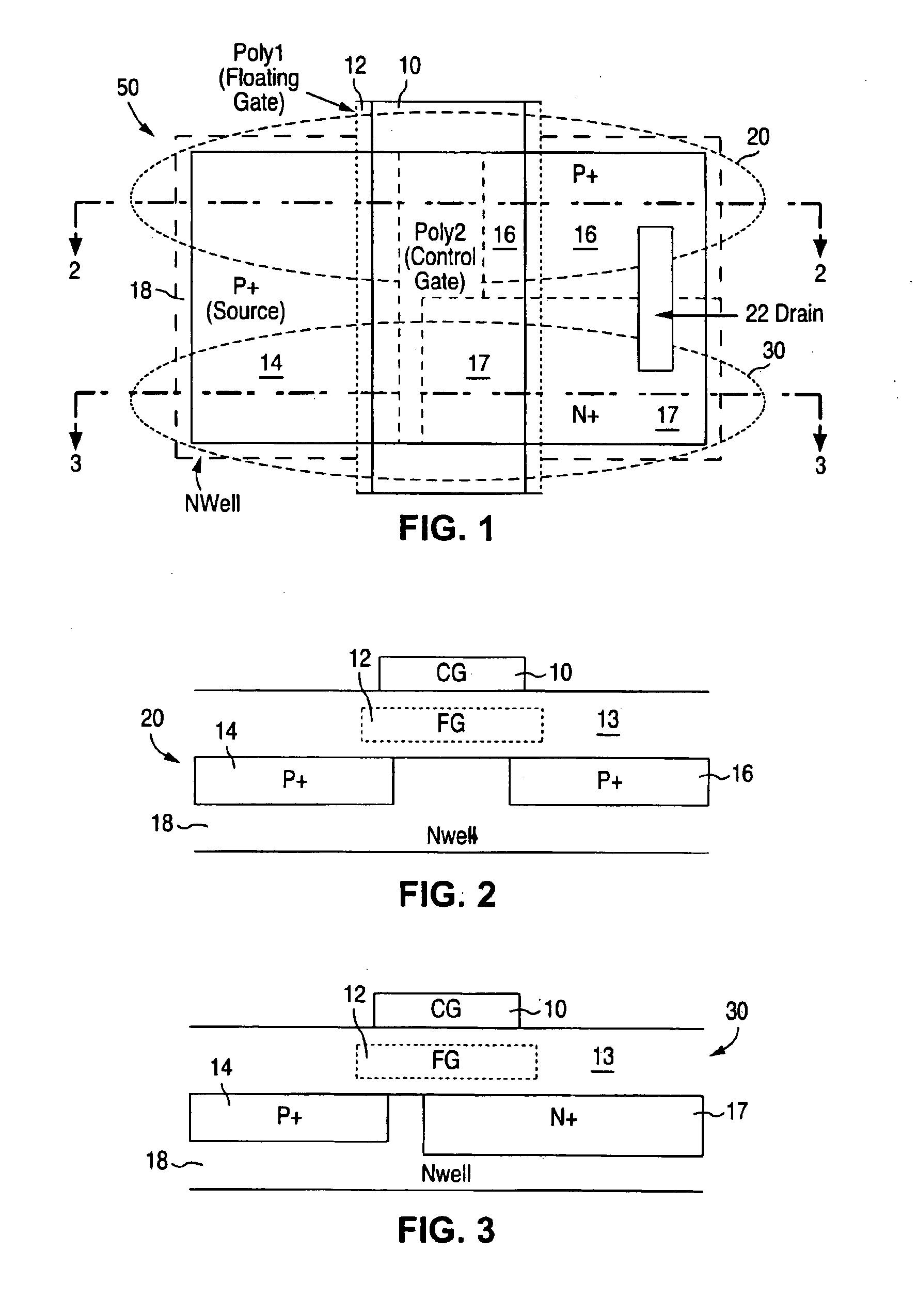

Non-volatile memory cell with gated diode and MOS transistor and method for using such cell

A non-volatile memory cell including a gated diode and a single readout transistor, methods for programming and reading out such a cell, and a memory including an array of such cells. The readout transistor is an MOS transistor. The transistor and gated diode are formed in a volume of semiconductor material of one type, and share a source region, a control gate, and a floating gate. The transistor has a drain region formed of semiconductor material of one type and the diode has a drain region formed of semiconductor material of the opposite type.

Owner:NAT SEMICON CORP

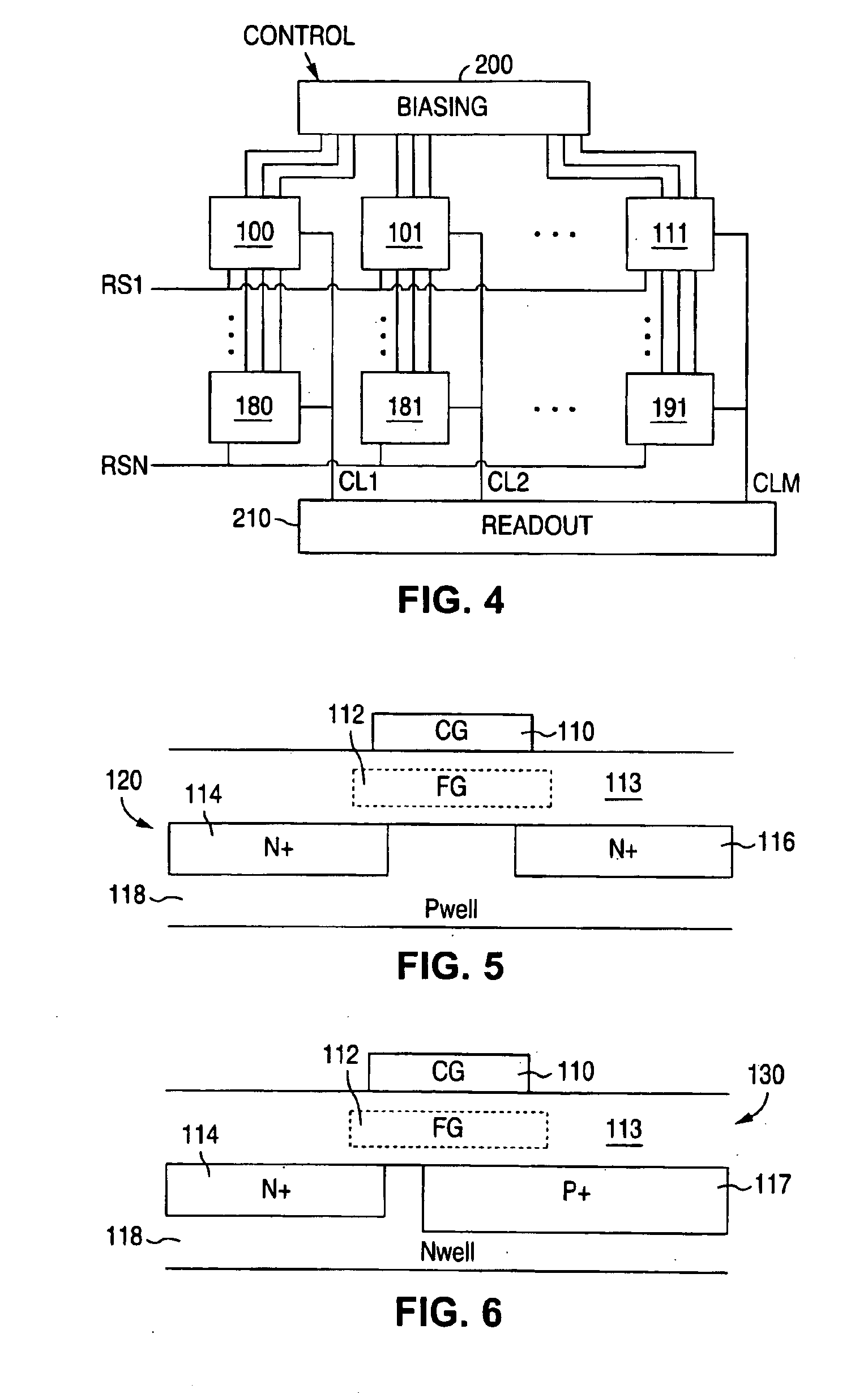

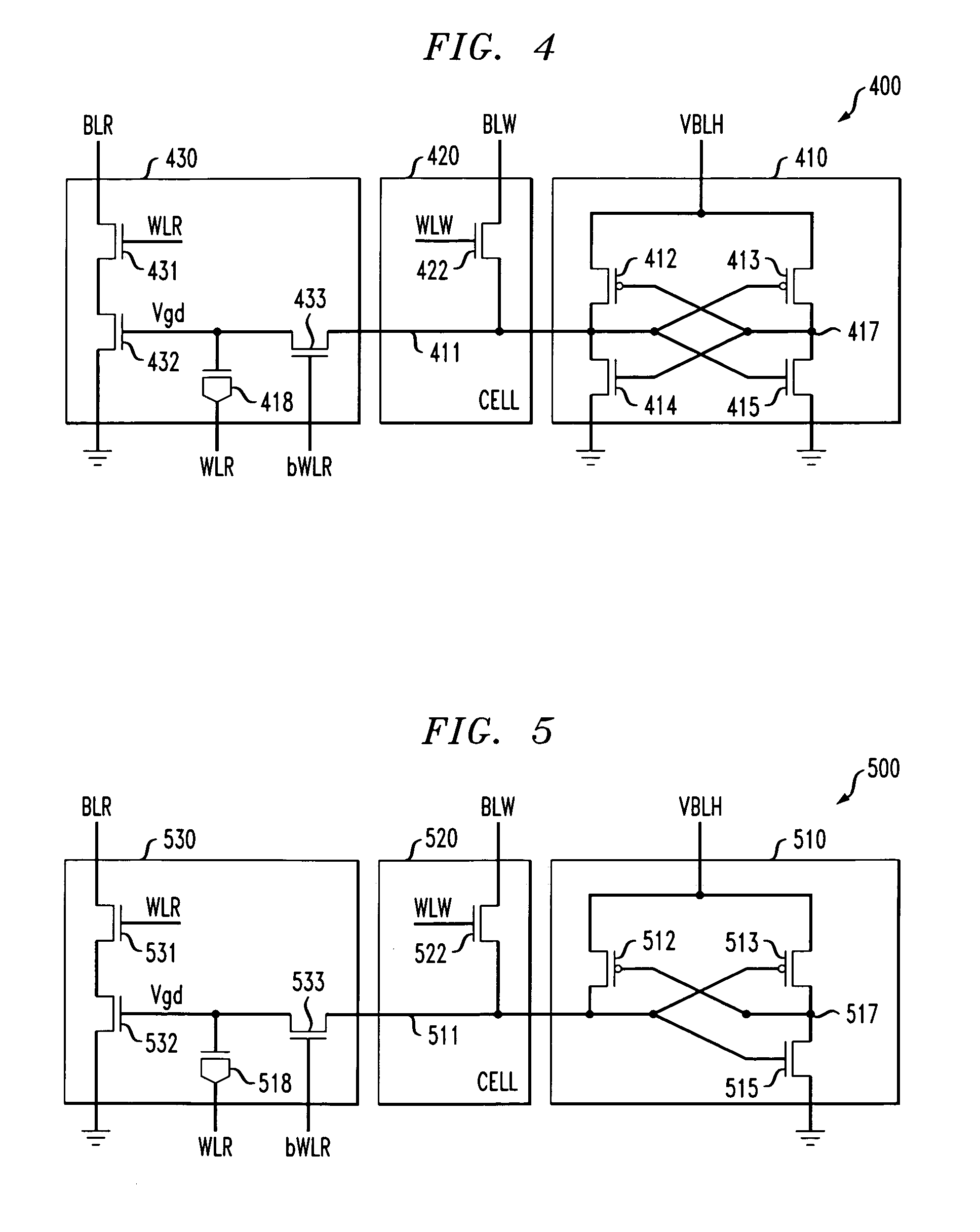

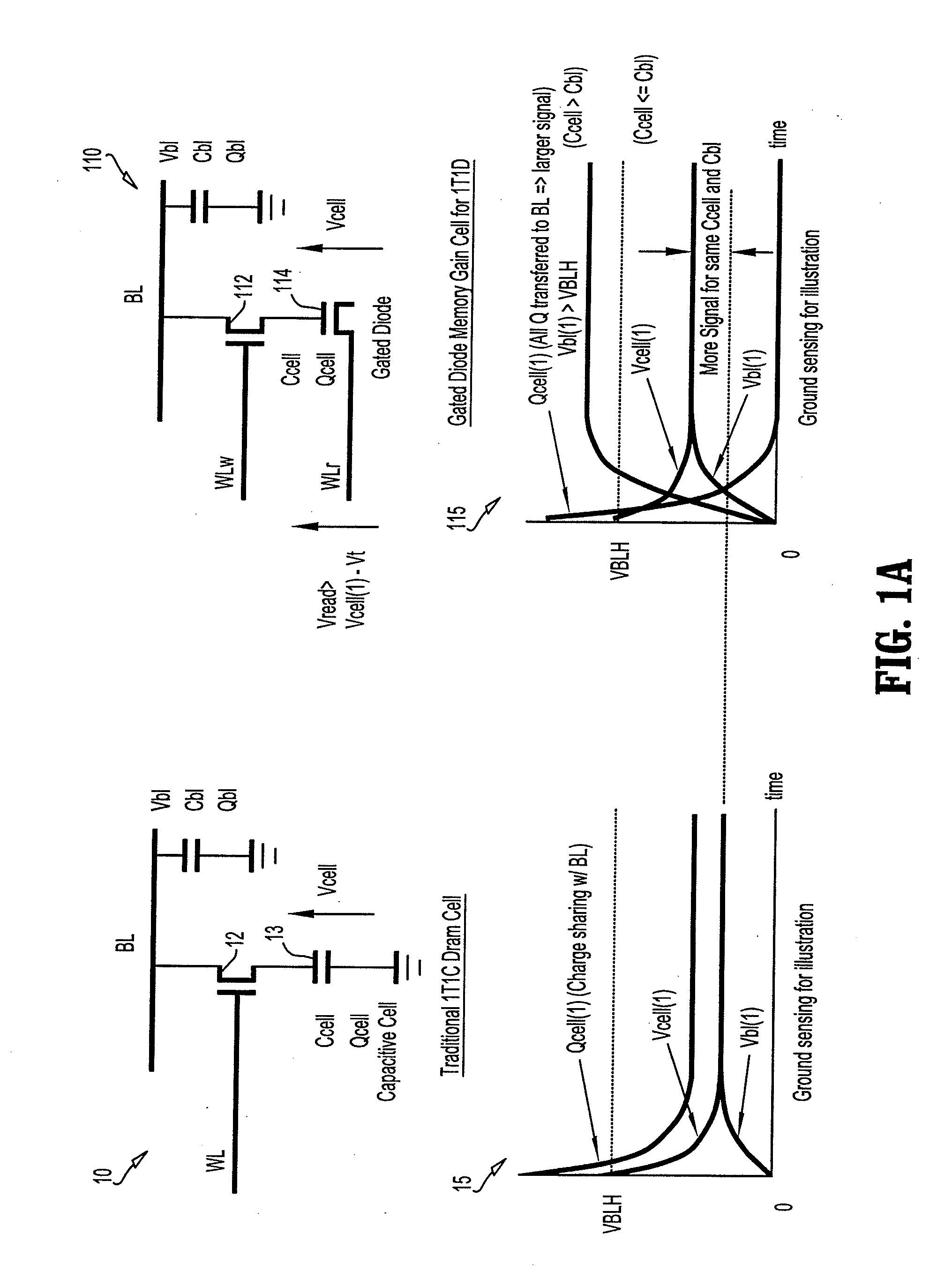

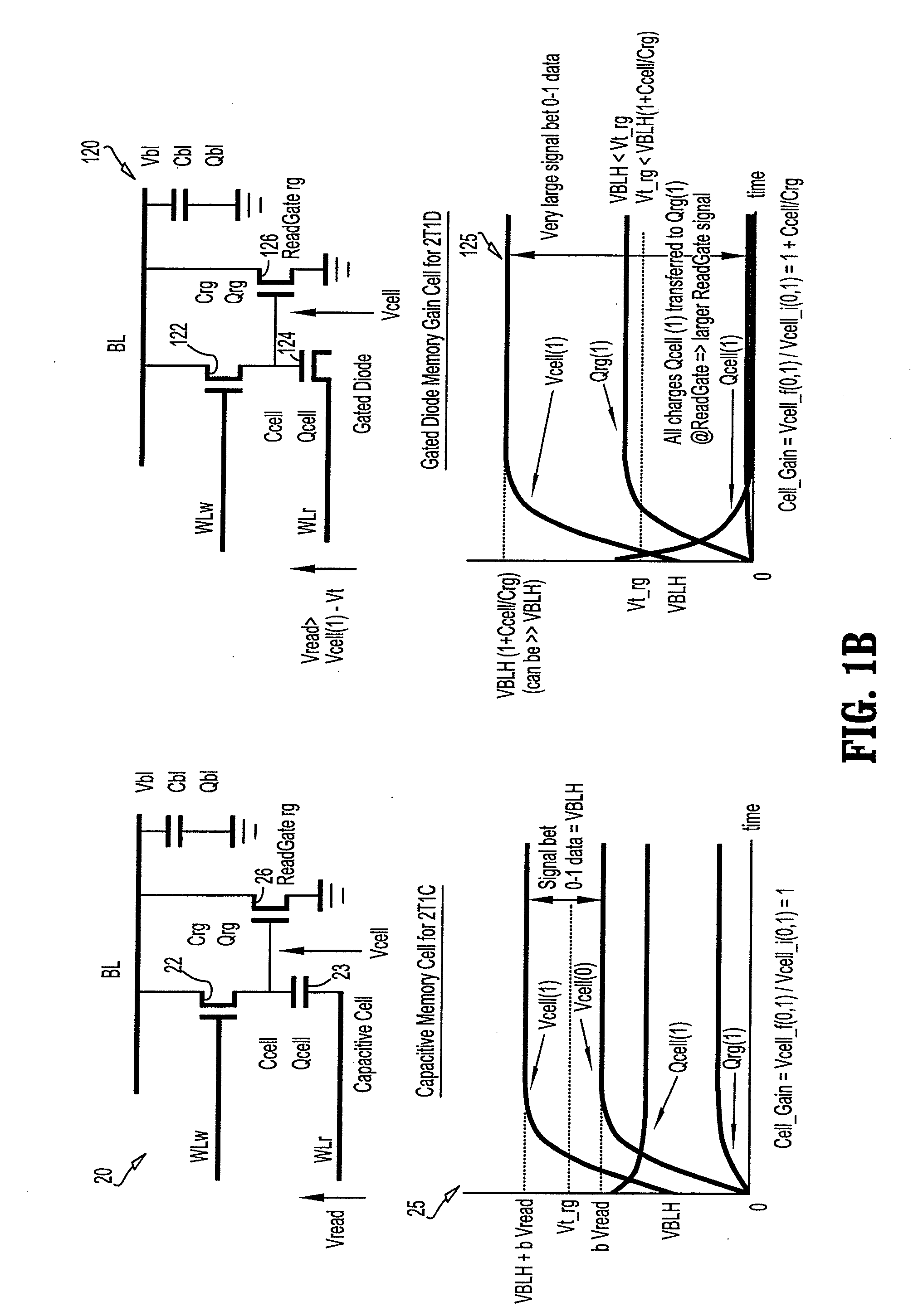

3T1D memory cells using gated diodes and methods of use thereof

Owner:GLOBALFOUNDRIES INC

HIGH THRESHOLD NMOS SOURCE-DRAIN FORMATION WITH As, P AND C TO REDUCE DAMAGE

ActiveUS20090179280A1Reduce leakage currentReduced GDLTransistorSemiconductor/solid-state device manufacturingHigh concentrationArsenic

Pipe defects in n-type lightly doped drain (NLDD) regions and n-type source / drain (NDS) regions are associated with arsenic implants, while excess diffusion in NLDD and NSD regions is mainly due to phosphorus interstitial movement. Carbon implanatation is commonly used to reduce phosphorus diffusion in the NLDD, but contributes to gated diode leakage (GDL). In high threshold NMOS transistors GDL is commonly a dominant off-state leakage mechanism. This invention provides a method of forming an NMOS transistor in which no carbon is implanted into the NLDD, and the NSD is formed by a pre-amorphizing implant (PAI), a phosphorus implant and a carbon species implant. Use of carbon in the NDS allows a higher concentration of phosphorus, resulting in reduced series resistance and reduced pipe defects. An NMOS transistor with less than 1·1014 cm−2 arsenic in the NSD and a high threshold NMOS transistor formed with the inventive method are also disclosed

Owner:TEXAS INSTR INC

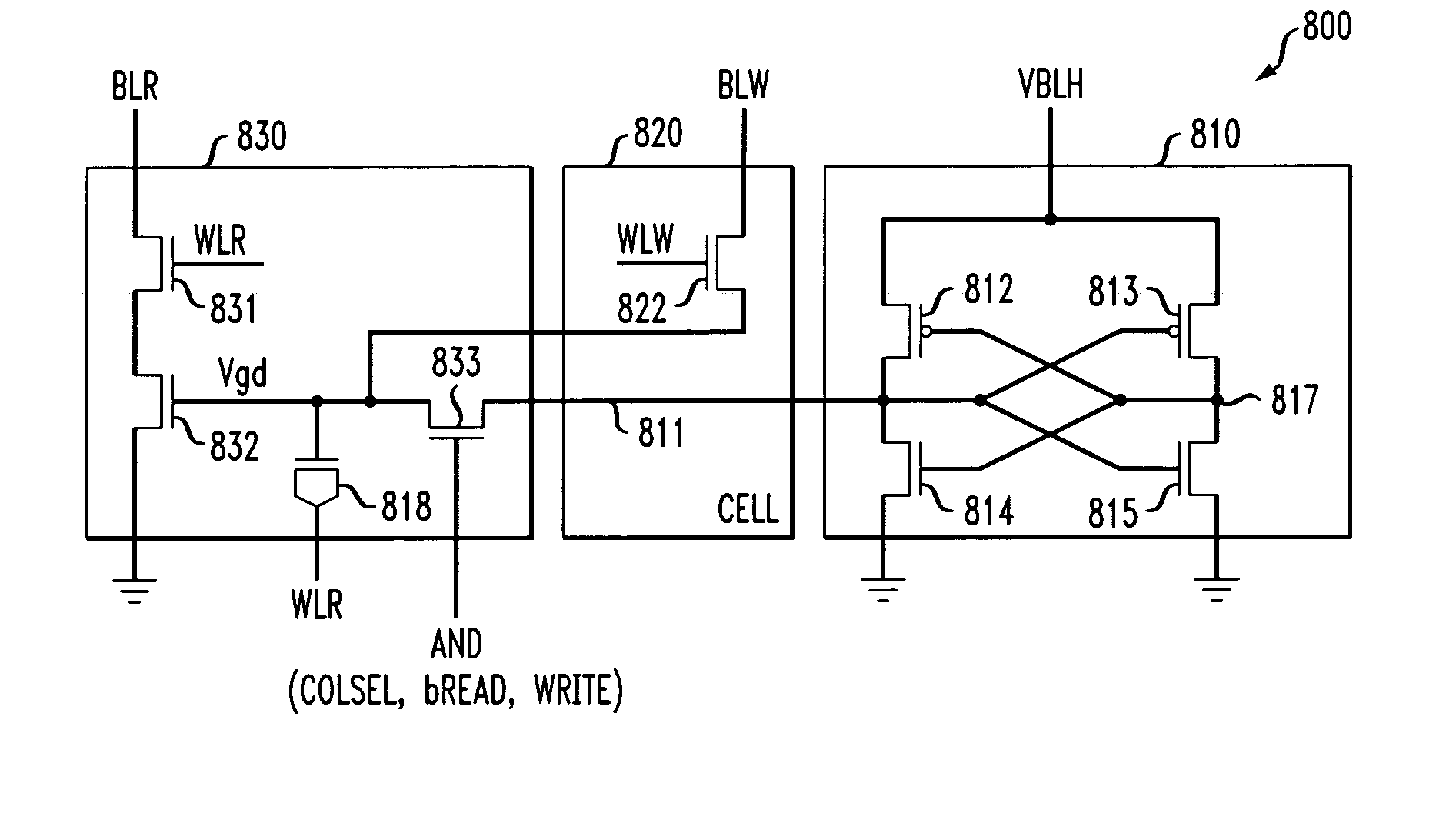

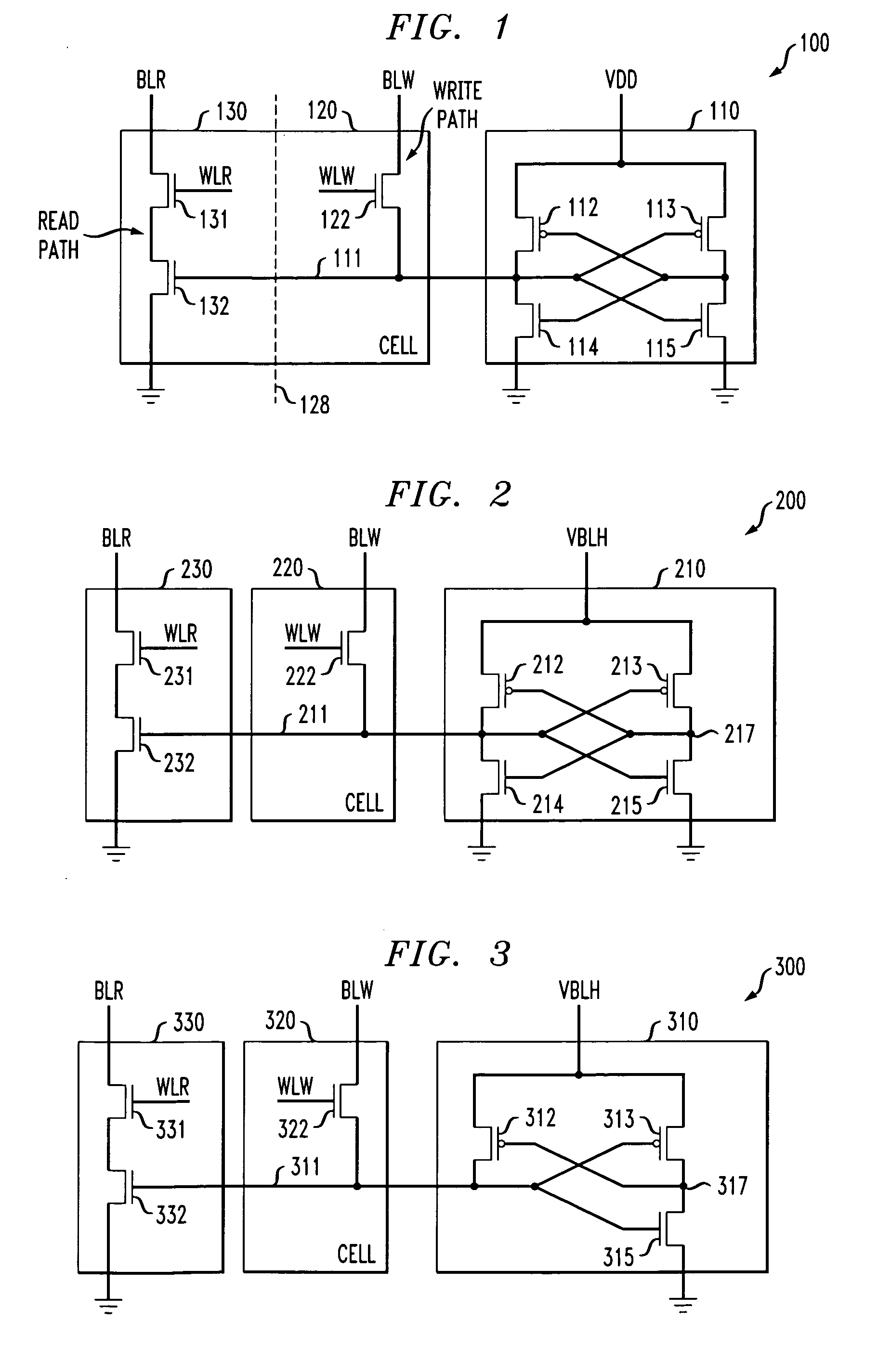

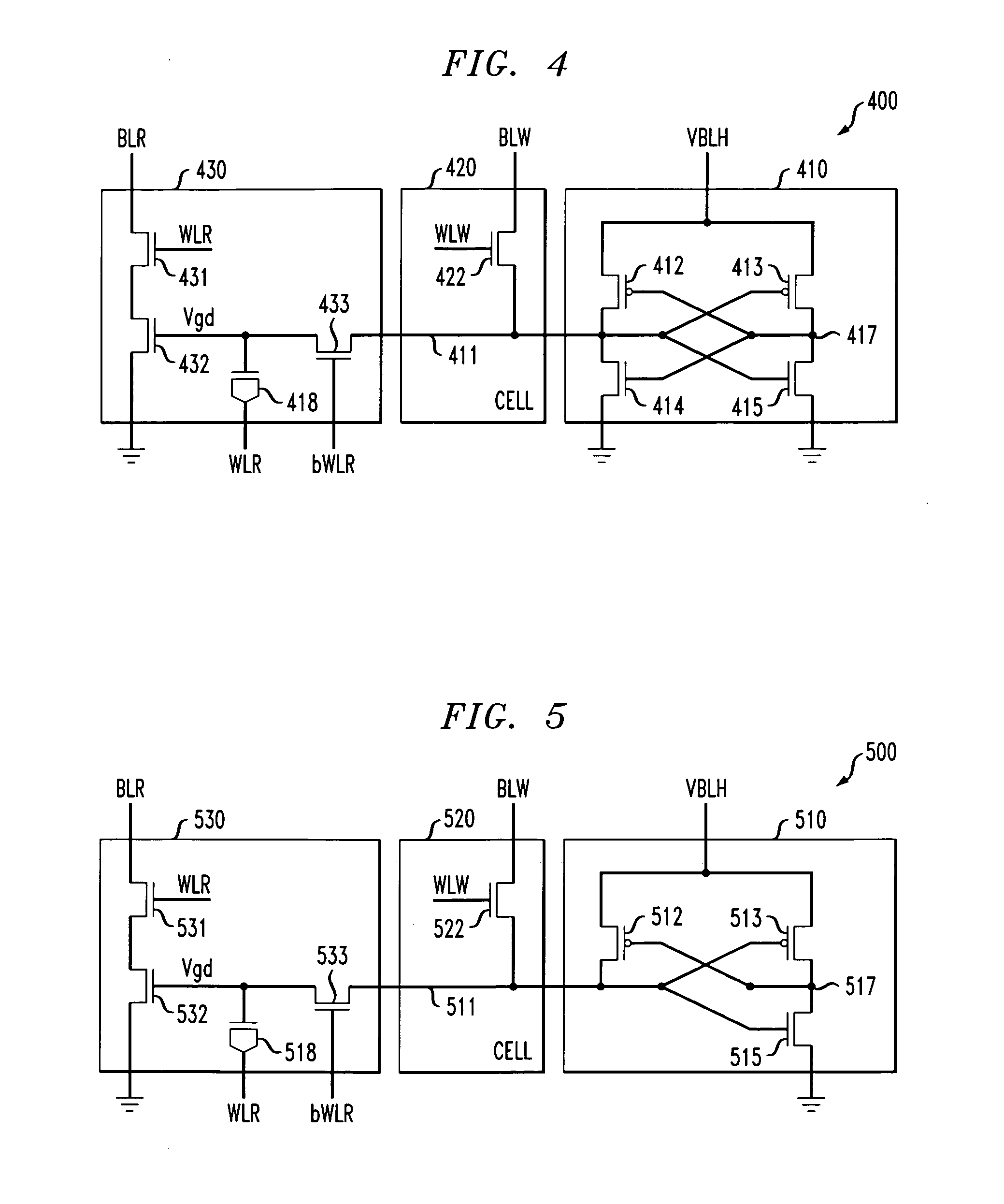

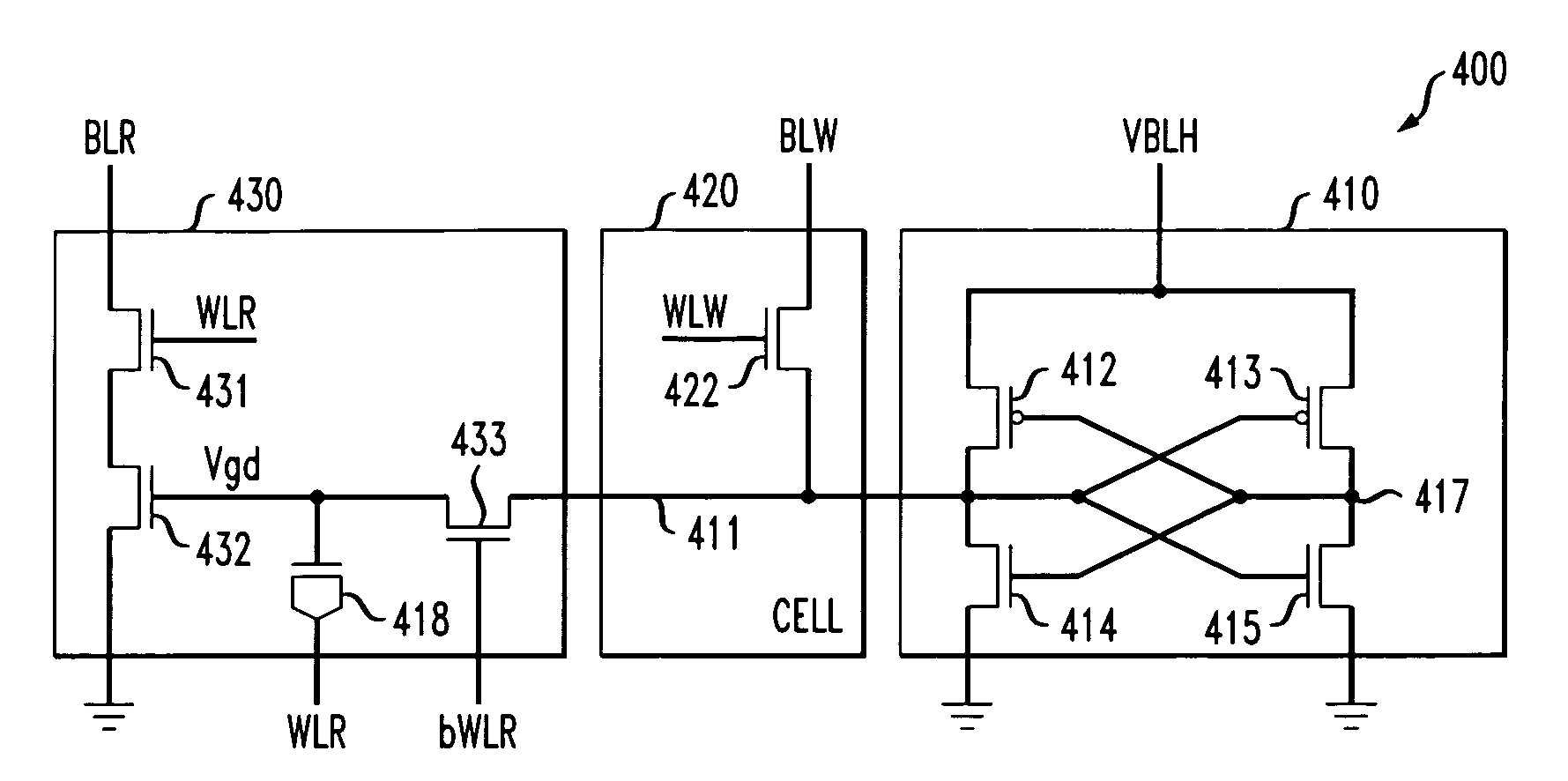

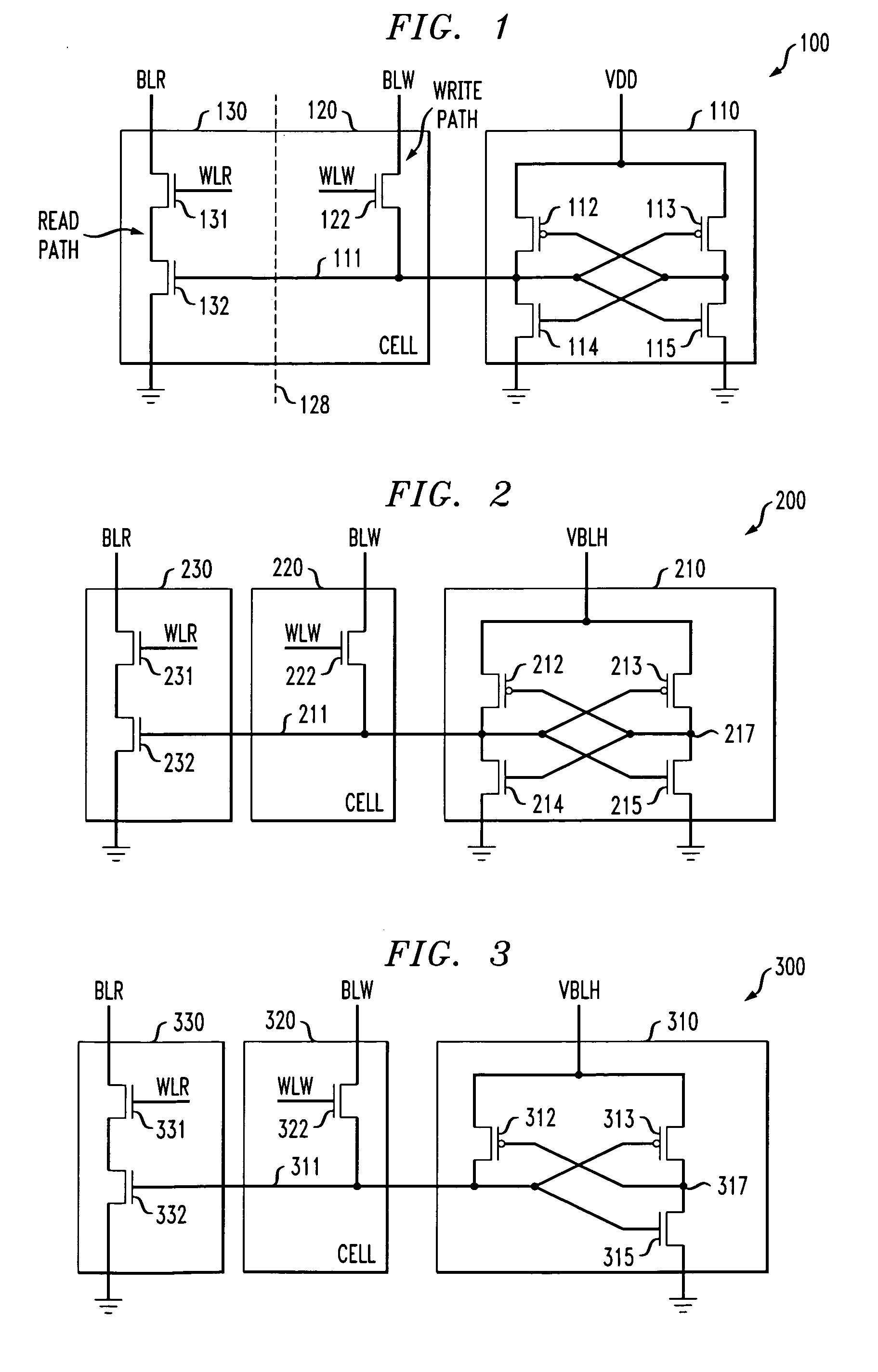

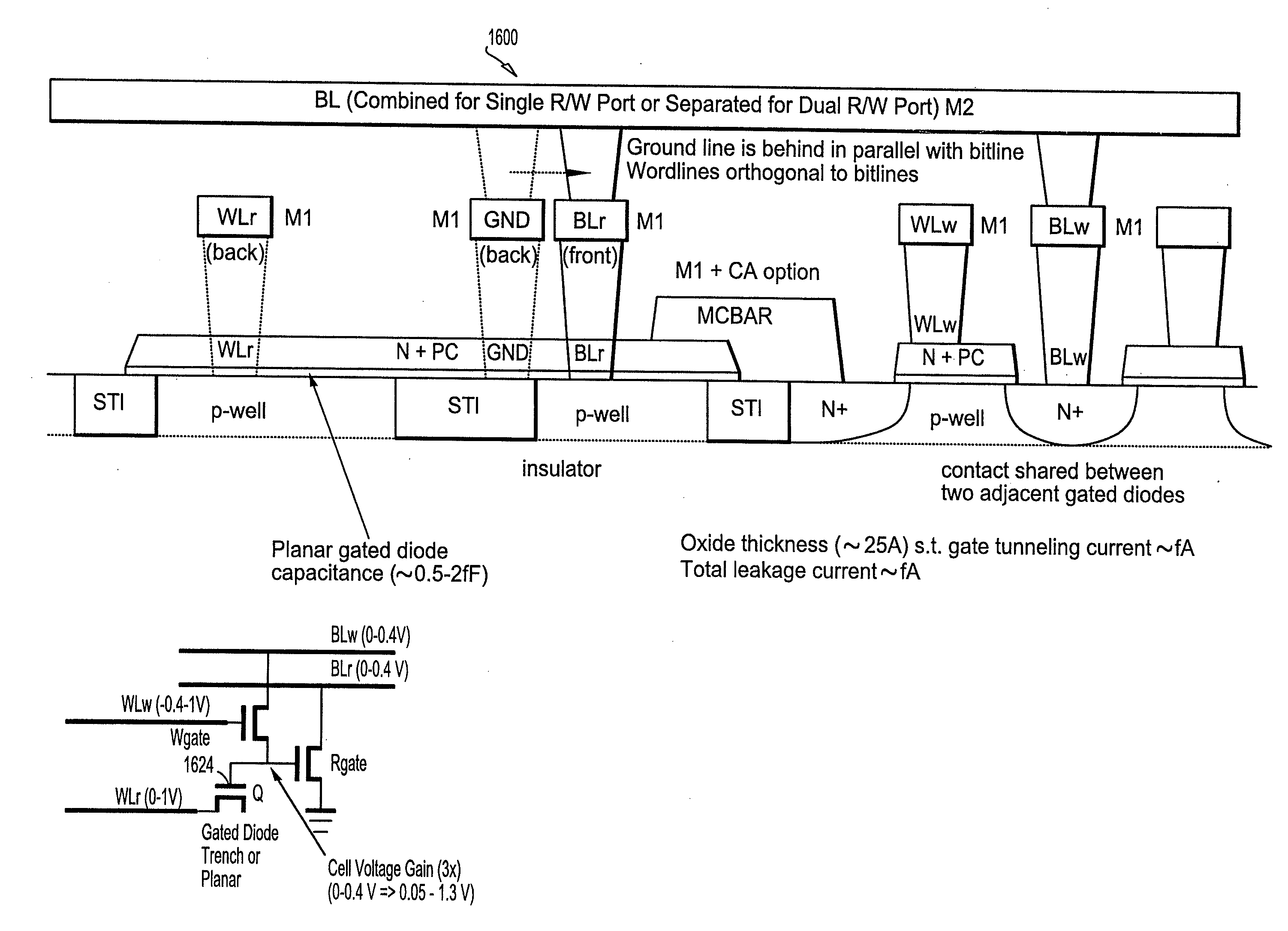

Static random access memory utilizing gated diode technology

ActiveUS20060198181A1Improve signal-to-noise ratioImprove scalabilityDigital storageExtensibilityStatic random-access memory

A new type of static RAM cell is disclosed that is based on a gated diode and its voltage amplification characteristic. The cell combines the advantages of a static RAM, in which data refresh is not needed, and those of gated diode cells, which are scalable to low voltages, have high signal to noise ratio, high signal margin, and tolerance to process variations, to form a single high performance static memory cell. This new cell has independent read and write paths, which allow for separate optimization of the read (R) and write (W) events, and enable dual-port R / W operation. Furthermore, storage node disturbance during the read and write operations are eliminated, which greatly improves cell stability and scalability for future technologies.

Owner:GLOBALFOUNDRIES US INC

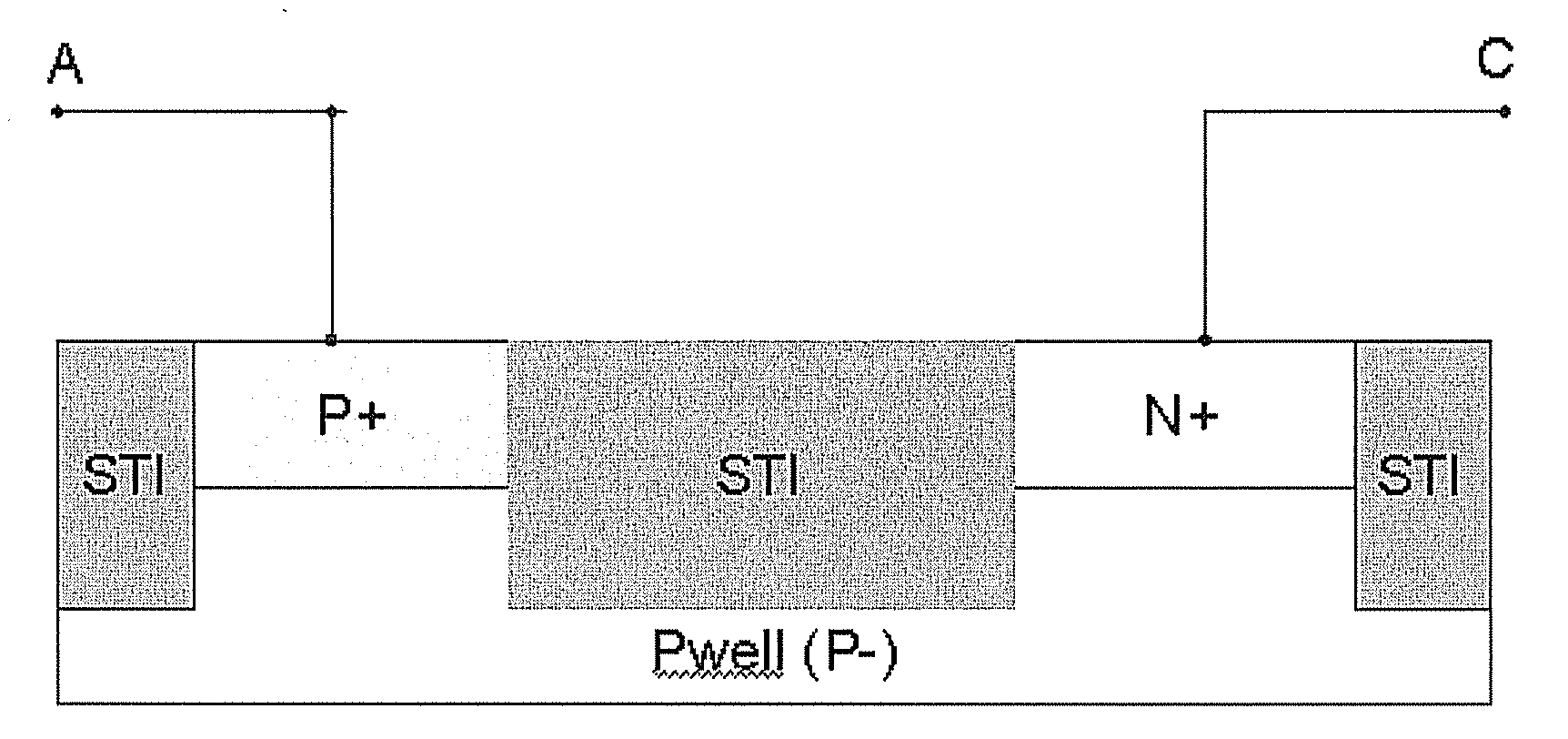

Electrostatic discharge protection circuit of non-gated diode and fabrication method thereof

InactiveUS6933573B2Improve pressure resistanceGood effectSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSilicon on insulator

A non-gated diode structure of a silicon-on-insulator, having a silicon-on-insulator substrate, a pair of isolating structures, a first type doped region and a second type doped region. The silicon-on-insulation substrate has a stack of a substrate, an insulation layer and a silicon layer. The isolating structures are located in the silicon layer to define a well region. The first and second type doped regions are located in the well and are adjacent to the isolating structures. Such a non-gated diode structure can be applied to an electrostatic discharge protection circuit to increase the electrostatic discharge protection voltage or current. In addition, a fabrication method of the non-gated diode is also introduced. This non-gated diode can be also fabricated in the general bulk CMOS process, and used in the on-chip ESD protection circuits.

Owner:UNITED MICROELECTRONICS CORP

Static random access memory utilizing gated diode technology

ActiveUS7136296B2Improve signal-to-noise ratioHigh signal marginDigital storageStatic random-access memorySignal-to-noise ratio (imaging)

A new type of static RAM cell is disclosed that is based on a gated diode and its voltage amplification characteristic. The cell combines the advantages of a static RAM, in which data refresh is not needed, and those of gated diode cells, which are scalable to low voltages, have high signal to noise ratio, high signal margin, and tolerance to process variations, to form a single high performance static memory cell. This new cell has independent read and write paths, which allow for separate optimization of the read (R) and write (W) events, and enable dual-port R / W operation. Furthermore, storage node disturbance during the read and write operations are eliminated, which greatly improves cell stability and scalability for future technologies.

Owner:GLOBALFOUNDRIES U S INC

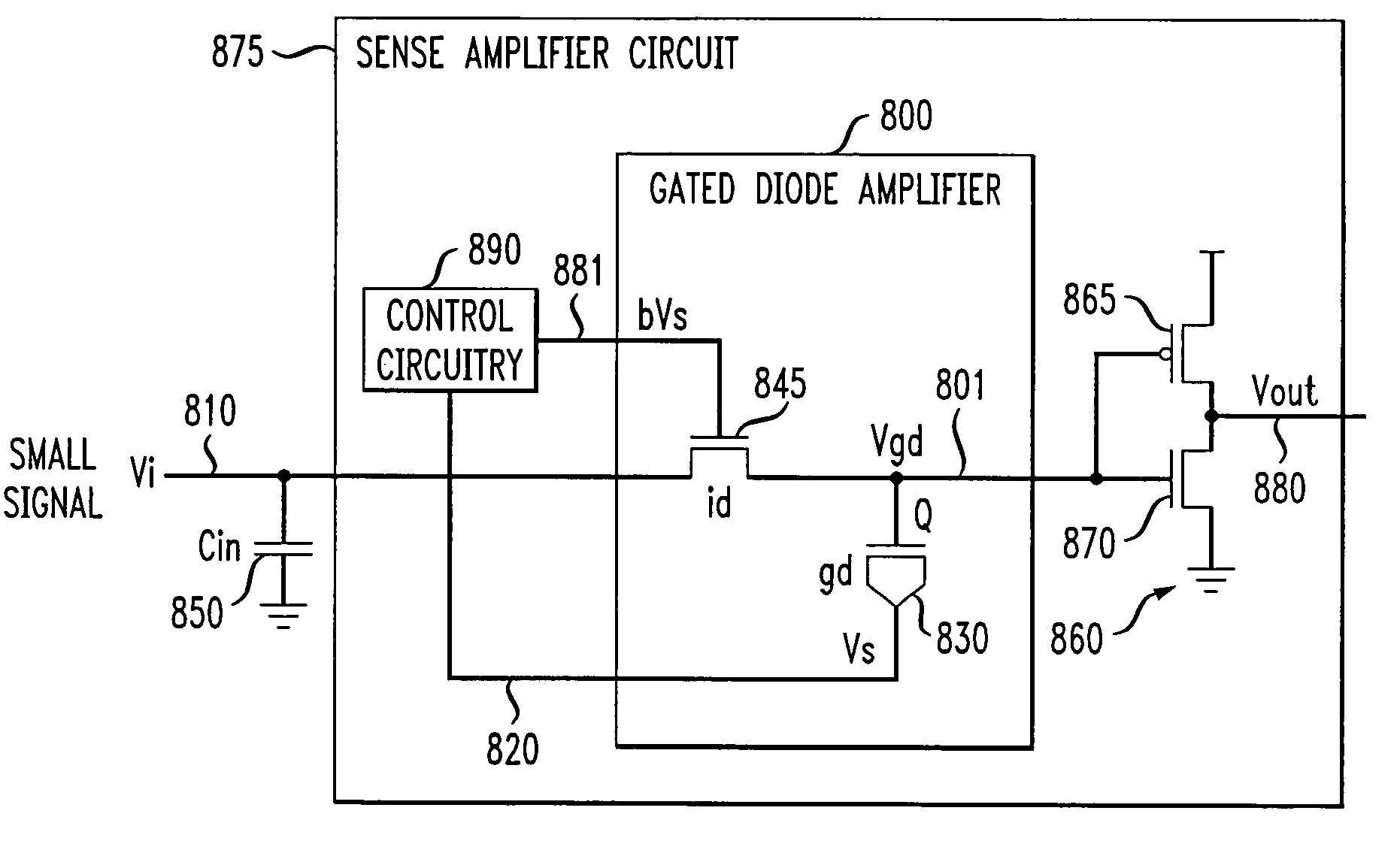

Sense amplifier circuits and high speed latch circuits using gated diodes

InactiveUS7116594B2Current/voltage measurementInstant pulse delivery arrangementsAudio power amplifierEngineering

A sense amplifier circuit comprises (1) an isolation device comprising a control terminal and first and second terminals, the first terminal of the isolation device coupled to a signal line, (2) a gated diode comprising first and second terminals, the first terminal of the gated diode coupled to the second terminal of the isolation device, and the second terminal of the gated diode coupled to a set line; and (3) control circuitry coupled to the control terminal of the isolation device and adapted to control voltage on the control terminal of the isolation device in order to enable and disable the isolation device. A latch circuit further comprises a precharge device comprising a control terminal and first and second terminals, the first terminal of the precharge device coupled to a power supply voltage, and the second terminal of the precharge device coupled to the first terminal of the isolation device.

Owner:GLOBALFOUNDRIES INC

Diode Having A Pocket Implant Blocked And Circuits And Methods Employing Same

ActiveUS20120074496A1Reducing area junction capacitanceLower junction capacitanceLiquid surface applicatorsSemiconductor/solid-state device detailsCapacitanceEngineering

Diodes, including gated diodes and shallow trench isolation (STI) diodes, manufacturing methods, and related circuits are provided without at least one halo or pocket implant thereby reducing capacitance of the diode. In this manner, the diode may be used in circuits and other devices having performance sensitive to load capacitance while still obtaining the performance characteristics of the diode. Such characteristics for a gated diode include fast turn-on times and high conductance, making the gated diodes well-suited for electro-static discharge (ESD) protection circuits as one example. Diodes include a semiconductor substrate having a well region and insulating layer thereupon. A gate electrode is formed over the insulating layer. Anode and cathode regions are provided in the well region. A P-N junction is formed. At least one pocket implant is blocked in the diode to reduce capacitance.

Owner:QUALCOMM INC

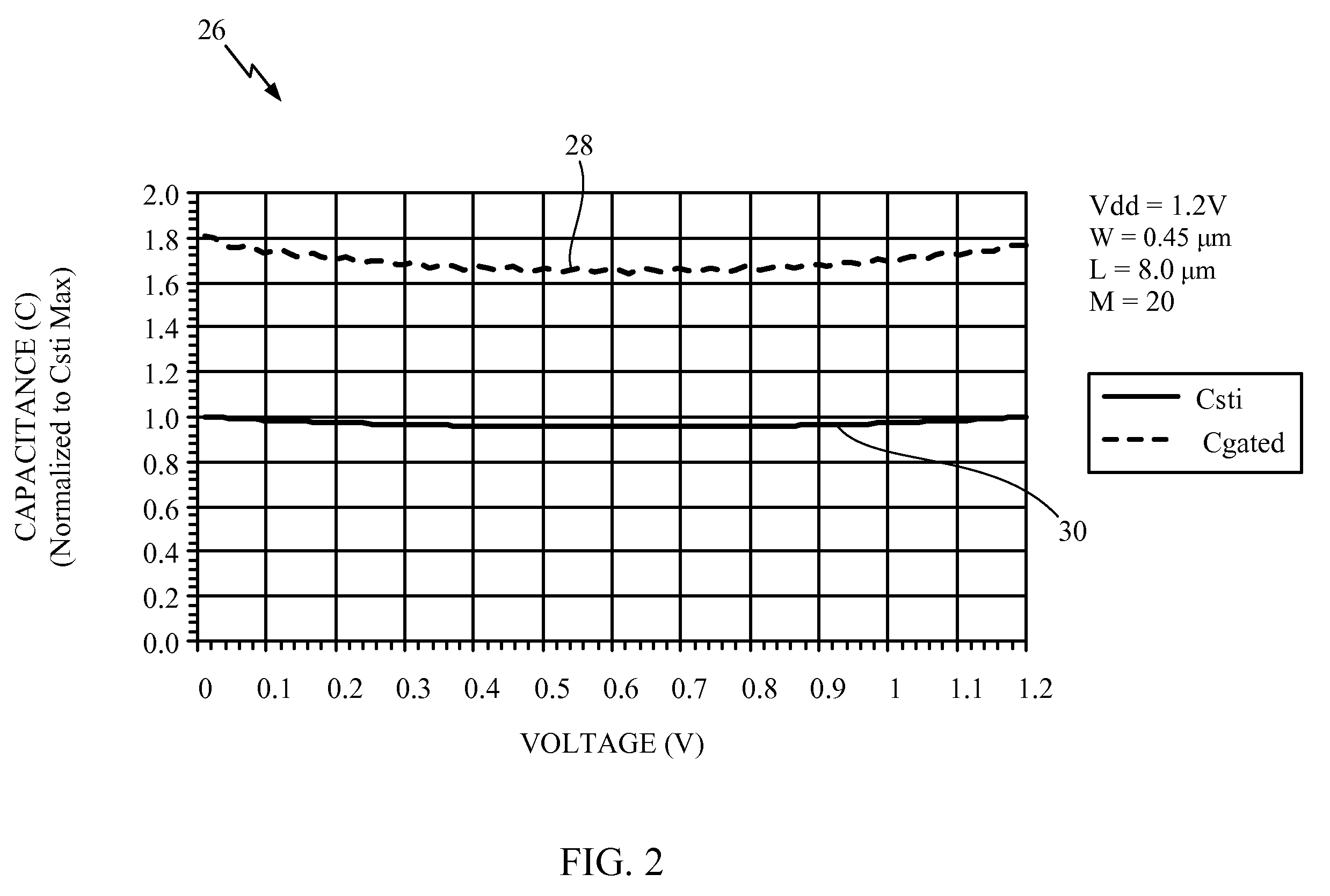

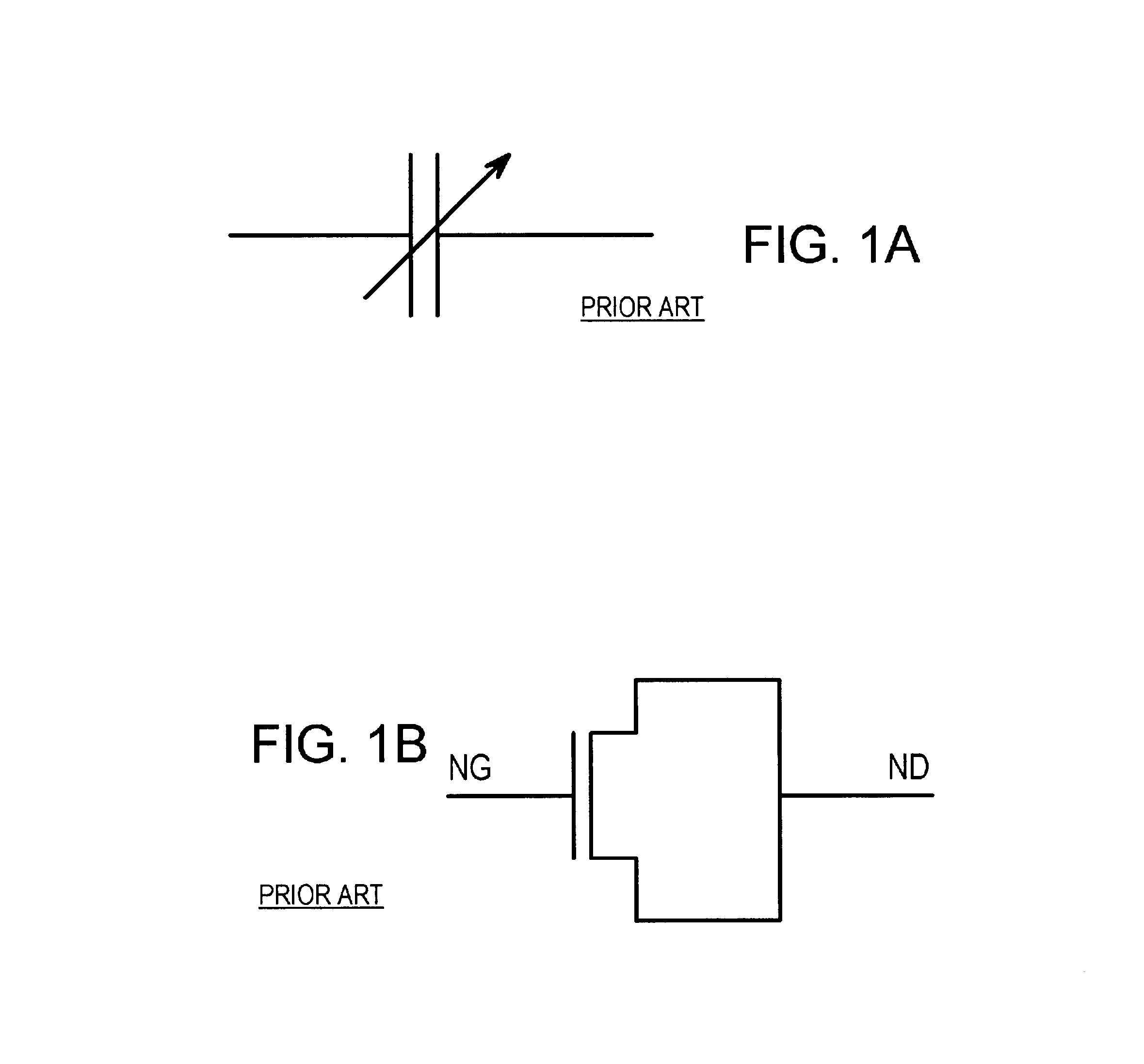

Variable capacitor using MOS gated diode with multiple segments to limit DC current

A voltage-variable capacitor uses the channel-to-substrate junction from a gated diode formed from a metal-oxide-semiconductor transistor. The transistor gate has at least two contacts that are biased to different voltages. The gate acts as a resistor with current flowing from an upper gate contact to a lower gate contact. The gate-to-source voltage varies as a function of the position. A critical voltage is where the gate-to-source voltage is equal to the transistor threshold. A portion of the gate that has gate voltages above the critical voltage has an inversion layer or conducting channel under the gate. Another portion of the gate has gate voltages below the critical voltage, and thus no channel forms. By varying either the gate voltages or the source voltage, the area of the gate that has a channel under it is varied, varying the channel-to-substrate capacitance. Separate gate arms reduce bias current.

Owner:DIODES INC

3T1D memory cells using gated diodes and methods of use thereof

InactiveUS20050146928A1Small capacitanceLeakage currentTransistorSolid-state devicesCapacitanceDevice material

A memory cell comprises: (1) a write switch, the first terminal of the write switch coupled to an at least one bitline, the control terminal of the write switch coupled to the first control line; (2) a two terminal semiconductor, the first terminal of the two terminal semiconductor device coupled to the second terminal of the write switch, and the second terminal of the two terminal semiconductor device coupled to an at least one second control line, wherein the two terminal semiconductor device has a capacitance when a voltage on the first terminal relative to the second terminal is above a threshold voltage and has a lower capacitance when the voltage on the first terminal relative to the second terminal is less than the threshold voltage; (3) a read select switch, the control terminal of the read select switch coupled to an at least one second control line, the first terminal of the read select switch coupled to the at least one bitline; and (4) a read switch, the control terminal of the read switch coupled to the first terminal of the gated diode and coupled to the second terminal of the write switch, the first terminal of the read switch coupled to the second terminal of the read select gate, and the second terminal of the read switch coupled to ground.

Owner:GLOBALFOUNDRIES INC

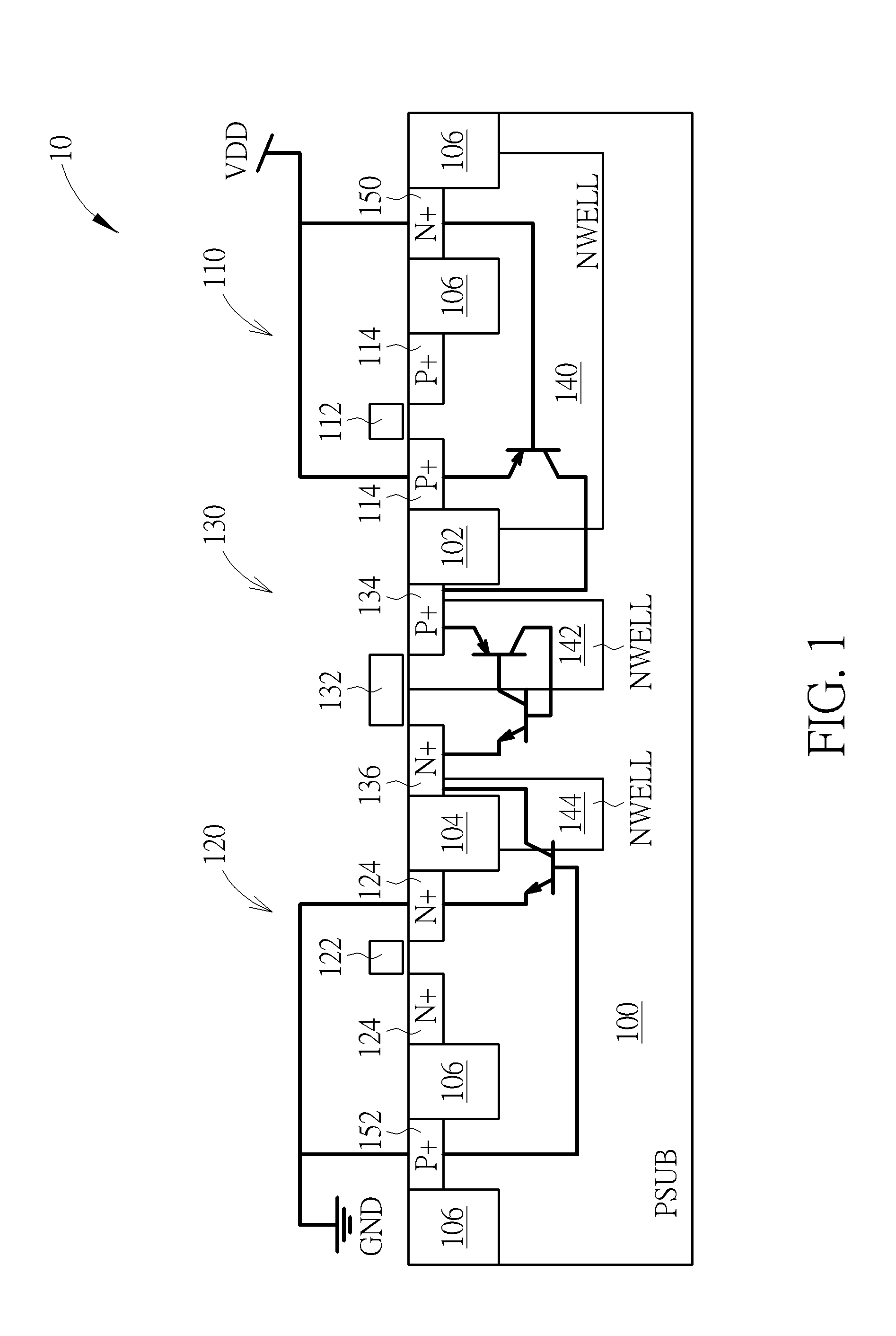

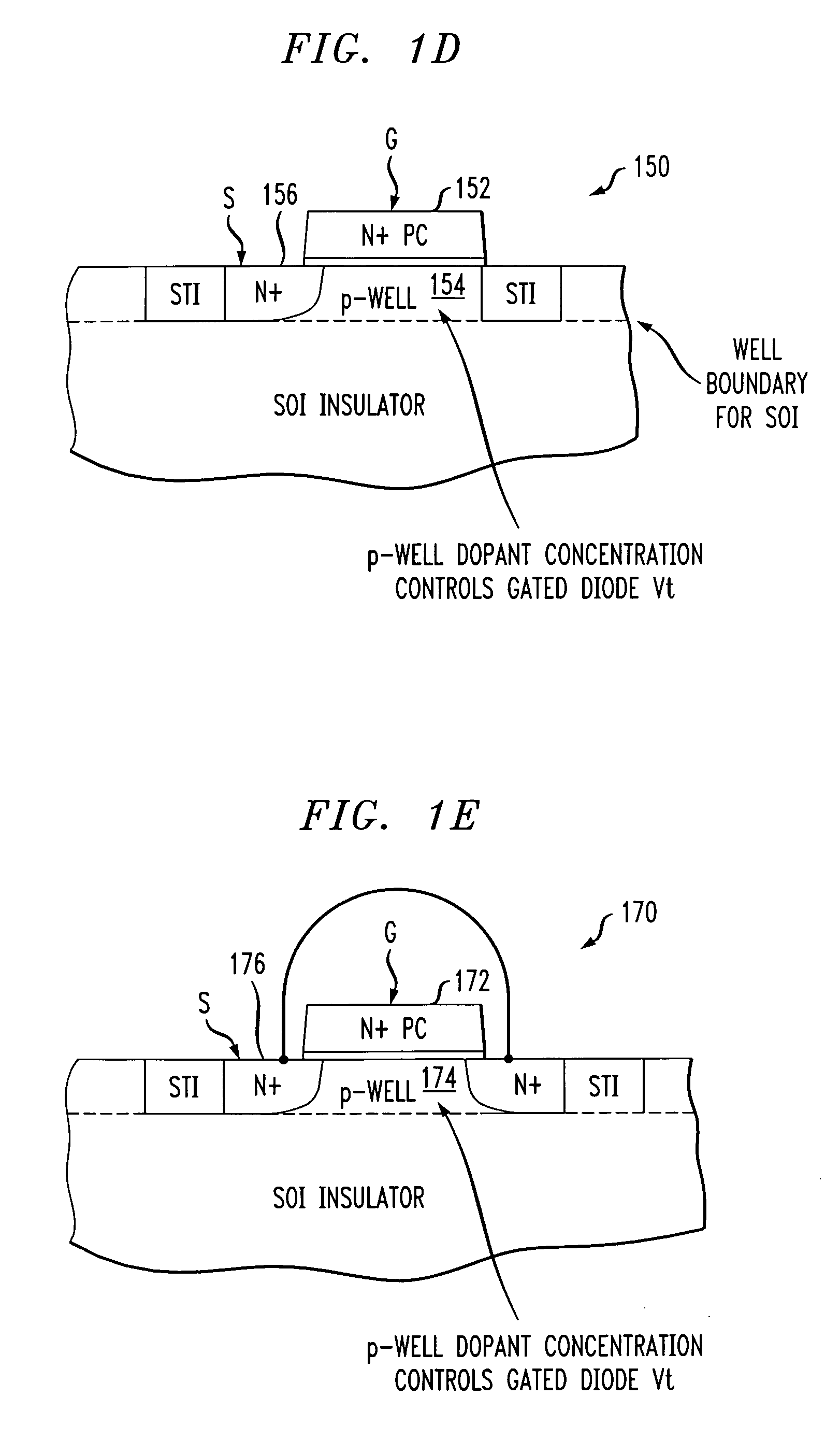

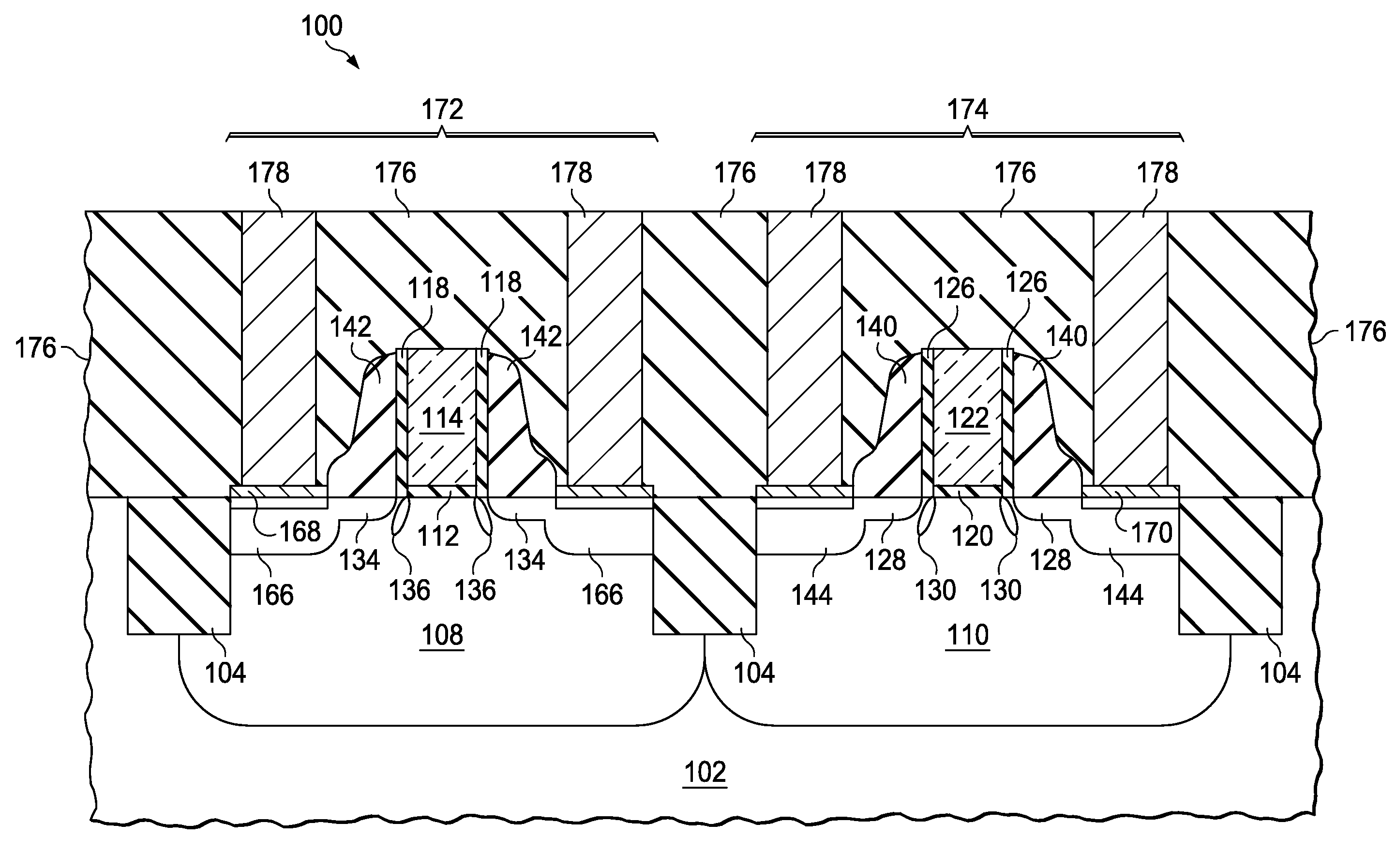

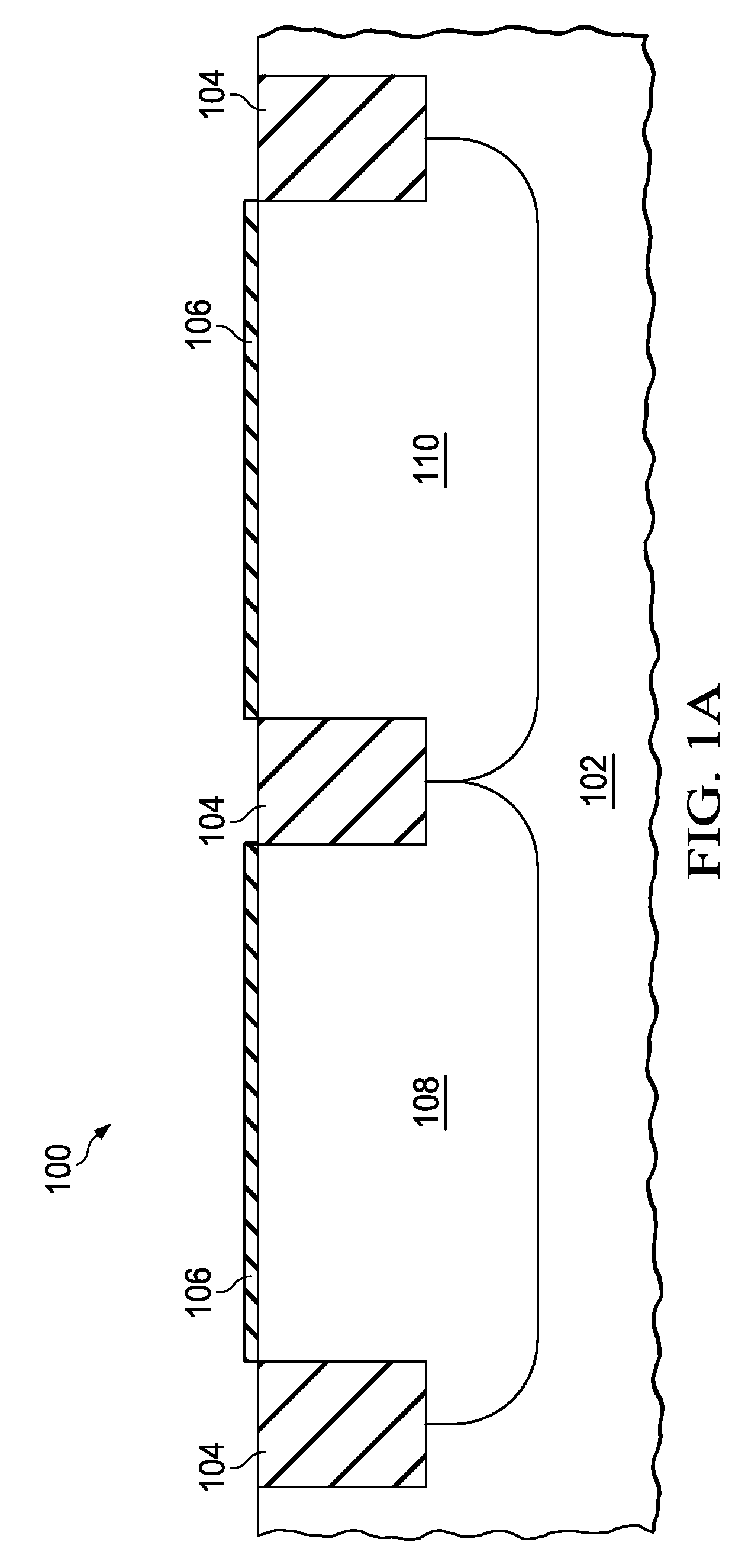

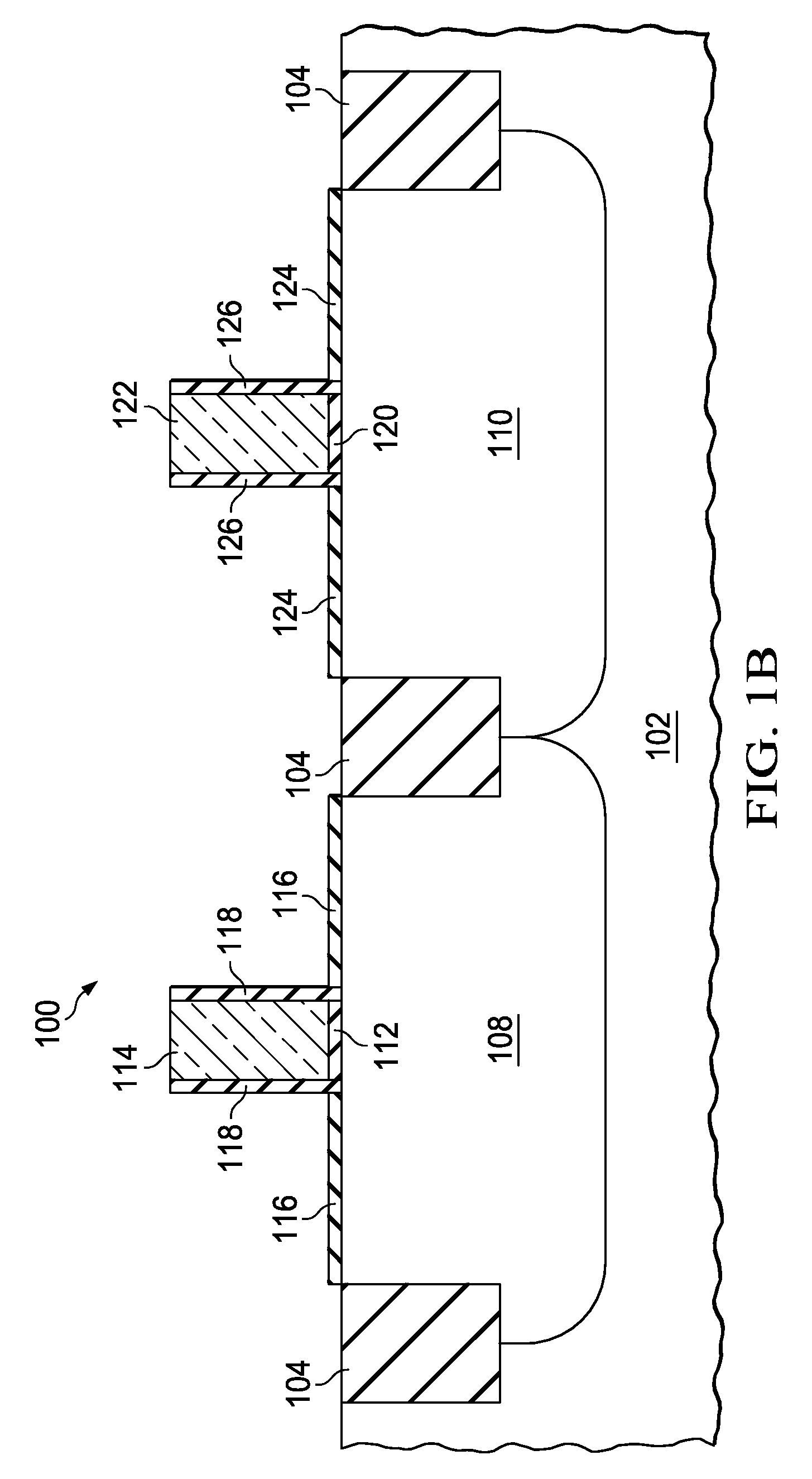

Complementary metal-oxide-semiconductor device

ActiveUS20150123184A1Increase holding voltageIncrease layout areaTransistorSemiconductor/solid-state device detailsCMOSEngineering

A CMOS device includes a substrate, a pMOS transistor and an nMOS transistor formed on the substrate, and a gated diode. The gated diode includes a floating gate formed on the substrate in between the pMOS transistor and the nMOS transistor and a pair of a p-doped region and an n-doped region formed in the substrate and between the pMOS transistor and the nMOS transistor. The n-doped region is formed between the floating gate and the nMOS transistor, and the p-doped region is formed between the floating gate and the pMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

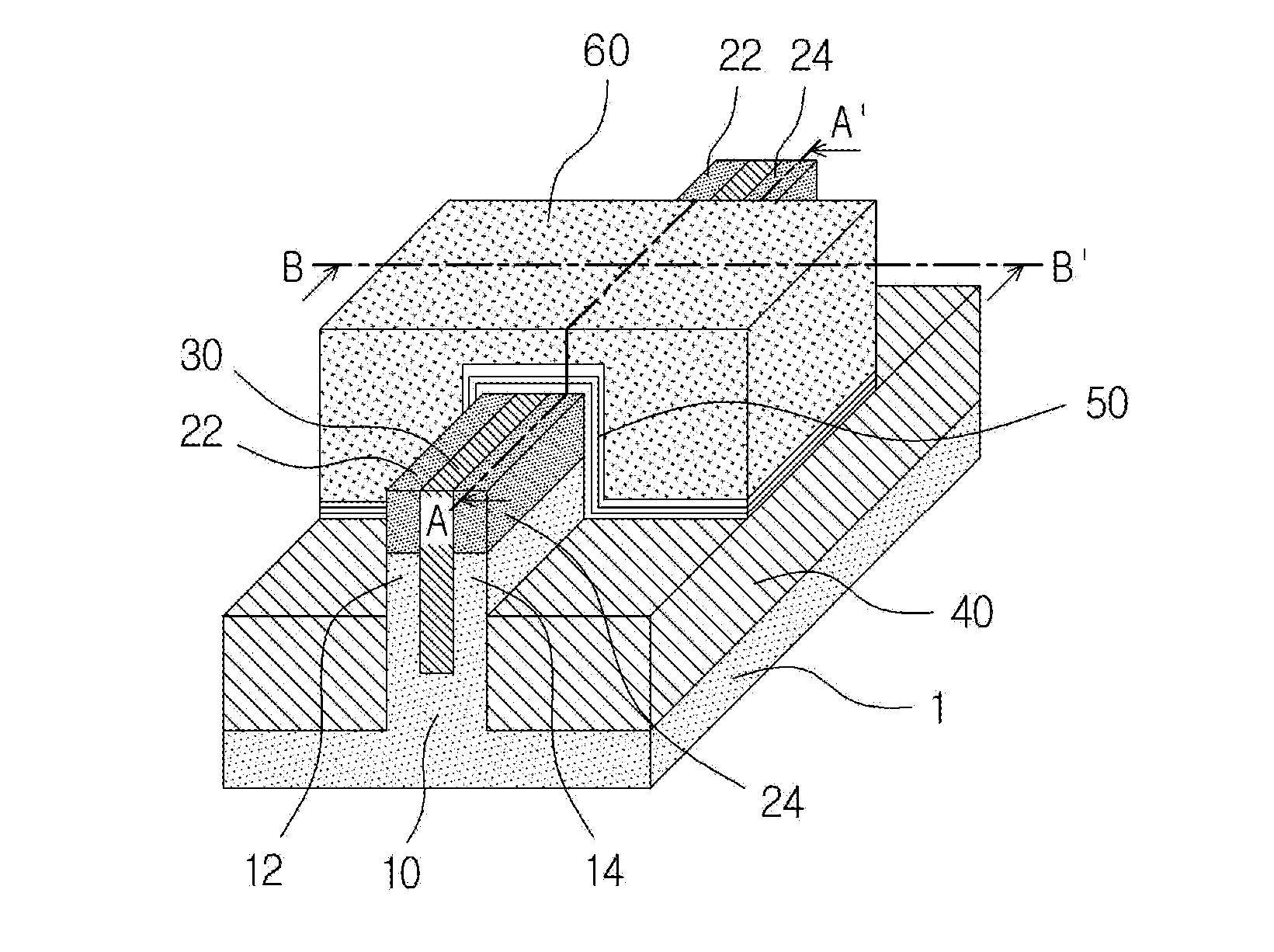

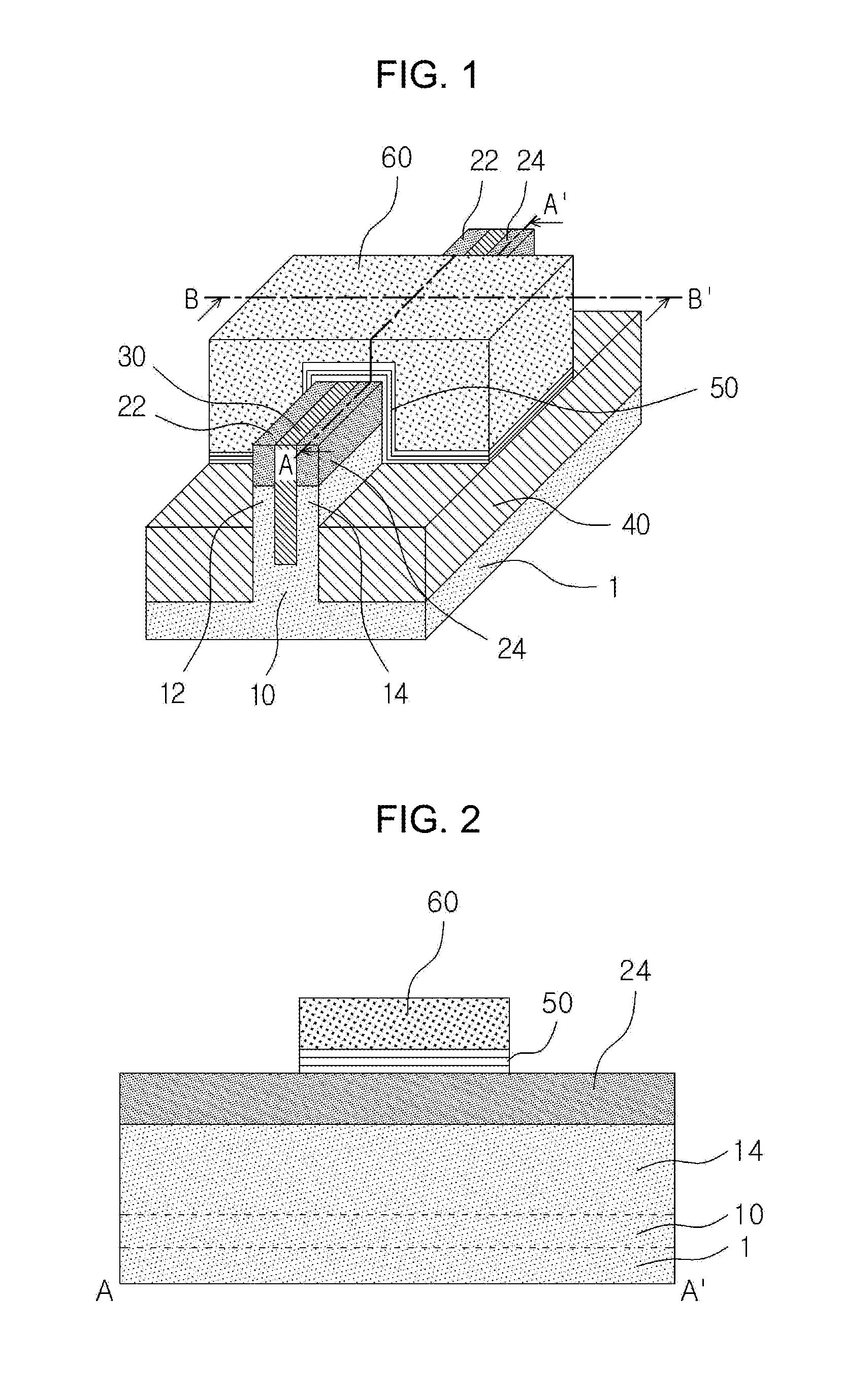

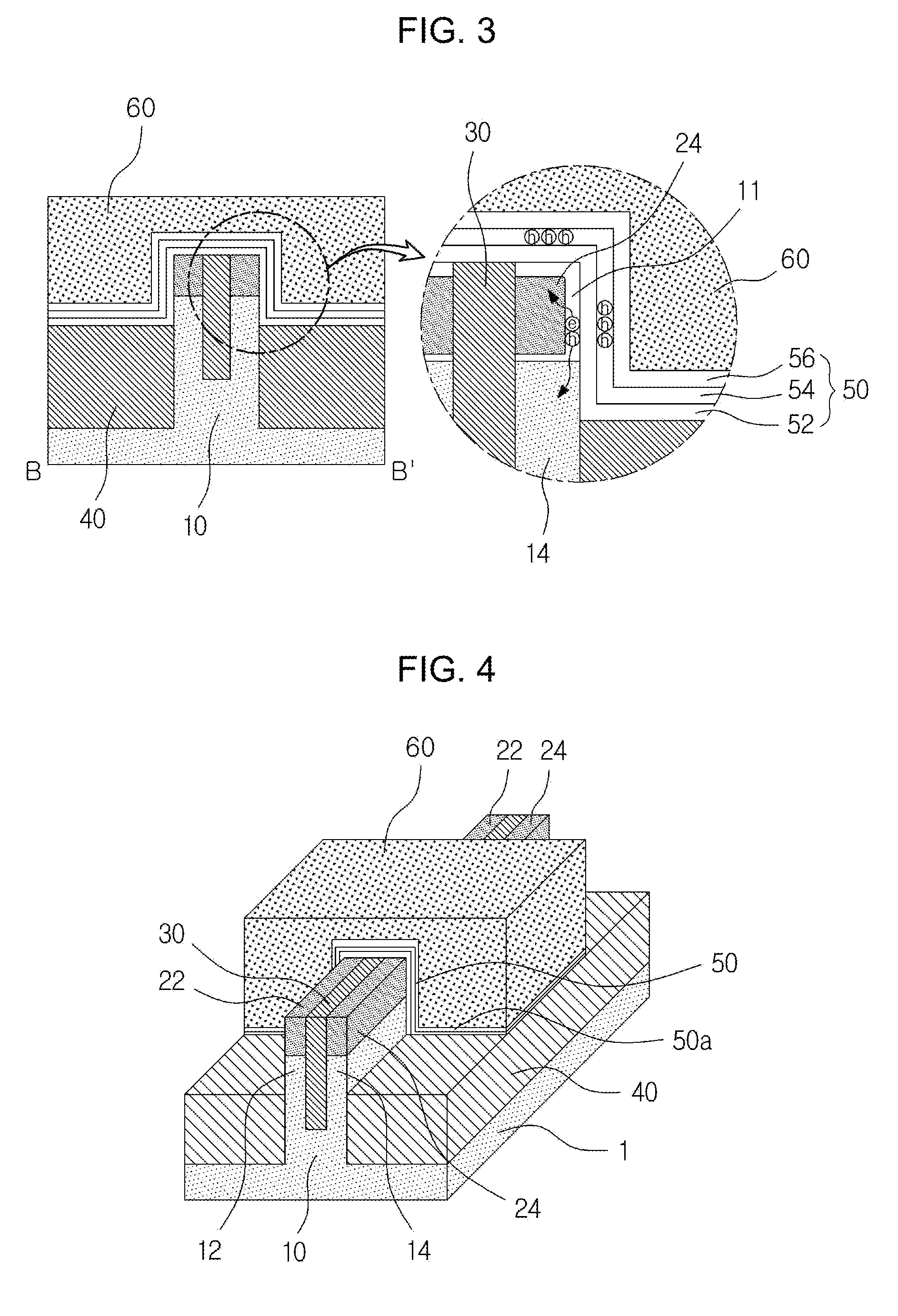

Memory cell string based on gated-diode cell and memory array using the same

ActiveUS20130329499A1Highly integratedAvoid interferenceSolid-state devicesRead-only memoriesP–n junctionStorage cell

The present invention provides a nonvolatile memory cell string and a memory array using the same. According to the present invention, a wall type semiconductor separated into twin fins and a memory cell string formed with memory cells having a gated diode structure along each fin are enabled to increase the degree of integration and basically prevent the interferences between adjacent cells. And a first semiconductor layer and a depletion region of a PN junction wrapped up by a gate electrode are enabled to remove GSL and CSL by GIDL memory operation and significantly increase the degree of integration for applying to a neuromorphic technology.

Owner:SEOUL NAT UNIV R&DB FOUND

Gated Diode Sense Amplifiers

InactiveUS20090103382A1Improve the sense of speedDecrease in source voltageLine/current collector detailsCurrent/voltage measurementAudio power amplifierSense amplifier

A sense amplifier for use in sensing a signal in an integrated circuit comprises an amplifier portion and an output portion. The amplifier portion comprises a gated diode having a gate terminal. The output portion comprises an output transistor in signal communication with the gate terminal of the gated diode and having a source terminal. A variable source voltage acts on the source terminal of the output transistor when the sense amplifier is in operation. The variable source voltage is temporarily altered when the sense amplifier is actively sensing the signal in the integrated circuit.

Owner:IBM CORP

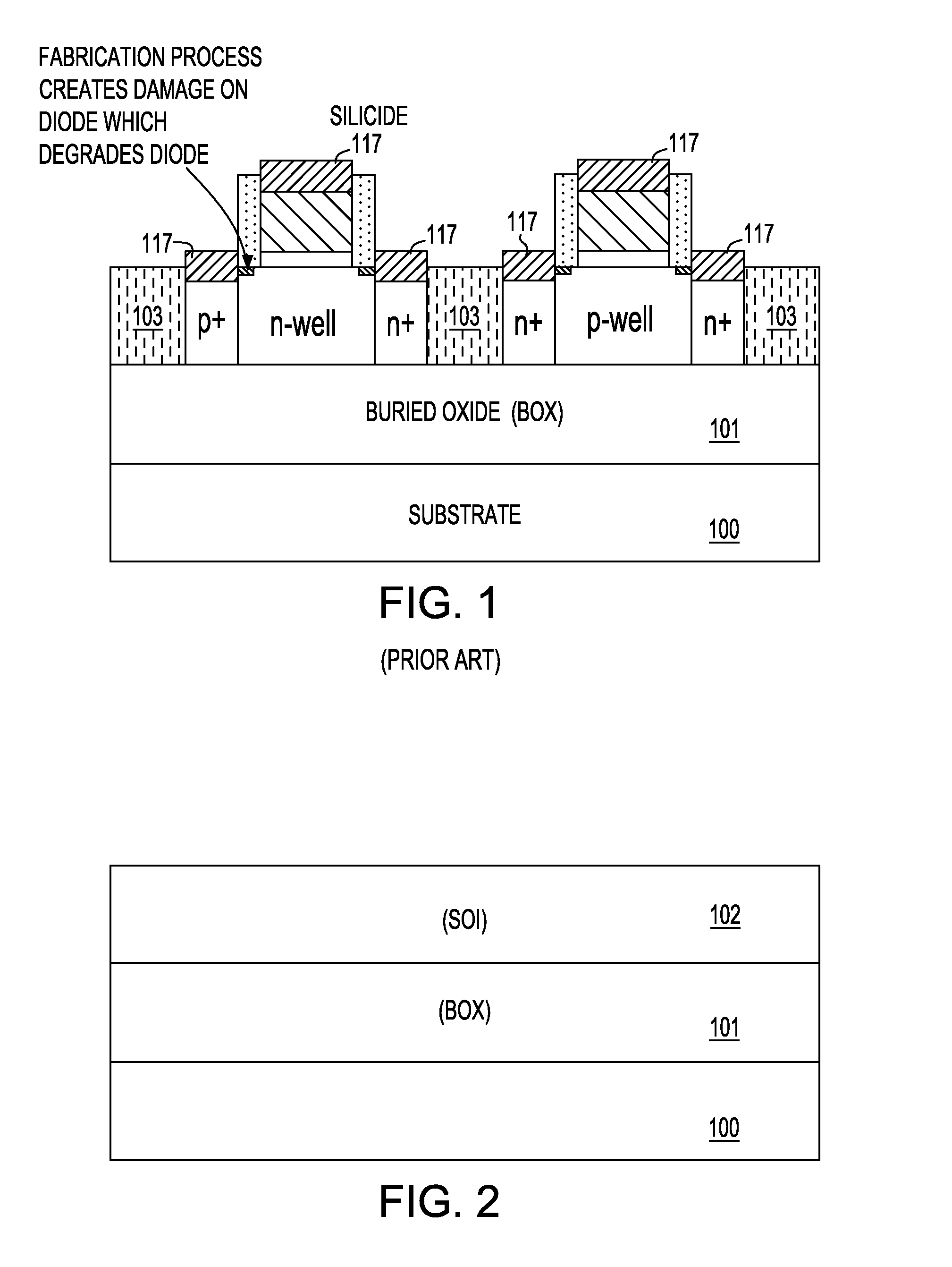

Electronic device and a process for forming the electronic device

An electronic device can include a gated diode, wherein the gated diode includes a junction diode structure including a junction. A first conductive member spaced apart from and adjacent to the junction can be connected to a first signal line. A second conductive member, spaced apart from and adjacent to the junction, can be both electrically connected to a second signal line and electrically insulated from the first conductive member. The junction diode structure can include a p-n or a p-i-n junction. A process for forming the electronic device is also described.

Owner:TAIWAN SEMICON MFG CO LTD

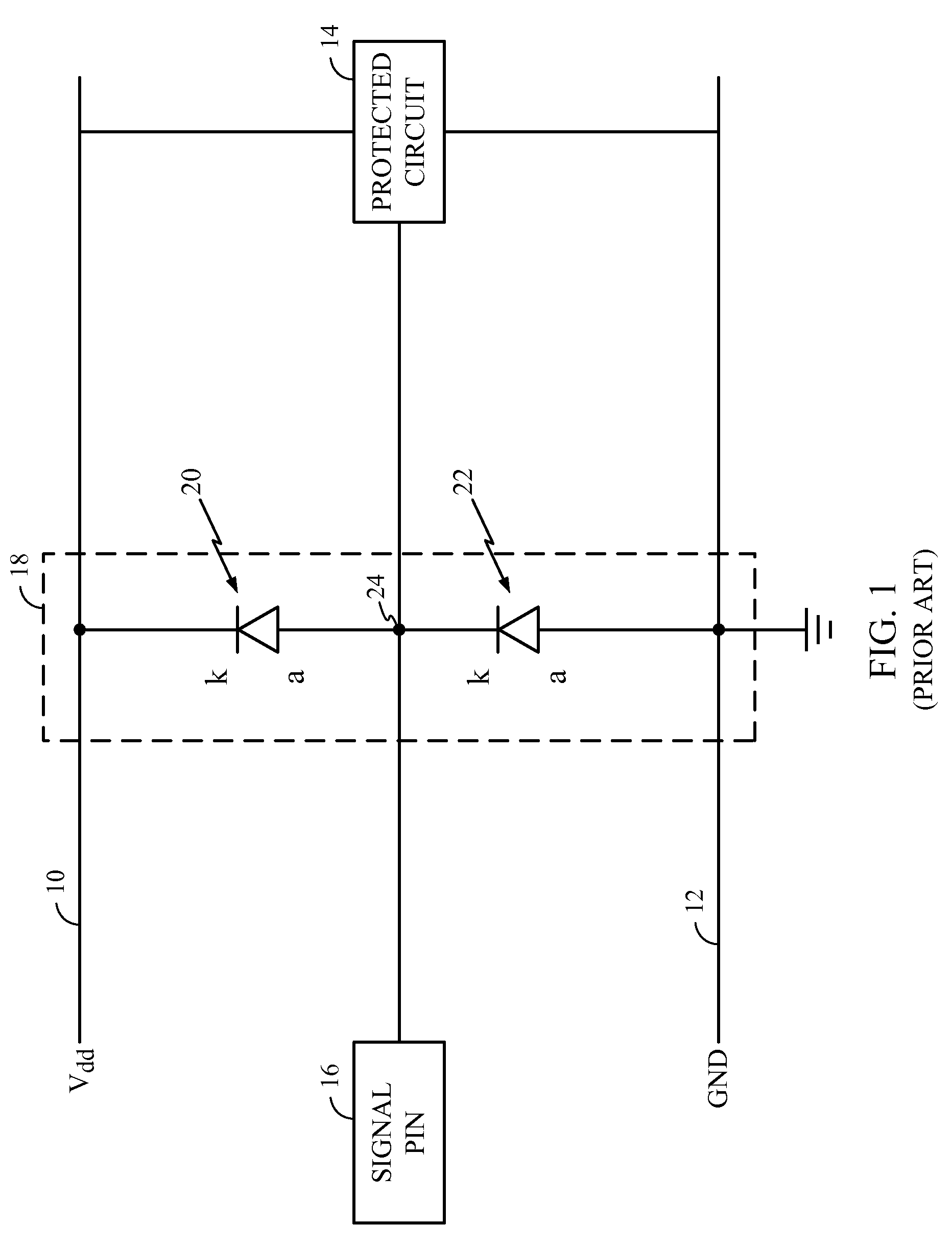

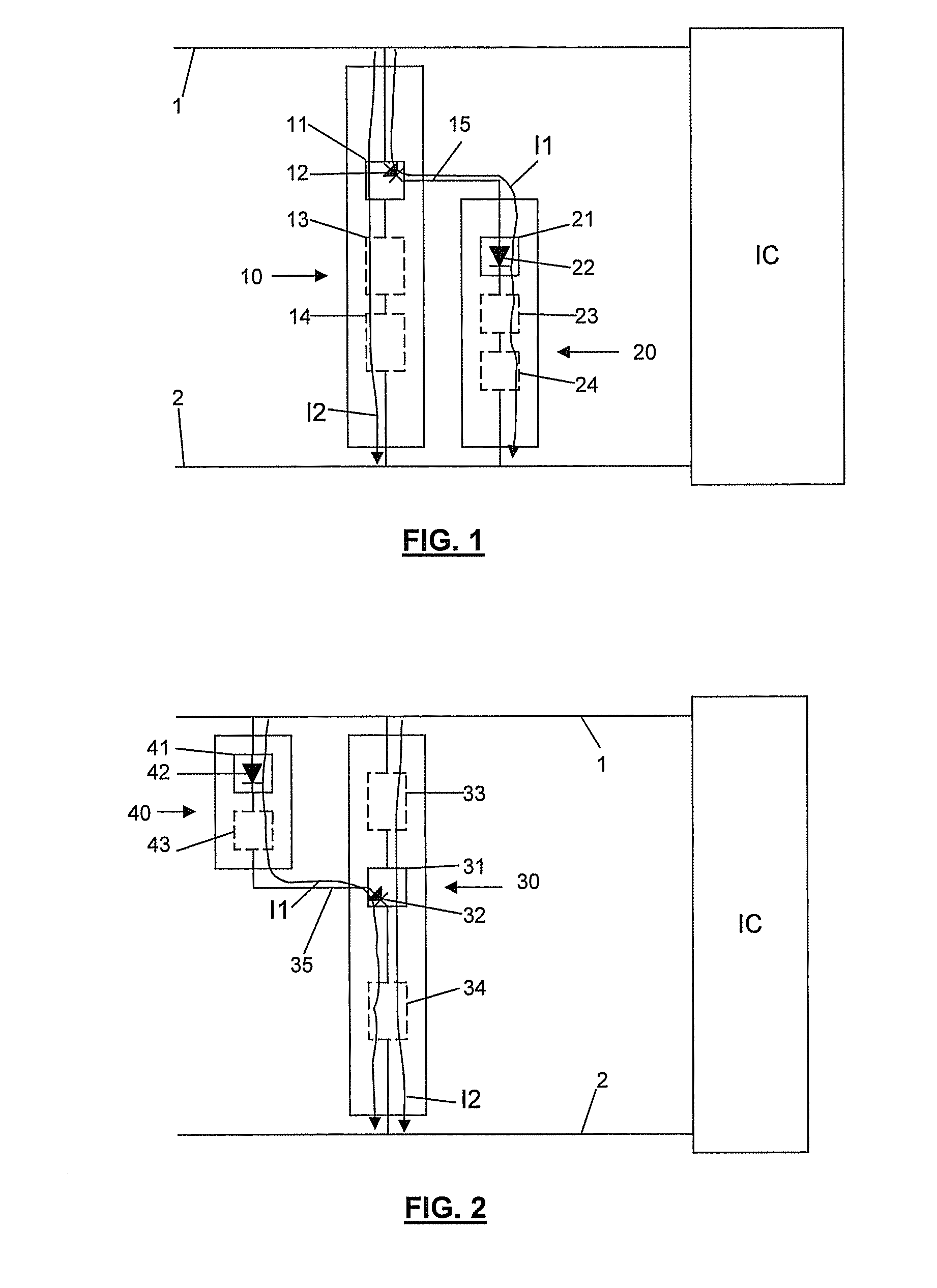

Fast Triggering ESD Protection Device and Method for Designing Same

InactiveUS20090073621A1Overshoot appearing over the IC can be further reducedComponent be accuratelyTransistorThyristorDesign methodsElectrical current

A method and apparatus for designing an ESD protection circuit comprising a main ESD device and a triggering device connected to a triggering node of the main ESD device by means of which the main ESD device can be triggered for conducting ESD current at a reduced voltage. The triggering device is located in an initial current path for the ESD current. In this initial current path, there is at least one triggering component which can be triggered from an off-state to an on-state. The triggering speed of this component is considered and its design is optimised in view of increasing its triggering speed. Further shown is an ESD protection circuit in which at least one triggering component is selected to be of a predetermined type for achieving a fast triggering speed, preferably of the gated diode type.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

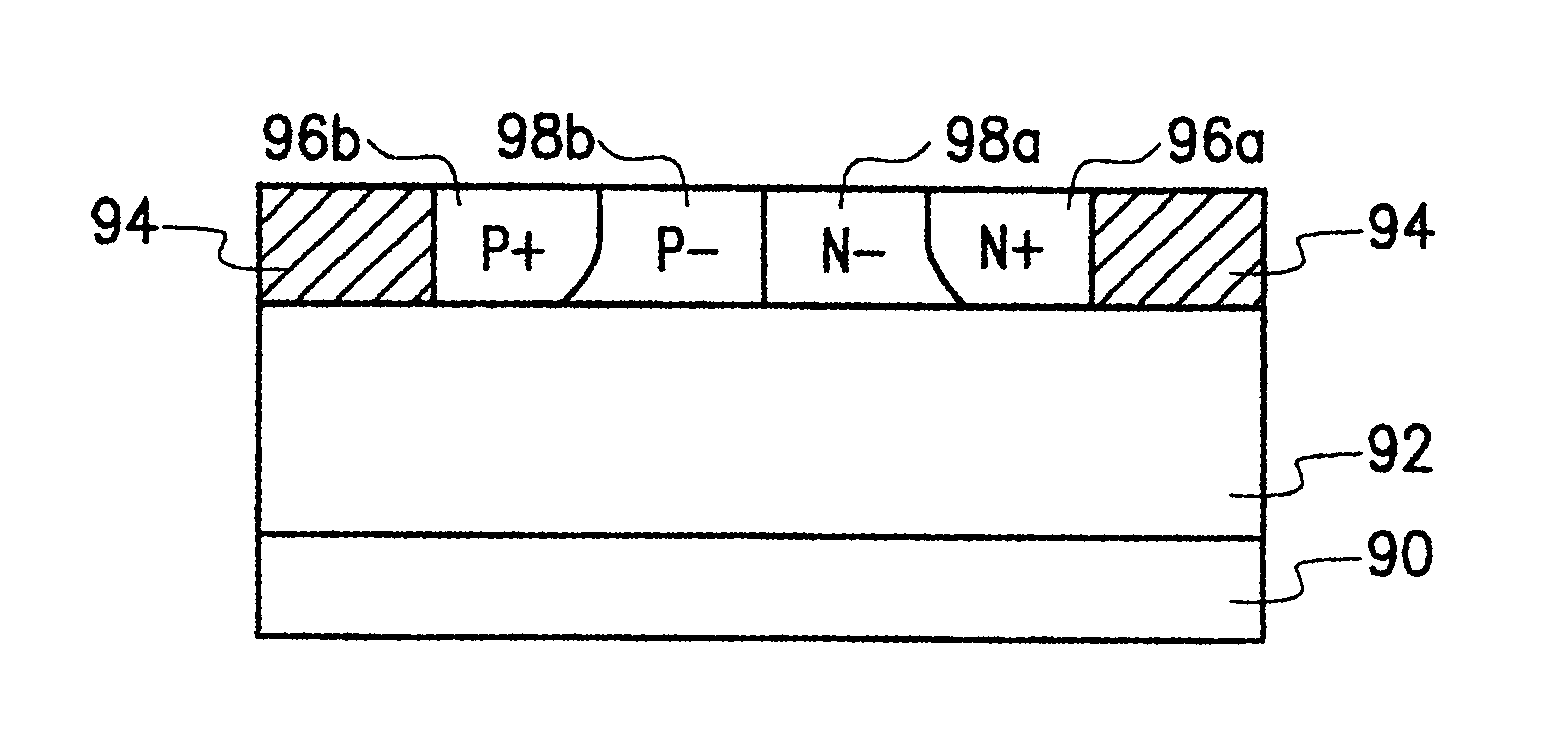

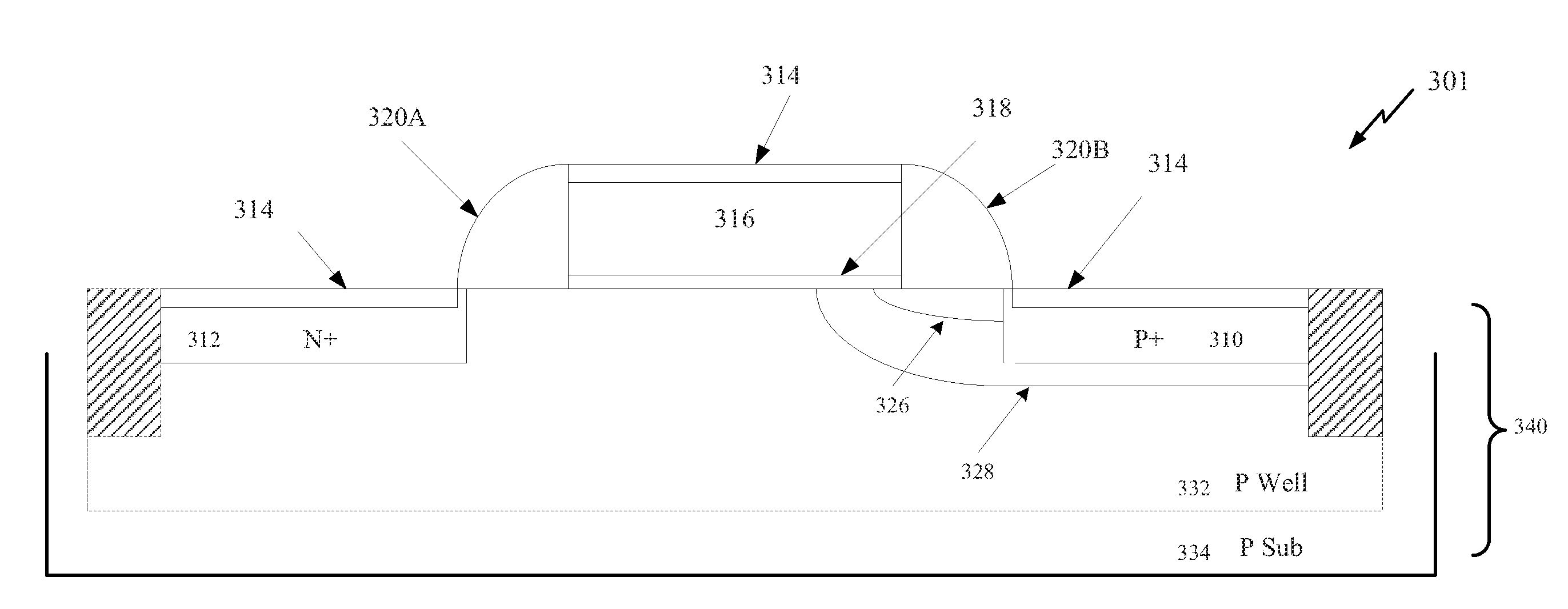

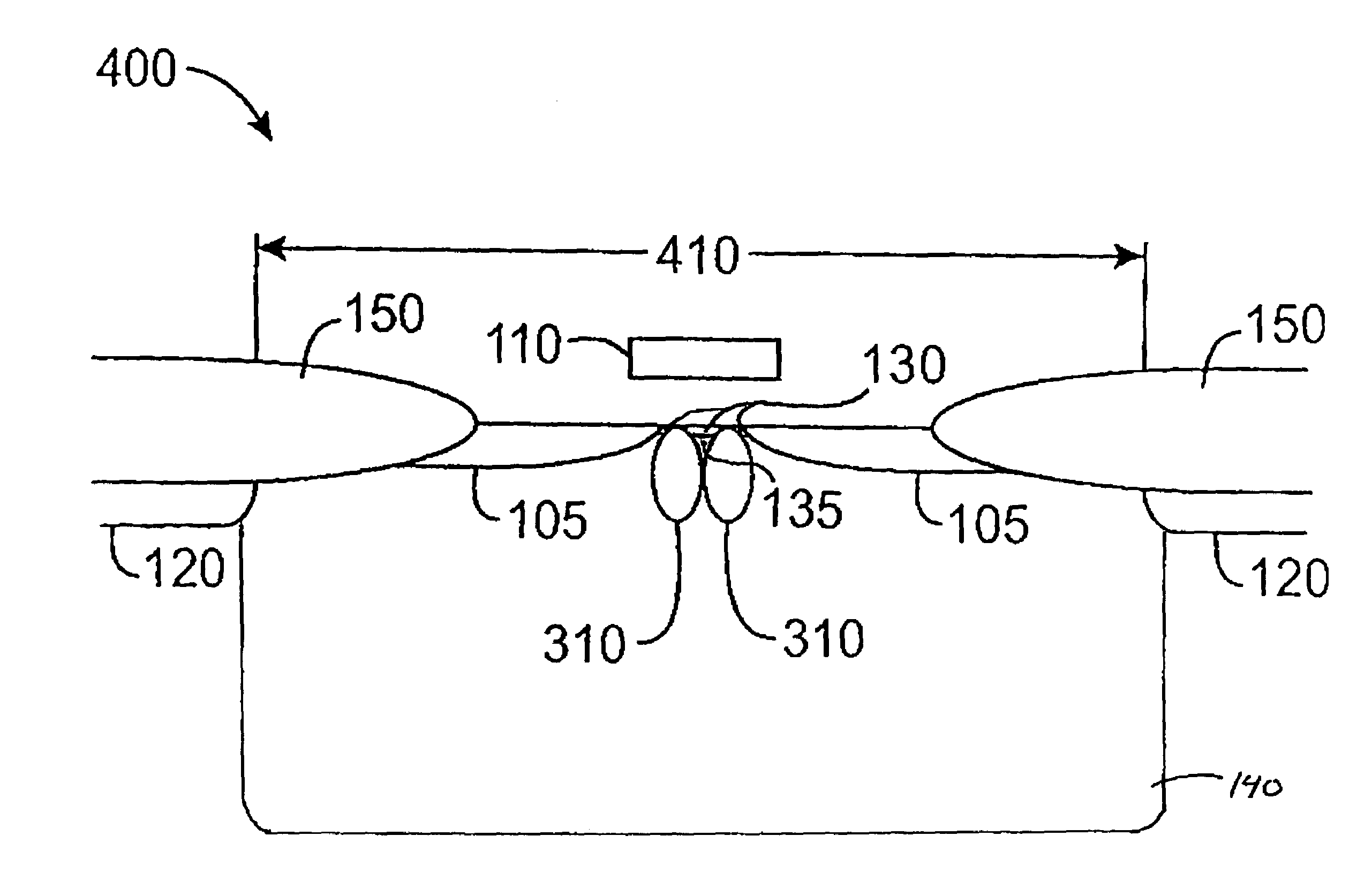

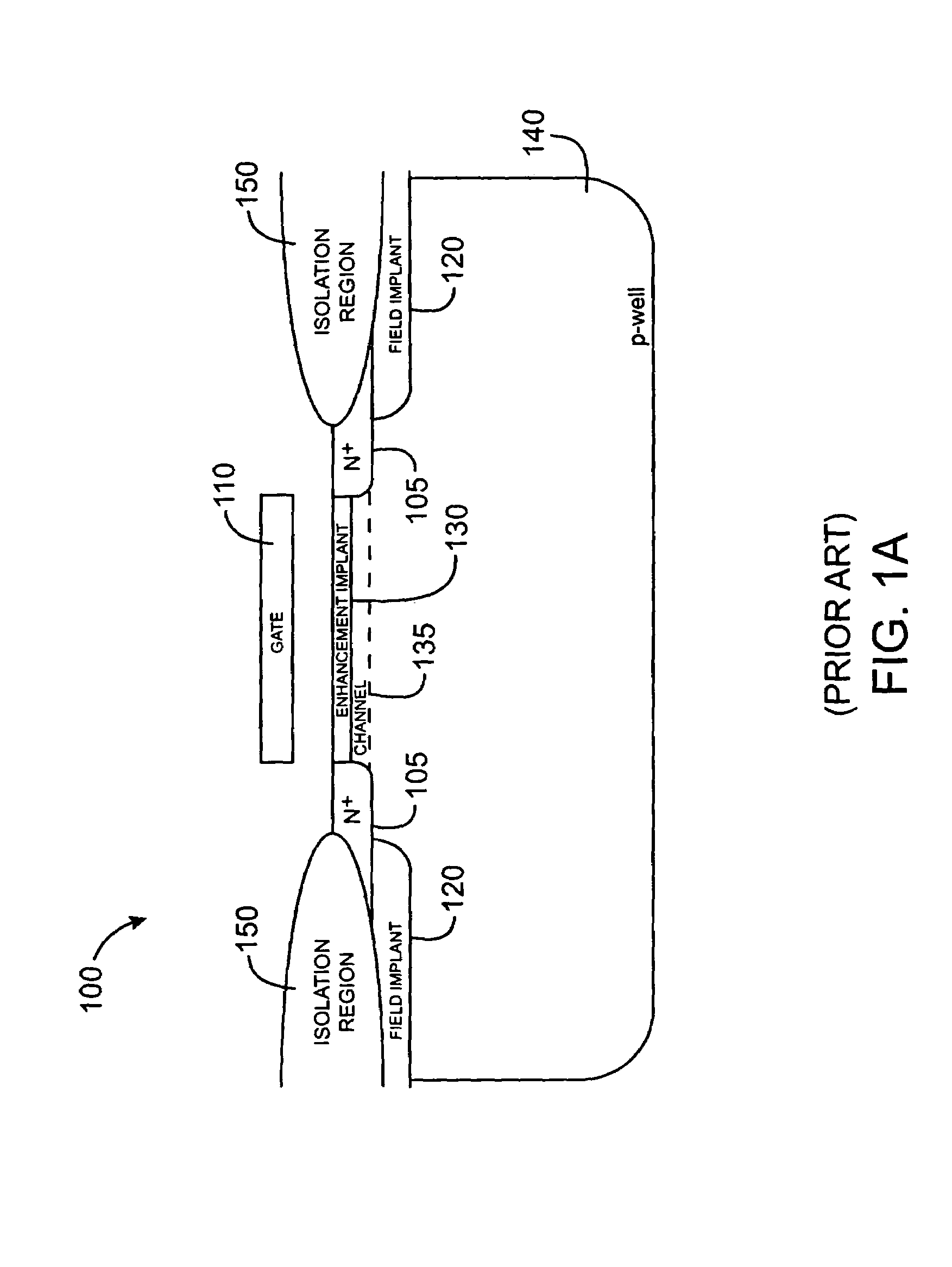

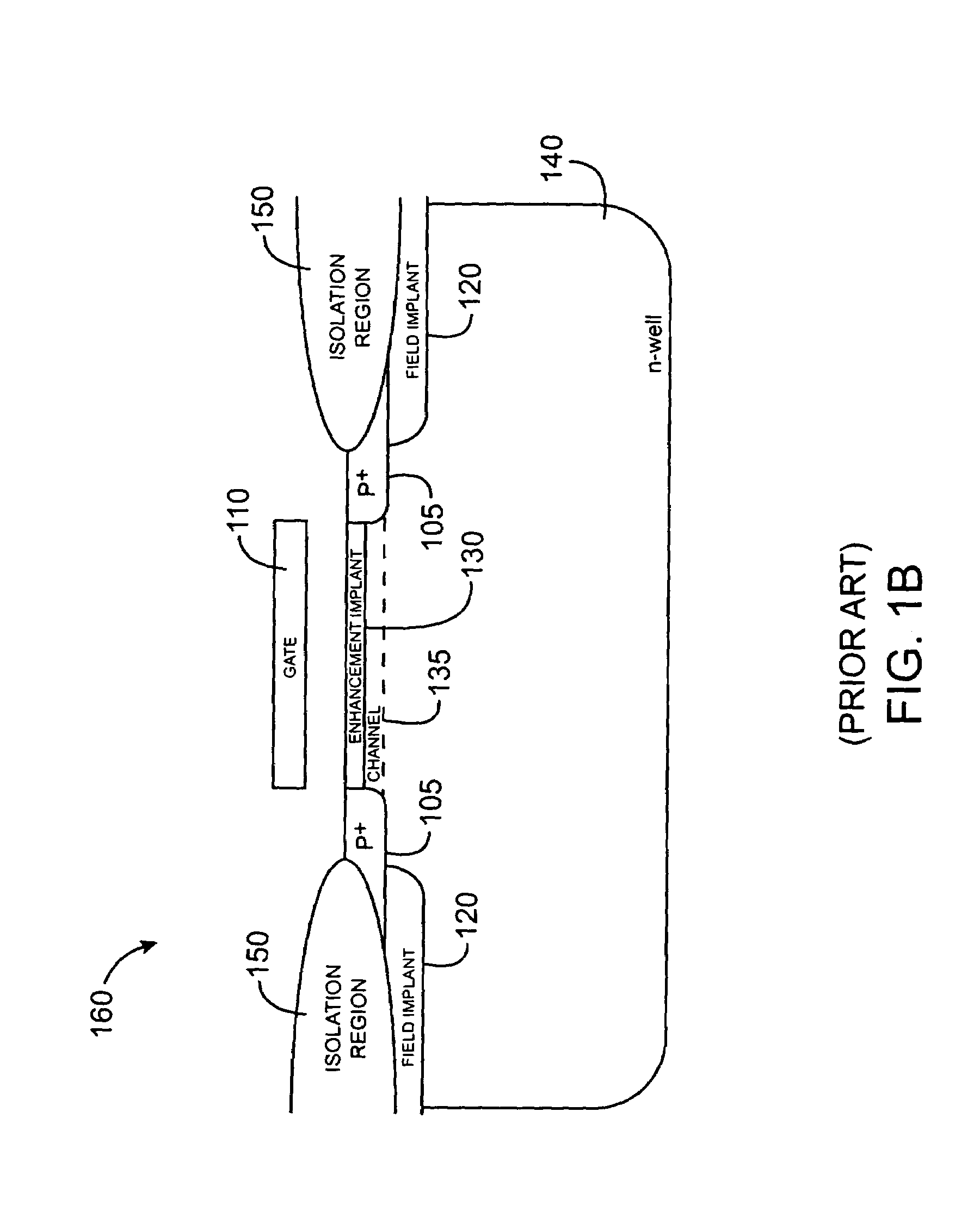

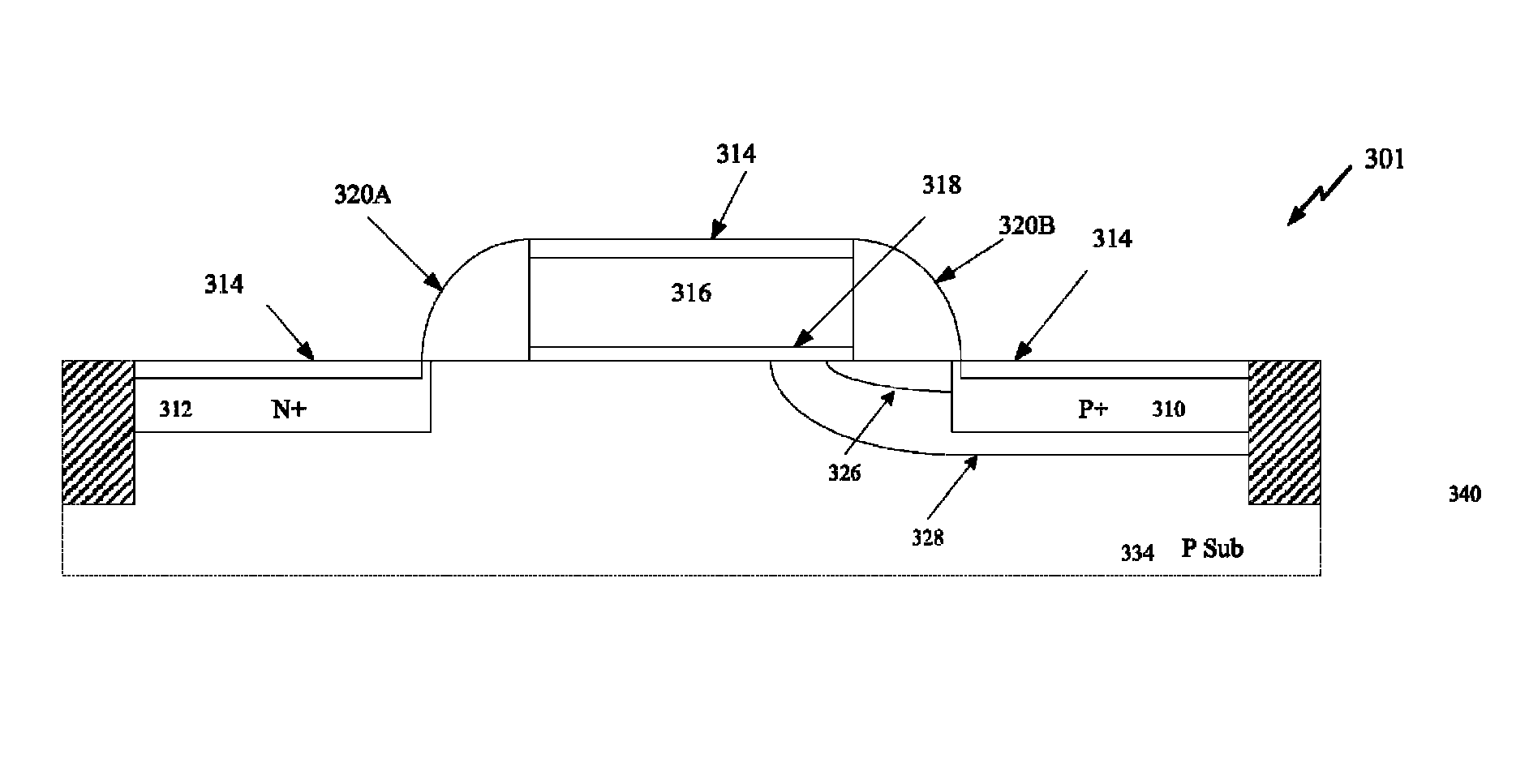

High voltage MOS devices with high gated-diode breakdown voltage and punch-through voltage

InactiveUS6972234B1Improve featuresDesign rule can be simplerSolid-state devicesSemiconductor/solid-state device manufacturingCMOSLow voltage

A method of fabricating CMOS devices suitable for high voltage and low voltage applications, while maintaining minimum channel lengths for the devices. In one embodiment, pocket implants (310) are formed in a minimum channel device causing a reverse channel effect. The reverse channel effect is optimized for the minimum channel length of the device. Field implants (120), enhancement implants (130), and wells (140) are all formed using a single mask.

Owner:ALTERA CORP

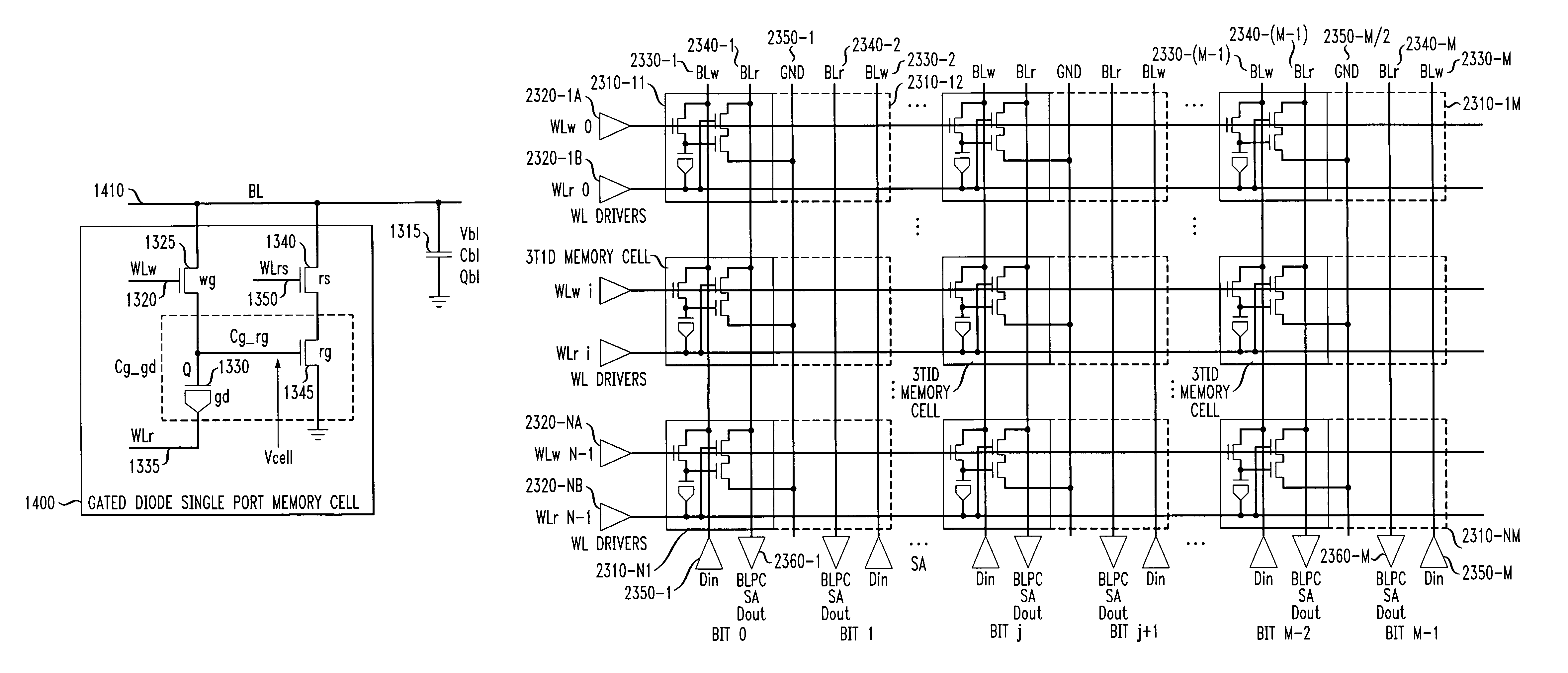

Gated Diode Memory Cells

A gated diode memory cell is provided, including one or more transistors, such as field effect transistors (“FETs”), and a gated diode in signal communication with the FETs such that the gate of the gated diode is in signal communication with the source of a first FET, wherein the gate of the gated diode forms one terminal of the storage cell and the source of the gated diode forms another terminal of the storage cell, the drain of the first FET being in signal communication with a bitline (“BL”) and the gate of the first FET being in signal communication with a write wordline (“WLw”), and the source of the gated diode being in signal communication with a read wordline (“WLr”).

Owner:GLOBALFOUNDRIES INC

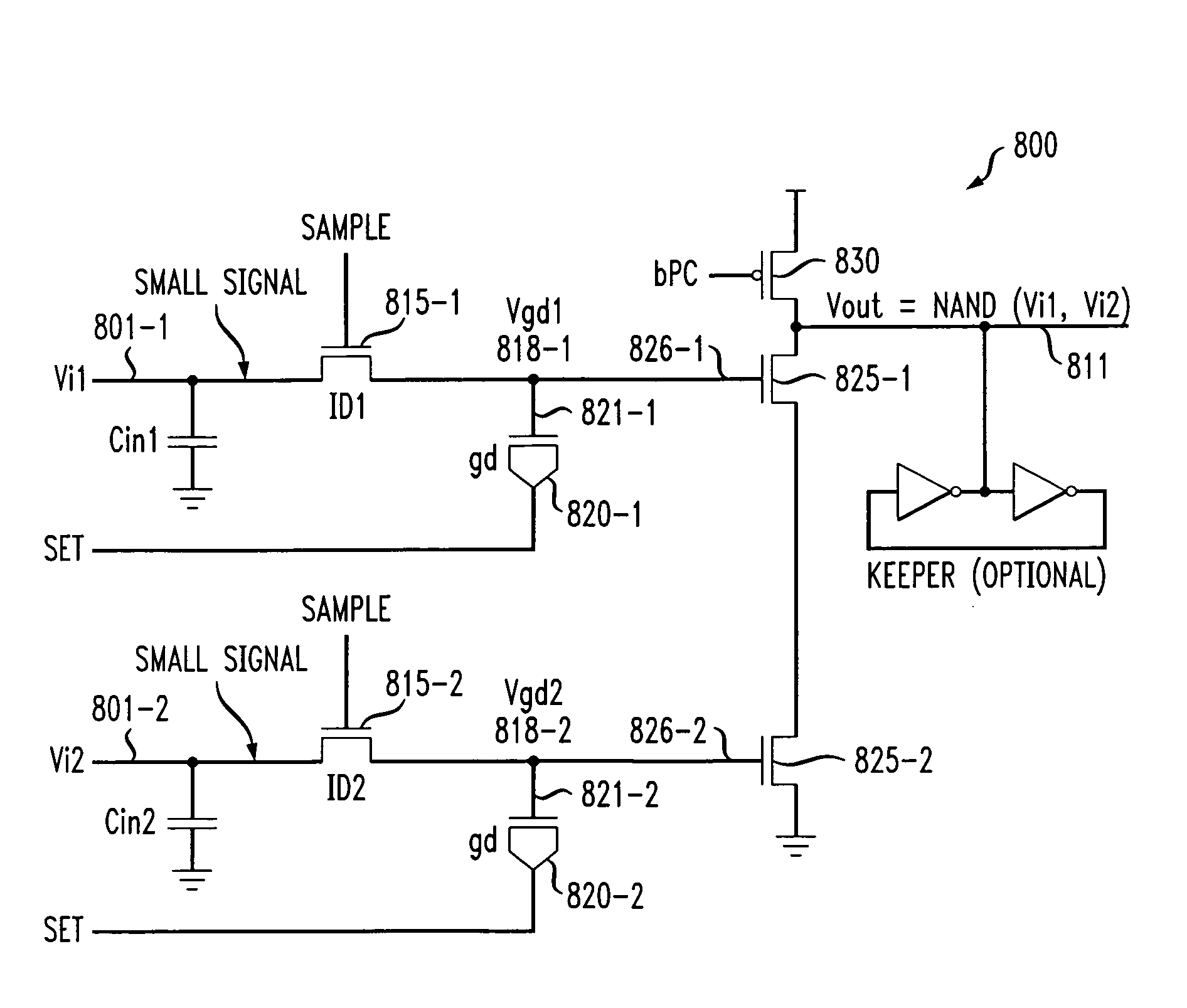

Logic circuits utilizing gated diode sensing

InactiveUS7230455B2Reliability increasing modificationsLogic circuits characterised by logic functionCMOSSmall amplitude

A family of logic circuits, called gated diode logic circuits, is disclosed wherein small amplitude signals, typically a fraction of the supply voltage, can be sensed and amplified by applying a small amplitude signal to a gate of a gated diode in a sampling mode and changing a voltage of a source of the gated diode in an evaluation mode. One or more isolation devices may be connected between each small amplitude signal and a gate of the gated diode, wherein the isolation device passes the small amplitude signal to the gate of the gated diode in the sampling mode, and isolates the small amplitude signal from the gate in the evaluation mode for amplification and performing fast logic operations (logic functions). The disclosed gated diode logic circuits overcome the Vt variation problem in FETs by detecting and amplifying the small logic signals utilizing gated diodes that have relatively low Vt variation. The amplified signals may then be processed by conventional logic circuits to perform certain logic functions in a gated diode logic circuit. The Vt variation of the gated diode is relatively small compared to the small logic signal amplitude and can be controlled relatively precisely. Typically, Vt of the gated diode can be set to a fraction of the small logic signal amplitude. Thus, in a gated diode logic circuit, the gated diode circuit can sense and amplify the small logic signals sufficiently to perform the various logic operations in conjunction with conventional logic circuits. The output(s) of the gated diode logic circuit can be of a standard full CMOS voltage swing, or can be scaled down in amplitude and further processed by other gated diode logic circuits.

Owner:GOOGLE LLC

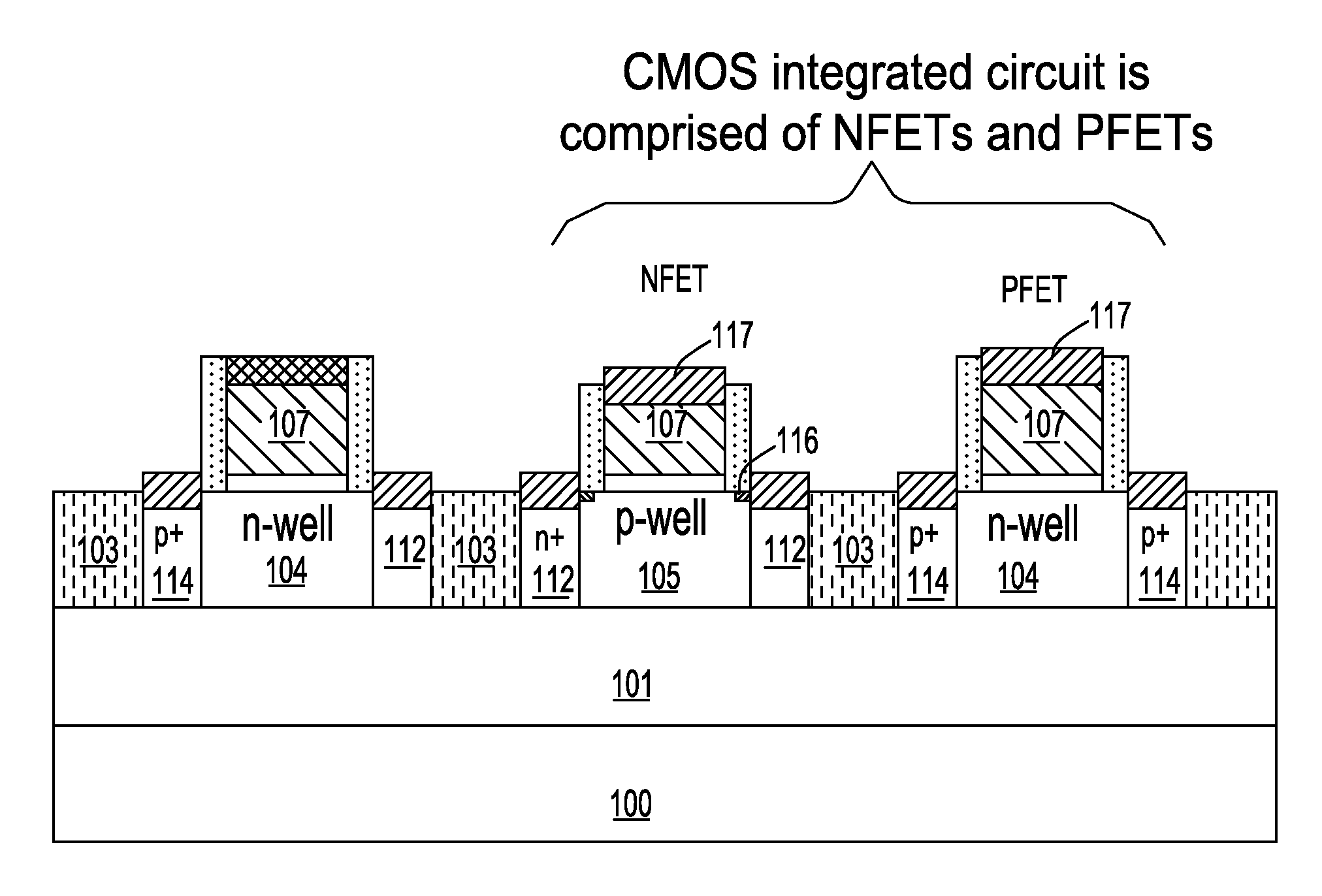

Gated diode structure for eliminating rie damage from cap removal

InactiveUS20130328124A1Increase resistanceExcellent diode idealityTransistorSolid-state devicesSemiconductor structureEngineering

A semiconductor structure provided with a plurality of gated-diodes having a silicided anode (p-doped region) and cathode (n-doped region) and a high-K gate stack made of non-silicided gate material, the gated-diodes being adjacent to FETs, each of which having a silicided source, a silicided drain and a silicided HiK gate stack. The semiconductor structure eliminates a cap removal RIE in a gate first High-K metal gate flow from the region of the gated-diode. The lack of silicide and the presence of a nitride barrier on the gate of the diode are preferably made during the gate first process flow. The absence of the cap removal RIE is beneficial in that diffusions of the diode are not subjected to the cap removal RIE, which avoids damage and allows retaining its highly ideal junction characteristics.

Owner:GLOBALFOUNDRIES INC

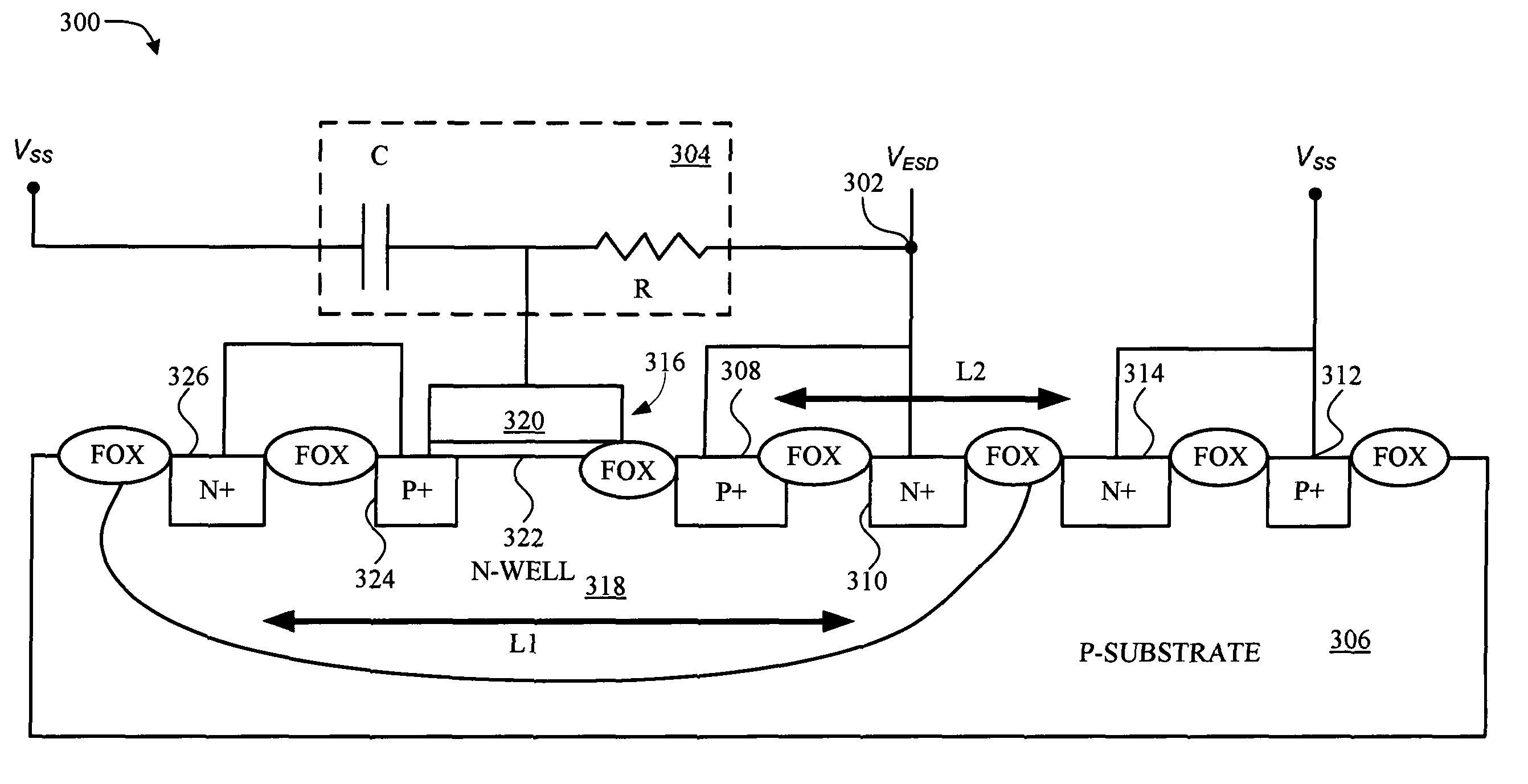

Capacitor triggered silicon controlled rectifier

ActiveUS8129788B1TransistorSemiconductor/solid-state device detailsSilicon-controlled rectifierDevice material

A protection circuit and method are provided for protecting semiconductor devices from electrostatic discharge (ESD). Generally, the ESD protection circuit includes a silicon controlled rectifier (SCR) formed in a substrate and configured to transfer charge from a protected node to a negative power supply, VSS, during an ESD event, and a trigger device to activate transfer of charge by the SCR when a voltage on the protected node reaches a predetermined trigger voltage. The trigger device includes a gated-diode and MOS capacitor formed in a well formed in the substrate, the trigger device configured to inject electrons into the well during charging of the MOS capacitor, forward biasing a node of the SCR, hence allowing fast triggering of the SCR device. The trigger voltage can be set independent of a holding voltage by adjusting the length of the well and area of the capacitor. Other embodiments are also disclosed.

Owner:CYPRESS SEMICON CORP

High threshold NMOS source-drain formation with As, P and C to reduce damage

ActiveUS7736983B2Reduce leakage currentReduced GDLTransistorSemiconductor/solid-state device manufacturingHigh concentrationTransistor

Pipe defects in n-type lightly doped drain (NLDD) regions and n-type source / drain (NDS) regions are associated with arsenic implants, while excess diffusion in NLDD and NSD regions is mainly due to phosphorus interstitial movement. Carbon implantation is commonly used to reduce phosphorus diffusion in the NLDD, but contributes to gated diode leakage (GDL). In high threshold NMOS transistors GDL is commonly a dominant off-state leakage mechanism. This invention provides a method of forming an NMOS transistor in which no carbon is implanted into the NLDD, and the NSD is formed by a pre-amorphizing implant (PAI), a phosphorus implant and a carbon species implant. Use of carbon in the NDS allows a higher concentration of phosphorus, resulting in reduced series resistance and reduced pipe defects. An NMOS transistor with less than 1·1014 cm−2 arsenic in the NSD and a high threshold NMOS transistor formed with the inventive method are also disclosed.

Owner:TEXAS INSTR INC

Diode having a pocket implant blocked and circuits and methods employing same

ActiveUS8665570B2Lower junction capacitanceReduce area junction capacitanceLiquid surface applicatorsSemiconductor/solid-state device detailsCapacitanceEngineering

Diodes, including gated diodes and shallow trench isolation (STI) diodes, manufacturing methods, and related circuits are provided without at least one halo or pocket implant thereby reducing capacitance of the diode. In this manner, the diode may be used in circuits and other devices having performance sensitive to load capacitance while still obtaining the performance characteristics of the diode. Such characteristics for a gated diode include fast turn-on times and high conductance, making the gated diodes well-suited for electro-static discharge (ESD) protection circuits as one example. Diodes include a semiconductor substrate having a well region and insulating layer thereupon. A gate electrode is formed over the insulating layer. Anode and cathode regions are provided in the well region. A P-N junction is formed. At least one pocket implant is blocked in the diode to reduce capacitance.

Owner:QUALCOMM INC

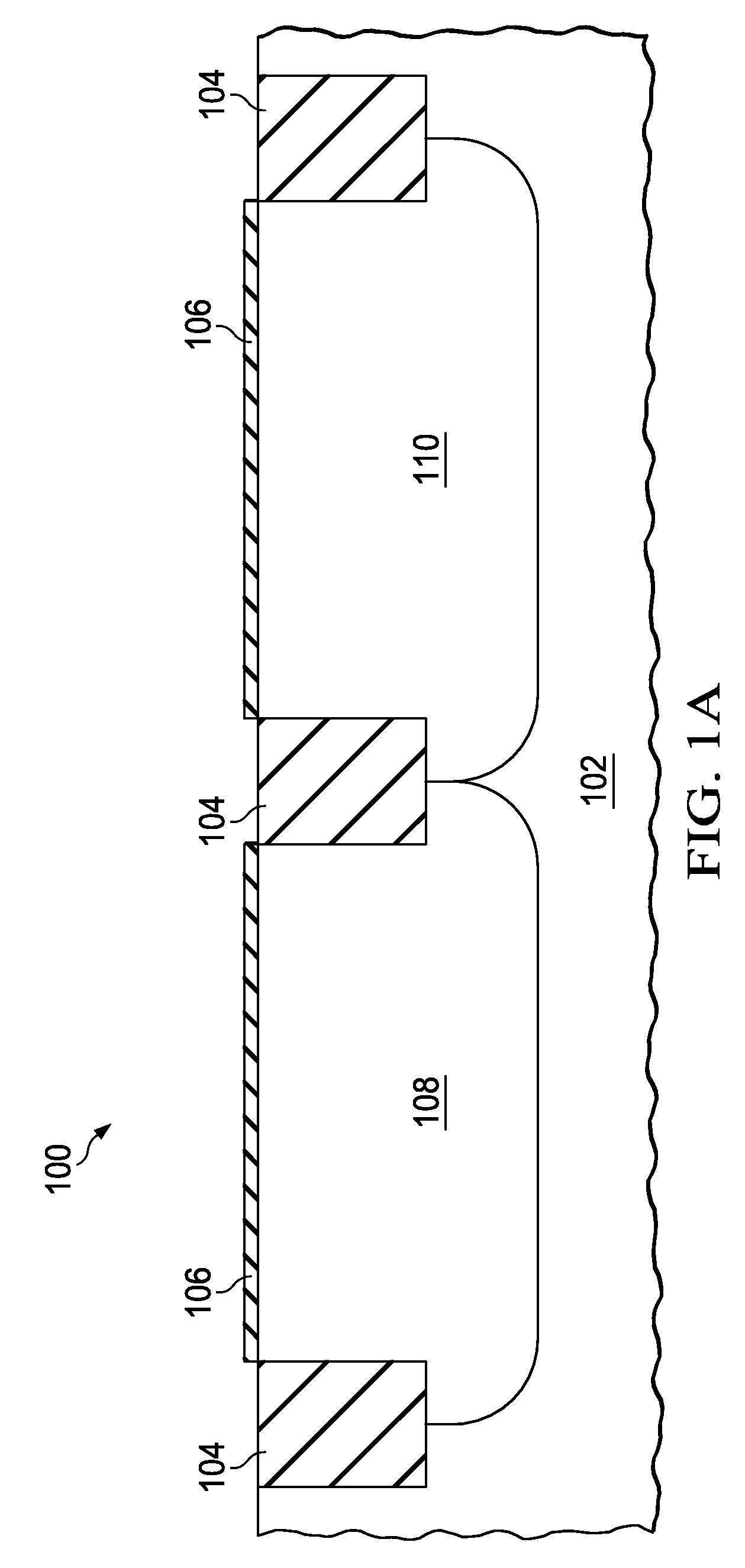

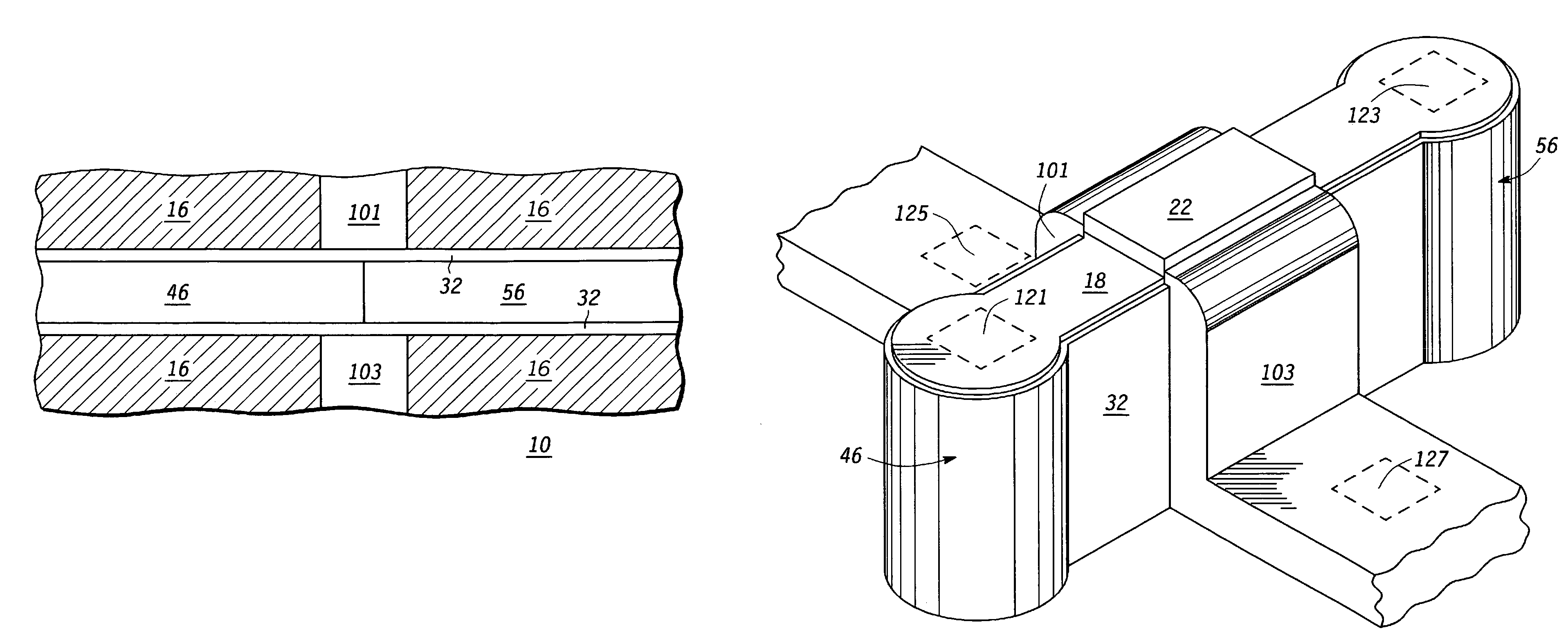

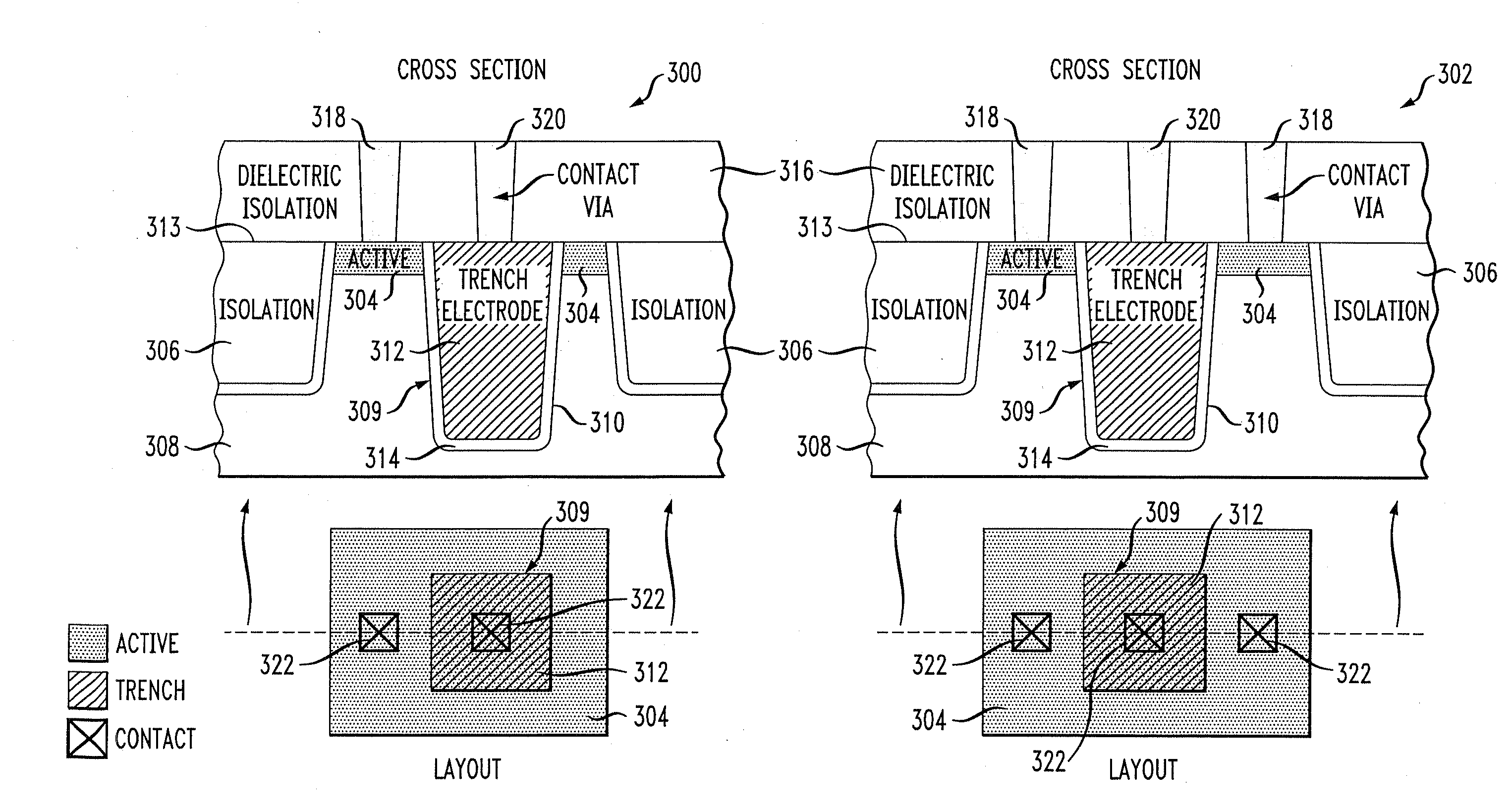

Area-Efficient Gated Diode Structure and Method of Forming Same

InactiveUS20080164507A1Improve area efficiencyIncrease layout areaTransistorSolid-state devicesCapacitanceSemiconductor

An area-efficient gated diode includes a semiconductor layer of a first conductivity type, an active region of a second conductivity type formed in the semiconductor layer proximate an upper surface thereof, and at least one trench electrode extending vertically through the active region and at least partially into the semiconductor layer. A first terminal of the gated diode is connected to the trench electrode, and a second terminal is connected to the active region. The gated diode is operative in one of at least first an second modes as a function of a voltage potential applied between the first and second terminals. The first mode is characterized by the creation of an inversion layer in the semiconductor layer surrounding the trench electrode. The gated diode has a first capacitance in the first mode and a second capacitance in the second mode, the first capacitance being greater than the second capacitance.

Owner:GLOBALFOUNDRIES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com