Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

151results about How to "Increase layout area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

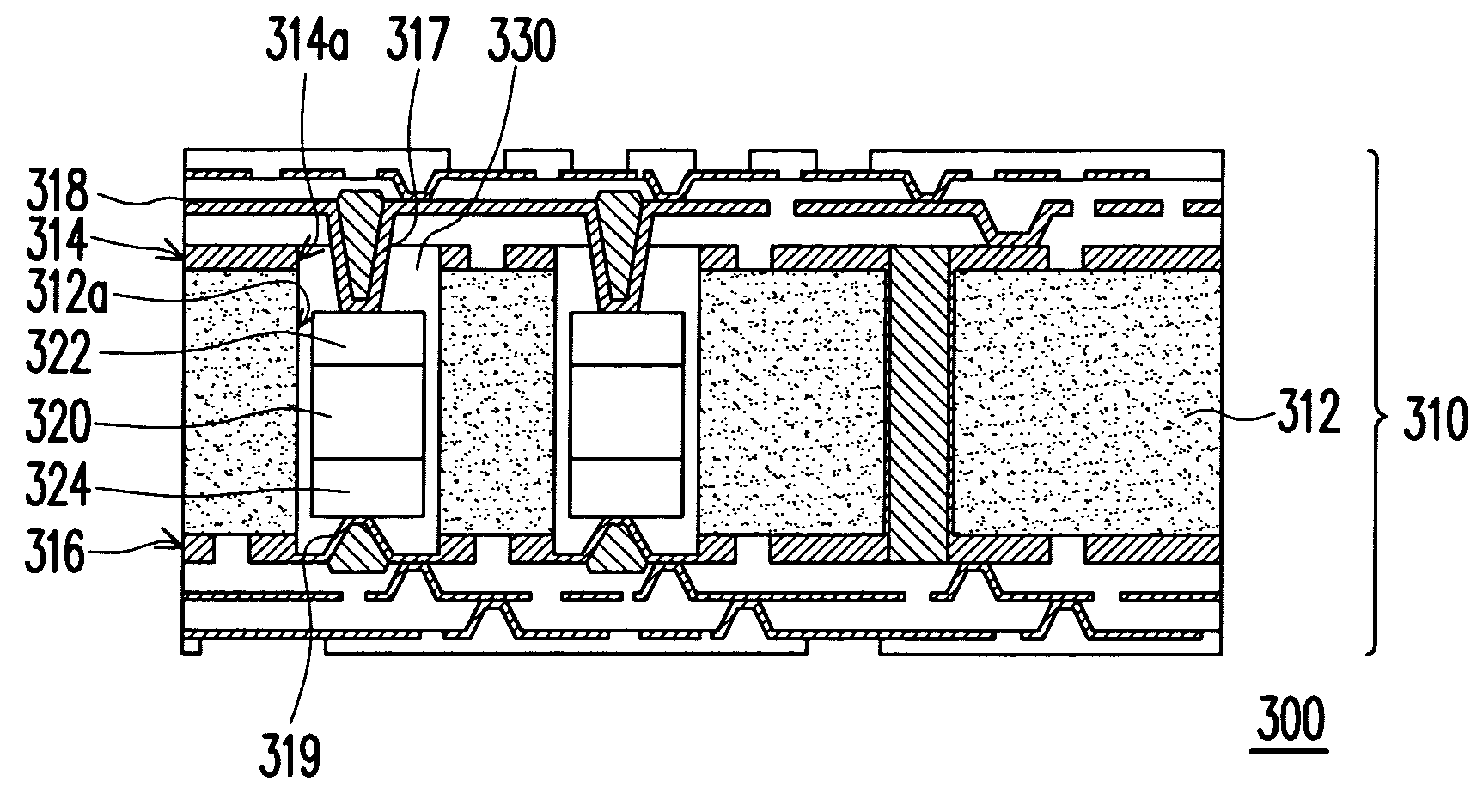

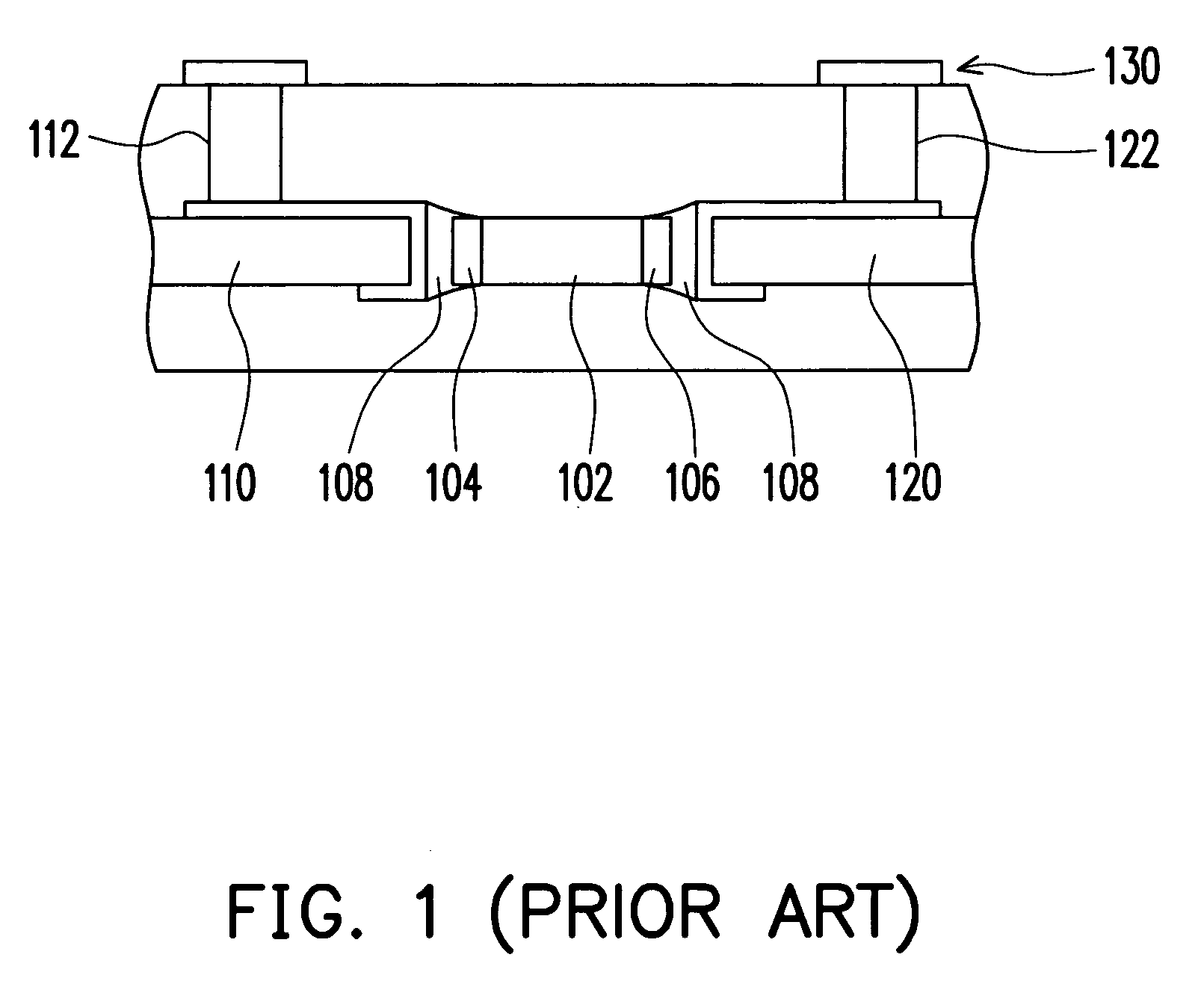

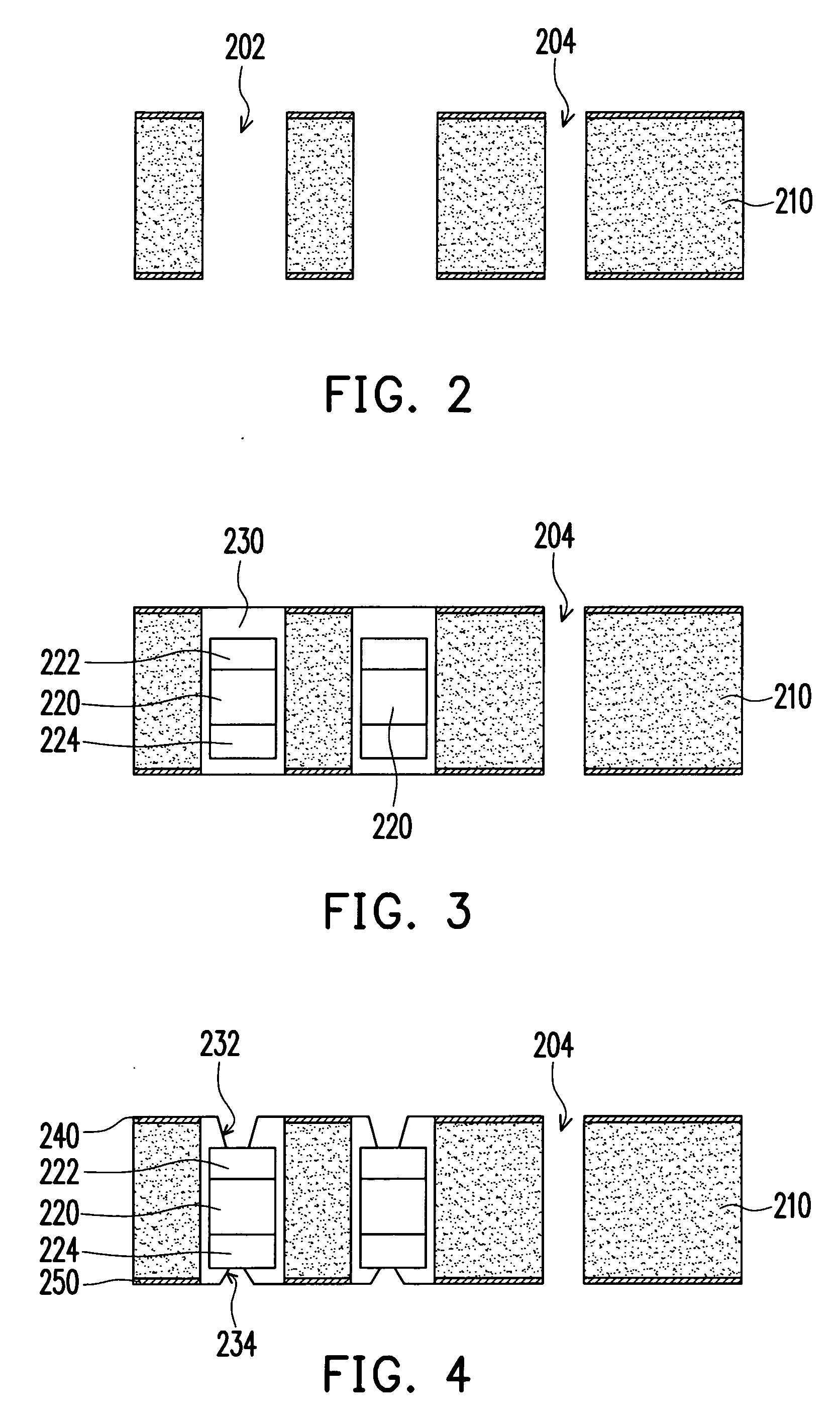

Assembly structure and method for embedded passive device

InactiveUS20060118931A1Improve convenienceImprove efficiencyFinal product manufactureSemiconductor/solid-state device detailsAssembly structureElectrical and Electronics engineering

An assembly structure for an embedded passive device is provided, including at least one passive device embedded in a through hole of a core layer in a circuit substrate. The embedded passive device comprises plural electrodes, which electrically connect through the top side and the bottom side of the core layer. Because the vertically embedded passive device does not occupy the layout area of internal circuit of the circuit substrate, the layout area of the circuit substrate can be increased, the signal transmission route can be reduced, and the performance of signal transmission can be enhanced.

Owner:VIA TECH INC

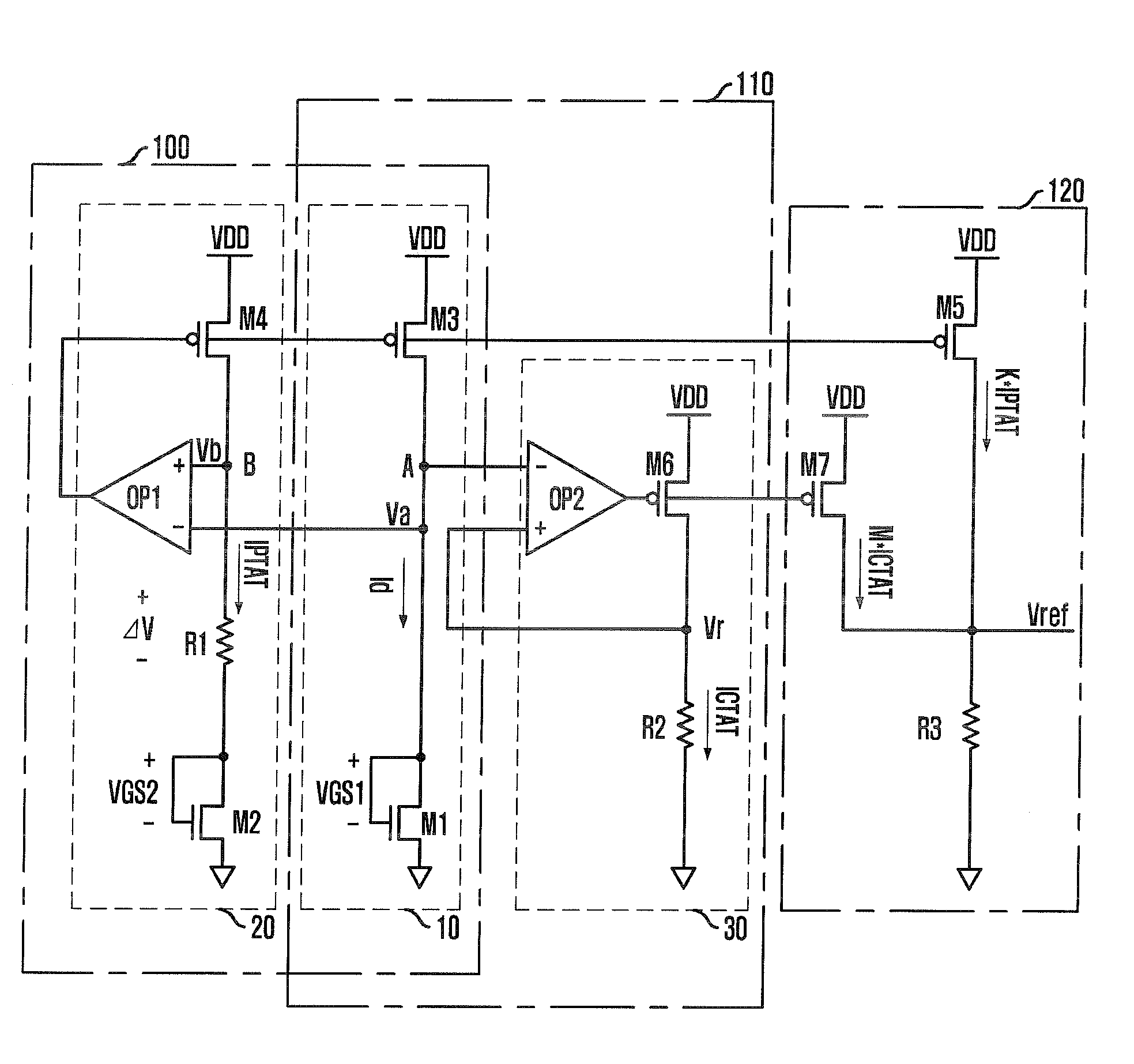

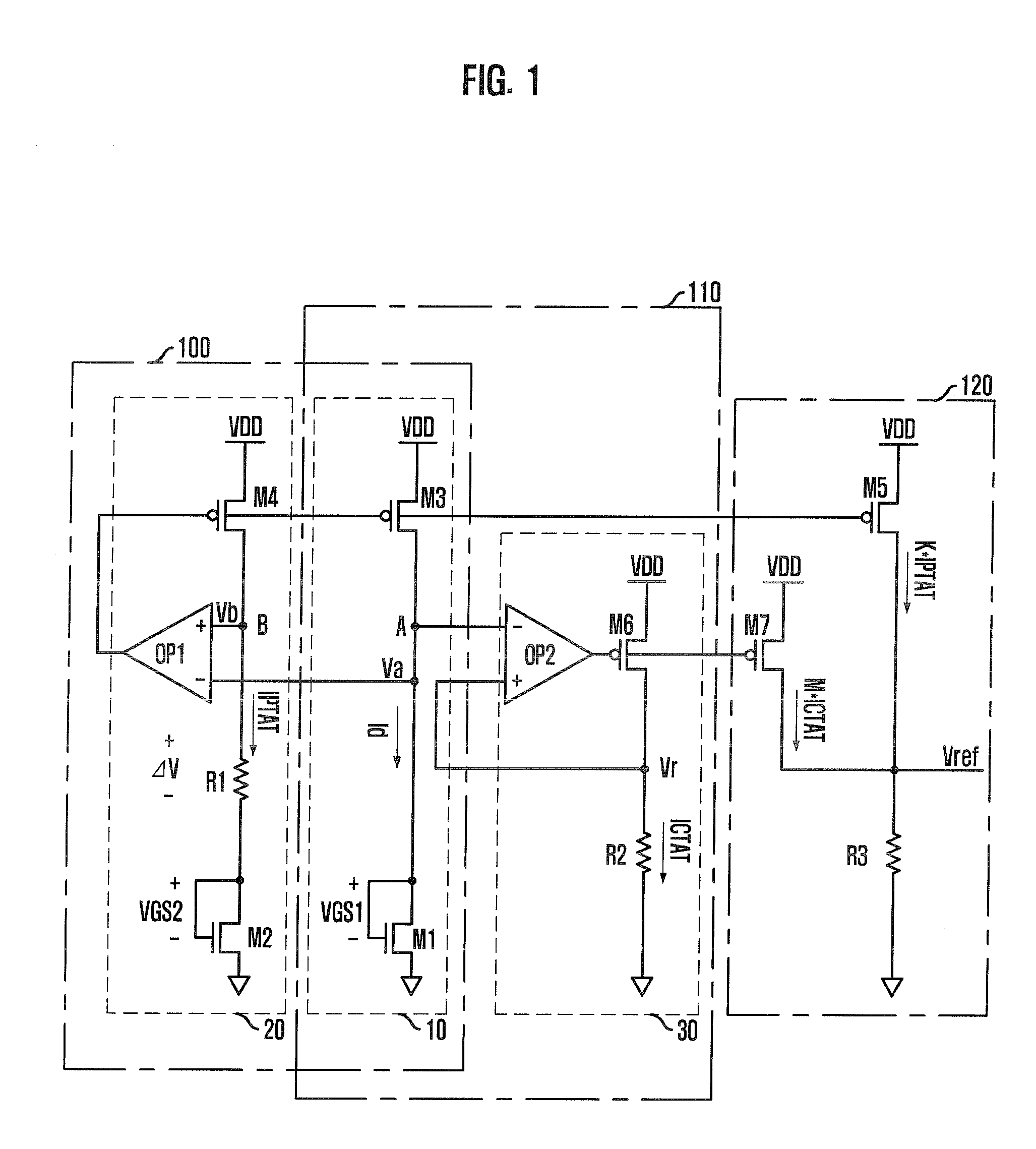

Bandgap reference voltage generation circuit in semiconductor memory device

InactiveUS20090121699A1Increase layout areaLimiting output levelDigital storageElectric variable regulationVoltage referenceCurrent generator

Bandgap reference voltage generation circuit in semiconductor memory device includes a first current generator configured to generate a first current proportional to a change of a temperature by using temperature characteristic of a diode-connected MOS transistor, a second current generator configured to generate a second current inversely proportional to the change of the temperature by using the temperature characteristic of a diode-connected MOS transistor and a summation unit configured to mirror and sum the output currents of the first current generator and the second current generator, and output a reference voltage.

Owner:SK HYNIX INC

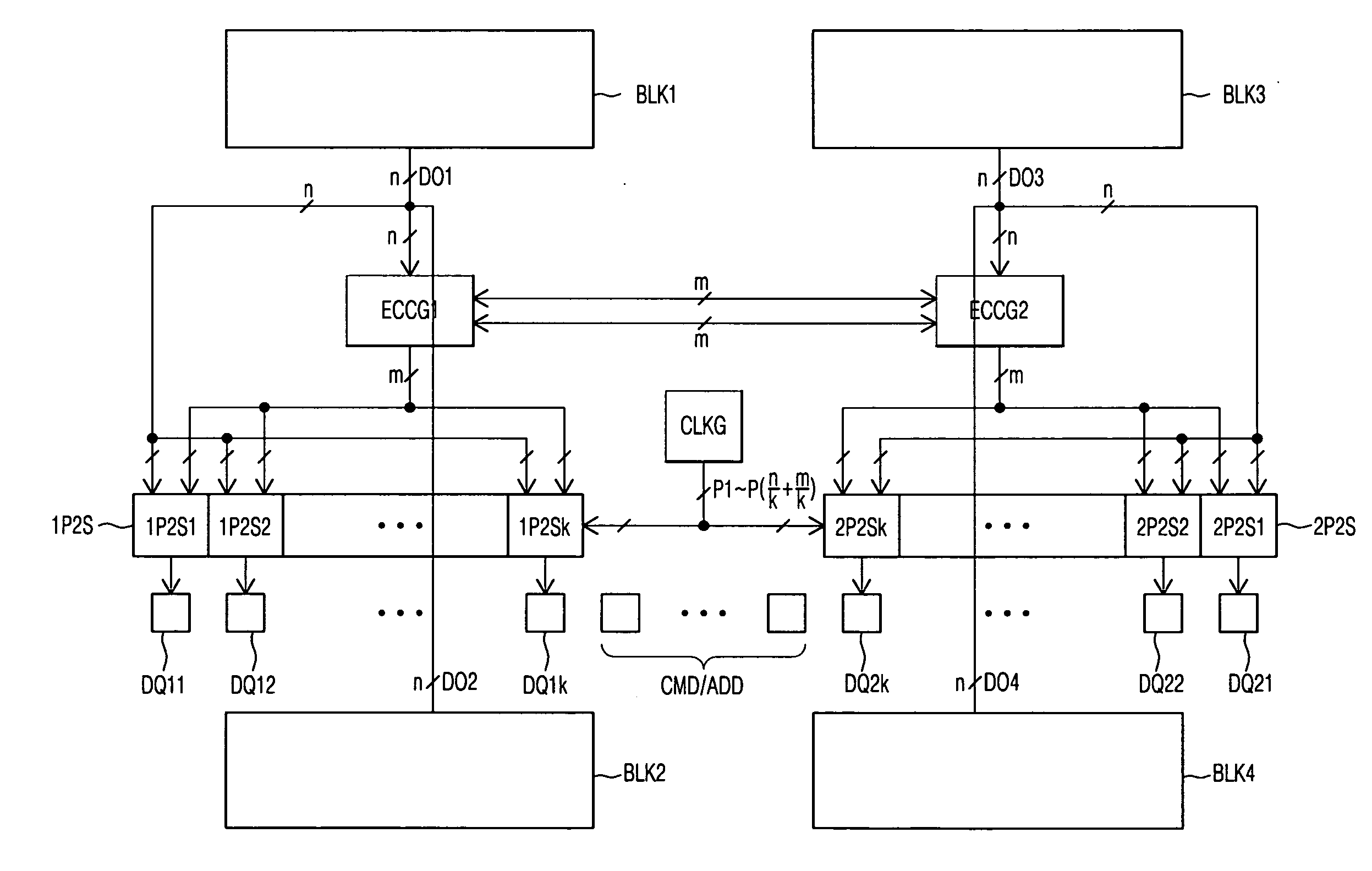

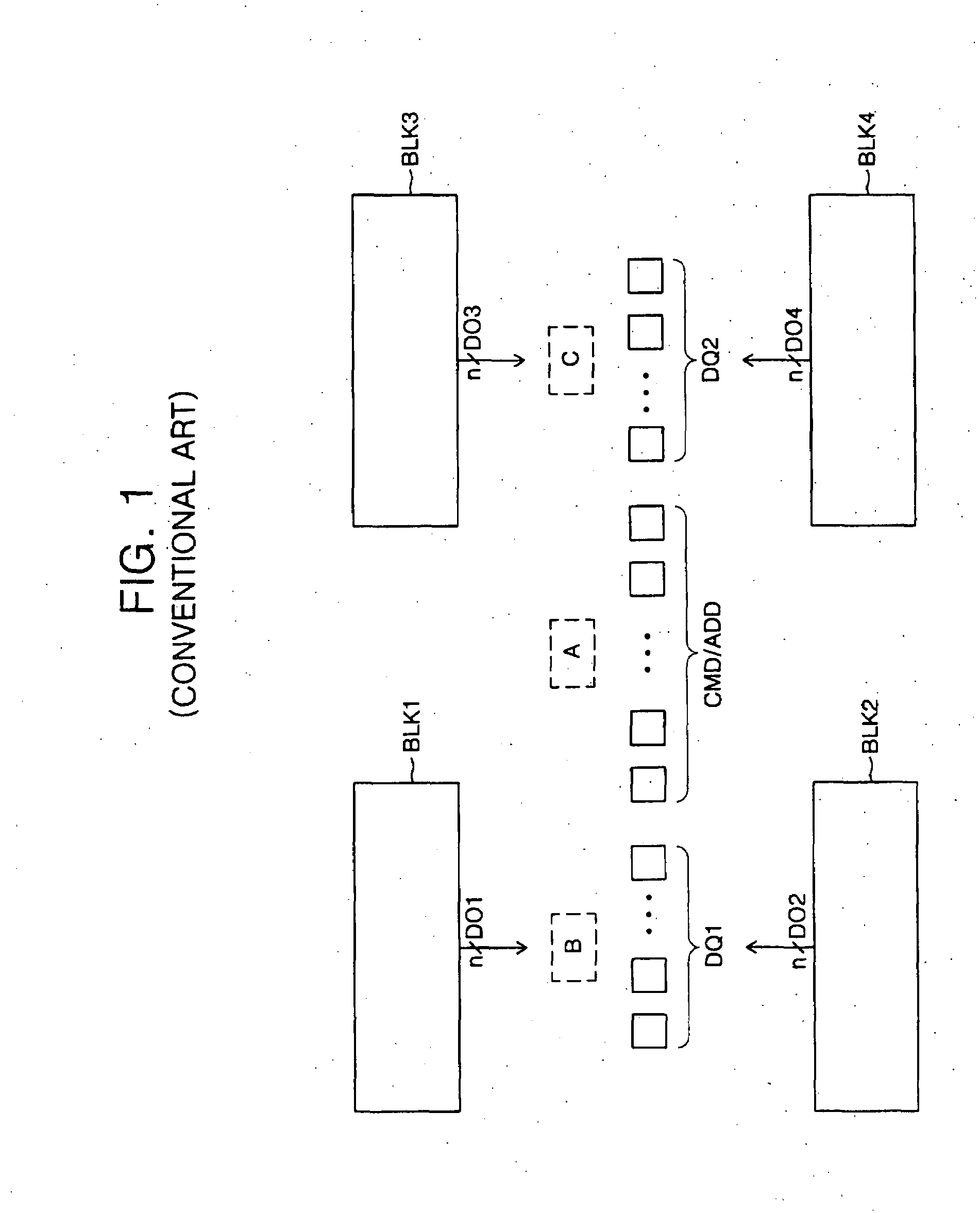

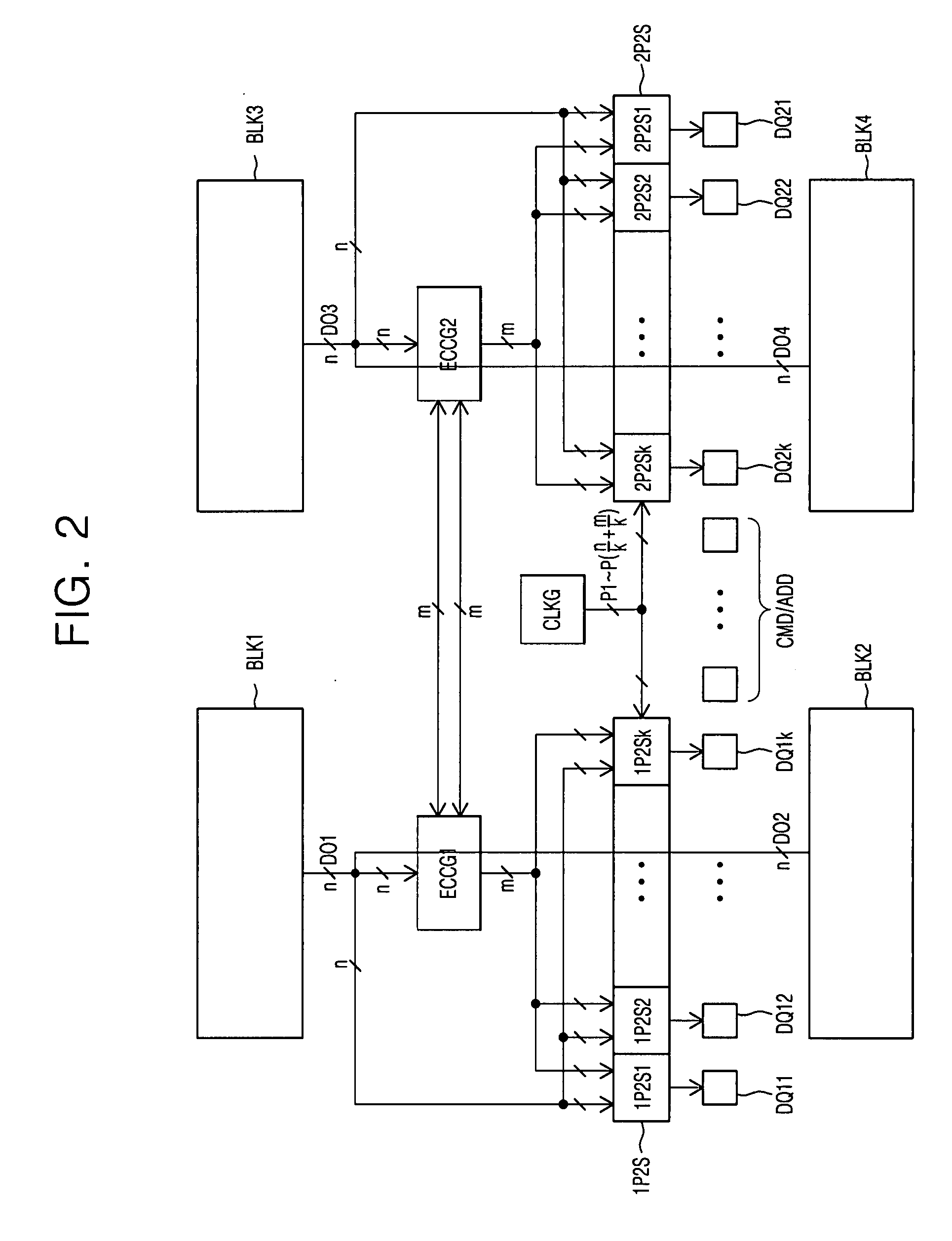

Semiconductor memory device and memory system including the same

ActiveUS20070204199A1Increase layout areaCode conversionMaterial strength using tensile/compressive forcesError detection codingSemiconductor

A semiconductor memory device and a memory system including the same are provided. The semiconductor memory device may include a first memory cell array block generating first data, a second memory cell array block generating second data, and first and second error detection code generators. The first error detection code generator may generate a first error detection code and may combine a portion of bits of the first error detection code with a portion of bits of a second error detection code to generate a first final error detection signal. The second error detection code generator may generate the second error detection code and may combine the remaining bits other than the portion of bits of the second error detection code with the remaining bits other than the portion of bits of the first error detection code to generate a second final error detection signal.

Owner:SAMSUNG ELECTRONICS CO LTD

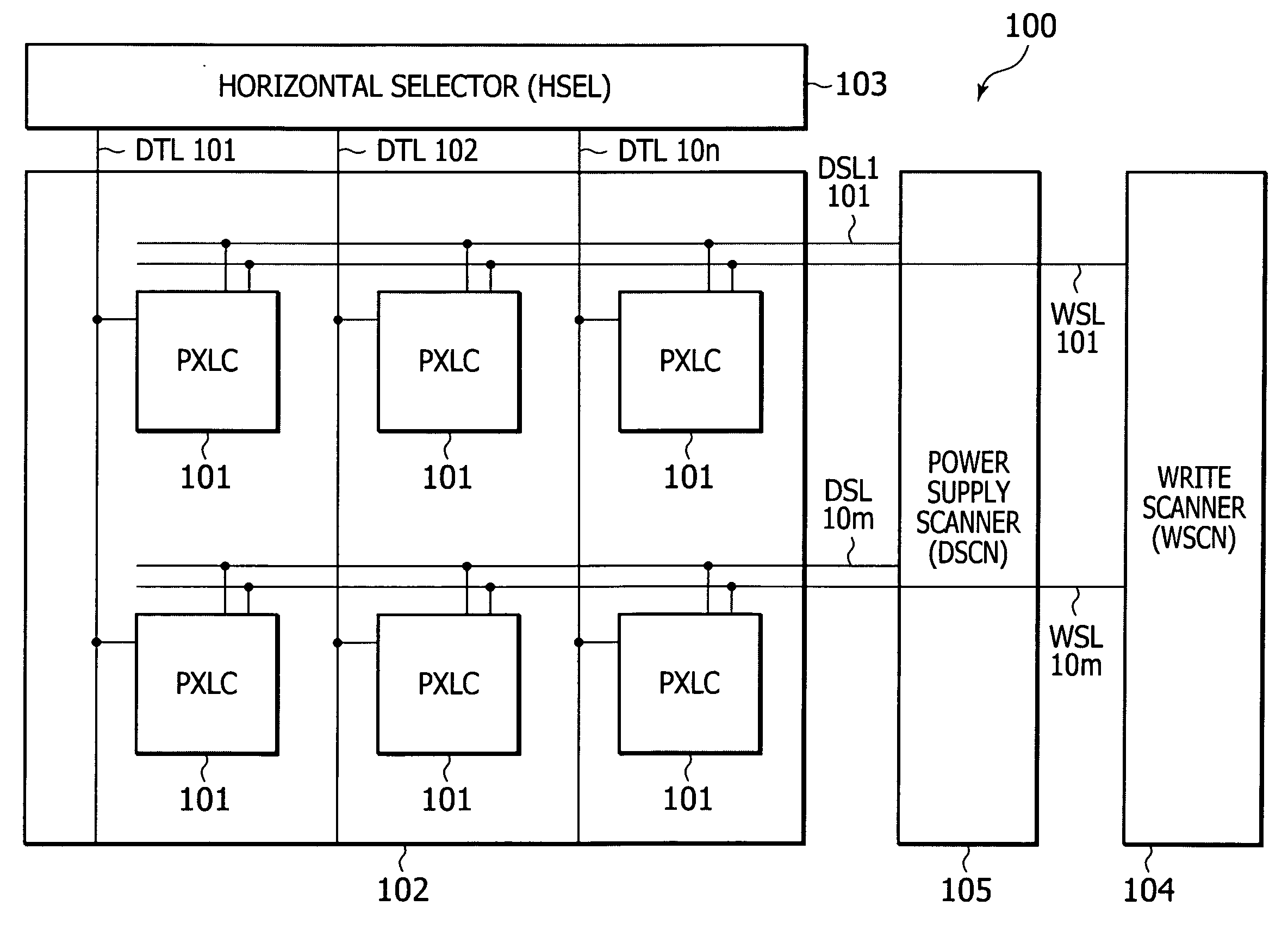

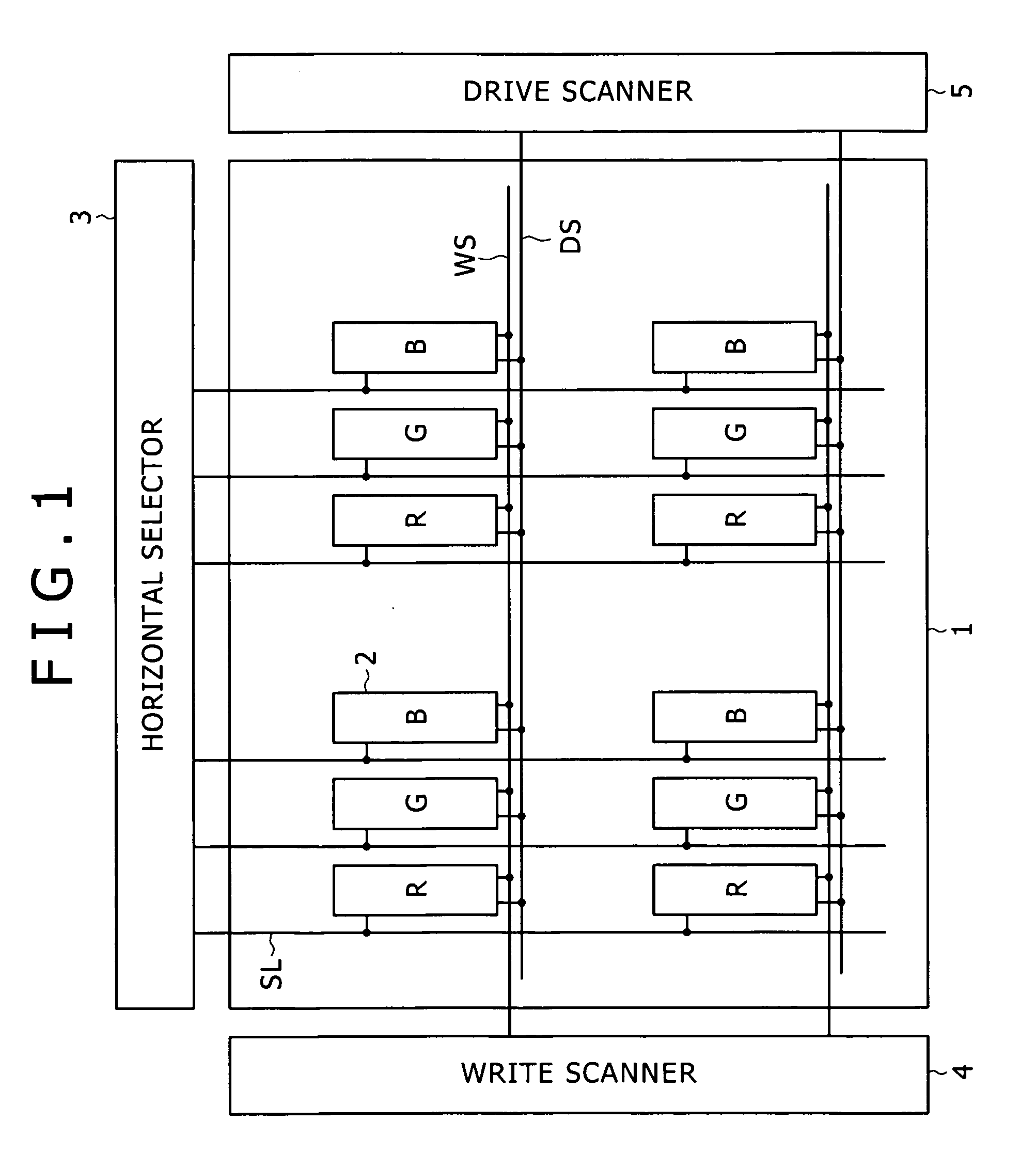

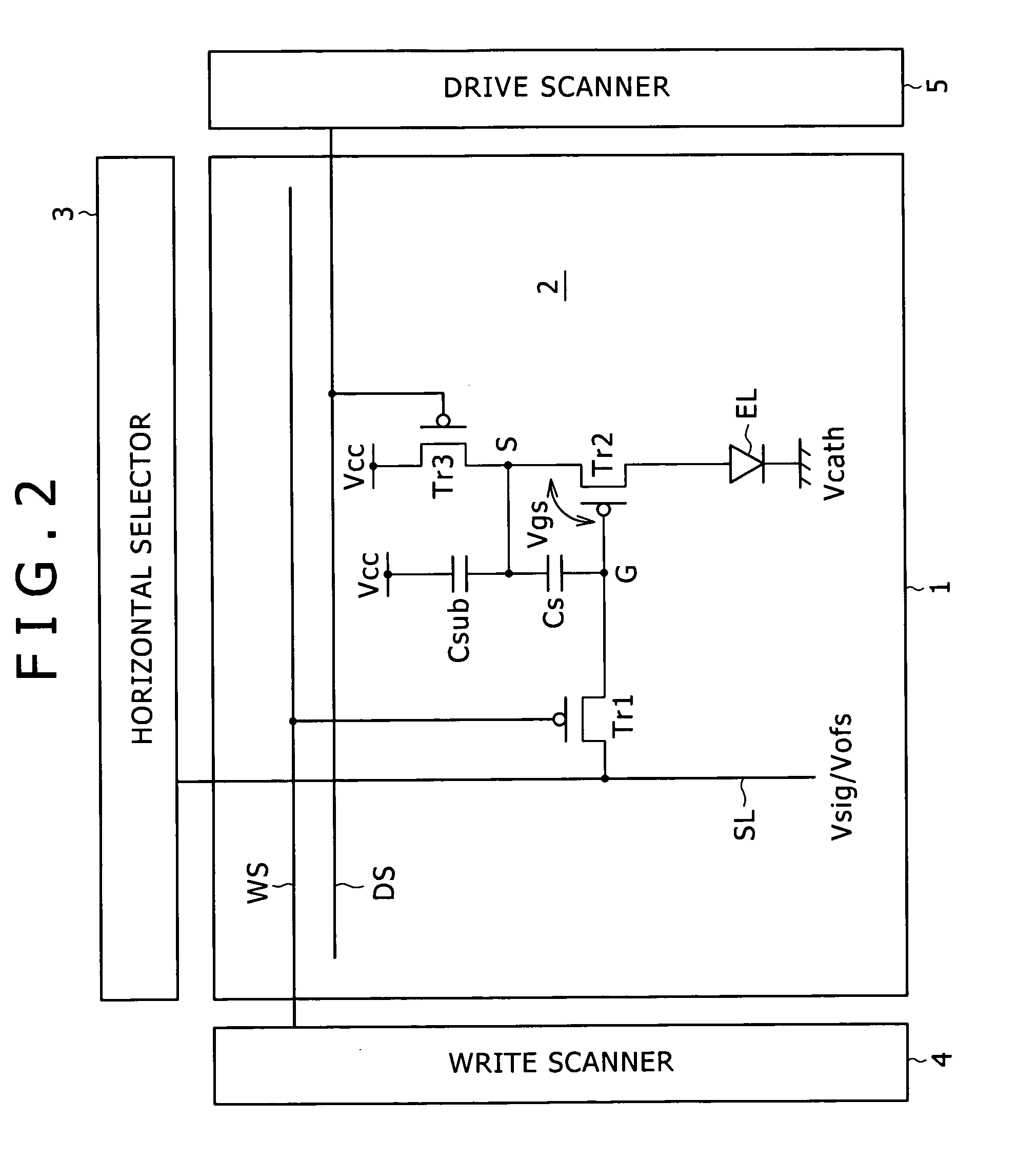

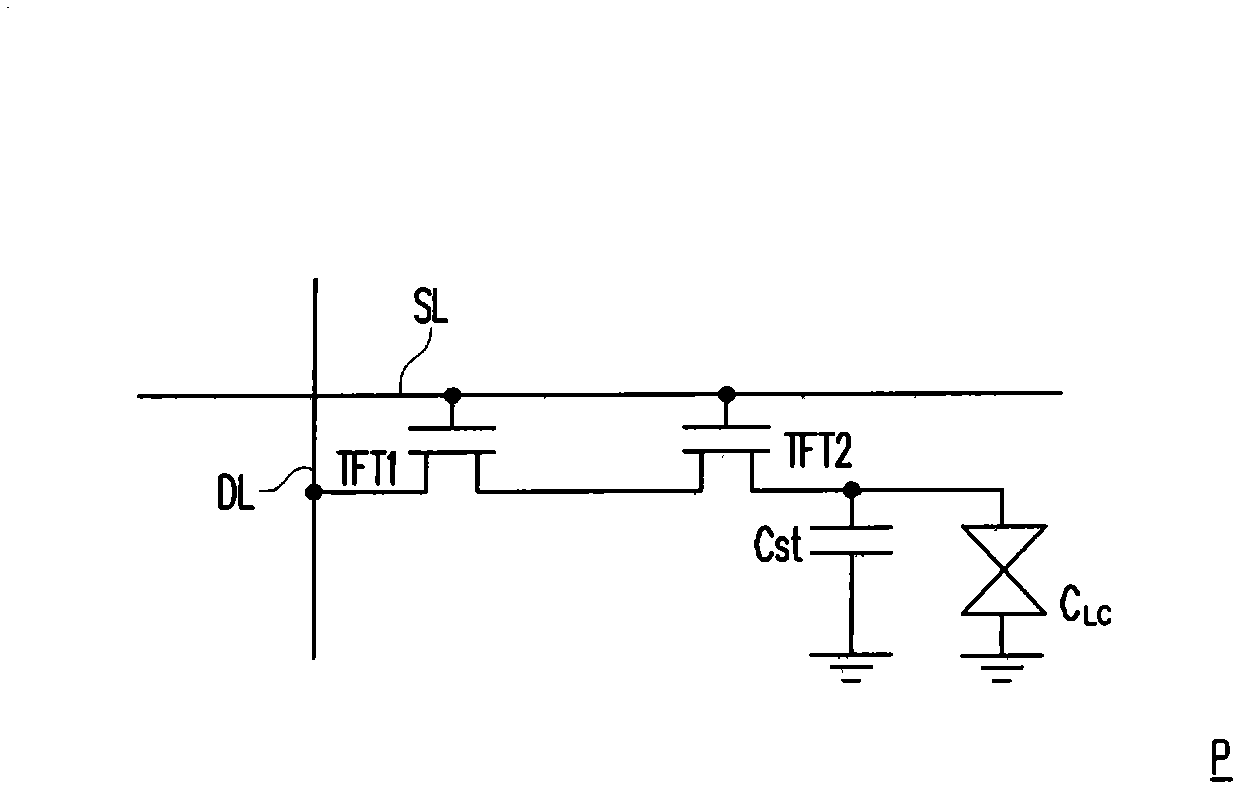

Display device, driving method thereof, and electronic apparatus

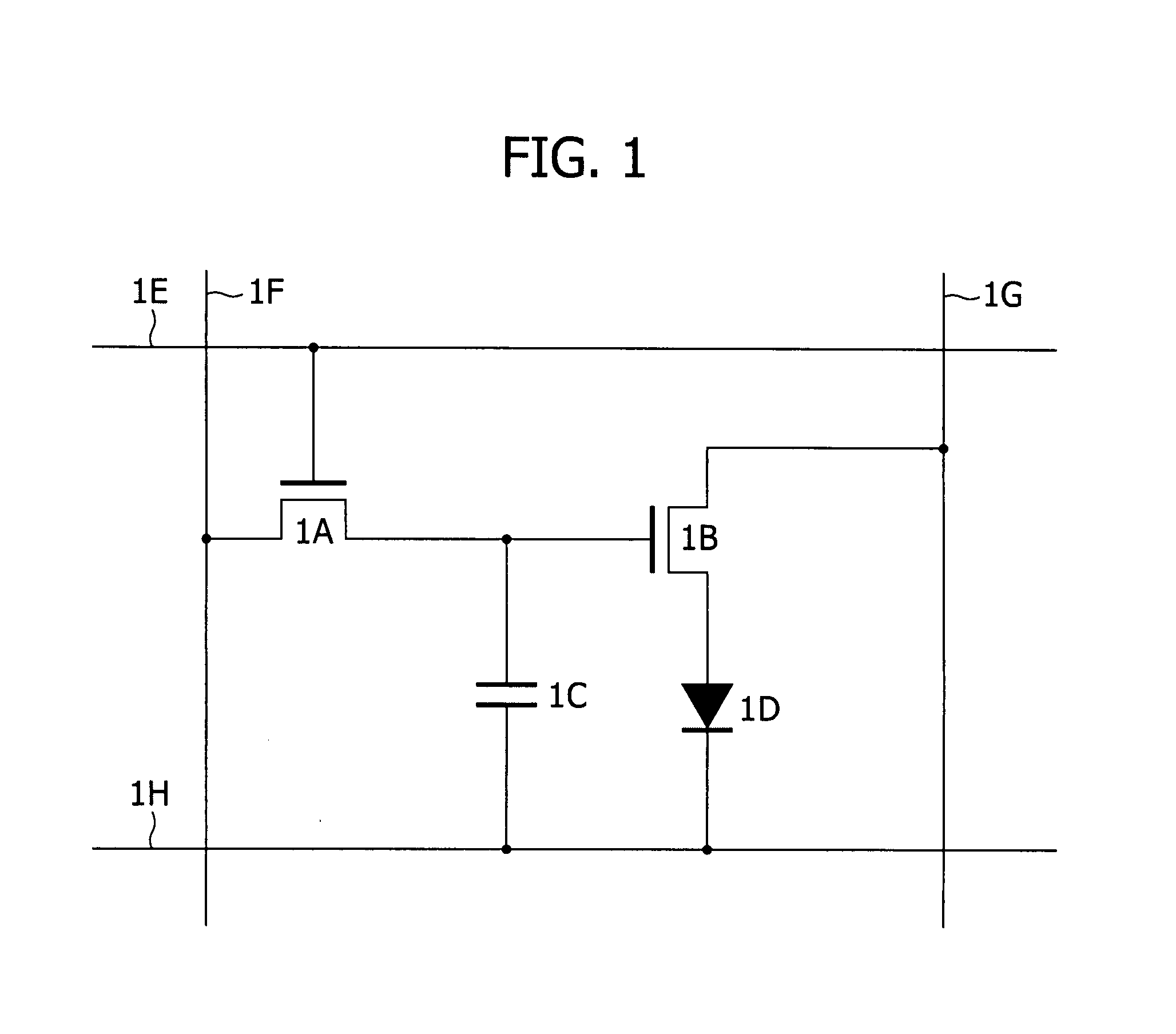

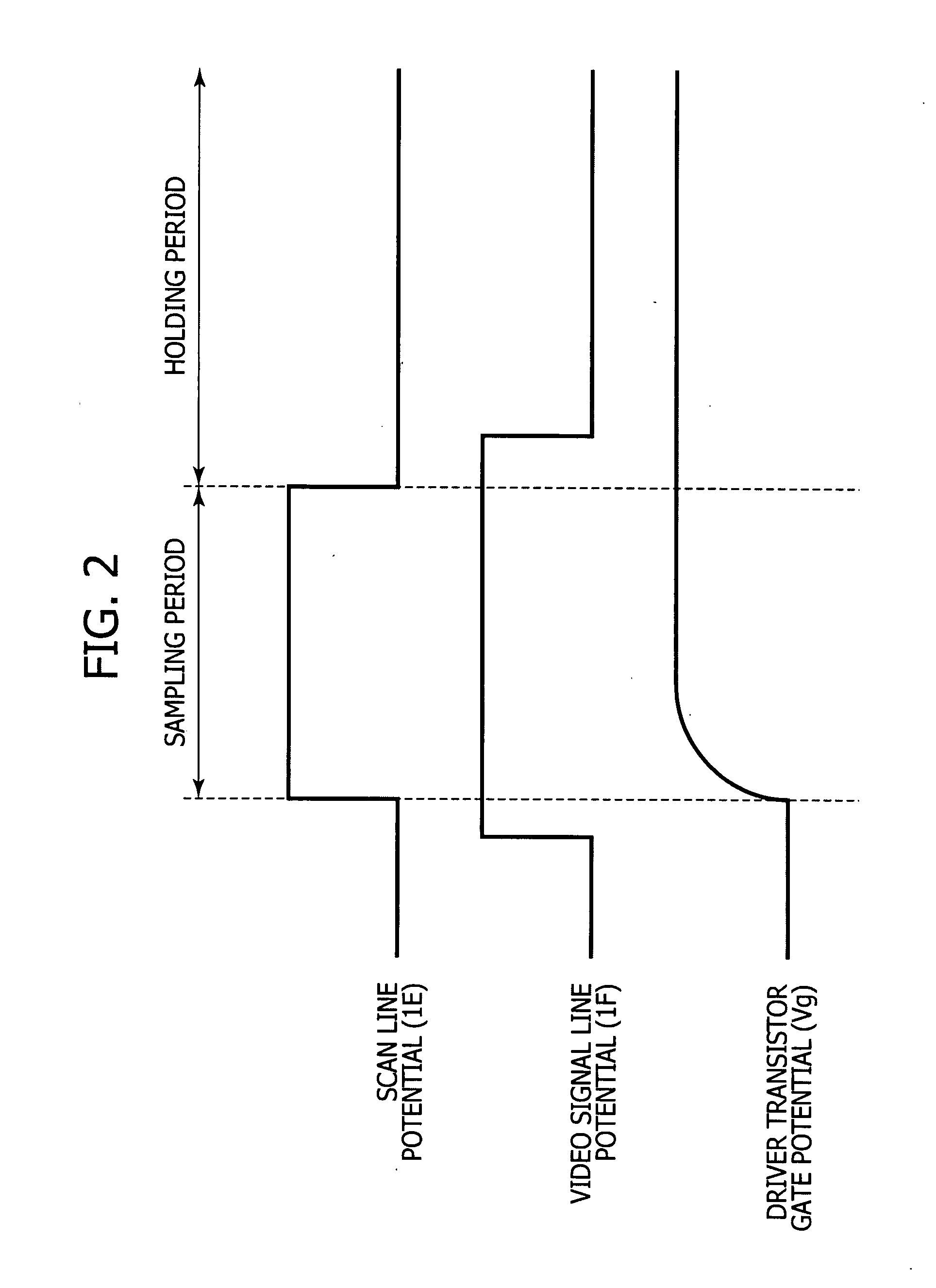

ActiveUS20080049007A1Accurate settingCorrection of mobilityElectrical apparatusElectroluminescent light sourcesDriving currentDisplay device

A display device includes a pixel array unit and a driver unit. A sampling transistor samples a signal potential to hold the signal potential in a holding capacitor. A driver transistor flows a drive current to a light emitting element in accordance with the signal potential held. A power supply scanner in the driver unit changes a power supply line from a first potential to a second potential before the sampling transistor samples the signal potential. A main scanner in the driver unit makes the sampling transistor conductive to apply a reference potential from the signal line to the gate of the driver transistor and to set the source of the driver transistor to a second potential. The power supply scanner changes the power supply line from the second potential to the first potential to hold a voltage corresponding to a threshold voltage off the driver transistor in the holding capacitor.

Owner:JOLED INC

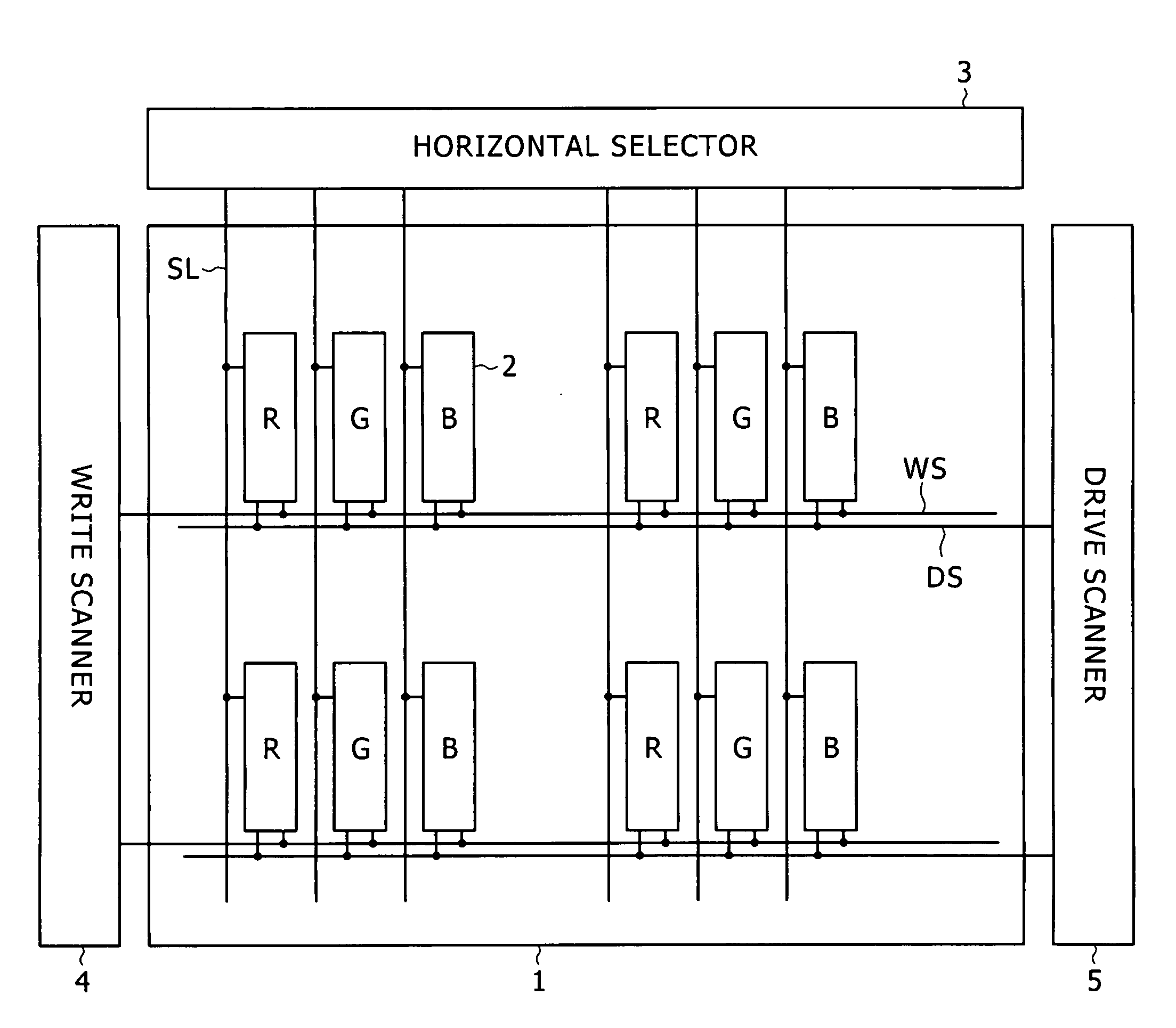

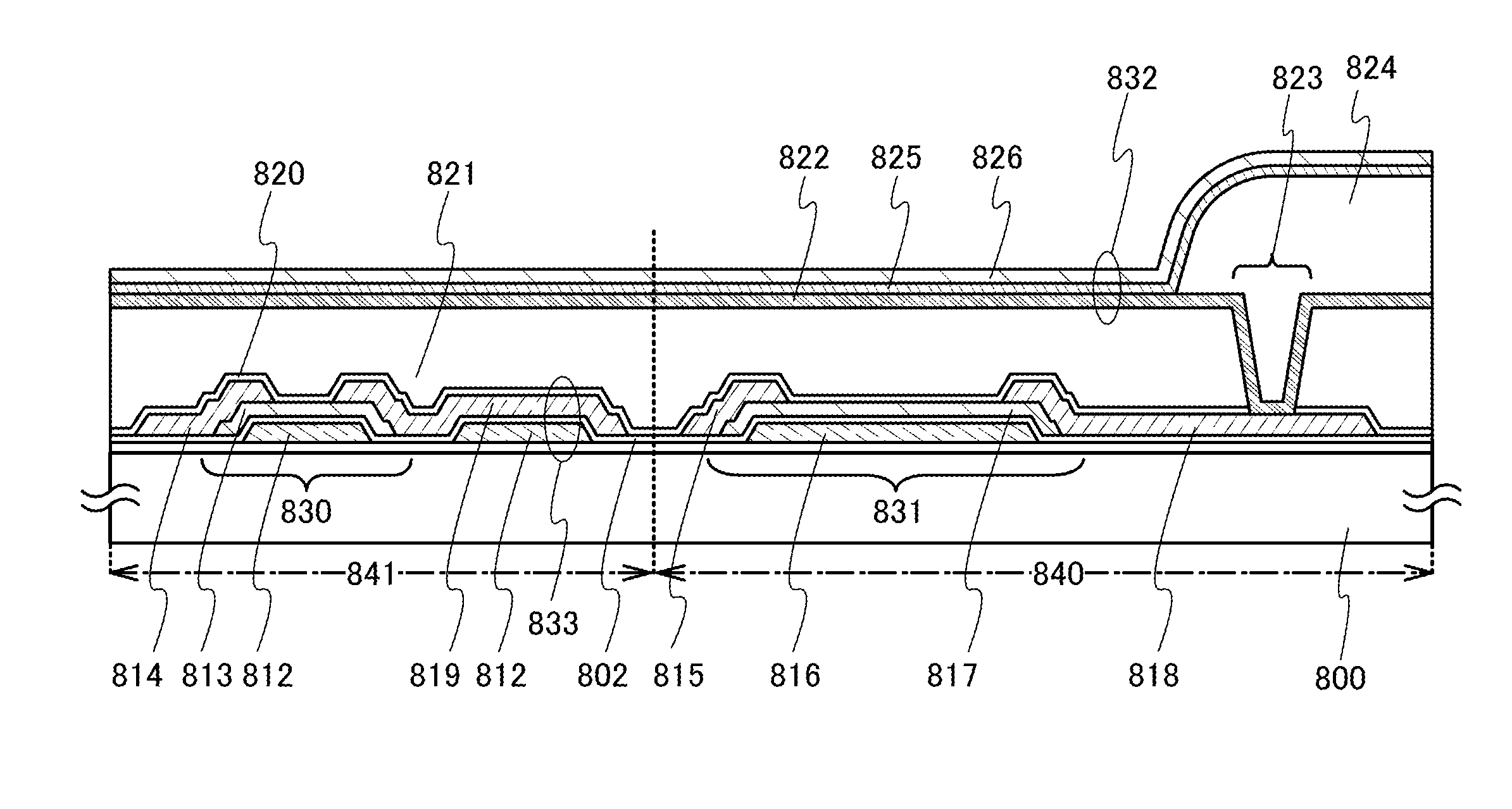

Display device, driving method thereof, and electronic device

ActiveUS20080291182A1Provide marginIncrease layout areaCathode-ray tube indicatorsInput/output processes for data processingCapacitanceControl signal

Disclosed herein is a display device including: a pixel array unit; and a driving unit; wherein said pixel array unit includes first scanning lines and second scanning lines in a form of rows, signal lines in a form of columns, and pixels in a form of a matrix, each pixel includes a drive transistor, a sampling transistor, a switching transistor, a retaining capacitance, and a light emitting element, said driving unit includes a write scanner for sequentially supplying a control signal to each first scanning line, a drive scanner for sequentially supplying a control signal to each second scanning line, and a signal selector for alternately supplying a signal potential as a video signal and a predetermined reference potential to each signal line.

Owner:JOLED INC

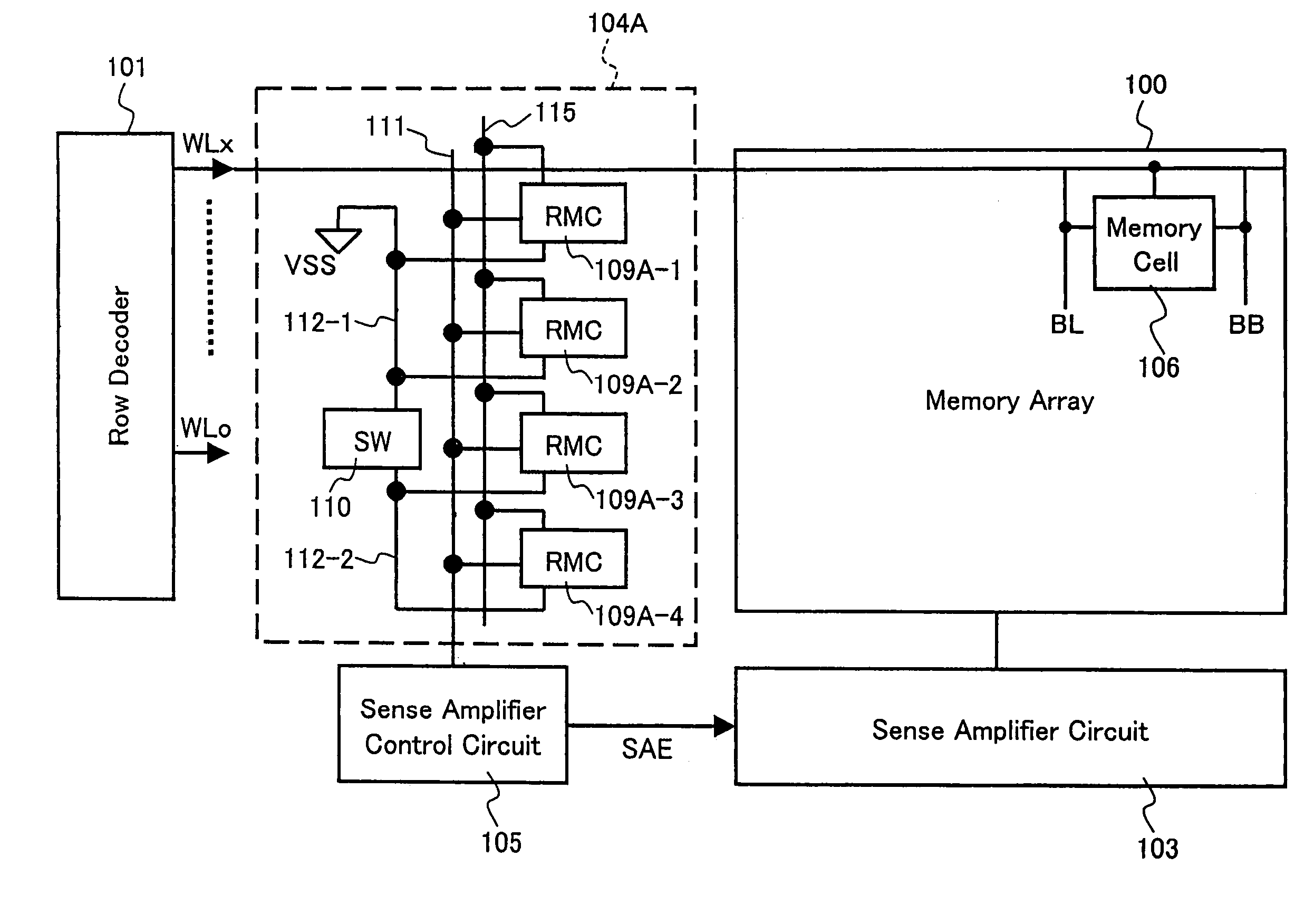

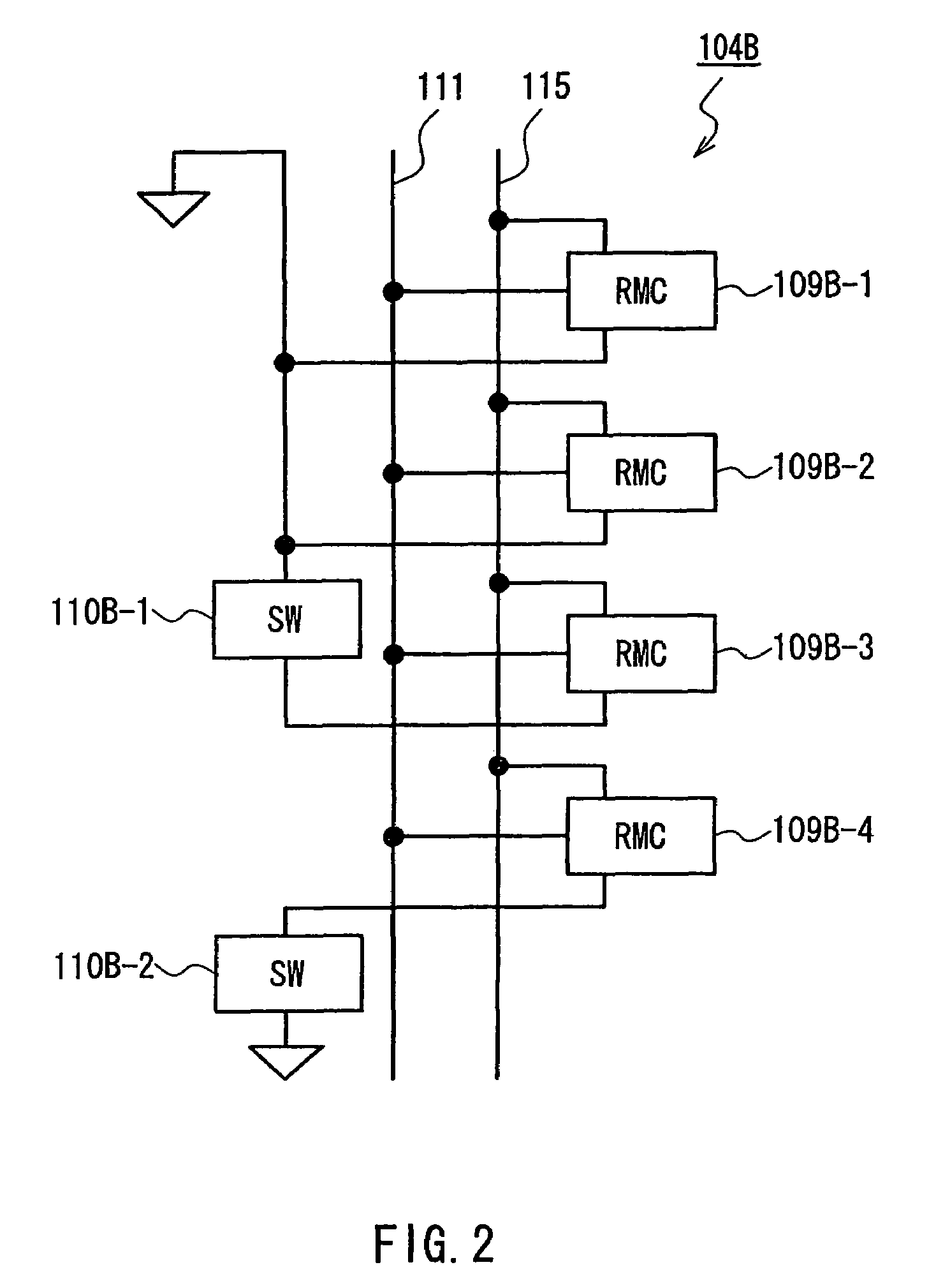

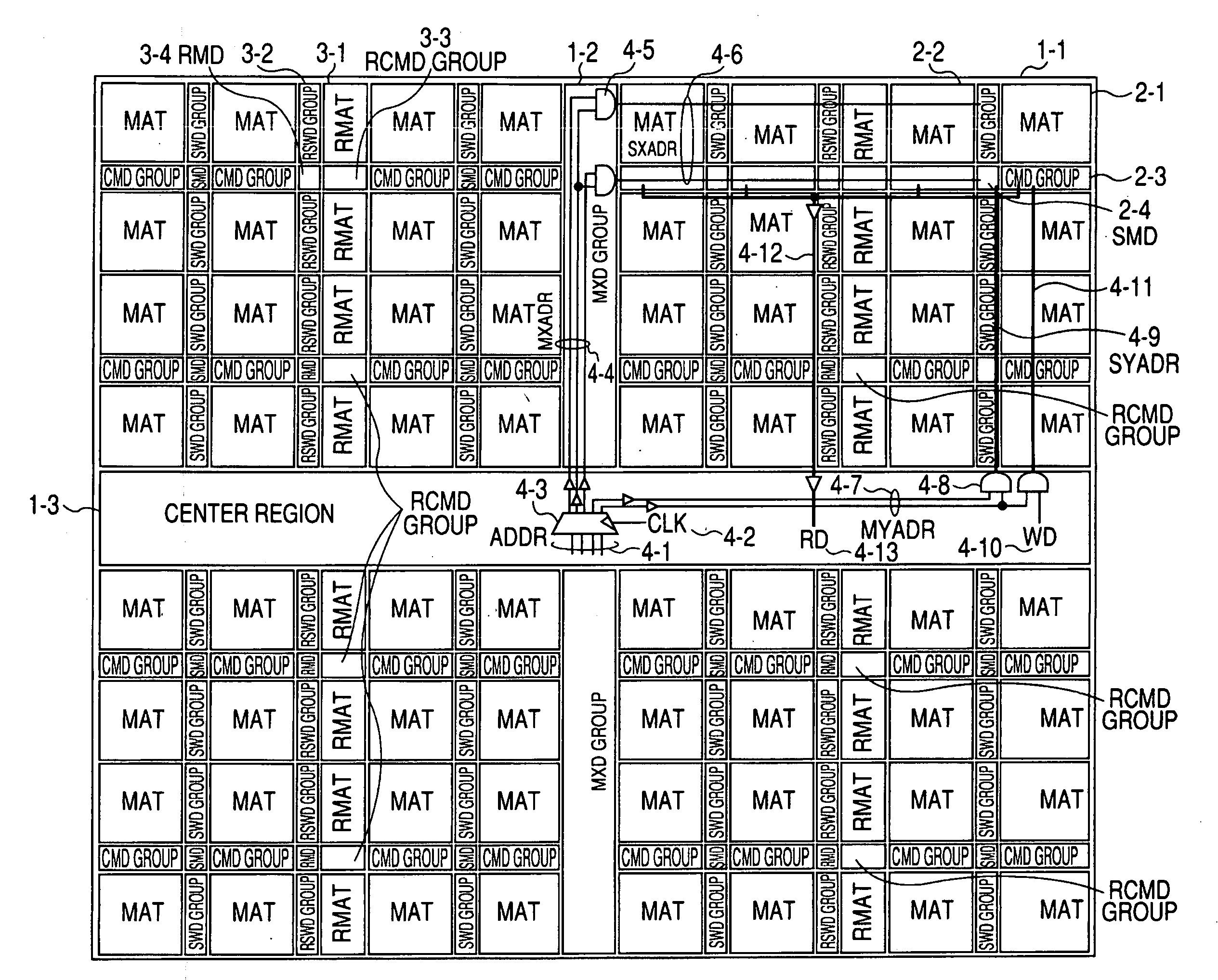

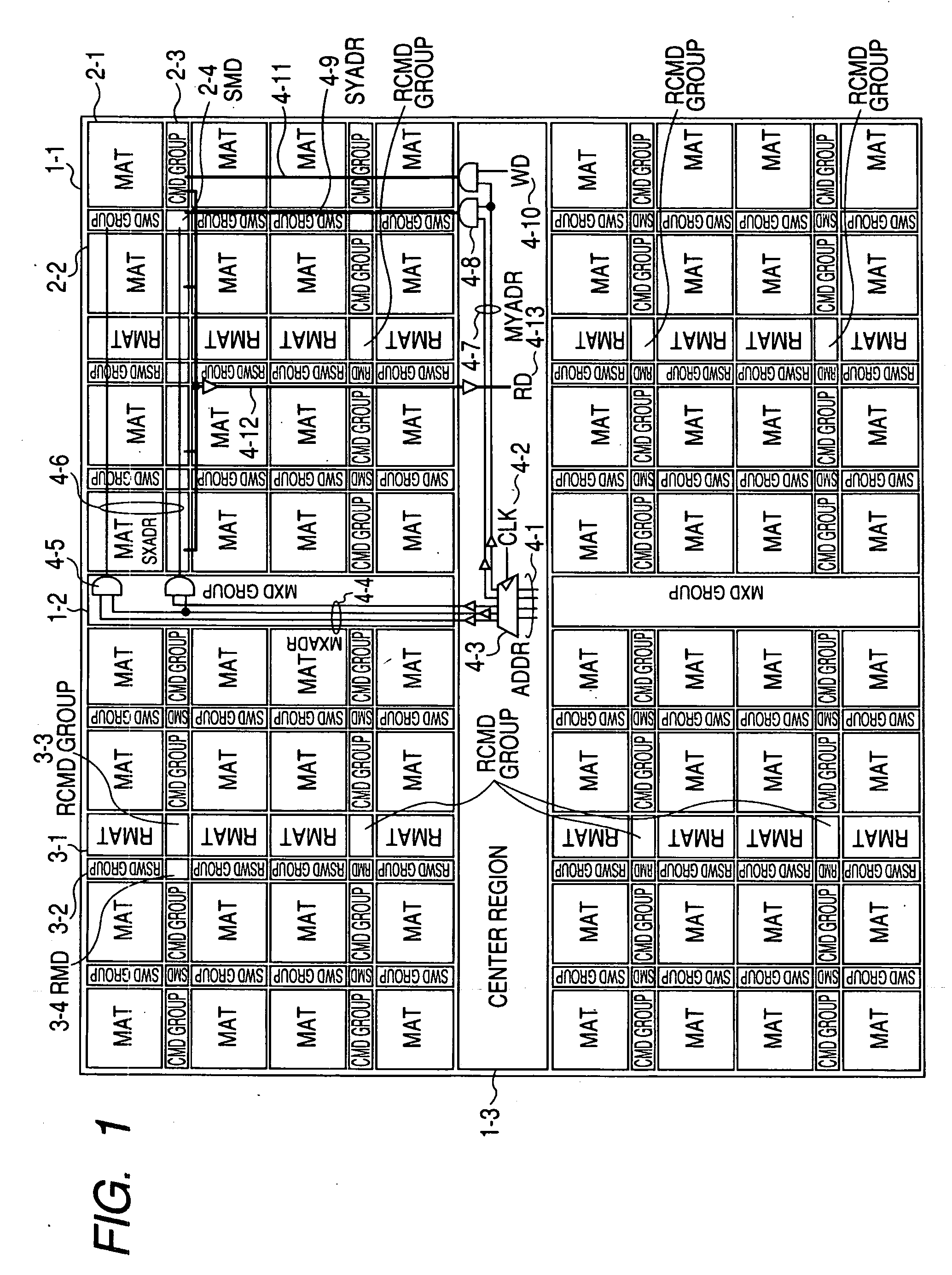

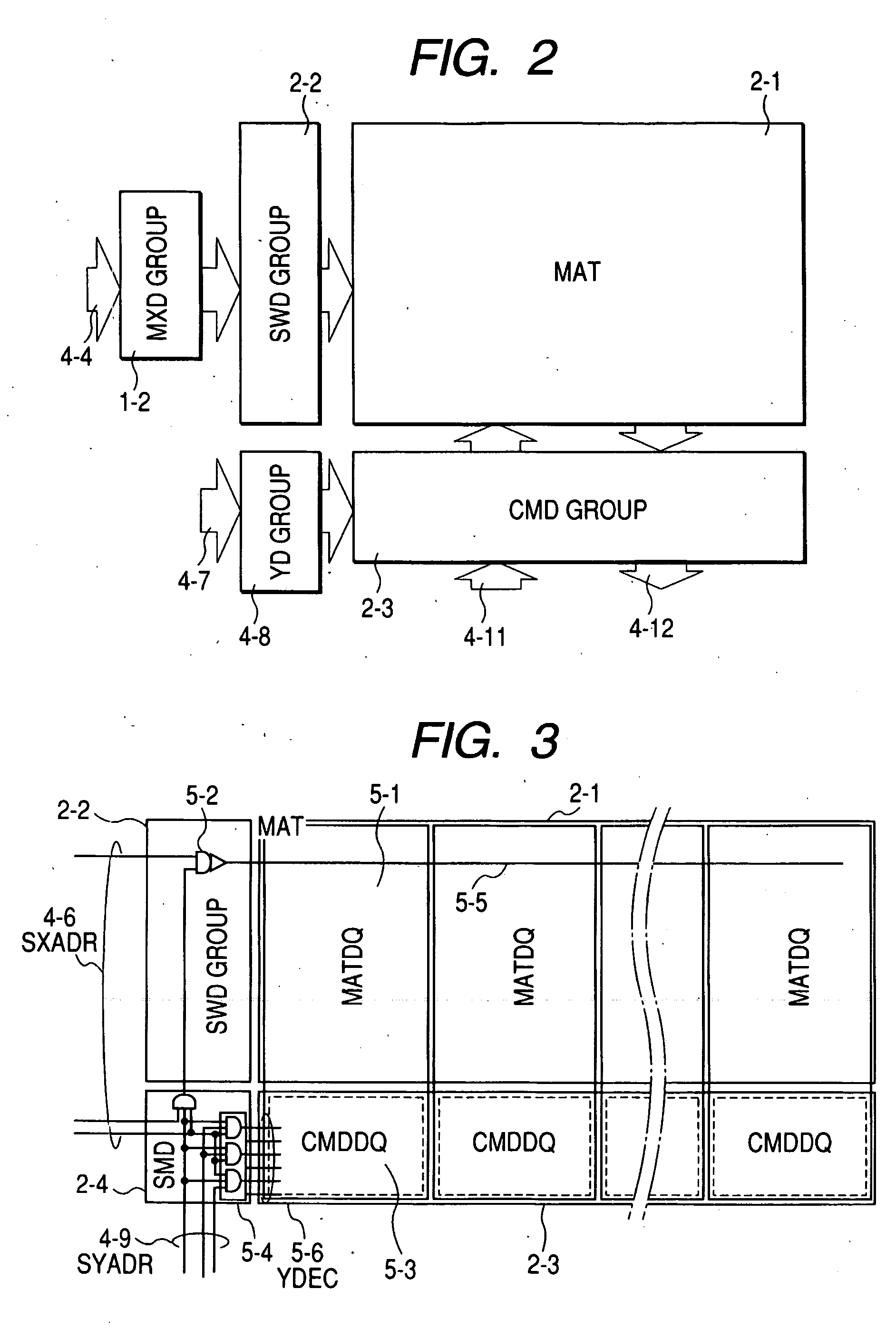

Semiconductor memory device

InactiveUS6982914B2Increase layout areaSolid-state devicesSemiconductor/solid-state device manufacturingBit lineAudio power amplifier

A semiconductor memory device includes a replica circuit including a plurality of replica cells (RMC) having the same elements as those of memory cells in a memory array and outputting signals with levels in the stage number to a common replica bit line, and a sense amplifier control circuit for receiving a signal of the replica bit line to control a timing of a signal SAE for starting a sense amplifier circuit. The replica circuit includes a switching circuit (SW) for switching the stage number of the replica cells to be activated among the plurality of replica cells in a programmable manner.

Owner:PANASONIC CORP

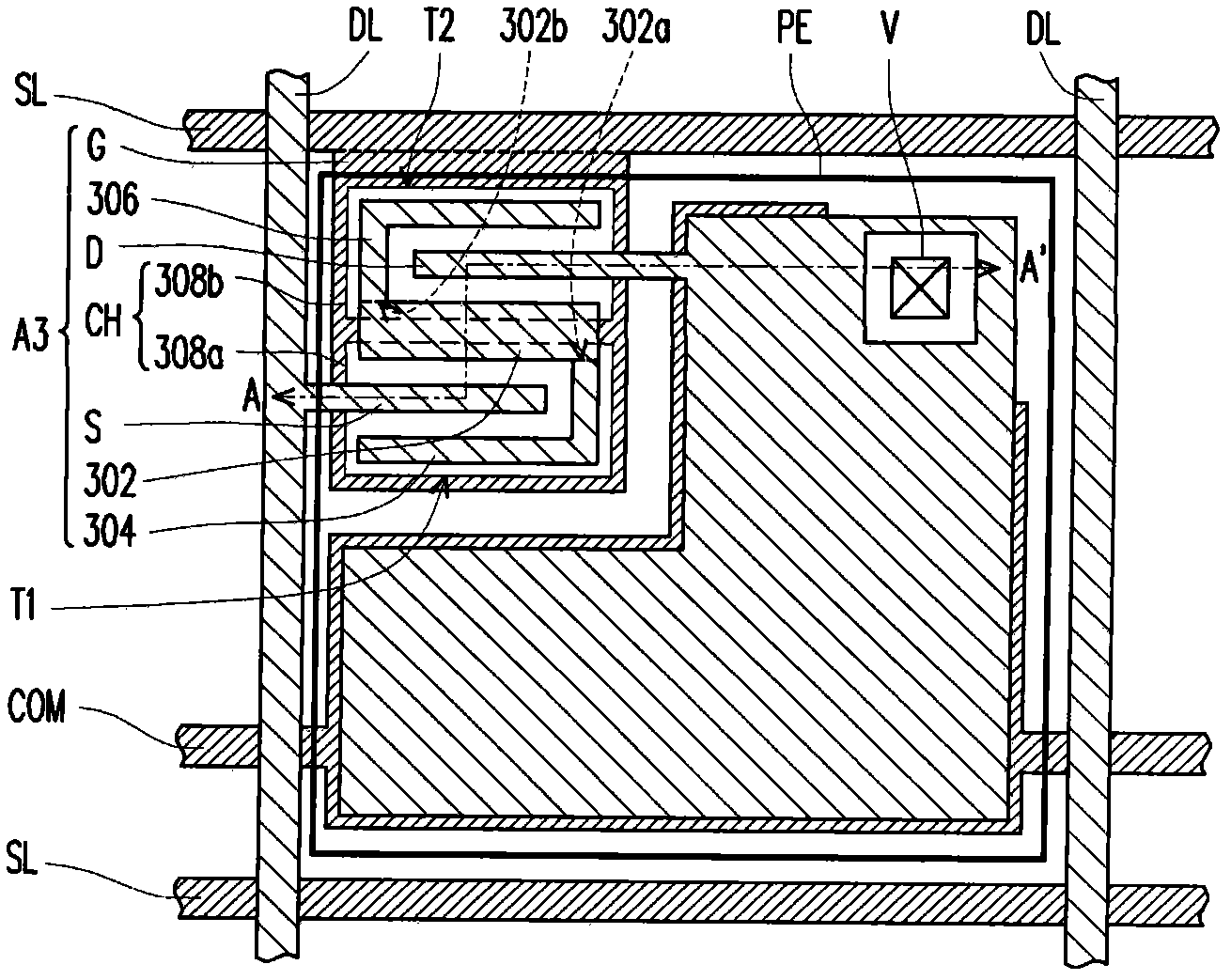

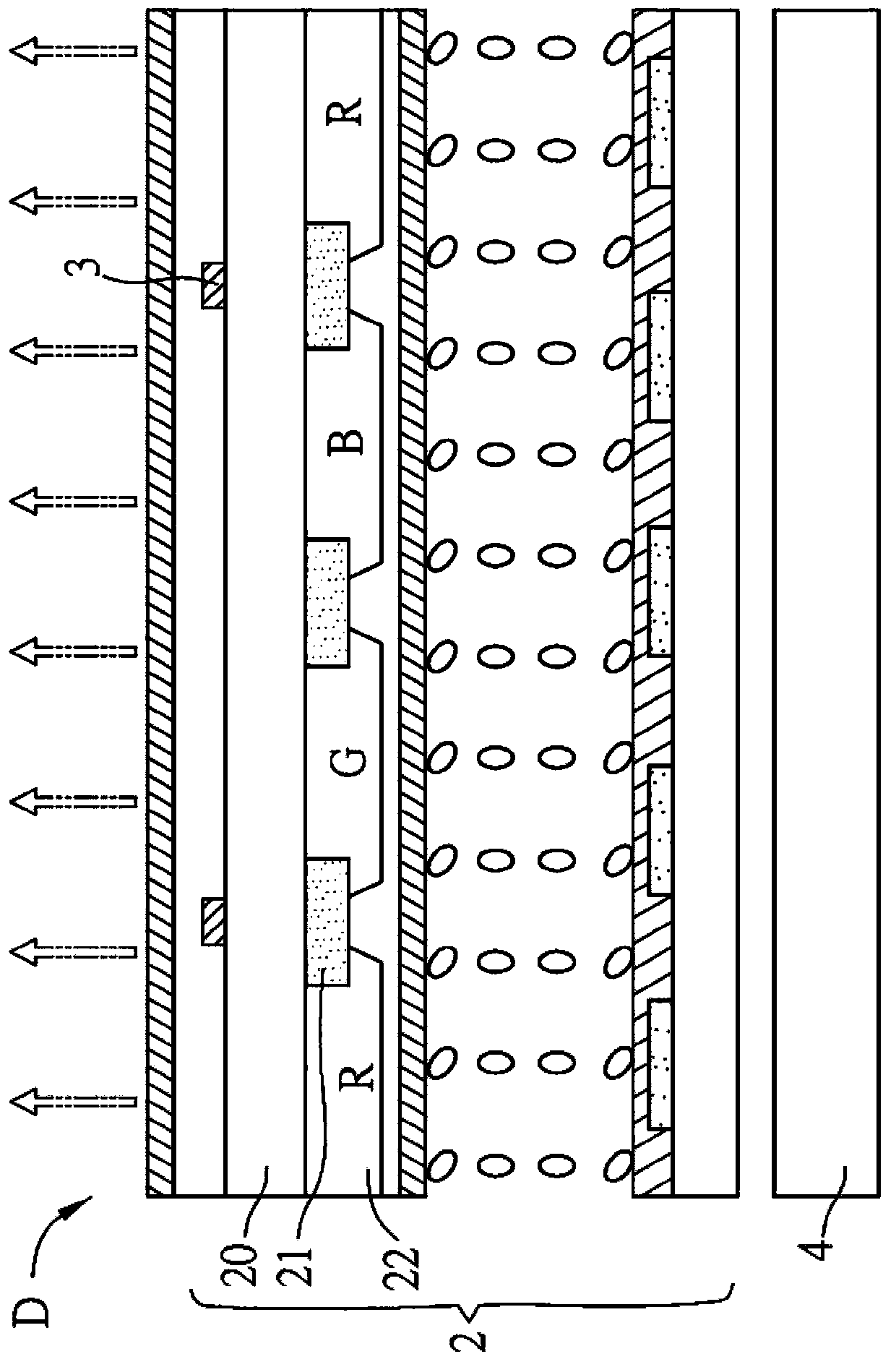

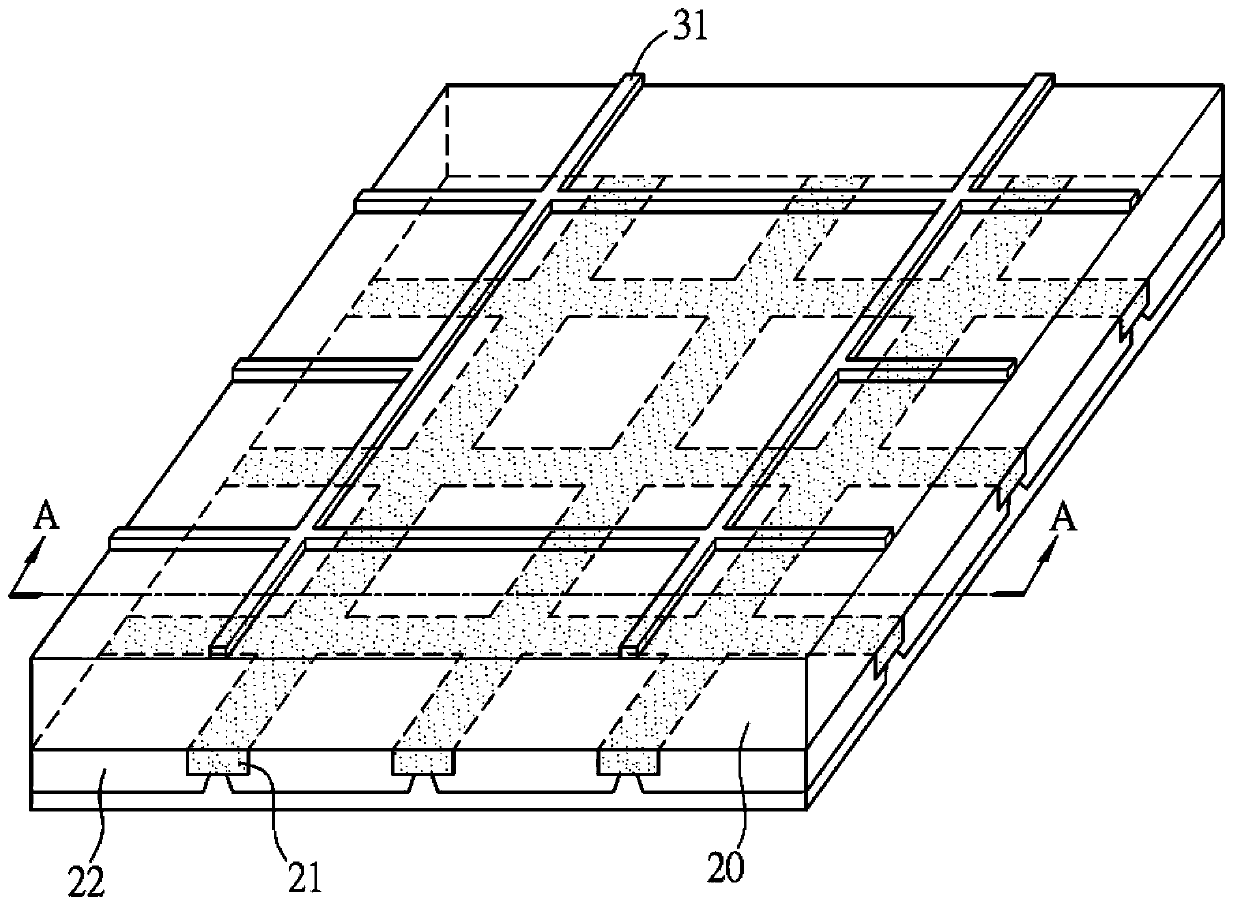

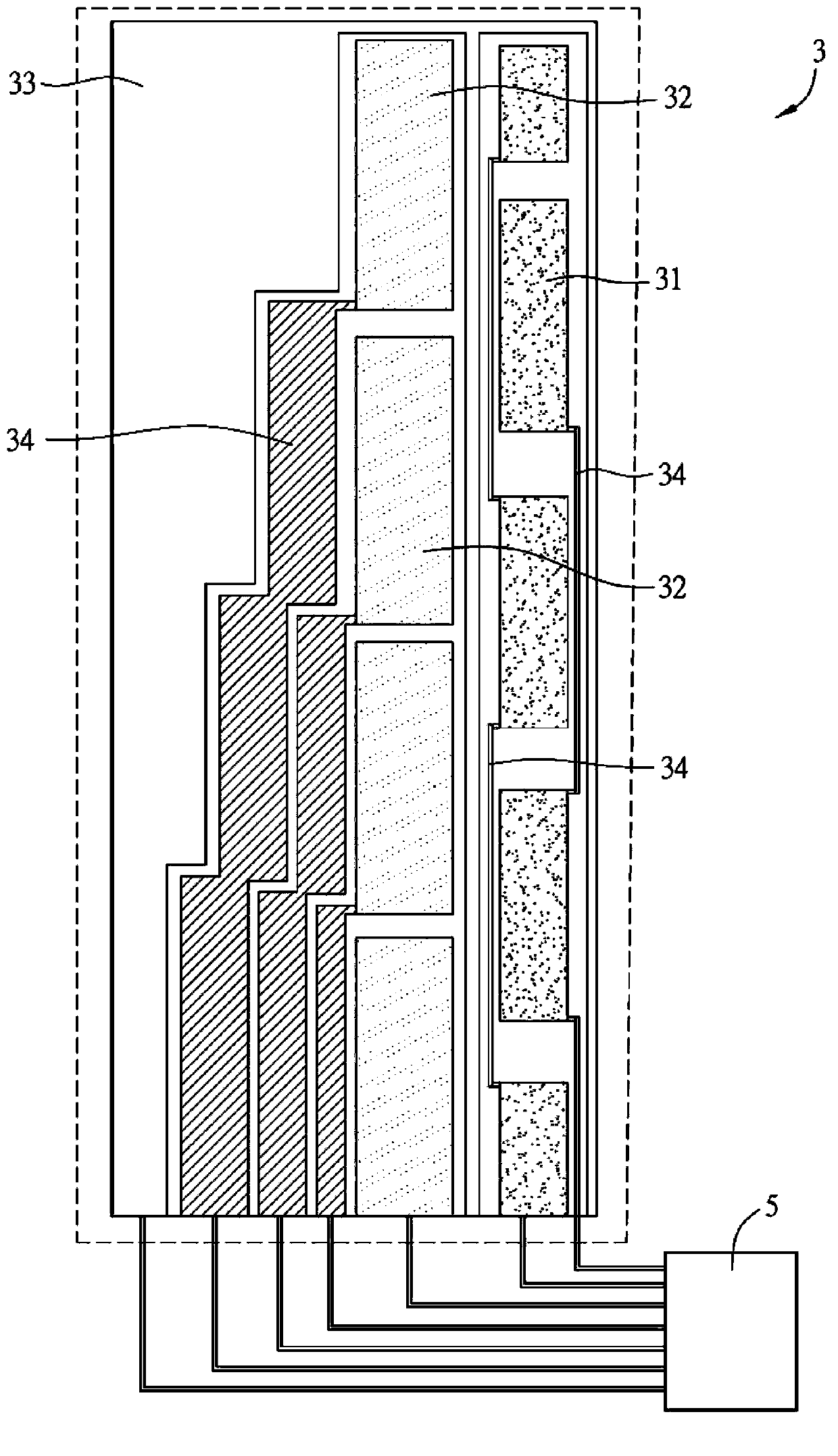

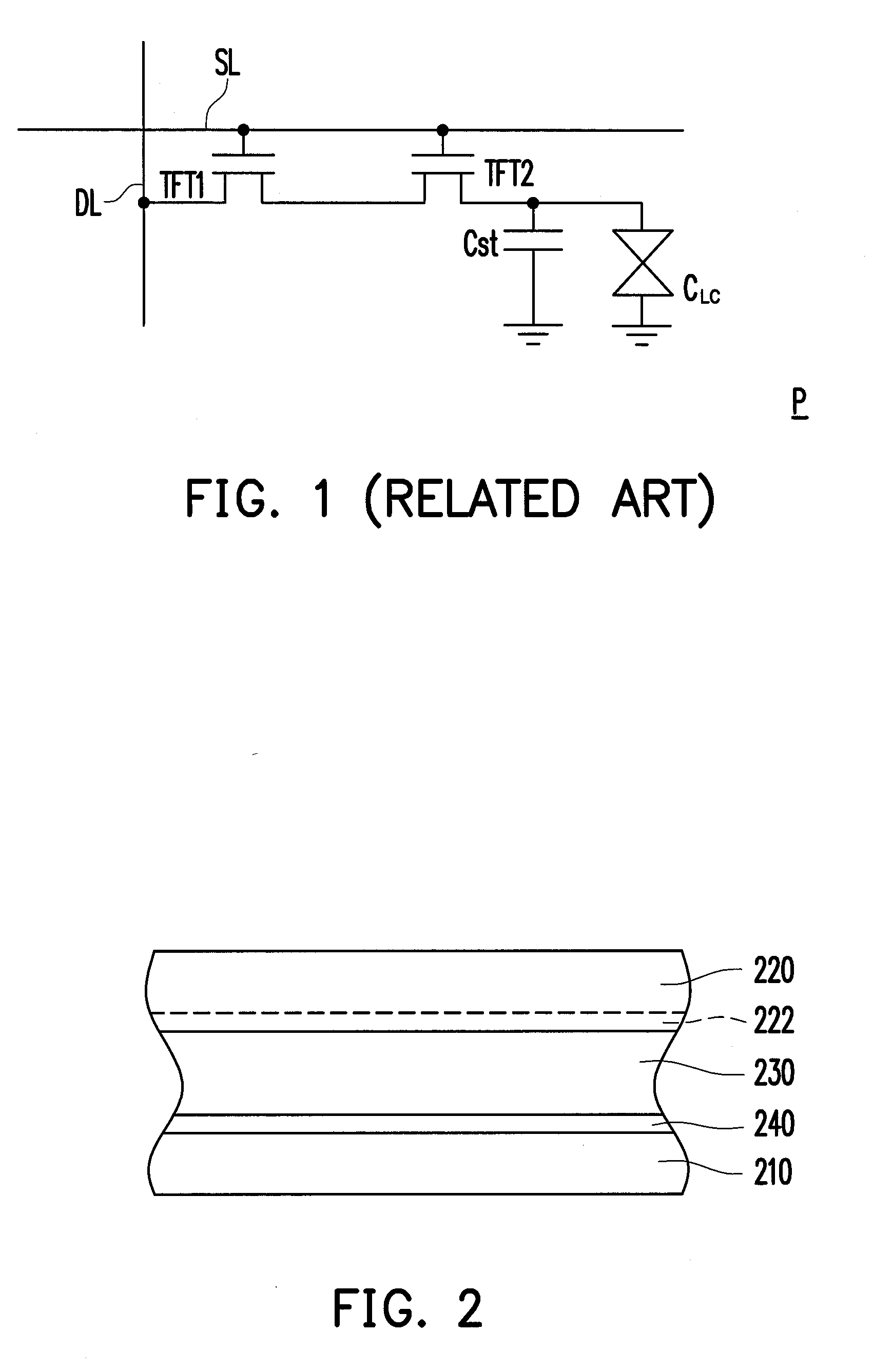

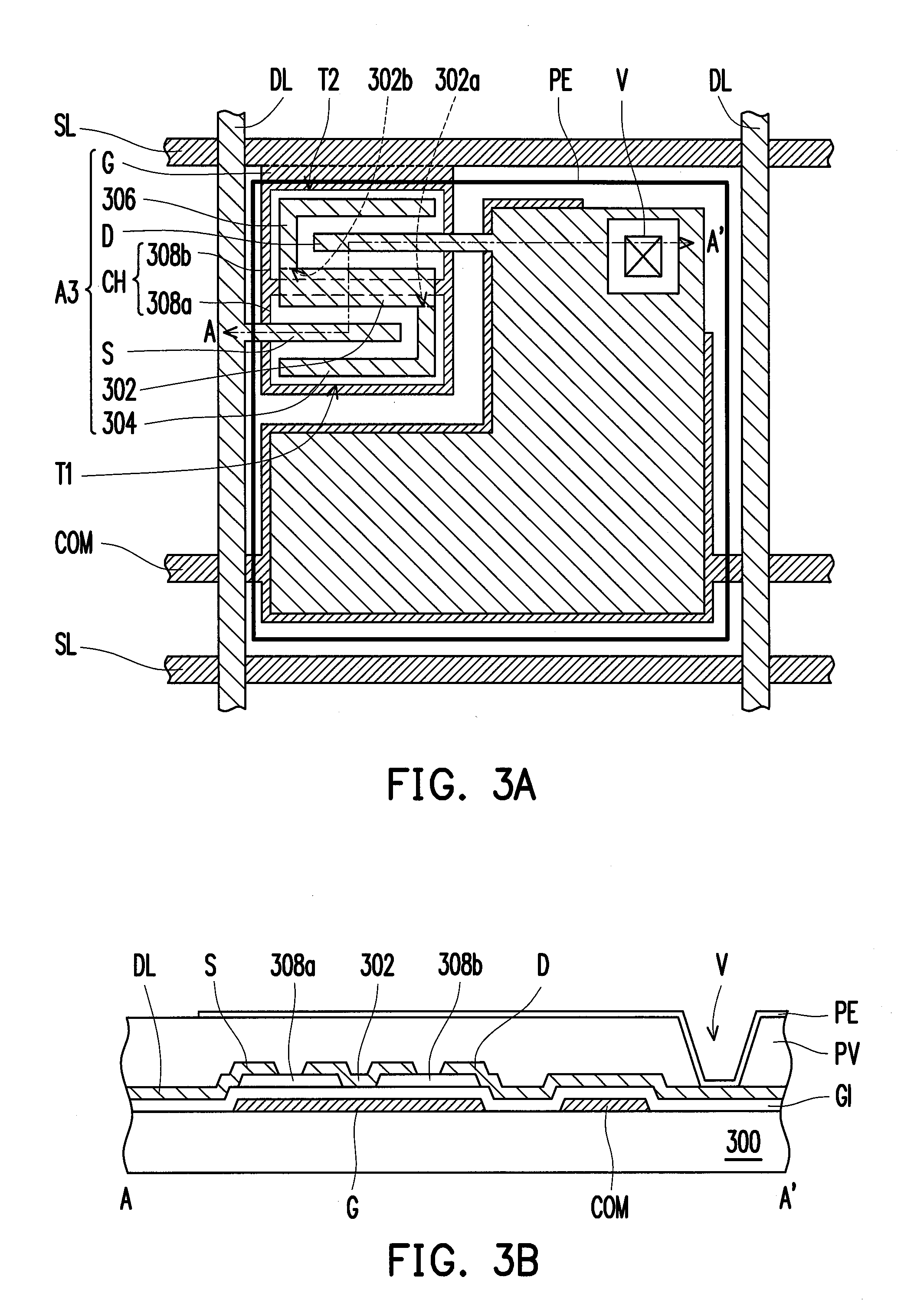

Pixel structure, active element array substrate and planar display panel

ActiveCN102402087AReduce layout areaIncrease layout areaSolid-state devicesNon-linear opticsOptoelectronicsData lines

The invention discloses a pixel structure, an active element array substrate and a planar display panel. The pixel structure comprises a pixel electrode and an active element. The active element comprises a grid electrode, a channel layer, a source electrode, a drain electrode, a connecting electrode, a first branch part and a second branch part. The grid electrode is electrically connected with a scanning line. The channel layer is located on one side of the grid electrode and electrically insulated from the grid electrode. The source electrode and the data line are electrically connected. The drain electrode and the pixel electrode are electrically connected. The source electrode, the drain electrode and the connecting electrode are equipped on parts of the channel layer. The connecting electrode is located between the source electrode and the drain electrode. The first branch part is equipped on the parts of the channel layer and connected with one end of the connecting electrode. The first branch part surrounds the source electrode located on the channel layer. The second branch part is equipped on parts of the channel layer and connected with the other end of the connecting electrode. The second branch part surrounds the drain electrode located on the channel layer.

Owner:AU OPTRONICS CORP

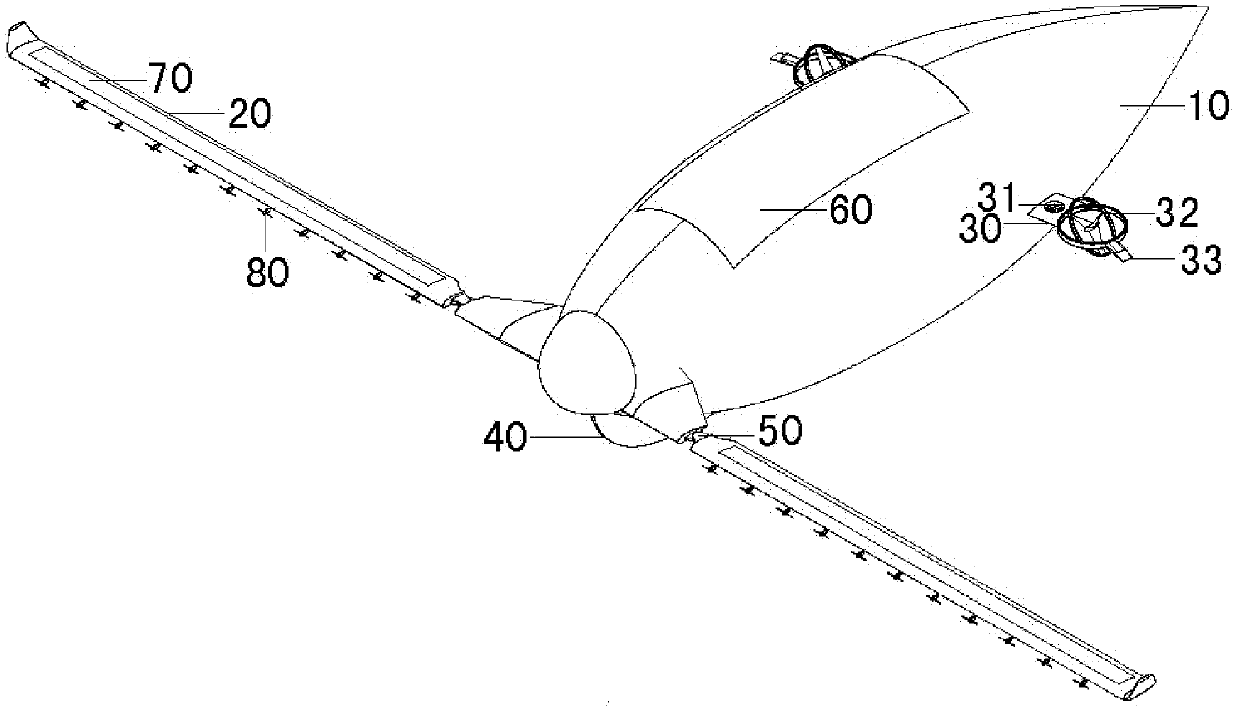

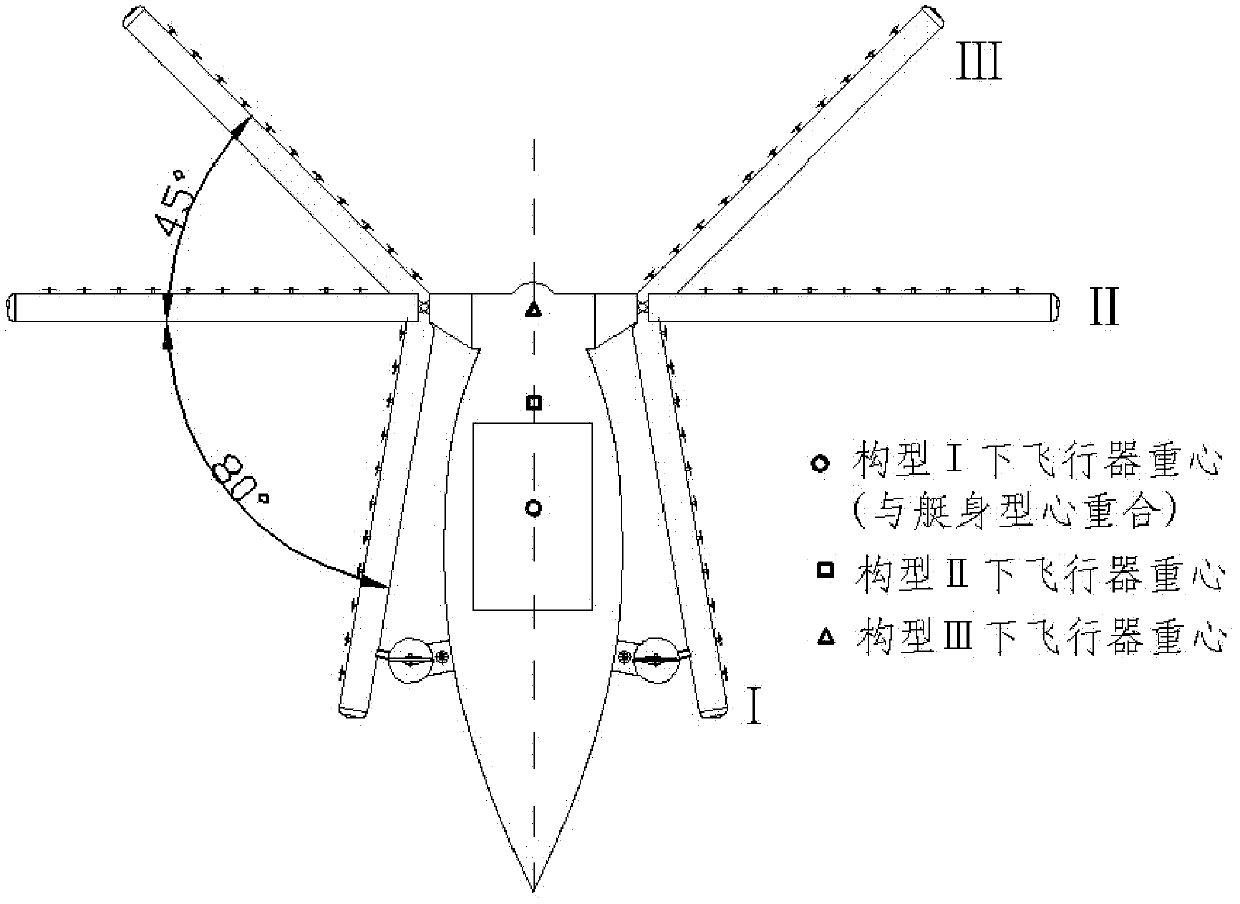

Near-space unmanned aircraft

The invention discloses a near-space unmanned aircraft. Helium gas is inflated into an inflatable aircraft, solar wings are mounted at the front end of the inflatable aircraft, can rotate around flatter positions of rotary shafts at the roots of the wings by an angle ranging from -45 degrees to 80 degrees and can be locked at the three positions of a -45-degree angle, a 0-degree angle and a 80-degree angle. A plurality of propellers are mounted on the solar wings, two slantingly-rotatable trust propellers and two directional-trust auxiliary propellers are mounted on the inflatable aircraft, and solar cell panels are distributed on the surface of the solar wings and the inflatable aircraft. The inflatable aircraft is divided into a front section, a middle section and a rear section, wherein the rear section has a soft structure, a middle section has a semi-hard structure, and the front section is a task loading cabin. The near-space unmanned aircraft can overcome the defects of high requirements to taking-off and landing fields, insufficiency in effective load, poor safety in low-altitude flying and the like of an existing unmanned aircraft, and meanwhile, higher flight altitude can be realized, hovering posture and flight path control performances of the near-space unmanned aircraft are improved, absorption and storage of solar energy are improved and time for staying in space is guaranteed.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

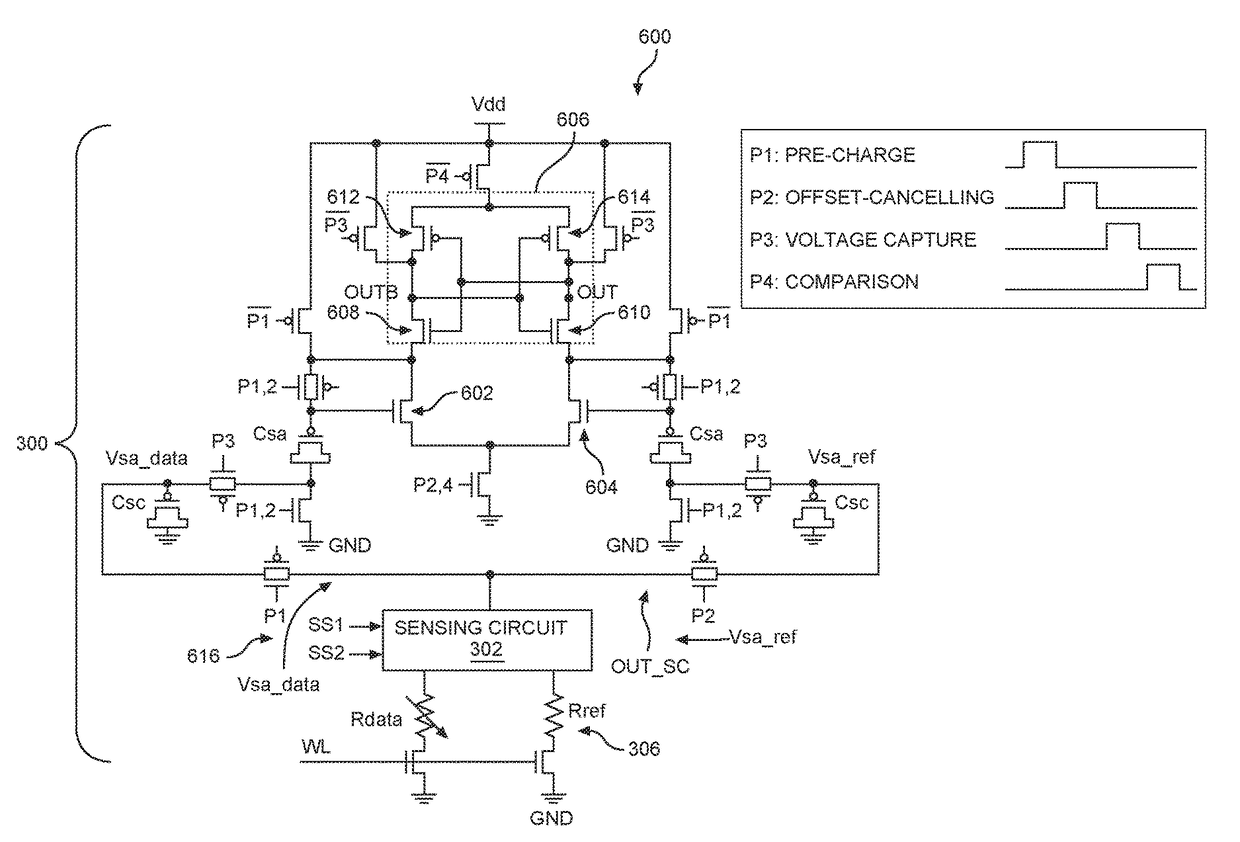

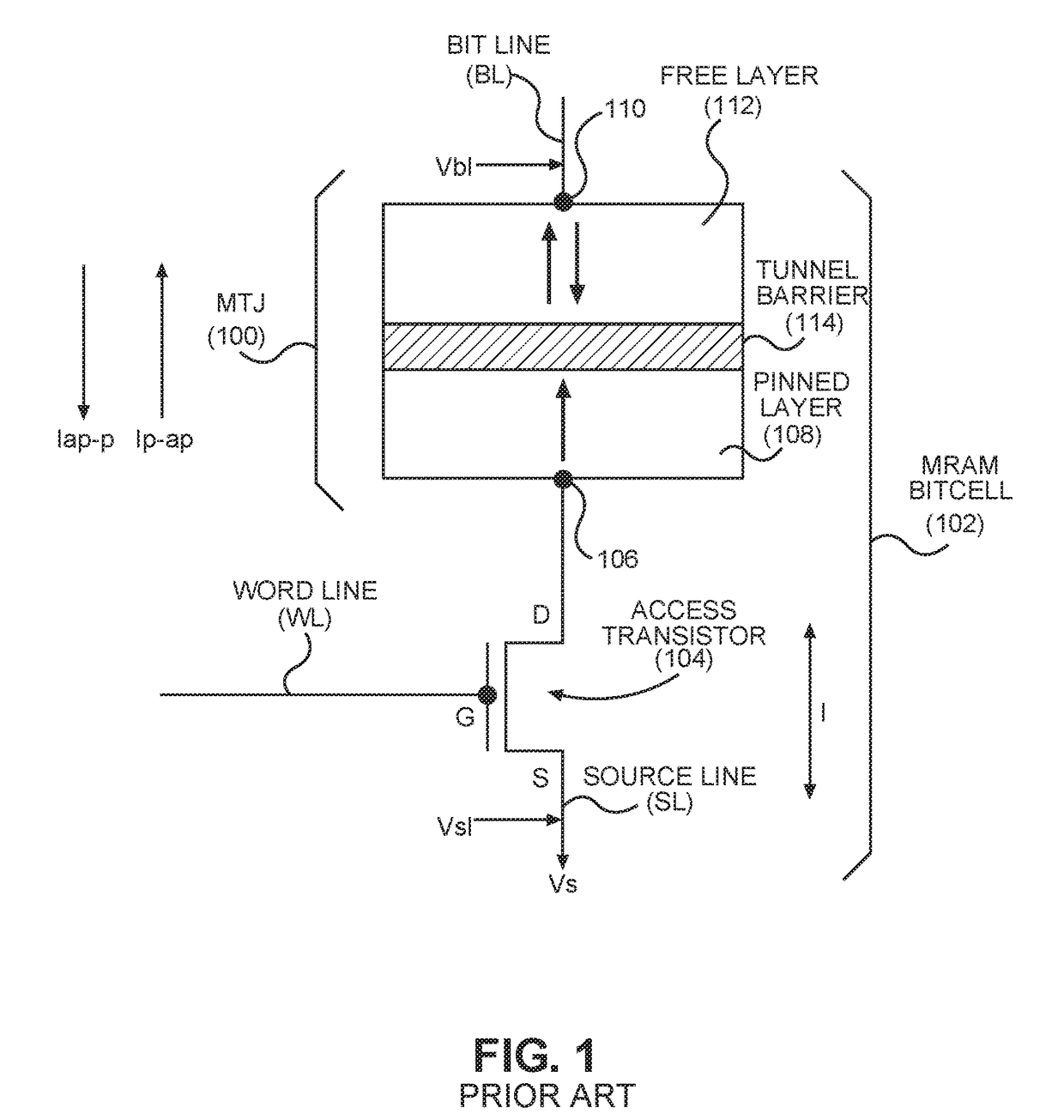

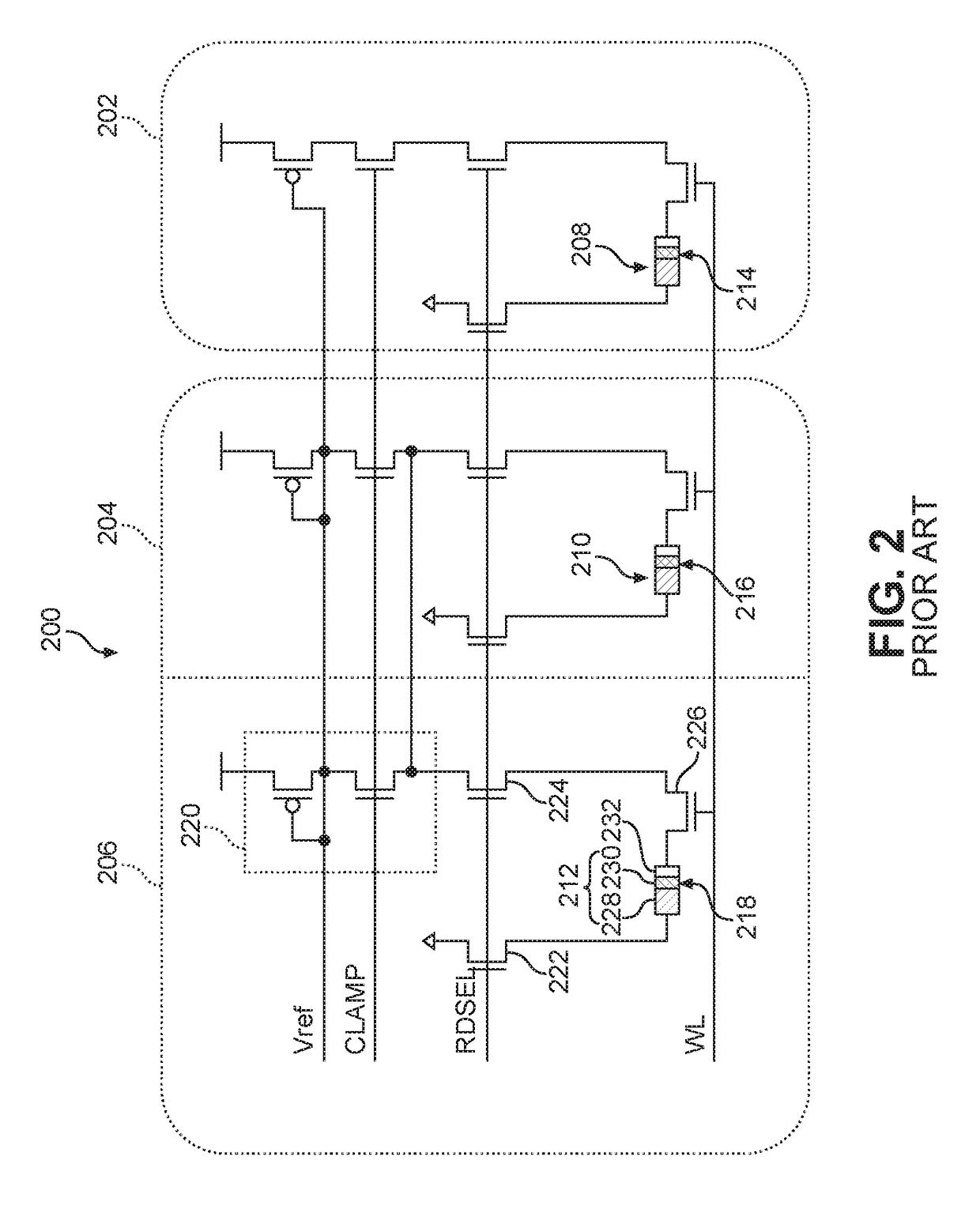

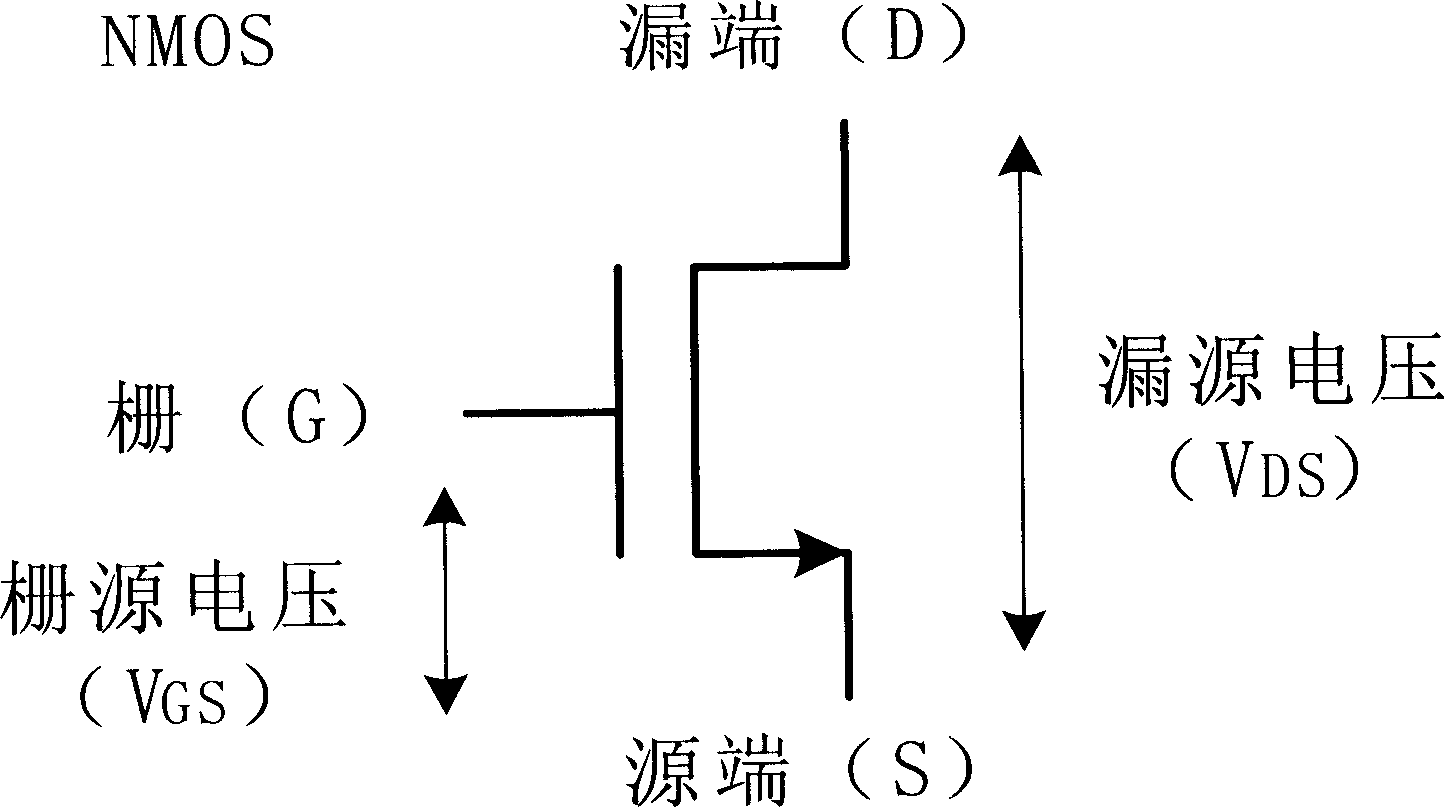

Metal-oxide semiconductor (MOS) transistor offset-cancelling (OC), zero-sensing (ZS) dead zone, current-latched sense amplifiers (SAs) (CLSAs) (OCZS-SAs) for sensing differential voltages

Metal-oxide semiconductor (MOS) transistor offset-cancelling (OC), zero-sensing (ZS) dead zone, current-latched sense amplifiers (SAs) (CLSAs) (OCZS-SAs) for sensing differential voltages are provided. An OCZS-SA is configured to amplify received differential data and reference input voltages with a smaller sense amplifier offset voltage to provide larger sense margin between different storage states of memory bitcell(s). The OCZS-SA is configured to cancel out offset voltages of input and complement input transistors, and keep the input and complement input transistors in their activated state during sensing phases so that sensing is not performed in their “dead zones” when their gate-to-source voltage (Vgs) is below their respective threshold voltages. In other aspects, sense amplifier capacitors are configured to directly store the data and reference input voltages at gates of the input and complement input transistors during voltage capture phases to avoid additional layout area that would otherwise be consumed with additional sensing capacitor circuits.

Owner:QUALCOMM TECHNOLOGIES INC +1

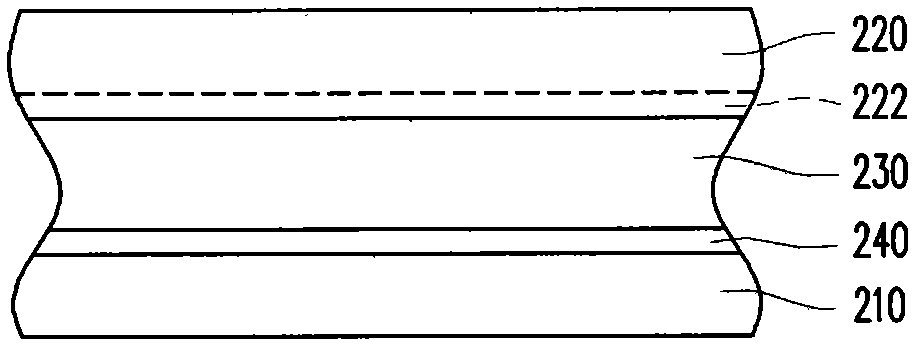

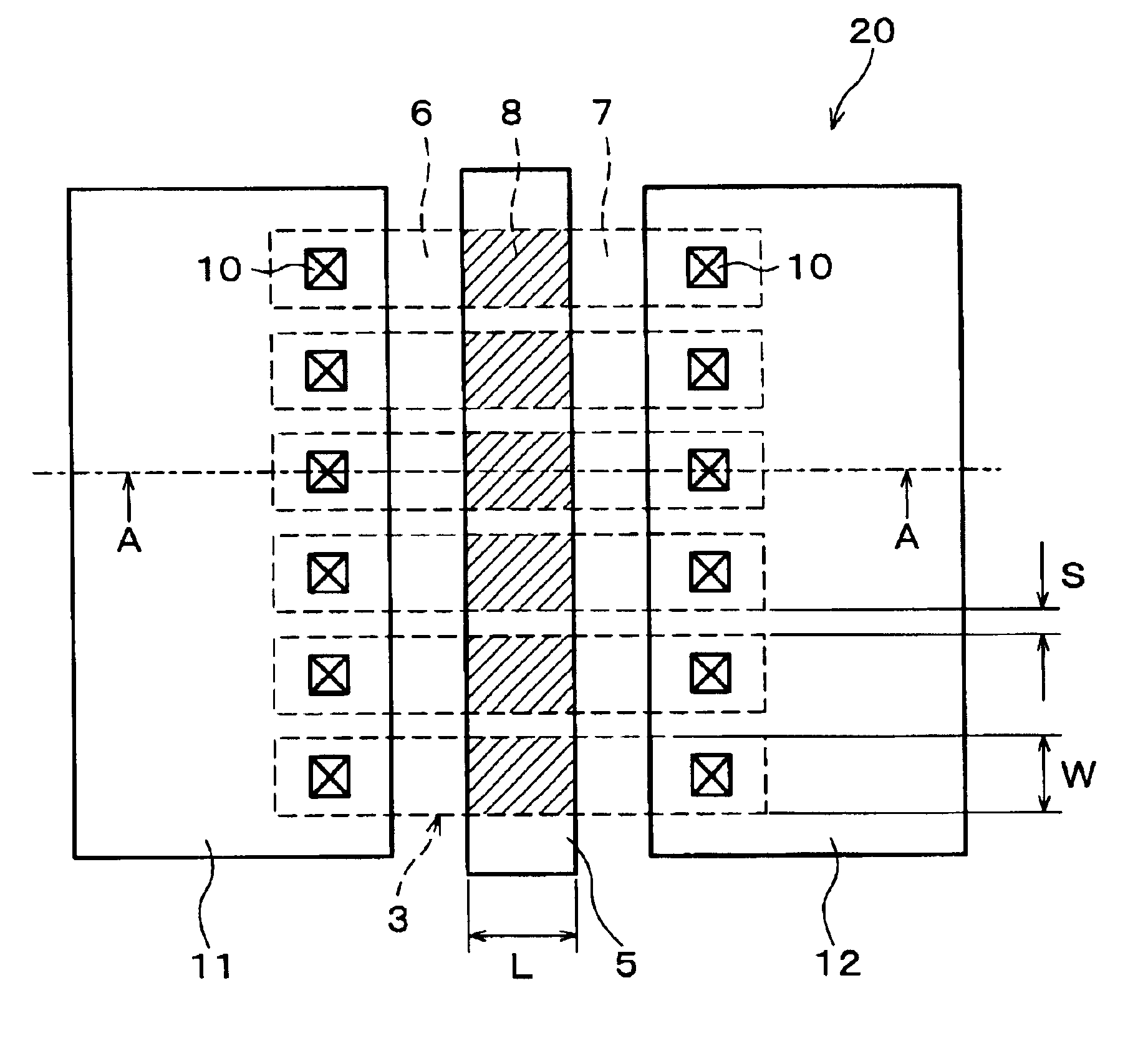

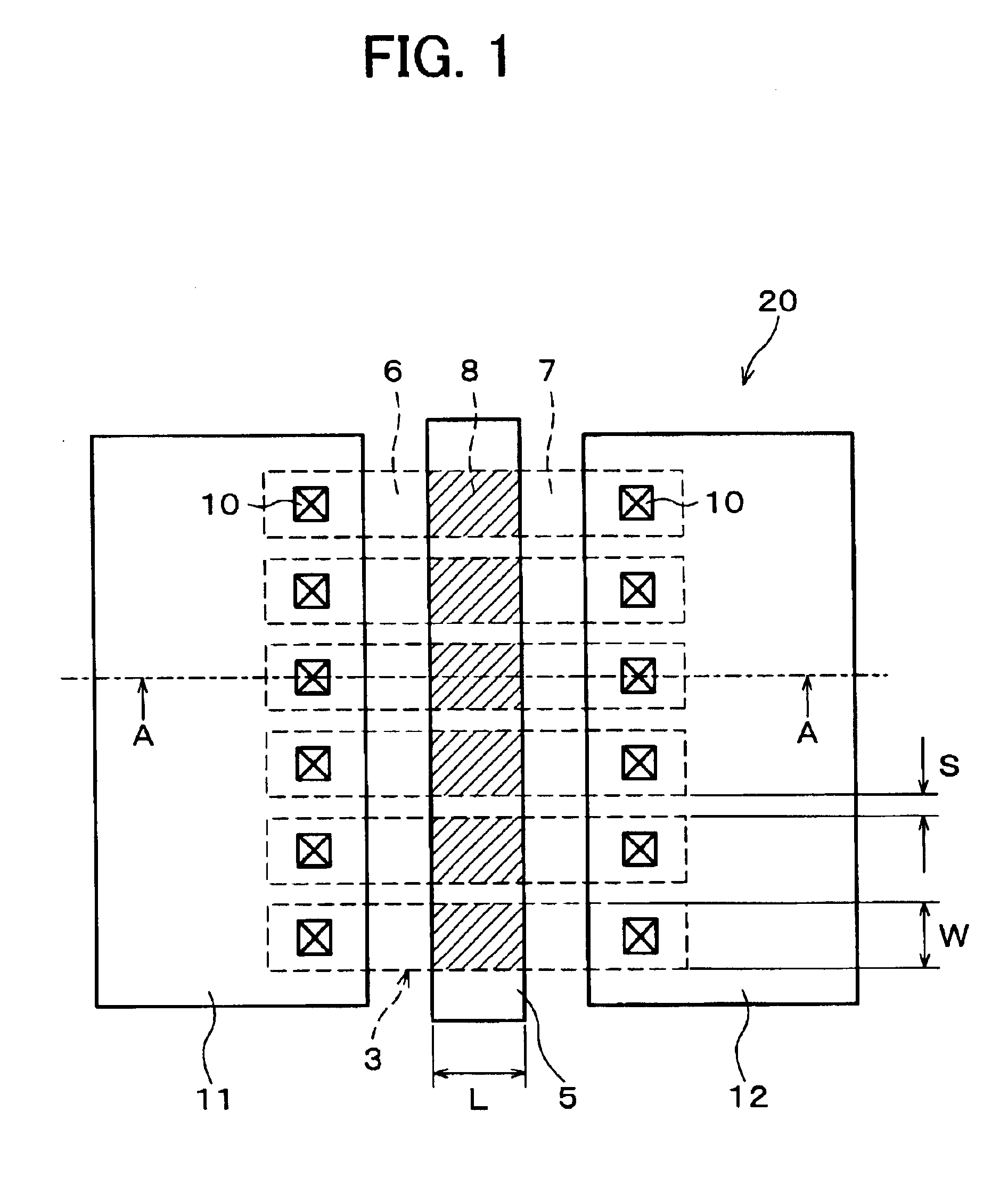

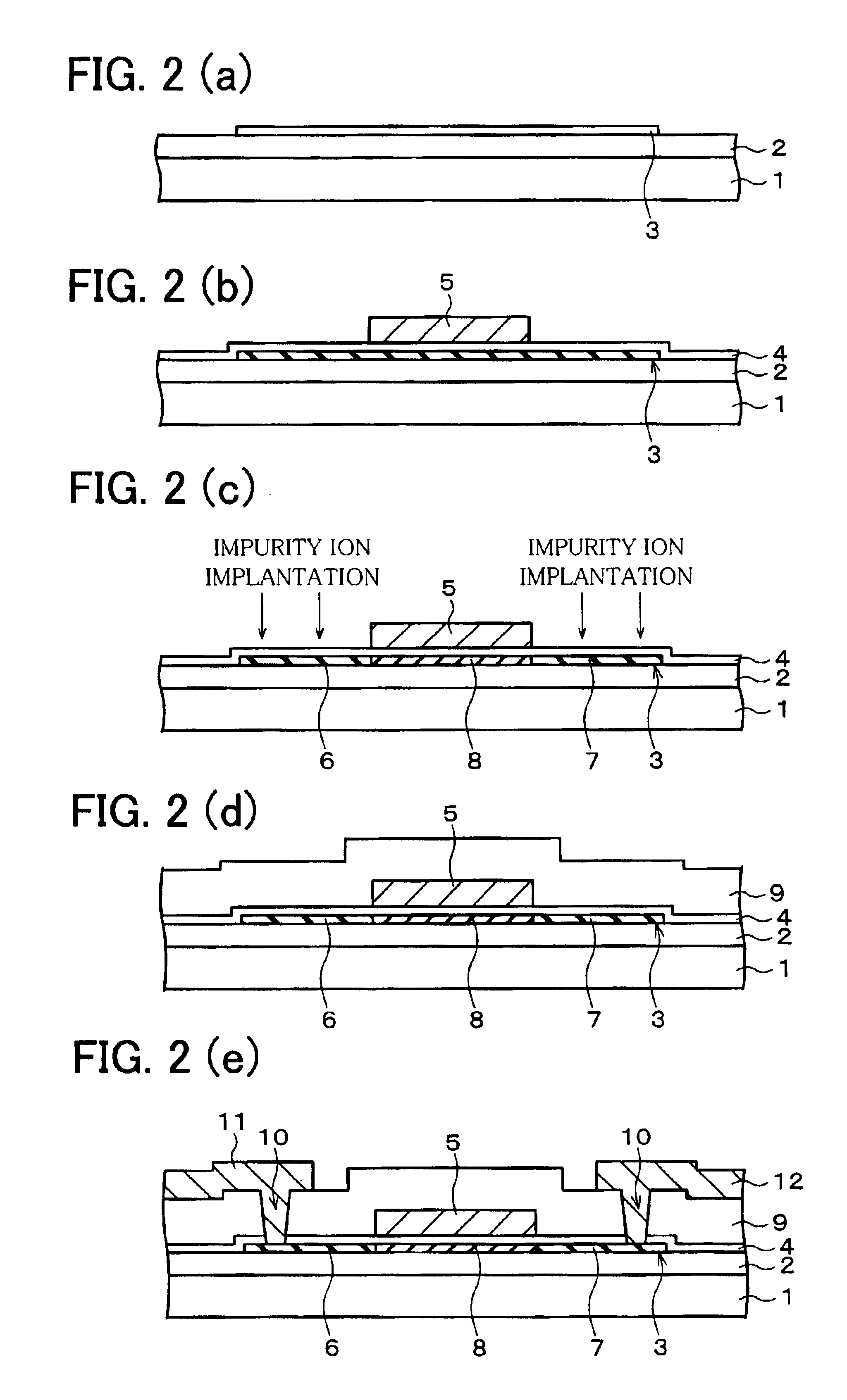

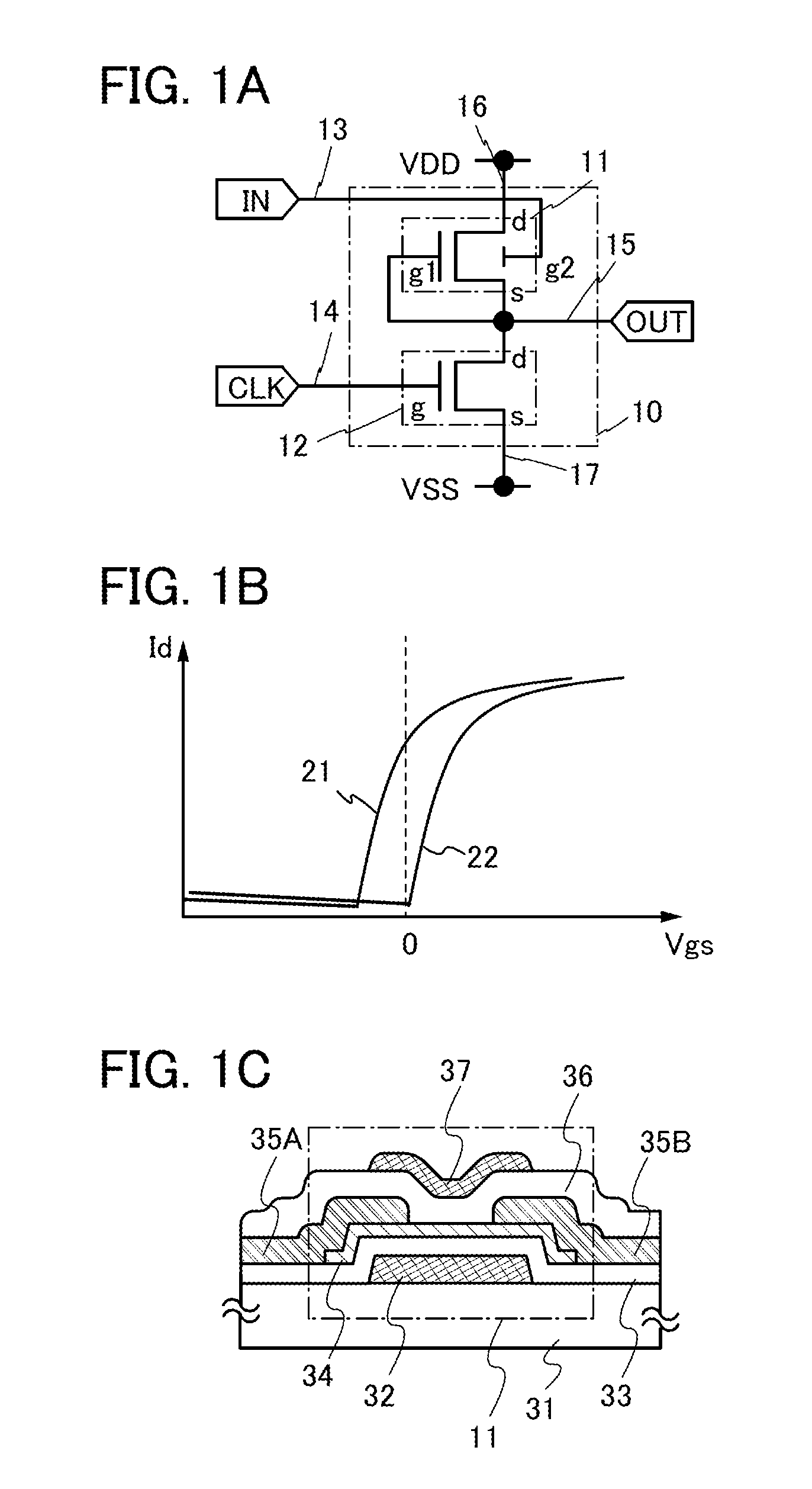

Thin film transistor, method for manufacturing same, and liquid crystal display device using same

InactiveUS6888182B2Increase layout areaLow reliabilityTransistorSolid-state devicesLiquid-crystal displayEngineering

A thin film transistor of the present invention is provided with (i) a plurality of divided channel regions formed under a gate electrode, and (ii) divided source regions and divided drain regions between which each of the divided channel regions is sandwiched, the divided source regions being connected with one another, and the divided drain regions being connected with one another. Here, the divided channel regions are so arranged that a spacing between the divided channel regions is smaller than a channel divided width which is a width of one divided channel region, the channel divided width is not more than 50 μm, and the spacing is not less than 3 μm. With this arrangement, it is possible to provide a thin film transistor capable of obtaining reliability with reducing the variation in threshold voltage by reducing the self-heating at the channel regions, as well as capable of reducing the increase of a layout area.

Owner:SHARP KK

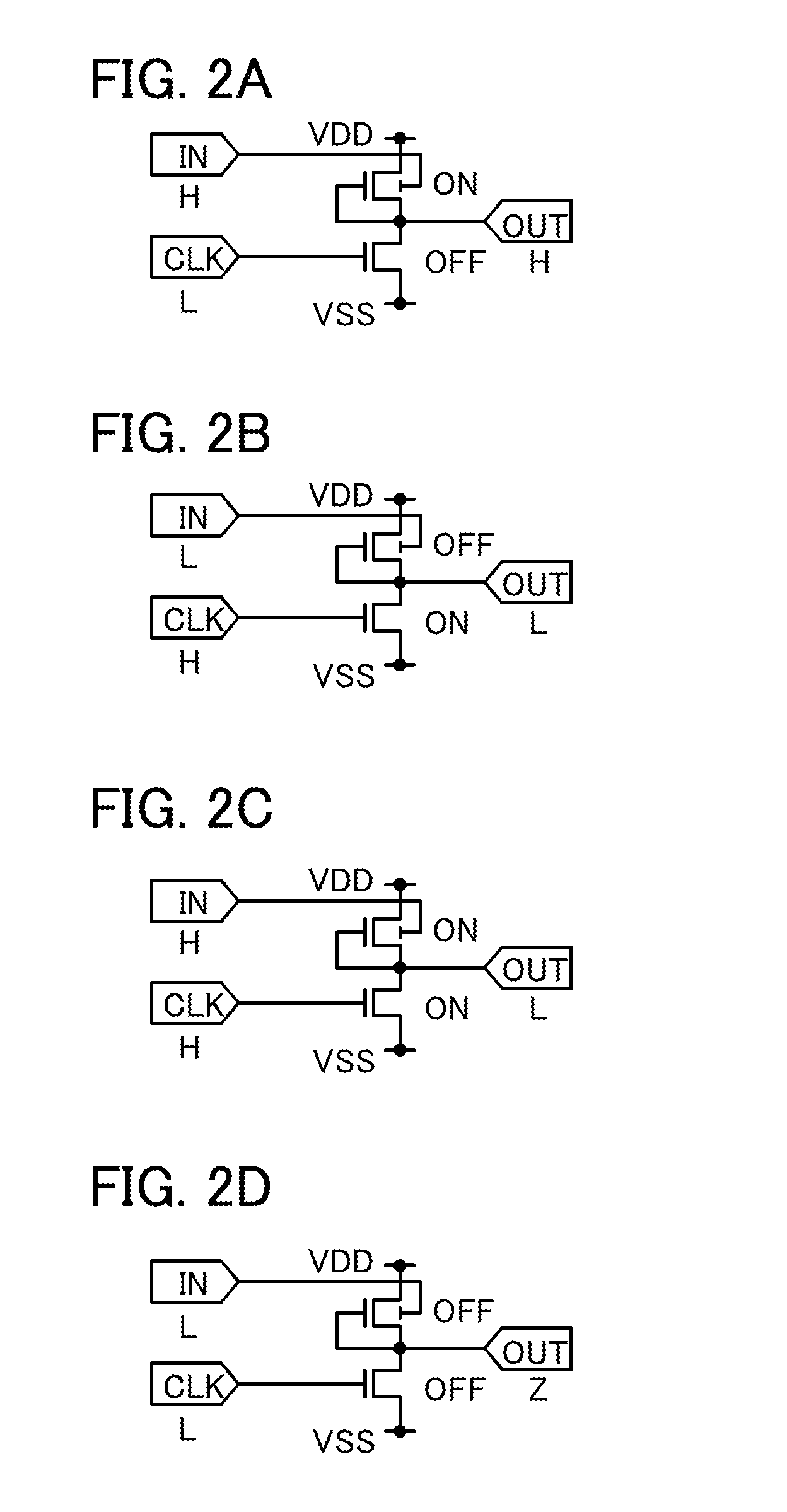

Semiconductor device

ActiveUS20130140617A1Decrease W/LRaise the gate potential of the transistor MTransistorStatic indicating devicesEngineeringCapacitor

A semiconductor device capable of high-speed operation. The semiconductor device includes a first transistor, a second transistor, and a capacitor. One of a source and a drain of the first transistor is supplied with a first signal. One of a source and a drain of the second transistor is supplied with a first potential. A gate of the second transistor is supplied with a second signal. A first electrode of the capacitor is electrically connected to the other of the source and the drain of the first transistor. A second electrode of the capacitor is electrically connected to the other of the source and the drain of the second transistor. In a first period, the first signal is low and the second signal is high. In a second period, the first signal is high and the second signal is either low or high.

Owner:SEMICON ENERGY LAB CO LTD

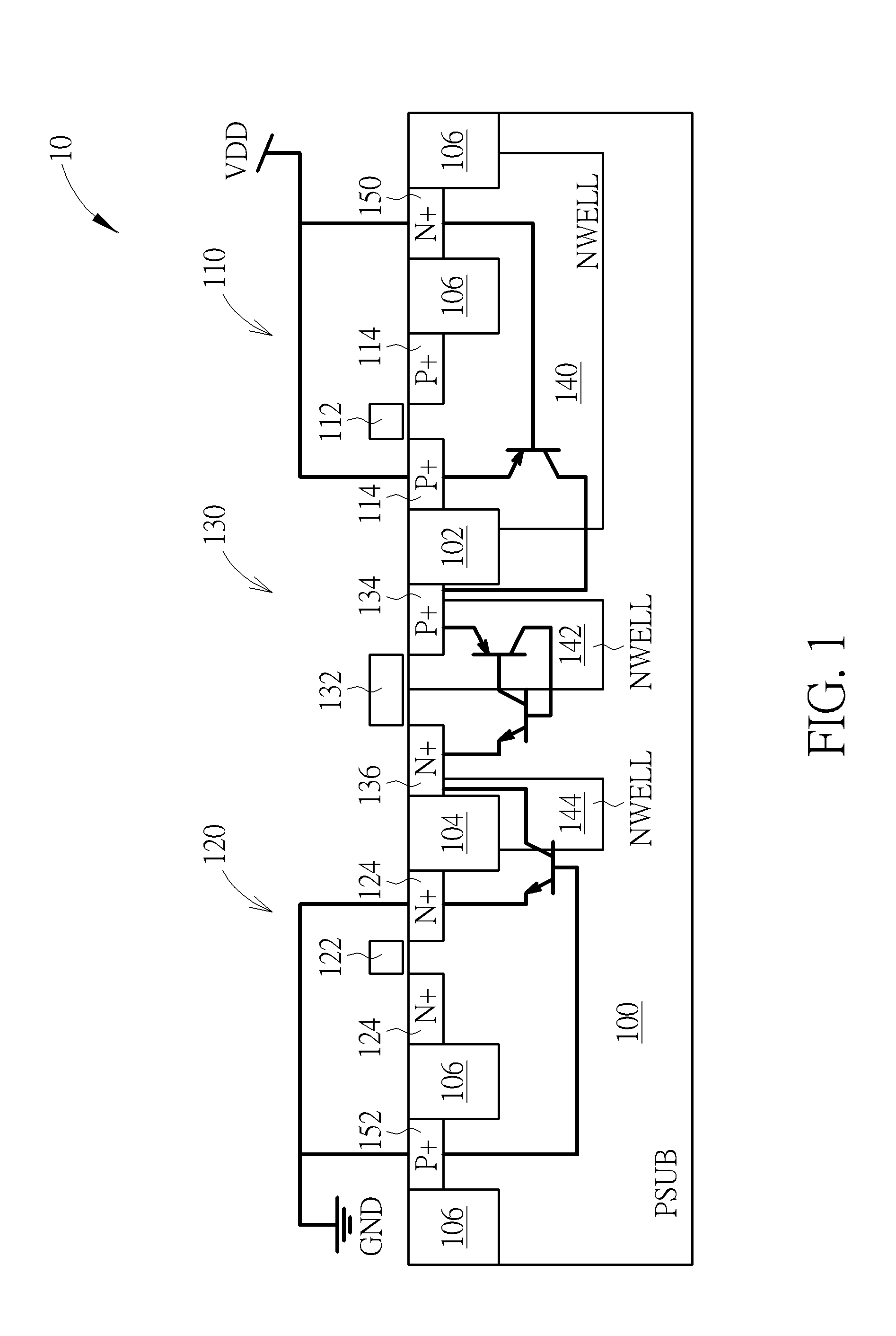

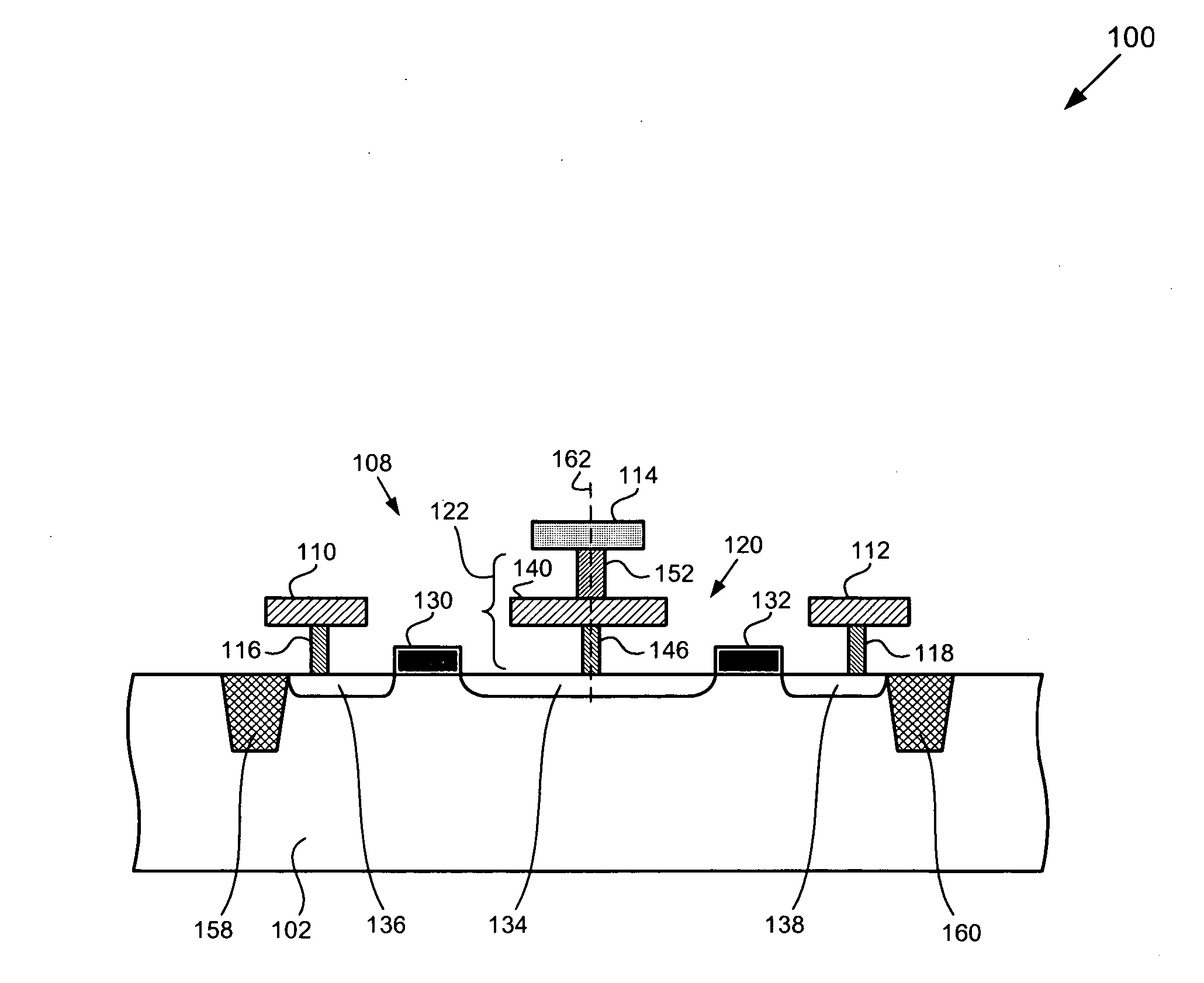

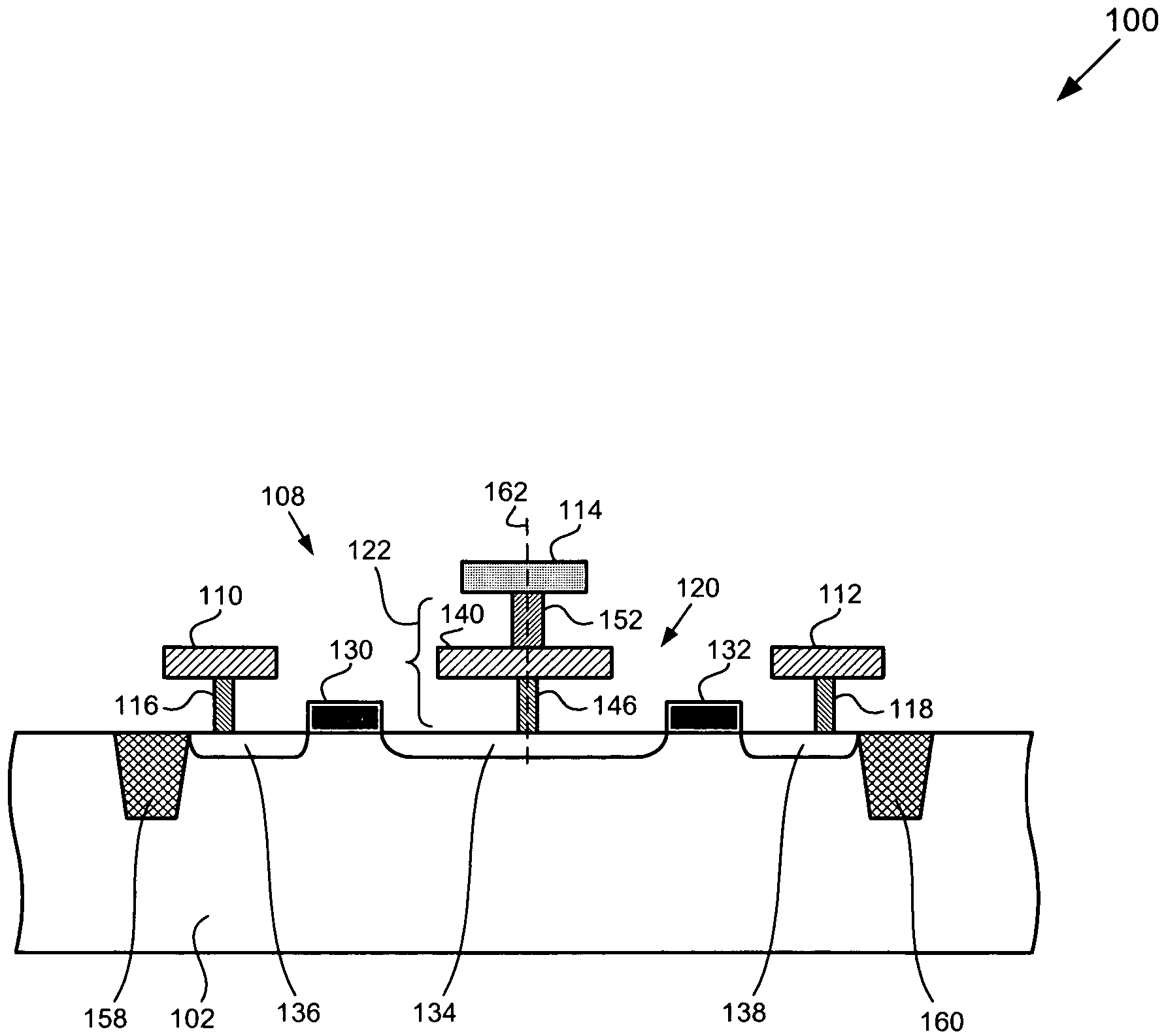

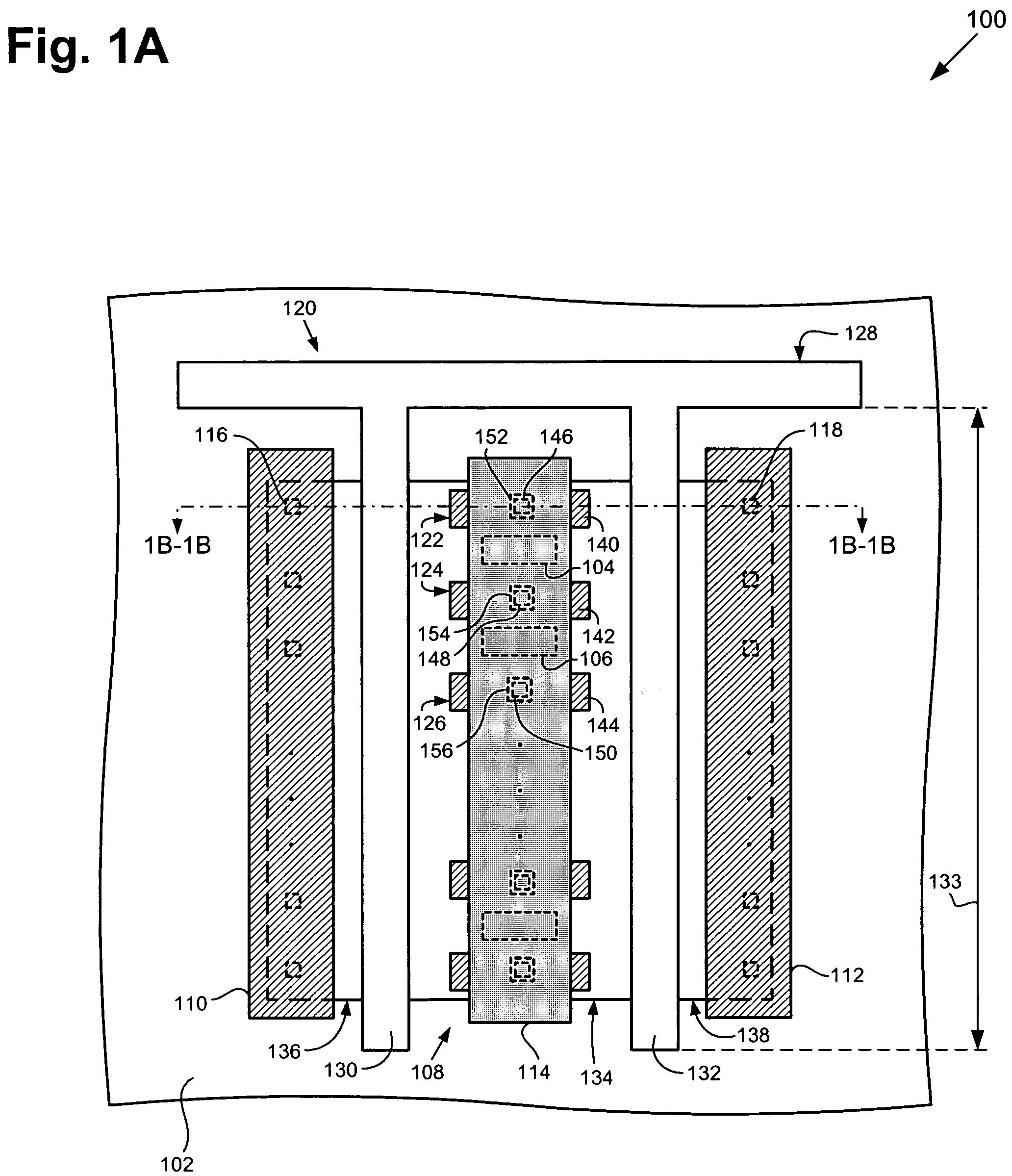

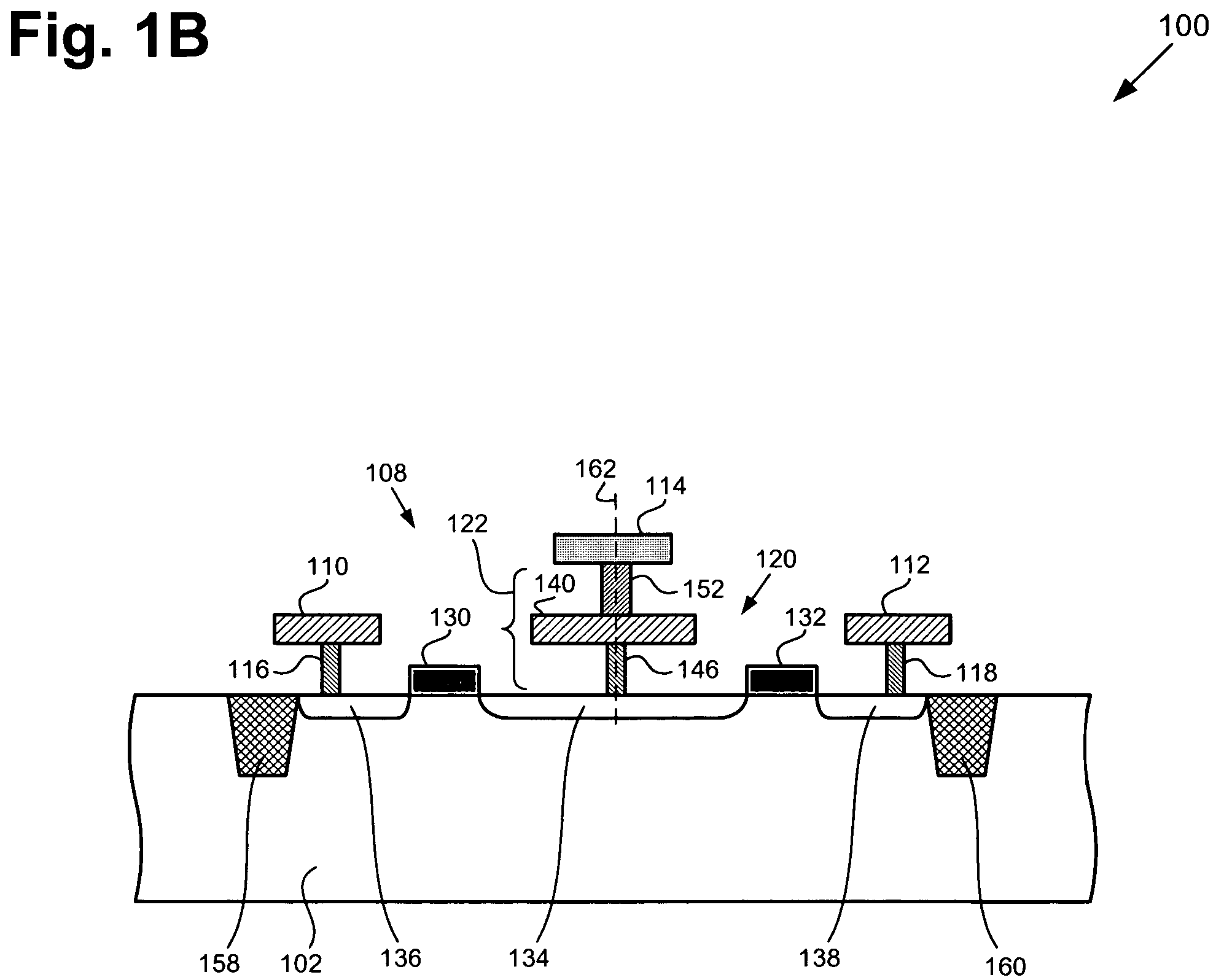

Complementary metal-oxide-semiconductor device

ActiveUS20150123184A1Increase holding voltageIncrease layout areaTransistorSemiconductor/solid-state device detailsCMOSEngineering

A CMOS device includes a substrate, a pMOS transistor and an nMOS transistor formed on the substrate, and a gated diode. The gated diode includes a floating gate formed on the substrate in between the pMOS transistor and the nMOS transistor and a pair of a p-doped region and an n-doped region formed in the substrate and between the pMOS transistor and the nMOS transistor. The n-doped region is formed between the floating gate and the nMOS transistor, and the p-doped region is formed between the floating gate and the pMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

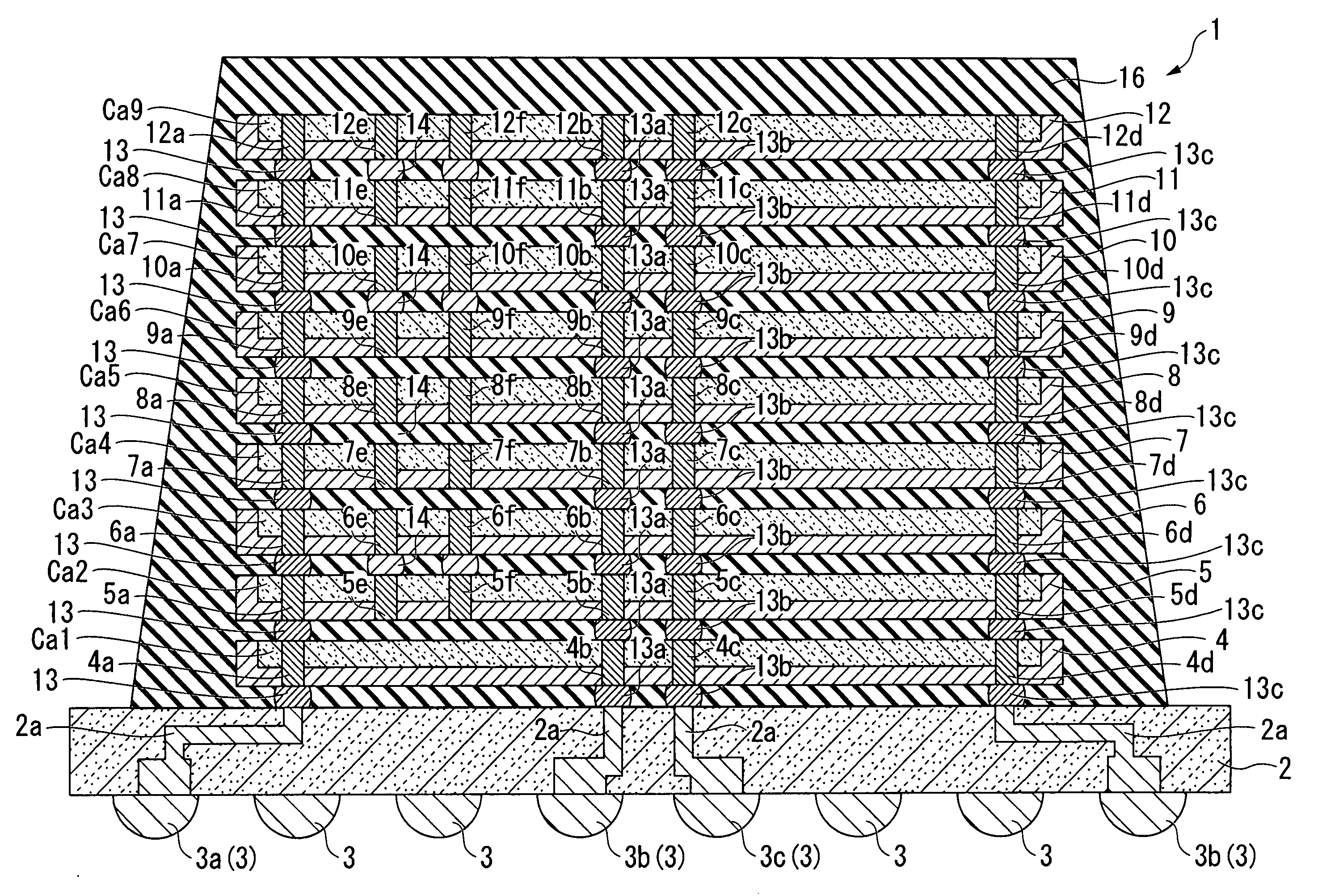

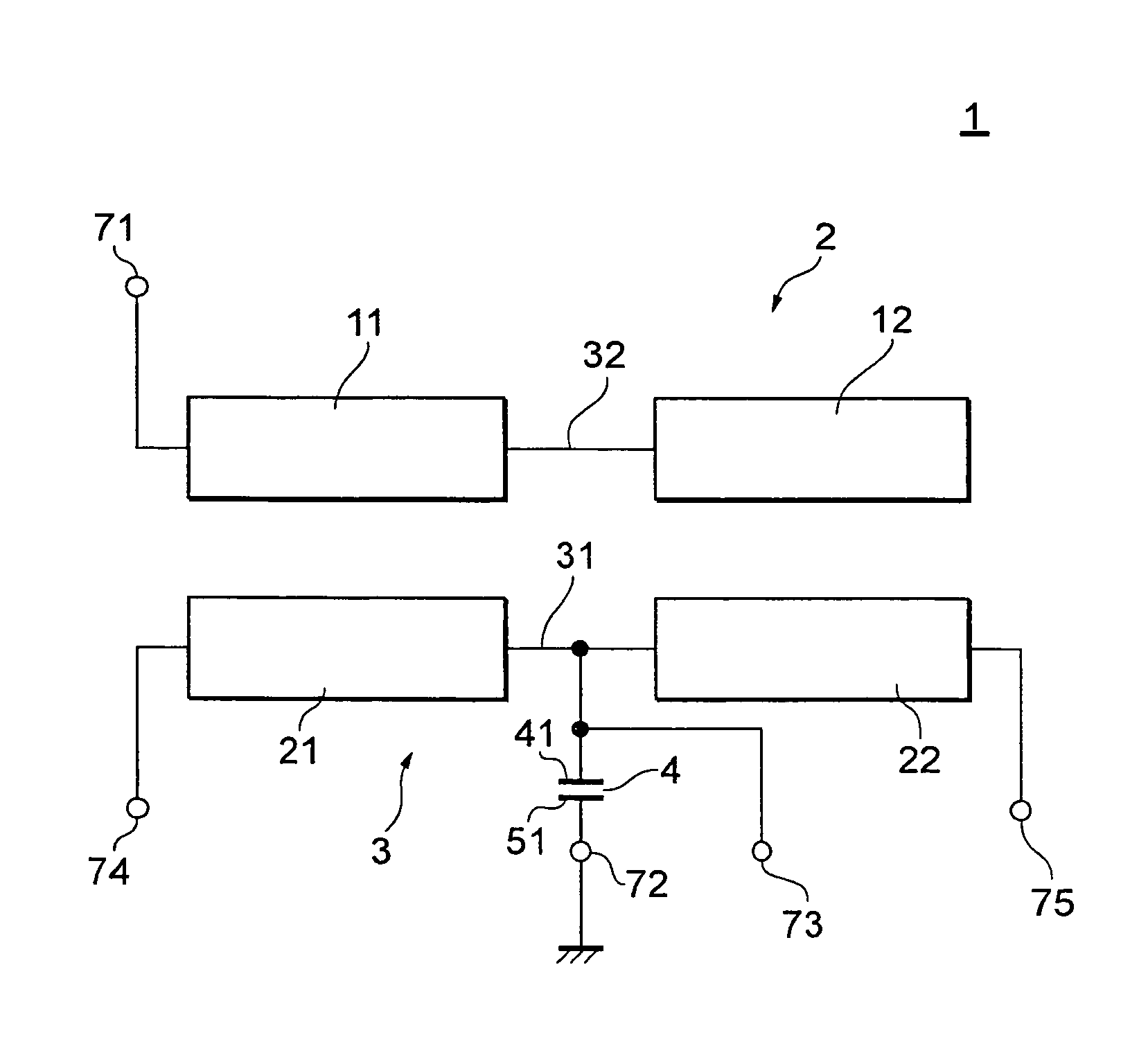

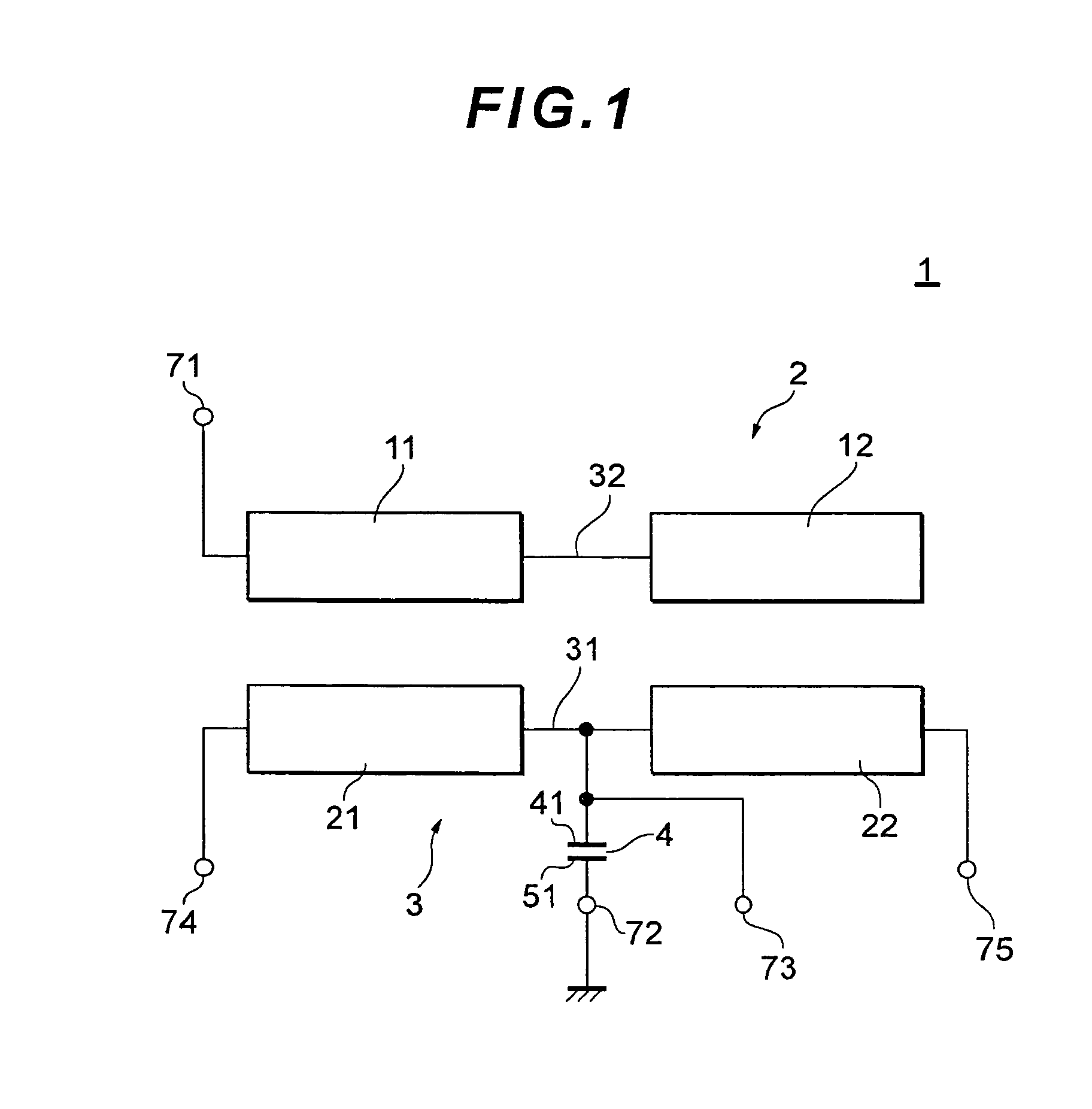

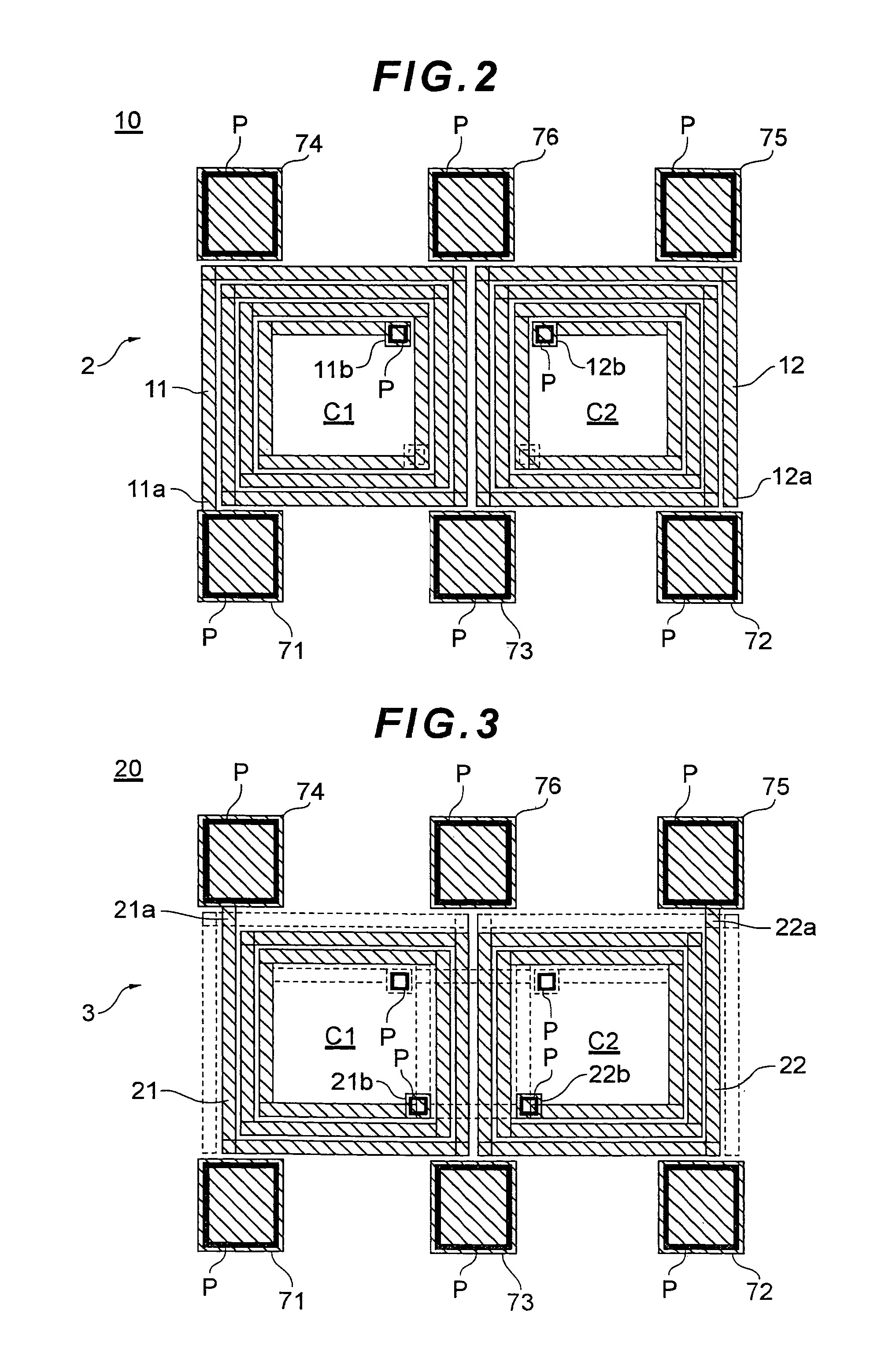

Semiconductor device

ActiveUS20090189293A1Increase layout areaHigh capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceChIP-on-chip

A semiconductor device having a chip-on-chip structure is constituted of a first semiconductor chip and even-numbered pairs of second semiconductor chips, all of which are laminated together on the surface of an interposer. The first semiconductor chip controls each pair of the second semiconductor chips so as to activate one second semiconductor chip while inactivating another second semiconductor chip. The second semiconductor chips are paired together in such a way that through-vias and electrodes thereof are positioned opposite to each other via bumps. Since drive voltage electrodes supplied with a drive voltage (VDD) and reference potential electrodes supplied with a reference potential (VSS) are mutually connected together between the paired second semiconductor chips, it is possible to increase the overall electrostatic capacitance of each second semiconductor chip so as to substantially reduce feed noise without increasing the overall layout area of the semiconductor device.

Owner:LONGITUDE LICENSING LTD

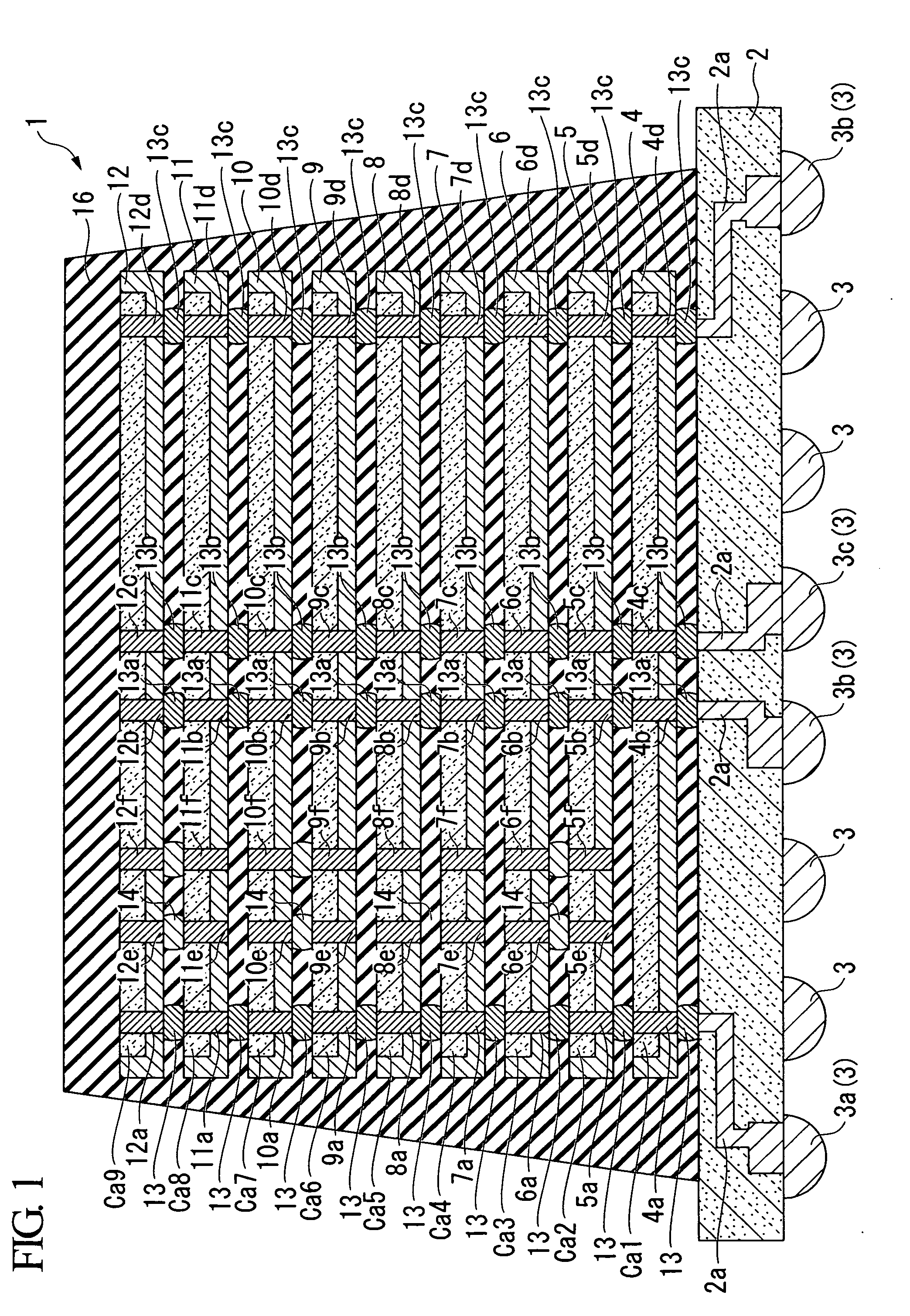

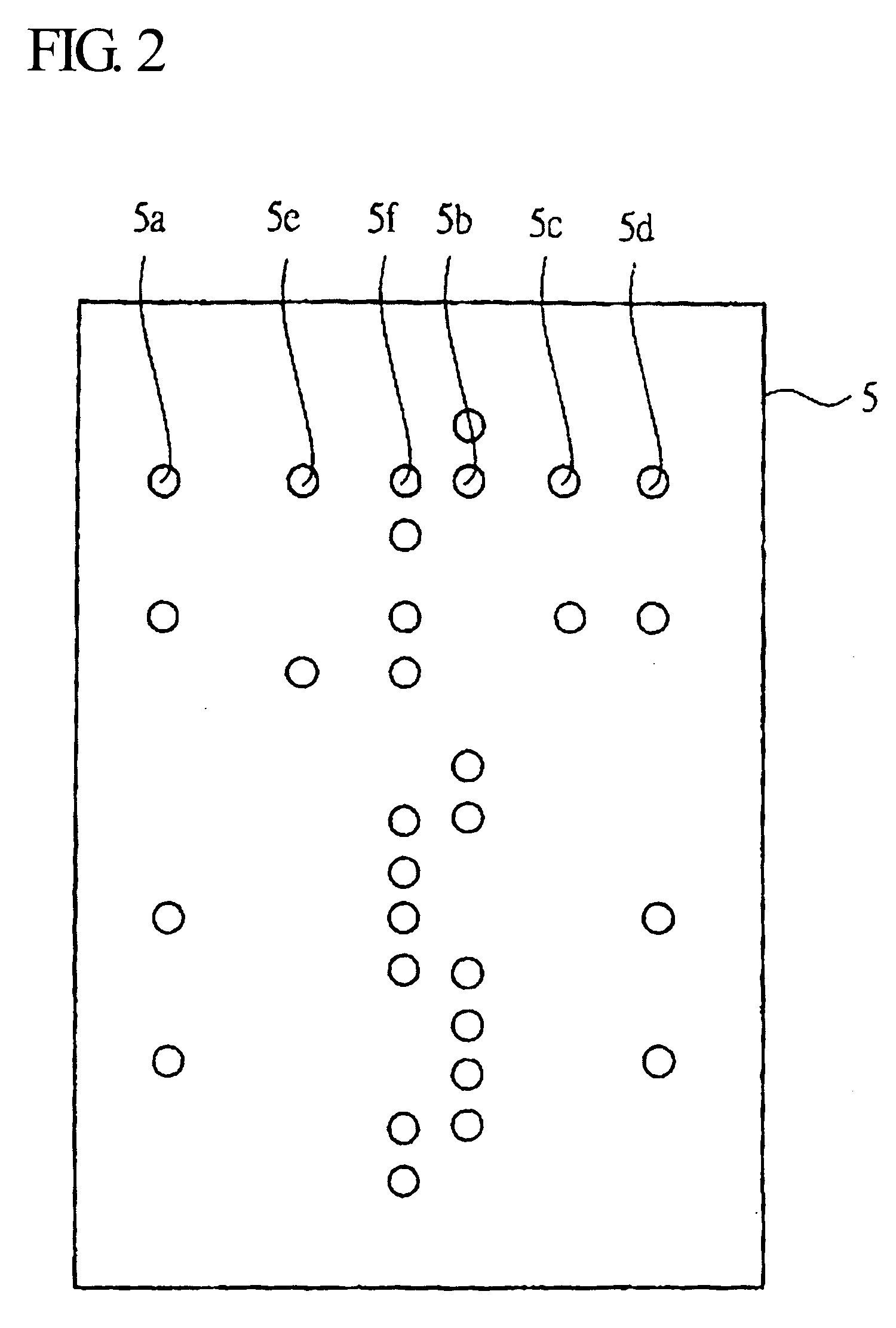

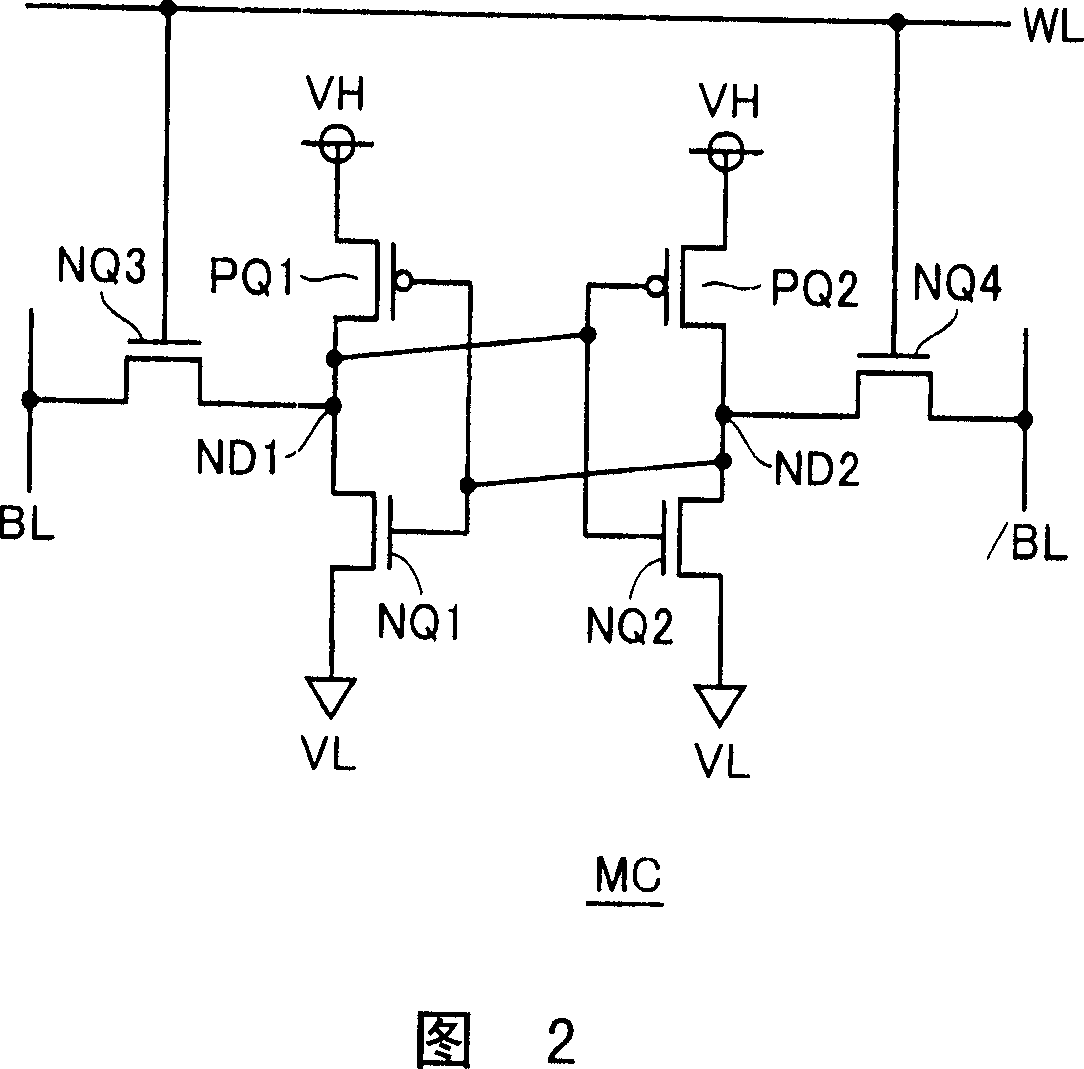

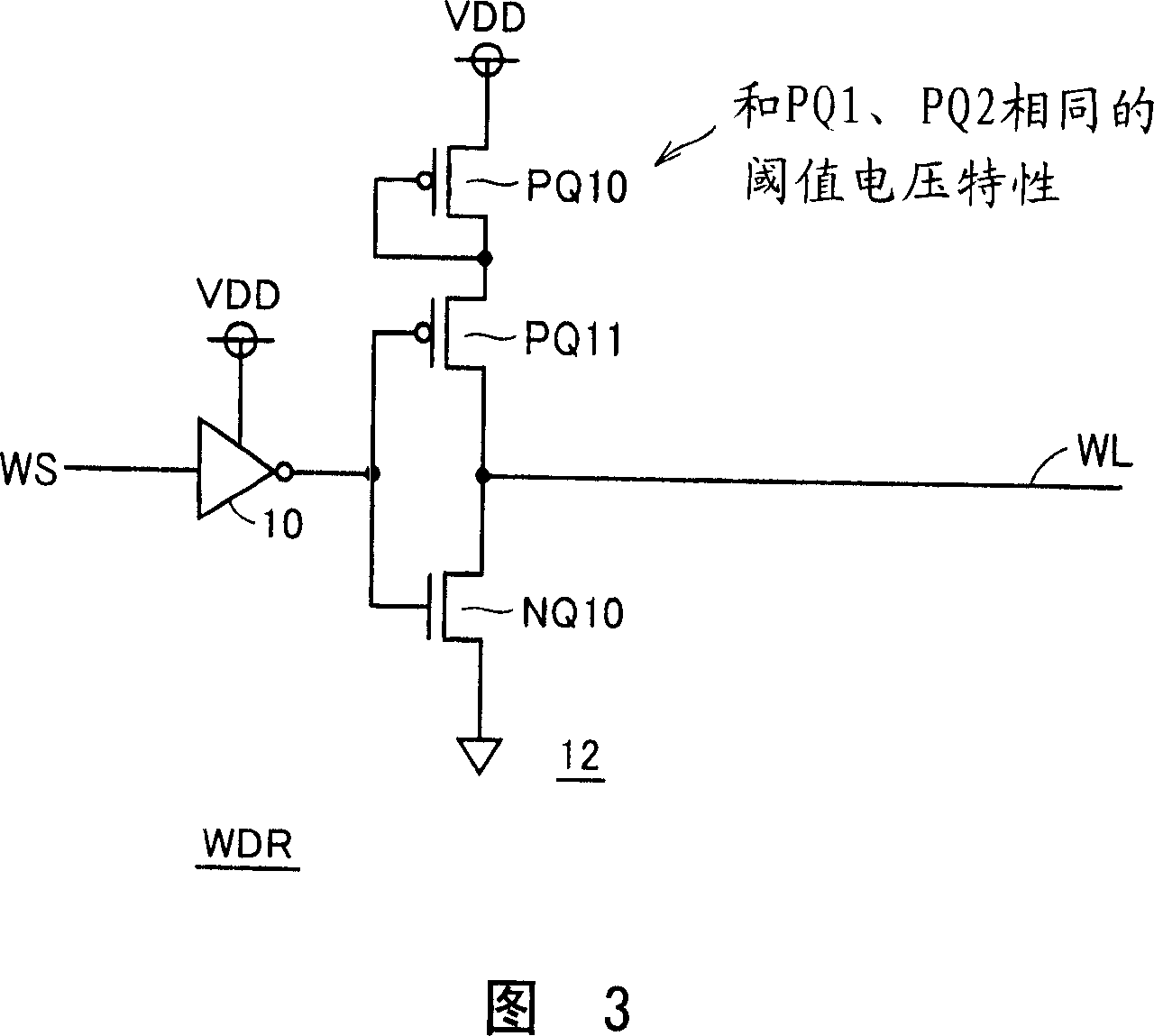

Semiconductor storage device

InactiveCN1956098ASimple structureIncrease layout areaDigital storageSemiconductor storage devicesSemiconductor

A level shift element adjusting a voltage level at the time of selection of a word line according to fluctuations in threshold voltage of a memory cell transistor is arranged for each word line. This level shift element lowers a driver power supply voltage, and transmits the level-shifted voltage onto a selected word line. The level shift element can be replaced with a pull-down element for pulling down the word line voltage according to the threshold voltage level of the memory cell transistor. In either case, the selected word line voltage level can be adjusted according to the fluctuations in threshold voltage of the memory cell transistor without using another power supply system. Thus, the power supply circuitry is not complicated, and it is possible to achieve a semiconductor memory device that can stably read and write data even with a low power supply voltage.

Owner:RENESAS TECH CORP

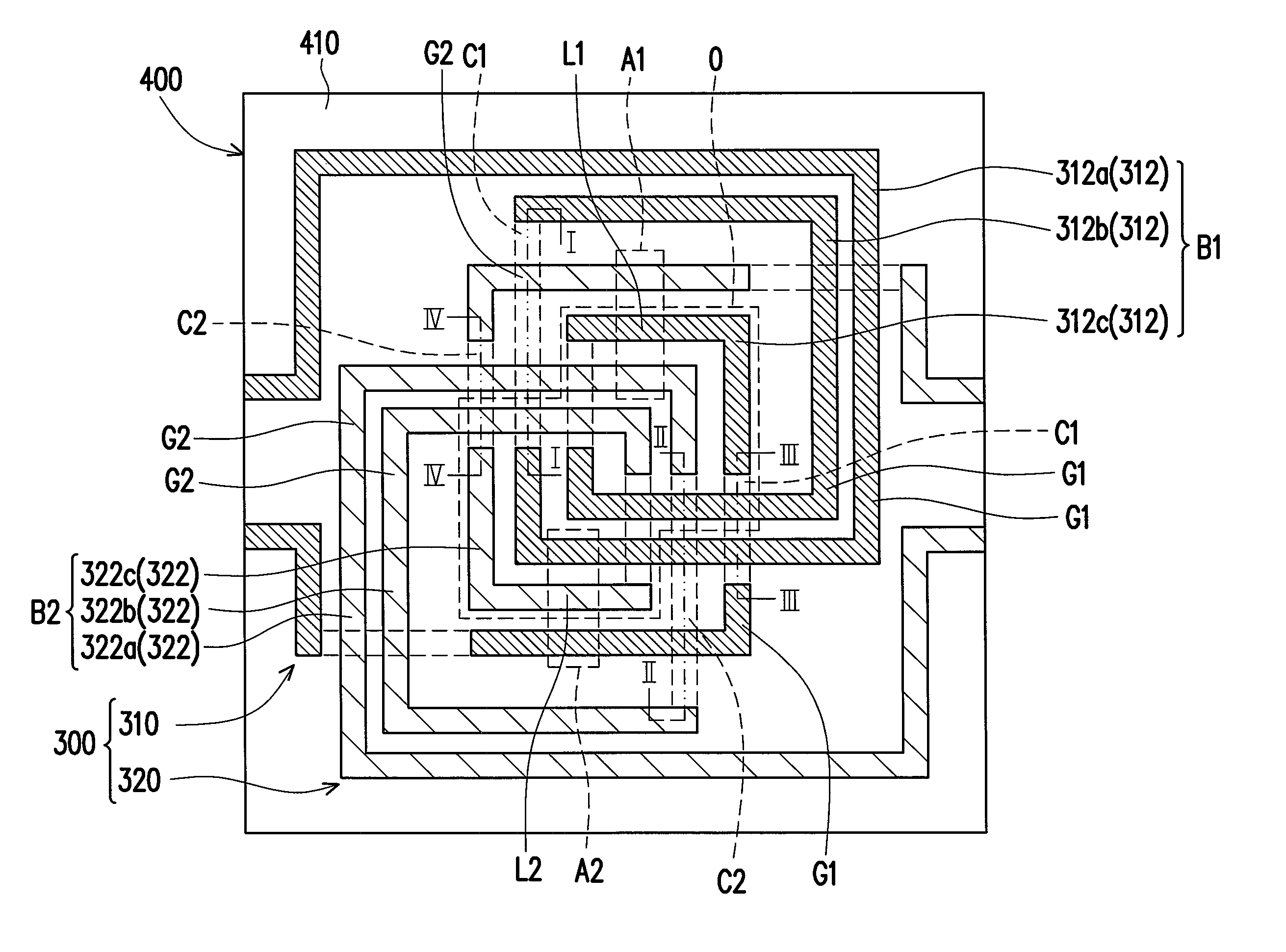

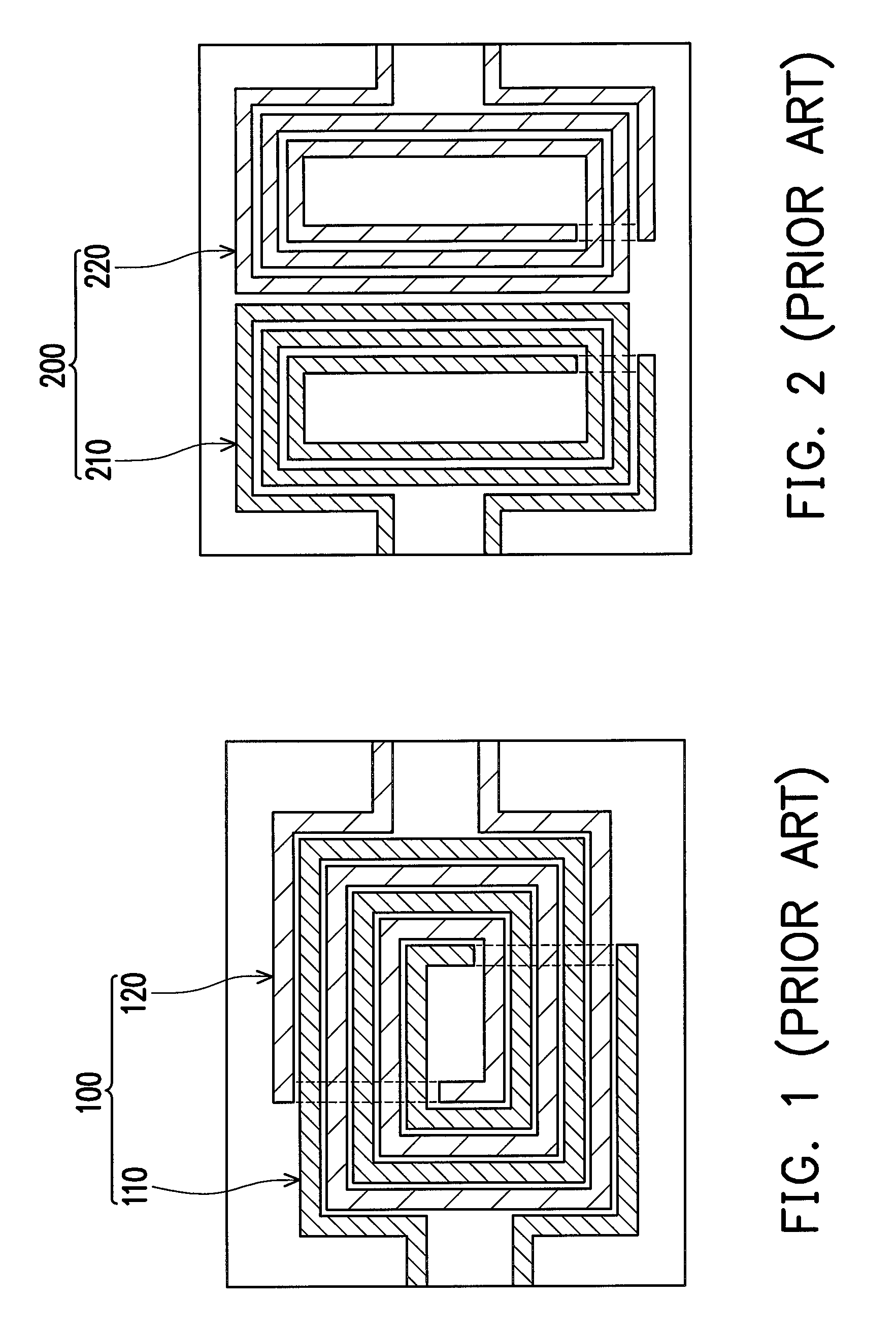

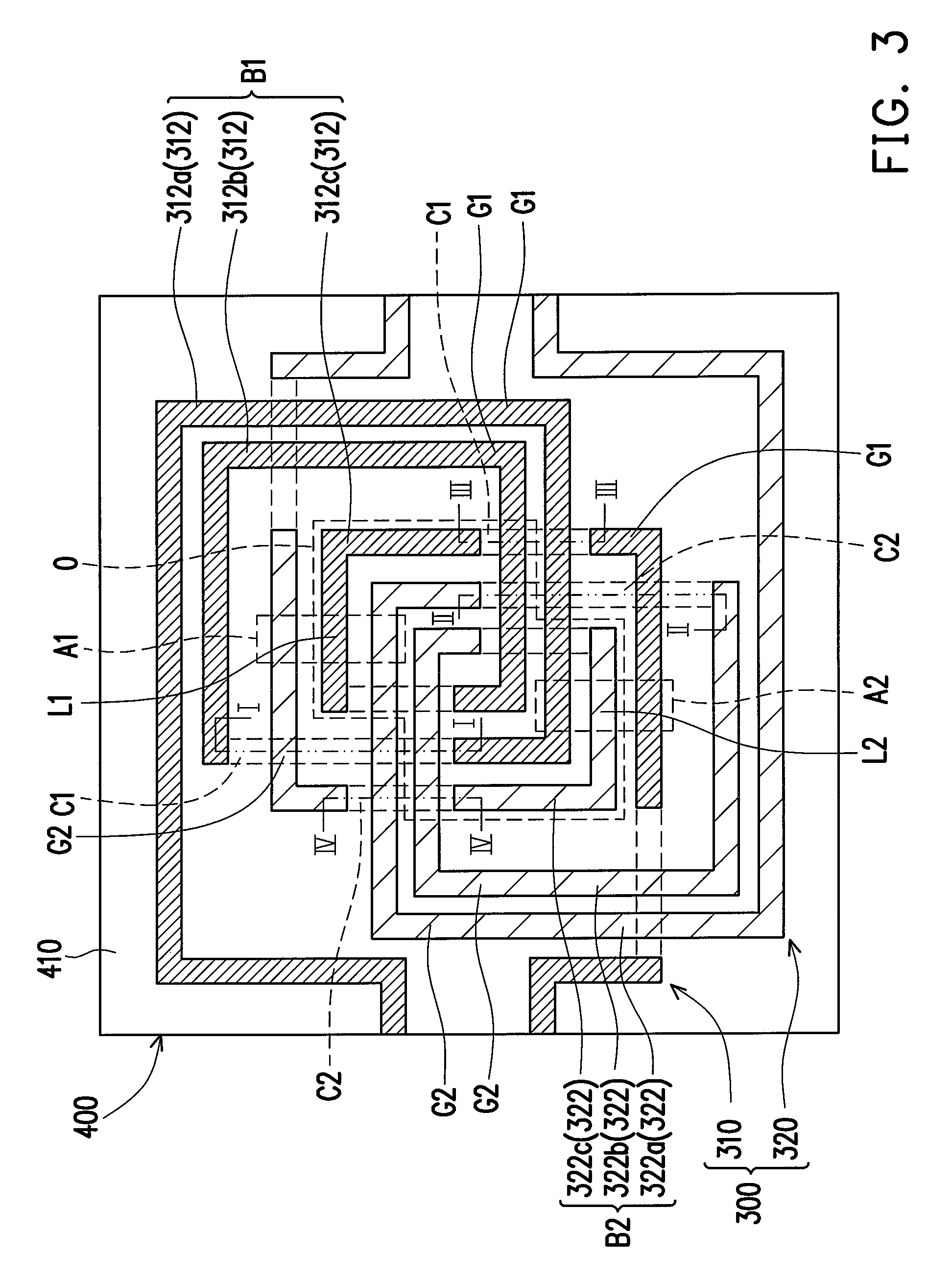

Transformer

ActiveUS7924135B2Improve design flexibilityIncrease layout areaTransformers/inductances coils/windings/connectionsElectromagnetsTransformerElectrical and Electronics engineering

Owner:ADVANCED SEMICON ENG INC

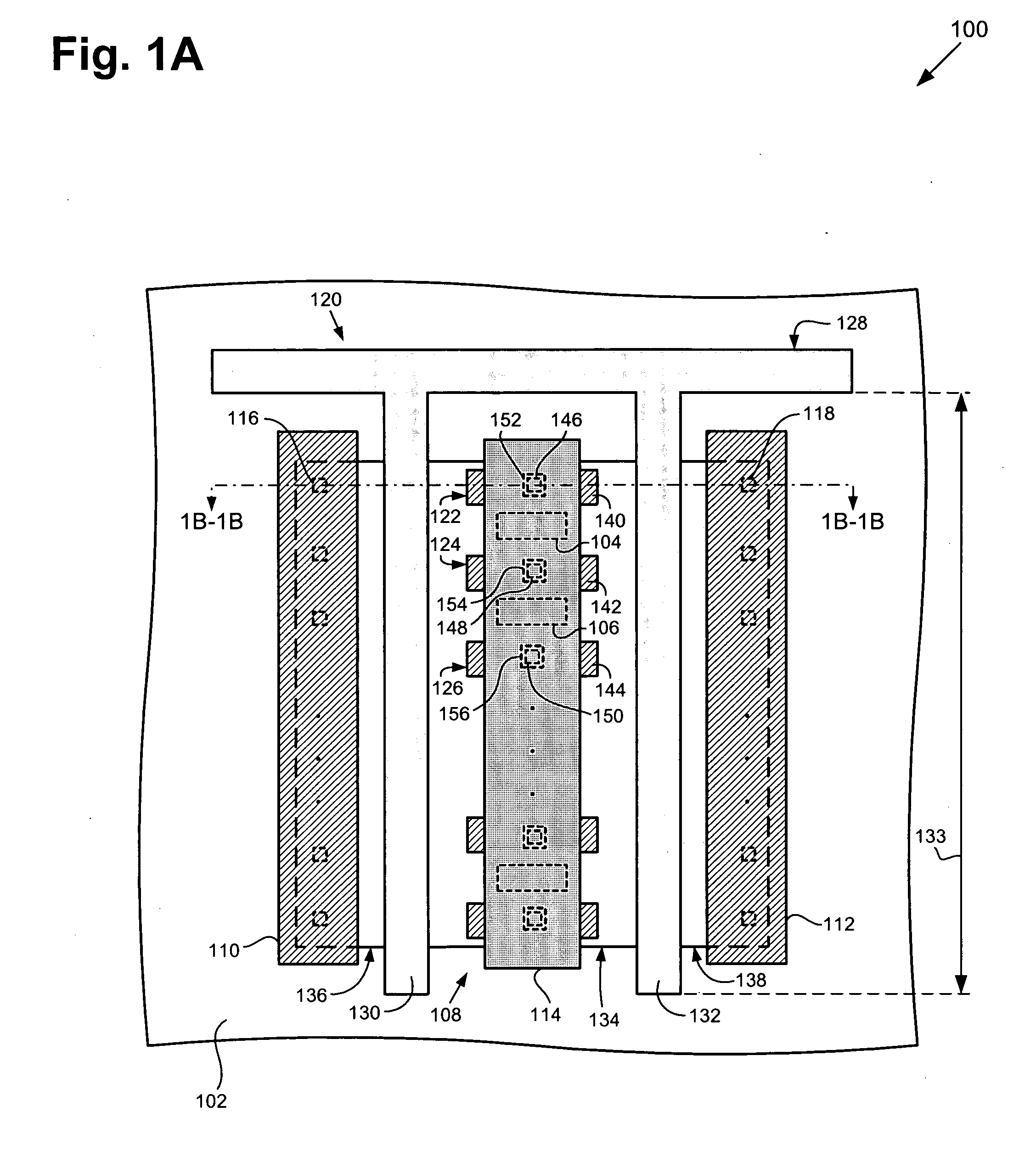

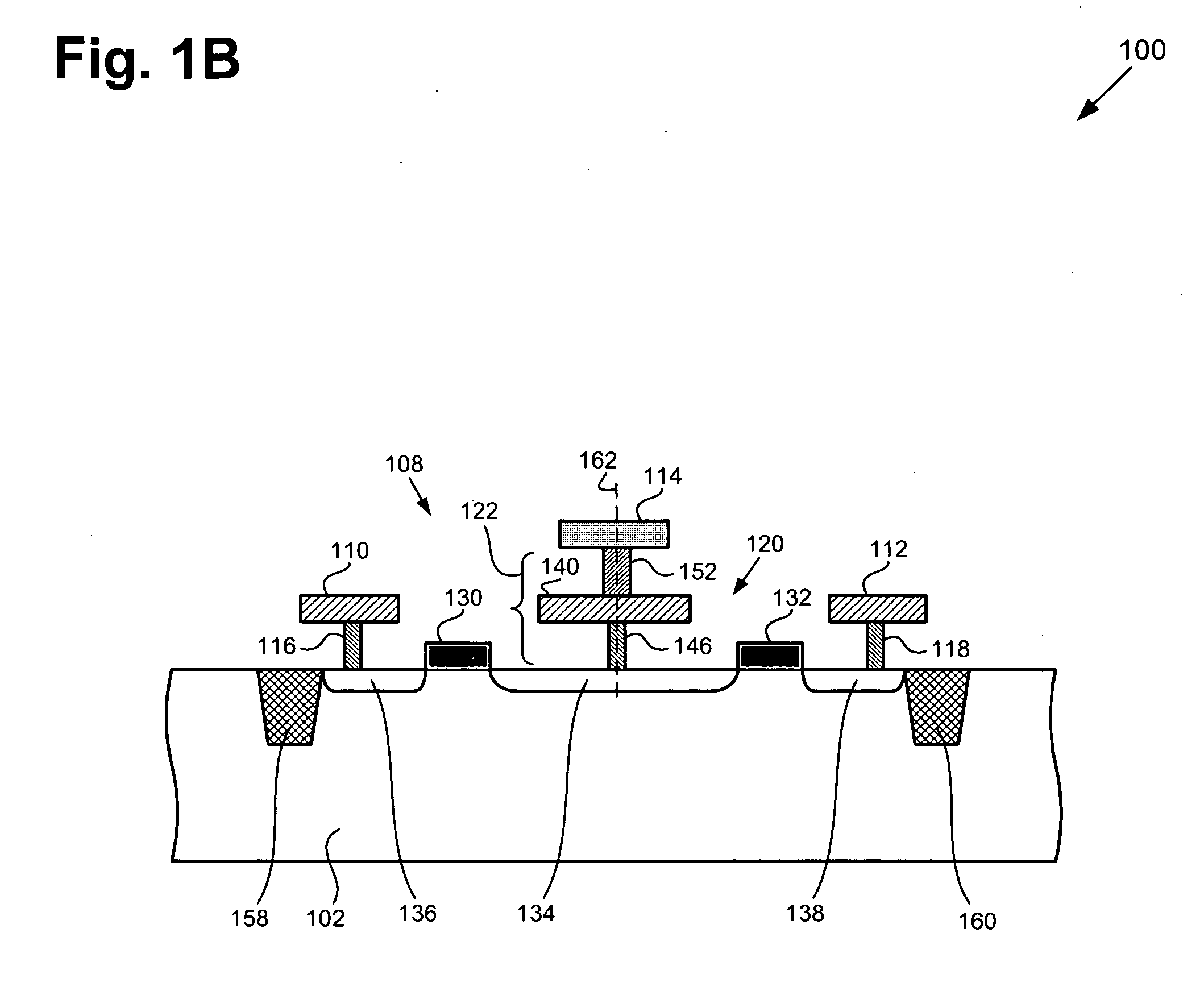

ESD protection structure using contact-via chains as ballast resistors

ActiveUS20070034960A1Increased ESD current distribution uniformityIncrease layout areaTransistorSemiconductor/solid-state device detailsBallast resistorCurrent distribution

According to an exemplary embodiment, an ESD protection structure situated in a semiconductor die includes a FET including a gate and first and second active regions, where the gate includes at least one gate finger, and where the at least one gate finger is situated between the first and second active regions. The ESD protection structure further includes at least one contact-via chain connected to the first active region, where the at least one contact-via chain includes a contact connected to a via. The at least one contact-via chain forms a ballast resistor for increased ESD current distribution uniformity. The contact is connected to the via by a first metal segment situated in a first interconnect metal layer of a die. The at least one contact-via chain is connected between the first active region and a second metal segment situated in a second interconnect metal layer of the die.

Owner:SKYWORKS SOLUTIONS INC

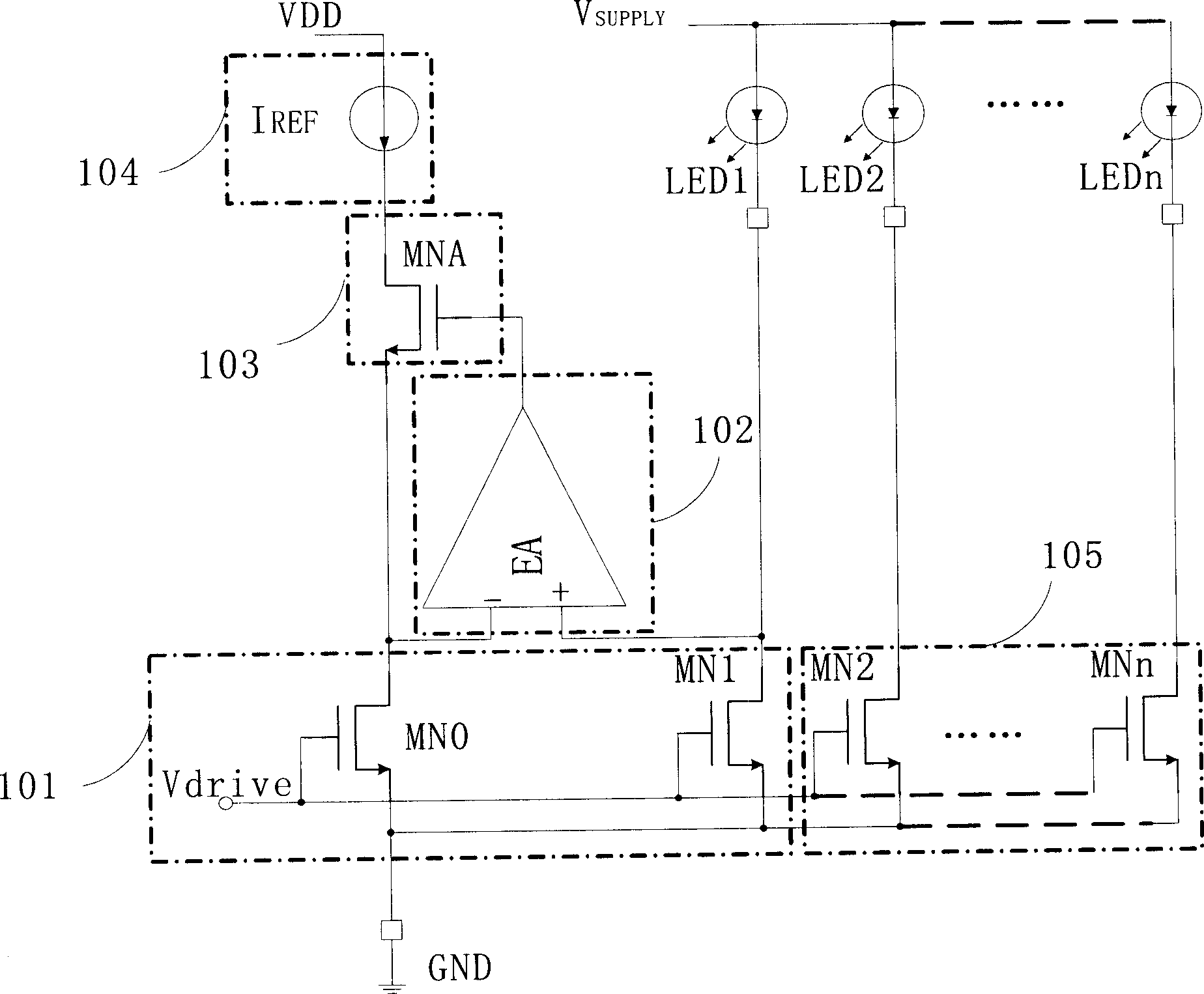

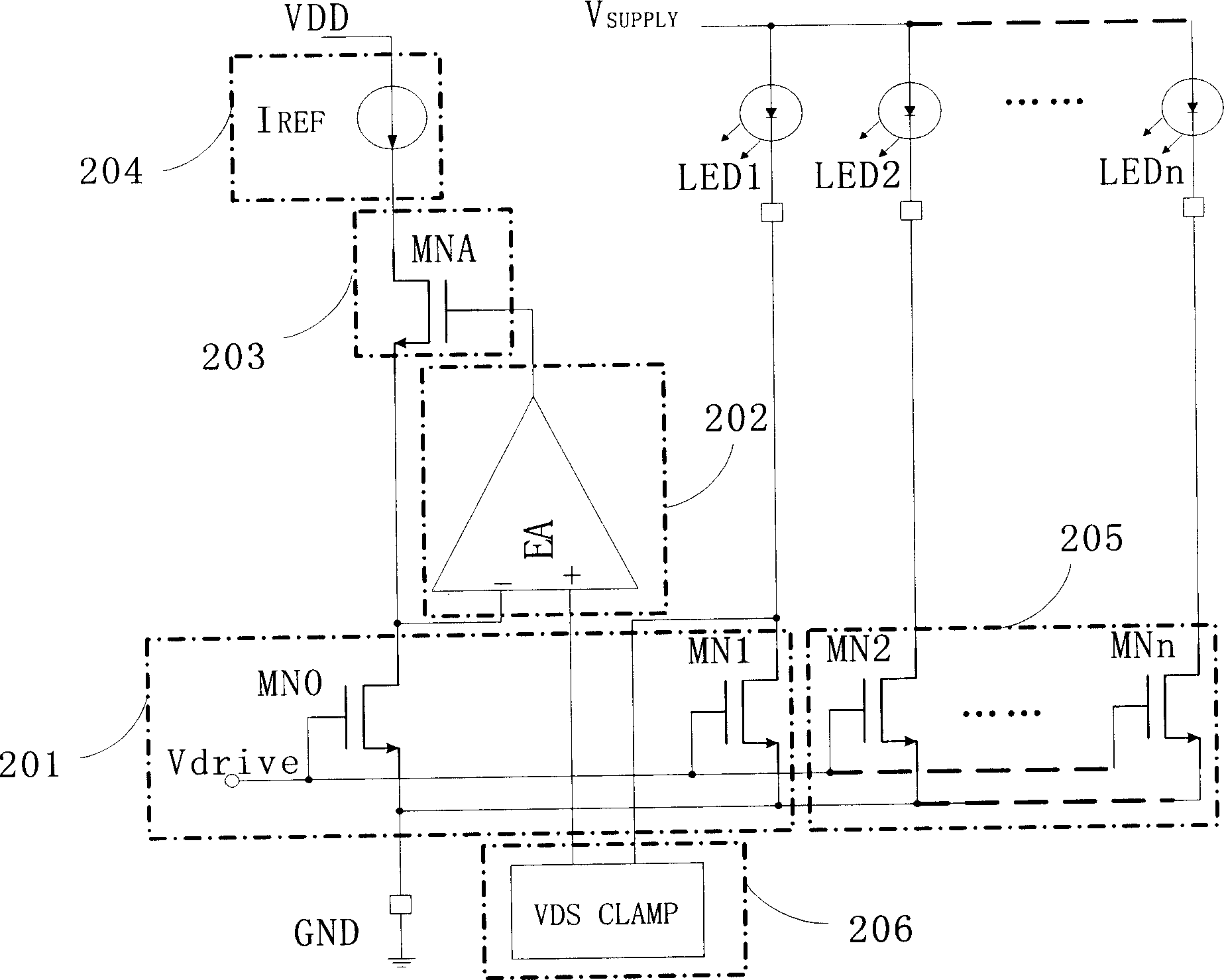

Current source circuit of multiplex parallel LED driven by one reference current

InactiveCN1913736AGood current matchingImprove work efficiencyElectrical apparatusElectric lighting sourcesWilson current mirrorReference current

A current source circuit for the multi-parallel circuited LED driven by a single reference current including: a current mirror, a error amplifier, a regulator tube, a reference current, other multi-driving tubes and VDS clamp circuit. The characteristic is that: the VDS clamp circuit respectively connects with the drain-leakage end of the MN1 and the input of the error amplifier. The current mirror and the grid terminals of other multi-driving tubes are driven by a common Vdrive signal. During the normal working hours, the MN0 and MN1 drain-leakage end voltages of the MOS tube keep consistent under the effects of the error amplifier and the regulator tubes, the other driving tubes and MN1 can obtain a good current-matching even there is a small difference between the drain-leakage end voltages. During the abnormal working hours, the VDS clamp circuit can provide an appropriate bias voltage to make sure that the other driving tubes do not guide a high current and keep the LED in a normal state regardless of the leakage of MN1.

Owner:CHIPHOMER TECH SHANGHAI

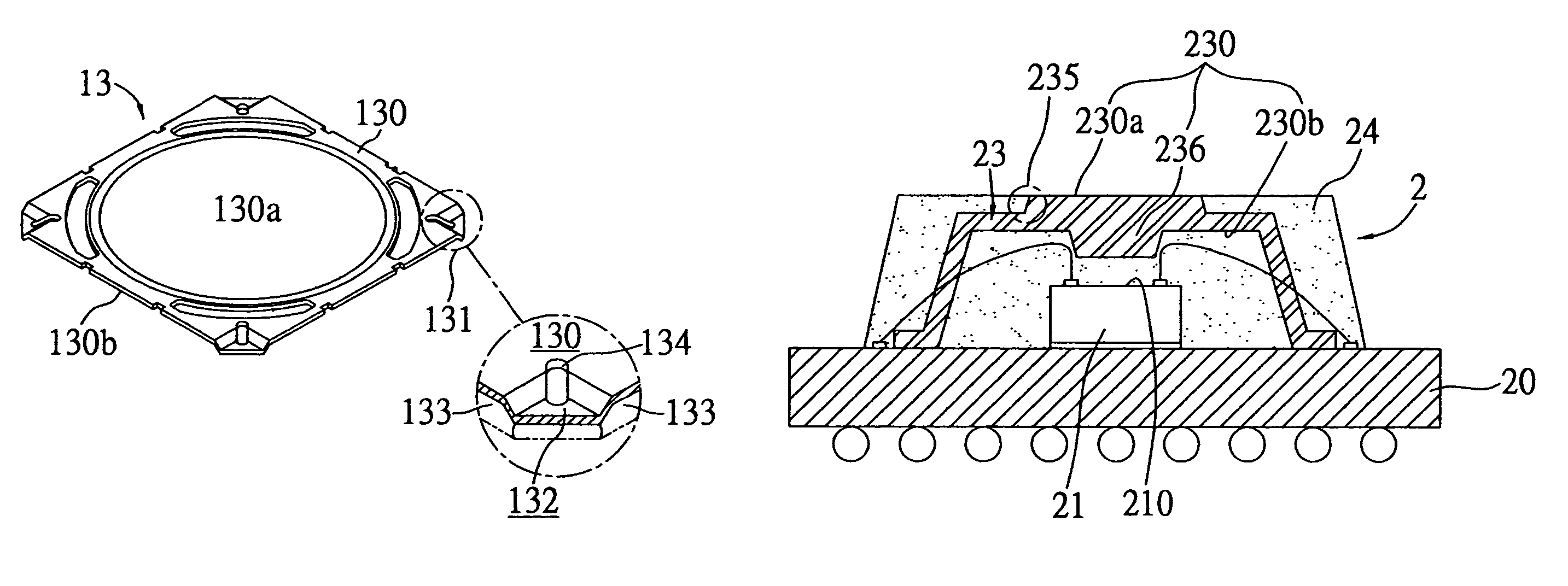

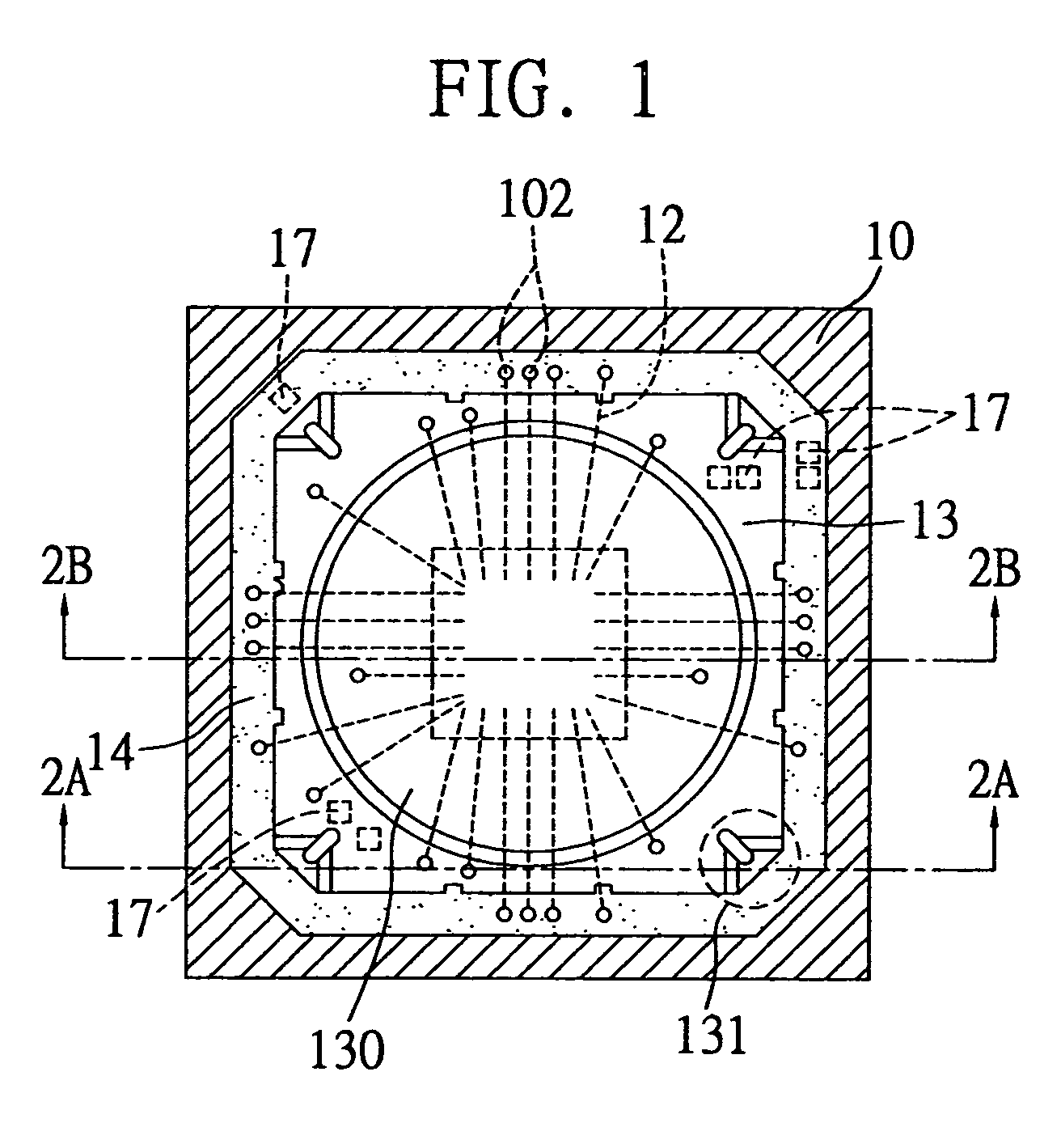

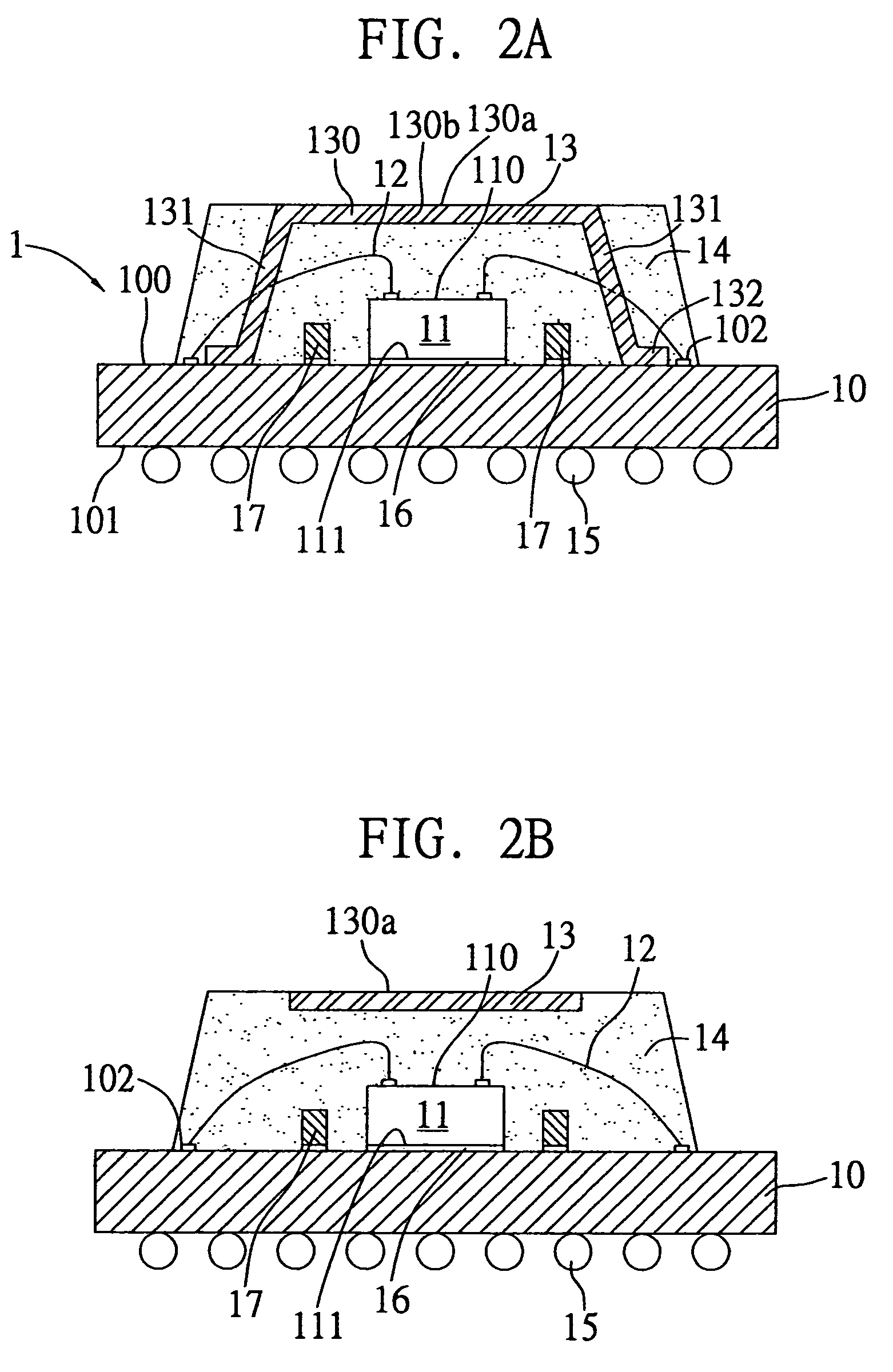

Semiconductor package with heat dissipating structure

InactiveUS7342304B2Increase flexibilityIncrease layout areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package with a heat dissipating structure is provided. The heat dissipating structure includes a flat portion, and a plurality of support portions formed at edge corners of the flat portion for supporting the flat portion above a chip mounted on a substrate. The support portions are mounted at predetermined area on the substrate without interfering with arrangement of the chip and bonding wires that electrically connect the chip to the substrate. The support portions are arranged to form a space embraced by adjacent supports and the flat portion, so as to allow the bonding wires to pass through the space to reach area on the substrate outside coverage of the heat dissipating structure; besides, passive components or other electronic components can be mounted on the substrate at area within or outside the coverage of the heat dissipating structure, thereby improving flexibility in component arrangement in the semiconductor package.

Owner:SILICONWARE PRECISION IND CO LTD

ESD protection structure using contact-via chains as ballast resistors

ActiveUS7397089B2Increase layout areaWithout degrading high-frequency performanceTransistorSemiconductor/solid-state device detailsBallast resistorCurrent distribution

According to an exemplary embodiment, an ESD protection structure situated in a semiconductor die includes a FET including a gate and first and second active regions, where the gate includes at least one gate finger, and where the at least one gate finger is situated between the first and second active regions. The ESD protection structure further includes at least one contact-via chain connected to the first active region, where the at least one contact-via chain includes a contact connected to a via. The at least one contact-via chain forms a ballast resistor for increased ESD current distribution uniformity. The contact is connected to the via by a first metal segment situated in a first interconnect metal layer of a die. The at least one contact-via chain is connected between the first active region and a second metal segment situated in a second interconnect metal layer of the die.

Owner:SKYWORKS SOLUTIONS INC

Semiconductor memory device

The present invention provides a semiconductor memory device in which the number of write amplifiers is decreased by increasing the number of bit line pairs connected to one pair of common write data lines. Further, by decreasing the number of bit line pairs connected to one pair of common read data lines, parasitic capacitance connected to the pair of common read data lines is reduced and, accordingly, time in which the potential difference between the pair of common read data lines increases is shortened. Thus, while preventing enlargement of the chip layout area, read time can be shortened.

Owner:RENESAS ELECTRONICS CORP

Touch control display panel and touch control display device

ActiveCN104182101AIncrease layout areaHigh sensitivityInput/output processes for data processingEngineeringElectrical and Electronics engineering

The invention relates to a touch control display panel, which comprises a substrate, a light shielding matrix layer and a sensing circuit, wherein the sensing circuit is positioned on one side surface of the substrate to form a single layer structure, is positioned in a vertical projection part of the light shielding matrix layer and comprises a plurality of driving electrodes, a plurality of sensing electrodes and a plurality of conducting wires, in addition, the driving electrodes and the sensing electrodes are mutually insulated and separated, and the conducting wires are respectively connected with each driving electrode and each sensing electrode, wherein the sensing electrodes, the driving electrodes and the conducting wires are all positioned in the single layer. The invention also discloses a touch control display device. The touch control display panel and the touch control display device provided by the invention have the advantages that under the condition of not increasing the light transmission loss, the distribution area of the sensing circuit can be increased, so that the goals of improving the sensitivity of the touch control display panel and the touch control display device, reducing the integral resistance-capacitance load and improving the integral efficiency are achieved.

Owner:INNOLUX CORP

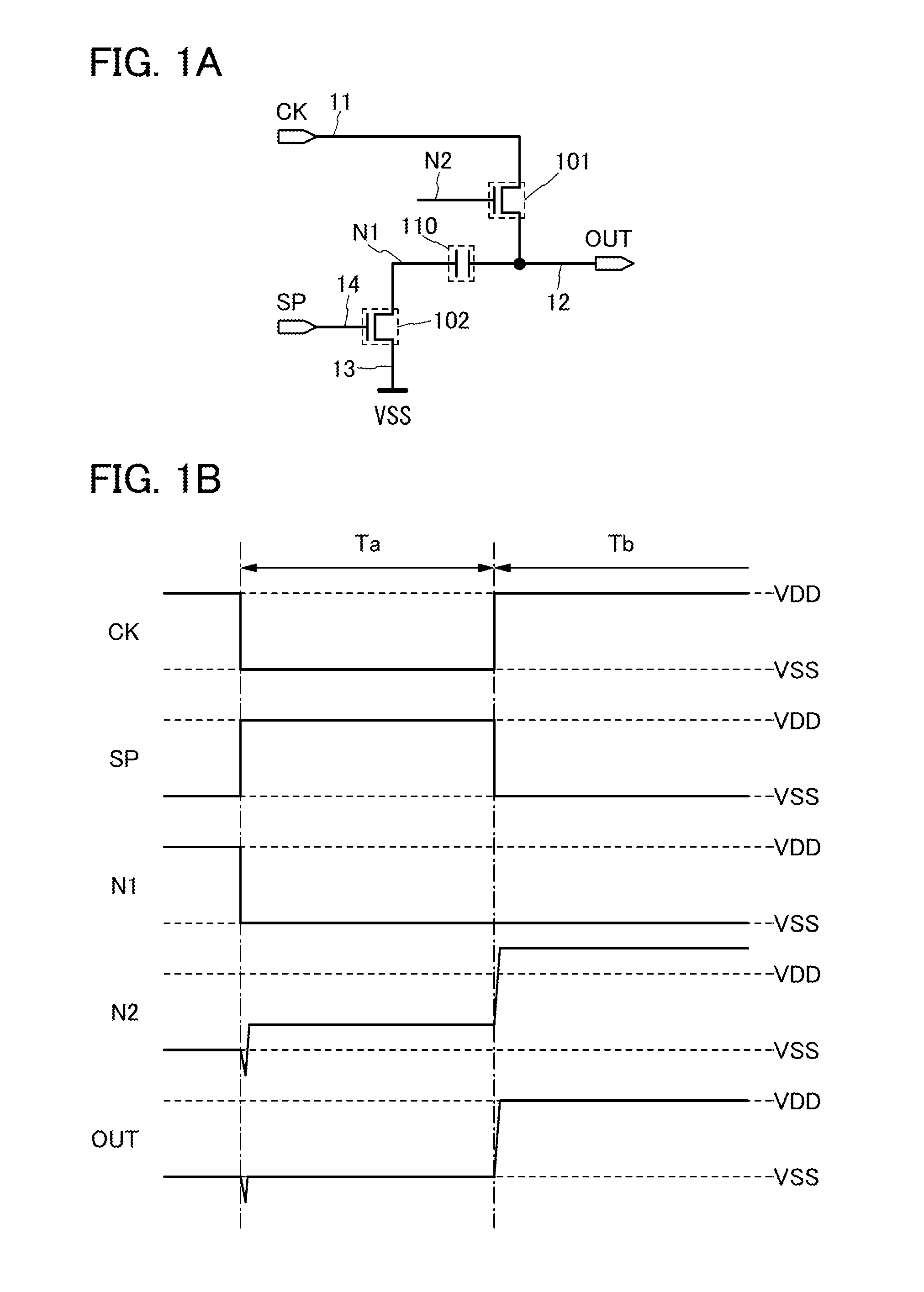

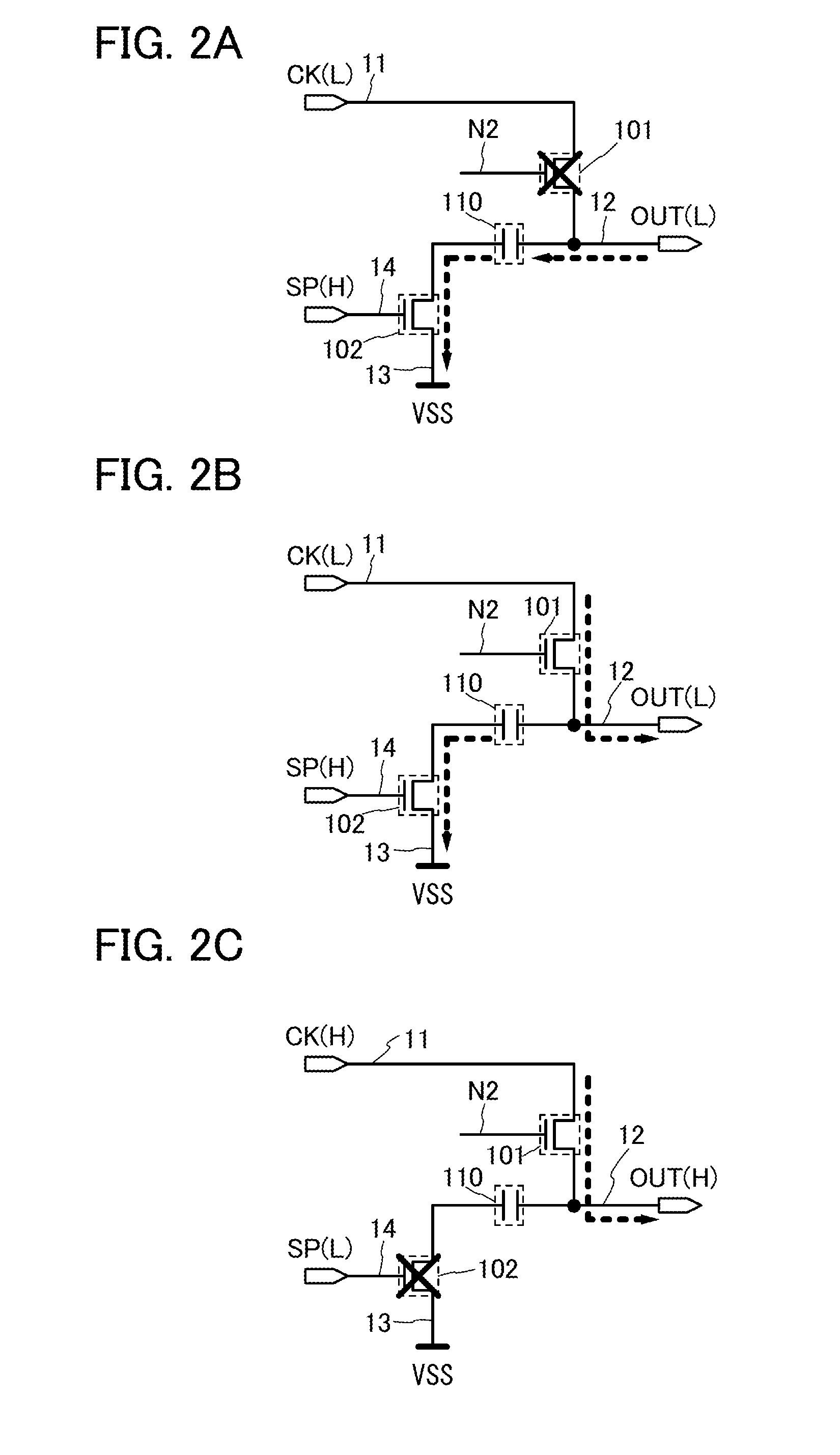

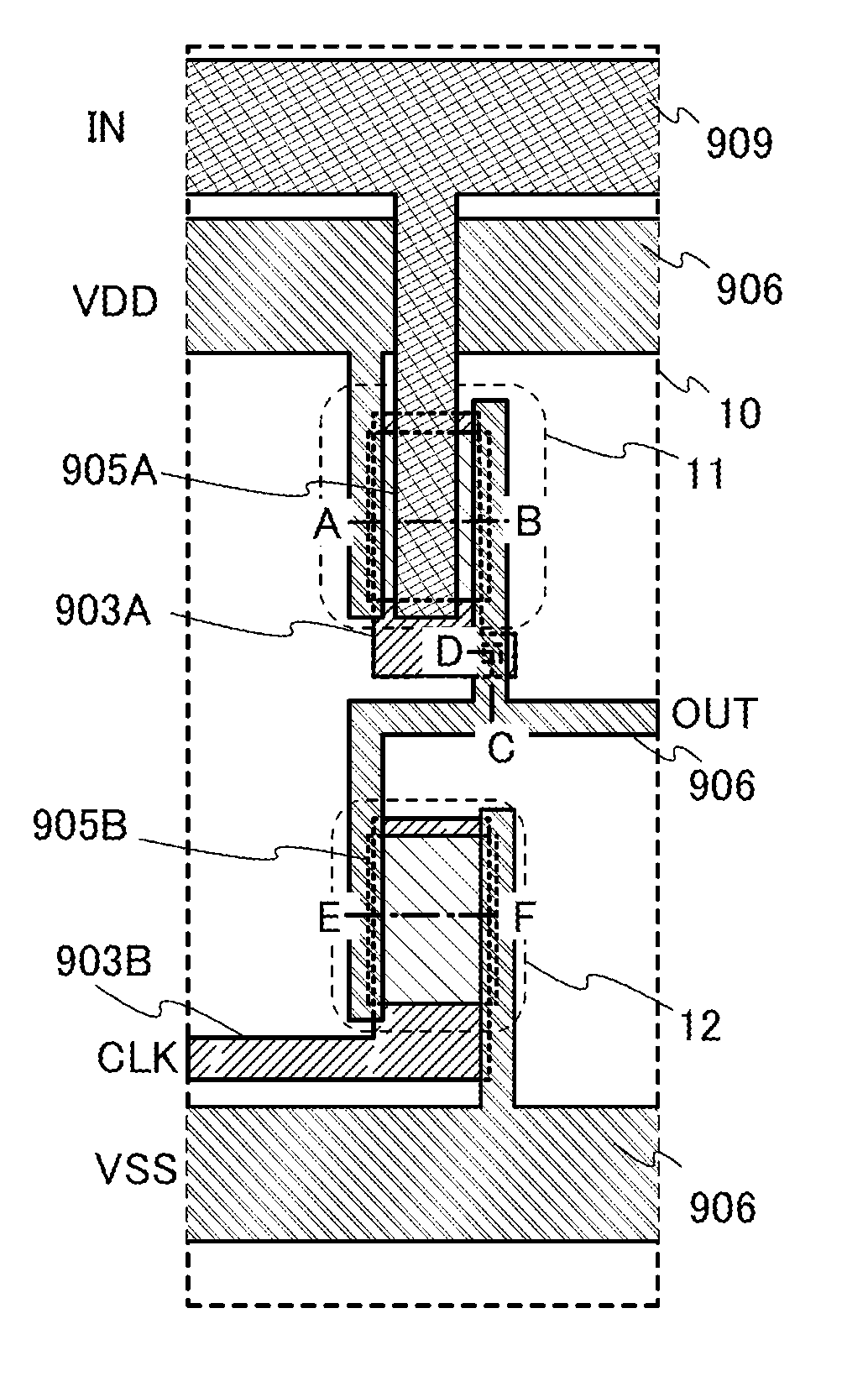

Shift register circuit

InactiveUS20130077735A1Reduce manufacturing costIncrease layout areaStatic indicating devicesSolid-state devicesShift registerEngineering

A shift register circuit including a logic circuit capable of controlling the threshold voltage of a transistor and outputting a signal corresponding to an input signal by changing only the potential of a back gate without changing the potential of a gate is provided. In a shift register circuit including a logic circuit with a first transistor and a second transistor having the same conductivity type, a first gate electrode of the first transistor is connected to a source electrode or a drain electrode of the first transistor, an input signal is supplied to a second gate electrode of the first transistor, a clock signal is supplied to a gate electrode of the second transistor, and the first gate electrode and the gate electrode are formed from the same layer.

Owner:SEMICON ENERGY LAB CO LTD

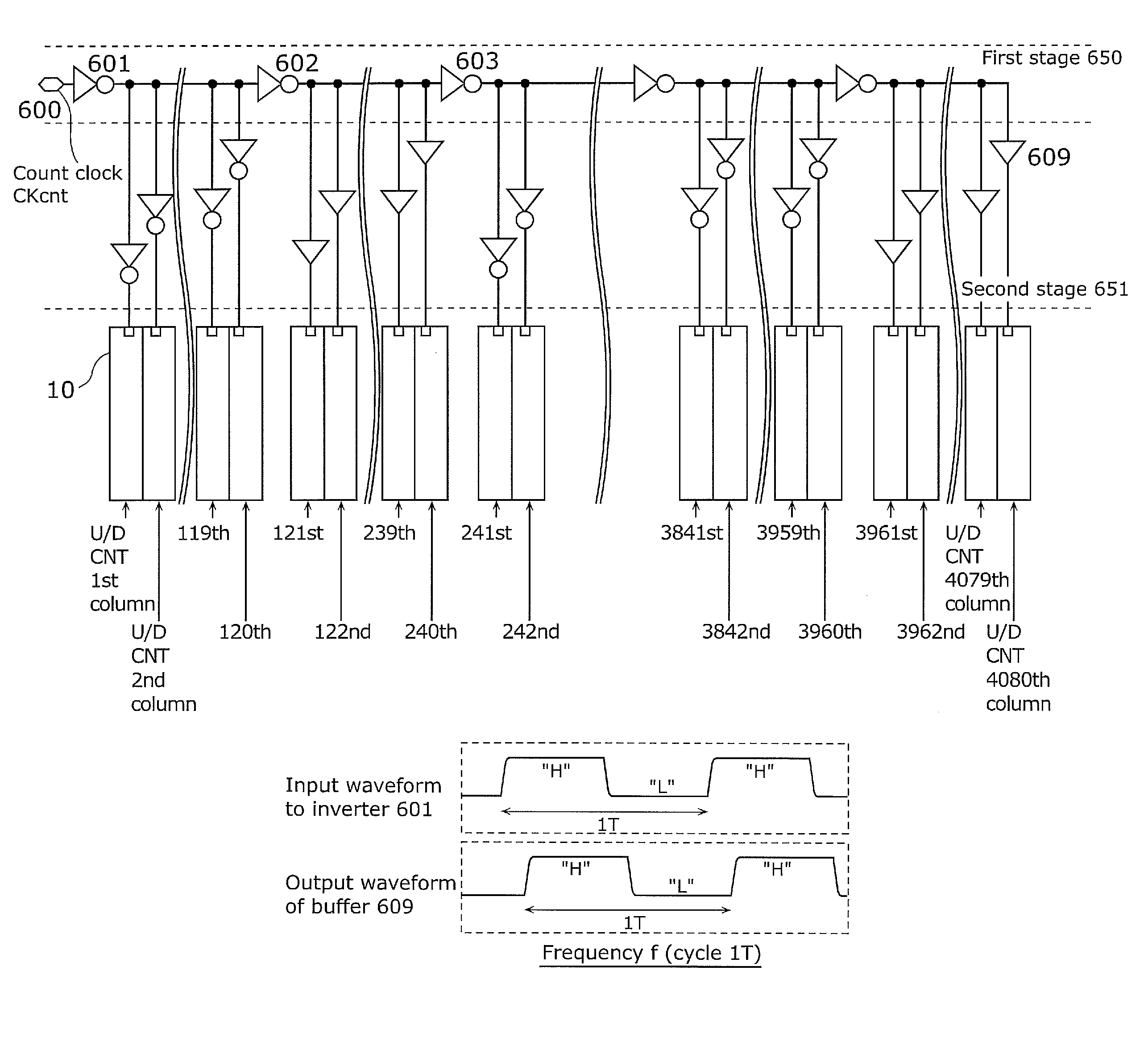

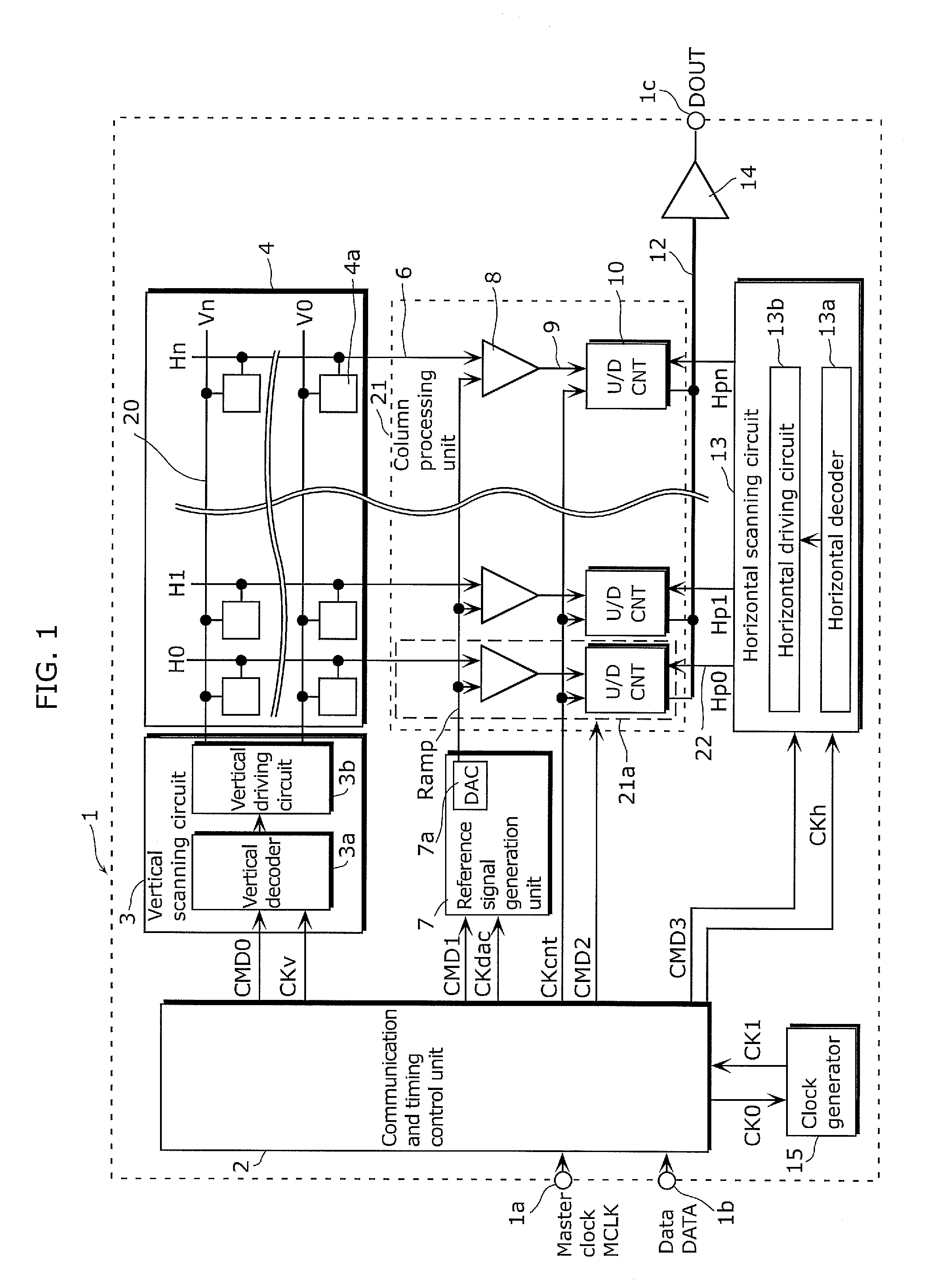

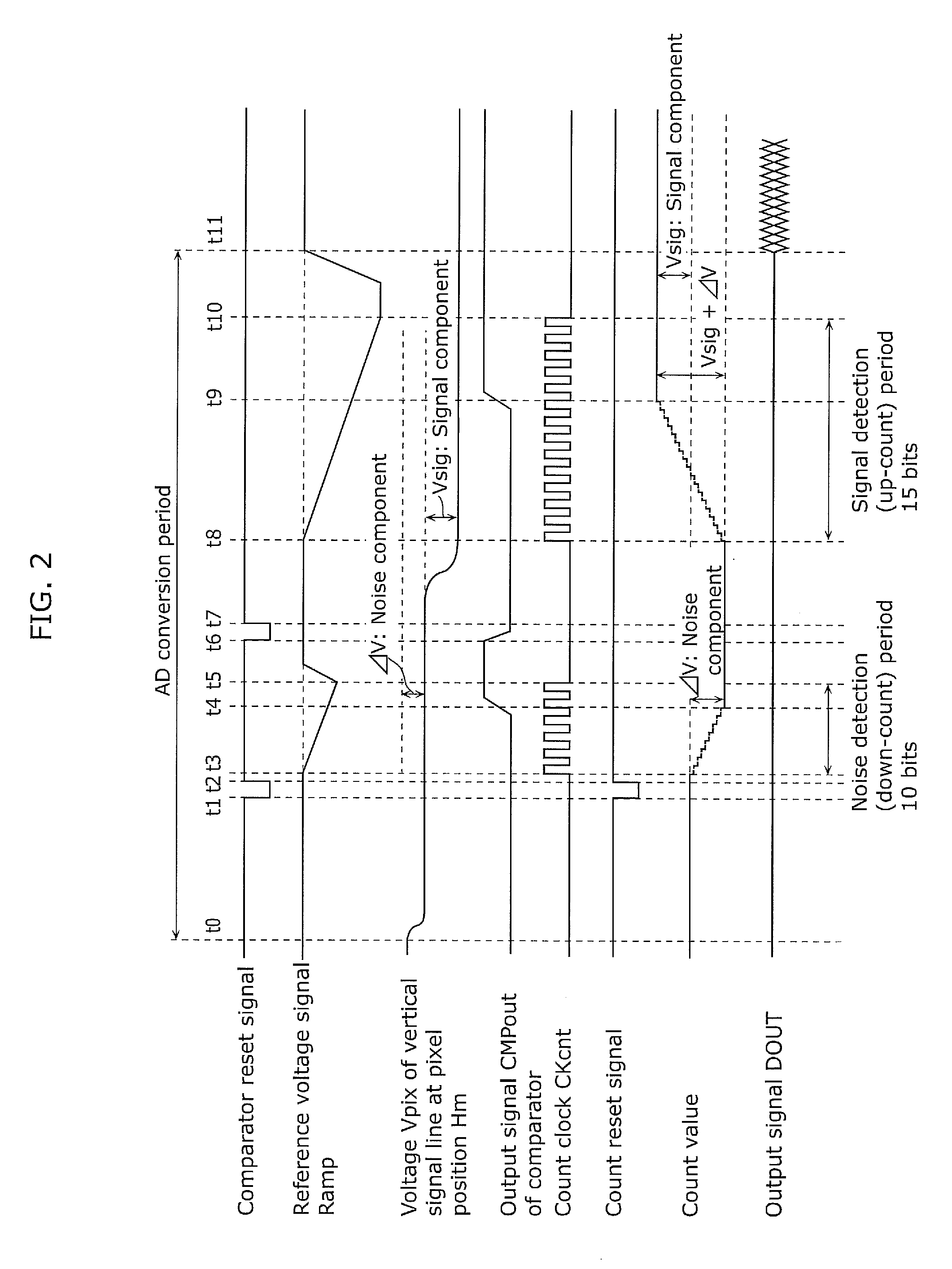

Solid-state imaging device comprising an analog to digital converter with column comparison circuits, column counter circuits, first and second inverters, and buffers

ActiveUS8735796B2Improve accuracyDecrease in the duty of the clock is restrictedAnalogue/digital conversionTelevision system detailsAnalog-to-digital converterClock signal

A solid-state imaging device includes: a column comparison circuit which compares a pixel signal with ramp waves and detects a timing at which the pixel signal and the ramp waves match; a counter circuit which is disposed for each of the pixel columns and measures the timing in the column comparison circuit by being supplied with a clock signal; and M first inverters which are equidistantly connected in series, wherein the counter circuit belongs to one of M groups corresponding to each of the M first inverters disposed in the upper clock stage, the odd-numbered group has second inverters disposed between the output terminal of the first inverter corresponding to the group and the counter circuit of the group, and the even-numbered group has buffers disposed between the output terminal of the first inverter corresponding to the group and the counter circuit of the group.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

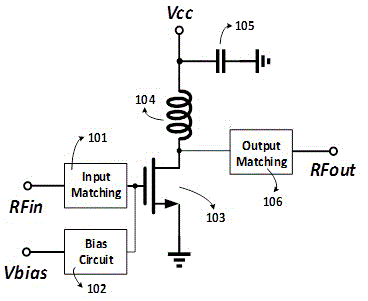

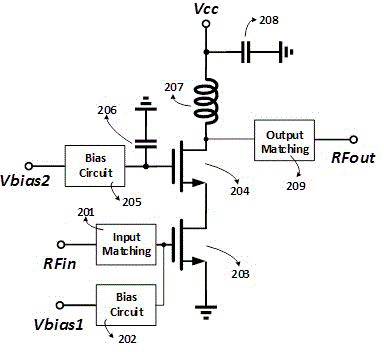

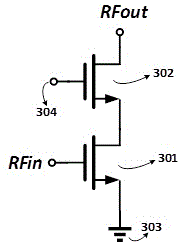

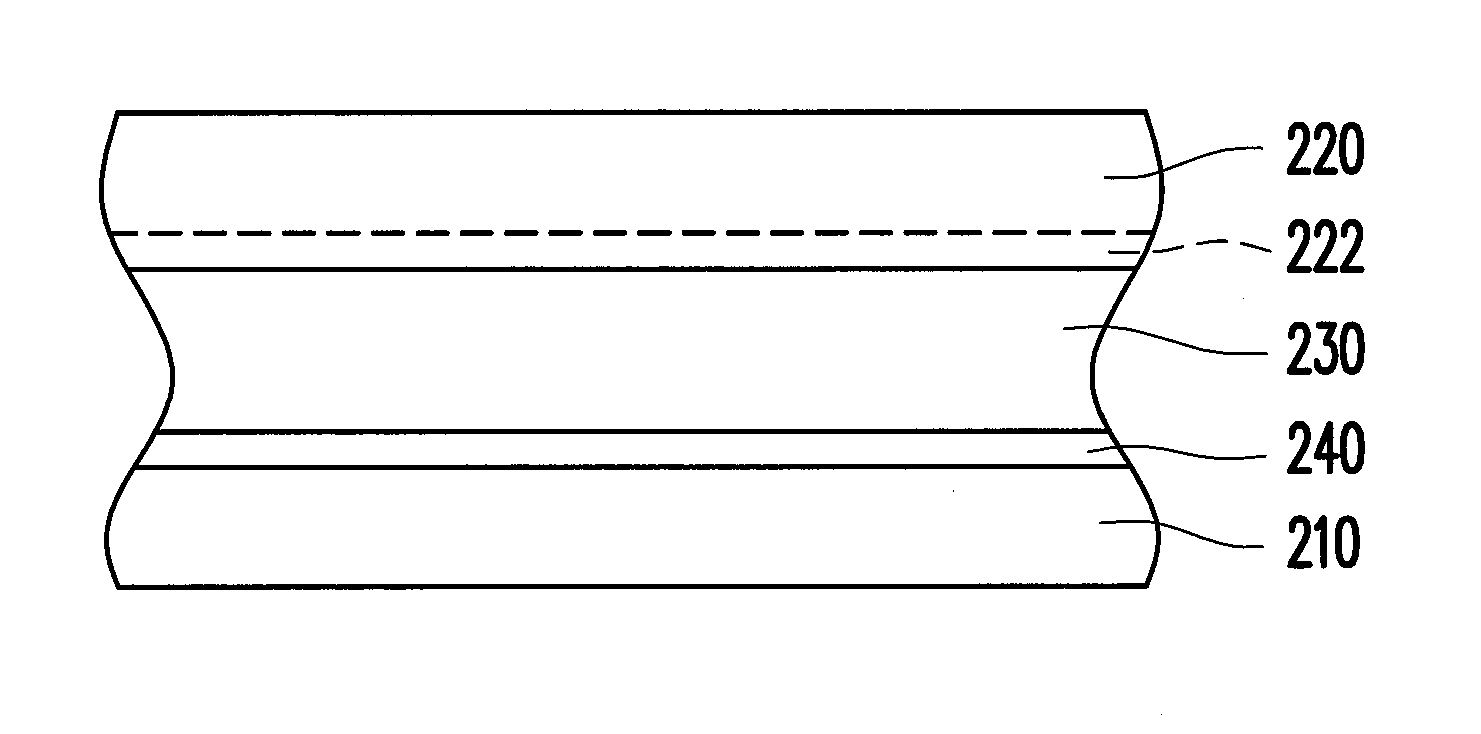

Improved cascode radio frequency power amplifier

InactiveCN104702226ACompact structureThe connection relationship is simplePower amplifiersCascodeHemt circuits

The invention discloses an improved cascode radio frequency power amplifier. A common-source-stage transistor grid electrode G1, a common-source-stage transistor source electrode S, a common-grid-stage transistor grid electrode G2 and a common-grid-stage transistor drain electrode D are transversely arranged on a substrate, a radio frequency input end RFin is connected with the common-source-stage transistor grid electrode G1 through a metal routing wire, the common-source-stage transistor source electrode S is connected with a grounding hole array through a metal routing wire, the common-grid-stage transistor grid electrode G2 is connected with a bias circuit through a metal routing wire, and the common-grid-stage transistor drain electrode D is connected with a radio frequency output end RFout through a metal routing wire. A cascode structure is adopted, and a layout structure is optimized, so that the improved cascode radio frequency power amplifier has the advantages of high gain, high power, high linearity, high efficiency and the like; layout area equivalent to that of a single-transistor common-source structure radio frequency power amplifier is maintained, so that low cost is realized.

Owner:ETRA SEMICON SUZHOU CO LTD

Pixel array, active device array substrate and flat display panel

ActiveUS20130010247A1Improve display image qualityQuality improvementDischarge tube luminescnet screensPrinted electric component incorporationScan lineDisplay device

A pixel array including a pixel electrode and an active device is provided. The active device includes a gate, a channel layer, a source, a drain, a connection electrode, a first branch portion and a second branch portion. The gate is electrically connected with a scan line. The channel layer located at a side of the gate is electrically isolated from the gate. The source, the drain and the connection electrode are disposed on a part region of the channel layer. The first branch portion disposed on a part region of the channel layer is connected with an end of the connection electrode. The first branch portion surrounds the source located on the channel layer. The second branch portion disposed on a part region of the channel layer is connected with the other end of the connection electrode. The second branch portion surrounds the drain located on the channel layer.

Owner:AU OPTRONICS CORP

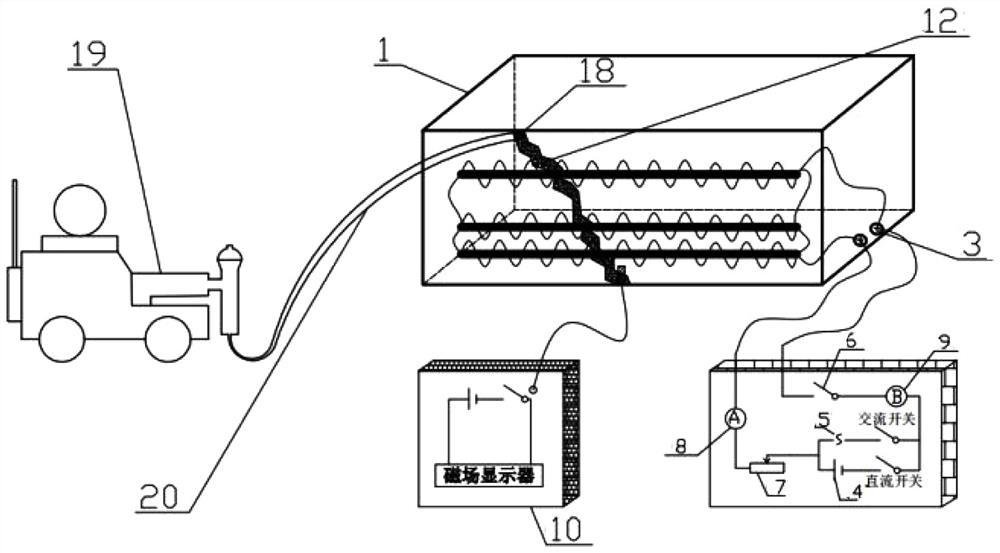

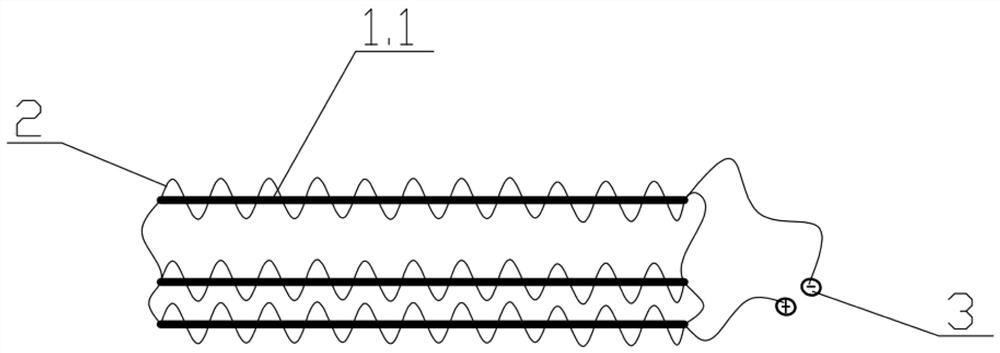

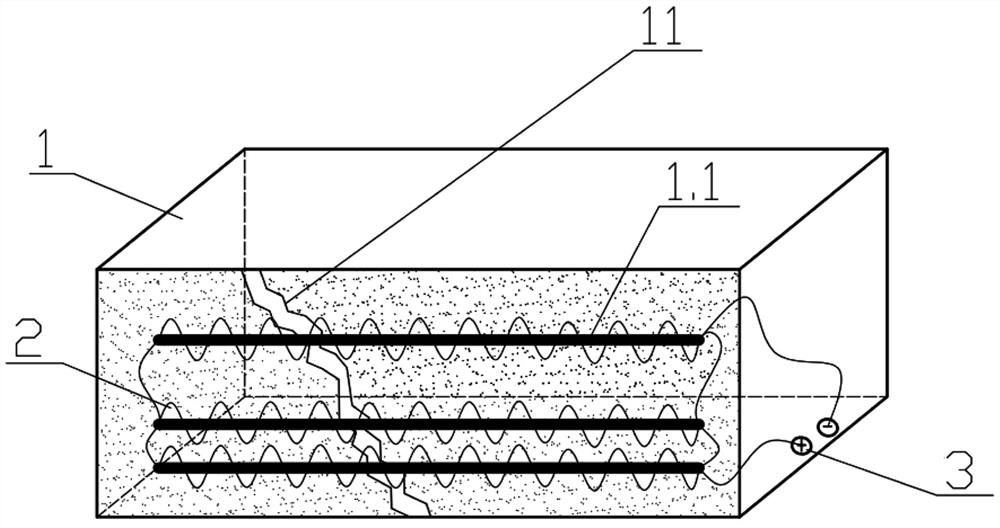

Pre-embedded and prefabricated magnetic attraction end guiding type building crack repairing device and method based on magnetic force

InactiveCN113250483AHas the effect of anti-oxidationWill not harmBuilding repairsTinningMagnetic tension force

The invention provides a pre-embedded and prefabricated magnetic attraction end guiding type building crack repairing device and a method based on magnetic force. The device comprises a steel bar pre-embedded in a reinforced concrete beam body; the steel bar is wound with a tinned copper wire; the tinned copper wire penetrates through a reserved wire interface pre-formed in the reinforced concrete beam body; the tinned copper wire is connected with an electromagnetic induction device used for providing current; a guide hole is formed in the position, where a crack easily occurs, of the reinforced concrete beam body; and the guide hole is connected with a high-pressure jet grouting machine through a grouting pipe, and then magnetic mortar is injected into the crack. The magnetic mortar is injected into a required position under the guide adsorption of different magnetic attraction ends, so that the sufficient grouting effect is achieved, and the crack repairing and filling rate is increased. According to the pre-embedded and prefabricated magnetic attraction end guiding type building crack repairing device and the method based on the magnetic force, the needed materials are simple, the assembly cost is low, and the device has prefabrication performance, is fast to operate, and is high in crack repair guiding effect and long in duration time.

Owner:CHINA THREE GORGES UNIV

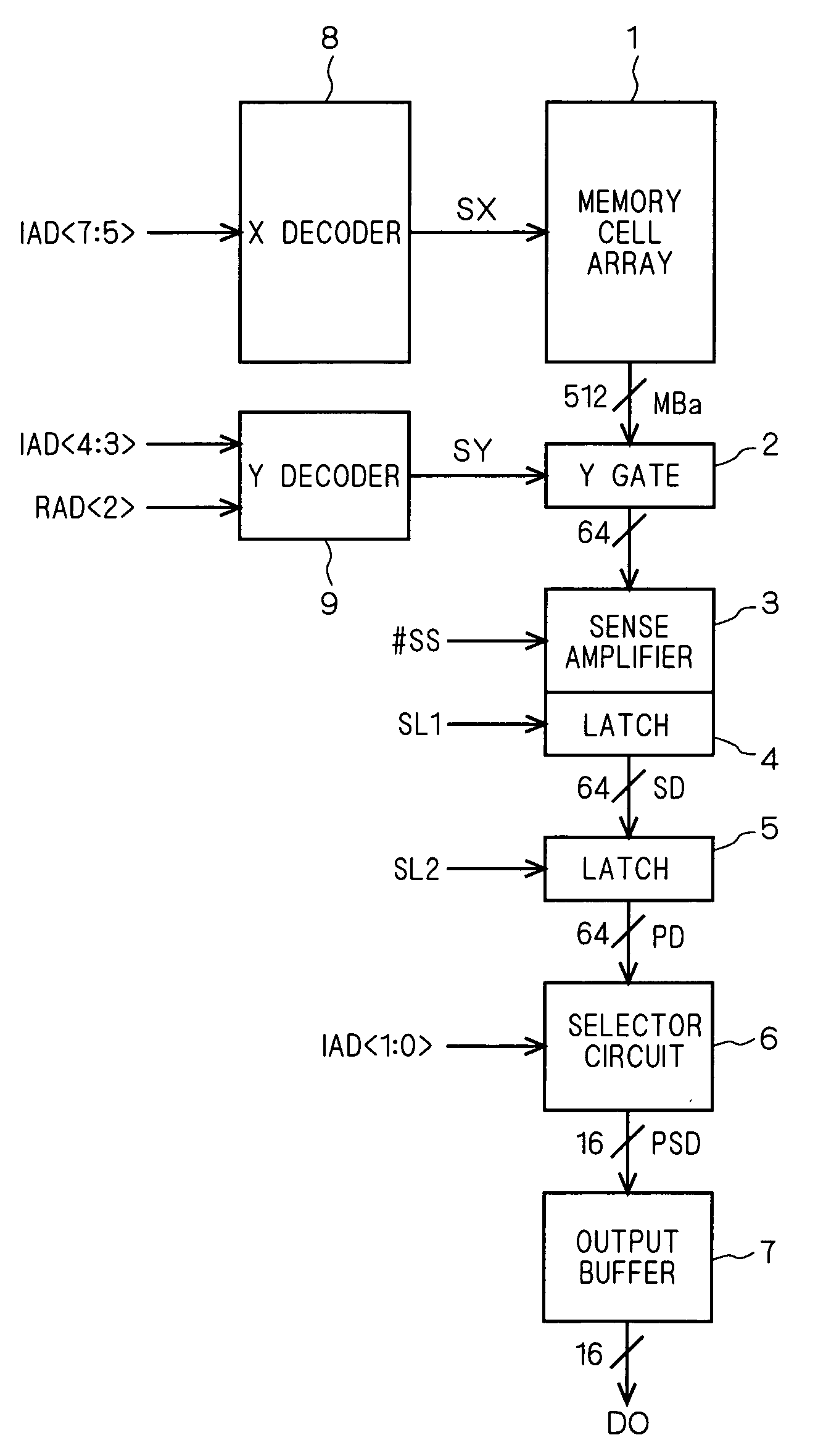

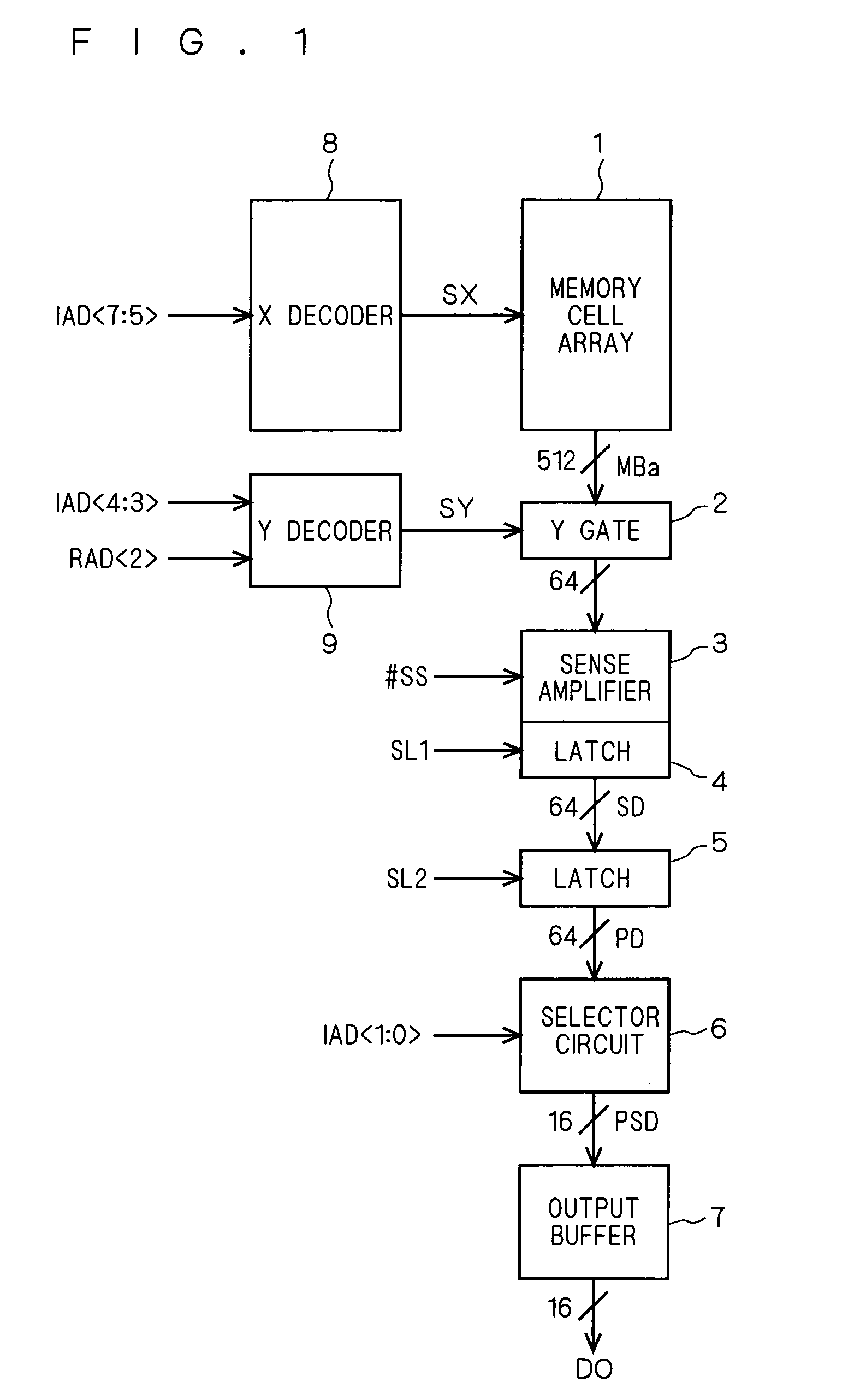

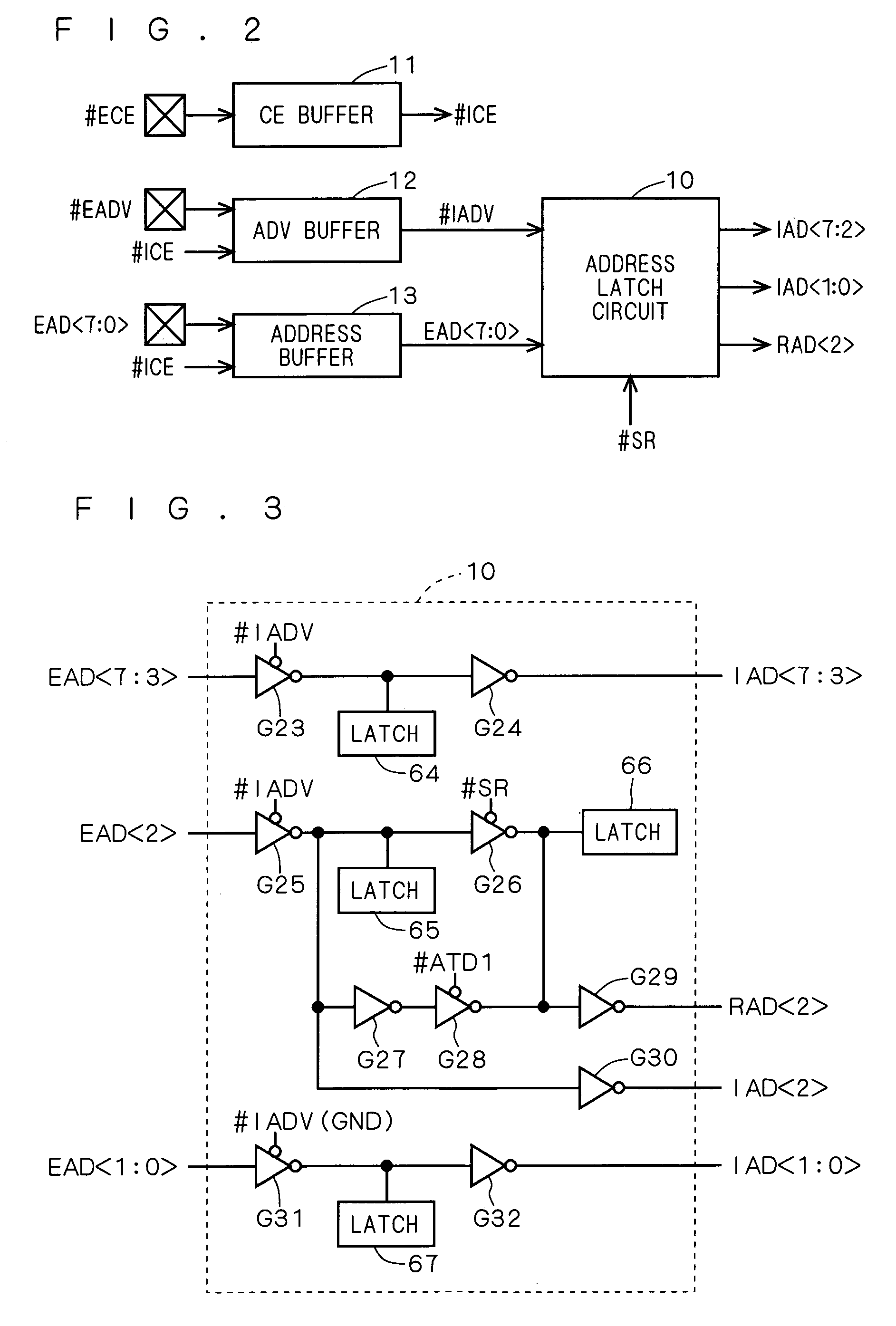

Semiconductor memory device with a page mode

InactiveUS7180824B2Minimise currentIncrease layout areaDigital storageSensing dataAudio power amplifier

A sense amplifier and a latch for sense data output the former 4 words of sense data to a latch for page data, and during a page mode reading period of the former 4 words of data as external data by the latch for page data, a selector circuit and an output buffer, perform a sense amplifying operation and a latch operation on the latter 4 words of memory cell information output from a Y gate under control of a sense signal and a latch signal.

Owner:RENESAS ELECTRONICS CORP

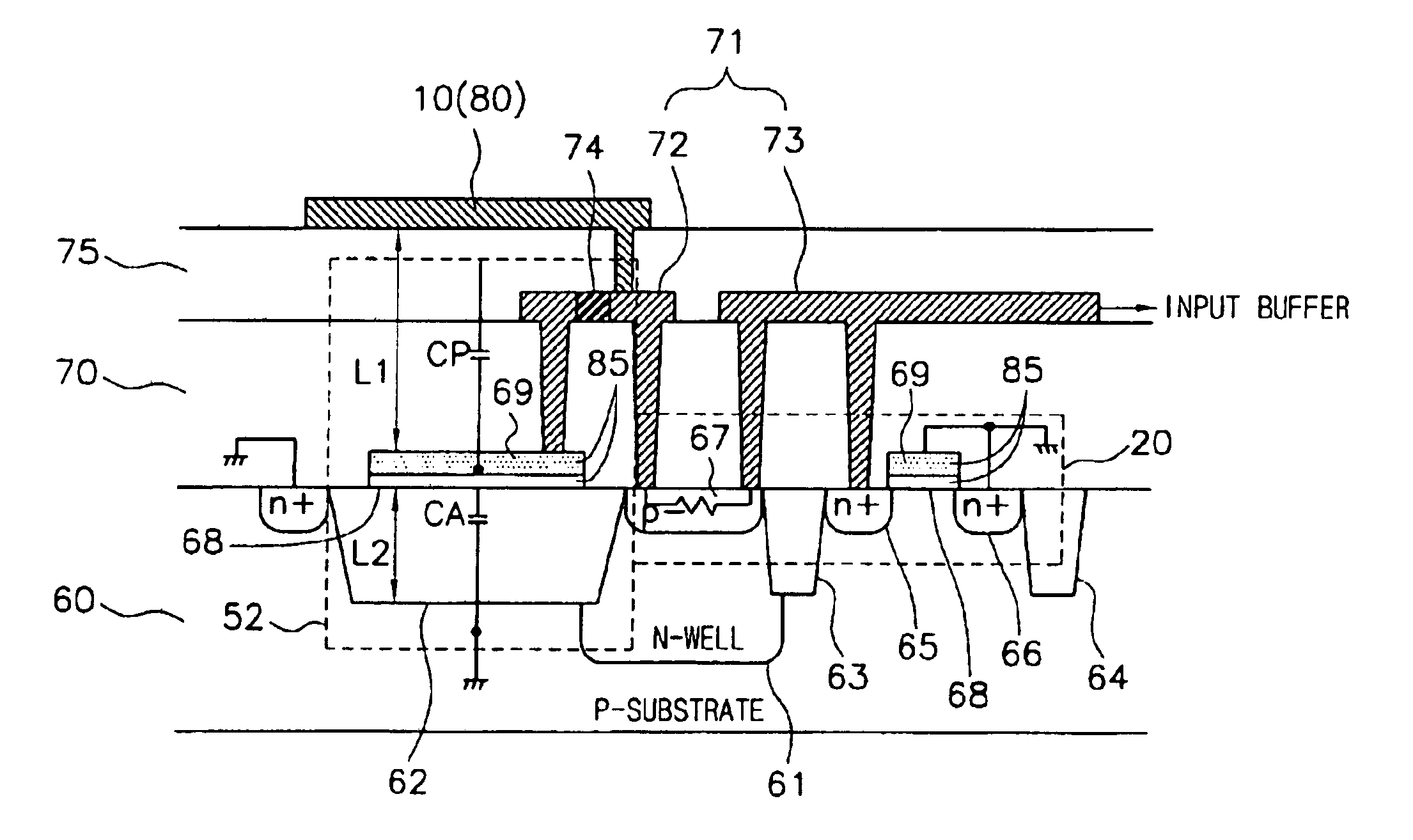

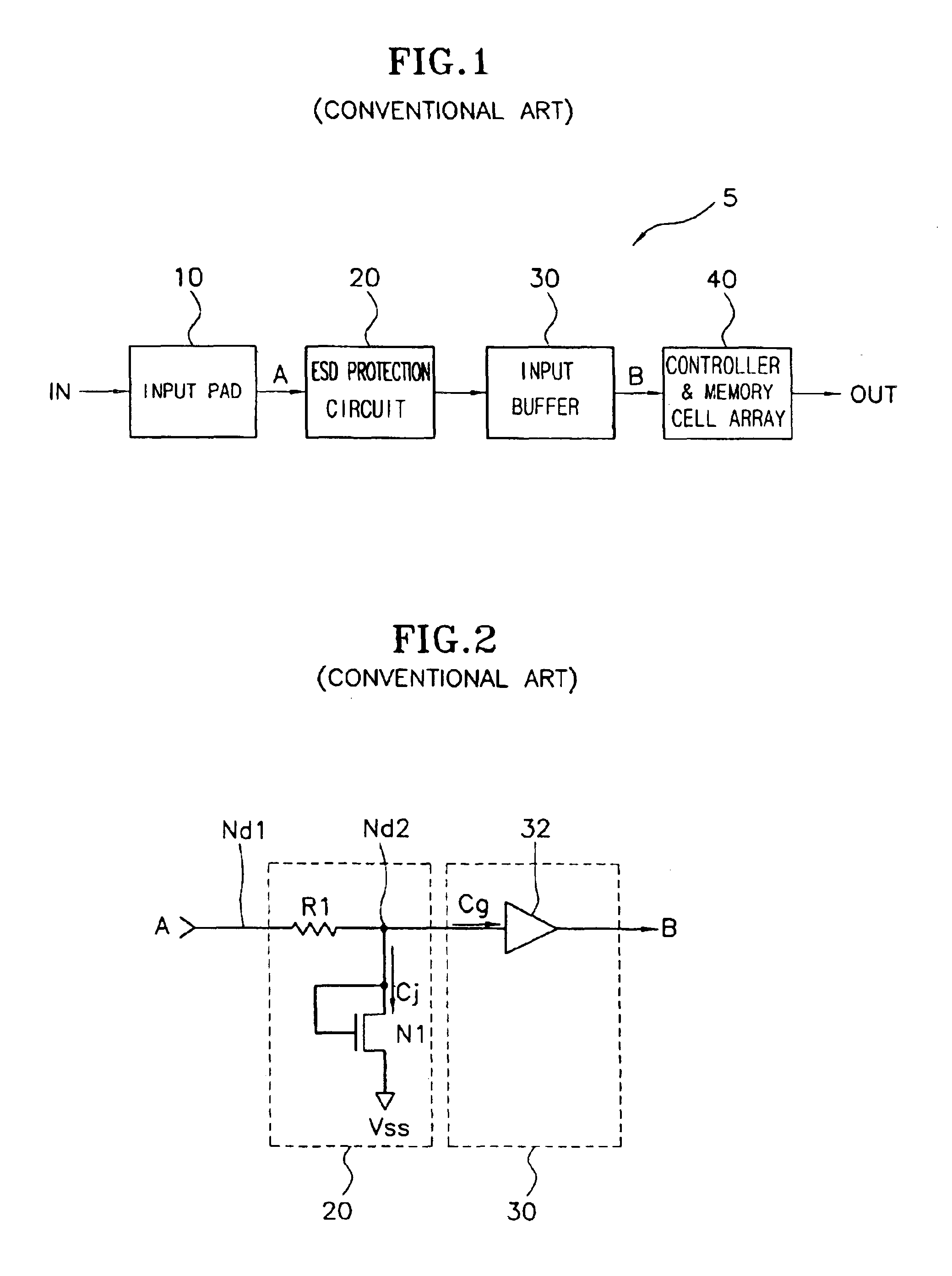

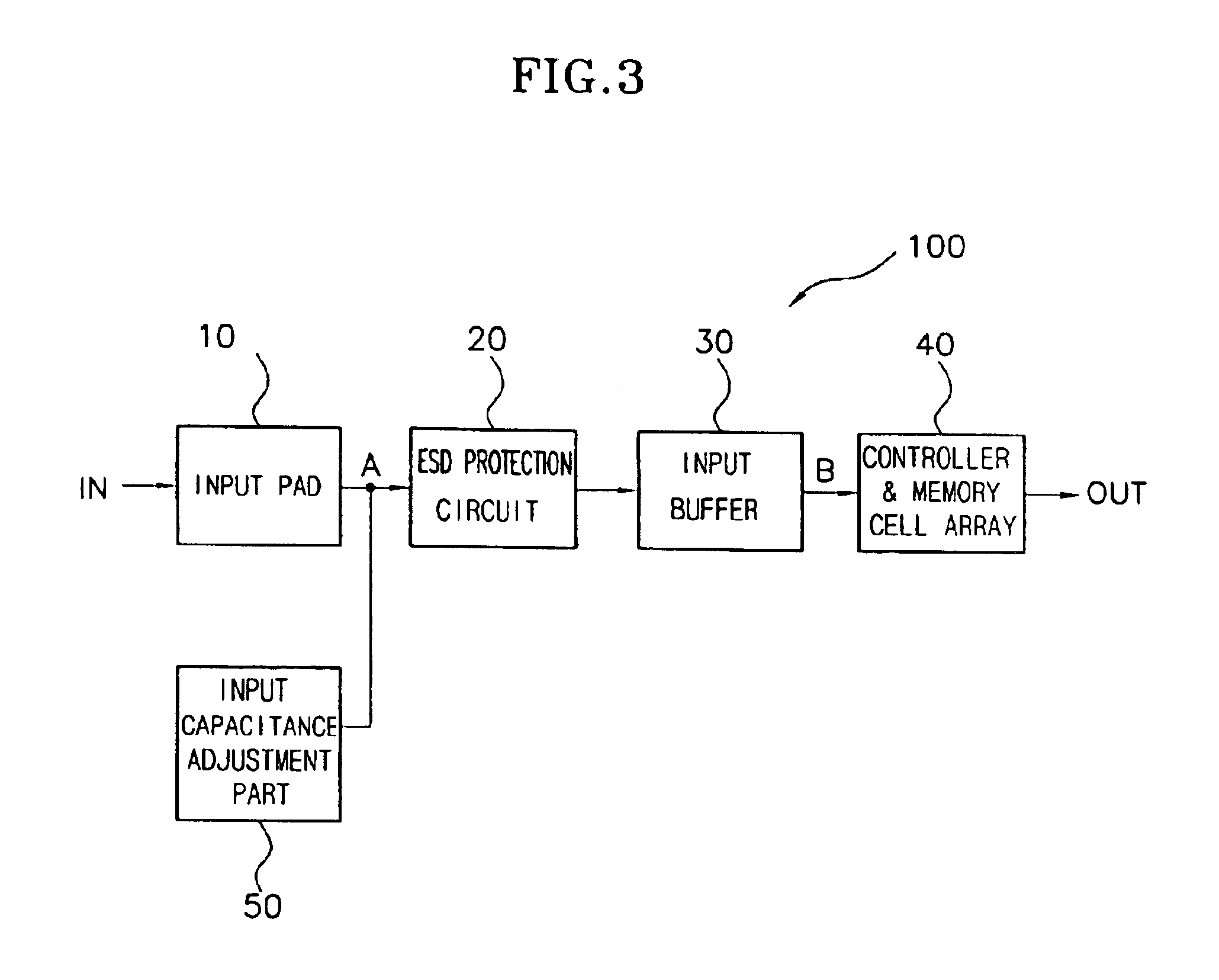

Apparatus for adjusting input capacitance of semiconductor device and fabricating method

InactiveUS6908821B2Easy to adjustIncrease layout areaBaseband system detailsSemiconductor/solid-state device detailsCapacitanceIsolation layer

An apparatus for finely adjusting the input capacitance of a semiconductor device and a method of fabricating the apparatus are disclosed. The invention adjusts finely the input capacitance without increasing a layout area of the device by using a capacitor constructed with a poly layer / device isolation layer / P-type substrate. The poly layer is formed on an unnecessary space provided by the device isolation layer under an input pad.

Owner:SK HYNIX INC

Thin film balun

ActiveUS8143968B2Improve balanceGood effectMultiple-port networksOne-port networksCapacitorBalanced line

A thin film balun includes: an unbalanced transmission line which includes two coils; a balanced transmission line which includes two coils and is electromagnetically coupled to the unbalanced transmission line; a first electrode which is connected to the balanced transmission line and constitutes a capacitor; and a second electrode which is connected to a ground terminal and disposed to be opposed to the first electrode and constitutes the capacitor. The second electrode has a section opposed to the coils configuring the unbalanced transmission line or the balanced transmission line, the section being integrally formed with a section opposed to the first electrode.

Owner:TDK CORPARATION

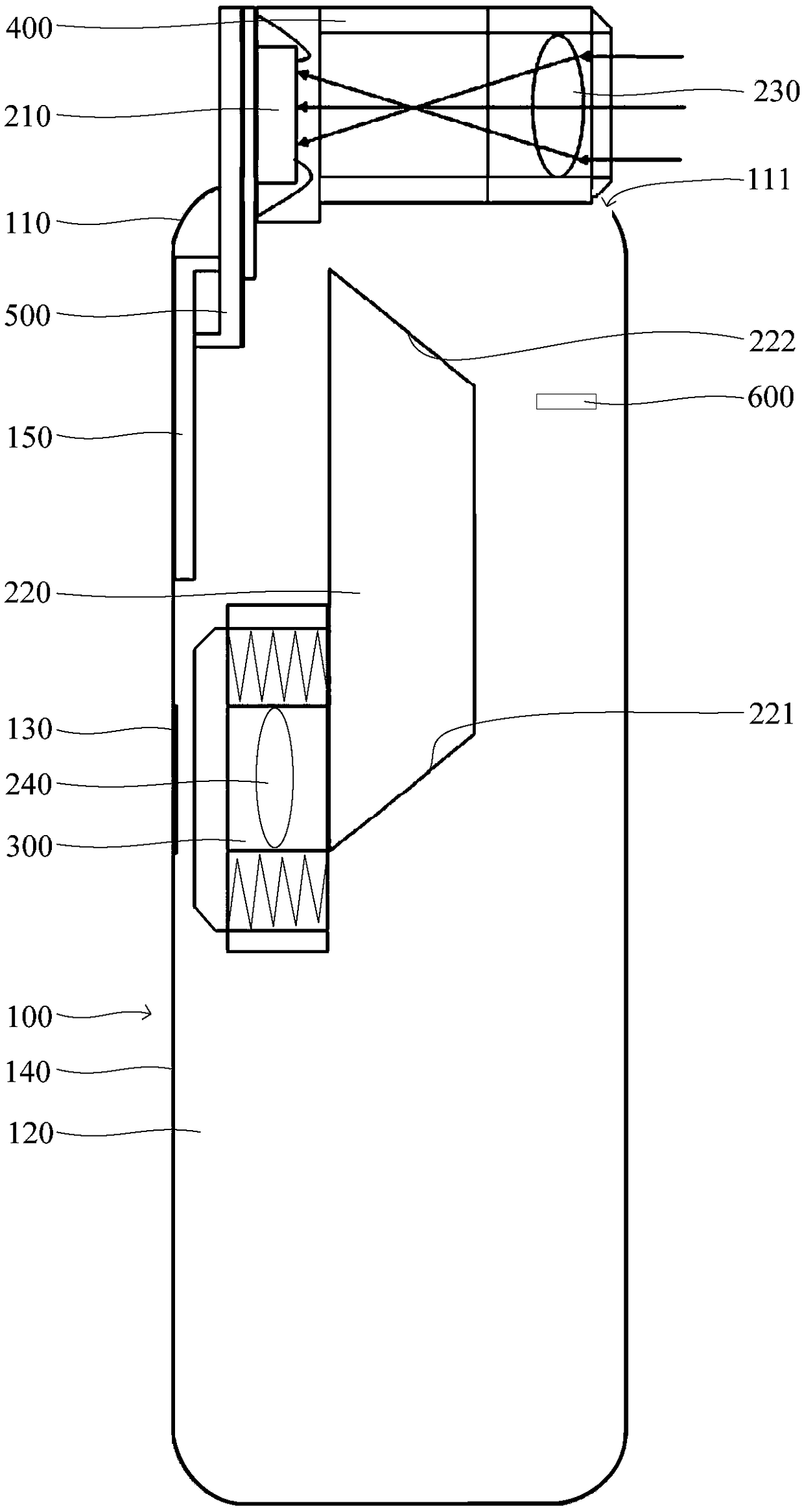

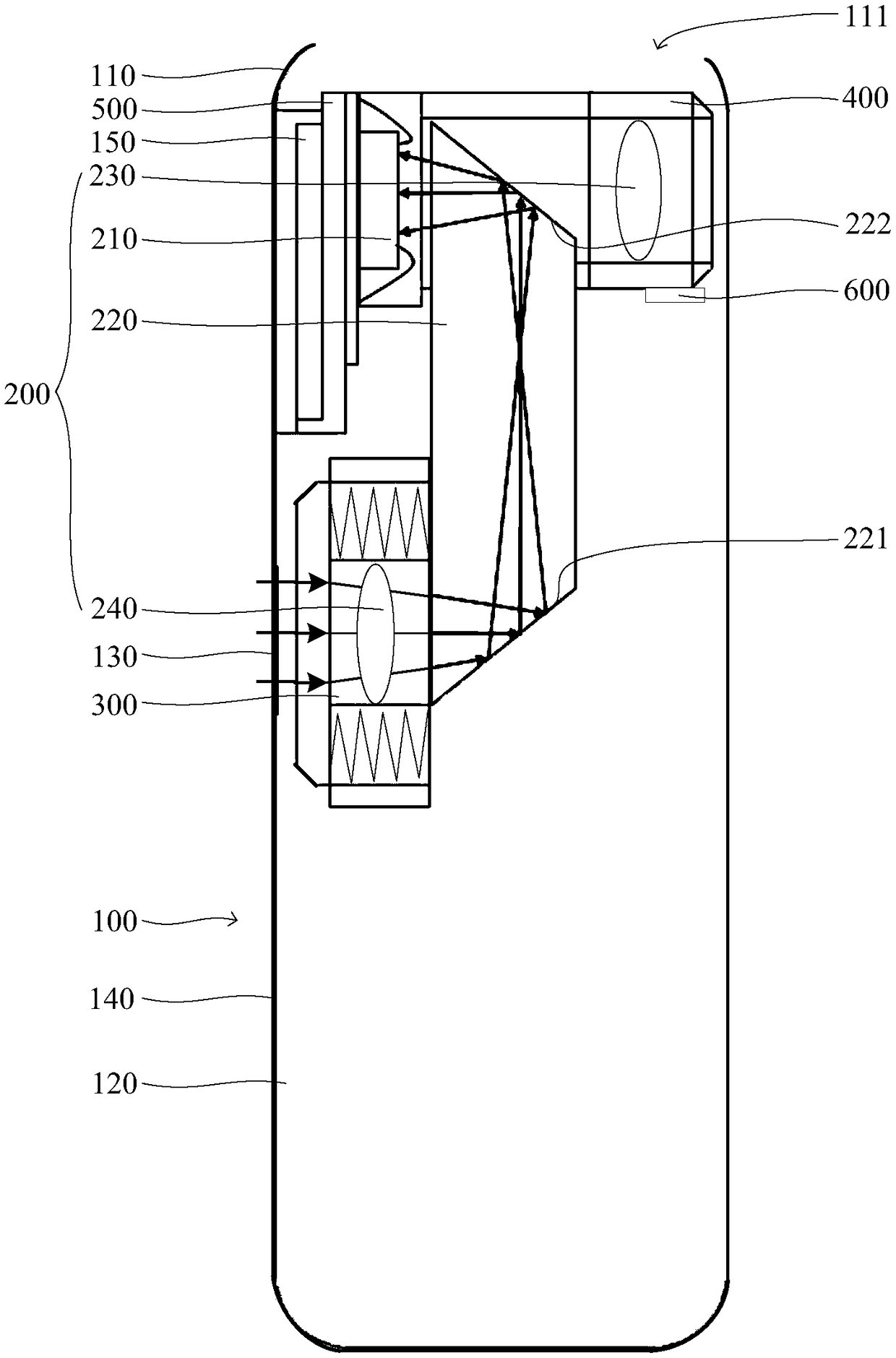

A mobile terminal

ActiveCN109005266AIncrease the screen ratioReduce occupancyTelevision system detailsColor television detailsCamera lensComputer science

A mobile terminal which includes a housing and an image pickup module disposed on the housing, the frame of the shell is provided with perforations, the image pickup module includes an image sensor, alight-transmitting device and a first lens and a second lens facing the front and rear sides of the mobile terminal, respectively, the image sensor is movably disposed on the housing, and switchablebetween a first position and a second position, the first lens is fixed on the image sensor, the second lens and the light transmitting device are fixed in the inner cavity of the housing, and the mobile terminal is provided with a window opposite to the second lens. When the image sensor is in the first position, the first lens extends out of the housing through the hole of the image sensor, andthe first lens is used for guiding light into the image sensor. When the image sensor is in the second position, the first lens moves with the image sensor into the lumen and is blocked by the housing, and the light transmitting device conducts light passing through the second lens to the image sensor. The scheme can solve the problem that the screen occupancy of the mobile terminal is relativelysmall.

Owner:VIVO MOBILE COMM CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com