Method of manufacturing semiconductor device having notched gate MOSFET

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will now be described more fully with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. It should be noted that, throughout the description, unless noted otherwise, when a layer is described as being formed on another layer or on a substrate, the layer may be formed directly on the other layer or on the substrate, or one or more layers may be interposed between the layer and the other layer or the substrate.

[0039] This application incorporates by reference the entire contents of another U.S. Patent Application, filed on even date herewith, assigned to Samsung Electronics Co., Ltd., entitled, “Transistor Having Gate Dielectric Layer of Partial Thickness Difference and Method of Fabricating the Same,” naming as inventors Byung-yong Choi, Chang-woo Oh, Dong-gun Park and Dong-won Kim.

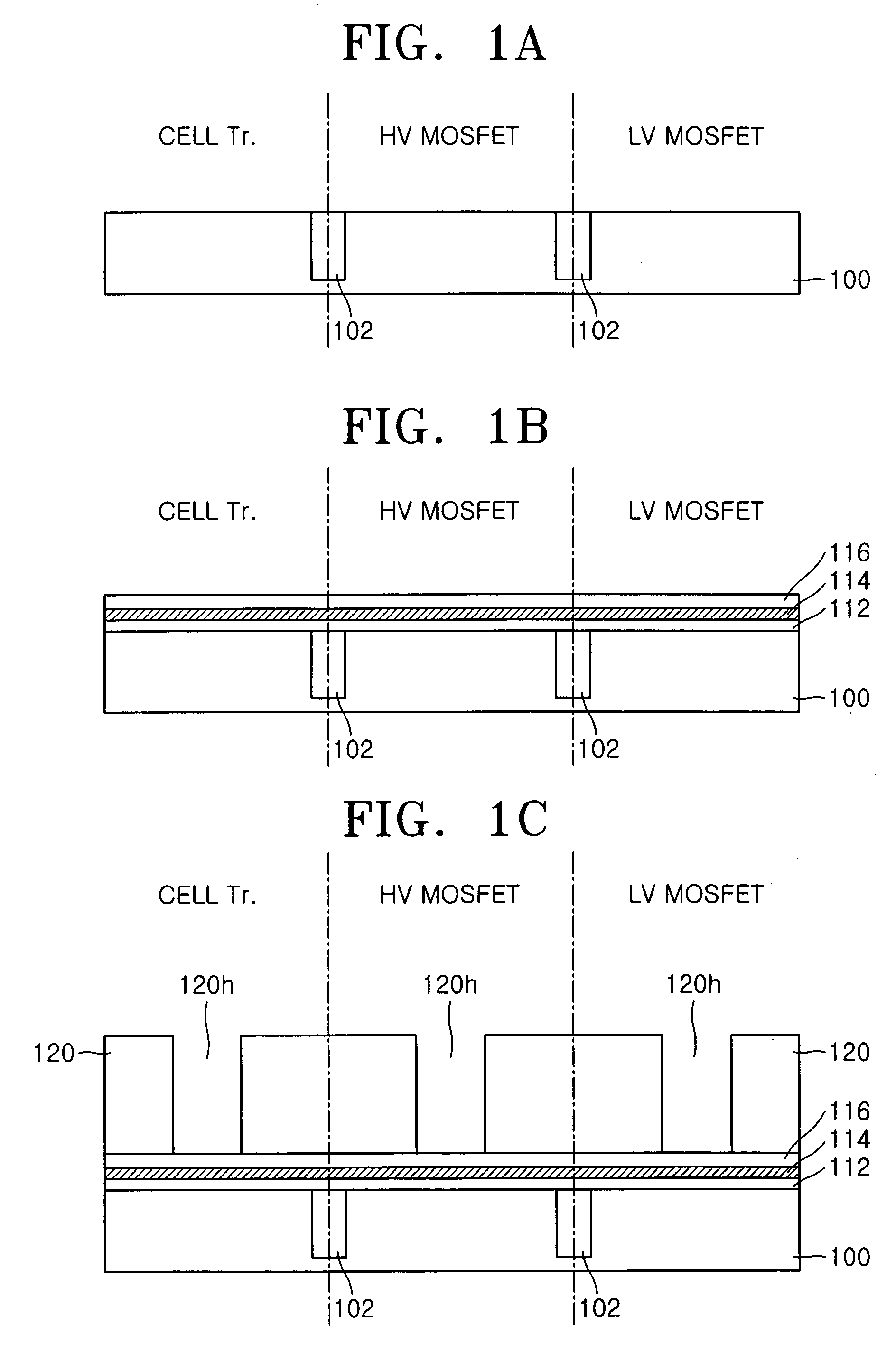

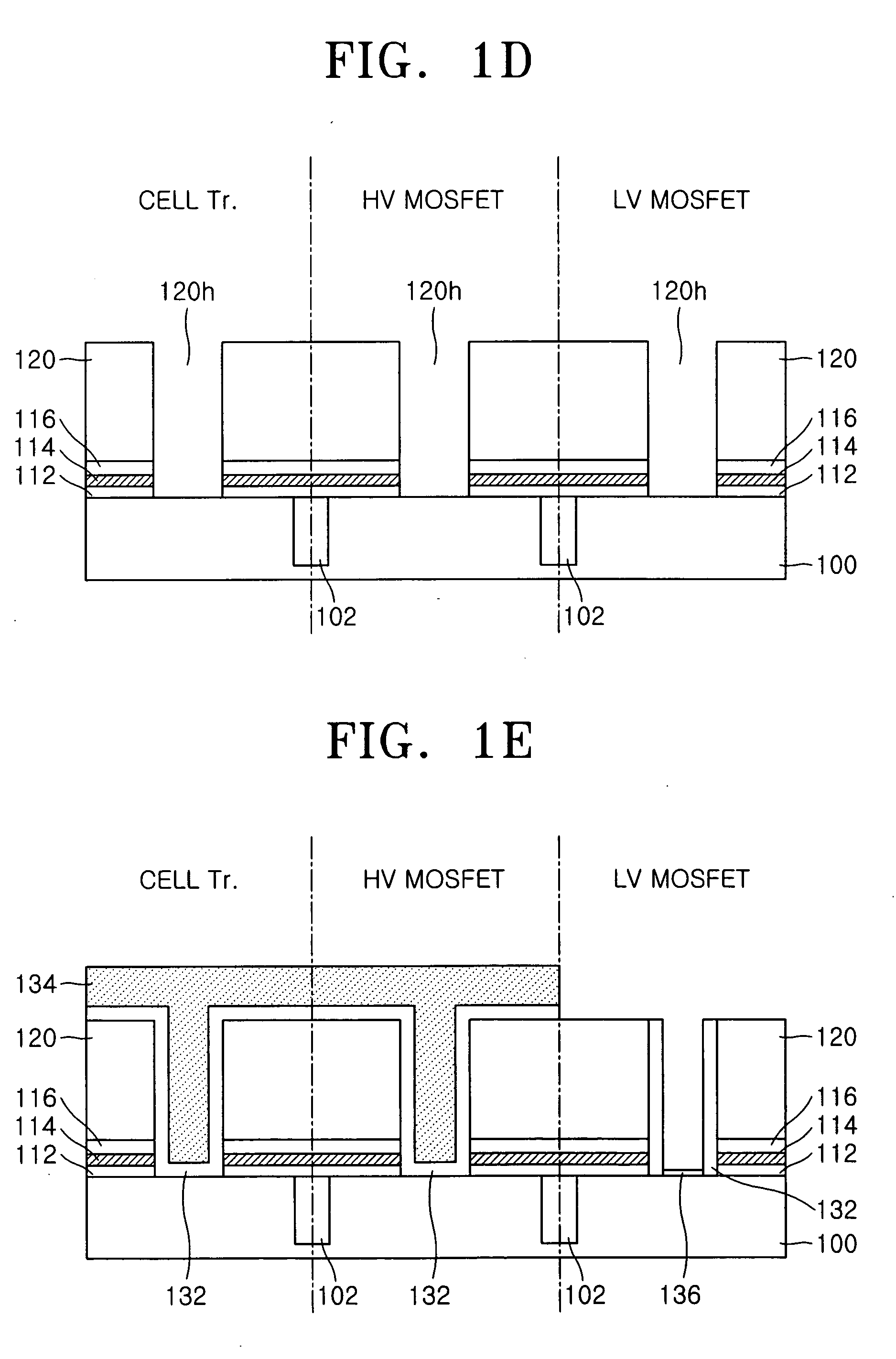

[0040]FIGS. 1A through 1O are cross-sectional views illustrating a method of manufacturing a semiconductor device according an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com