Power trench MOSFET having SiGe/Si channel structure

A channel region, trench gate technology, applied in sustainable manufacturing/processing, climate sustainability, semiconductor devices, etc., can solve problems such as limiting device performance, limiting power efficiency, limiting converter efficiency, etc., to improve device performance. characteristics, the effect of reducing parasitic gate resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

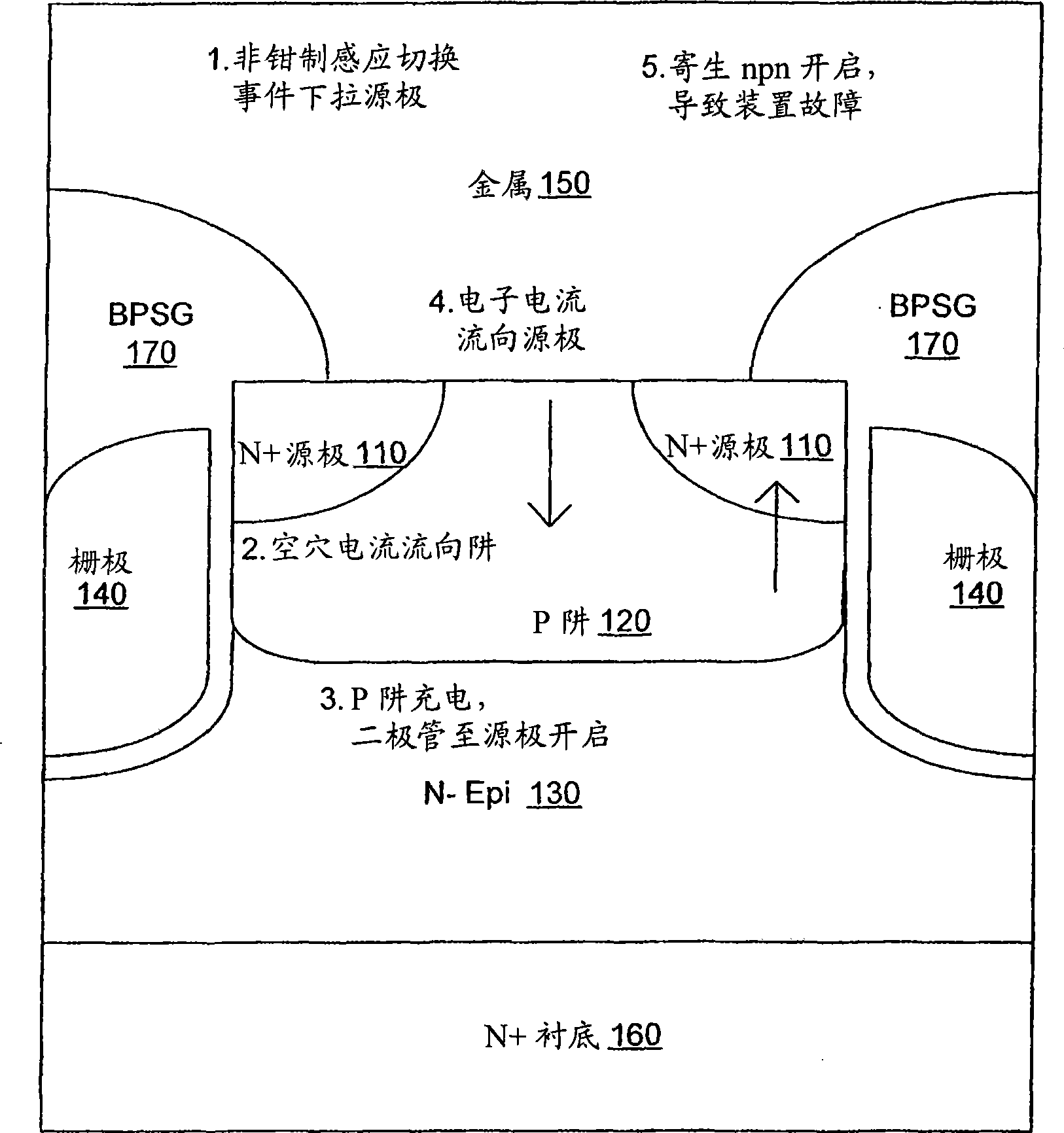

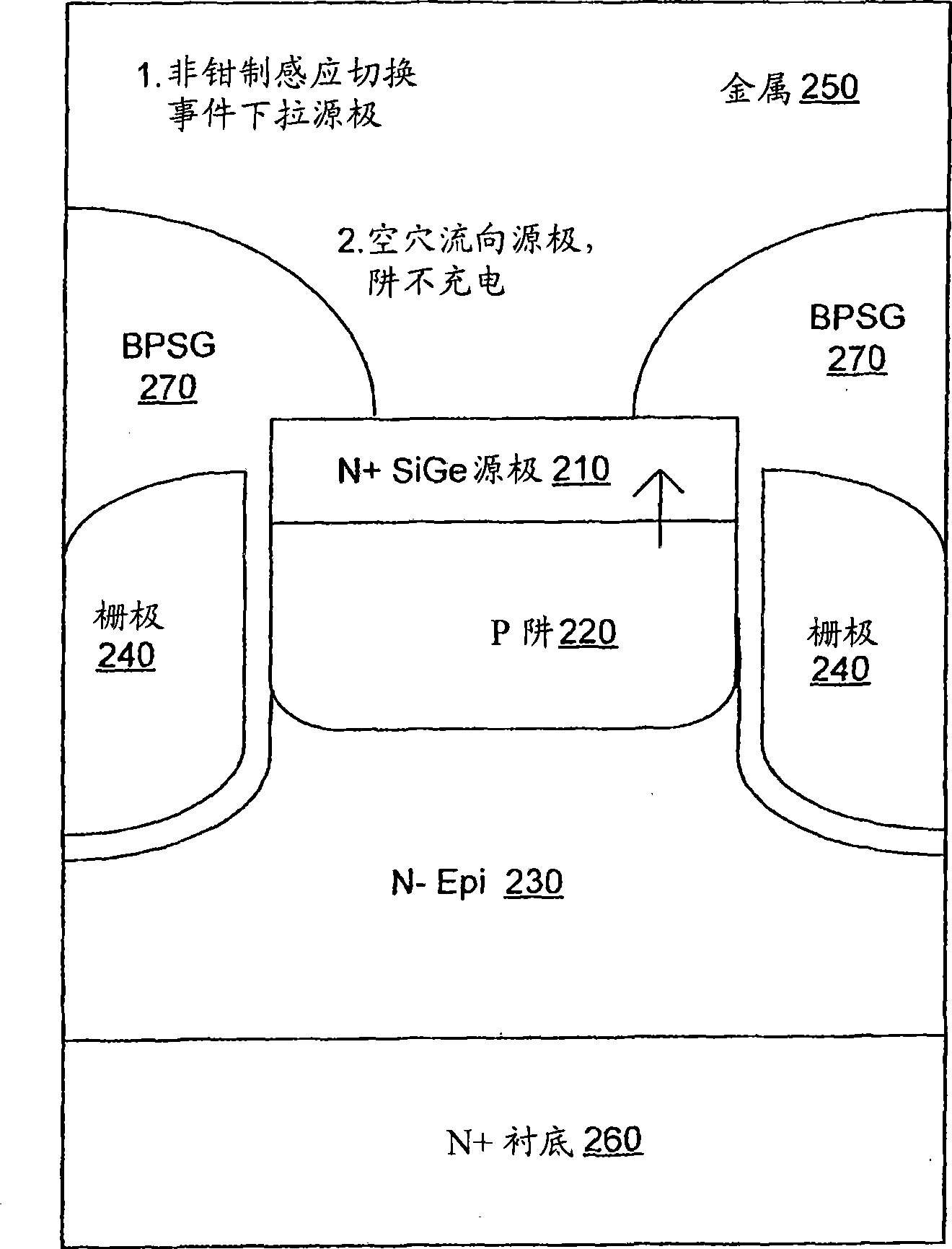

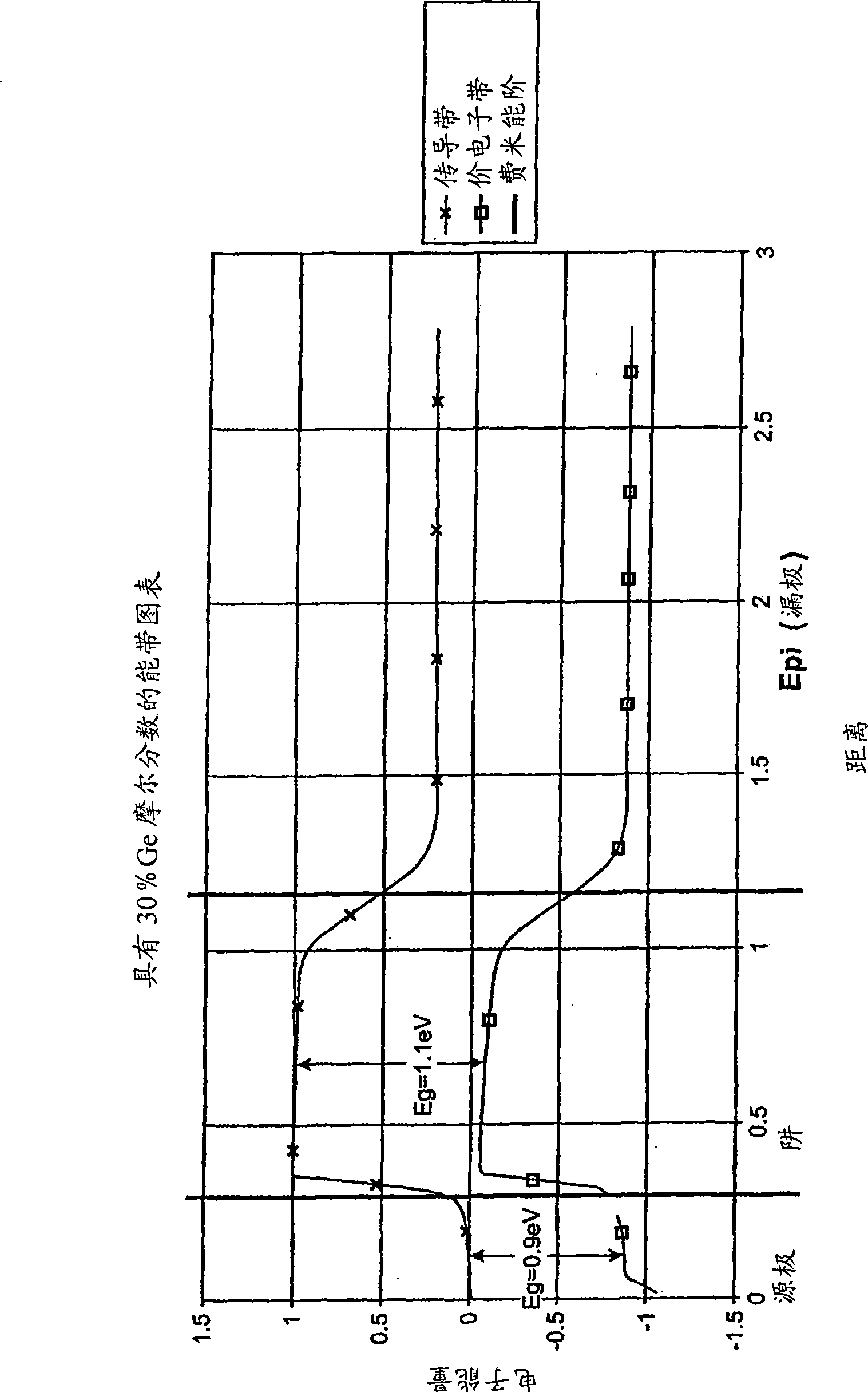

[0039] figure 1 It is a cross-sectional view of an n-channel trench gate power MOSFET improved by combining the embodiment of the present invention. The device includes an n-type source region 110 , a body formed by a p-well 120 , an n-type drain region 130 , a substrate 160 , a gate 140 , and a metal contact 150 .

[0040] Parasitic npn bipolar transistors are inherent in this structure. Specifically, the emitter of the parasitic device is the source region 110 , the base thereof is the body or well region 120 , while the collector of the parasitic device corresponds to the epi region 130 . If this parasitic transistor is biased into its active-forward mode of operation, destructive failure will occur. This can occur, for example, during avalanche breakdown caused by an unclamped inductive switching (UIS) event. Holes generated by impact ionization may flow through the base formed by the P-well 120, causing an ohmic voltage drop. If this voltage drop exceeds about 0.6V, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com