Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

87 results about "Parasitic impedance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

With standard inductive coupling, the parasitic impedance of the inductors, primarily the parasitic impedance of the transmitter inductor, affects the performance of the interface circuitry. The quality factor Q=ωL/Rs of the inductor must be increased to enhance power transmission, where Rs is the parasitic resistance of the inductors.

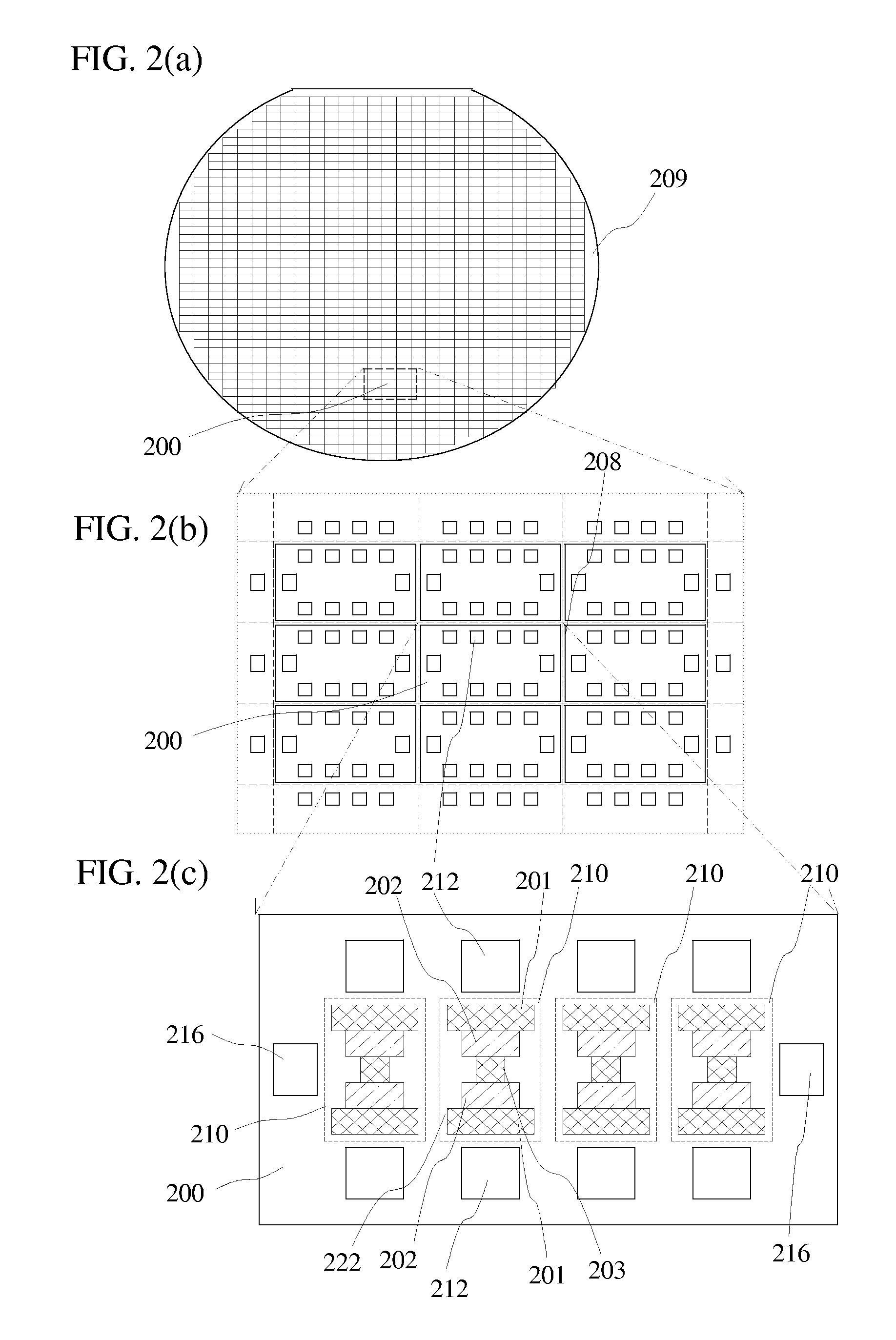

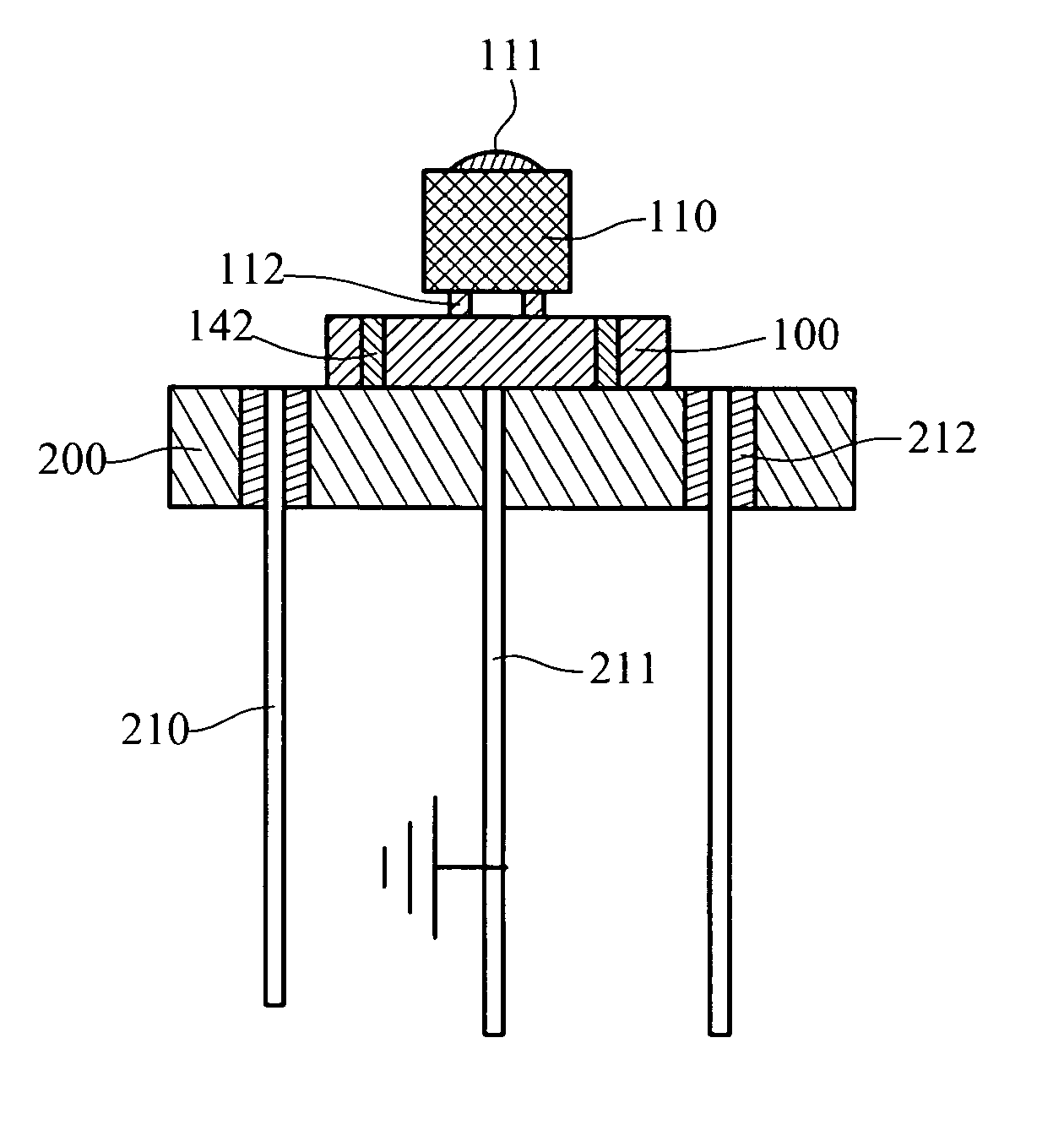

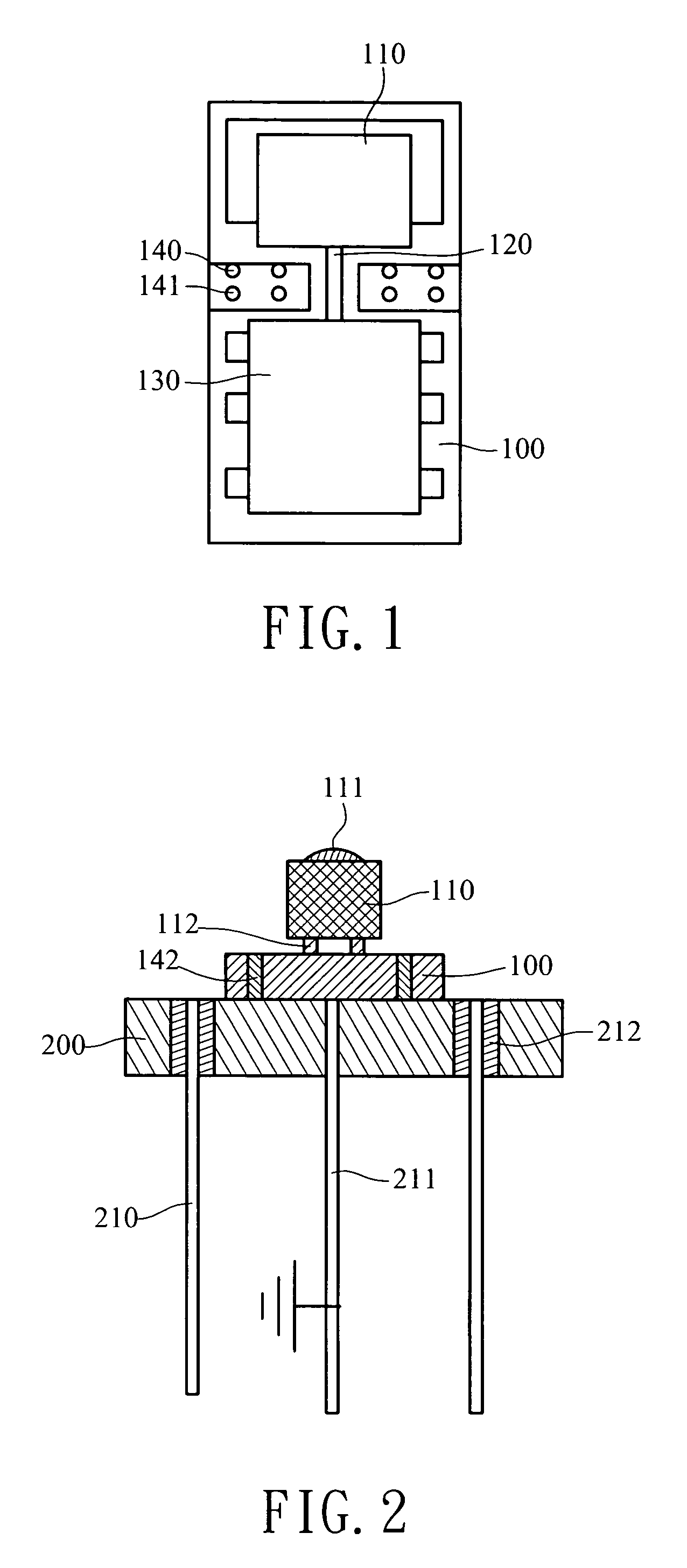

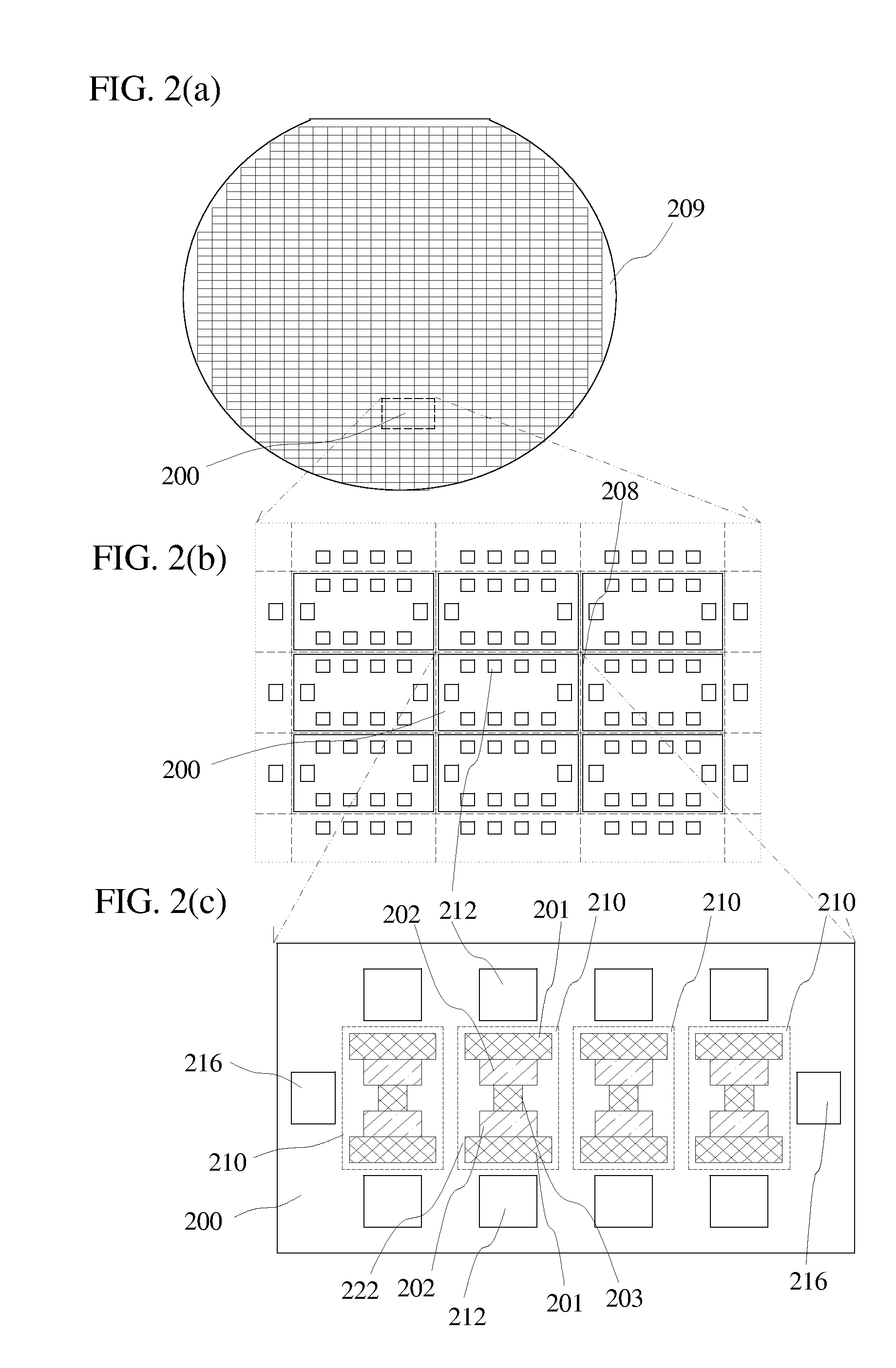

Multibeam arrays of optoelectronic devices for high frequency operation

ActiveUS7949024B2Increase powerReduces parasitic impedance characteristicSemiconductor laser optical deviceLaser cooling arrangementsContact padDevice form

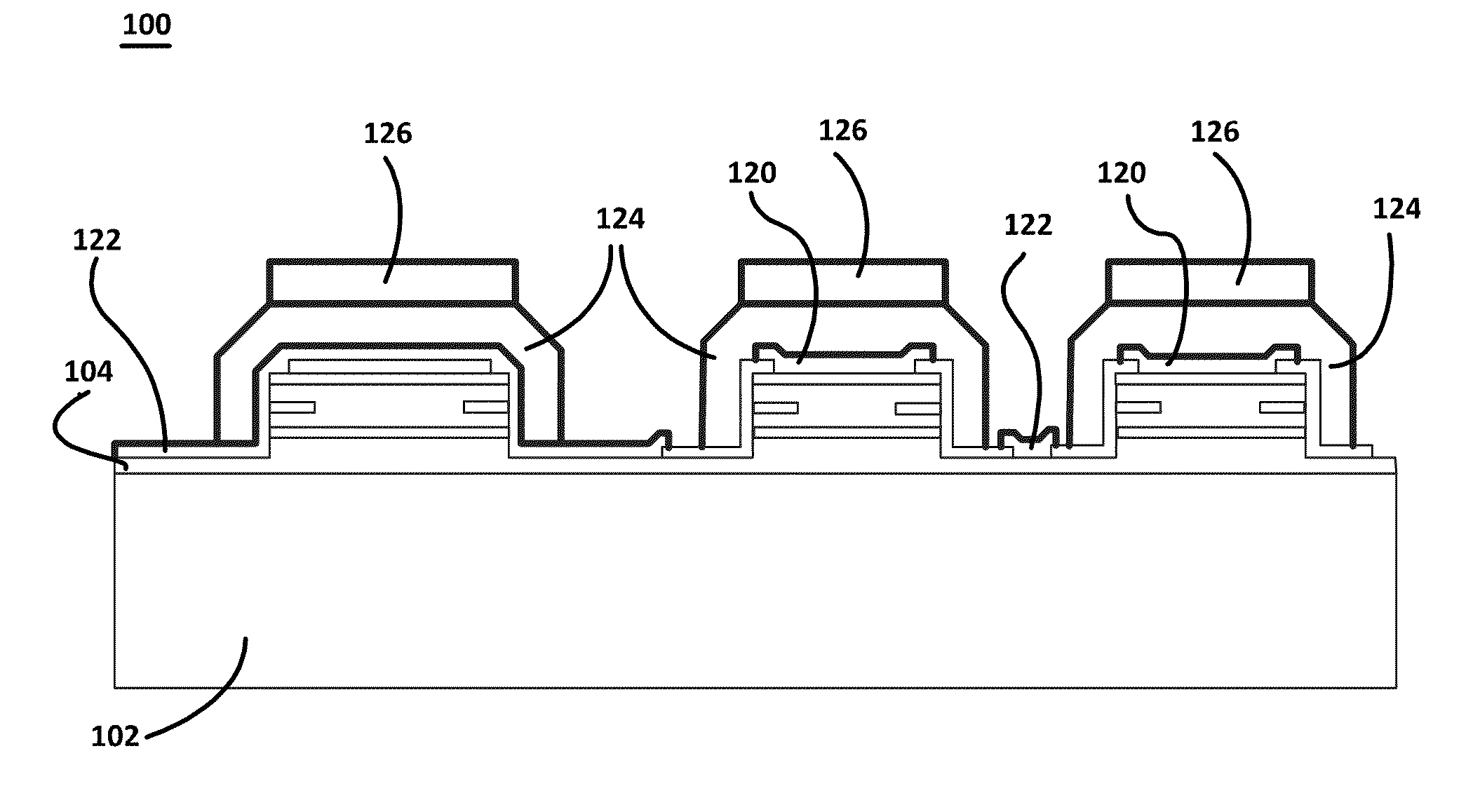

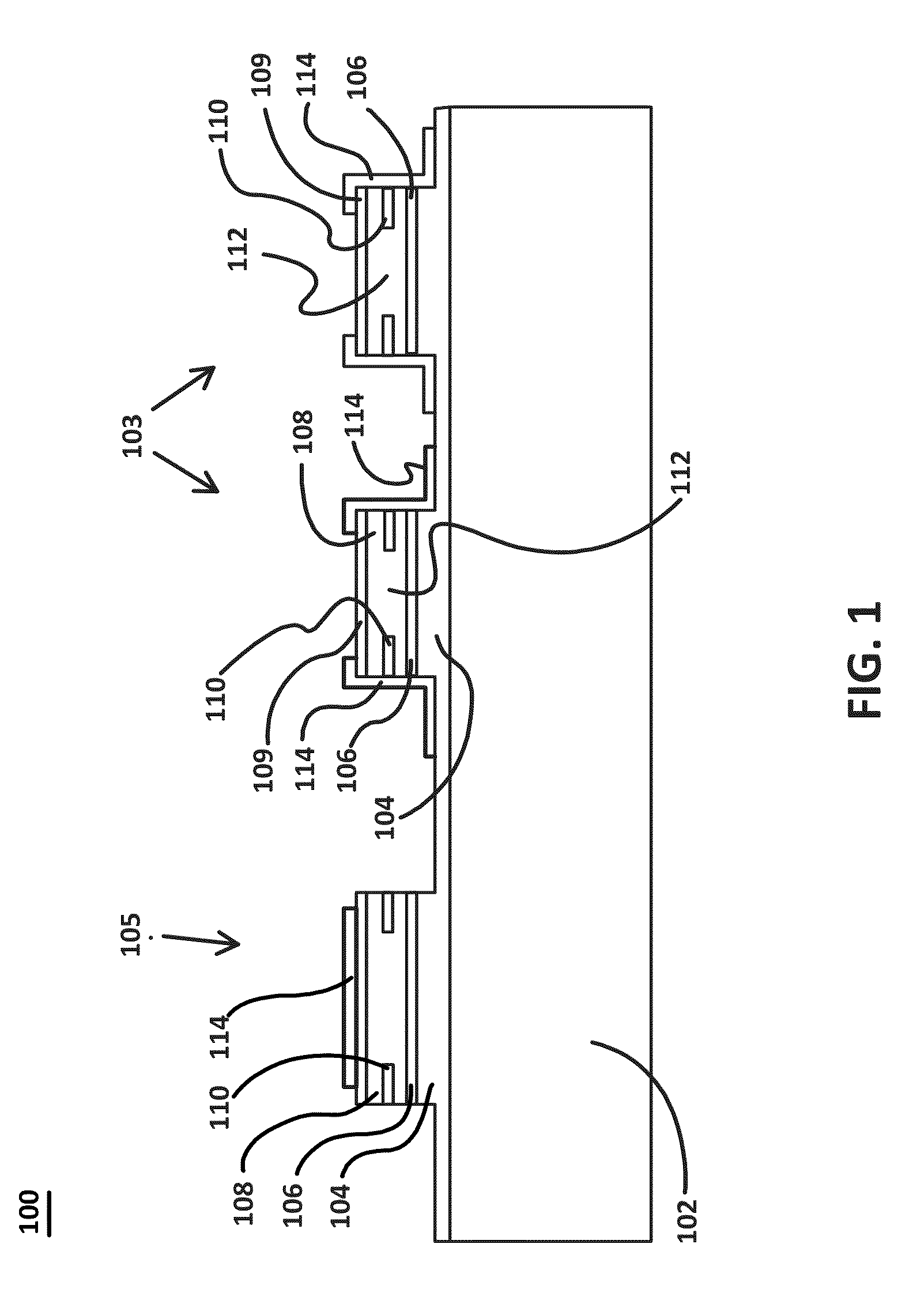

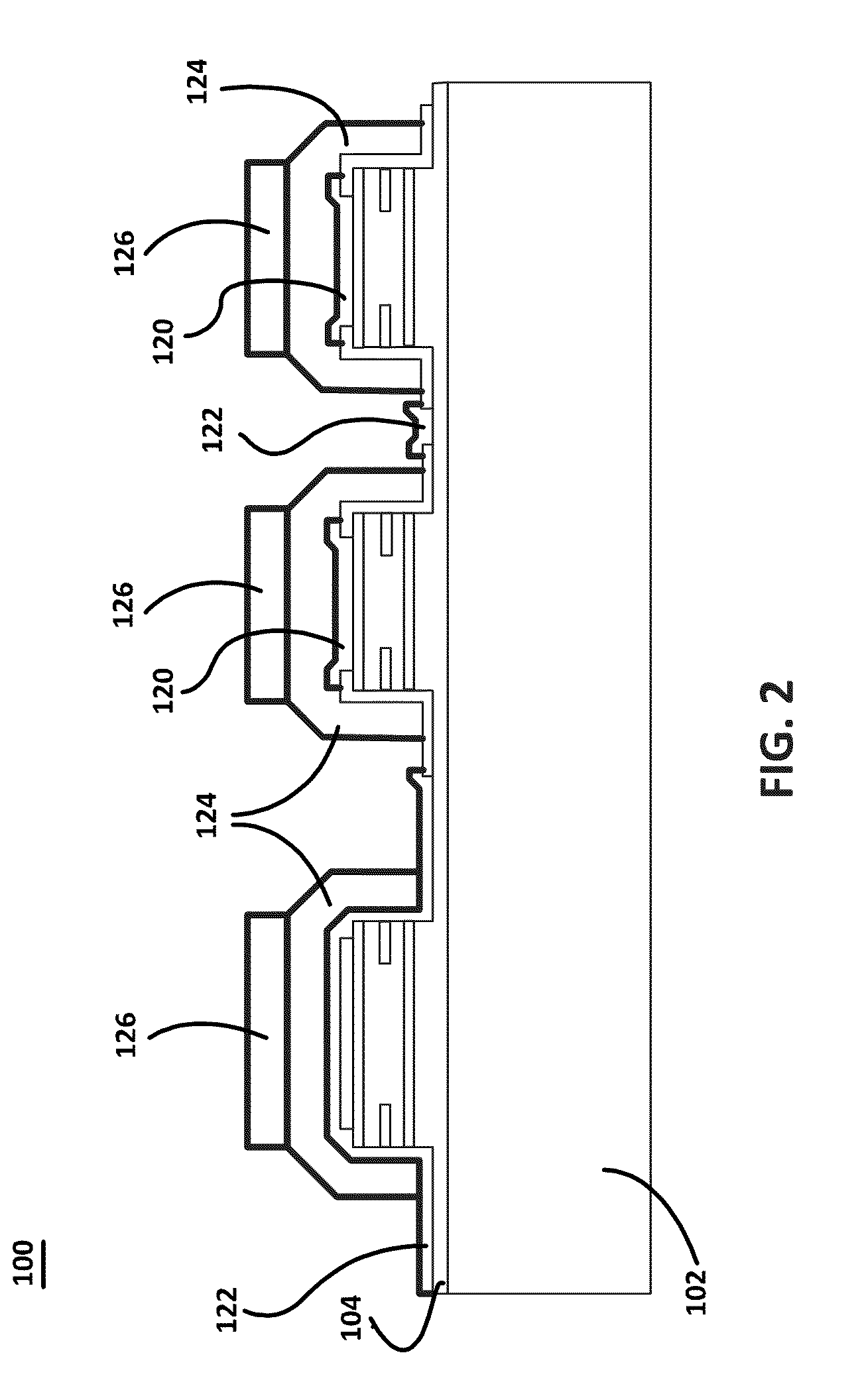

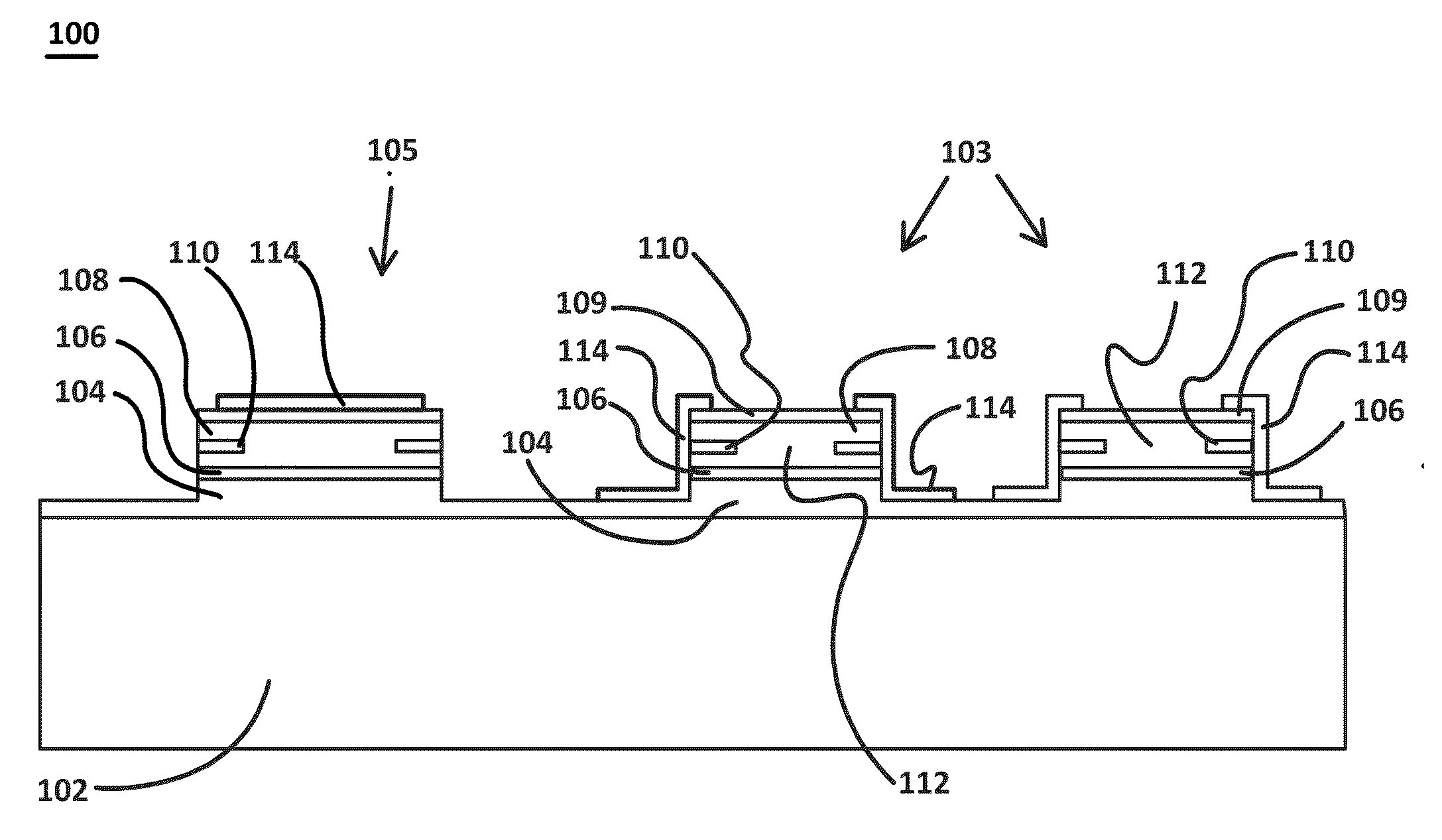

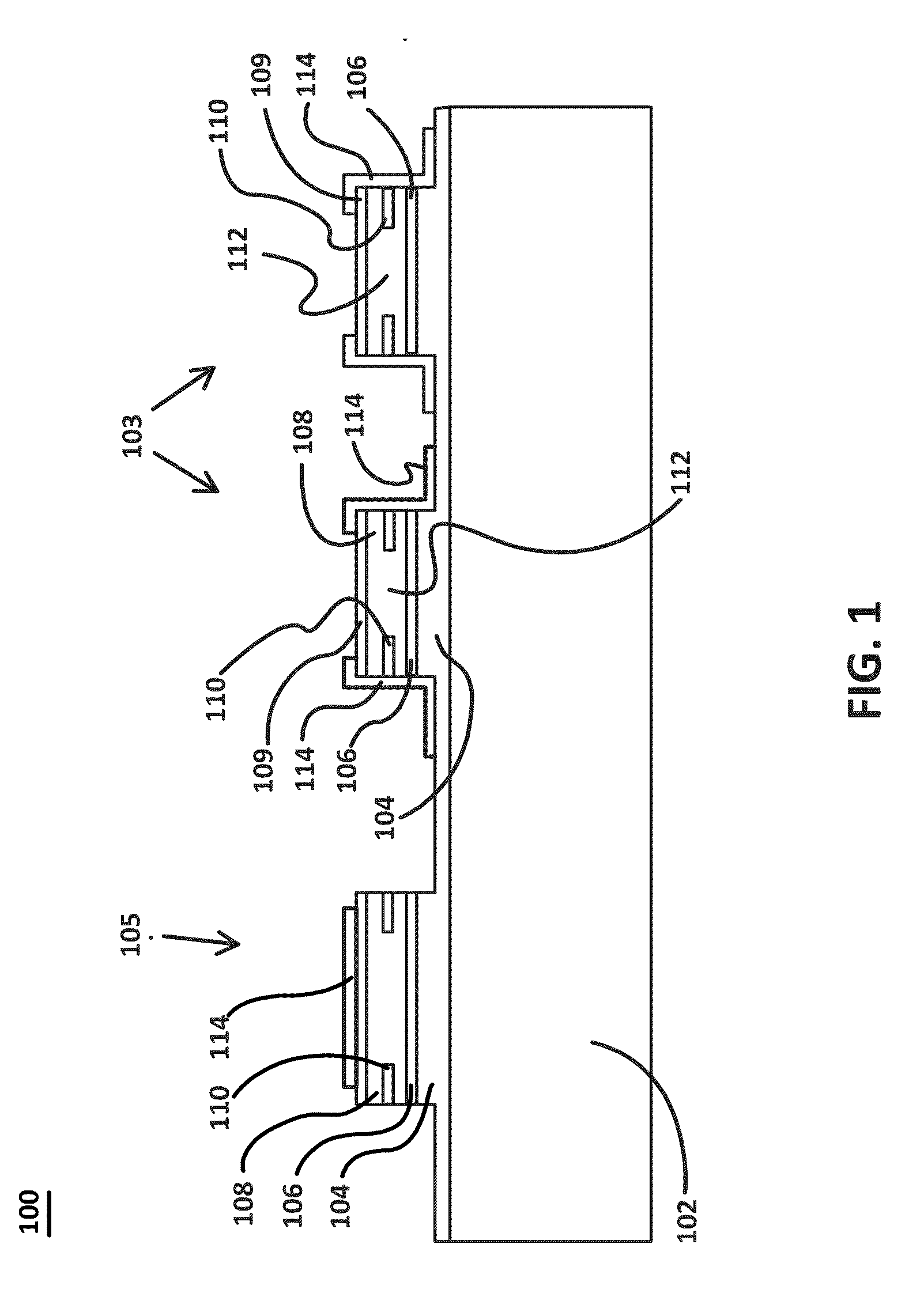

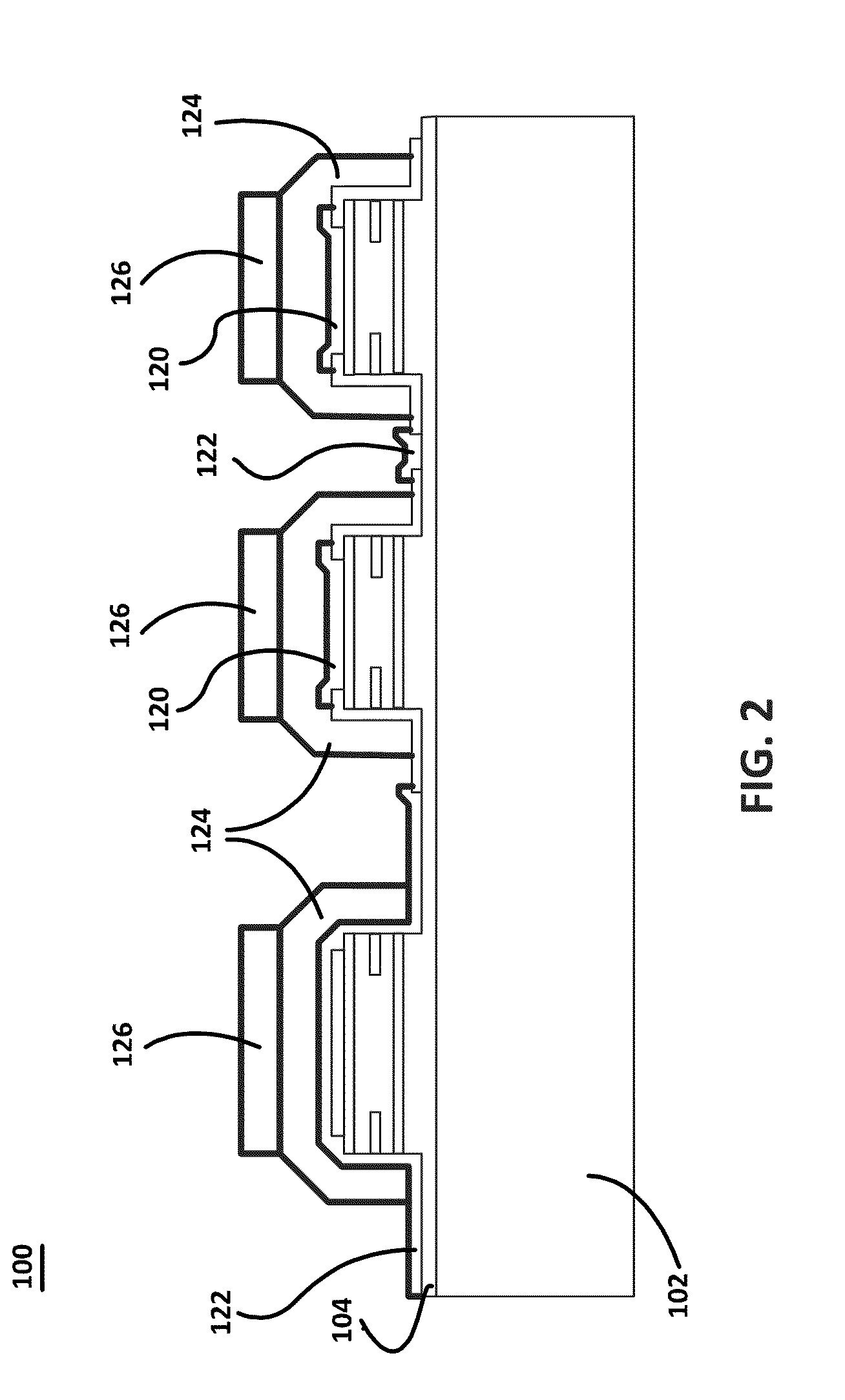

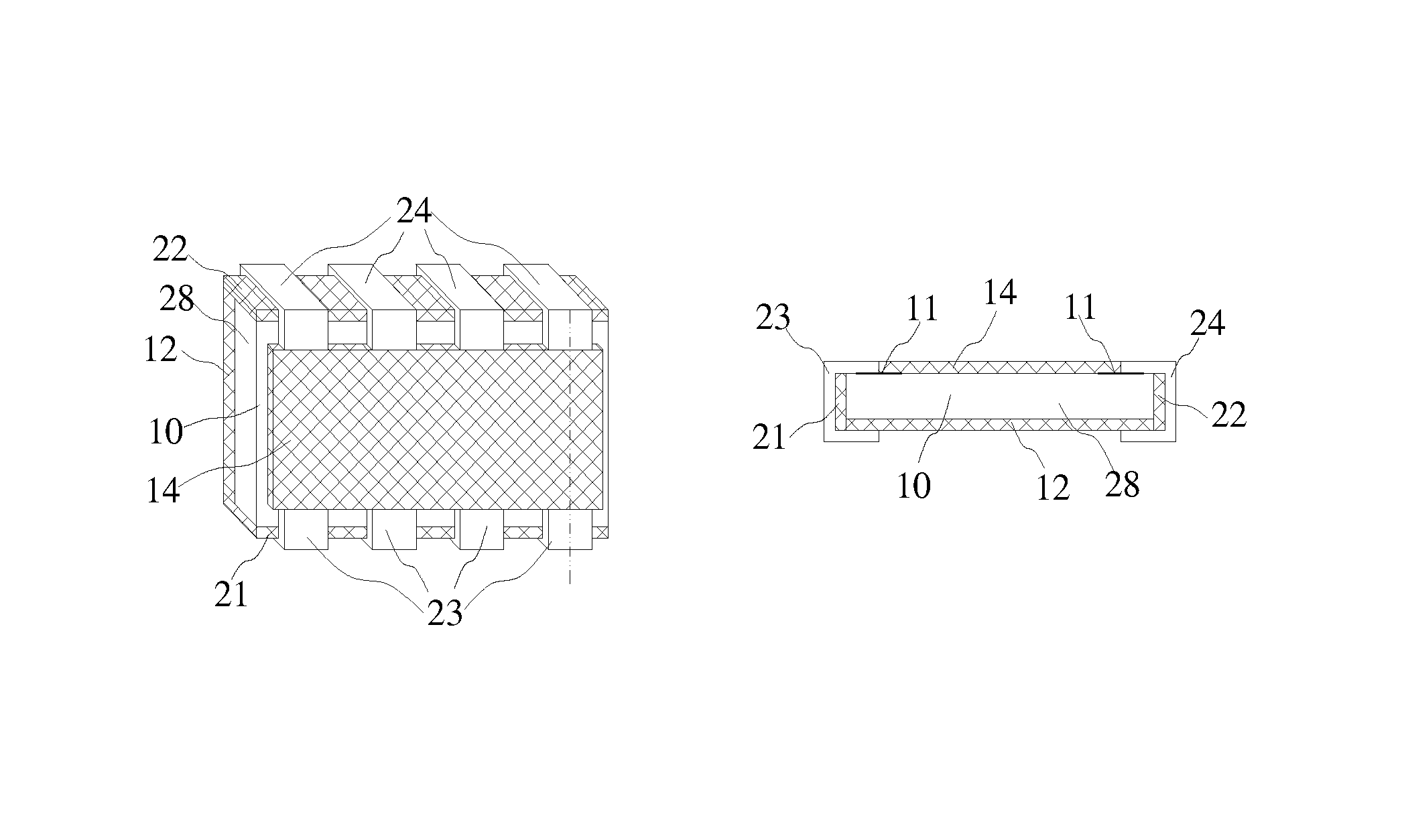

A VCSEL array device formed of a monolithic array of VCSELs and short circuited mesas is disclosed. The VCSELs can be spaced symmetrically or asymmetrical, in a manner to improve power or speed, or in phase and in parallel. The VCSELs are connected to a first metal contact pad formed on a heat-spreading substrate. The short-circuited mesas are formed alongside the VCSELs and are bonded to and form a short circuit to a second metal contact pad on the grounding substrate. Each VCSEL is encompassed by a thick metal heat sink to increase the height of VCSEL mesas. The structure of the heat sink, the VCSELs and the shorting mesas reduce parasitic impedance thereby increasing output power and high frequency response. The VCSELs and shorting mesas can be packaged as a coplanar waveguide in a ground-signal-ground configuration that improves signal modulation characteristics.

Owner:LUMENTUM OPERATIONS LLC

Multibeam Arrays of Optoelectronic Devices for High Frequency Operation

ActiveUS20100303113A1Increase powerReduces parasitic impedance characteristicSemiconductor laser optical deviceLaser cooling arrangementsContact padDevice form

A VCSEL array device formed of a monolithic array of VCSELs and short circuited mesas is disclosed. The VCSELs can be spaced symmetrically or asymmetrical, in a manner to improve power or speed, or in phase and in parallel. The VCSELs are connected to a first metal contact pad formed on a heat-spreading substrate. The short-circuited mesas are formed alongside the VCSELs and are bonded to and form a short circuit to a second metal contact pad on the grounding substrate. Each VCSEL is encompassed by a thick metal heat sink to increase the height of VCSEL mesas. The structure of the heat sink, the VCSELs and the shorting mesas reduce parasitic impedance thereby increasing output power and high frequency response. The VCSELs and shorting mesas can be packaged as a coplanar waveguide in a ground-signal-ground configuration that improves signal modulation characteristics.

Owner:LUMENTUM OPERATIONS LLC

High-temperature, wirebondless, injection-molded, ultra-compact hybrid power module

ActiveUS8120153B1Cost-effectiveImprove long-term reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipPolymer

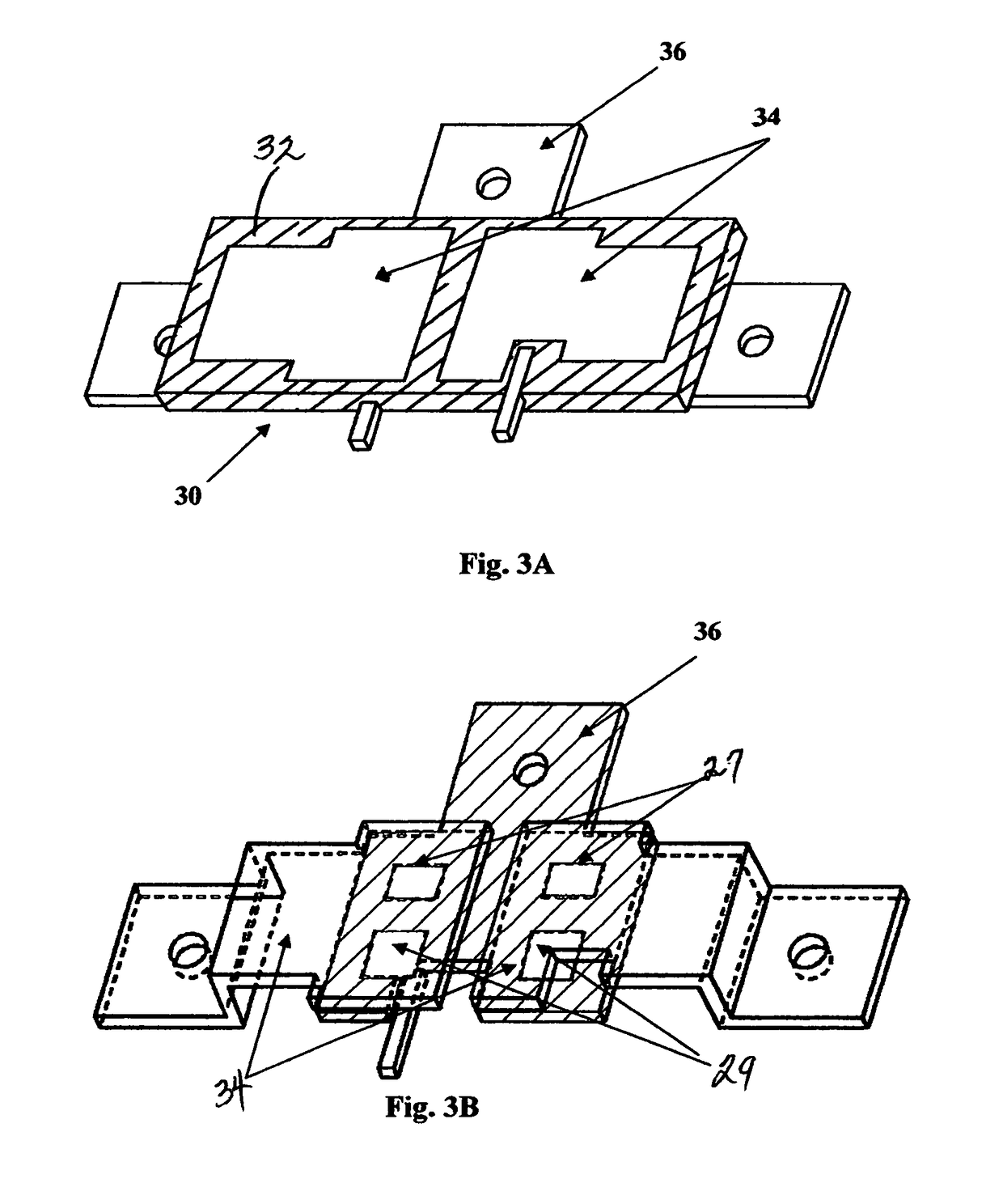

A cost-effective, ultra-compact, hybrid power module packaging system and method for making allows device operation in conventional and high temperature ranges over 300° C. Double metal leadframes are directly bonded to the front- and backside of semiconductor chips, and injection-molded high temperature polymer materials encapsulate the module. The invention eliminates the use of unreliable metal wirebonds and solders joints, and expensive aluminum nitride ceramic substrates commonly used in conventional and high temperature hybrid power modules. Advantages of the new power modules include high current carrying capability, low package parasitic impedance, low thermo-mechanical stress under high temperature cycling, low package thermal resistance (double-side cooling), modularity for easy system-level integration, and low-cost manufacturing of devices compatible with current electronic packaging industry. A first embodiment uses molybdenum leadframes for operation in temperatures over 300° C.; a second embodiment of the invention, uses copper and copper alloy leadframes, provides benefits for conventional temperature electronics.

Owner:UNIV OF CENT FLORIDA RES FOUND INC

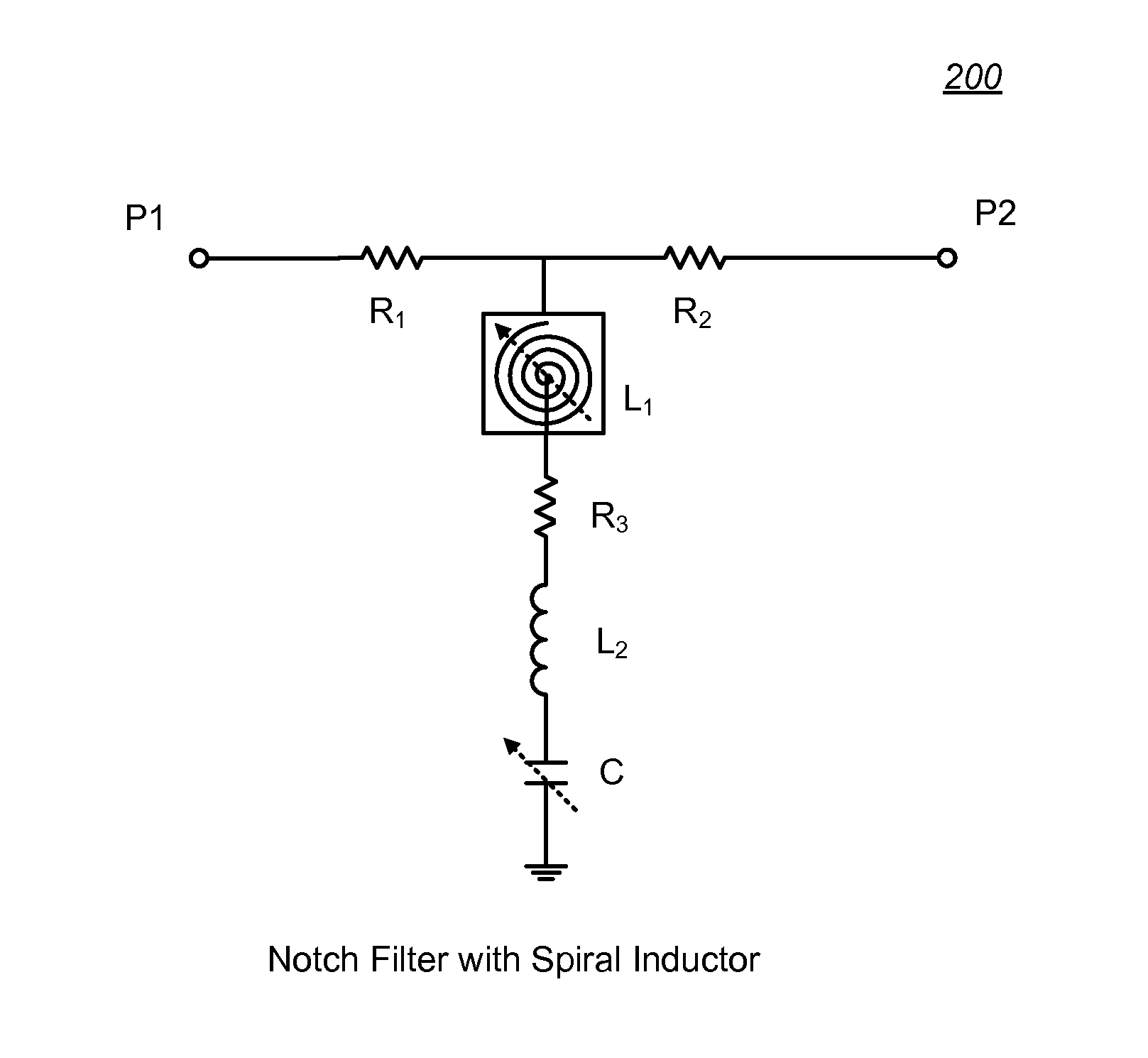

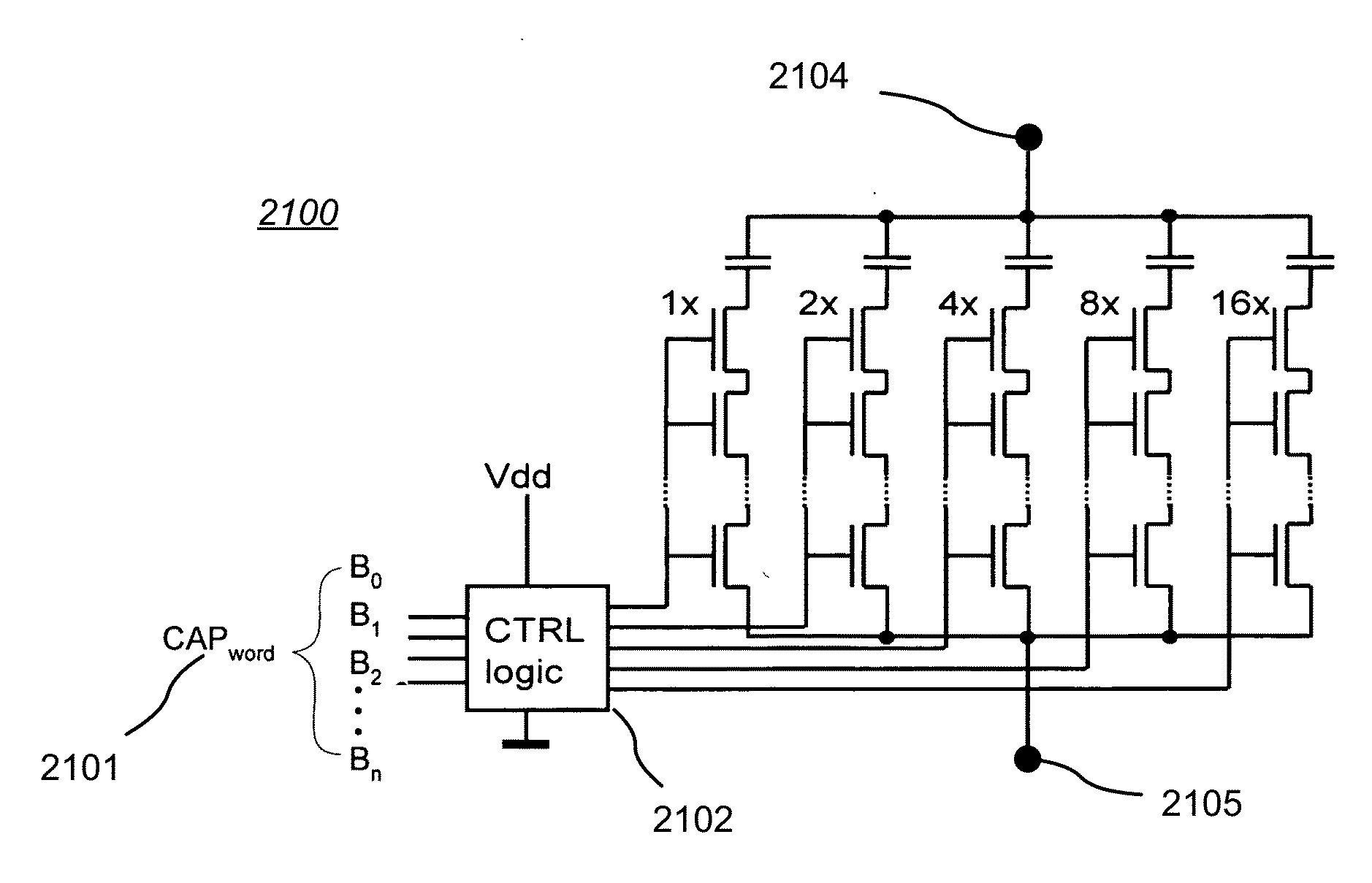

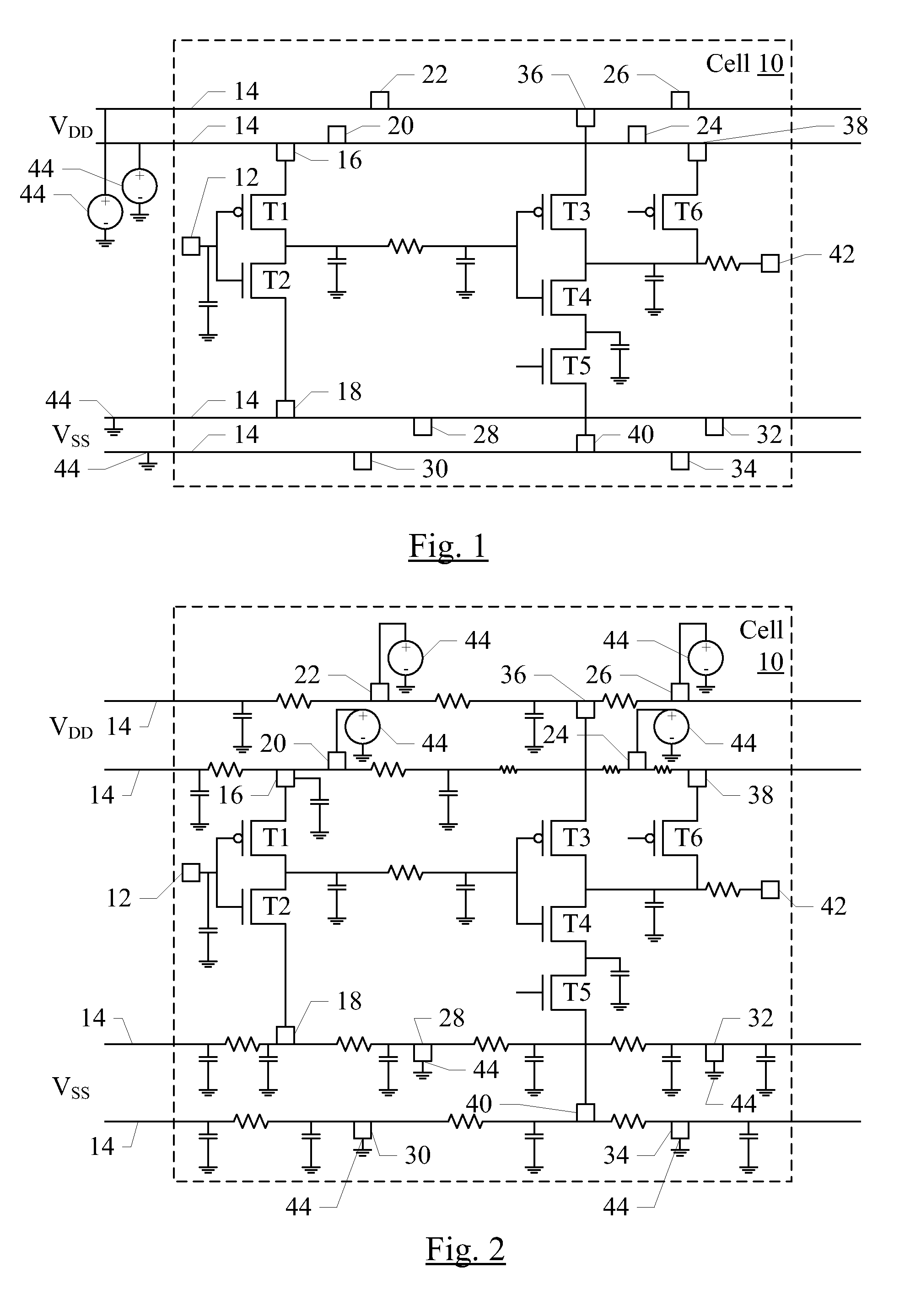

Integrated tunable filter architecture

ActiveUS9673155B2Large insertion lossLoss of impactMultiple-port networksSemiconductor/solid-state device detailsBandpass filteringEngineering

Owner:PSEMI CORP

Integrated Tunable Filter Architecture

ActiveUS20150235971A1Large insertion lossLoss of impactMultiple-port networksPrinted circuit assemblingBandpass filteringMultiple frequency

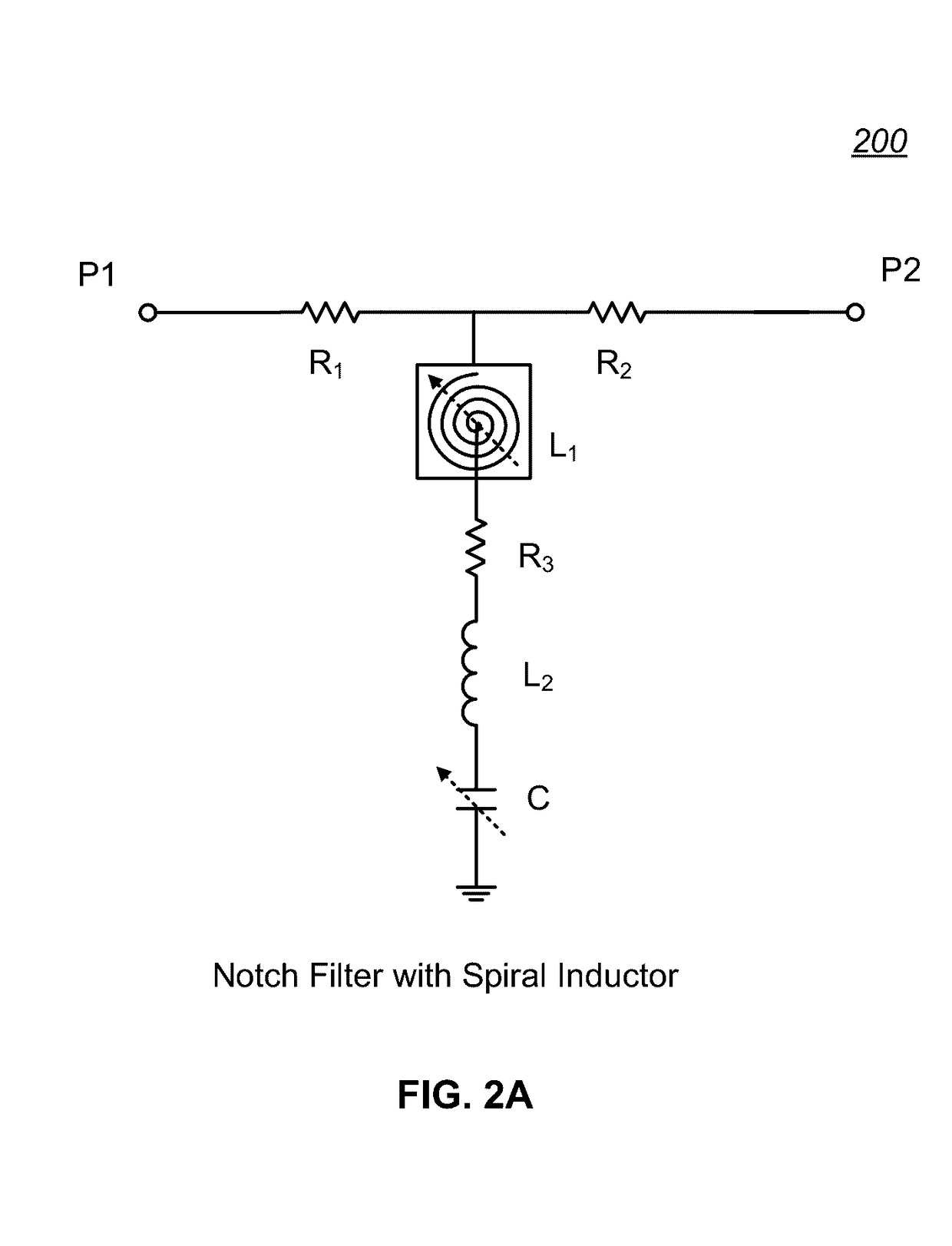

An apparatus and method for a frequency based integrated circuit that selectively filters out unwanted bands or regions of interfering frequencies utilizing one or more tunable notch or bandpass filters or tunable low or high pass filters capable of operating across multiple frequencies and multiple bands in noisy RF environments. The tunable filters are fabricated within the same integrated circuit package as the associated frequency based circuitry, thus minimizing R, L, and C parasitic values, and also allowing residual and other parasitic impedance in the associated circuitry and IC package to be absorbed and compensated.

Owner:PSEMI CORP

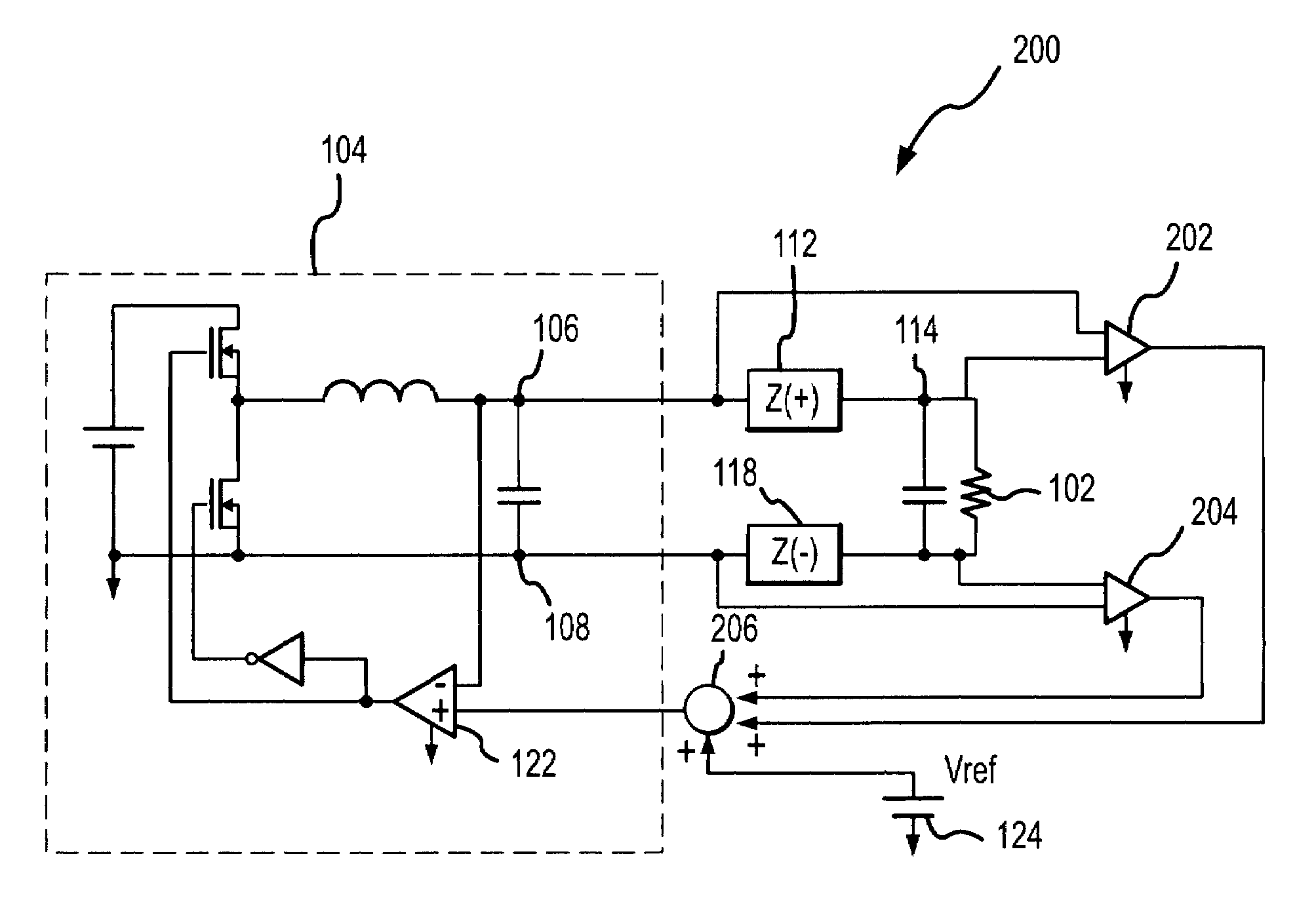

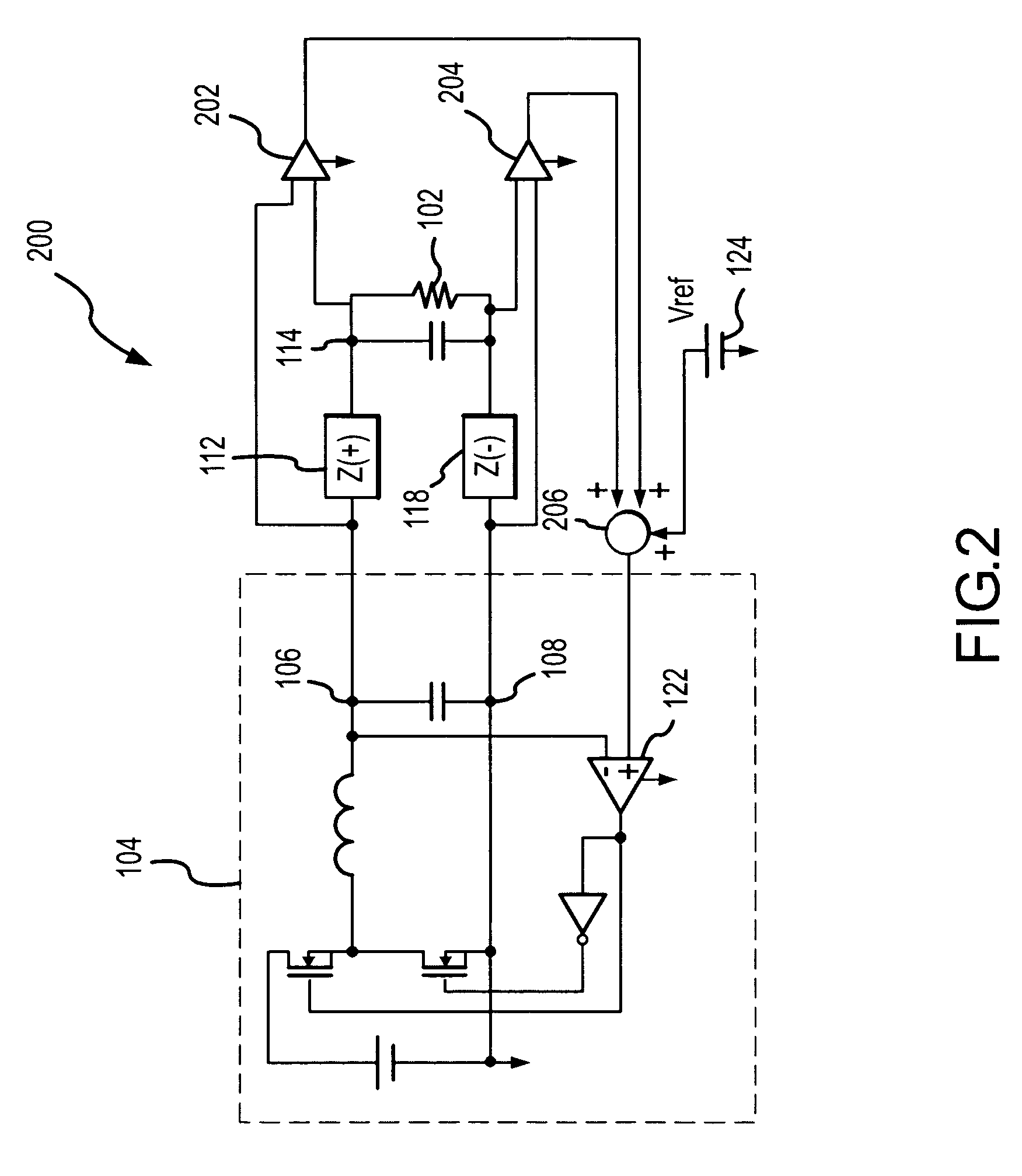

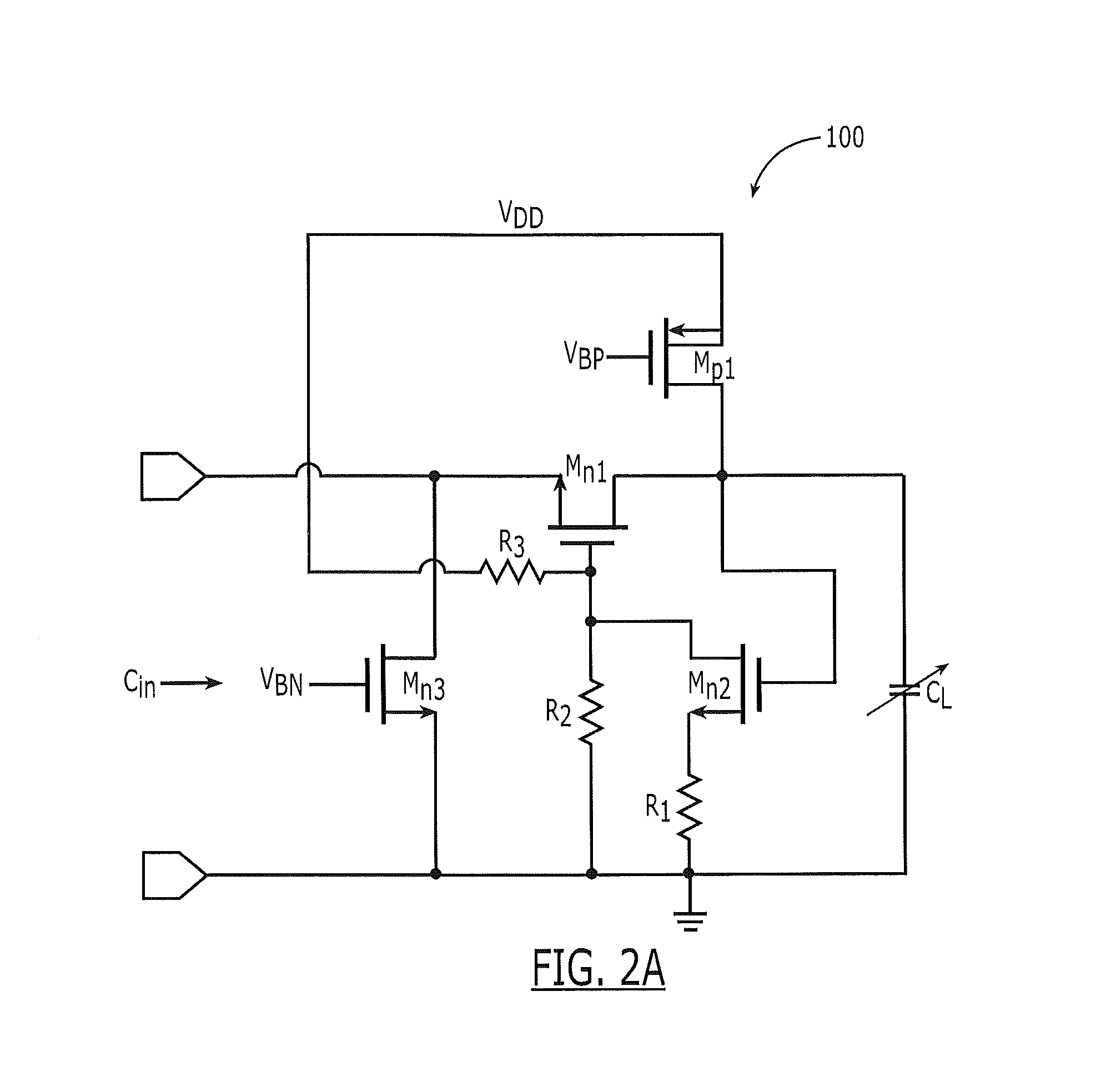

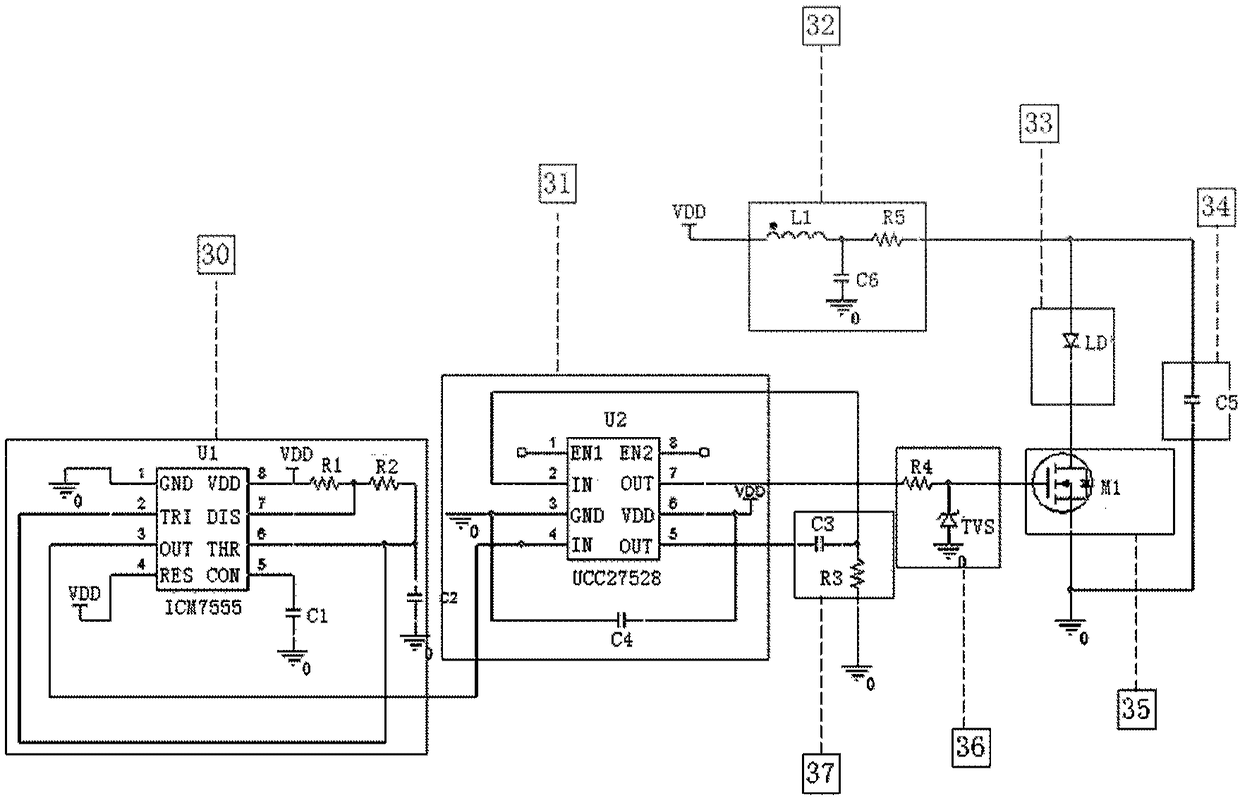

Method and apparatus for voltage compensation for parasitic impedance

InactiveUS7242169B2Efficient power electronics conversionDc-dc conversionAudio power amplifierVoltage drop

An apparatus and method for regulating a voltage to a load to compensate for one or more parasitic impedances. A first amplifier measures the voltage drop due to a first parasitic impedance, and a second amplifier measures the voltage drop due to a second parasitic impedance. An offset generator sums the first and second voltage drops with a reference voltage, and drives a DC-to-DC converter to produce an input voltage matching the summed voltages. Accordingly, the voltage at a load between the parasitic impedances matches the reference voltage. The load may be, for example, a computer microprocessor or central processing unit.

Owner:APPLE INC

Area reduction for surface mount package chips

InactiveUS20110133337A1Reduce areaCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSurface mounting

Using side-wall conductor leads deposited on the side-walls of a base substrate to form package level conductor leads for active circuits manufactured on silicon substrate(s) stacked on the base substrate, the preferred embodiments of the present invention significantly reduces the areas of surface mount package chips. Besides area reduction, these methods also provide significant cost saving and reduction in parasitic impedance.

Owner:SHAU JENG JYE

Integrated Tunable Filter Architecture

ActiveUS20150236671A1Minimize signal propagationReduce parasitic capacitanceMultiple-port networksDigital technique networkBandpass filteringEngineering

An apparatus and method for a frequency based integrated circuit that selectively filters out unwanted bands or regions of interfering frequencies utilizing one or more tunable notch or bandpass filters or tunable low or high pass filters capable of operating across multiple frequencies and multiple bands in noisy RF environments. The tunable filters are fabricated within the same integrated circuit package as the associated frequency based circuitry, thus minimizing R, L, and C parasitic values, and also allowing residual and other parasitic impedance in the associated circuitry and IC package to be absorbed and compensated.

Owner:PSEMI CORP

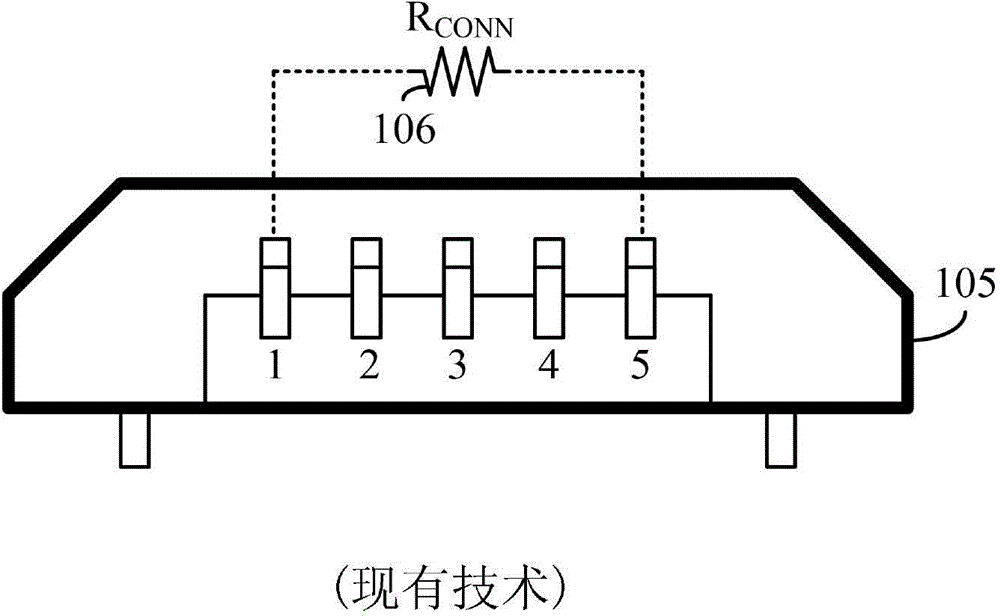

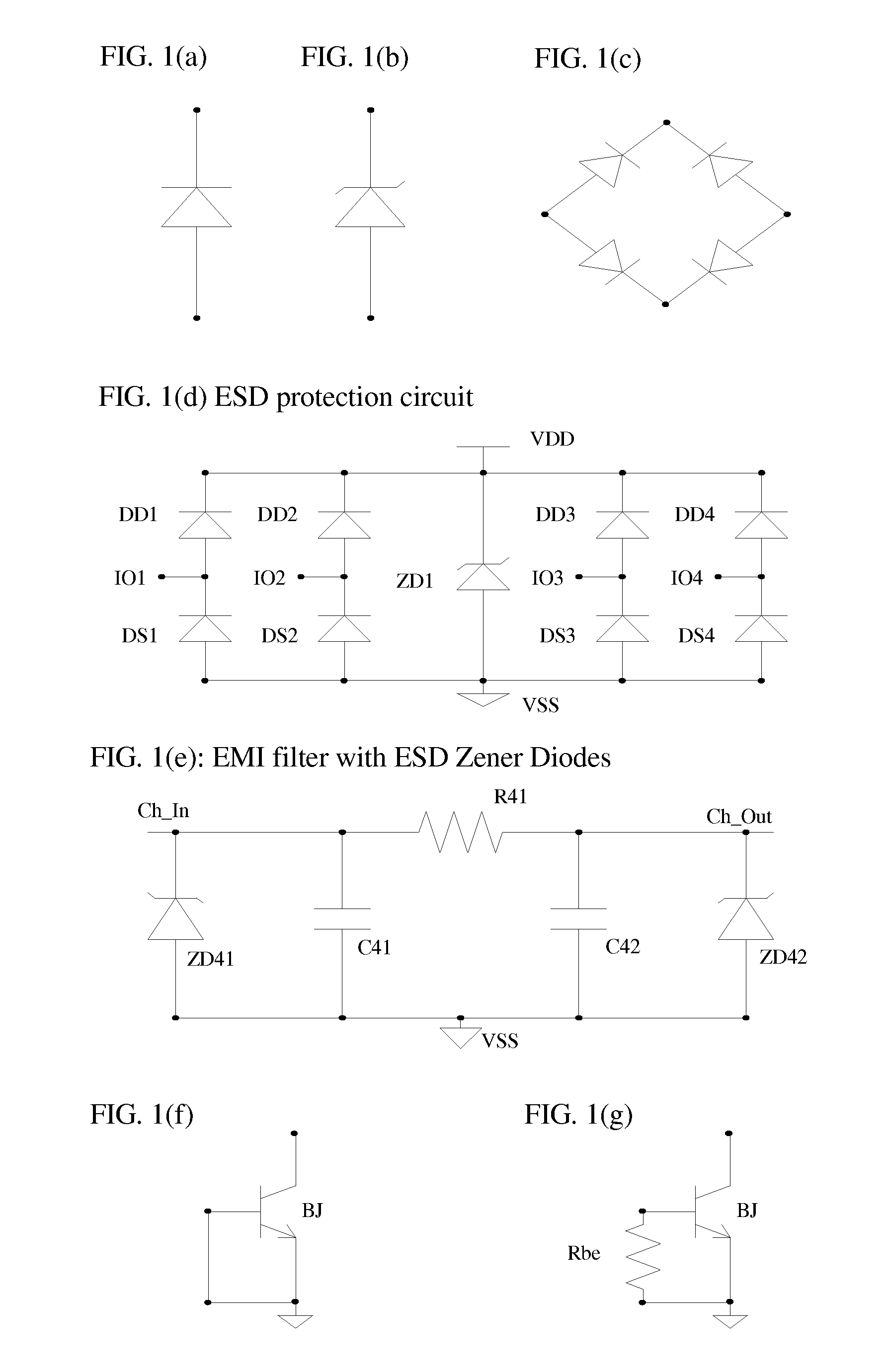

Protection circuit for a standard connector adapter and protection method thereof

ActiveCN104836208AEmergency protection detectionArrangements resposive to fault currentElectrical resistance and conductanceEngineering

This document discusses, among other things, a protection system and method configured to detect a parasitic impedance between first and second pins of a standard connector and to remove a current path between a power source and a supply pin of the standard connector if a low-impedance is detected, in certain examples, without adding a current sense resistance to a return path between a ground pin of the standard connector and the power source.

Owner:FAIRCHILD SEMICON SUZHOU +1

Integrated tunable filter architecture

ActiveUS9438196B2Minimize signal propagationReduce parasitic capacitanceMultiple-port networksDigital technique networkBandpass filteringMultiple frequency

An apparatus and method for a frequency based integrated circuit that selectively filters out unwanted bands or regions of interfering frequencies utilizing one or more tunable notch or bandpass filters or tunable low or high pass filters capable of operating across multiple frequencies and multiple bands in noisy RF environments. The tunable filters are fabricated within the same integrated circuit package as the associated frequency based circuitry, thus minimizing R, L, and C parasitic values, and also allowing residual and other parasitic impedance in the associated circuitry and IC package to be absorbed and compensated.

Owner:PSEMI CORP

Voltage controlled oscillator

ActiveUS8957738B1Increase ratingsImprove thermal stabilityAngle modulation by variable impedencePulse automatic controlCapacitancePhase noise

A voltage controlled oscillator including an RF output terminal and a DC control terminal, an active circuit, and a resonant circuit interconnected with the active circuit and including a plurality of series resonators each having an electrically variable capacitance and fixed inductor; the active circuit includes at least one transistor having an operating current density which is approximately 35% or less of the peak fT operating current density and / or the active circuit includes a multi-transistor bank disposed in at least two separate sections, each pair of sections spaced apart to provide improved thermal uniformity among the transistors without substantially increasing parasitic impedance among them for providing an improved lower phase noise output at said RF output terminal.

Owner:HITTITE MICROWAVE LLC

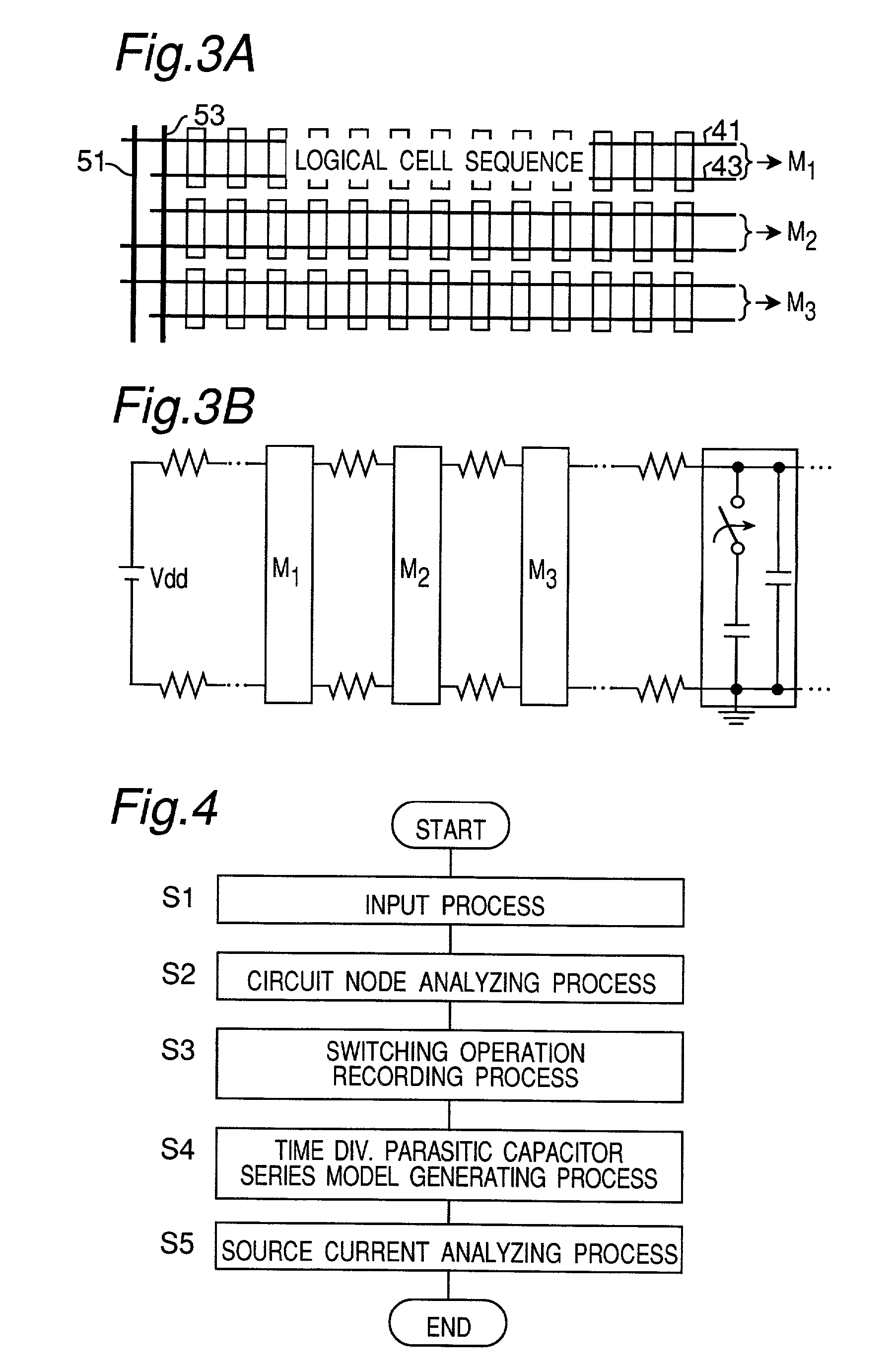

Method and apparatus for analyzing a source current waveform in a semiconductor integrated circuit

InactiveUS7039536B2Increase speedImprove accuracyAnalog circuit testingNoise figure or signal-to-noise ratio measurementParasitic capacitorCapacitance

The invention provides a method of analyzing a source current at a higher speed and an enhanced accuracy in a semiconductor integrated circuit including a digital circuit. The method to analyze a waveform of the source current, with consideration of re-distribution of charges throughout the digital circuit in the semiconductor integrated circuit, expressing the digital circuit with series of parasitic capacitors ΣCch, ↑ (nT) and ΣCch, ↓ (nT) to be charged and connected between the source and the ground lines. The capacitor series are calculated in time series based on the distribution of switching operations of the logic gates included in the digital circuit. An analysis model for determining the waveform of the source current in the digital circuit is obtained by connecting the parasitic capacitor series with a couple of respective parasitic impedances Zd and Zg of the source line and the ground line.

Owner:A R TEC CORP

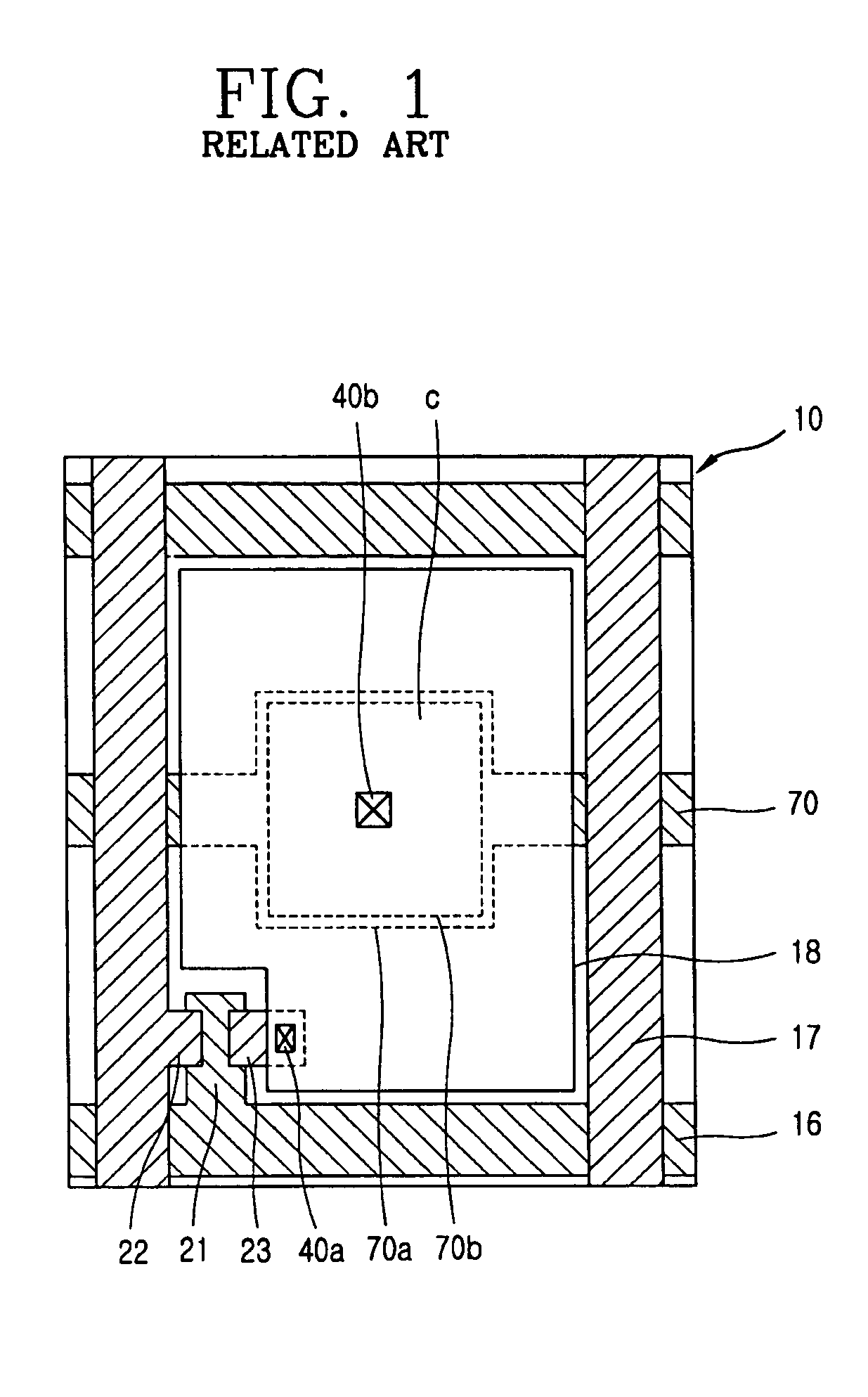

Liquid crystal display panel with reduced parasitic impedance

A liquid crystal display includes an array substrate, a data line, a gate line, a first and a second storage wiring, and a second substrate. The data line is disposed on the array substrate and intersects the gate line near a first pixel region. A second substrate, such as a color filter substrate, includes a second pixel region that corresponds to the first pixel region. The first storage wiring is positioned near an edge of the array substrate and the second storage wiring is disposed on the second substrate near an edge of the second substrate.

Owner:LG DISPLAY CO LTD

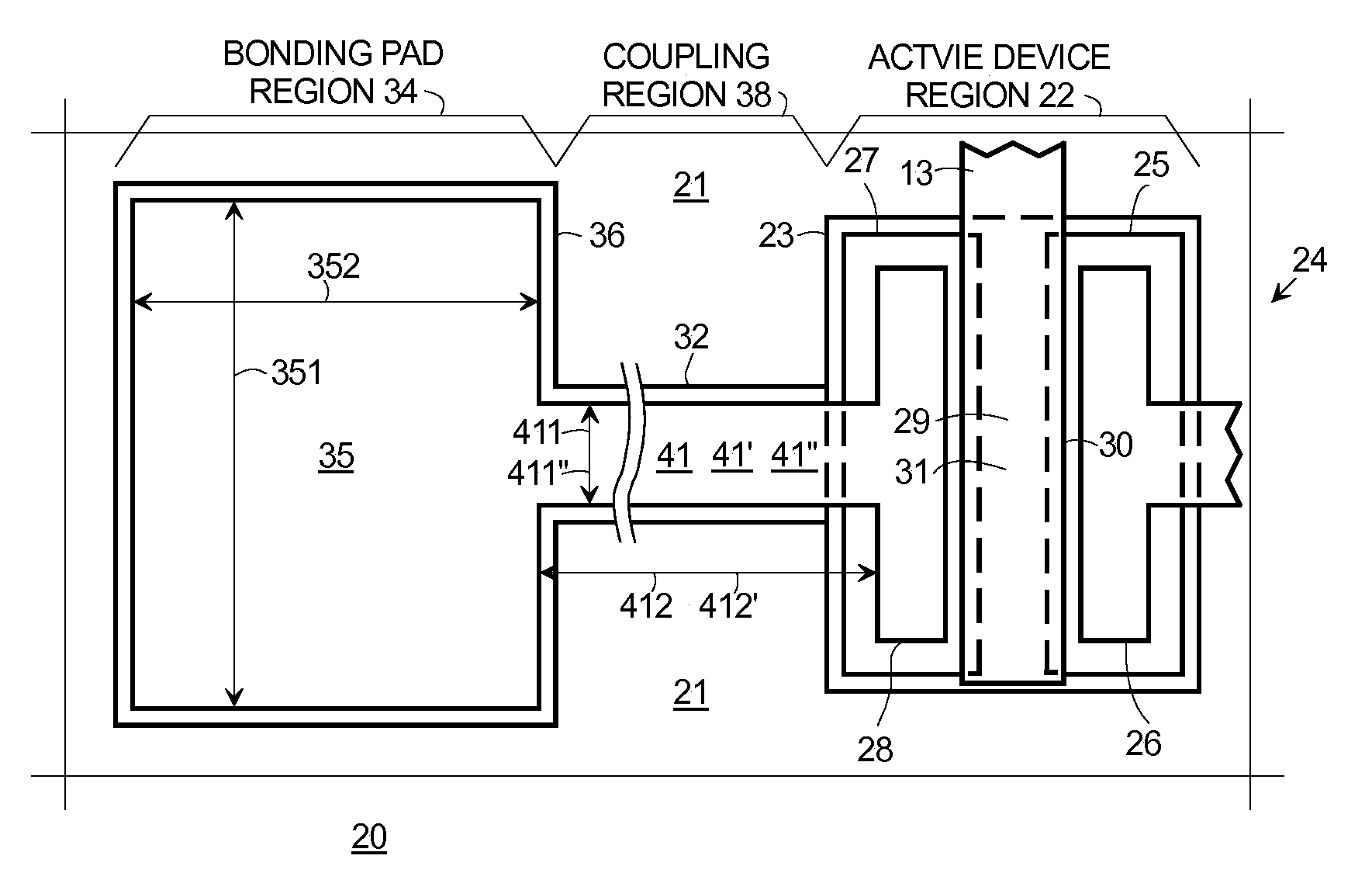

RF device and method with trench under bond pad feature

ActiveUS20100140814A1Semiconductor/solid-state device detailsSolid-state devicesAmorphous siliconSilicon oxide

Electronic elements (44, 44′, 44″) having an active device region (46) and bonding pad (BP) region (60) on a common substrate (45) desirably include a dielectric region underlying the BP (35) to reduce the parasitic impedance of the BP (35) and its interconnection (41) as the electronic elements (44, 44′, 44″) are scaled to higher power and / or operating frequency. Mechanical stress created by plain (e.g., oxide only) dielectric regions (36′) can adversely affect performance, manufacturing yield, pad-to-device proximity and occupied area. This can be avoided by providing a composite dielectric region (62, 62′, 62″) having electrically isolated inclusions (65, 65′, 65′) of a thermal expansion coefficient (TEC) less than that of the dielectric material (78, 78′, 78″) in which they are embedded and / or closer to the substrate (45) TEC. For silicon substrates (45), poly or amorphous silicon is suitable for the inclusions (65, 65′, 65″) and silicon oxide for the dielectric material (78, 78′, 78″). The inclusions (65, 65′, 65″) preferably have a blade-like shape separated by and enclosed within the dielectric material (78, 78′, 78″).

Owner:NXP USA INC

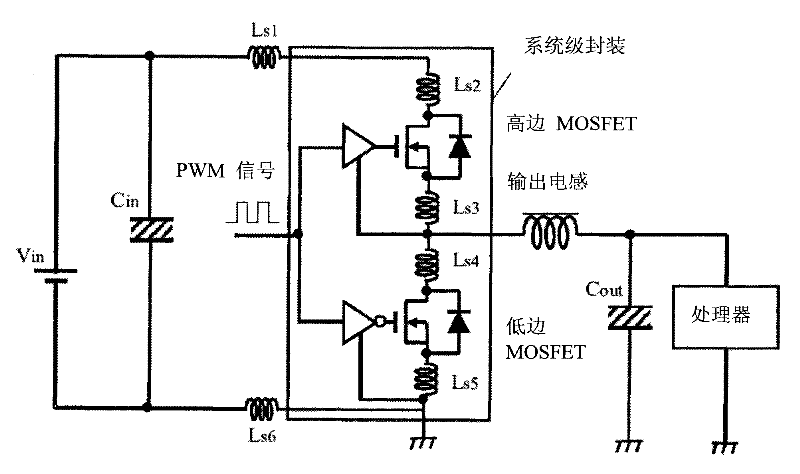

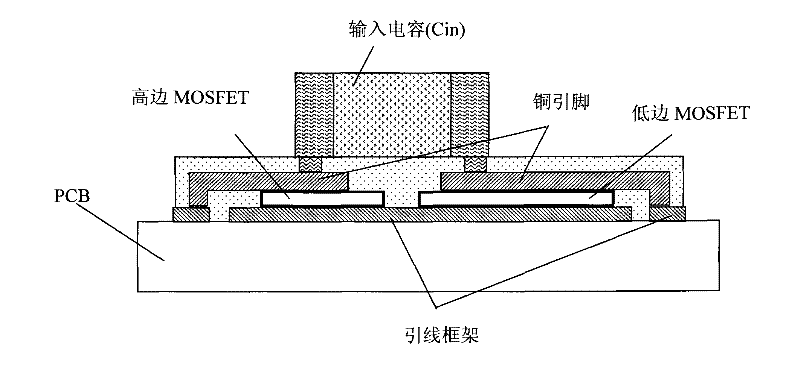

Compact semiconductor package with integrated bypass capacitor and method

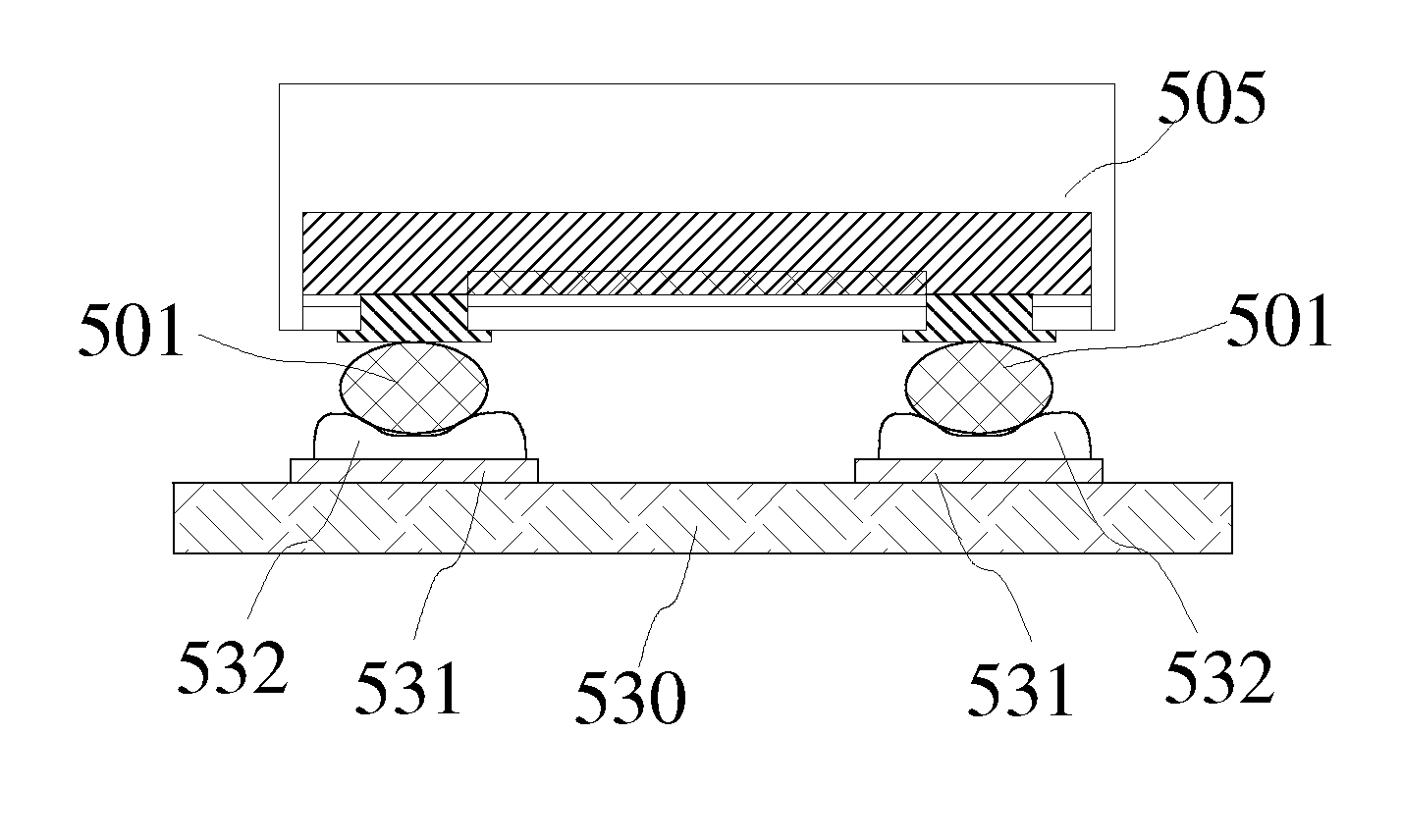

ActiveCN101752358ASemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A top-side cooled compact semiconductor package with integrated bypass capacitor is disclosed. The top-side cooled compact semiconductor package includes a circuit substrate with terminal leads, numerous semiconductor dies bonded atop the circuit substrate, numerous elevation-adaptive interconnection plates for bonding and interconnecting top contact areas of the semiconductor dies with the circuit substrate, a first member of the elevation-adaptive interconnection plates has a first flat-top area and a second member of the elevation-adaptive interconnection plates has a second flat-top area in level with the first flat-top area, a bypass capacitor, having two capacitor terminals located at its ends, stacked atop the two interconnection plate members while being bonded thereto via the first flat-top area and the second flat-top area for a reduced interconnection parasitic impedance.

Owner:重庆万国半导体科技有限公司

Suppression method and structure for reducing a via stub effect of a substrate

InactiveUS20070132527A1Reduce stub effectExtra costMultiple-port networksHigh frequency circuit adaptationsImpedance matchingParasitic impedance

A suppression method for suppressing a via stub effect of a substrate is disclosed. The suppression method is applicable to a substrate having a via, a first conductive line and a second conductive line connected through the via to the first conductive line. The suppression method includes changing a first width of a first conductive segment of the first conductive line connected to the via, and changing a second width of a second conductive segment of the second conductive line connected to the via, so as to change impedances of the first conductive line and the second conductive line to match with a stub impedance of the via, reduce a parasite impedance of the via stub, reach an impedance match at a designed frequency point, and improve an integrity of a signal after traveling from the first conductive line, the via and the second conductive line.

Owner:INVENTEC CORP

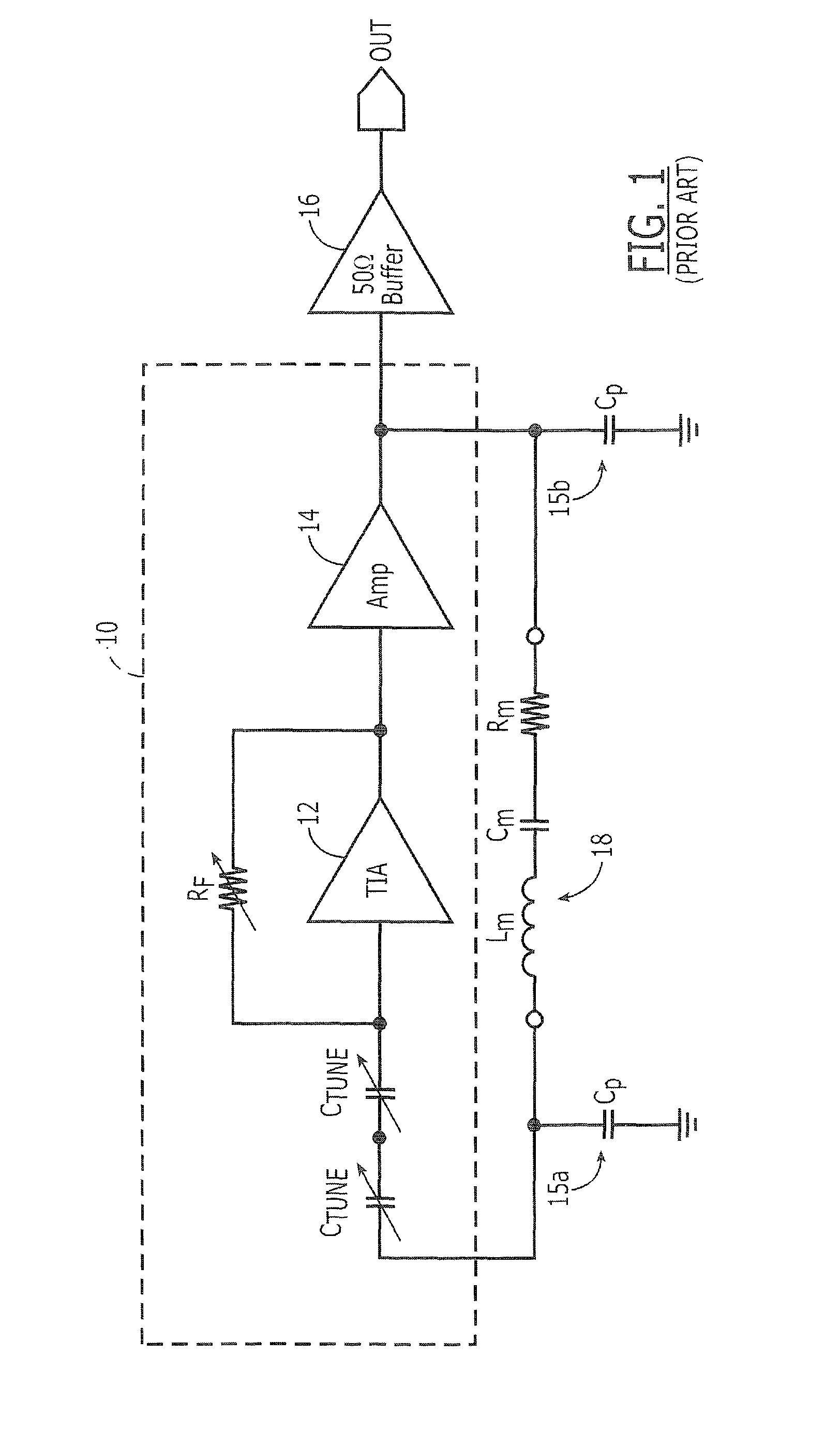

Integrated Circuit Oscillators Having Microelectromechanical Resonators Therein with Parasitic Impedance Cancellation

InactiveUS20100308930A1Increase tuning rangePulse automatic controlOscillations generatorsAudio power amplifierResonator

An integrated circuit oscillator includes a microelectromechanical (MEM) resonator having input and output terminals. An oscillation sustaining circuit is provided. The oscillation sustaining circuit is electrically coupled between the input and output terminals of the microelectromechanical resonator. The oscillation sustaining circuit includes a sustaining amplifier and a negative impedance circuit electrically coupled to the sustaining amplifier. The negative impedance circuit is configured to increase a tuning range of the oscillator by at least partially cancelling a parasitic shunt capacitance associated with the microelectromechanical resonator.

Owner:GEORGIA TECH RES CORP

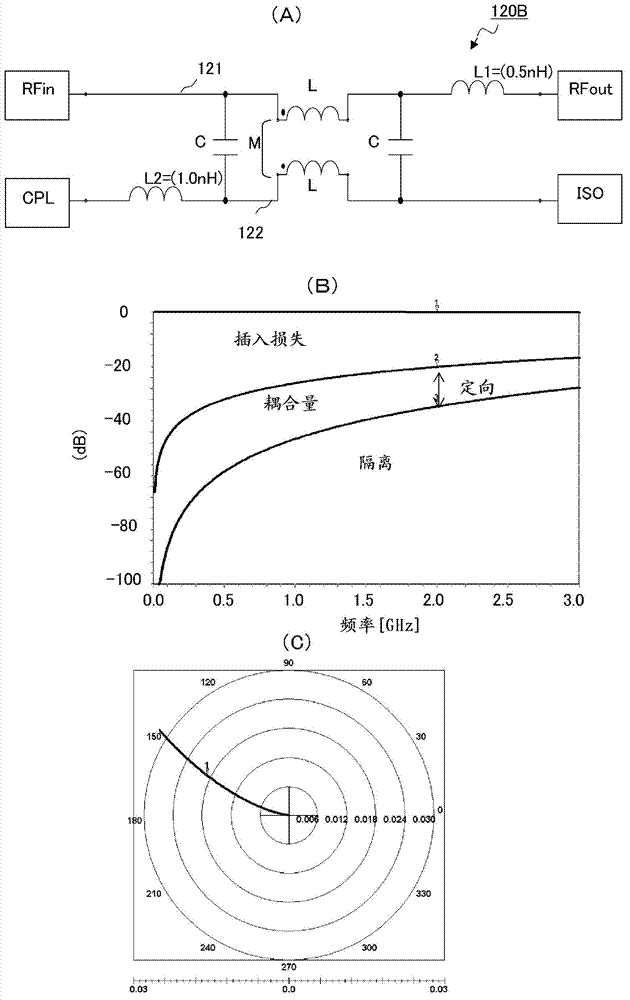

Directional coupler

ActiveCN103201899ASuppression of upsizingImprove isolation characteristicsCoupling devicesCapacitanceMagnetic field coupling

In the present invention, while minimizing increases in the size of a directional coupler, said directional coupler is provided with good isolation characteristics even in the presence of parasitic impedance. A transmission-line directional coupler (20A) is provided with a main line (21) and a coupled line (22) that is coupled to the main line (21) by electric-field coupling and magnetic-field coupling. The main line (21) has a signal-input port (RFin) and a signal-output port (RFout), and the coupled line (22) has a coupling port (CPL) and an isolation port (ISO). A series capacitance is connected to either the signal-output port (RFout) or the coupling port (CPL), but not both.

Owner:MURATA MFG CO LTD

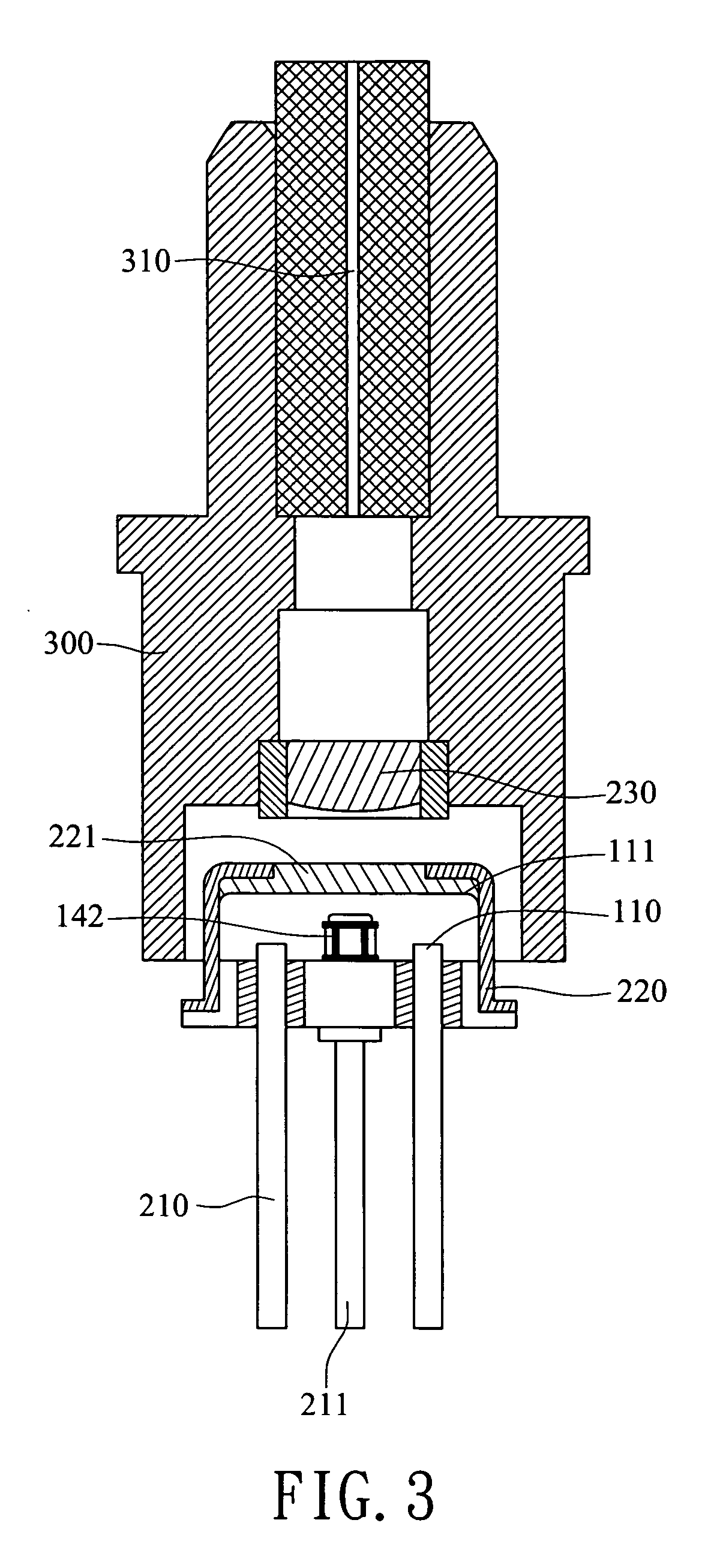

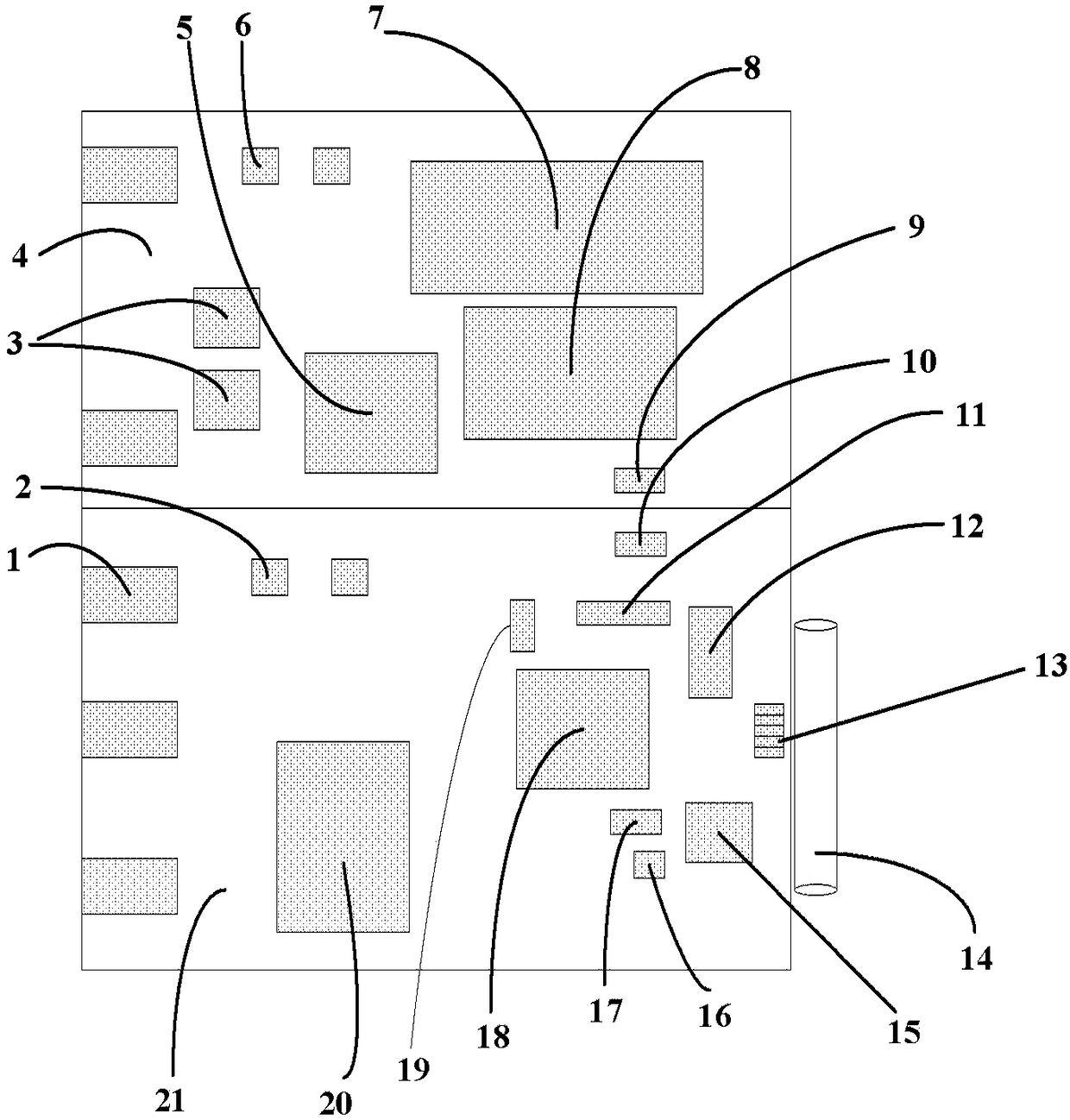

Receiver optical subassembly

InactiveUS20050121736A1Effective alignmentImprove performanceSolid-state devicesOptical light guidesAudio power amplifierEngineering

A receiver optical subassembly for transforming received optical signal into electrical signal includes at least a ceramic substrate, a photo receiver and a transimpedance amplifier. There are high-speed traces formed on the substrate. The positive and negative pads of the photo receiver are coplanar and connected to the traces without wire bonding so as to reduce the parasitic impedance effect and improve the high-speed performance of the optical subassembly. The transimpedance amplifier is electrically connected to the traces via flip chip, wire bonding or other methods. The photo receiver and the transimpedance amplifier are connected via the high-speed traces formed on the substrate.

Owner:IND TECH RES INST

Area reduction for die-scale surface mount package chips

InactiveUS20110089557A1Reduce areaCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSurface mounting

Using side-wall conductor leads to form package level conductor leads for active circuits manufactured on silicon substrate, the preferred embodiments of the present invention significantly reduces the areas of die-scale surface mount package chips. Besides area reduction, these methods also provide significant cost saving and reduction in parasitic impedance.

Owner:SHAU JENG JYE

Area reduction for surface mount package chips

InactiveUS20110089555A1Reduce areaCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSurface mounting

Using side-wall conductor leads insulated by side-wall insulators to form package level conductor leads for active circuits manufactured on silicon substrate, the preferred embodiments of the present invention significantly reduces the areas of surface mount package chips. Besides area reduction, these methods also provide significant cost saving and reduction in parasitic impedance.

Owner:SHAU JENG JYE

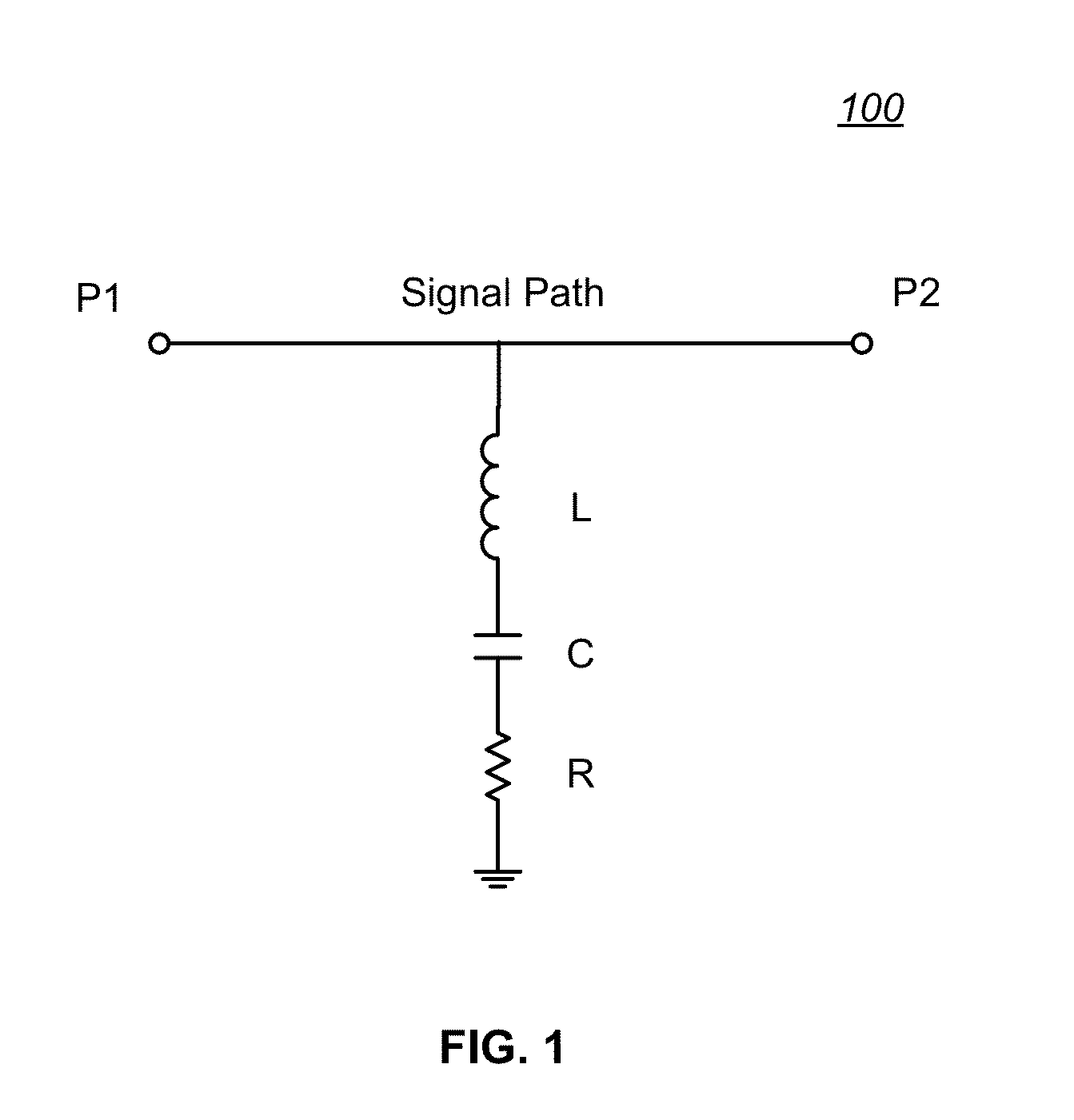

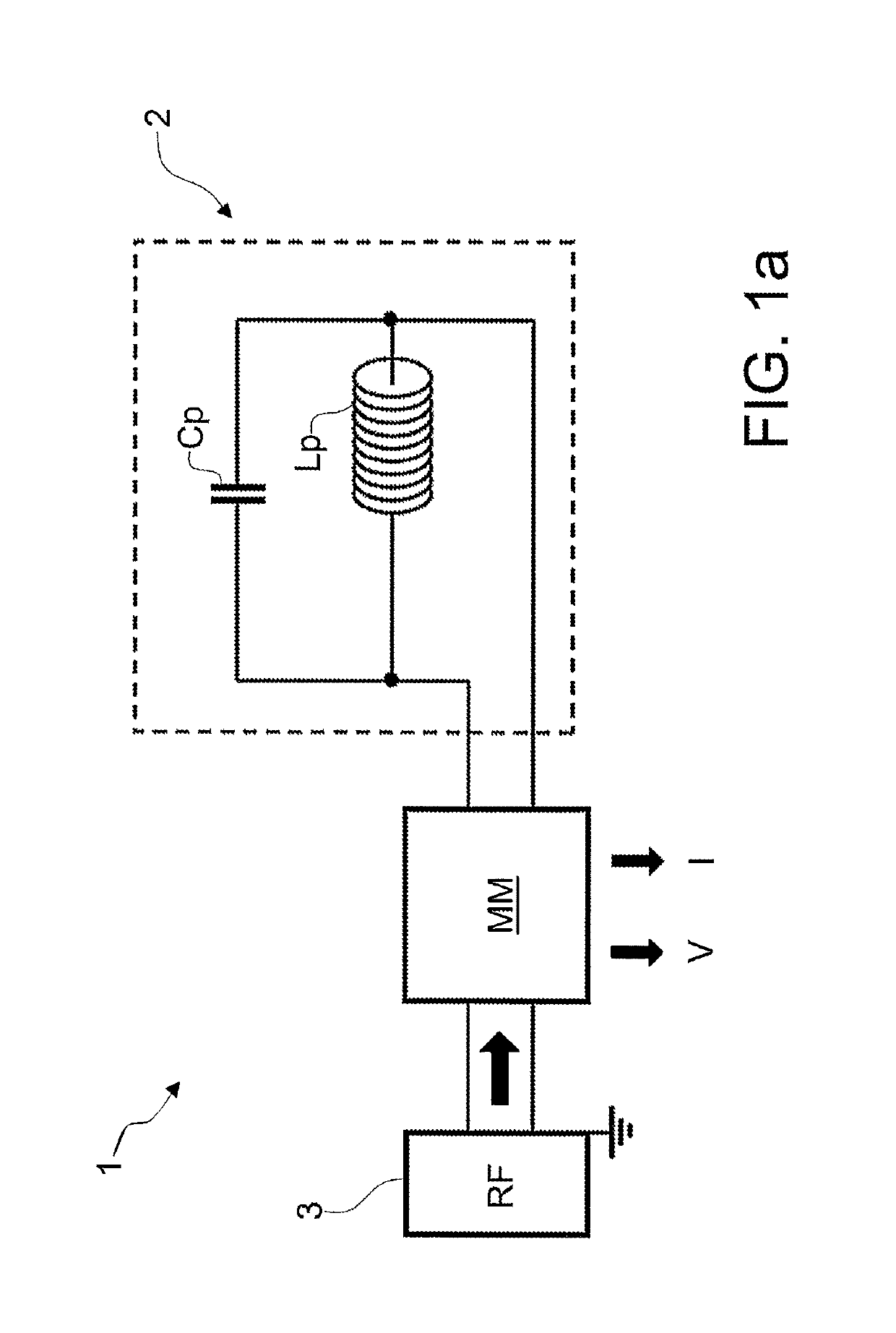

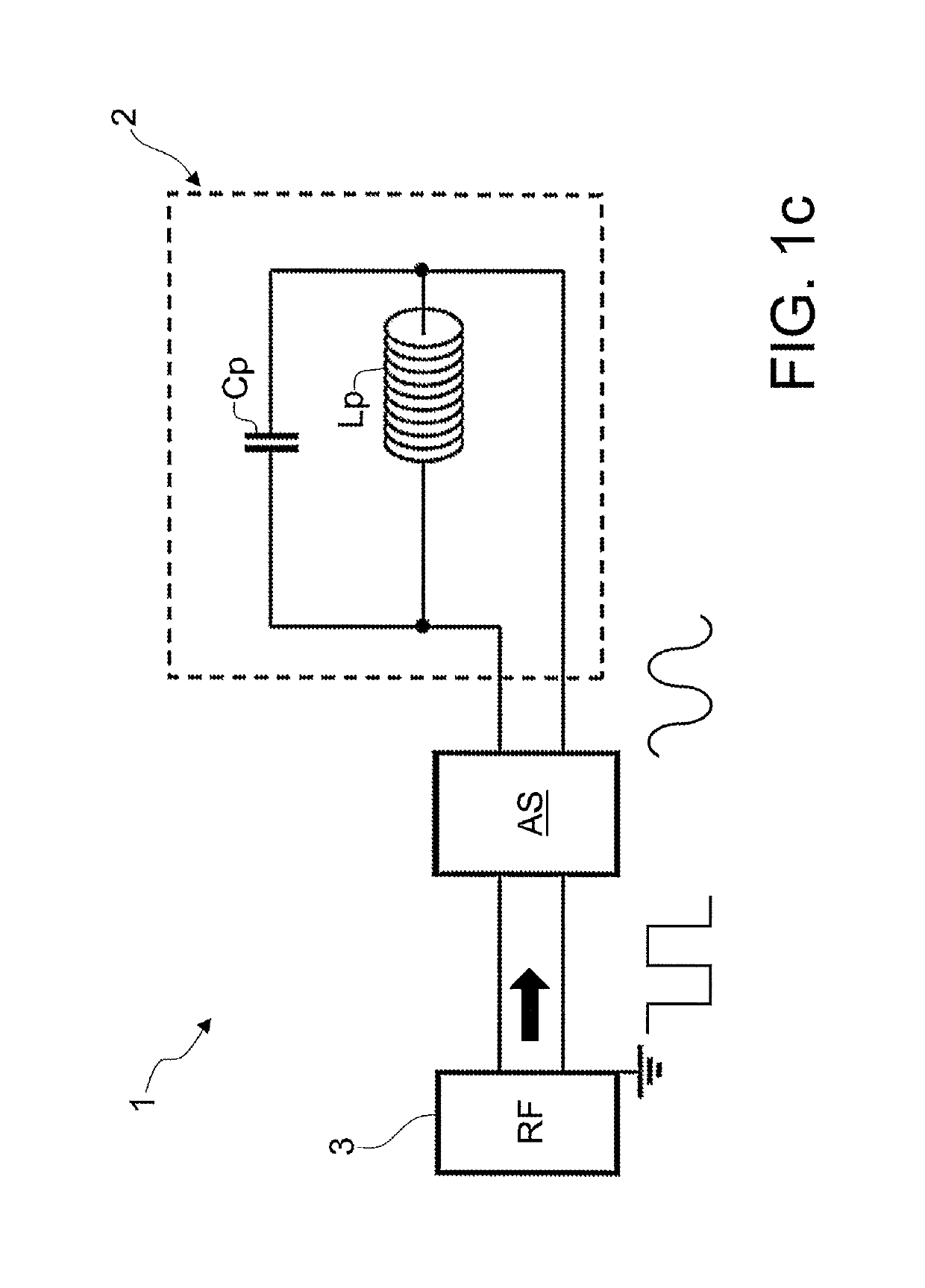

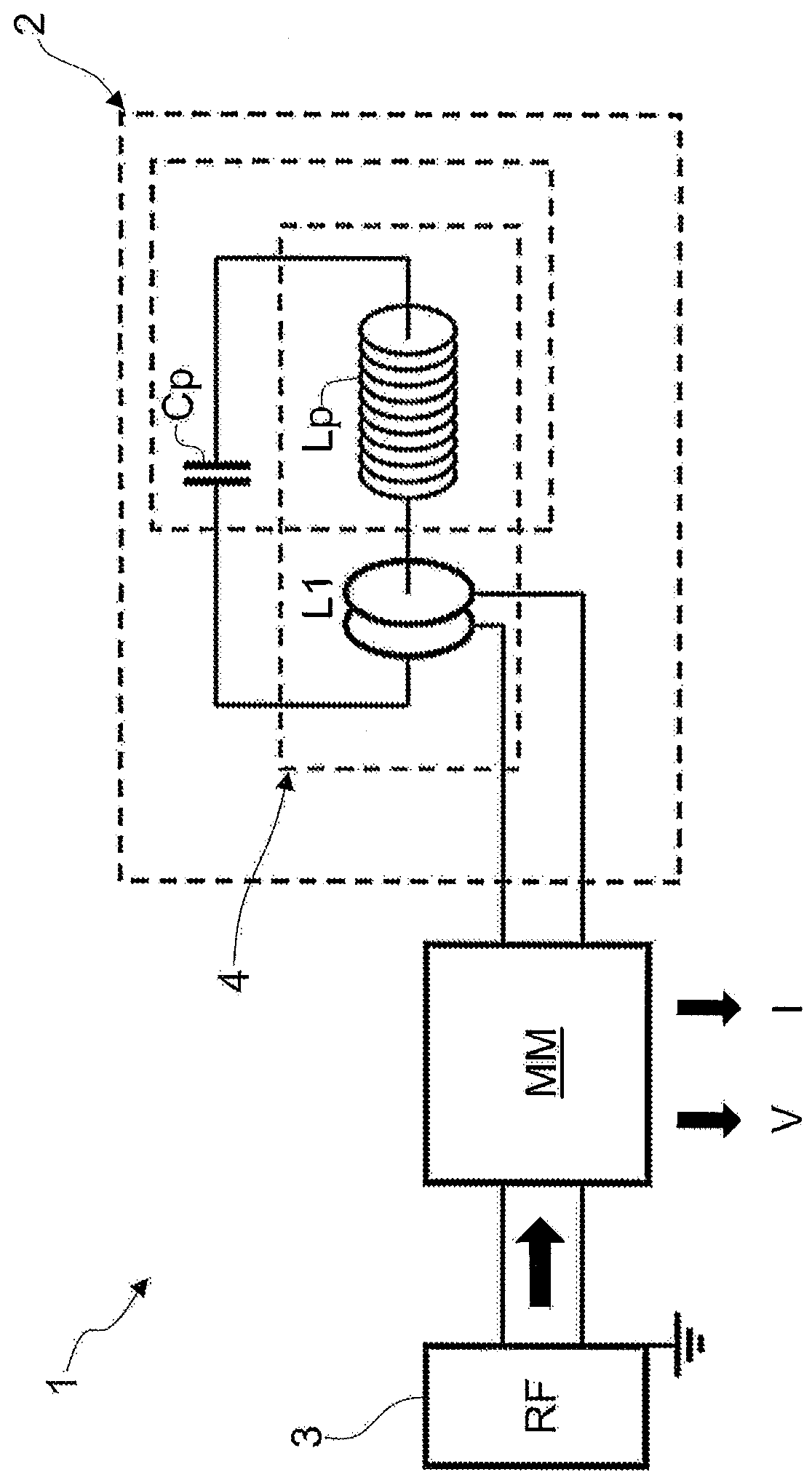

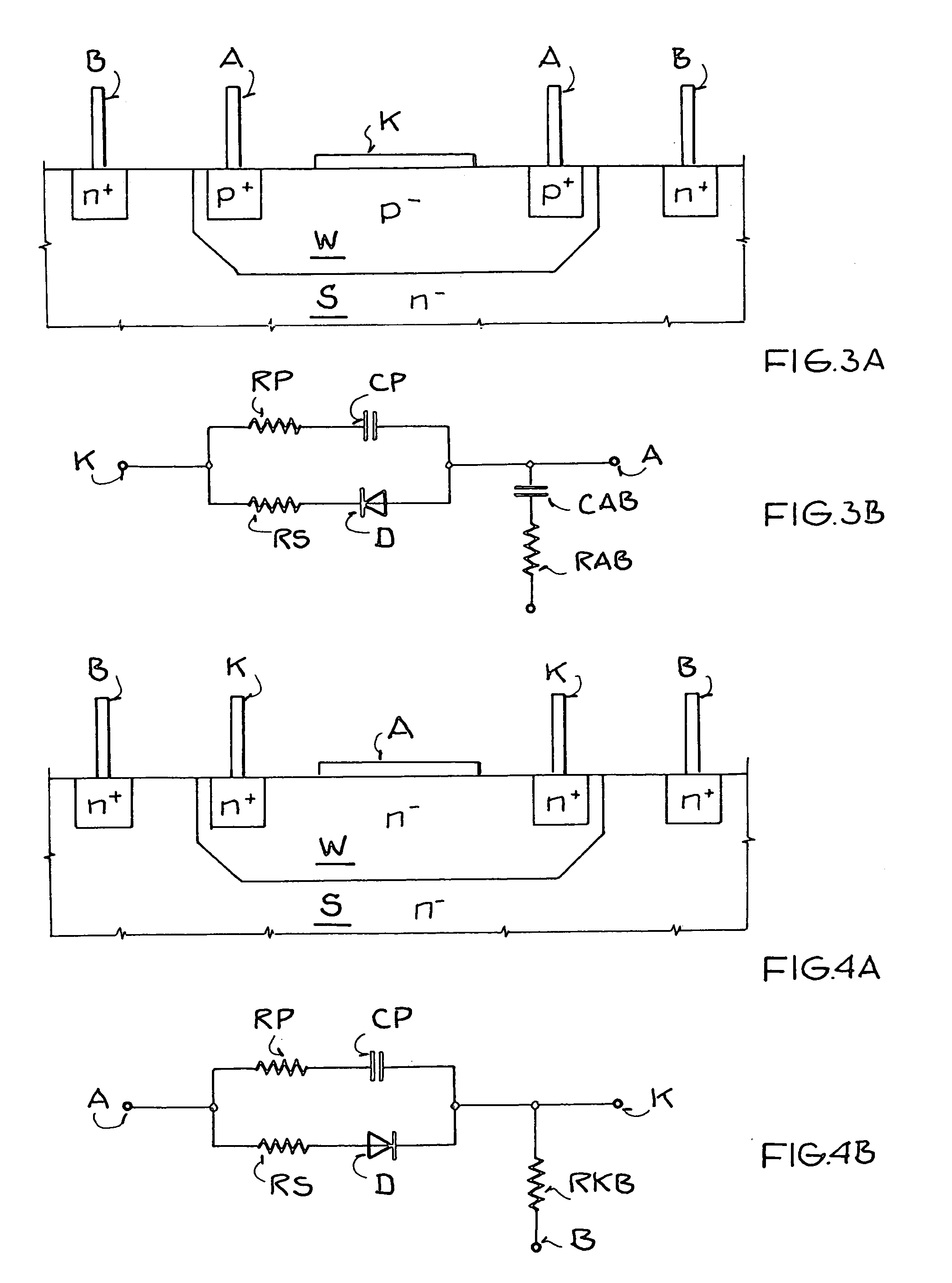

Device intrinsically designed to resonate, suitable for RF power transfer as well as group including such device and usable for the production of plasma

ActiveUS10879043B2Good conditionDrawback can be solvedElectric discharge tubesPlasma techniqueCapacitanceElectrical resistance and conductance

The present invention regards a device intrinsically designed to resonate, suitable for RF power transfer, particularly usable for the production of plasma and electrically connectable downstream of a radio frequency power supply with fixed or variable frequency, comprising at least one inductive element (Lp), which can be powered, during use, by such at least one power supply; at least one capacitive element (Cp) electrically connected at the terminals of such at least one inductive element (Lp); such at least one device having a resonance angular frequency equal to: ωo=1 / √LpCp. The capacitive element (Cp) and the inductive element (Lp) have values such that, at resonance state, they provide an equivalent impedance, measured at the terminals of such device, substantially of resistive type and much greater than the value of the parasitic impedance upstream of such terminals of such device, such that the effect of such parasitic impedance is, during use, substantially negligible.

Owner:TREZZOLANI FABIO +3

Methods for forming an RF device with trench under bond pad feature

ActiveUS7998852B2Semiconductor/solid-state device detailsSolid-state devicesAmorphous siliconEngineering

Owner:NXP USA INC

Area reduction for surface mount package chips

InactiveUS8710645B2Reduce areaReduce the parasitic inductanceLine/current collector detailsElectrically conductive connectionsElectrical conductorSurface mounting

Using side-wall conductor leads insulated by side-wall insulators to form package level conductor leads for active circuits manufactured on silicon substrate, the preferred embodiments of the present invention significantly reduces the areas of surface mount package chips. Besides area reduction, these methods also provide significant cost saving and reduction in parasitic impedance.

Owner:SHAU JENG JYE

A device intrinsically designed to resonate, suitable for RF power transfer as well as group including such device and usable for the production of plasma

ActiveUS20180269035A1Good conditionDrawback can be solvedElectric discharge tubesPlasma techniqueElectricityCapacitance

The present invention regards a device intrinsically designed to resonate, suitable for RF power transfer, particularly usable for the production of plasma and electrically connectable downstream of a radio frequency power supply with fixed or variable frequency, comprising at least one inductive element (Lp), which can be powered, during use, by such at least one power supply; at least one capacitive element (Cp) electrically connected at the terminals of such at least one inductive element (Lp); such at least one device having a resonance angular frequency equal to: ωo=1 / √LpCp. The capacitive element (Cp) and the inductive element (Lp) have values such that, at resonance state, they provide an equivalent impedance, measured at the terminals of such device, substantially of resistive type and much greater than the value of the parasitic impedance upstream of such terminals of such device, such that the effect of such parasitic impedance is, during use, substantially negligible.

Owner:TREZZOLANI FABIO +3

Integrated circuit oscillators having microelectromechanical resonators therein with parasitic impedance cancellation

InactiveUS8022779B2Pulse automatic controlElectric windingAudio power amplifierMicroelectromechanical systems

An integrated circuit oscillator includes a microelectromechanical (MEM) resonator having input and output terminals. An oscillation sustaining circuit is provided. The oscillation sustaining circuit is electrically coupled between the input and output terminals of the microelectromechanical resonator. The oscillation sustaining circuit includes a sustaining amplifier and a negative impedance circuit electrically coupled to the sustaining amplifier. The negative impedance circuit is configured to increase a tuning range of the oscillator by at least partially cancelling a parasitic shunt capacitance associated with the microelectromechanical resonator.

Owner:GEORGIA TECH RES CORP

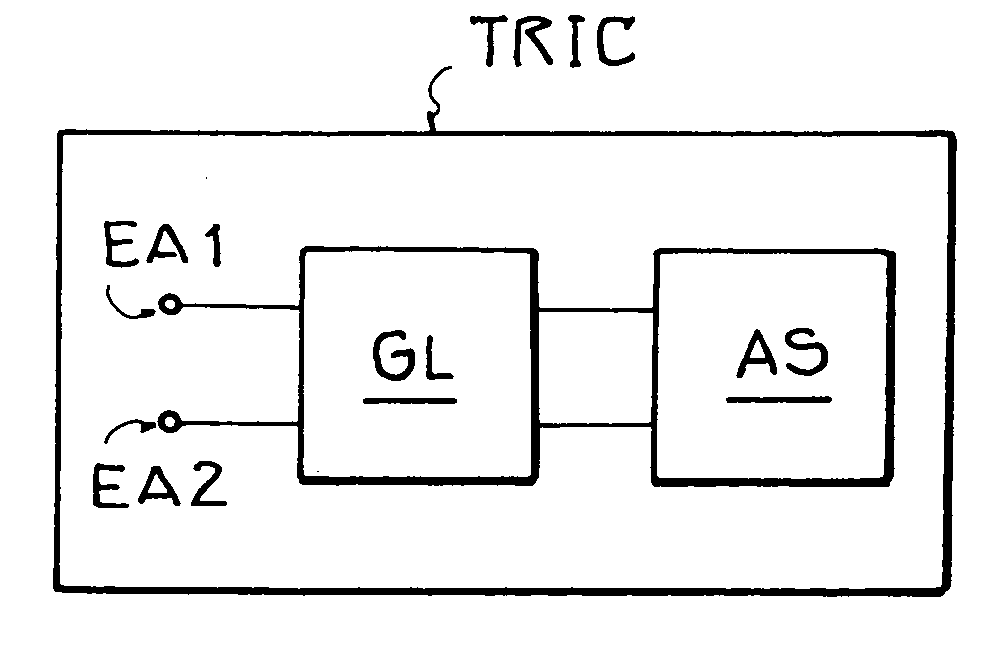

Integrated circuit for a transponder

ActiveUS20040245344A1Reduces parasitic impedanceExpand the transmission rangeAc-dc conversionEmergency protective circuit arrangementsElectricityElectrical conductor

An integrated circuit is combined with a transponder to function either as a voltage or power supply for the transponder by extracting energy out of an electromagnetic field transmitted by a base station or as a detector in the transponder to act as a remote sensor. For this purpose the integrated circuit comprises diode rectifiers. Each of the diode rectifiers has a first and a second service terminal and a reference terminal. In order to reduce a parasitic impedance between the first service terminal and the reference terminal, the first service terminal of at least one rectifier diode is electrically connected to a reference potential such as ground. Parasitic diode characteristics are further reduced by surrounding the respective diode or diodes by an electrical conductor path also connected to the reference potential.

Owner:ATMEL GERMANY +1

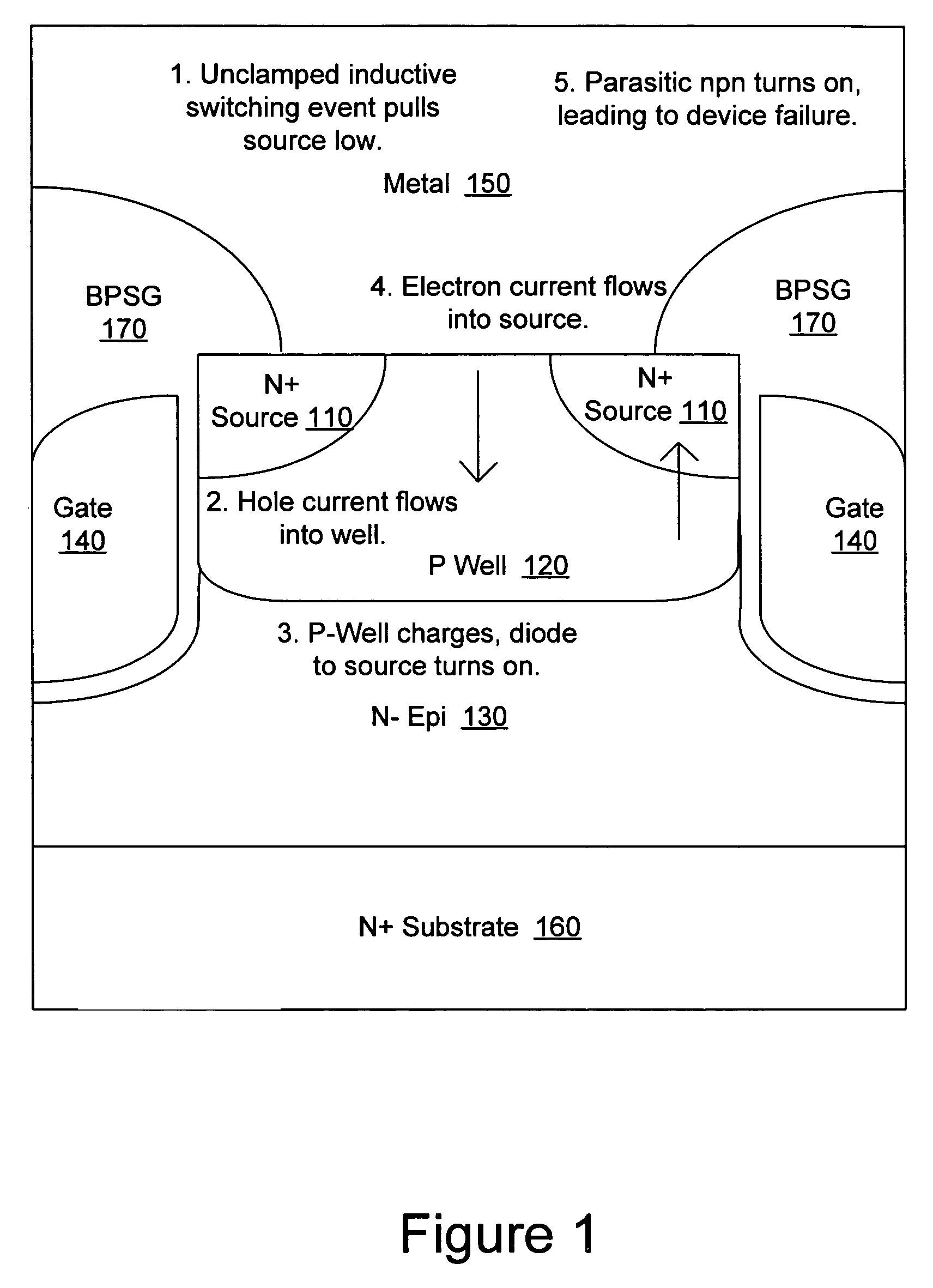

Bandgap engineered MOS-gated power transistors

ActiveUS7755137B2Improve immunityLower impedanceFinal product manufactureSemiconductor/solid-state device manufacturingElectrical resistance and conductanceReverse recovery

Devices, methods, and processes that improve immunity to transient voltages and reduce parasitic impedances. Immunity to unclamped inductive switching events is improved. For example, a trench-gated power MOSFET device having a SiGe source is provided, where the SiGe source reduces parasitic npn transistor gain by reducing hole current in the body or well region, thereby decreasing the likelihood of a latch-up condition. A body tie on this device can also be eliminated to reduce transistor cell size. A trench-gated power MOSFET device having a SiGe body or well region is also provided. A SiGe body reduces hole current when the body diode is turned on, thereby reducing reverse recovery power losses. Device characteristics are also improved. For example, parasitic gate impedance is reduced through the use of a poly SiGe gate, and channel resistance is reduced through the use of a SiGe layer near the device's gate.

Owner:SEMICON COMPONENTS IND LLC

IR(voltage) drop analysis in integrated circuit timing

InactiveUS8712752B2Analogue computers for nuclear physicsComputer aided designAnalysis methodStandard cell

In one embodiment, an IR drop analysis methodology may include characterizing standard cells without including power parasitic impedances, extracting the power parasitic impedances for the standard cells, and characterizing the standard cells with the power parasitic impedances. A set of timing parameters (such as minimum delays and maximum delays through the cells) may be generated from each characterization. The methodology may include comparing the timing parameters from each characterization, and identifying cells for which additional design effort should be expended to improve the power supply grid (e.g. to reduce the power parasitic impedances). For example, a margin may be budgeted for speed loss (delay increase) due to IR drop. If the difference in the timing parameters exceeds the margin, additional design effort may be warranted.

Owner:APPLE INC

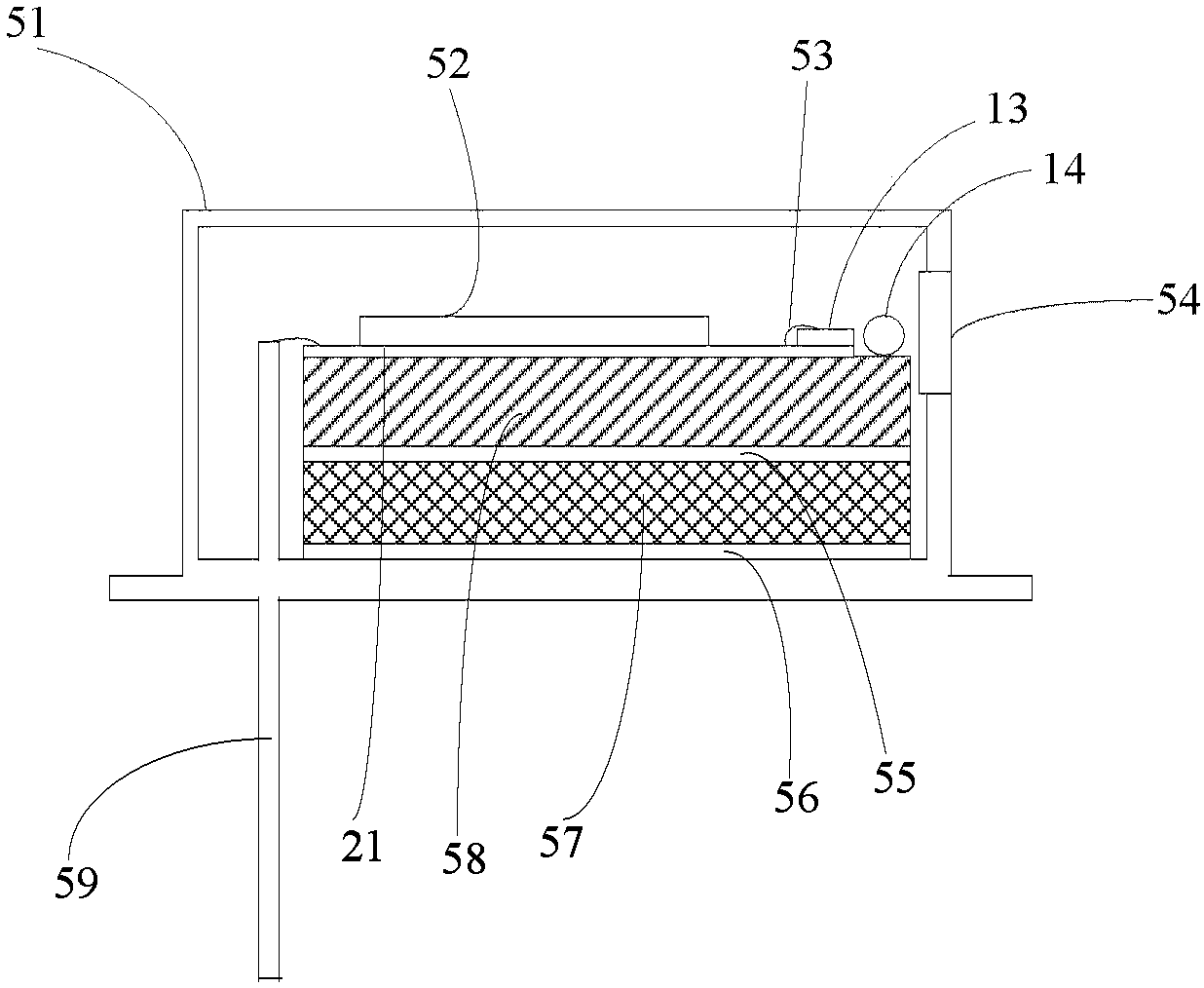

Laser emitter

InactiveCN108512030AReduce parasitic impedanceReduce power lossLaser detailsSemiconductor laser structural detailsTemperature controlOptoelectronics

The invention discloses a laser emitter which comprises a driving circuit, an AlN substrate and a laser tube core. Components of the driving circuit are integrated on the AlN substrate; the laser tubecore is attached to the AlN substrate; and the driving circuit is electrically connected with the laser tube core. According to the laser emitter, components of the driving circuit and a laser arrayare integrated, the parasitic impedance of the driving circuit and a laser path is reduced, fewer technical steps are included, heave-current narrow-pulse laser emission under a temperature control condition can be provided, and an optical collimation function is provided.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com