Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

826 results about "Heterojunction bipolar transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

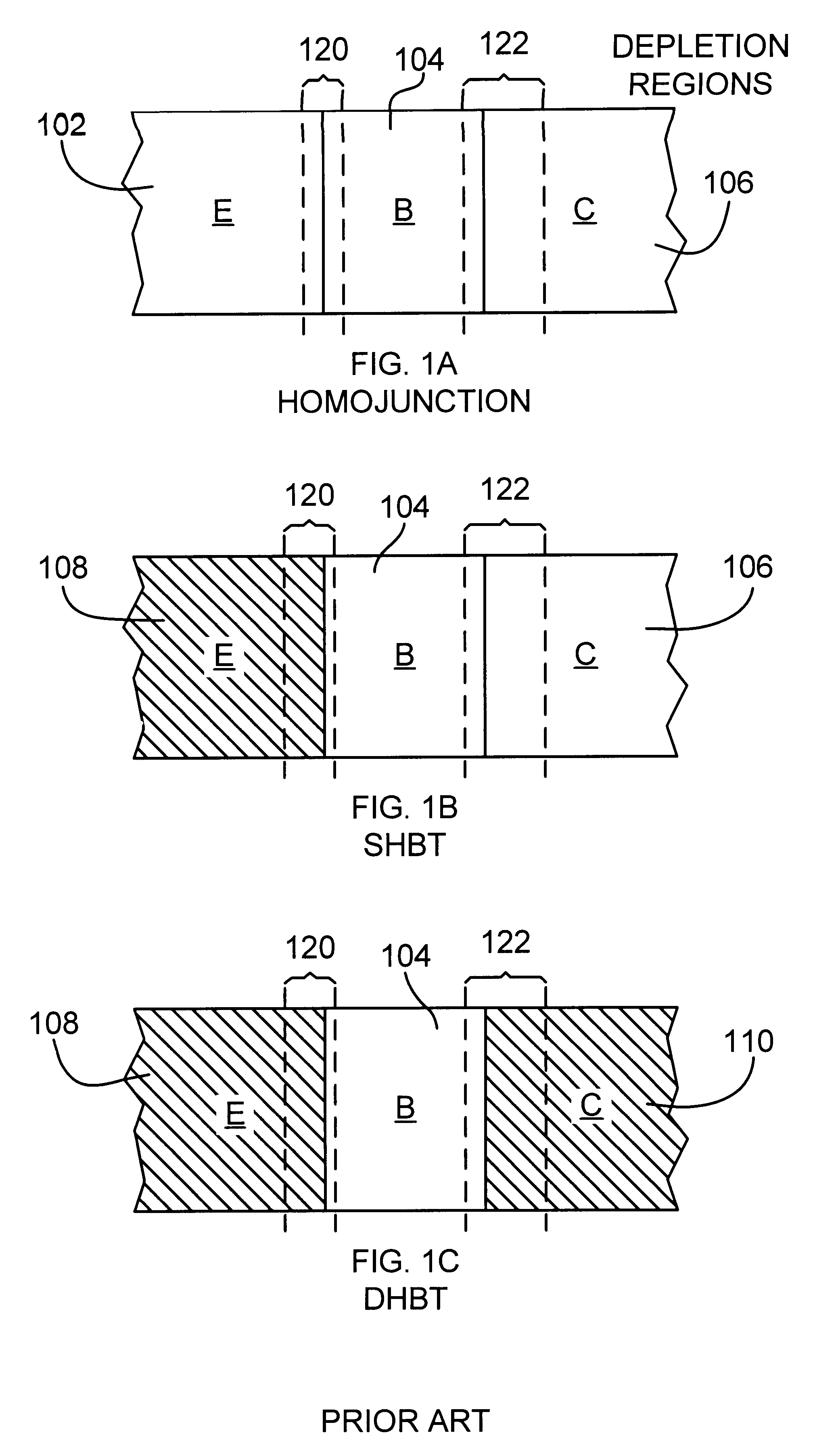

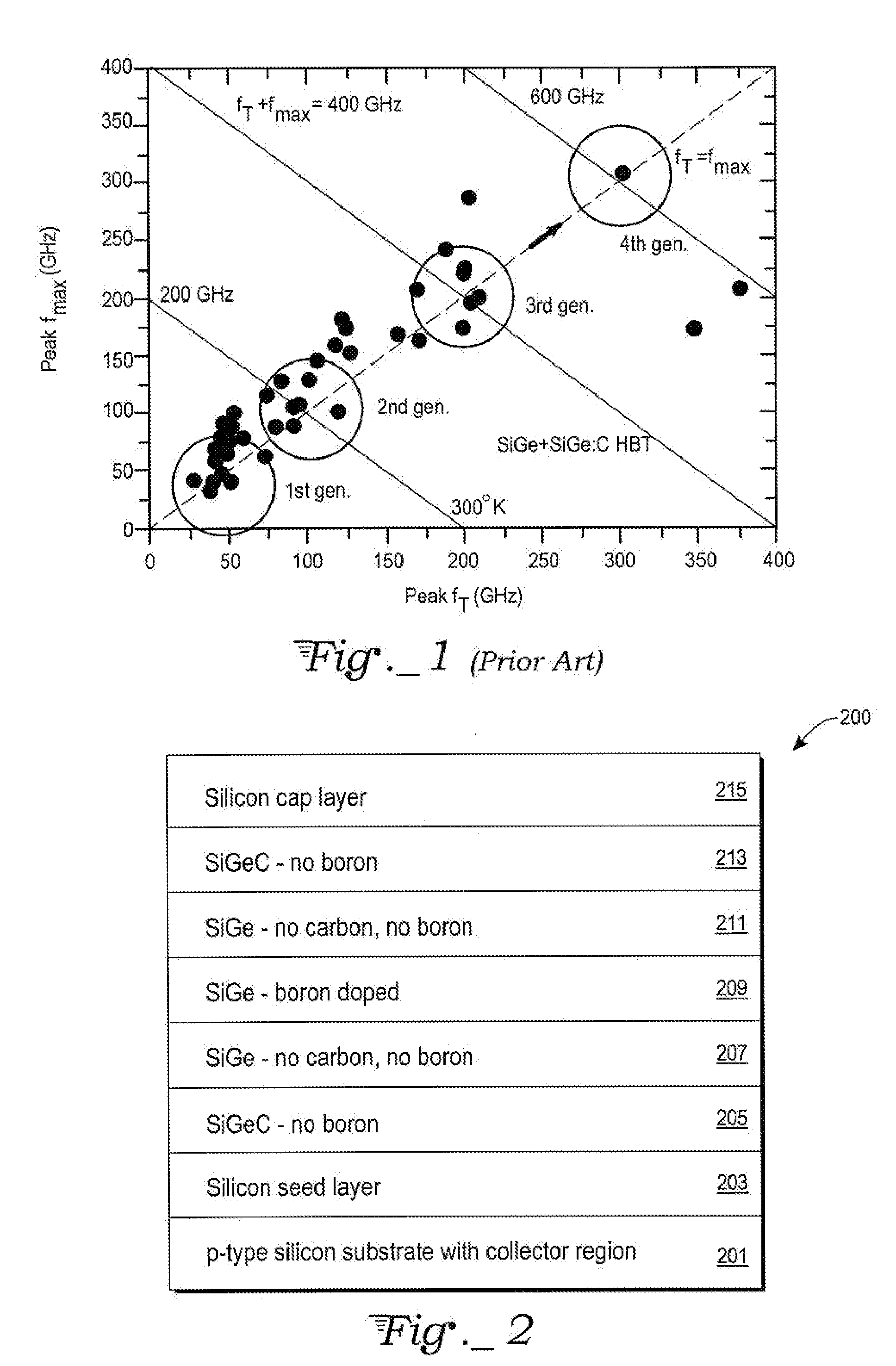

The heterojunction bipolar transistor (HBT) is a type of bipolar junction transistor (BJT) which uses differing semiconductor materials for the emitter and base regions, creating a heterojunction. The HBT improves on the BJT in that it can handle signals of very high frequencies, up to several hundred GHz. It is commonly used in modern ultrafast circuits, mostly radio-frequency (RF) systems, and in applications requiring a high power efficiency, such as RF power amplifiers in cellular phones. The idea of employing a heterojunction is as old as the conventional BJT, dating back to a patent from 1951. Detailed theory of heterojunction bipolar transistor was developed by Herbert Kroemer in 1957.

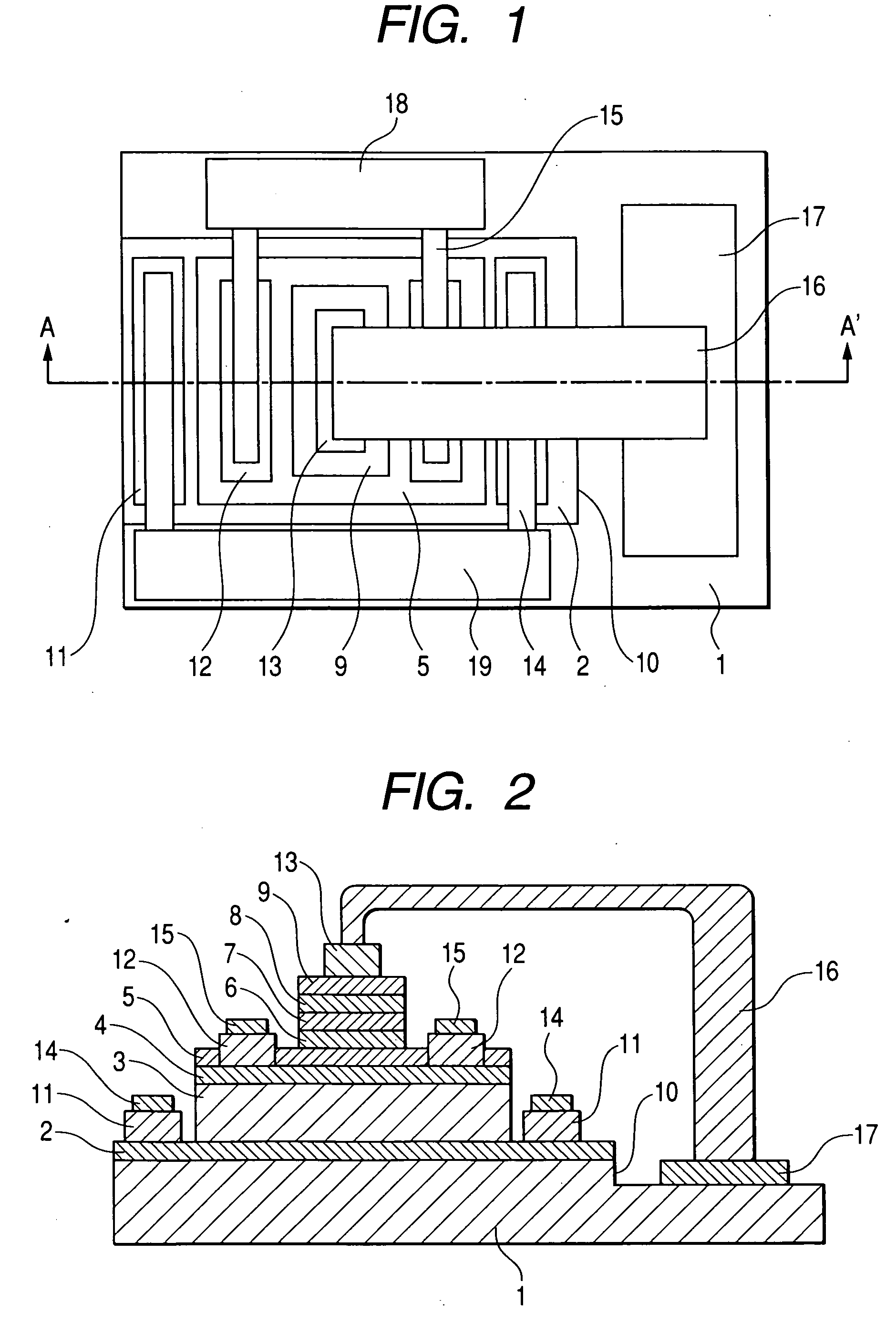

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

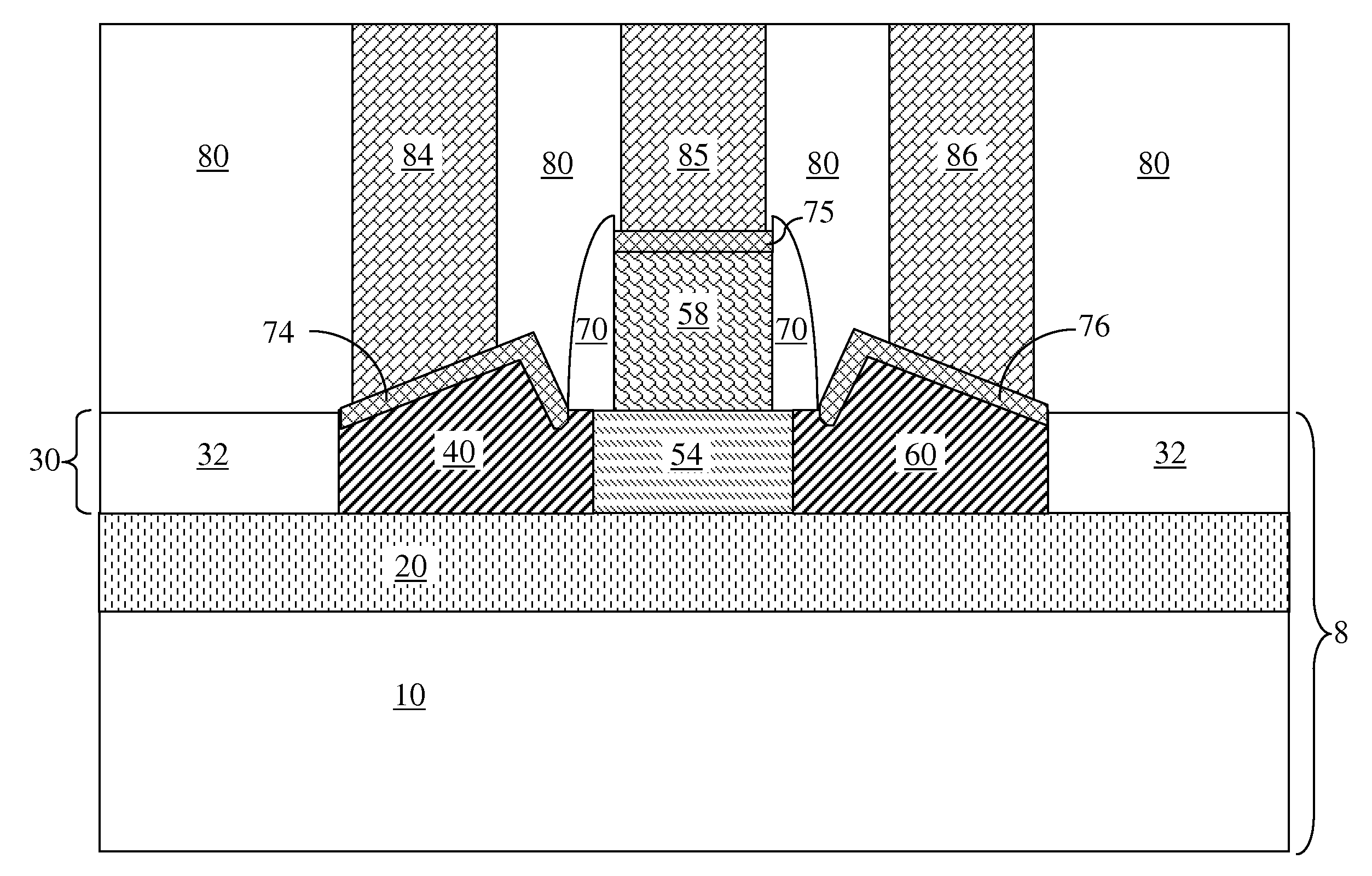

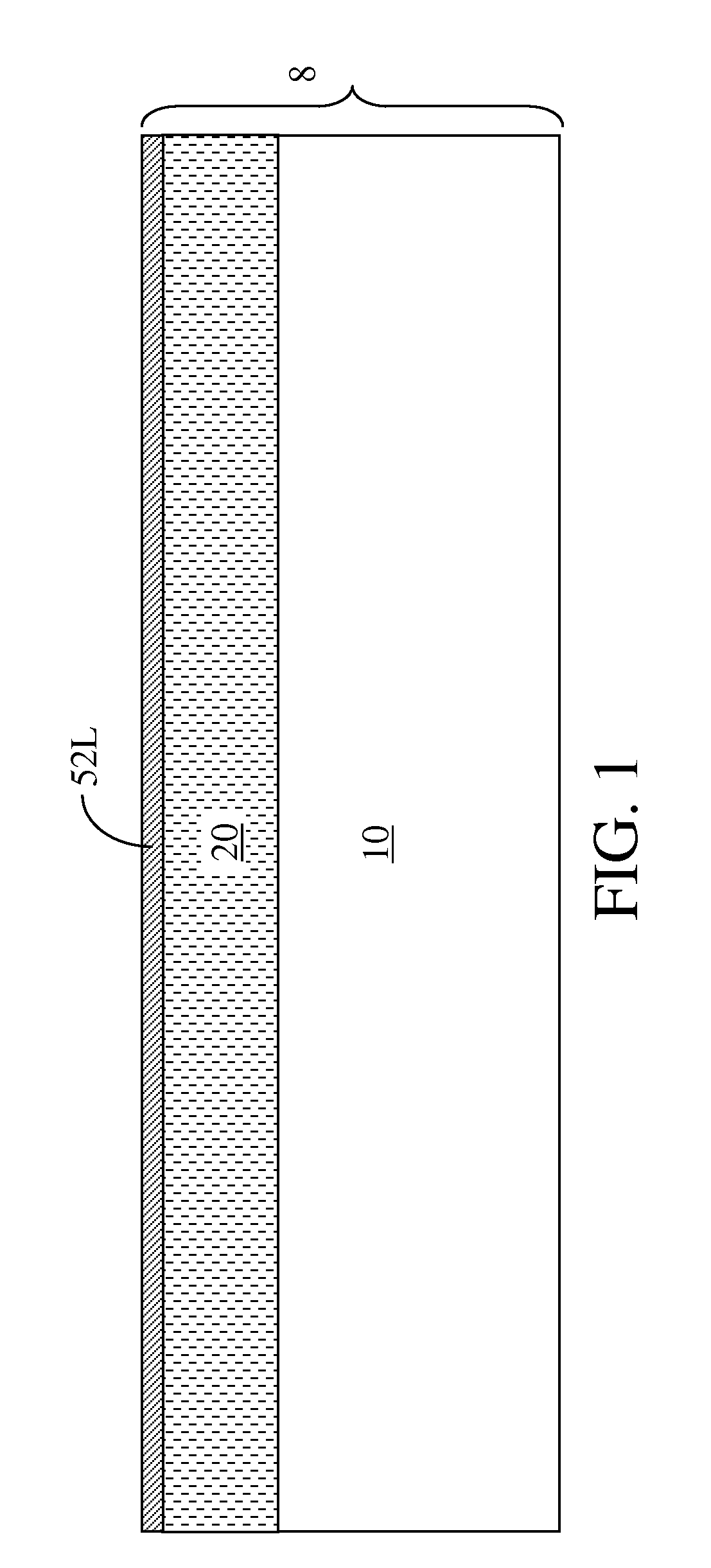

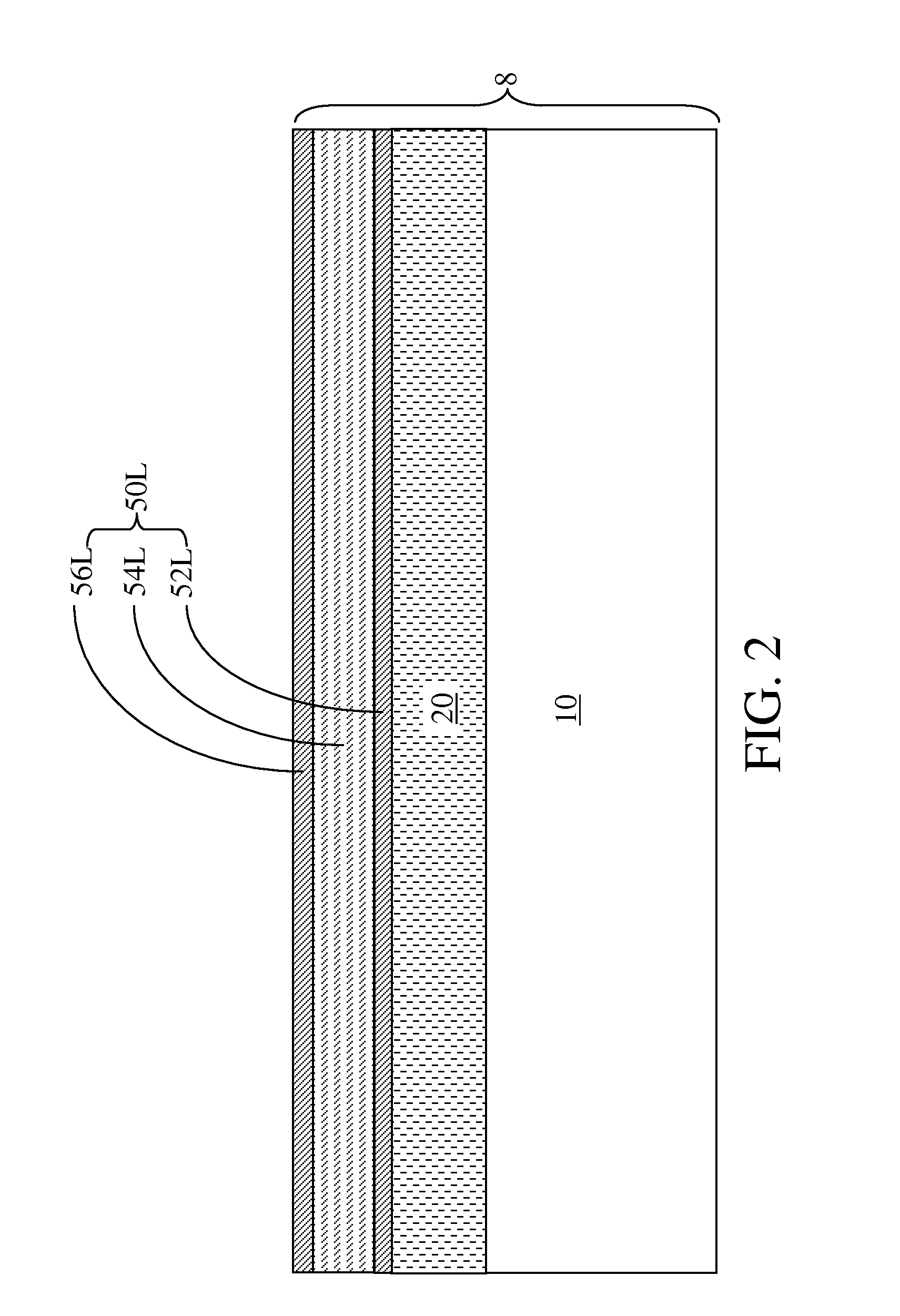

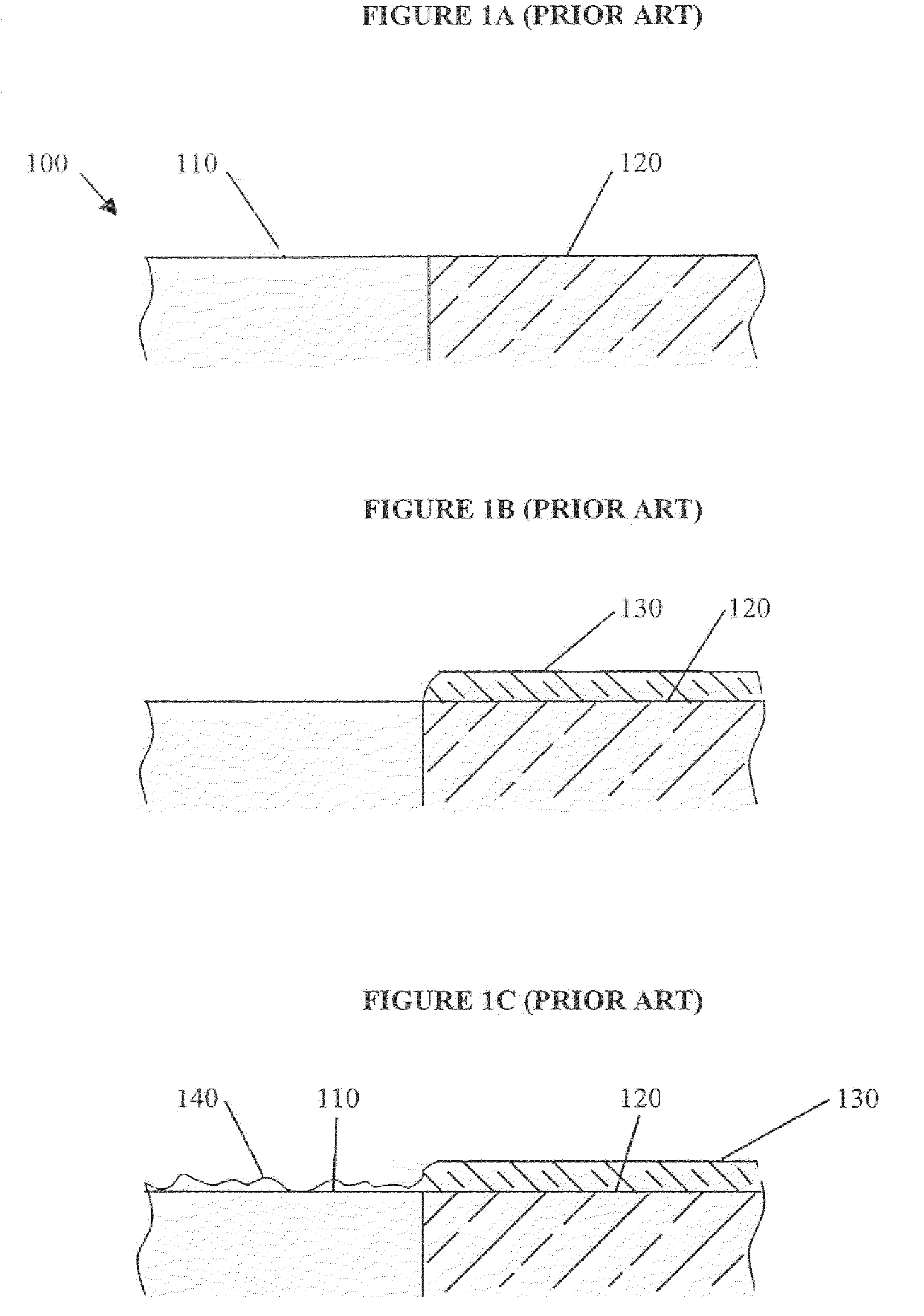

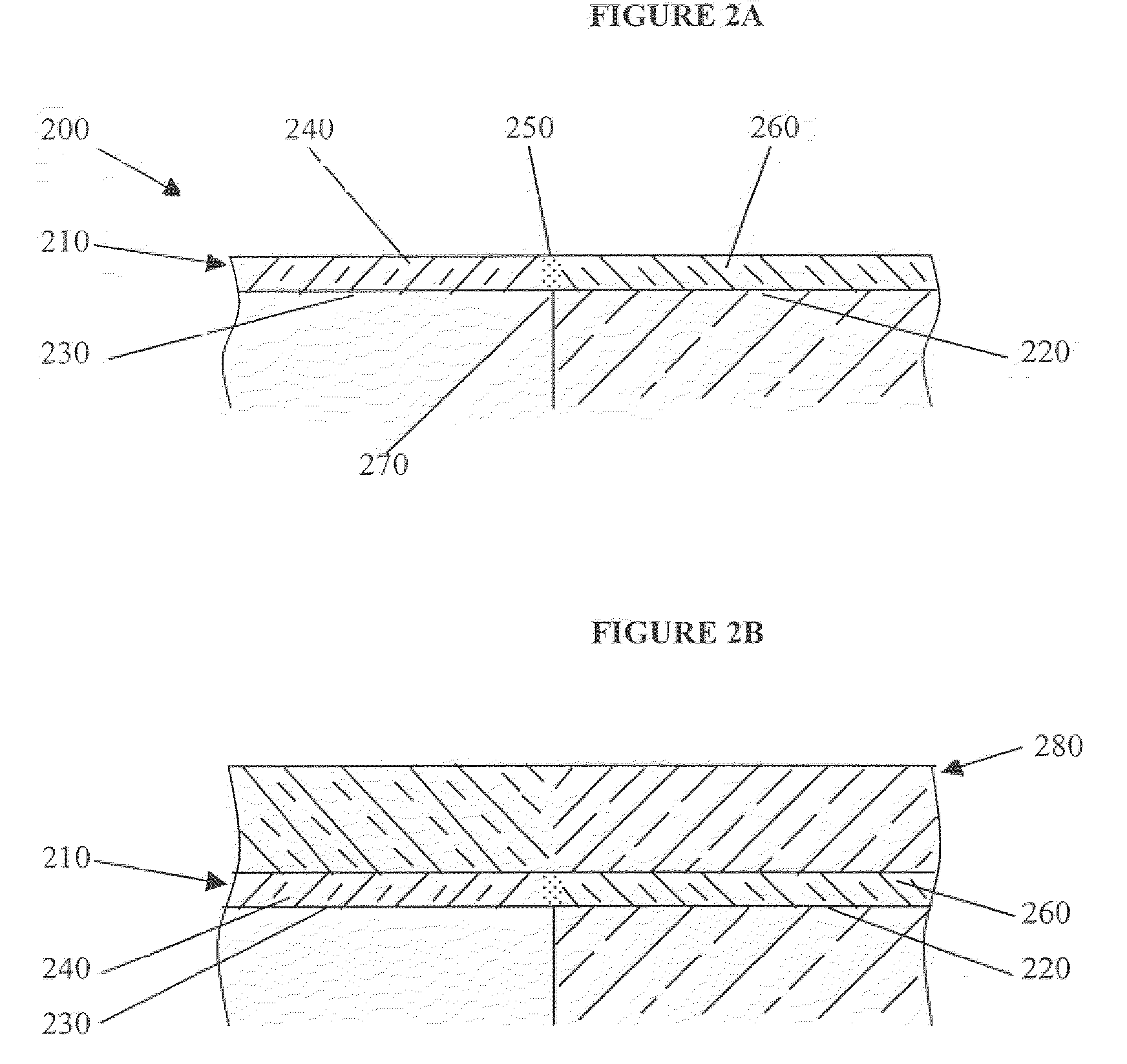

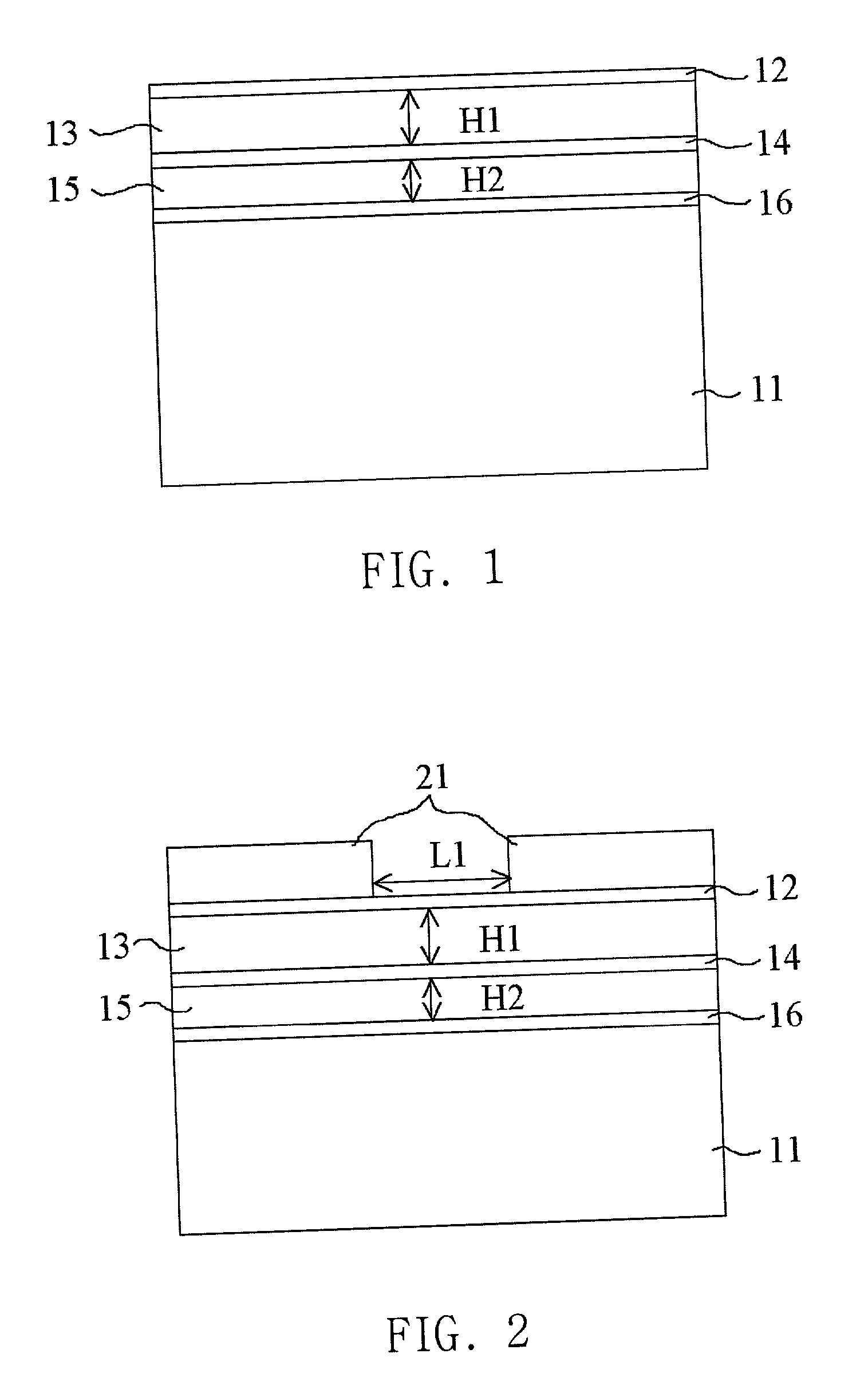

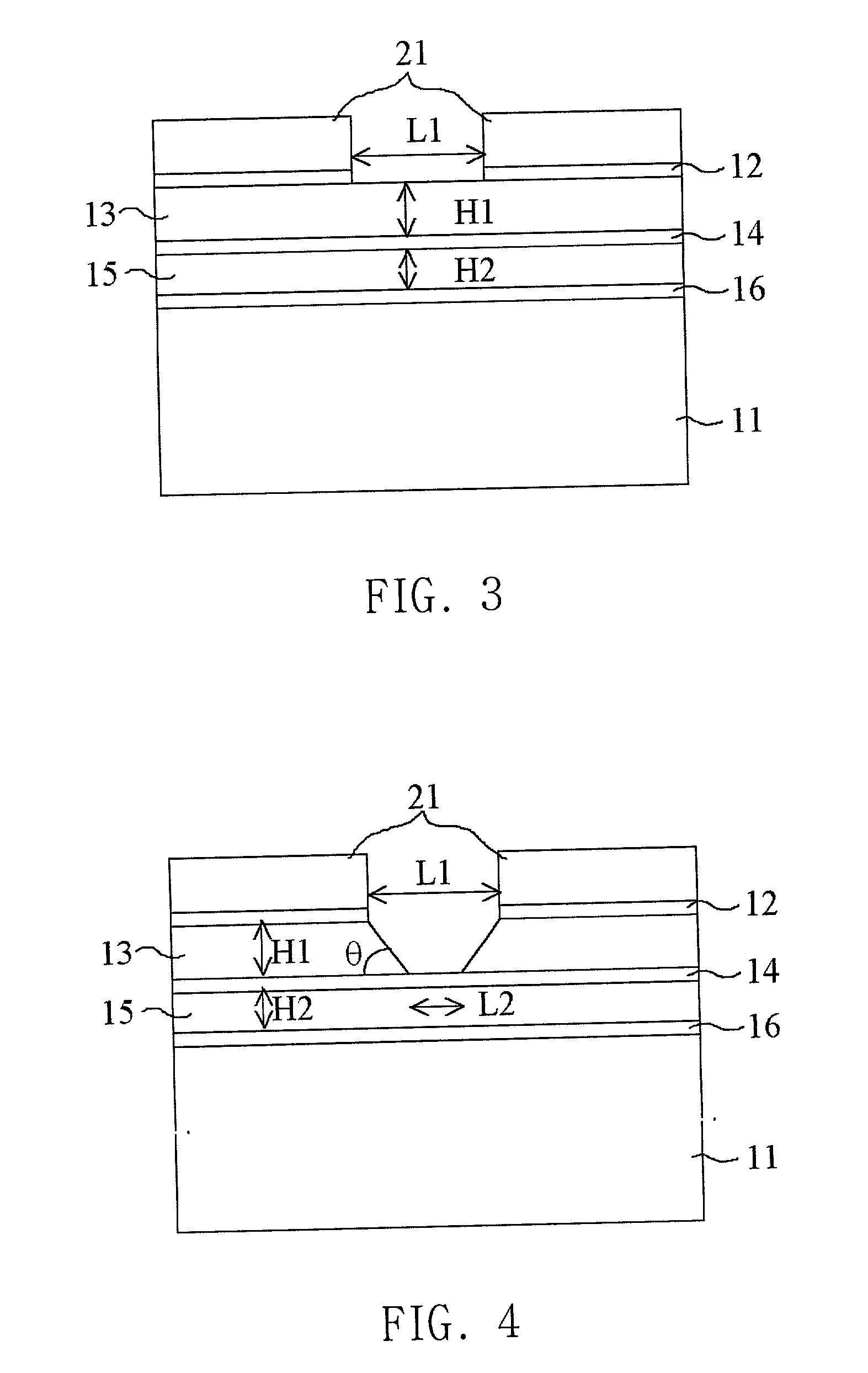

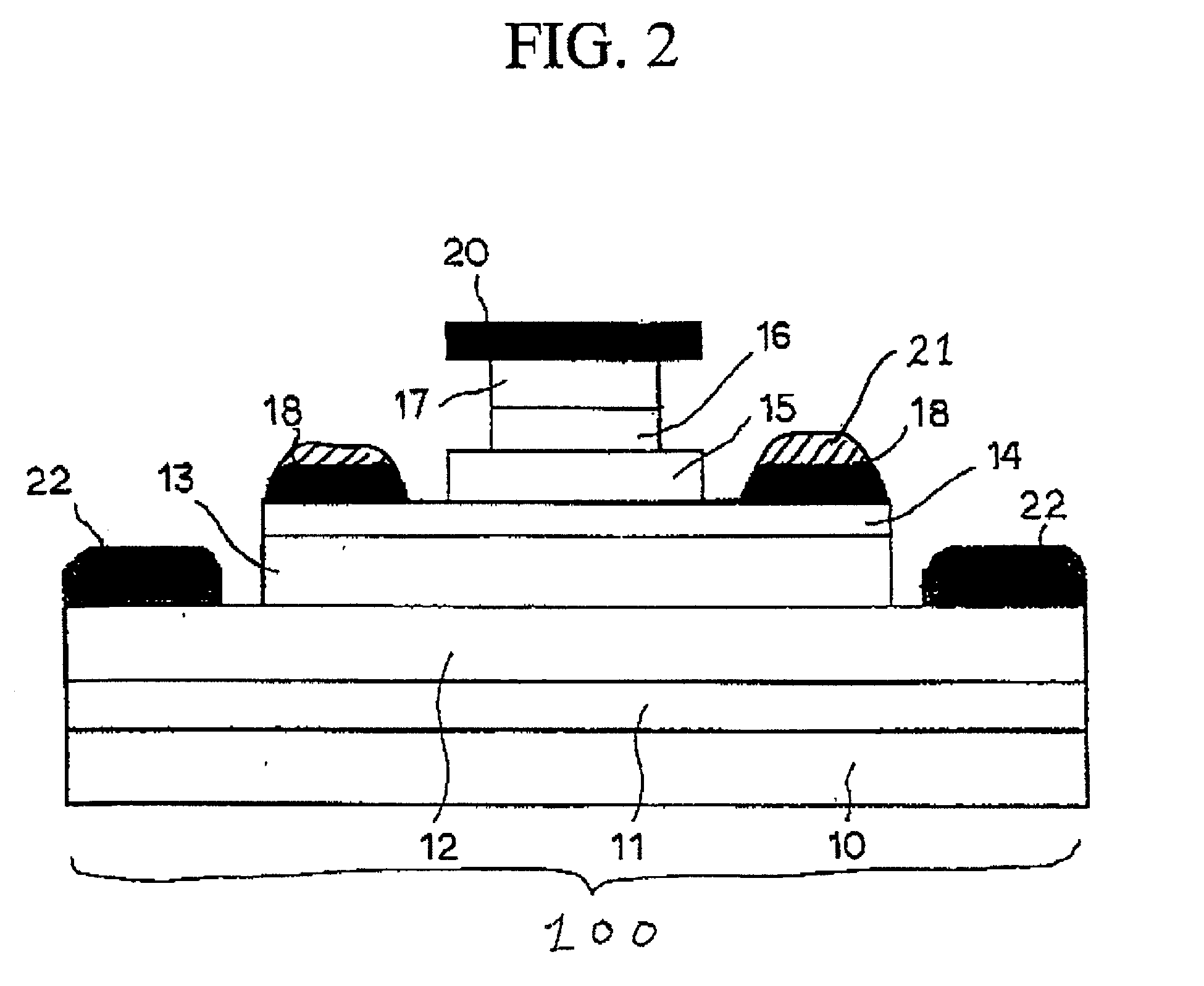

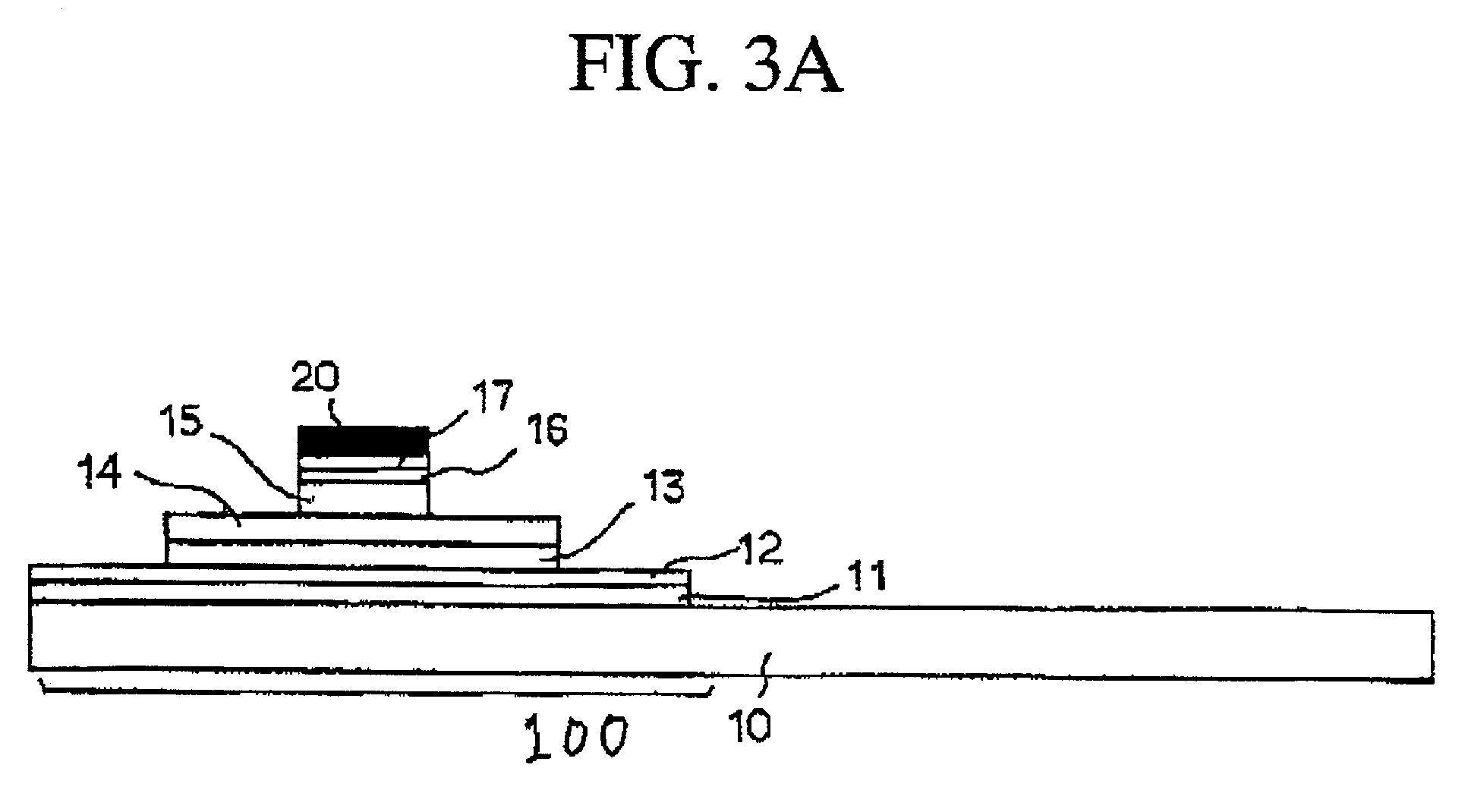

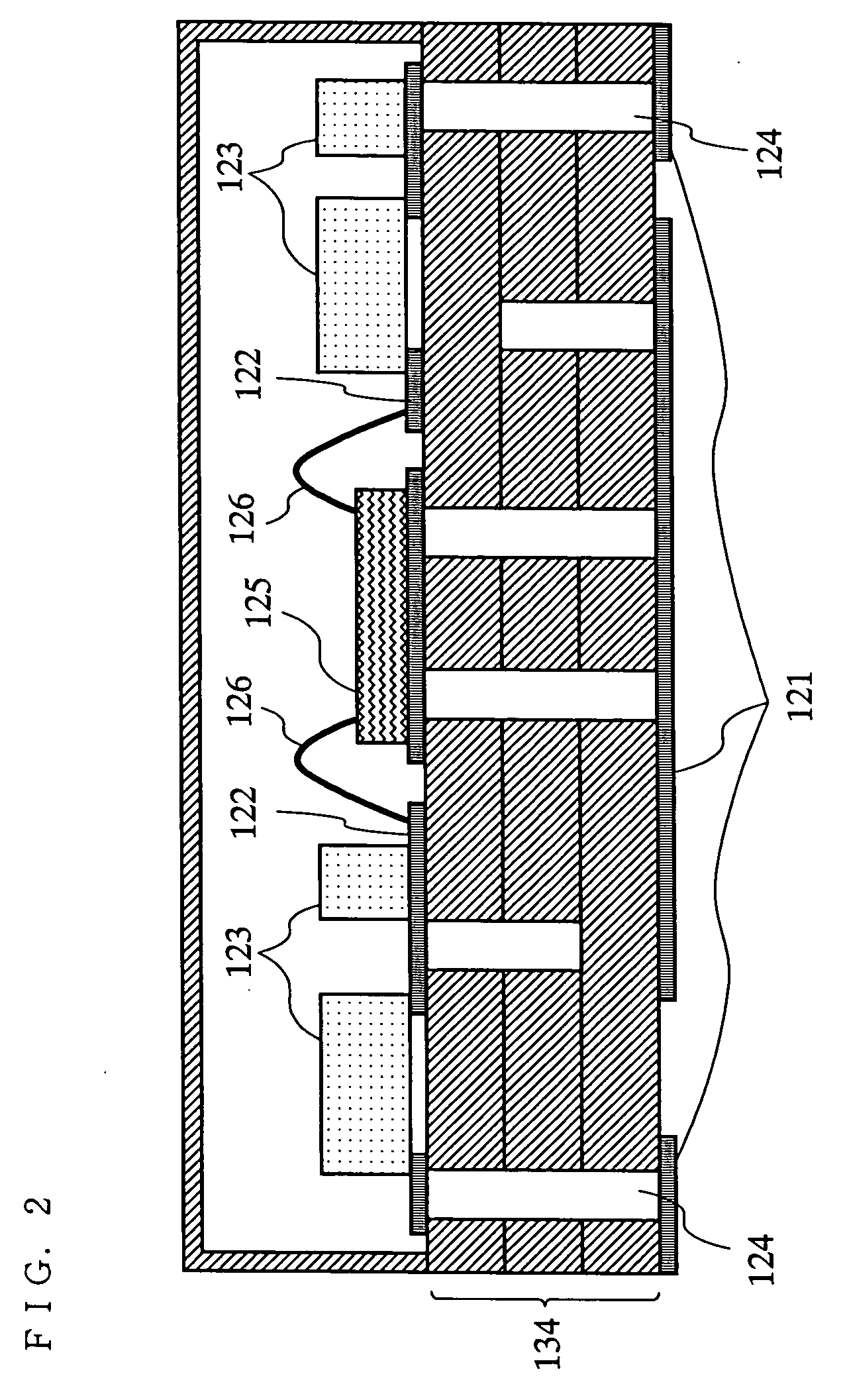

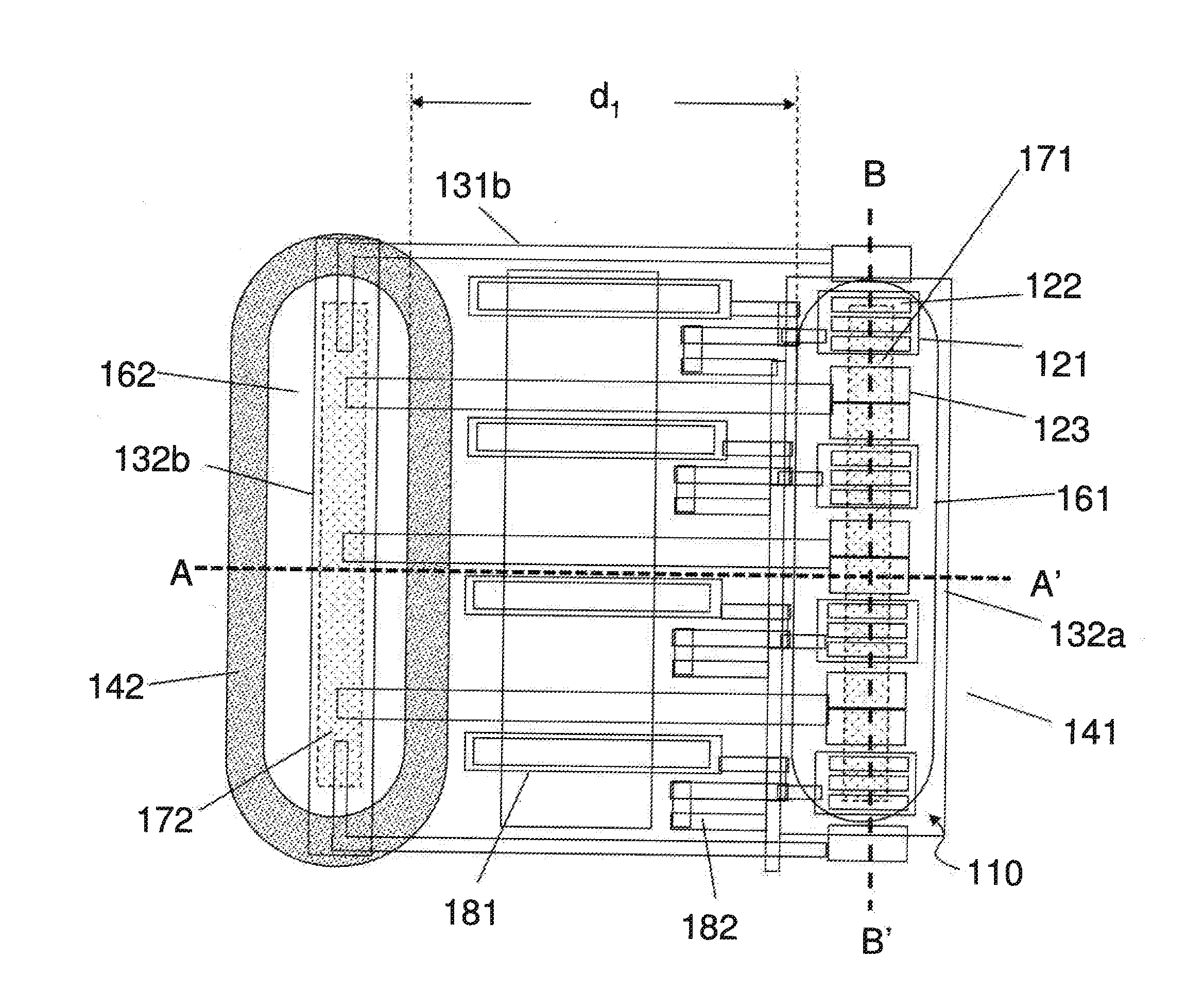

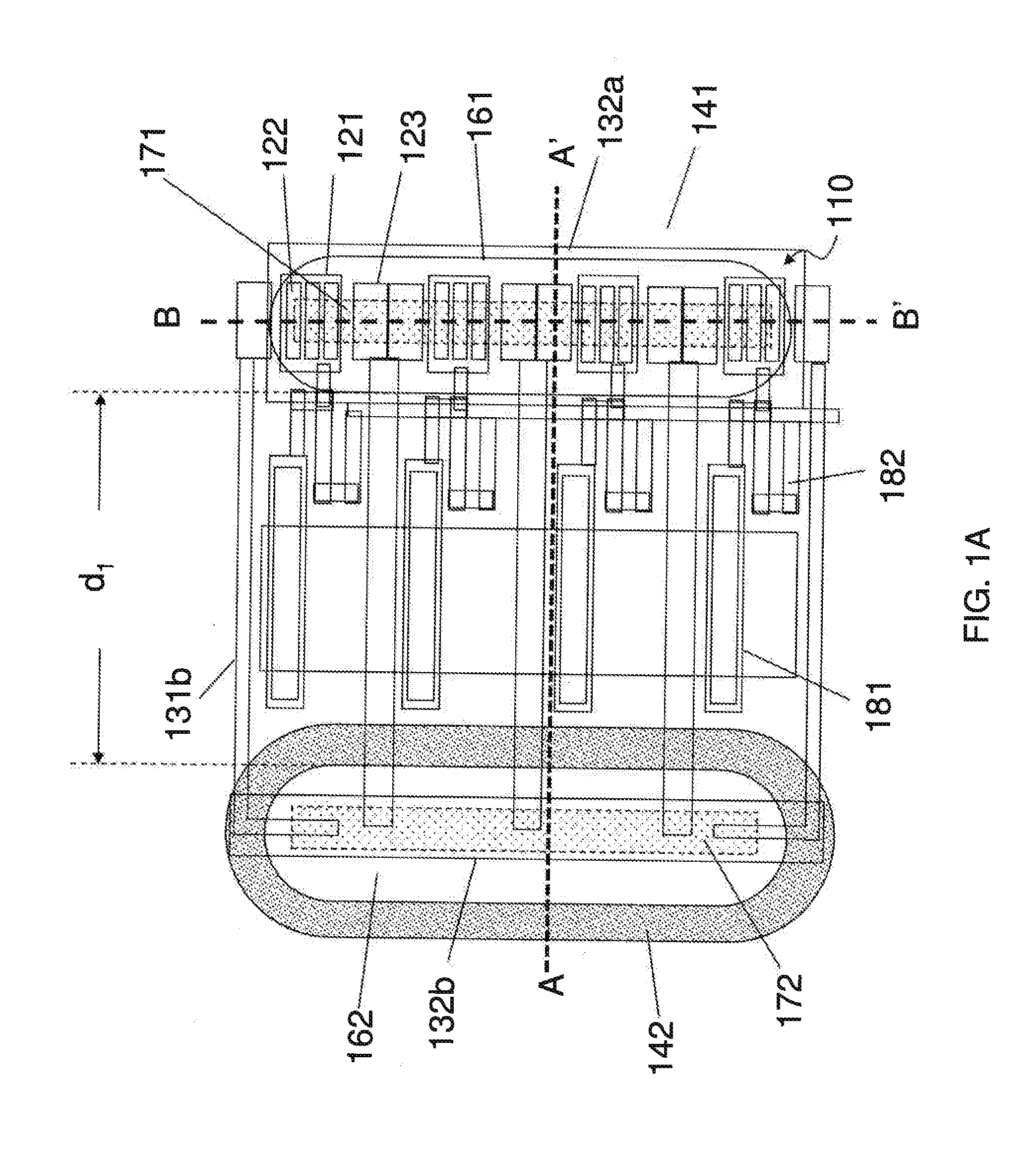

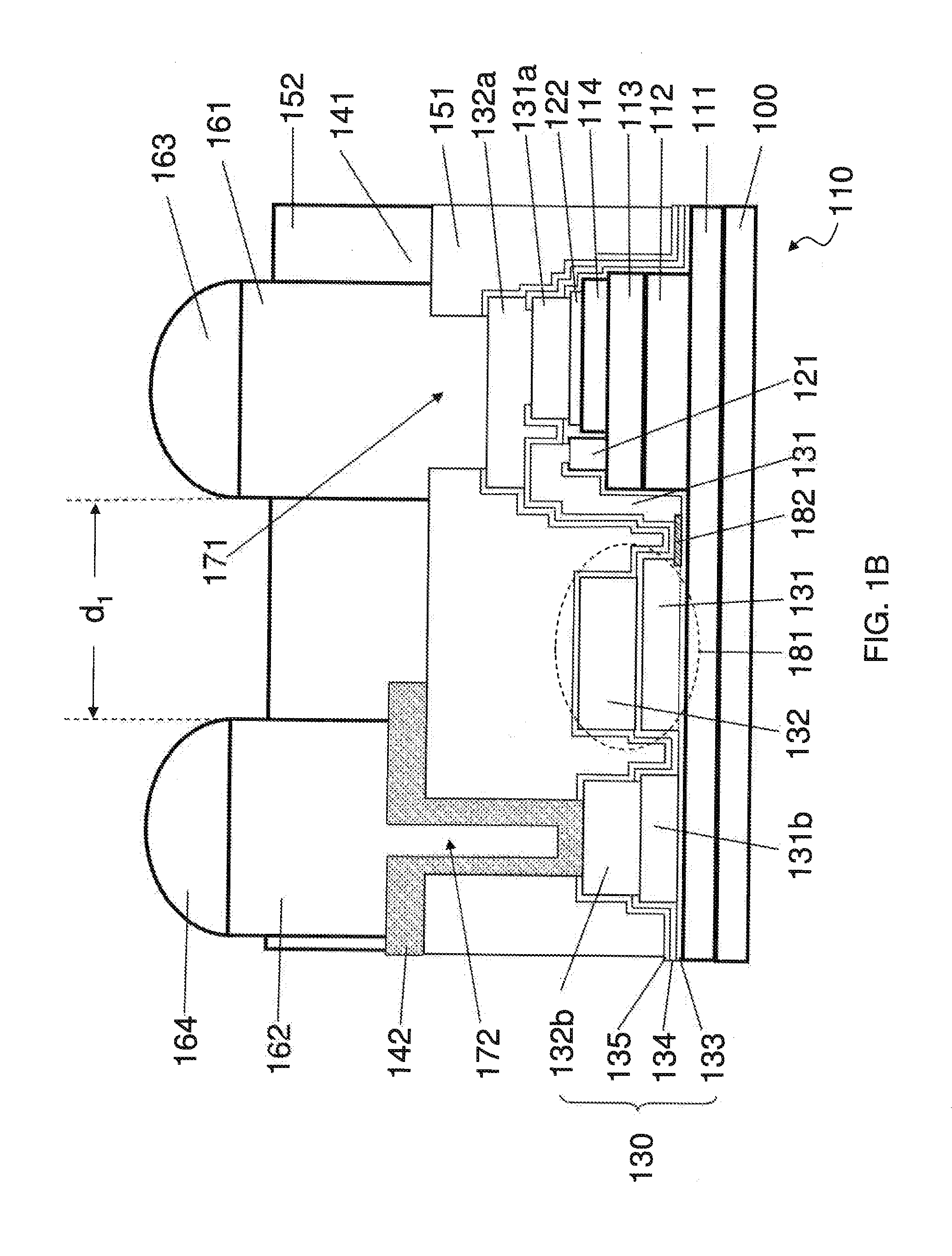

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

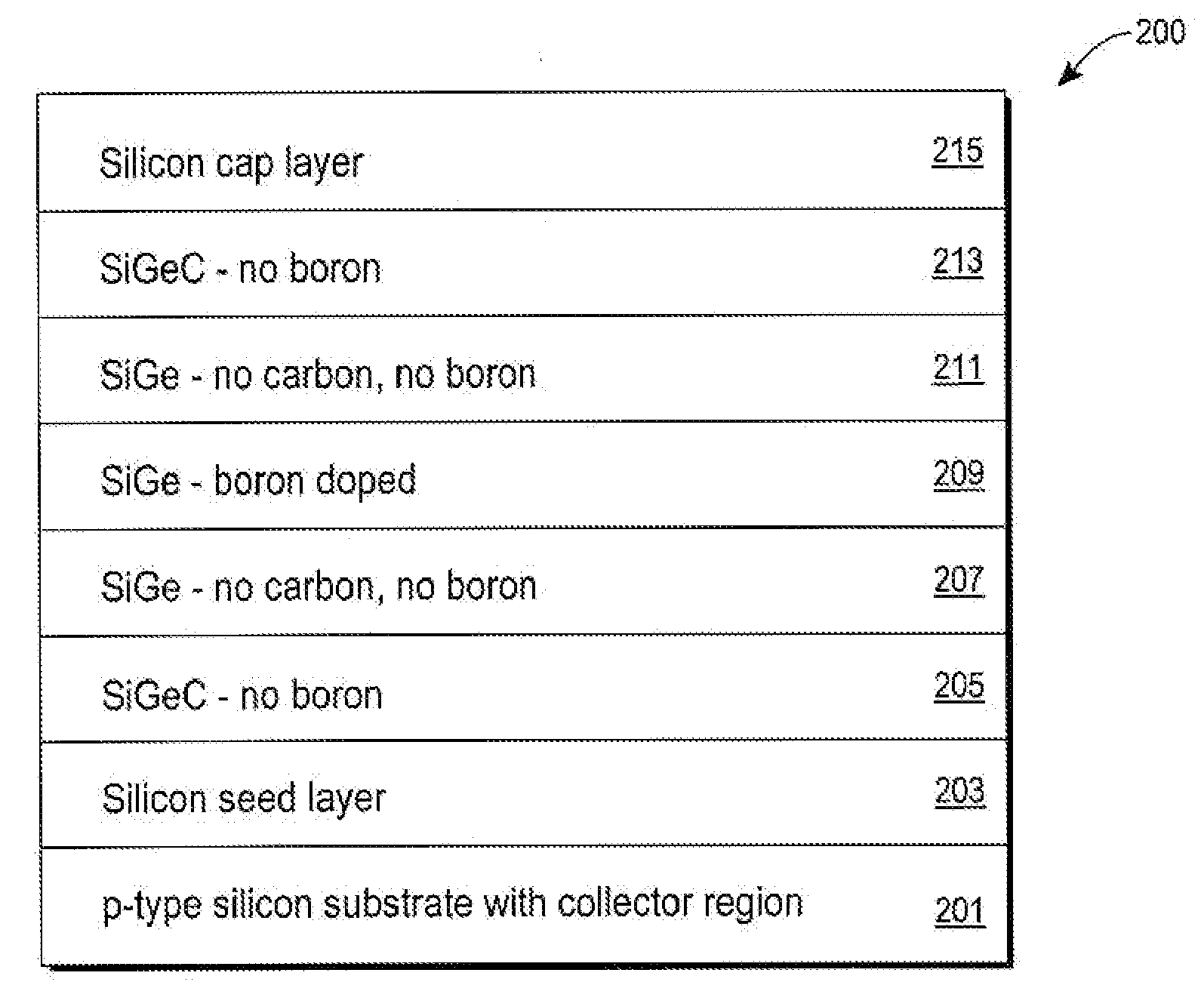

Deposition Over Mixed Substrates

<heading lvl="0">Abstract of Disclosure< / heading> Chemical vapor deposition methods are used to deposit silicon-containing films over mixed substrates. Such methods are useful in semiconductor manufacturing to provide a variety of advantages, including uniform deposition over heterogeneous surfaces, high deposition rates, and higher manufacturing productivity. An example is in forming the base region of a heterojunction bipolar transistor, including simultaneous deposition over both single crystal semiconductor surfaces and amorphous insulating regions.

Owner:ASM IP HLDG BV

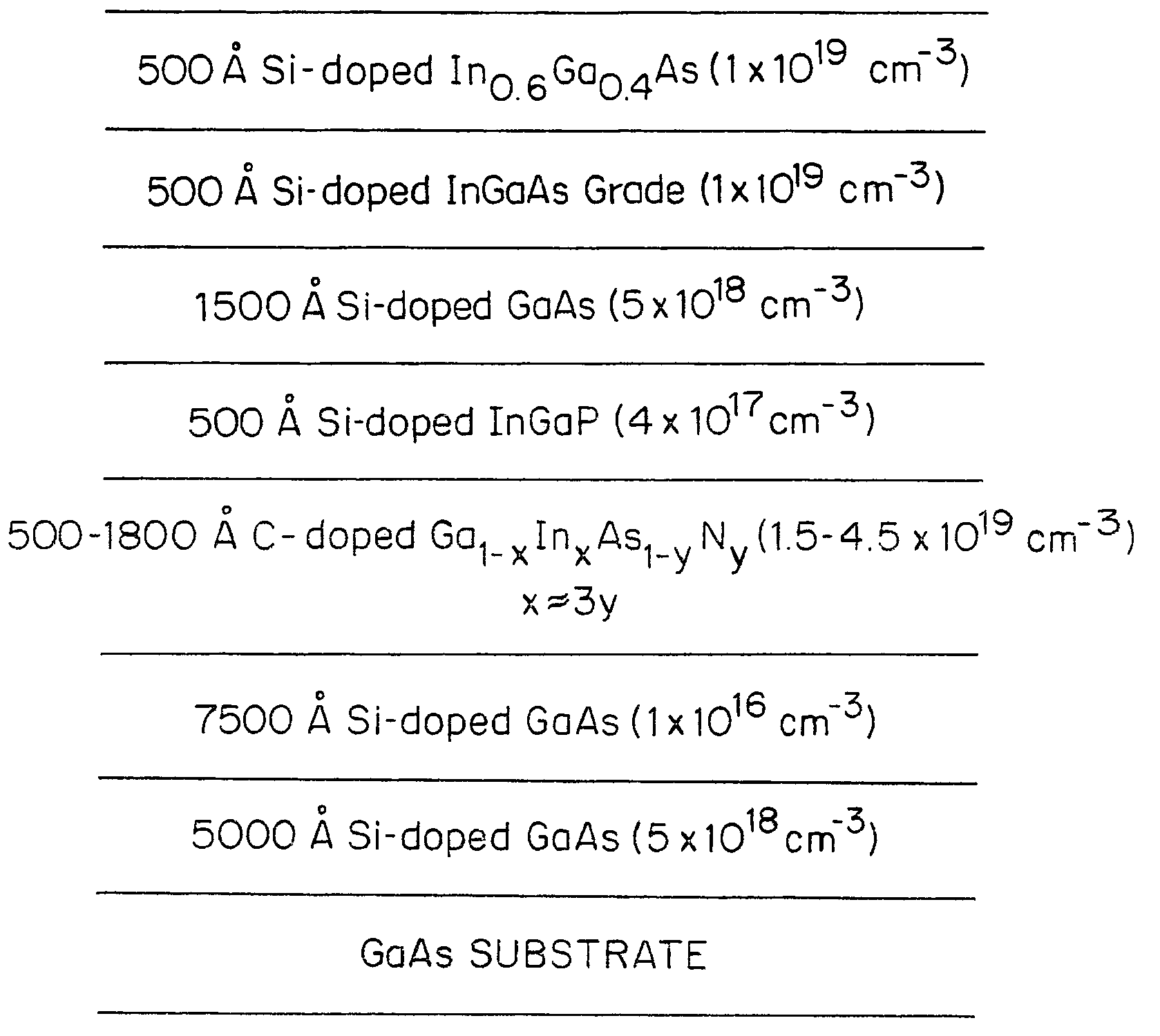

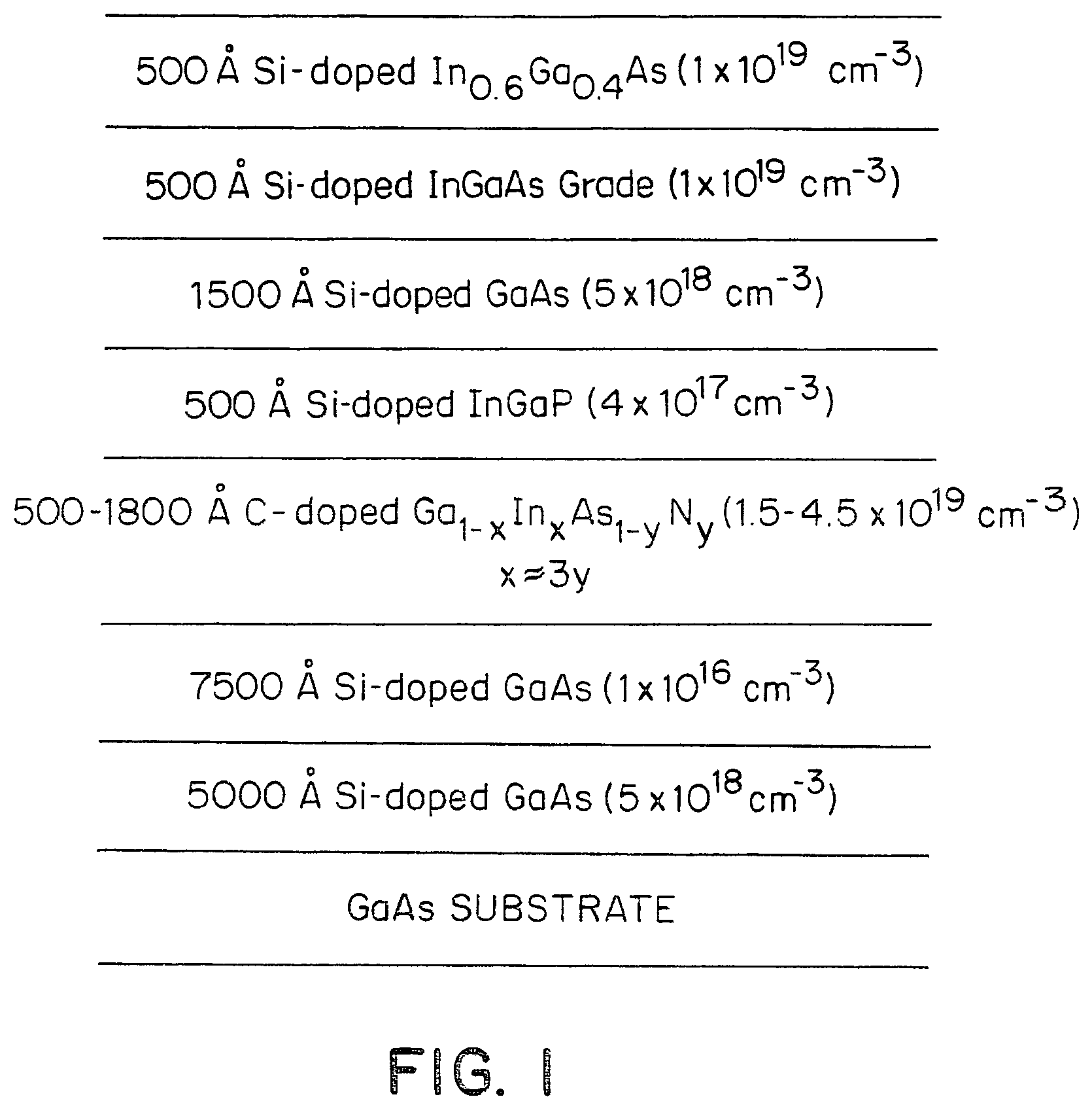

Bipolar transistor with lattice matched base layer

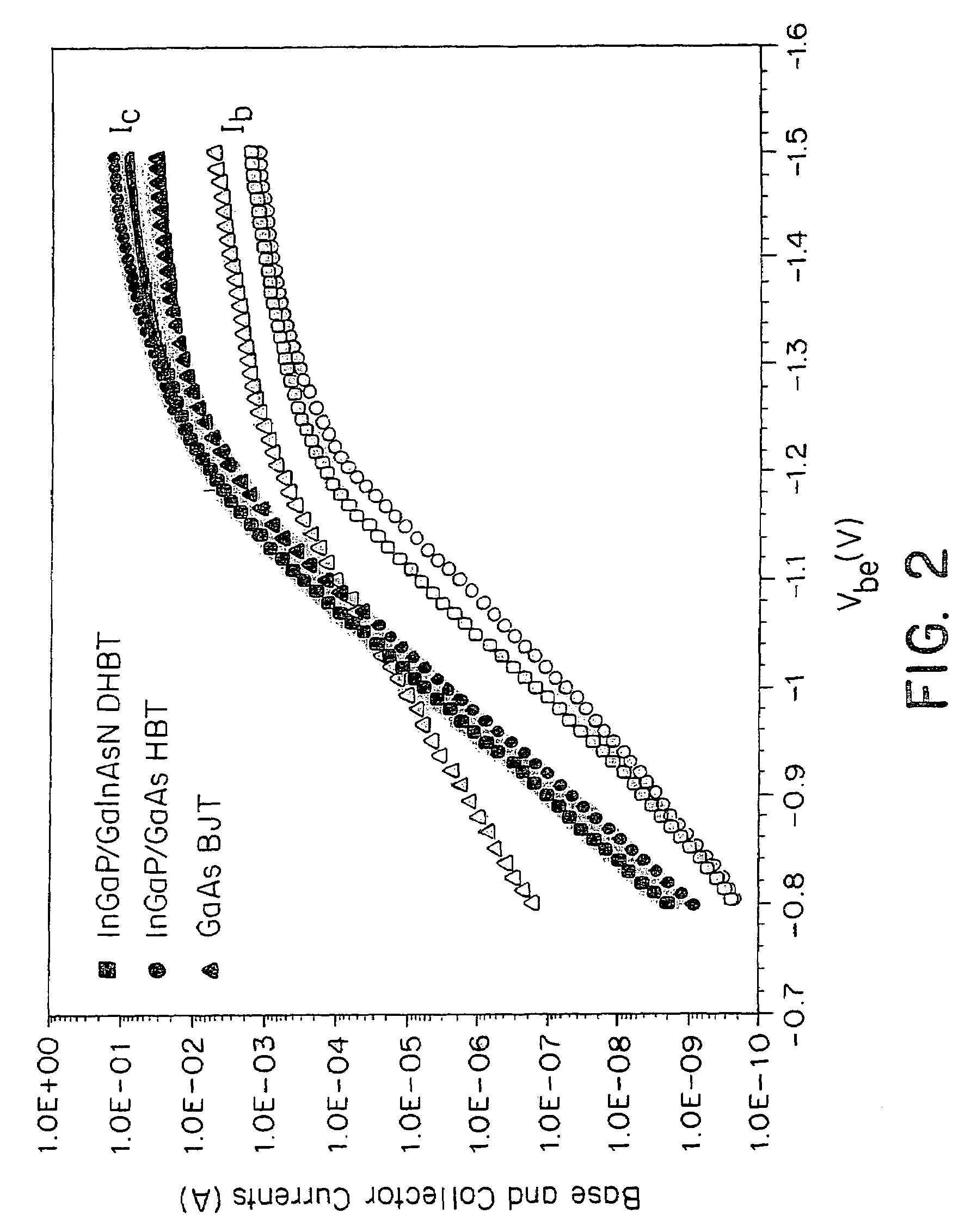

InactiveUS7186624B2Reduce gapLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDopant

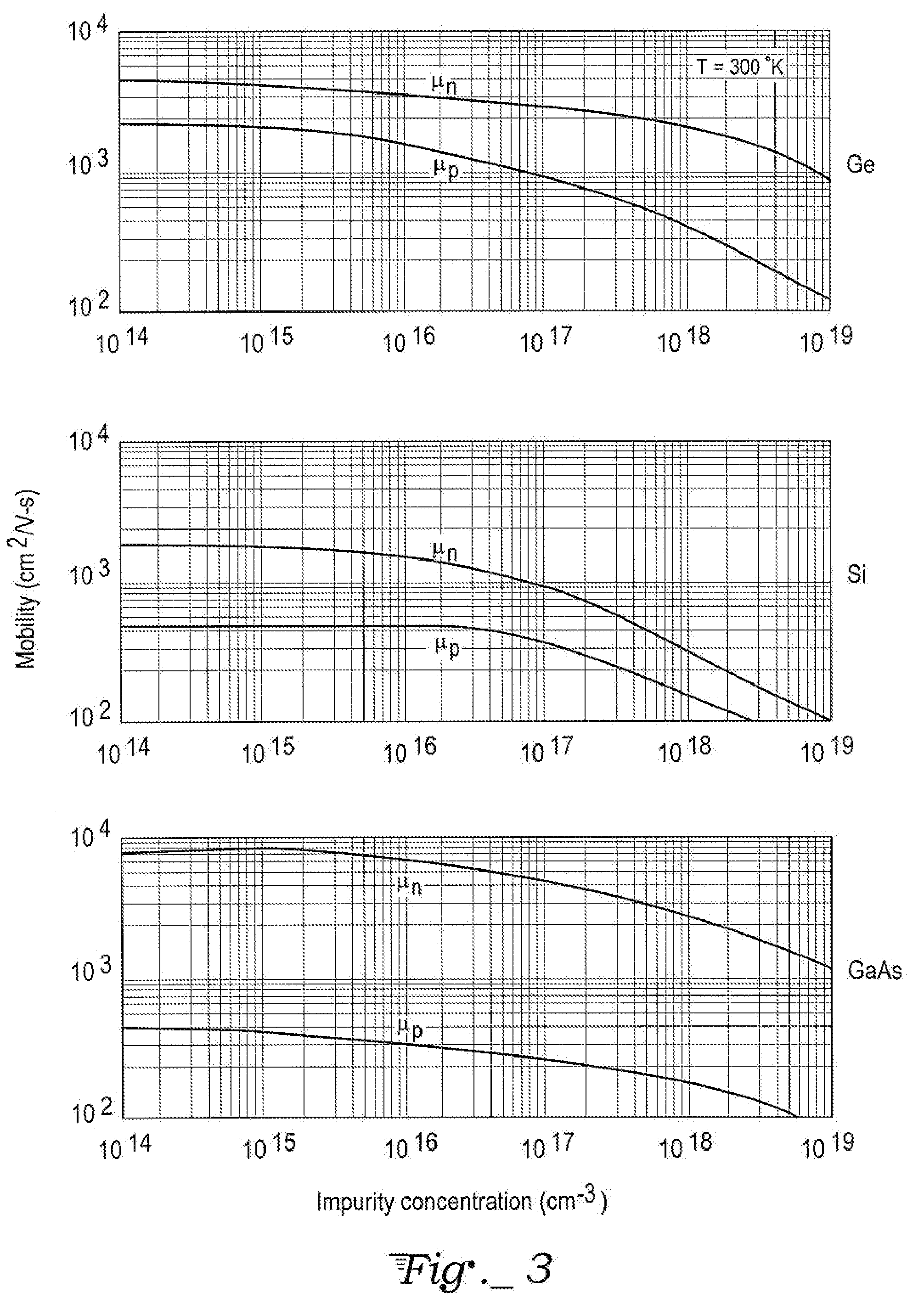

A semiconductor material which has a high carbon dopant concentration and is composed of gallium, indium, arsenic and nitrogen is disclosed. The material is useful in forming the base layer of gallium arsenide based heterojunction bipolar transistors because it can be lattice matched to gallium arsenide by controlling the concentration of indium and nitrogen. The disclosed semiconductor materials have a low sheet resistivity because of the high carbon dopant concentration obtained.

Owner:IQE KC

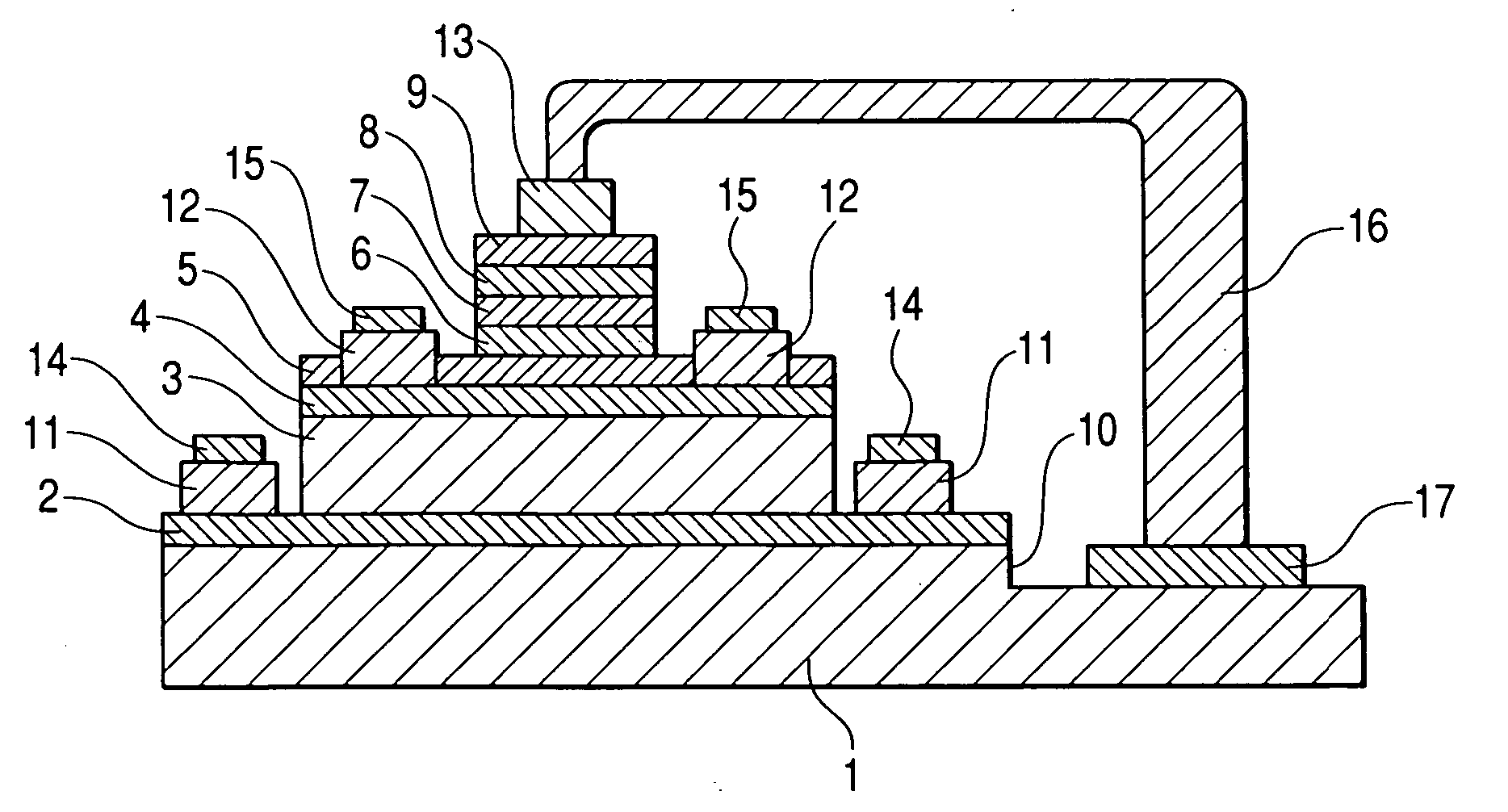

High-frequency power amplifier

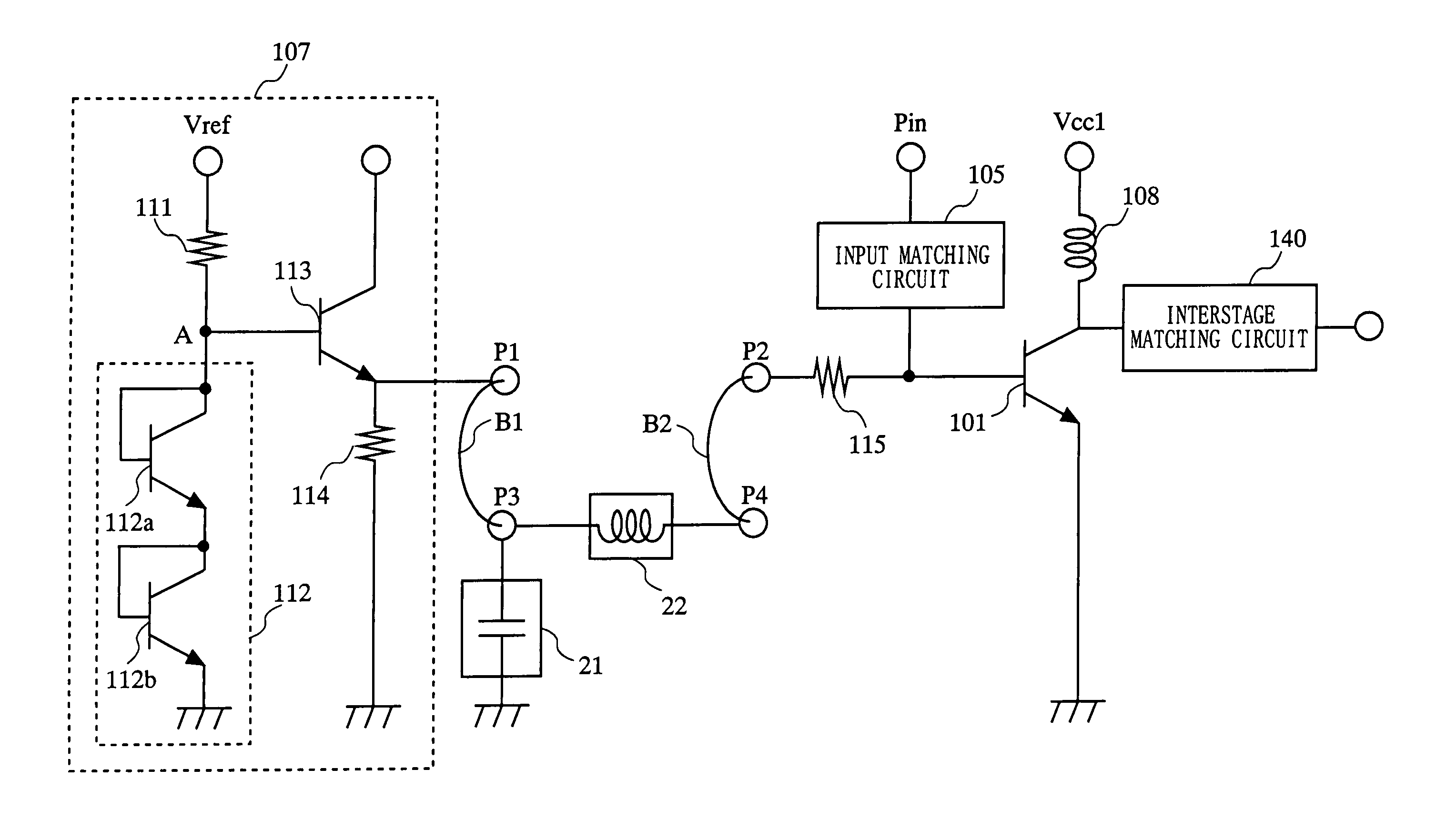

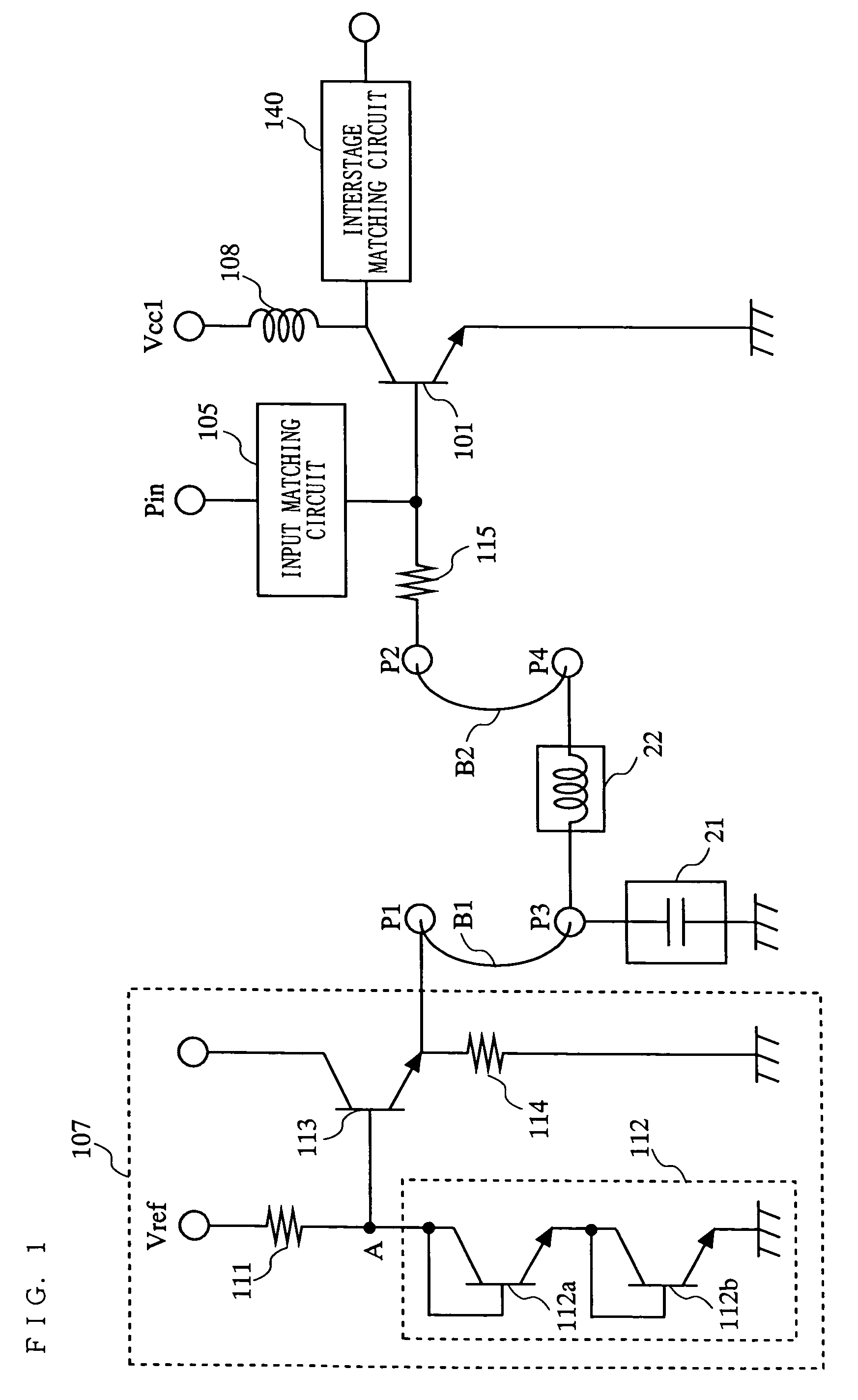

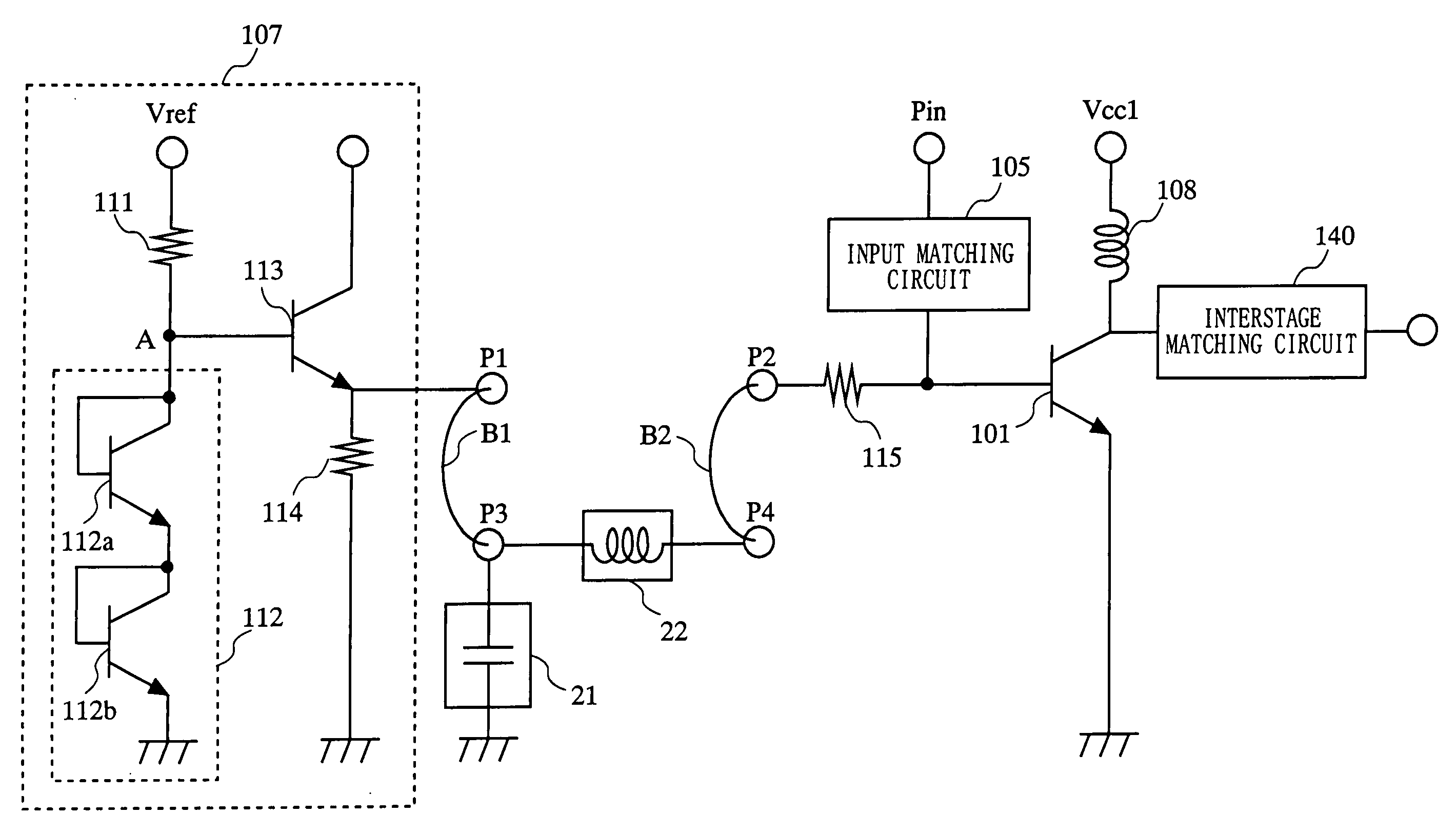

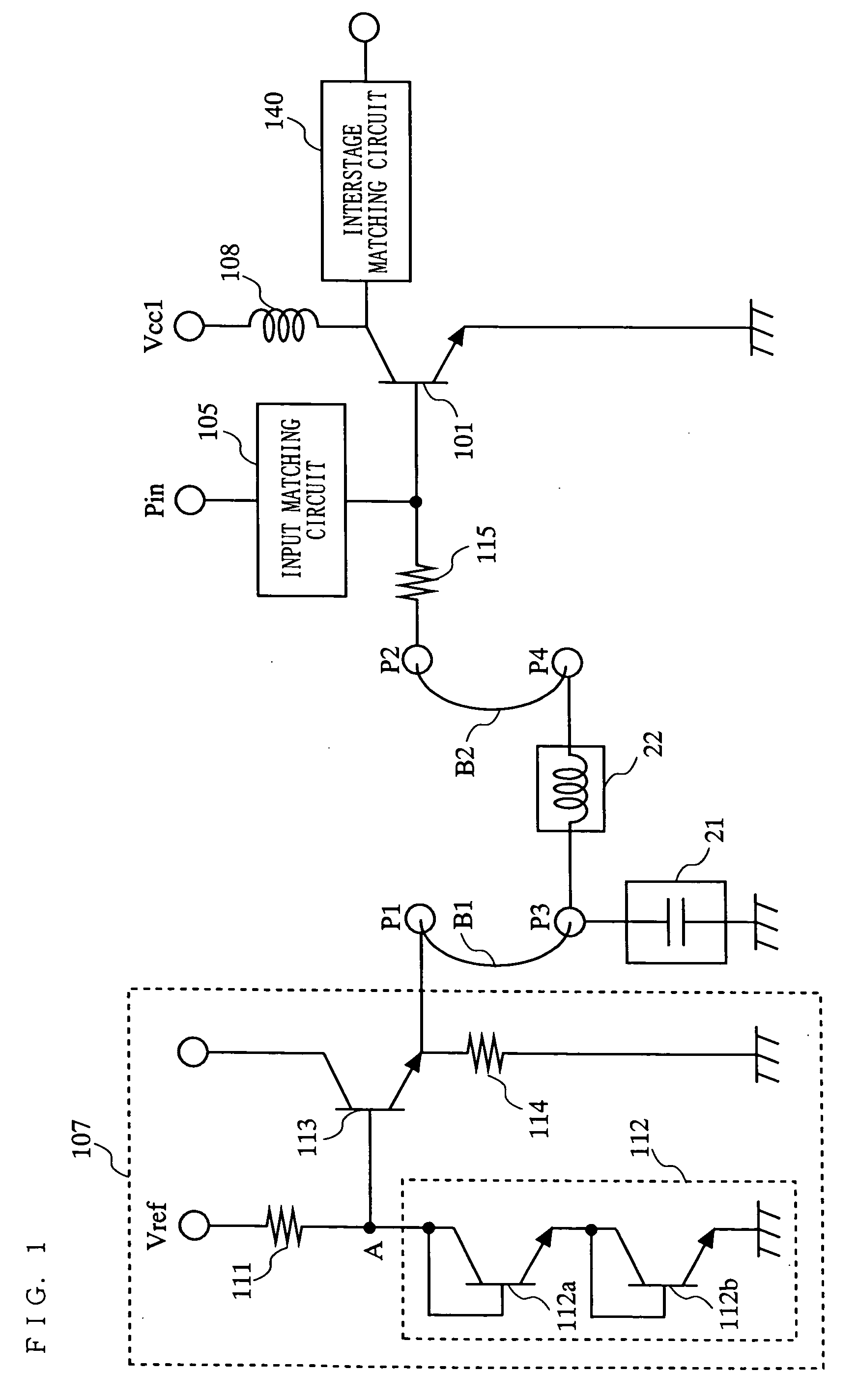

The present invention provides a compact and low-cost high-frequency power amplifier including GaAs heterojunction bipolar transistors (HBTs) but having a low level of noise in the transmission band. In the high-frequency power amplifier of the present invention, a chip capacitor 21 is connected at one end to an upstream stage bias circuit 107 via a bonding wire B1, and grounded at the other end. Also, a chip inductor 22 is connected to a base electrode of a high-frequency signal amplification HBT 101 via a bonding wire B2. In the high-frequency power amplifier of the present invention, the chip capacitor 21 causes noise generated within the upstream stage bias circuit 107 to flow to the ground, thereby reducing noise in the reception band. Also, the chip inductor 22 reduces a power loss of a high-frequency signal which is caused because the high-frequency signal flows to the ground.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

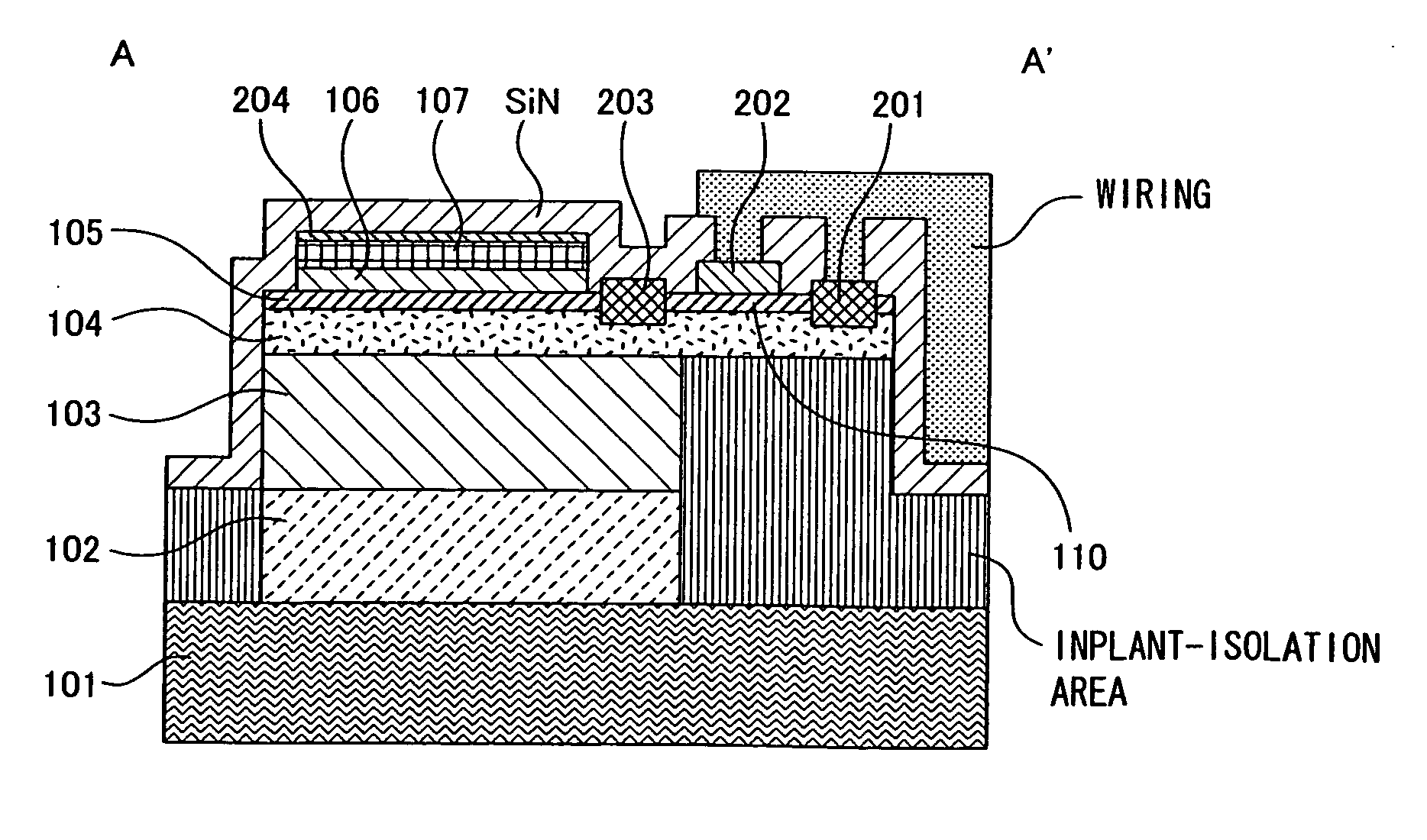

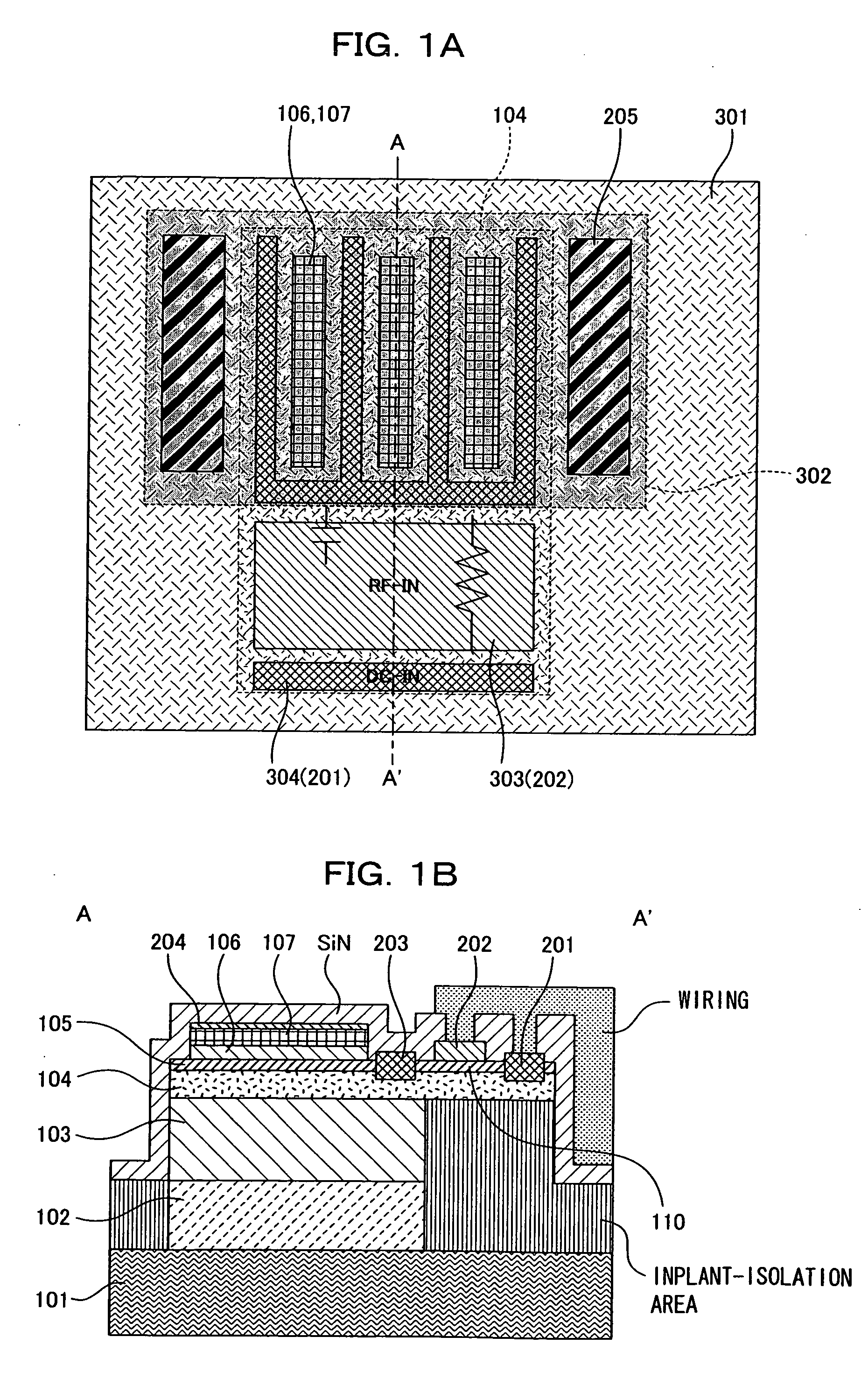

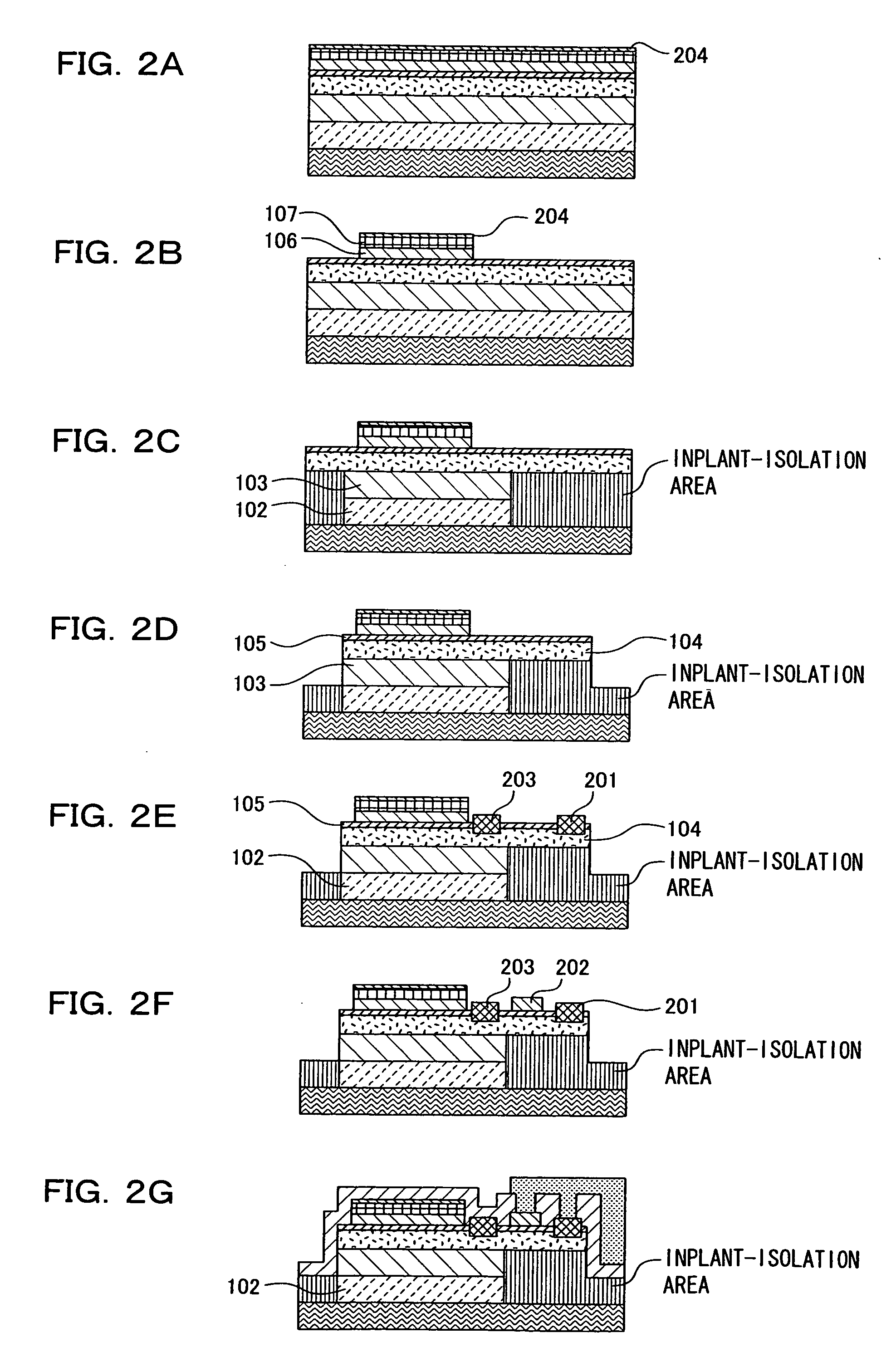

Hetero-junction bipolar transistor and manufacturing method of the same

InactiveUS20060267047A1Improve fracture resistanceImprove thermal stabilitySemiconductor devicesCapacitanceEngineering

Ion implantation is performed on a collector area under an external base area, and a capacitance film is provided on the external base area above the collector area.

Owner:PANASONIC CORP

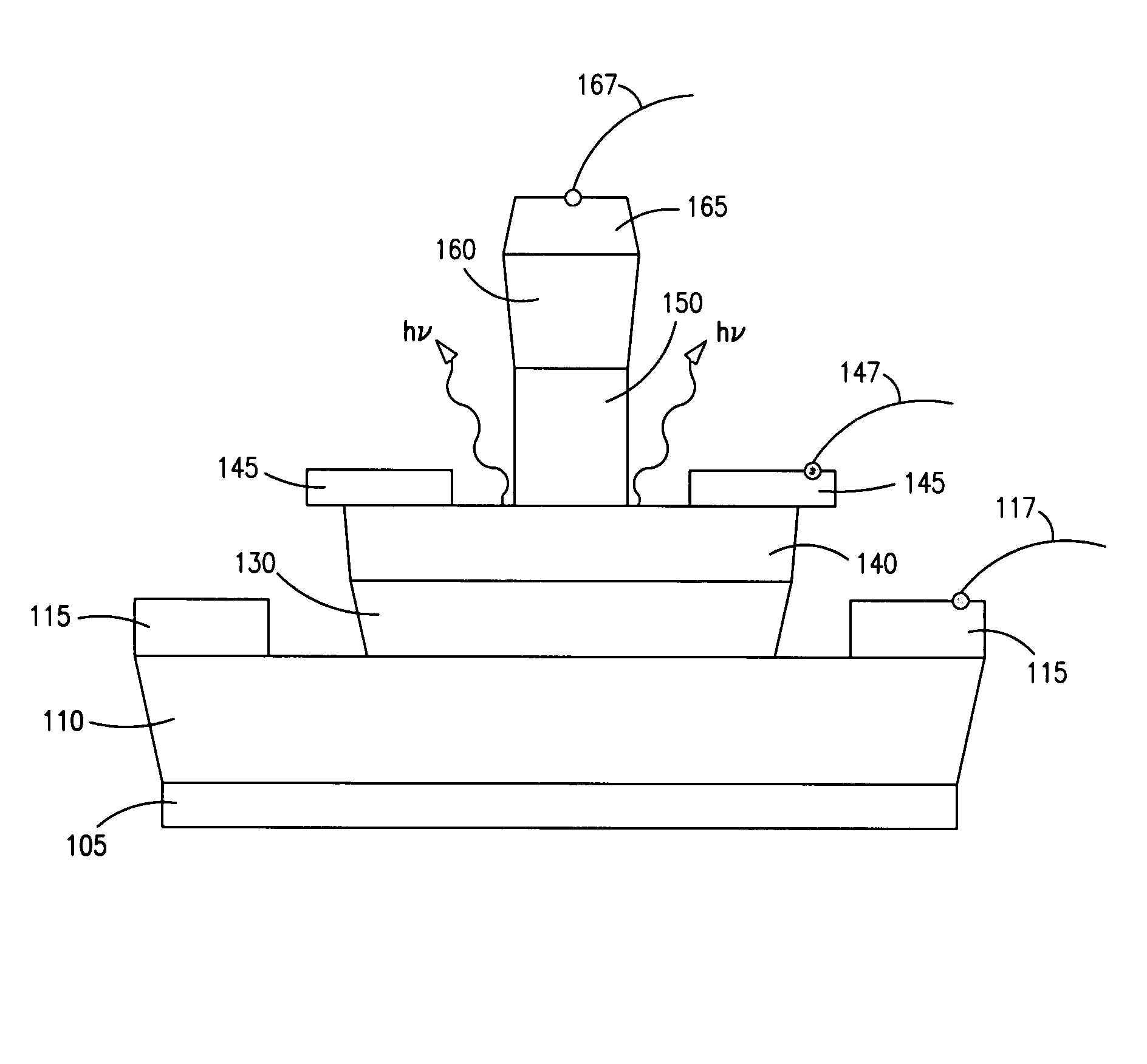

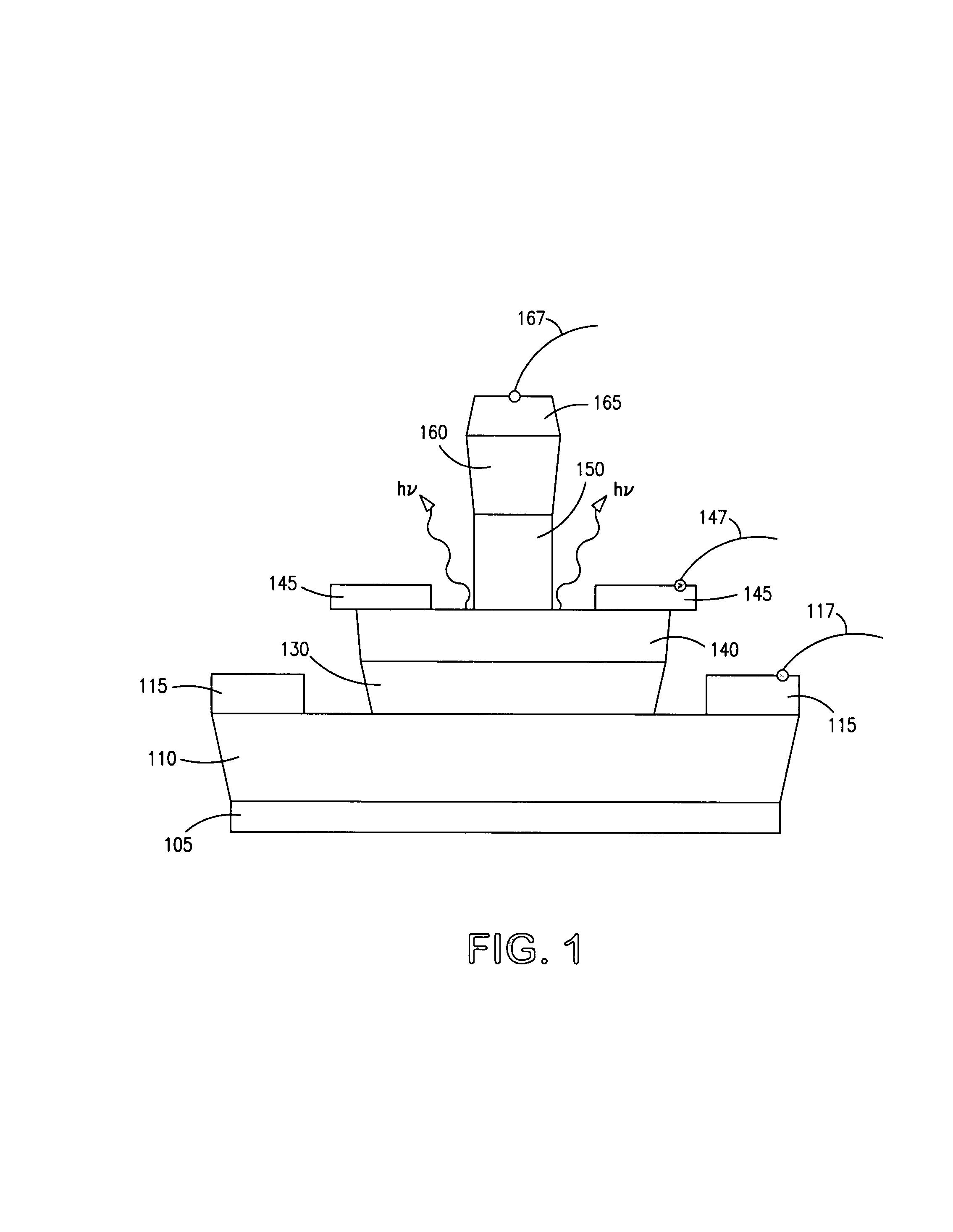

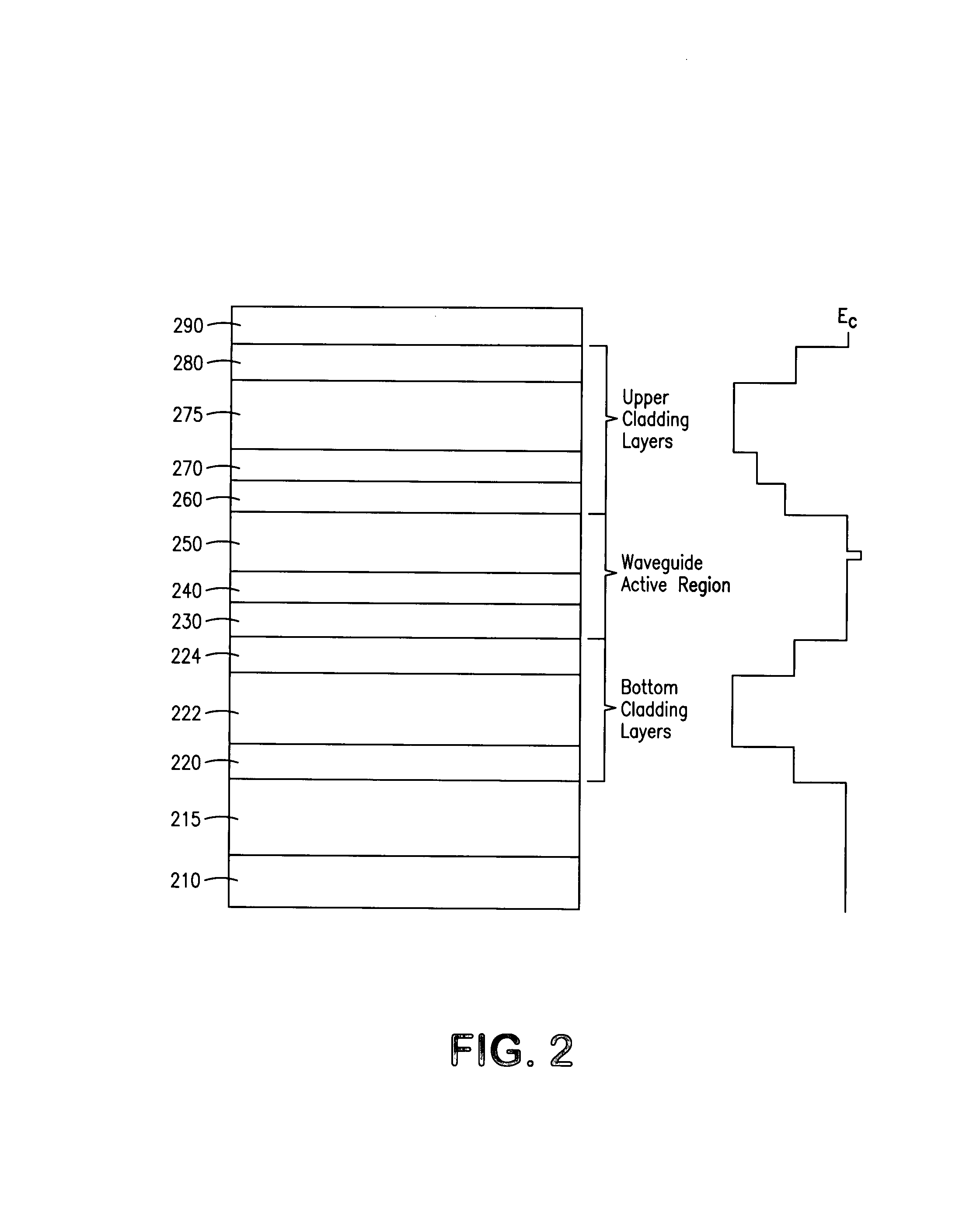

Semiconductor laser devices and methods

InactiveUS7286583B2Increase speedImprove mobilityLaser detailsNanoopticsResonant cavitySemiconductor materials

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

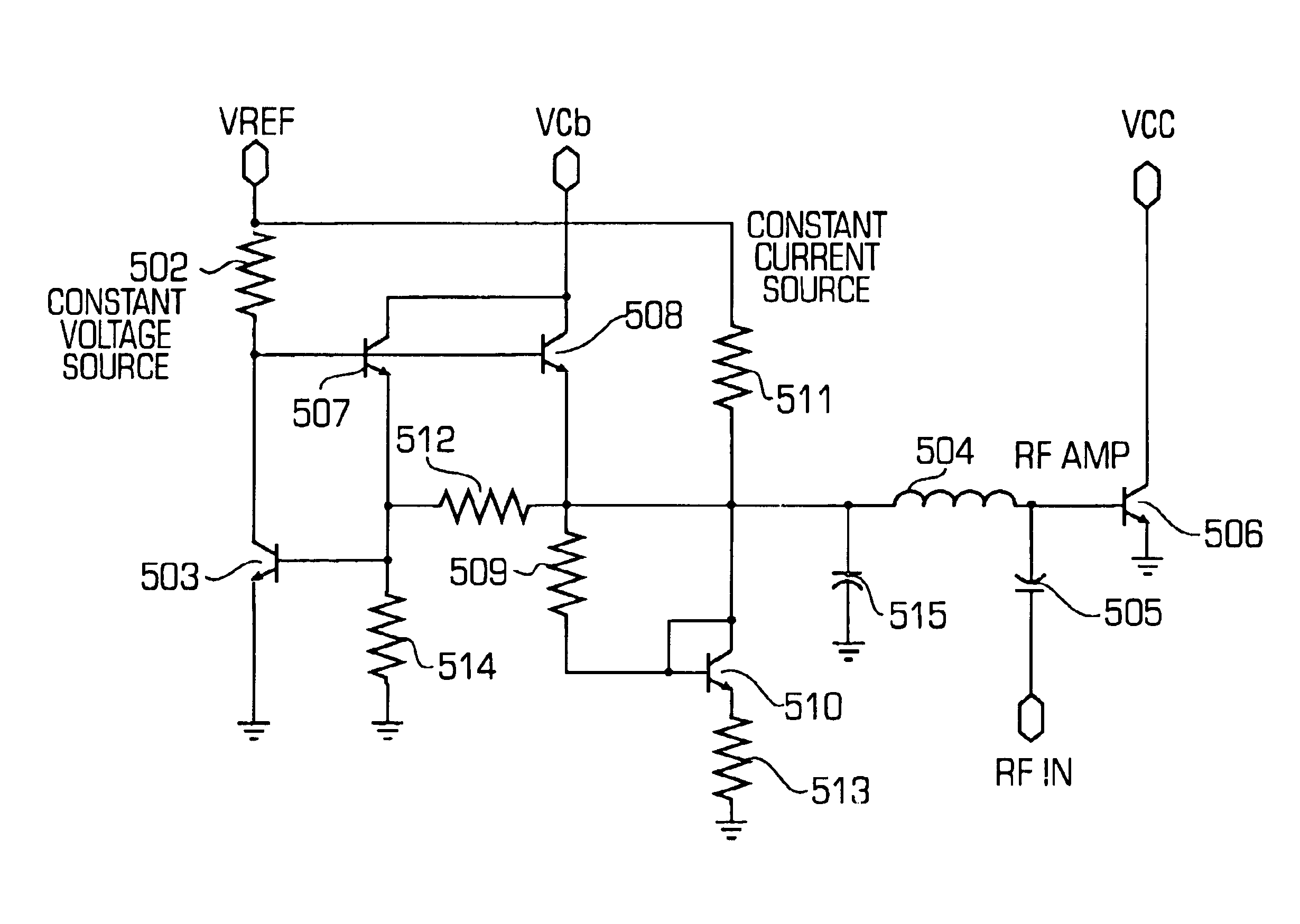

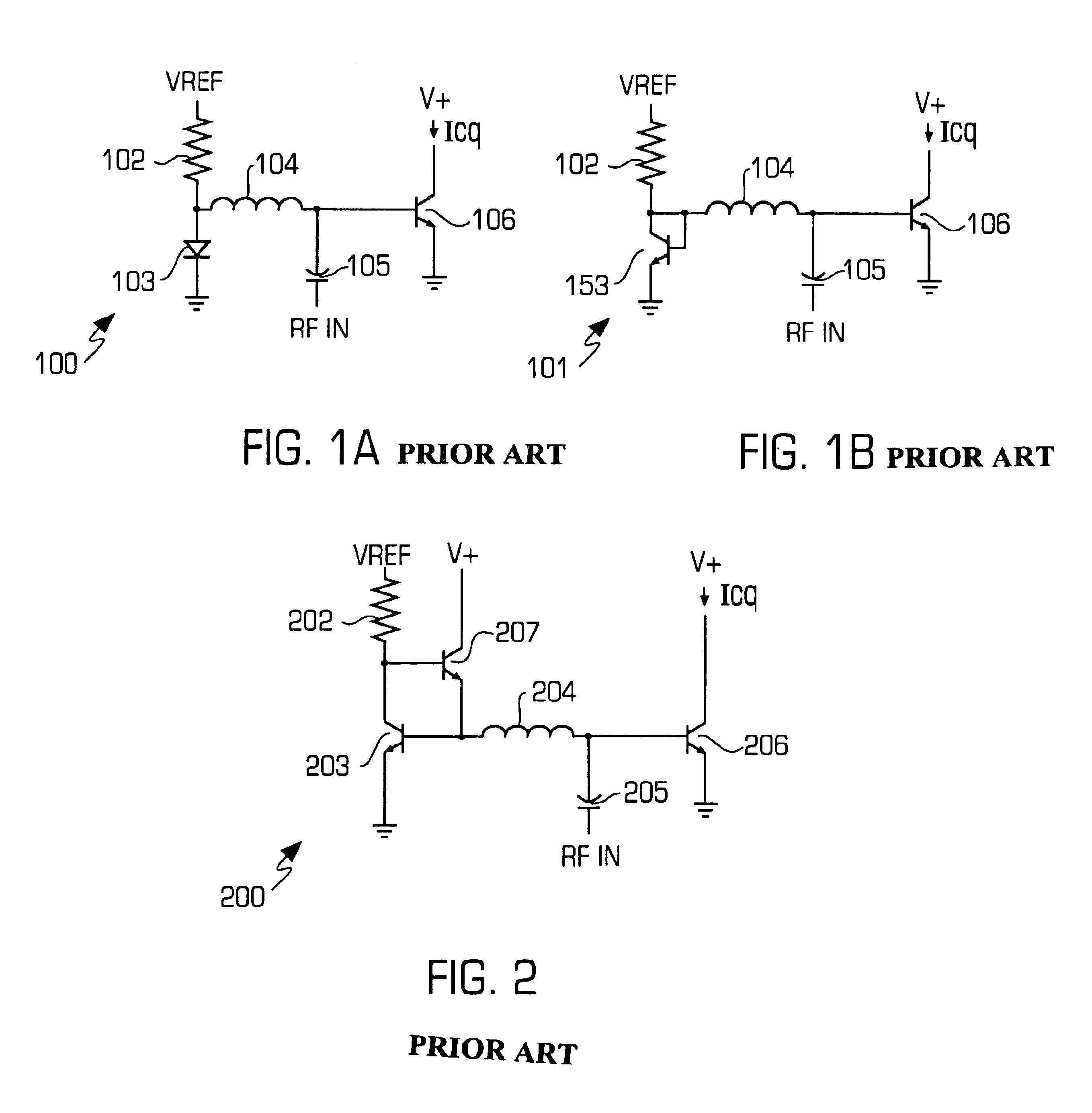

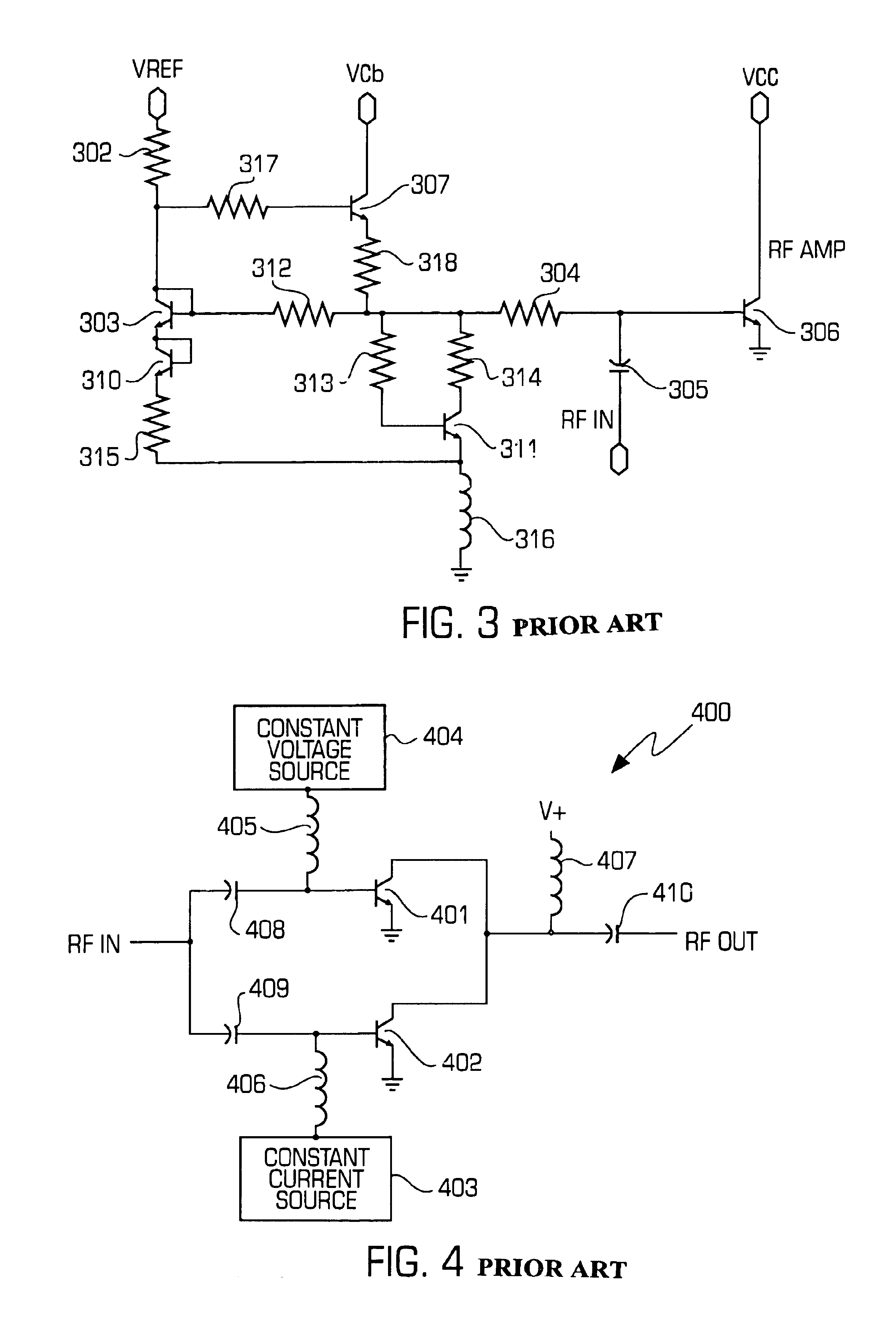

Dual (constant voltage/constant current) bias supply for linear power amplifiers

ActiveUS6922107B1Amplifier modifications to reduce non-linear distortionHigh frequency amplifiersAudio power amplifierLinear power amplifier

An RF amplifier comprises a power amplifier and a dual bias circuit. A dual bias circuit comprises a constant current source and a constant voltage source for biasing the power amplifier. The power may include a heterojunction bipolar transistor (HBT) or a bipolar junction transistor (BJT).

Owner:CALLAHAN CELLULAR L L C

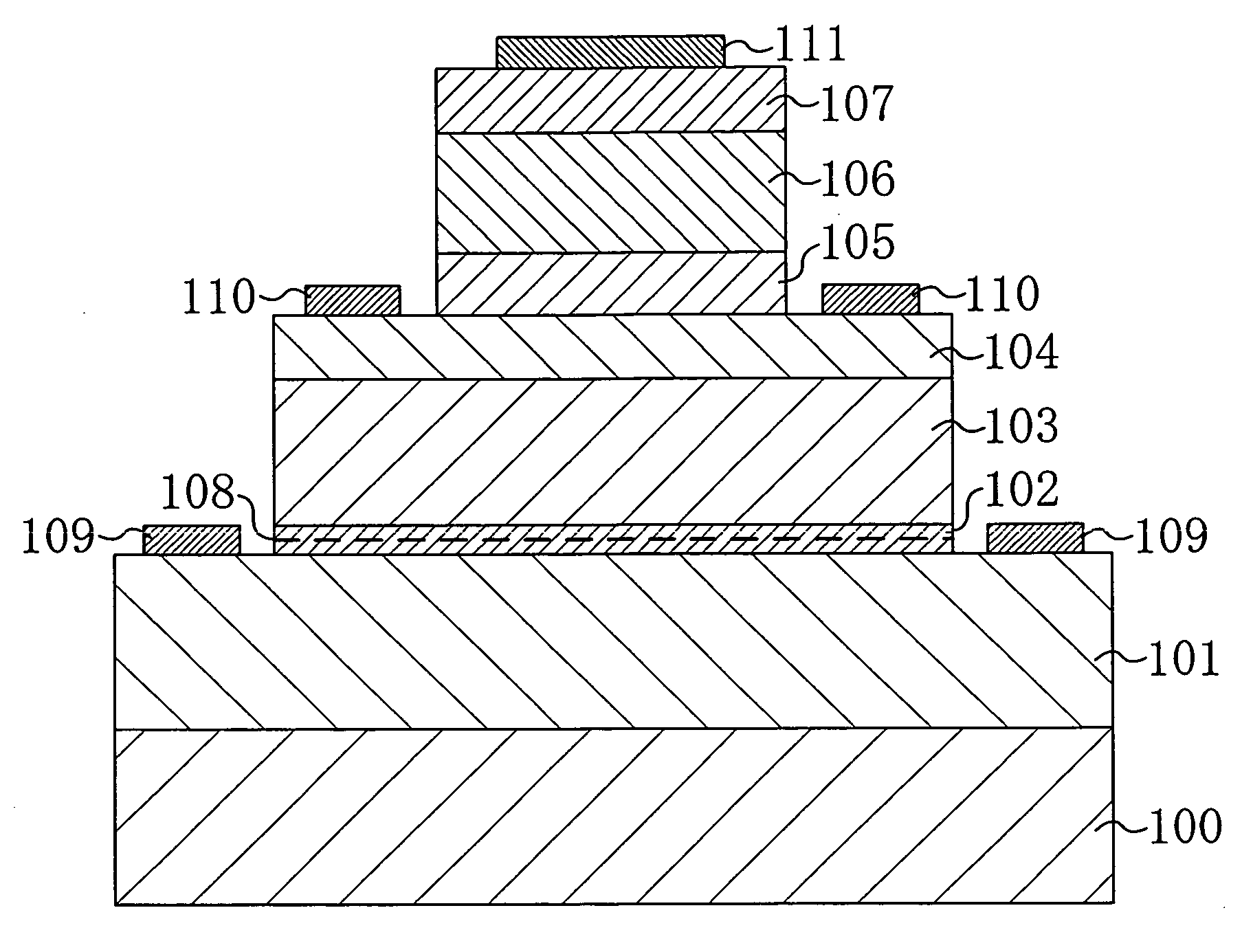

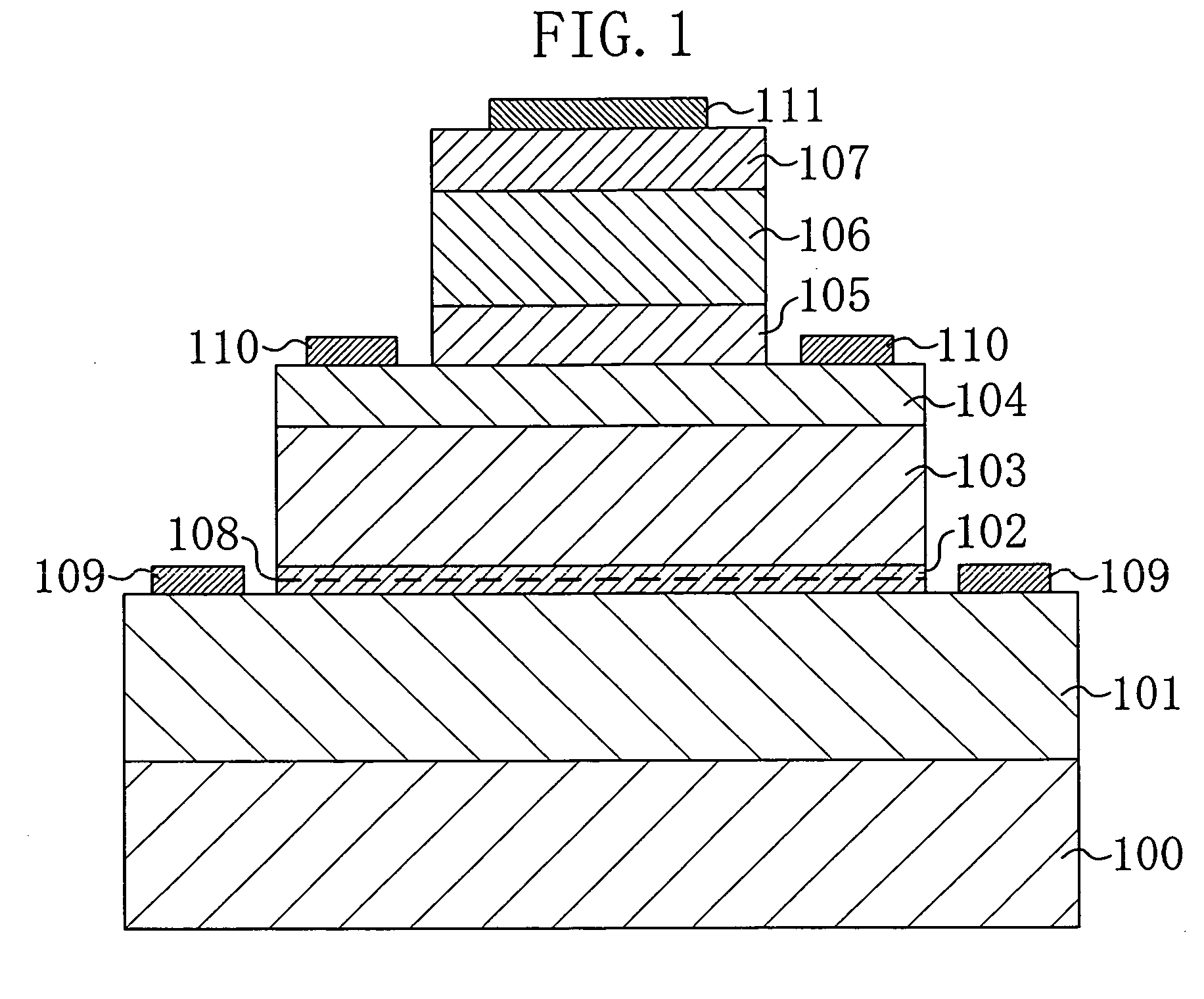

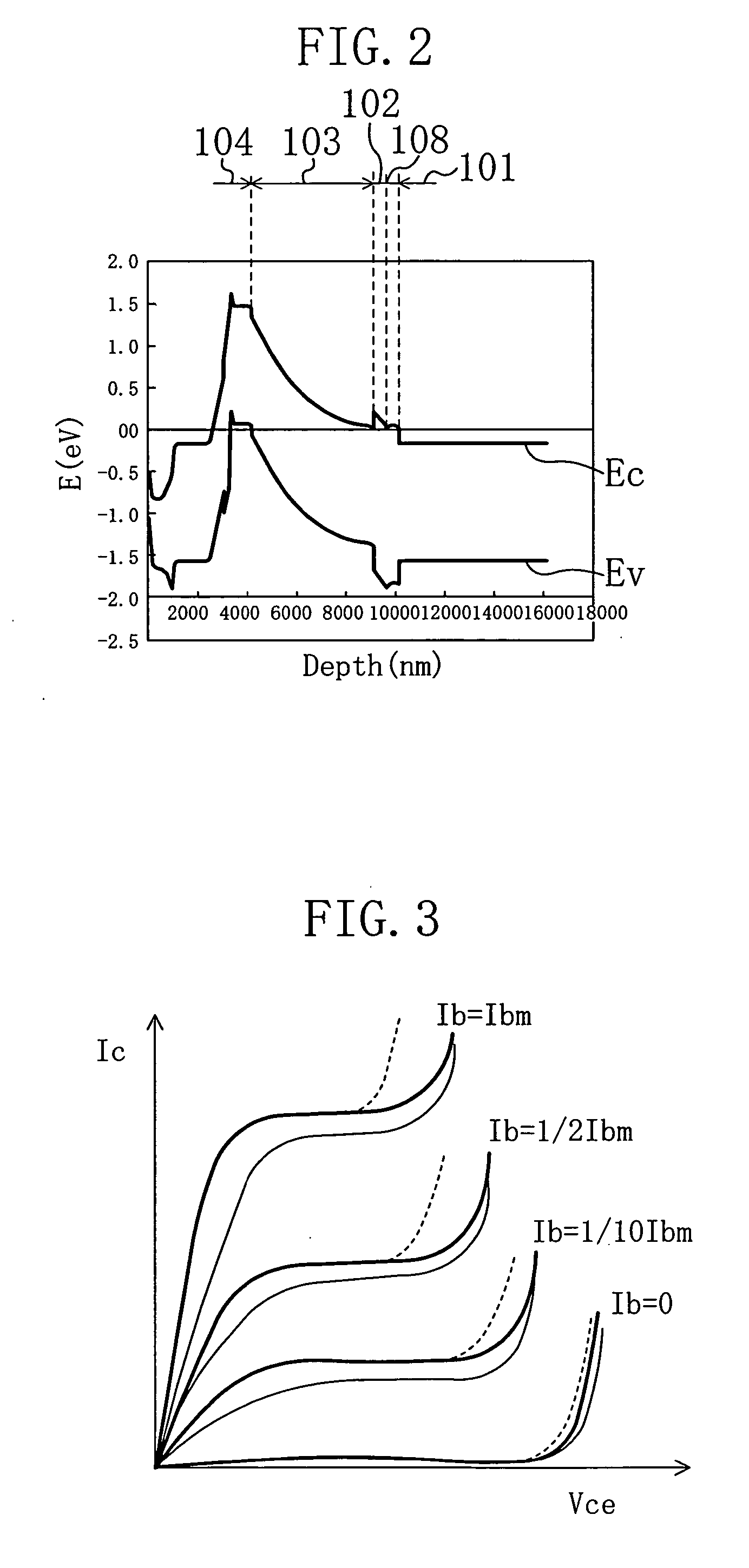

Hetero-junction bipolar transistor

InactiveUS20070120148A1High breakdown resistanceExcellent high-frequency characteristicSemiconductor devicesDelta dopingOptoelectronics

A hetero-junction bipolar transistor includes a sub-collector layer formed on a substrate and having conductivity, a first collector layer formed on the sub-collector layer and a second collector layer formed on the first collector layer and having the same conductive type as a conductive type of the sub-collector layer. In the first collector layer, a delta-doped layer is provided.

Owner:PANASONIC CORP

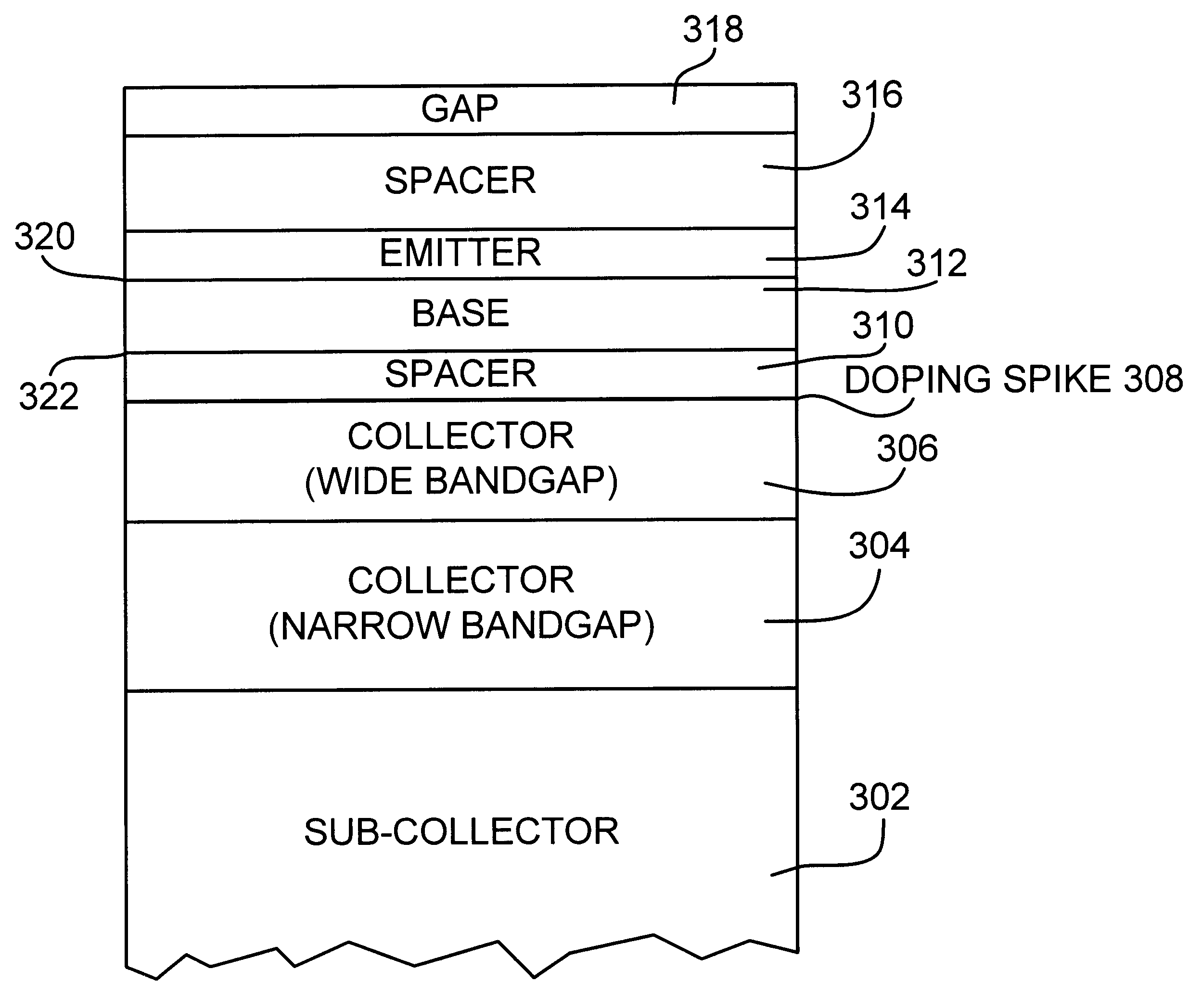

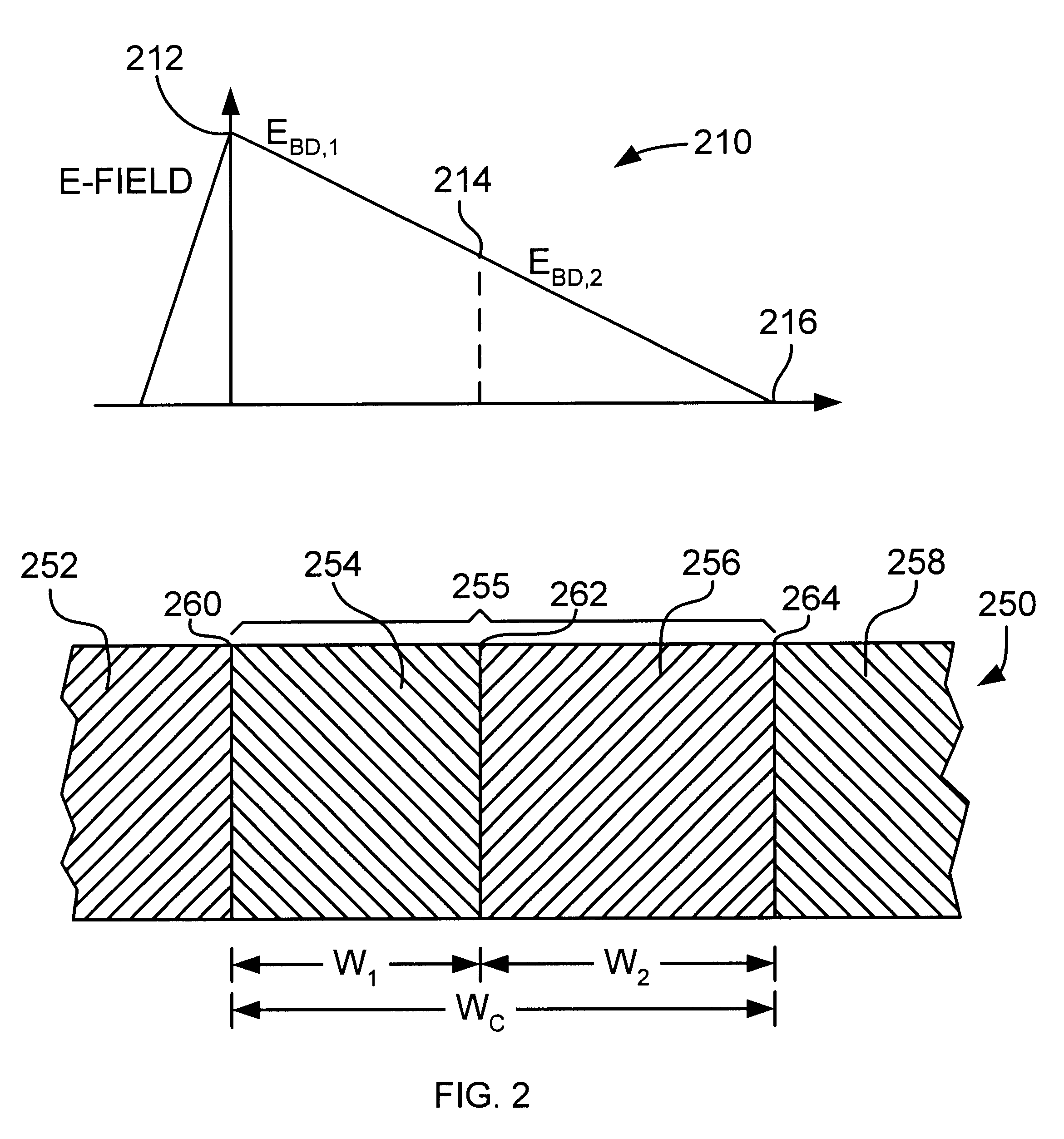

Methods and apparatus for a composite collector double heterojunction bipolar transistor

InactiveUS6563145B1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringWideband

A compound collector double heterojunction bipolar transistor (CCHBT) incorporates a collector comprising two layers: a wide bandgap collector region (e.g., GaAs), and a narrow bandgap collector region (e.g., InGaP). The higher electric field is supported in the wide bandgap region, thereby increasing breakdown voltage and reducing offset voltage. At the same time, the use of wide bandgap material in the depleted portion of the collector, and a higher mobility material toward the end and outside of the depletion region, reduces series resistance as well as knee voltage.

Owner:SKYWORKS SOLUTIONS INC

Heterojunction bipolar transistor and method for manufacturing the same, and power amplifier using the same

InactiveUS20050156194A1Reliable electrical conduction and thermal stabilityReliable conductionTransistorPower amplifiersAudio power amplifierEngineering

A heterojunction bipolar transistor with InGaP as the emitter layer and capable of both reliable electrical conduction and thermal stability wherein a GaAs layer is inserted between the InGaP emitter layer and AlGaAs ballast resistance layer, to prevent holes reverse-injected from the base layer from diffusing and reaching the AlGaAs ballast resistance layer.

Owner:RENESAS ELECTRONICS CORP

Hetrojunction bipolar transistor (HBT) with periodic multilayer base

InactiveUS20080050883A1Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSemiconductor materials

Owner:ATMEL CORP

Fabrication method of submicron gate using anisotropic etching

InactiveUS20010026985A1Reduce distanceLower base resistanceTransistorSemiconductor/solid-state device manufacturingEngineeringAnisotropic etching

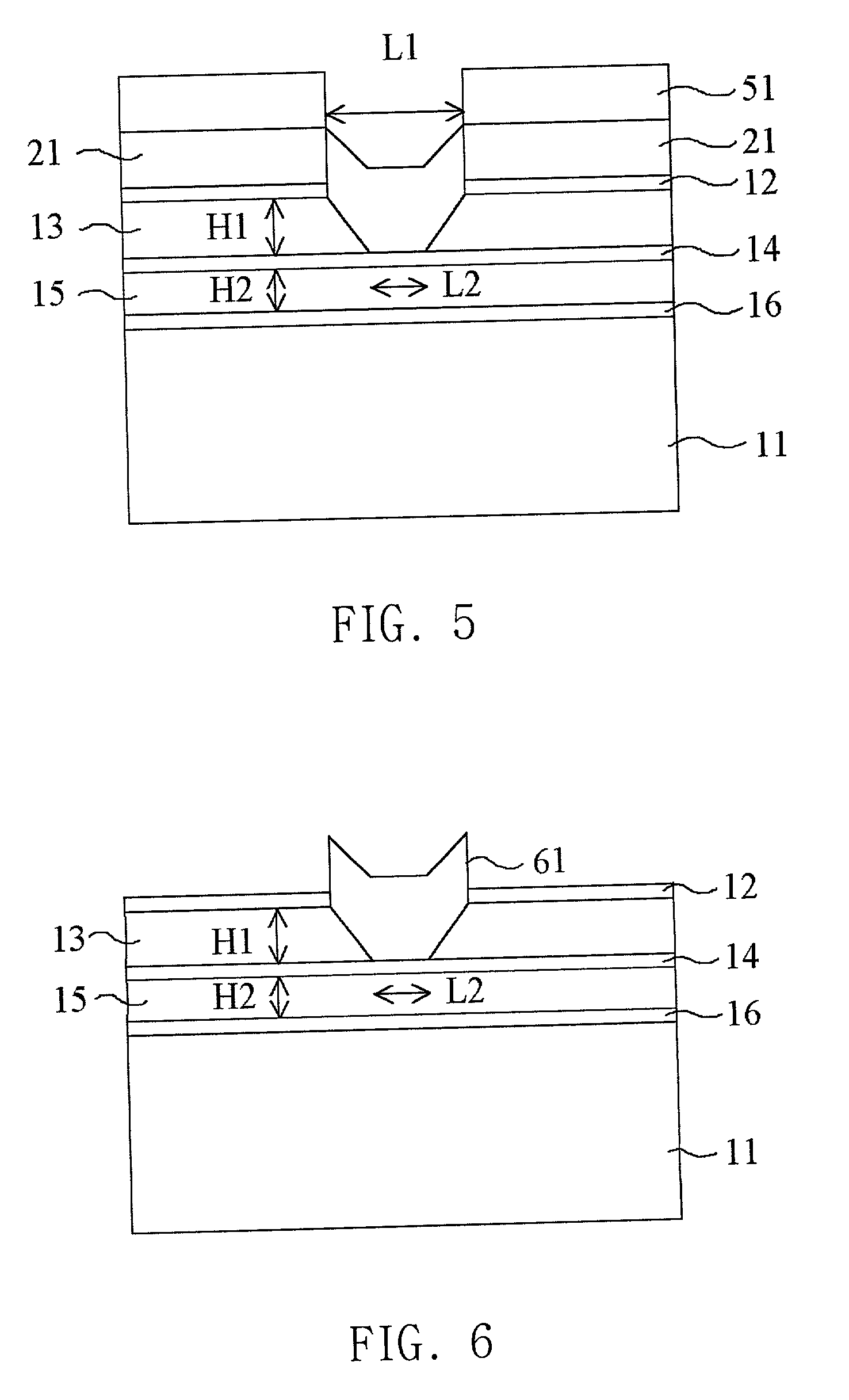

Disclosed is a method for fabricating a self-aligned submicron gate electrode using an anisotropic etching process. The method involves the steps of laminating a dummy emitter defining a dummy emitter region over a heterojunction bipolar transistor structure including layers sequentially formed over a semiconductor substrate to define a base region, an emitter region, and an emitter cap region, respectively, defining a line having a width of about 1 micron on the dummy emitter by use of a photoresist while using a contact aligner, selectively anisotropic etching the dummy emitter at a region where the line is defined, to allow the dummy emitter to have an etched portion having a bottom surface with a width less than the width of the line defined by the photoresist, and depositing a contact metal on the etched portion of the dummy emitter, thereby forming a gate. In accordance with the present invention, a reliable submicron gate can be fabricated using a simple anisotropic wet etch process and an inexpensive contact aligner. Accordingly, the manufacturing costs can be reduced. In the formation of a base electrode involved in the fabrication of an HBT device, the present invention also provides an effect of reducing the distance between a base and an emitter, thereby achieving a reduction in base resistance, by virtue of a self-alignment using a V-shaped submicron gate.

Owner:KOREA ADVANCED INST OF SCI & TECH

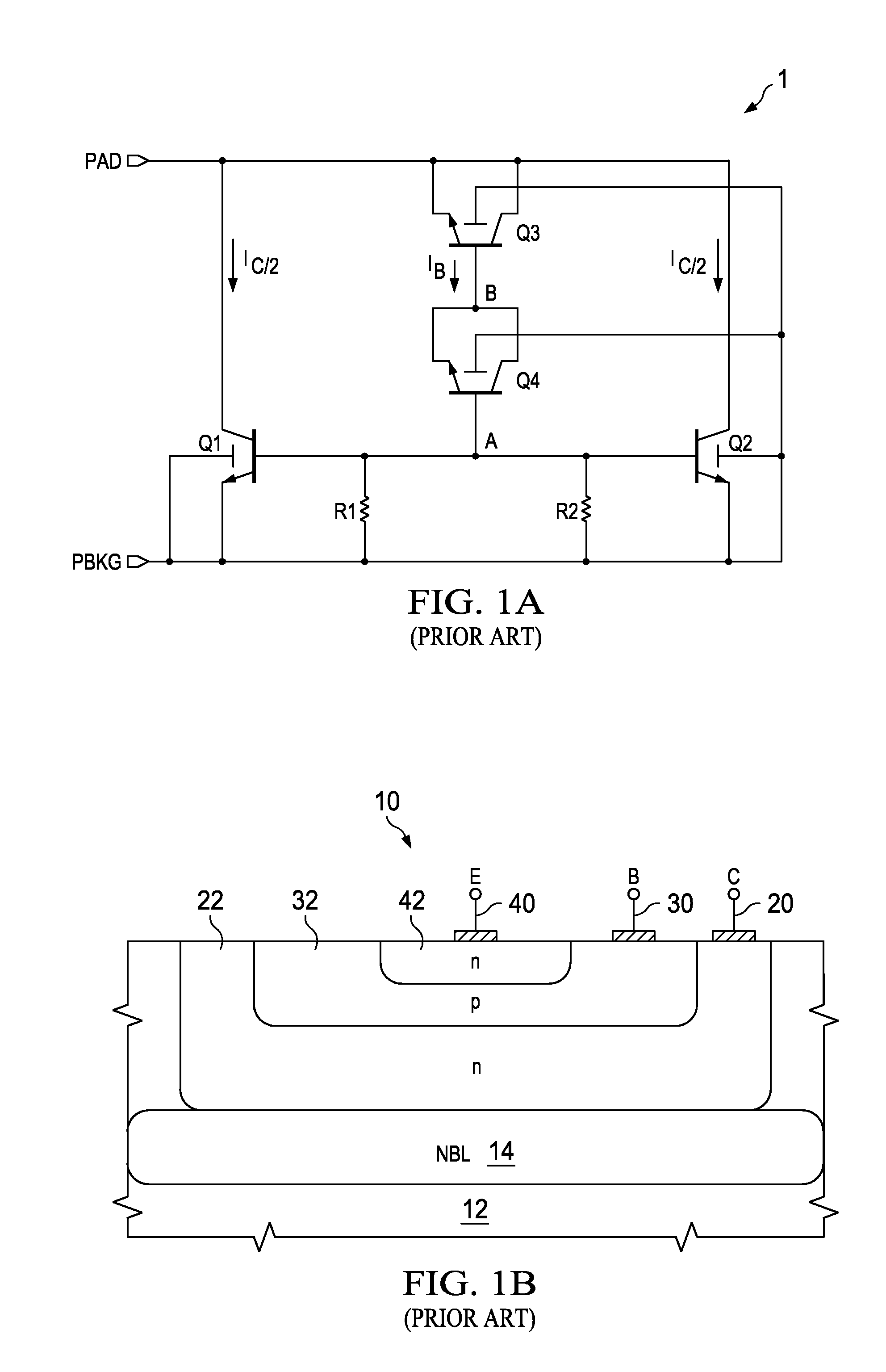

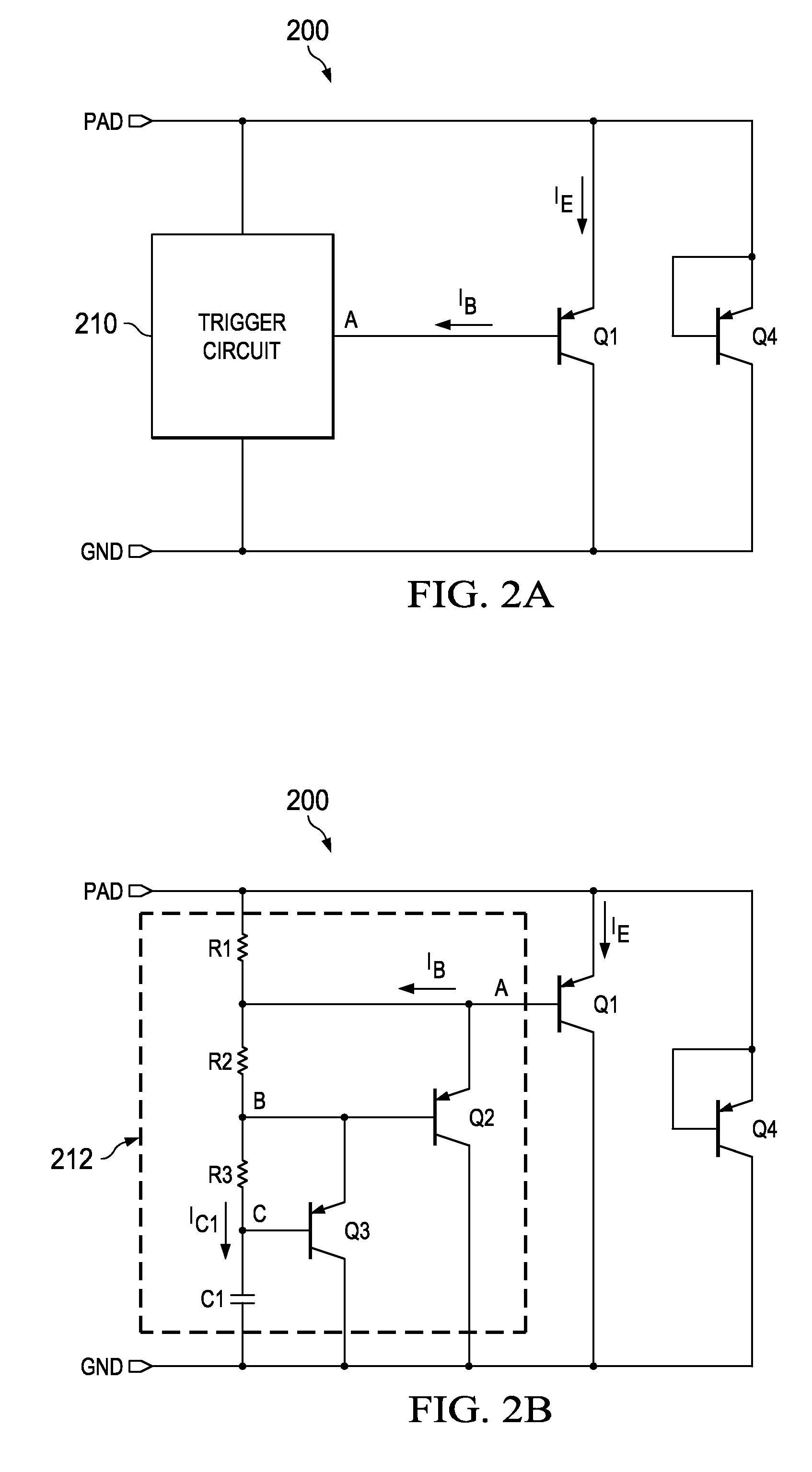

High voltage ESD protection featuring pnp bipolar junction transistor

InactiveUS20080316659A1Reduce decreaseReduce riskTransistorEmergency protective arrangements for limiting excess voltage/currentCapacitanceDriving current

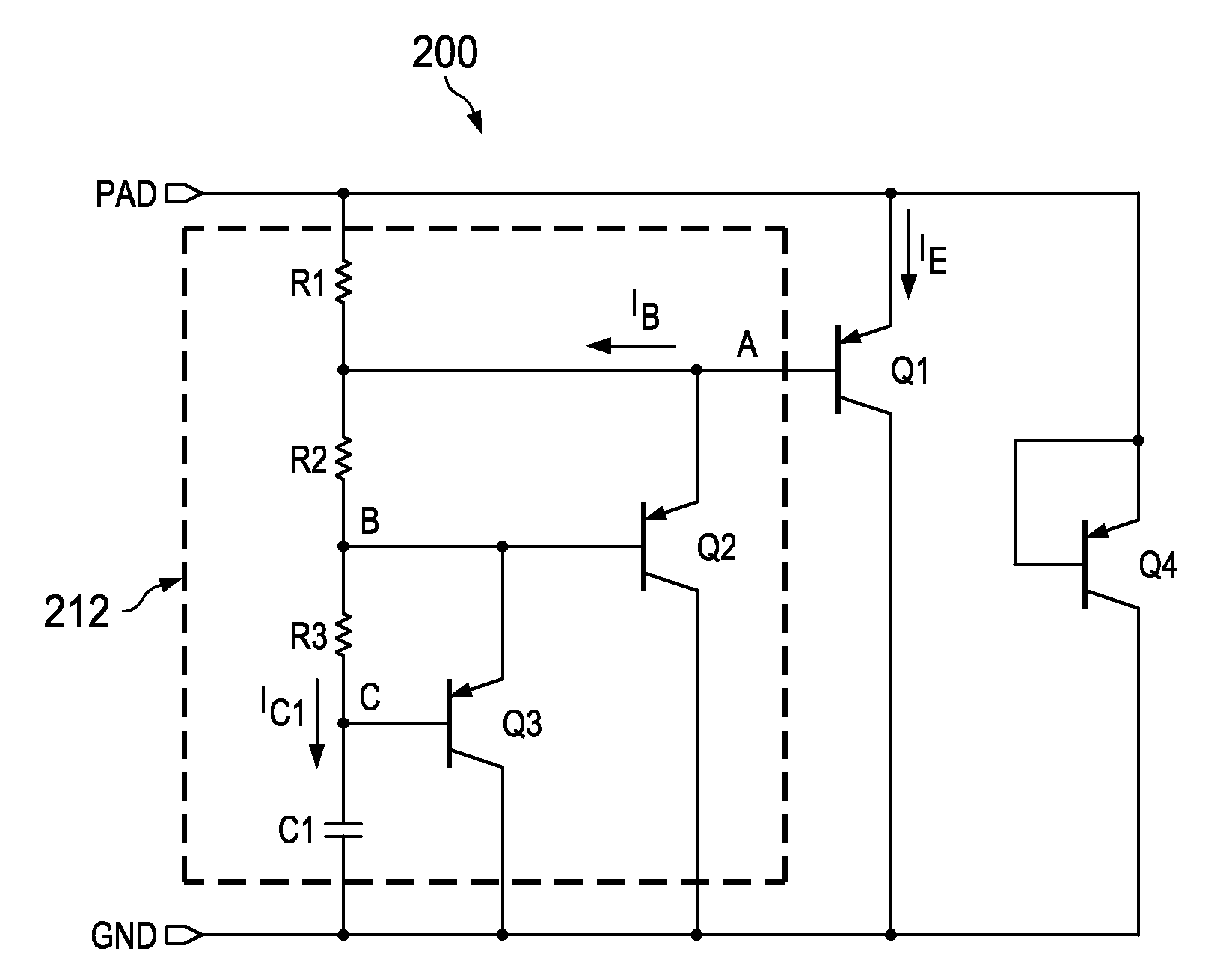

A protection circuit is disclosed that protects a semiconductor device from damage due to an electrostatic discharge. One such protection circuit comprises a vertical pnp hetero-junction bipolar transistor (HBT) connected between terminals such as supply terminals of the device, configured to conduct during an electrostatic discharge. The protection circuit also comprises a trigger circuit, such as a transient activated RC circuit connected between the terminals to detect the electrostatic discharge and control the transistor based on the detected electrostatic discharge. A Darlington transistor pair in the trigger circuit can be used to multiply the effective capacitance and HBT drive current. The HBT transistor absorbs energy from the electrostatic discharge and clamps the over-voltage across the terminals. The protection circuit may also be used across other I / O terminals of the device.

Owner:TEXAS INSTR INC

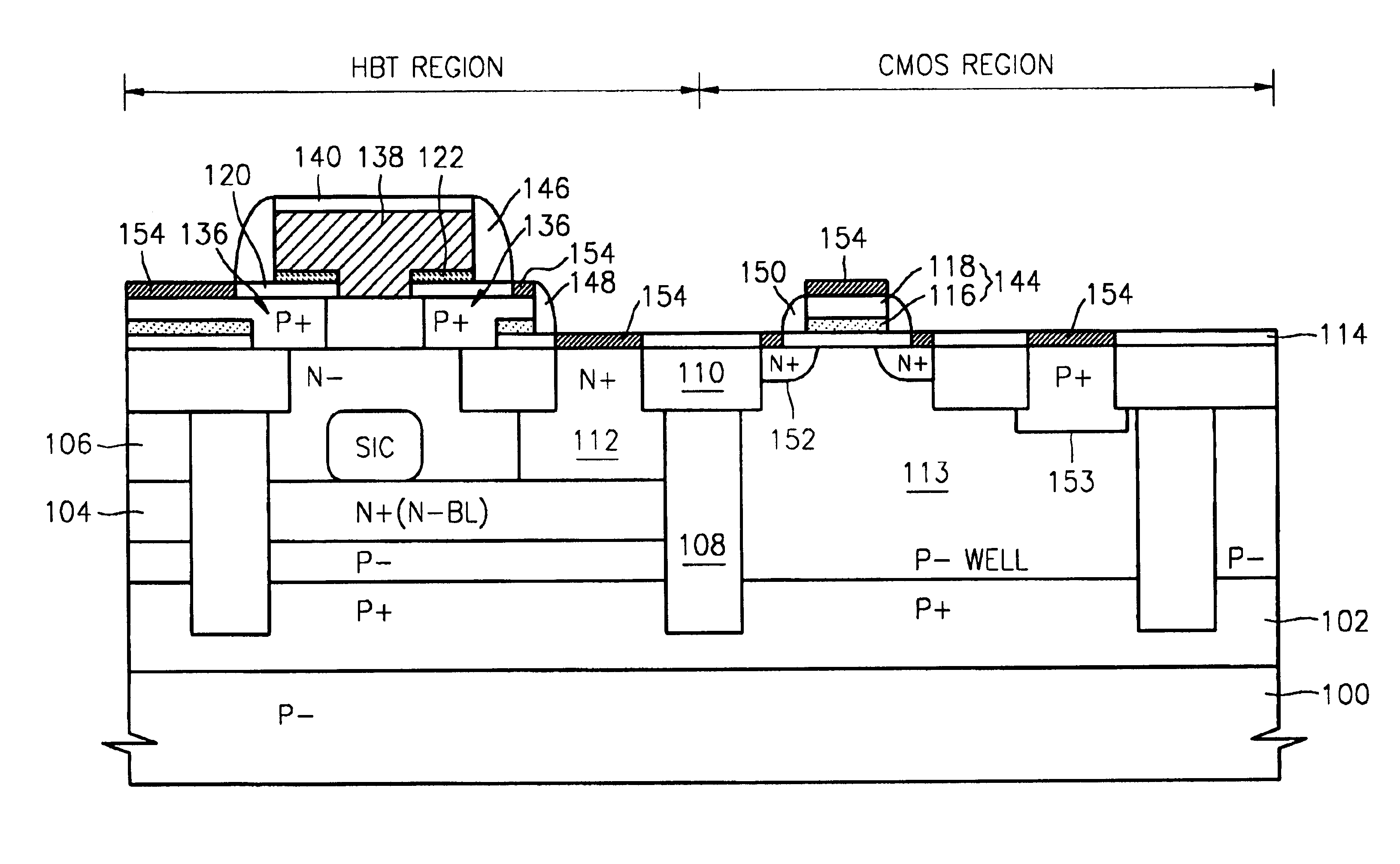

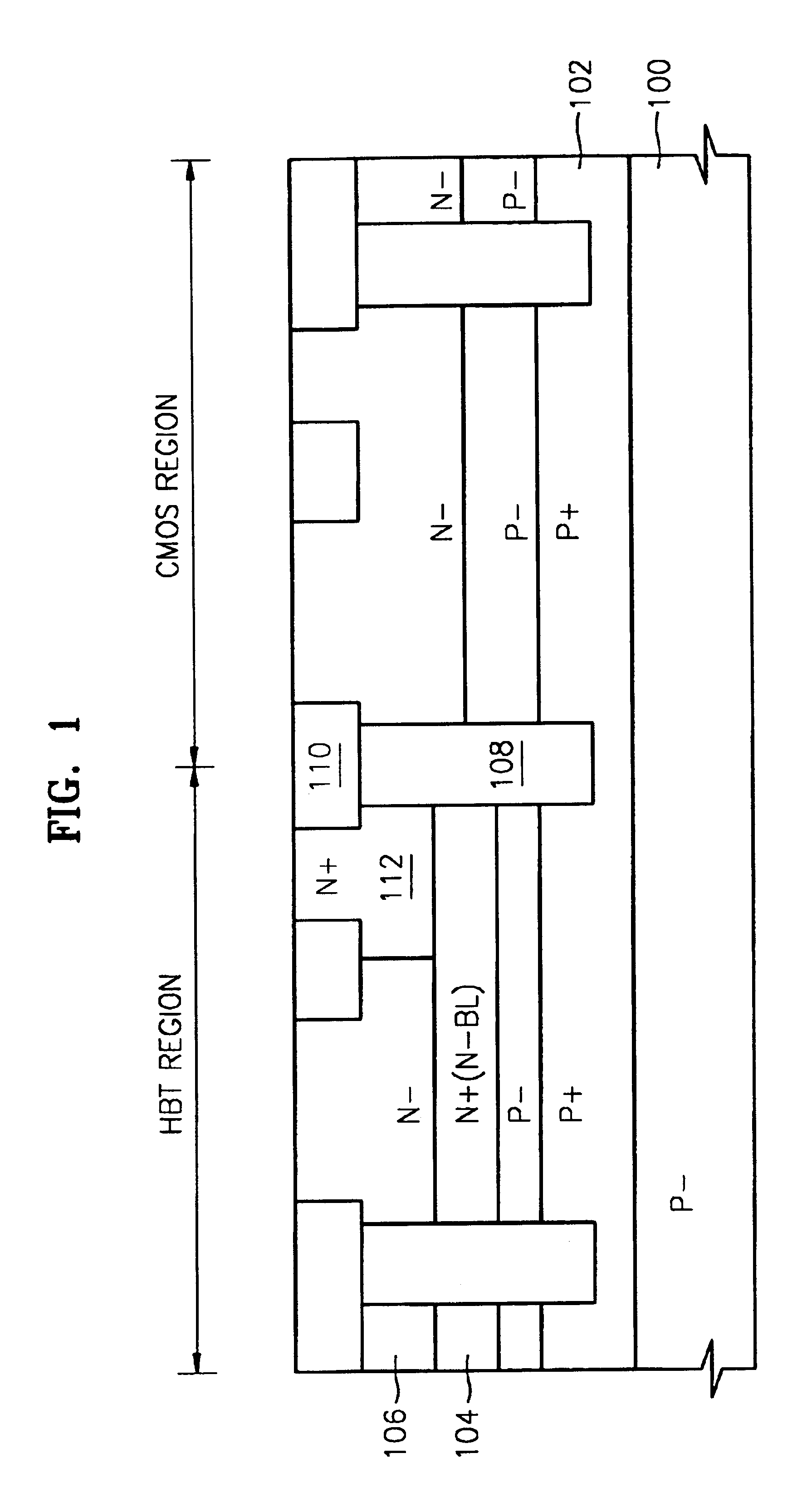

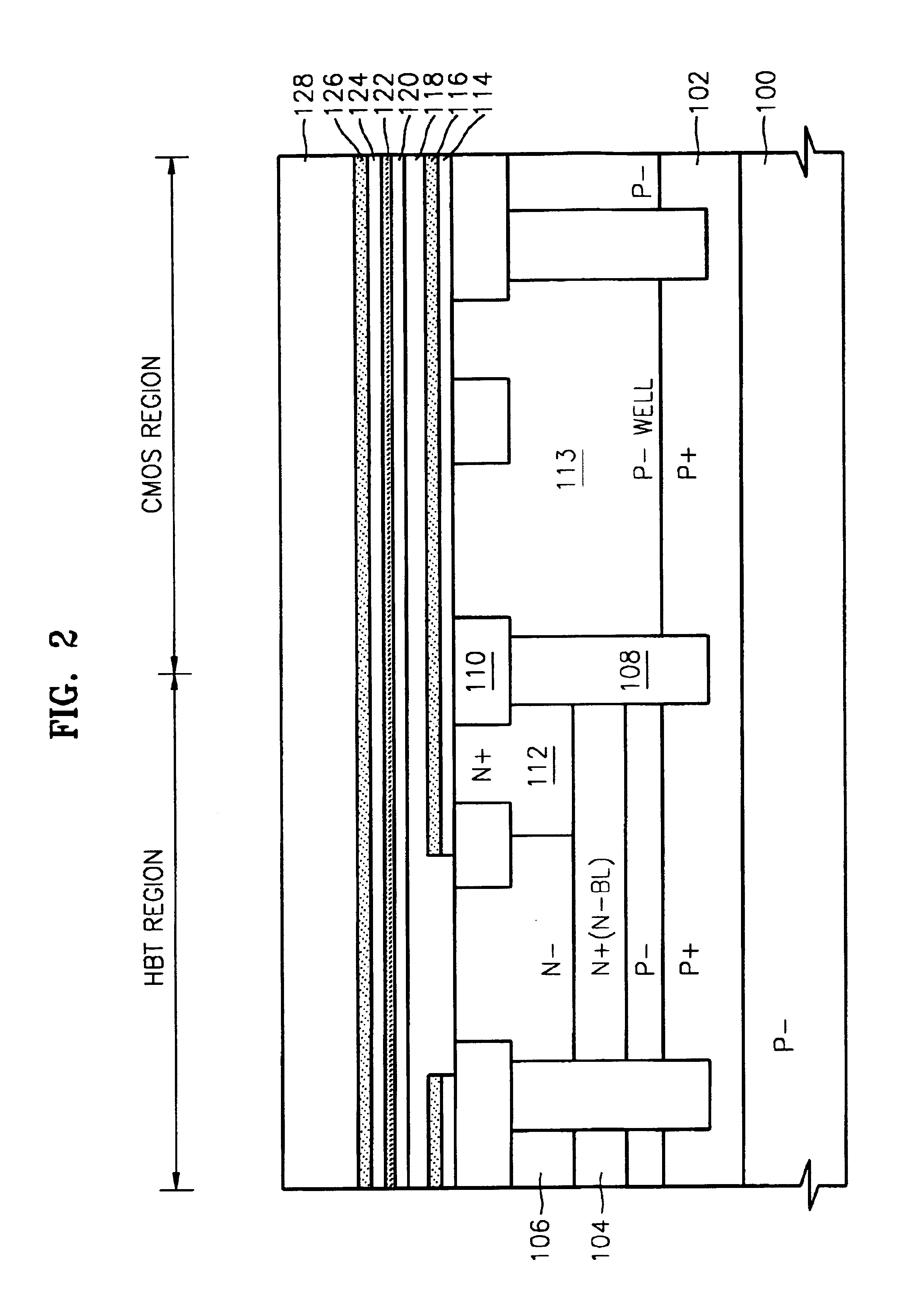

BiCMOS technology on SOI substrates

InactiveUS6936910B2Simple and reliable processIncrease resistanceTransistorSolid-state devicesSoi substrateBicmos technology

A method and a BICMOS structure are provided. The BiCMOS structure includes an SOI substrate having a bottom Si-containing layer, a buried insulating layer located atop the bottom Si-containing layer, a top Si-containing layer atop the buried insulating layer and a sub-collector which is located in an upper surface of the bottom Si-containing layer. The sub-collector is in contact with a bottom surface of the buried insulating layer. The structure also includes an extrinsic base heterojunction bipolar transistor located in an opening provided in a bipolar device area of the SOI substrate in which a base region of the bipolar transistor is located directly atop the sub-collector

Owner:GLOBALFOUNDRIES US INC

Heterojunction bipolar transistor using reverse emitter window

ActiveUS20050079678A1Lower base resistanceImprove Noise PerformanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

A heterojunction bipolar transistor (HBT), and manufacturing method therefor, comprising a semiconductor substrate having a collector region, an intrinsic base region of a compound semiconductive material over the collector region, an extrinsic base region, an emitter structure, an interlevel dielectric layer over the collector region, extrinsic base region and emitter structure, and connections through the interlevel dielectric layer to the base region, the emitter structure, and the collector region. The emitter structure is formed by forming a reverse emitter window over the intrinsic base region, which subsequently is etched to form an emitter window having a multi-layer reverse insulating spacer therein.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Method for manufacturing self-aligned BiCMOS

Provided is a method for manufacturing a self-aligned BiCMOS including a SiGe heterojunction bipolar transistor (HBT) for performing high-frequency operations. In this method, an extrinsic base and a selective ion-implanted collector (SIC) are formed by a self-alignment process.

Owner:SAMSUNG ELECTRONICS CO LTD

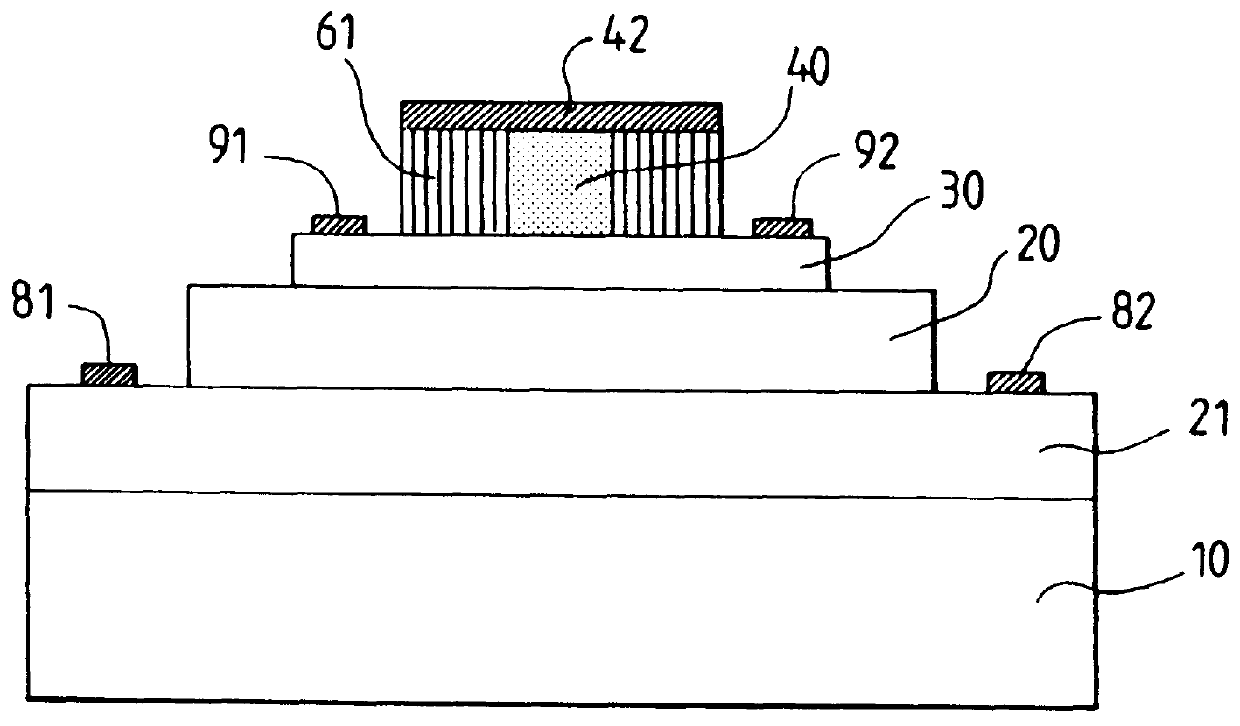

Monolithic compound semiconductor integrated circuit and method of forming the same

InactiveUS20010042867A1Improve high frequency performanceLow costTransistorSemiconductor/solid-state device detailsEngineeringElectrode Contact

A monolithically integrated semiconductor device comprises: a hetero-junction bipolar transistor having at least an electrode contact layer which contacts directly with at least one of collector, base and emitter electrodes; and at least a passive device having at least a passive device electrode and at least a resistive layer, wherein the electrode contact layer and the resistive layer comprise the same compound semiconductor layer.

Owner:NEC ELECTRONICS CORP

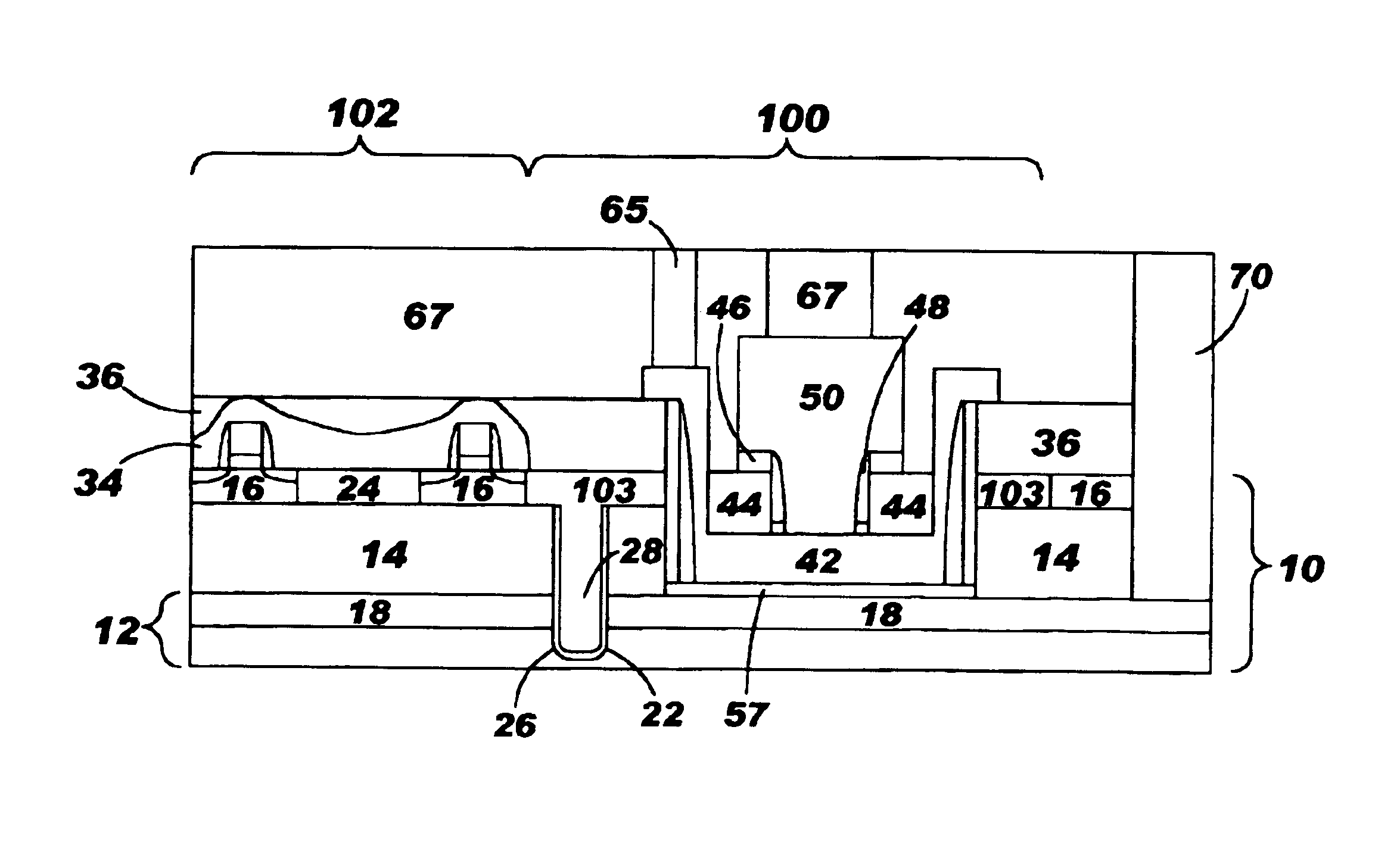

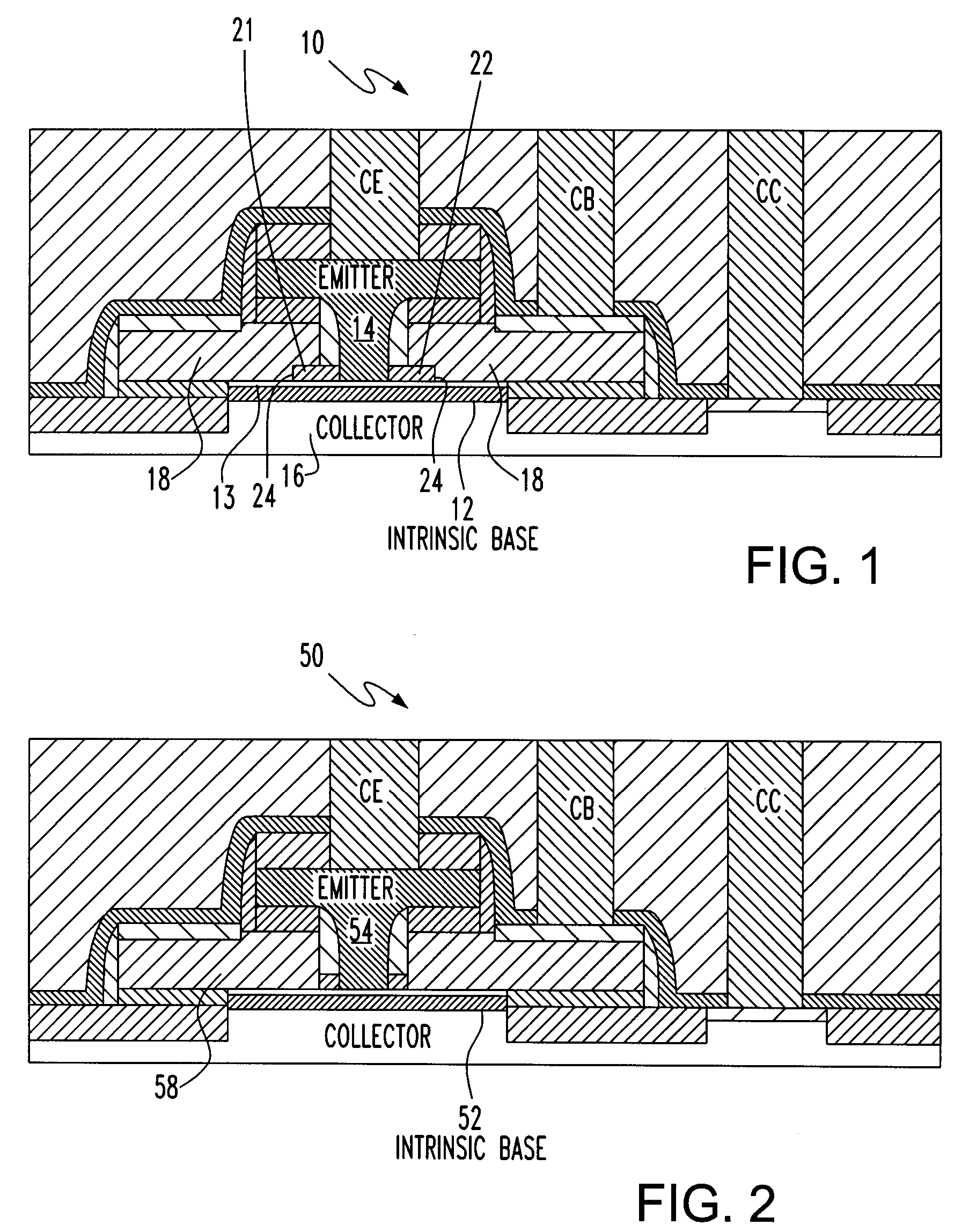

Bipolar device having shallow junction raised extrinsic base and method for making the same

A raised extrinsic base, silicon germanium (SiGe) heterojunction bipolar transistor (HBT), and a method of making the same is disclosed herein. The heterojunction bipolar transistor includes a substrate, a silicon germanium layer formed on the substrate, a collector layer formed on the substrate, a raised extrinsic base layer formed on the silicon germanium layer, and an emitter layer formed on the silicon germanium layer. The silicon germanium layer forms a heterojunction between the emitter layer and the raised extrinsic base layer. The bipolar transistor further includes a base electrode formed on a portion of the raised extrinsic base layer, a collector electrode formed on a portion of the collector layer, and an emitter electrode formed on a portion of the emitter layer. Thus, the heterojunction bipolar transistor includes a self-aligned raised extrinsic base, a minimal junction depth, and minimal interstitial defects influencing the base width, all being formed with minimal thermal processing. The heterojunction bipolar transistor simultaneously improves three factors that affect the speed and performance of bipolar transistors: base width, base resistance, and base-collector capacitance.

Owner:INTELLECTUAL DISCOVERY INC

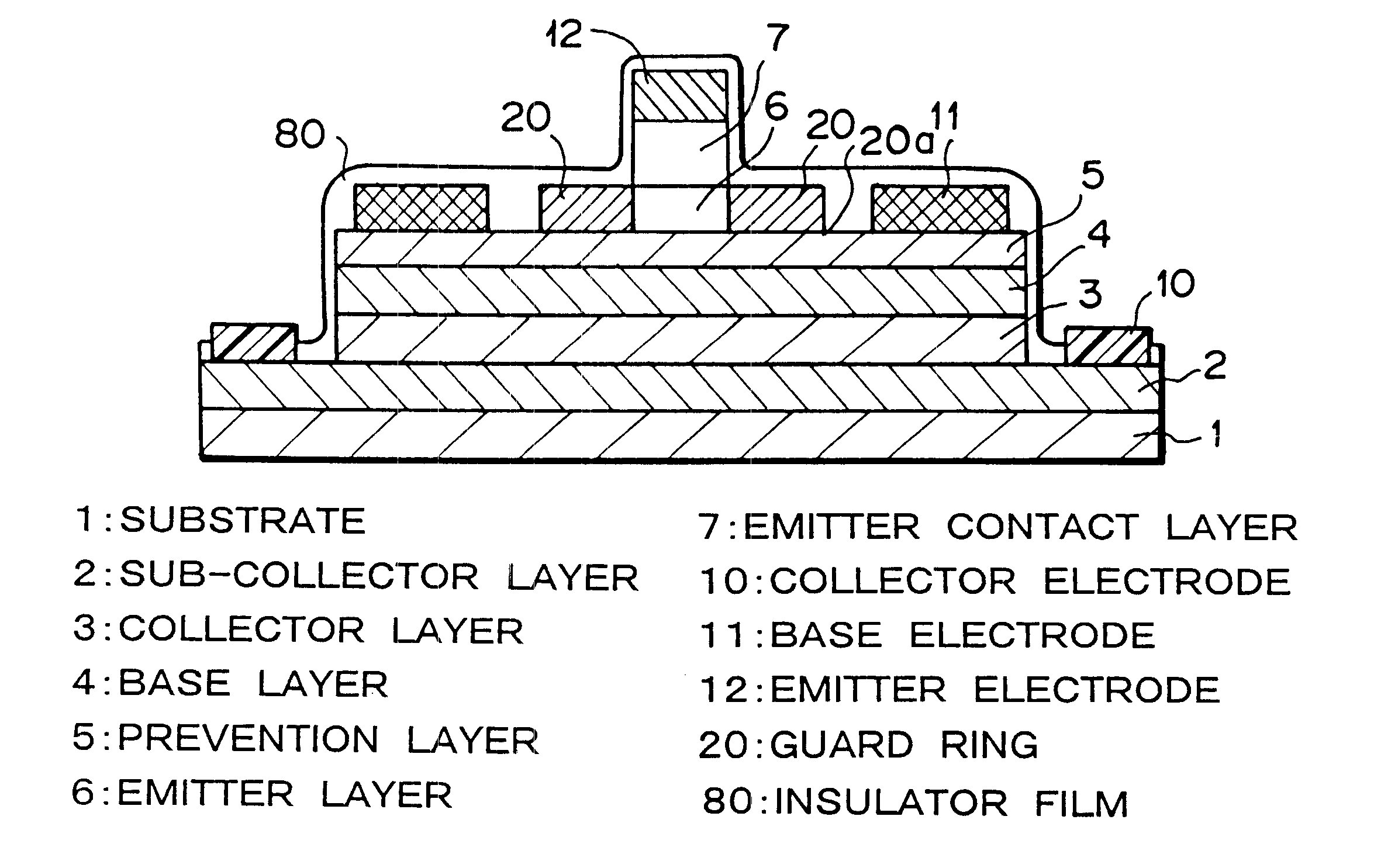

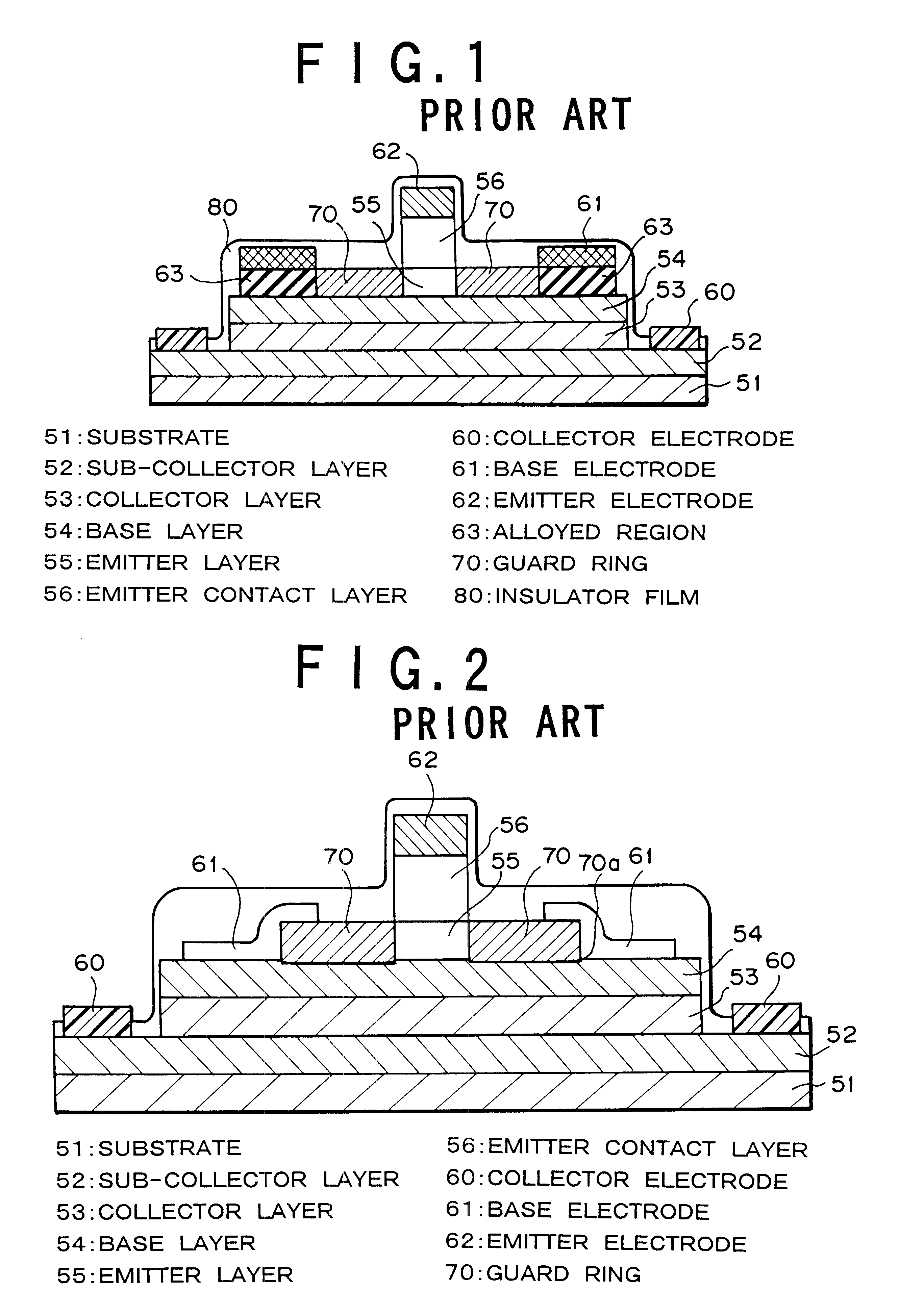

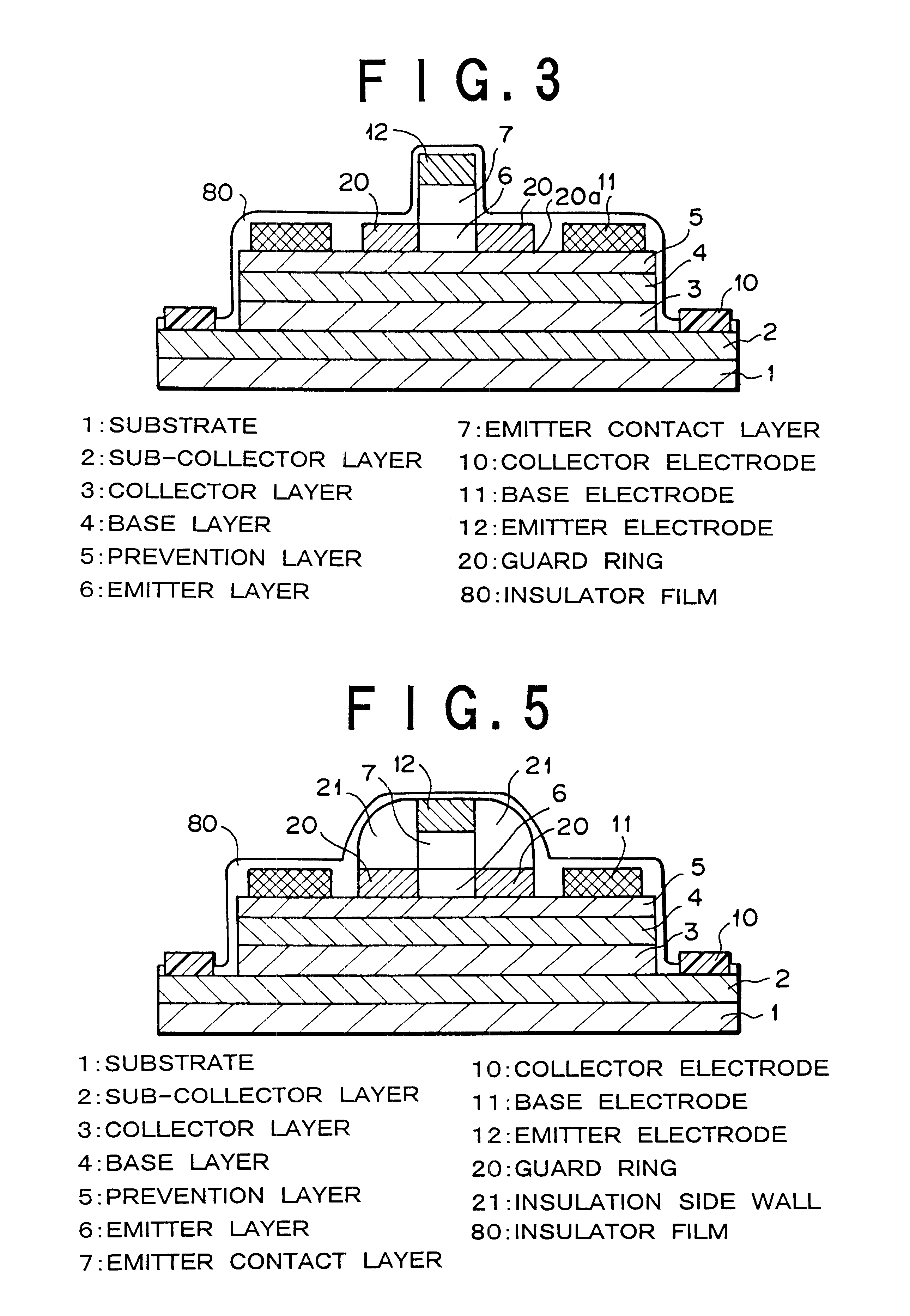

Heterojunction bipolar transistor having prevention layer between base and emitter

A bipolar transistor is disclosed, that comprises a collector layer of first conduction type, a base layer of second conduction type, formed on the collector layer, a prevention layer, formed on the base layer, for preventing carriers from being recombined, an emitter layer of first conduction type, formed on a first part of the prevention layer, and a base electrode, formed on a second part separated from the first part of the prevention layer.

Owner:RENESAS ELECTRONICS CORP

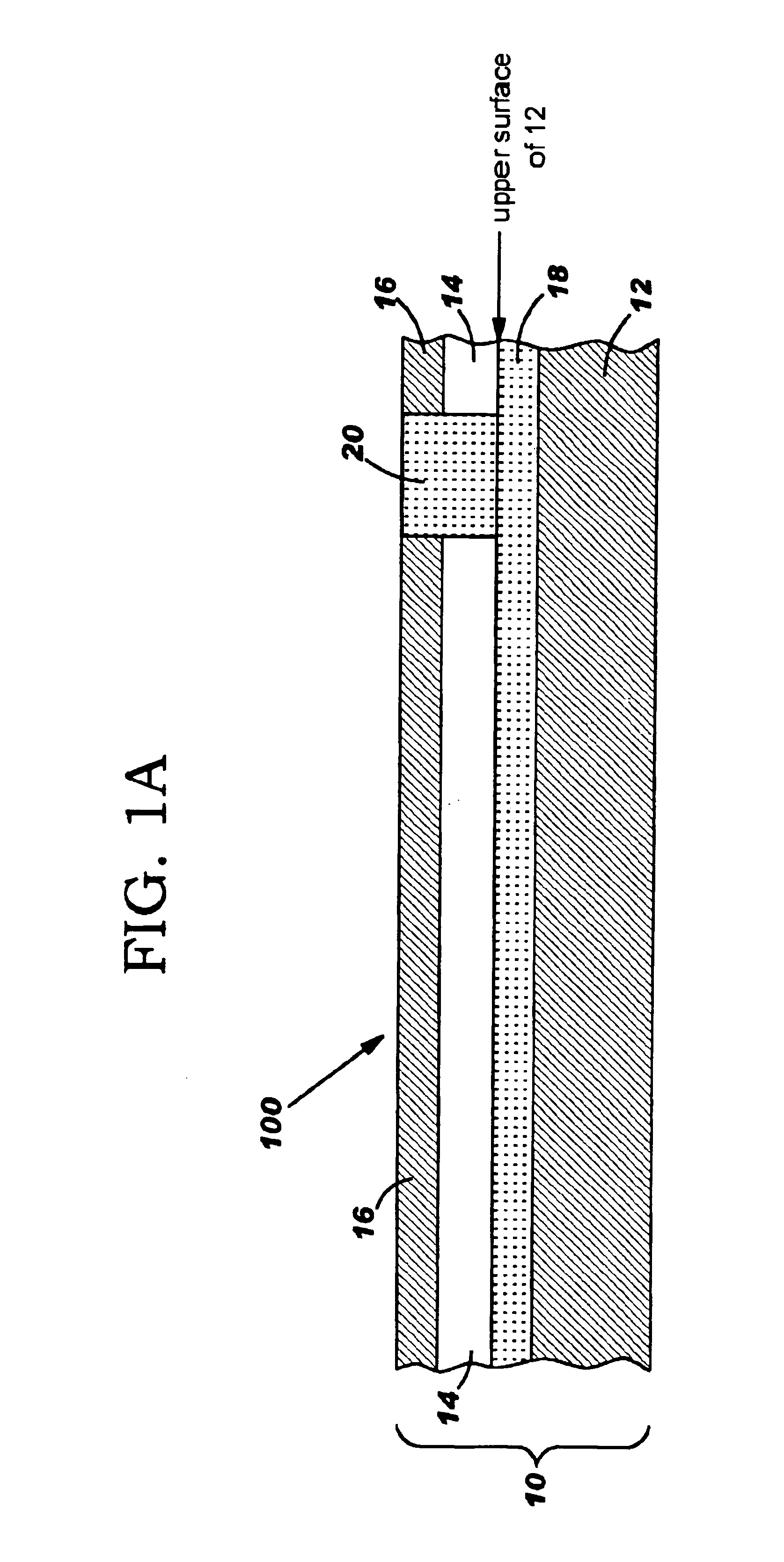

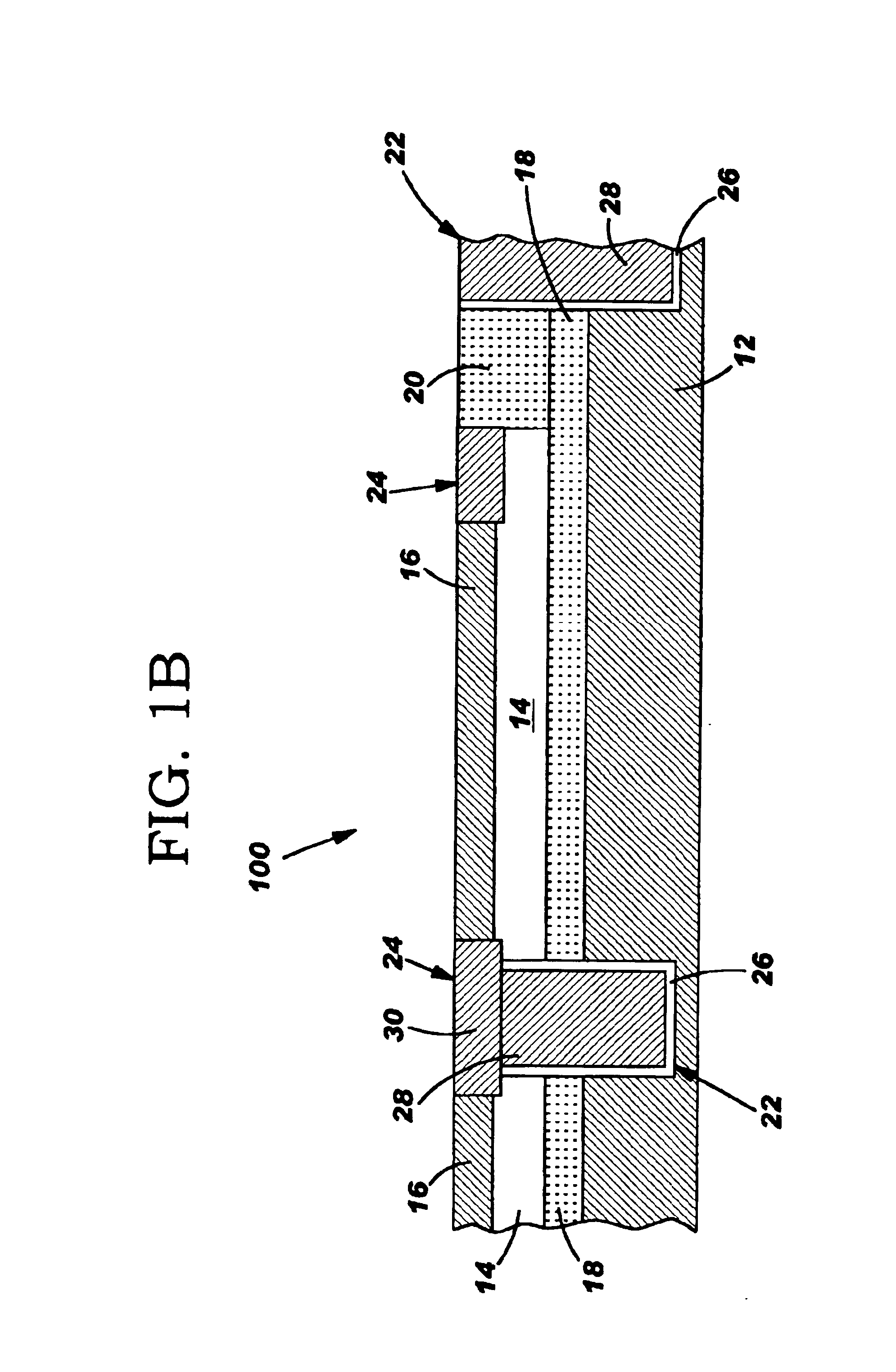

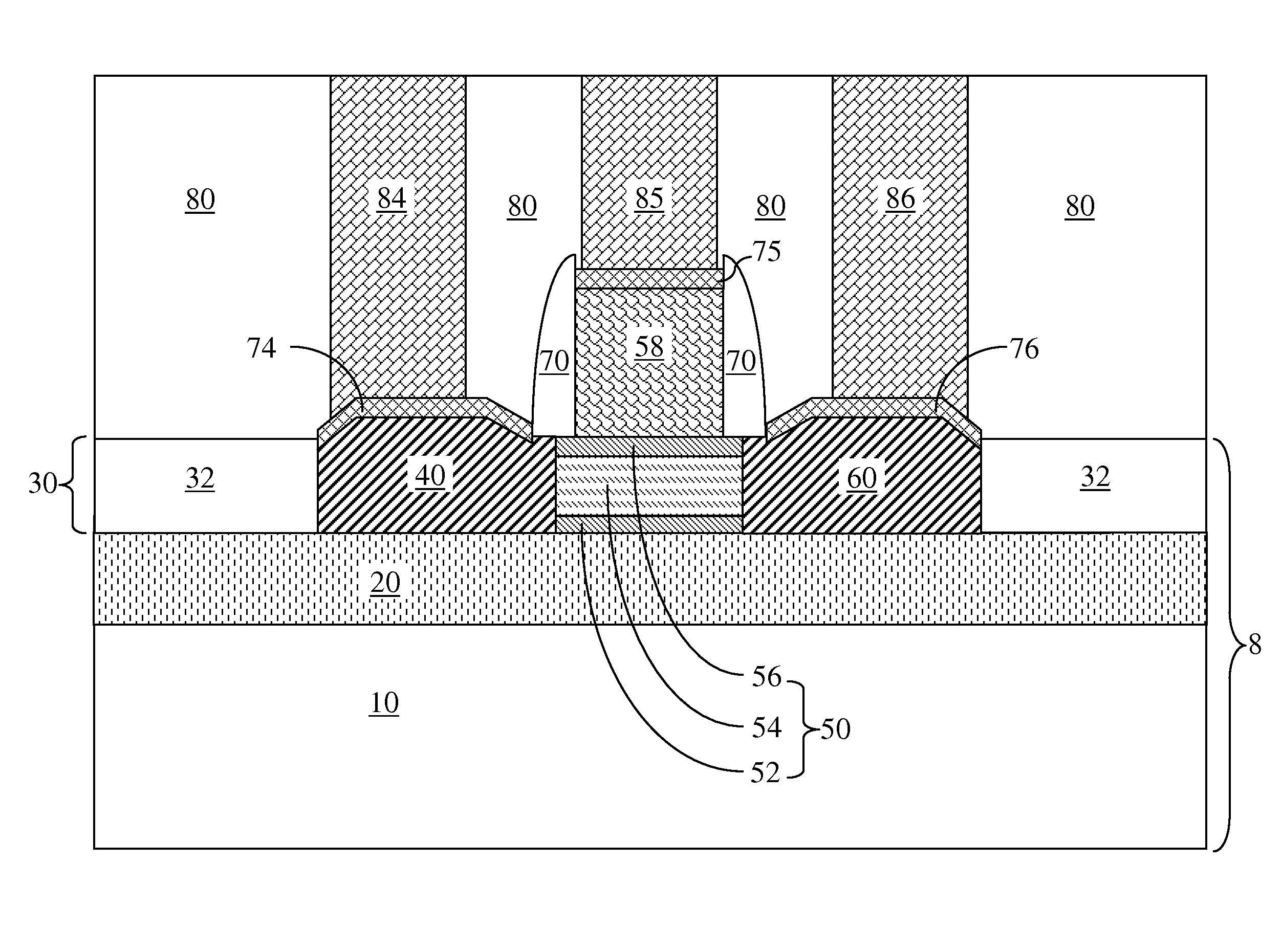

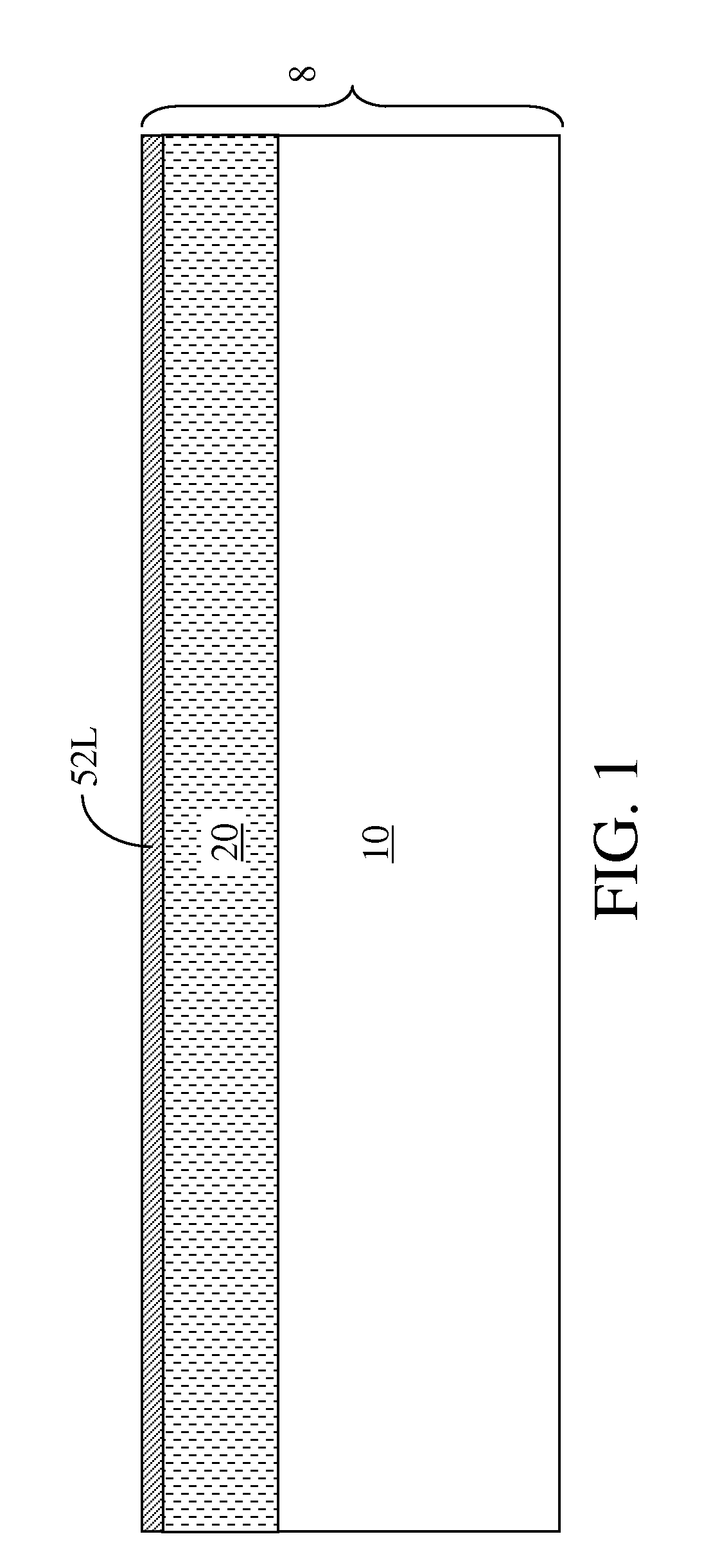

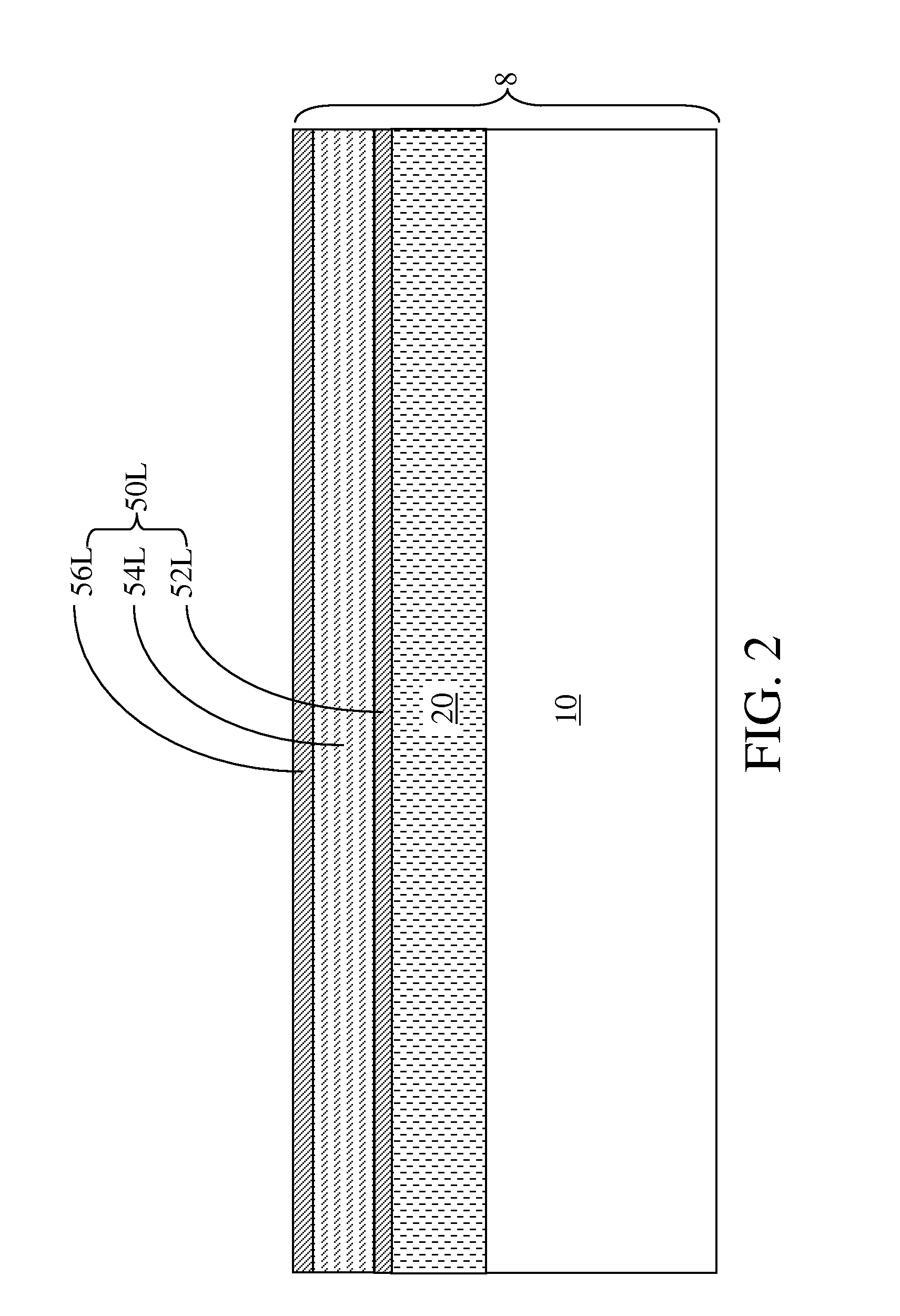

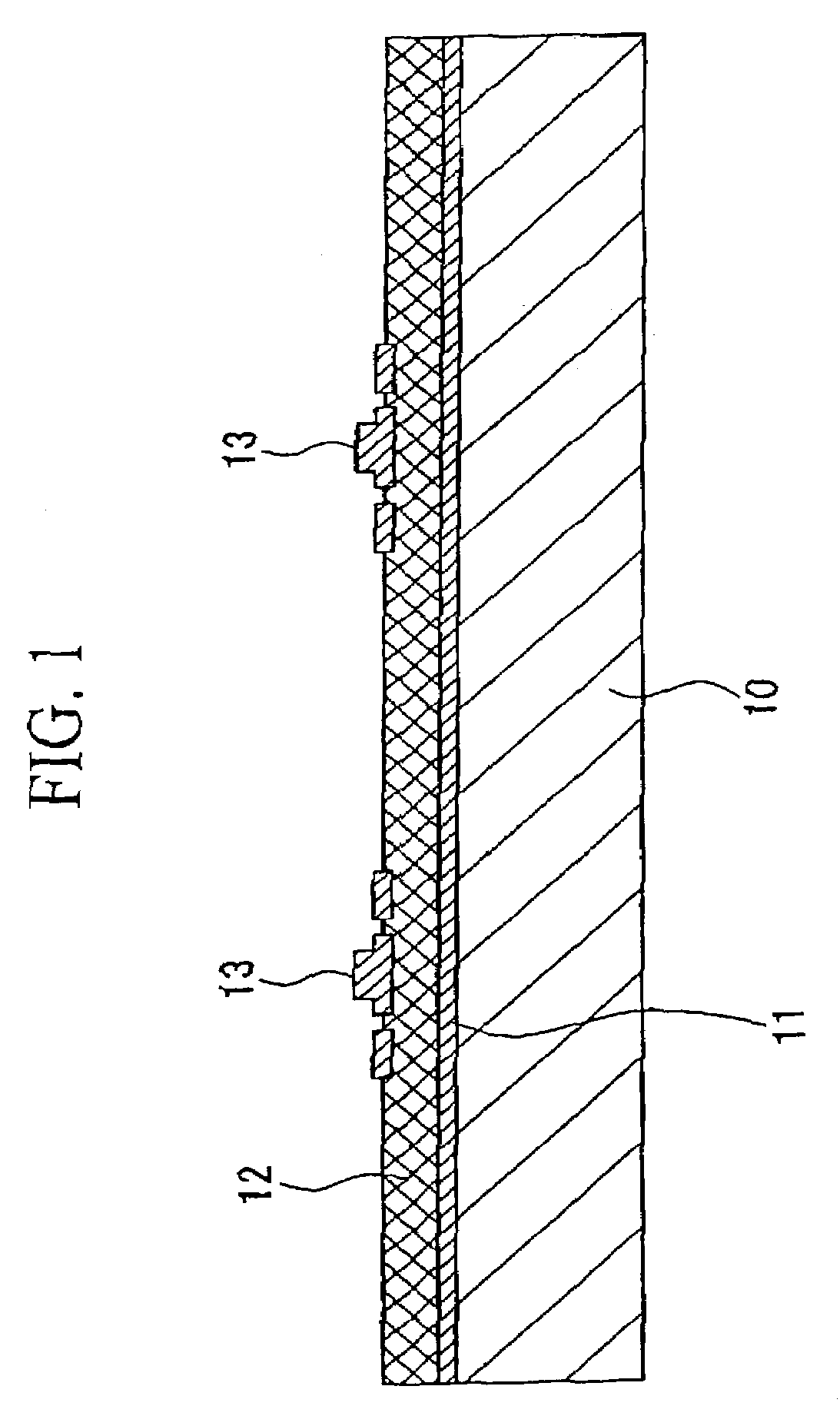

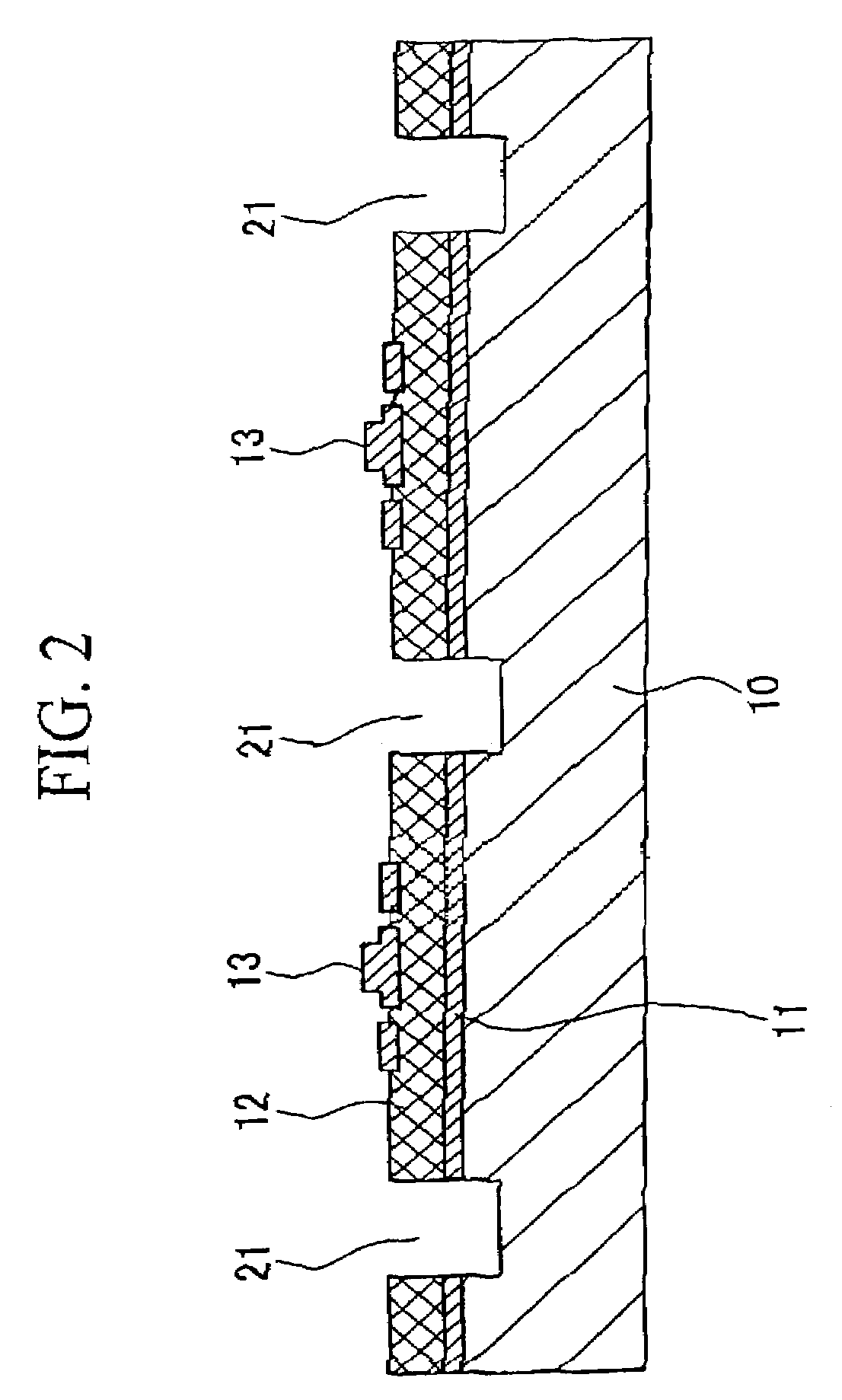

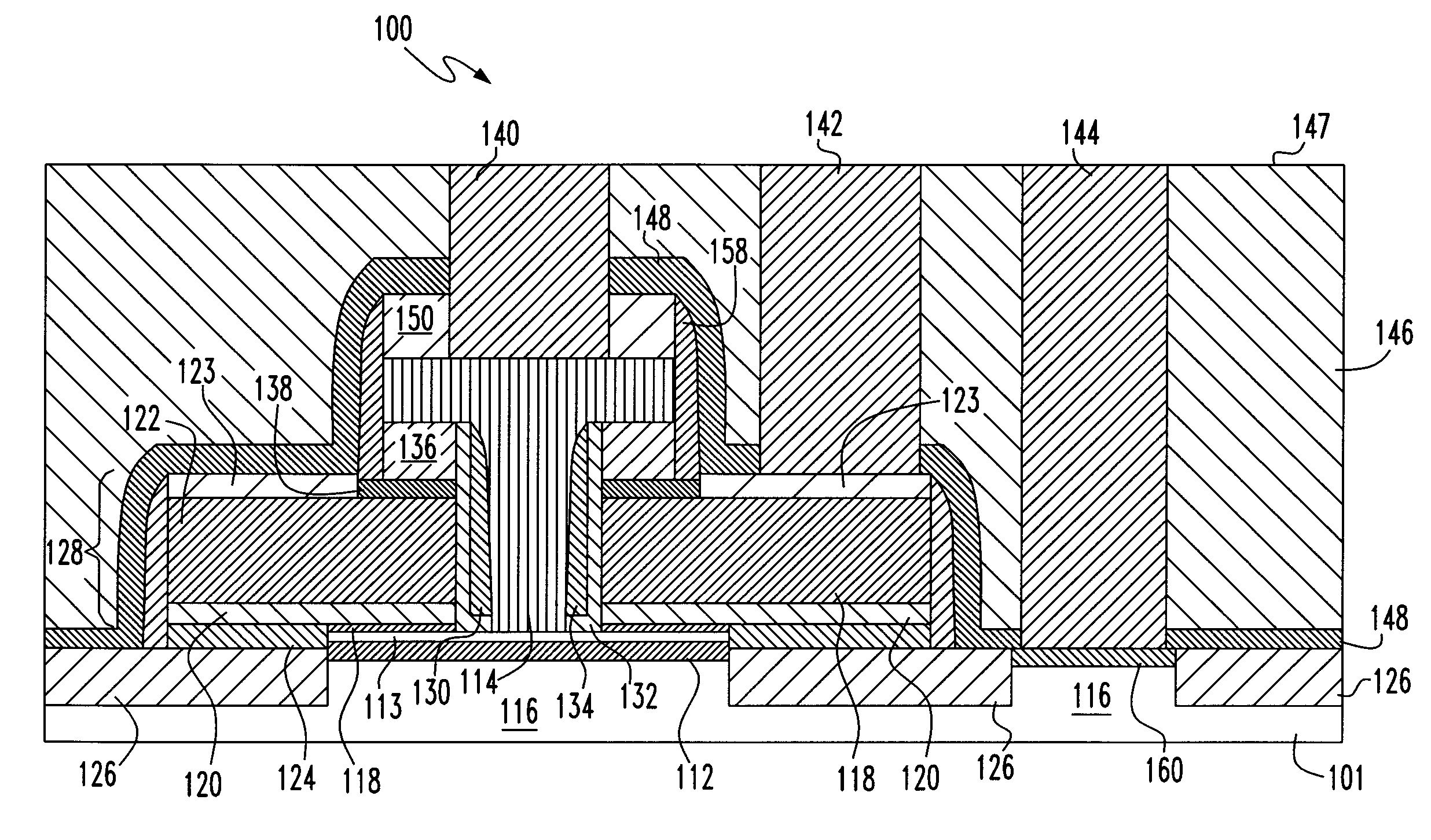

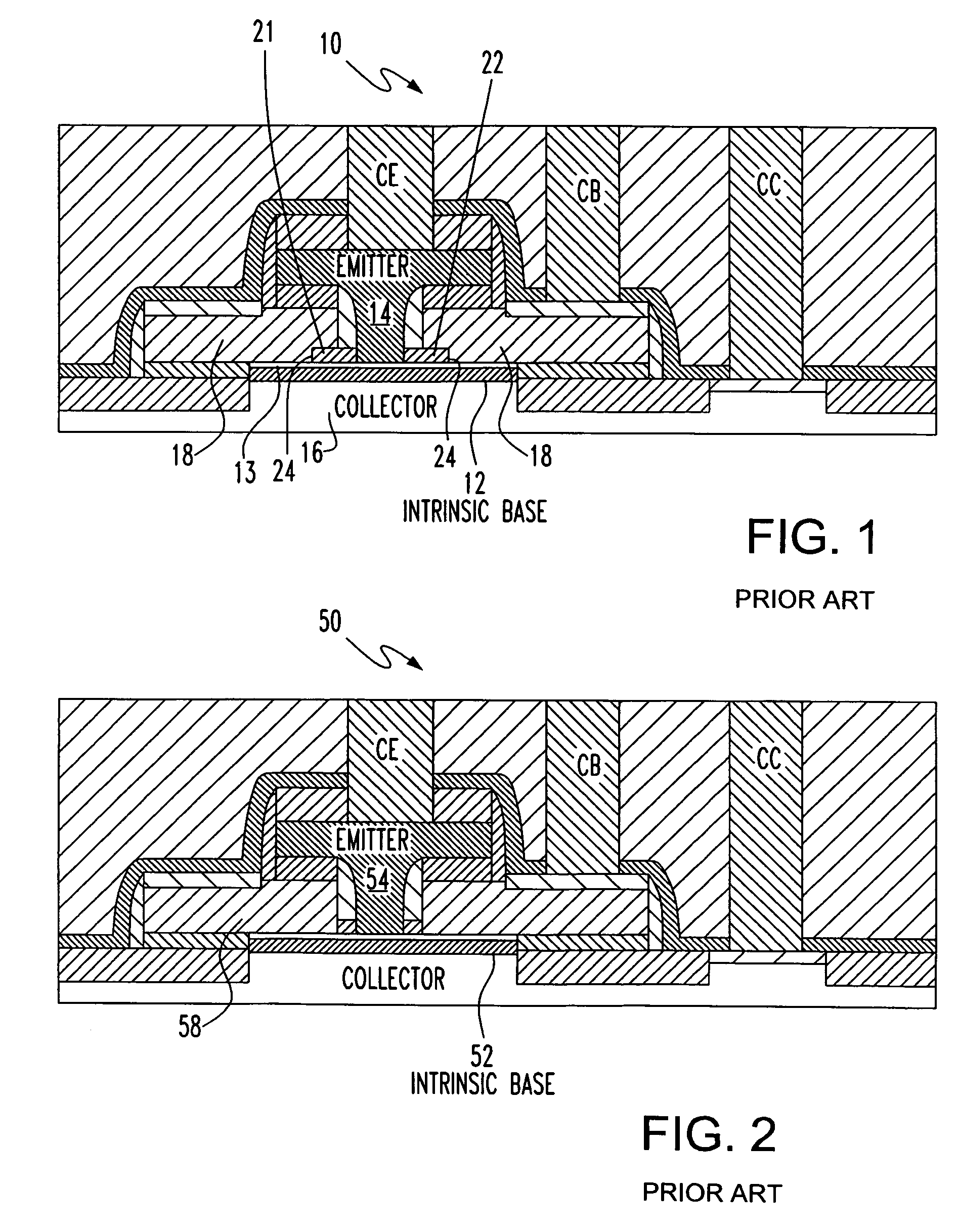

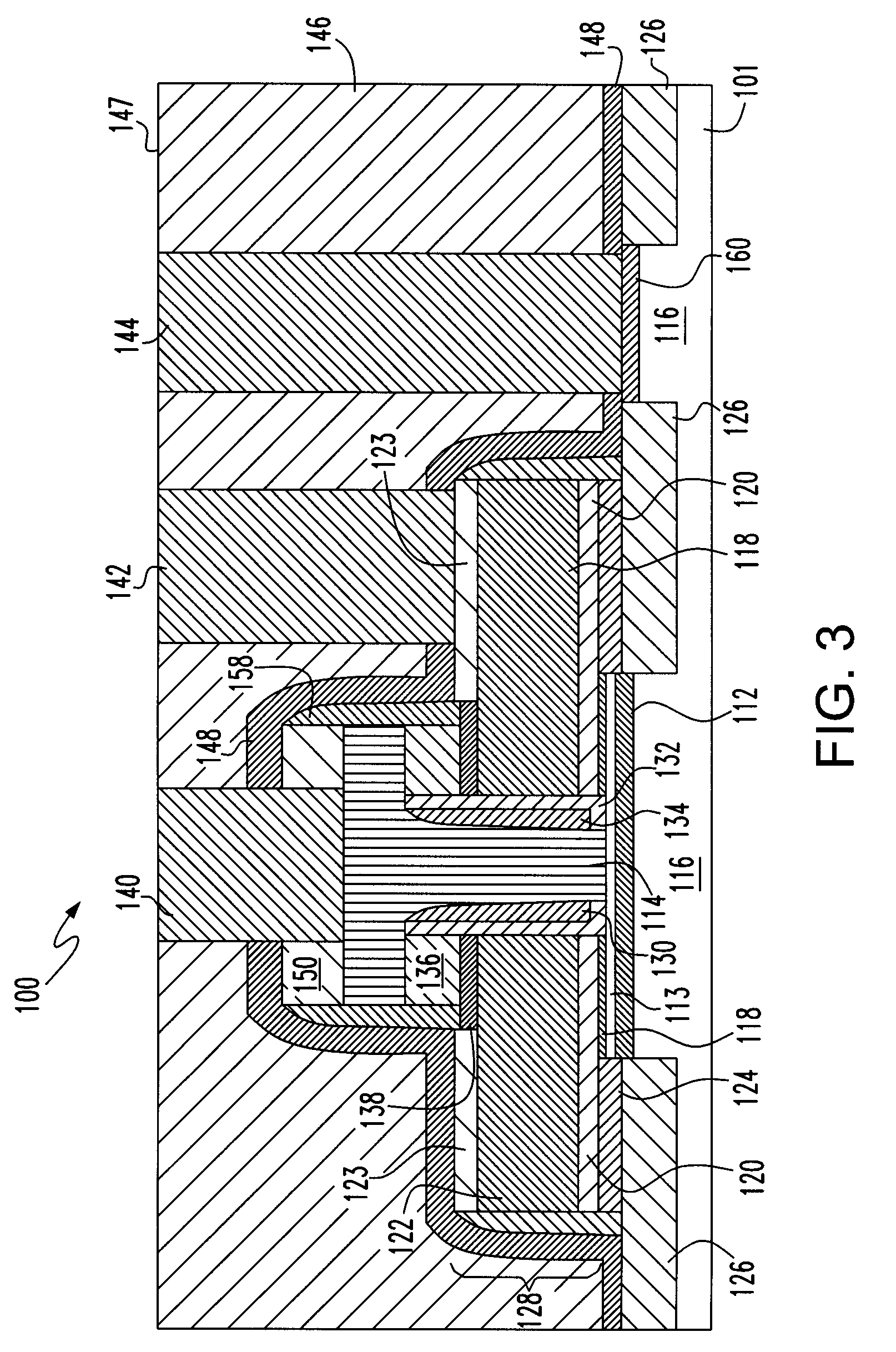

SOI SiGe-base lateral bipolar junction transistor

ActiveUS8288758B2Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

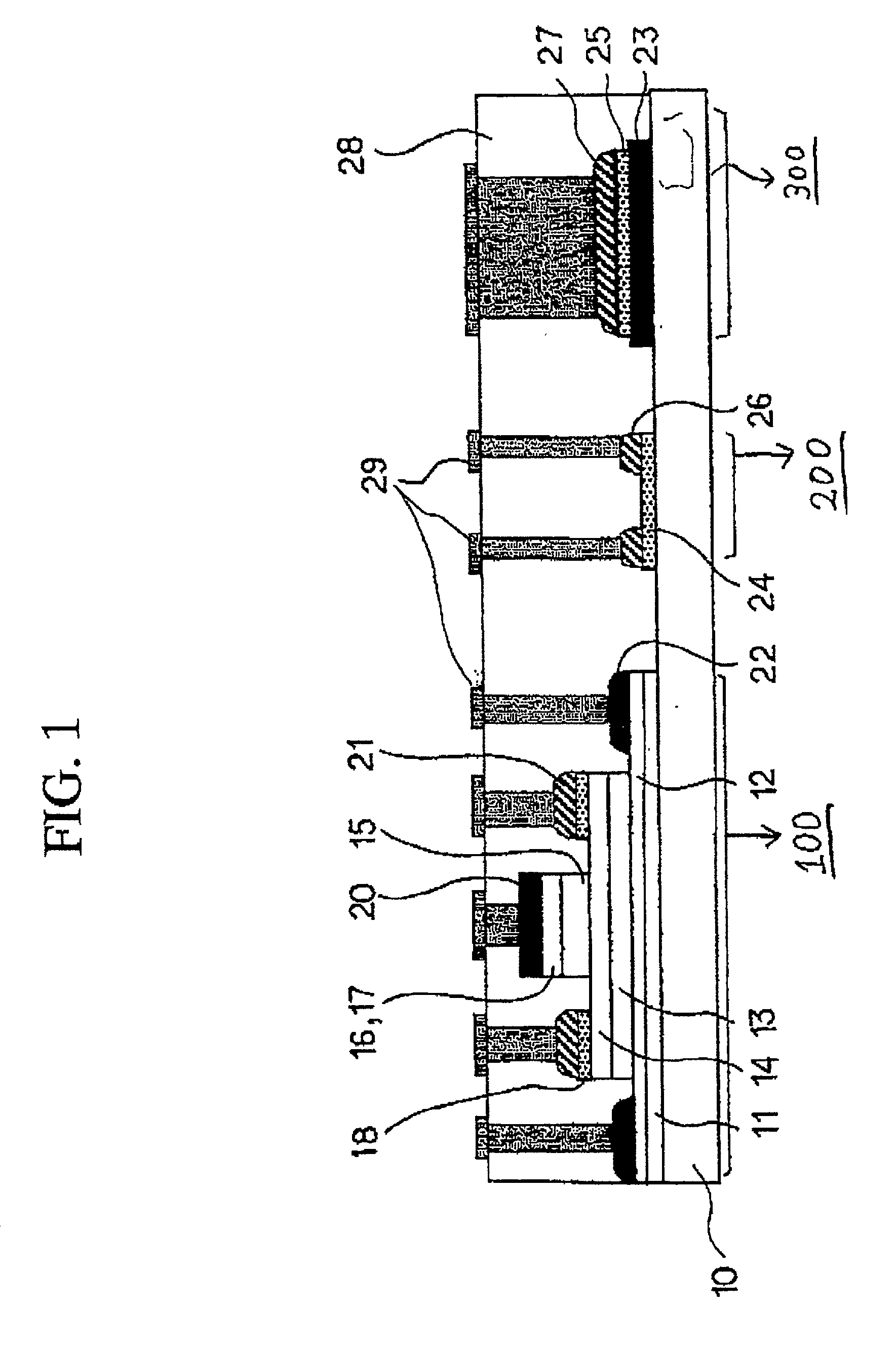

High-frequency power amplifier

ActiveUS20050077964A1Lower levelHigh frequency amplifiersGain controlHeterojunctionHigh frequency power

The present invention provides a compact and low-cost high-frequency power amplifier including GaAs heterojunction bipolar transistors (HBTs) but having a low level of noise in the transmission band. In the high-frequency power amplifier of the present invention, a chip capacitor 21 is connected at one end to an upstream stage bias circuit 107 via a bonding wire B1, and grounded at the other end. Also, a chip inductor 22 is connected to a base electrode of a high-frequency signal amplification HBT 101 via a bonding wire B2. In the high-frequency power amplifier of the present invention, the chip capacitor 21 causes noise generated within the upstream stage bias circuit 107 to flow to the ground, thereby reducing noise in the reception band. Also, the chip inductor 22 reduces a power loss of a high-frequency signal which is caused because the high-frequency signal flows to the ground.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

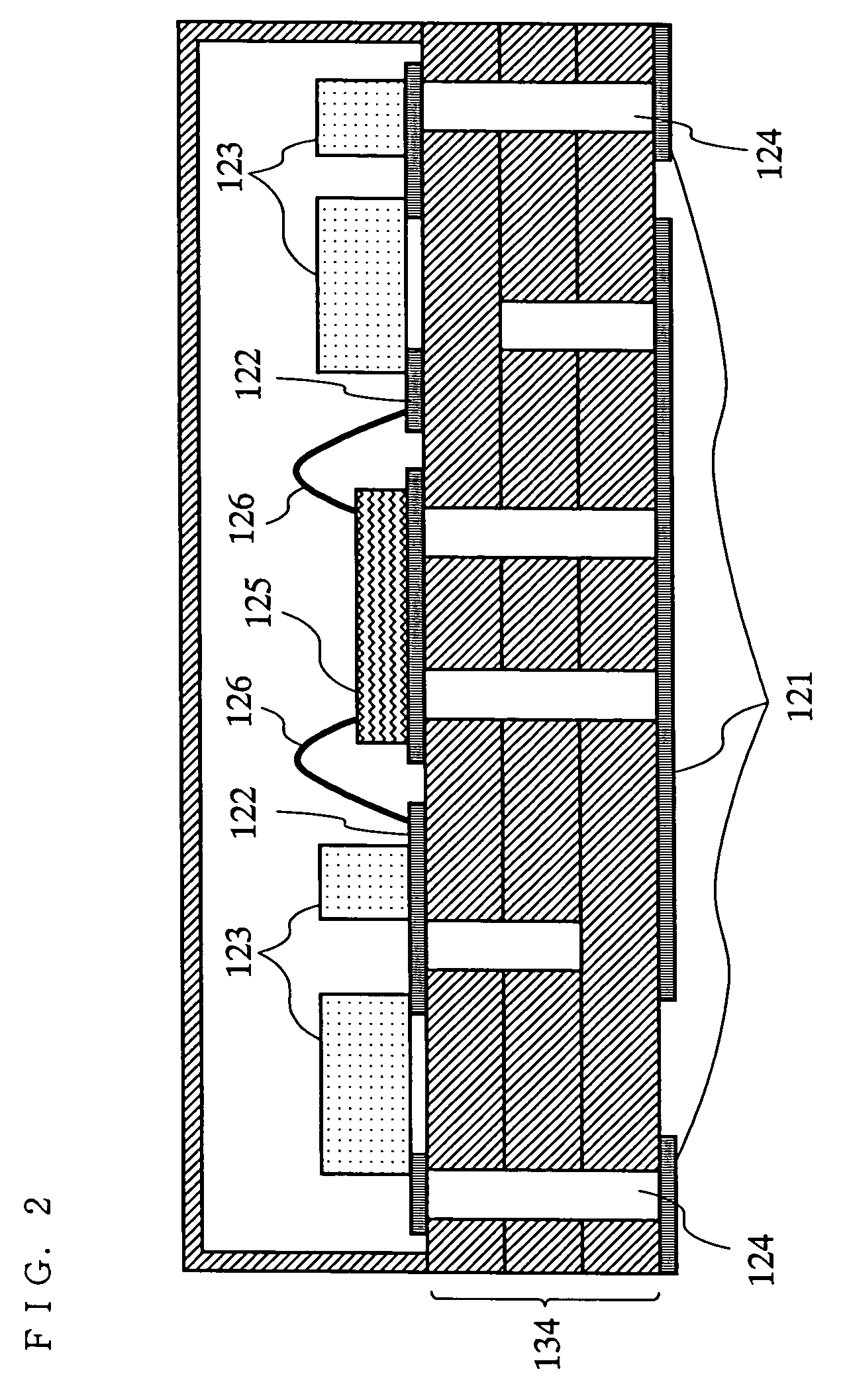

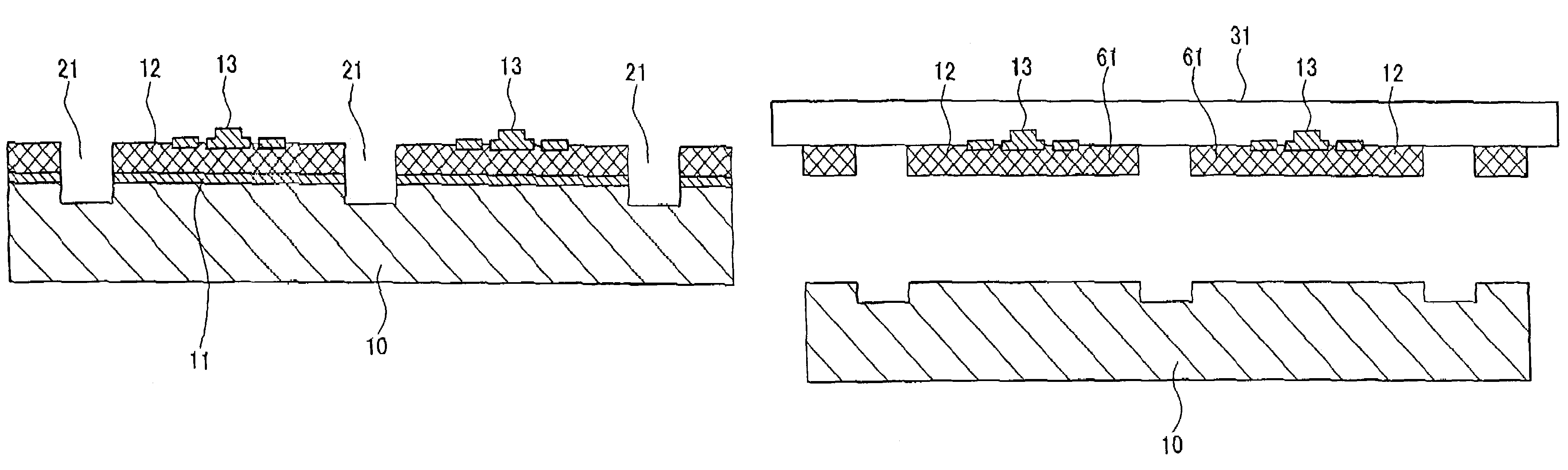

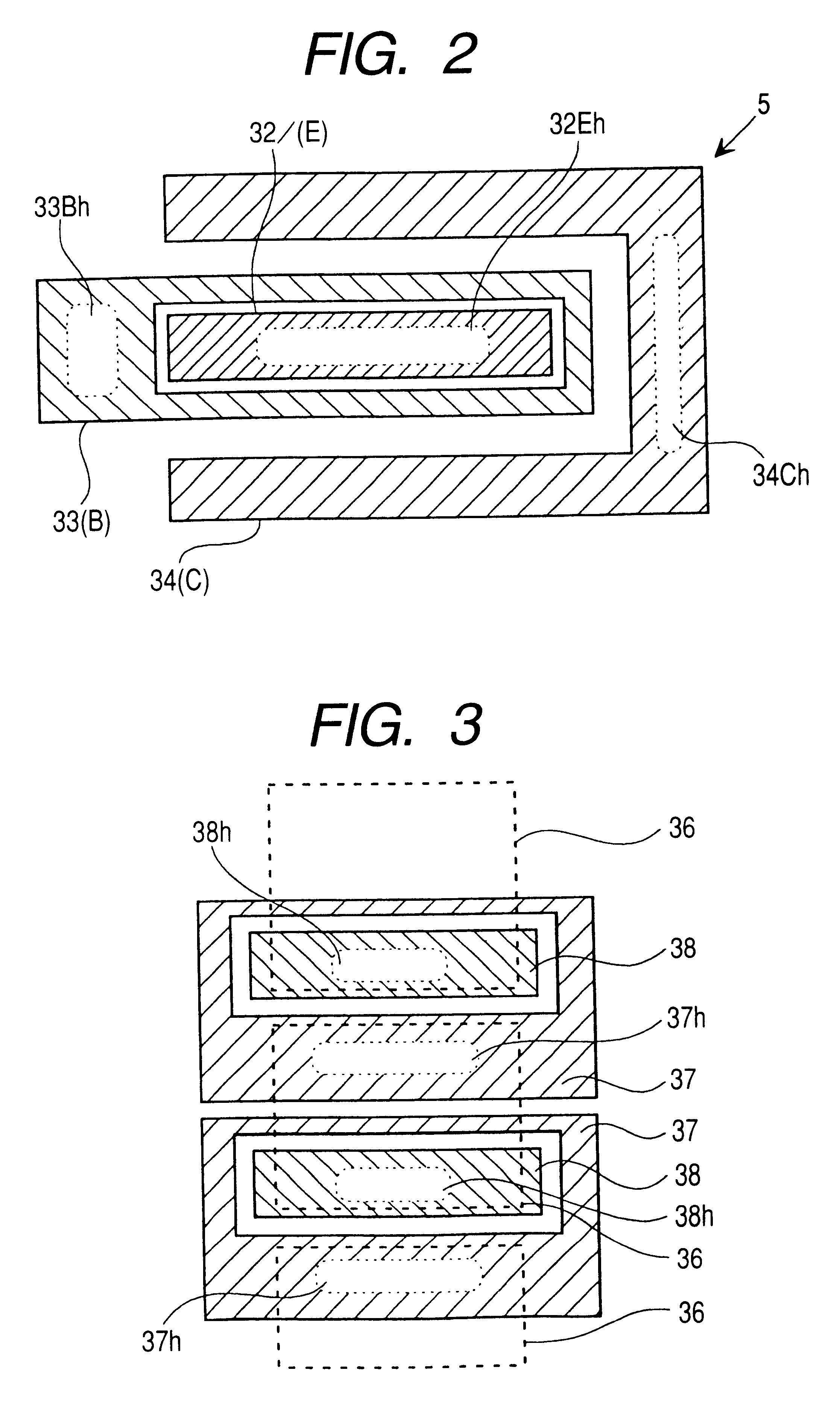

Layout Structure of Heterojunction Bipolar Transistors

ActiveUS20140312390A1Improve cooling efficiencyDifference in heightTransistorSemiconductor/solid-state device detailsHeterojunctionRedistribution layer

A layout structure of HBTs comprising one or more HBTs, each of which comprises a base electrode, an emitter electrode, and a collector electrode. A passive layer, a first dielectric layer, a collector redistribution layers, one or more emitter copper pillars, and one or more collector copper pillars are formed above the one or more HBTs. The passive layer comprises a collector and an emitter pads. The first dielectric layer has one or more emitter and collector via holes. The emitter copper pillar is disposed on the emitter via hole and forms an electrical connection to the emitter electrode. The collector copper pillar is disposed on the collector redistribution layer and forms electrical connection to the collector electrode. The layout design of the emitter and collector copper pillars is therefore flexible, and the heat dissipation efficiency is improved.

Owner:WIN SEMICON

Method for manufacturing semiconductor integrated circuit

ActiveUS7244662B2Improve efficiencyUnnecessary activity in of integratedTransistorSolid-state devicesEngineeringPhotodiode

A method for manufacturing a semiconductor integrated circuit includes steps of forming a semiconductor element on a semiconductor substrate and separating only a function layer including the semiconductor element, which is a surface layer of the semiconductor substrate, from the semiconductor substrate. The semiconductor element is preferably a compound semiconductor device including at least one of a light emitting diode, a vertical cavity surface emitting laserdiode, a photodiode, a high electron mobility transistor, an inductor, a capacitor, a resistor, and a heterojunction bipolar transistor.

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

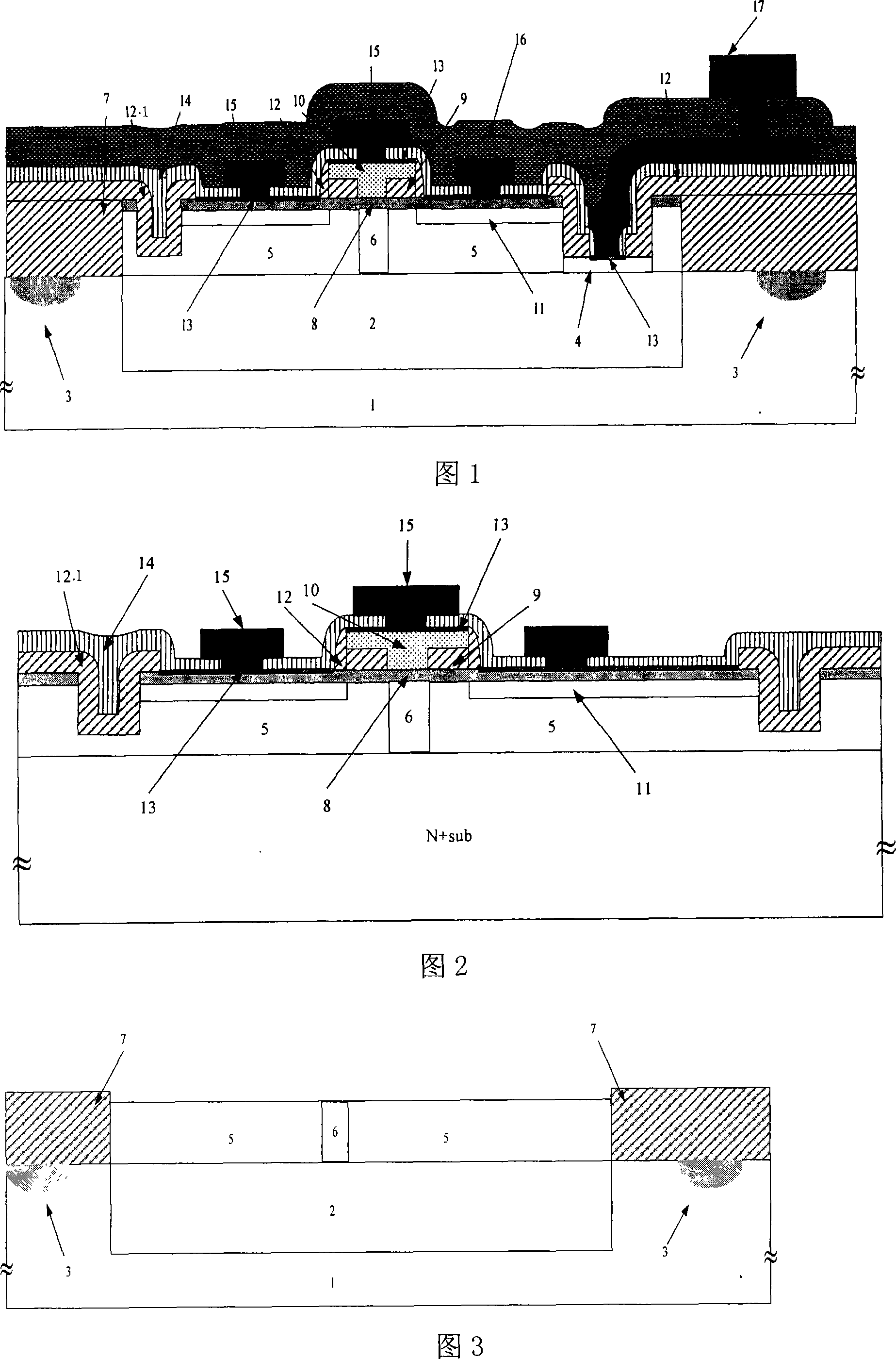

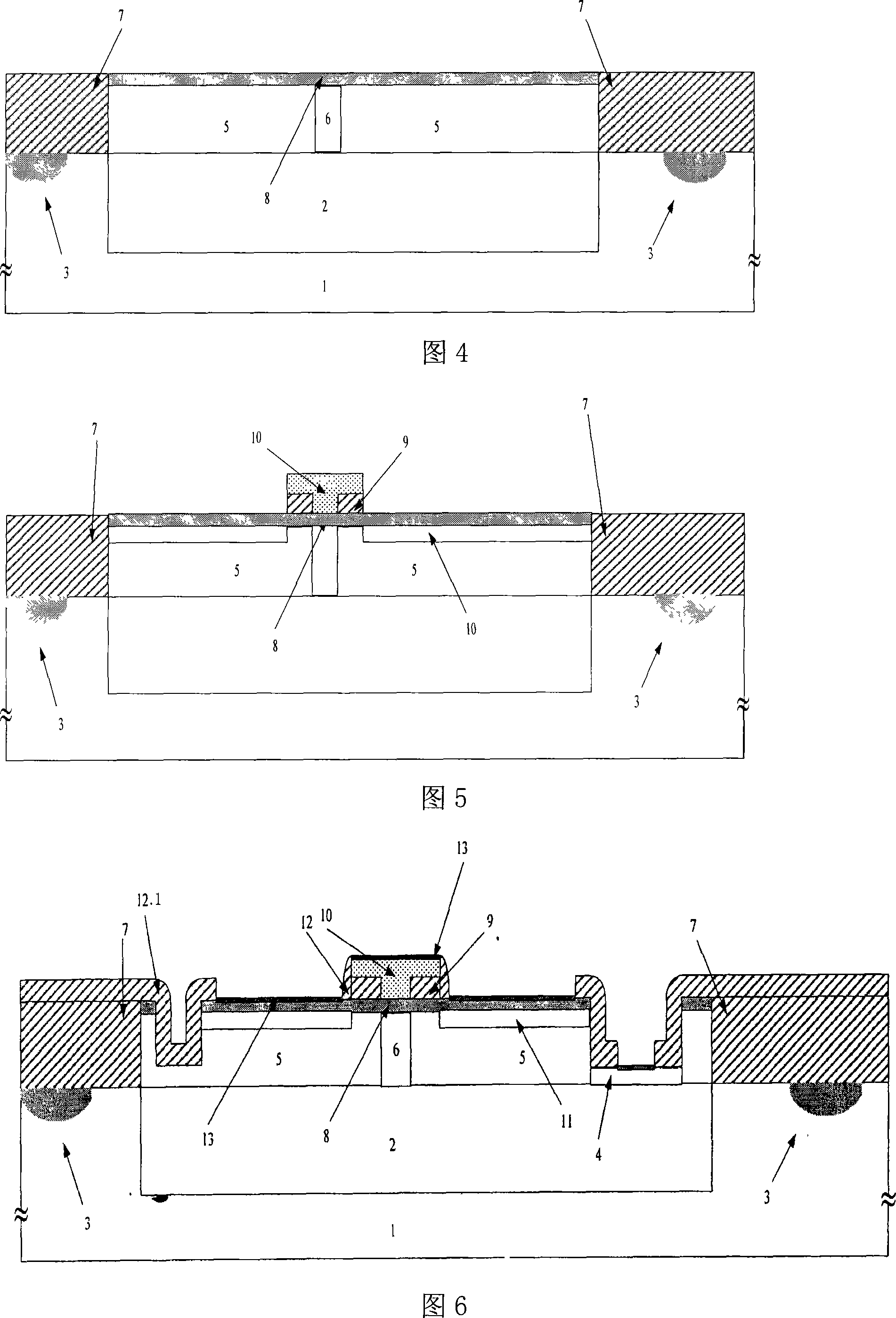

NPN type germanium-silicon heterogenous dual-pole transistor and its making method

InactiveCN101101922AQuality is not affectedInjection activationSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactImpurity

The invention is concerned with a kind of NPN type of SiGe heterojunction bipolar transistor and its preparation method, belonging to semiconductor device preparation technology field. Implant selectivity ion into impure collector, and carry epitaxial growth of SiGe base area after high temperature annealing. It activates the implanted impurity primely and keeps the quality of SiGe layer. Product integrating circuit unit apparatus, and its collector is at a same plane with base pole and emitter. This method carries epitaxial growth of N- collector and SiGe area to reduce autoeciousness parameter of apparatus. It uses sidewall to separate and form silicide on outside base area and emitter to reduce resistance between base pole and emitter and enhance high frequency capability of apparatus.

Owner:中国电子信息产业集团有限公司 +1

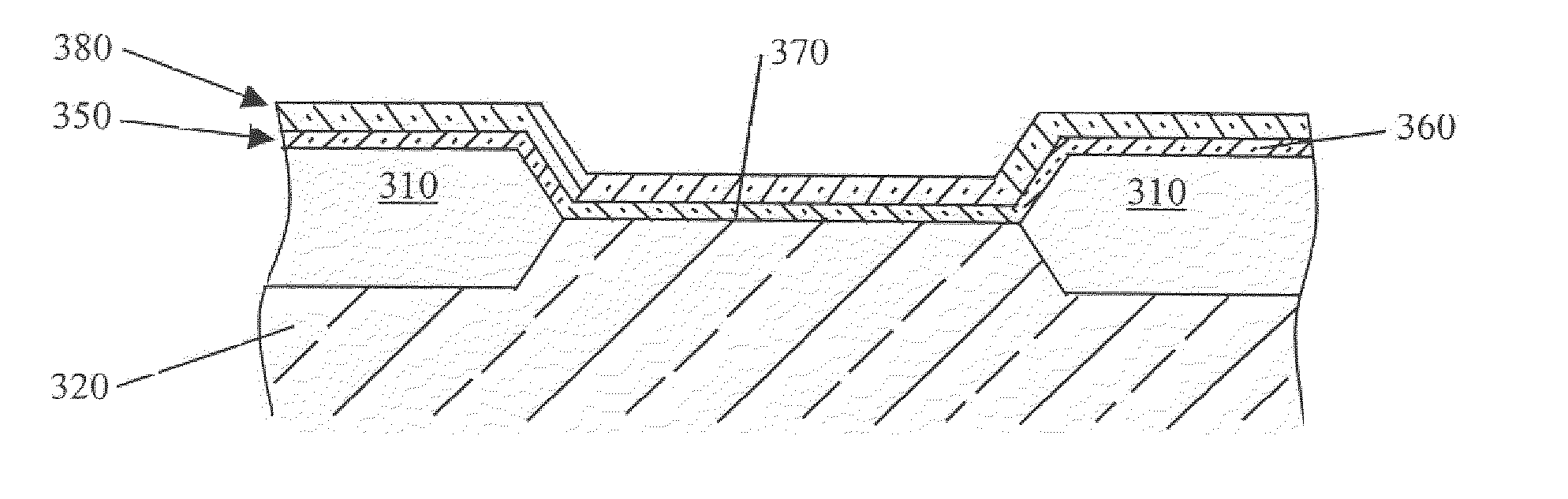

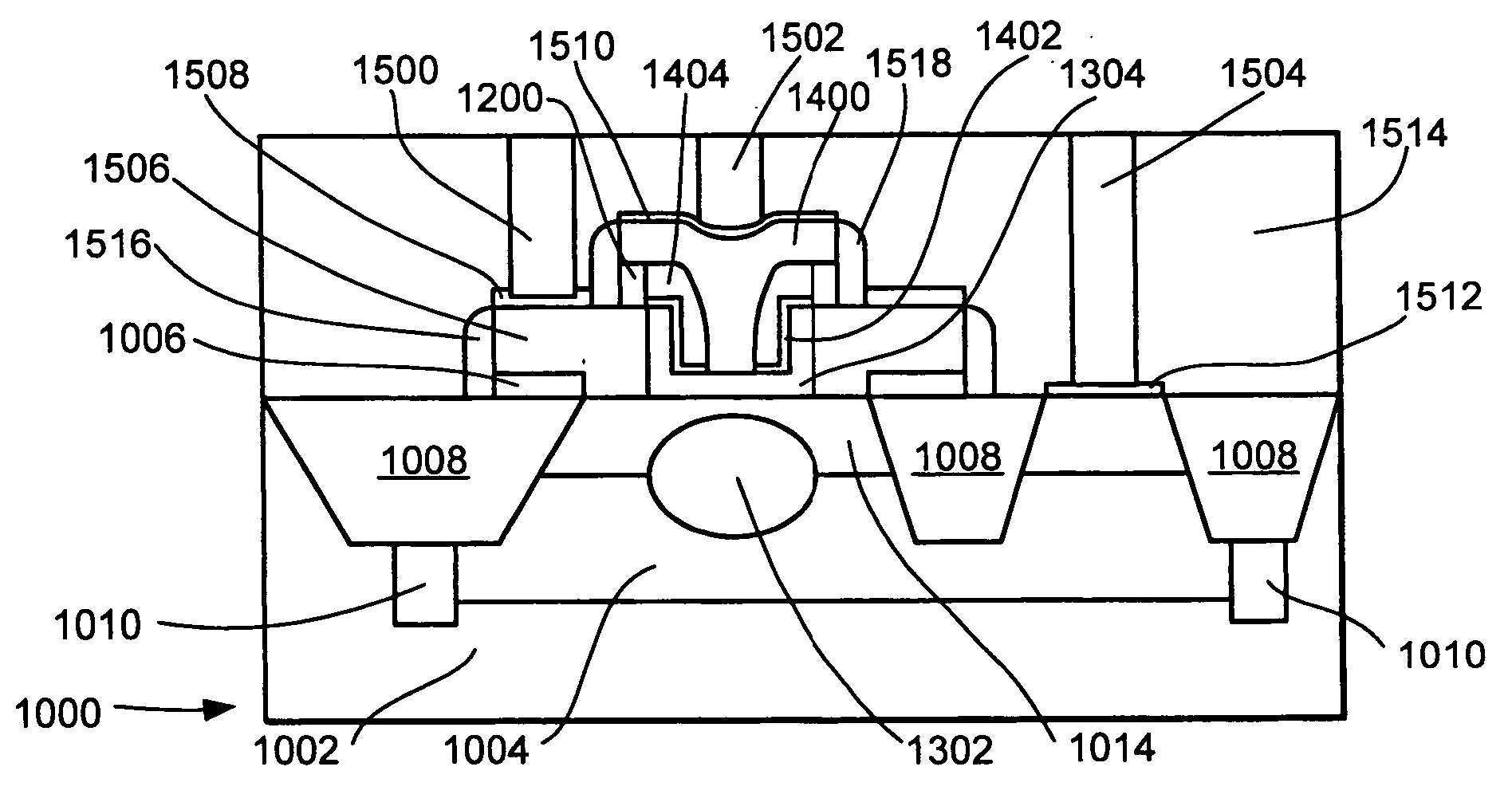

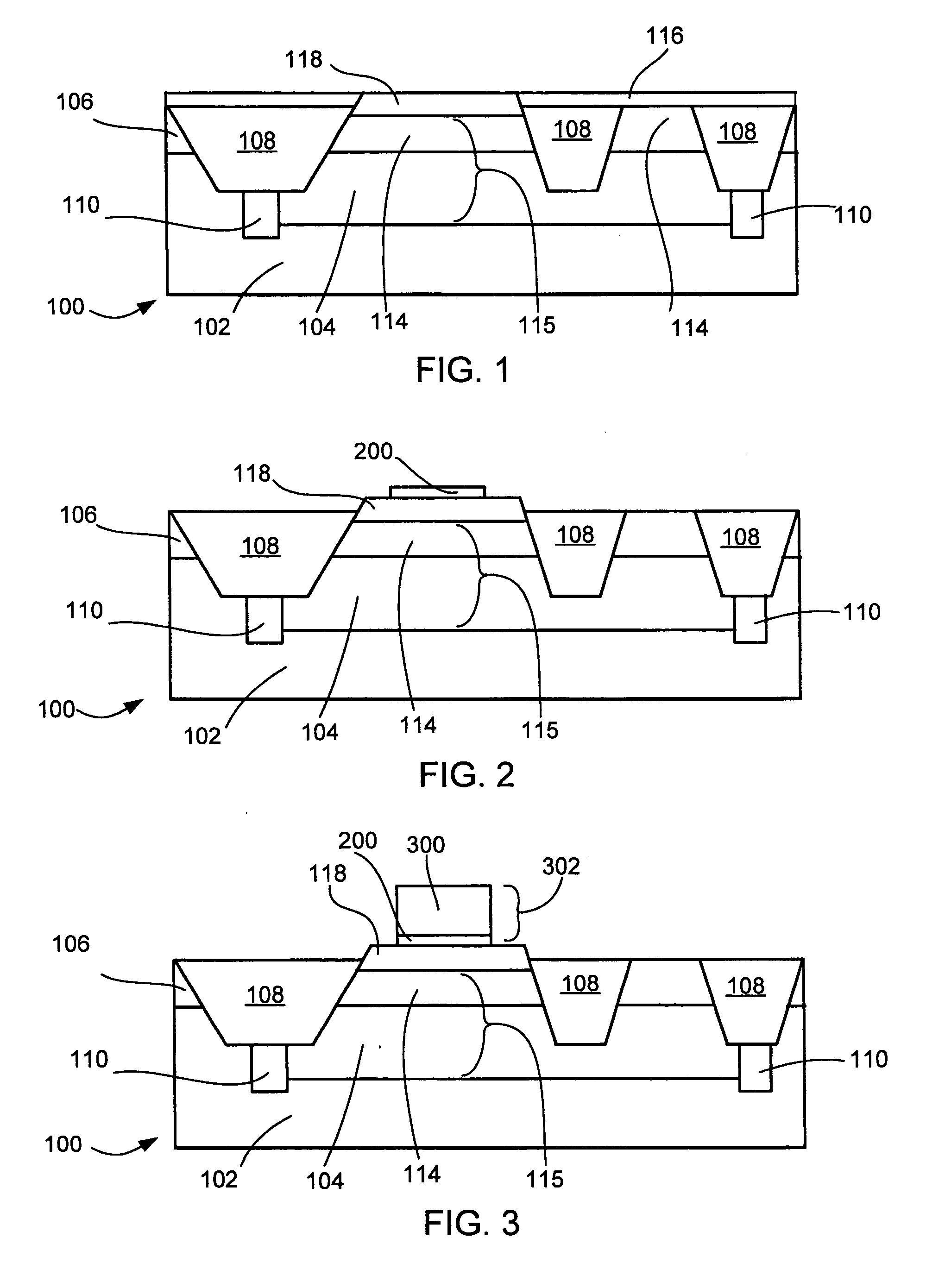

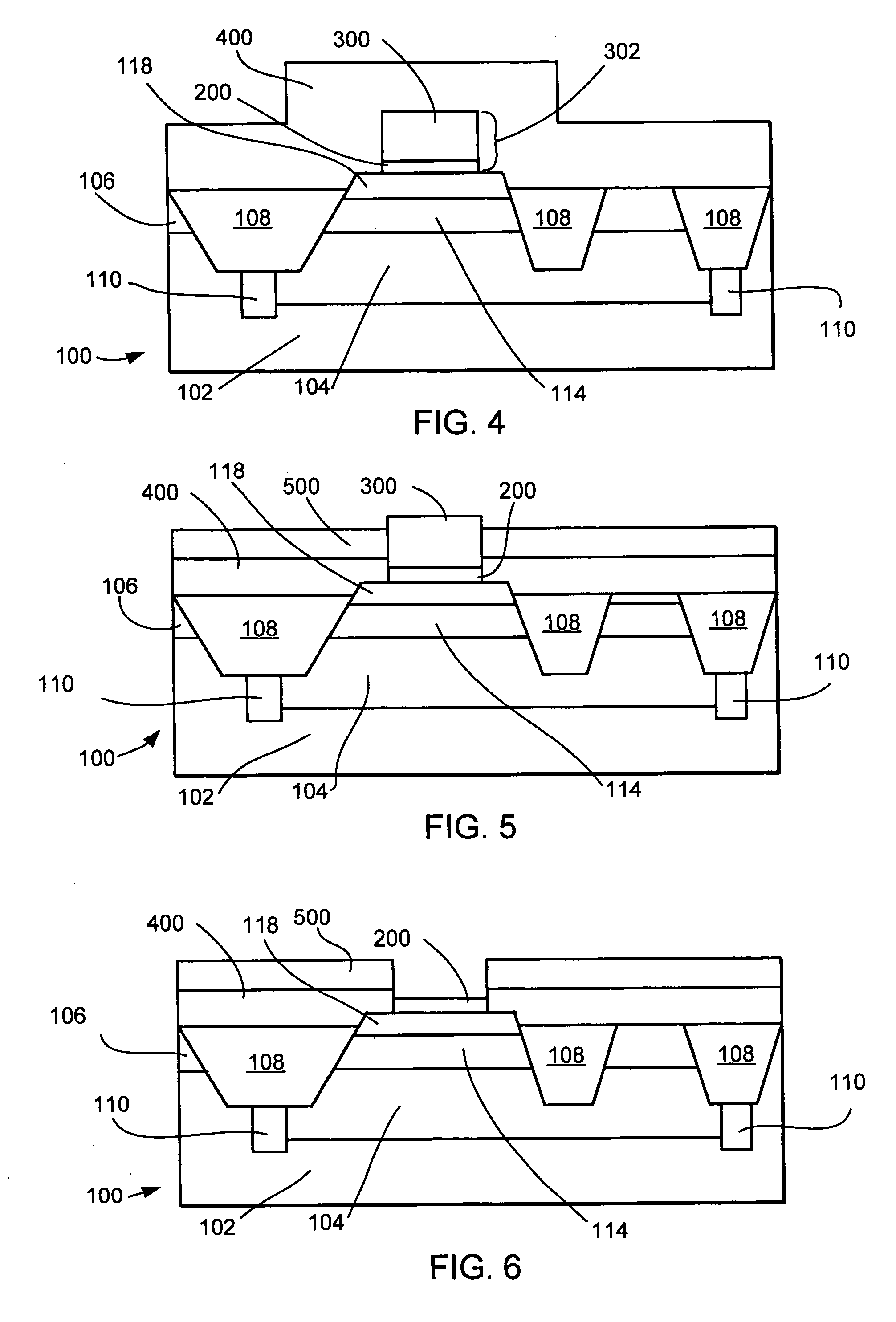

Structure and method of making heterojunction bipolar transistor having self-aligned silicon-germanium raised extrinsic base

InactiveUS20050151165A1High selectivityLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor alloys

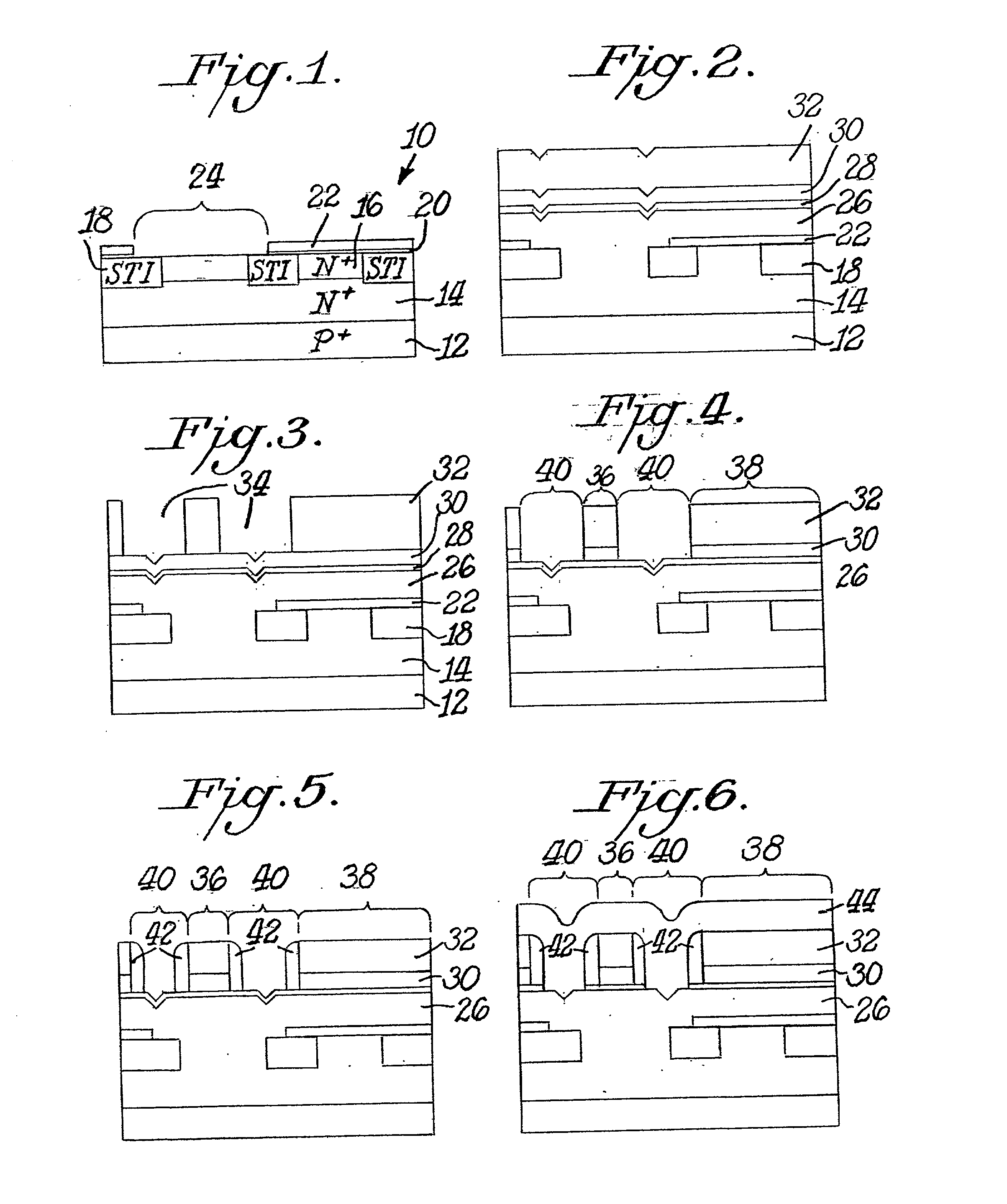

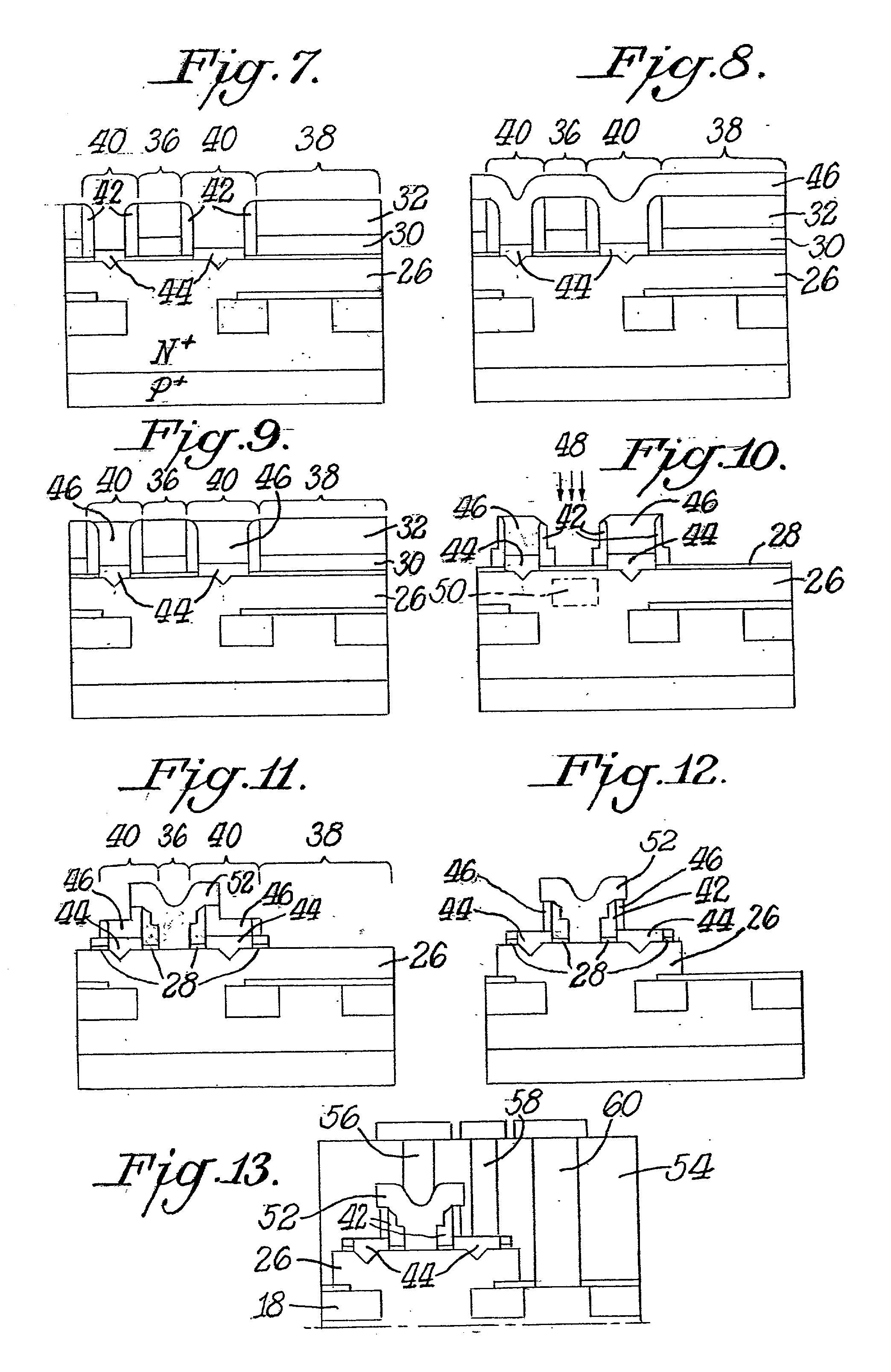

A heterojunction bipolar transistor (HBT) and method of making an HBT are provided. The HBT includes a collector, and an intrinsic base overlying the collector. The intrinsic base includes a layer of a single-crystal semiconductor alloy. The HBT further includes a raised extrinsic base having a first semiconductive layer overlying the intrinsic base and a second semiconductive layer formed on the first semiconductive layer. An emitter overlies the intrinsic base, and is disposed in an opening of the first and second semi-conductive layers, such that the raised extrinsic base is self-aligned to the emitter.

Owner:IBM CORP

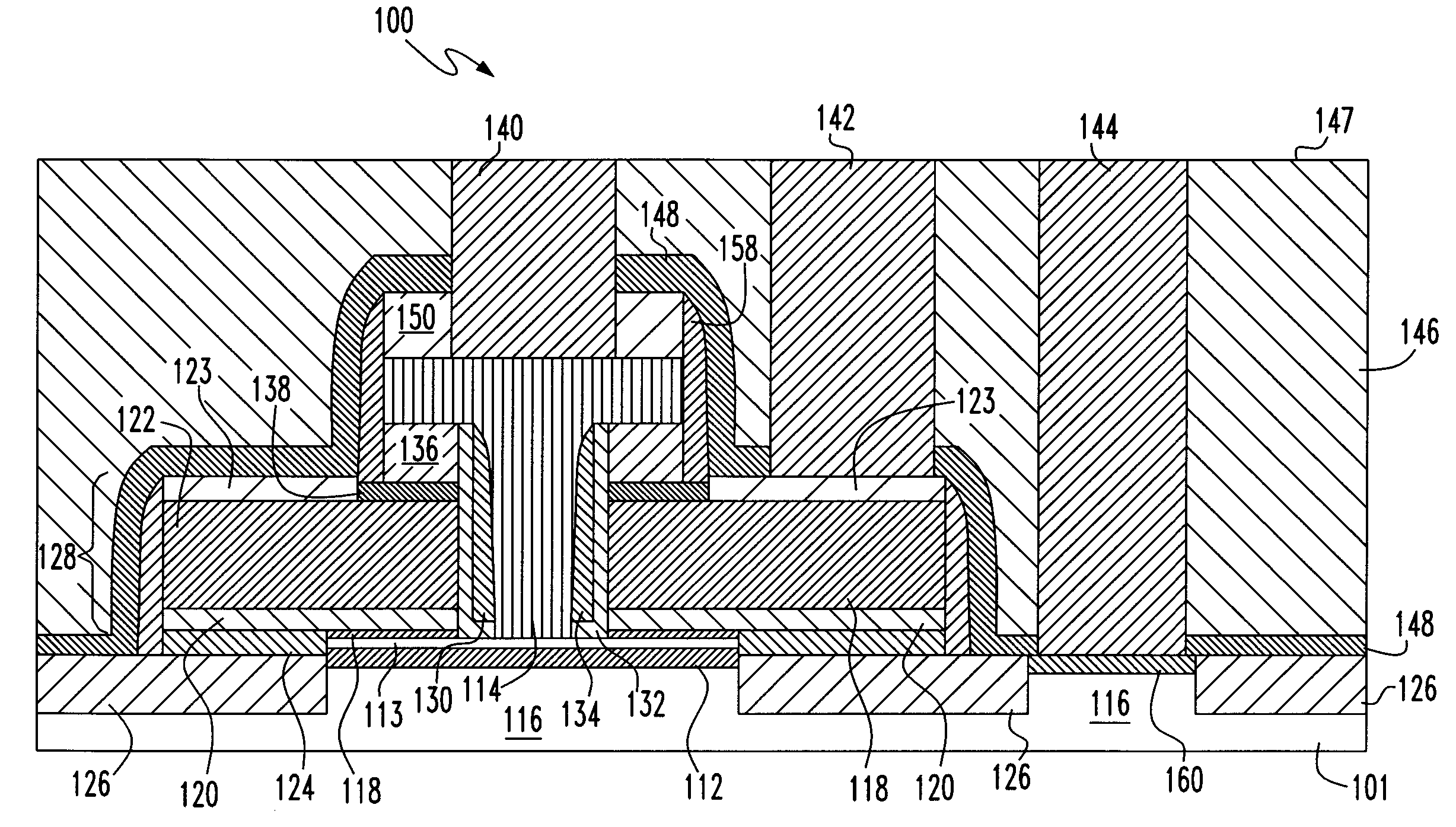

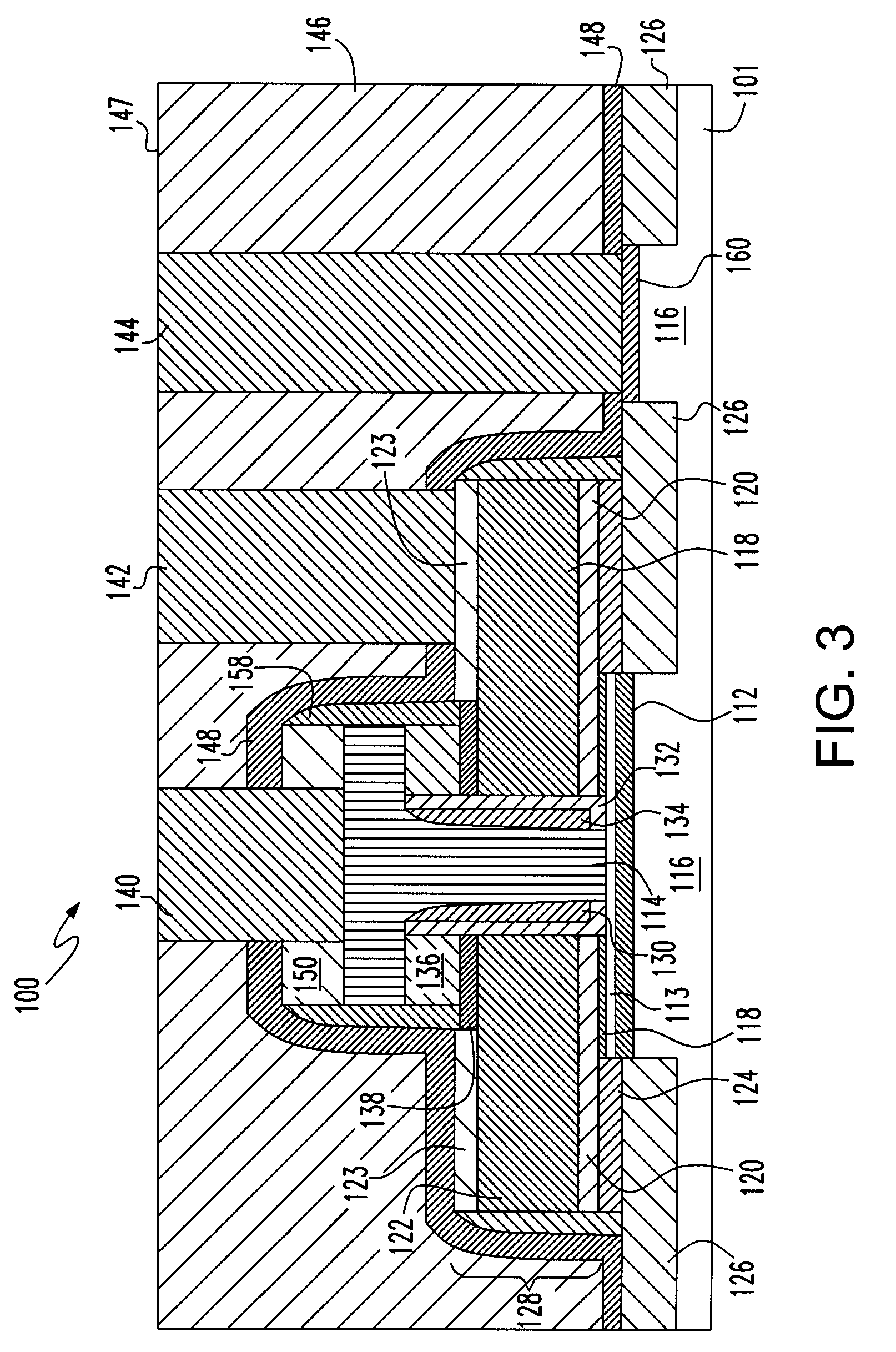

Structure and method for making heterojunction bipolar transistor having self-aligned silicon-germanium raised extrinsic base

InactiveUS6982442B2High selectivityLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor alloys

A heterojunction bipolar transistor (HBT) and method of making an HBT are provided. The HBT includes a collector, and an intrinsic base overlying the collector. The intrinsic base includes a layer of a single-crystal semiconductor alloy. The HBT further includes a raised extrinsic base having a first semiconductive layer overlying the intrinsic base and a second semiconductive layer formed on the first semiconductive layer. An emitter overlies the intrinsic base, and is disposed in an opening of the first and second semiconductive layers, such that the raised extrinsic base is self-aligned to the emitter.

Owner:INT BUSINESS MASCH CORP

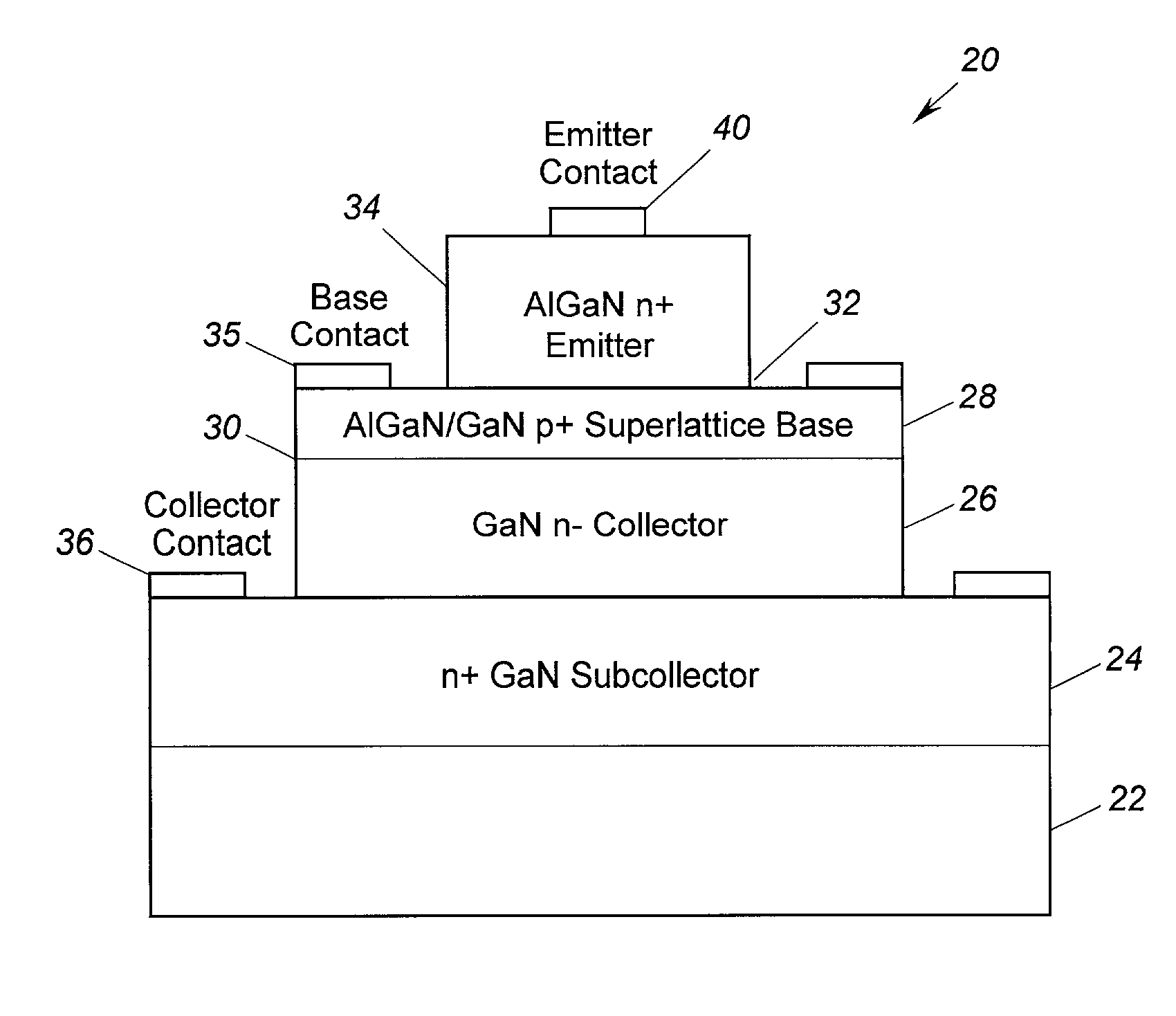

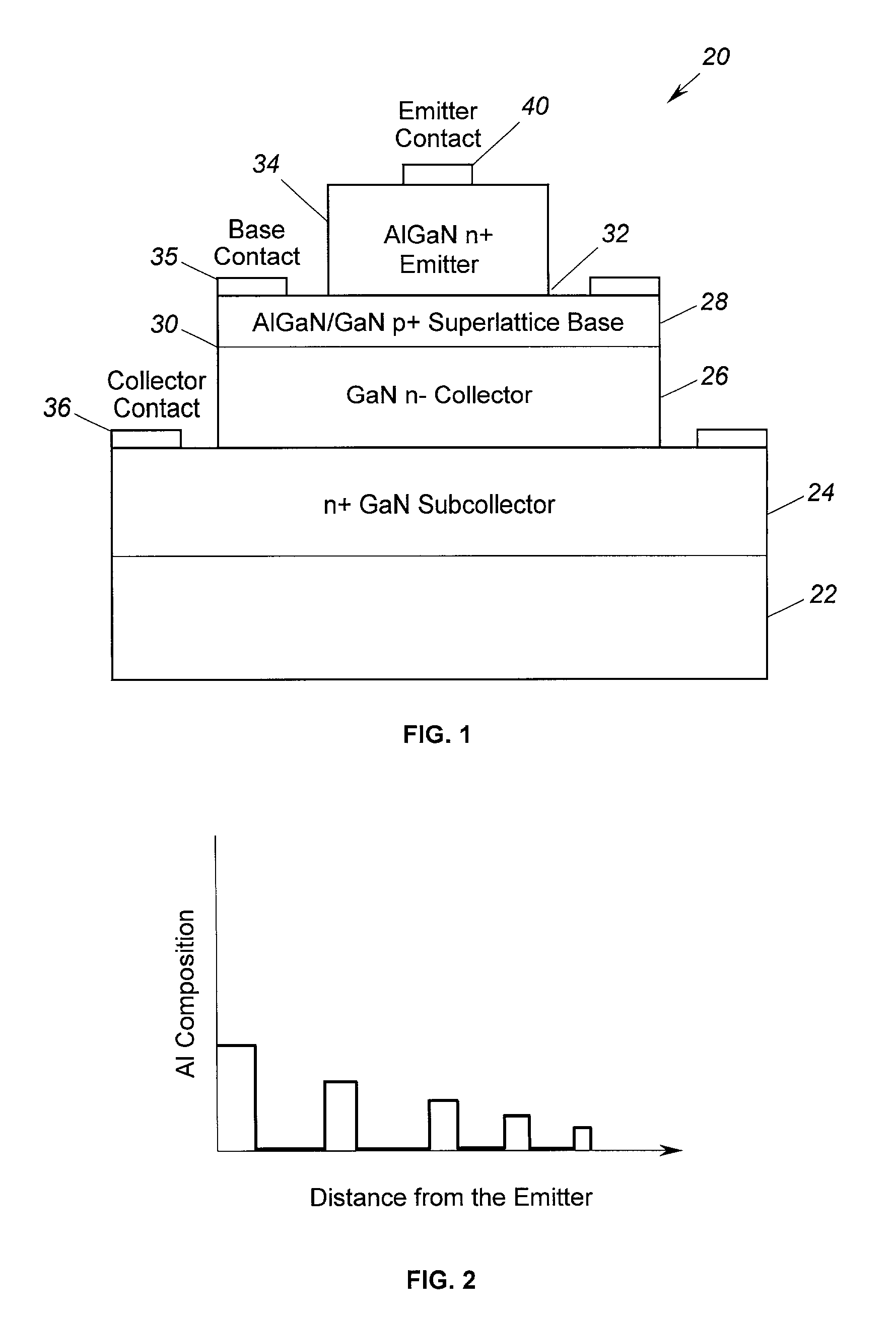

GaN HBT superlattice base structure

InactiveUS20020149033A1Semiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierThin layer

A heterojunction bipolar transistor (HBT) (20) with alternating layers of gallium nitride (GaN) and aluminum gallium nitride (AlGaN) with varying Al composition forming a graded superlattice structure in the base layer (28) includes. The thin layers of AlGaN in the base layer (28) increases the base p-type carrier concentration. Grading of the Al composition in the thin AlGaN layers induces an electrostatic field across the base layer (28) that increases the carrier velocity and reduces the carrier transit time. The structure thus decreases the transit time and at the same time increases the p-type carrier concentration to improve the operating efficiency of the device.

Owner:NORTHROP GRUMAN CORP

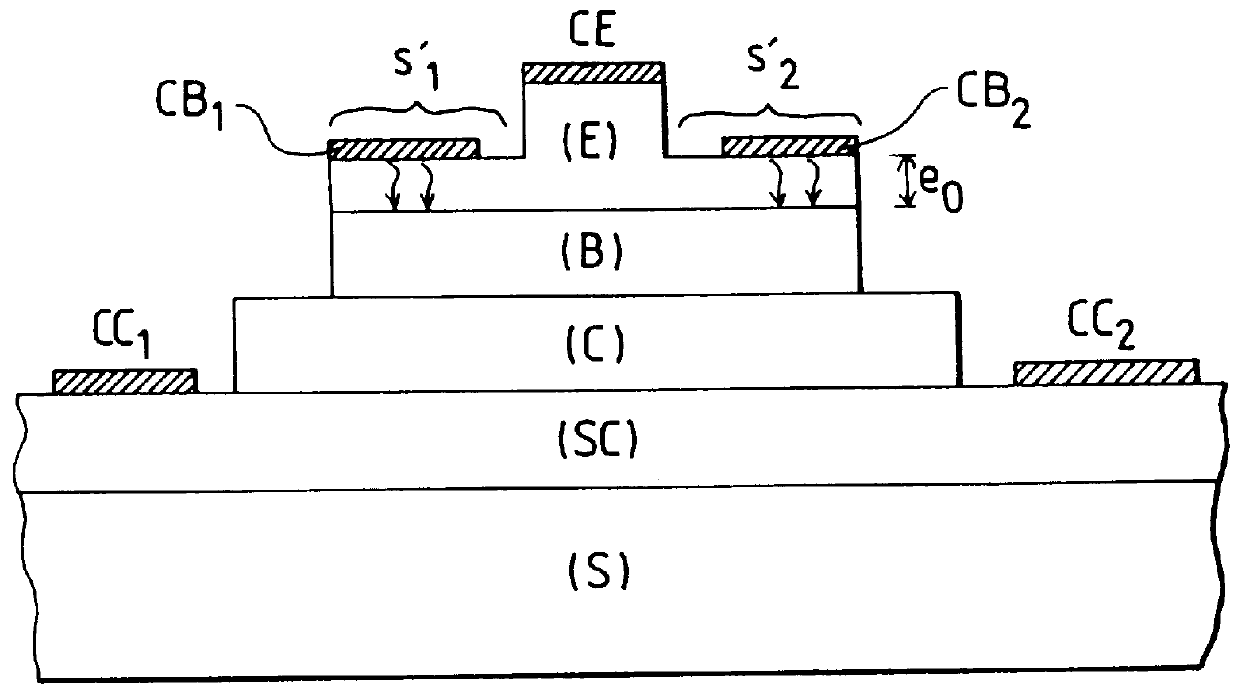

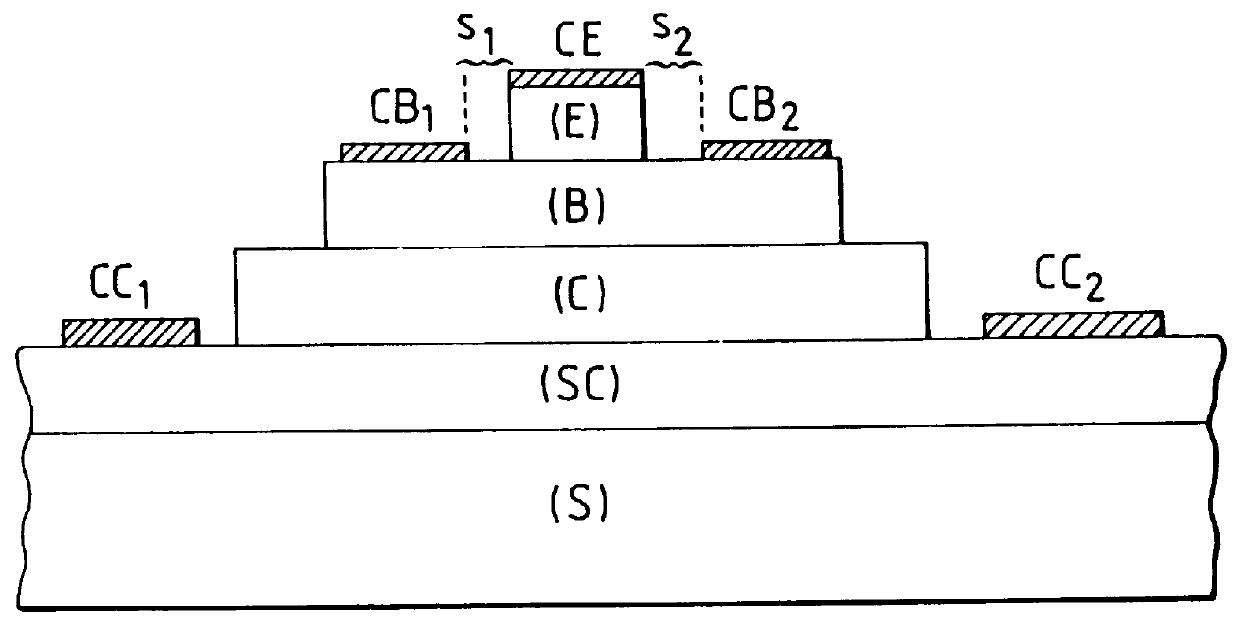

Bipolar transistor stabilized with electrical insulating elements

A semiconductor component of the heterojunction bipolar transistor type comprises, on a substrate, a collector, a base and a mesa-shaped emitter resting on the base. The bipolar transistor furthermore comprises electrically insulating elements in contact with the base and the flanks of the emitter mesa, said elements having a width of the same magnitude as the width of the mesa and providing the component with greater stability. Furthermore, a method for the manufacture of a component of this kind comprises in particular a step for the ion implantation of insulating ions through the constituent layer of the emitter mesa so as to define the electrically insulating elements.

Owner:THOMSON CSF SA

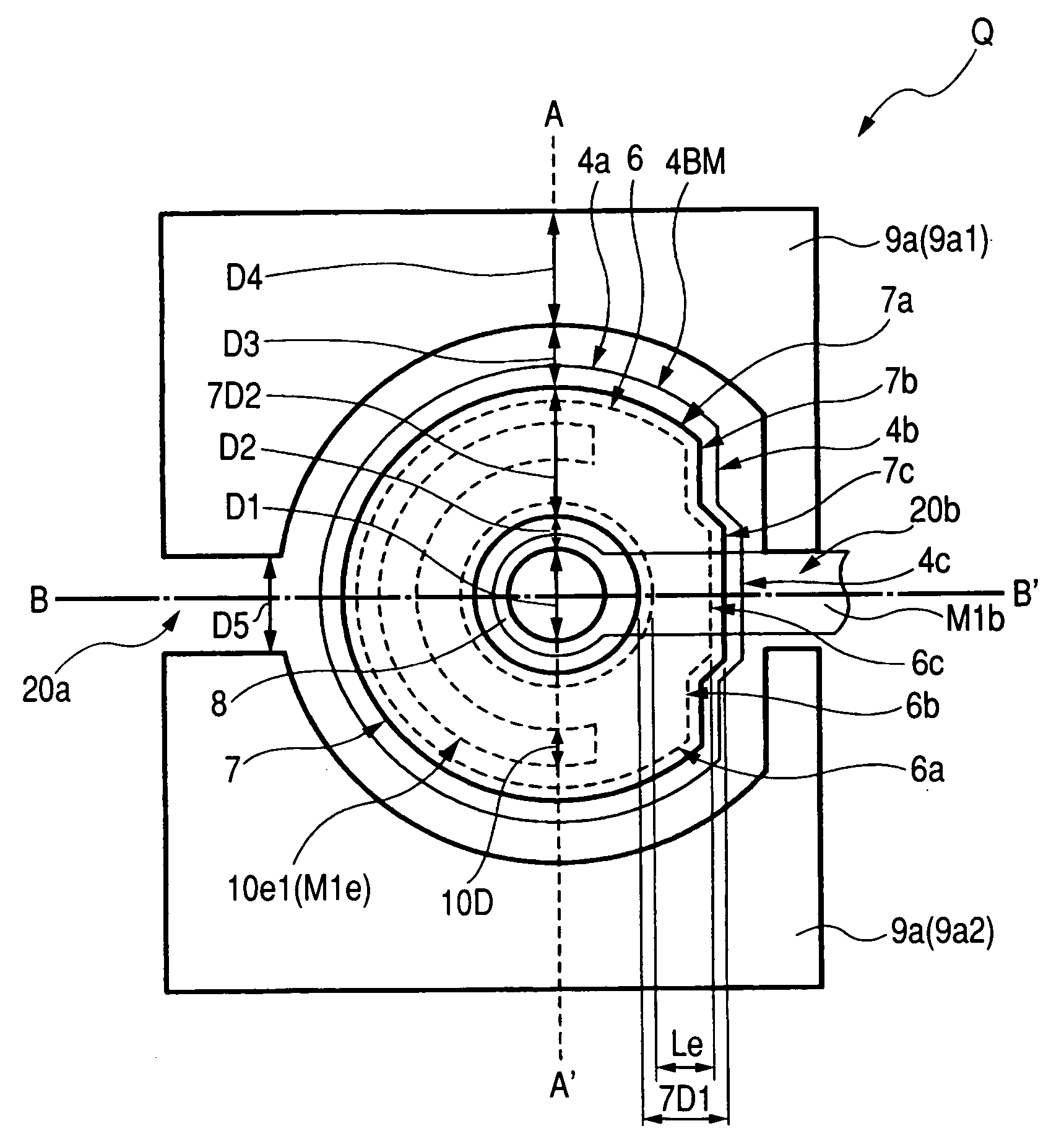

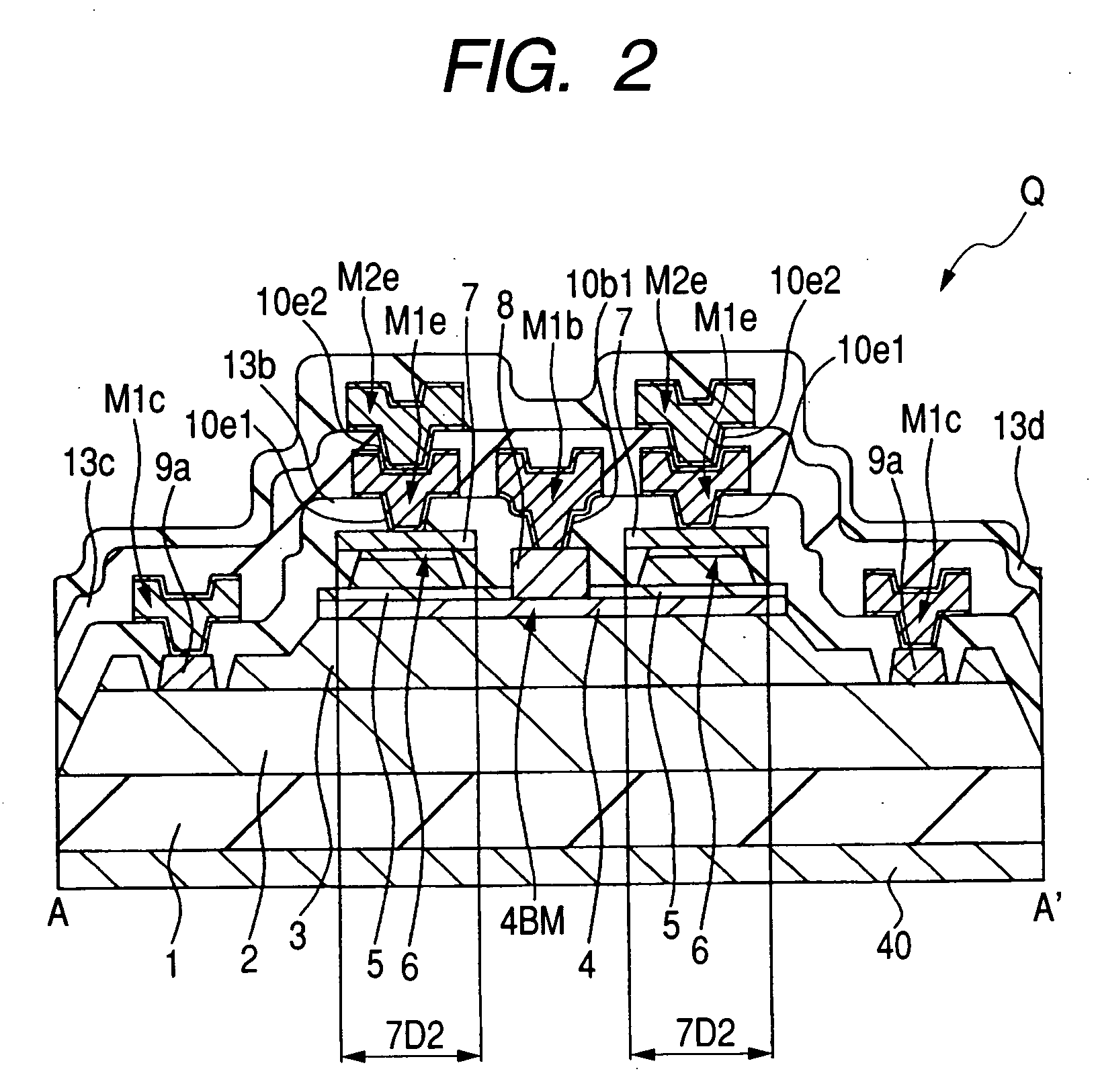

Semiconductor device, manufacturing method of the same, and electronic device

InactiveUS20060108665A1Improve featuresReduce areaTransistorHigh frequency amplifiersLower limitDevice material

The invention is directed to improve characteristics of an HBT (Hetero-junction Bipolar Transistor). An HBT has a collector layer, a base layer, and an emitter layer formed in order on a main surface of a substrate made of a compound semiconductor and a collector electrode, a base electrode, and an emitter electrode electrically connected to the collector layer, the base layer, and the emitter layer, respectively, and further has an emitter contact layer formed between the emitter electrode and the emitter layer. The plane shape of the emitter contact layer and the emitter electrode is an almost annular shape surrounding the base electrode in a plane parallel with the main surface of the substrate, and the lower limit of the emitter contact layer is 1.2 μm or larger.

Owner:RENESAS TECH CORP

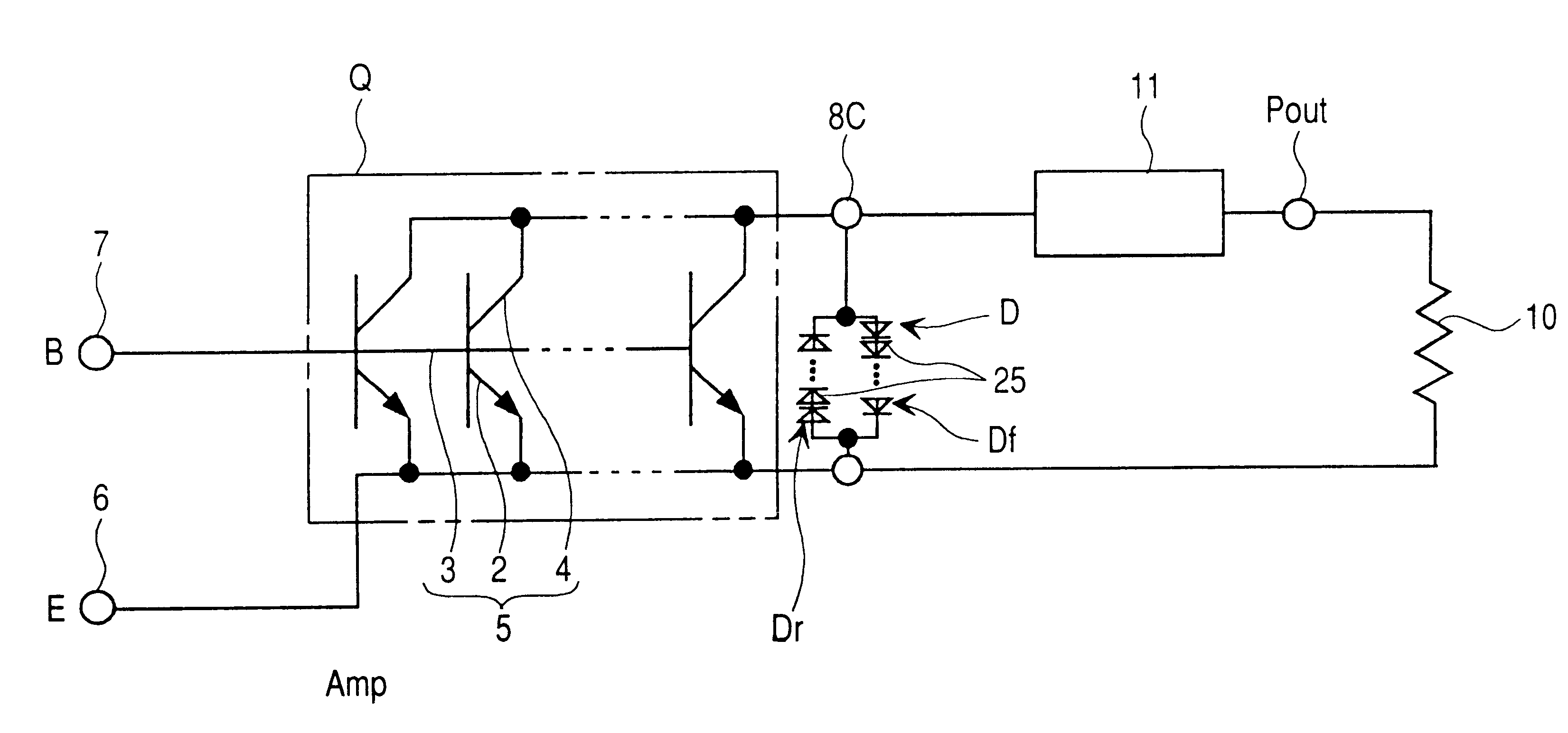

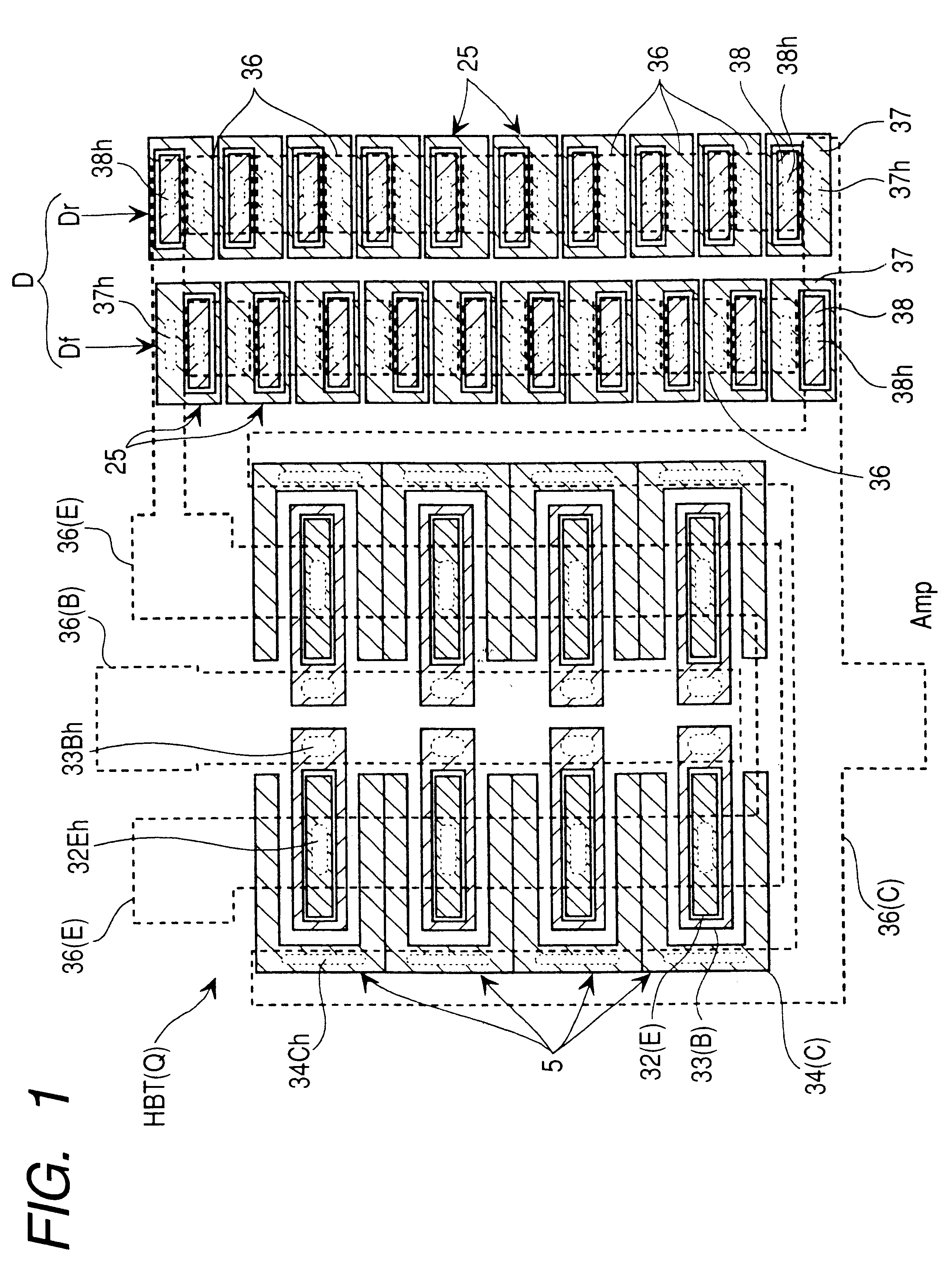

High-frequency power amplification module and radio communication device

InactiveUS6636118B1Stable communicationConvenient wireless communicationPulse automatic controlHigh frequency amplifiersHeterojunctionOvervoltage

In a high frequency power amplifier module of a multi-stage structure in which a plurality of heterojunction bipolar transistors (npn-type HBTs) are cascade-connected, a protection circuit in which a plurality of pn junction diodes are connected in series is connected between the collector and emitter of each HBT. The p-side is connected to the collector side, and the n-side is connected to the emitter side. A protection circuit in which pn junction diodes of the number equal to or smaller than that of the pn junction diodes are connected in series is connected between the base and the emitter. The p-side is connected to the base side, and the n-side is connected to the emitter side. With the configuration, in the case where an overvoltage is applied across the collector and emitter due to a fluctuation in load on the antenna side, the collector terminal is clamped by an ON-state voltage of the protection circuits, so that the HBT can be prevented from being destroyed. Since the similar protection circuit is assembled between the base and emitter, even when the operator touches the module at the time of manufacturing the high frequency power amplifier module, the HBT can be prevented from being destroyed by the clamping effect of the protection circuit between the base and emitter and the protection circuit between the collector and emitter. Thus, an improved manufacturing yield of the high frequency power amplifier module and a wireless communication apparatus can be achieved, and destruction caused by fluctuation in load impedance of the wireless communication apparatus can be prevented.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com