Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

295 results about "Semiconductor alloys" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Low resistance contacts including intermetallic alloy of nickel, platinum, titanium, aluminum and type iv semiconductor elements

ActiveUS20180068950A1Semiconductor/solid-state device detailsSolid-state devicesPlatinumSemiconductor materials

A method of forming a contact to a semiconductor device is provided that forms an alloy composed of nickel (Ni), platinum (Pt), aluminum (Al), titanium (Ti) and a semiconductor material. The methods may include forming a nickel and platinum semiconductor alloy at a base of a via. A titanium layer having an angstrom scale thickness is deposited in the via in contact with the nickel platinum semiconductor alloy. An aluminum containing fill is deposited atop the titanium layer. A forming gas anneal including an oxygen containing atmosphere is applied to the structure to provide a contact alloy comprising nickel, platinum, aluminum, titanium and a semiconductor element from the contact surface of the semiconductor device.

Owner:IBM CORP

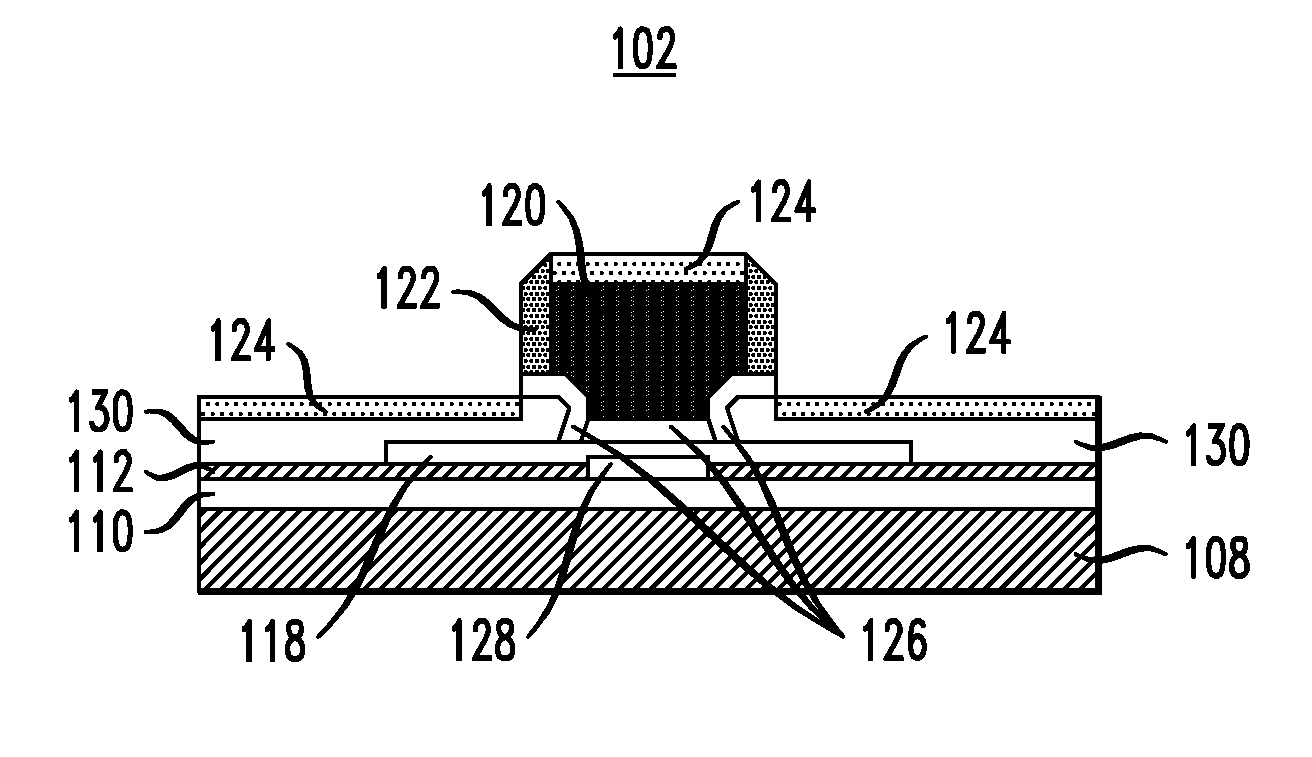

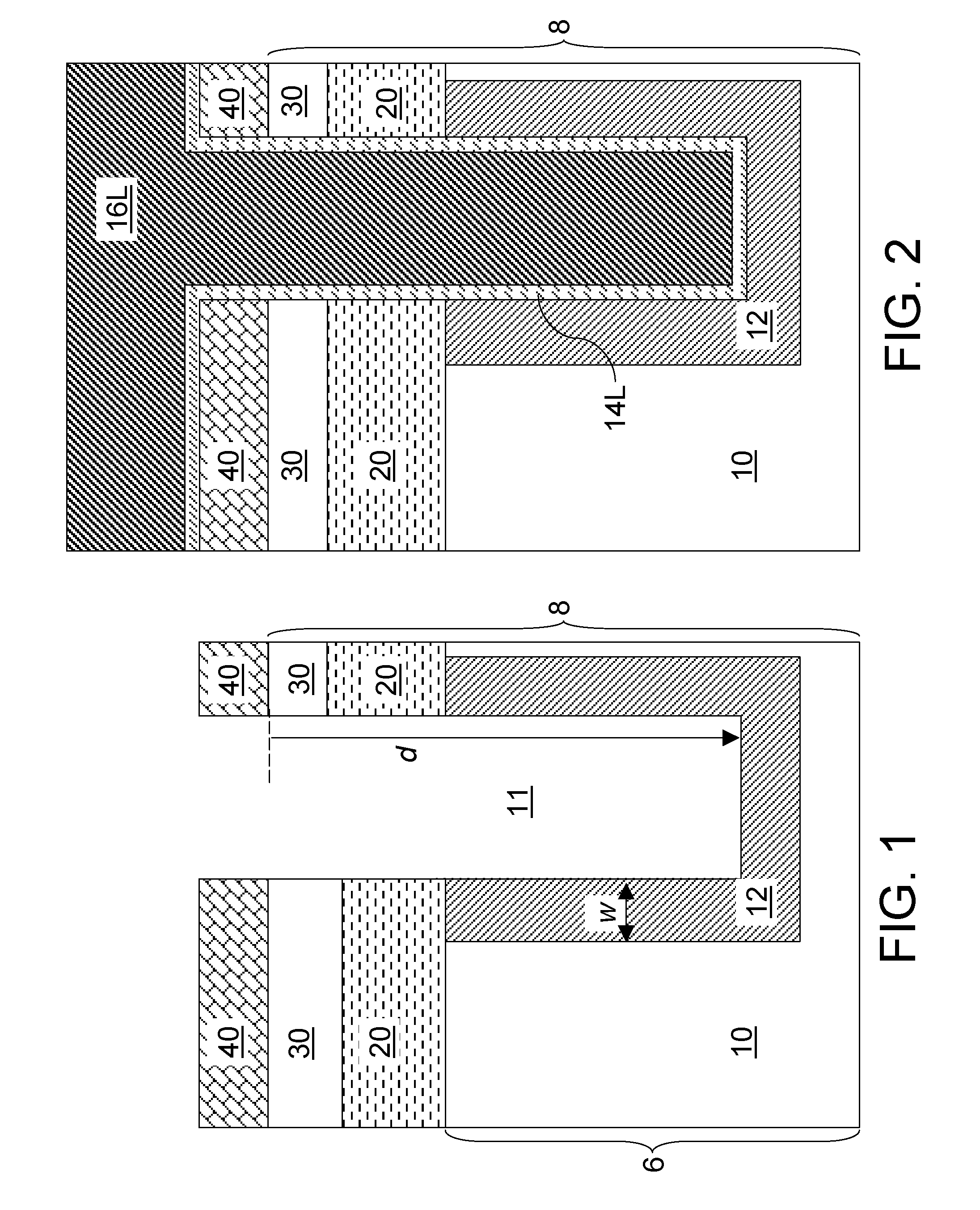

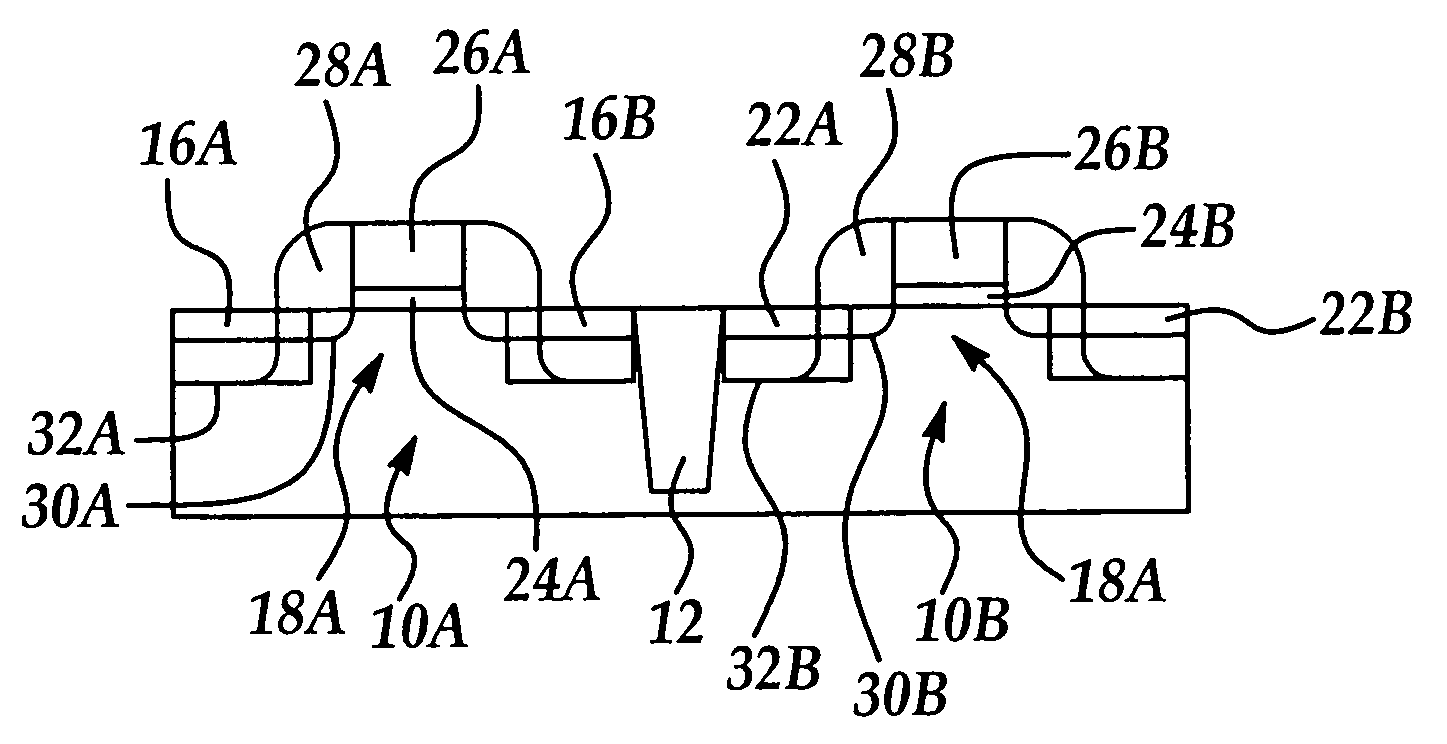

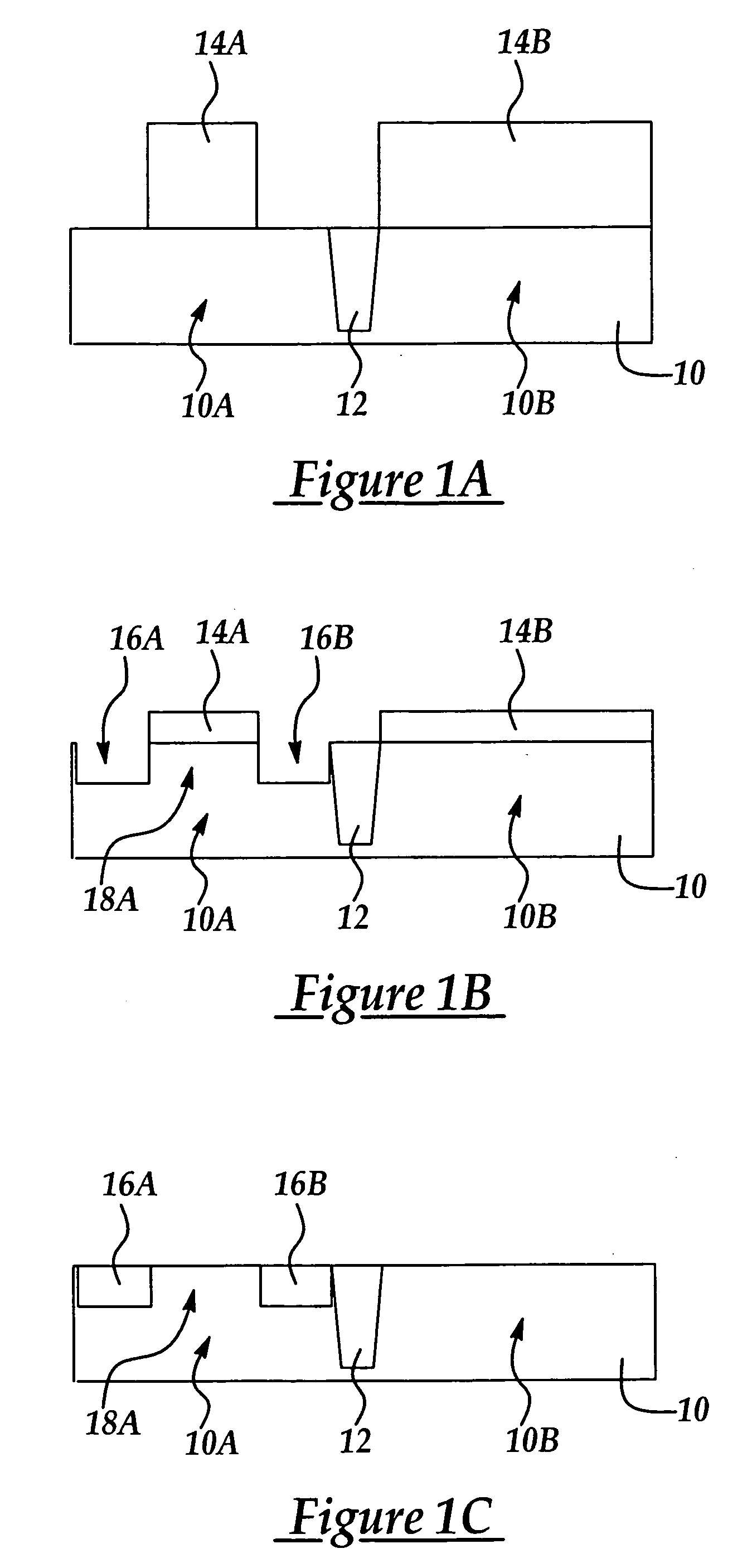

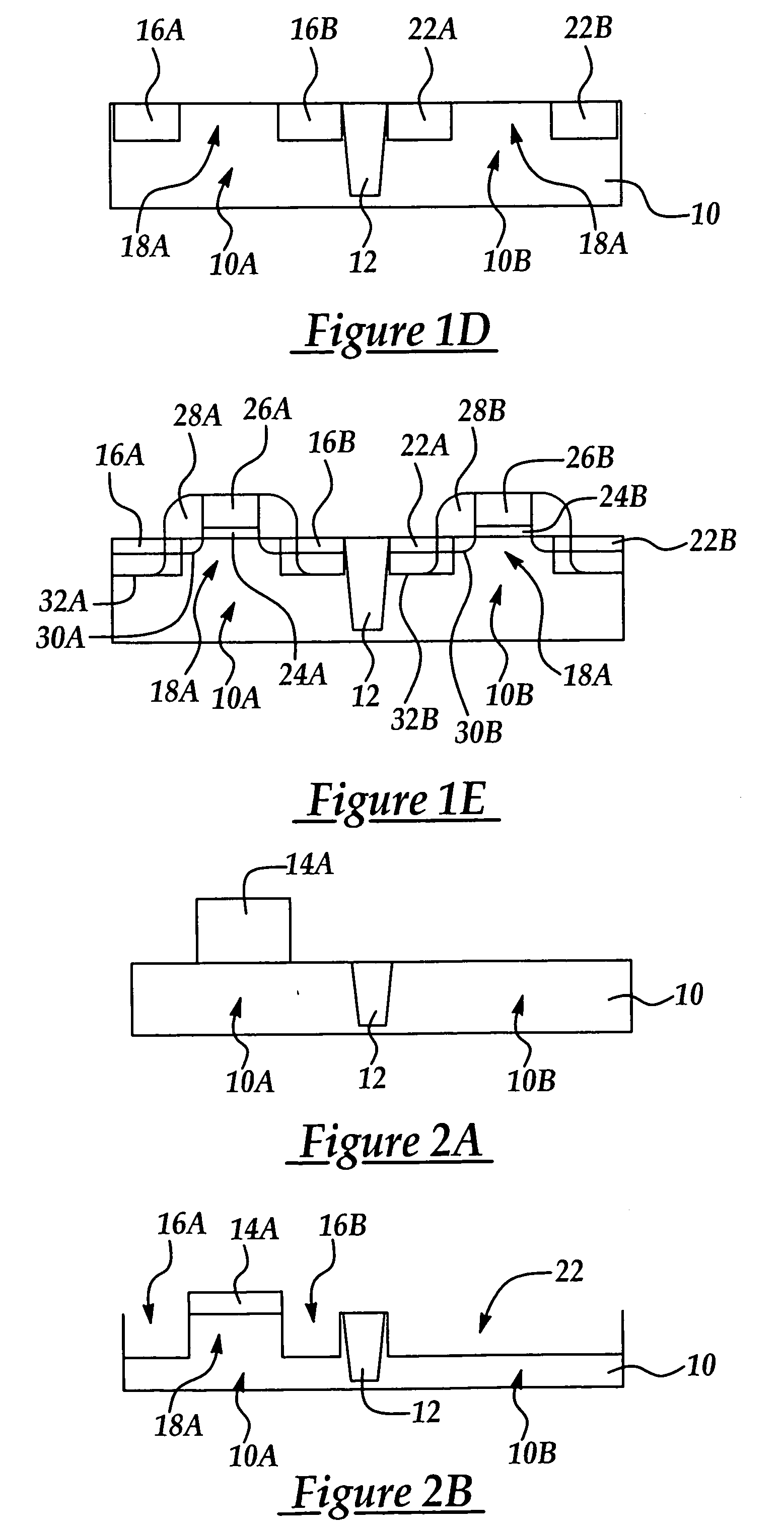

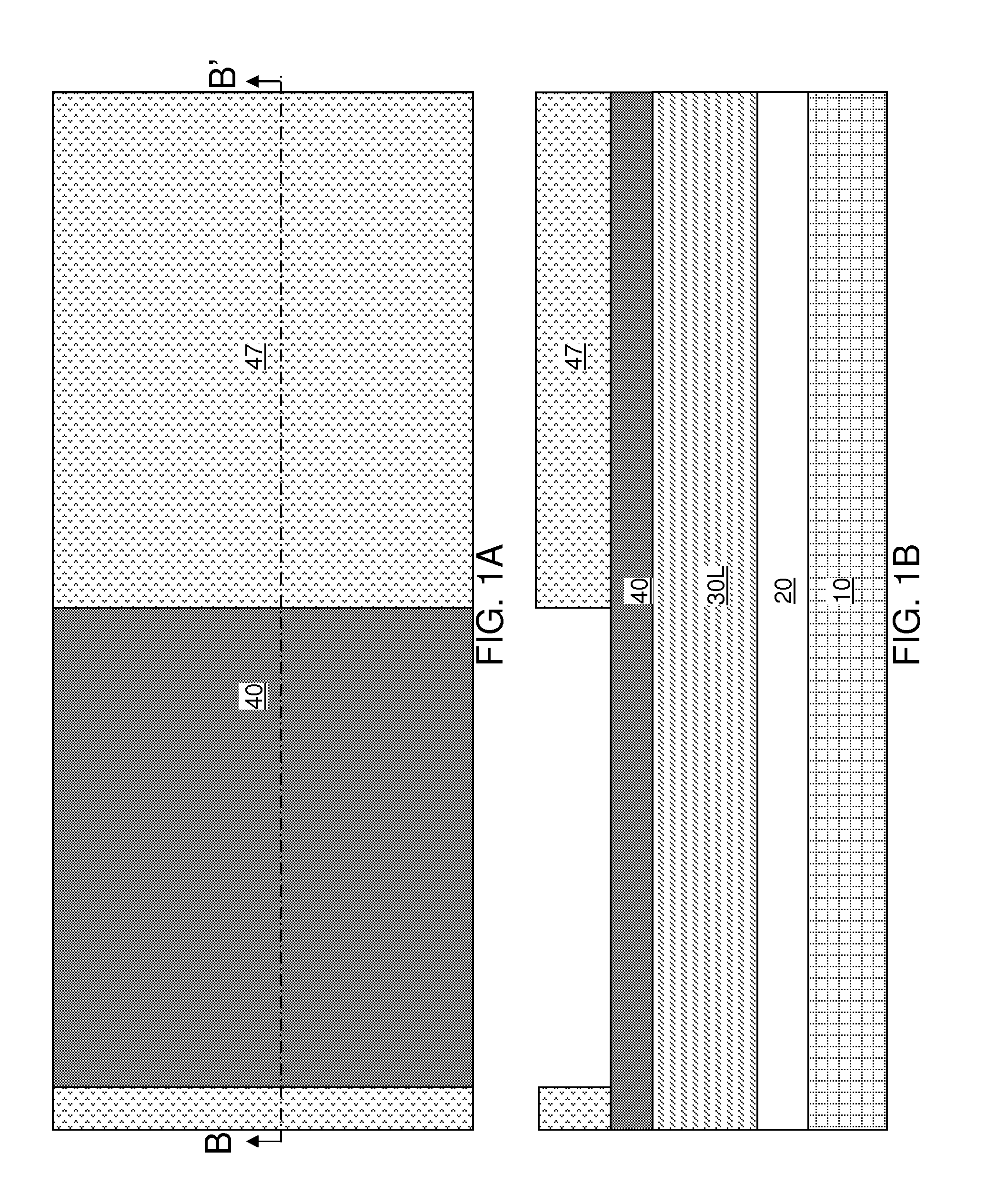

Metal semiconductor alloy structure for low contact resistance

InactiveUS20120032275A1TransistorSemiconductor/solid-state device detailsSemiconductor materialsSemiconductor alloys

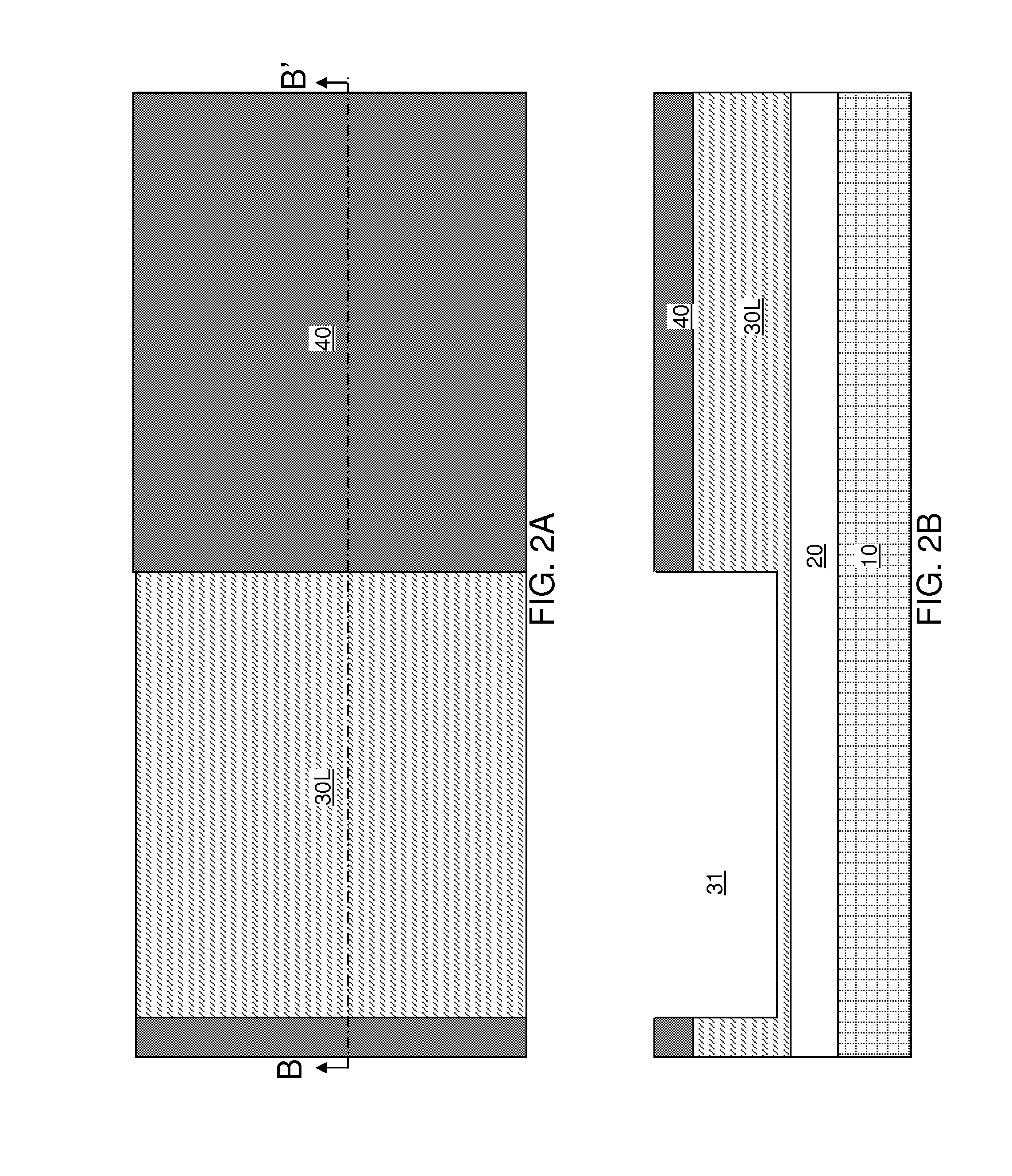

Contact via holes are etched in a dielectric material layer overlying a semiconductor layer to expose the topmost surface of the semiconductor layer. The contact via holes are extended into the semiconductor material layer by continuing to etch the semiconductor layer so that a trench having semiconductor sidewalls is formed in the semiconductor material layer. A metal layer is deposited over the dielectric material layer and the sidewalls and bottom surface of the trench. Upon an anneal at an elevated temperature, a metal semiconductor alloy region is formed, which includes a top metal semiconductor alloy portion that includes a cavity therein and a bottom metal semiconductor alloy portion that underlies the cavity and including a horizontal portion. A metal contact via is formed within the cavity so that the top metal semiconductor alloy portion laterally surrounds a bottom portion of a bottom portion of the metal contact via.

Owner:IBM CORP

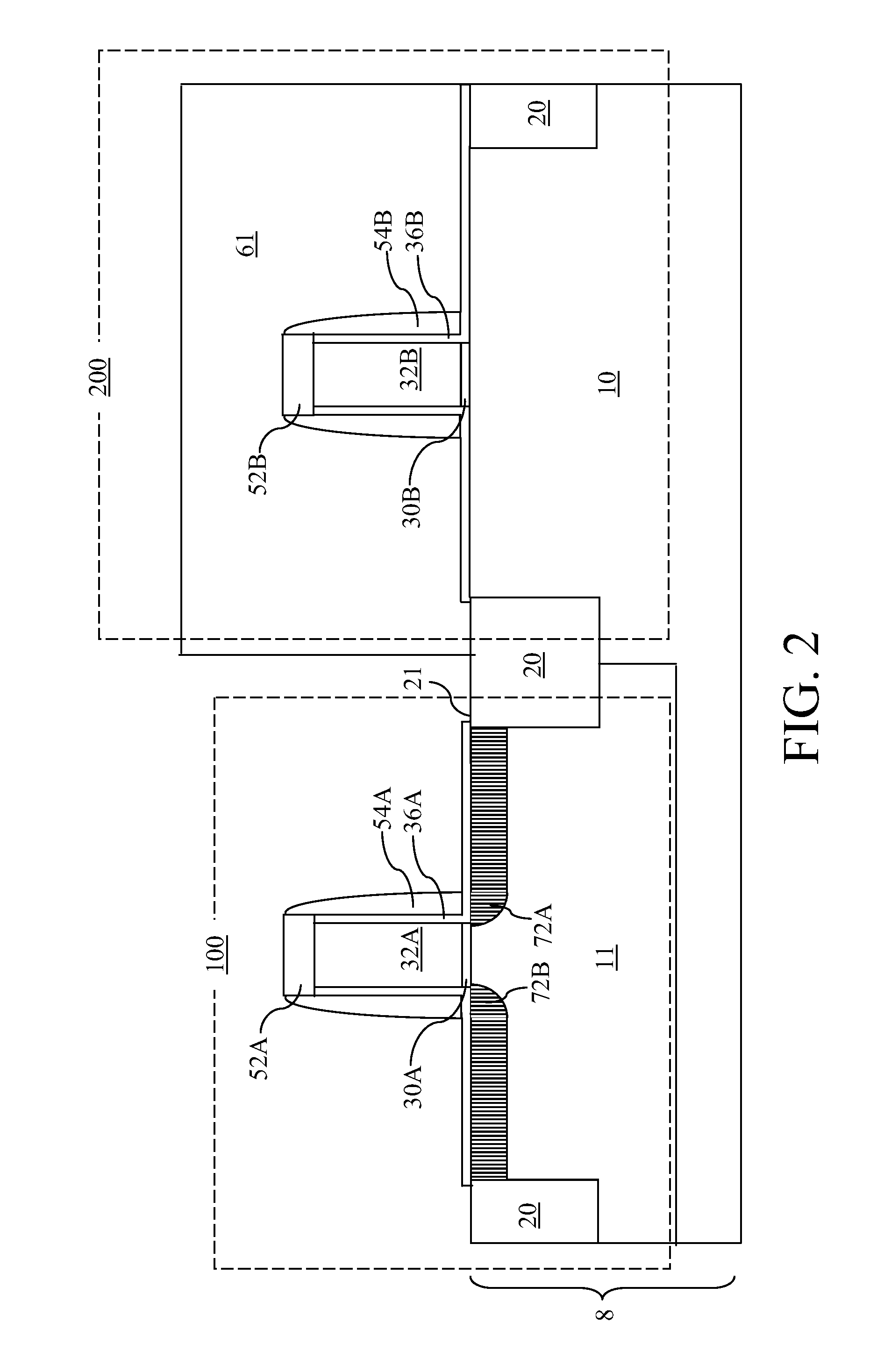

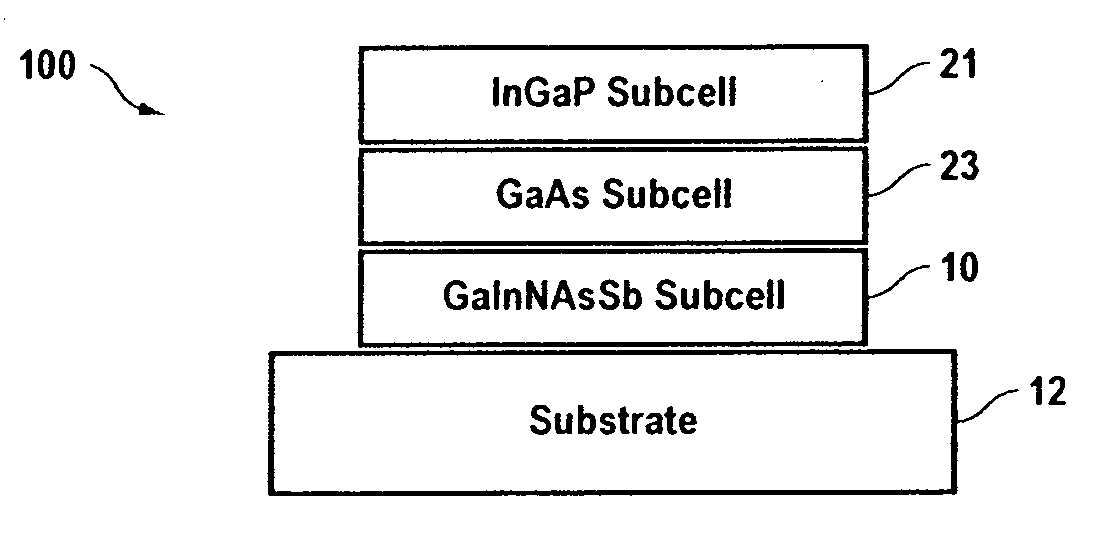

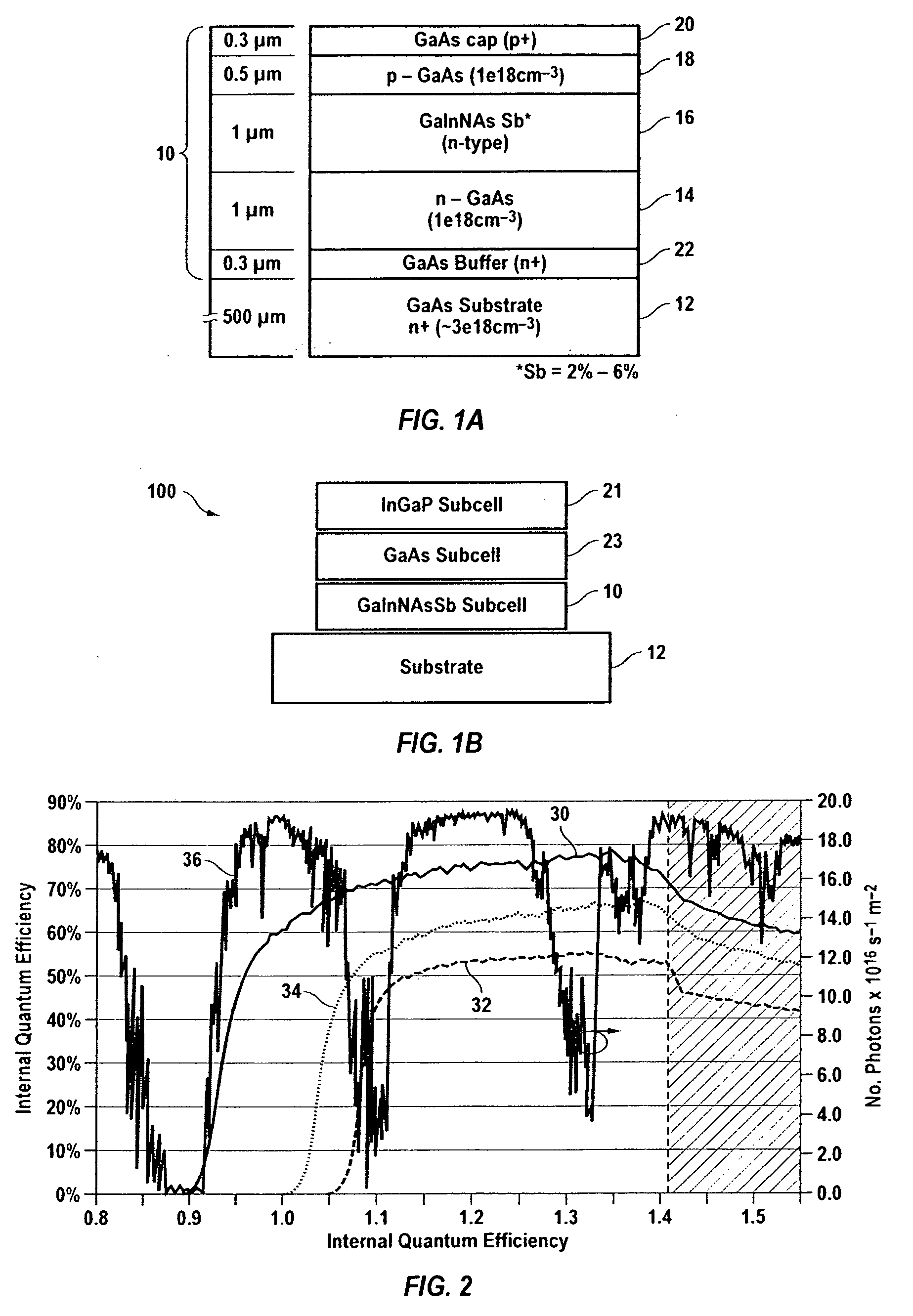

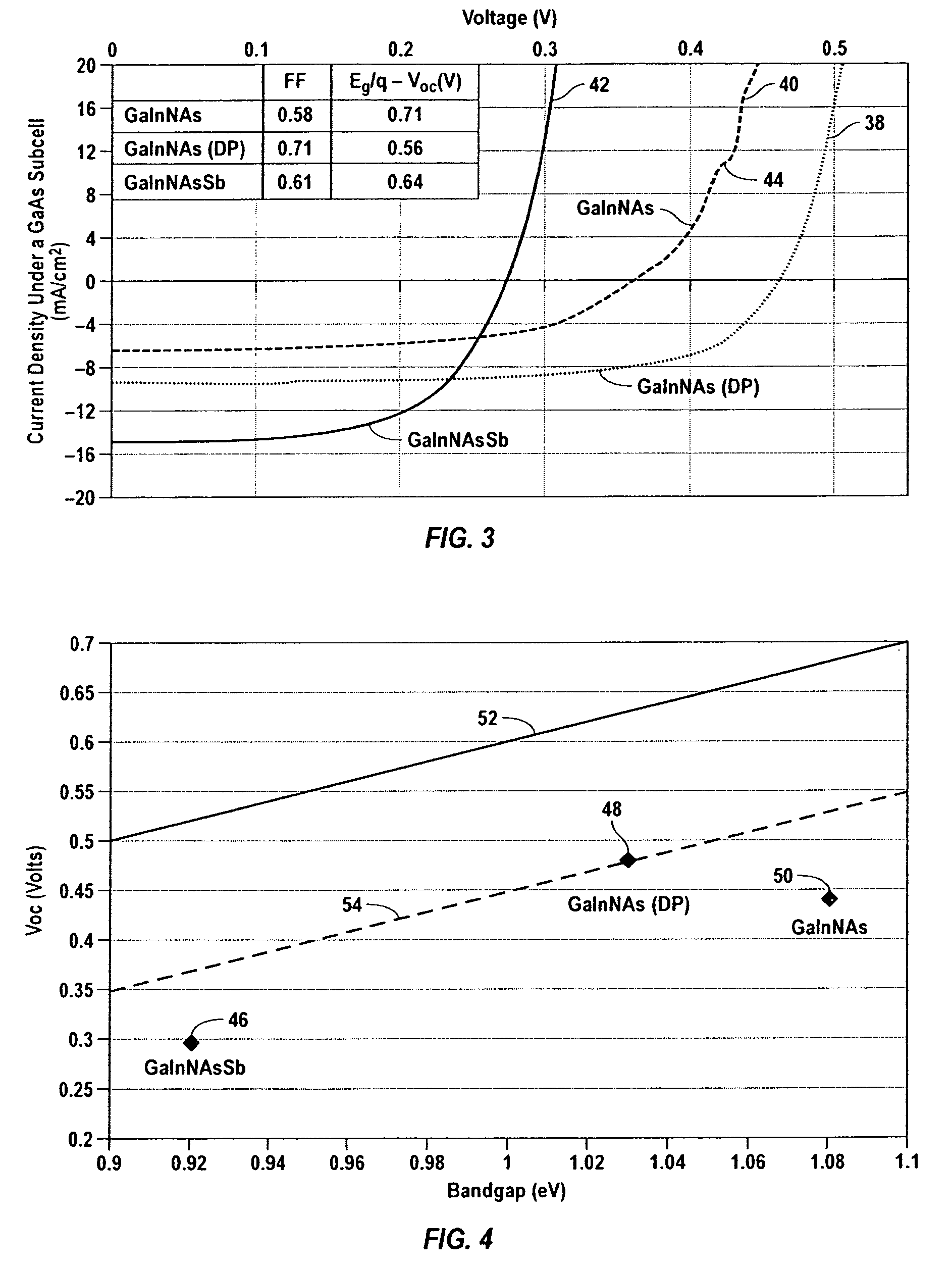

GaInNAsSb solar cells grown by molecular beam epitaxy

InactiveUS20090014061A1Improve featuresPromote efficient solar energy conversionFinal product manufacturePhotovoltaic energy generationIndiumSemiconductor alloys

A high efficiency triple-junction solar cell and method of manufacture therefor is provided wherein junctions are formed between different types of III-V semiconductor alloy materials, one alloy of which contains a combination of an effective amount of antimony (Sb) with gallium (Ga), indium (In), nitrogen (N, the nitride component) and arsenic (As) to form the dilute nitride semiconductor layer GaInNAsSb which has particularly favorable characteristics in a solar cell. In particular, the bandgap and lattice matching promote efficient solar energy conversion.

Owner:CACTUS MATERIALS INC +1

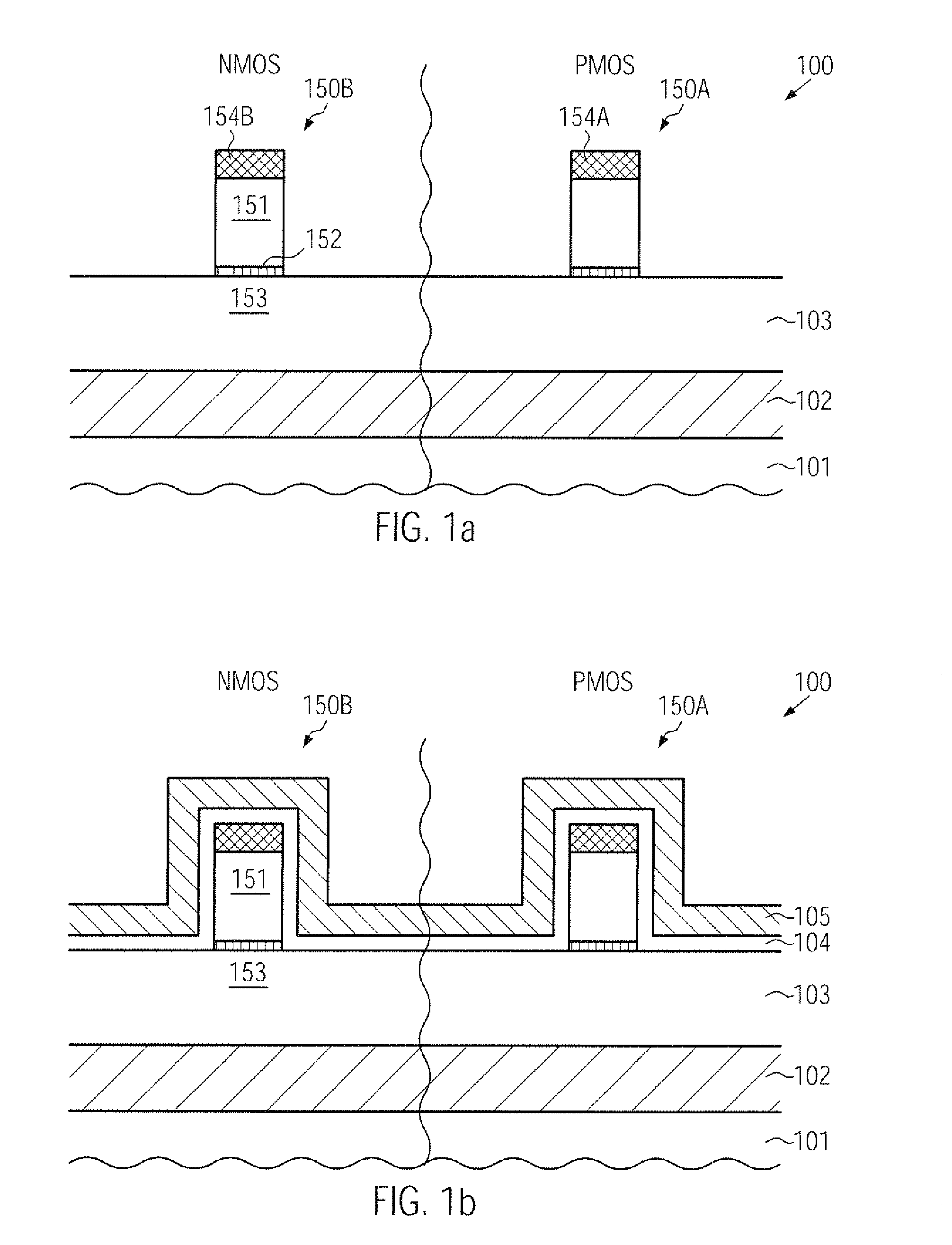

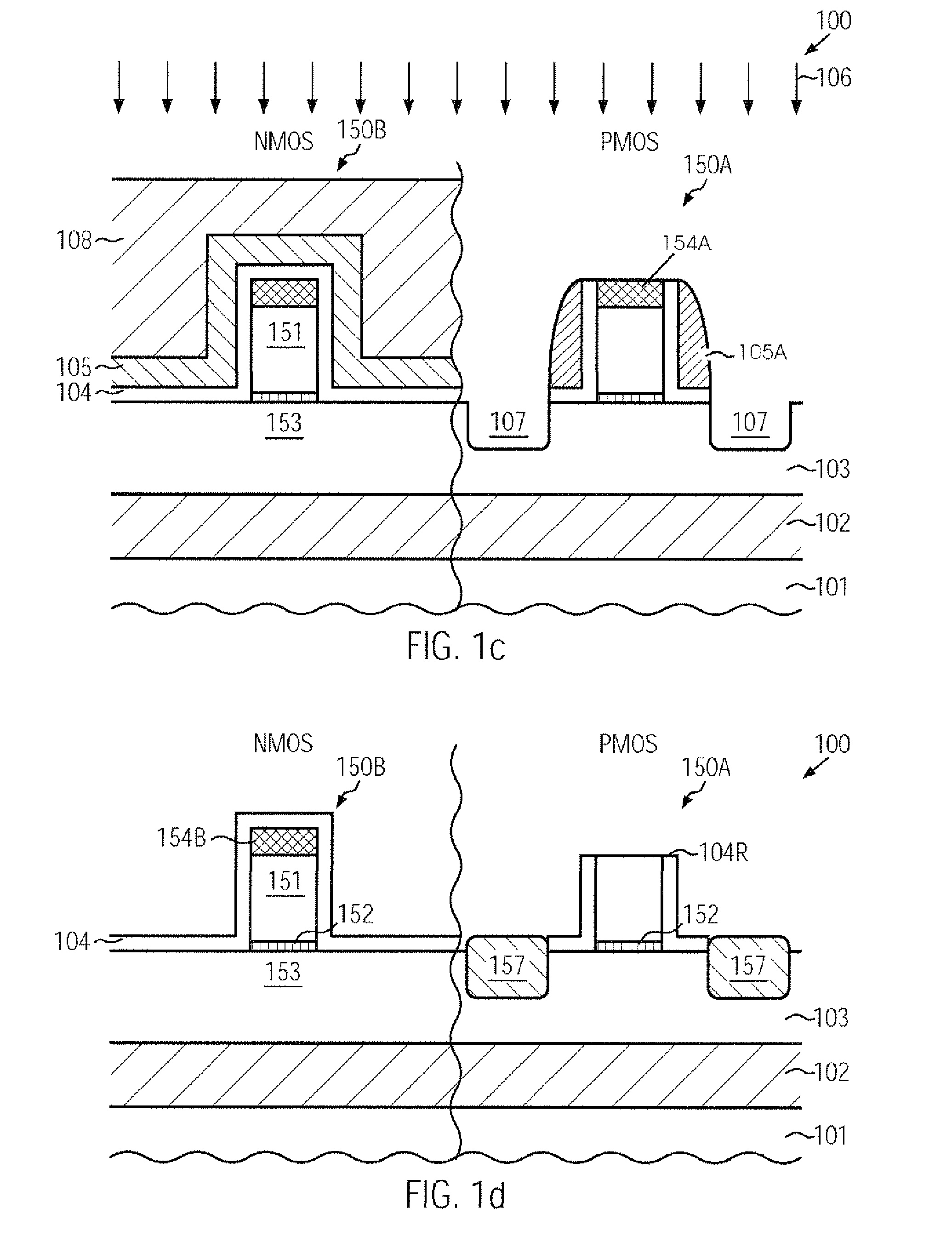

Transistor with an embedded strain-inducing material having a gradually shaped configuration

ActiveUS20120223363A1Improve controllabilityIncrease flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor alloysAlloy

Owner:CHENGDU HAIGUANG MICROELECTRONICS TECH CO LTD

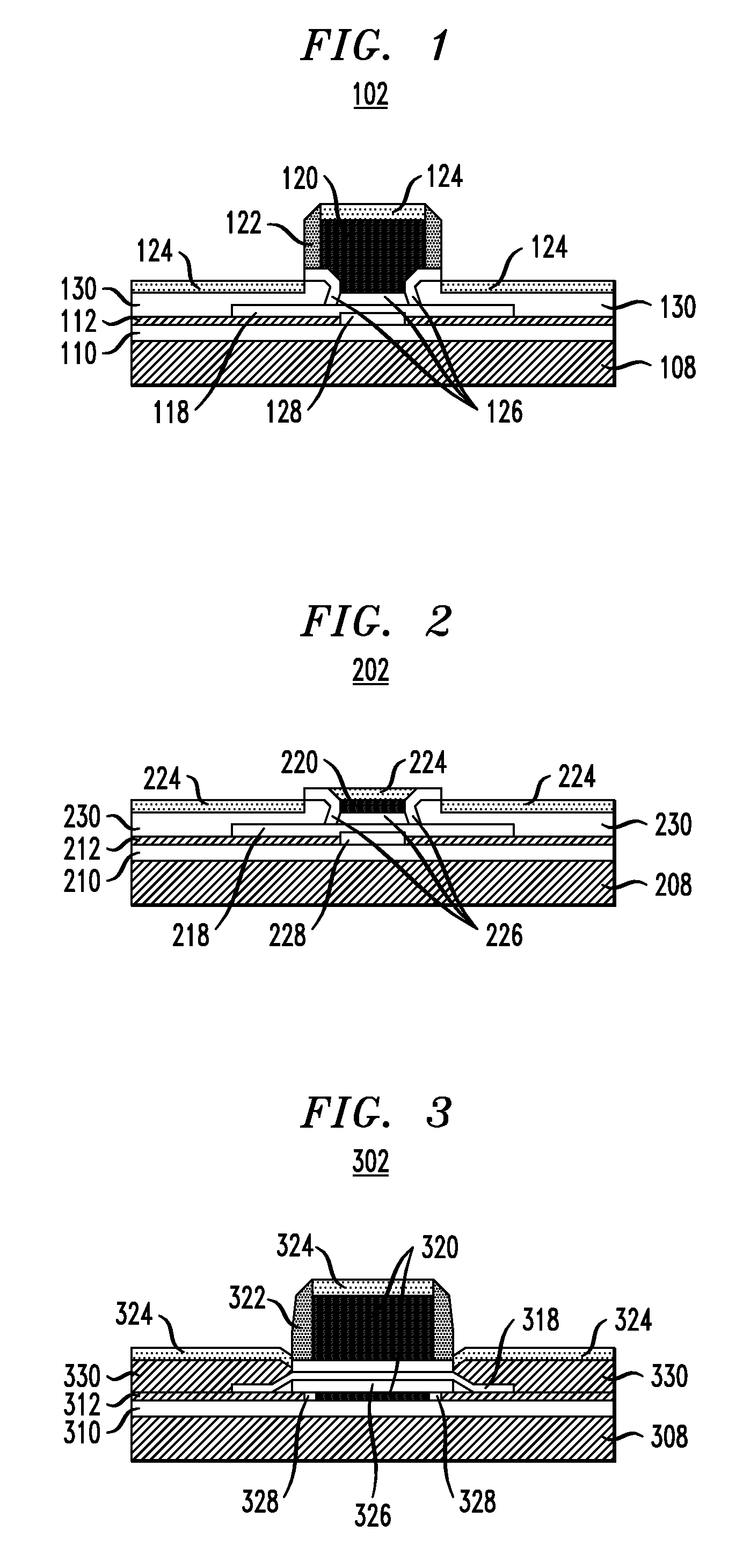

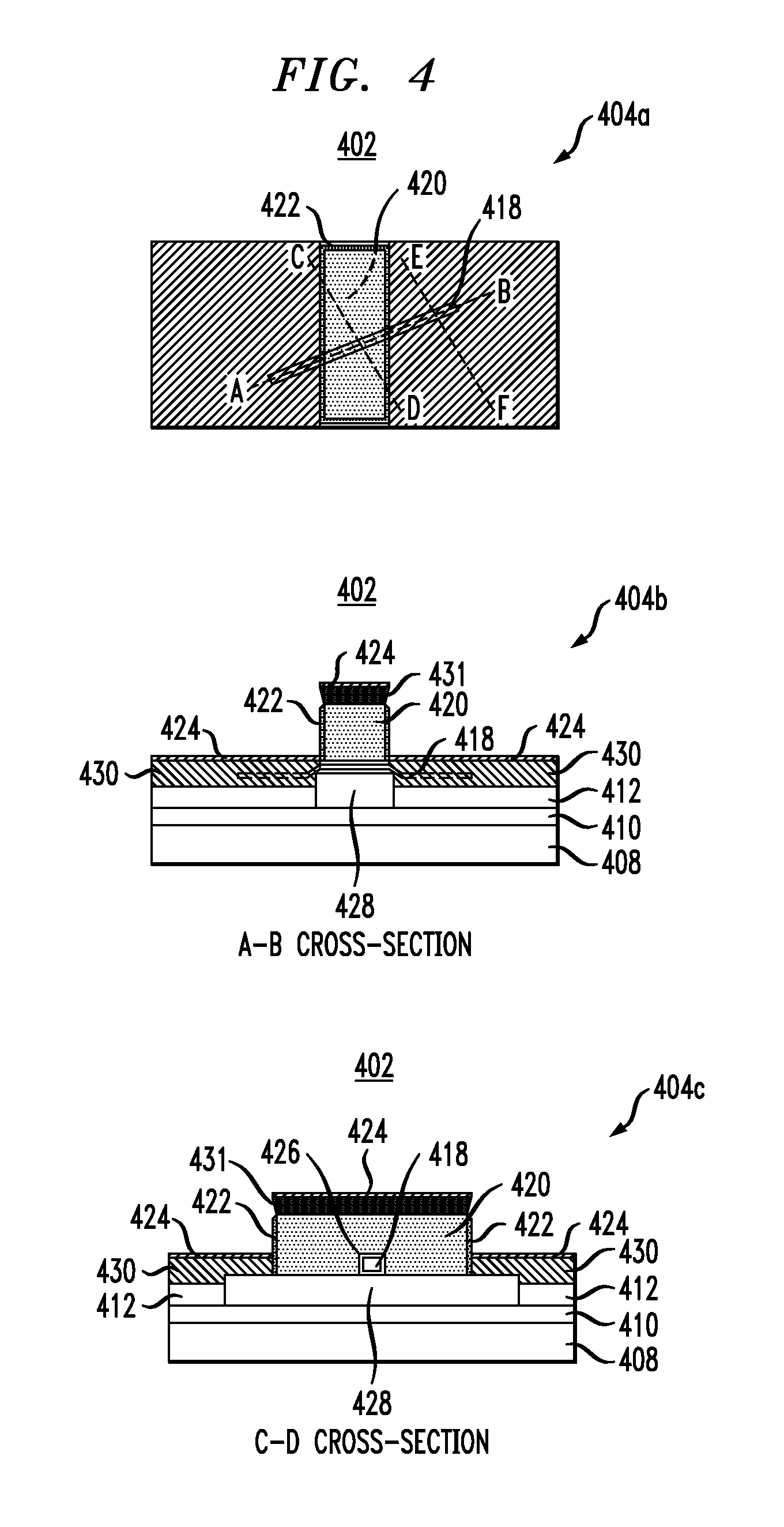

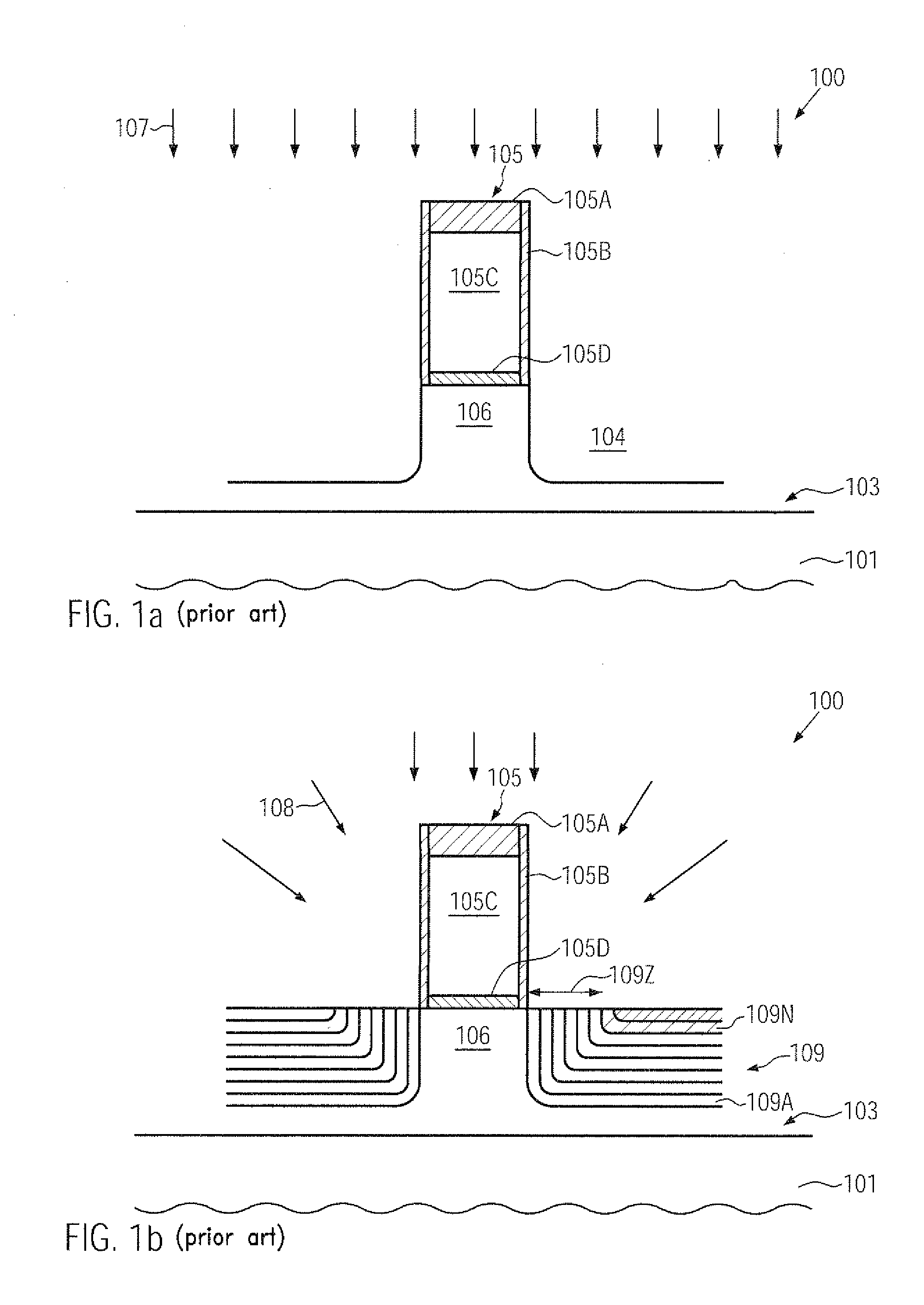

Techniques for Fabricating Nanowire Field-Effect Transistors

ActiveUS20090061568A1NanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

Techniques for the fabrication of field-effect transistors (FETs) having nanowire channels are provided. In one aspect, a method of fabricating a FET is provided comprising the following steps. A substrate is provided having a silicon-on-insulator (SOI) layer. At least one nanowire is deposited over the SOI layer. A sacrificial gate is formed over the SOI layer so as to cover a portion of the nanowire that forms a channel region. An epitaxial semiconductor material is selectively grown from the SOI layer that covers the nanowire and attaches the nanowire to the SOI layer in a source region and in a drain region. The sacrificial gate is removed. An oxide is formed that divides the SOI layer into at least two electrically isolated sections, one section included in the source region and the other section included in the drain region. A gate dielectric layer is formed over the channel region. A gate is formed over the channel region separated from the nanowire by the gate dielectric layer. A metal-semiconductor alloy is formed over the source and drain regions.

Owner:GLOBALFOUNDRIES US INC

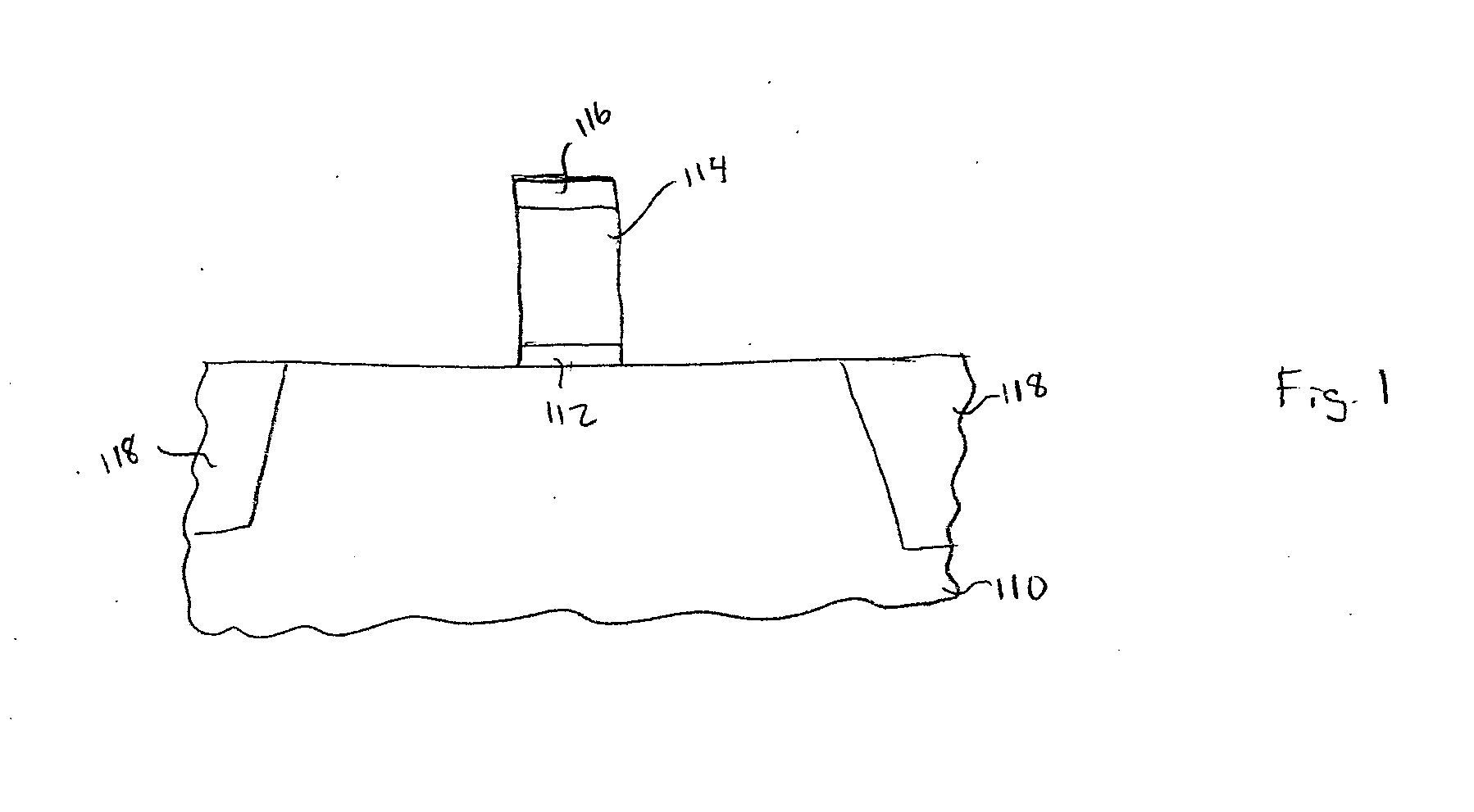

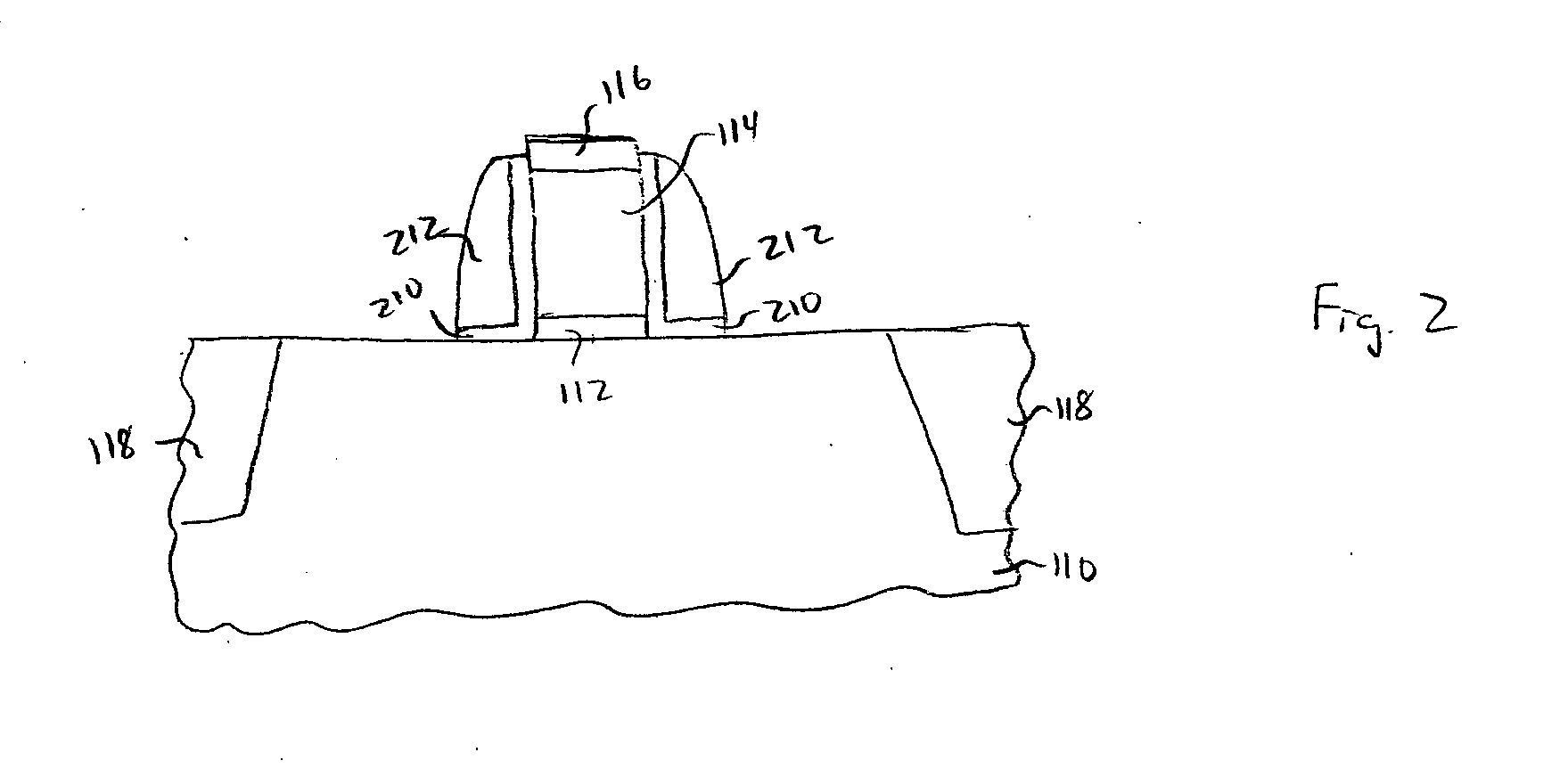

Structure and method for making strained channel field effect transistor using sacrificial spacer

A field effect transistor (“FET”) is provided which includes a gate stack overlying a single-crystal semiconductor region of a substrate, a pair of first spacers disposed over sidewalls of said gate stack, and a pair of regions consisting essentially of a single-crystal semiconductor alloy which are disposed on opposite sides of the gate stack. Each of the semiconductor alloy regions is spaced a first distance from the gate stack. The source region and drain region of the FET are at least partly disposed in respective ones of the semiconductor alloy regions, such that the source region and the drain region are each spaced a second distance from the gate stack by a first spacer of the pair of first spacers, the second distance being different from the first distance.

Owner:TOSHIBA ELECTRONICS DEVICES & STORAGE CORPORARTION +1

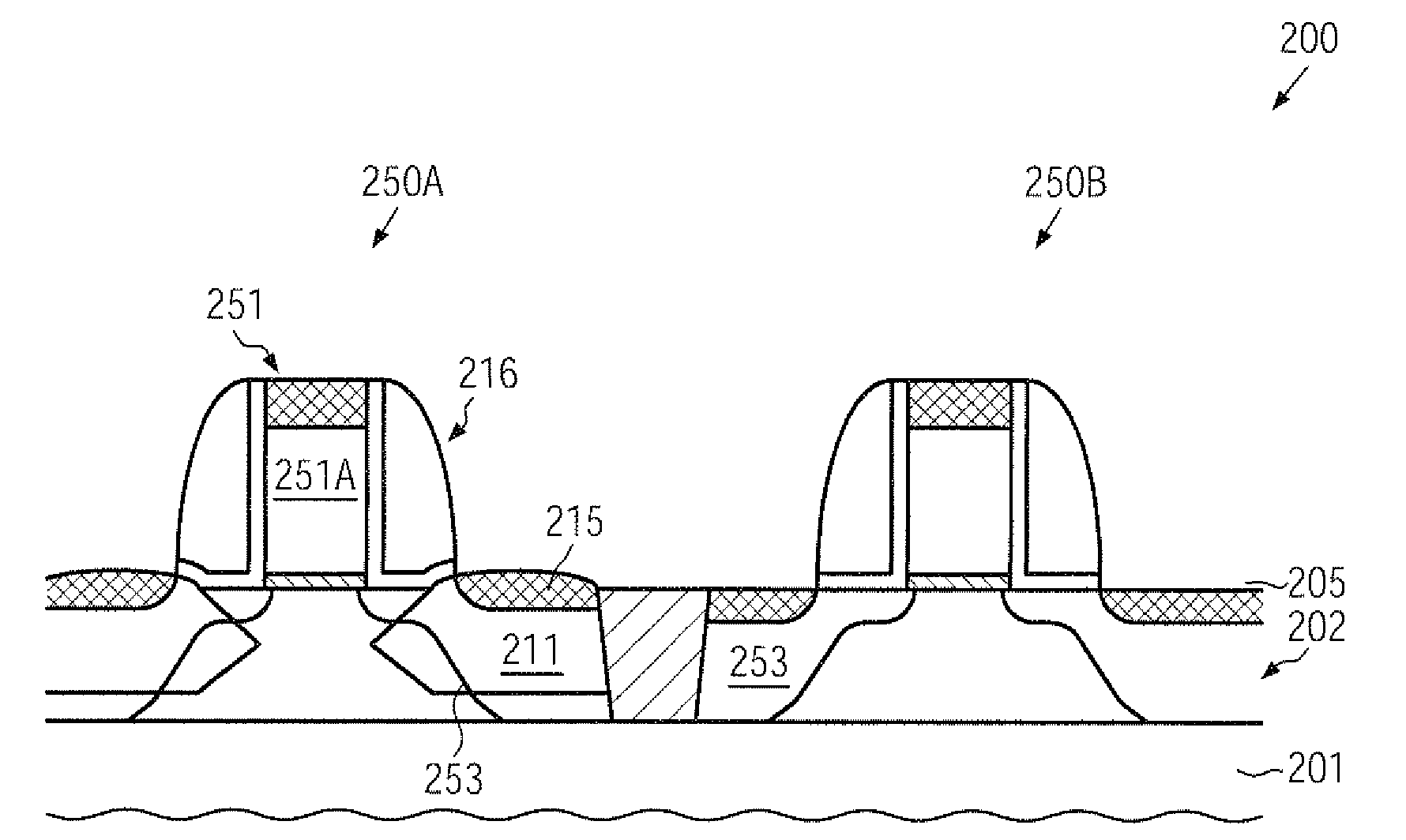

Performance enhancement in pmos and nmos transistors on the basis of silicon/carbon material

InactiveUS20100025771A1Improve production efficiencyImprove featuresTransistorSolid-state devicesTensile strainPerformance enhancement

A silicon / germanium material and a silicon / carbon material may be provided in transistors of different conductivity type on the basis of an appropriate manufacturing regime without unduly contributing to overall process complexity. Furthermore, appropriate implantation species may be provided through exposed surface areas of the cavities prior to forming the corresponding strained semiconductor alloy, thereby additionally contributing to enhanced overall transistor performance. In other embodiments a silicon / carbon material may be formed in a P-channel transistor and an N-channel transistor, while the corresponding tensile strain component may be overcompensated for by means of a stress memorization technique in the P-channel transistor. Thus, the advantageous effects of the carbon species, such as enhancing overall dopant profile of P-channel transistors, may be combined with an efficient strain component while enhanced overall process uniformity may also be accomplished.

Owner:ADVANCED MICRO DEVICES INC

Diffusion layer for semiconductor devices

ActiveUS20070190731A1Improve equipment reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor alloysAlloy

A diffusion layer for semiconductor devices is provided. In accordance with embodiments of the present invention, a semiconductor device, such as a transistor, comprises doped regions surrounded by a diffusion barrier. The diffusion barrier may be formed by recessing regions of the substrate and implanting fluorine or carbon ions. A silicon layer may be epitaxially grown over the diffusion barrier in the recessed regions. Thereafter, the recessed regions may be filled and doped with a semiconductor or semiconductor alloy material. In an embodiment, a semiconductor alloy material, such as silicon carbon, is selected to induce a tensile stress in the channel region for an NMOS device, and a semiconductor alloy material, such as silicon germanium, is selected to induce a compressive stress in the channel region for a PMOS device.

Owner:TAIWAN SEMICON MFG CO LTD

Multi-nary group ib and via based semiconductor

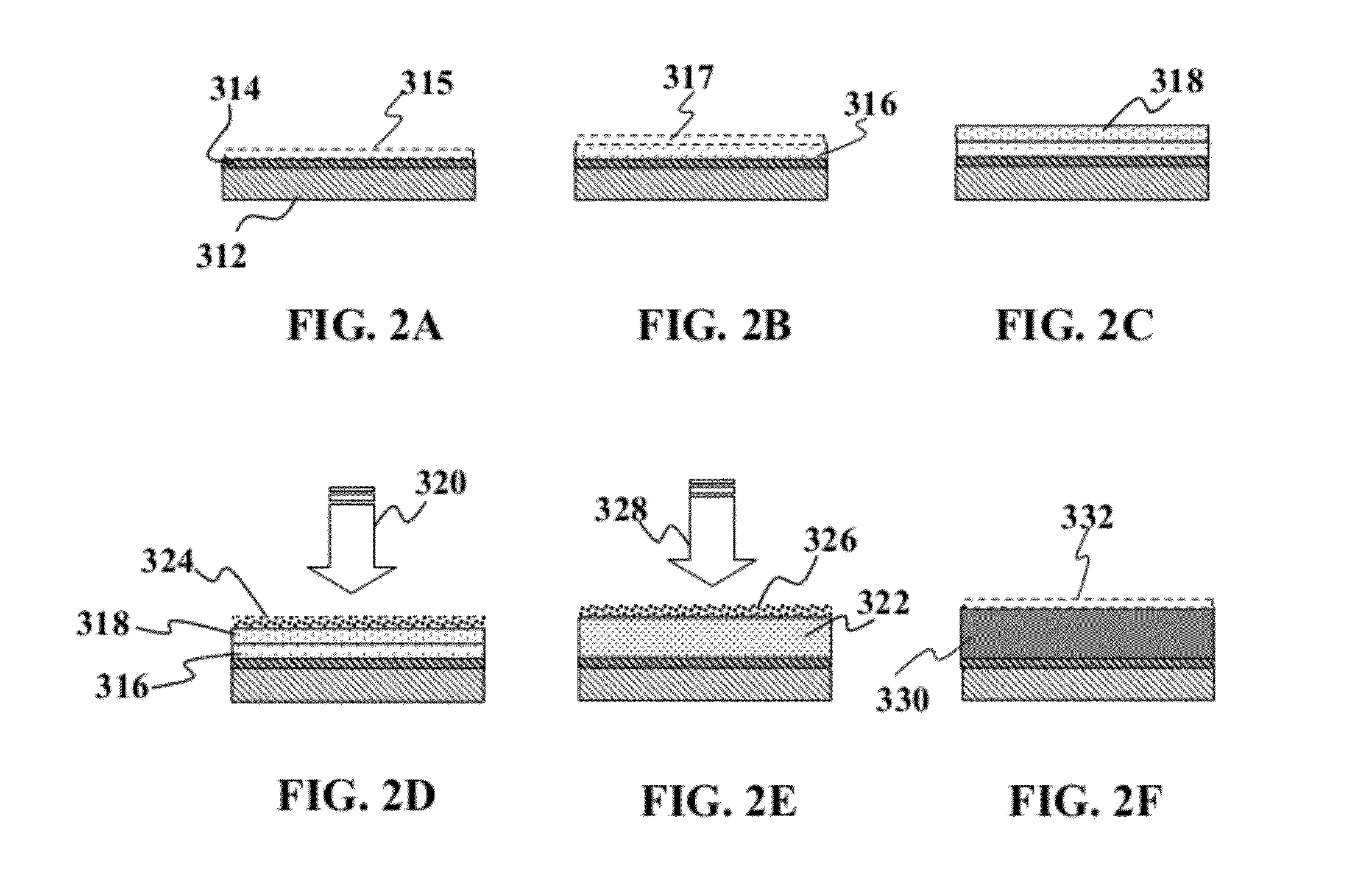

InactiveUS20120313200A1Increase the open circuit voltageLow costSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor alloysSulfur

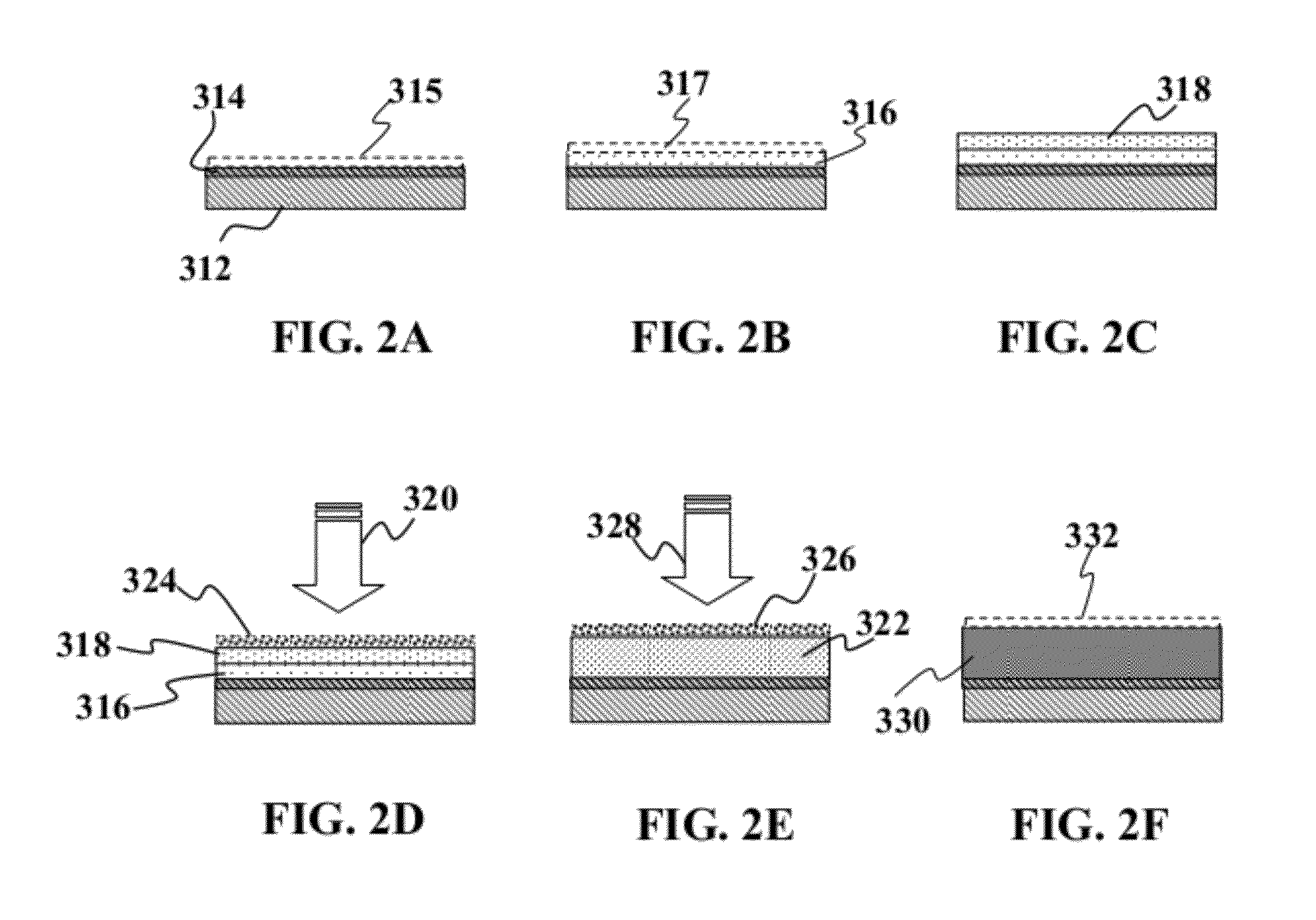

Methods and devices are provided for forming multi-nary semiconductor. In one embodiment, a method is provided comprising of depositing a precursor material onto a substrate, wherein the precursor material may include or may be used with an additive to minimize concentration of group IIIA material such as Ga in the back portion of the final semiconductor layer. The additive may be a non-copper Group IB additive in elemental or alloy form. Some embodiments may use both selenium and sulfur, forming a senary or higher semiconductor alloy. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:AERIS CAPITAL SUSTAINABLE IP

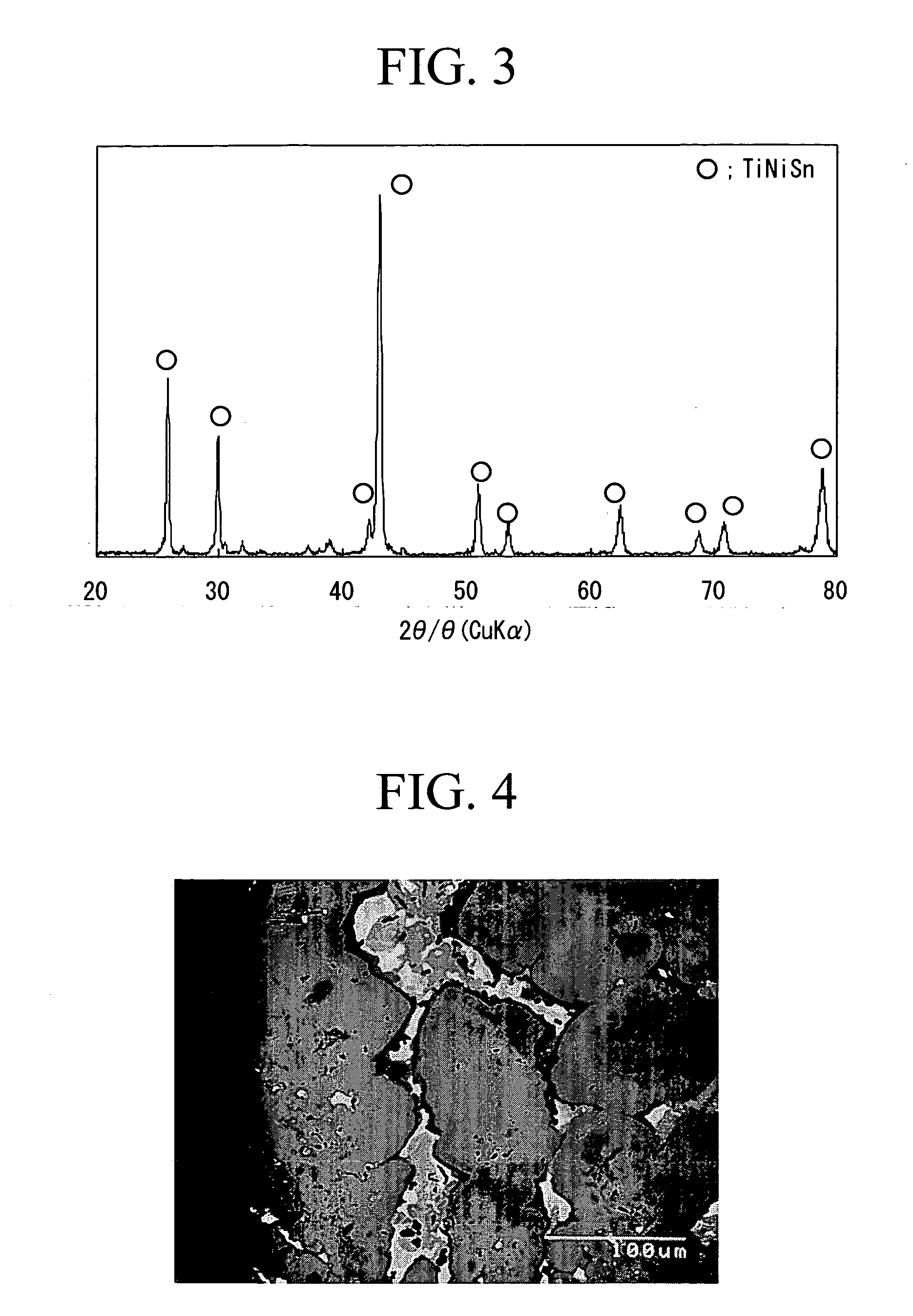

Production Method of Thermoelectric Semiconductor Alloy, Thermoelectric Conversion Module and Thermoelectric Power Generating Device

InactiveUS20080092940A1Improve performanceLow costThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentSemiconductor alloysThermoelectric conversion

The present invention provides a method for producing a half Heuslar alloy including quench-solidifying a molten alloy at a cooling rate of 1×102 to 1×103° C. / sec to produce a Heuslar alloy represented by the formula: ABC (wherein A and B each is at least one member selected from transition metals such as Fe, Co, Ni, Ti, V, Cr, Zr, Hf, Nb, Mo, Ta and W, and C is at least one member selected from Group 13 or 14 element such as Al, Ga, In, Si, Ge and Sn), and a high-performance thermoelectric power generating device using the thermoelectric semiconductor alloy.

Owner:SHOWA DENKO KK

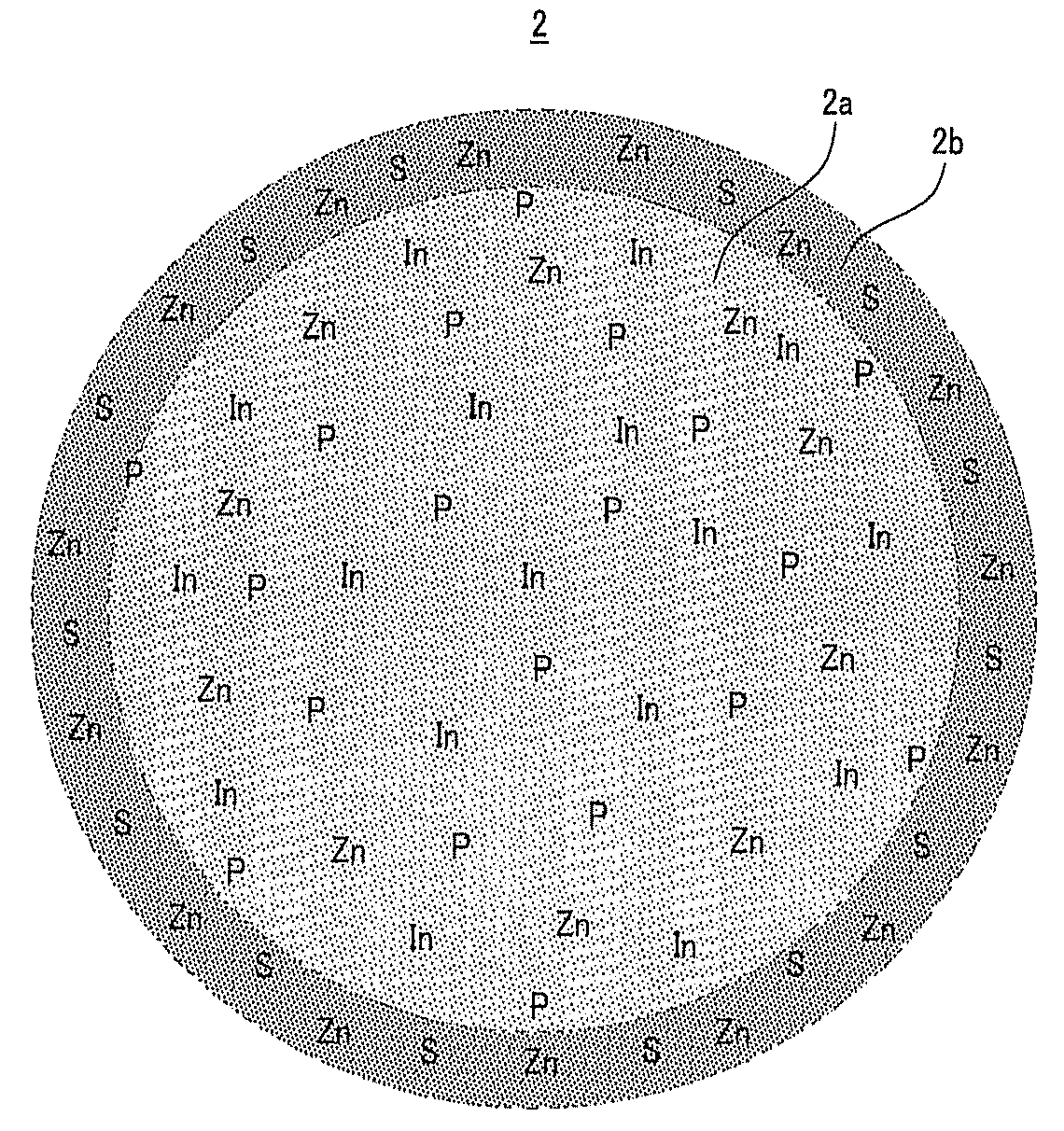

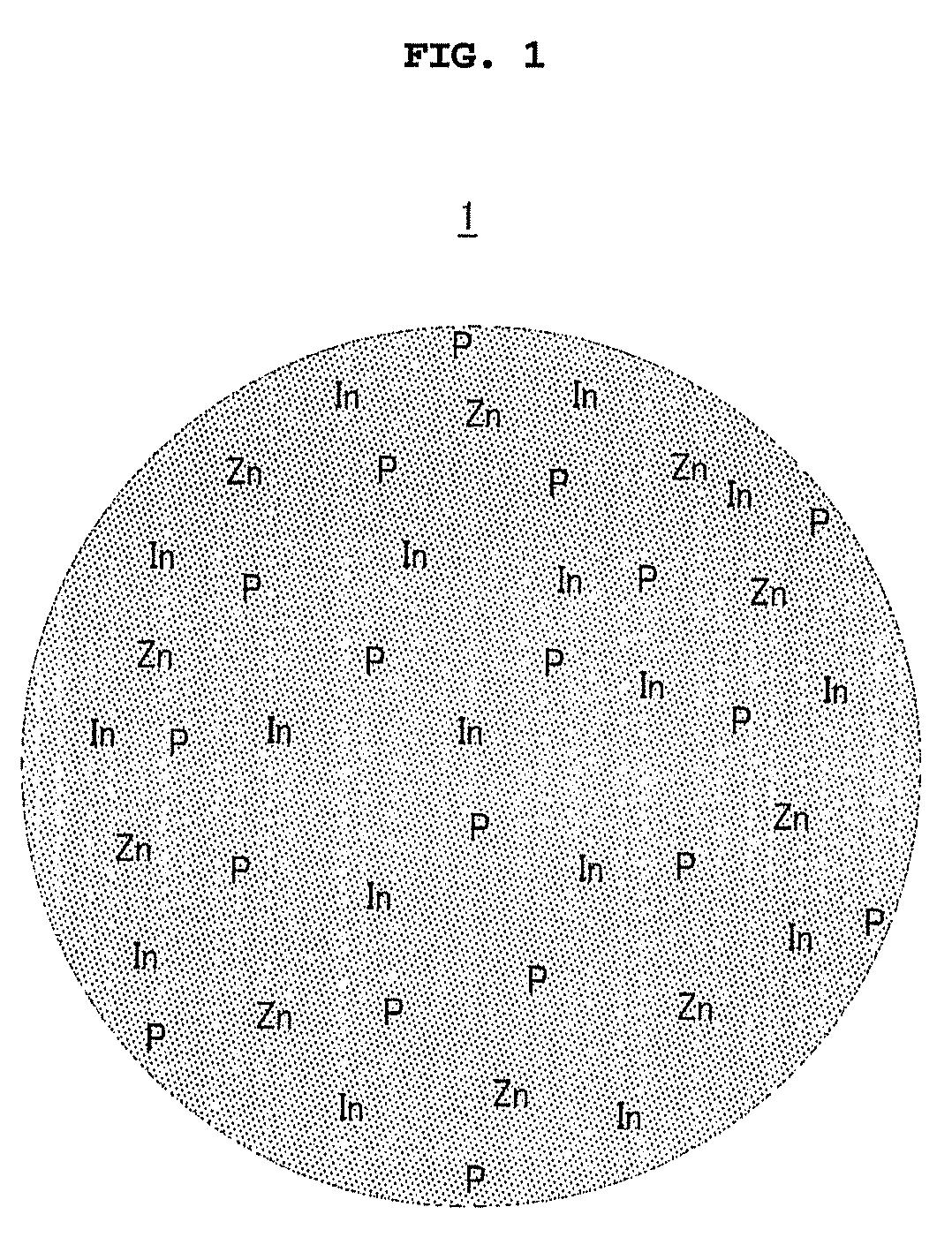

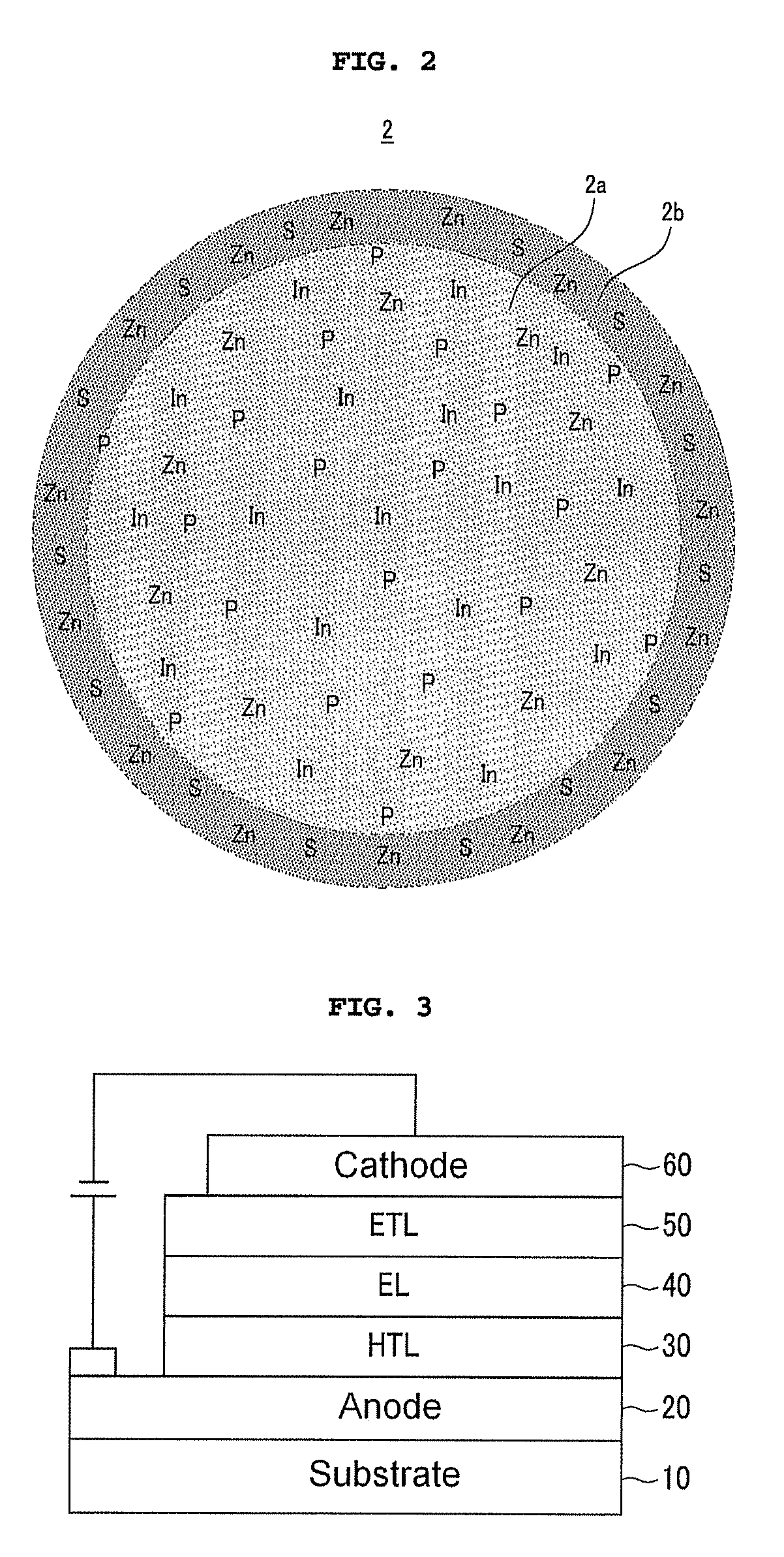

Semiconductor nanocrystals and preparation methods thereof

A nanocrystal includes a core including a Group III-V semiconductor and a transition metal alloyed with the Group III-V semiconductor, wherein the transition metal is present at a higher molar concentration in an outermost surface layer of the core than in a central portion of the core.

Owner:SAMSUNG ELECTRONICS CO LTD

Techniques for fabricating nanowire field-effect transistors

ActiveUS7534675B2NanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

Techniques for the fabrication of field-effect transistors (FETs) having nanowire channels are provided. In one aspect, a method of fabricating a FET is provided comprising the following steps. A substrate is provided having a silicon-on-insulator (SOI) layer. At least one nanowire is deposited over the SOI layer. A sacrificial gate is formed over the SOI layer so as to cover a portion of the nanowire that forms a channel region. An epitaxial semiconductor material is selectively grown from the SOI layer that covers the nanowire and attaches the nanowire to the SOI layer in a source region and in a drain region. The sacrificial gate is removed. An oxide is formed that divides the SOI layer into at least two electrically isolated sections, one section included in the source region and the other section included in the drain region. A gate dielectric layer is formed over the channel region. A gate is formed over the channel region separated from the nanowire by the gate dielectric layer. A metal-semiconductor alloy is formed over the source and drain regions.

Owner:GLOBALFOUNDRIES U S INC

Structure and method for making strained channel field effect transistor using sacrificial spacer

Owner:TOSHIBA ELECTRONICS DEVICES & STORAGE CORPORARTION +1

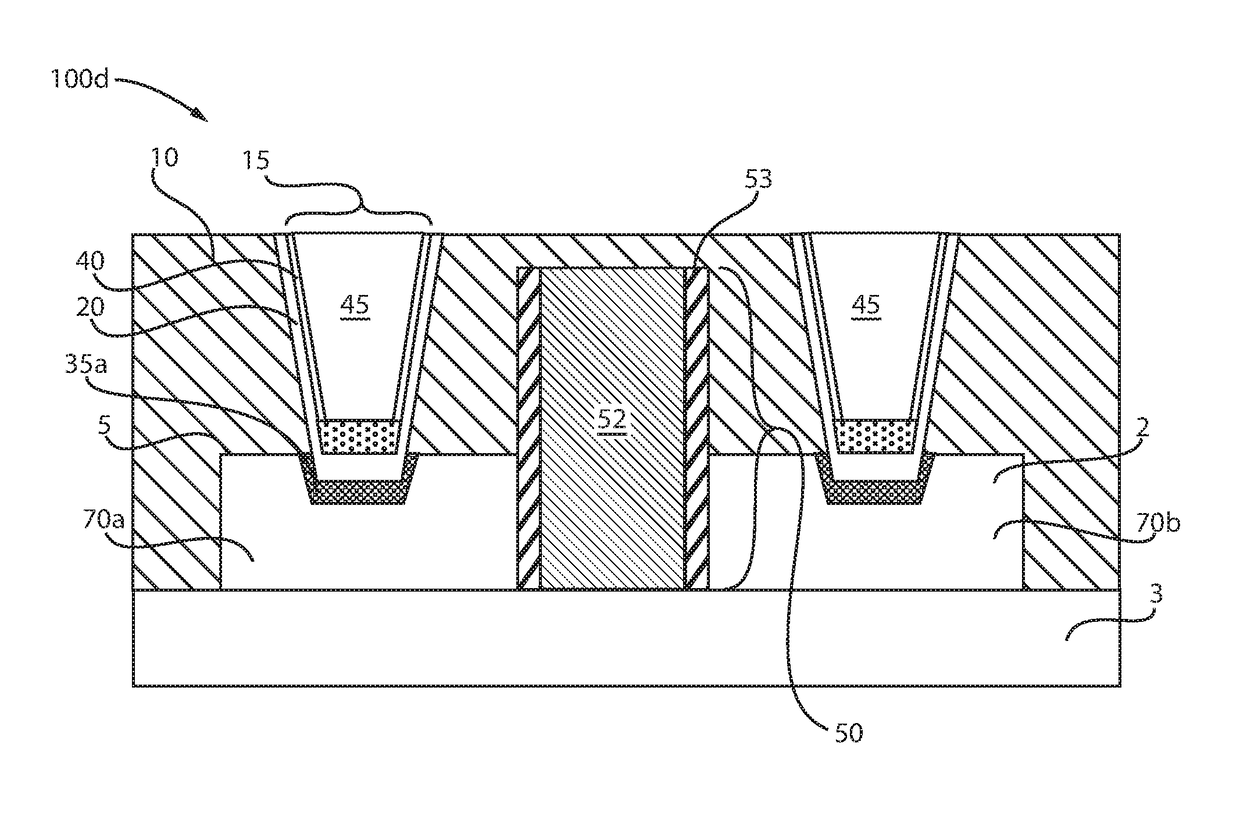

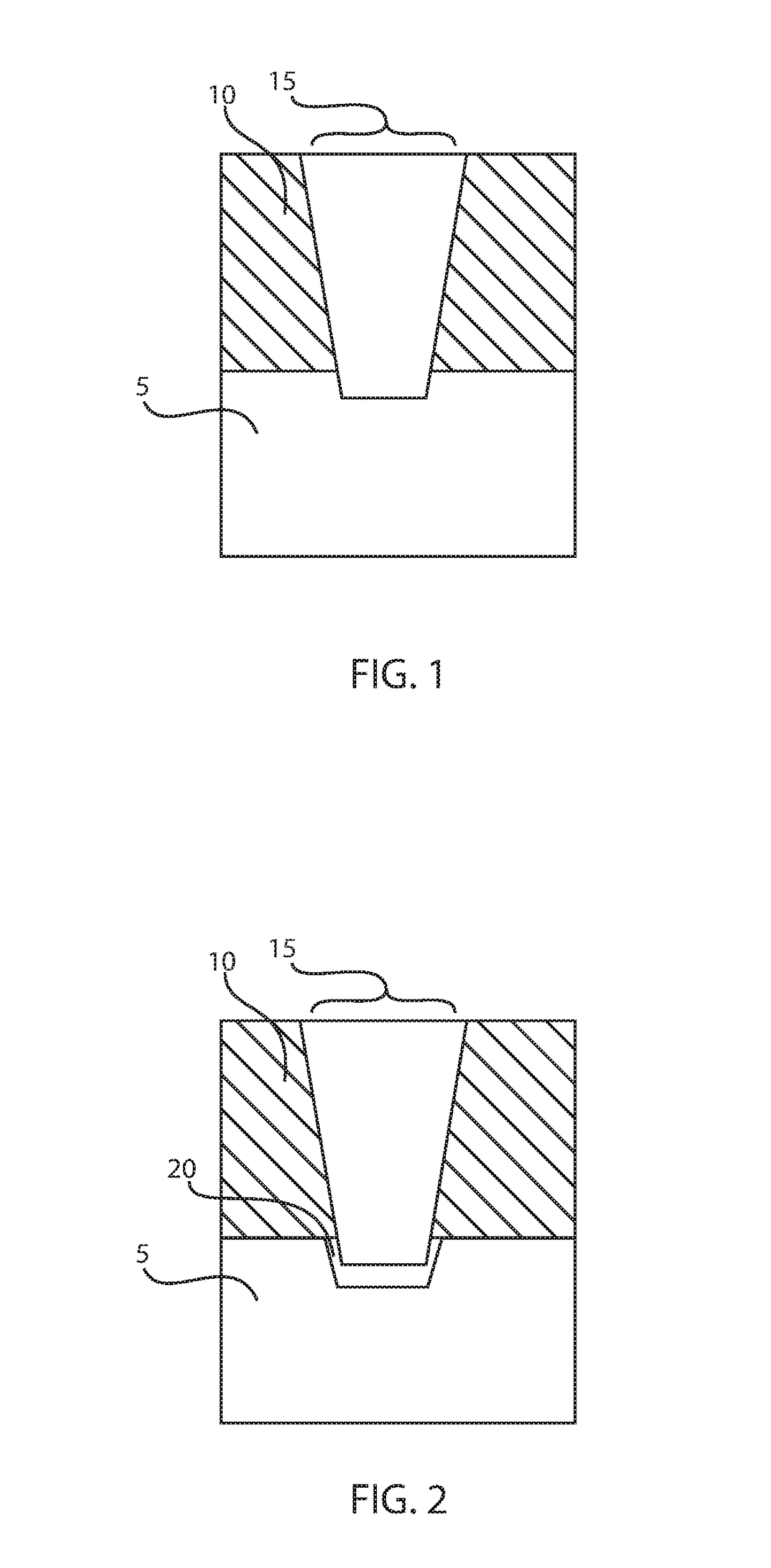

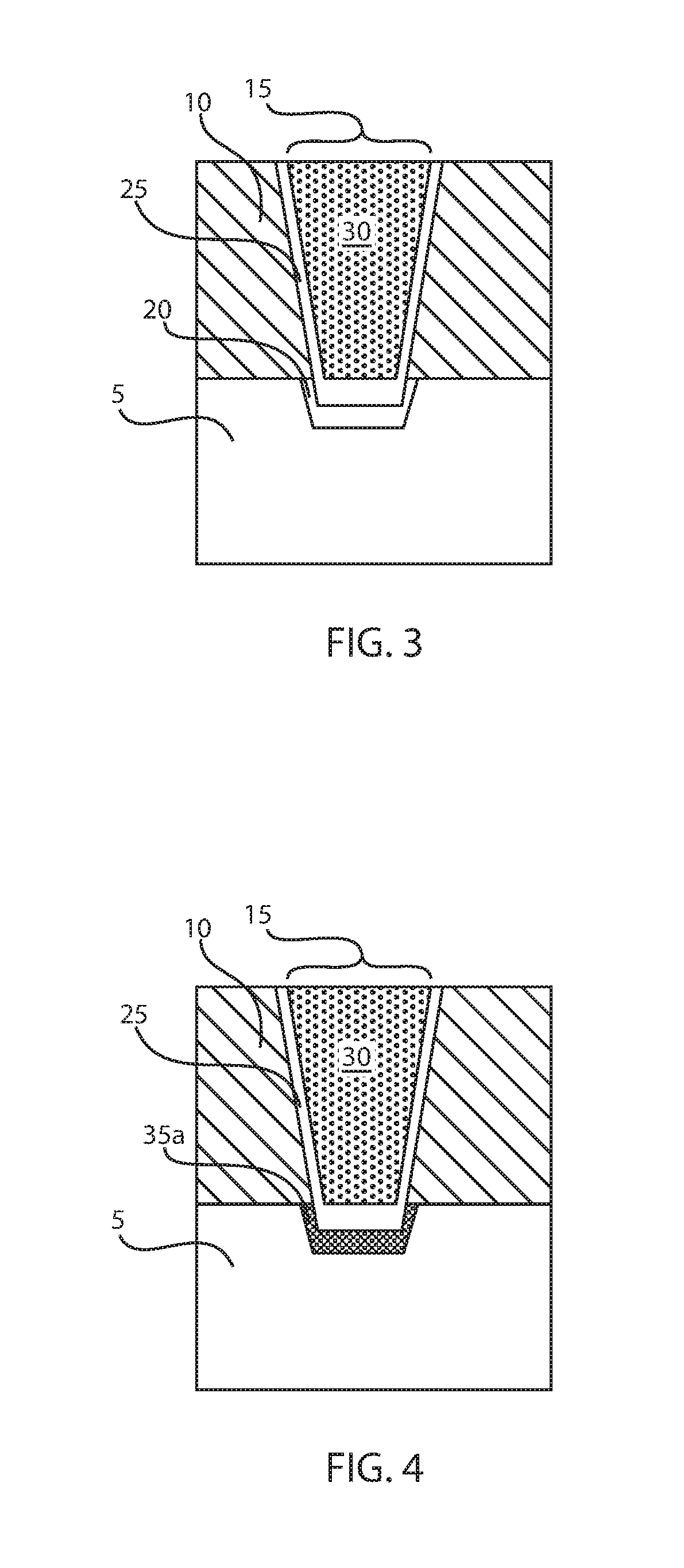

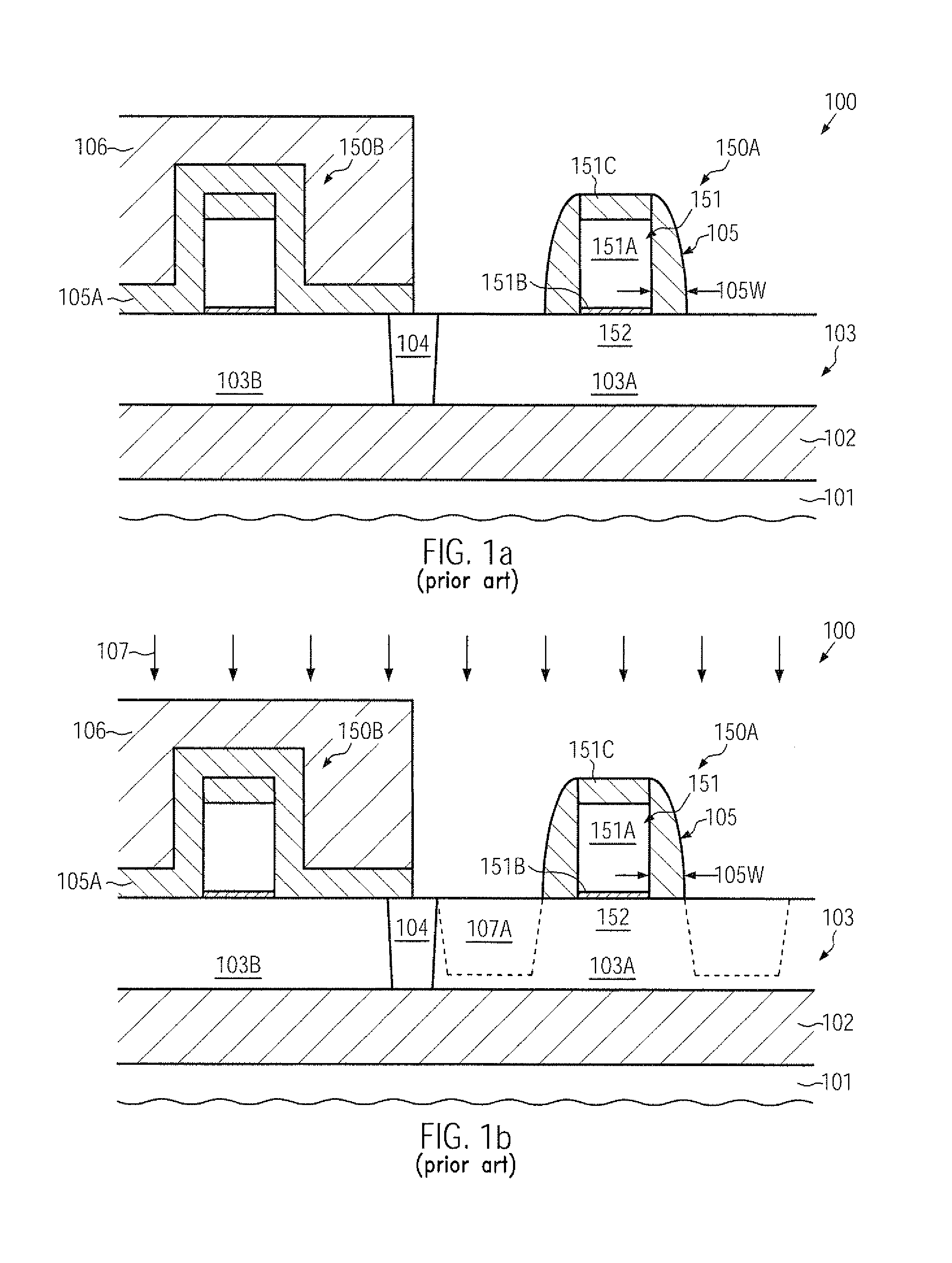

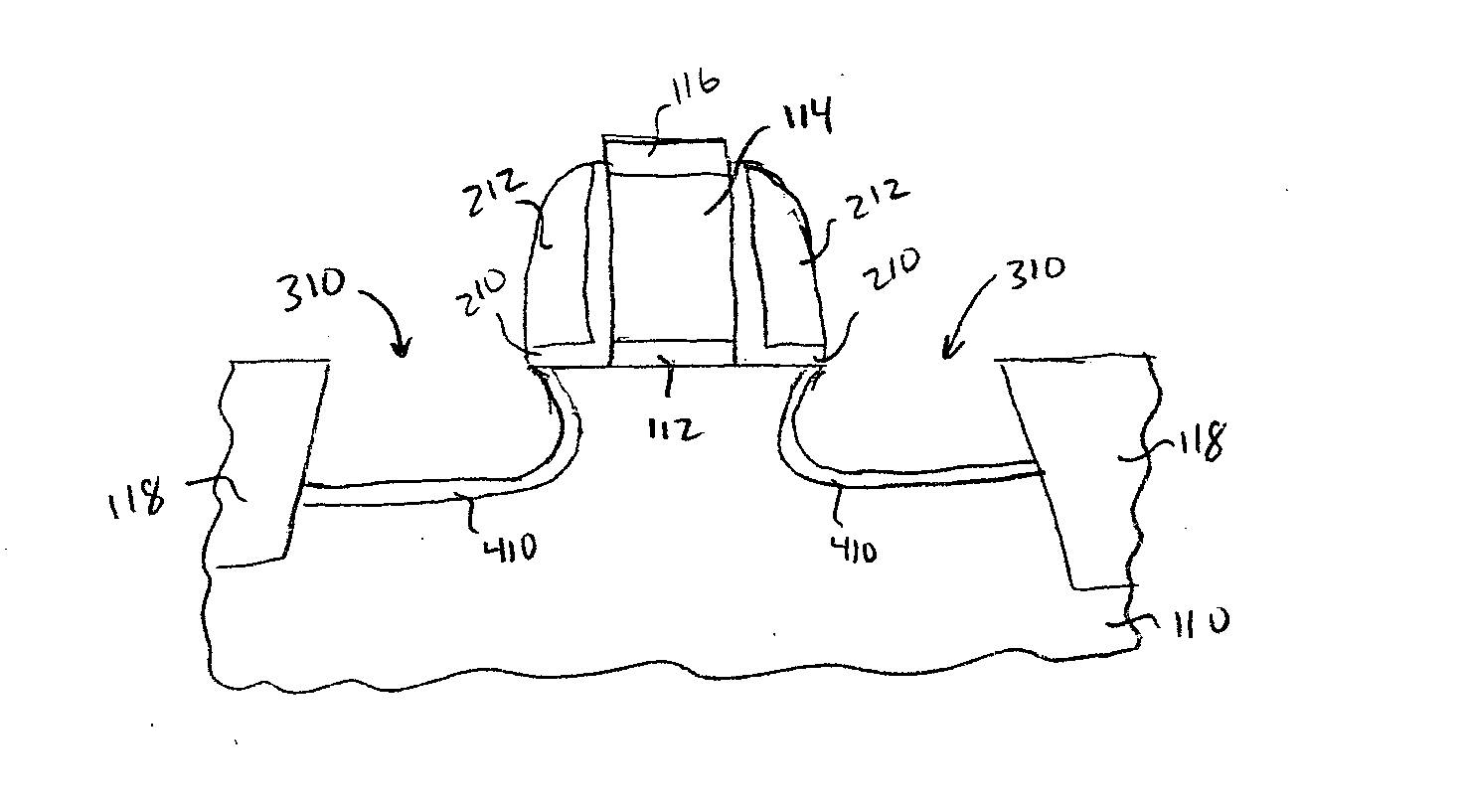

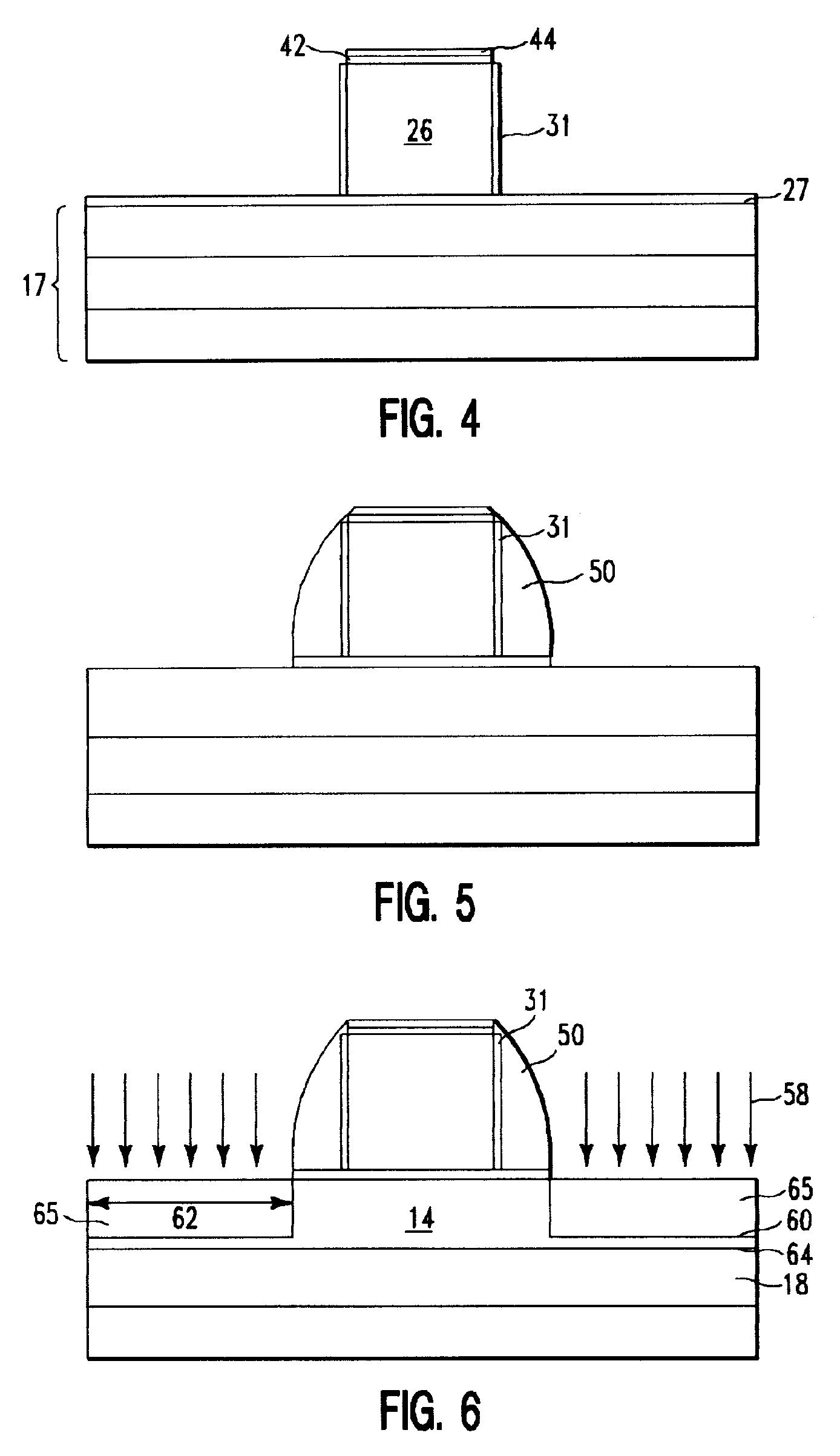

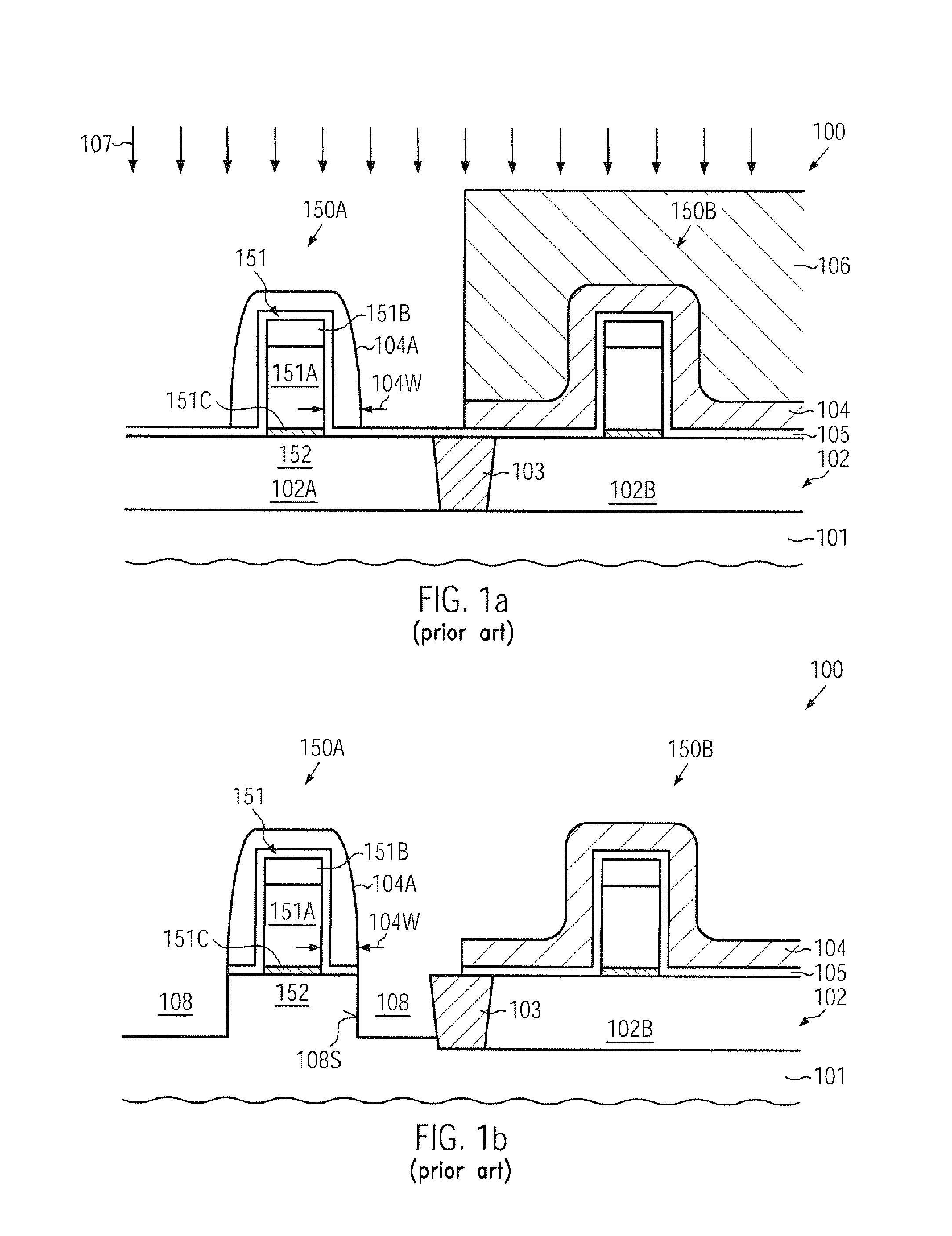

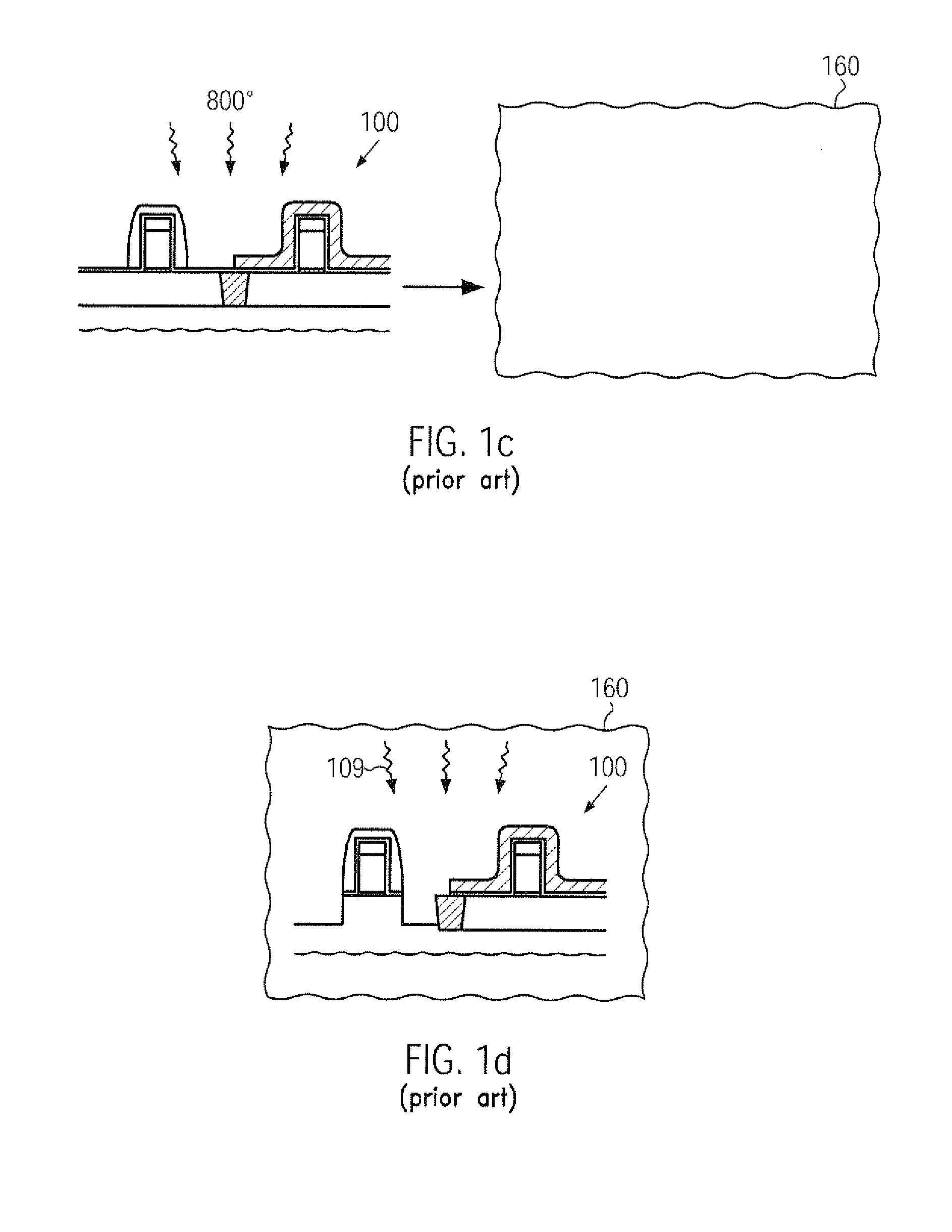

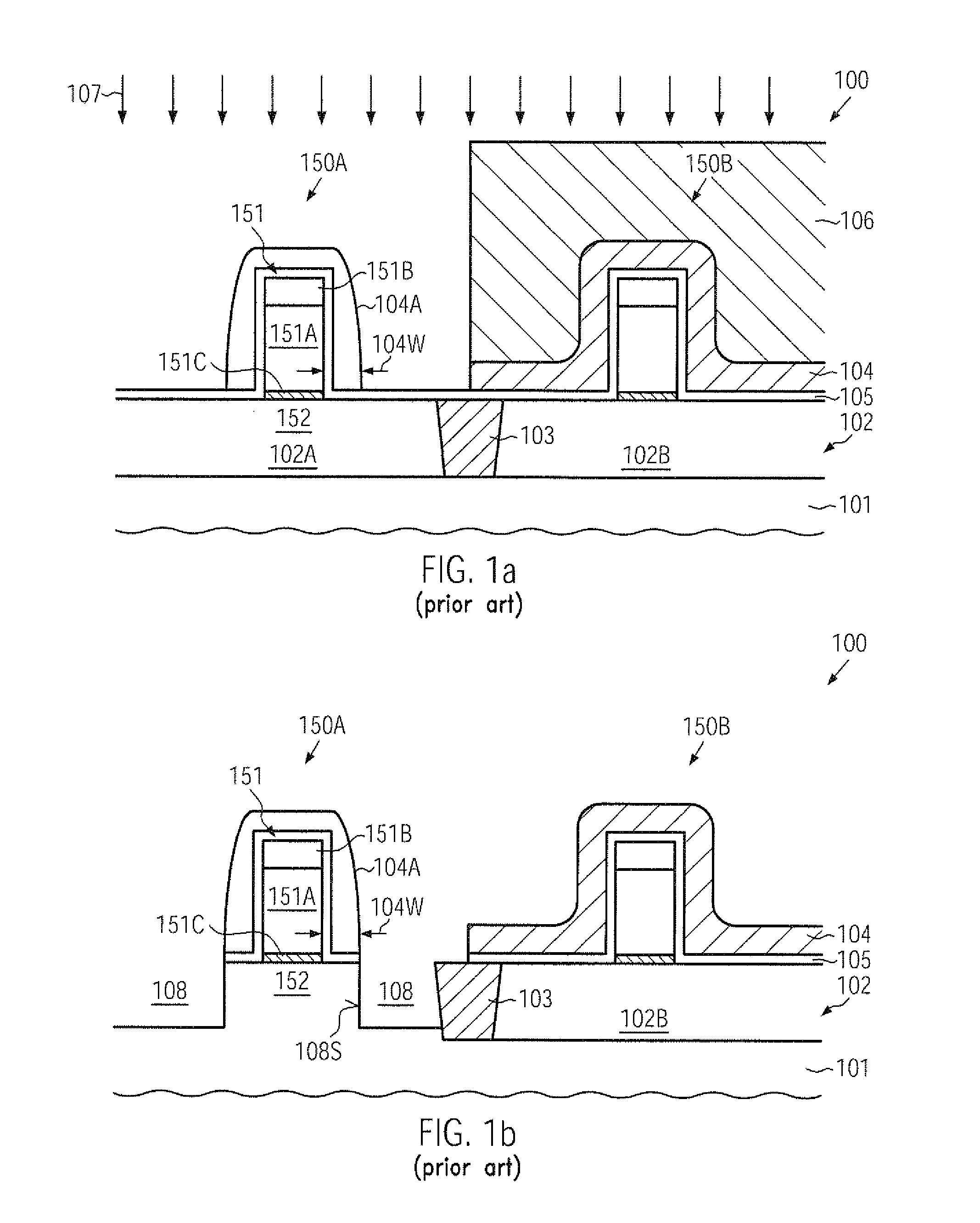

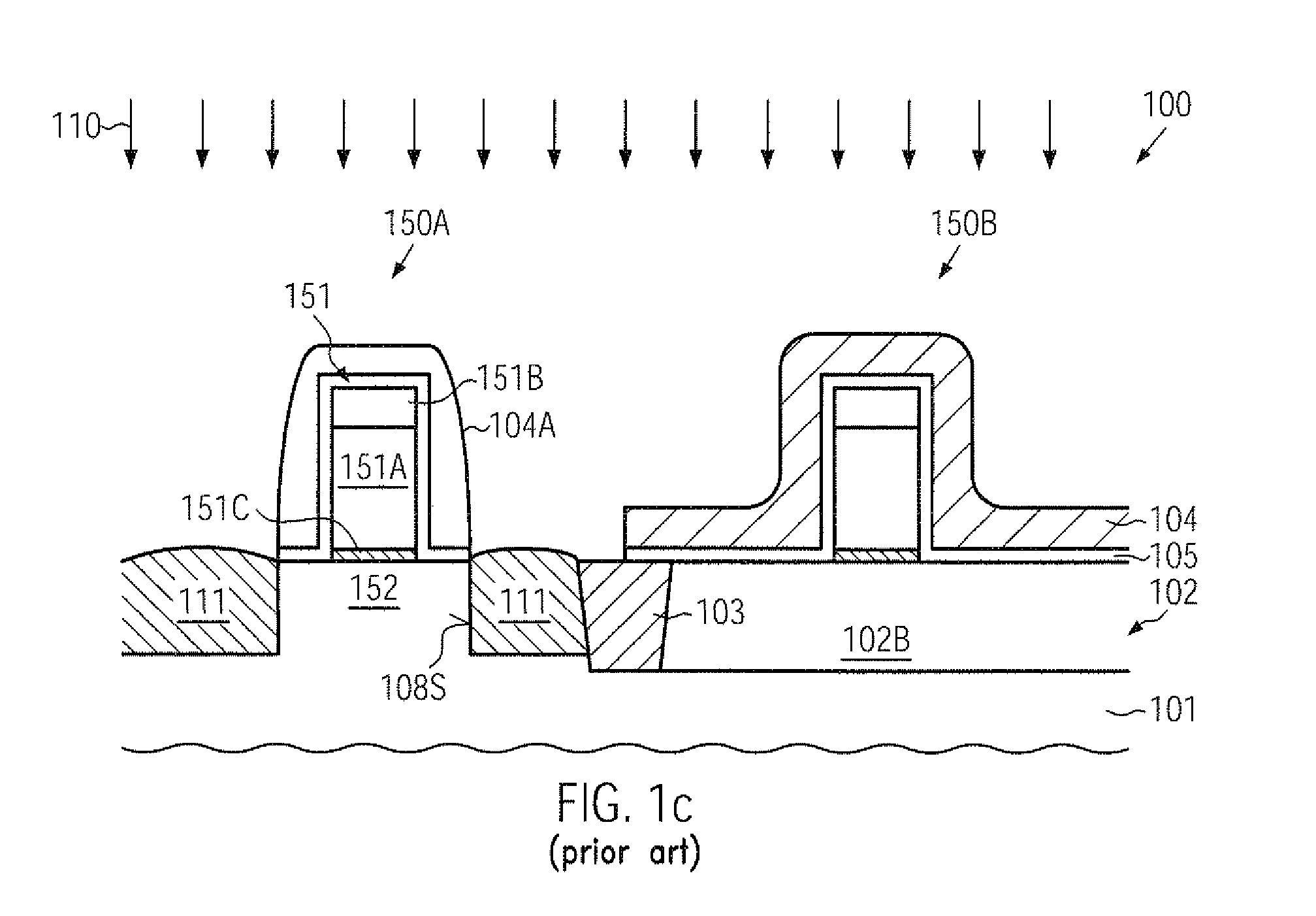

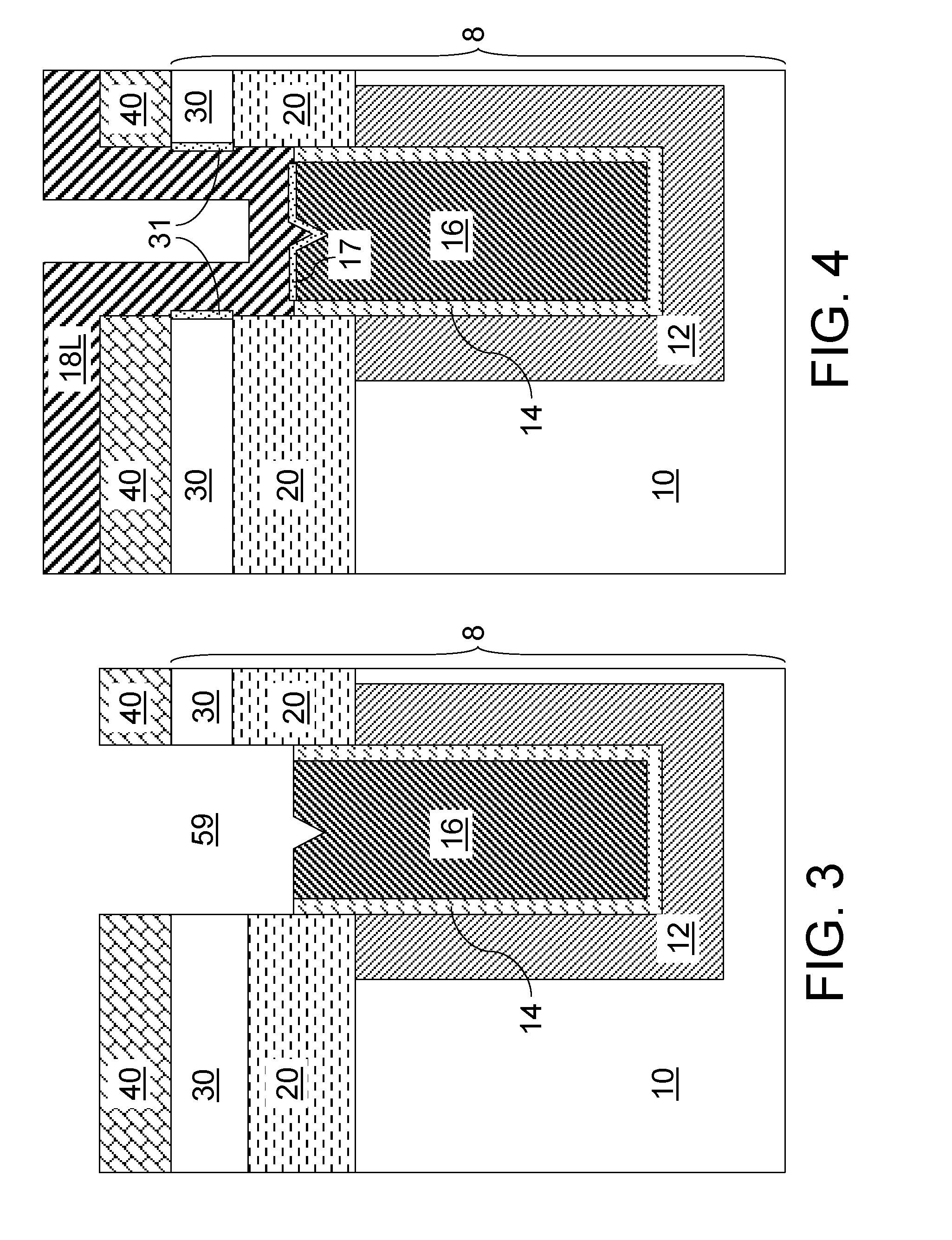

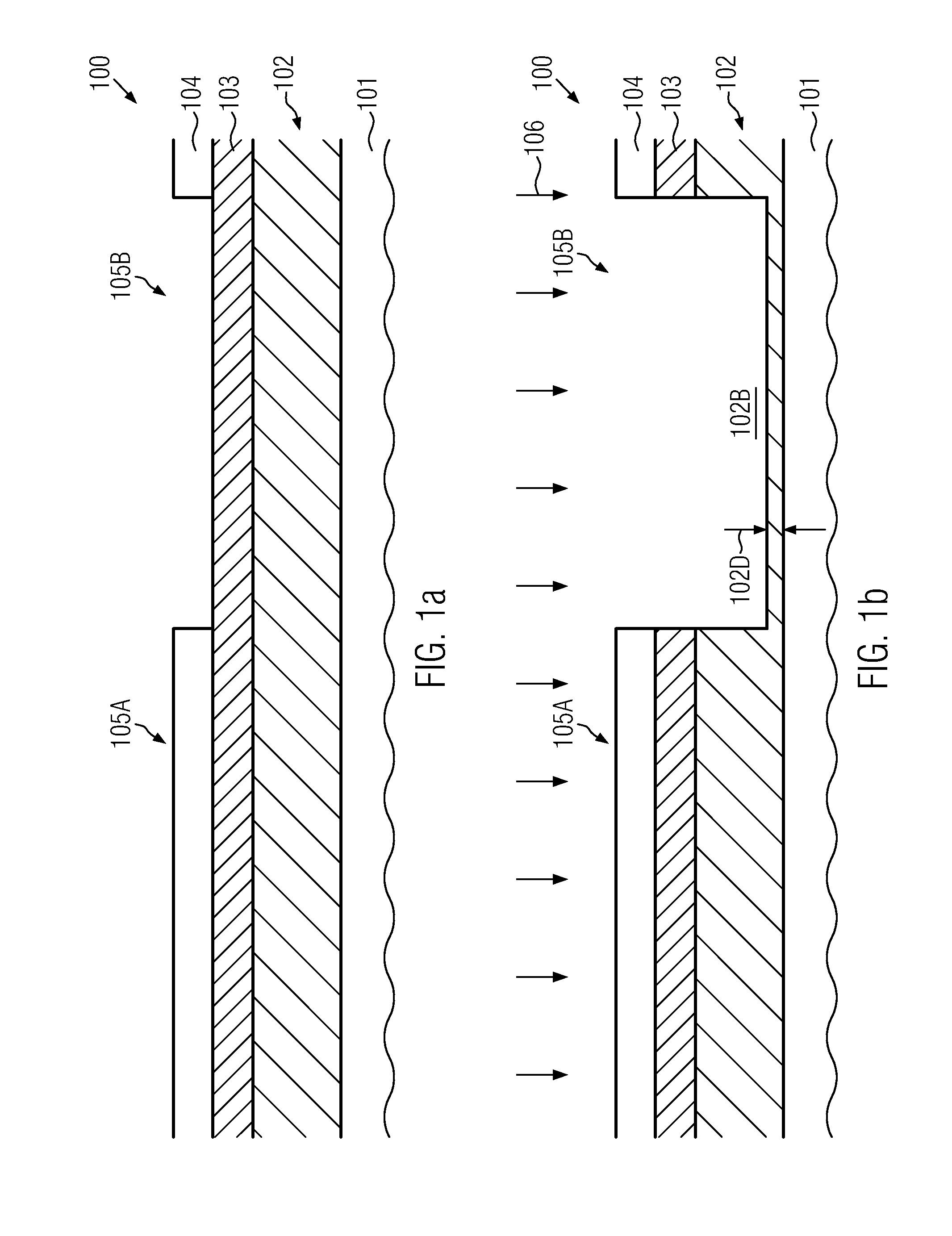

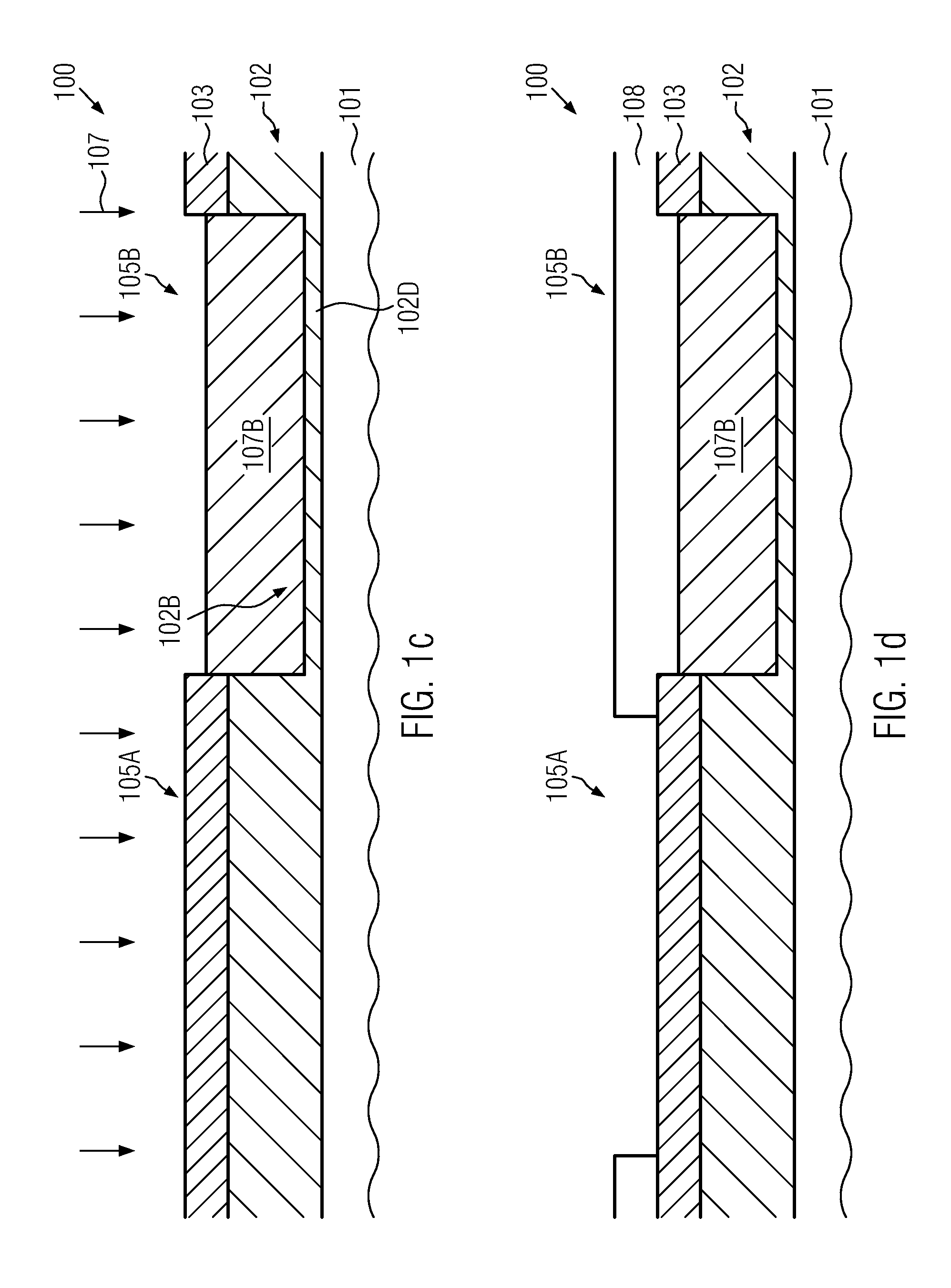

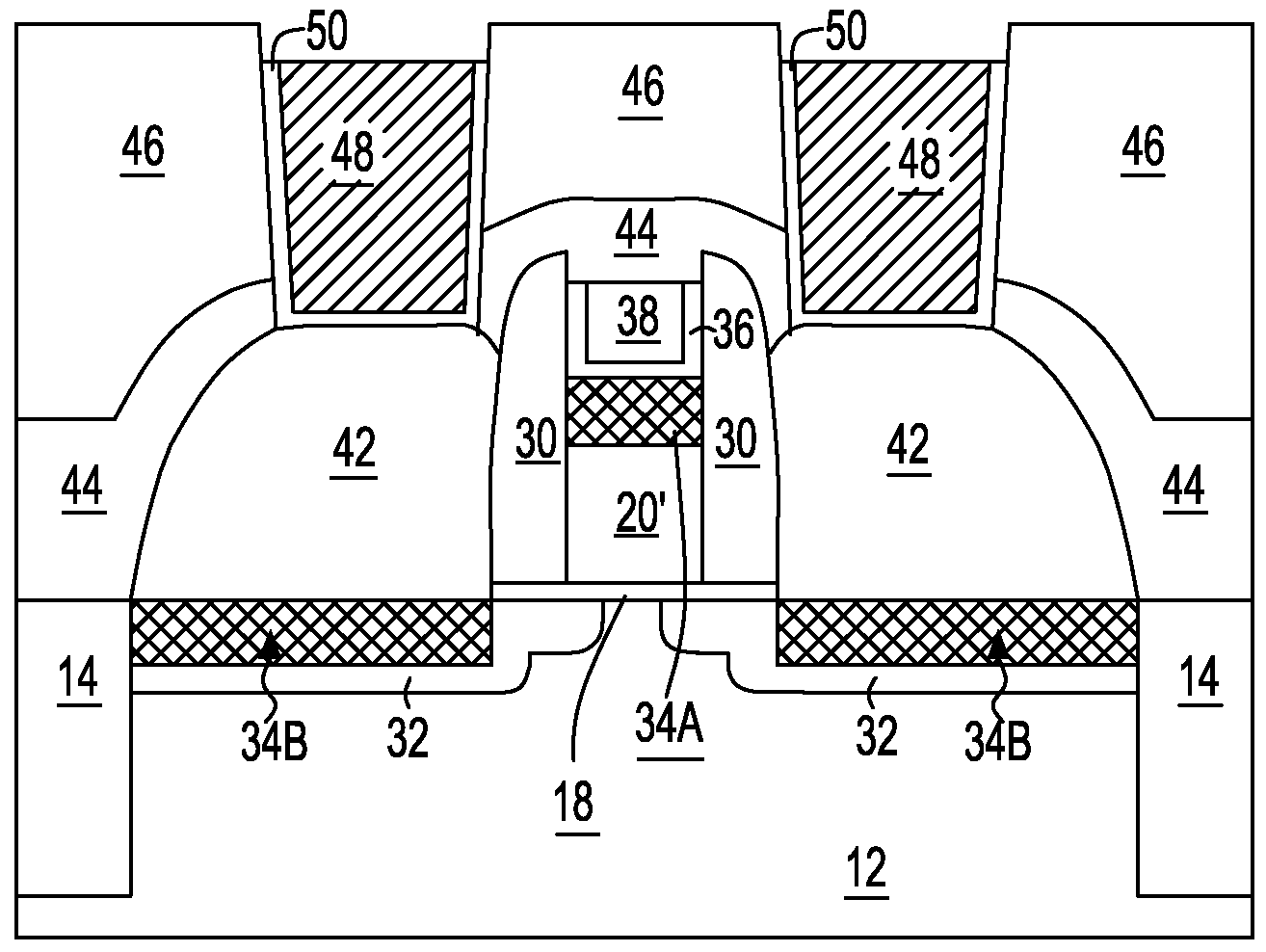

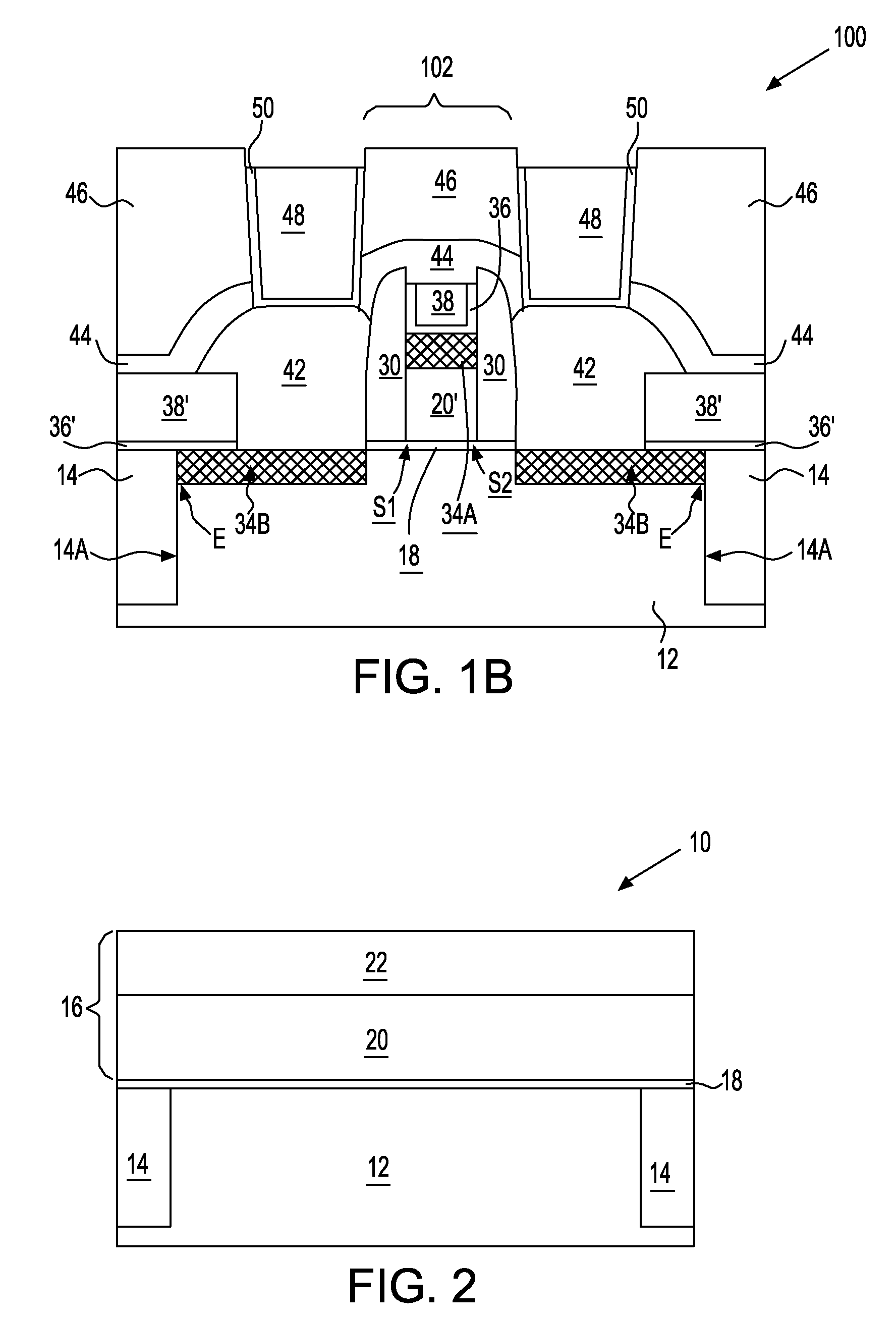

Transistor with embedded si/ge material having reduced offset to the channel region

ActiveUS20100078689A1Prevent backflowIncrease flexibilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemiconductor alloys

A strain-inducing semiconductor alloy may be formed on the basis of cavities which may have a non-rectangular shape, which may be maintained even during corresponding high temperature treatments by providing an appropriate protection layer, such as a silicon dioxide material. Consequently, a lateral offset of the strain-inducing semiconductor material may be reduced, while nevertheless providing a sufficient thickness of corresponding offset spacers during the cavity etch process, thereby preserving gate electrode integrity. For instance, P-channel transistors may have a silicon / germanium alloy with a hexagonal shape, thereby significantly enhancing the overall strain transfer efficiency.

Owner:ADVANCED MICRO DEVICES INC

Adjusting of a non-silicon fraction in a semiconductor alloy during transistor fabrication by an intermediate oxidation process

ActiveUS20100221883A1High degree of process uniformitySpeed up the processTransistorSemiconductor/solid-state device manufacturingSemiconductor alloysAlloy

The concentration of a non-silicon species in a semiconductor alloy, such as a silicon / germanium alloy, may be increased after a selective epitaxial growth process by oxidizing a portion of the semiconductor alloy and removing the oxidized portion. During the oxidation, preferably the silicon species may react to form a silicon dioxide material while the germanium species may be driven into the remaining semiconductor alloy, thereby increasing the concentration thereof. Consequently, the threshold adjustment of sophisticated transistors may be accomplished with enhanced process uniformity on the basis of a given parameter setting for the epitaxial growth process while nevertheless providing a high degree of flexibility in adjusting the composition of the threshold adjusting material. In other cases, in addition to or alternatively to forming a threshold adjusting semiconductor alloy, a strain-inducing semiconductor alloy may also be provided with enhanced flexibility using the above-described process sequence.

Owner:GLOBALFOUNDRIES US INC

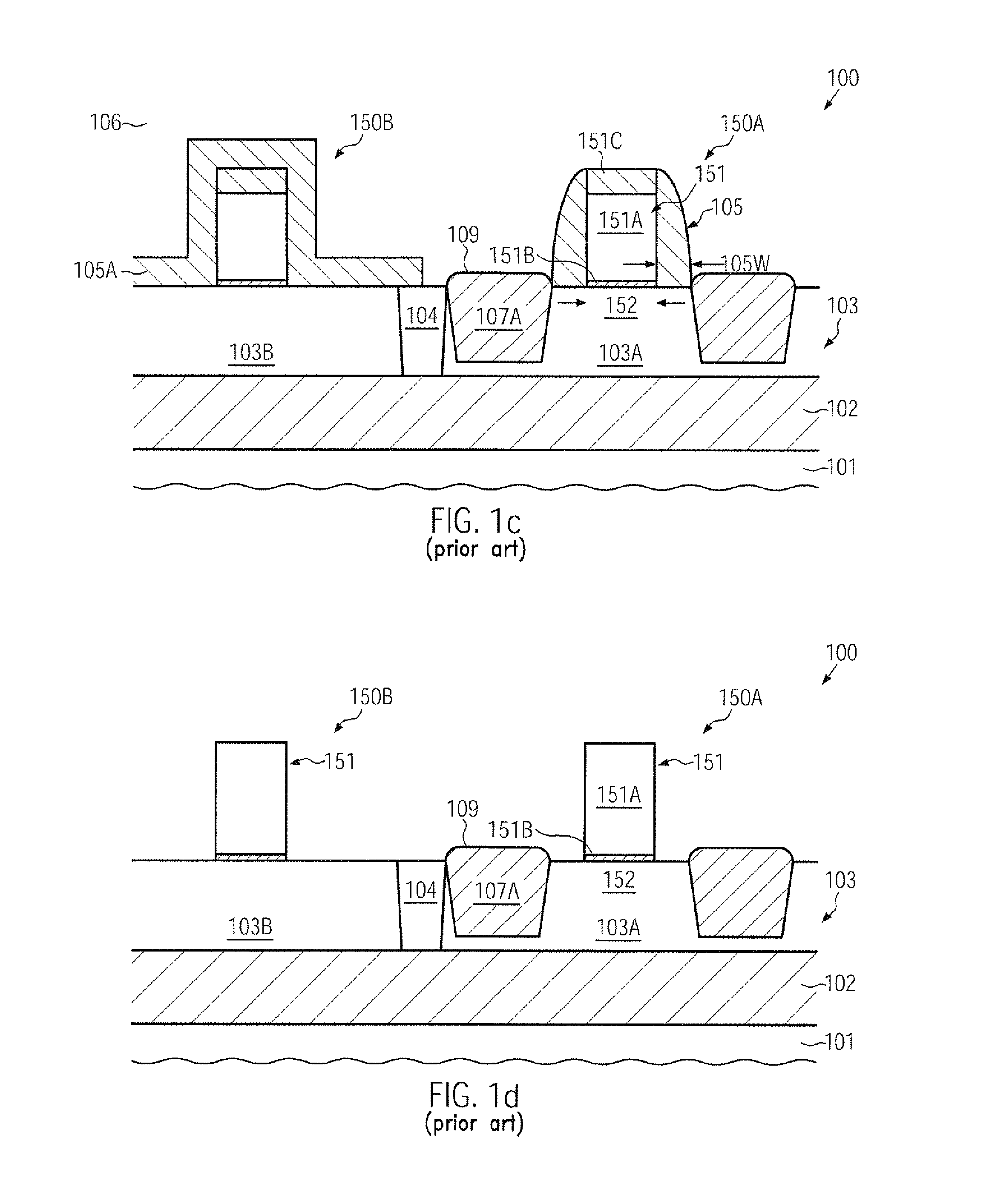

Transistor comprising an embedded semiconductor alloy in drain and source regions extending under the gate electrode

InactiveUS20100219474A1Maintain integrityAvoid contactSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor alloysEngineering

A strain-inducing semiconductor alloy may be formed on the basis of cavities that may extend deeply below the gate electrode structure, which may be accomplished by using a sequence of two etch processes. In a first etch process, the cavity may be formed on the basis of a well-defined lateral offset to ensure integrity of the gate electrode structure and, in a subsequent etch process, the cavity may be increased in a lateral direction while nevertheless reliably preserving a portion of the channel region. Consequently, the strain-inducing efficiency may be increased by appropriately positioning the strain-inducing material immediately below the channel region without compromising integrity of the gate electrode structure.

Owner:ALSEPHINA INNOVATIONS INC

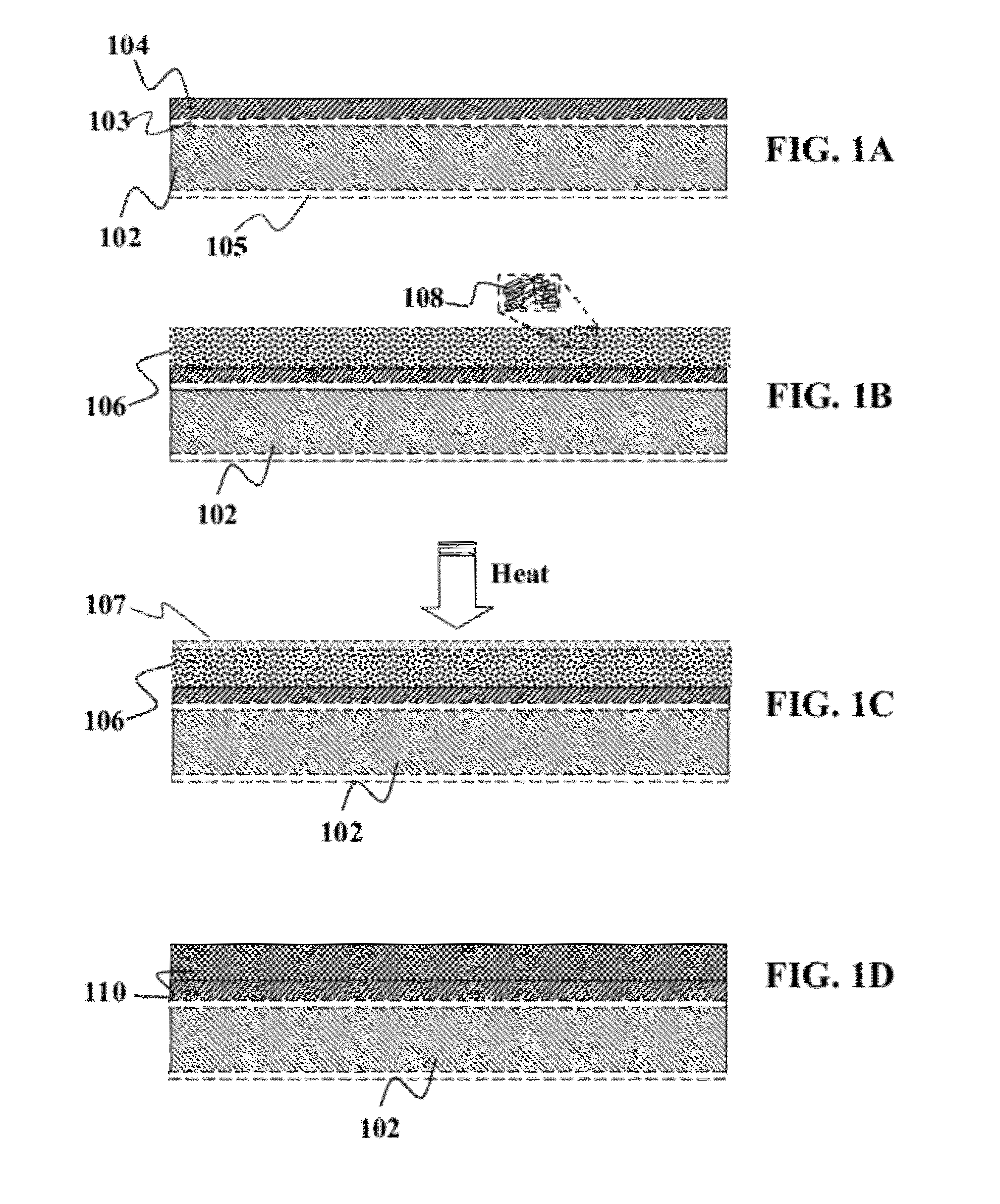

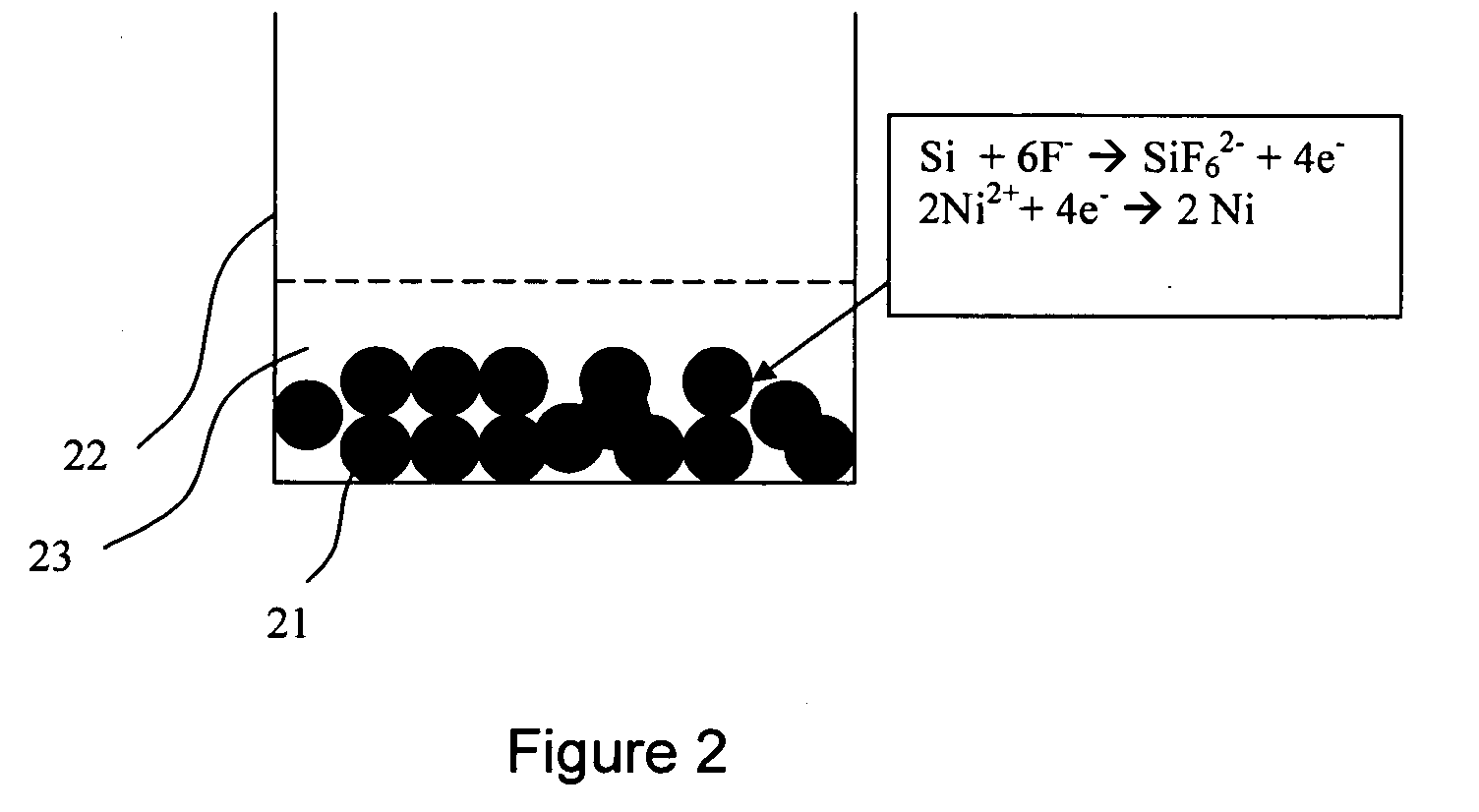

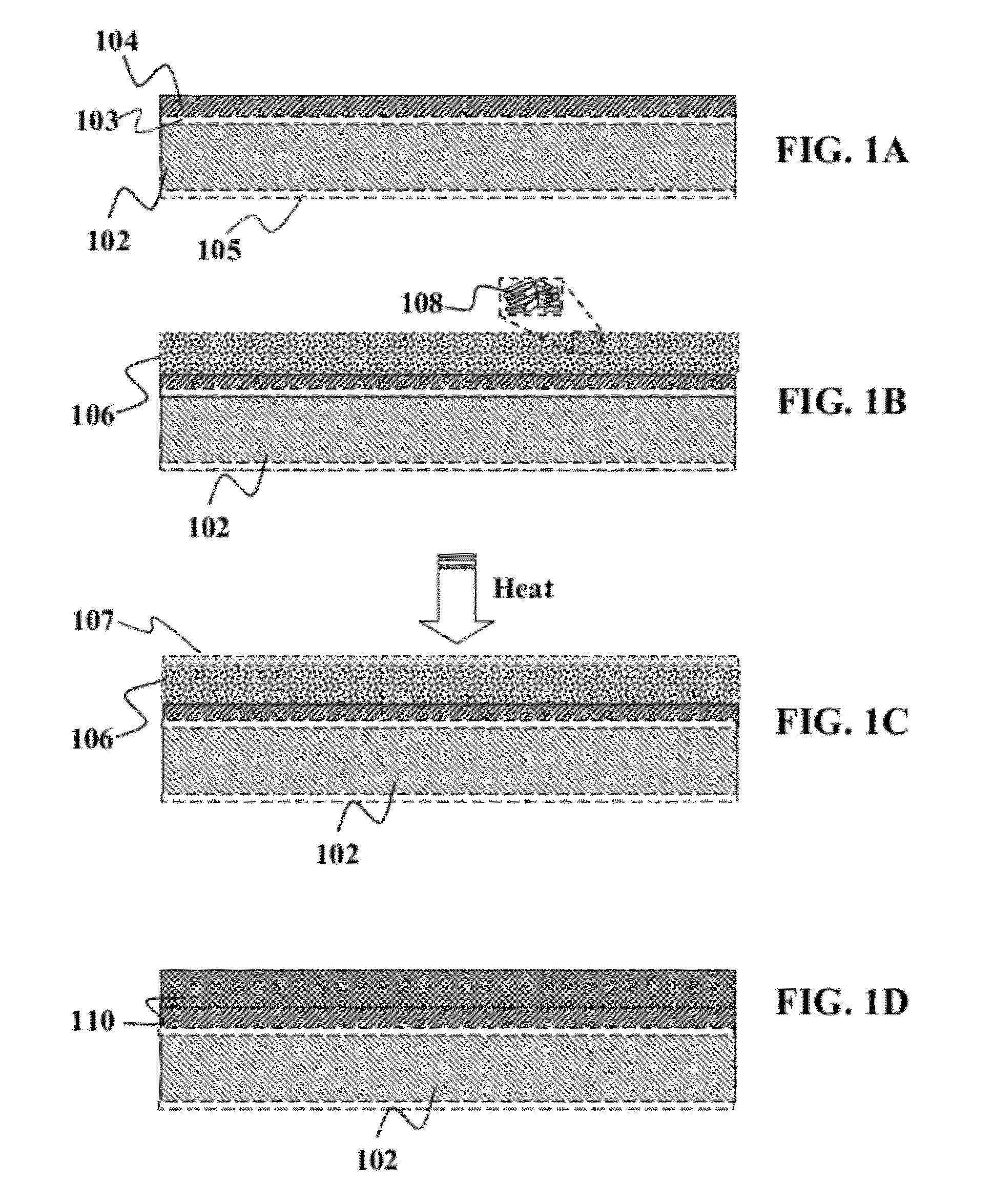

Anode material having a uniform metal-semiconductor alloy layer

ActiveUS20090263716A1Metal being depositedSemiconductor/solid-state device manufacturingNegative electrodesParticulatesSemiconductor materials

The present invention relates to methods for producing anode materials for use in nonaqueous electrolyte secondary batteries. In the present invention, a metal-semiconductor alloy layer is formed on an anode material by contacting a portion of the anode material with a solution containing metals ions and a dissolution component. When the anode material is contacted with the solution, the dissolution component dissolves a part of the semiconductor material in the anode material and deposit the metal on the anode material. After deposition, the anode material and metal are annealed to form a uniform metal-semiconductor alloy layer. The anode material of the present invention can be in a monolithic form or a particle form. When the anode material is in a particle form, the particulate anode material can be further shaped and sintered to agglomerate the particulate anode material.

Owner:ENOVIX CORP

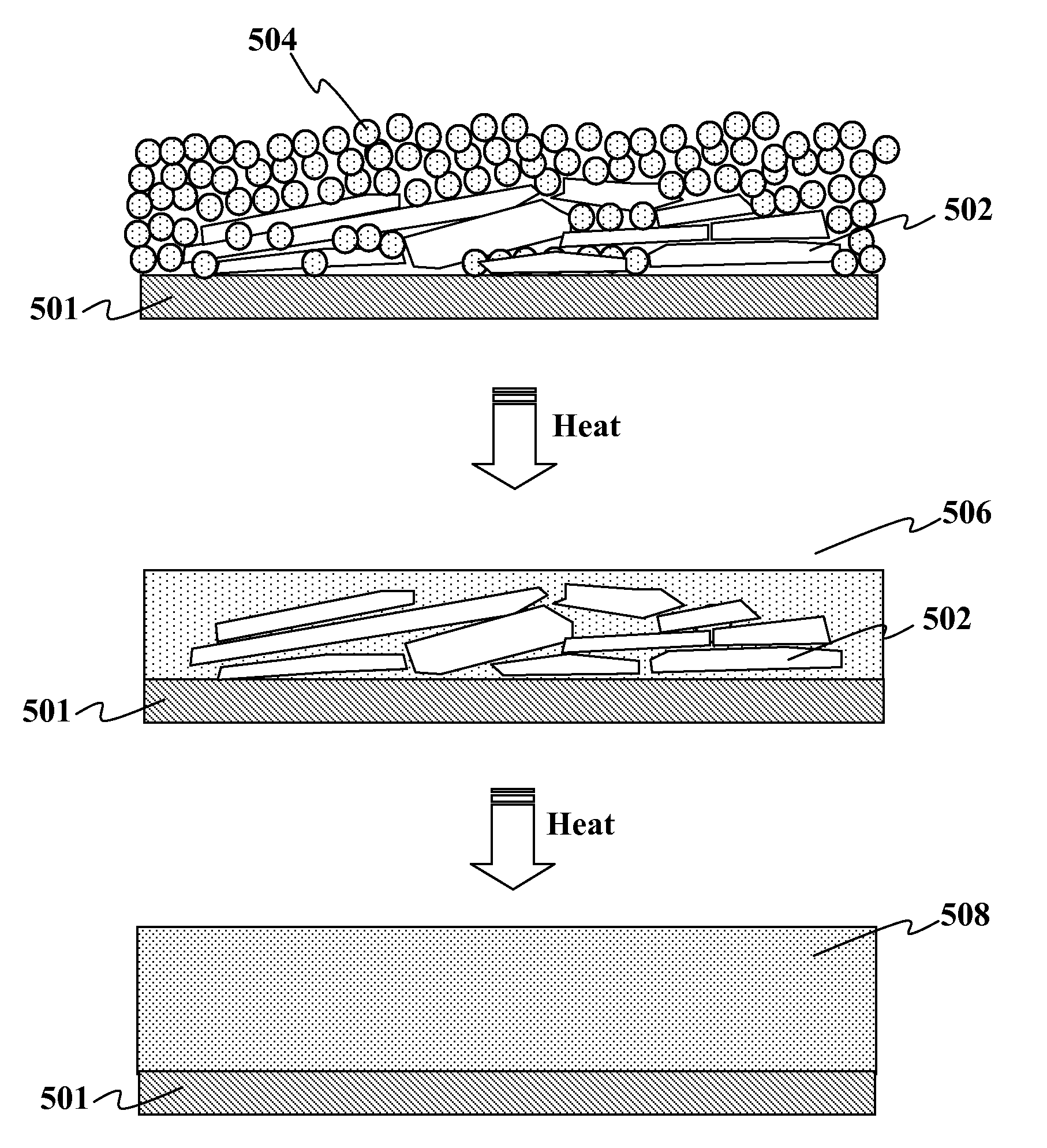

Multi-nary group ib and via based semiconductor

InactiveUS20120168910A1Increase the open circuit voltageLow costFinal product manufactureSemiconductor/solid-state device manufacturingSulfurSemiconductor alloys

Methods and devices are provided for forming multi-nary semiconductor. In one embodiment, a method is provided comprising of depositing a precursor material onto a substrate, wherein the precursor material may include or may be used with an additive to minimize concentration of group IIIA material such as Ga in the back portion of the final semiconductor layer. The additive may be a non-copper Group IB additive in elemental or alloy form. Some embodiments may use both selenium and sulfur, forming a senary or higher semiconductor alloy.

Owner:AERIS CAPITAL SUSTAINABLE IP

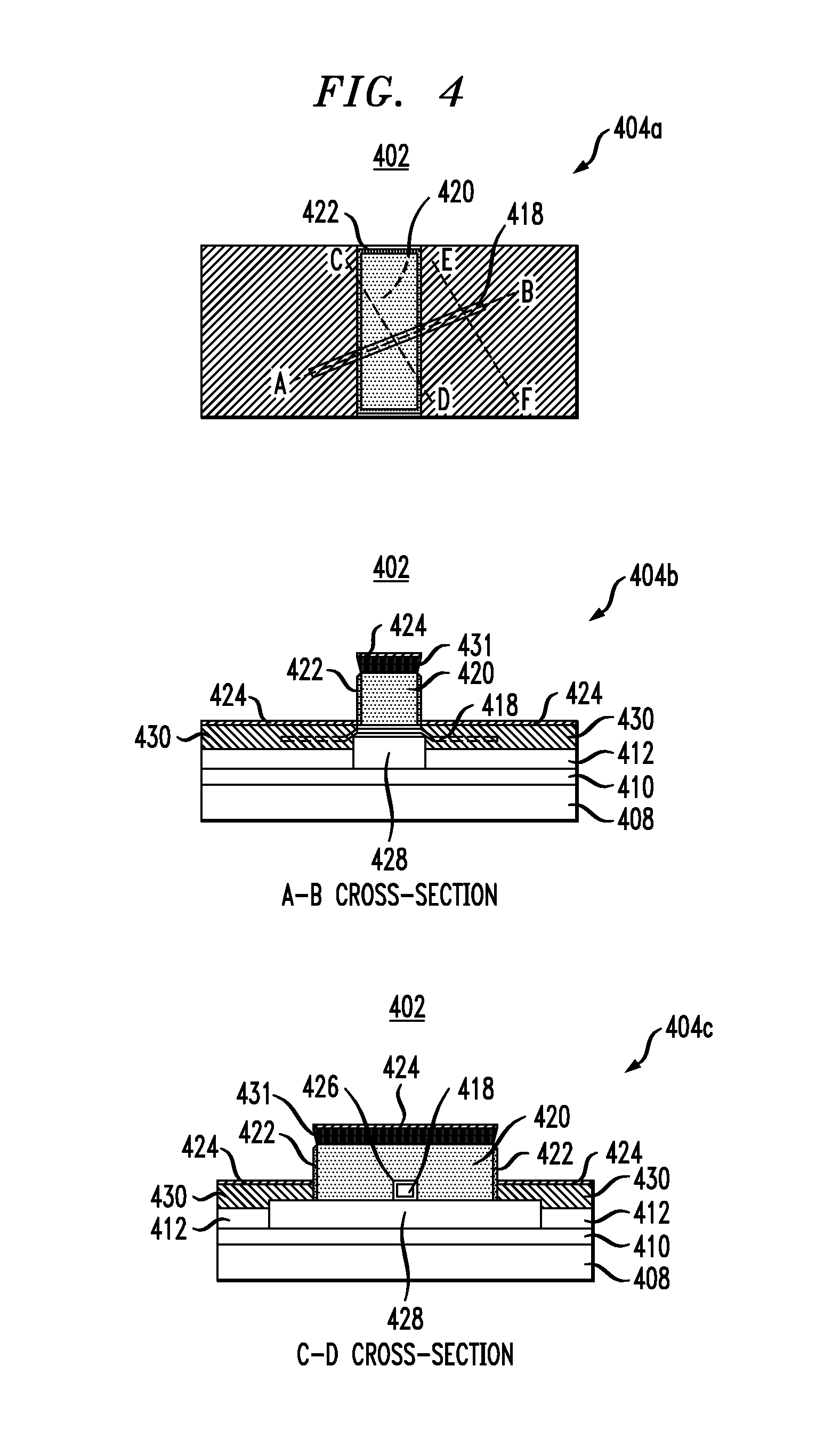

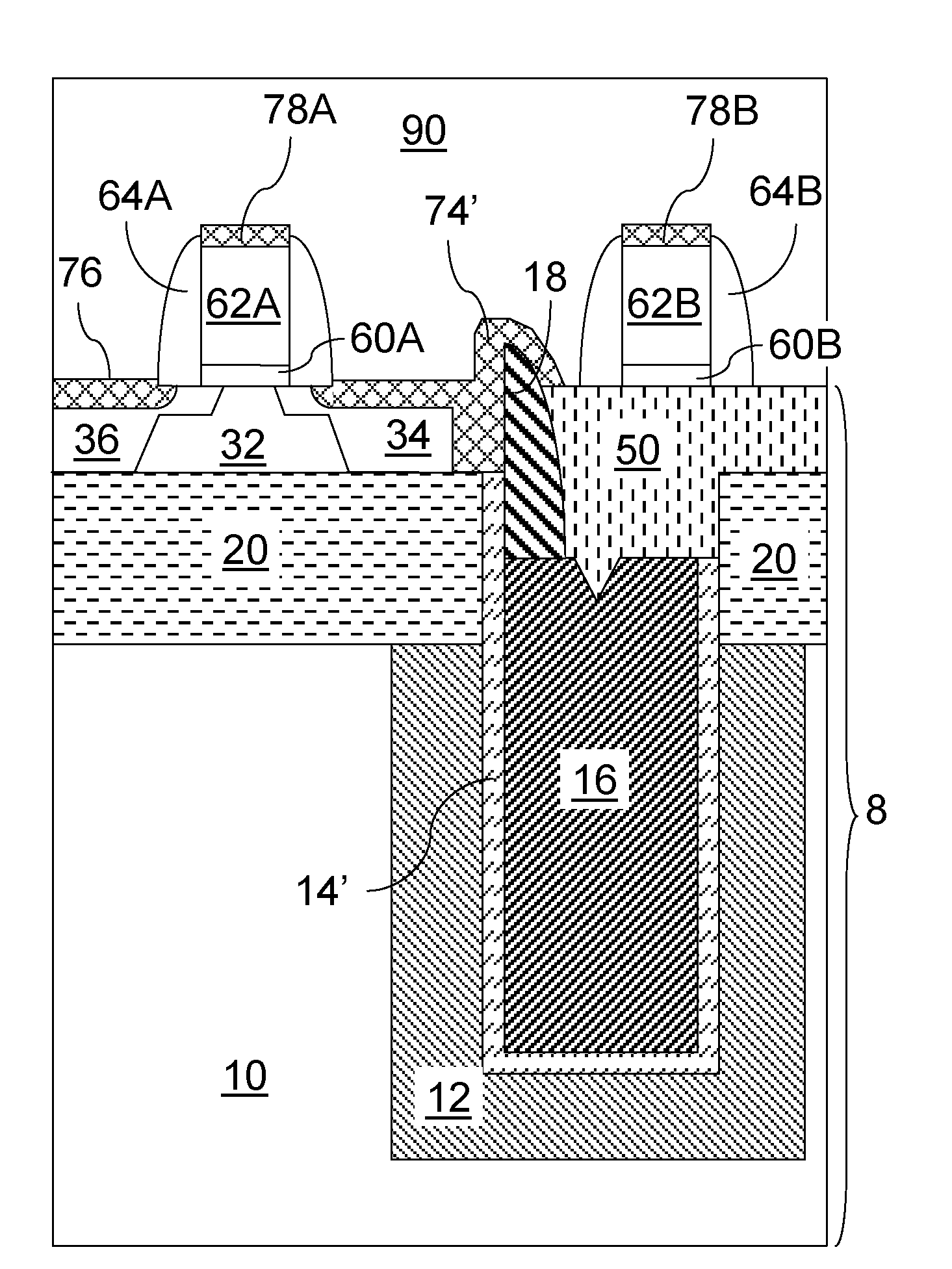

Metallized conductive strap spacer for soi deep trench capacitor

ActiveUS20090256185A1Reliable electrical connectionTransistorSolid-state devicesSemiconductor alloysElectrical connection

A conductive strap spacer is formed within a buried strap cavity above an inner electrode recessed below a top surface of a buried insulator layer of a semiconductor-on-insulator (SOI) substrate. A portion of the conductive strap spacer is metallized by reacting with a metal to form a strap metal semiconductor alloy region, which is contiguous over the conductive strap spacer and a source region, and may extend to a top surface of the buried insulator layer along a substantially vertical sidewall of the conductive strap spacer. The conductive strap spacer and the strap metal semiconductor alloy region provide a stable electrical connection between the inner electrode of the deep trench capacitor and the source region of the access transistor.

Owner:IBM CORP

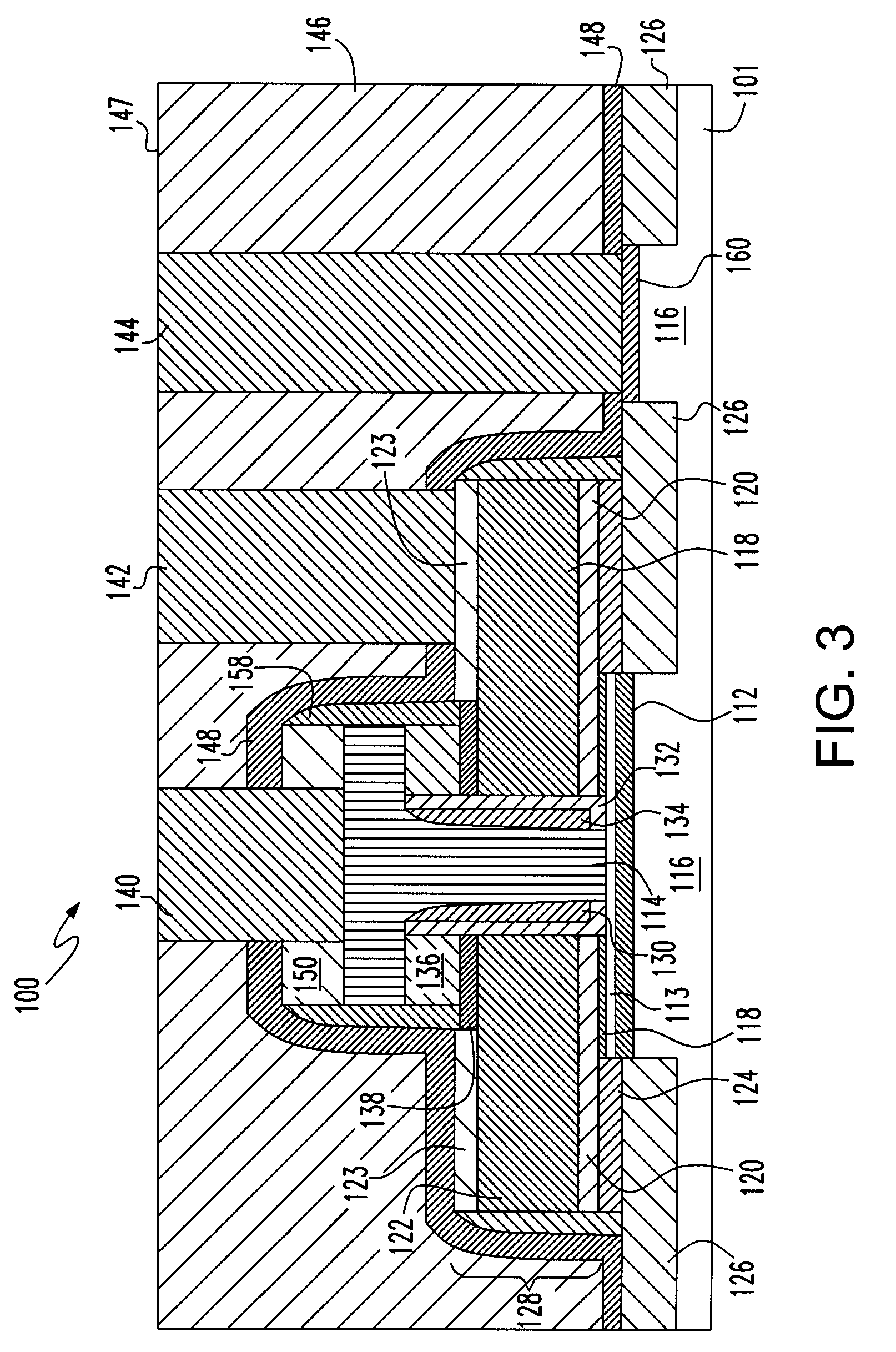

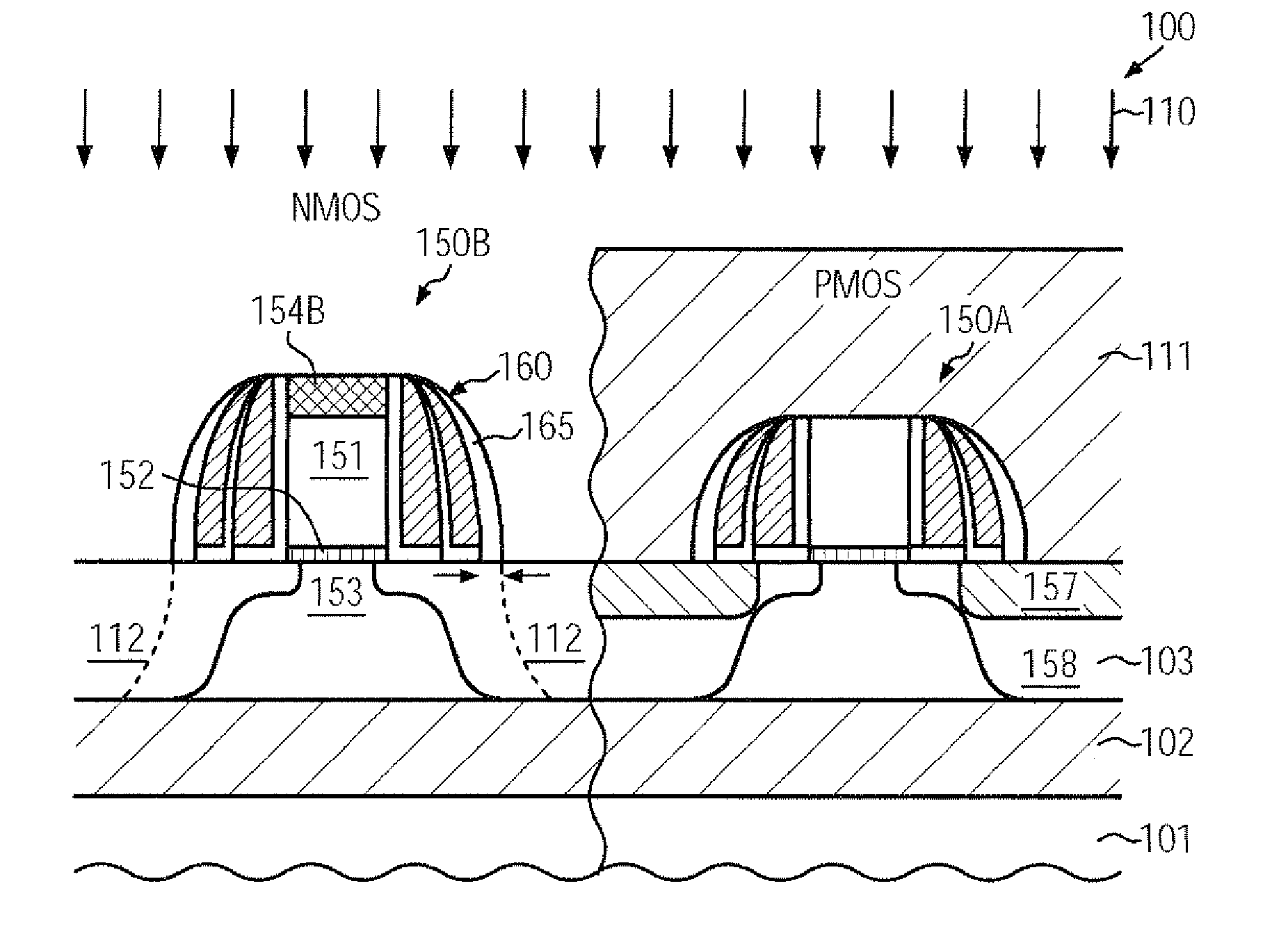

CMOS device with selectively formed and backfilled semiconductor substrate areas to improve device performance

InactiveUS20060118878A1TransistorSemiconductor/solid-state device manufacturingCMOSSemiconductor alloys

An NMOS and PMOS device pair having a selected stress level and type exerted on a respective channel region and method for forming the same, the method including providing a semiconductor substrate; forming isolation regions to separate active areas comprising a PMOS device region and an NMOS device region; lithographically patterning the semiconductor substrate and etching respective recessed areas including the respective NMOS and PMOS device regions into the silicon semiconductor substrate to a predetermined depth; backfilling the respective recessed areas with at least one semiconductor alloy; and, forming gate structures and offset spacers over the respective NMOS and PMOS device regions.

Owner:TAIWAN SEMICON MFG CO LTD

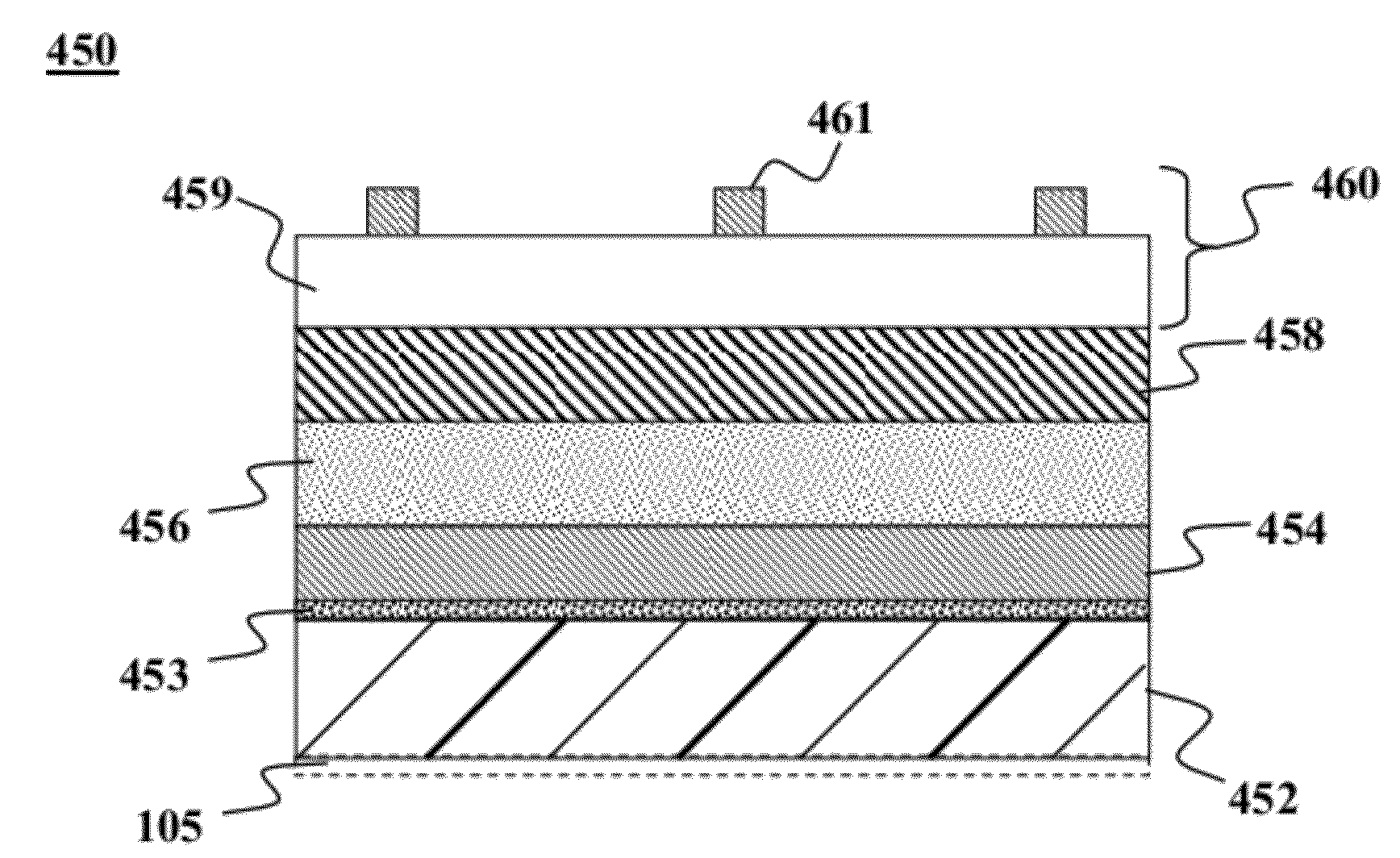

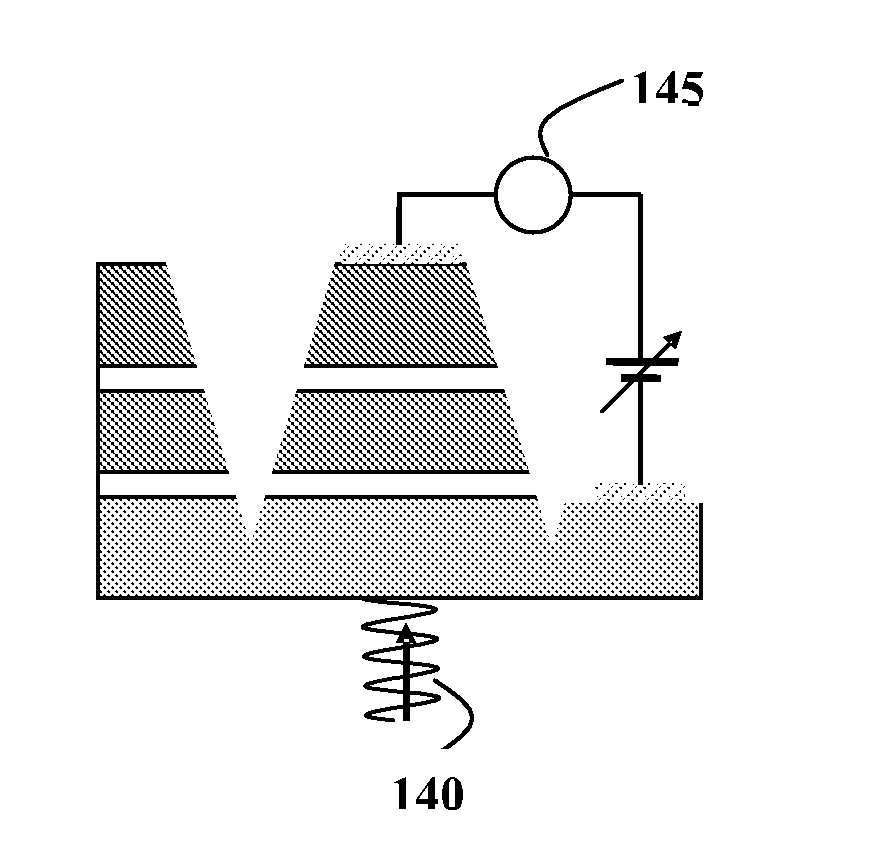

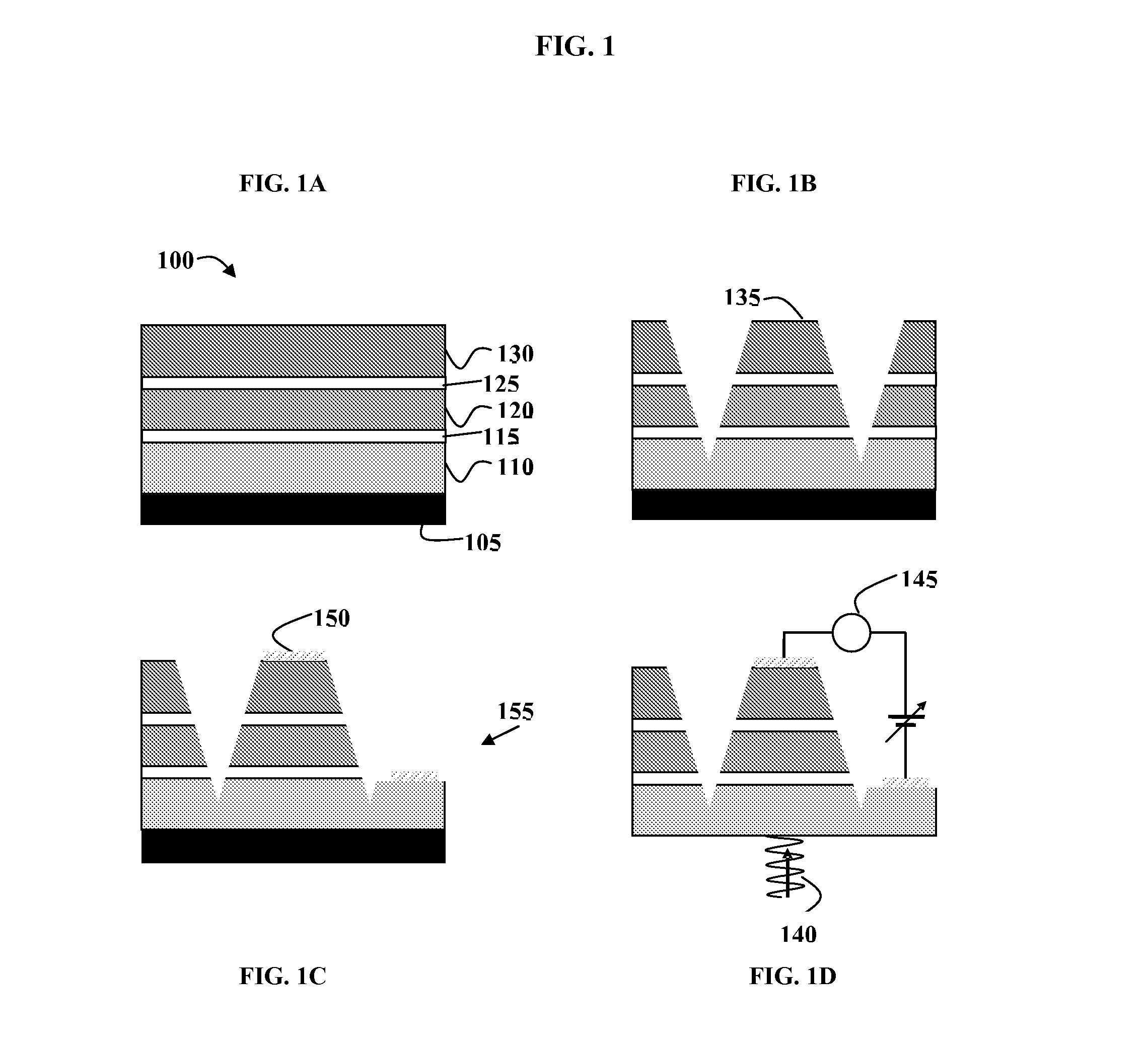

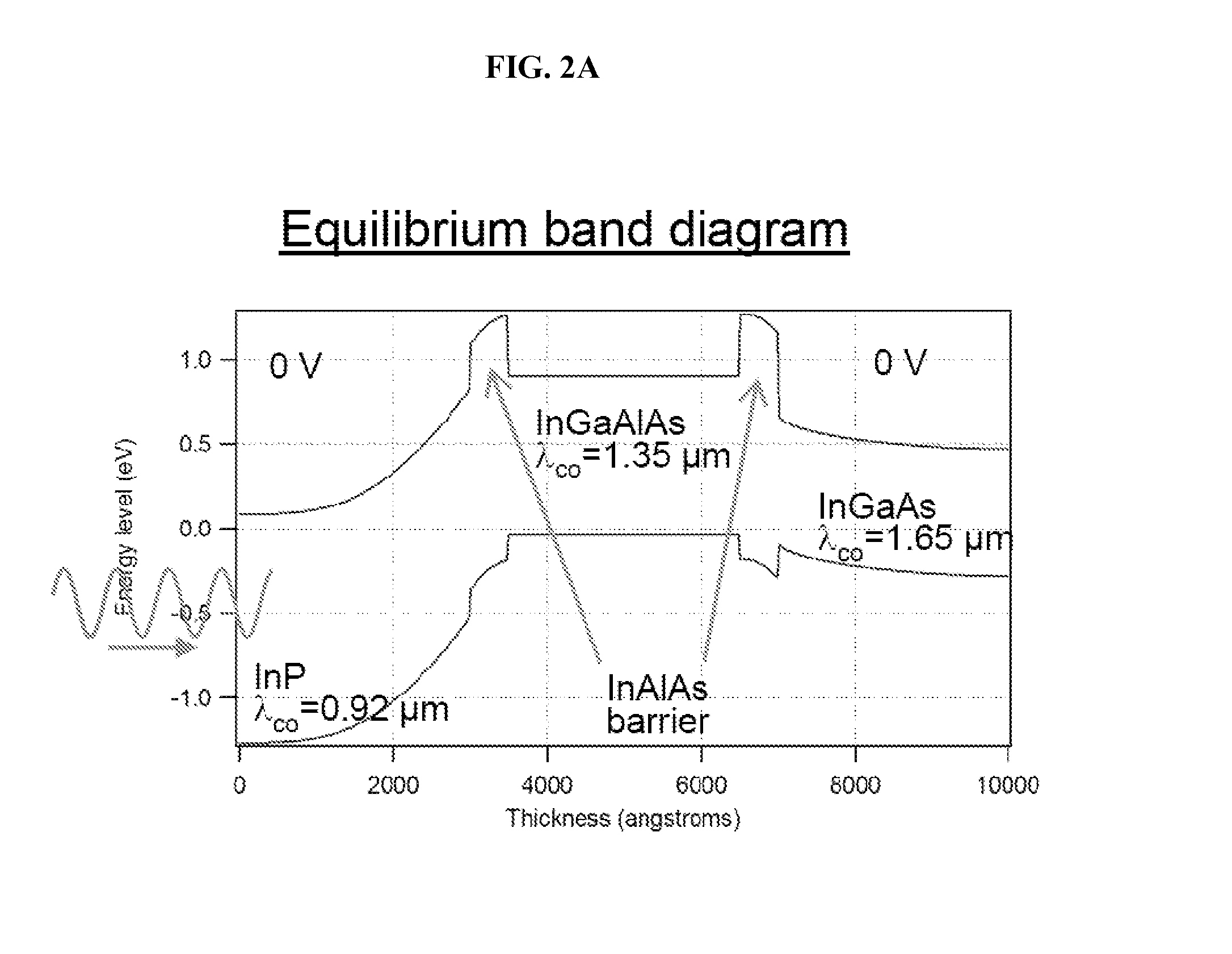

Methods and apparatus for three-color infrared sensors

ActiveUS8093559B1Reduce dark currentApplication of bias voltageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor alloysAlloy

The present invention provides a two-terminal infrared detector capable of detecting a plurality of bands, such as three bands, over the visible and short-wave infrared bands. Detection of three colors enables one to construct composite imagery that provide significantly added contract in comparison to typical grayscale images. In some variations, the device includes multiple absorber and barrier layers that consist of distinct engineered semiconductor alloys which are closely lattice matched to InP.

Owner:HRL LAB

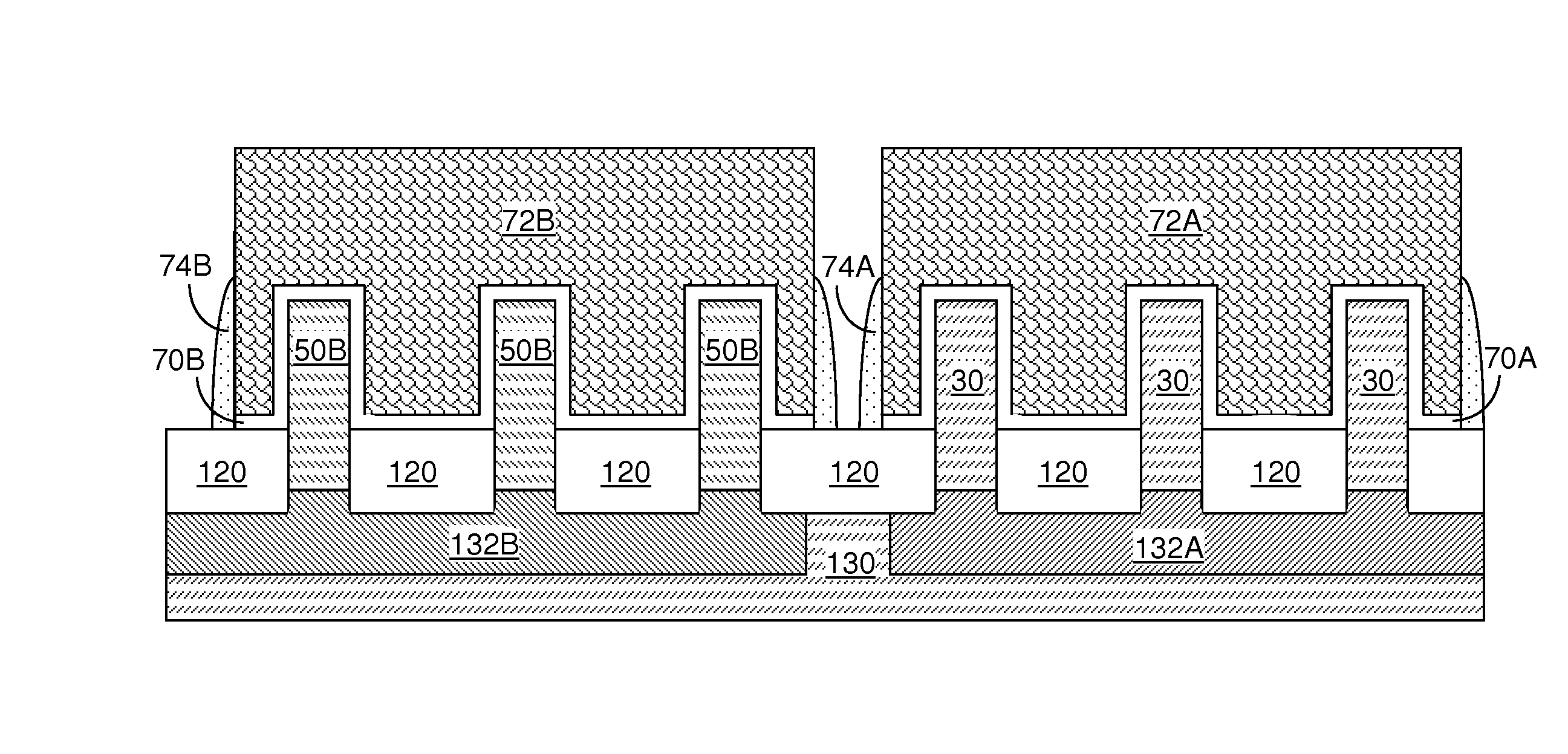

Semiconductor alloy fin field effect transistor

ActiveUS20140097518A1Inhibited DiffusionSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor materials

Semiconductor alloy fin structures can be formed by recessing a semiconductor material layer including a first semiconductor material to form a trench, and epitaxially depositing a semiconductor alloy material of the first semiconductor material and a second semiconductor material within the trench. The semiconductor alloy material is epitaxially aligned to the first semiconductor material in the semiconductor material layer. First semiconductor fins including the first semiconductor material and second semiconductor fins including the semiconductor alloy material can be simultaneously formed. In one embodiment, the first and second semiconductor fins can be formed on an insulator layer, which prevents diffusion of the second semiconductor material to the first semiconductor fins. In another embodiment, shallow trench isolation structures and reverse biased wells can be employed to provide electrical insulation among neighboring semiconductor fins.

Owner:GLOBALFOUNDRIES US INC

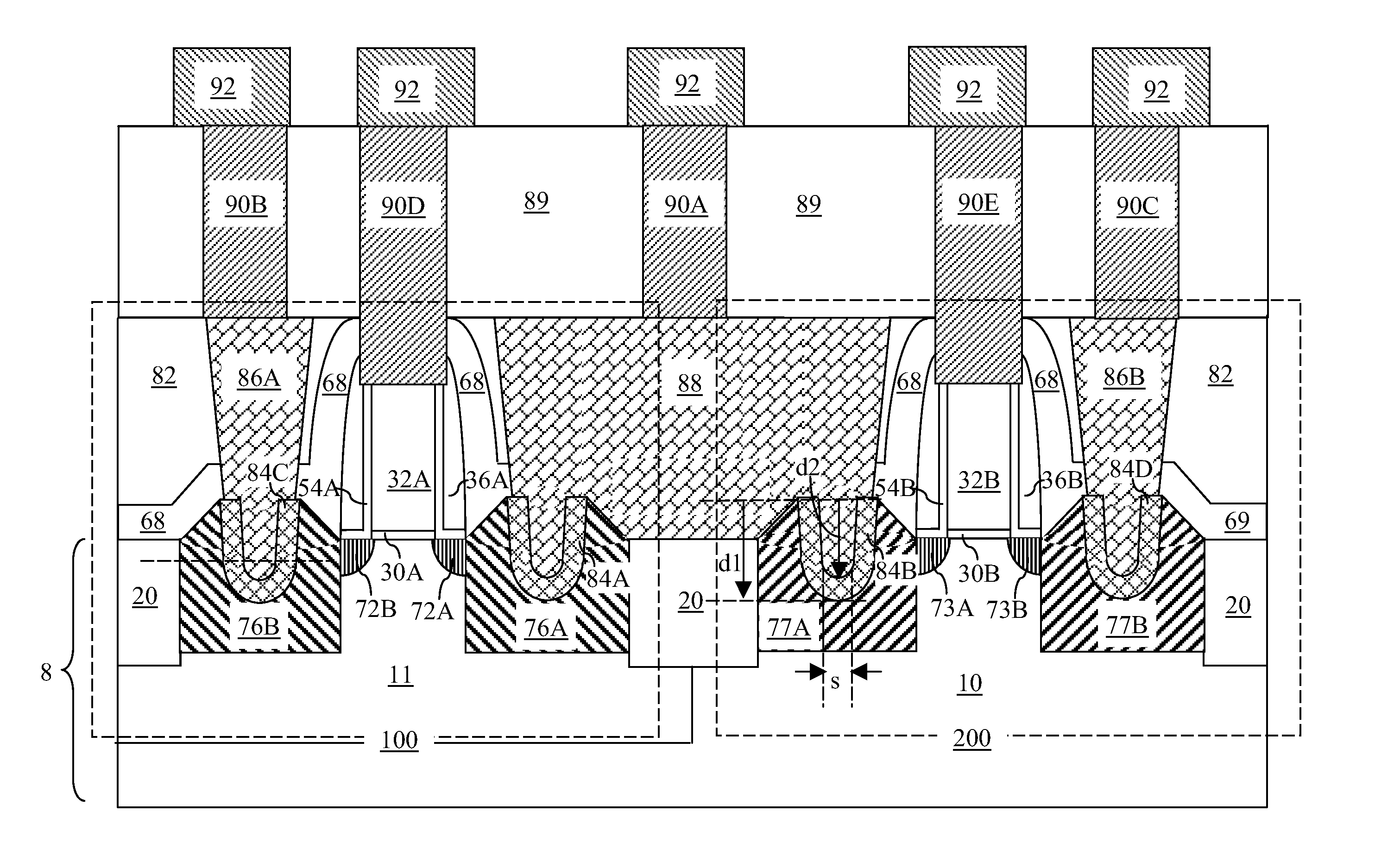

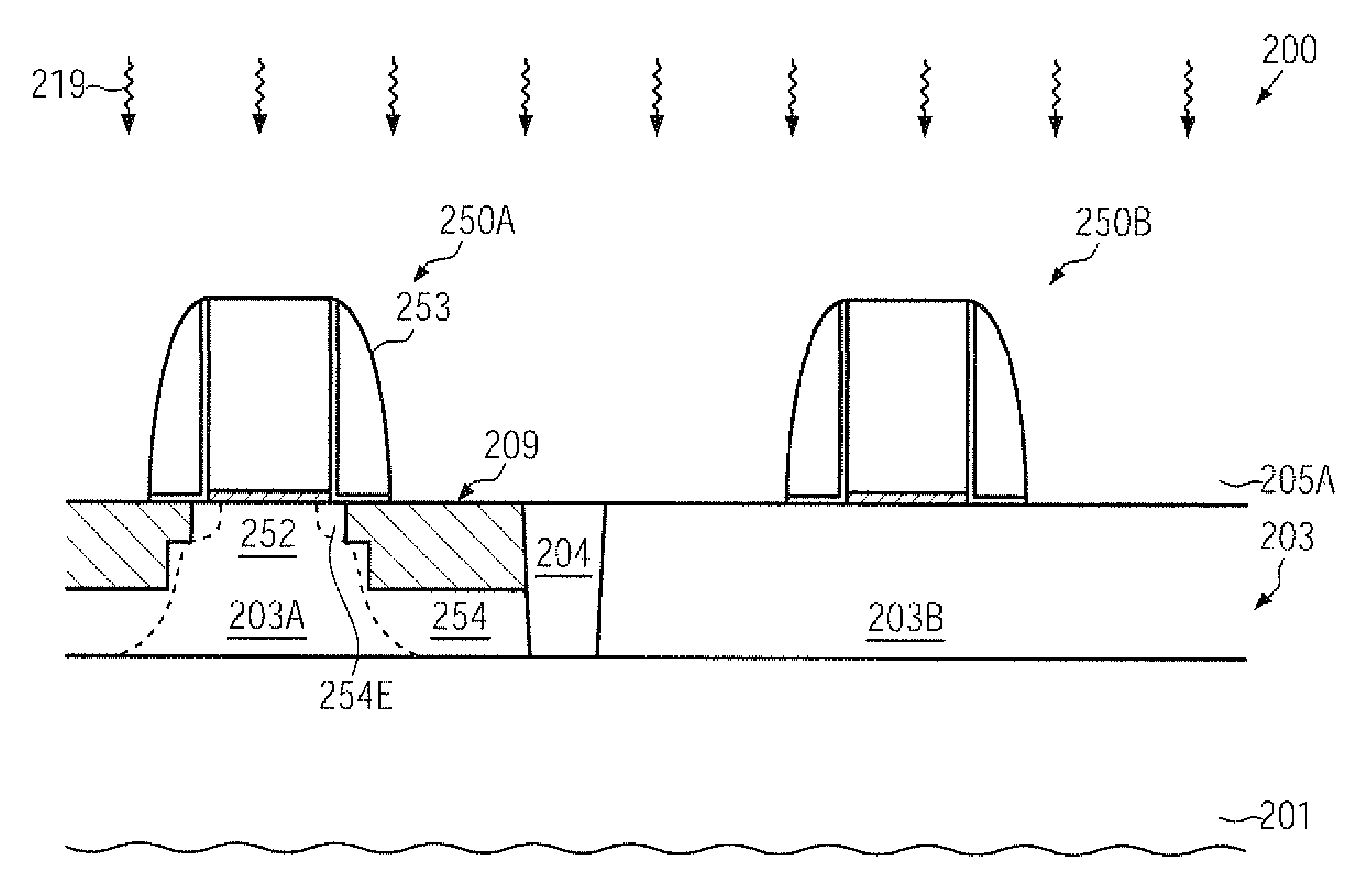

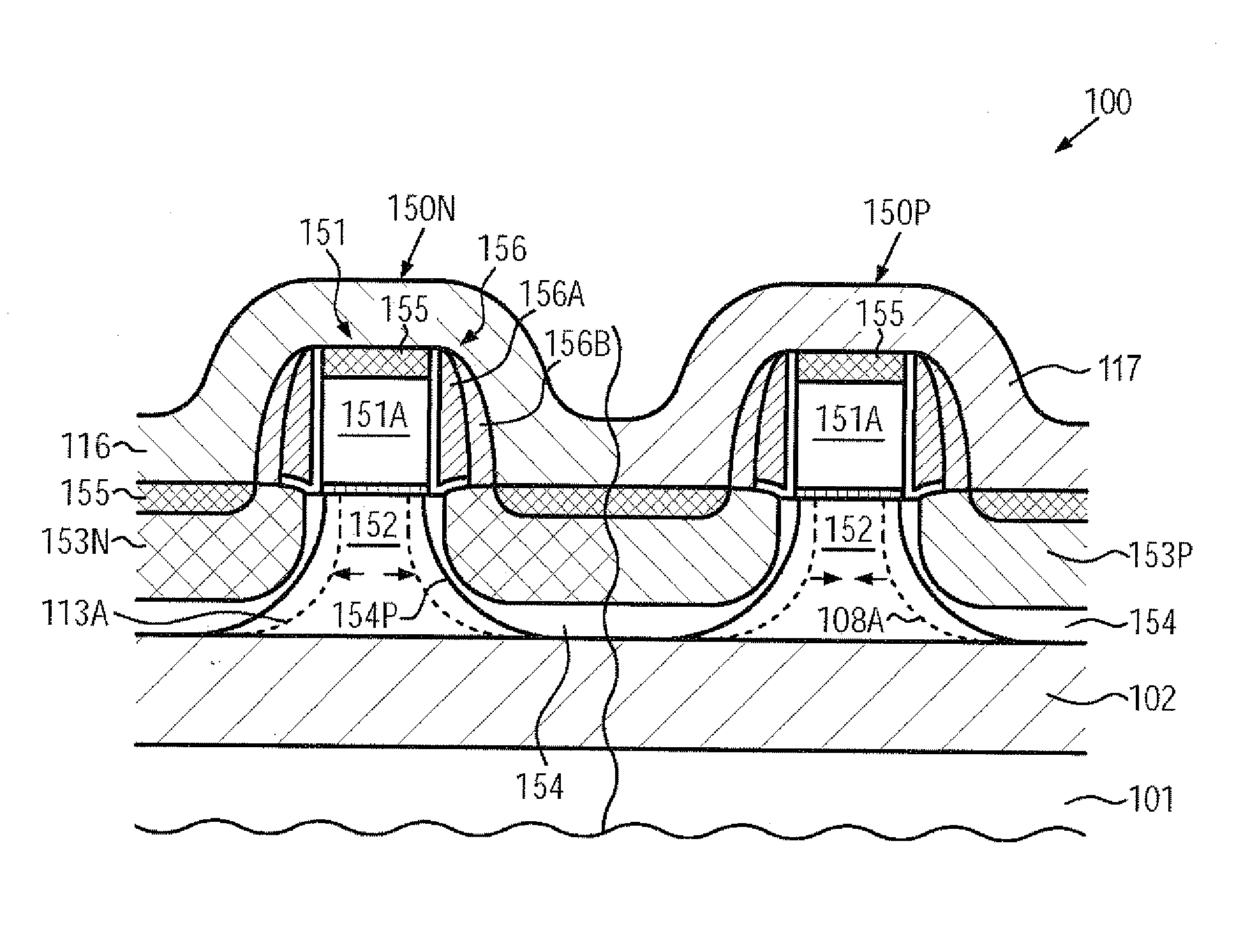

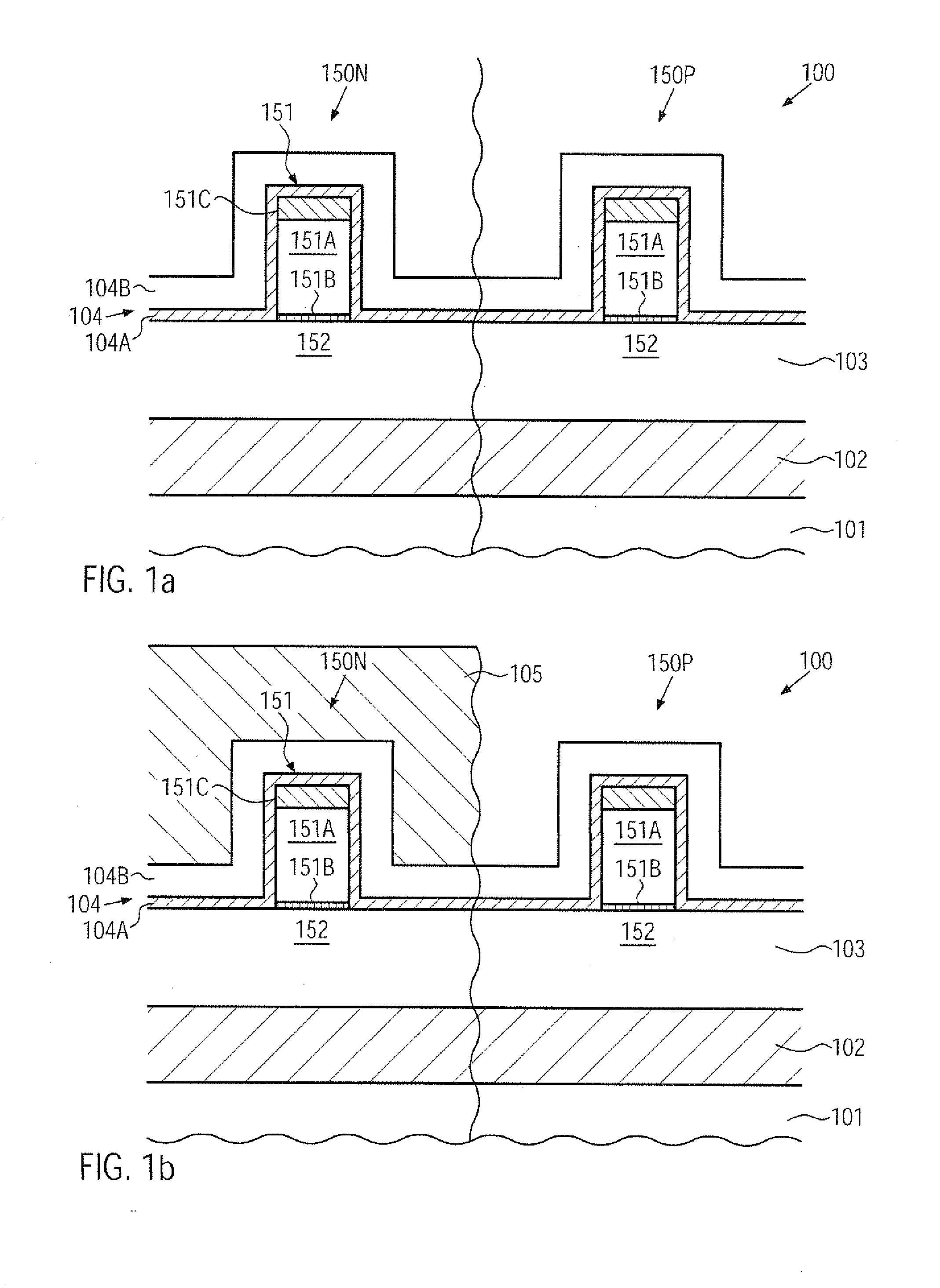

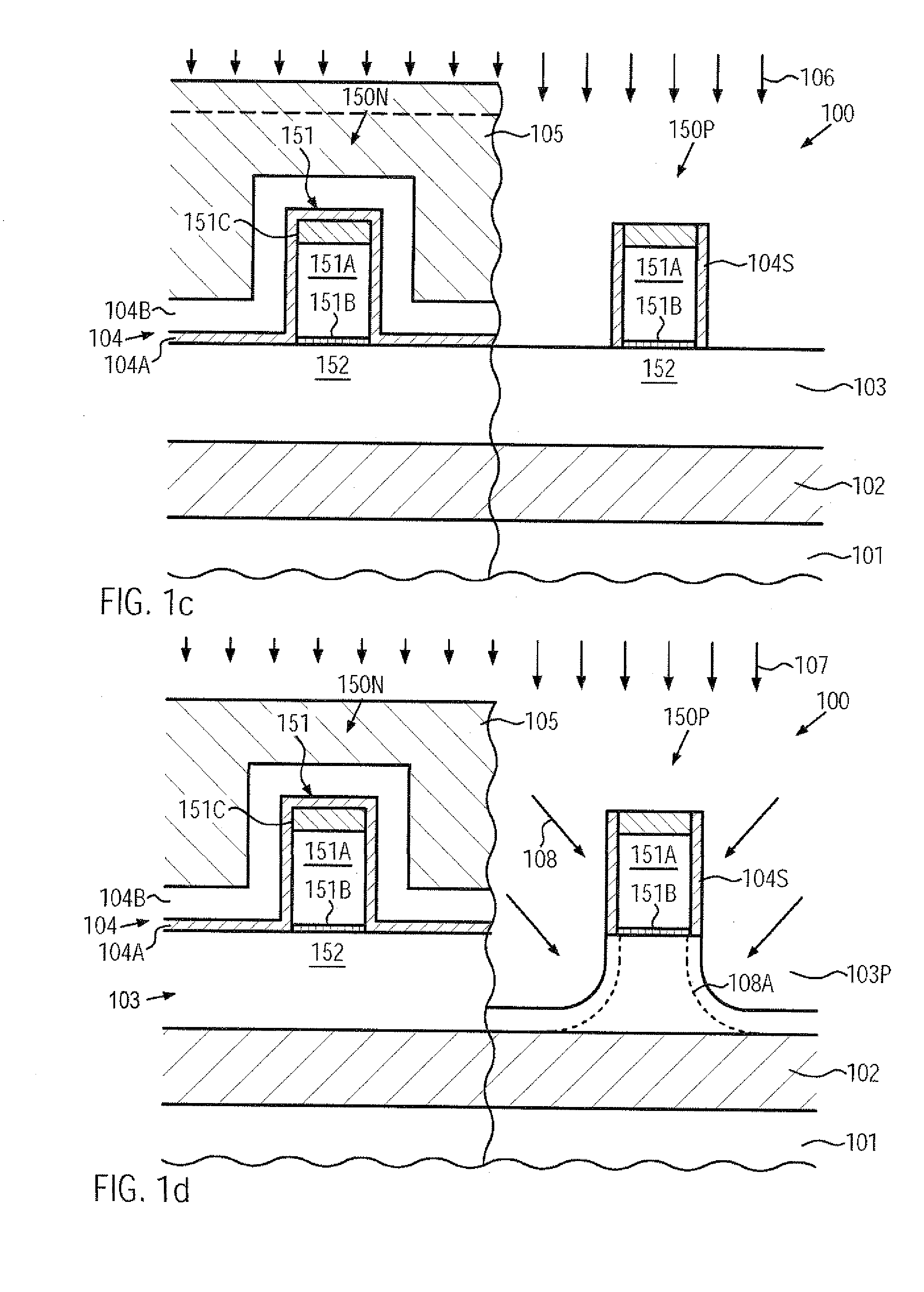

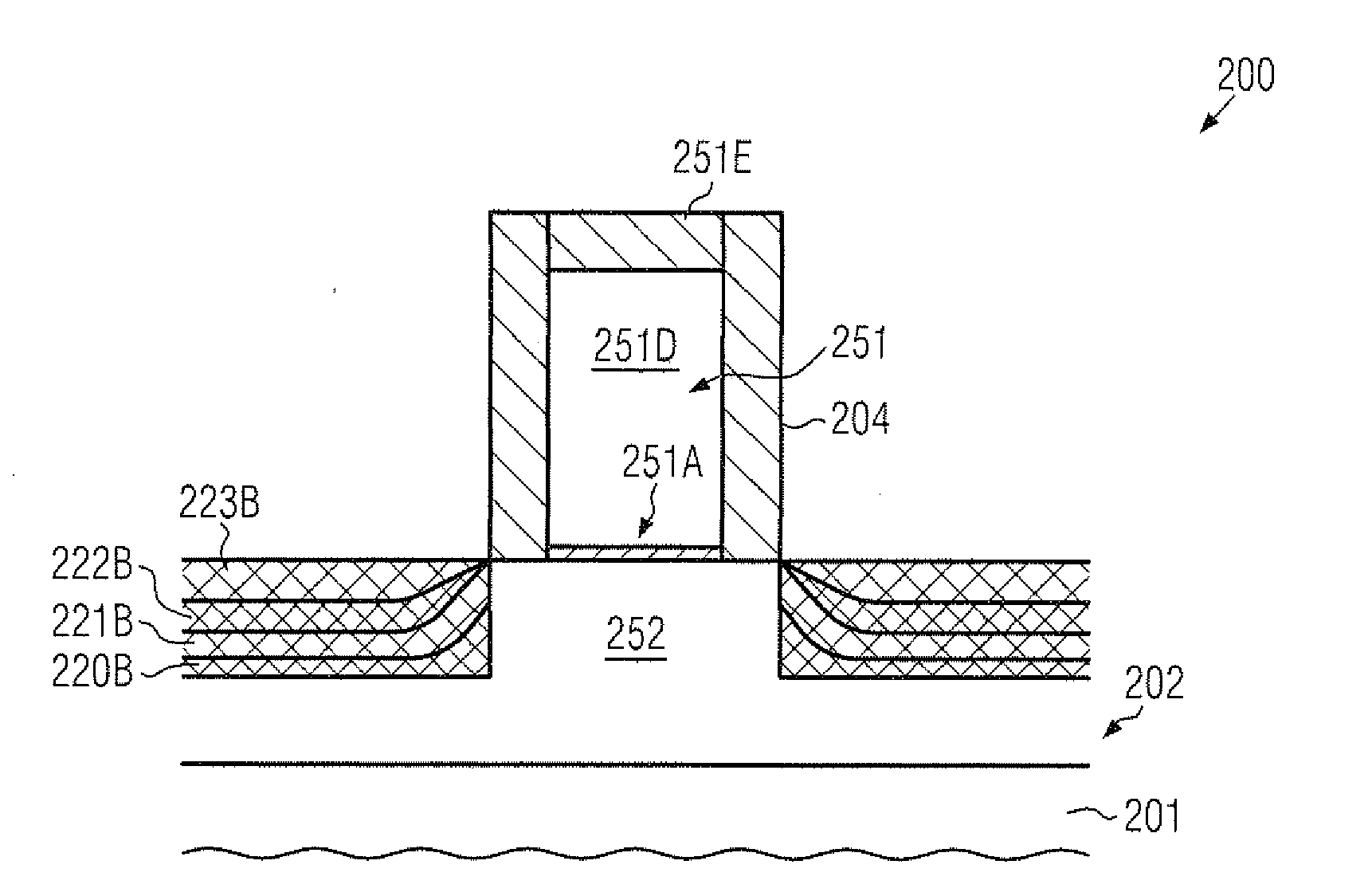

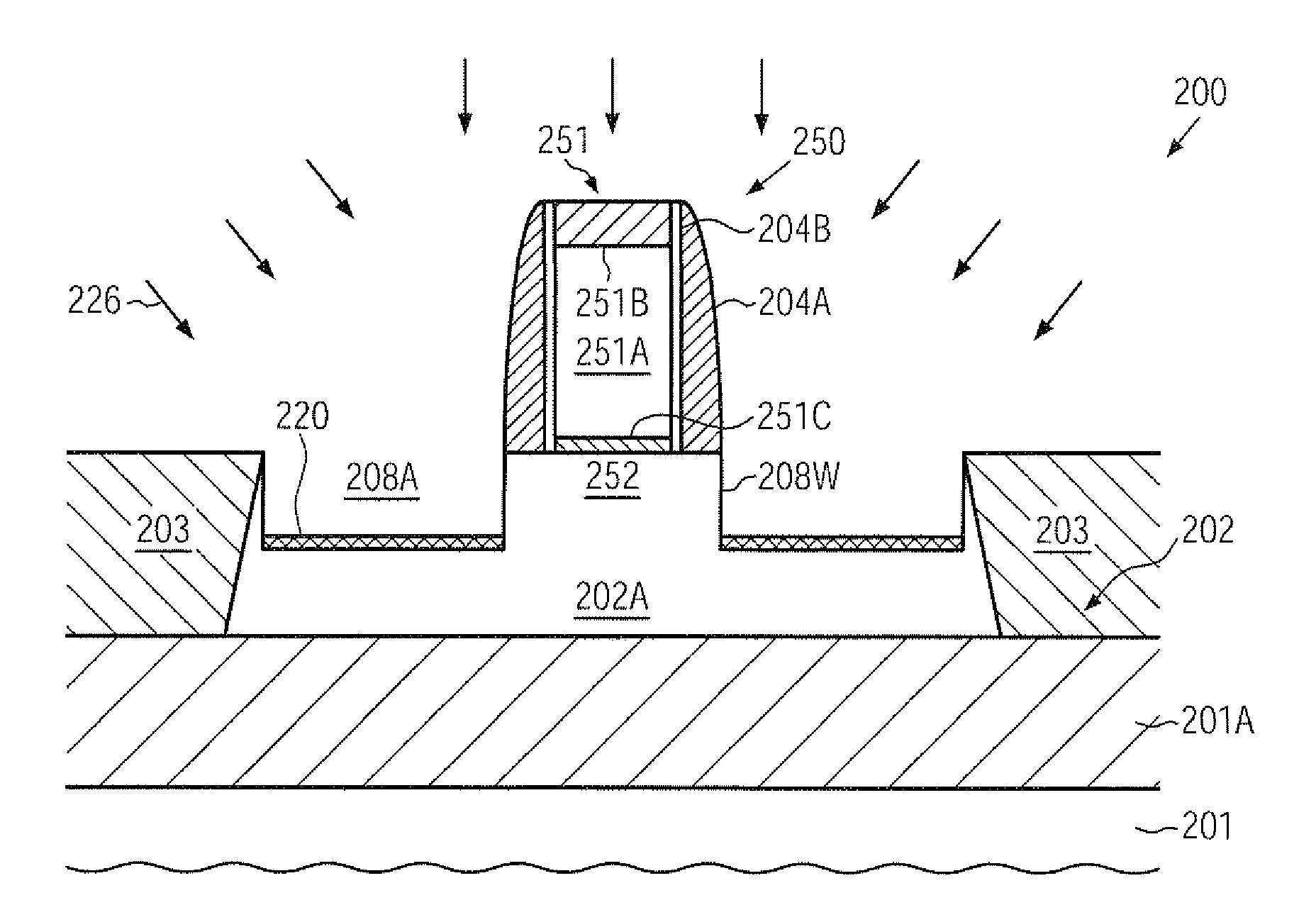

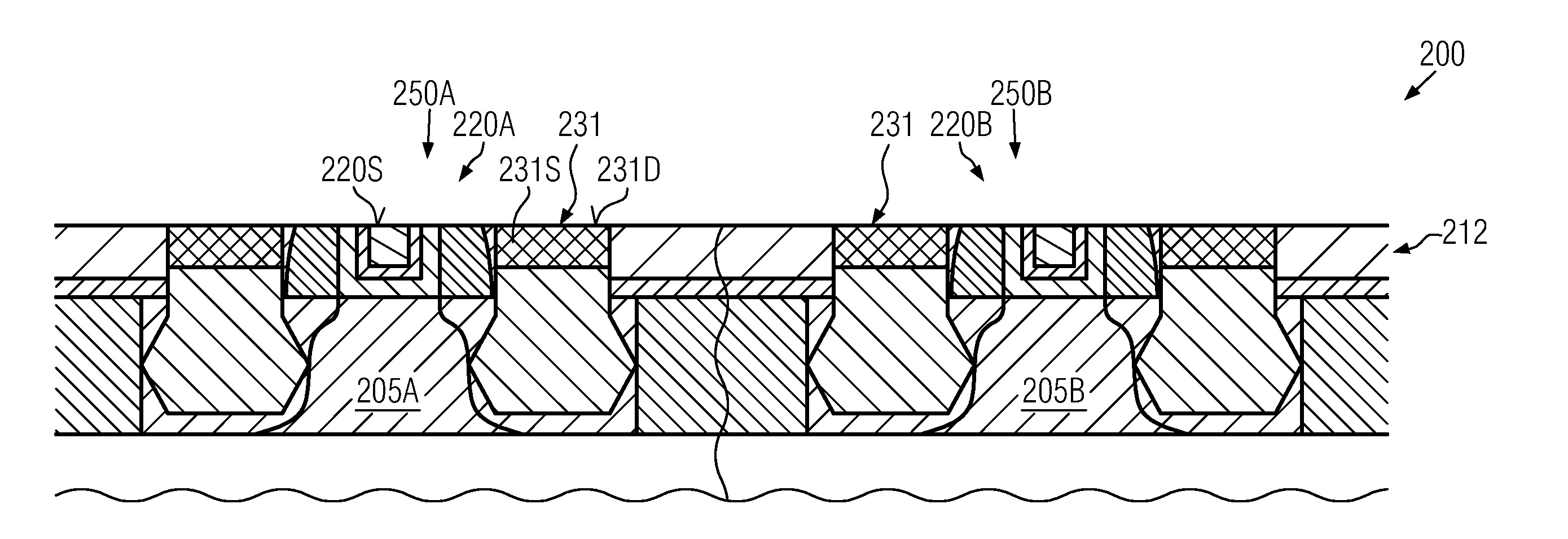

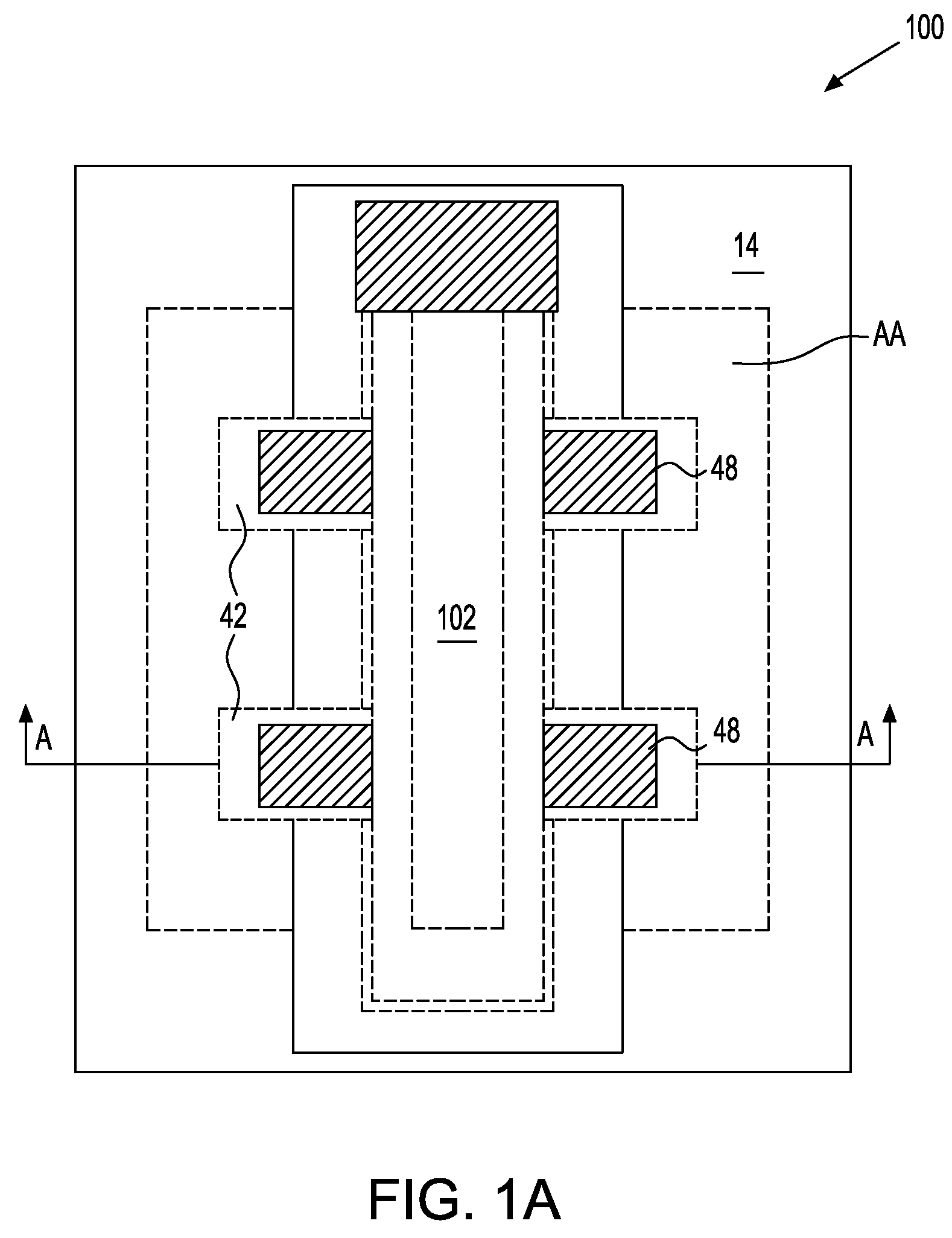

Transistors Comprising High-K Metal Gate Electrode Structures and Embedded Strain-Inducing Semiconductor Alloys Formed in a Late Stage

ActiveUS20120025266A1Improve performance efficiencyImprove production efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsSemiconductor alloys

In sophisticated semiconductor devices, replacement gate approaches may be applied in combination with a process strategy for implementing a strain-inducing semiconductor material, wherein superior proximity of the strain-inducing semiconductor material and / or superior robustness of the replacement gate approach may be achieved by forming the initial gate electrode structures with superior uniformity and providing at least one cavity for implementing the strained channel regions in a very advanced manufacturing stage, i.e., after completing the basic transistor configuration.

Owner:GLOBALFOUNDRIES US INC

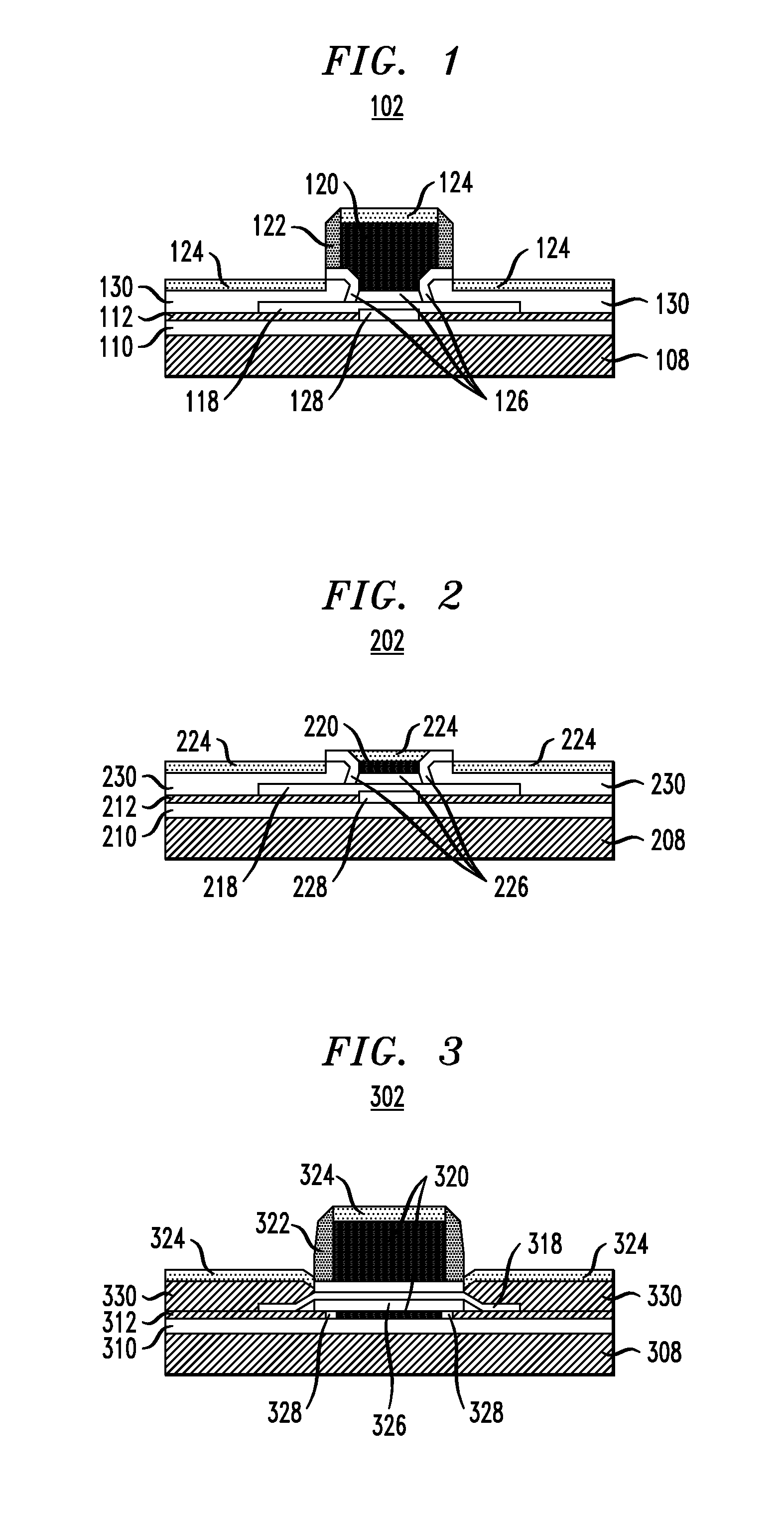

Structure and method for fabricating self-aligned metal contacts

InactiveUS20090108378A1Semiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor alloys

A semiconductor structure including at least one transistor is provided which has a stressed channel region that is a result of having a stressed layer present atop a gate conductor that includes a stack comprising a bottom polysilicon (polySi) layer and a top metal semiconductor alloy (i.e., metal silicide) layer. The stressed layer is self-aligned to the gate conductor. The inventive structure also has a reduced external parasitic S / D resistance as a result of having a metallic contact located atop source / drain regions that include a surface region comprised of a metal semiconductor alloy. The metallic contact is self-aligned to the gate conductor.

Owner:AURIGA INNOVATIONS INC

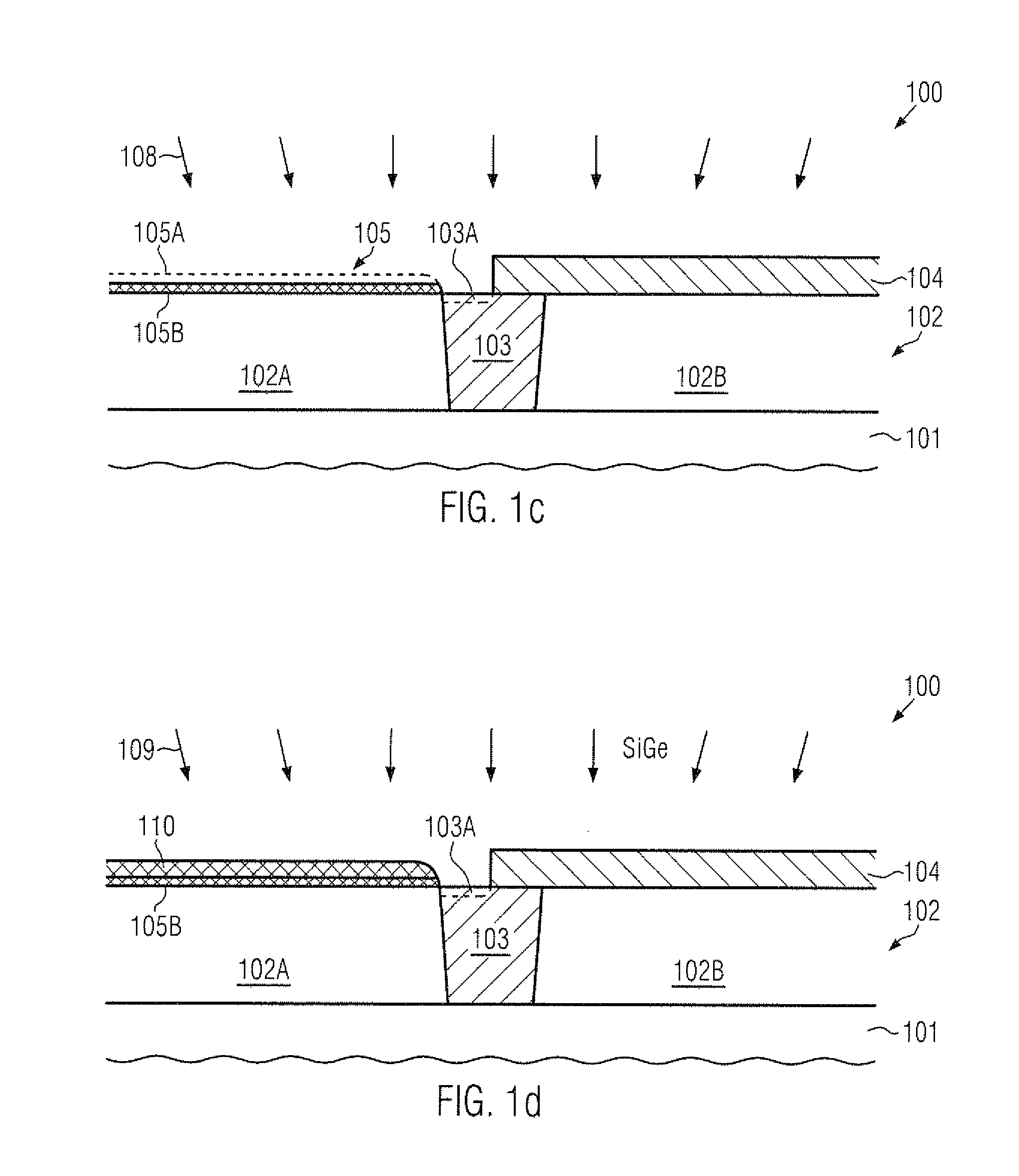

Shallow pn junction formed by in situ doping during selective growth of an embedded semiconductor alloy by a cyclic growth/etch deposition process

ActiveUS20100025779A1Increase strainImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingIn situ dopingUltra-high vacuum

A silicon / carbon alloy may be formed in drain and source regions, wherein another portion may be provided as an in situ doped material with a reduced offset with respect to the gate electrode material. For this purpose, in one illustrative embodiment, a cyclic epitaxial growth process including a plurality of growth / etch cycles may be used at low temperatures in an ultra-high vacuum ambient, thereby obtaining a substantially bottom to top fill behavior.

Owner:ADVANCED MICRO DEVICES INC

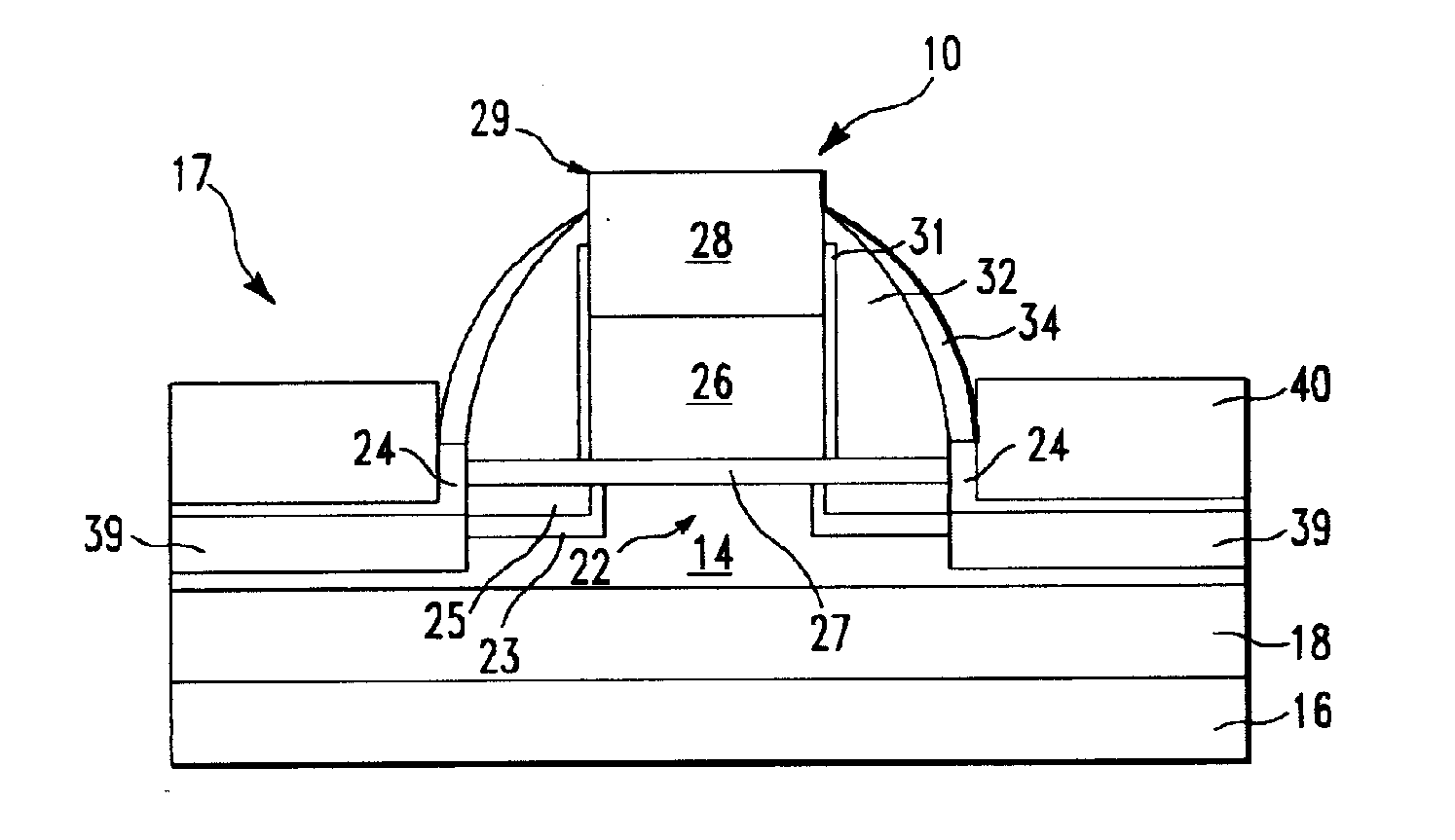

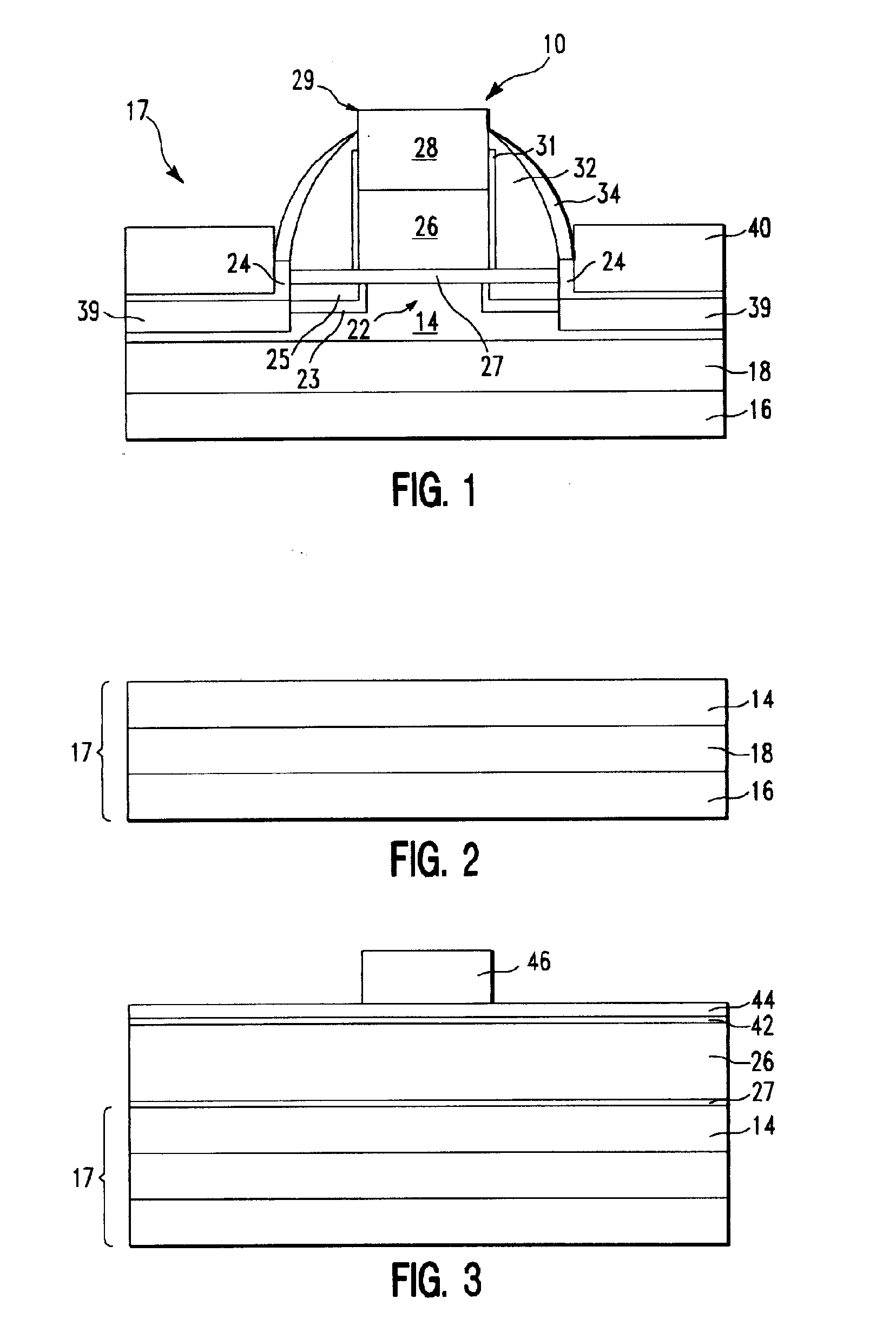

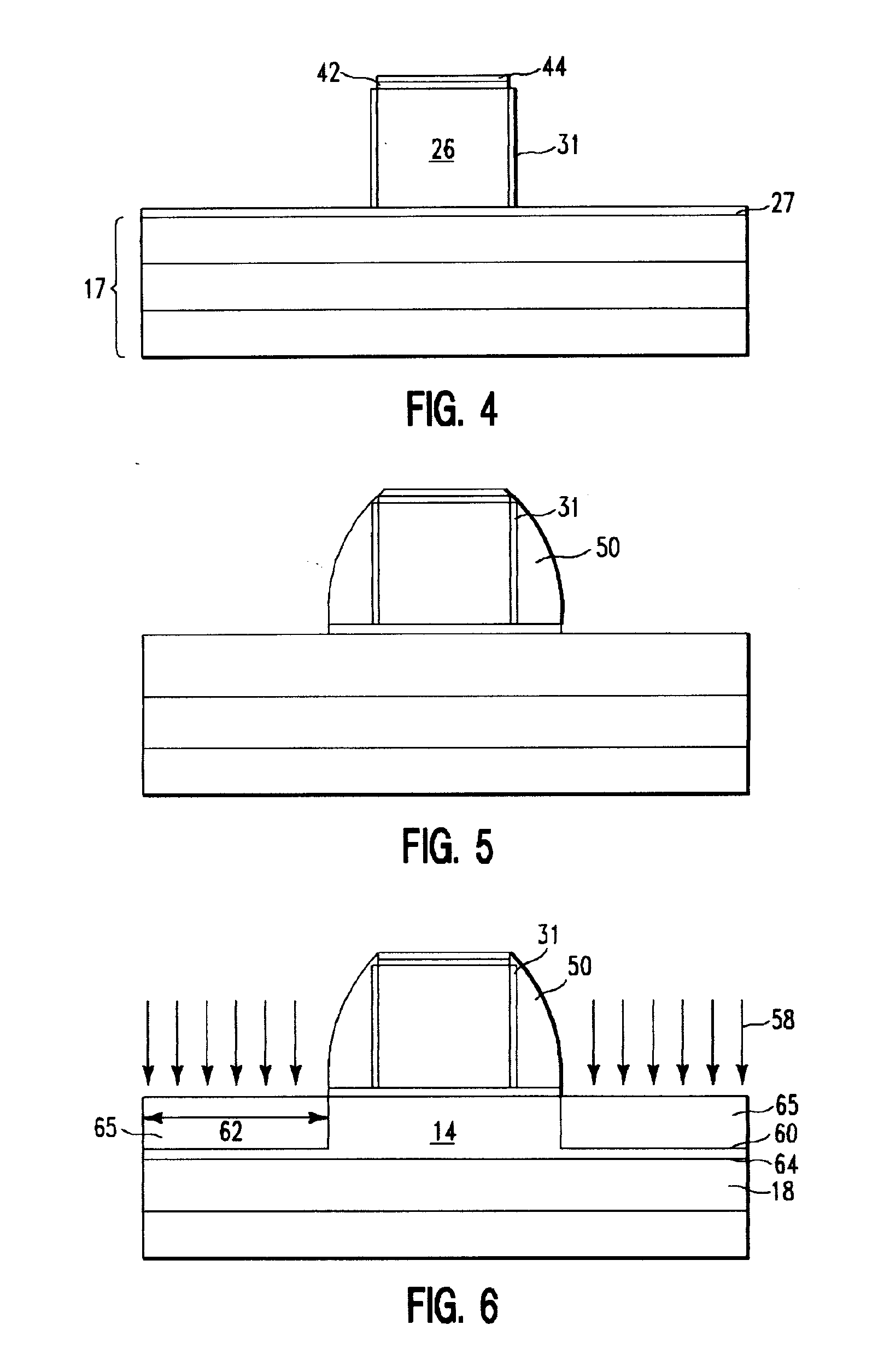

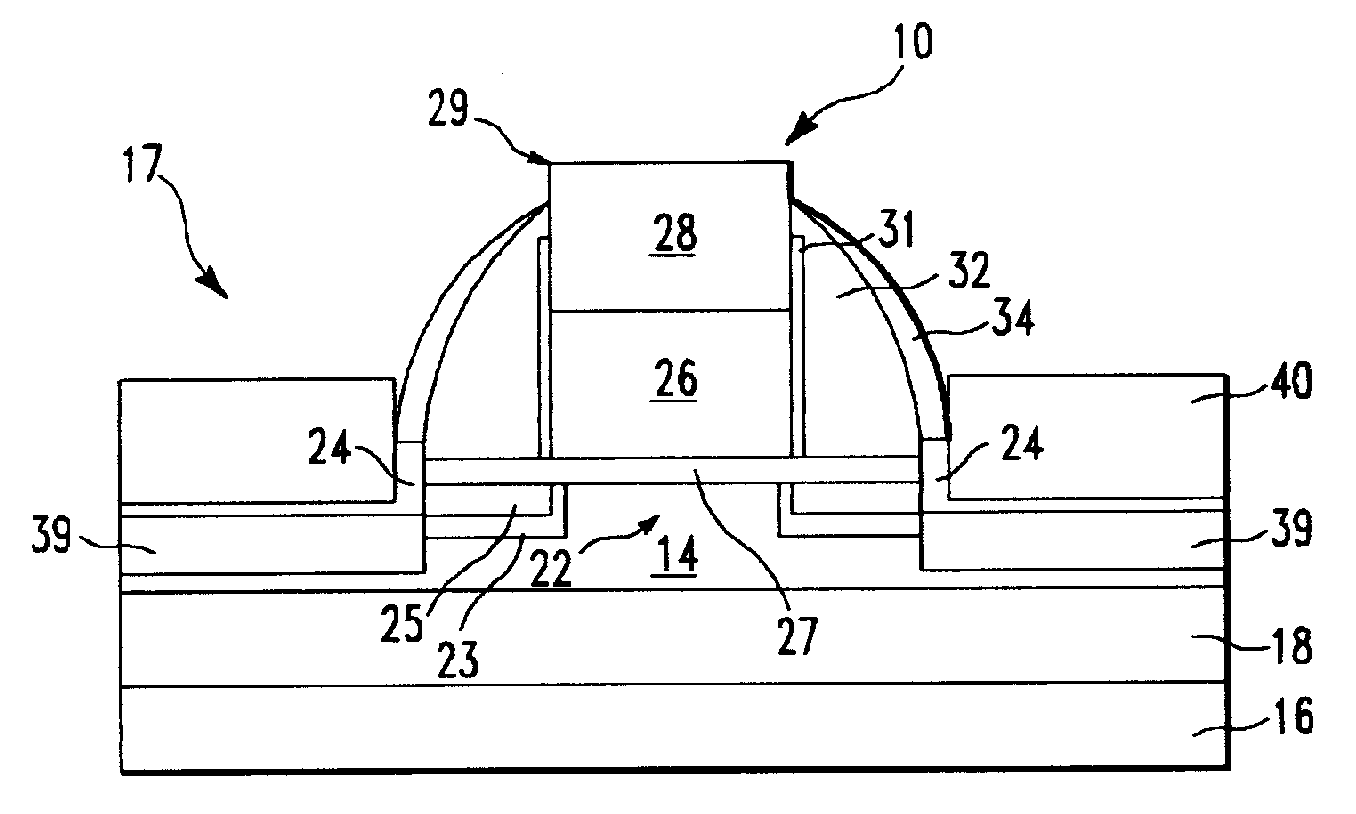

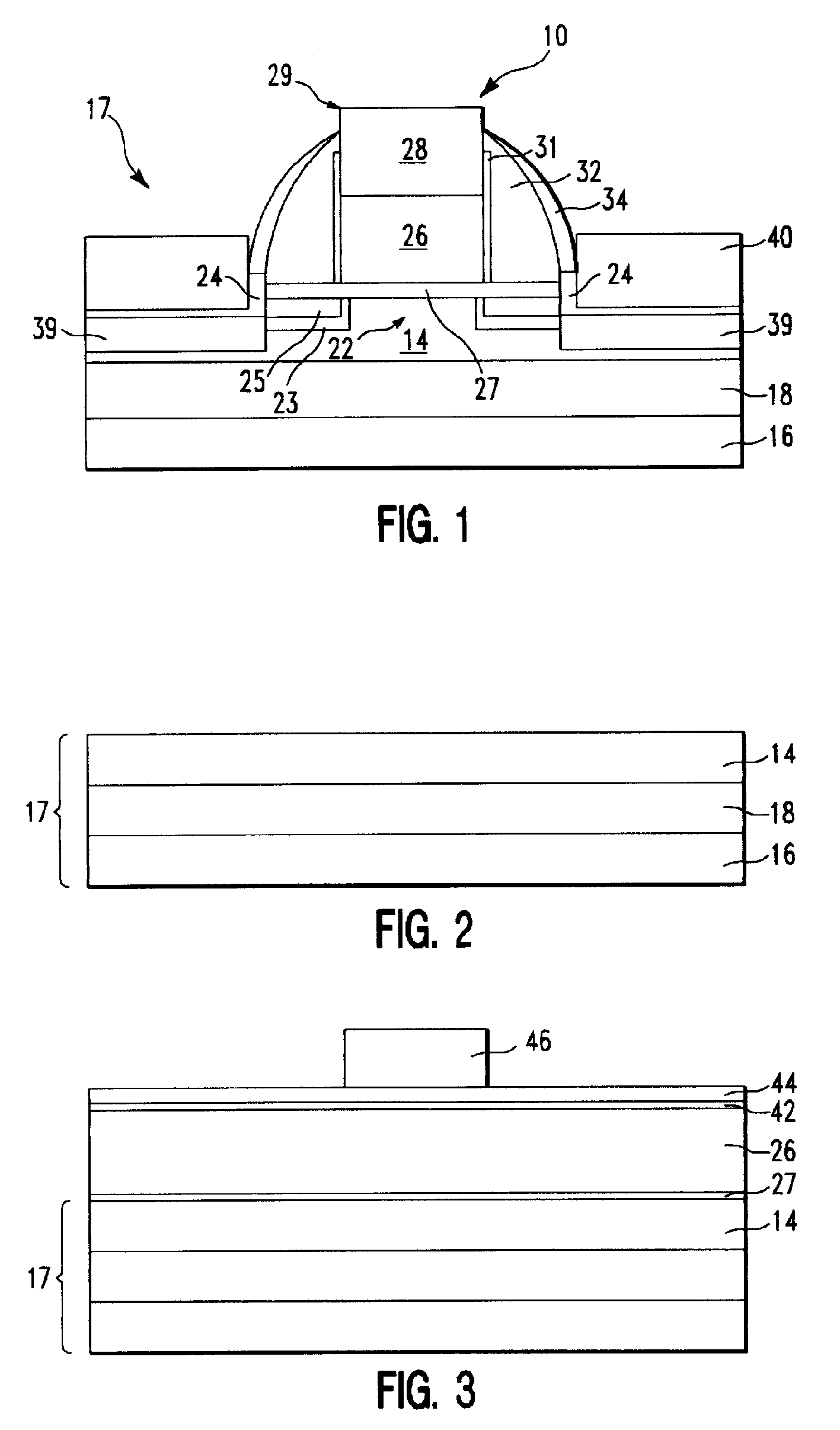

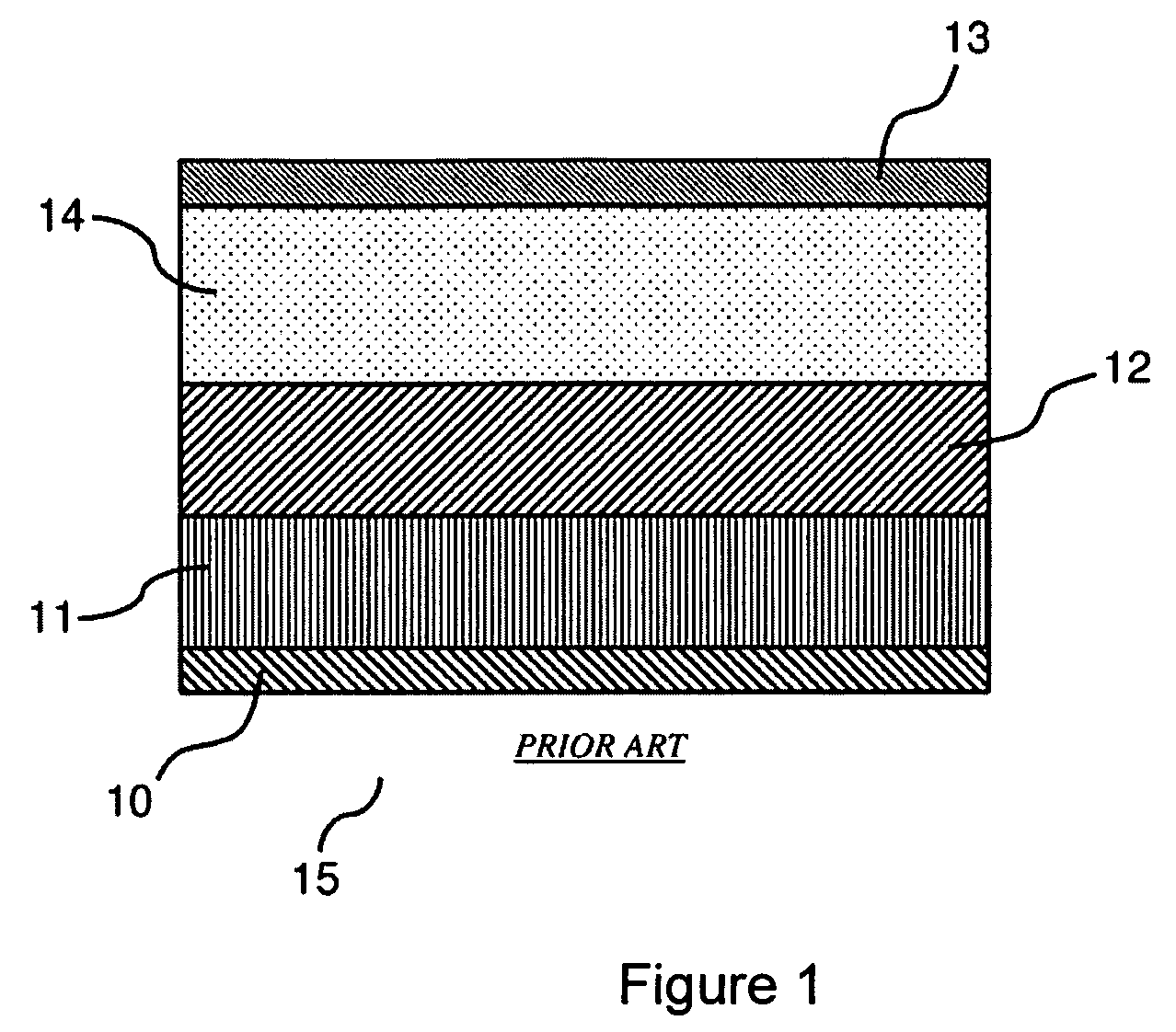

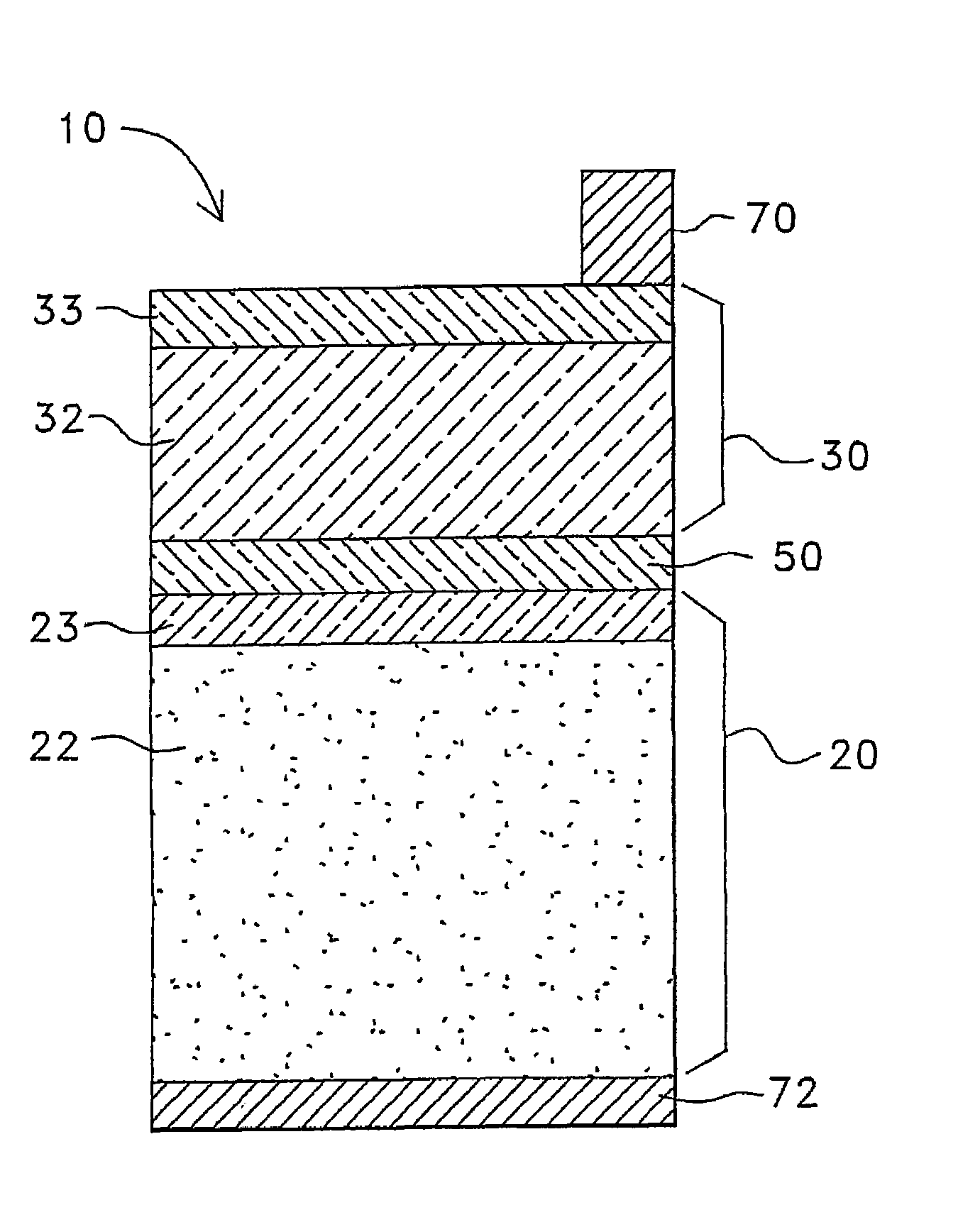

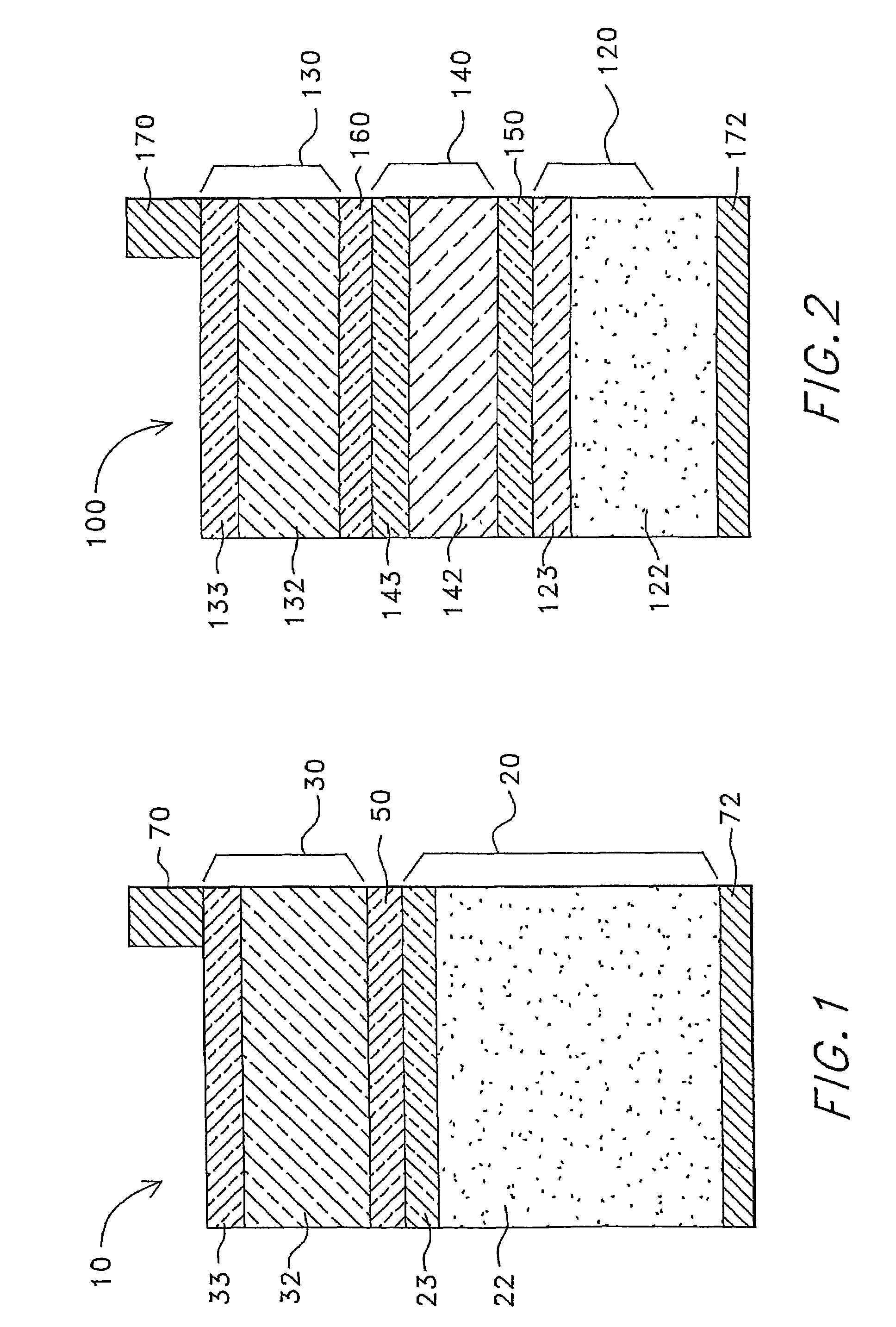

Multi-junction solar cell device

InactiveUS7309832B2Not affectPV power plantsSemiconductor/solid-state device manufacturingChemical structureAlloy

A multi-junction solar cell device (10) is provided. The multi-junction solar cell device (10) comprises either two or three active solar cells connected in series in a monolithic structure. The multi-junction device (10) comprises a bottom active cell (20) having a single-crystal silicon substrate base and an emitter layer (23). The multi-junction device (10) further comprises one or two subsequent active cells each having a base layer (32) and an emitter layer (23) with interconnecting tunnel junctions between each active cell. At least one layer that forms each of the top and middle active cells is composed of a single-crystal III-V semiconductor alloy that is substantially lattice-matched to the silicon substrate (22). The polarity of the active p-n junction cells is either p-on-n or n-on-p. The present invention further includes a method for substantially lattice matching single-crystal III-V semiconductor layers with the silicon substrate (22) by including boron and / or nitrogen in the chemical structure of these layers.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

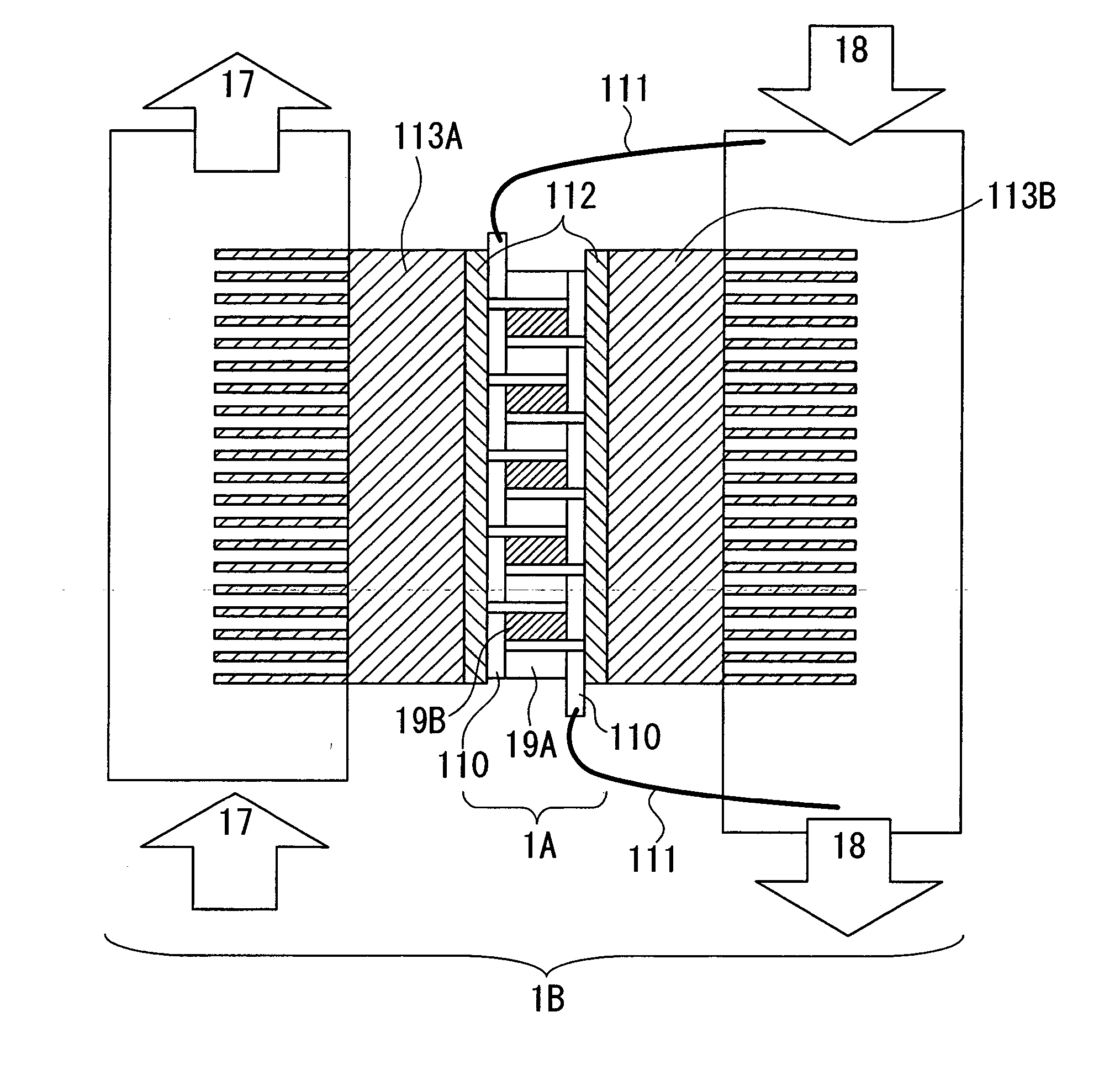

Process for producing thermoelectric semiconductor alloy, thermoelectric conversion module, thermoelectric power generating device, rare earth alloy, producing process thereof, thermoelectric conversion material, and thermoelectric conversion system using filled skutterudite based alloy

InactiveUS20070034245A1Improve power generation efficiencyEffective measure against global warmingThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentSkutteruditeSemiconductor alloys

The present invention is a process for producing a rare earth alloy including heating a raw material alloy which is compounded so as to have a composition represented by the formula: A3−XBXC (wherein A and B each is at least one member selected from transition metals consisting of Fe, Co, Ni, Ti, V, Cr, Zr, Hf, Nb, Mo, Ta and W, and C is at least one member selected from Group 13 or 14 elements consisting of Al, Ga, In, Si, Ge and Sn) to be a molten ally, and quench-solidifying the molten alloy at a cooling rate of 1×102 to 1×103° C. / sec.

Owner:SHOWA DENKO KK

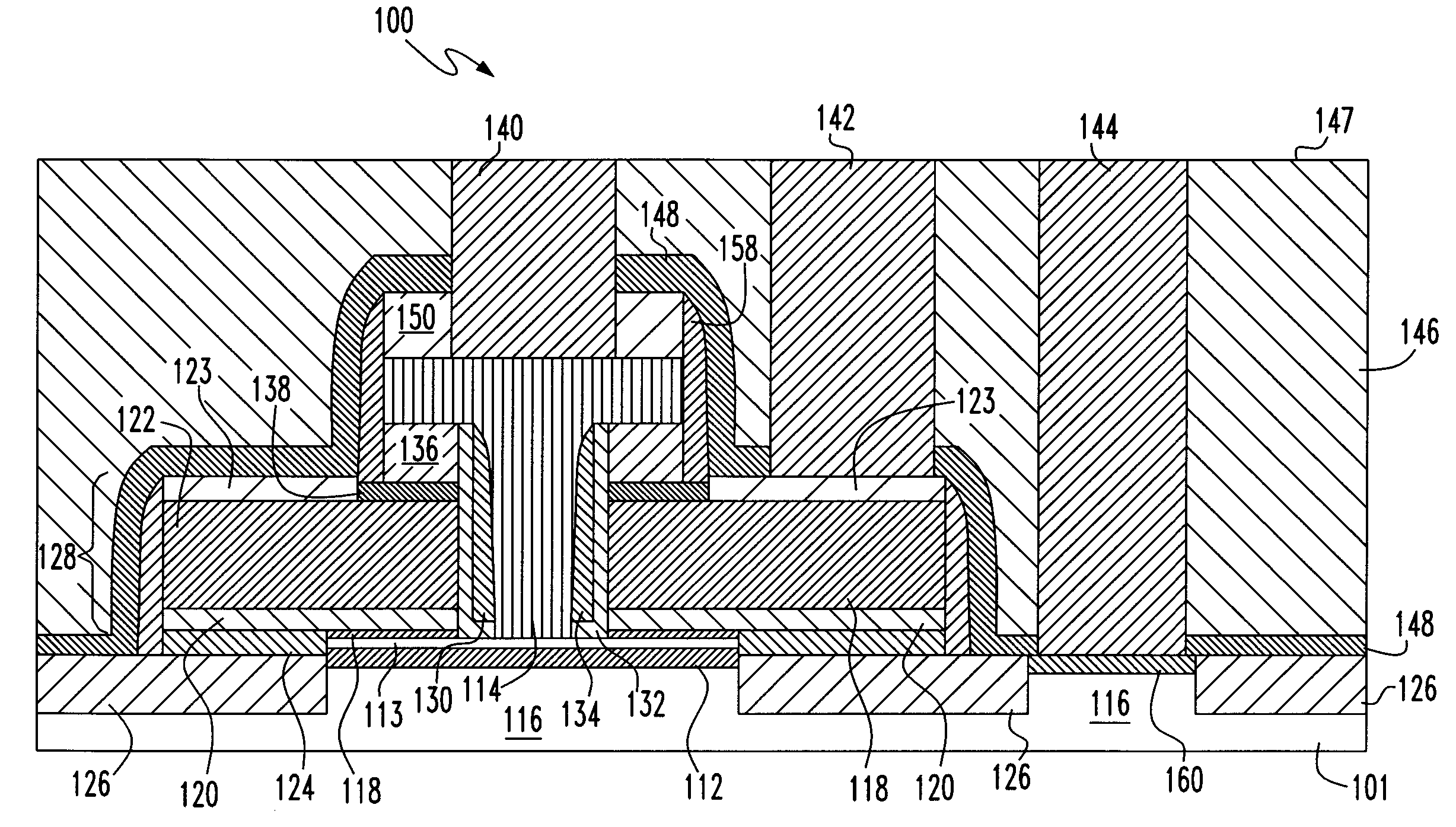

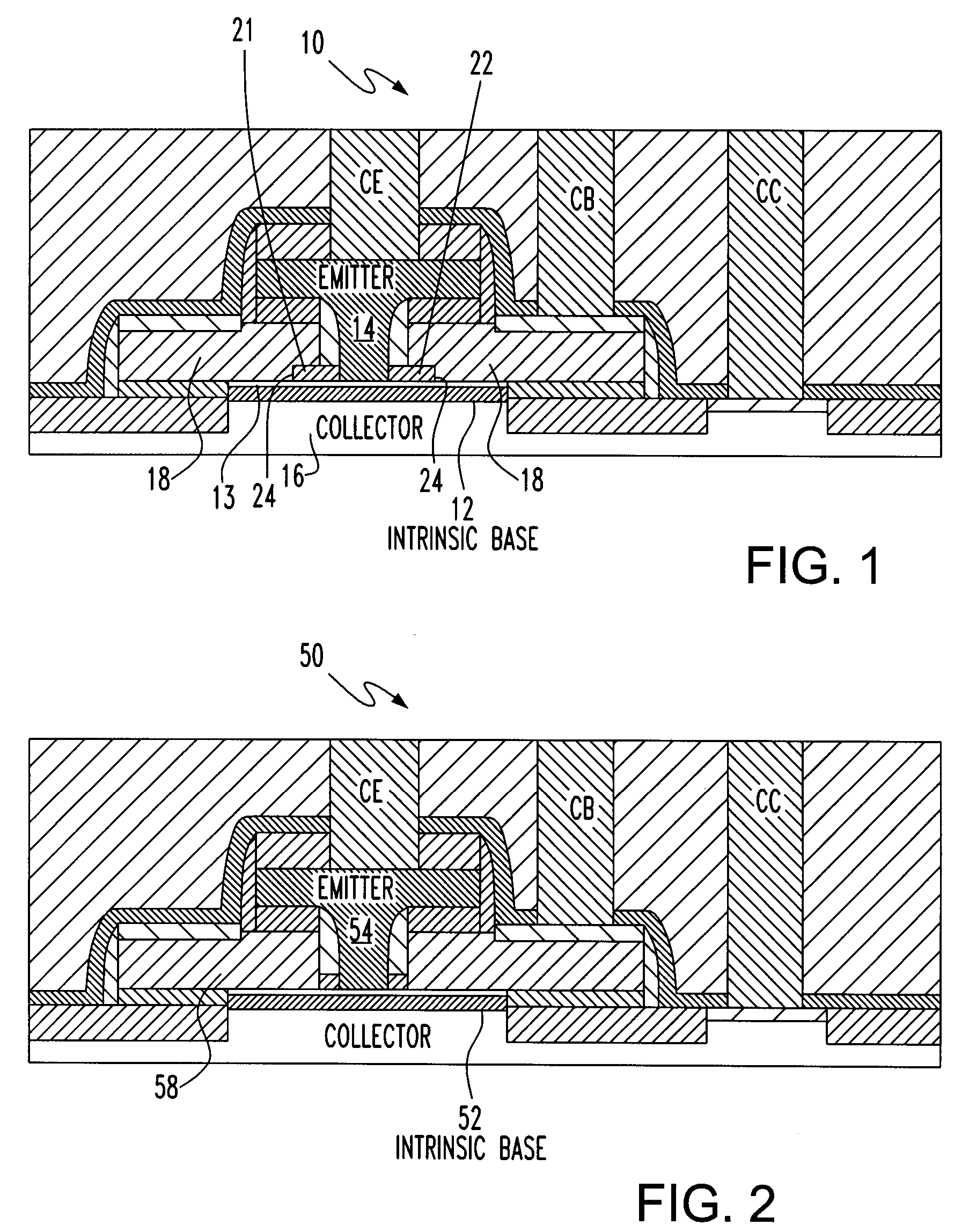

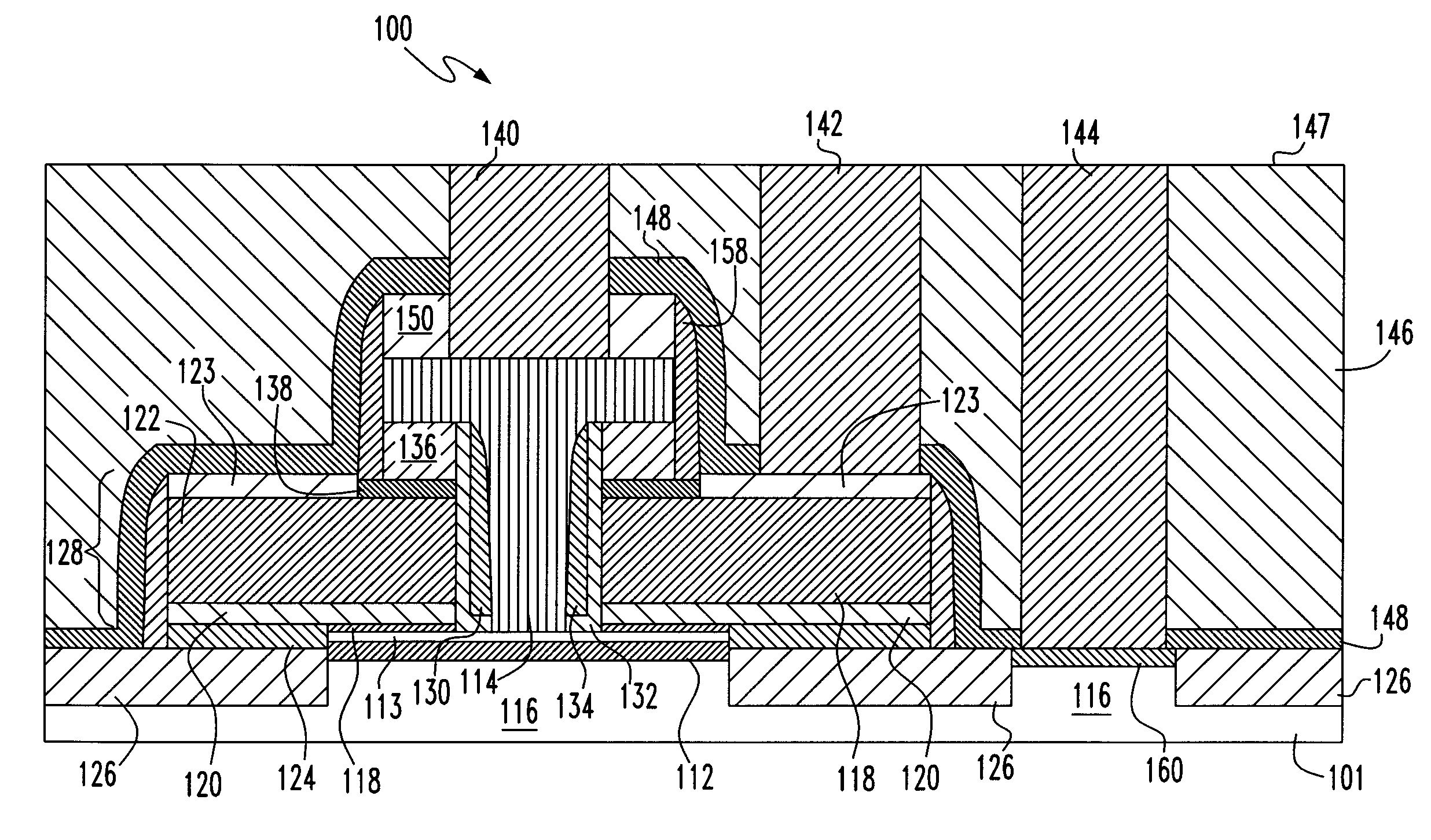

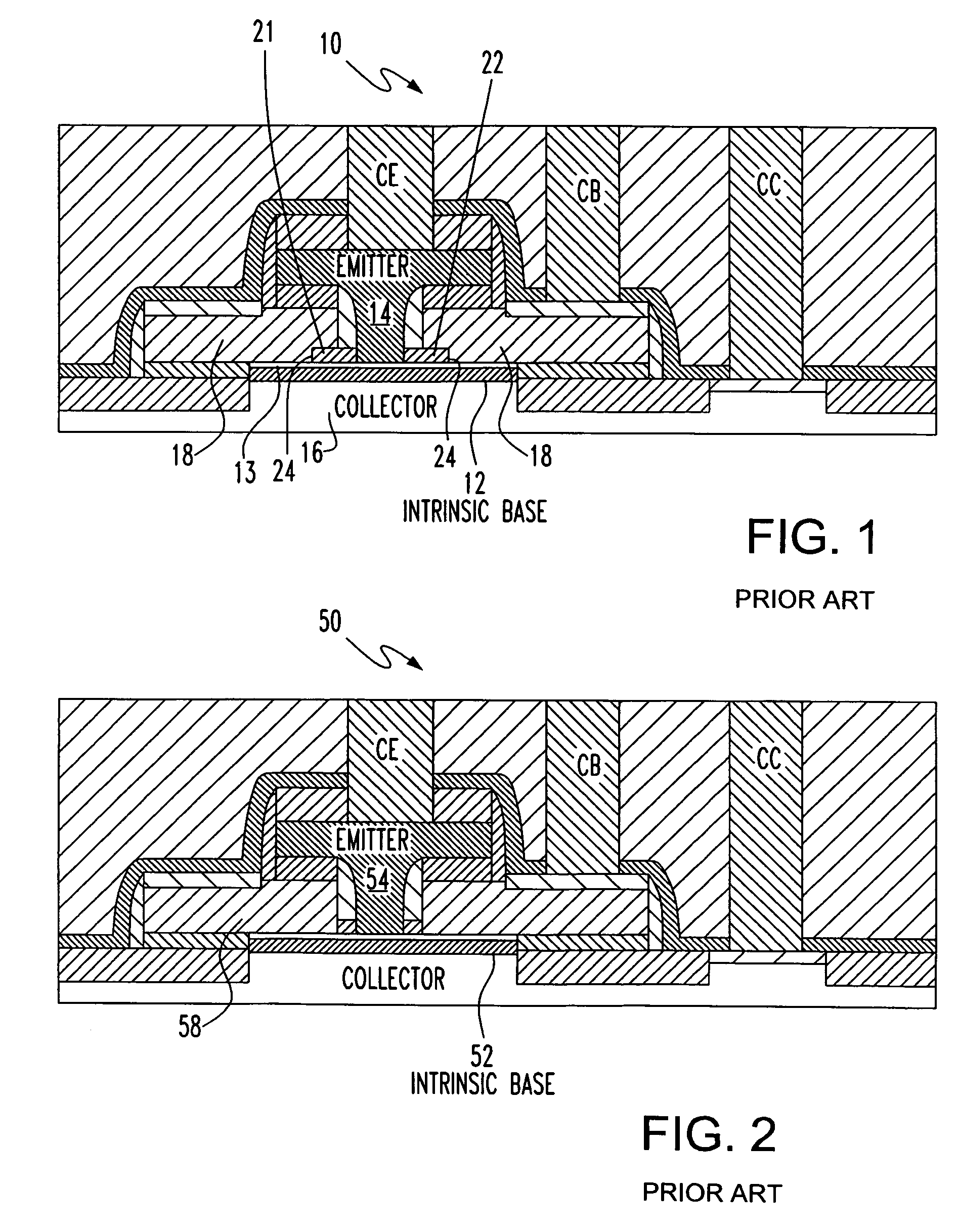

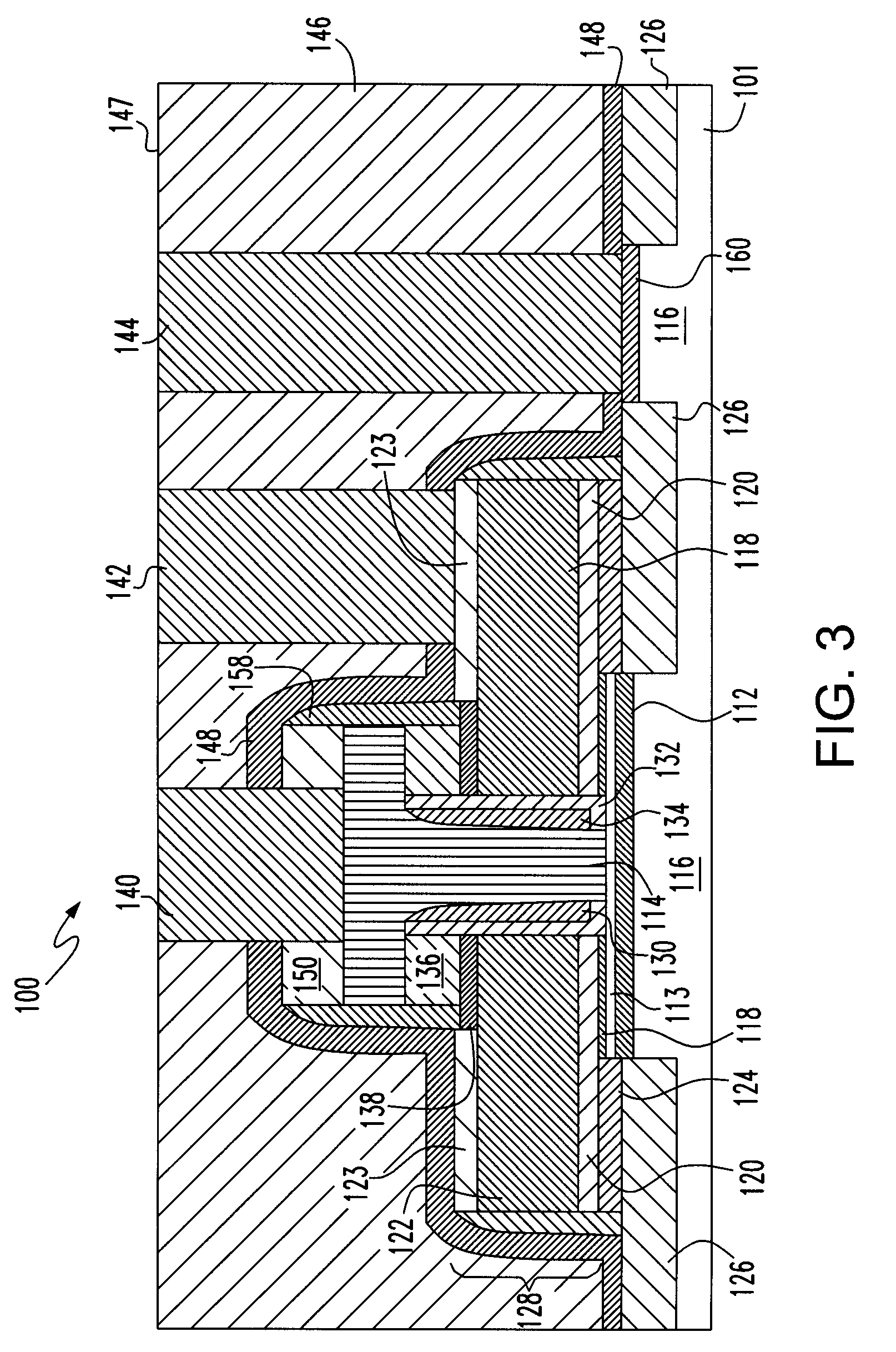

Structure and method of making heterojunction bipolar transistor having self-aligned silicon-germanium raised extrinsic base

InactiveUS20050151165A1High selectivityLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor alloys

A heterojunction bipolar transistor (HBT) and method of making an HBT are provided. The HBT includes a collector, and an intrinsic base overlying the collector. The intrinsic base includes a layer of a single-crystal semiconductor alloy. The HBT further includes a raised extrinsic base having a first semiconductive layer overlying the intrinsic base and a second semiconductive layer formed on the first semiconductive layer. An emitter overlies the intrinsic base, and is disposed in an opening of the first and second semi-conductive layers, such that the raised extrinsic base is self-aligned to the emitter.

Owner:IBM CORP

Structure and method for making heterojunction bipolar transistor having self-aligned silicon-germanium raised extrinsic base

InactiveUS6982442B2High selectivityLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor alloys

A heterojunction bipolar transistor (HBT) and method of making an HBT are provided. The HBT includes a collector, and an intrinsic base overlying the collector. The intrinsic base includes a layer of a single-crystal semiconductor alloy. The HBT further includes a raised extrinsic base having a first semiconductive layer overlying the intrinsic base and a second semiconductive layer formed on the first semiconductive layer. An emitter overlies the intrinsic base, and is disposed in an opening of the first and second semiconductive layers, such that the raised extrinsic base is self-aligned to the emitter.

Owner:INT BUSINESS MASCH CORP

CMOS device comprising an nmos transistor with recessed drain and source areas and a pmos transistor having a silicon/germanium material in the drain and source areas

InactiveUS20090218633A1Enhanced transistor performanceImprove compatibilityTransistorSolid-state devicesCMOSSemiconductor alloys

A recessed transistor configuration may be provided selectively for one type of transistor, such as N-channel transistors, thereby enhancing strain-inducing efficiency and series resistance, while a substantially planar configuration or raised drain and source configuration may be provided for other transistors, such as P-channel transistors, which may also include a strained semiconductor alloy, while nevertheless providing a high degree of compatibility with CMOS techniques. For this purpose, an appropriate masking regime may be provided to efficiently cover the gate electrode of one transistor type during the formation of the corresponding recesses, while completely covering the other type of transistor.

Owner:ADVANCED MICRO DEVICES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com