Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Enhanced transistor performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

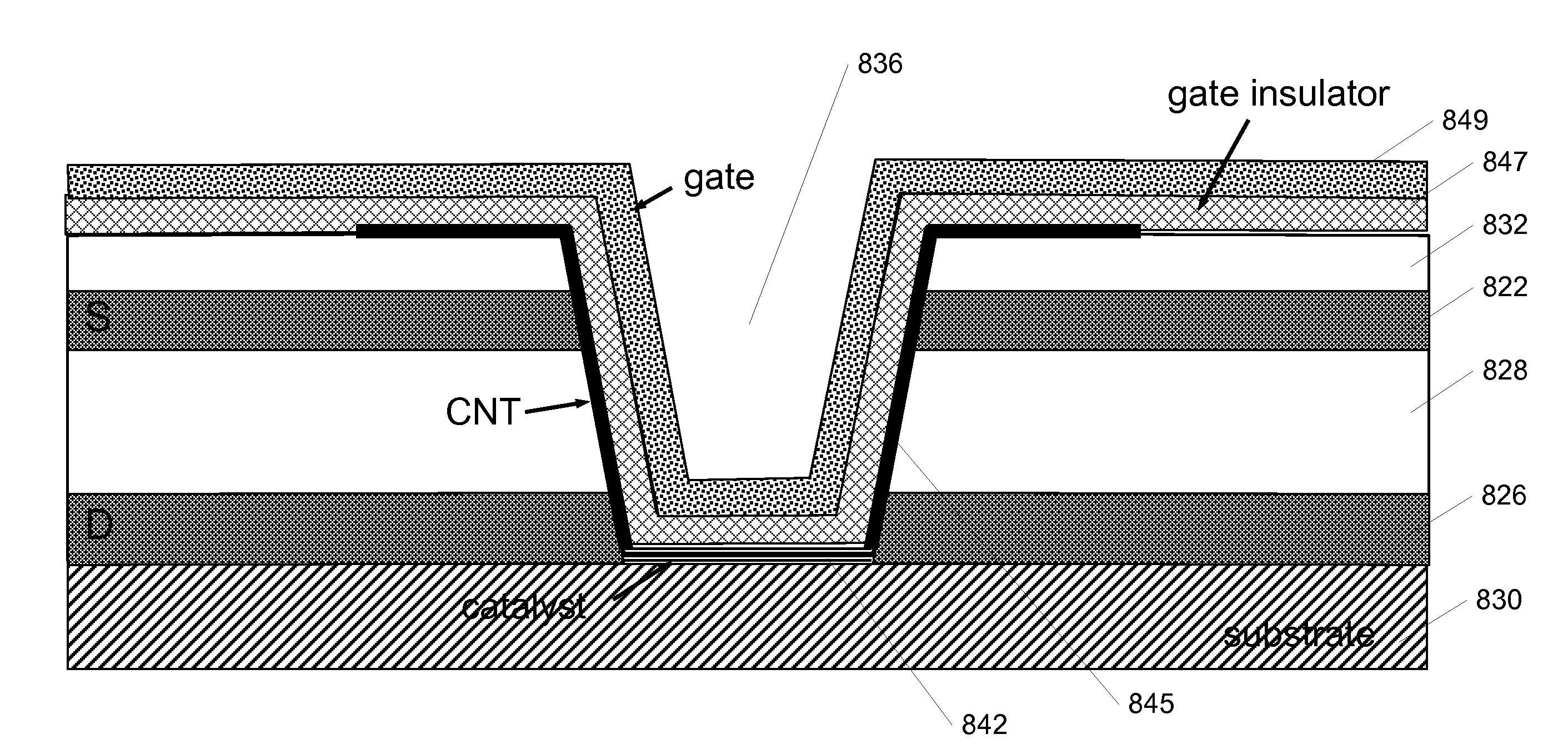

Edge-Contacted Vertical Carbon Nanotube Transistor

InactiveUS20090166686A1Maximize Power DensityDensely packedNanoinformaticsSolid-state devicesCarbon nanotubeField-effect transistor

A vertical device geometry for a carbon-nanotube-based field effect transistor has one or multiple carbon nanotubes formed in a trench.

Owner:ETAMOTA CORP

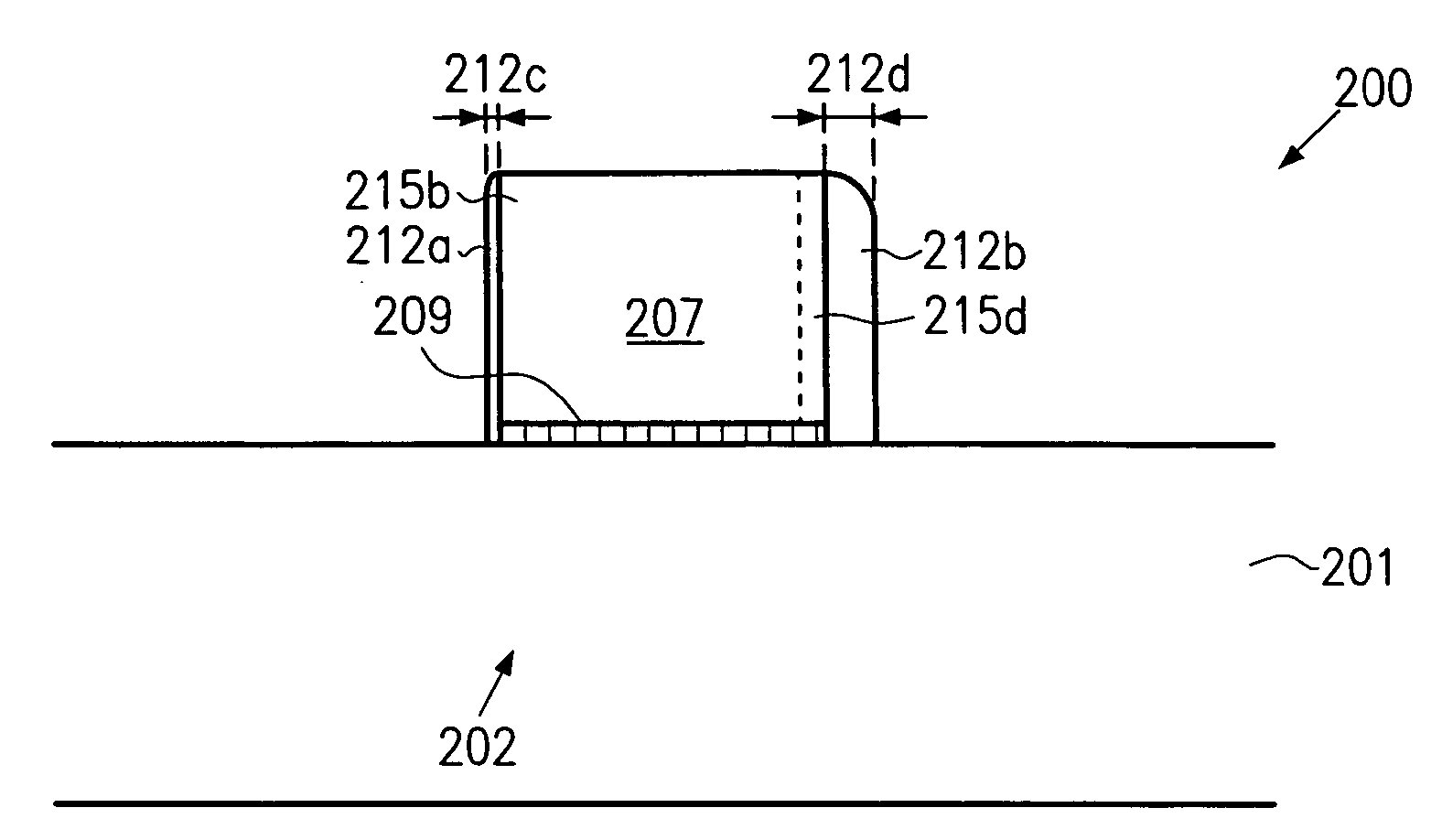

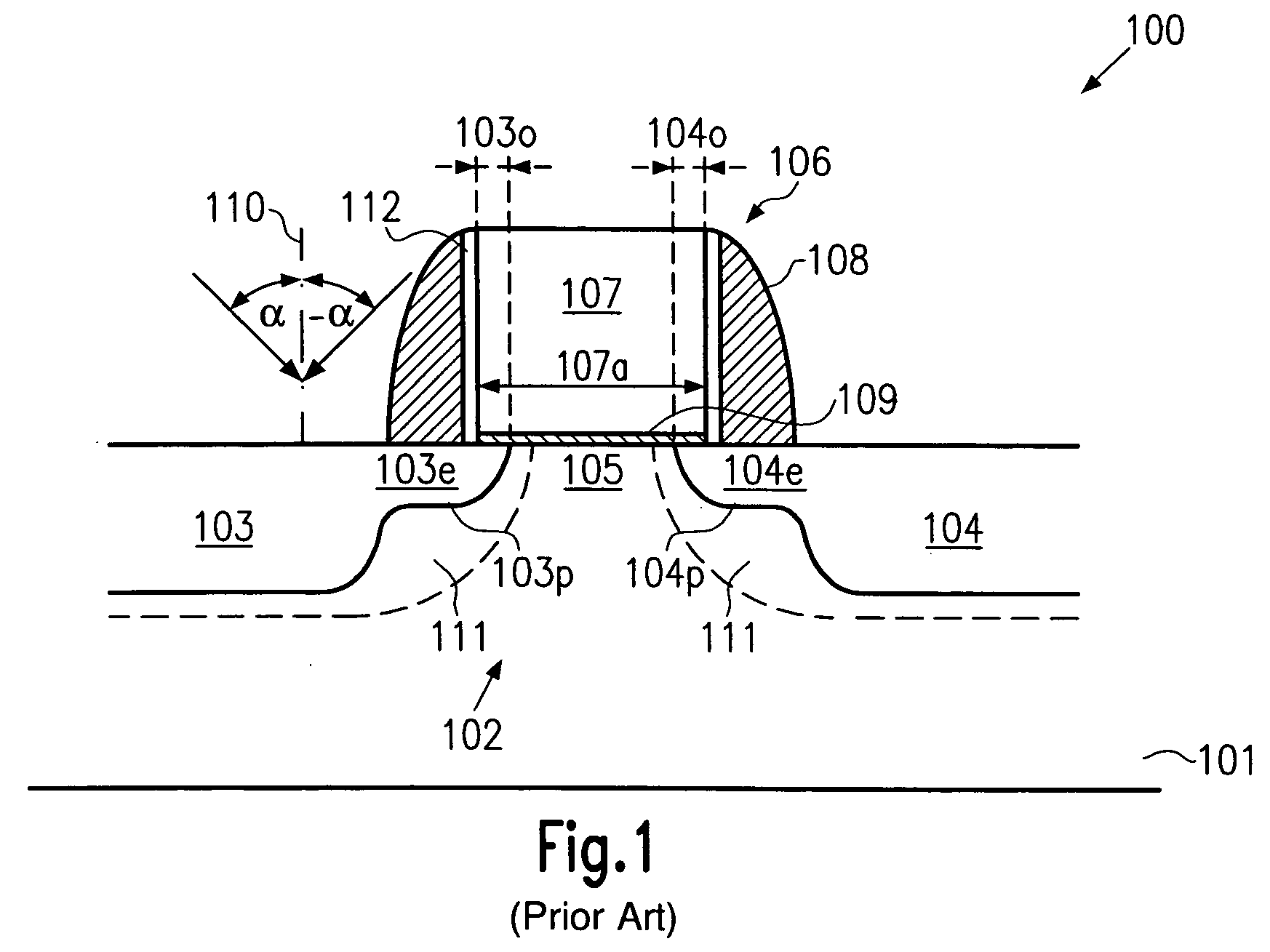

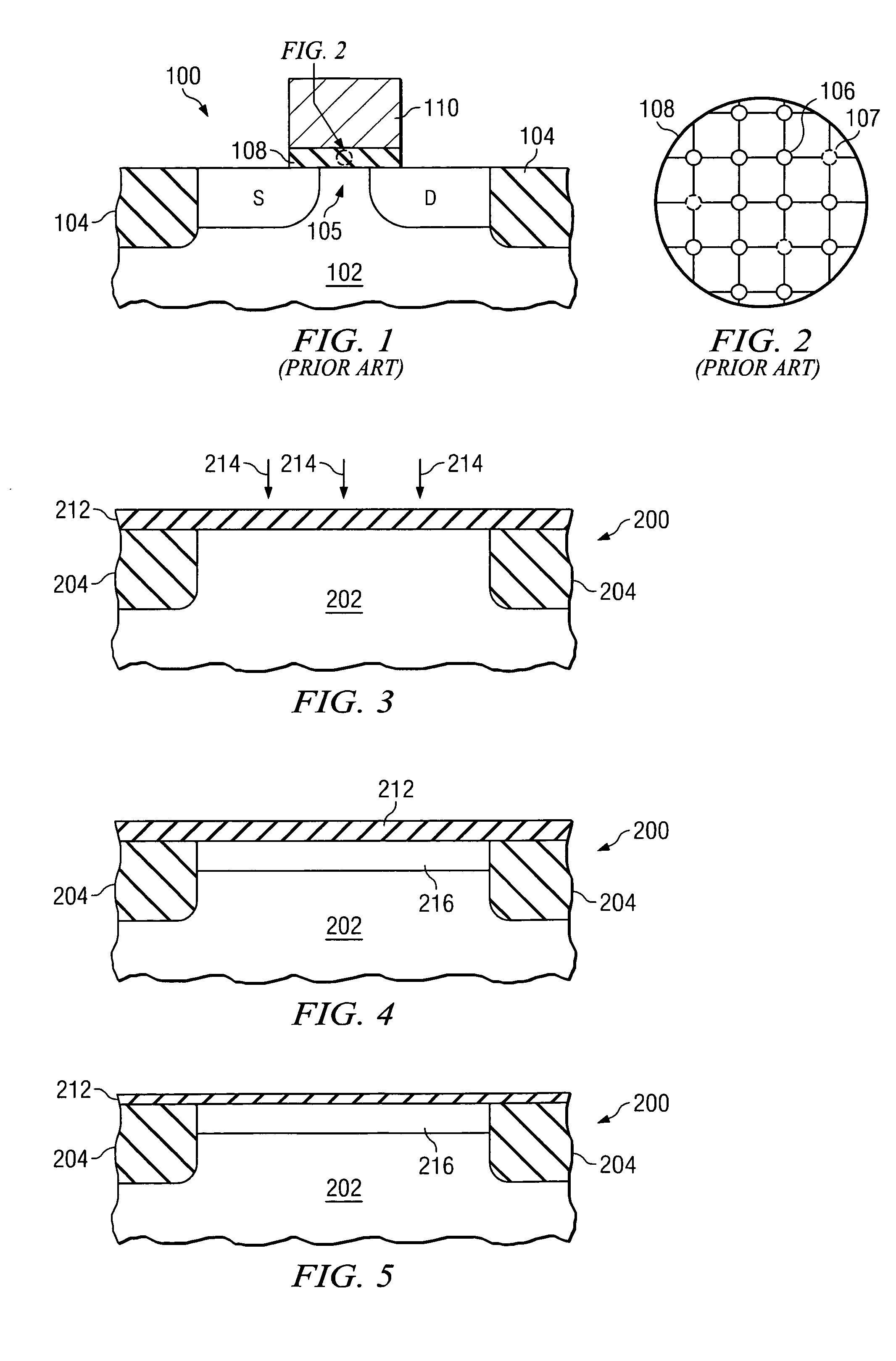

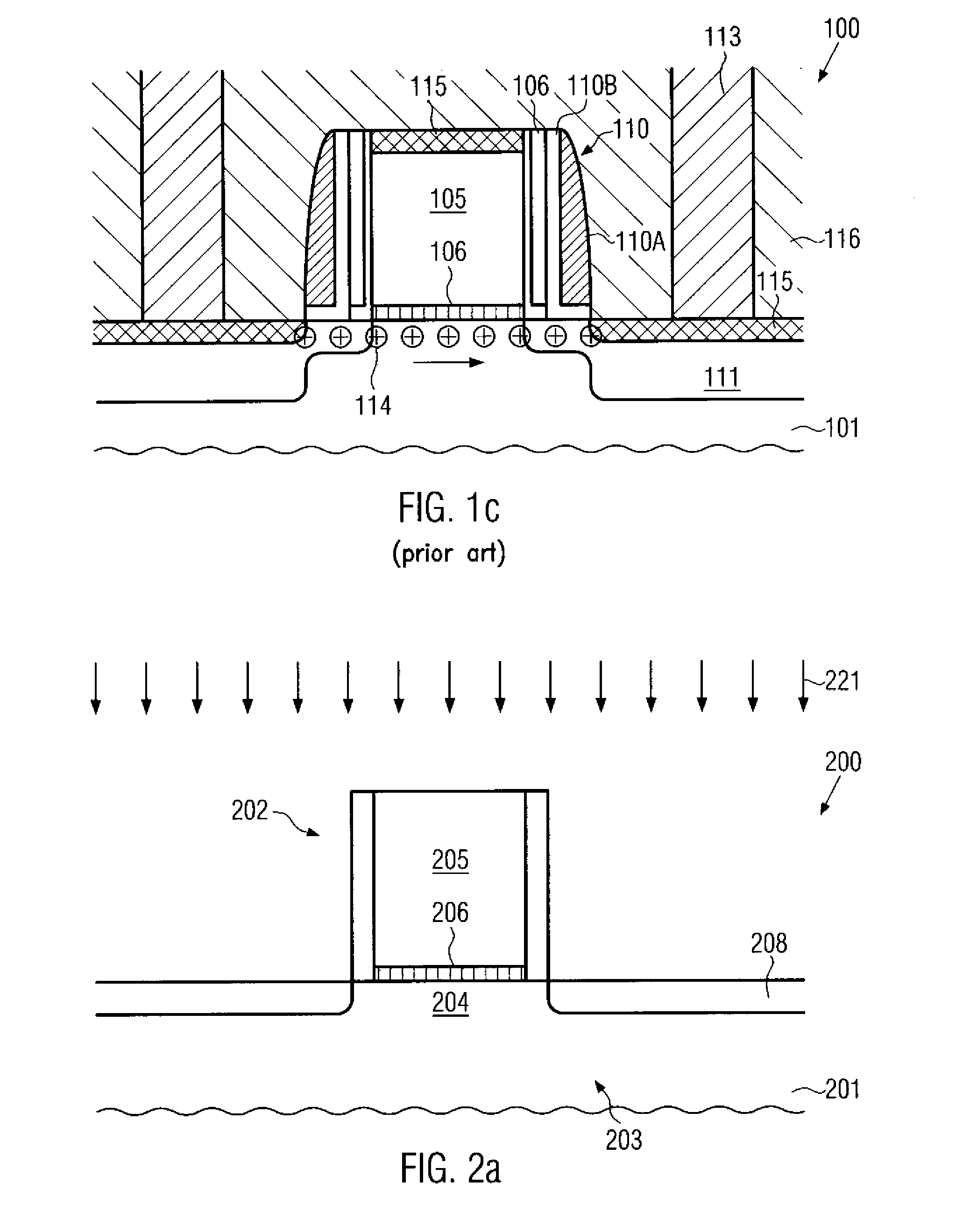

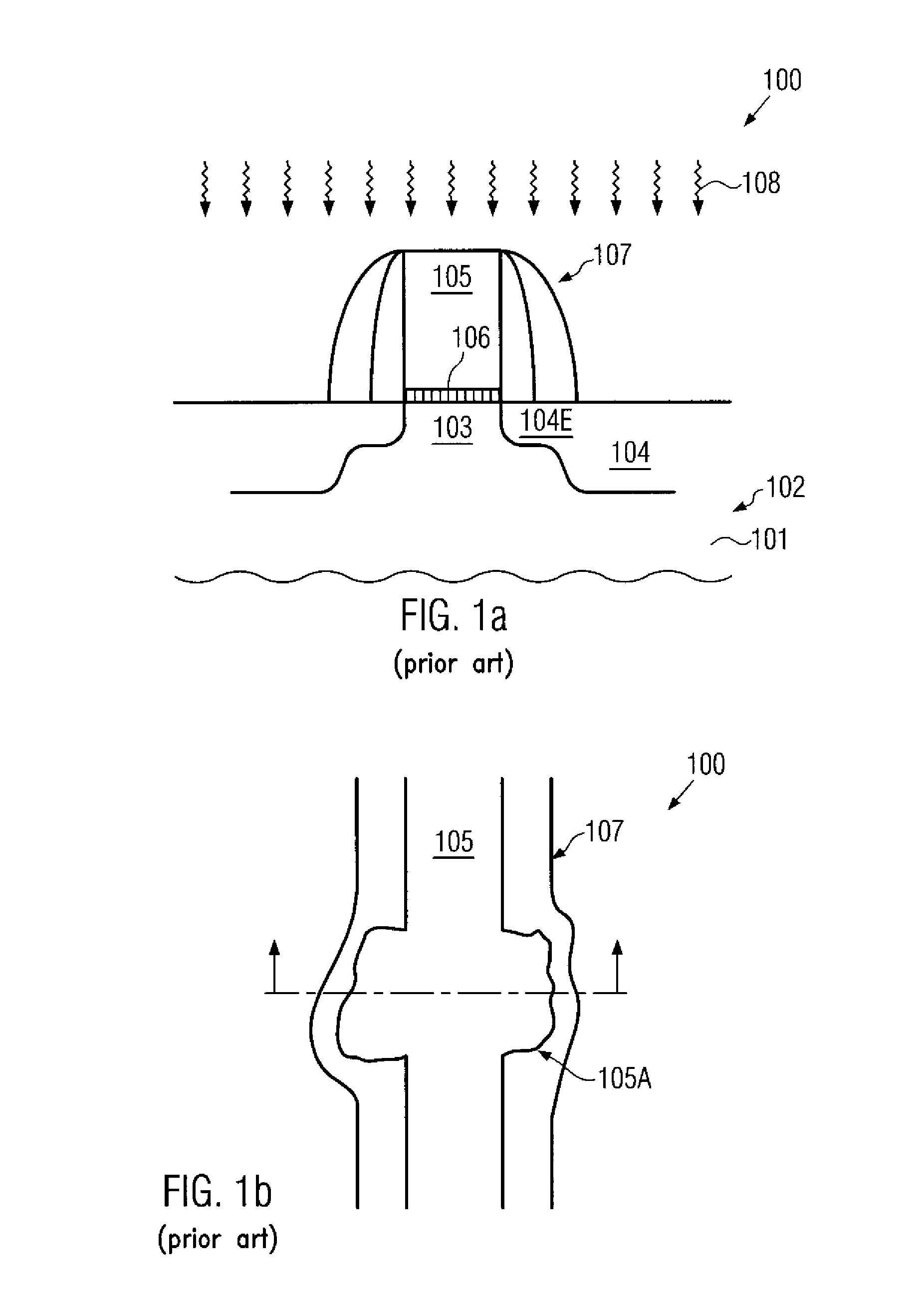

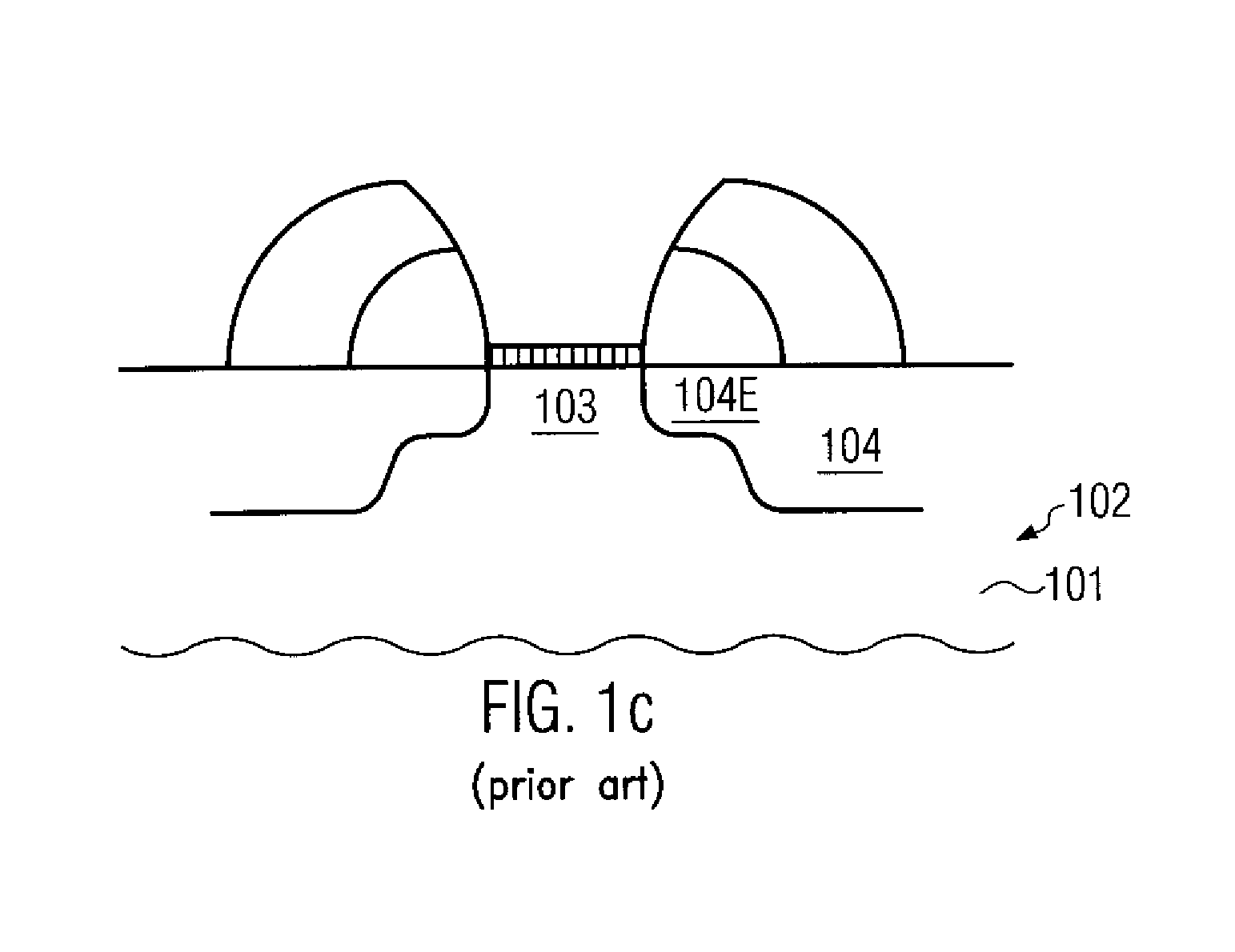

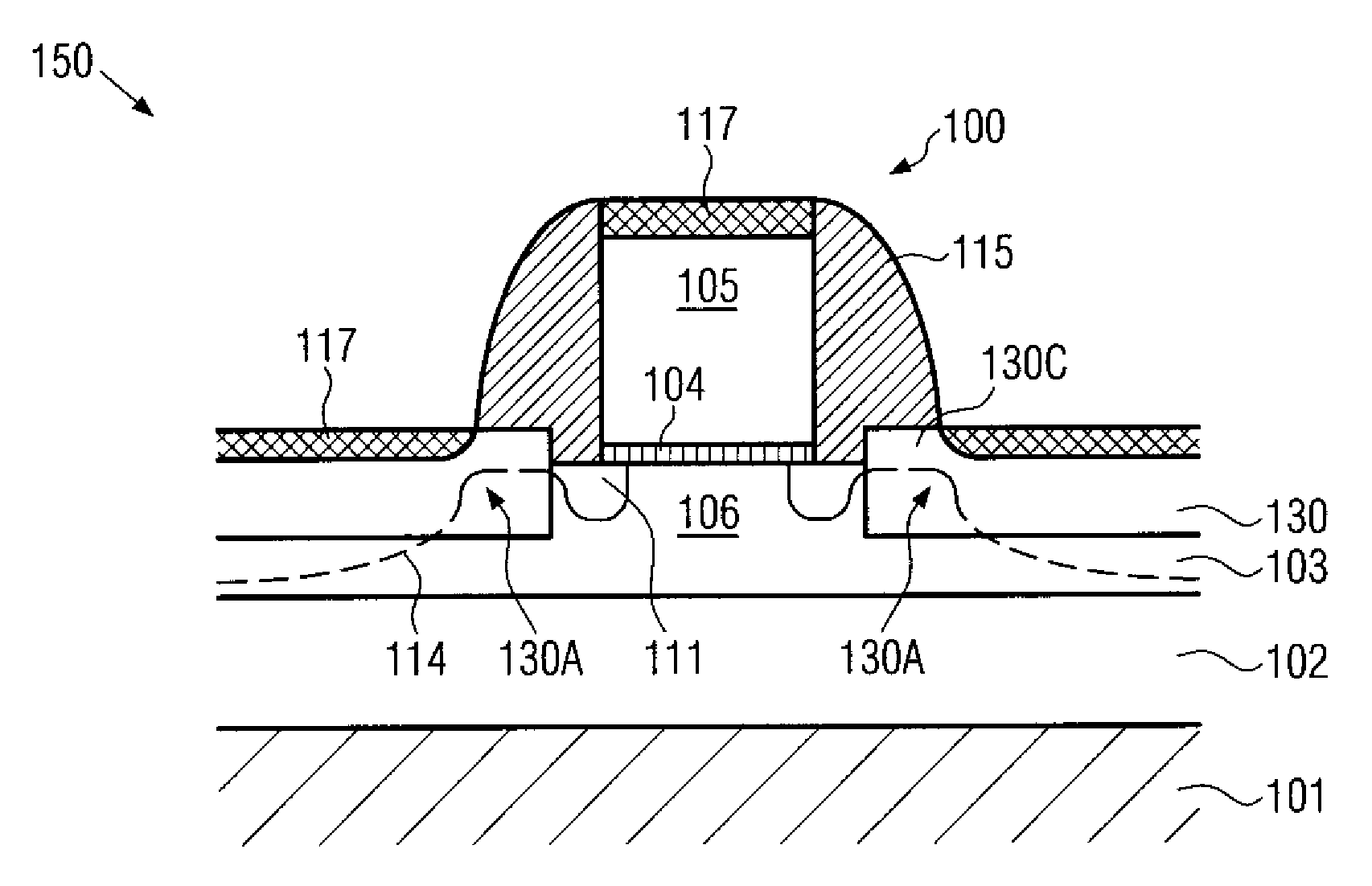

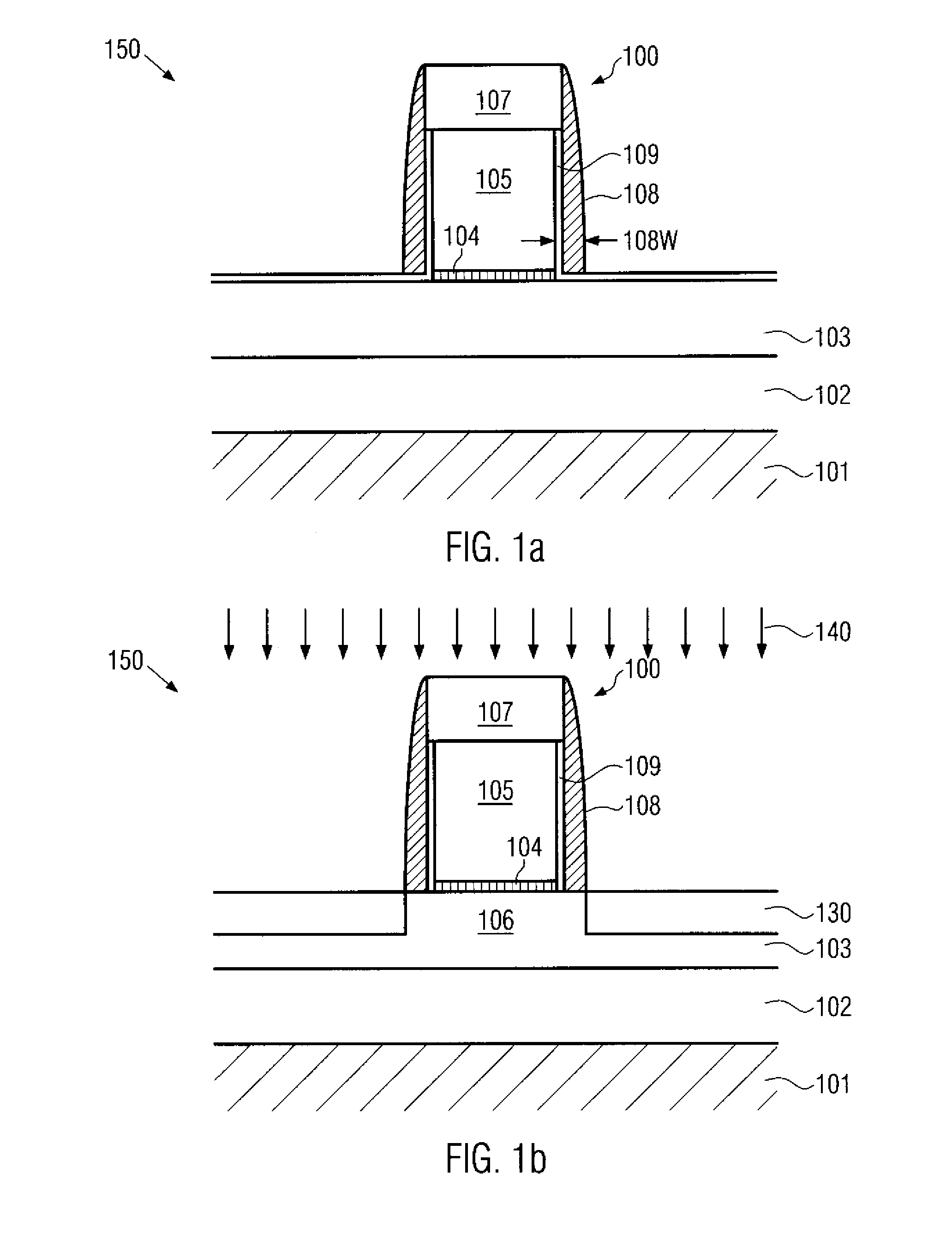

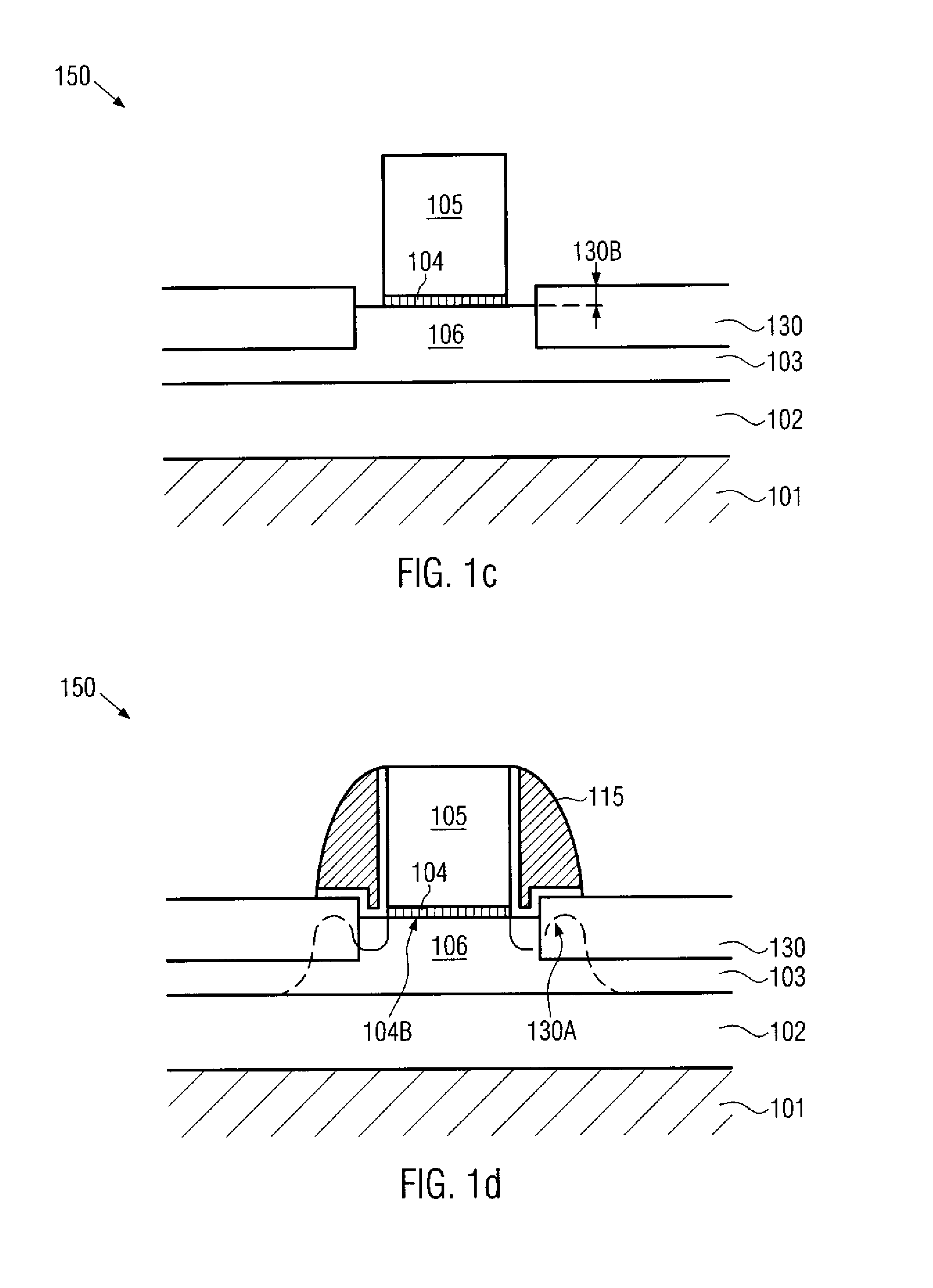

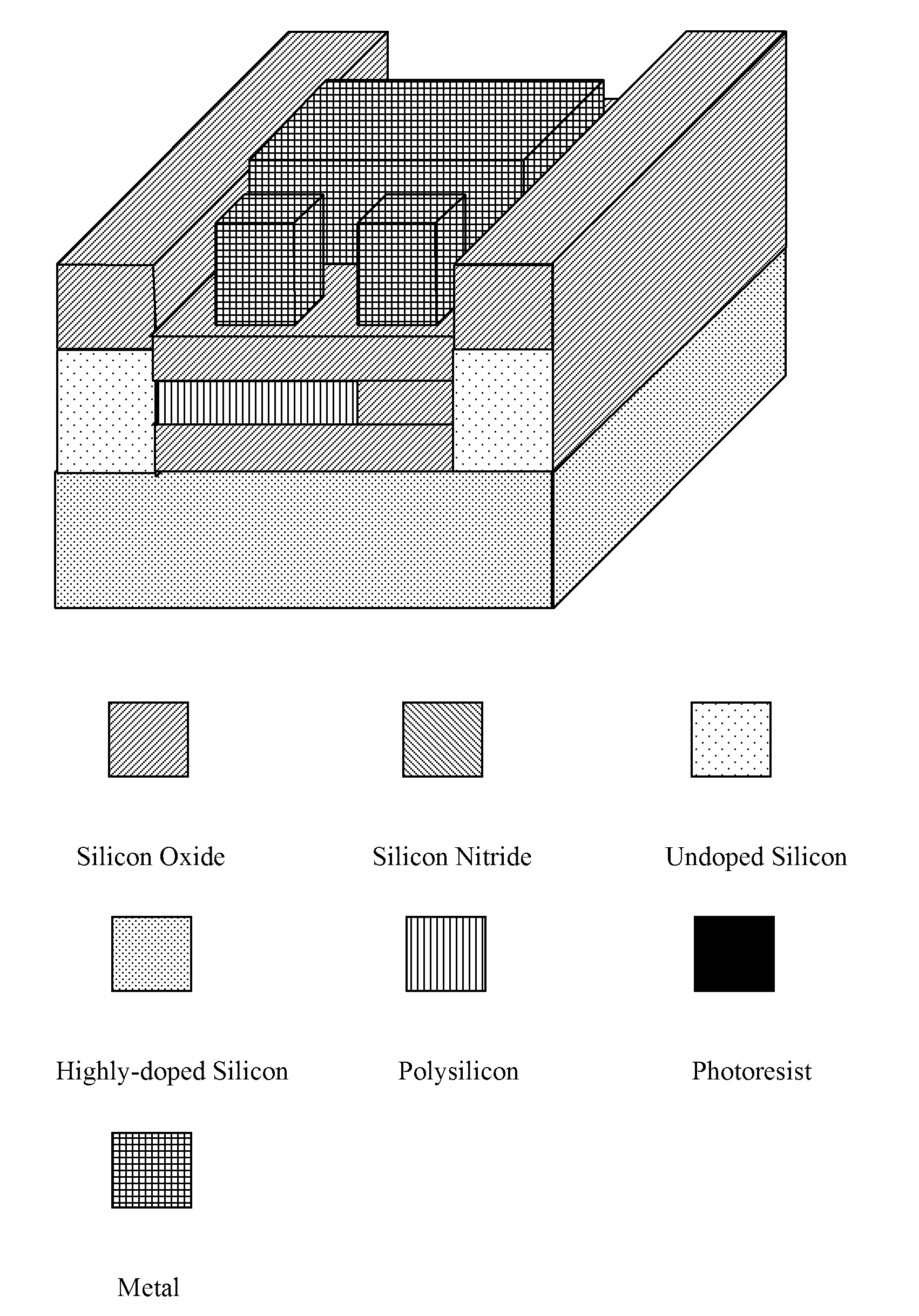

Gate structure and a transistor having asymmetric spacer elements and methods of forming the same

ActiveUS20060194381A1Improve current drive capabilityReduce staticSemiconductor/solid-state device manufacturingSemiconductor devicesNon symmetricEngineering

Methods for forming asymmetric gate structures comprising spacer elements disposed on the opposed sides of a gate electrode and having a different width are disclosed. The asymmetric gate structures are employed to form an asymmetric design of a halo region and extension regions of a field effect transistor using a symmetric implantation scheme, or to further enhance the effectiveness of asymmetric implantation schemes. The transistor performance may be significantly enhanced for a given basic transistor architecture. In particular, a large overlap area may be created at the source side with a steep concentration gradient of the PN junction due to the provision of the halo region, whereas the drain overlap may be significantly reduced or may even be completely avoided to further enhance the transistor performance.

Owner:ADVANCED MICRO DEVICES INC

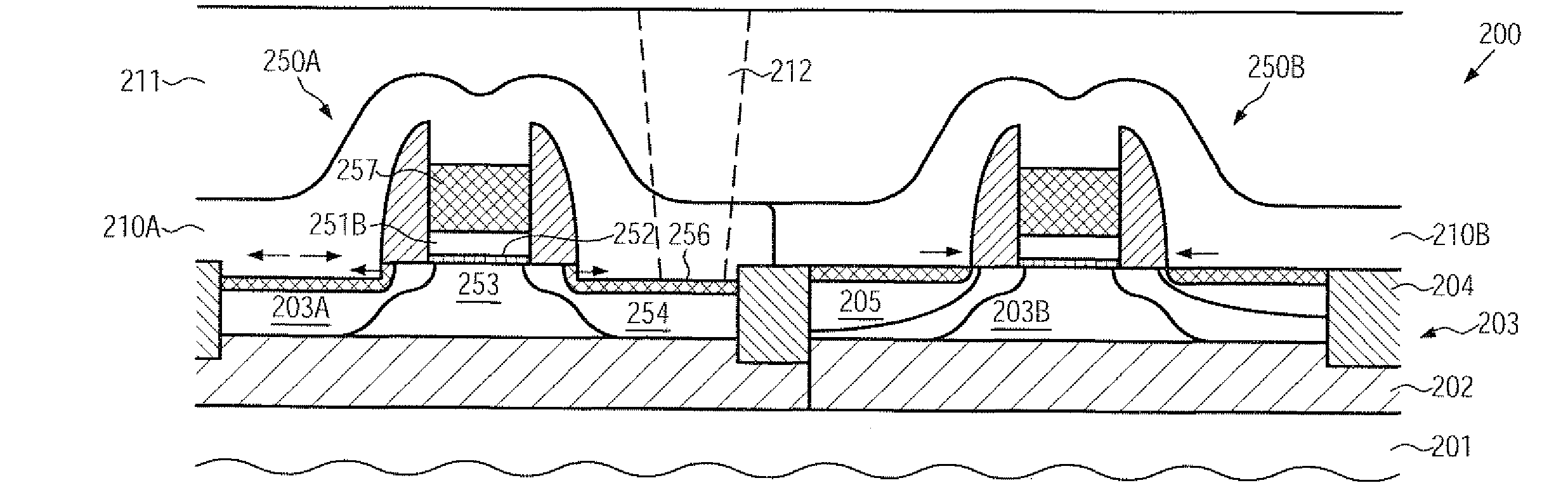

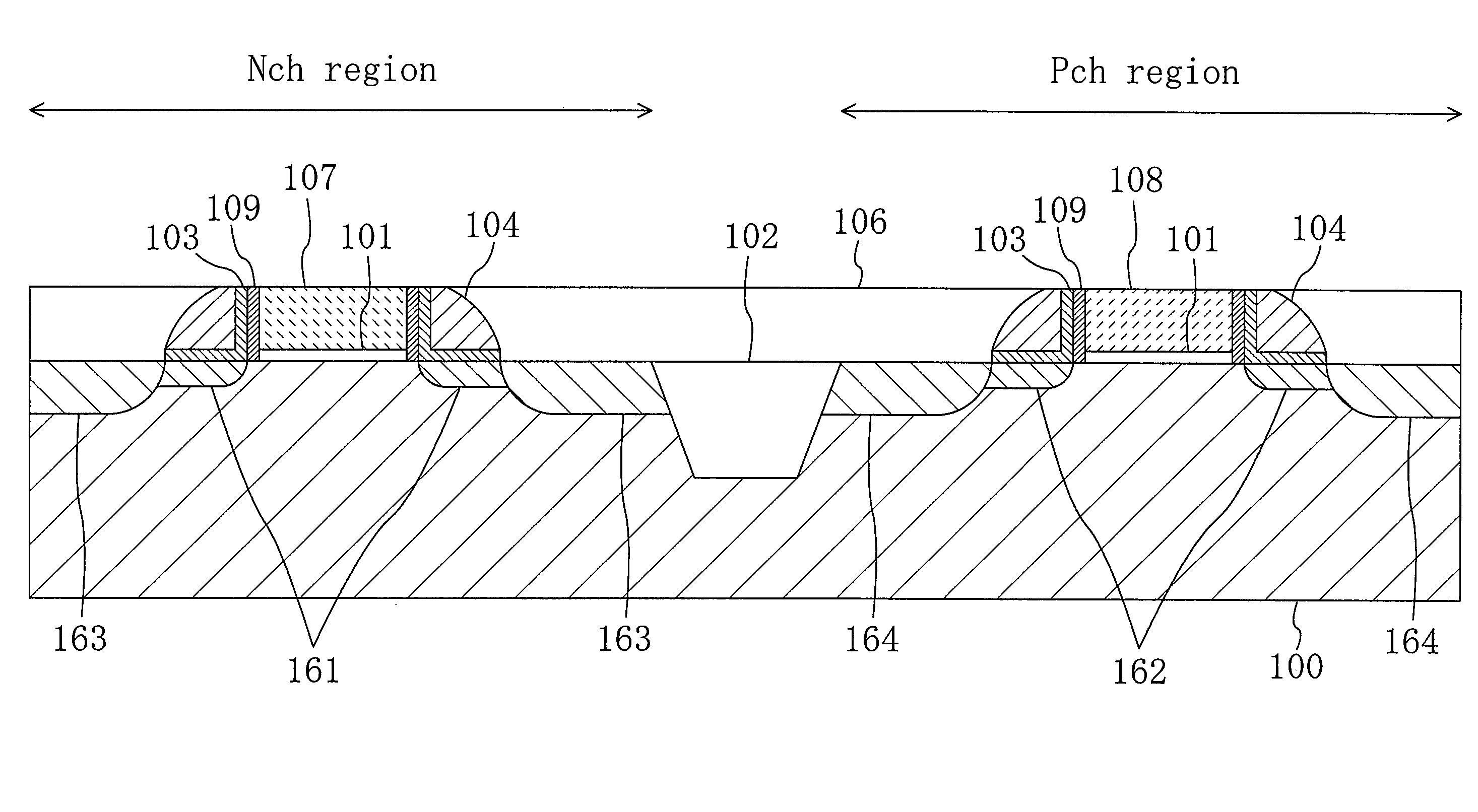

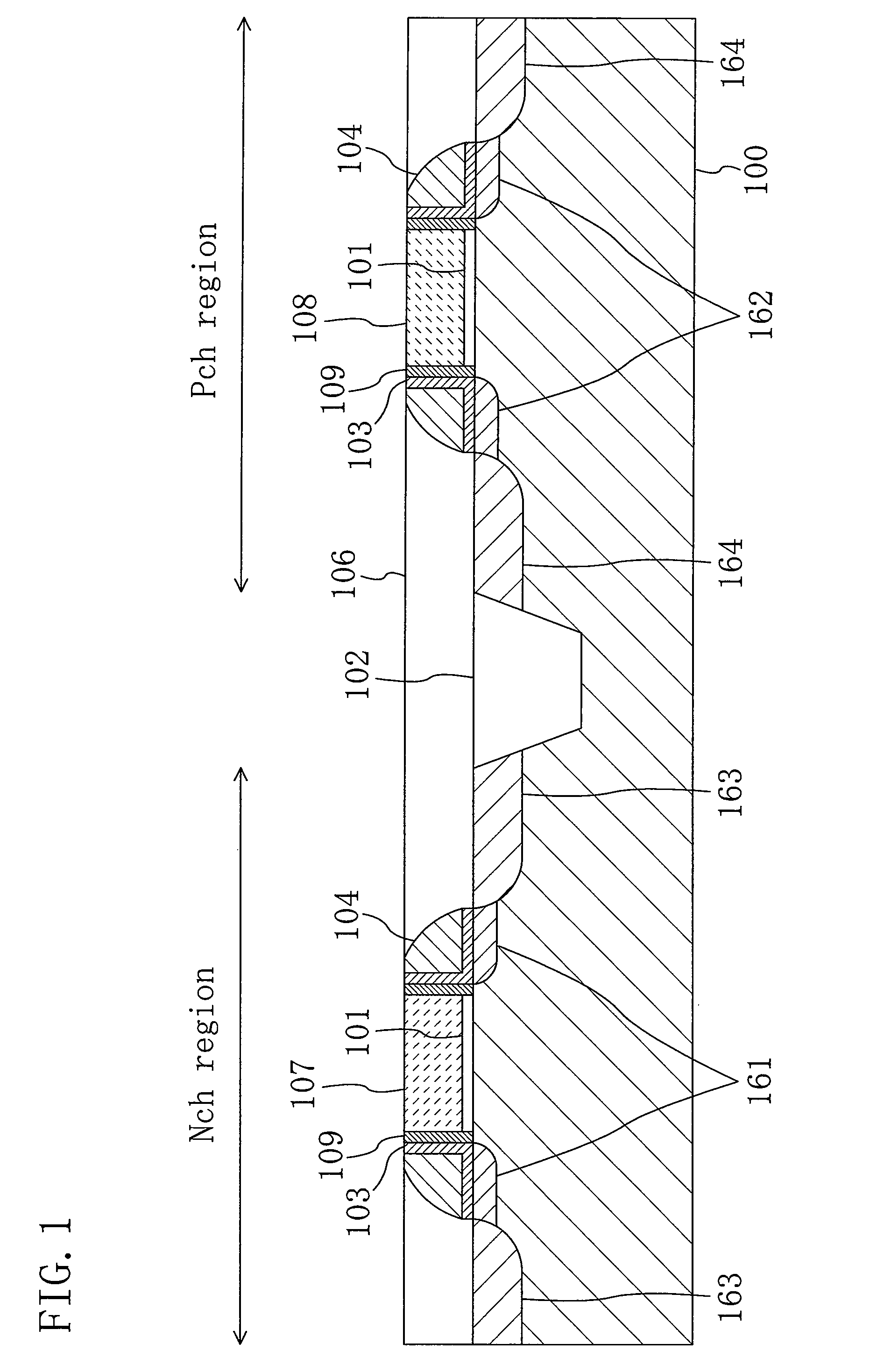

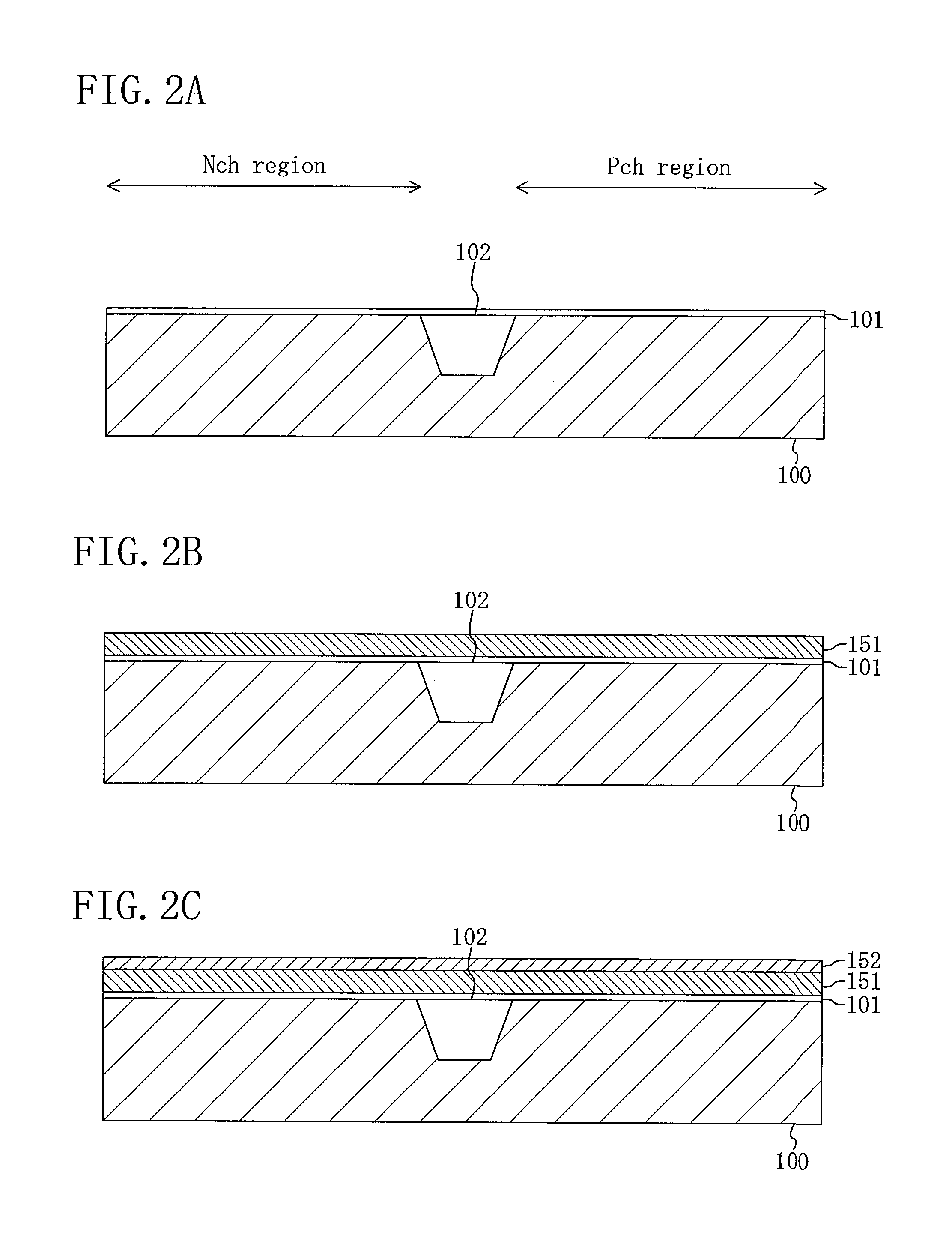

CMOS device comprising mos transistors with recessed drain and source areas and a si/ge material in the drain and source areas of the pmos transistor

InactiveUS20090321843A1High degree of compatibilityEnhanced transistor performanceTransistorSemiconductor/solid-state device manufacturingCMOSSource area

The present disclosure relates to semiconductor devices and a process sequence in which a semiconductor alloy, such as silicon / germanium, may be formed in an early manufacturing stage, wherein other performance-increasing mechanisms, such as a recessed drain and source configuration, possibly in combination with high-k dielectrics and metal gates, may be incorporated in an efficient manner while still maintaining a high degree of compatibility with conventional process techniques.

Owner:GLOBALFOUNDRIES US INC

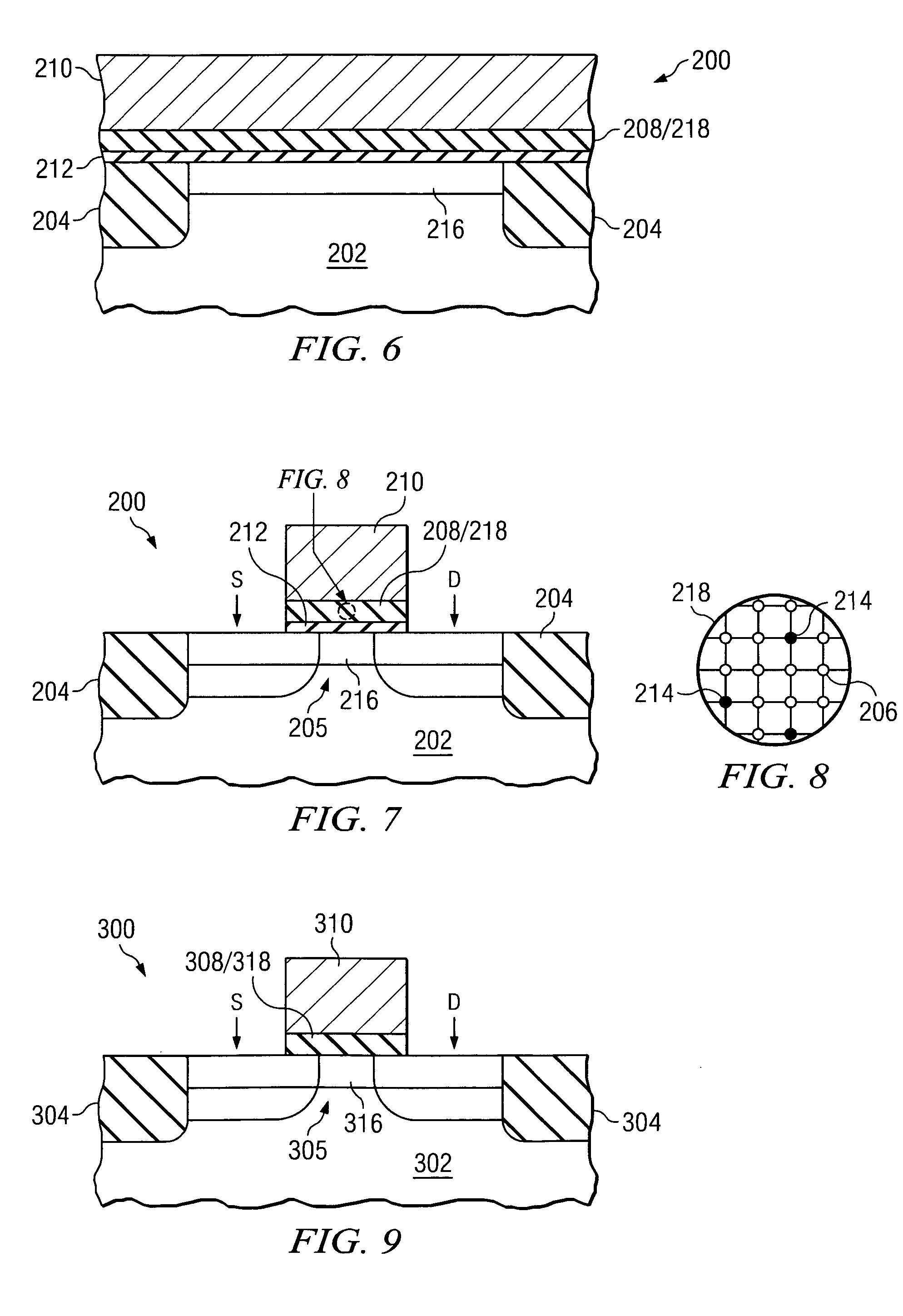

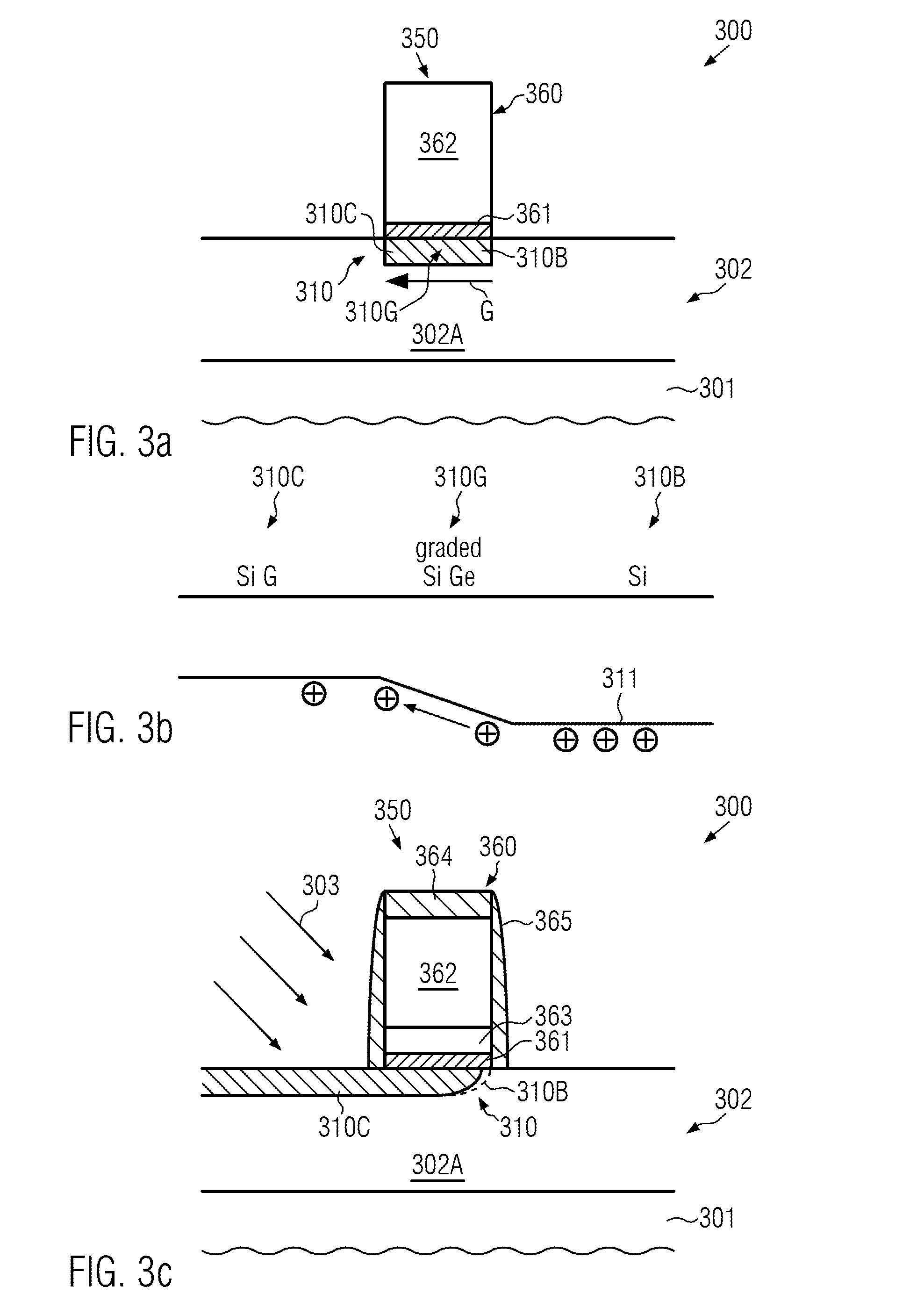

Transistor device having an increased threshold stability without drive current degradation

ActiveUS20070202641A1Improve behaviorReduced threshold varianceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentSemiconductor materials

By removing a portion of a halo region or by avoiding the formation of the halo region within the extension region, which may be subsequently formed on the basis of a re-grown semiconductor material, the threshold roll off behavior may be significantly improved, wherein an enhanced current drive capability may simultaneously be achieved.

Owner:OCEAN SEMICON LLC

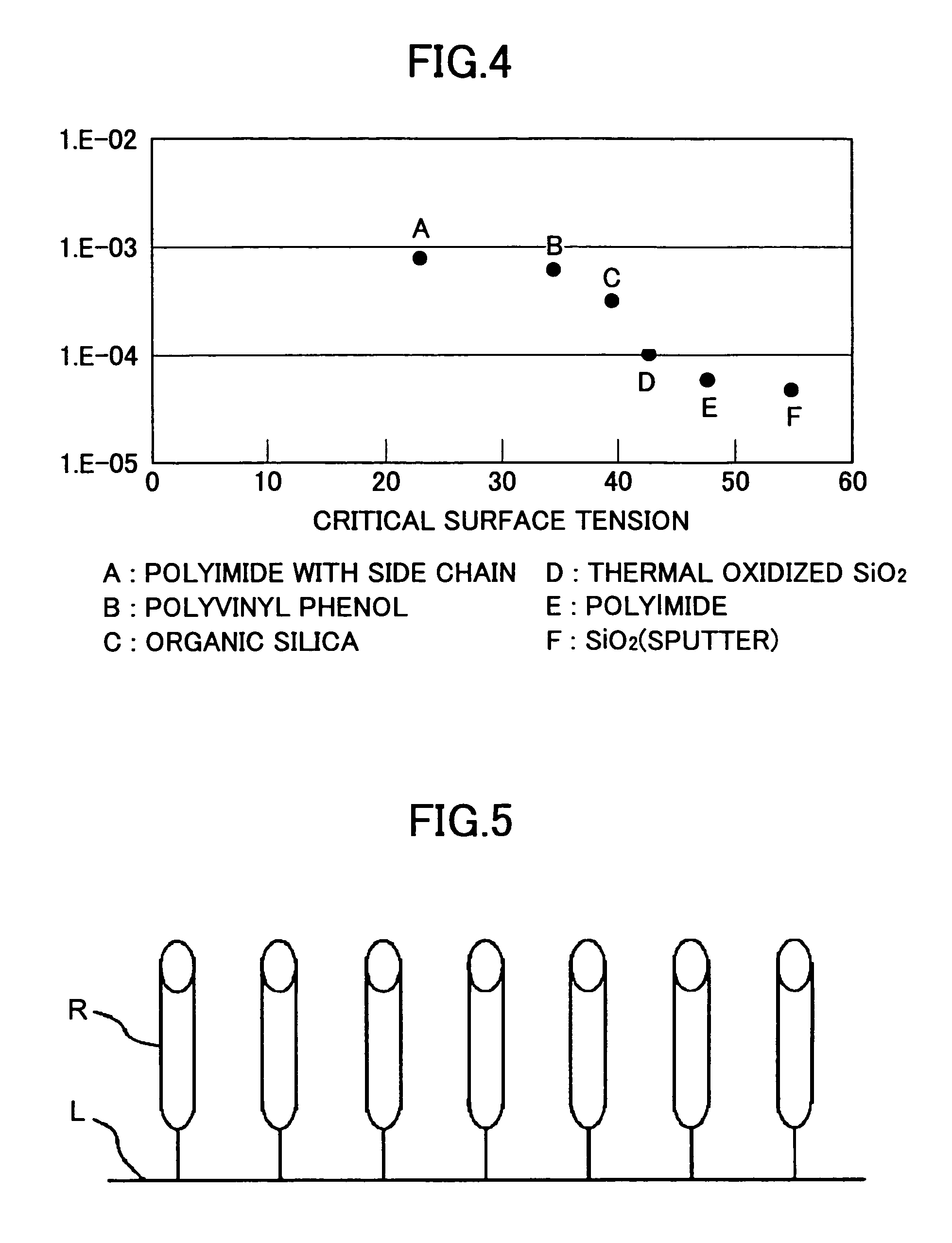

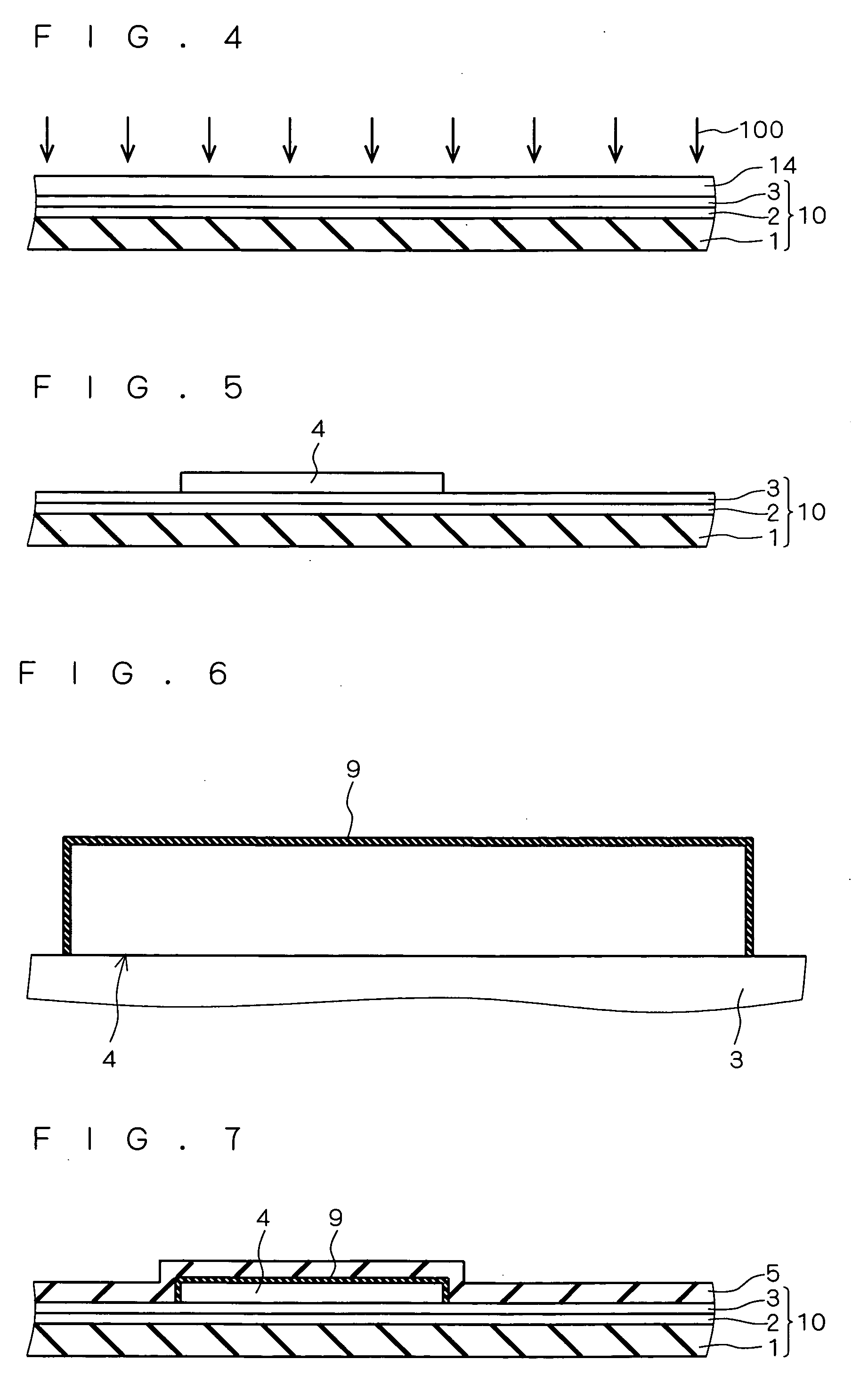

Layered structure for electron device including regions of different wettability, electron device and electron device array that uses such a layered structure

InactiveUS7612455B2Low costReduce usageTransistorSemiconductor/solid-state device detailsHigh surfaceElectron

A layered structure comprises a variable wettability layer including a material that changes a critical surface tension in response to energy provided thereto, the wettability changing layer including at least a high surface energy part of large critical surface tension and a low surface energy part of low critical surface tension, a conductive layer formed on the variable wettability layer at the high surface energy tension part, and a semiconductor layer formed on the variable wettability layer at the low surface energy part.

Owner:RICOH KK

CMOS transistors and methods of forming same

InactiveUS20050059260A1Easy to operateEasy to optimizeTransistorSemiconductor/solid-state device manufacturingCMOSDriving current

The present invention teaches the formation of CMOS transistors using interfacial nitrogen at the interface between the lightly doped extension regions and an overlying insulating layer in combination with a capping layer of silicon nitride, both prior to the final source / drain anneal. Doses and energies may be increased for the P-channel lightly-doped drain, source and drain regions. The resulting transistors exhibit desirably high drive current and low off-state leakage current and overlap capacitance.

Owner:TEXAS INSTR INC

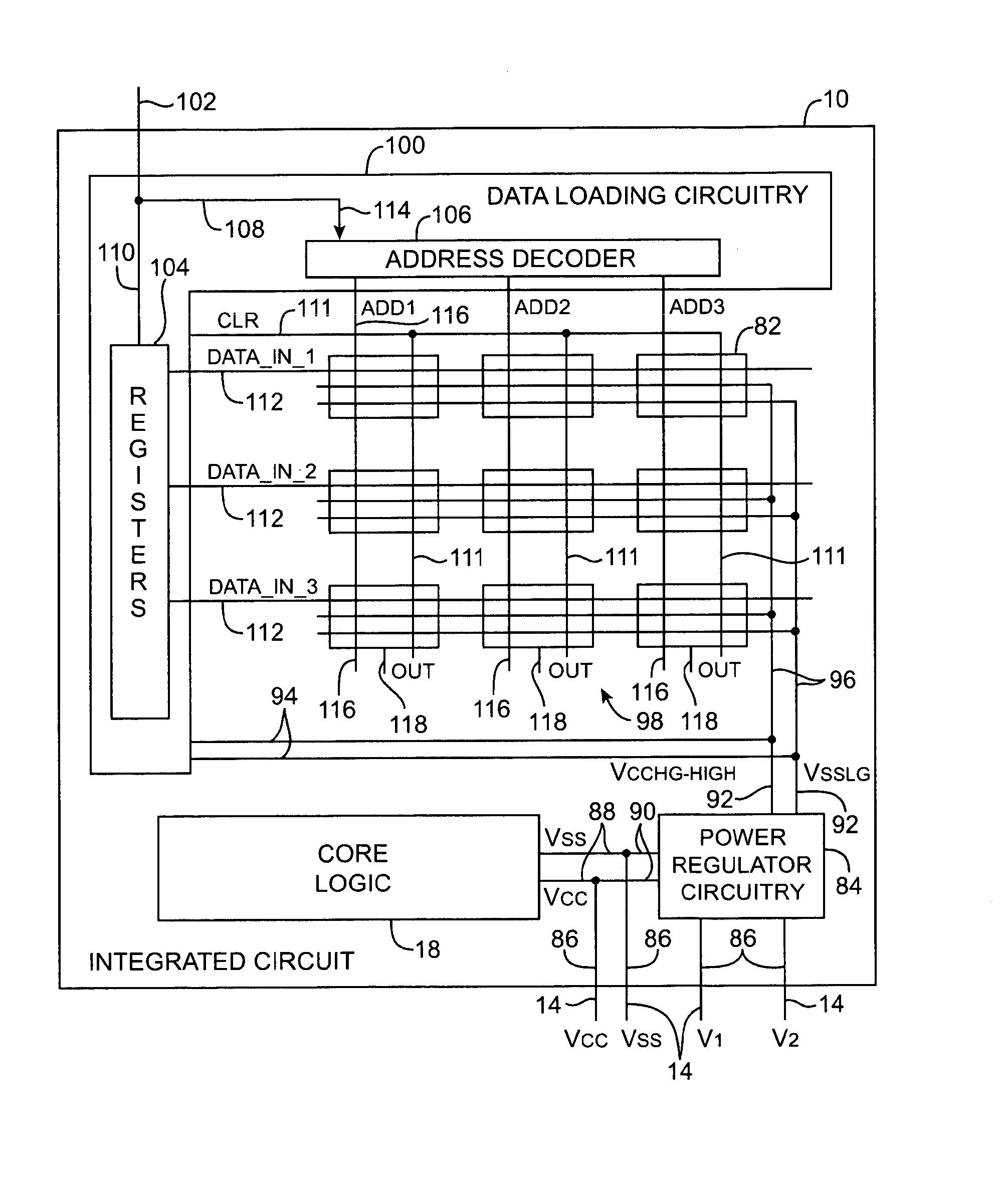

Volatile memory elements with elevated power supply levels for programmable logic device integrated circuits

ActiveUS7411853B2Reduce leakage currentEnhanced transistor performanceSolid-state devicesRead-only memoriesProgrammable logic deviceEngineering

Integrated circuits are provided that have volatile memory elements. The memory elements produce output signals. The integrated circuits may be programmable logic device integrated circuits containing programmable core logic including transistors with gates. The core logic is powered using a core logic power supply level defined by a core logic positive power supply voltage and a core logic ground voltage. When loaded with configuration data, the memory elements produce output signals that are applied to the gates of the transistors in the core logic to customize the programmable logic device. The memory elements are powered with a memory element power supply level defined by a memory element positive power supply voltage and a memory element ground power supply voltage. The memory element power supply level is elevated with respect to the core logic power supply level.

Owner:TAHOE RES LTD

Transistor with doped gate dielectric

ActiveUS20050167764A1Increase speedImproving transistor 's performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricVoltage stability

A transistor and method of manufacture thereof. A semiconductor workpiece is doped before depositing a gate dielectric material. Using a separate anneal process or during subsequent anneal processes used to manufacture the transistor, dopant species from the doped region of the workpiece are outdiffused into the gate dielectric, creating a doped gate dielectric. The dopant species fill vacancies in the atomic structure of the gate dielectric, resulting in a transistor having increased speed, reduced power consumption, and improved voltage stability.

Owner:INFINEON TECH AG

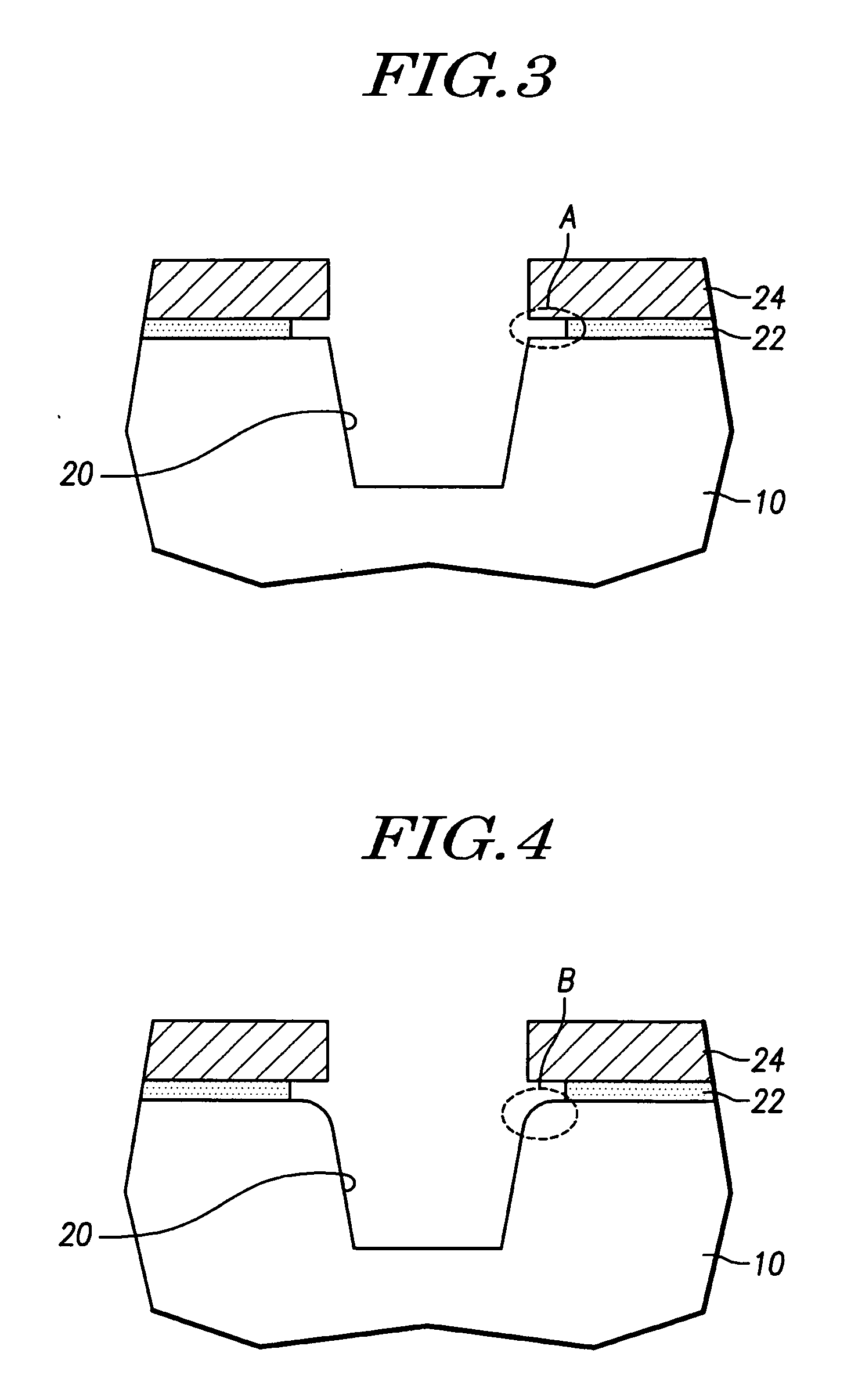

Method for forming shallow trench isolation in semiconductor device

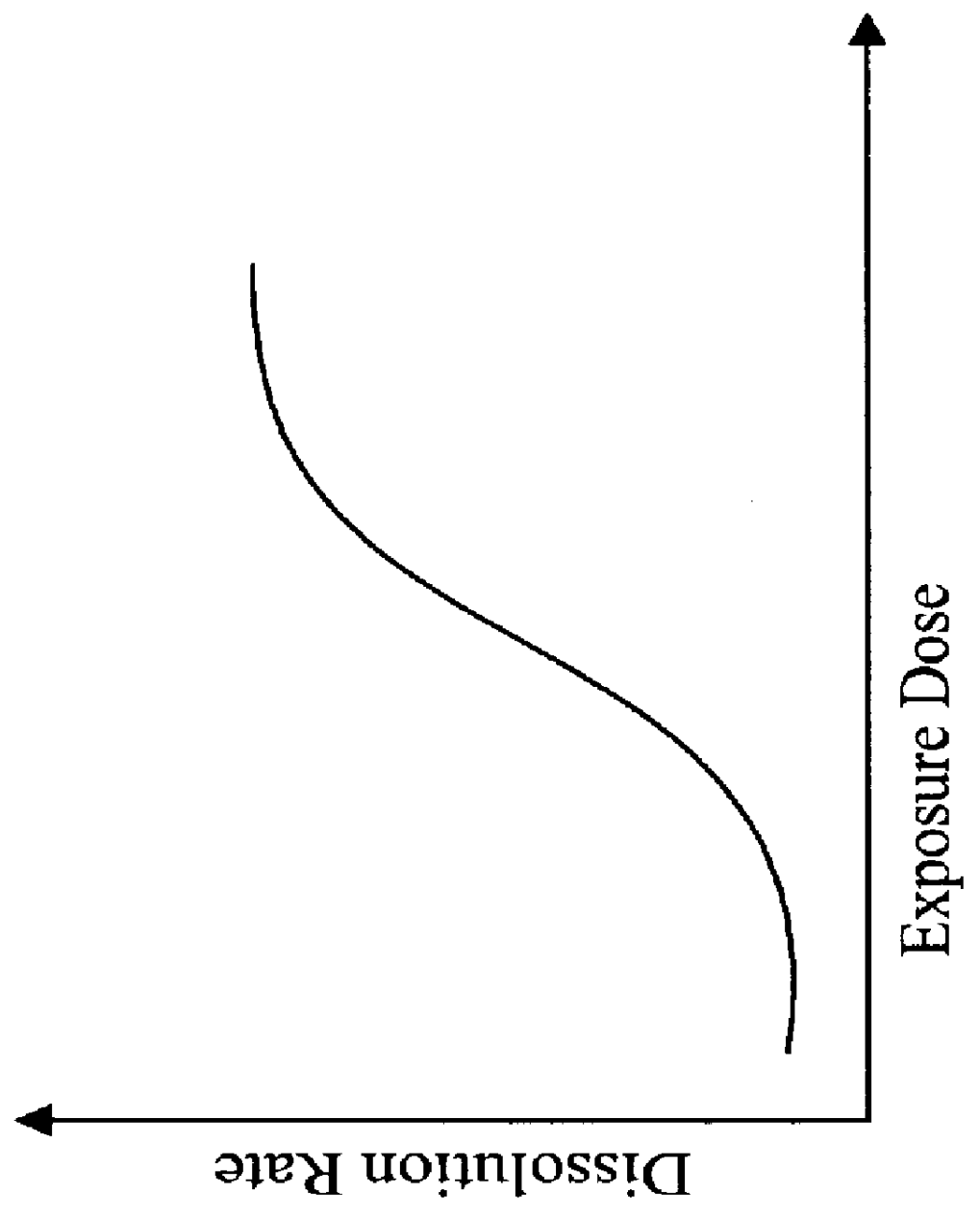

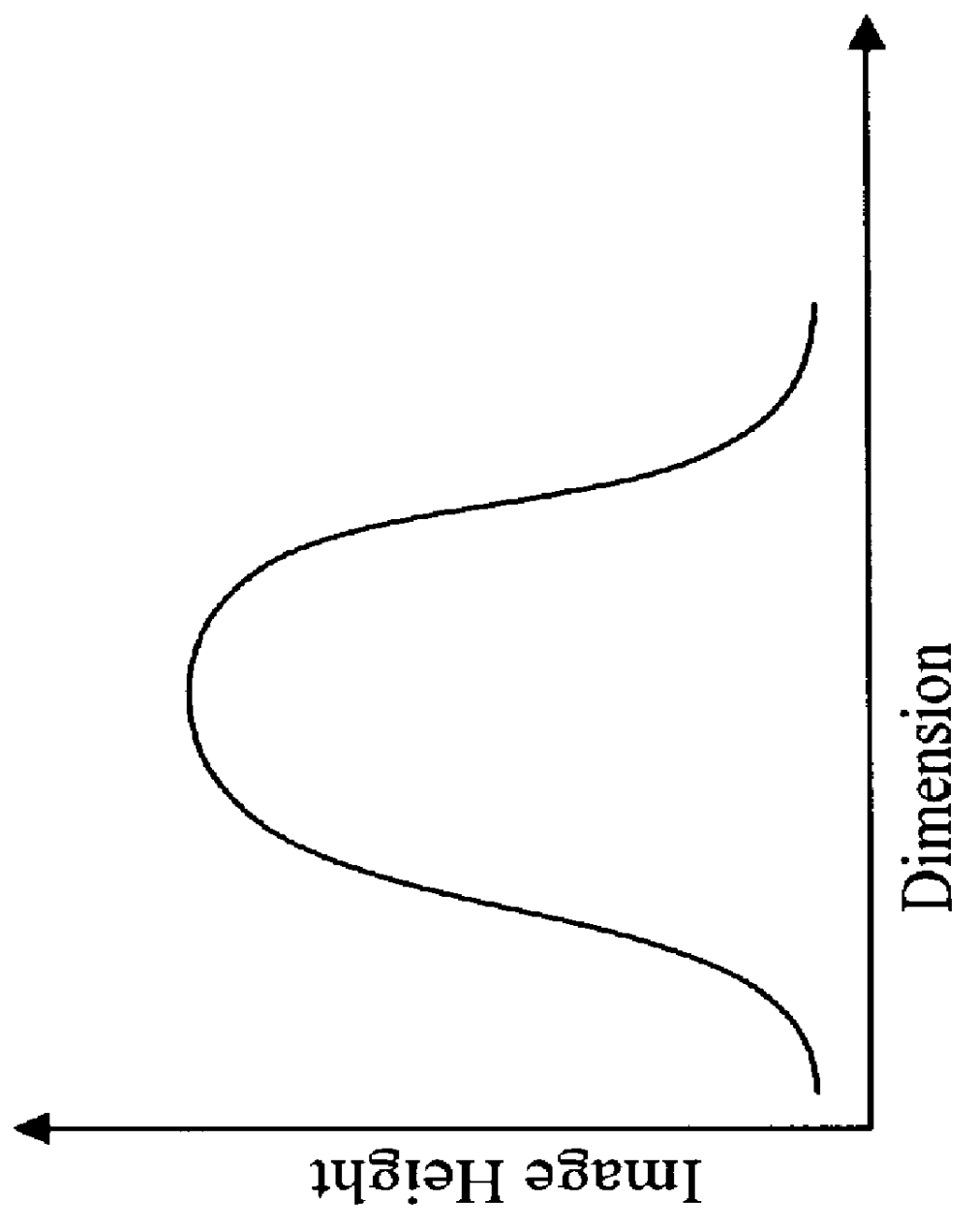

InactiveUS20060141731A1Enhance the imageEnhanced transistor performanceSemiconductor/solid-state device manufacturingDevice materialCompound (substance)

A method for forming shallow trench isolation in a semiconductor device. The method includes forming a pad oxide and a pad nitride on a semiconductor substrate in successive order, forming a trench in the substrate by etching the pad nitride, the pad oxide and the substrate, removing a portion of the pad oxide to expose top corners of the trench, and rounding the exposed portion of the top corners of the trench by a wet chemical etch.

Owner:DONGBU ELECTRONICS CO LTD

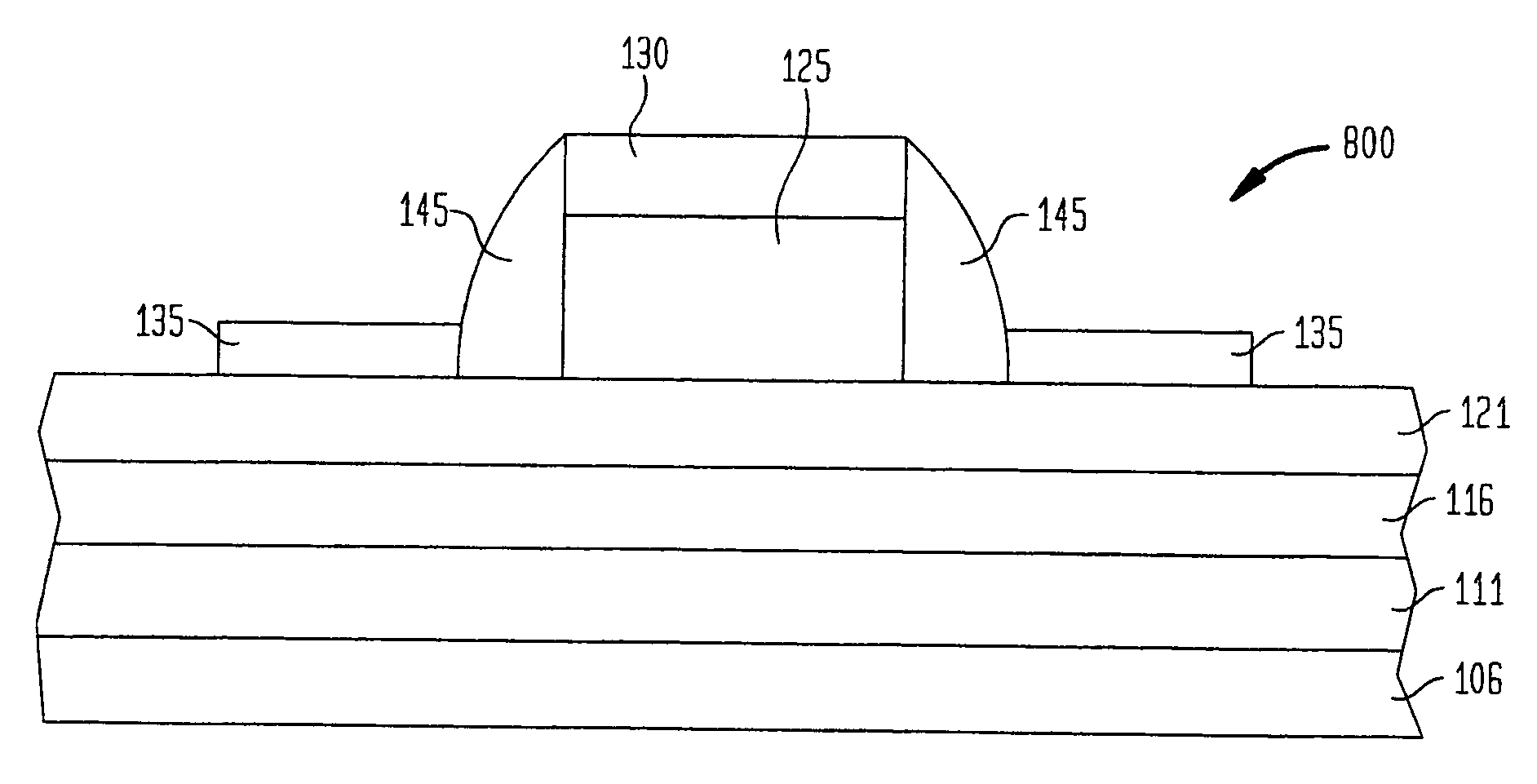

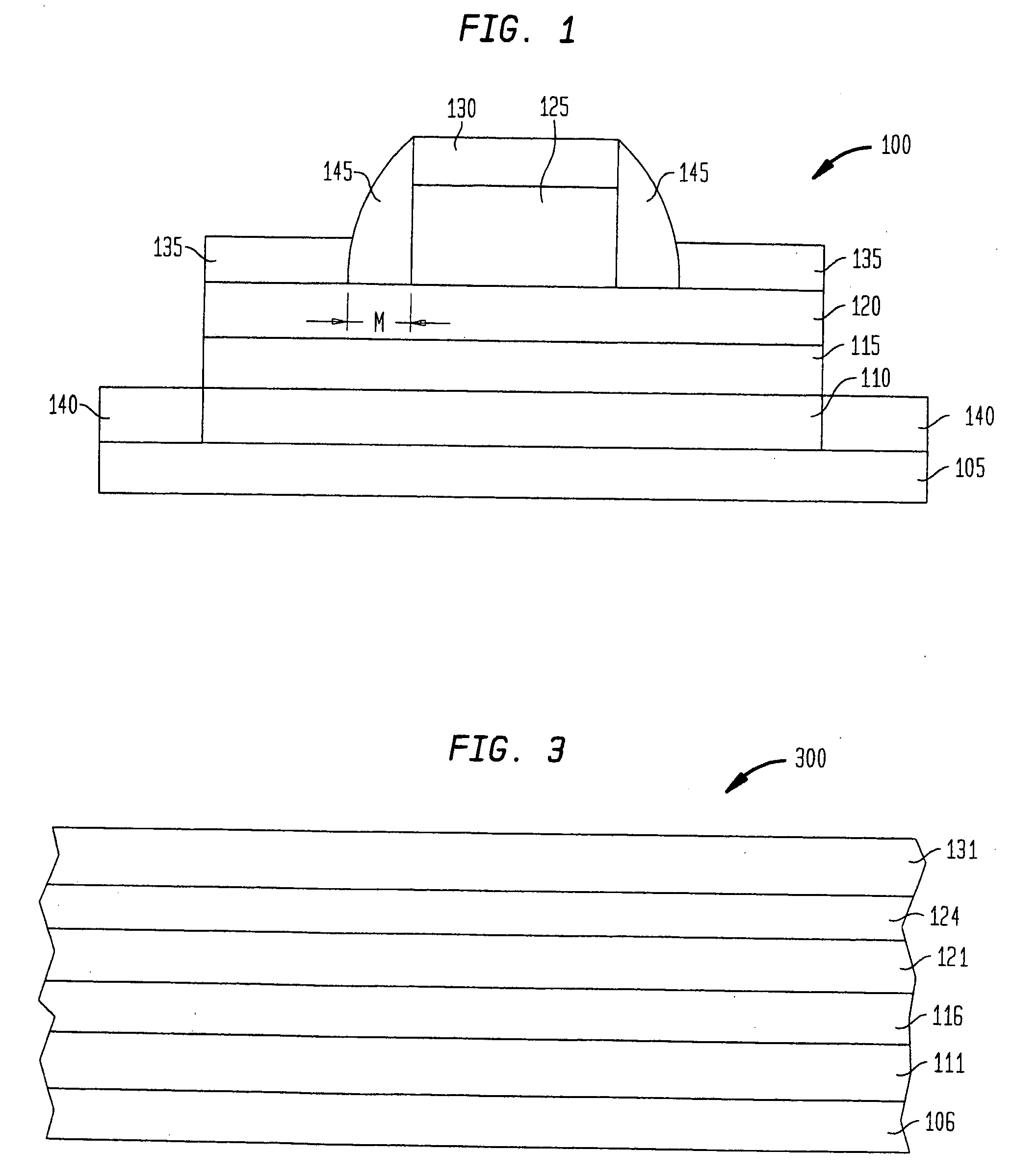

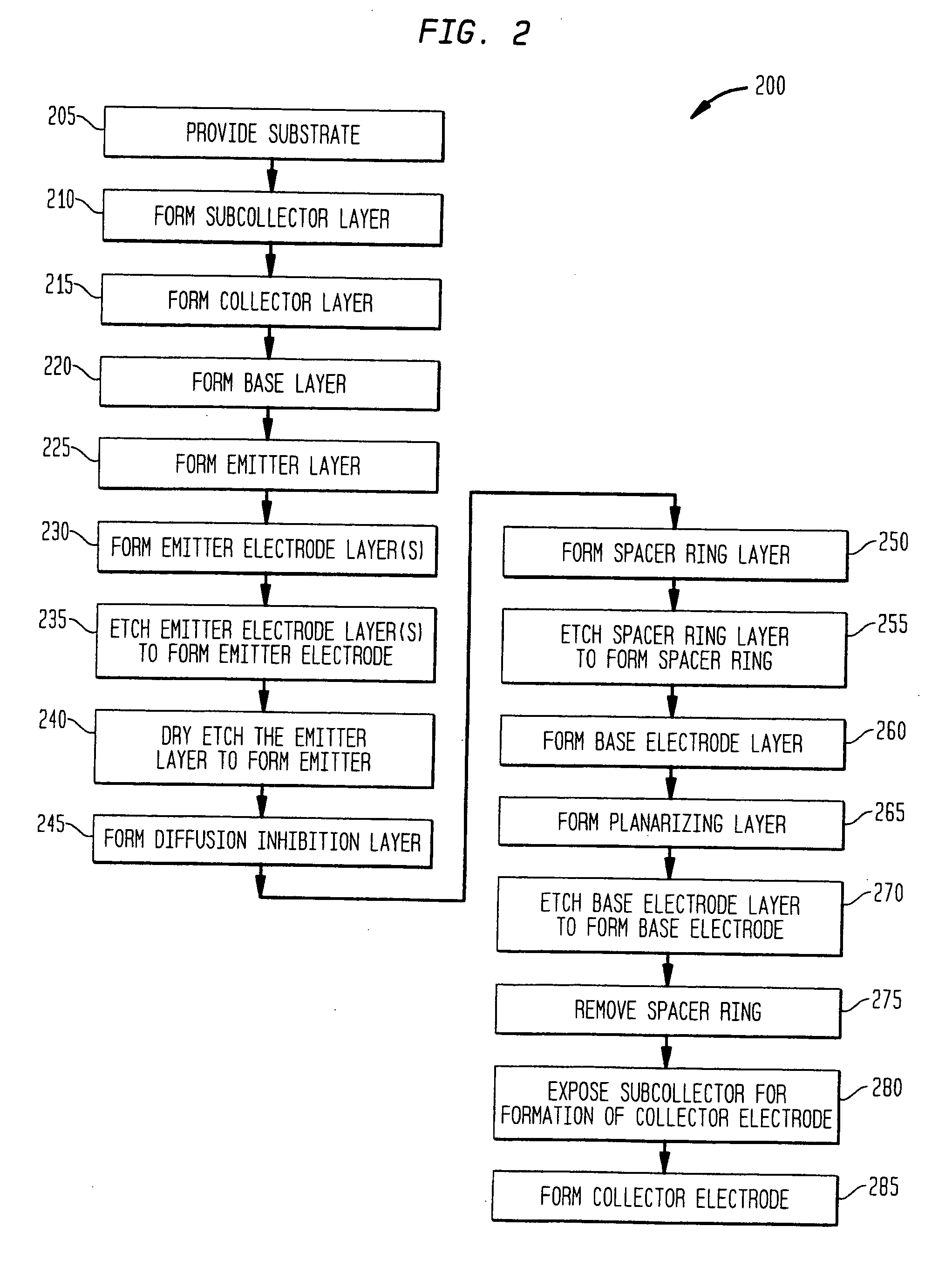

Transistors amd methods for making the same

ActiveUS20050269594A1Reduced base access resistanceEnhanced transistor performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSecondary layerCharge carrier

Apparatus comprising: a first compound semiconductor composition layer doped to have a first charge carrier polarity; a second compound semiconductor composition layer doped to have a second charge carrier polarity and located on the first layer; a third compound semiconductor composition layer doped to have the first charge carrier polarity and located on the second layer; a base electrode on the second layer; and a spacer ring interposed between and defining a charge carrier access path distance between the base electrode and the third layer, the path distance being within a range of between about 200 Å and about 1000 Å. Techniques for making apparatus. Apparatus is useful as a heterobipolar transistor, particularly for high frequency applications.

Owner:ALCATEL-LUCENT USA INC +1

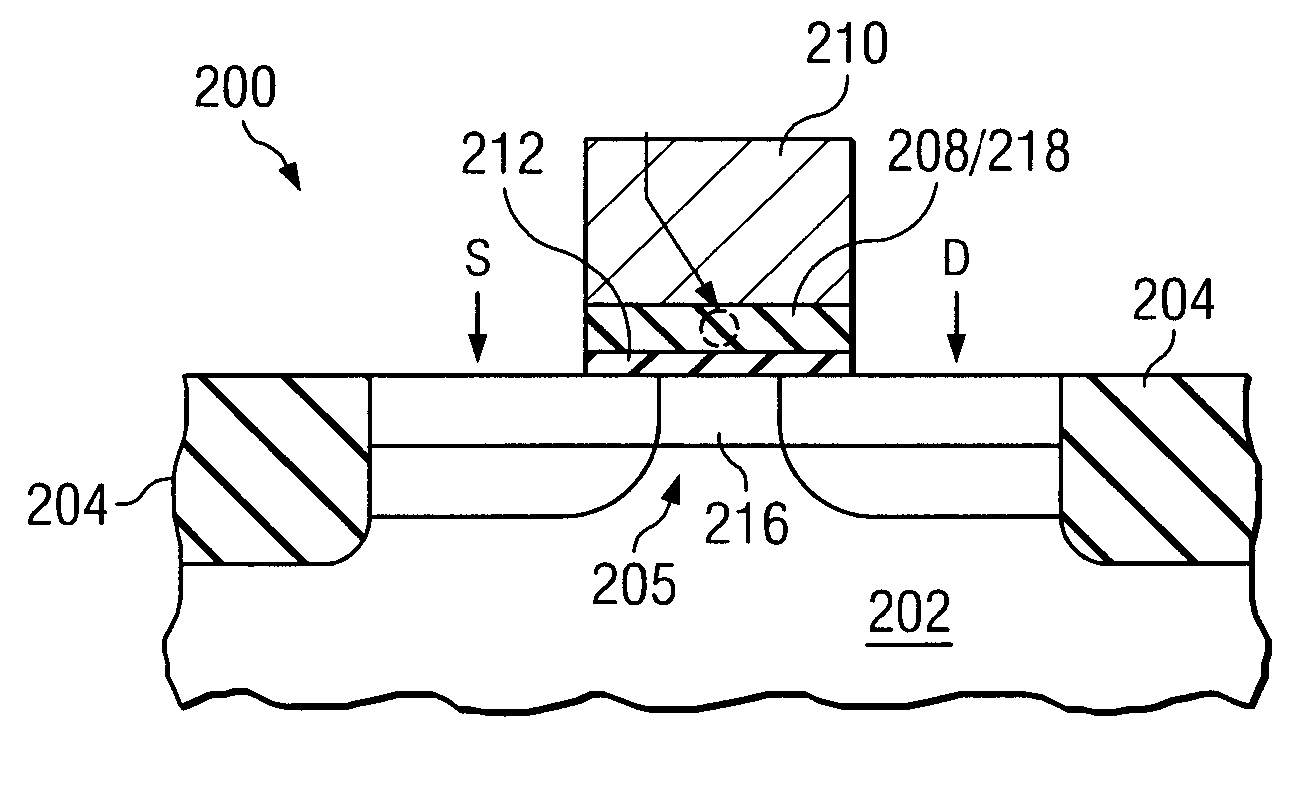

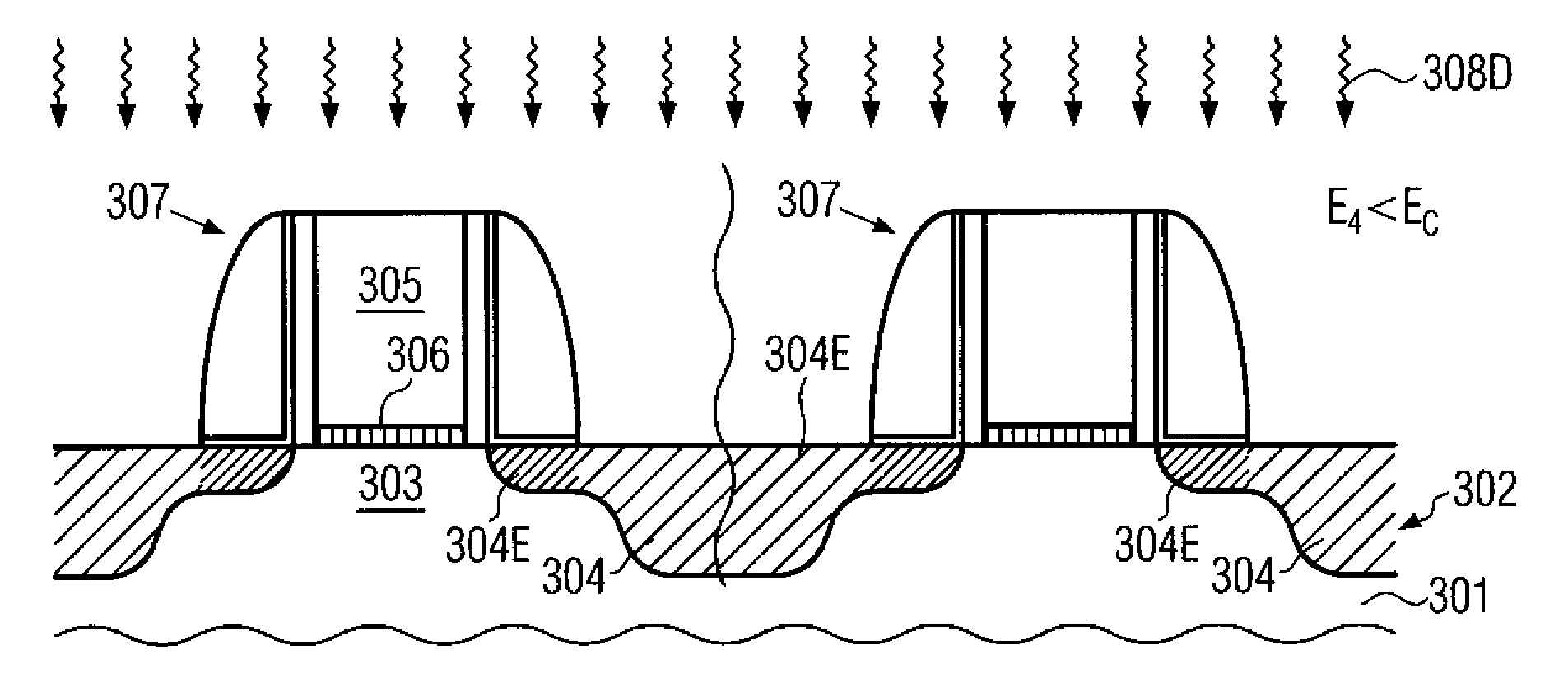

Recessed drain and source areas in combination with advanced silicide formation in transistors

ActiveUS20100109091A1Enhanced transistor performanceHeight of gate be reducedTransistorSolid-state devicesSalicideMetal silicide

During the manufacturing process for forming sophisticated transistor elements, the gate height may be reduced and a recessed drain and source configuration may be obtained in a common etch sequence prior to forming respective metal silicide regions. Since the corresponding sidewall spacer structure may be maintained during the etch sequence, controllability and uniformity of the silicidation process in the gate electrode may be enhanced, thereby obtaining a reduced degree of threshold variability. Furthermore, the recessed drain and source configuration may provide reduced overall series resistance and enhanced stress transfer efficiency.

Owner:ADVANCED MICRO DEVICES INC

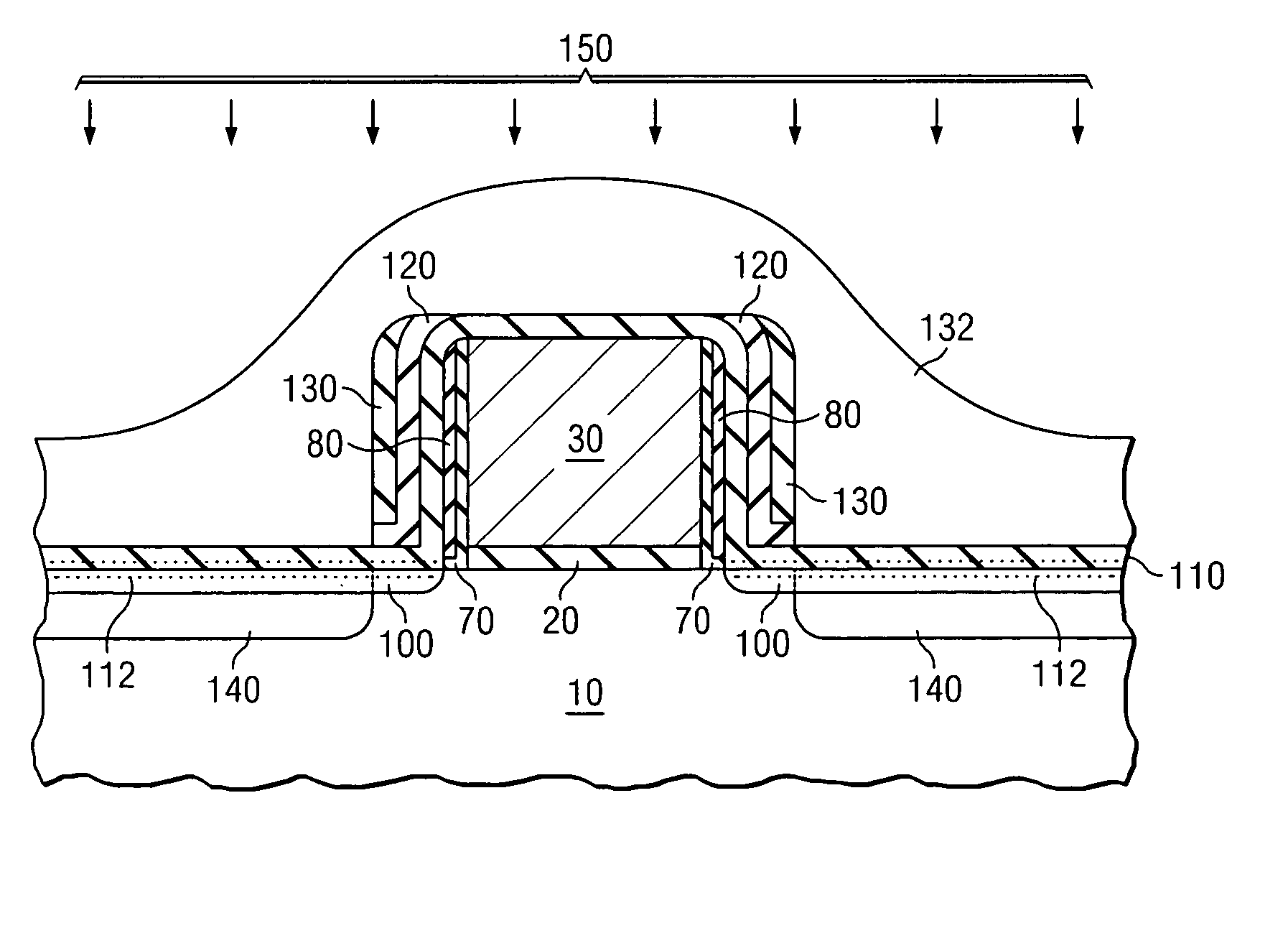

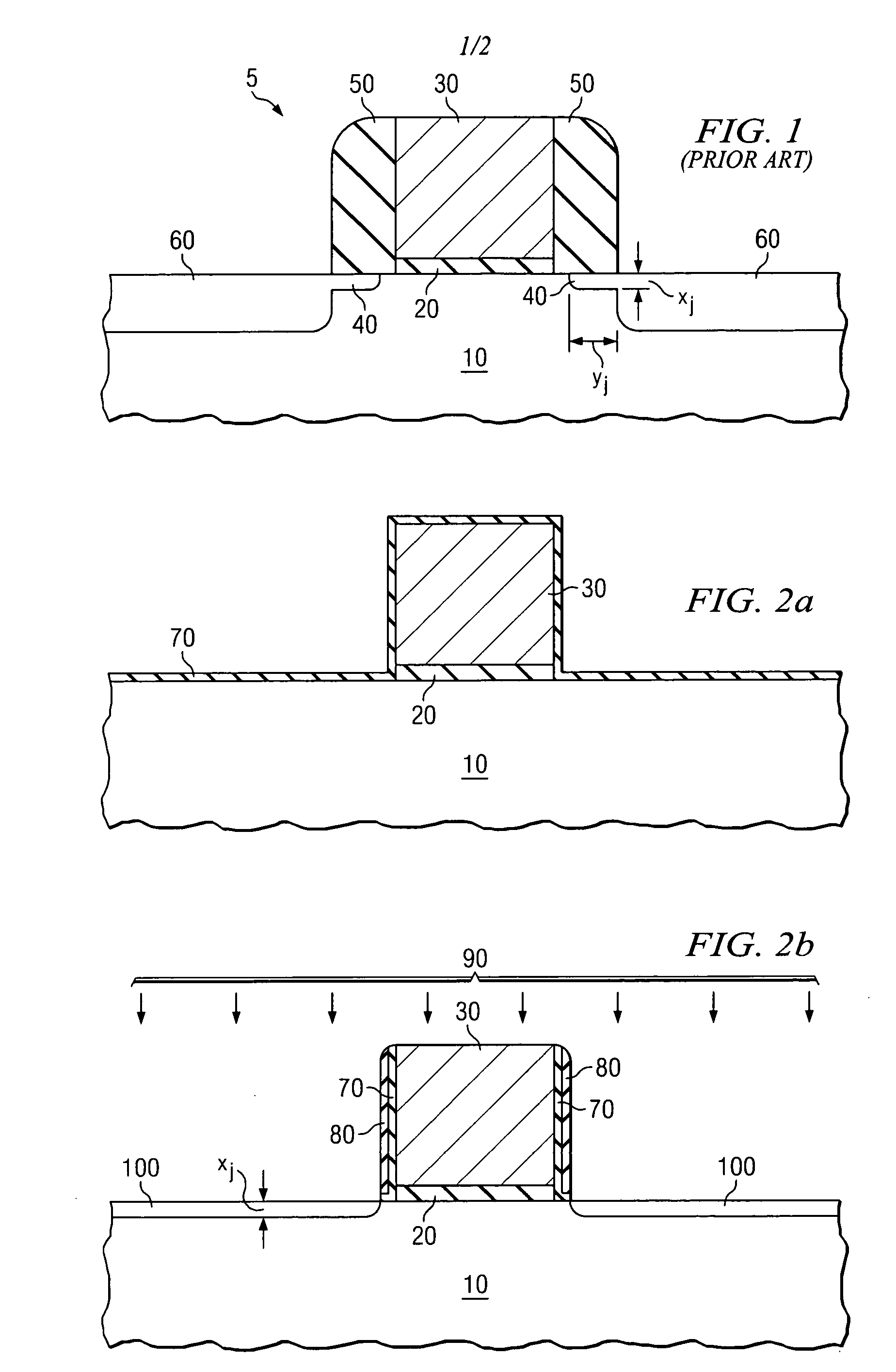

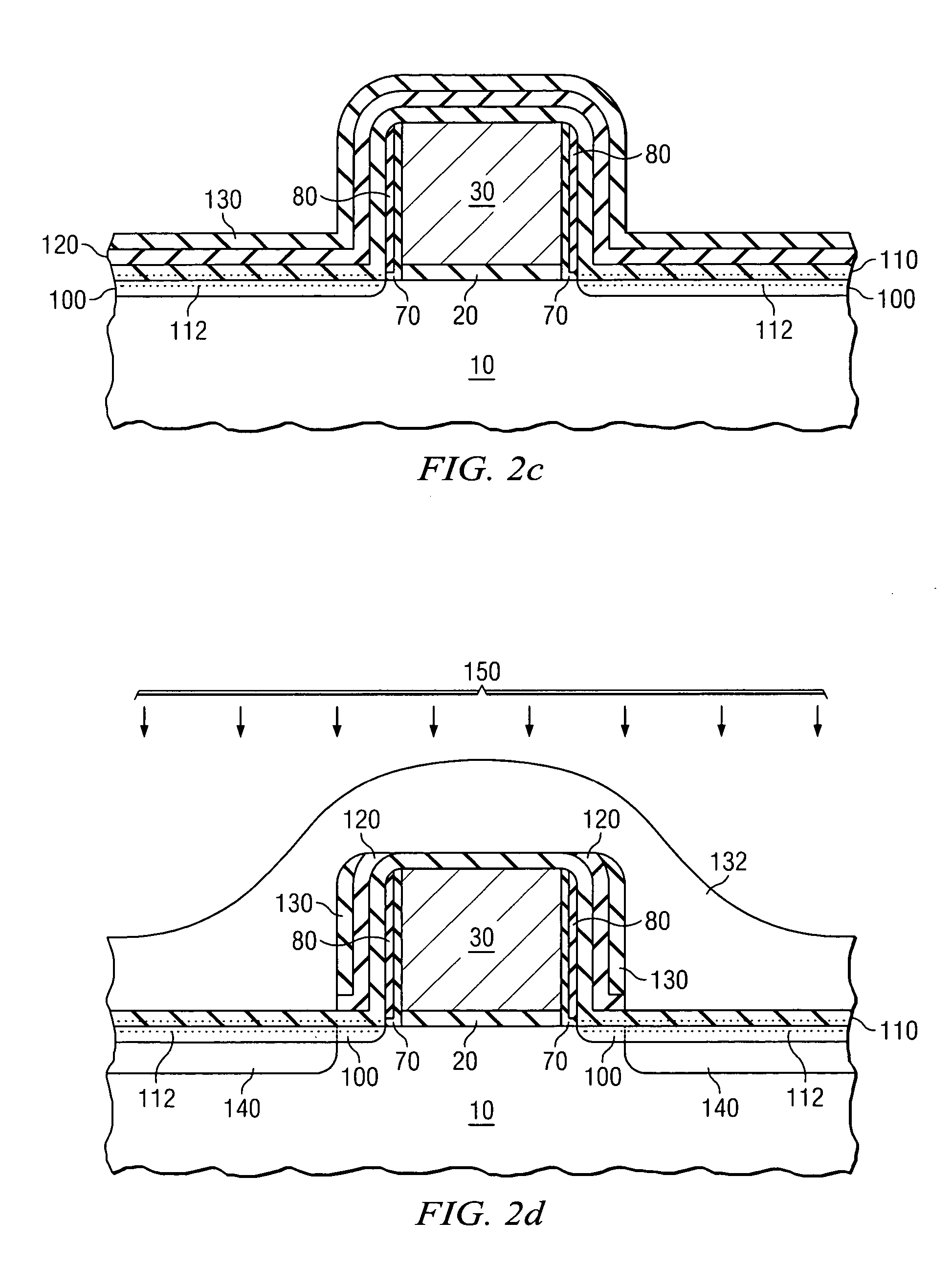

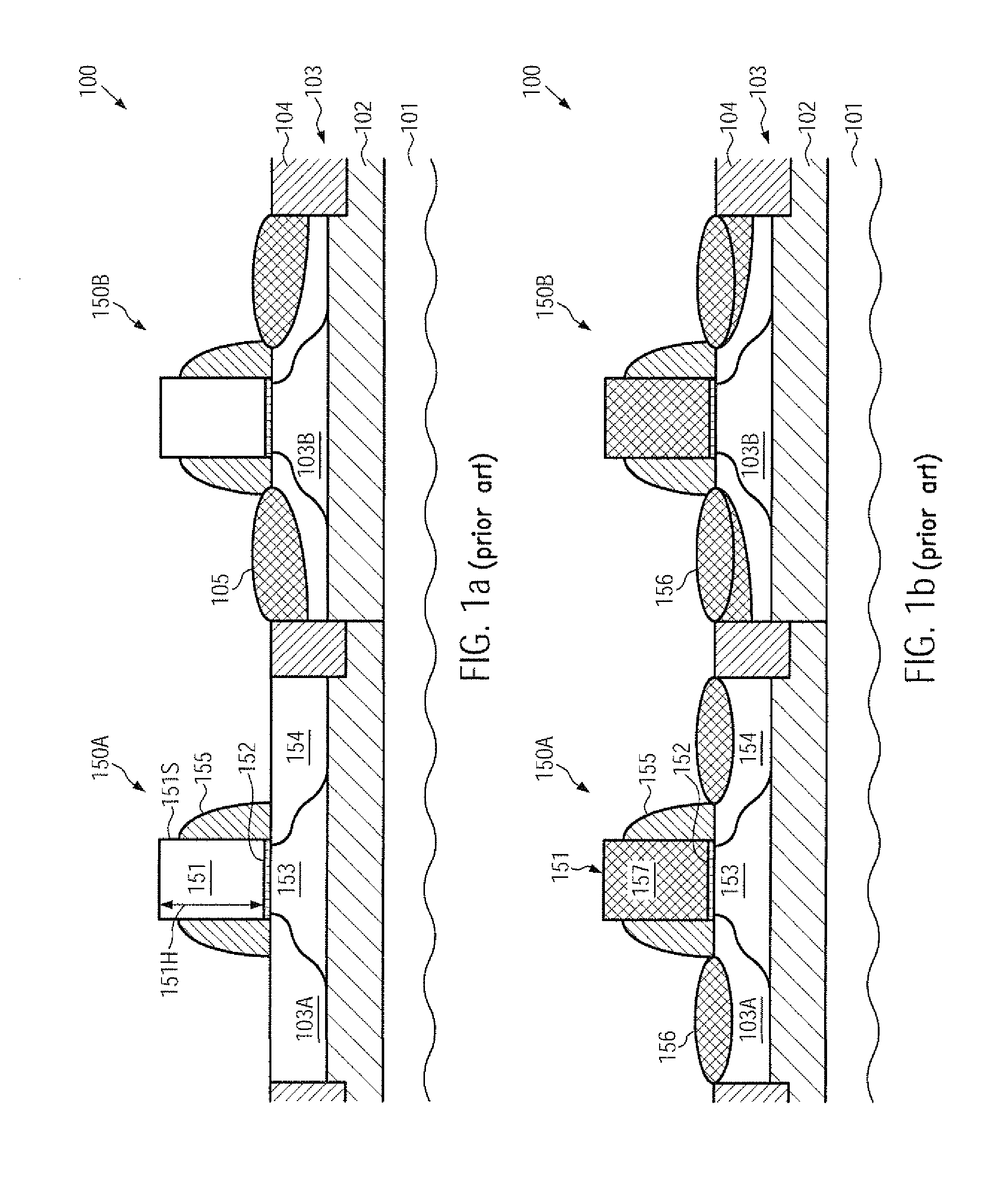

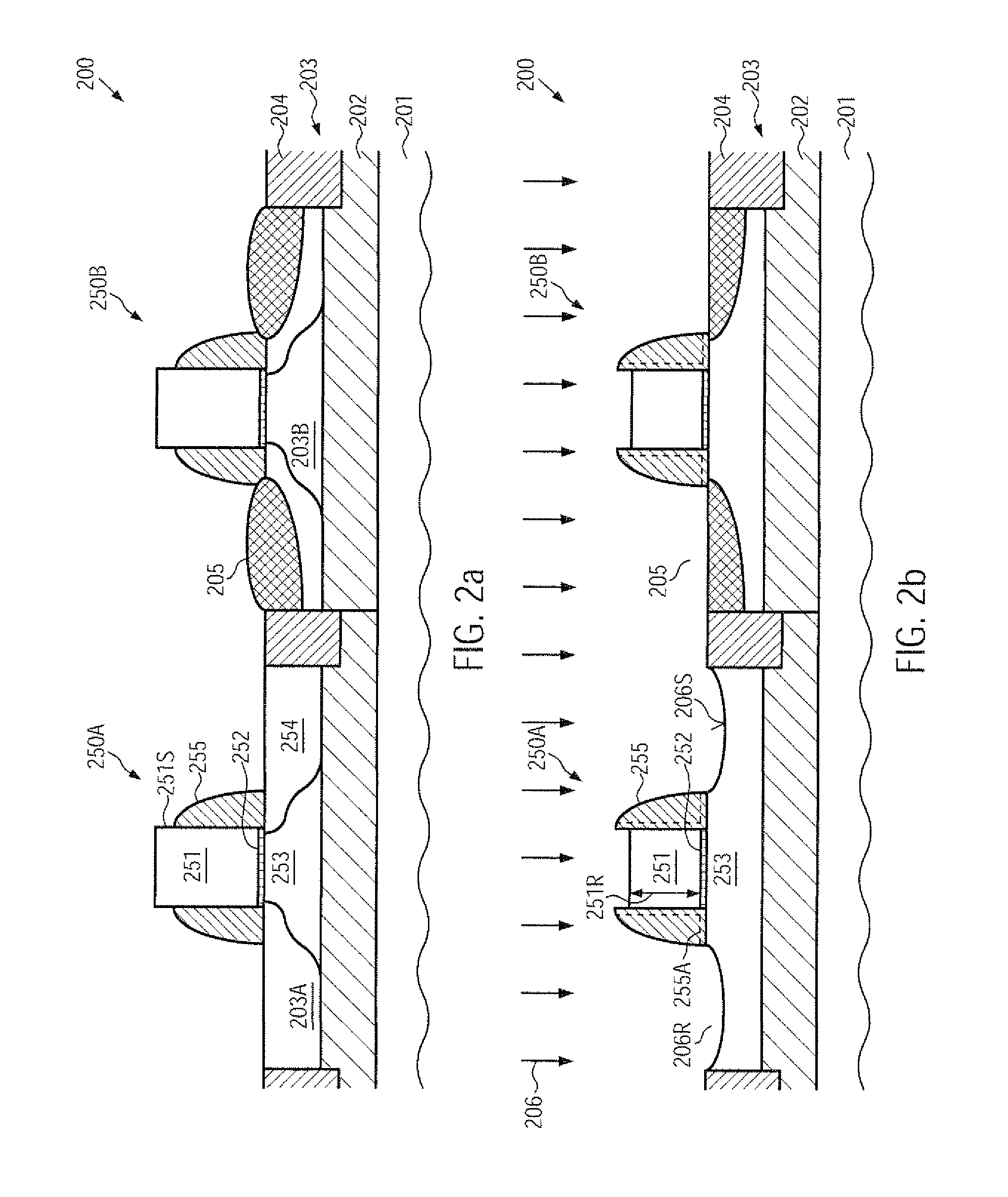

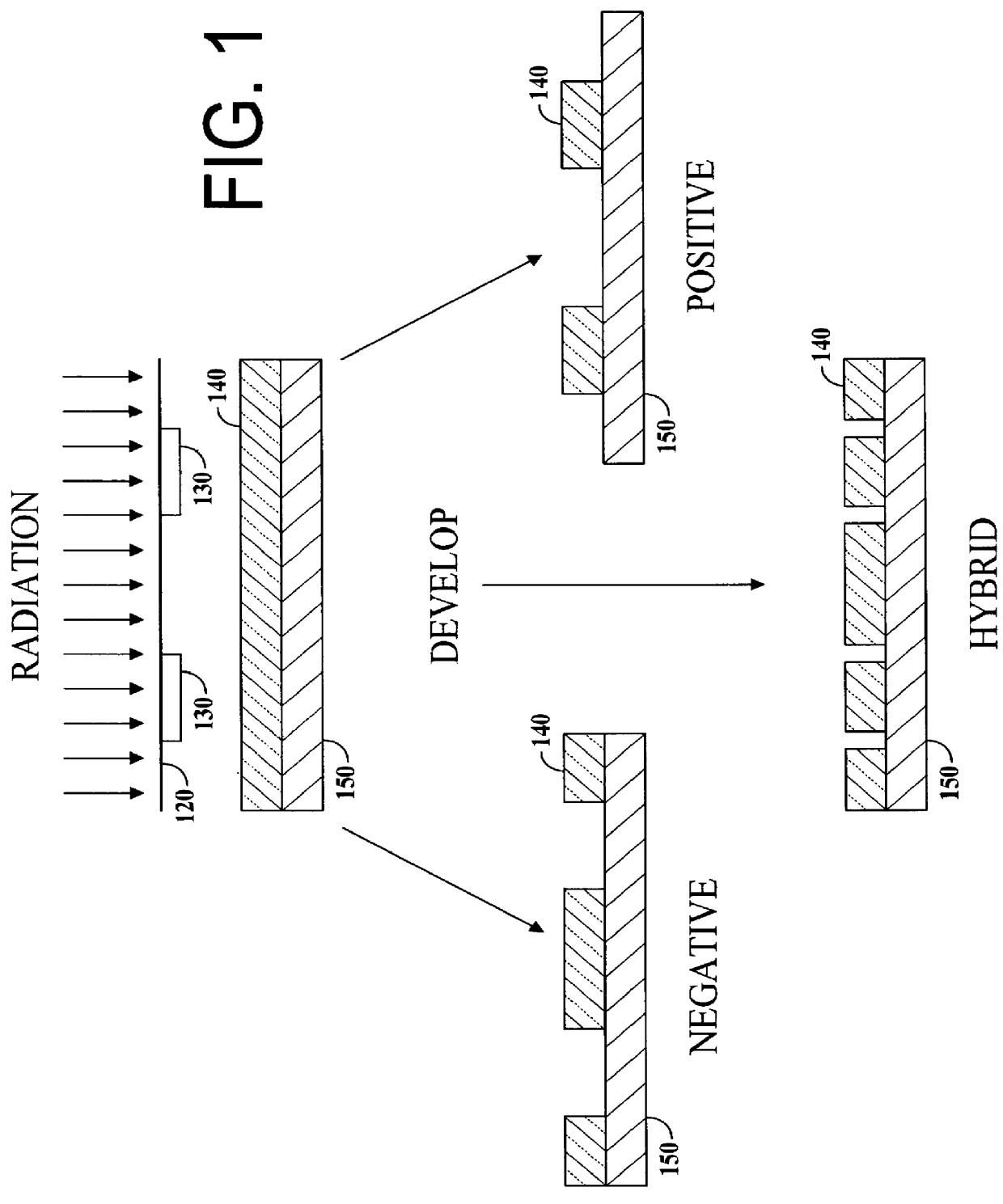

Method for forming transistors with raised source and drains and device formed thereby

InactiveUS6100013AEnhanced transistor performanceOvercome limitationsTransistorDecorative surface effectsCapacitanceResist

The preferred embodiment of the present invention provides a transistor structure and method for fabricating the same that overcomes the disadvantages of the prior art. In particular, the preferred structure and method results in lower leakage and junction capacitance by using raised source and drains which are partially isolated from the substrate by a dielectric layer. The raised source and drains are preferably fabricated from the same material layer used to form the transistor gate. The preferred method for fabricating the transistor uses hybrid resist to accurately pattern the gate material layer into regions for the gate, the source and the drain. The source and drain regions are then connected to the substrate by growing silicon. The preferred method thus results in an improved transistor structure while not requiring excessive fabrication steps.

Owner:IBM CORP

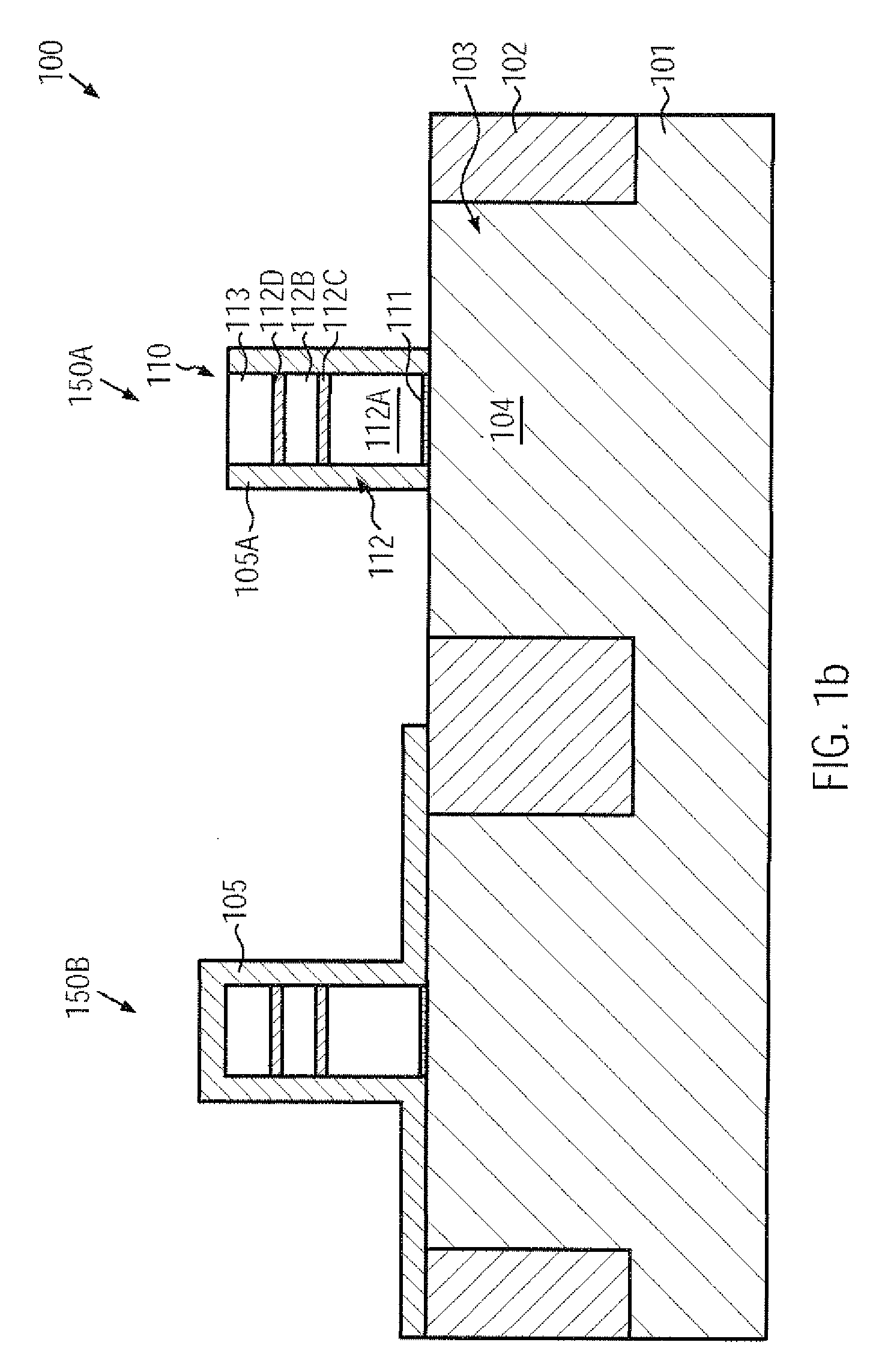

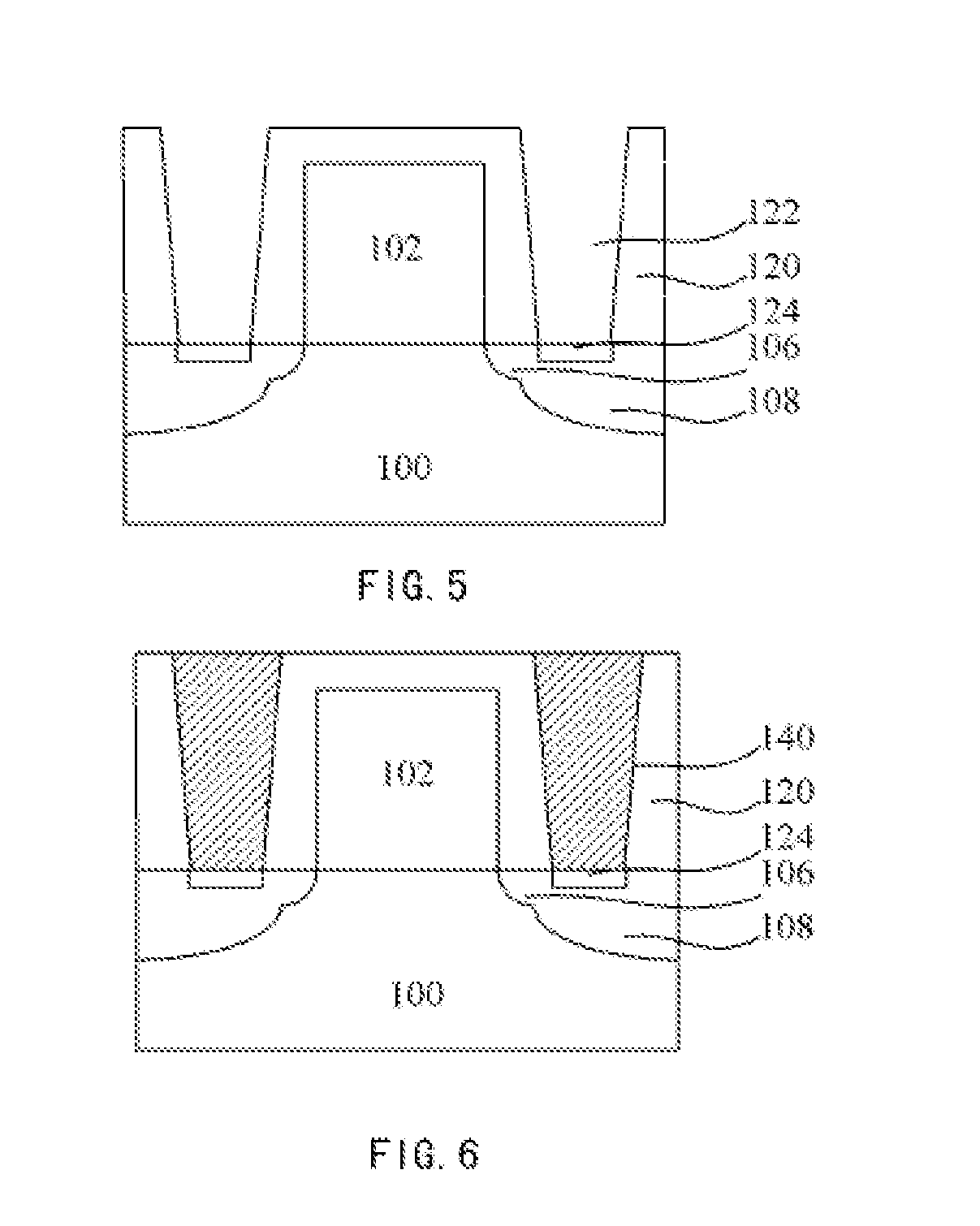

Enhancing mosfet performance by optimizing stress properties

InactiveUS20110127588A1Enhanced transistor performanceTransistorSemiconductor/solid-state device manufacturingShadow effectMOSFET

A device and method for improving performance of a transistor includes gate structures formed on a substrate having a spacing therebetween. The gate structures are formed in an operative relationship with active areas fainted in the substrate. A stress liner is formed on the gate structures. An angled ion implantation is applied to the stress liner such that ions are directed at vertical surfaces of the stress liner wherein portions of the stress liner in contact with the active areas are shielded from the ions due to a shadowing effect provided by a height and spacing between adjacent structures.

Owner:ALSEPHINA INNOVATIONS INC

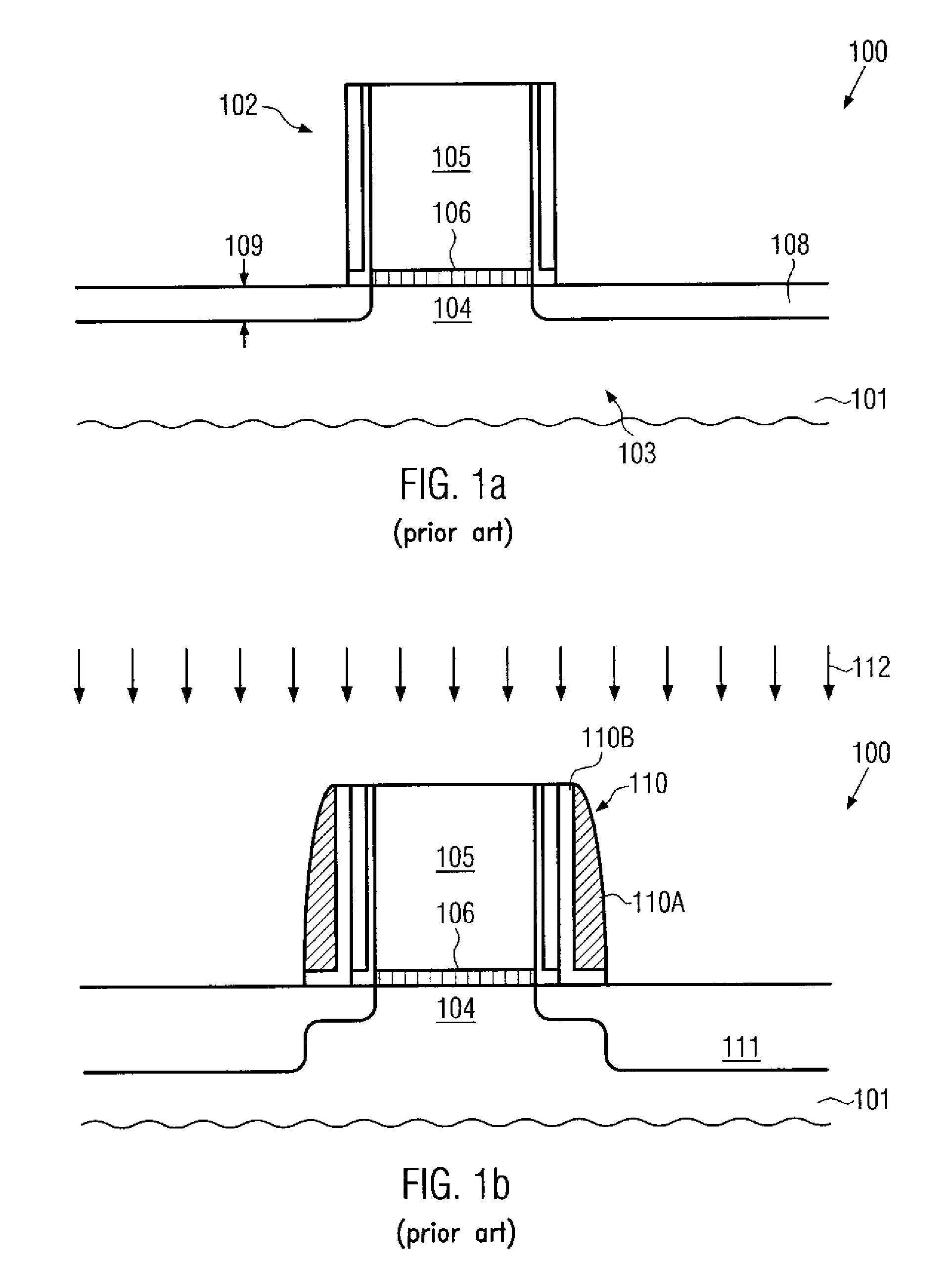

Drain/source extension structure of a field effect transistor with reduced boron diffusion

ActiveUS20080001191A1Reduction of dopant lossDegrades transistor performanceTransistorSemiconductor/solid-state device manufacturingDopantDiffusion

By modifying the dielectric liner for a spacer structure so as to exhibit an enhanced diffusion blocking characteristic, for instance by incorporating nitrogen, the out-diffusion of P-dopants, such as boron, into the dielectric material may be significantly reduced. Consequently, transistor performance, especially of P-type transistors, may be significantly enhanced while nevertheless a high degree of compatibility with conventional techniques may be maintained.

Owner:GLOBALFOUNDRIES US INC

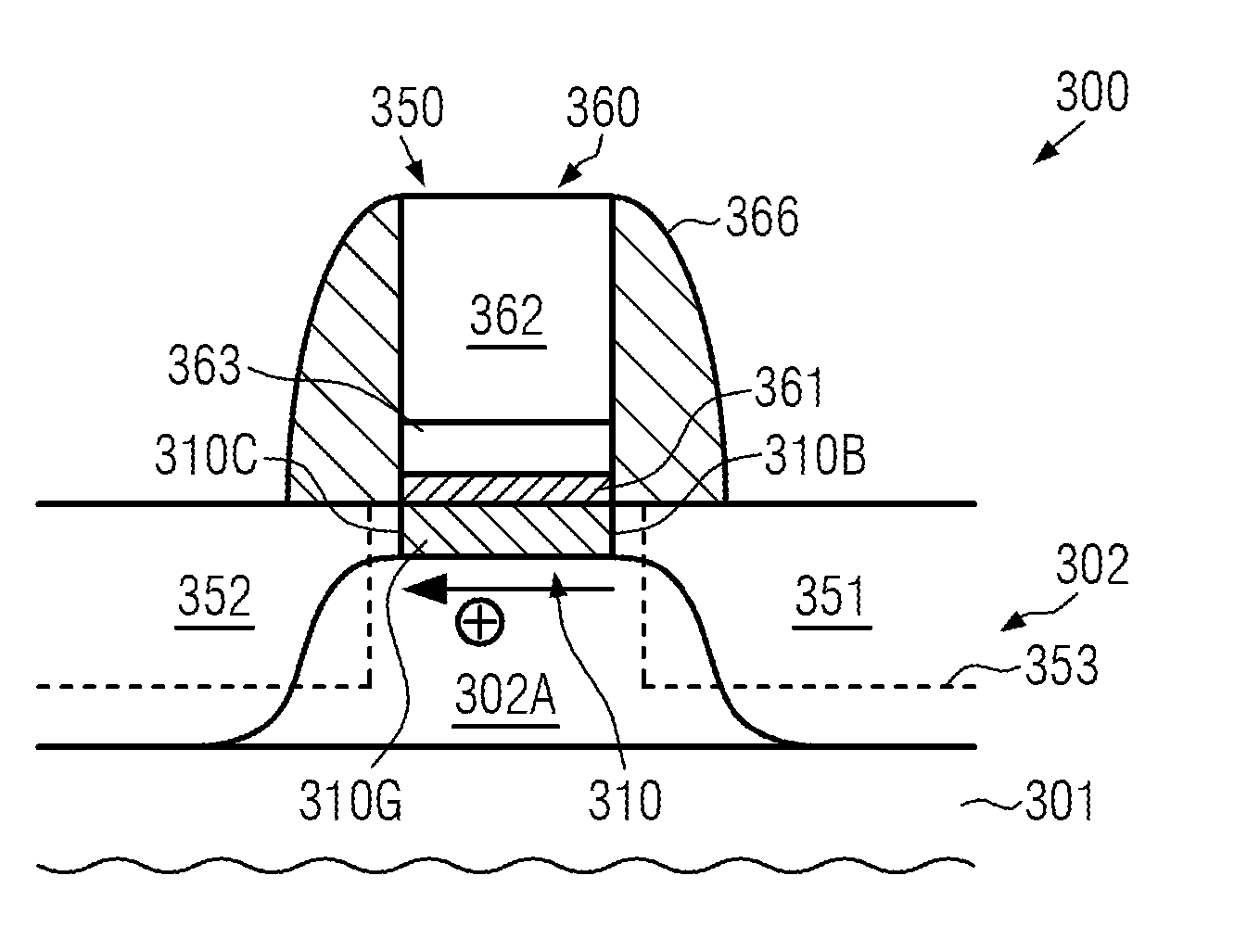

Drive Current Increase in Field Effect Transistors by Asymmetric Concentration Profile of Alloy Species of a Channel Semiconductor Alloy

ActiveUS20120193708A1Increased charge carrier velocitySuperior transistor performanceSemiconductor/solid-state device manufacturingSemiconductor devicesNon symmetricAlloy

When forming sophisticated transistors, the channel region may be provided such that the gradient of the band gap energy of the channel material may result in superior charge carrier velocity. For example, a gradient in concentration of germanium, carbon and the like may be implemented along the channel length direction, thereby obtaining higher transistor performance.

Owner:GLOBALFOUNDRIES US INC

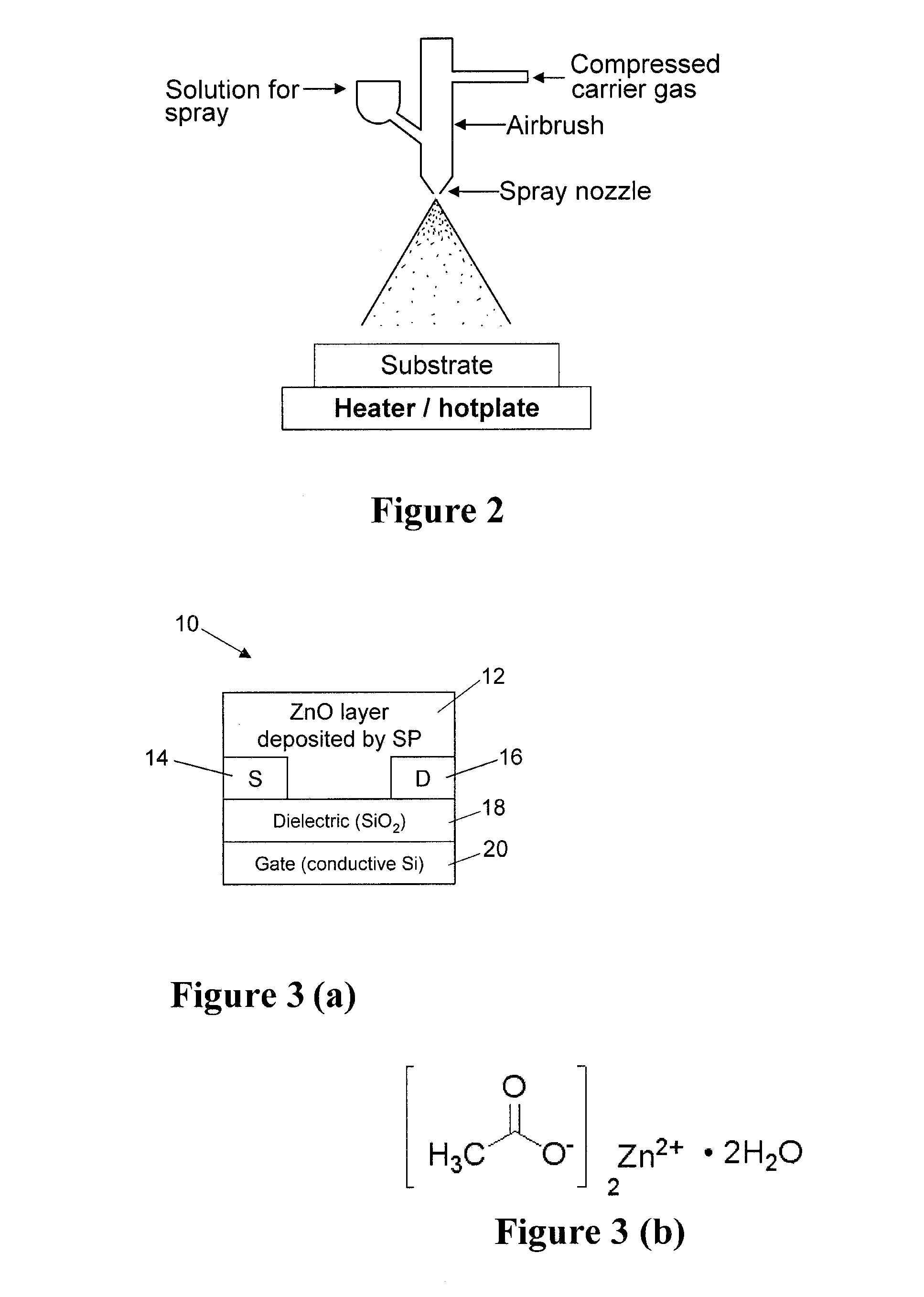

Fabrication method for thin-film field-effect transistors

InactiveUS20120058597A1Enhanced transistor performanceEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingMixed oxideSulfur

A thin-film field-effect transistor is formed by forming a dielectric layer adjacent a gate, forming a source region and a drain region, and forming a semiconductor layer on the dielectric layer. The semiconductor layer is deposited by spray pyrolysis and comprises a material selected from a group comprising: oxides; oxide-based materials; mixed oxides; metallic type oxides; group I-IV, II-VI, III-VI, IV-VI, V-VI and VIII-VI binary chalcogenides; and group I-II-VI, II-II-VI, II-III-VI, II-VI-VI and V-II-VI ternary chalcogenides.

Owner:IMPERIAL INNOVATIONS LTD

Silicon on insulator device with partially recessed gate

ActiveUS20150228777A1Enhanced transistor performanceSuppression of short channel effectsSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDopant

Transistors having partially recessed gates are constructed on silicon-on-insulator (SOI) semiconductor wafers provided with a buried oxide layer (BOX), for example, FD-SOI and UTBB devices. An epitaxially grown channel region relaxes constraints on the design of doped source and drain profiles. Formation of a partially recessed gate and raised epitaxial source and drain regions allow further improvements in transistor performance and reduction of short channel effects such as drain induced barrier lowering (DIBL) and control of a characteristic subthreshold slope. Gate recess can be varied to place the channel at different depths relative to the dopant profile, assisted by advanced process control. The partially recessed gate has an associated high-k gate dielectric that is initially formed in contact with three sides of the gate. Subsequent removal of the high-k sidewalls and substitution of a lower-k silicon nitride encapsulant lowers capacitance between the gate and the source and drain regions.

Owner:STMICROELECTRONICS SRL

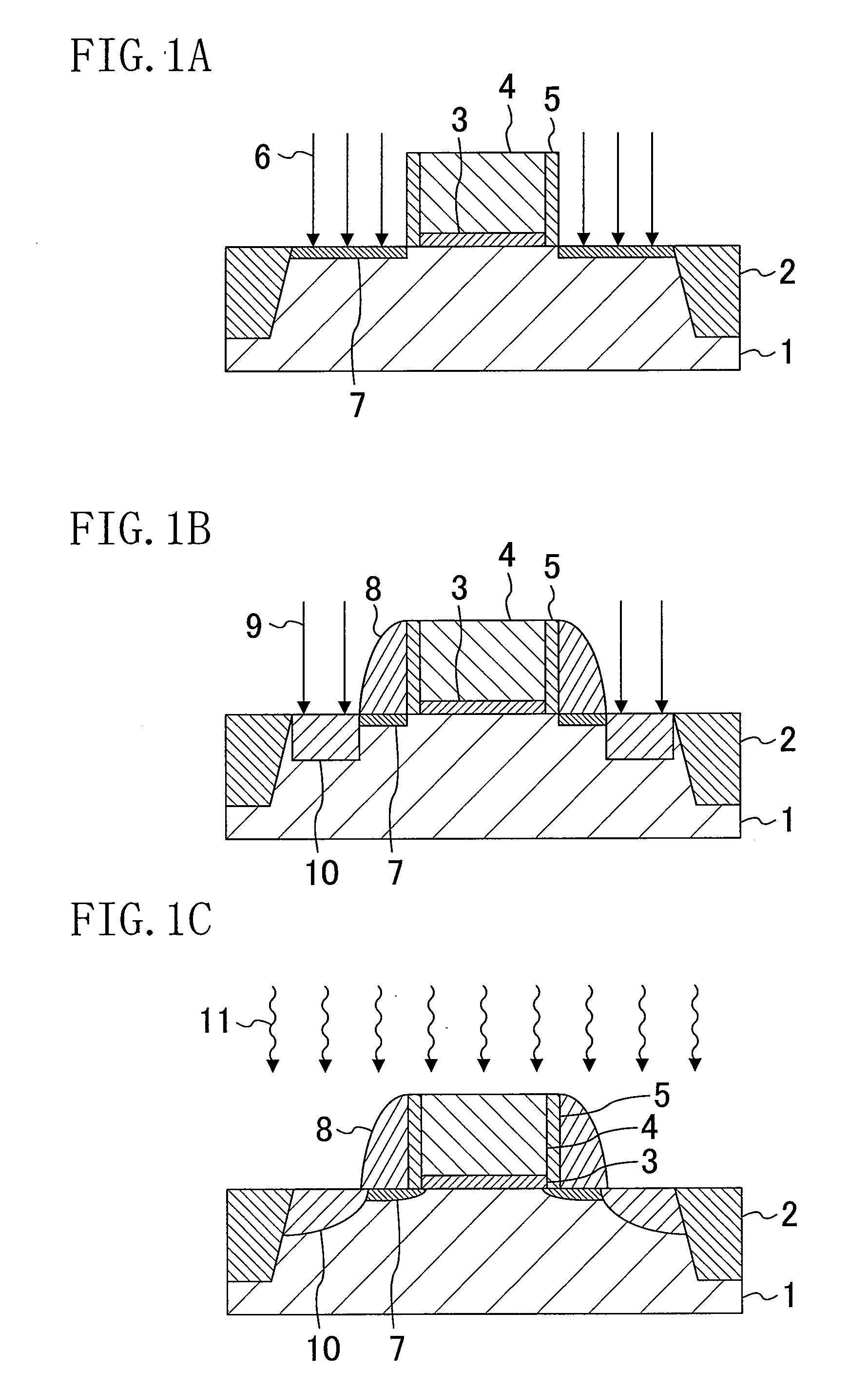

Technique for enhancing dopant activation by using multiple sequential advanced laser/flash anneal processes

InactiveUS20080268597A1Enhanced transistor performanceReduce probabilitySemiconductor/solid-state device manufacturingEngineeringDopant Activation

By performing multiple radiation-based anneal processes on the basis of less critical process parameters, the overall risk for creating anneal-induced damage, such as melting of gate portions, may be substantially avoided while nevertheless the respective degree of dopant activation may be enhanced for each individual anneal process. Consequently, the sheet resistance of advanced transistor devices may be reduced with a decreasing number of sequential anneal processes.

Owner:ADVANCED MICRO DEVICES INC

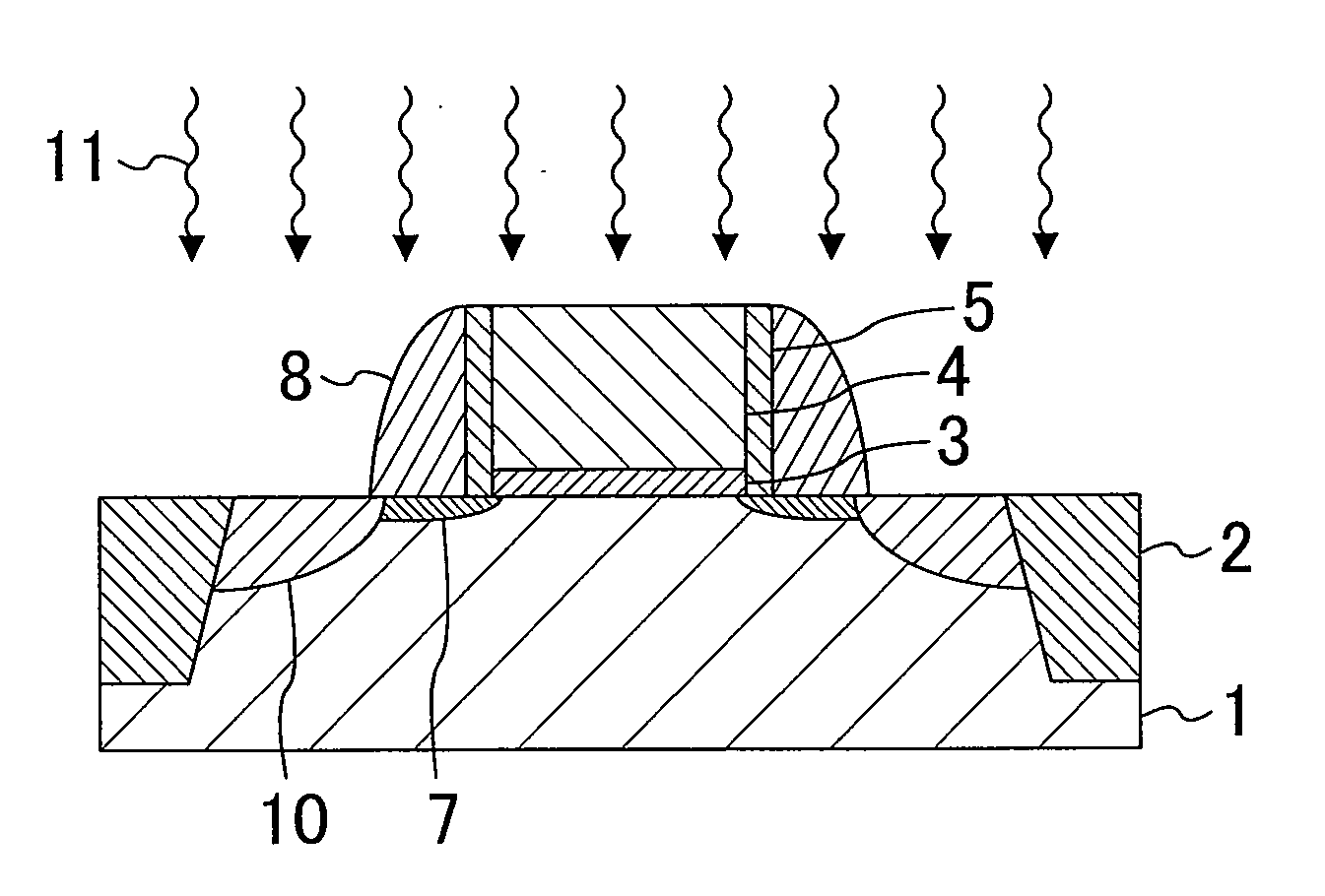

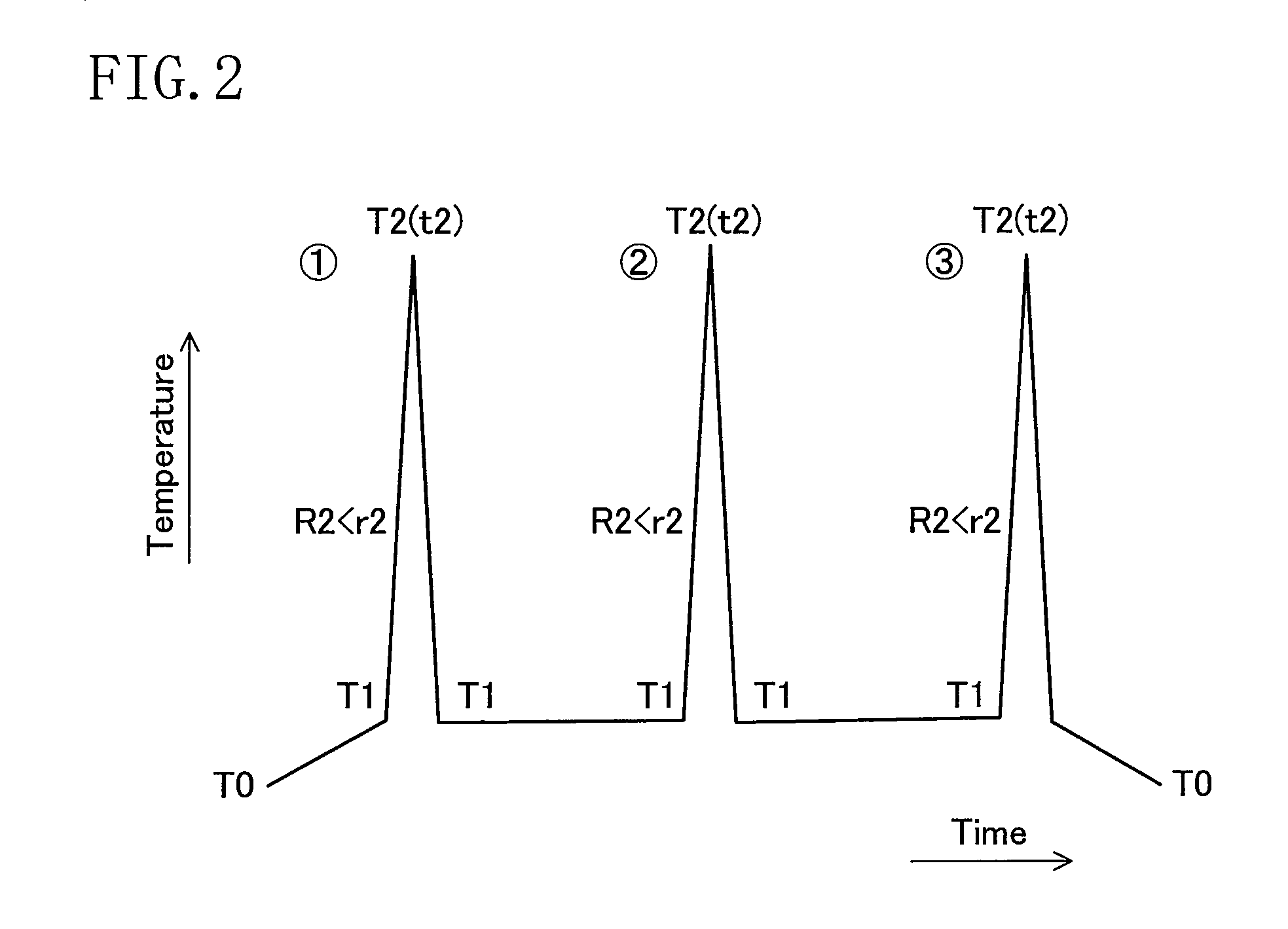

Impurity-activating thermal process method and thermal process appartus

ActiveUS20090197427A1Improve impurity activation rateWithout increasing impurity diffusion lengthTransistorDomestic stoves or rangesArbitrary rateImpurity

A thermal cycle includes: increasing a temperature from an initial temperature to a temperature T1 at an arbitrary rate R1 (° C. / sec); holding the temperature at the temperature T1 for an arbitrary period t1 (sec); increasing the temperature from the temperature T1 to a temperature T2 at a rate R2 (° C. / sec) of 1.0×107 (° C. / sec) or less; and holding the temperature at the temperature T2 for a period t2 (sec) of 50 msec or less. The thermal cycle thereafter includes: decreasing the temperature from the temperature T2 to the temperature T1 at a rate R1′ (° C. / sec) of 1.0×107 (° C. / sec) or less; holding the temperature T1 for an arbitrary period t3 (sec); and decreasing the temperature from the temperature T1 to a final temperature at an arbitrary rate R2′ (° C. / sec). Such a thermal cycle is successively repeated in a plurality of iterations.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

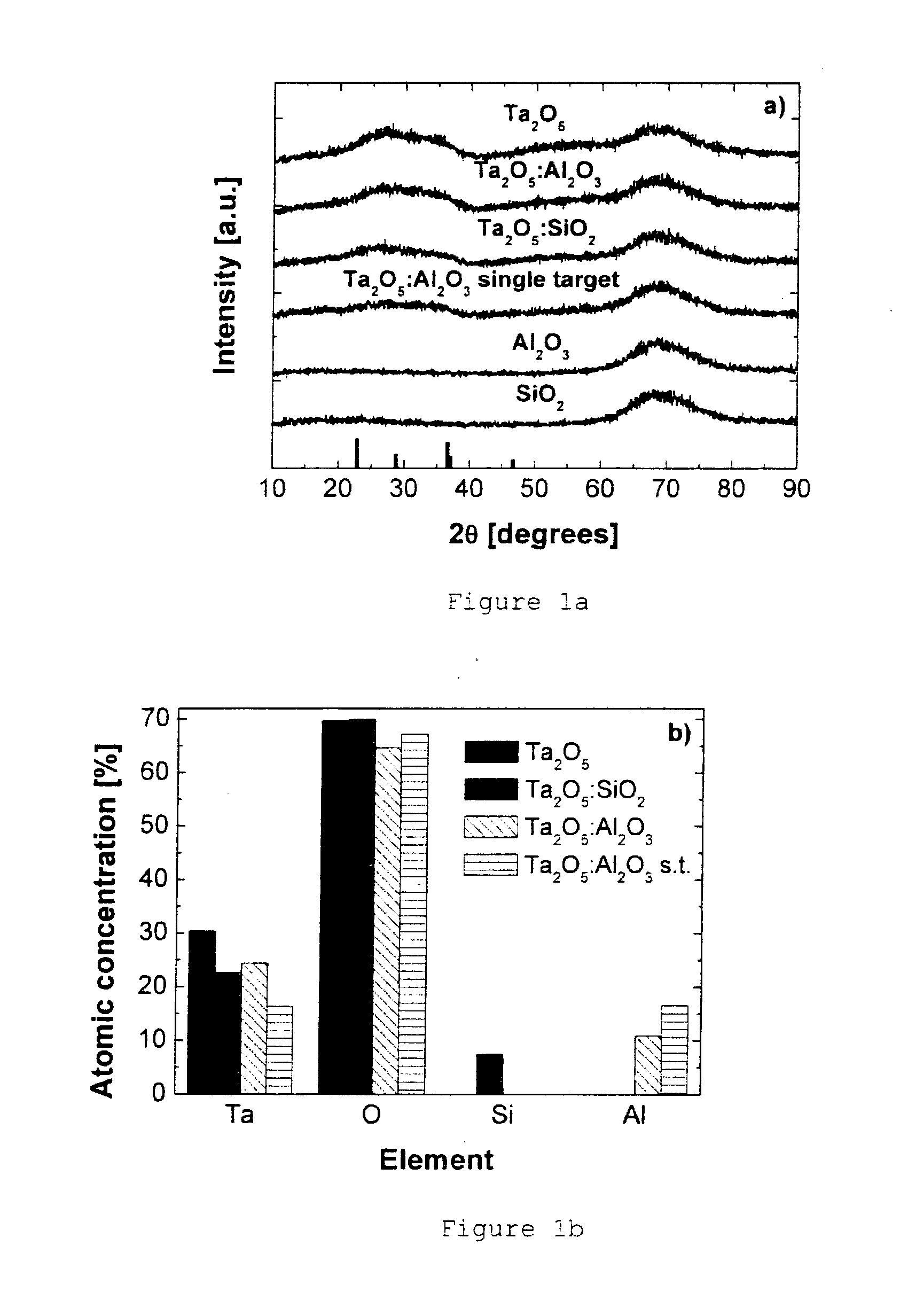

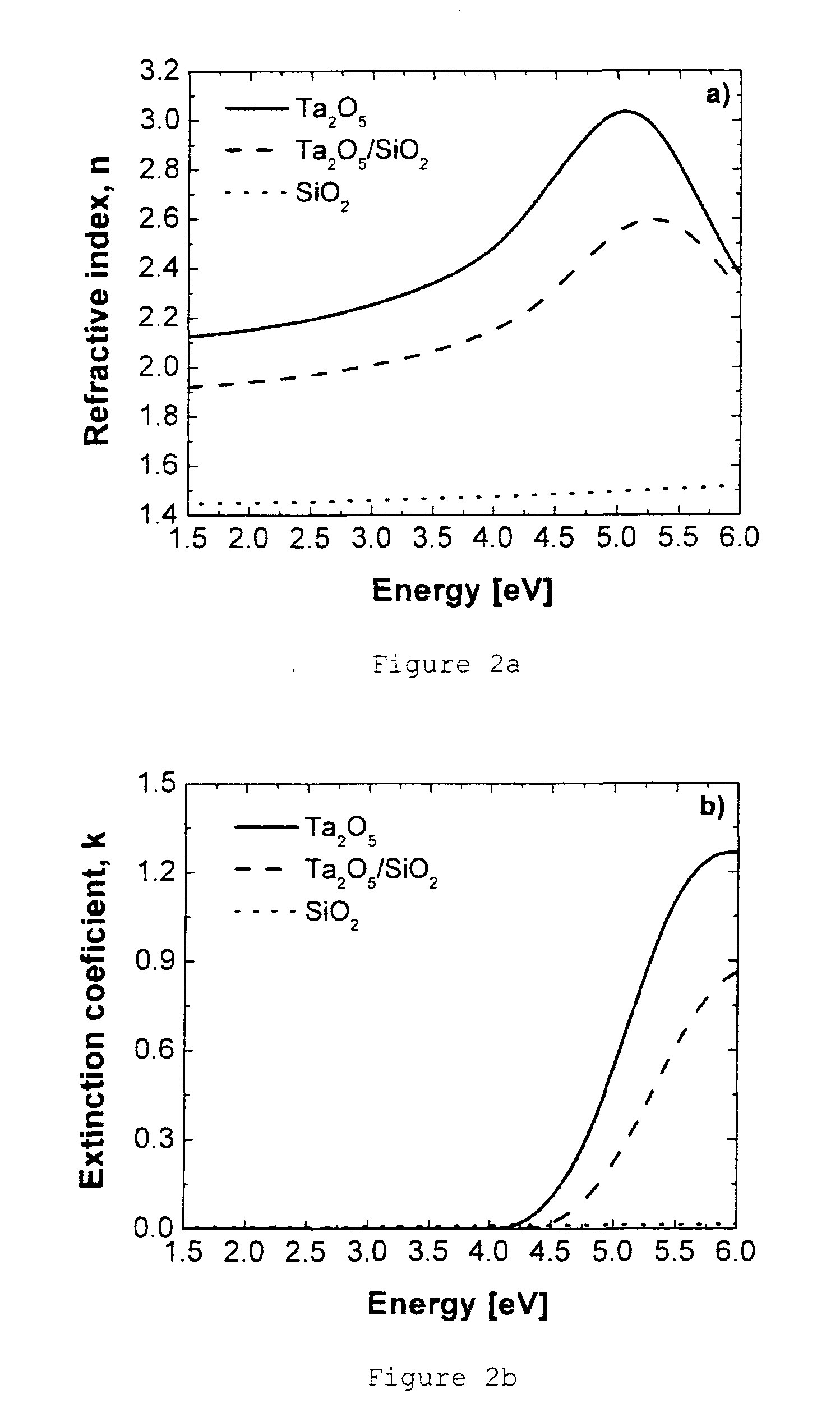

Amorphous multicomponent dielectric based on the mixture of high band gap and high k materials, respective devices and manufacture

InactiveUS20120248445A1Improve interface propertiesEnhanced transistor performanceTransistorSemiconductor/solid-state device detailsLow leakageHigh dielectric permittivity

High performance thin-film, transistors are entirely processed at temperatures not exceeding 150° C., using amorphous multi component dielectrics based on the mixture of high band gap and high dielectric constant (K) materials. The sputtered or ink jet printed mixed dielectric materials such as Ta2O5 with SiO2 or Al2O3 or HfO2 with SiO2 or Al2O3 are used. These multicomponent dielectrics allow producing amorphous dielectrics to be introduced in high stable electronic devices with low leakage currents, while preserving a high dielectric constant. This results in producing thin film transistors with remarkable electrical properties, such as the ones produced based on Ga—In—Zn oxide as channel layers and where the dielectric was the combination of the mixture Ta2O5:SiO2, exhibiting field-effect mobility exceeding 35 cm2 V−1 s−1, close to 0 V turn-on voltage, on / off ratio higher than 106 and subthreshold slope below 0.24 V dec−1.

Owner:FACULDADE DE CIENCIAS E TECHA DA UNIV NOVA DE LISBOA +2

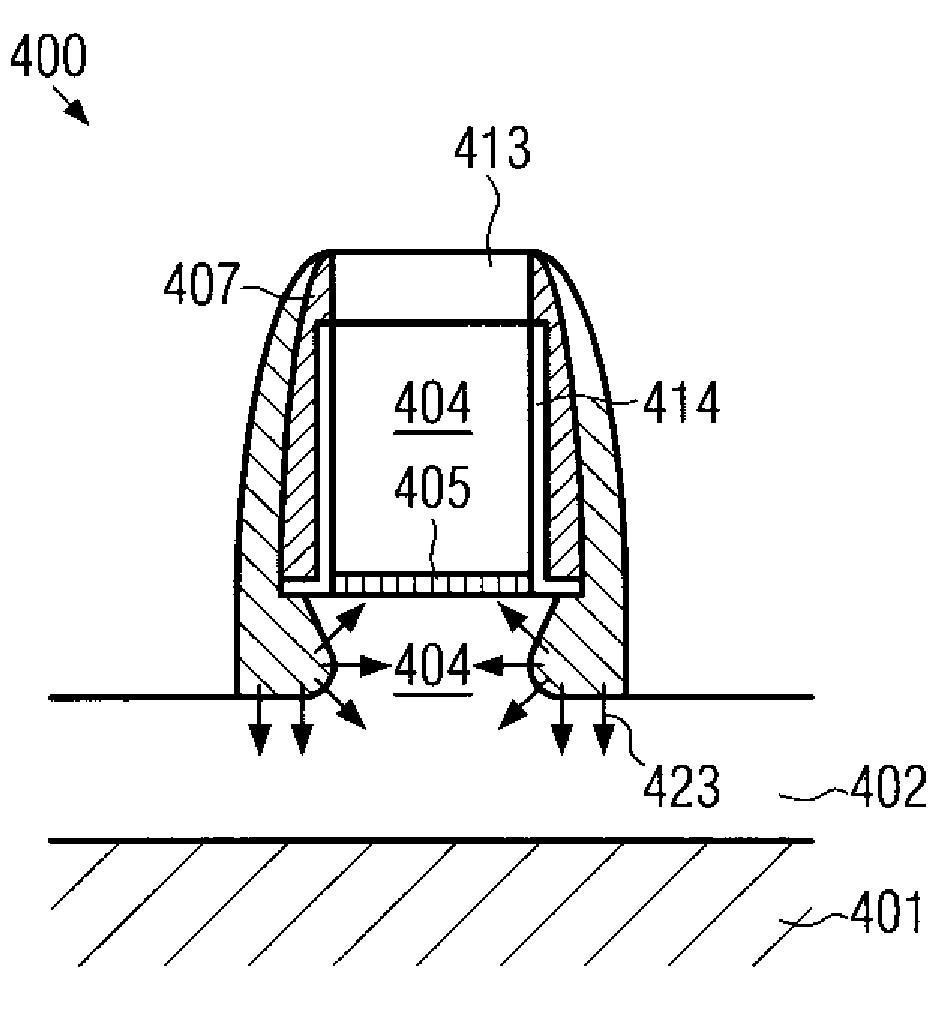

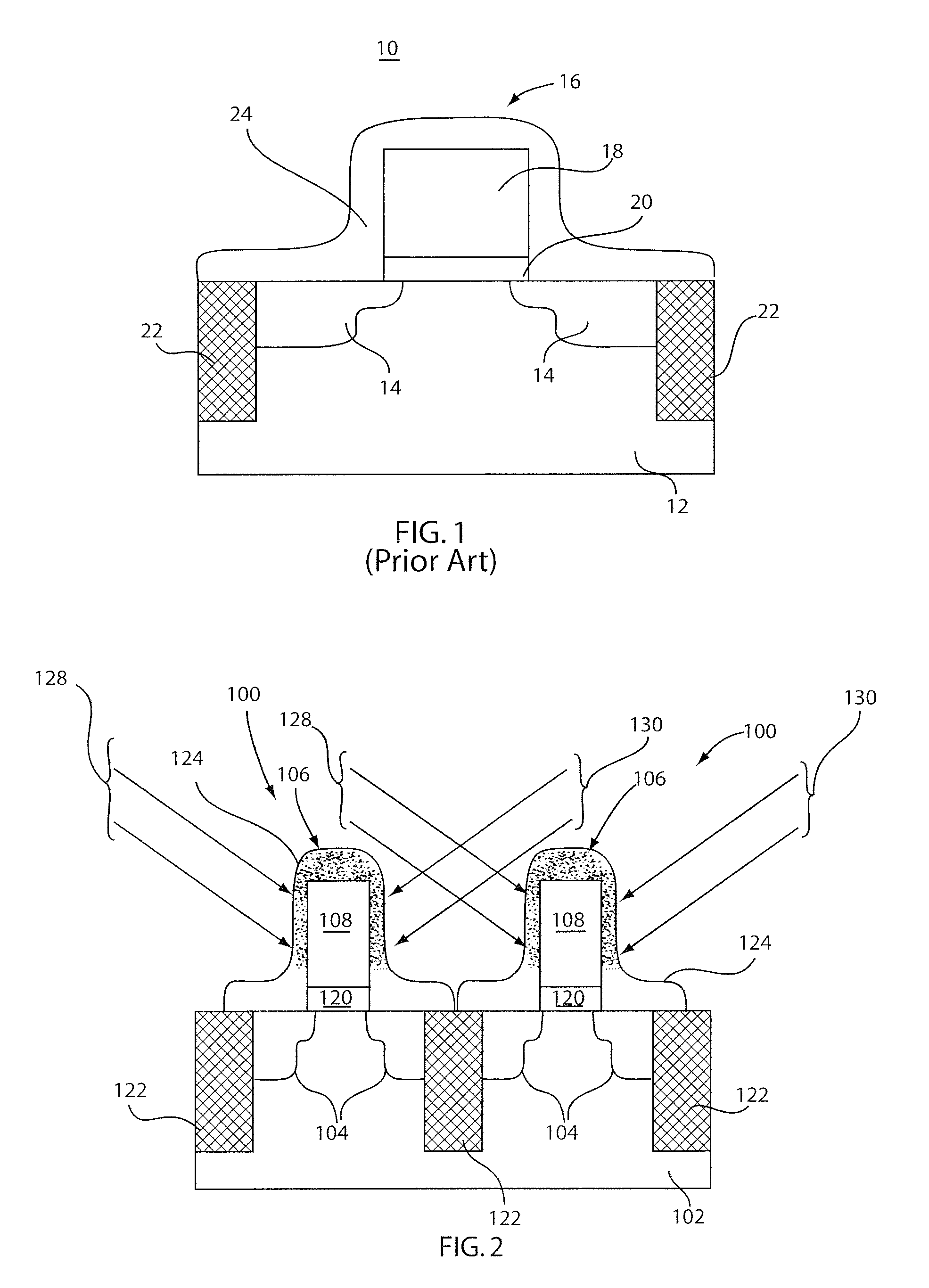

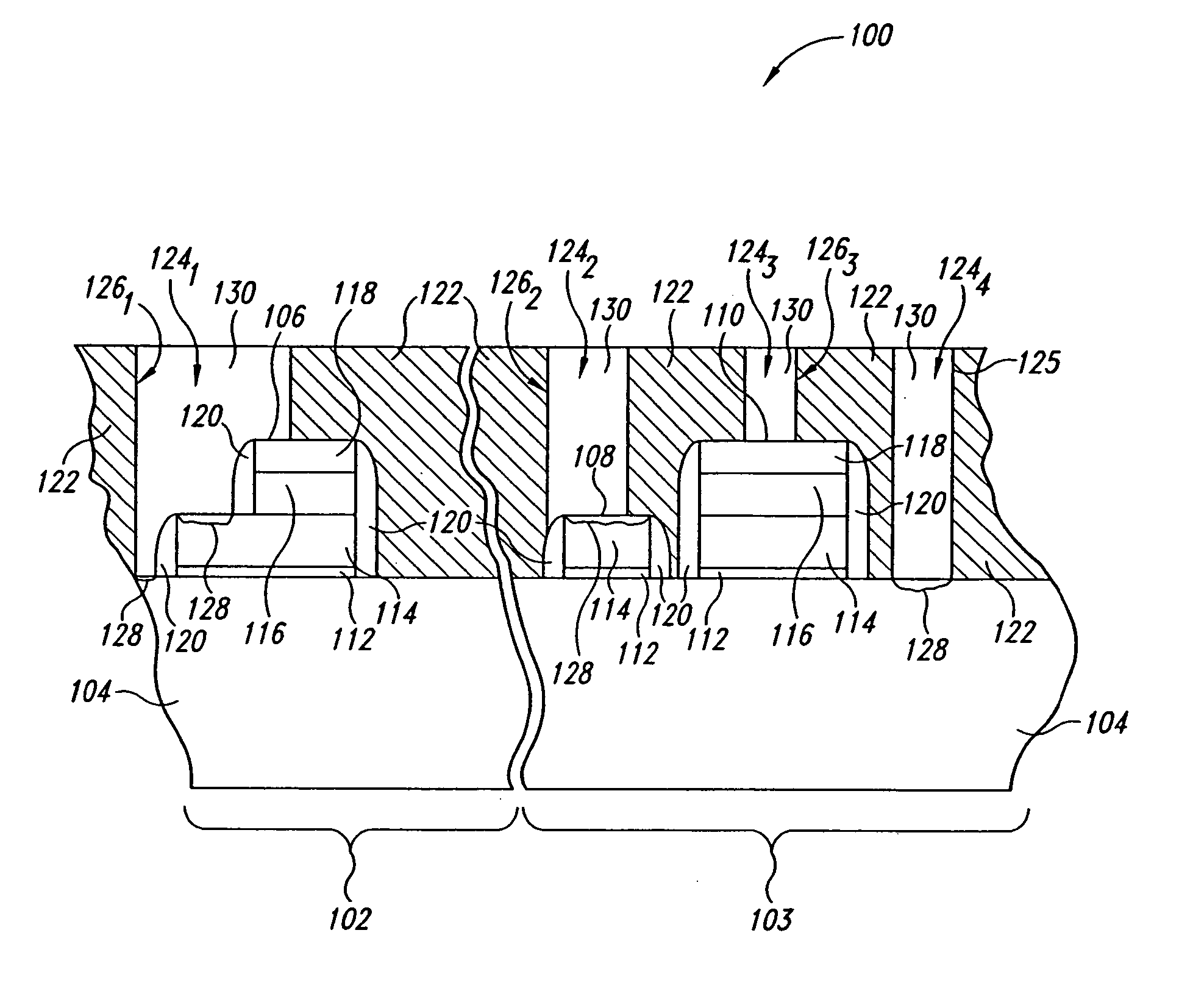

Technique for providing stress sources in mos transistors in close proximity to a channel region

ActiveUS20070228357A1Enhanced transistor performanceIncrease strainSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideRelaxation effect

A strained semiconductor material may be positioned in close proximity to the channel region of a transistor, such as an SOI transistor, while reducing or avoiding undue relaxation effects of metal silicides and extension implantations, thereby providing enhanced efficiency for the strain generation.

Owner:ADVANCED MICRO DEVICES INC

Fabrication method of vertical silicon nanowire field effect transistor

ActiveUS20130011980A1Reduce leakage currentImprove gate control abilityNanoinformaticsSemiconductor/solid-state device manufacturingElectrical resistance and conductanceSilicon nanowires

The present invention discloses a fabrication method of a vertical silicon nanowire field effect transistor having a low parasitic resistance, which relates to a field of an ultra-large-integrated-circuit fabrication technology. As compared with a conventional planar field effect transistor, on one hand the vertical silicon nanowire field effect transistor fabricated by the present invention can provide a good ability for suppressing a short channel effect due to the excellent gate control ability caused by the one-dimensional structure, and reduce a leakage current and a drain-induced barrier lowering (DIBL). On the other hand, an area of the transistor is further reduced and an integration degree of an IC system is increased.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device and manufacturing method thereof

InactiveUS20100078730A1Enhanced transistor performanceImprove performanceTransistorSemiconductor/solid-state device manufacturingSemiconductorDevice material

A semiconductor device includes a gate electrode. The gate electrode includes a silicide layer obtained by siliciding porous silicon or organic silicon.

Owner:PANASONIC CORP

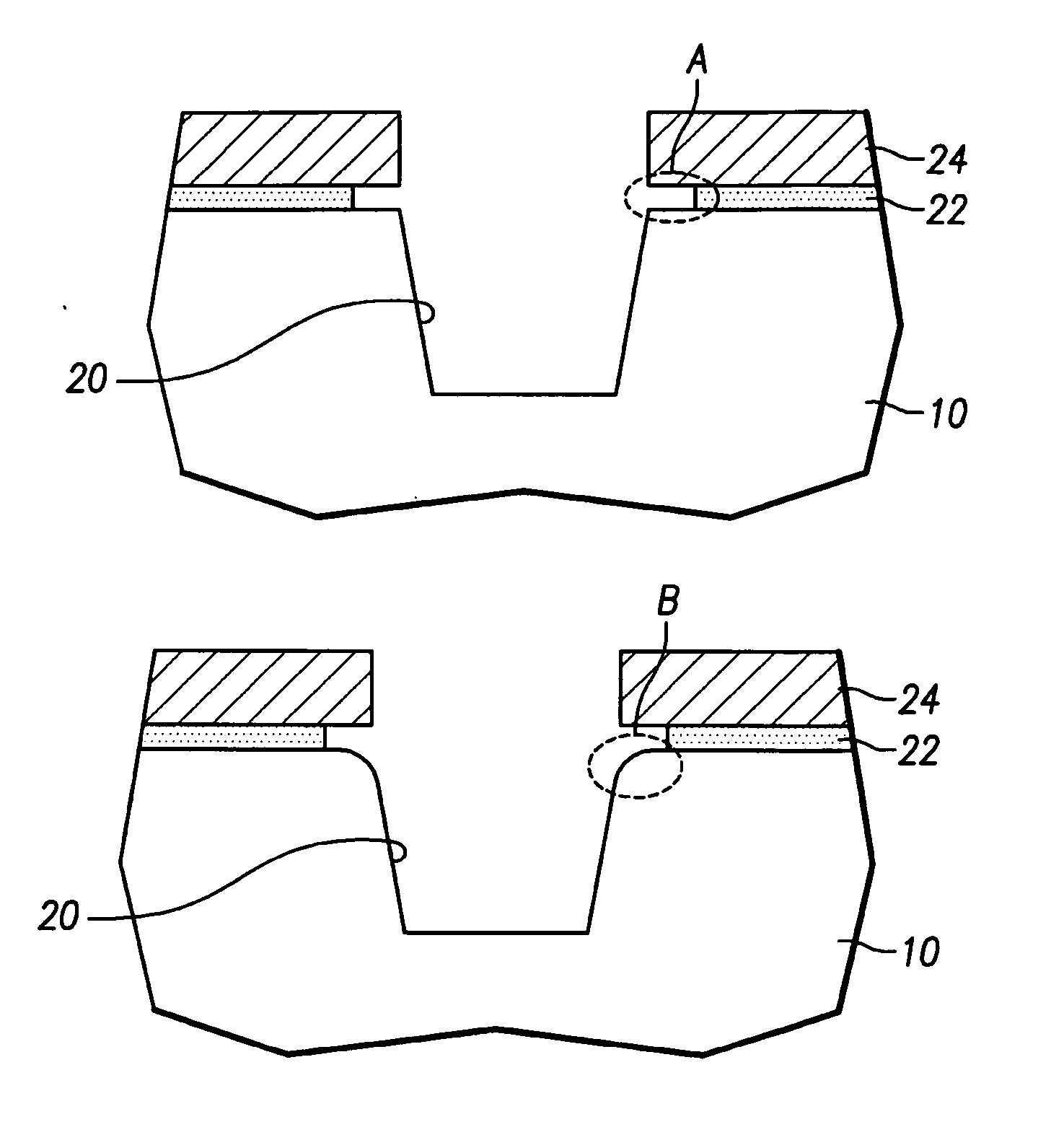

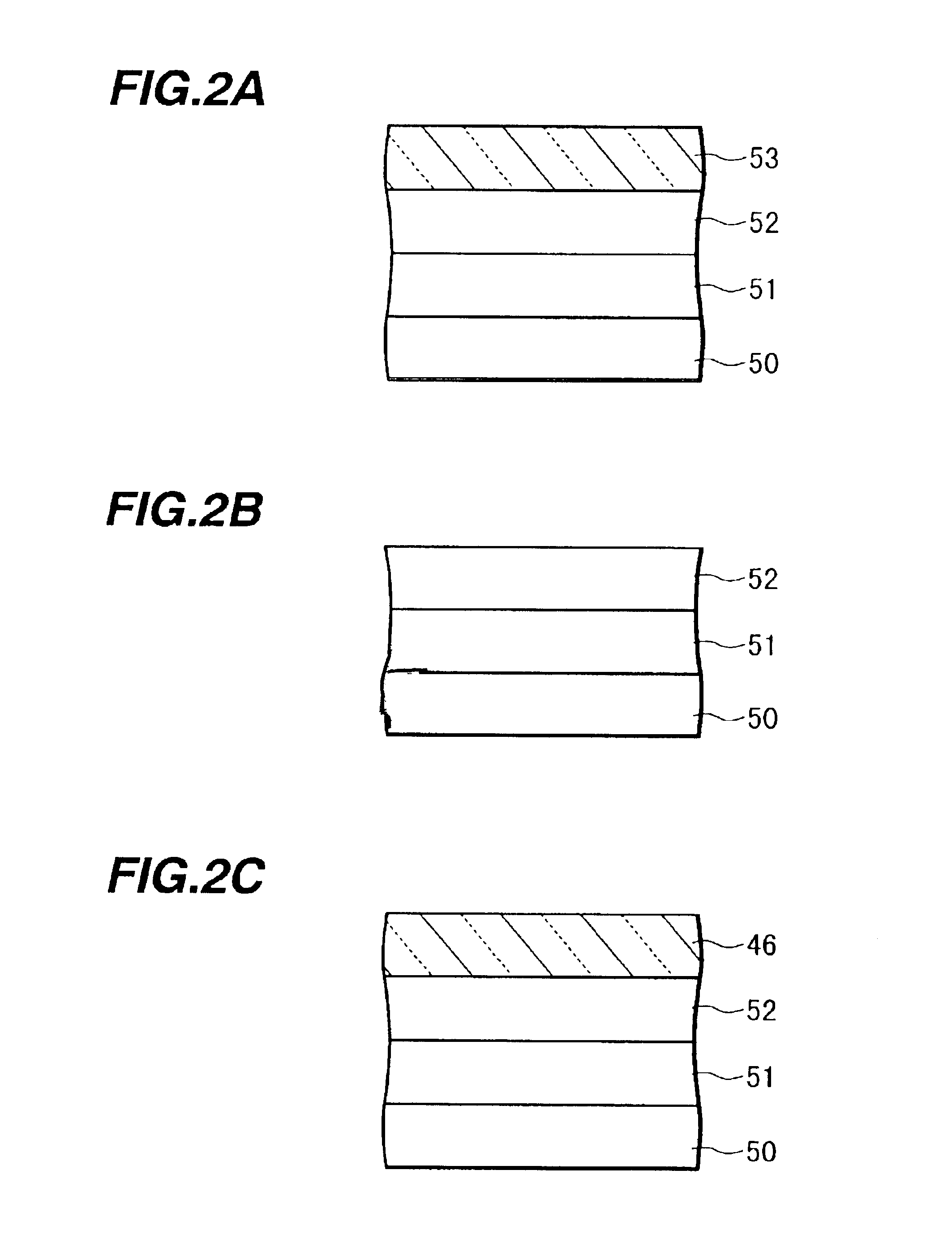

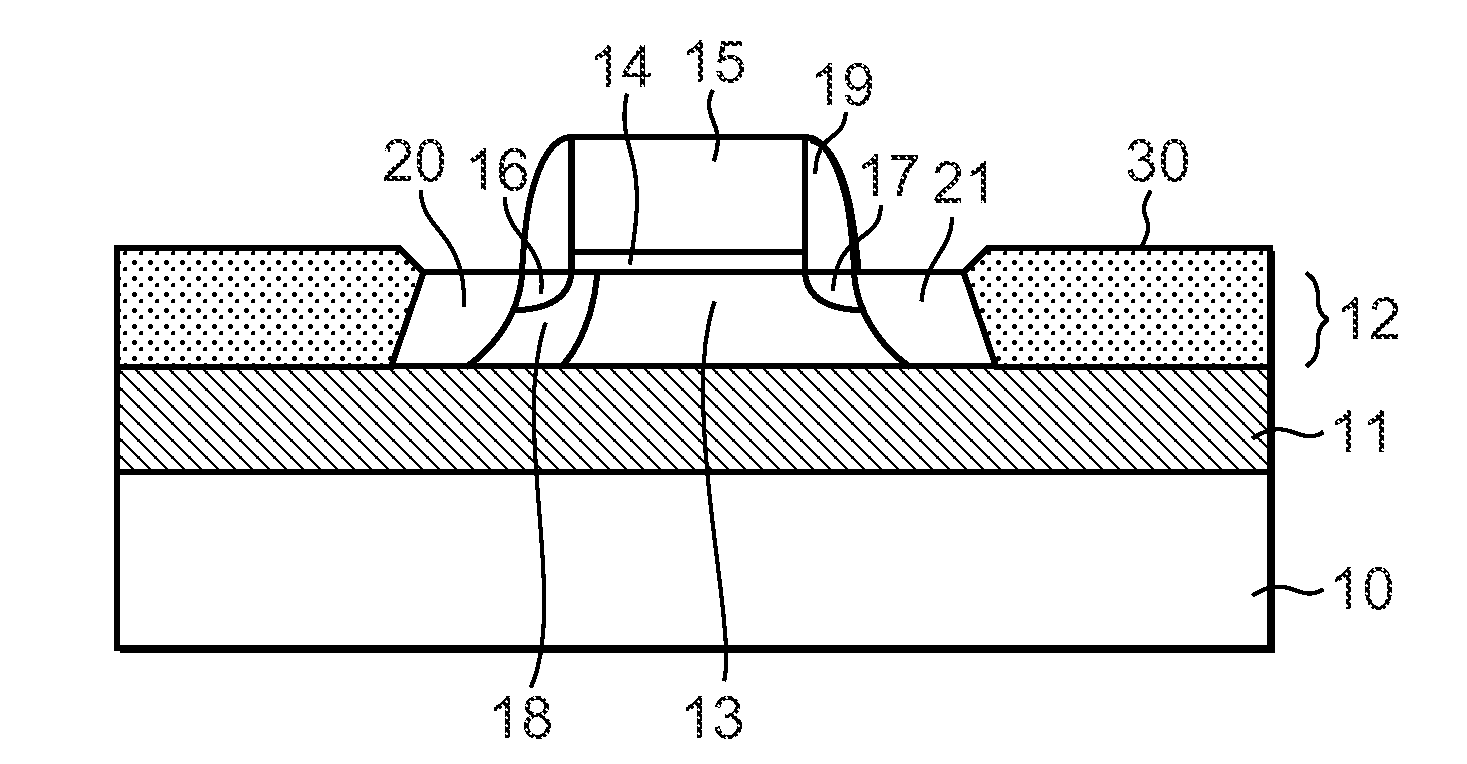

Semiconductor device and method of manufacturing the same

InactiveUS20060267115A1Enhanced transistor performanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A gate insulating film of a thin-film transistor is formed on a polysilicon film in which a source region and a drain region of the thin-film transistor are formed. A gate electrode of the thin-film transistor is formed on the gate insulating film. An insulating layer containing a silicon atom, a dangling bond of which is terminated with a nitrogen atom or an ON group, is provided in an interface between the polysilicon film and the gate insulating film.

Owner:MITSUBISHI ELECTRIC CORP

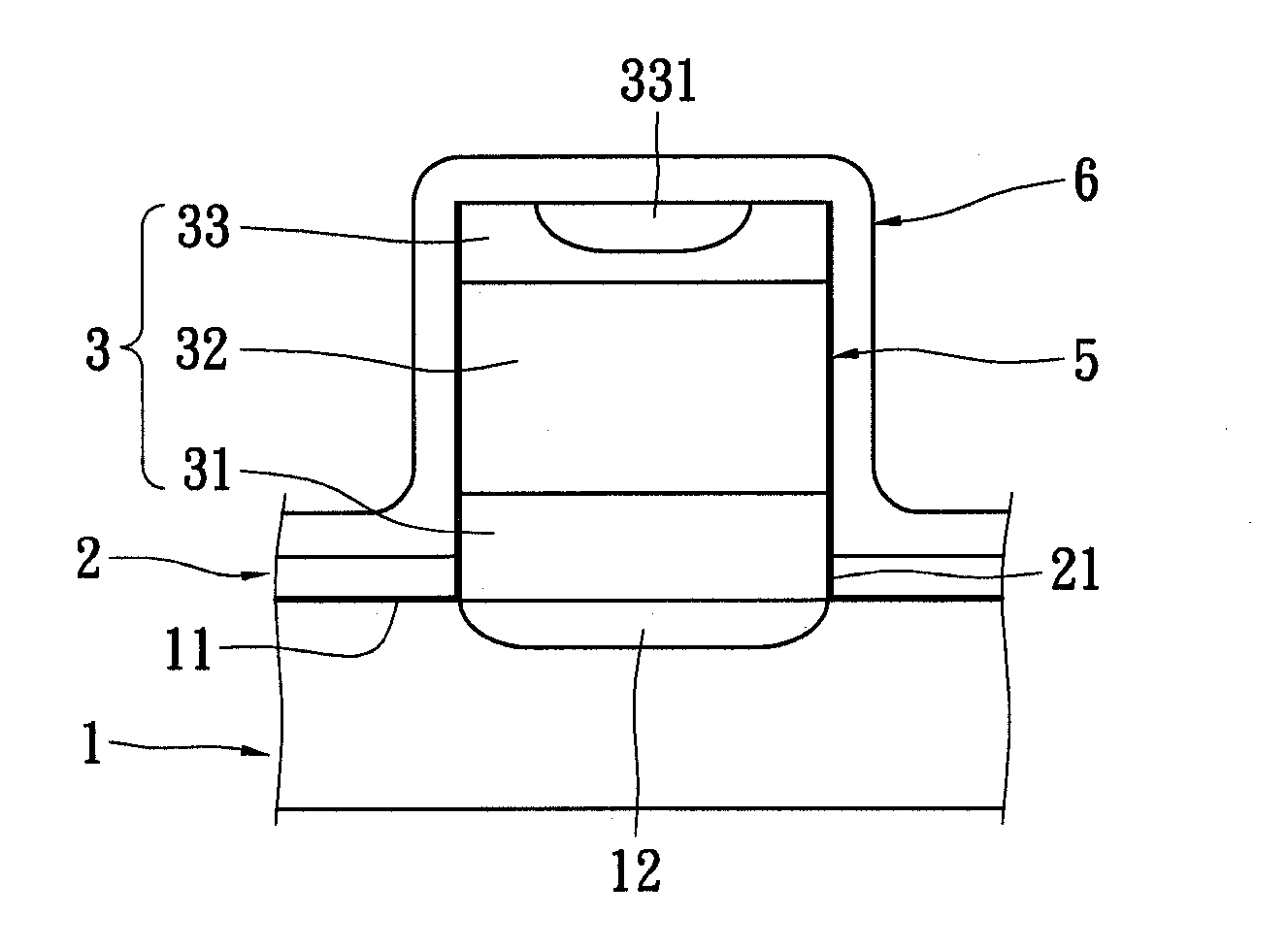

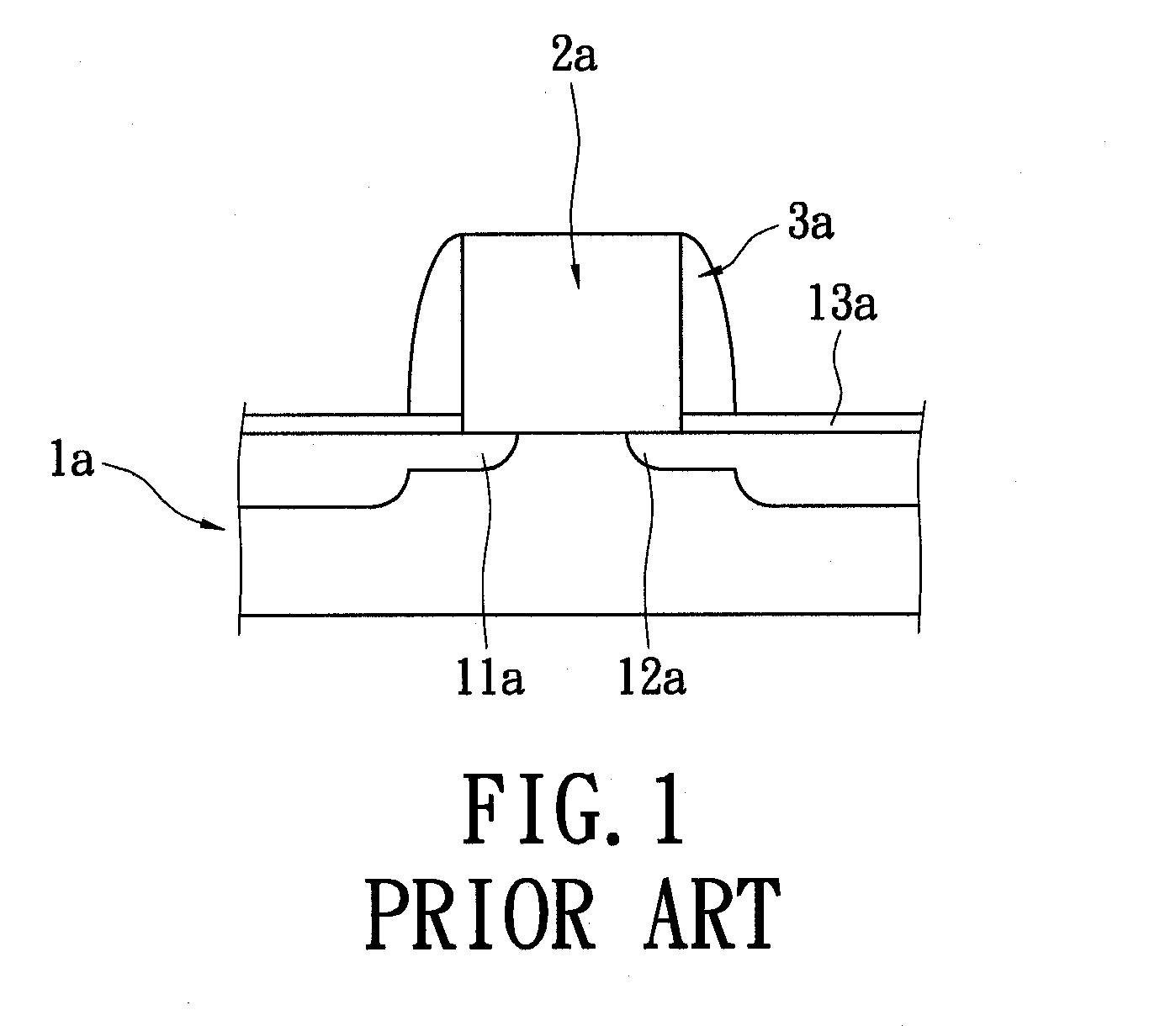

Vertical PMOS field effect transistor and manufacturing method thereof

ActiveUS20110133248A1Enhanced transistor performanceTransistor area can be reducedSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerGate stack

A PMOS field effect transistor includes a substrate, a first nitride layer, a mesa structure, two gate oxide films, a gate stack layer and a second nitride layer. The substrate has a oxide layer and a first doping area. The first nitride layer is located on the oxide layer. The mesa structure includes a first strained Si—Ge layer, an epitaxial Si layer and a second strained Si—Ge layer. The first strained Si—Ge layer is located on the oxide layer and the first nitride layer. The epitaxial Si layer is located on the first strained Si—Ge layer. The second strained Si—Ge layer is located on the epitaxial Si layer. In the surface layer of the second strained Si—Ge layer, there is a second doping area. The two gate oxide films are located at two sides of the mesa structure.

Owner:MICRON TECH INC

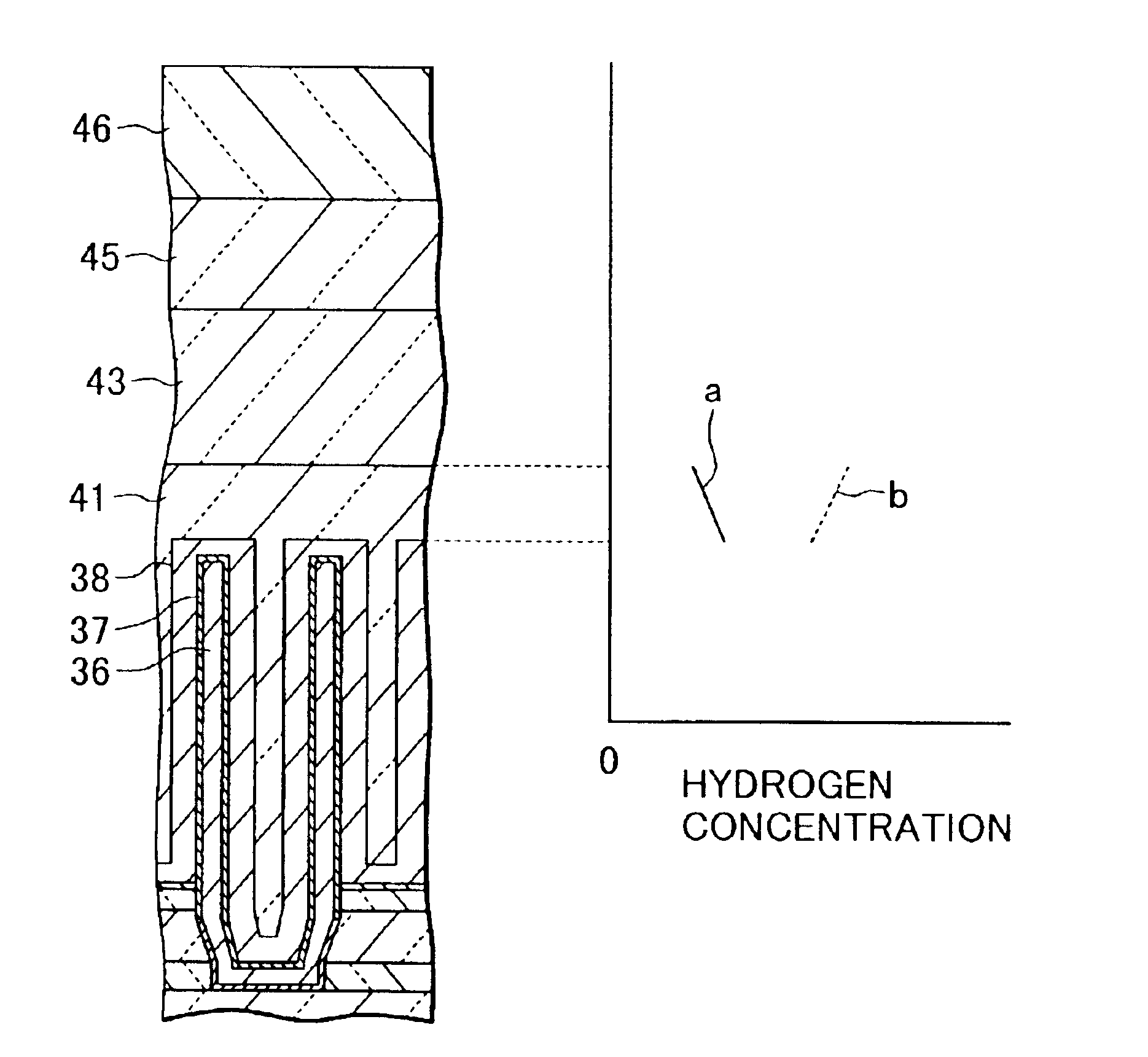

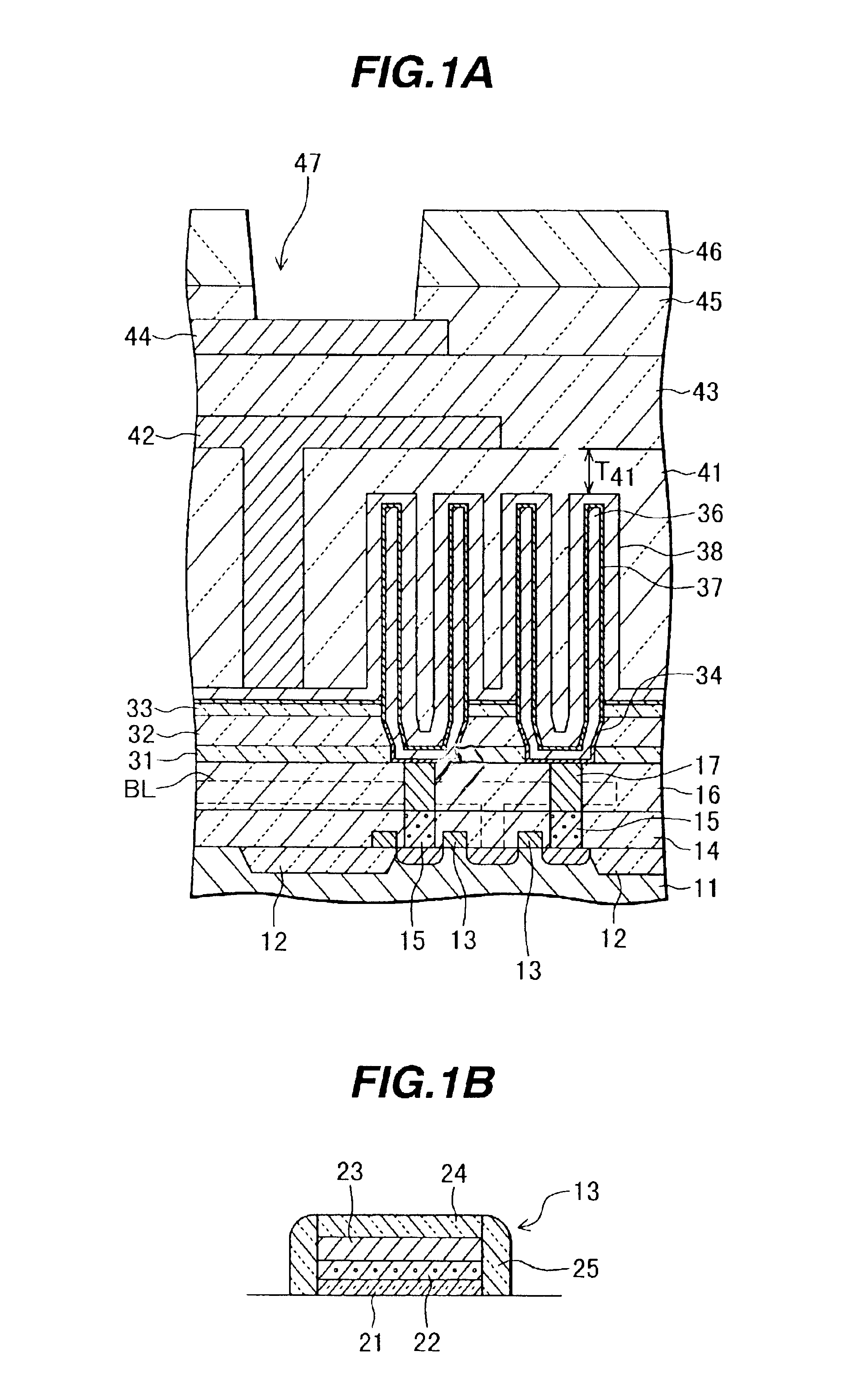

Semiconductor device with transistor and capacitor and its manufacture method

InactiveUS6849894B2Enhanced transistor performanceReduce leakage currentTransistorSolid-state devicesEngineeringHeat treated

On a semiconductor substrate, a transistor and a capacitor electrically connected to the transistor are formed, the capacitor having two electrodes made of metal and a capacitor dielectric layer between the two electrodes made of oxide dielectric material. A temporary protective film is formed over the capacitor, the temporary protective film covering the capacitor. The semiconductor substrate with the temporary protective film is subjected to a heat treatment in a reducing atmosphere. The temporary protective film is removed. The semiconductor substrate with the temporary protective film removed is subjected to a heat treatment in an inert gas atmosphere or in a vacuum state. A protective film is formed over the capacitor, the protective film covering the capacitor. With these processes, leak current of the capacitor can be reduced.

Owner:FUJITSU SEMICON LTD +1

Method for manufacturing transistor and semiconductor device

InactiveUS20130040435A1Enhanced transistor performanceReduce capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceGate stack

A method for manufacturing a transistor and a semiconductor device is provided. The method for manufacturing a transistor may comprise: defining an active area on a semiconductor substrate, and forming on the active area a gate stack or a dummy gate stack, a source / drain extension region, a spacer and a source / drain region, wherein the source / drain extension region is embedded in the active area and self-aligned on both sides of the gate stack or dummy gate stack, the spacer surrounds the gate stack or dummy gate stack, and the source / drain region is embedded in the active area and self-aligned outside the spacer; removing at least a portion of the spacer to expose a portion of the active area; and forming an interlayer dielectric layer which covers the gate stack or dummy gate stack, the spacer and the exposed active area, wherein the dielectric constant of the material of the interlayer dielectric layer is smaller than that of the removed material of the spacer. It is beneficial for reducing the capacitance between the gate region and the source / drain region as well as between the gate region and the contact plug.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

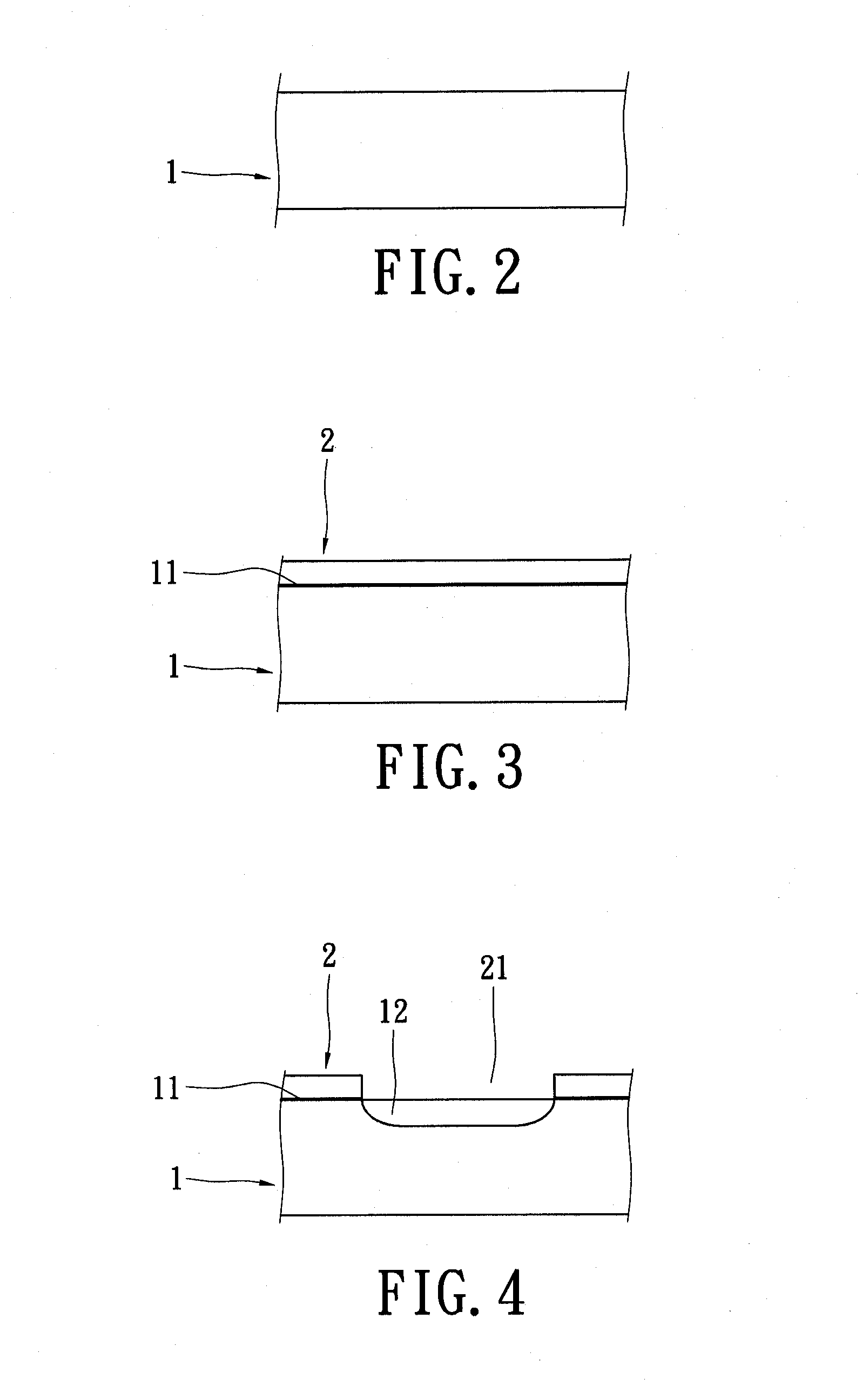

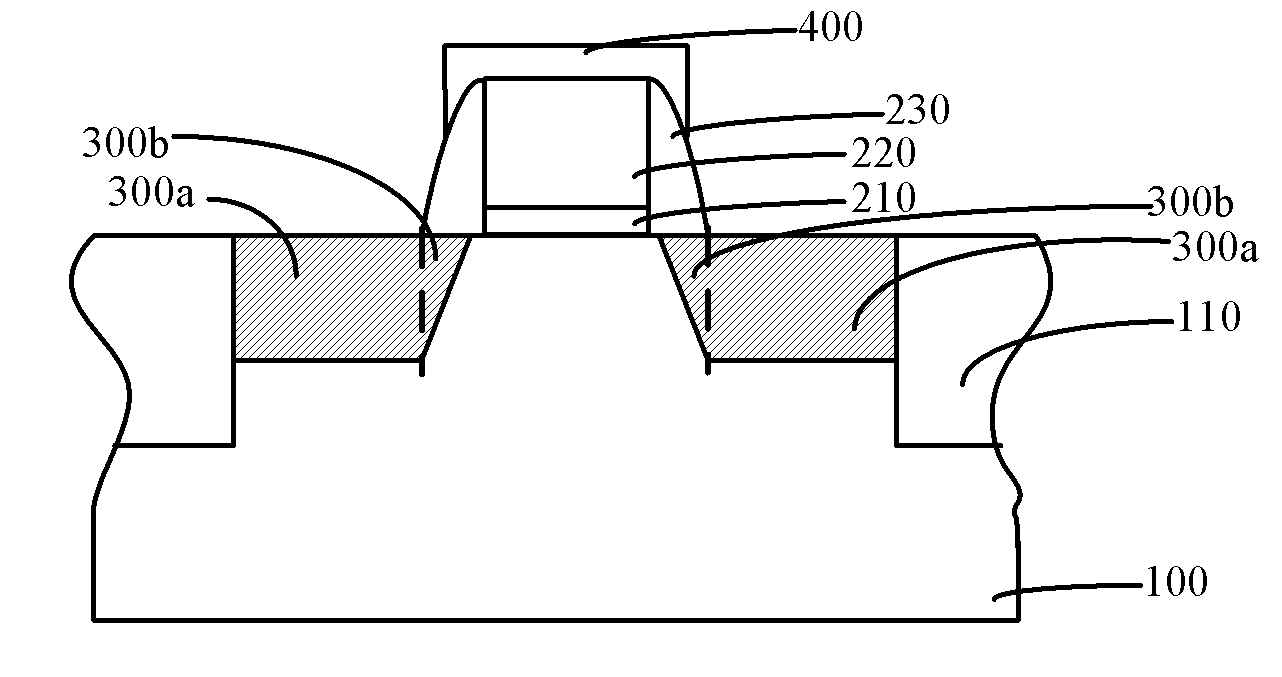

Semiconductor device and method for forming the same

ActiveUS20120139016A1Increase pressureEnhanced transistor performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor

A semiconductor device and a method for forming the same are provided. The method includes: providing a substrate having a gate structure and first spacers on both sidewalls of the gate structure formed on a top surface of the substrate; forming first openings in the substrate by using the first spacers as a mask, wherein the first openings are located on both sides of the gate structure; forming second openings by etching the first openings with an etching gas, wherein each of the second openings is an expansion of a corresponding one of the first openings toward the gate structure and extends to underneath an adjacent first spacer; and forming epitaxial layers in the first openings and the second openings.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Methods for making semiconductor structures having high-speed areas and high-density areas

InactiveUS20050173747A1Decrease horizontal resistanceEnhanced transistor performanceTransistorSolid-state devicesEngineeringSemiconductor structure

Methods for making a semiconductor structure are discussed. The methods include forming openings in a high-density area and a high-speed area, and forming a metallization layer simultaneously into the high-density area and the high-speed area. The metallization layer includes a combination of substances and compounds that reduce vertical resistance, reduce horizontal resistance, and inhibit cross-diffusion.

Owner:MICRON TECH INC

Mosfet and manufacturing method thereof

InactiveUS20090261413A1Enhanced transistor performanceImprove the level ofSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate oxide

The present invention provides a MOSFET capable of improving the basic performance of a transistor such as saturation current characteristics, input follow-up and an offleak current at high levels, and a manufacturing method thereof. The MOSFET comprises a semiconductor layer, a gate electrode formed over the semiconductor layer through a gate oxide film interposed therebetween, a pair of drain / source regions each provided at a position where the regions interpose a channel region lying below the gate oxide film therebetween inside the semiconductor layer and each having a conductivity type different from a conductivity type of the semiconductor layer, a pair of extension regions which are respectively provided adjacent to the drain / source regions at the position and which are identical in conductivity type to the drain / source regions and lower in impurity concentration than the drain / source regions, and an interposition layer having a conductivity type different from the conductivity type of the source region, the interposition layer being provided adjacent only to the source region and the extension region adjacent thereto inside the semiconductor layer.

Owner:LAPIS SEMICON CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com