Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

645 results about "Metal semiconductor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

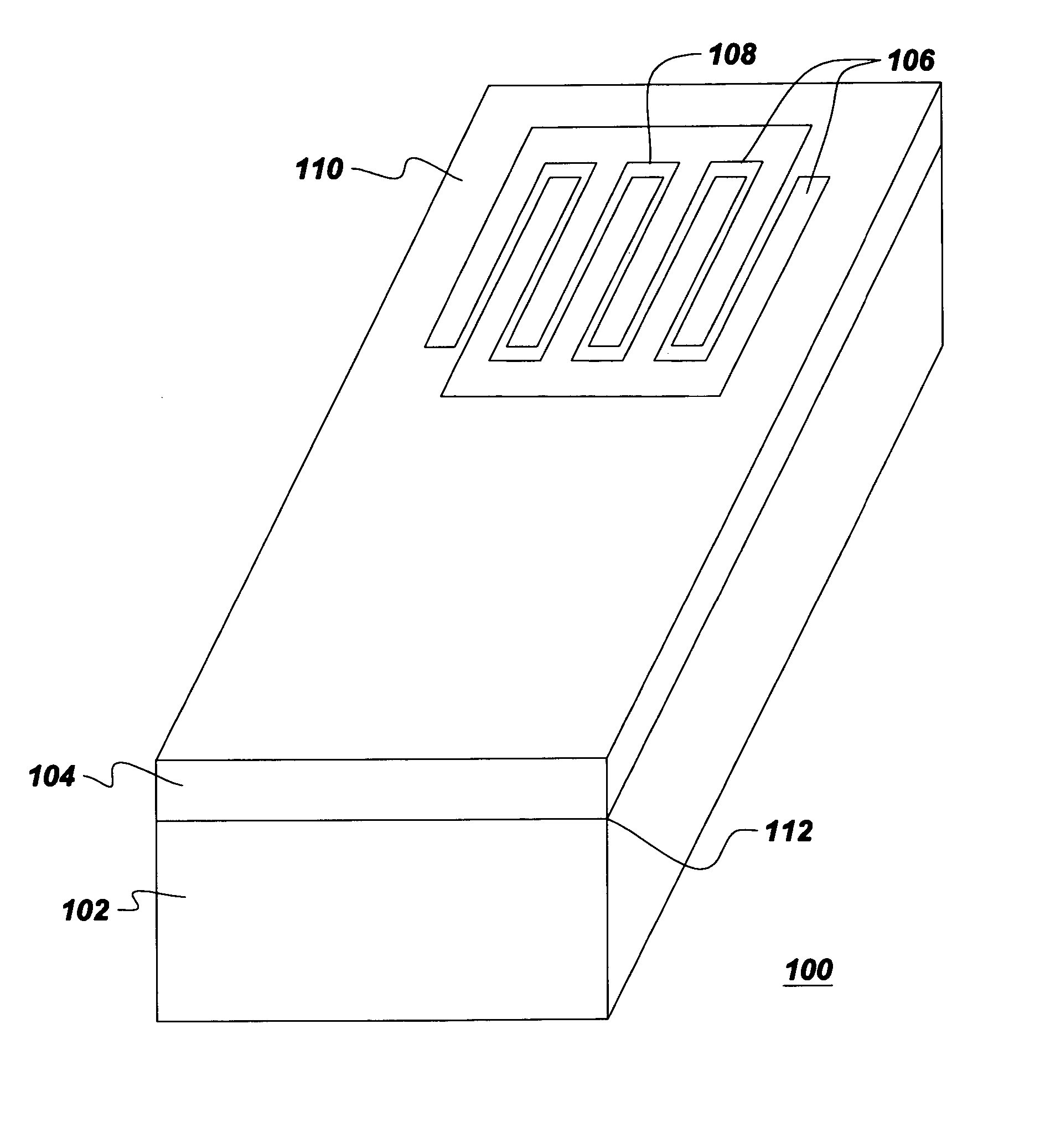

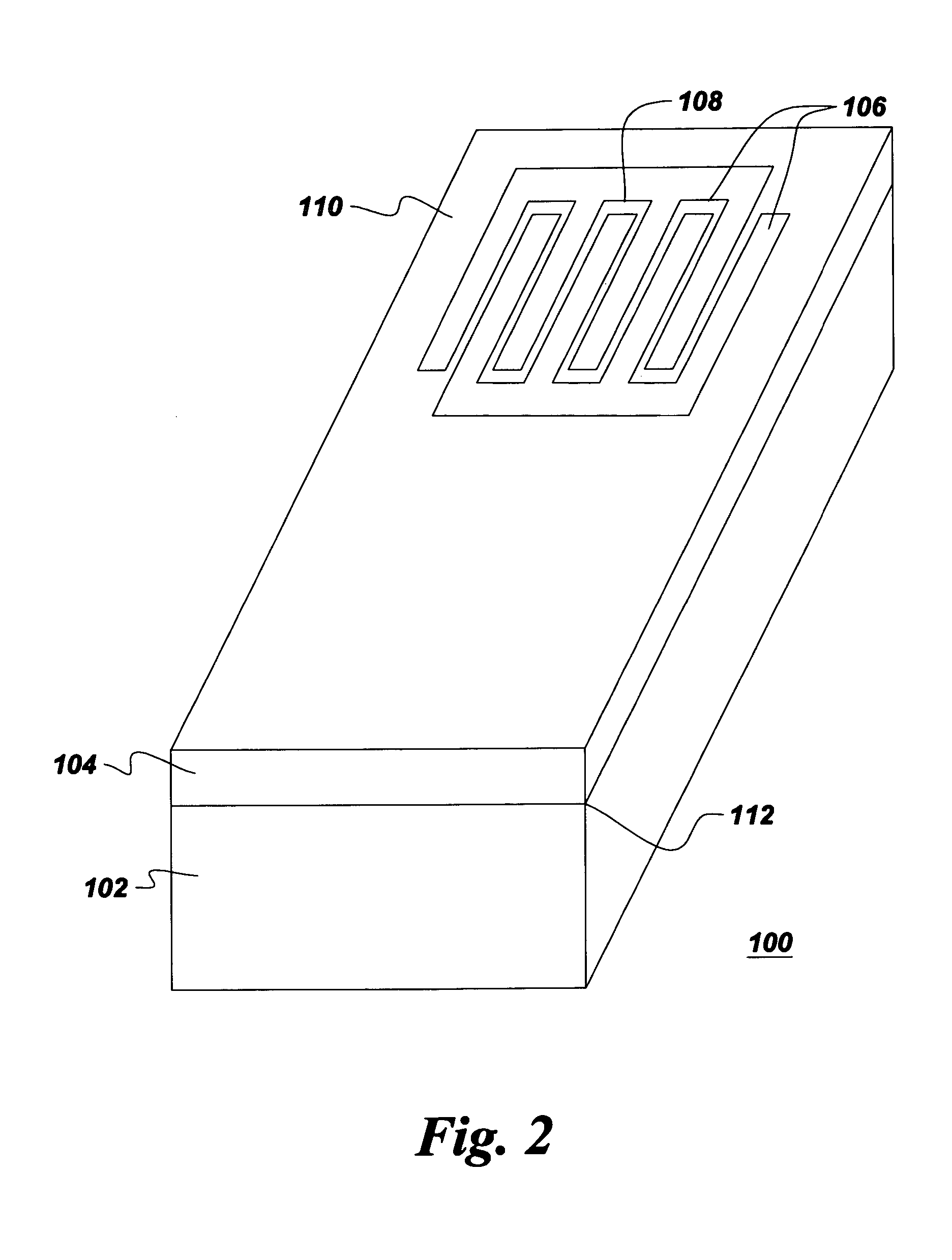

Monolithic microwave integrated circuit (MMIC) waveguide resonators having a tunable ferroelectric layer

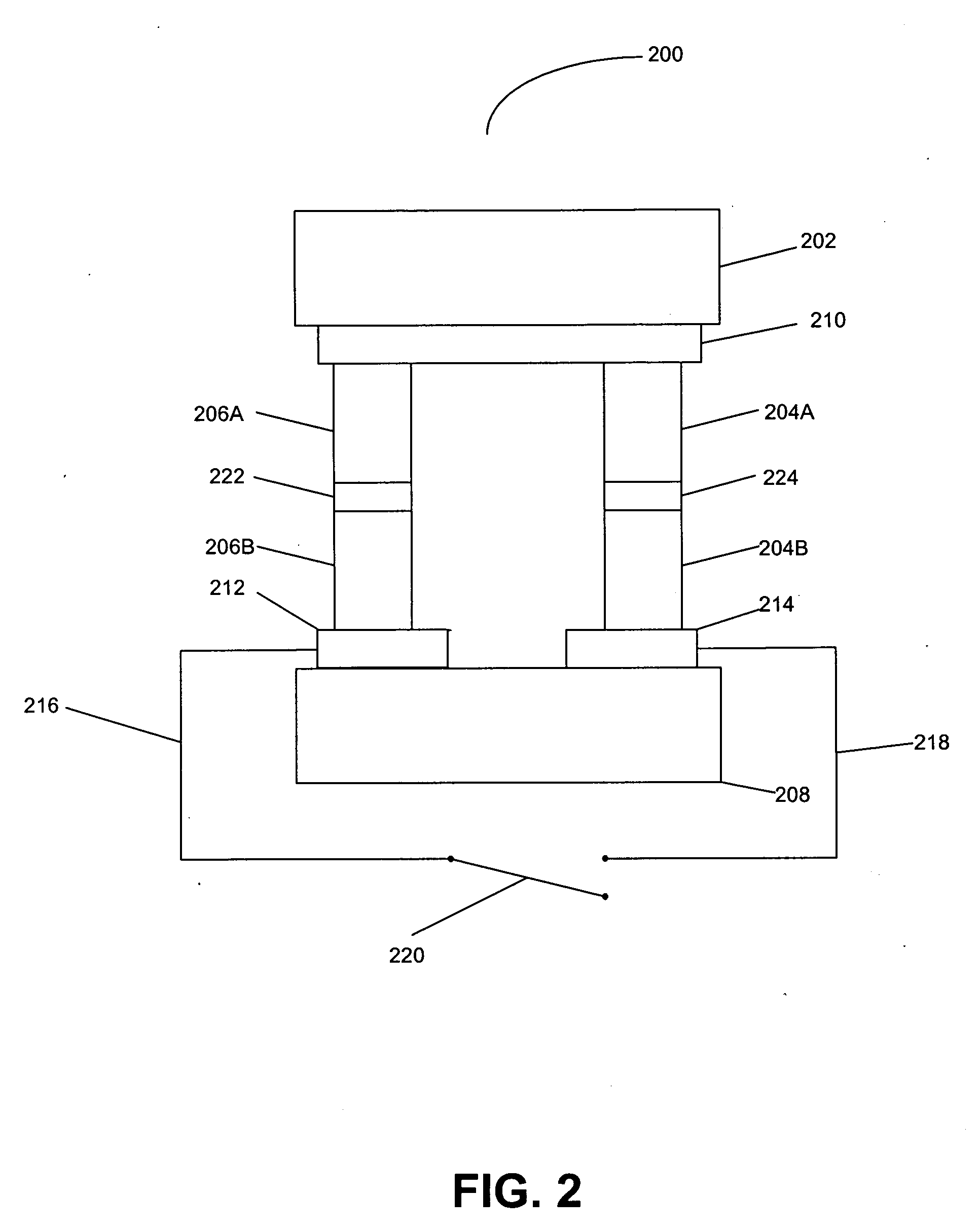

ActiveUS7570137B2Improve scalabilityEasy to integrateResonatorsOscillations generatorsElectromagnetic couplingResonant cavity

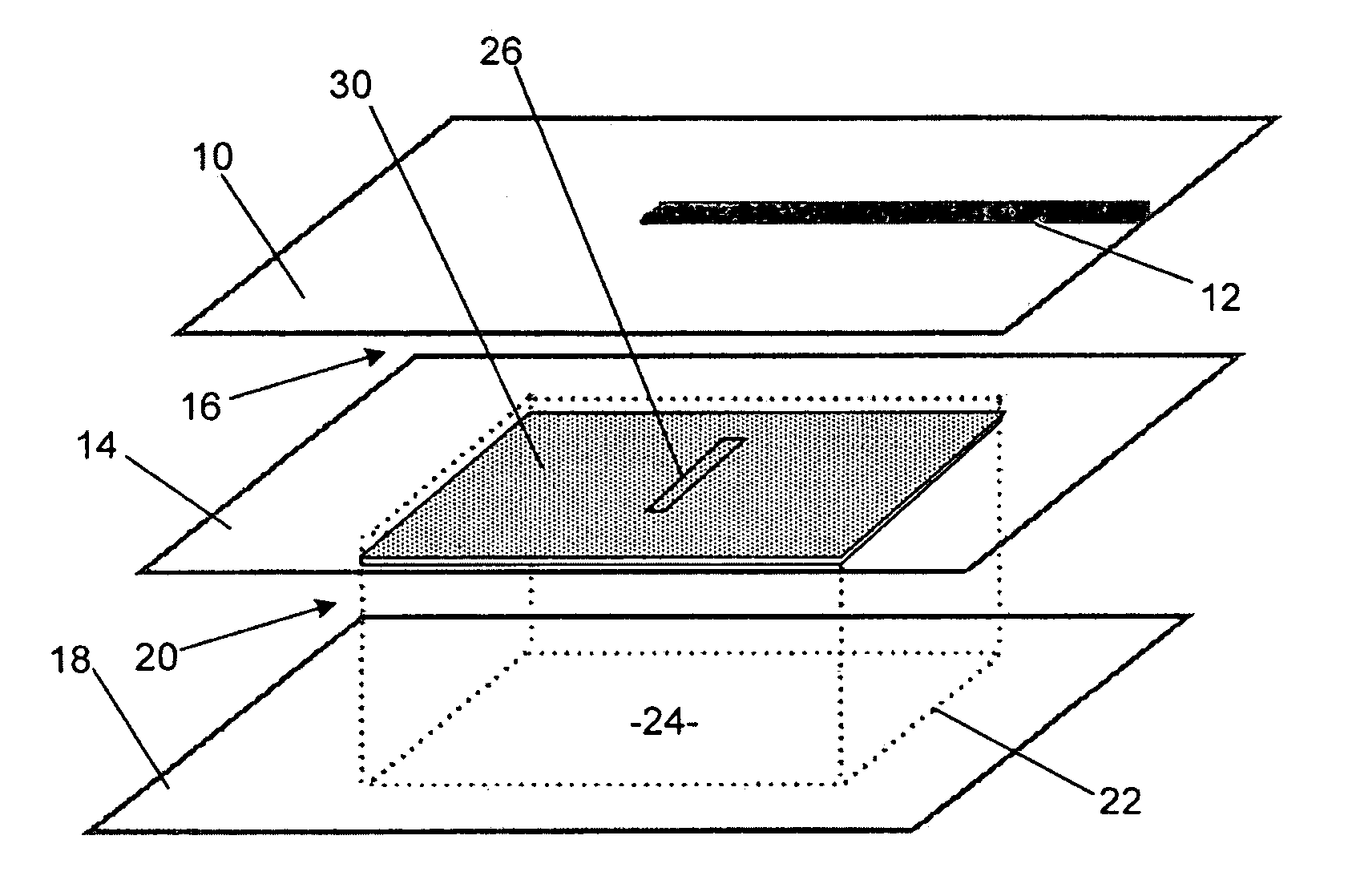

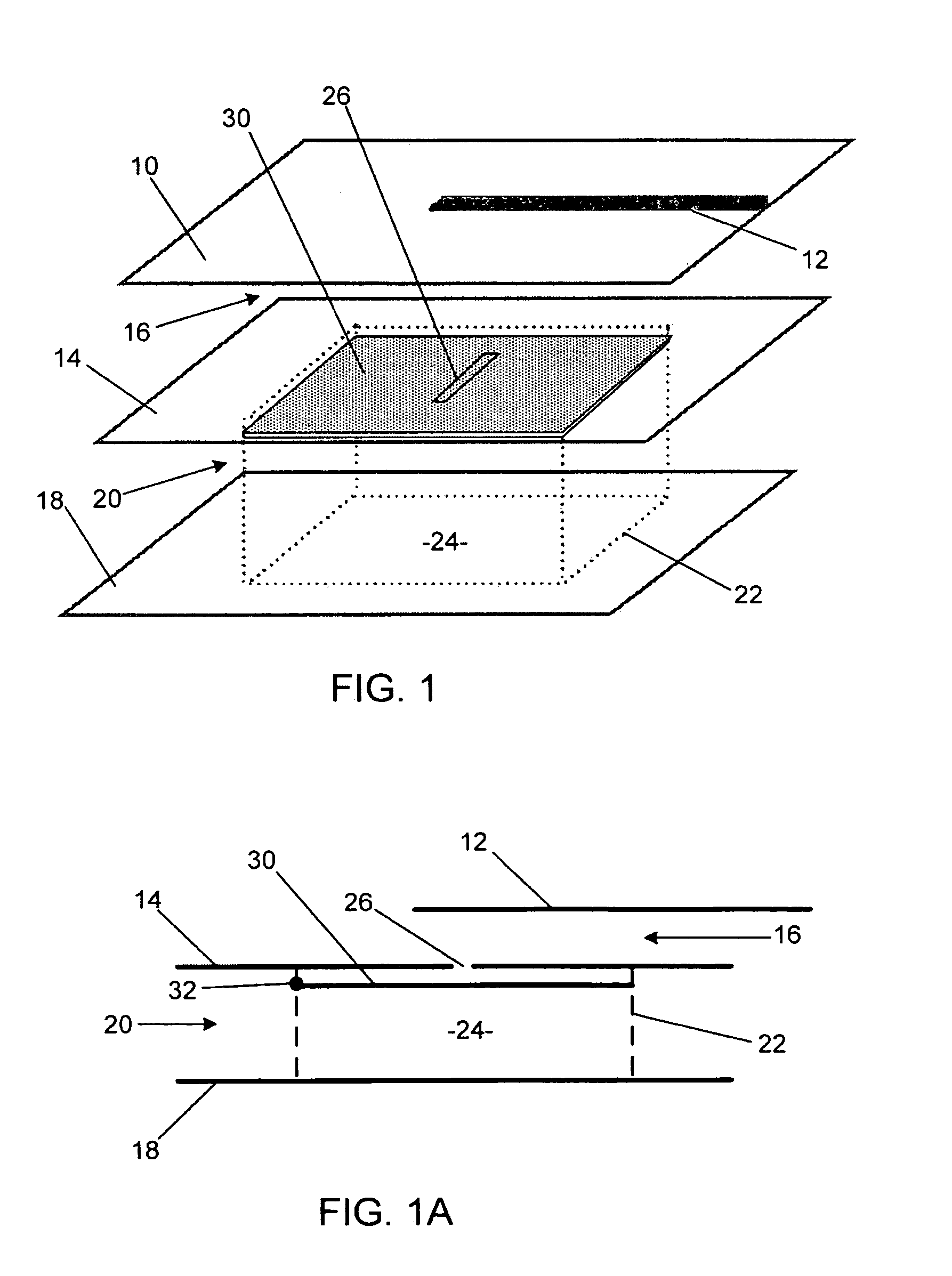

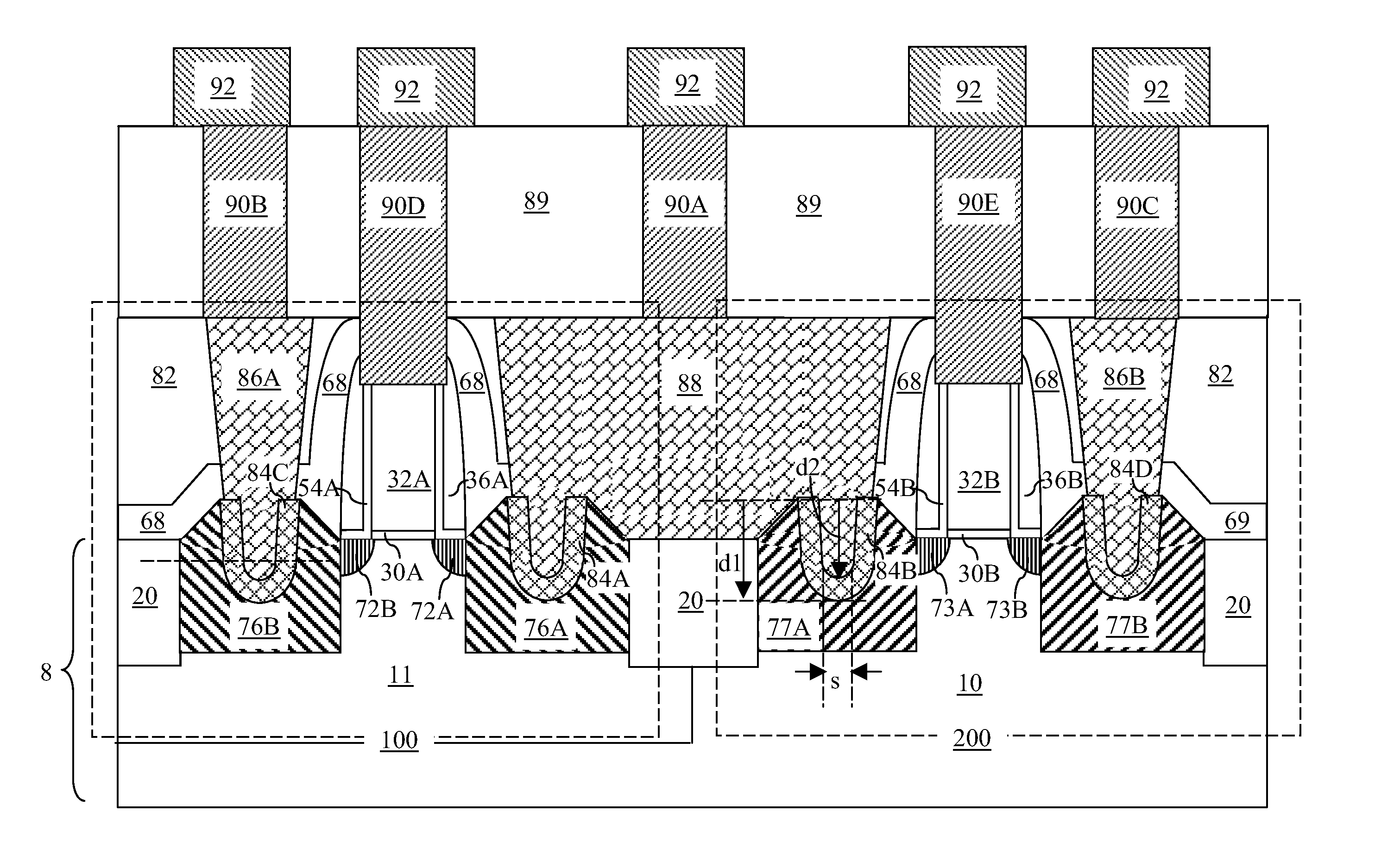

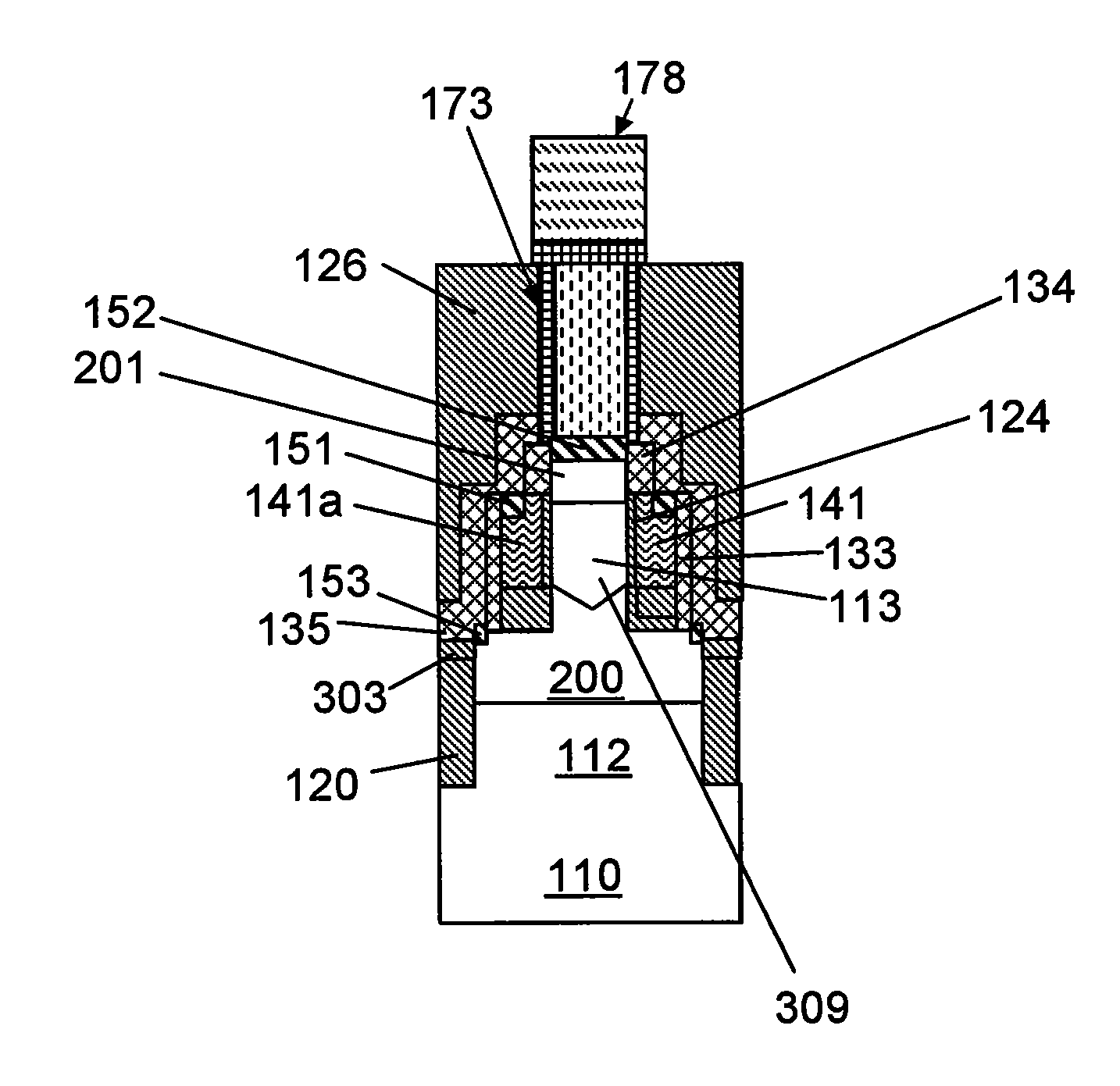

A ferroelectric loaded waveguide resonator capable of operation at microwave, millimeter-wave and higher frequencies and suitable for integration into a three-dimensional monolithic microwave integrated circuit (3D MMIC) is disclosed. The resonator includes a resonator cavity, which, in one form of the invention, is formed by two parallel metal layers and a metallized wall structure extending between the metal layers. The cavity is filled with dielectric material and includes a layer of ferroelectric material, which is used to control the resonant frequency by varying a voltage bias applied to the ferroelectric layer. The cavity includes a slot in one of the metal layers and a coupling strip formed adjacent to the slot to provide electromagnetic coupling to other components, such as a voltage controlled oscillator (VCO). The invention can also be applied to other multi-metal semiconductor or wafer level packaging technologies.

Owner:NORTHROP GRUMMAN SYST CORP

Metal semiconductor alloy structure for low contact resistance

InactiveUS20120032275A1TransistorSemiconductor/solid-state device detailsSemiconductor materialsSemiconductor alloys

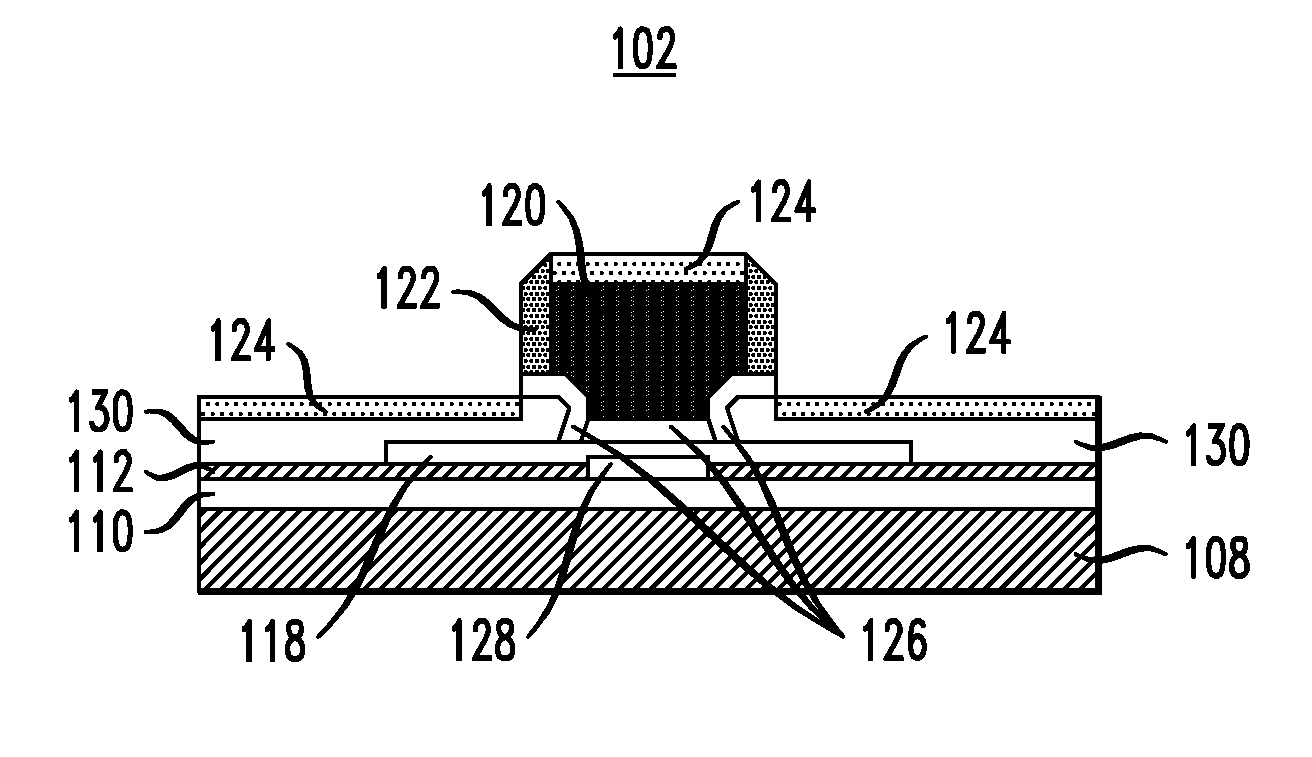

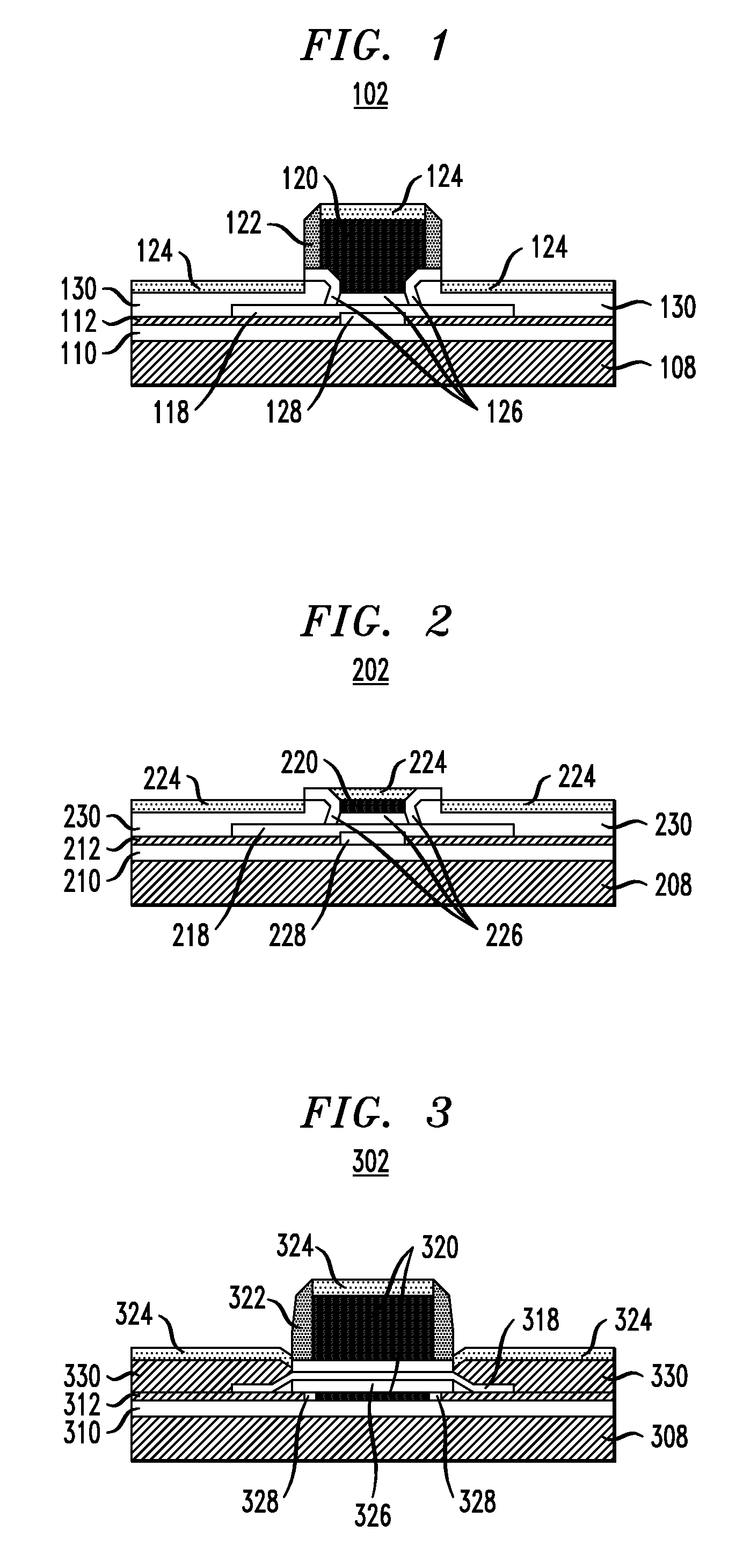

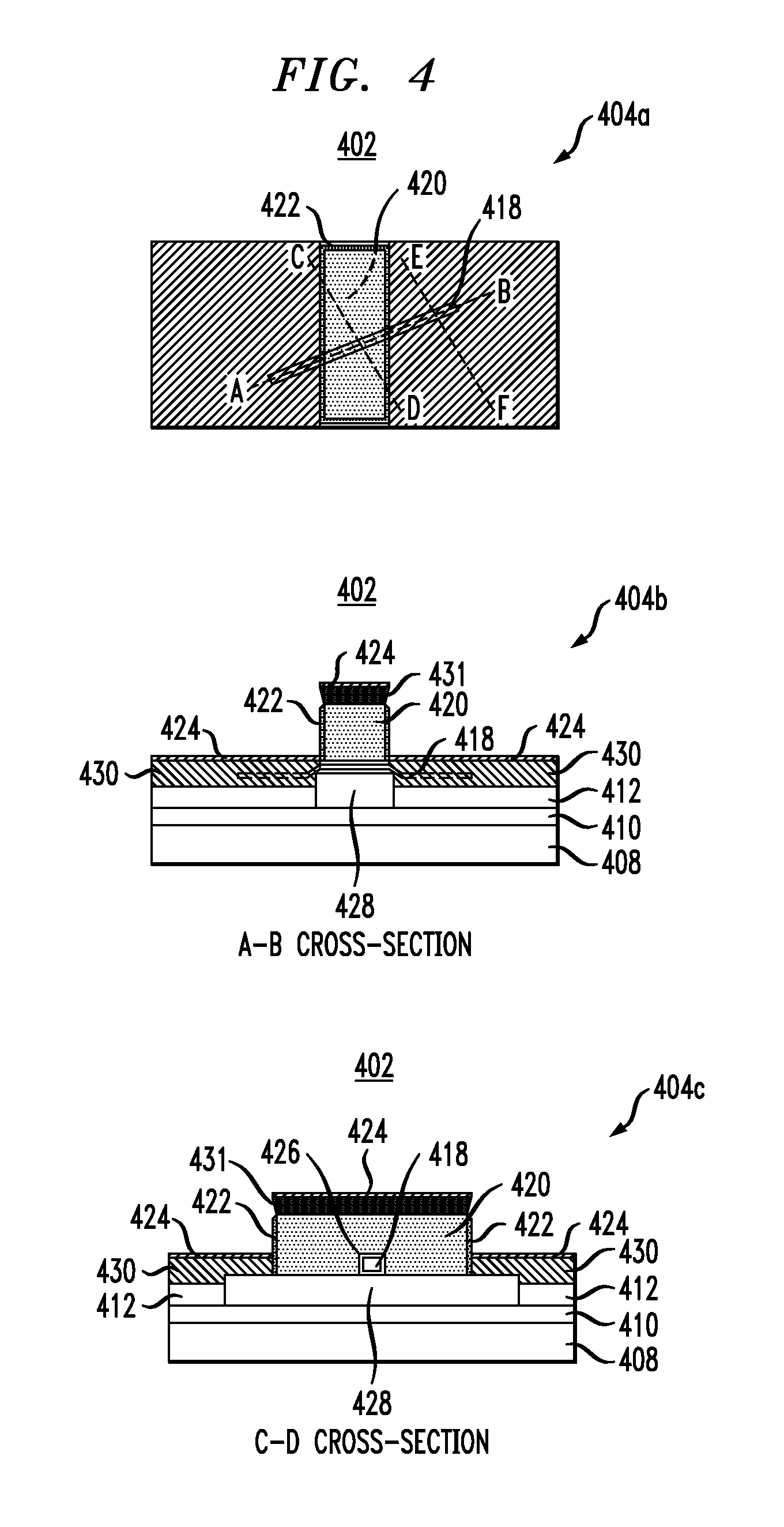

Contact via holes are etched in a dielectric material layer overlying a semiconductor layer to expose the topmost surface of the semiconductor layer. The contact via holes are extended into the semiconductor material layer by continuing to etch the semiconductor layer so that a trench having semiconductor sidewalls is formed in the semiconductor material layer. A metal layer is deposited over the dielectric material layer and the sidewalls and bottom surface of the trench. Upon an anneal at an elevated temperature, a metal semiconductor alloy region is formed, which includes a top metal semiconductor alloy portion that includes a cavity therein and a bottom metal semiconductor alloy portion that underlies the cavity and including a horizontal portion. A metal contact via is formed within the cavity so that the top metal semiconductor alloy portion laterally surrounds a bottom portion of a bottom portion of the metal contact via.

Owner:IBM CORP

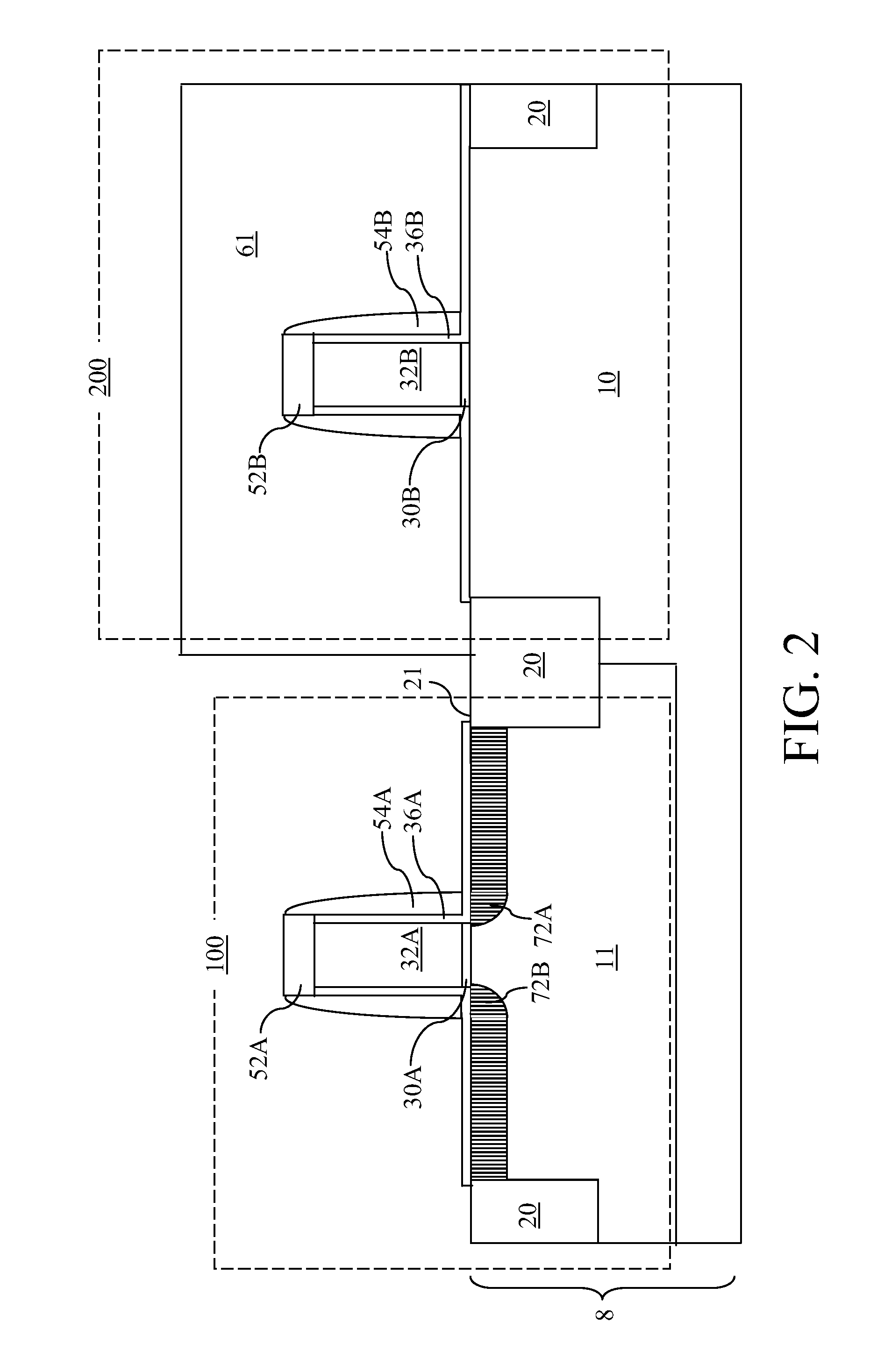

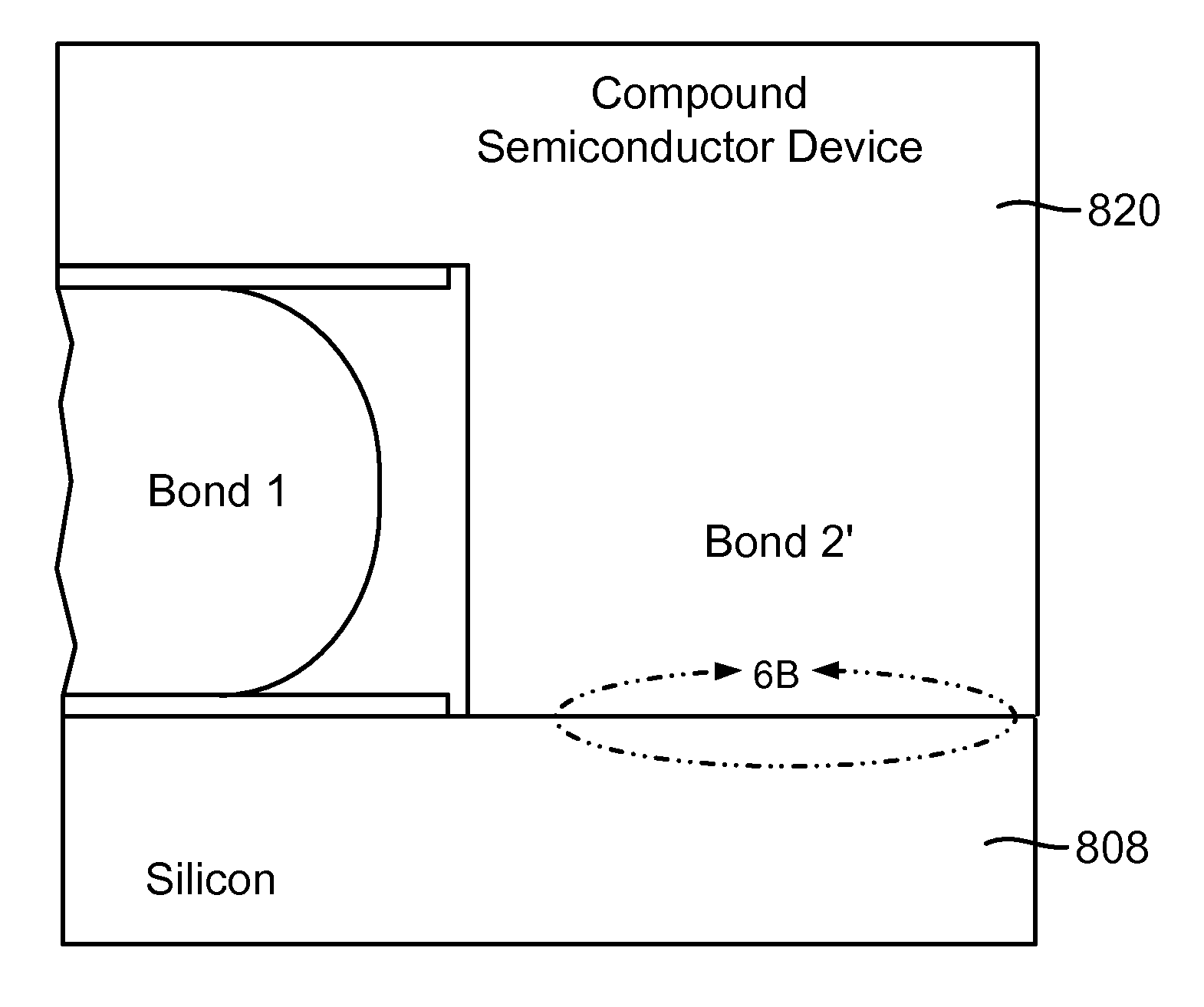

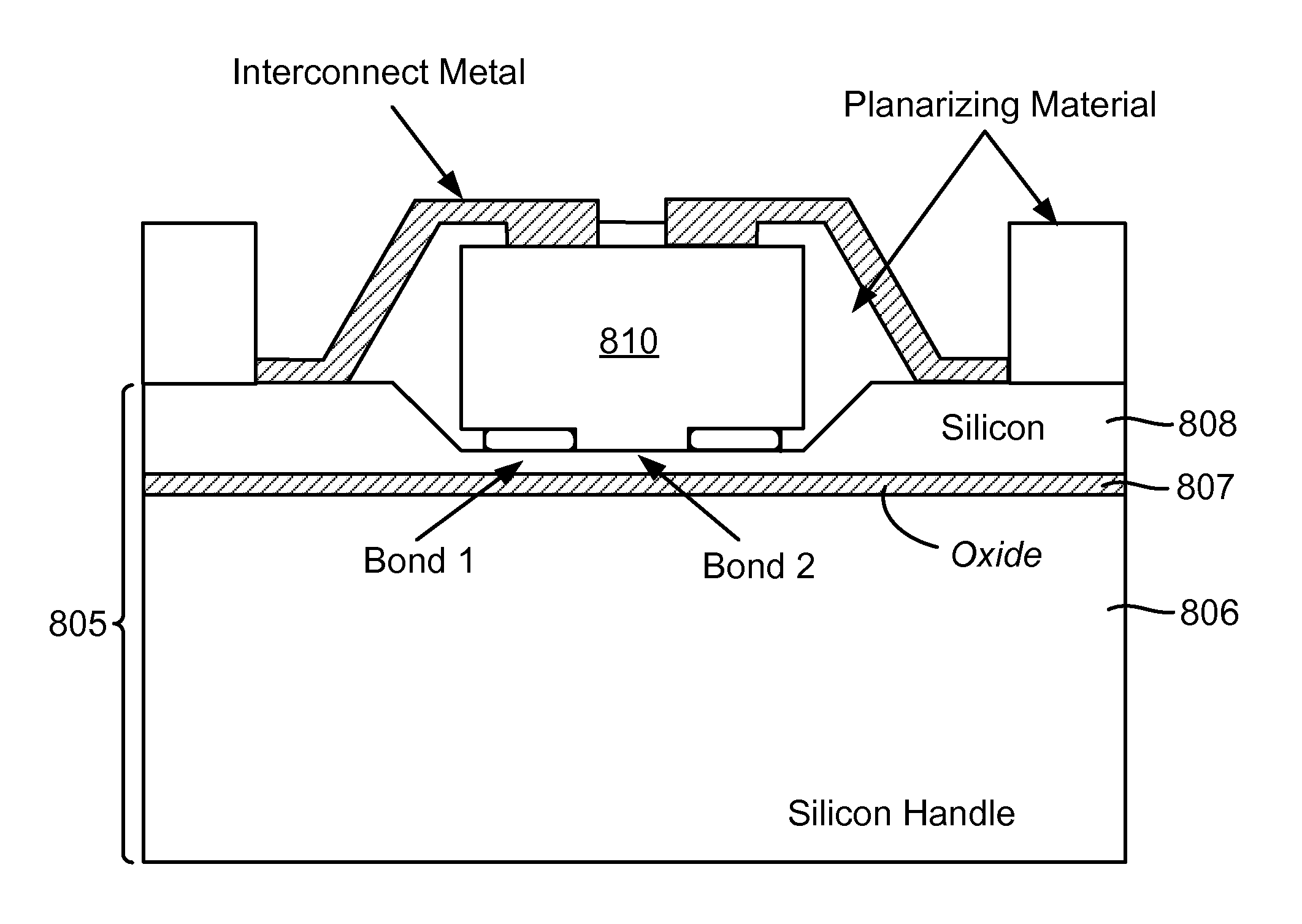

Method and system of heterogeneous substrate bonding for photonic integration

ActiveUS8630326B2Semiconductor/solid-state device detailsSolid-state devicesPhotonicsInterface layer

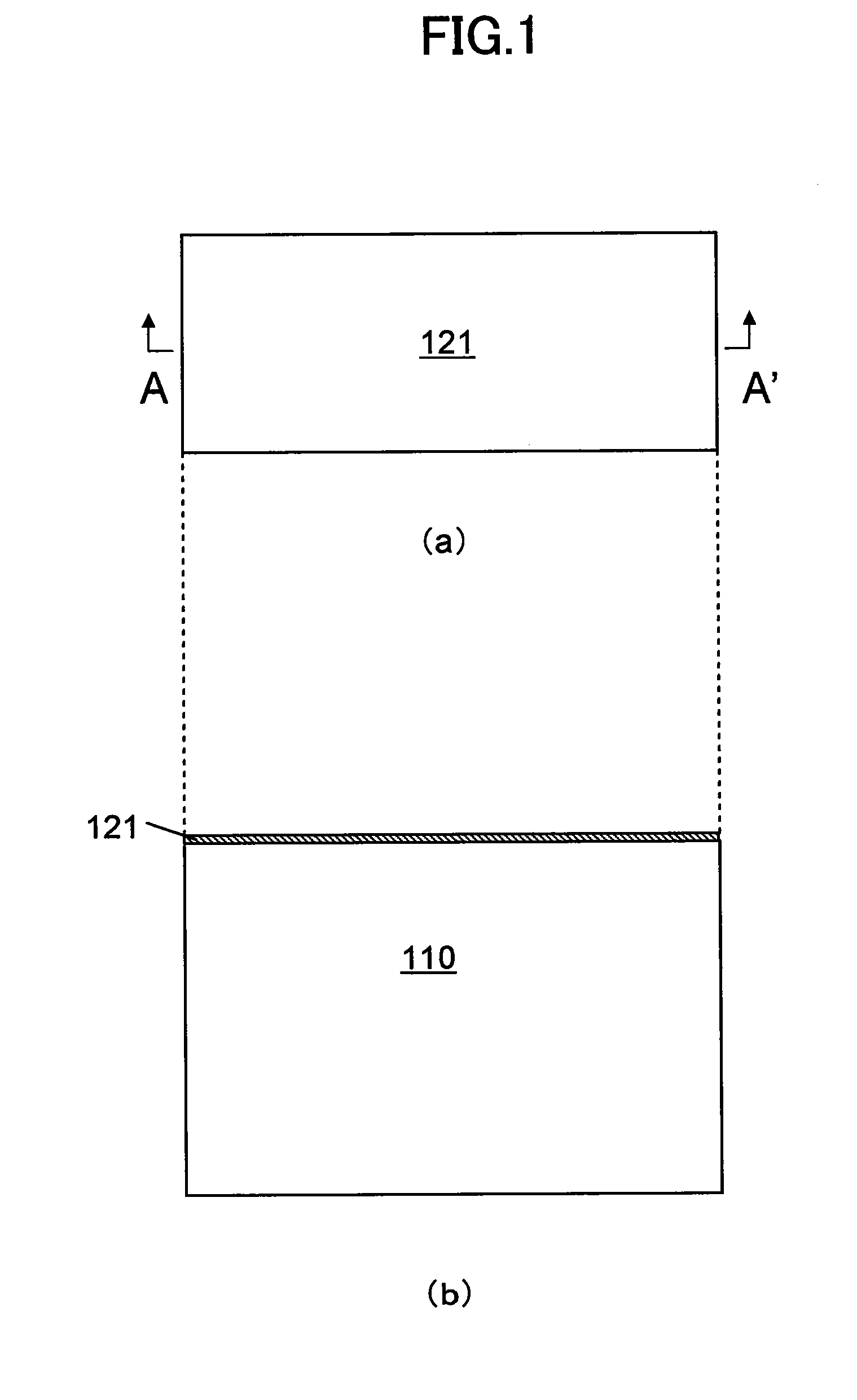

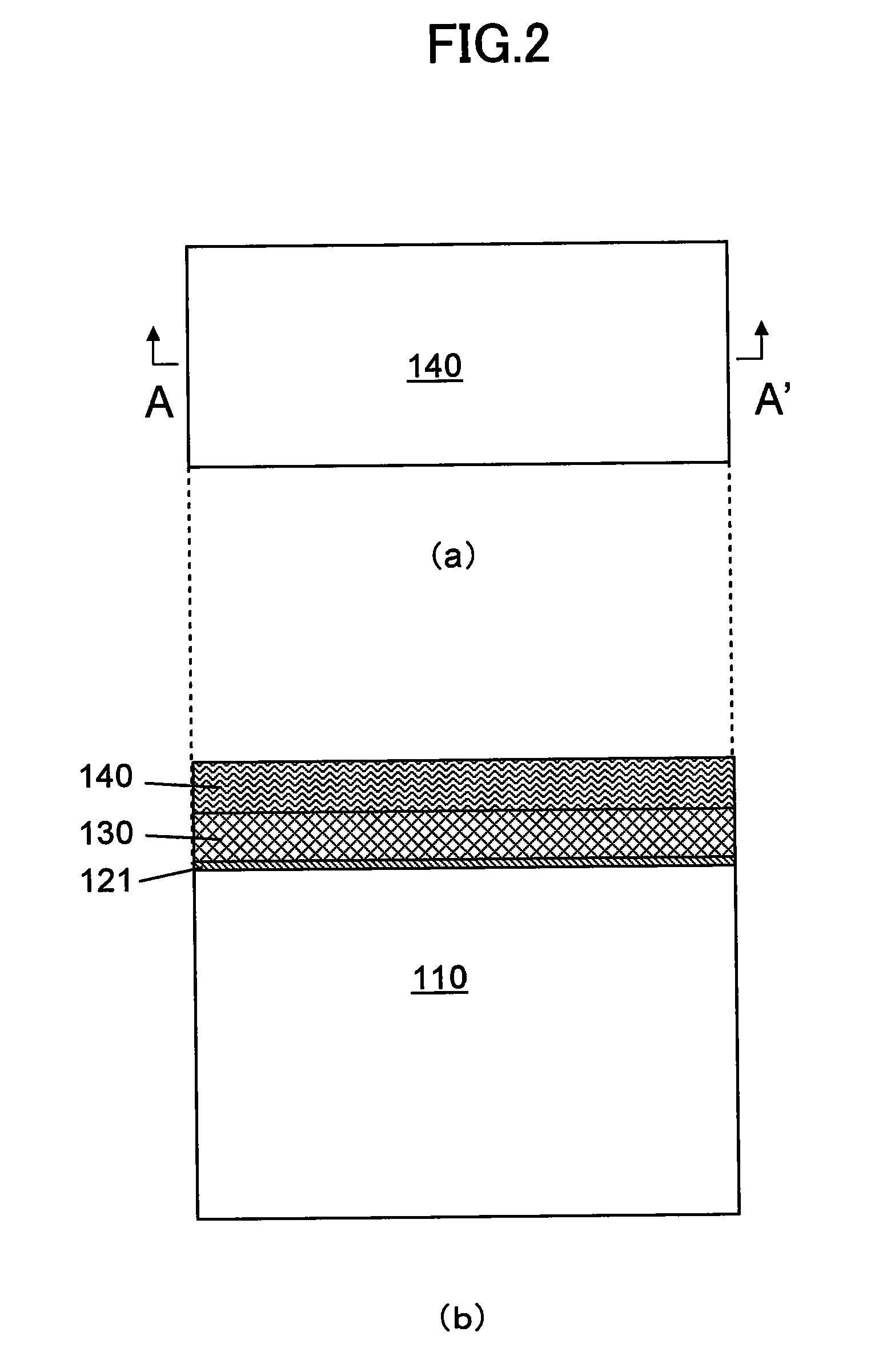

A hybrid integrated optical device includes a substrate comprising a silicon layer and a compound semiconductor device bonded to the silicon layer. The device also includes a bonding region disposed between the silicon layer and the compound semiconductor device. The bonding region includes a metal-semiconductor bond at a first portion of the bonding region. The metal-semiconductor bond includes a first pad bonded to the silicon layer, a bonding metal bonded to the first pad, and a second pad bonded to the bonding metal and the compound semiconductor device. The bonding region also includes an interface assisted bond at a second portion of the bonding region. The interface assisted bond includes an interface layer positioned between the silicon layer and the compound semiconductor device, wherein the interface assisted bond provides an ohmic contact between the silicon layer and the compound semiconductor device.

Owner:SKORPIOS TECH

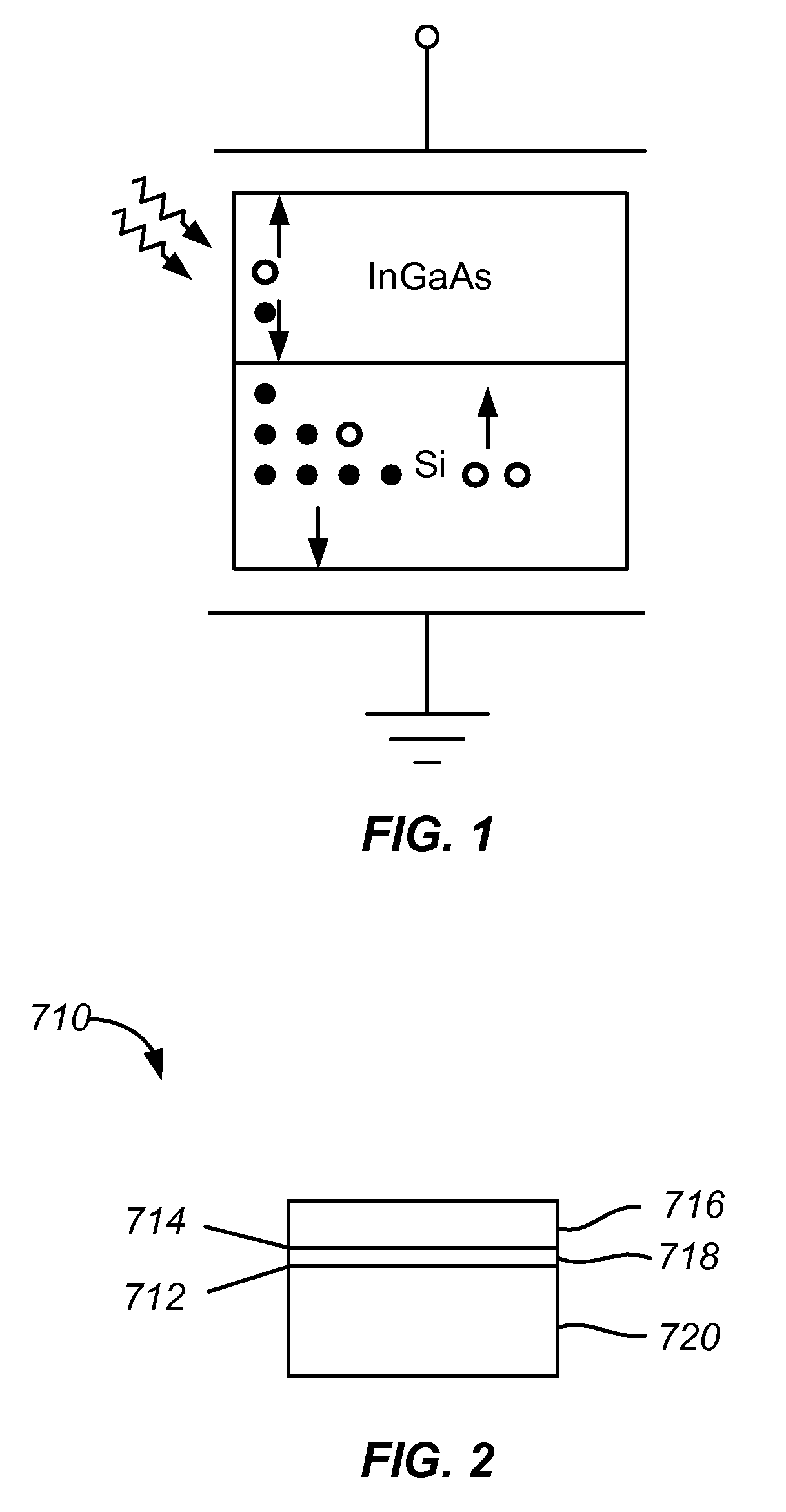

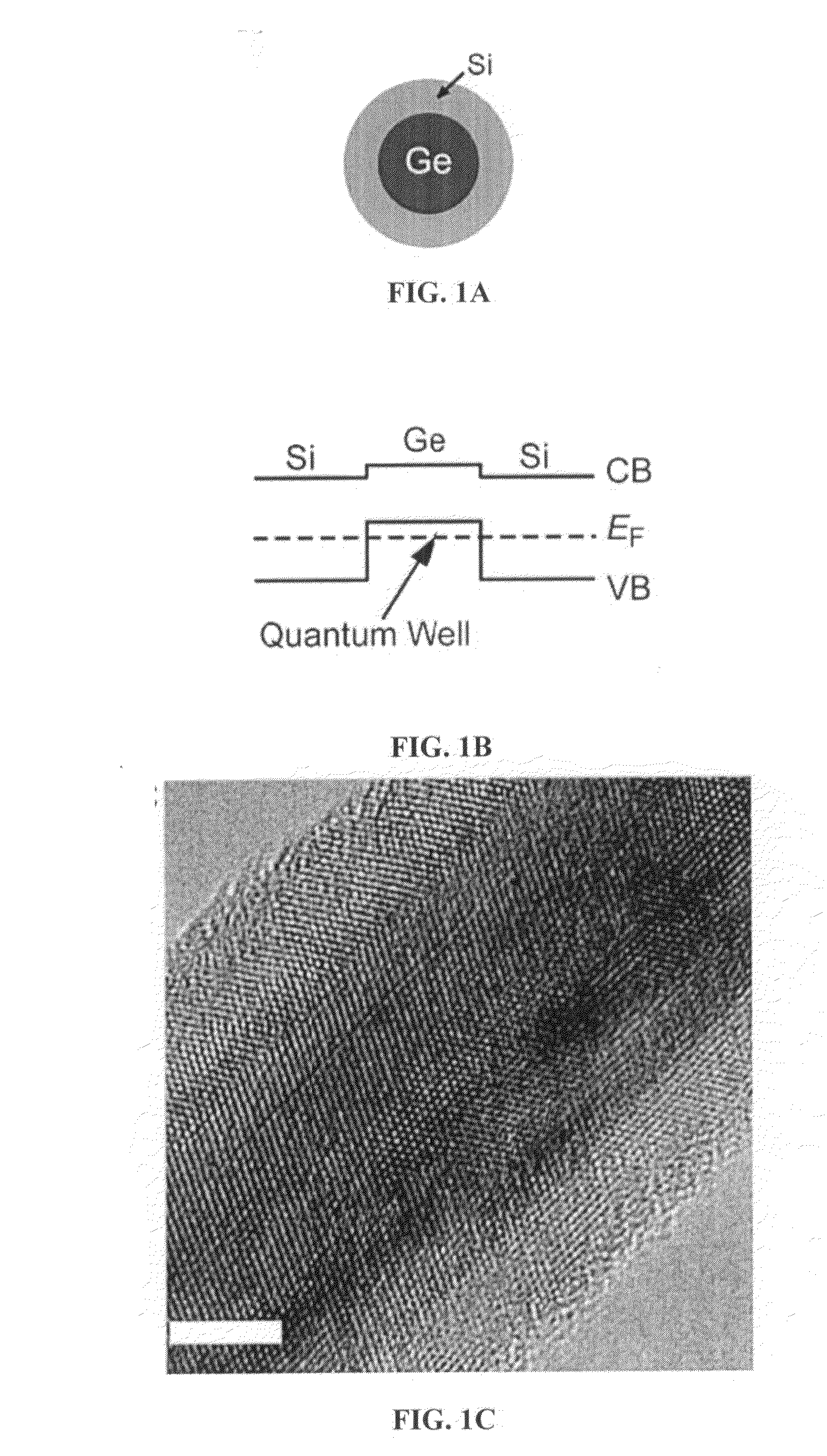

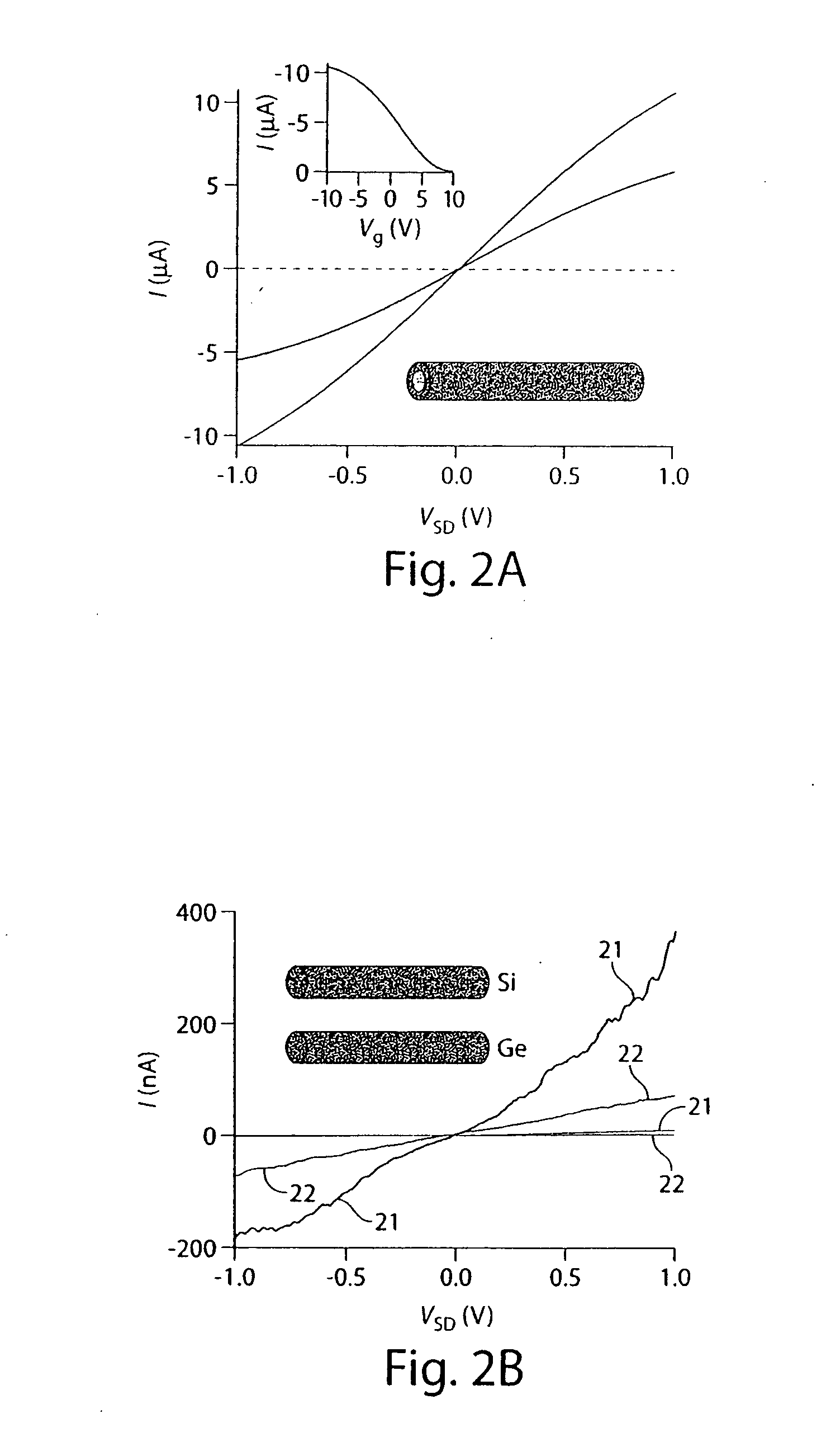

Nanowire heterostructures

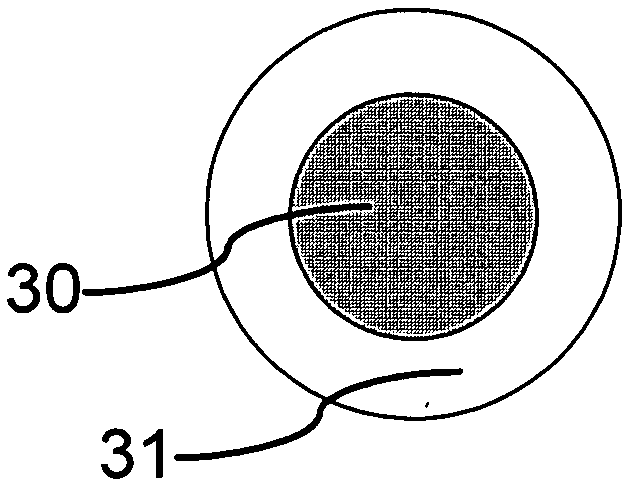

ActiveUS20080191196A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireMetal electrodes

The present invention generally relates to nanoscale heterostructures and, in some cases, to nanowire heterostructures exhibiting ballistic transport, and / or to metal-semiconductor junctions that that exhibit no or reduced Schottky barriers. One aspect of the invention provides a solid nanowire having a core and a shell, both of which are essentially undoped. For example, in one embodiment, the core may consist essentially of undoped germanium and the shell may consist essentially of undoped silicon. Carriers are injected into the nanowire, which can be ballistically transported through the nanowire. In other embodiments, however, the invention is not limited to solid nanowires, and other configurations, involving other nanoscale wires, are also contemplated within the scope of the present invention. Yet another aspect of the invention provides a junction between a metal and a nanoscale wire that exhibit no or reduced Schottky barriers. As a non-limiting example, a nanoscale wire having a core and a shell may be in physical contact with a metal electrode, such that the Schottky barrier to the core is reduced or eliminated. Still other aspects of the invention are directed to electronic devices exhibiting such properties, and techniques for methods of making or using such devices.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

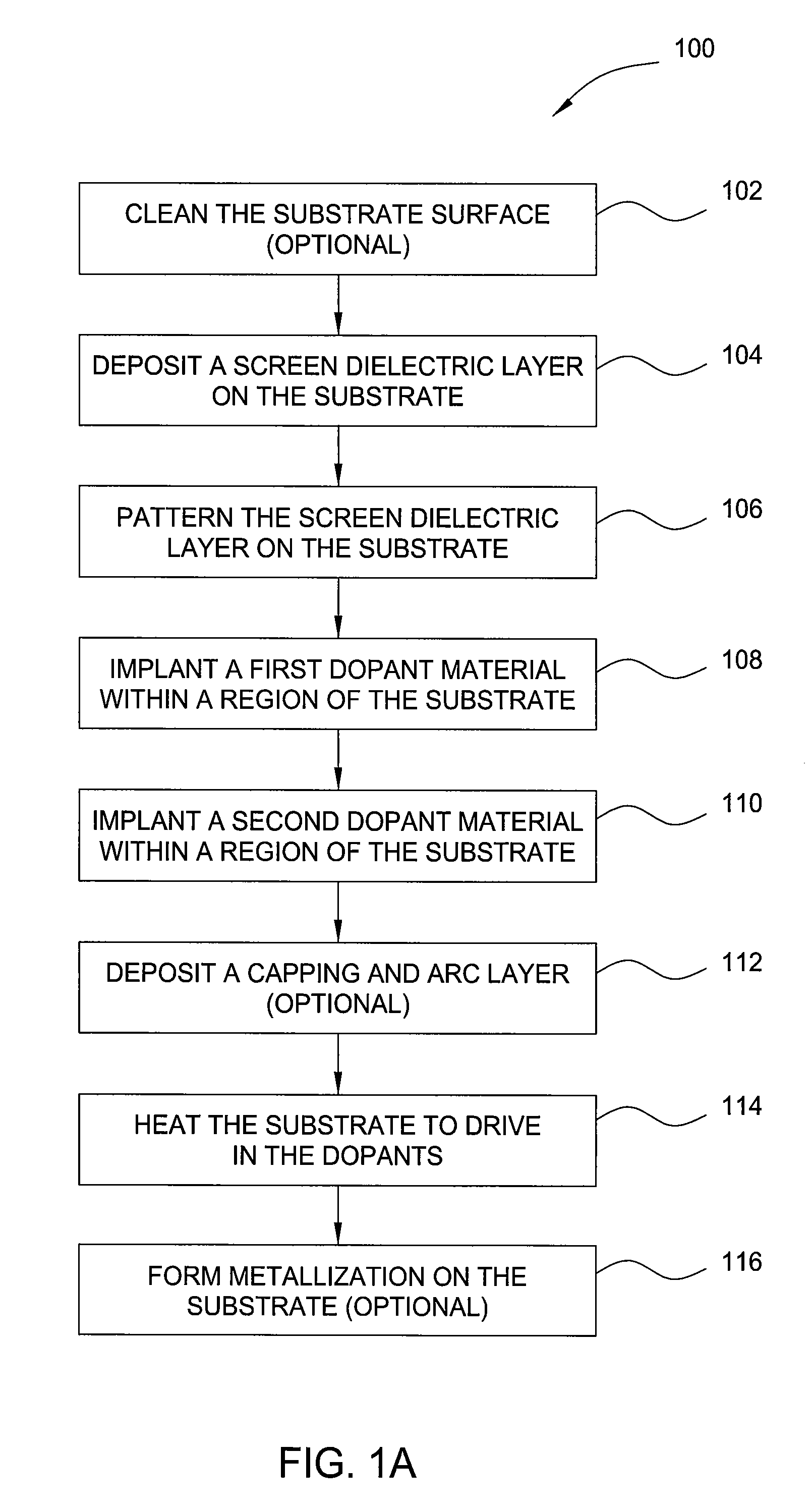

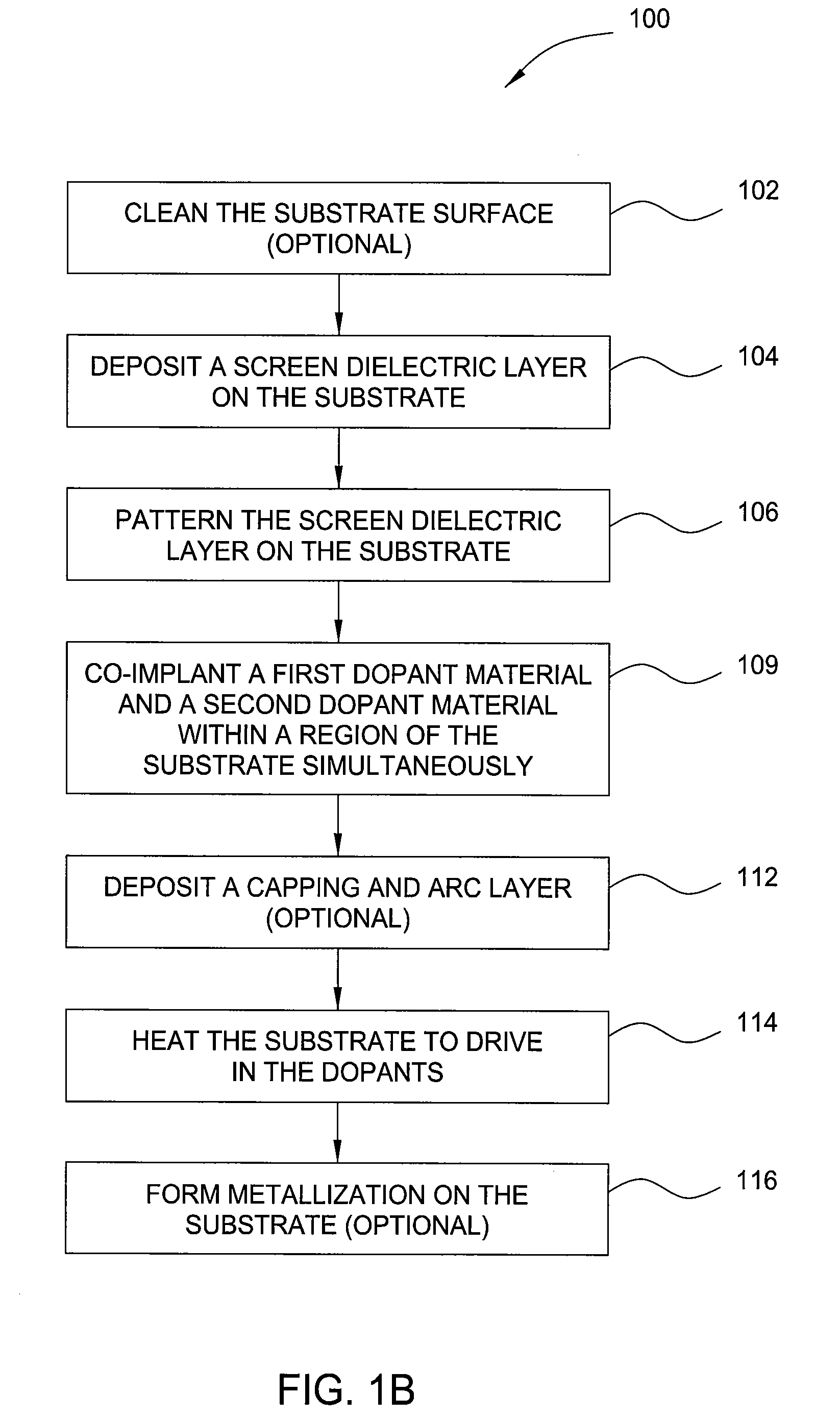

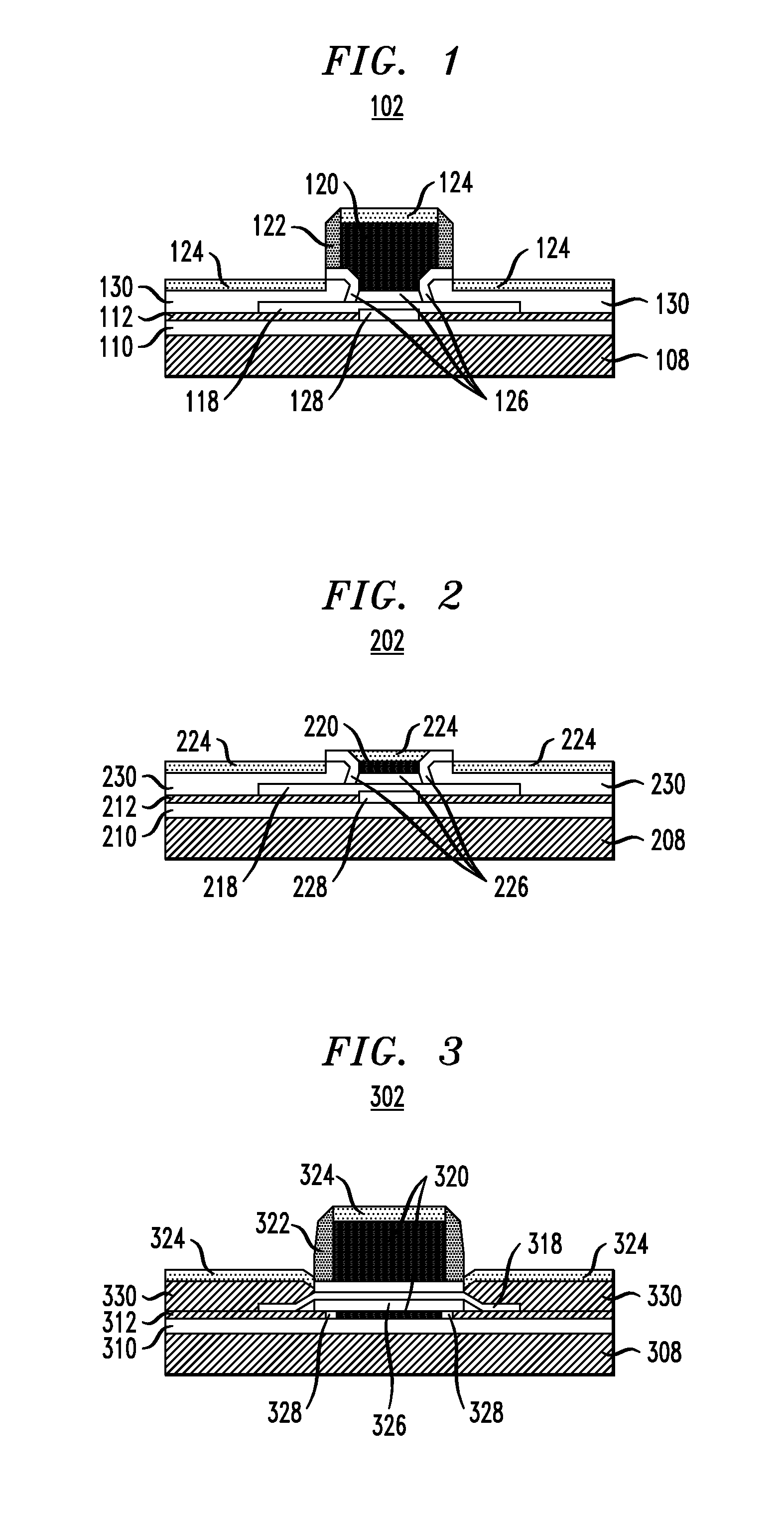

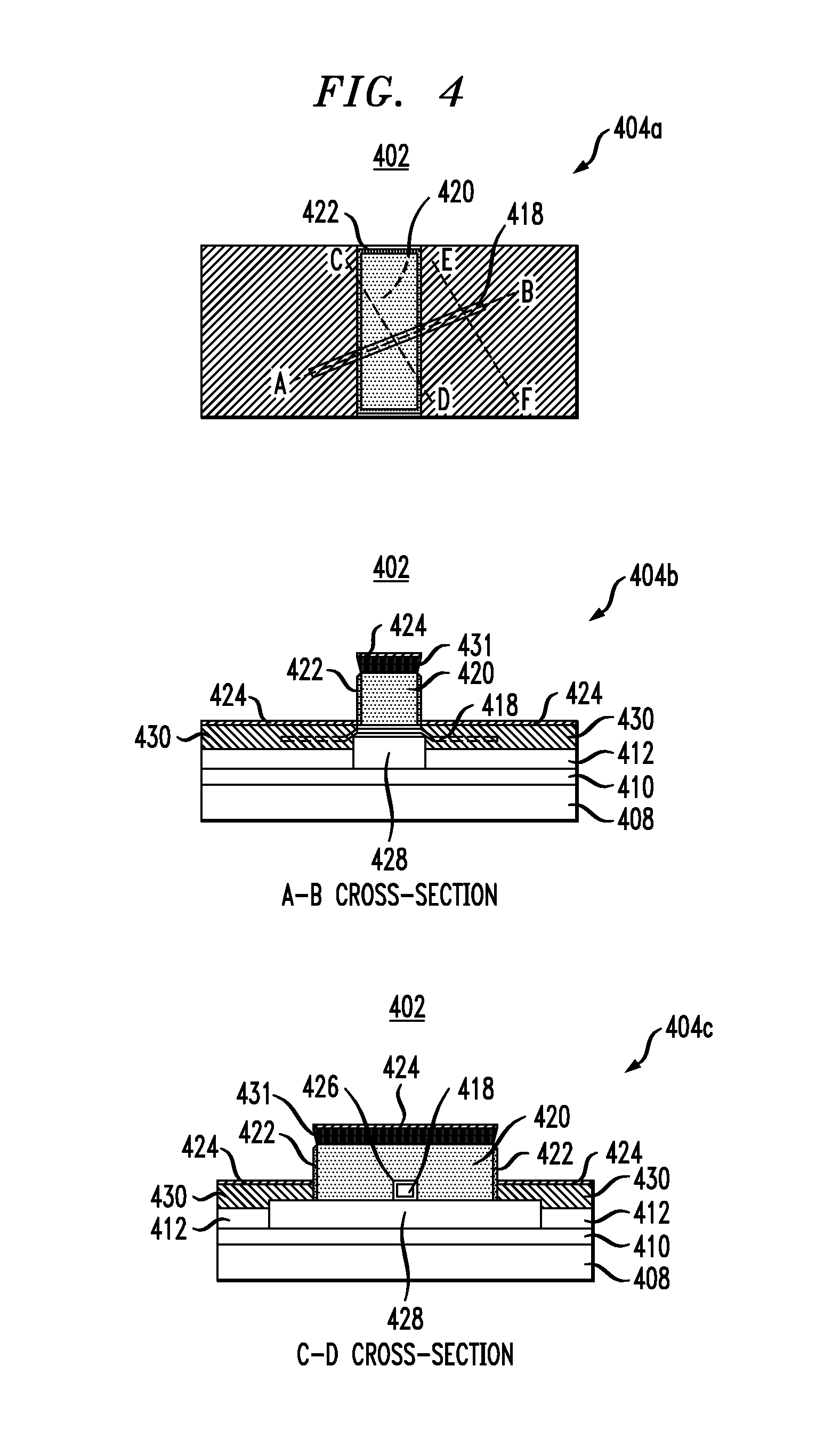

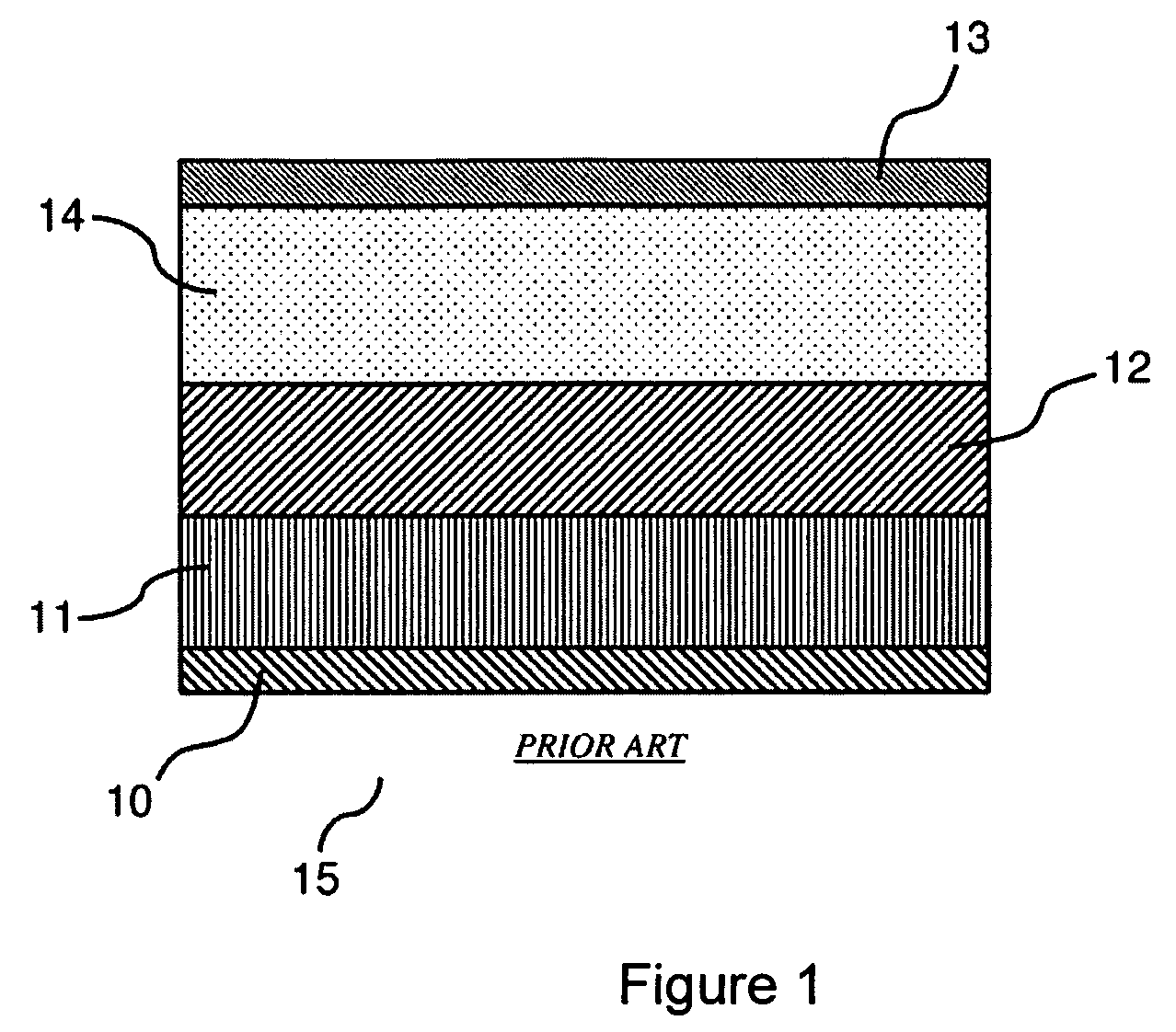

Methods of emitter formation in solar cells

InactiveUS20090068783A1Final product manufactureSemiconductor/solid-state device manufacturingDopantElectrical resistance and conductance

Embodiments of the invention contemplate high efficiency emitters in solar cells and novel methods for forming the same. One embodiment of the improved emitter structure, called a high-low type emitter, optimizes the solar cell performance by equally providing low contact resistance to minimize ohmic losses and isolation of the high surface recombination metal-semiconductor interface from the junction to maximize cell voltage. Another embodiment, called an alternating doping type emitter, provides regions of alternating doping type for use with point contacts in the back-contact solar cells. One embodiment of the methods includes depositing and patterning a doped or undoped dielectric layer on a surface of a substrate, implanting a fast-diffusing dopant and / or a slow-diffusing dopant into the substrate either simultaneously or sequentially, and annealing the substrate to drive in the dopants. Another embodiment of the methods includes using a physical mask to form a patterned dopant distribution in a substrate.

Owner:APPLIED MATERIALS INC

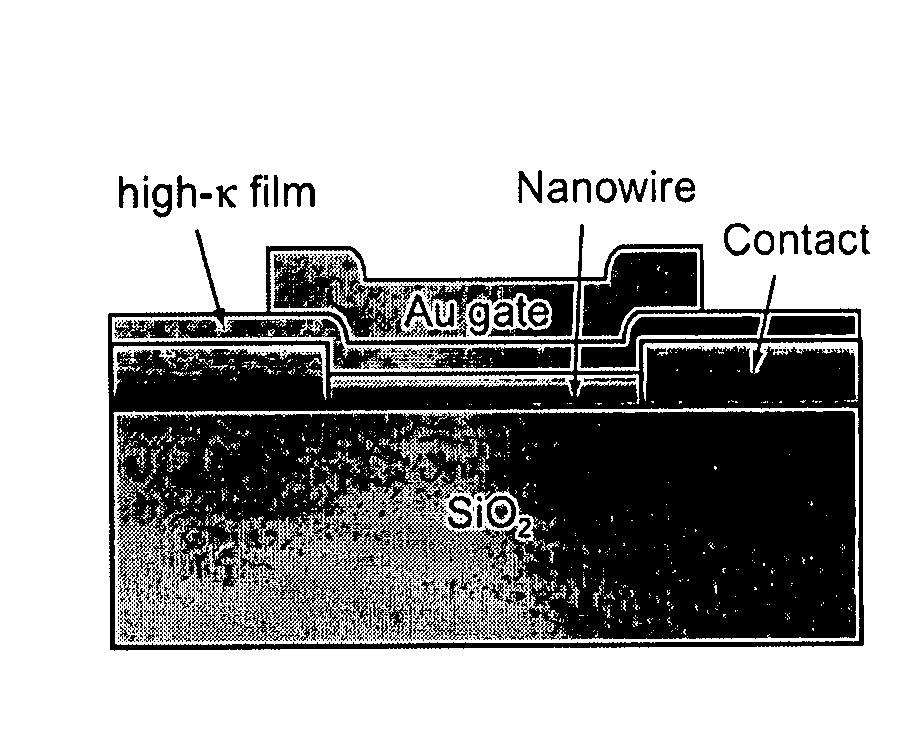

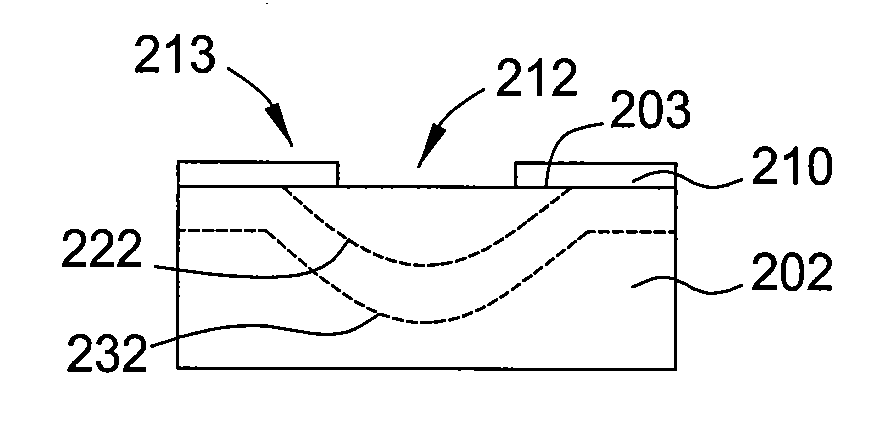

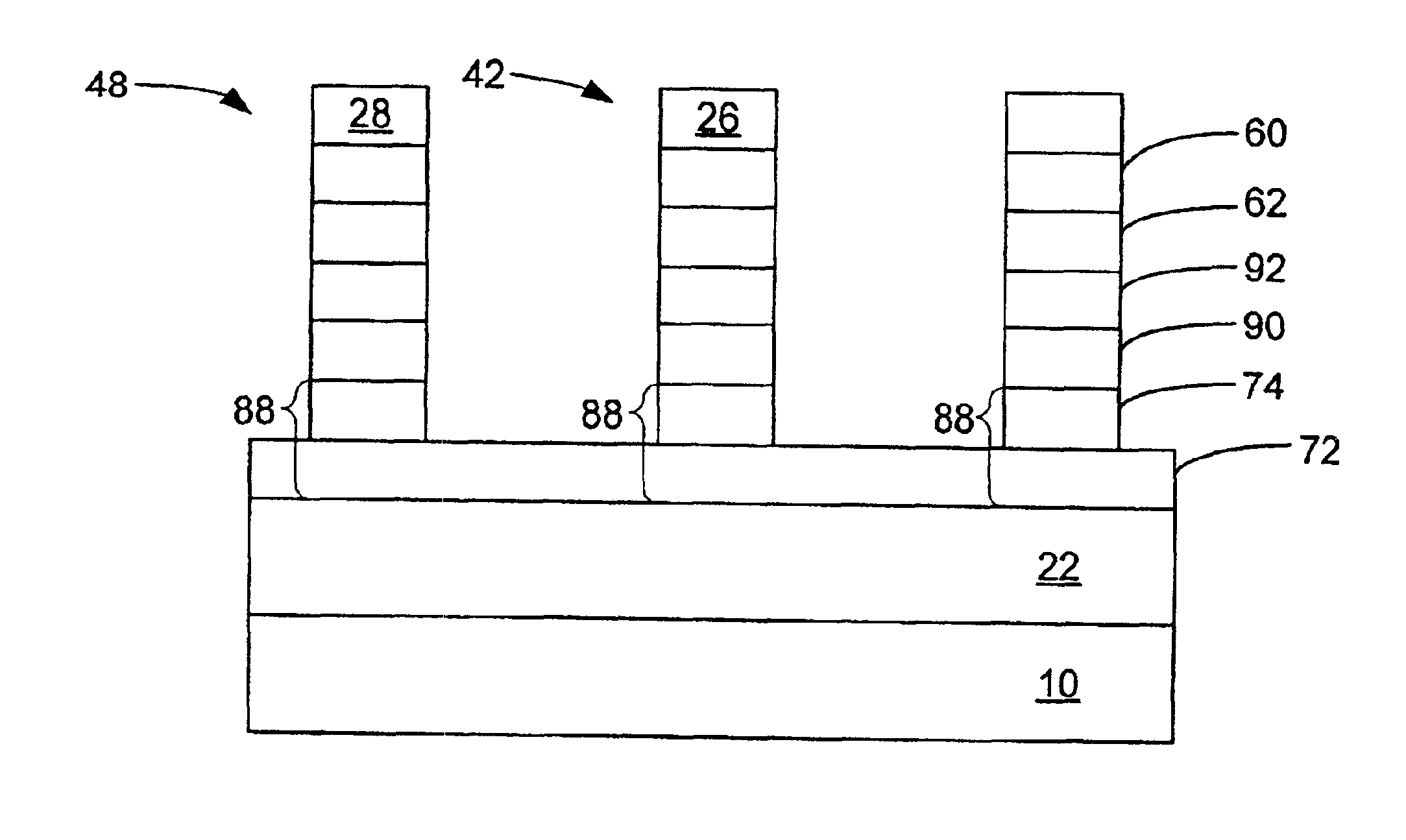

Techniques for Fabricating Nanowire Field-Effect Transistors

ActiveUS20090061568A1NanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

Techniques for the fabrication of field-effect transistors (FETs) having nanowire channels are provided. In one aspect, a method of fabricating a FET is provided comprising the following steps. A substrate is provided having a silicon-on-insulator (SOI) layer. At least one nanowire is deposited over the SOI layer. A sacrificial gate is formed over the SOI layer so as to cover a portion of the nanowire that forms a channel region. An epitaxial semiconductor material is selectively grown from the SOI layer that covers the nanowire and attaches the nanowire to the SOI layer in a source region and in a drain region. The sacrificial gate is removed. An oxide is formed that divides the SOI layer into at least two electrically isolated sections, one section included in the source region and the other section included in the drain region. A gate dielectric layer is formed over the channel region. A gate is formed over the channel region separated from the nanowire by the gate dielectric layer. A metal-semiconductor alloy is formed over the source and drain regions.

Owner:GLOBALFOUNDRIES US INC

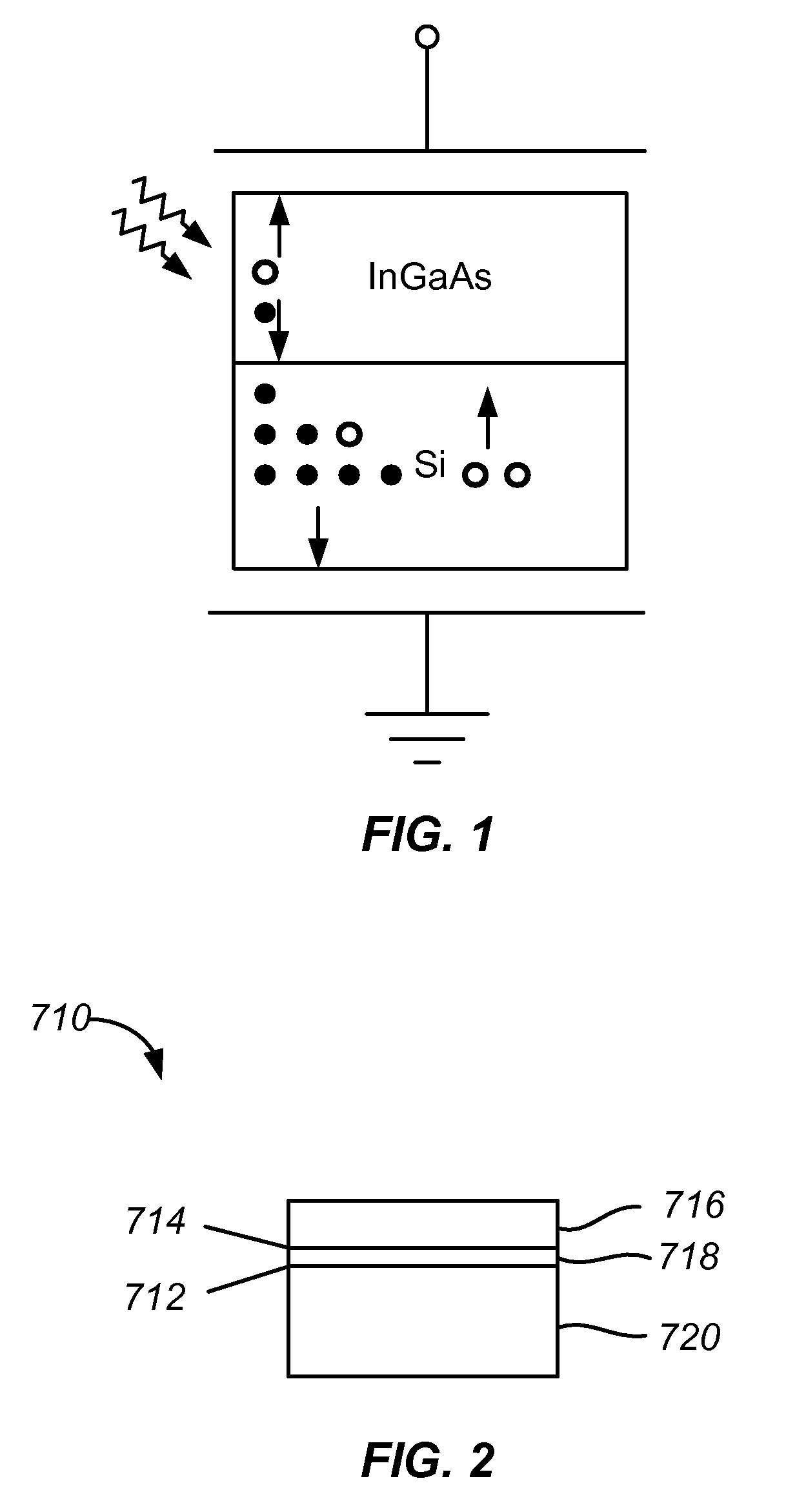

Metal/semiconductor/metal (MSM) back-to-back Schottky diode

ActiveUS20070015330A1Inhibit currentHigh voltageSolid-state devicesSemiconductor/solid-state device manufacturingGas phaseEngineering

A method is provided for forming a metal / semiconductor / metal (MSM) back-to-back Schottky diode from a silicon (Si) semiconductor. The method deposits a Si semiconductor layer between a bottom electrode and a top electrode, and forms a MSM diode having a threshold voltage, breakdown voltage, and on / off current ratio. The method is able to modify the threshold voltage, breakdown voltage, and on / off current ratio of the MSM diode in response to controlling the Si semiconductor layer thickness. Generally, both the threshold and breakdown voltage are increased in response to increasing the Si thickness. With respect to the on / off current ratio, there is an optimal thickness. The method is able to form an amorphous Si (a-Si) and polycrystalline Si (polySi) semiconductor layer using either chemical vapor deposition (CVD) or DC sputtering. The Si semiconductor can be doped with a Group V donor material, which decreases the threshold voltage and increases the breakdown voltage.

Owner:XENOGENIC DEV LLC

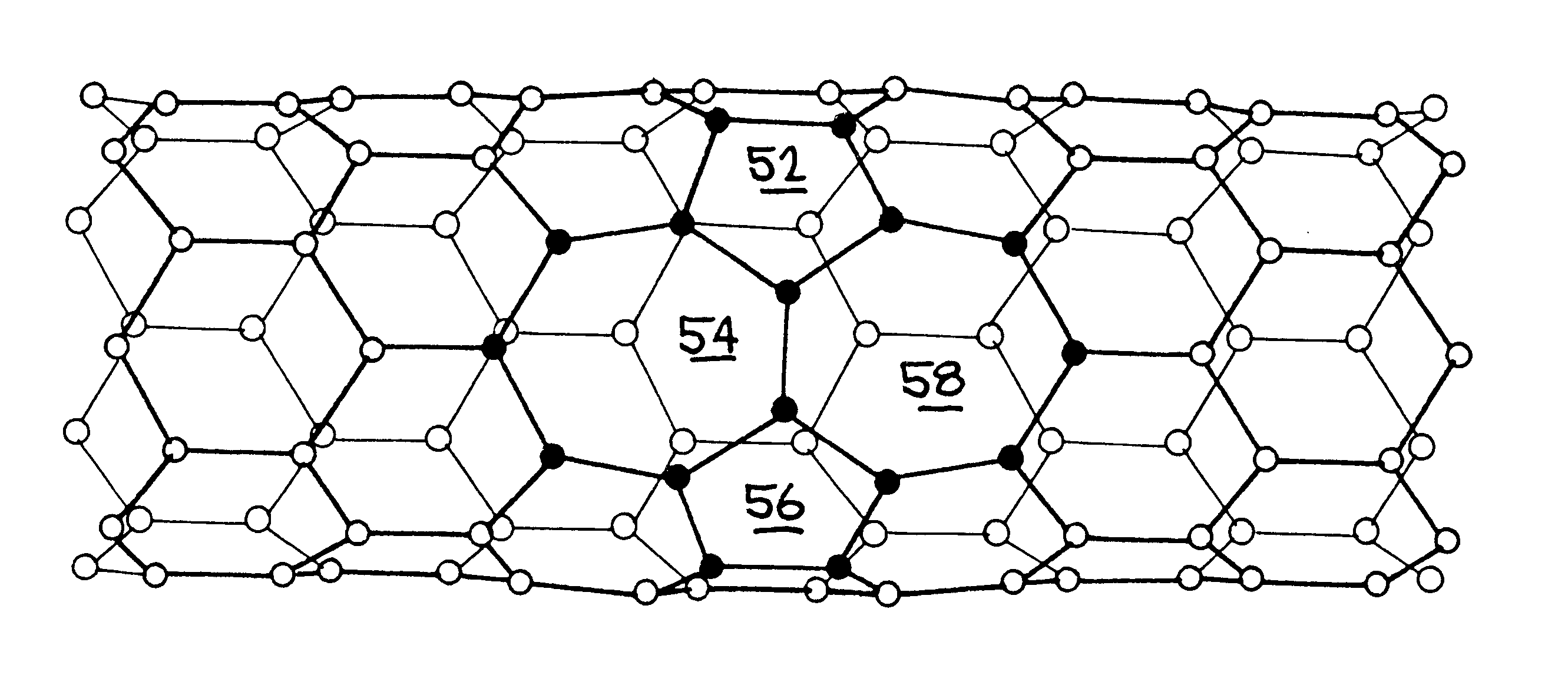

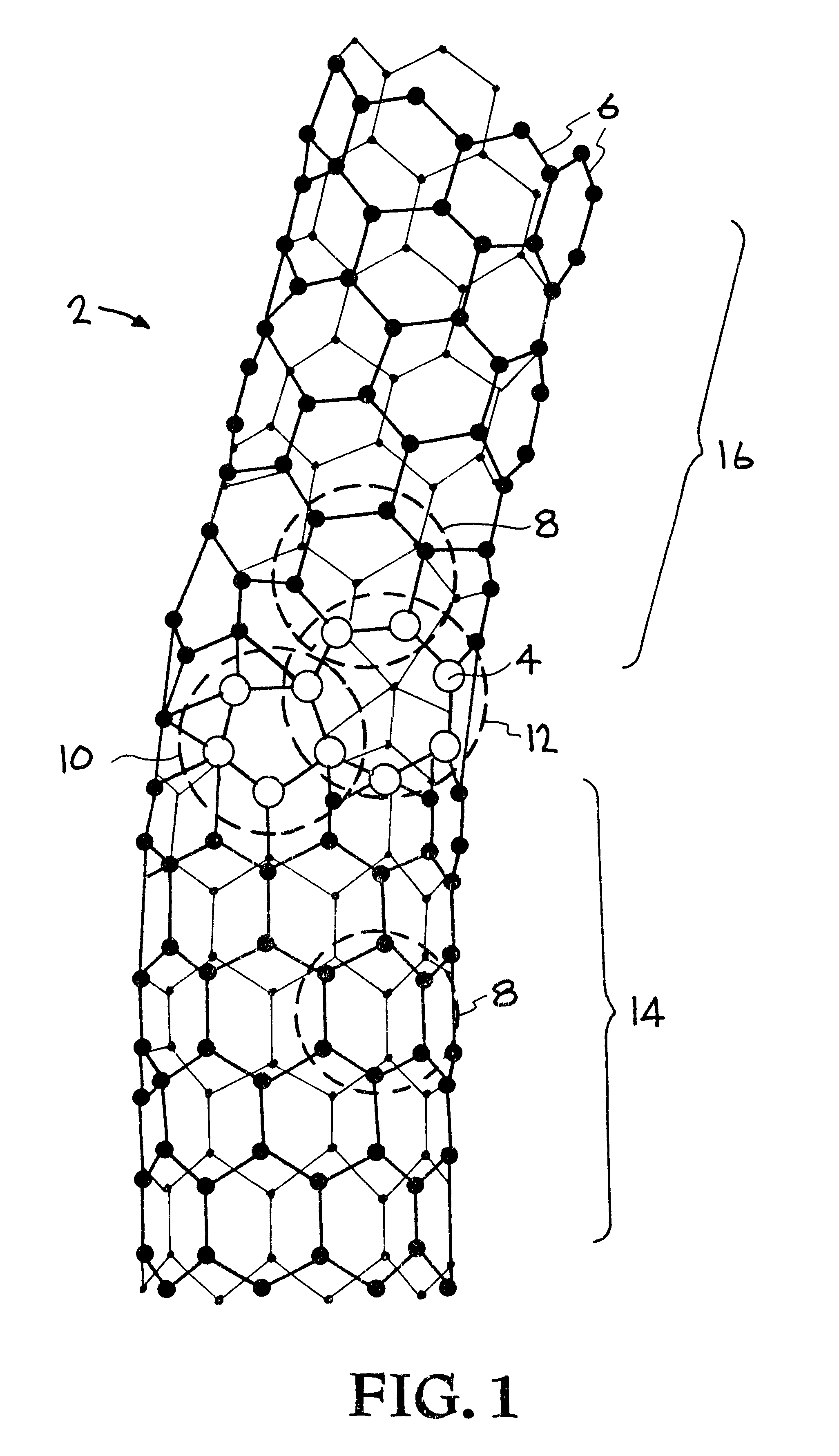

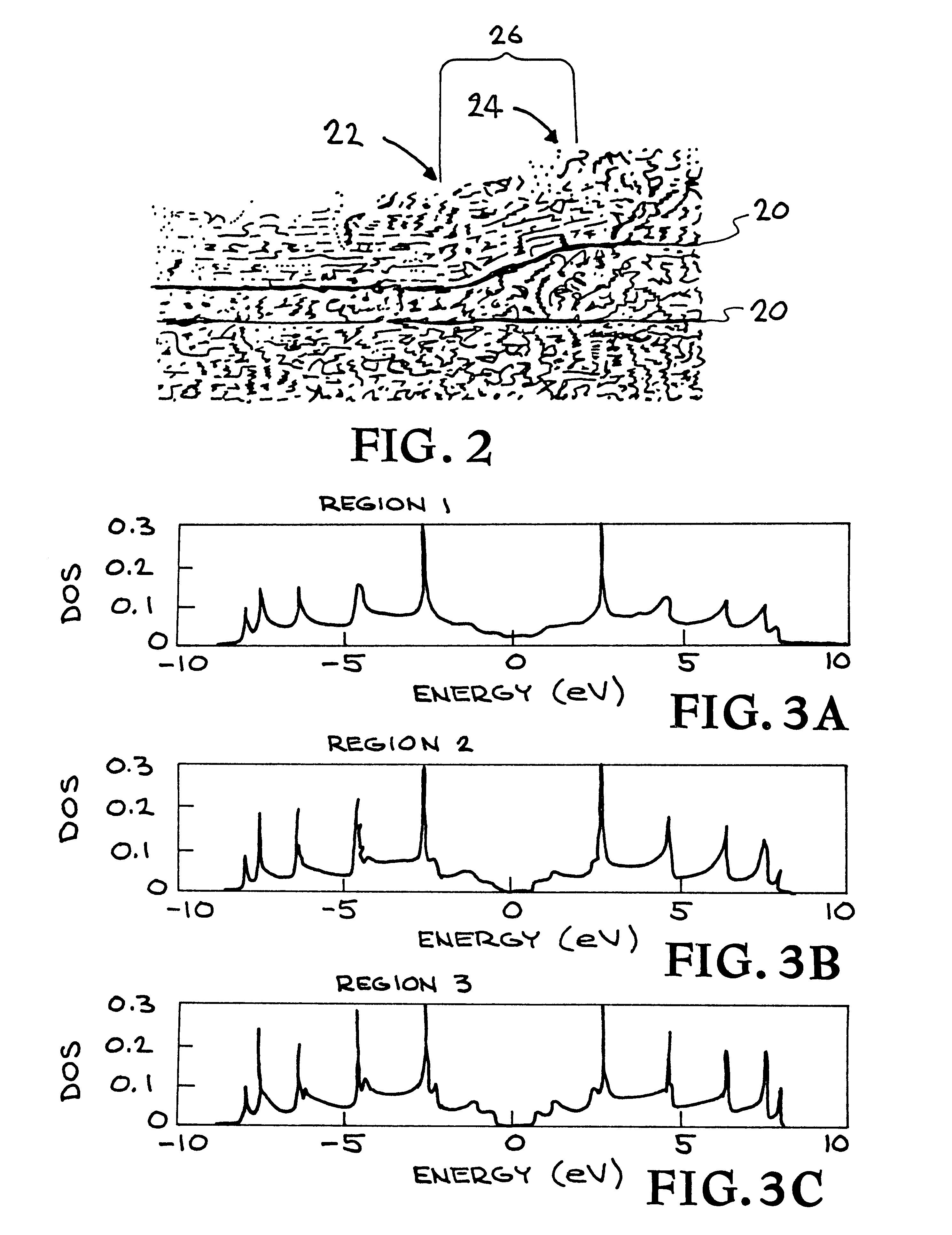

Nanotube junctions

The present invention comprises a new nanoscale metal-semiconductor, semiconductor-semiconductor, or metal-metal junction, designed by introducing topological or chemical defects in the atomic structure of the nanotube. Nanotubes comprising adjacent sections having differing electrical properties are described. These nanotubes can be constructed from combinations of carbon, boron, nitrogen and other elements. The nanotube can be designed having different indices on either side of a junction point in a continuous tube so that the electrical properties on either side of the junction vary in a useful fashion. For example, the inventive nanotube may be electrically conducting on one side of a junction and semiconducting on the other side. An example of a semiconductor-metal junction is a Schottky barrier. Alternatively, the nanotube may exhibit different semiconductor properties on either side of the junction. Nanotubes containing heterojunctions, Schottky barriers, and metal-metal junctions are useful for microcircuitry.

Owner:RGT UNIV OF CALIFORNIA

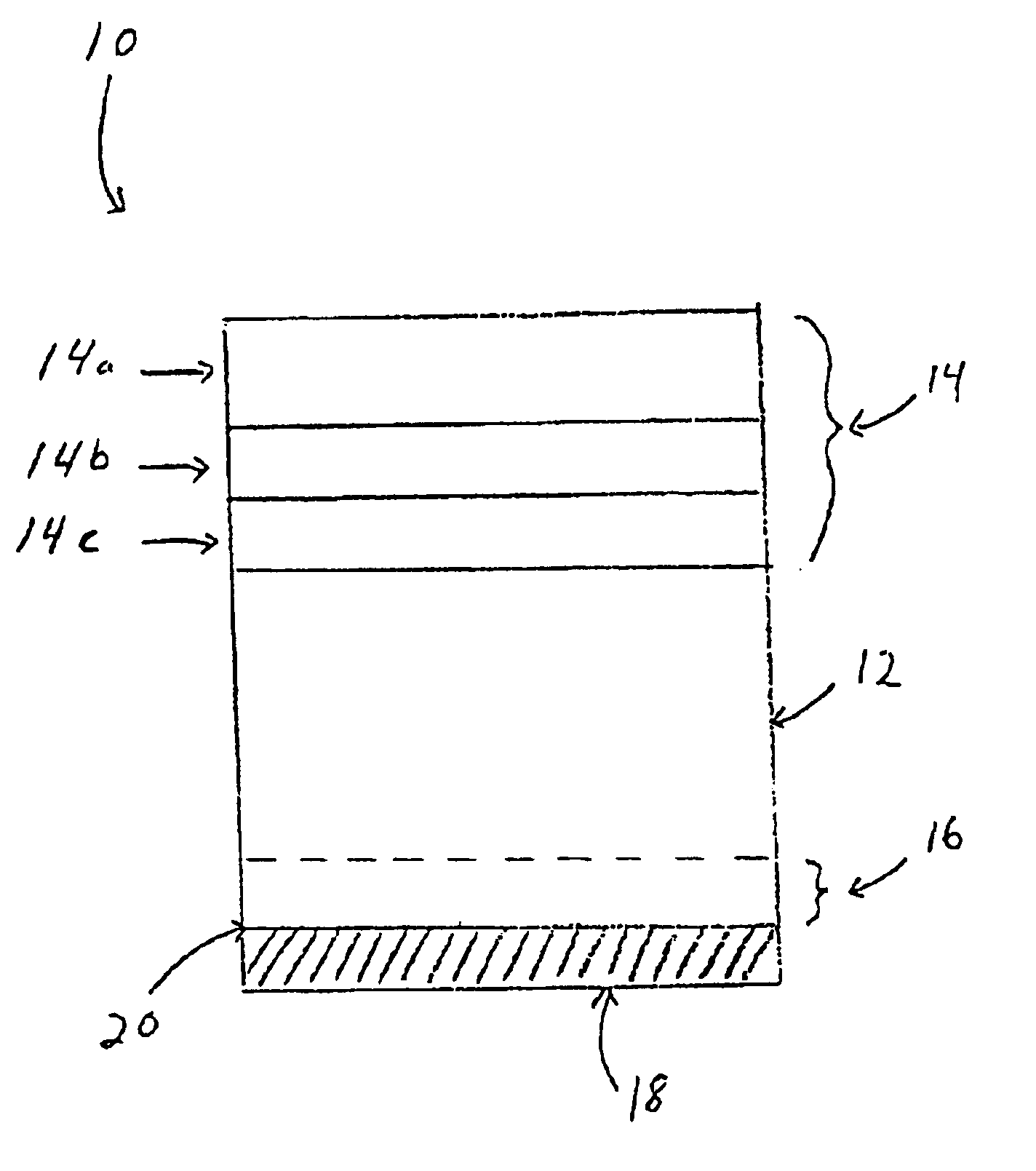

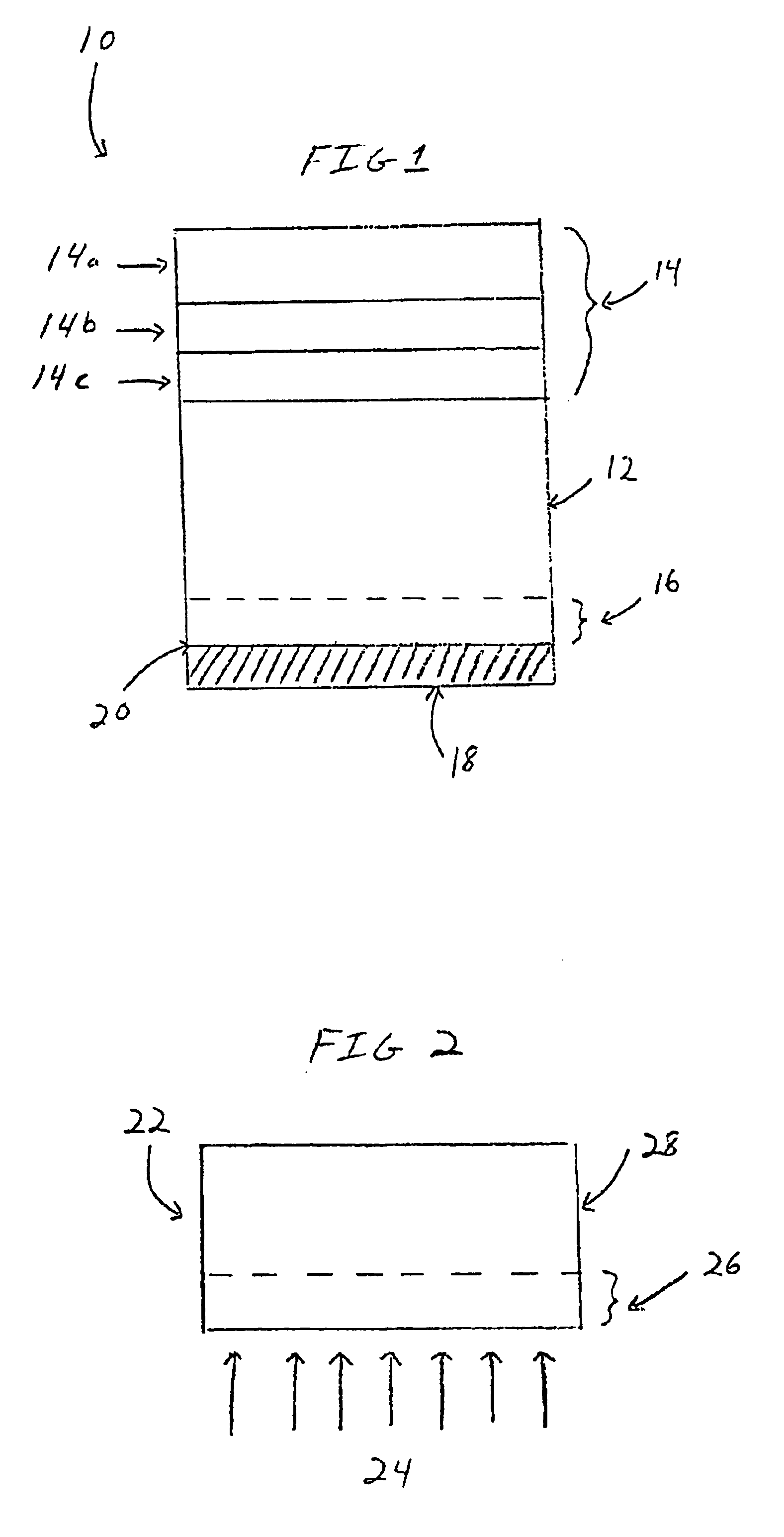

Low temperature formation of backside ohmic contacts for vertical devices

InactiveUS6884644B1Reduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactEngineering

The invention comprises a method for forming a metal-semiconductor ohmic contact (18) for use in a semiconductor device (10) having a plurality of epitaxial layers (14a-c) wherein the ohmic contact (18) is preferably formed after deposition of the epitaxial layers (14a-c). The invention also comprises a semiconductor device comprising a plurality of epitaxial layers and an ohmic contact.

Owner:WOLFSPEED INC

Method and system of heterogeneous substrate bonding for photonic integration

ActiveUS20110085577A1Good light transmissionImprove conductivityLaser detailsSolid-state devicesPhotonicsInterface layer

A hybrid integrated optical device includes a substrate comprising a silicon layer and a compound semiconductor device bonded to the silicon layer. The device also includes a bonding region disposed between the silicon layer and the compound semiconductor device. The bonding region includes a metal-semiconductor bond at a first portion of the bonding region. The metal-semiconductor bond includes a first pad bonded to the silicon layer, a bonding metal bonded to the first pad, and a second pad bonded to the bonding metal and the compound semiconductor device. The bonding region also includes an interface assisted bond at a second portion of the bonding region. The interface assisted bond includes an interface layer positioned between the silicon layer and the compound semiconductor device, wherein the interface assisted bond provides an ohmic contact between the silicon layer and the compound semiconductor device.

Owner:SKORPIOS TECH

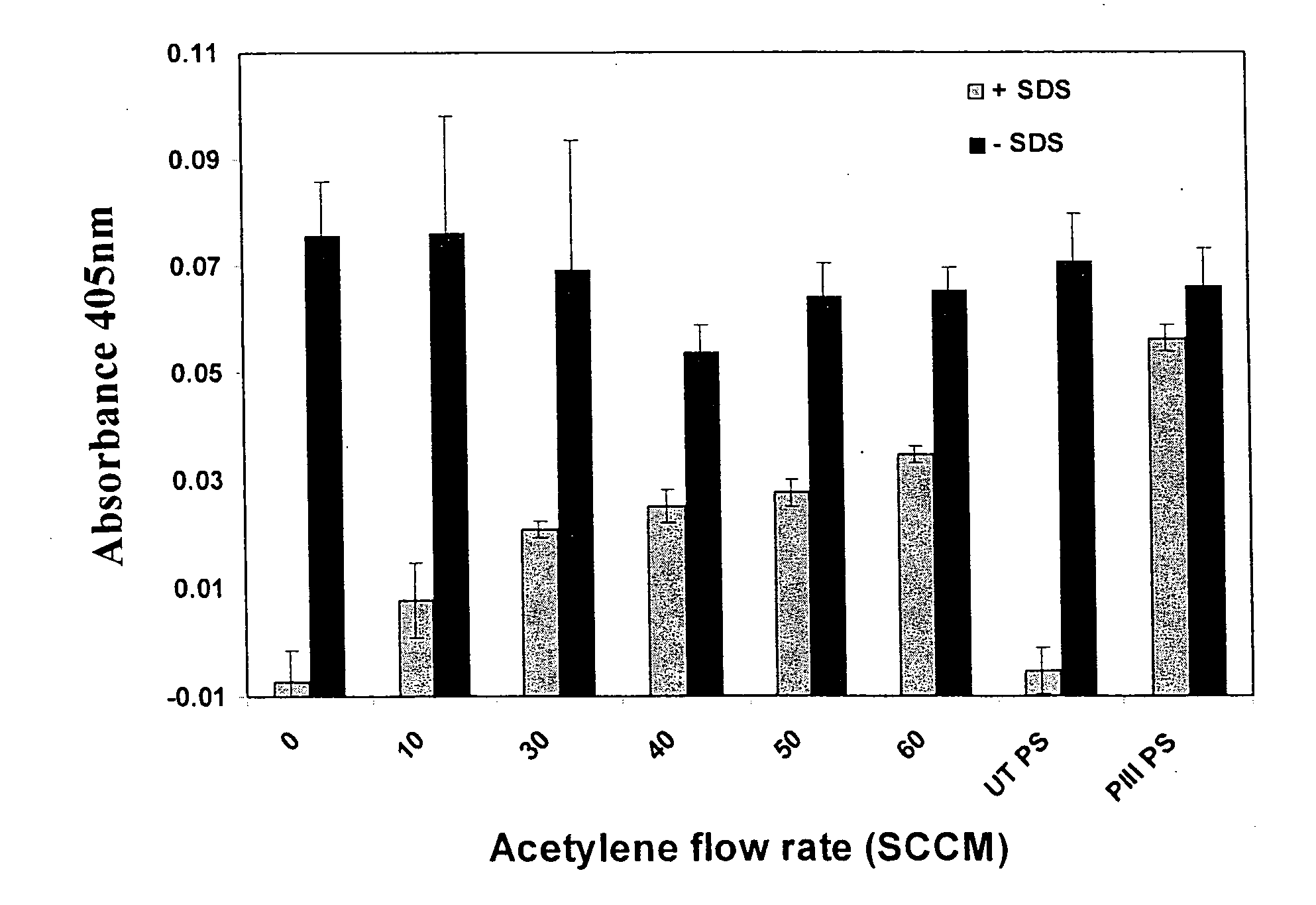

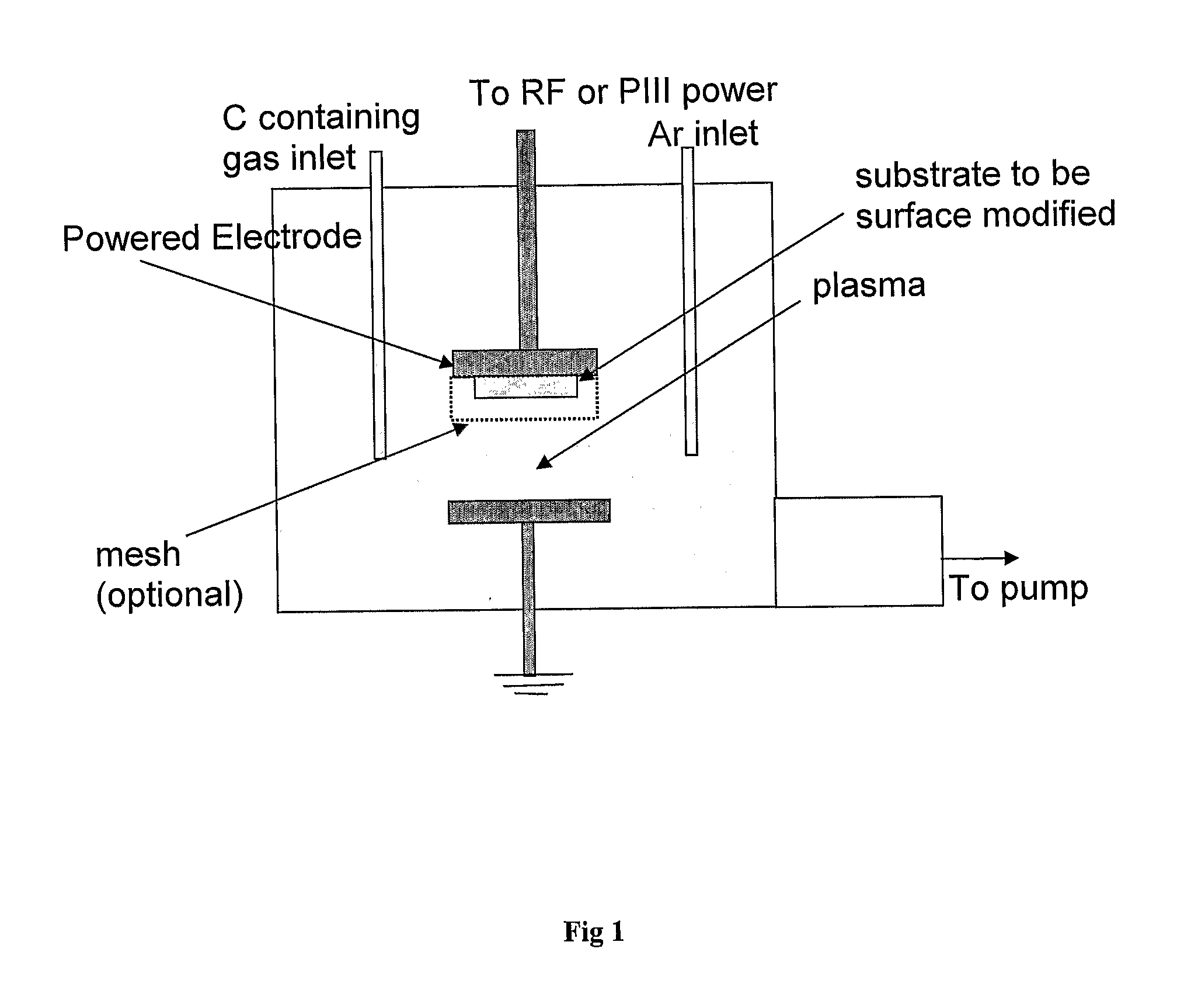

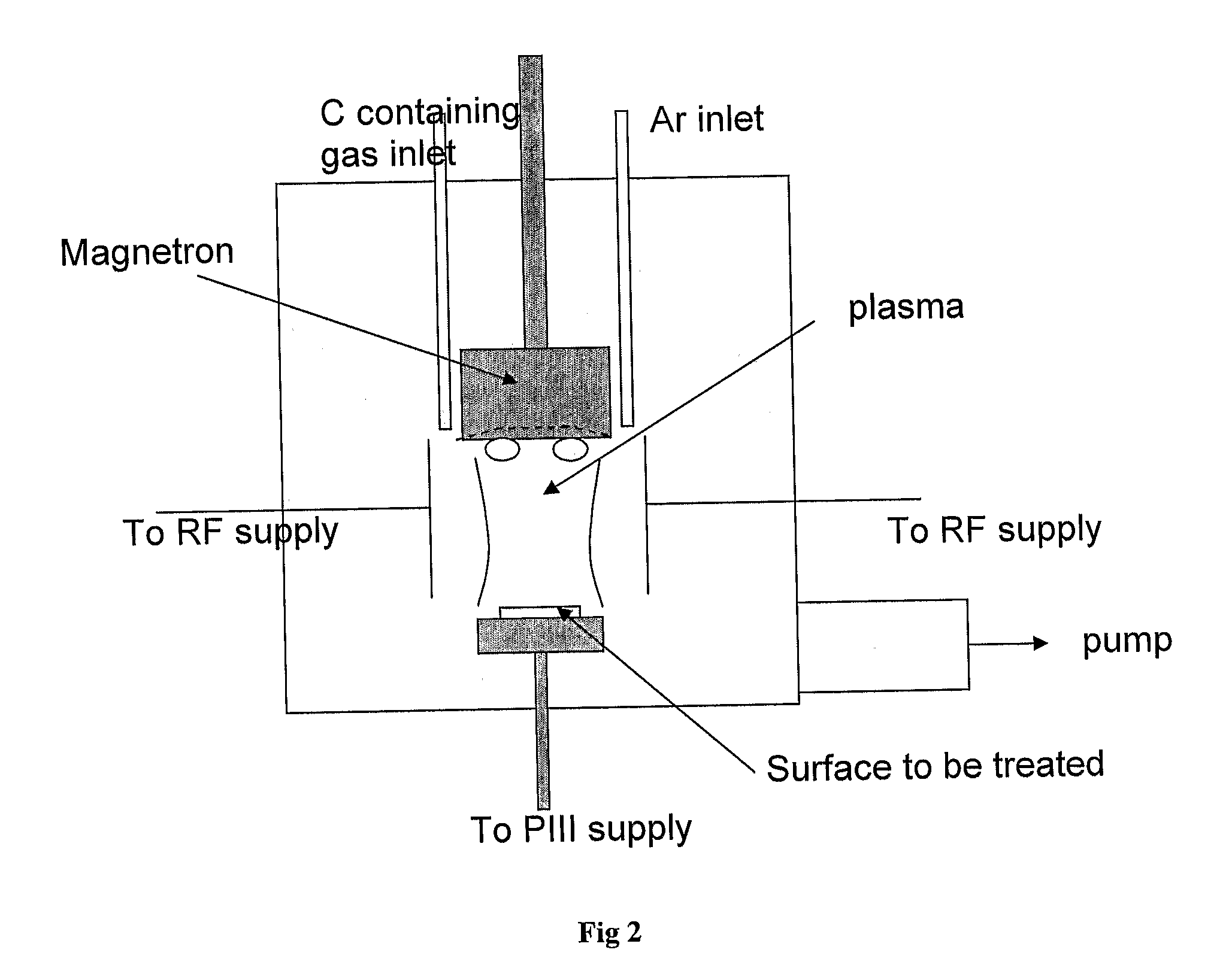

Biological functionalisation of substrates

InactiveUS20100227372A1Improve surface stabilityMaintaining conformationLiquid surface applicatorsSynthetic resin layered productsCross-linkPolymeric surface

The invention relates to an activated metallic, semiconductor, polymer, composite and / or ceramic substrate, the substrate being bound through a mixed or graded interface to a hydrophilic polymer surface that is activated to enable direct covalent binding to a functional biological molecule, the polymer surface comprising a sub-surface that includes a plurality of cross-linked regions, as well as to such activated substrates that have been functionalised with a biological molecule and to devices comprising such functionalised substrates. Such substrates can be produced by a method comprising steps of: a. exposing a surface of the substrate to any or more of (i) to (iii): (i) plasma ion implantation with carbon containing species; (ii) co-deposition under conditions in which substrate material is deposited with carbon containing species while gradually reducing substrate material proportion and increasing carbon containing species proportion; (iii) deposition of a plasma polymer surface layer with energetic ion bombardment; incubating the surface treated according to step (a) with a desired biological molecule.

Owner:SYDNEY THE UNIV OF

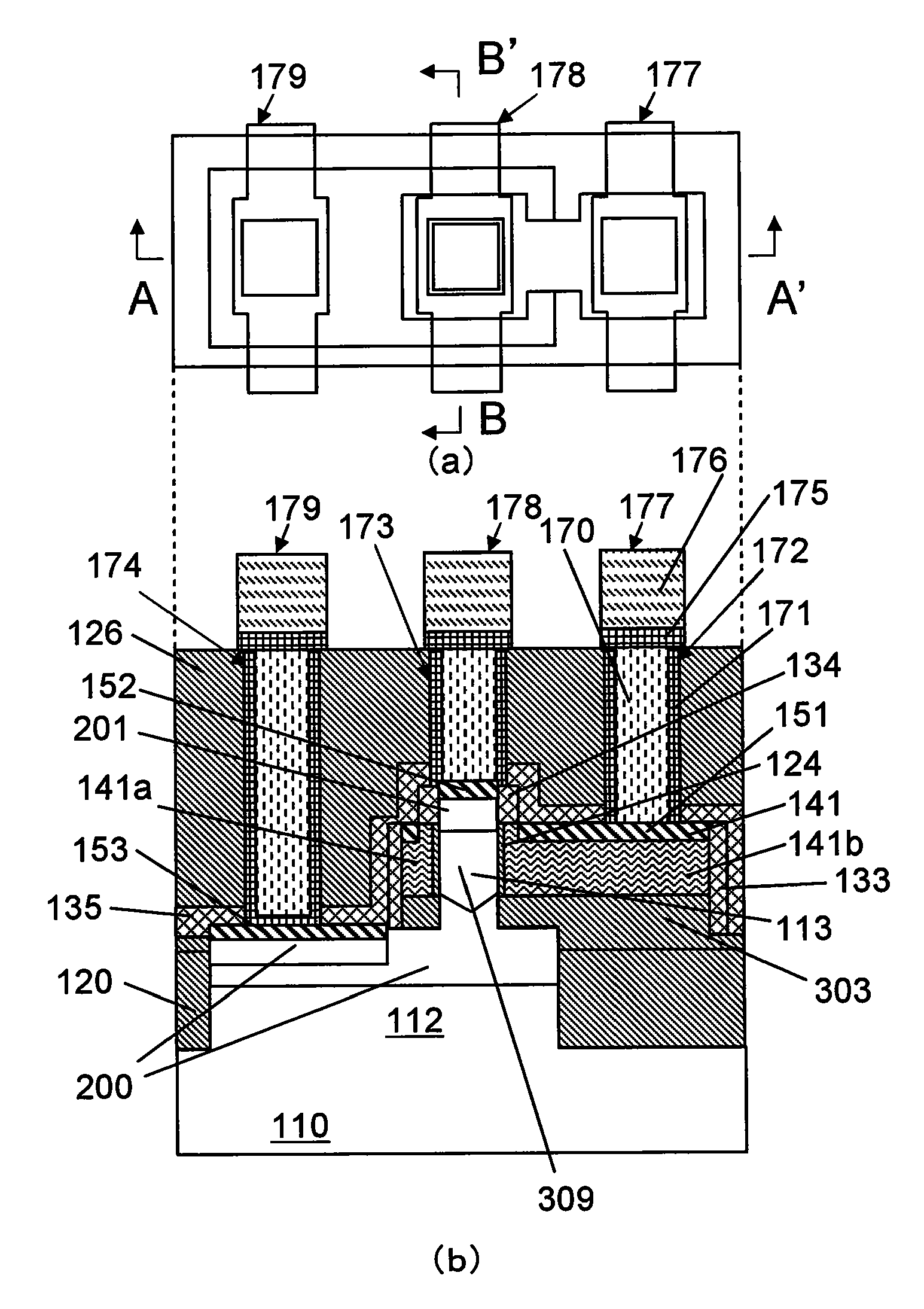

Semiconductor device and manufacturing method thereof

ActiveUS8080458B2Reduce resistanceReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSilicon

A method of manufacturing a semiconductor device includes the steps of forming a first columnar semiconductor layer on a substrate forming a first flat semiconductor layer forming a first semiconductor layer of a second conductive type, and forming a first insulating film. The method further includes the steps of forming a gate insulating film and a gate electrode, forming a second semiconductor layer of the second conductive type, forming a semiconductor layer of a first conductive type and forming a metal-semiconductor compound. The first insulating film has a thickness larger than that of the gate insulating film formed around the first columnar silicon layer.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

Techniques for fabricating nanowire field-effect transistors

ActiveUS7534675B2NanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanowire

Techniques for the fabrication of field-effect transistors (FETs) having nanowire channels are provided. In one aspect, a method of fabricating a FET is provided comprising the following steps. A substrate is provided having a silicon-on-insulator (SOI) layer. At least one nanowire is deposited over the SOI layer. A sacrificial gate is formed over the SOI layer so as to cover a portion of the nanowire that forms a channel region. An epitaxial semiconductor material is selectively grown from the SOI layer that covers the nanowire and attaches the nanowire to the SOI layer in a source region and in a drain region. The sacrificial gate is removed. An oxide is formed that divides the SOI layer into at least two electrically isolated sections, one section included in the source region and the other section included in the drain region. A gate dielectric layer is formed over the channel region. A gate is formed over the channel region separated from the nanowire by the gate dielectric layer. A metal-semiconductor alloy is formed over the source and drain regions.

Owner:GLOBALFOUNDRIES U S INC

Semiconductor device and manufacturing method thereof

ActiveUS20100264485A1Lower gate resistanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor package

This invention provides a method of manufacturing a semiconductor device, which comprises the steps of: forming a first columnar semiconductor layer on a first flat semiconductor layer; forming a first semiconductor layer of a second conductive type in a lower portion of the first columnar semiconductor layer; forming a first insulating film around a lower sidewall of the first columnar silicon layer; forming a gate insulating film and a gate electrode around the first columnar silicon layer; forming a sidewall-shaped second insulating film to surround an upper sidewall of the first columnar silicon layer; forming a semiconductor layer of a first conductive type between the first semiconductor layer of the second conductive type and a second semiconductor layer of the second conductive type; and forming a metal-semiconductor compound on an upper surface of the first semiconductor layer of the second conductive type.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

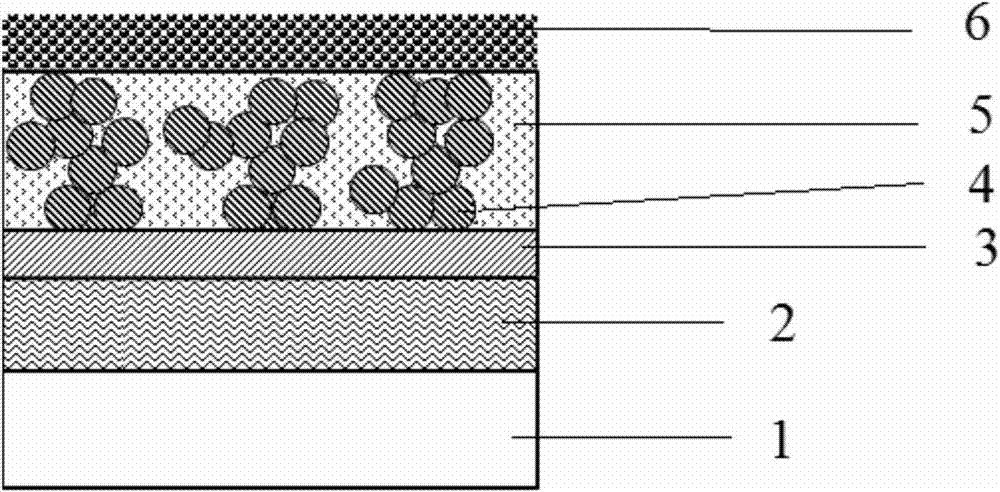

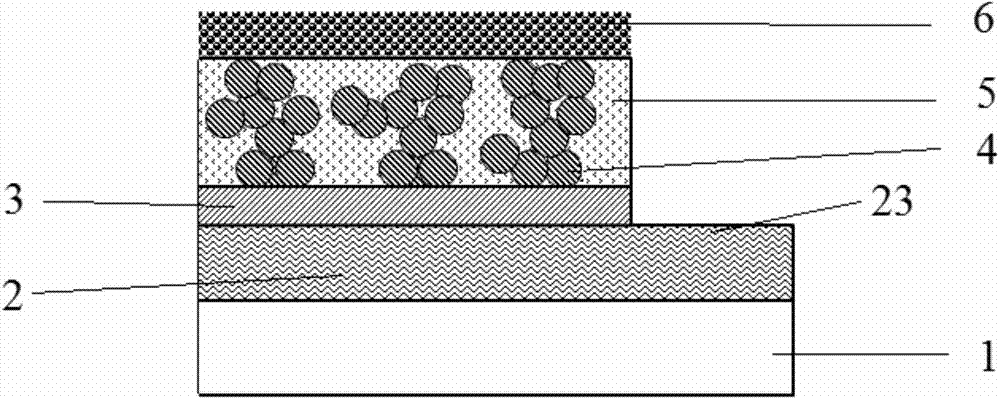

Perovskite-based thin film solar cell and method for preparing same

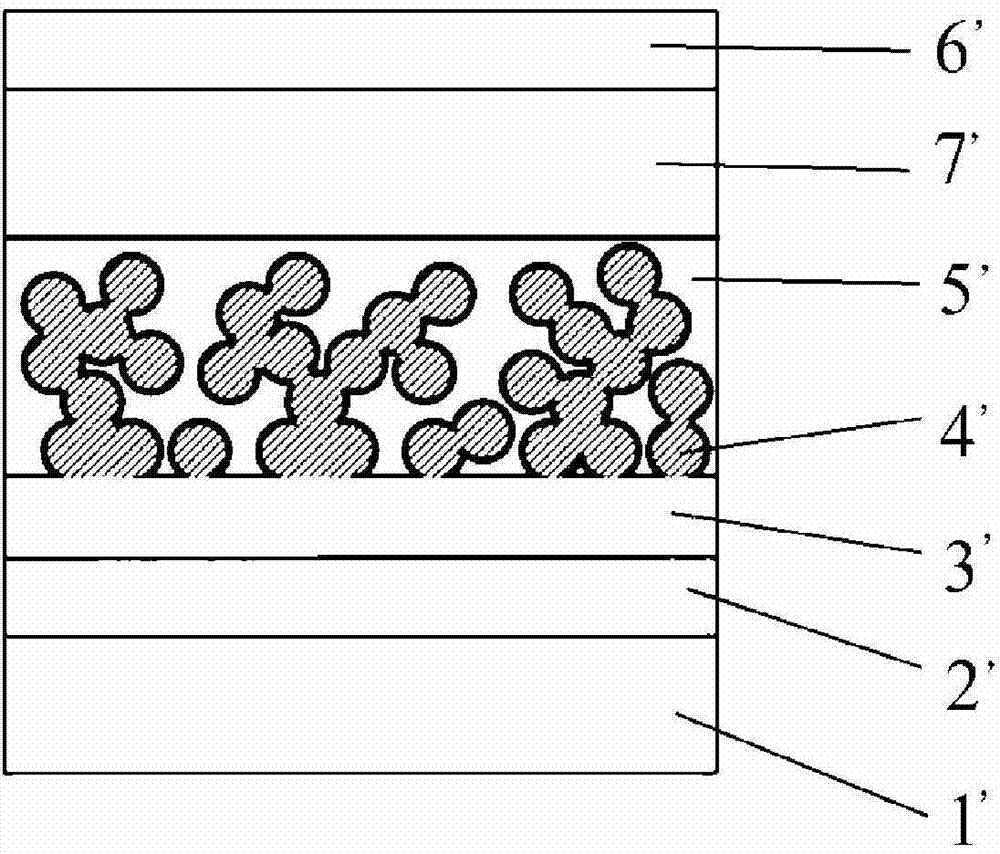

ActiveCN103490011ASolve problems that are difficult to achieve large-scale productionLow costFinal product manufactureSolid-state devicesSemiconductor materialsPorous carbon

The invention provides a perovskite-based thin film solar cell and a method for preparing the perovskite-based thin film solar cell. The perovskite-based thin film solar cell comprises a transparent substrate, a transparent conducting layer formed on the transparent substrate, a compact layer which is formed on the transparent conducting layer and made of semiconductor materials, a porous insulating layer formed on the compact layer, a porous carbon counter electrode layer formed on the porous insulating layer, and an organic metal semiconductor light absorption material which is filled into pores inside the porous insulating layer and has a perovskite structure. The invention provides application of carbon counter electrodes in the perovskite-based thin film solar cell. Compared with an existing method for preparing the perovskite-based thin film solar cell, the method has the advantages that the counter electrodes are made of carbon materials instead of expensive precious metal materials, and therefore the cost is greatly reduced. The vacuum coating method is replaced by a simple and rapid silk screen print method which allows large-scale production to be achieved, therefore, the cost is further saved, and the achievement of industrial production of the perovskite-based thin film solar cell is facilitated.

Owner:深圳市华物光能技术有限公司

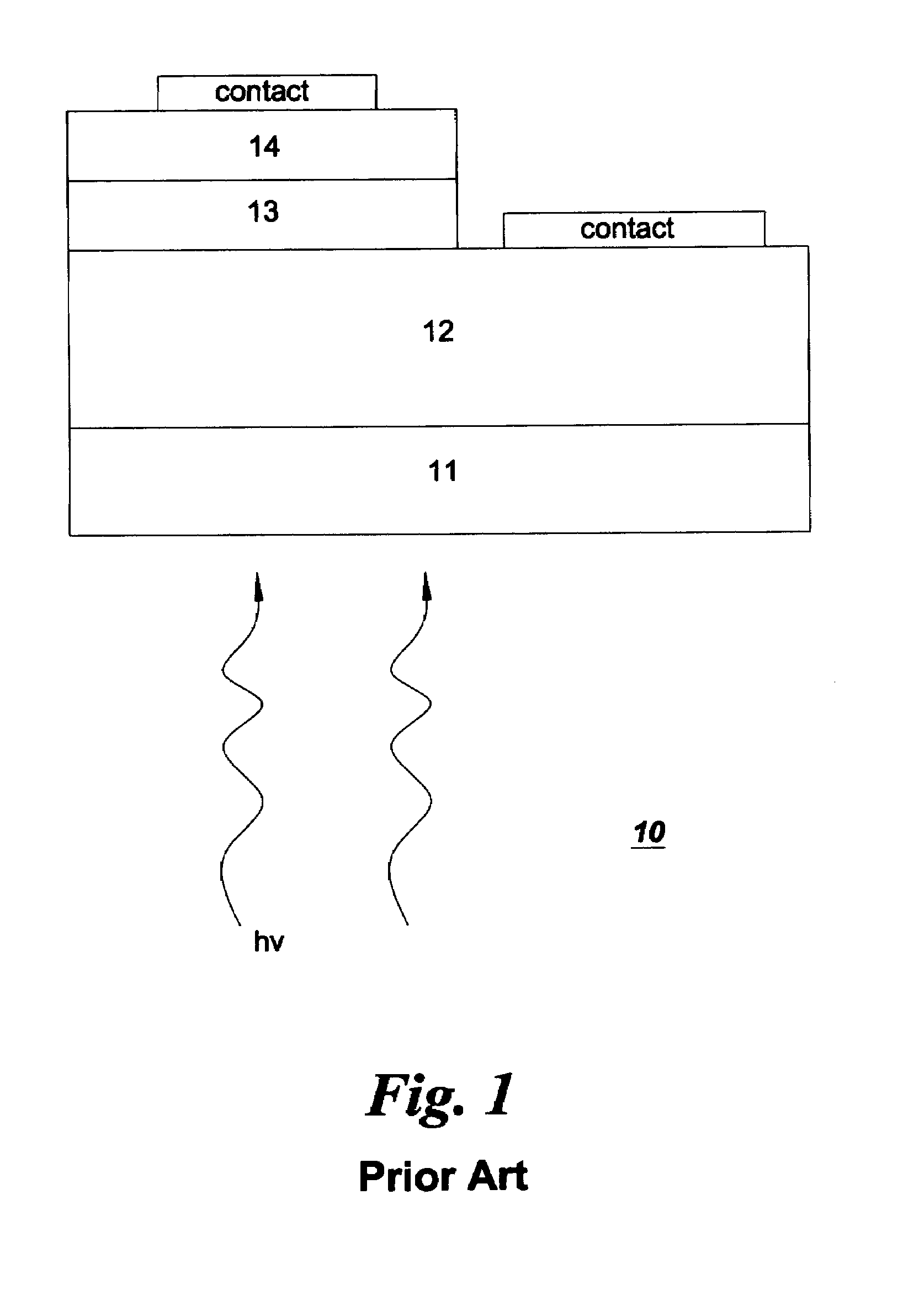

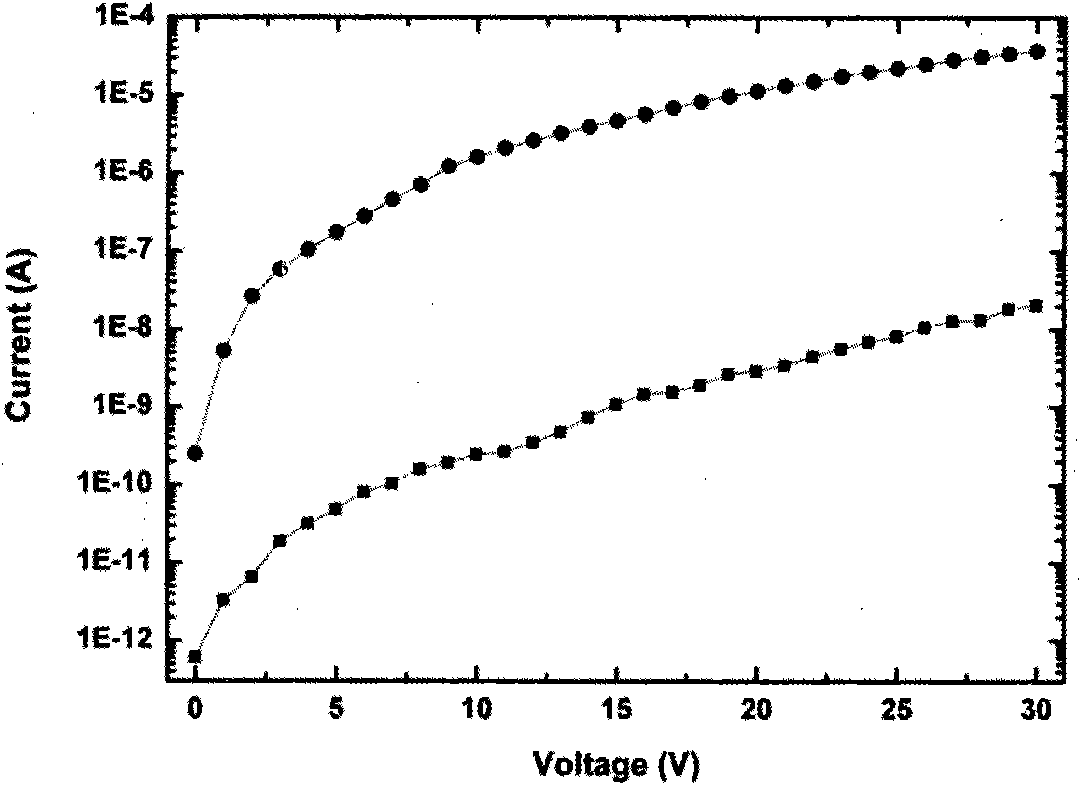

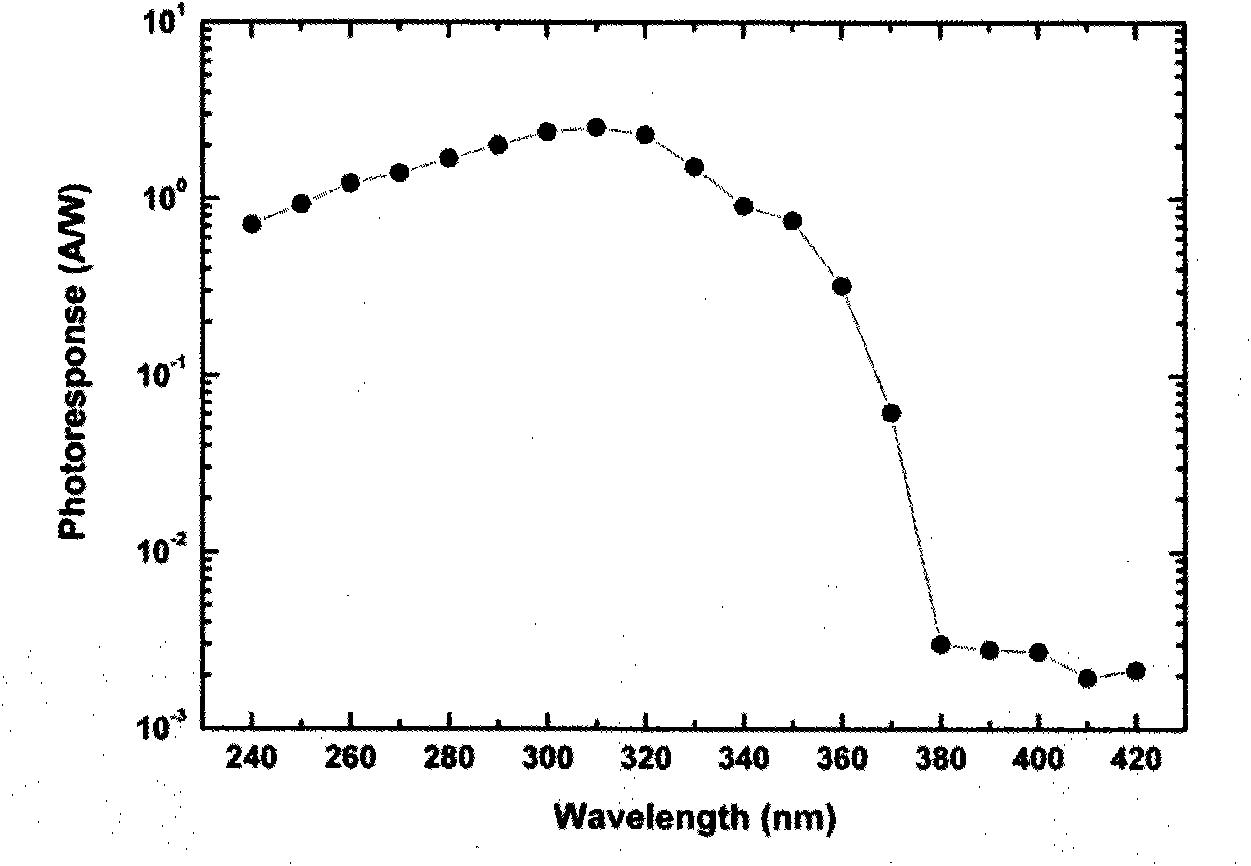

Homoepitaxial gallium nitride based photodetector and method of producing

InactiveUS7291544B2Final product manufactureSemiconductor/solid-state device manufacturingPhotovoltaic detectorsSchottky barrier

Owner:SLT TECH

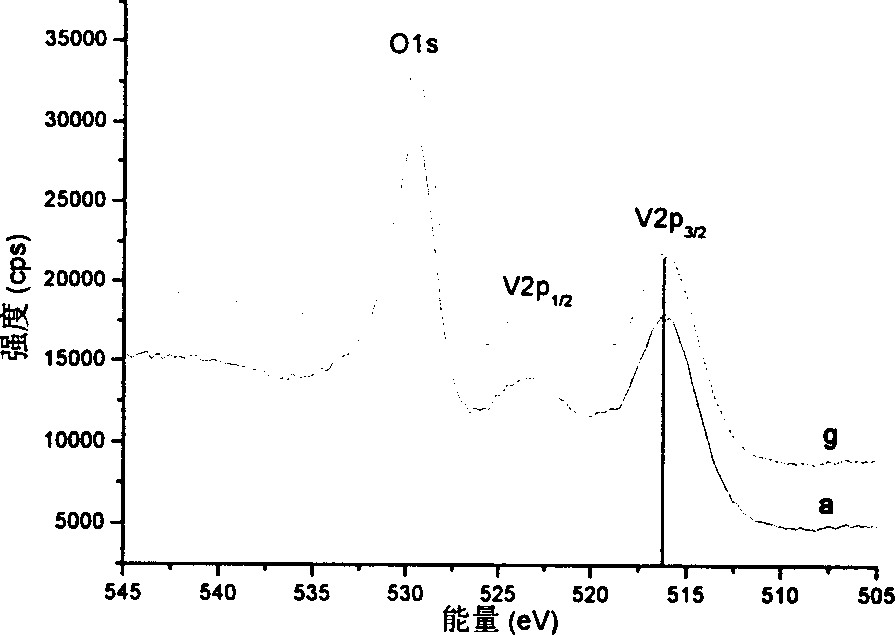

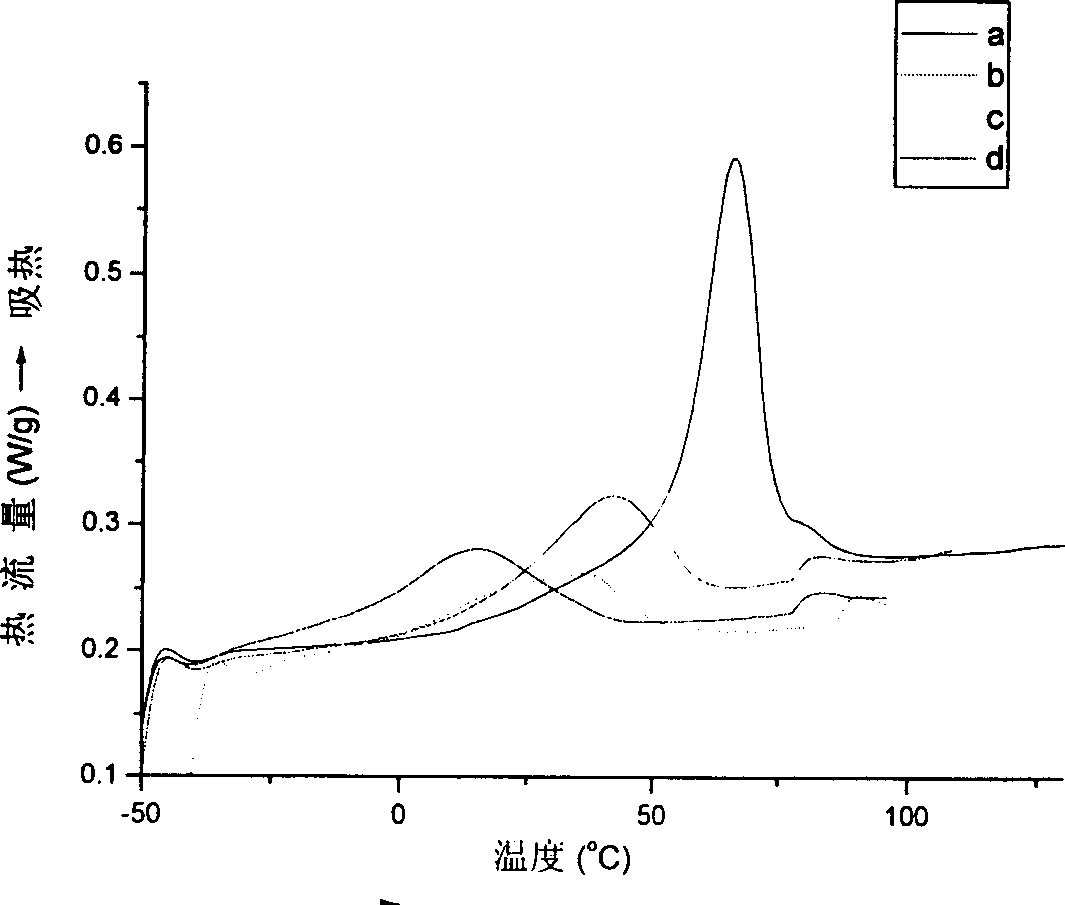

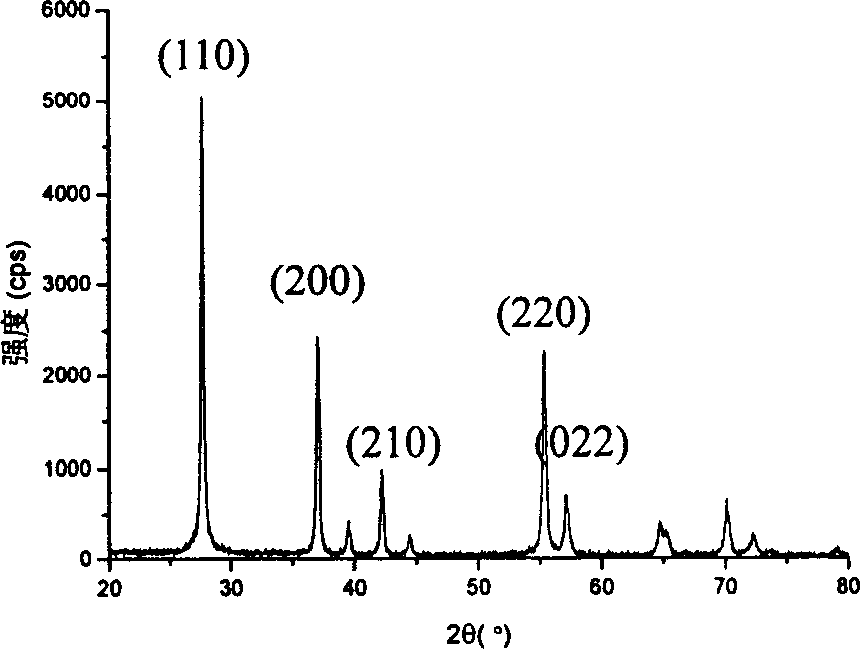

Phase-transition intelligent materials with adjustable phase-transition temperature and process for preparing same

InactiveCN1837061AReduce infrared transmittanceIt has the function of intelligent temperature controlOther chemical processesVanadium oxidesVanadium dioxideMaterials science

The invention relates to an intelligent phase-change material with adjustable phase-change temperature and its preparing process, which comprises making doped vanadium dioxide precursor through liquid phase precipitation method, carrying out filtering, scouring, drying, heating and crystallizing. The crystal grain dimension of the obtained phase-change material is less than 100 nanometers, thus can be applied into intelligent window coating material and temperature measurement resistors.

Owner:FUDAN UNIV

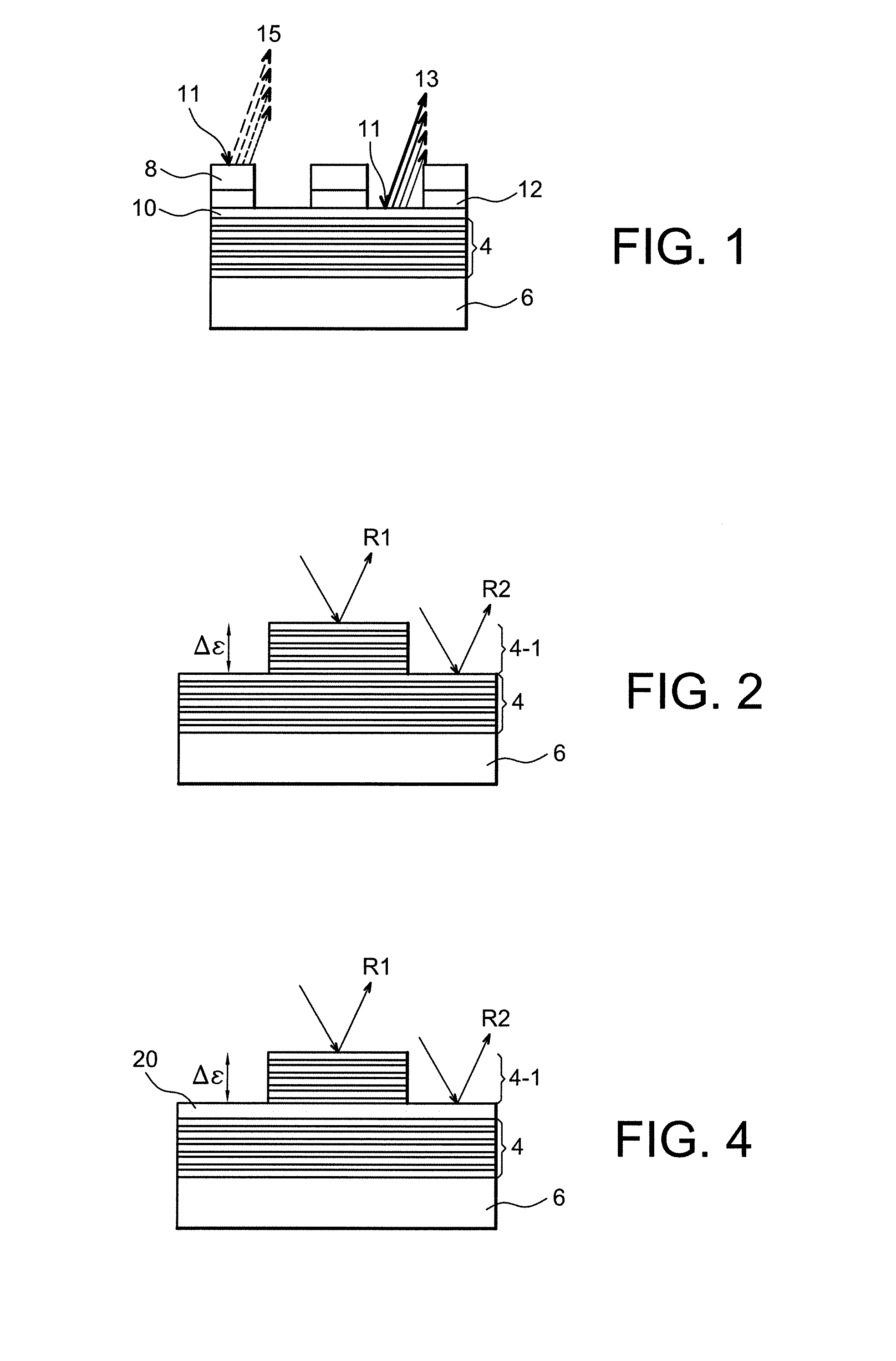

Adjustable Mask Blank Structure for an Euv Phase-Shift Mask

The invention concerns a process for forming an optical component comprising:a—formation of a multi-layer stack (32, 34) with an adjustment layer (30) made of a metal-semiconductor mix formed in or on the stack,b—etching a part of the multi-layer stack, including at least a part of the adjustment layer,c—an annealing step to contract the adjustment layer within less than 1 nm.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

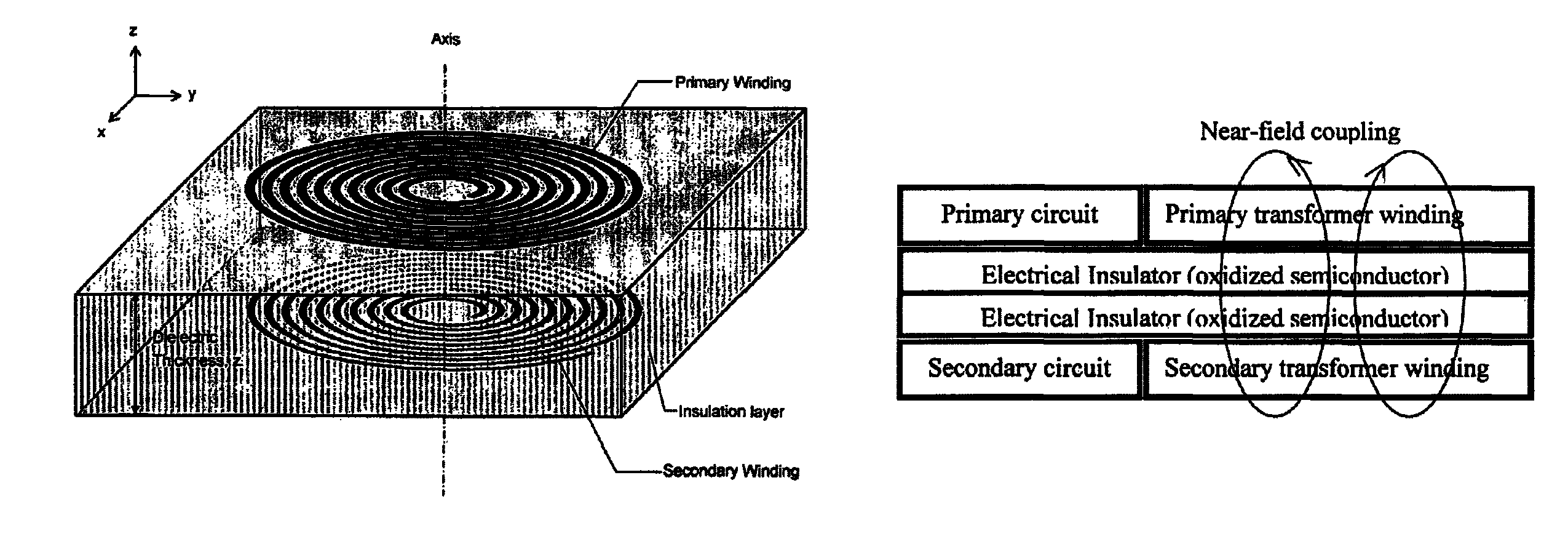

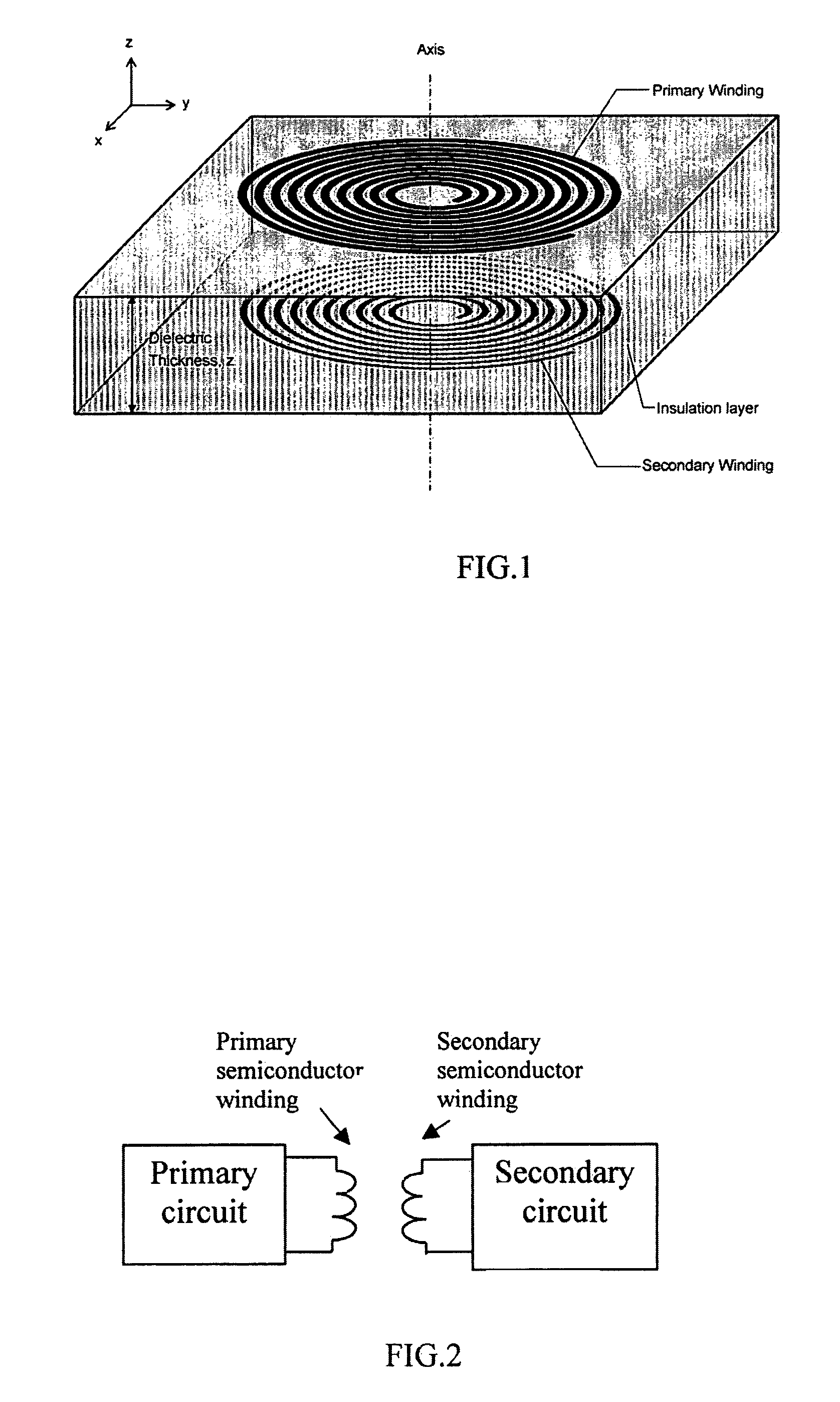

Semiconductor transformers

ActiveUS8049301B2Improve conductivityHigh coefficient of thermal expansionEmergency protective circuit arrangementsSolid-state devicesSalicideElectricity

A planar transformer structure, which can be constructed in an integrated semiconductor circuit without using traditional metallic windings. To avoid large thermal expansion of metallic spiral windings and associated mechanical stress on a metal-semiconductor interface, it is suggested that highly doped semiconductor materials with or without silicides and salicides can be used to form windings or conducting paths because their thermal expansion coefficients are similar to that of semiconductor material. The planar semiconductor transformer may find application for low-power and signal transfer that needs electrical isolation.

Owner:CITY UNIVERSITY OF HONG KONG

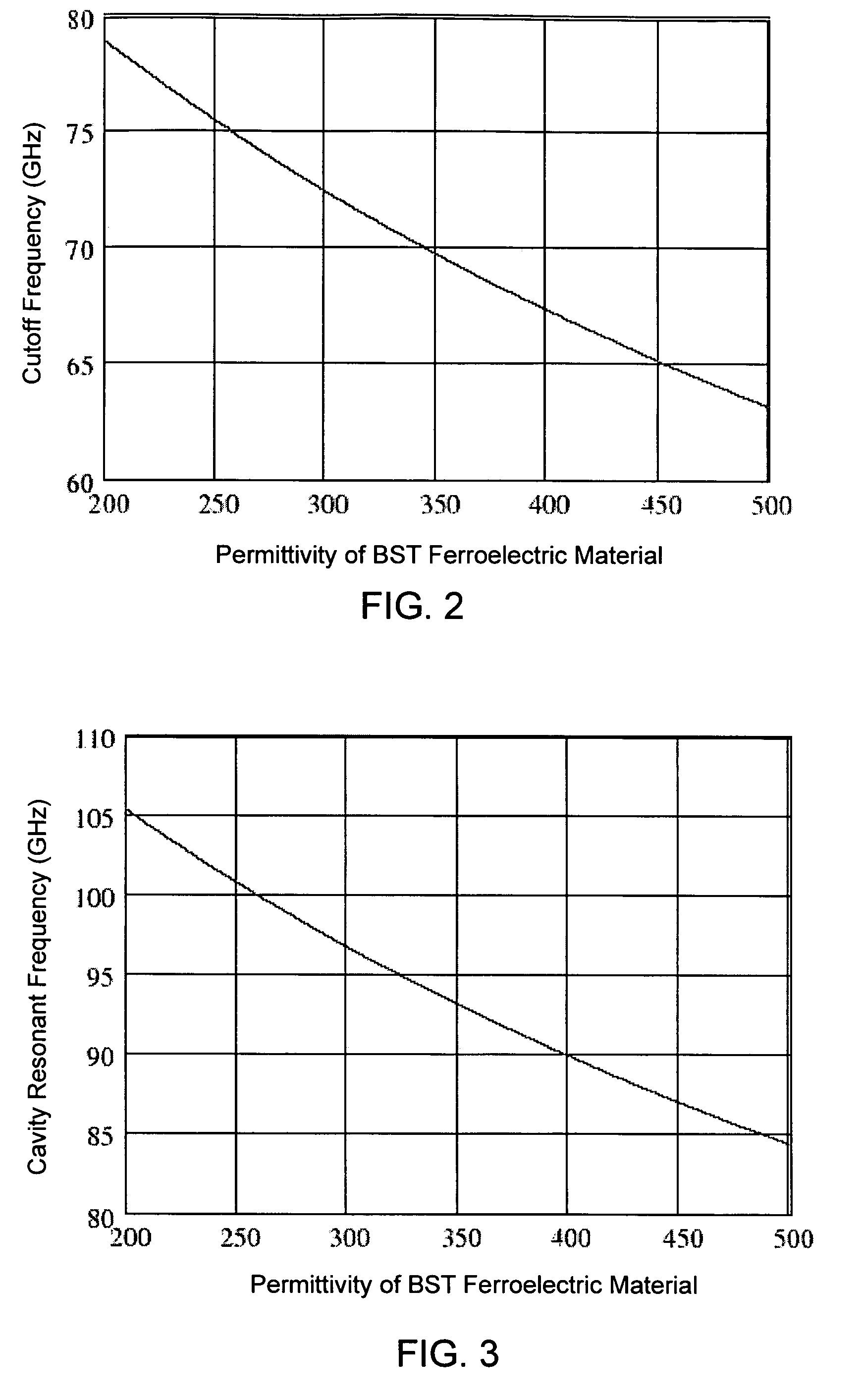

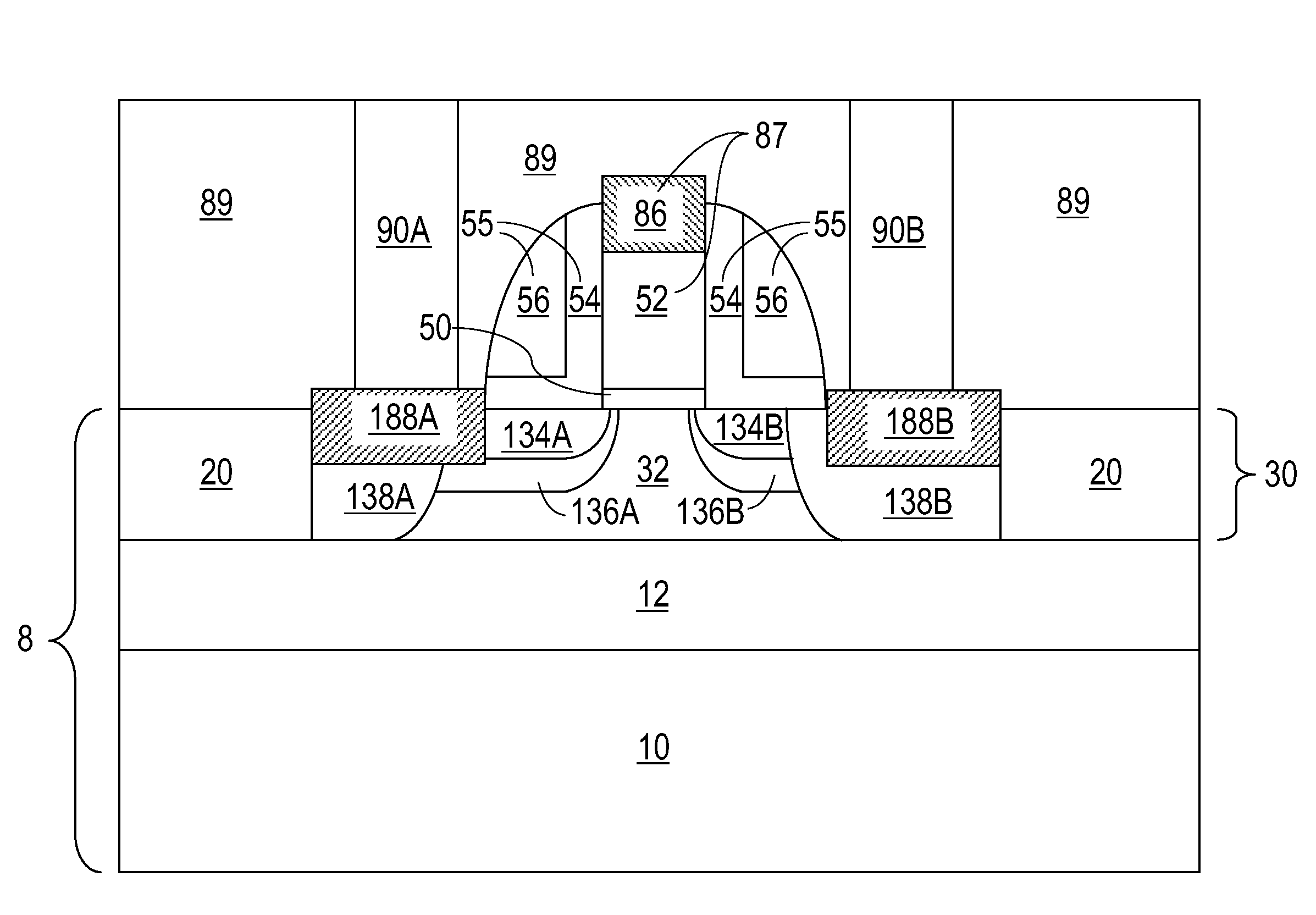

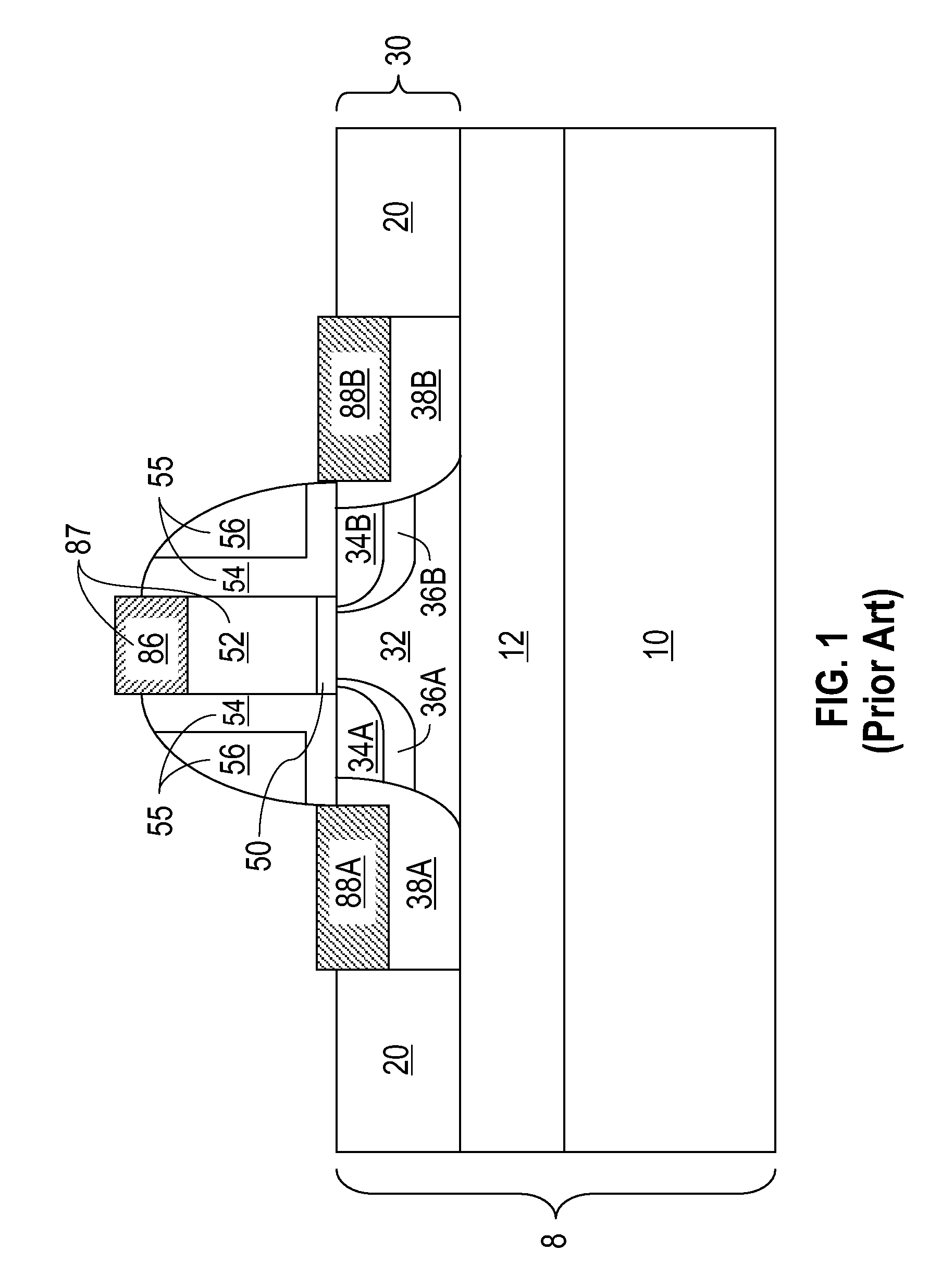

Partially depleted soi field effect transistor having a metallized source side halo region

Source and drain extension regions and source side halo region and drain side halo region are formed in a top semiconductor layer aligned with a gate stack on an SOI substrate. A deep source region and a deep drain region are formed asymmetrically in the top semiconductor layer by an angled ion implantation. The deep source region is offset away from one of the outer edges of the at least spacer to expose the source extension region on the surface of the semiconductor substrate. A source metal semiconductor alloy is formed by reacting a metal layer with portions of the deep source region, the source extension region, and the source side halo region. The source metal semiconductor alloy abuts the remaining portion of the source side halo region, providing a body contact tied to the deep source region to the partially depleted SOI MOSFET.

Owner:TAIWAN SEMICON MFG CO LTD

Thermoelectric tunnelling device

InactiveUS20070137687A1Thermoelectric device with peltier/seeback effectElectric discharge tubesCold platePhonon

Methods and apparatuses for making a thermotunneling device. A method in accordance with the present invention comprises metal / semiconductor or semiconductor / semiconductor bonded material combinations that allows current flow between a hot plate and a cold plate of a thermoelectric device, and interrupting a flow of phonons between the hot plate and the cold plate of the thermoelectric device, wherein the interrupted flow is caused by a nanogap, said nanogap being formed by applying a small voltage or current between the two sides of the thermoelectric device.

Owner:THE BOEING CO

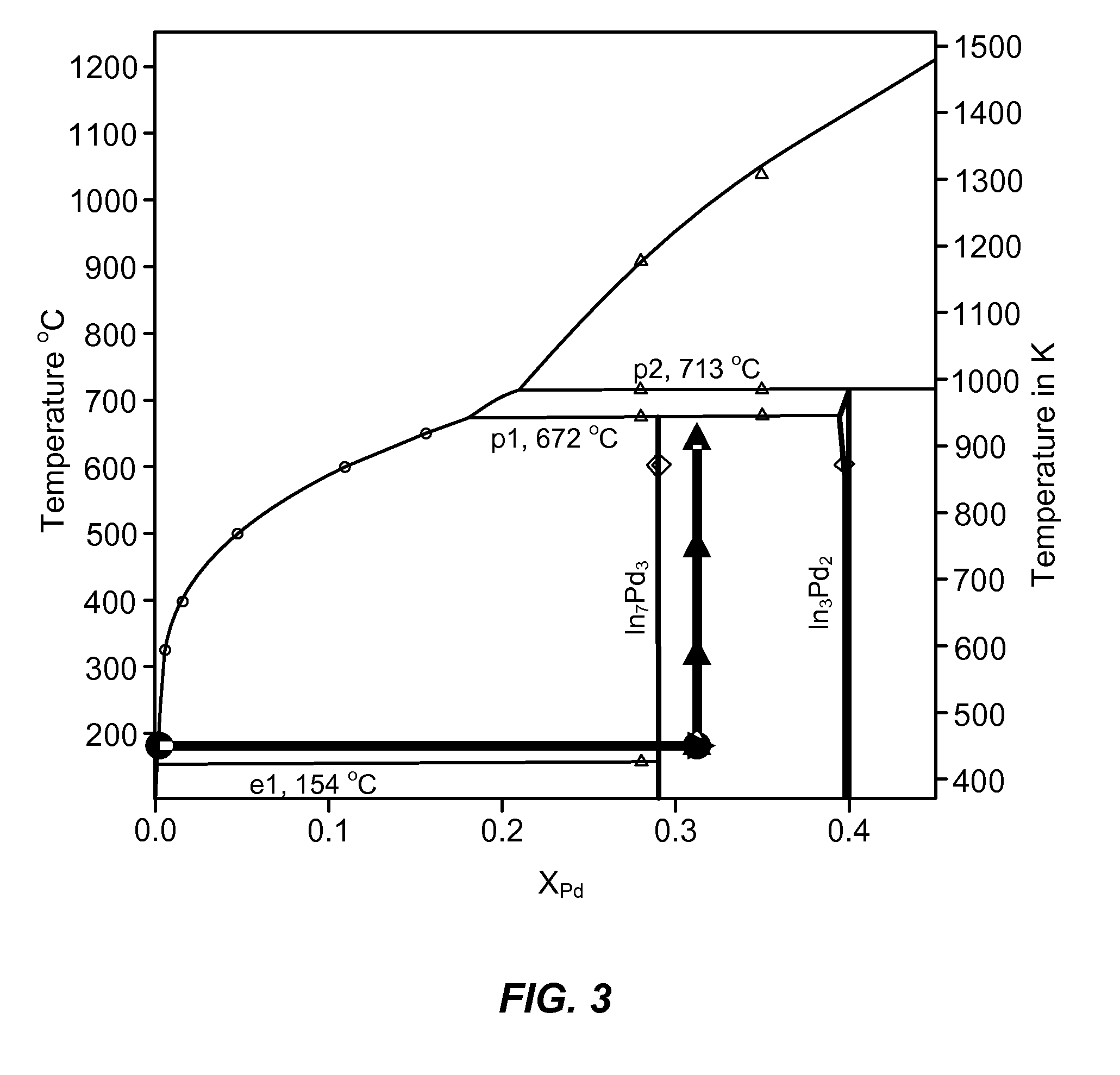

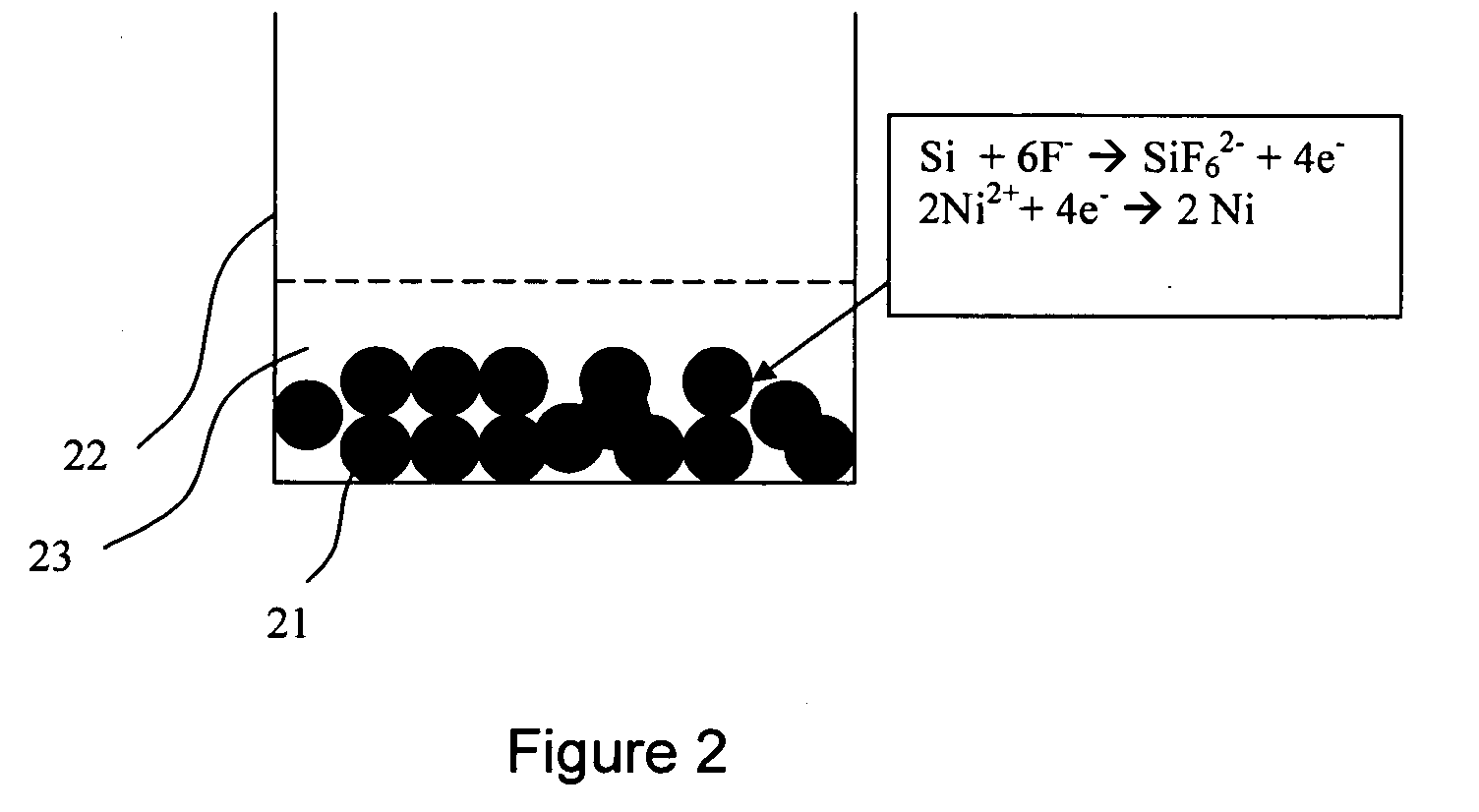

Anode material having a uniform metal-semiconductor alloy layer

ActiveUS20090263716A1Metal being depositedSemiconductor/solid-state device manufacturingNegative electrodesParticulatesSemiconductor materials

The present invention relates to methods for producing anode materials for use in nonaqueous electrolyte secondary batteries. In the present invention, a metal-semiconductor alloy layer is formed on an anode material by contacting a portion of the anode material with a solution containing metals ions and a dissolution component. When the anode material is contacted with the solution, the dissolution component dissolves a part of the semiconductor material in the anode material and deposit the metal on the anode material. After deposition, the anode material and metal are annealed to form a uniform metal-semiconductor alloy layer. The anode material of the present invention can be in a monolithic form or a particle form. When the anode material is in a particle form, the particulate anode material can be further shaped and sintered to agglomerate the particulate anode material.

Owner:ENOVIX CORP

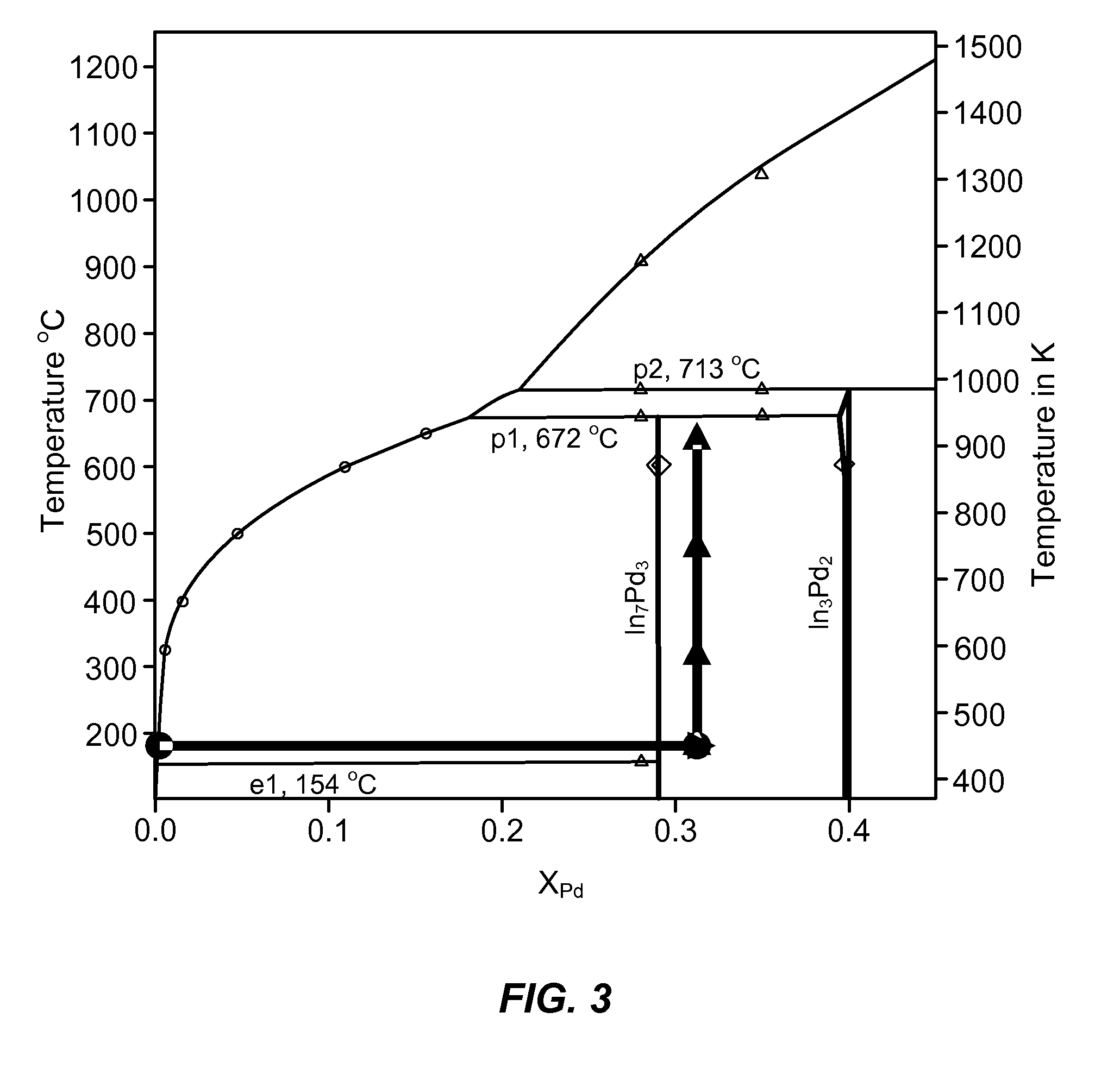

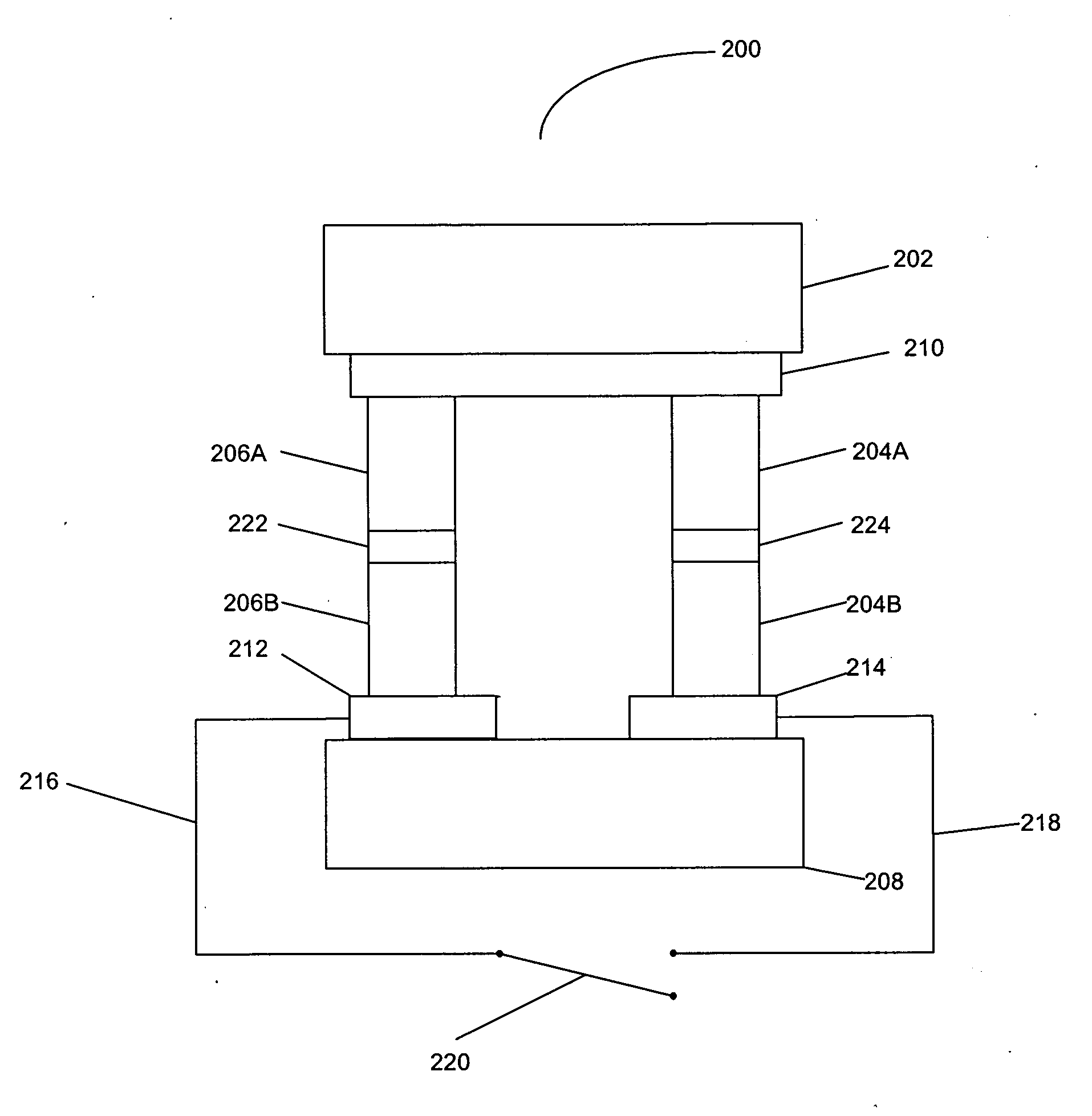

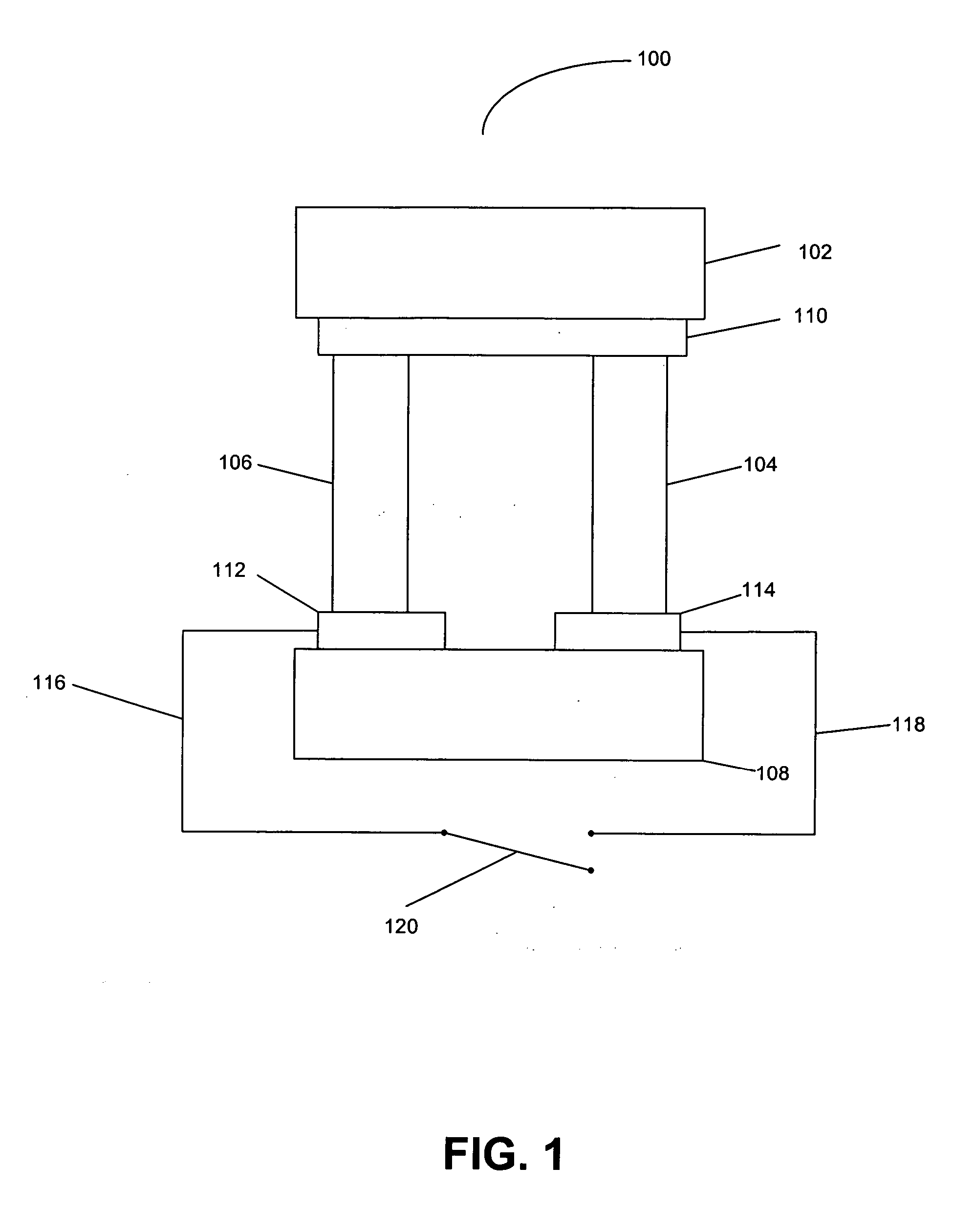

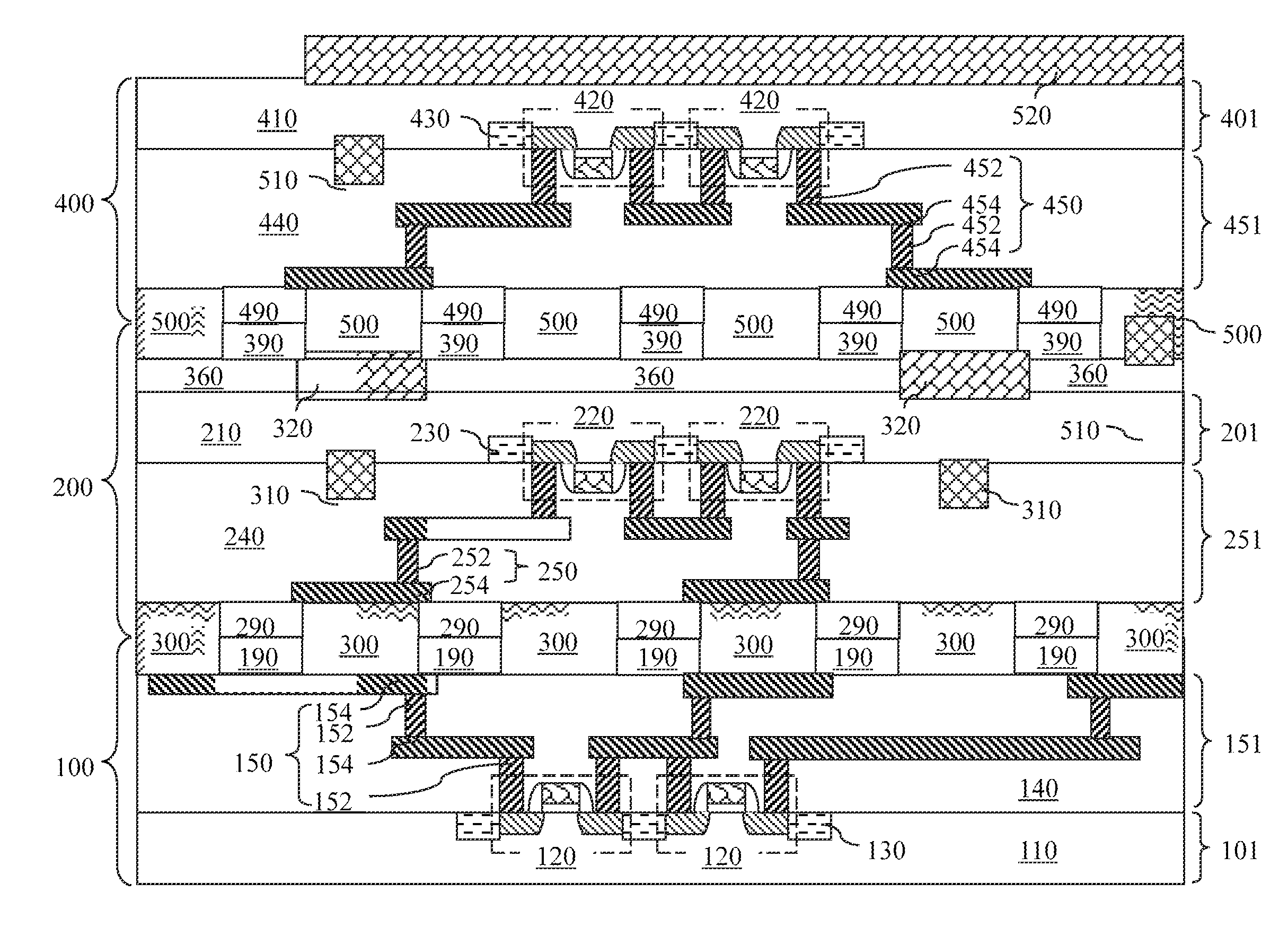

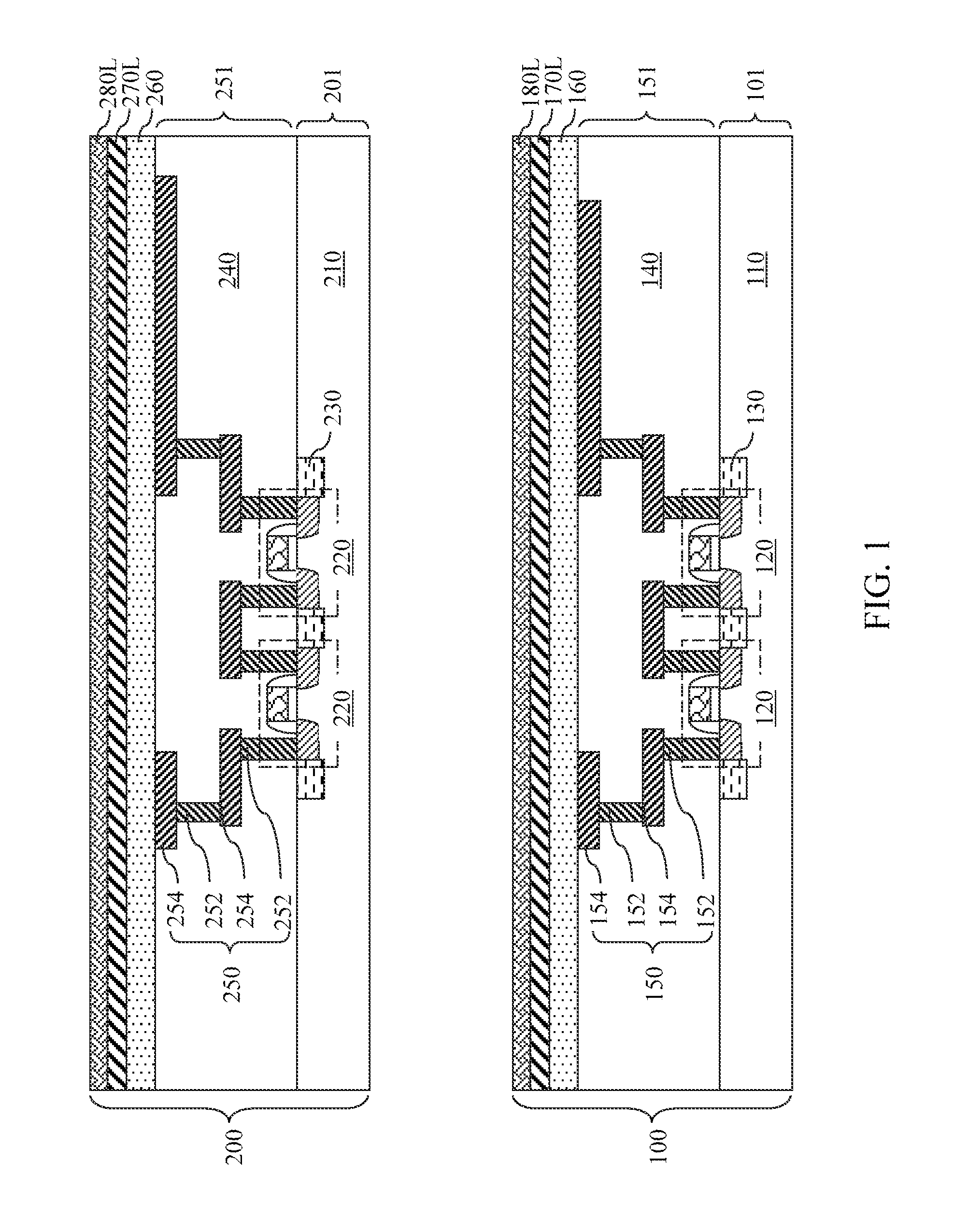

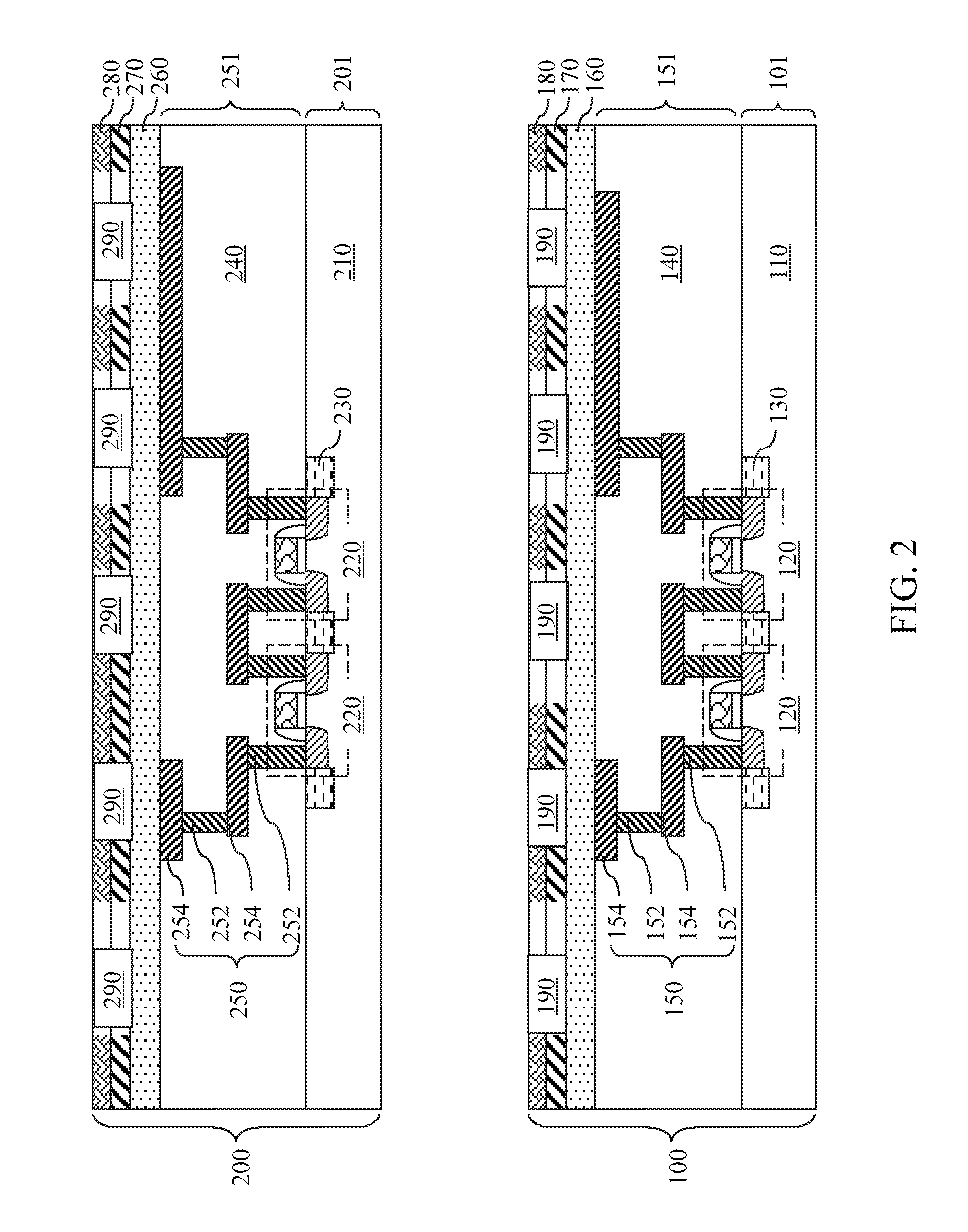

Bonded structure employing metal semiconductor alloy bonding

ActiveUS20110168434A1Solid-state devicesSemiconductor/solid-state device manufacturingAlloyMetal semiconductor

Vertical stacks of a metal portion and a semiconductor portion formed on a first substrate are brought into physical contact with vertical stacks of a metal portion and a semiconductor portion formed on a second substrate. Alternately, vertical stacks of a metal portion and a semiconductor portion formed on a first substrate are brought into physical contact with metal portions formed on a second substrate. The assembly of the first and second substrates is subjected to an anneal at a temperature that induces formation of a metal semiconductor alloy derived from the semiconductor portions and the metal portions. The first substrate and the second substrate are bonded through metal semiconductor alloy portions that adhere to the first and second substrates.

Owner:IBM CORP

Diode for use in MRAM devices and method of manufacture

A data storage device is disclosed that has a plurality of word lines, a plurality of bit lines, and a resistive crosspoint array of memory cells. Each memory cell is connected to a bit line and connected to an isolation diode that further connects to a respective word line. The isolation diode provides a unidirectional conductive path from the bit line to the word line. Each word line provides a common metal-semiconductor contact with each diode sharing the word line such that each diode has a separate metal contact located between the semiconductor portion of the common metal-semiconductor contact and its respective memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

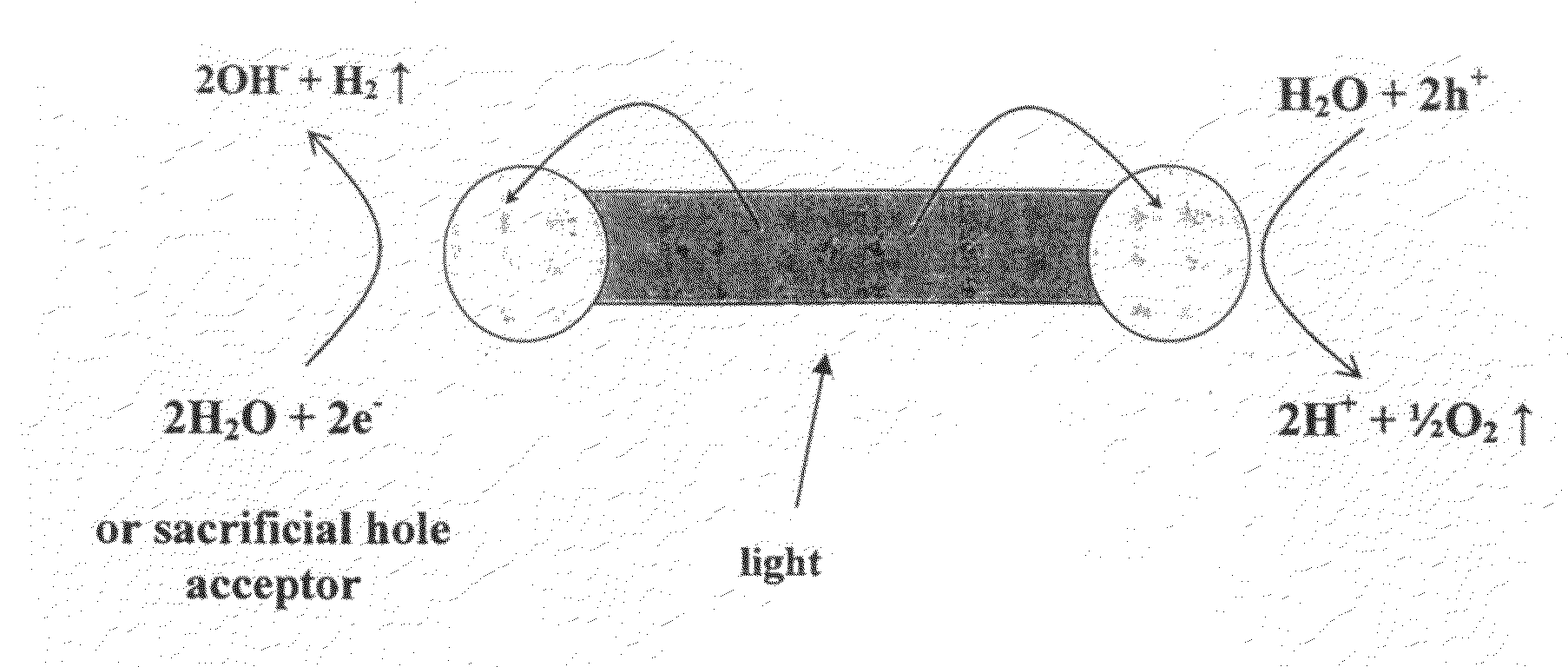

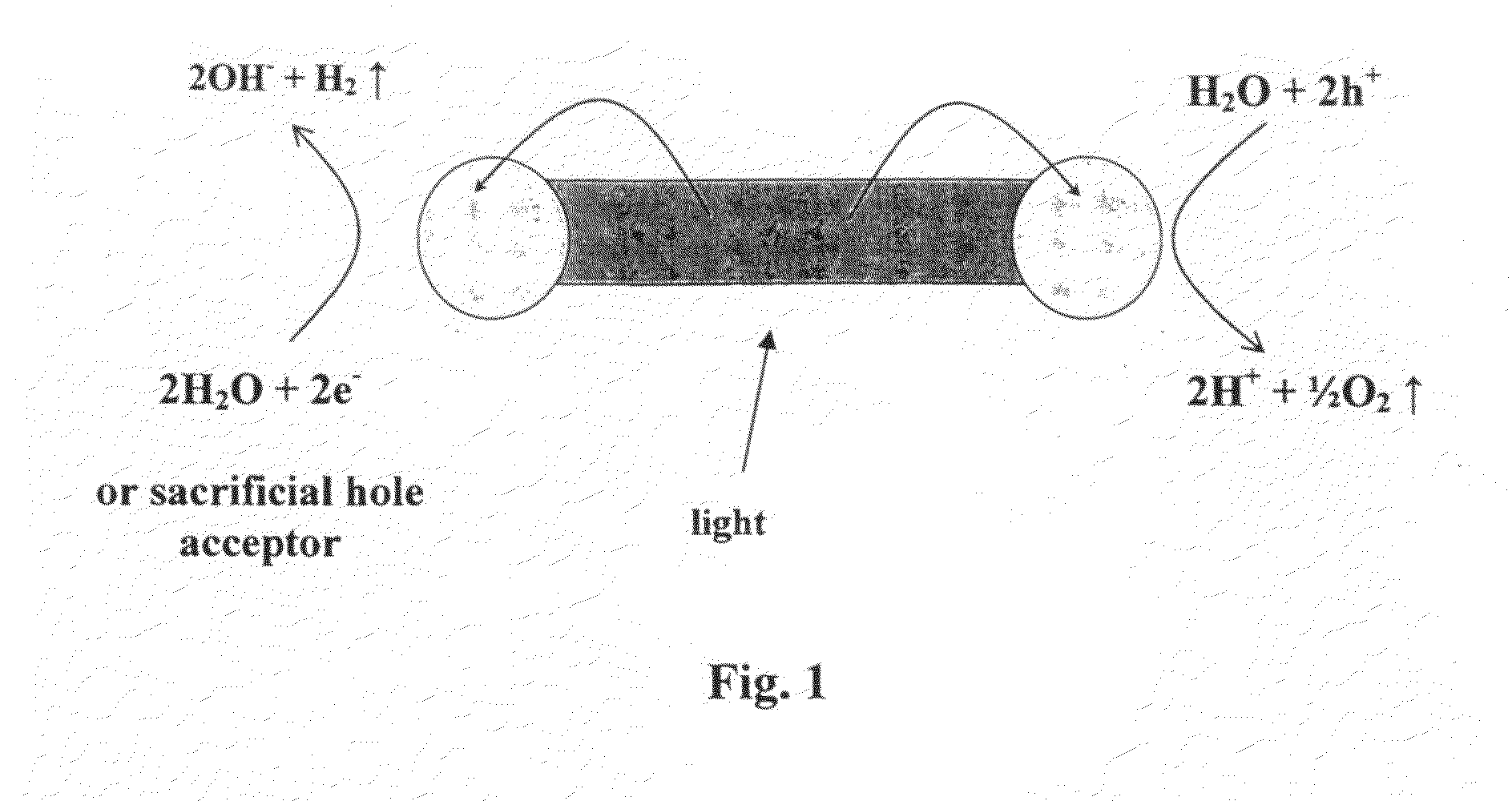

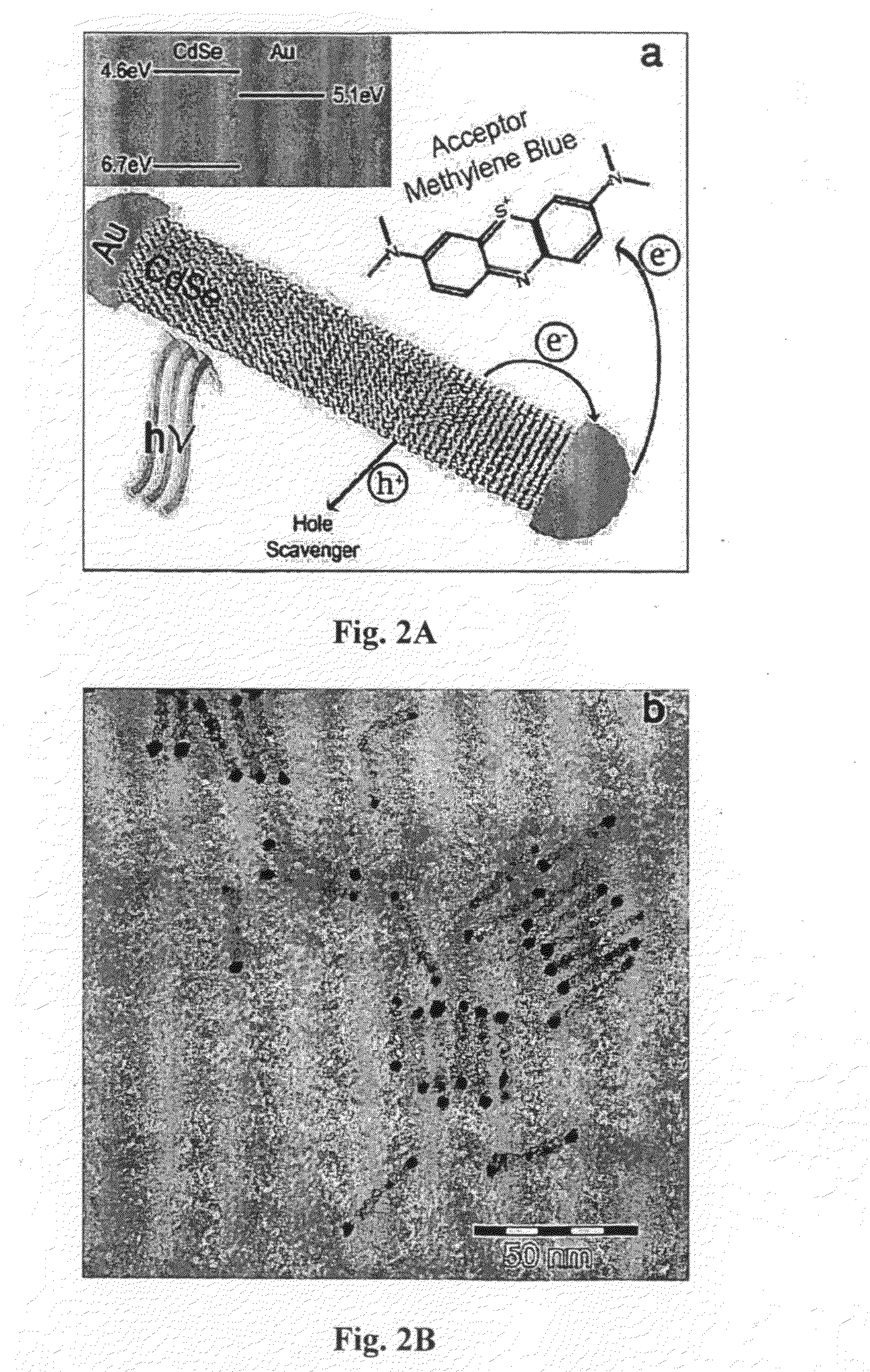

Hybrid metal-semiconductor nanoparticles and methods for photo-inducing charge separation and applications thereof

InactiveUS20100044209A1Easy to controlEfficient use ofMaterial nanotechnologyLight-sensitive devicesChemical reactionOxidation-Reduction Agent

The development and use of hybrid metal-semiconductor nanoparticles for photocatalysis of a variety of chemical reactions such as redox reactions and water-splitting, is provided.

Owner:YISSUM RES DEV CO OF THE HEBREWUNIVERSITY OF JERUSALEM LTD

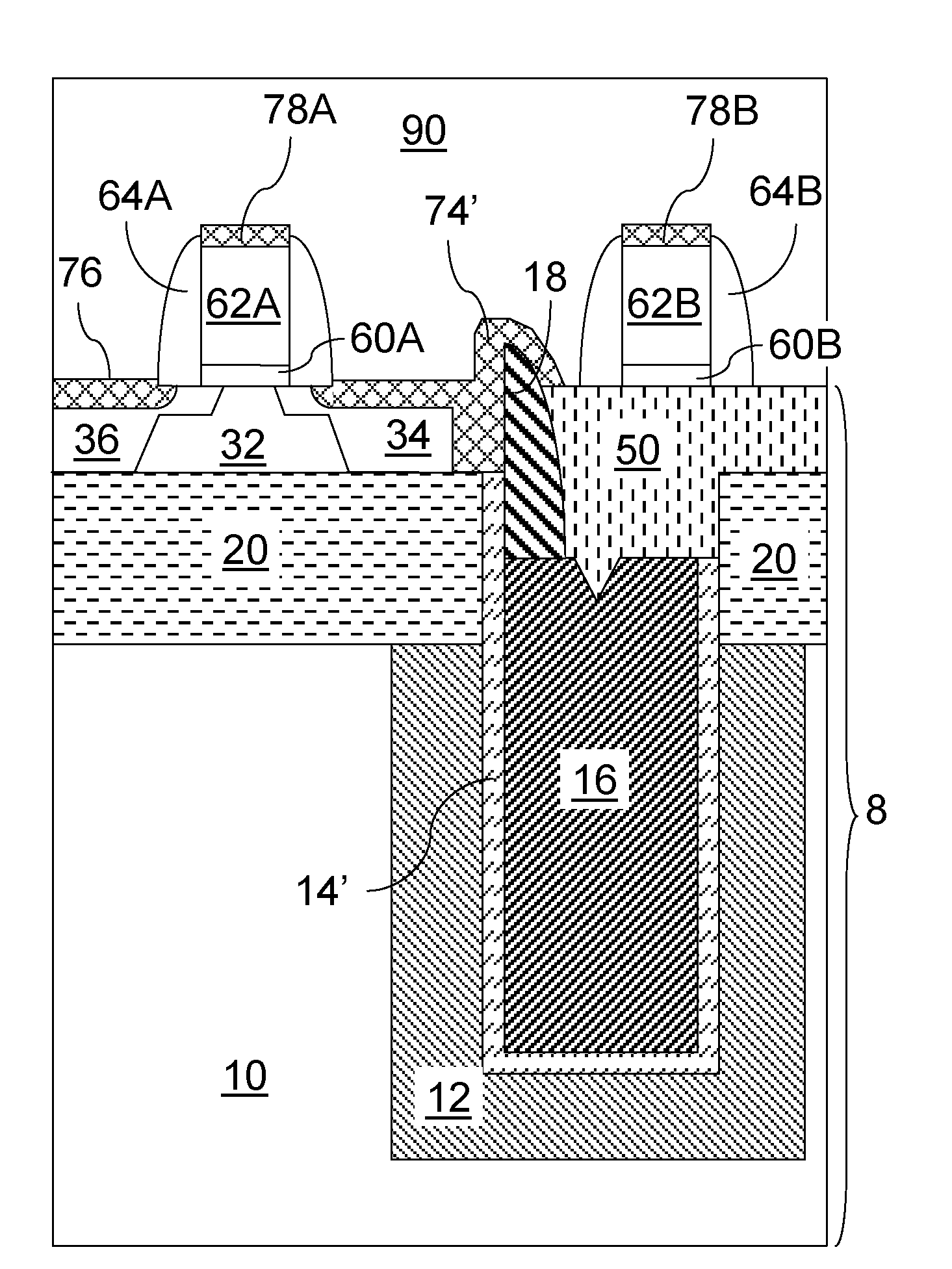

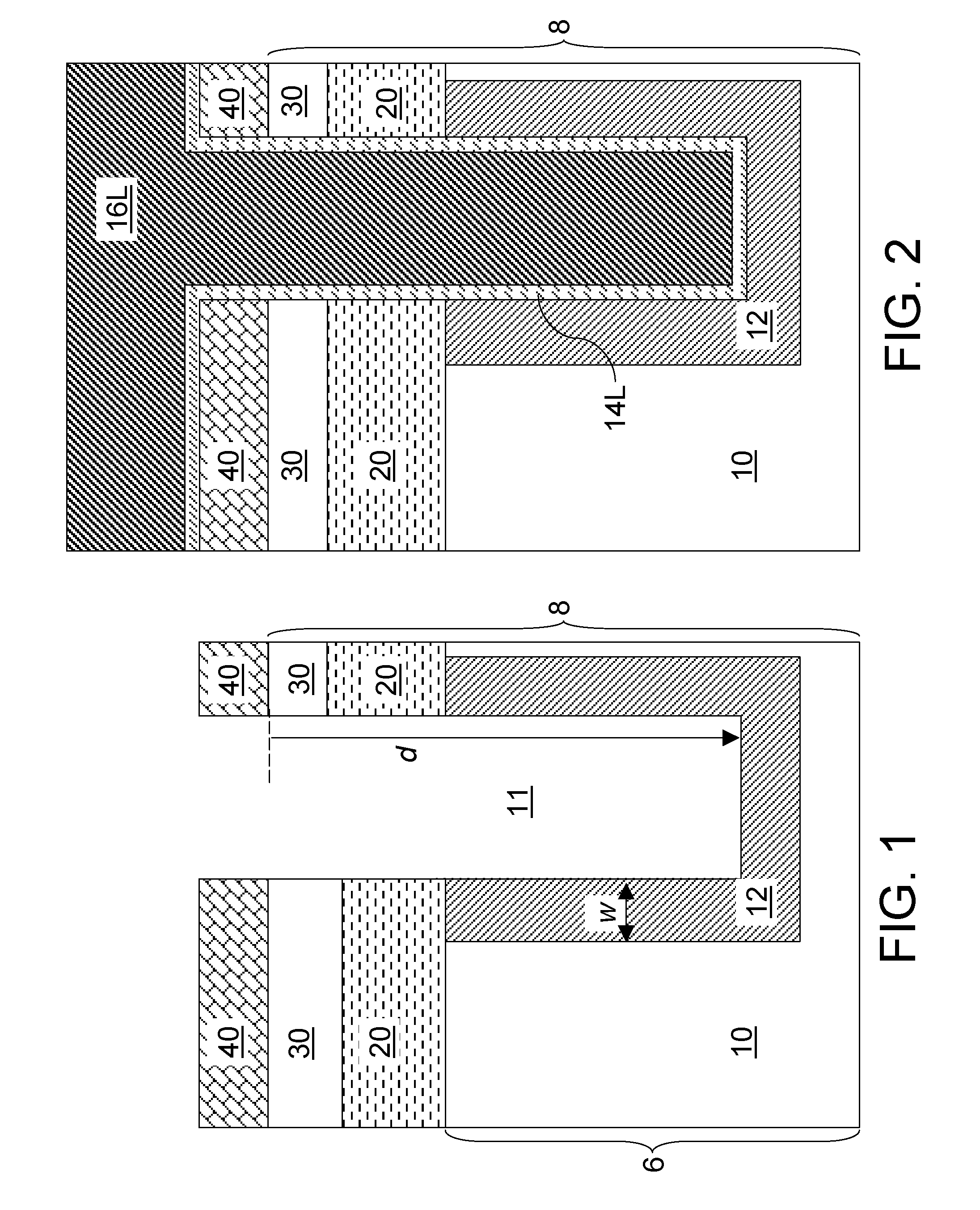

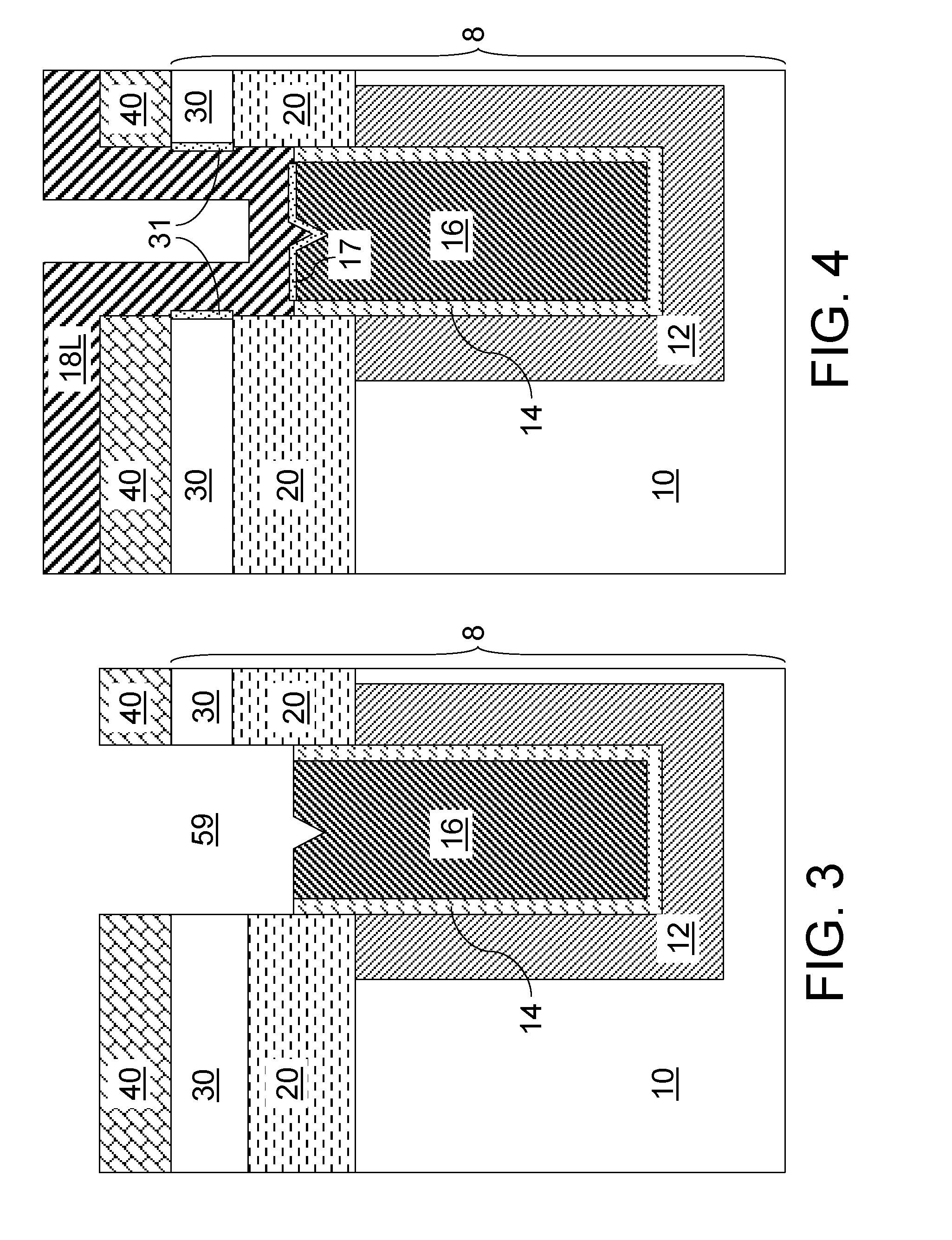

Metallized conductive strap spacer for soi deep trench capacitor

ActiveUS20090256185A1Reliable electrical connectionTransistorSolid-state devicesSemiconductor alloysElectrical connection

A conductive strap spacer is formed within a buried strap cavity above an inner electrode recessed below a top surface of a buried insulator layer of a semiconductor-on-insulator (SOI) substrate. A portion of the conductive strap spacer is metallized by reacting with a metal to form a strap metal semiconductor alloy region, which is contiguous over the conductive strap spacer and a source region, and may extend to a top surface of the buried insulator layer along a substantially vertical sidewall of the conductive strap spacer. The conductive strap spacer and the strap metal semiconductor alloy region provide a stable electrical connection between the inner electrode of the deep trench capacitor and the source region of the access transistor.

Owner:IBM CORP

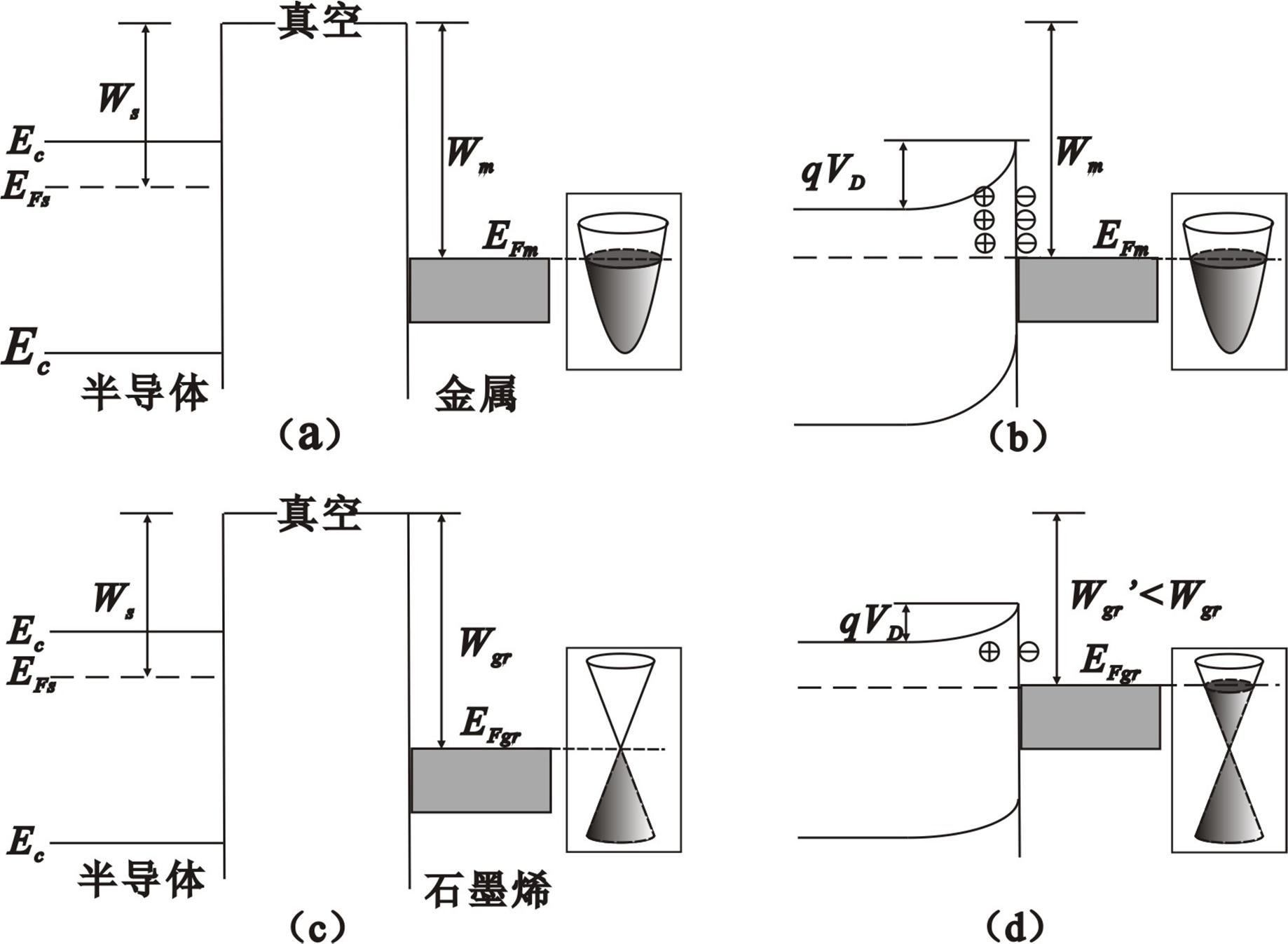

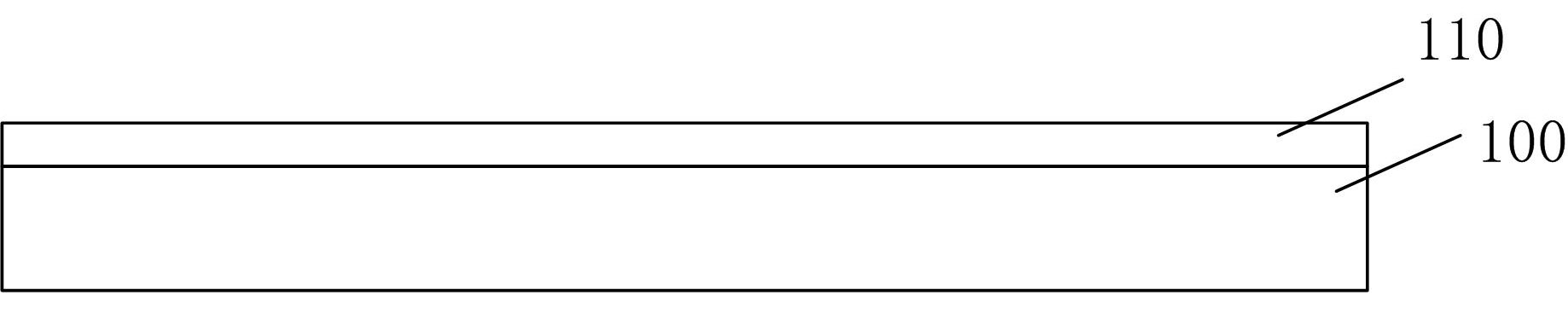

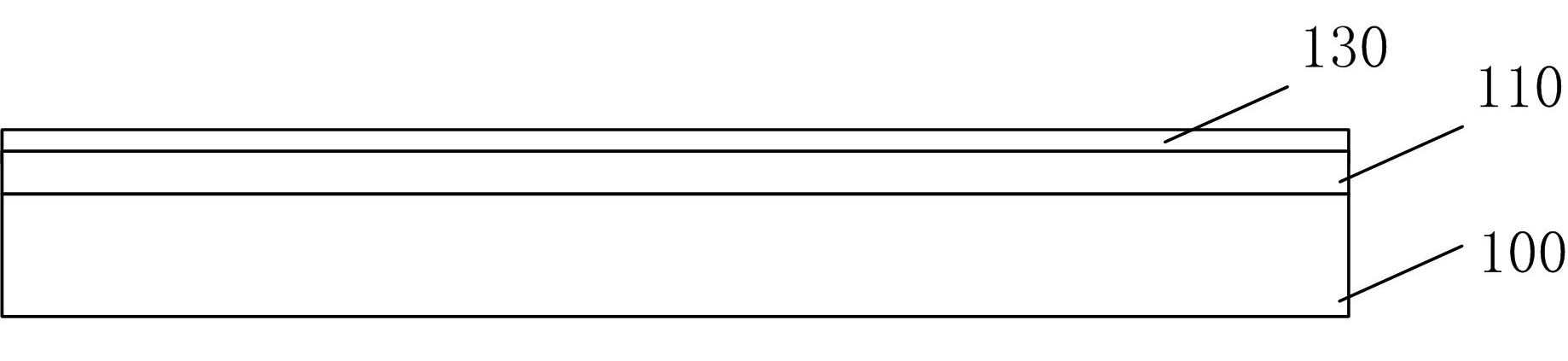

Metal-semiconductor electrode structure and preparation method thereof

InactiveCN102064189ALower the barrierImprove energy band statusSemiconductor/solid-state device manufacturingSemiconductor devicesMicro nanoSemiconductor electrode

The invention relates to a metal-semiconductor electrode structure which comprises a semiconductor layer and a metal electrode, and a graphene layer is further arranged between the semiconductor layer and the metal electrode to reduce the contact resistance between the metal electrode and the semiconductor layer. The metal-semiconductor electrode structure provided by the invention has the advantages of improving the energy band state of metal-semiconductor contact by inserting the graphene layer between the metal and the semiconductor layer, being widely applicable to metals with different work functions and semiconductors with different doping types and doping concentrations, and reducing the contact potential barrier, thereby playing the function of reducing the contact resistance. The metal-semiconductor electrode structure provided by the invention has simple preparation method, stable performance, good repeatability and low cost and plays an important role in realizing micro nano semiconductor electronic devices with high performance and low cost.

Owner:SUZHOU NANOWIN SCI & TECH +1

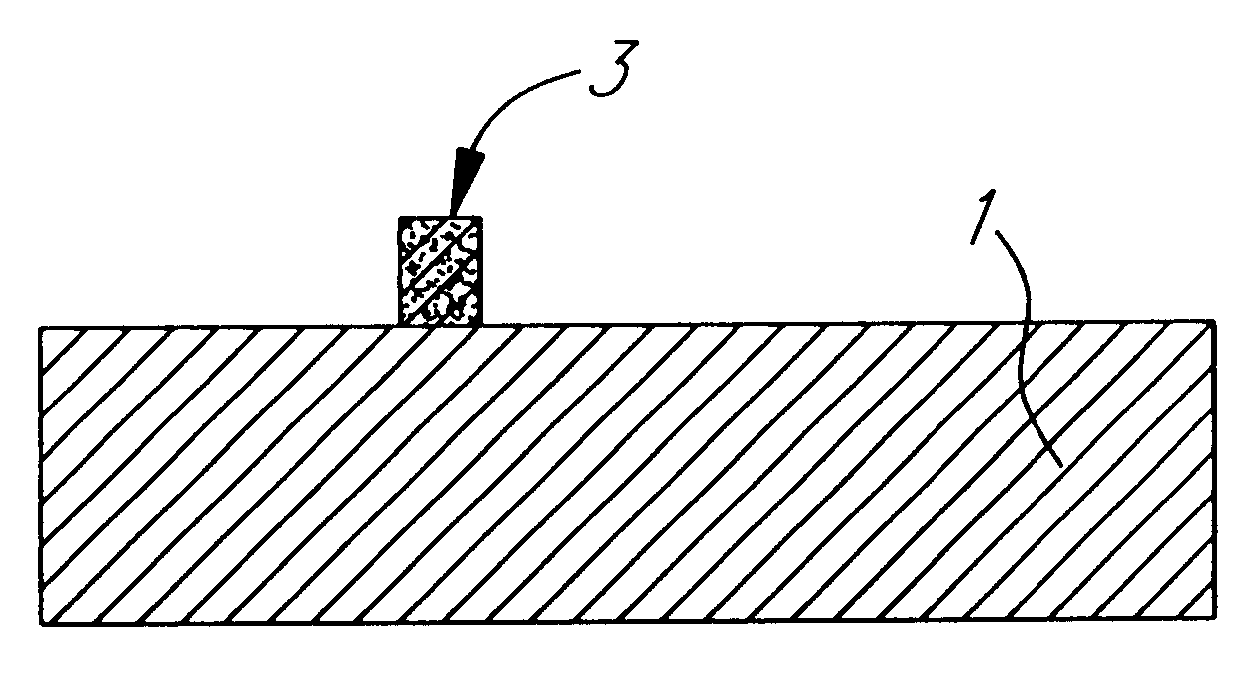

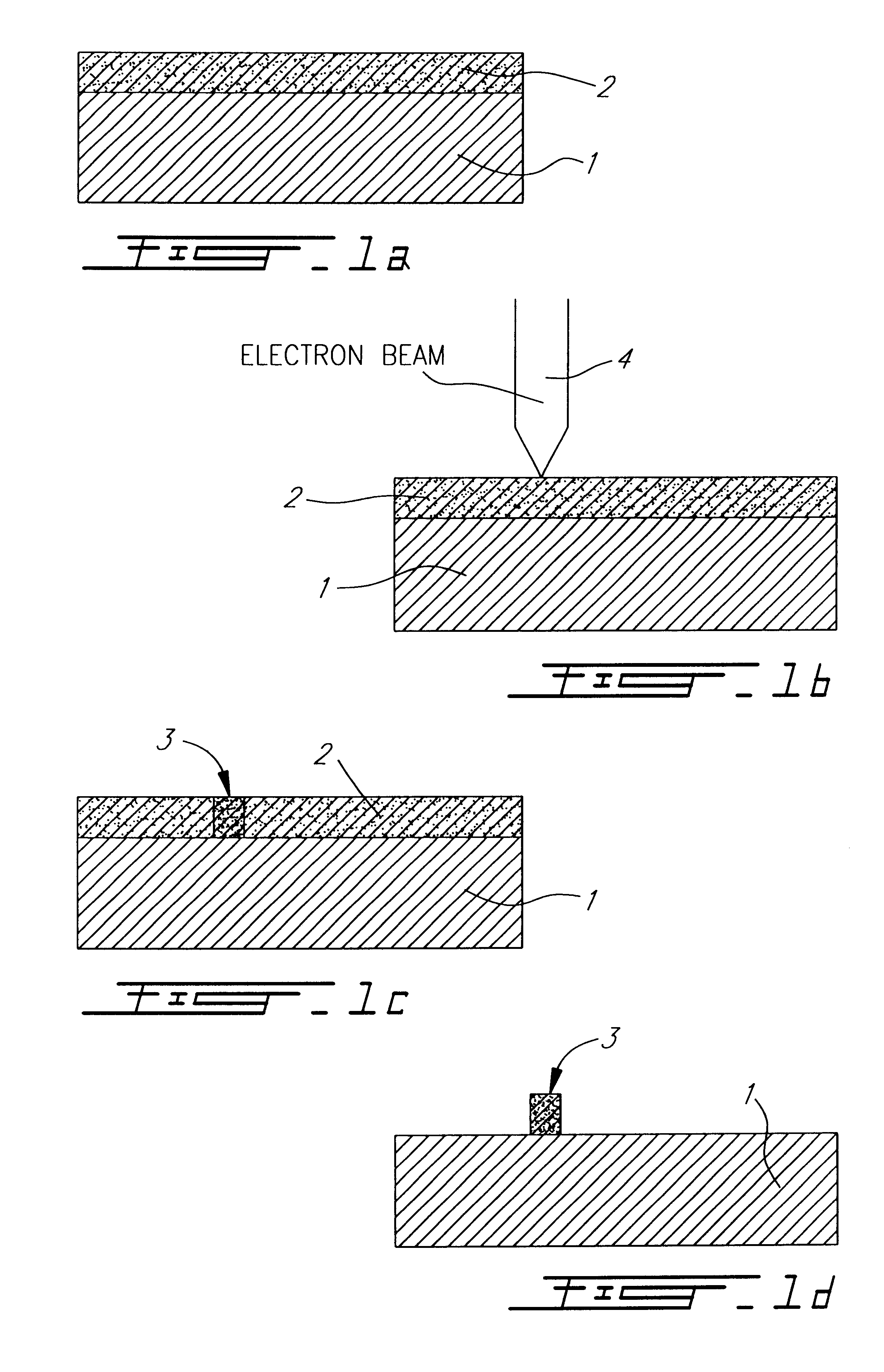

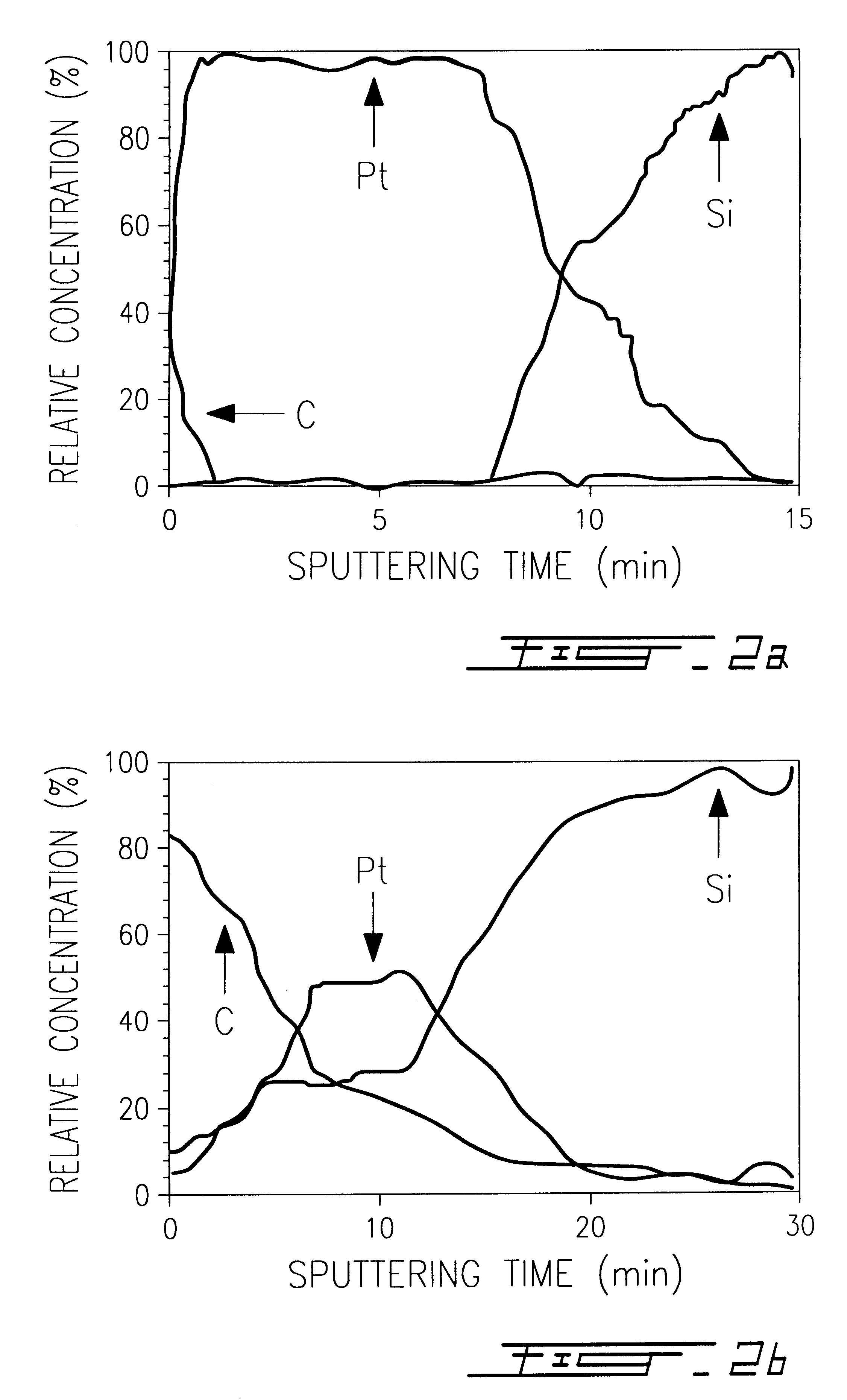

Fabrication of sub-micron etch-resistant metal/semiconductor structures using resistless electron beam lithography

InactiveUS6261938B1NanoinformaticsSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor structure

A method for fabricating a sub-micron structure of etch-resistant metal / semiconductor compound on a substrate of semiconductor material comprises the step of depositing onto the substrate a layer of metal capable of reacting with the semiconductor material to form etch-resistant metal / semiconductor compound, and the step of producing a focused electron beam. The focused electron beam is applied to the layer of metal to locally heat the metal and semiconductor material and cause diffusion of the metal and semiconductor material in each other to form etch-resistant metal / semiconductor compound. The focused electron beam is displaced onto the layer of metal to form the structure of etch-resistant metal / semiconductor compound. Finally, the layer of metal is wet etched to leave on the substrate only the structure of metal / semiconductor compound. Following wet etching of the layer of metal, an oxygen plasma etch can be conducted to remove a carbon deposit formed at the surface of the structure of etch-resistant metal / semiconductor compound. Also, the substrate may be subsequently etched to remove a thin layer of metal rich semiconductor material formed at the surface of the substrate by reaction, at room temperature, of the metal and semiconductor material with each other.

Owner:SCOPRA SCI & GENIE SEC

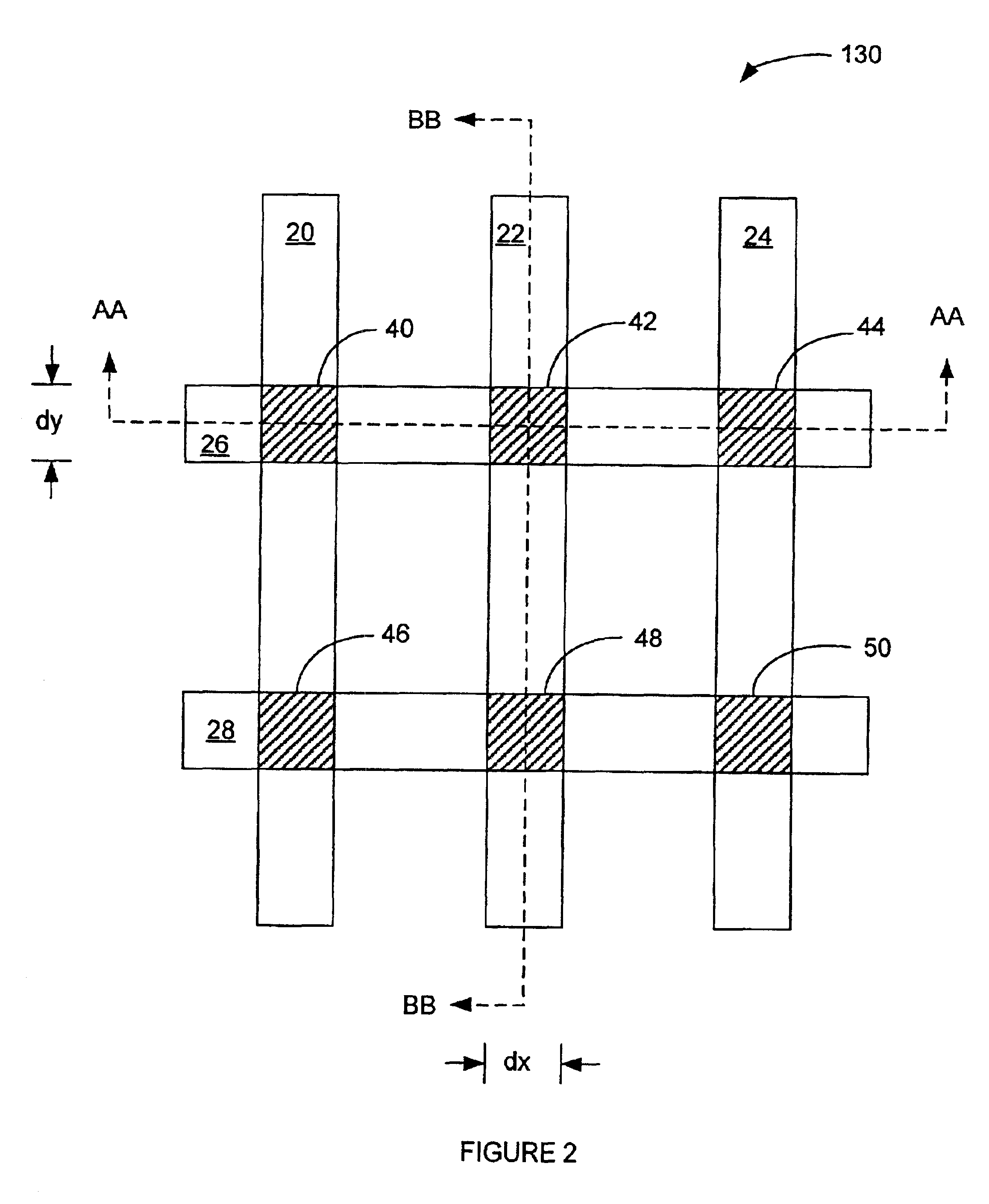

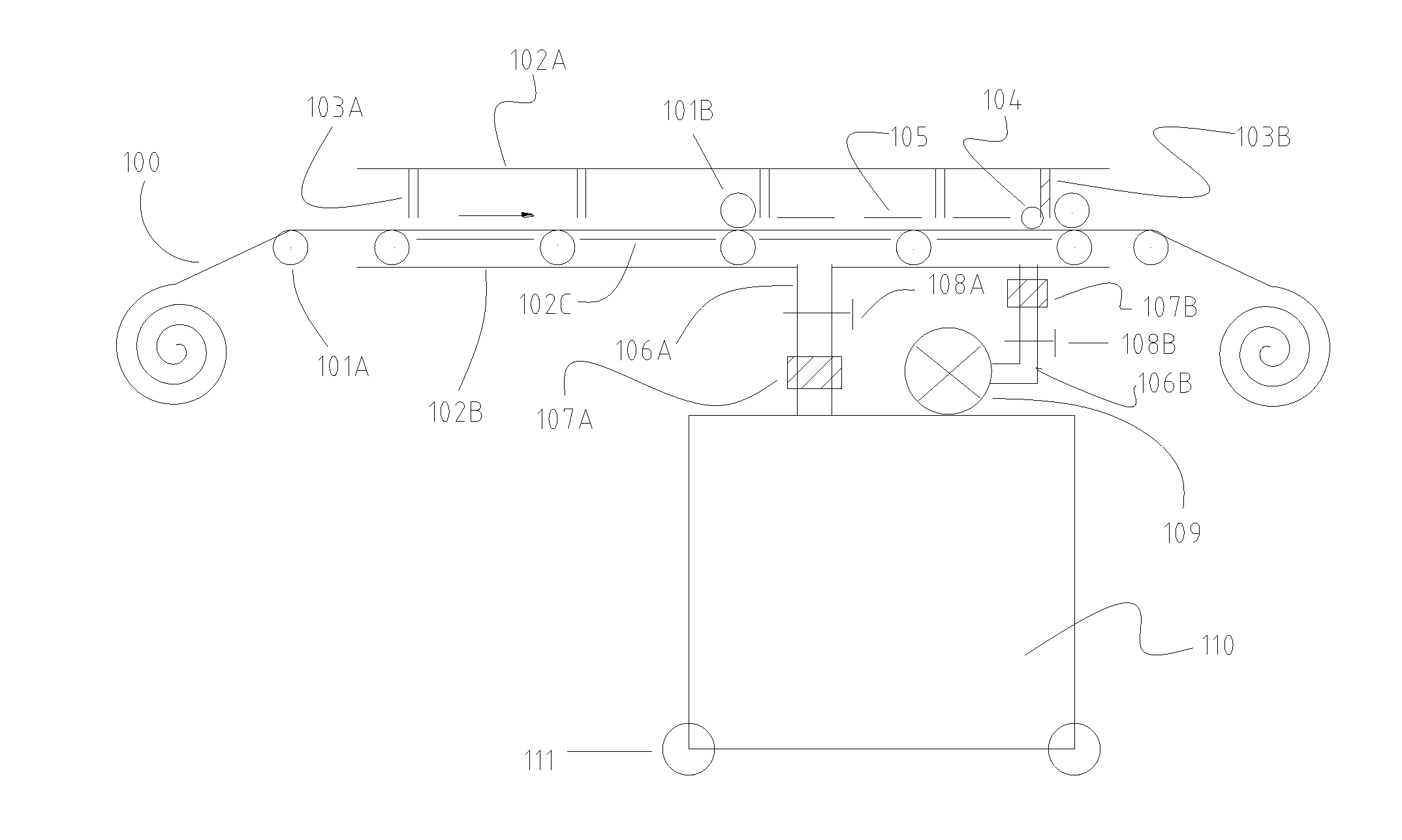

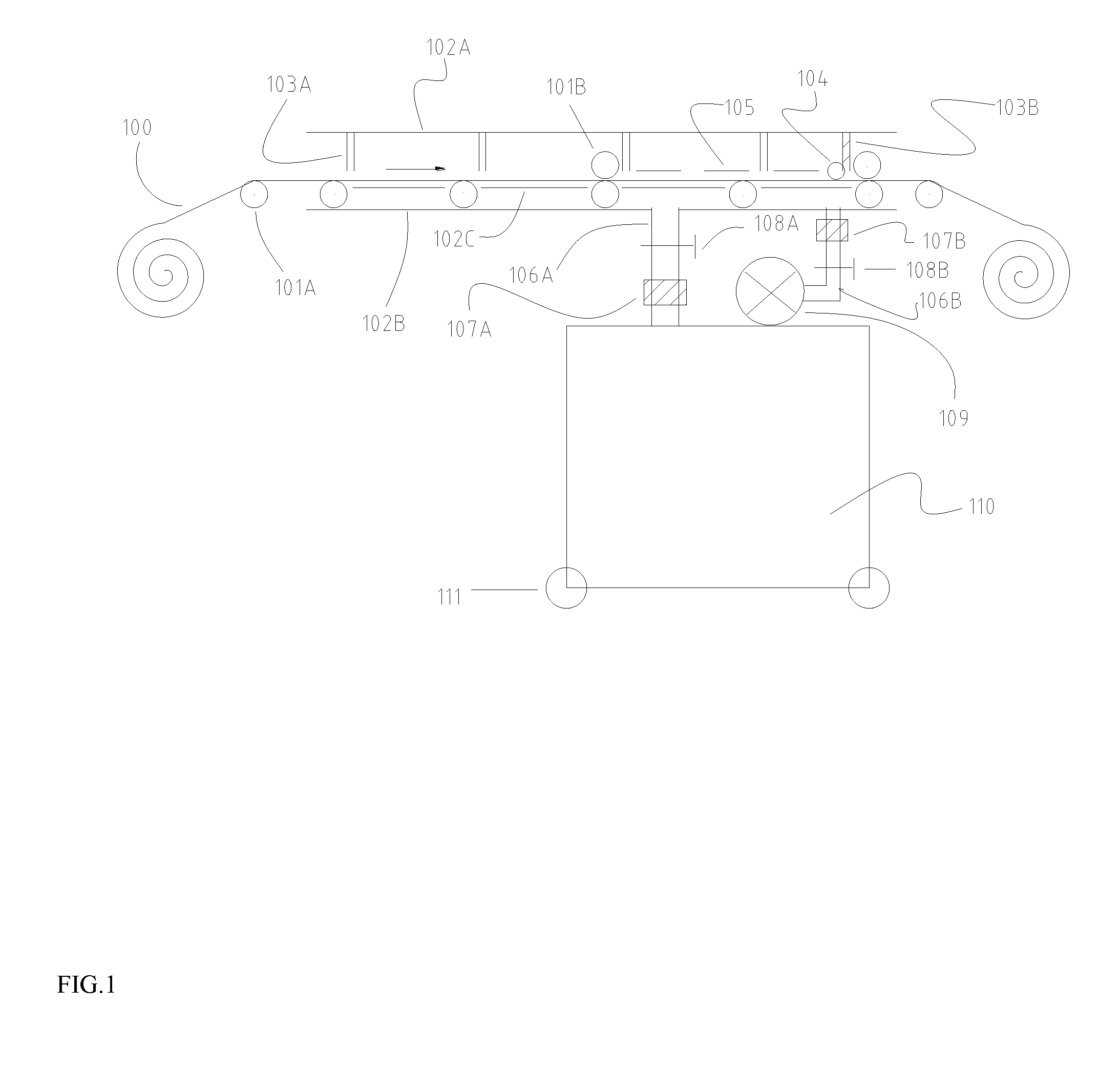

Continuous Electroplating Apparatus with Assembled Modular Sections for Fabrications of Thin Film Solar Cells

An electroplating production line or apparatus that can be assembled with modular plating sections in a roll-to-roll or reel-to-reel continuous plating process is provided. The length of the plating cell for a modular plating section can be readily changed to fit different current densities required in a roll-to-roll or reel-to-reel process. In addition, the electrolyte solution tanks can be simply connected or disconnected from the modular plating sections and moved around. With these designs, a multiple layers of coating with different metals, semiconductors or their alloys can be electrodeposited on this production line or apparatus with a flexibility to easily change the plating orders of different materials. This apparatus is particularly useful in manufacturing Group IB-IIIA-VIA and Group IIB-VIA thin film solar cells such as CIGS and CdTe solar cells on flexible conductive substrates through a continuous roll-to-roll or reel-to-reel process.

Owner:WANG JIAXIONG

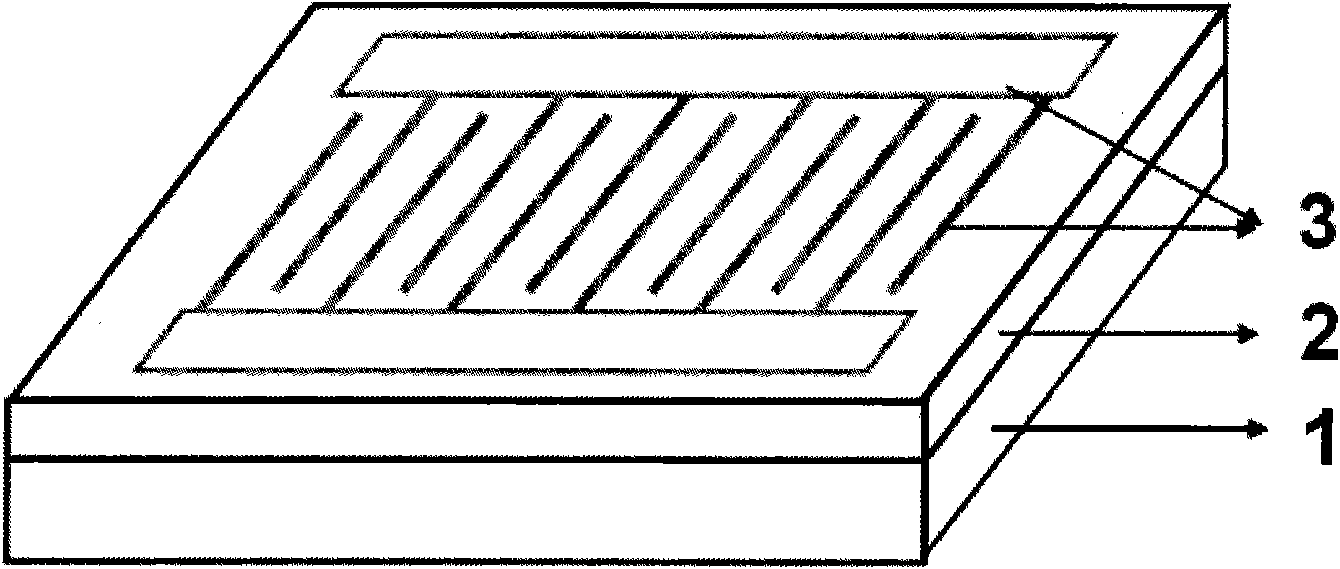

Method for preparing titanium dioxide ultraviolet photoelectric detector

InactiveCN101820016AReduce dark currentImproved UV-Vis suppression ratioFinal product manufactureVacuum evaporation coatingUltraviolet detectorsPhotovoltaic detectors

The invention discloses a method for preparing a titanium dioxide ultraviolet photoelectric detector, relates to a semiconductor photoelectric detection device, and provides a titanium dioxide ultraviolet photoelectric detector with low dark current and a preparation method thereof. The detector has a metal-semiconductor-metal structure, and comprises an insulating substrate, a polycrystal TiO2 film deposited on the insulating substrate by using magnetron sputtering technology and an interdigital metal electrode prepared on the TiO2 film by using magnetron sputtering or electron beam evaporation technology from the bottom to the top. The high-quality polycrystal TiO2 film is deposited by adopting optimized sputtering process parameters, and the deposited film has ideal chemical proportion and high compactness and crystallinity. The MSM structural ultraviolet detector prepared by using the film as a matrix has the advantages of high response degree, low dark current, high ultraviolet visible suppression ratio and the like. The preparation method has simple process and low cost; if the detector is manufactured on a Si-based substrate, the method can be compatible with the mature Si process; and the method is favorable for photoelectric integration and easy for industrialization.

Owner:XIAMEN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com