Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

135 results about "Delta doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

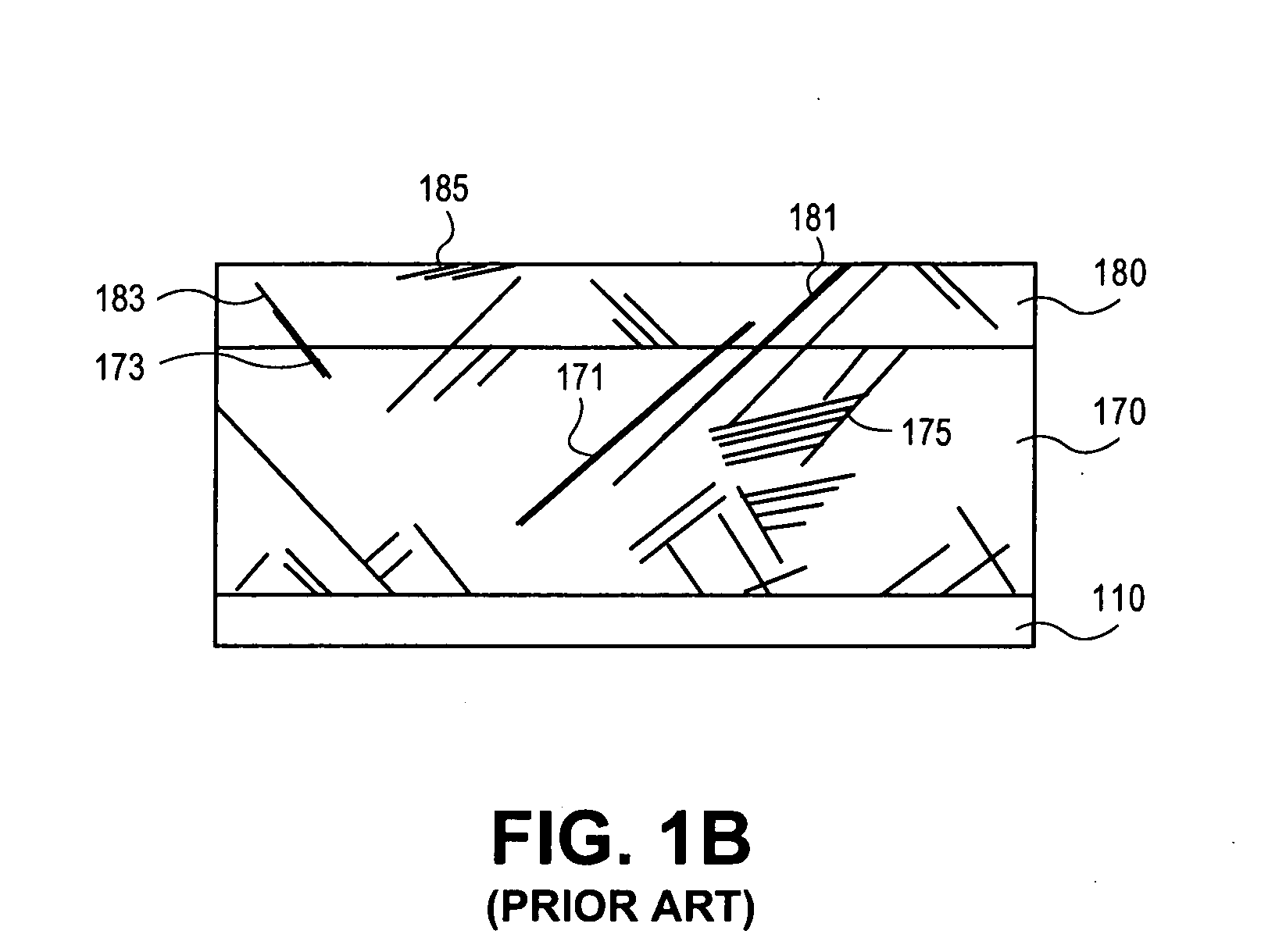

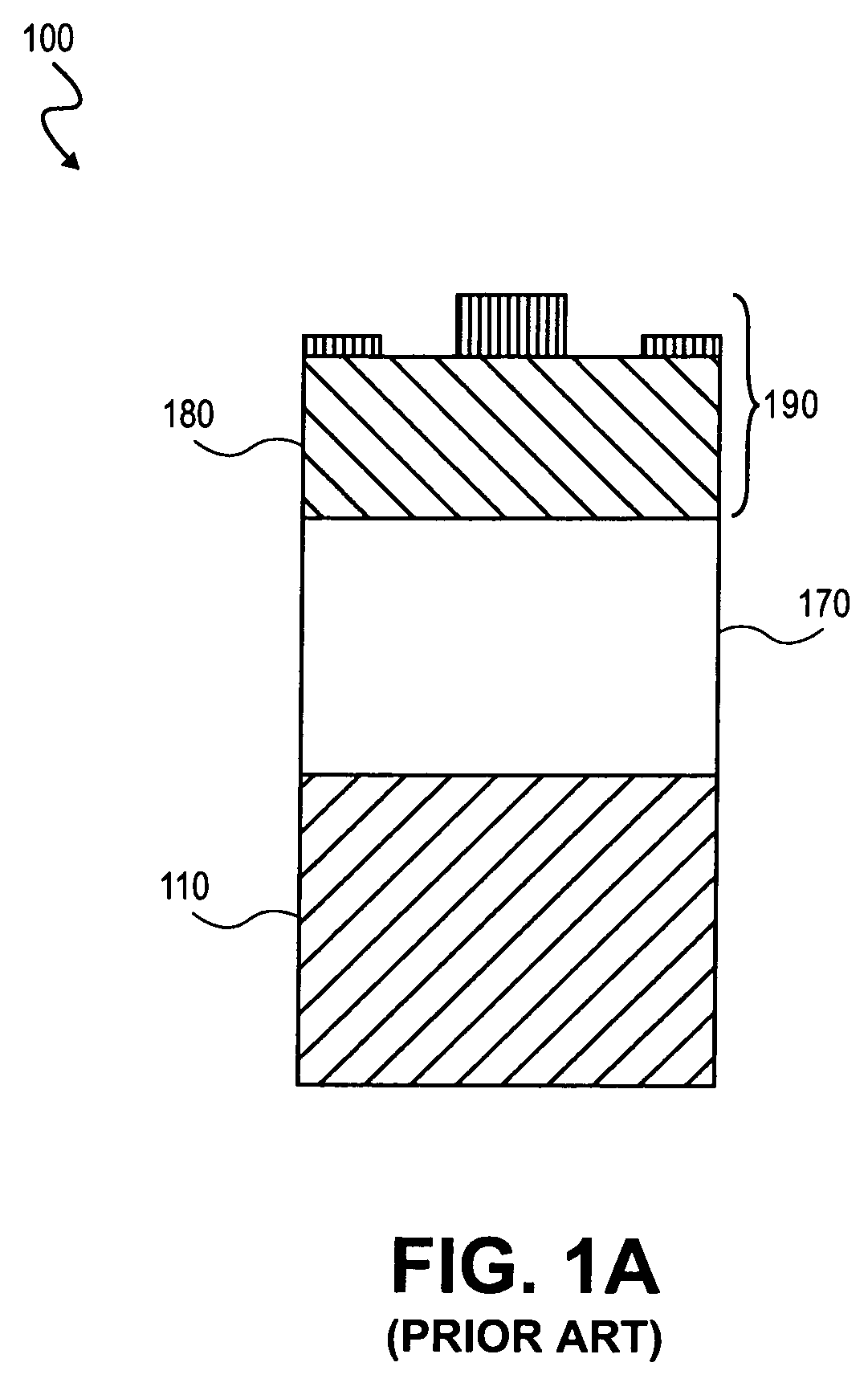

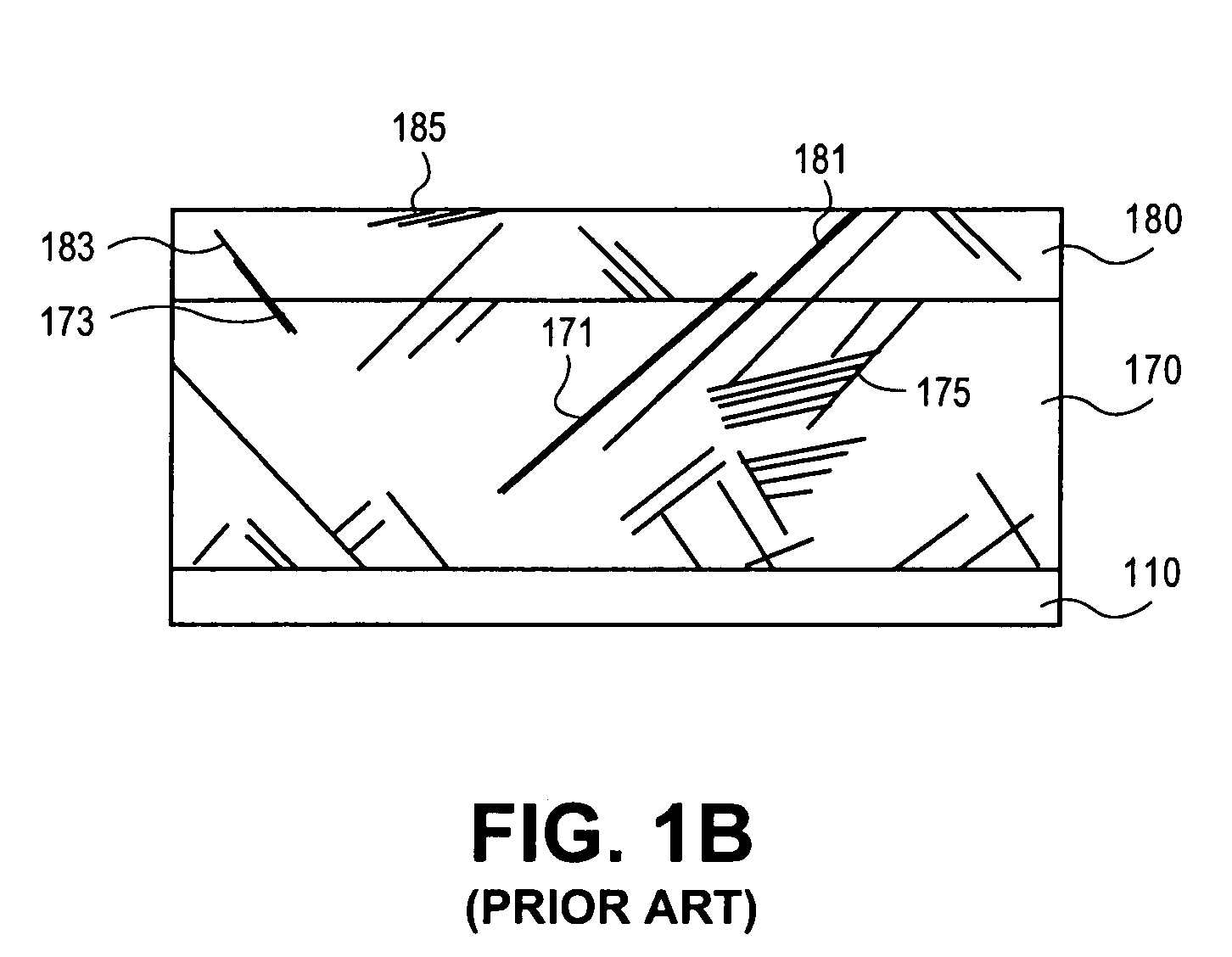

DELTA AND SUPERLATTICE DOPING. Delta or superlattice doping is the deposition using molecular beam epitaxy (MBE) to deposit one to six Boron and Silicon layers. This is a multistep process where the number of layers is a trade off between the Modulation transfer function (MTF) and durability at the target frequency and power resiliance.

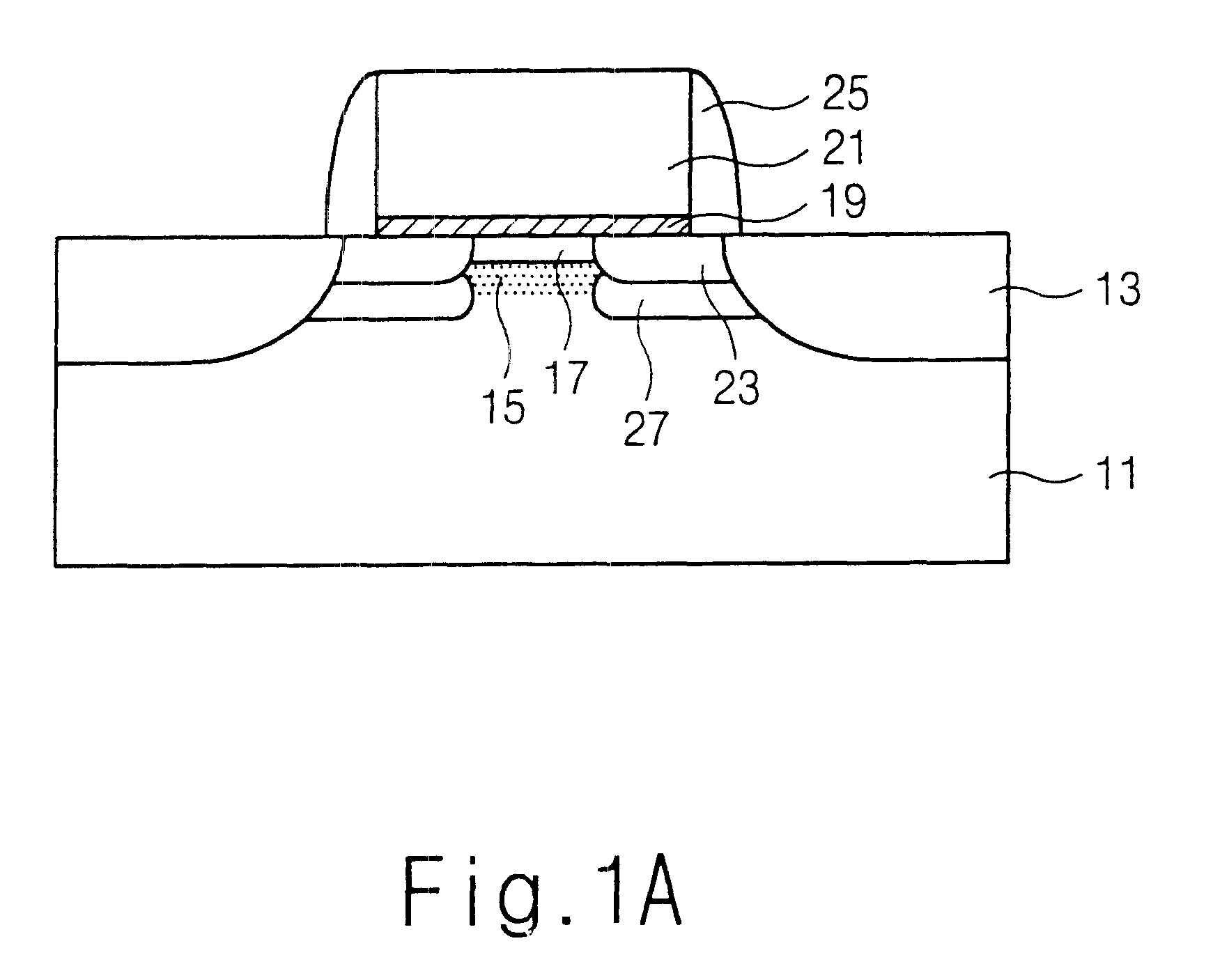

Method for forming transistor of semiconductor device

InactiveUS6667200B2Highly integratedRapid heat treatmentTransistorSemiconductor/solid-state device manufacturingDelta dopingHydrogen

A method for forming a transistor of a semiconductor device, including the step of forming channel layers of a first and a second conductive types, performing high temperature thermal process to form stabilized channel layers and forming an epitaxial channel structure having a super-steep-retrograde delta-doped layer by growing undoped silicon epitaxial layers, treating the entire surface of the resulting structure with hydrogen, forming an epitaxial channel structure by growing undoped silicon epitaxial layers on the stabilized channel layers, forming gate insulating films and gate electrodes on the epitaxial channel structures, re-oxidizing the gate insulating films for repairing damaged portions of the gate insulating films; and forming a source / drain region and performing a low temperature thermal process.

Owner:SK HYNIX INC

Compound semiconductor FET

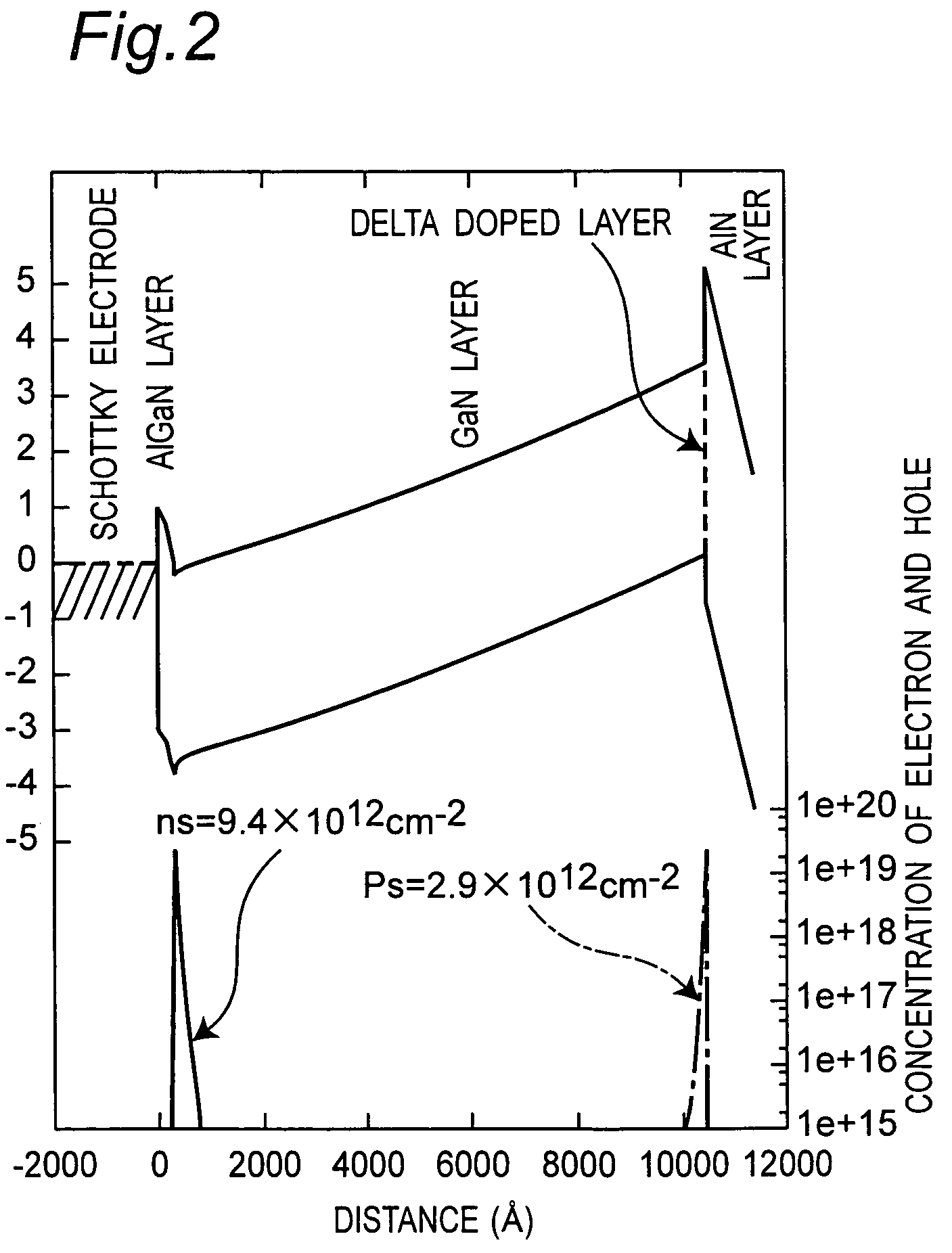

InactiveUS7538364B2Solve and reduce parallel conductionSolve and reduce and gate leakTransistorSolid-state devicesDelta dopingAND gate

On a substrate of a GaN FET, an undoped AlN layer, a GaN delta doped layer, an undoped GaN layer, and an undoped Al0.2Ga0.8N layer are formed in sequence. Arranged on the undoped Al0.2Ga0.8N layer are a Ti / Al / Pt / Au source ohmic electrode, a Pt / Au gate Schottky electrode, and a Ti / Al / Pt / Au drain ohmic electrode. Parallel conduction and gate leak are reduced or eliminated by the GaN delta doped layer.

Owner:SHARP KK

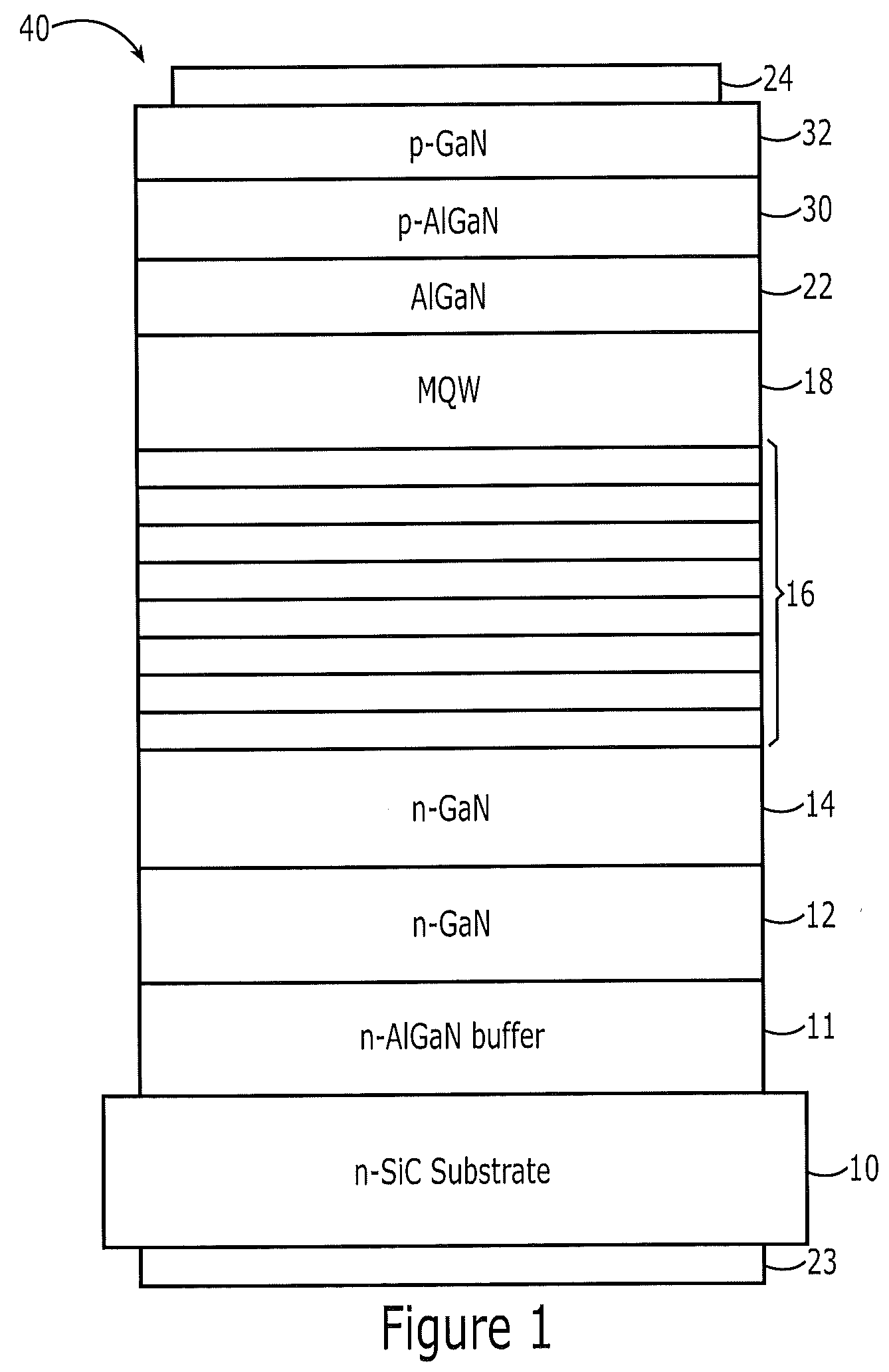

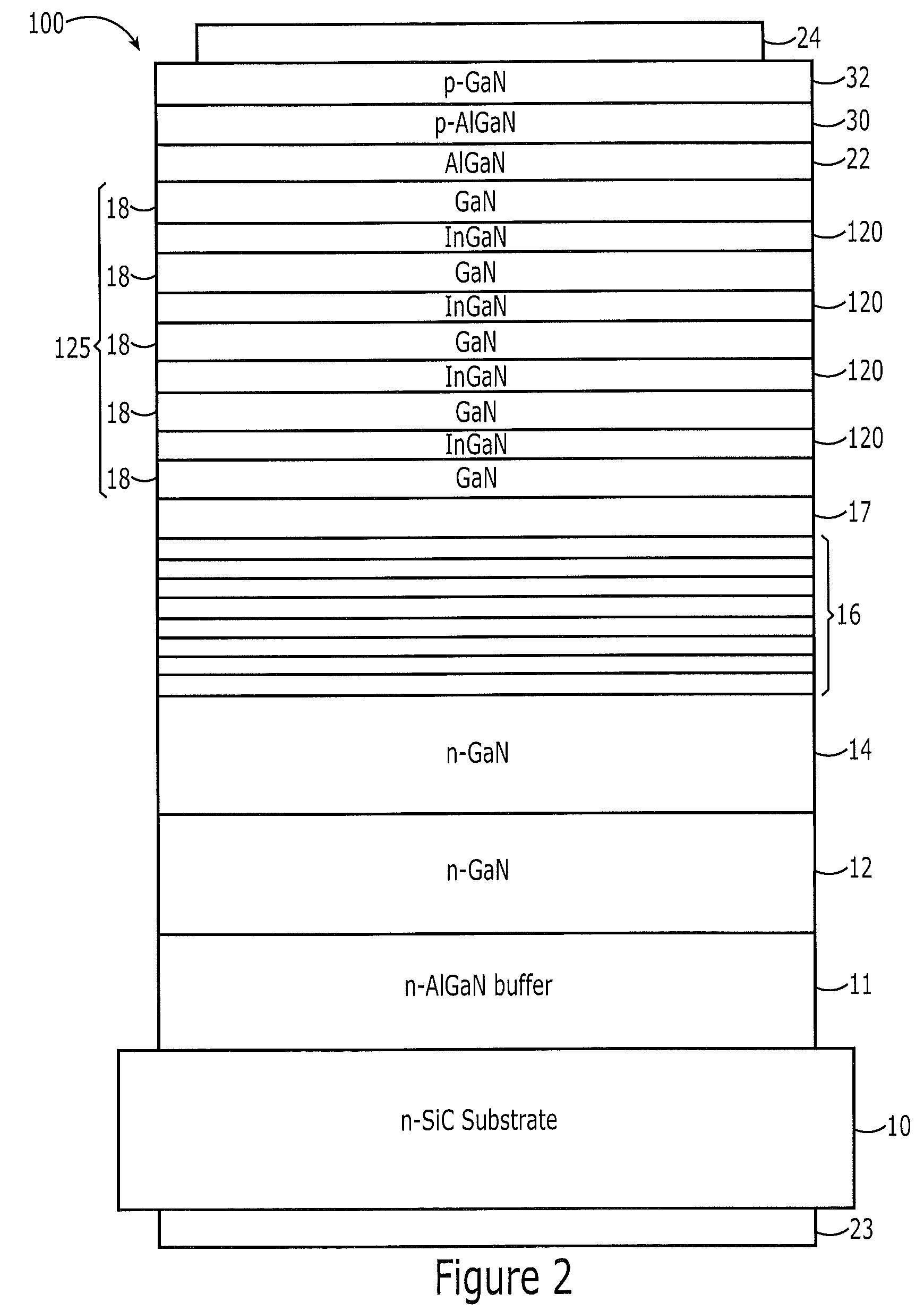

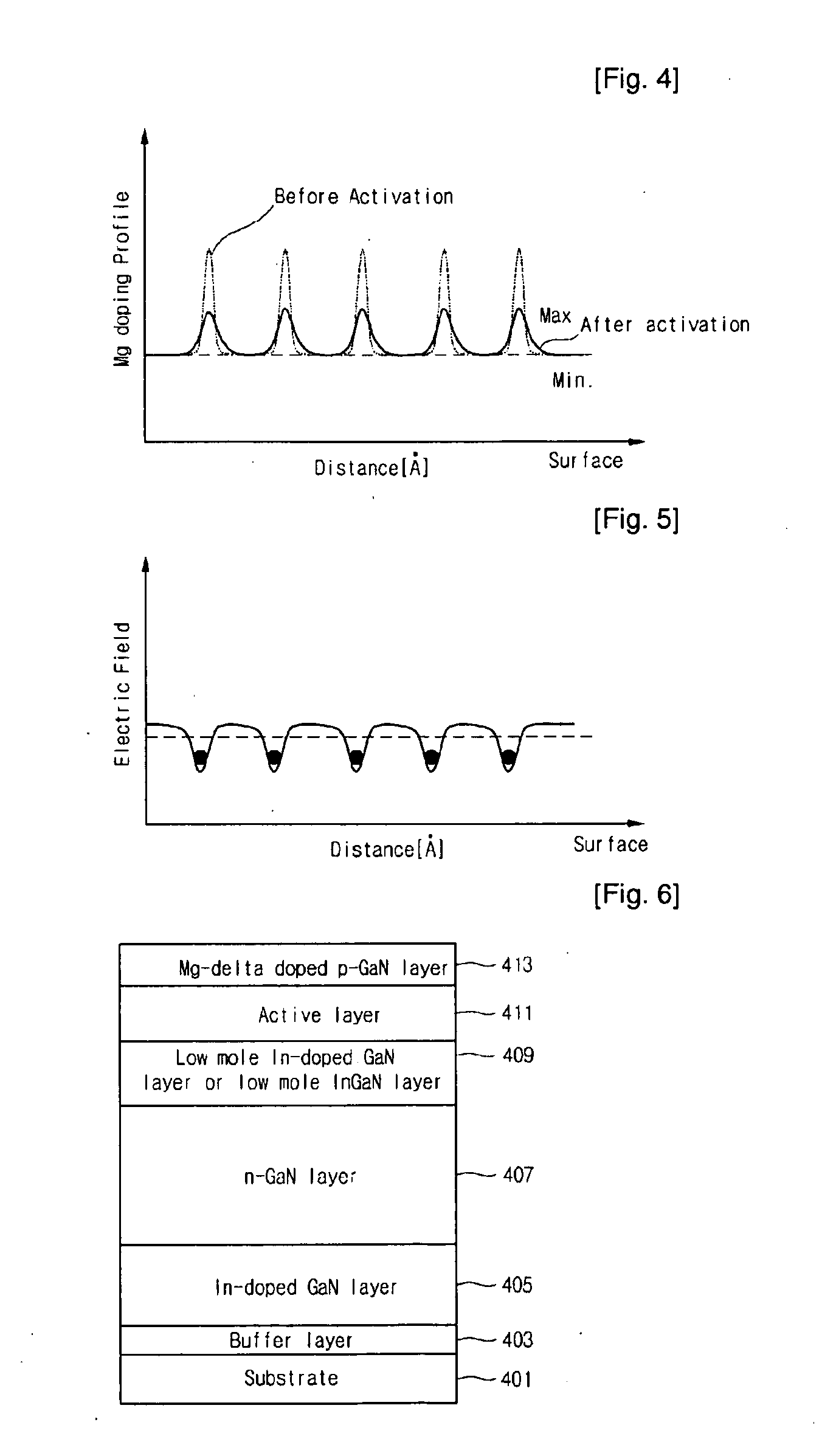

Nitride Semiconductor Light Emitting Device and Fabrication Method Thereof

ActiveUS20080142781A1Reduce lightCrystallinitySolid-state devicesSemiconductor/solid-state device manufacturingDelta dopingOptical power

Provided is a nitride semiconductor light emitting device including: a first nitride semiconductor layer; an active layer formed above the first nitride semiconductor layer; and a delta doped second nitride semiconductor layer formed above the active layer. According to the present invention, the optical power of the nitride semiconductor light emitting device is enhanced, optical power down phenomenon is improved and reliability against ESD (electro static discharge) is enhanced.

Owner:SUZHOU LEKIN SEMICON CO LTD

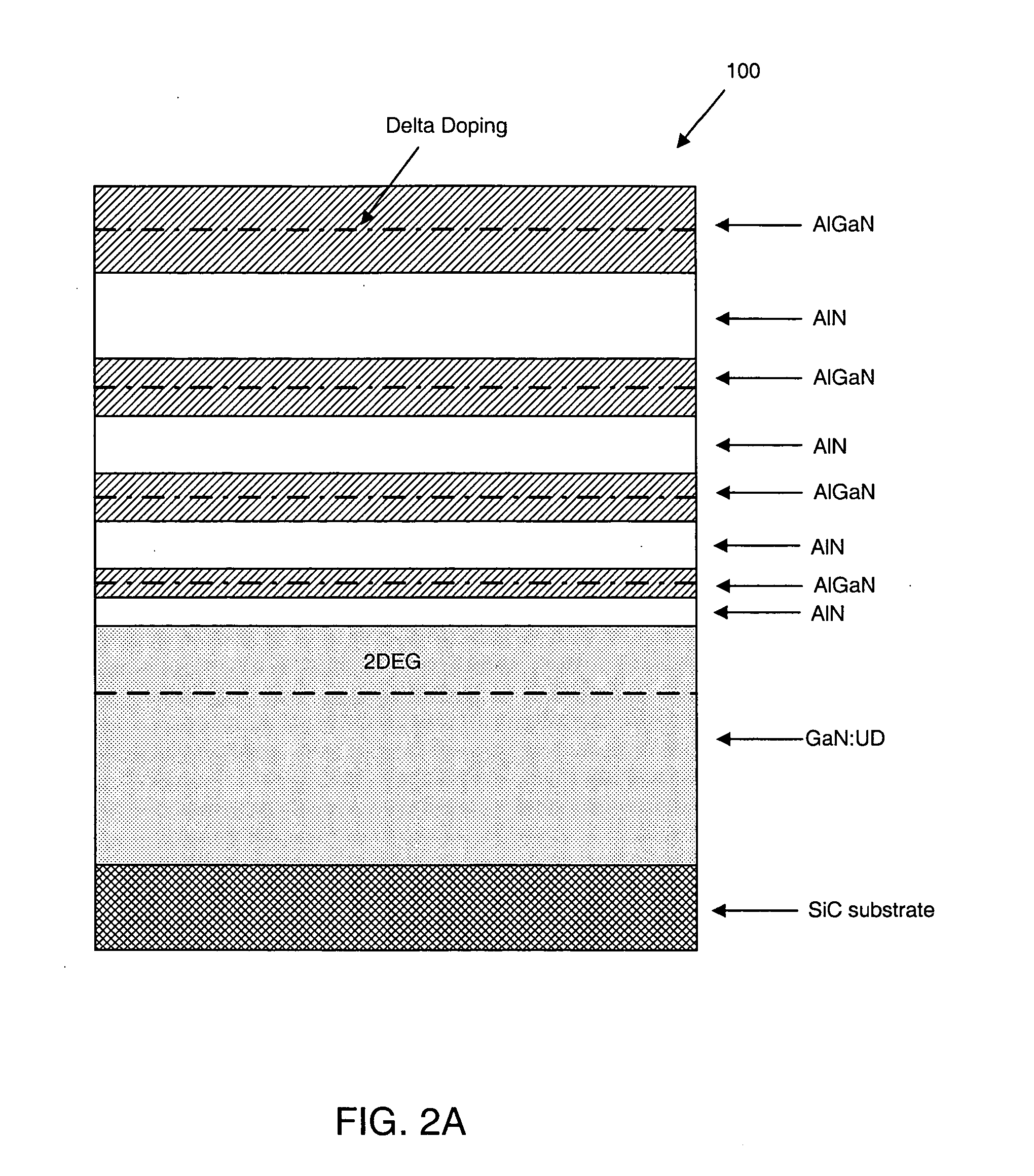

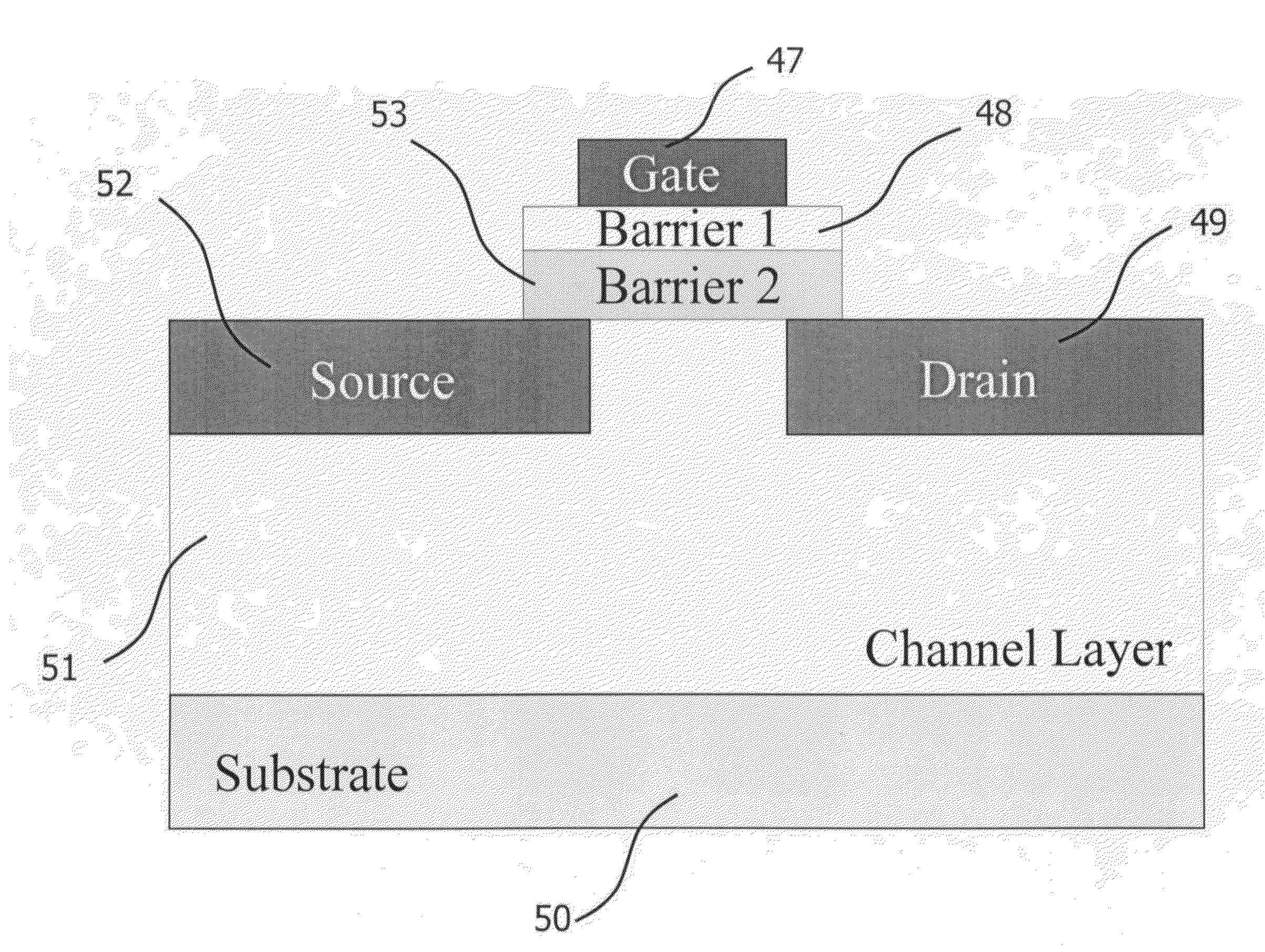

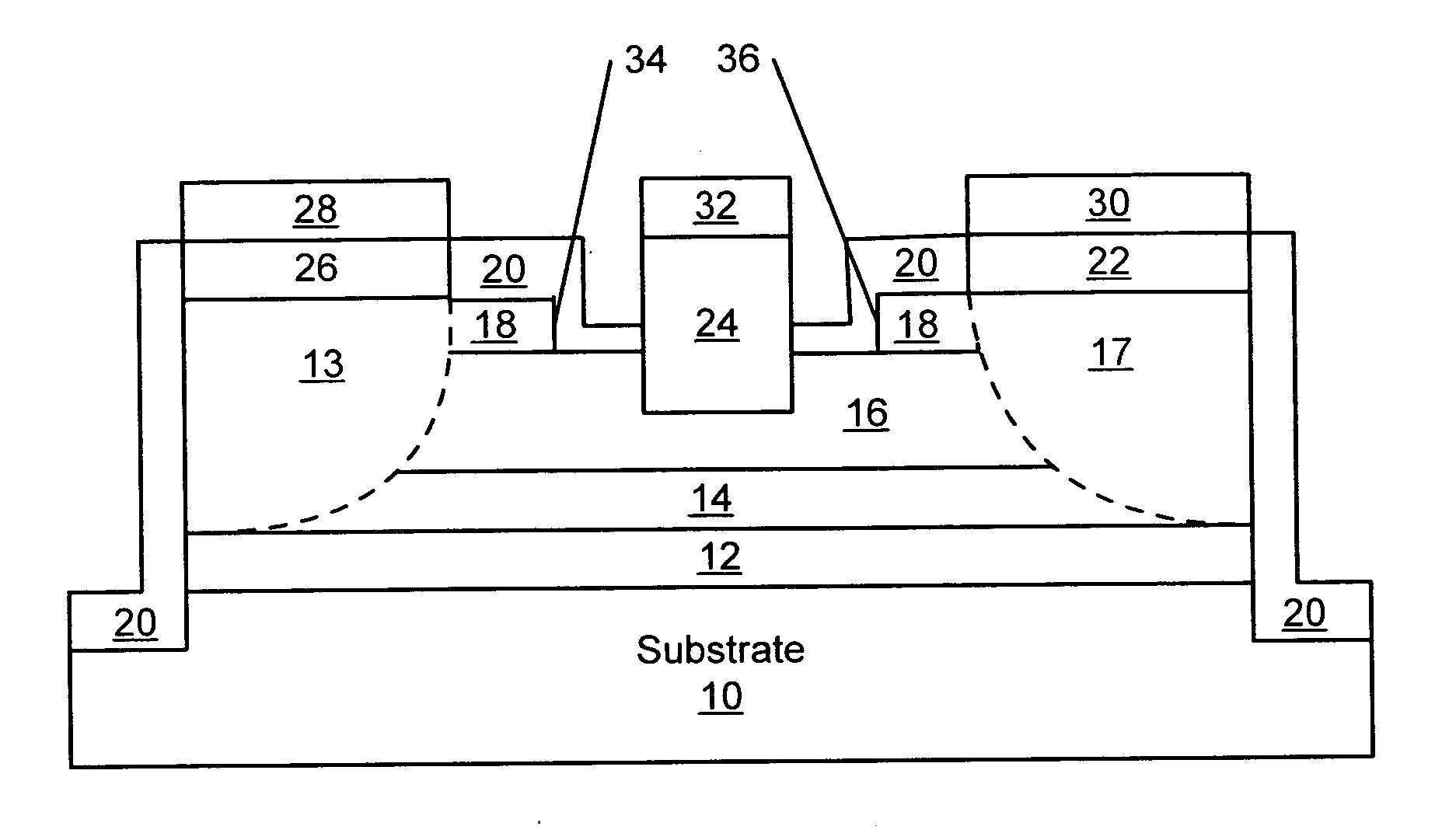

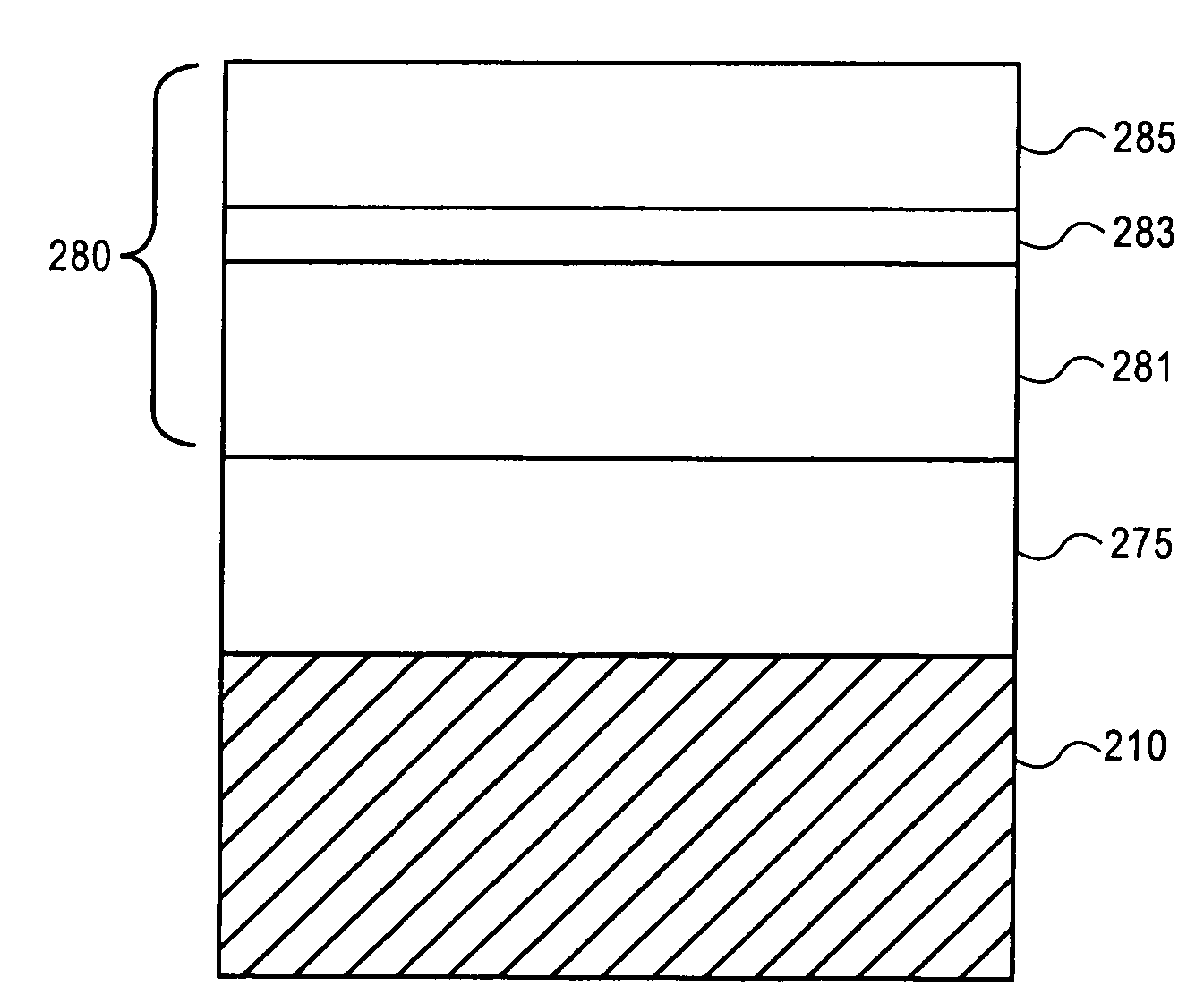

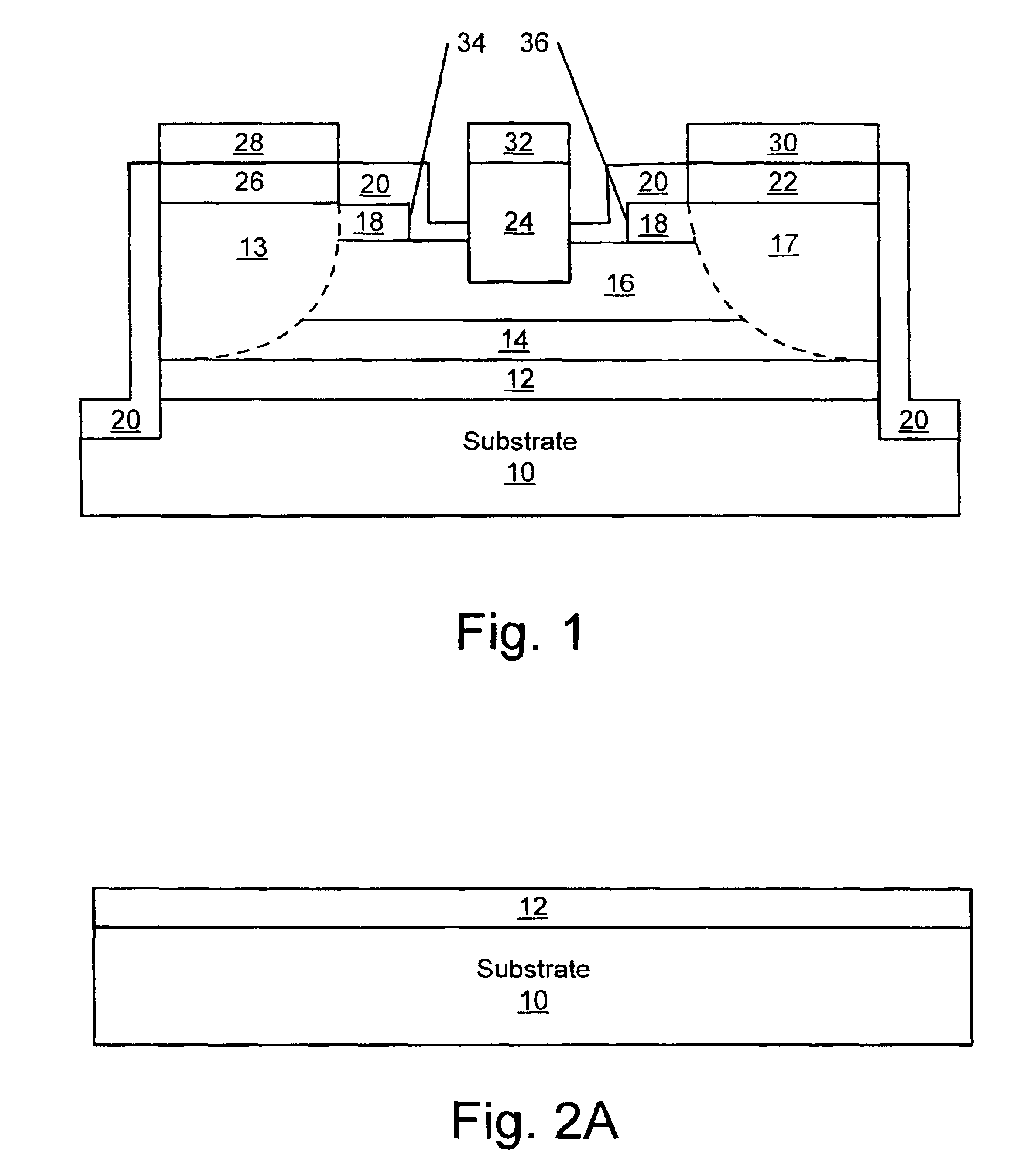

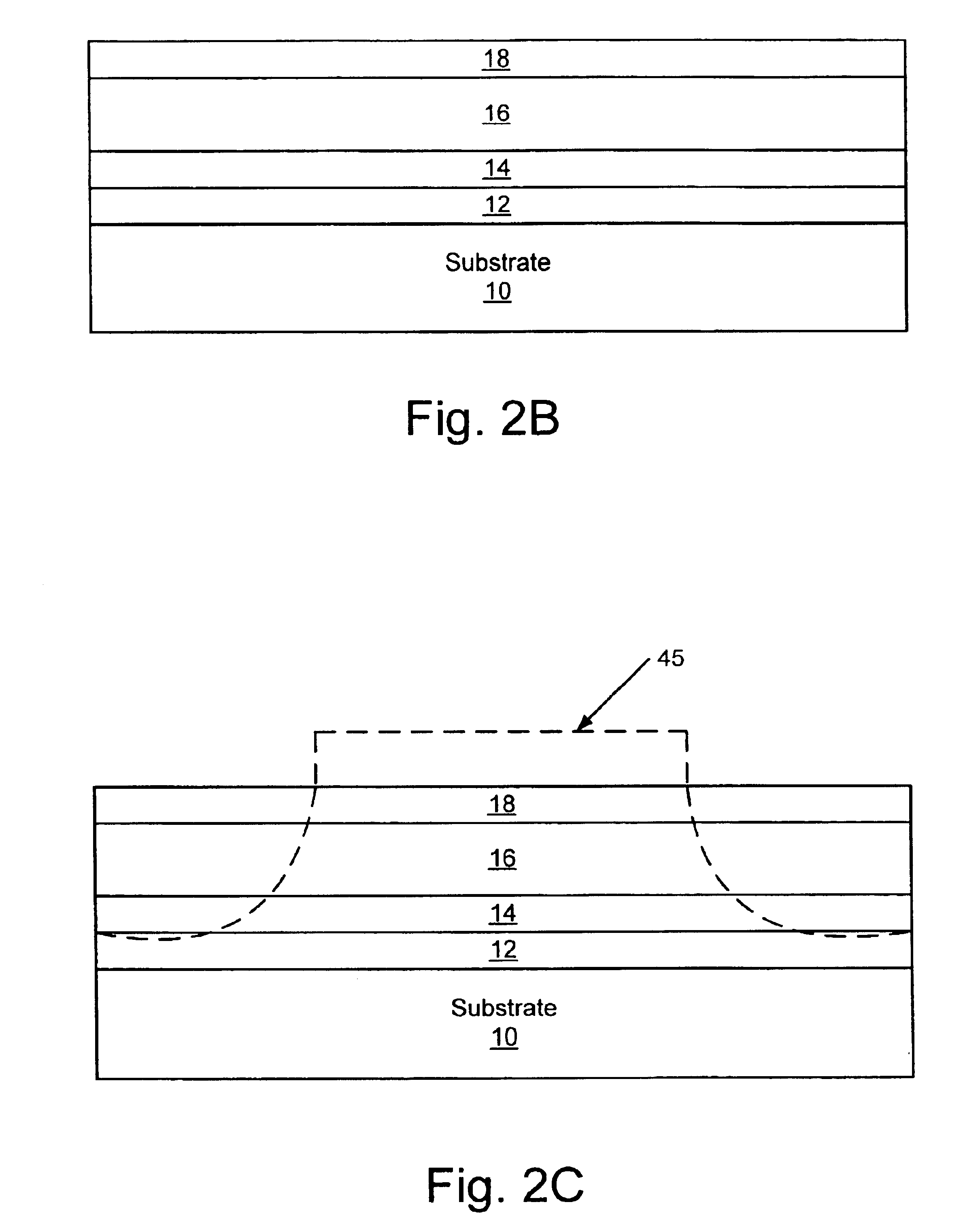

Semiconductor electronic devices and methods

InactiveUS20050006639A1Semiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionEngineering

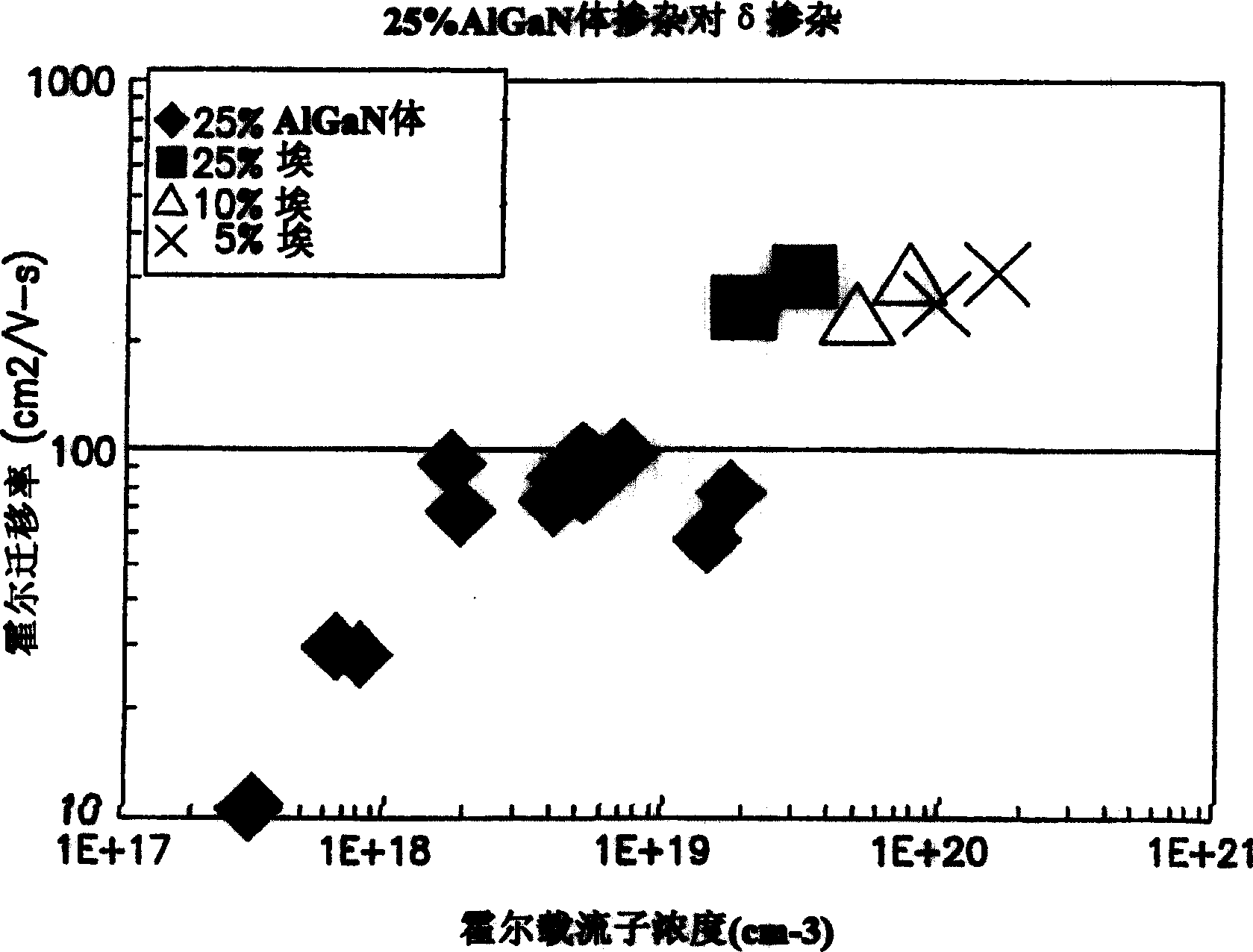

Embodiments disclosed herein include electronic device designs based upon electronic properties of Group III-N materials and quantum-mechanical effects of specialized heterostructures. Such electronic device designs may include, for example, heterojunction field-effect transistors (HFETs) and high-electron-mobility transistors (HEMTs). The design concepts permit high power, high-frequency, and high-temperature operation of advanced electronic circuits, including devices for radar, collision-avoidance systems, and wireless communications. Designs disclosed may include one or more AlN layers and / or one or more SMASH superlattice barriers combined with one or more n-type delta-doped regions. Alternately, in certain embodiments, one or more AlN layers and one or more SMASH superlattice barriers may be combined without the n-type delta-doped regions.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

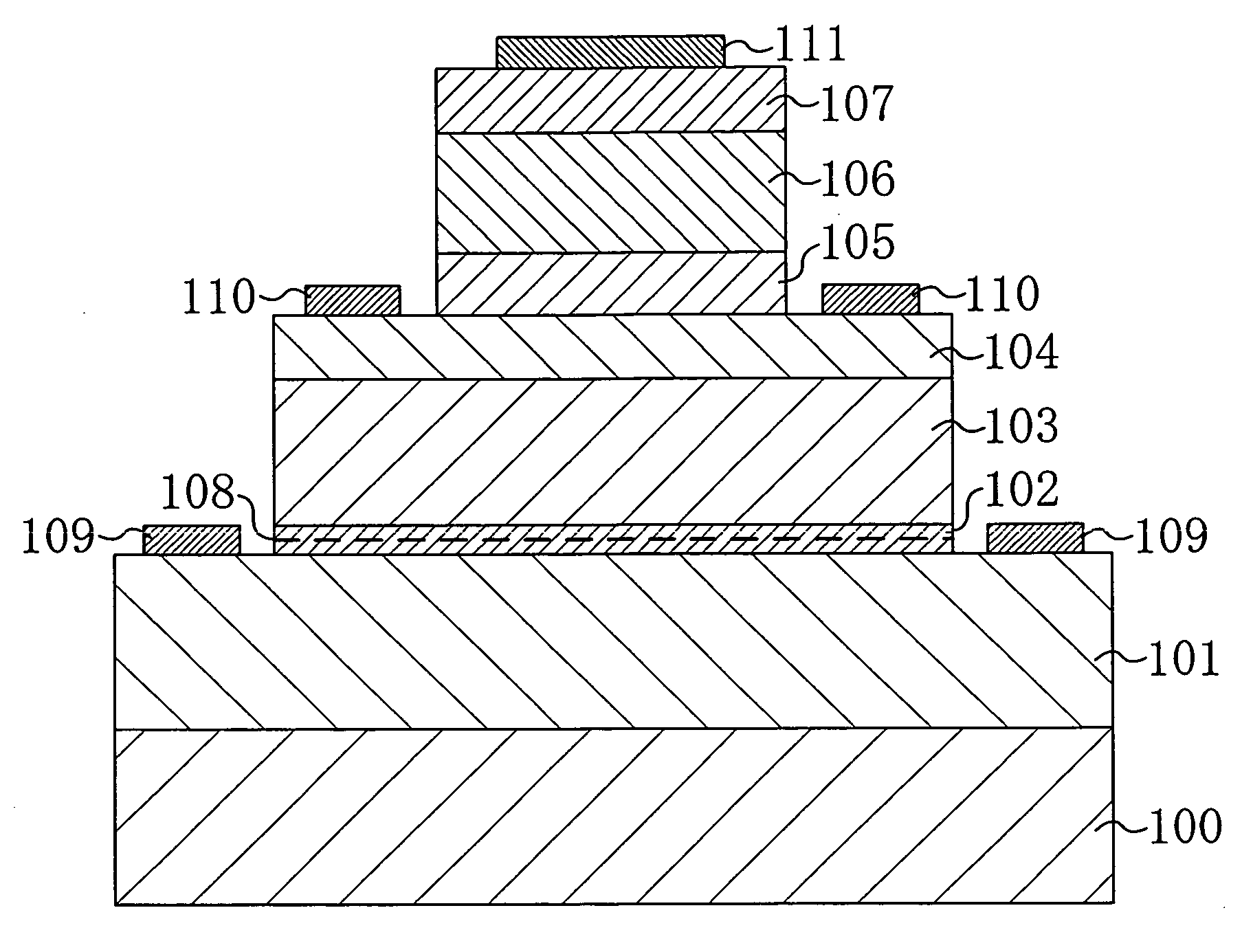

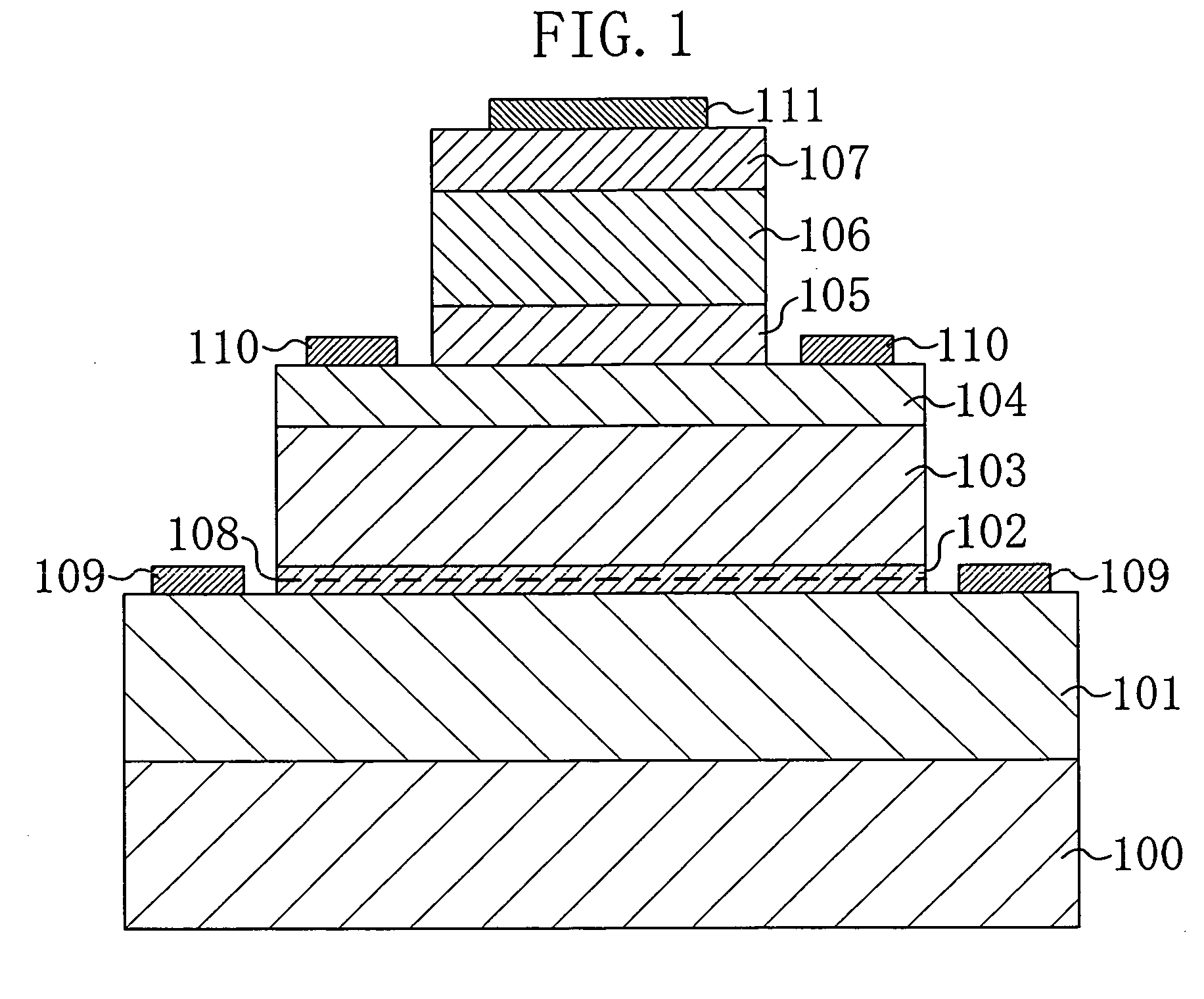

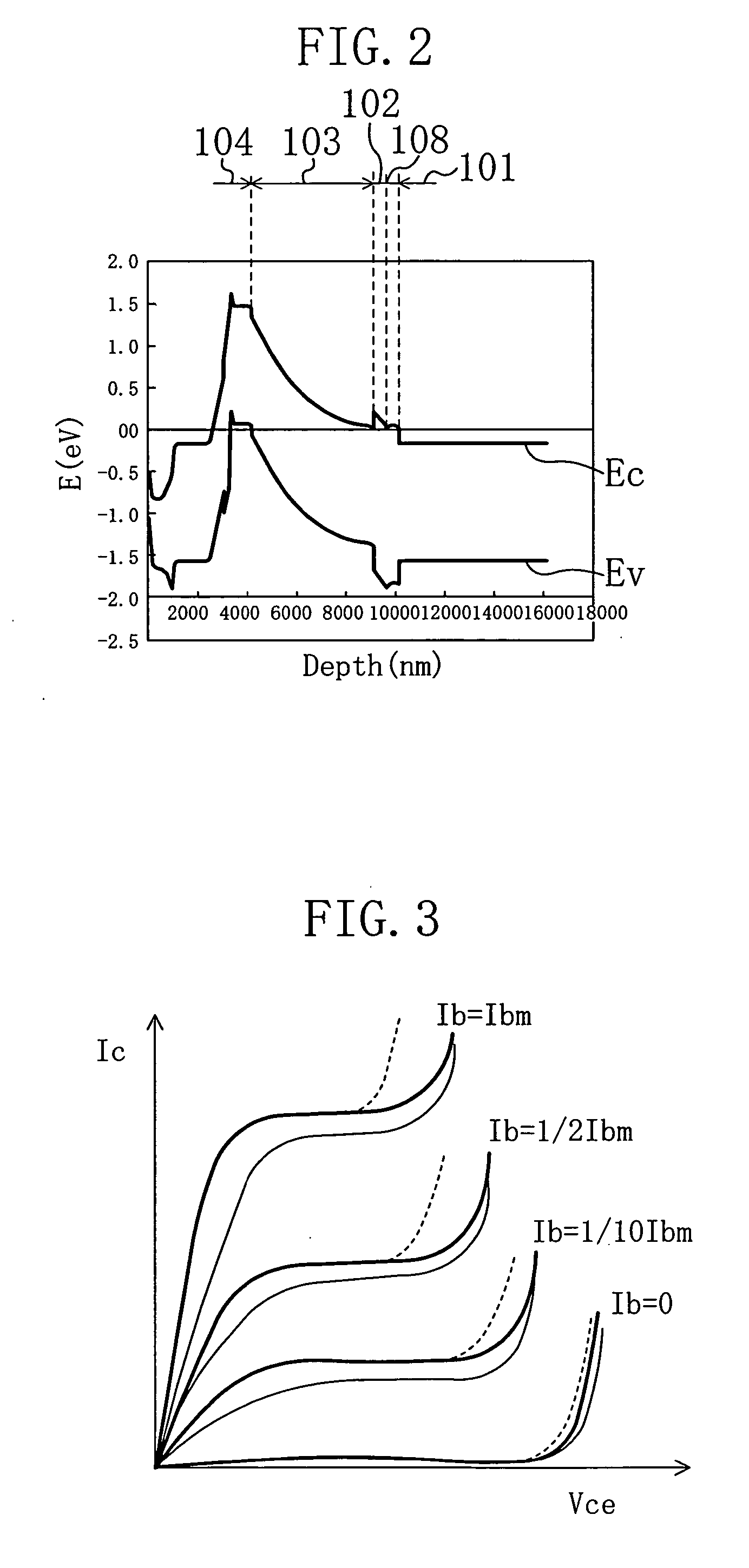

Hetero-junction bipolar transistor

InactiveUS20070120148A1High breakdown resistanceExcellent high-frequency characteristicSemiconductor devicesDelta dopingOptoelectronics

A hetero-junction bipolar transistor includes a sub-collector layer formed on a substrate and having conductivity, a first collector layer formed on the sub-collector layer and a second collector layer formed on the first collector layer and having the same conductive type as a conductive type of the sub-collector layer. In the first collector layer, a delta-doped layer is provided.

Owner:PANASONIC CORP

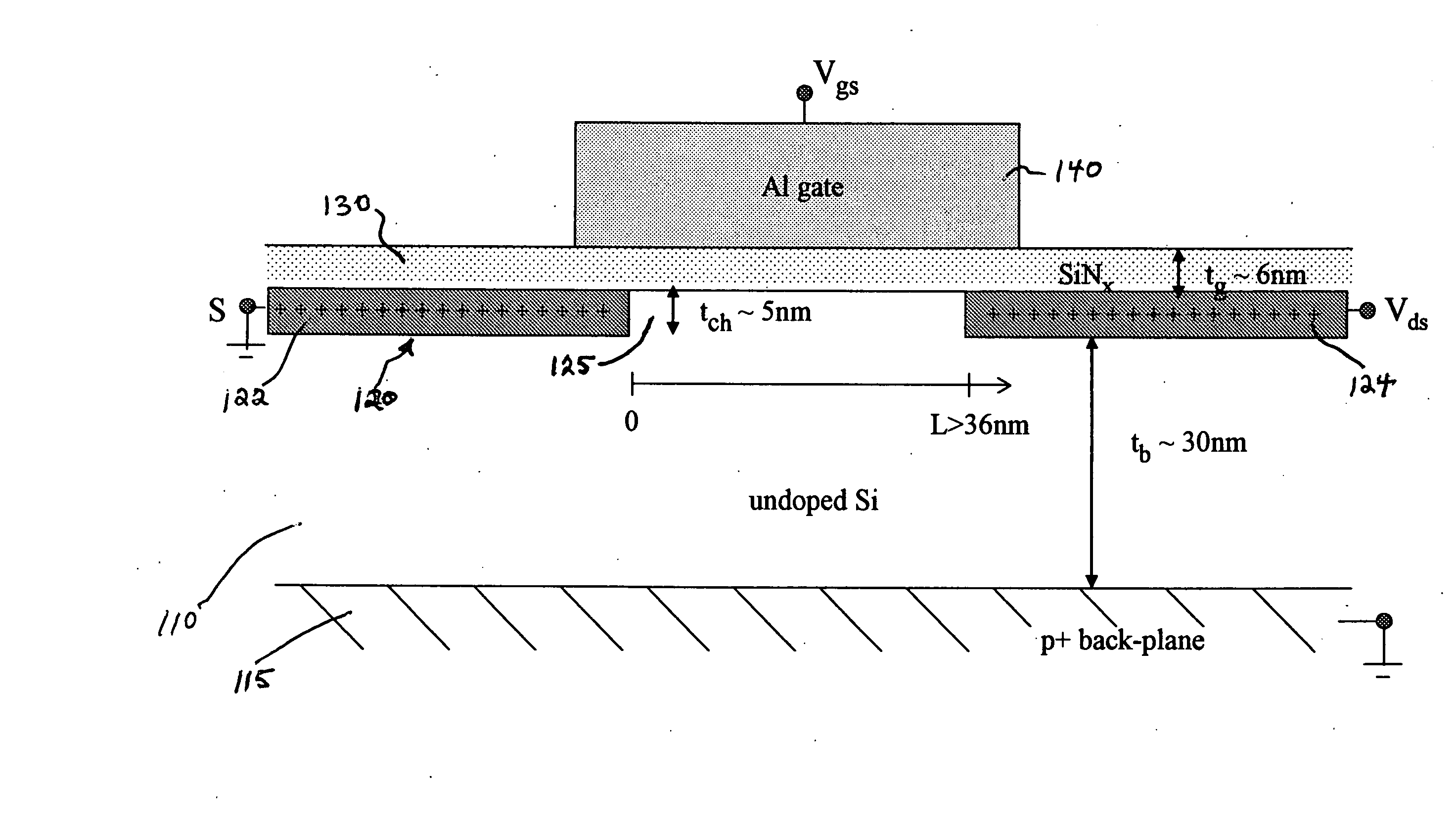

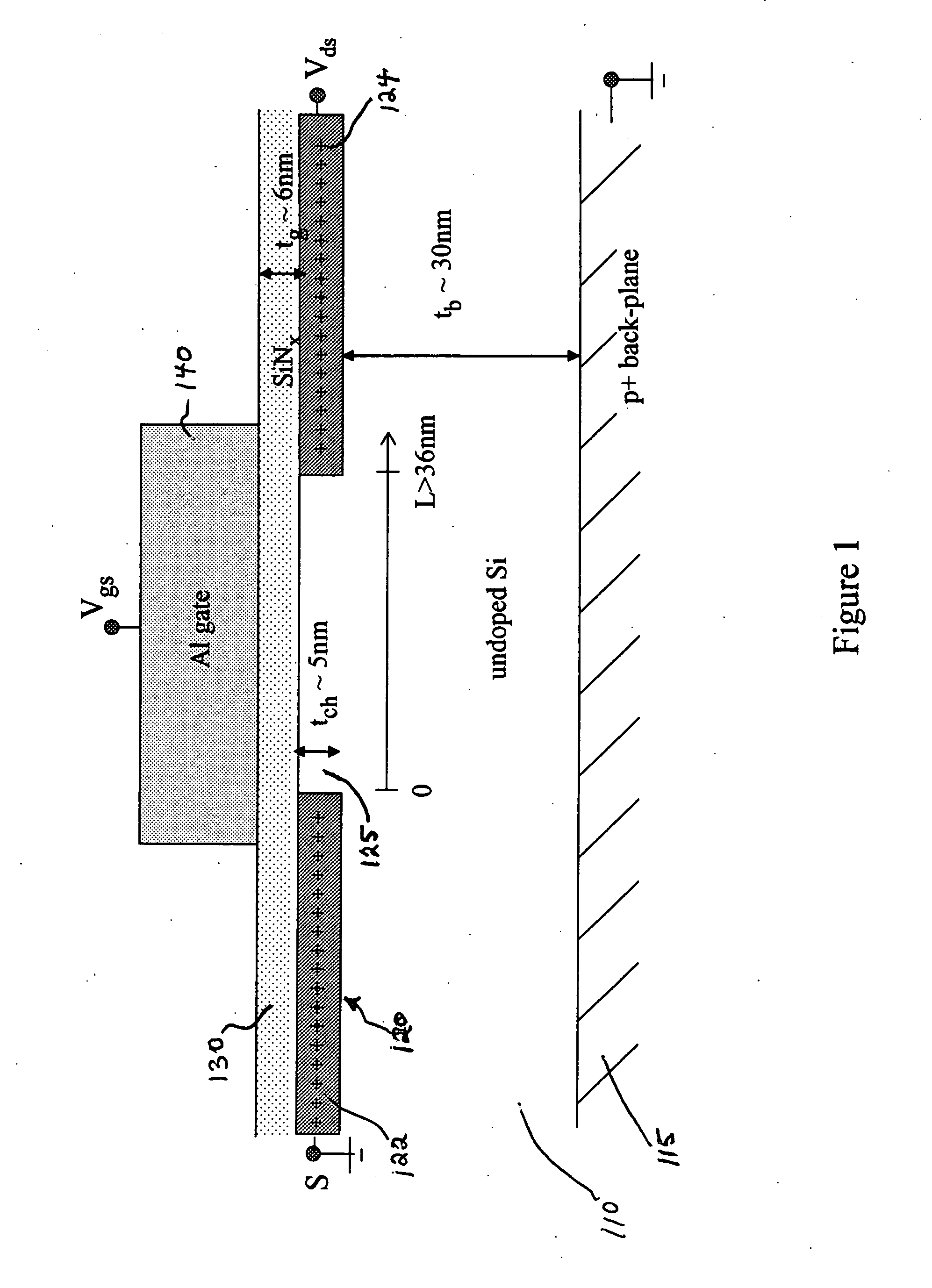

Field effect transistor devices and methods

InactiveUS20070290193A1Reduce device sizeLocal connectionTransistorSolid-state devicesDopantDelta doping

A field-effect transistor device is provided, including: a substrate; a vertically stacked layered semiconductor structure on the substrate including the following layers: a first quantum well layer having laterally spaced-apart drain and source regions that are each delta-doped with a dopant of a first conductivity type, the drain and source regions being laterally separated by a channel region; and a second quantum well layer vertically spaced from the first quantum well layer by a gate spacing layer, the second quantum well layer having a gate region, above the channel region, which is delta-doped with a dopant; and couplings for applying electrical potentials with respect to said source, drain, and gate regions.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

CASCODE STRUCTURES WITH GaN CAP LAYERS

A transistor device including a cap layer is described. One embodiment of such a device includes cap layer between a gate and a semiconductor layer. In one embodiment, the thickness of the cap layer is between 5 nm and 100 nm. In another embodiment, the cap layer can be doped, such as delta-doped or doped in a region remote from the semiconductor layer. Devices according to the present invention can show capacitances which are less drain bias dependent, resulting in improved linearity.

Owner:CREE INC

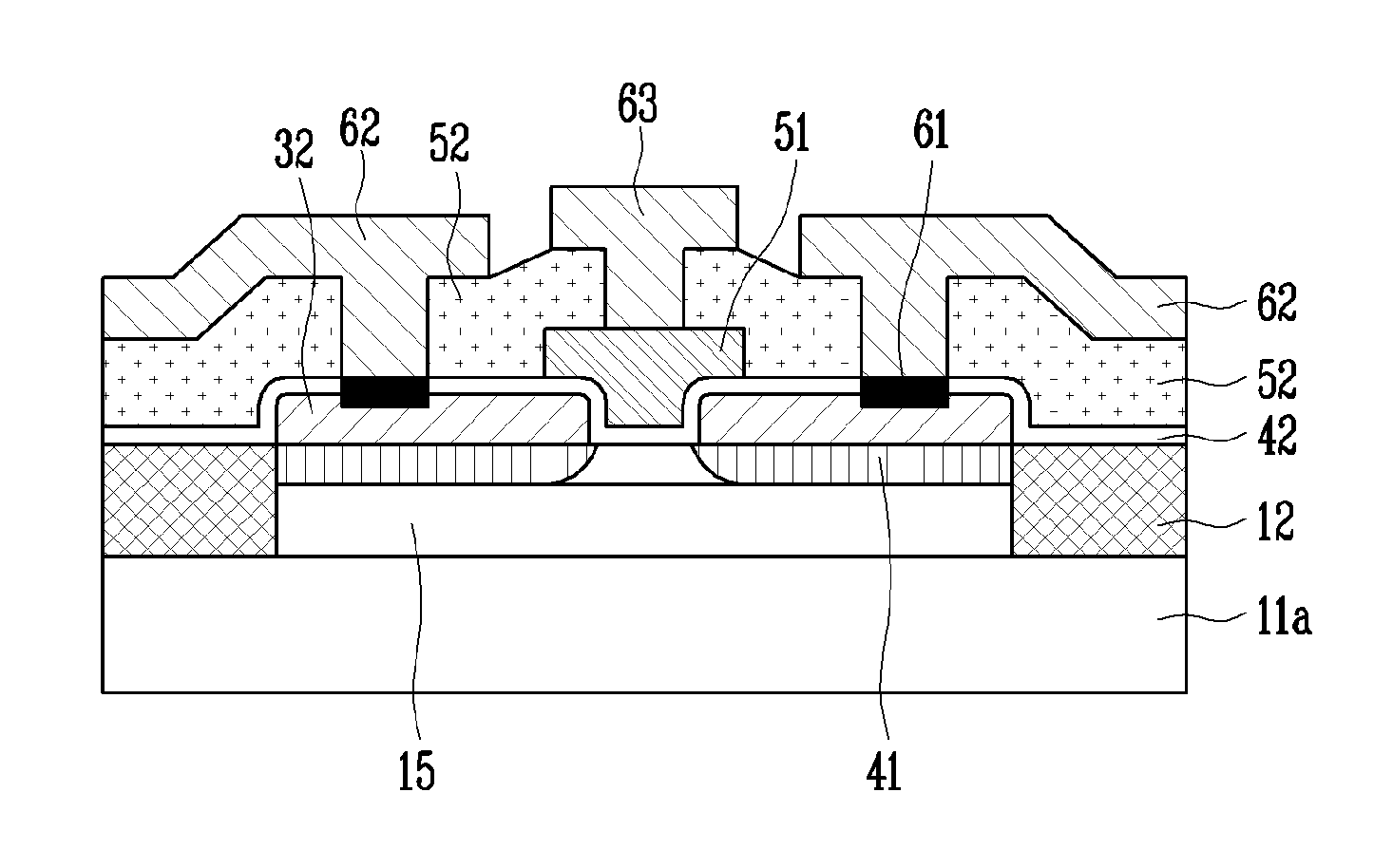

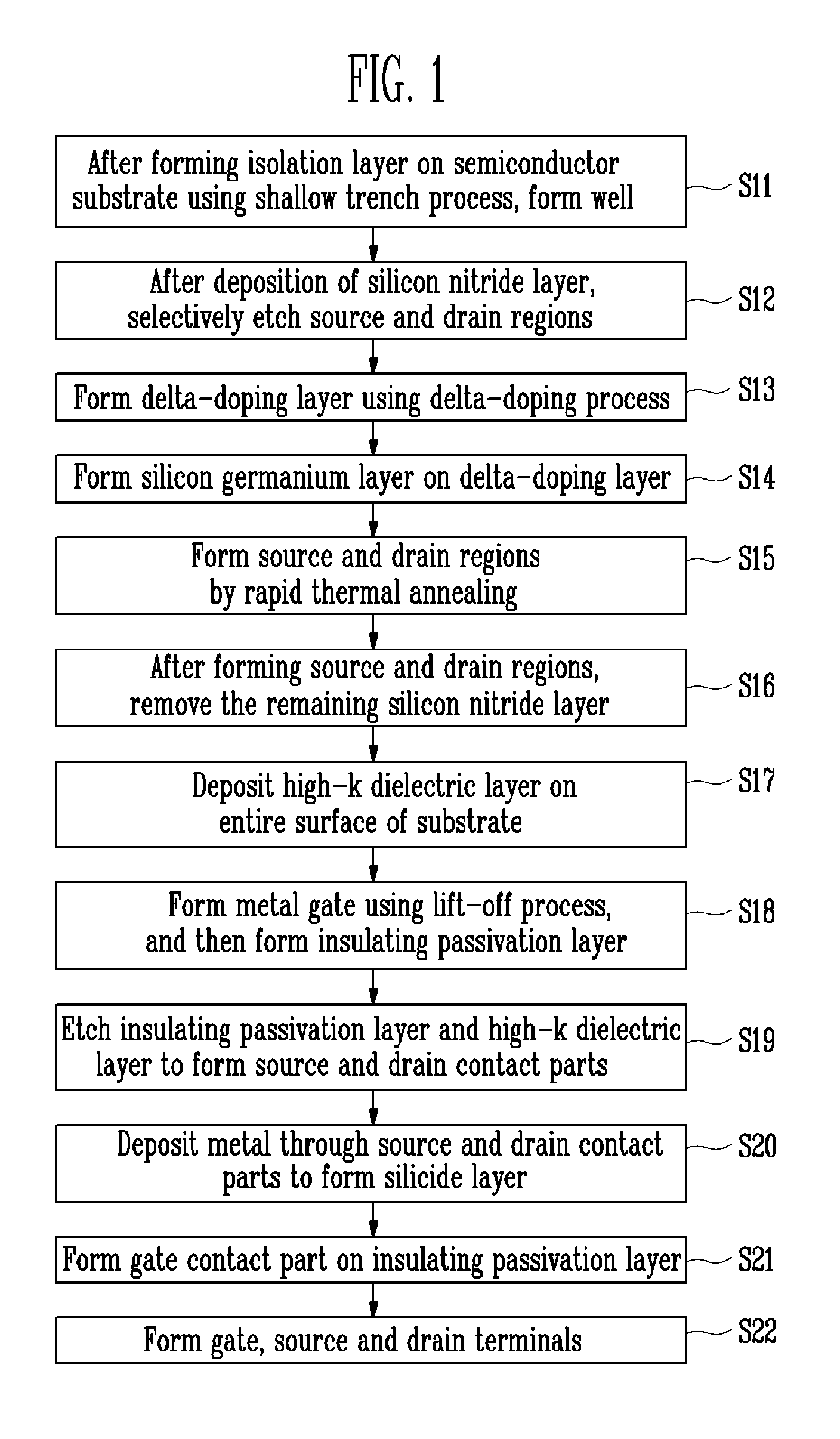

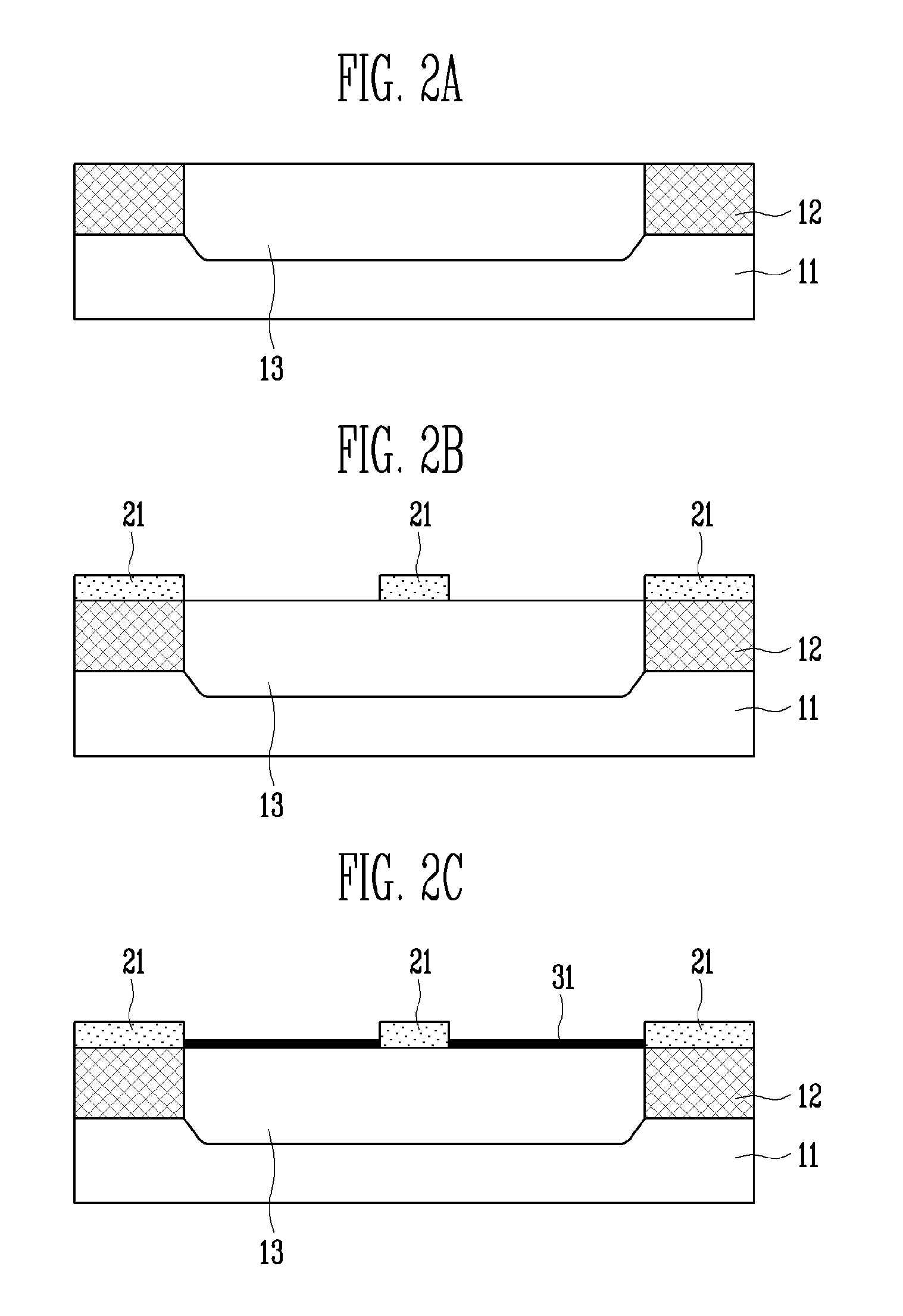

Germanium semiconductor device and method of manufacturing the same

InactiveUS20080135878A1Reduce contact resistanceIncrease currentTransistorSolid-state devicesHigh concentrationDevice material

A germanium semiconductor device and a method of manufacturing the same are provided. The method includes the steps of: forming an isolation layer on a substrate using a shallow trench; forming a silicon-nitride layer on the substrate, and selectively etching the silicon nitride layer to expose source and drain regions; injecting impurities onto a surface of the substrate over the exposed source and drain regions using delta-doping to form a delta-doping layer; selectively growing a silicon germanium layer containing impurities on the delta-doping layer; rapidly annealing the substrate and forming source and drain regions by diffusion of the impurities; depositing an insulating layer on the entire surface of the substrate; etching the insulating layer and forming source and drain contact parts to be in contact with source and drain terminals; depositing metal over the insulating layer having the source and drain contact parts thereon and forming a metal silicide layer; and after forming the silicide layer, forming the source and drain terminals to be in contact with the silicide layer. Accordingly, the source and drain regions having a shallow junction depth may be ensured by forming the source and drain regions through annealing after delta-doping and selectively growing the silicon germanium layer containing high-concentration impurities. Also, the germanium silicide layer is stably formed by the silicon germanium layer grown in the source and drain regions, and thus contact resistance is lowered and driving current of the device is improved.

Owner:ELECTRONICS & TELECOMM RES INST +1

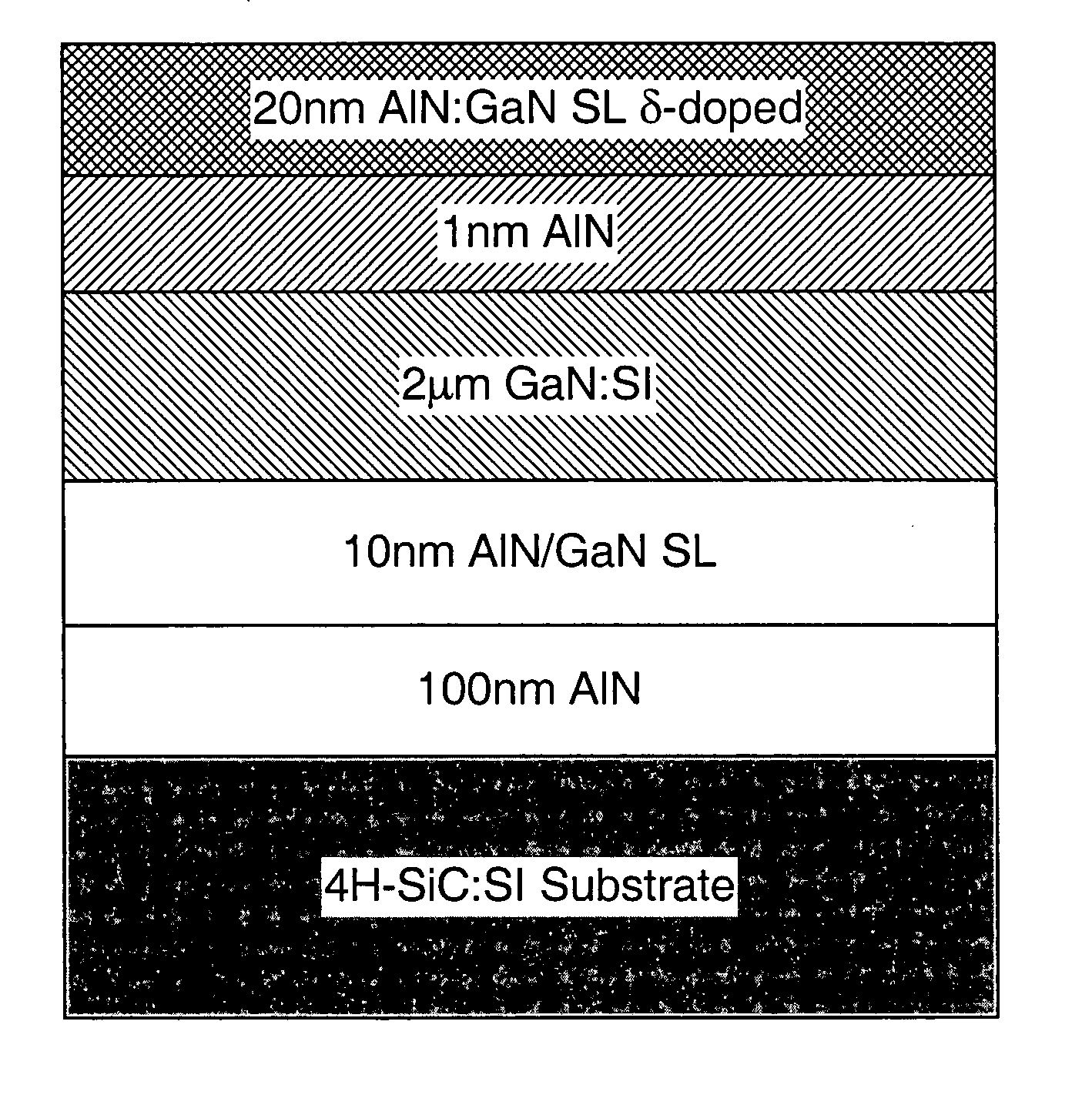

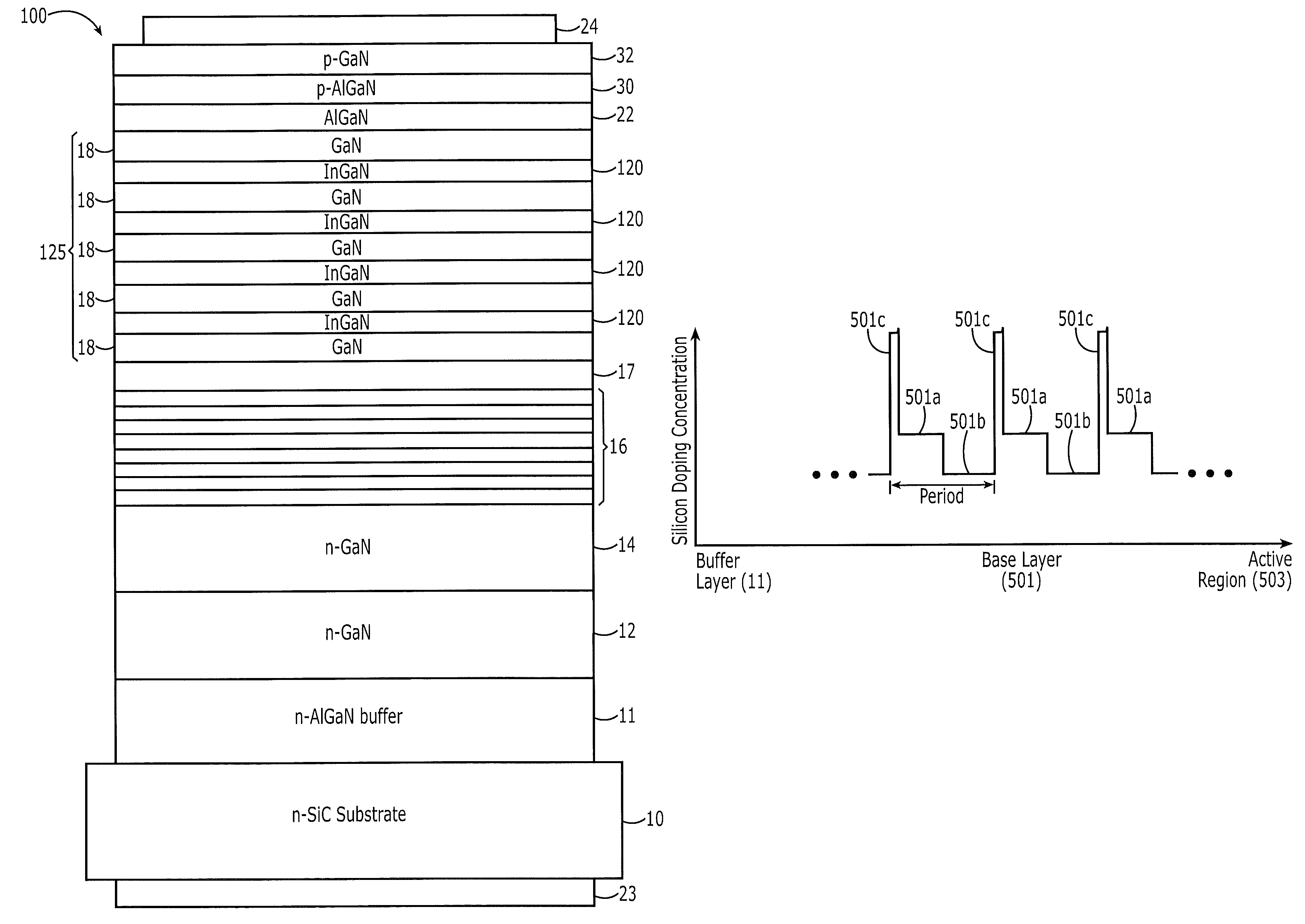

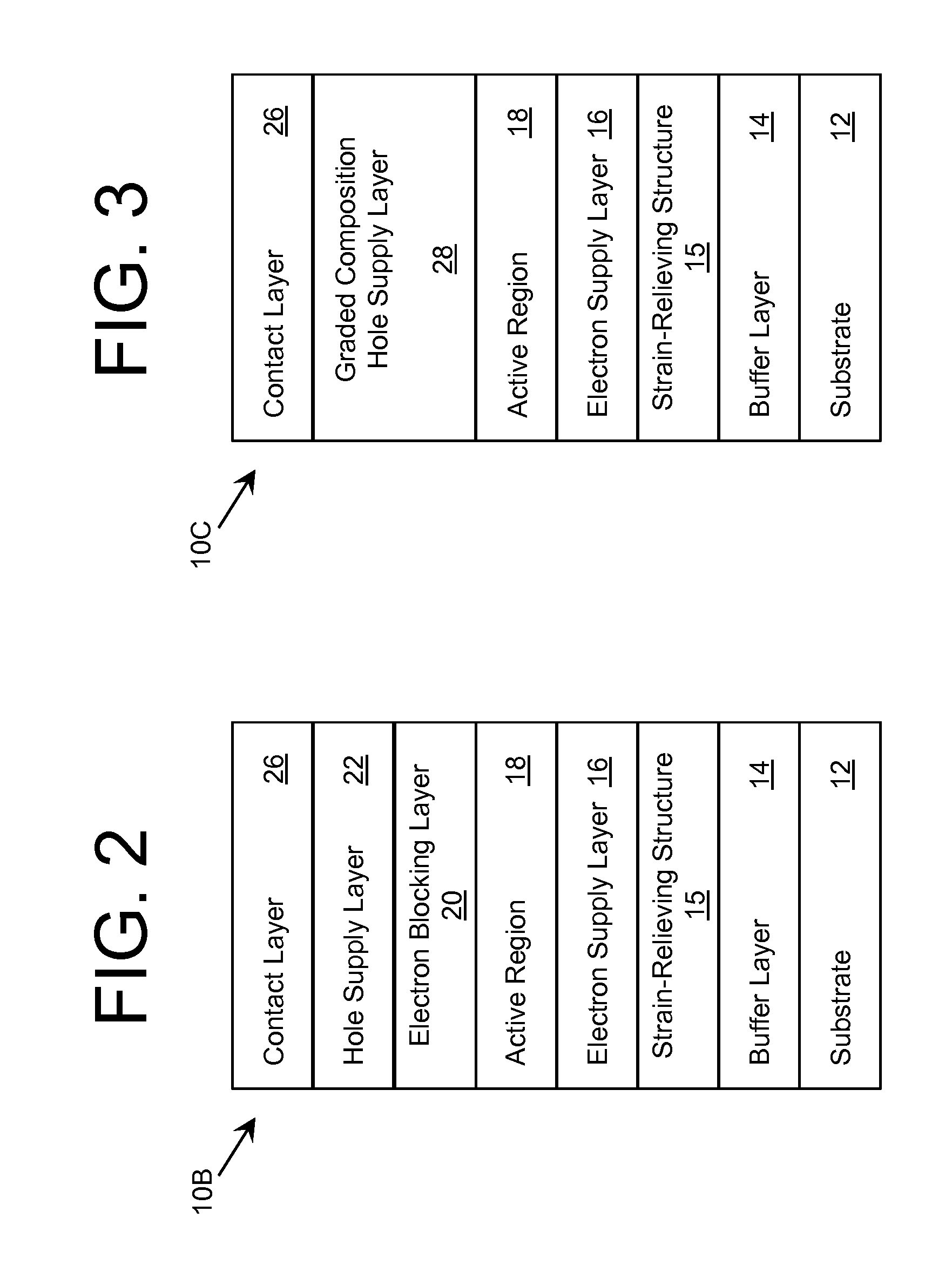

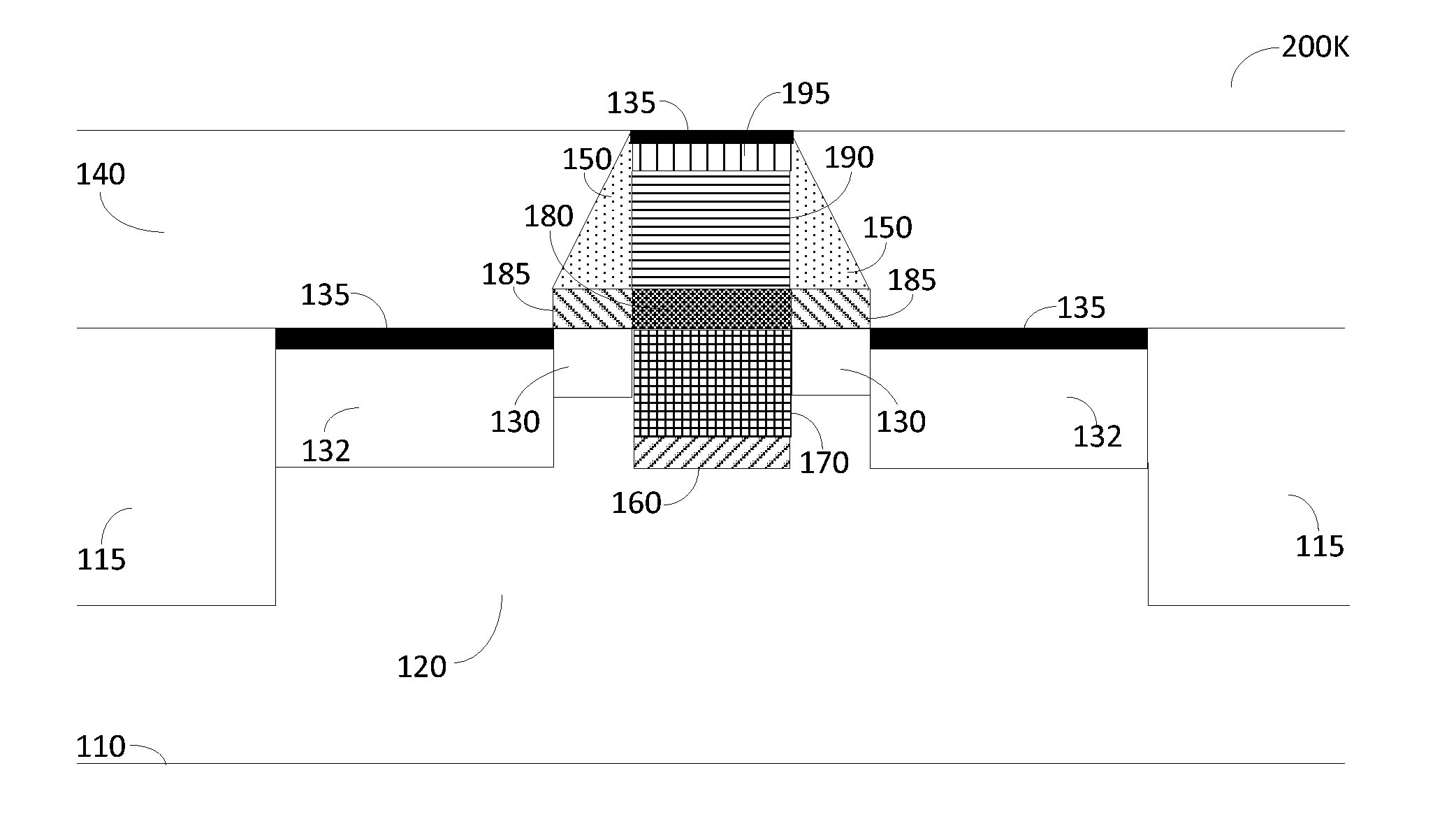

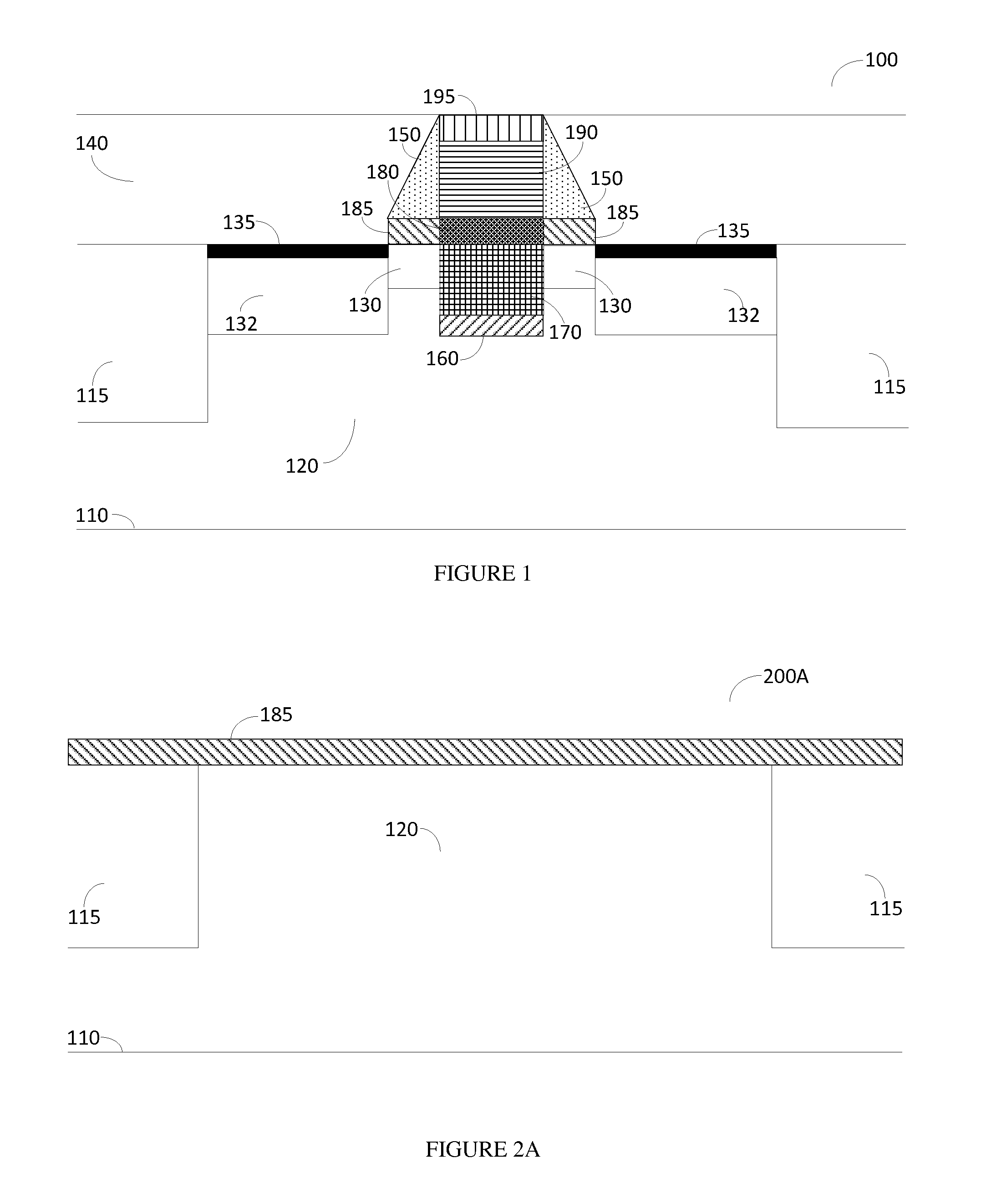

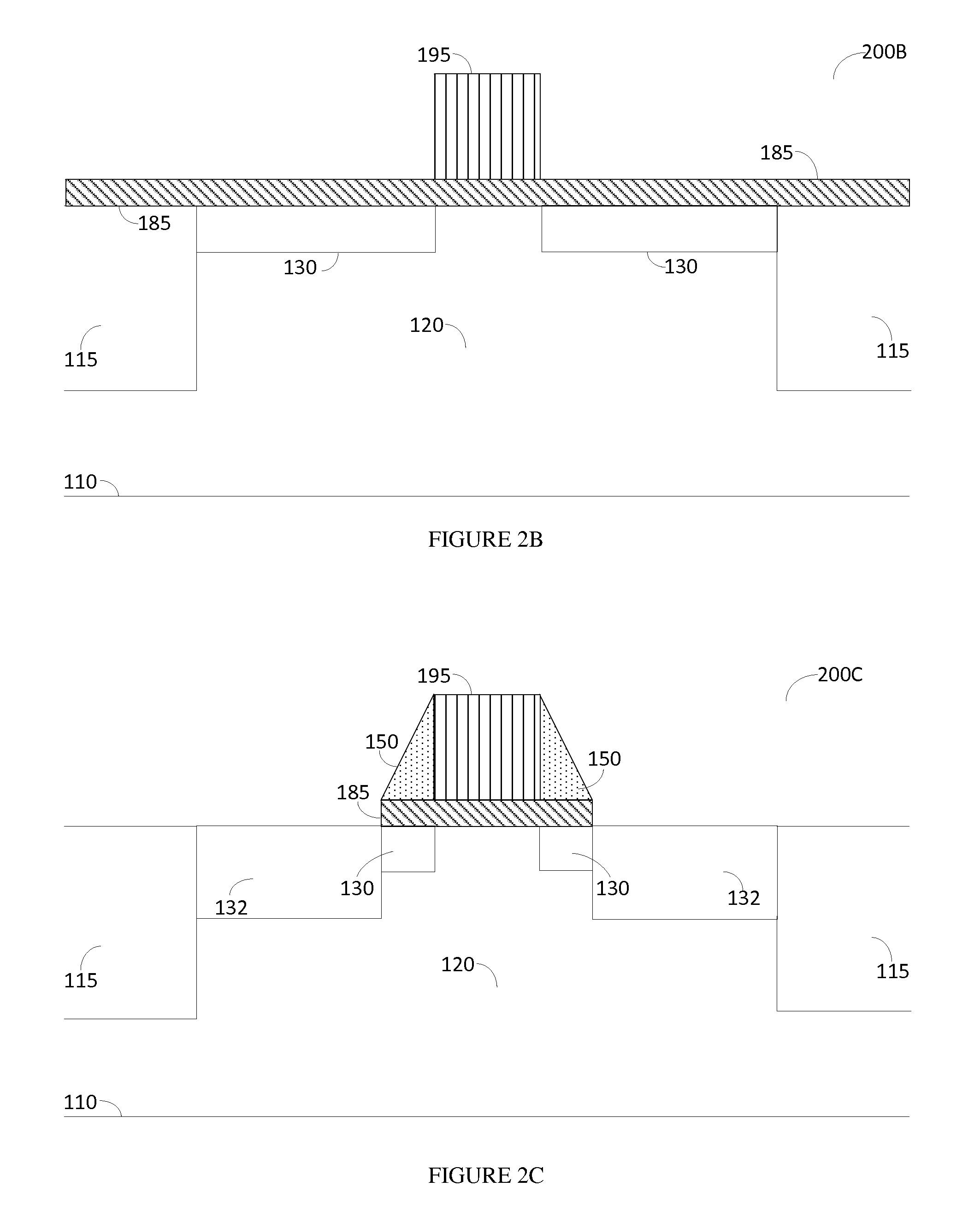

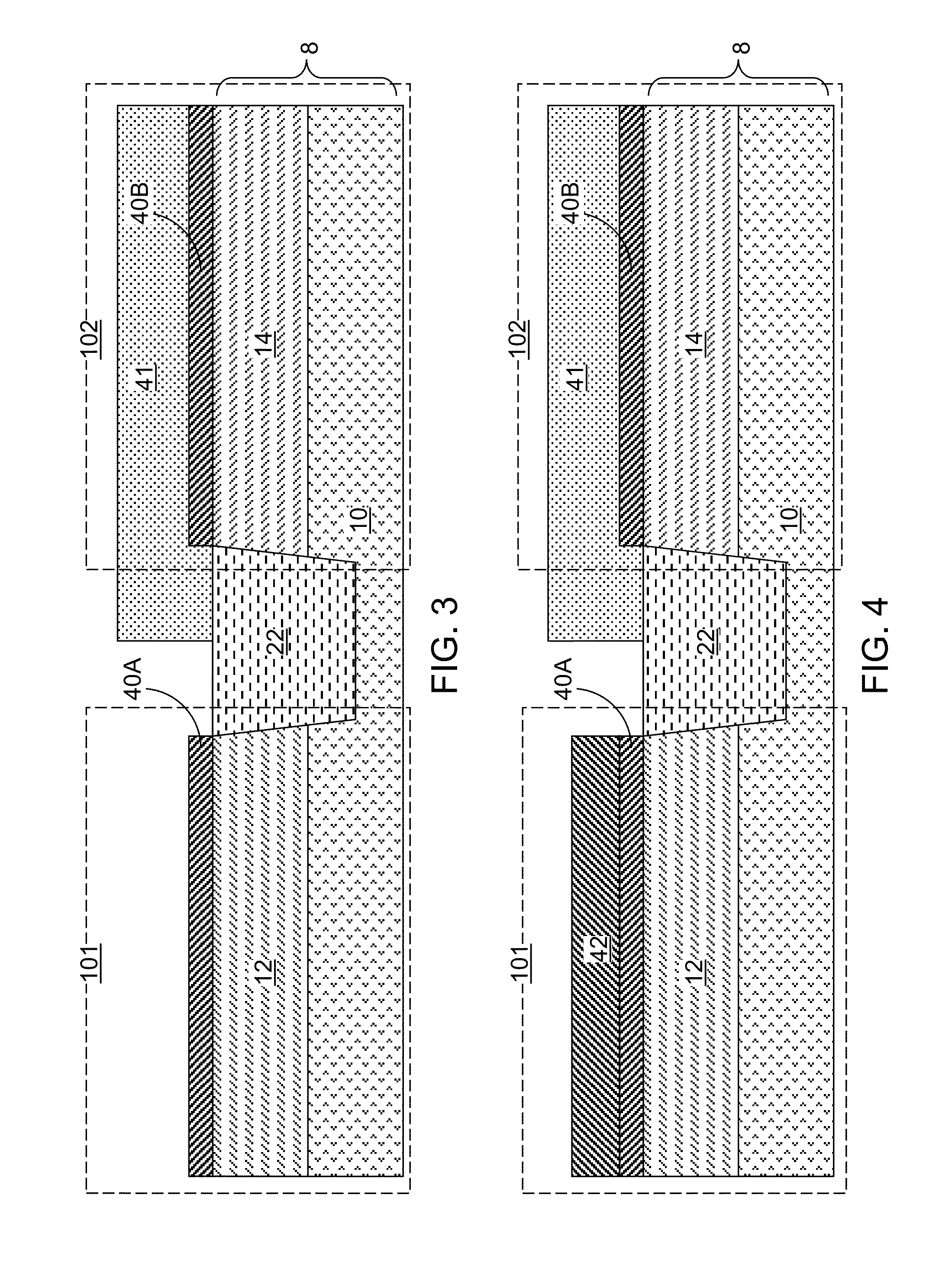

Semiconductor device structures with modulated and delta doping and related methods

ActiveUS8536615B1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantDelta doping

Owner:CREE INC

HFET with low access resistance

InactiveUS20130032860A1SpecificEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceAccess resistance

A novel semiconductor power transistor is presented. The semiconductor structure is simple and is based on a Hetero-structure FET structure, where the access regions have been eliminated so as to effectively obtain a lower specific on-resistance, and a higher control on the transport properties of the device, drastically reducing the dispersion phenomena associated with these regions. The present invention can be realized both with polar and non-polar (or semi-polar) materials, without requiring delta doping implantation. It can be fabricated as an enhancement or depletion mode device with much higher control on the device threshold voltage with respect to state-of-the-art HFET devices, and achieving superior RF switching performance. Furthermore, due to the absence of access regions, enhancement mode devices can be realized without discontinuity in the channel conductivity, which results in an even lower on-resistance.

Owner:QUALCOMM INC

Diamond Transistor And Method Of Manufacture Thereof

InactiveUS20080099768A1Reduce surface roughnessLower step heightTransistorPolycrystalline material growthDelta dopingSingle crystal

Owner:DIAMOND MICROWAVE DEVICES

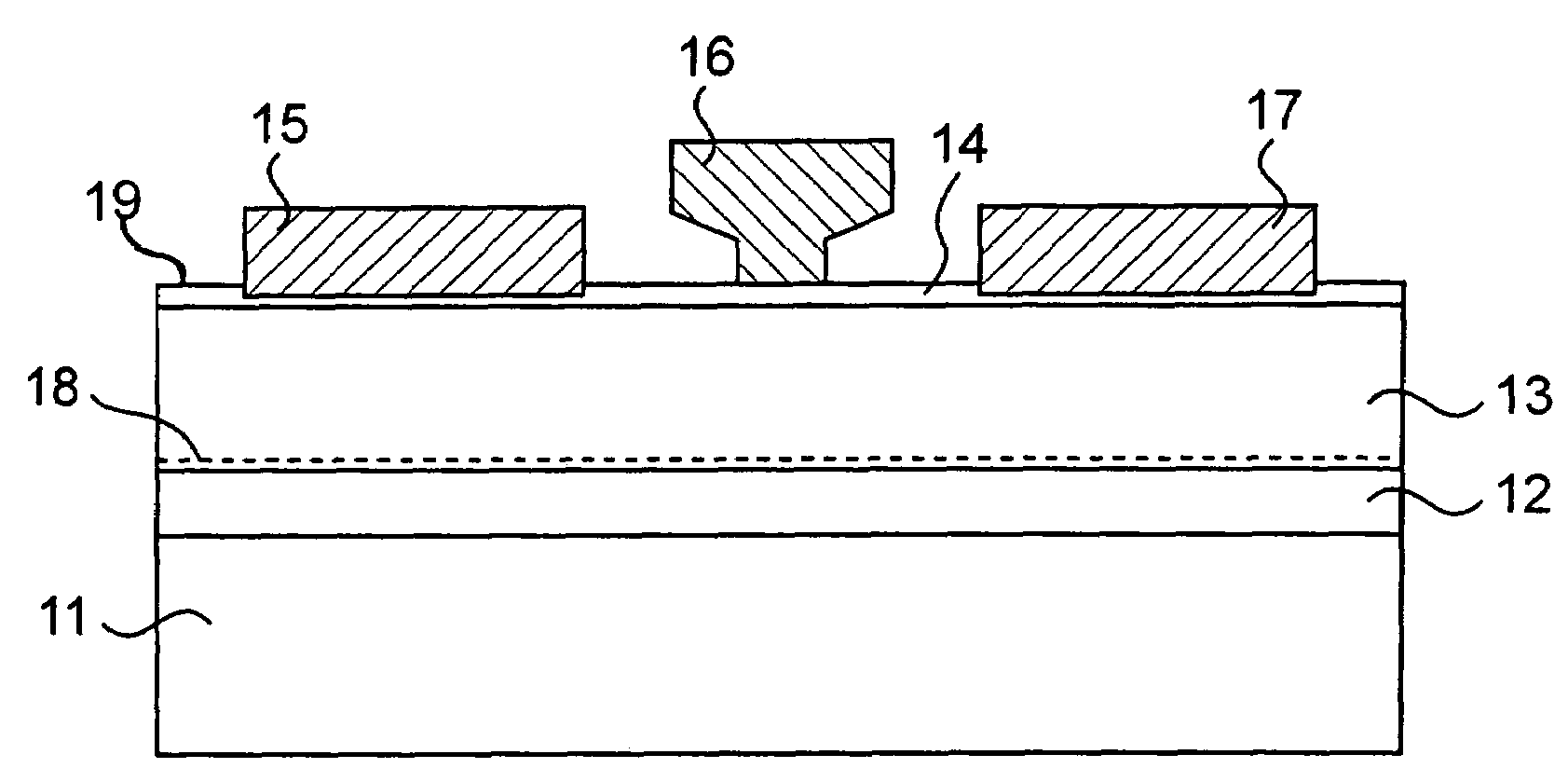

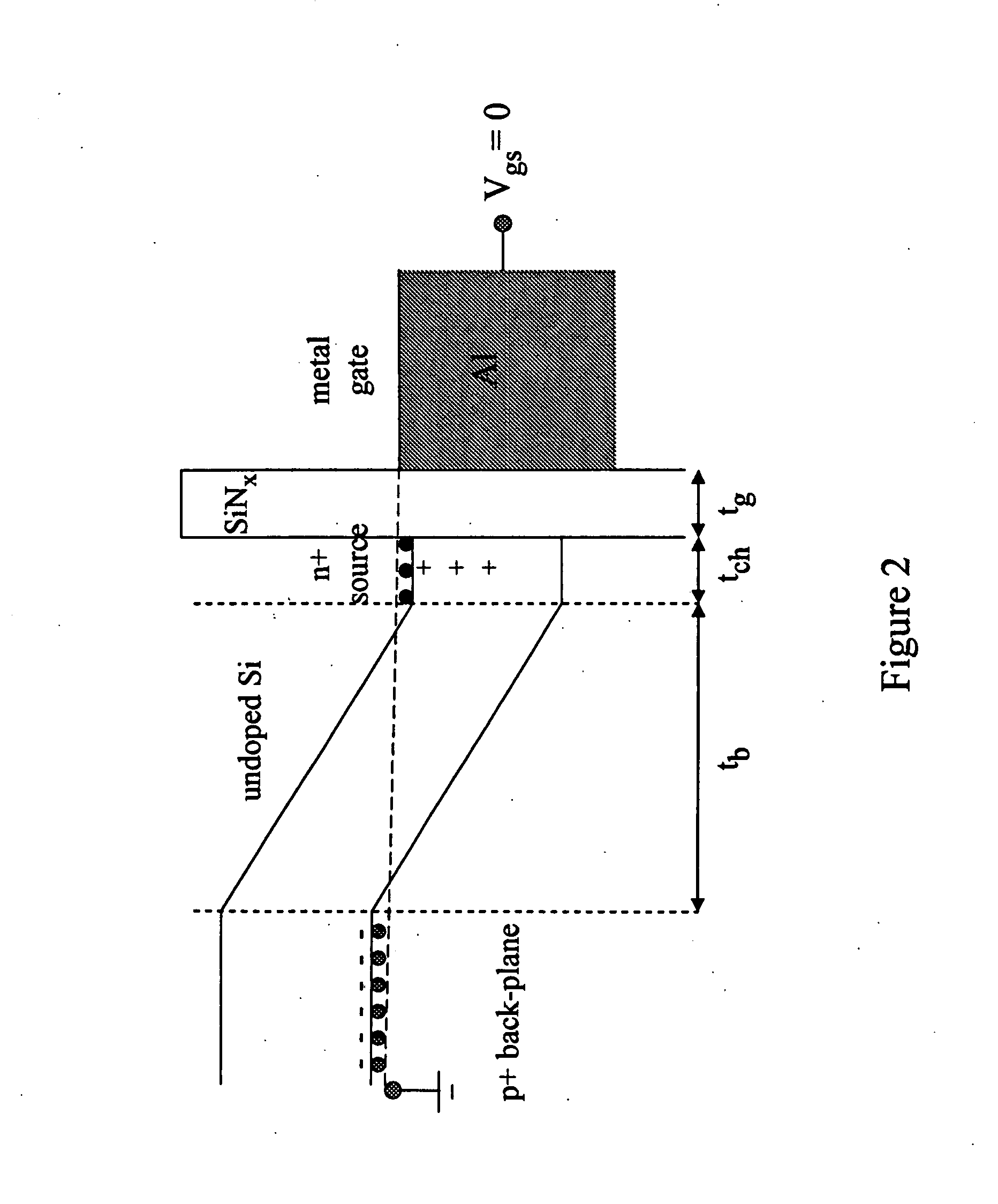

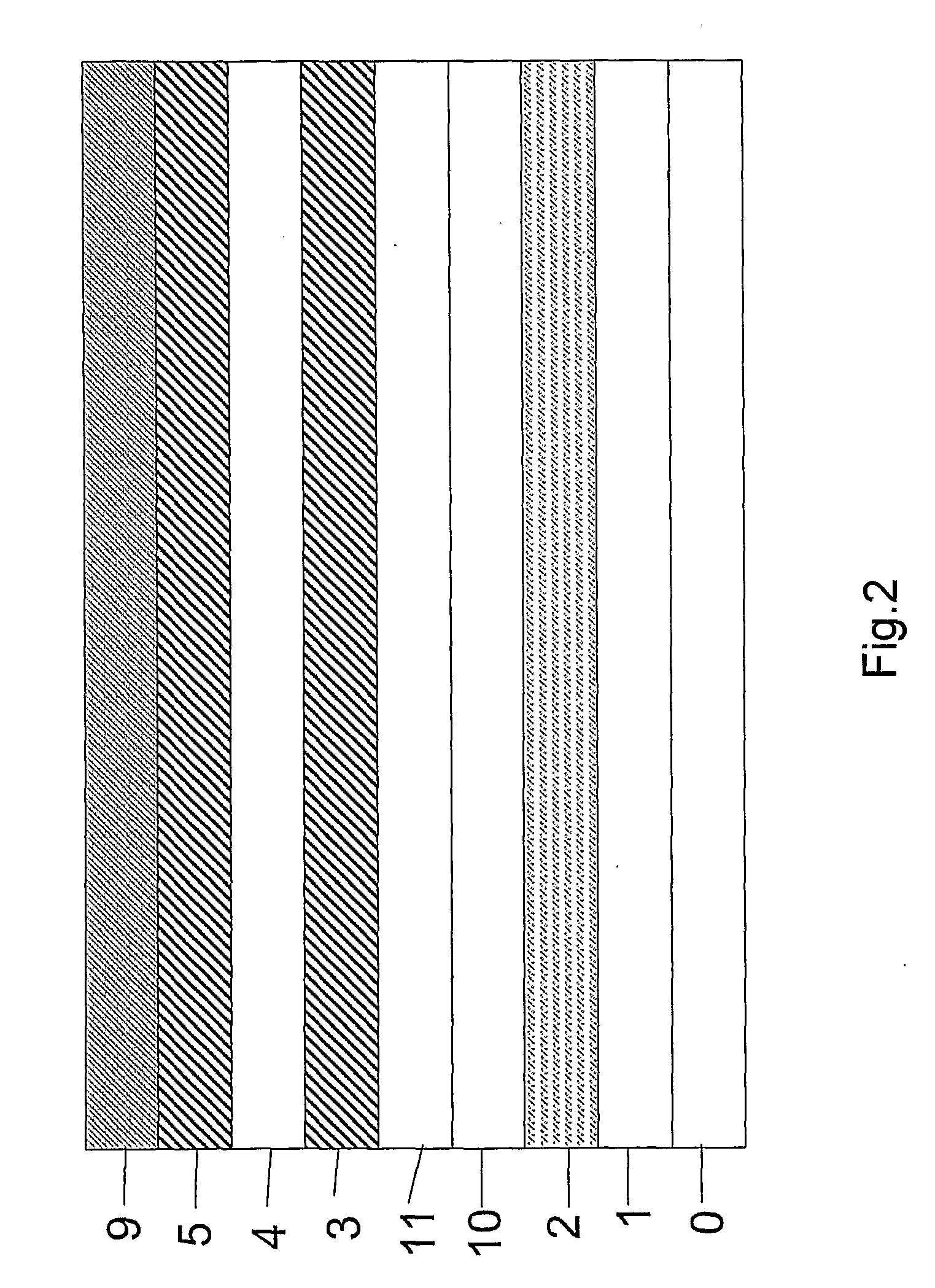

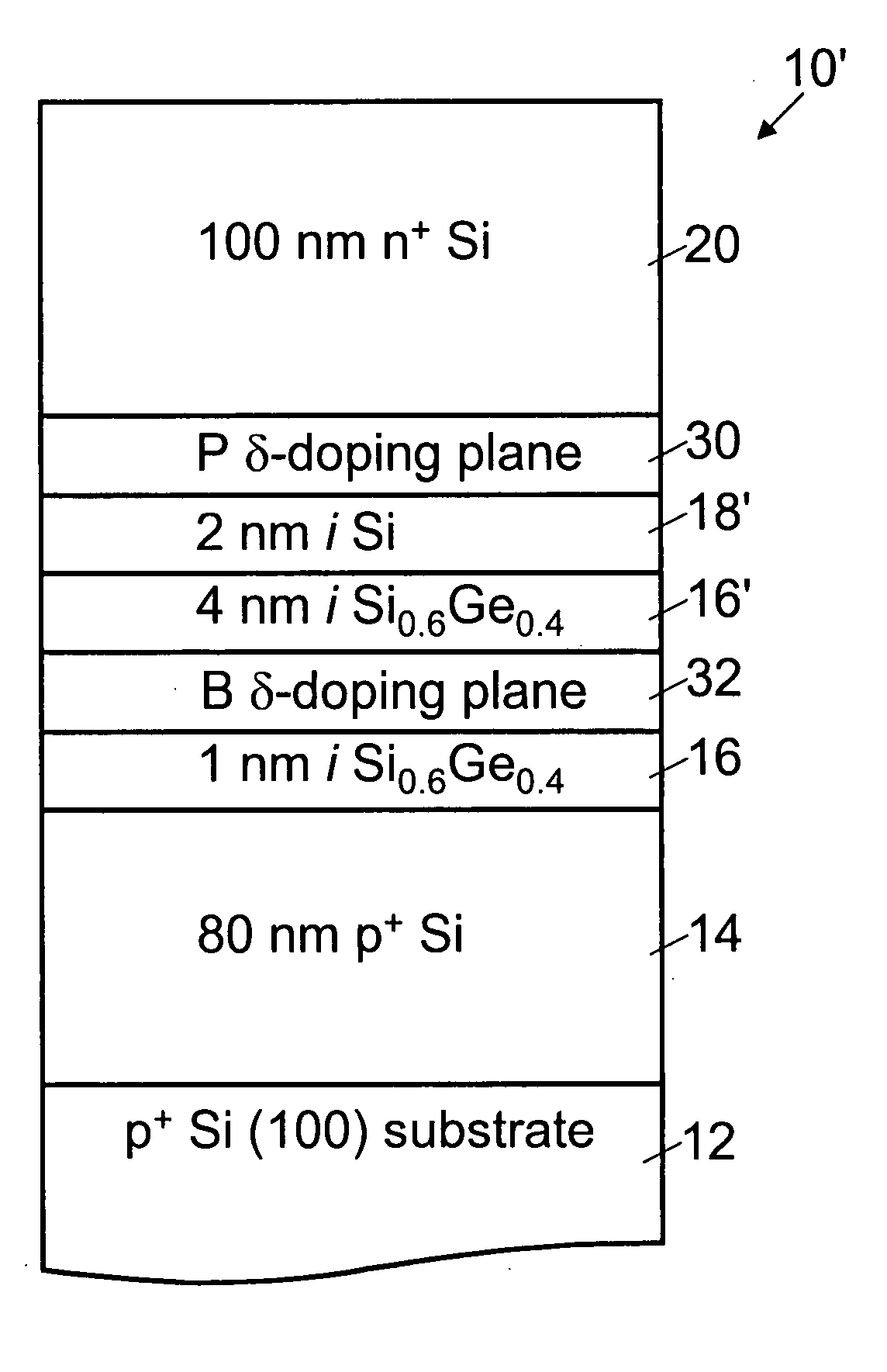

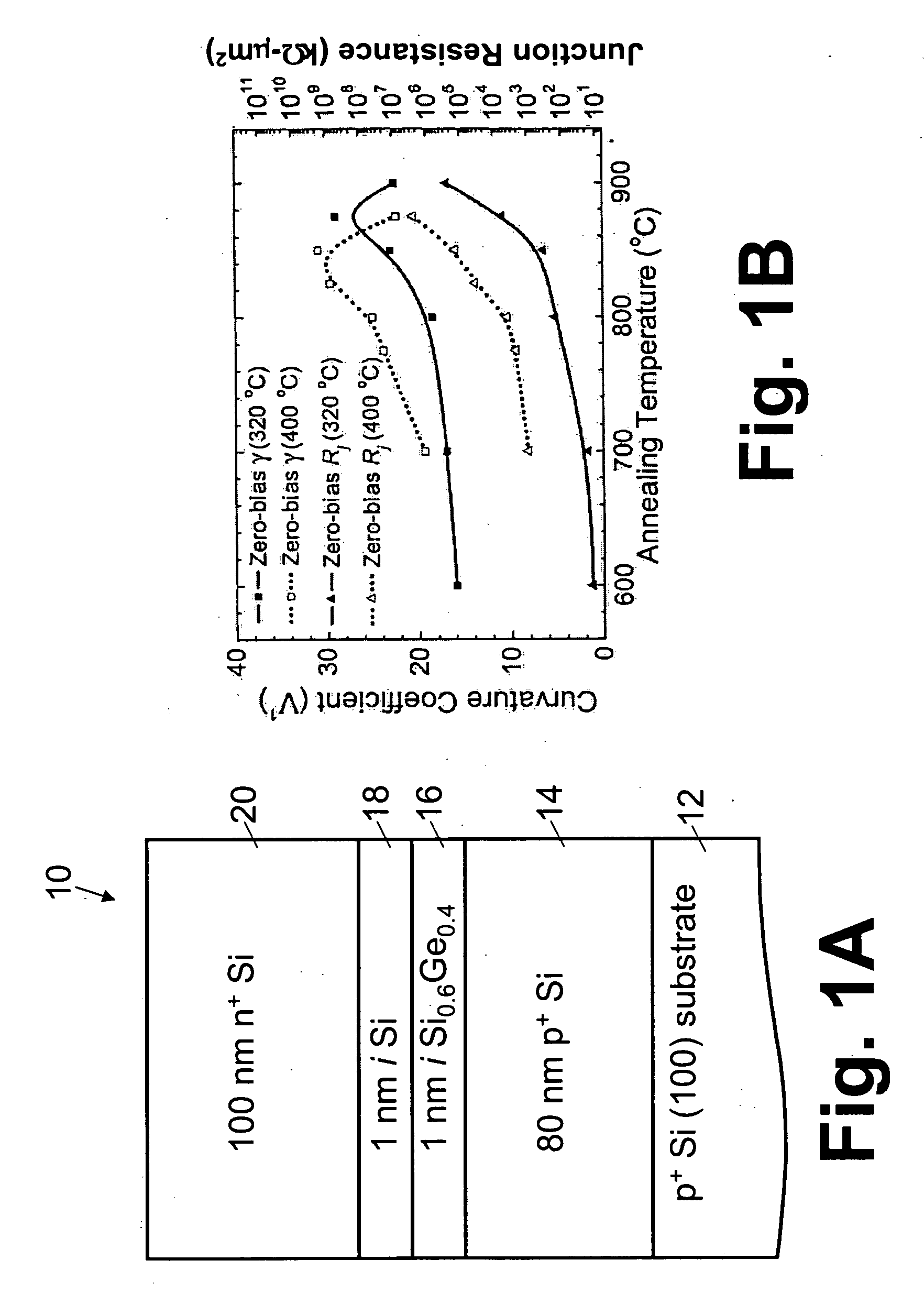

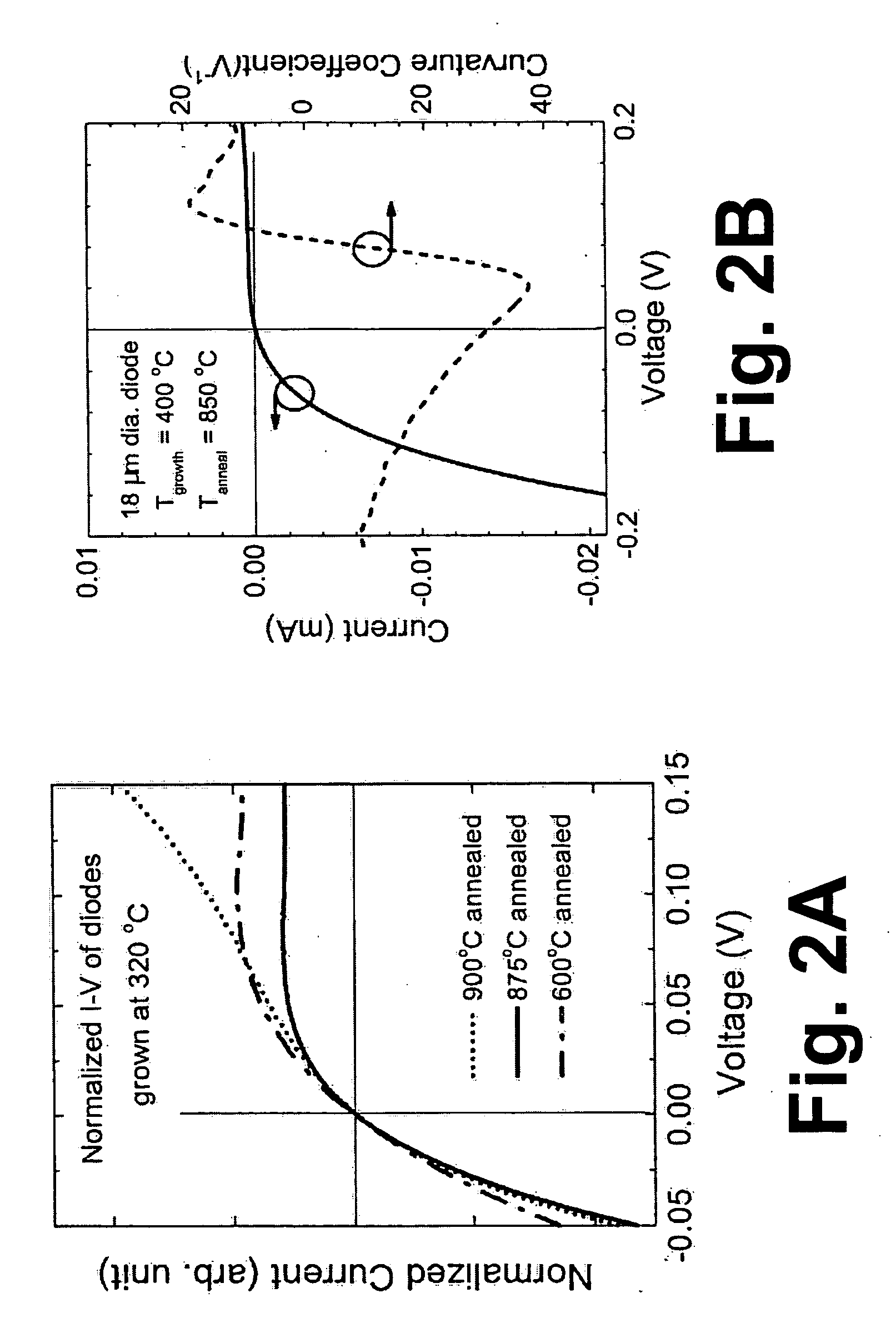

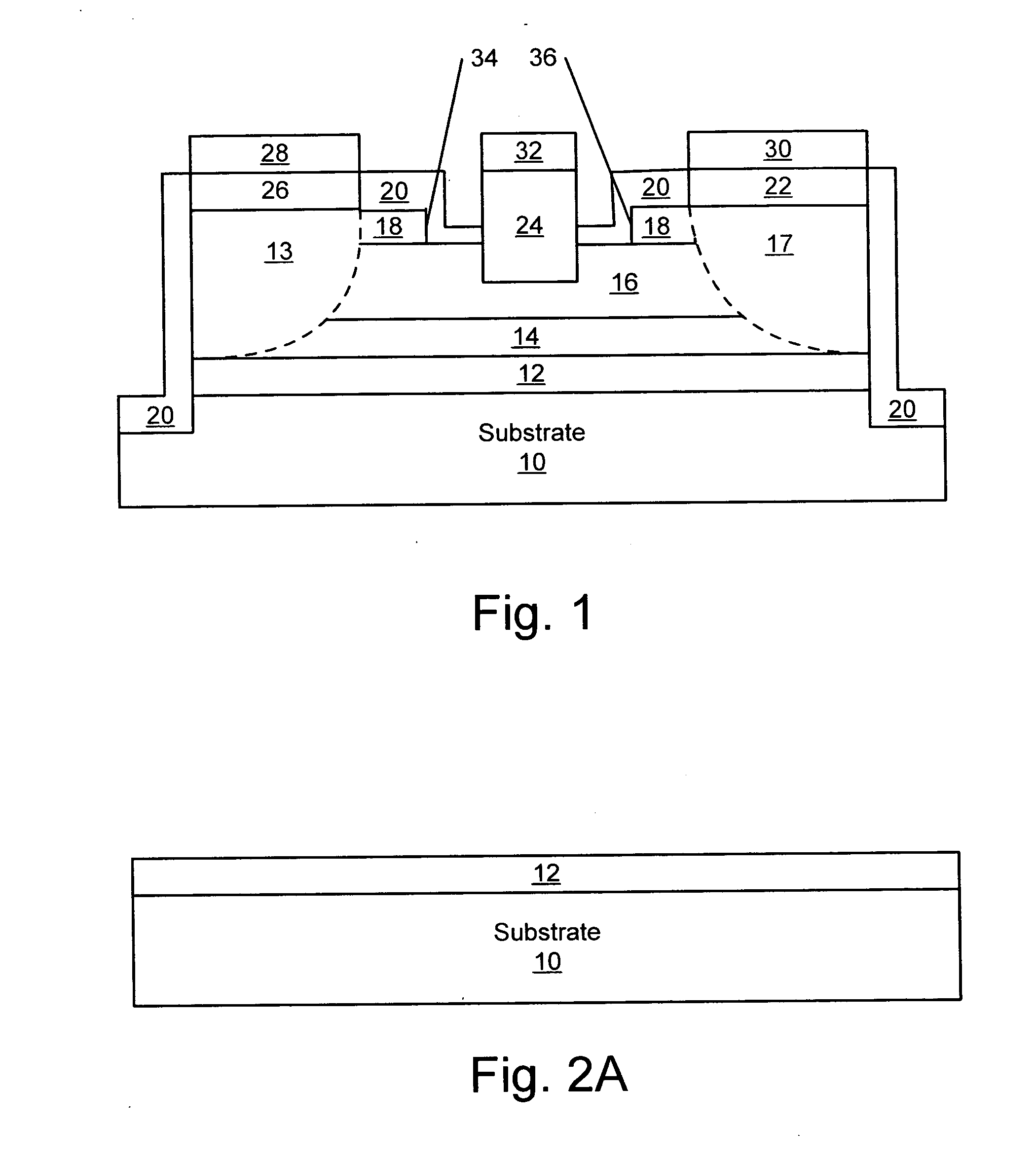

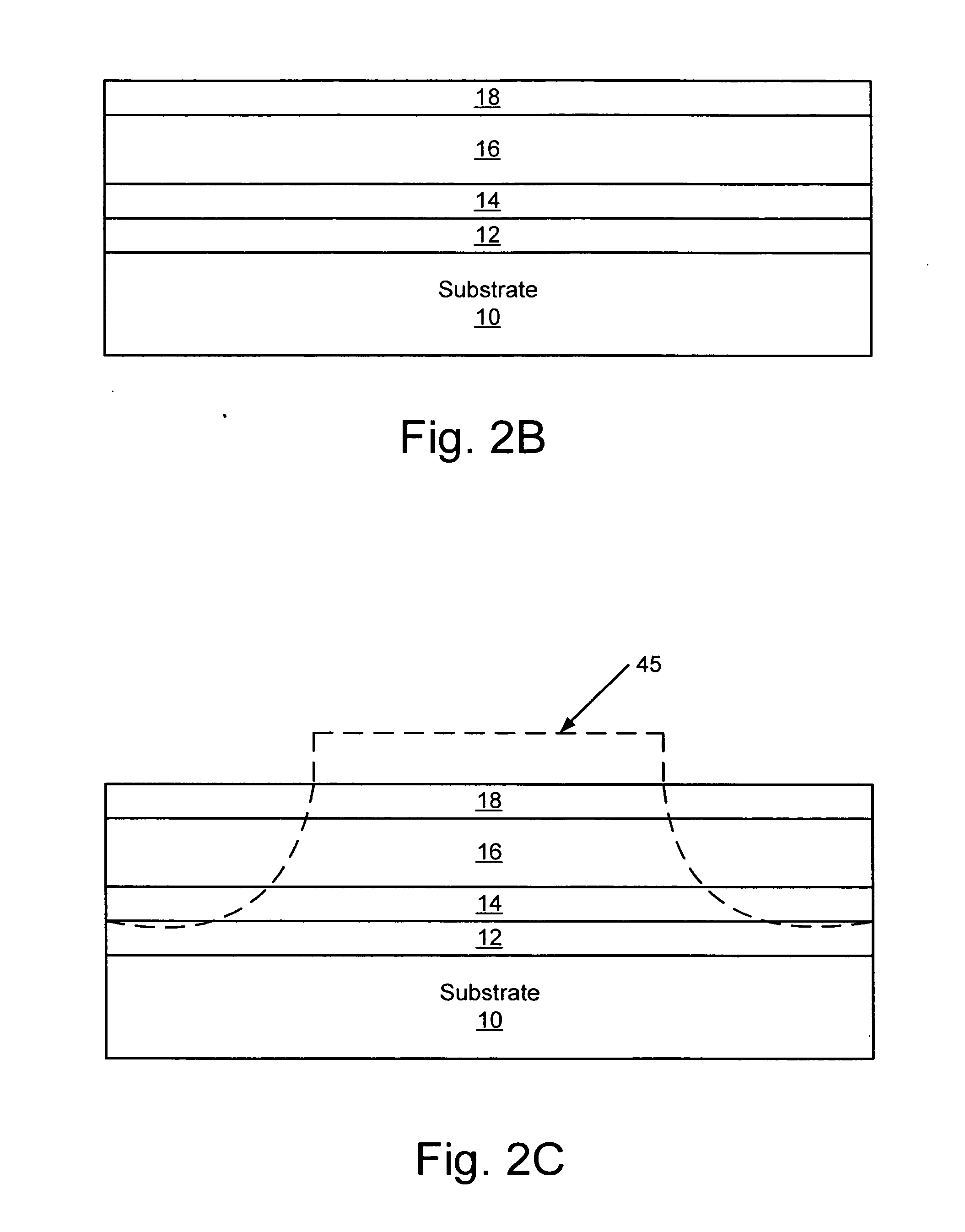

Silicon-based backward diodes for zero-biased square law detection and detector arrays of same

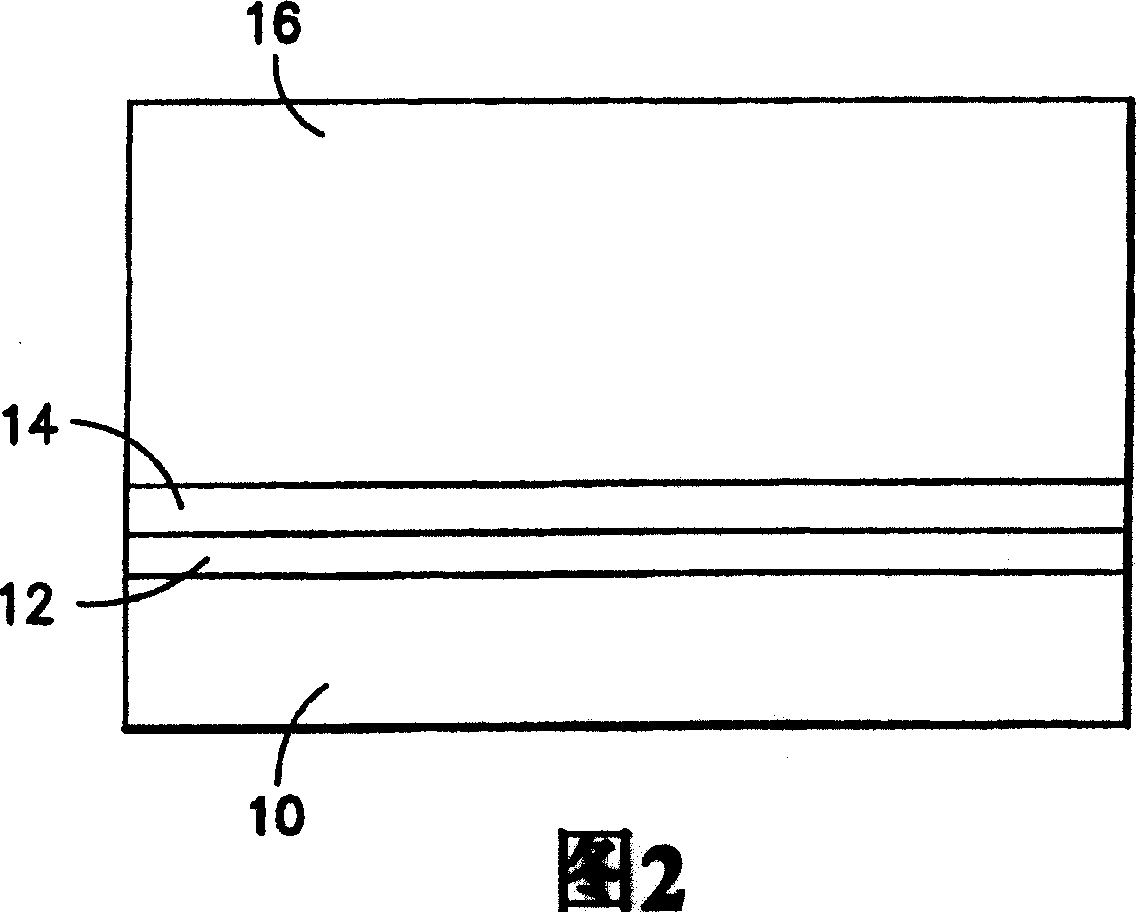

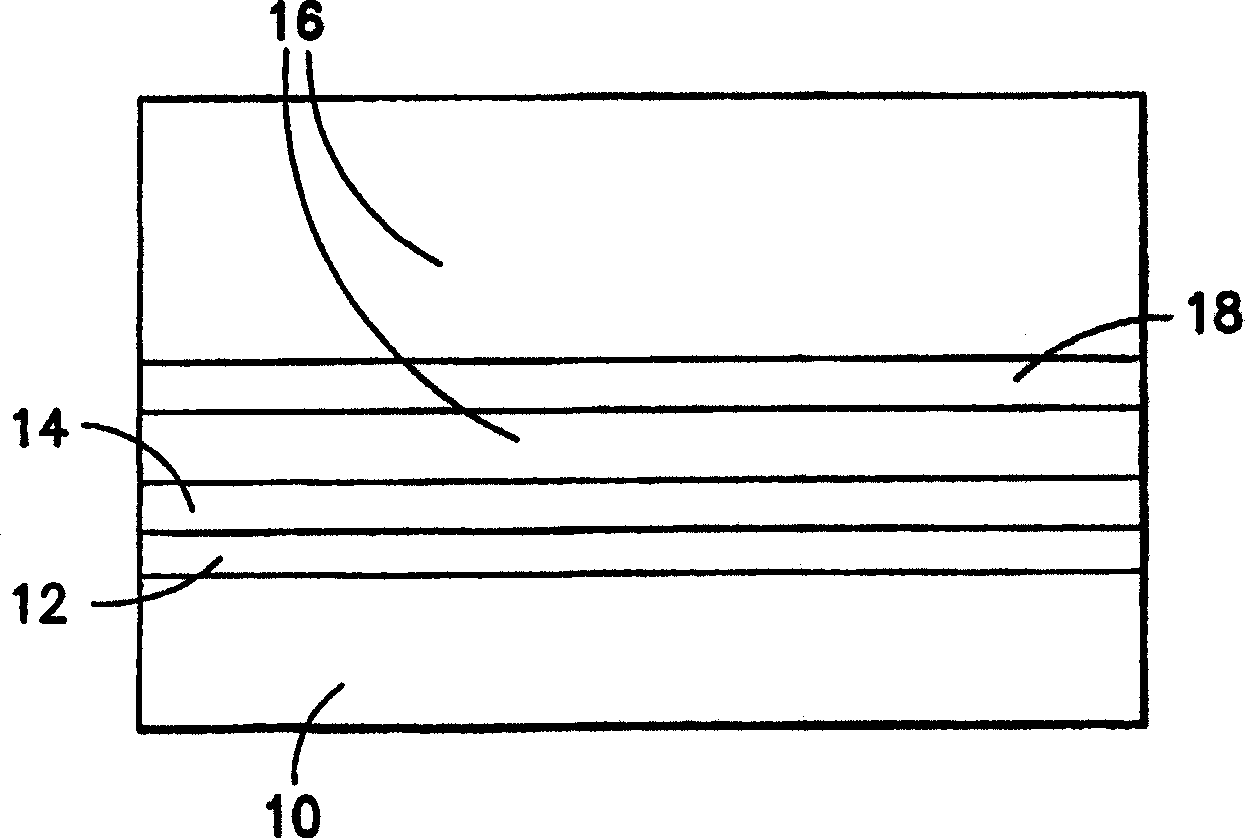

A Si-based diode (10, 10′, 100) is formed by epitaxially depositing a Si-based diode structure on a silicon substrate. The Si-based diode structure includes a Si-based pn junction (16, 16′, 18, 18′, 30, 32, 160, 161) having a backward diode current-voltage characteristic in which the forward tunneling current is substantially smaller than the backward tunneling current at comparable voltage levels. In some embodiments, the Si-based pn junction includes at least one non-silicon or silicon alloy layer such as at least one SiGe layer (16, 16′, 160, 161). In some embodiments, at least one delta doping (30, 32) is disposed on the silicon substrate in or near the pn junction, that together with the Si-based pn junction define an electrical junction having the backward diode current-voltage characteristic. A large area detector array may include a plurality of such Si-based diodes (10, 10′, 100).

Owner:THE OHIO STATES UNIV +1

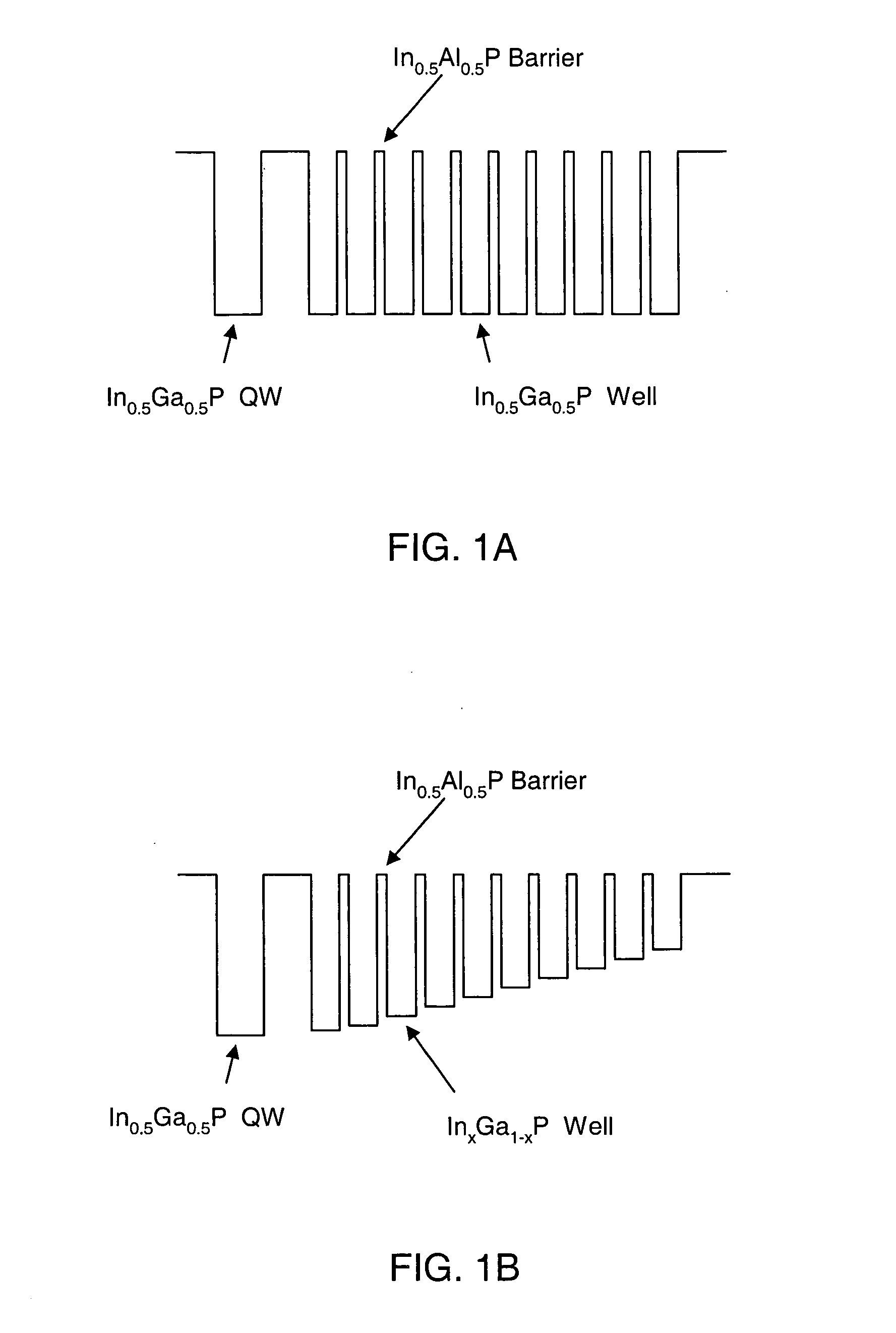

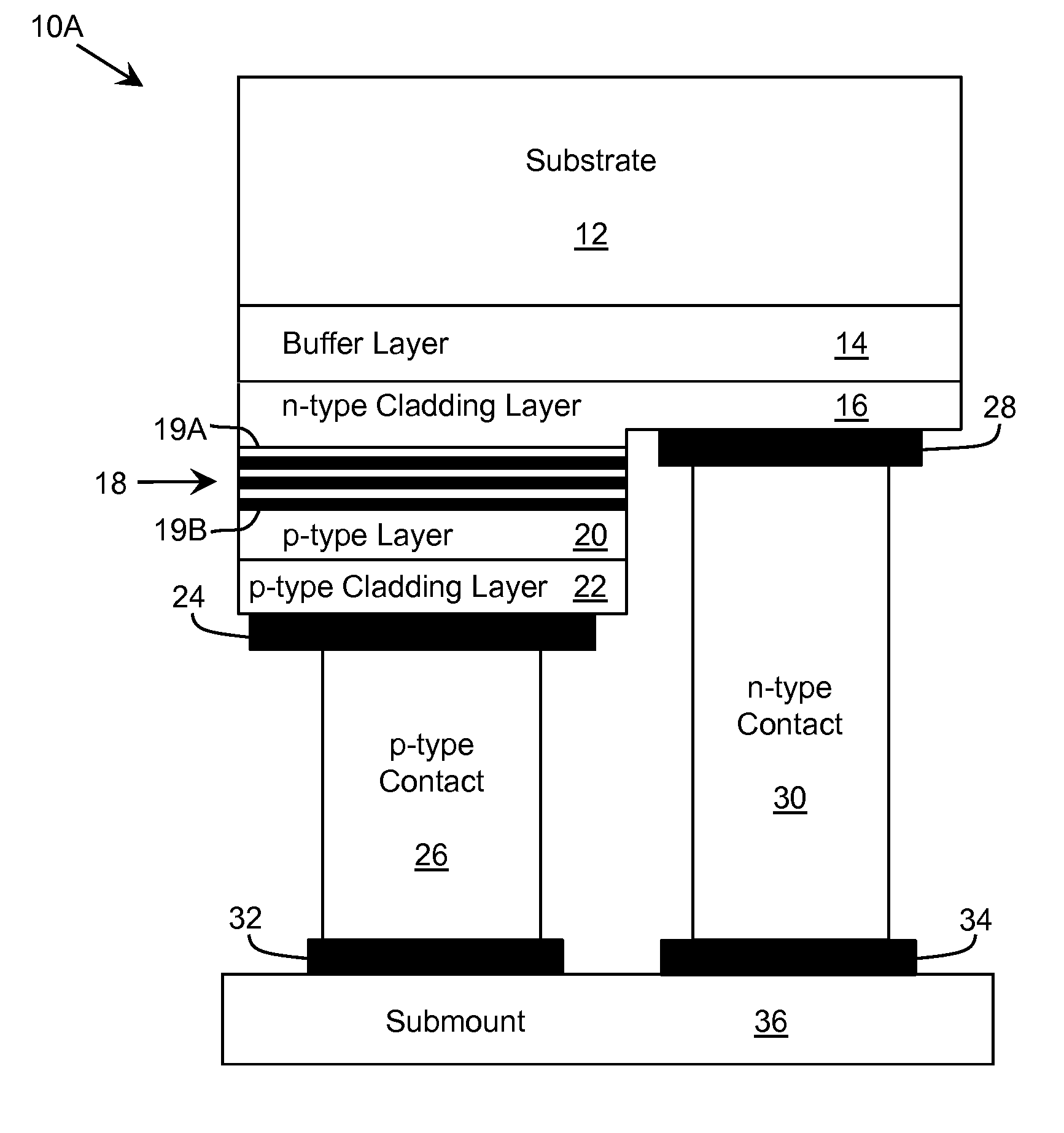

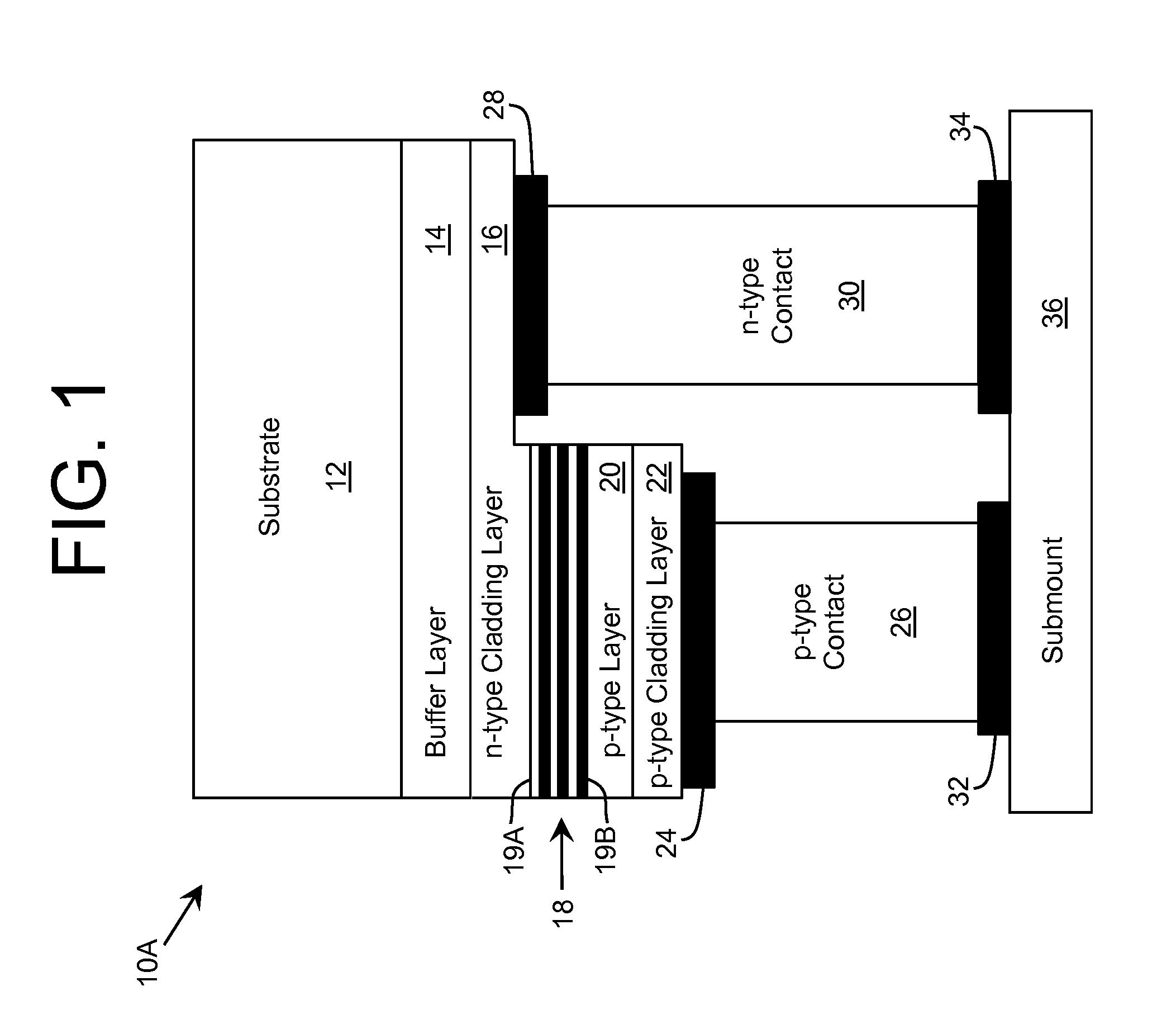

Light Emitting Diode with Polarization Control

ActiveUS20120217473A1Easy to optimizeSemiconductor/solid-state device manufacturingSemiconductor lasersDelta dopingQuantum well

An improved light emitting heterostructure is provided. The heterostructure includes an active region having a set of barrier layers and a set of quantum wells, each of which is adjoined by a barrier layer. The quantum wells have a delta doped p-type sub-layer located therein, which results in a change of the band structure of the quantum well. The change can reduce the effects of polarization in the quantum wells, which can provide improved light emission from the active region.

Owner:SENSOR ELECTRONICS TECH

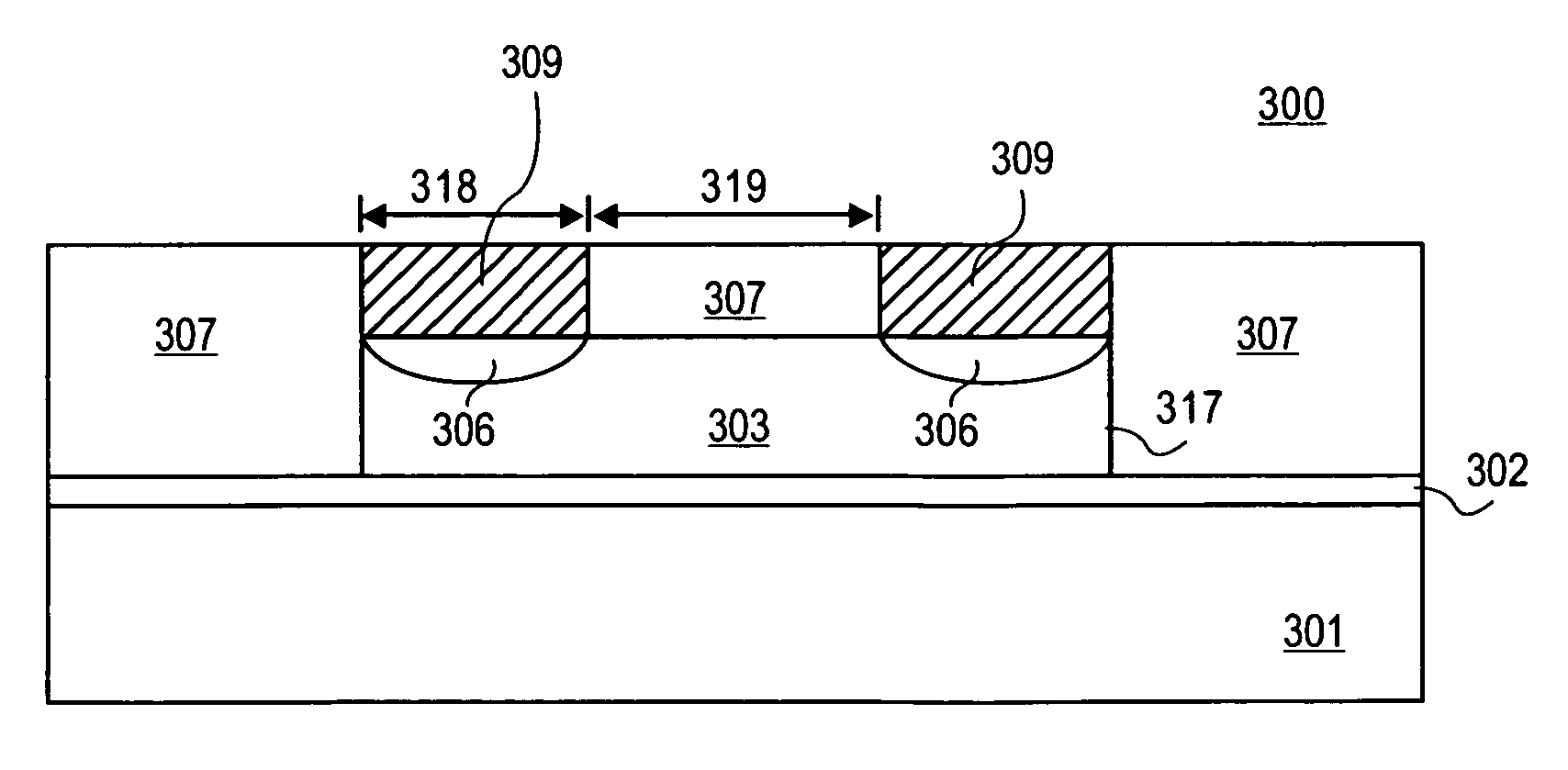

Methods of fabricating delta doped silicon carbide metal-semiconductor field effect transistors having a gate disposed in a double recess structure

InactiveUS20050023535A1Improve breakdown voltageReduce resistanceTransistorSemiconductor/solid-state device manufacturingDelta dopingMESFET

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a delta doped silicon carbide MESFET having a source, a drain and a gate. The gate is situated between the source and the drain and extends into a doped channel layer of a first conductivity type. Regions of silicon carbide adjacent to the source and the drain extend between the source and the gate and the drain and the gate, respectively. The regions of silicon carbide have carrier concentrations that are greater than a carrier concentration of the doped channel layer and are spaced apart from the gate.

Owner:CREE INC

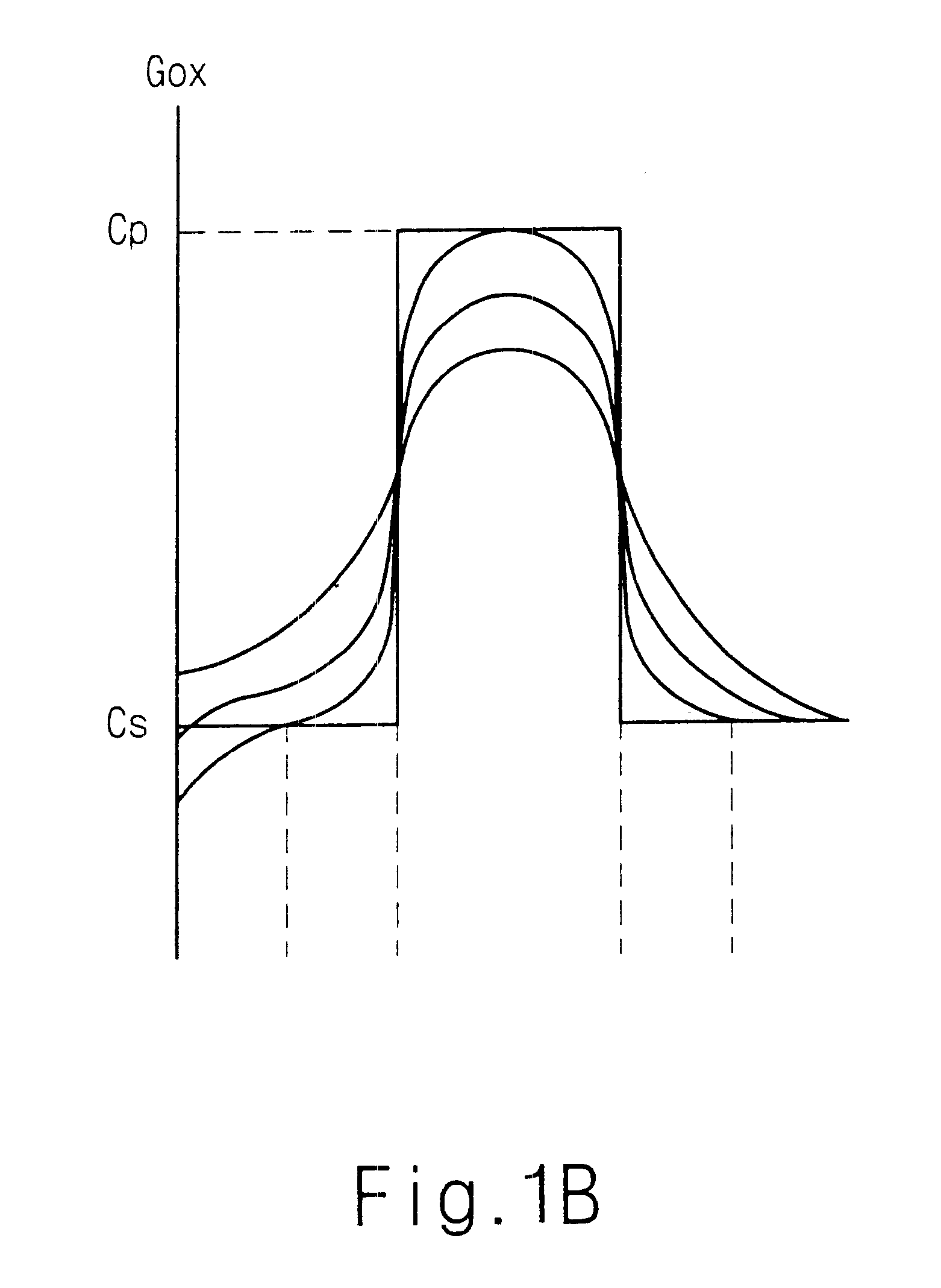

Variation Resistant Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET)

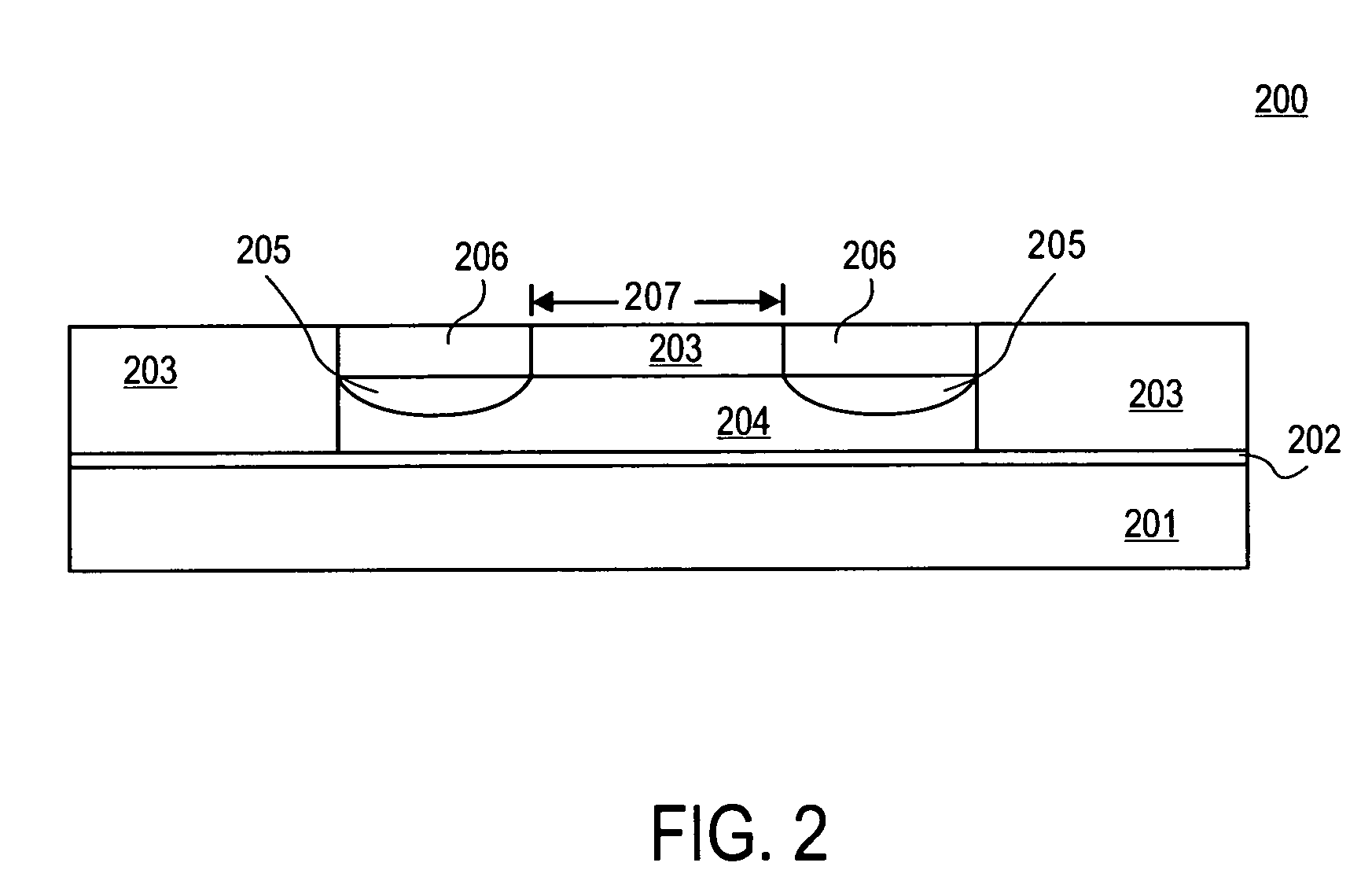

Variation resistant metal-oxide-semiconductor field effect transistors (MOSFETs) are manufactured using a high-K, metal-gate ‘channel-last’ process. A cavity is formed between spacers formed over a well area having separate drain and source areas, and then a recess into the well area is formed. The active region is formed in the recess, comprising an optional narrow highly doped layer, essentially a buried epitaxial layer, over which a second un-doped or lightly doped layer is formed which is a channel epitaxial layer. The high doping beneath the low doped epitaxial layer can be achieved utilizing low-temperature epitaxial growth with single or multiple delta doping, or slab doping. A high-K dielectric stack is formed over the channel epitaxial layer, over which a metal gate is formed within the cavity boundaries. In one embodiment of the invention a cap of poly-silicon or amorphous silicon is added on top of the metal gate.

Owner:SEMIWISE

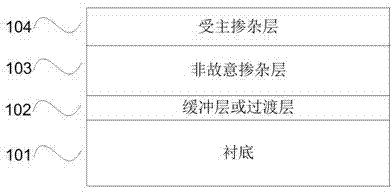

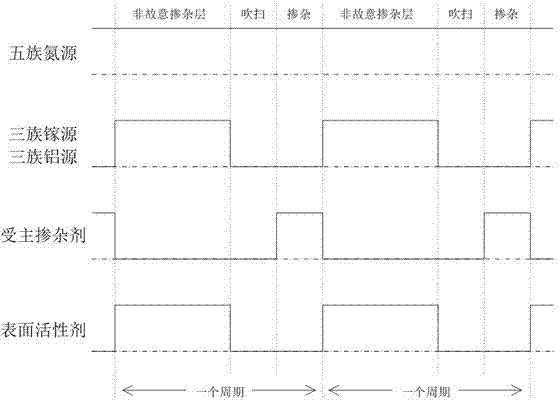

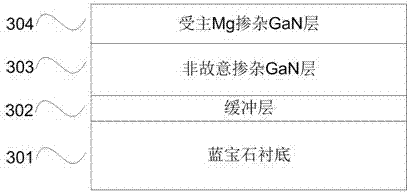

Preparation method of p type GaN and AlGaN semiconductor material

ActiveCN102903615AEasy to desorbImprove bindingSemiconductor/solid-state device manufacturingDimethylhydrazineSemiconductor materials

The invention discloses a preparation method of a p type GaN and AlGaN semiconductor material. A substrate, and a buffer layer or a transition layer, an unintended doped layer and an acceptor doped layer grown on the substrate from bottom to top are contained; in a growth process of the structure, ammonia or nitrogen dimethylhydrazine is used as a five-group nitrogen source; trimethyl gallium or TEGa used as a three-group gallium source, trimethylaluminium or triethyl aluminum used as a three-group aluminium source, and trimethylindium or TEIn used as a three-group indium source are collectively called three-group metal sources; and the trimethylindium or the TEIn is also used as a surface active agent and used in the acceptor doped layer. According to the method, the trimethylindium or the TEIn is used as the surface active agent to assist growth, and simultaneously, the acceptor doped layer is prepared by adopting a delta doping method. According to the method, the doping efficiency of acceptor doped magnesium atoms is increased, and simultaneously, the self-compensation effect is suppressed, so that the p type GaN and AlGaN semiconductor material with favorable crystalline quality and high hole concentration is obtained.

Owner:SUN YAT SEN UNIV

Dopant confinement in the delta doped layer using a dopant segregation barrier in quantum well structures

InactiveUS20080157058A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantDelta doping

A device grade III-V quantum well structure and method of manufacture is described. Embodiments of the present invention enable III-V InSb quantum well device layers with defect densities below 1×108 cm−2 to be formed. In an embodiment of the present invention, a delta doped layer is disposed on a dopant segregation barrier in order to confine delta dopant within the delta doped layer and suppress delta dopant surface segregation.

Owner:INTEL CORP

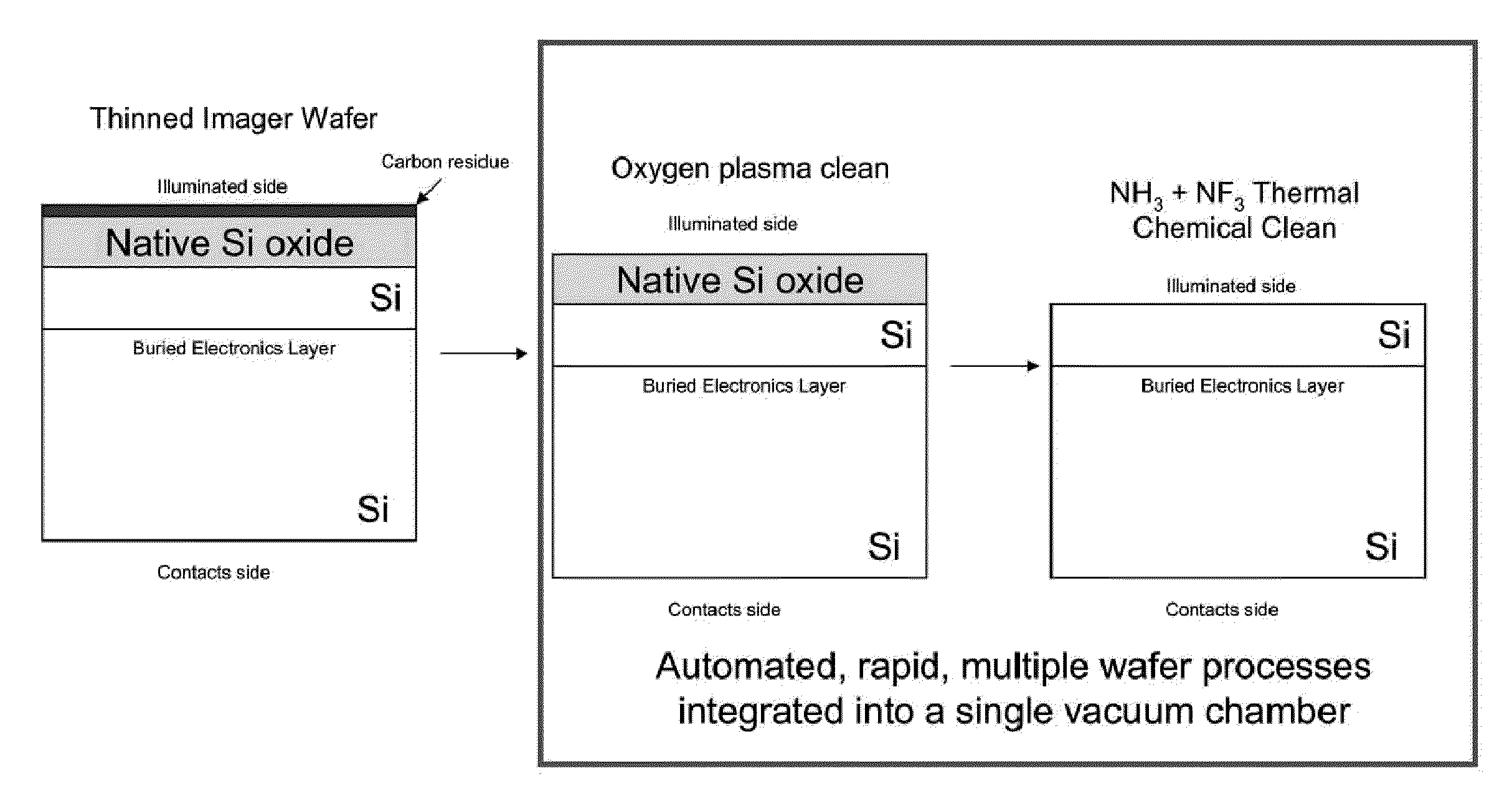

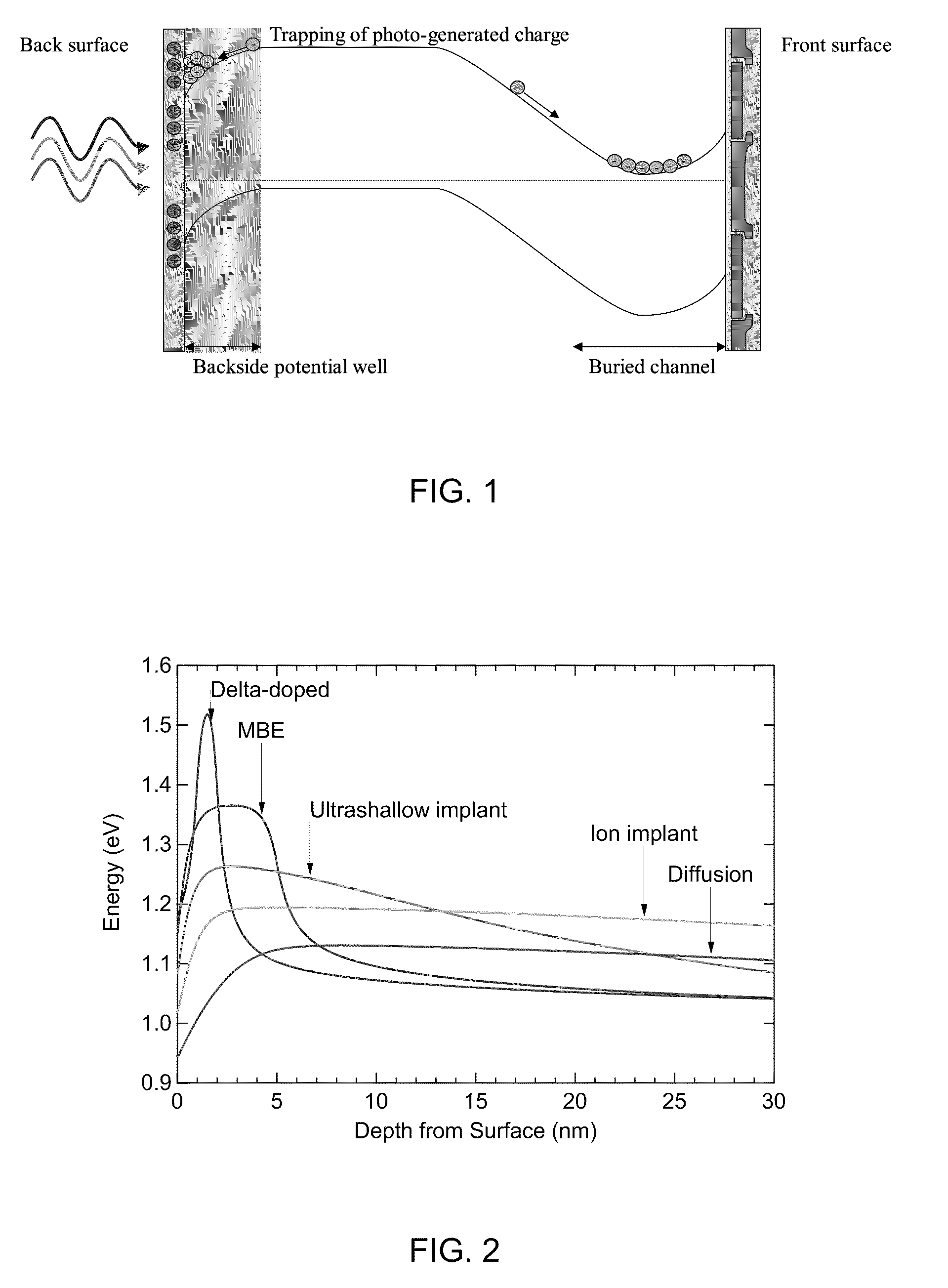

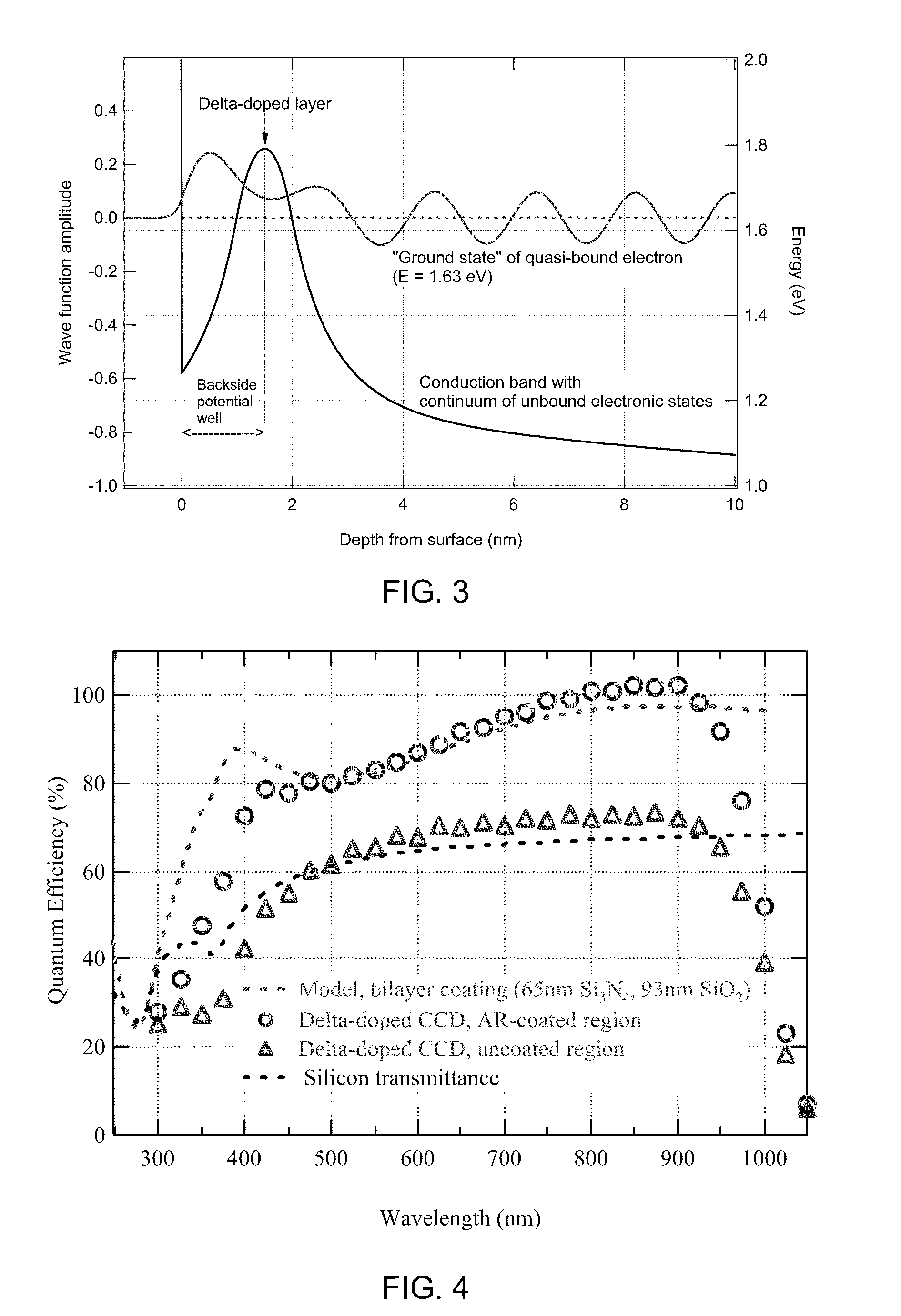

Delta-doping at wafer level for high throughput, high yield fabrication of silicon imaging arrays

ActiveUS20110140246A1Avoid interactionStabilizes electronic propertyVacuum evaporation coatingSolid-state devicesQuantum efficiencyDelta doping

Systems and methods for producing high quantum efficiency silicon devices. A silicon MBE has a preparation chamber that provides for cleaning silicon surfaces using an oxygen plasma to remove impurities and a gaseous (dry) NH3+NF3 room temperature oxide removal process that leaves the silicon surface hydrogen terminated. Silicon wafers up to 8 inches in diameter have devices that can be fabricated using the cleaning procedures and MBE processing, including delta doping.

Owner:CALIFORNIA INST OF TECH

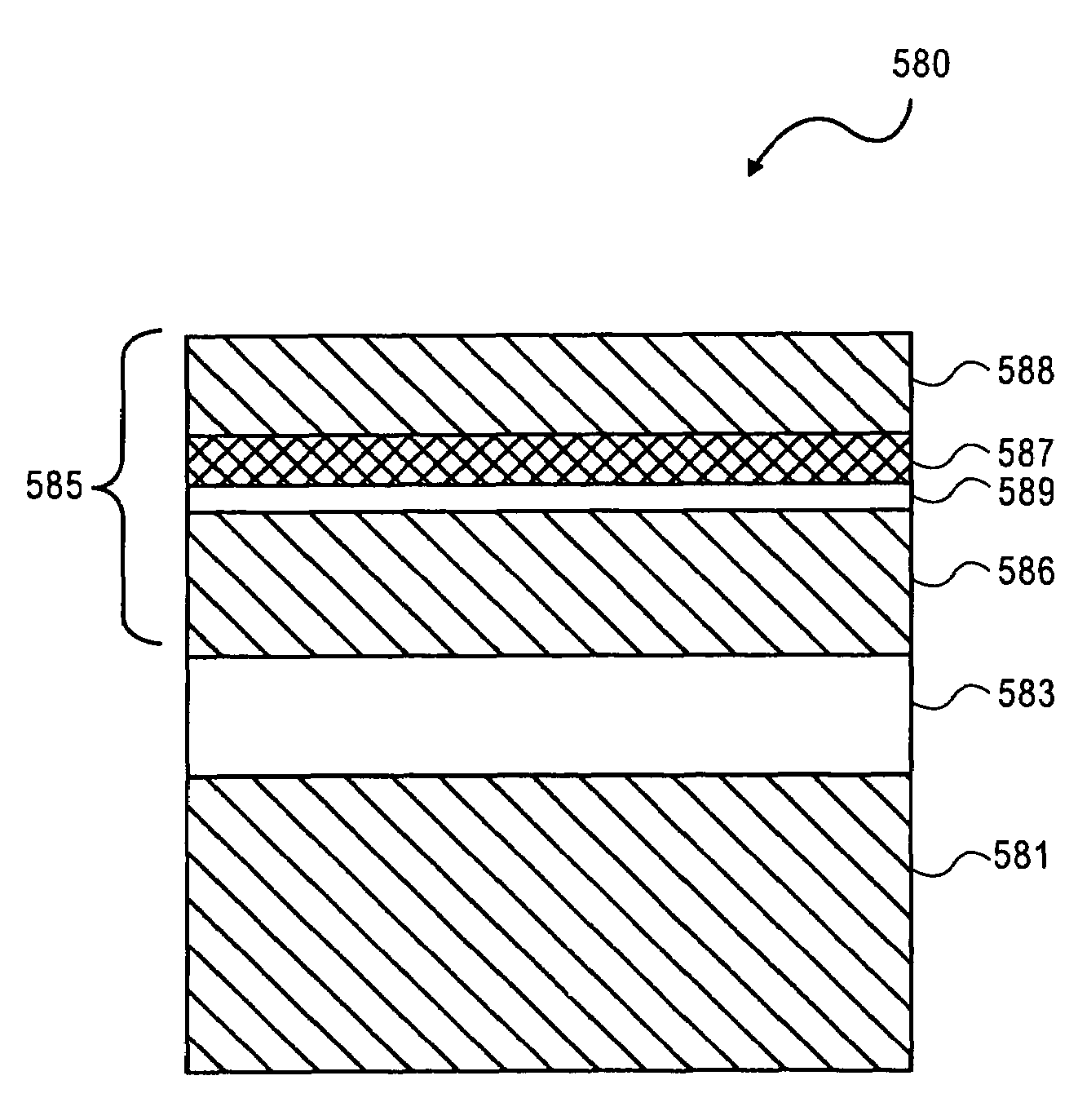

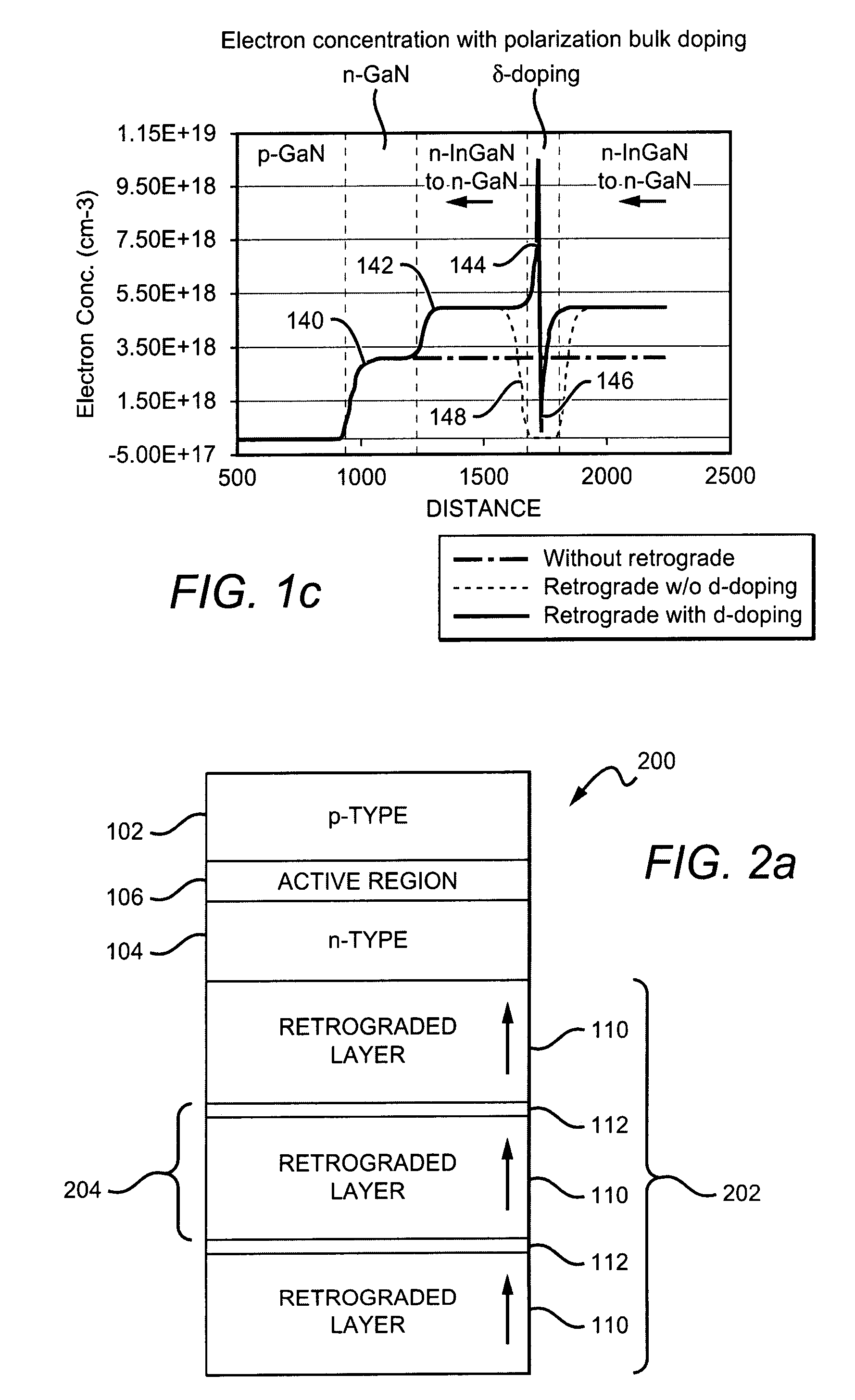

Polarization doping in nitride based diodes

A light emitting device comprising a three-dimensional polarization-graded (3DPG) structure that improves lateral current spreading within the device without introducing additional dopant impurities in the epitaxial structures. The 3DPG structure can include a repeatable stack unit that may be repeated several times within the 3DPG. The stack unit includes a compositionally graded layer and a silicon (Si) delta-doped layer. The graded layer is compositionally graded over a distance from a first material to a second material, introducing a polarization-induced bulk charge into the structure. The Si delta-doped layer compensates for back-depletion of the electron gas at the interface of the graded layers and adjacent layers. The 3DPG facilitates lateral current spreading so that current is injected into the entire active region, increasing the number of radiative recombination events in the active region and improving the external quantum efficiency and the wall-plug efficiency of the device.

Owner:CREELED INC

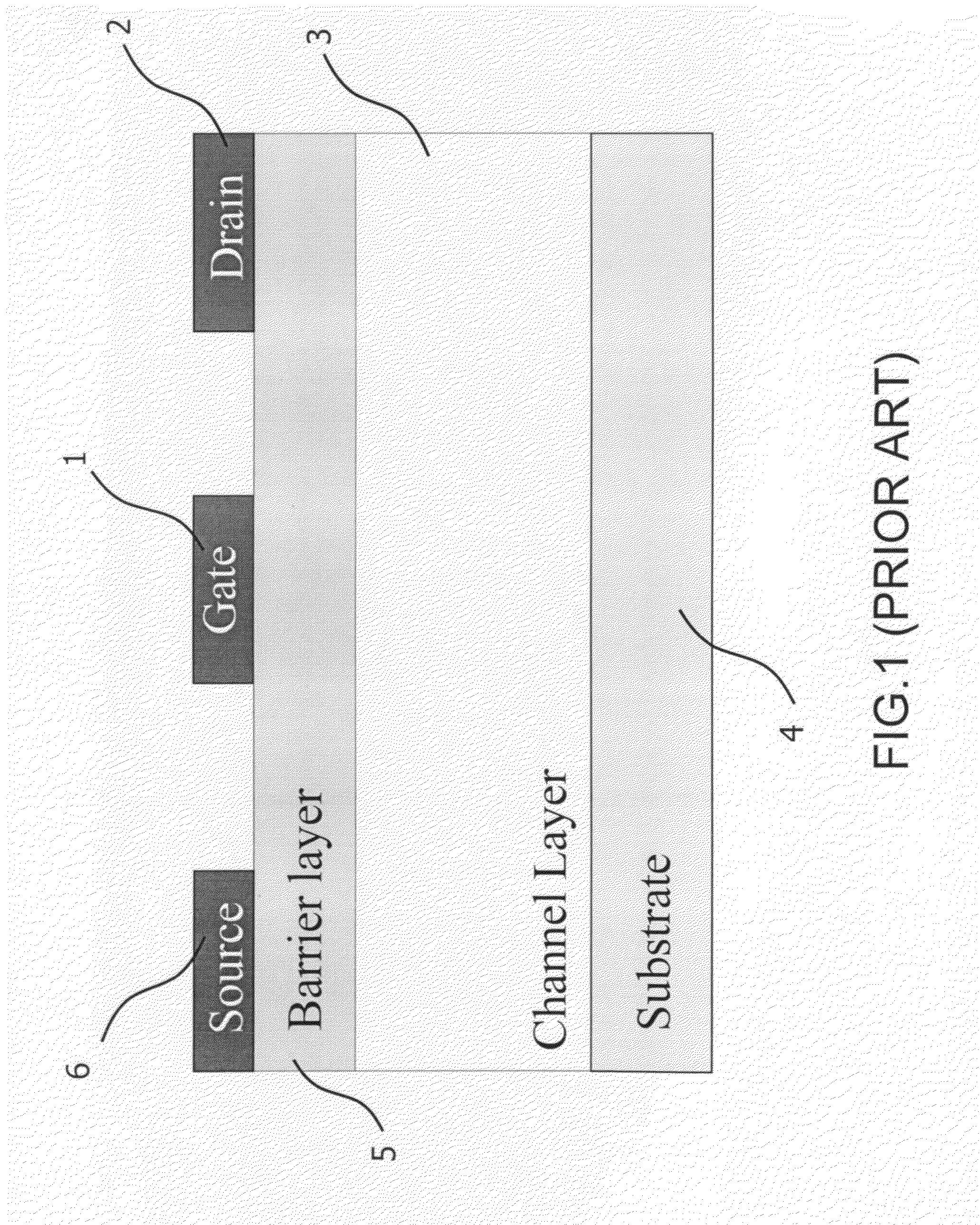

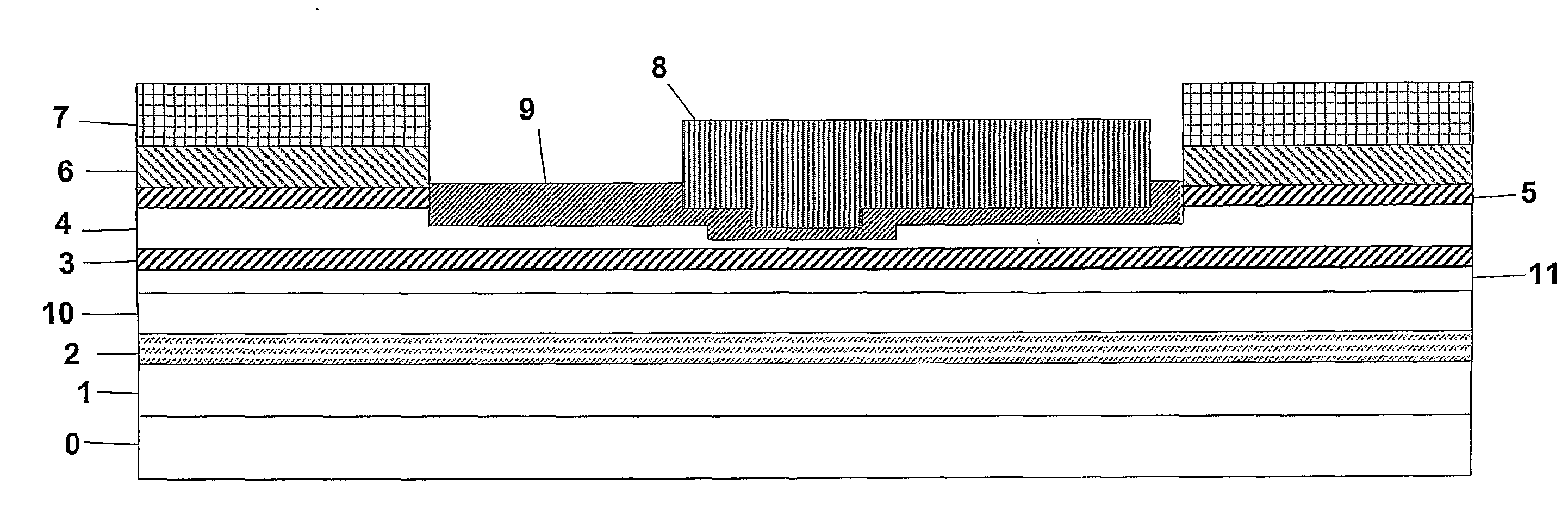

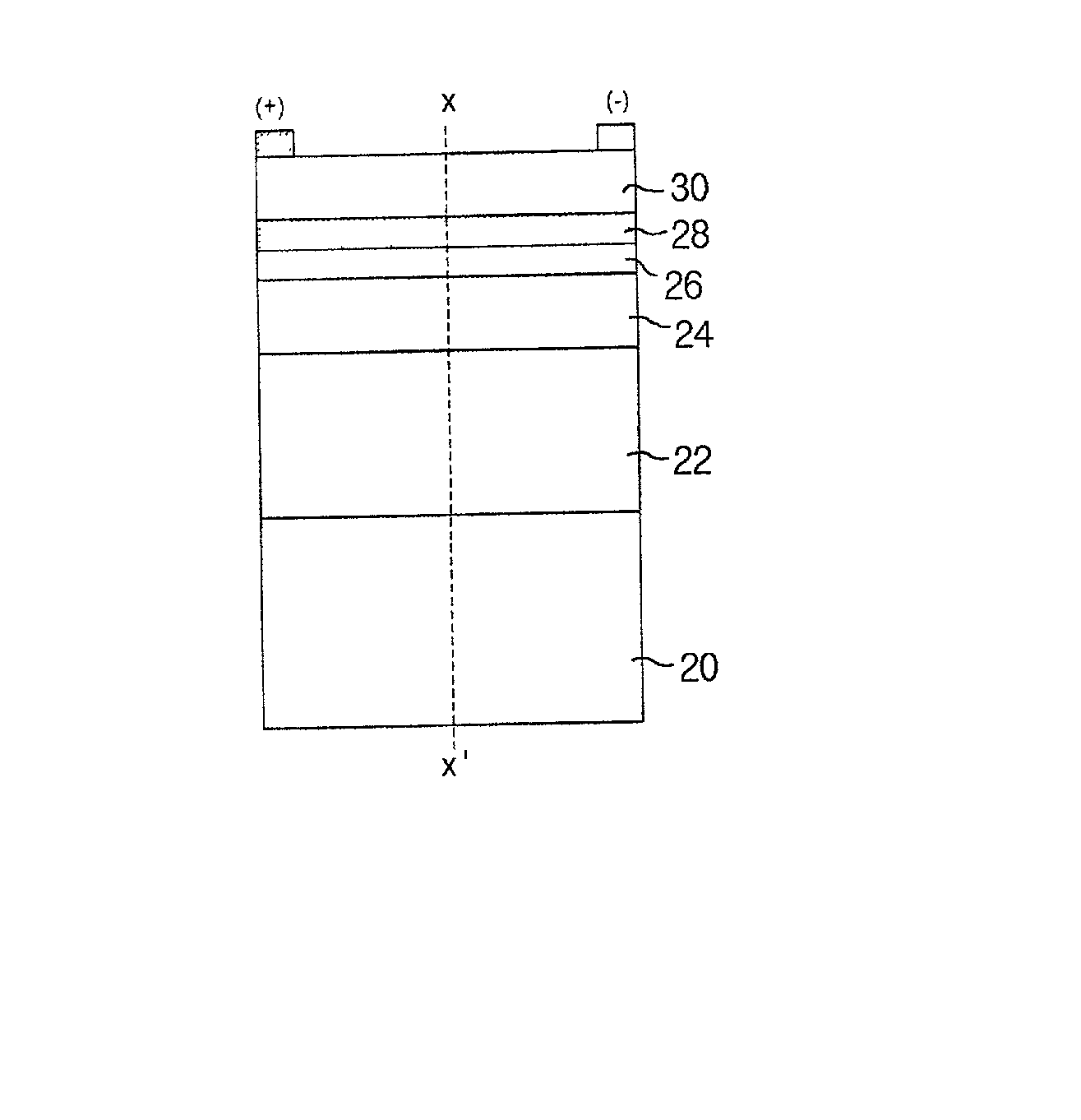

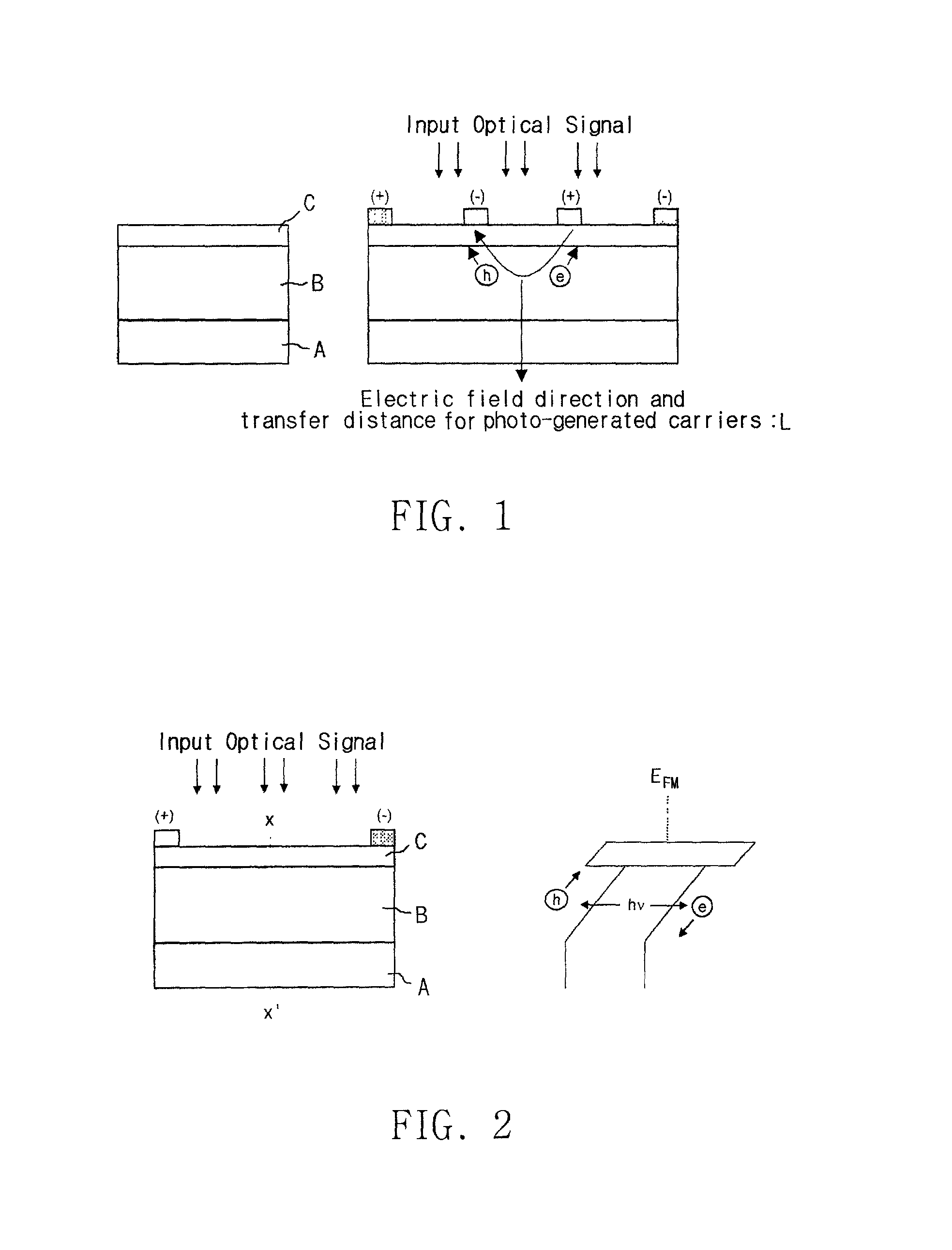

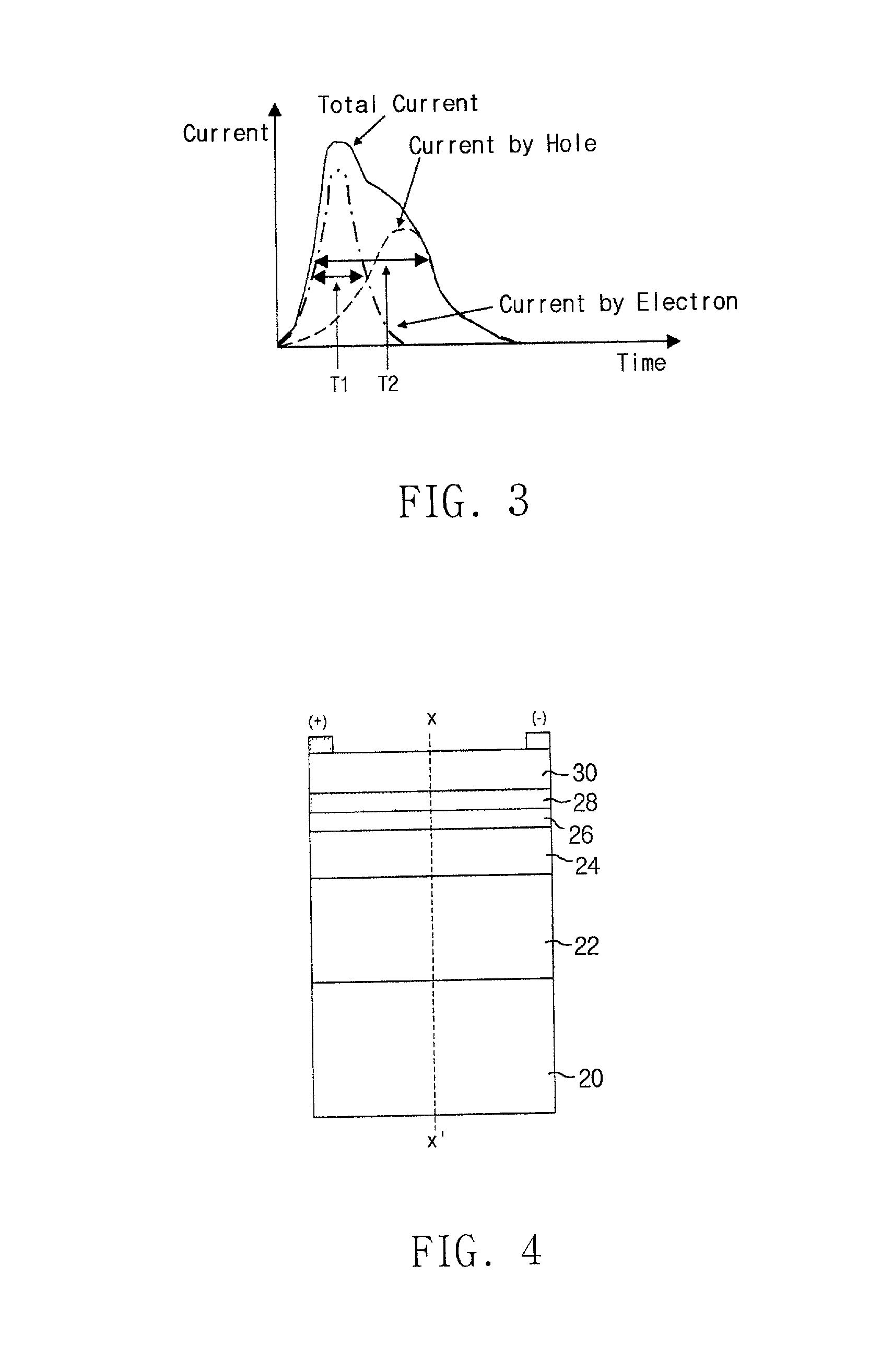

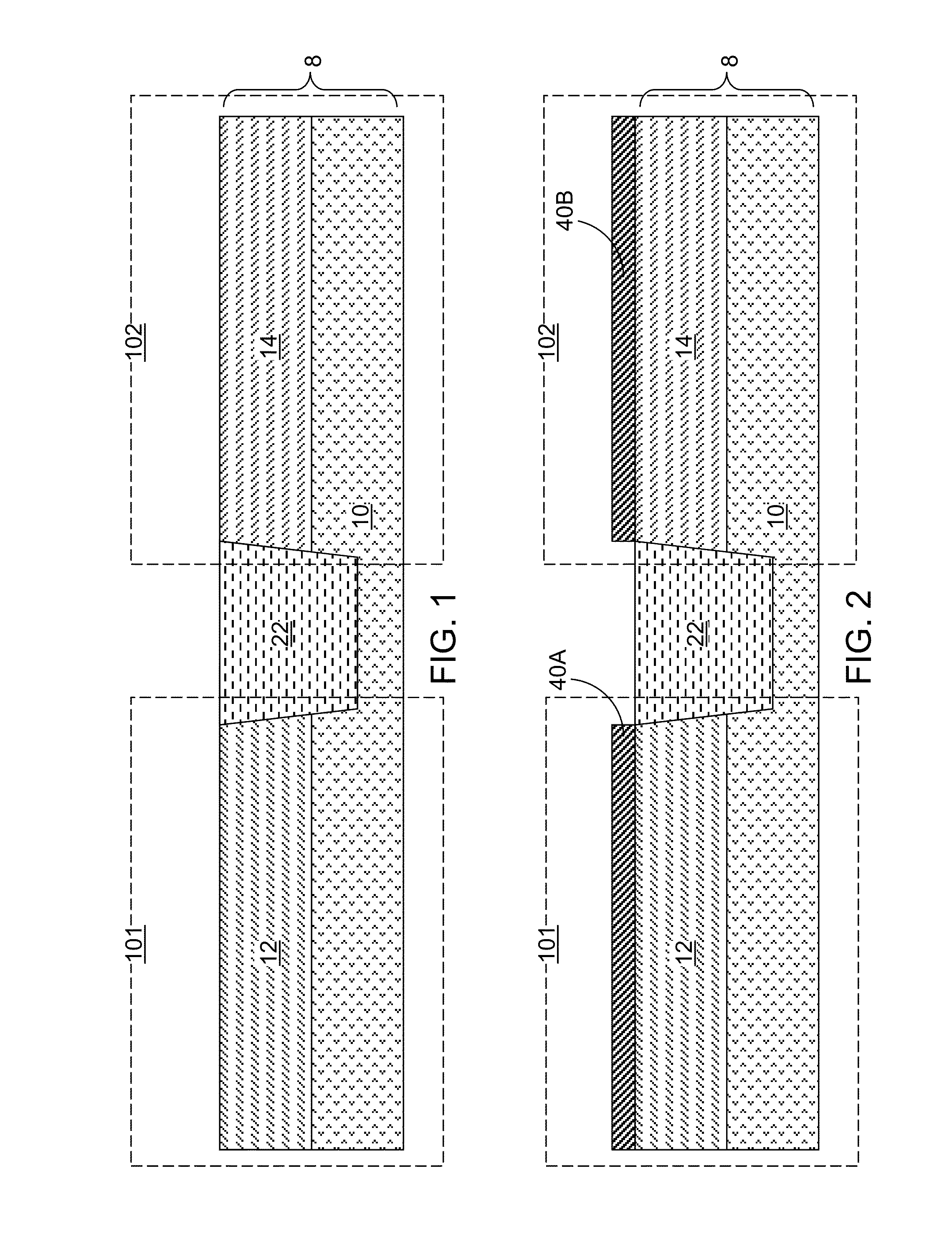

Photodetector utilizing a HEMTstructure

The present invention relates to MSM photodetectors based on the high electron mobility transistor (HEMT) structure. More specifically, the present invention relates to MSM photodetectors based on the high electron mobility transistor (HEMT) structure that use a barrier layer of the HEMT structure as a Schottky barrier layer of the photodetector and use the channel layer of the HEMT structure as an absorption layer of the photodetector by doping the bottom part of the channel layer with a p-type dopant. Modification of the HEMT structure for the MSM photodetector can enhance electron current and suppress hole current, resulting in an impulse photocurrent response having a narrow pulse width. The present invention comprises an undoped buffer layer grown on the semi-insulating substrate, a p-doped channel layer that is used as an absorption layer grown on the said buffer layer, an undoped channel layer that is used as an absorption layer grown on the said channel layer, an undoped barrier layer that is composed of a material having a larger band gap energy than the said channel layers grown on the said undoped channel layer, a heavily n-type delta-doped barrier layer that is composed of a material having a larger band gap energy than the said channel layers grown on the said undoped barrier layer, and an undoped barrier layer that is composed of a material having a larger band gap energy than the said channel layers grown on the said heavily n-type delta-doped barrier layer.

Owner:GWANGJU INST OF SCI & TECH

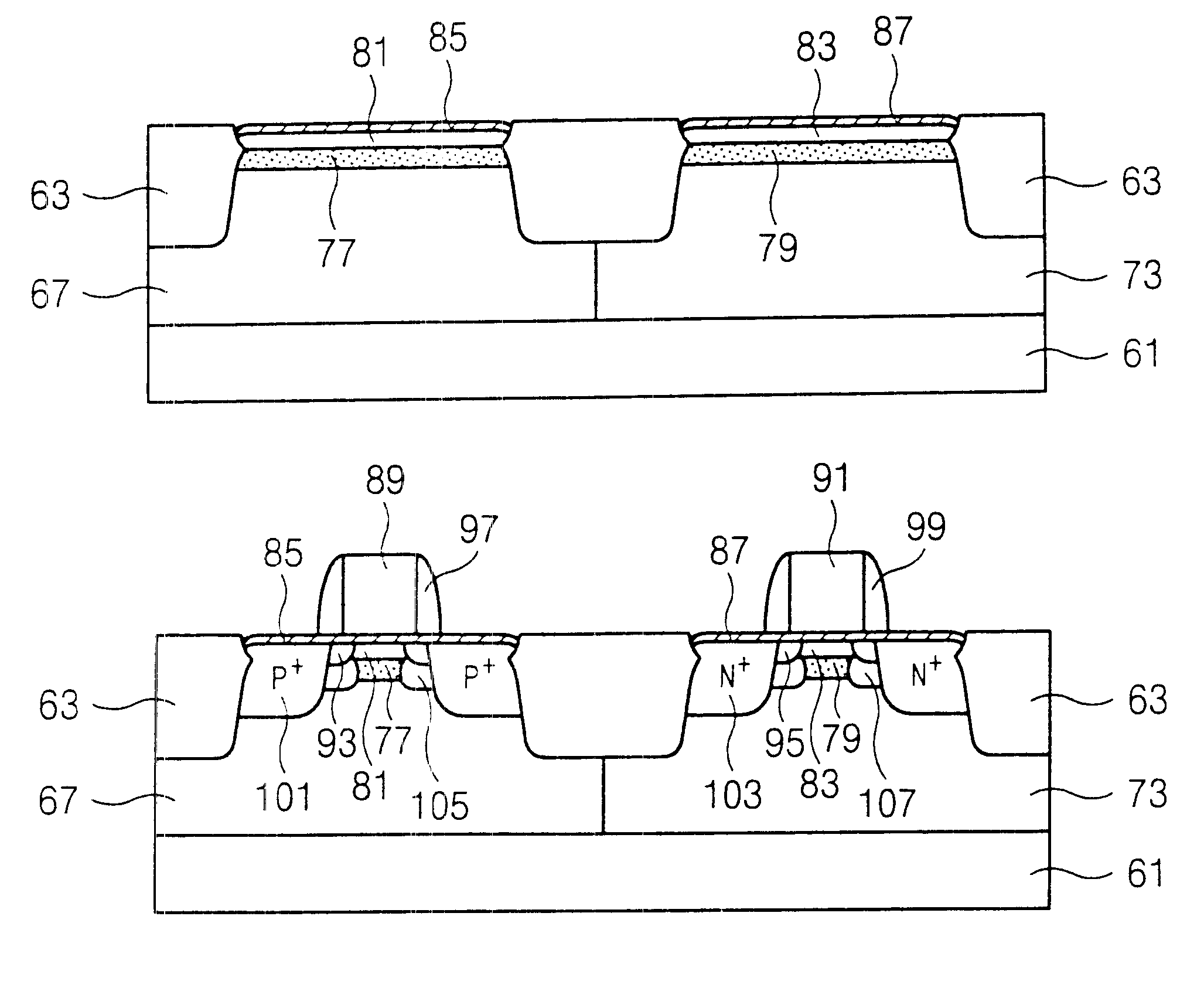

CMOS having a SiC/SiGe alloy stack

A delta doping of silicon by carbon is provided on silicon surfaces by depositing a silicon carbon alloy layer on silicon surfaces, which can be horizontal surfaces of a bulk silicon substrate, horizontal surfaces of a top silicon layer of a semiconductor-on-insulator substrate, or vertical surfaces of silicon fins. A p-type field effect transistor (PFET) region and an n-type field effect transistor (NFET) region can be differentiated by selectively depositing a silicon germanium alloy layer in the PFET region, and not in the NFET region. The silicon germanium alloy layer in the PFET region can overlie or underlie a silicon carbon alloy layer. A common material stack can be employed for gate dielectrics and gate electrodes for a PFET and an NFET. Each channel of the PFET and the NFET includes a silicon carbon alloy layer, and is differentiated by the presence or absence of a silicon germanium layer.

Owner:GLOBALFOUNDRIES US INC

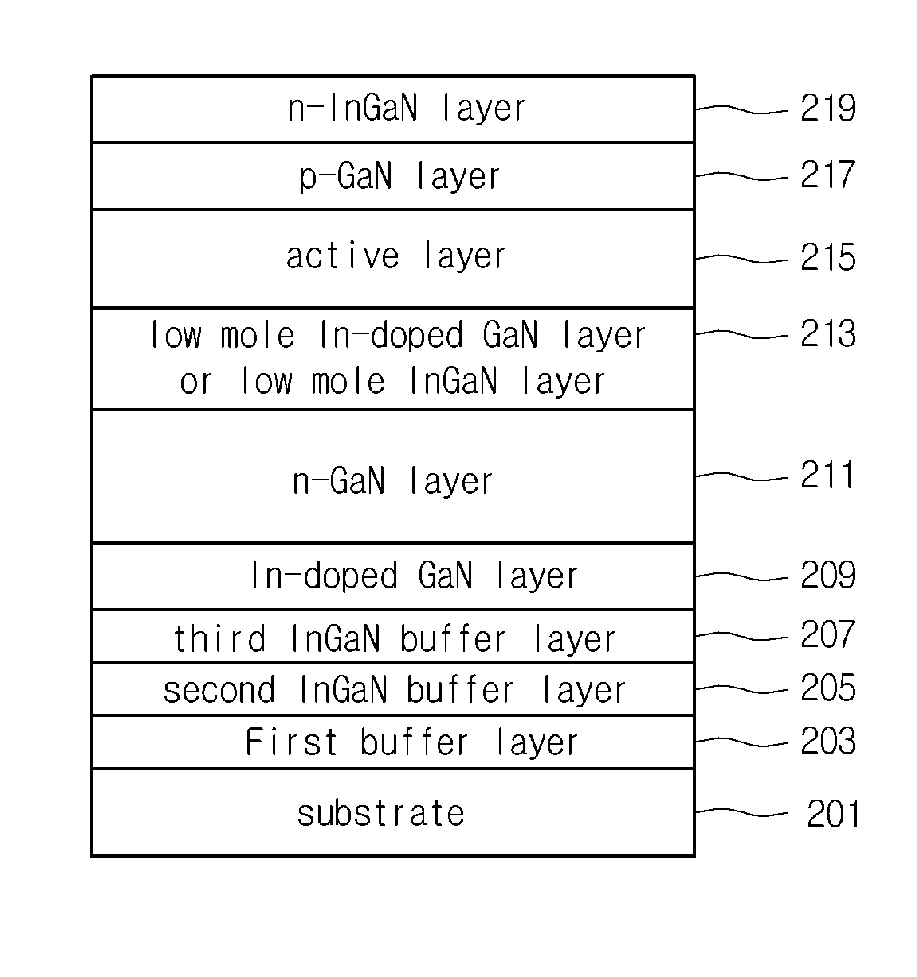

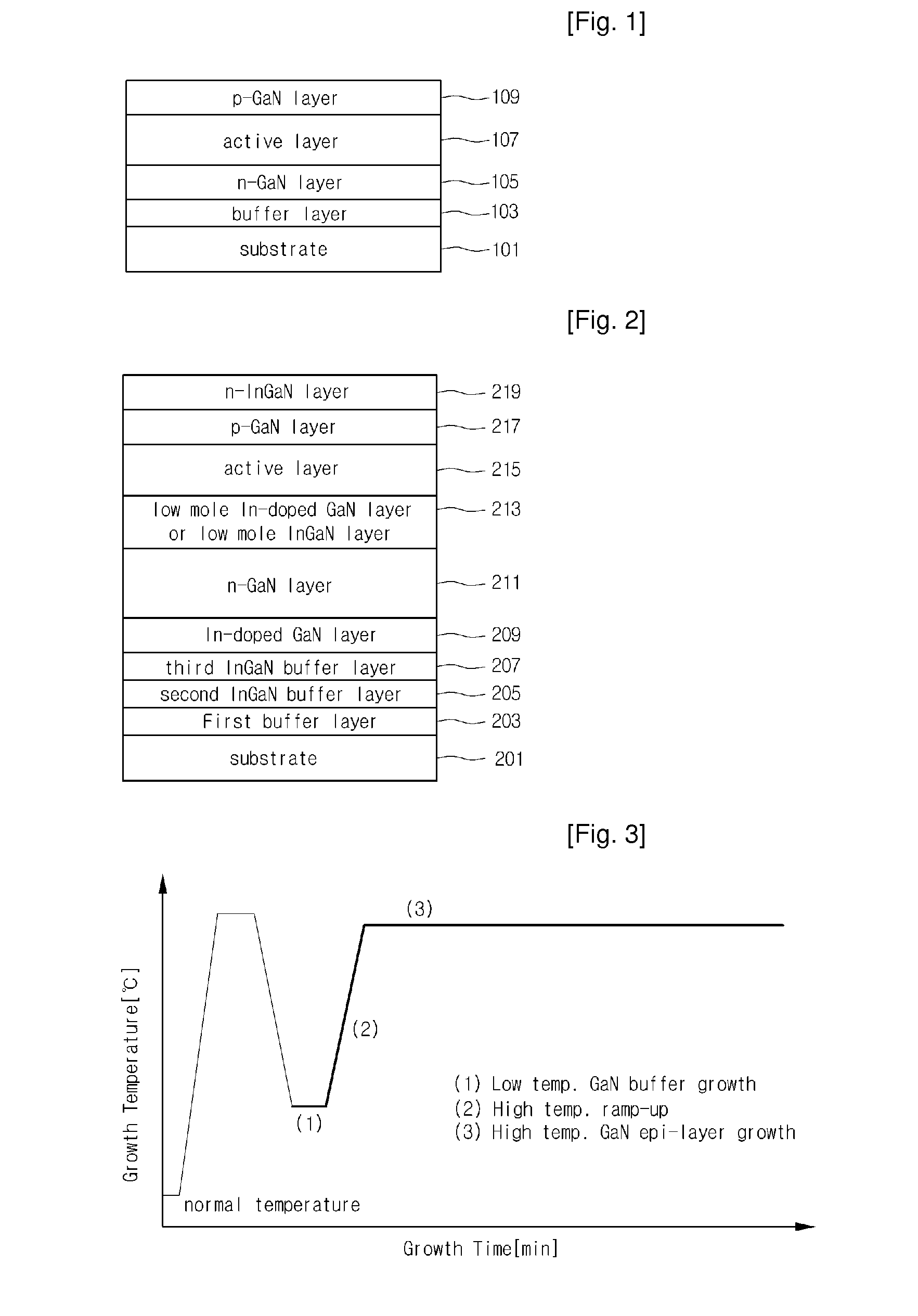

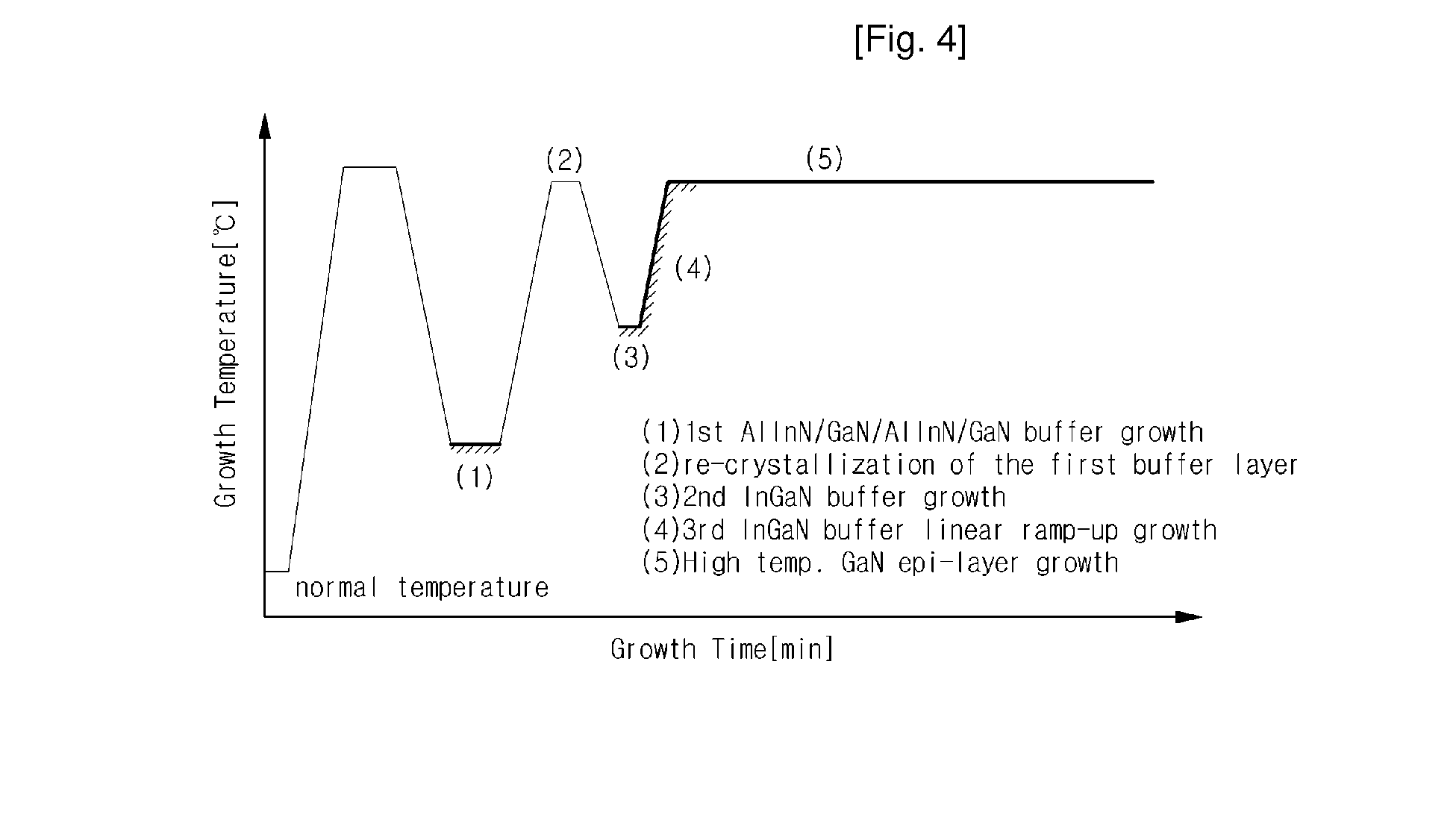

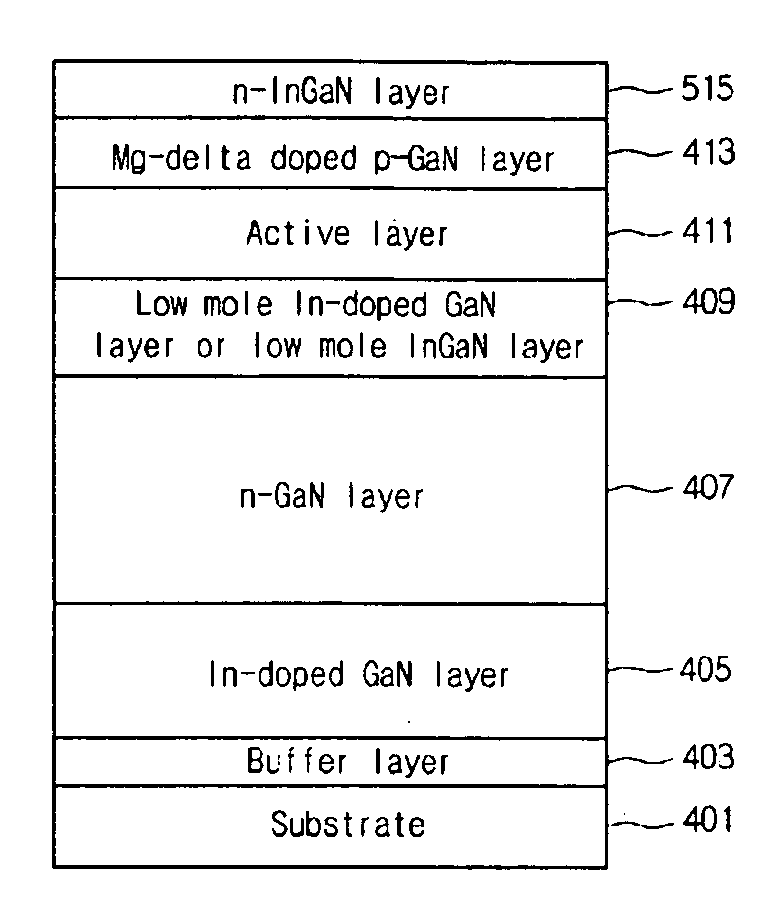

Nitride Semiconductor Light Emitting Device and Fabrication Method Thereof

ActiveUS20090166606A1Enhance layeringIncrease optical powerSolid-state devicesSemiconductor/solid-state device manufacturingDelta dopingOptical power

Provided is a nitride semiconductor light emitting device including: a first nitride semiconductor layer; an active layer formed above the first nitride semiconductor layer; and a delta doped second nitride semiconductor layer formed above the active layer. According to the present invention, the optical power of the nitride semiconductor light emitting device is enhanced, optical power down phenomenon is improved and reliability against ESD (electro static discharge) is enhanced.

Owner:SUZHOU LEKIN SEMICON CO LTD

Theta-doped 4HSiC avalanche ultraviolet photoelectric detector and its production

The invention is concerned with delta-doped 4H-SiC ultraviolet avalanche photodetector and its production, involved with a kind of ultraviolet photodetector. Thedelta-doped 4H-SiC ultraviolet avalanche photodetector and production can enhance the capability of device, eliminate the restrict of quantum yield and respond time to avalanche device, control the thickness of elevated area, the concentration of surface charge and the length of absorbing area. The table-board owns n+ type of 4H-SiC under lay, and there is n+ type buffer layer, super-low-doped n- type layer, delta-doped n type layer, low-doped n- type layer and high-doped p+ type layer on the table-board one by one. The super-low-doped n- type layer, delta-doped n type layer, low-doped n- type layer form active layer. It has at least three table-boards, the lowest one sets on the n+ type buffer layer to isolation of device, the other table-boards set on active layer of device, while the surface of device owns compact Silica passivation film with p type and n type poles.

Owner:XIAMEN UNIV

Doped group III-V nitride materials, and microelectronic devices and device precursor structures comprising same

A Group III-V nitride microelectronic device structure including a delta doped layer and / or a doped superlattice. A delta doping method is described, including the steps of: depositing semiconductor material on a substrate by a first epitaxial film growth process; terminating the deposition of semiconductor material on the substrate to present an epitaxial film surface; delta doping the semiconductor material at the epitaxial film surface, to form a delta doping layer thereon; terminating the delta doping; resuming deposition of semiconductor material to deposit semiconductor material on the delta doping layer, in a second epitaxial film growth process; and continuing the semiconductor material second epitaxial film growth process to a predetermined extent, to form a doped microelectronic device structure, wherein the delta doping layer is internalized in semiconductor material deposited in the first and second epitaxial film growth processes.

Owner:CREELED INC

Dopant confinement in the delta doped layer using a dopant segregation barrier in quantum well structures

InactiveUS7601980B2Semiconductor/solid-state device manufacturingSemiconductor devicesDopantDelta doping

Owner:INTEL CORP

Schottky barrier metal-germanium contact in metal-germanium-metal photodetectors

Metal-Semiconductor-Metal (“MSM”) photodetectors and methods to fabricate thereof are described. The MSM photodetector includes a thin heavily doped (“delta doped”) layer deposited at an interface between metal contacts and a semiconductor layer to reduce a dark current of the MSM photodetector. In one embodiment, the semiconductor layer is an intrinsic semiconductor layer. In one embodiment, the thickness of the delta doped layer is less than 100 nanometers. In one embodiment, the delta doped layer has a dopant concentration of at least 1×1018 cm−3. A delta doped layer is formed on portions of a semiconductor layer over a substrate. Metal contacts are formed on the delta doped layer. A buffer layer may be formed between the substrate and the semiconductor layer. In one embodiment, the substrate includes silicon, and the semiconductor layer includes germanium.

Owner:INTEL CORP

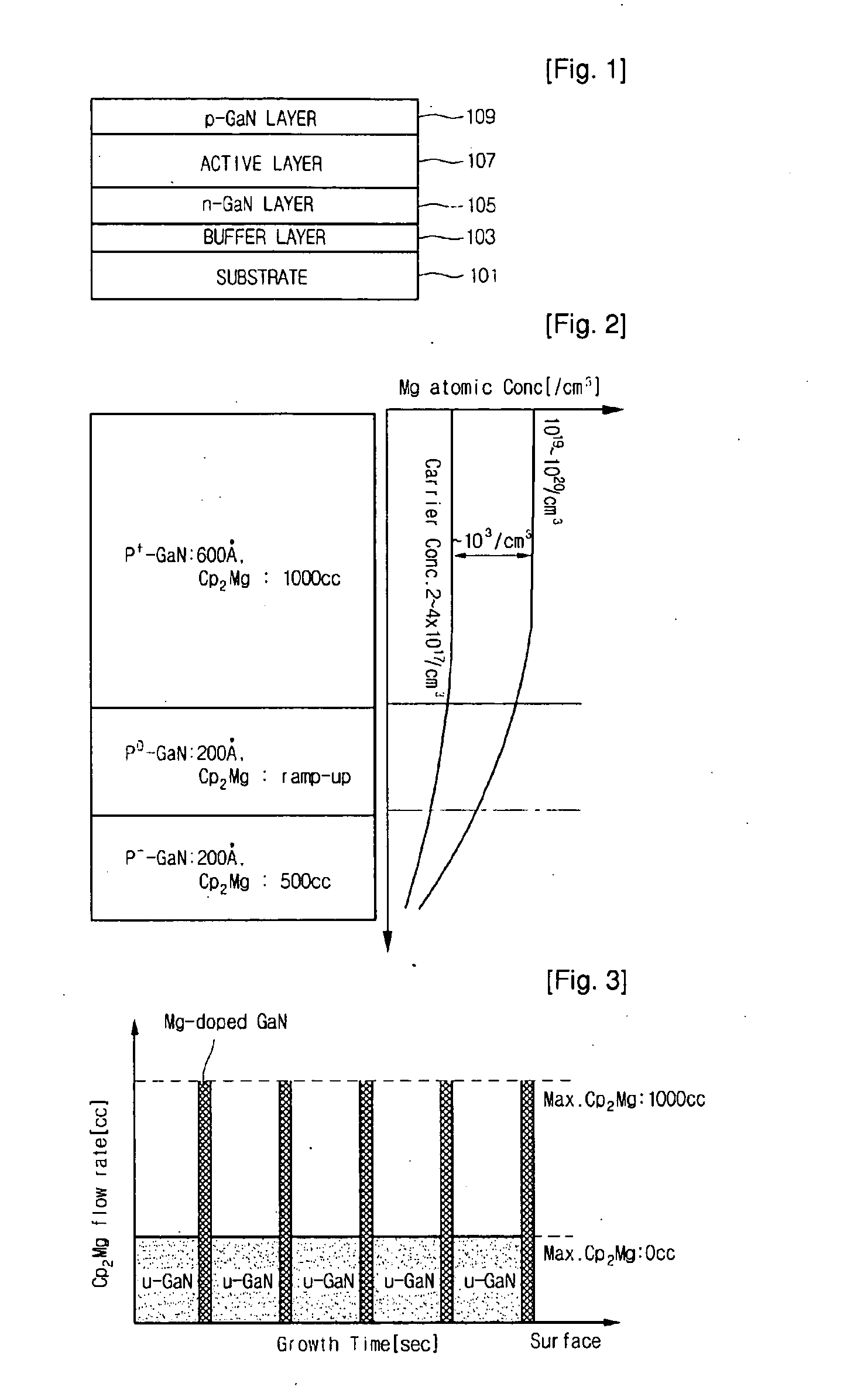

LED epitaxial layer growing method and LED epitaxial layer

InactiveCN103996759AImprove crystal qualityIncrease contactSemiconductor devicesDelta dopingTotal thickness

The invention provides an LED epitaxial layer growing method and an LED epitaxial layer. The method for growing a P-type GaN layer comprises the steps that A, NH3 and Cp2Mg are introduced in a reaction chamber at the temperature of 900 DEG C to 950 DEG C, wherein pressure of a reaction cavity ranges from 200 mbar to 600 mbar, TMGa is closed, and pretreatment of doping Mg is carried out for 10 minutes-20 minutes; B, TMGa is introduced, Cp2Mg is closed, a GaN layer grows for 20 minutes-40 minutes, and the thickness of GaN is 5 nm-10 nm; the step A and the step B are repeated ten to twenty times until the total thickness of the P-type GaN layer is 80 nm-200 nm. According to the method, delta doping is used for growing the P-type GaN layer, the crystal quality of the P-type GaN layer is improved, the dislocation density is reduced, and hole concentration and the migration rate of P-type GaN are improved; more hole-electron pairs can be provided for light-emitting active areas of an LED device, the composite probability is improved, the brightness is promoted, and therefore photoelectric property of the LED device is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

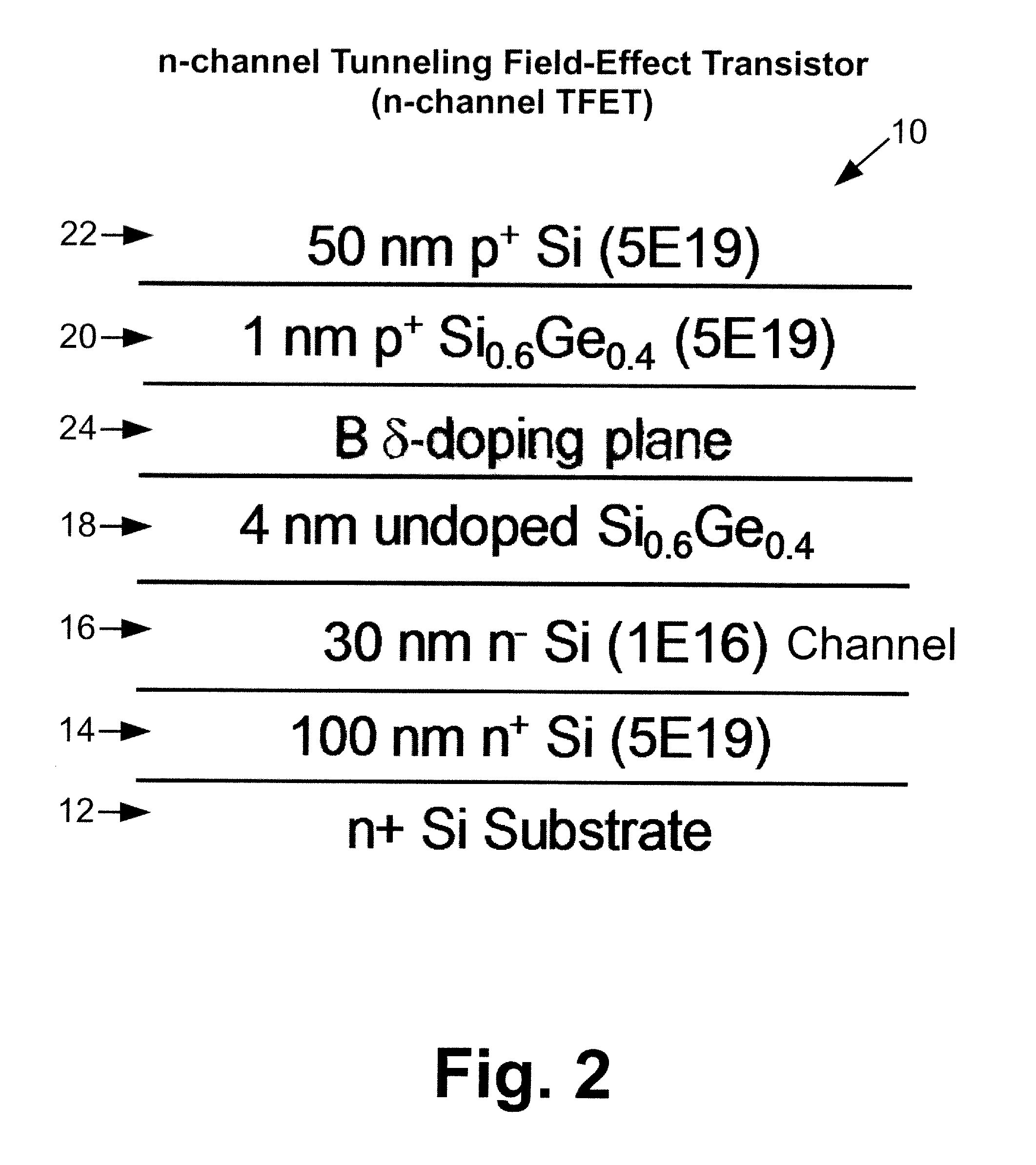

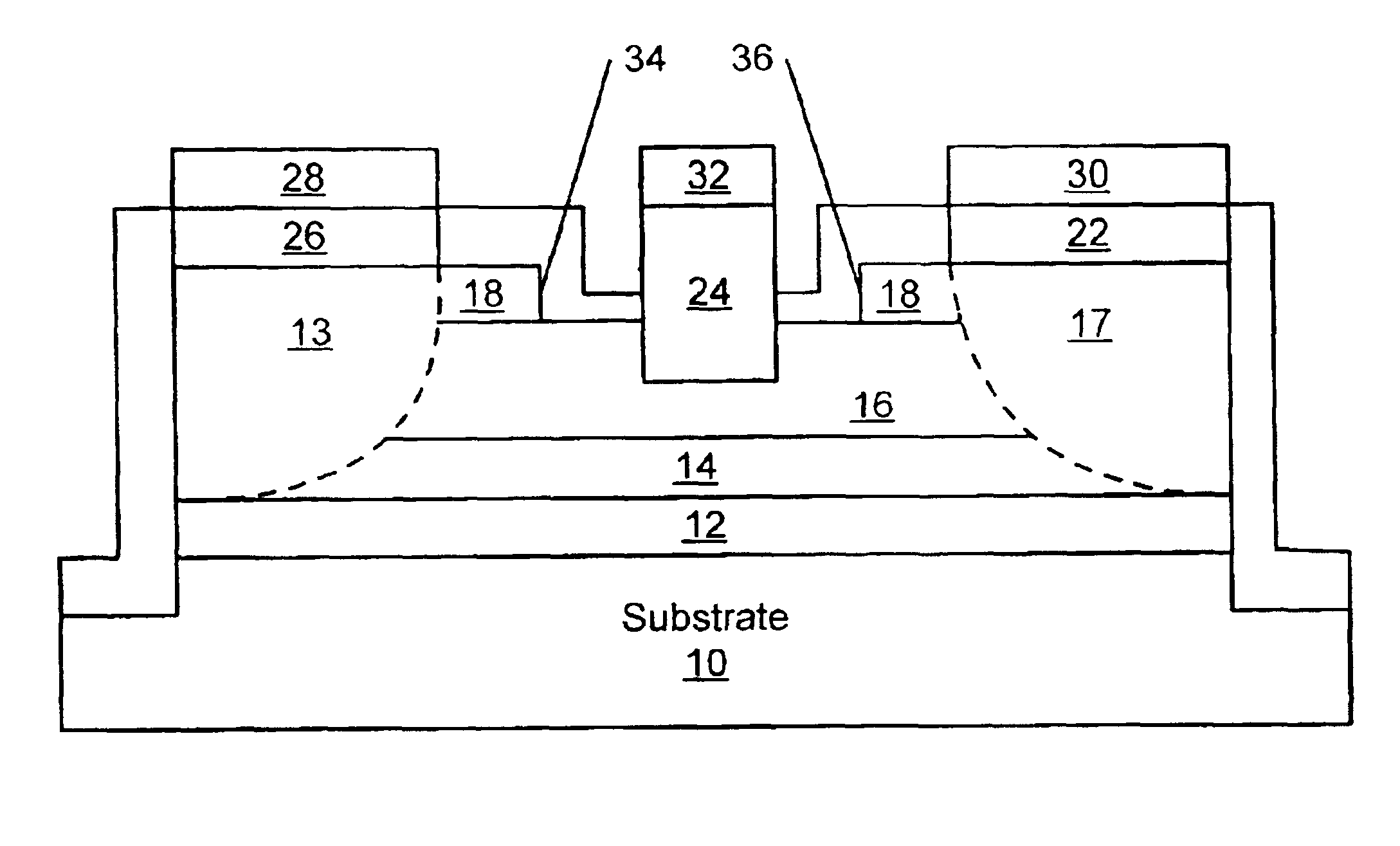

Silicon-based tunneling field effect transistors and transistor circuitry employing same

ActiveUS20120199814A1TransistorSemiconductor/solid-state device manufacturingDelta dopingTransistor circuits

A p-channel tunneling field effect transistor (TFET) is selected from a group consisting of (i) a multi-layer structure of group IV layers and (u) a multi-layer structure of group III-V layers. The p-channel TFET includes a channel region comprising one of a silicon-germanium alloy with non-zero germanium content and a ternary III-V alloy. An n-channel TFET is selected from a group consisting of (i) a multi-layer structure of group IV layers and (u) a multi-layer structure of group III-V layers. The n-channel TFET includes an n-type region, a p-type region with a p-type delta doping, and a channel region disposed between and spacing apart the n-type region and the p-type region. The p-channel TFET and the n-channel TFET may be electrically connected to define a complementary field-effect transistor element. TFETs may be fabricated from a silicon-germanium TFET layer structure grown by low temperature (500 degrees Centigrade) molecular beam epitaxy.

Owner:THE OHIO STATES UNIV

Methods of fabricating delta doped silicon carbide metal-semiconductor field effect transistors having a gate disposed in a double recess structure

InactiveUS6902964B2Improve breakdown voltageReduce resistanceTransistorSemiconductor/solid-state device manufacturingDelta dopingCharge carrier

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a delta doped silicon carbide MESFET having a source, a drain and a gate. The gate is situated between the source and the drain and extends into a doped channel layer of a first conductivity type. Regions of silicon carbide adjacent to the source and the drain extend between the source and the gate and the drain and the gate, respectively. The regions of silicon carbide have carrier concentrations that are greater than a carrier concentration of the doped channel layer and are spaced apart from the gate.

Owner:CREE INC

Polarization doping in nitride based diodes

Owner:CREELED INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com