Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

70 results about "Bicmos technology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

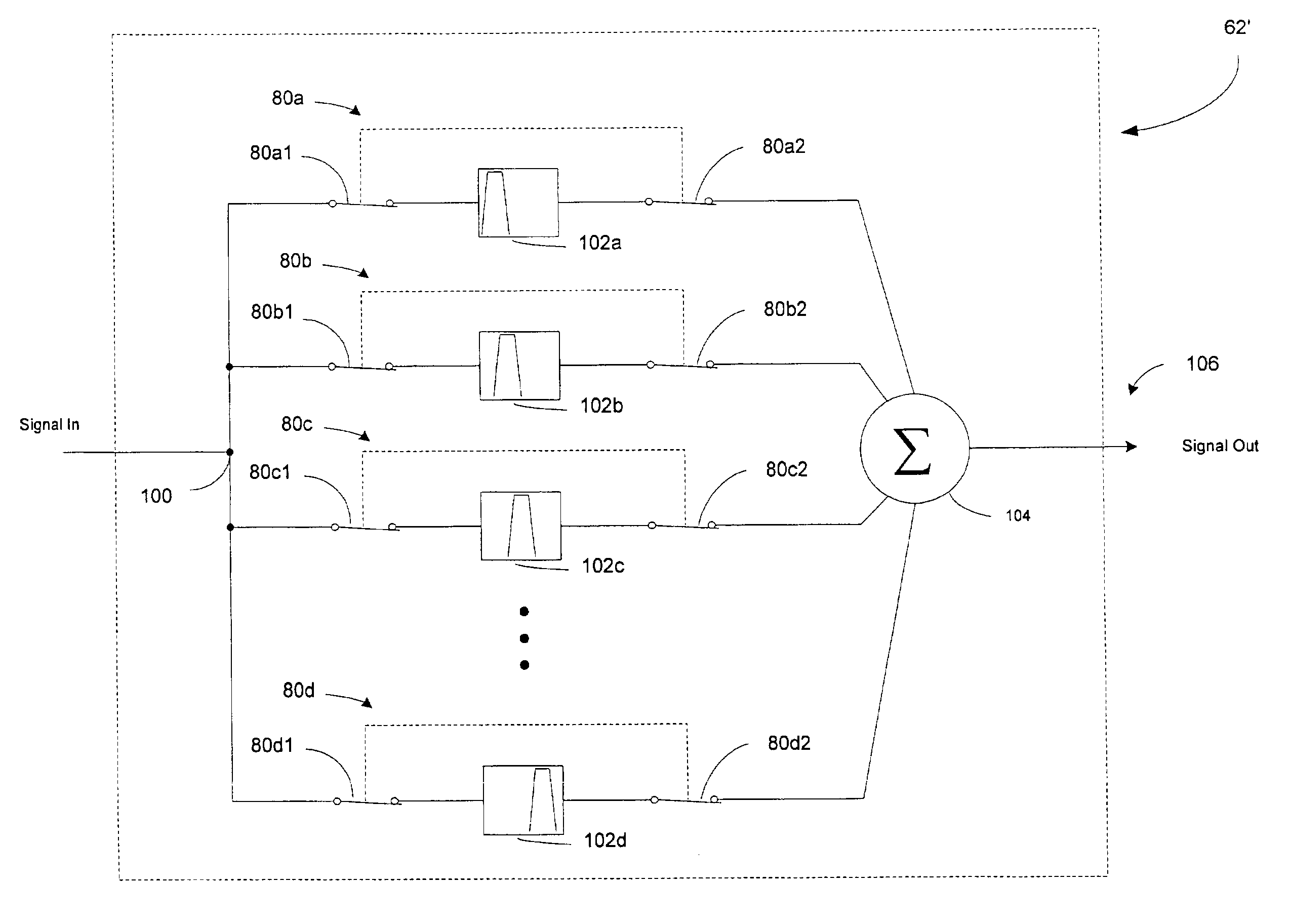

Mixed technology MEMS/SiGe BiCMOS digitalized analog front end with direct RF sampling

A digitizing analog front end (DAFE) using mixed technology on a single substrate is described. SiGe BiCMOS technology is implemented for the semiconductor components, which include a low noise amplifier and an analog-to-digital converter. Micro Electro Mechanical System (MEMS) switches are used to change the filtering characteristics of several filters, including an anti-aliasing filter and a pre-select and anti-jamming filter.

Owner:RAYTHEON CO

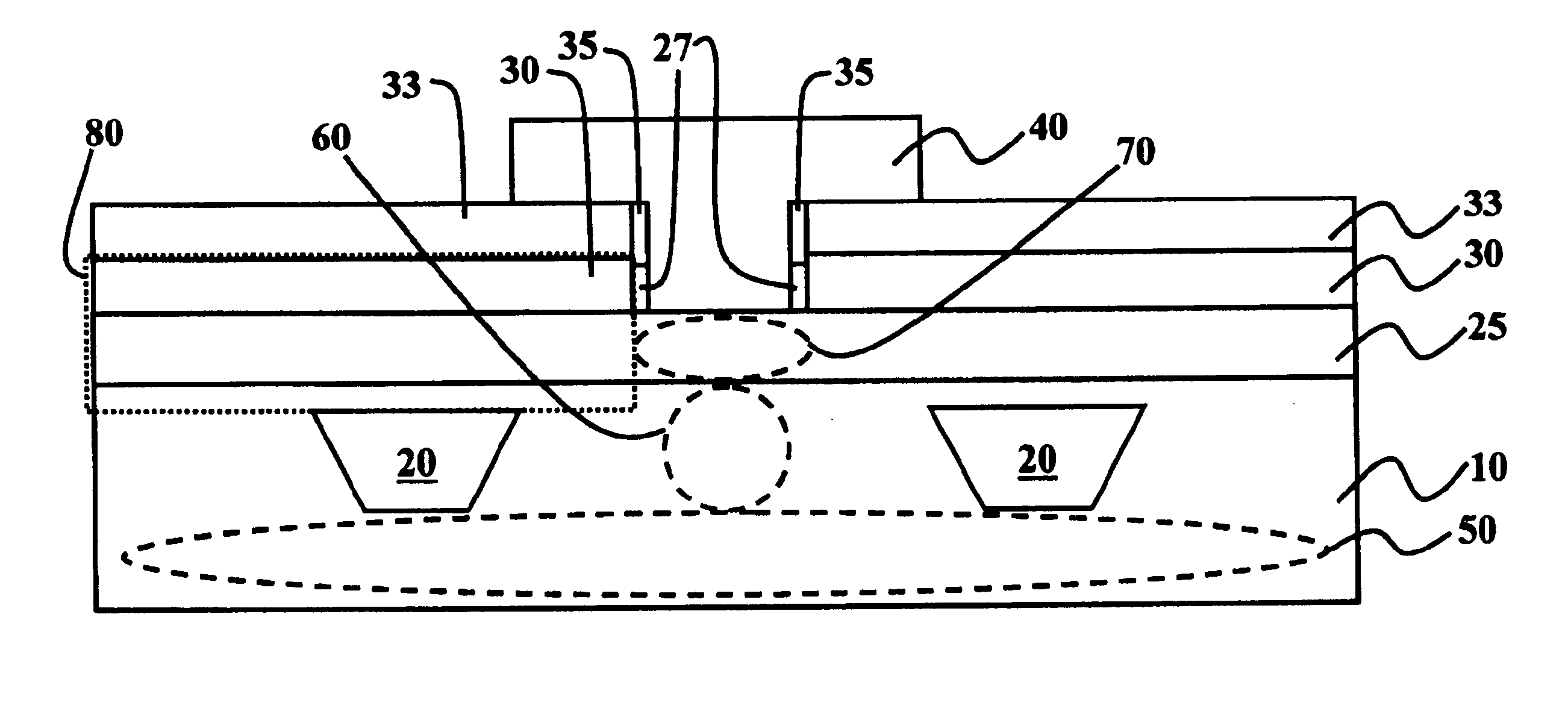

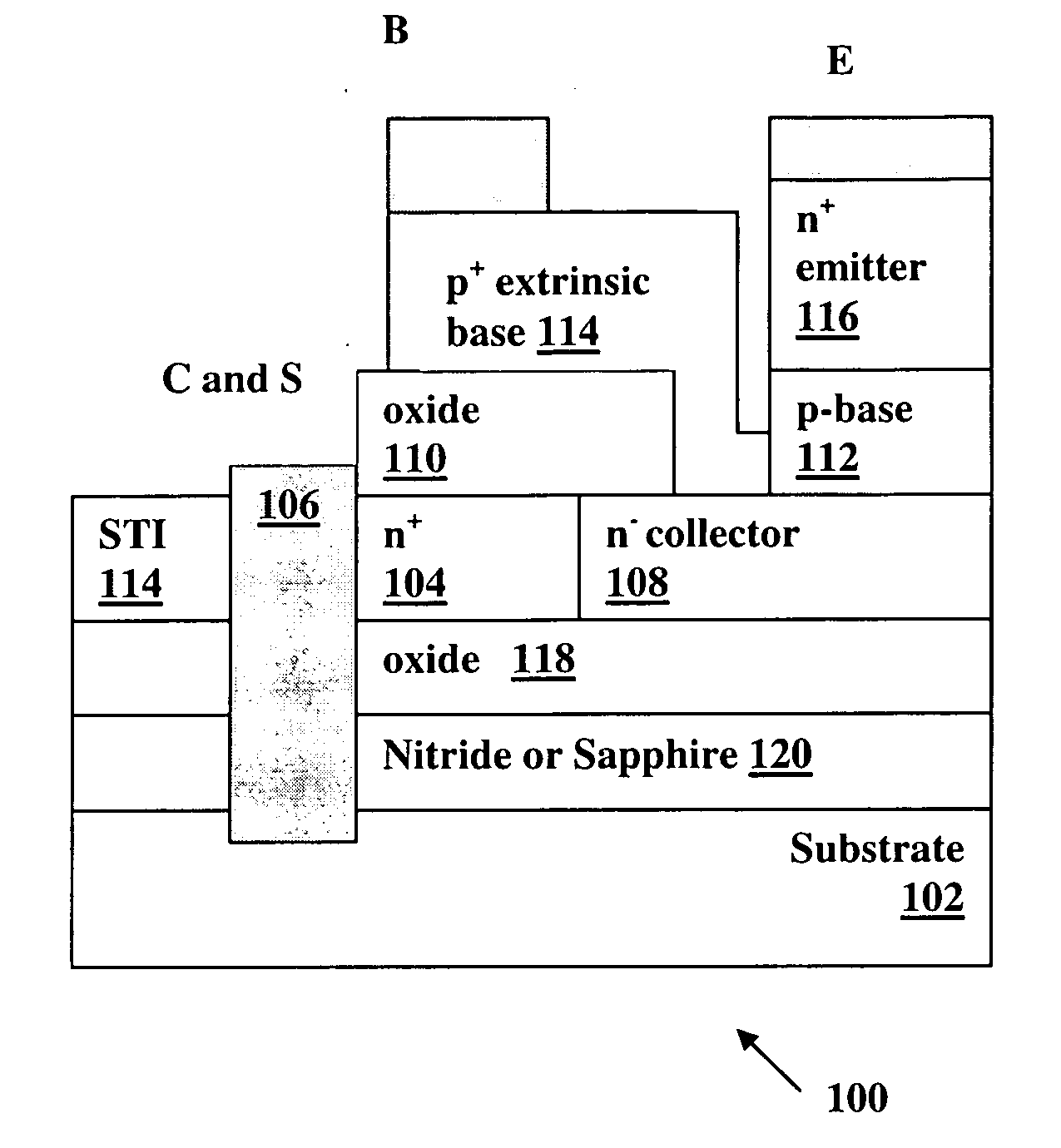

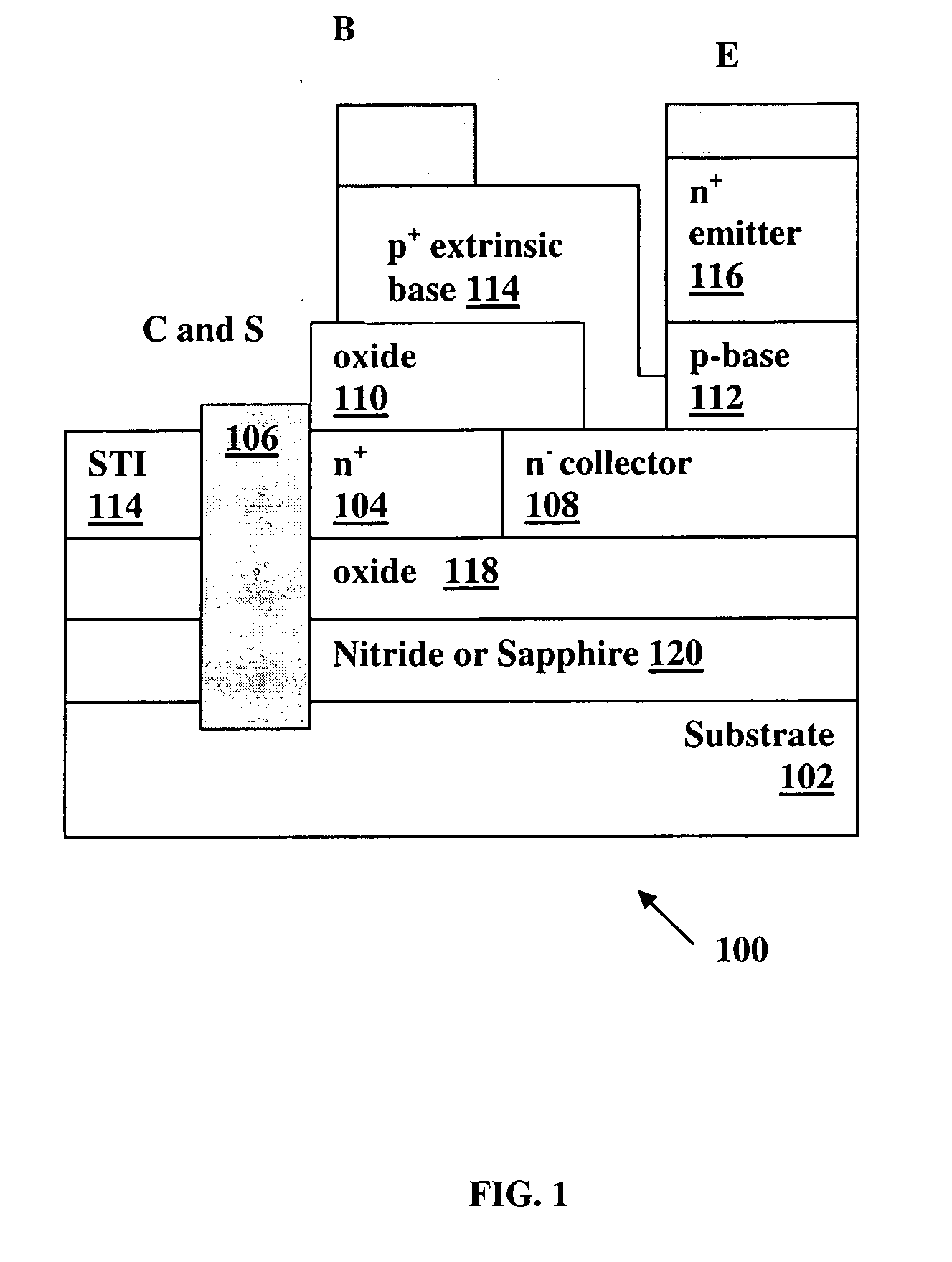

BiCMOS technology on SOI substrates

InactiveUS6936910B2Simple and reliable processIncrease resistanceTransistorSolid-state devicesSoi substrateBicmos technology

A method and a BICMOS structure are provided. The BiCMOS structure includes an SOI substrate having a bottom Si-containing layer, a buried insulating layer located atop the bottom Si-containing layer, a top Si-containing layer atop the buried insulating layer and a sub-collector which is located in an upper surface of the bottom Si-containing layer. The sub-collector is in contact with a bottom surface of the buried insulating layer. The structure also includes an extrinsic base heterojunction bipolar transistor located in an opening provided in a bipolar device area of the SOI substrate in which a base region of the bipolar transistor is located directly atop the sub-collector

Owner:GLOBALFOUNDRIES US INC

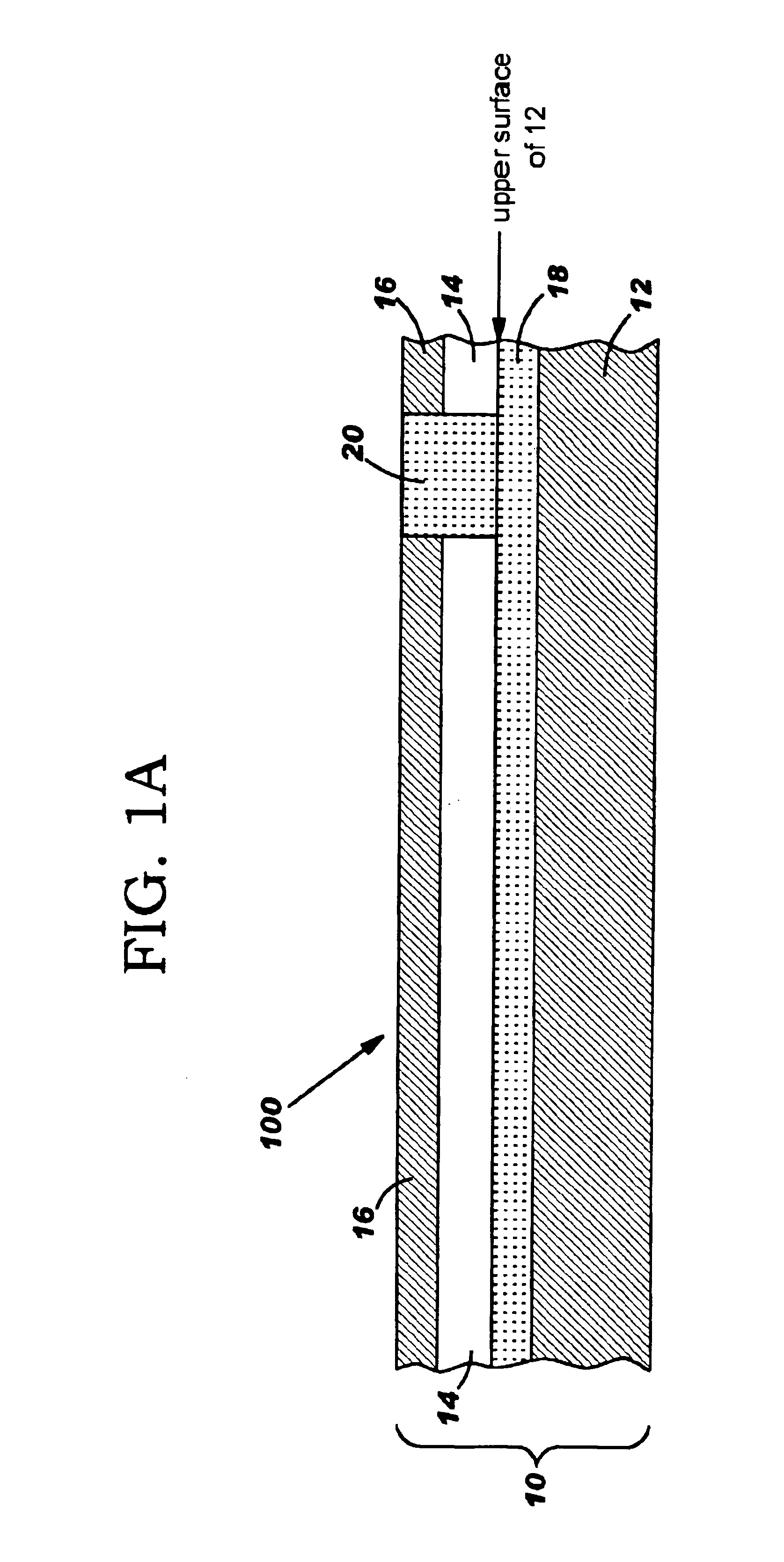

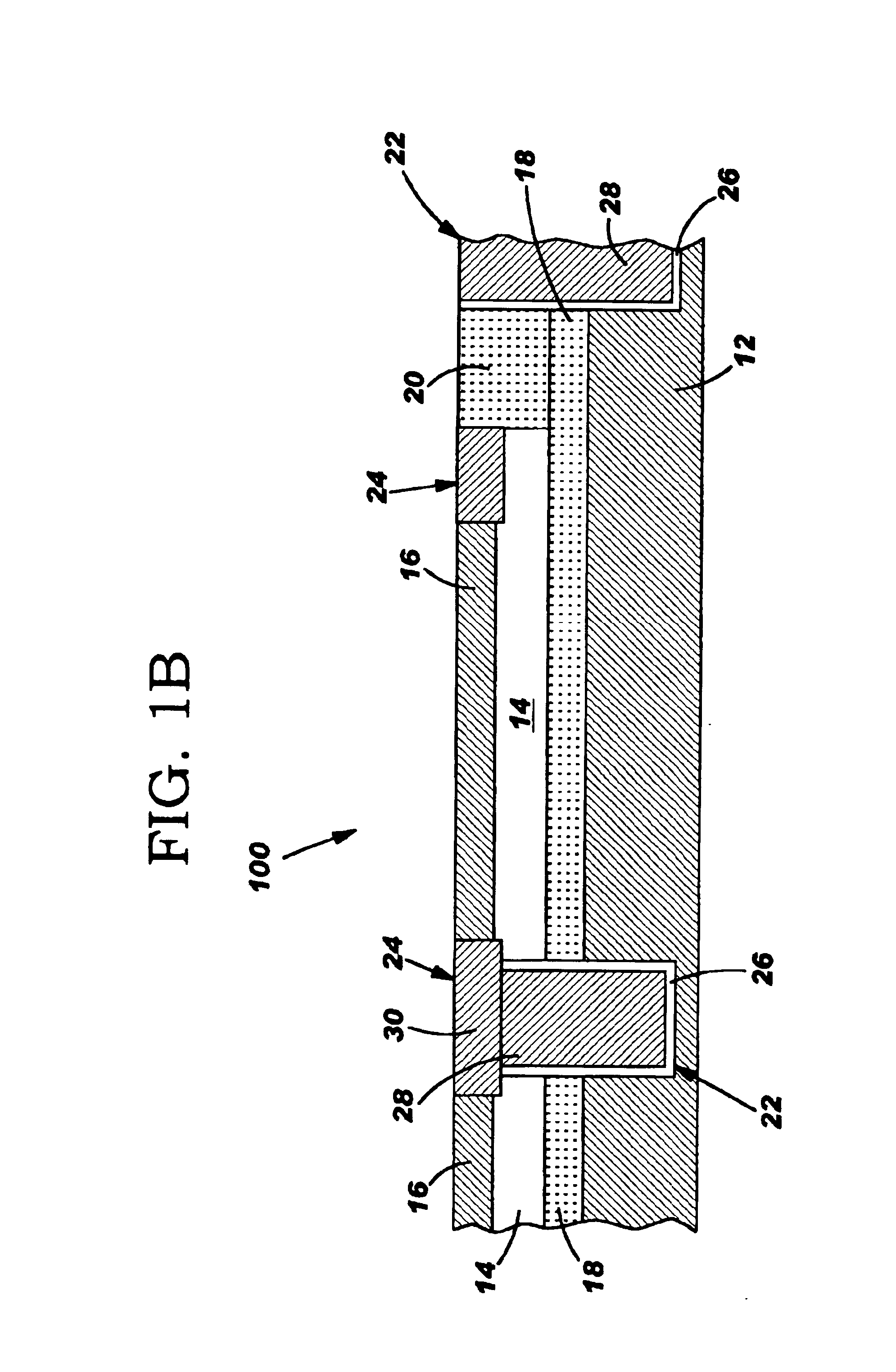

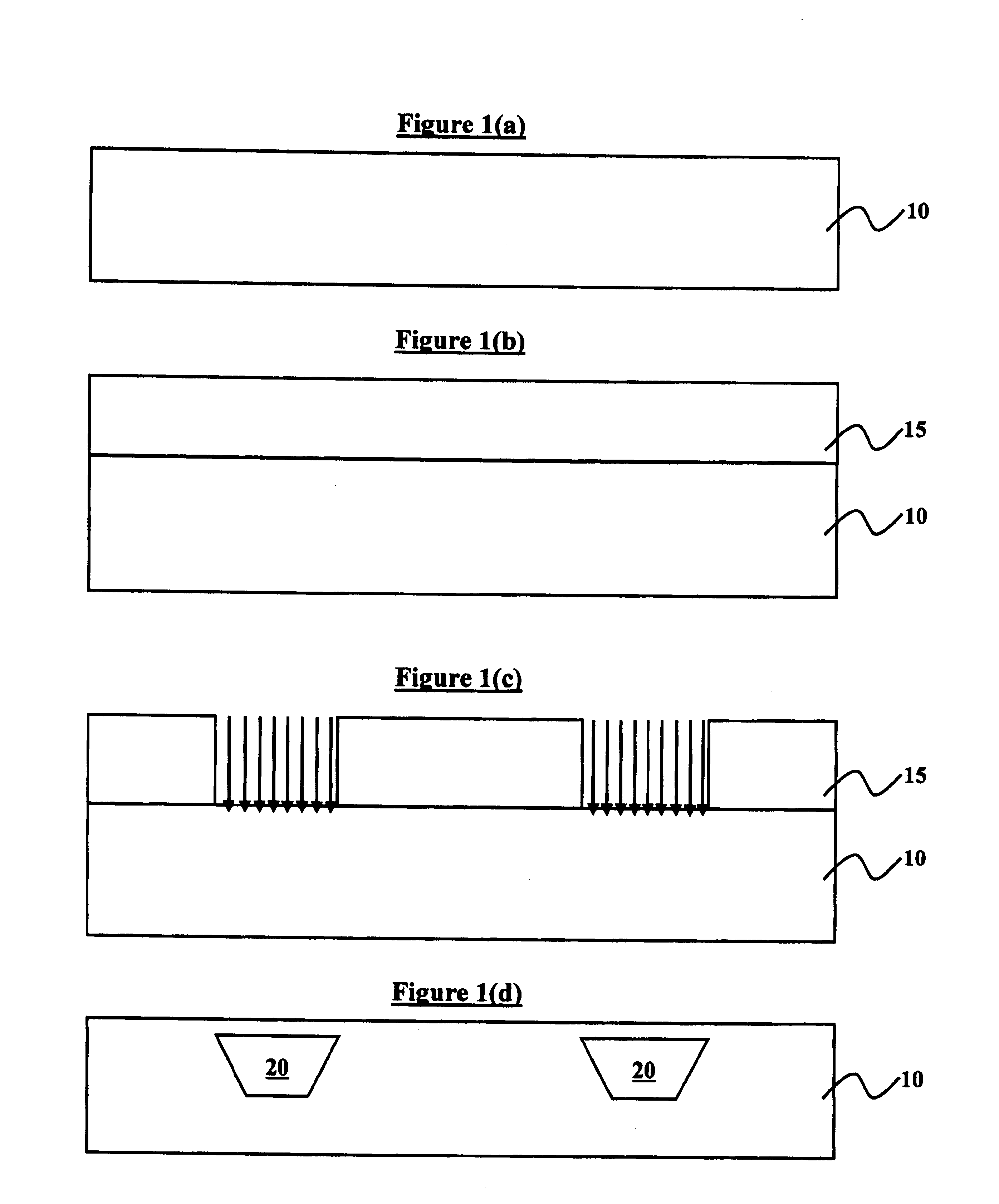

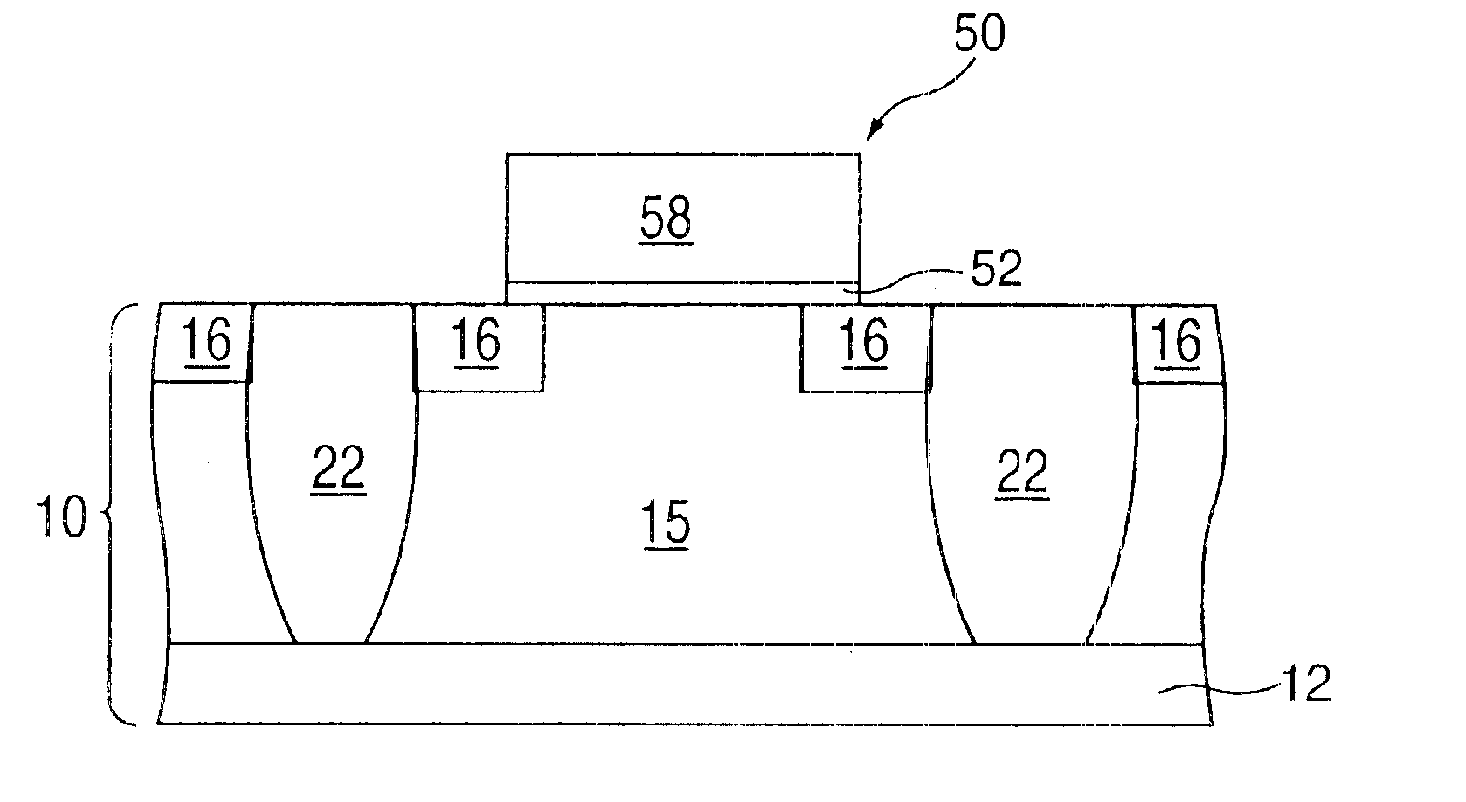

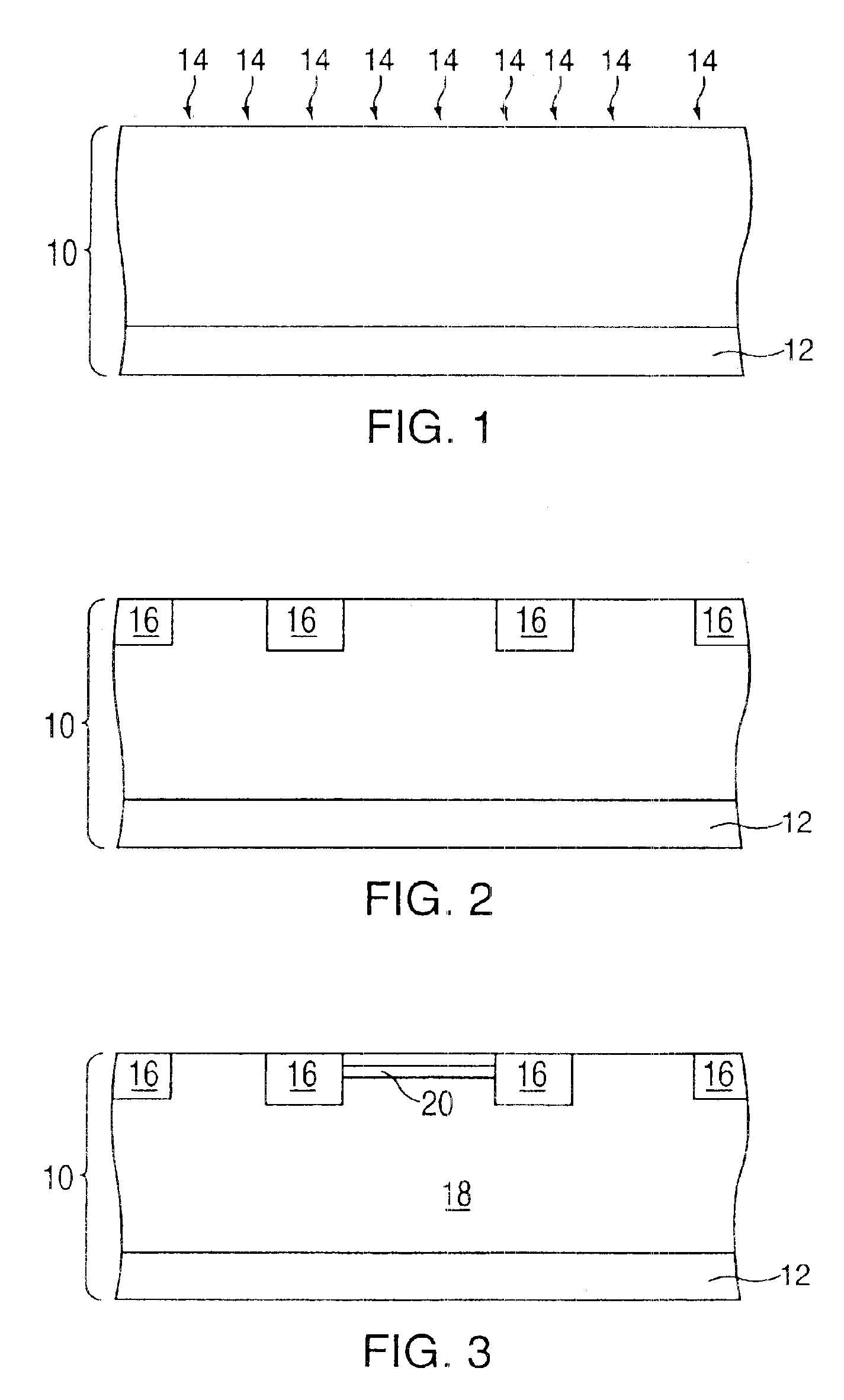

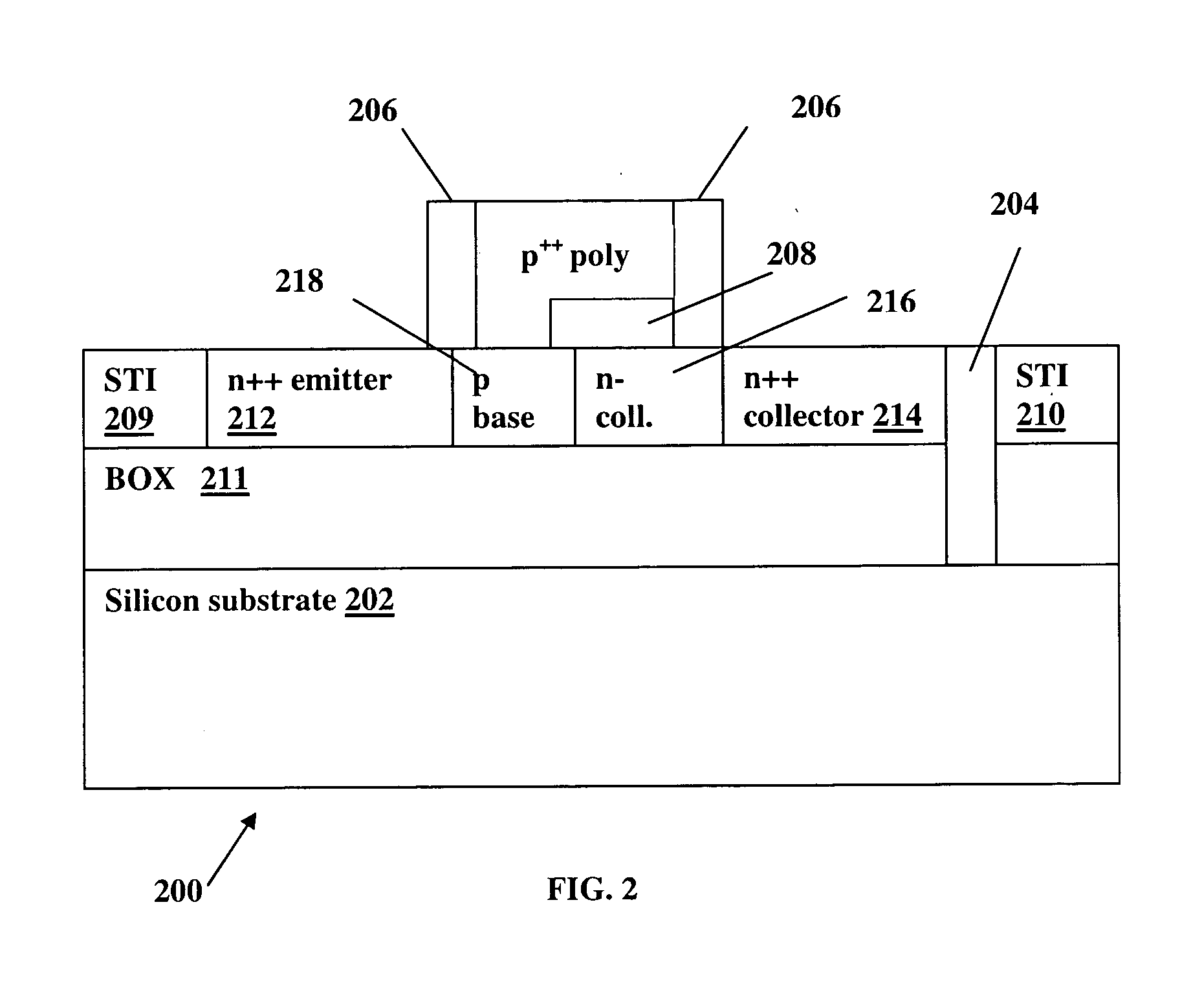

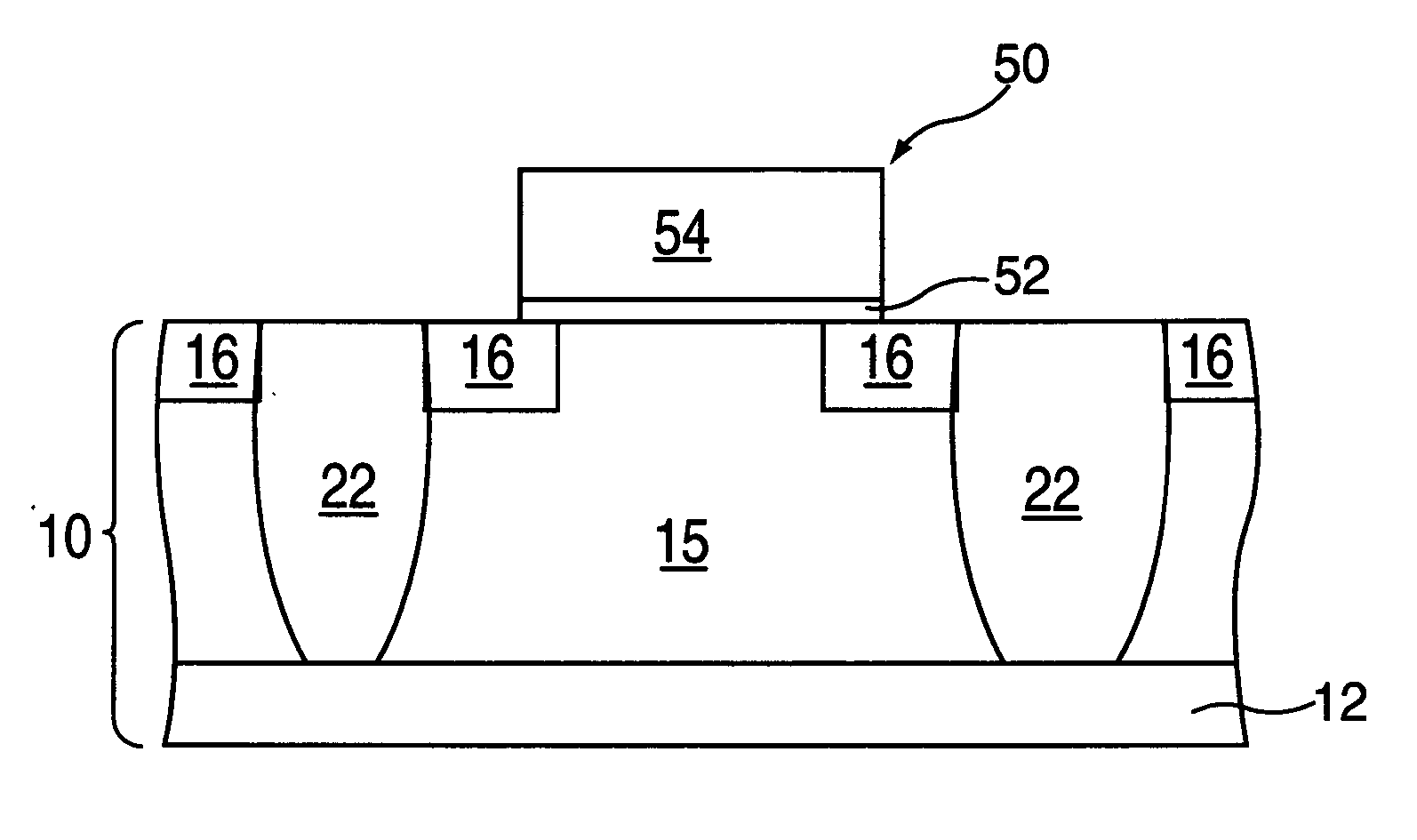

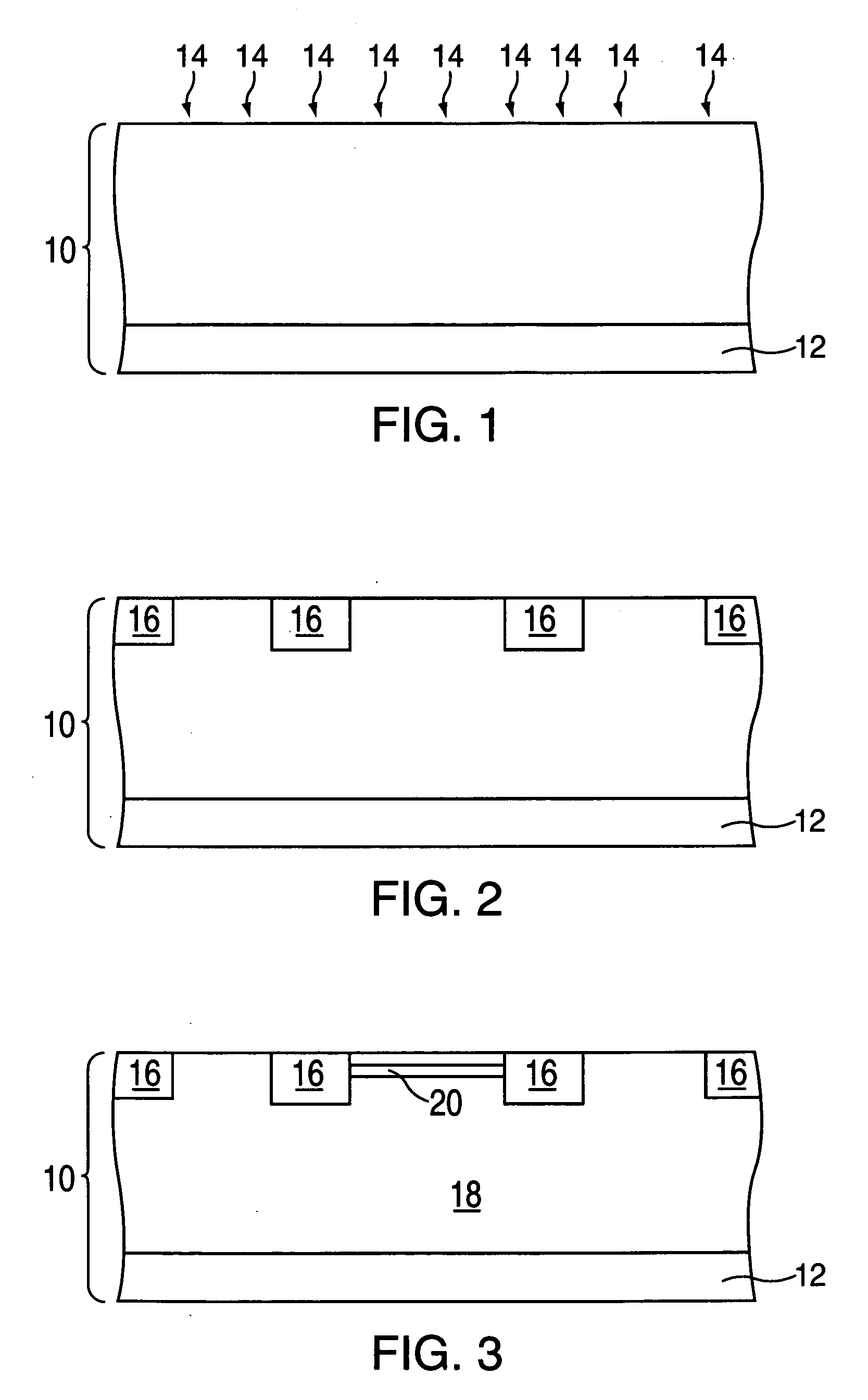

BICMOS technology on SIMOX wafers

InactiveUS6888221B1Reduce power consumptionImprove current drive capabilityTransistorSemiconductor/solid-state device manufacturingEngineeringSingle crystal

A method and structure for a bipolar transistor comprising a patterned isolation region formed below an upper surface of a semiconductor substrate and a single crystal extrinsic base formed on an upper surface of the isolation region. The single crystal extrinsic base comprises a portion of the semiconductor substrate located between the upper surface of the isolation region and the upper surface of the semiconductor substrate. The bipolar transistor further comprises a single crystal intrinsic base, wherein a portion of the single crystal extrinsic base merges with a portion of the single crystal intrinsic base. The isolation region electrically isolates the extrinsic base from a collector. The intrinsic and extrinsic bases separate the collector from an emitter. The extrinsic base comprises epitaxially-grown silicon. The isolation region comprises an insulator, which comprises oxide, and the isolation region comprises any of a shallow trench isolation region and a deep trench isolation region.

Owner:GLOBALFOUNDRIES INC

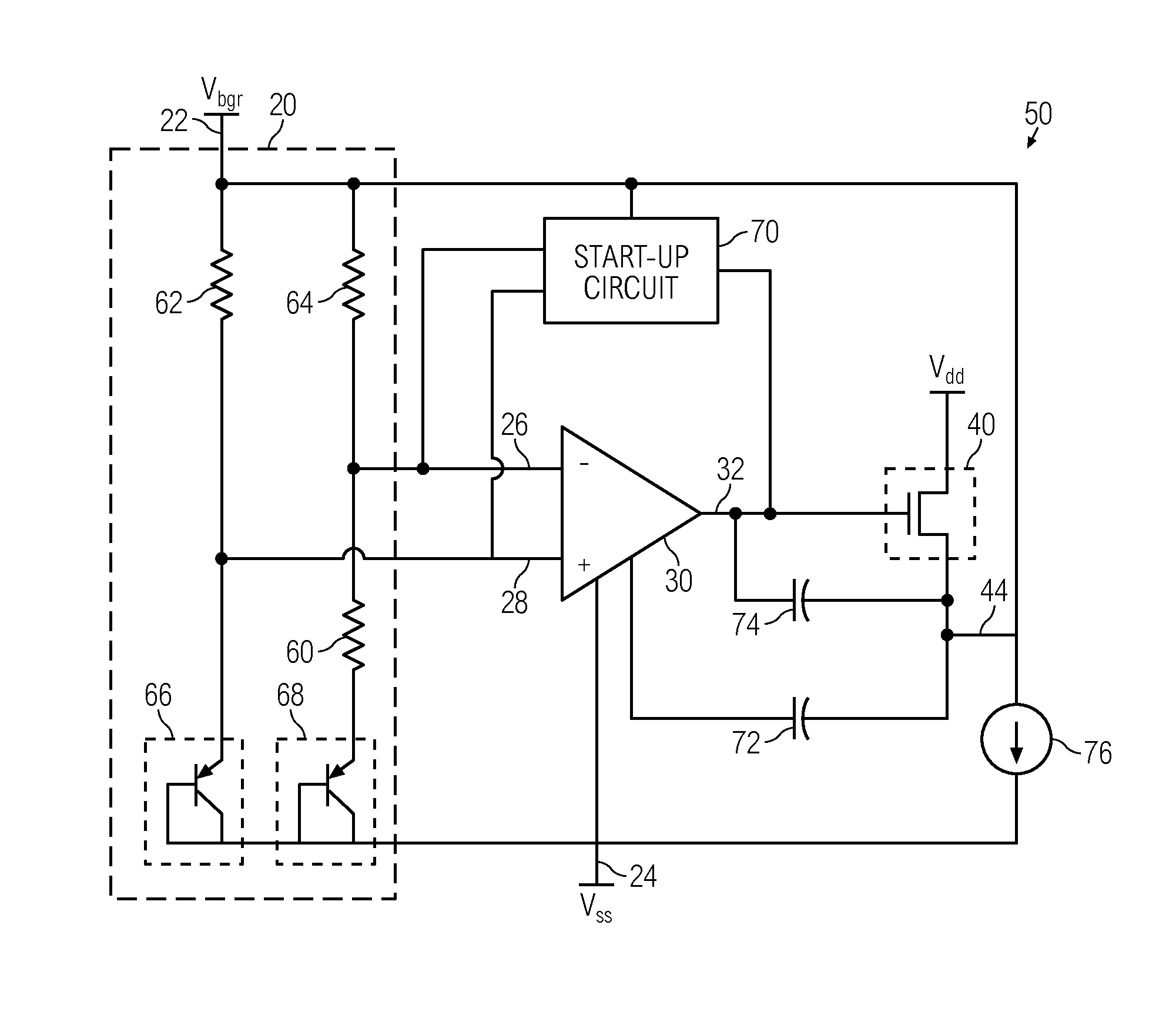

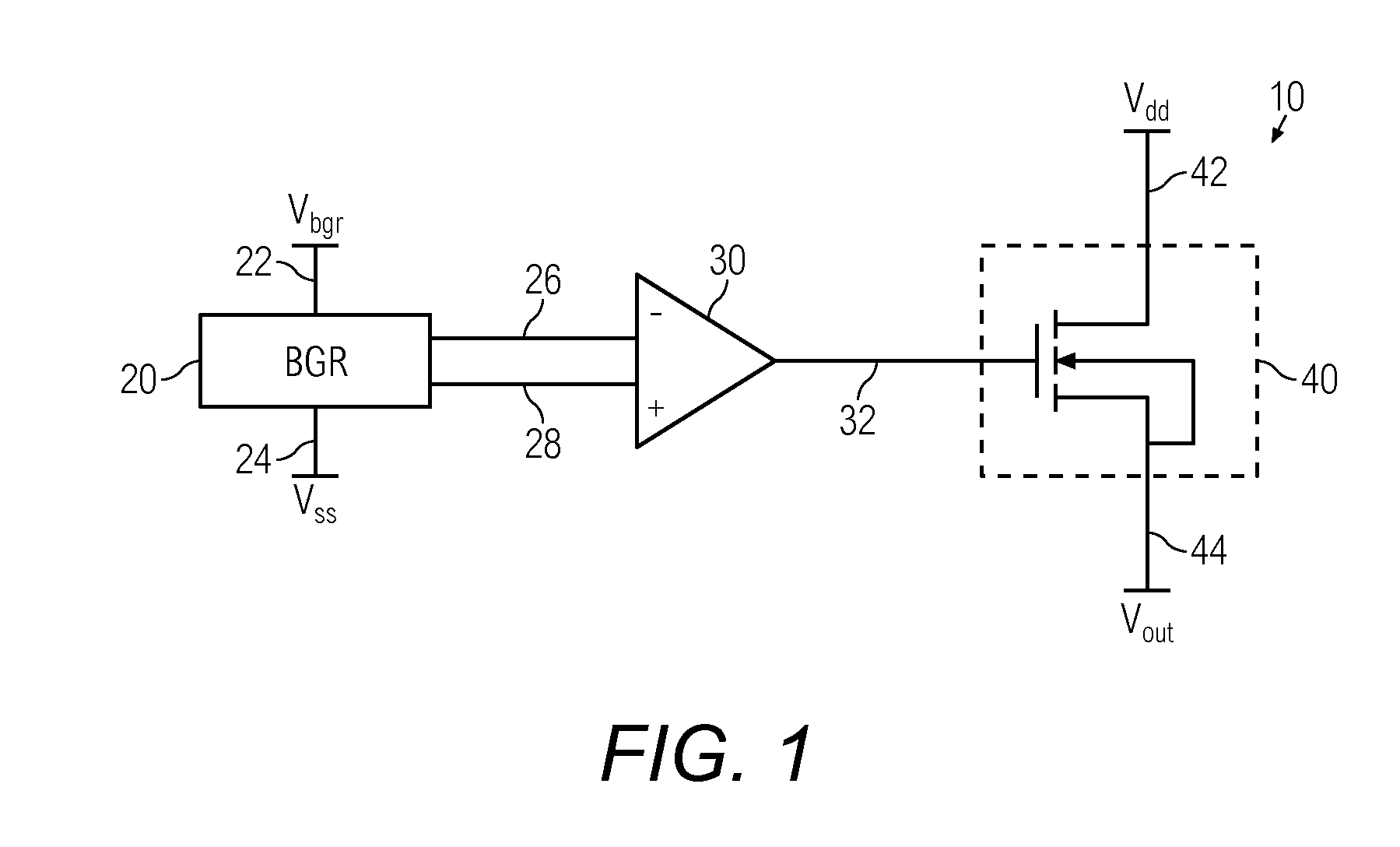

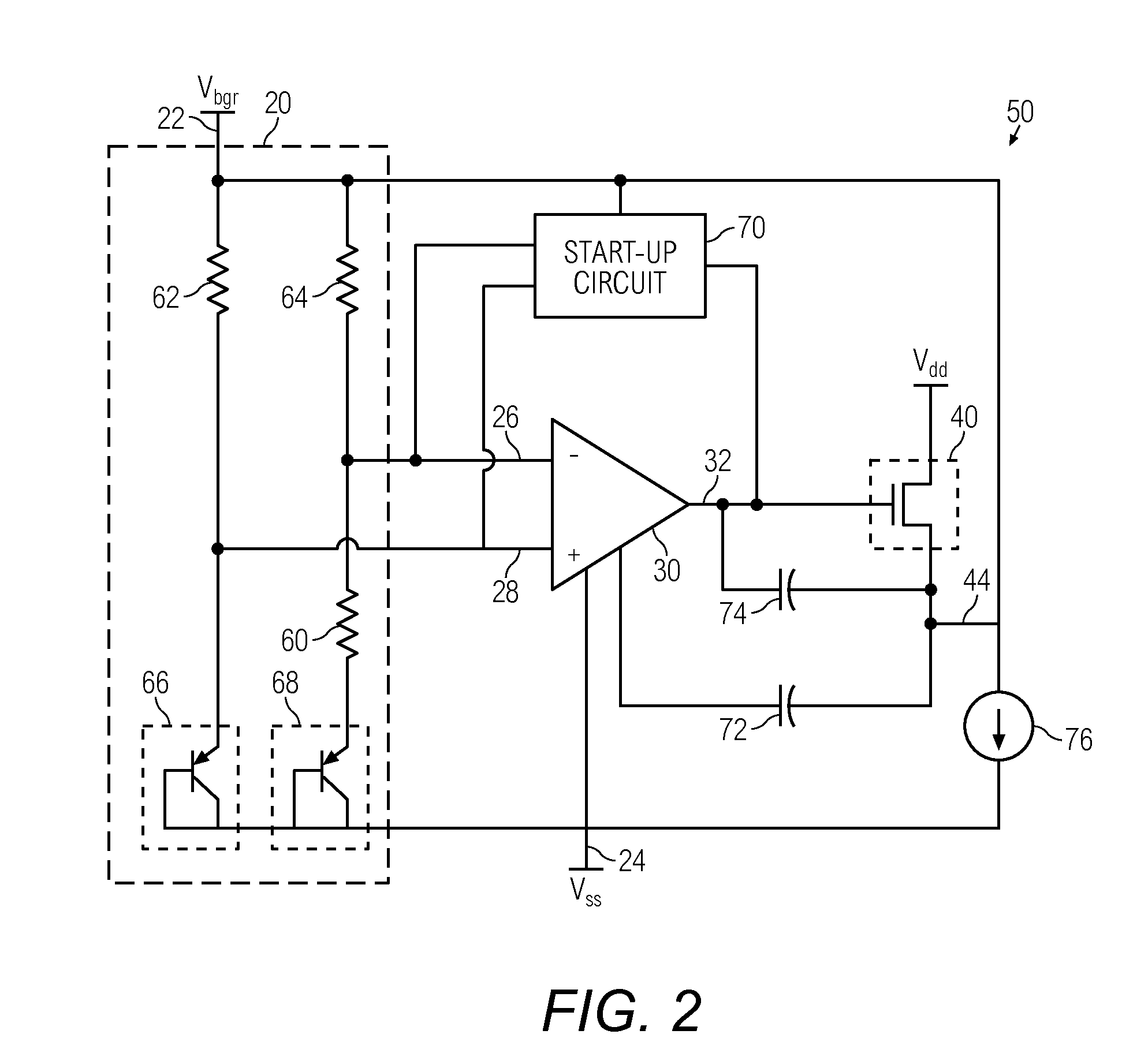

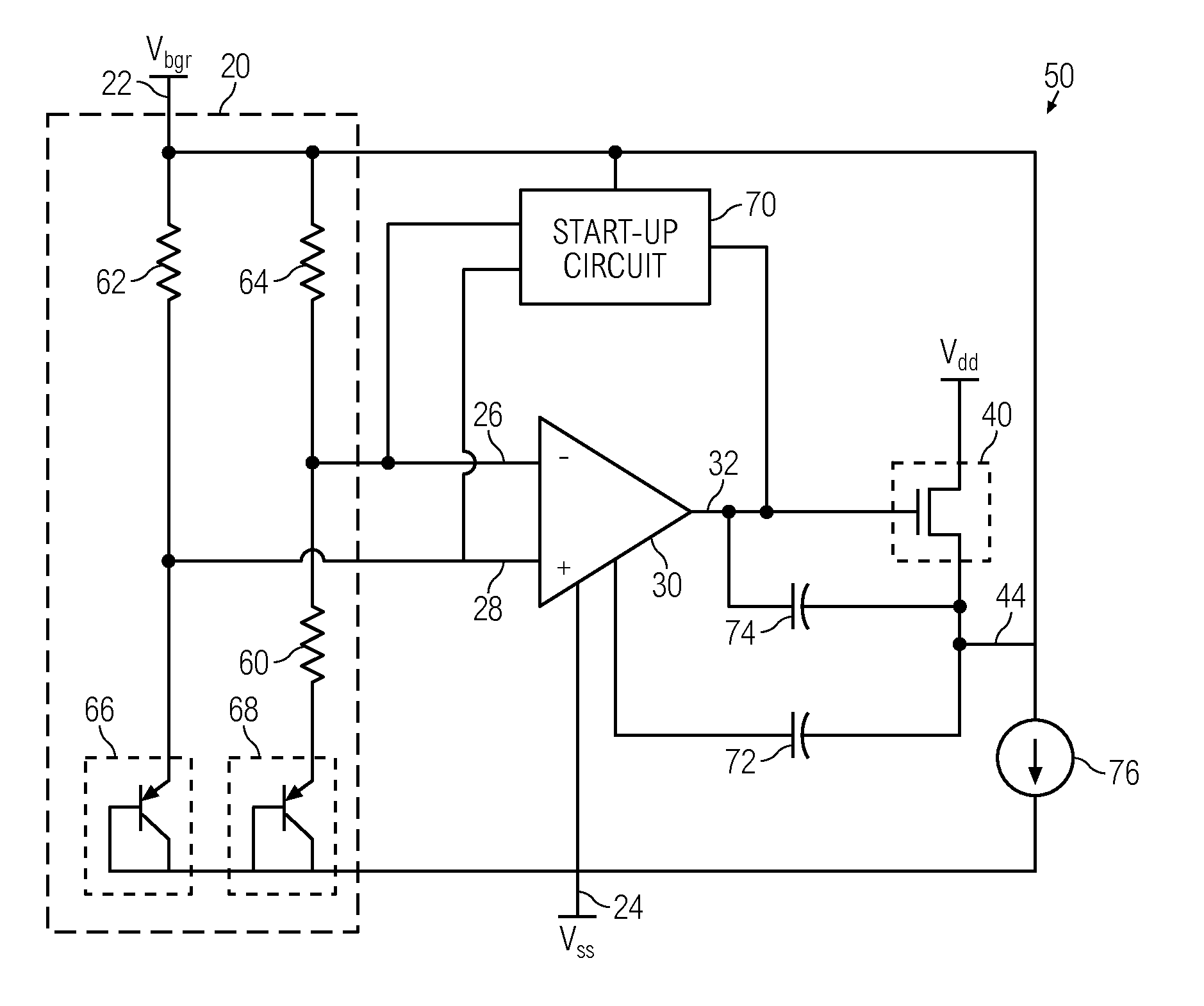

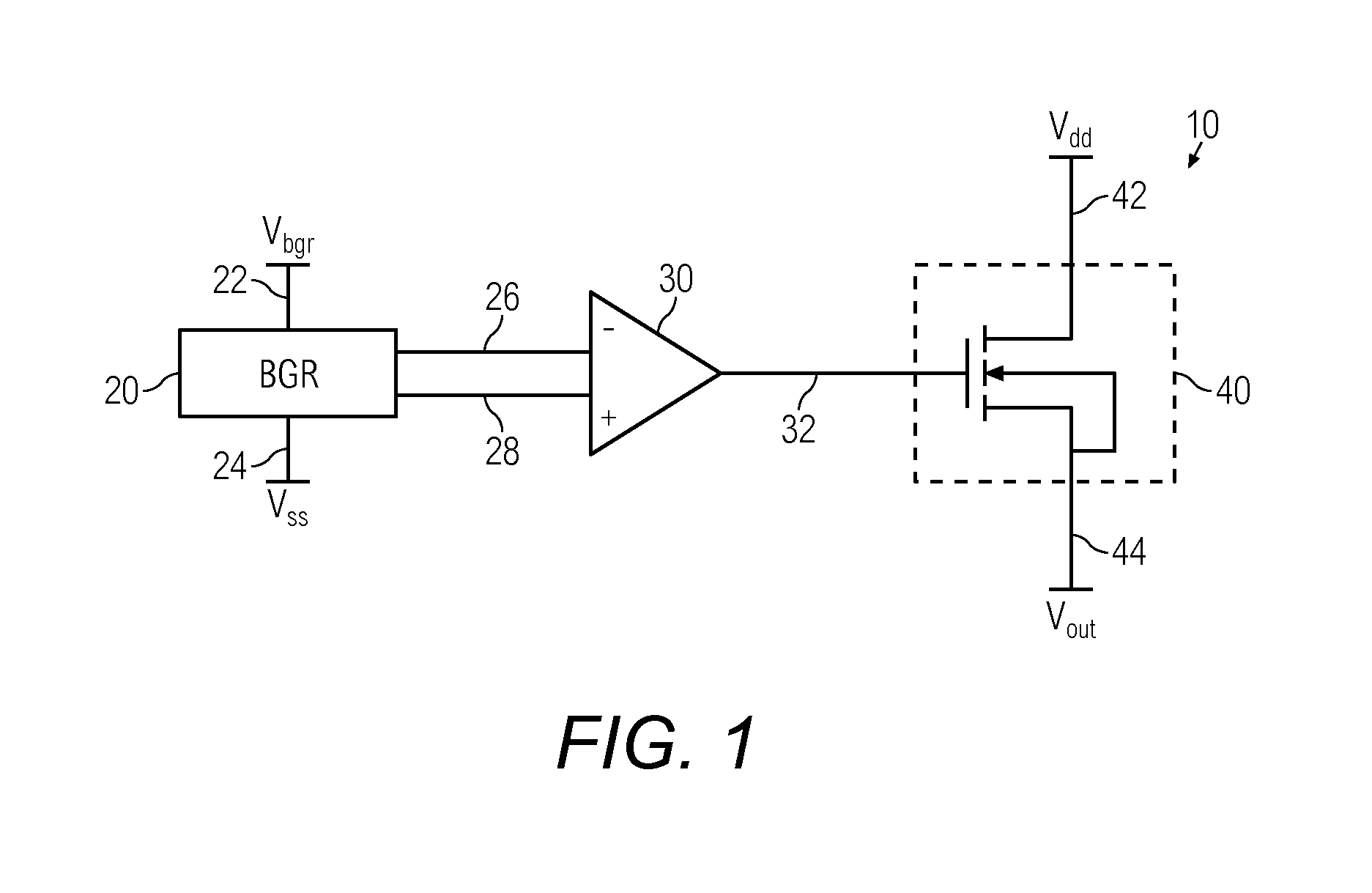

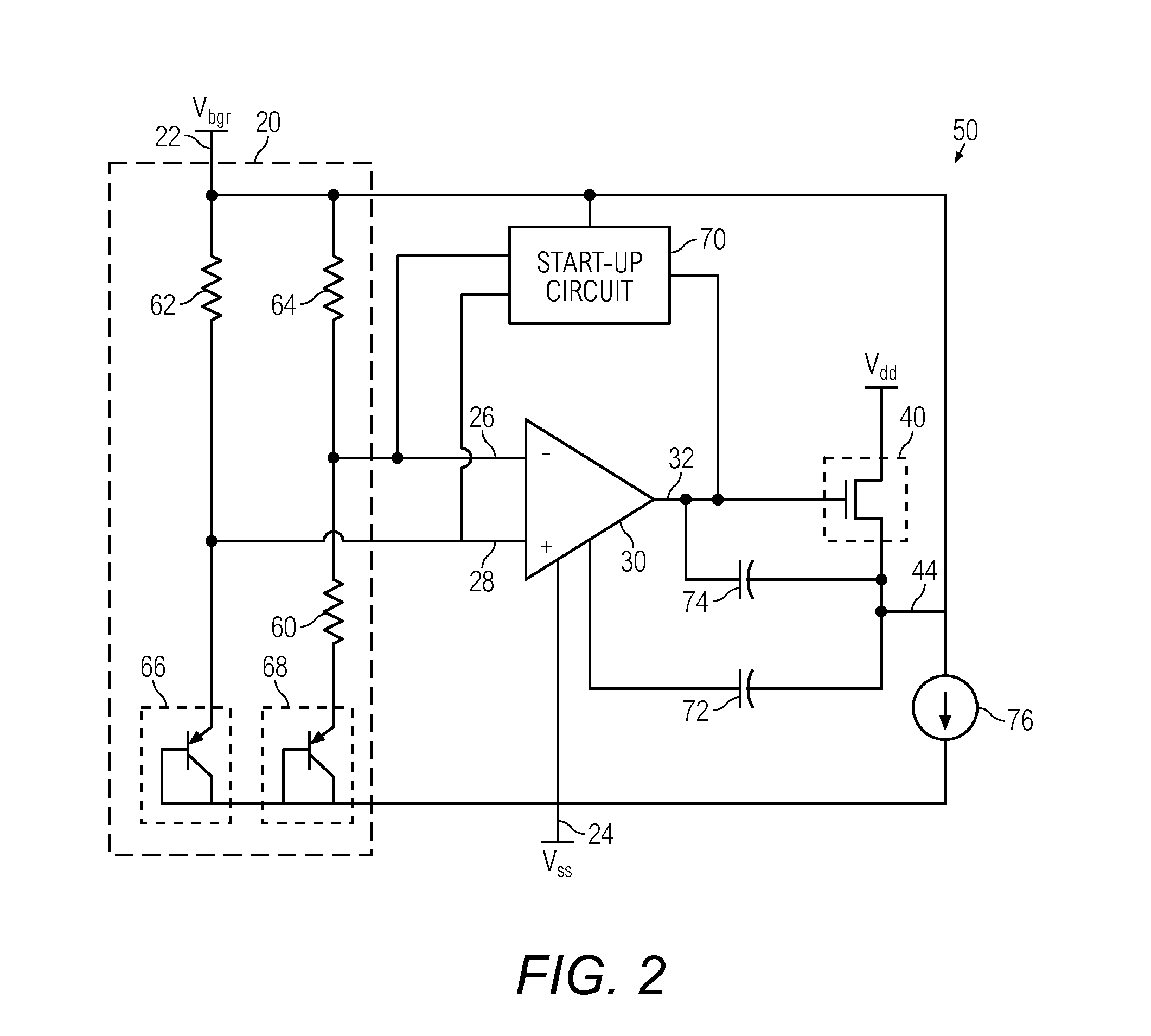

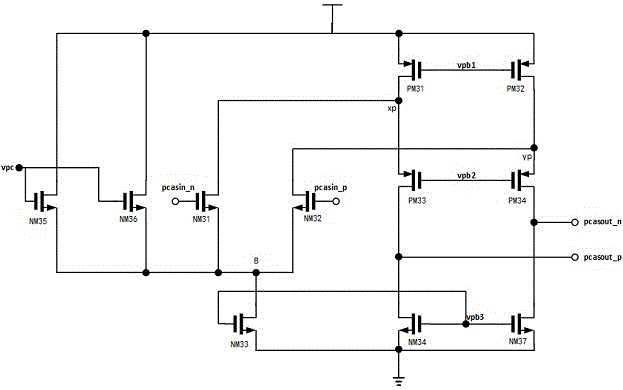

Bandgap reference circuit and regulator circuit with common amplifier

InactiveUS20140015509A1Power supply linesElectric variable regulationElectrical resistance and conductanceCMOS

A bandgap voltage reference and voltage regulator system includes a bandgap voltage reference circuit and a voltage regulator circuit that share a single, common amplifier. The amplifier acts as a gain stage for the reference circuit and as an error amplifier for a driver stage of the regulator circuit. The regulator circuit has an input reference generated by the reference circuit, and the reference circuit acts as a load to the driver stage, obviating the need for a bias resistance network. By sharing the amplifier and obviating the need for a resistance network, the area and overall quiescent current of the system are reduced. The system can be implemented in CMOS / BiCMOS technology and is suited for low power applications.

Owner:NXP USA INC

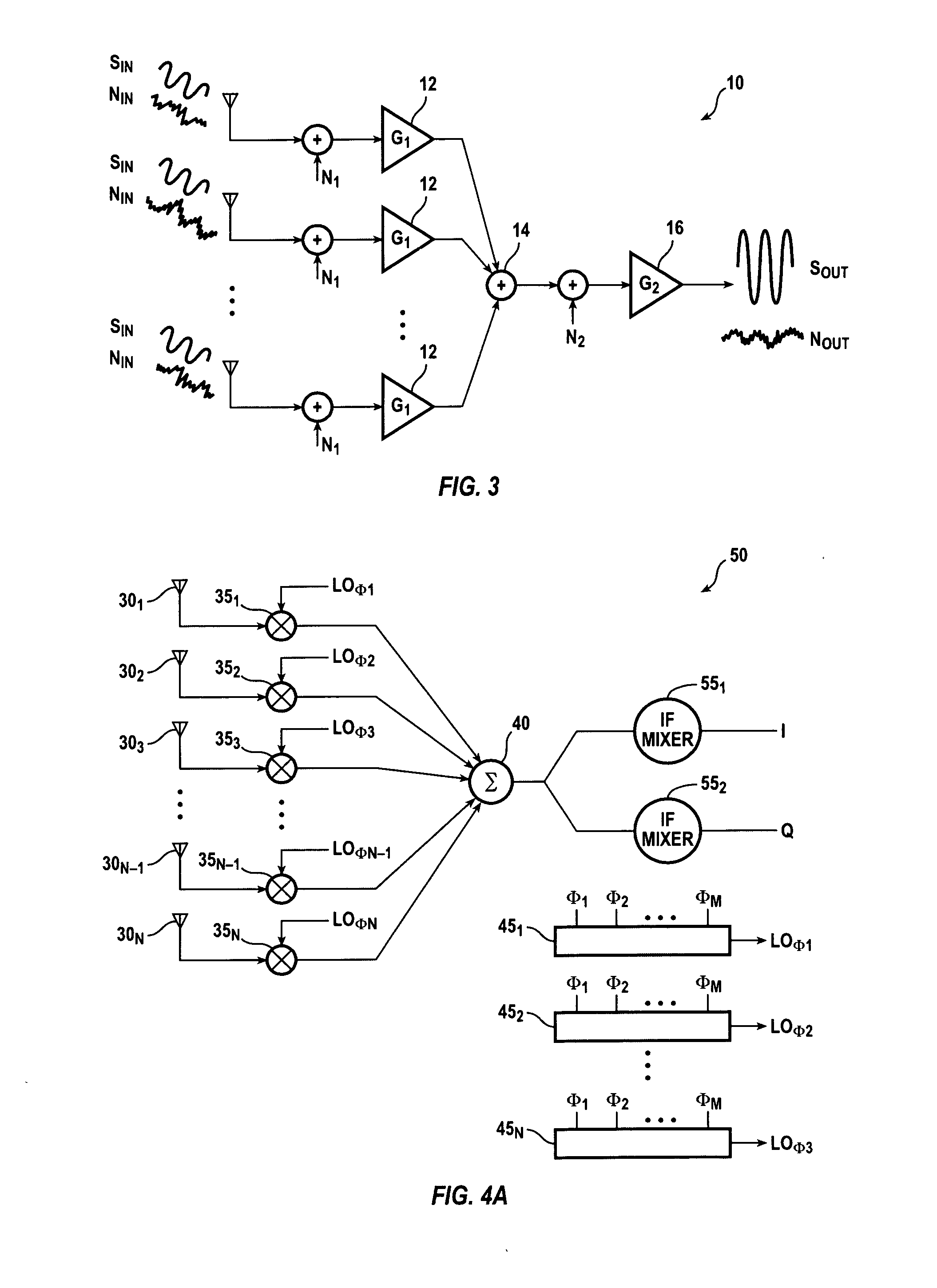

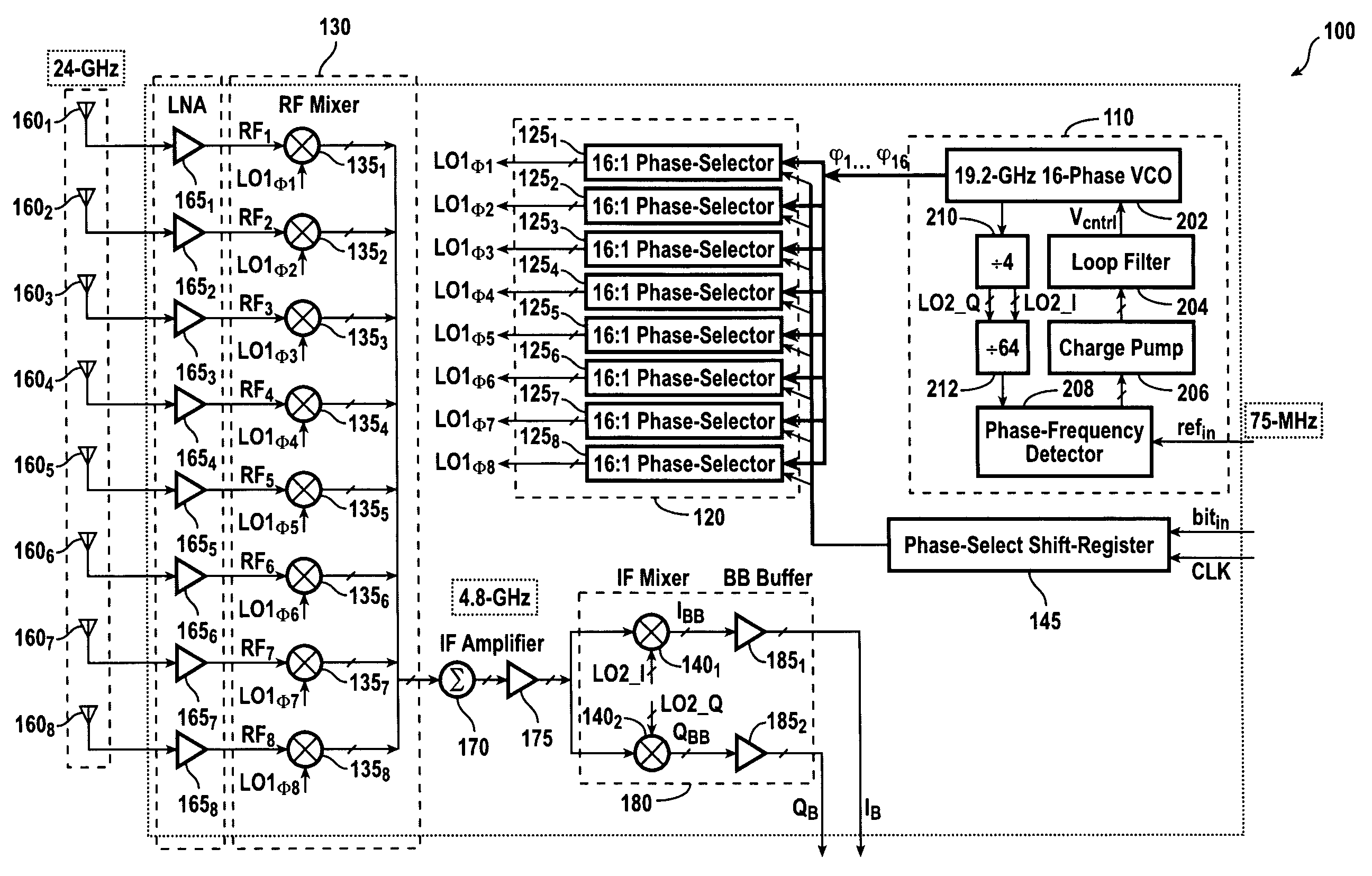

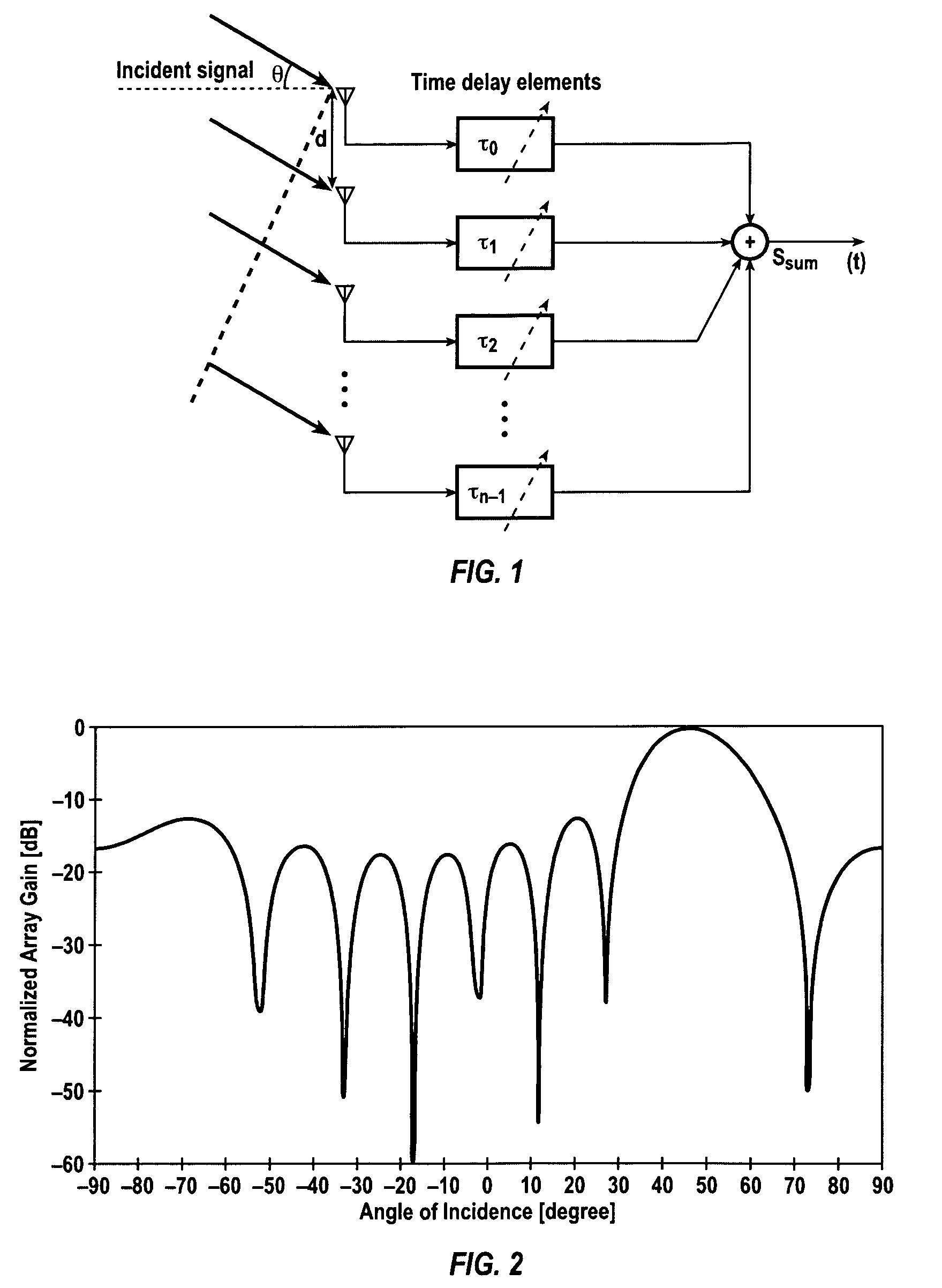

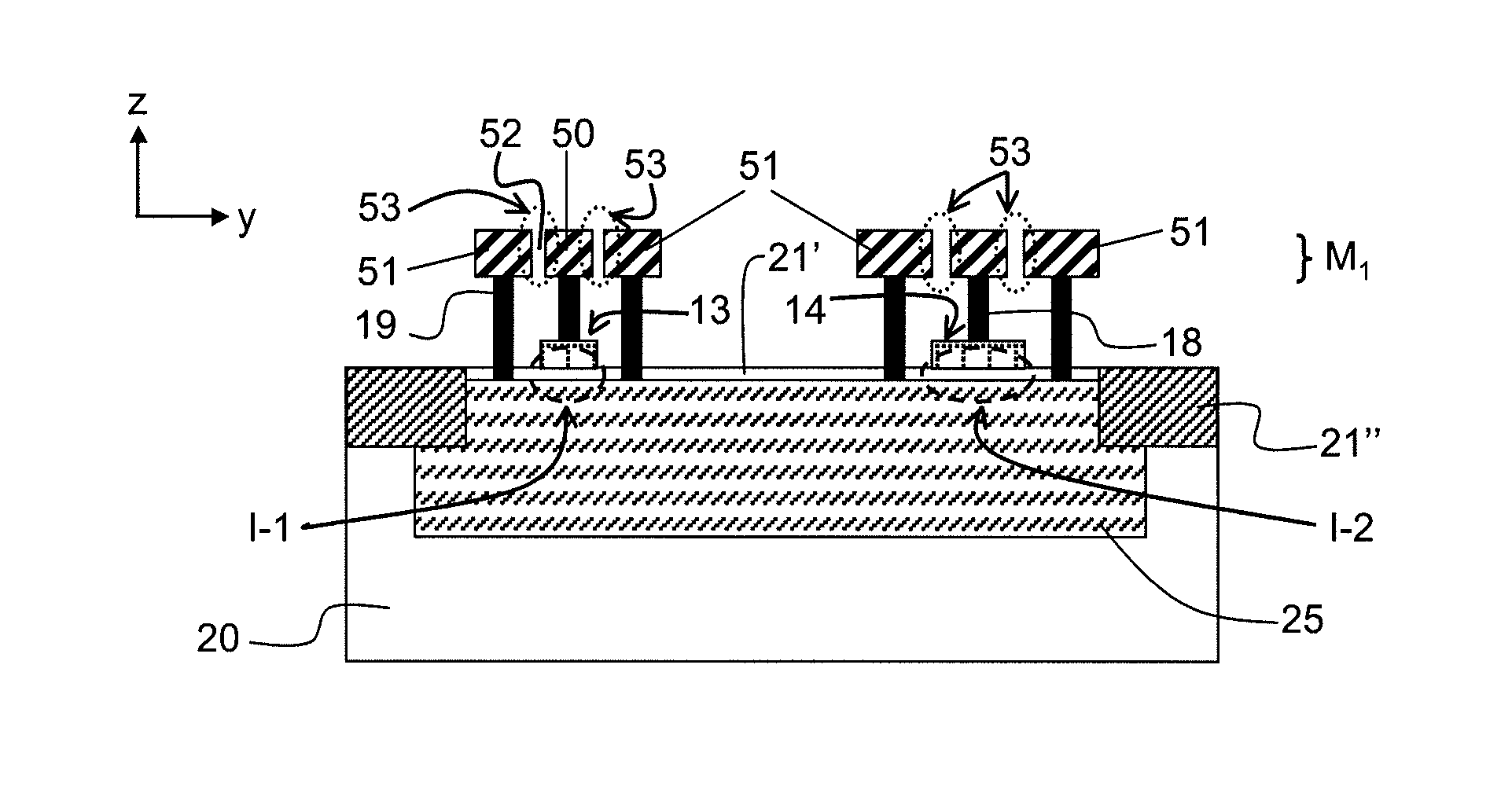

Monolithic silicon-based phased arrays for communications and radars

A phased-array receiver is adapted so as to be fully integrated and fabricated on a single silicon substrate. The phased-array receiver is operative to receive a 24 GHz signal and may be adapted to include 8-elements formed in a SiGe BiCMOS technology. The phased-array receiver utilizes a heterodyne topology, and the signal combining is performed at an IF of 4.8 GHz. The phase-shifting with 4 bits of resolution is realized at the LO port of the first down-conversion mixer. A ring LC VCO generates 16 different phases of the LO. An integrated 19.2 GHz frequency synthesizer locks the VCO frequency to a 75 MHz external reference. Each signal path achieves a gain of 43 dB, a noise figure of 7.4 dB, and an IIP3 of −11 dBm. The 8-path array achieves an array gain of 61 dB, a peak-to-null ratio of 20 dB, and improves the signal-to-noise ratio at the output by 9 dB.

Owner:CALIFORNIA INST OF TECH

Silicone substrate high-linearity low-phase-shift ultra-broad-band digital attenuator

ActiveCN103427781AOvercoming lossTo overcome the large additional phase shiftMultiple-port networksEngineeringField-effect transistor

The invention discloses a silicone substrate high-linearity low-phase-shift ultra-broad-band digital attenuator which comprises a 1dB attenuating module, a 2dB attenuating module, a 4dB attenuating module, a 8dB attenuating module and a 16dB attenuating module. Two NMOS field effect transistors which are of a channel parallel-connection resistor structure and of a solid suspension structure and manufactured through SiGe BiCMOS technology are adopted to be used as control switches, five sets of complementary digital signals are used for controlling the five attenuating modules independently to work, a low-pass network is used for conducting phase compensation, inductance is used for matching between the adjacent attenuating modules, matching between the input end of the1dB attenuating module and 50 omega input impedance and matching between the output end of the 16dB attenuating module and 50 omega output impedance are realized through transmission wires, the working frequency range is 1-25GHz, and low-differential-loss low-phase-shift attenuation of signal amplitudes under 32 states can be realized with the 1dB length stepping in the attenuating range of 0-31dB. The silicone substrate high-linearity low-phase-shift ultra-broad-band digital attenuator has the advantages of being low in differential loss, low in accessory phase shift, high in linearity, low in production cost and low in chip area, and can be used for large-amplitude signal processing and single chip integration.

Owner:XIDIAN UNIV

Monolithic silicon-based phased arrays for communications and radars

A phased-array receiver is adapted so as to be fully integrated and fabricated on a single silicon substrate. The phased-array receiver is operative to receive a 24 GHz signal and may be adapted to include 8-elements formed in a SiGe BiCMOS technology. The phased-array receiver utilizes a heterodyne topology, and the signal combining is performed at an IF of 4.8 GHz. The phase-shifting with 4 bits of resolution is realized at the LO port of the first down-conversion mixer. A ring LC VCO generates 16 different phases of the LO. An integrated 19.2 GHz frequency synthesizer locks the VCO frequency to a 75 MHz external reference. Each signal path achieves a gain of 43 dB, a noise figure of 7.4 dB, and an IIP3 of −11 dBm. The 8-path array achieves an array gain of 61 dB, a peak-to-null ratio of 20 dB, and improves the signal-to-noise ratio at the output by 9 dB.

Owner:CALIFORNIA INST OF TECH

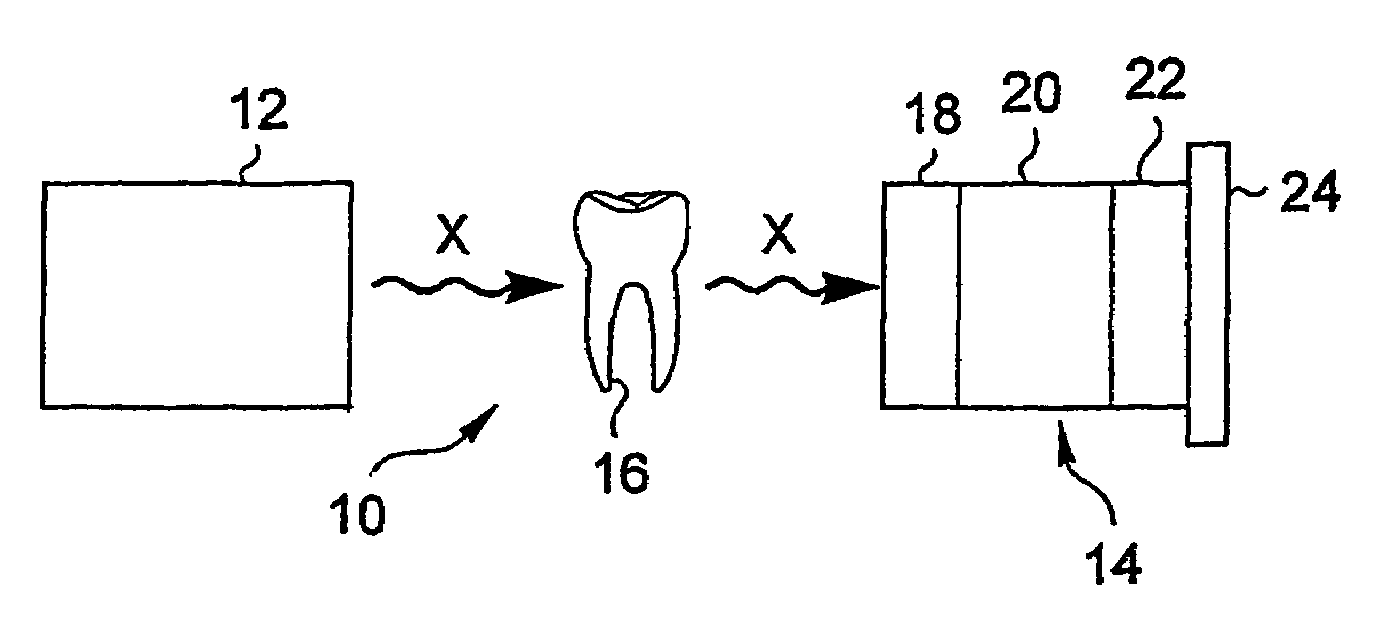

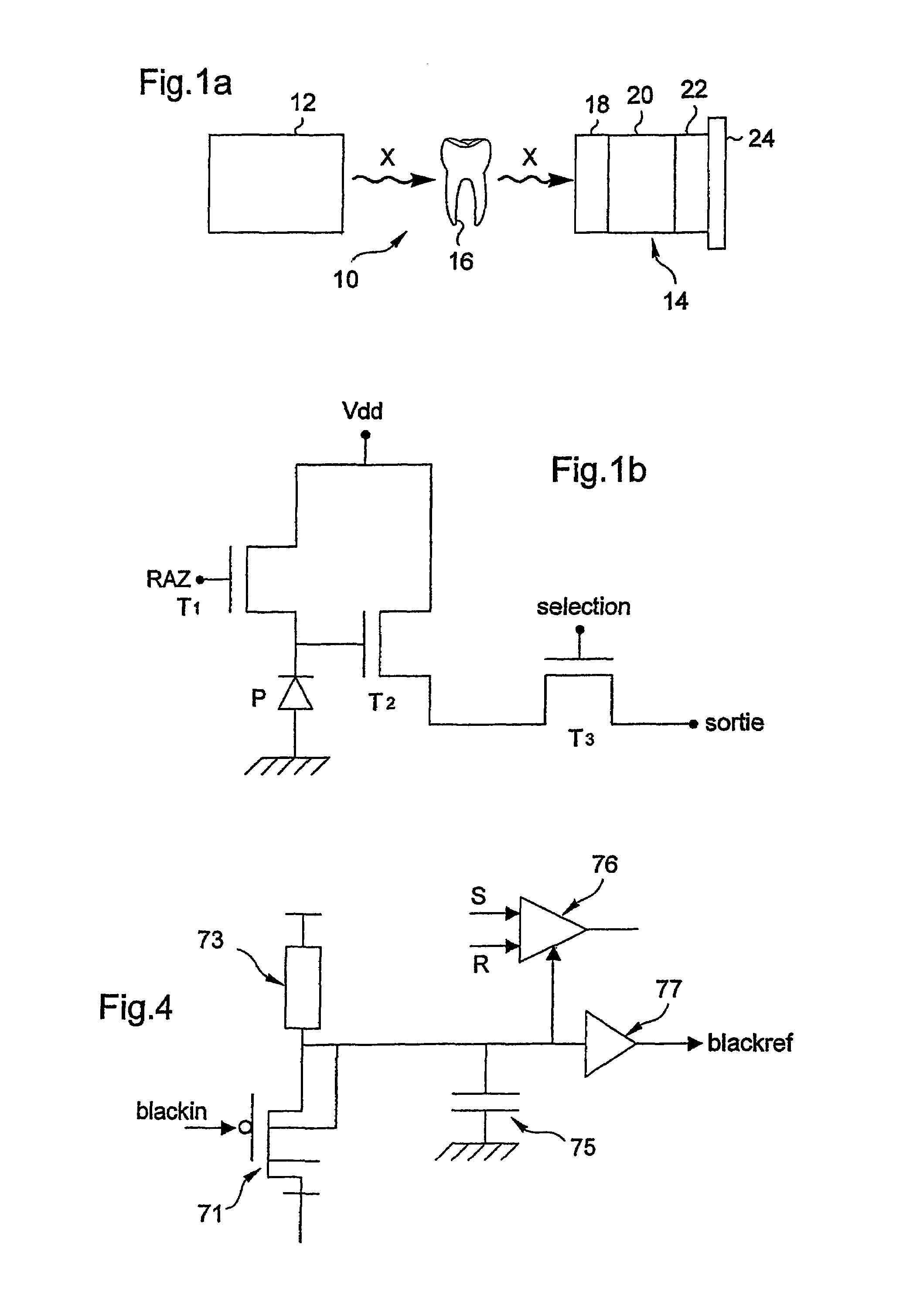

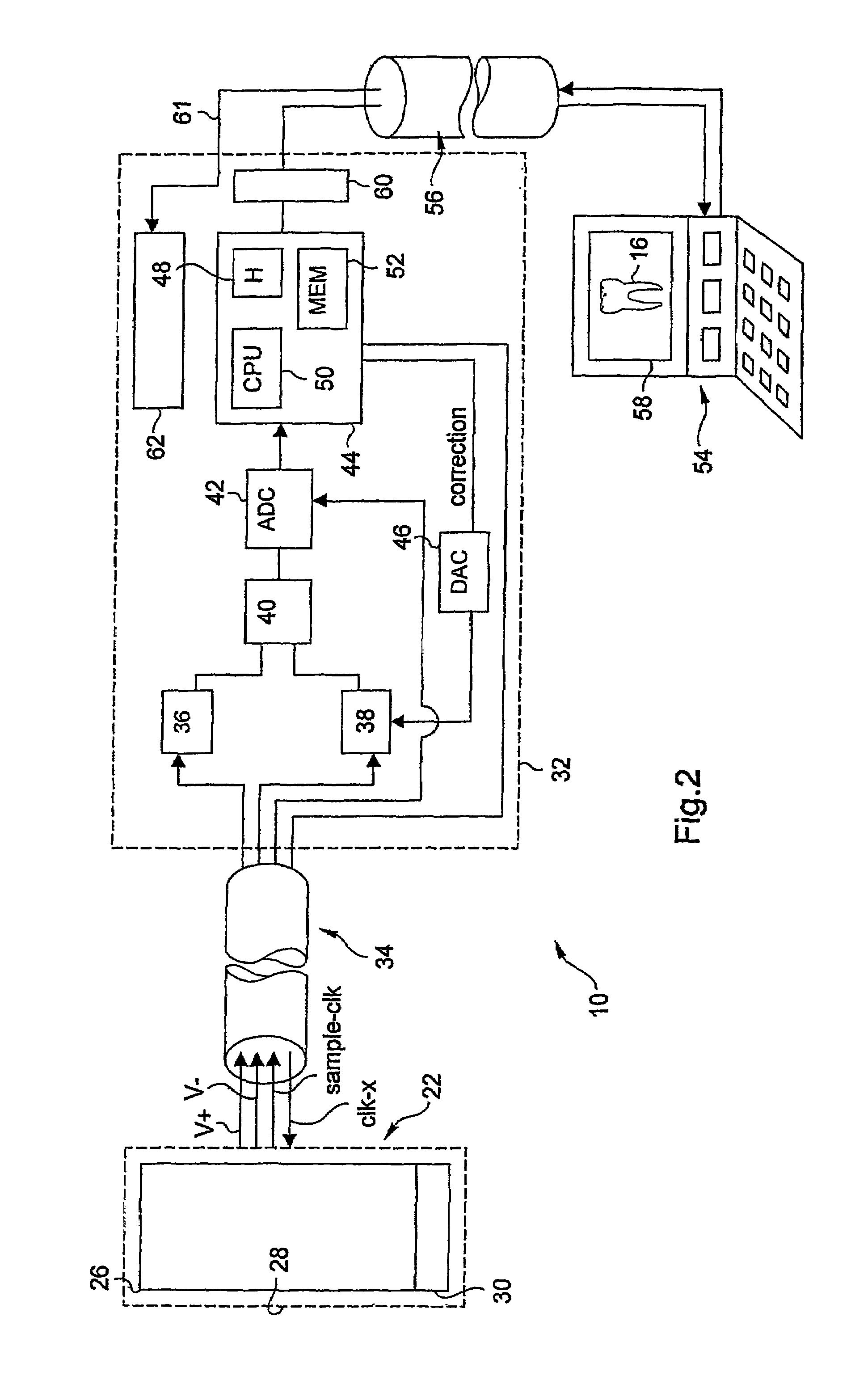

Dental radiology apparatus and signal processing method used therewith

ActiveUS7608834B2Avoid deteriorating detector 's signal-to-noise ratioIntroduce any reading noiseTelevision system detailsSolid-state devicesX-rayComputer module

The invention relates to a dental radiology apparatus, characterized in that it comprises: an intraoral sensor comprising a detector that includes an active pixel array produced using biCMOS technology and converting a received x-ray into at least one analog electrical output signal, an electronic module encapsulated in a case and which has at least one detector activation device, the module being linked to the sensor by a wire link for the transmission to said sensor of a detector activation signal generated in the module and for the transmission to the module of said at least one analog electrical output signal, the module having analog-digital means for converting said at least one analog electrical output signal into at least one digital output signal, a remote processing and display unit of said at least one digital output signal which is linked to the electronic module by a wire link intended to ensure the transmission to the unit of said at least one digital output signal.

Owner:CARESTREAM DENTAL TECH TOPCO LTD

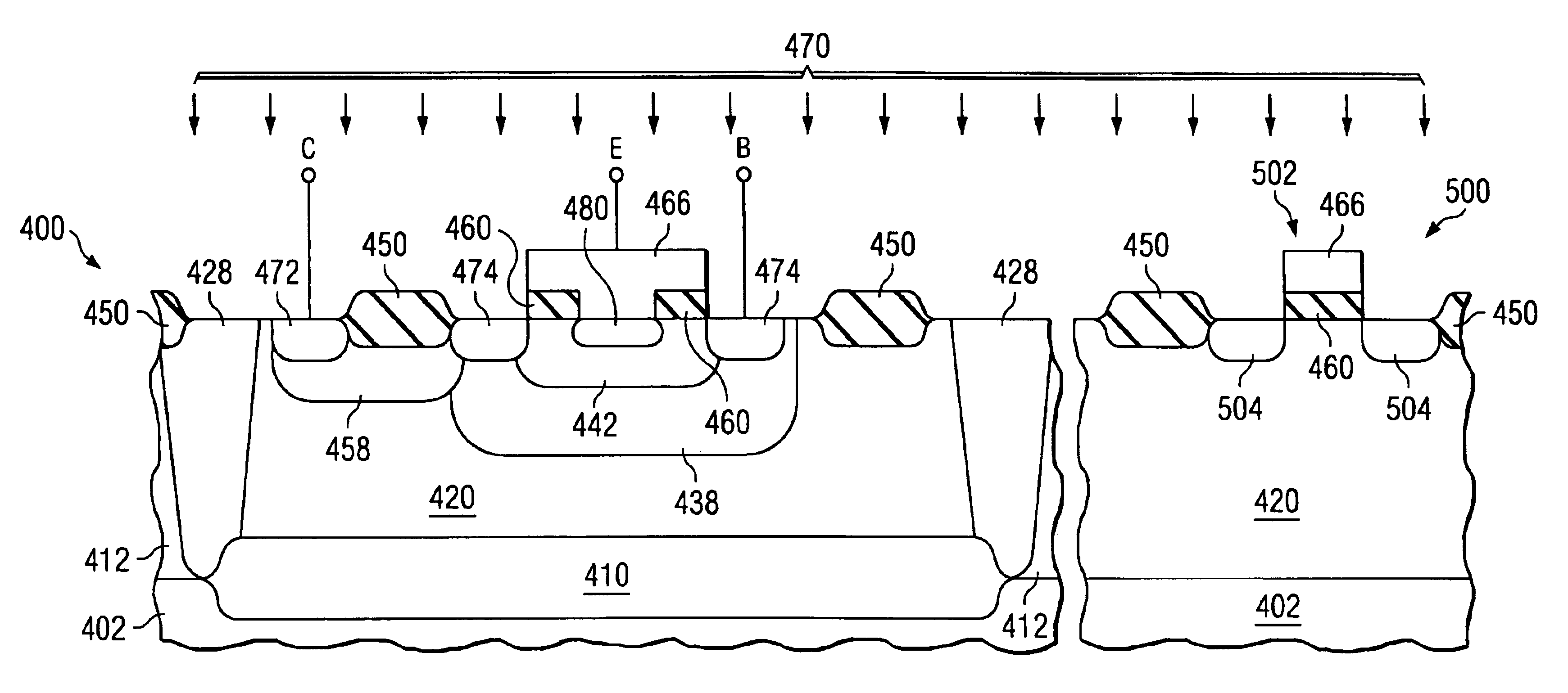

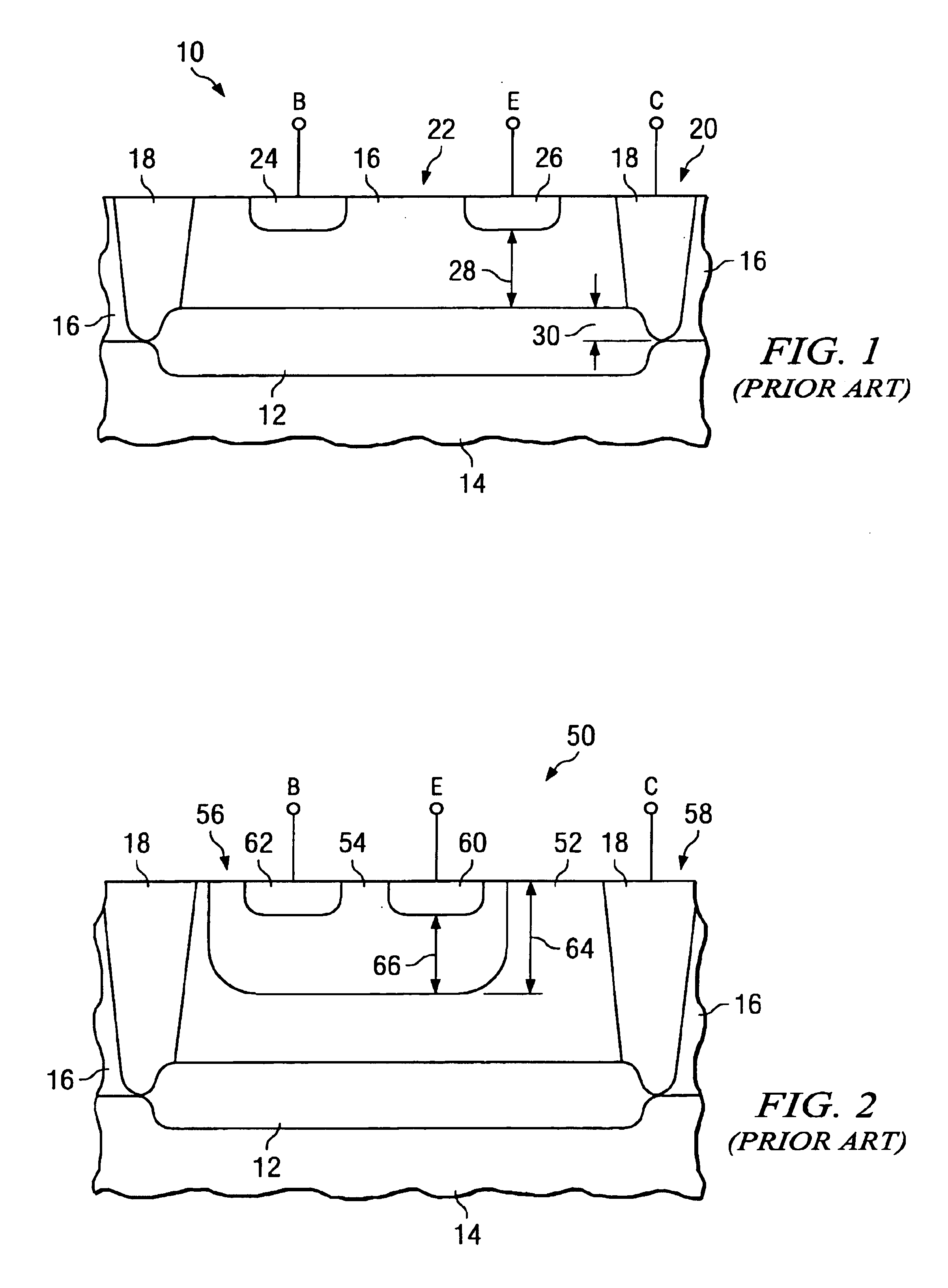

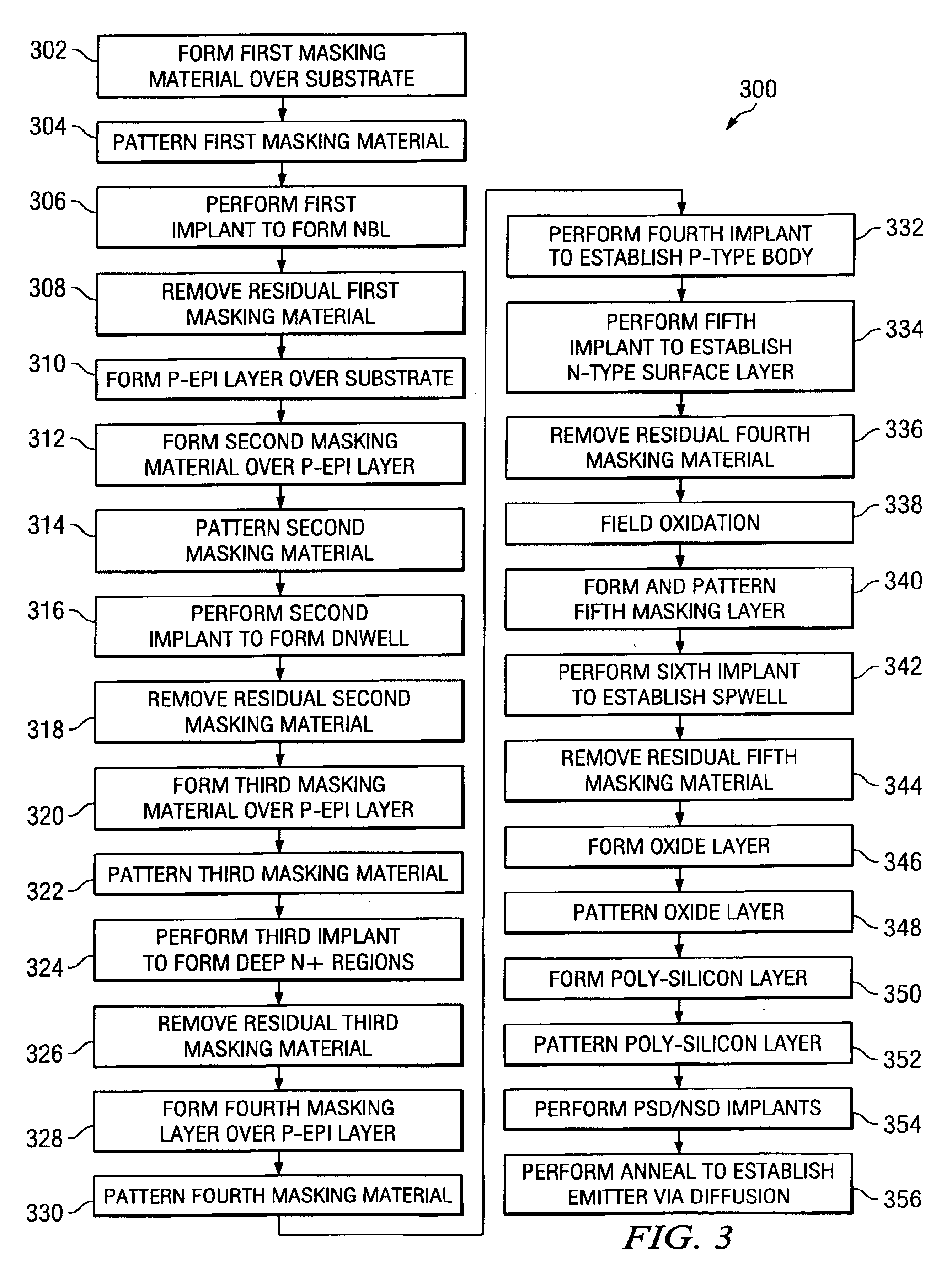

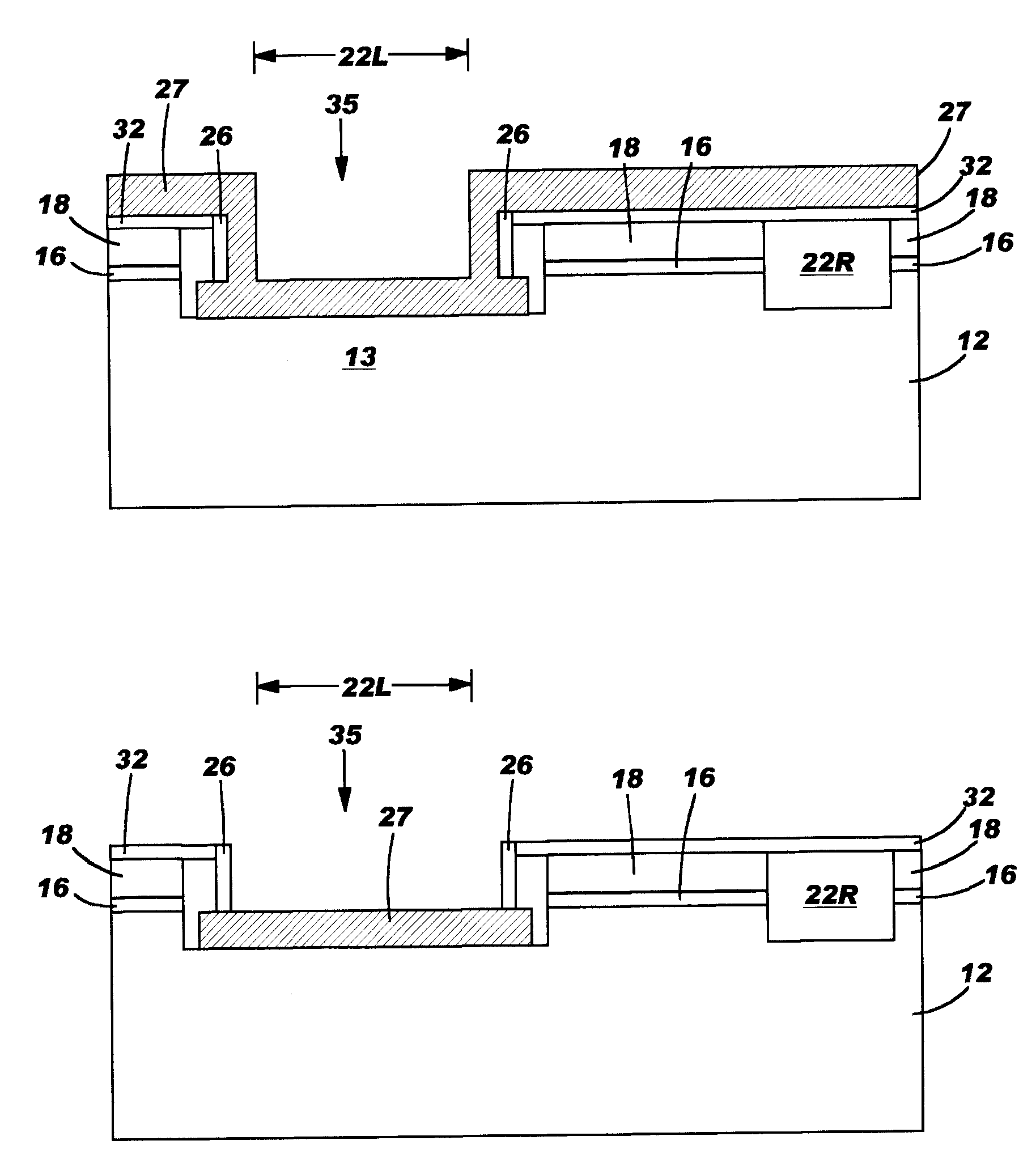

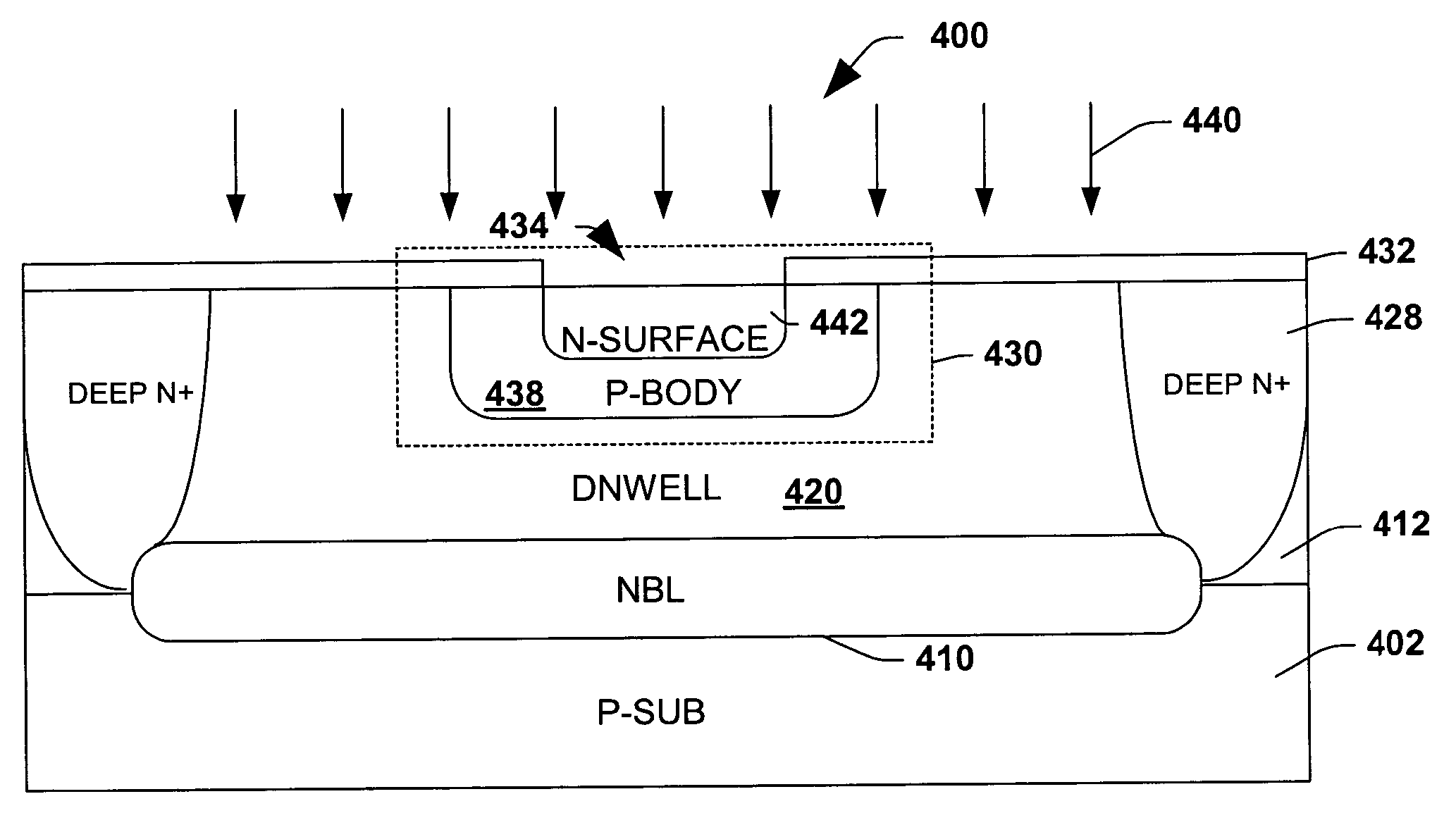

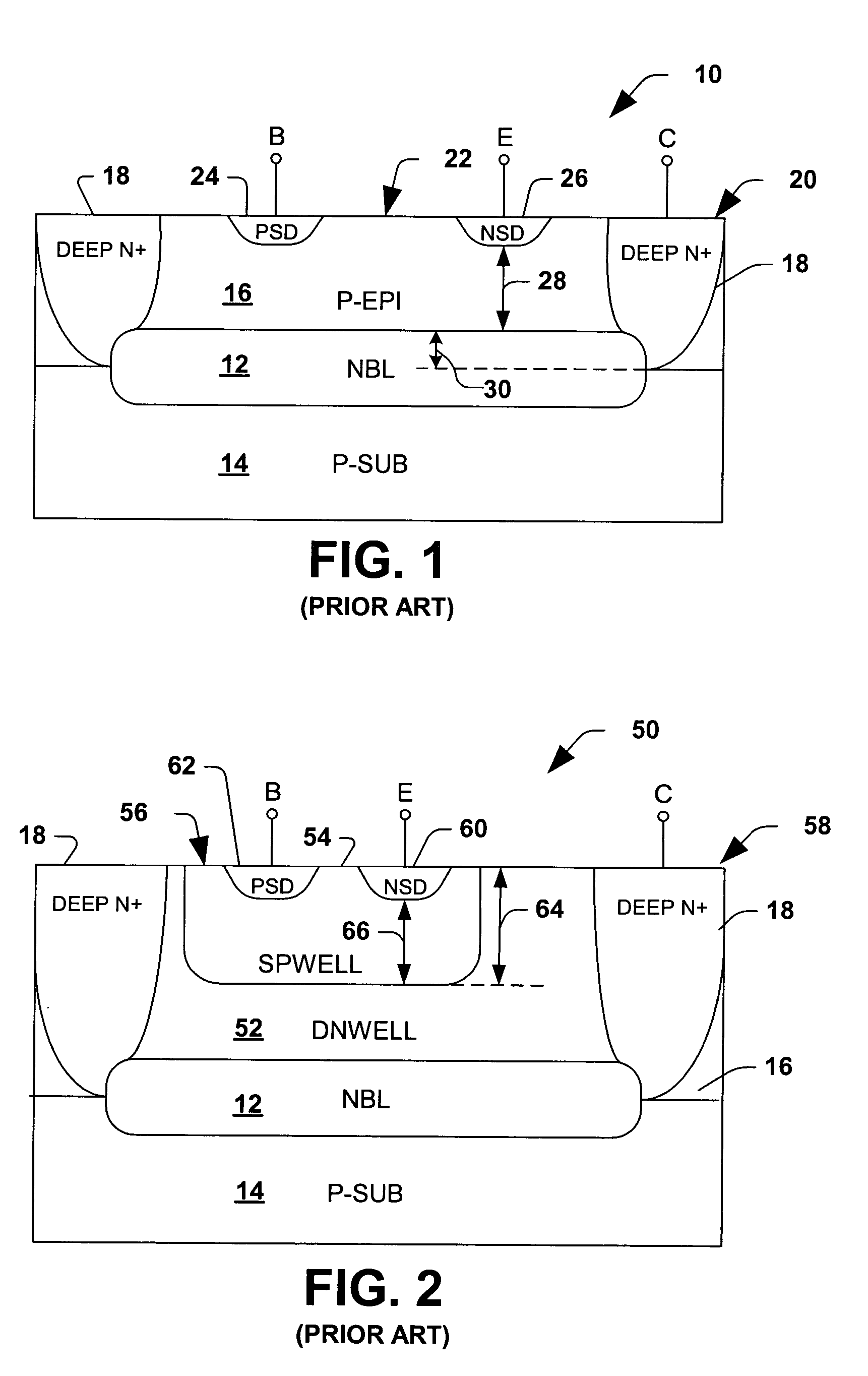

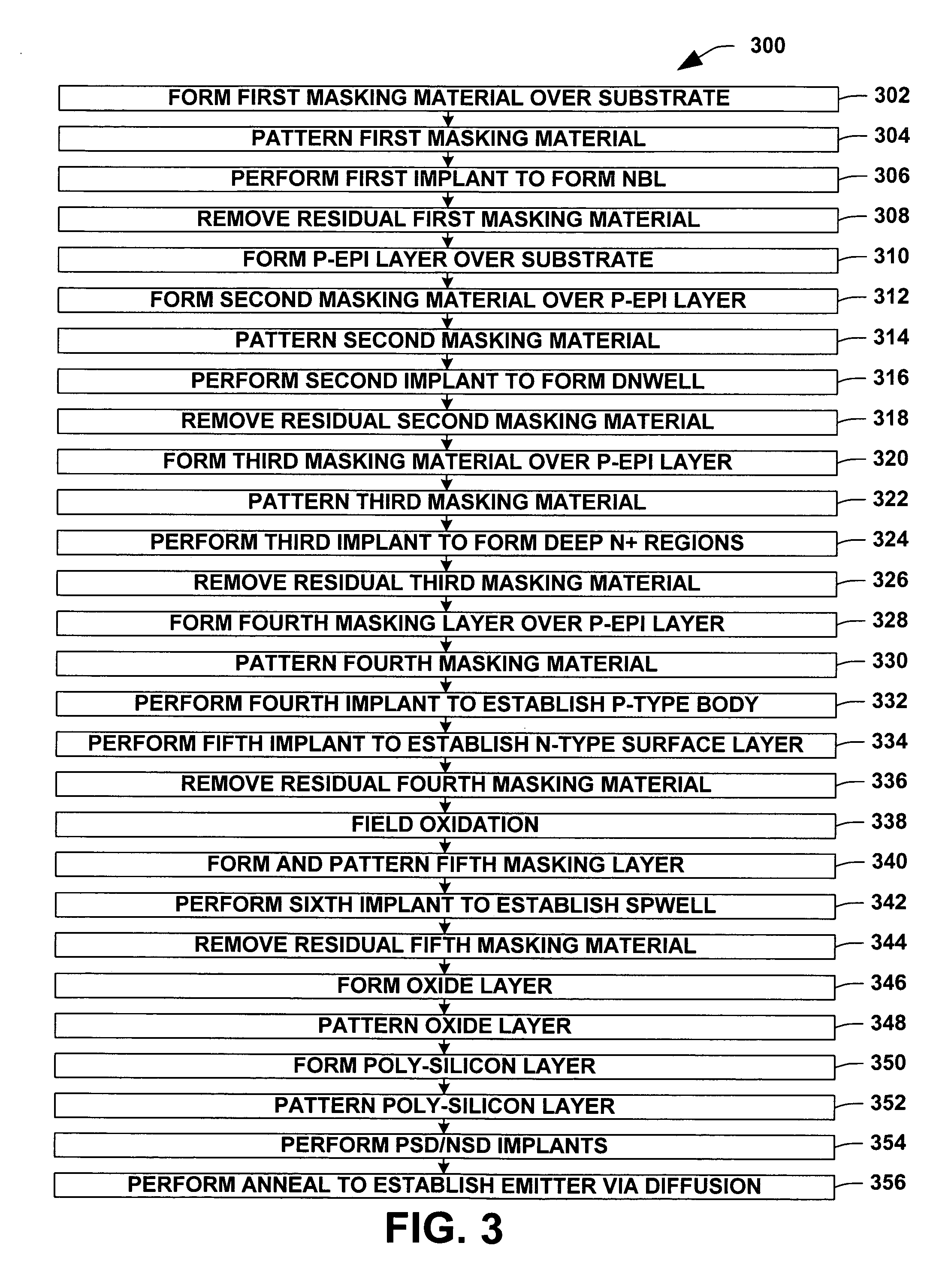

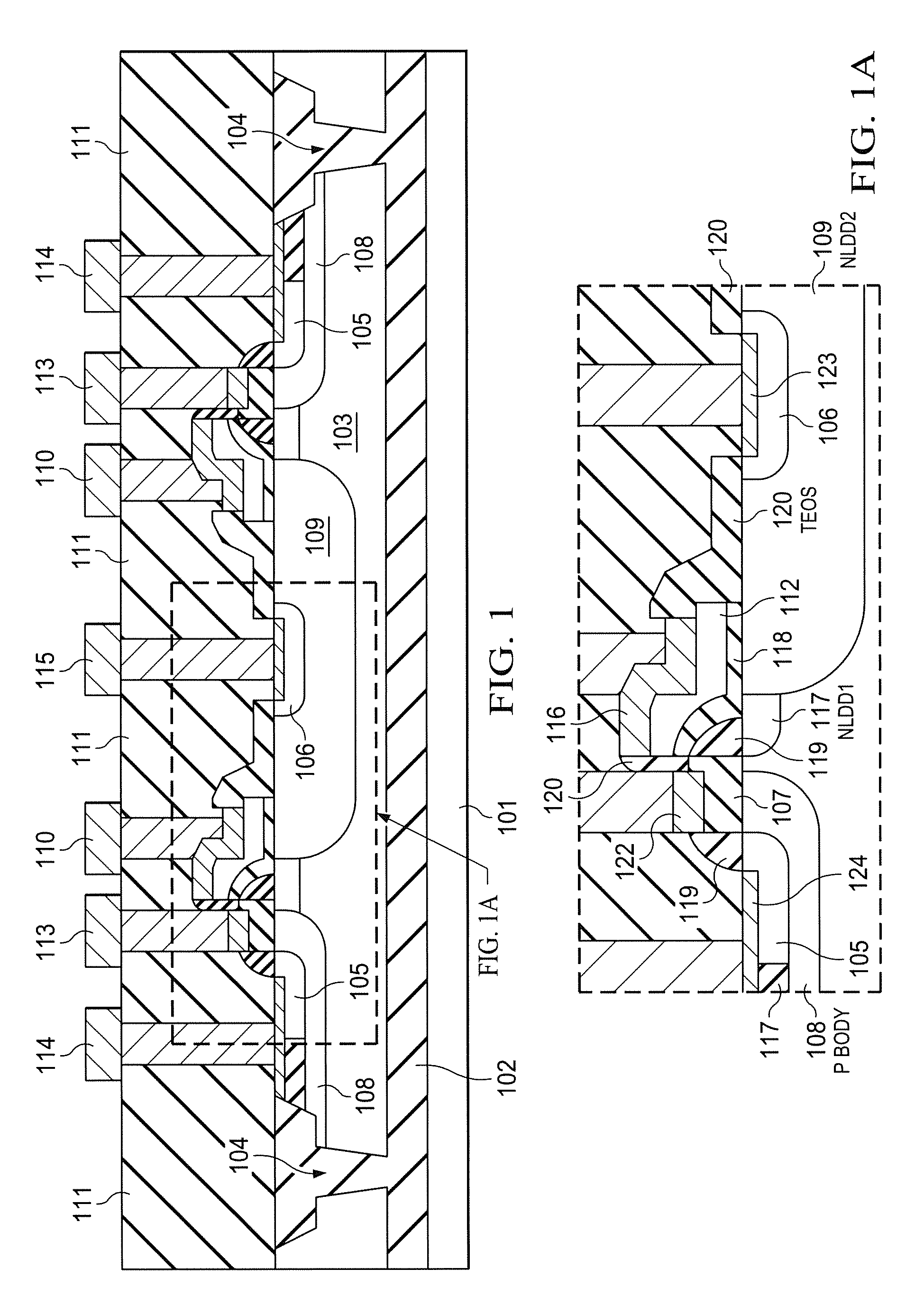

Single poly-emitter PNP using DWELL diffusion in a BiCMOS technology

InactiveUS6949424B2Small formatSolid-state devicesSemiconductor/solid-state device manufacturingCMOSSurface layer

A method of forming a bipolar transistor device, and more particularly a vertical poly-emitter PNP transistor, as part of a BiCMOS type manufacturing process is disclosed. The formation of the PNP transistor during a CMOS / DMOS fabrication process requires merely one additional mask to facilitate formation of a very small emitter in a portion of an N-type surface layer of a double diffused well (DWELL). Unlike conventional PNP transistors, a separate mask is not required to establish the base of the transistor as the transistor base is formed from a portion of the double diffused well and the DWELL includes a P-type body layer formed via implantation through the same opening in the same mask utilized to establish the N-type surface layer of the double diffused well. The base is also thin thus improving the transistor's frequency and gain.

Owner:TEXAS INSTR INC

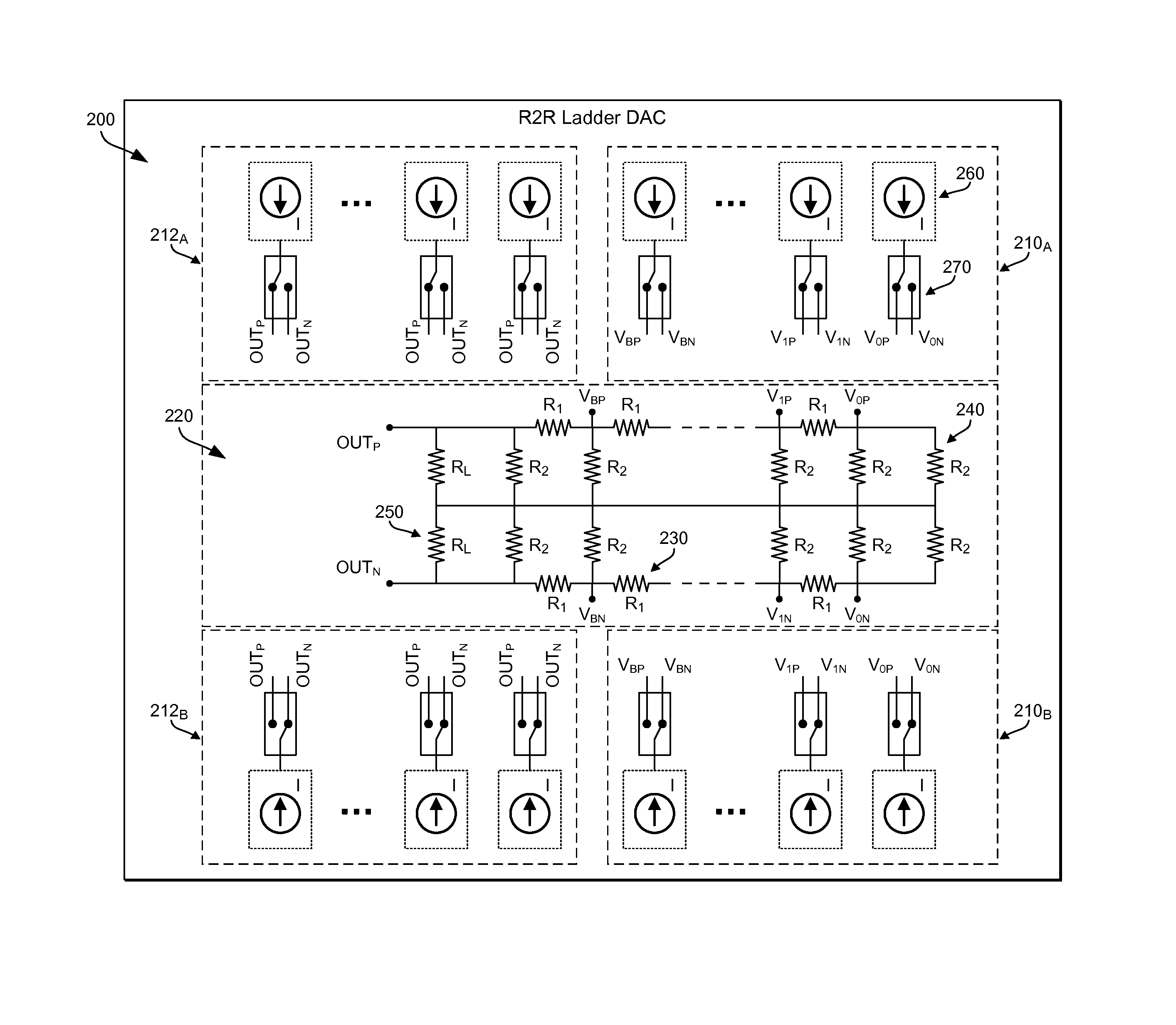

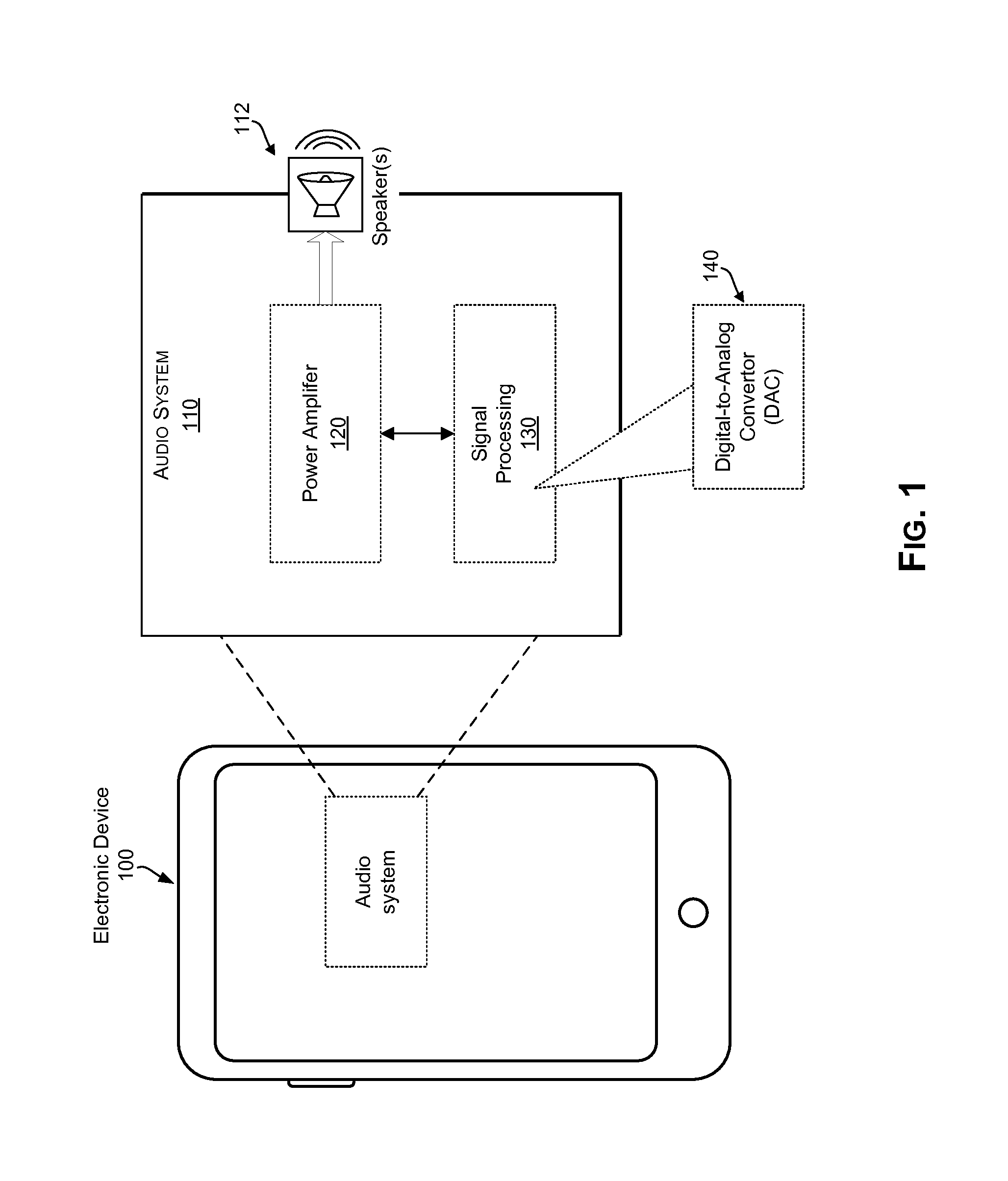

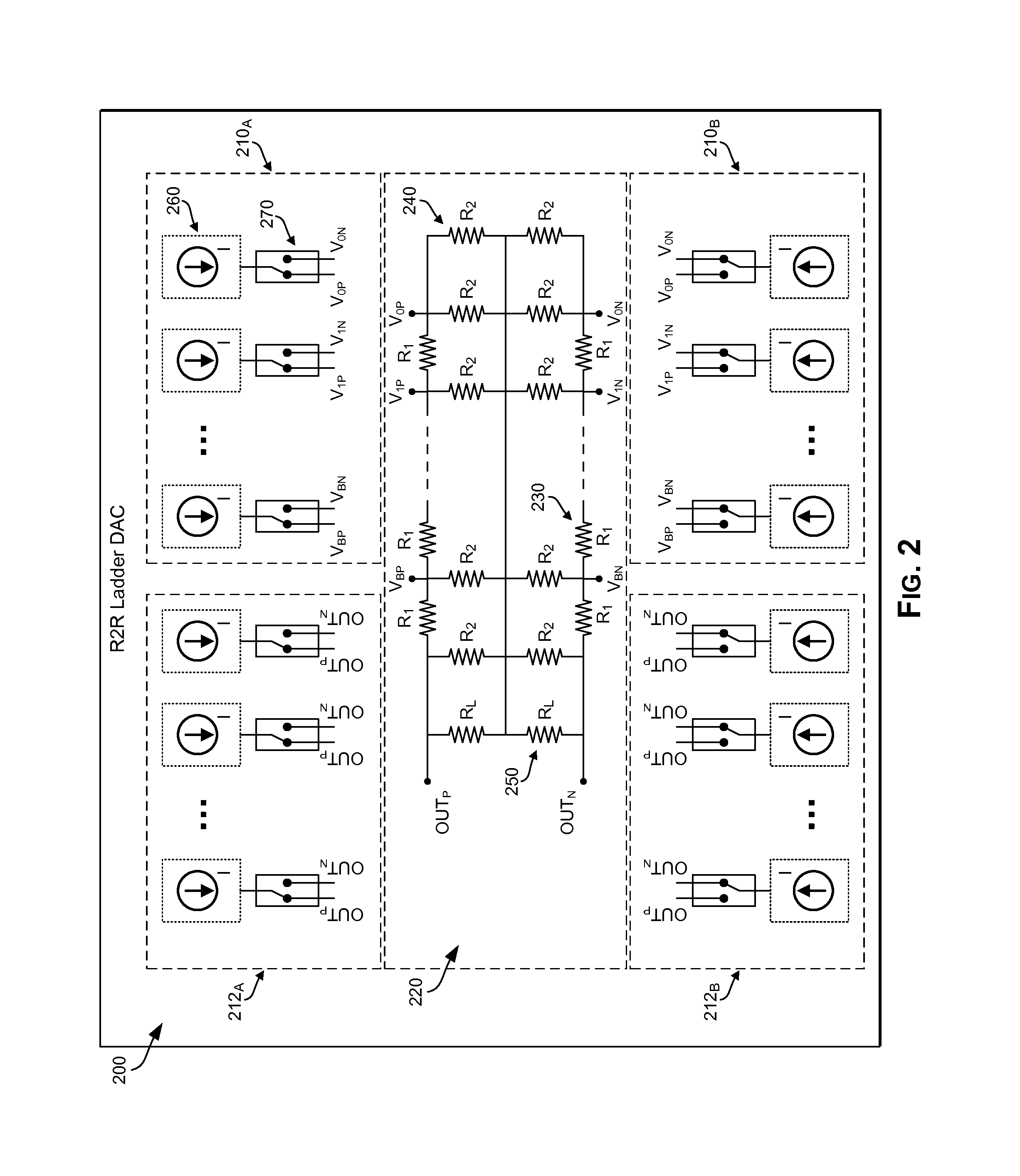

Calibration of an R2R ladder based current digital-to-analog converter (DAC)

InactiveUS8576101B1Electric signal transmission systemsDigital-analogue convertorsPower flowDigital analog converter

A R2R ladder circuit implementation of a digital-to-analog convertor (DAC) may be configured to compensate for mismatch in each of a plurality of current sources in the R2R ladder circuit. The compensating of mismatch in each of the plurality of current sources may be achieved by adding one or more auxiliary current sources associated with each of the plurality of current sources, which may be used to provide pre-configured auxiliary current that would enable compensating for mismatch in current of an associated one of the plurality of current sources. For example, each of the plurality of current sources may have two auxiliary current sources, connected in parallel therewith, with one of two auxiliary current sources being switched to the positive-side and the other auxiliary current source being switched to the negative-side. The switching structure of the modified R2R ladder circuit may be implemented in any semiconductor technology (e.g., BiCMOS technology).

Owner:GOOGLE LLC

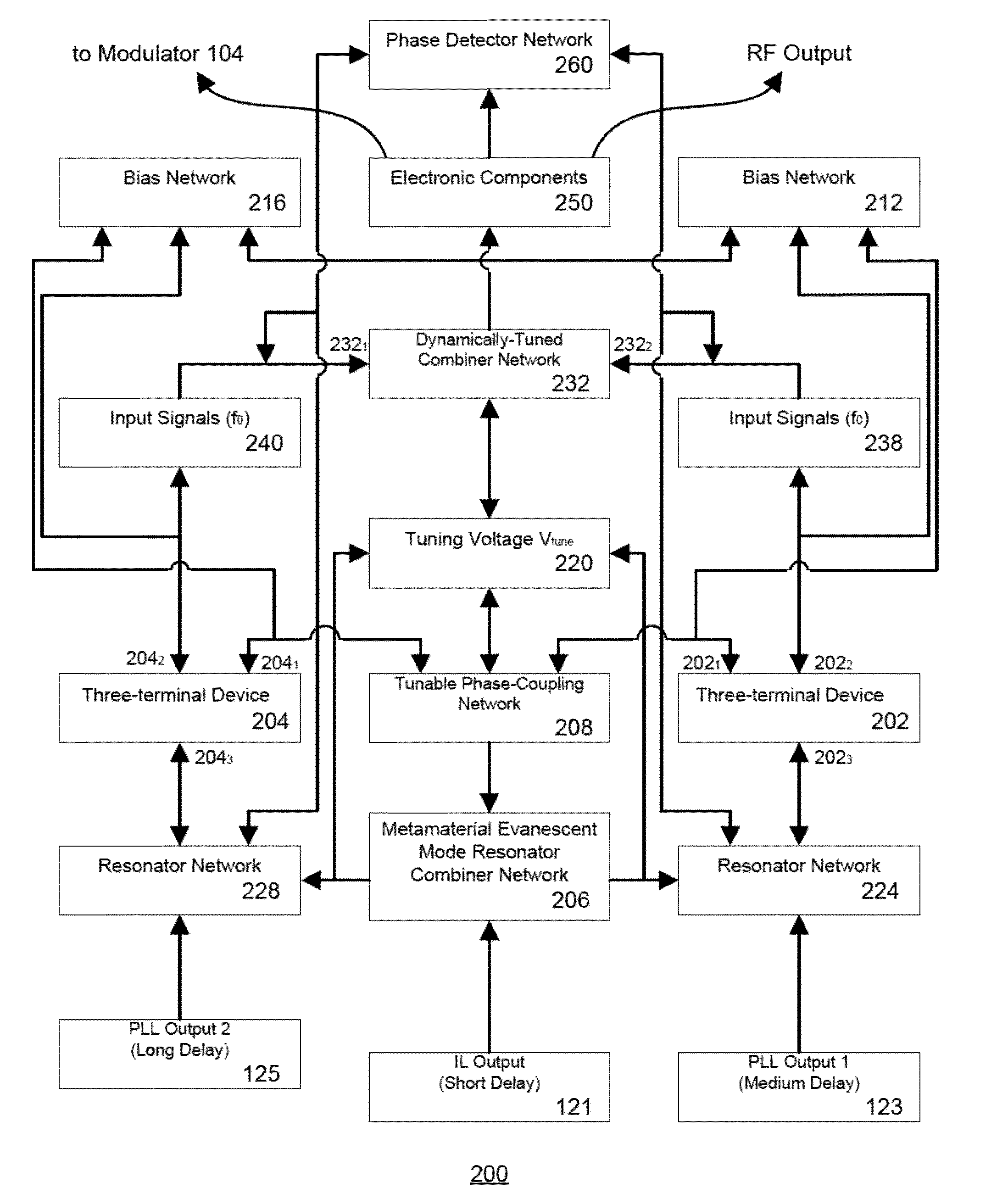

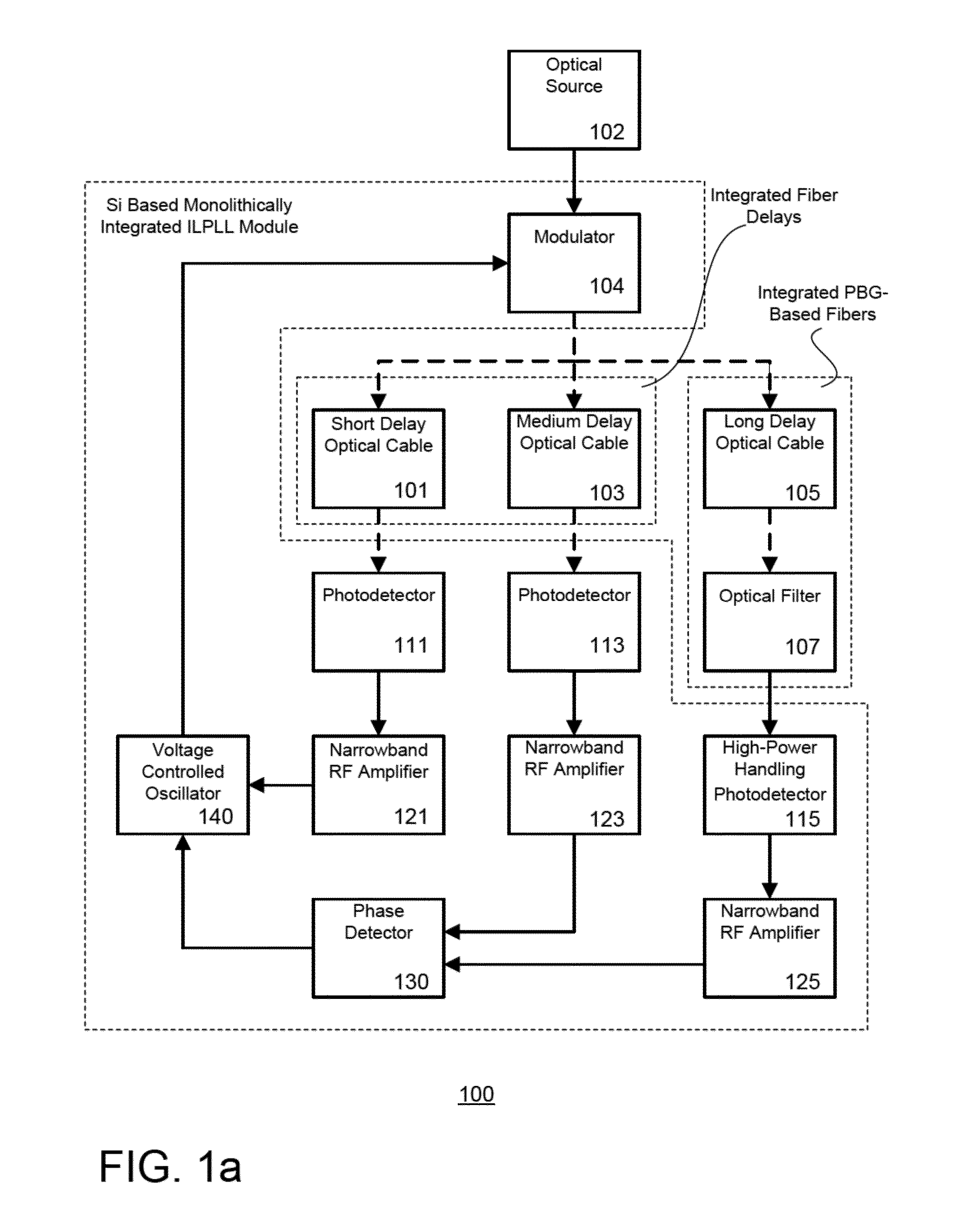

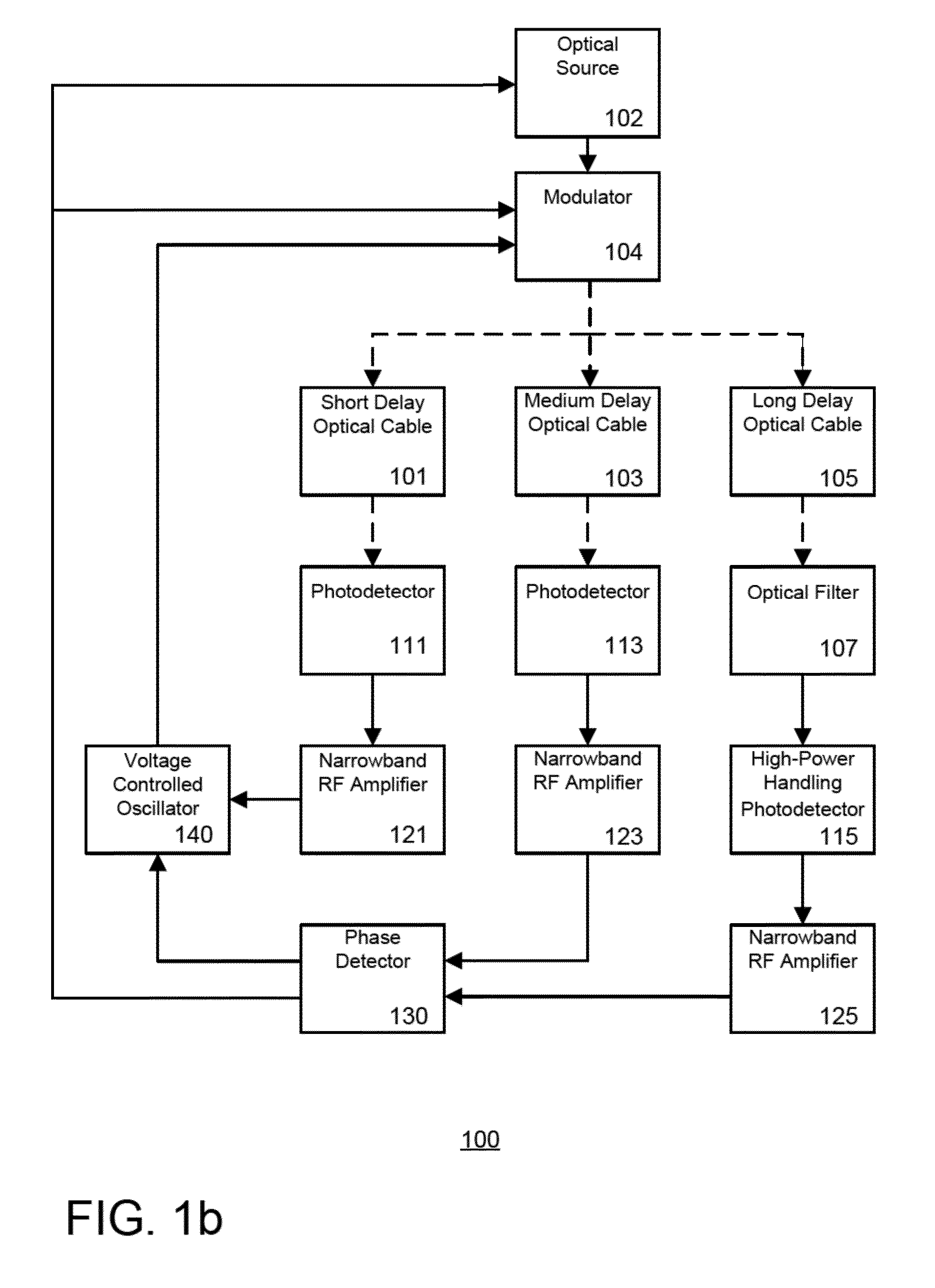

Integrated production of self injection locked self phase loop locked optoelectronic oscillator

ActiveUS20140270786A1Reduce power consumptionEliminate needElectromagnetic transmittersOscillations generatorsPhotonicsRf filters

The present invention details fabrication guidelines of integrated optoelectronic oscillators with frequency and phase stability, having higher frequency selectivity in a relatively small size (compared to the larger size of a higher order electrically realized RF filter), reduced temperature sensitivity, and minimized frequency drift. The integrated photonic components and RF oscillator may use Silicon photonics and microelectronic integration using CMOS and BiCMOS technology, eliminating the need for bulky and / or discrete optical and microwave components.

Owner:SYNERGY MICROWAVE CORP

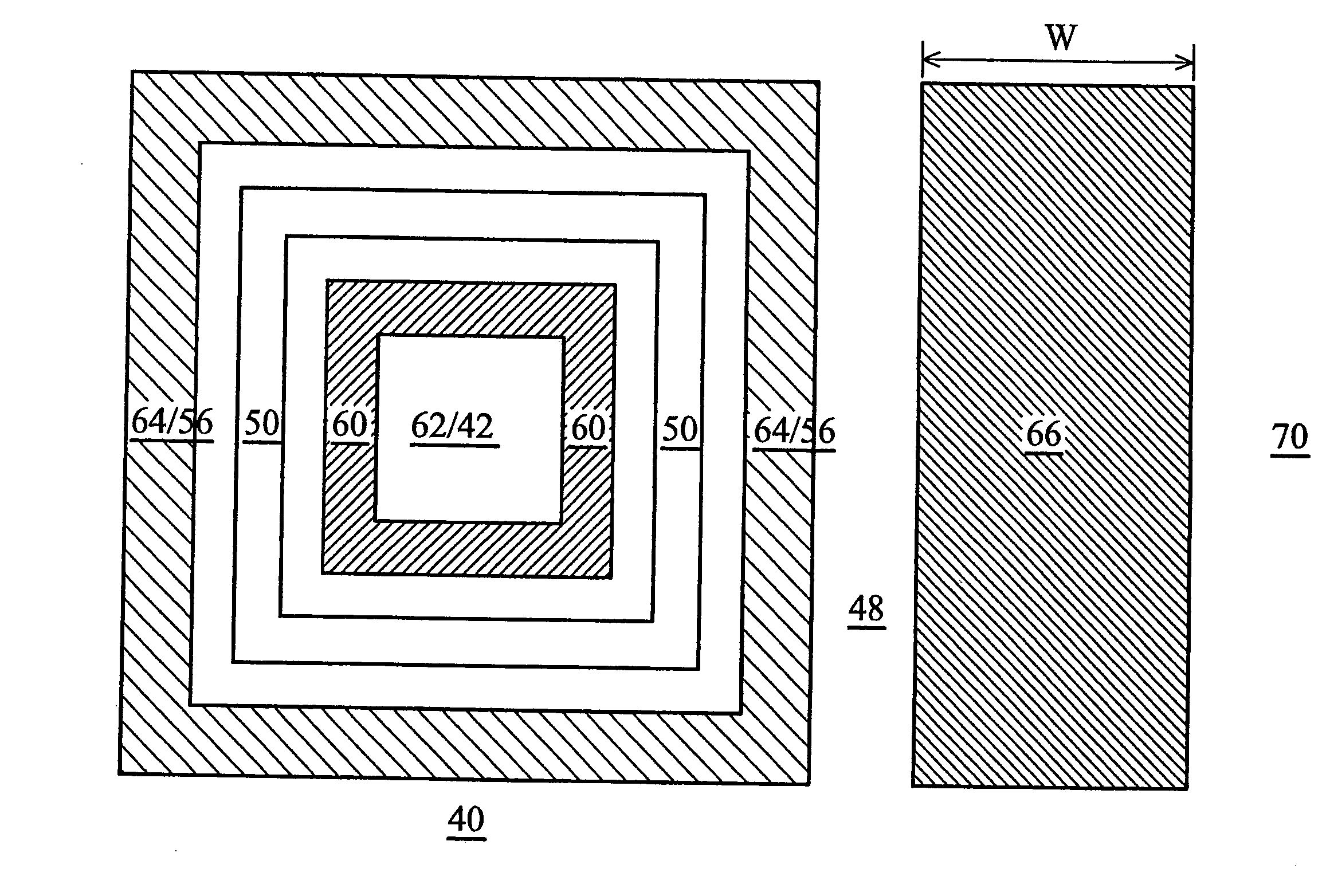

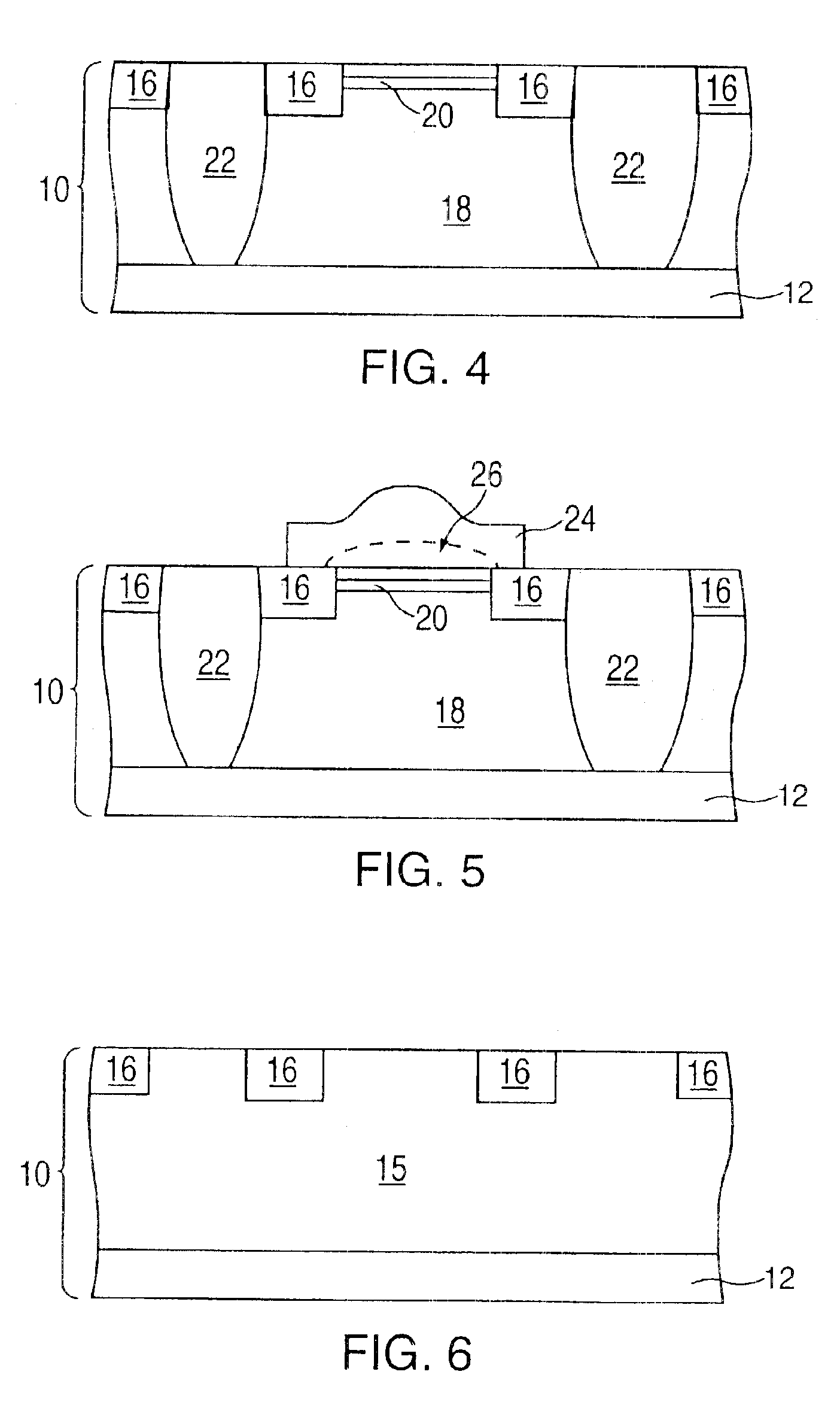

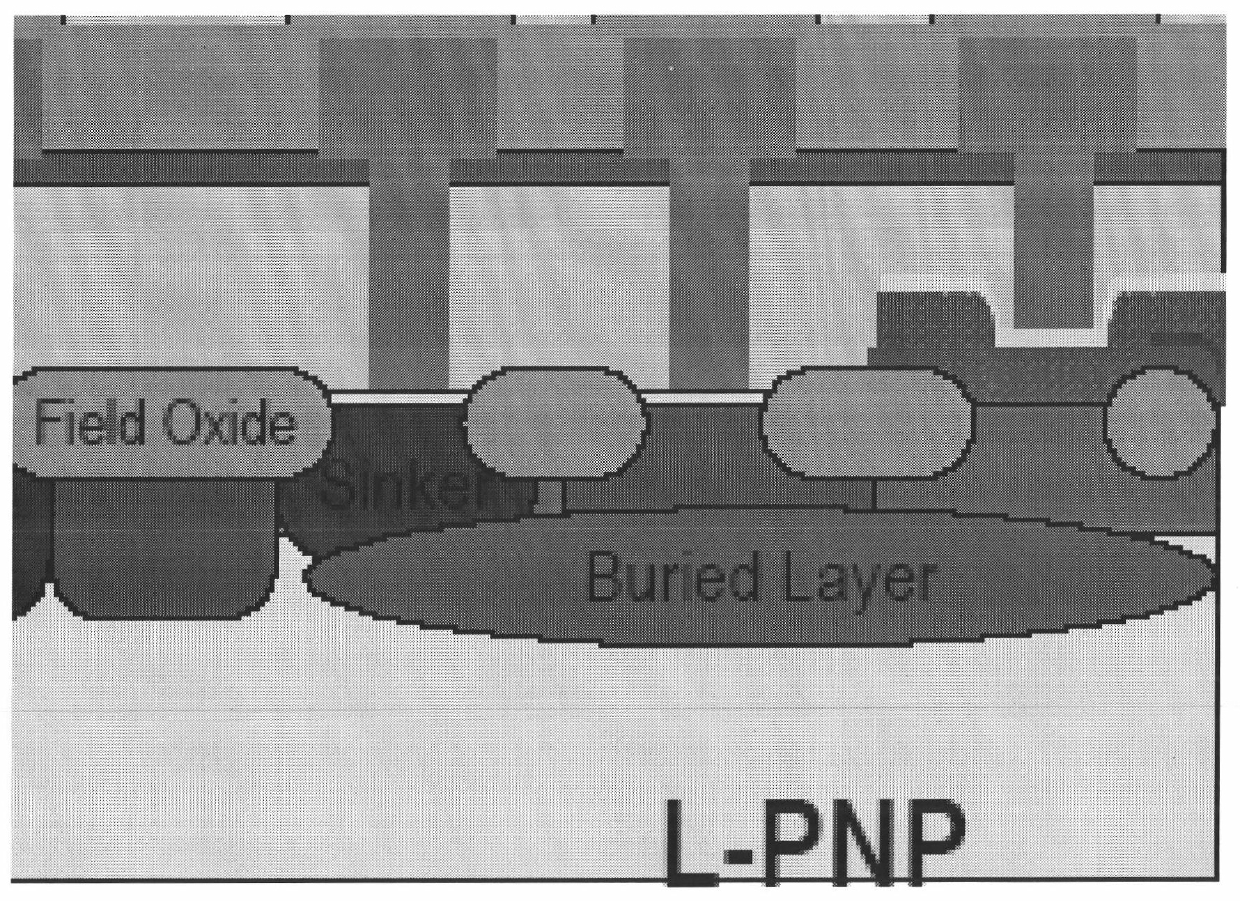

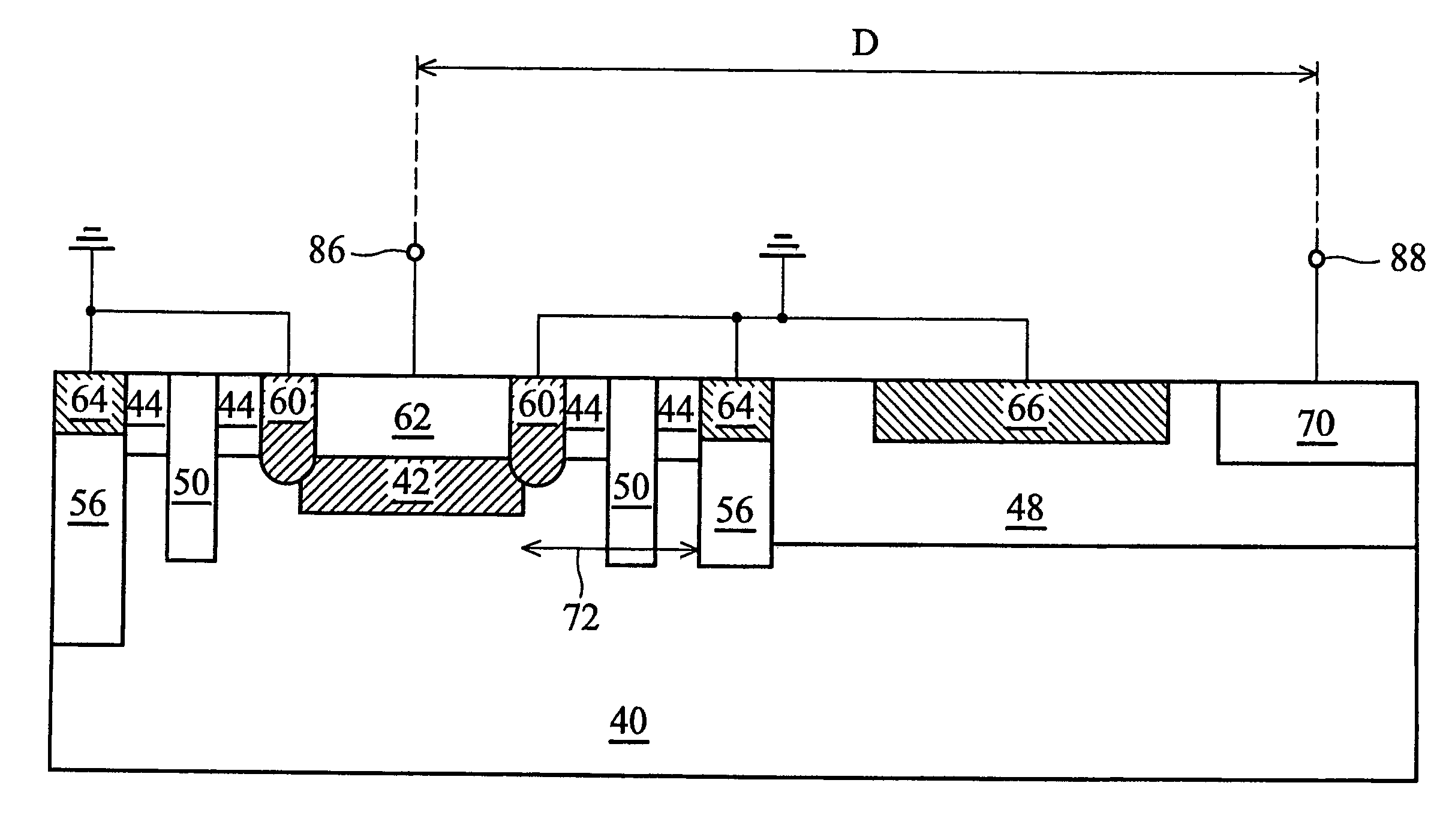

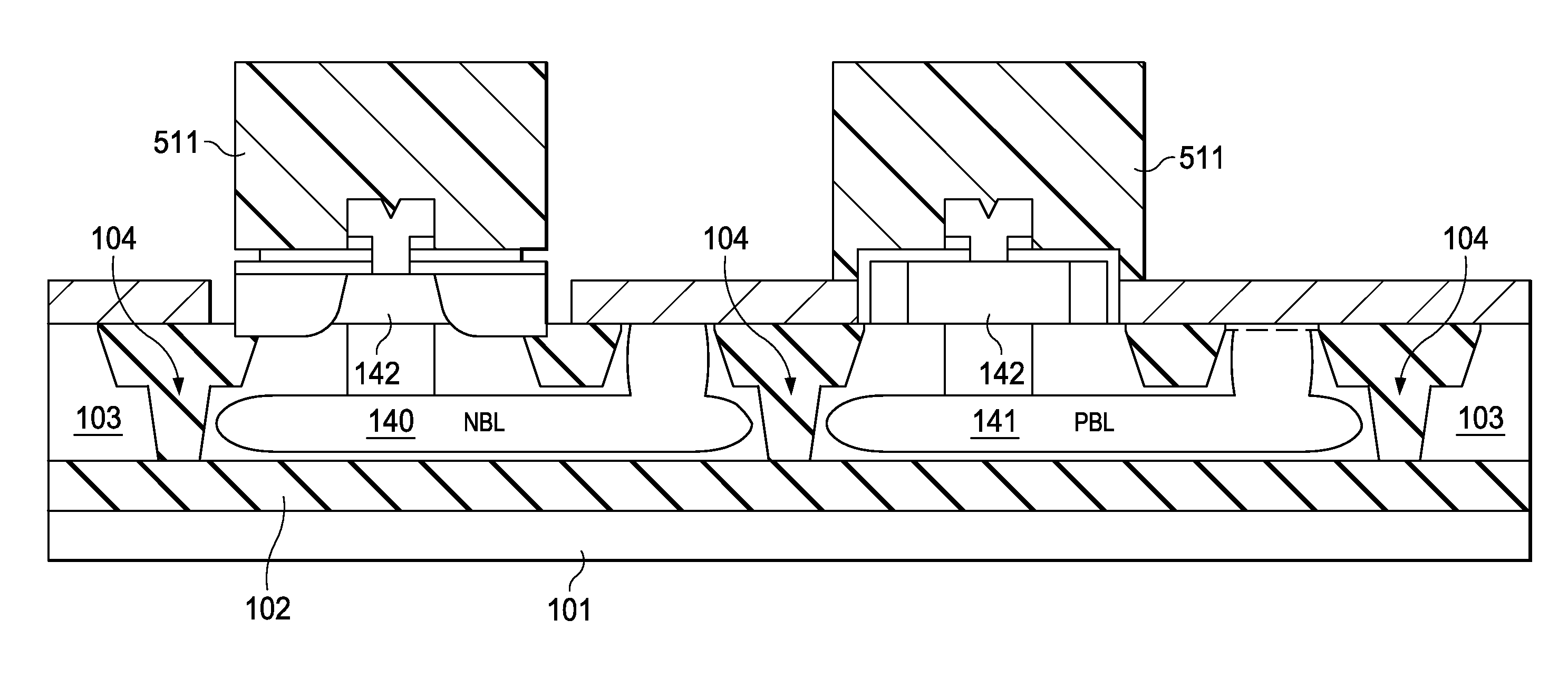

Design of high-frequency substrate noise isolation in BiCMOS technology

A high-frequency noise isolation structure and a method for forming the same are provided. The noise isolation structure isolates a first device region and a second device region over a semiconductor substrate. The noise isolation structure preferably includes a sinker region substantially encircling a first device region, a buried layer underlying the first device region and joining the sinker region, a deep guard ring substantially encircling the sinker region, and a deep trench oxide region substantially encircling the sinker region. The isolation structure further includes a wide guard ring between the first and the second device regions. The sinker region and the buried region preferably have a high impurity concentration. Integrated circuits to be noise decoupled are preferably formed in the respective first and second device regions.

Owner:TAIWAN SEMICON MFG CO LTD

Method for creation of the gate shield in analog/rf power ed-cmos in sige bicmos technologies

A method of fabricating a MOSFET transistor in a SiGe BICMOS technology and resulting structure having a drain-gate feedback capacitance shield formed between a gate electrode and the drain region. The shield does not overlap the gate and thereby minimizes effect on the input capacitance of the transistor. The process does not require complex or costly processing since the shield is composed of bipolar base material commonly used in SiGe BICMOS technologies.

Owner:TEXAS INSTR INC

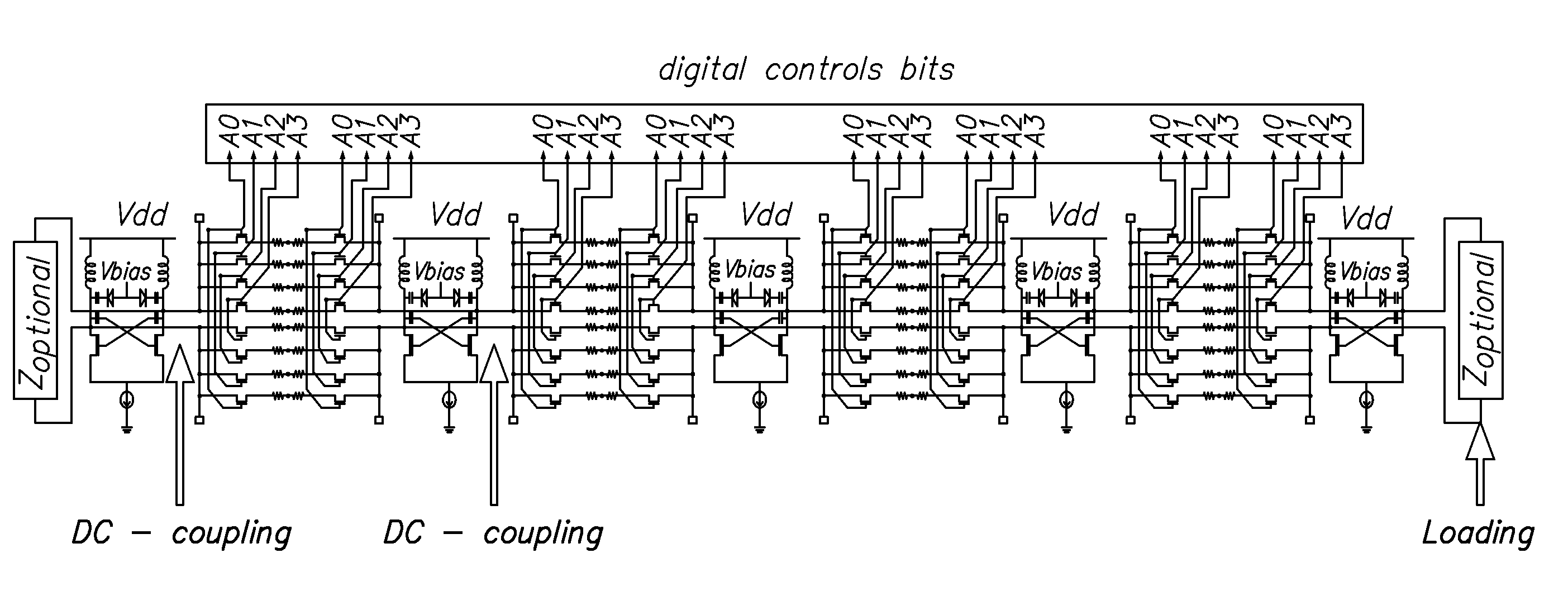

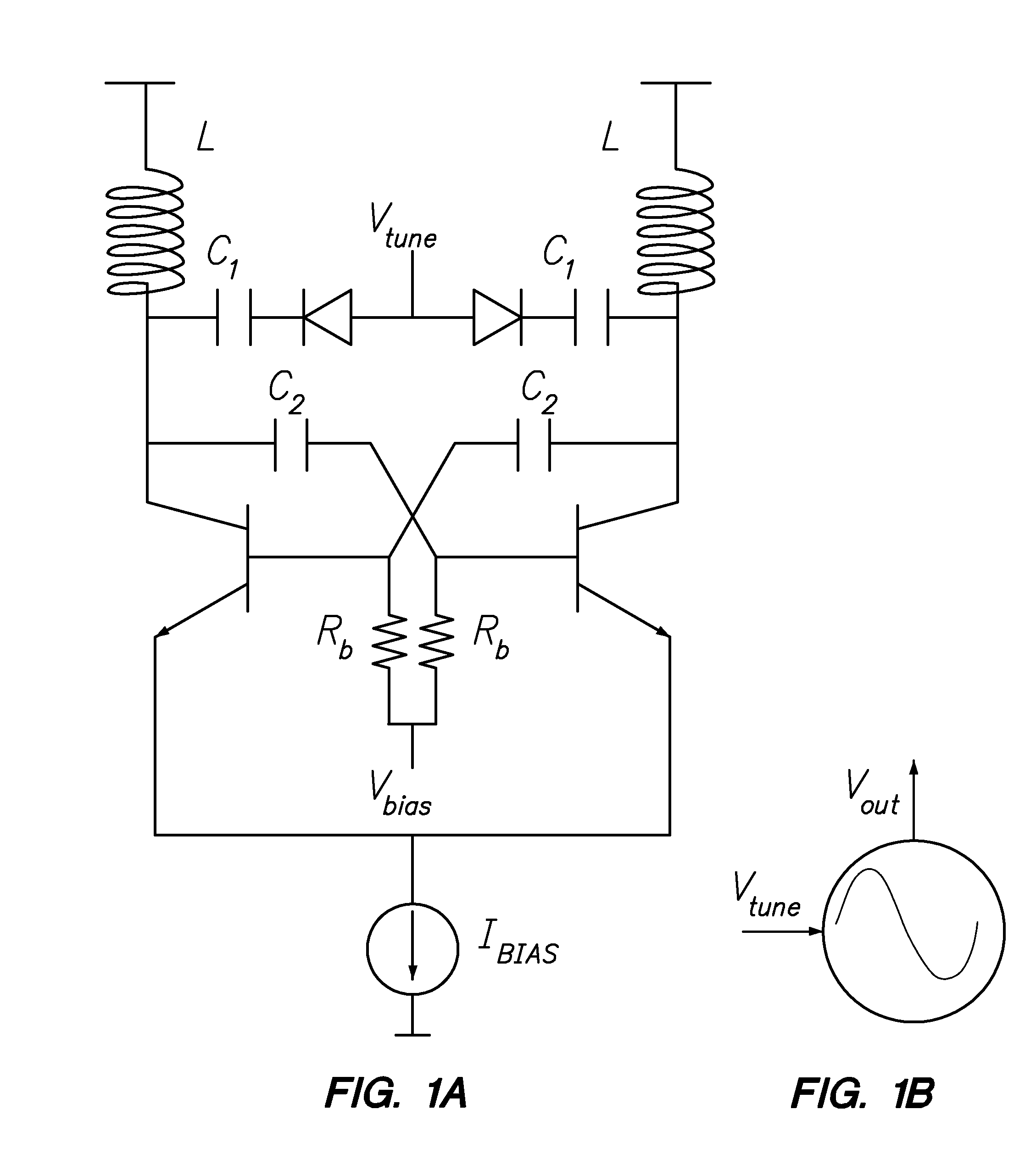

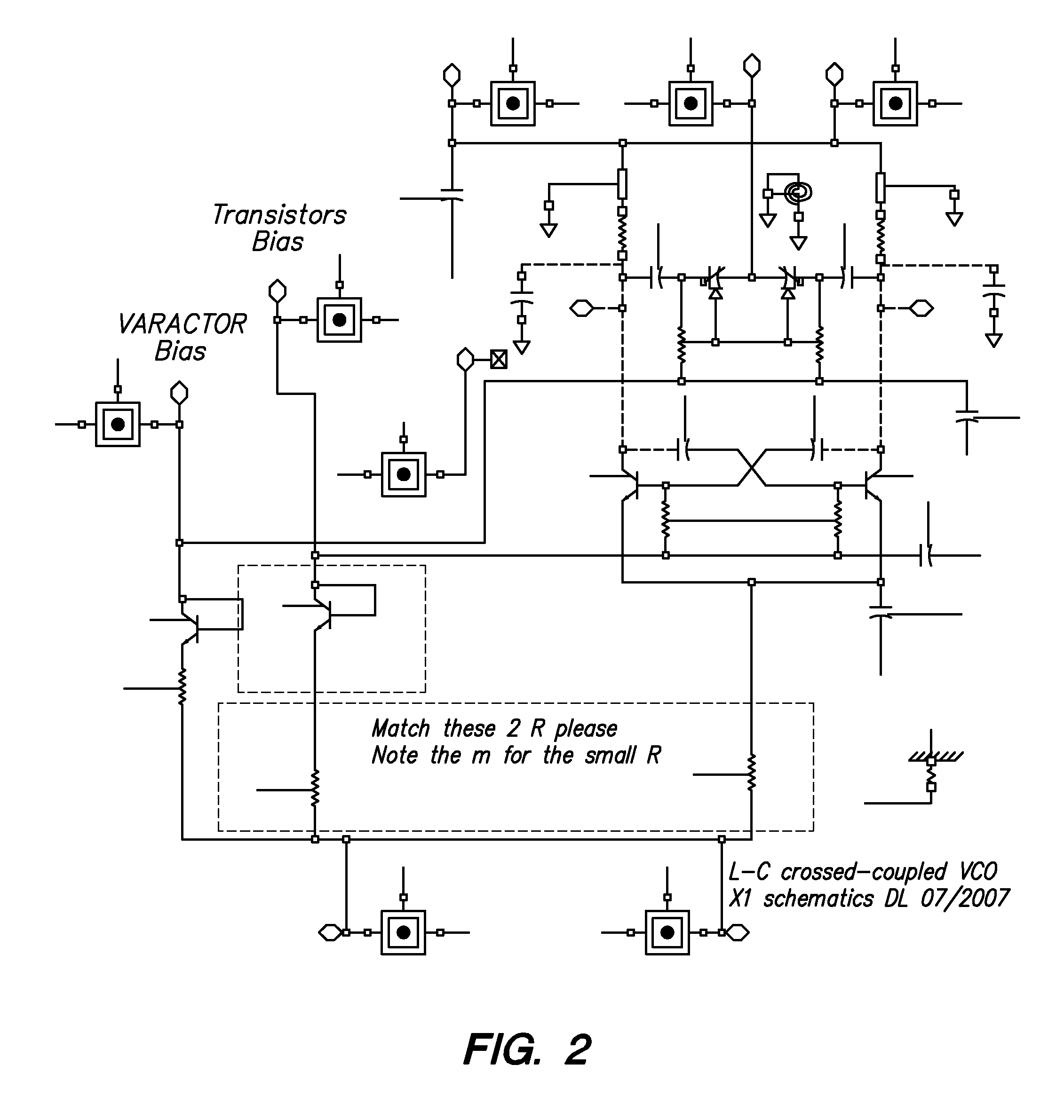

Frequency tuning and phase shifting techniques using 1-dimensional coupled voltage-controlled-oscillator arrays for active antennas

InactiveUS8558625B1Reduce phase noiseLarge tuning rangePulse generation by logic circuitsOscillations generatorsPhase noiseBeam steering

A technique for enhancing the frequency tuning range for monolithic RF source generation using fully-integrated coupled Voltage-Controlled-Oscillator (VCO) arrays that contain an odd number of VCOs. Fully-monolithic SiGe VCO arrays using on-chip inductor and varactor with on-chip bias current sources have been carefully designed and simulated in IBM 7HP 0.18 μm BiCMOS technology and taped out for fabrication. The SPICE simulated frequency and phase tuning of the 1-D VCO×5 array is dependent on the edge VCOs termination impedance, the tuning voltages, and the VCO coupling strength. The simulated data suggests that the enhanced tuning range and beam steering can be accomplished using coupled-VCO arrays without needing complex and bulky phase shifters. This design technique imposes no apparent phase noise penalty but can provide simulated RF frequency tuning range of ˜40% and also ˜+ / −25° beam steering for active antennas applications.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

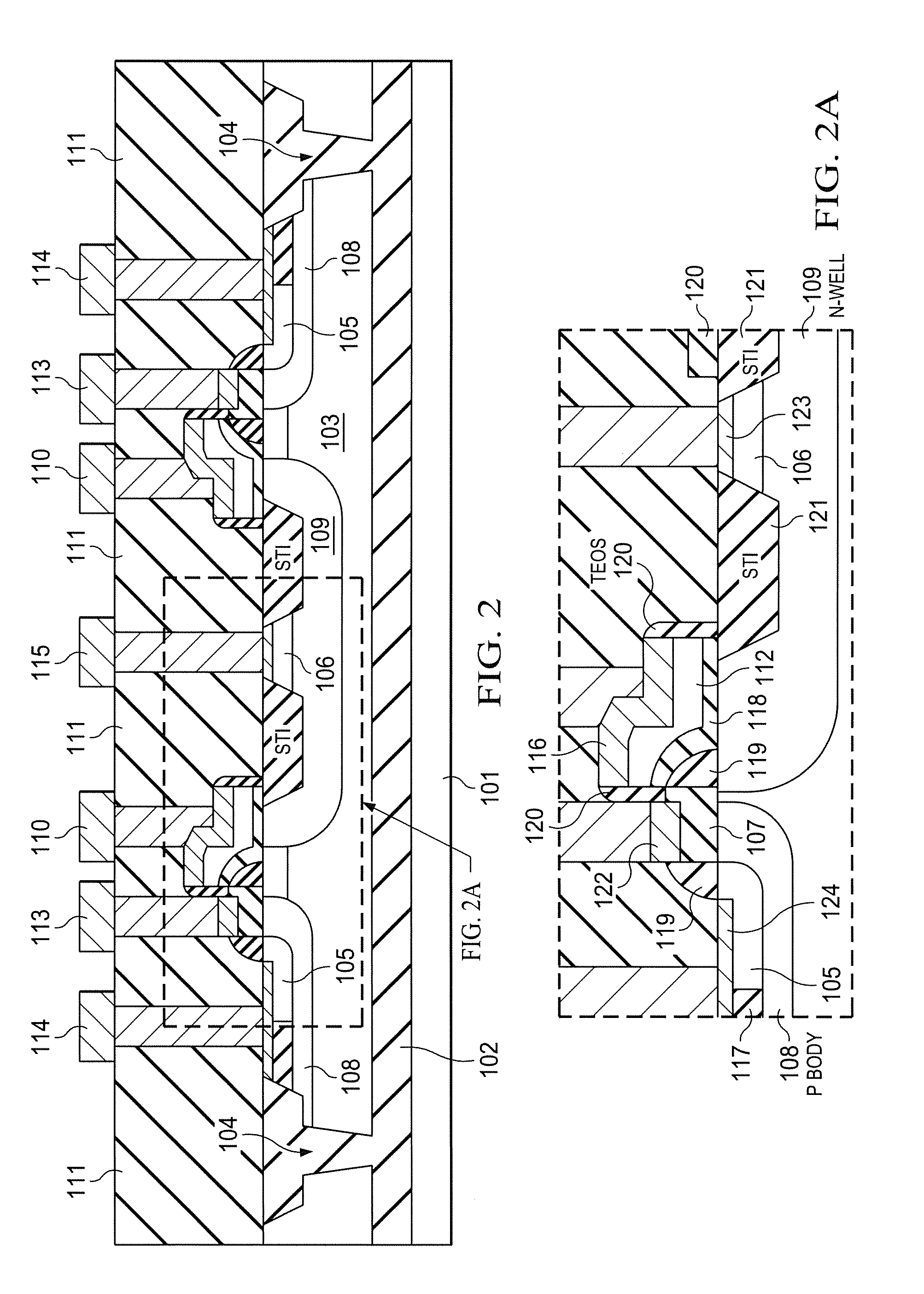

Varactors for CMOS and BiCMOS technologies

Varactors are provided which have a high tunability and / or a high quality factor associated therewith as well as methods for fabricating the same. One type of varactor disclosed is a quasi hyper-abrupt base-collector junction varactor which includes a substrate having a collector region of a first conductivity type atop a subcollector region, the collector region having a plurality of isolation regions present therein; reach-through implant regions located between at least a pair of the isolation regions; a SiGe layer atop a portion of the substrate not containing a reach-through implant region, the SiGe layer having an extrinsic base region of a second conductivity type which is different from the first conductivity type; and an antimony implant region located between the extrinsic base region and the subcollector region. Another type of varactor disclosed is an MOS varactor which includes at least a poly gate region and a well region wherein the poly gate region and the well region have opposite polarities.

Owner:IBM CORP

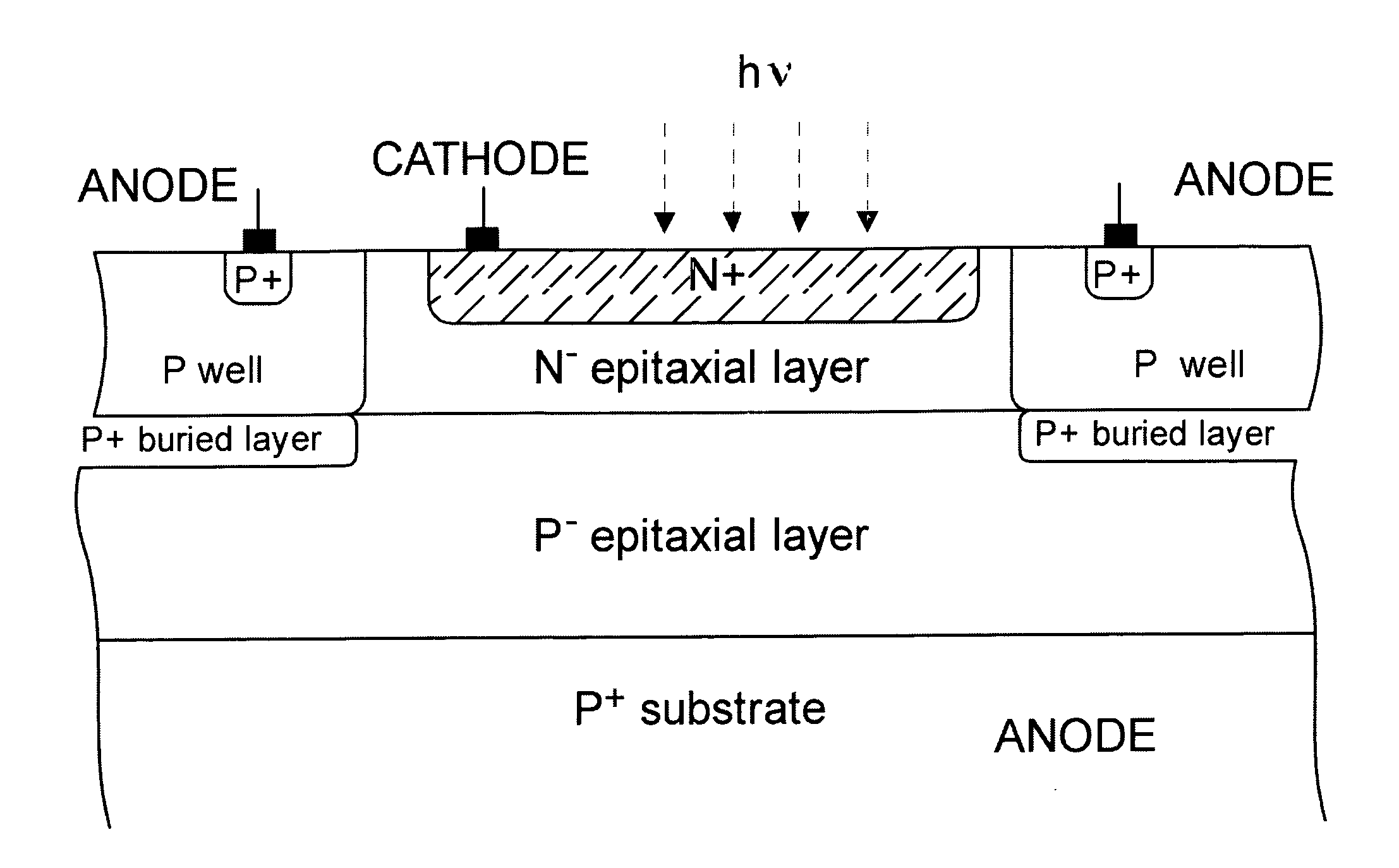

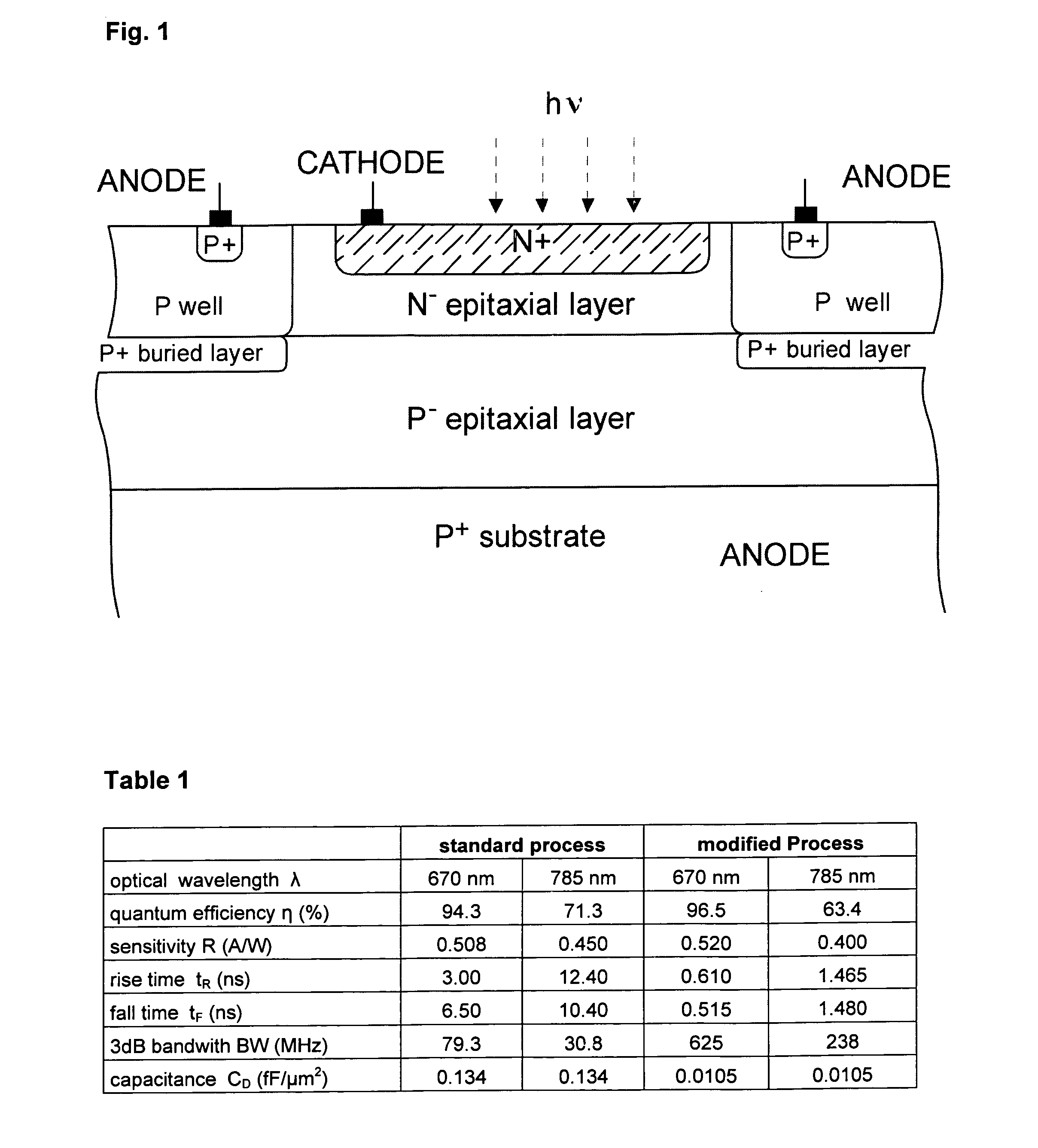

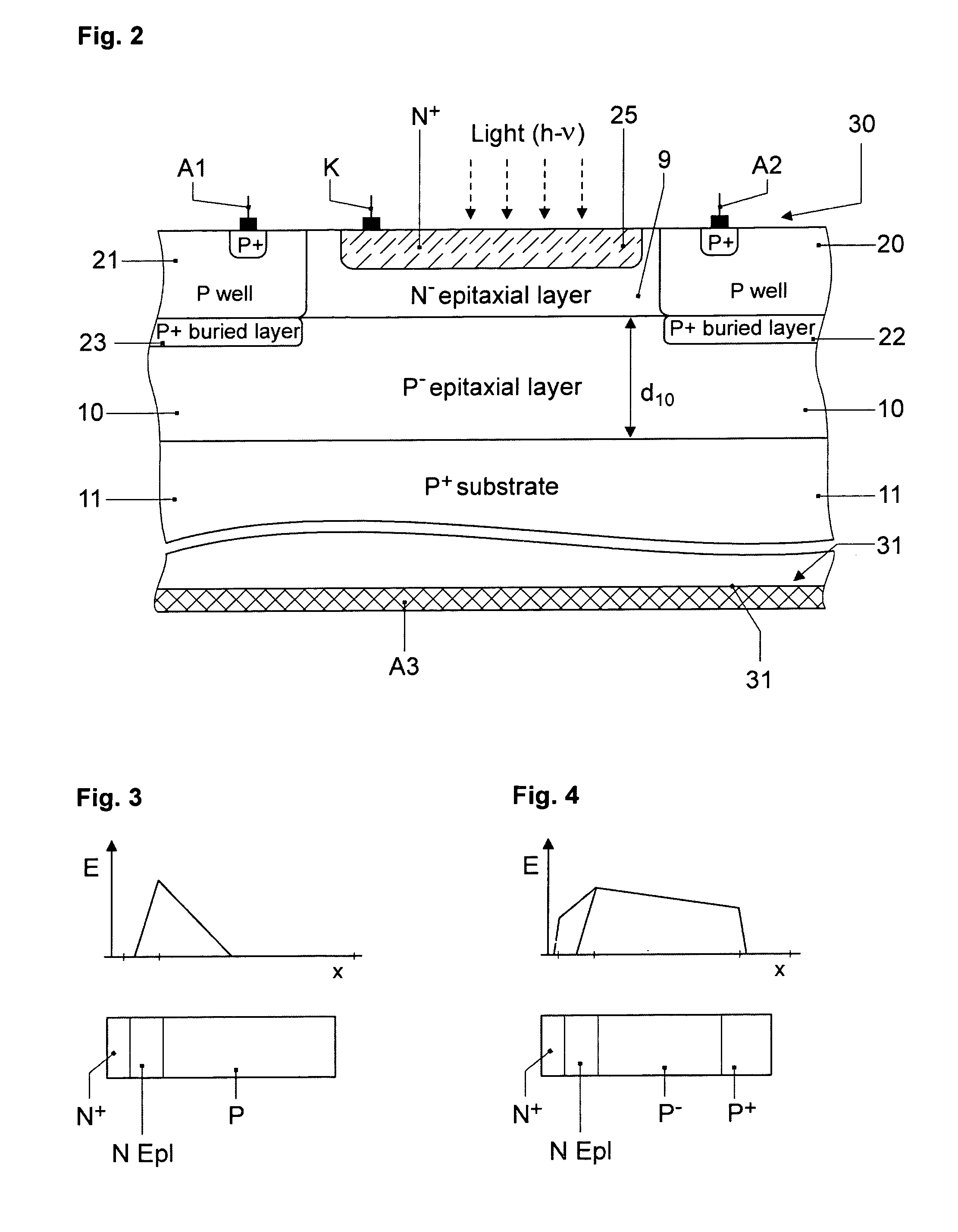

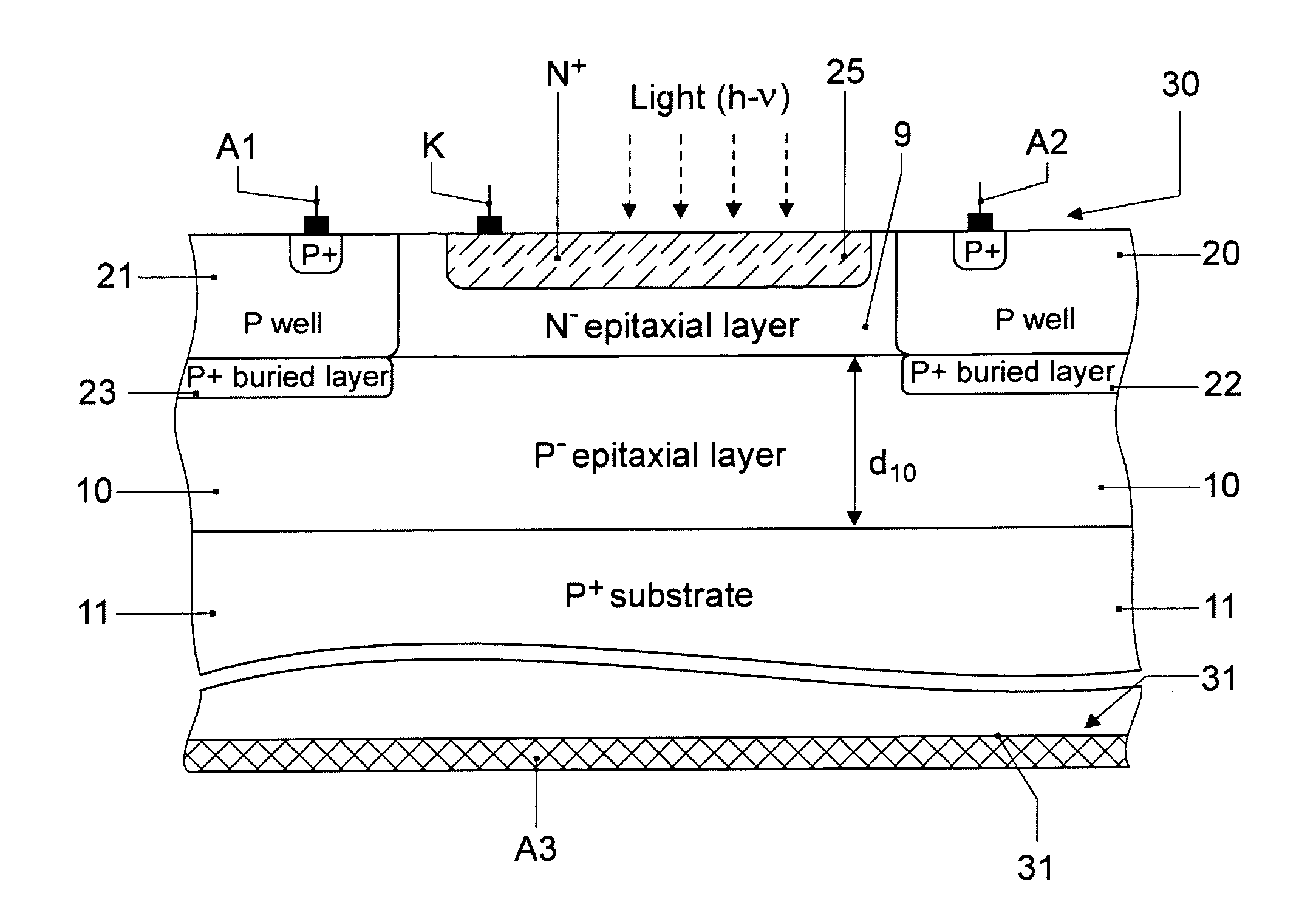

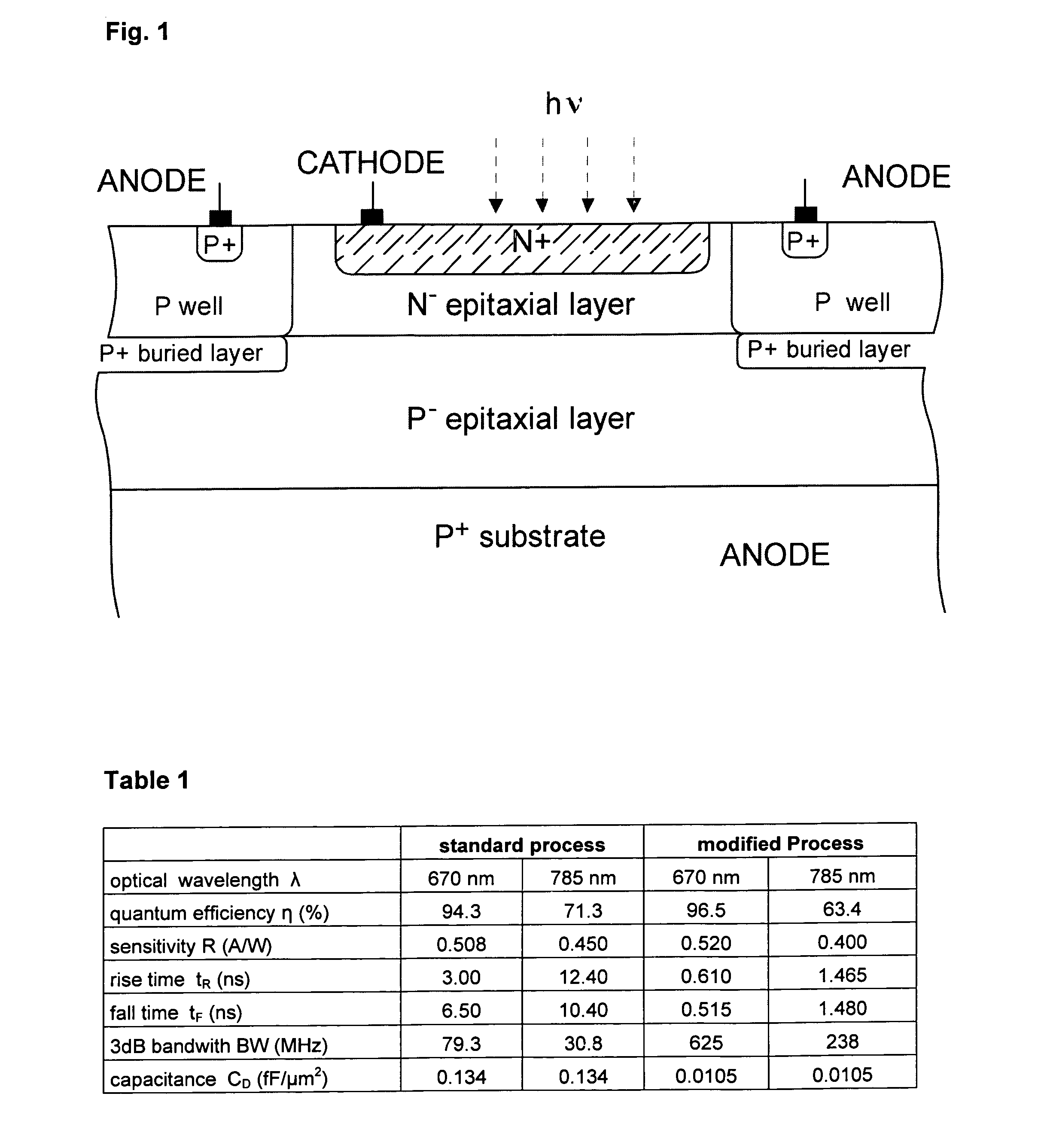

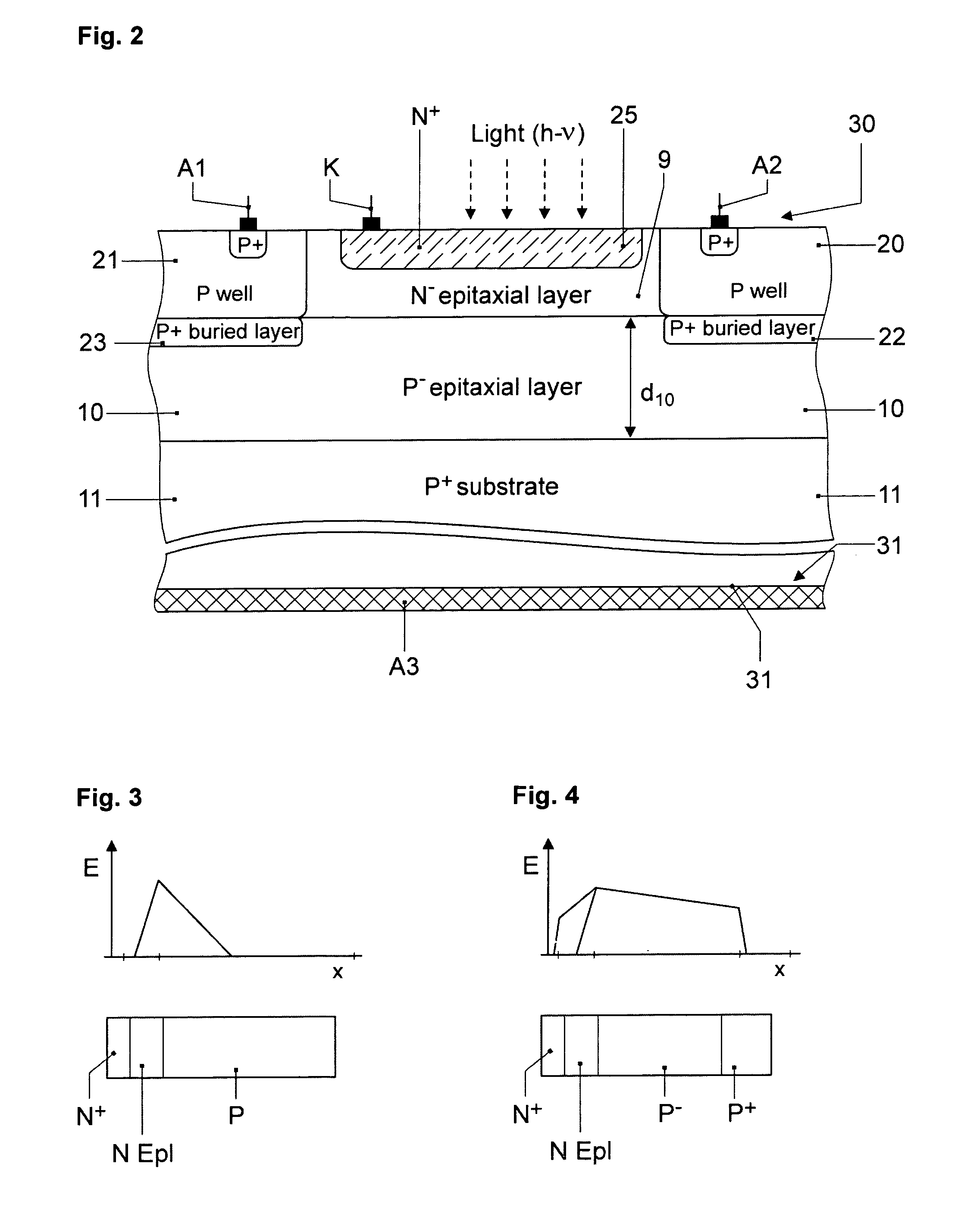

Monolithically integrated vertical pin photodiode used in bicmos technology

ActiveUS20070018268A1Reduced series resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBicmos technologyPhotodiode

The invention relates to a monolithically integrated vertical pin photodiode which is produced according to BiCMOS technology and comprises a planar surface facing the light and a rear face and anode connections located across p areas on a top face of the photodiode. An i-zone of the pin photodiode is formed by combining a low doped first p-epitaxial layer, which has maximum thickness and doping concentration, placed upon a particularly high doped p substrate, with a low doped second n− epitaxial layer that borders the first layer, and n+ cathode of the pin photodiode being integrated into the second layer. The p areas delimit the second n epitaxial layer in a latent direction while another anode connecting area of the pin diode is provided on the rear face in addition to the anode connection.

Owner:X FAB SEMICON FOUNDRIES

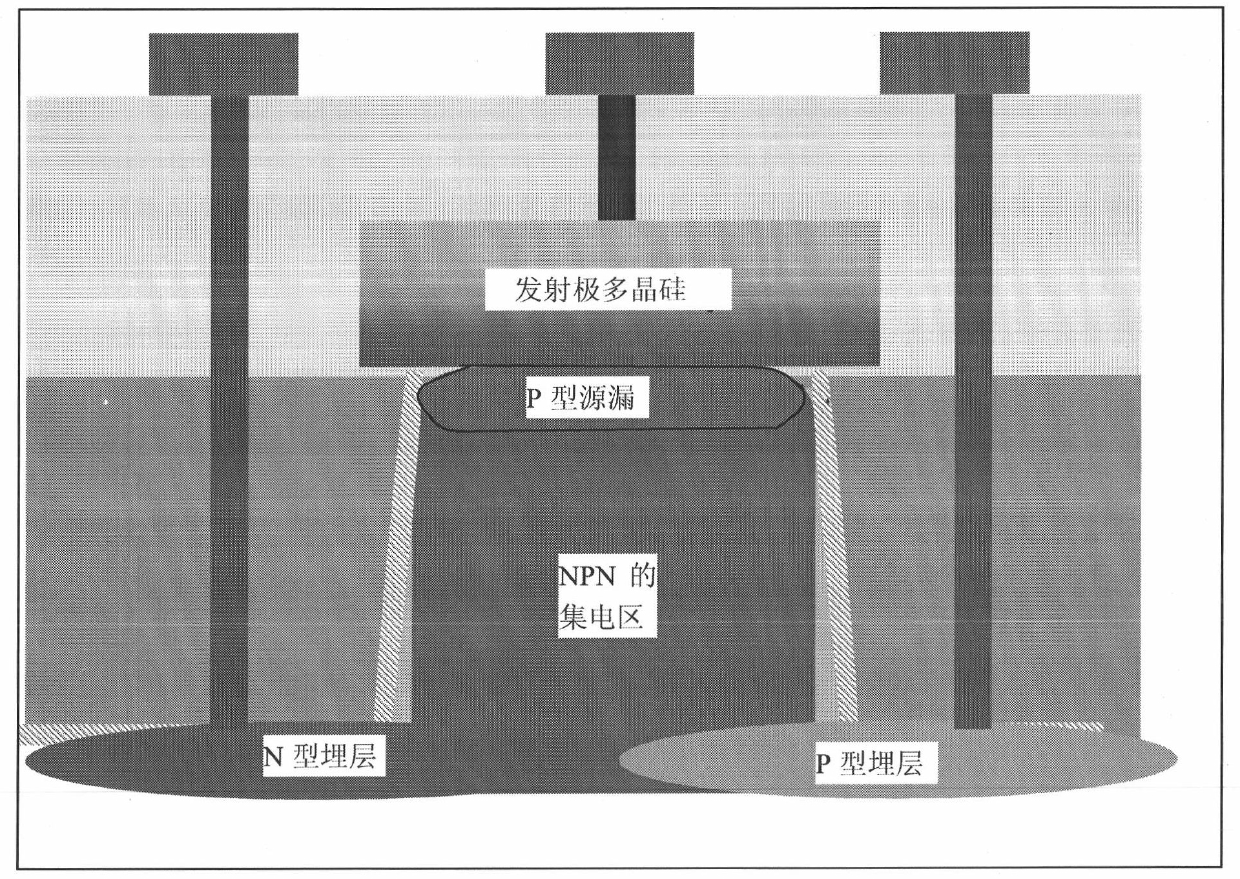

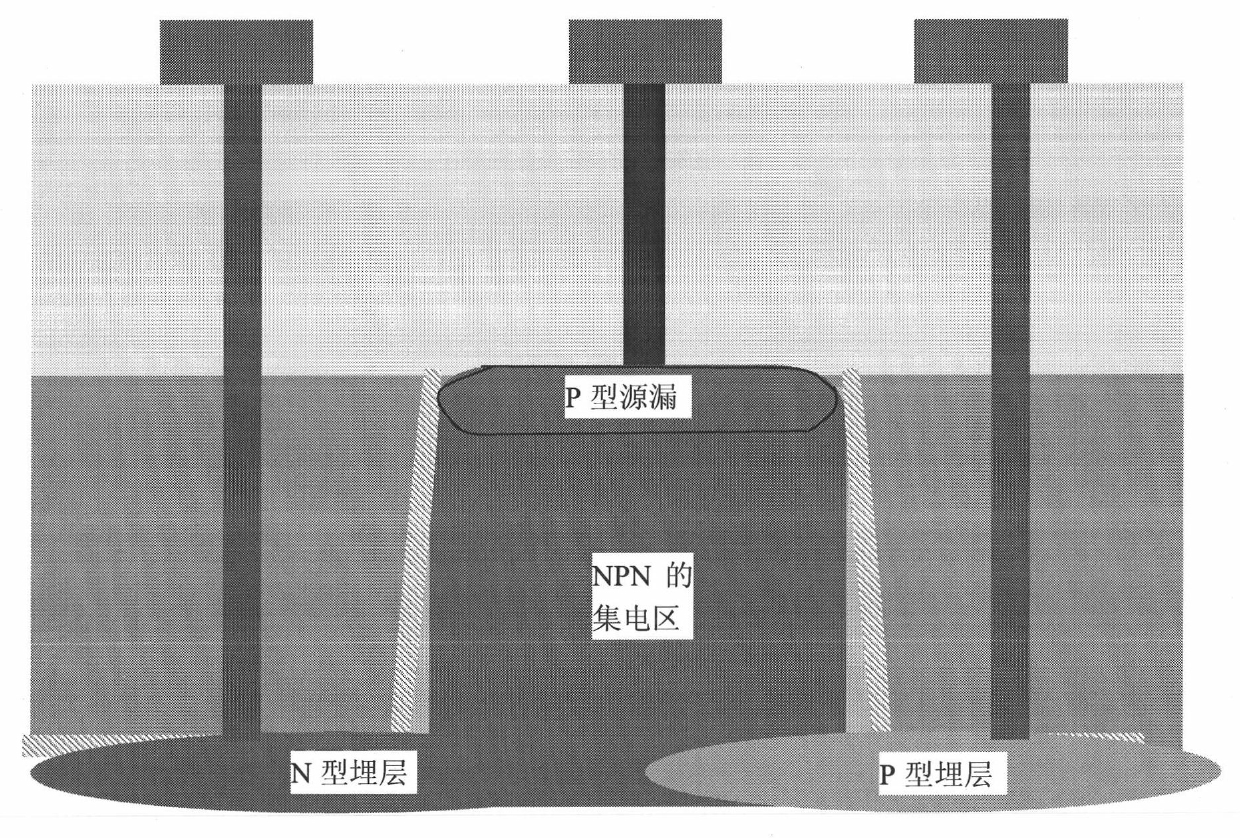

PNP bipolar transistor in SiGe BiCMOS technology

ActiveCN102088029AReduce areaIncreased current amplification factorSemiconductor/solid-state device manufacturingSemiconductor devicesBicmos technologyIon implantation

The present invention discloses a PNP bipolar transistor in a SiGe BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) technology, an active region of the bipolar transistor is isolated by making use of shallow groove field oxide layers and comprises a collector region, a base region and an emitter region, wherein the collector region is formed by a P-type buried layer located at the bottom of the shallow groove, and led out by making a deep trap contact on the field oxide layers; the base region is formed by N-type ion implantation in the active region, peripheral sides of the base region are the shallow groove field oxide layers, width of the base region is equal to depth of the shallow groove, and the bottom of the base region is connected with the collector region; an N-type buried layer is formed at the bottom of the shallow groove located at the opposite side of the collector region, the base region is connected with the N-type buried layer and led out by making the deep trap contact on the field oxide layer on the N-type buried layer; and the emitter region is formed by a P-type ion implantation layer formed above the base region or by further providing a P-type polycrystalline silicon. The PNP bipolar transistor in the present invention can reduce area of the PNP transistor and raise current amplification factor of the PNP transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

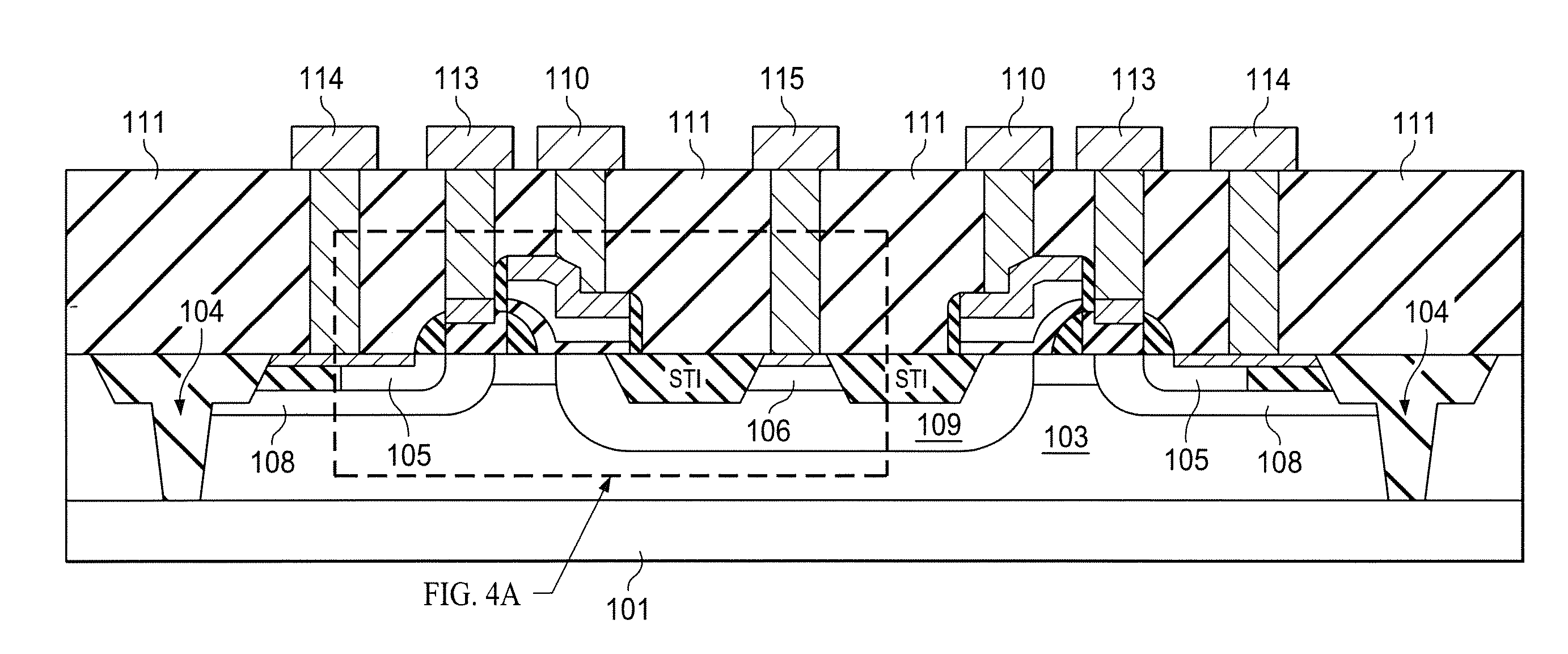

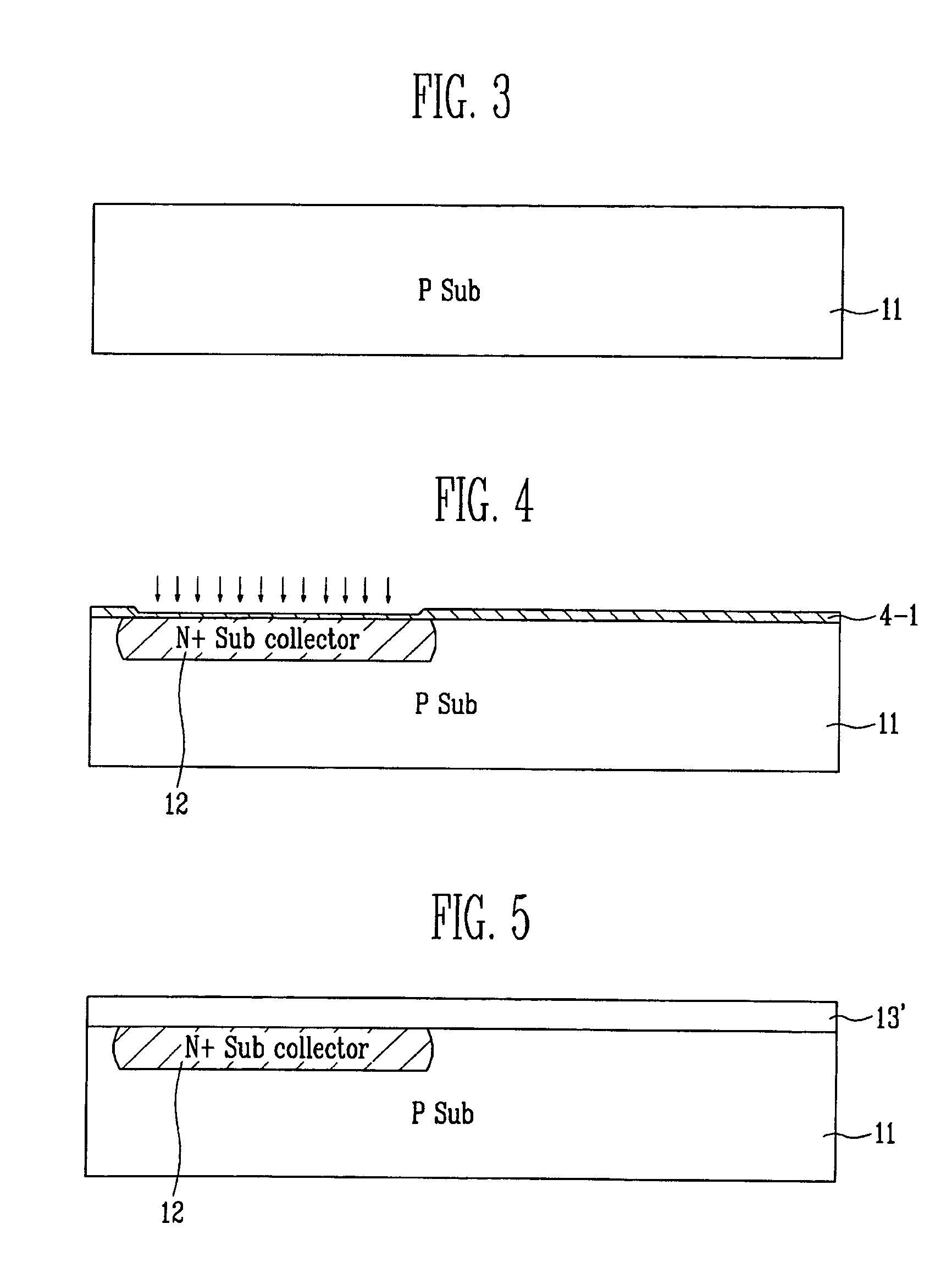

Method of collector formation in BiCMOS technology

ActiveUS7002190B1Minimally disturbing BiCMOS process flowLower resistance subcollectorTransistorSemiconductor/solid-state device manufacturingBicmos technologySilicide

A heterobipolar transistor (HBT) for high-speed BiCMOS applications is provided in which the collector resistance, Rc, is lowered by providing a buried refractory metal silicide layer underneath the shallow trench isolation region on the subcollector of the device. Specifically, the HBT of the present invention includes a substrate including at least a subcollector; a buried refractory metal silicide layer located on the subcollector; and a shallow trench isolation region located on a surface of the buried refractory metal silicide layer. The present invention also provides a method of fabricating such a HBT. The method includes forming a buried refractory metal silicide underneath the shallow trench isolation region on the subcollector of the device.

Owner:ELPIS TECH INC

Bandgap reference circuit and regulator circuit with common amplifier

A bandgap voltage reference and voltage regulator system includes a bandgap voltage reference circuit and a voltage regulator circuit that share a single, common amplifier. The amplifier acts as a gain stage for the reference circuit and as an error amplifier for a driver stage of the regulator circuit. The regulator circuit has an input reference generated by the reference circuit, and the reference circuit acts as a load to the driver stage, obviating the need for a bias resistance network. By sharing the amplifier and obviating the need for a resistance network, the area and overall quiescent current of the system are reduced. The system can be implemented in CMOS / BiCMOS technology and is suited for low power applications.

Owner:NXP USA INC

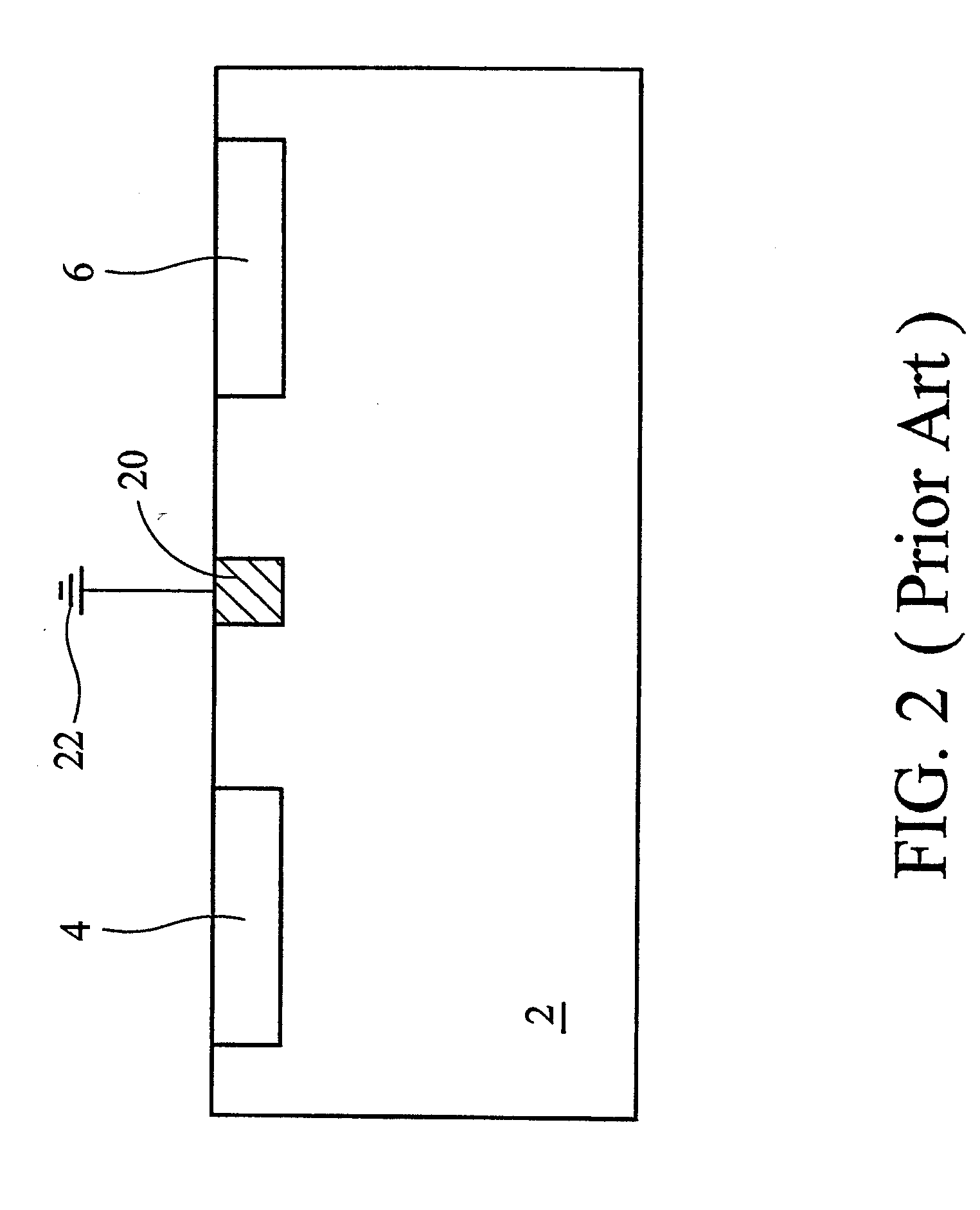

Single poly-emitter PNP using DWELL diffusion in a BiCMOS technology

InactiveUS20050045948A1Small formatSolid-state devicesSemiconductor/solid-state device manufacturingCMOSSurface layer

A method of forming a bipolar transistor device, and more particularly a vertical poly-emitter PNP transistor, as part of a BiCMOS type manufacturing process is disclosed. The formation of the PNP transistor during a CMOS / DMOS fabrication process requires merely one additional mask to facilitate formation of a very small emitter in a portion of an N-type surface layer of a double diffused well (DWELL). Unlike conventional PNP transistors, a separate mask is not required to establish the base of the transistor as the transistor base is formed from a portion of the double diffused well and the DWELL includes a P-type body layer formed via implantation through the same opening in the same mask utilized to establish the N-type surface layer of the double diffused well. The base is also thin thus improving the transistor's frequency and gain.

Owner:TEXAS INSTR INC

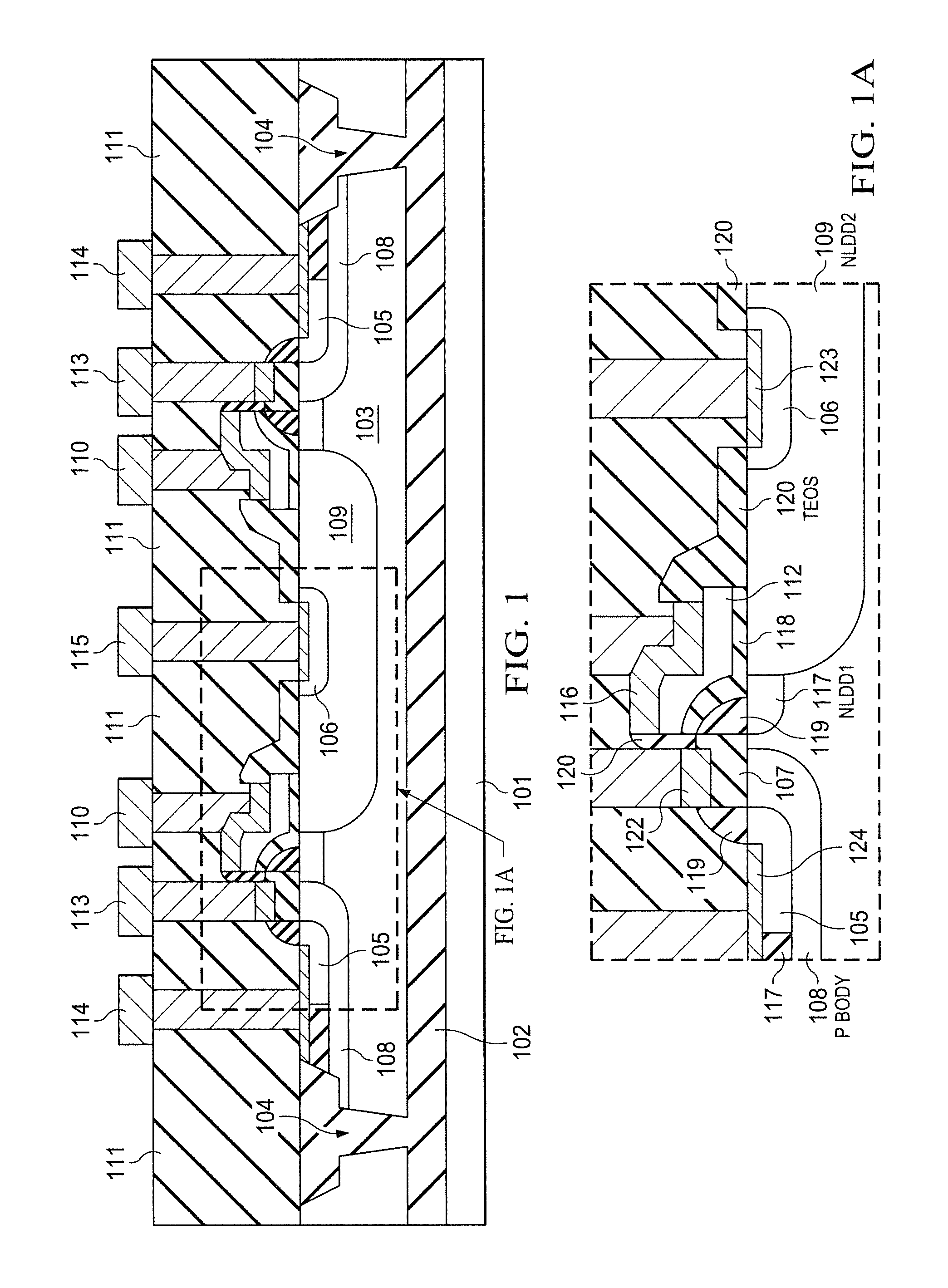

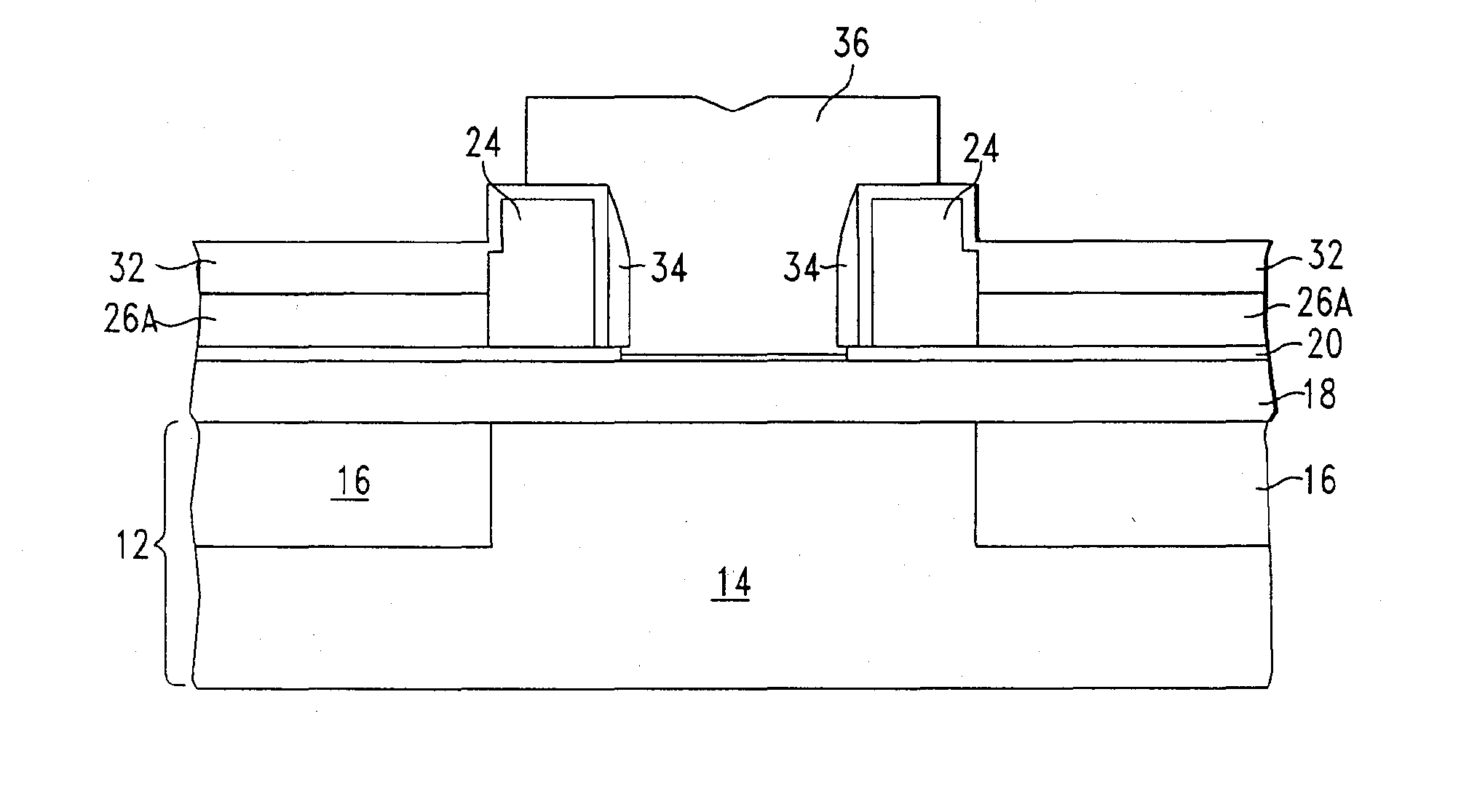

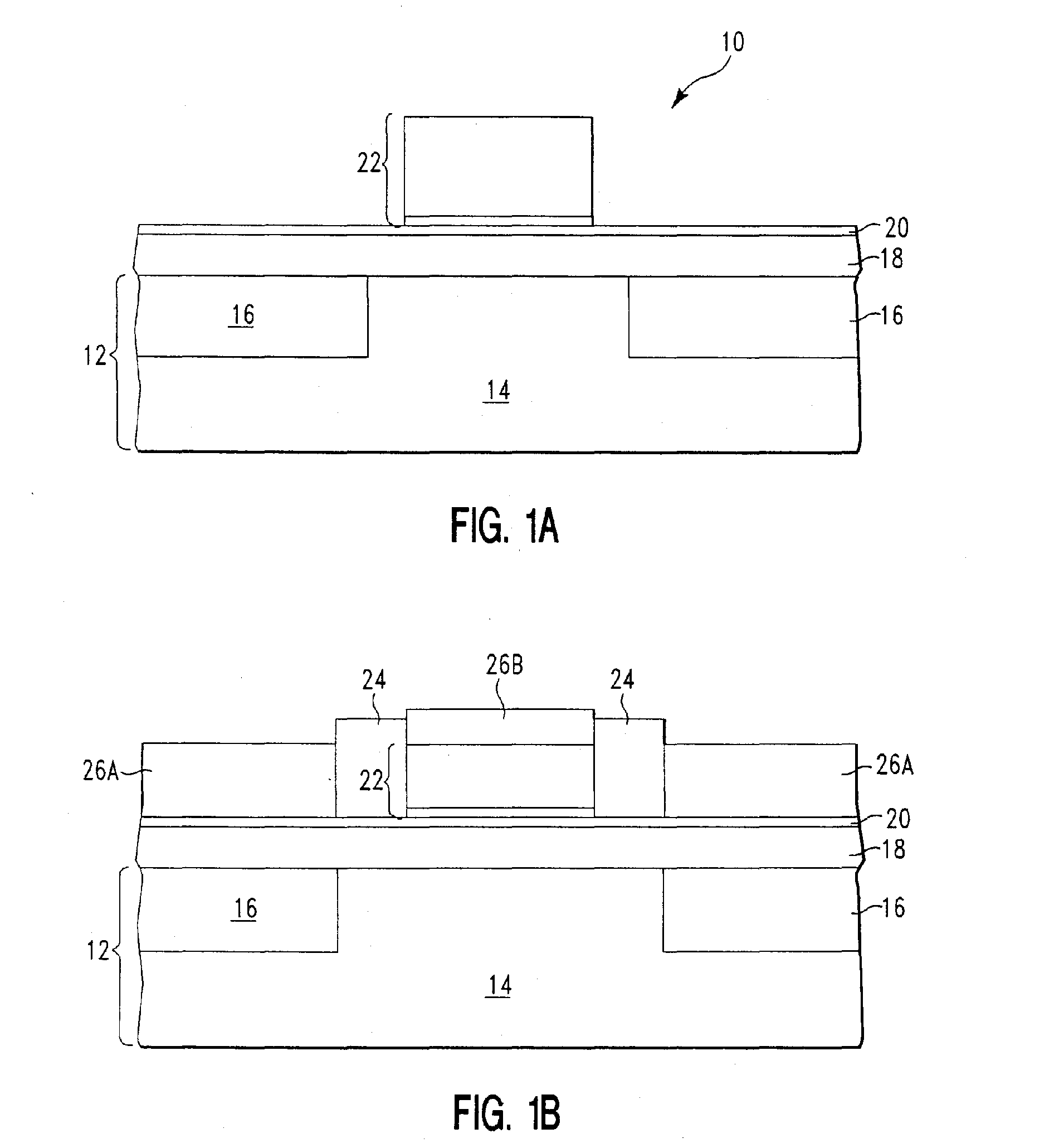

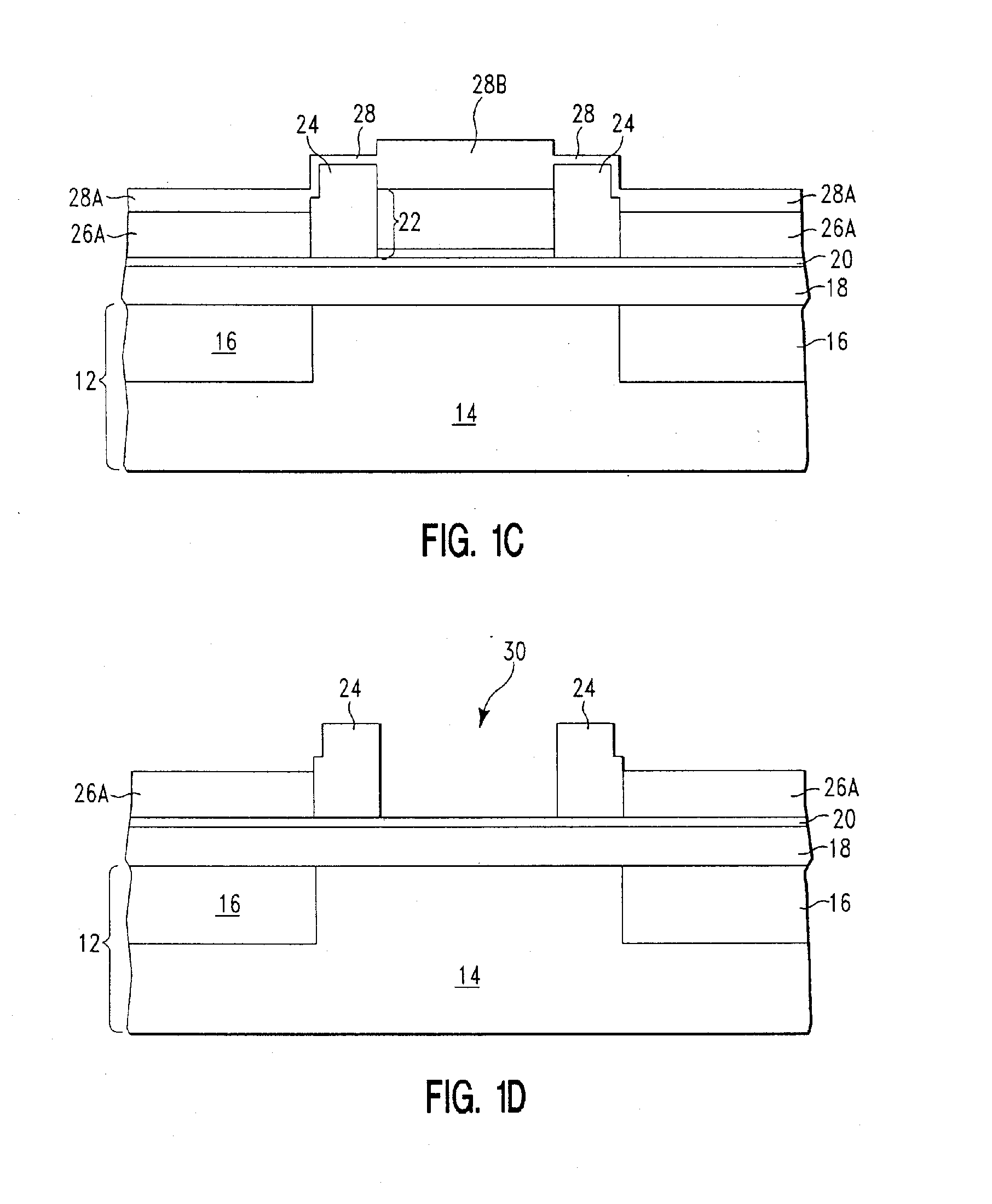

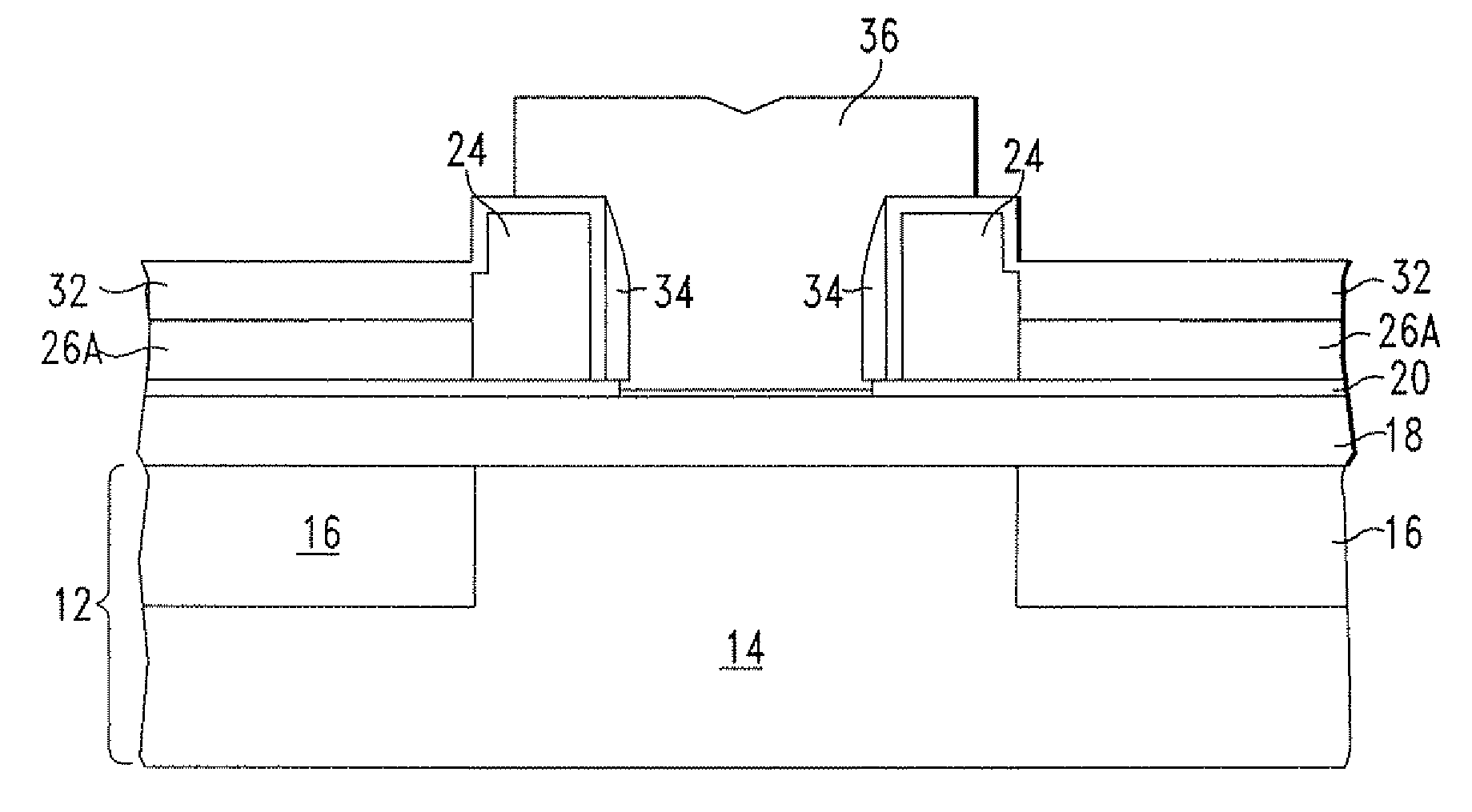

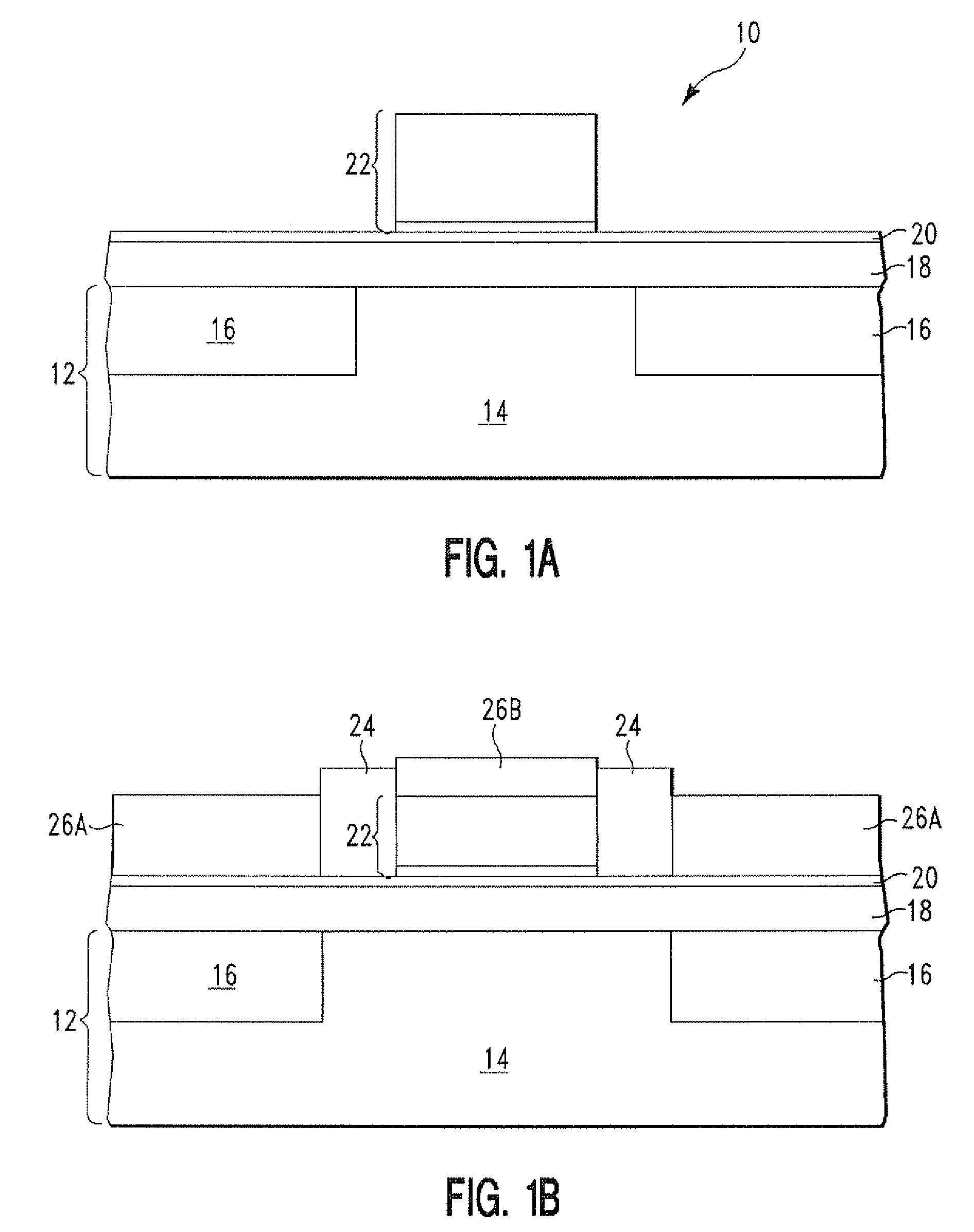

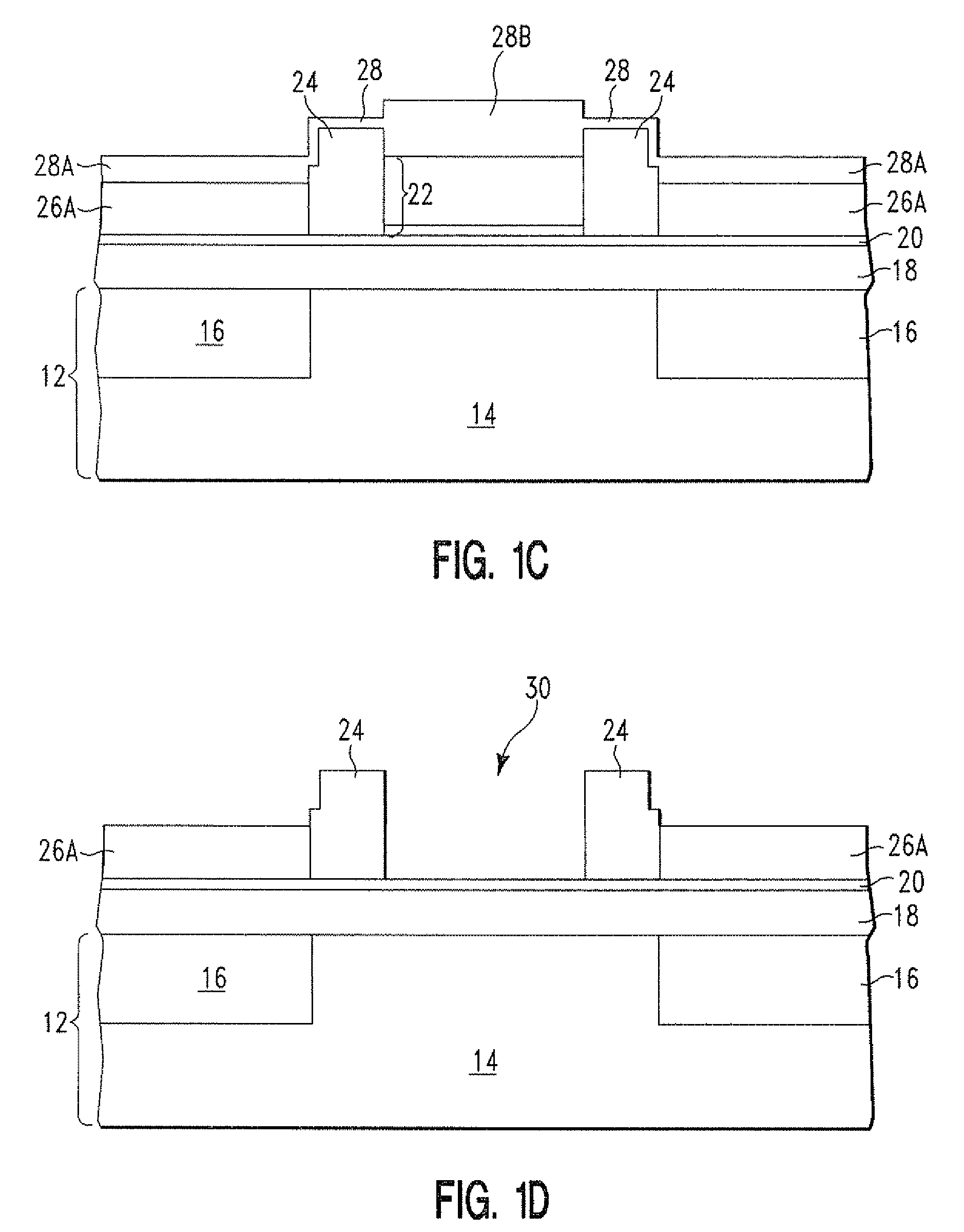

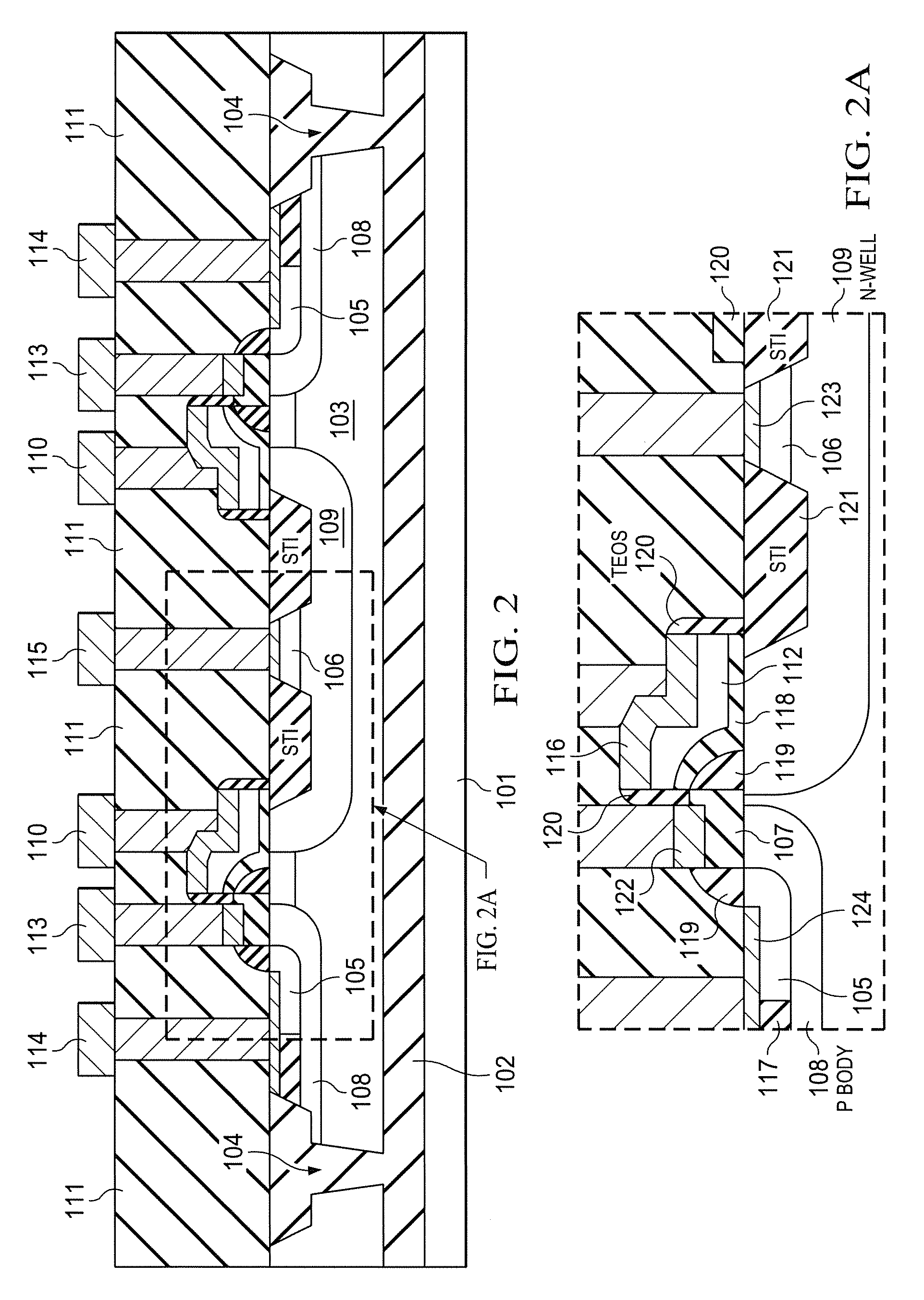

METHOD TO BUILD SELF-ALIGNED NPN IN ADVANCED BiCMOS TECHNOLOGY

ActiveUS20060060886A1Semiconductor/solid-state device manufacturingSemiconductor devicesMetallurgyHigh pressure

The present invention provides a method of forming a self-aligned heterobipolar transistor (HBT) device in a BiCMOS technology. The method includes forming a raised extrinsic base structure by using an epitaxial growth process in which the growth rate between single crystal silicon and polycrystalline silicon is different and by using a low temperature oxidation process such as a high-pressure oxidation (HIPOX) process to form a self-aligned emitter / extrinsic base HBT structure.

Owner:TAIWAN SEMICON MFG CO LTD

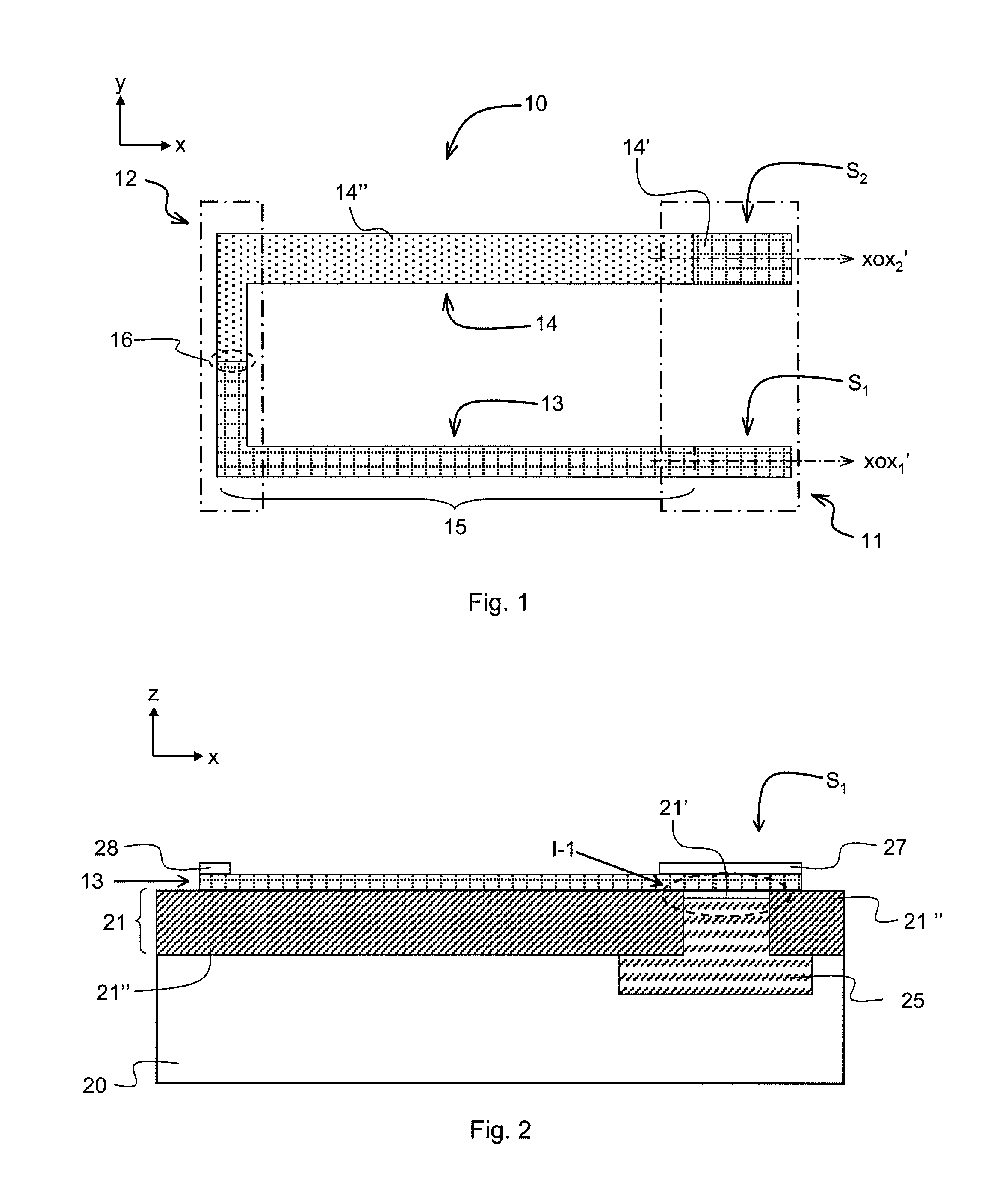

Differential temperature sensor and its capacitors in cmos/bicmos technology

InactiveUS20140015089A1Efficient detectionEfficient communicationThermoelectric device manufacture/treatmentThermometers using electric/magnetic elementsCMOSCapacitance

The sensor is made on a semiconductor substrate covered with an electrically insulating layer. The electrically insulating layer separates a thermocouple from the substrate. It includes a first portion presenting a first value of capacitance per unit area and a second portion presenting a second value of capacitance per unit area, which is lower than the first value. The sensor includes first and second output terminals connected to the thermocouple. The first output terminal includes a first capacitor having a first electrode formed by a first leg made of an electrically conducting material. The second electrode of the capacitor is formed by a part of the substrate facing said first leg and separated from the first electrode by the first portion of the electrically insulating layer. The first leg connects the thermocouple while overlapping the second portion of the electrically insulating layer.

Owner:ST ERICSSON SA +1

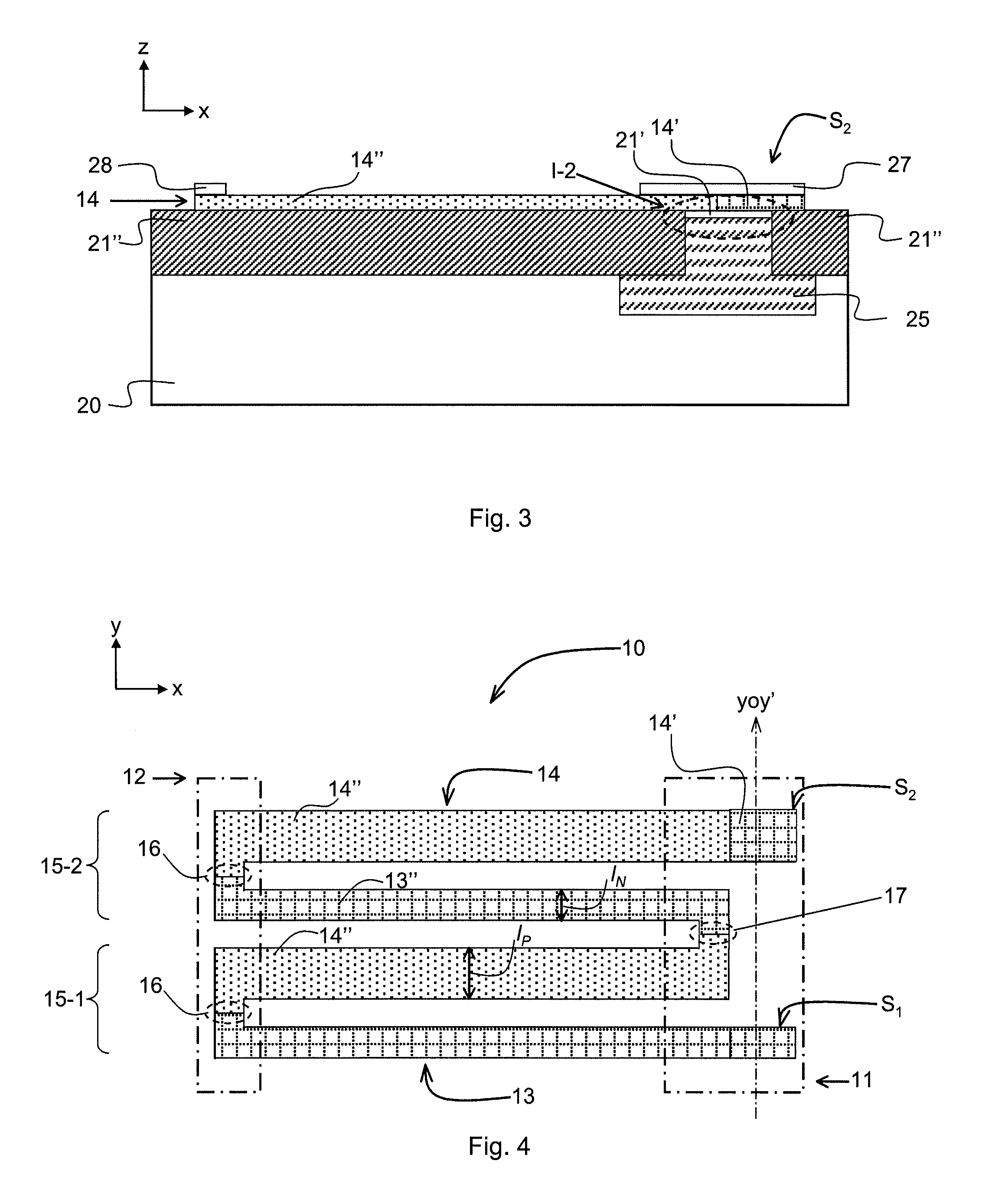

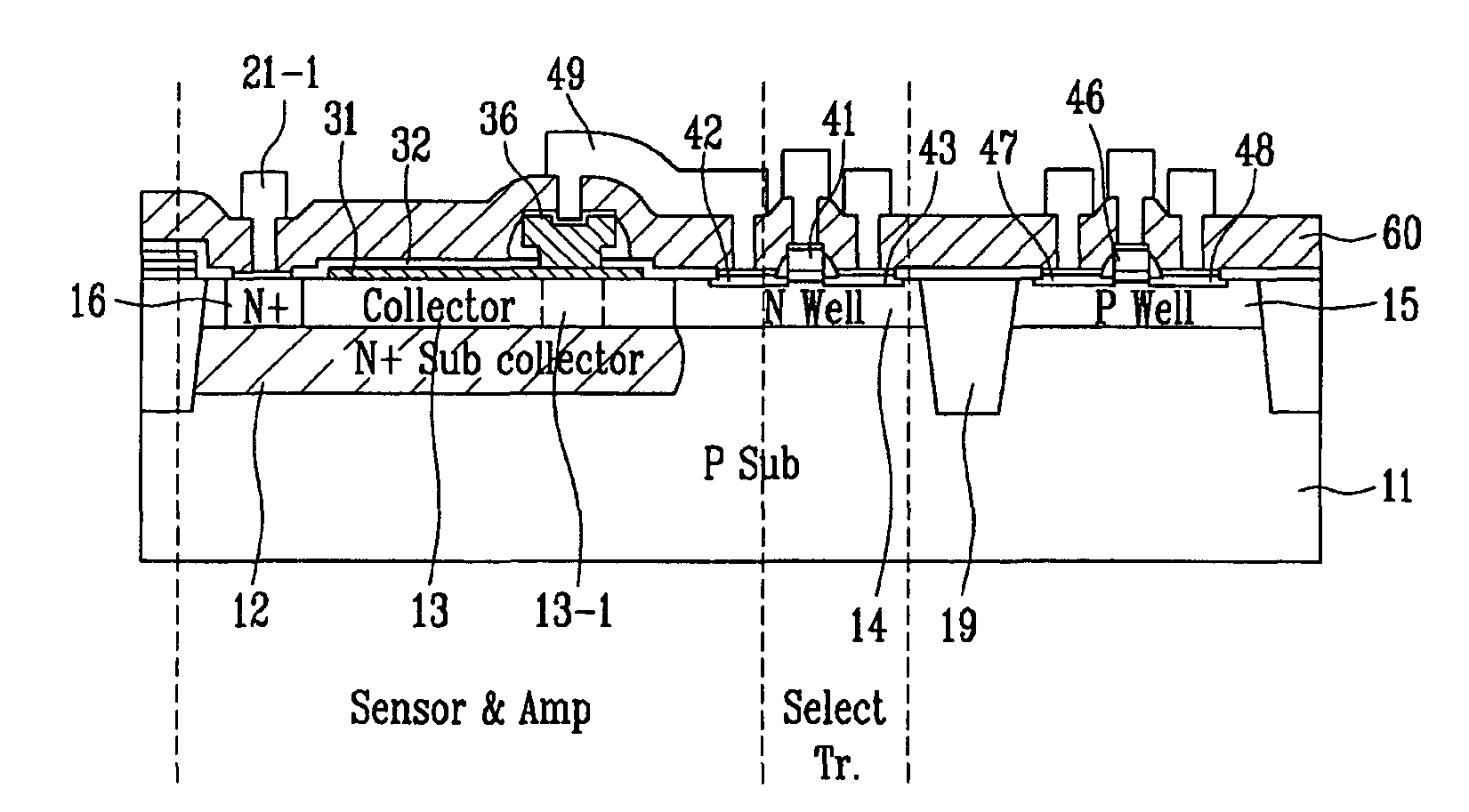

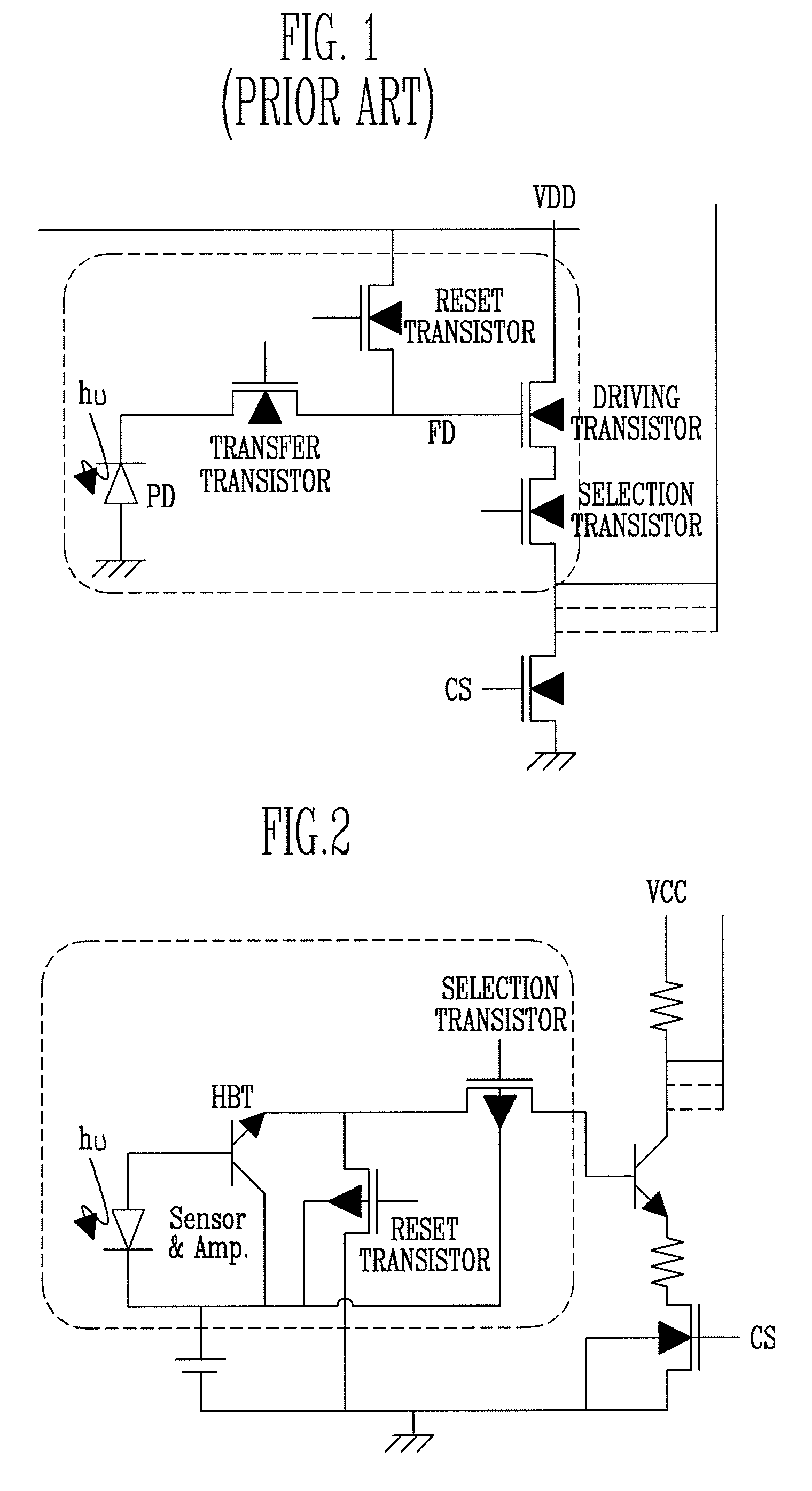

Image sensor having heterojunction bipolar transistor and method of fabricating the same

InactiveUS7902577B2Reduce in quantityPrevent degradationTransistorSolid-state devicesPower flowLength wave

Provided is an image sensor having a heterojunction bipolar transistor (HBT) and a method of fabricating the same. The image sensor is fabricated by SiGe BiCMOS technology. In the image sensor, a PD employs a floating-base-type SiGe HBT. A floating base of the SiGe HBT produces a positive voltage with respect to a collector during an exposure process, and the HBT performs a reverse bipolar operation due to the positive voltage so that the collector and an emitter exchange functions. The SiGe HBT can sense an optical current signal and also amplify the optical current signal. The image sensor requires only three transistors in a pixel so that the degree of integration can increase. The image sensor has an improved sensitivity of signals in the short wavelength region and a sensing signal has excellent linearity such that both a sensing mechanism and control circuit are very simple.

Owner:ELECTRONICS & TELECOMM RES INST

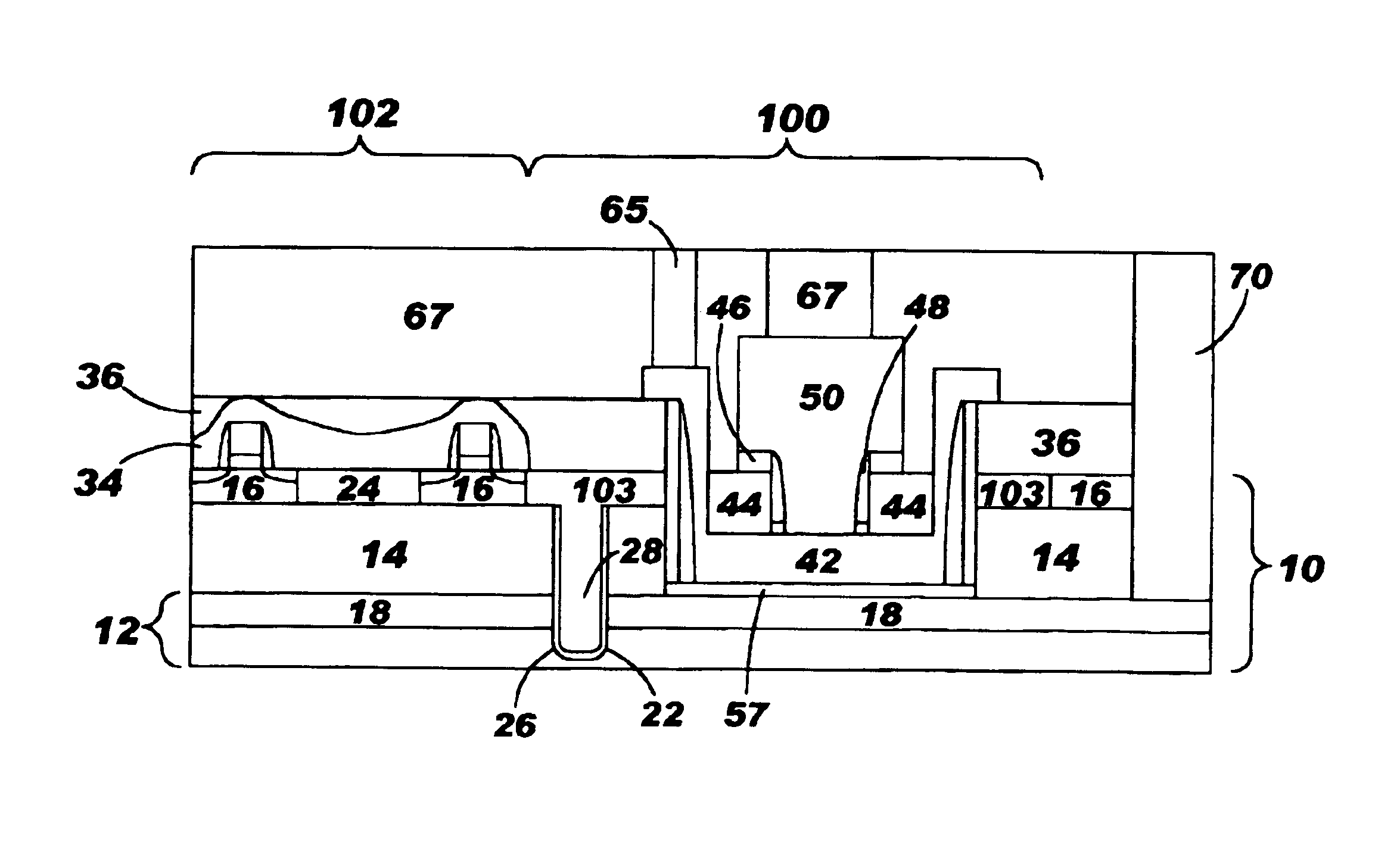

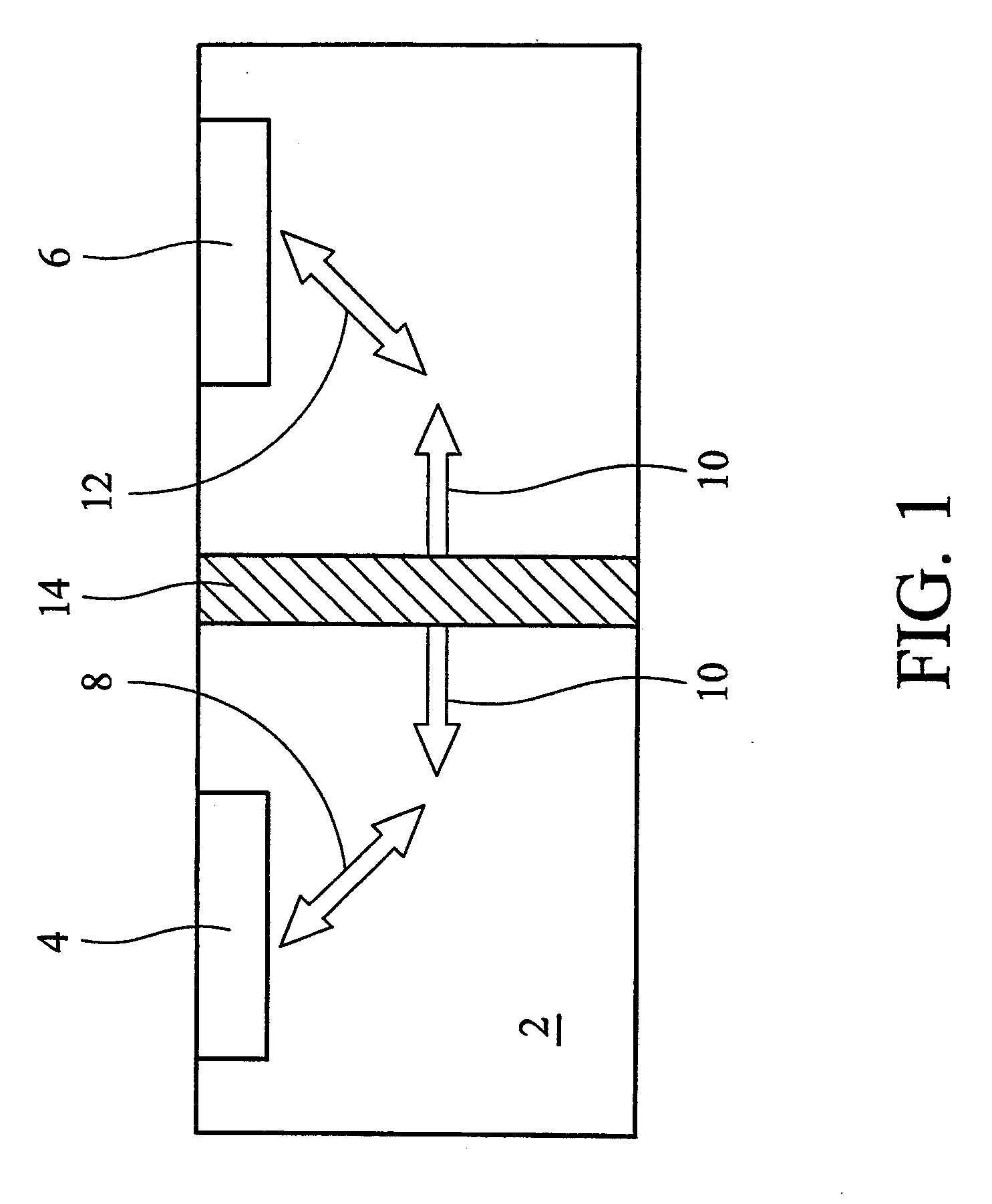

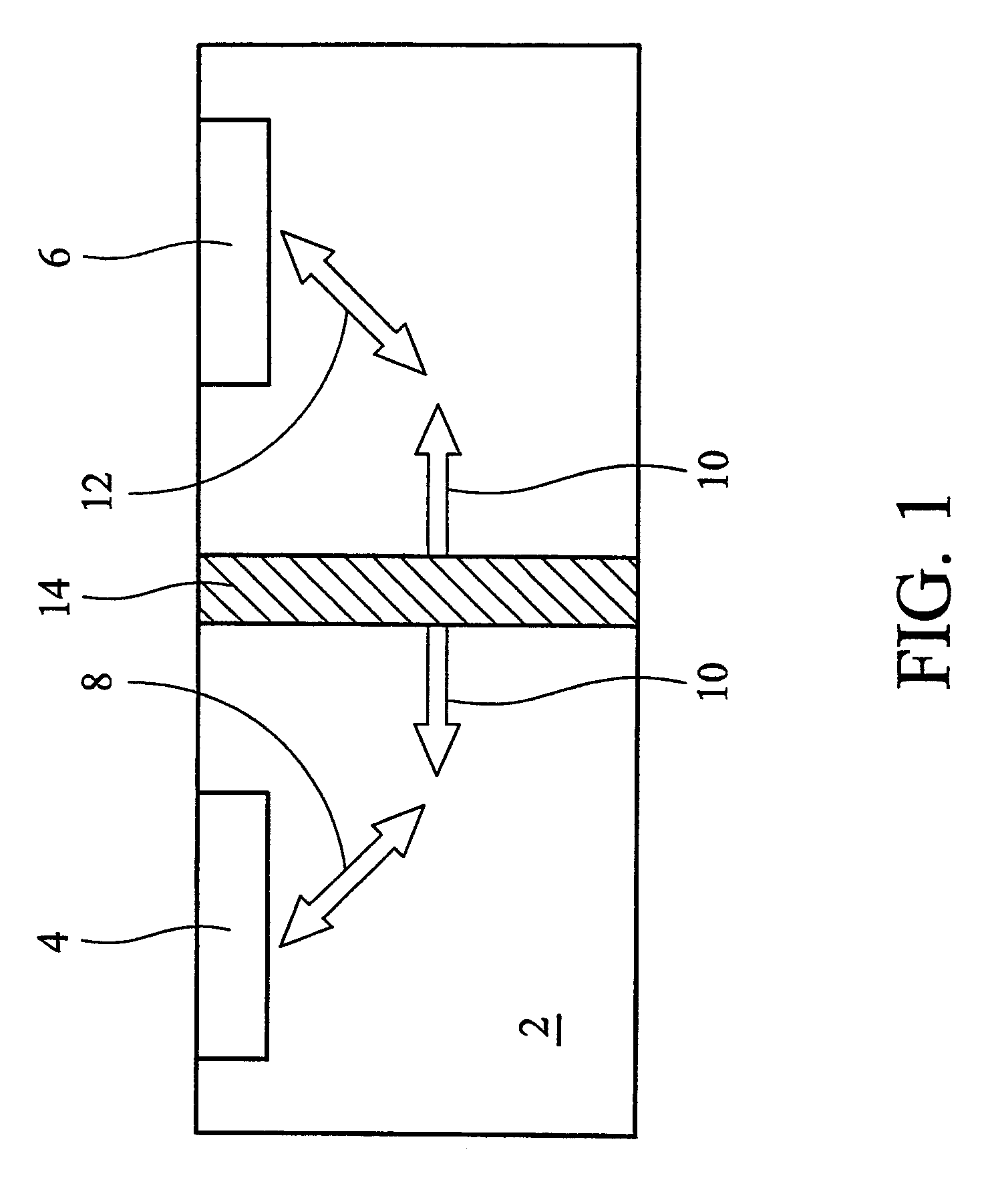

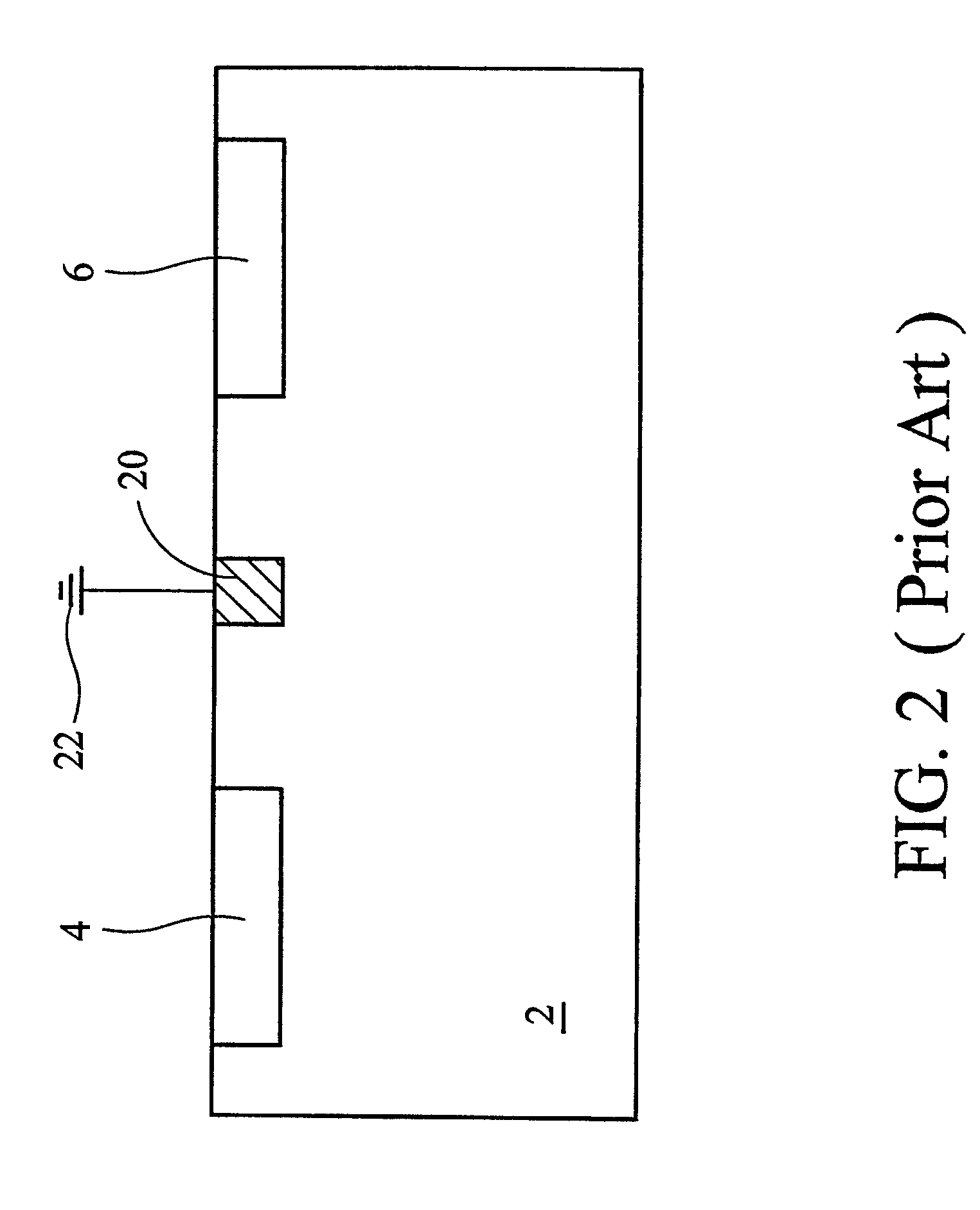

SOI bipolar transistors with reduced self heating

A bipolar transistor includes a collector located over a substrate; and a heat conductive path connecting the substrate to the collector. The heat conductive path is filled with a heat conductive material such as metal or polysilicon. In one embodiment the heat conductive path runs through the collector to extract heat from the collector and drain it to the substrate. In alternate embodiments, the transistor can be a vertical or a lateral device. According to another embodiment, an integrated circuit using BiCMOS technology comprises pnp and npn bipolar transistors with heat conduction from collector to substrate and possibly p-channel and n-channel MOSFETS. According to yet another embodiment, a method for making a transistor in an integrated network comprises steps of etching the heat conducting path through the collector and to the substrate and fill with heat conductive material to provide a heat drain for the transistor comprising the collector.

Owner:GOOGLE LLC

Method to build self-aligned NPN in advanced BiCMOS technology

ActiveUS7265018B2Semiconductor/solid-state device manufacturingSemiconductor devicesMetallurgyHigh pressure

Owner:TAIWAN SEMICON MFG CO LTD

Design of high-frequency substrate noise isolation in BiCMOS technology

A high-frequency noise isolation structure and a method for forming the same are provided. The noise isolation structure isolates a first device region and a second device region over a semiconductor substrate. The noise isolation structure preferably includes a sinker region substantially encircling a first device region, a buried layer underlying the first device region and joining the sinker region, a deep guard ring substantially encircling the sinker region, and a deep trench oxide region substantially encircling the sinker region. The isolation structure further includes a wide guard ring between the first and the second device regions. The sinker region and the buried region preferably have a high impurity concentration. Integrated circuits to be noise decoupled are preferably formed in the respective first and second device regions.

Owner:TAIWAN SEMICON MFG CO LTD

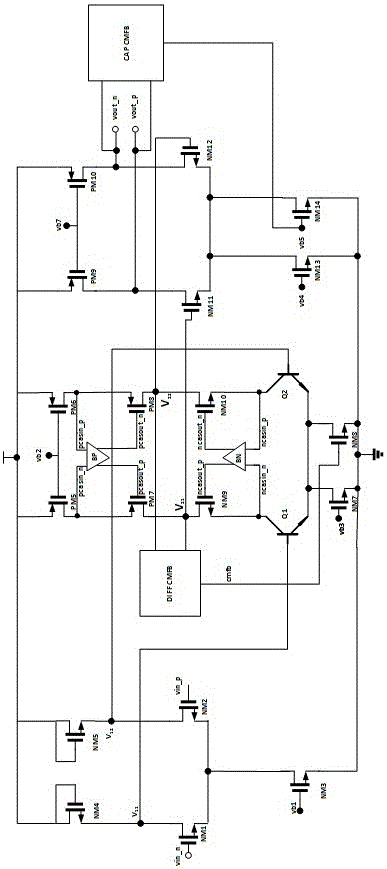

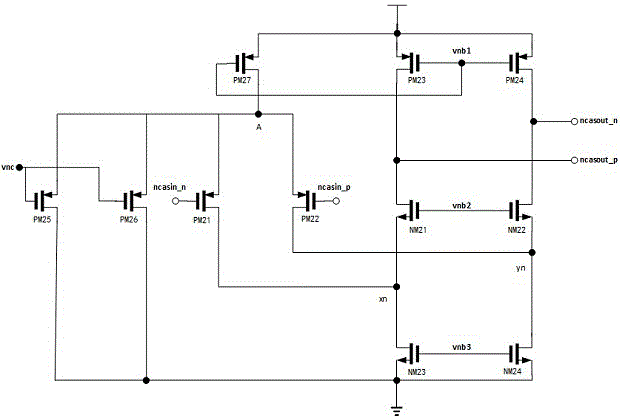

Operational amplifier

ActiveCN105846788AHigh gainHigh speedDifferential amplifiersDc-amplifiers with dc-coupled stagesCMOSBicmos technology

The invention discloses a BiCMOS technical design operational amplifier comprising a first stage amplification module, a second stage amplification module, a third stage amplification module, a common mode feedback module DIFF CMFB circuit using two differential pairs, and a switch capacitance common mode feedback module CAP CMFB circuit; the operational amplifier is realized by a bipolar transistor and CMOS transistor BiCMOS technology, so low input impedance and high gain of an ambipolar circuit can be provided, and low power consumption and high integrated level of the CMOS circuit can be added, thus improving amplifier gains, reducing signal main channel parasitic capacitance, improving whole operational circuit speed, and improving ADC circuit speed and stability.

Owner:南京德睿智芯电子科技有限公司

Novel varactors for CMOS and BiCMOS technologies

InactiveUS20050245038A1Easy to implementEasy to adjustSolid-state devicesSemiconductor/solid-state device manufacturingCMOSEngineering

Varactors are provided which have a high tunability and / or a high quality factor associated therewith as well as methods for fabricating the same. One type of varactor disclosed is a quasi hyper-abrupt base-collector junction varactor which includes a substrate having a collector region of a first conductivity type atop a subcollector region, the collector region having a plurality of isolation regions present therein; reach-through implant regions located between at least a pair of the isolation regions; a SiGe layer atop a portion of the substrate not containing a reach-through implant region, the SiGe layer having an extrinsic base region of a second conductivity type which is different from the first conductivity type; and an antimony implant region located between the extrinsic base region and the subcollector region. Another type of varactor disclosed is an MOS varactor which includes at least a poly gate region and a well region wherein the poly gate region and the well region have opposite polarities.

Owner:INT BUSINESS MASCH CORP

Monolithically integrated vertical pin photodiode used in biCMOS technology

ActiveUS7535074B2Reduced series resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBicmos technologyPhotodiode

The invention relates to a monolithically integrated vertical pin photodiode which is produced according to BiCMOS technology and comprises a planar surface facing the light and a rear face and anode connections located across p areas on a top face of the photodiode. An i-zone of the pin photodiode is formed by combining a low doped first p-epitaxial layer, which has maximum thickness and doping concentration, placed upon a particularly high doped p substrate, with a low doped second n− epitaxial layer that borders the first layer, and n+ cathode of the pin photodiode being integrated into the second layer. The p areas delimit the second n epitaxial layer in a latent direction while another anode connecting area of the pin diode is provided on the rear face in addition to the anode connection.

Owner:X FAB SEMICON FOUNDRIES

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com