Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1302 results about "Low input" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

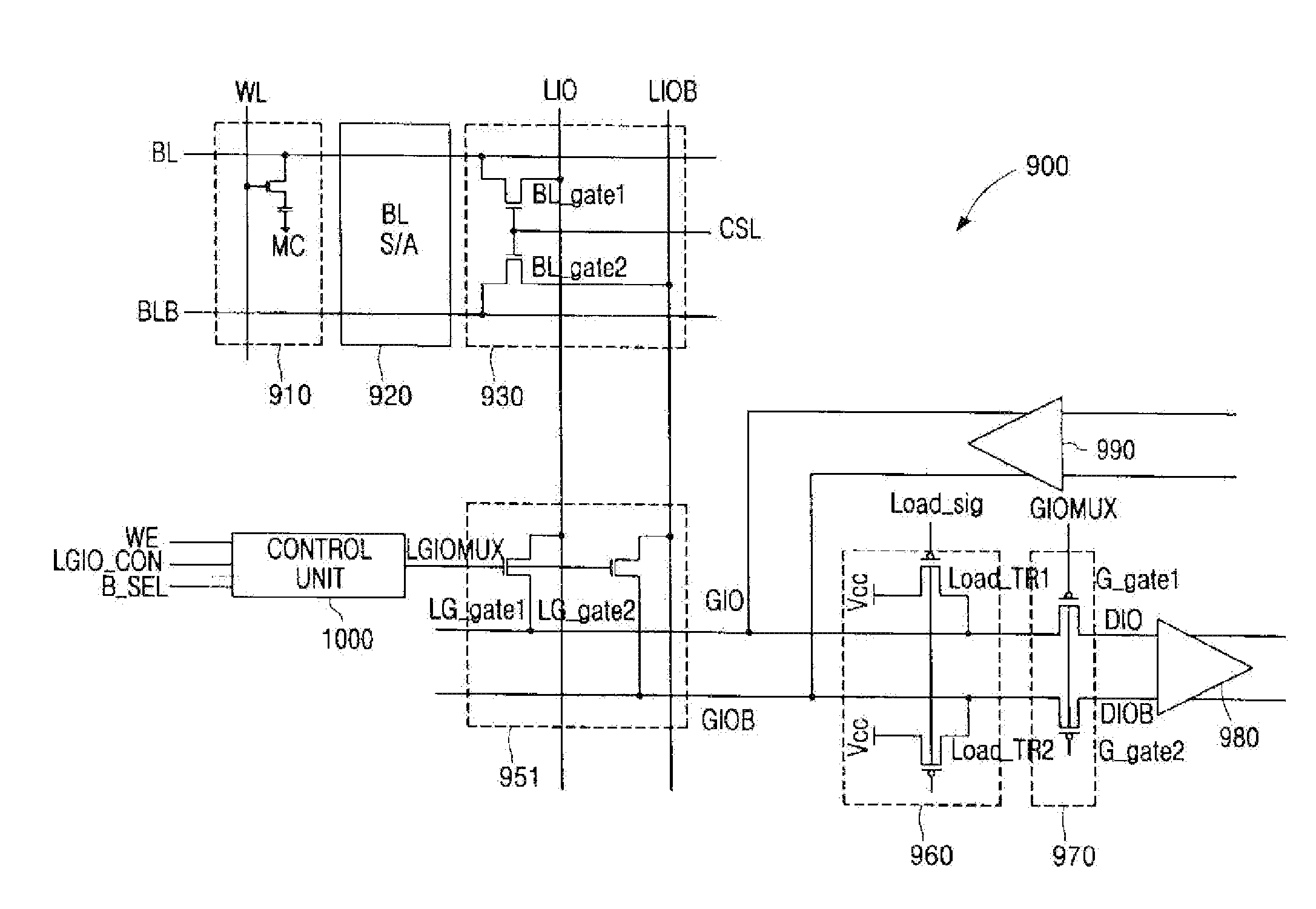

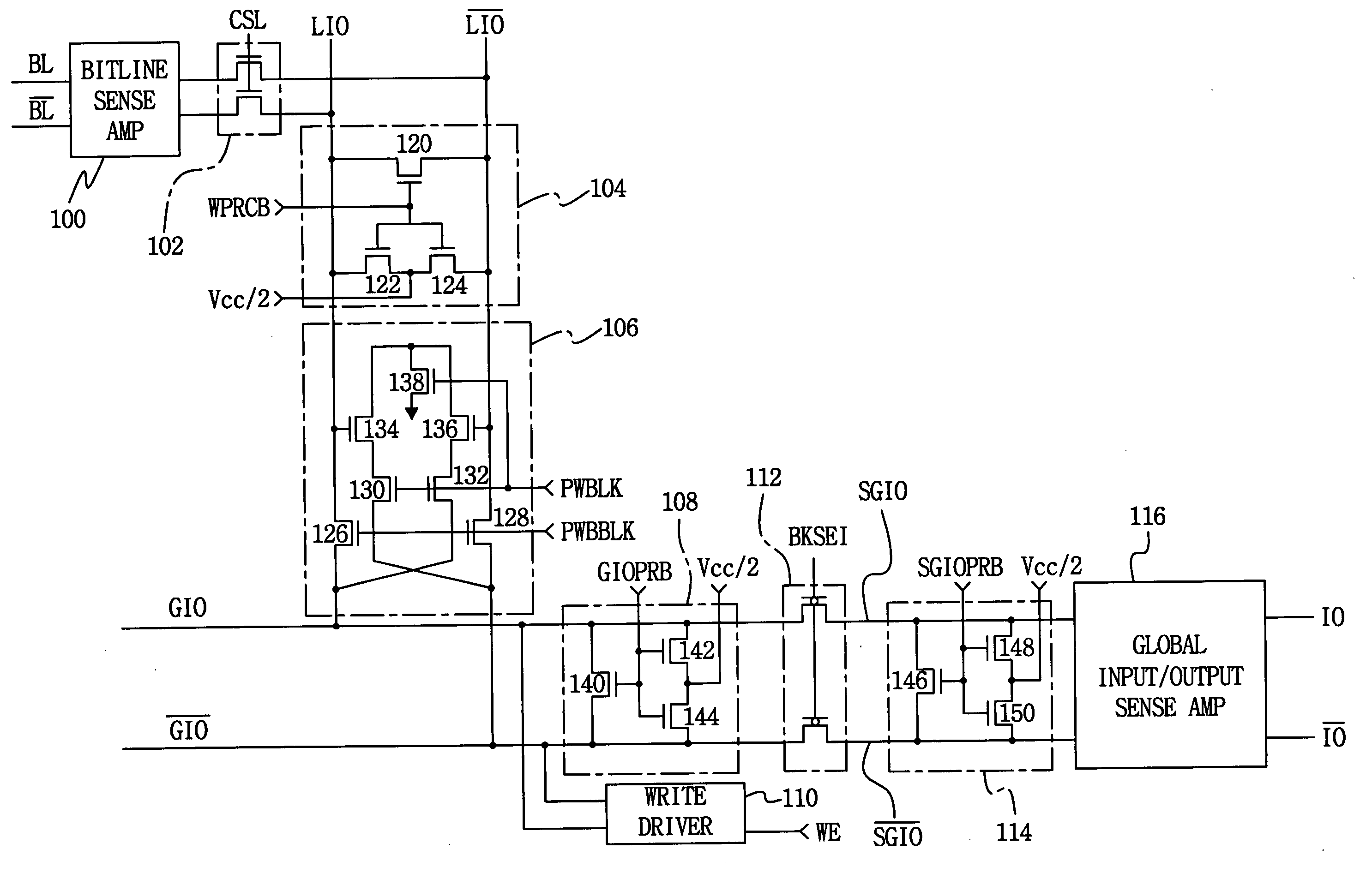

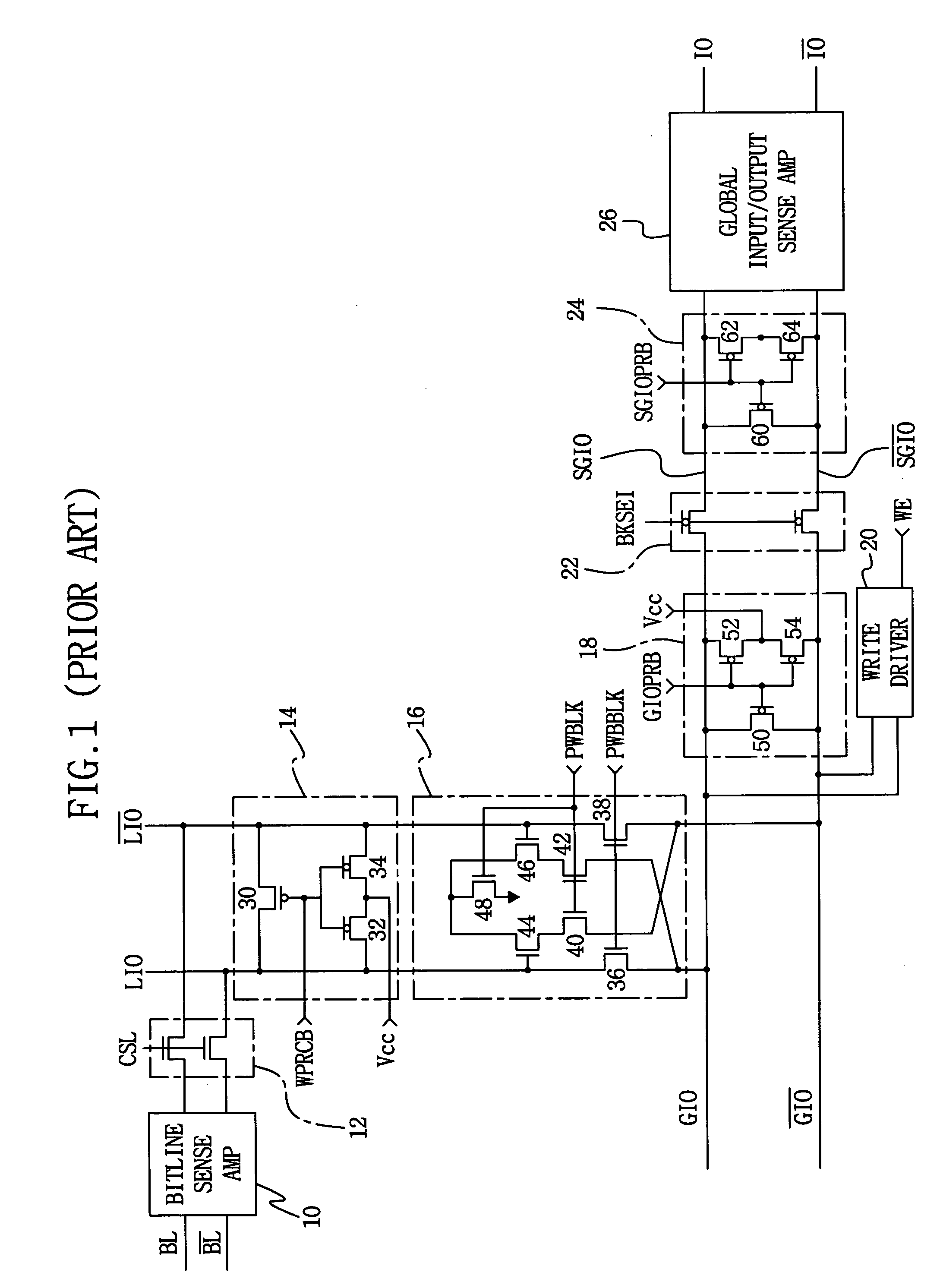

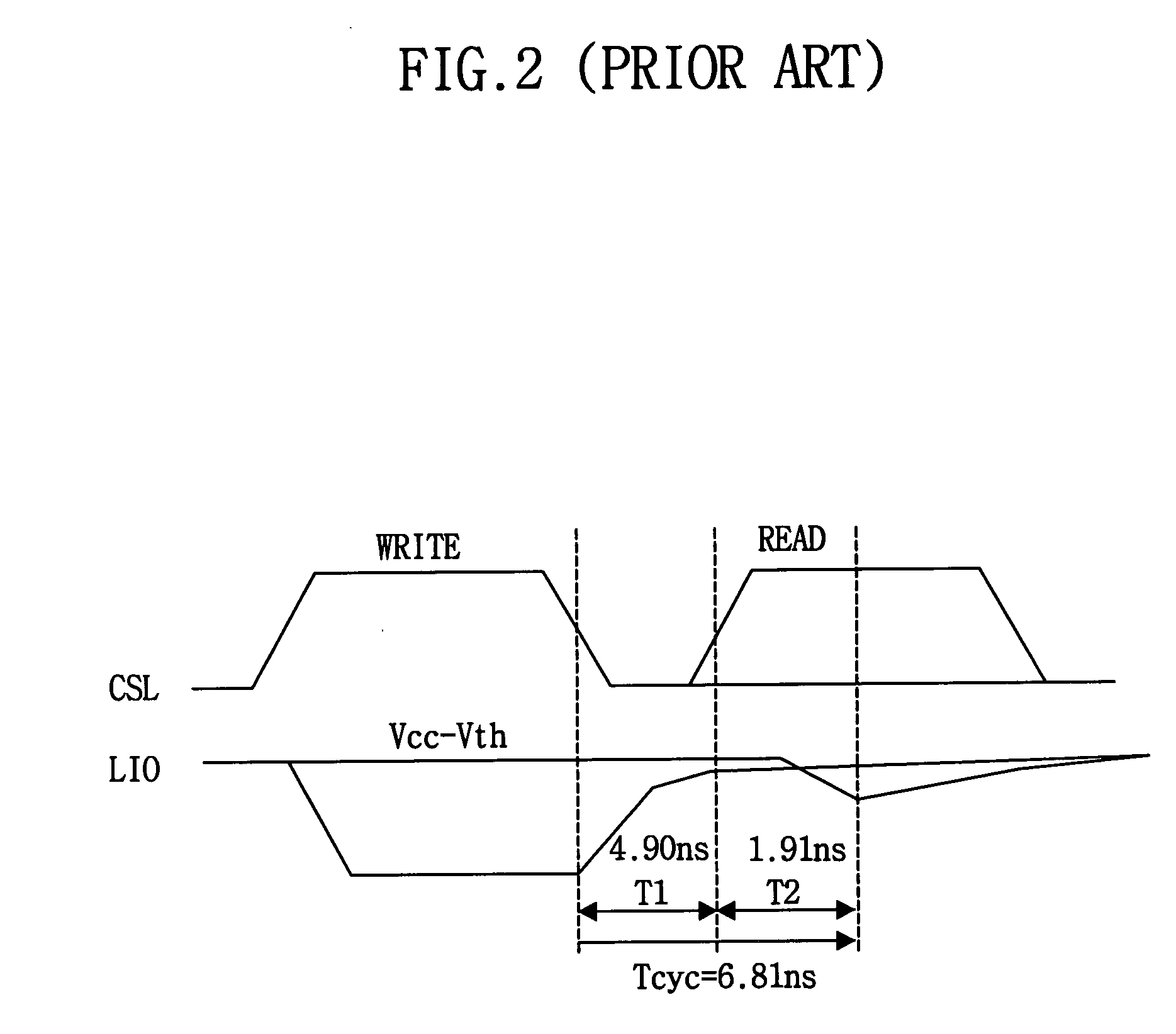

Memory device with separate read and write gate voltage controls

A circuit and method are provided for controlling the gate voltage of a transistor acting between local and global input / output lines of a memory device, the circuit including a local input / output line, a local from / to global input / output multiplexer in signal communication with the local input / output line, a global input / output line in signal communication with the local from / to global input / output multiplexer, and a local from / to global input / output controller having an input node and an output node, the input node disposed for receiving a signal indicative of an input or output operation, and the output node in signal communication with a gate of the local from / to global input / output multiplexer for providing a gate signal of a first or second level in the presence of the output operation, and a gate signal of a third level in the presence of the input operation.

Owner:SAMSUNG ELECTRONICS CO LTD

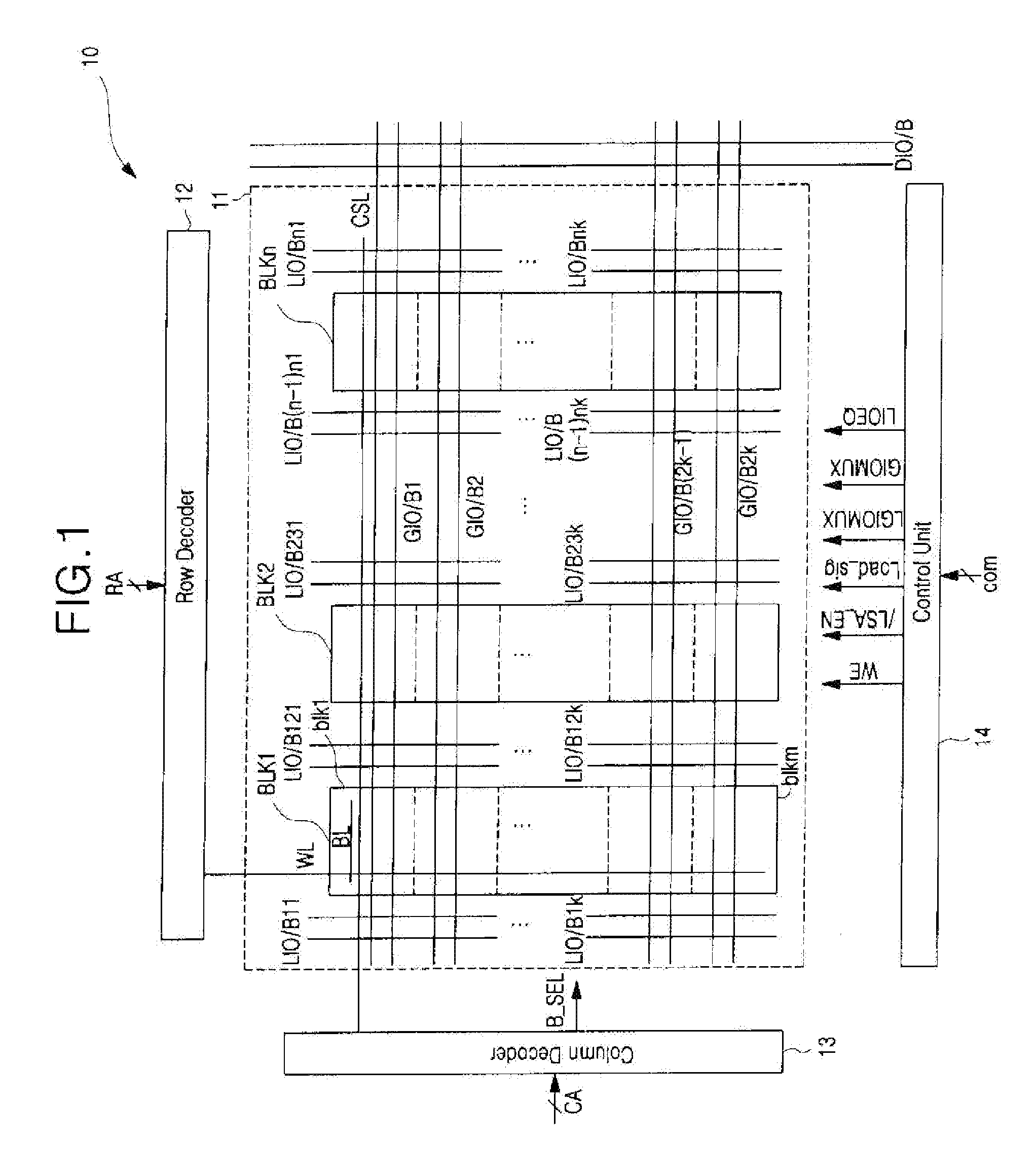

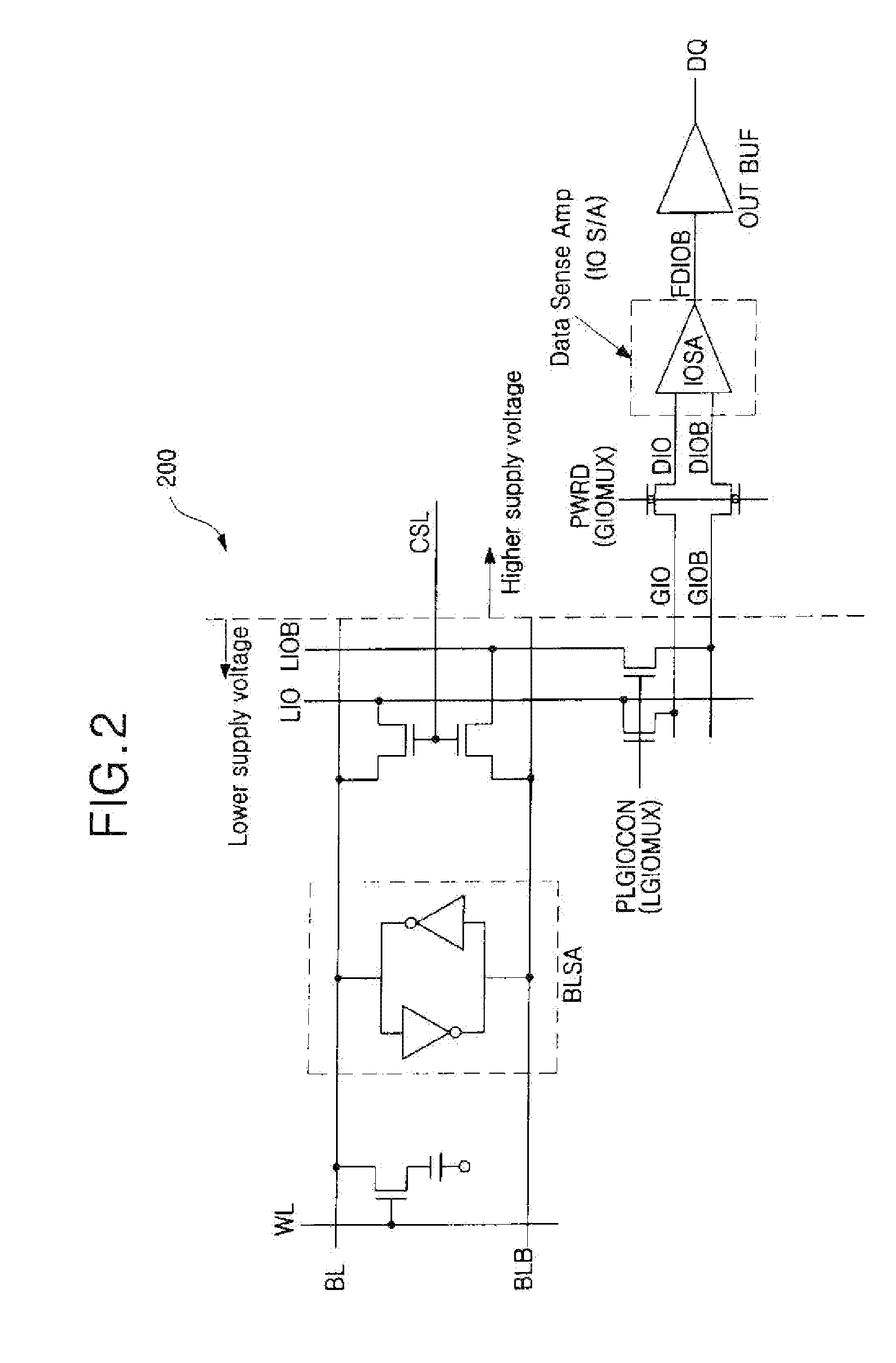

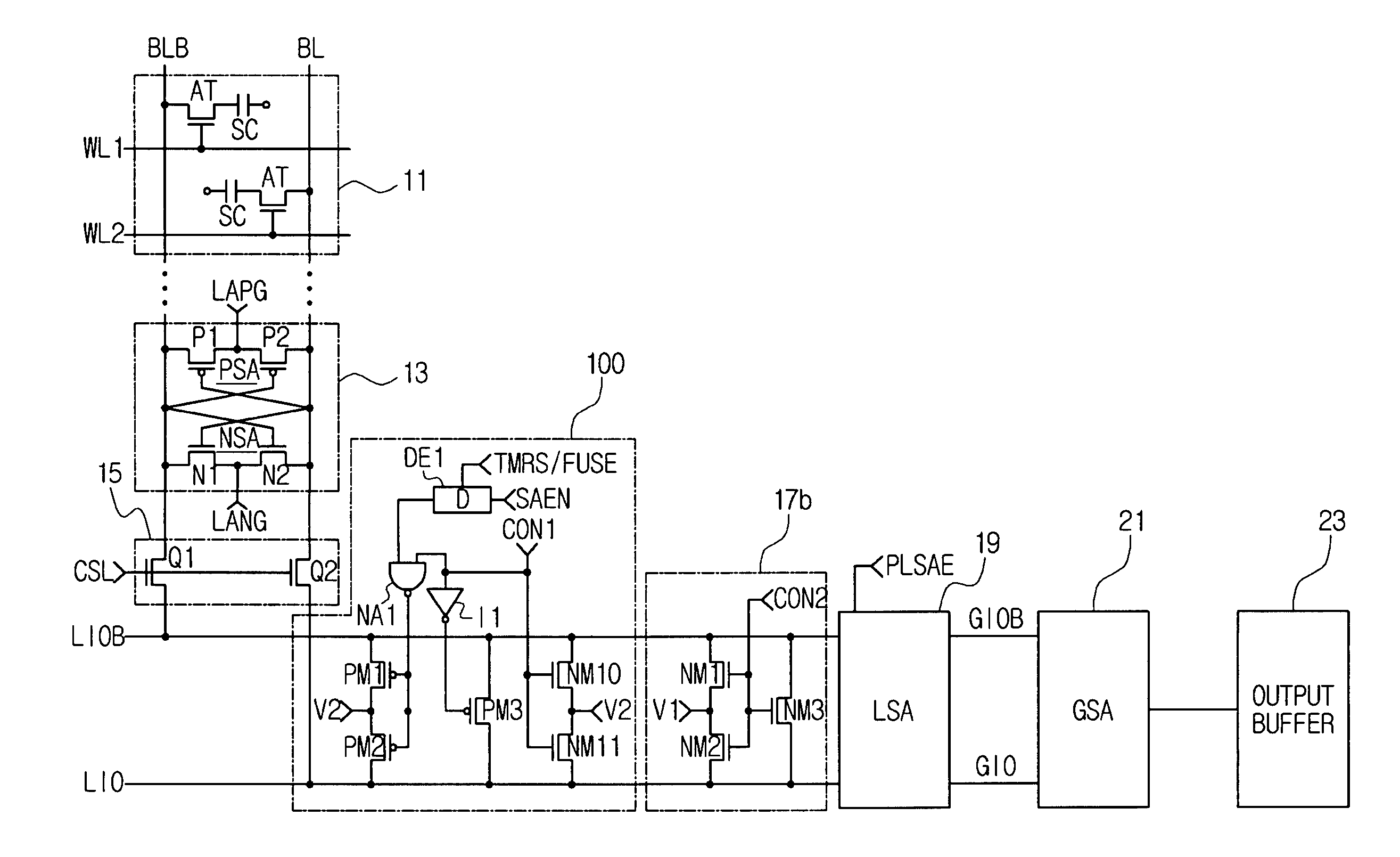

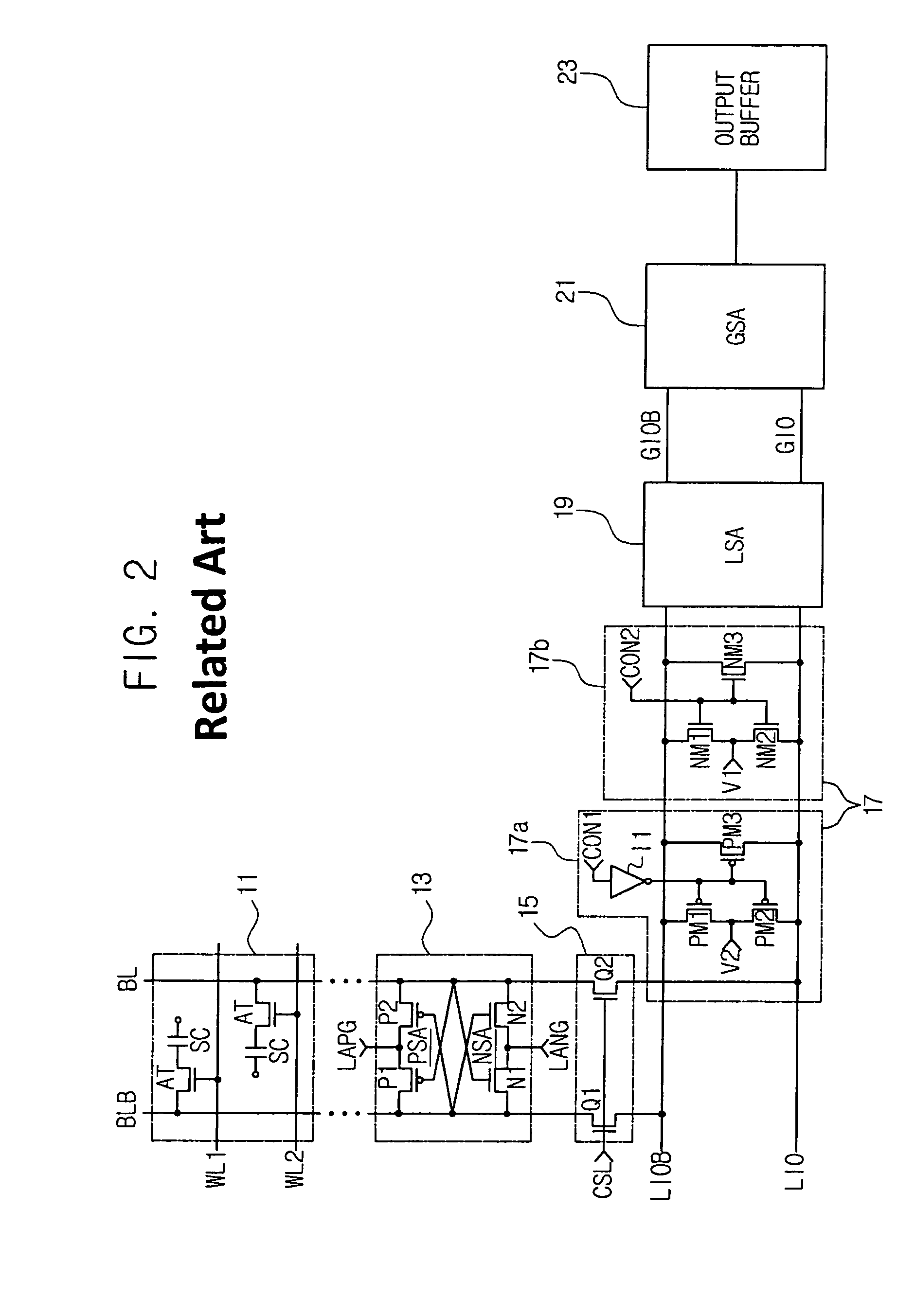

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

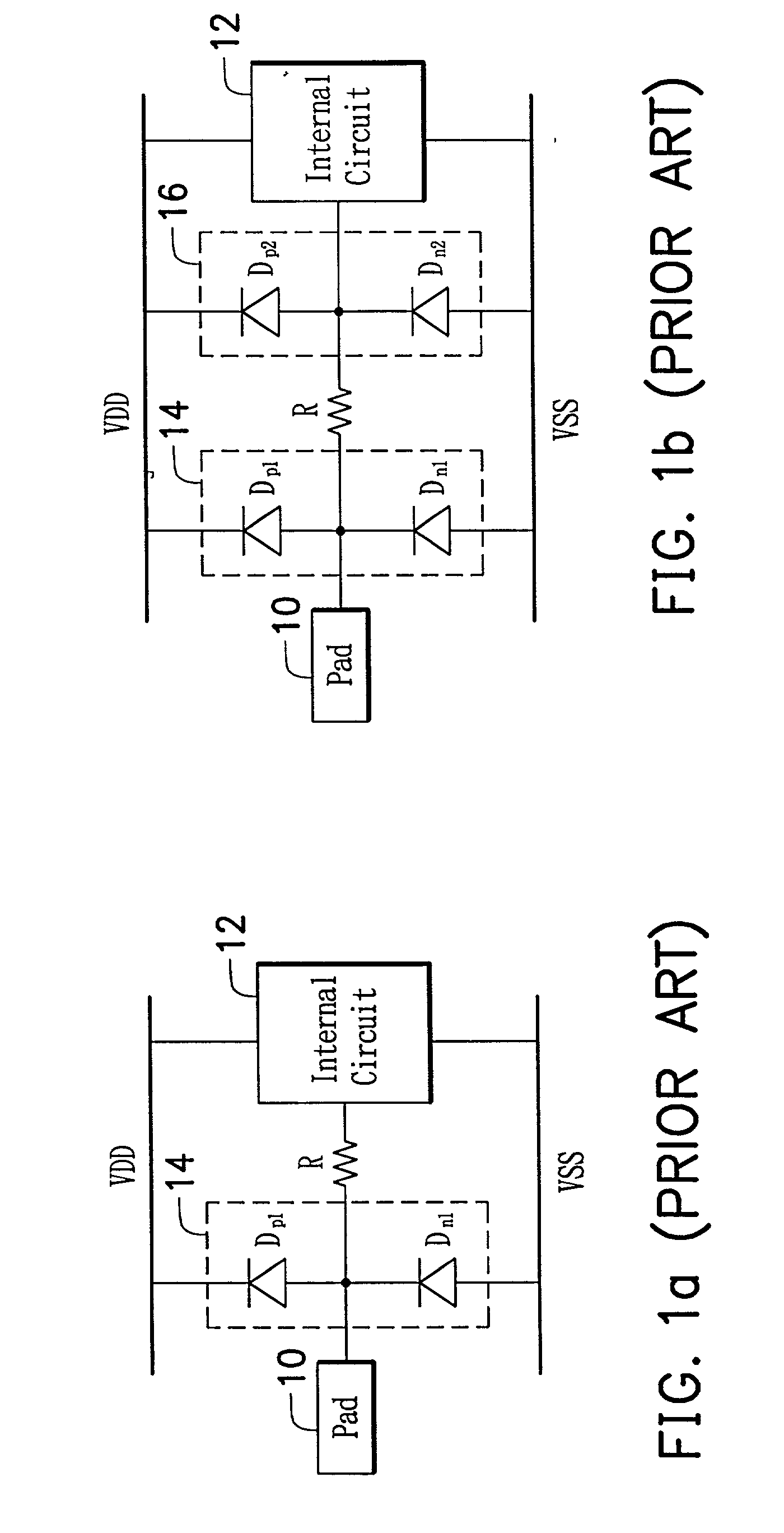

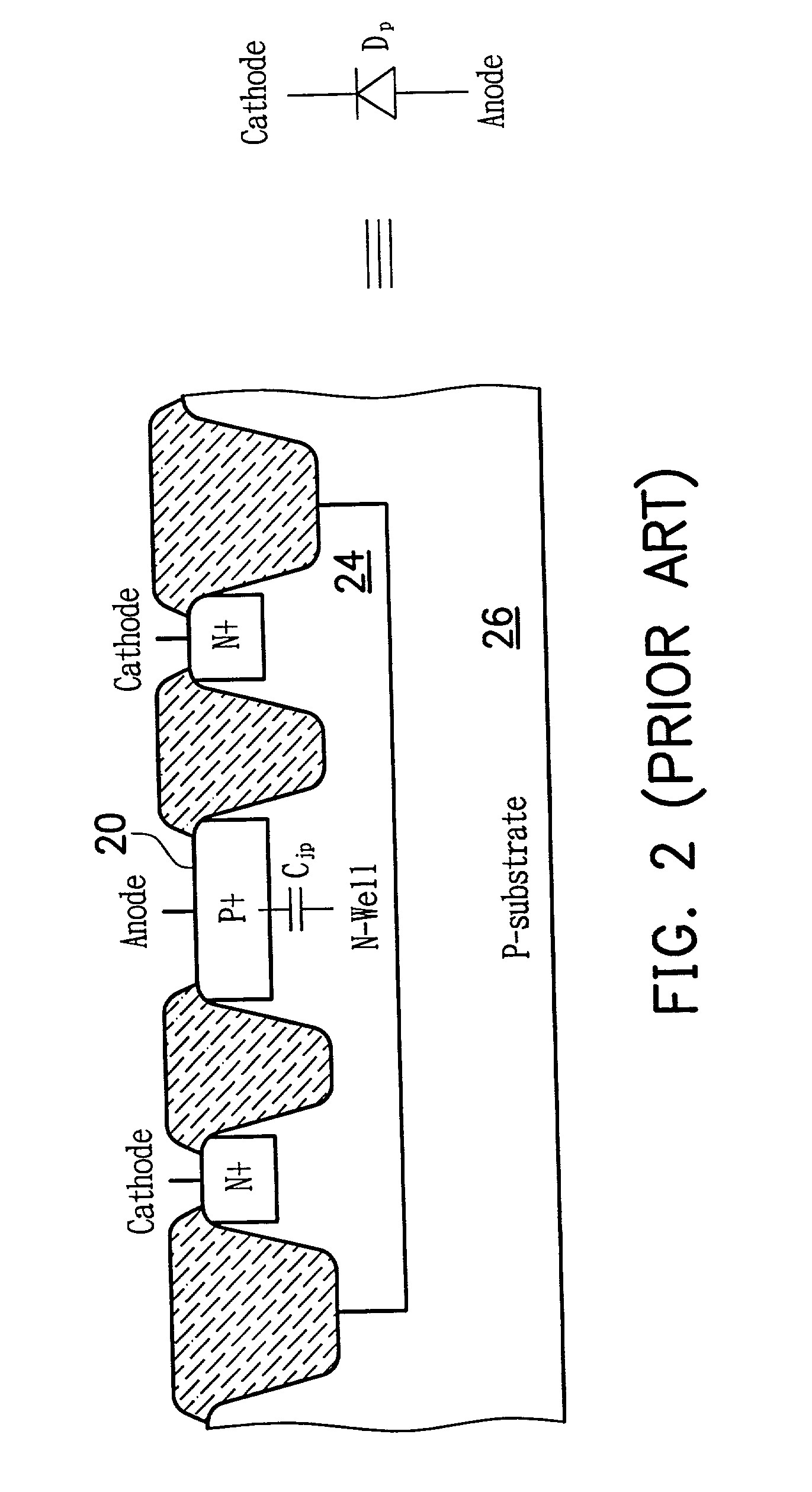

ESD protection circuit with very low input capacitance for high-frequency I/O ports

InactiveUS20020130390A1Reduce chip areaReduce input capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEquivalent input

The present invention proposes an ESD protection circuit with low input capacitance, suitable for an I / O pad. The ESD protection circuit includes a plurality of diodes and a power-rail ESD clamp circuit between power lines. The diodes are stacked and coupled between a first power line and the I / O pad. The ESD protection circuit between power lines is coupled between the first power line and a second power line. During normal operation, the diodes are reverse-biased and the ESD protection circuit between power lines is turned off. When an ESD event between the power line and the I / O pad occurs, the diodes are forward-biased, and the ESD protection circuit between power lines is turned on to conduct ESD current. The equivalent input capacitance of the ESD protection circuit of the present invention is very small, making it particularly suitable for the I / O port of high-frequency or high-speed IC.

Owner:TAIWAN SEMICON MFG CO LTD

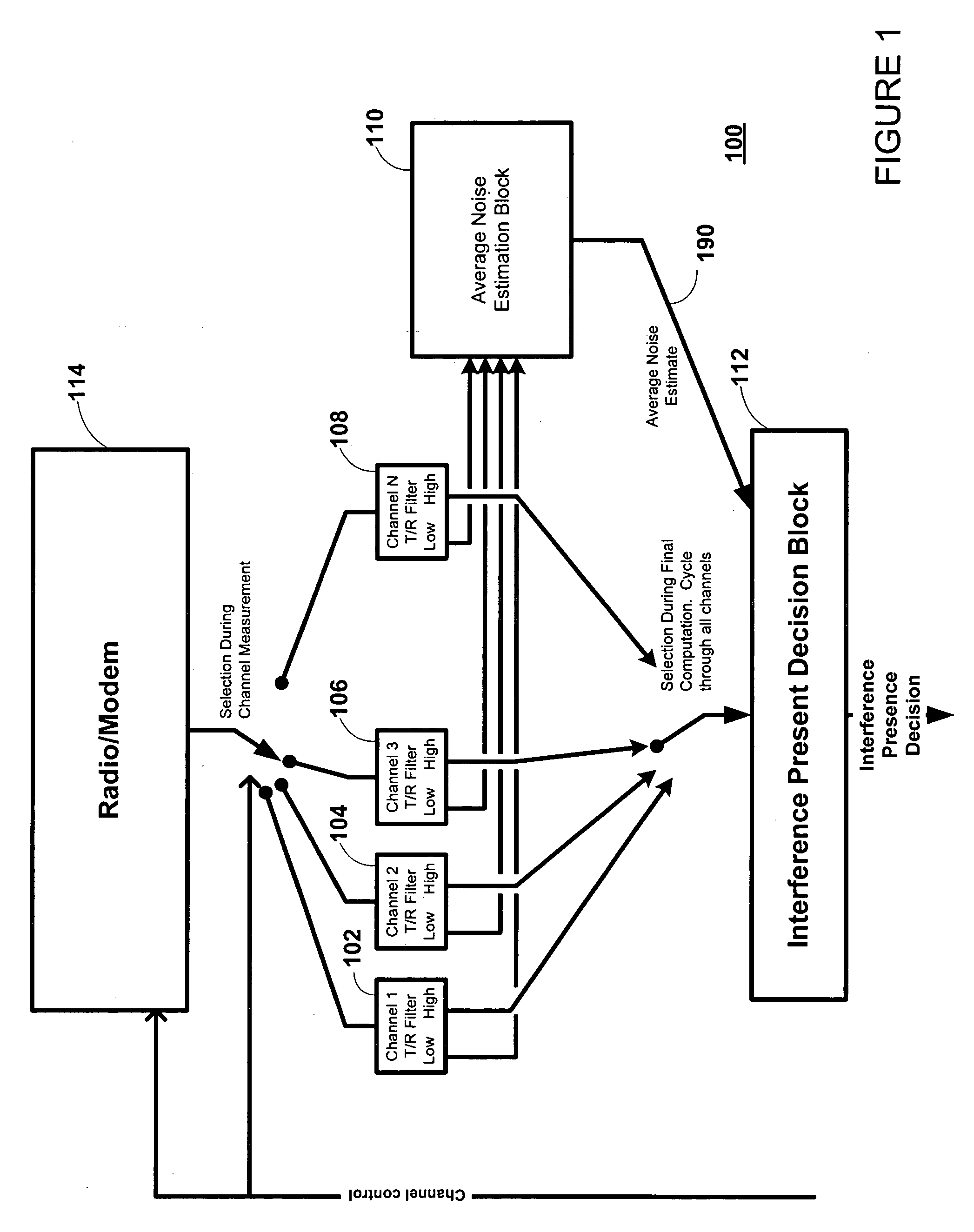

Method and apparatus determining the presence of interference in a wireless communication channel

ActiveUS7103316B1Reduce observationReduce processTransmission monitoringTransmission noise suppressionWireless dataLow input

A method and apparatus for estimating the presence of RF interference in a wireless data channel is described. The method and apparatus comprises a set of identical tracking / register (T / R) filter blocks, each T / R filter block associated and corresponding to an RF channel of interest. Each T / R filter block includes a pair of tracking / register (T / R) filters. Power / magnitude estimates from an RSSI calculation are input to the T / R filter blocks. One T / R filter is used to estimate the noise floor (in the absence of interference). The T / R filter latches and filters the lowest input values received from a power / magnitude circuit. The other T / R filter estimates the level of an interferer, if present, by latching and filtering the largest valued outputs of the power / magnitude circuit.

Owner:QUALCOMM INC

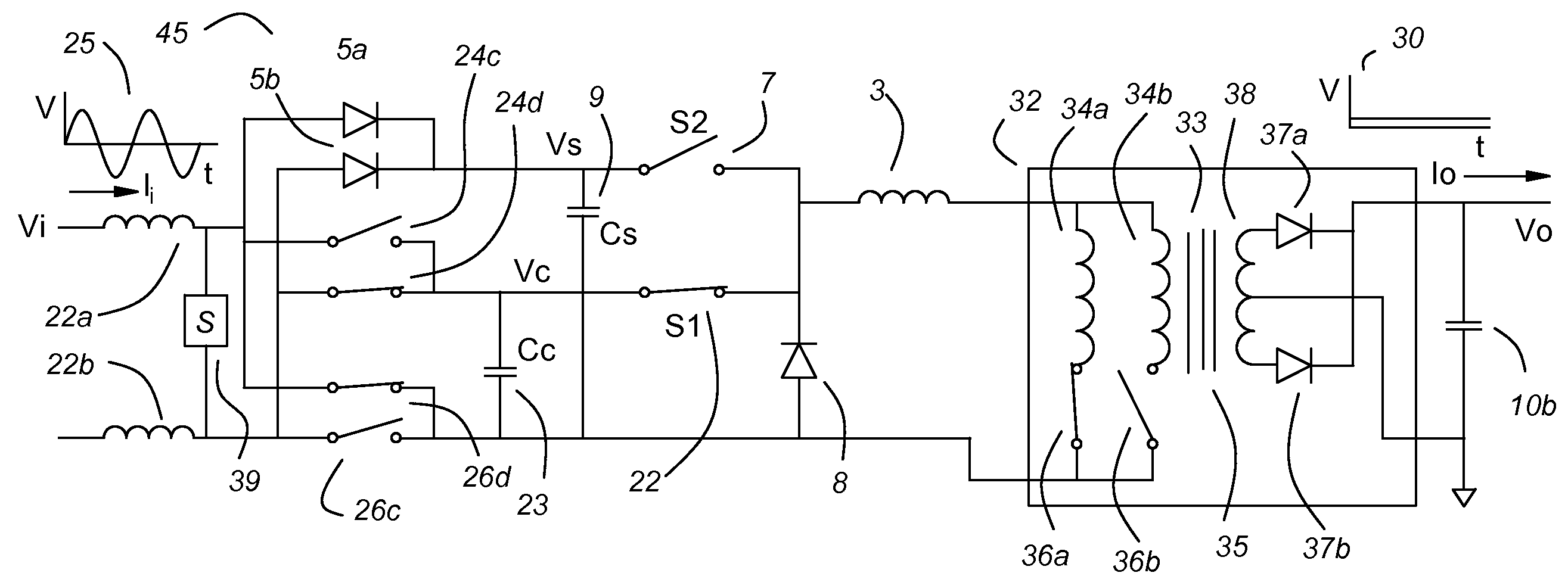

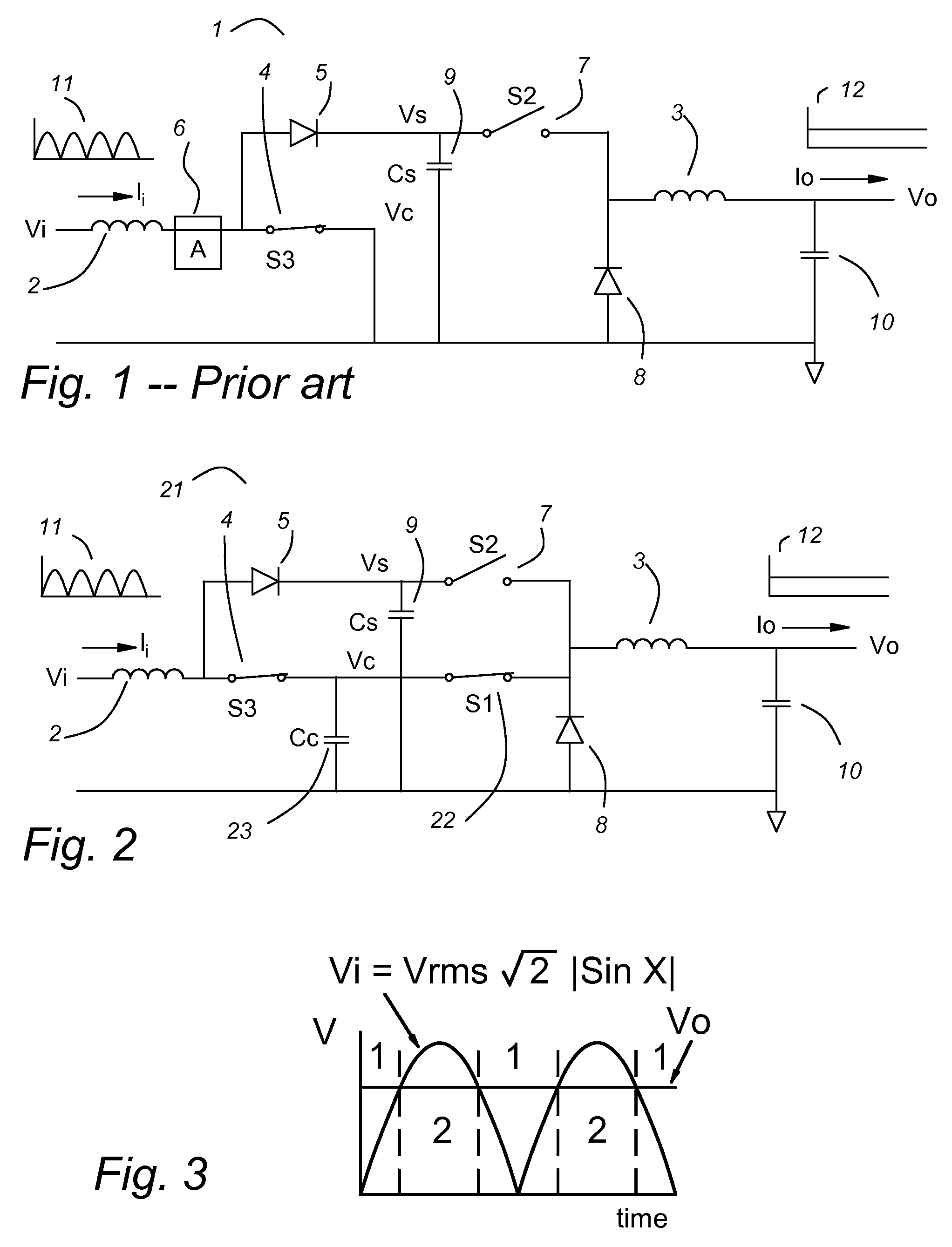

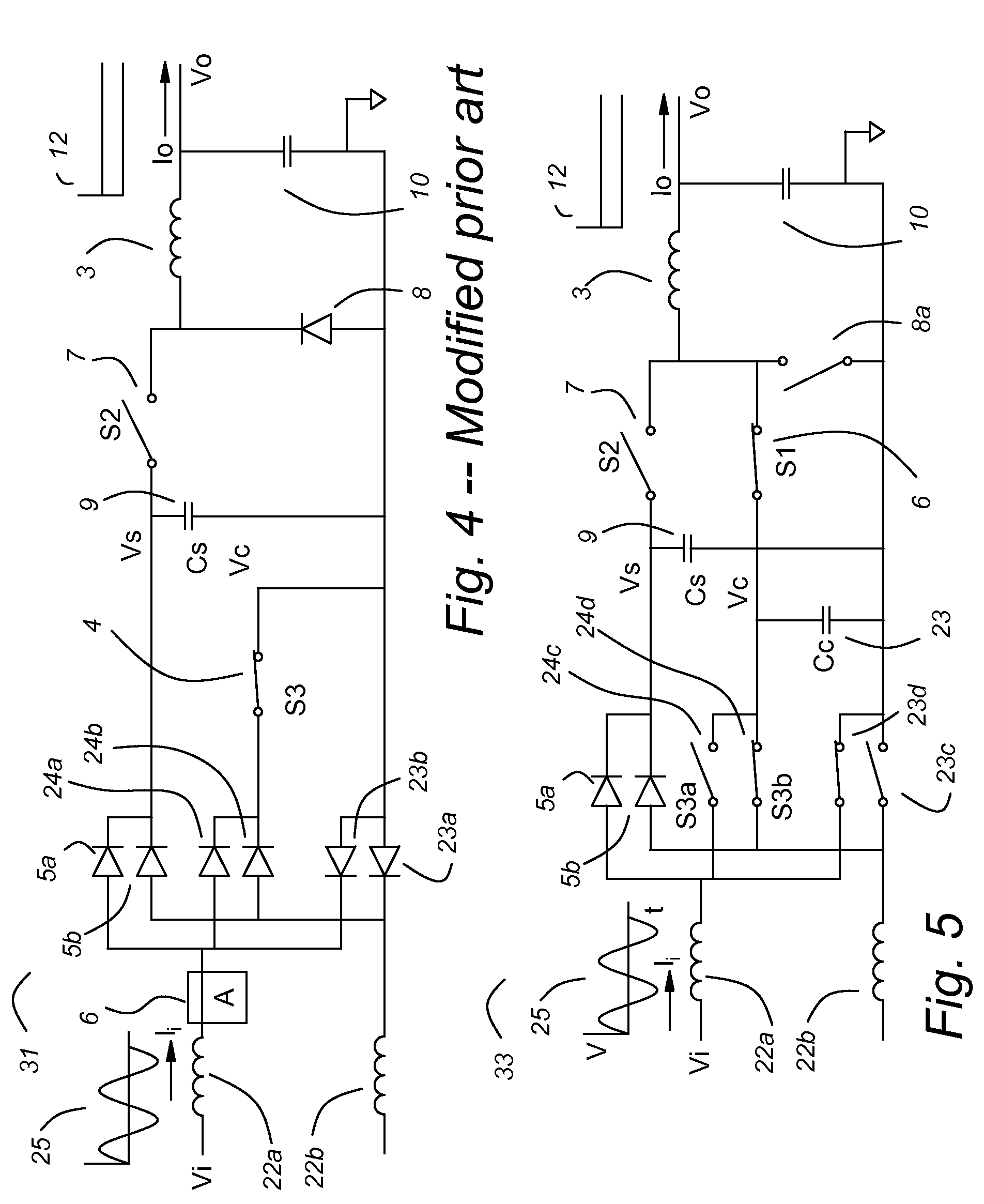

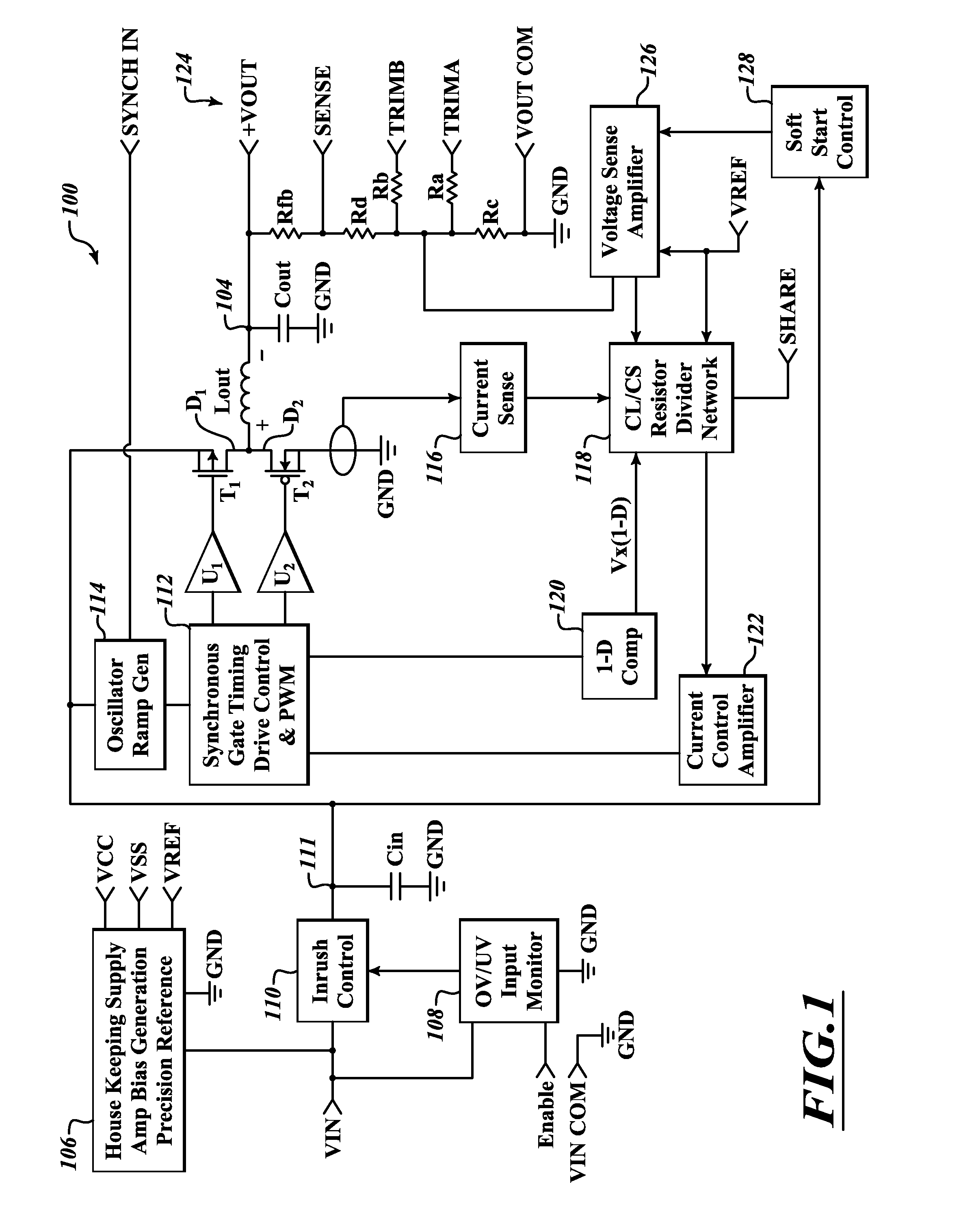

Power factor corrected single-phase AC-DC power converter using natural modulation

InactiveUS7564706B1Reduce lossesMost efficientAc-dc conversion without reversalEfficient power electronics conversionLevel shiftingElectric power system

A power factor corrected (pfc) ac-dc converter has a modified boost input and a modified buck output. Unlike the prior art boost input, the boost switch returns to the output, not to ground. Unlike the prior art buck output stage, a third switch connects to the input. This allows much of the input current to pass through the converter to the output. There is no input current measurement, but nearly ideal power factor correction is achieved through “natural modulation.” A preferred pfc ac-dc converter uses a variable dc-dc transformer on its output, as a post regulator, to provide dielectric isolation and to provide voltage level shifting. The output of the pfc ac-dc converter has the control characteristics of a buck converter, so it is a natural mate for the variable dc-dc transformer. An ac-dc buck converter is most efficient at its maximum duty cycle. It cannot regulate for a lower input voltage, but it can reduce its duty-cycle to control for higher input voltages. A variable dc-dc transformer is most efficient at its maximum ratio. It cannot regulate for a higher input voltage, but it can reduce its effective turns ratio to control for a lower input voltage. With a small overlap in their control ranges, both parts of the power system can operate at maximum efficiency. The variable dc-dc transformer controls the output voltage for nominal and low input voltage. The ac-dc buck converter limits over-voltage transients.

Owner:HERBERT EDWARD

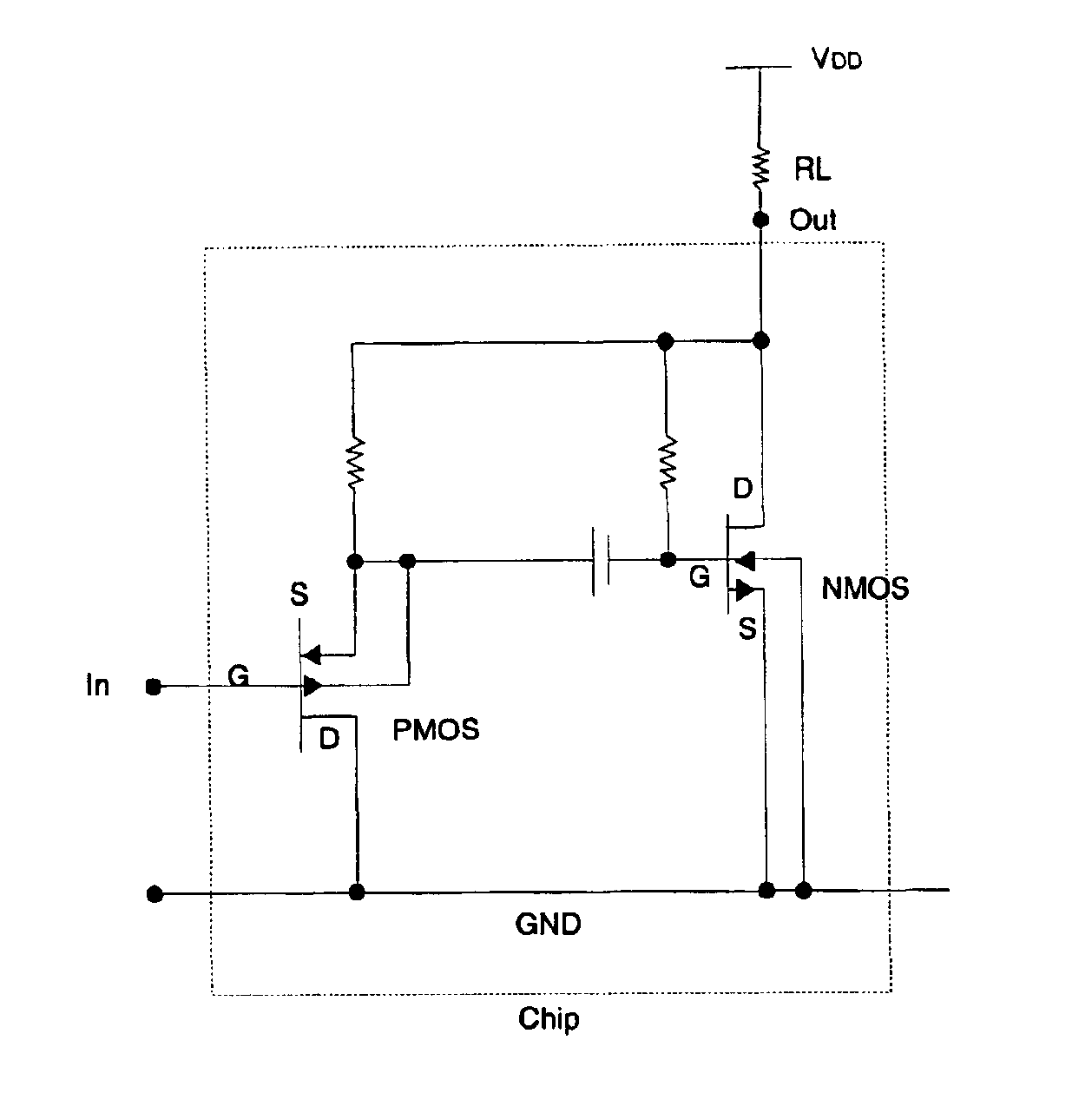

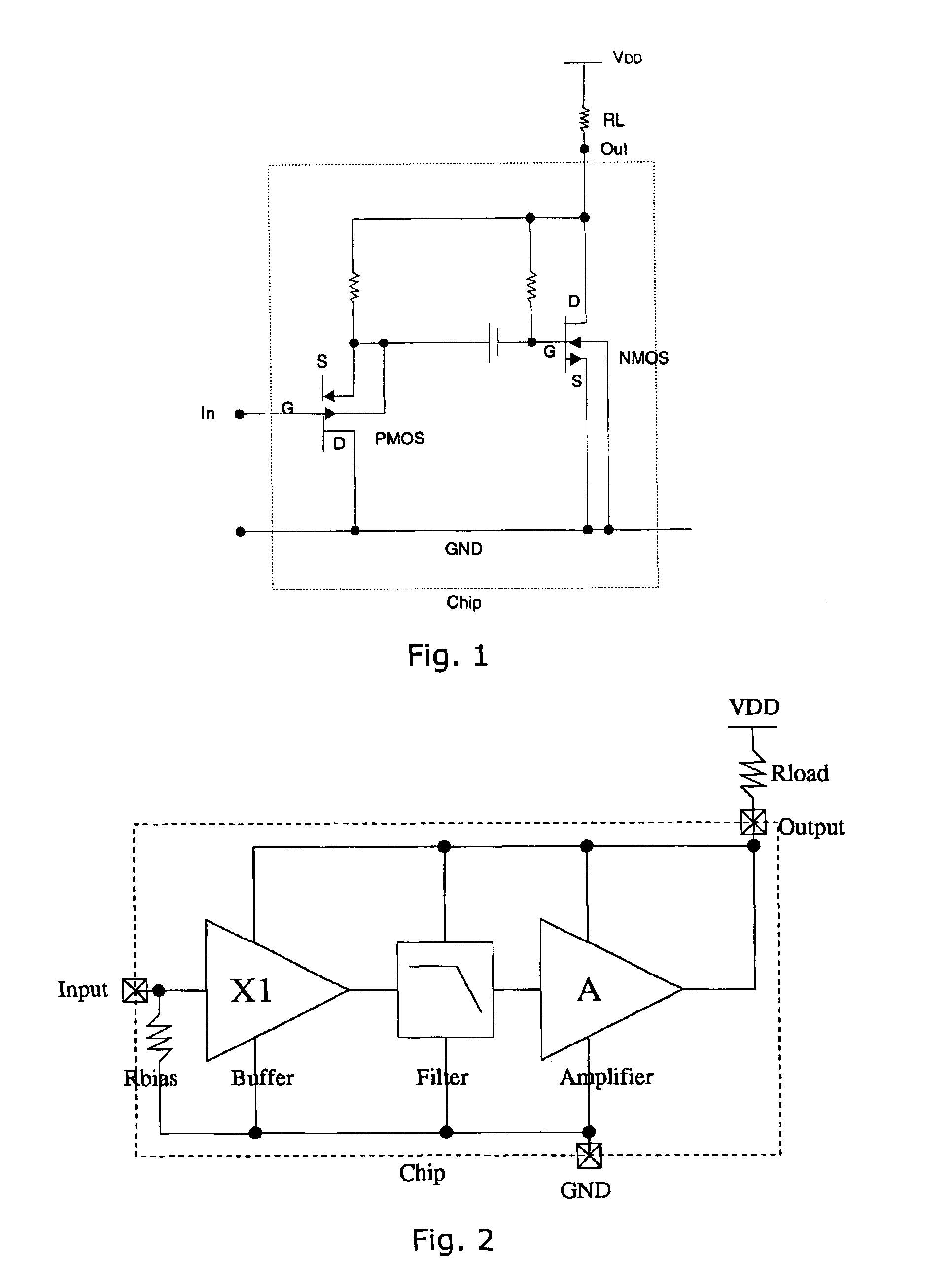

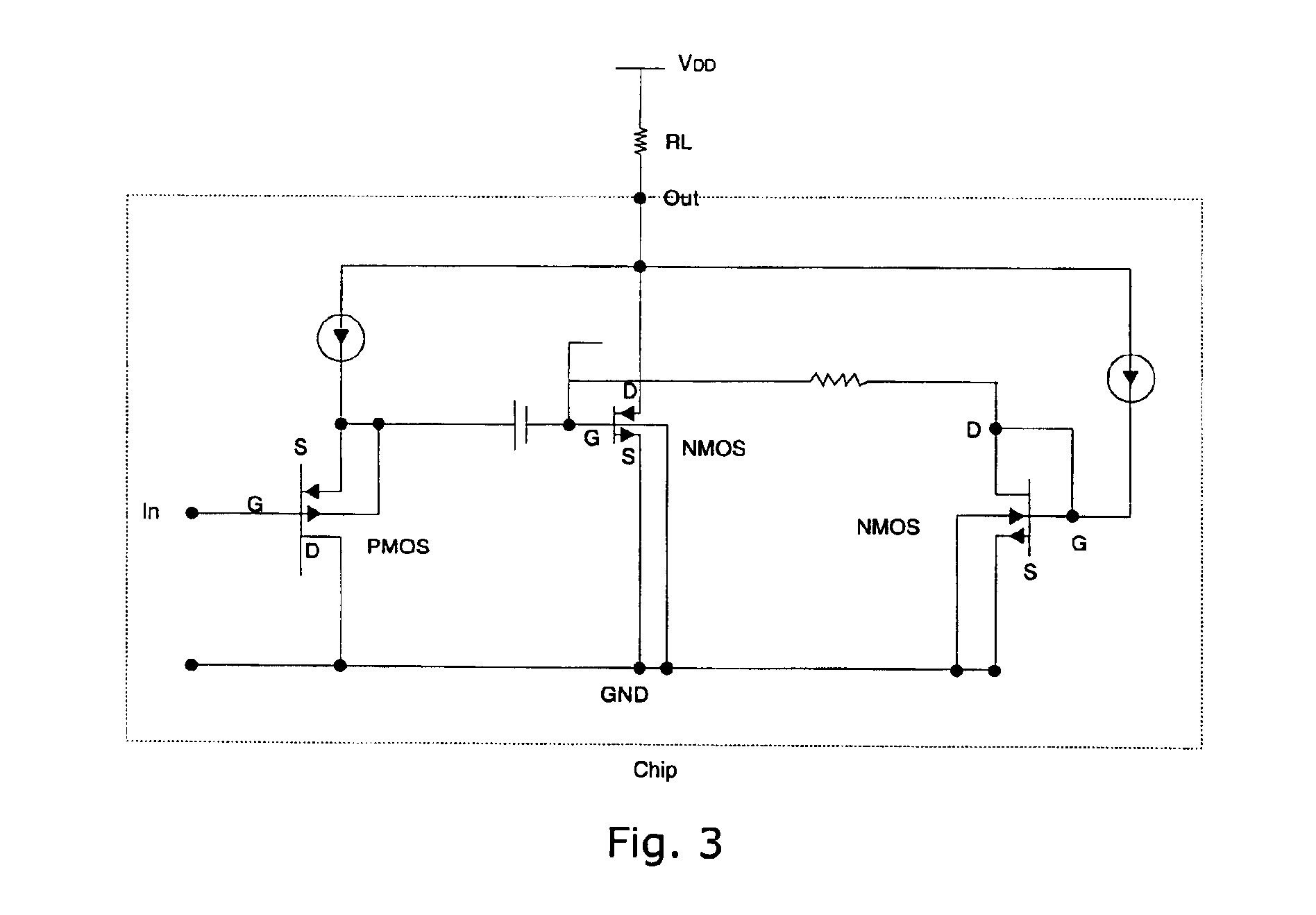

Preamplifier for two terminal electret condenser microphones

ActiveUS6888408B2Low costLimited space availableLow frequency amplifiersAmplifier combinationsCapacitanceAudio power amplifier

The present invention relates to a preamplifier suitable for use with Electret Condenser Microphones such as used within telecommunication equipment. More particularly the invention relates to a preamplifier specially suited for the demands to such a preamplifier within telecommunication equipment: low input capacitance, gain and a combined terminal for output and supply voltage, thus making the preamplifier suitable for two terminal microphone assemblies. These features are obtained with a two stage amplifier with a first stage optimised for low input capacitance and the second stage being able to provide gain. The preamplifier may be implemented using an ASIC, thus making the preamplifier suitable for applications with very limited space available, such as for integration within microphone assemblies.

Owner:SONION

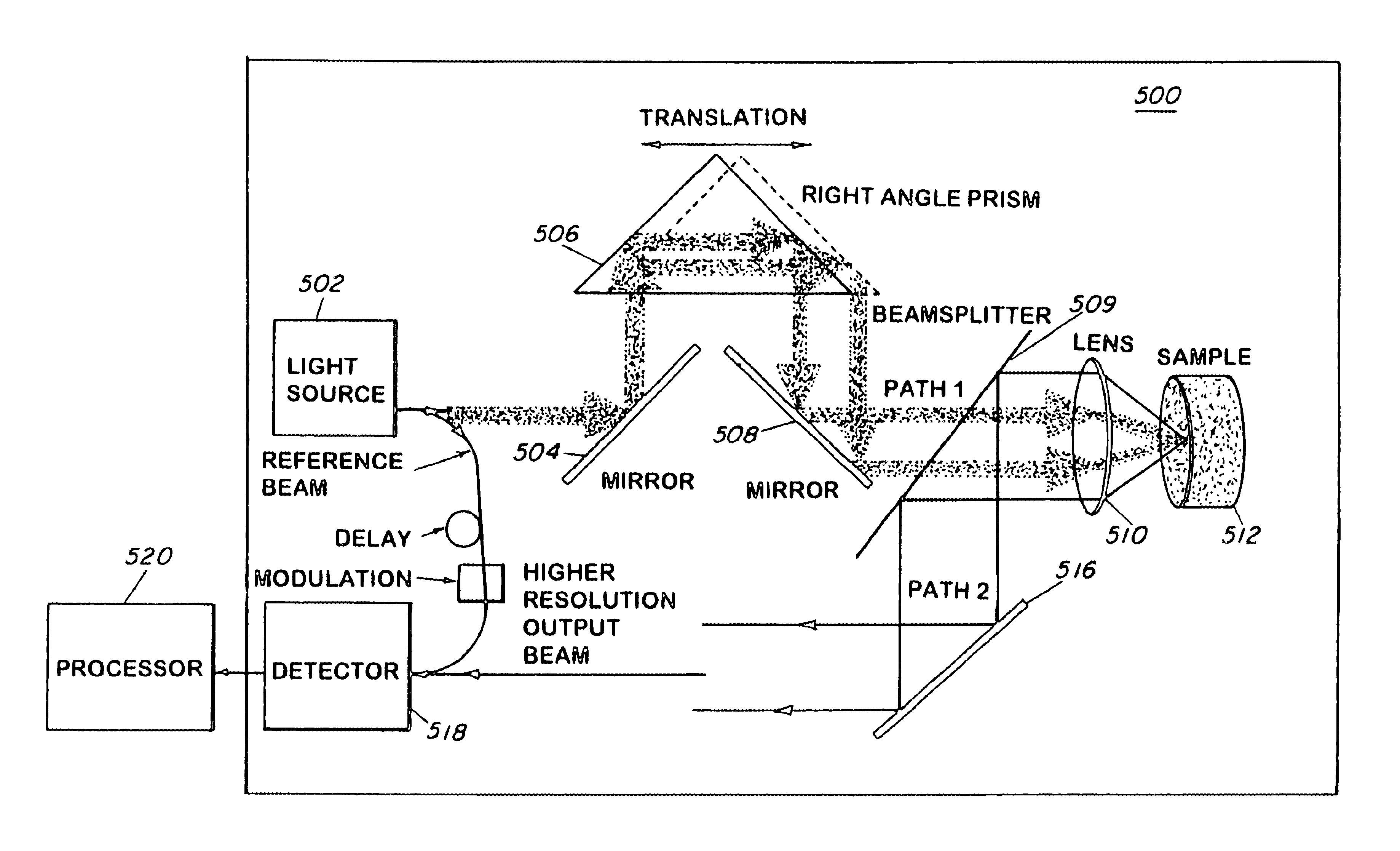

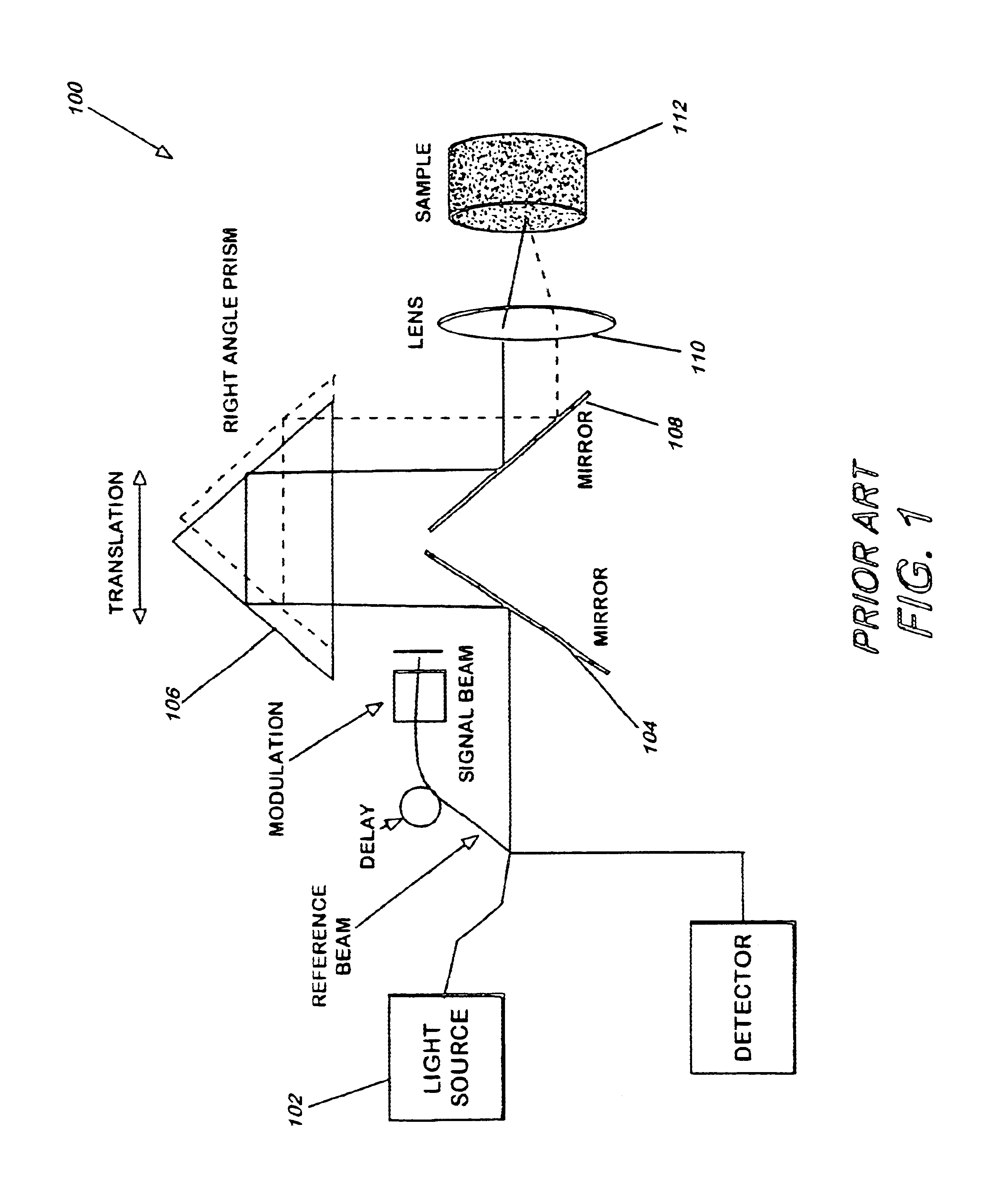

Method and apparatus for reducing speckle in optical coherence tomography images

InactiveUS6847449B2Simple and inexpensive methodImprove resolutionScattering properties measurementsLight polarisation measurementImage resolutionLow input

A method and apparatus for reducing speckle due to MSL, without any loss of resolution, by averaging over different angles of the incident light at low input resolution, while collecting the backscattered light at a full resolution of a lens is described. The present invention allows discrimination against the speckle due to coherent MSL.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

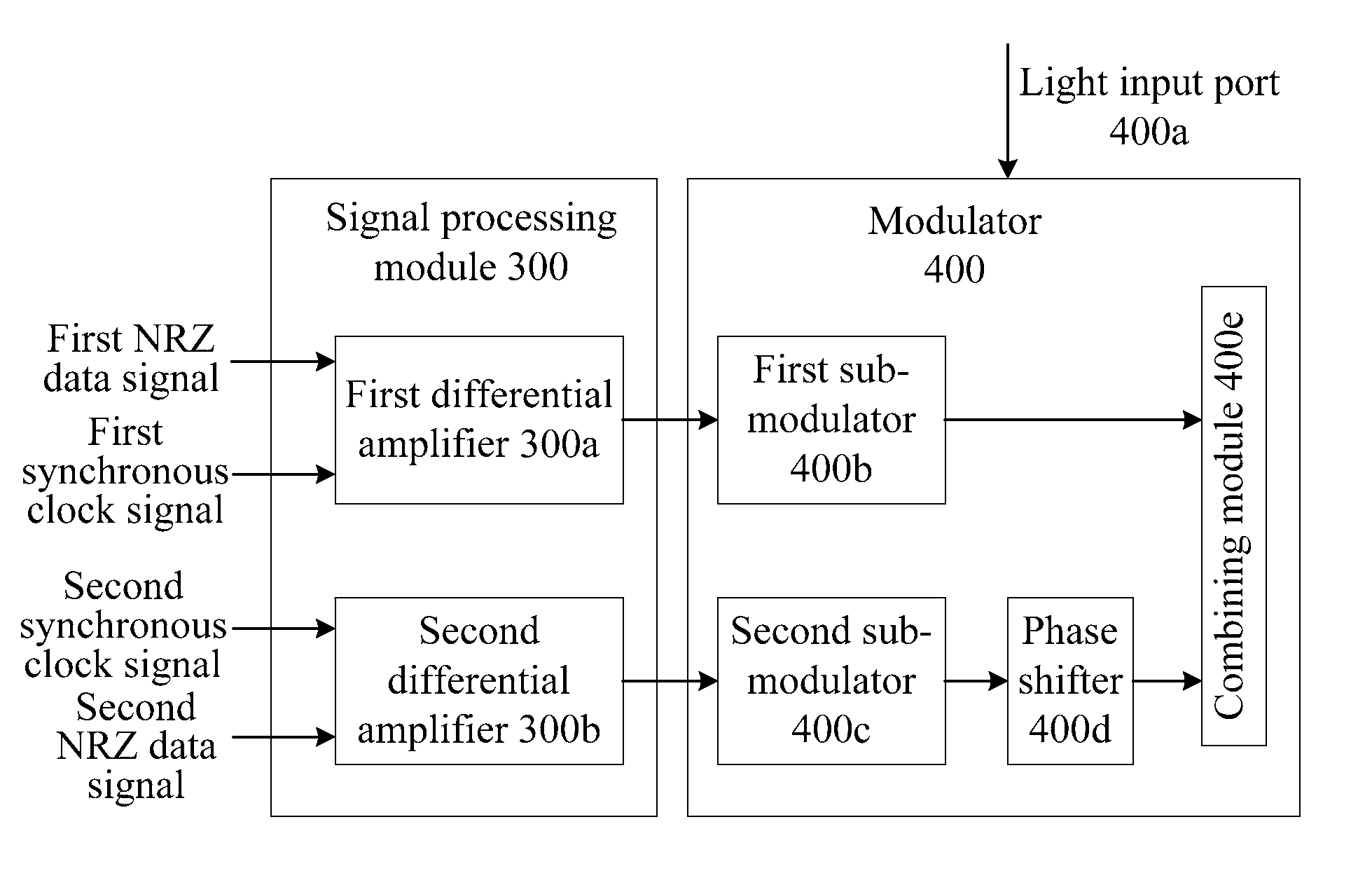

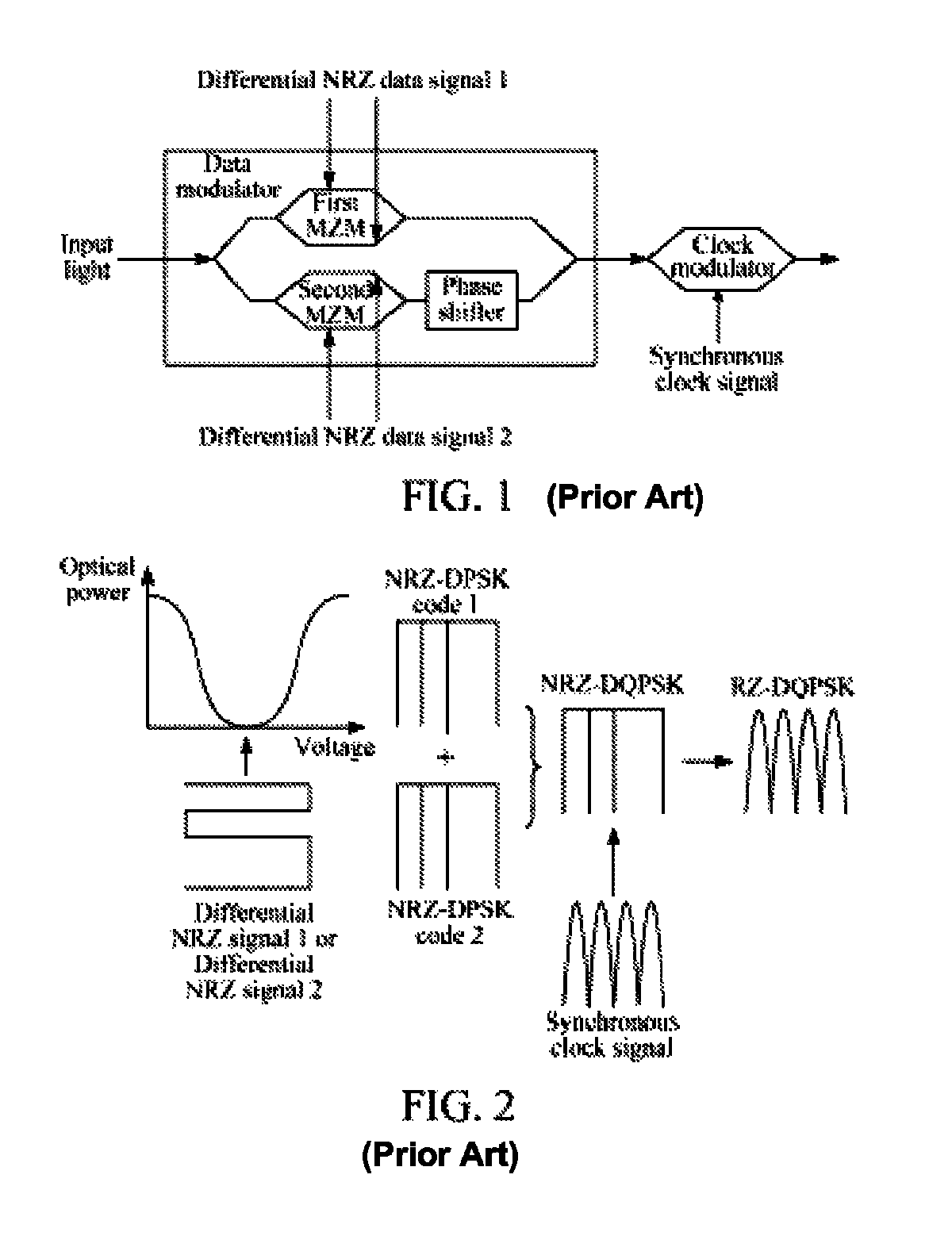

Method and device for generating optical signals

ActiveUS8831440B2Simple structureLow costElectromagnetic transmittersOptical NRZ to RZ conversionReturn-to-zeroSoftware engineering

The method includes: receiving a first Non Return to Zero (NRZ) data signal and a synchronous clock signal, and performing Return to Zero (RZ) processing to generate a first complementary RZ data signal pair; receiving a second NRZ data signal and a synchronous clock signal, and performing RZ processing to generate a second complementary RZ data signal pair; and modulating the first complementary RZ data signal pair and the second complementary RZ data signal pair on light to generate an RZ-Differential Quadrature Phase Shift Keying (RZ-DQPSK) optical signal. Through the method and device, RZ processing are performed on the NRZ data signals to generate the complementary RZ data signal pairs, and the complementary RZ data signal pairs are modulated on the light, thereby reducing the cost and the insertion loss of the entire device, lowering the requirements for input optical power and reducing the complexity of loop circuit control.

Owner:HUAWEI TECH CO LTD

Bistable all optical devices in non-linear photonic crystals

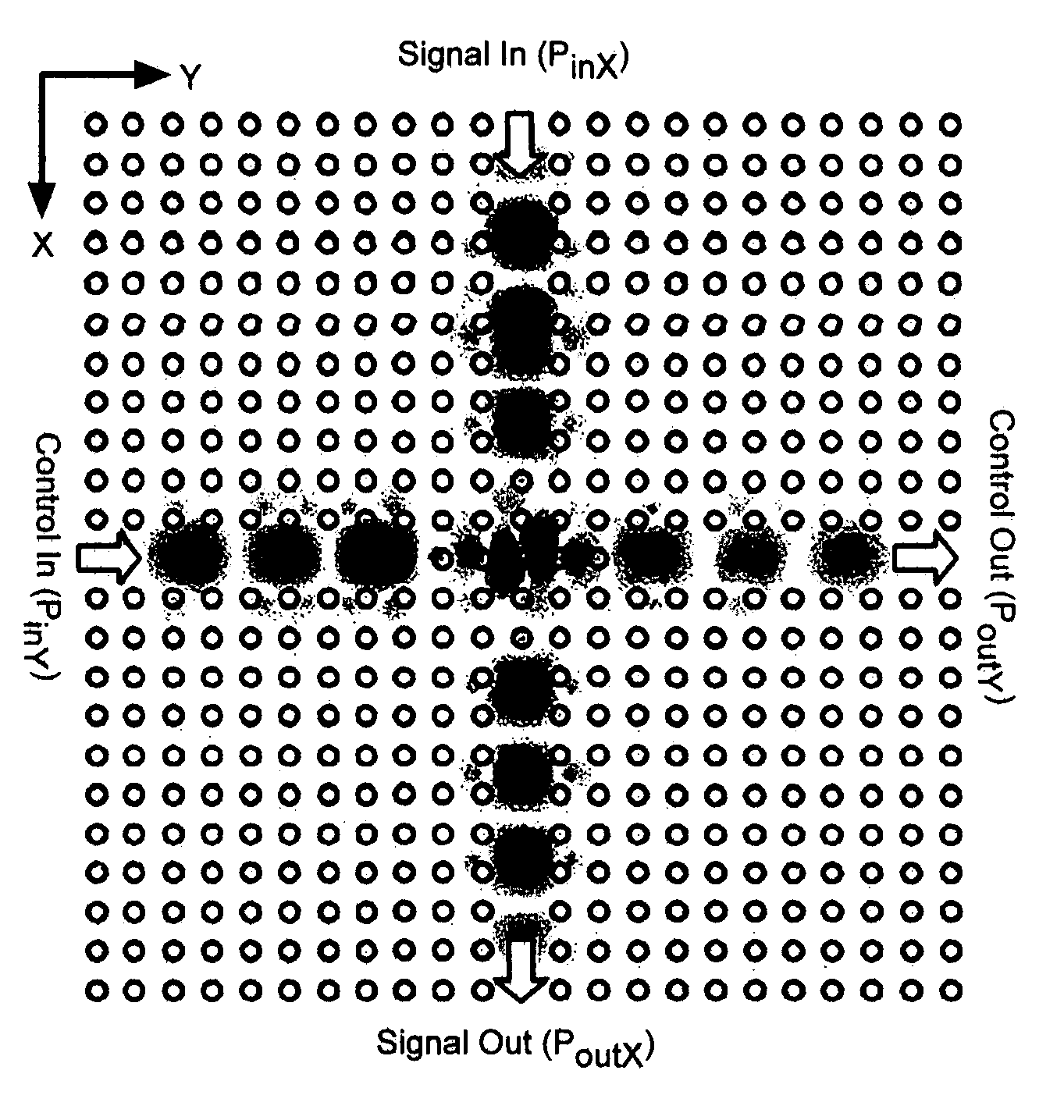

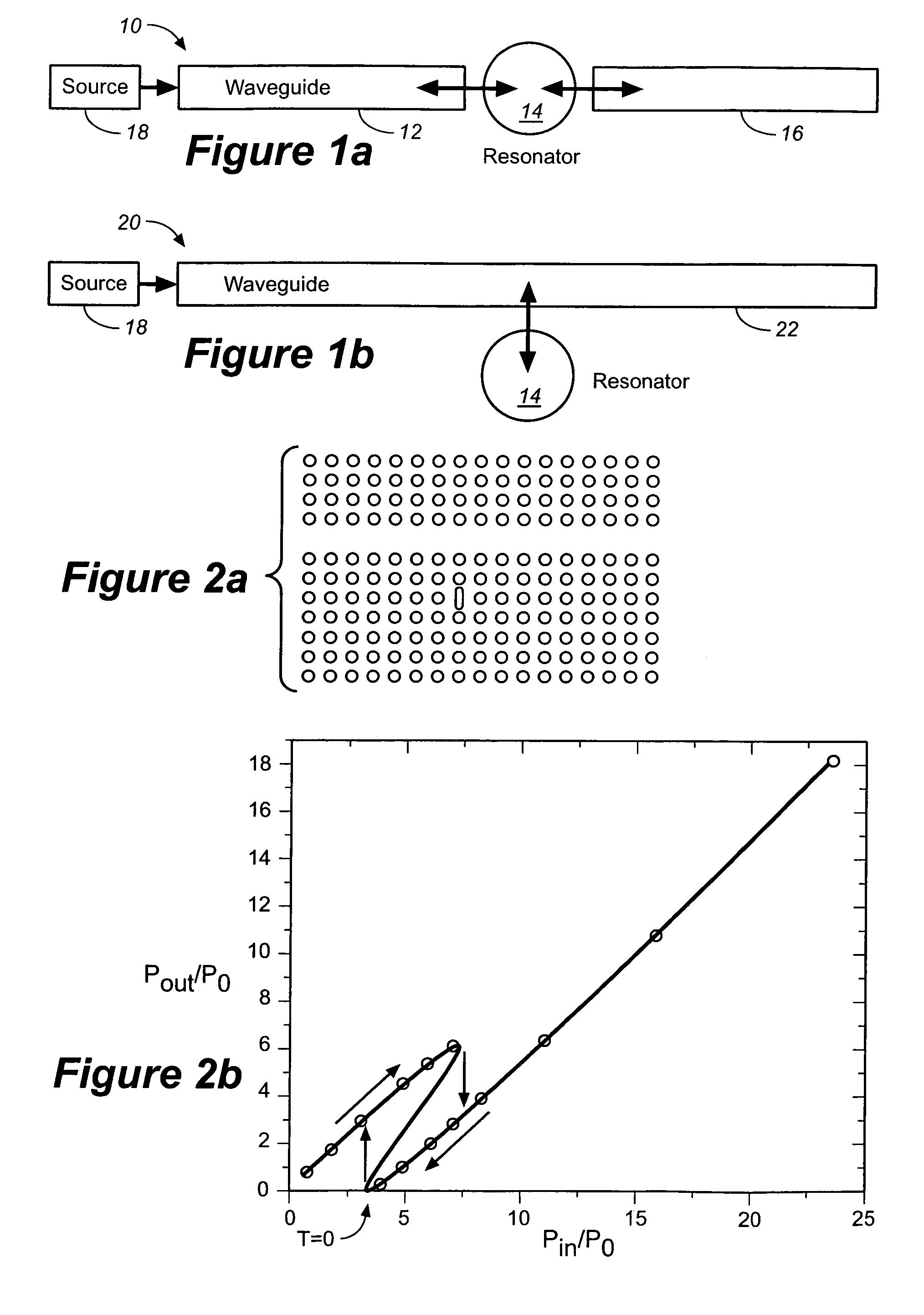

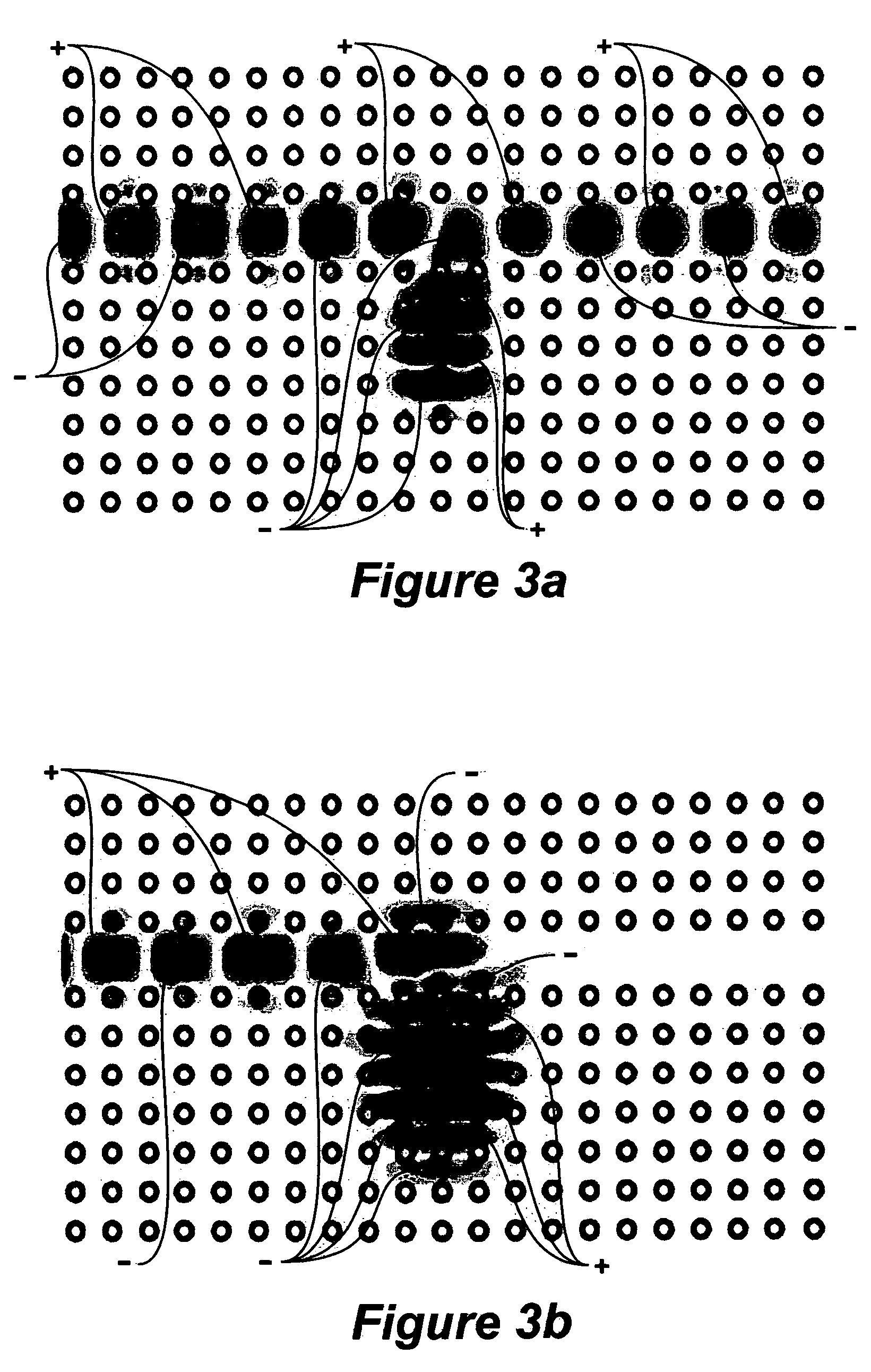

InactiveUS20060062507A1Reduce input powerIncrease contrastNanoopticsCoupling light guidesPhotonicsEngineering

A bistable photonic crystal configuration comprises a waveguide sided coupled to a single-mode cavity. This configuration can generate extremely high contrast between the bistable states in its transmission with low input power. All-optical switching action is also achieved in a nonlinear photonic crystal cross-waveguide geometry, in which the transmission of a signal can be reversibly switched on and off by a control input, or irreversibly switched, depending on the input power level.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV +1

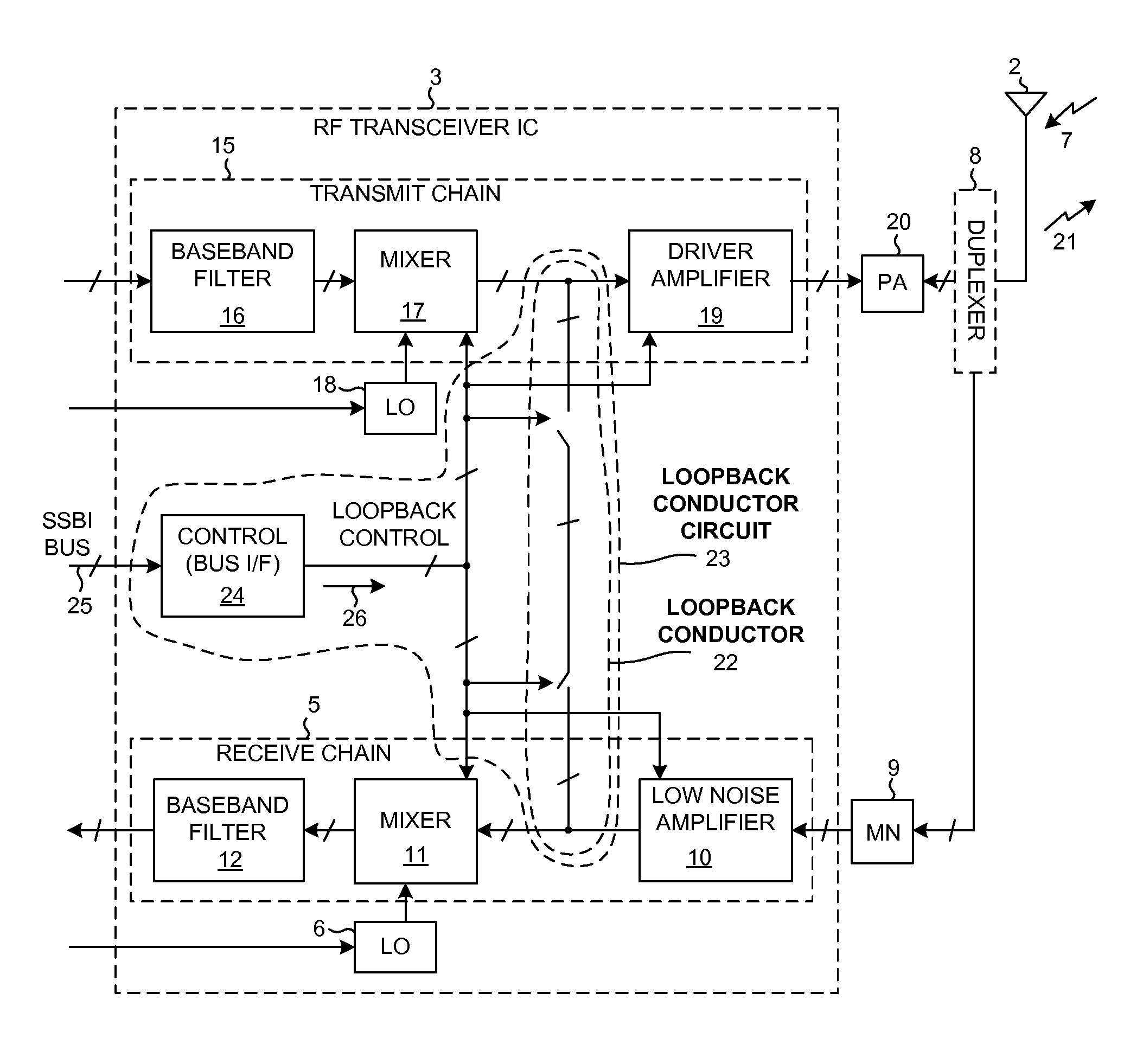

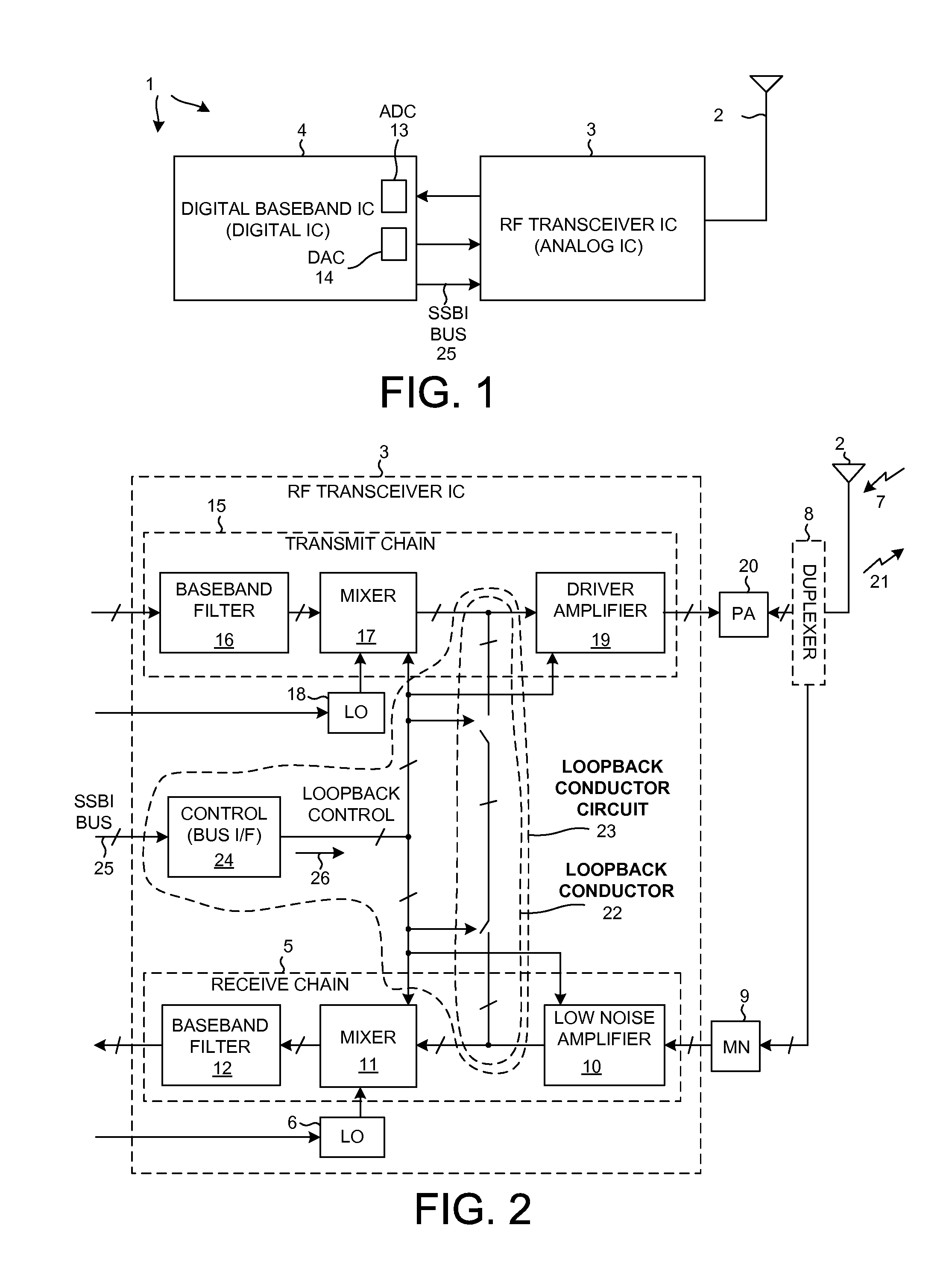

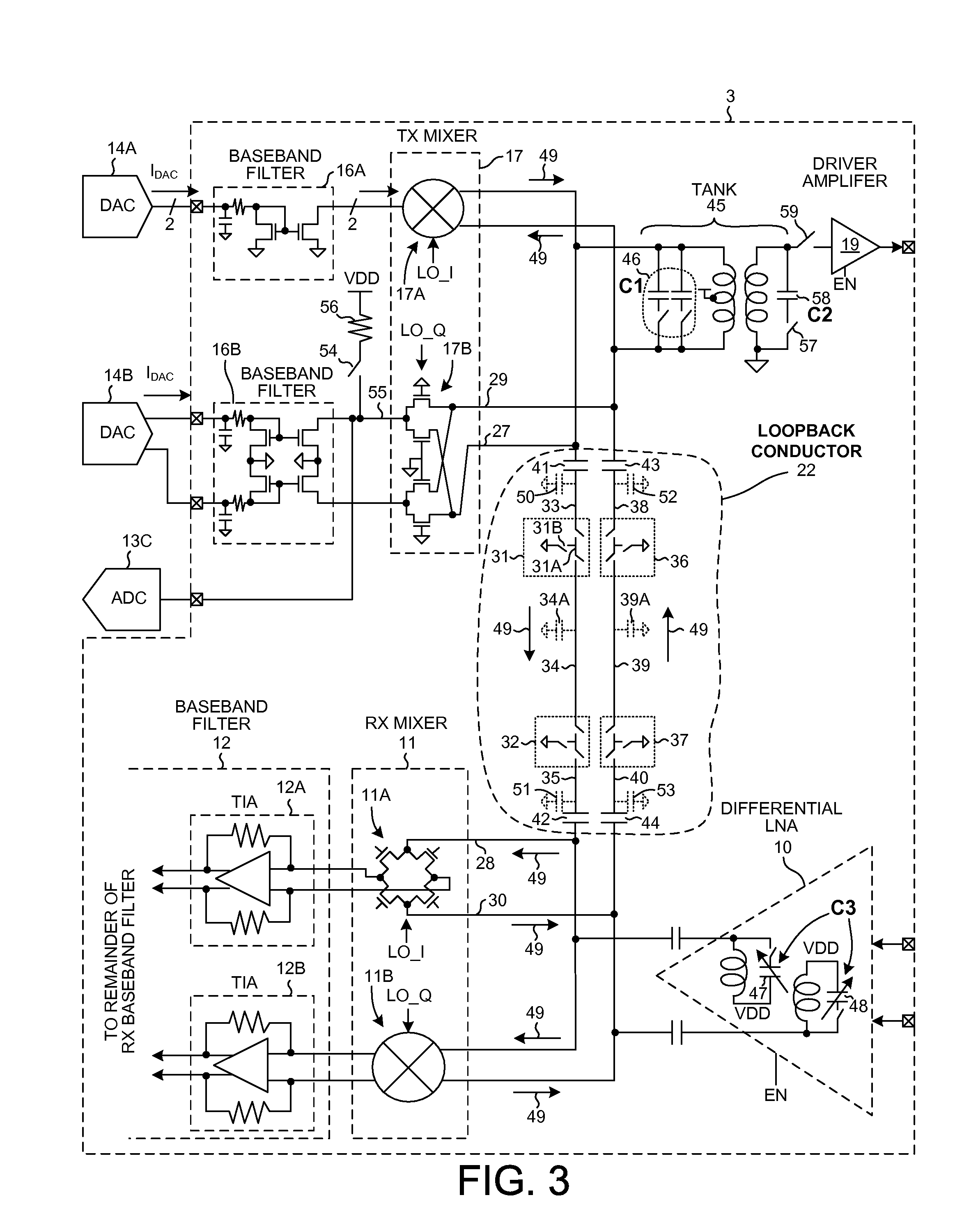

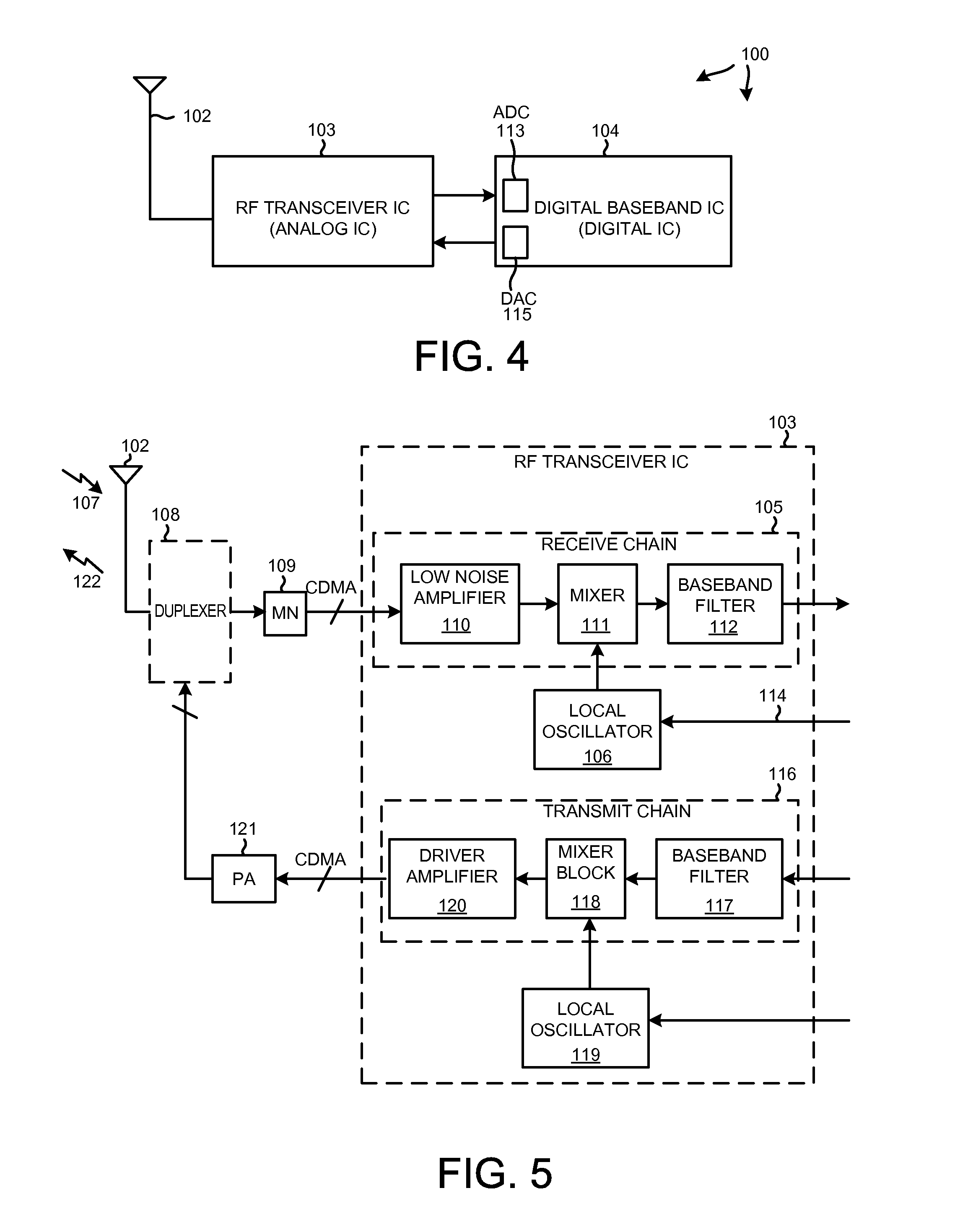

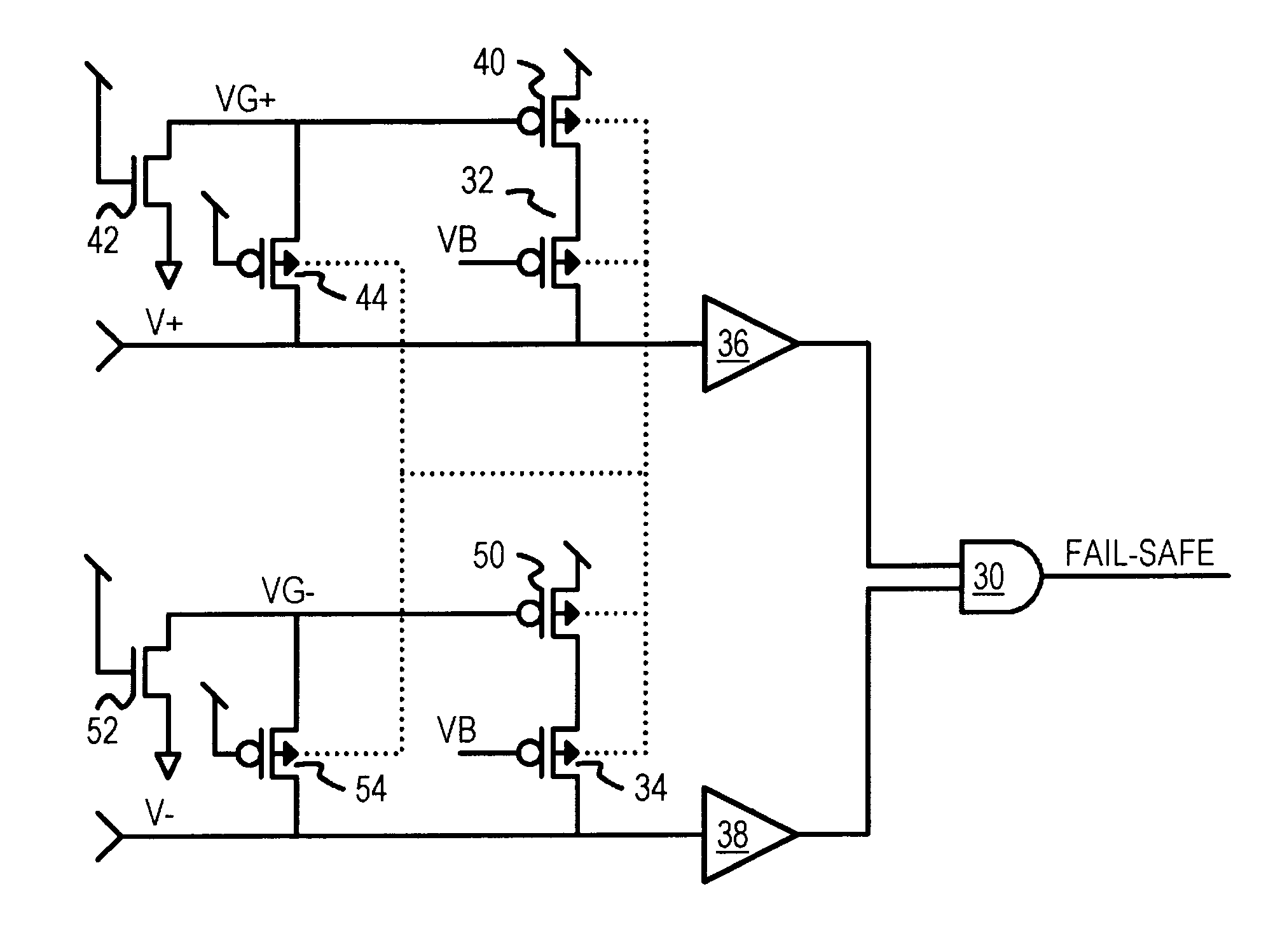

RF transceiver IC having internal loopback conductor for ip2 self test

ActiveUS20100120369A1Lower input impedanceMaximize power transferTelevision system detailsModulation transferenceElectrical conductorTransceiver

An RF transceiver integrated circuit has a novel segmented, low parasitic capacitance, internal loopback conductor usable for conducting IP2 self testing and / or calibration. In a first novel aspect, the transmit mixer of the transceiver is a current mode output mixer. The receive mixer is a passive mixer that has a low input impedance. In the loopback mode, the transmit mixer drives a two tone current signal to the passive mixer via the loopback conductor. In a second novel aspect, only one quadrature branch of the transmit mixer is used to generate both tones required for carrying out an IP2 test. In a third novel aspect, a first calibration test is performed using one quadrature branch of the transmit mixer at the same time that a second calibration test is performed using the other quadrature branch, thereby reducing loopback test time and power consumption.

Owner:QUALCOMM INC

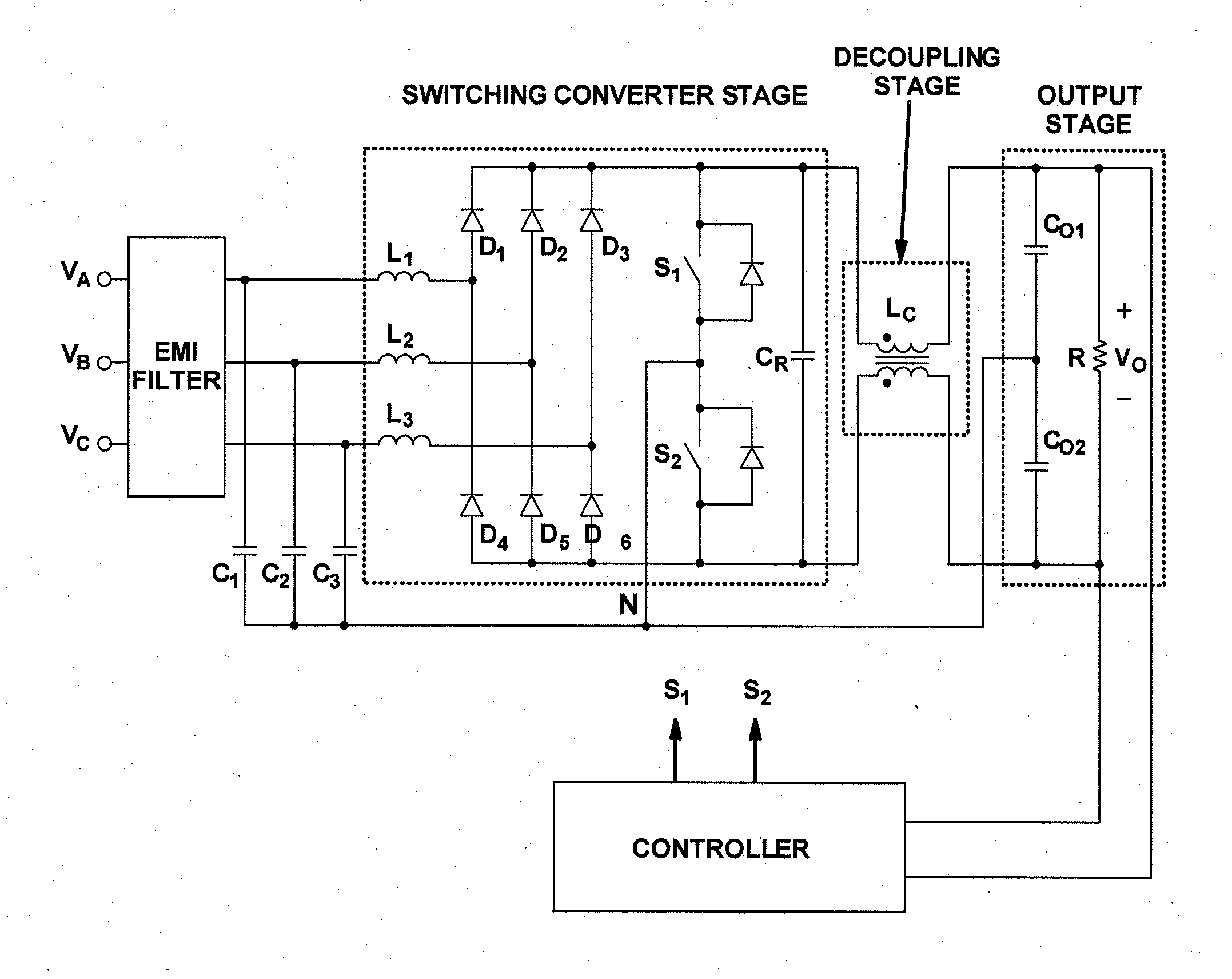

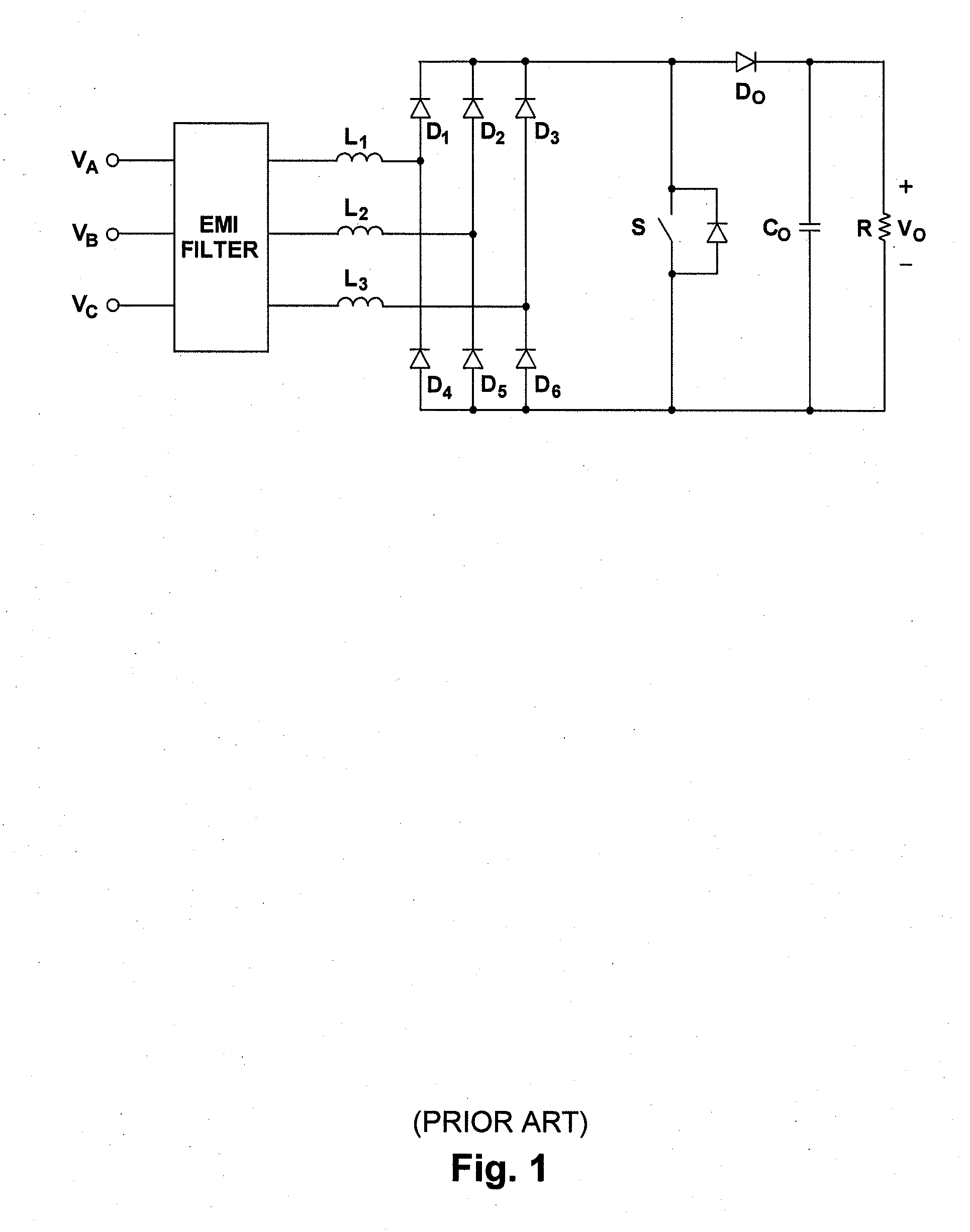

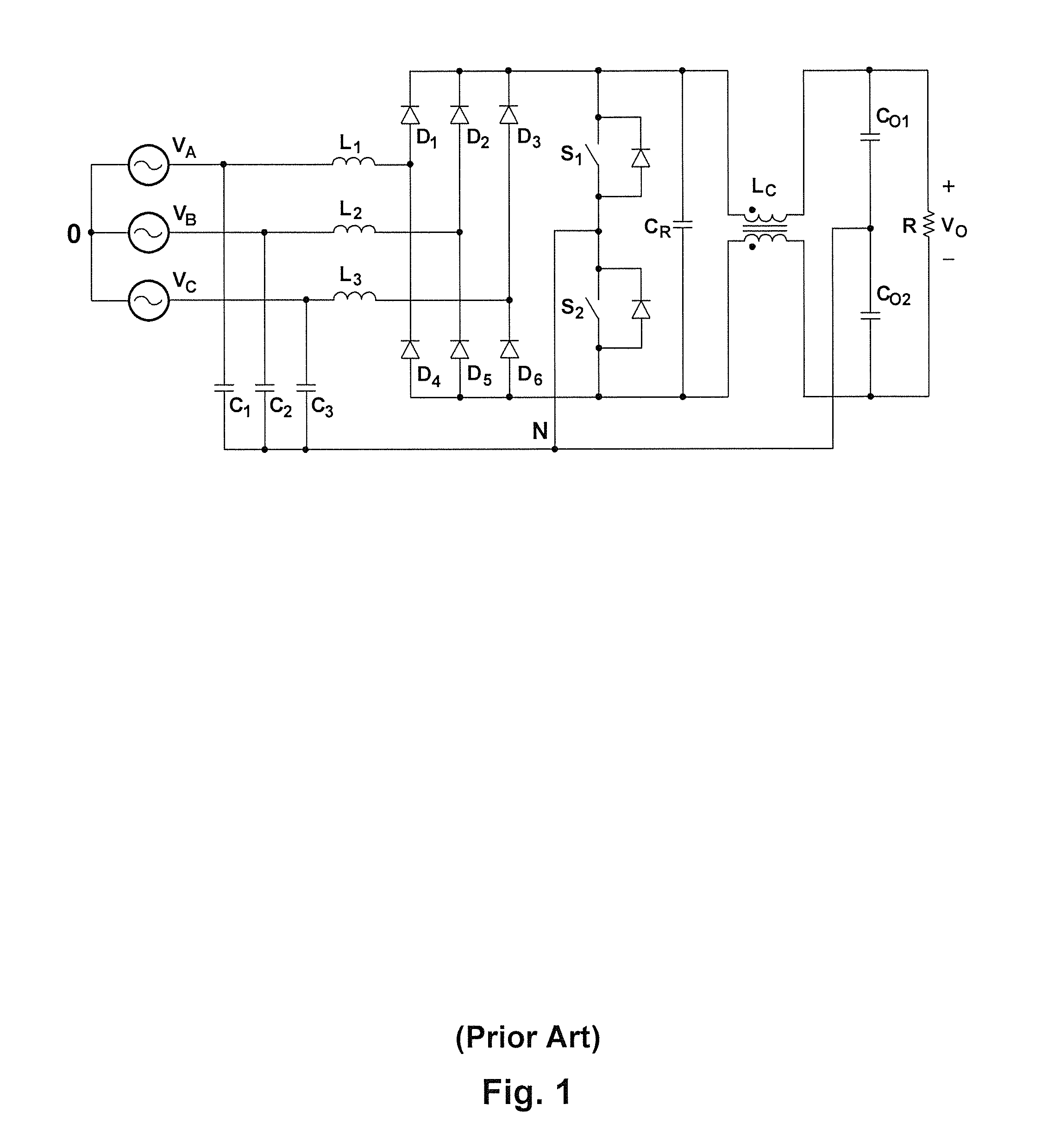

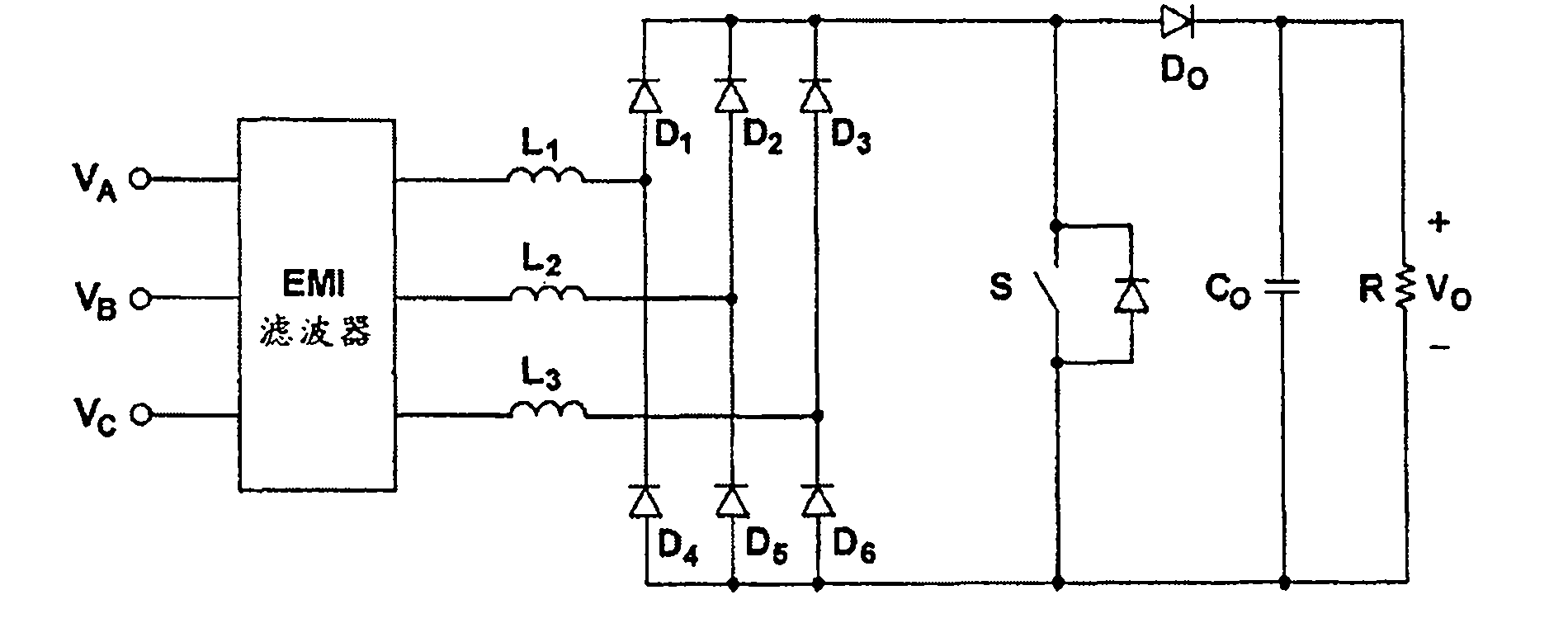

Three-phase soft-switched pfc rectifiers

A low input-current harmonic three-phase boost rectifier includes an input stage for receiving a three-phase input voltage in relation to a neutral node and an output stage adapted to couple to at least one load. The rectifier further includes one or more switching converter stages, each having a plurality of switches coupled to the neutral node, the plurality of switches operating with a fixed duty cycle, the fixed duty cycle being a substantially 50% duty cycle. The rectifier further includes one or more controllers adapted to vary the switching frequency of the plurality of switches based on at least one of a condition of the at least one load or the input voltage and includes one or more decoupling stages, each including one or more inductive elements adapted to inductively decouple the output stage from at least one of the one or more switching converter stages.

Owner:DELTA ELECTRONICS INC

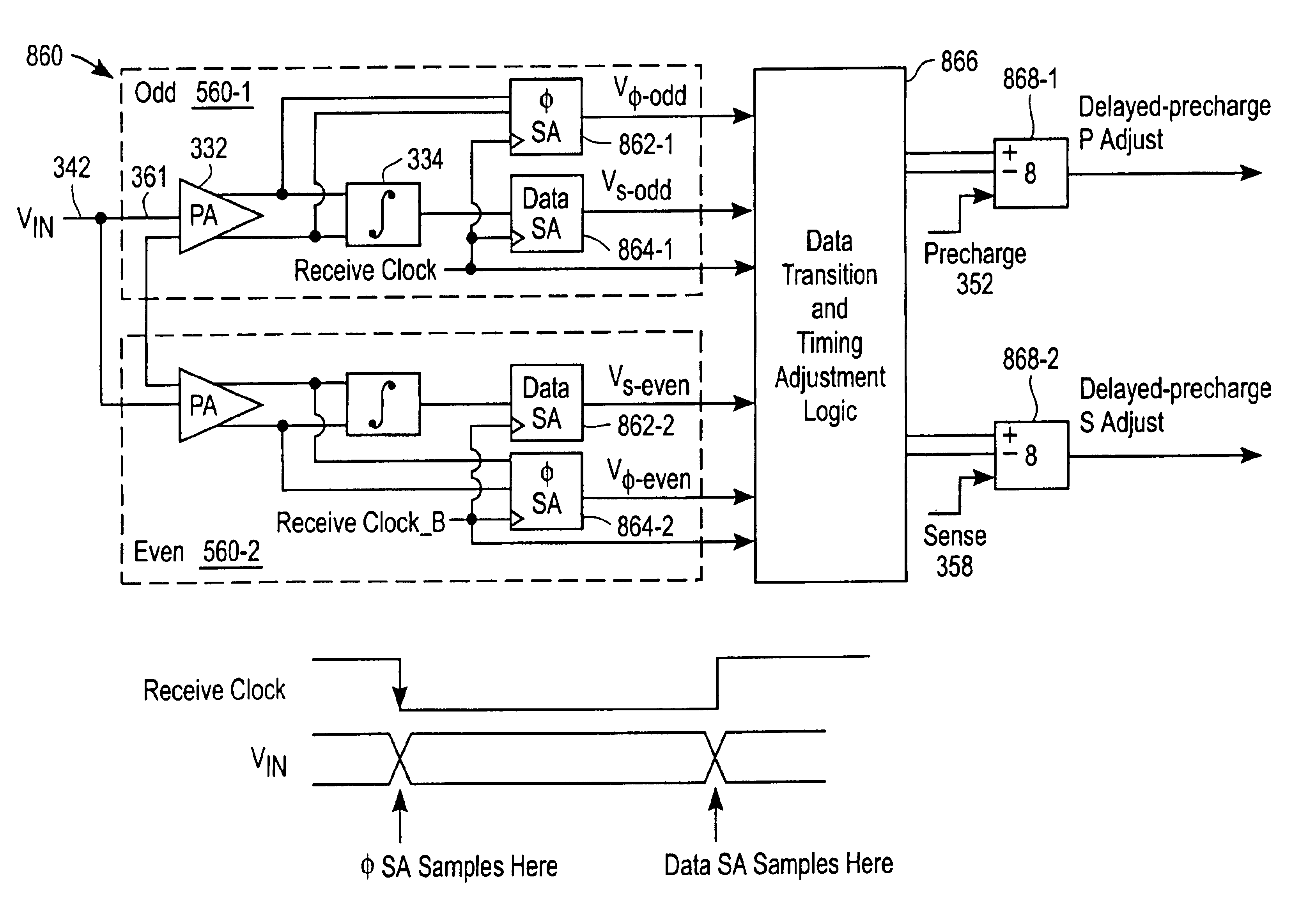

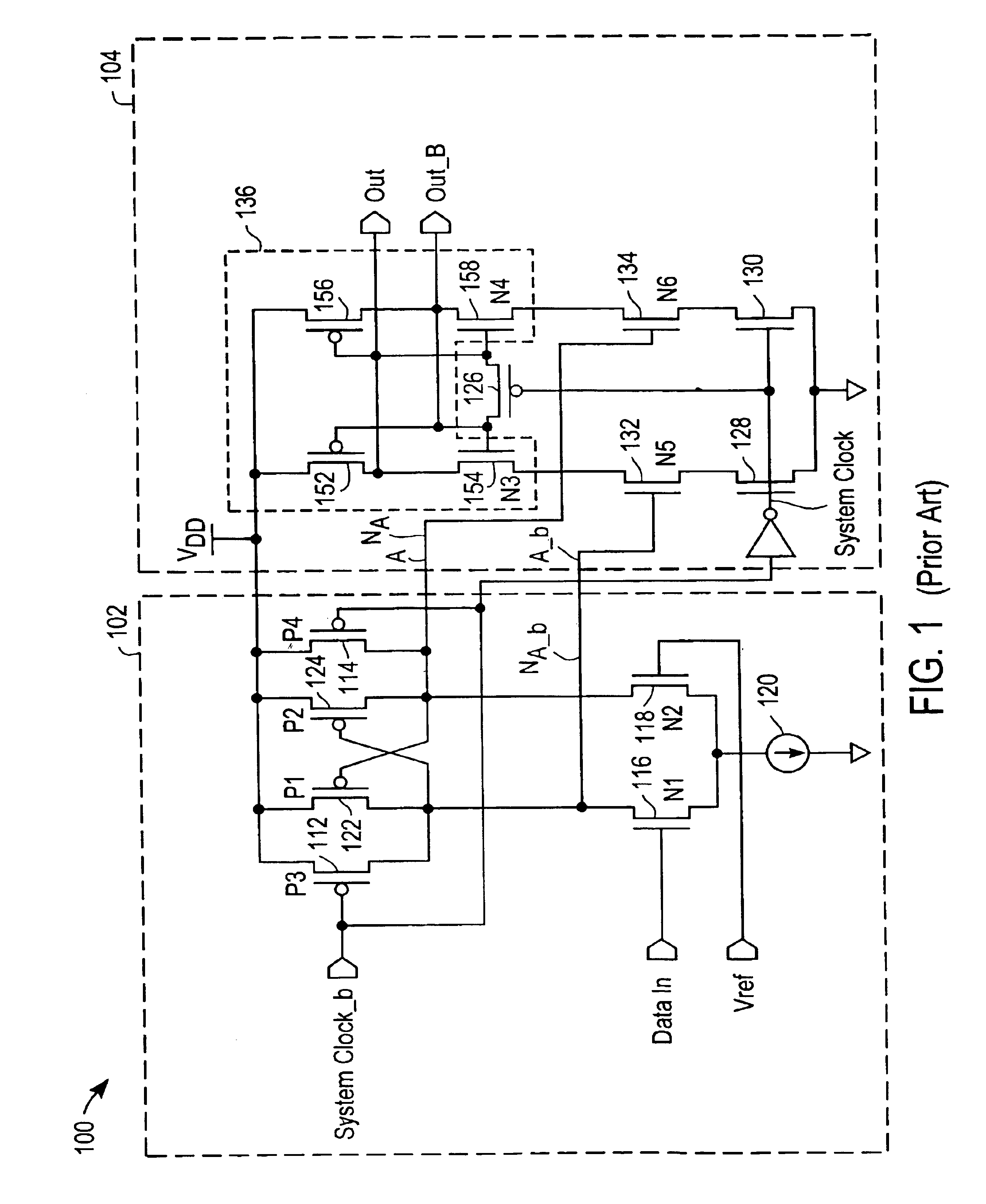

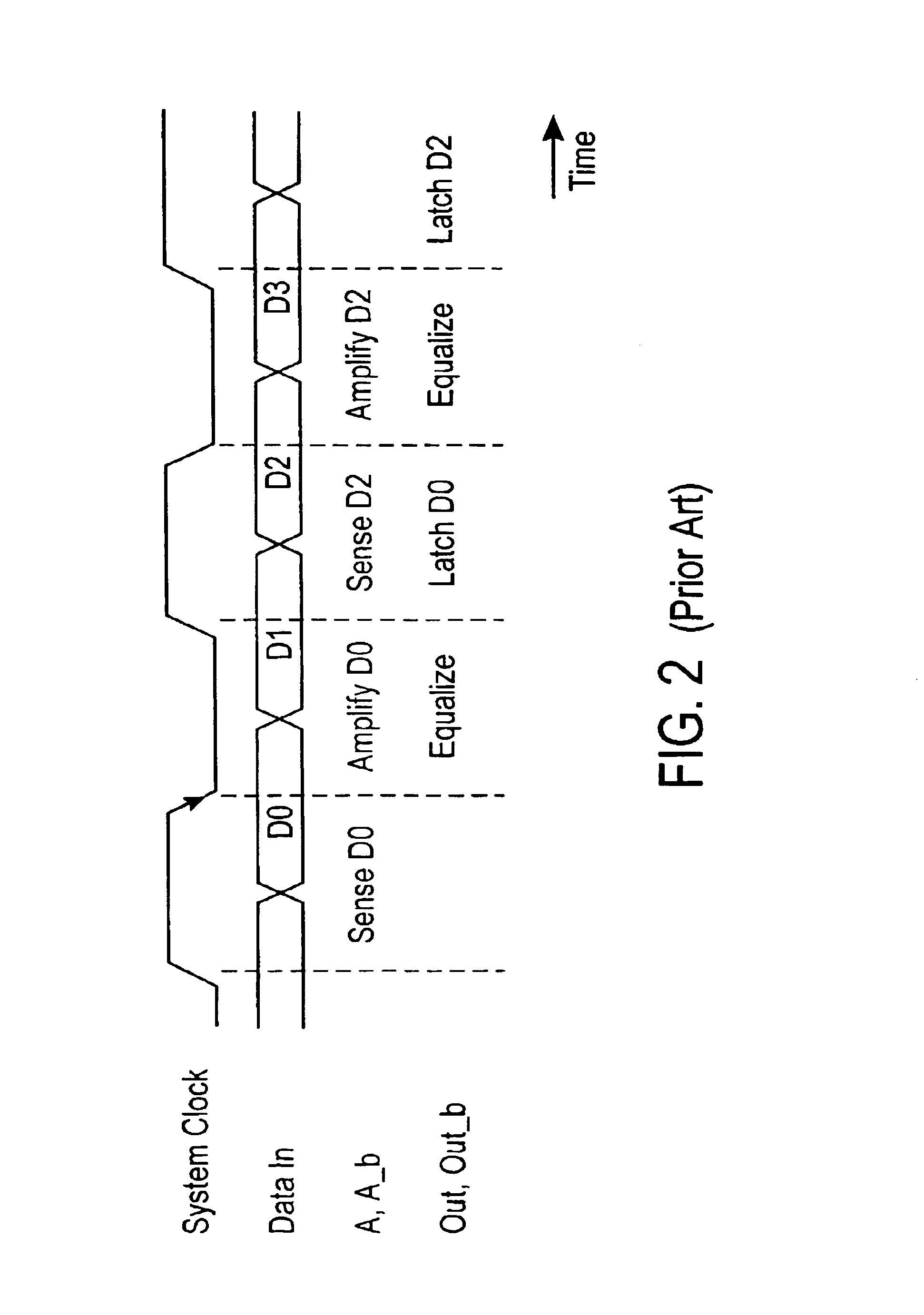

Method and apparatus for receiving high speed signals with low latency

InactiveUS6965262B2Reduces input-to-output latencyReduce static power consumptionDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

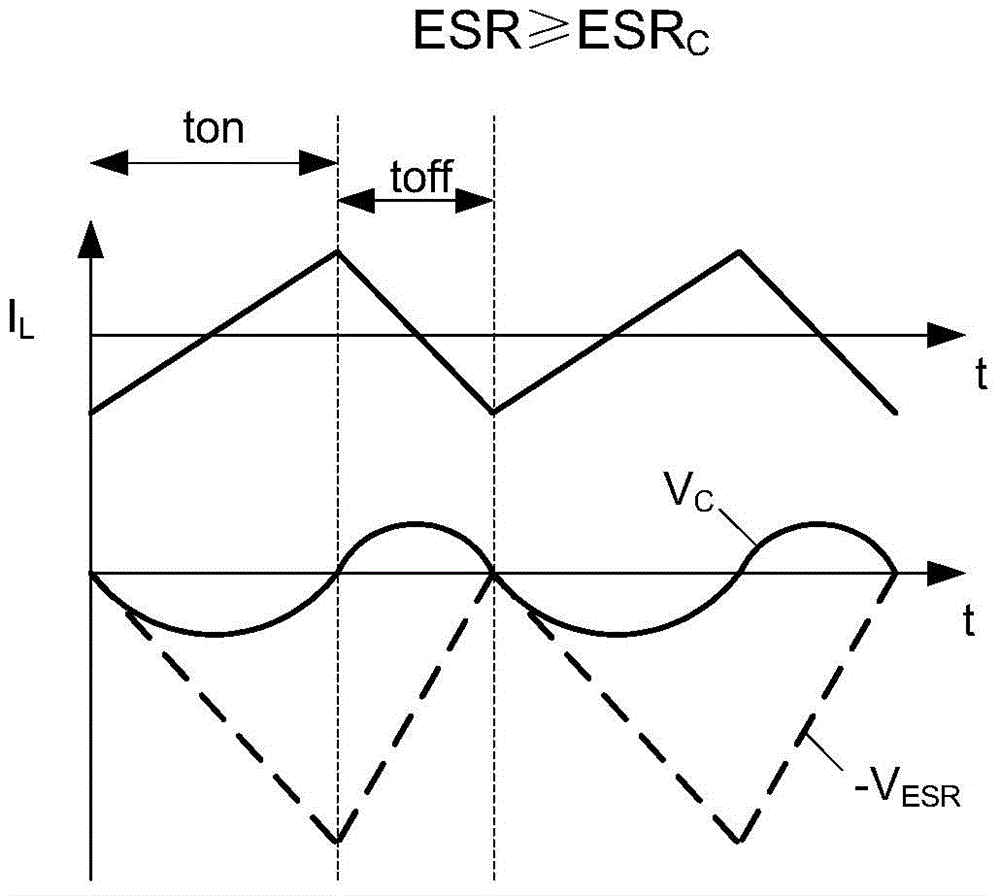

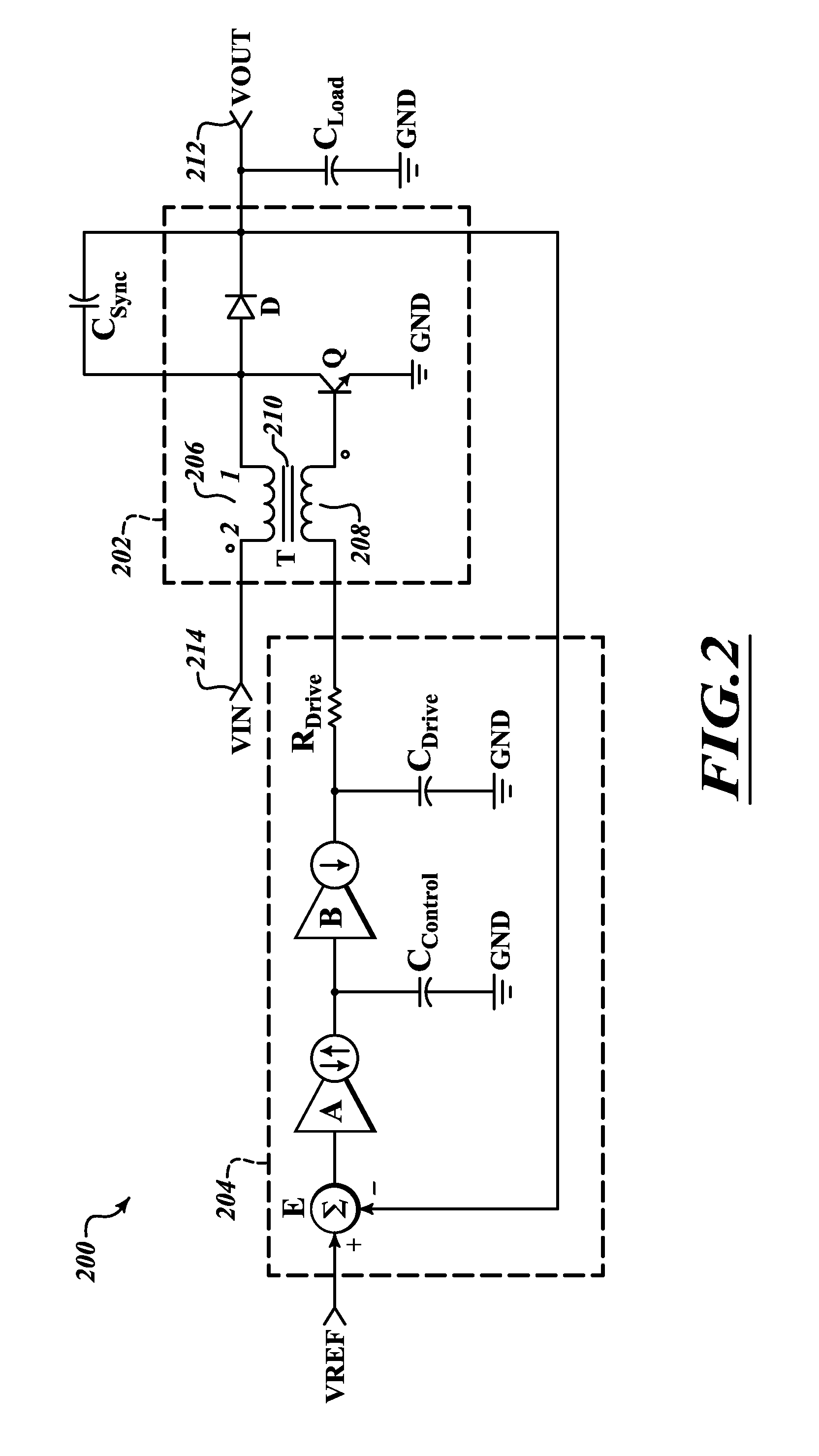

Switch converter and control circuit and method thereof

ActiveCN104022648AAvoid jitterAvoid Subharmonic OscillationDc-dc conversionElectric variable regulationSubharmonic oscillationControl signal

The invention discloses a switch converter with constant connection time control, and a control circuit and method thereof. A compensation control signal is generated according to the input voltage or a control signal, and a compensation signal is adjusted according to the compensation control signal so that the compensation signal can be adjusted to a proper value within a wide input range. Compared with the prior art, jittering and subharmonic oscillation under low input can be avoided, and dynamic response and load adjusting rate under high input are improved.

Owner:CHENGDU MONOLITHIC POWER SYST

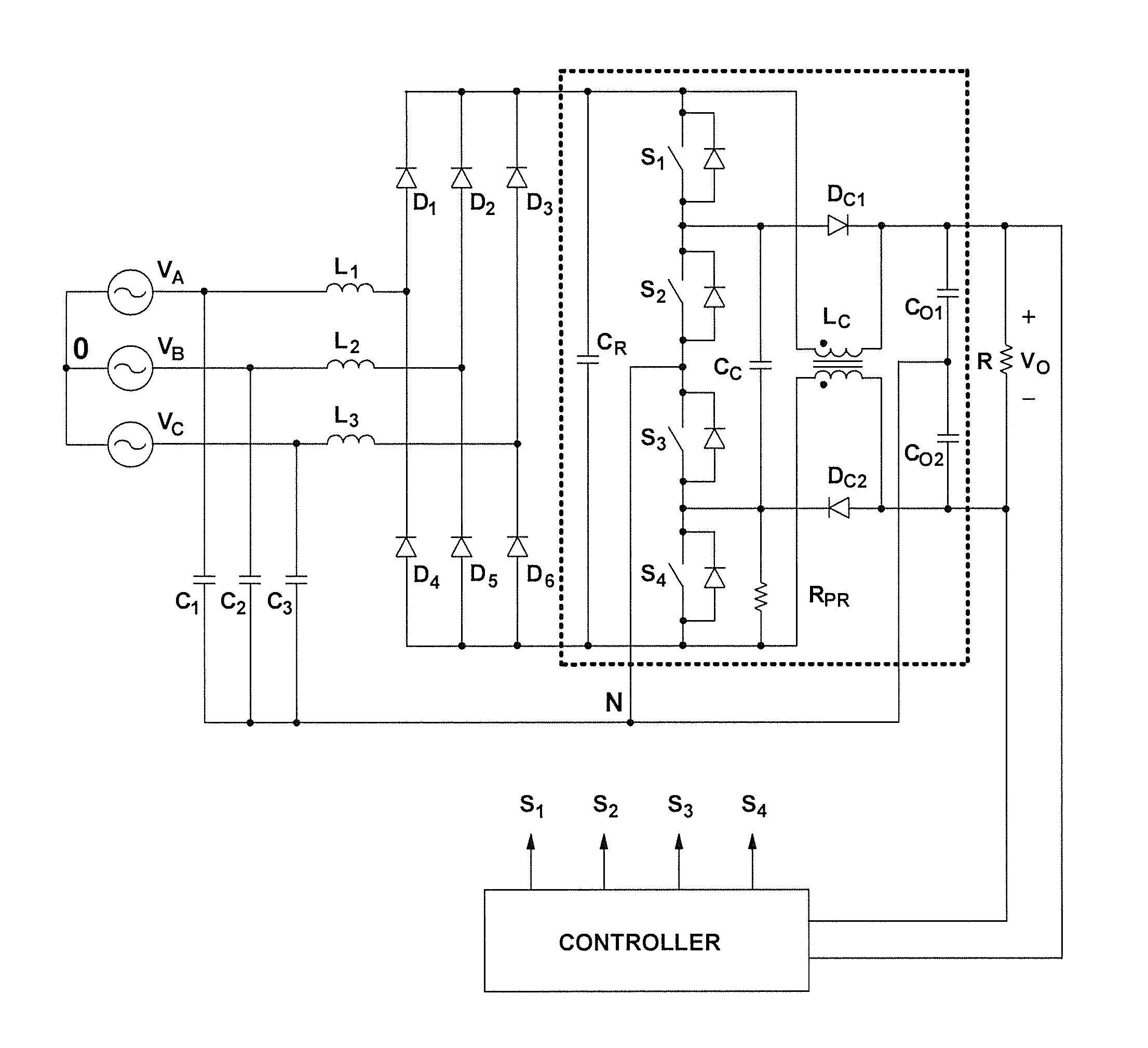

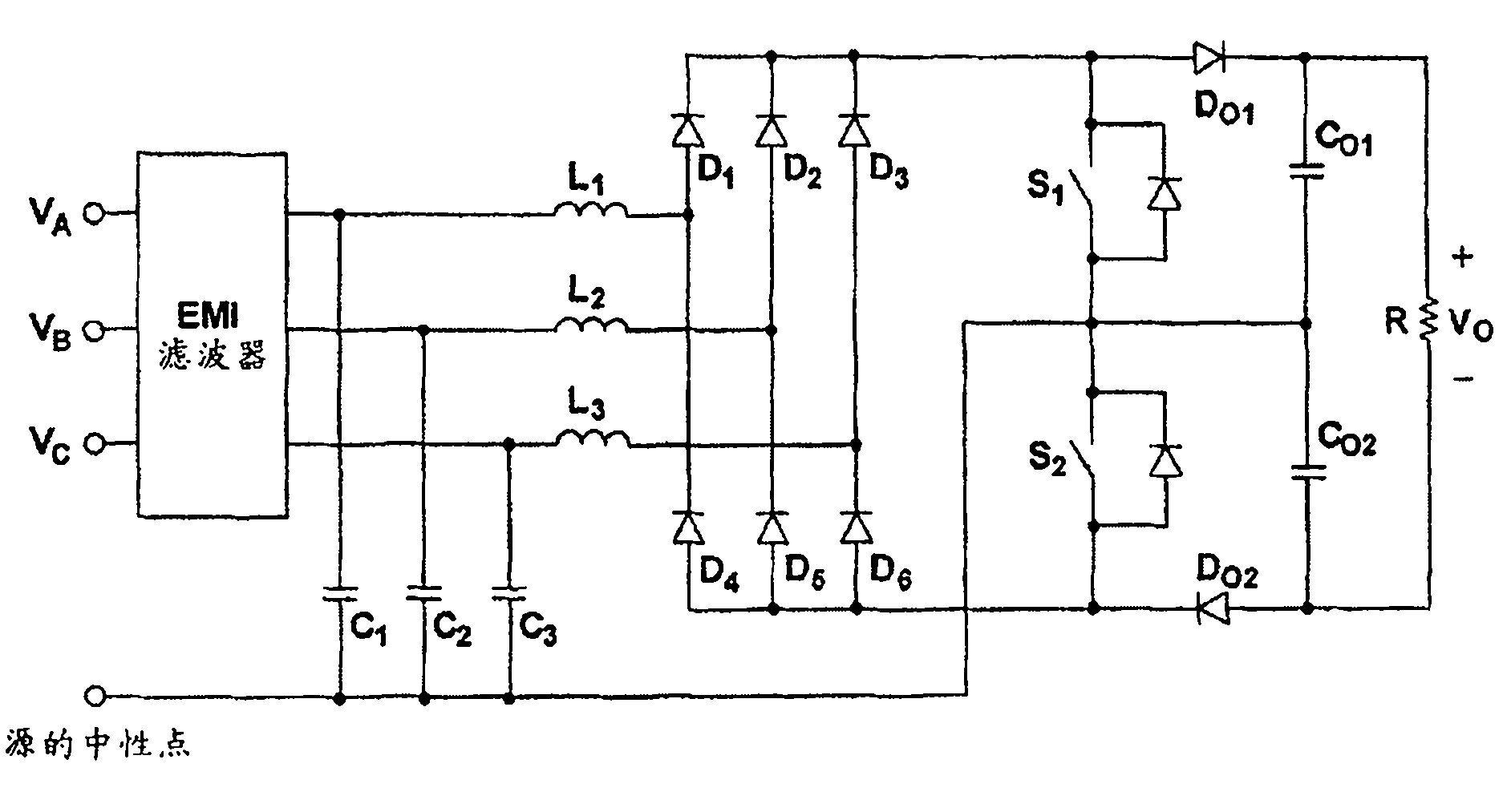

Three-phase three-level soft-switched pfc rectifiers

ActiveUS20130235626A1Low rateReduce conduction lossAc-dc conversion without reversalEfficient power electronics conversionClamp capacitorThree level

A low input-current-harmonic three-phase three-level boost rectifier includes an input stage for receiving a three-phase input voltage in relation to a neutral node and an output stage adapted to couple to at least one load. The rectifier further includes one or more switching converter stages, each having a plurality of serially-connected switches coupled to the neutral node, one of the serially-connected switches operating with a fixed duty cycle while the other of the serially-connected switches operating with a variable duty cycle, the fixed duty cycle being a substantially 50% duty cycle and the variable duty cycle being less than or equal to a substantially 50% duty cycle. The serially-connected switches are coupled to clamping diodes and clamping capacitors. The rectifier further includes one or more controllers adapted to vary the switching frequency and / or duty cycle of the plurality of switches based on at least one of a condition of the at least one load or the input voltage and includes one or more decoupling stages, each including one or more inductive elements adapted to inductively decouple the output stage from at least one of the one or more switching converter stages.

Owner:DELTA ELECTRONICS INC

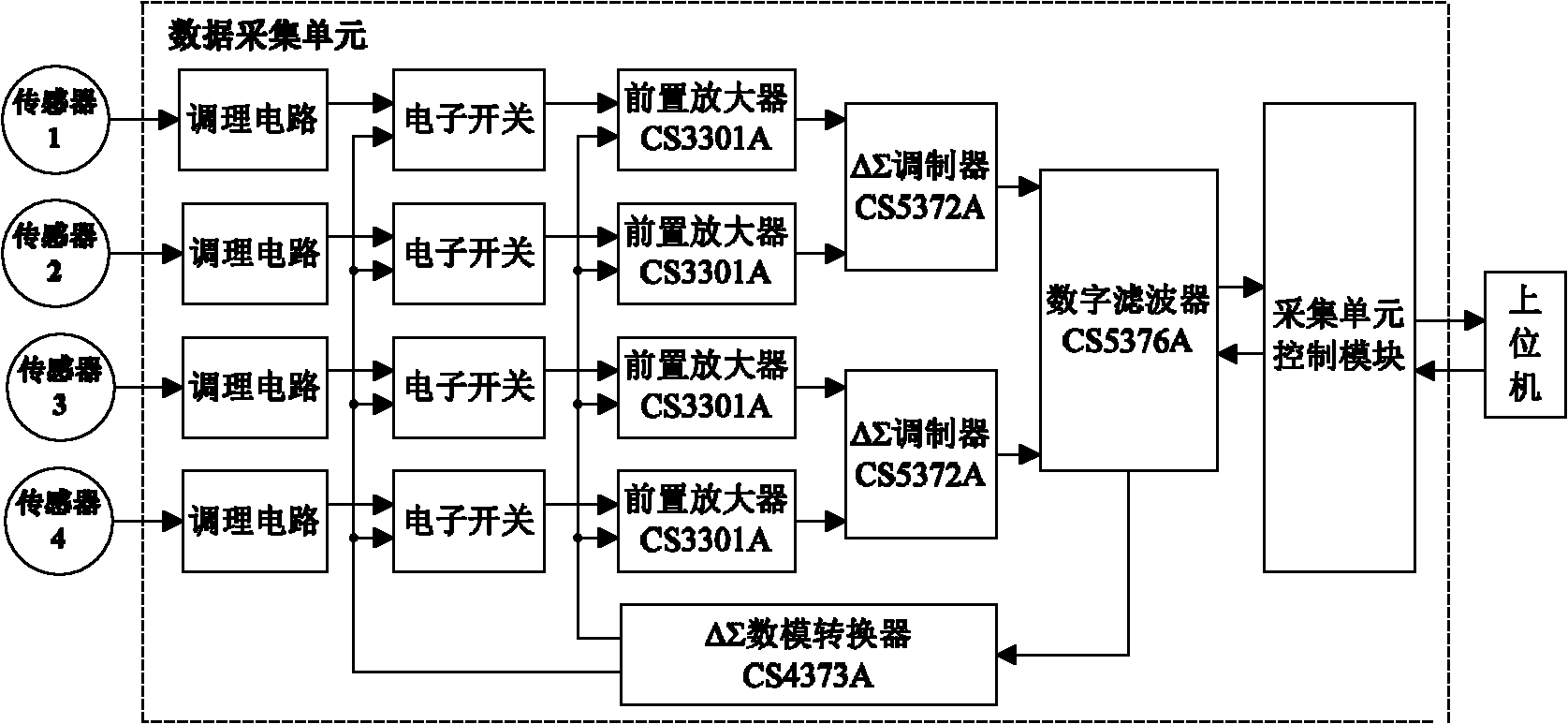

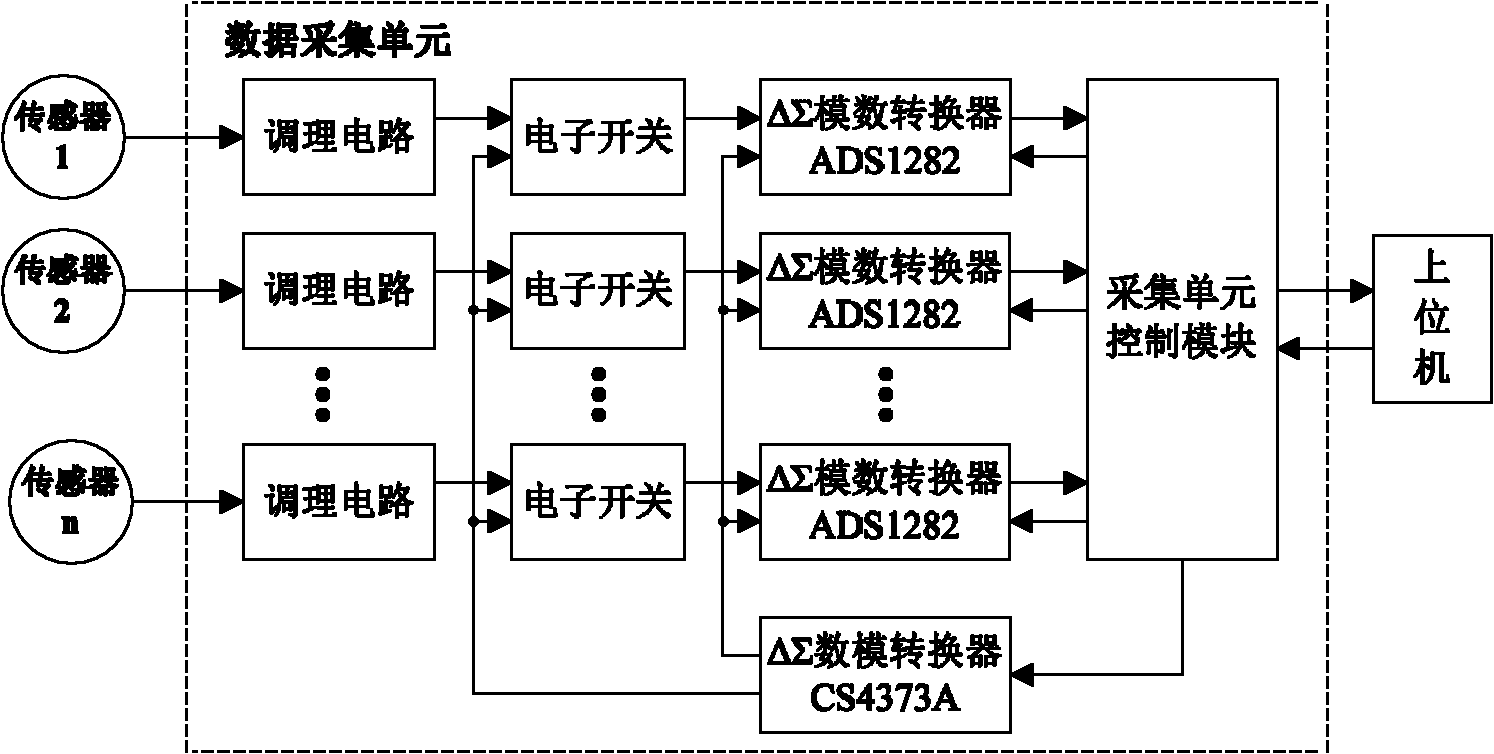

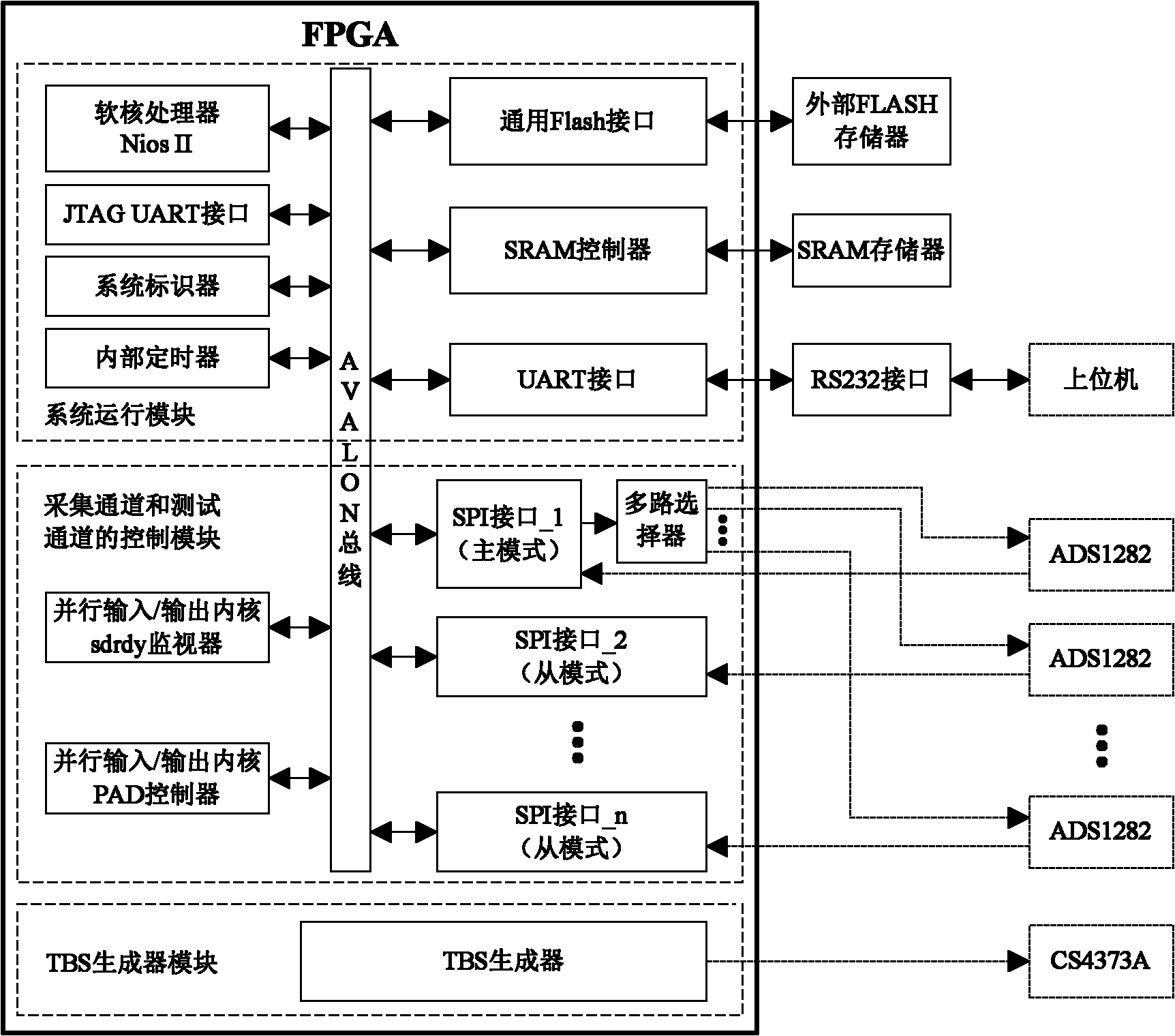

Multi-channel data collection unit

InactiveCN102201014AExpensive to fixImprove performanceData acquisition and loggingData acquisitionElectronic switch

The invention relates to a multi-channel data collection unit, belonging to the technical field of data collection in testing and measurement. The collection unit consists of a plurality of collection channels, a testing channel and a collection unit control module, wherein each collection channel comprises a conditioning circuit which consists of a conventional filter circuit and a voltage protective circuit, an electric switch and a delta sigma analog to digital converter; the testing channel is formed by a delta sigma digital to analog converter; the collection unit control module is realized on the basis of a programmable logic controller; the plurality of collection channels are connected with the collection unit control module; the input end of the delta sigma digital to analog converter is connected with the output end of the collection unit control module; and the output end of the delta sigma digital to analog converter is connected with each electric switch and each delta sigma analog to digital converter of the collection channel respectively. By the multi-channel data collection unit, high dynamic range, low input nose, low harmonic distortion, low crosstalk and high common mode rejection ratio can be realized, and the requirement of low power consumption and low cost can be fulfilled.

Owner:TSINGHUA UNIV

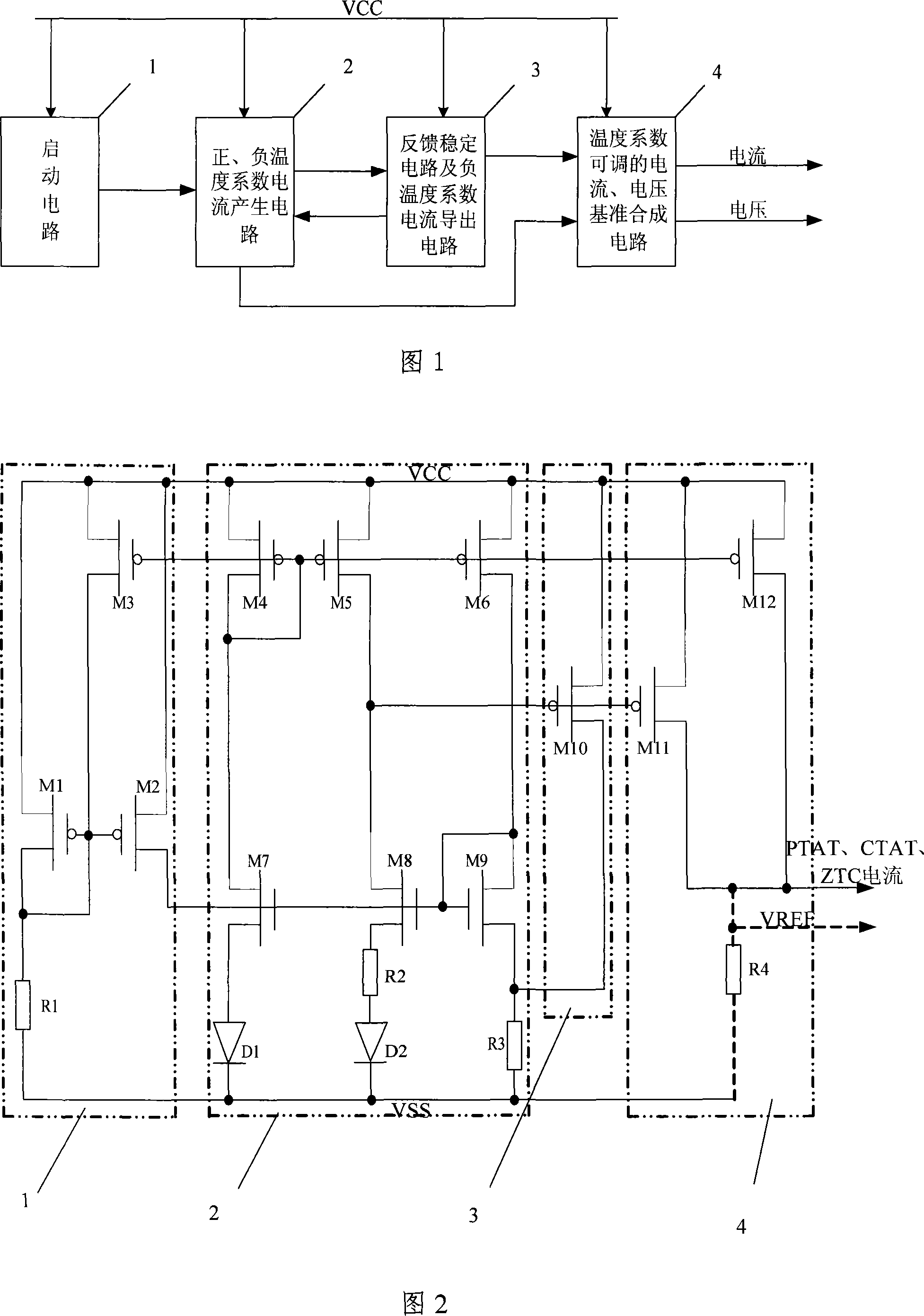

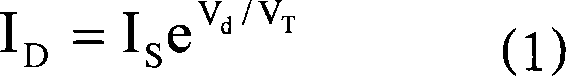

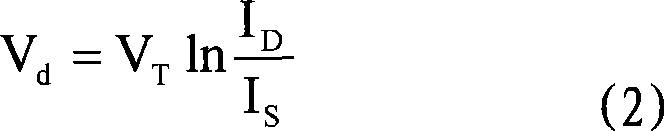

Circuit outputting adjustable positive and negative or zero-temperature coefficient electrical current and voltage reference

InactiveCN101178610ASimple structureReduce layout areaElectric variable regulationNegative temperatureReference current

The invention provides a circuit for outputting adjustable positive, negative or zero temperature coefficient current and voltage reference, including: a start-up circuit, a positive and negative temperature coefficient current generation circuit, a feedback stable and negative temperature coefficient current derivation circuit, and the temperature coefficient can be Adjusted current reference, voltage reference synthesis circuit. The invention is realized under the standard CMOS technology, has simple structure, low input voltage, and can generate current reference and voltage (VREF) reference with adjustable temperature coefficient, which can be positive, negative or zero temperature coefficient.

Owner:XIAN BIAOXIN ELECTRONICS SCI & TECH

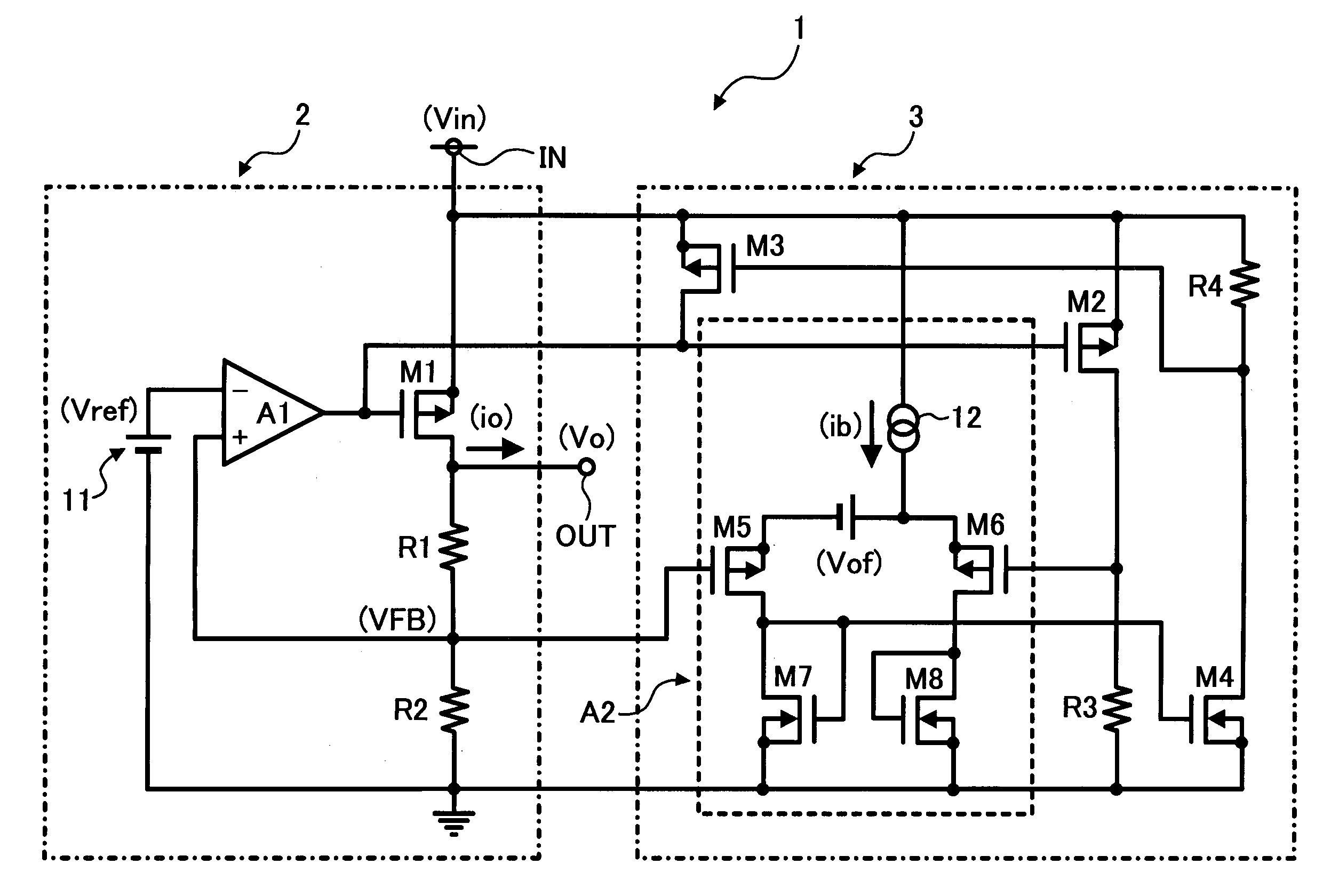

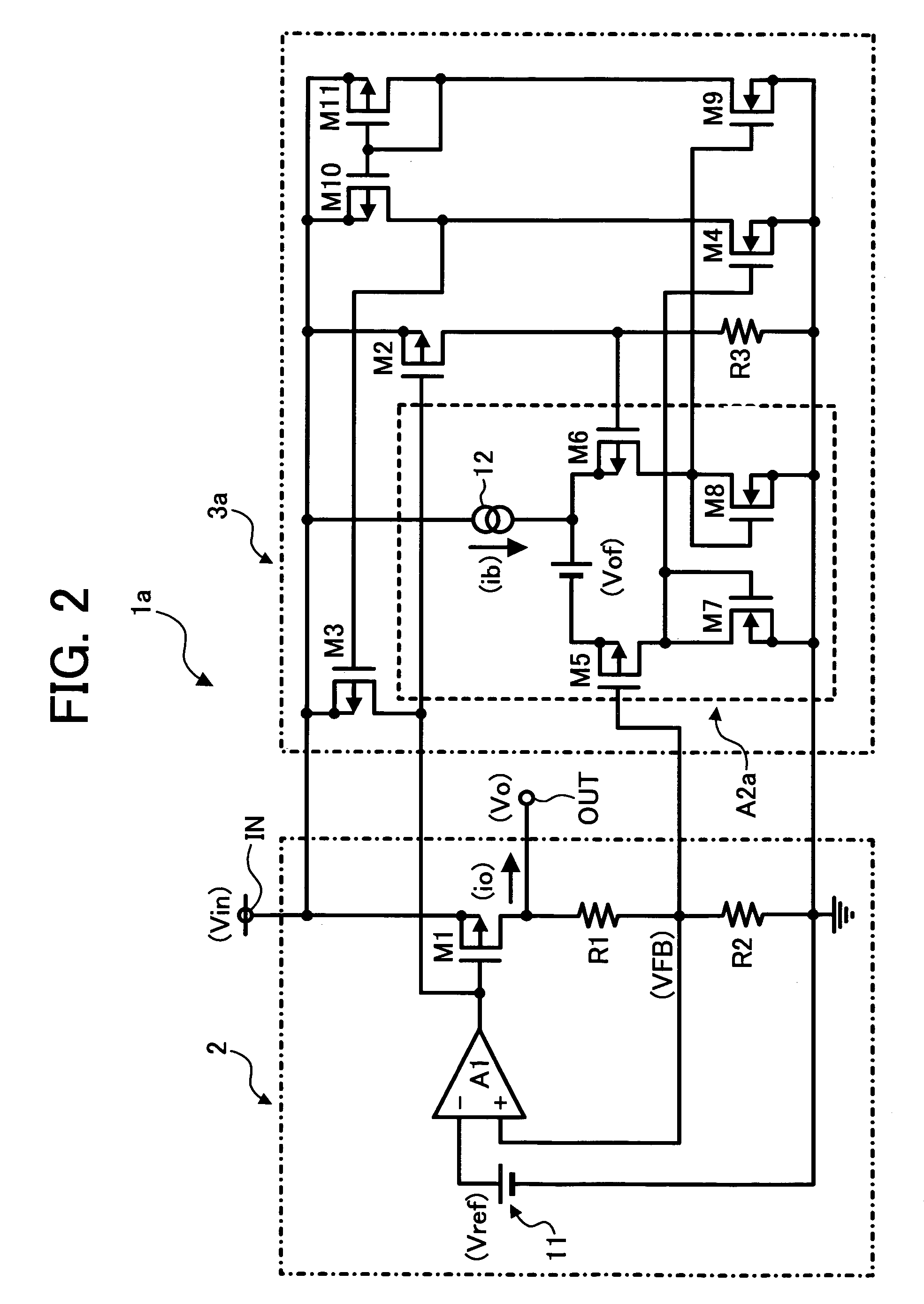

Constant-voltage power circuit with fold back current limiting capability

InactiveUS7183755B2Reduce eliminateArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentSmall amplitudeCurrent limiting

A constant-voltage power circuit incorporating an over-current protection circuit having a fold back current limiting capability operative through low input voltages, and being capable of arbitrarily setting current outputs. The constant-voltage power supply circuit is configured so that a voltage output with small amplitude from a differential amplifier circuit is subjected to amplitude expansion to be amplified to range fully from the ground potential approximately to the input voltage by means of an amplitude expansion circuit, which includes an inverter consisting of an NMOS transistor and a resistor, and that the voltage resulting from the amplitude expansion is subsequently input to the gate of a PMOS transistor configured to directly control an output transistor.

Owner:RICOH ELECTRONIC DEVICES CO LTD

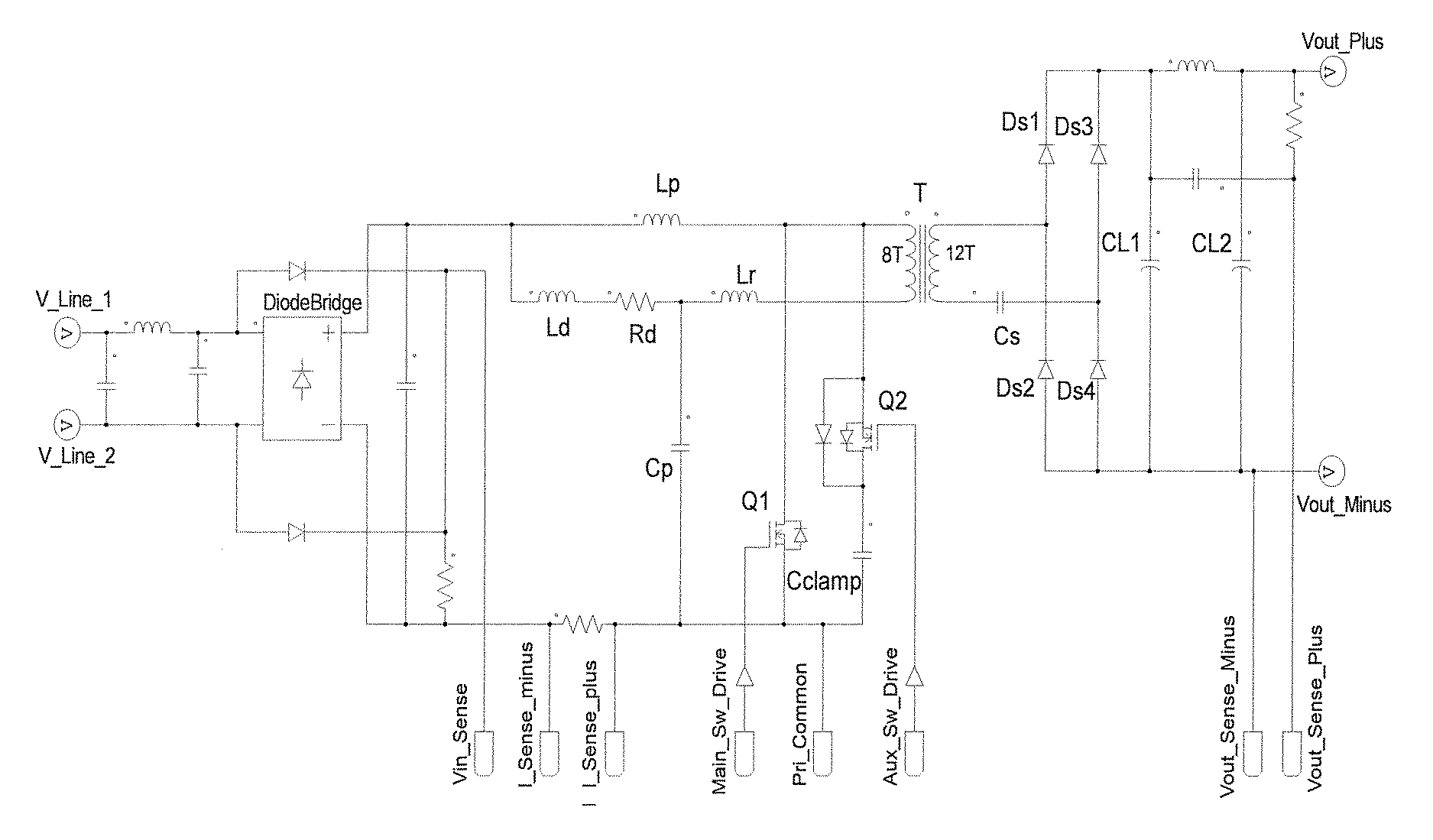

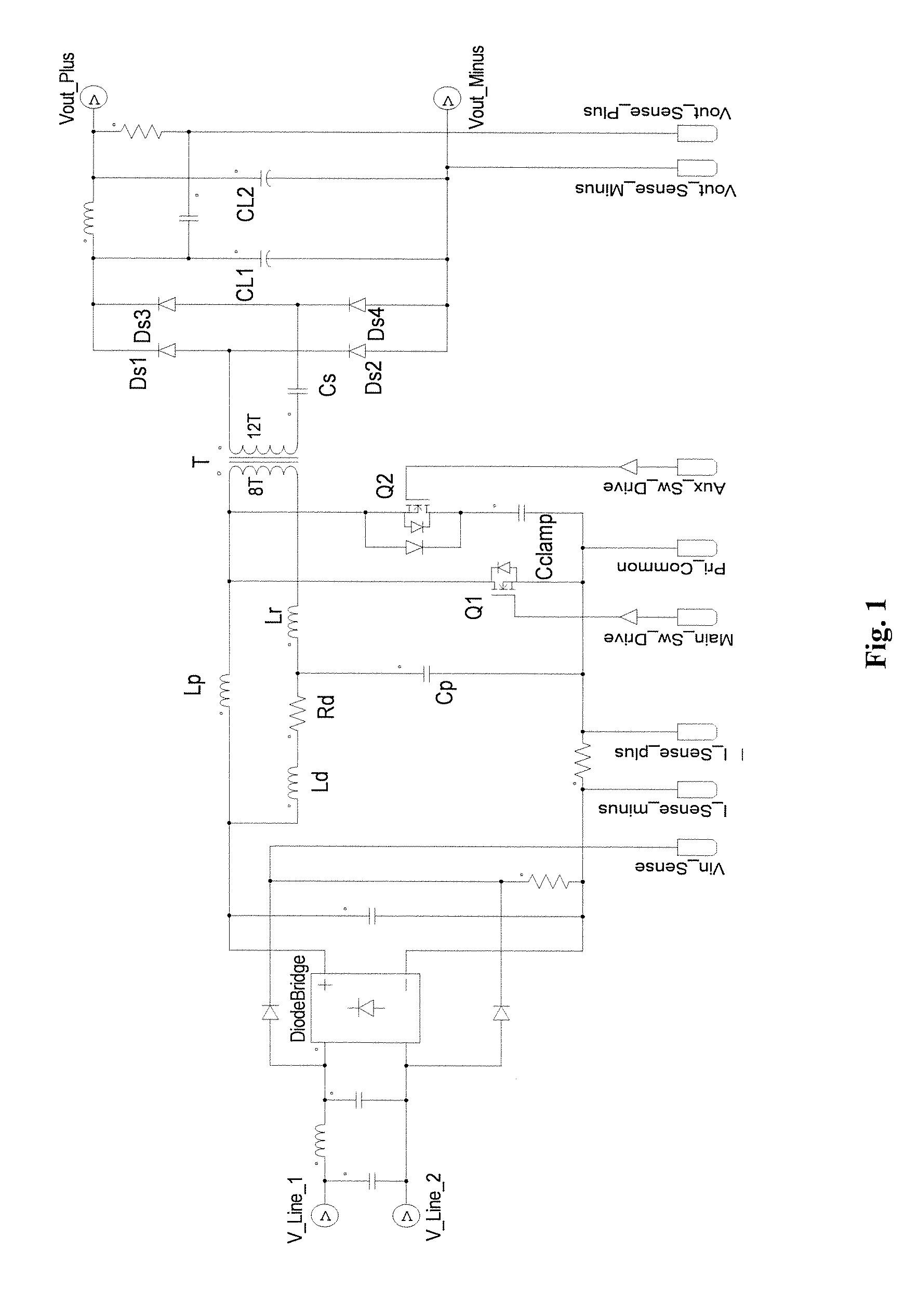

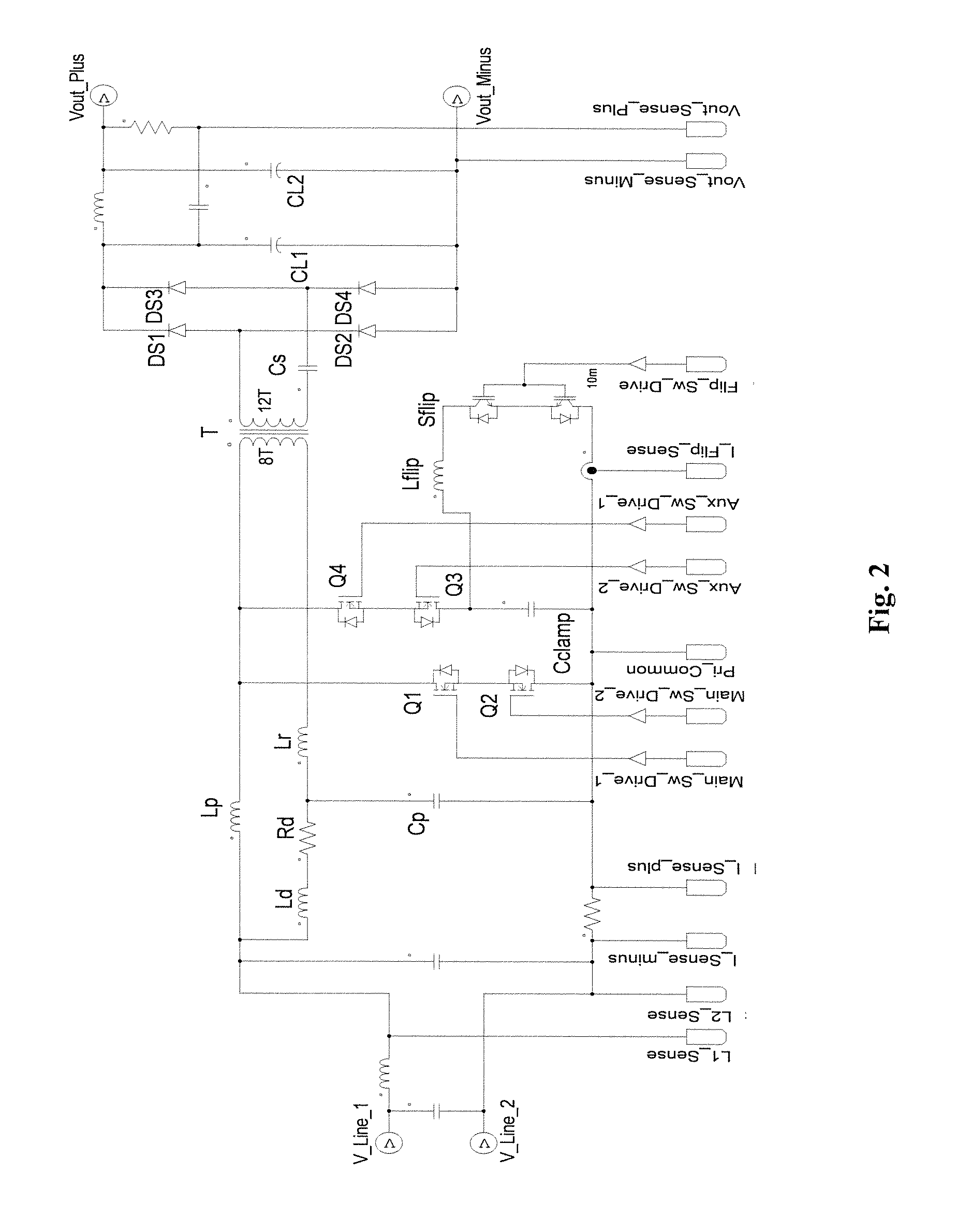

Single stage isolated ac/dc power factor corrected converter

ActiveUS20170025962A1Improve efficiencyReduce the burden onEfficient power electronics conversionDc-dc conversionClamp capacitorSingle stage

Two versions of an isolated single stage converter AC / DC Power Factor Corrected (PFC) converter topology have been invented. One is with a full bridge rectifier at its input and the other is a True Bridgeless version. The two versions of the topology feature new configurations and circuitry including a simplified damper circuit and a clamp capacitor flipping circuit and control methods that allow them to realize improved single stage isolated power factor converters which are suitable for high power operation, features Zero Voltage Switching to maximize conversion efficiency and to minimize Electro-Magnetic Interference generation, does not need an additional circuit to limit the inrush current, achieves reasonably low input current Total Harmonic Distortion (THD), and is easy to control. The second version provides a true bridgeless single stage isolated power factor converter with even higher efficiency and lower input current THD.

Owner:DAVIDSON CHRISTOPHER DONOVAN

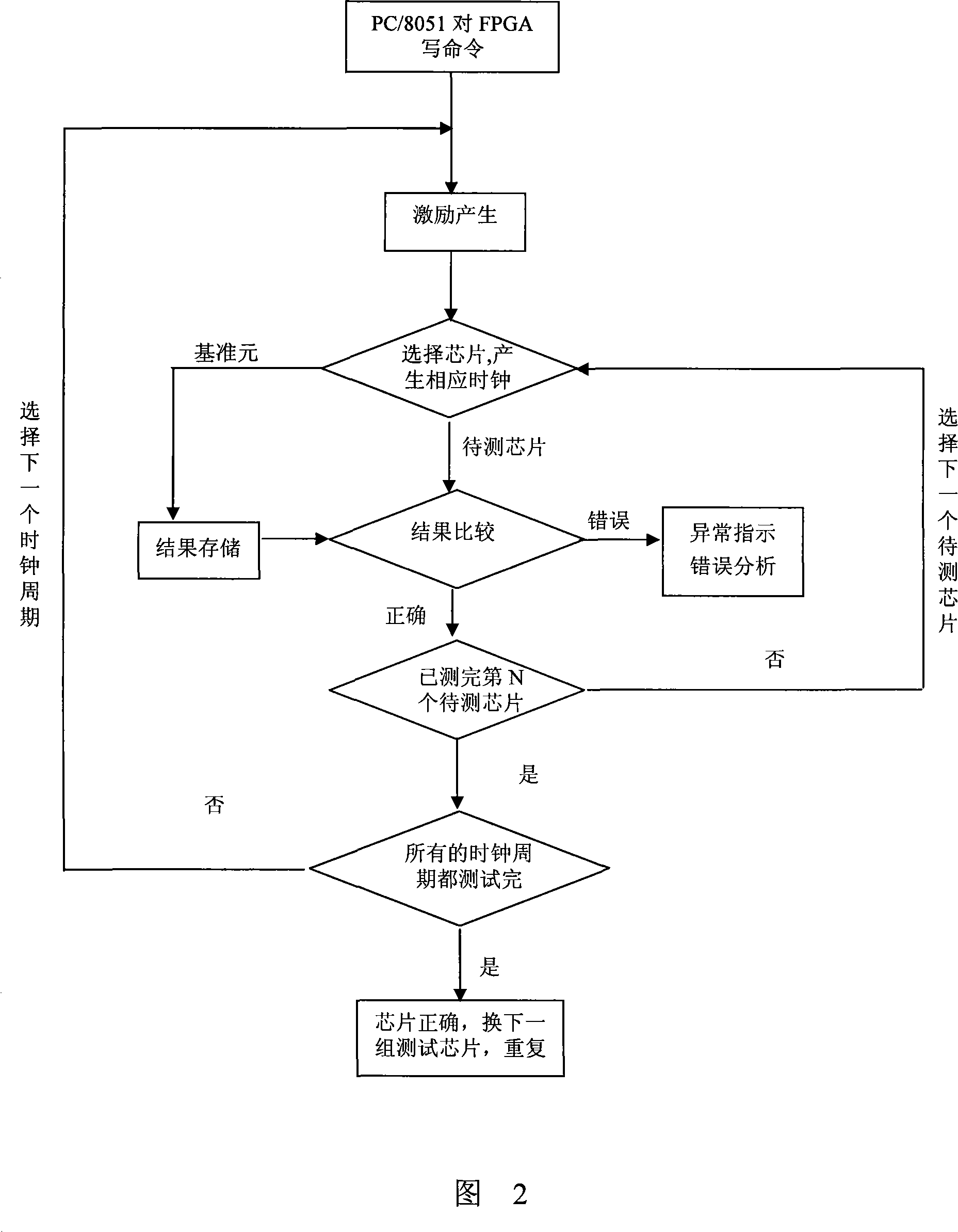

Multiple chips automatic test method based on programmable logic device

InactiveCN101158708AMeet the test requirementsImplement automated testingDigital circuit testingProgrammable logic deviceField-programmable object array

The invention relates to an automatic testing technology for molectron, in particular to an automatic testing method for multiple chips based on field programmable gate array (FPGA). According to the technical scheme provided by the invention, the field programmable gate array comprises the sample circuits that are connected to each other, a circuit of digital comparator, an encoder, and a pulse generating circuit. The technical scheme is characterized in that the input end of the circuit of digital comparator is connected with the output end of a multiplexer, the input end of the sample circuit is connected with a plurality of chips being tested; and the pulse generating circuit is connected with a plurality of chips being tested and a tested chip respectively; the output end of the encoder circuit is connected with the multiplexer. The invention uses the field programmable gate array (FPGA) to set up a simple automatic testing system, in which the automatic testing of a single or a plurality of chips can be implemented simultaneously on a testing board, The invention achieves automatic testing and has low input cost and rapid development, thus completely satisfying the requirement for the testing of small-lot products.

Owner:无锡汉柏信息技术有限公司

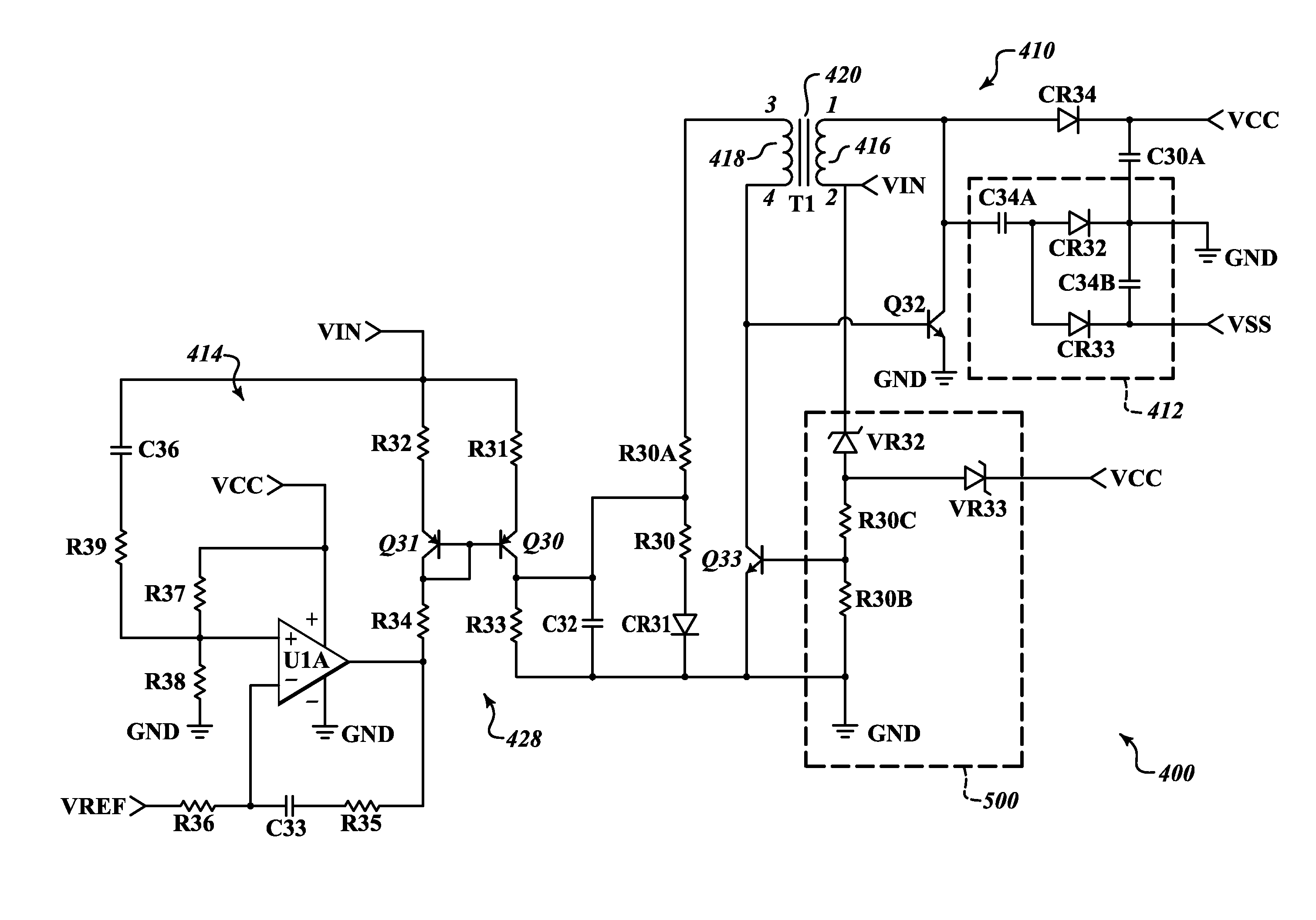

Self synchronizing power converter apparatus and method suitable for auxiliary bias for dynamic load applications

ActiveUS8824167B2Reduce input voltageReducing switching interactionElectric signal transmission systemsConversion with intermediate conversion to dcEngineeringPeak value

An auxiliary power supply or bias voltage supply employs a step up switch mode DC / DC power converter topology to supply regulated bias supply voltages, from very low input voltages (e.g., less than 2V). The supply will synchronize to dynamic loads making it particularly useful in circuits with periodic high peak current power demands, for example, gate drive circuits employed in regulated switched mode power converters. When unladed, the supply will efficiently adjust its cycle period to the minimum required to maintain the desired boosted output voltage. Additional transformer windings or a charge pump may be used to generate additional vias voltage sources.

Owner:CRANE ELECTRONICS INC

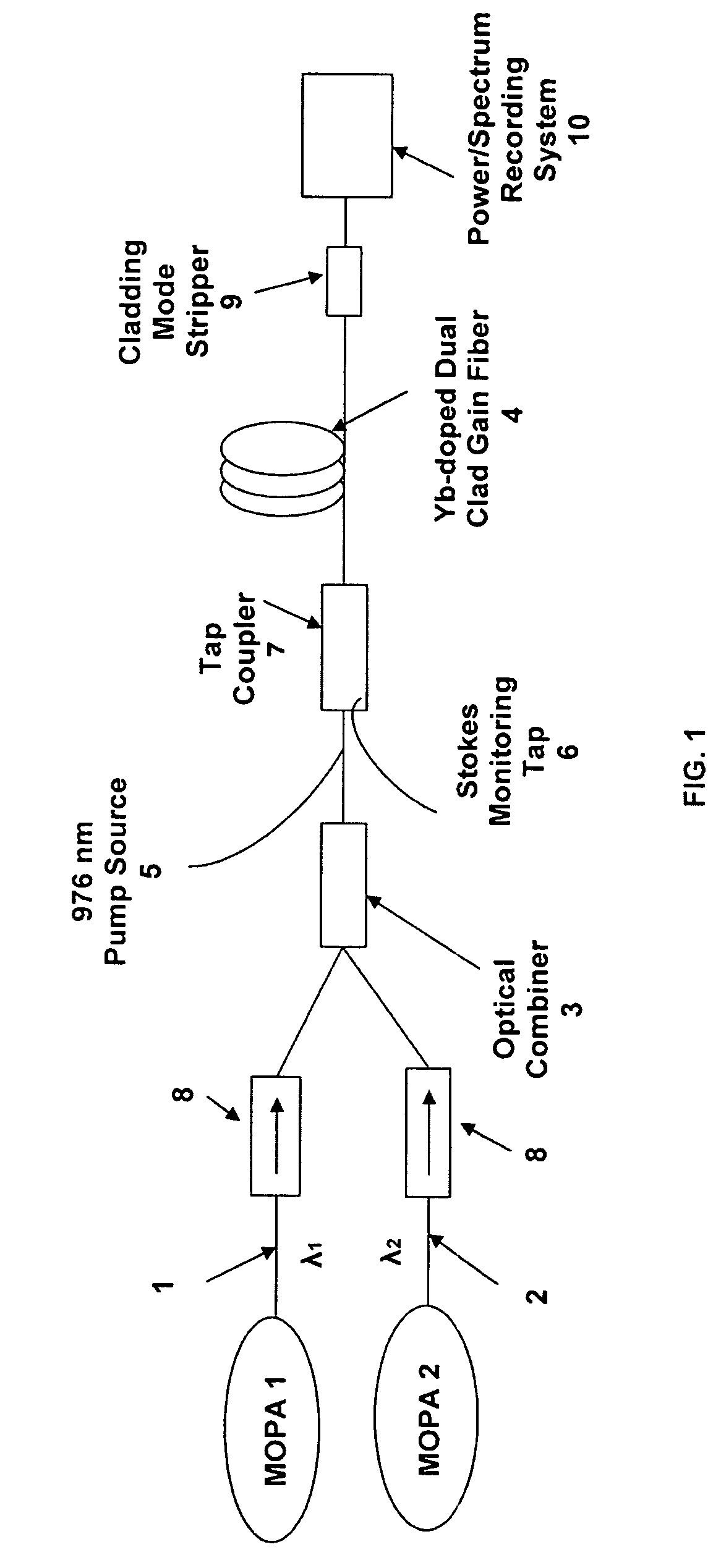

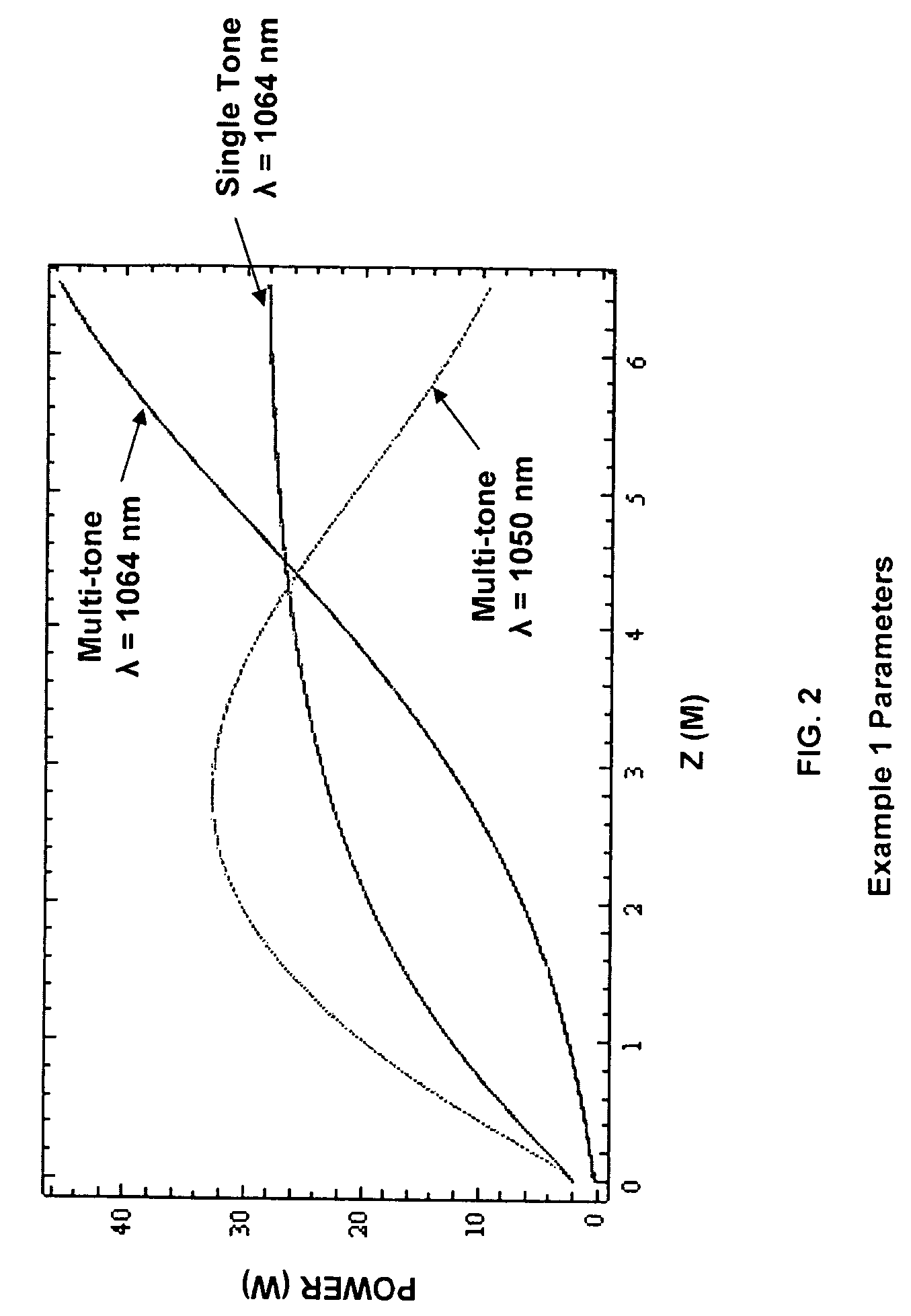

Multi-tone driven high-power narrow-linewidth rare earth doped fiber amplifier

A method to increase the output power of narrow-linewidth rare earth-doped fiber amplifiers by suppressing simulated Brillouin scattering. The fiber amplifier is seeded with two or more lasers having frequencies and input powers that are sufficiently different. The seed signal with the highest emission cross section (e.g., signal 2) initially experiences the greatest gain. If signal 2 is also given sufficiently greater input power than signal 1, it will be amplified to its maximum value before the seed signals have reached the midpoint of the gain fiber. Beyond that point, the signal having the lower emission and absorption cross sections (signal 1) and significantly lower input power will continue to experience gain by power transfer from both signal 2 and the pump light, attaining a power output well beyond what the maximum output would have been had the amplifier been illuminated with a single frequency beam. This technique effectively reduces the Stokes light of signal 1, whereby higher power narrow-linewidth optical fiber amplifiers may be realized.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

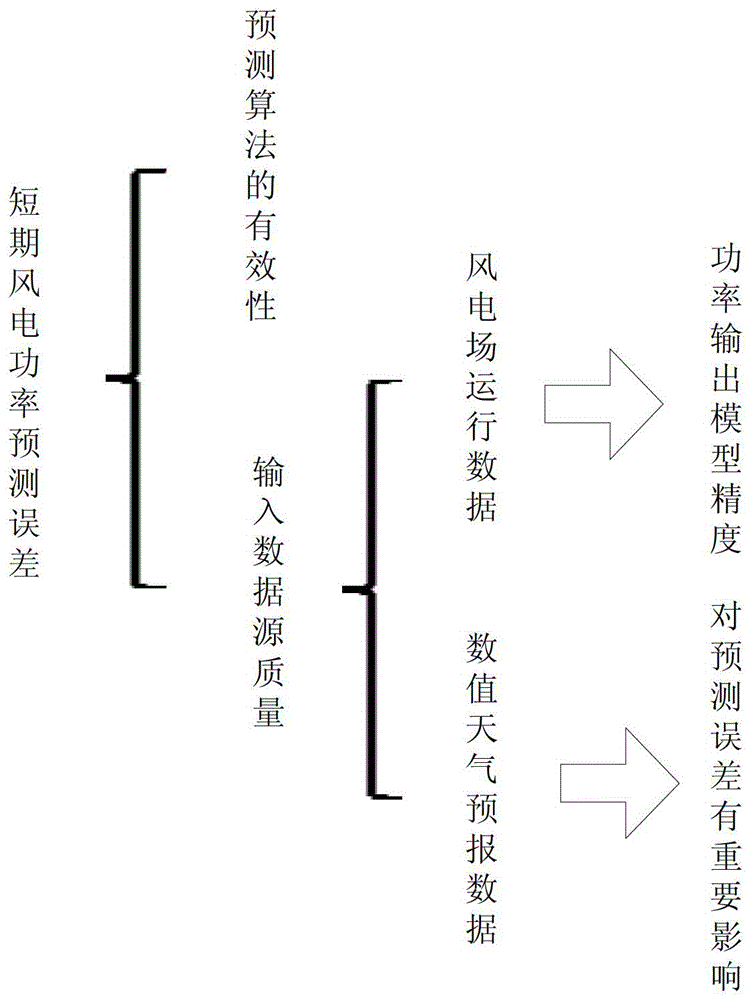

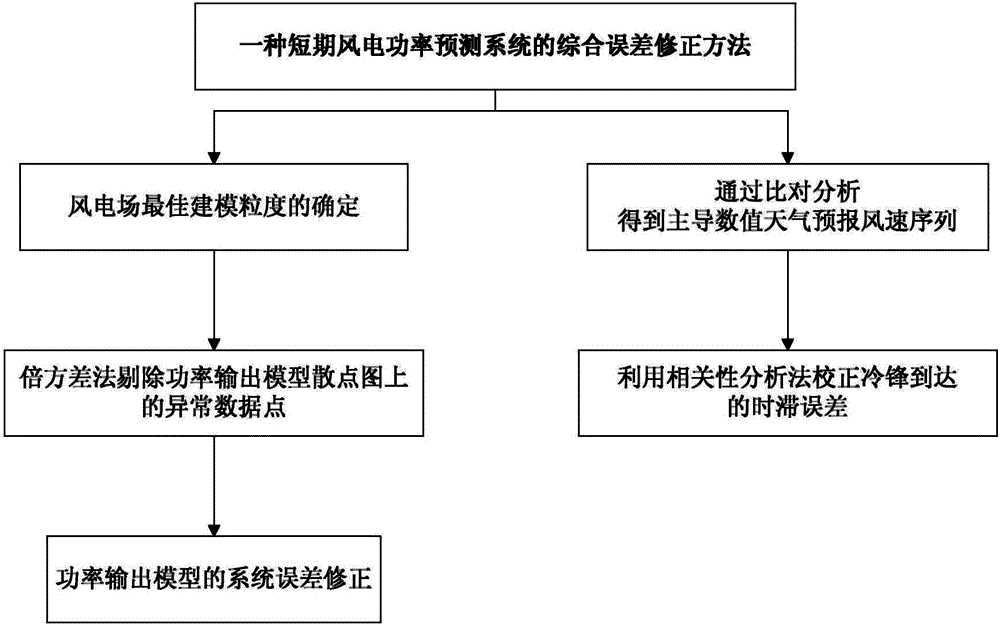

Comprehensive error correction method of short-period wind power prediction system

ActiveCN102914969AImprove modeling accuracyImprove forecast accuracyAdaptive controlPredictive methodsCorrelation analysis

The invention discloses a comprehensive error correction method of a short-period wind power prediction system. The method comprises wind power plant power output link error correction and numerical value weather forecast link error correction; the step of correcting an error of a wind power plant power output link comprises the steps of calculating the best modeling granularity of a power output model, accumulating after modeling by a plurality of fans instead of a single unit, rejecting an abnormal data point on a scatter diagram of the power output model with a times-variance method, and correcting the system error of the power output model by related factors; the step of correcting an error of a numerical value weather forecast link comprises the steps of obtaining a leading value weather forecast wind speed sequence by comparing actually measured wind speed with related coefficients of the numerical value weather forecast wind speeds in different time and space and correcting the system error, and correcting a cold front arrival time-delay error by a correlation analysis method. As to the problem of low input data quality of the existing short-period wind power prediction system, the comprehensive error correction method is generally applicable to various short-period wind power prediction methods, and can be conveniently applied to actual engineering, so that the modeling precision and the prediction precision of the short-period wind power prediction can be obviously improved.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

Three-phase soft-switched PCF rectifiers

Owner:DELTA ELECTRONICS INC

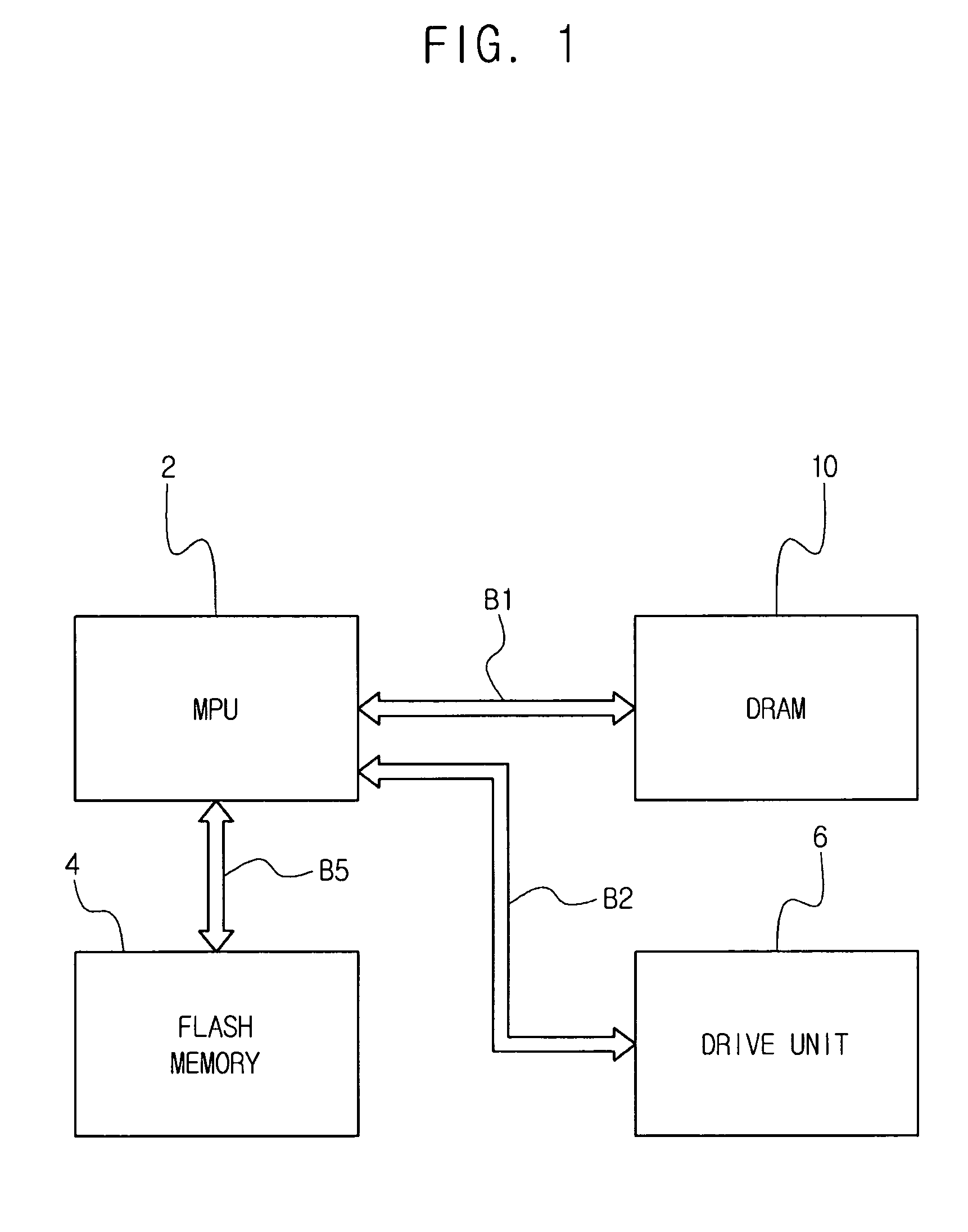

Semiconductor memory device having hierarchical structure of data input/output line and precharge method thereof

A semiconductor memory device having a hierarchical structure of data input / output lines and a precharge method thereof. A precharge method in a semiconductor memory device having a hierarchical structure includes precharging the global input / output line pairs with half of a memory cell array voltage, and precharging the local input / output line pairs with the half of the memory cell array voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

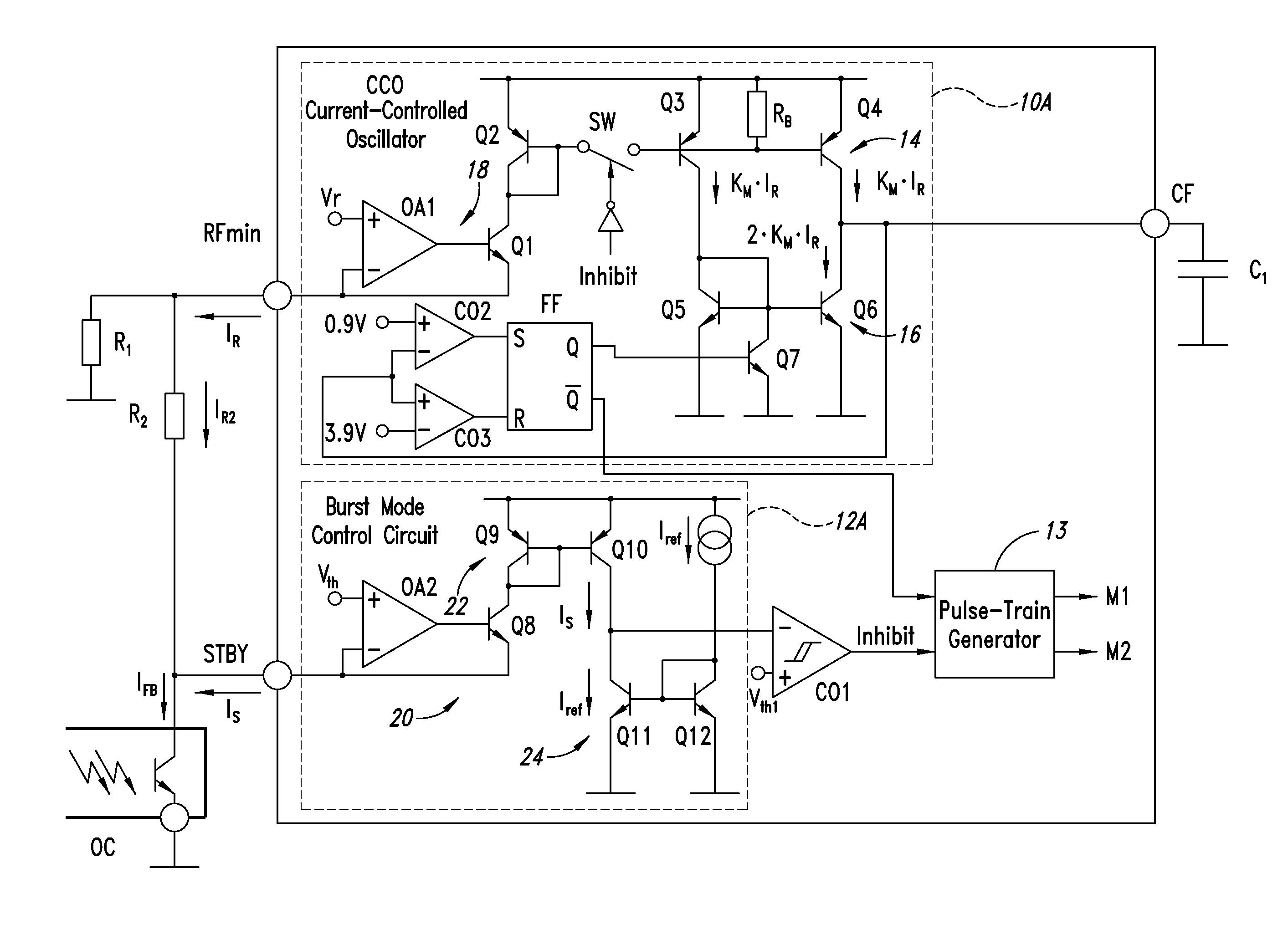

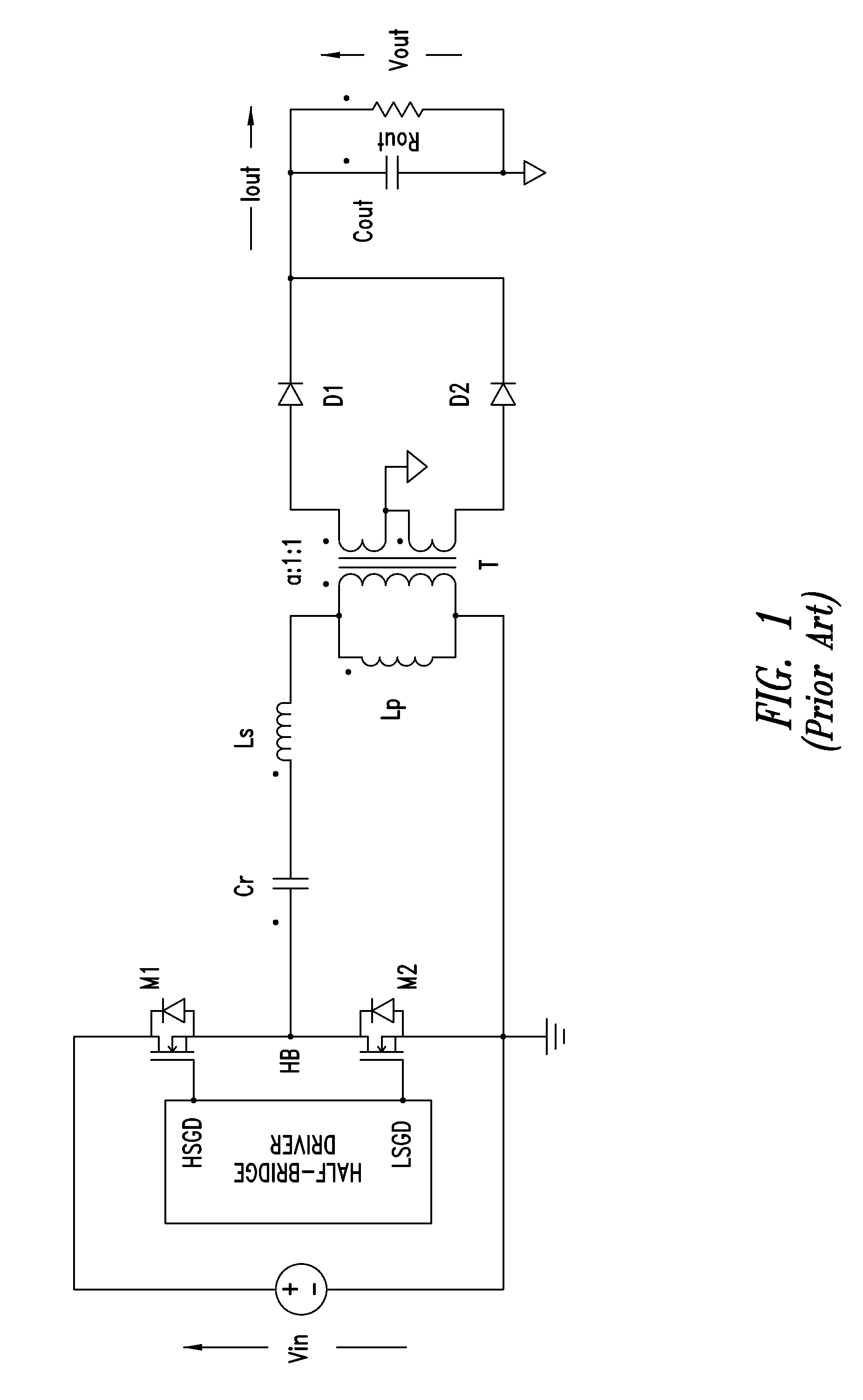

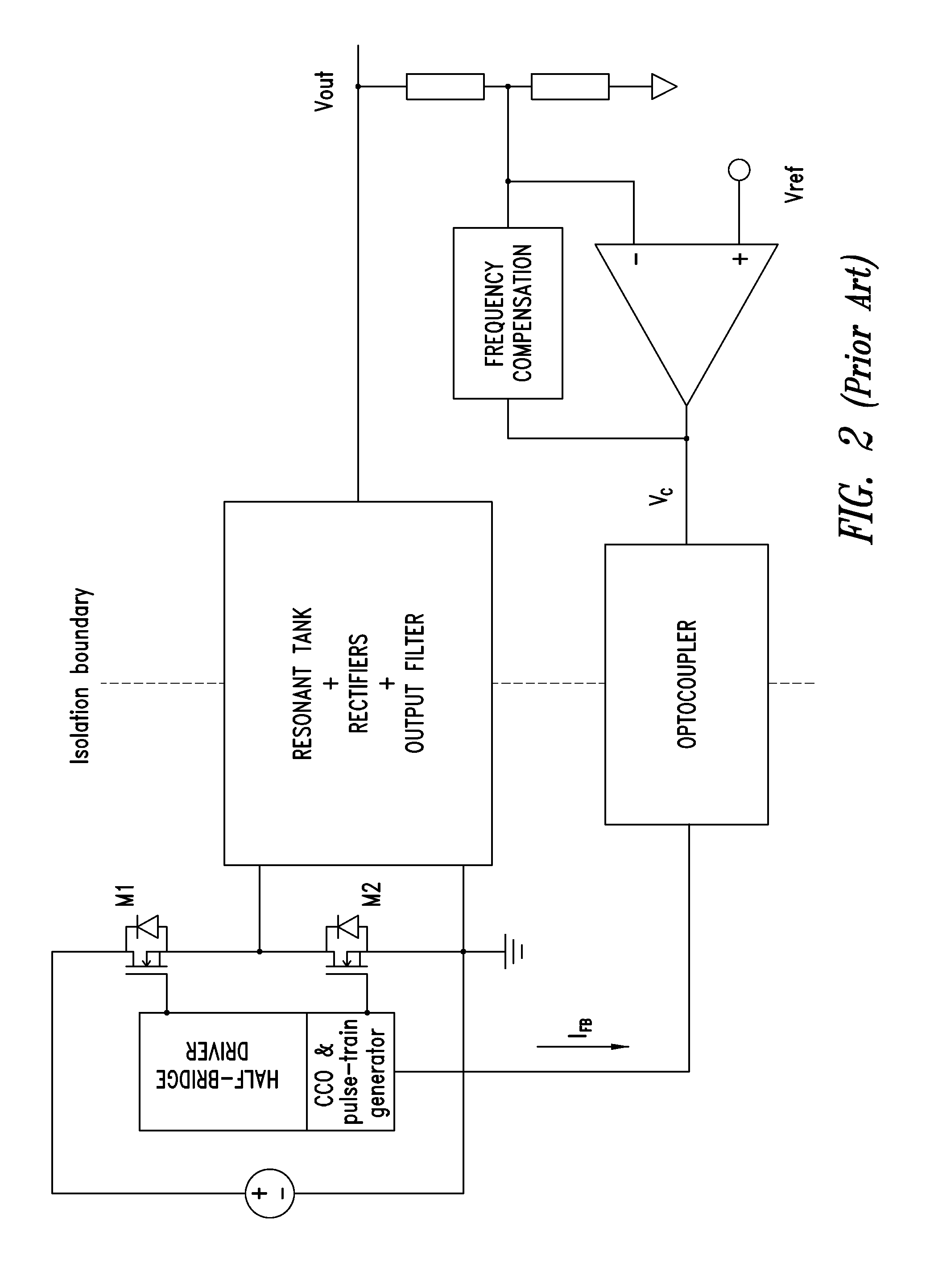

Burst-mode control method for low input power consumption in resonant converters and related control device

ActiveUS20140016362A1Improve efficiencySuppression of shortcomingsEfficient power electronics conversionDc-dc conversionMicrocontrollerMode control

An effective method enhances energy saving at low load in a resonant converter with a hysteretic control scheme for implementing burst-mode at light load. The method causes a current controlled oscillator of the converter to stop oscillating when a feedback control current of the output voltage of the converter reaches a first threshold value, and introduces a nonlinearity in the functional relation between the frequency of oscillation and said feedback control current or in a derivative of the functional relation, while the control current is between a lower, second threshold value and the first threshold value, such that the frequency of oscillation remains equal or smaller than the frequency of oscillation when the control current is equal to the second threshold value. Several circuital implementations are illustrated, all of simple realization without requiring any costly microcontroller.

Owner:STMICROELECTRONICS INT NV

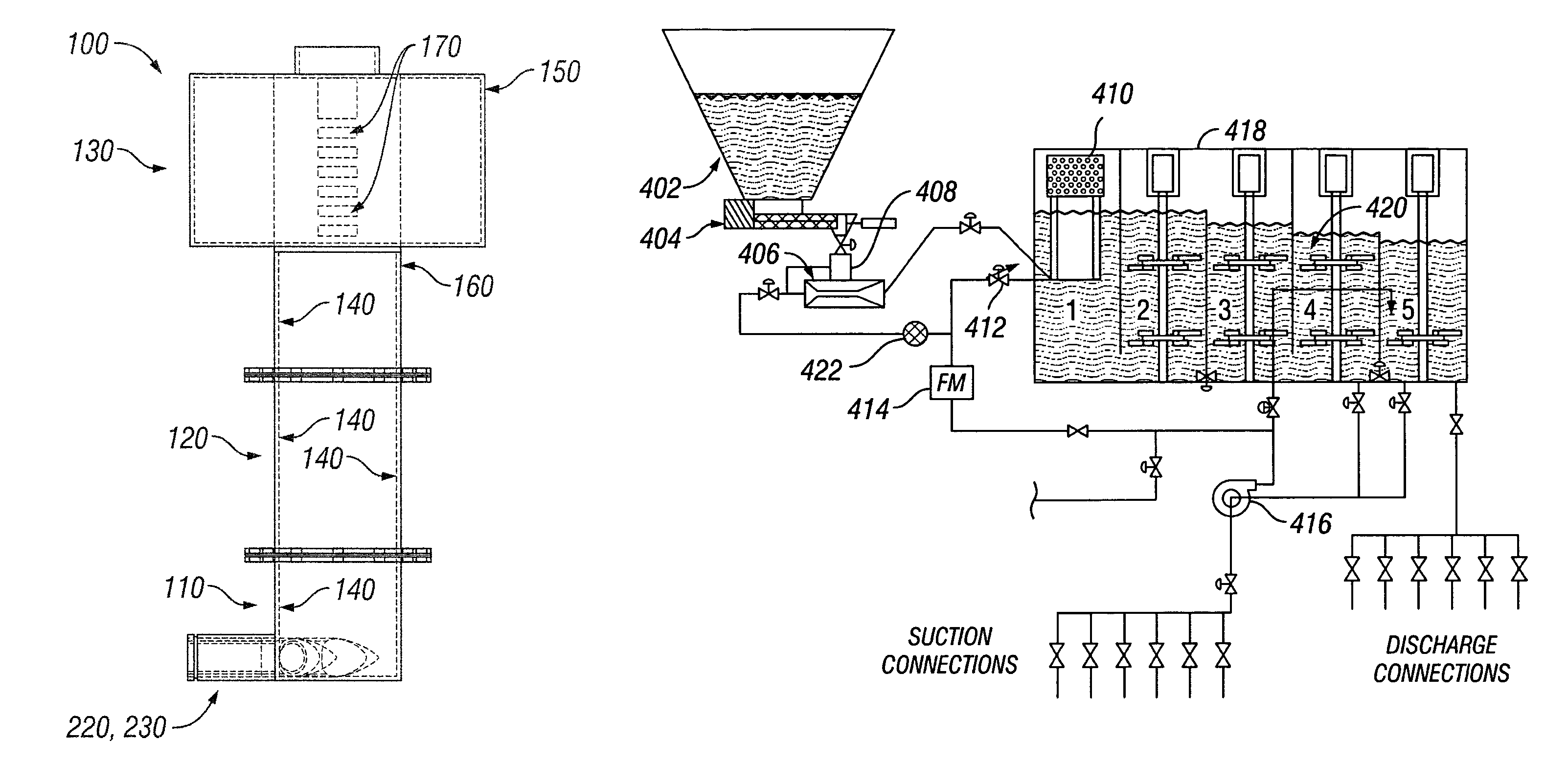

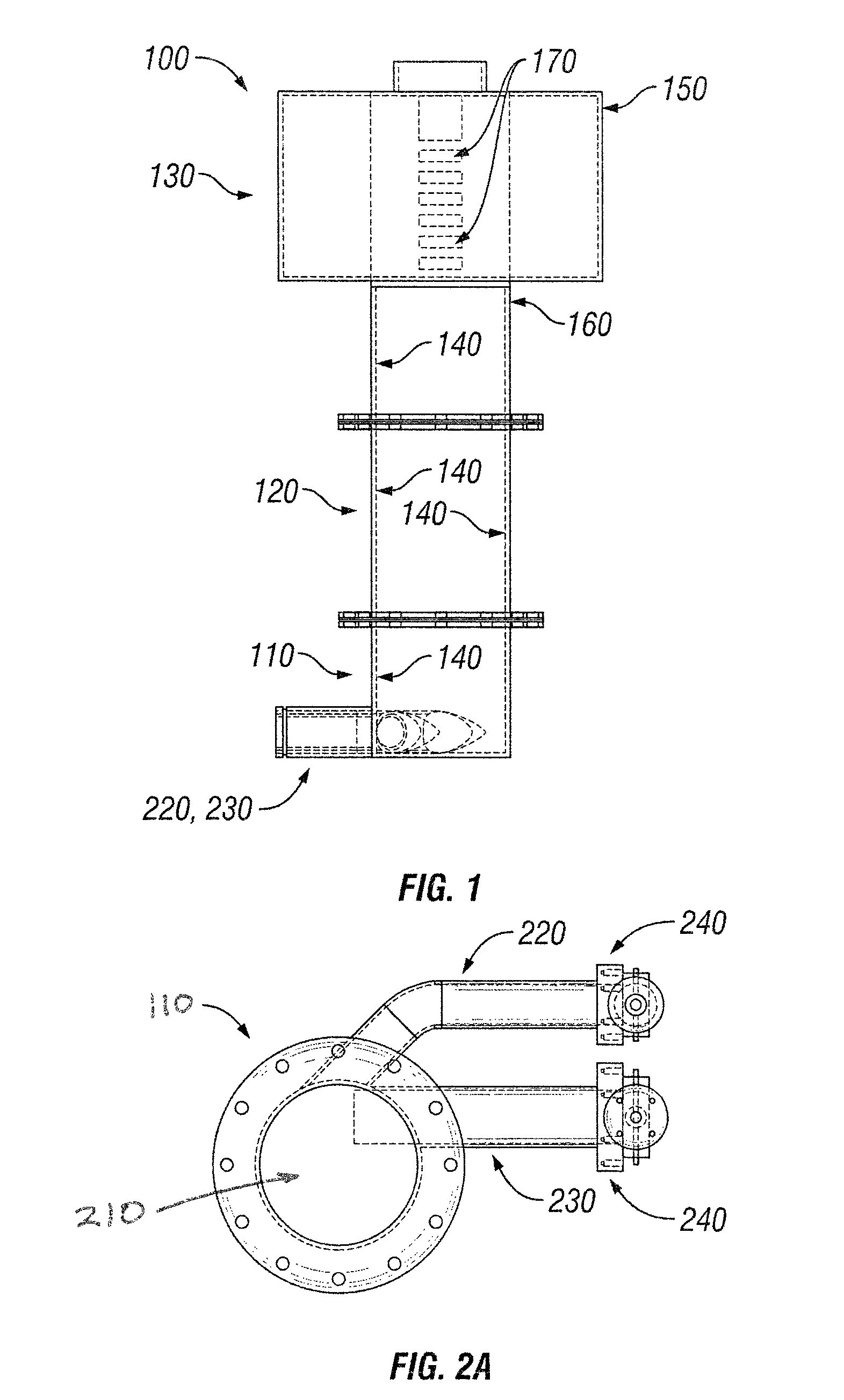

Dry polymer hydration apparatus and methods of use

InactiveUS7794135B2Easy to operateReduce the introductionFlow mixersMixing methodsImpellerWater source

Disclosed are apparatus and methods for preparing wellbore viscous treatment gels from dry polymer and water. The apparatus includes an eductor which slurries dry polymer with water, at least two input tubes, wherein one input tube is connected with the eductor, and another to a water source. The apparatus also includes a mixing chimney connected to the input tubes. The mixing chimney includes a lower input section with inlets connected to the input tubes wherein a jet of metered dilution water is applied at high pressure to the incoming polymer-water slurry stream. This mixture is then accelerated in a circular, and preferably upward, motion where it is sheared against the wall of a central section of the chimney, without the use of an impeller. The chimney further includes an output section that comprising holes circumferentially located, through which the mixture passes from the central section and into a hydration tank. The mixture exiting the chimney is polymer-water gel which is essentially fully mixed and de-aerated, and at least partially hydrated.

Owner:SCHLUMBERGER TECH CORP

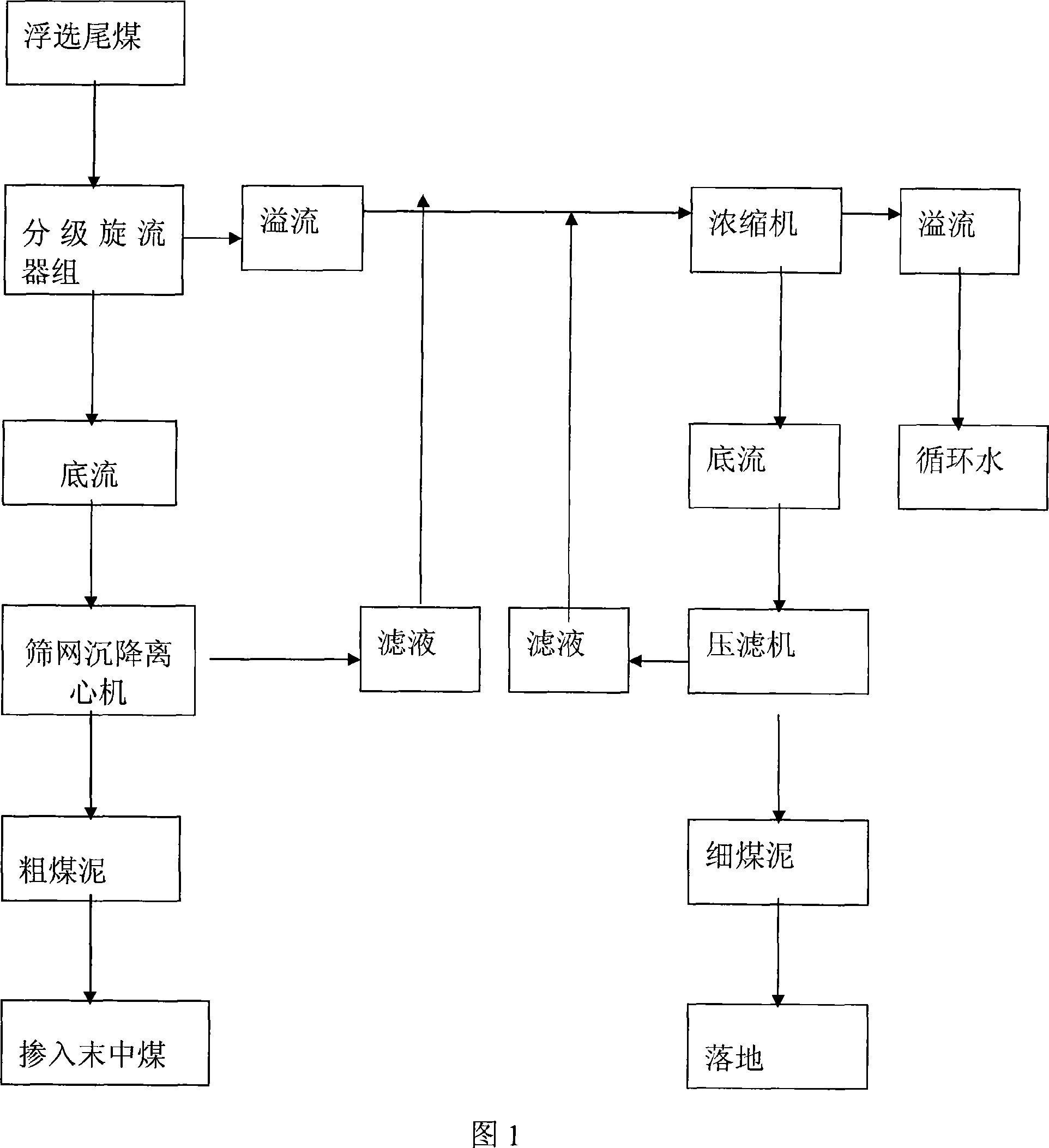

Floating tail-coal graded recovering process

The invention relates to a technology method of flotation tailings classification recovery process, belongs to solid-liquid separation technology area, used to solve maximize recovery of flotation tailings issue. It uses classification Cyclone group to grade flotation tailings, the products moisture after dehydration is 14-18%, the particle size of recovery is 0.045-3mm, it occupy55-60% of floatation tailings quantity; the pressure filter recover fine fuel, the product after dehydration occupy 40-45% of floatation tailings quantity. The invention method filled the flotation tailings bank of use the technology at home and abroad, supplies a low input, high efficiency, simple process, a high degree automation of flotation tailings recovery method, has a simple system, low-moisture products, a bulk materials, can into the coal or other late Medium steam coal advantages. Six months can recover the investment, with good economic and social benefits.

Owner:开滦(集团)有限责任公司煤业分公司

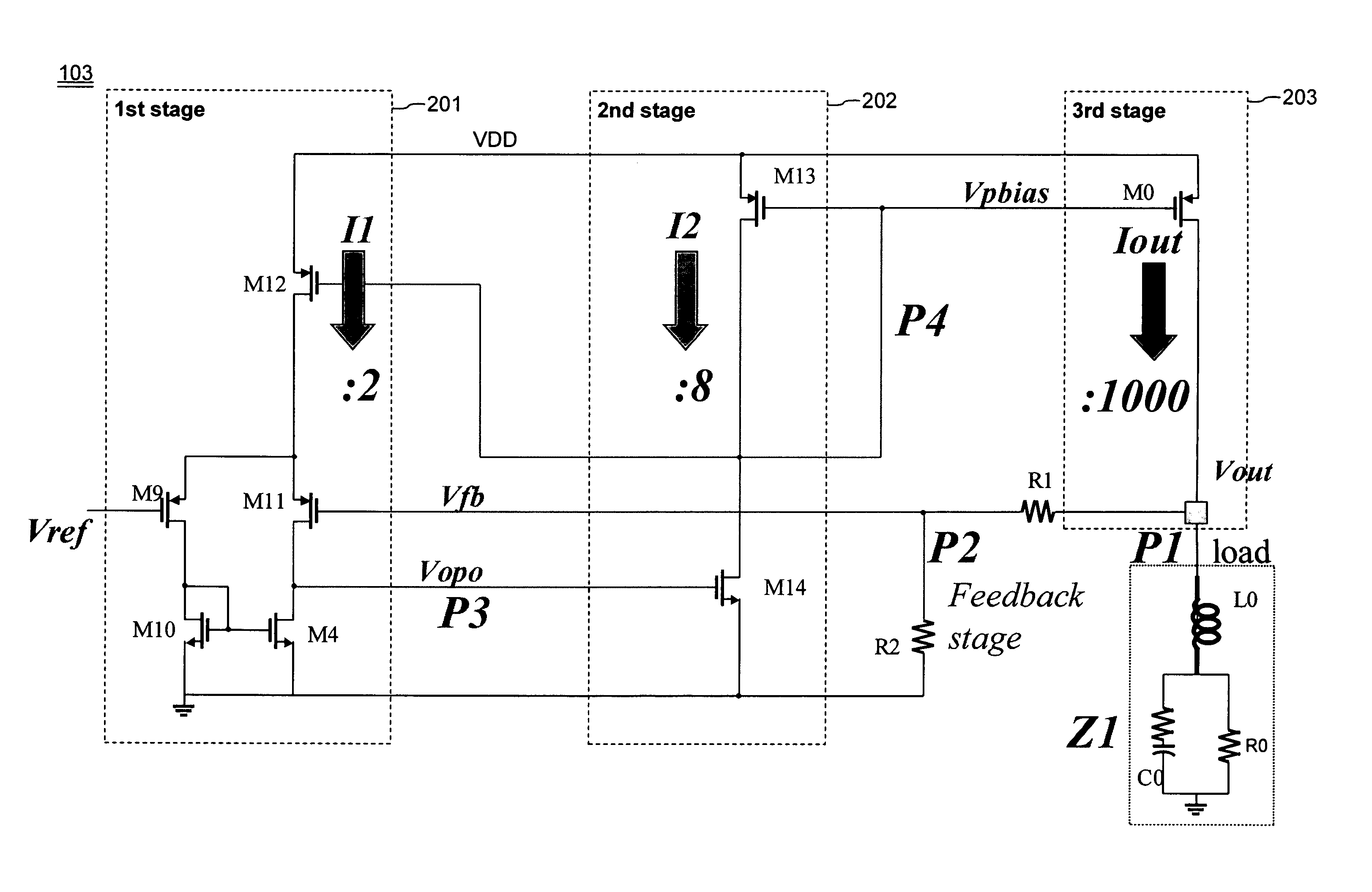

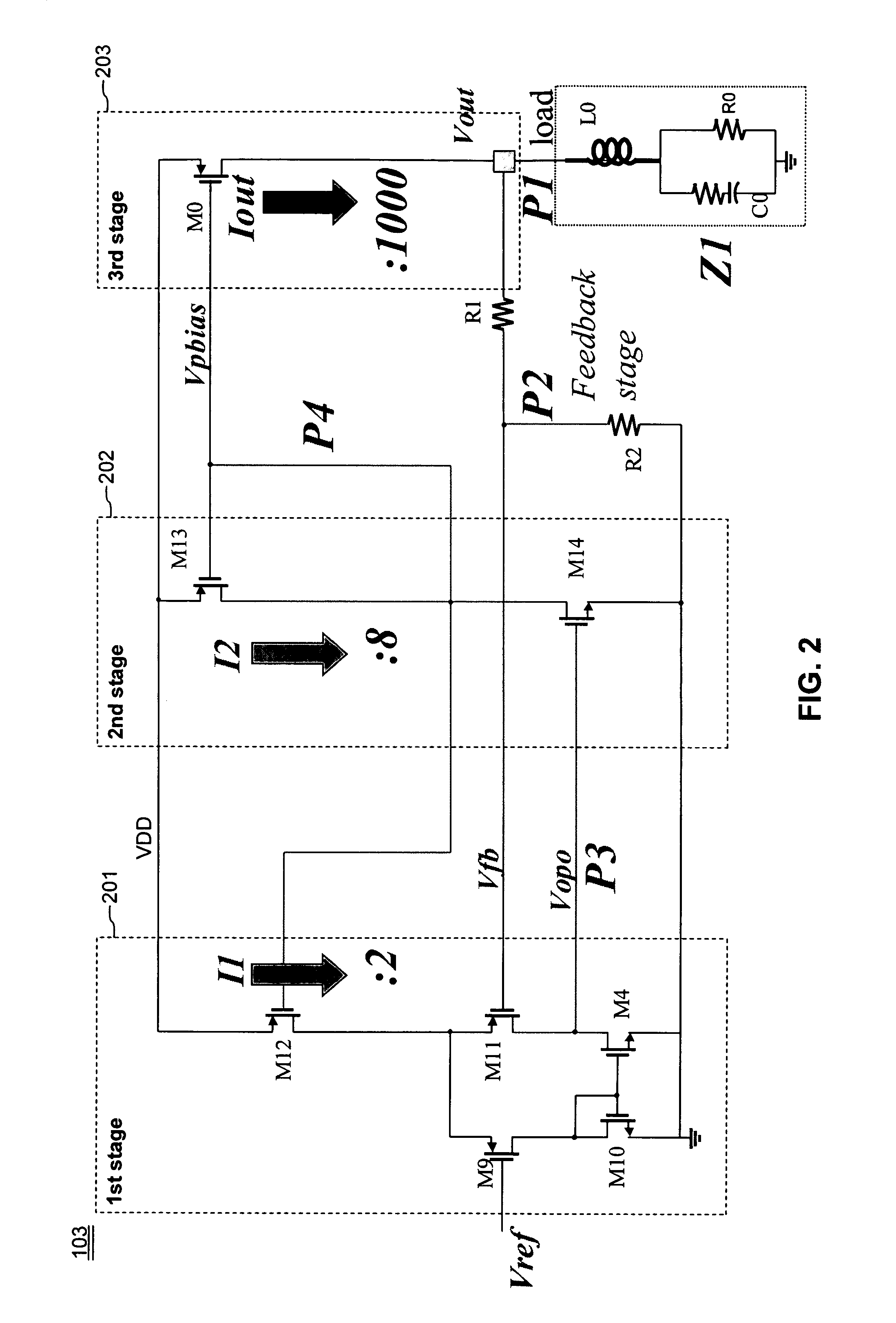

Power management unit for use in portable applications

A voltage regulator includes a first stage capable of receiving a reference voltage and capable of having a first current flowing through the first stage. A second stage is capable of having a second current flowing through the second stage. A third stage is capable of outputting an output voltage and capable of having a third current flowing through the second stage. The first, second and third currents are proportional to each other throughout a range of operation of the voltage regulator between substantially zero output current and maximum output current. The first stage drives the second stage as a low input impedance load.

Owner:AVAGO TECH INT SALES PTE LTD

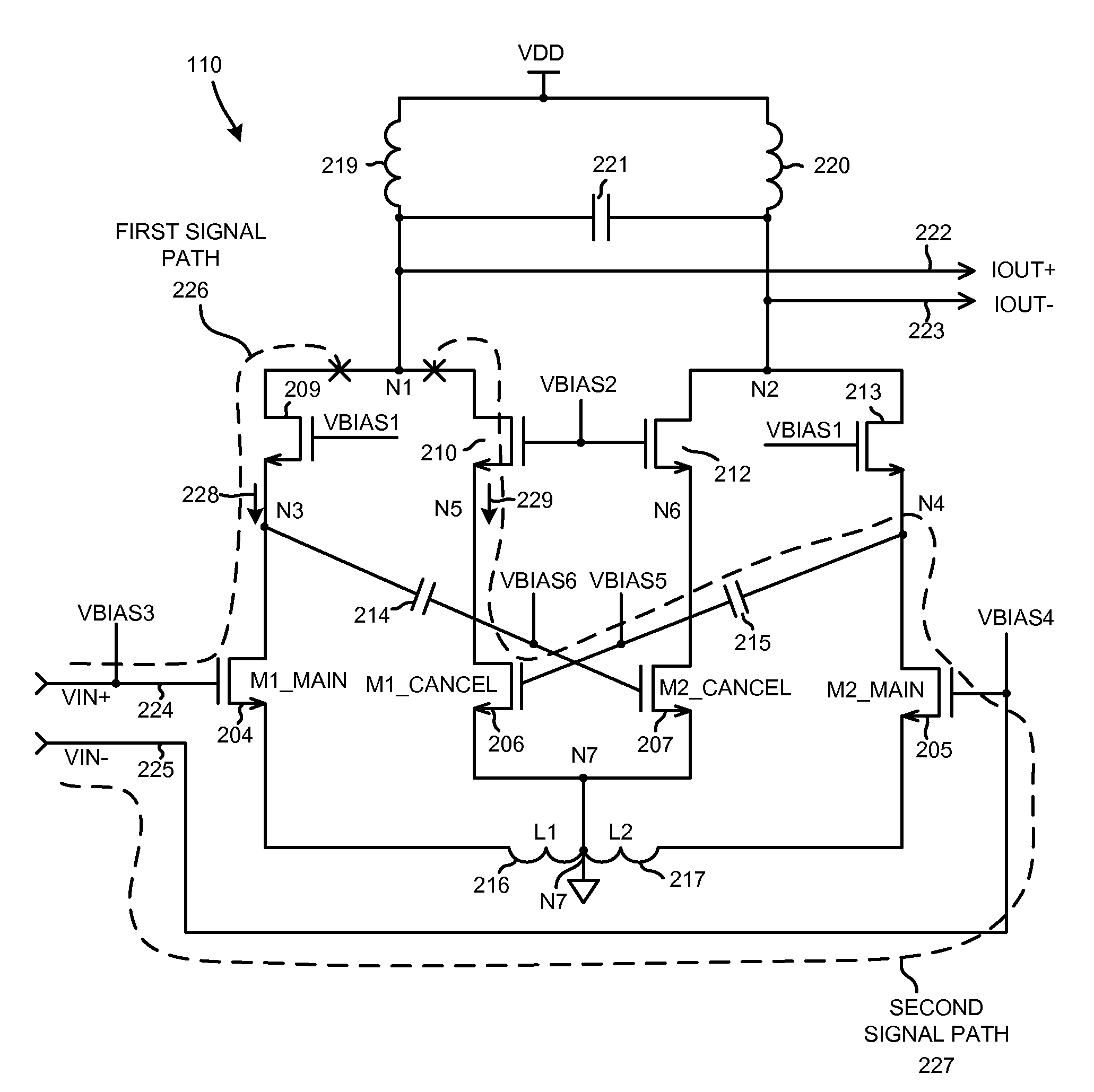

Low noise and low input capacitance differential mds lna

ActiveUS20090153244A1Reduce input capacitanceReduce noise contributionGain controlDifferential amplifiersCapacitanceLow noise

A differential low noise amplifier (LNA) involves two main amplifying transistors biased in saturation, and two cancel transistors biased in sub-threshold. In one example, the gates of the cancel transistors are coupled to the drains of main transistors, in a symmetrical and cross-coupled fashion. The main transistors are source degenerated. Because the gates of cancel transistors are not coupled to the differential input leads of the LNA, the input capacitance of the LNA is reduced. Noise introduced into the LNA output due to the cancel transistors being biased in the sub-threshold region is reduced because there are two stages. The first stage involves the main transistors, and the second stage involves the cancel transistors. By increasing the gain of the first stage and decreasing the gain of the second stage, overall LNA gain is maintained while reducing the noise that the sub-threshold biased transistors contribute to the LNA output.

Owner:QUALCOMM INC

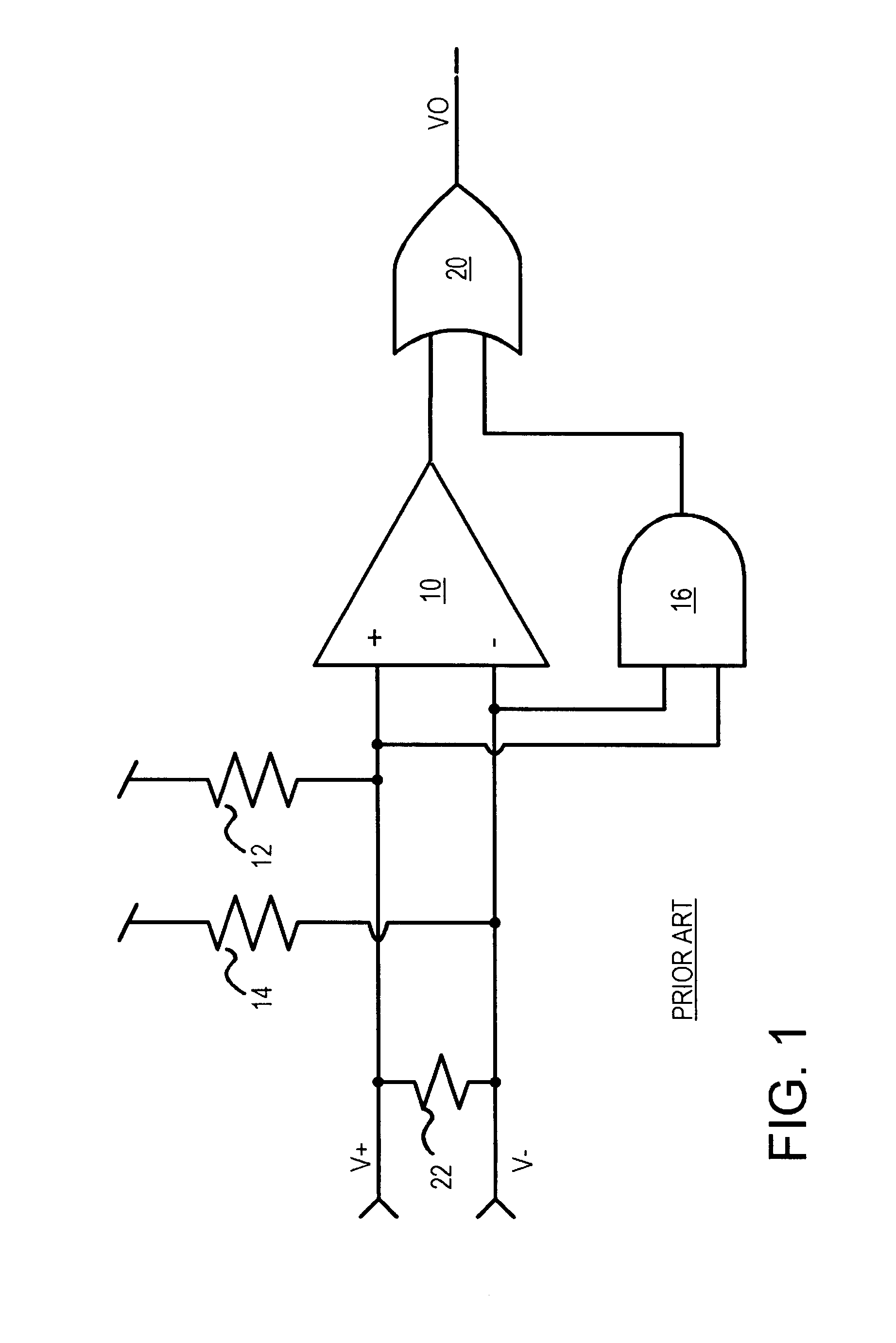

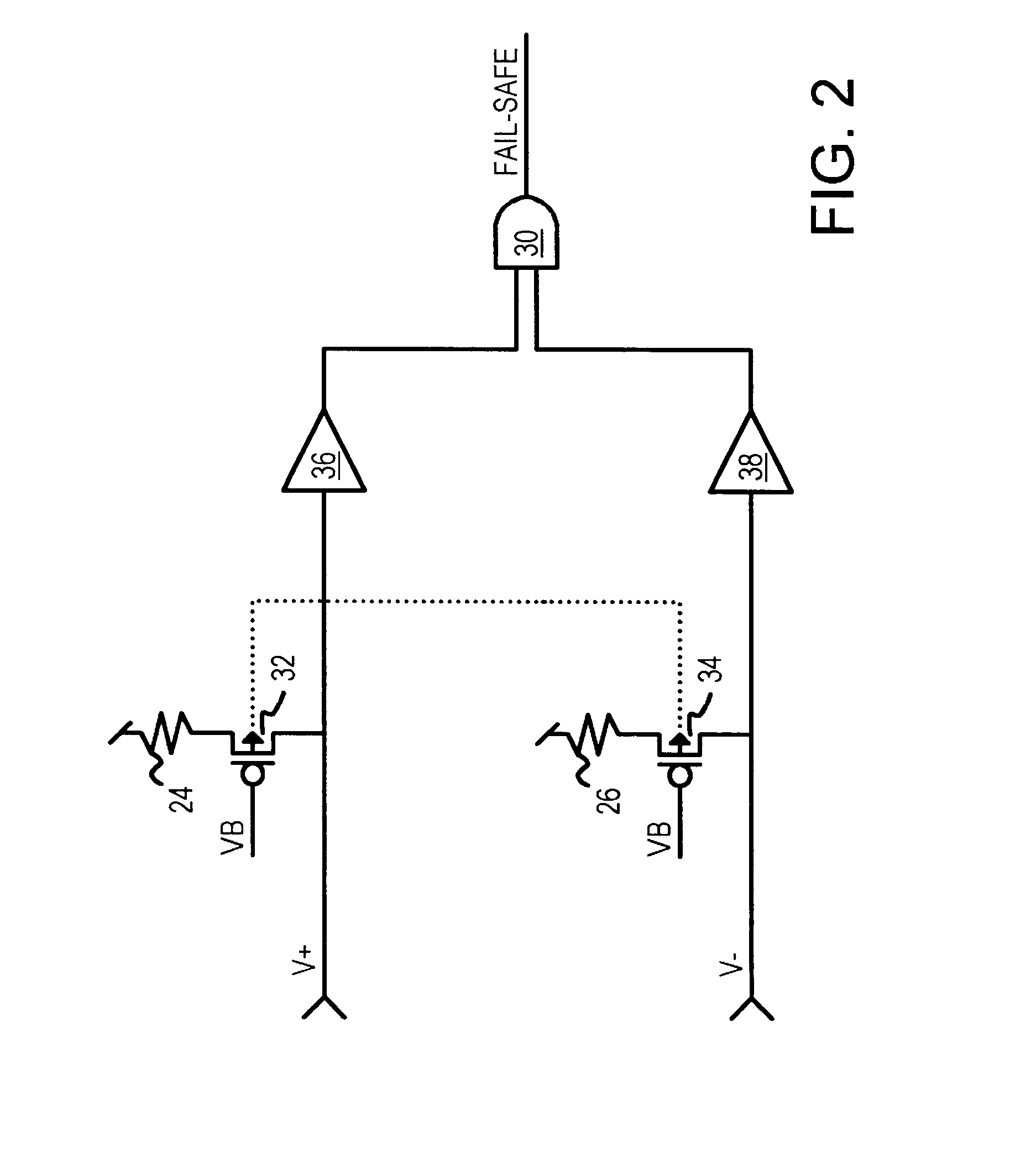

Fail-safe circuit with low input impedance using active-transistor differential-line terminators

InactiveUS6525559B1Reliability increasing modificationsFail-safe circuitsEngineeringPull-up resistor

A fail-safe circuit for a pair of differential input lines detects when one or both lines are open. Each line has a pull-up of a switched p-channel transistor in series with a resistor or another p-channel transistor that has its effective resistance controlled by a gate bias. The gate of the switched p-channel transistor is driven to ground when power is applied to the gate of a grounding n-channel transistor. When power is off, a p-channel connecting transistor charges the gate node from the differential input line when a positive voltage is applied to the input line, such as during a leakage test. Charging the gate node prevents the switched p-channel transistor from turning on, blocking a leakage current path through the pull-up. An N-well bias circuit can be added, which connects the N-well under p-channel transistors to power or the gate node or the input line.

Owner:DIODES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com