Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1876 results about "Power Management Unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Power Management Unit (PMU) is a microcontroller that governs power functions of digital platforms. This microchip has many similar components to the average computer, including firmware and software, memory, a CPU, input/output functions, timers to measure intervals of time, and analog to digital converters to measure the voltages of the main battery or power source of the computer. The PMU is one of the few items to remain active even when the computer is completely shut down, powered by the backup battery.

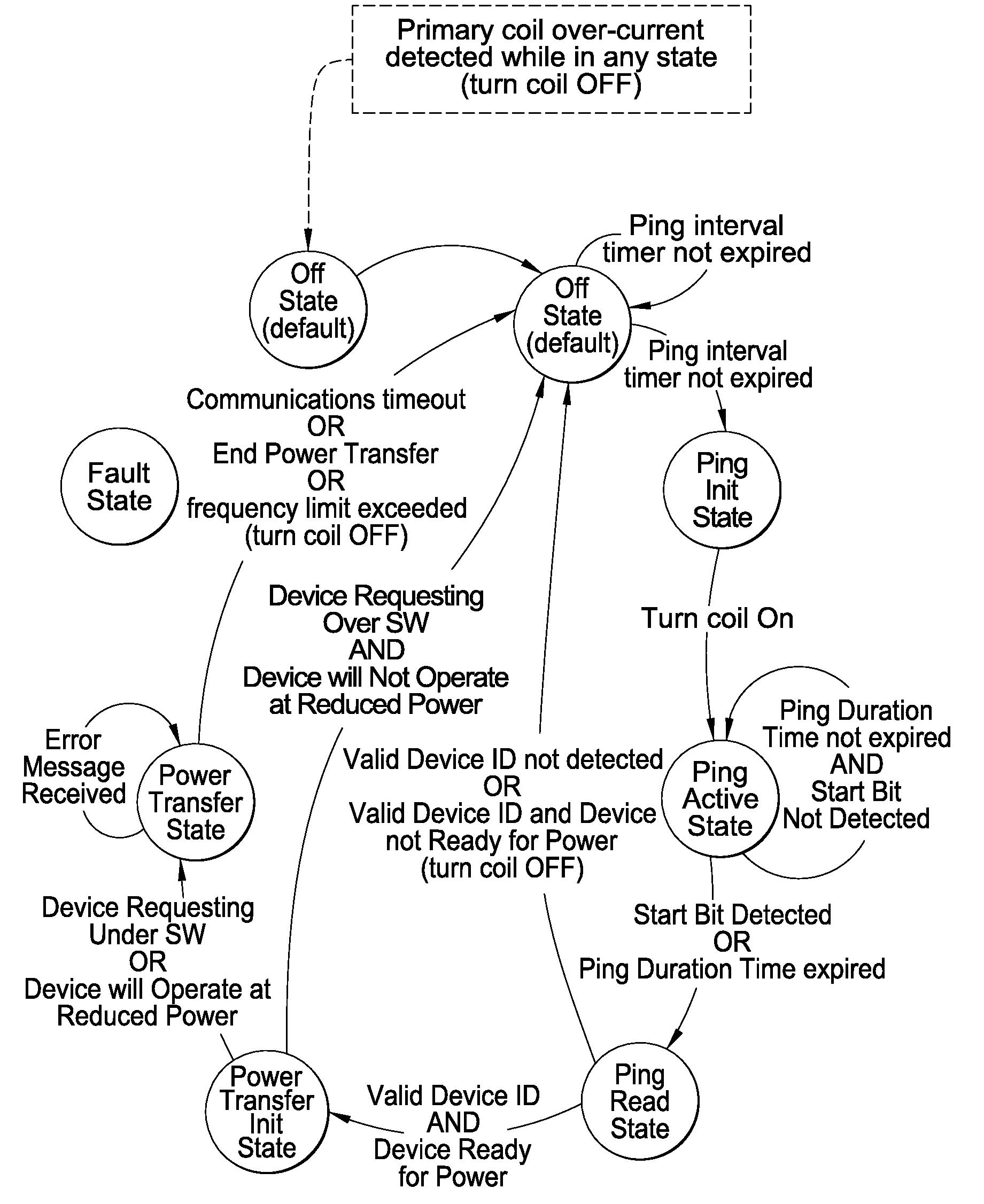

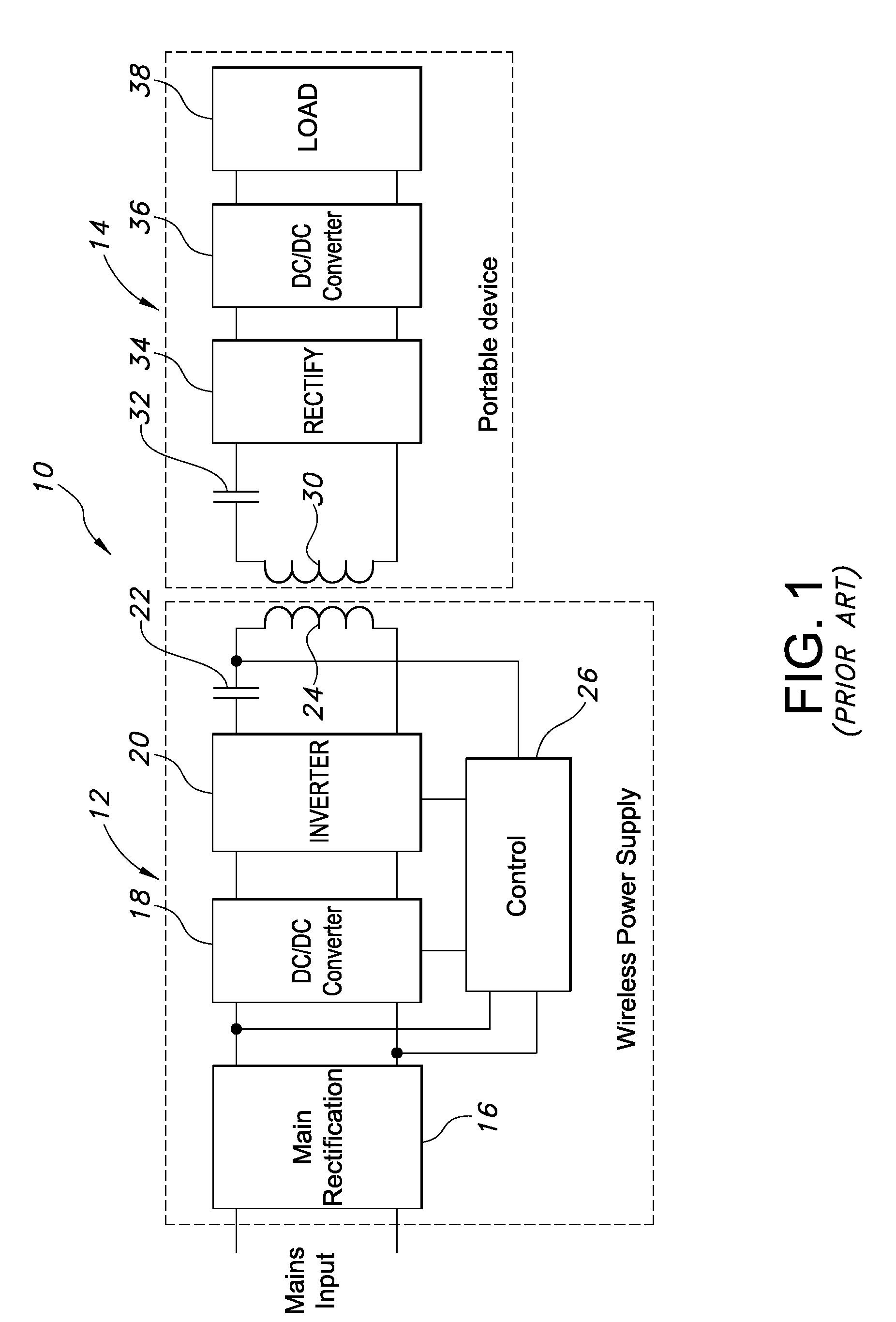

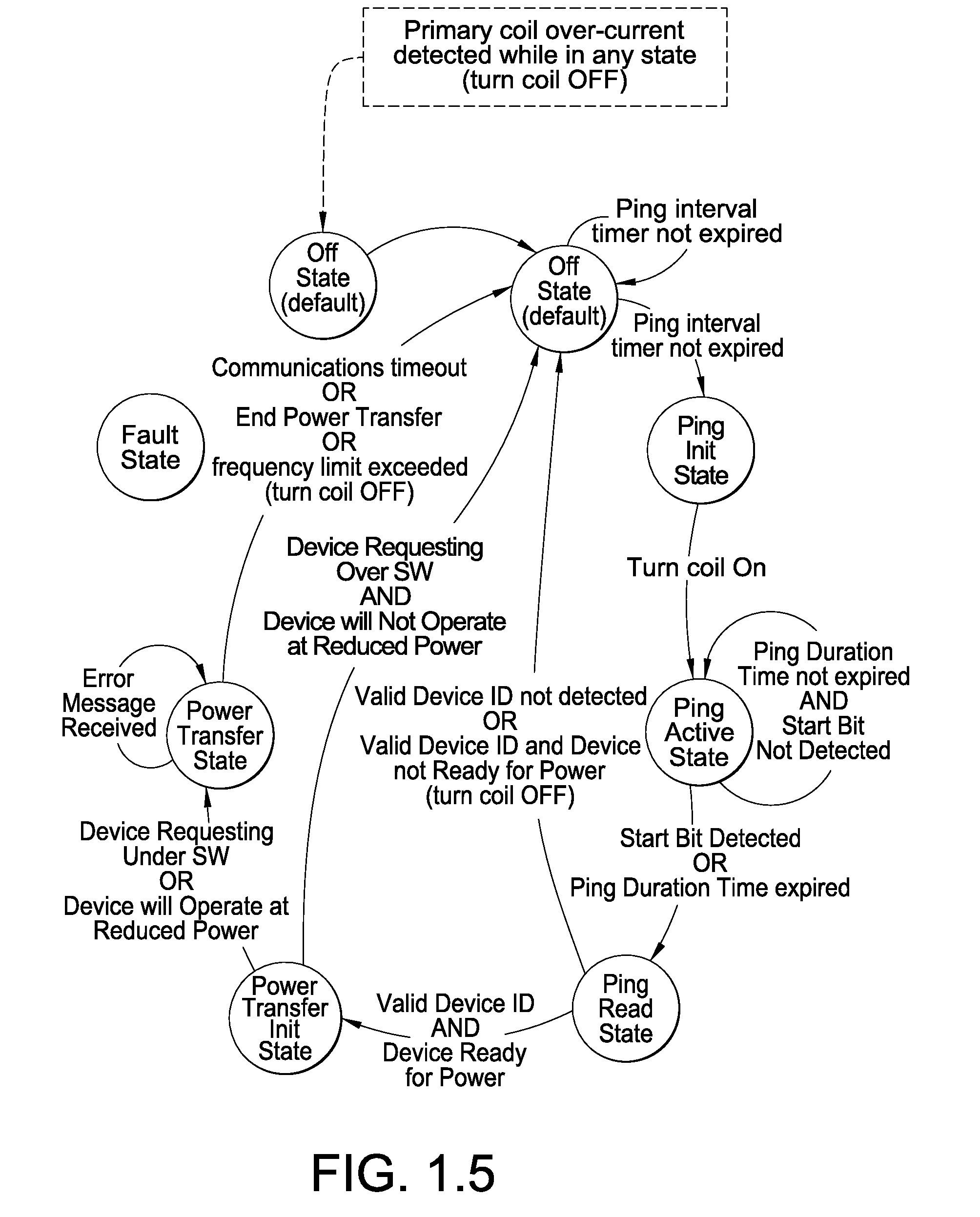

Wireless charging system with device power compliance

ActiveUS20100171461A1Reduce power levelEnhanced power complianceTransformersElectric powerPower Management UnitEngineering

A method of controlling an inductive charging system on those occasions in which the combined power requests of a plurality of secondary devices exceed the power capacity of the power supply. The method includes at least one of (a) powering each device at a level below its requested level, (b) powering each device sequentially, and / or (c) powering each device in a repetitive pattern (e.g. time multiplexing). Also disclosed is a method of controlling an inductive charging system at least partially as a function of information received from the power management unit (PMU) of each secondary device.

Owner:PHILIPS IP VENTURES BV

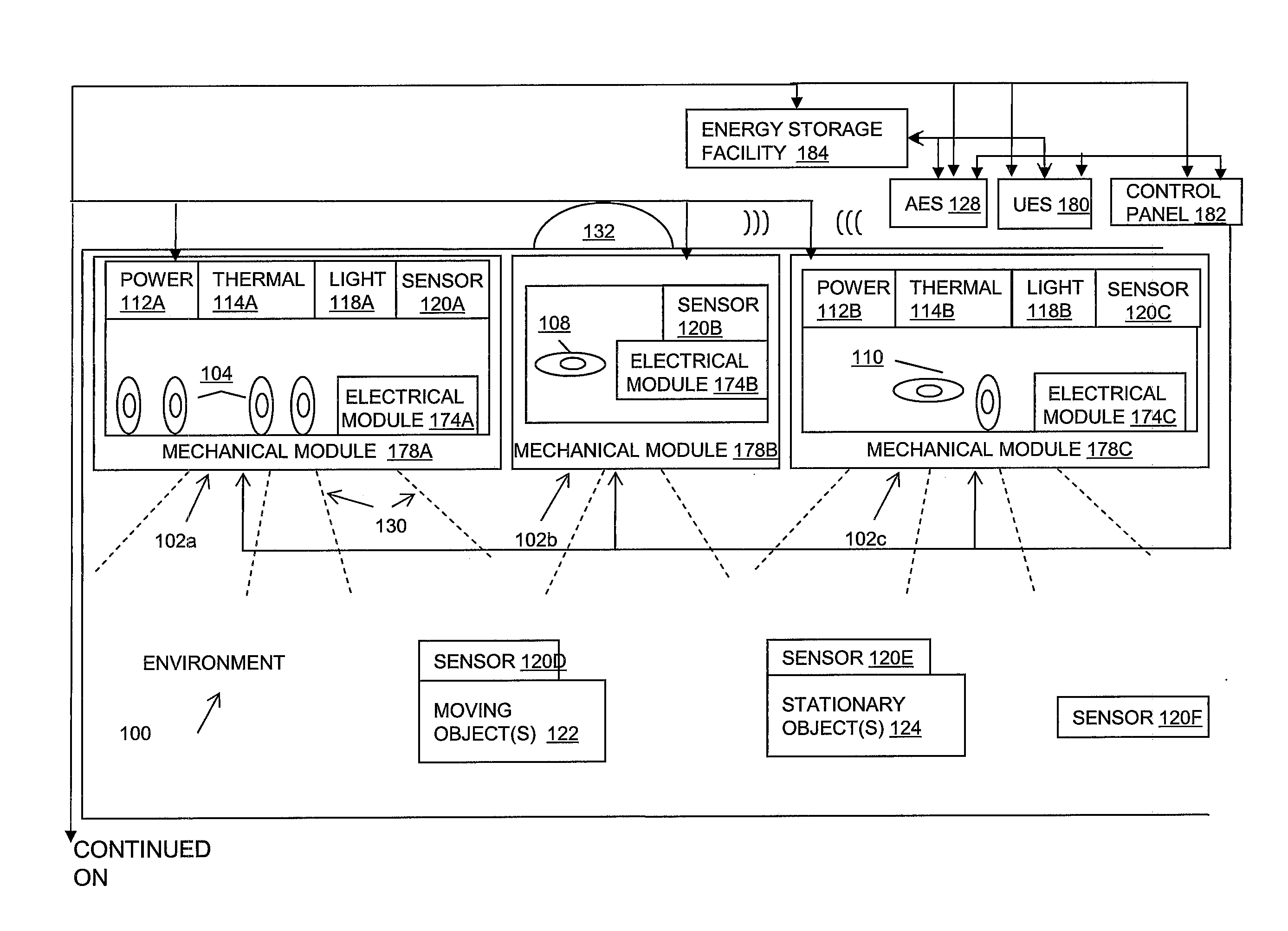

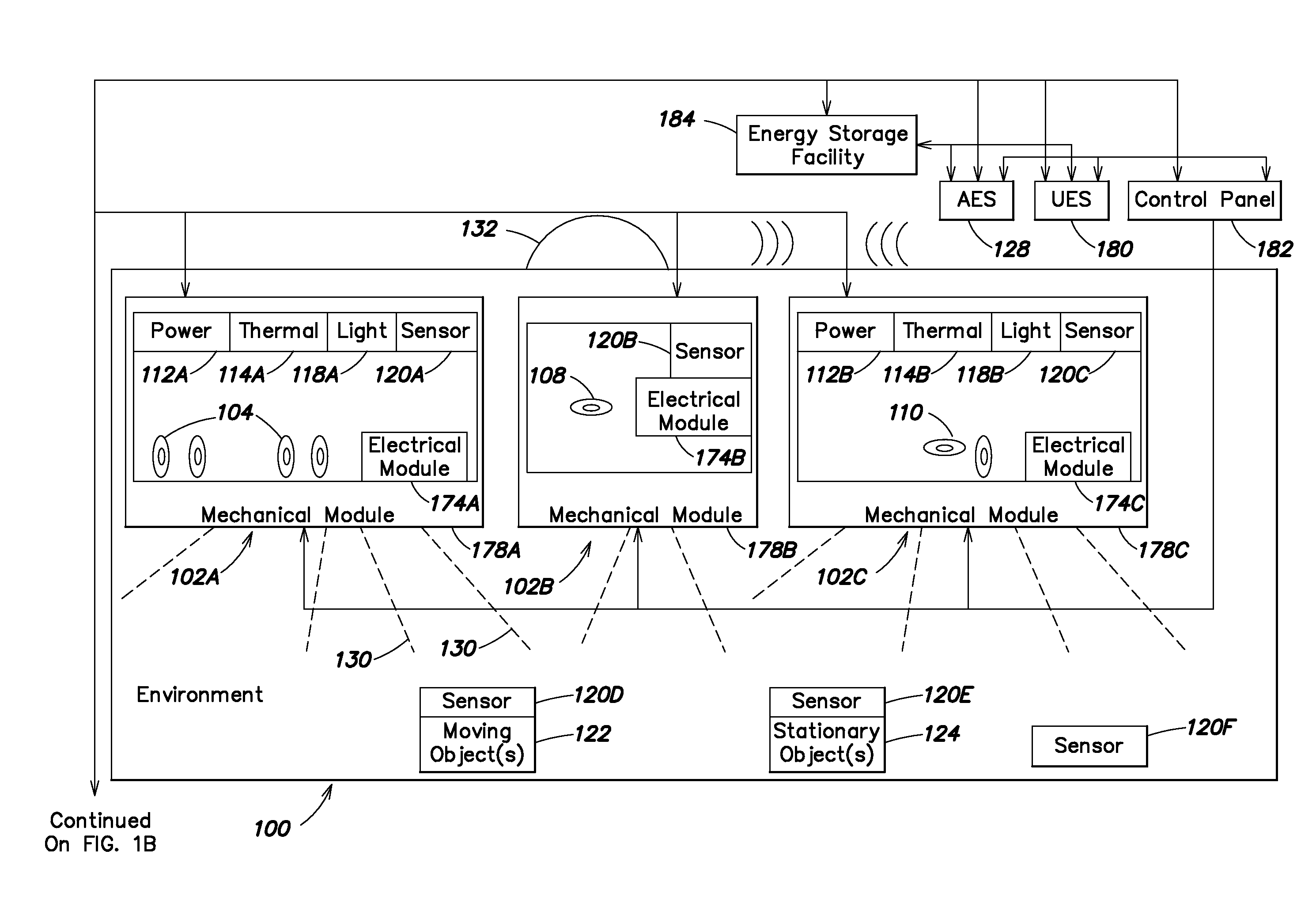

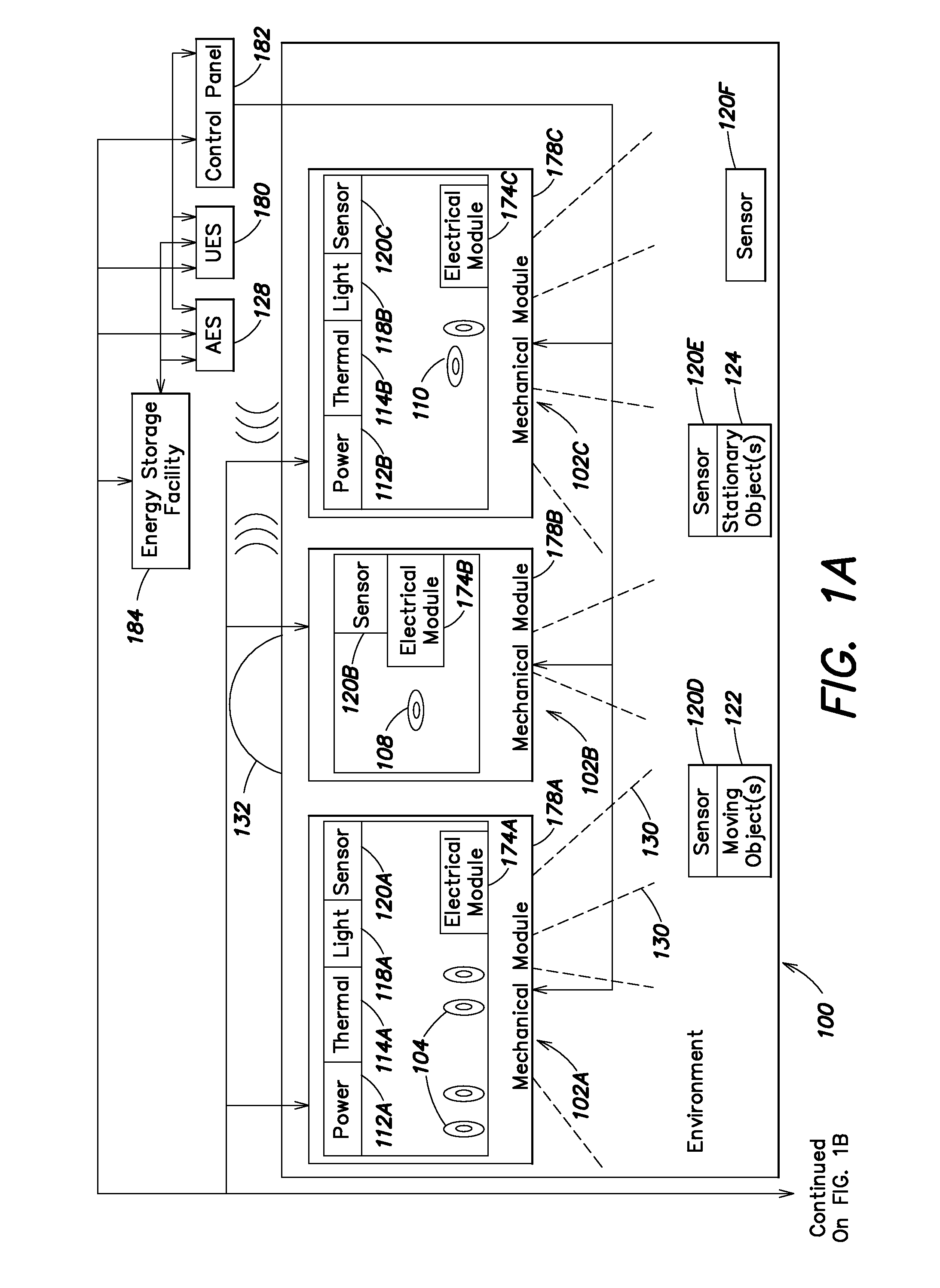

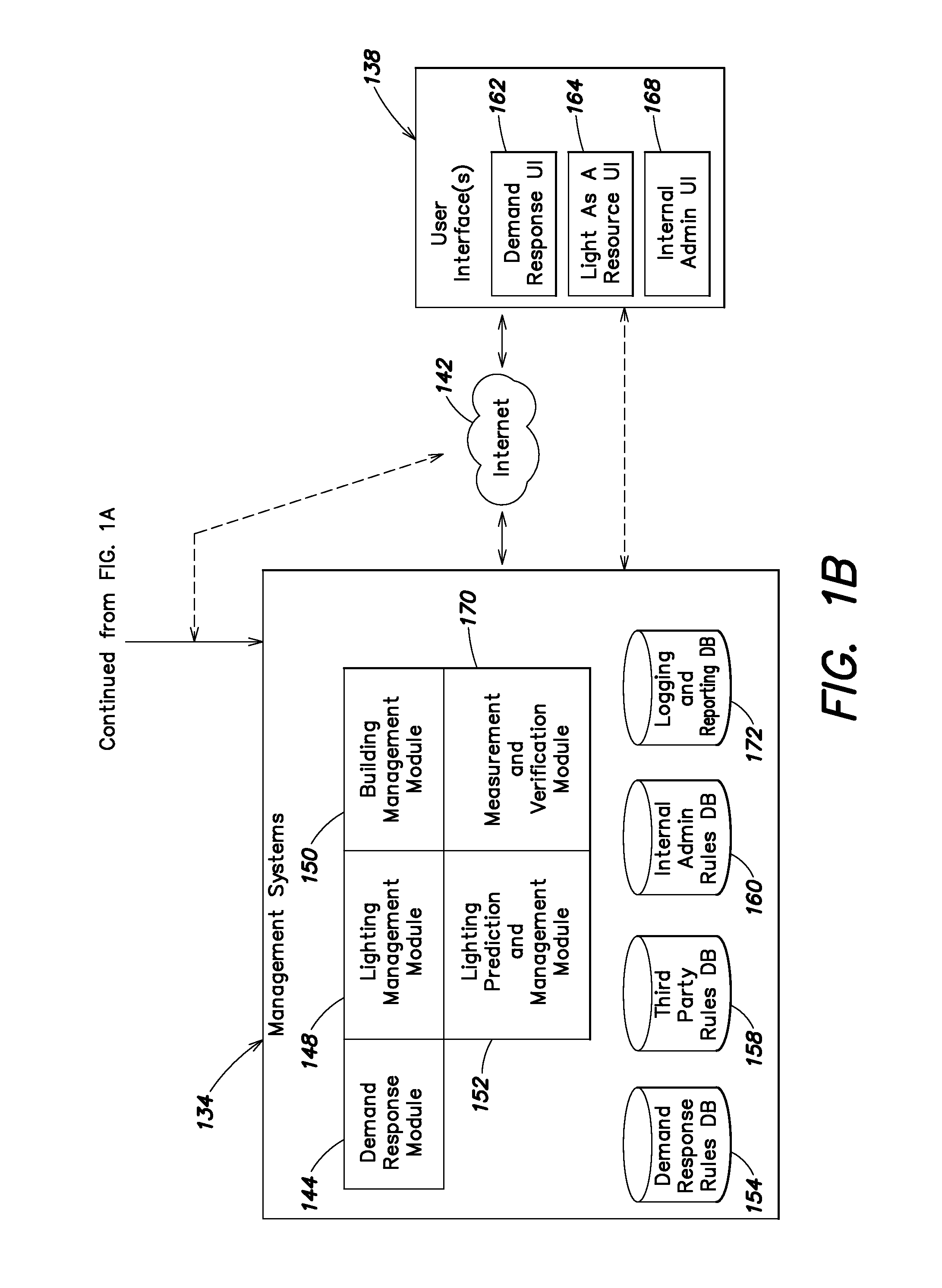

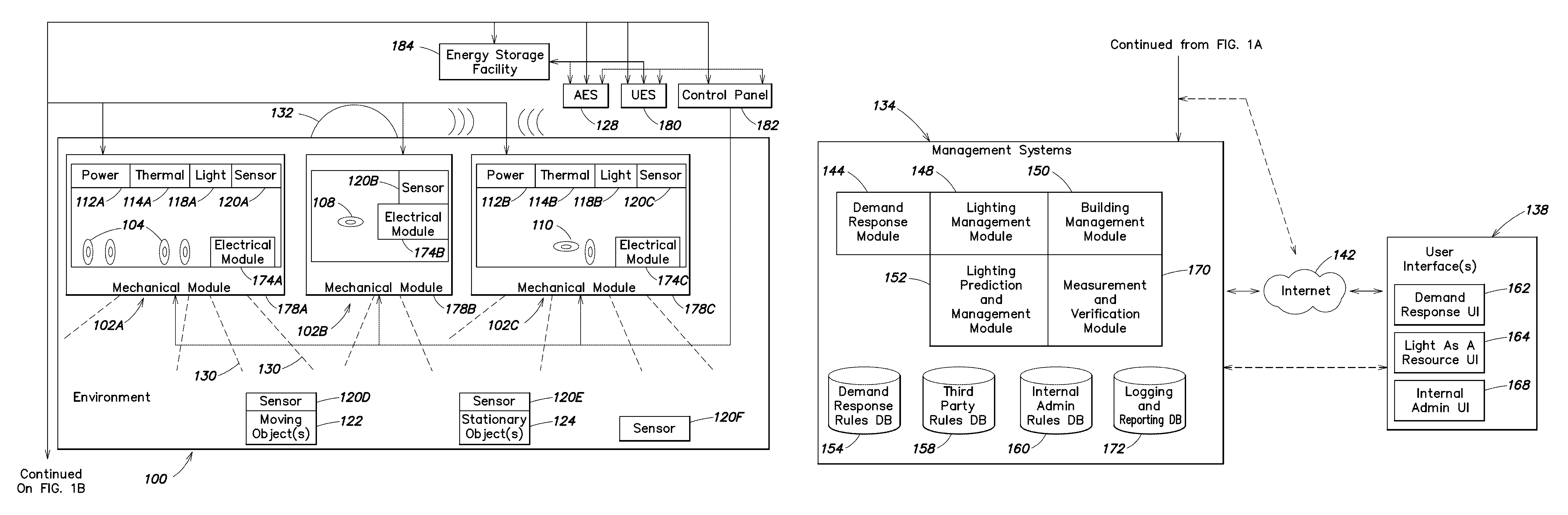

Power Management Unit with Temperature Protection

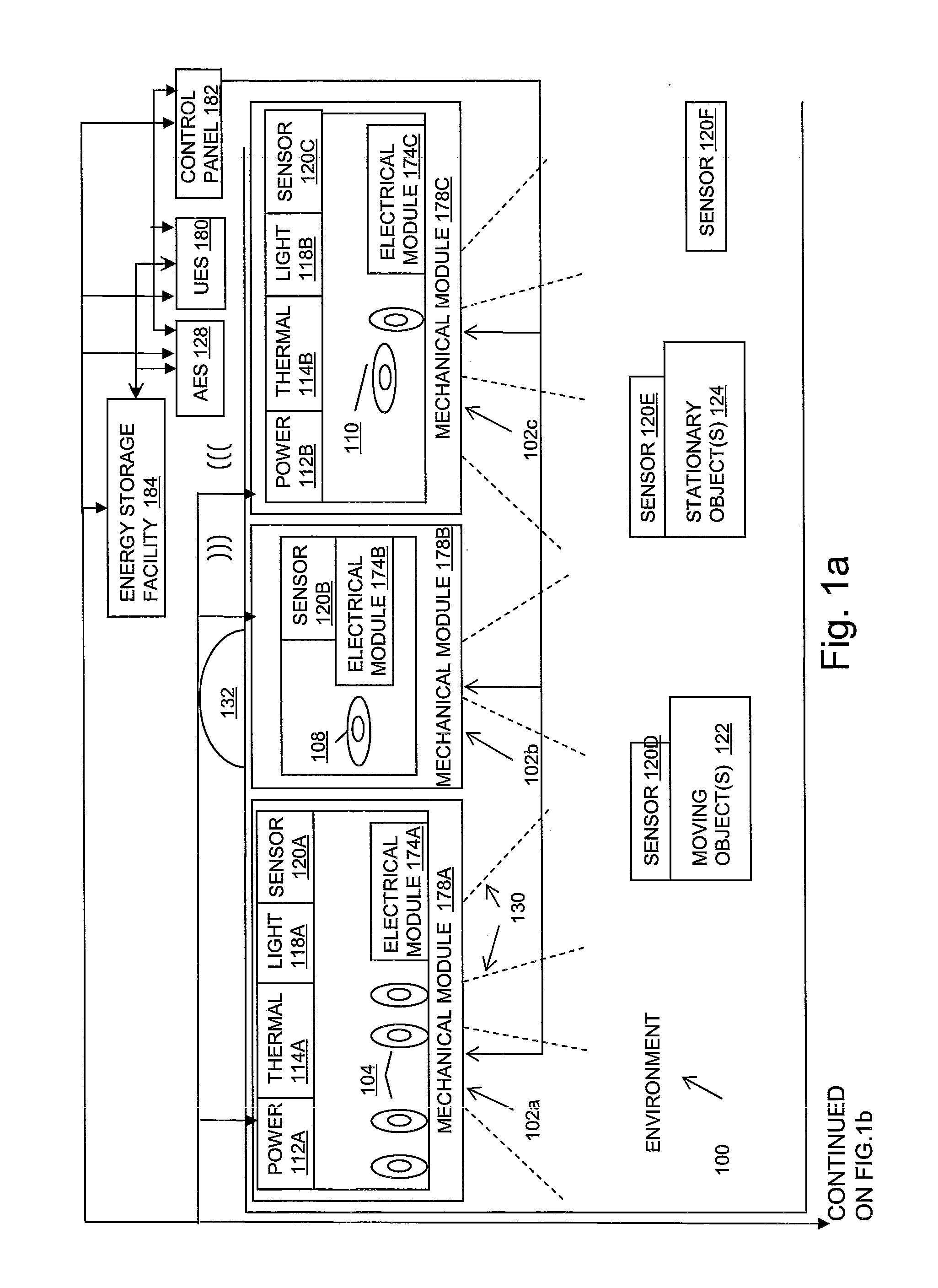

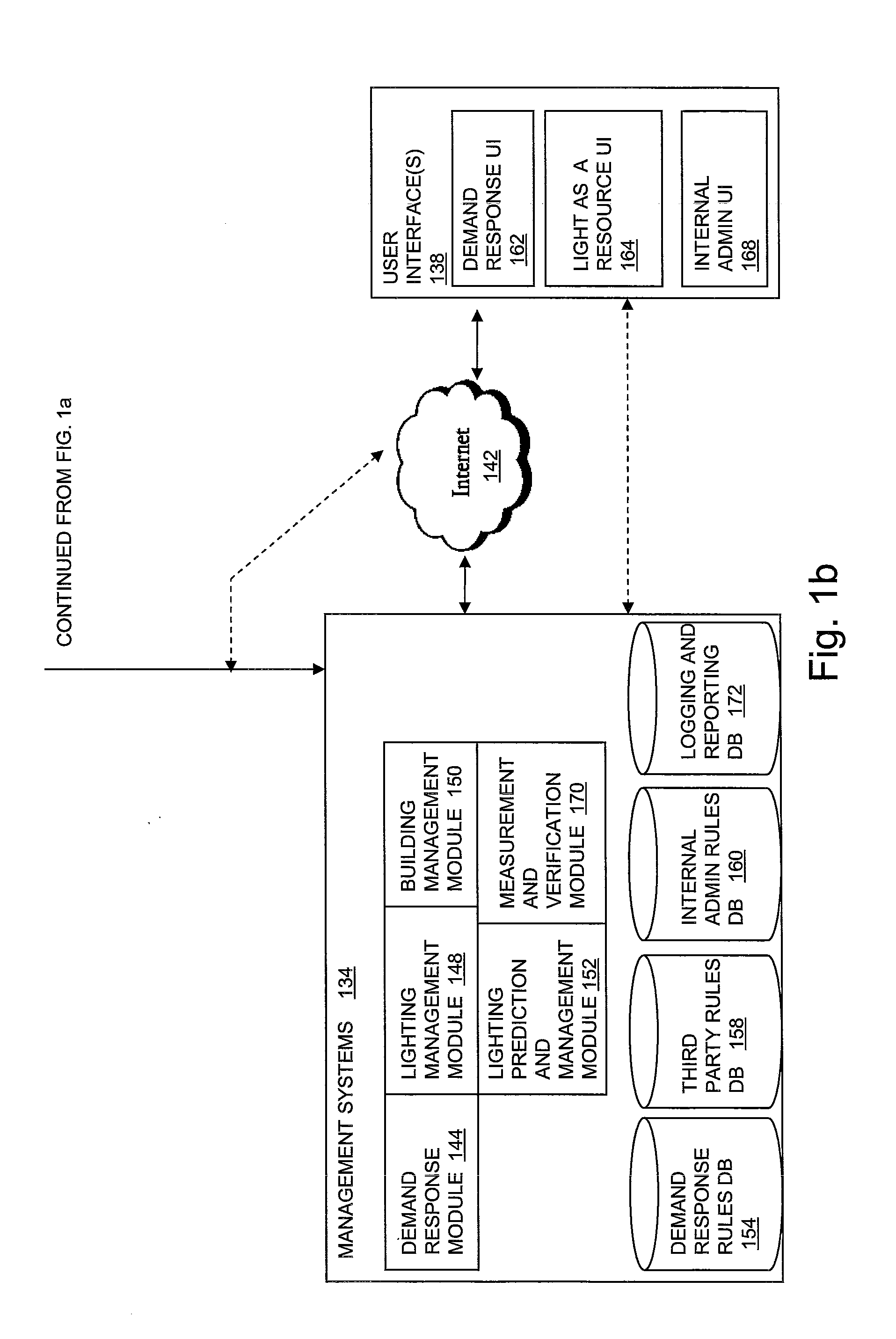

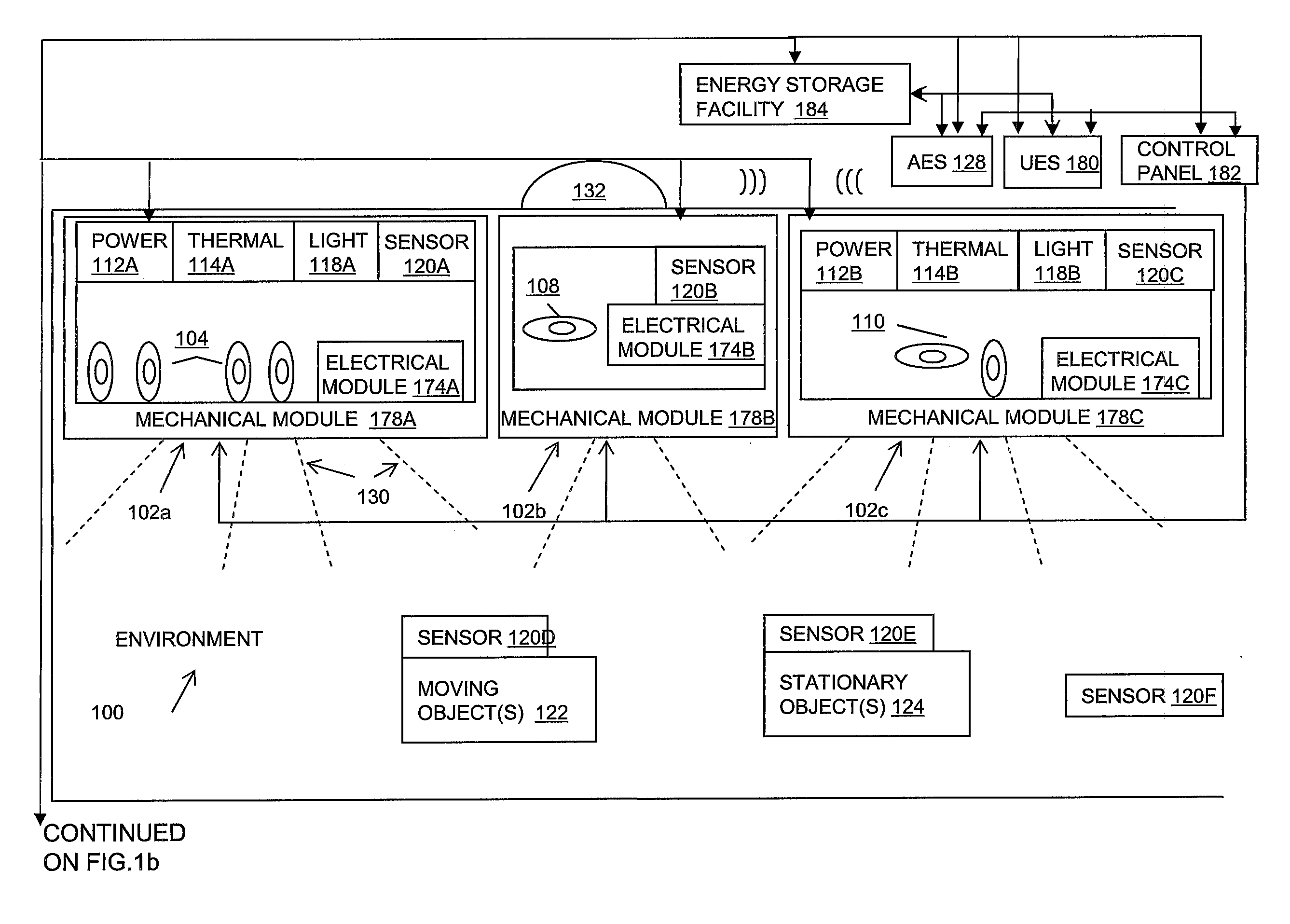

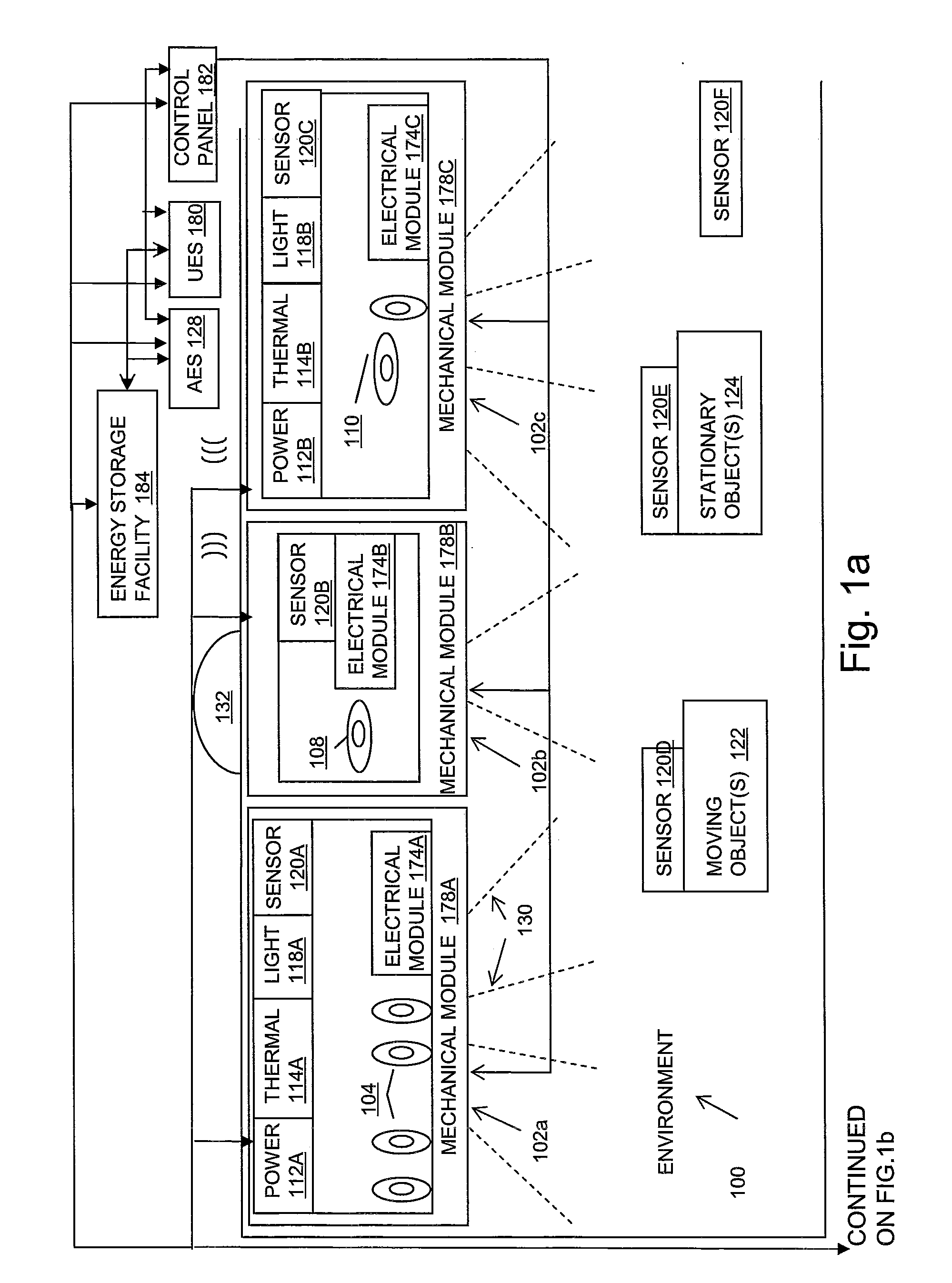

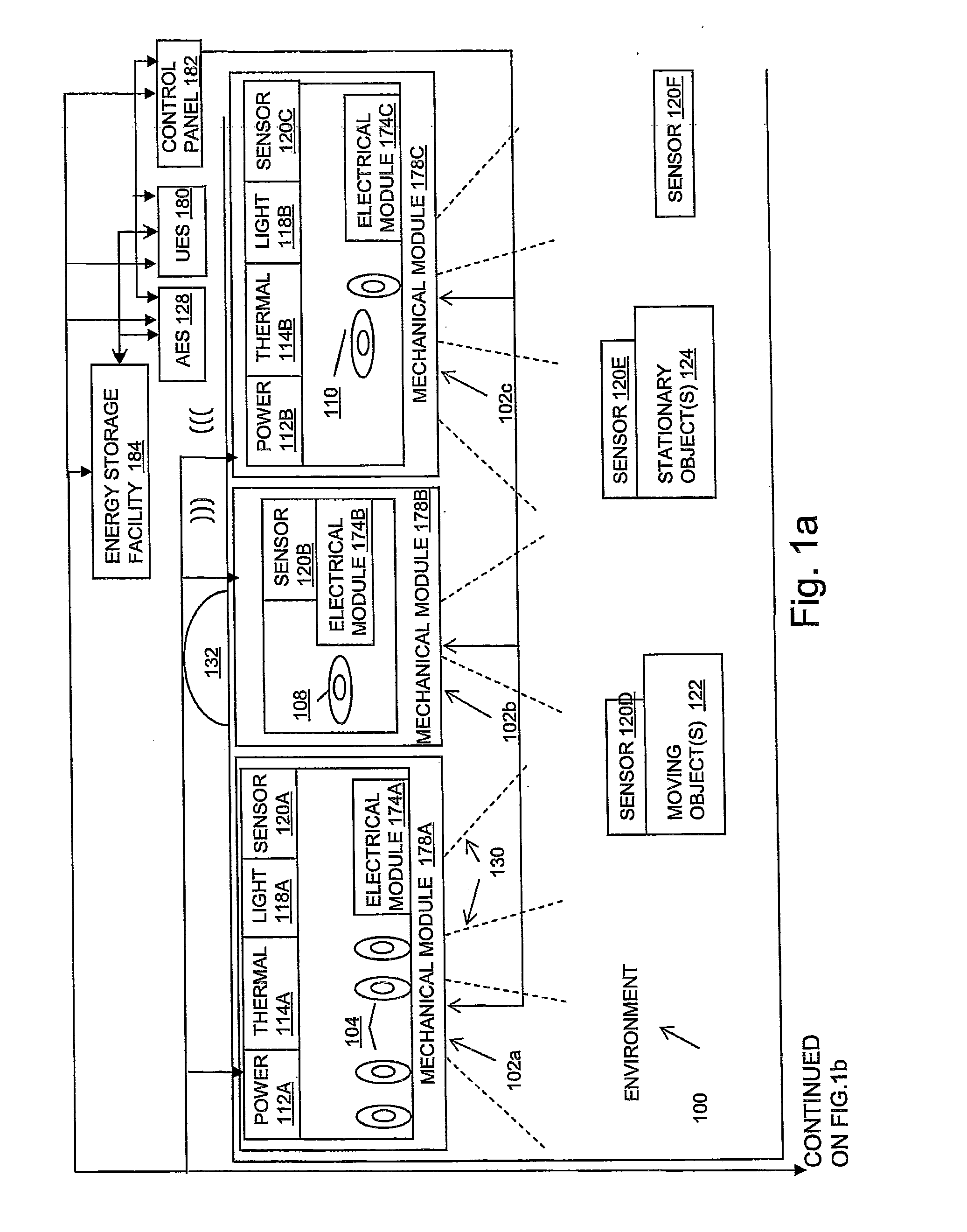

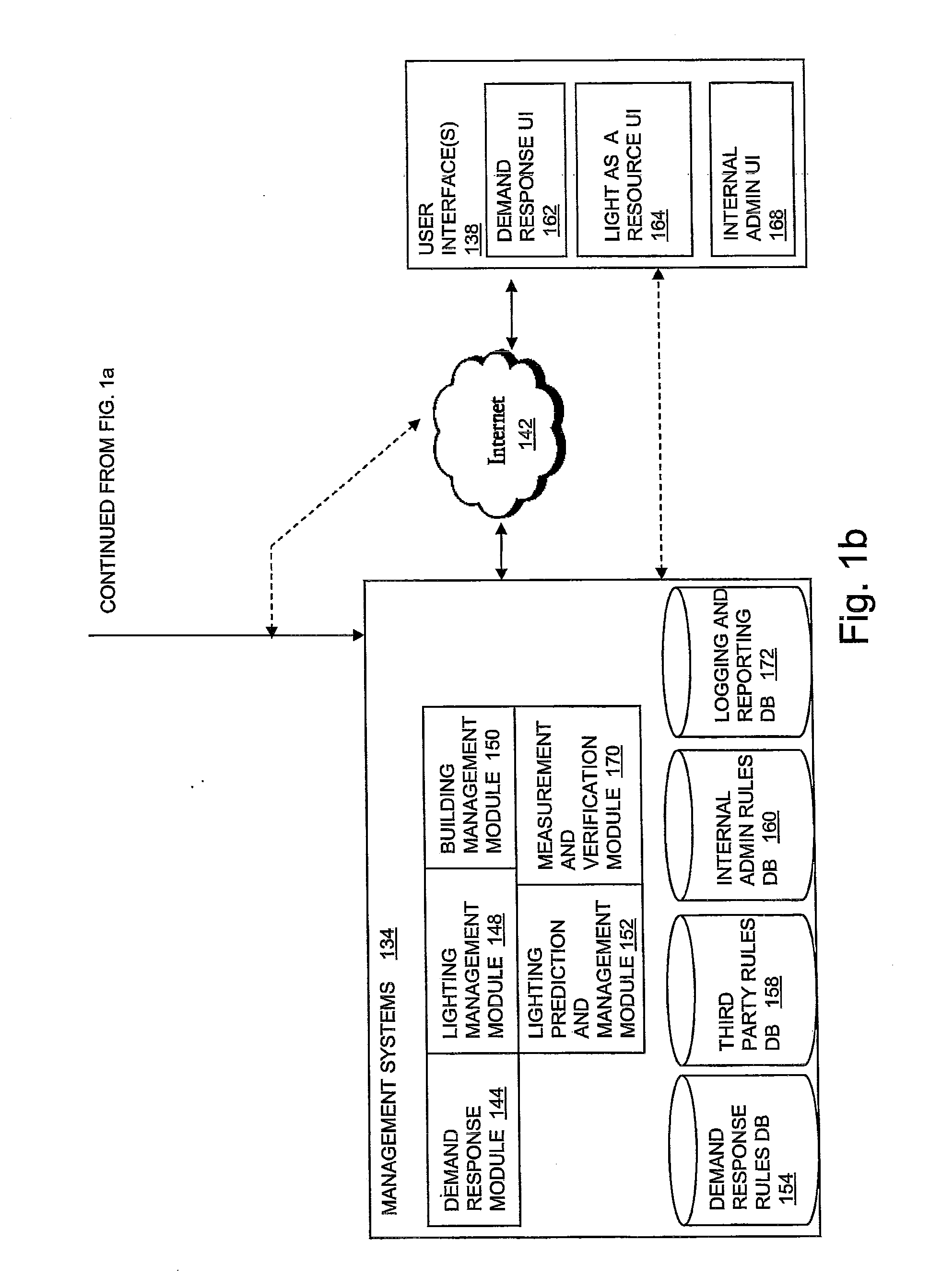

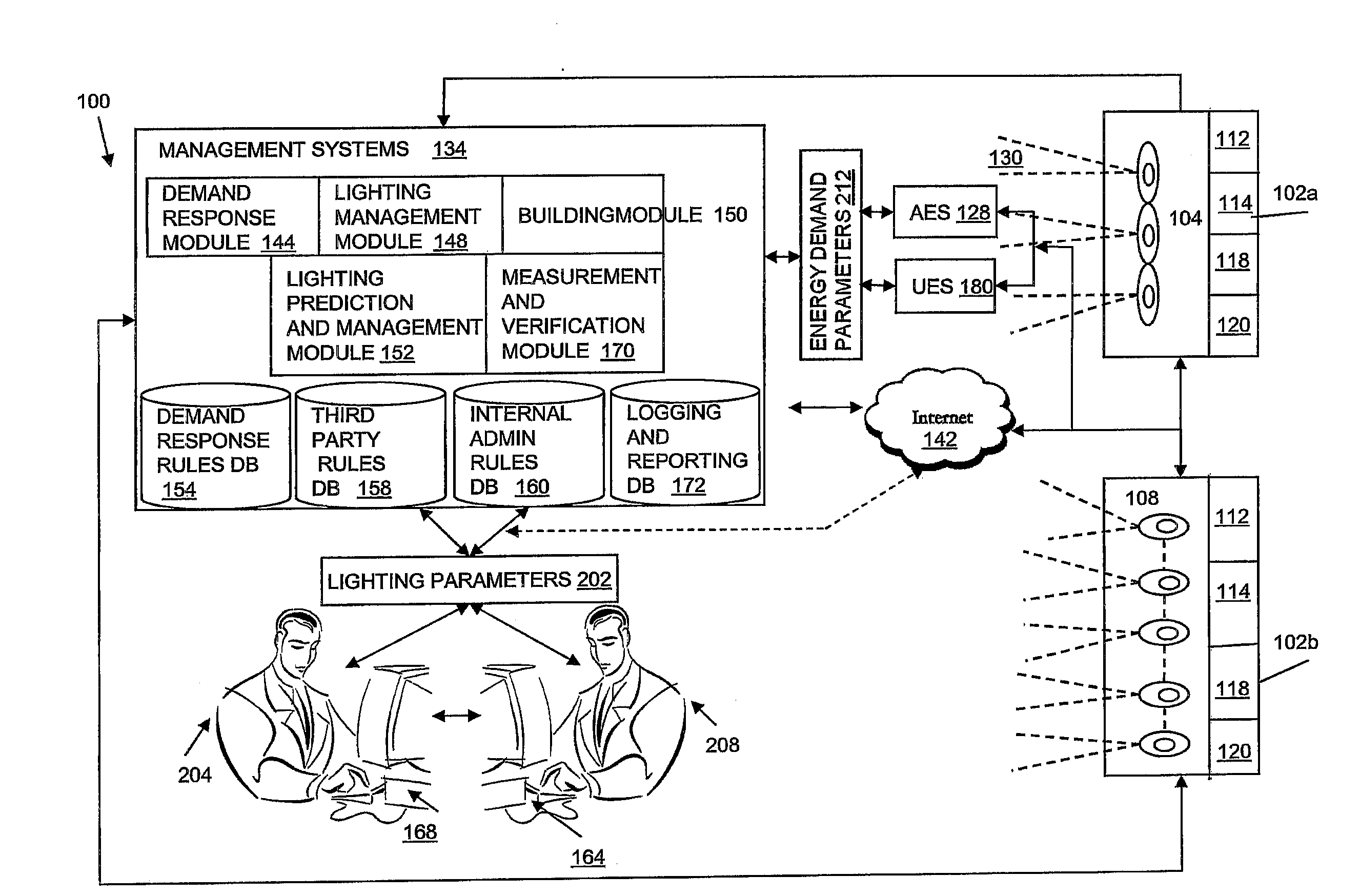

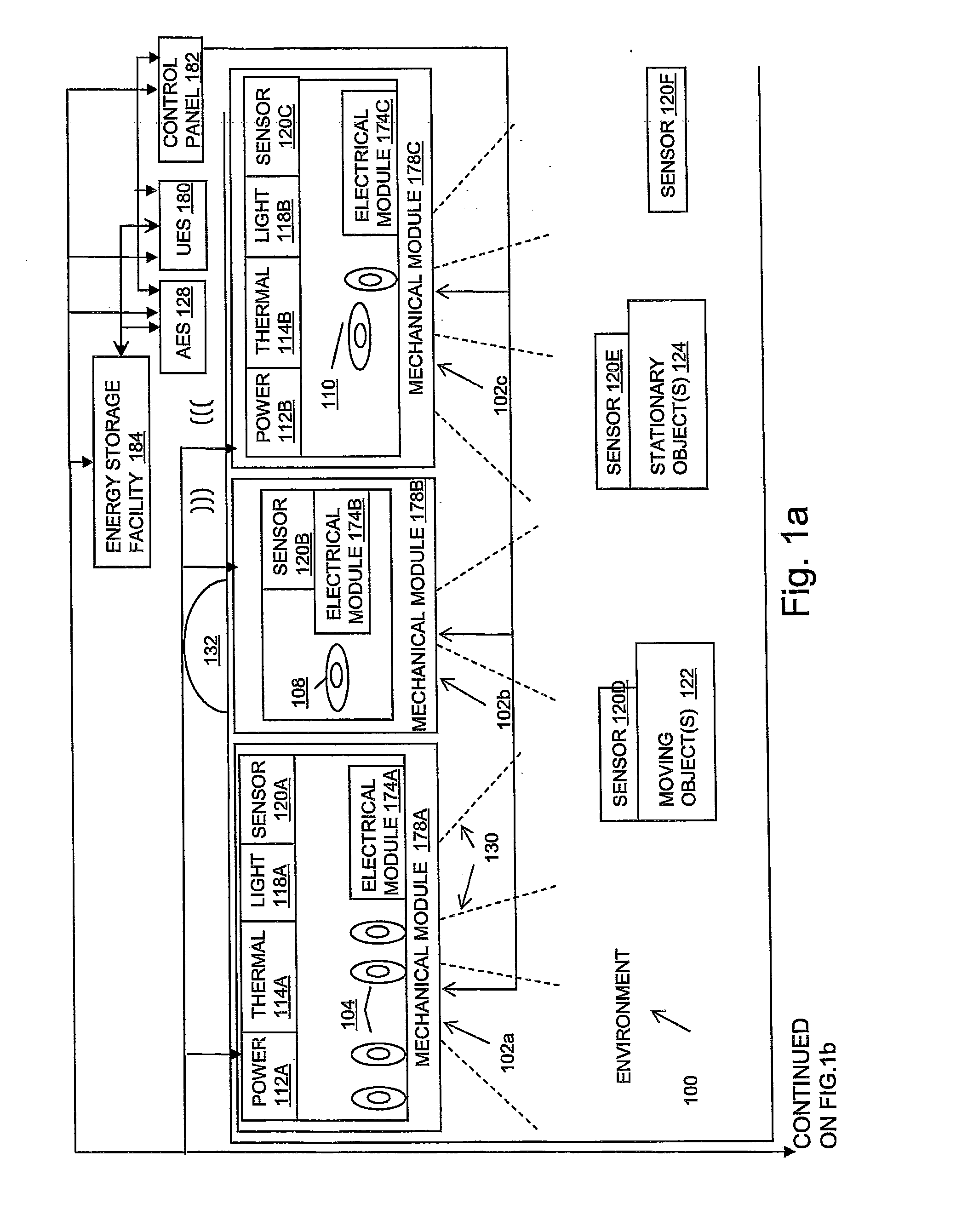

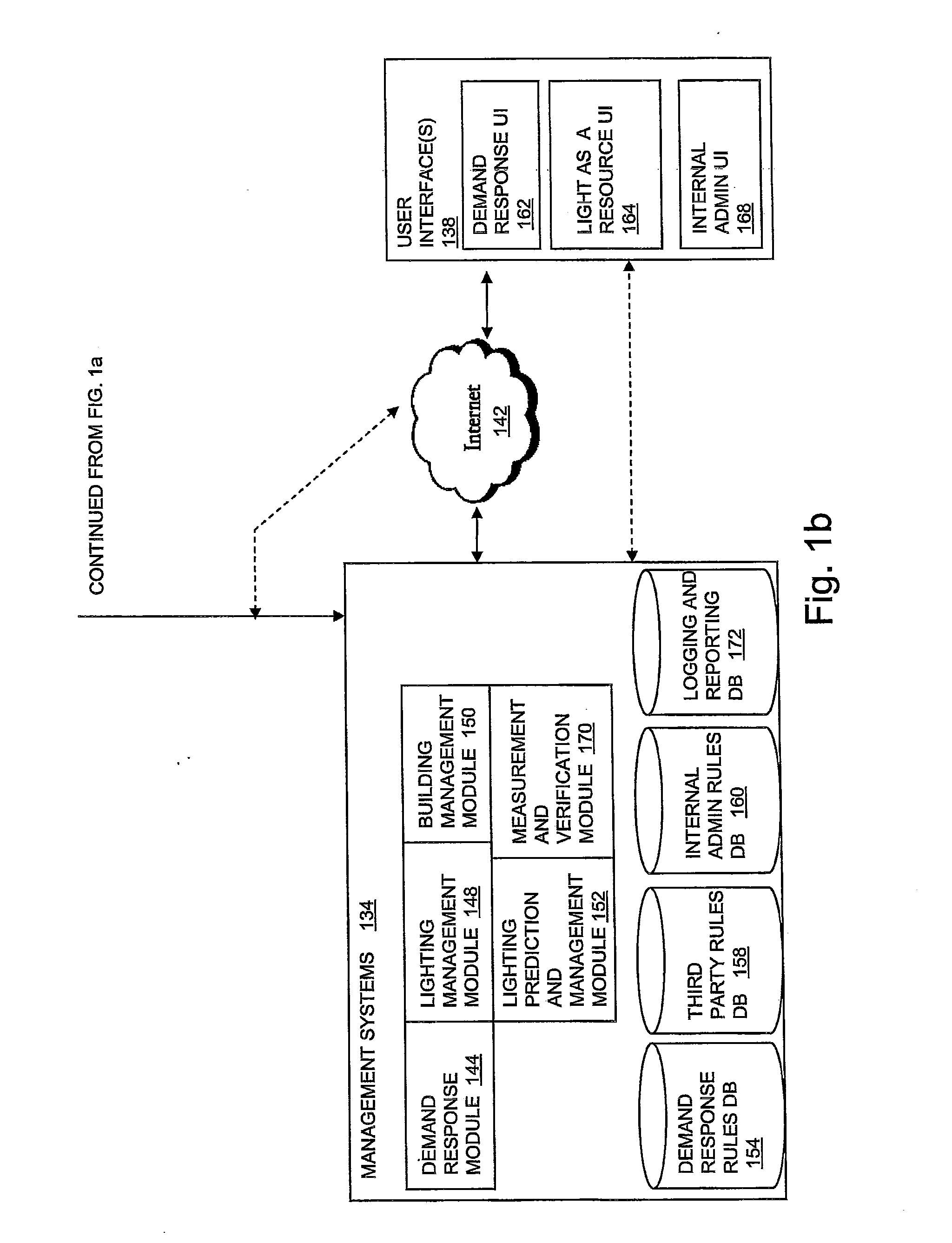

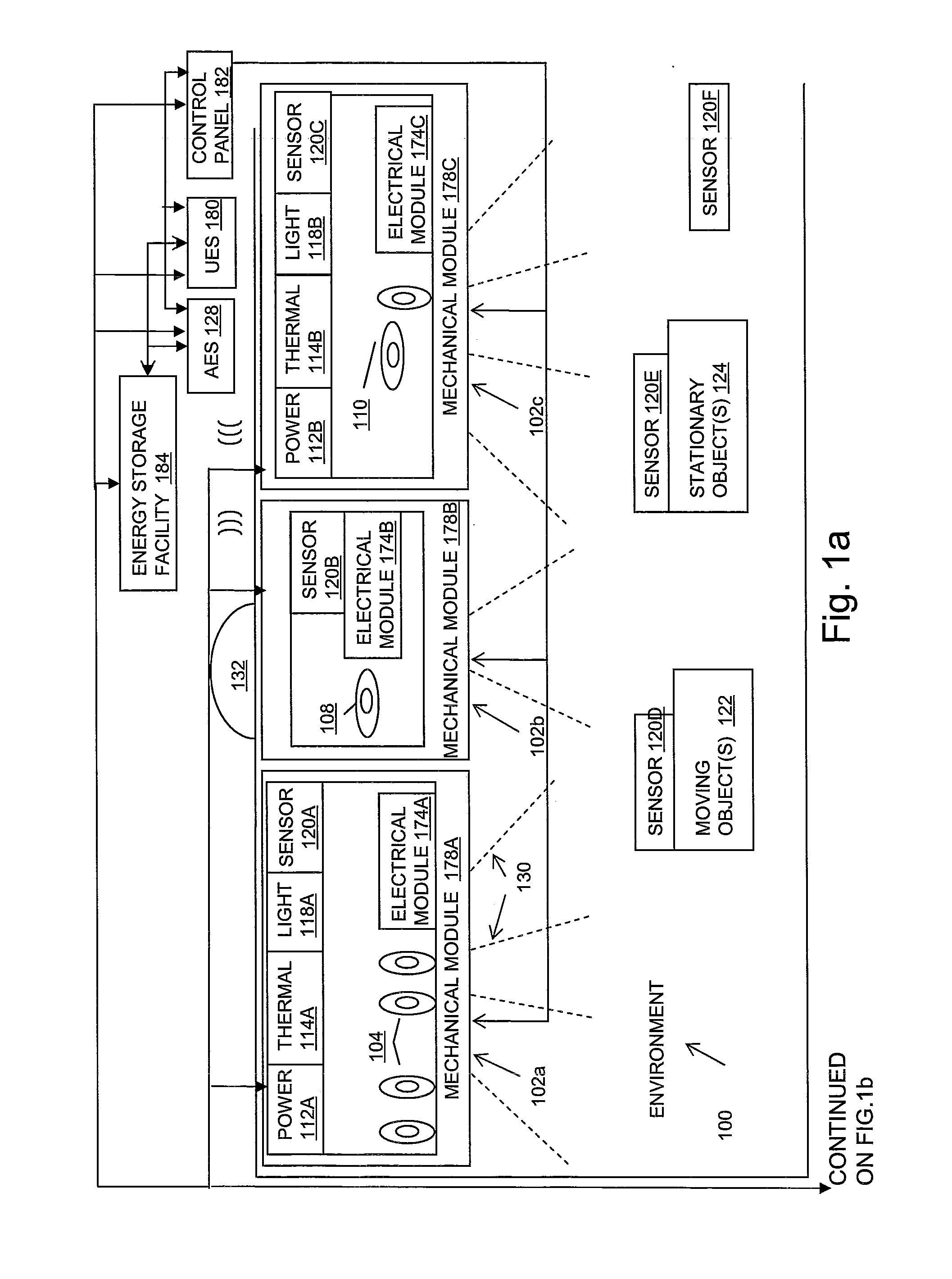

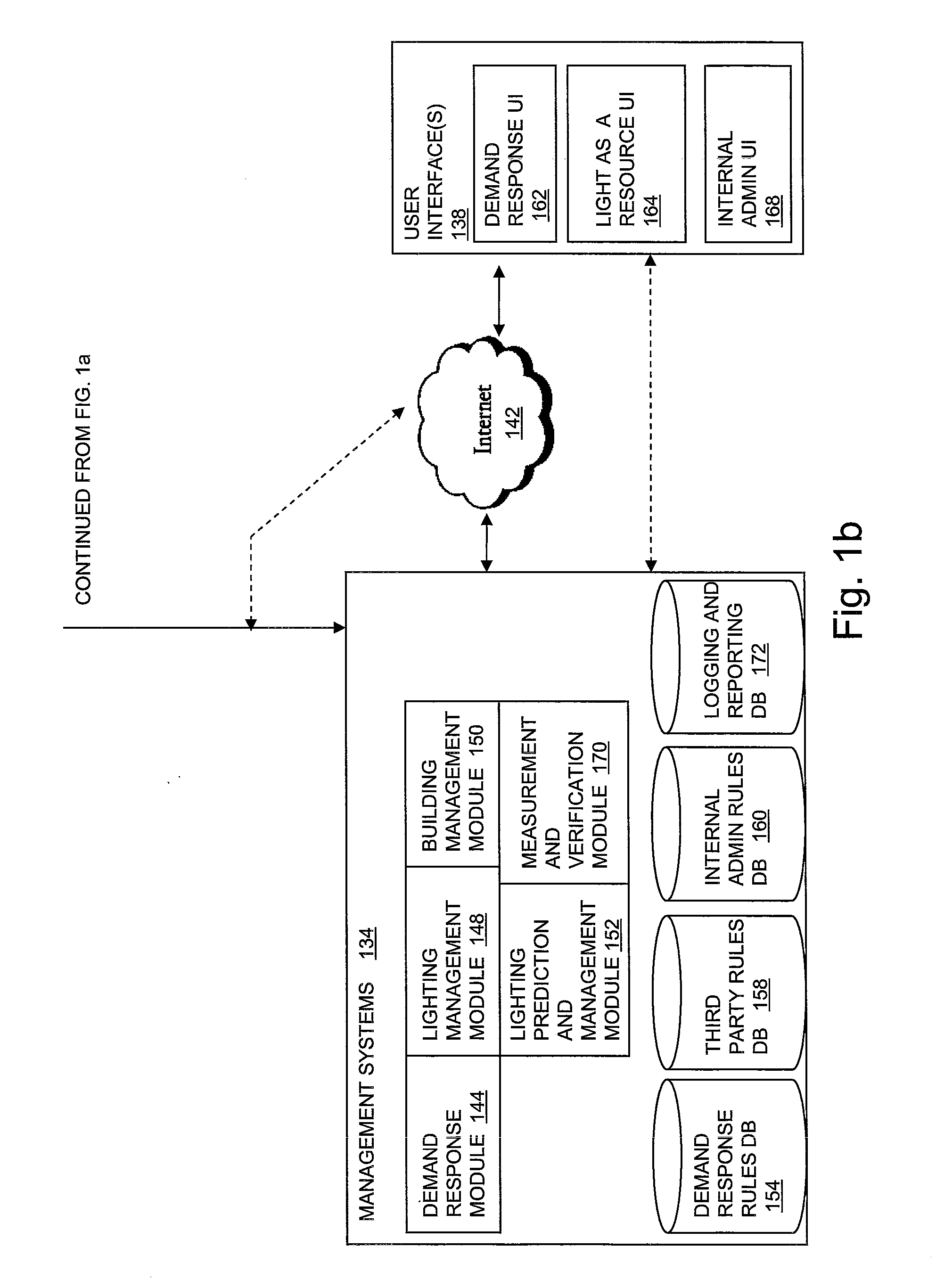

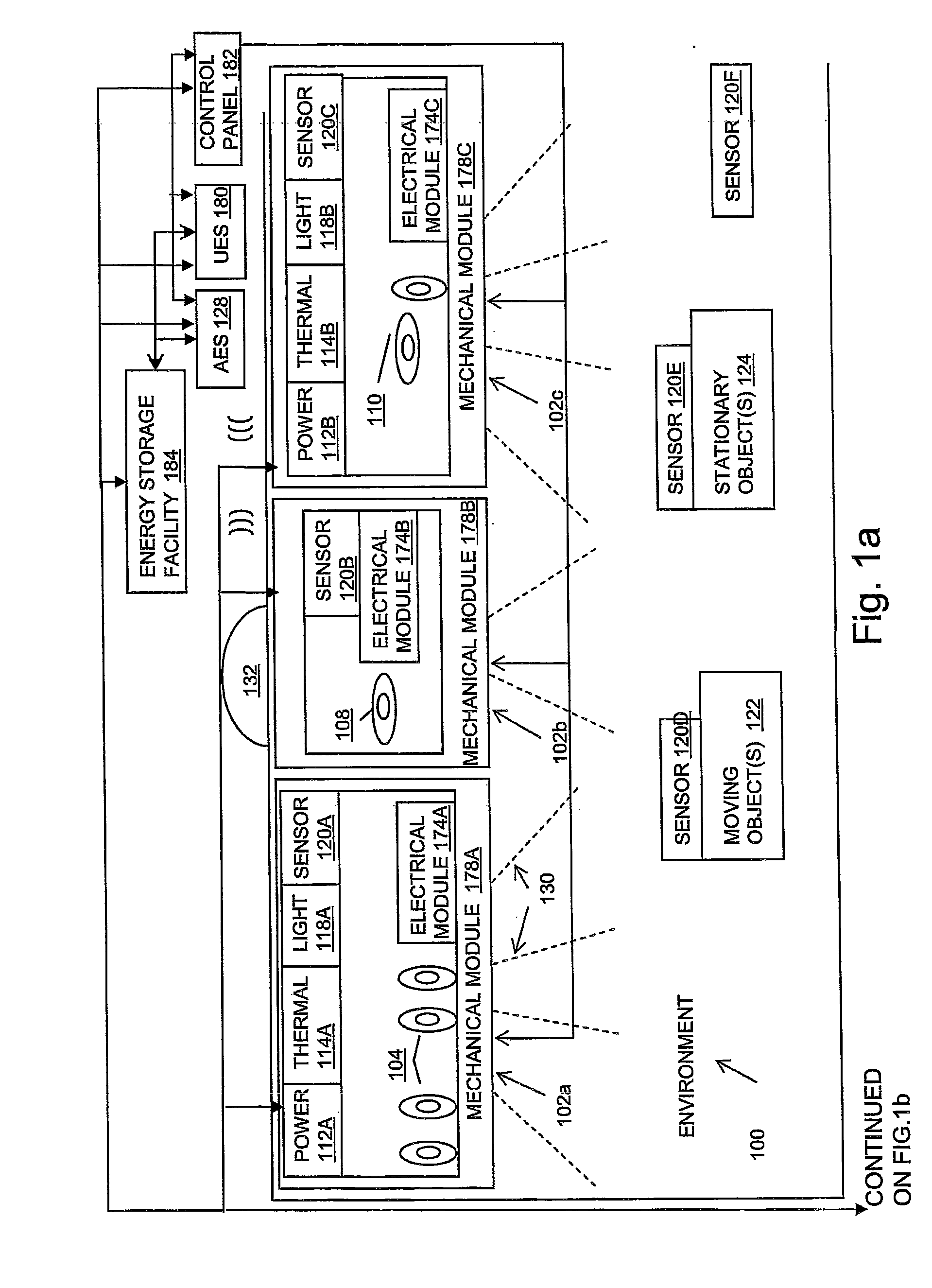

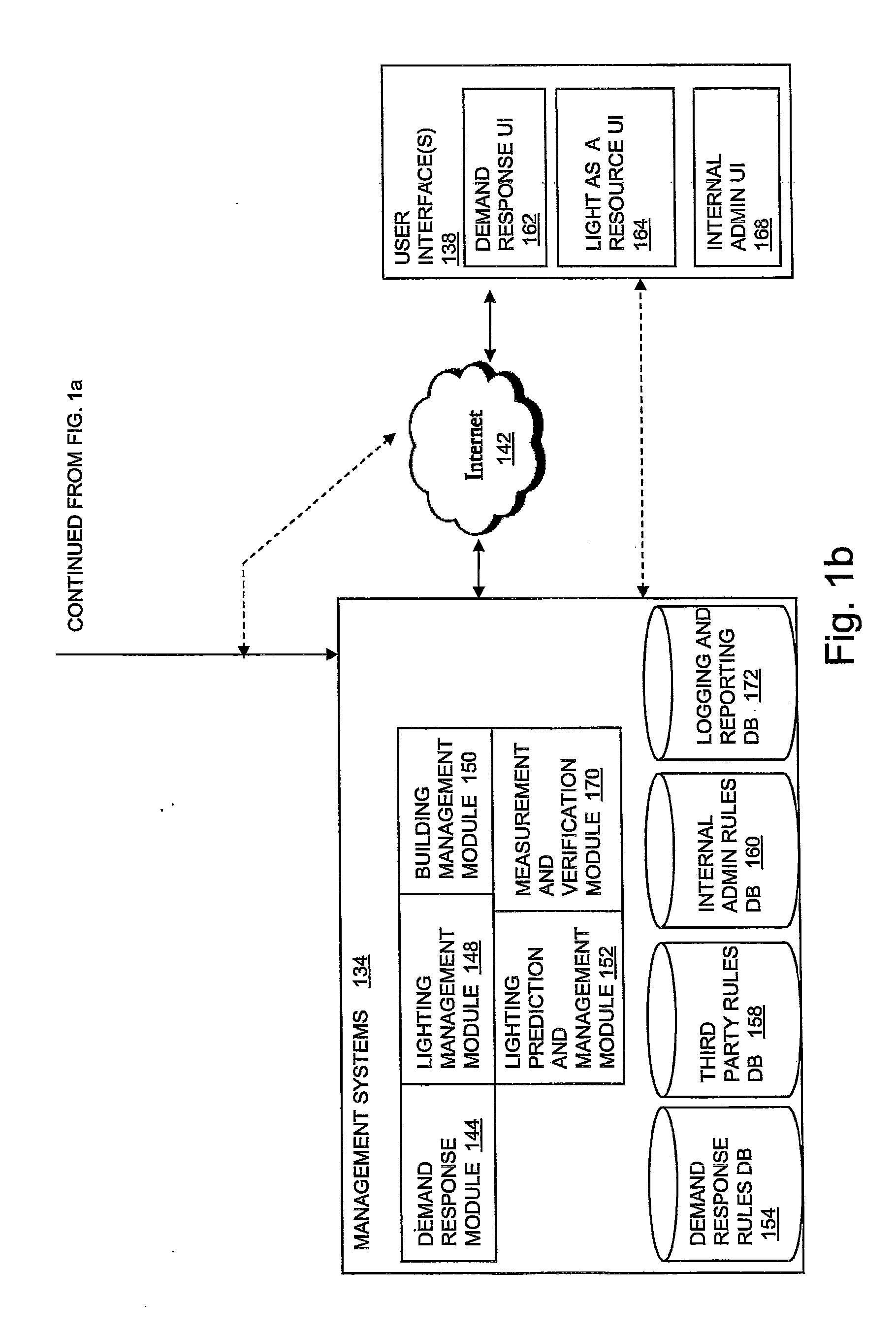

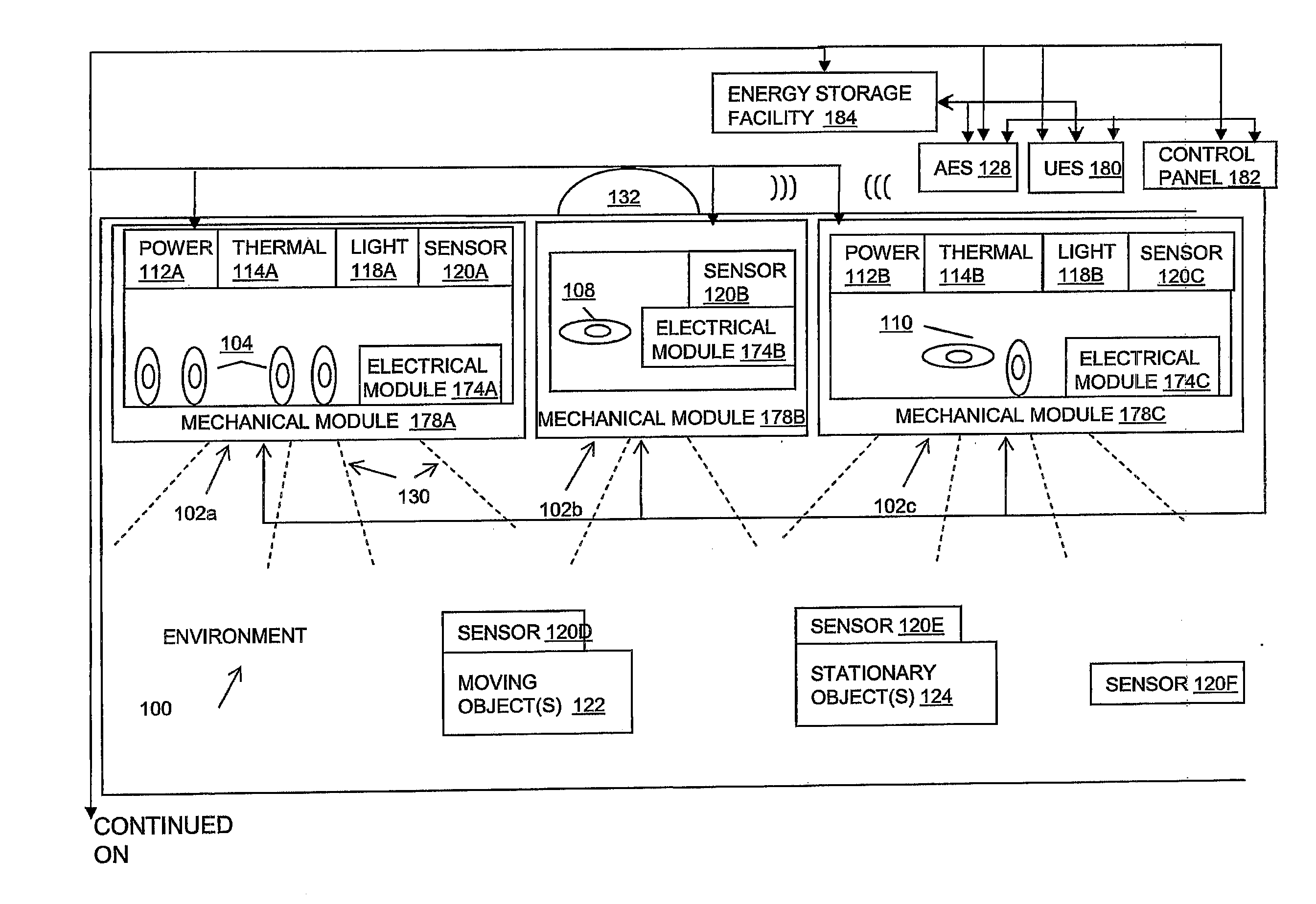

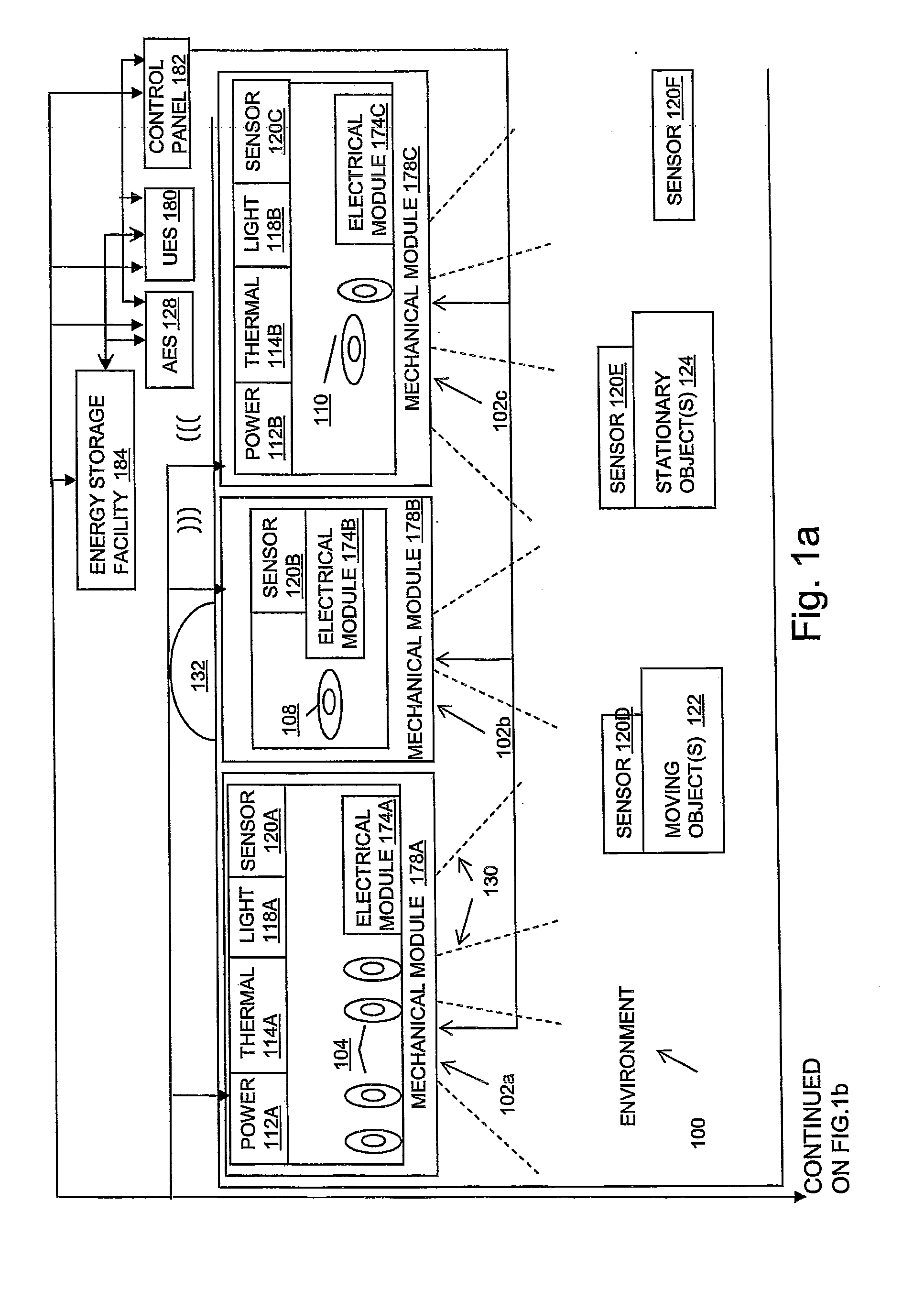

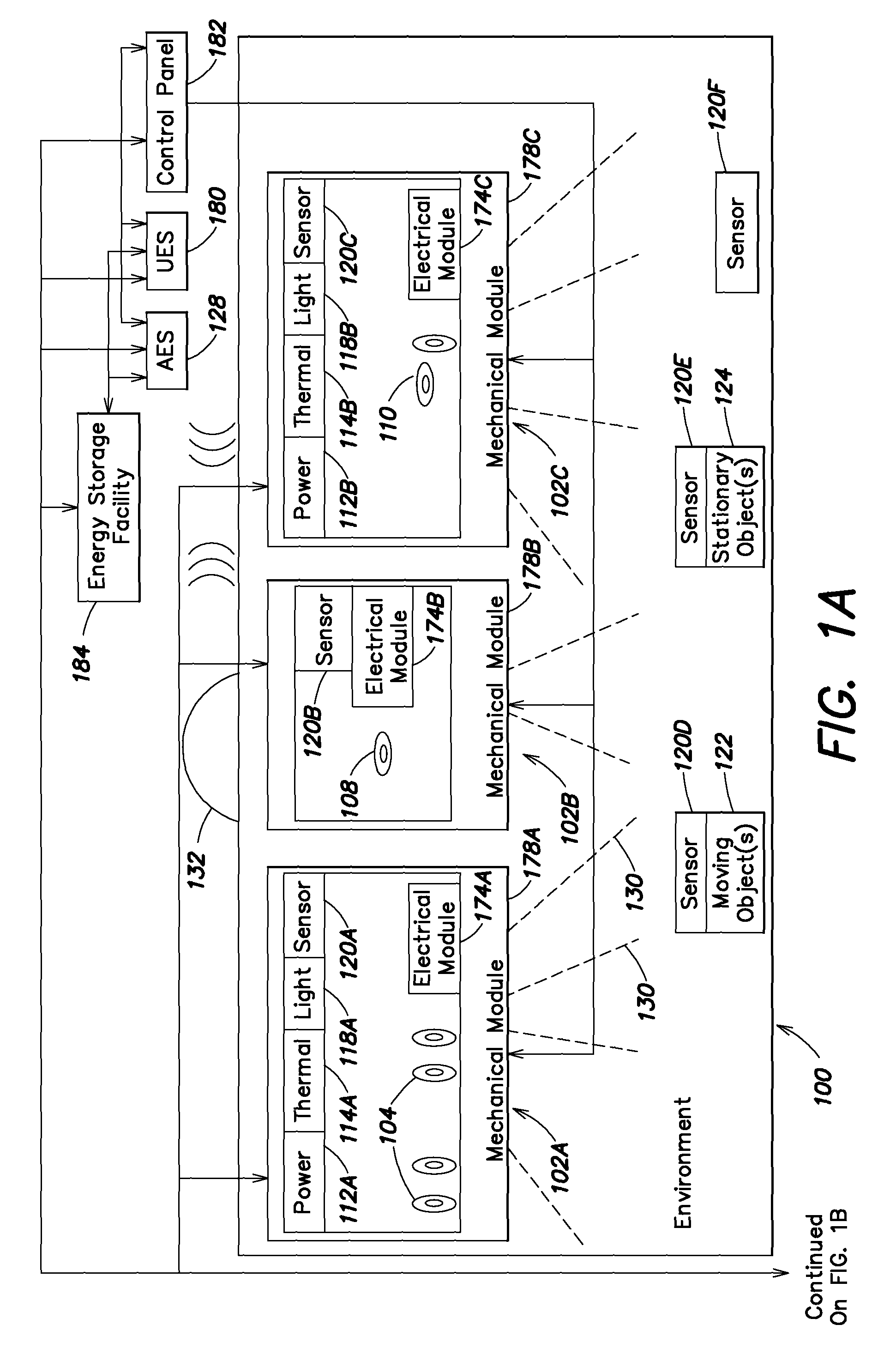

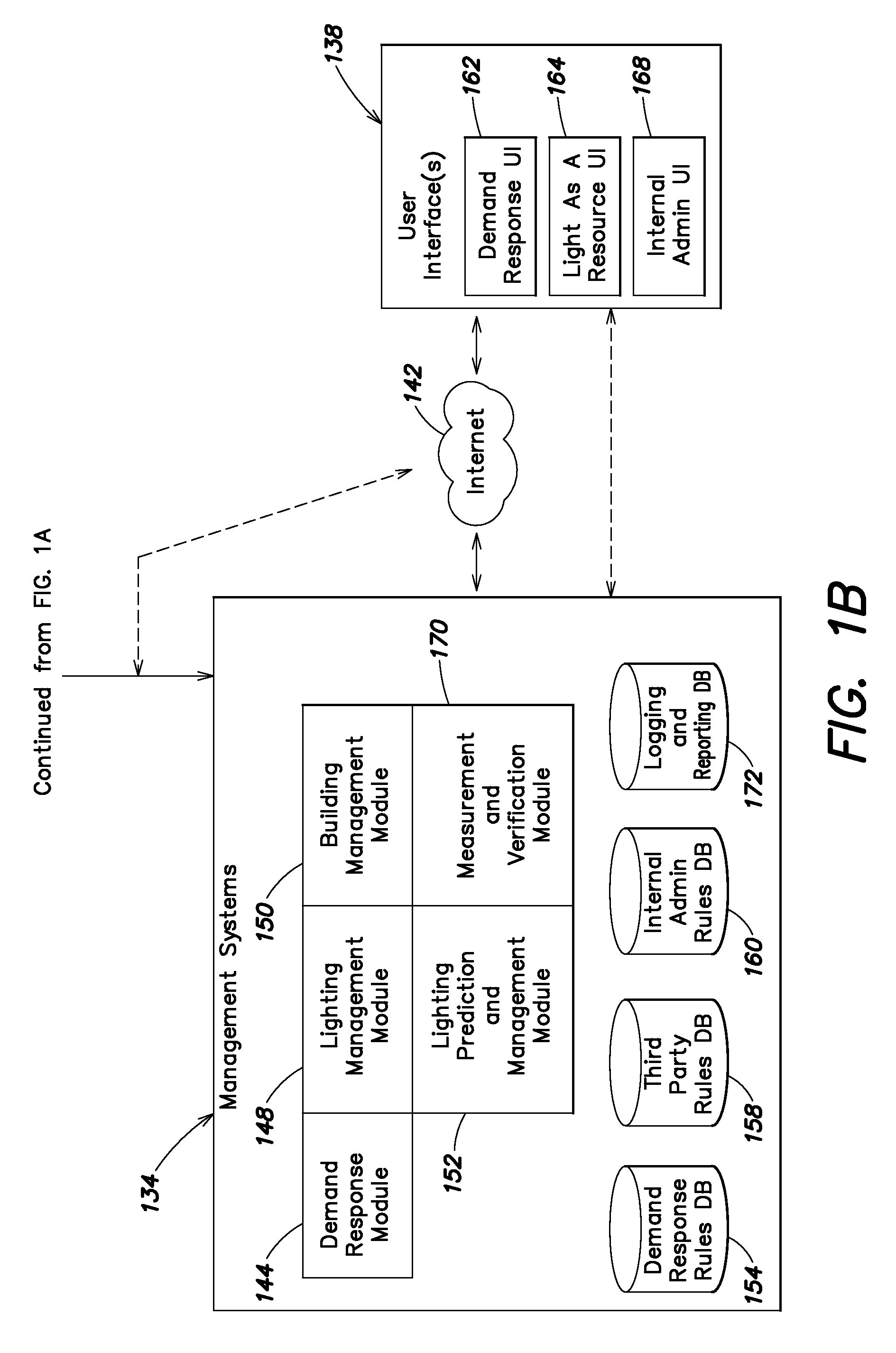

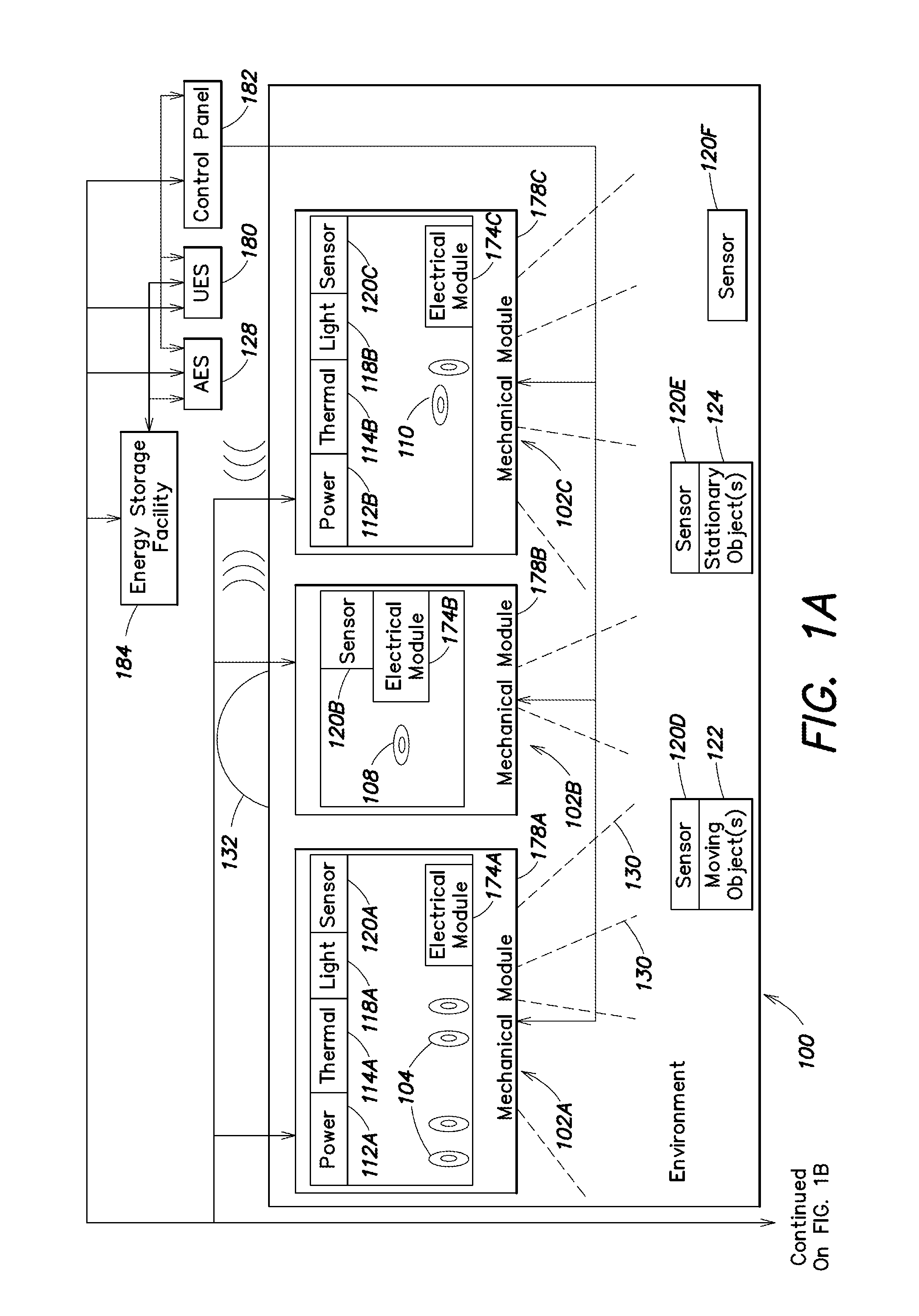

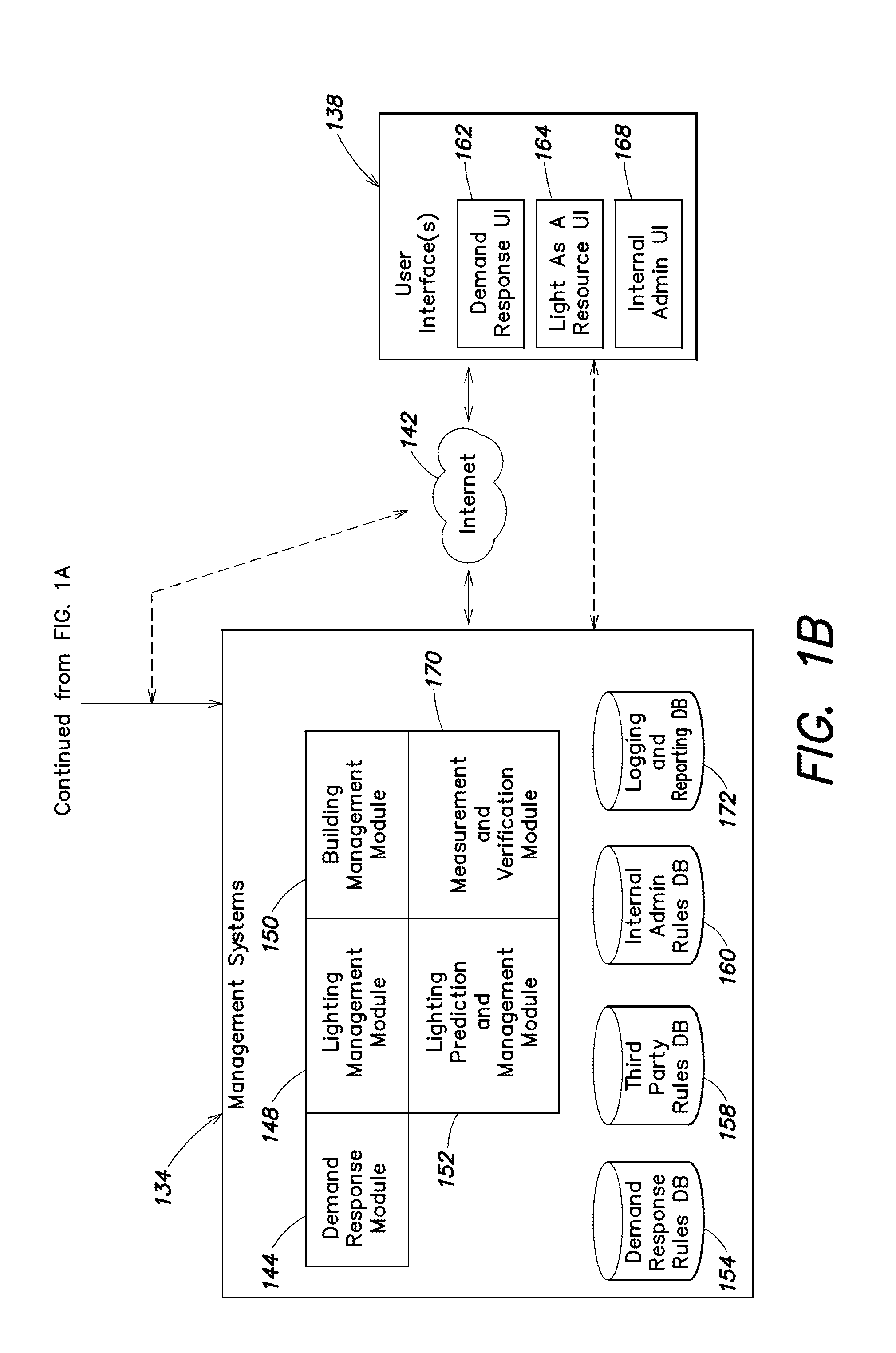

ActiveUS20110001438A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementIntelligent lightingPower Management Unit

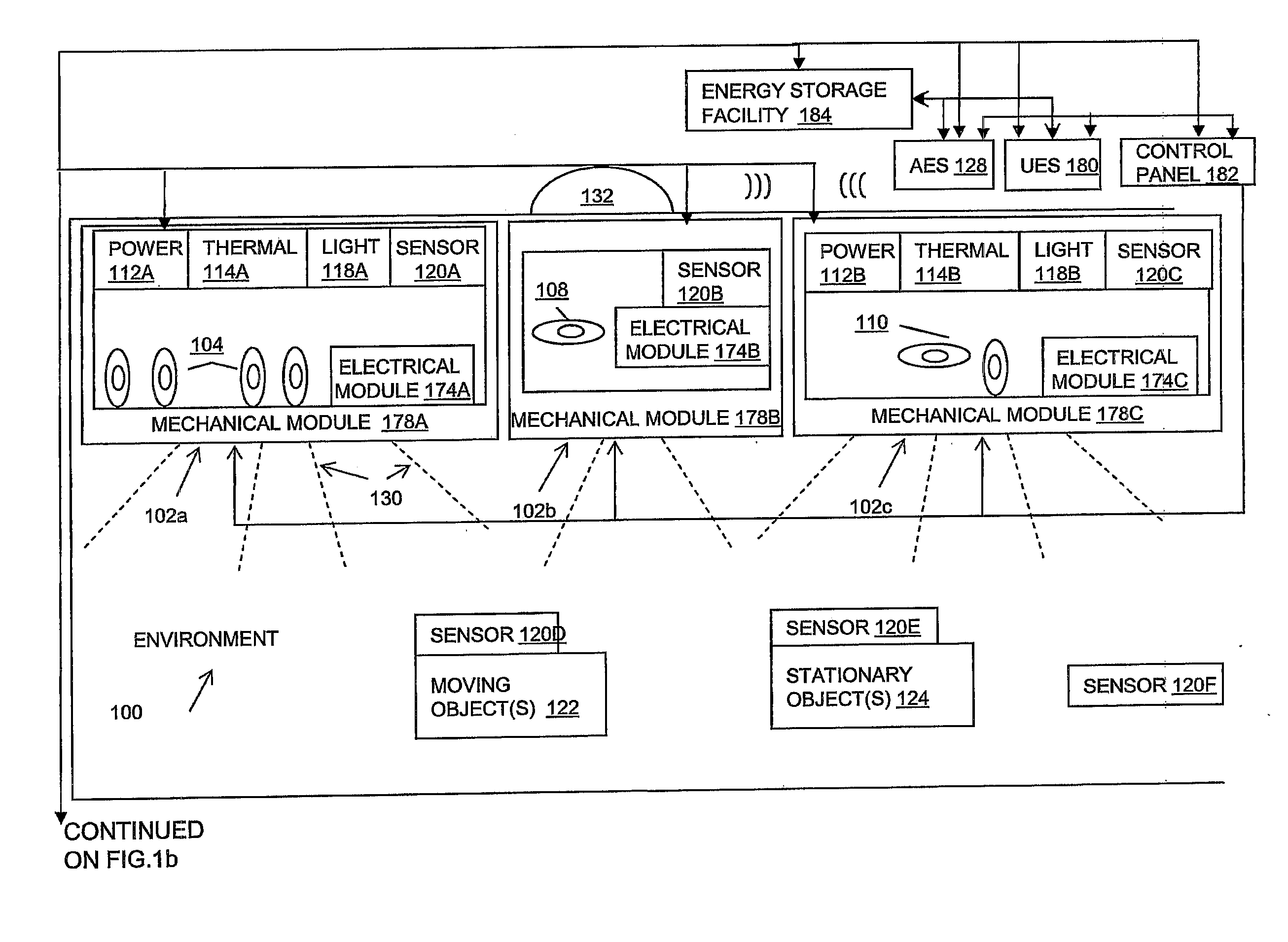

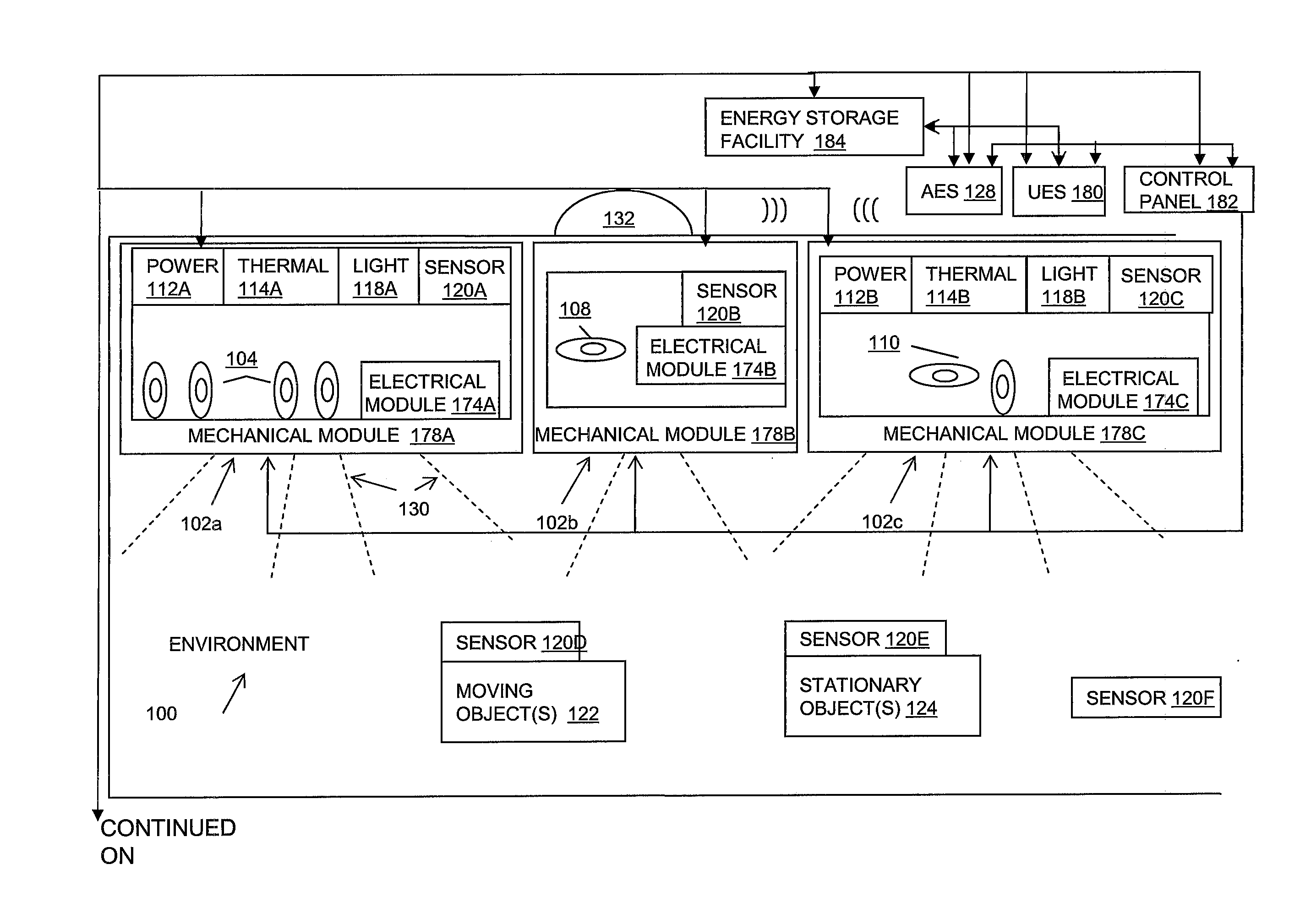

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Power Management Unit with Adaptive Dimming

ActiveUS20100264846A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementSmart lightingDesign improvement

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Power Management Unit with Power Metering

ActiveUS20100270933A1Failure to compensateMaintain lightDischarge tube incandescent screensPlanar light sourcesDesign improvementSmart lighting

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

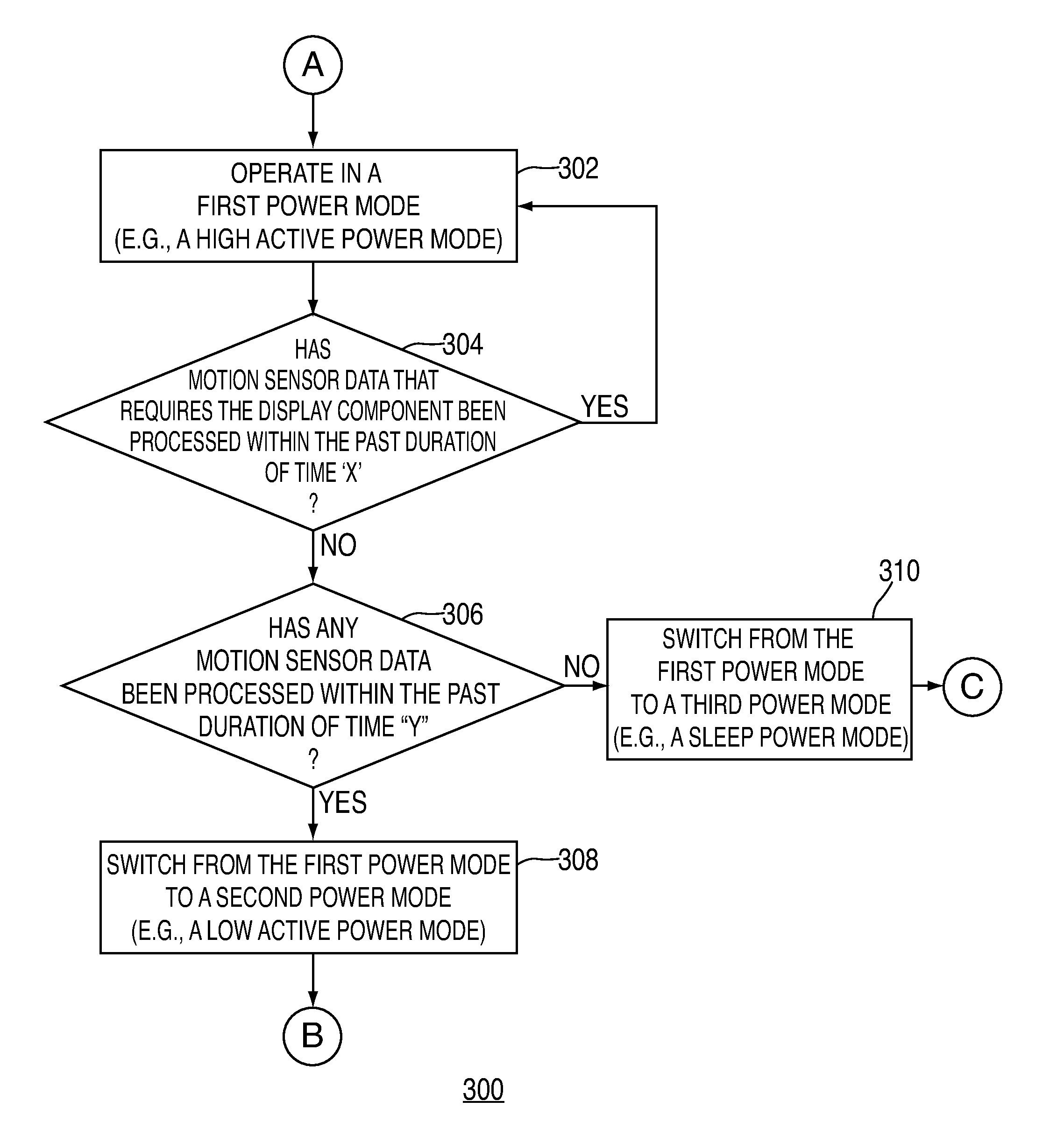

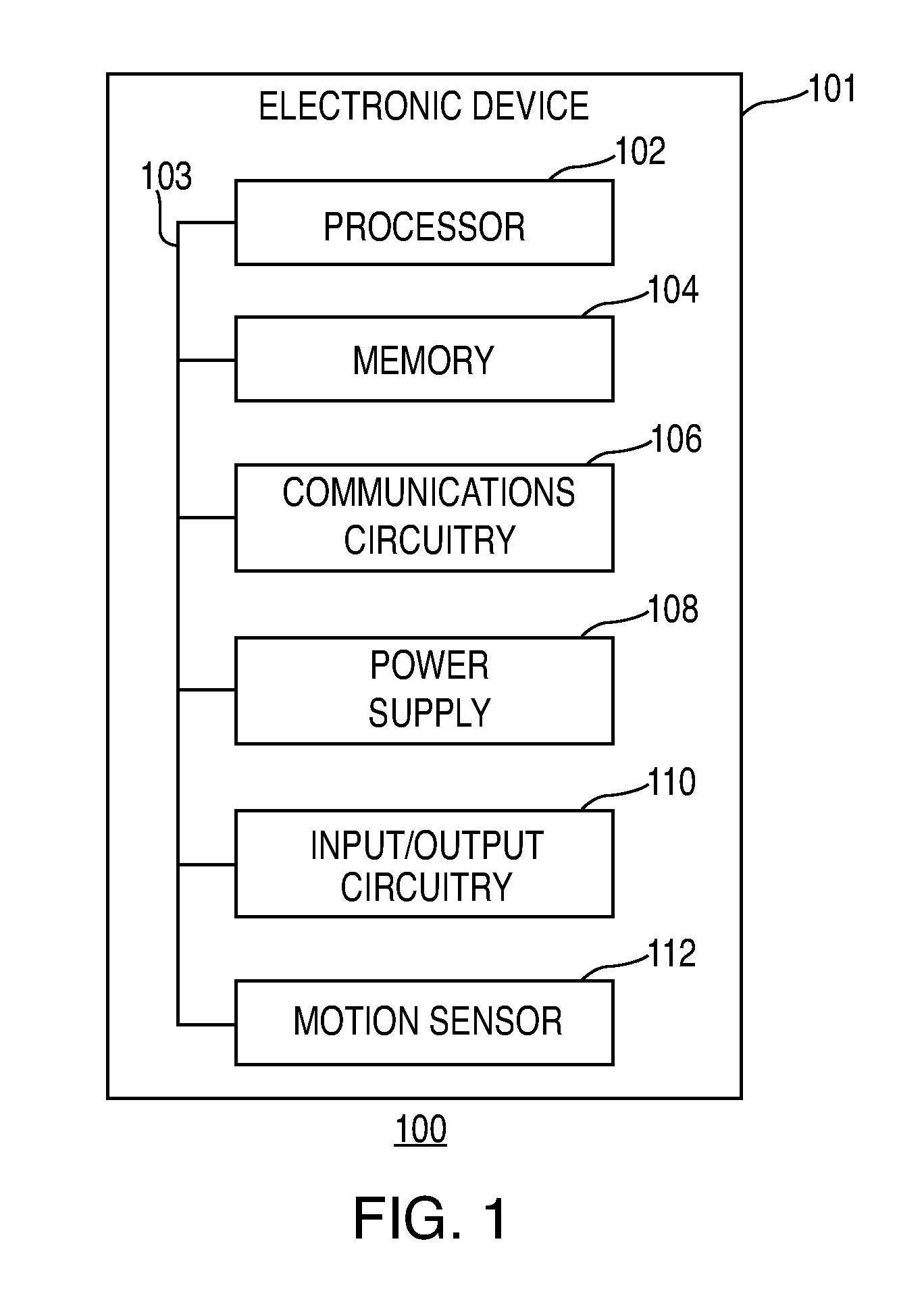

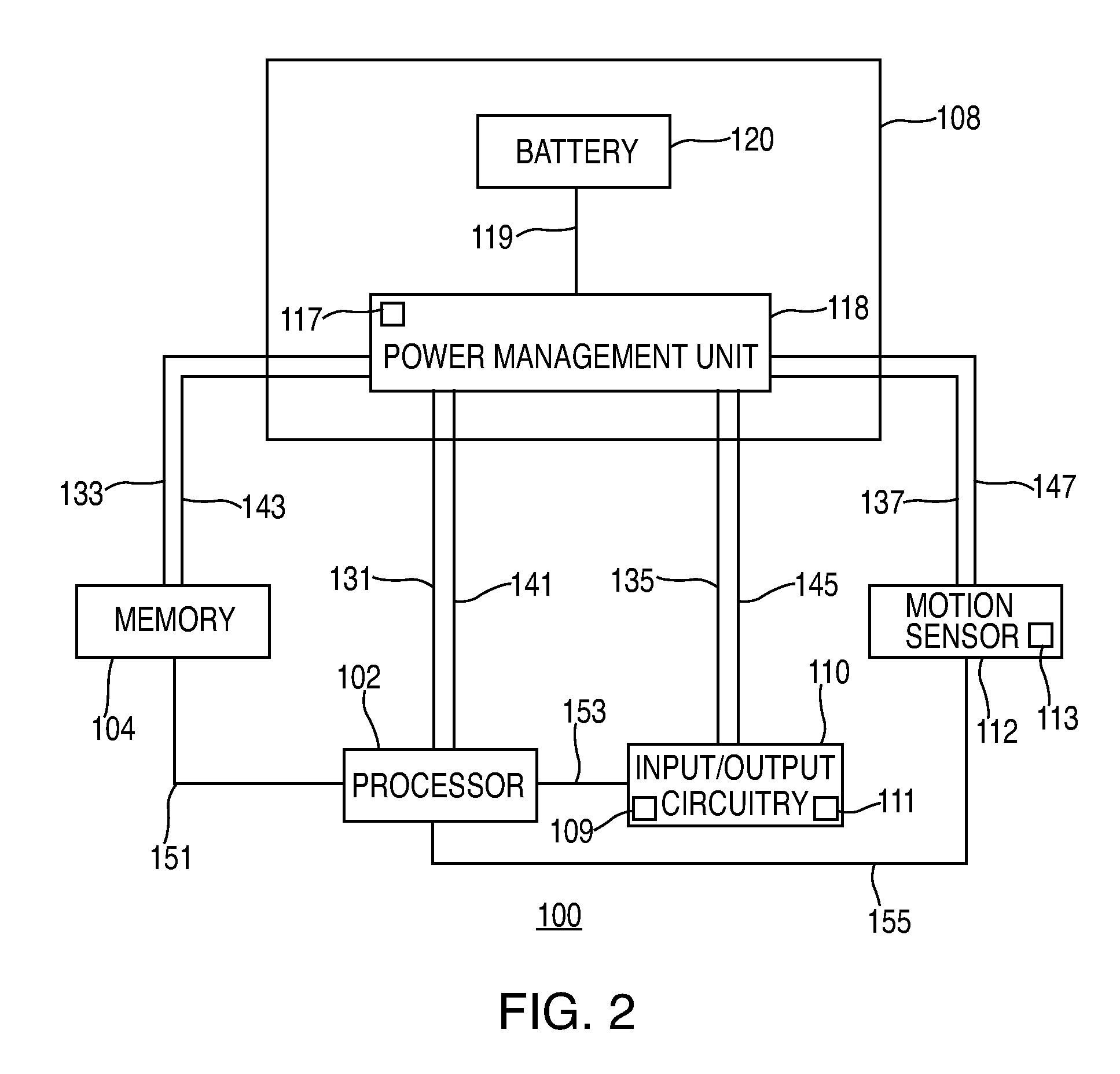

Motion sensor data processing using various power management modes

Systems and methods for processing motion sensor data using various power management modes of an electronic device are provided. Power may be provided to a motion sensor during a first power mode of the device. In response to the motion sensor detecting a motion event with a magnitude exceeding a threshold, the sensor may transmit a wake up signal to a power management unit of the device. In response to receiving the wake up signal, the power management unit may switch the device to a second power mode. The device may provide power to a processor and load the processor with a motion sensing application when switching to the second power mode. During the second power mode, motion sensor data may be processed to determine that the motion event is not associated with an intentional user input and the device may return to the first power mode.

Owner:APPLE INC

Power Management Unit with Light Module Identification

ActiveUS20110001436A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementDesign improvementSmart lighting

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Power Management Unit with Multi-Input Arbitration

ActiveUS20100295482A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementMulti inputDesign improvement

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

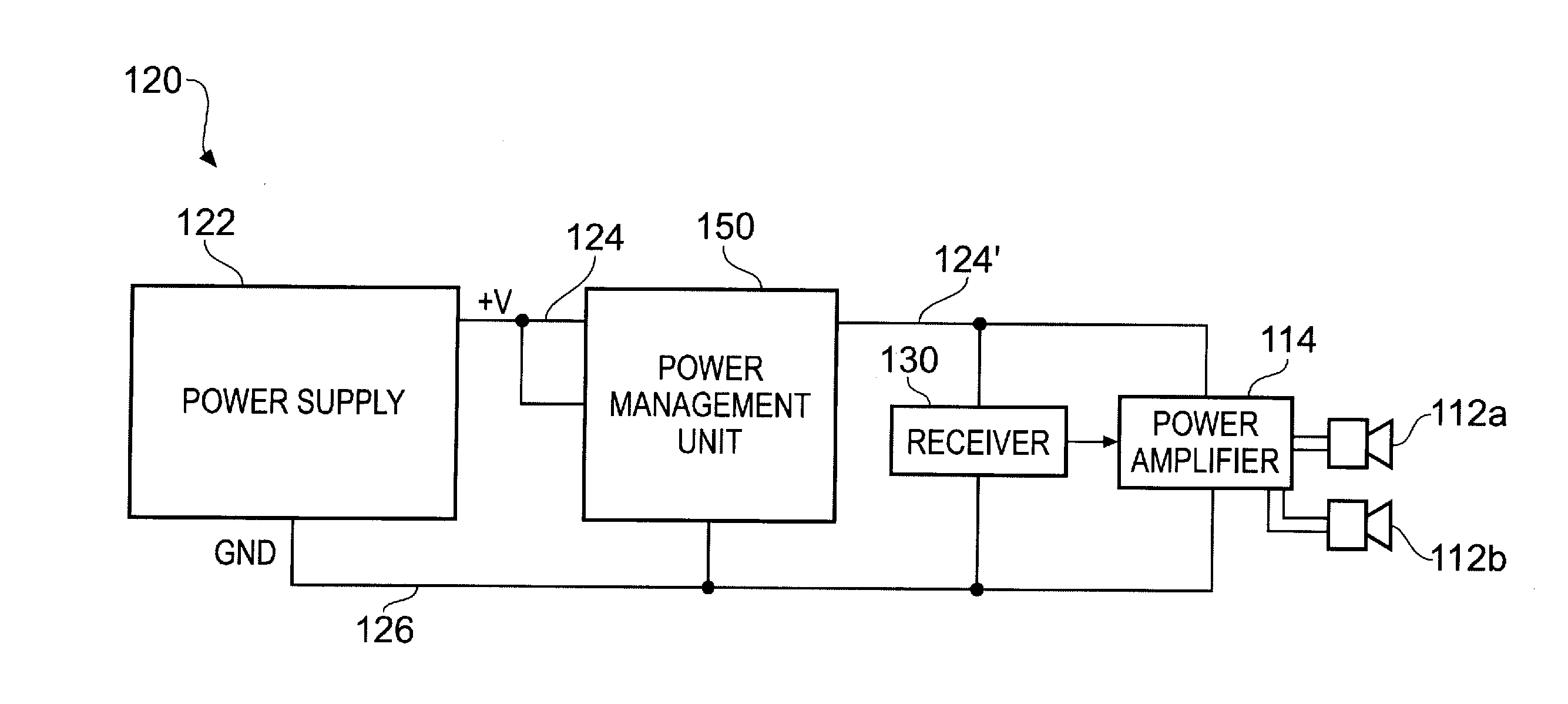

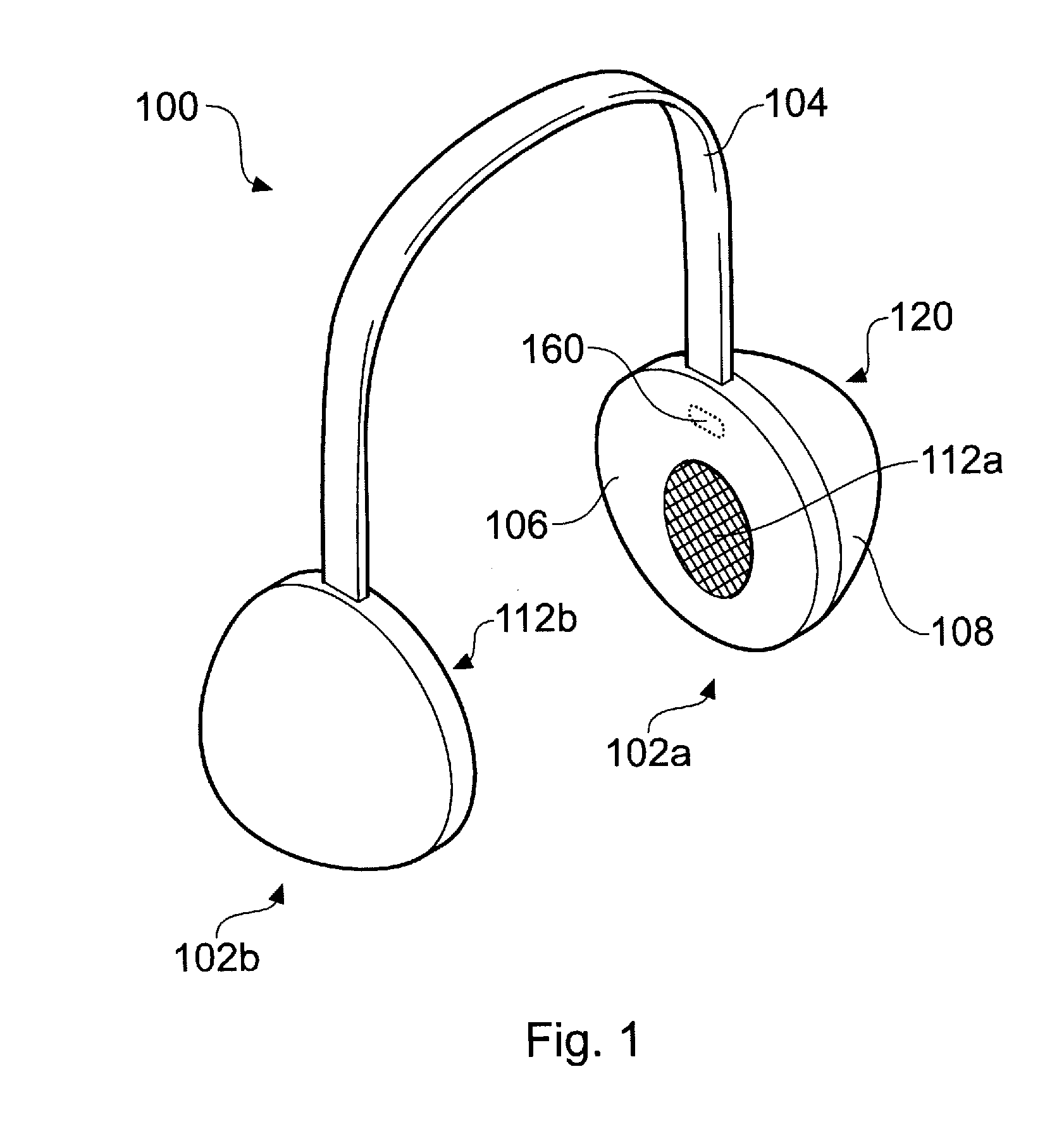

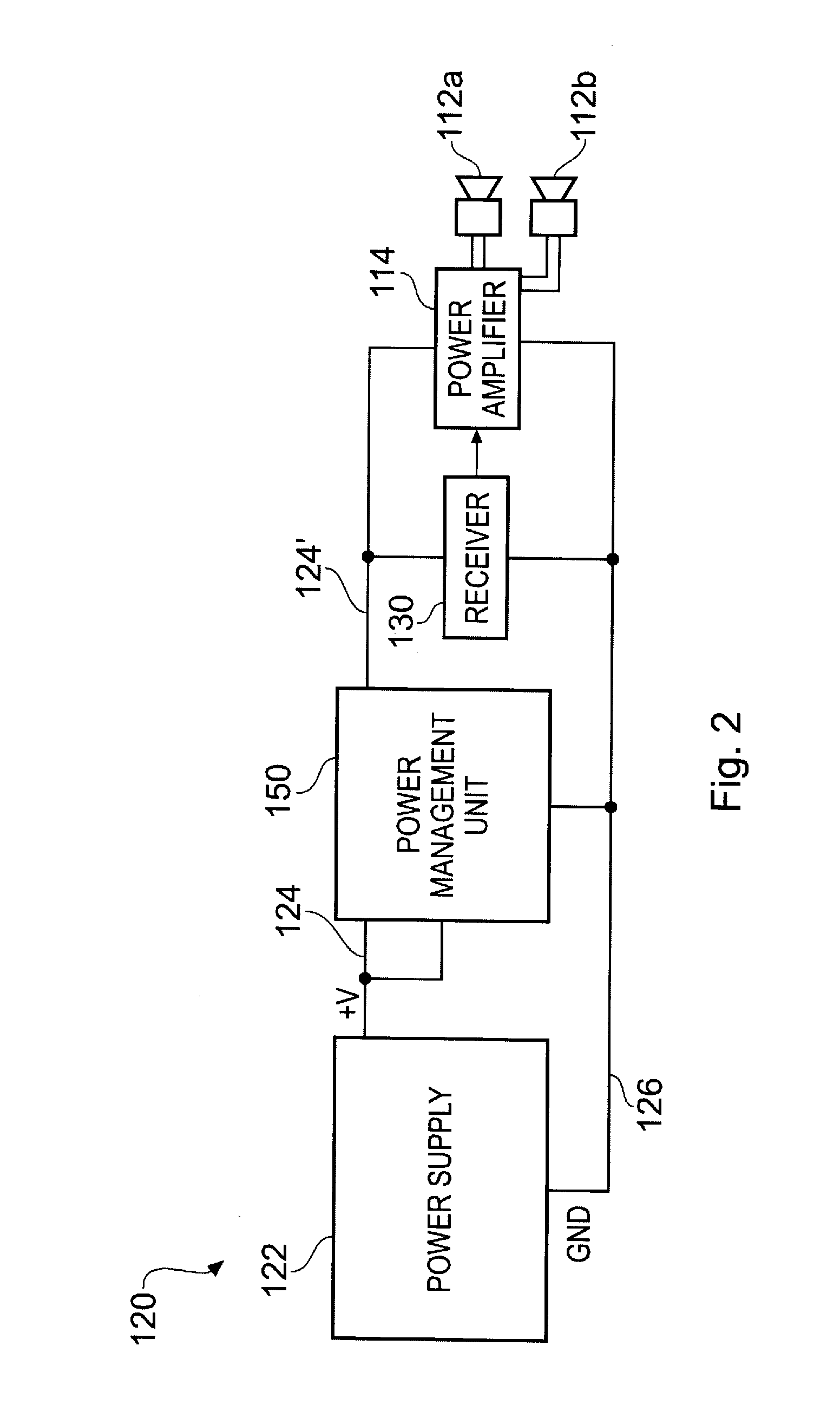

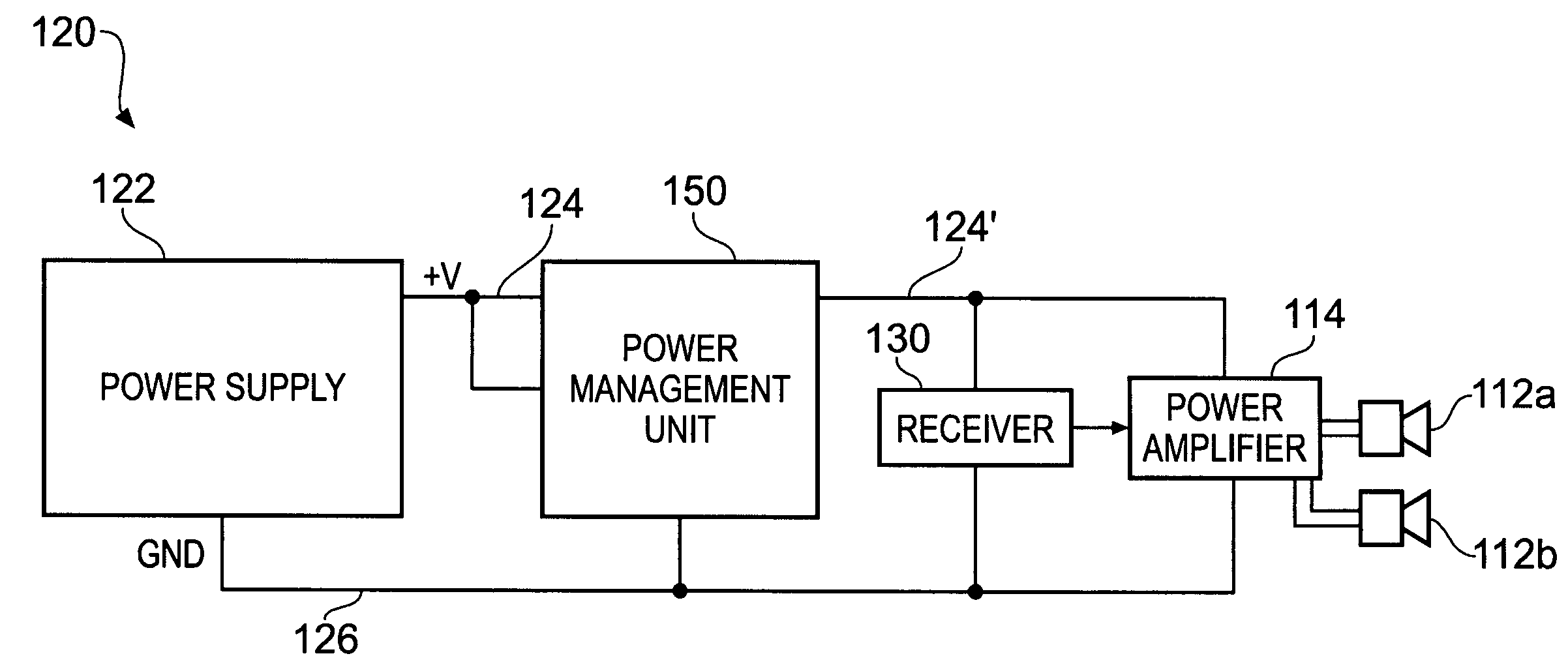

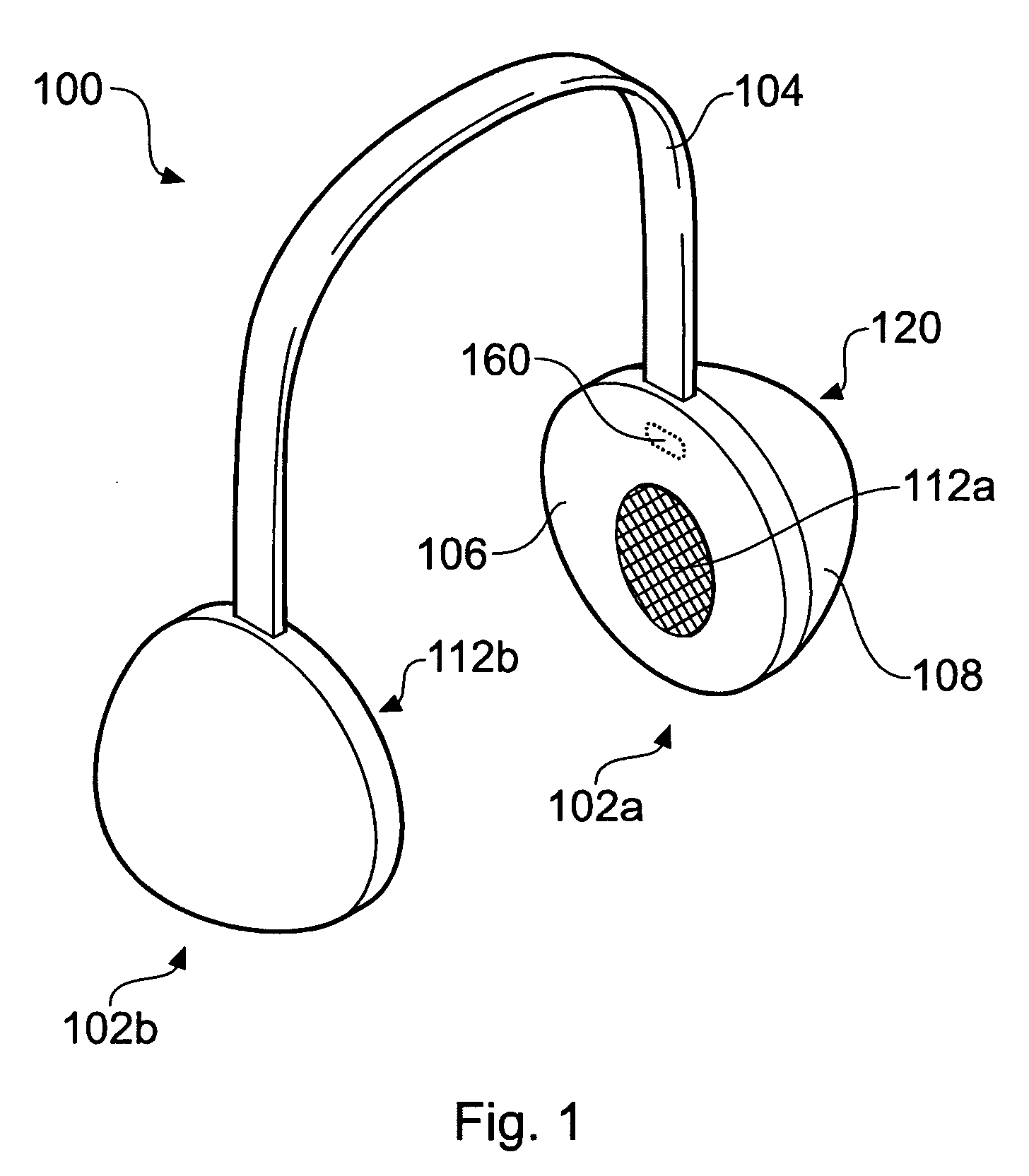

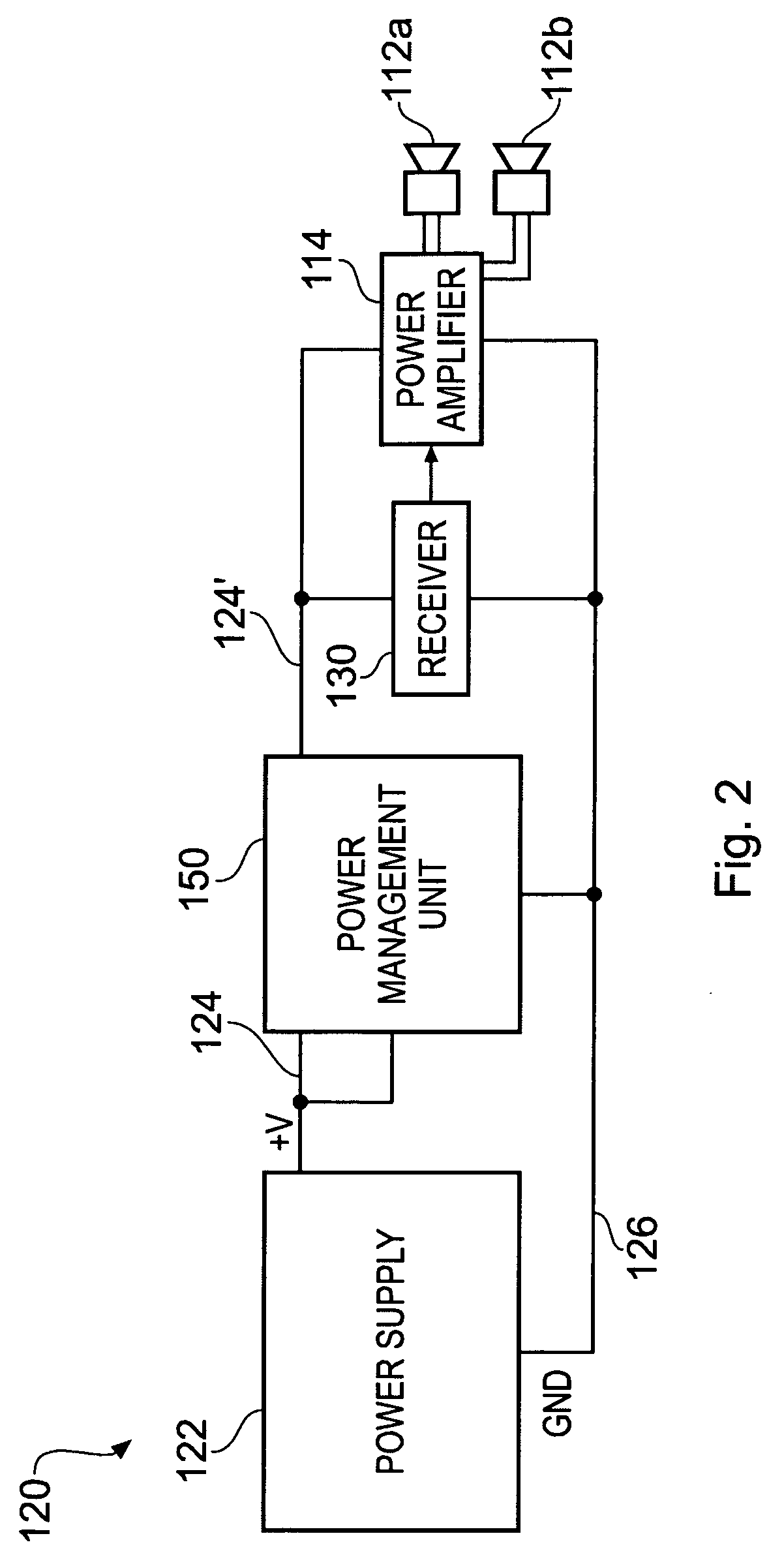

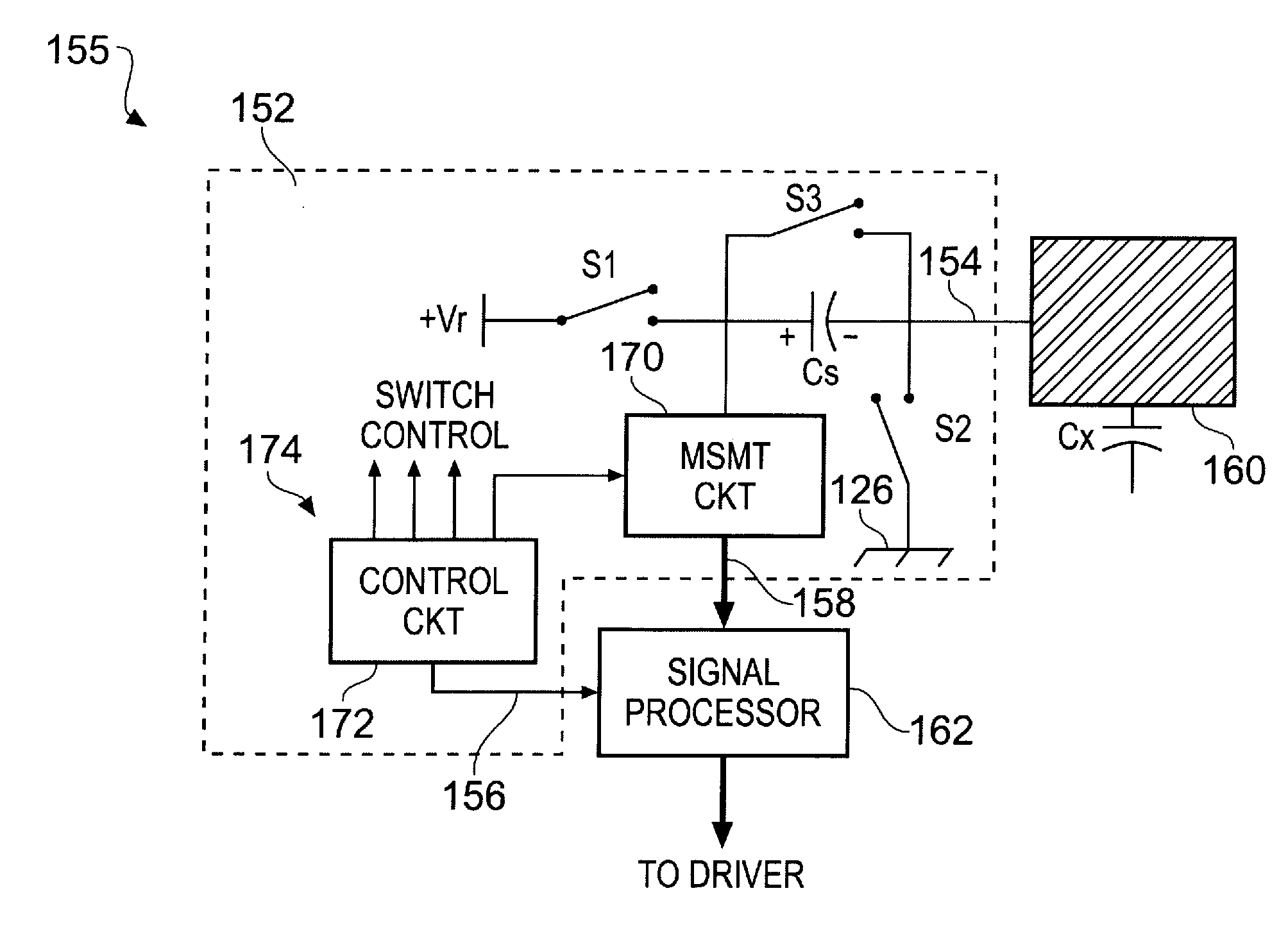

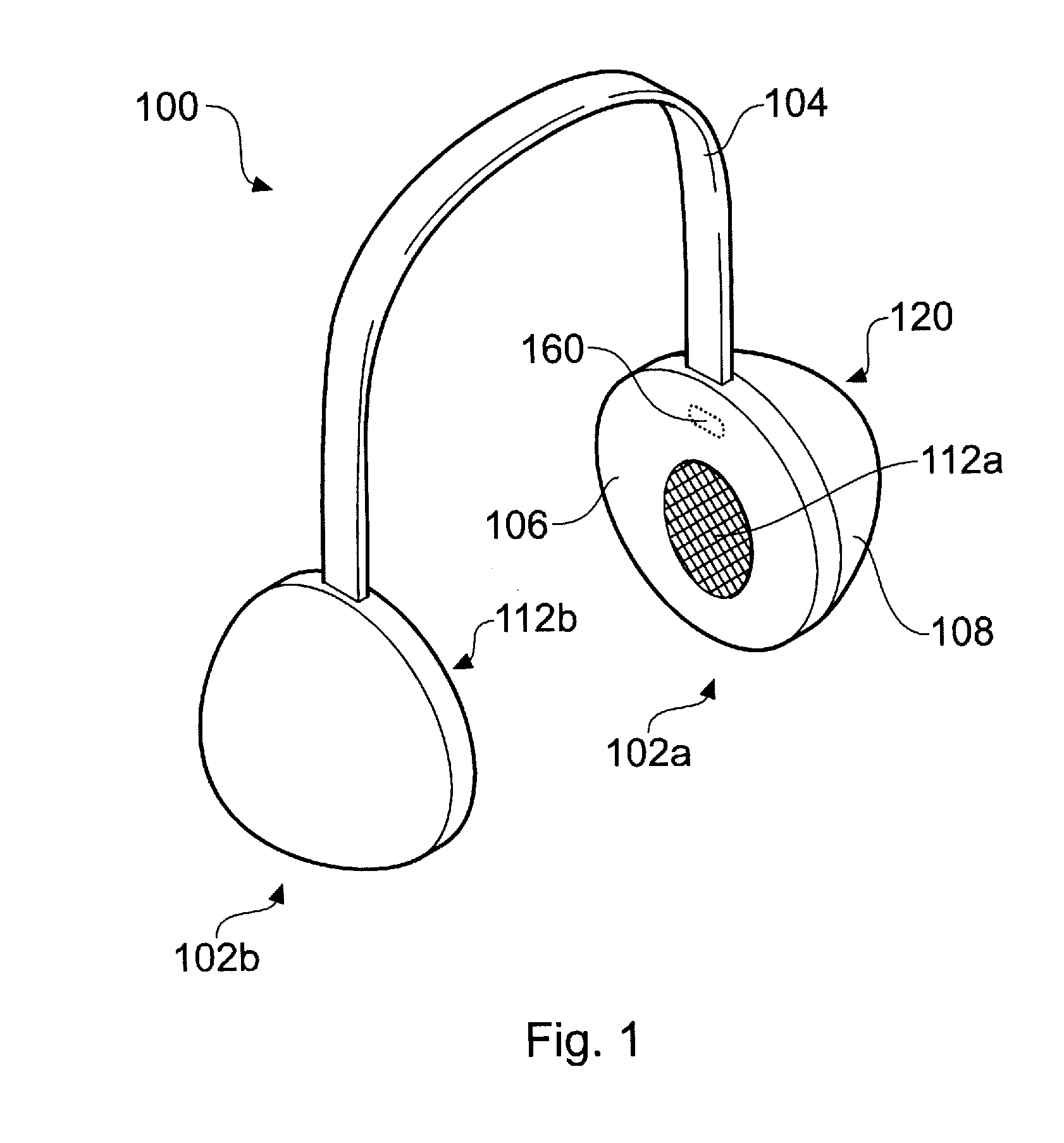

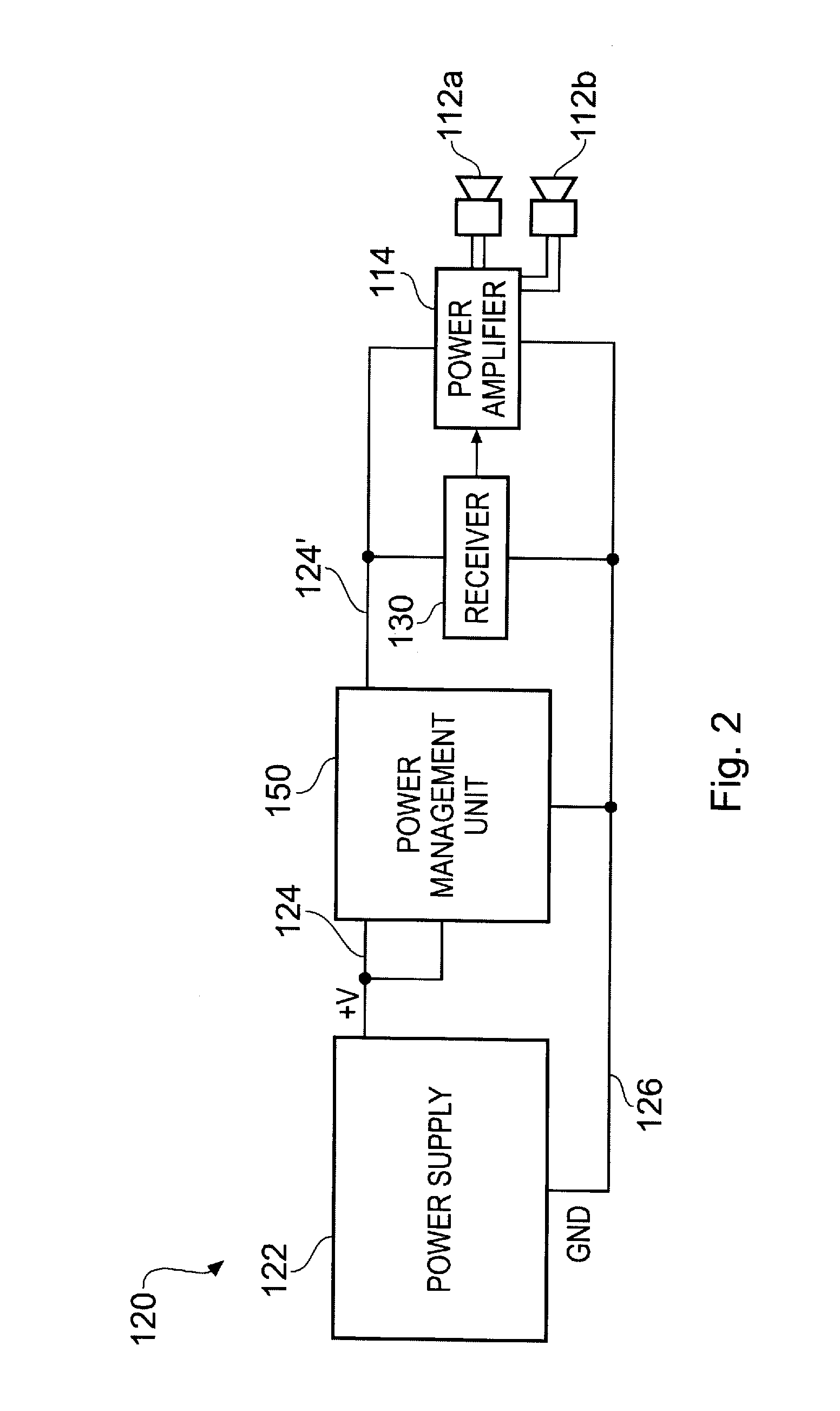

Headsets and Headset Power Management

ActiveUS20070076897A1Limited functionReduce power consumptionSignal processingHeadphones for stereophonic communicationPower Management UnitEngineering

The invention relates to an energy saving headset that comprises a power management unit operable to reduce the power consumption of the headset when a user is not present. The power management unit uses capacitive sensing to detect the presence of the user. Capacitive sensing is advantageous since it provides a flexible and reliable sensor that can accurately detect the presence or absence of a user either by detecting user proximity or user contact. Moreover, in various embodiments, the sensitivity of a capacitive sensor may be adjusted to account for user movement or changes in environmental conditions, such as, for example, the presence of water, or sweat, on the headset to further improve sensing reliability. The invention further relates to headsets using user presence signals based on capacitive sensing to control other functions of the headset or to control external devices to which the headset is connected, either wirelessly or by wires.

Owner:ATMEL CORP

Autonomous Sensing Module, a System and a Method of Long-Term Condition Monitoring of Structures

InactiveUS20100271199A1Sufficient protectionEasy to useMaterial analysis using wave/particle radiationAnti-theft devicesPower Management UnitDependability

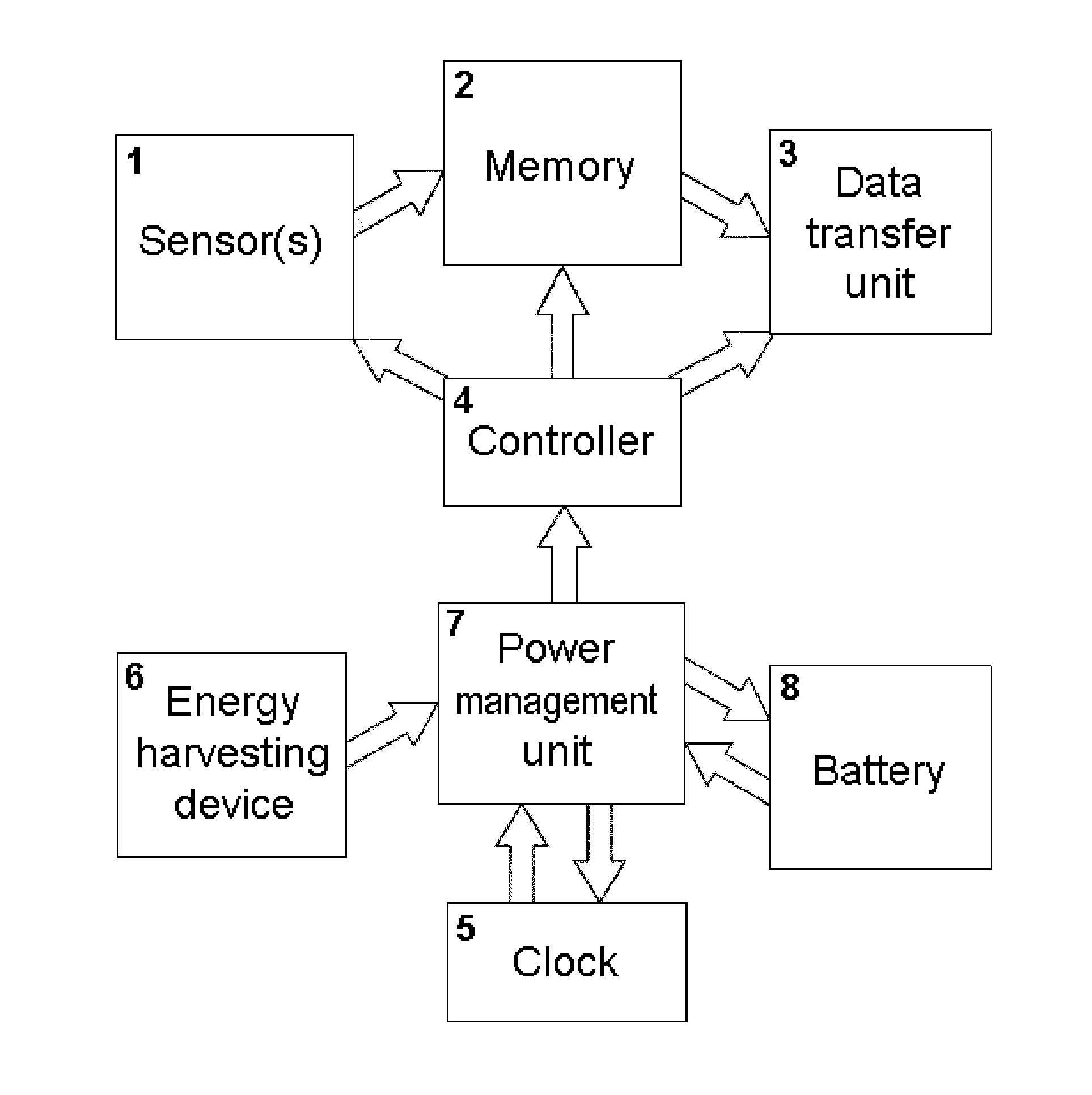

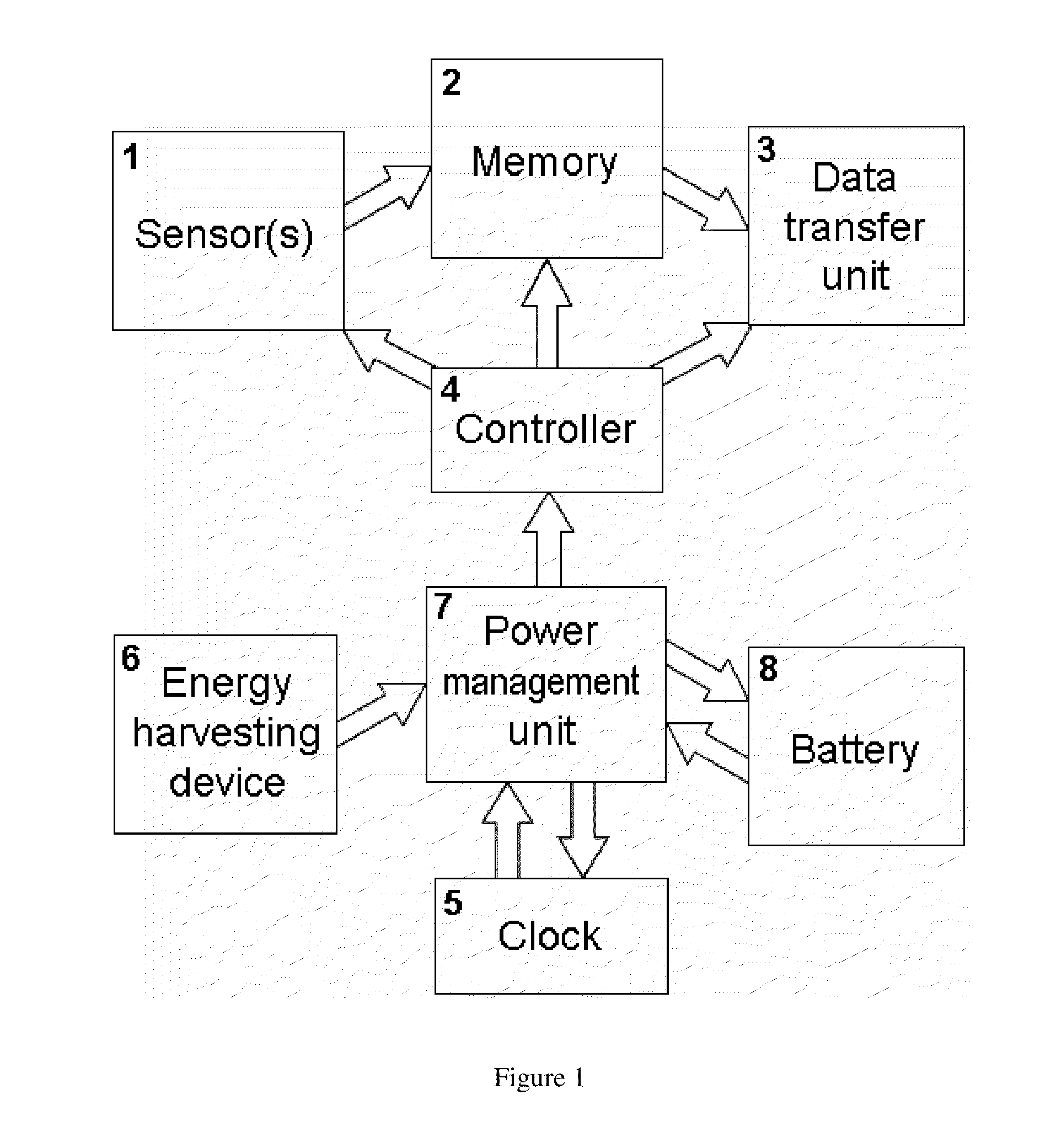

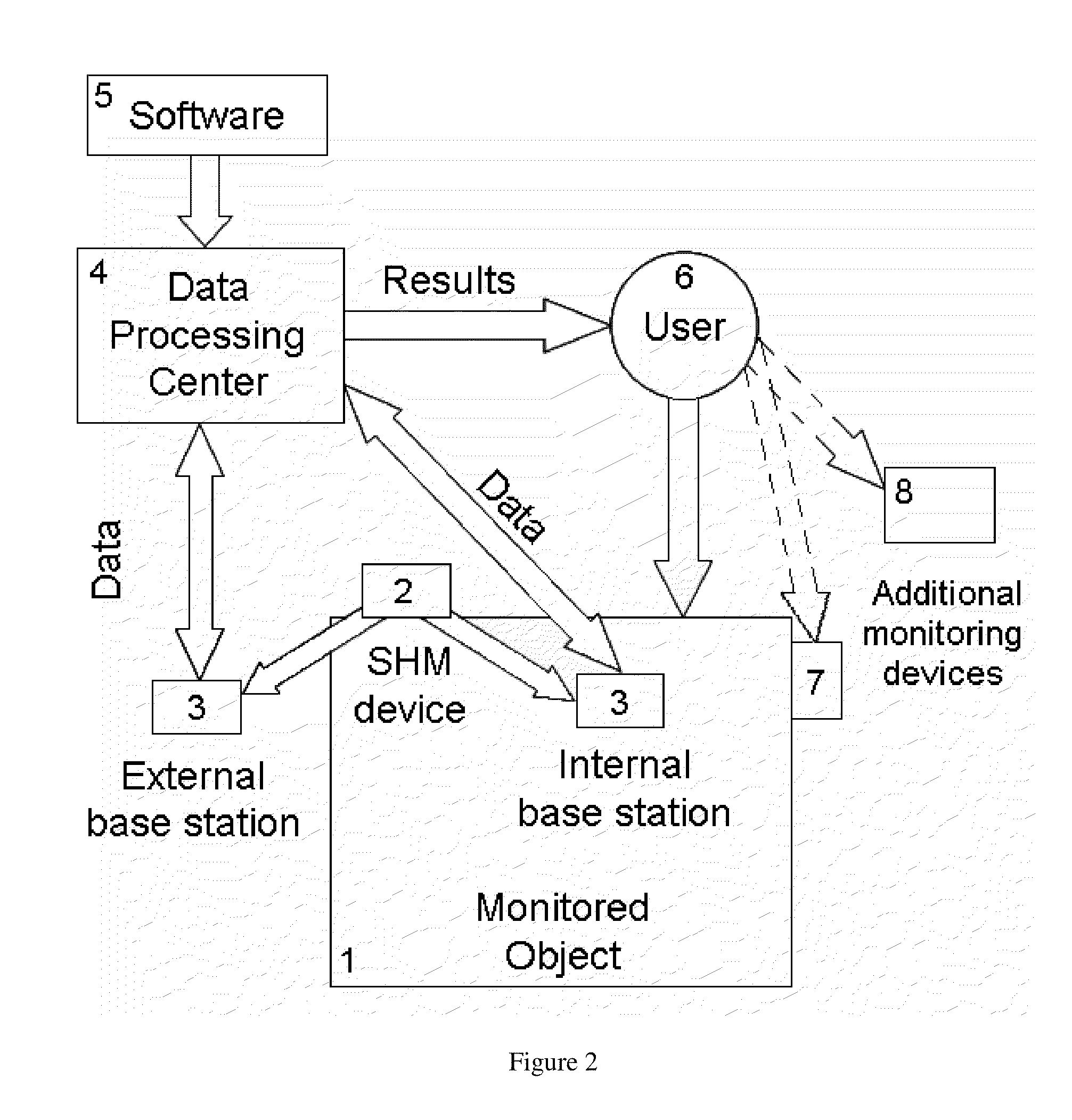

A system and a method of long-term condition monitoring of structures are based on use of autonomous sensing modules, centers for storing and processing data and software for data analysis. An autonomous sensing module contains a set of sensors for measurements of parameters related to the condition of a monitored structure, a non-volatile memory, a wireless data transfer unit, a controller, a clock circuit, a battery, an energy harvesting device and a power management unit. The autonomous sensing module provides a very long-term (40 years or more) functionality and reliability due to both use of at least near hermetic packages for the controller, the non-volatile memory, the battery, the clock circuit and the power management unit and choosing the duration of periods when the sensing module works in active mode in such a way that the average energy consumed by the autonomous sensing module is fully compensated by the average energy harvested by the energy harvesting device.

Owner:KOLOS INT

Power Management Unit with Remote Reporting

ActiveUS20100301769A1Failure to compensateMaintain lightPlanar light sourcesMechanical apparatusSmart lightingDesign improvement

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

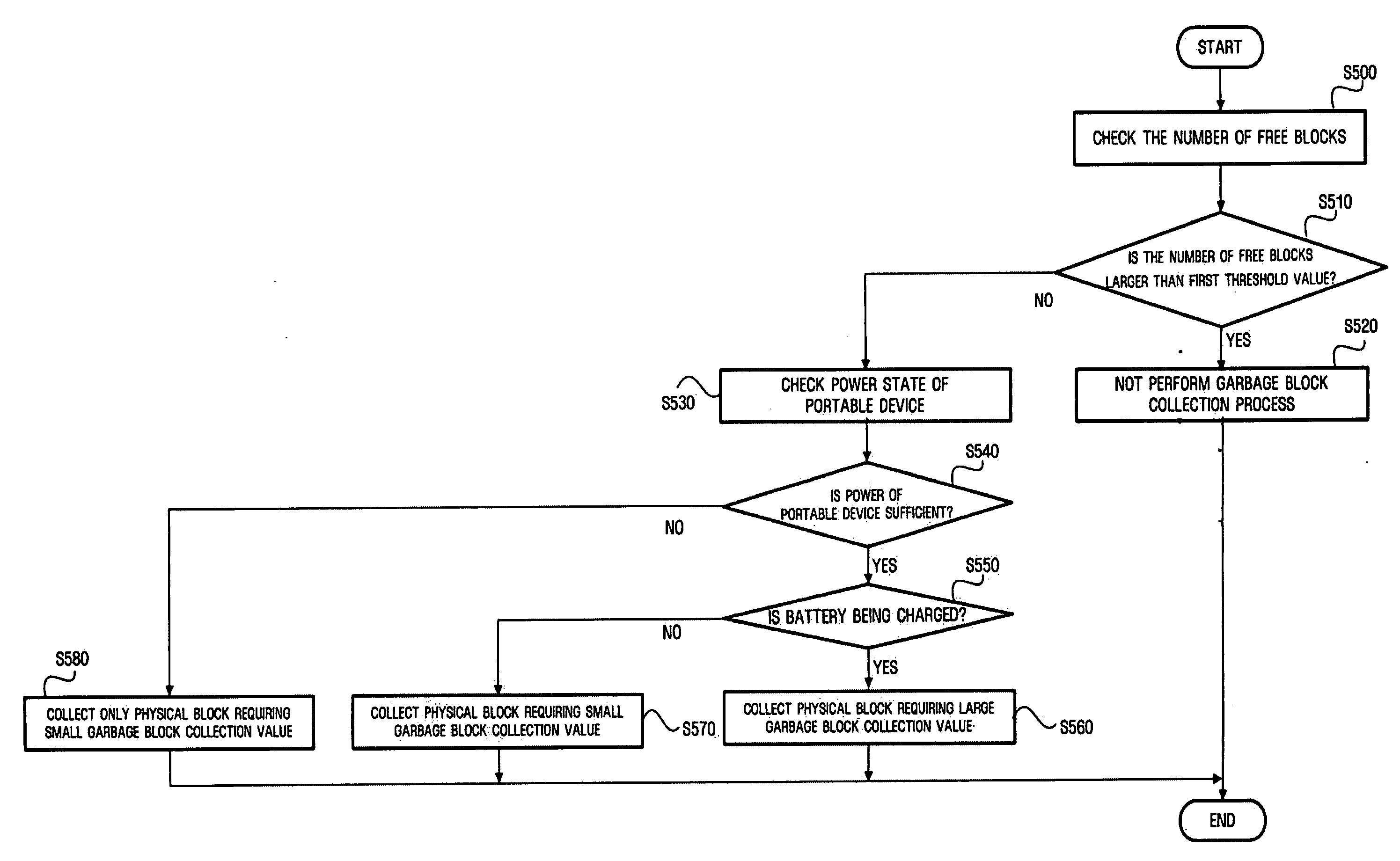

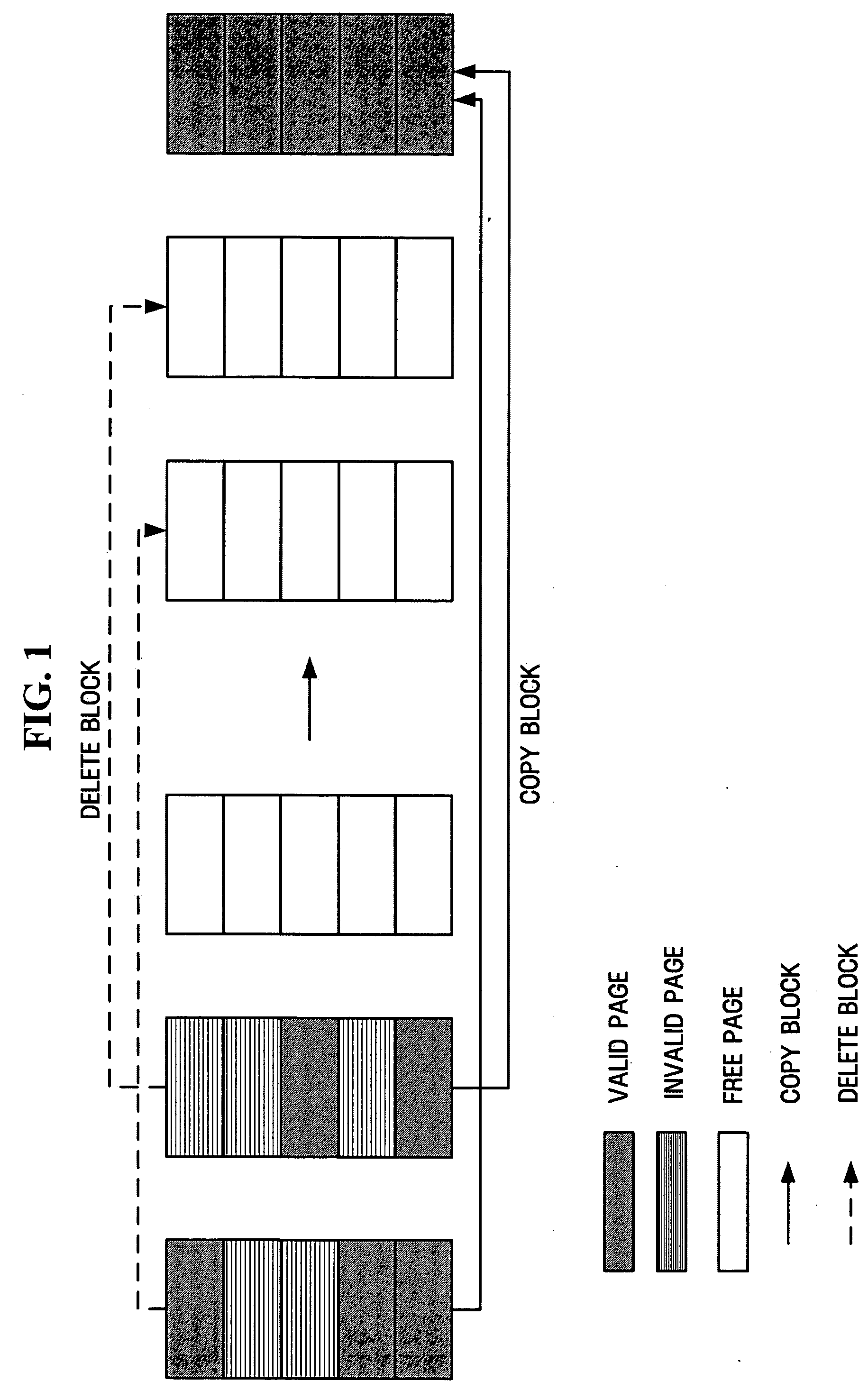

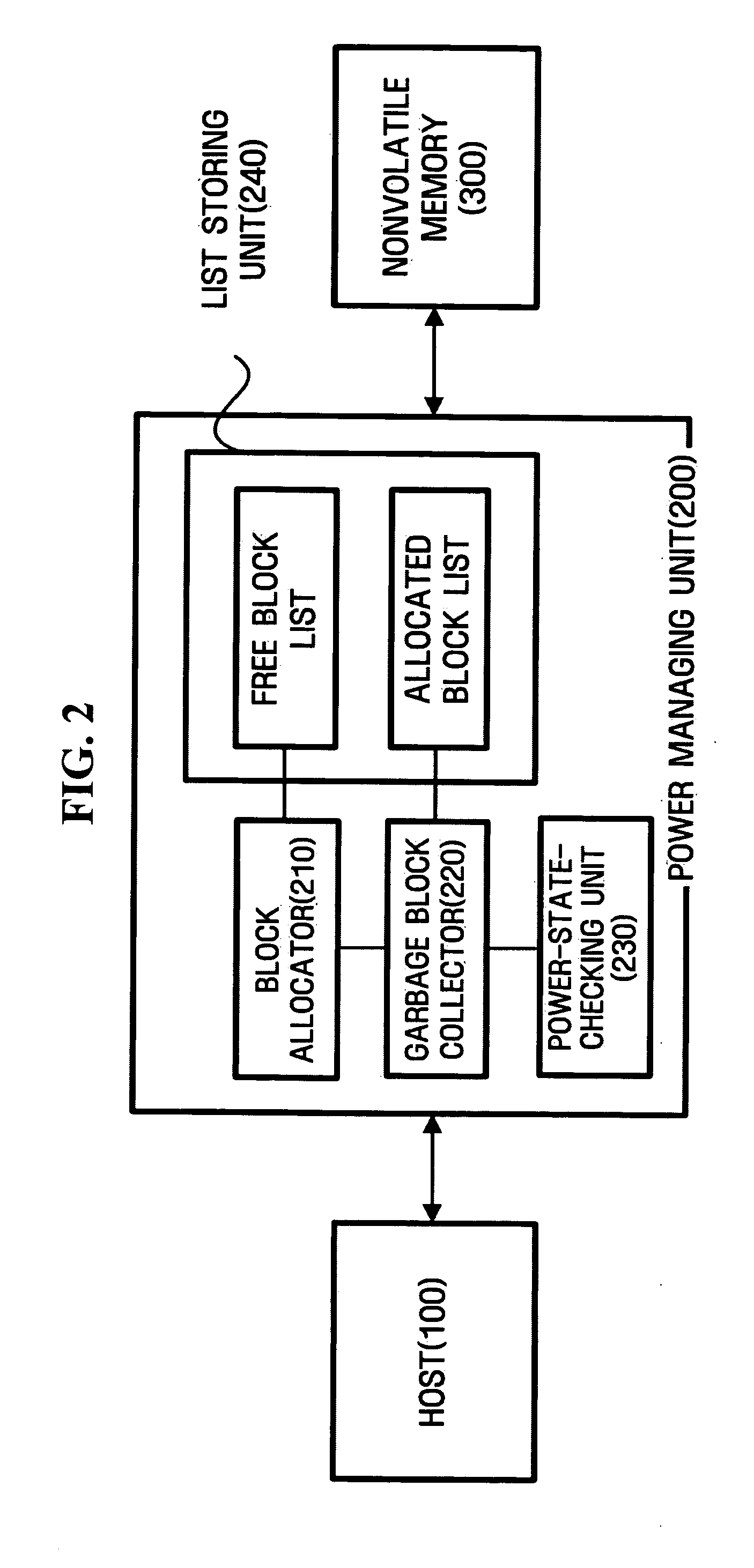

Apparatus for collecting garbage block of nonvolatile memory according to power state and method of collecting the same

ActiveUS20070174579A1Efficient consumptionMemory architecture accessing/allocationEnergy efficient ICTPower Management UnitComputer science

Owner:SAMSUNG ELECTRONICS CO LTD

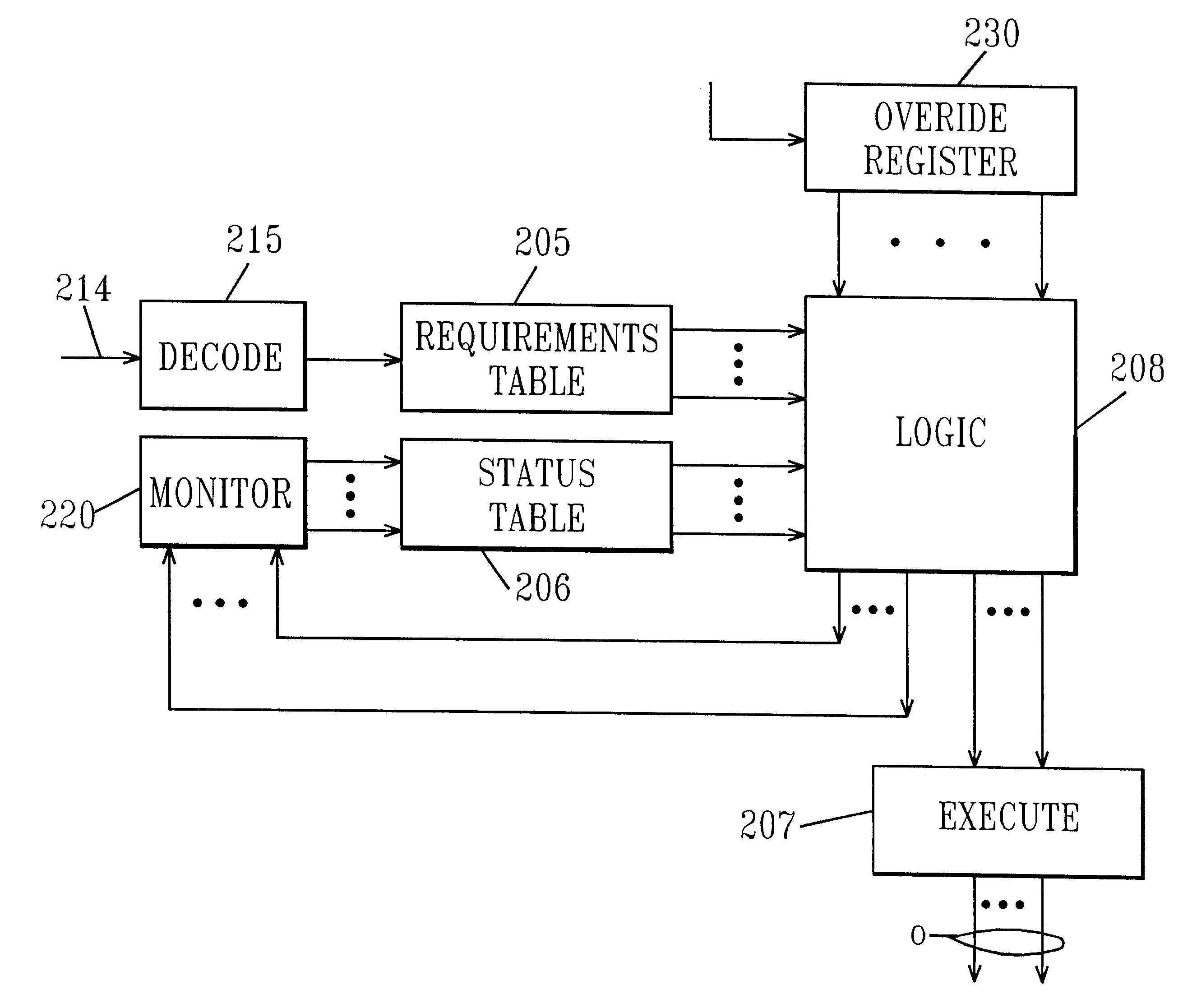

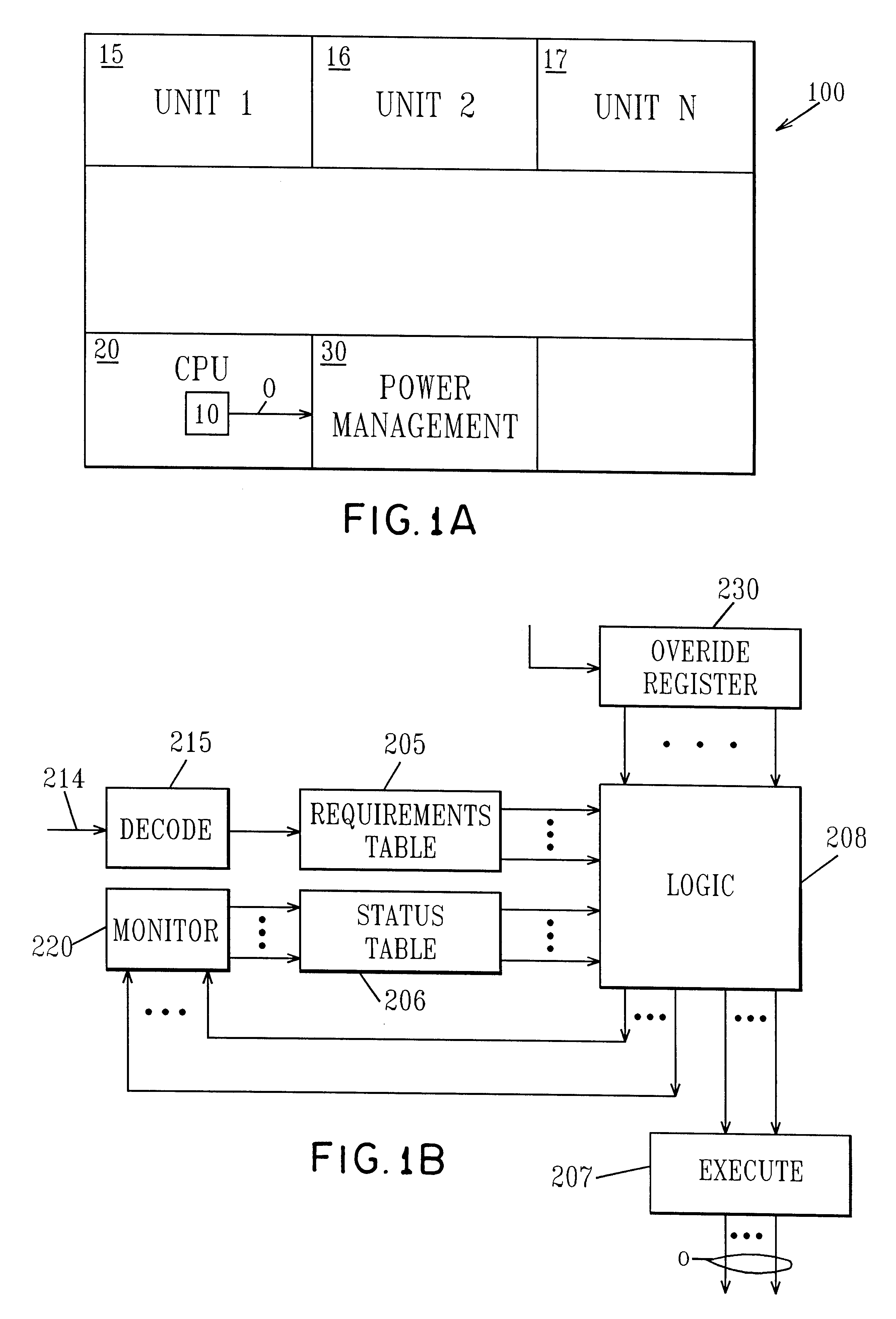

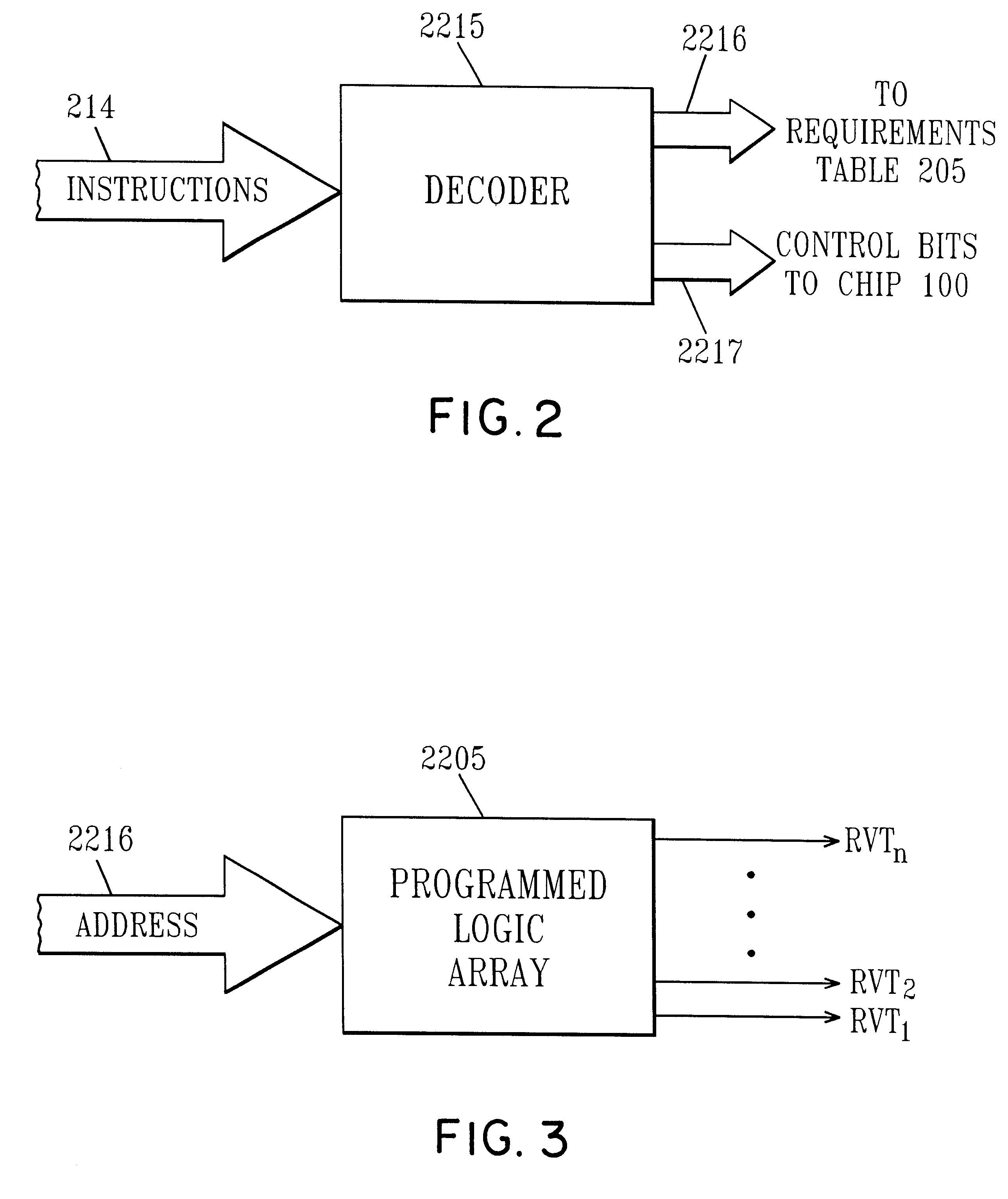

Managing Vt for reduced power using a status table

InactiveUS6345362B1Improve performanceReduce power consumptionEnergy efficient ICTVolume/mass flow measurementHemt circuitsLow power dissipation

An integrated circuit includes a CPU, a power management unit and plural functional units each dedicated to executing different functions. The power management unit controls the threshold voltage of the different functional units to optimize power / performance operation of the circuit and intelligent power management control responds to the instruction stream and decodes each instruction in turn. This information identifies which of the functional units are required for the particular instruction and by comparing that information to power status, the intelligent power control determines whether the functional units required to execute the command are at the optimum power level. If they are, the command is allowed to proceed, otherwise the intelligent power control either stalls the instruction sequence or modifies process speed.

Owner:GLOBALFOUNDRIES INC

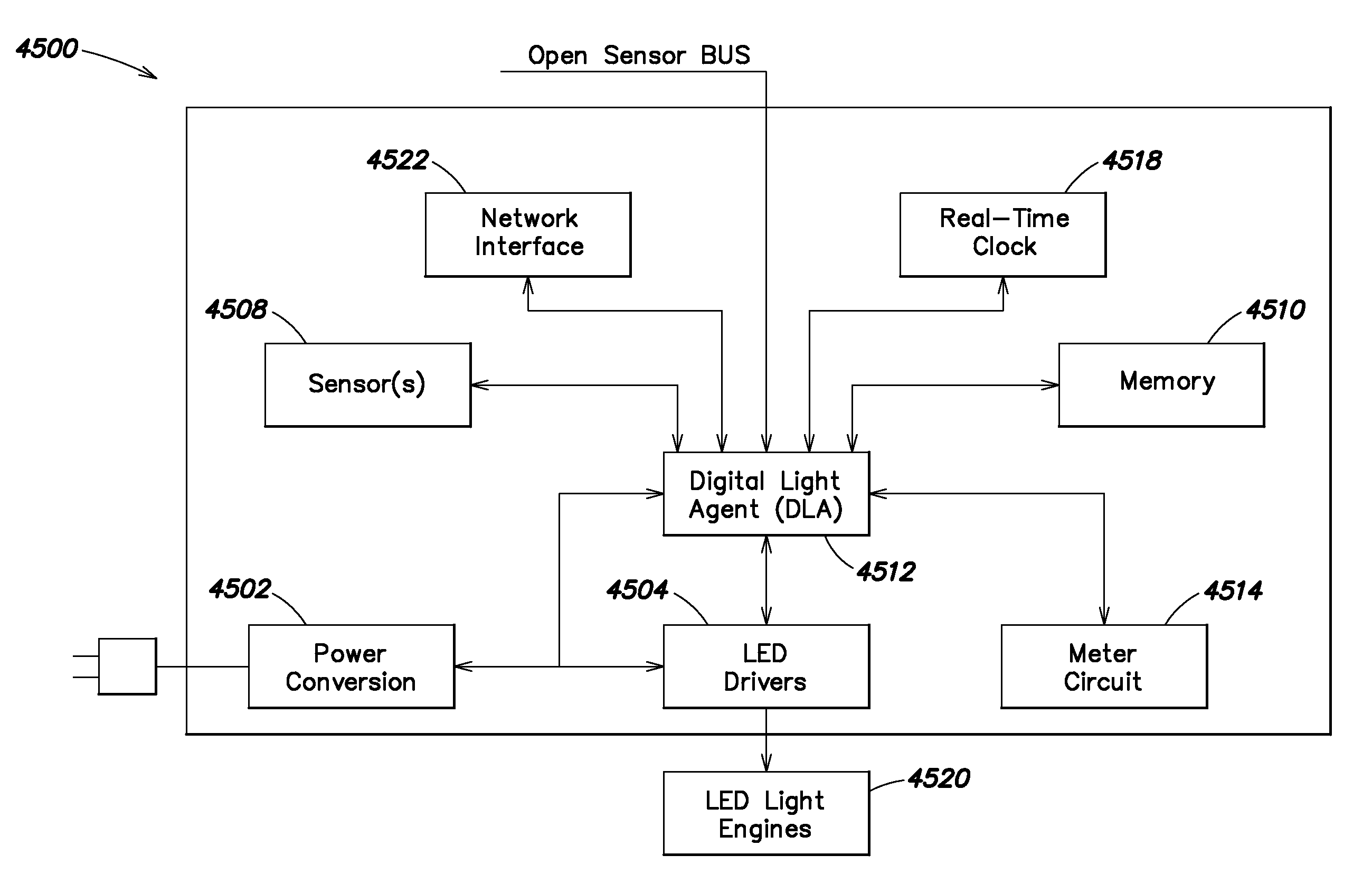

Power Management Unit with Modular Sensor Bus

ActiveUS20100295474A1Failure to compensateMaintain lightMechanical power/torque controlLevel controlDesign improvementSmart lighting

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Power Management Unit with Real Time Clock

ActiveUS20100301768A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementReal-time clockSmart lighting

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Power Management Unit with Power Source Arbitration

ActiveUS20100301771A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementDesign improvementSmart lighting

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Power Management Unit with Sensor Logging

ActiveUS20100295473A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementSmart lightingDesign improvement

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC +1

Power management unit with power metering

ActiveUS8339069B2Discharge tube incandescent screensPlanar light sourcesDesign improvementSmart lighting

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

Headset power management

ActiveUS20070121959A1Reduce power consumptionLimited functionEar treatmentSubstation equipmentPower Management UnitEngineering

Owner:ATMEL CORP

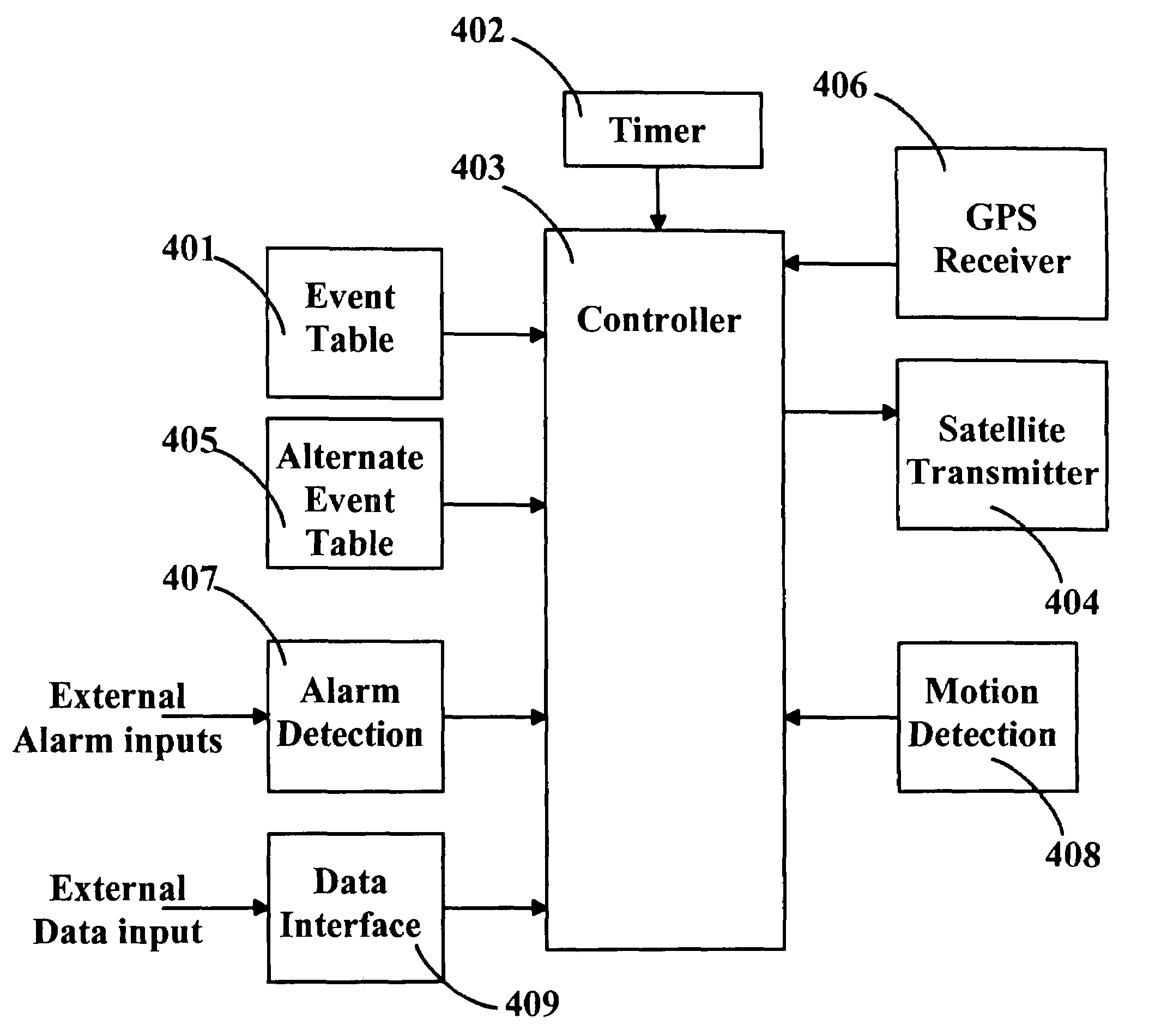

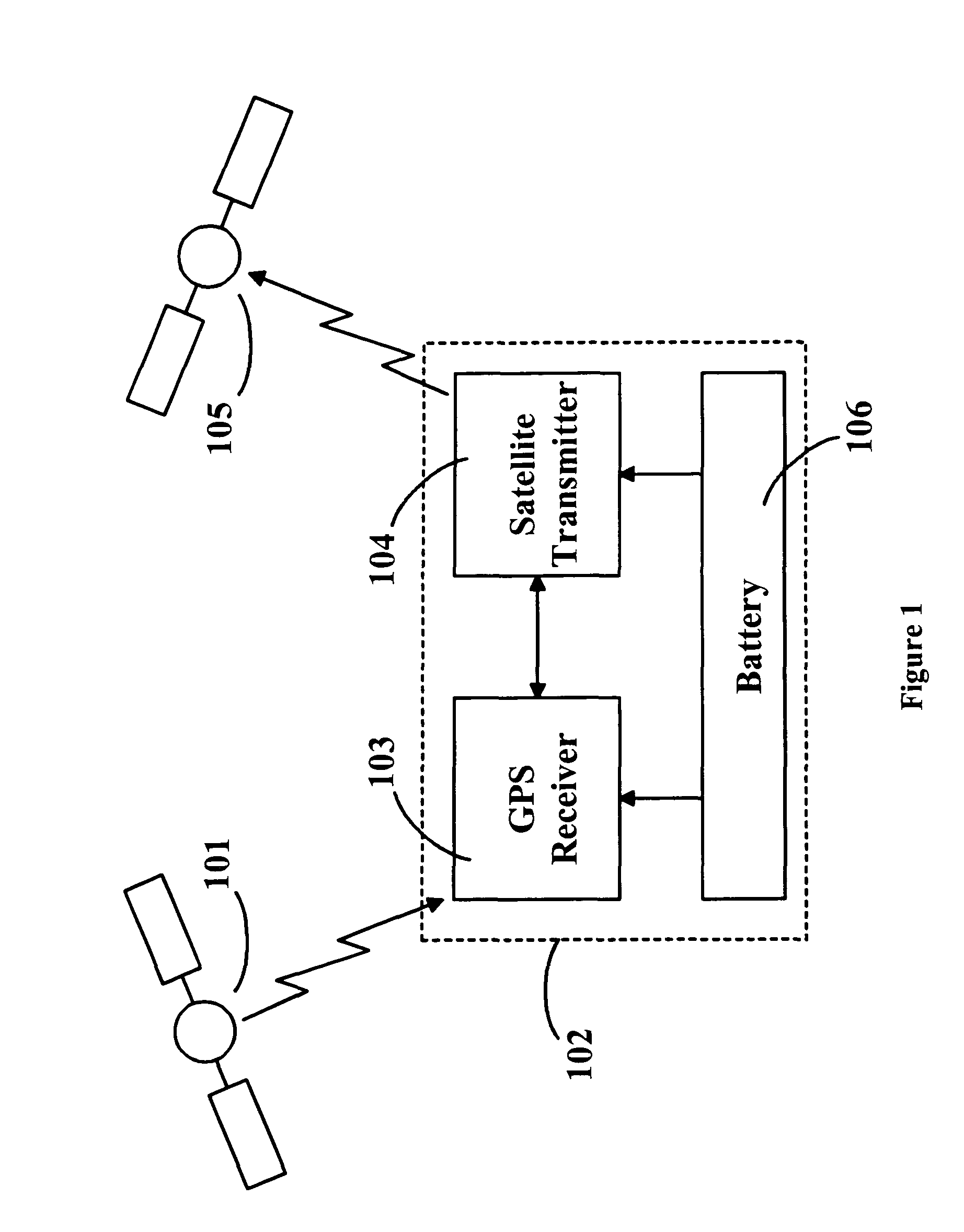

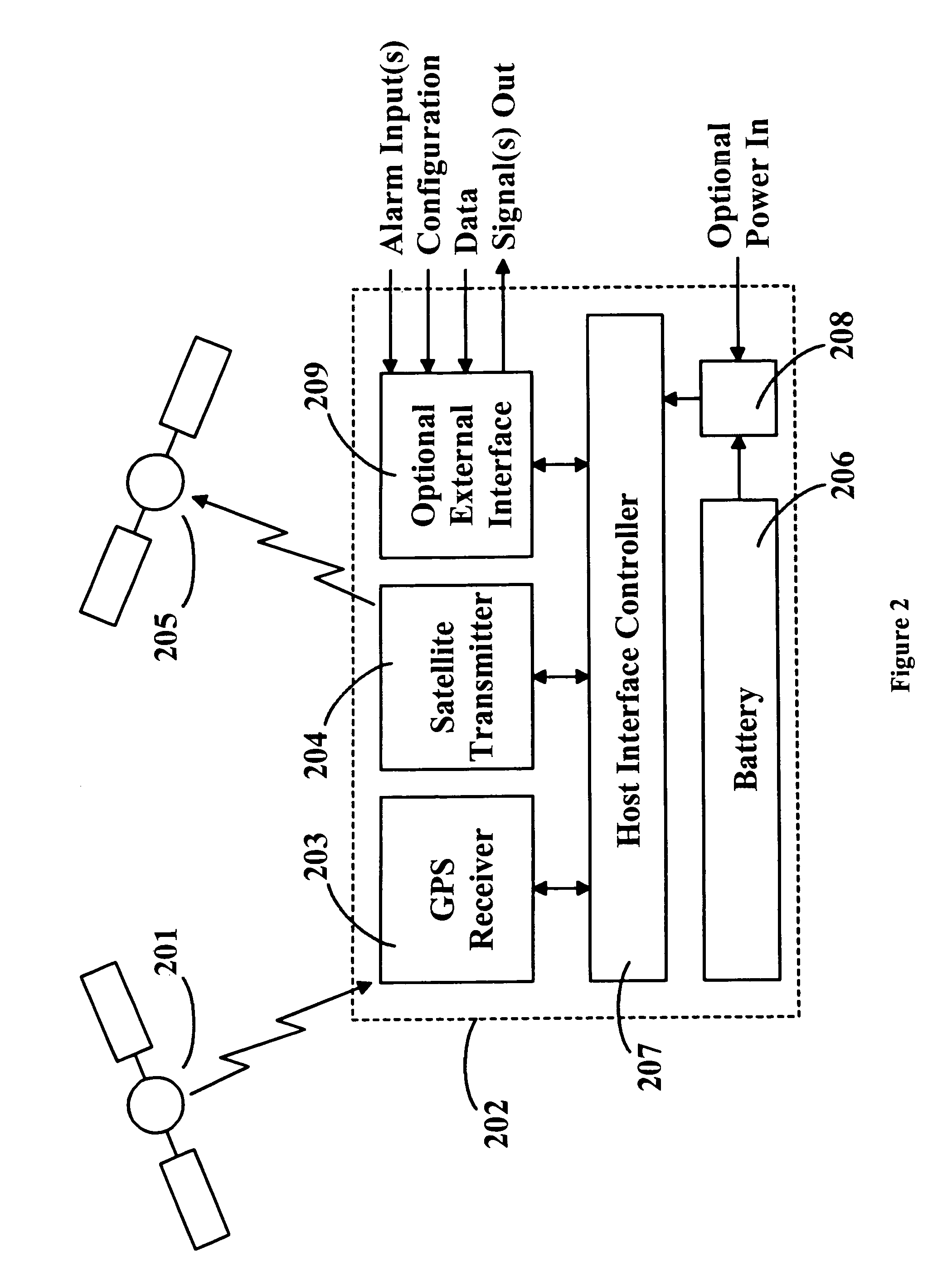

Location monitoring and transmitting device, method, and computer program product using a simplex satellite transmitter

InactiveUS7099770B2Efficient and reliable location determinationReduce power consumptionAnalogue computers for vehiclesInstruments for road network navigationSatellite transmitterTelecommunications

A device, method, and computer program product for monitoring and transmitting a location and a local status of a remote device using a simplex satellite transmitter. The monitoring device includes a position location unit, a simplex satellite transmitter, a power source, and a controller. The position location unit is configured to determine a location of the remote device. The simplex satellite transmitter is configured to transmit the location to one or more satellites in low earth orbit. The controller includes a power management unit configured to control a power state of the position location unit and the simplex satellite transmitter, and to periodically enable and disable power from the power source to the position location unit and the simplex satellite transmitter.

Owner:BNP PARIBAS AS SECURITY AGENT

Power management unit with modular sensor bus

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

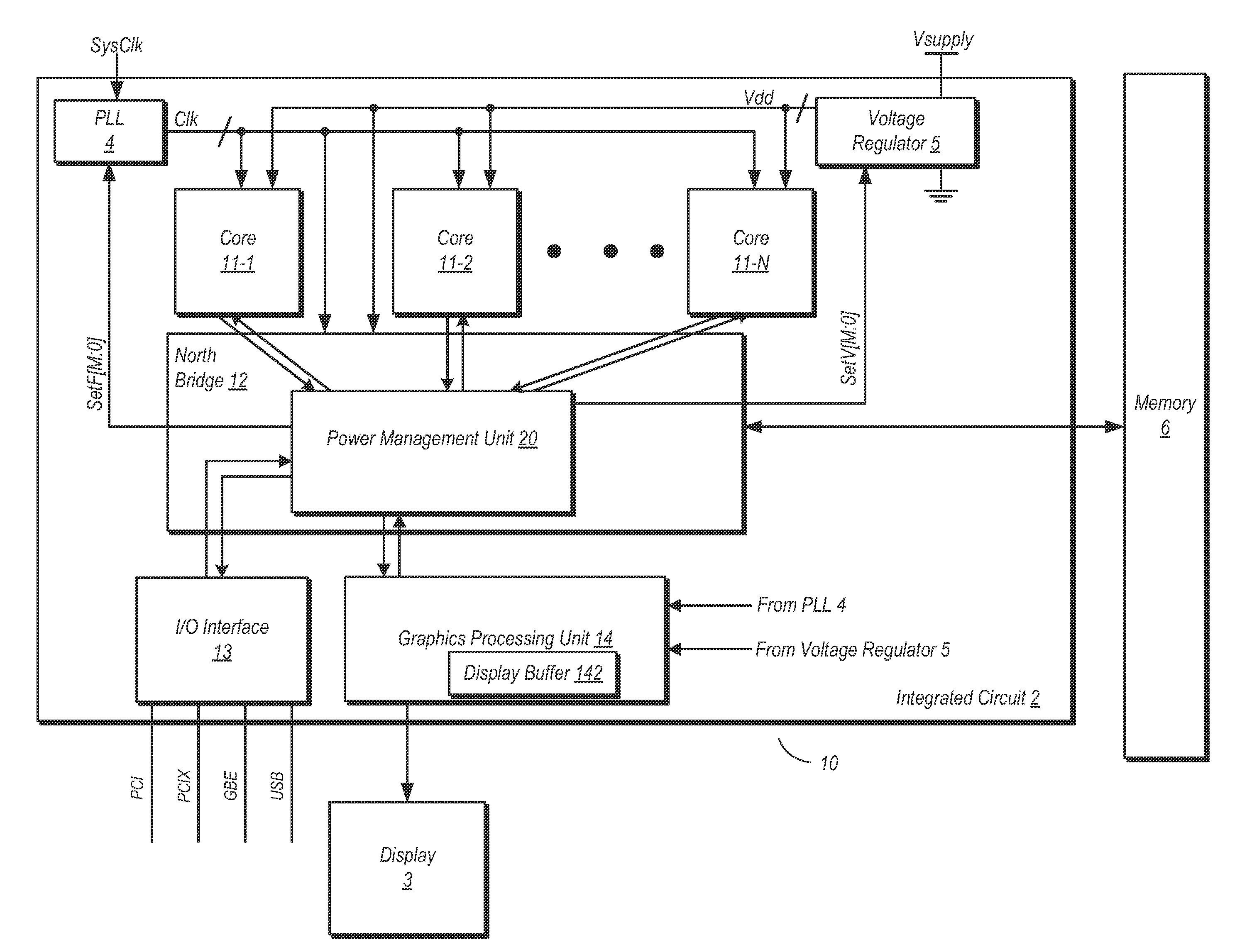

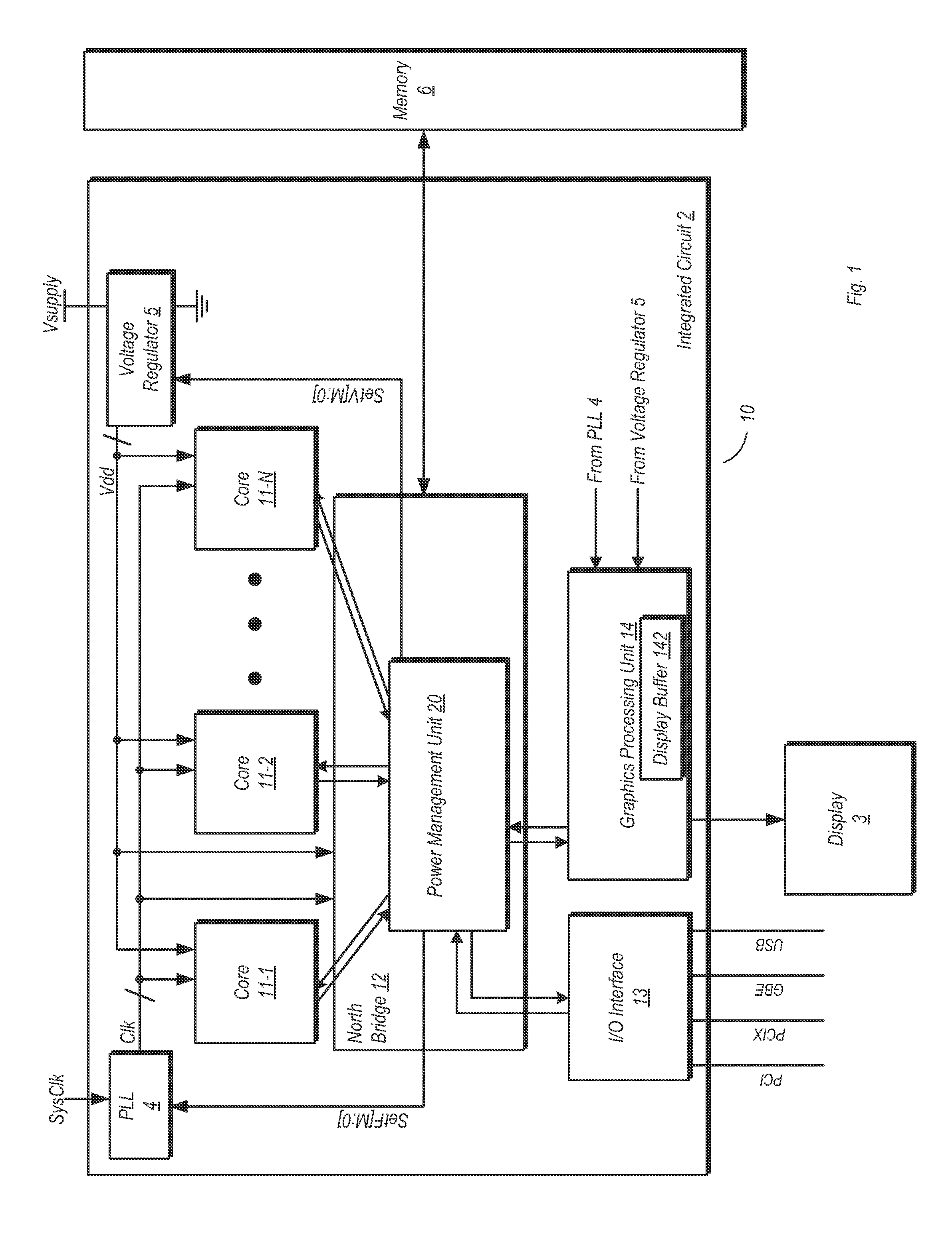

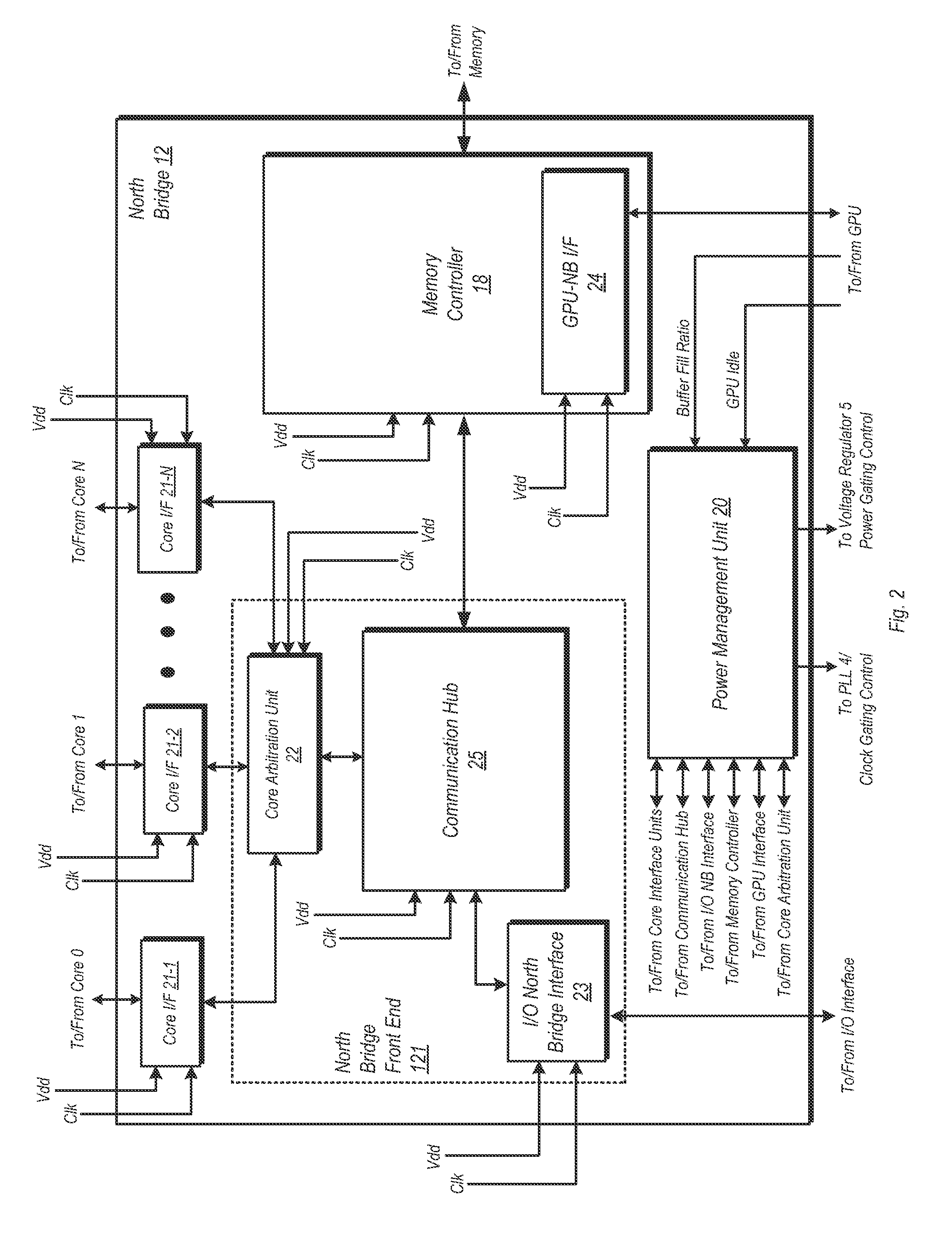

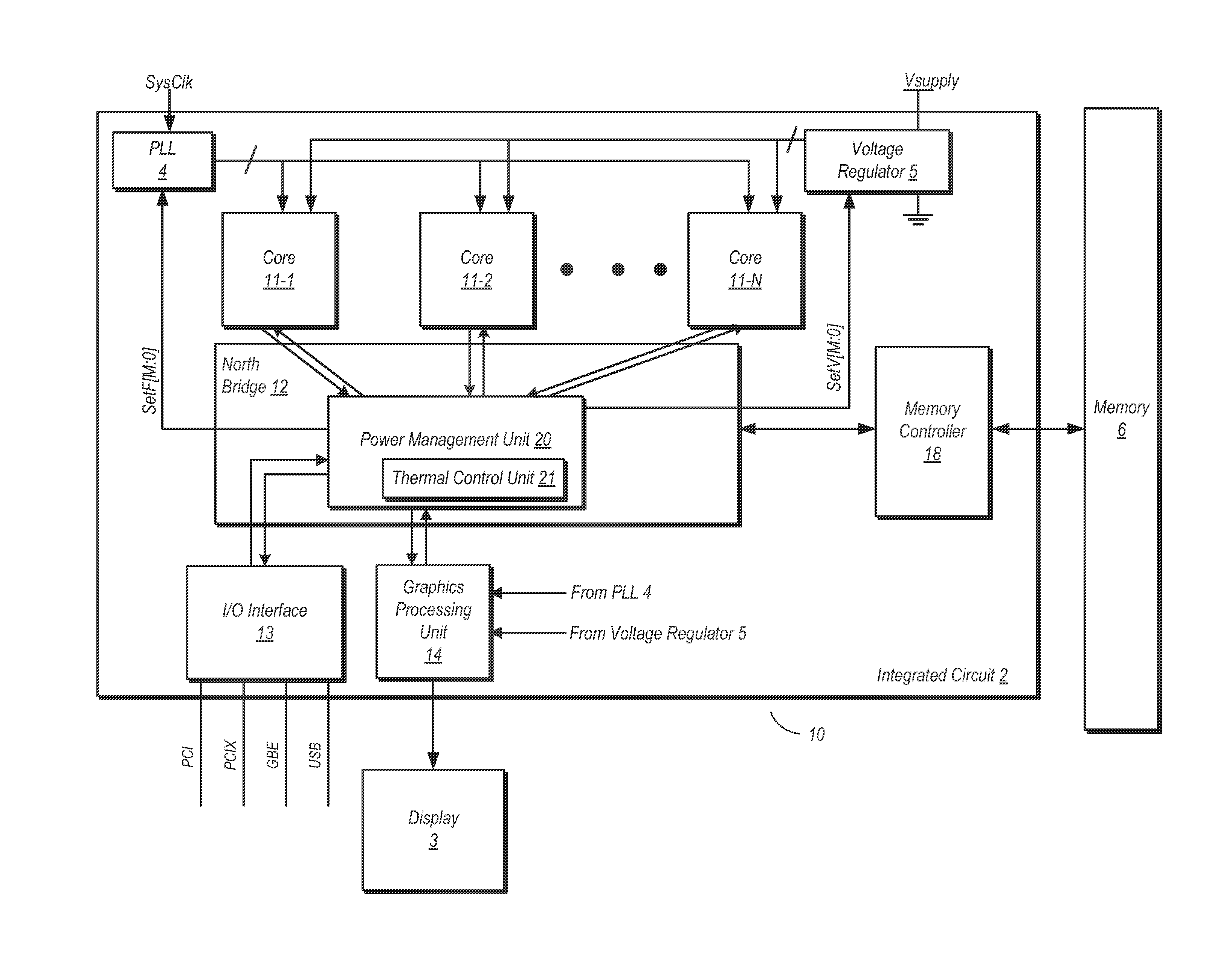

Function based dynamic power control

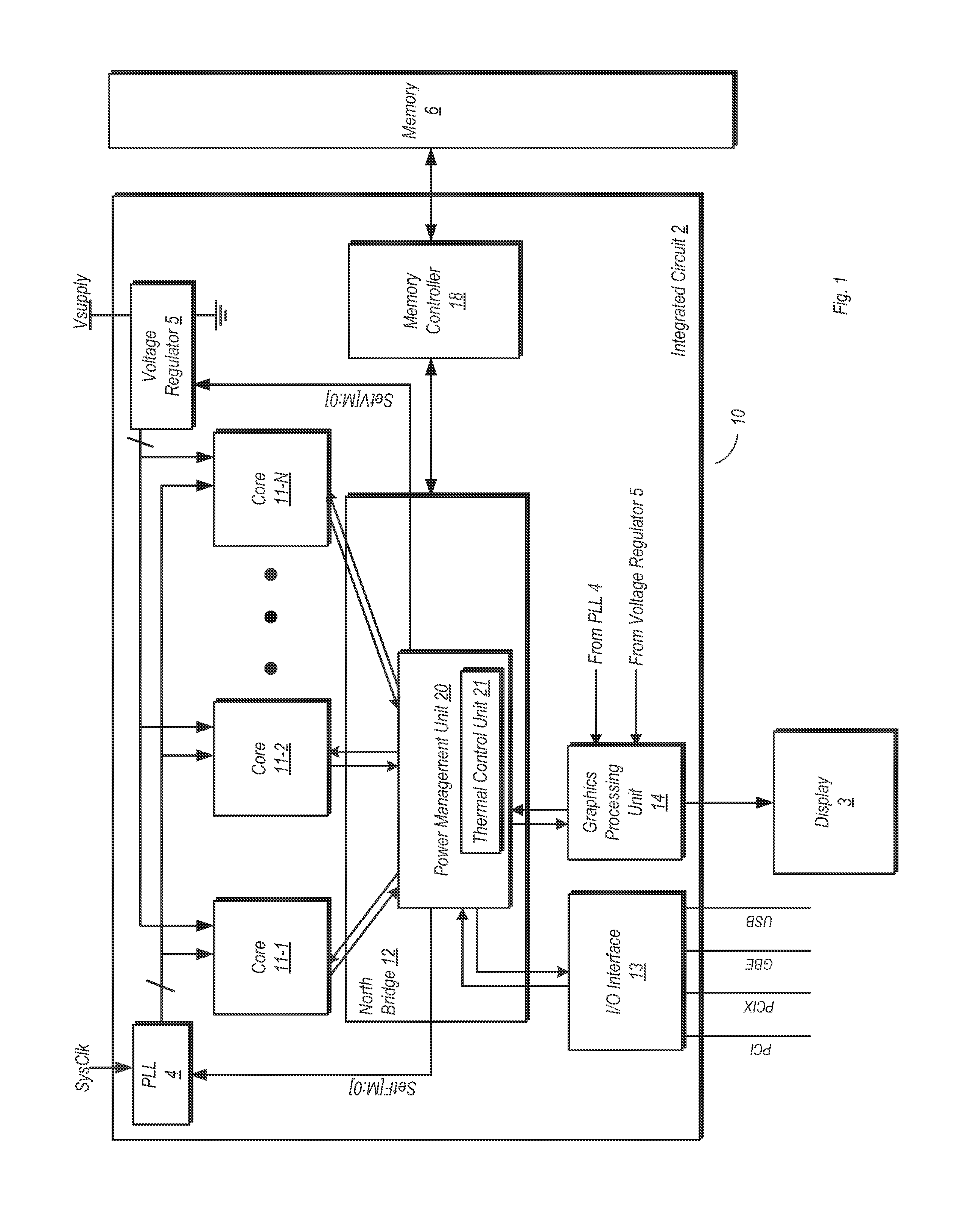

ActiveUS20120102344A1Energy efficient ICTGenerating/distributing signalsPower Management UnitMemory controller

A system and method for dynamic function based power control is disclosed. In one embodiment, a system includes a bridge unit having a memory controller and a communication hub coupled to the memory controller. The system further includes a power management unit, wherein the power management unit is configured to clock-gate the communication hub responsive to determining that each of a plurality of processor cores are in an idle state and that an I / O interface unit has been idle for an amount of time exceeding a first threshold. The power management unit is further configured to clock-gate the memory controller responsive to clock-gating the communication hub and determining that a memory coupled to the memory controller is in a first low power state. The power management unit may also perform power-gating of functional units subsequent to clock-gating the same.

Owner:ADVANCED MICRO DEVICES INC

Power management unit with ballast interface

ActiveUS8552664B2Electrical apparatusElectric light circuit arrangementSmart lightingPower Management Unit

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

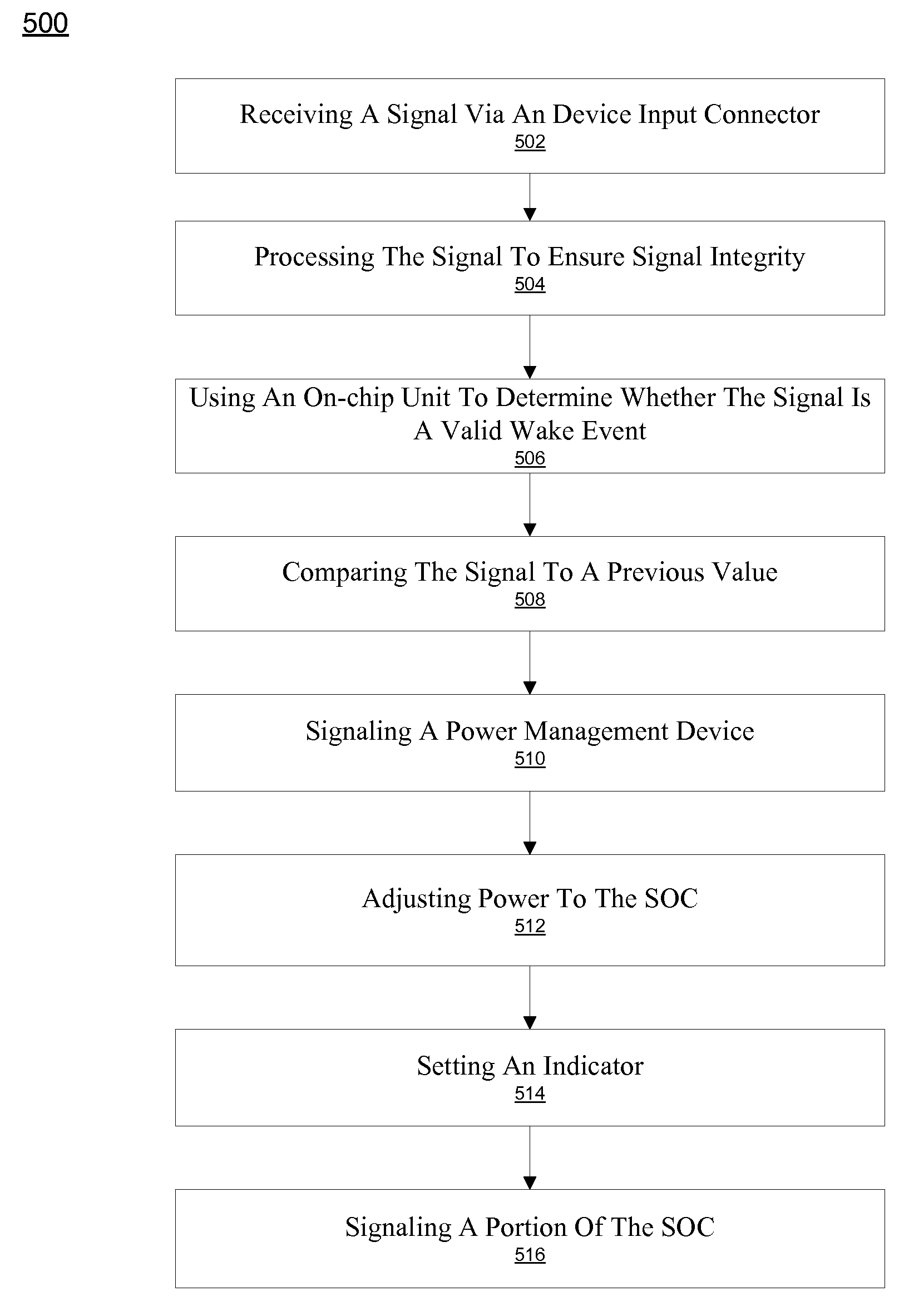

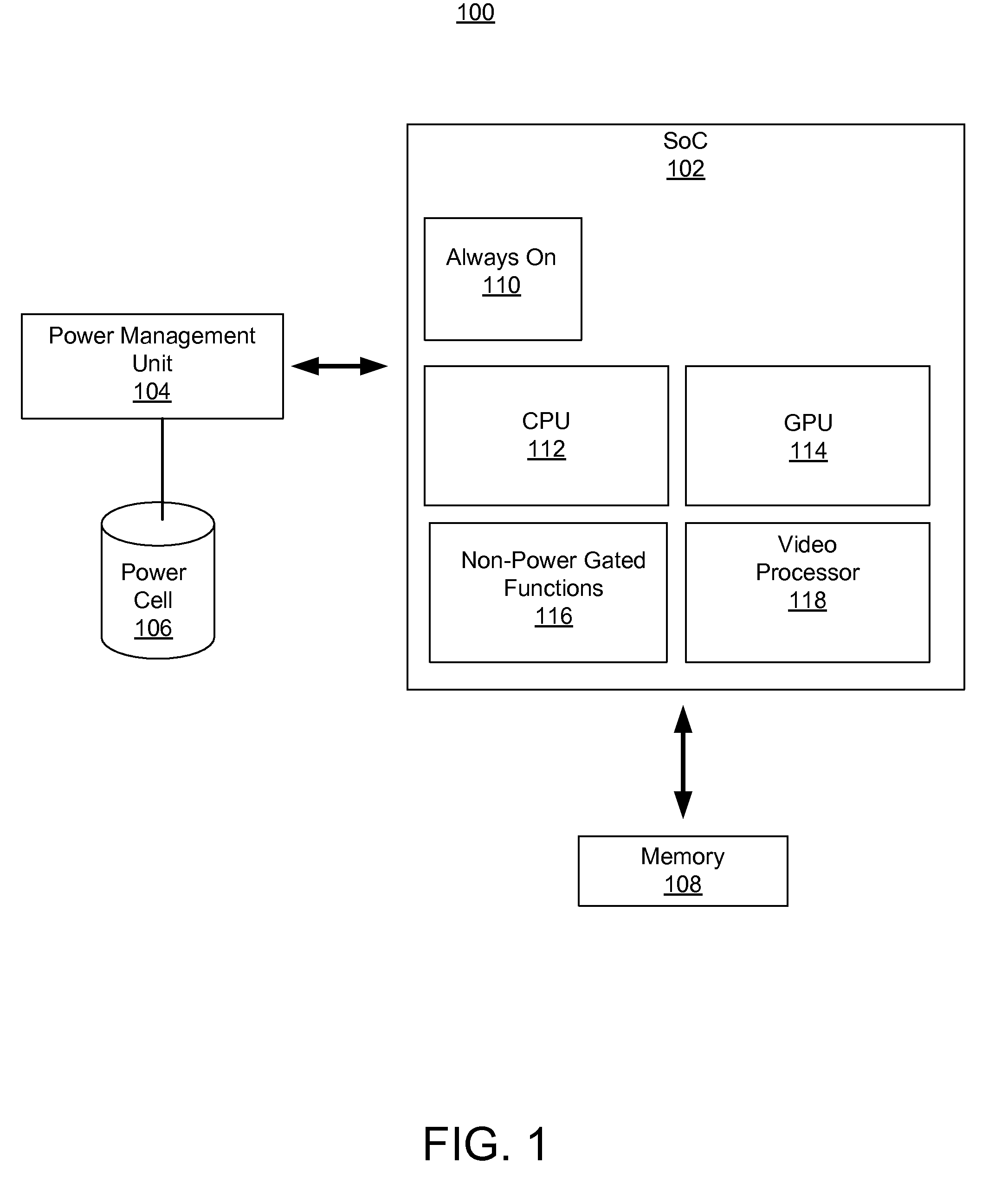

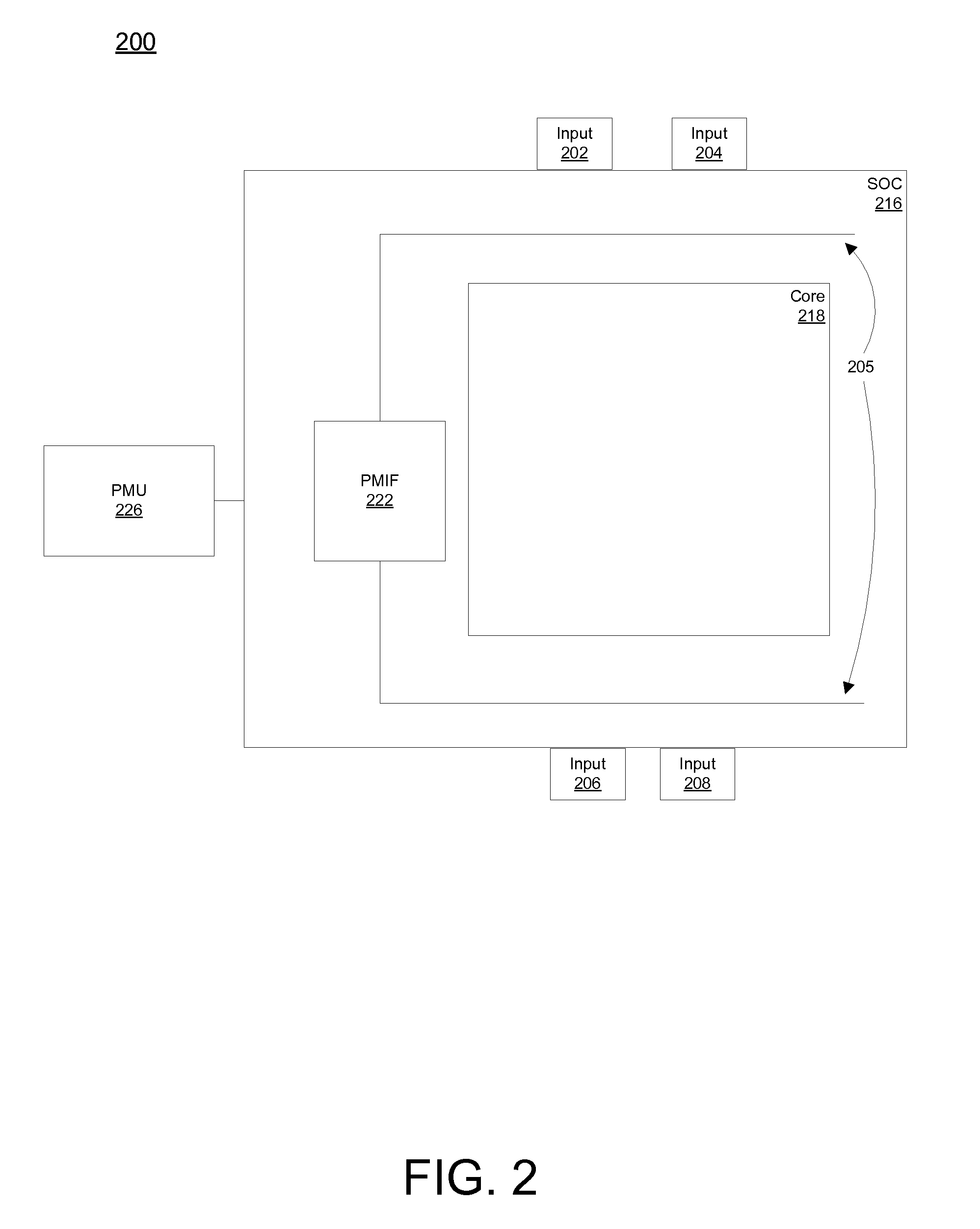

System and method for using inputs as wake signals

InactiveUS20090204834A1Facilitate low power and sleep stateReduce leakagePower supply for data processingEnergy efficient computingControl powerPower Management Unit

A system and method for waking up a portion of a programmable system on a chip (SoC). The system includes a power management unit for controlling power levels to the SoC and one or more inputs for receiving inputs from a coupled device. The system further includes a power management interface coupled to the one or more inputs. The power management interface signals the power management unit to adjust power levels to the SoC in response to receiving a signal via the one or more inputs corresponding to a wake event.

Owner:NVIDIA CORP

Headsets and headset power management

ActiveUS7945297B2Limited functionReduce power consumptionSignal processingHeadphones for stereophonic communicationPower Management UnitEngineering

The invention relates to an energy saving headset that comprises a power management unit operable to reduce the power consumption of the headset when a user is not present. The power management unit uses capacitive sensing to detect the presence of the user. Capacitive sensing is advantageous since it provides a flexible and reliable sensor that can accurately detect the presence or absence of a user either by detecting user proximity or user contact. Moreover, in various embodiments, the sensitivity of a capacitive sensor may be adjusted to account for user movement or changes in environmental conditions, such as, for example, the presence of water, or sweat, on the headset to further improve sensing reliability. The invention further relates to headsets using user presence signals based on capacitive sensing to control other functions of the headset or to control external devices to which the headset is connected, either wirelessly or by wires.

Owner:ATMEL CORP

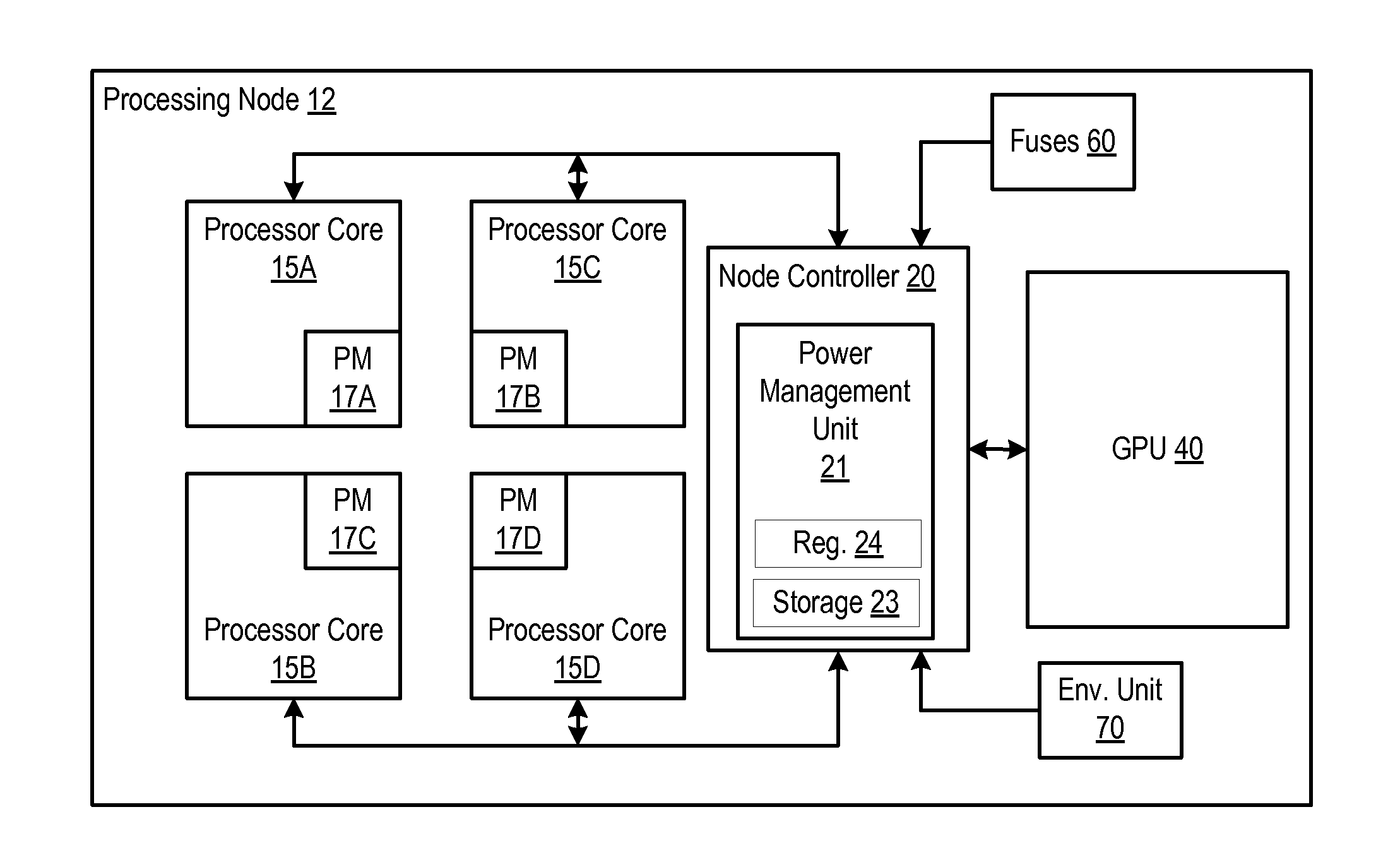

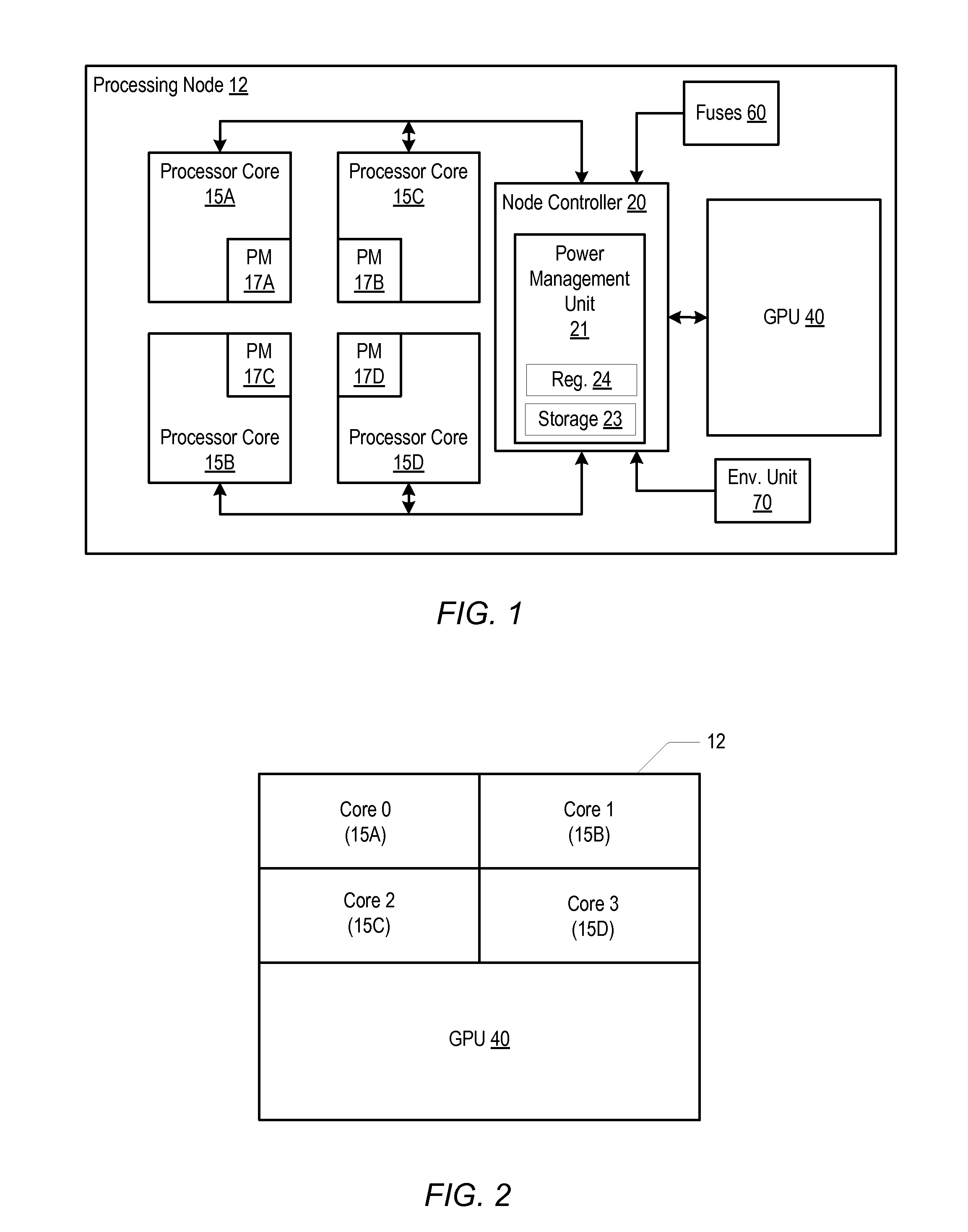

Mechanism for controlling power consumption in a processing node

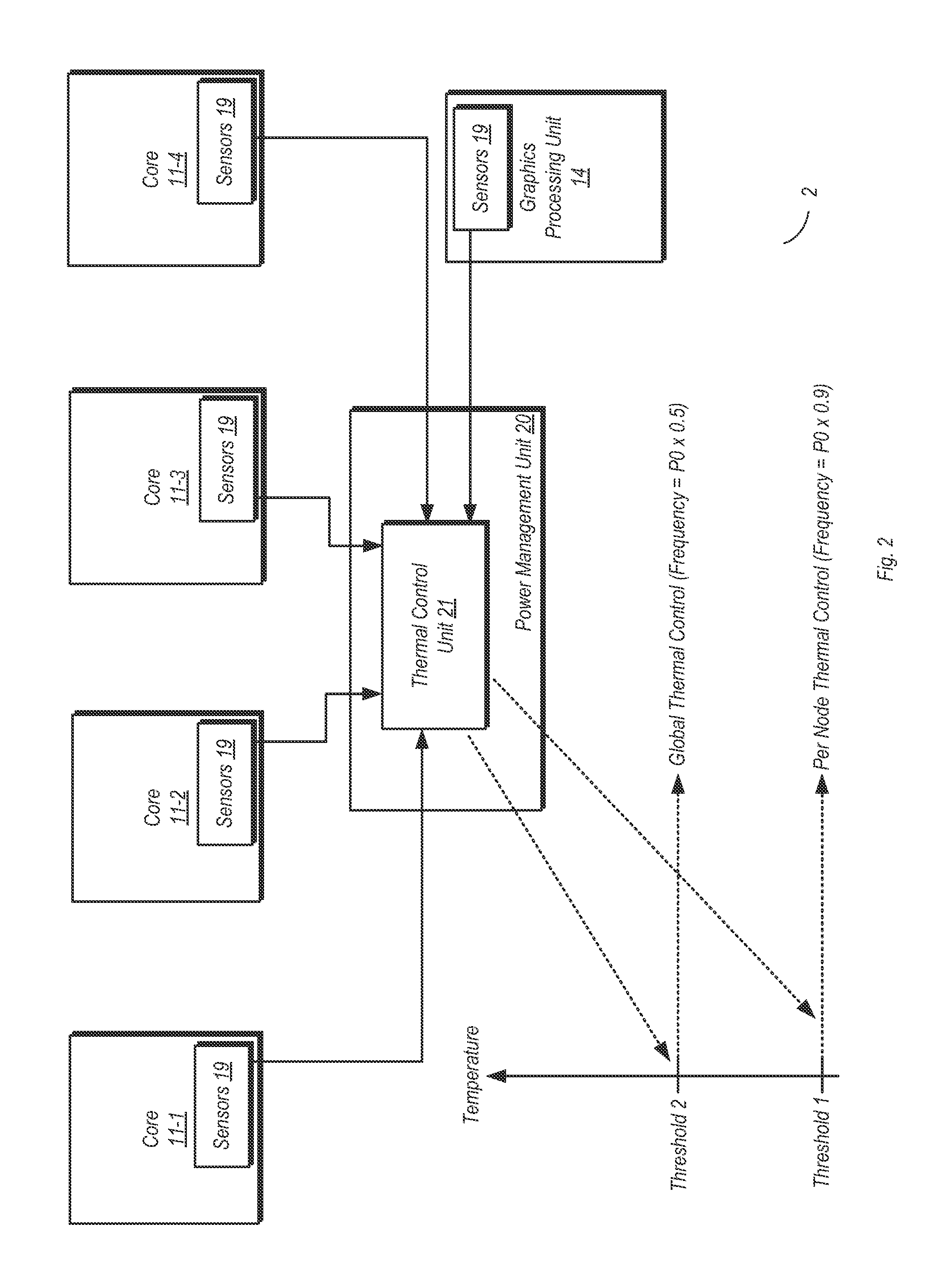

ActiveUS20120066535A1Increase powerLower performance requirementsVolume/mass flow measurementHardware monitoringControl powerPower Management Unit

A system includes a plurality of processor cores and a power management unit. The power management unit may be configured to independently control the performance of the processor cores by selecting a respective thermal power limit for each of the plurality of processor cores dependent upon an operating state of each of the processor cores and a relative physical proximity of each processor core to each other processor core. In response to the power management unit detecting that a given processor core is operating above the respective thermal power limit, the power management unit may reduce the performance of the given processor core, and thereby reduce the power consumed by that core.

Owner:ADVANCED MICRO DEVICES INC

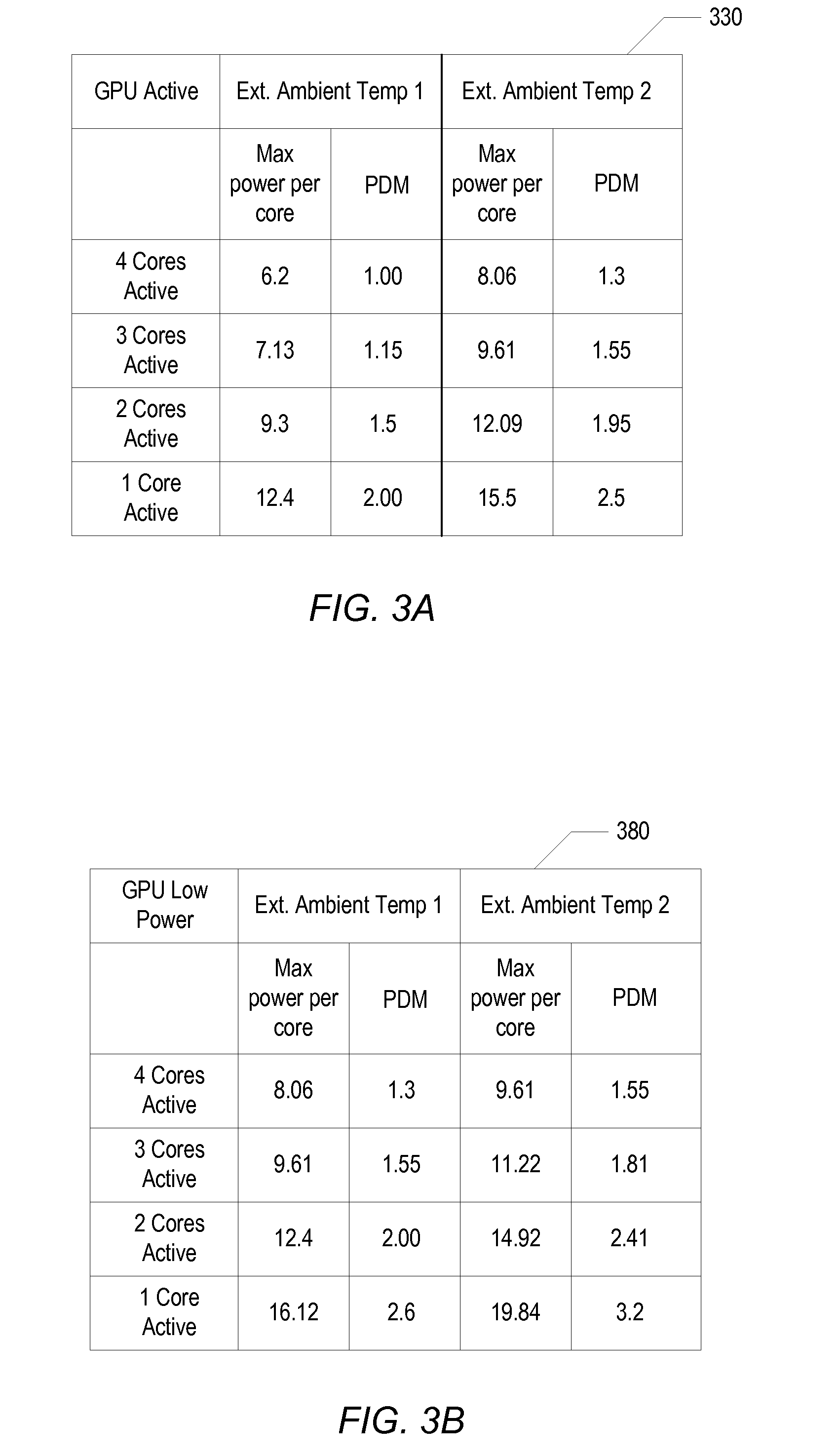

Method for adaptive performance optimization of the soc

ActiveUS20130246820A1Energy efficient ICTVolume/mass flow measurementPower Management UnitPower limits

An apparatus and method for dynamically adjusting power limits for processing nodes and other components, such as peripheral interfaces, is disclosed. The apparatus includes multiple processing nodes and other components, and further includes a power management unit configured to set a first frequency limit for at least one of the processing nodes responsive to receiving an indication of a first detected temperature greater than a first temperature threshold. Initial power limits are set below guard-band power limits for components that do not have reliable reporting of power consumption or for cost or power saving reasons. The amount of throttling of processing nodes is used to adjust the power limits for the processing nodes and these components.

Owner:ADVANCED MICRO DEVICES INC

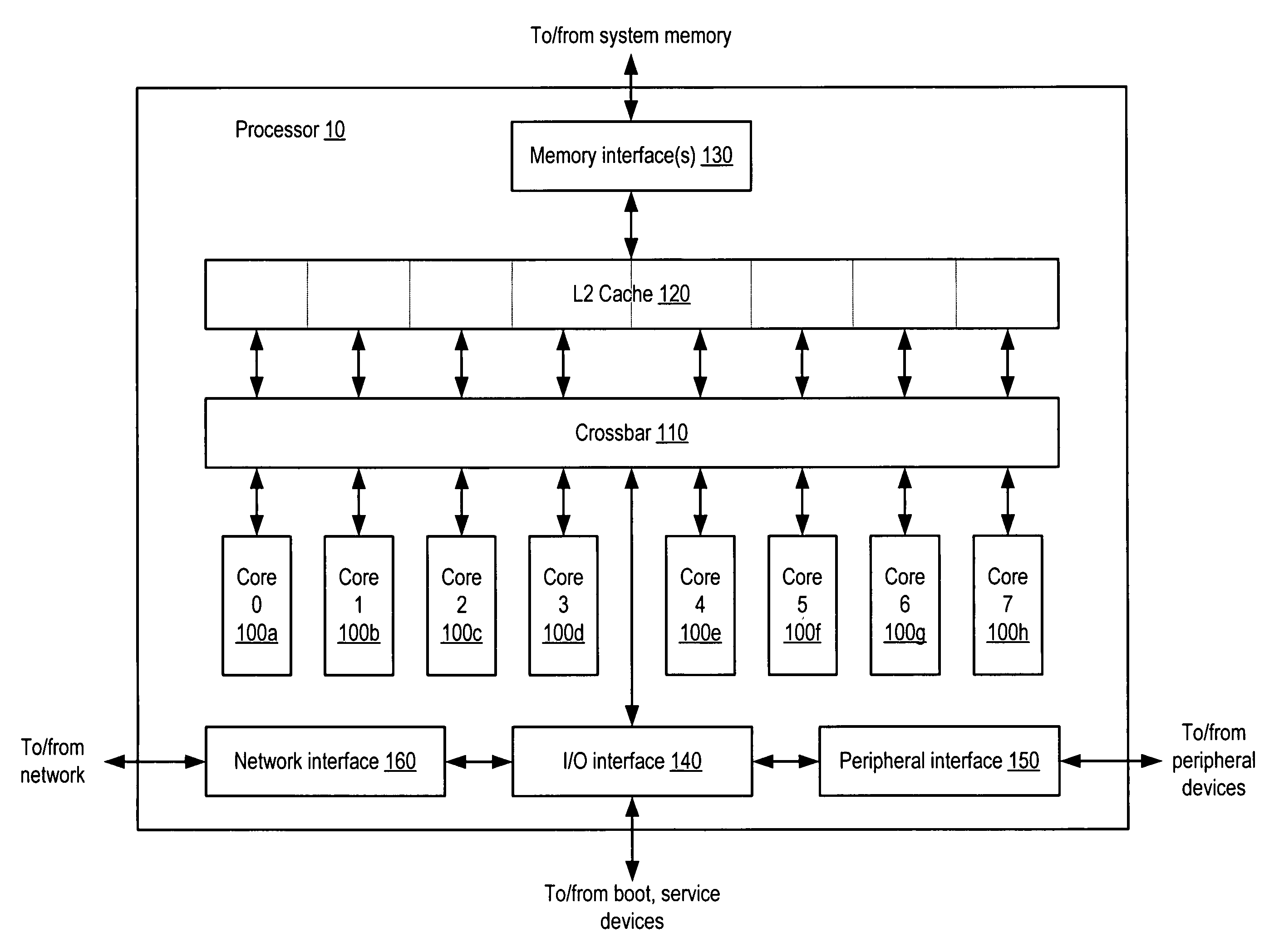

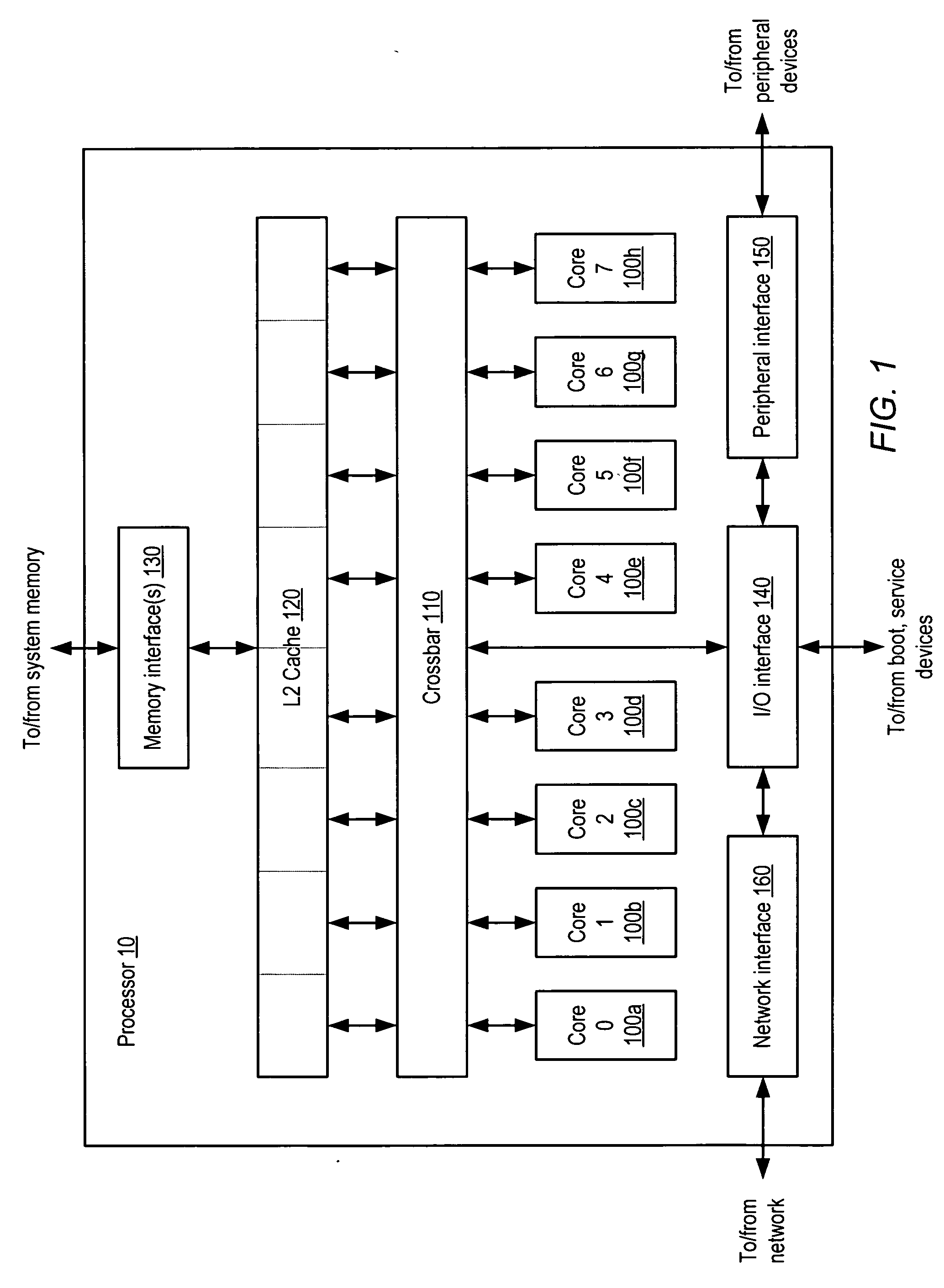

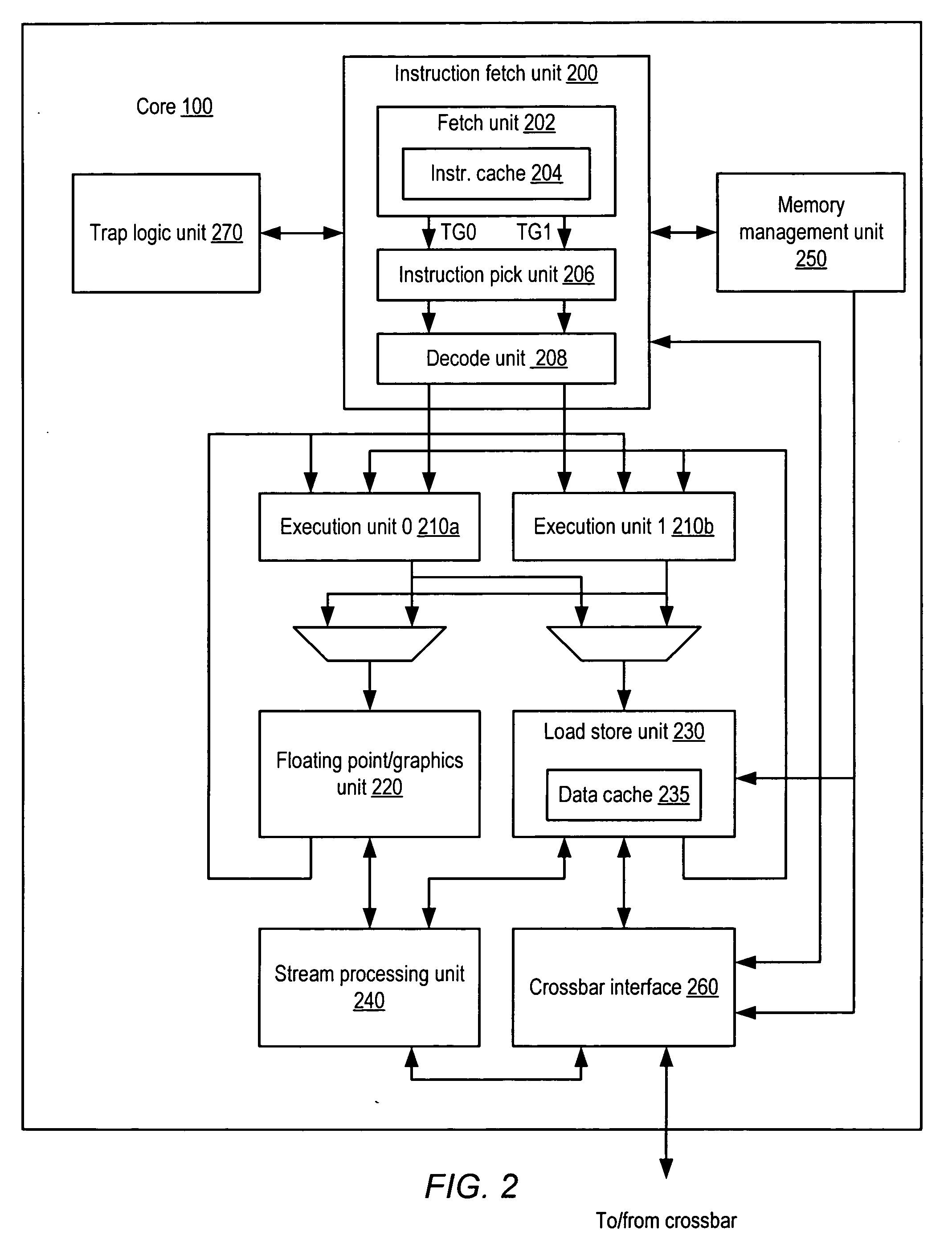

Method and appratus for power throttling in a multi-thread processor

ActiveUS20060020831A1Save powerRegister arrangementsVolume/mass flow measurementControl powerParallel computing

A method and apparatus for controlling power consumption in a processor. In one embodiment, a processor includes a pipeline. The pipeline includes logic for fetching instructions, issuing instructions, and executing instructions. The processor also includes a power management unit. The power management unit is configured to input M stalls into the pipeline every N instruction cycles (where M and N are integer value and wherein M is less than N).

Owner:SUN MICROSYSTEMS INC

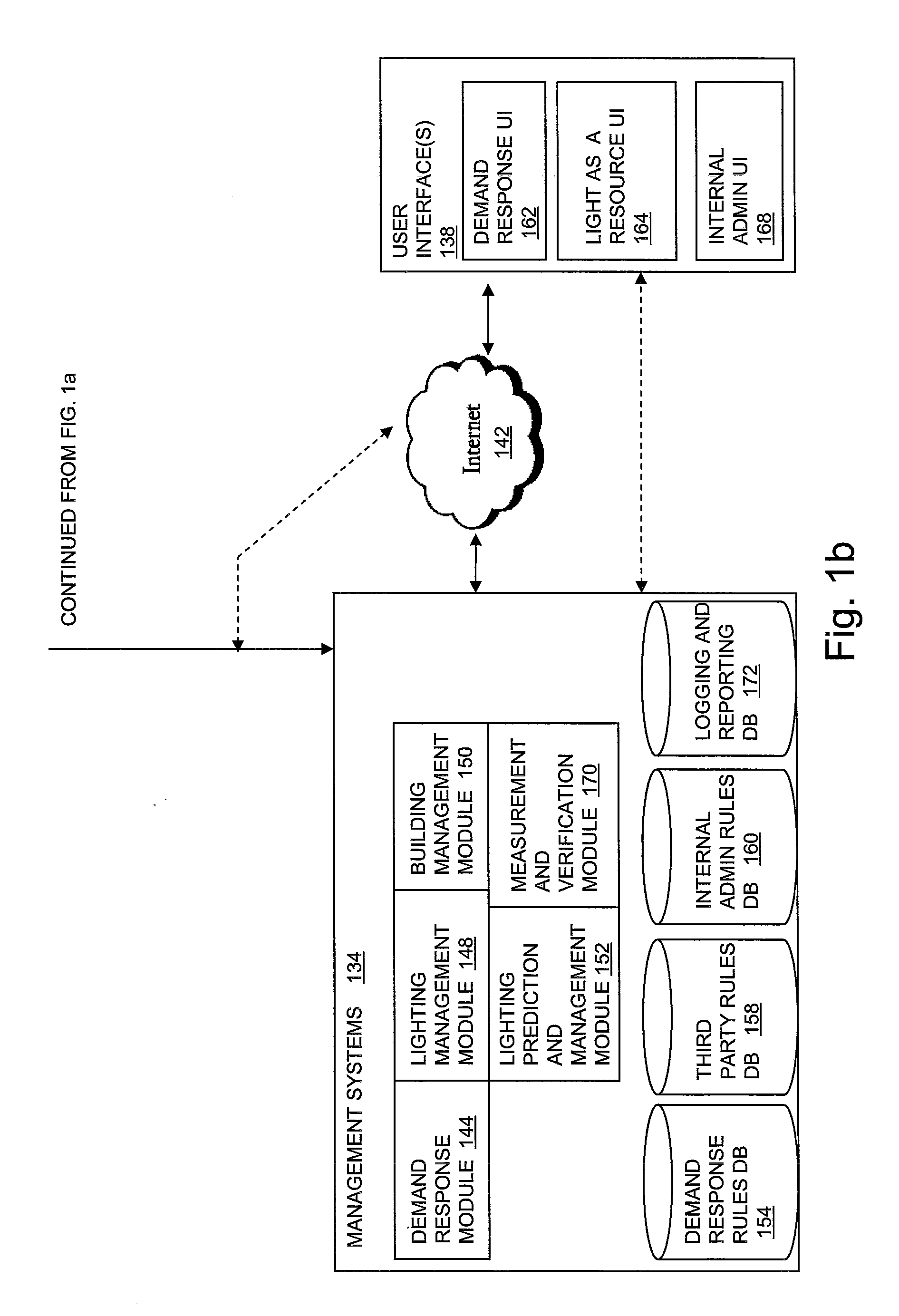

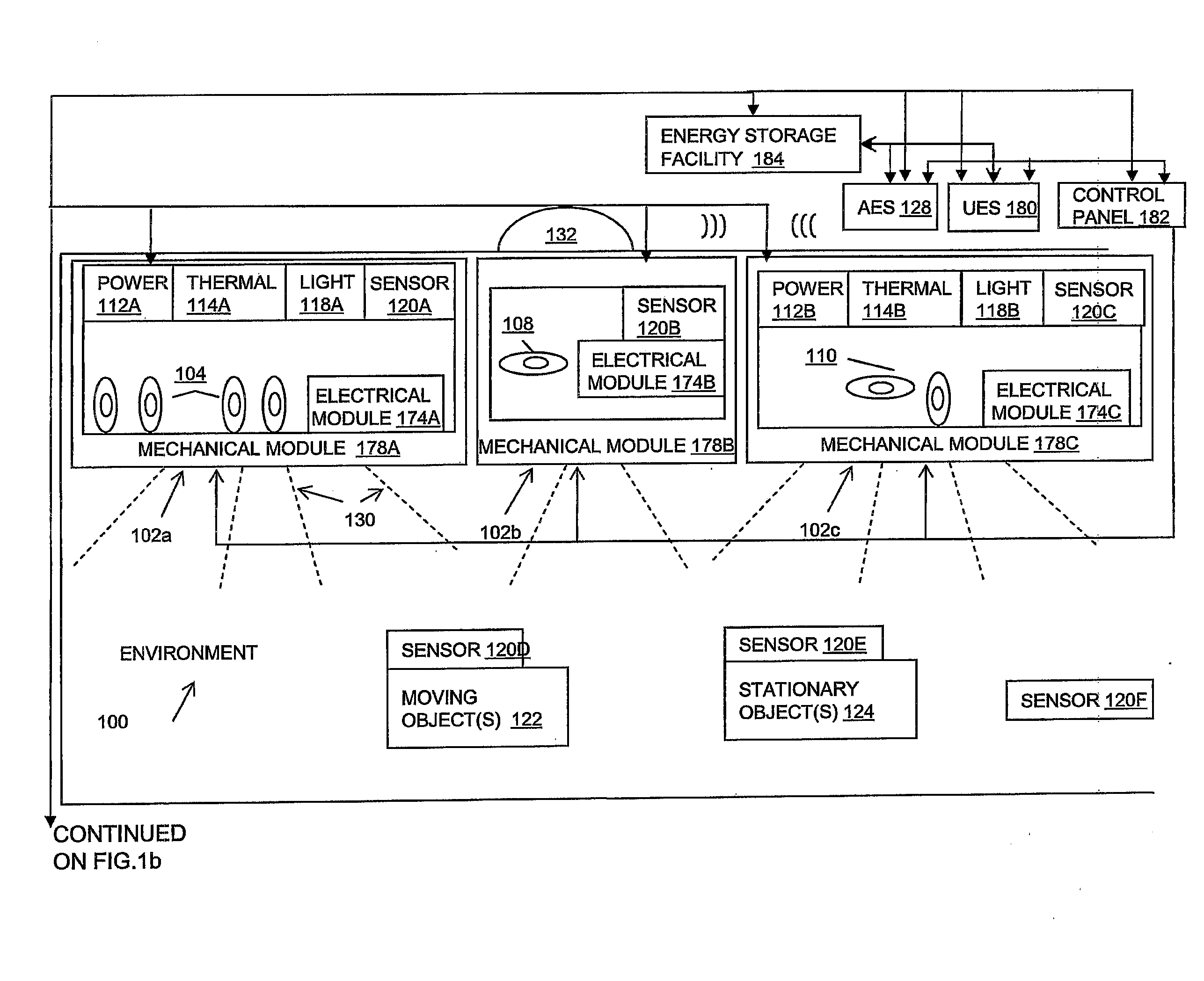

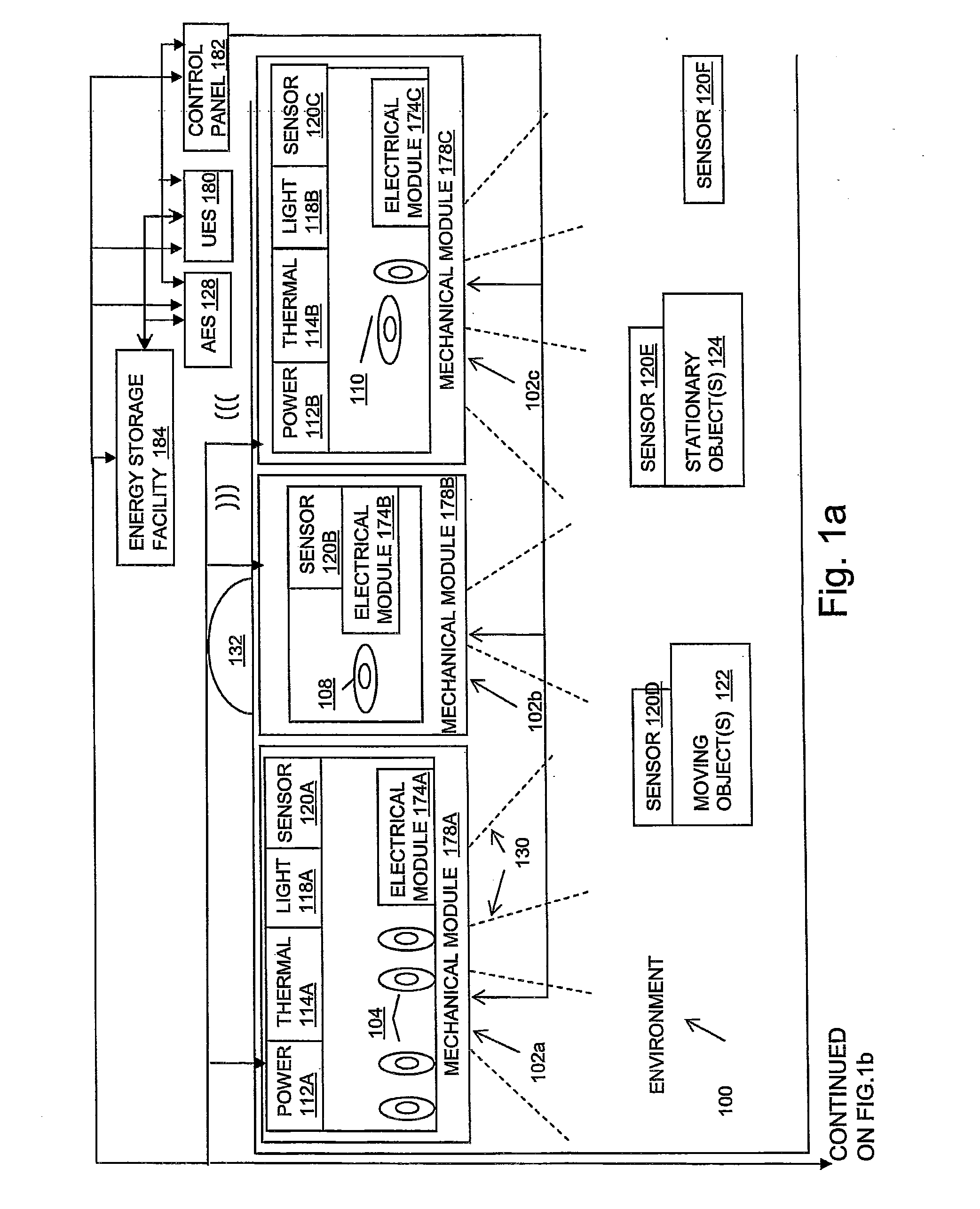

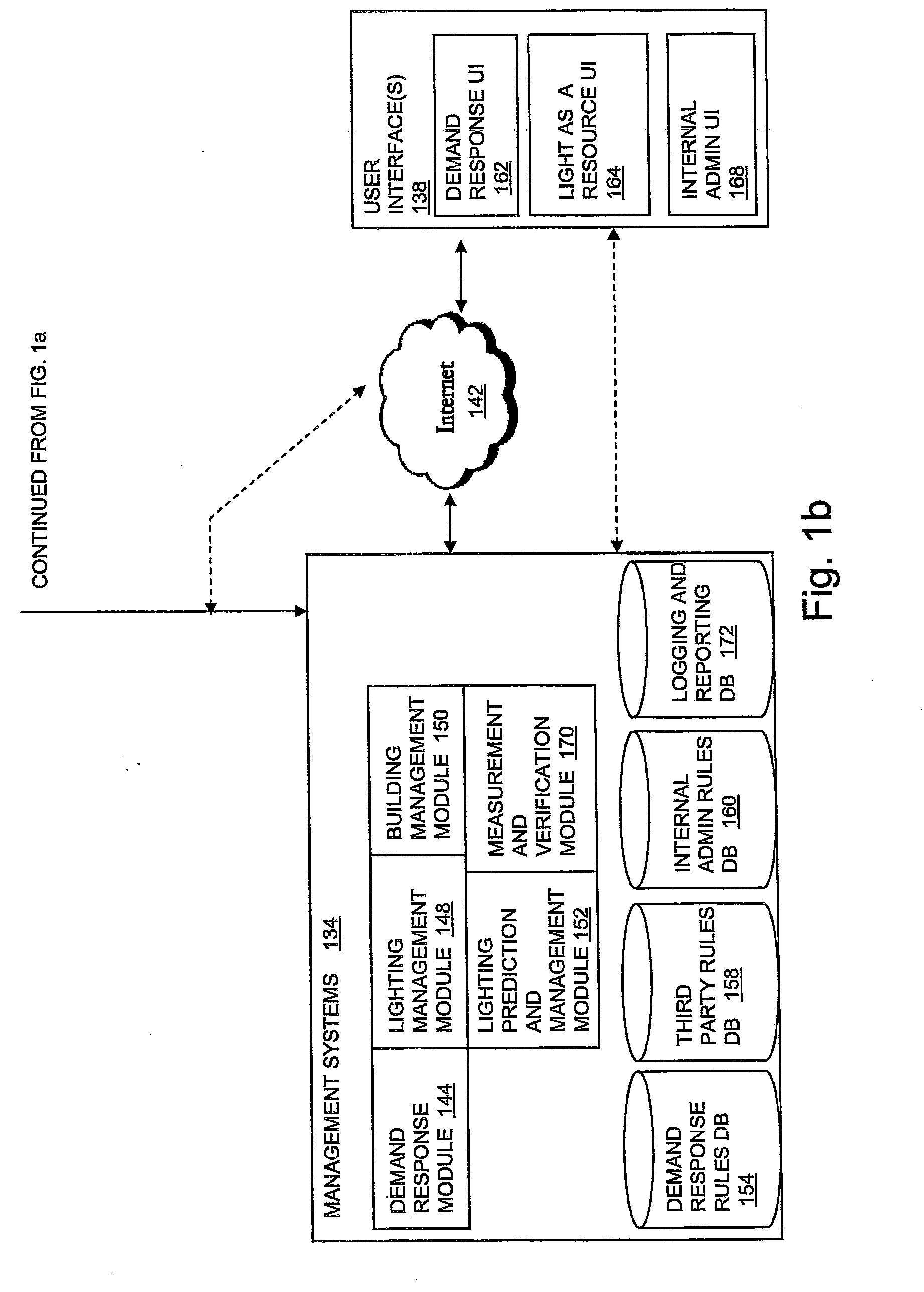

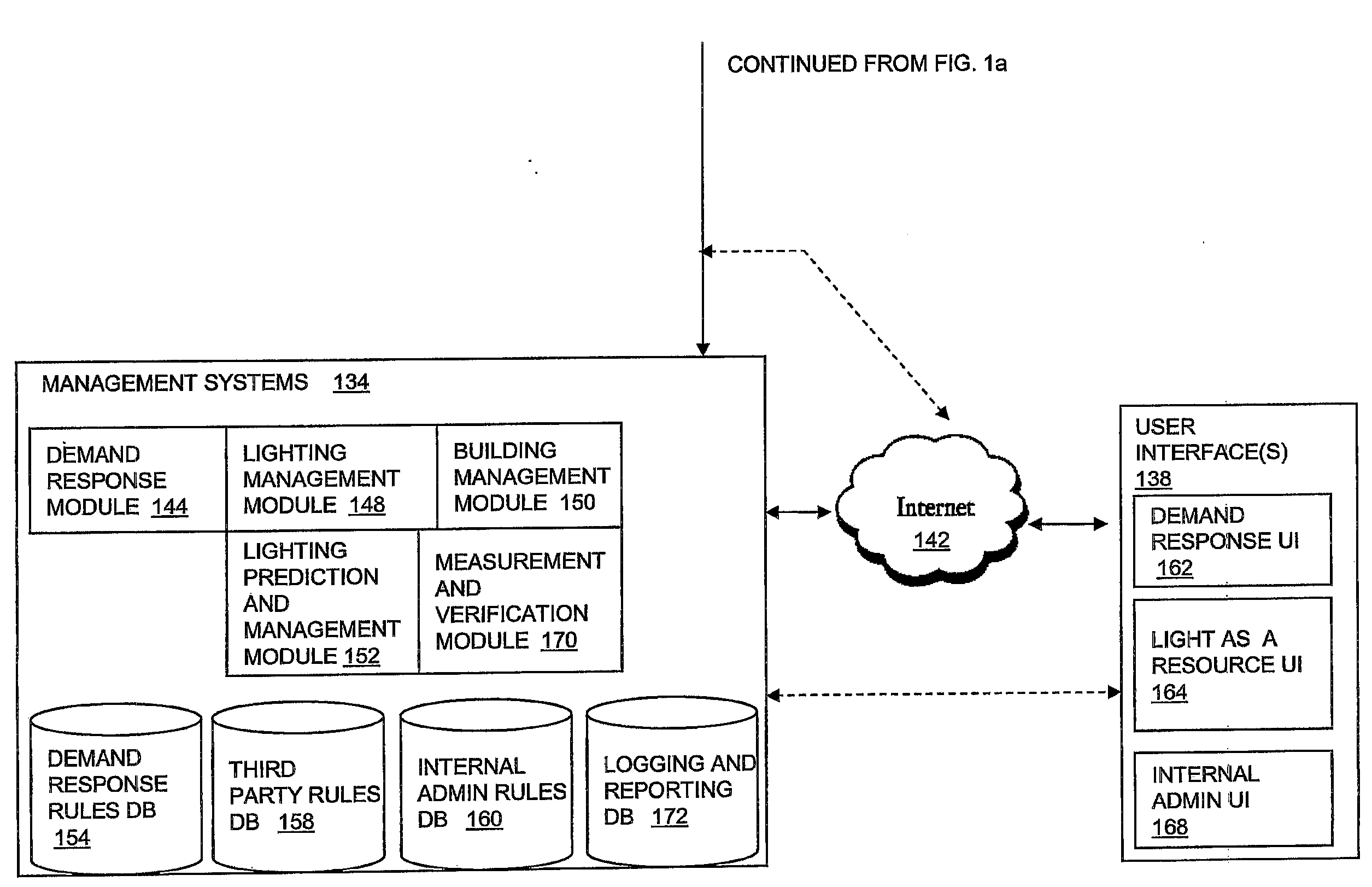

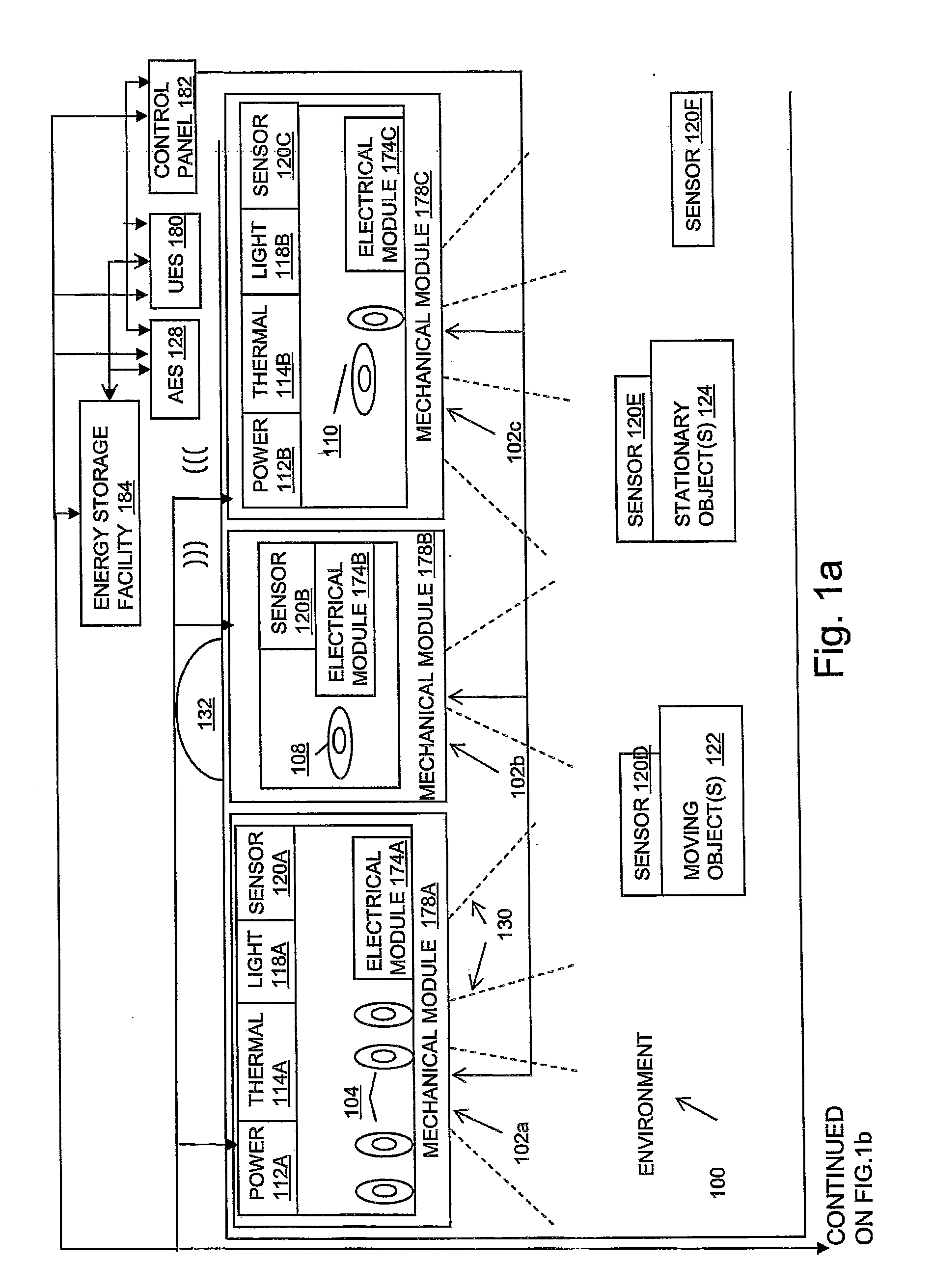

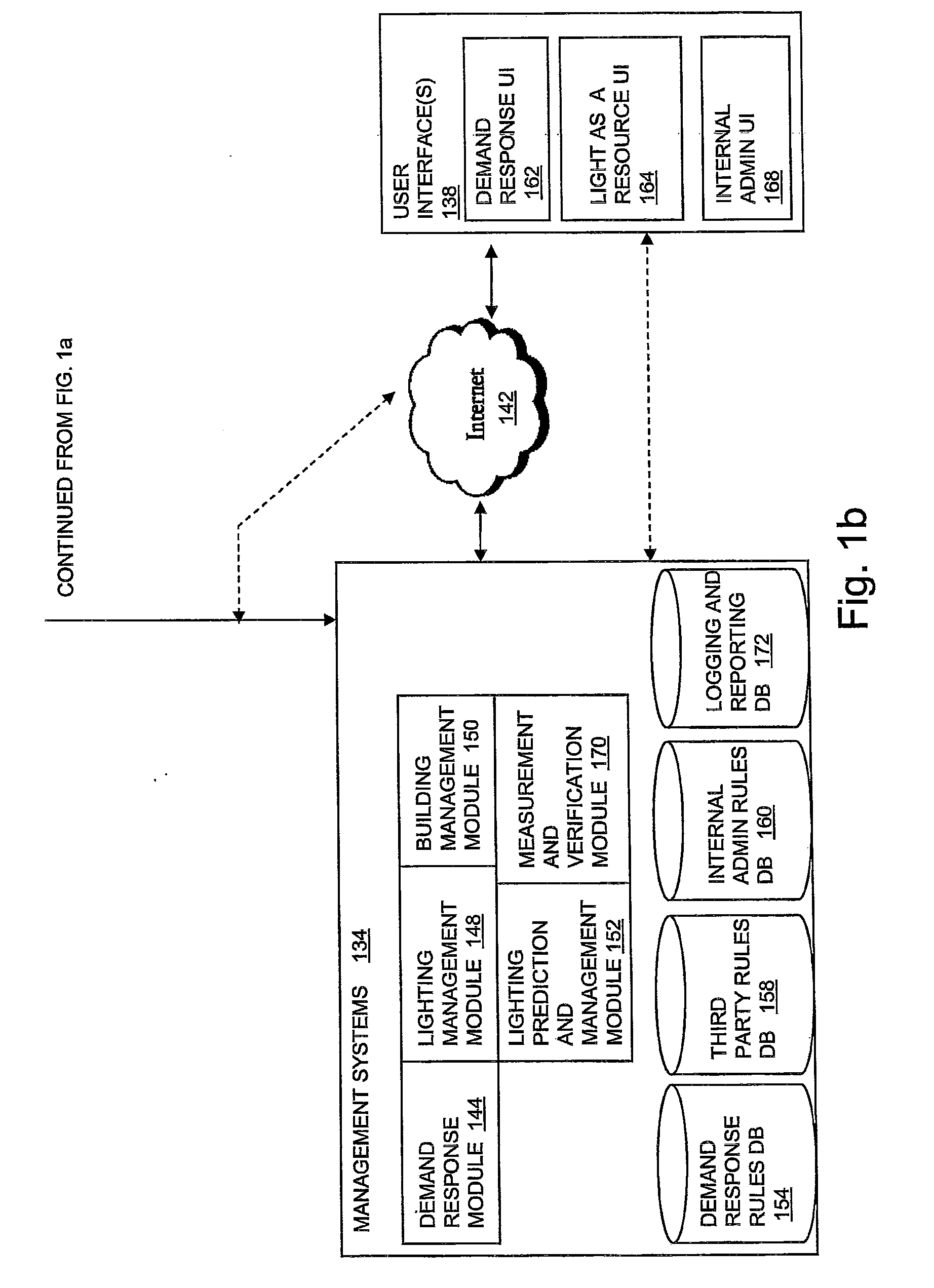

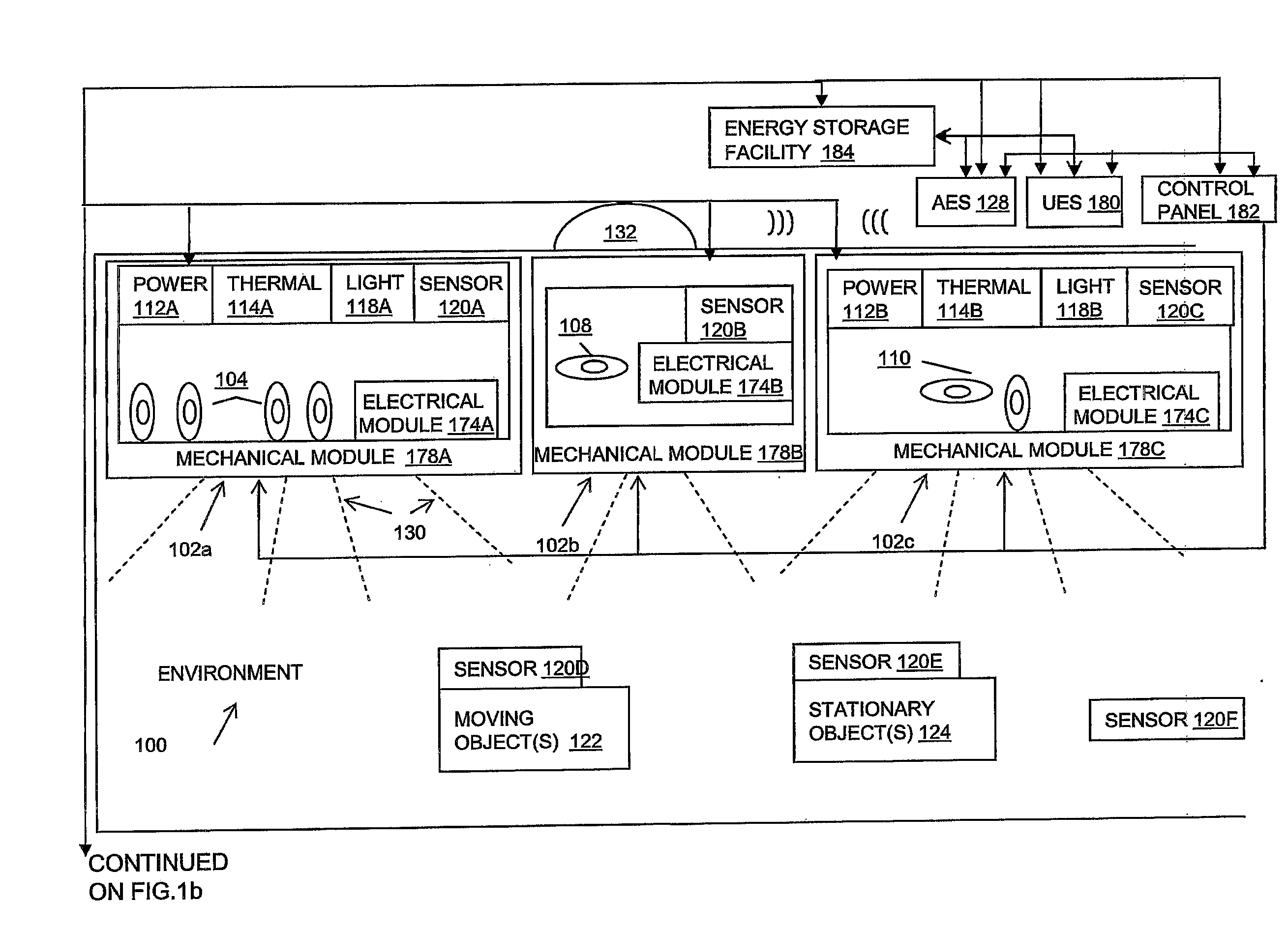

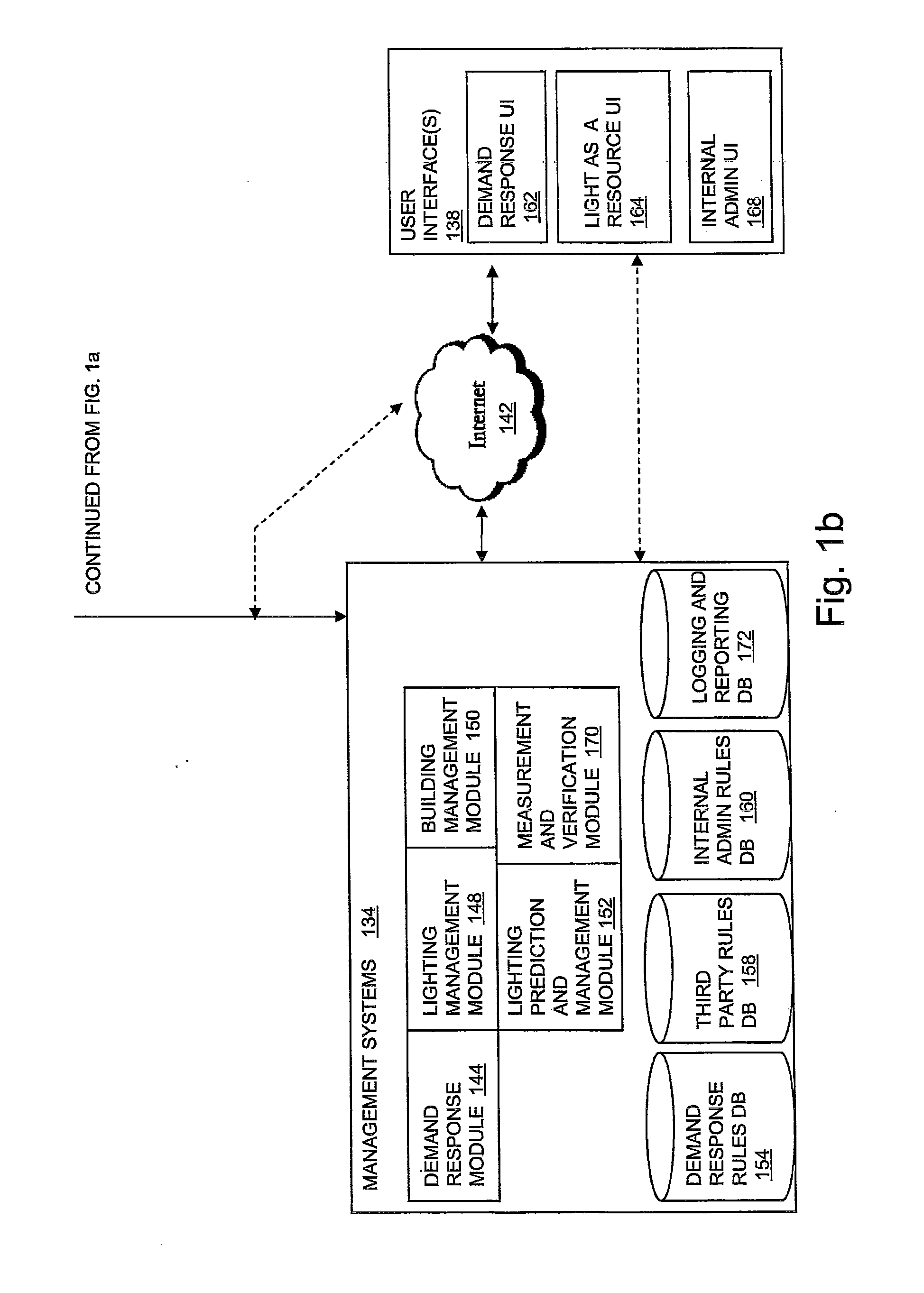

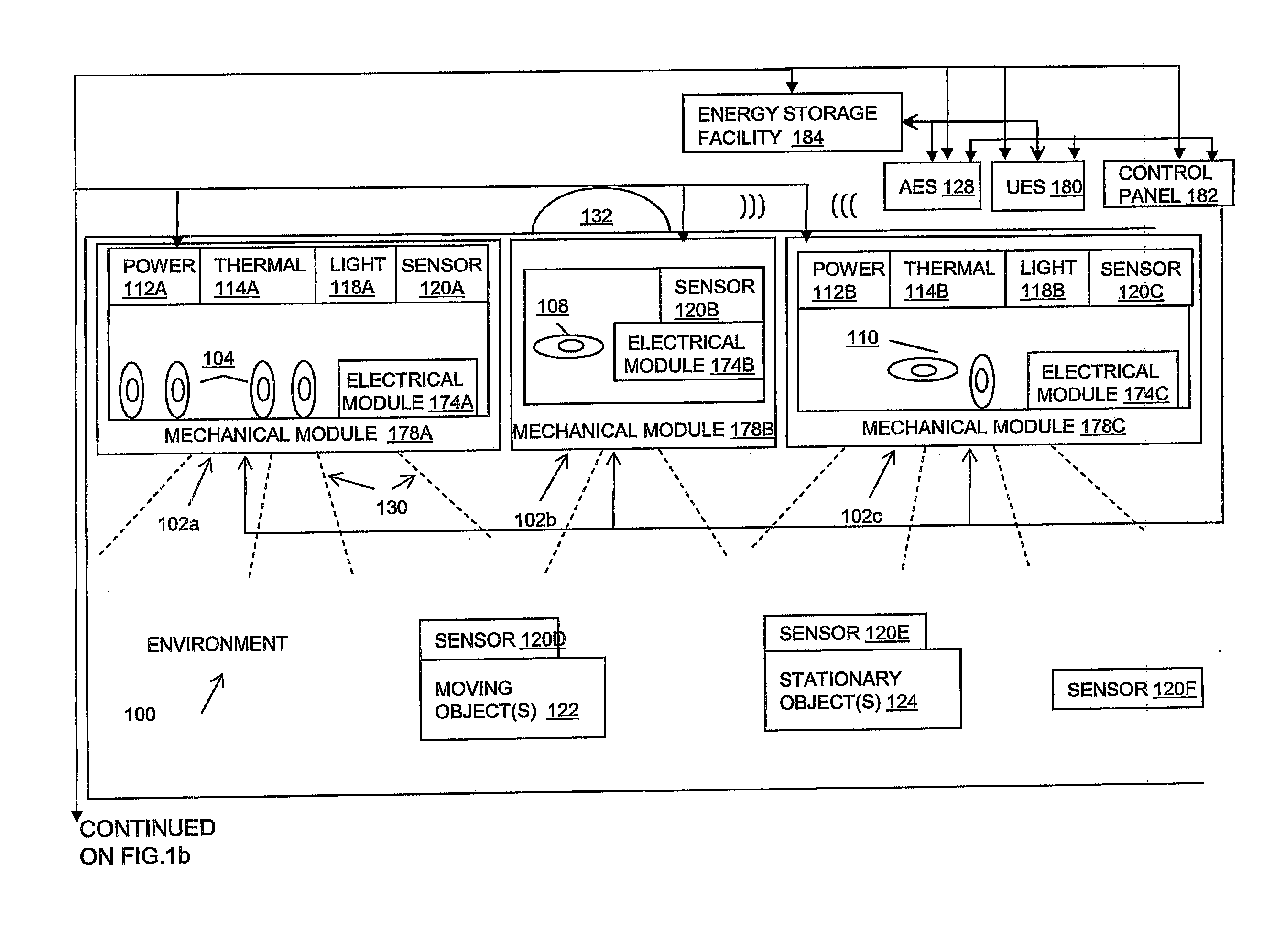

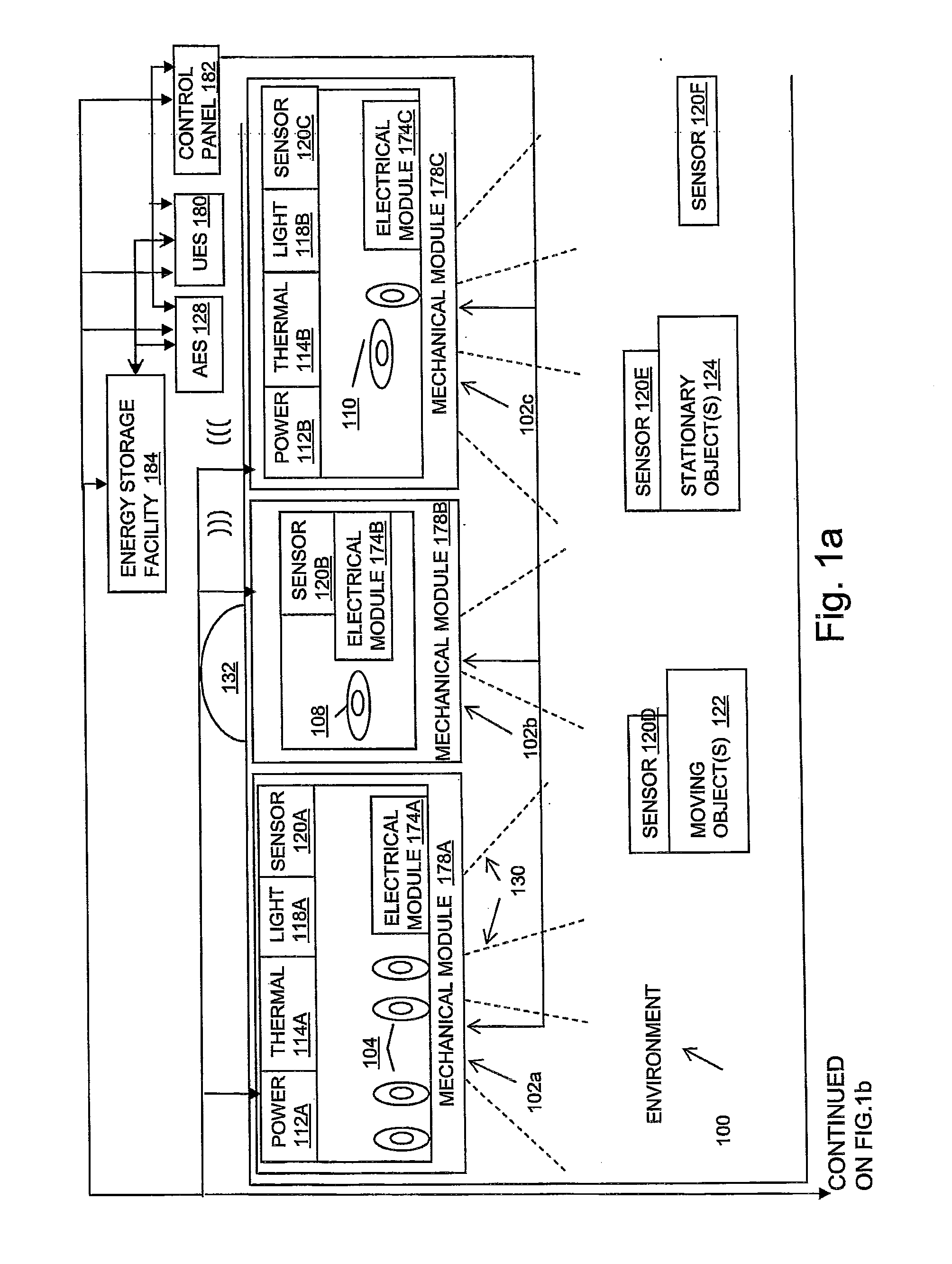

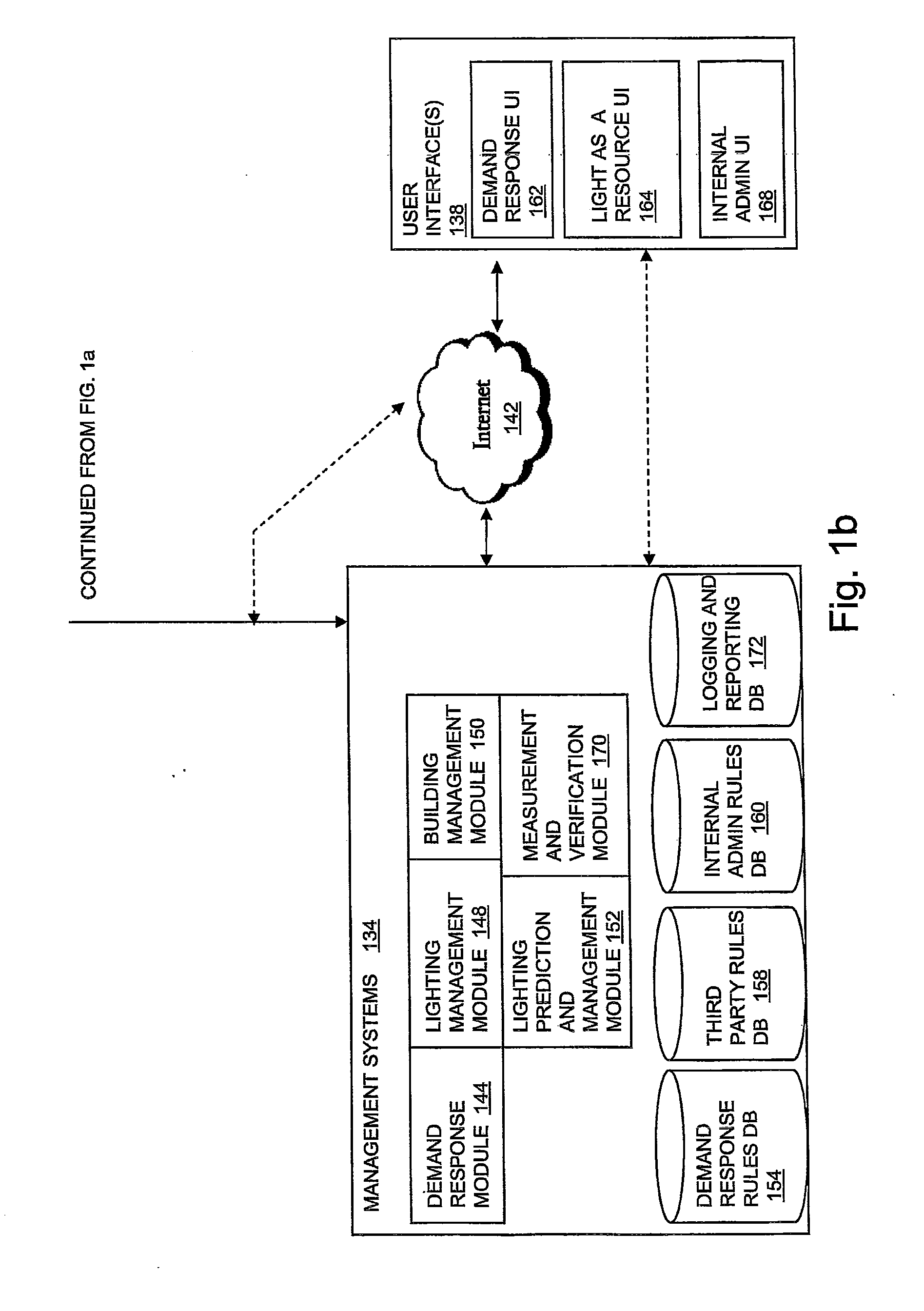

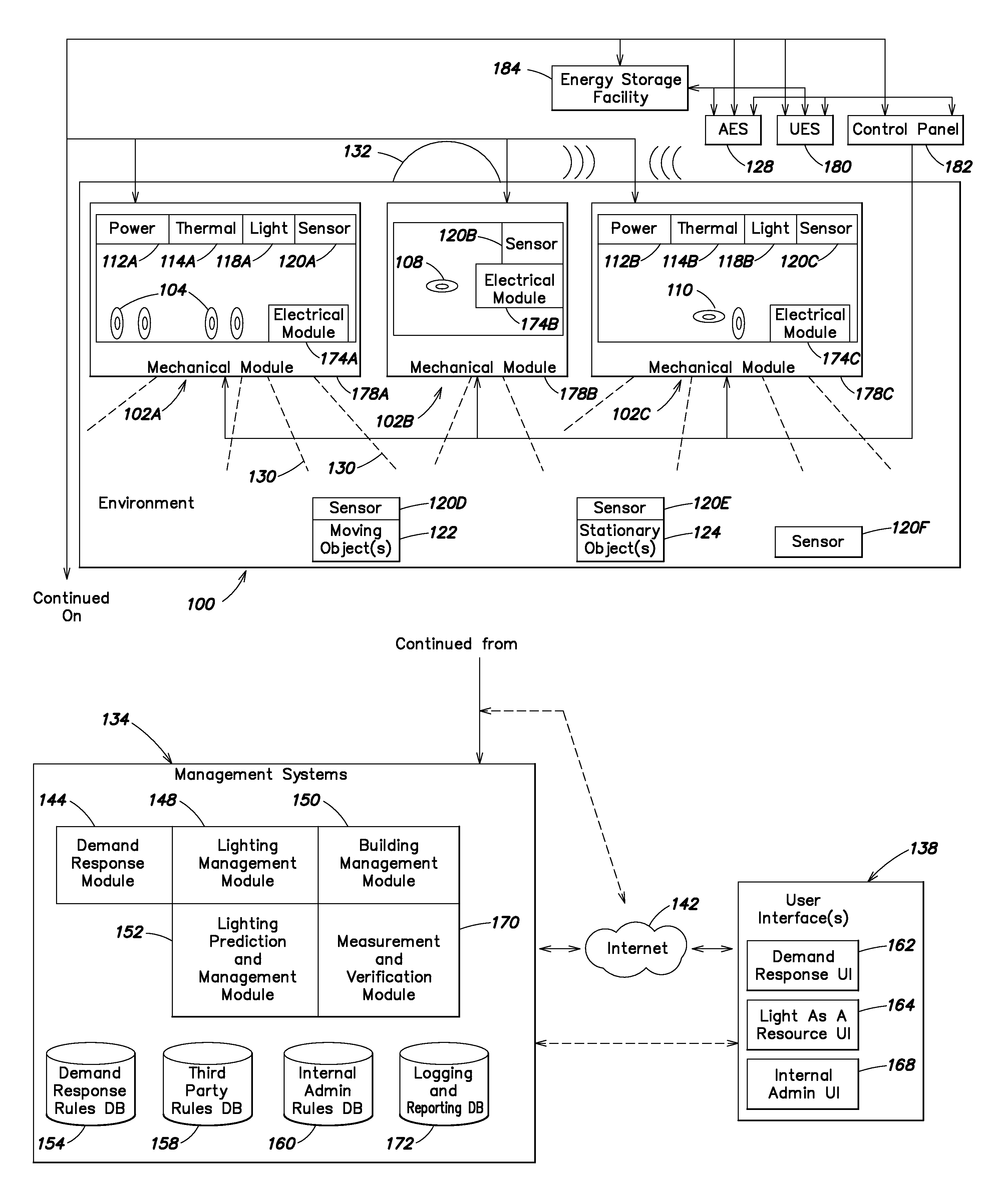

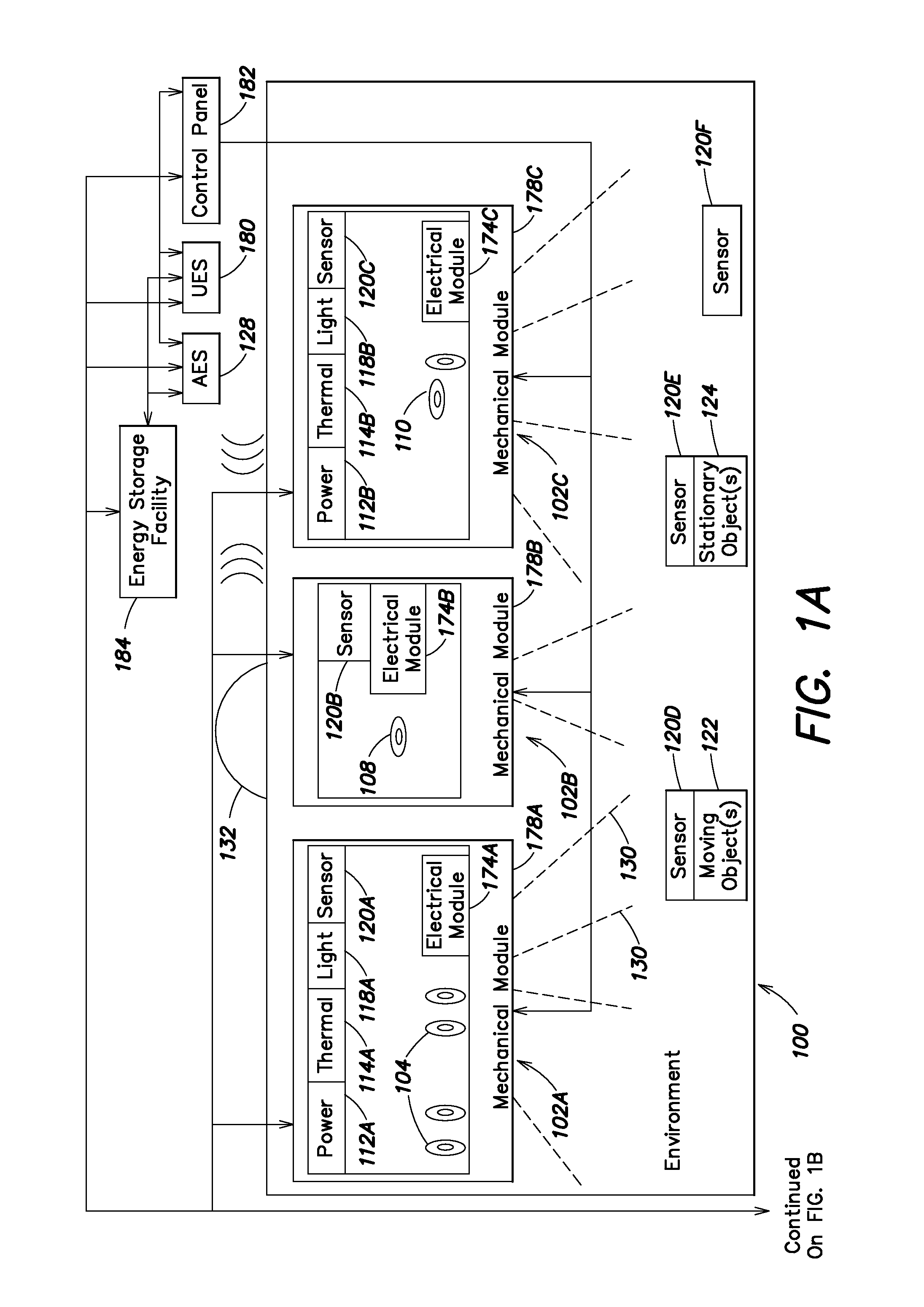

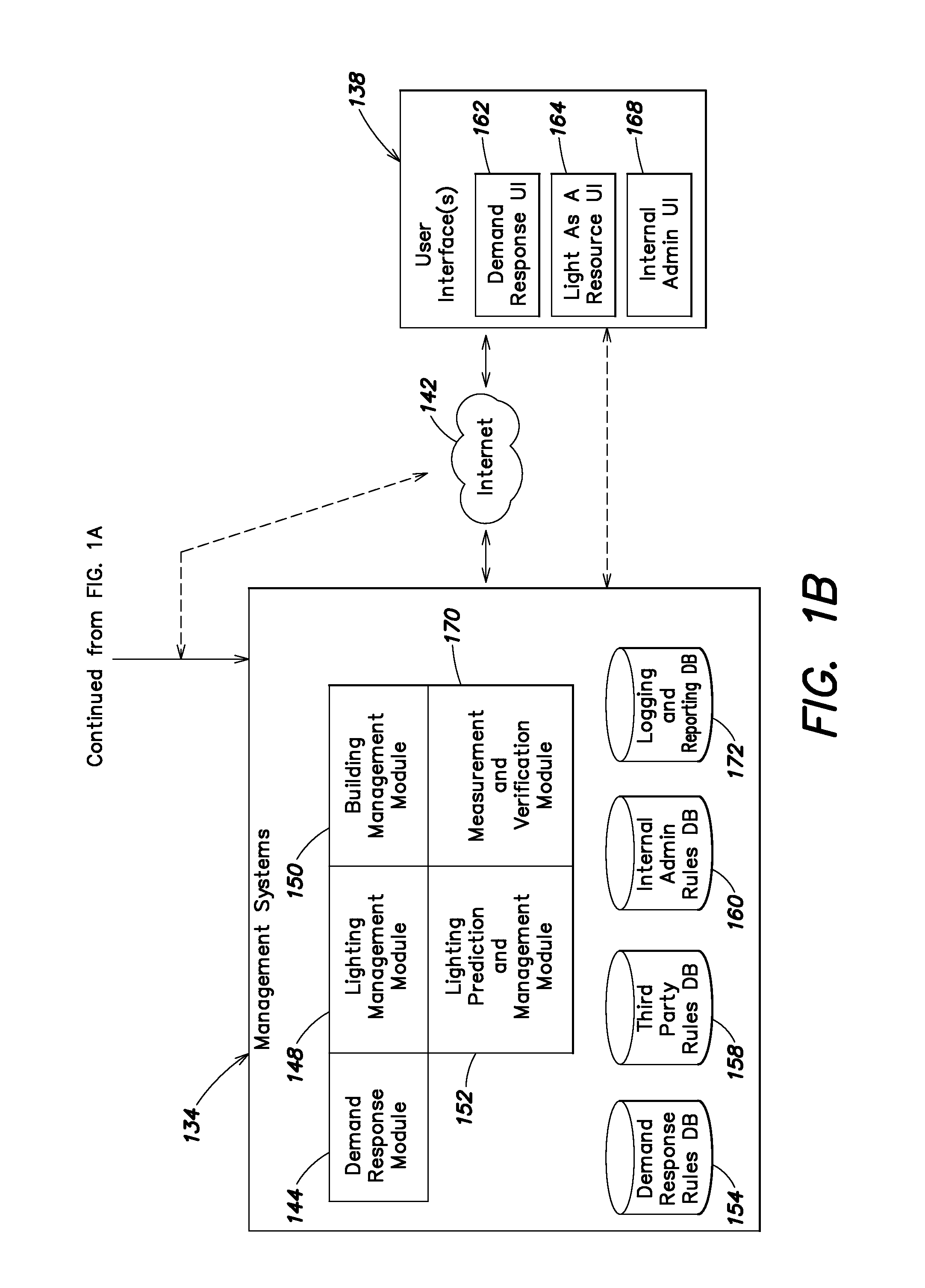

Power management unit with rules-based power consumption management

ActiveUS8368321B2Electrical apparatusElectric light circuit arrangementSmart lightingManagement unit

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

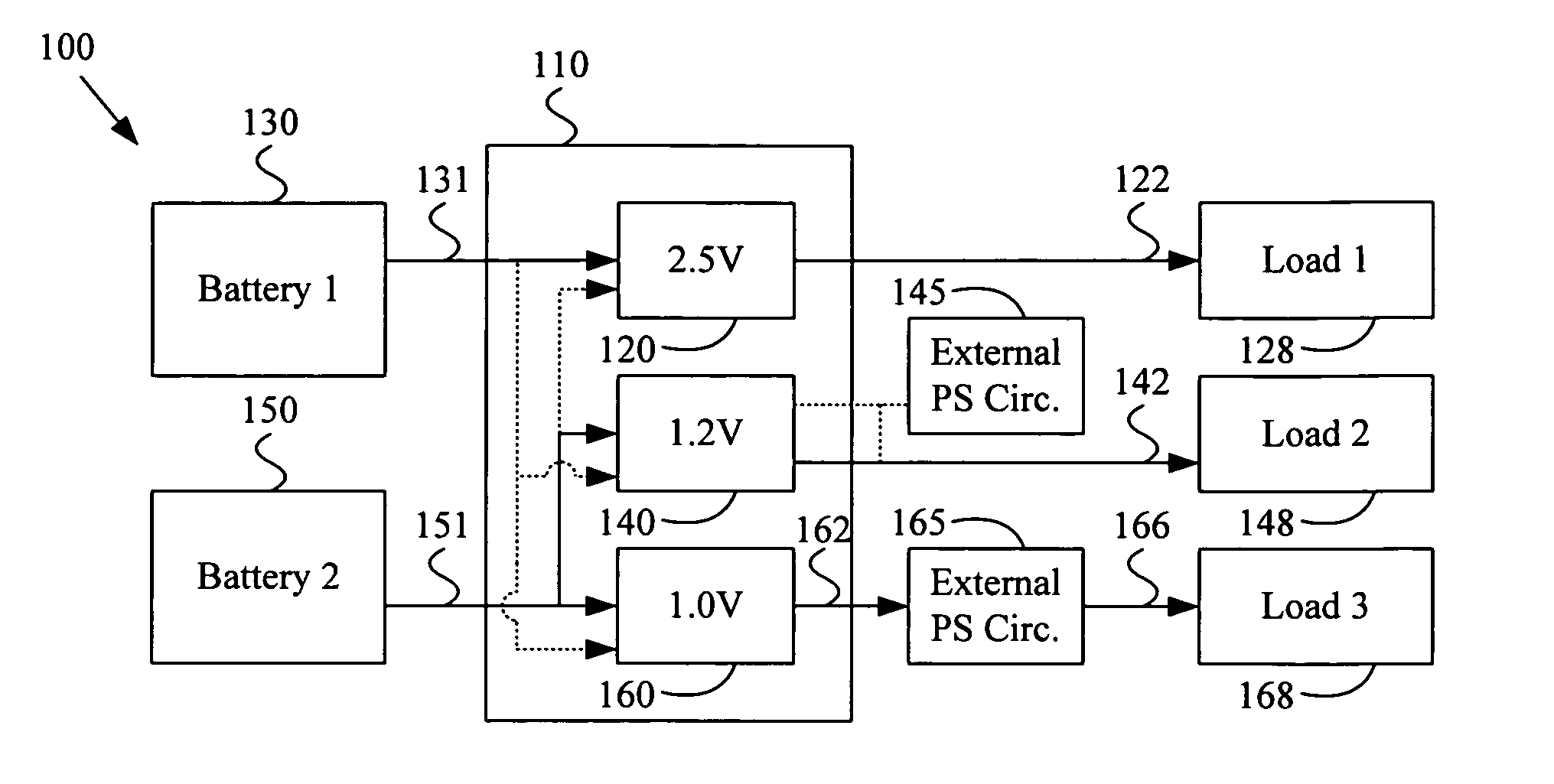

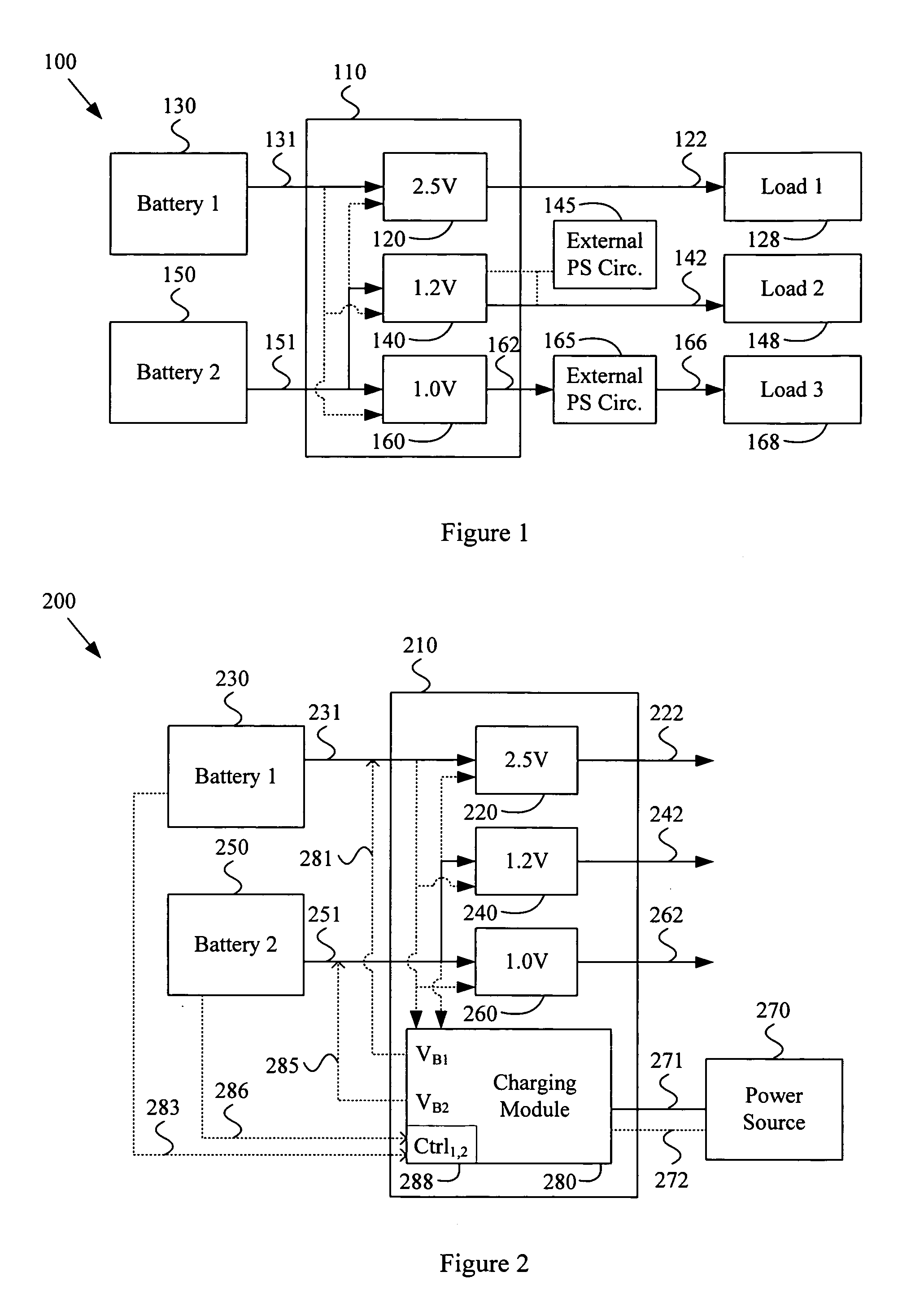

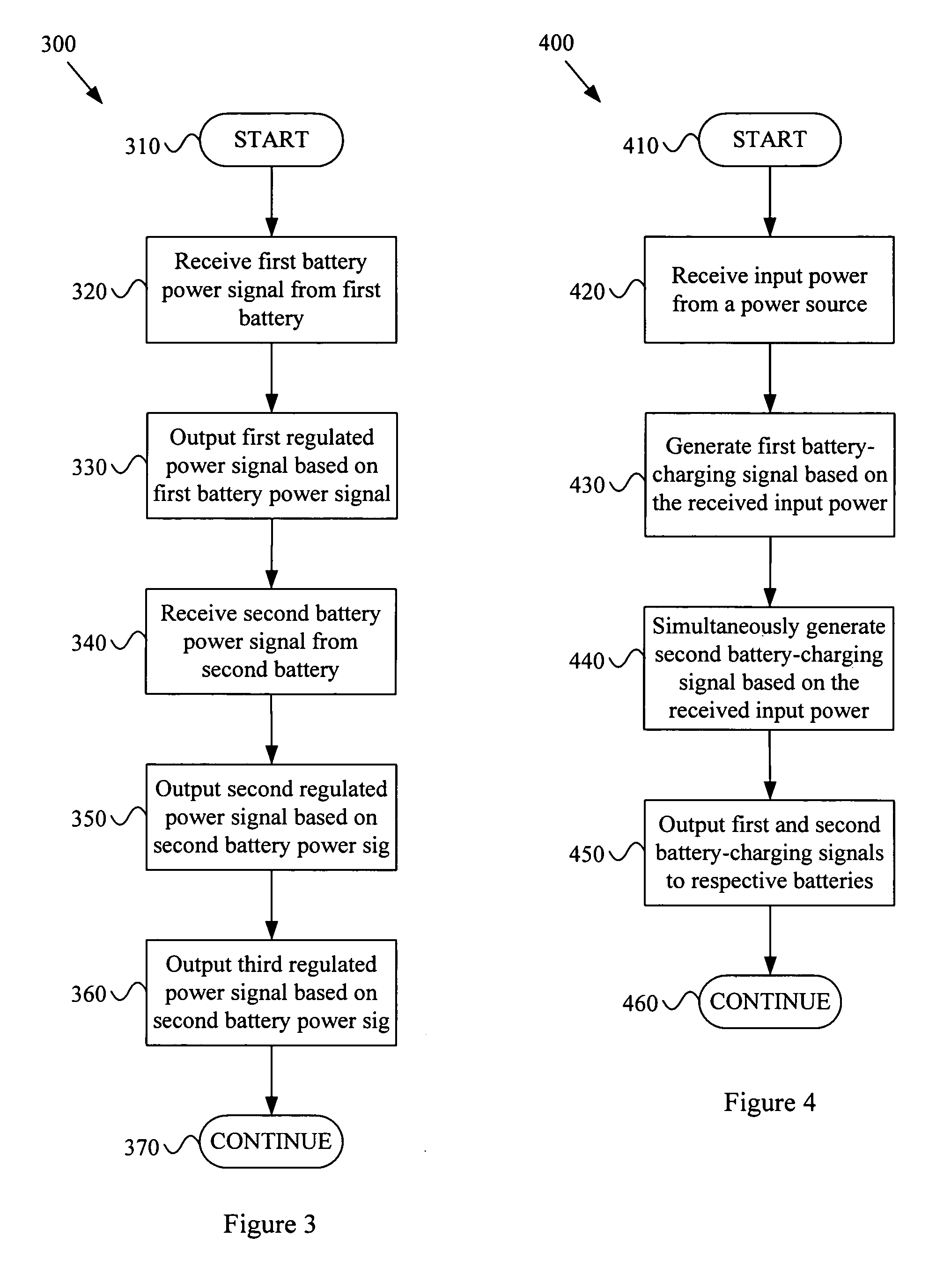

Multi-voltage multi-battery power management unit

InactiveUS20050289375A1Volume/mass flow measurementPower supply for data processingElectrical batteryPower Management Unit

A system and method for implementing a multi-voltage multi-battery power management integrated circuit. Various aspects of the present invention provide a power management integrated circuit. The power management IC may comprise a first regulator module that receives a first battery power signal from a first battery characterized by a first battery voltage and outputs a first regulated power signal, based at least in part on the first battery power signal. The power management IC may also comprise a second regulator module that receives a second battery power signal from a second battery characterized by a second battery voltage and outputs a second regulated power signal, based at least in part on the second battery power signal. The second battery voltage may, for example, be substantially different than the first battery voltage. The power first and second regulated power signals may, for example, correspond to substantially different power supply voltages.

Owner:AVAGO TECH INT SALES PTE LTD

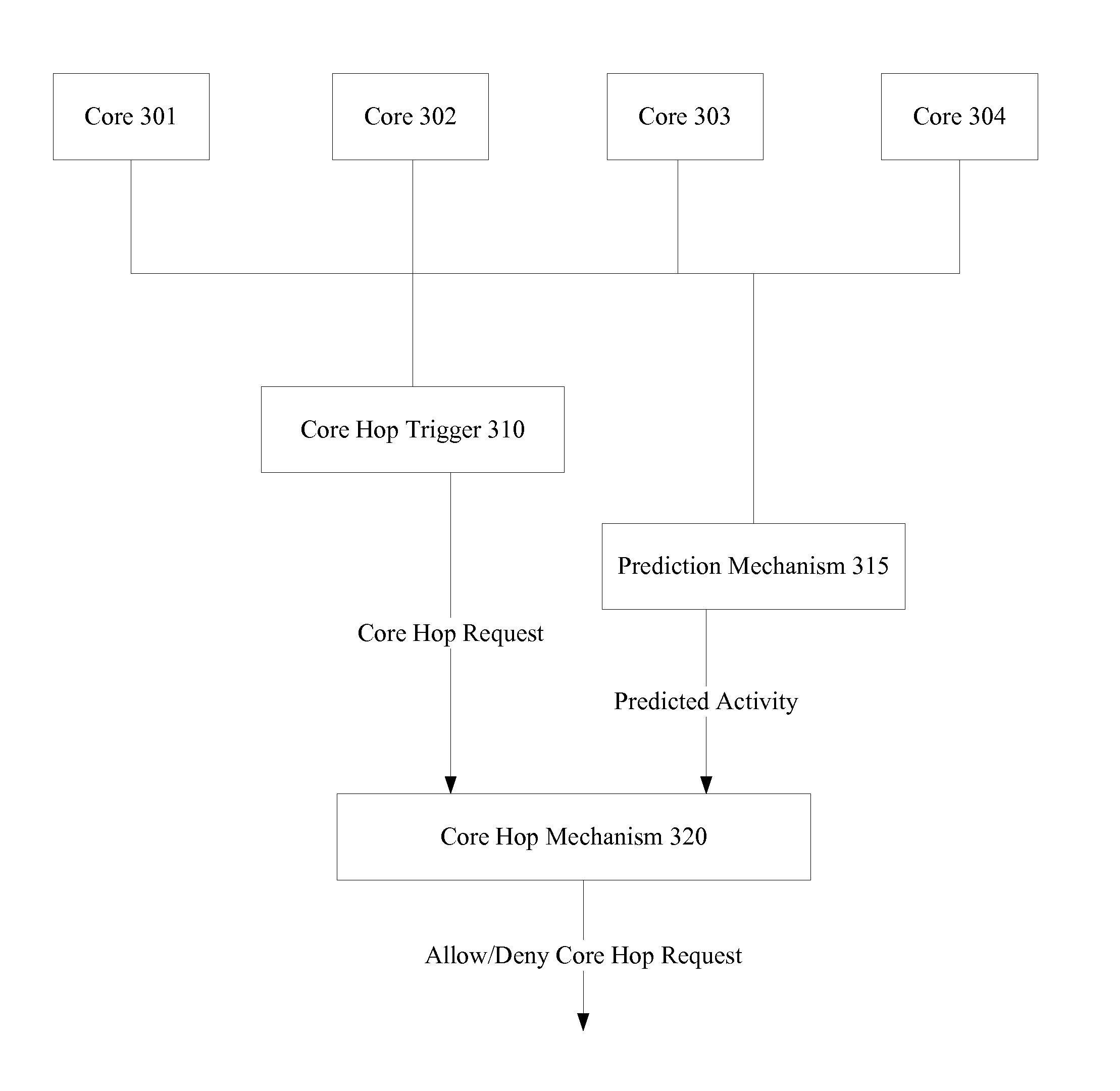

Mechanisms to avoid inefficient core hopping and provide hardware assisted low-power state selection

InactiveUS20110161627A1Energy efficient ICTConditional code generationPower Management UnitComputer science

An apparatus and method is described herein for avoiding inefficient core hopping and providing hardware assisted power state selection. Future idle-activity of cores is predicted. If the residency of activity patterns for efficient core hop scenarios is predicted to be large enough, a core is determined to be efficient and allowed. However, if efficient activity patterns are not predicted to be resident for long enough—inefficient patterns are instead predicted to be resident for longer—then a core hop request is denied. As a result, designers may implement a policy for avoiding core hops that weighs the potential gain of the core hop, such as alleviation of a core hop condition, against a penalty for performing the core hop, such as a temporal penalty for the core hop. Separately, idle durations associated with hardware power states for cores may be predicted in hardware. Furthermore, accuracy of the idle duration prediction is determined. Upon receipt of a request for a core to enter a power state, a power management unit may select either the hardware predicted power state, if the accuracy is high enough, or utilize the requested power state, if the accuracy of the hardware prediction is not high enough.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com