Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

8356 results about "Silicon based" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

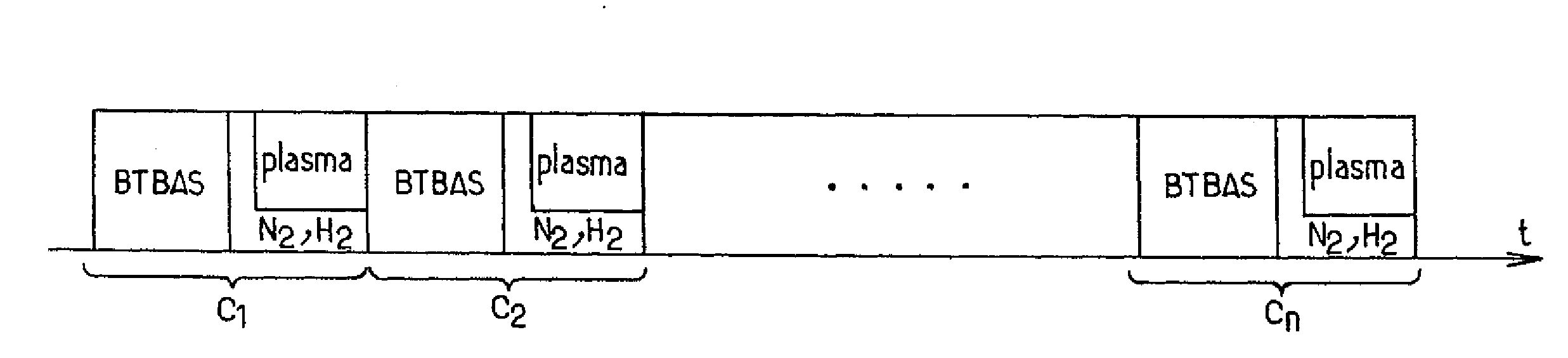

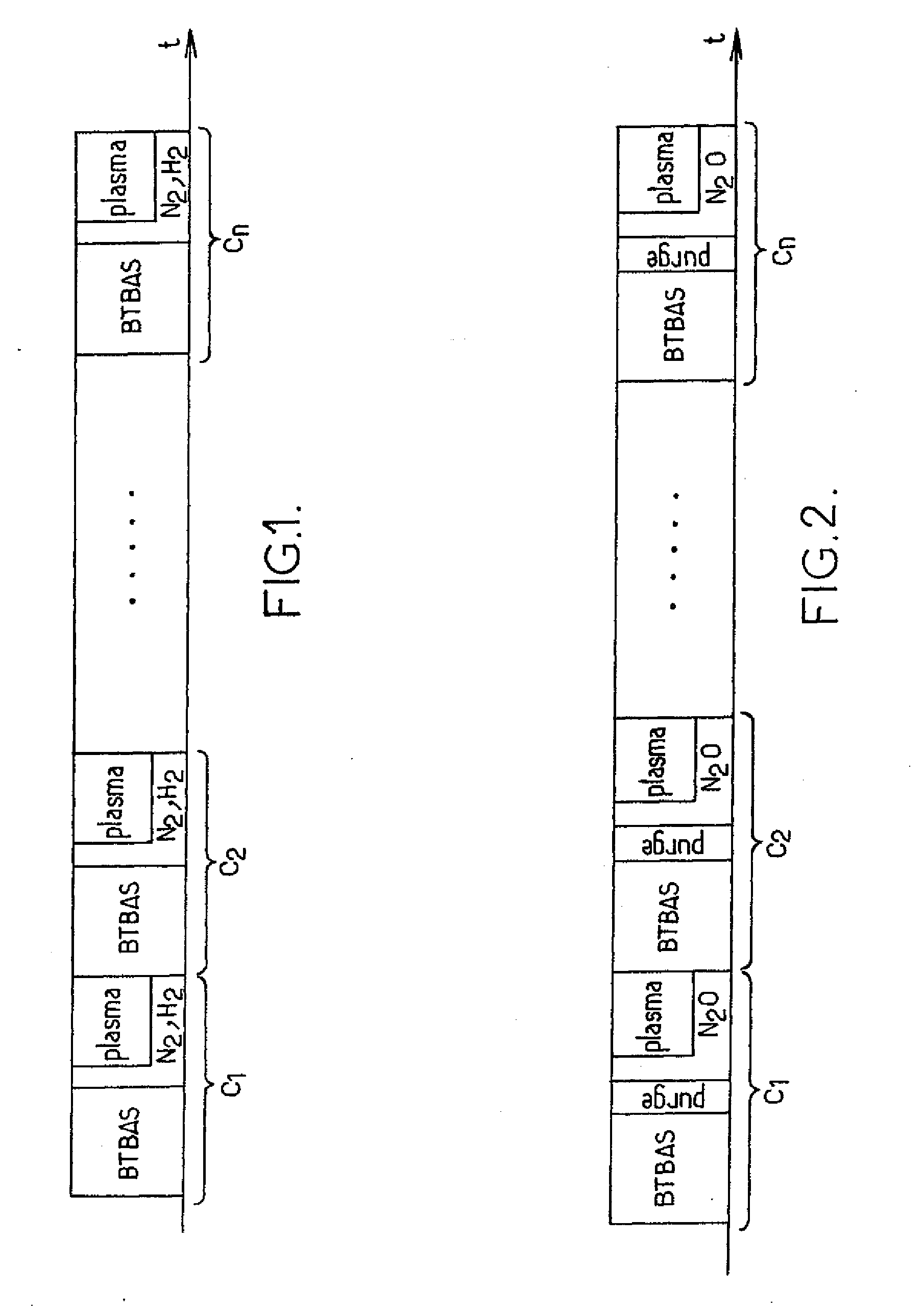

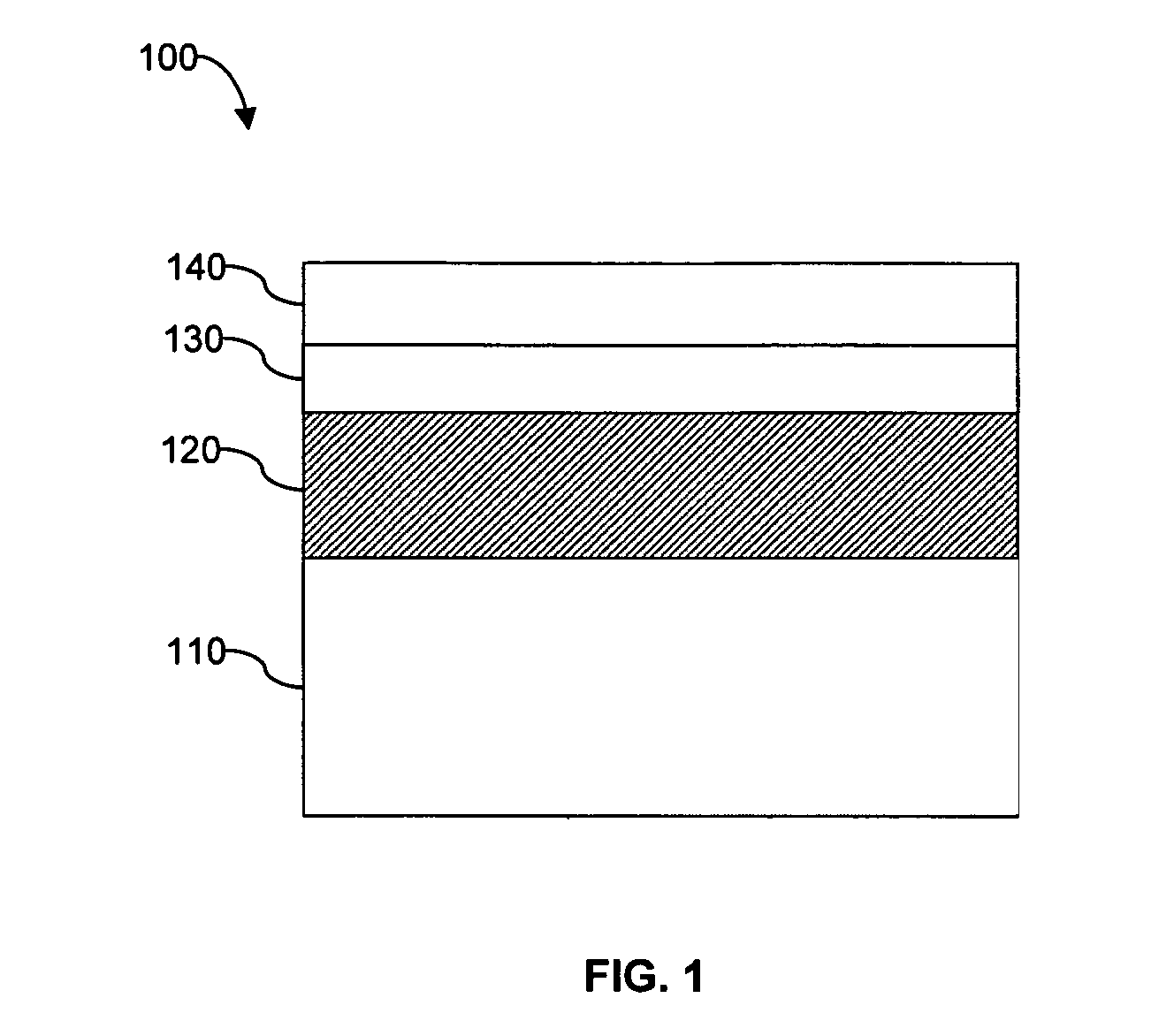

PEALD Deposition of a Silicon-Based Material

InactiveUS20070251444A1Avoiding considerable slow-downInhibition formationPolycrystalline material growthFrom chemically reactive gasesAtomic layer depositionSemiconductor

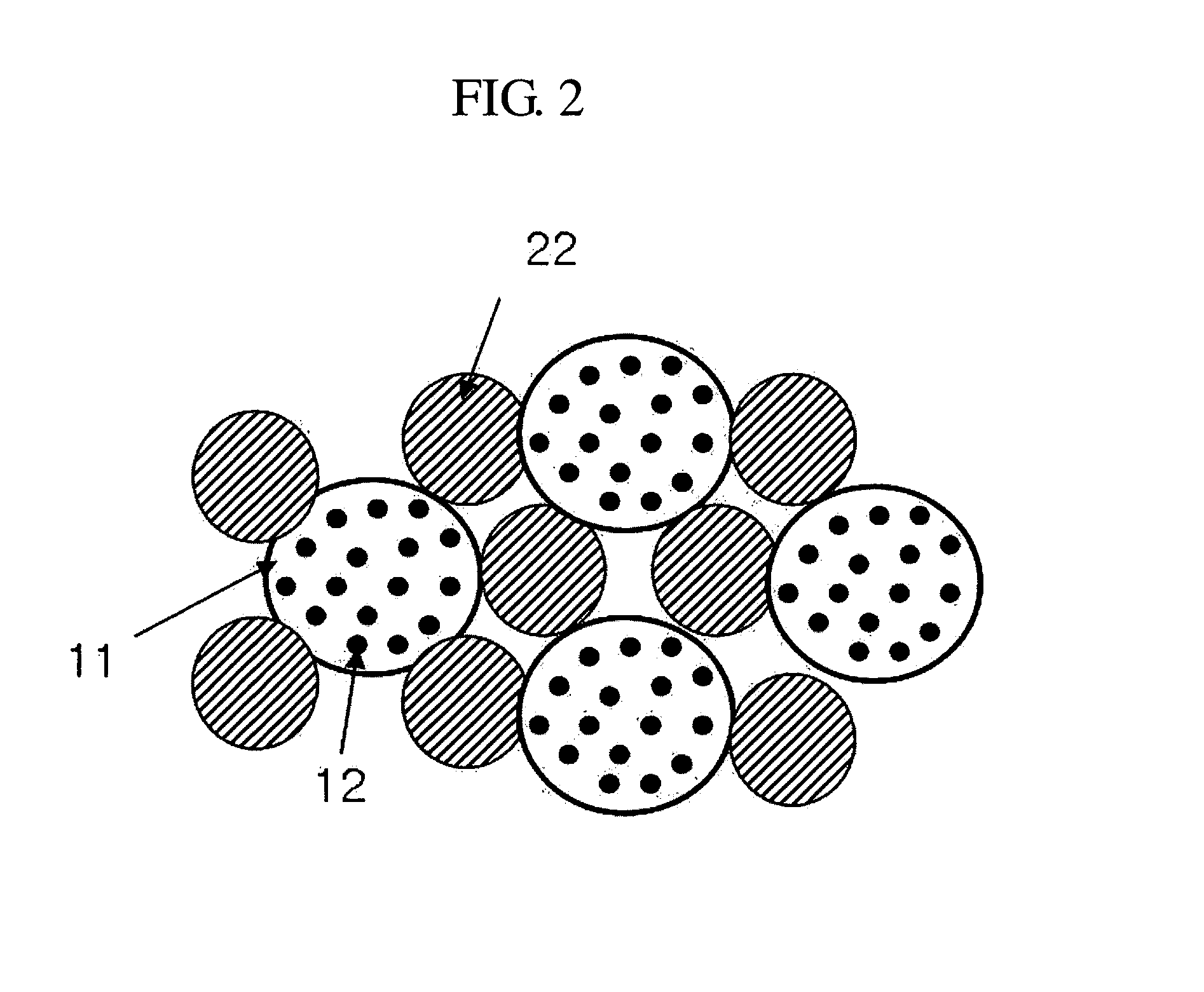

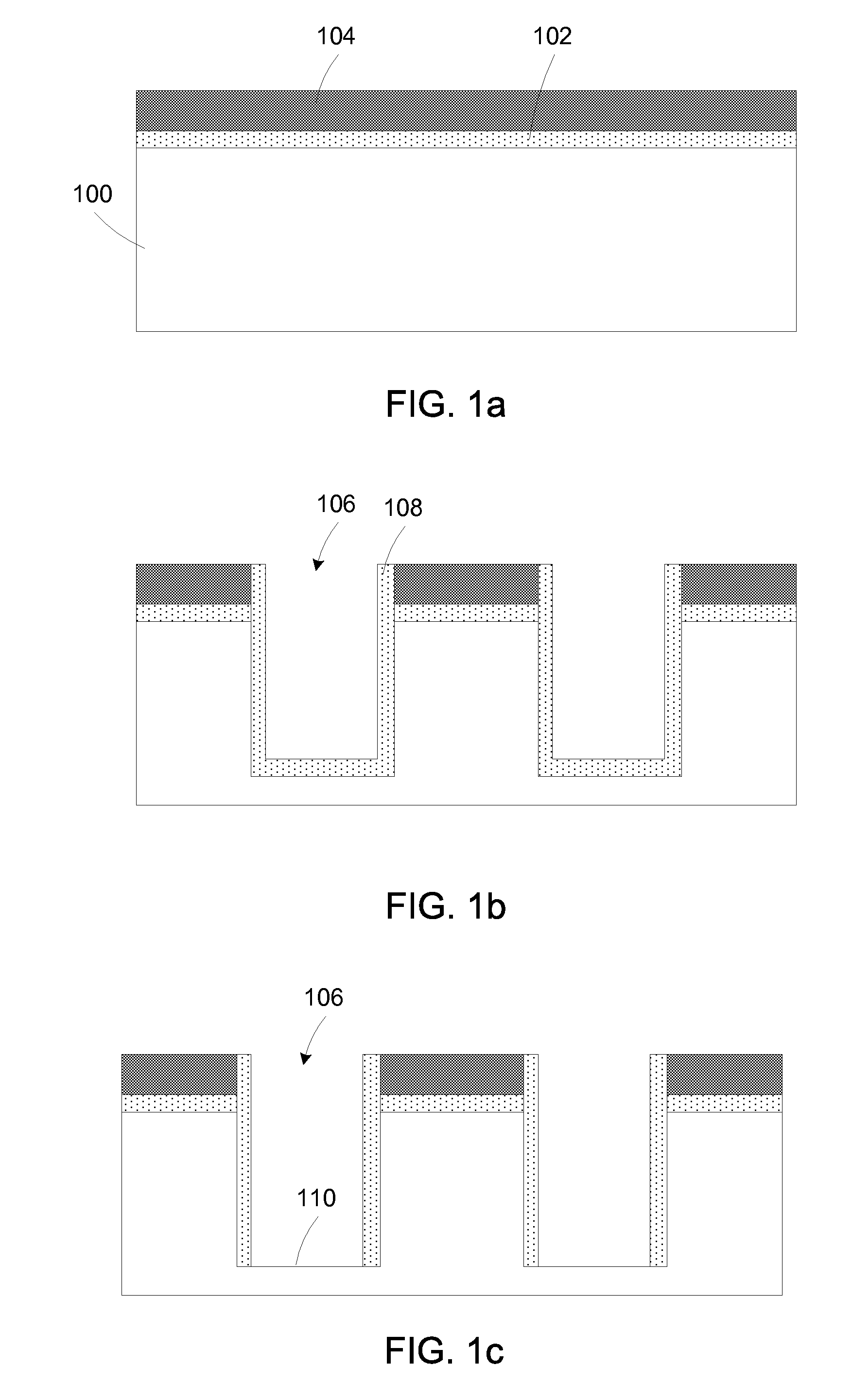

A process for depositing a silicon-based material on a substrate uses the technology of plasma-enhanced atomic layer deposition. The process is carried out over several cycles, wherein each cycle includes: exposing the substrate to a first precursor, which is an organometallic silicon precursor; and applying a plasma of at least a second precursor, different from the first precursor. Semiconductor products such as 3D capacitors, vertical transistor gate spacers, and conformal transistor stressors are made from the process.

Owner:STMICROELECTRONICS SRL

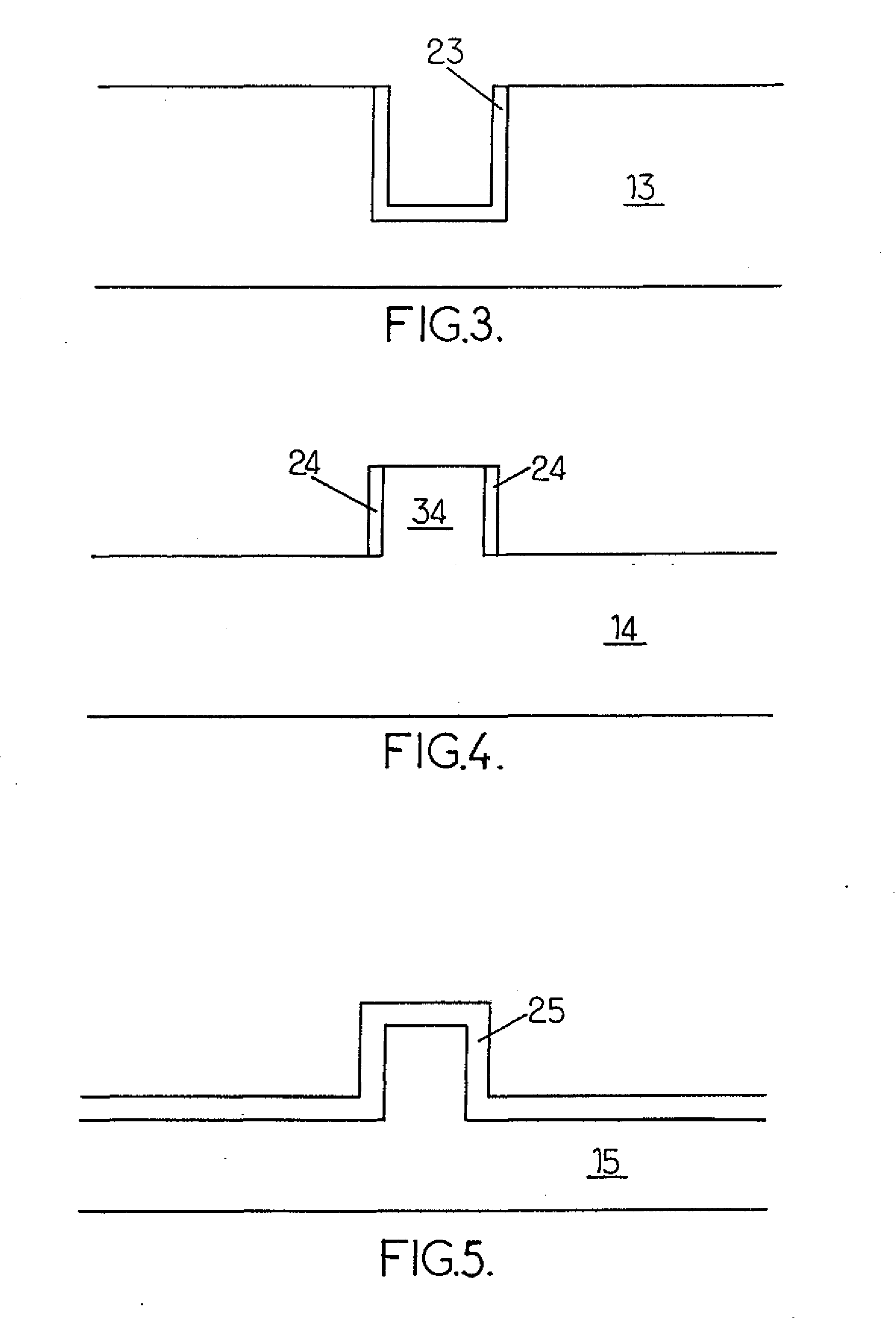

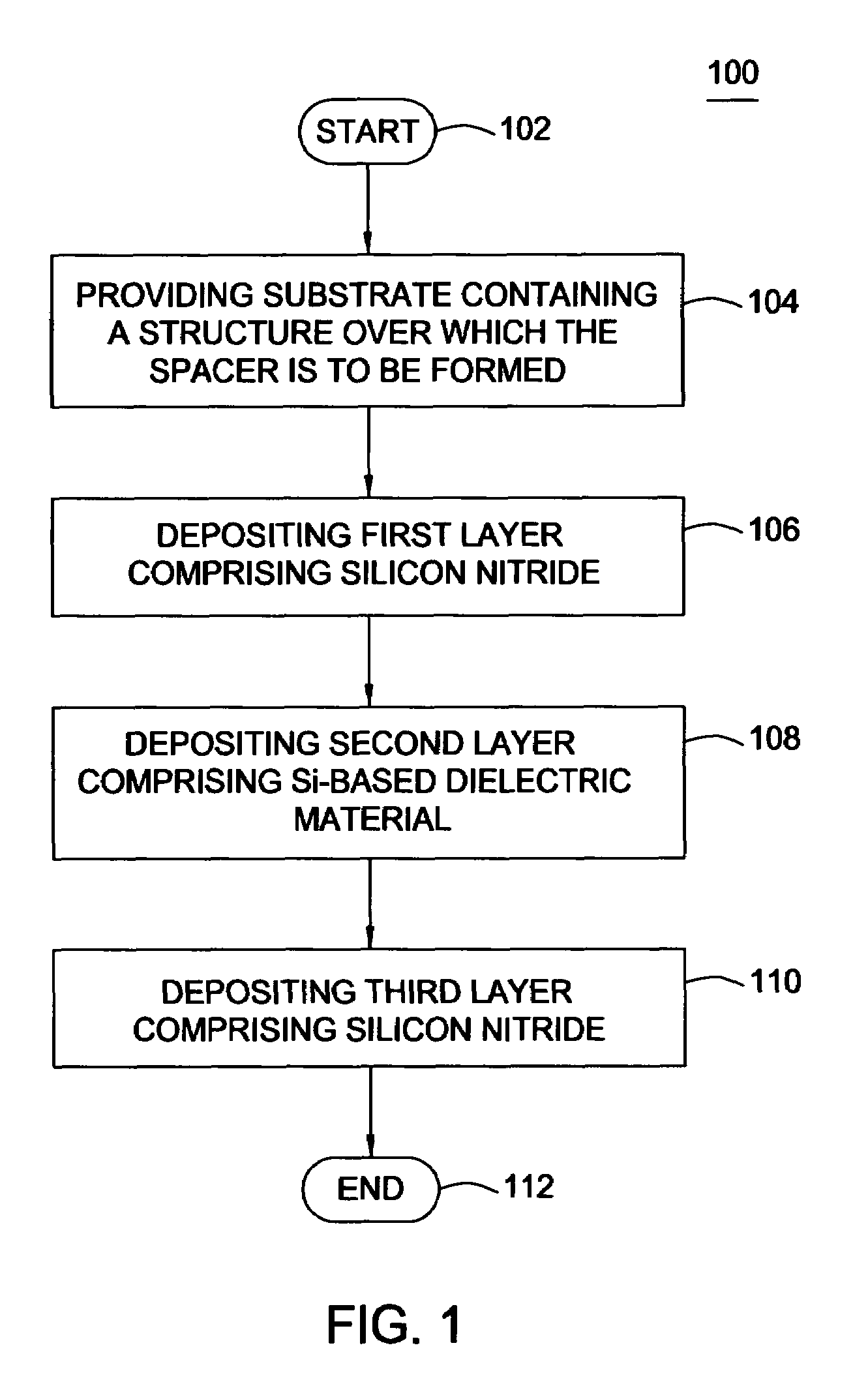

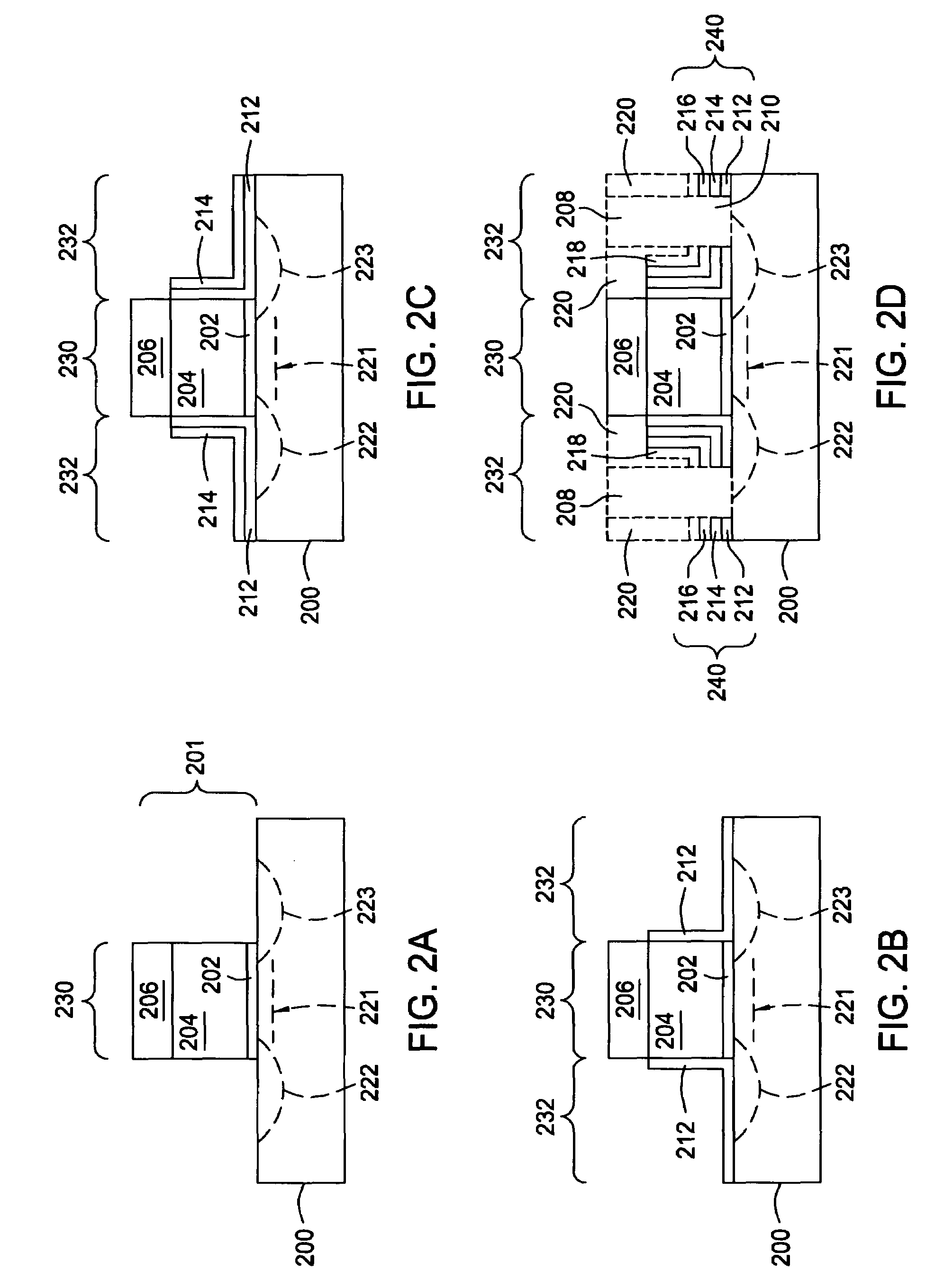

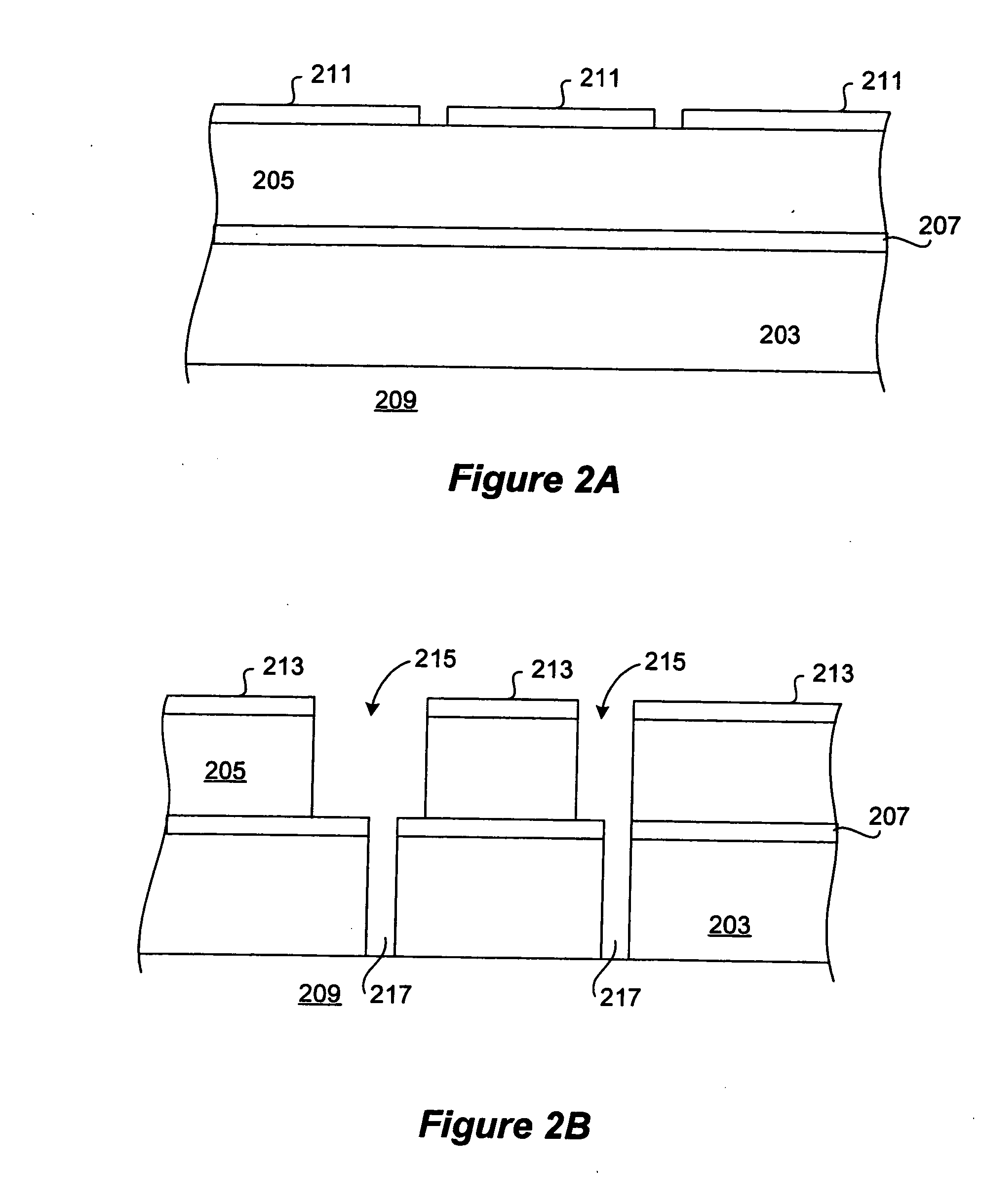

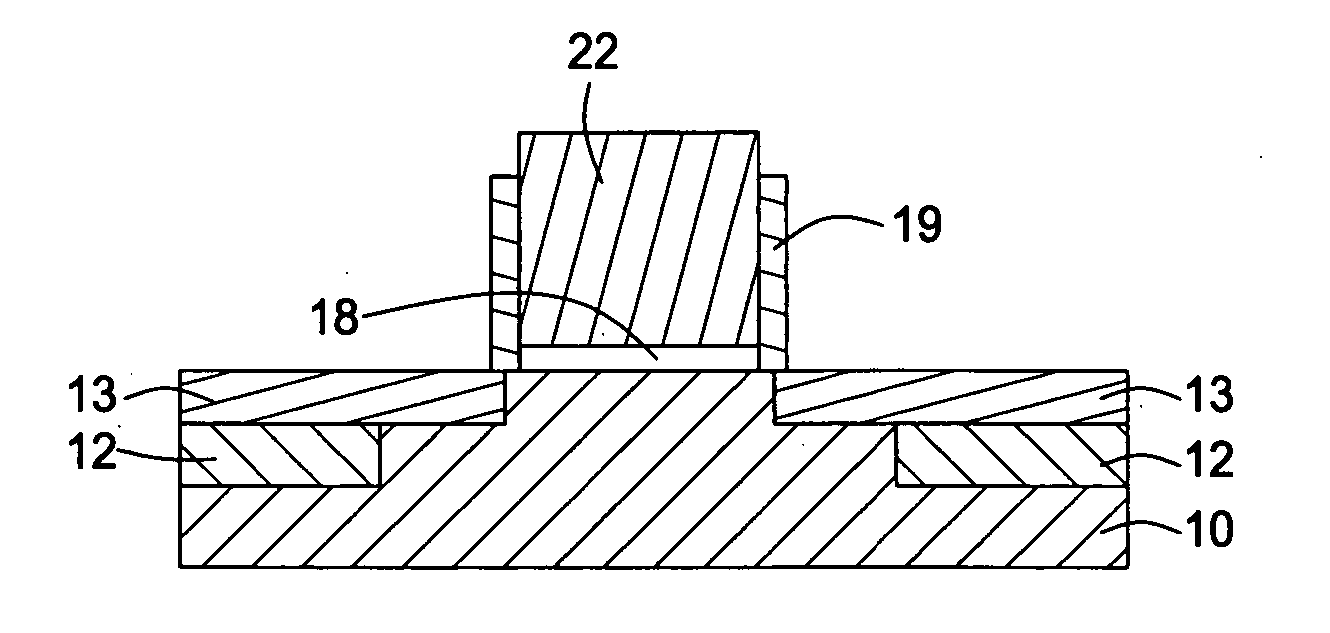

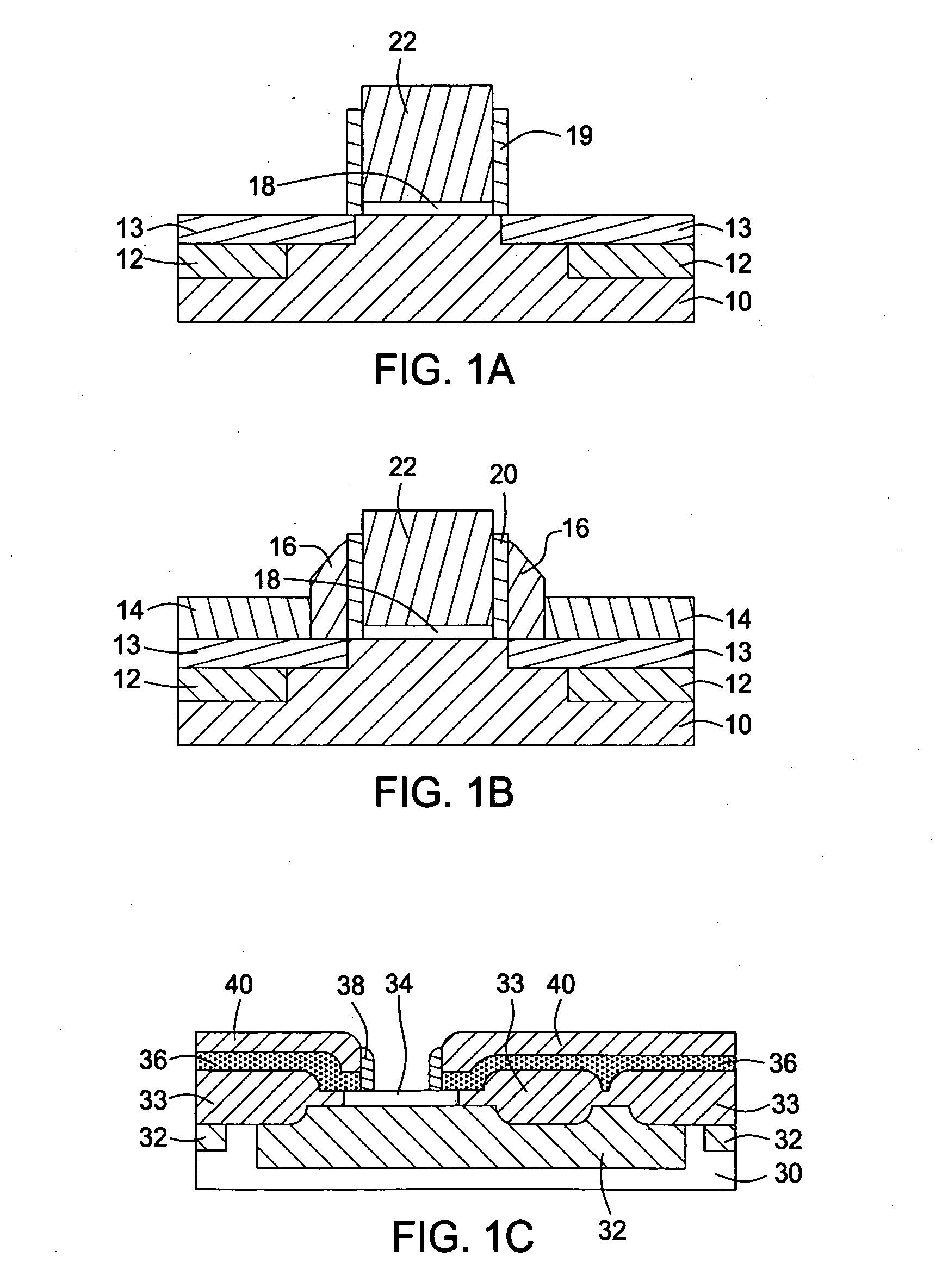

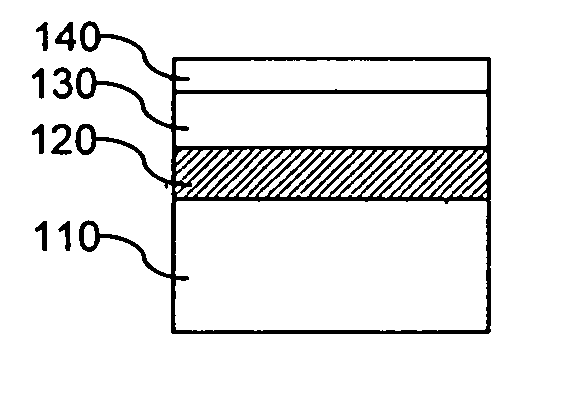

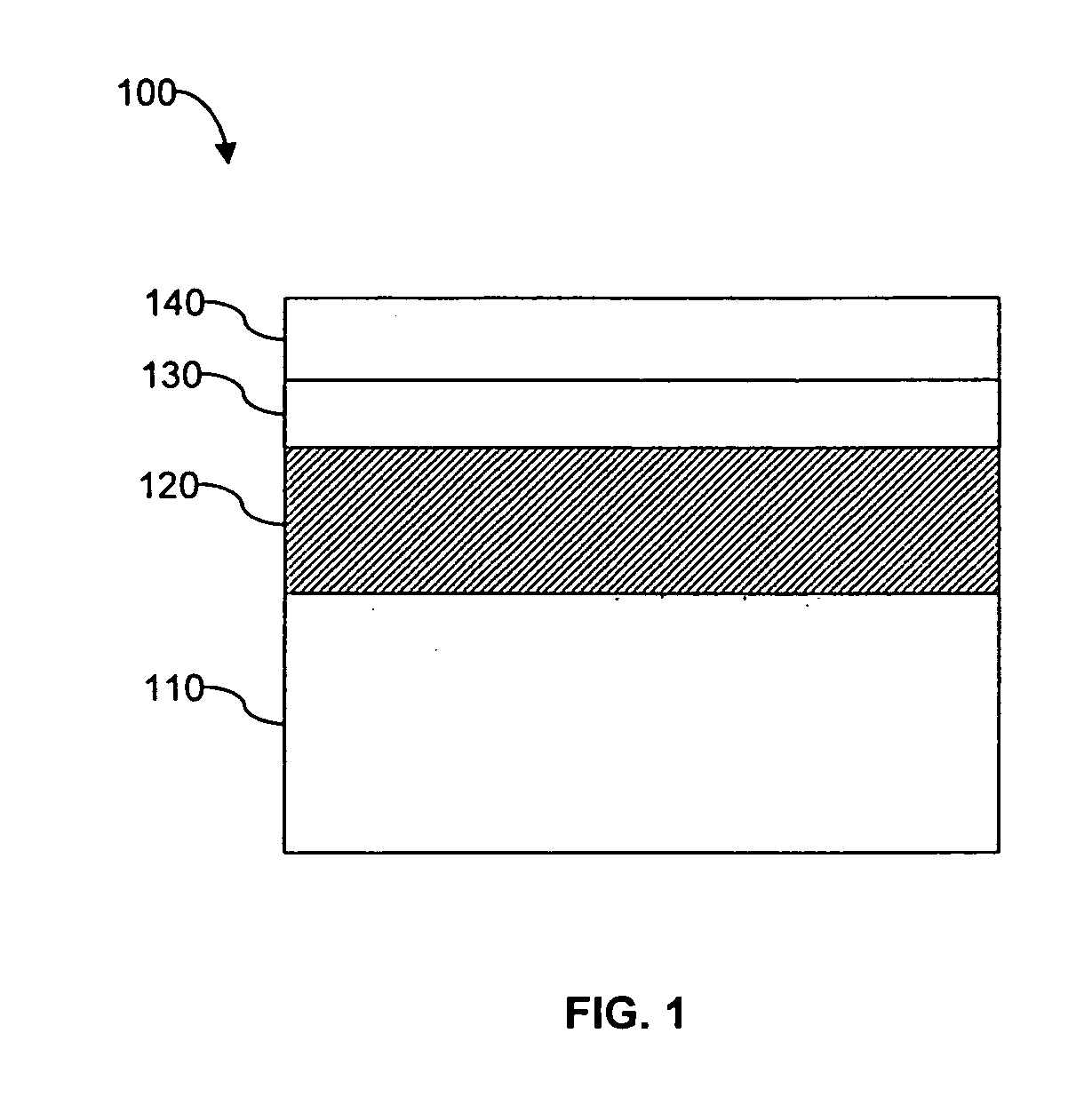

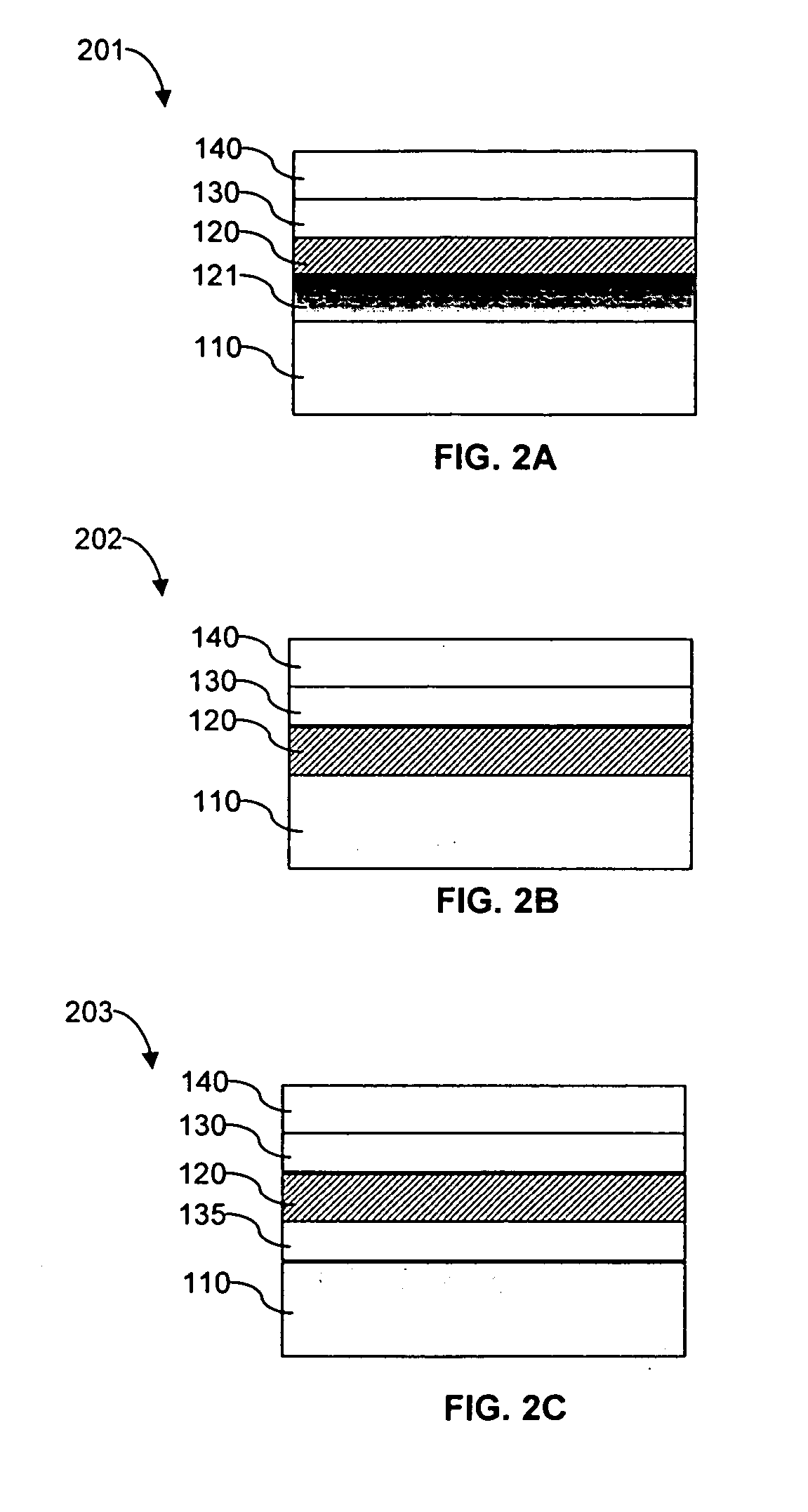

Method for fabricating silicon nitride spacer structures

ActiveUS7294581B2Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricSemiconductor

Embodiments of methods for fabricating a spacer structure on a semiconductor substrate are provided herein. In one embodiment, a method for fabricating a spacer structure on a semiconductor substrate includes providing a substrate containing a base structure over which the spacer structure is to be formed. The spacer structure may be formed over the base structure by depositing a first layer comprising silicon nitride on the base structure, depositing a second layer comprising a silicon-based dielectric material on the first layer, and depositing a third layer comprising silicon nitride on the second layer. The first, second, and third layers are deposited in a single processing reactor.

Owner:APPLIED MATERIALS INC

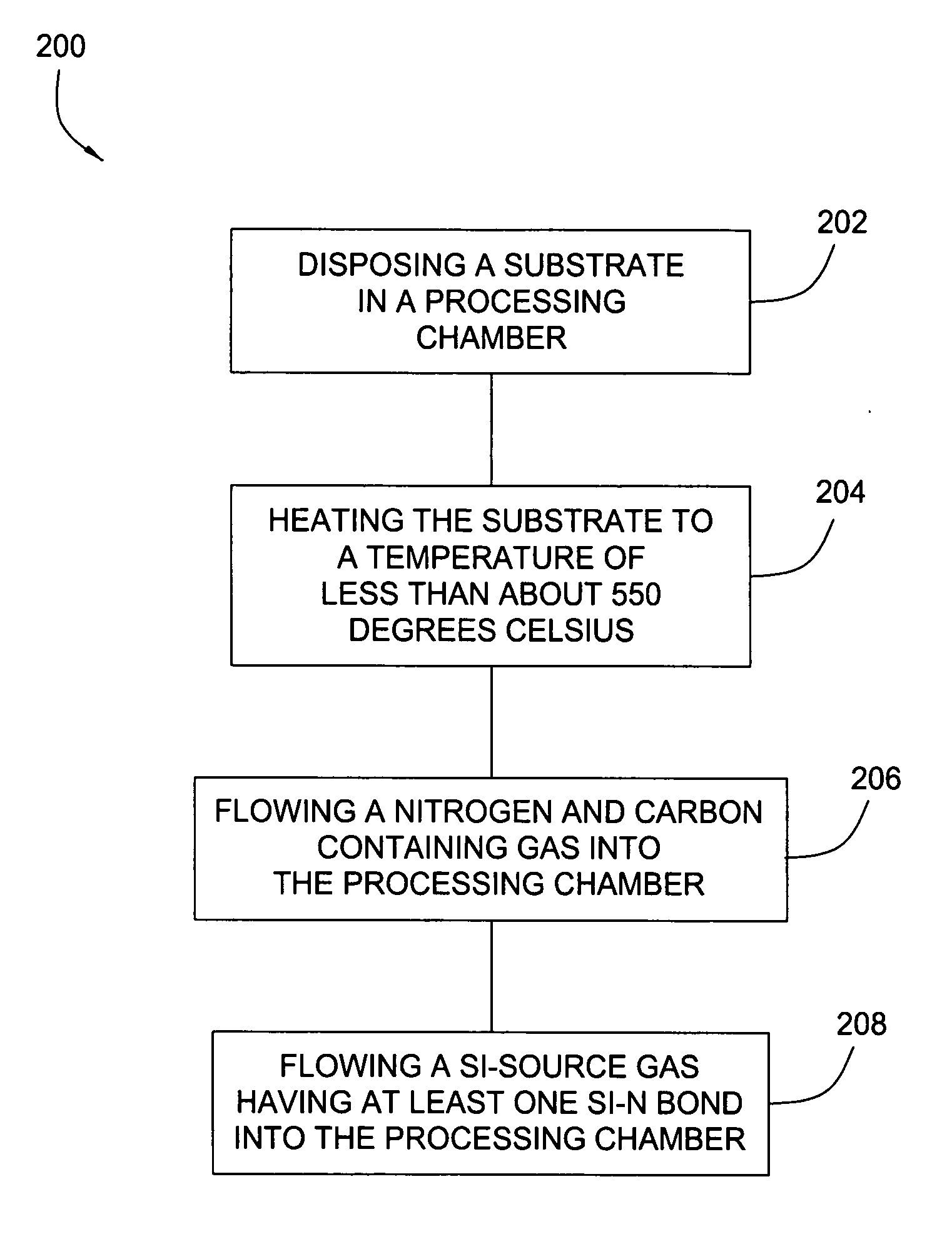

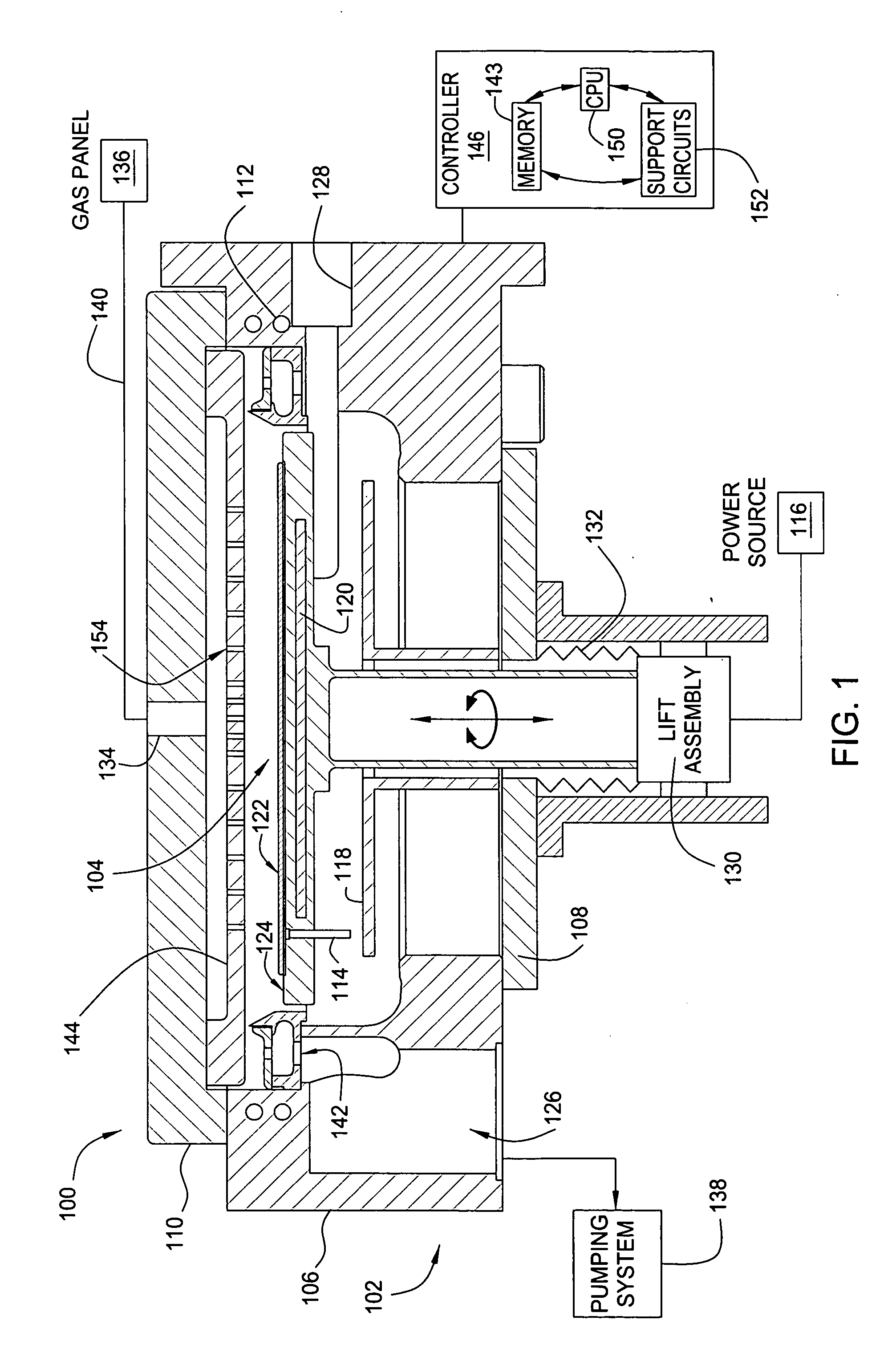

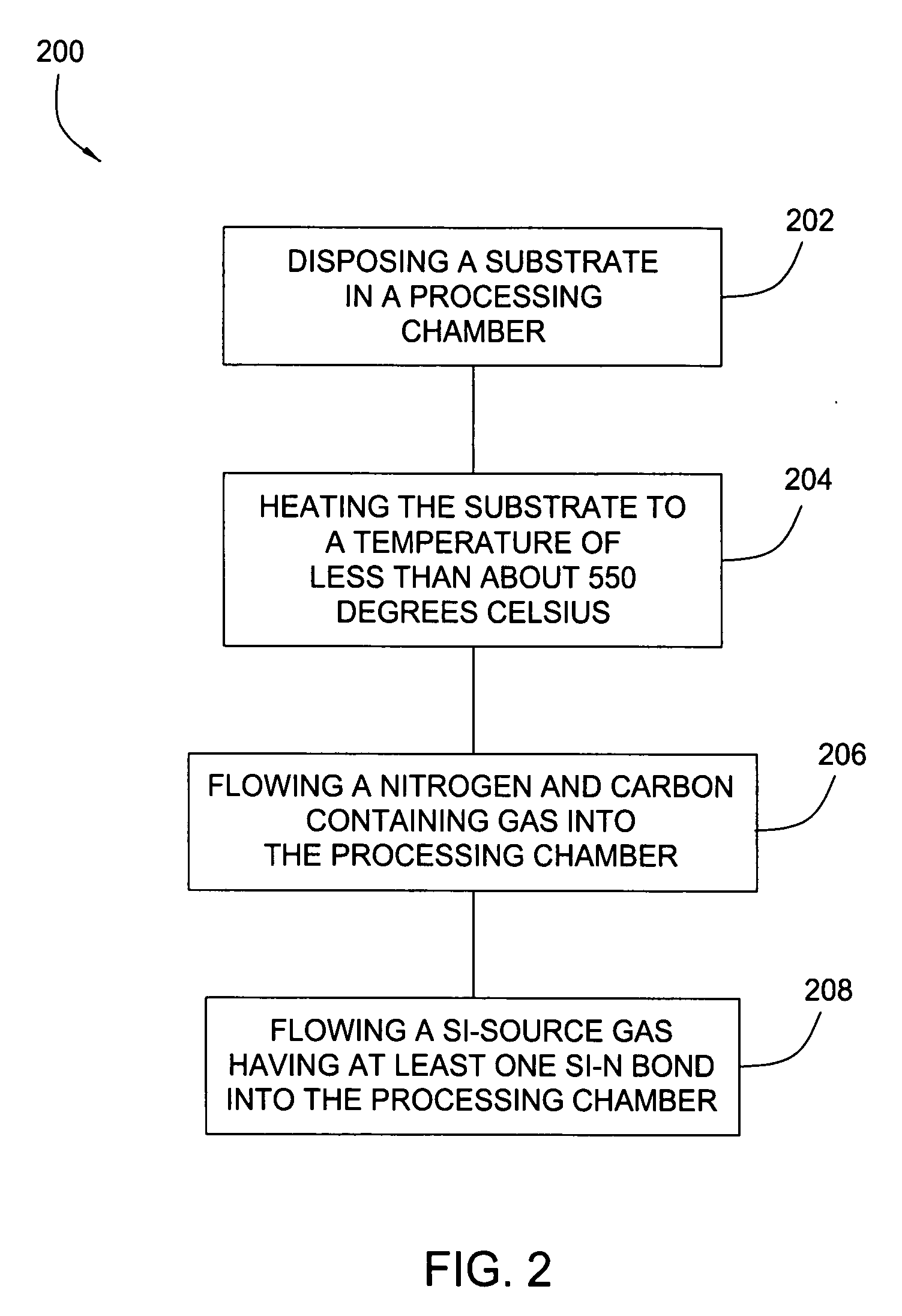

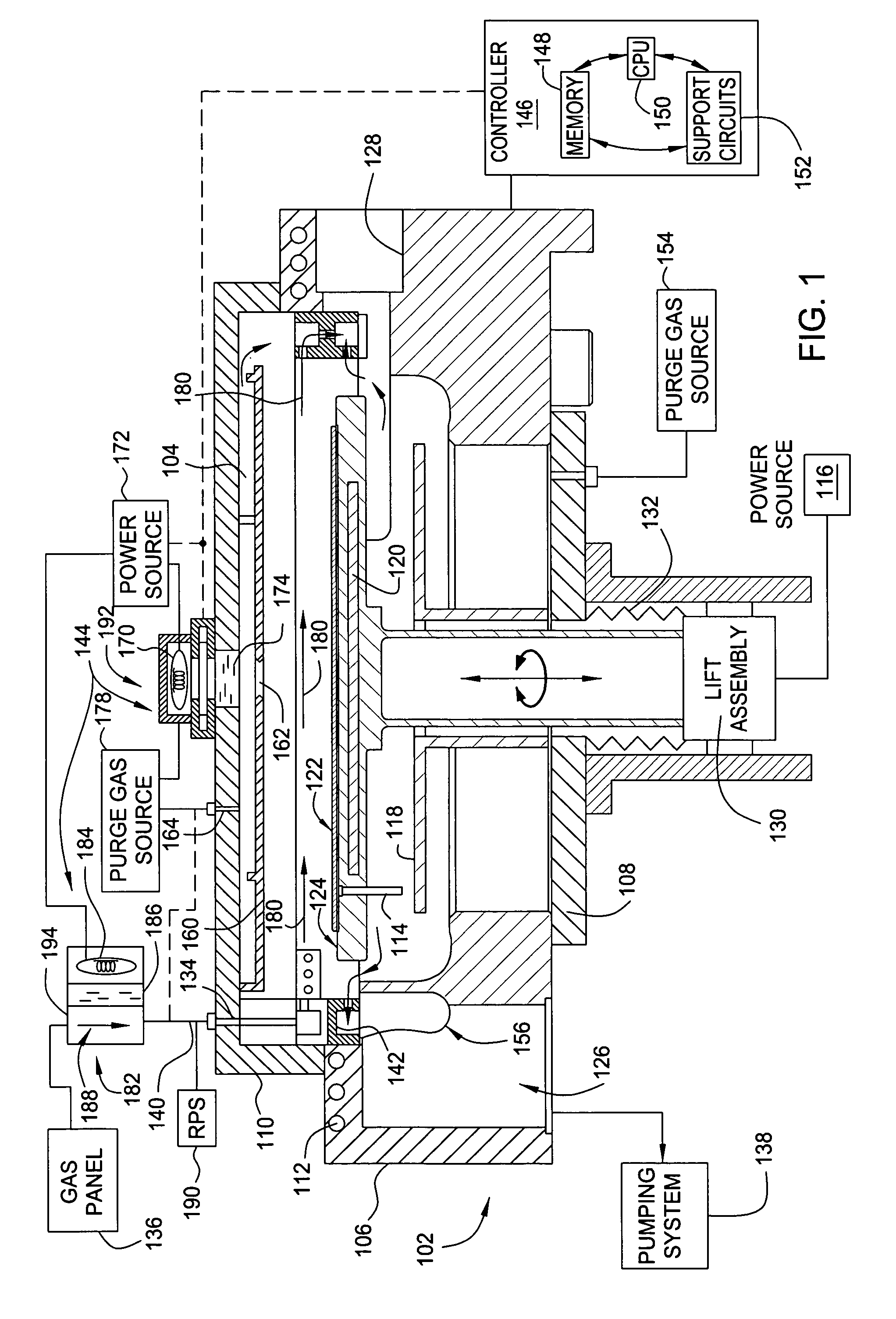

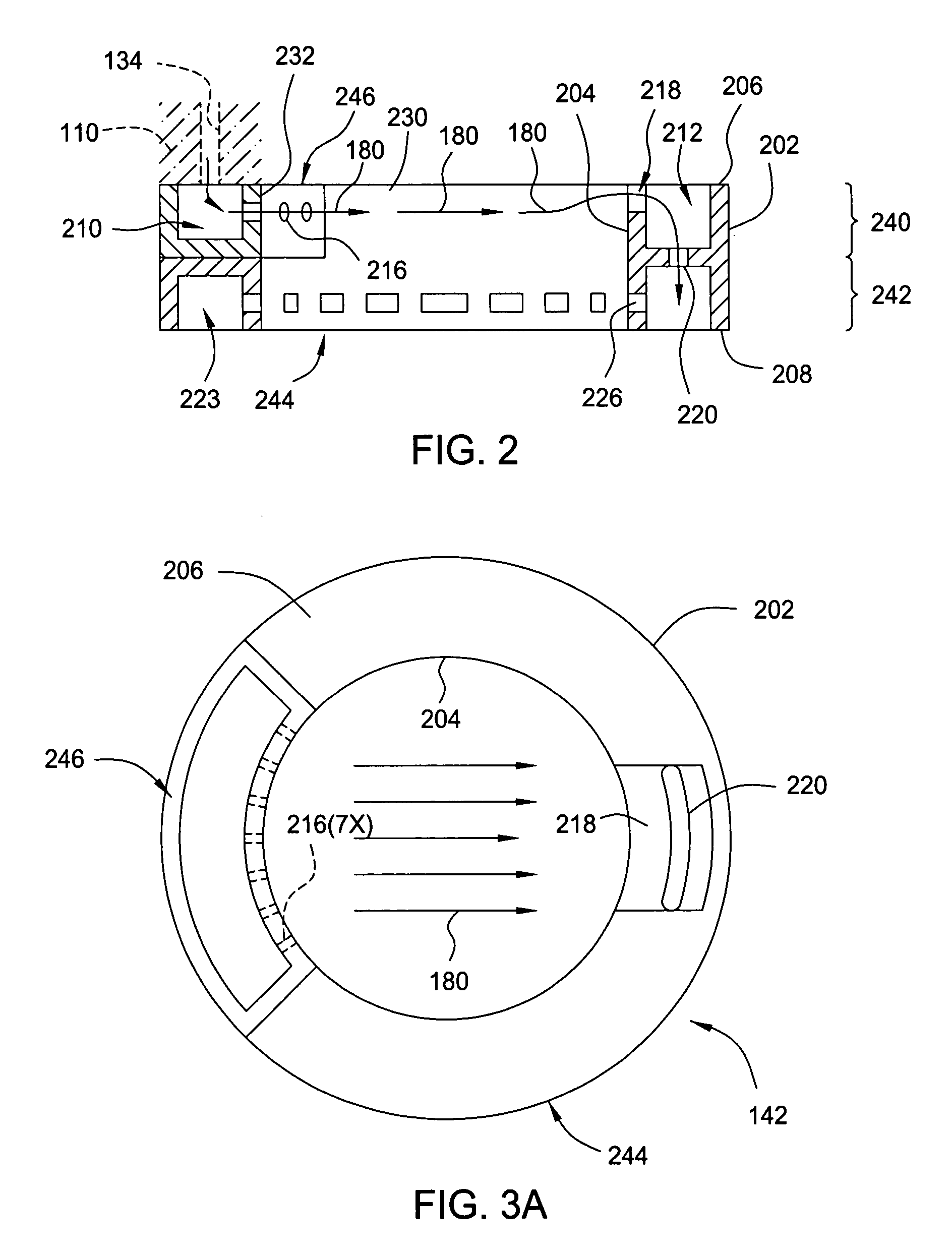

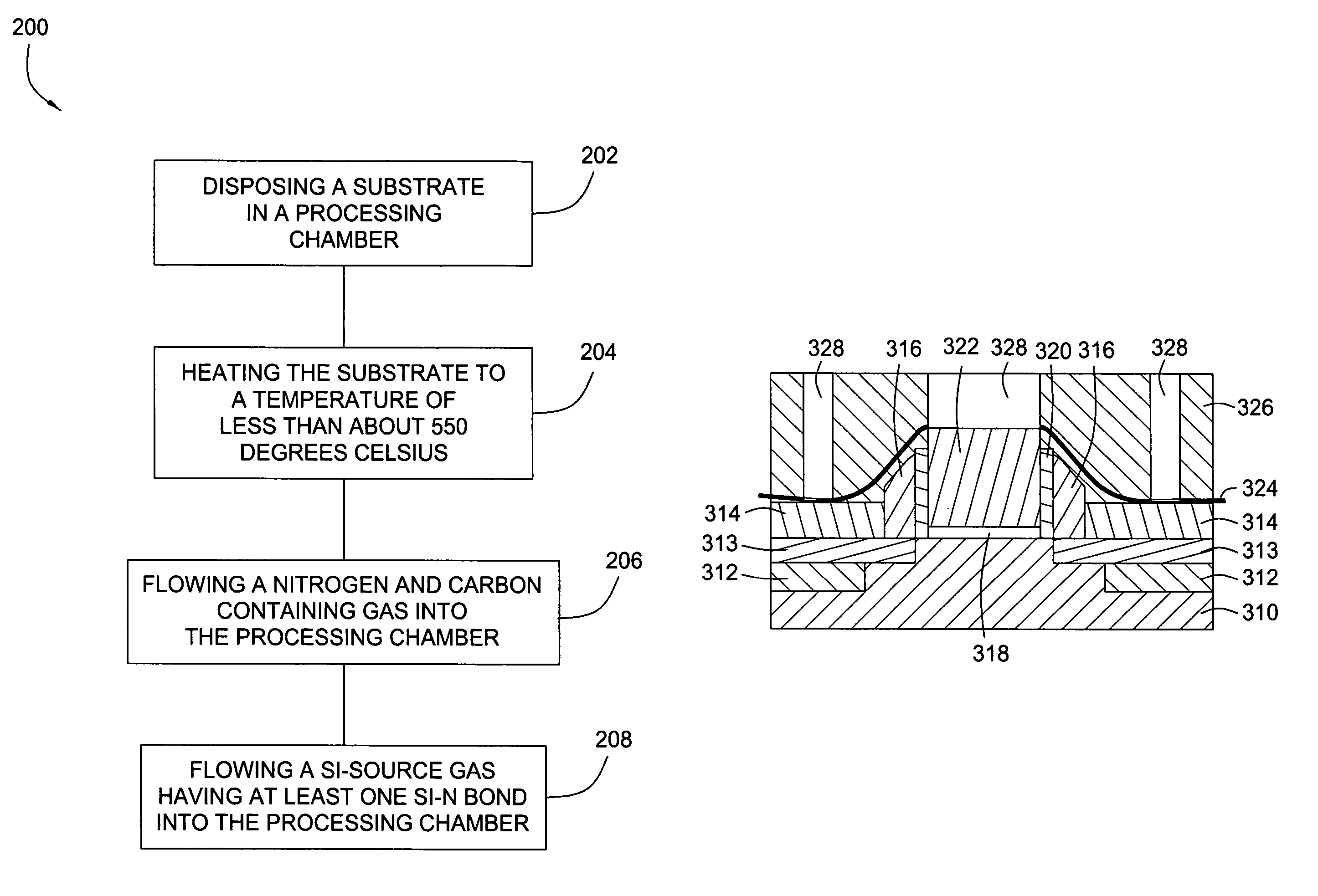

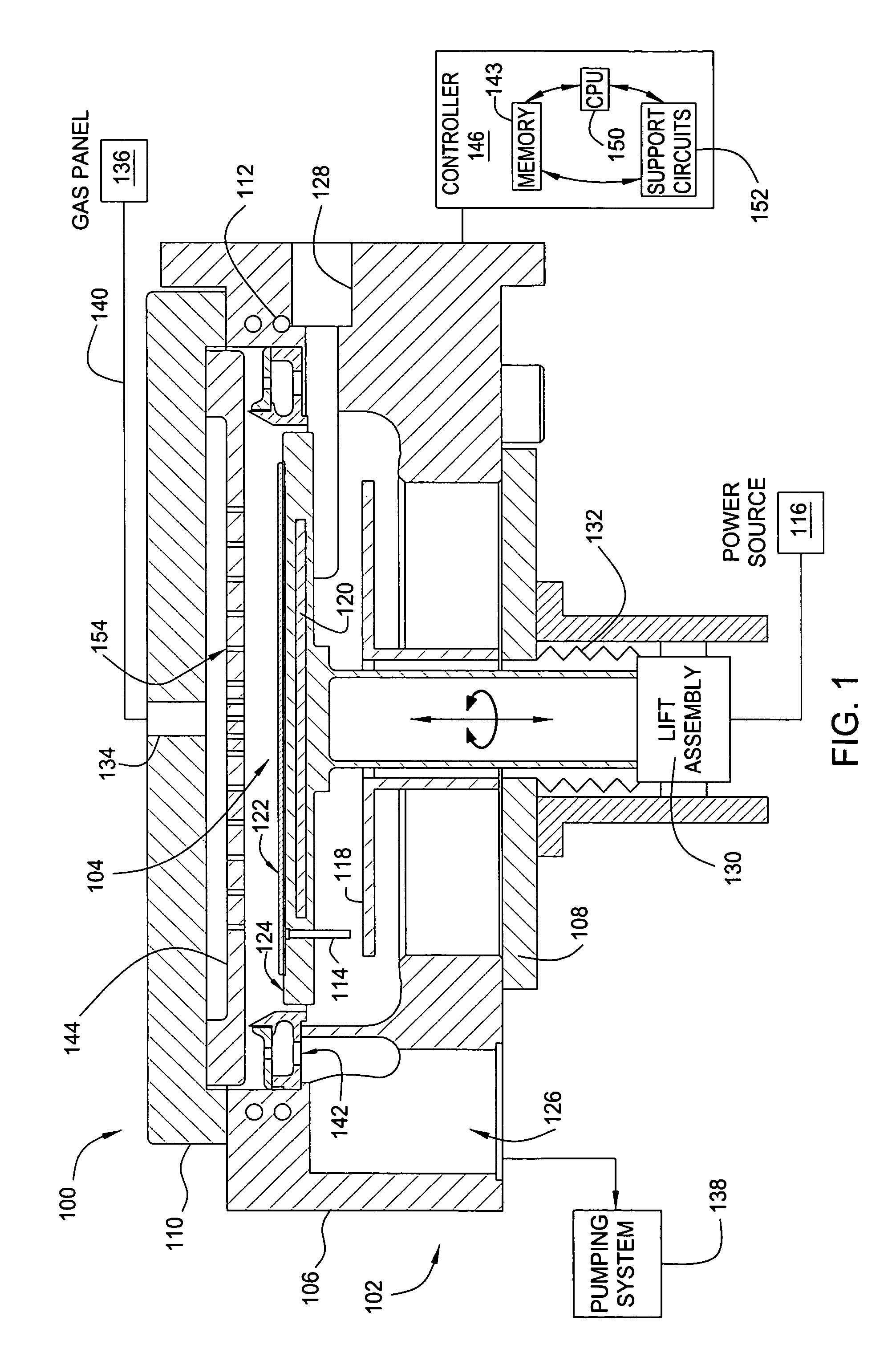

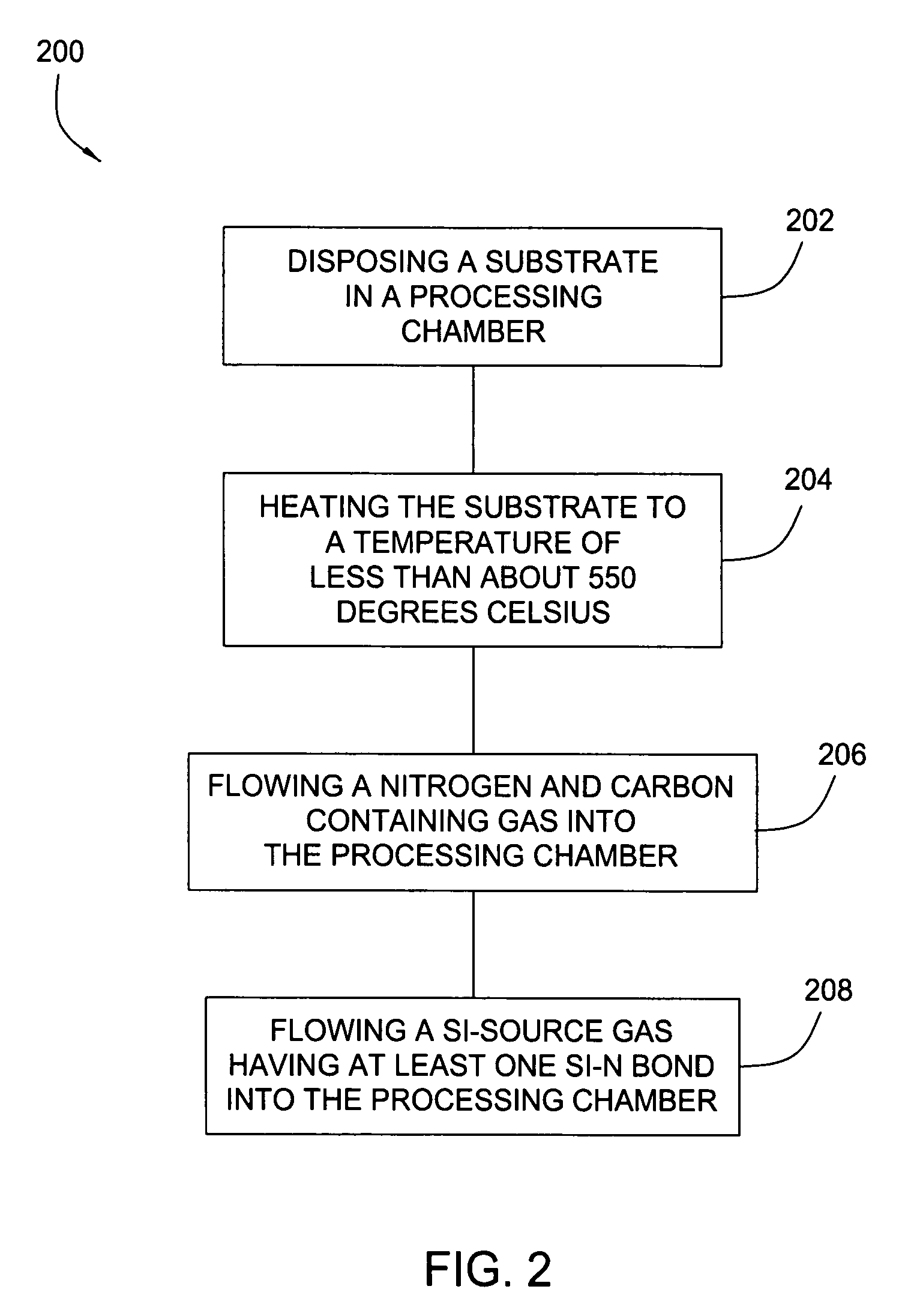

Method for silicon based dielectric chemical vapor deposition

InactiveUS20060286818A1TransistorSemiconductor/solid-state device manufacturingDielectricCelsius Degree

Embodiments of the invention generally provide a method for depositing silicon-containing films. In one embodiment, a method for depositing silicon-containing material film on a substrate includes flowing a nitrogen and carbon containing chemical into a deposition chamber, flowing a silicon-containing source chemical having silicon-nitrogen bonds into the processing chamber, and heating the substrate disposed in the chamber to a temperature less than about 550 degrees Celsius. In another embodiment, the silicon containing chemical is trisilylamine and the nitrogen and carbon containing chemical is (CH3)3—N.

Owner:APPLIED MATERIALS INC

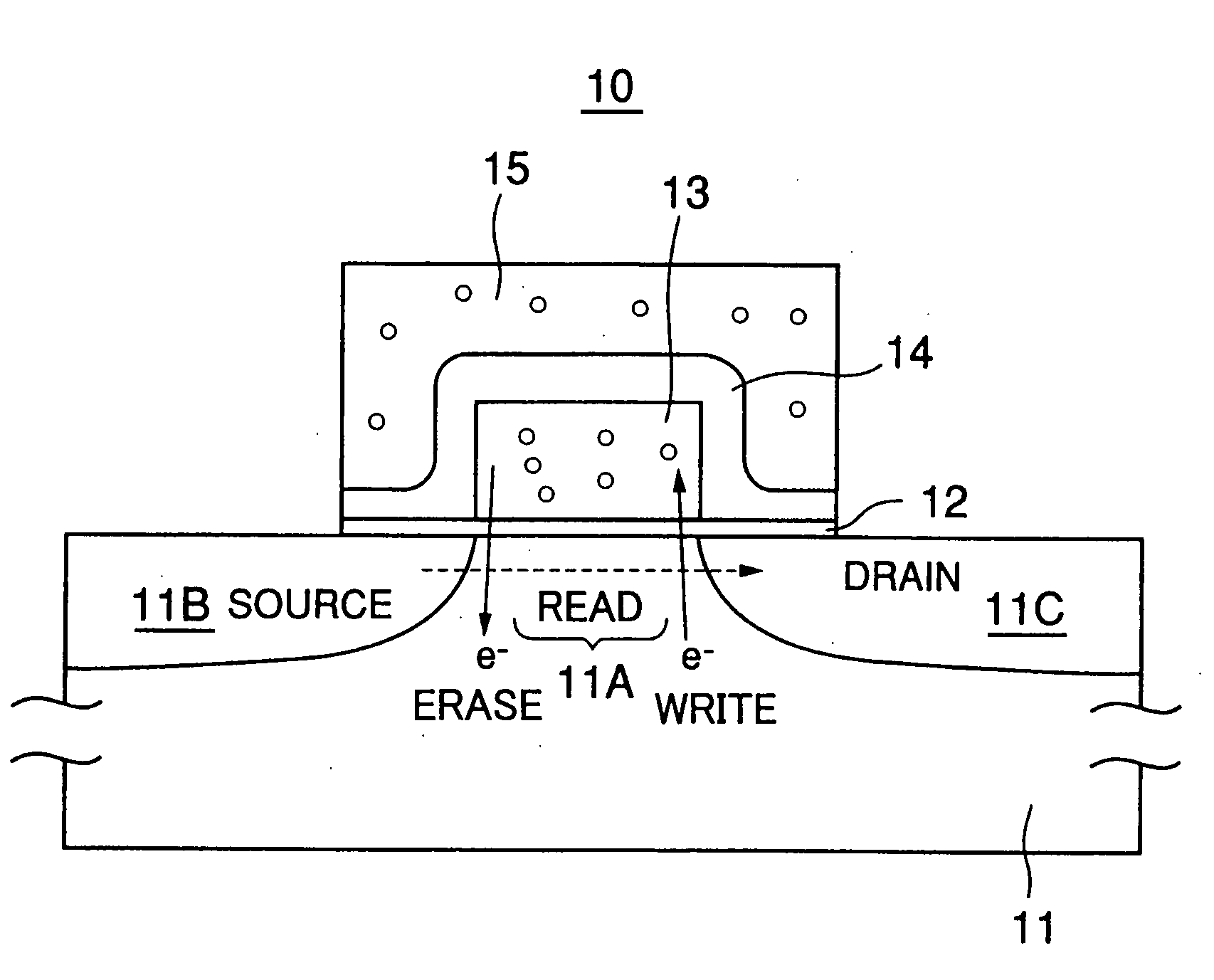

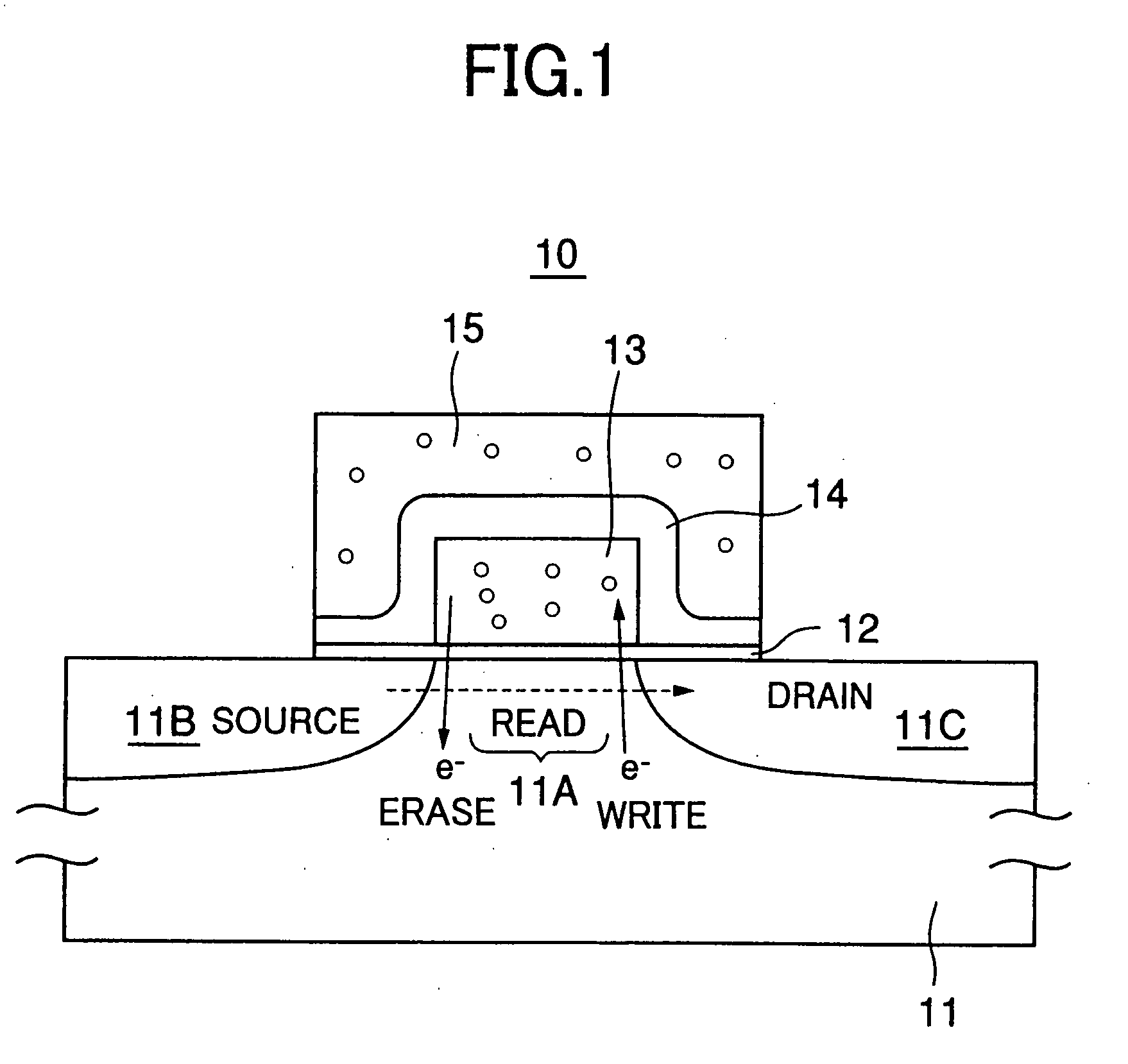

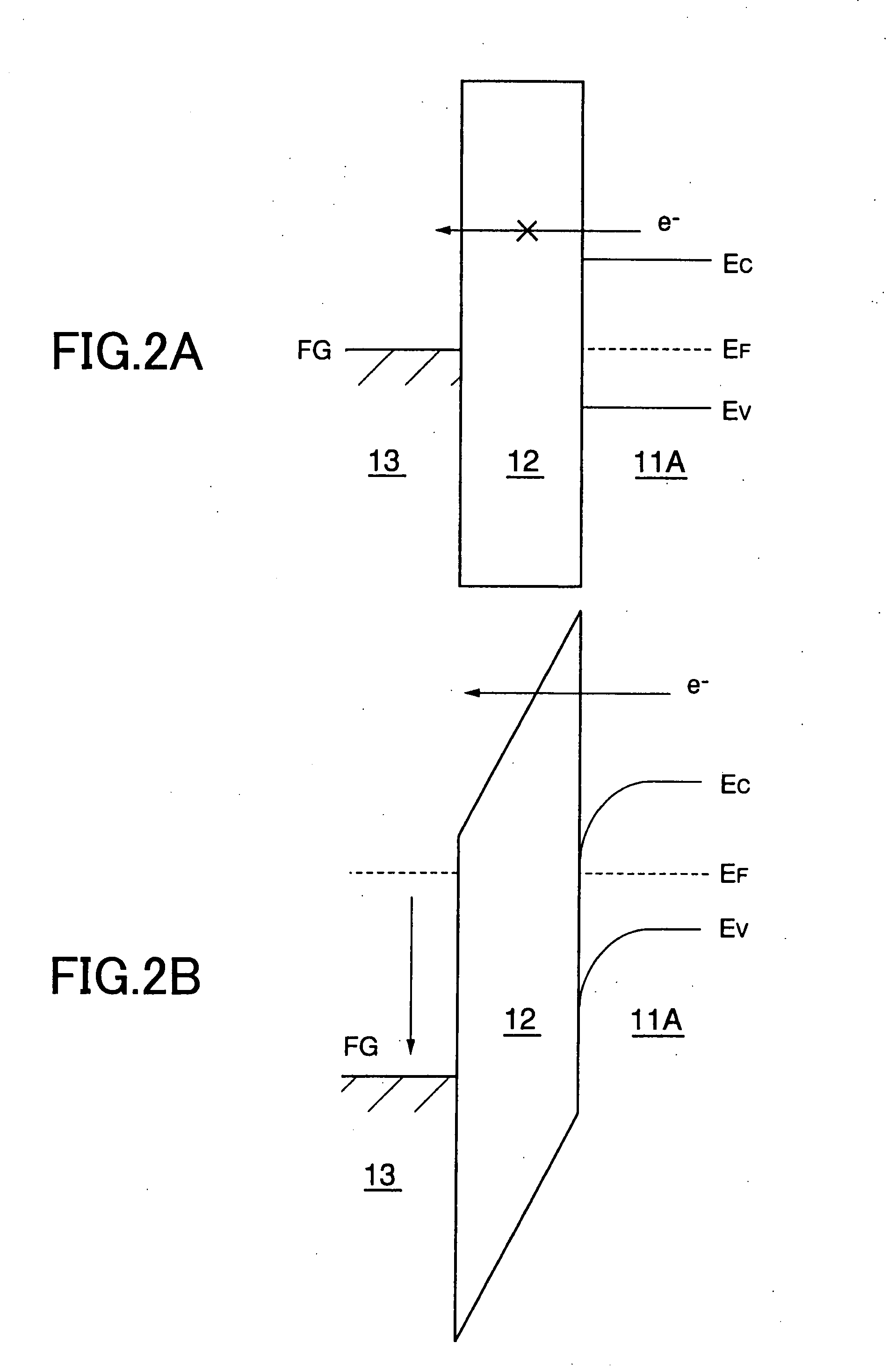

Dielectric film and formation method thereof, semiconductor device, non-volatile semiconductor memory device, and fabrication method for a semiconductor device

InactiveUS20080277715A1Improve wiring speedLow working voltageTransistorSemiconductor/solid-state device detailsDielectricHydrogen

Owner:FOUND FOR ADVANCEMENT OF INT SCI

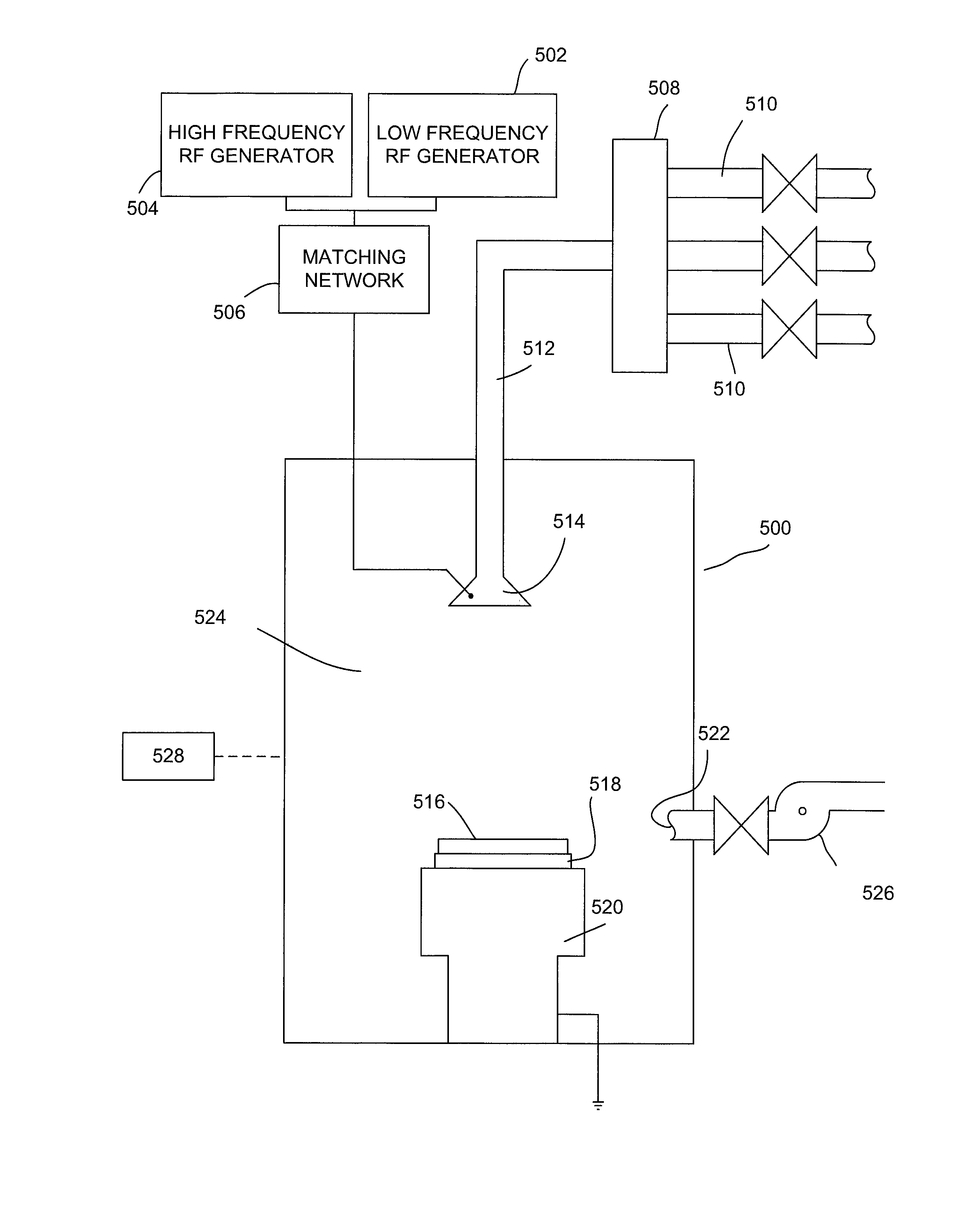

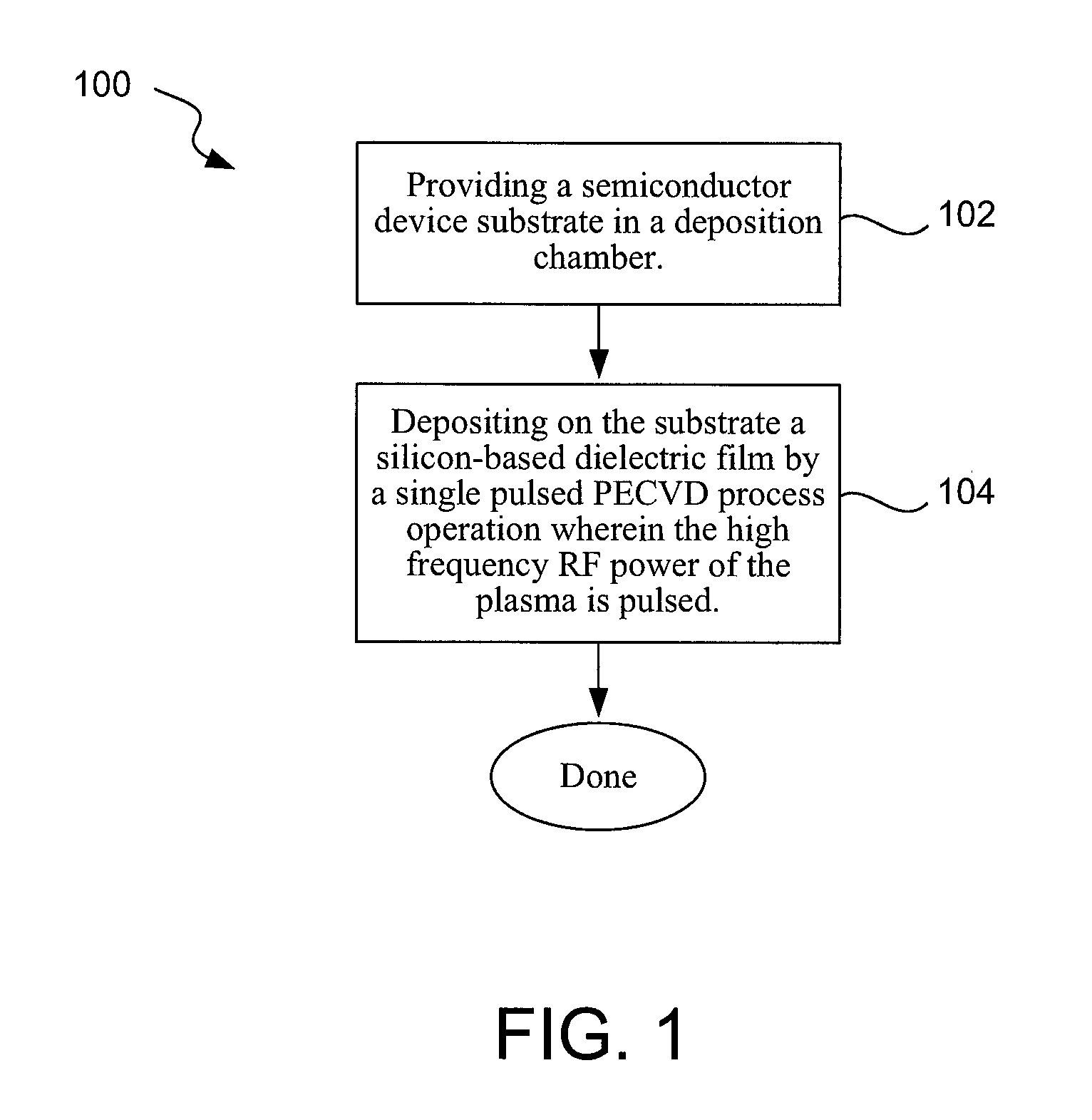

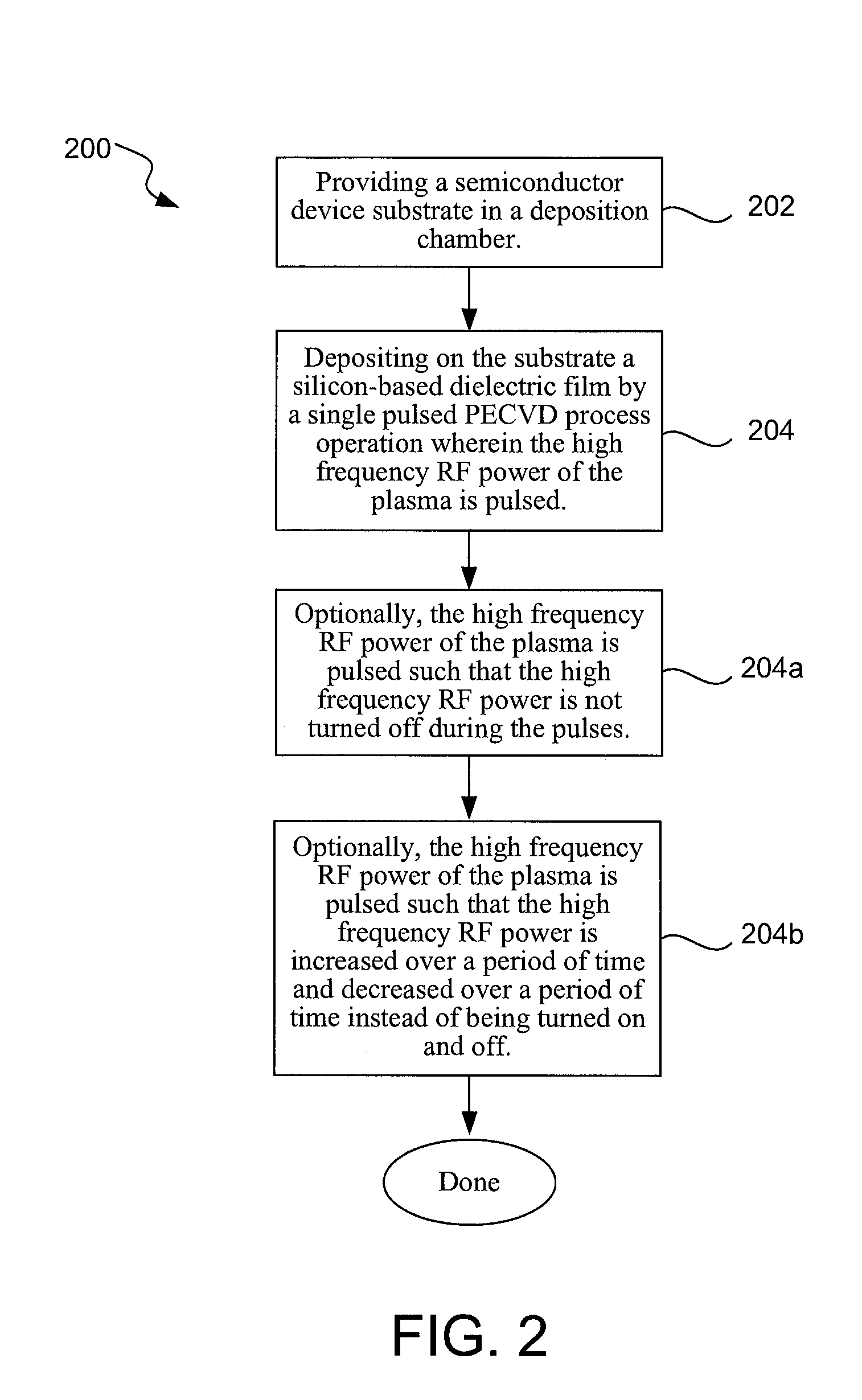

Method for improving process control and film conformality of PECVD film

ActiveUS7745346B2More controllable depositionIncrease depositionLiquid surface applicatorsSemiconductor/solid-state device manufacturingDielectricEngineering

A method for forming a silicon-based dielectric film on a substrate with a single deposition process operation using pulsed plasma enhanced chemical vapor deposition (PECVD) wherein the high frequency radio frequency power of the plasma is pulsed, allows enhanced control, efficiency and product quality of the PECVD process. Pulsing the high frequency RF power of the plasma reduces the deposited film thickness per unit time the high frequency RF power of the plasma is on. This yields silicon-based dielectric films that are both thin and conformal.

Owner:NOVELLUS SYSTEMS

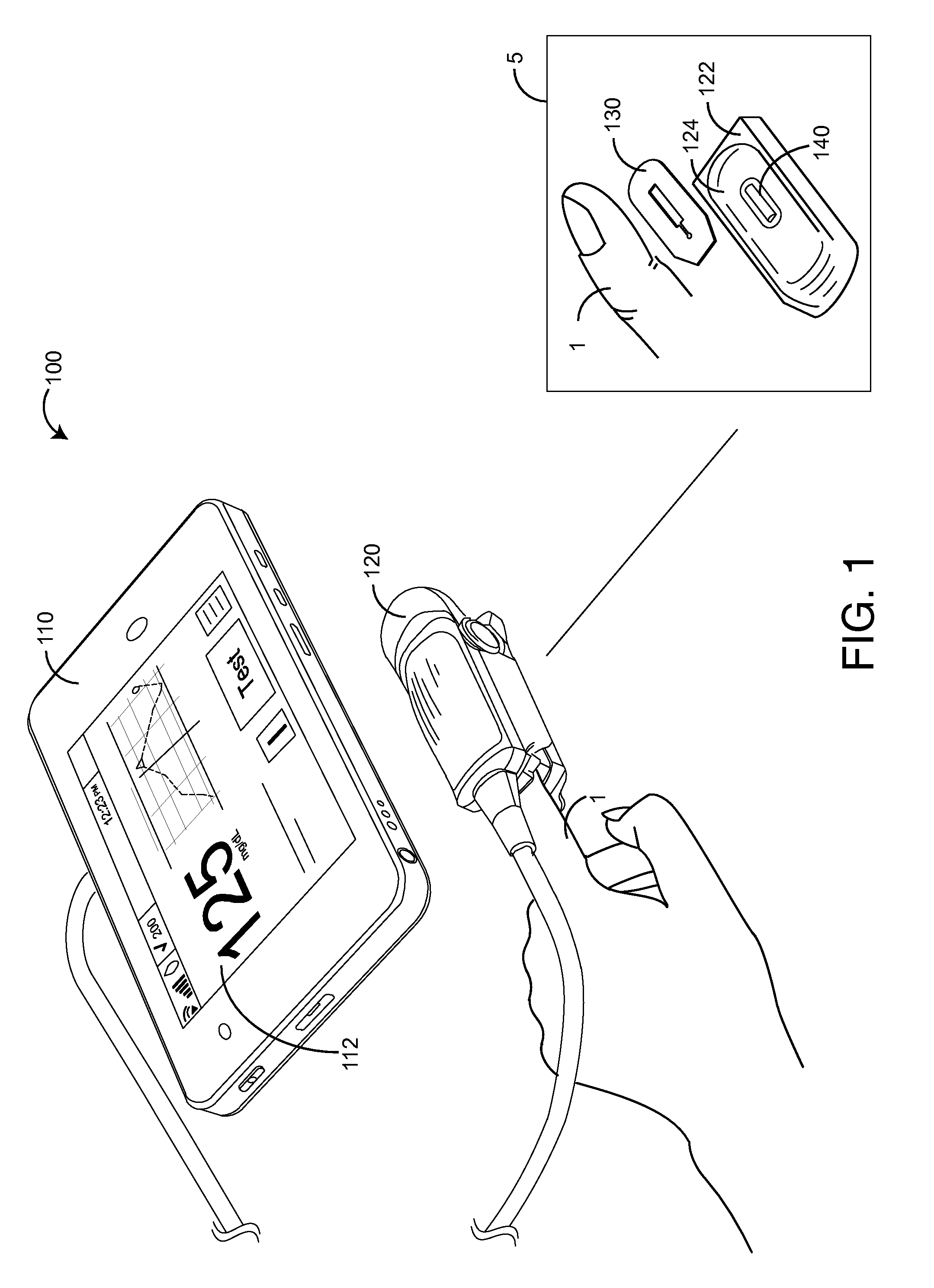

Finger-placement sensor tape

InactiveUS20150005600A1Easy to disassembleEasy to installSensorsBlood characterising devicesEngineeringAcrylic adhesive

A finger-placement sensor tape aligns and removably secures a finger to a sensor pad of a reusable finger-clip optical sensor so as to assure the finger is repeatably aligned between the sensors emitters and detectors and that the finger stays aligned during a test procedure. The sensor tape has a double-sided tape layer having a silicon-based adhesive on a finger side and an acrylic adhesive on a sensor-side. An aperture is defined in the tape layer so as to allow emitters disposed in a top sensor pad to emit light through the tape layer to detectors disposed in a bottom sensor pad. A finger-side release layer is removably disposed over the silicon-based adhesive. A sensor-side release layer is removably disposed over the acrylic adhesive.

Owner:MASIMO CORP

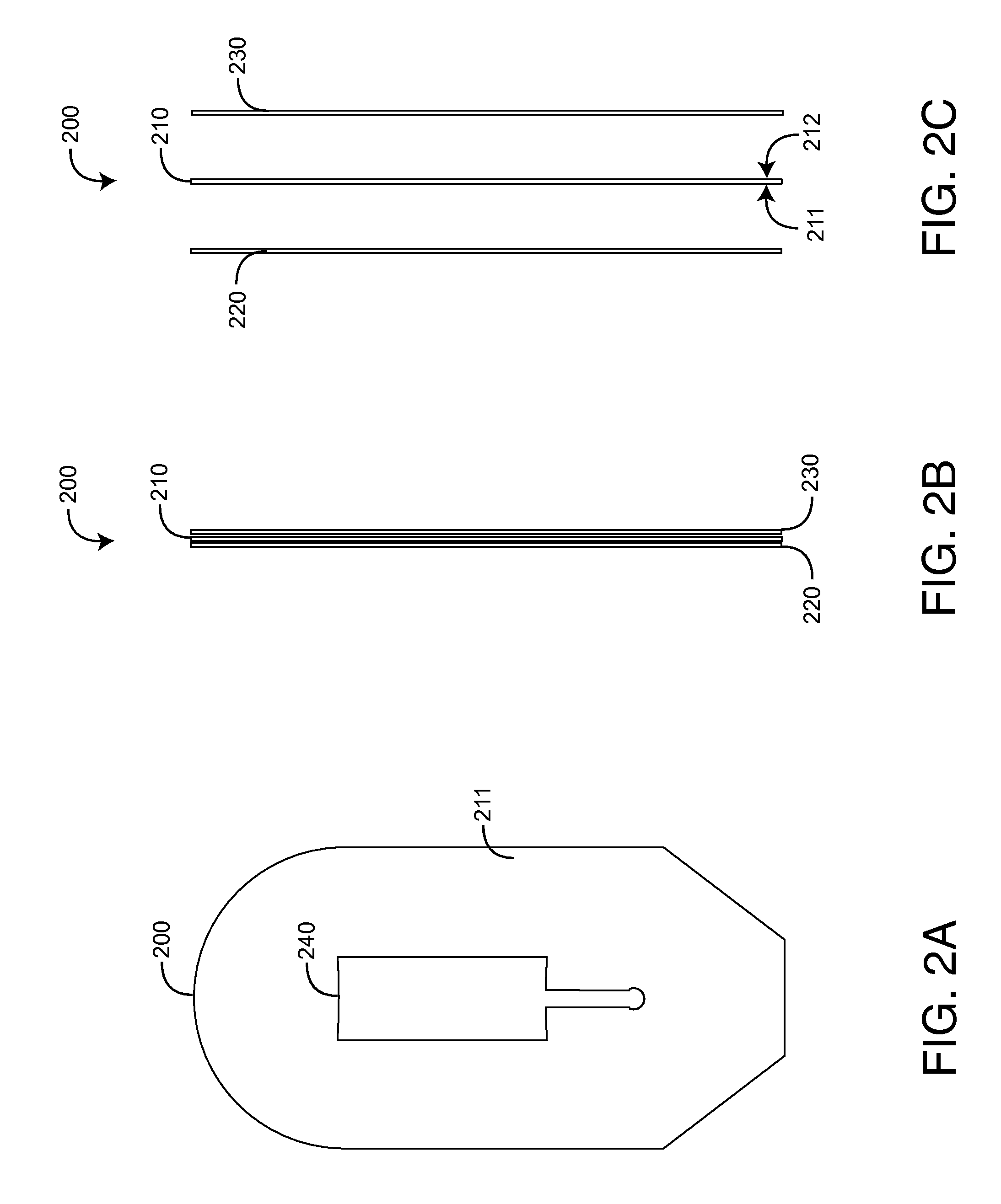

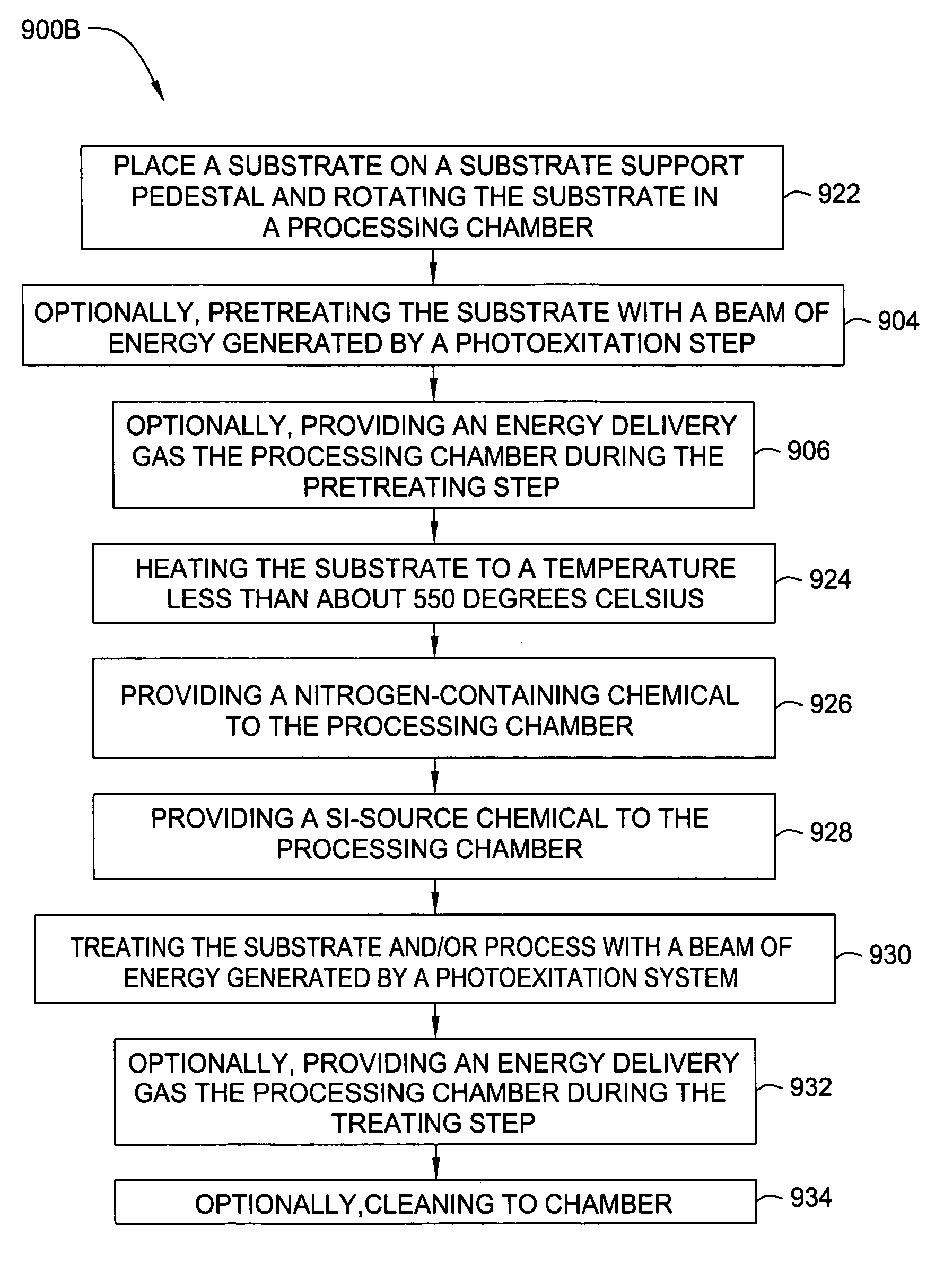

Method for silicon based dielectric deposition and clean with photoexcitation

InactiveUS20060286819A1Enhancing chamber cleaningSpeed up the processSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricCompound (substance)

Embodiments of the invention generally provide a method for depositing films using photoexcitation. The photoexcitation may be utilized for at least one of treating the substrate prior to deposition, treating substrate and / or gases during deposition, treating a deposited film, or for enhancing chamber cleaning. In one embodiment, a method for depositing silicon and nitrogen-containing film on a substrate includes heating a substrate disposed in a processing chamber, generating a beam of energy of between about 1 to about 10 eV, transferring the energy to a surface of the substrate; flowing a nitrogen-containing chemical into the processing chamber, flowing a silicon-containing chemical with silicon-nitrogen bonds into the processing chamber, and depositing a silicon and nitrogen-containing film on the substrate.

Owner:APPLIED MATERIALS INC

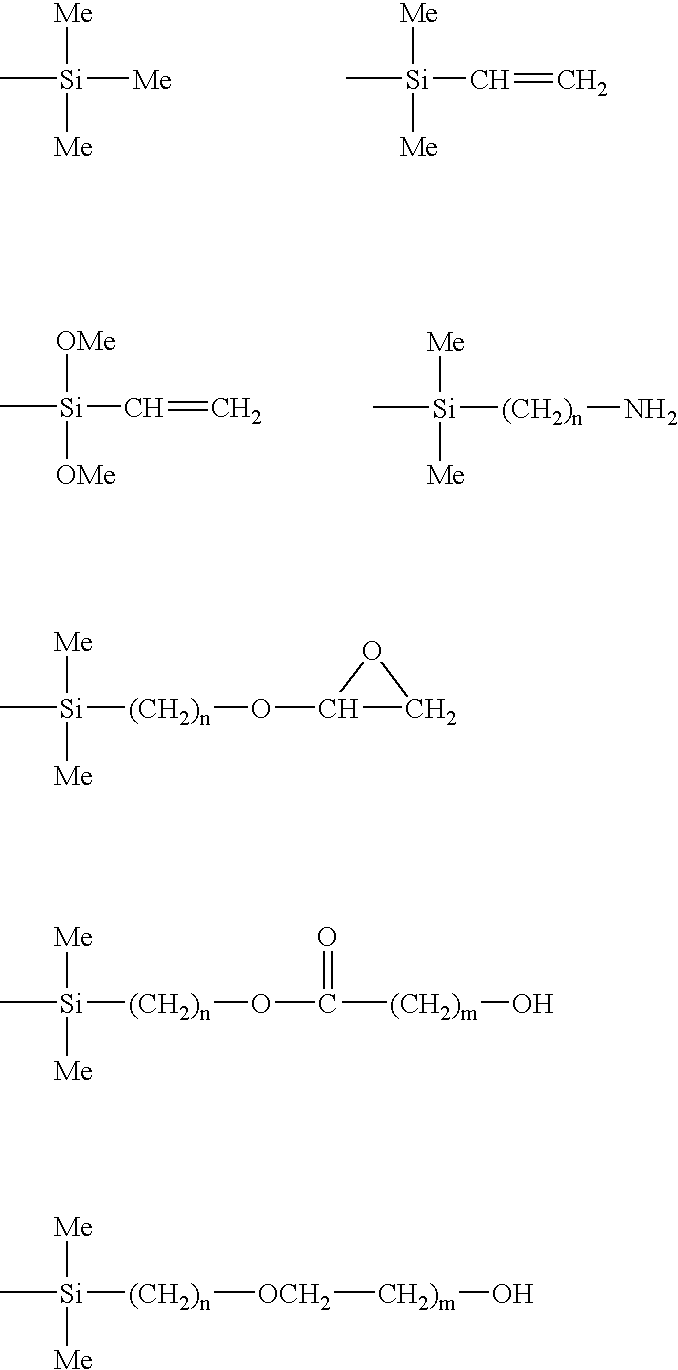

Home and personal care compositions comprising silicon-based lubricants

InactiveUS7465439B2Cosmetic preparationsOrganic detergent compounding agentsPersonal carePolymer science

A composition for personal, home, or laundry treatment comprising a polymer made up of one or more crosslinked rake or comb silicone copolymer segments. A process for making copolymers for use in such compositions involves hydrosilylation in the presence of a catalyst.

Owner:CONOPCO INC D B A UNILEVER

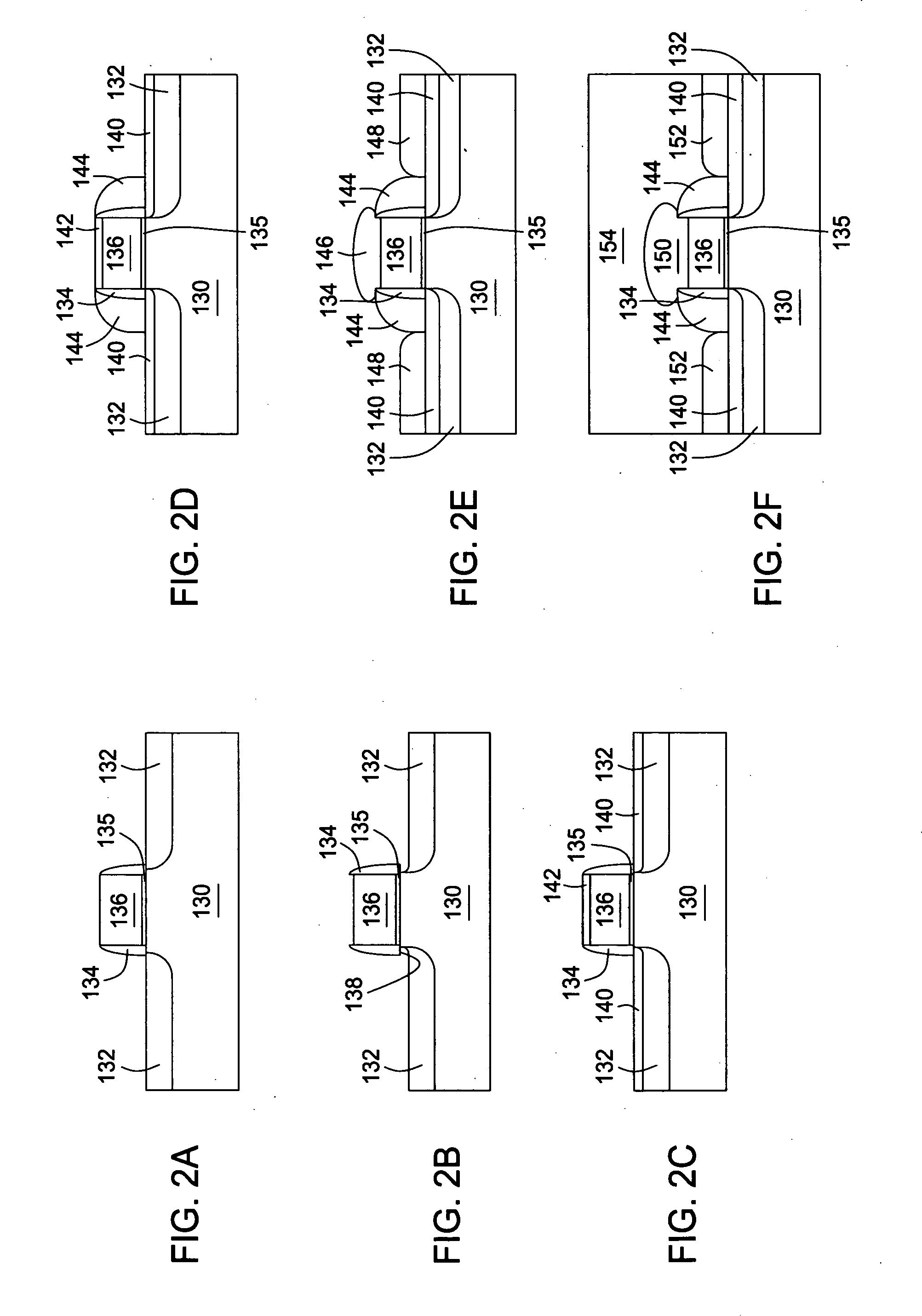

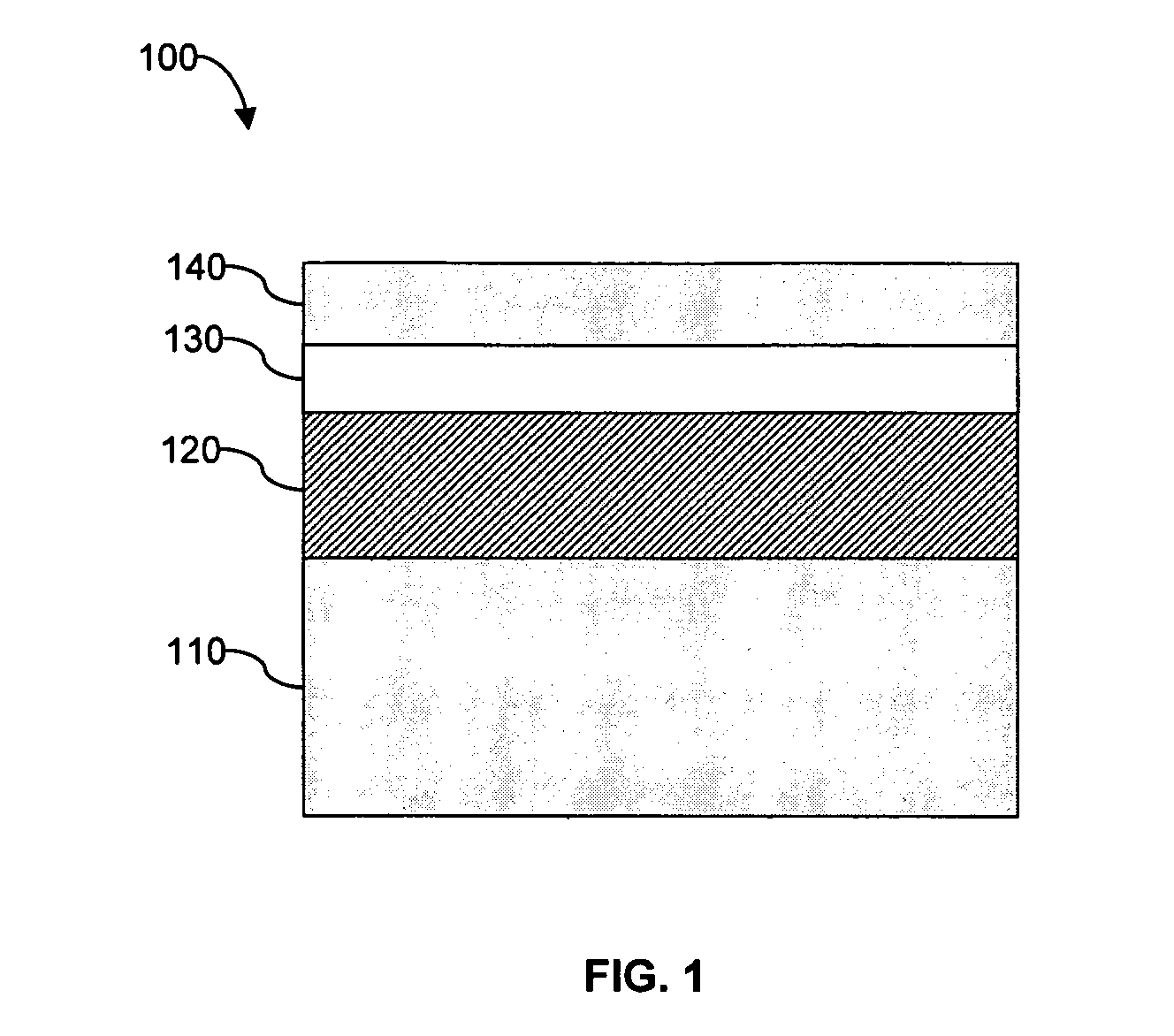

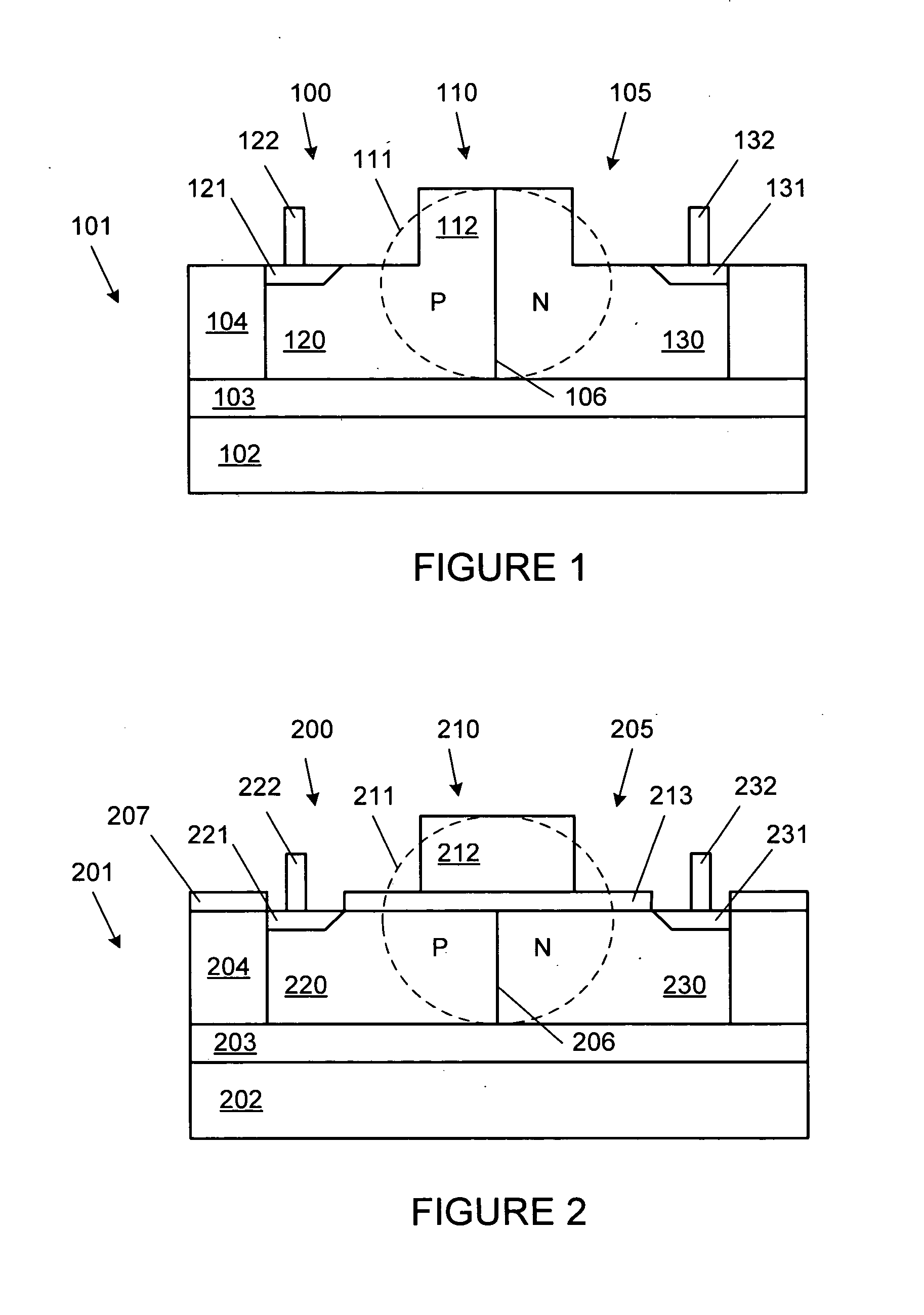

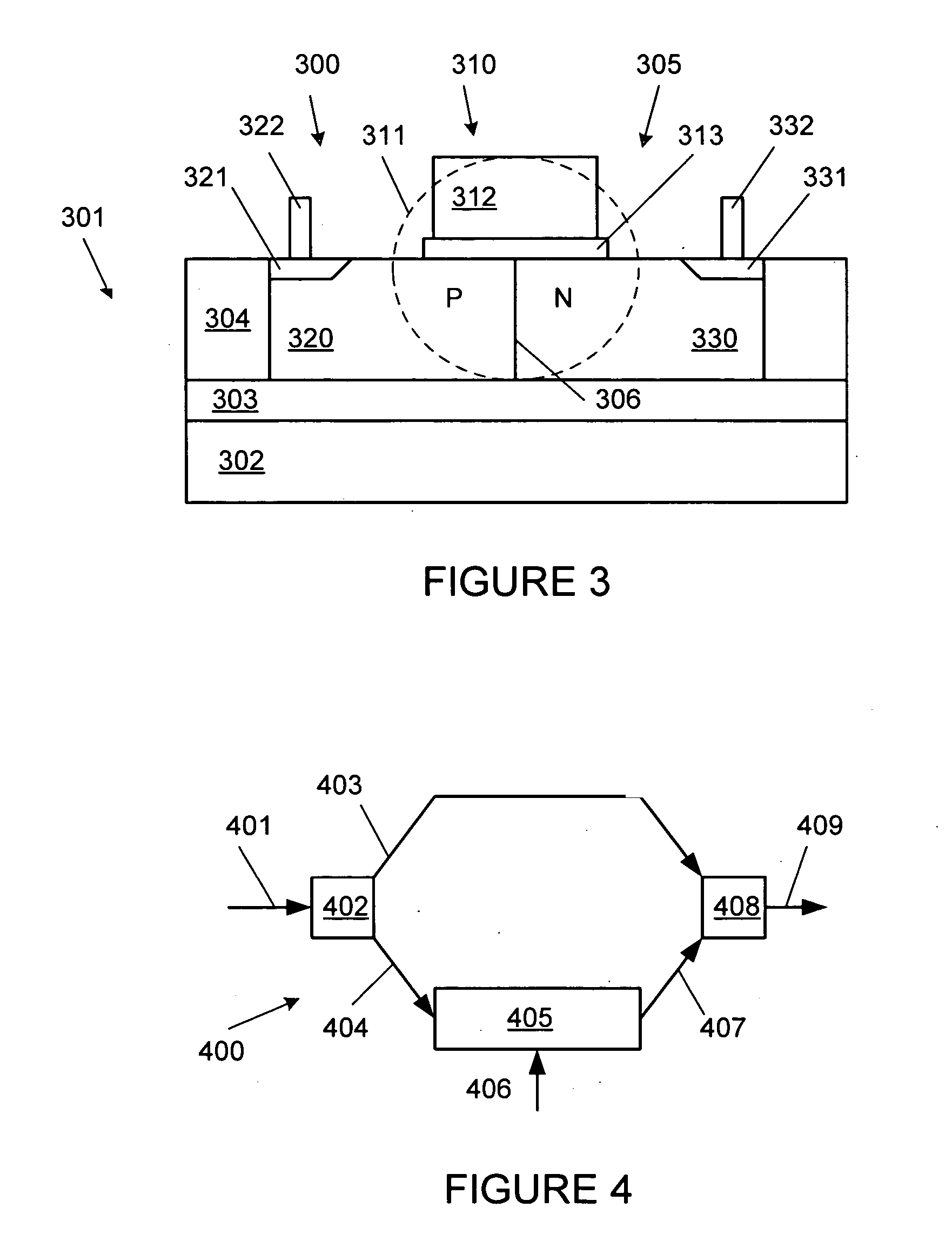

SOI SiGe-Base Lateral Bipolar Junction Transistor

ActiveUS20120139009A1Great current densityNoise minimizationSolid-state devicesSemiconductor/solid-state device manufacturingCarrier scatteringParasitic capacitance

A lateral heterojunction bipolar transistor (HBT) is formed on a semiconductor-on-insulator substrate. The HBT includes a base including a doped silicon-germanium alloy base region, an emitter including doped silicon and laterally contacting the base, and a collector including doped silicon and laterally contacting the base. Because the collector current is channeled through the doped silicon-germanium base region, the HBT can accommodate a greater current density than a comparable bipolar transistor employing a silicon channel. The base may also include an upper silicon base region and / or a lower silicon base region. In this case, the collector current is concentrated in the doped silicon-germanium base region, thereby minimizing noise introduced to carrier scattering at the periphery of the base. Further, parasitic capacitance is minimized because the emitter-base junction area is the same as the collector-base junction area.

Owner:IBM CORP

Method for silicon based dielectric chemical vapor deposition

Embodiments of the invention generally provide a method for depositing silicon-containing films. In one embodiment, a method for depositing silicon-containing material film on a substrate includes flowing a nitrogen and carbon containing chemical into a deposition chamber, flowing a silicon-containing source chemical having silicon-nitrogen bonds into the processing chamber, and heating the substrate disposed in the chamber to a temperature less than about 550 degrees Celsius. In another embodiment, the silicon containing chemical is trisilylamine and the nitrogen and carbon containing chemical is (CH3)3—N.

Owner:APPLIED MATERIALS INC

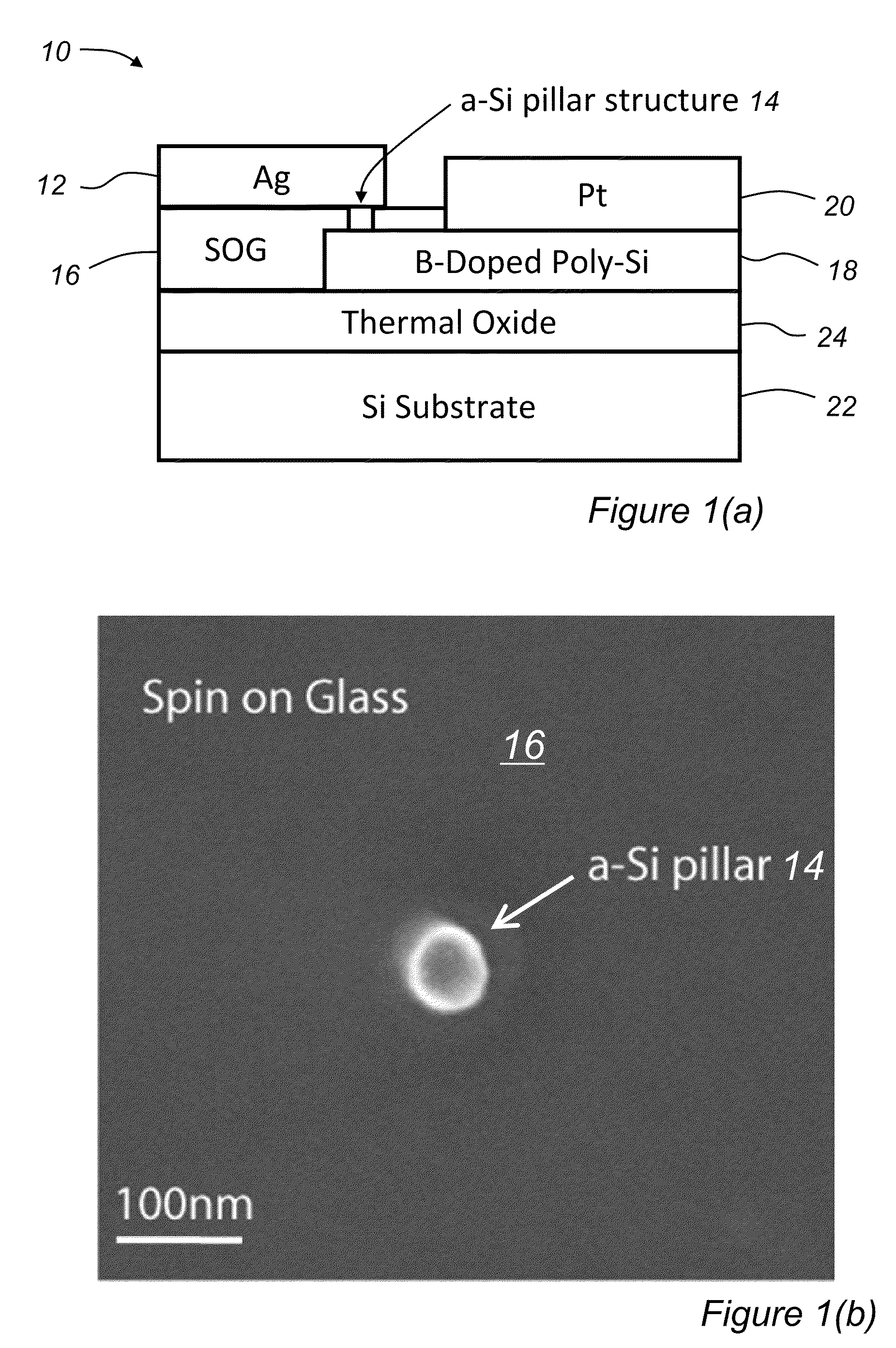

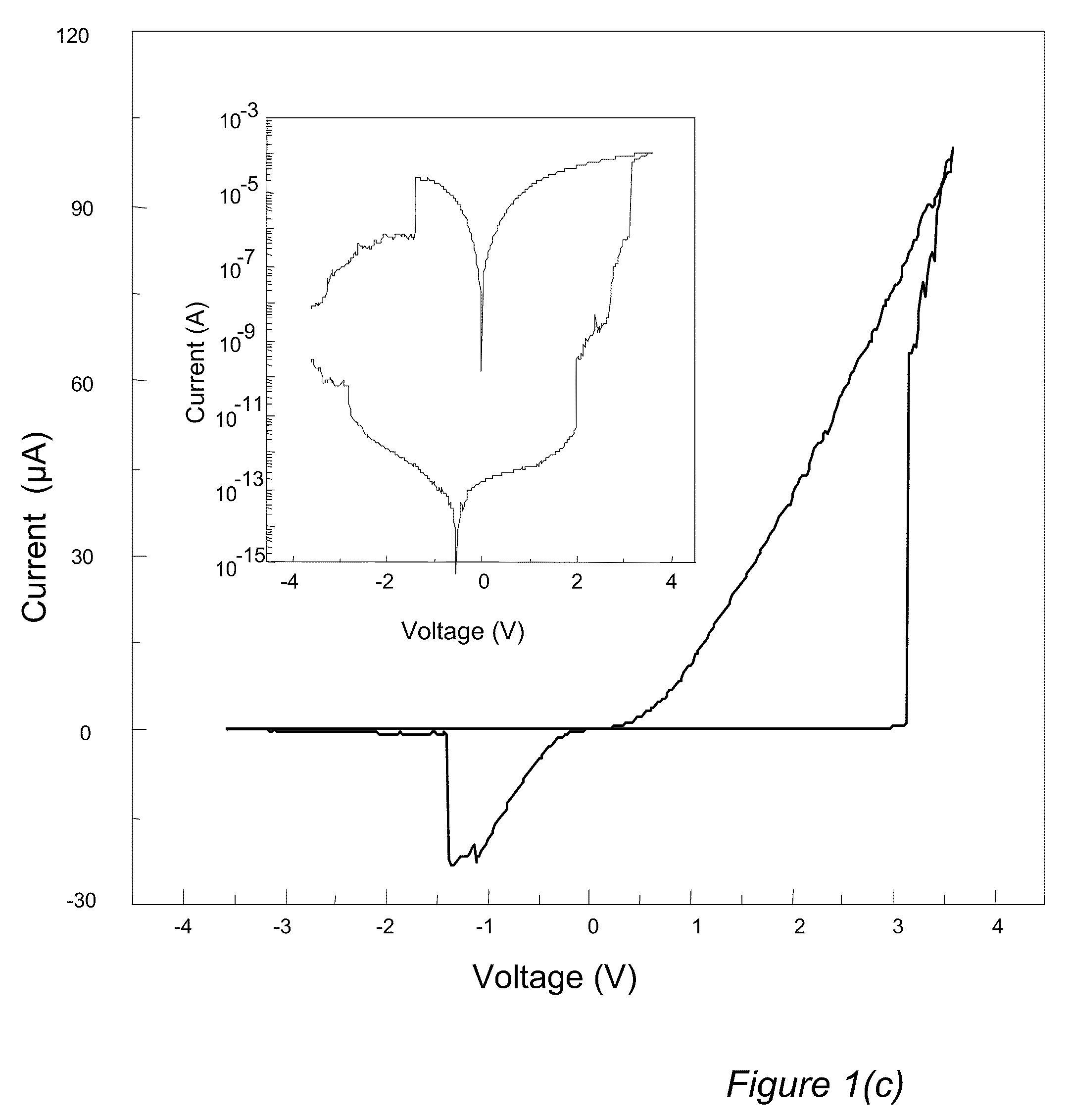

Silicon-based nanoscale resistive device with adjustable resistance

A non-volatile solid state resistive device that includes a first electrode, a p-type poly-silicon second electrode, and a non-crystalline silicon nanostructure electrically connected between the electrodes. The nanostructure has a resistance that is adjustable in response to a voltage being applied to the nanostructure via the electrodes. The nanostructure can be formed as a nanopillar embedded in an insulating layer located between the electrodes. The first electrode can be a silver or other electrically conductive metal electrode. A third (metal) electrode can be connected to the p-type poly-silicon second electrode at a location adjacent the nanostructure to permit connection of the two metal electrodes to other circuitry. The resistive device can be used as a unit memory cell of a digital non-volatile memory device to store one or more bits of digital data by varying its resistance between two or more values.

Owner:RGT UNIV OF MICHIGAN

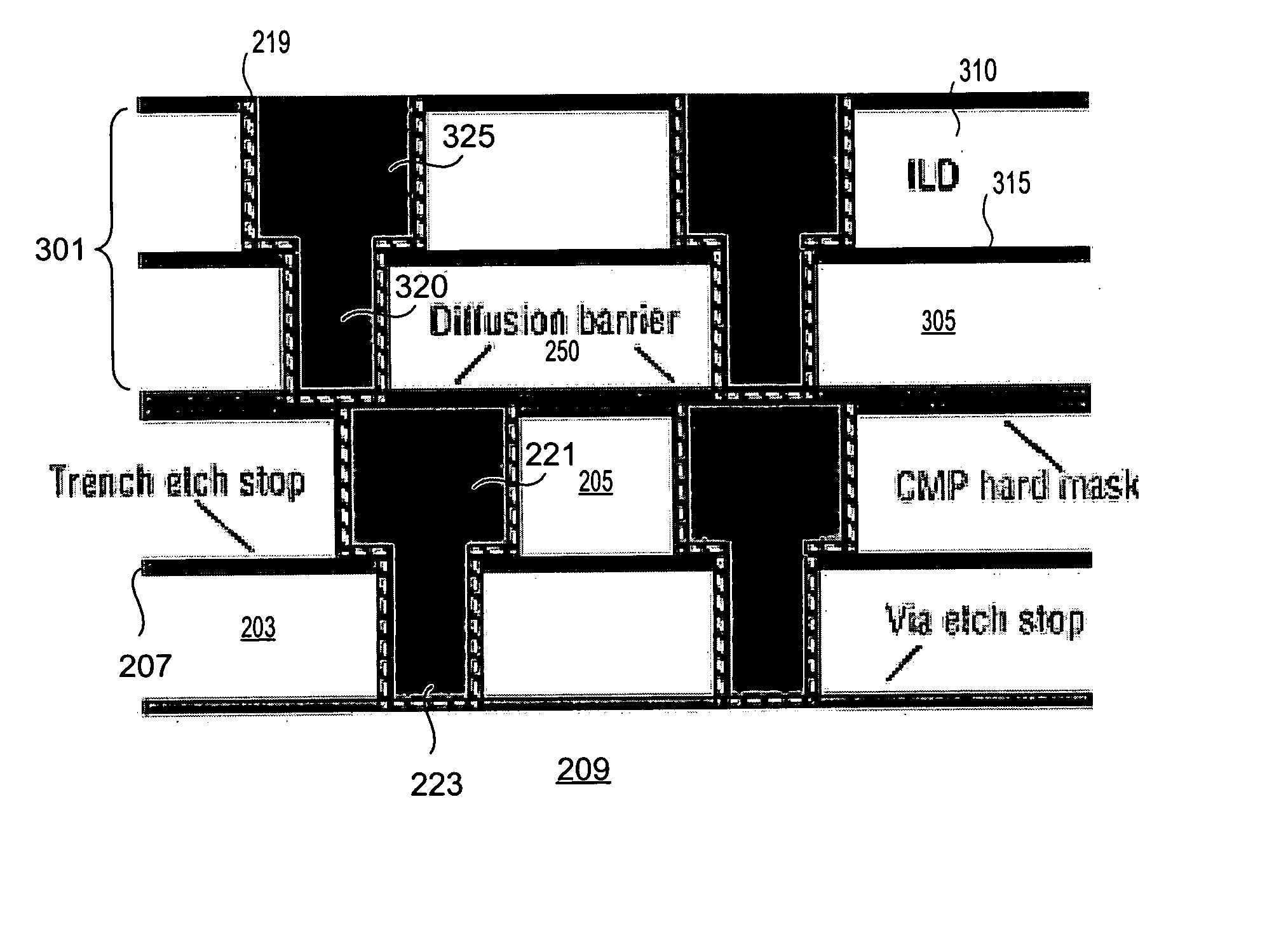

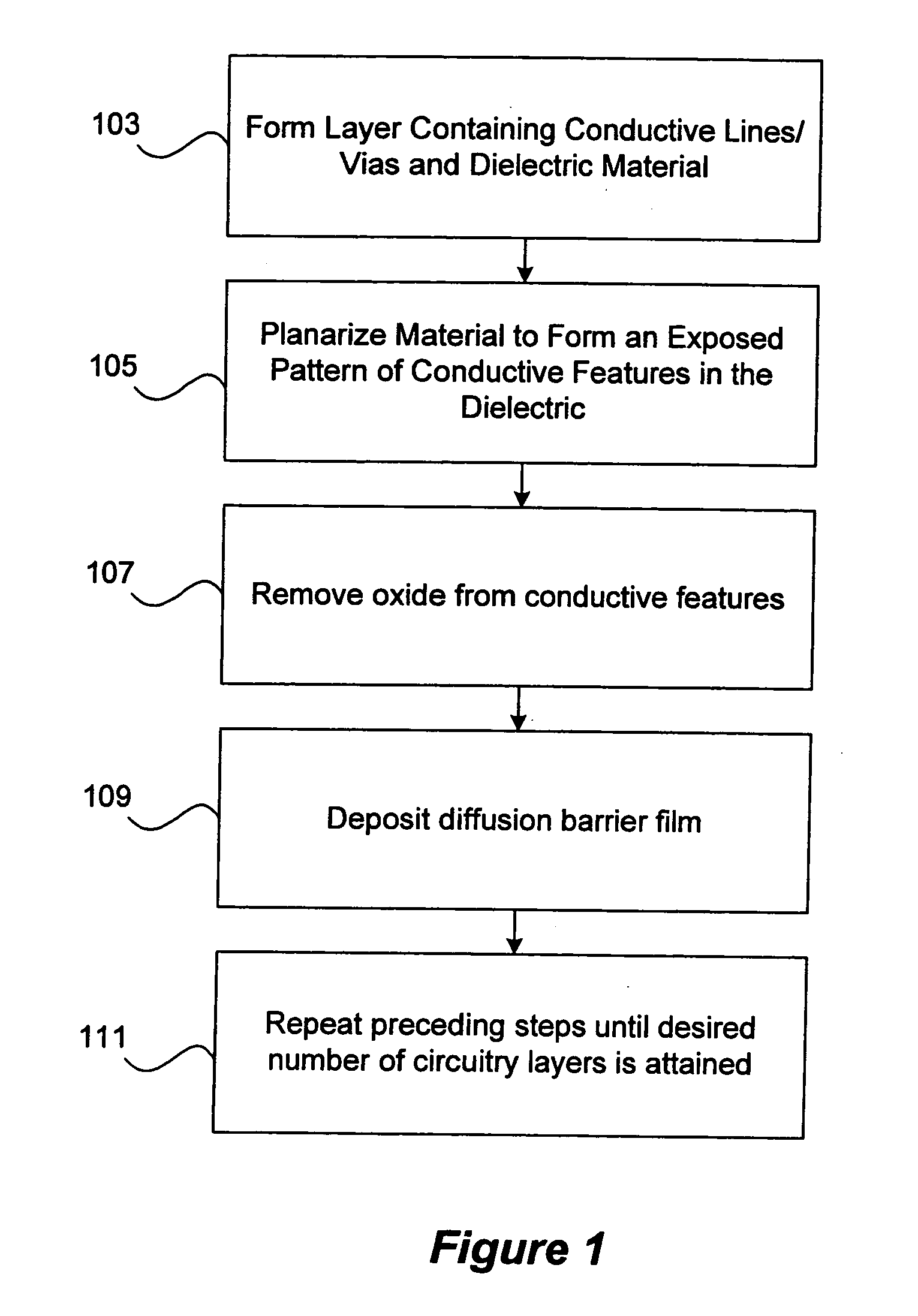

Novel film for copper diffusion barrier

InactiveUS20060019486A1Semiconductor/solid-state device detailsSolid-state devicesAtmospheric airBoron nitride

The present invention provides a low dielectric constant copper diffusion barrier film suitable for use in a semiconductor device and methods for fabricating such a film. Some embodiments of the film are formed of a silicon-based material doped with boron. Other embodiments are formed, at least in part, of boron nitride. Some such embodiments include a moisture barrier film that includes oxygen and / or carbon. Preferred embodiments of the copper diffusion barrier maintain a stable dielectric constant of less than 4.5 in the presence of atmospheric moisture.

Owner:NOVELLUS SYSTEMS

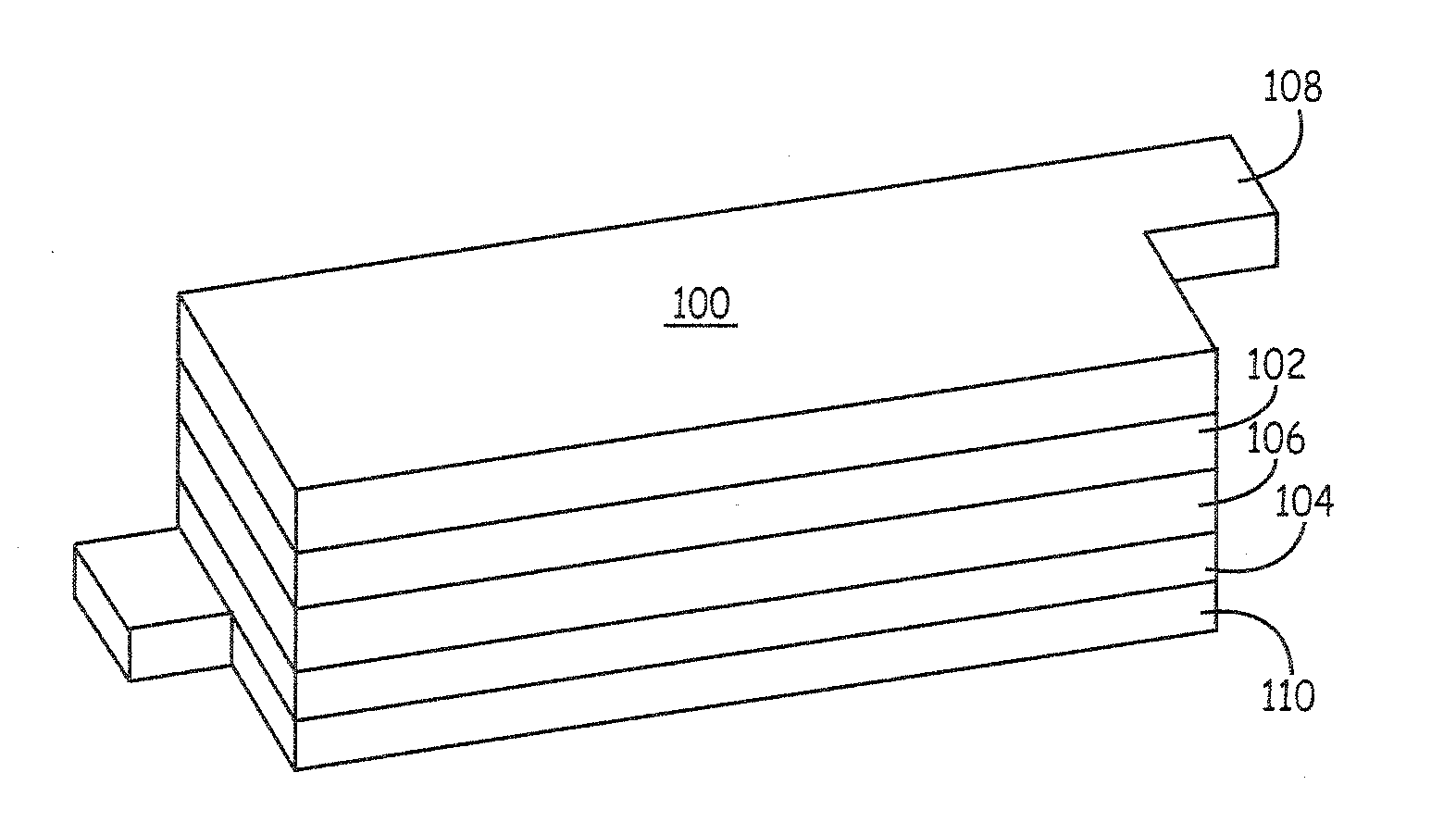

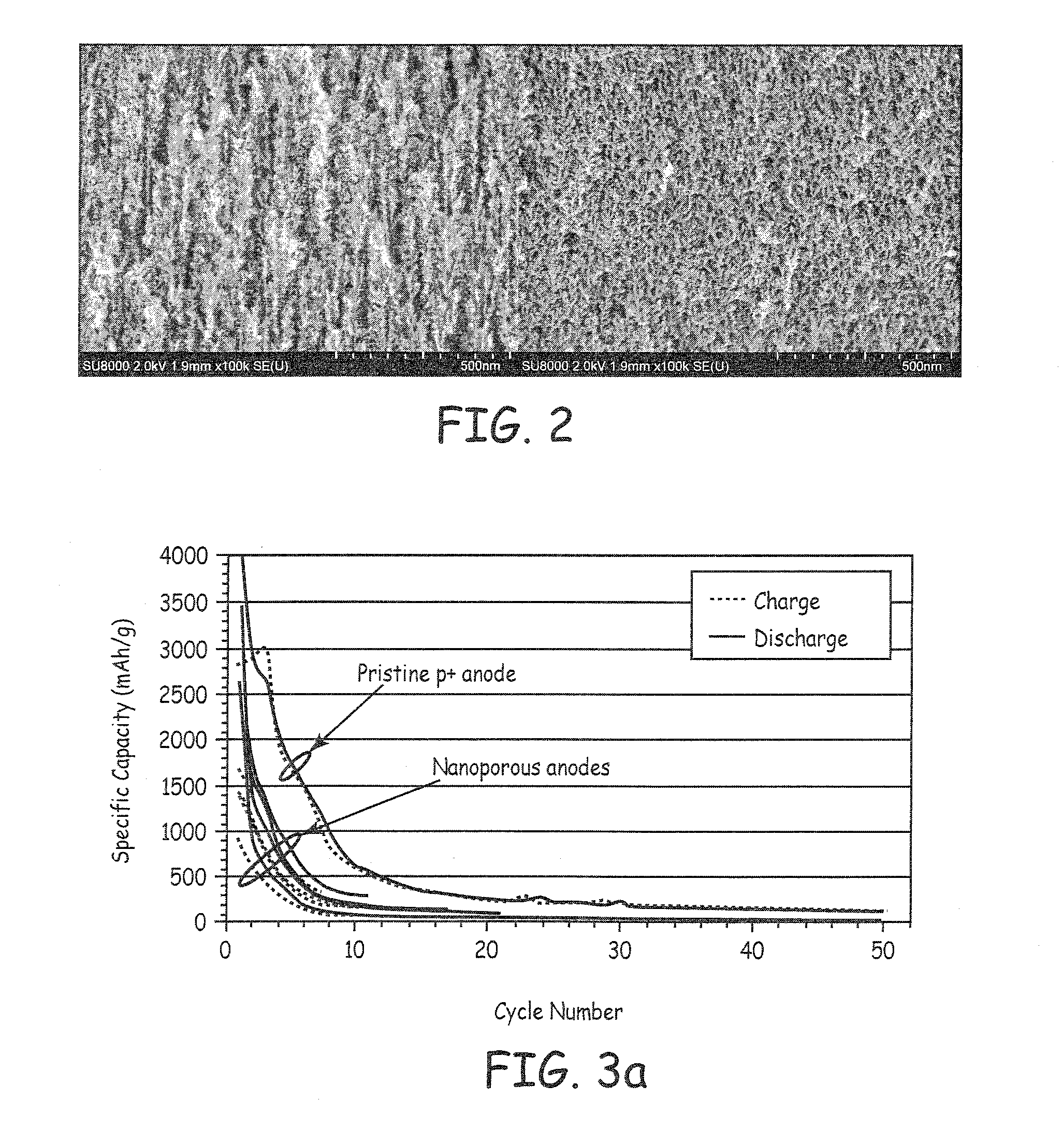

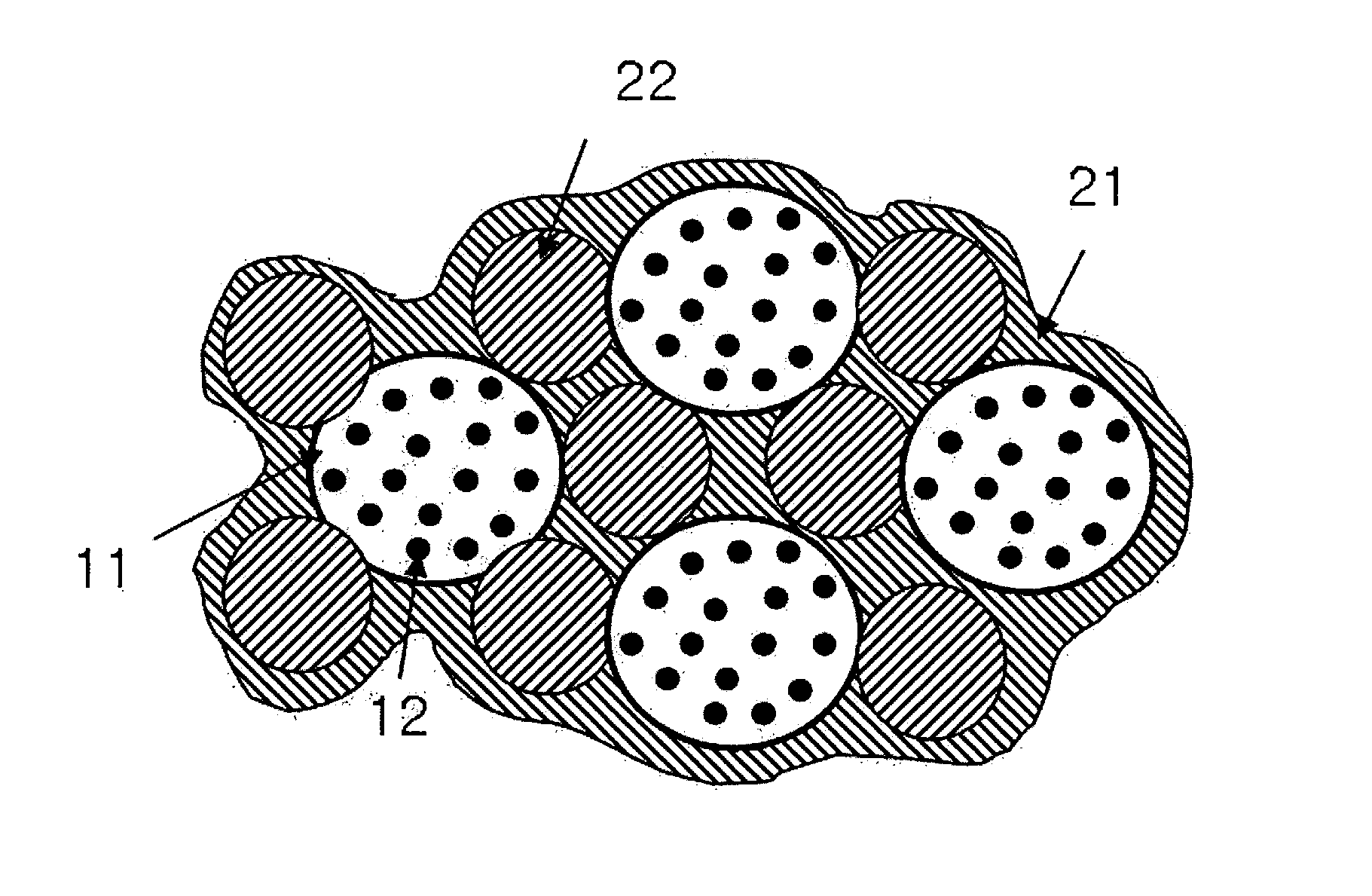

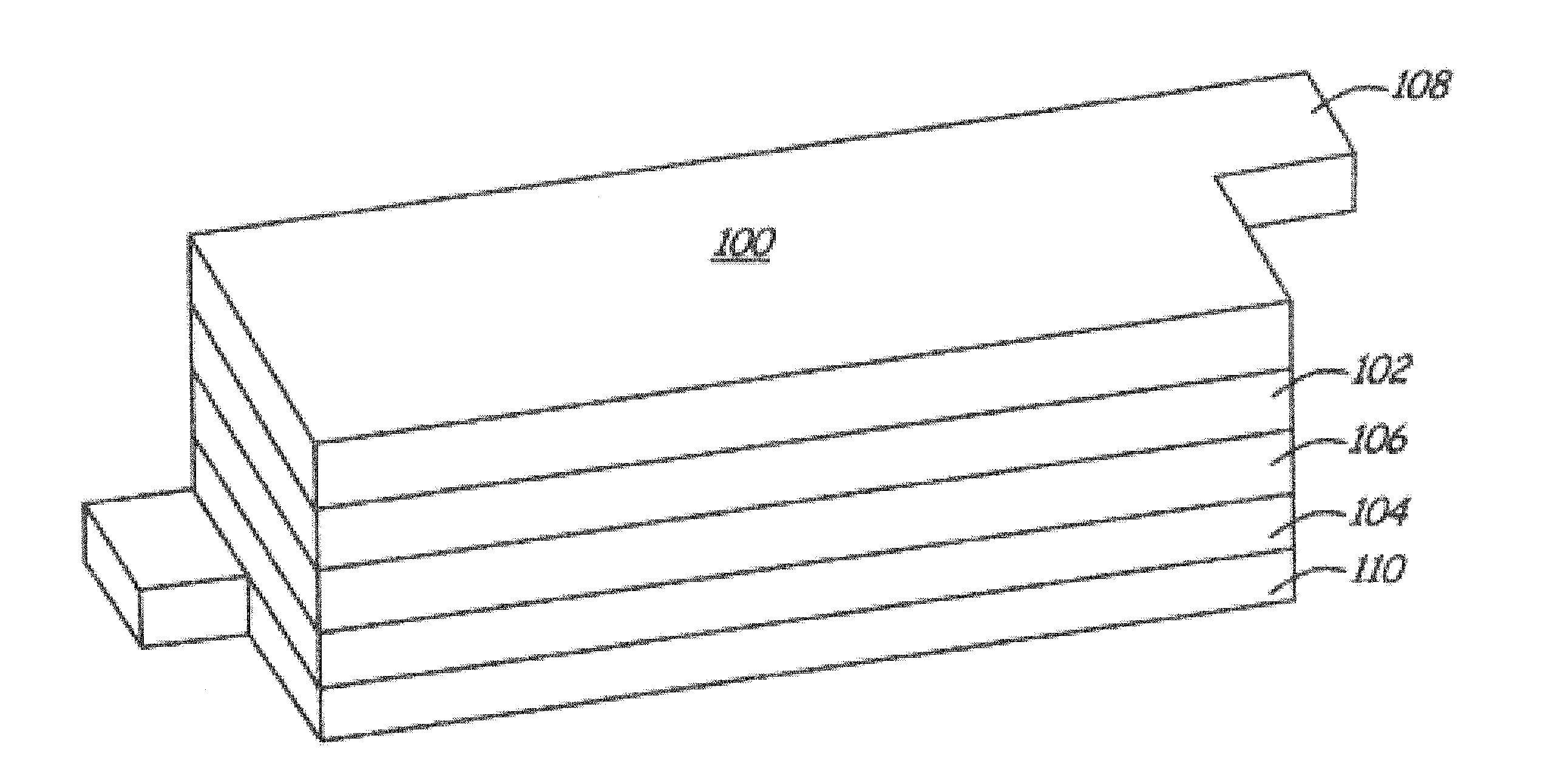

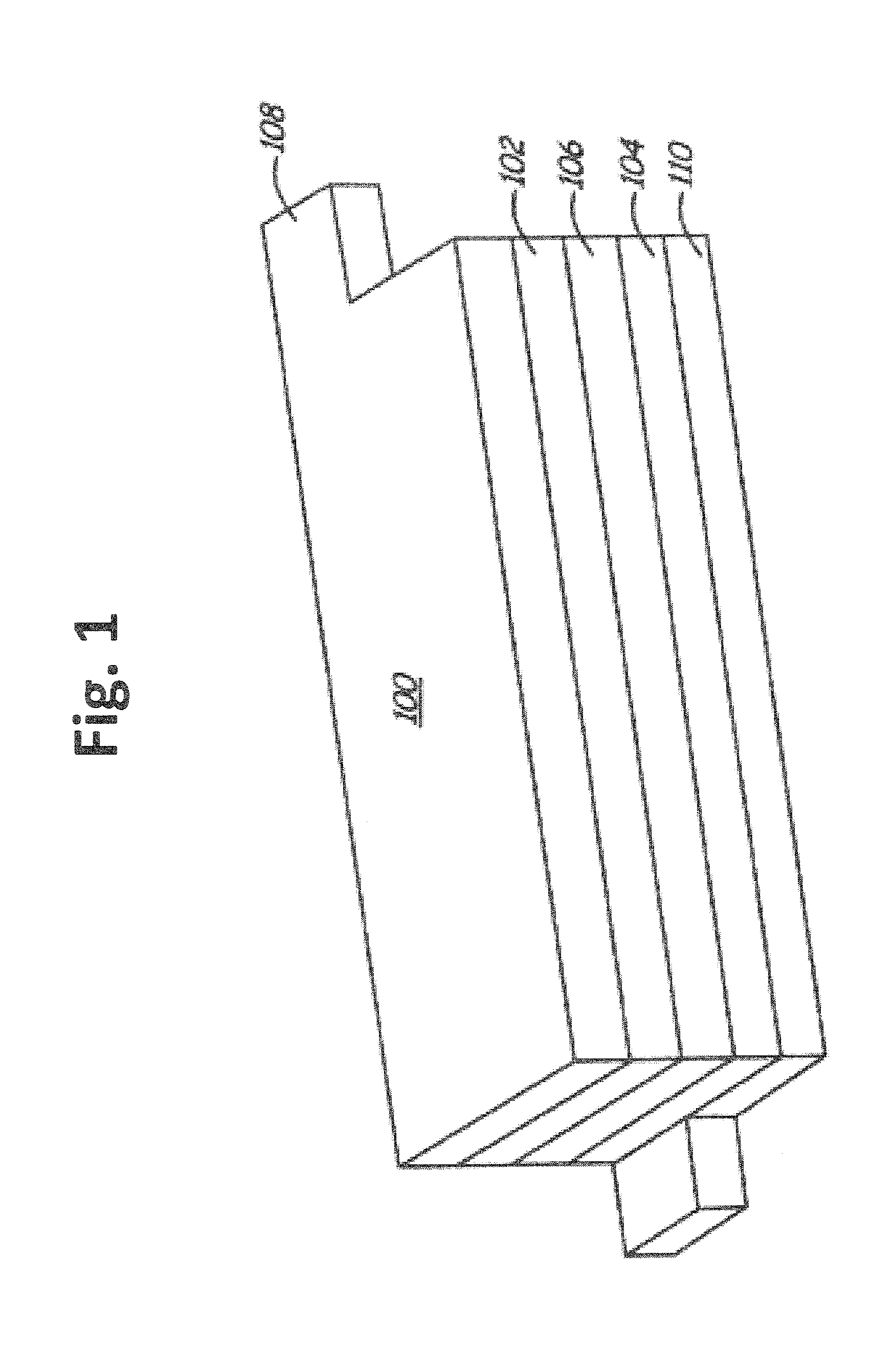

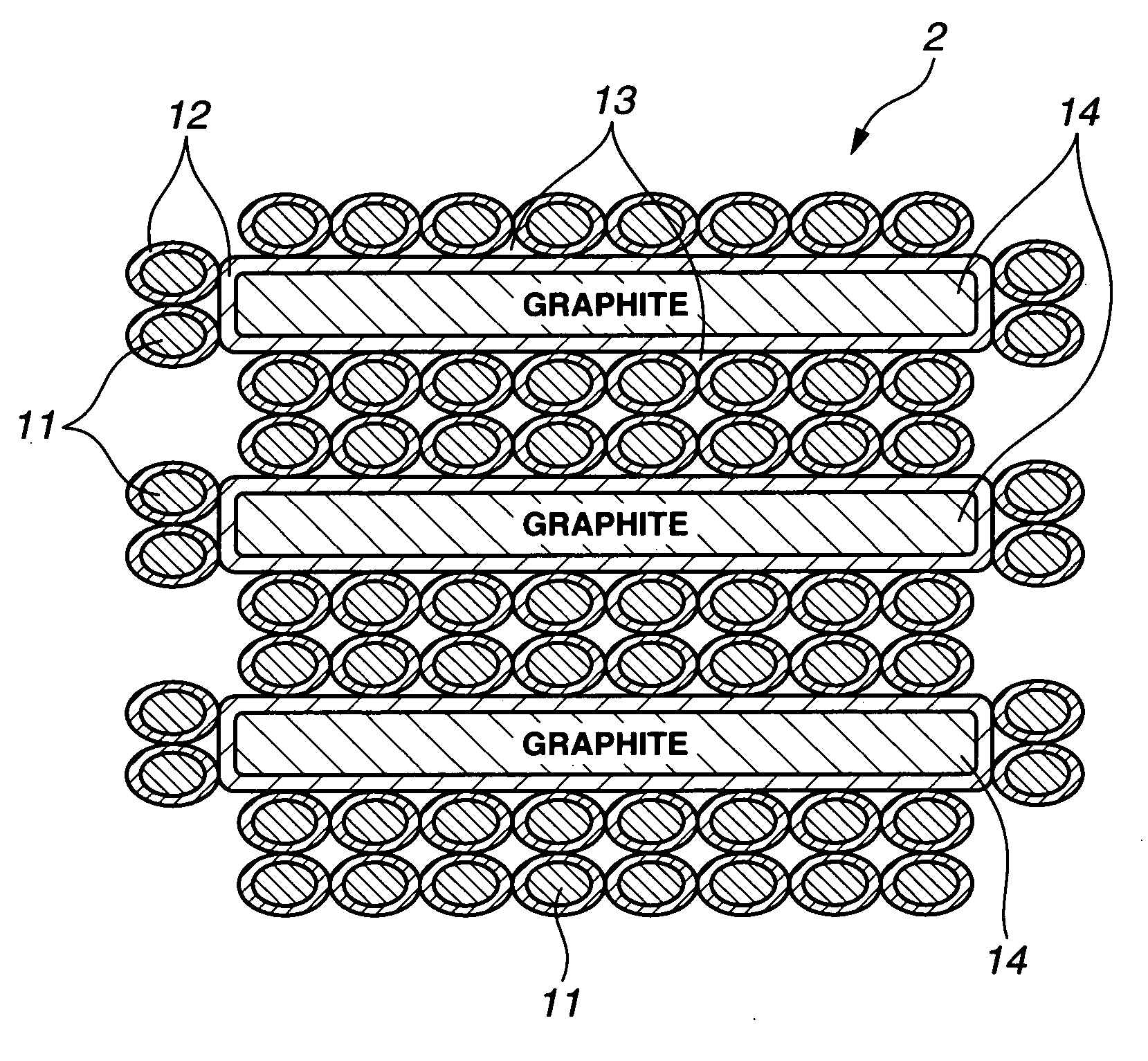

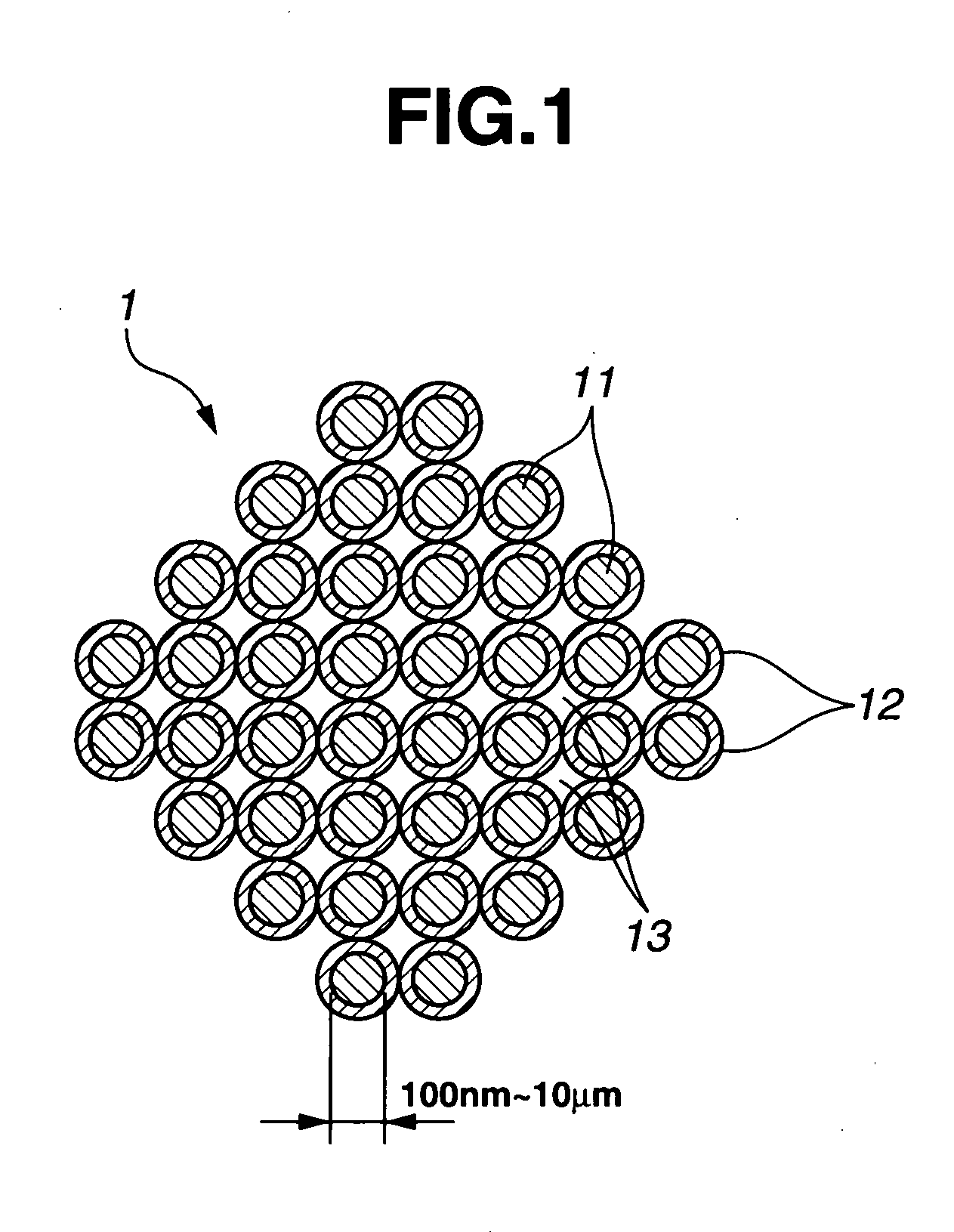

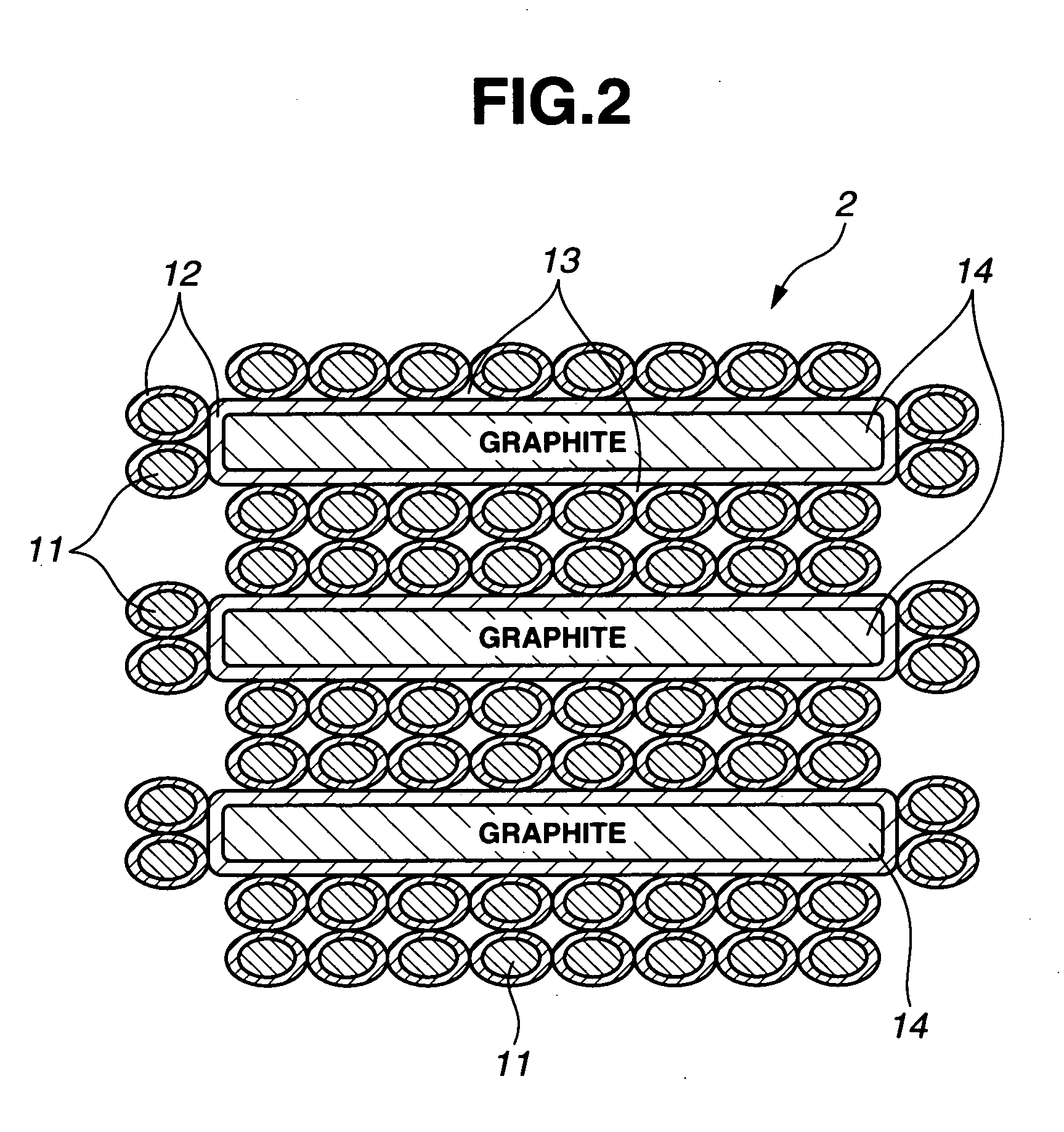

High Capacity Anode Materials for Lithium Ion Batteries

High capacity silicon based anode active materials are described for lithium ion batteries. These materials are shown to be effective in combination with high capacity lithium rich cathode active materials. Supplemental lithium is shown to improve the cycling performance and reduce irreversible capacity loss for at least certain silicon based active materials. In particular silicon based active materials can be formed in composites with electrically conductive coatings, such as pyrolytic carbon coatings or metal coatings, and composites can also be formed with other electrically conductive carbon components, such as carbon nanofibers and carbon nanoparticles. Additional alloys with silicon are explored.

Owner:IONBLOX INC

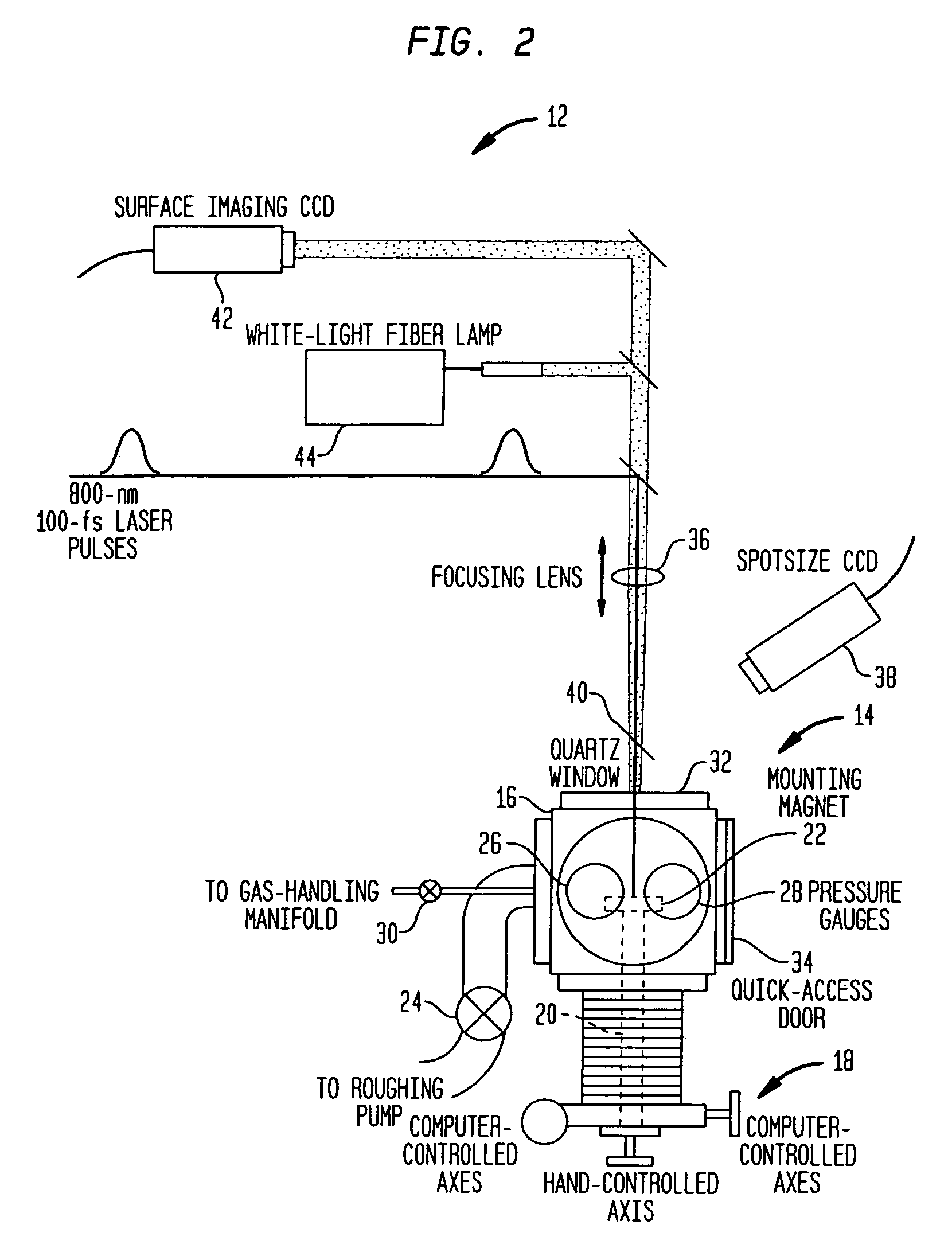

Silicon-based visible and near-infrared optoelectric devices

InactiveUS7057256B2Promote generationFinal product manufactureSemiconductor/solid-state device manufacturingPhotovoltaic detectorsSurface layer

In one aspect, the present invention provides a silicon photodetector having a surface layer that is doped with sulfur inclusions with an average concentration in a range of about 0.5 atom percent to about 1.5 atom percent. The surface layer forms a diode junction with an underlying portion of the substrate. A plurality of electrical contacts allow application of a reverse bias voltage to the junction in order to facilitate generation of an electrical signal, e.g., a photocurrent, in response to irradiation of the surface layer. The photodetector exhibits a responsivity greater than about 1 A / W for incident wavelengths in a range of about 250 nm to about 1050 nm, and a responsivity greater than about 0.1 A / W for longer wavelengths, e.g., up to about 3.5 microns.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

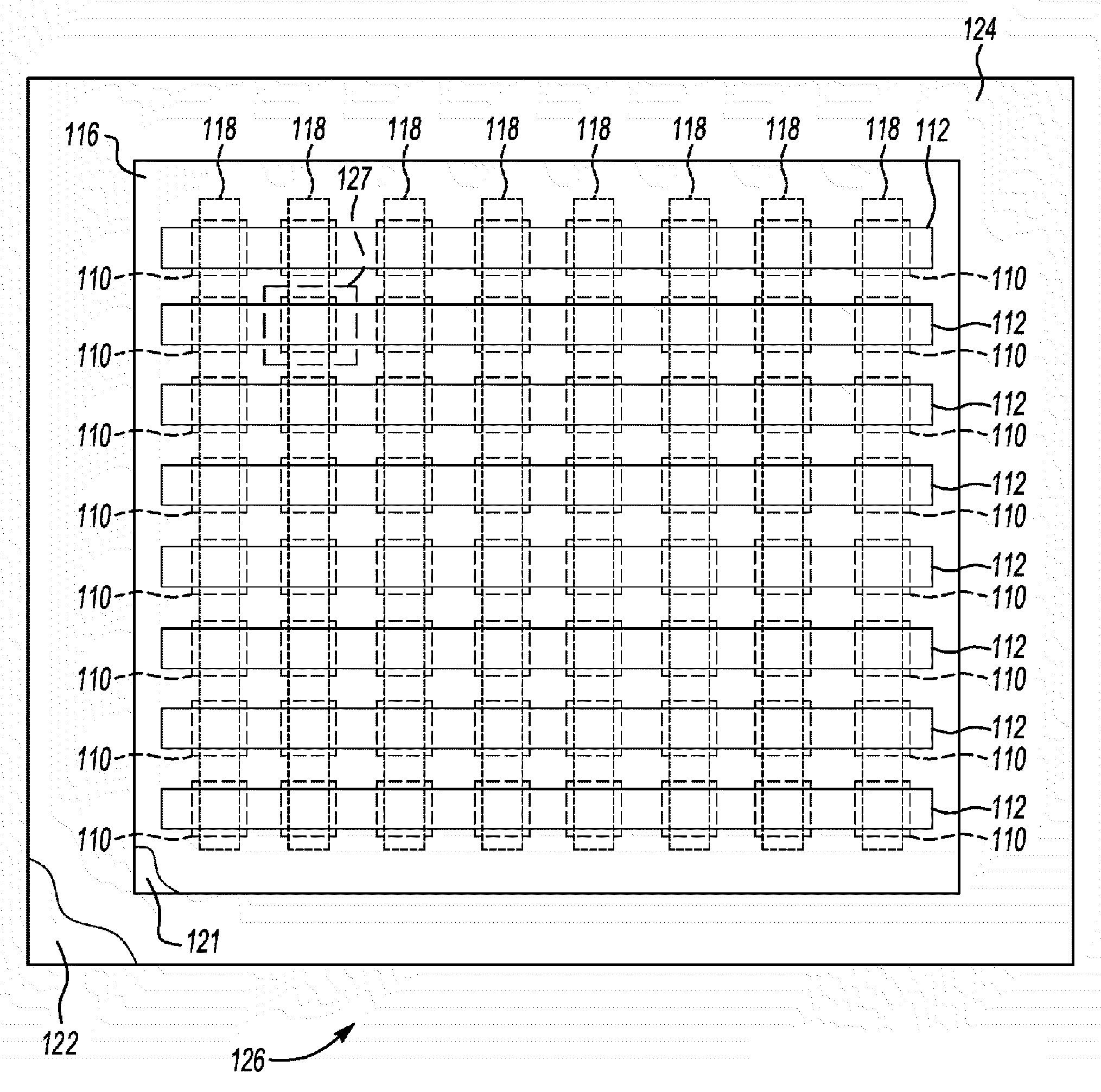

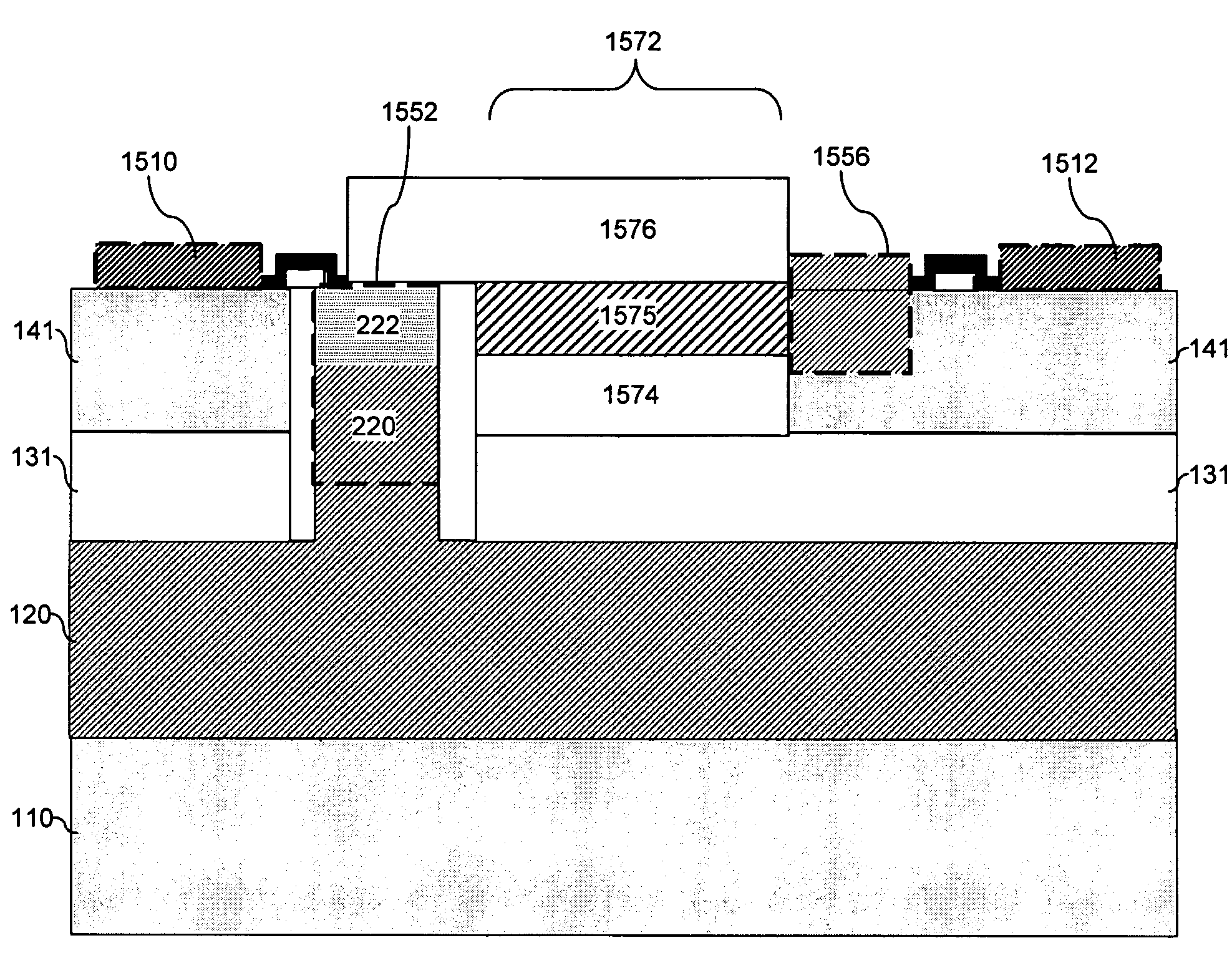

Monolithically integrated light emitting devices

ActiveUS7535089B2Layered productsSemiconductor/solid-state device detailsSingle crystalLattice constant

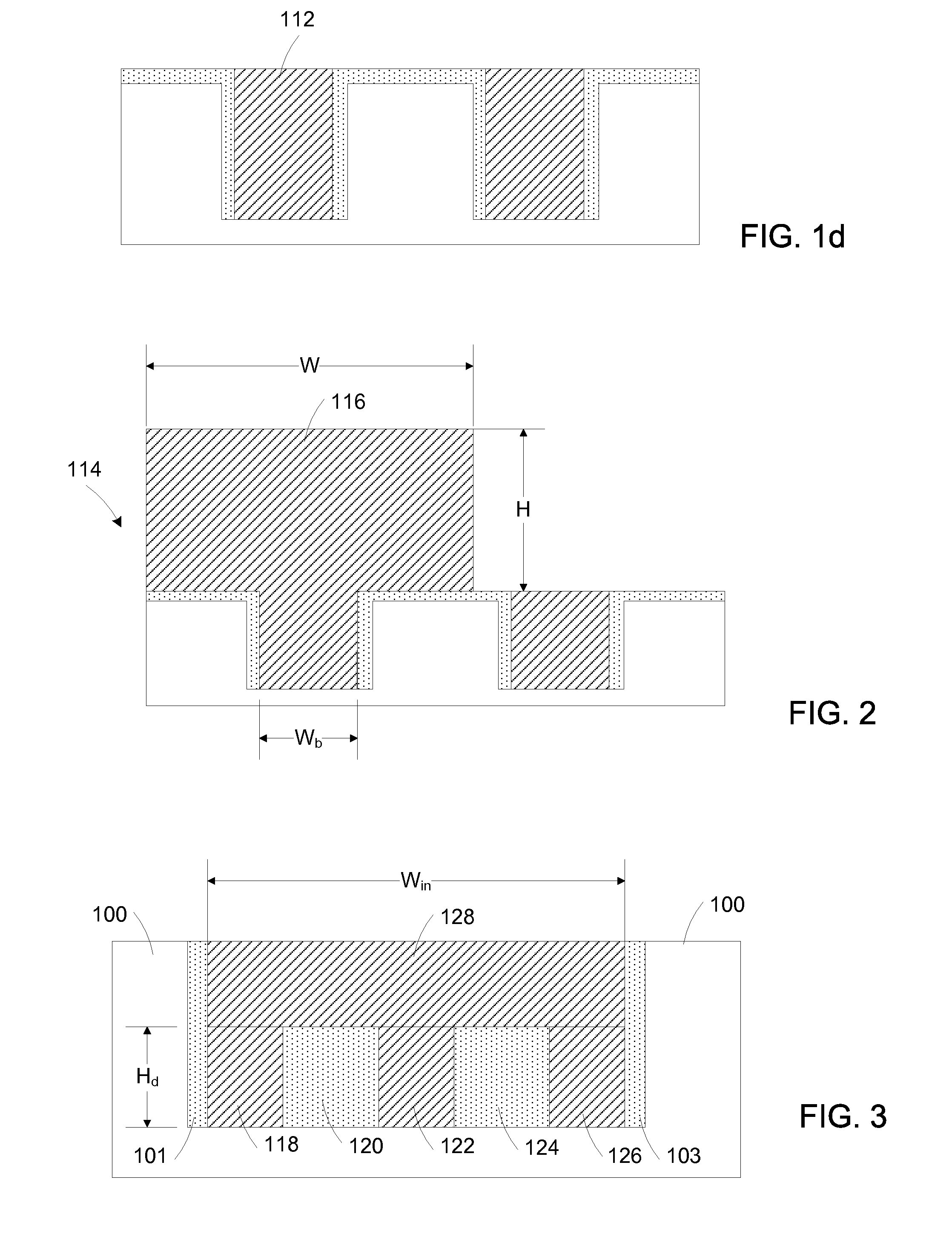

Methods and structures for monolithically integrating monocrystalline silicon and monocrystalline non-silicon materials and devices are provided. In one structure, a monolithically integrated semiconductor device structure comprises a silicon substrate and a first monocrystalline semiconductor layer disposed over the silicon substrate, wherein the first monocrystalline semiconductor layer has a lattice constant different from a lattice constant of relaxed silicon. The structure further includes an insulating layer disposed over the first monocrystalline semiconductor layer in a first region and a monocrystalline silicon layer disposed over the insulating layer in the first region. The structure includes at least one silicon-based electronic device including an element including at least a portion of the monocrystalline silicon layer. The structure also includes a second monocrystalline semiconductor layer disposed over at least a portion of the first monocrystalline semiconductor layer in a second region and absent from the first region, wherein the second monocrystalline semiconductor layer has a lattice constant different from the lattice constant of relaxed silicon. The structure includes at least one III-V light-emitting device including an active region including at least a portion of the second monocrystalline semiconductor layer.

Owner:MASSACHUSETTS INST OF TECH

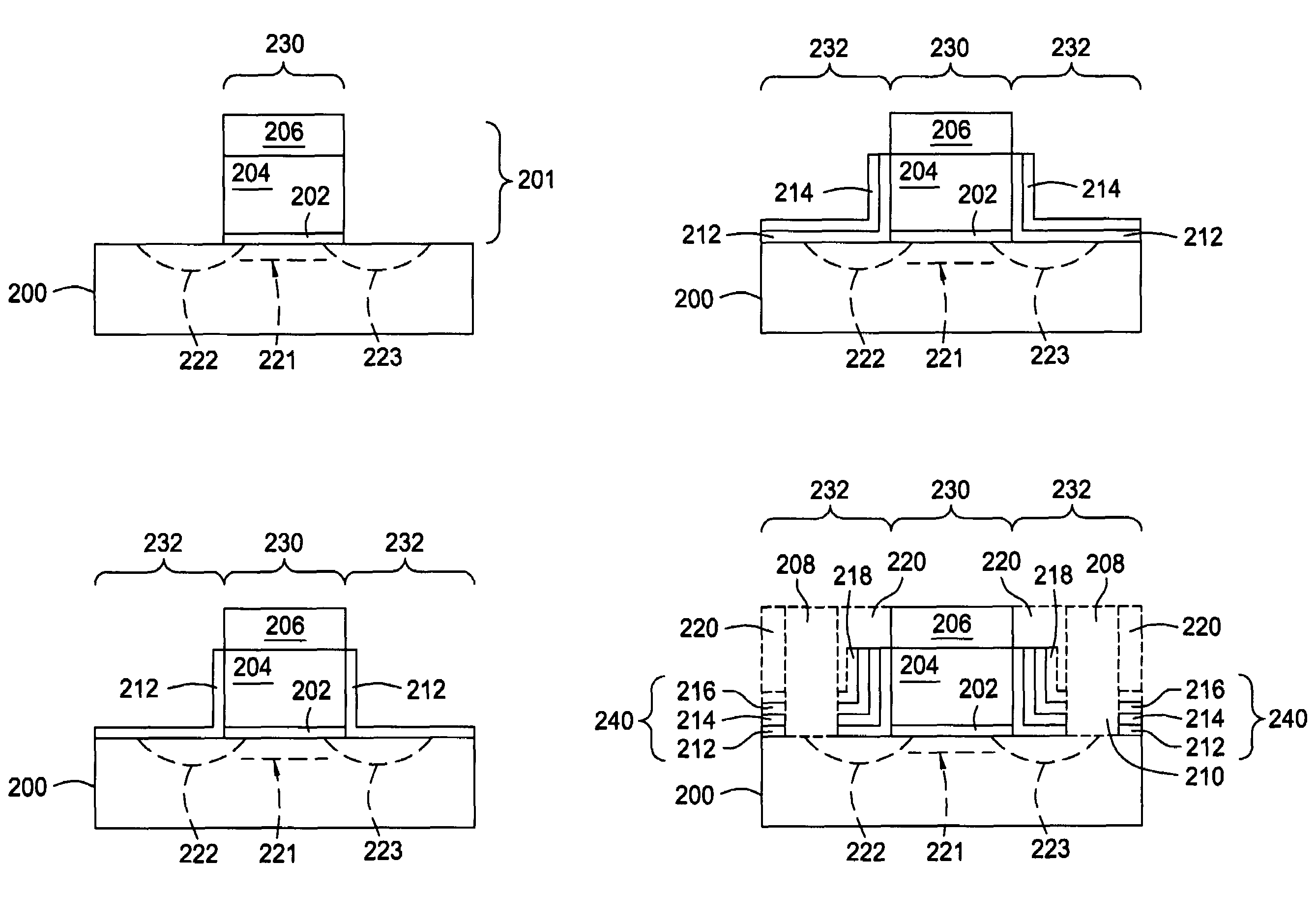

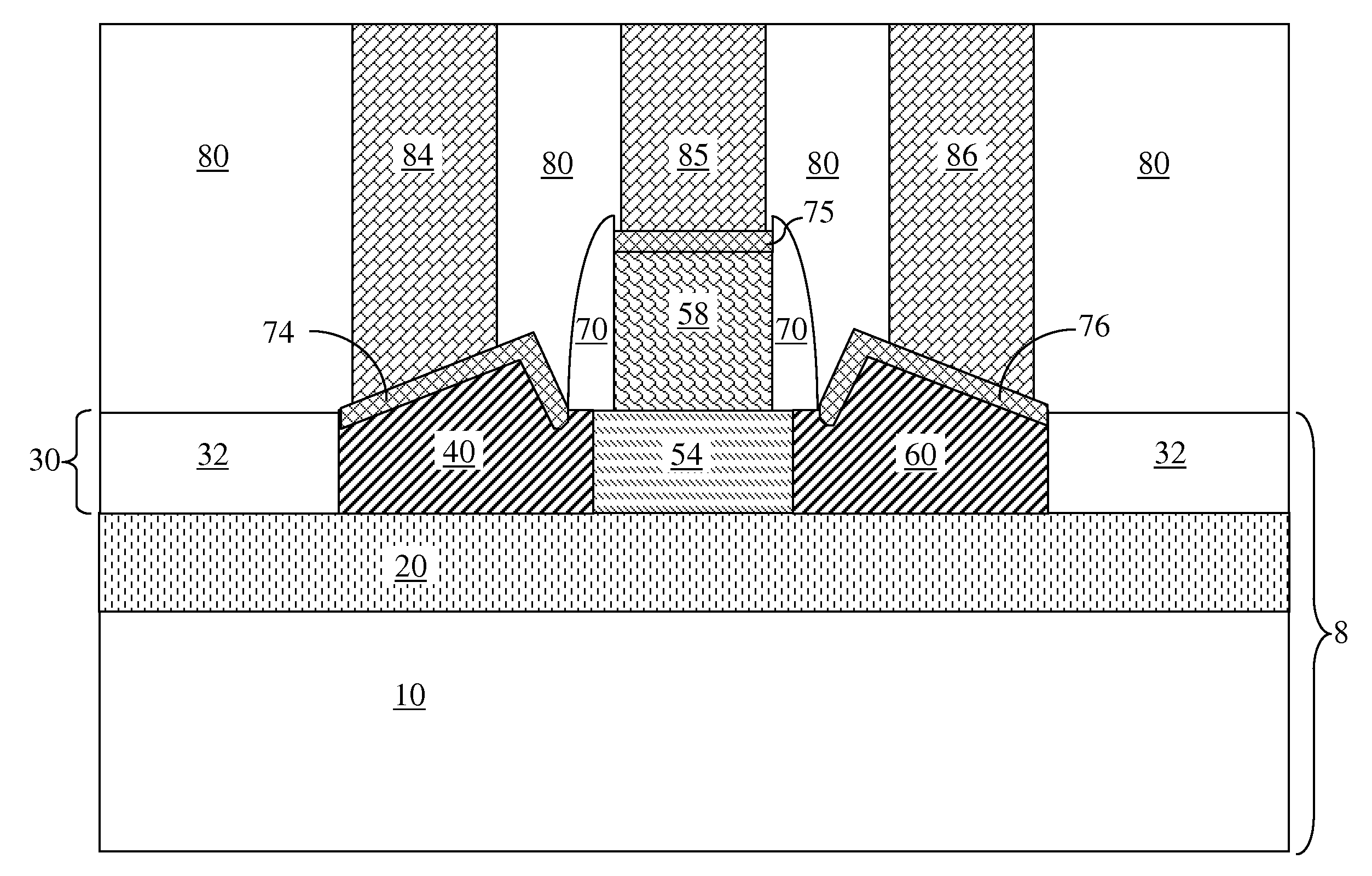

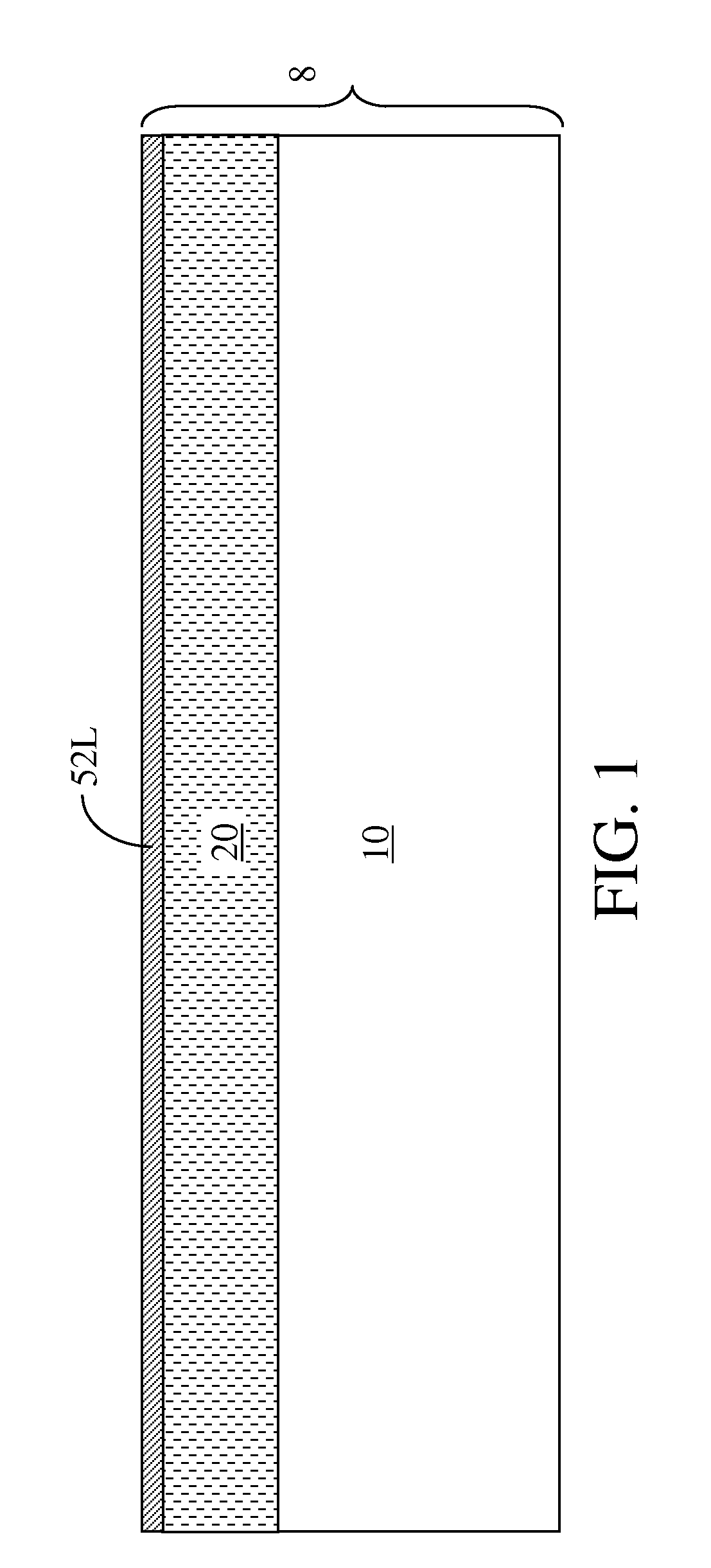

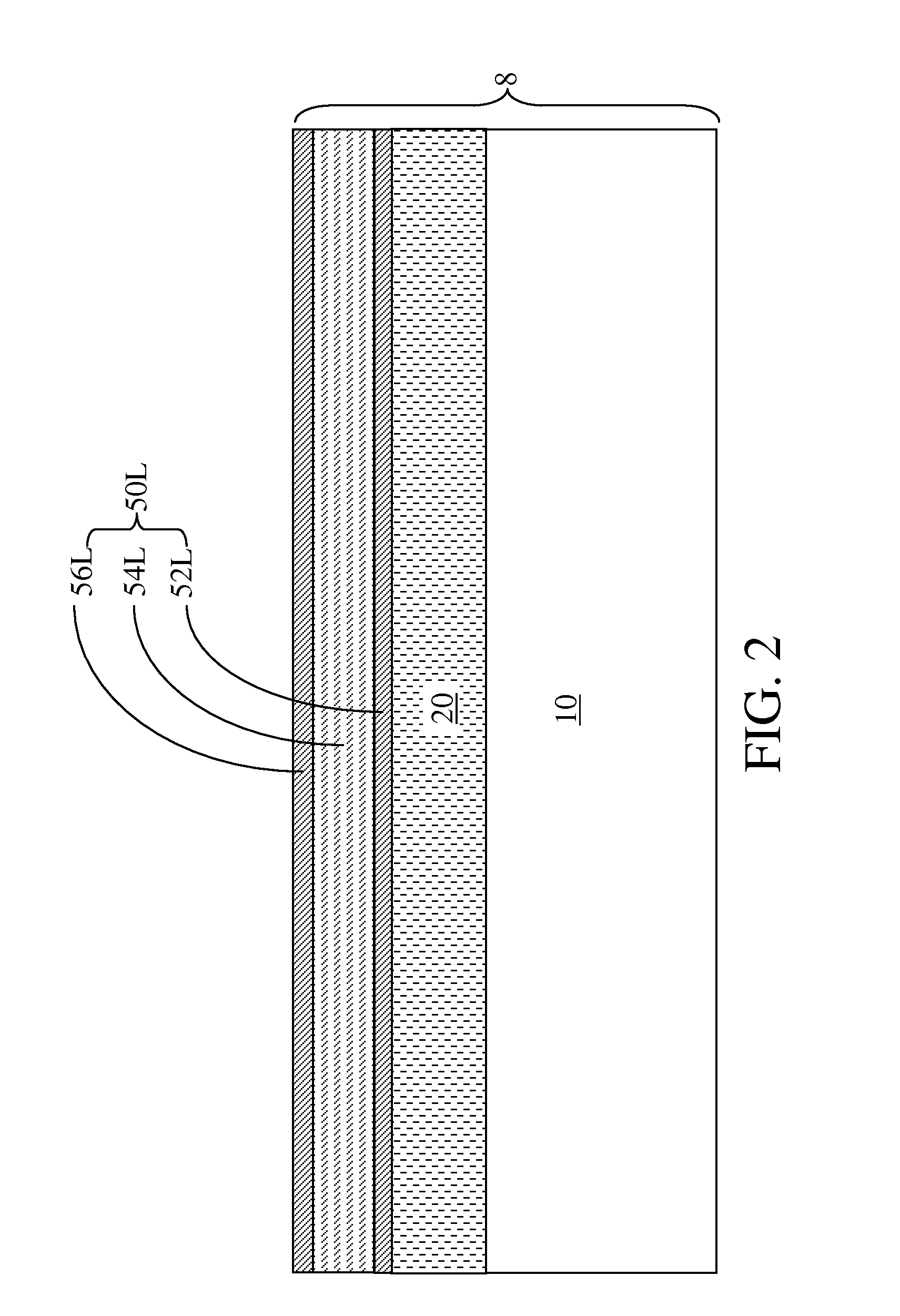

Methods to fabricate MOSFET devices using selective deposition process

ActiveUS20050079692A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMOSFETSelective deposition

In one embodiment, a method for fabricating a silicon-based device on a substrate surface is provided which includes depositing a first silicon-containing layer by exposing the substrate surface to a first process gas comprising Cl2SiH2, a germanium source, a first etchant and a carrier gas and depositing a second silicon-containing layer by exposing the first silicon-containing layer to a second process gas comprising SiH4 and a second etchant. In another embodiment, a method for depositing a silicon-containing material on a substrate surface is provided which includes depositing a first silicon-containing layer on the substrate surface with a first germanium concentration of about 15 at % or more. The method further provides depositing on the first silicon-containing layer a second silicon-containing layer wherein a second germanium concentration of about 15 at % or less, exposing the substrate surface to air to form a native oxide layer, removing the native oxide layer to expose the second silicon-containing layer, and depositing a third silicon-containing layer on the second silicon-containing layer. In another embodiment, a method for depositing a silicon-containing material on a substrate surface is provided which includes depositing epitaxially a first silicon-containing layer on the substrate surface with a first lattice strain, and depositing epitaxially on the first silicon-containing layer a second silicon-containing layer with a second lattice strain greater than the first lattice strain.

Owner:APPLIED MATERIALS INC

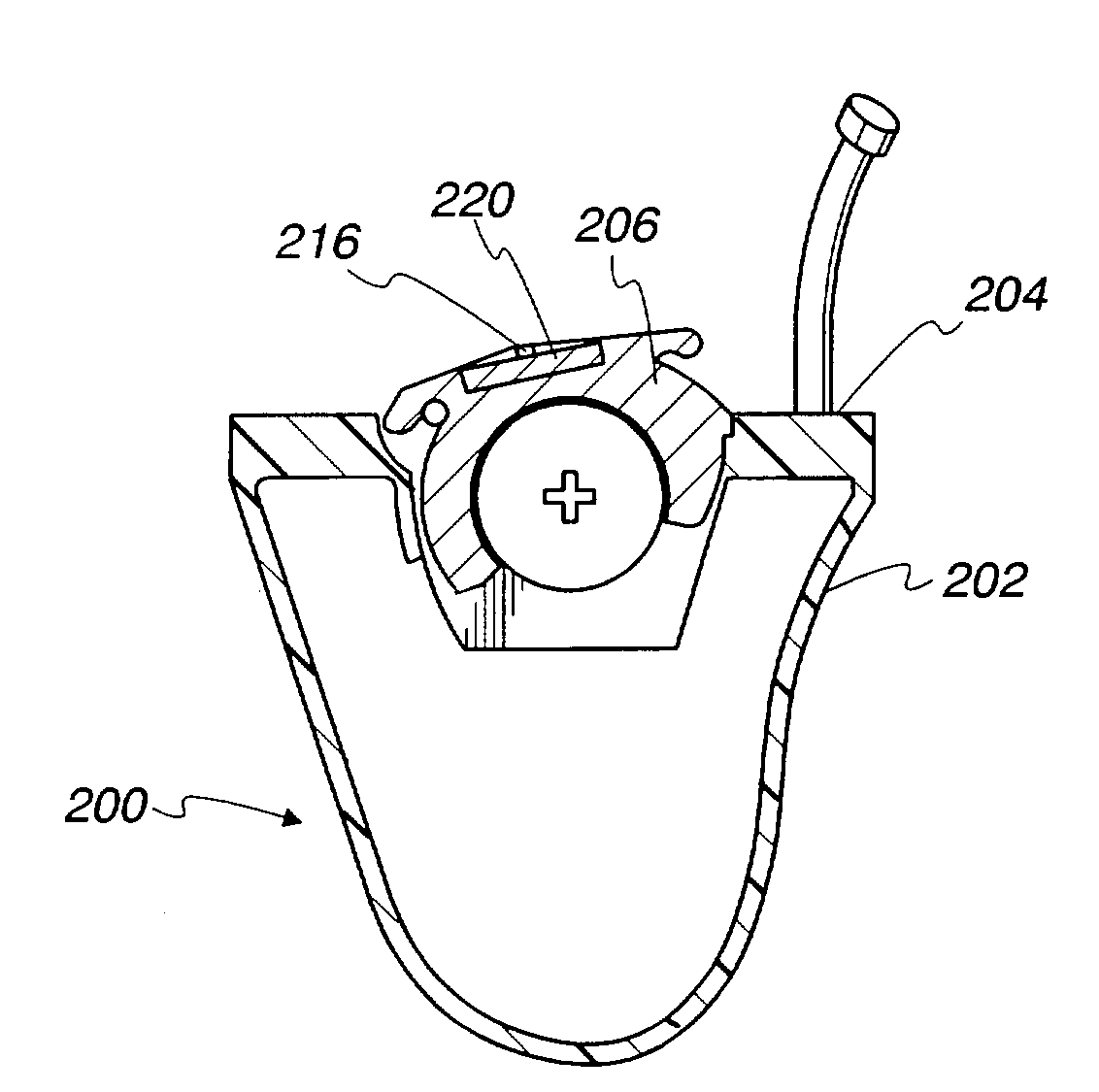

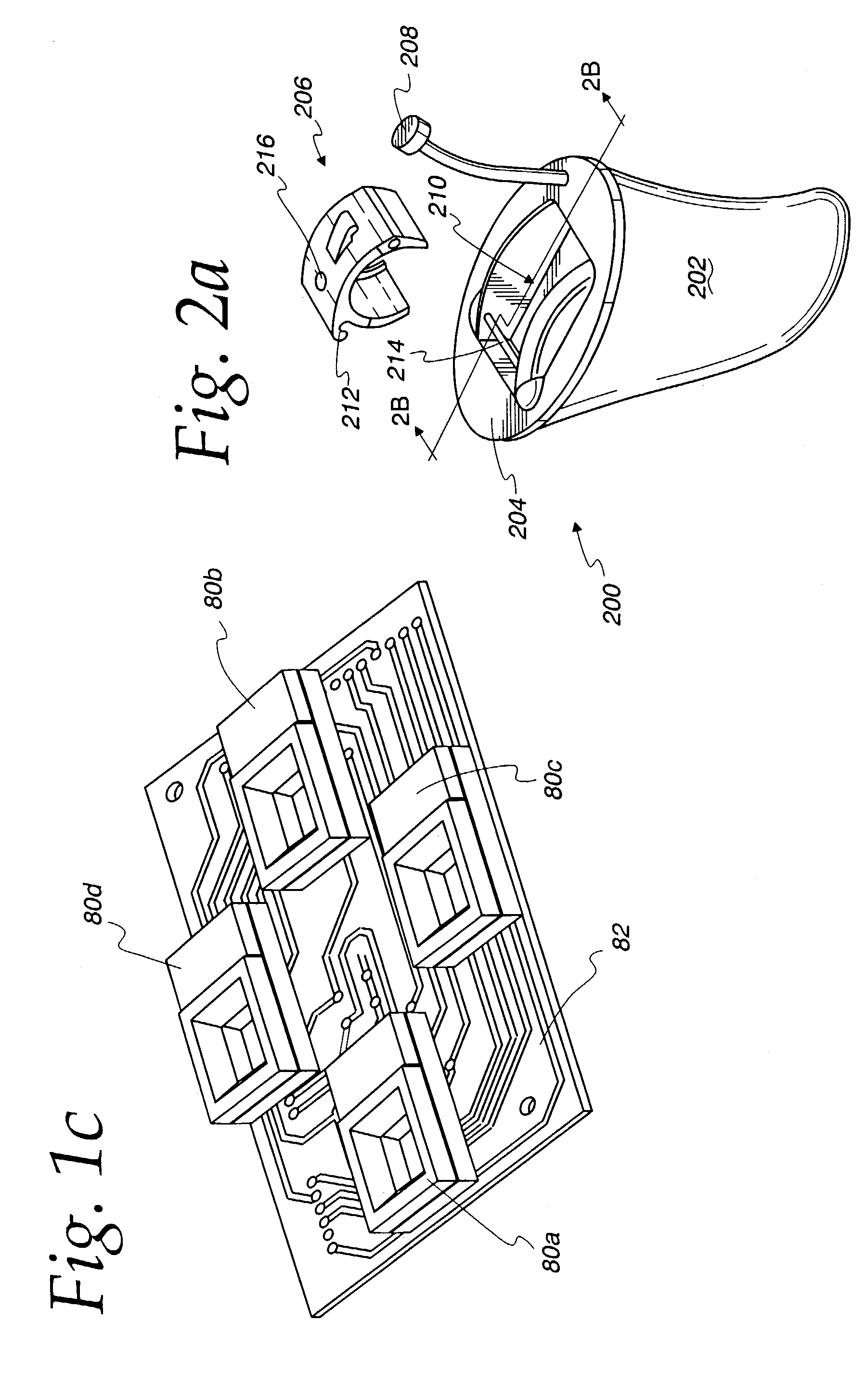

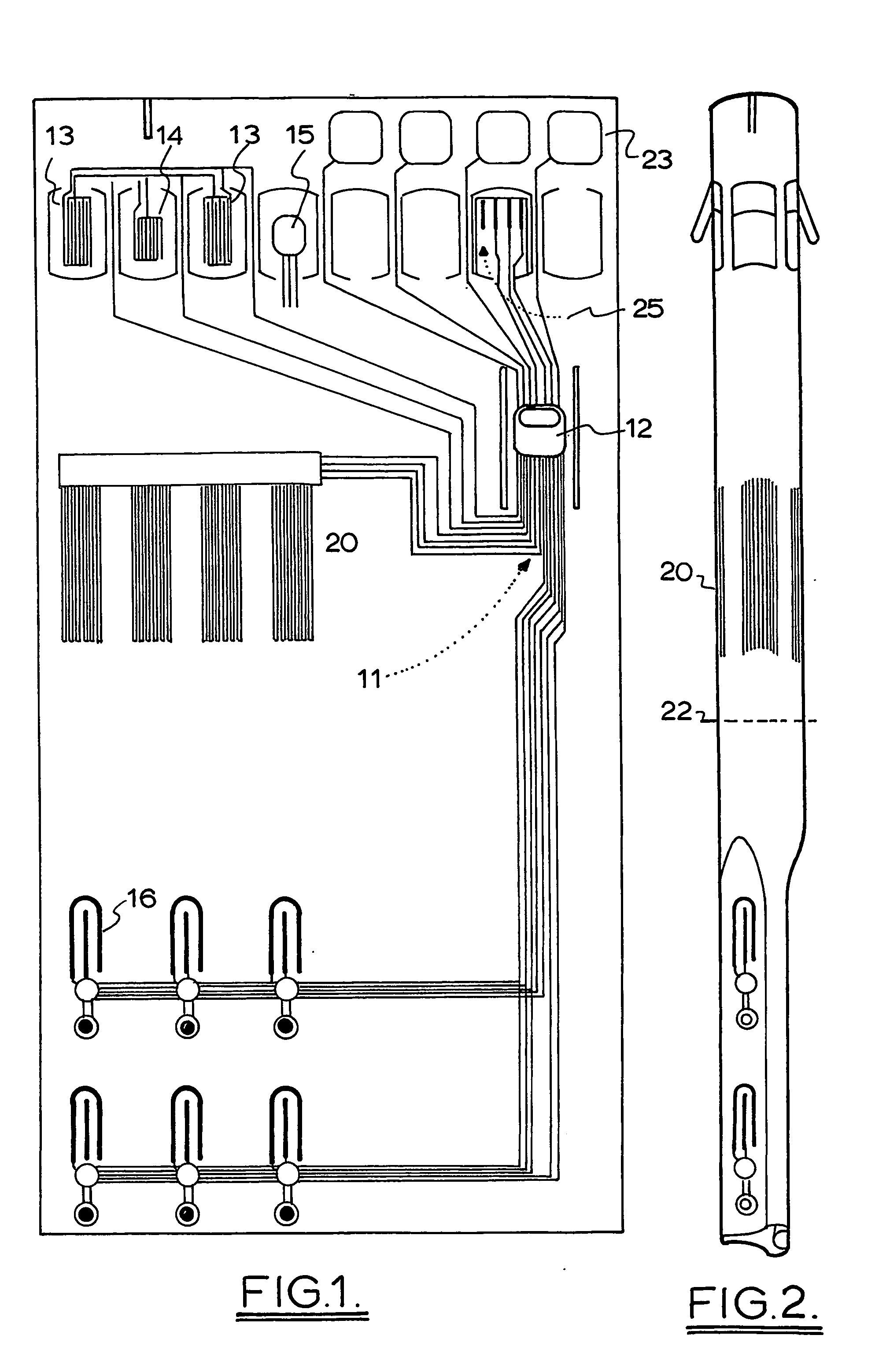

Silicon-based transducer for use in hearing instruments and listening devices

InactiveUS7142682B2Improve signal-to-noise ratioAdditive manufacturing apparatusSemiconductor electrostatic transducersConvertersAudio power amplifier

A silicon-based transducer assembly coupled to a movable structure in a hearing instrument. The transducer assembly includes at least one microphone chip and an ASIC having multiple integrated components such as any combination of a DSP, an A / D converter, an amplifier, a filter, or a wireless interface. The movable structure may be a battery access door, a volume dial, a switch, or a touch pad. A protection strip can be disposed across the battery access door to prevent debris from clogging the silicon-based transducer assembly. The transducer assembly may also include an array of microphone chips to achieve adaptive beam steering or directionality. When equipped with a wireless interface, the hearing instrument wirelessly communicates with another hearing instrument or with a network.

Owner:TDK CORPARATION

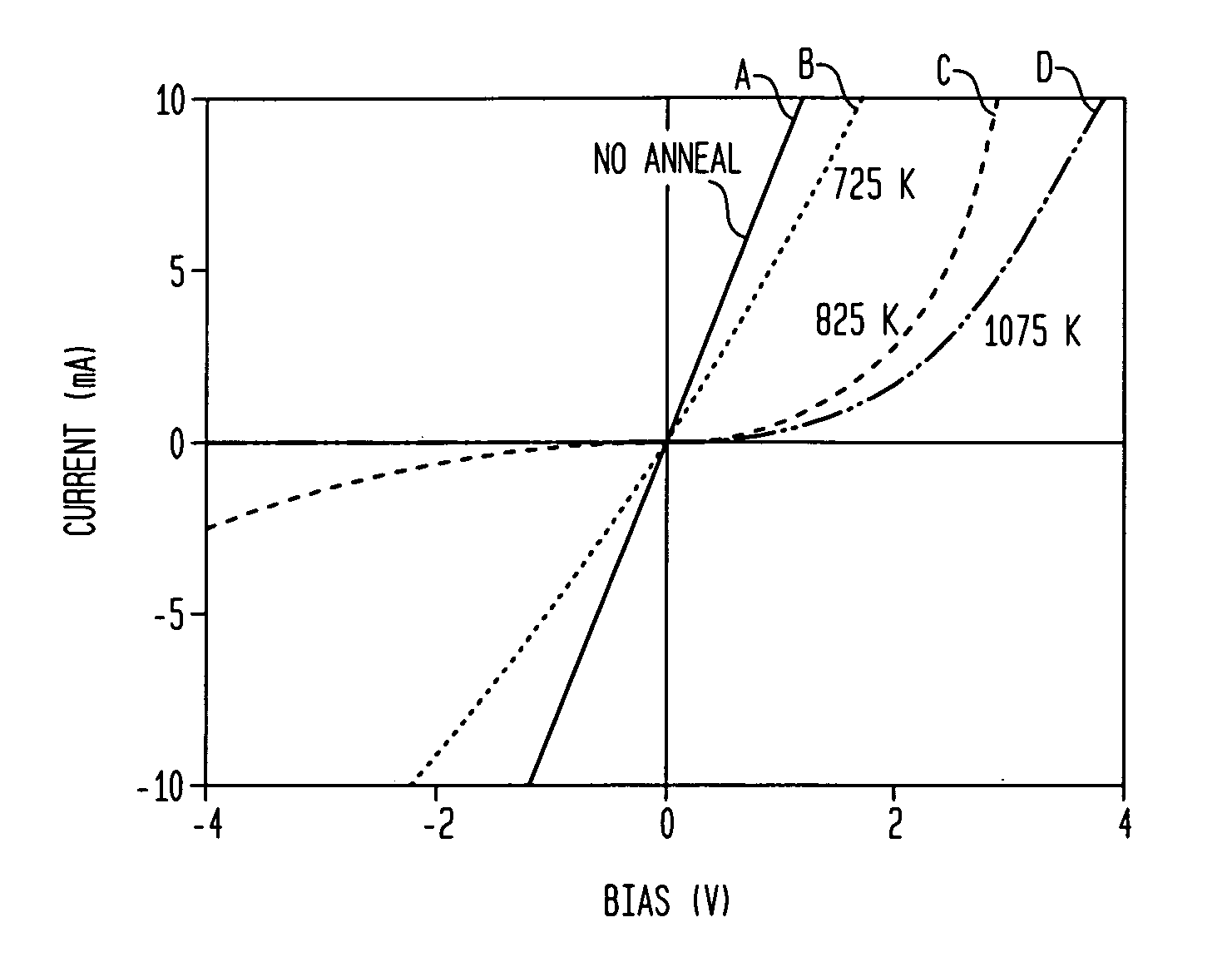

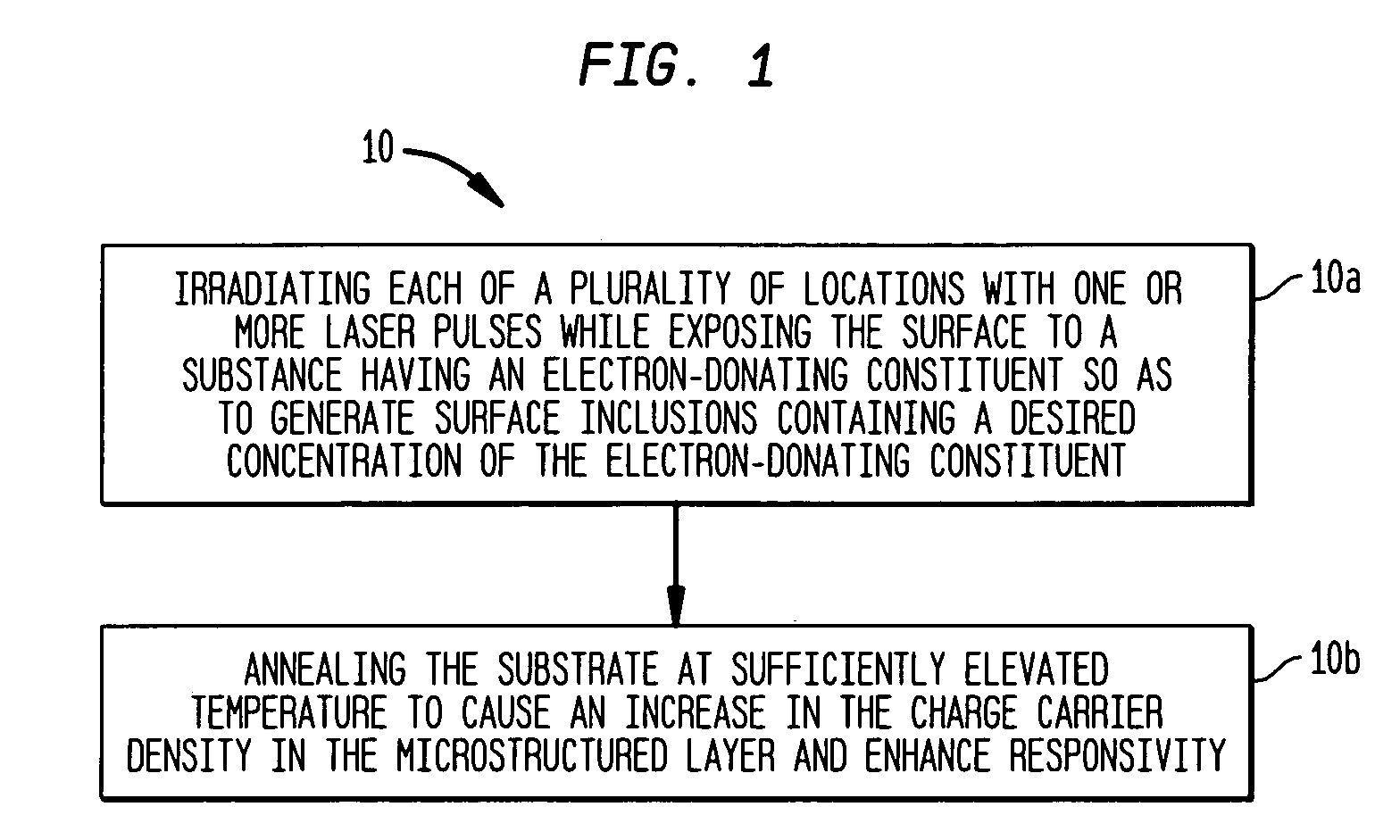

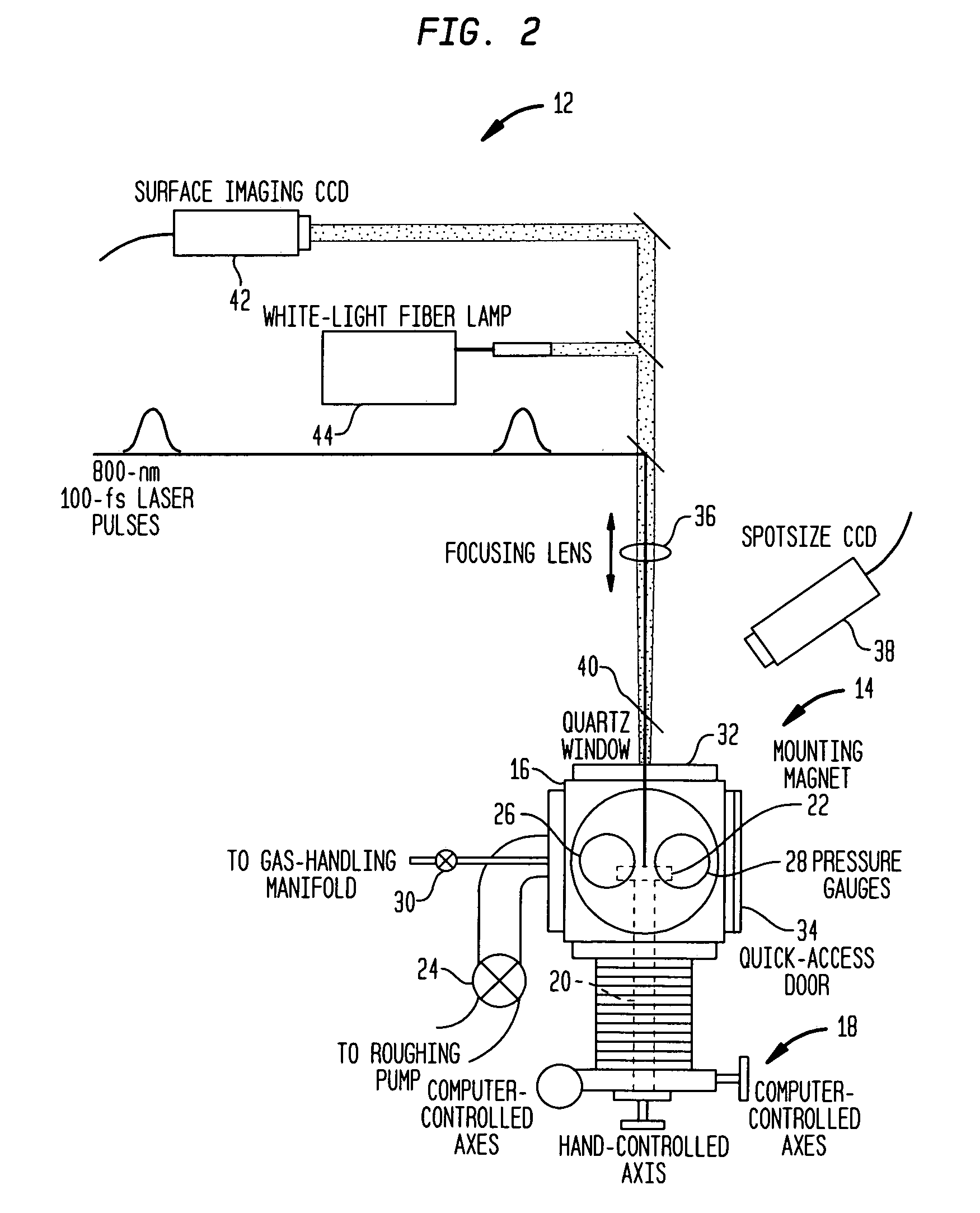

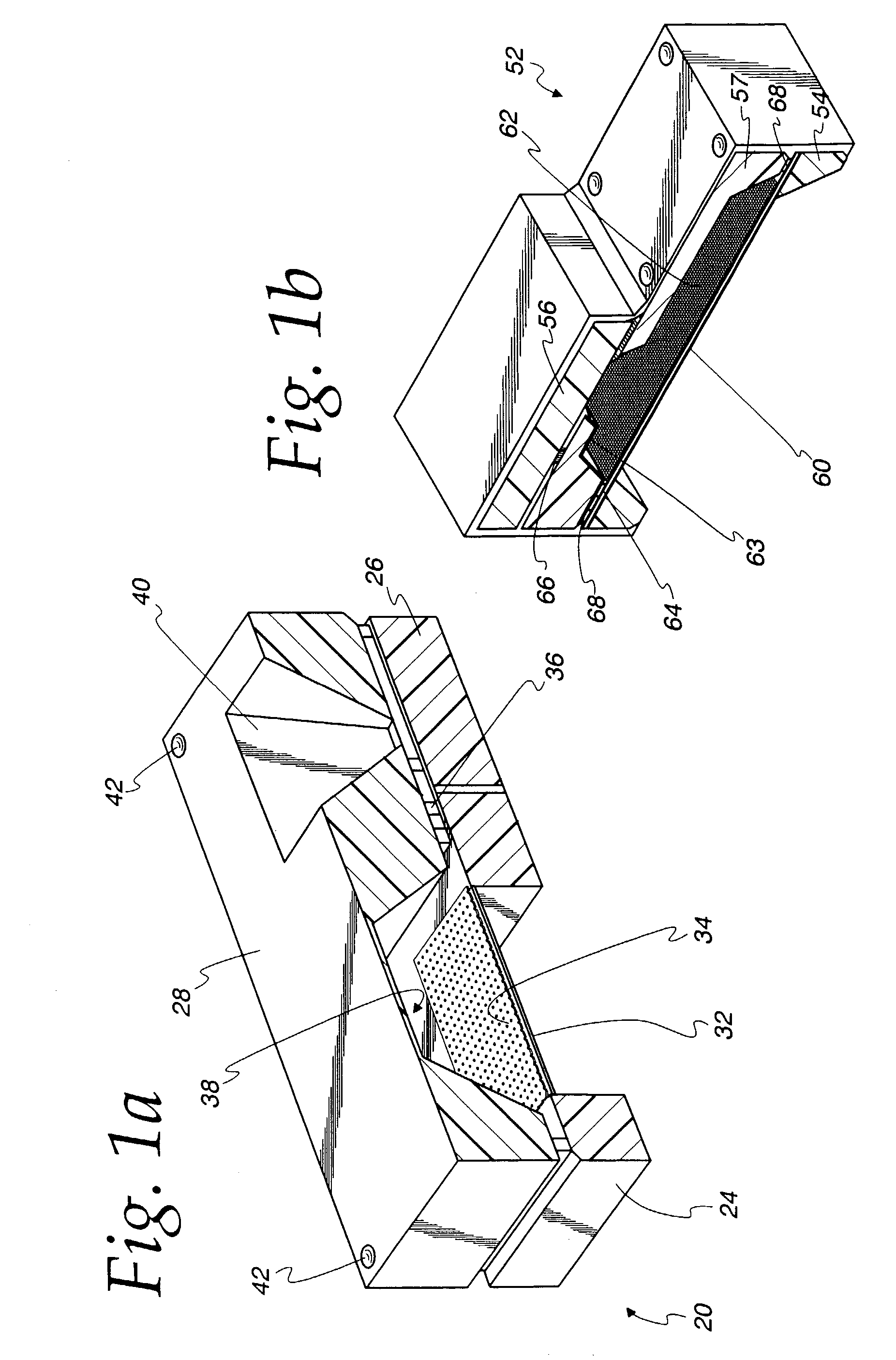

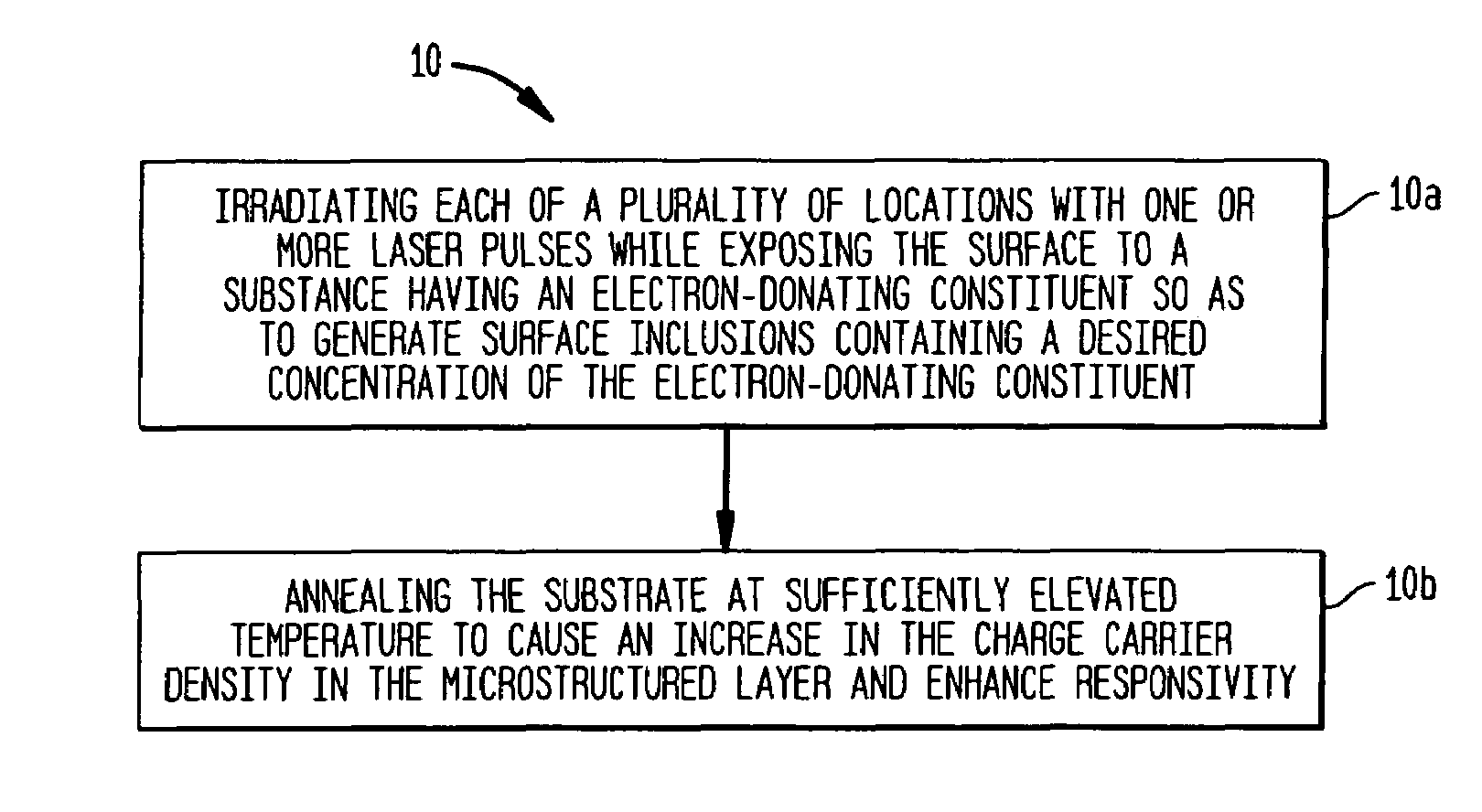

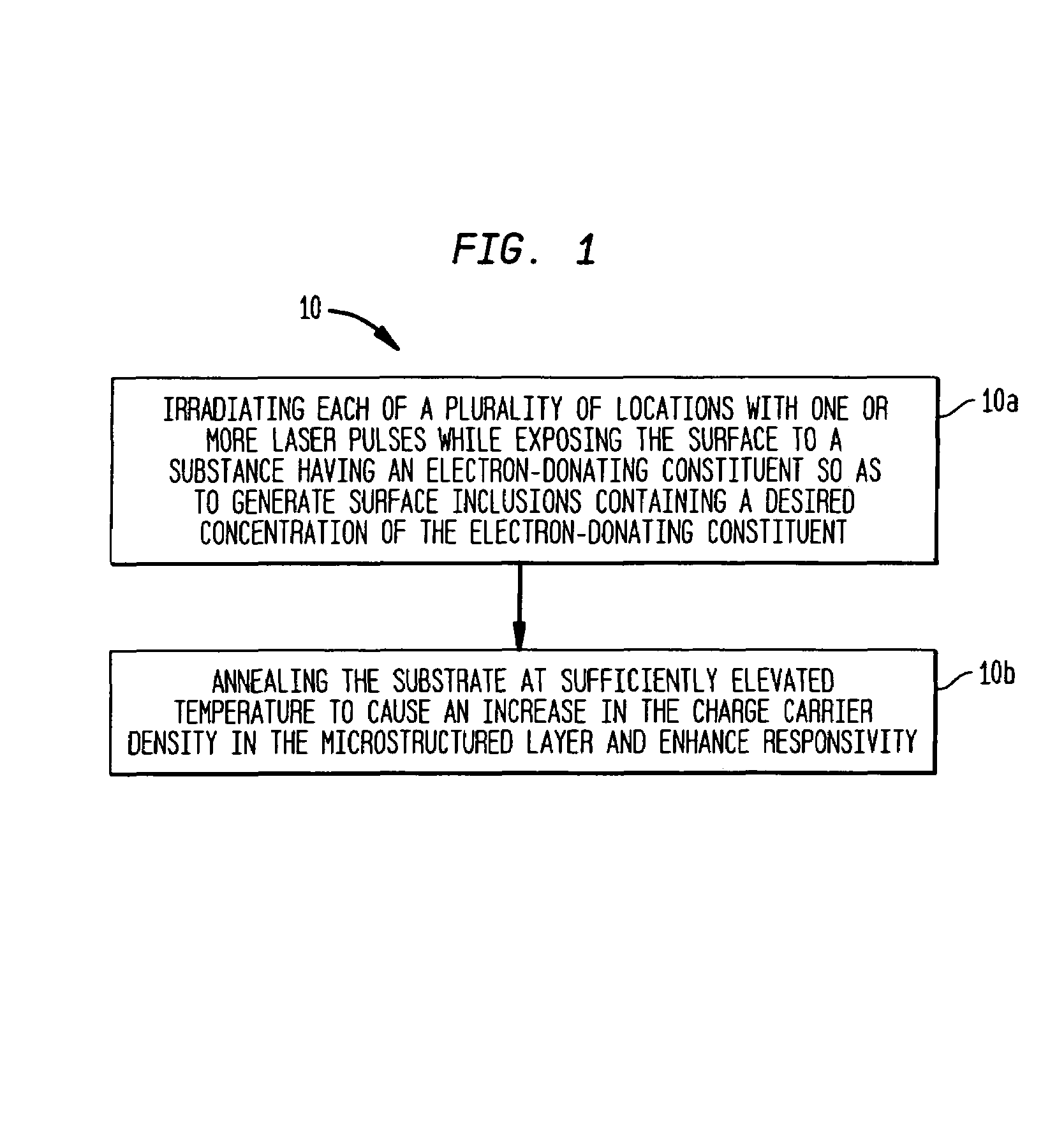

Manufacture of silicon-based devices having disordered sulfur-doped surface layers

InactiveUS7354792B2Final product manufactureSemiconductor/solid-state device manufacturingSurface layerCharge-carrier density

The present invention provides methods of fabricating a radiation-absorbing semiconductor wafer by irradiating at least one surface location of a silicon substrate, e.g., an n-doped crystalline silicon, by a plurality of temporally short laser pulses, e.g., femtosecond pulses, while exposing that location to a substance, e.g., SF6, having an electron-donating constituent so as to generate a substantially disordered surface layer (i.e., a microstructured layer) that incorporates a concentration of that electron-donating constituent, e.g., sulfur. The substrate is also annealed at an elevated temperature and for a duration selected to enhance the charge carrier density in the surface layer. For example, the substrate can be annealed at a temperature in a range of about 700 K to about 900 K.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Negative active material for a rechargeable lithium battery, a method of preparing the same, and a rechargeable lithium battery comprising the same

ActiveUS20050233213A1Improved cycle-life characteristic and charge and discharge characteristicIncrease chanceElectrode manufacturing processesNon-aqueous electrolyte accumulatorsHigh rateSilicon oxide

The present invention relates to a negative active material for a rechargeable lithium battery, which includes a silicon-based composite having a silicon oxide of the form SiOX where x≦1.5 and at least one element selected from the group consisting of B, P, Li, Ge, Al, and V, and a carbonaceous material. The negative active material of the present invention can improve the cycle-life and high-rate charge / discharge characteristics of a rechargeable lithium battery.

Owner:SAMSUNG SDI CO LTD

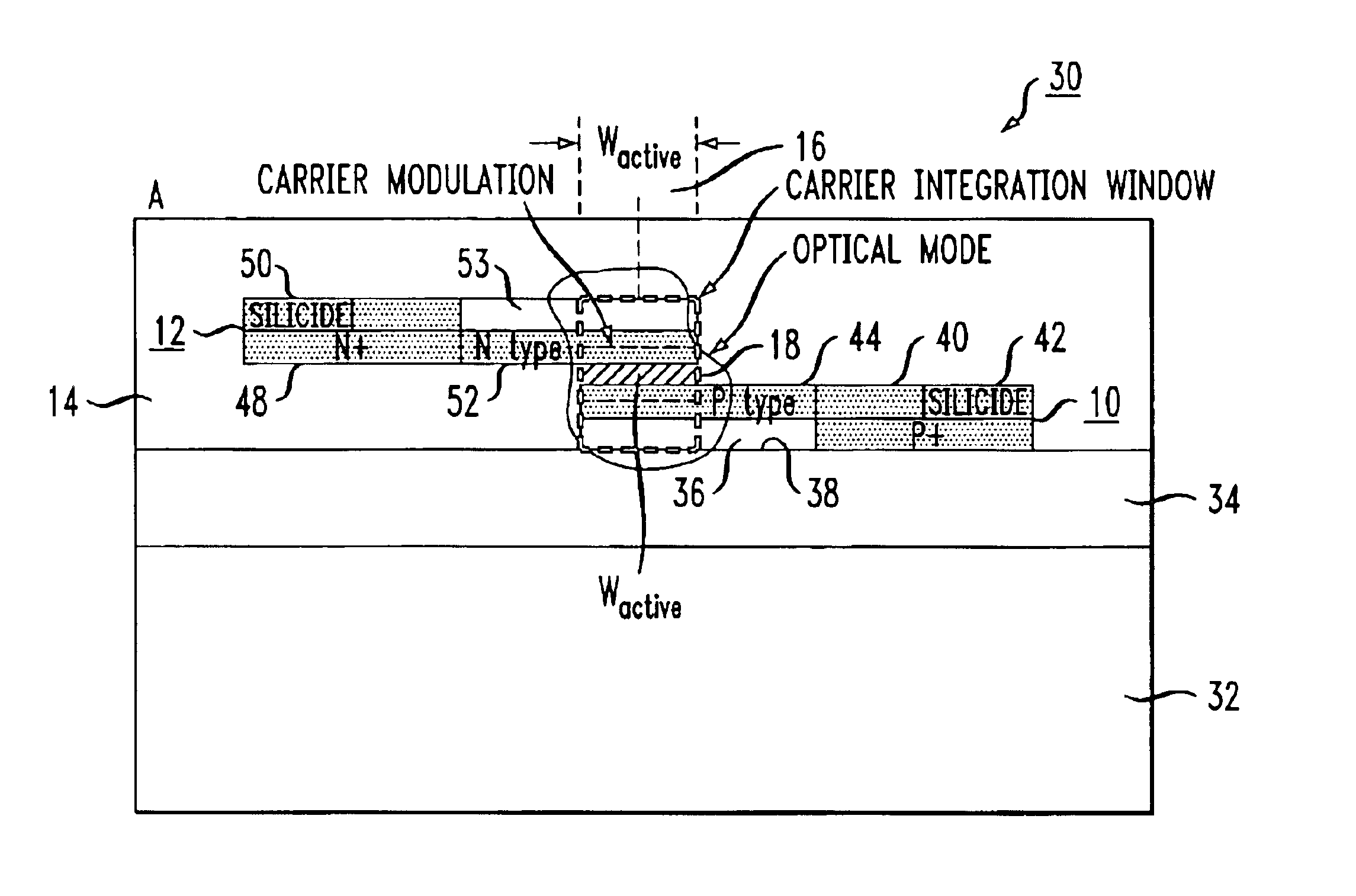

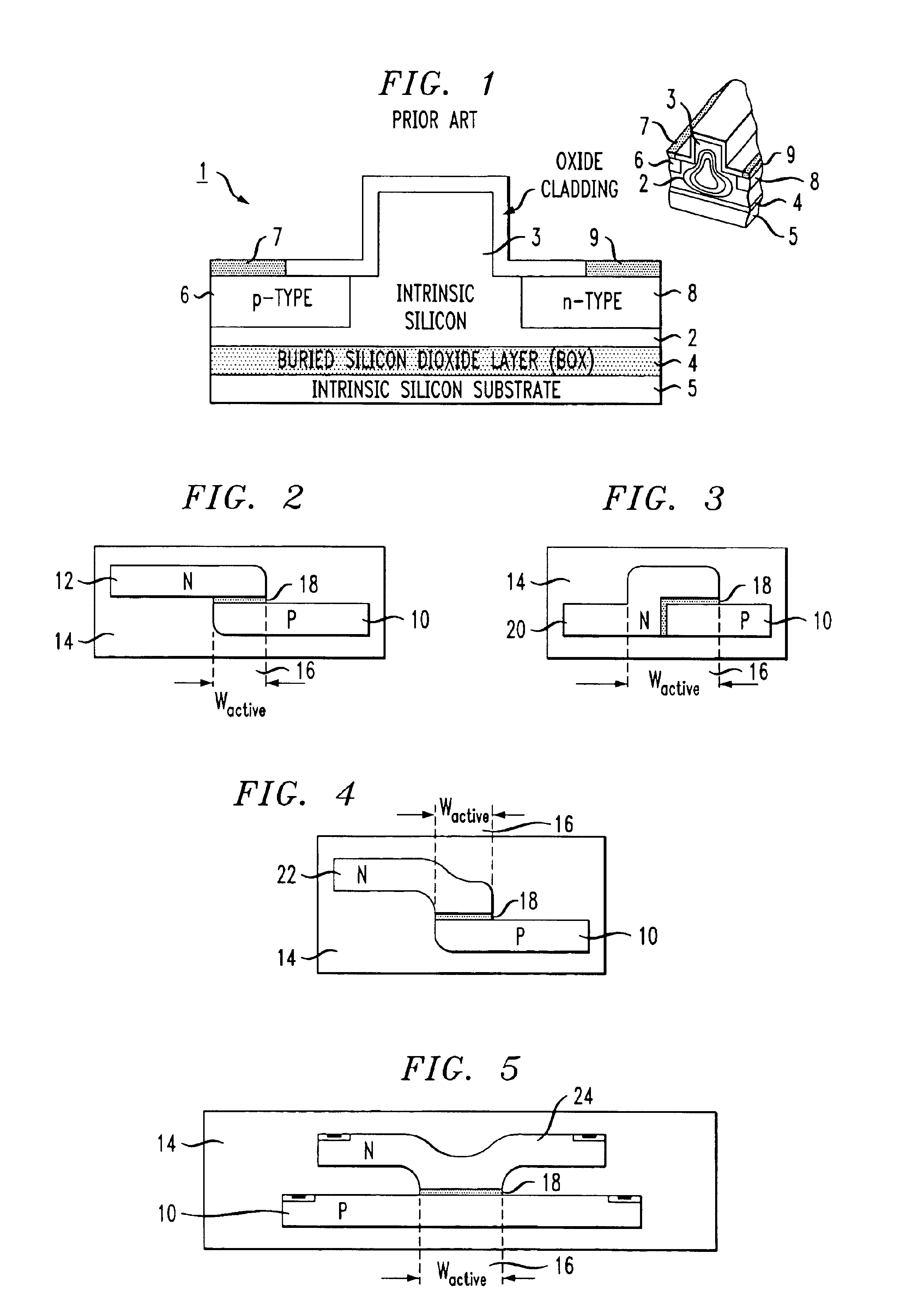

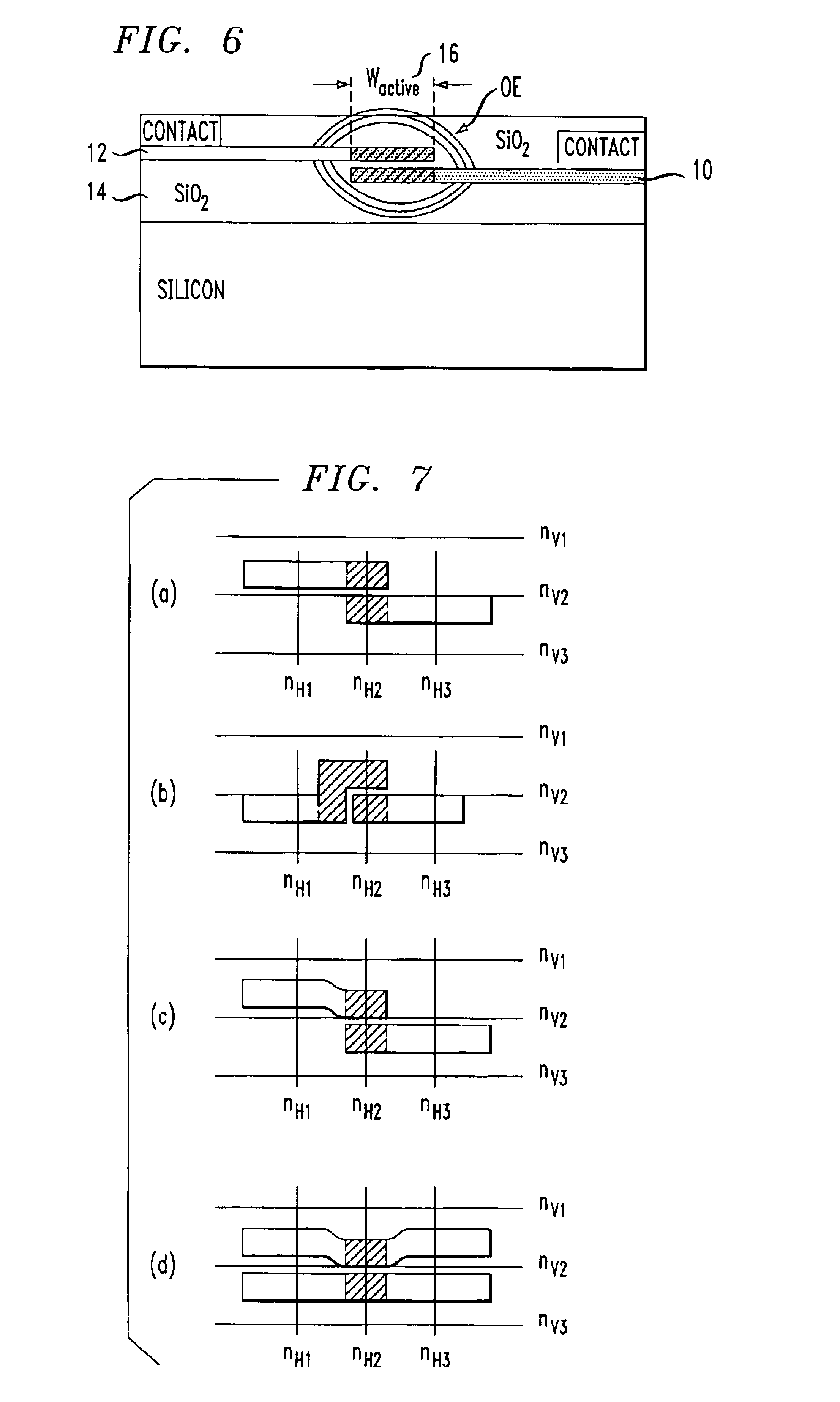

High-speed silicon-based electro-optic modulator

ActiveUS6845198B2Series resistance is minimizedLower optical lossCoupling light guidesOptical waveguide light guideElectricitySurface layer

A silicon-based electro-optic modulator is based on forming a gate region of a first conductivity to partially overly a body region of a second conductivity type, with a relatively thin dielectric layer interposed between the contiguous portions of the gate and body regions. The modulator may be formed on an SOI platform, with the body region formed in the relatively thin silicon surface layer of the SOI structure and the gate region formed of a relatively thin silicon layer overlying the SOI structure. The doping in the gate and body regions is controlled to form lightly doped regions above and below the dielectric, thus defining the active region of the device. Advantageously, the optical electric field essentially coincides with the free carrier concentration area in this active device region. The application of a modulation signal thus causes the simultaneous accumulation, depletion or inversion of free carriers on both sides of the dielectric at the same time, resulting in high speed operation.

Owner:CISCO TECH INC

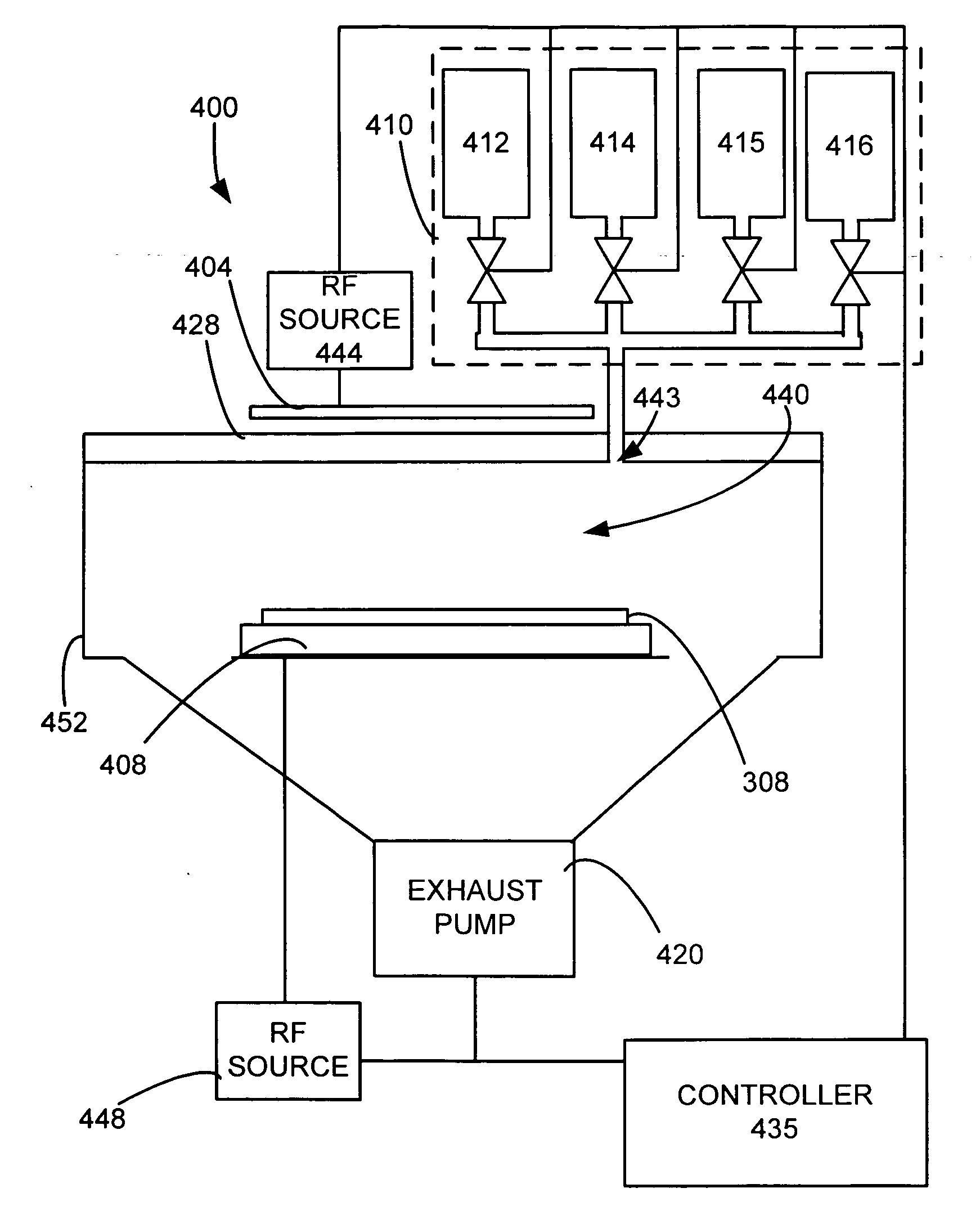

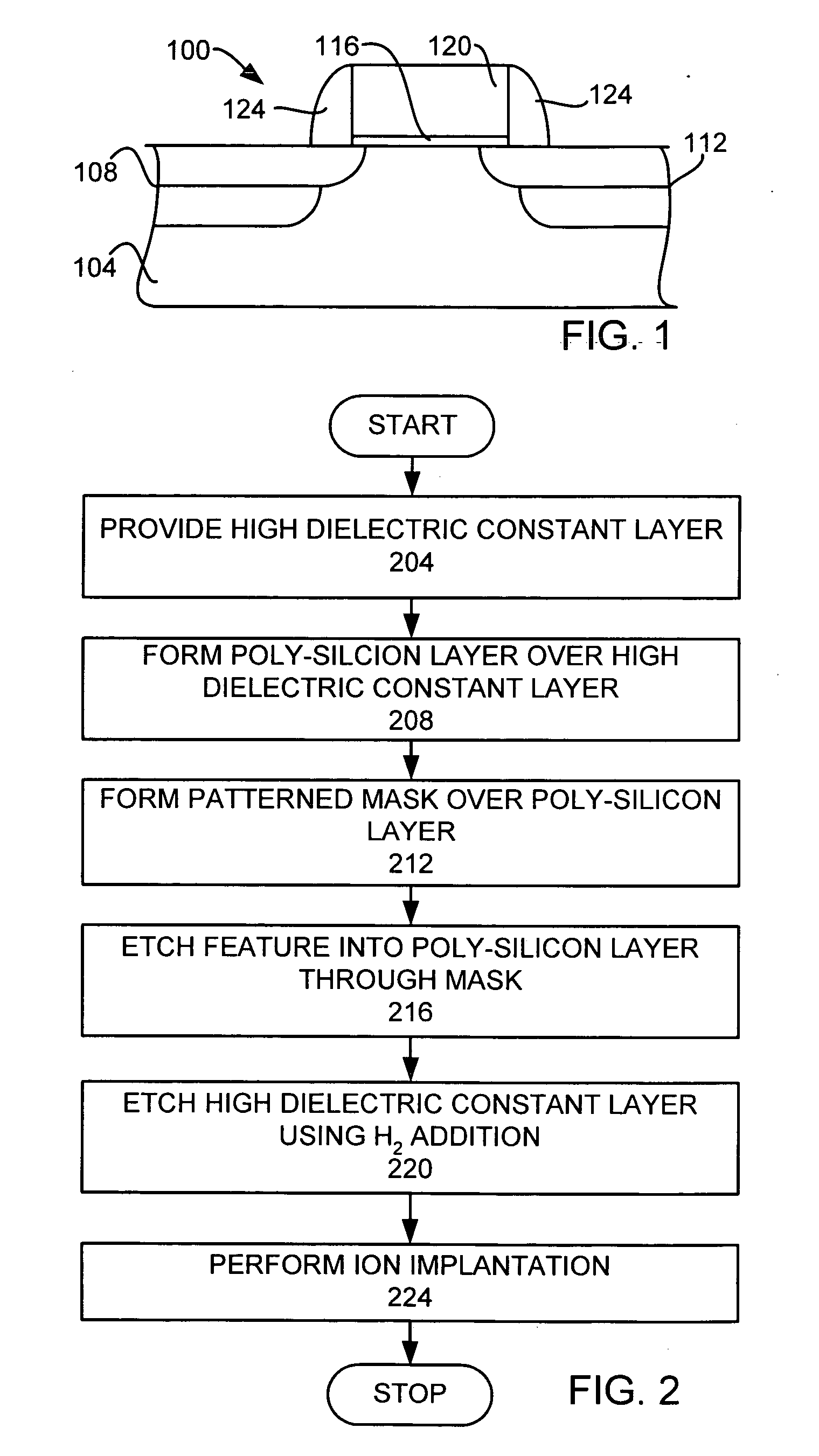

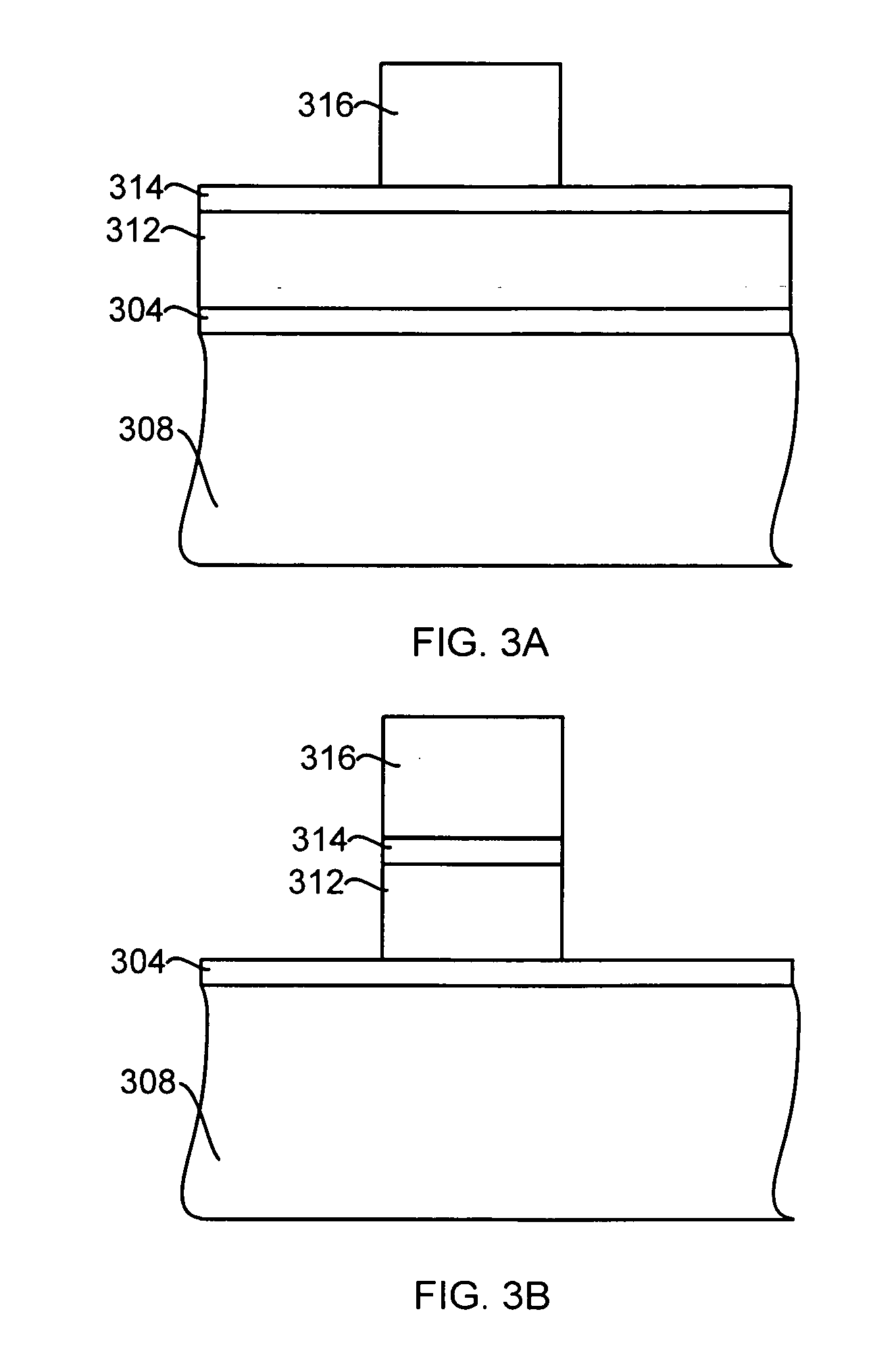

Selective etch of films with high dielectric constant with H2 addition

InactiveUS20070056925A1Decorative surface effectsSemiconductor/solid-state device manufacturingAtomic physicsHigh dielectric permittivity

A method for selectively etching a high k layer with respect to a silicon based material is provided. The high k layer is placed into an etch chamber. An etchant gas is provided into the etch chamber, wherein the etchant gas comprises H2. A plasma is generated from the etchant gas to selectively etch the high k layer with respect to a silicon based material.

Owner:LAM RES CORP

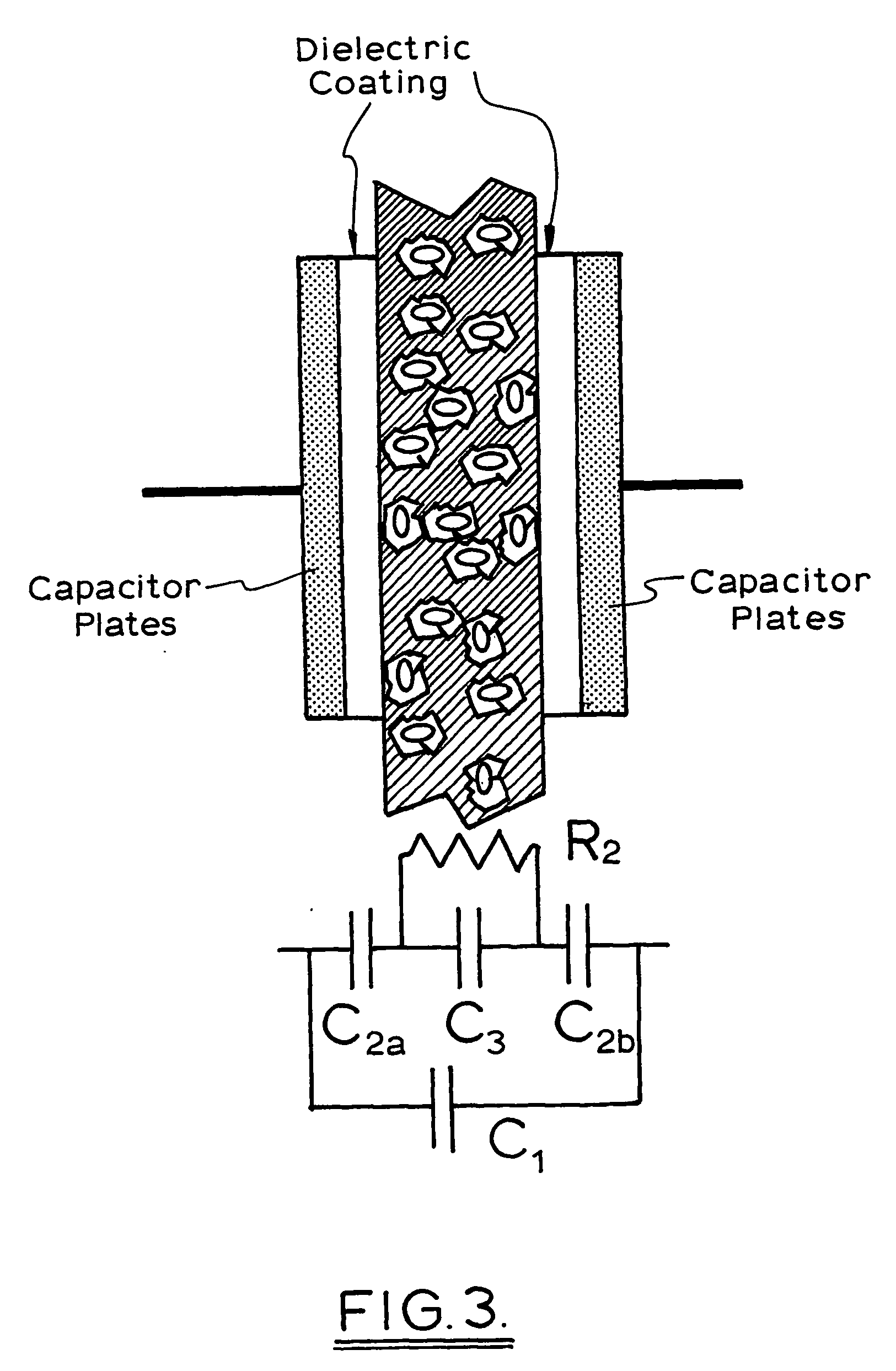

Environmental sensor

InactiveUS20070273394A1Calibration is unnecessaryQuality improvementResistance/reactance/impedenceVolume/mass flow measurementAbove groundEngineering

Multi functional sensors are described. A silicon based sensor utilizes metal layers arranged as resistors around a central pair if resistors separated by a humidity sensitive polymer with one of the central resistors being a heater. This enables temperature humidity wind speed and direction to be measured. In another embodiment an array of resistors is printed onto a flexible substrate to form the basis of an array of sensors. A soil moisture sensor, which is also useful as a leaf wetness sensor, incorporates a novel self calibrating capacitive sensor structure. The flexible substrate is rolled into a stake that can be inserted in the soil so that below ground sensors measure soil moisture and above ground sensors measure temperature, light, humidity, wind speed and direction.

Owner:M B T L

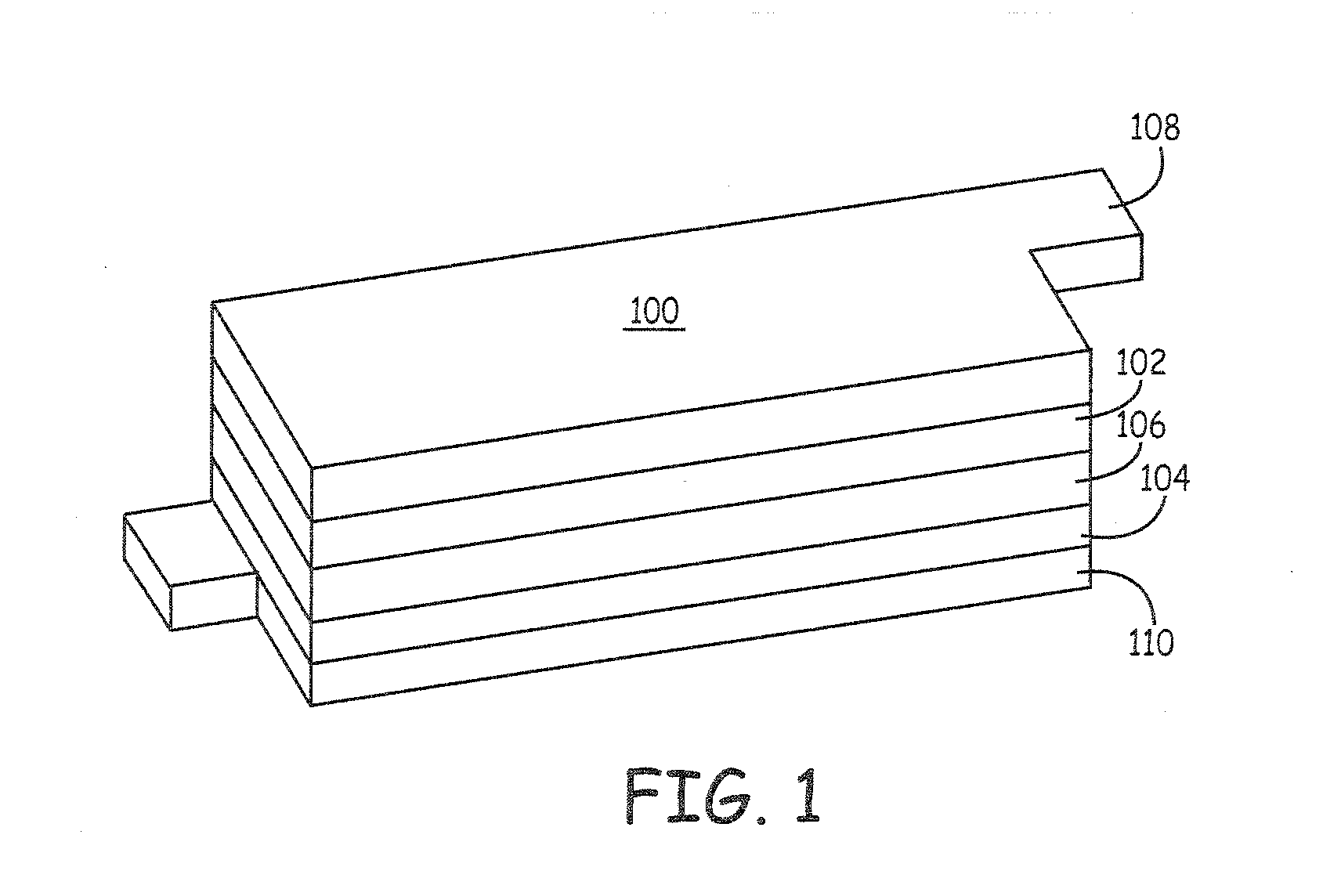

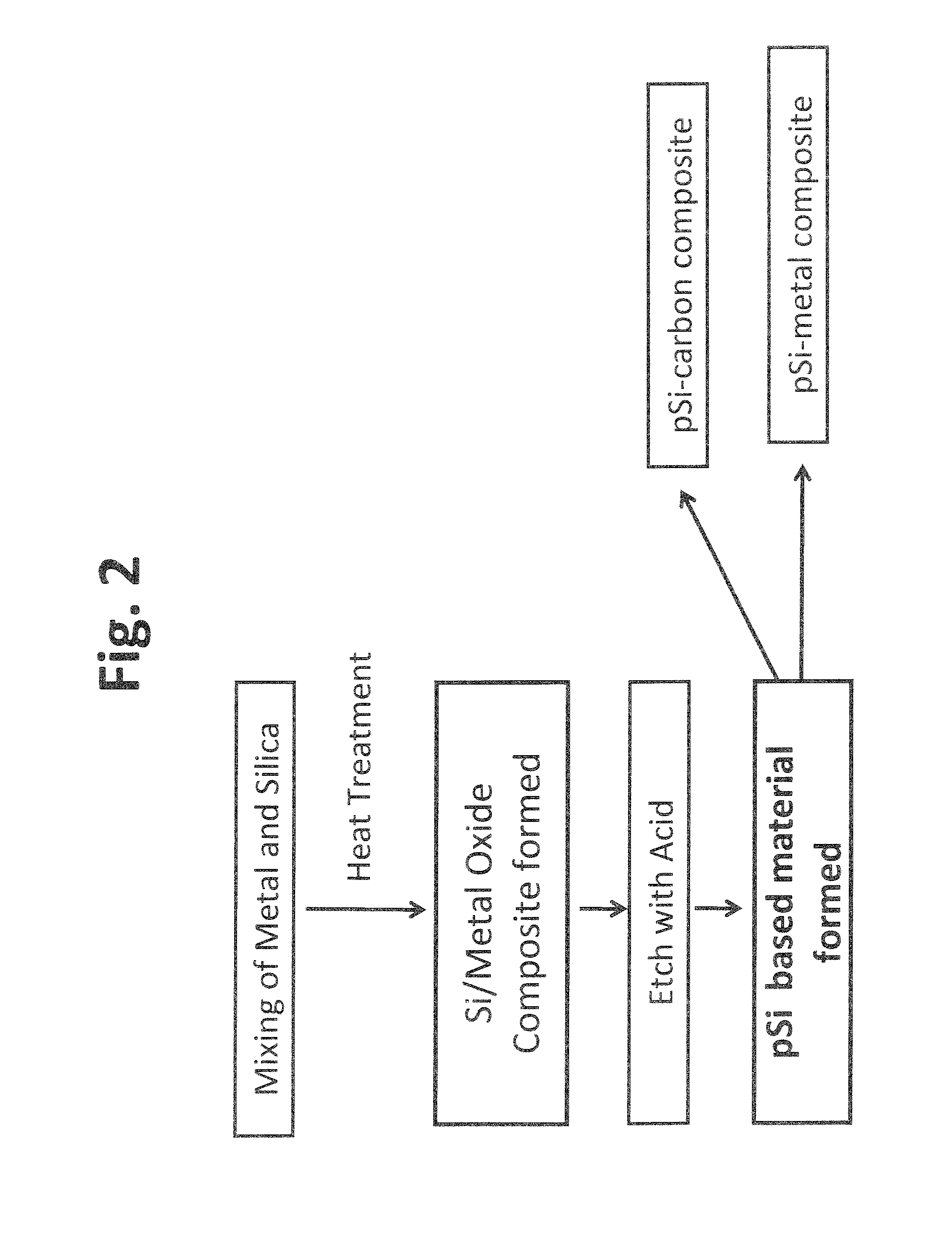

Porous silicon based anode material formed using metal reduction

A porous silicon based material comprising porous crystalline elemental silicon formed by reducing silicon dioxide with a reducing metal in a heating process followed by acid etching is used to construct negative electrode used in lithium ion batteries. Gradual temperature heating ramp(s) with optional temperature steps can be used to perform the heating process. The porous silicon formed has a high surface area from about 10 m2 / g to about 200 m2 / g and is substantially free of carbon. The negative electrode formed can have a discharge specific capacity of at least 1800 mAh / g at rate of C / 3 discharged from 1.5V to 0.005V against lithium with in some embodiments loading levels ranging from about 1.4 mg / cm2 to about 3.5 mg / cm2. In some embodiments, the porous silicon can be coated with a carbon coating or blended with carbon nanofibers or other conductive carbon material.

Owner:IONBLOX INC

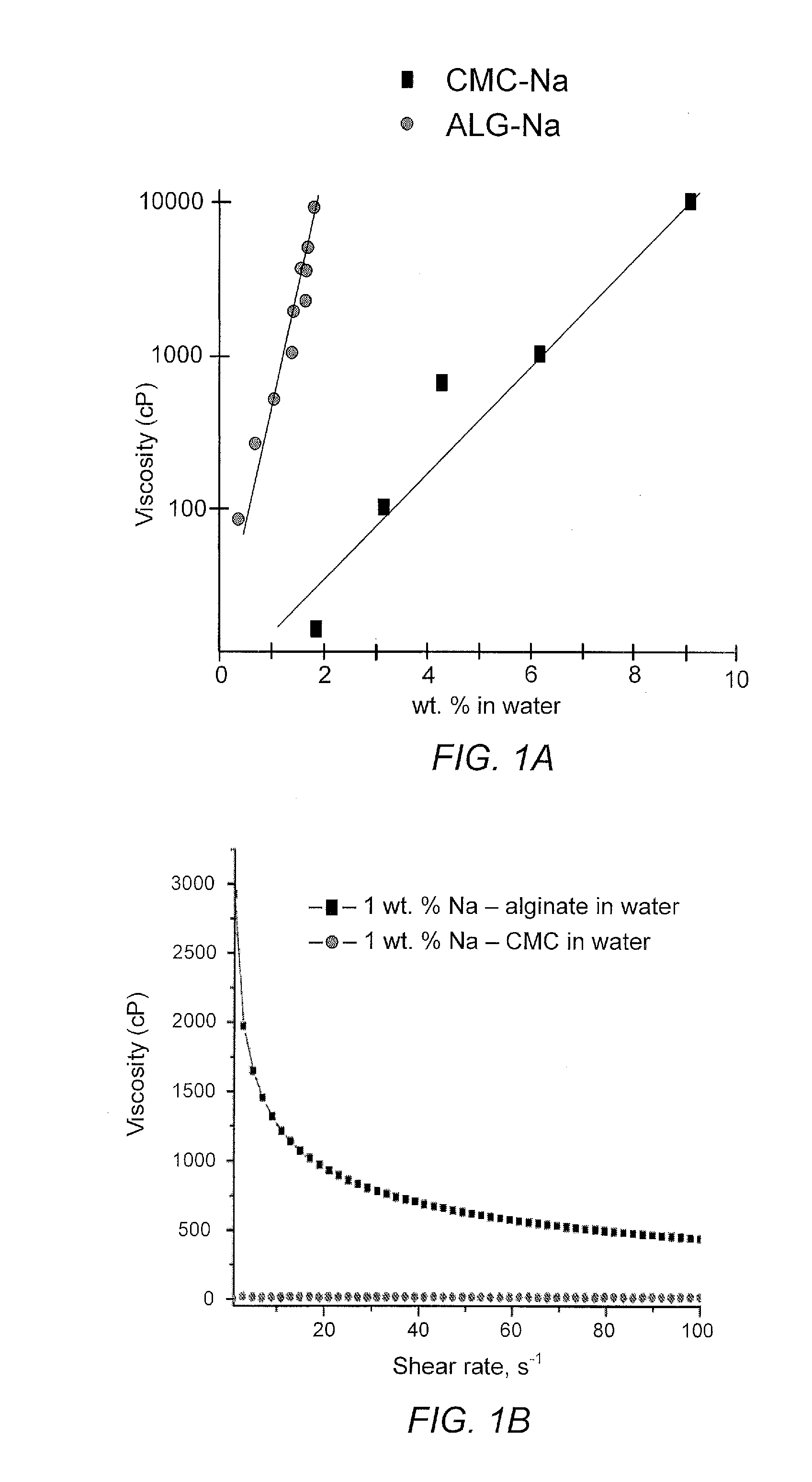

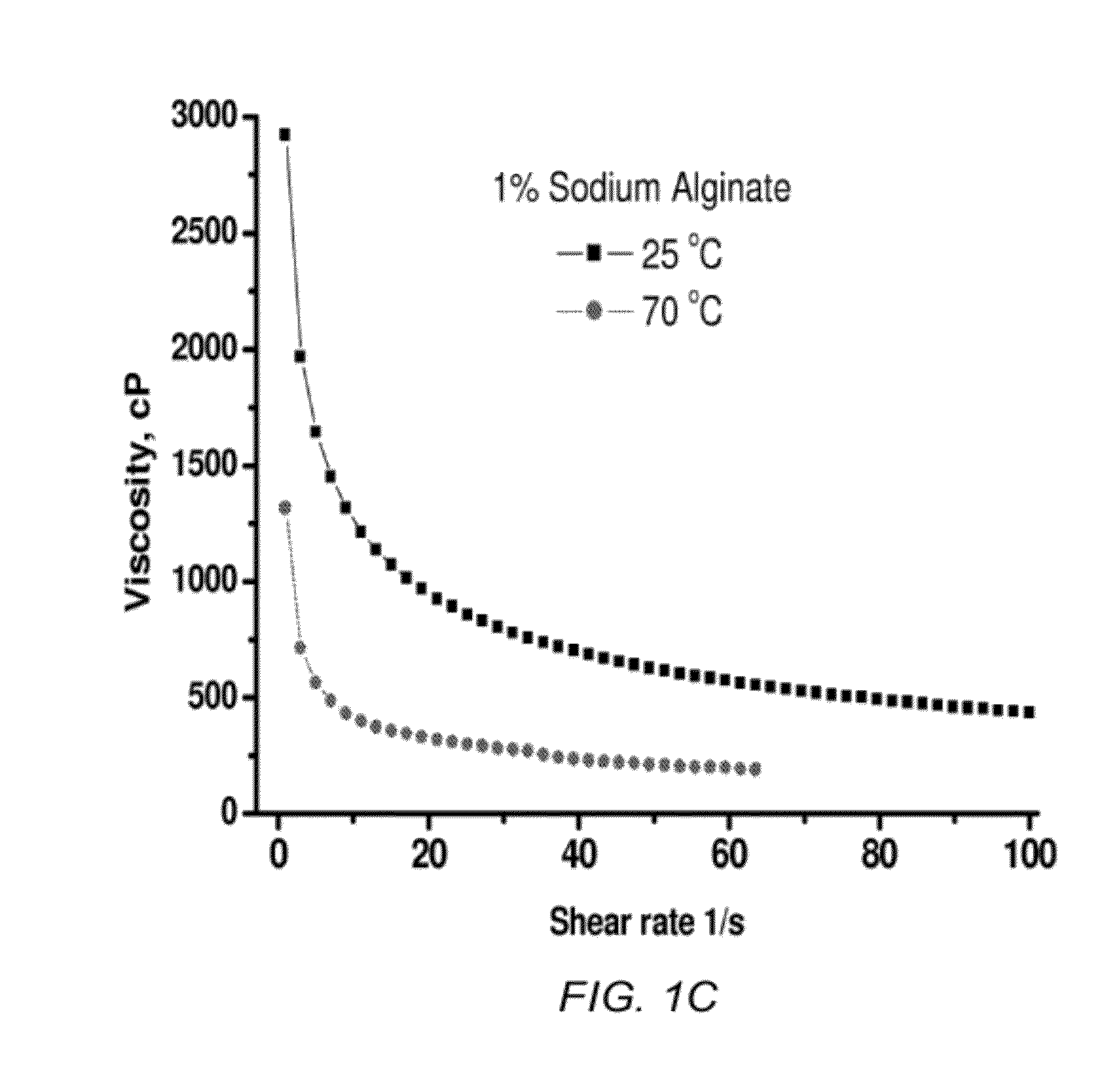

Alginate-containing compositions for use in battery applications

ActiveUS20120088155A1Material nanotechnologyCell seperators/membranes/diaphragms/spacersHydrogenMaterials science

A silicon-based anode comprises an alginate-containing binder. The many carboxy groups of alginate bind to a surface of silicon, creating strong, rigid hydrogen bonds that withstand battery cycling. The alginate-containing binder provides good performance to the anode by (1) improving the capacity of the anode in comparison to other commercially-available binders, (2) improving Columbonic efficiency during charging and discharging cycles, and (3) improving stability during charging and discharging cycles.

Owner:CLEMSON UNIV RES FOUND +1

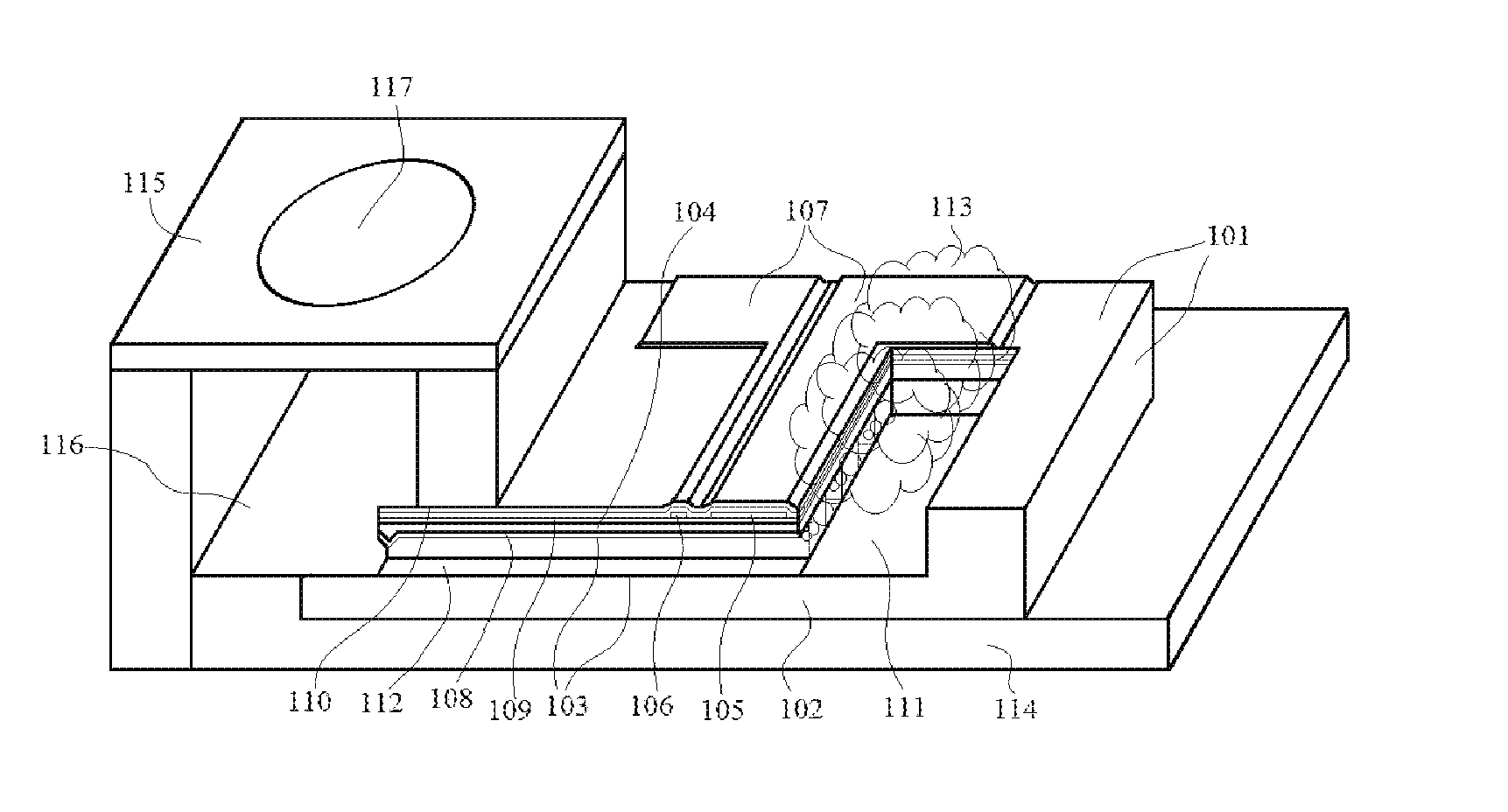

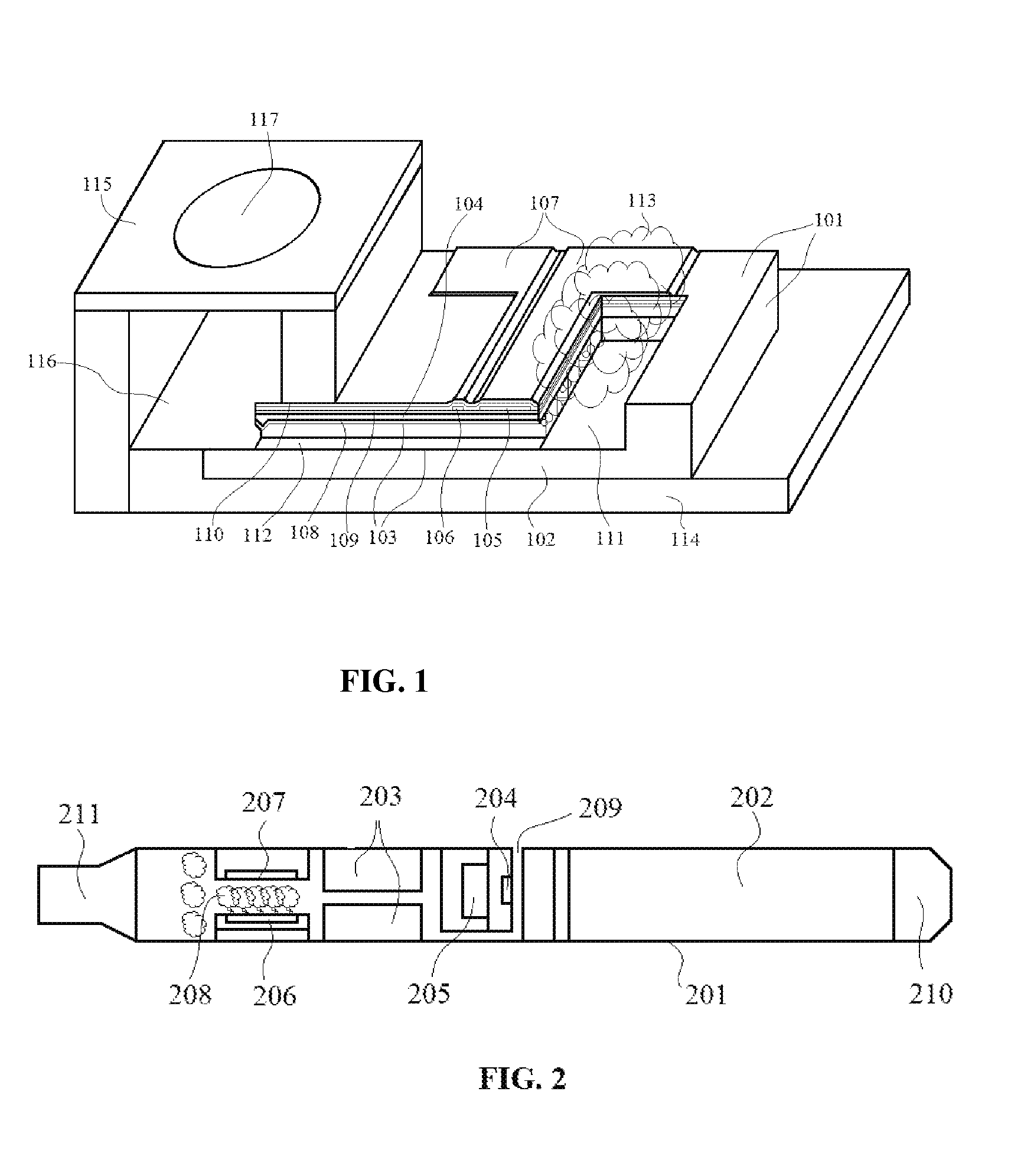

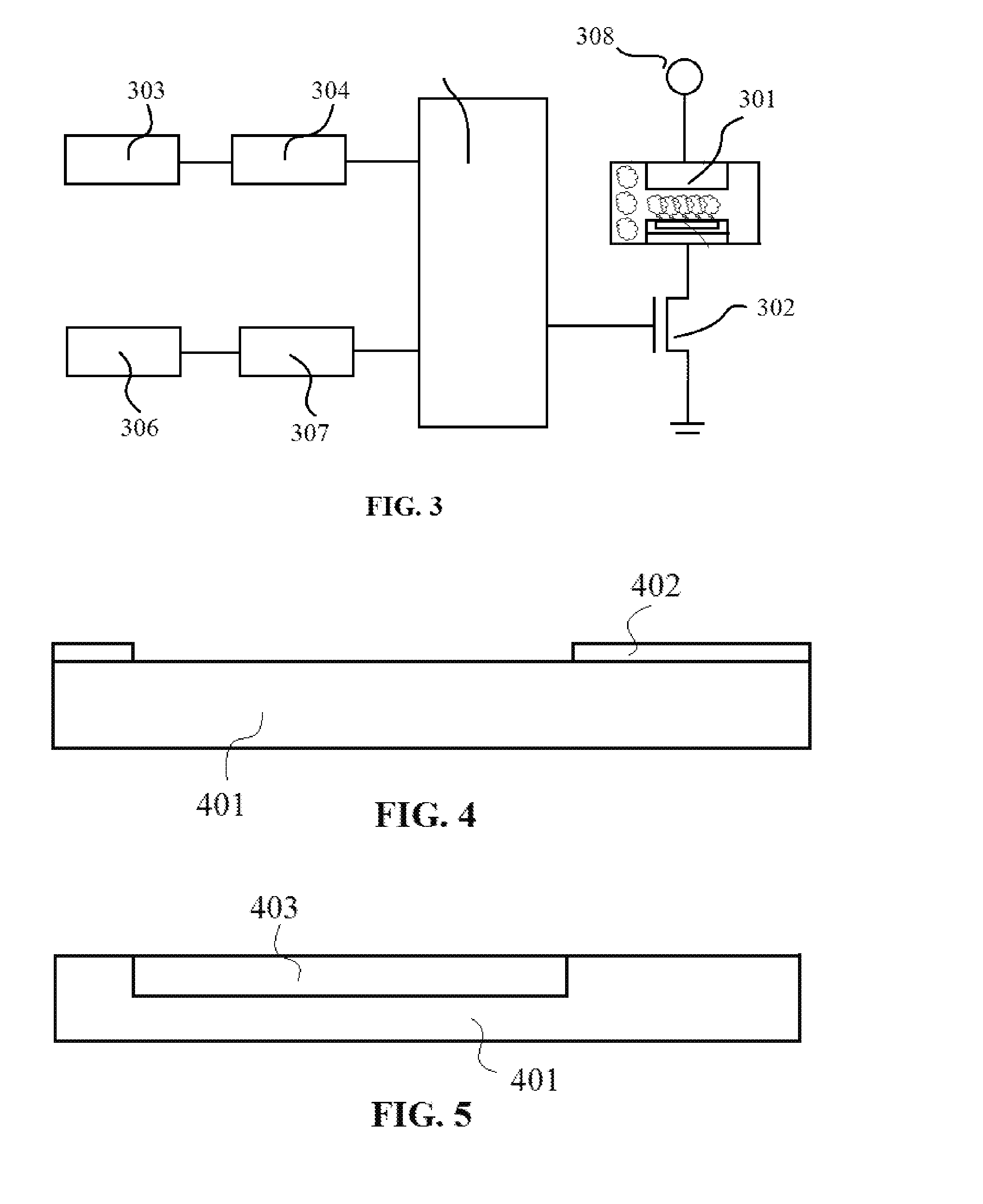

MEMS Vaporizer

ActiveUS20160007653A1Low costImprove reliabilityExhaust apparatusSemiconductor/solid-state device manufacturingEngineeringElectronic cigarette

A MEMS vaporizer is described which can be used for electronic cigarettes. The vaporizer mainly composes: a silicon substrate, a micro-channel array, a membrane suspending over the micro-channel array and supported by the silicon substrate, a resistance heater and a resistance temperature sensor are disposed on the membrane. Since the vaporizer is a silicon-based integrated actuator which provides advantages including small size, compact structure, lower power consumption, lower cost, increased reliability, higher precision, and more environmental friendliness.

Owner:POSIFA TECH LTD

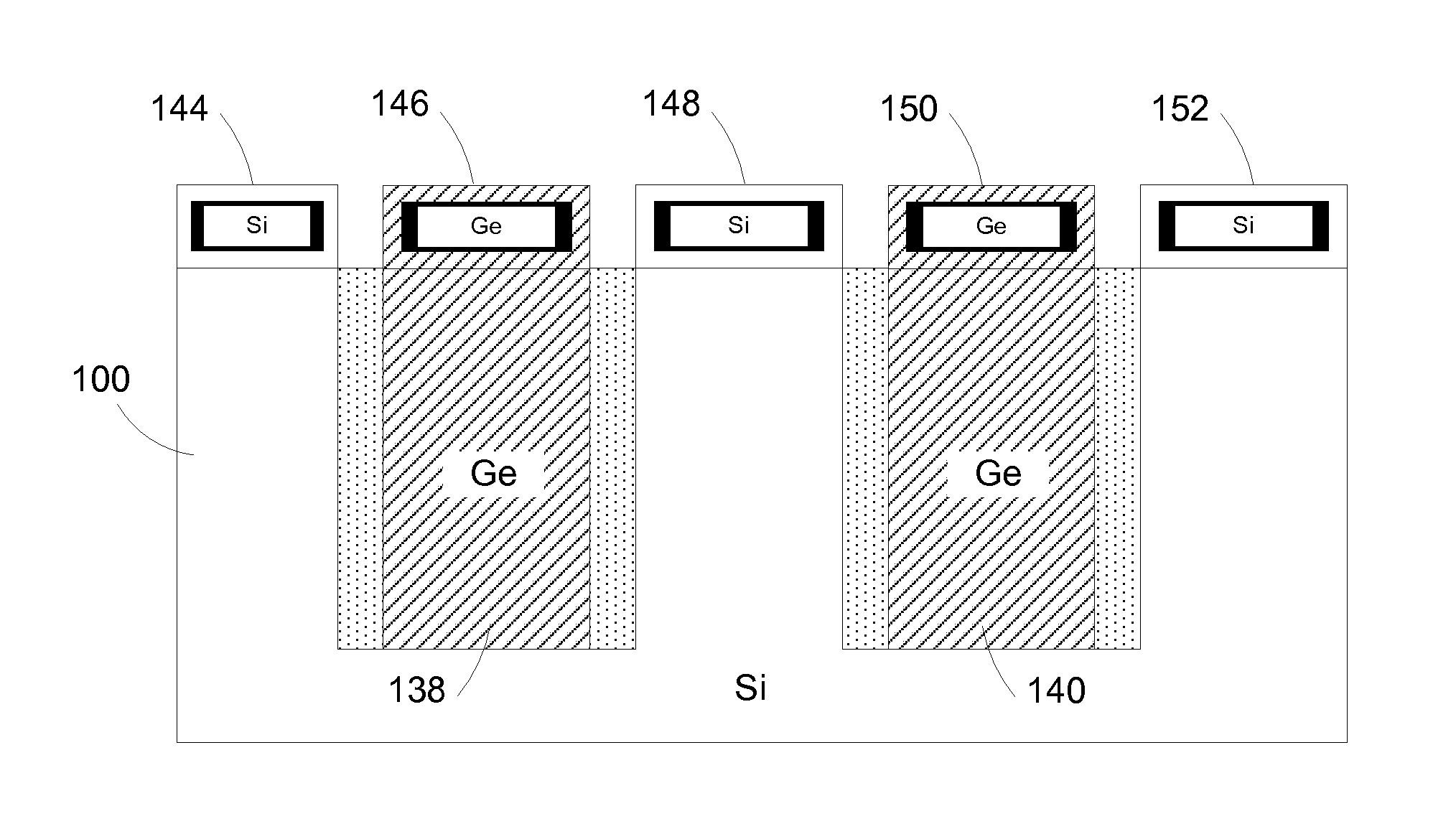

Semiconductor sensor structures with reduced dislocation defect densities and related methods for the same

Non-silicon based semiconductor devices are integrated into silicon fabrication processes by using aspect-ratio-trapping materials. Non-silicon light-sensing devices in a least a portion of a crystalline material can output electrons generated by light absorption therein. Exemplary light-sensing devices can have relatively large micron dimensions. As an exemplary application, complementary-metal-oxide-semiconductor photodetectors are formed on a silicon substrate by incorporating an aspect-ratio-trapping technique.

Owner:TAIWAN SEMICON MFG CO LTD

Monolithically integrated light emitting devices

ActiveUS20070105256A1Layered productsSemiconductor/solid-state device detailsDevice materialSingle crystal

Methods and structures for monolithically integrating monocrystalline silicon and monocrystalline non-silicon materials and devices are provided. In one structure, a monolithically integrated semiconductor device structure comprises a silicon substrate and a first monocrystalline semiconductor layer disposed over the silicon substrate, wherein the first monocrystalline semiconductor layer has a lattice constant different from a lattice constant of relaxed silicon. The structure further includes an insulating layer disposed over the first monocrystalline semiconductor layer in a first region and a monocrystalline silicon layer disposed over the insulating layer in the first region. The structure includes at least one silicon-based electronic device including an element including at least a portion of the monocrystalline silicon layer. The structure also includes a second monocrystalline semiconductor layer disposed over at least a portion of the first monocrystalline semiconductor layer in a second region and absent from the first region, wherein the second monocrystalline semiconductor layer has a lattice constant different from the lattice constant of relaxed silicon. The structure includes at least one III-V light-emitting device including an active region including at least a portion of the second monocrystalline semiconductor layer.

Owner:MASSACHUSETTS INST OF TECH

PN diode optical modulators fabricated in rib waveguides

ActiveUS20060008223A1Reduce speedSemiconductor/solid-state device manufacturingOptical waveguide light guideLow speedPhase shifted

Owner:CISCO TECH INC

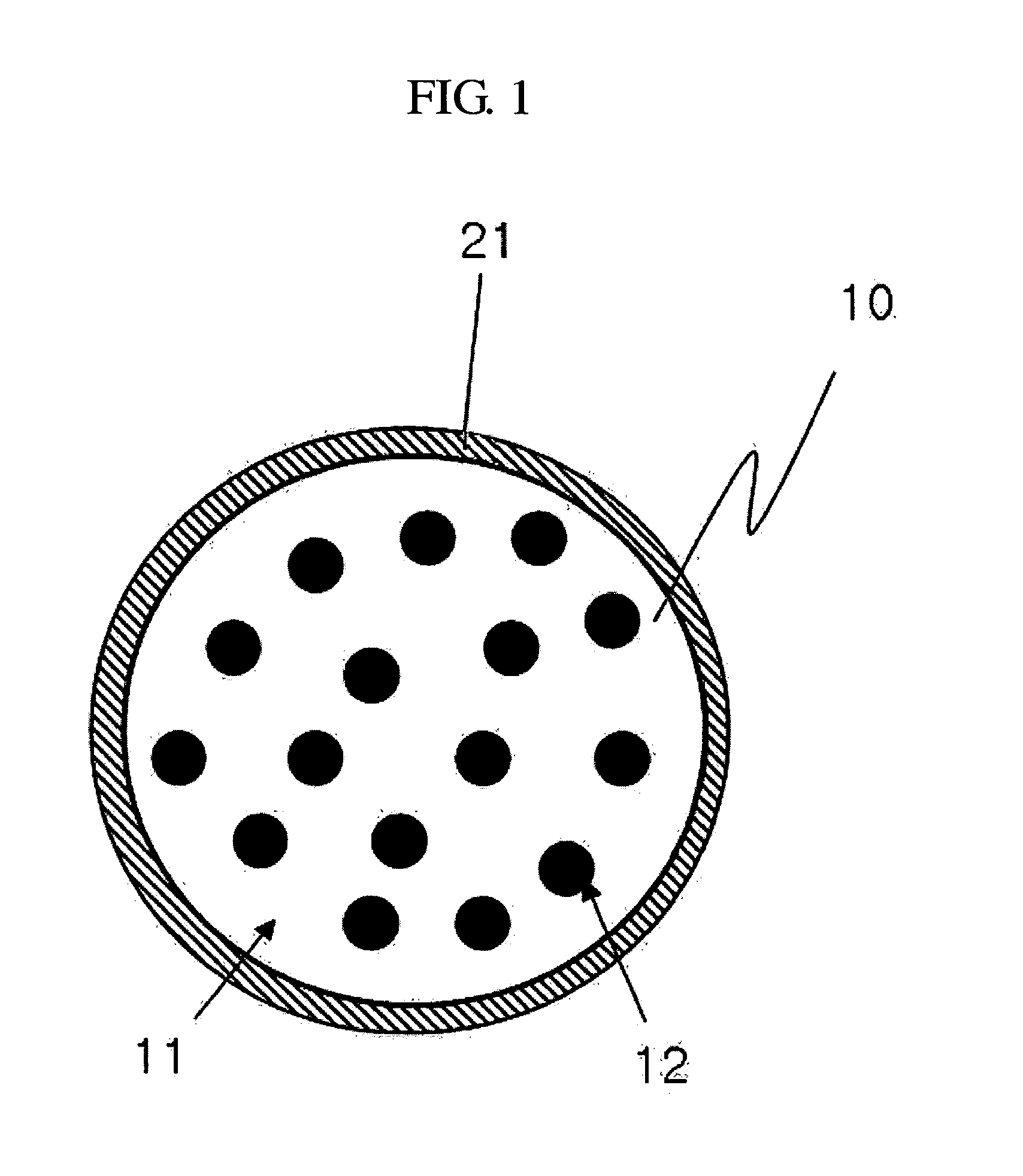

Silicon composite particles, preparation thereof, and negative electrode material for non-aqueous electrolyte secondary cell

ActiveUS20050214644A1Improve cycle performanceMinimize changesSilicaNitrogen compoundsSilicon alloyInorganic compound

Silicon composite particles are prepared by sintering primary fine particles of silicon, silicon alloy or silicon oxide together with an organosilicon compound. Sintering of the organosilicon compound results in a silicon-base inorganic compound which serves as a binder. Each particle has the structure that silicon or silicon alloy fine particles are dispersed in the silicon-base inorganic compound binder, and voids are present within the particle.

Owner:SHIN ETSU CHEM IND CO LTD

Monolithically integrated silicon and III-V electronics

Methods and structures for monolithically integrating monocrystalline silicon and monocrystalline non-silicon materials and devices are provided. In one structure, a monolithically integrated semiconductor device structure comprises a silicon substrate and a first monocrystalline semiconductor layer disposed over the silicon substrate, wherein the first monocrystalline semiconductor layer has a lattice constant different from a lattice constant of relaxed silicon. The structure also includes an insulating layer disposed over the first monocrystalline semiconductor layer in a first region and a monocrystalline silicon layer disposed over the insulating layer in the first region. The structure includes at least one silicon-based electronic device comprising an element including at least a portion of the monocrystalline silicon layer. The structure includes a second monocrystalline semiconductor layer disposed over at least a portion of the first monocrystalline semiconductor layer in a second region and absent from the first region, wherein the second monocrystalline semiconductor layer has a lattice constant different from the lattice constant of relaxed silicon. The structure also includes at least one III-V electronic device comprising an element including at least a portion of the second monocrystalline semiconductor layer.

Owner:MASSACHUSETTS INST OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com