Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

529 results about "Combustion chemical vapor deposition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Combustion chemical vapor deposition (CCVD) is a chemical process by which thin-film coatings are deposited onto substrates in the open atmosphere.

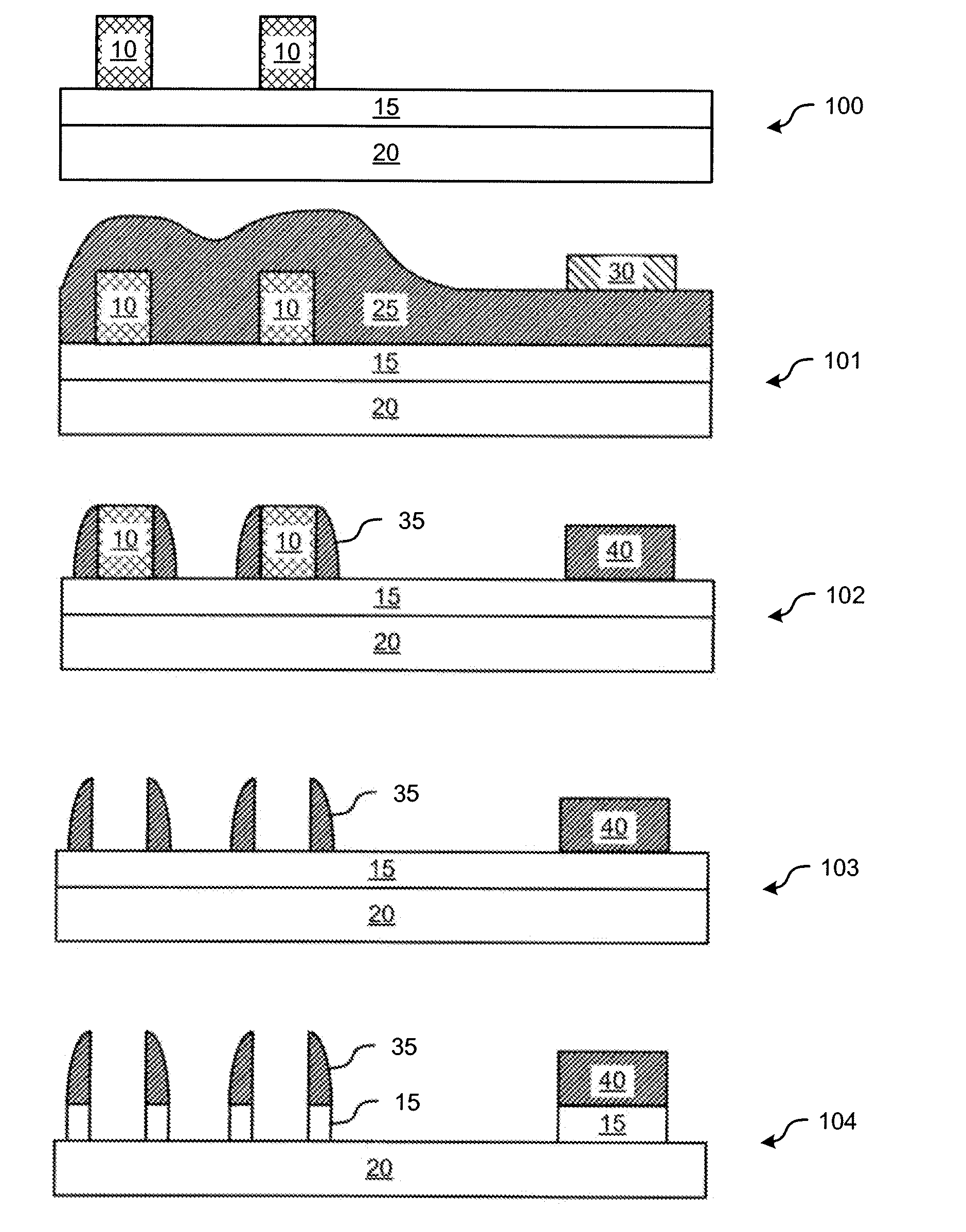

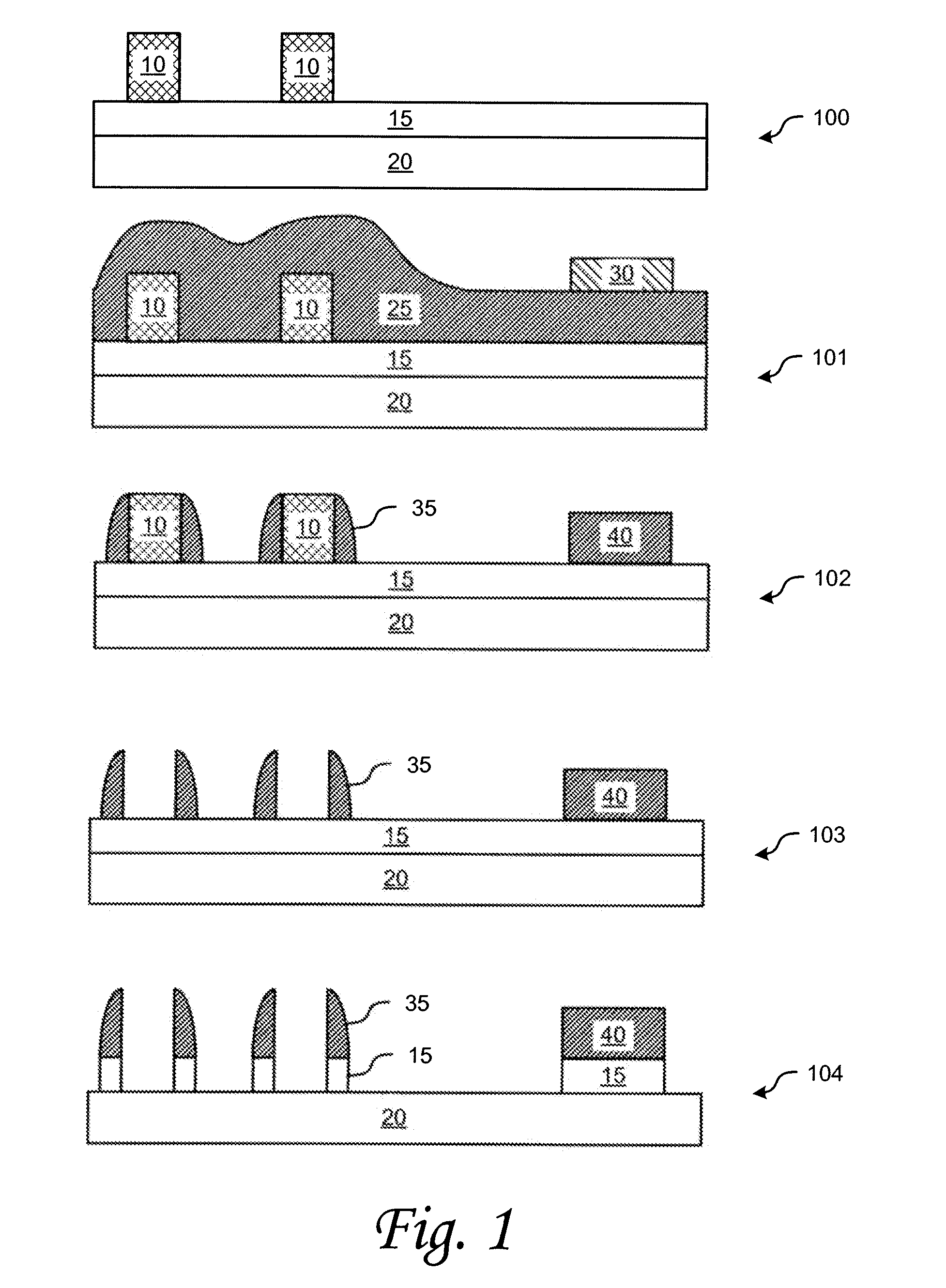

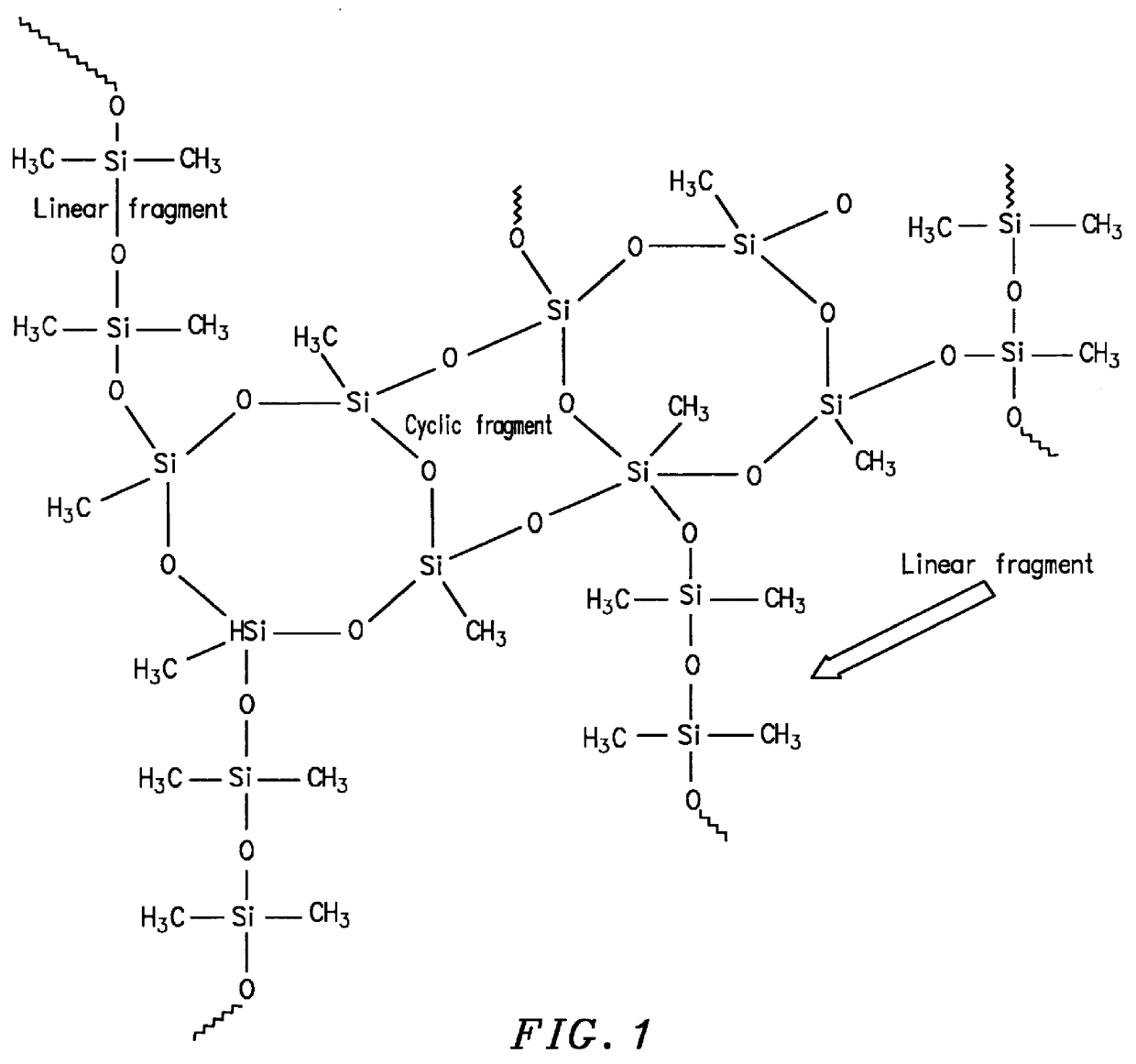

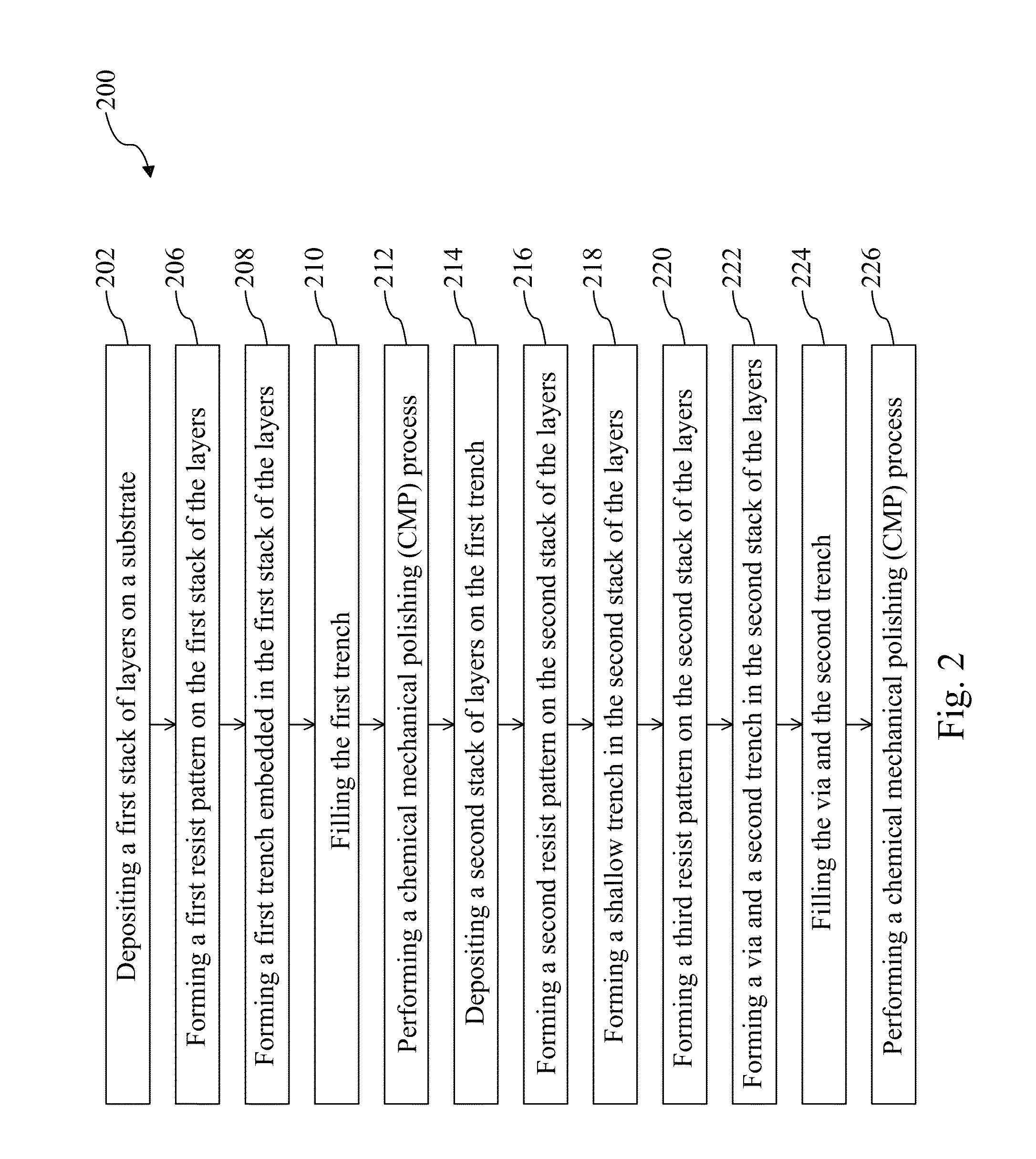

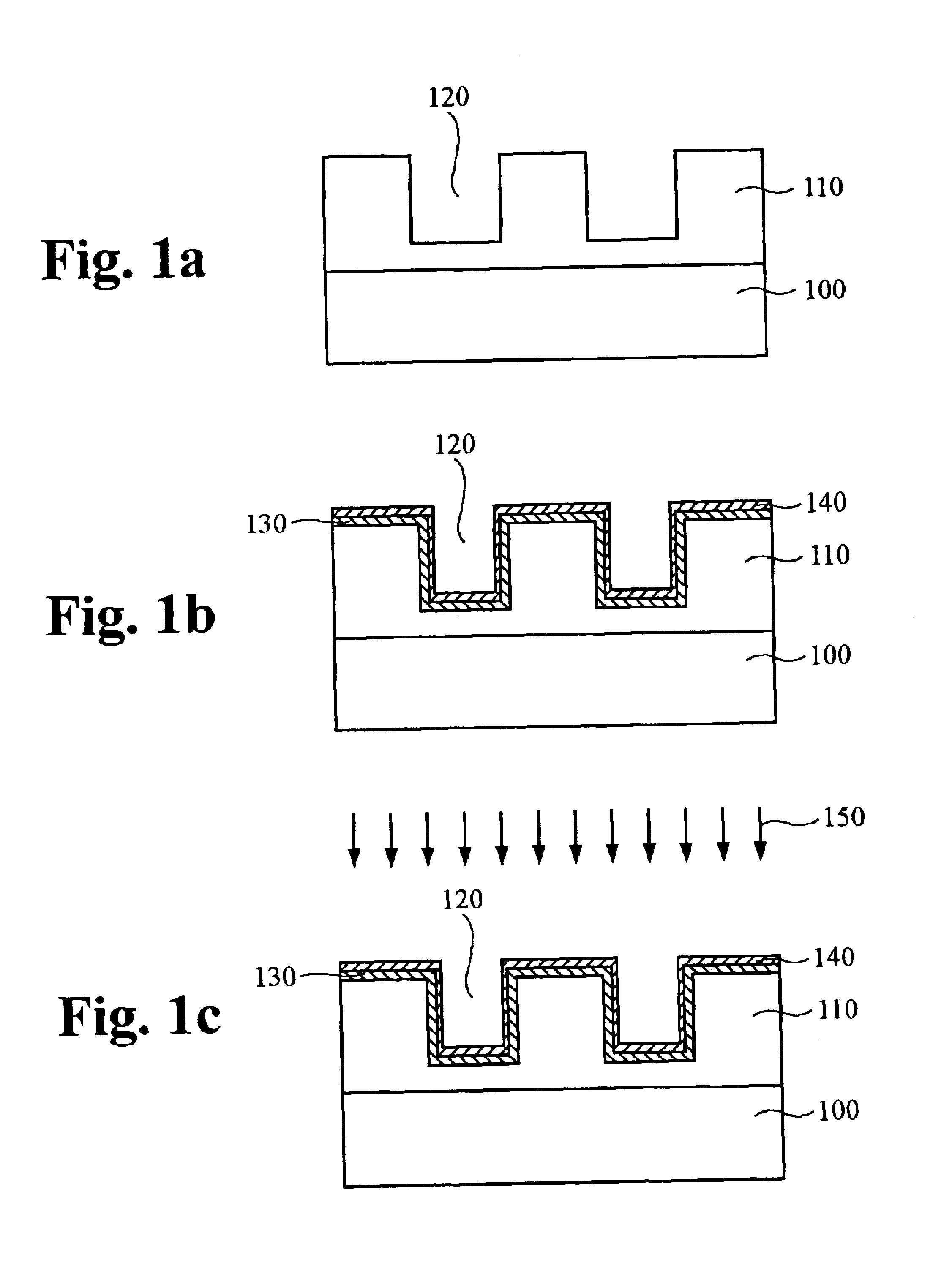

Method of eliminating a lithography operation

ActiveUS20090146322A1Semiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

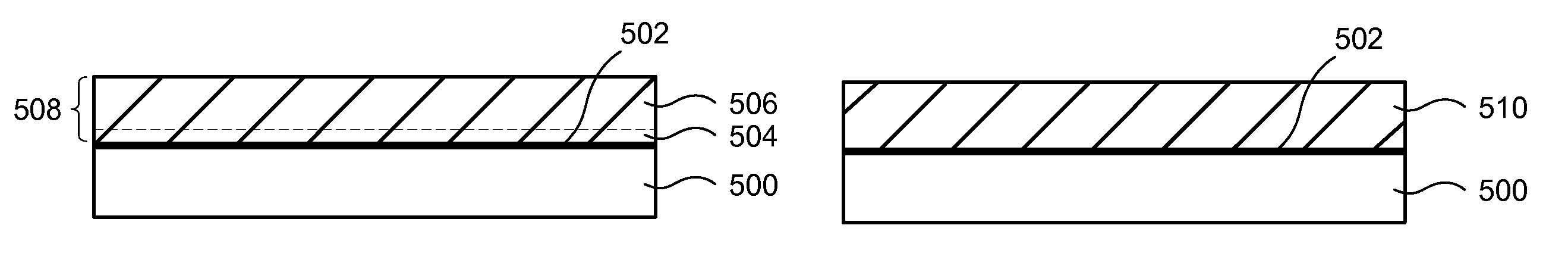

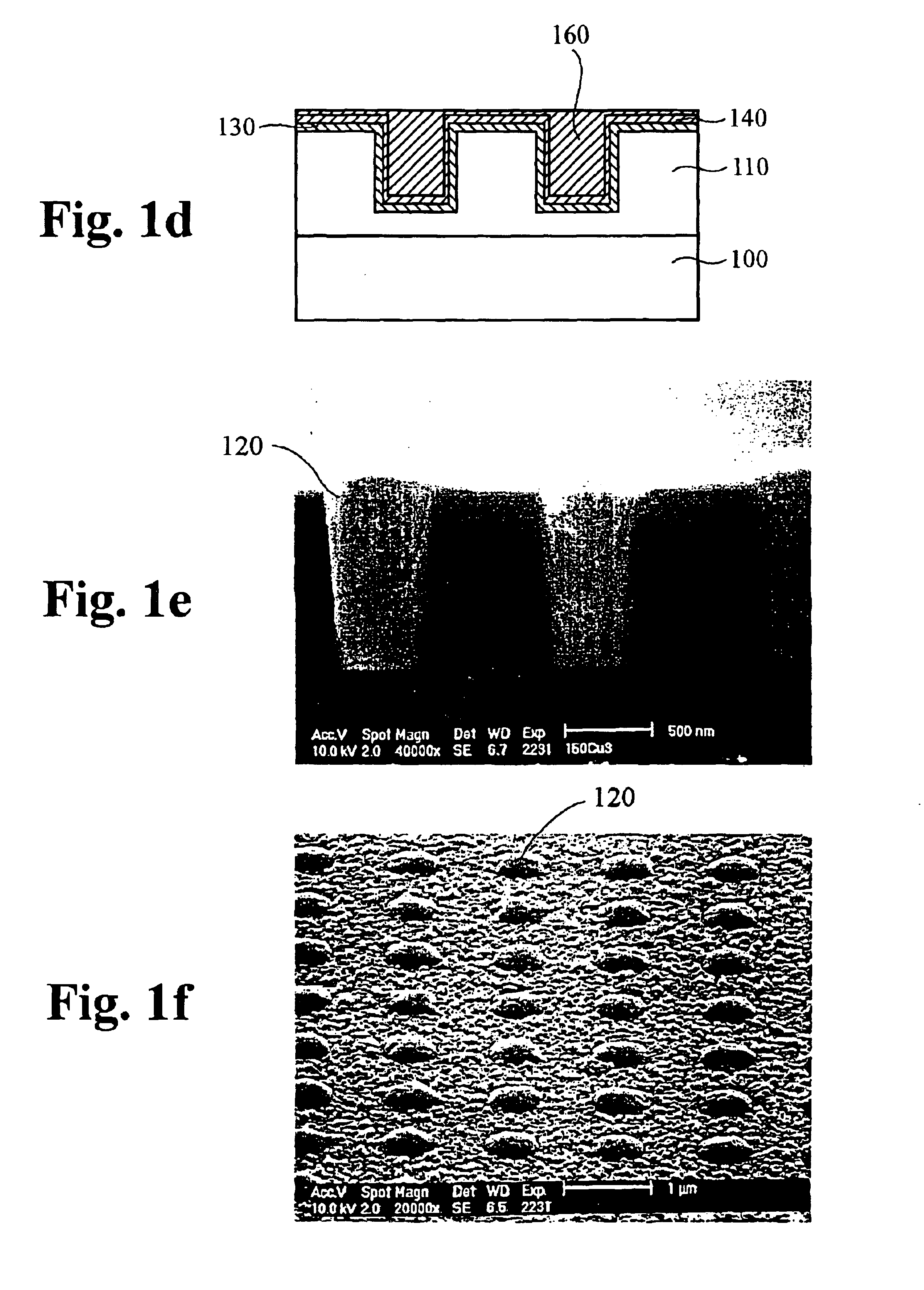

Methods of semiconductor device fabrication are disclosed. An exemplary method includes processes of depositing a first pattern on a semiconductor substrate, wherein the first pattern defines wide and narrow spaces; depositing spacer material over the first pattern on the substrate; etching the spacer material such that the spacer material is removed from horizontal surfaces of the substrate and the first pattern but remains adjacent to vertical surfaces of a wide space defined by the first pattern and remains within narrow a space defined by the first pattern; and removing the first pattern from the substrate. In one embodiment, the first pattern can comprise sacrificial material, which can include, for example, polysilicon material. The deposition can comprise physical vapor deposition, chemical vapor deposition, electrochemical deposition, molecular beam epitaxy, atomic layer deposition or other deposition techniques. According to another embodiment, features for lines and logic device components having a width greater than that of the lines are formed in the spacer material in the same mask layer.

Owner:CADENCE DESIGN SYST INC

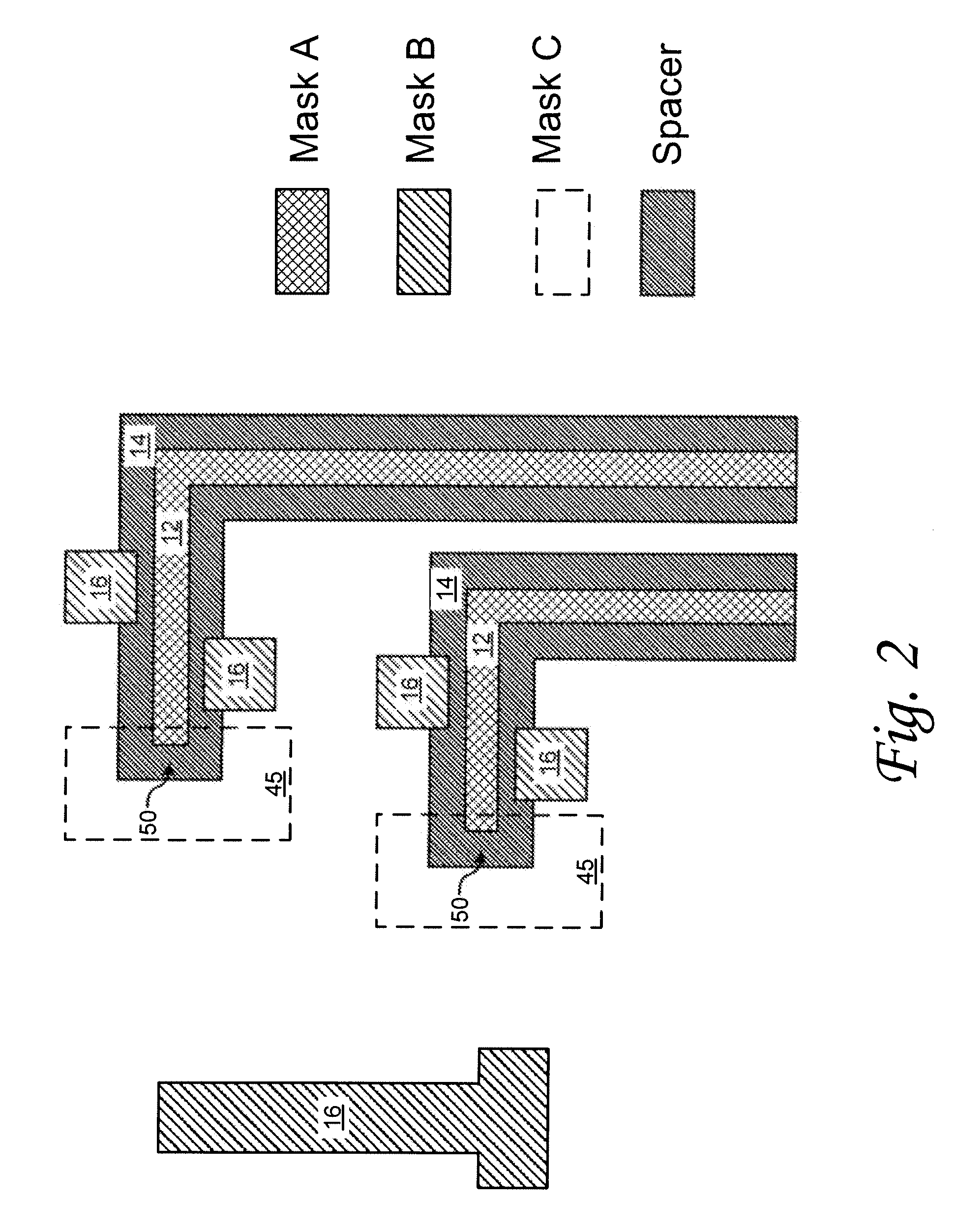

Method of making low kappa dielectric inorganic/organic hybrid films

InactiveUS6068884AImprove thermal stabilityLow dielectric constantLayered productsSemiconductor/solid-state device detailsThermal chemical vapor depositionSemiconductor

A method of depositing a dielectric film exhibiting a low dielectric constant in a semiconductor and / or integrated circuit by chemical vapor deposition (CVD) is provided. The film is deposited using an organosilicon precursor in a manner such that the film is comprised of a backbone made substantially of Si-O-Si or Si-N-Si groups with organic side groups attached to the backbone.

Owner:APPLIED MATERIALS INC

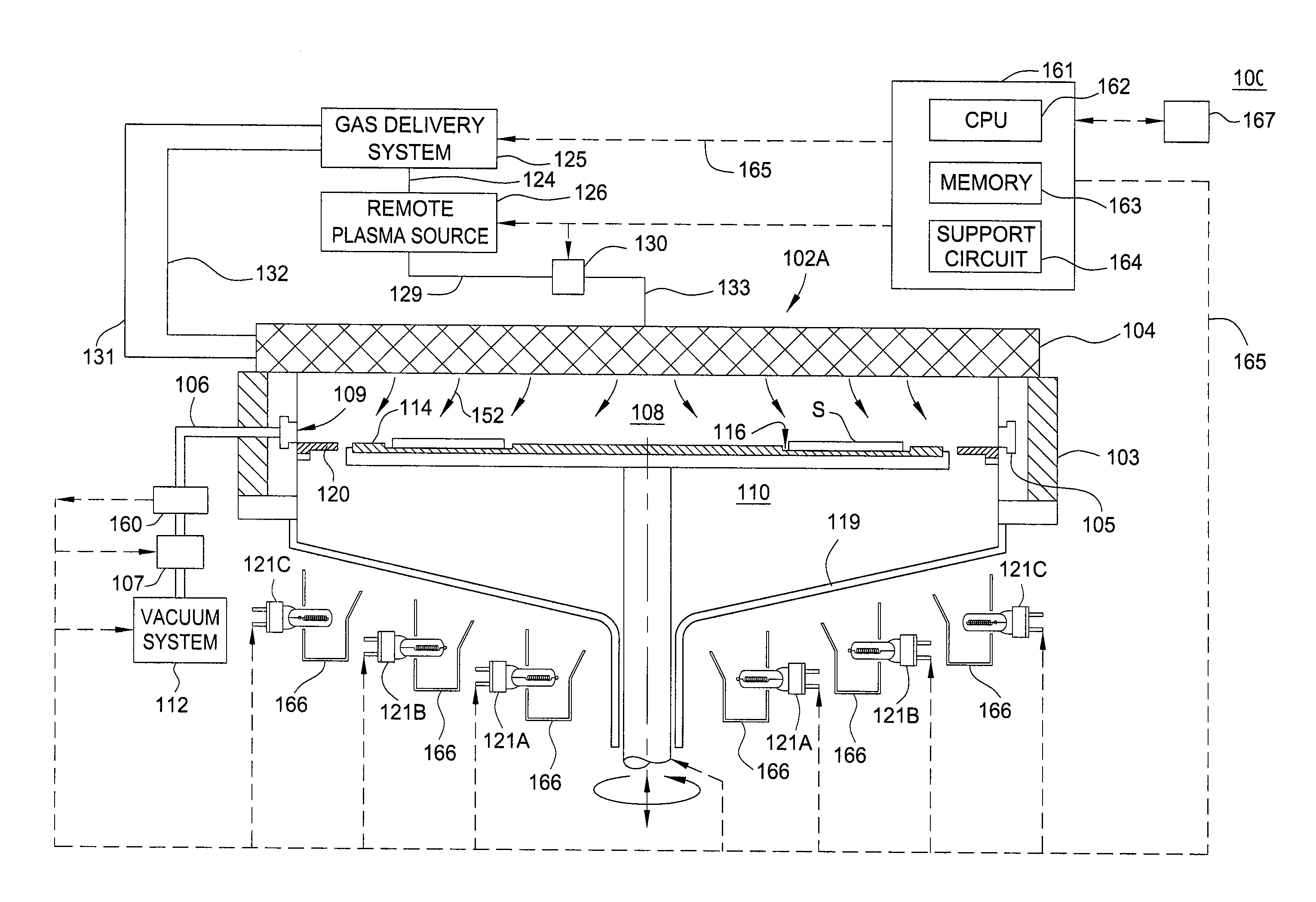

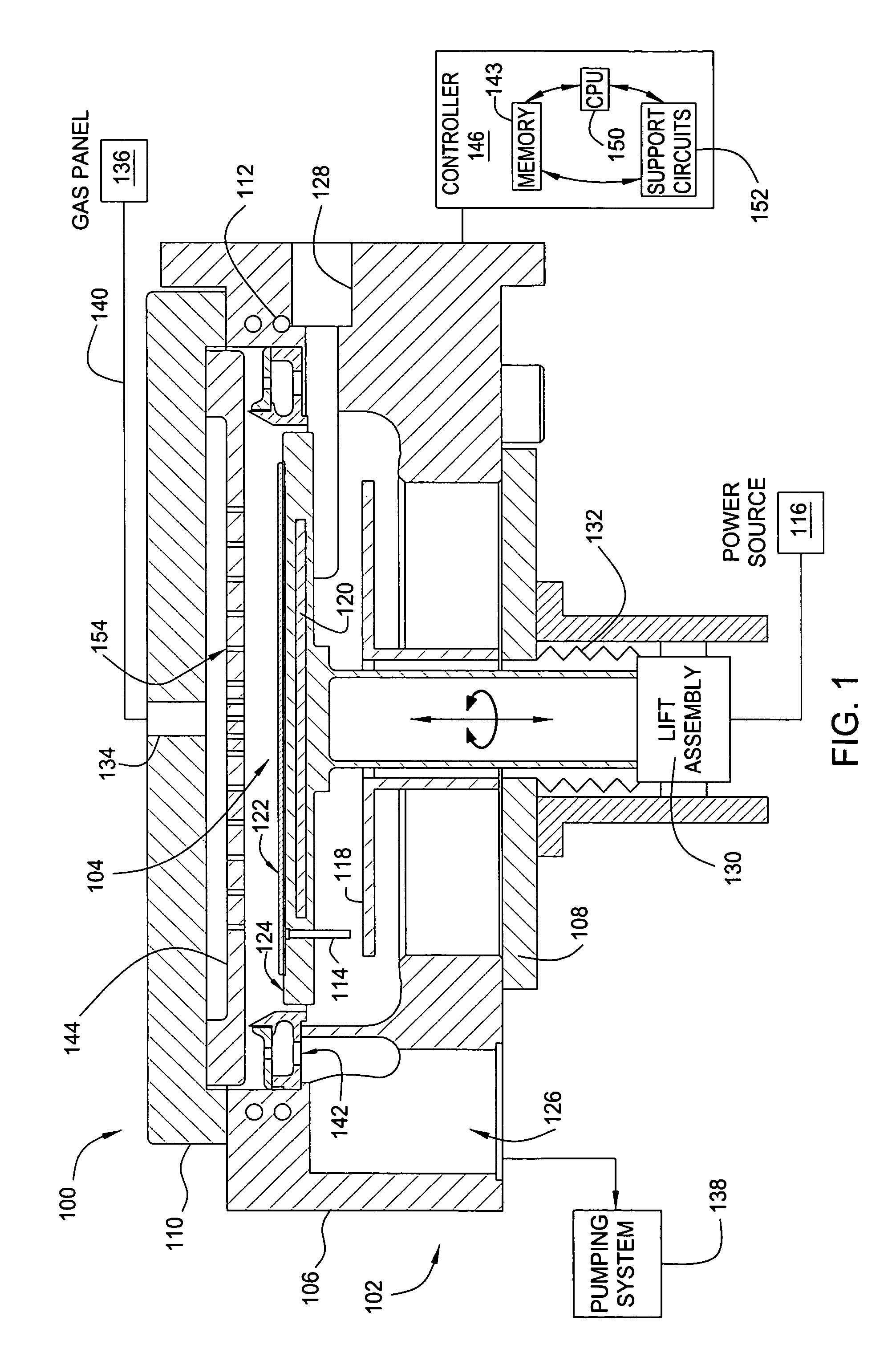

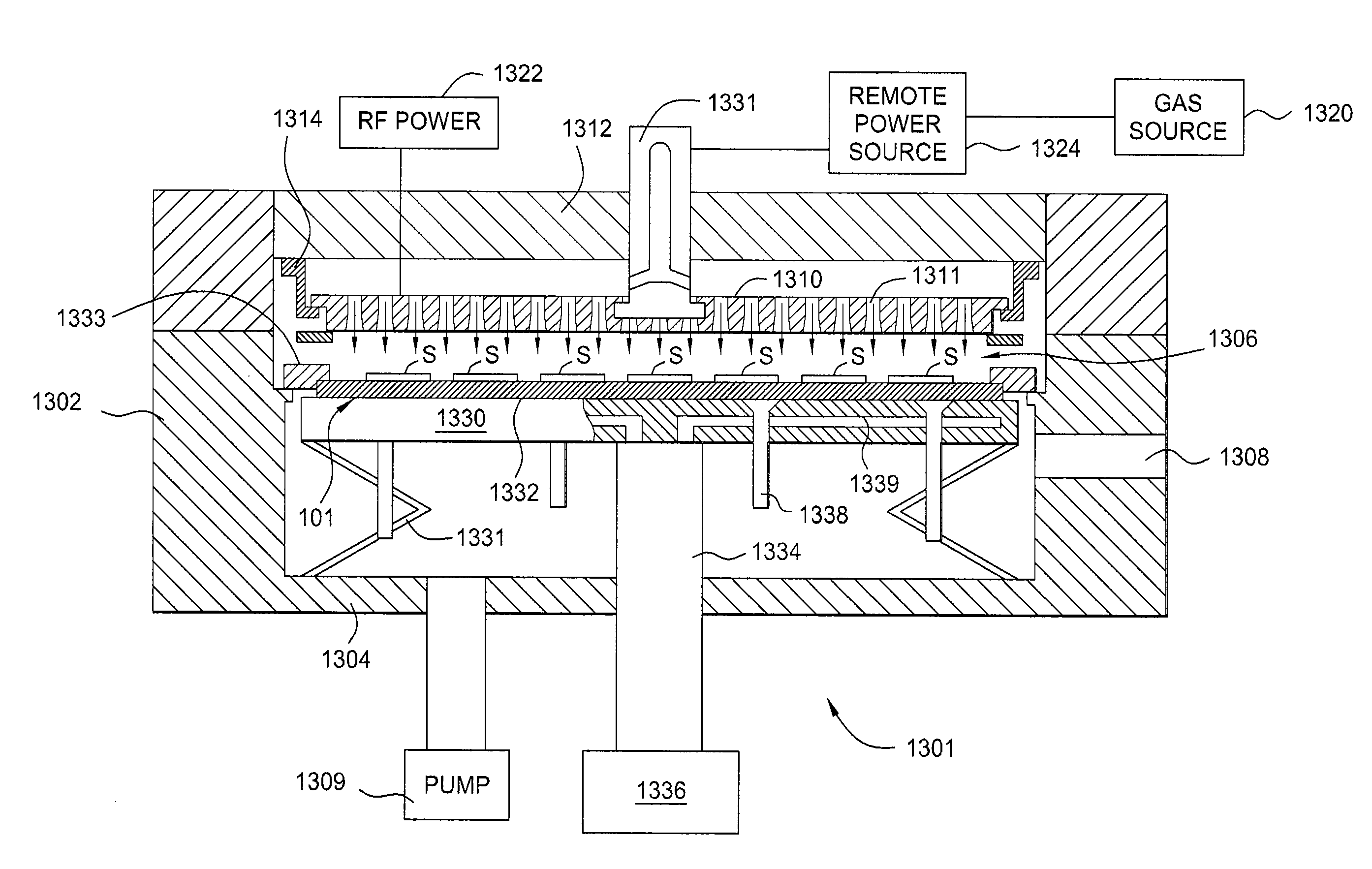

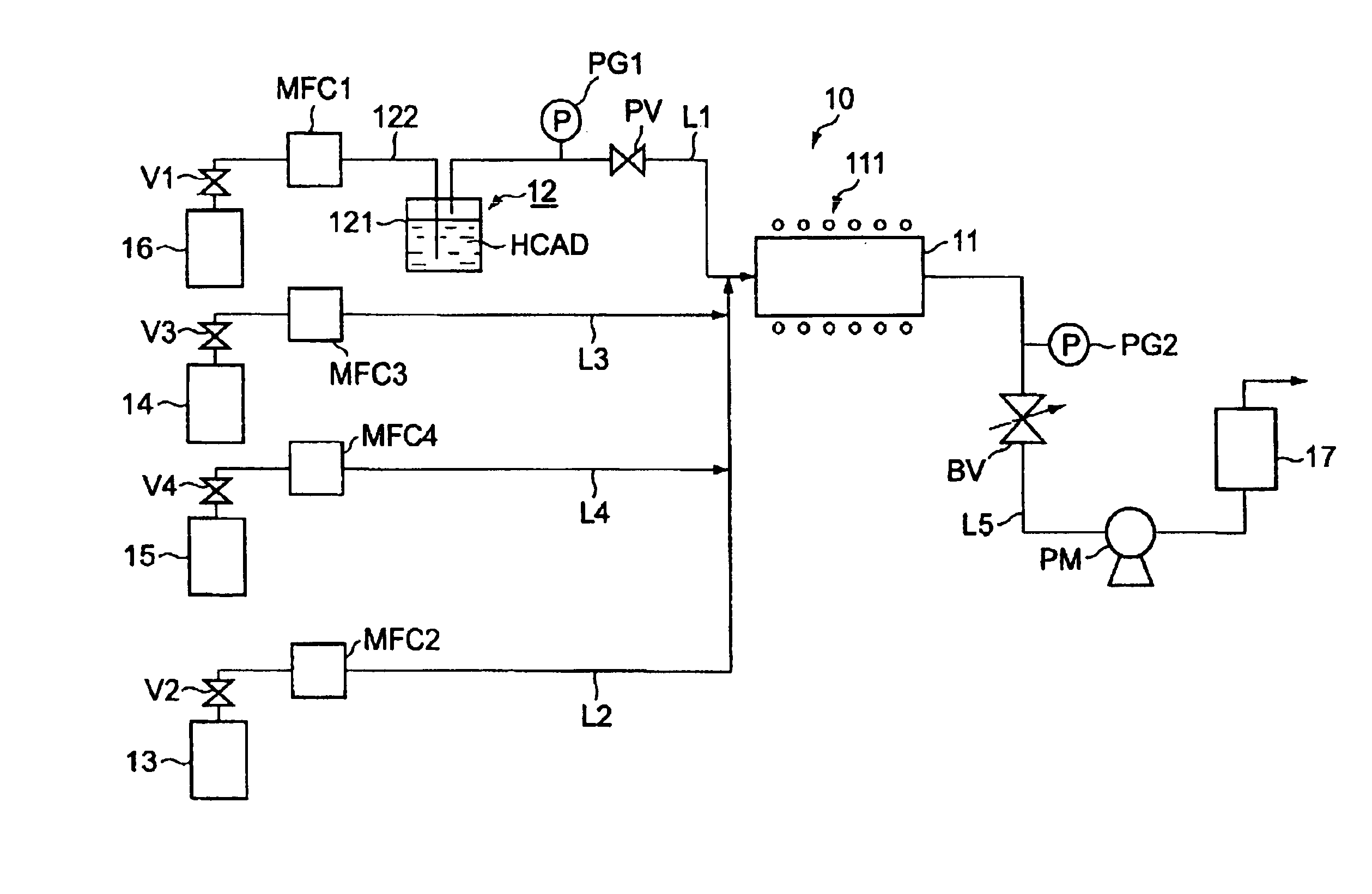

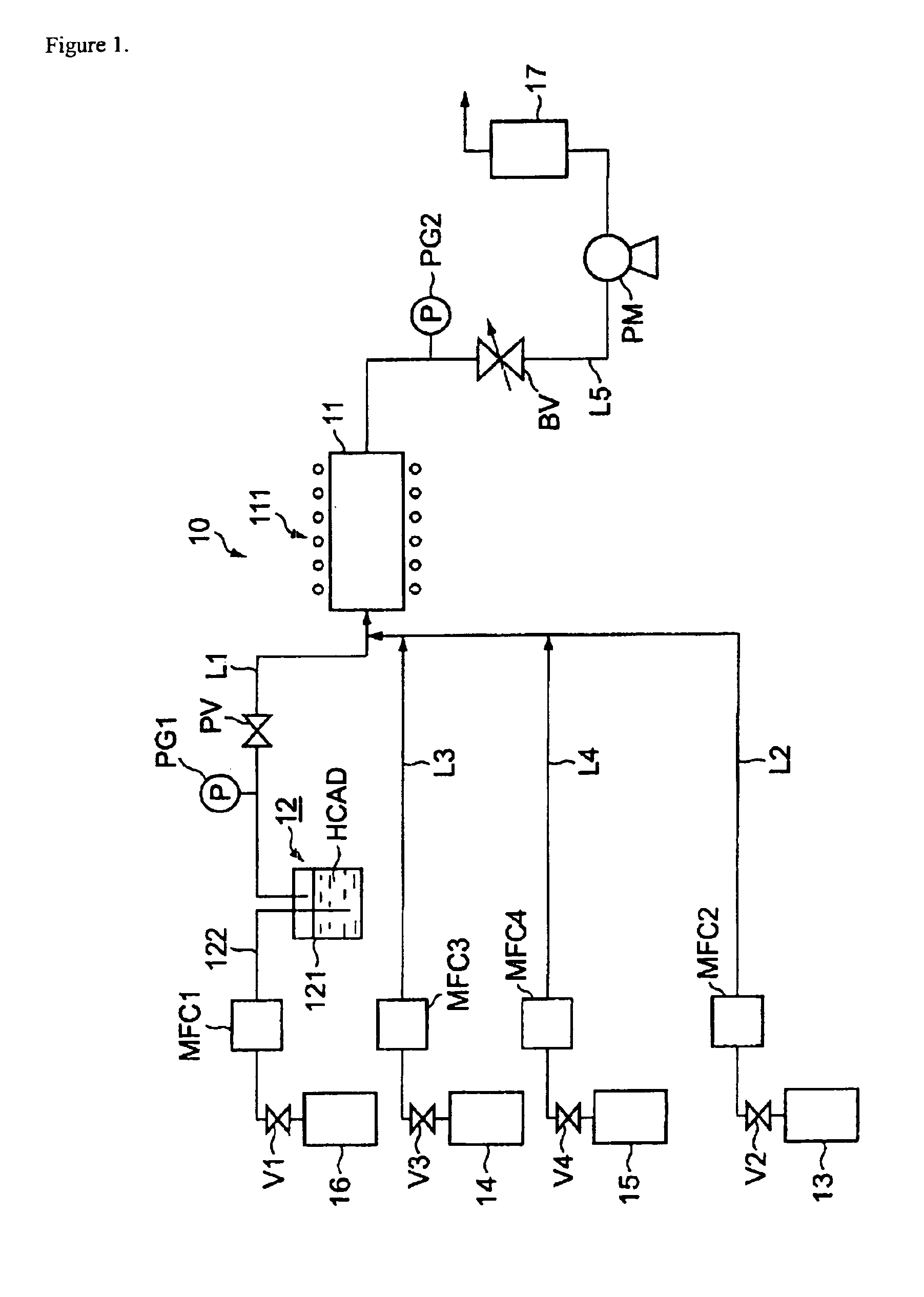

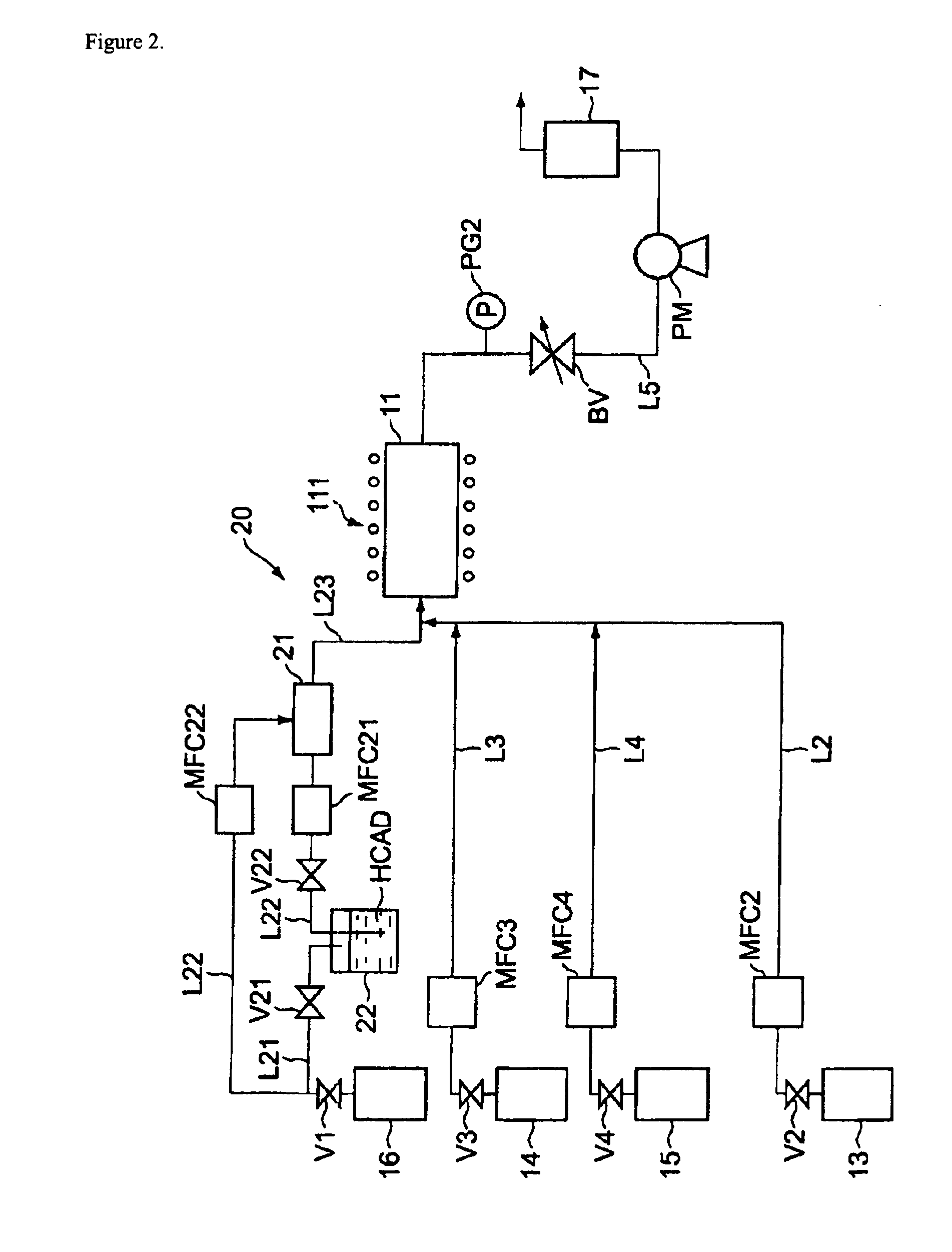

Closed loop mocvd deposition control

InactiveUS20110308453A1Liquid surface applicatorsSemiconductor/solid-state device manufacturingGas phaseControl system

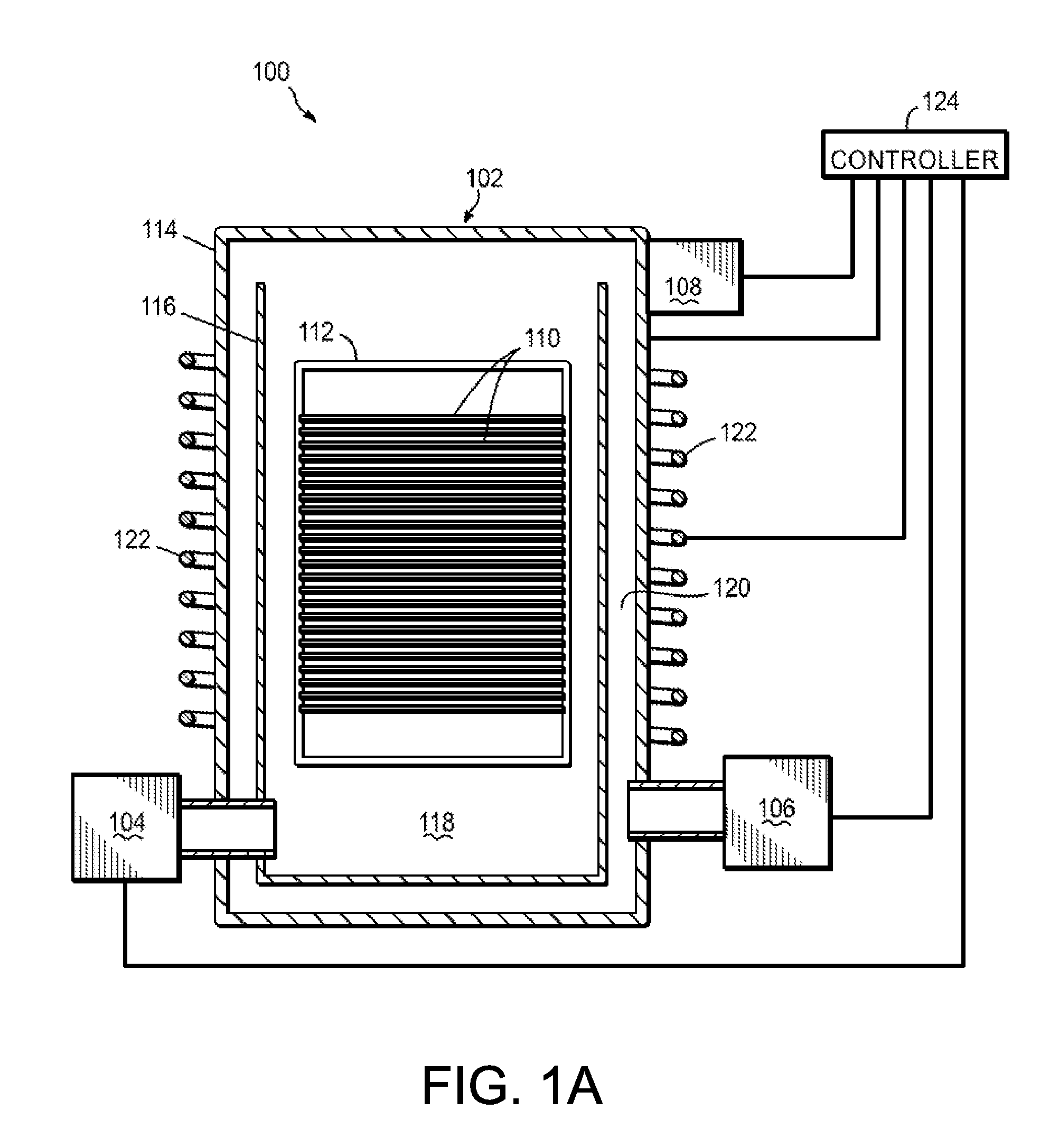

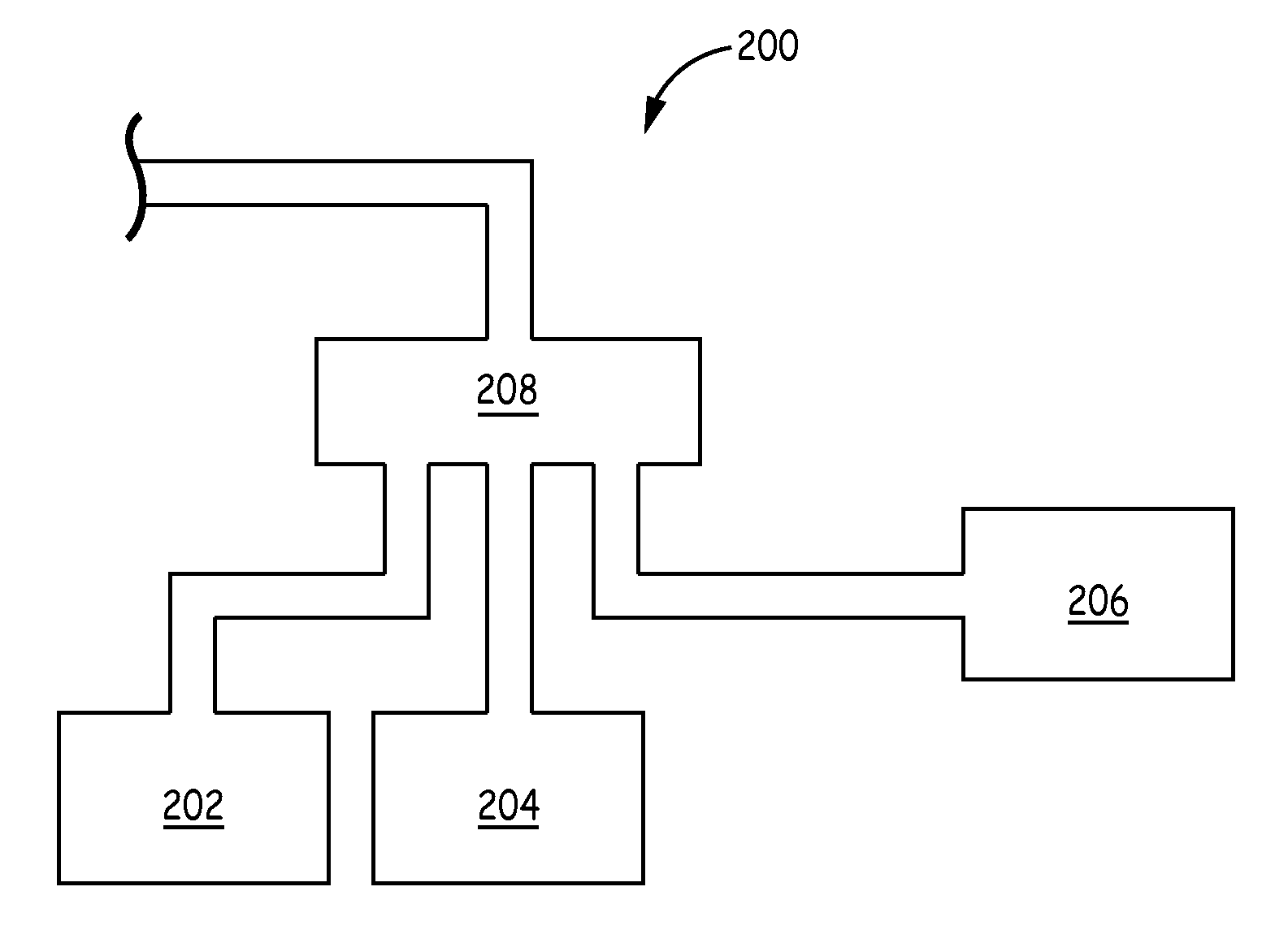

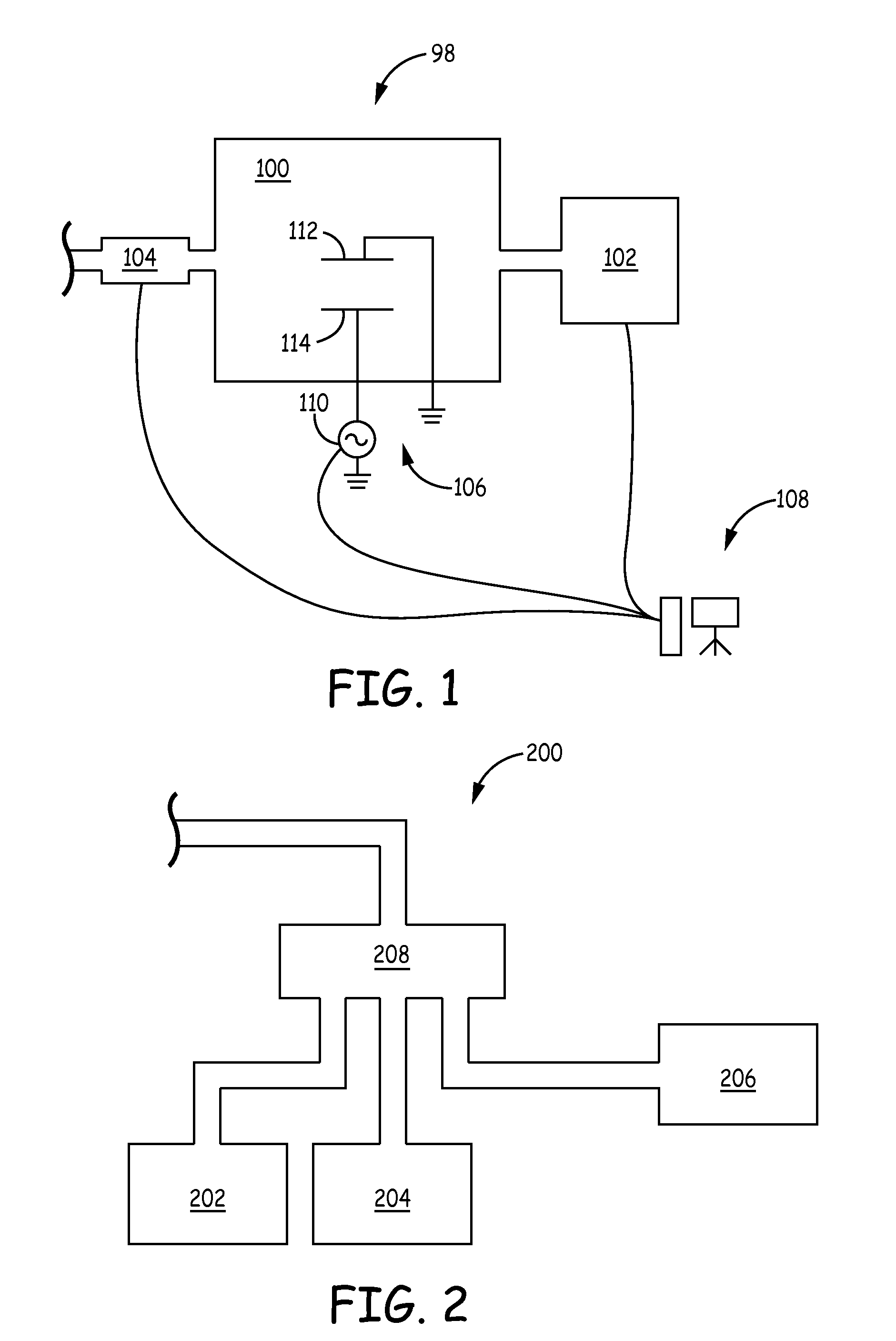

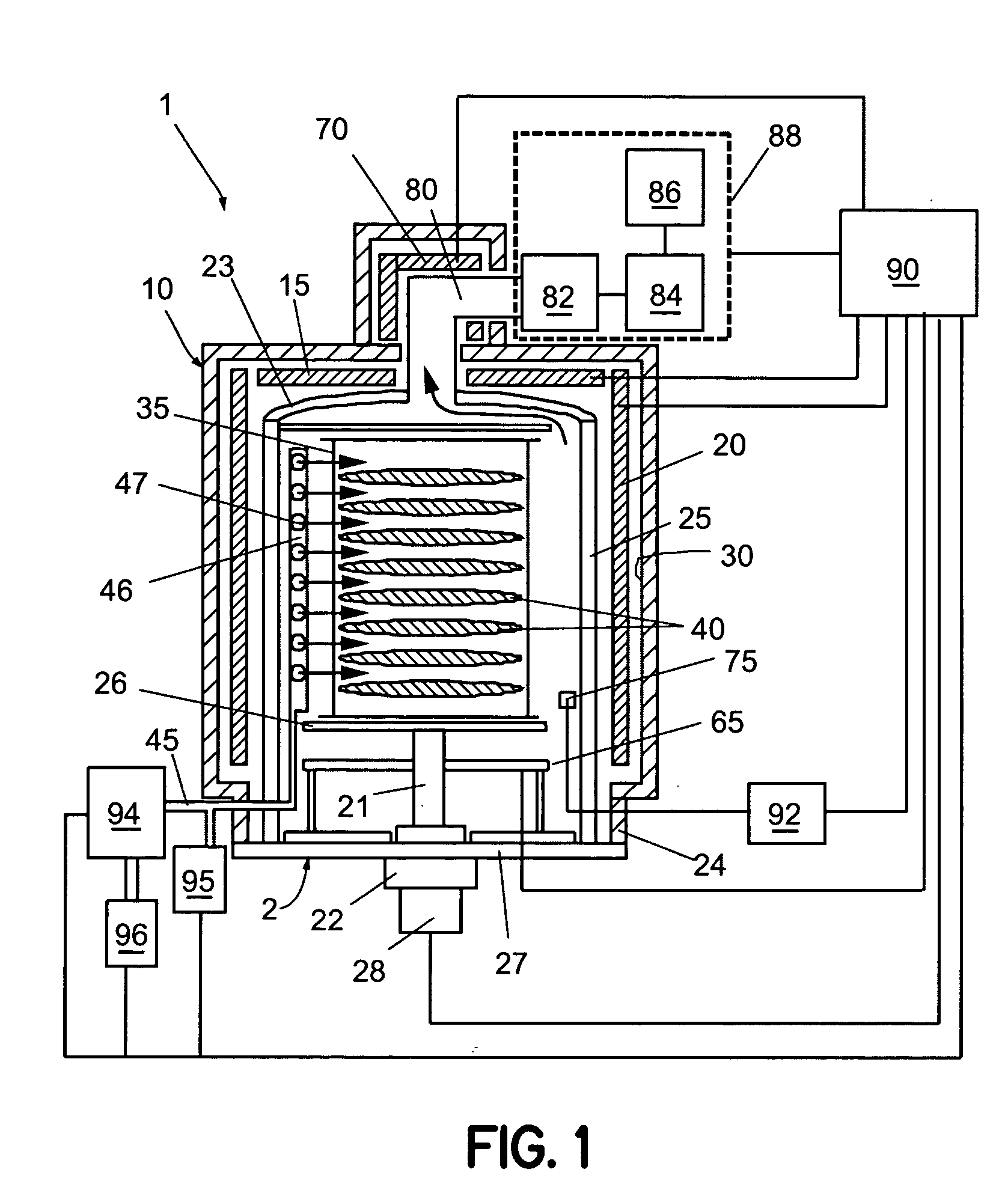

A method and apparatus are provided for monitoring and controlling substrate processing parameters for a cluster tool that utilizes chemical vapor deposition and / or hydride vapor phase epitaxial (HVPE) deposition. In one embodiment, a metal organic chemical vapor deposition (MOCVD) process is used to deposit a Group III-nitride film on a plurality of substrates within a processing chamber. A closed-loop control system performs in-situ monitoring of the Group III-nitride film growth rate and adjusts film growth parameters as required to maintain a target growth rate. In another embodiment, a closed-loop control system performs in-situ monitoring of film growth parameters for multiple processing chambers for one or more film deposition systems.

Owner:APPLIED MATERIALS INC

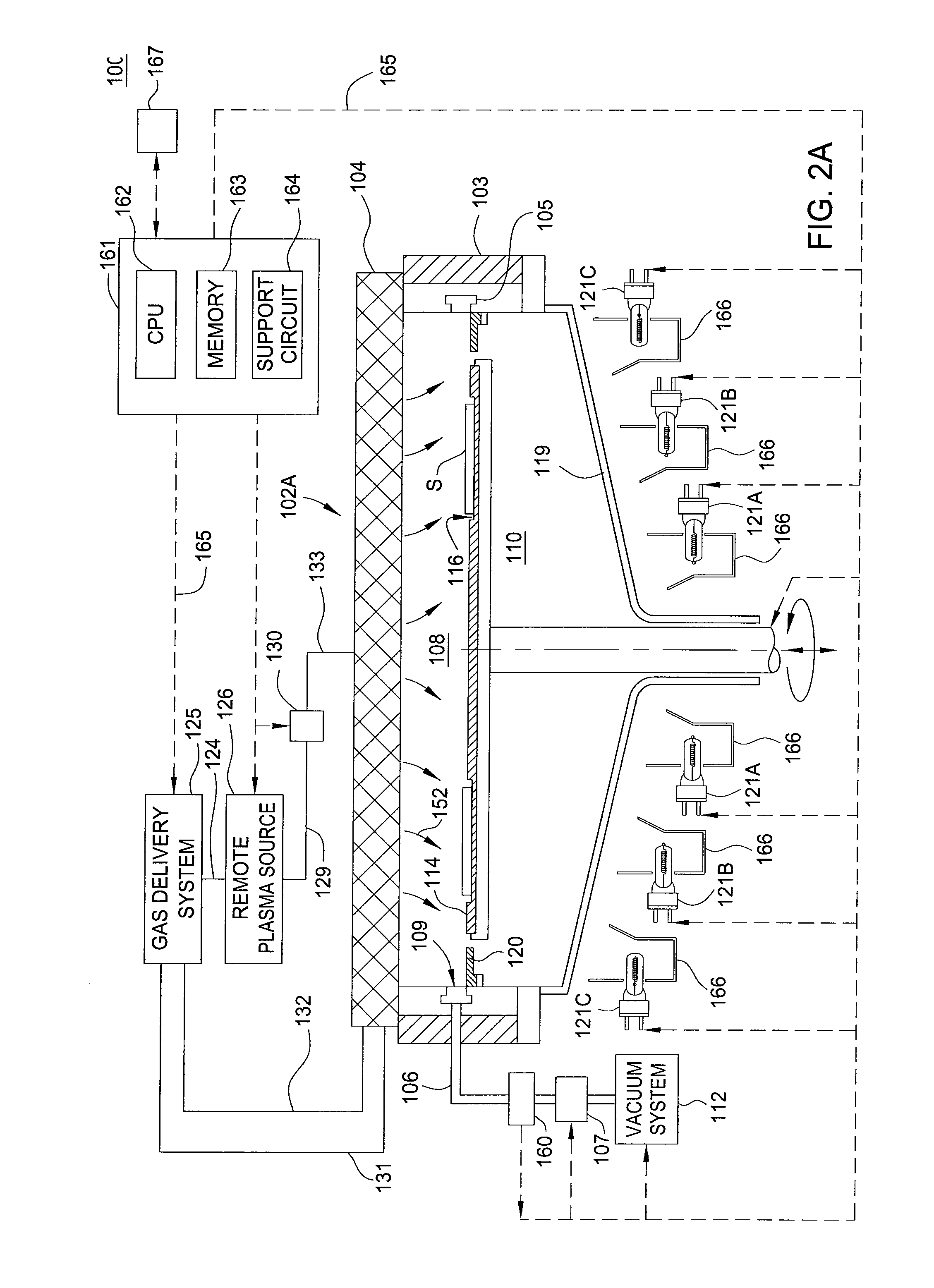

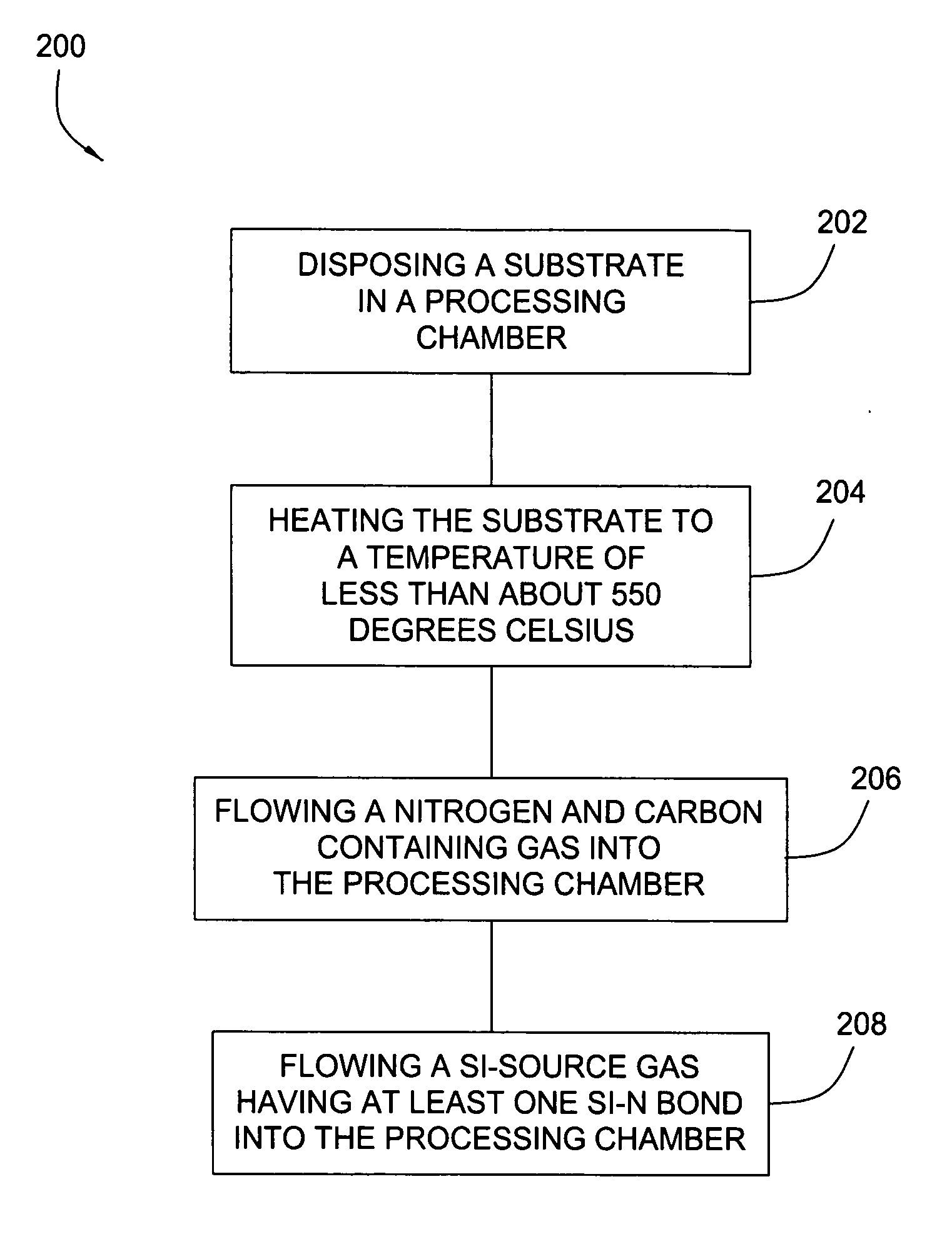

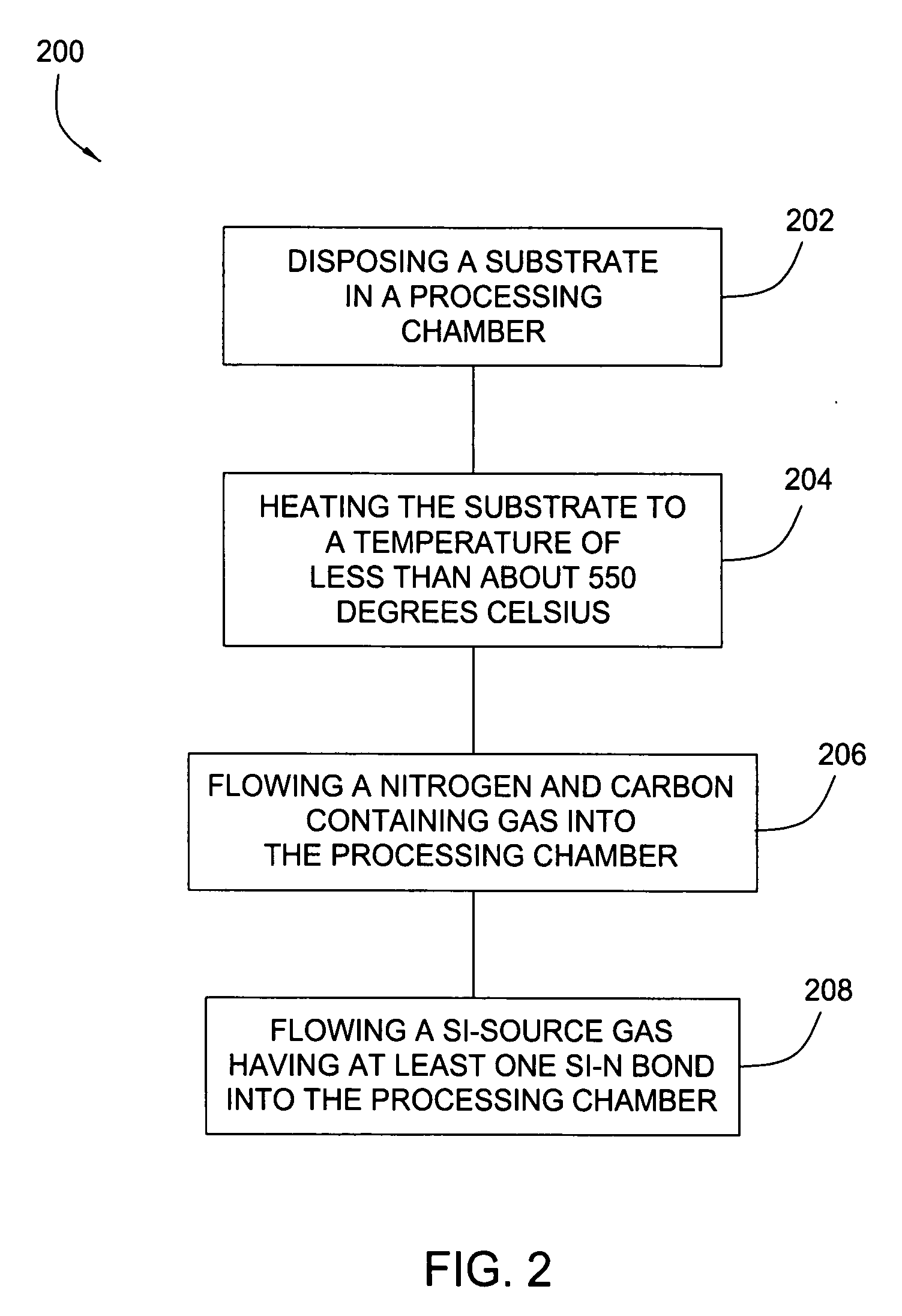

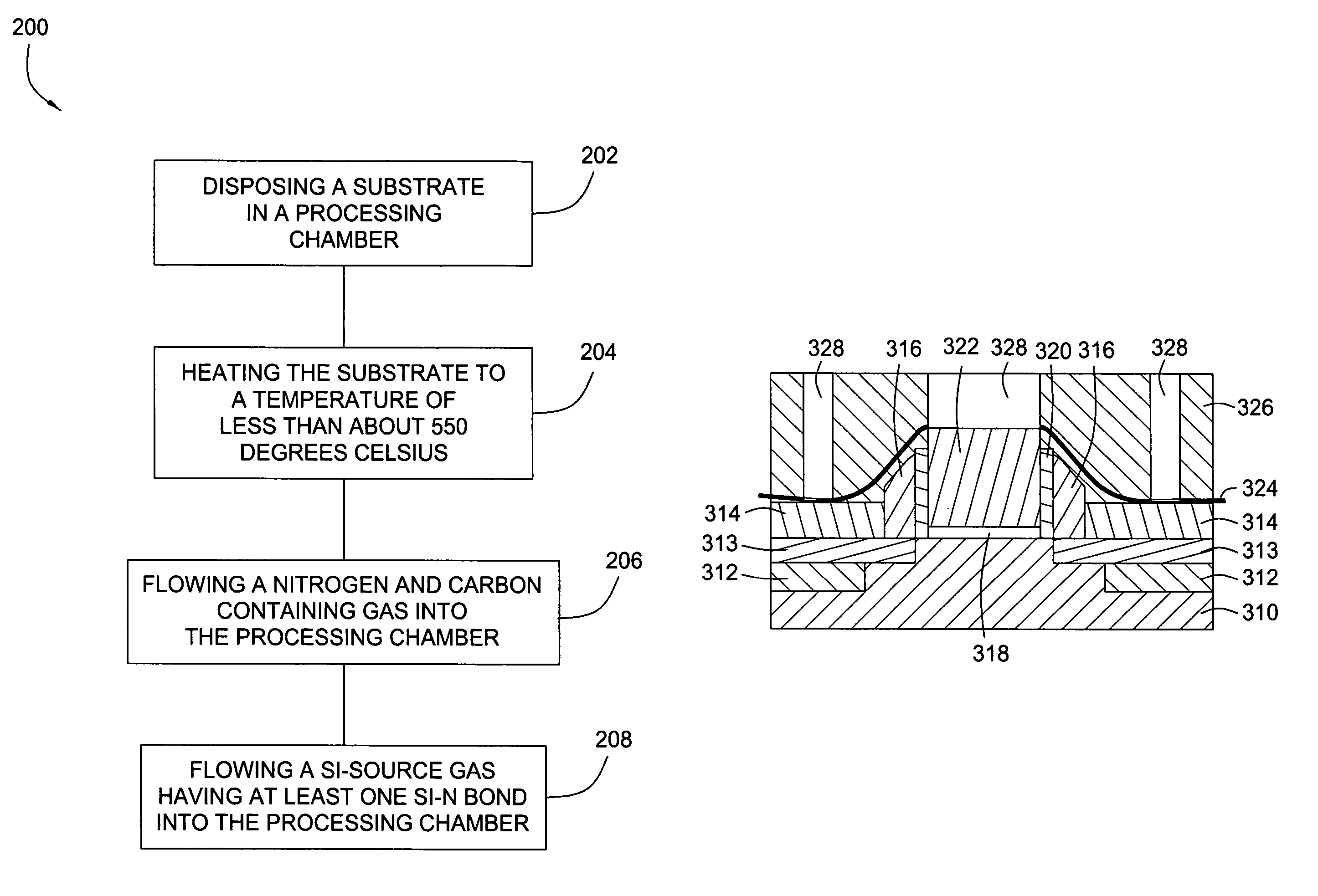

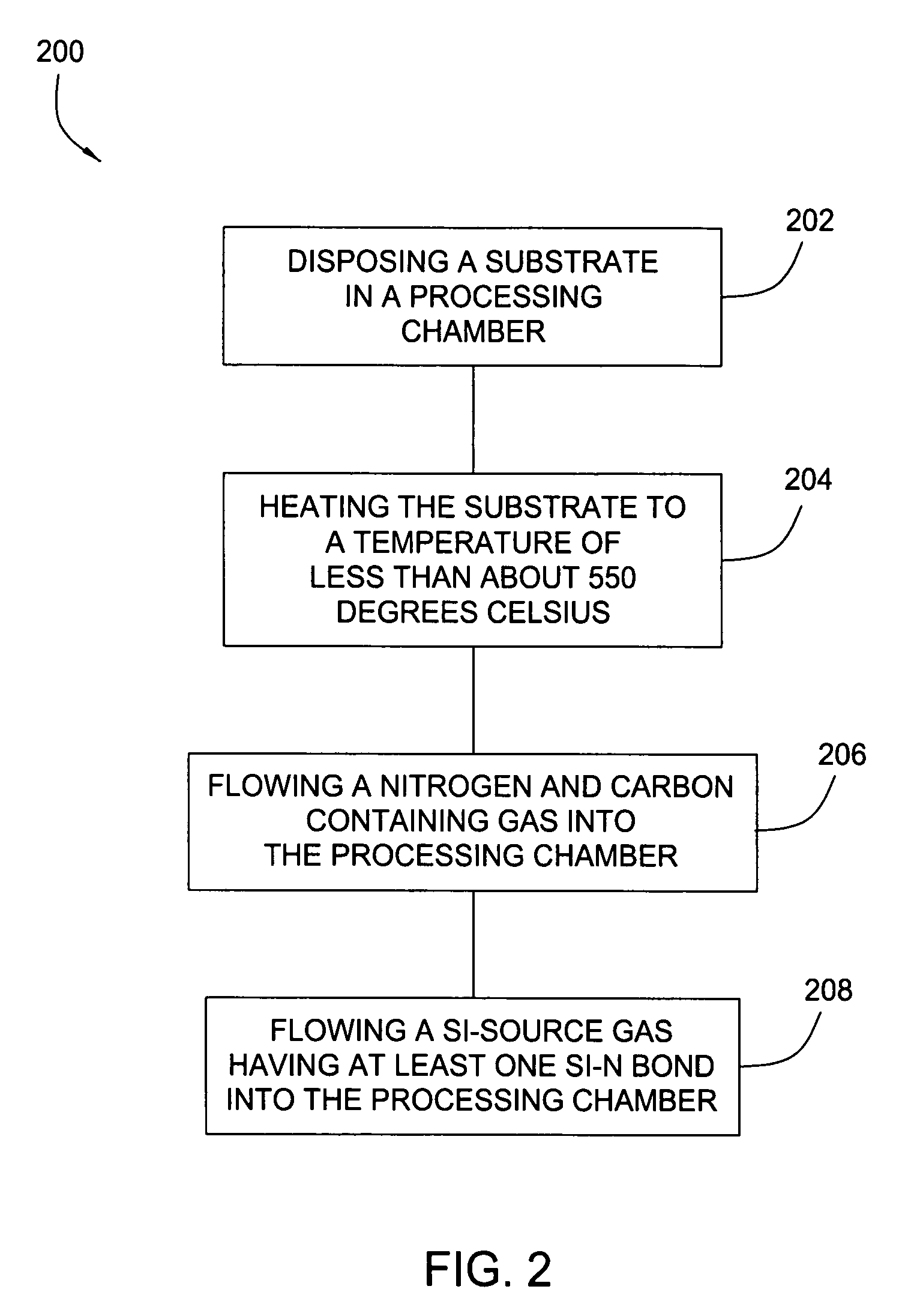

Method for silicon based dielectric chemical vapor deposition

InactiveUS20060286818A1TransistorSemiconductor/solid-state device manufacturingDielectricCelsius Degree

Embodiments of the invention generally provide a method for depositing silicon-containing films. In one embodiment, a method for depositing silicon-containing material film on a substrate includes flowing a nitrogen and carbon containing chemical into a deposition chamber, flowing a silicon-containing source chemical having silicon-nitrogen bonds into the processing chamber, and heating the substrate disposed in the chamber to a temperature less than about 550 degrees Celsius. In another embodiment, the silicon containing chemical is trisilylamine and the nitrogen and carbon containing chemical is (CH3)3—N.

Owner:APPLIED MATERIALS INC

In-situ hybrid deposition of high dielectric constant films using atomic layer deposition and chemical vapor deposition

InactiveUS7816278B2Rapid temperature measurementIncrease deposition rateSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricBatch processing

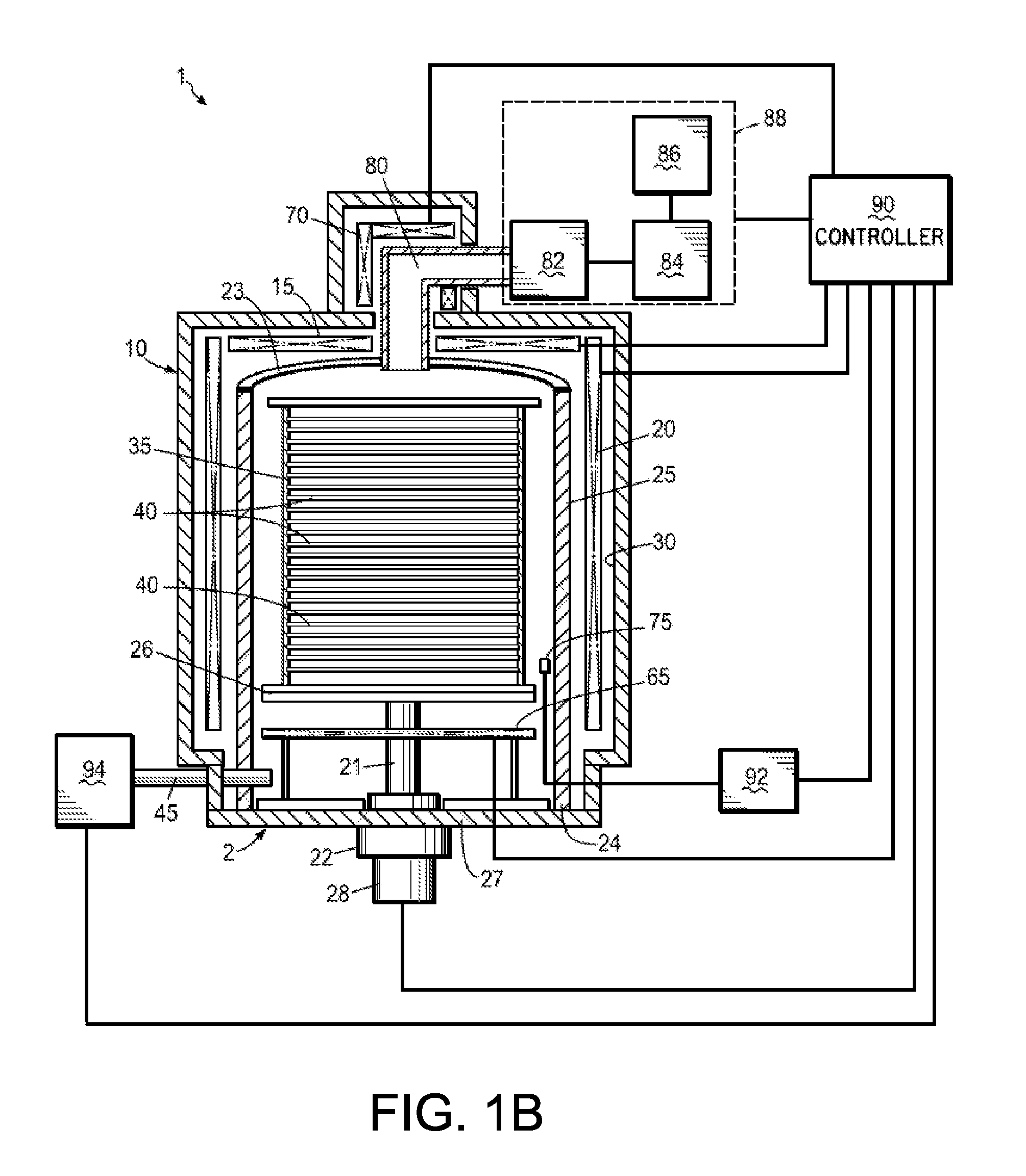

An in-situ hybrid film deposition method for forming a high-k dielectric film on a plurality of substrates in a batch processing system. The method includes loading the plurality of substrates into a process chamber of the batch processing system, depositing by atomic layer deposition (ALD) a first portion of a high-k dielectric film on the plurality of substrates, after depositing the first portion, and without removing the plurality of substrates from the process chamber, depositing by chemical vapor deposition (CVD) a second portion of the high-k dielectric film on the first portion, and removing the plurality of substrates from the process chamber. The method can further include alternatingly repeating the deposition of the first and second portions until the high-k dielectric film has a desired thickness. The method can still further include pre-treating the substrates and post-treating the high-k dielectric film in-situ prior to the removing.

Owner:TOKYO ELECTRON LTD

Sequential UV induced chemical vapor deposition

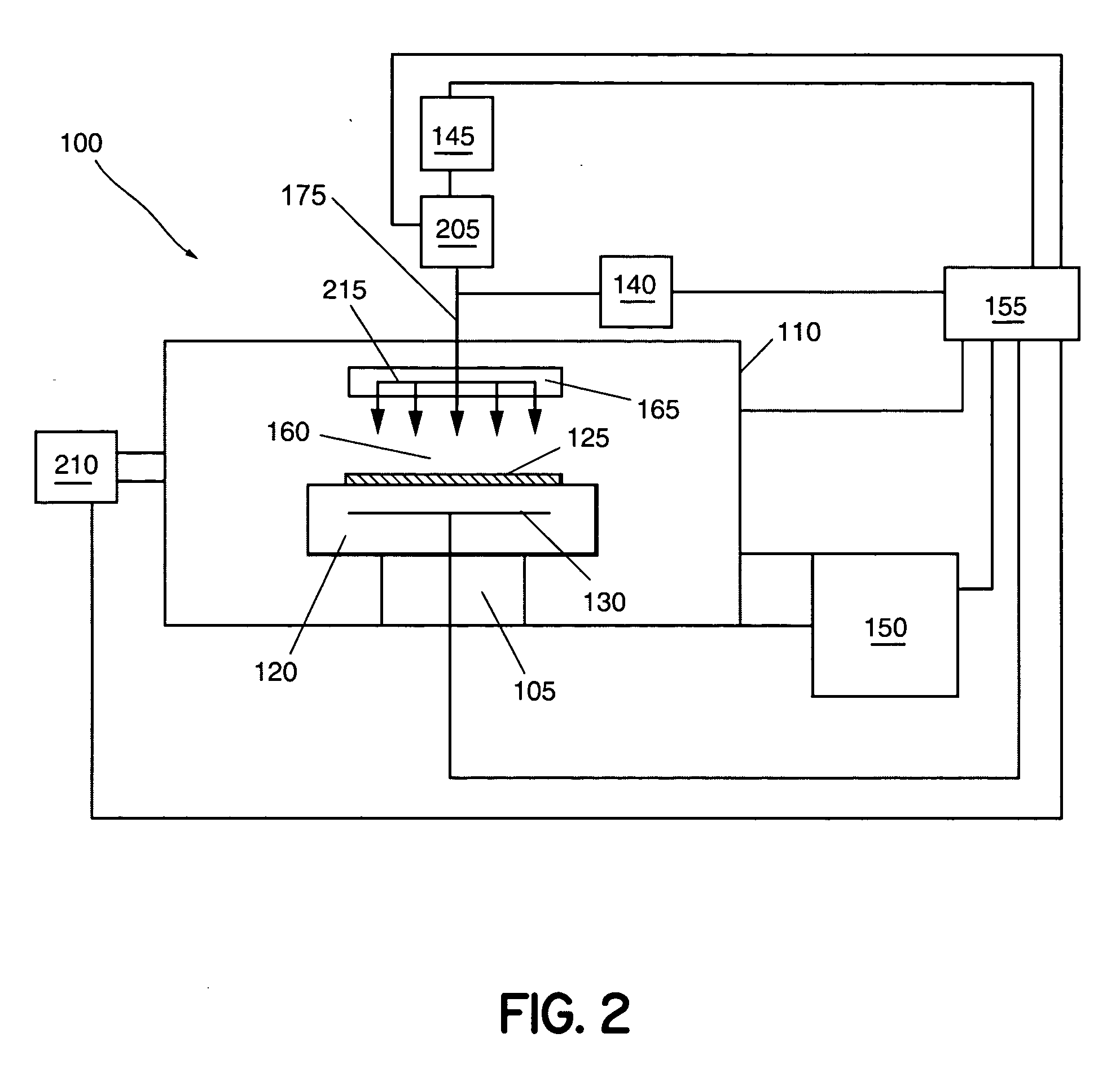

Ion-induced, UV-induced, and electron-induced sequential chemical vapor deposition (CVD) processes are disclosed where an ion flux, a flux of ultra-violet radiation, or an electron flux, respectively, is used to induce the chemical reaction in the process. The process for depositing a thin film on a substrate includes introducing a flow of a first reactant gas in vapor phase into a process chamber where the gas forms an adsorbed saturated layer on the substrate and exposing the substrate to a flux of ions, a flux of ultra-violet radiation, or a flux of electrons for inducing a chemical reaction of the adsorbed layer of the first reactant gas to form the thin film. A second reactant gas can be used to form a compound thin film. The ion-induced, UV-induced, and electron-induced sequential CVD process of the present invention can be repeated to form a thin film of the desired thickness.

Owner:NOVELLUS SYSTEMS

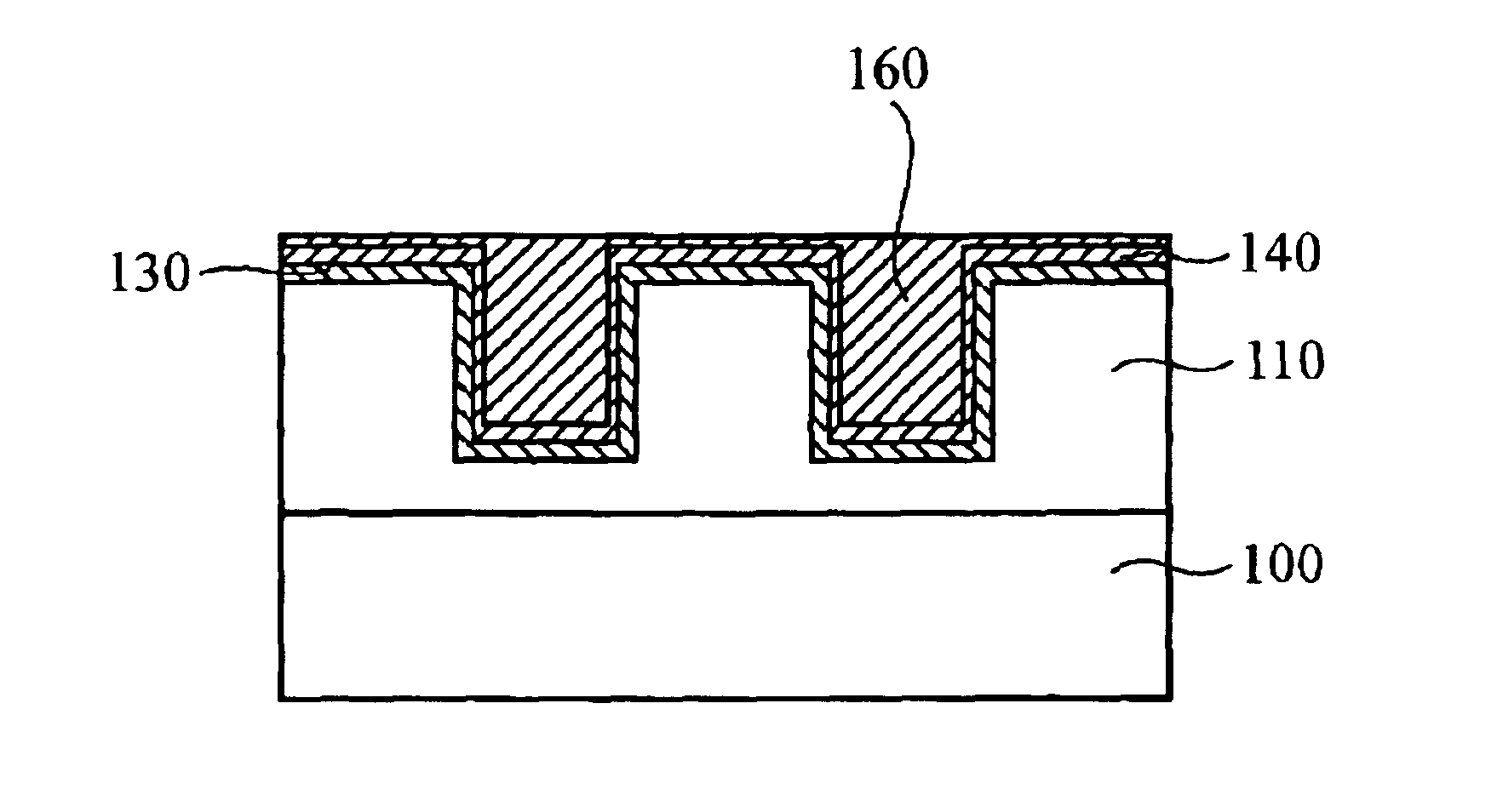

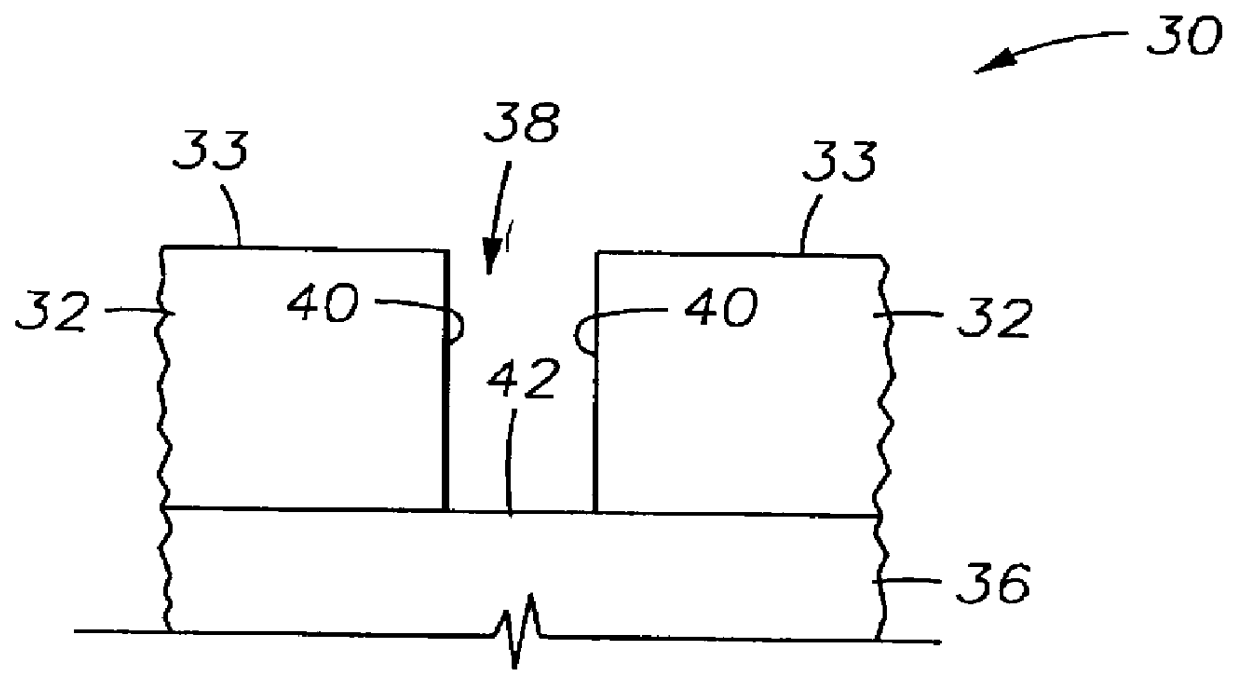

Device for reducing contact resistance of a metal

ActiveUS8736056B2Semiconductor/solid-state device detailsSolid-state devicesChemical vapor depositionAtomic layer deposition

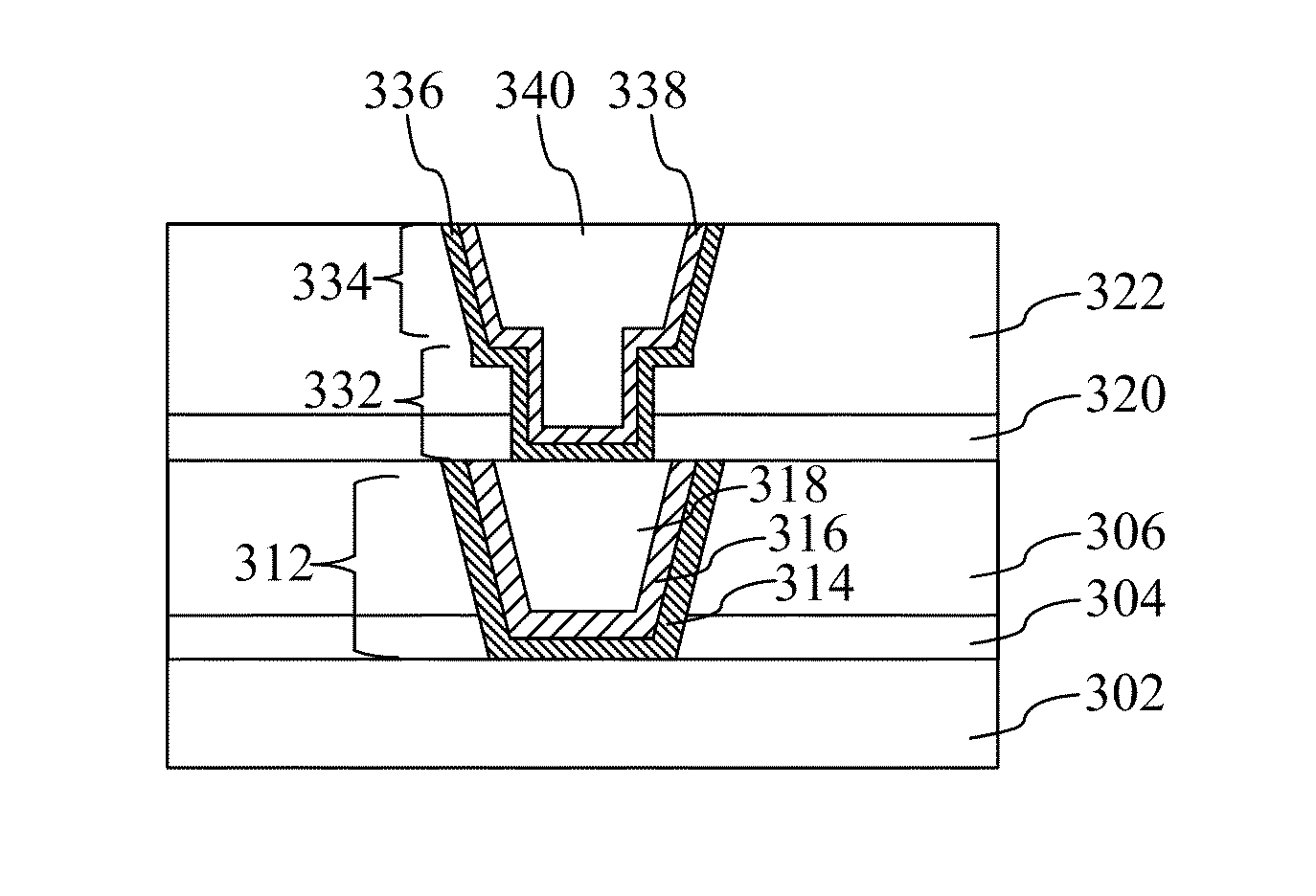

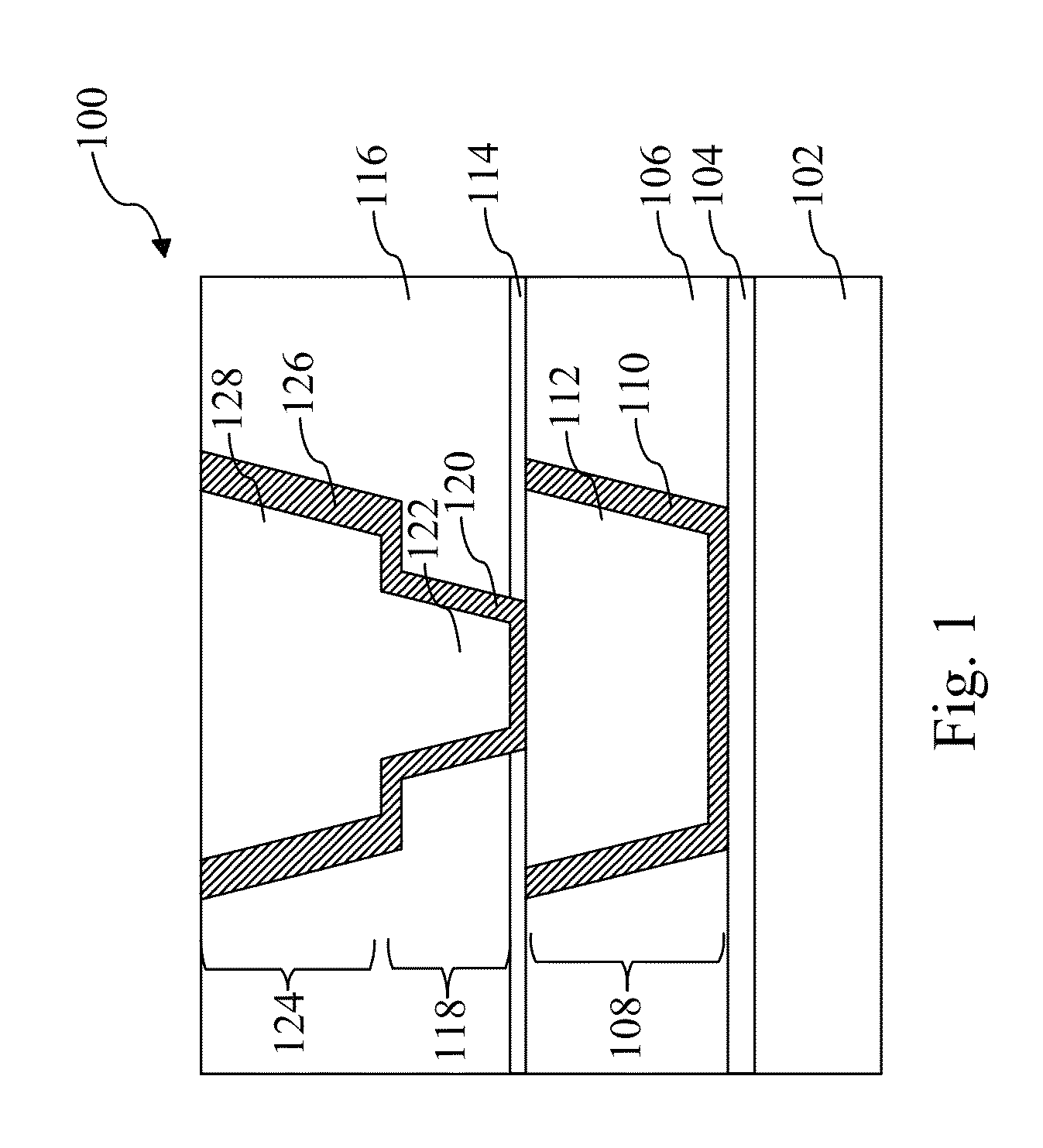

A structure for an integrated circuit with reduced contact resistance is disclosed. The structure includes a substrate, a cap layer deposited on the substrate, a dielectric layer deposited on the cap layer, and a trench embedded in the dielectric layer. The trench includes an atomic layer deposition (ALD) TaN or a chemical vapor deposition (CVD) TaN deposited on a side wall of the trench, a physical vapor deposition (PVD) Ta or a combination of the PVD Ta and a PVD TaN deposited on the ALD TaN or CVD TaN, and a Cu deposited on the PVD Ta or the combination of the PVD Ta and the PVD TaN deposited on the ALD TaN or the CVD TaN. The structure further includes a via integrated into the trench at bottom of the filled trench.

Owner:TAIWAN SEMICON MFG CO LTD

Method for silicon based dielectric chemical vapor deposition

Embodiments of the invention generally provide a method for depositing silicon-containing films. In one embodiment, a method for depositing silicon-containing material film on a substrate includes flowing a nitrogen and carbon containing chemical into a deposition chamber, flowing a silicon-containing source chemical having silicon-nitrogen bonds into the processing chamber, and heating the substrate disposed in the chamber to a temperature less than about 550 degrees Celsius. In another embodiment, the silicon containing chemical is trisilylamine and the nitrogen and carbon containing chemical is (CH3)3—N.

Owner:APPLIED MATERIALS INC

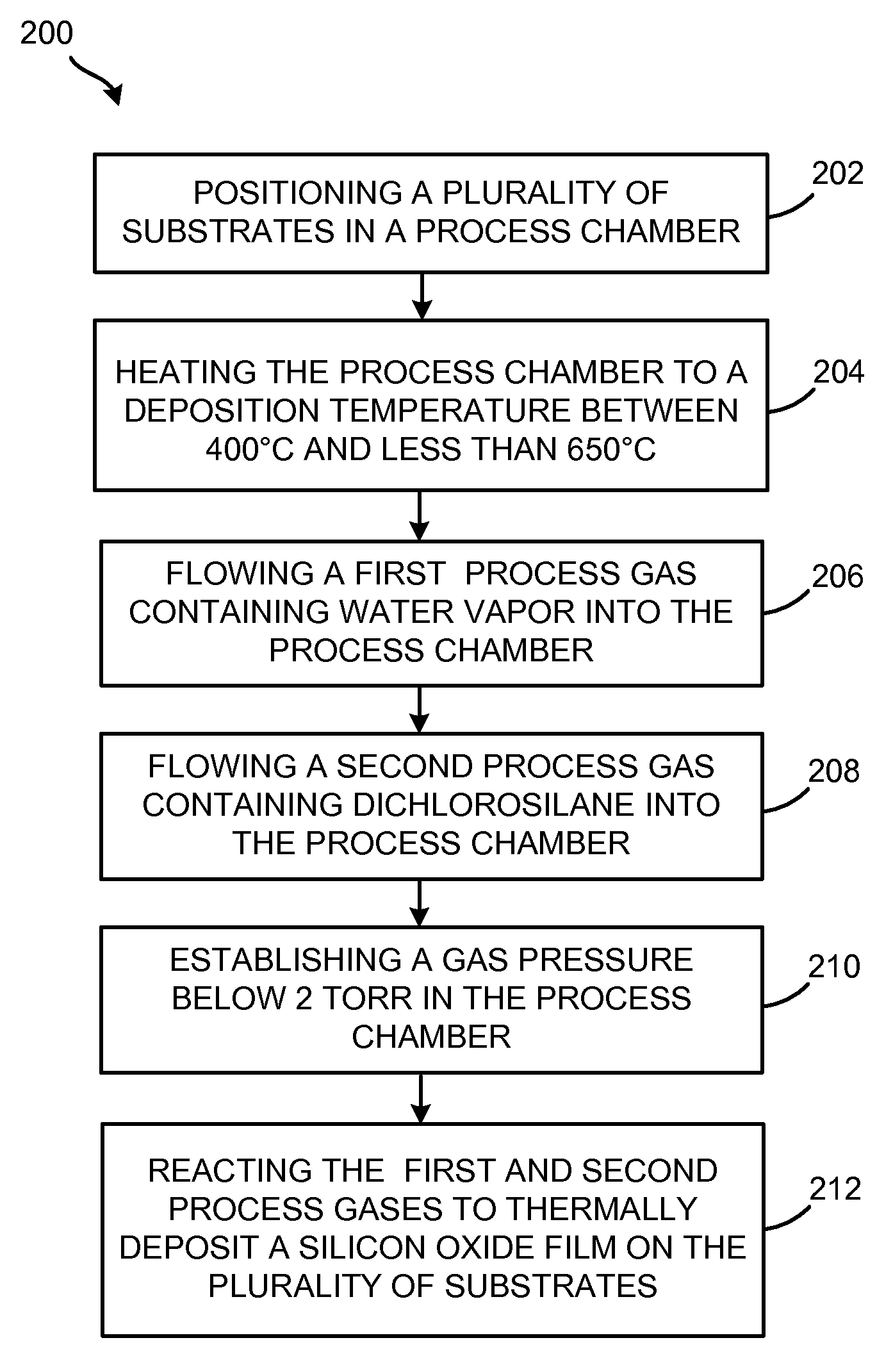

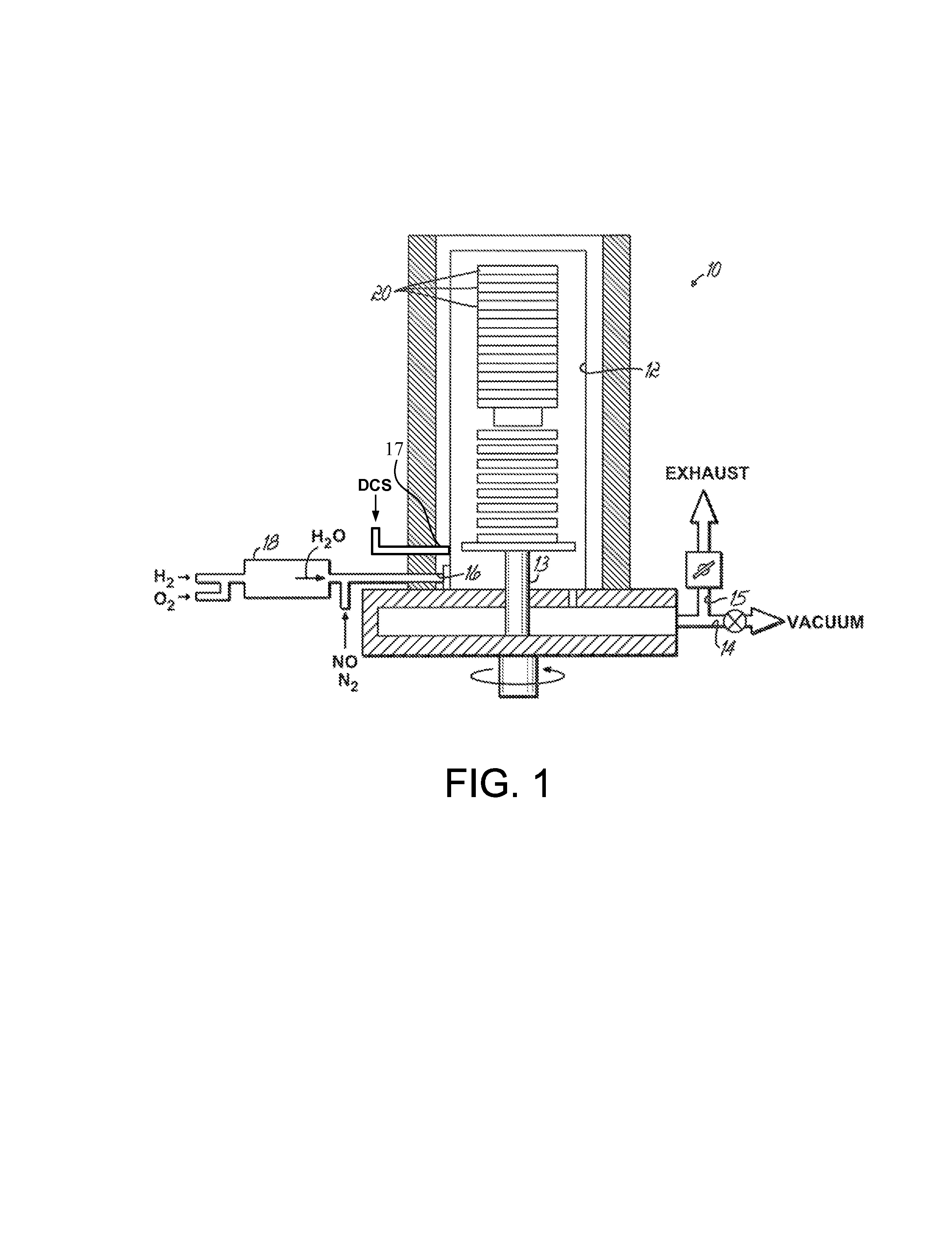

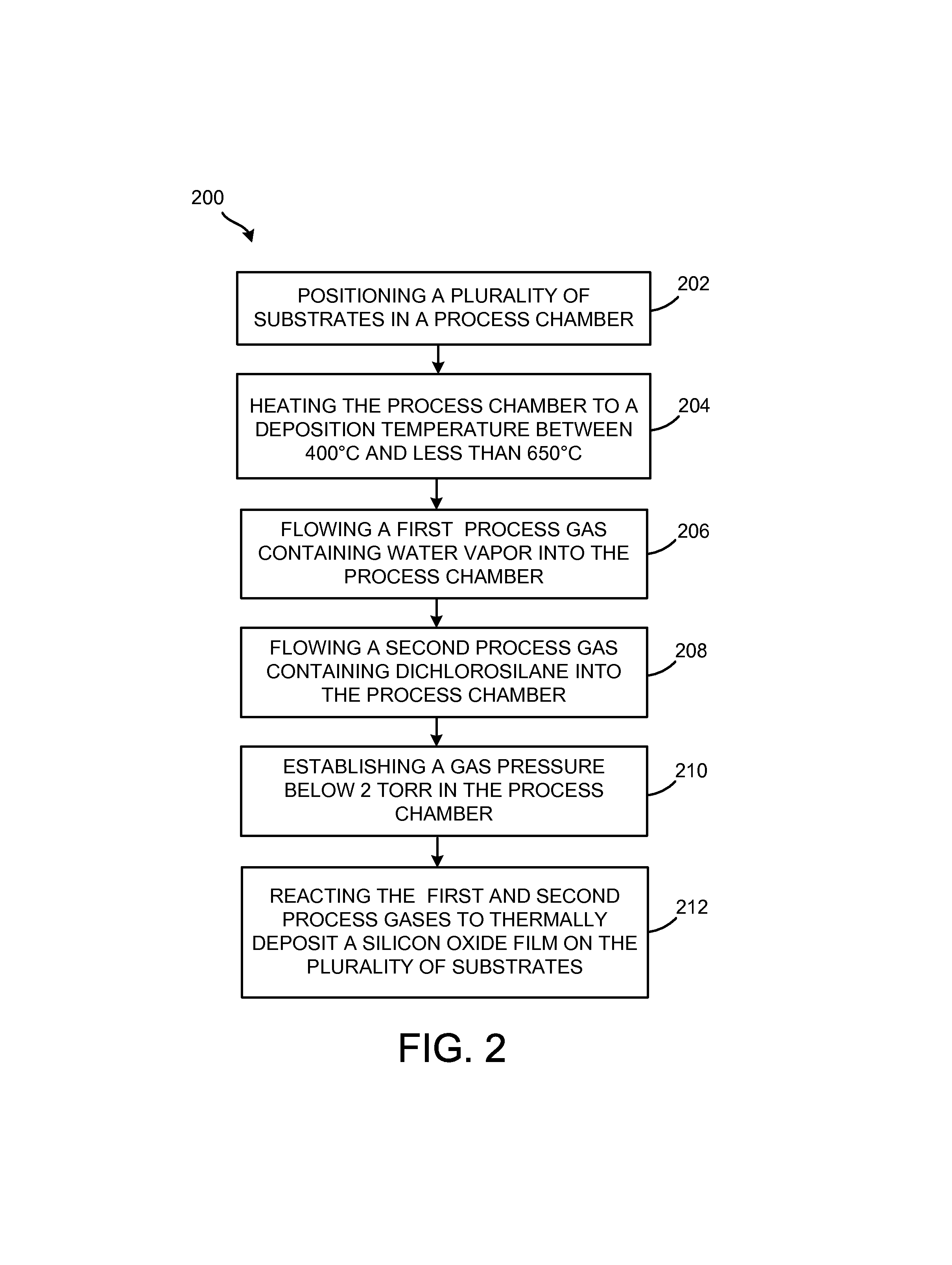

Low-temperature dielectric film formation by chemical vapor deposition

InactiveUS7994070B1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricWater vapor

A method for depositing a dielectric film on a substrate includes positioning a plurality of substrates in a process chamber, heating the process chamber to a deposition temperature between 400° C. and less than 650° C., flowing a first process gas comprising water vapor into the process chamber, flowing a second process gas comprising dichlorosilane (DCS) into the process chamber, establishing a gas pressure of less than 2 Torr, and reacting the first and second process gases to thermally deposit a silicon oxide film on the plurality of substrates. One embodiment further includes flowing a third process gas comprising nitric oxide (NO) gas into the process chamber while flowing the first process gas and the second process gas; and reacting the oxide film with the third process gas to form a silicon oxynitride film on the substrate.

Owner:TOKYO ELECTRON LTD

Apparatus and methods for plasma enhanced chemical vapor deposition of polymer coatings

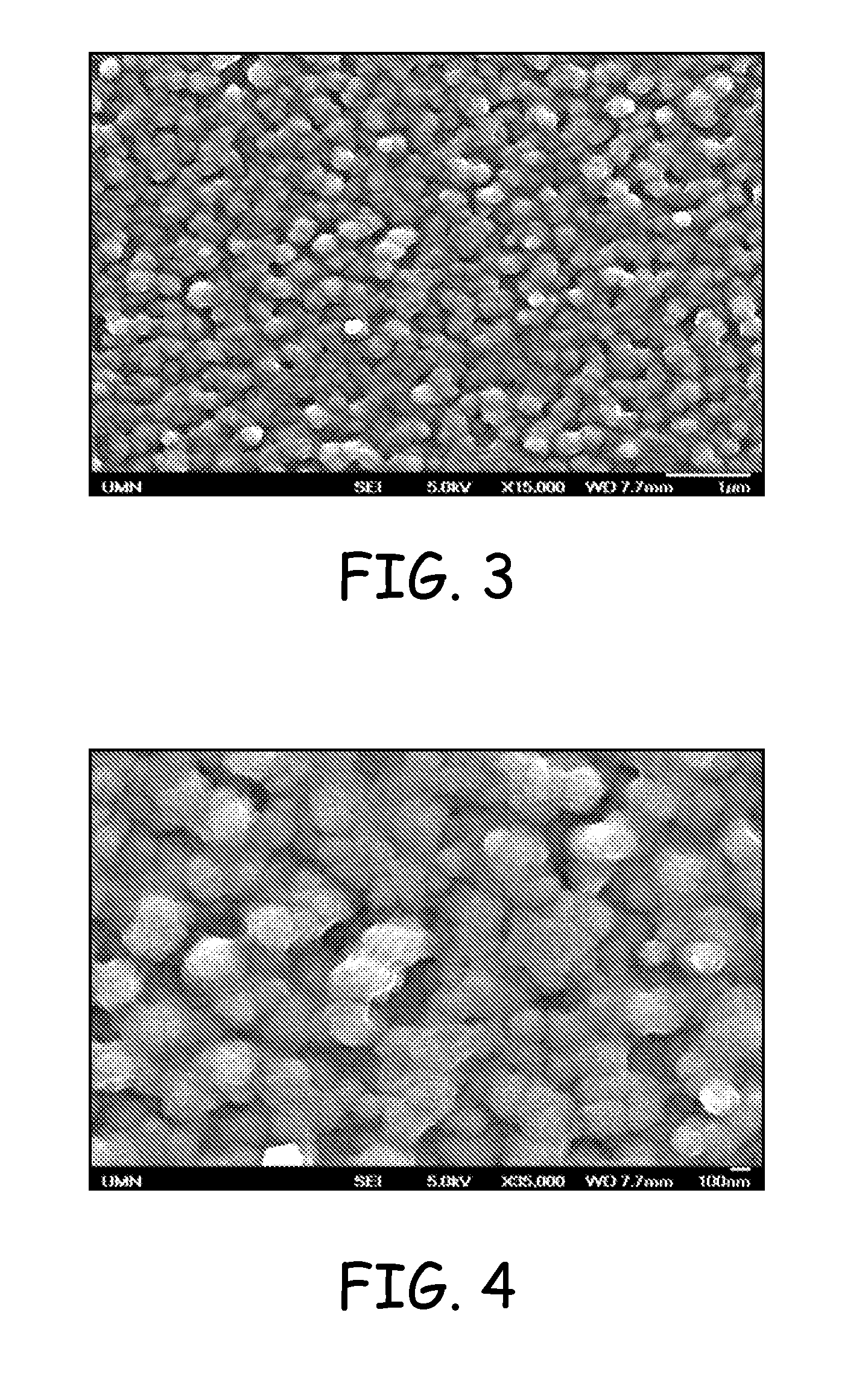

Apparatuses and methods are described that involve the deposition of polymer coatings on substrates. The polymer coatings generally comprise an electrically insulating layer and / or a hydrophobic layer. The hydrophobic layer can comprise fused polymer particles have an average primary particle diameter on the nanometer to micrometer scale. The polymer coatings are deposited on substrates using specifically adapted plasma enhanced chemical vapor deposition approaches. The substrates can include computing devices and fabrics.

Owner:LIQUIPEL IP

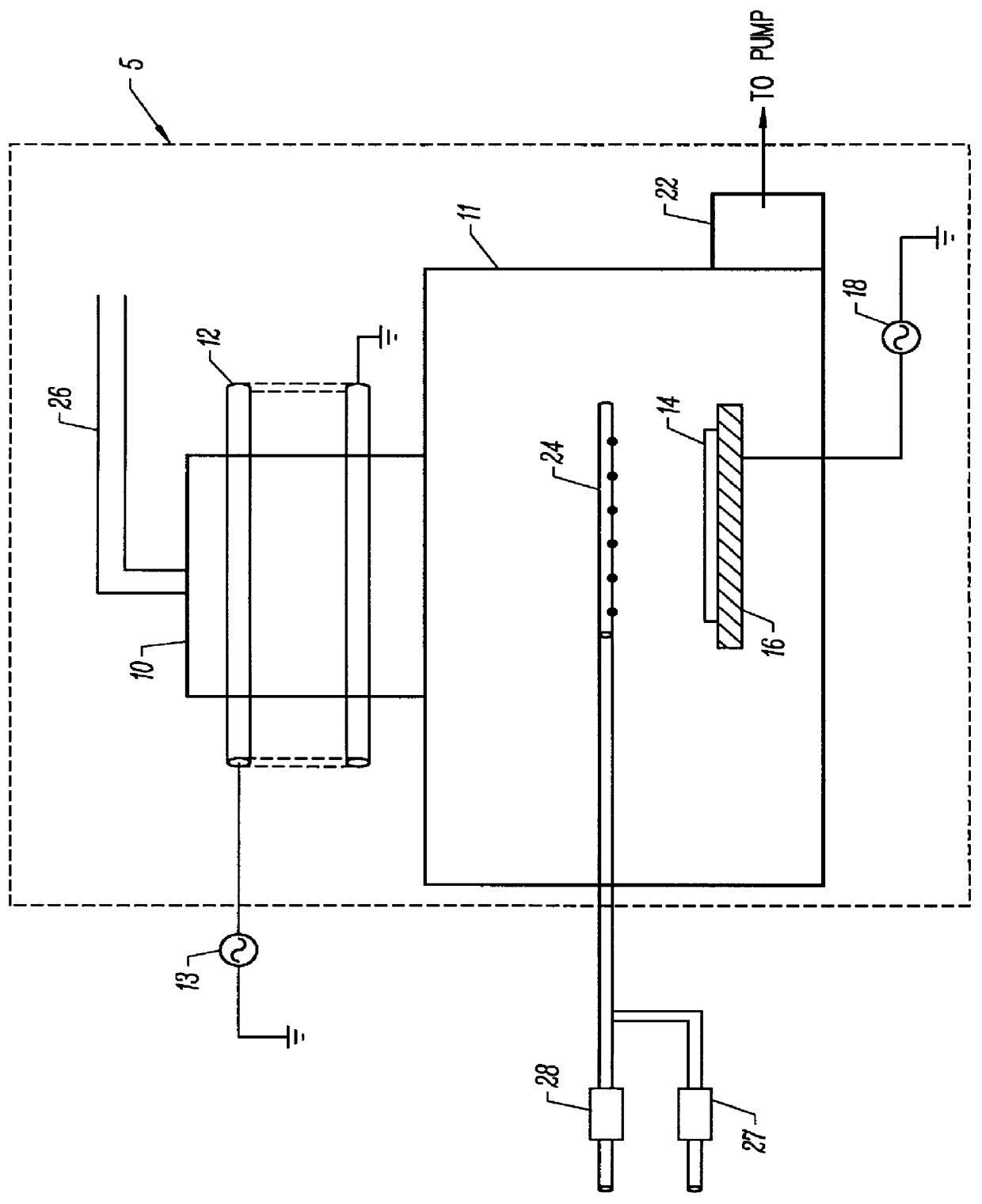

Chemical vapor deposition reactor

InactiveUS8778079B2Improve the deposition effectOptimize geometrySemiconductor/solid-state device manufacturingLiquid transferring devicesGas phaseProcess engineering

Owner:VALENCE PROCESS EQUIP

Method of forming copper interconnections and thin films using chemical vapor deposition with catalyst

InactiveUS6720262B2Semiconductor/solid-state device detailsSolid-state devicesCopper conductorSource material

A method of forming copper conductors for interconnecting active and passive elements as well as signal and power lines for circuits and devices on silicon wafers is disclosed. The method disclosed herein involves with using catalysts in conjunction with a chemical vapor deposition(CVD) process with typically using copper as a source material for forming interconnecting conductors. Interconnecting method for filling trenches, via holes, contacts, large trenches and holes for power devices and lines as well as for forming large passive elements is also disclosed. Disclosed herein are also a method of filling narrow and deep trenches and small in diameter and deep holes, and a method of forming very thin film on the flat top surface so that an etchback process, such as wet or dry etchback as well as plasma etchback processes, can be used for removing a thin film in preparation for subsequent processing steps, thereby rather expensive chemical mechanical polishing(CMP) process need not be used.

Owner:ASM KOREA LTD

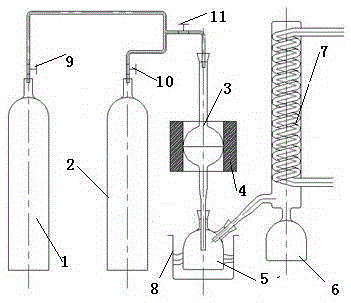

Method for preparing precursor for chemical vapor deposition of metallic rhenium

The invention discloses a method for preparing a precursor for chemical vapor deposition of metallic rhenium and belongs to the technical field of material preparation. According to the method, ReCl5 is made to react in an oxidizing atmosphere, efficient solid-liquid-gas separation is conducted on reactants and products with a sand core filter bulb so that reactants, reaction products and waste gas can be effectively separated, the reaction products ReOCl4 and ReO3Cl are gathered in a collection vessel heated by an oil bath pan at the same time, oxygen introduction is stopped after reaction ends, circulation of inert gases is maintained, a tube furnace is cooled, the oil bath pan is heated at the same time to enable ReO3Cl to volatilize to enter a rectification unit to be collected, ReOCl4 is purified, and then the high-purity precursor ReOCl4 for chemical vapor deposition of metallic rhenium is obtained. By the adoption of the method, reaction efficiency is high, ReOCl4 and ReO3Cl are separated through rectification, and the purity of the product ReOCl4 is improved.

Owner:海朴精密材料(苏州)有限责任公司

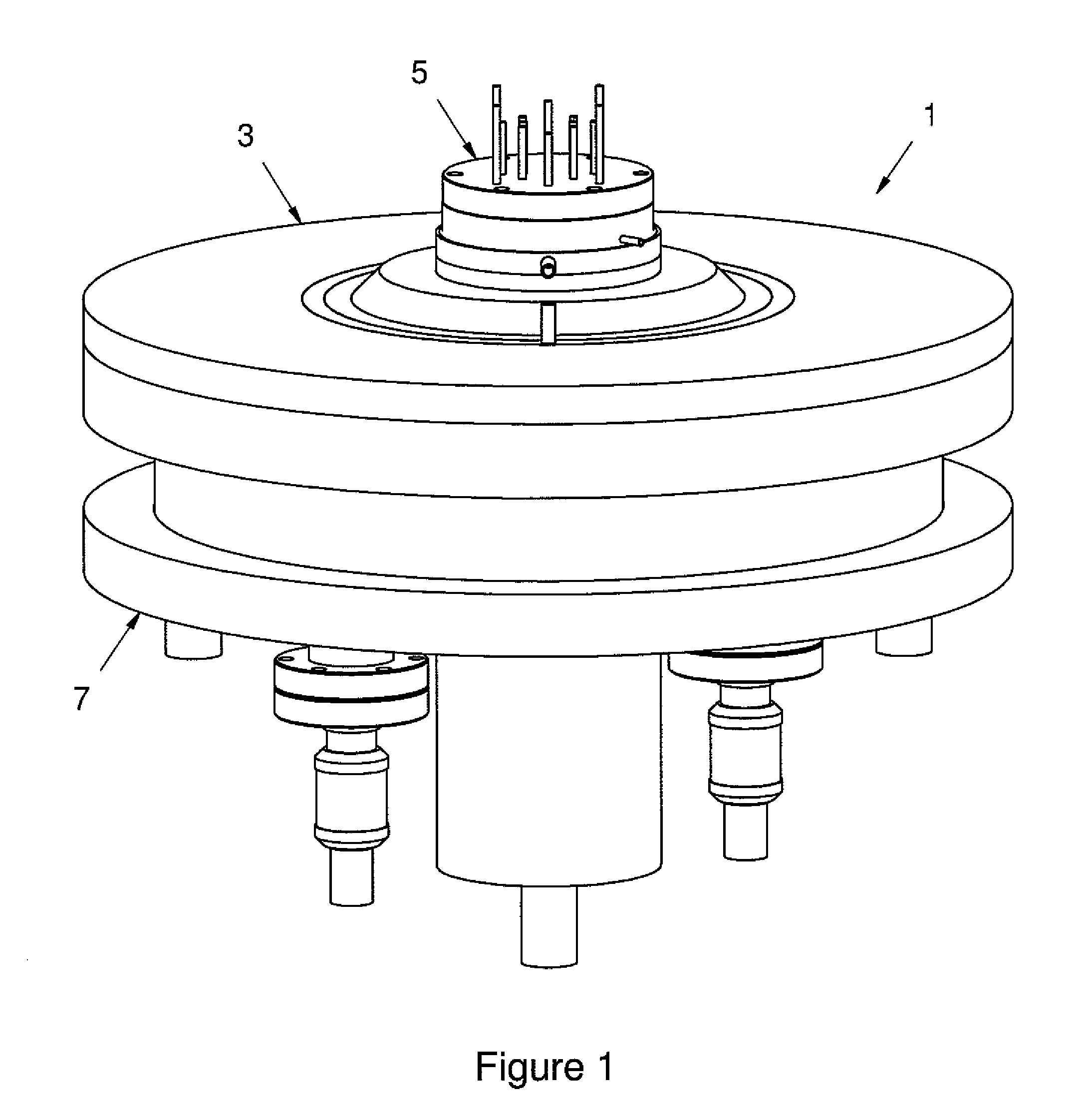

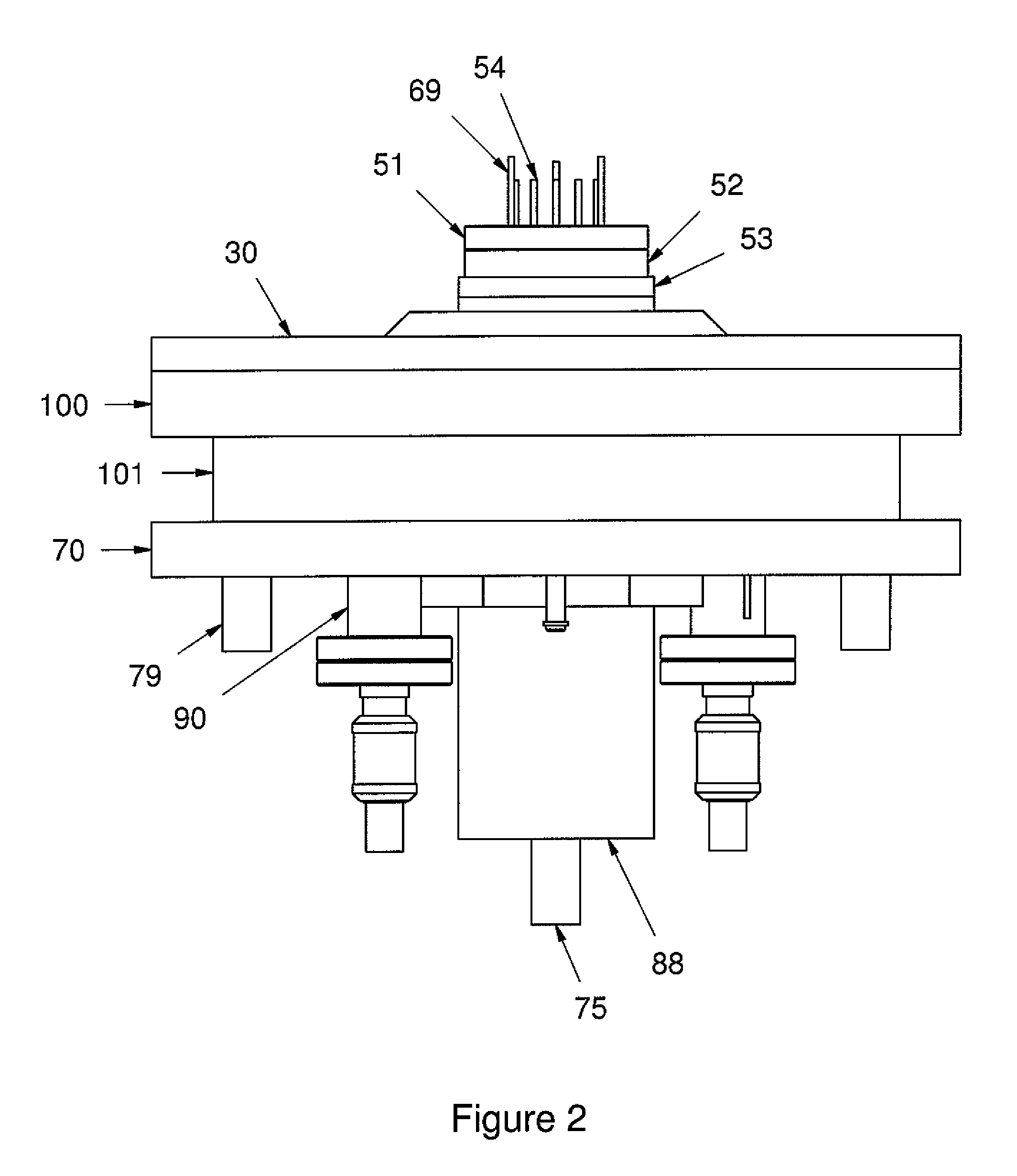

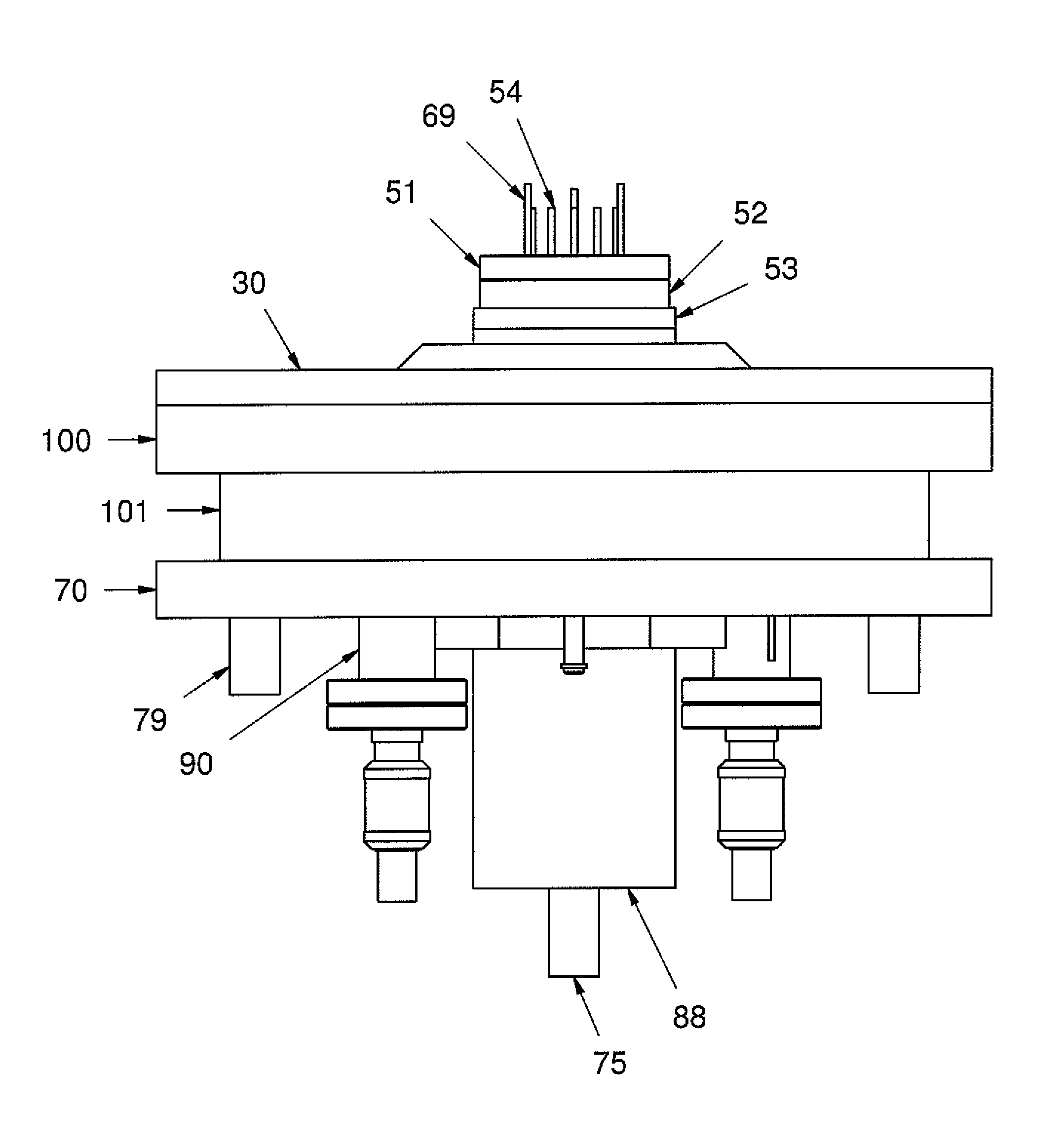

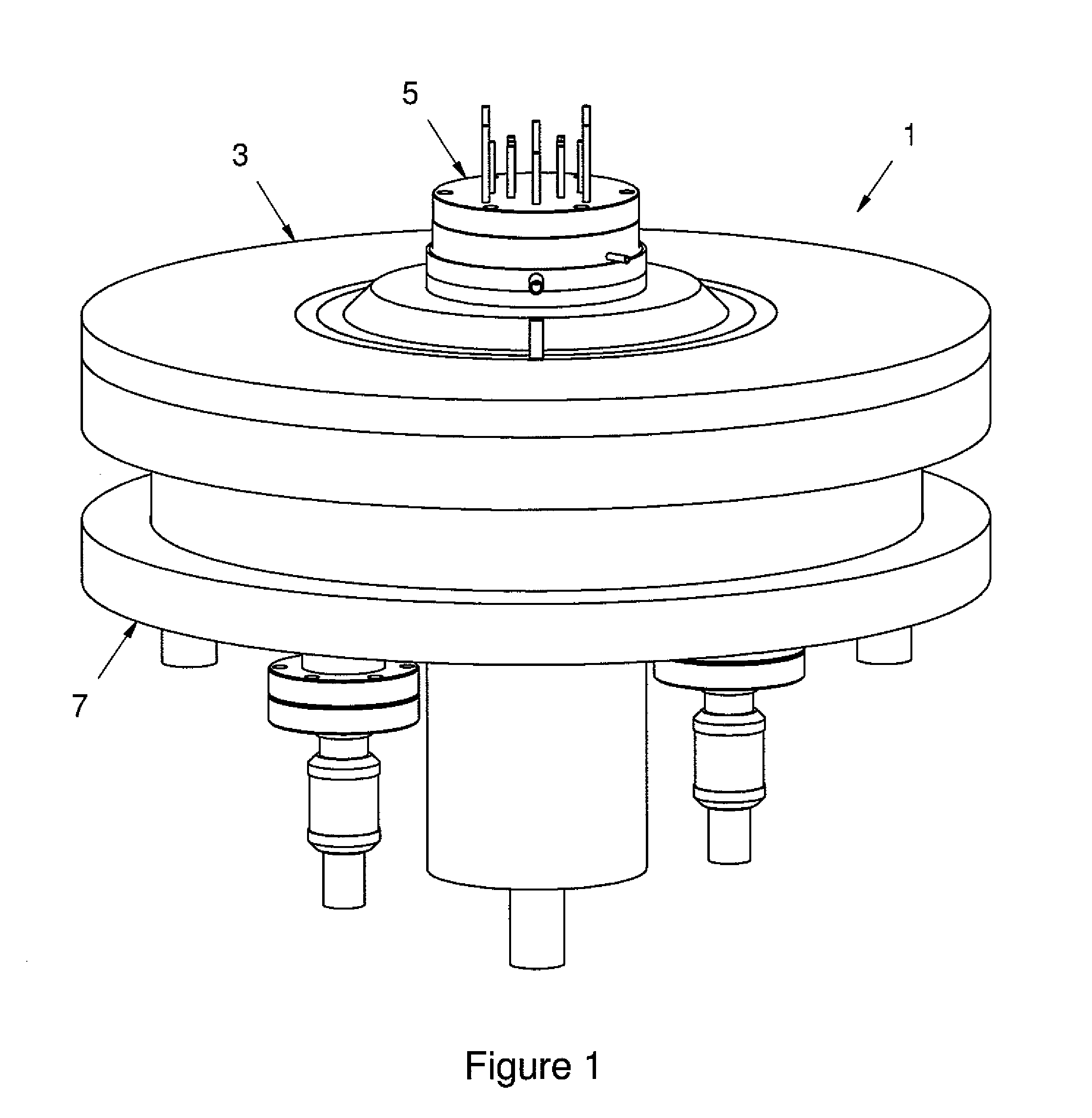

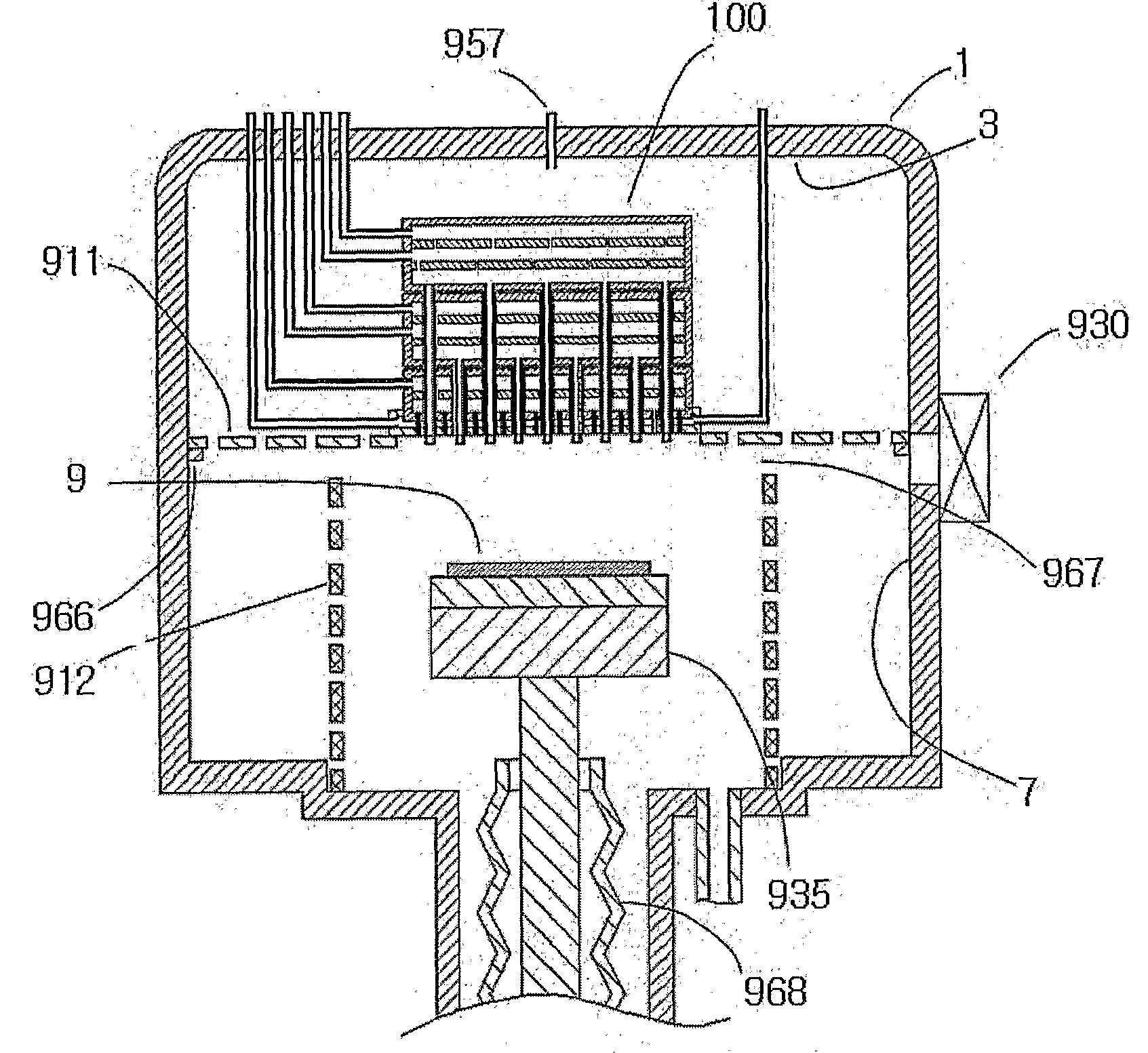

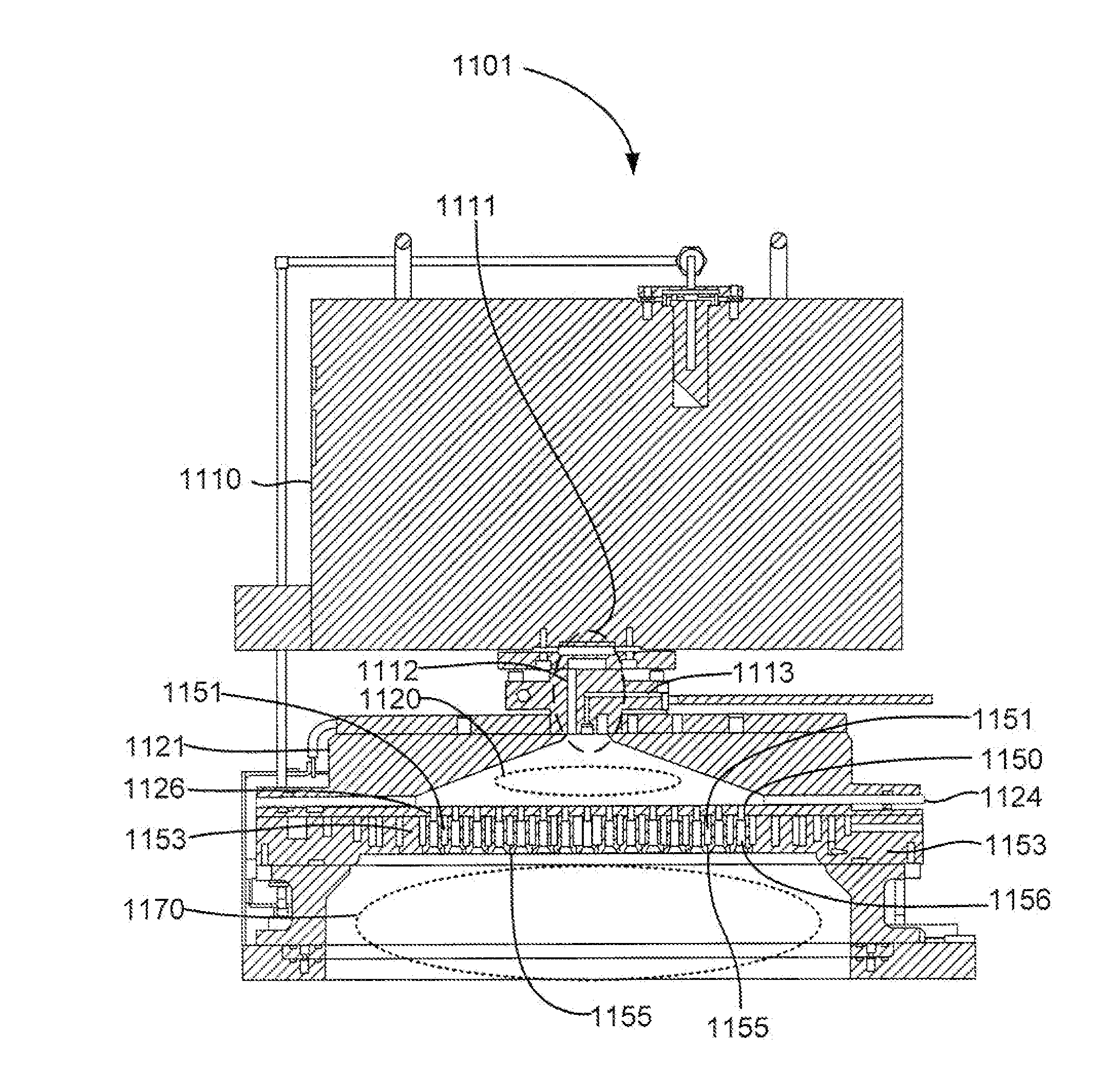

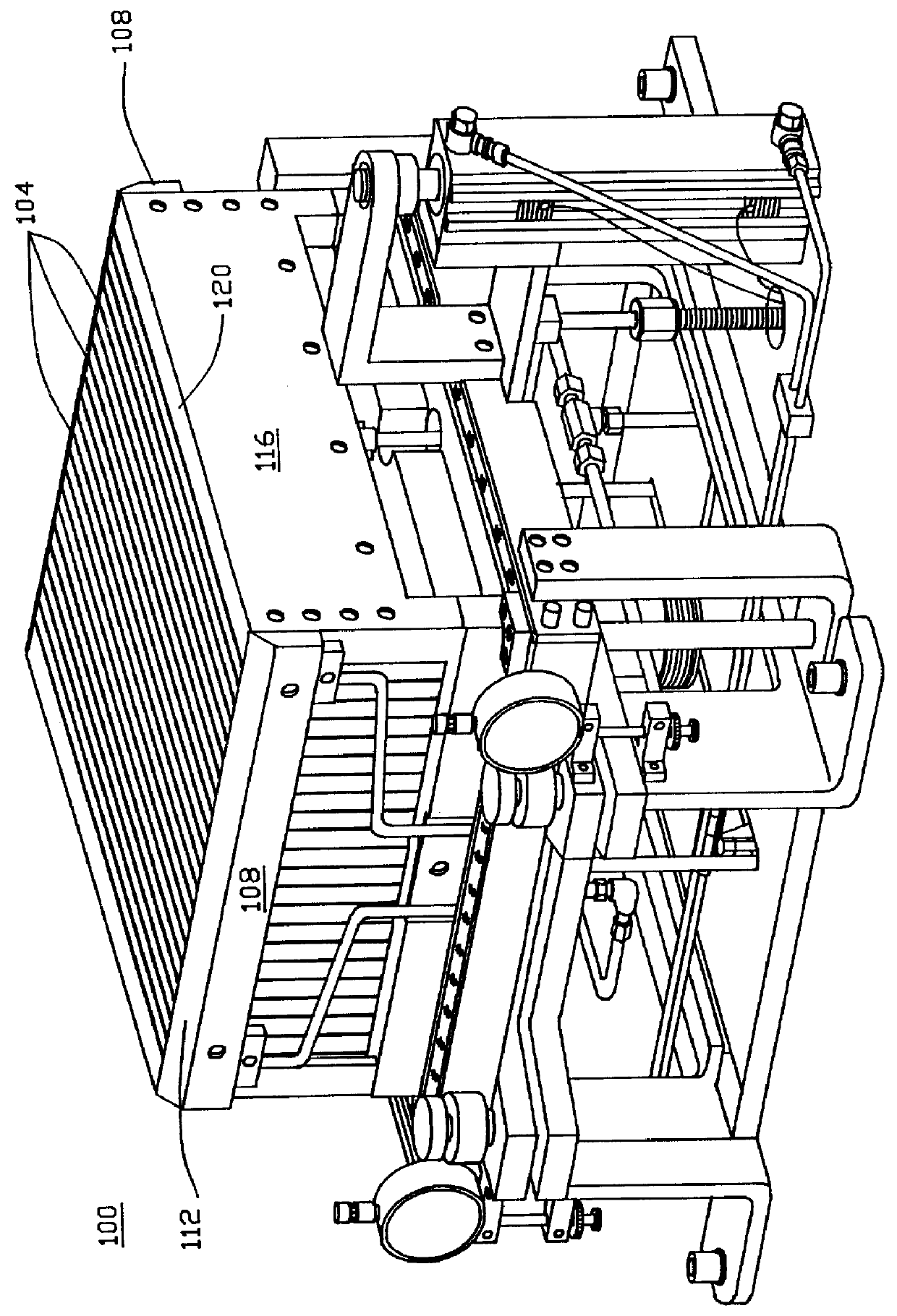

Chemical vapor deposition reactor

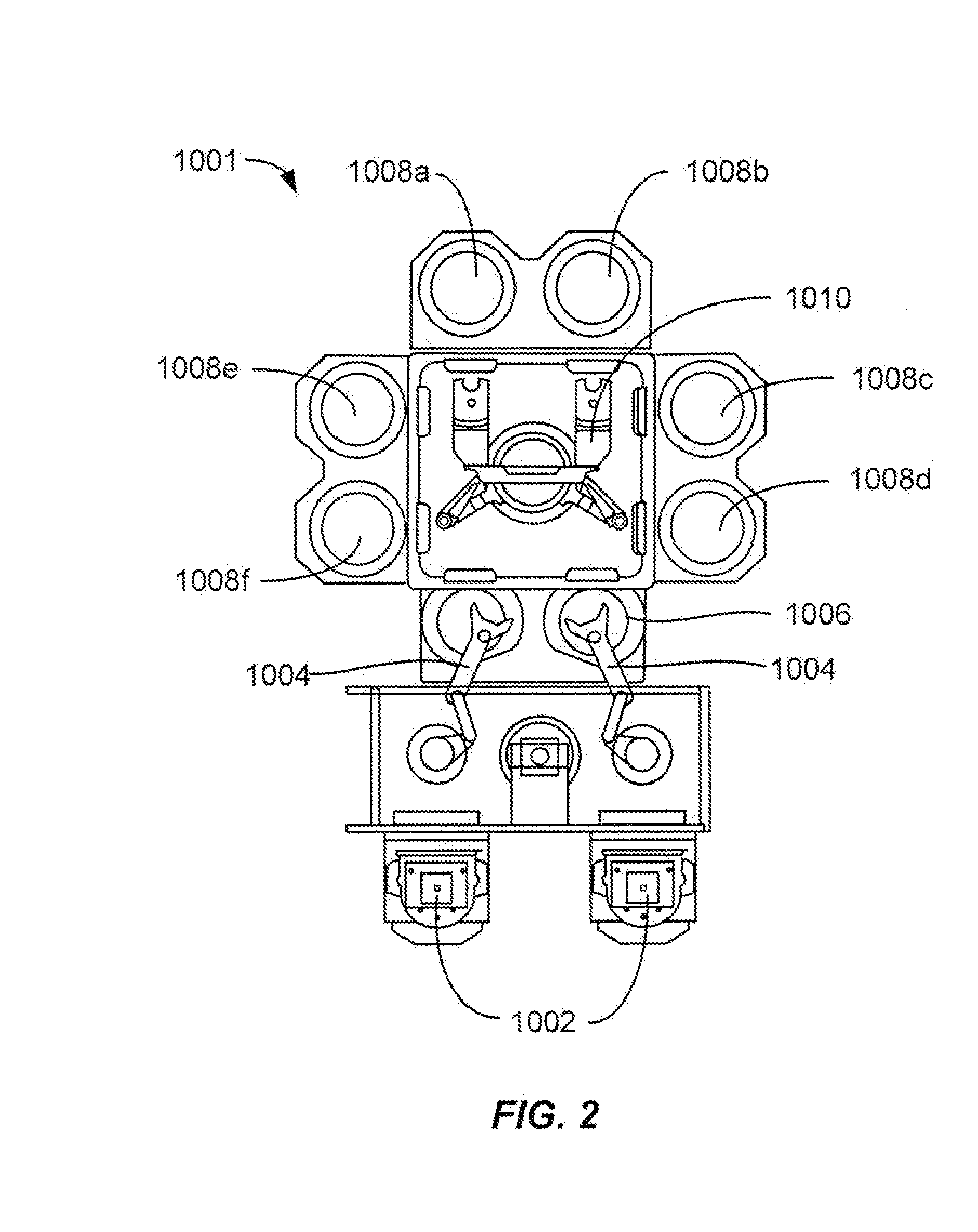

InactiveUS20120111271A1Improve the deposition effectOptimize geometrySemiconductor/solid-state device manufacturingLiquid transferring devicesGas phaseProcess engineering

A CVD reactor, such as a MOCVD reactor conducting metalorganic chemical vapor deposition of epitaxial layers, is provided. The CVD or MOCVD reactor generally comprises a flow flange assembly, adjustable proportional flow injector assembly, a chamber assembly, and a multi-segment center rotation shaft. The reactor provides a novel geometry to specific components that function to reduce the gas usage while also improving the performance of the deposition.

Owner:VALENCE PROCESS EQUIP

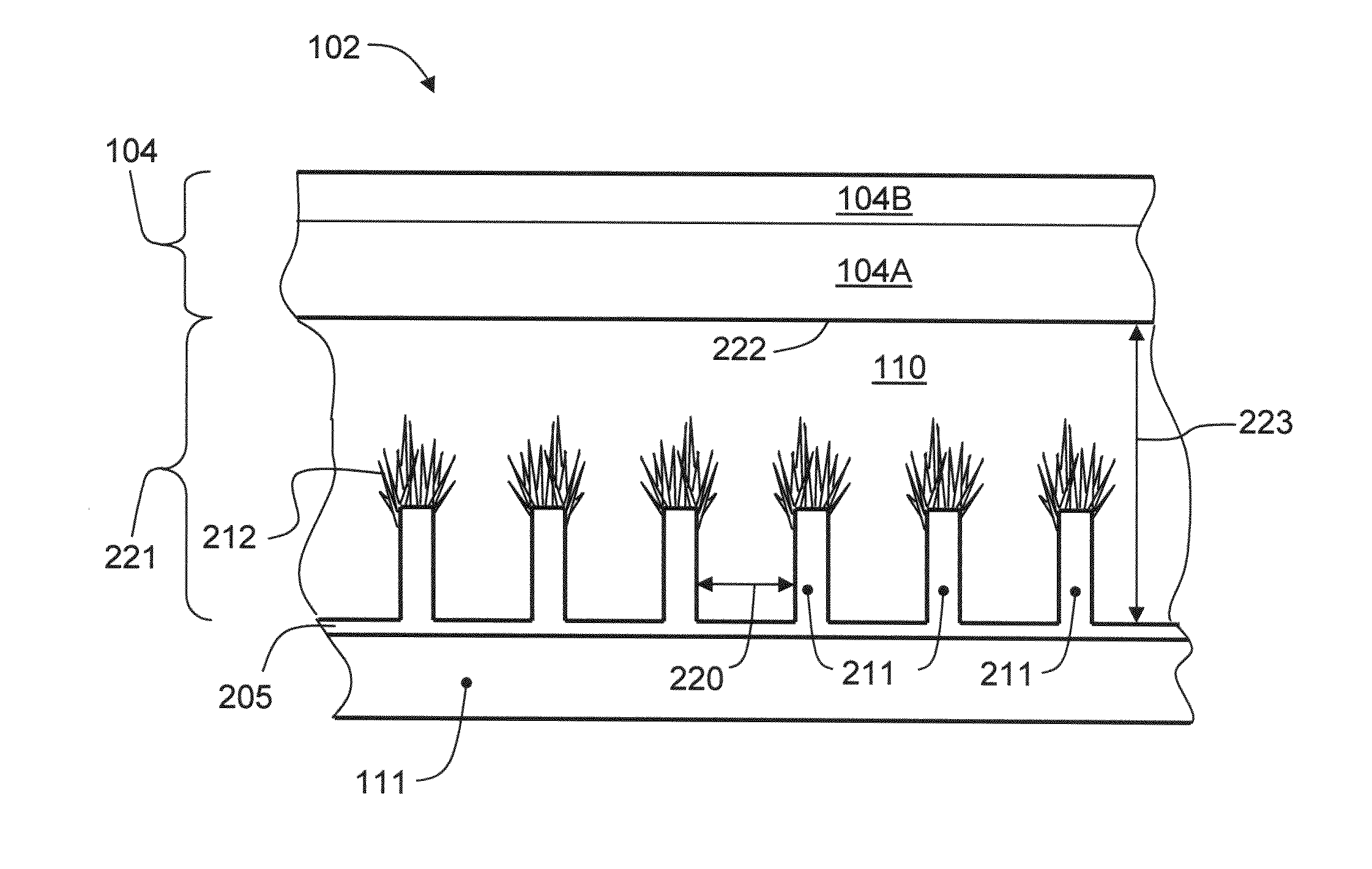

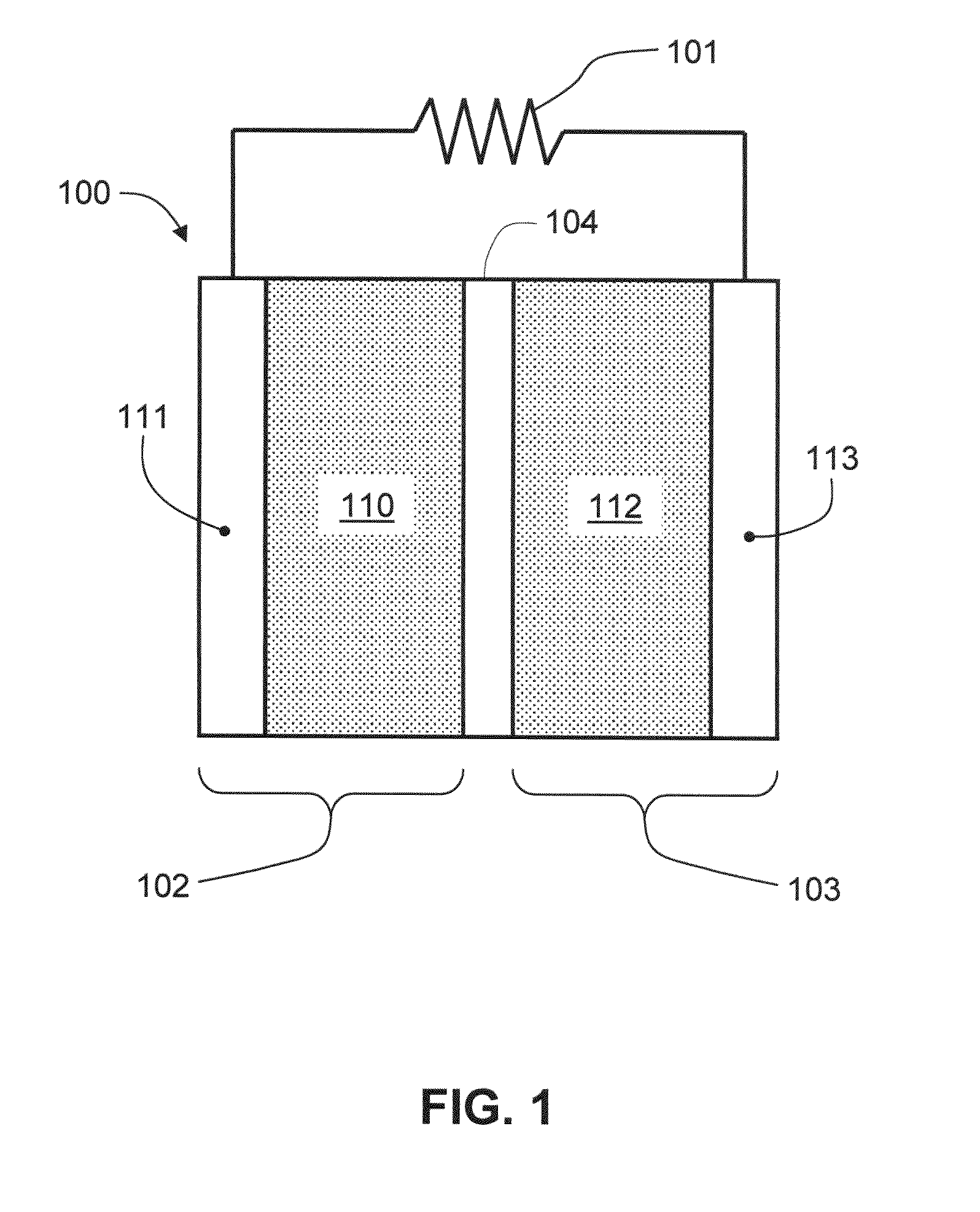

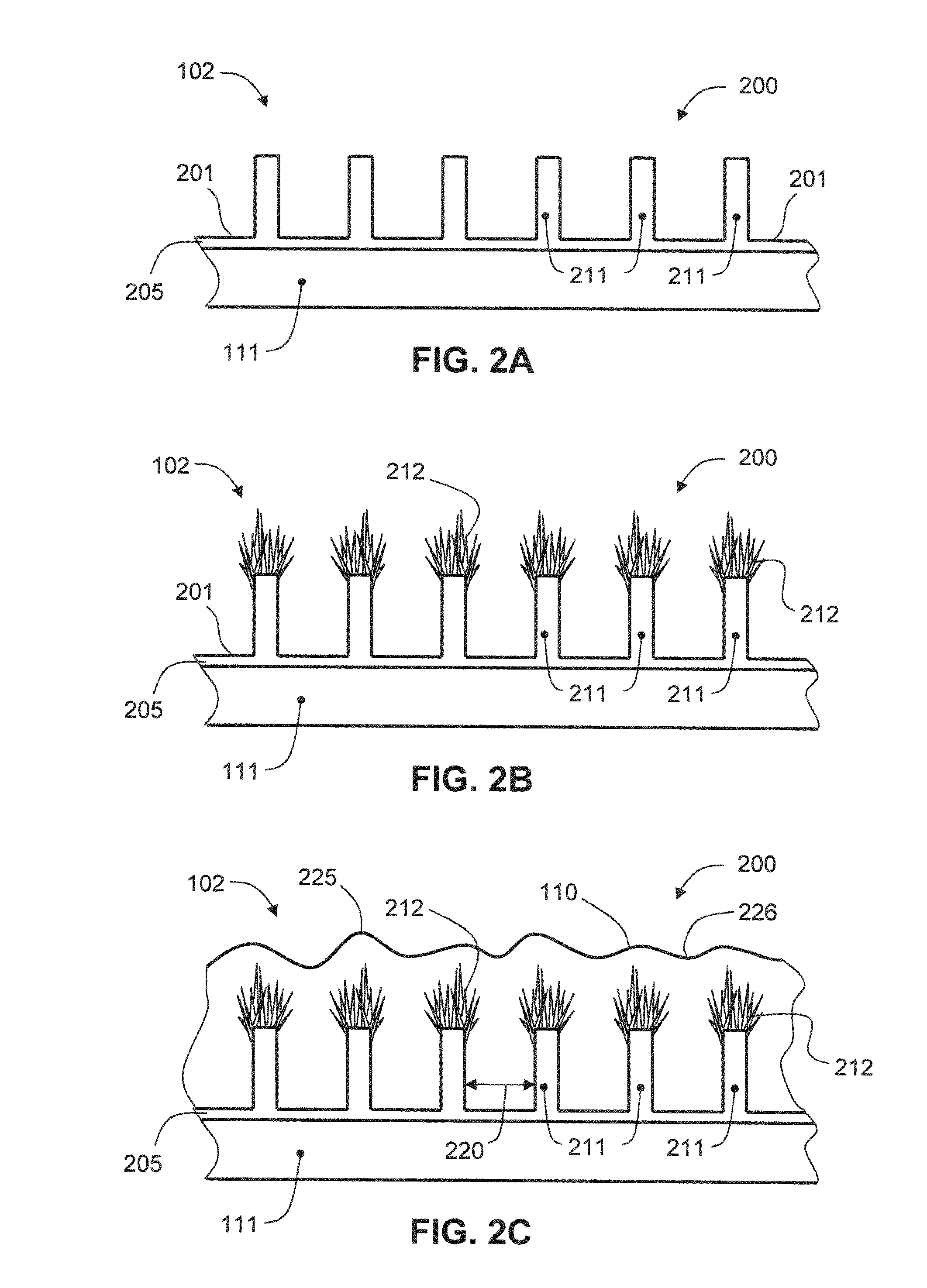

Thin film electrochemical energy storage device with three-dimensional anodic structure

InactiveUS20100216026A1Final product manufactureElectrode carriers/collectorsPorosityMicro structure

A method for forming a battery from via thin-film deposition processes is disclosed. A mesoporous carbon material is deposited onto a surface of a conductive substrate that has high surface area, conductive micro-structures formed thereon. A porous, dielectric separator layer is then deposited on the layer of mesoporous carbon material to form a half cell of an energy storage device. The mesoporous carbon material is made up of CVD-deposited carbon fullerene “onions” and carbon nano-tubes, and has a high porosity capable of retaining lithium ions in concentrations useful for storing significant quantities of electrical energy. Embodiments of the invention further provide for the formation of an electrode having a high surface area conductive region that is useful in a battery structure. In one configuration the electrode has a high surface area conductive region comprising a porous dendritic structure that can be formed by electroplating, physical vapor deposition, chemical vapor deposition, thermal spraying, and / or electroless plating techniques.

Owner:APPLIED MATERIALS INC

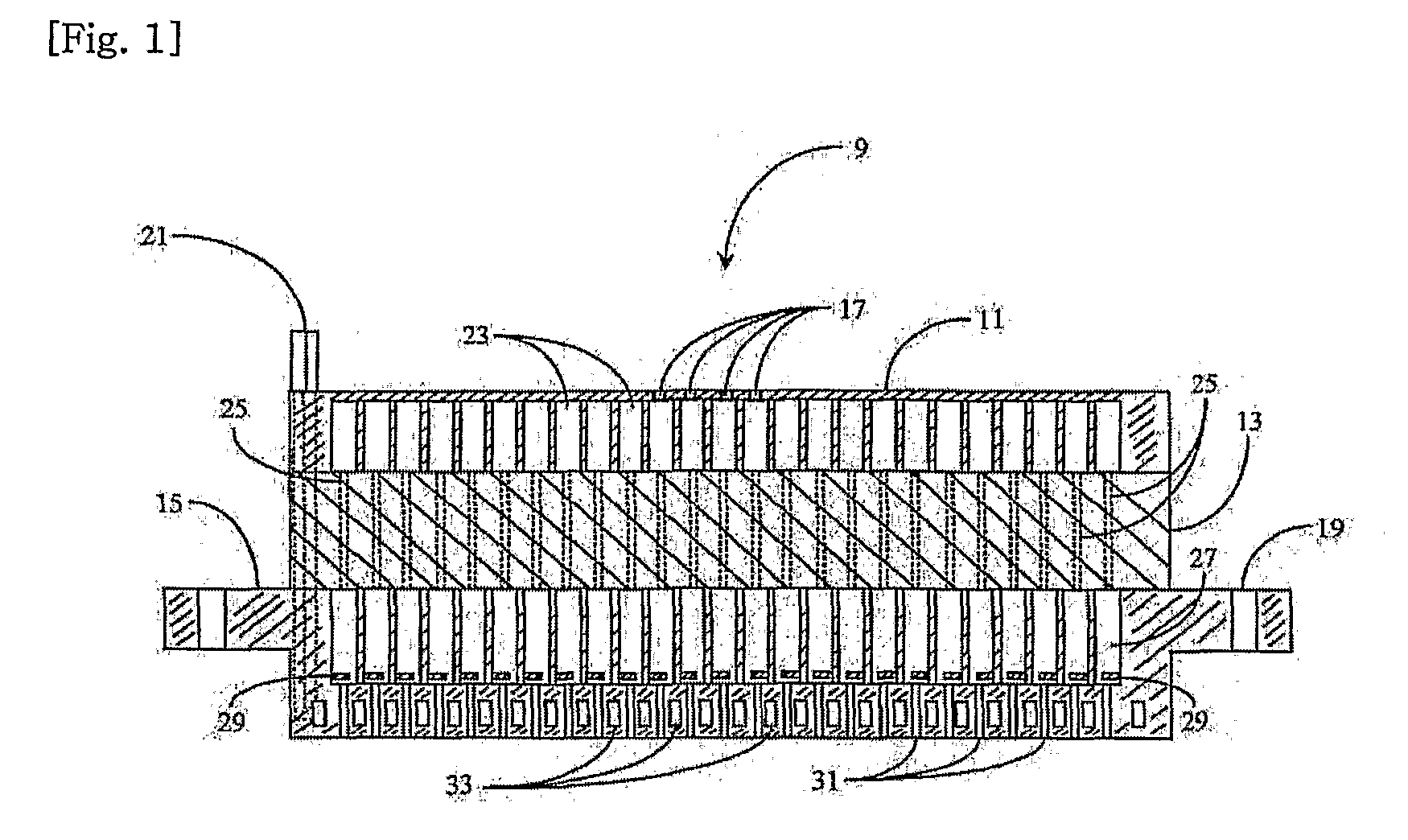

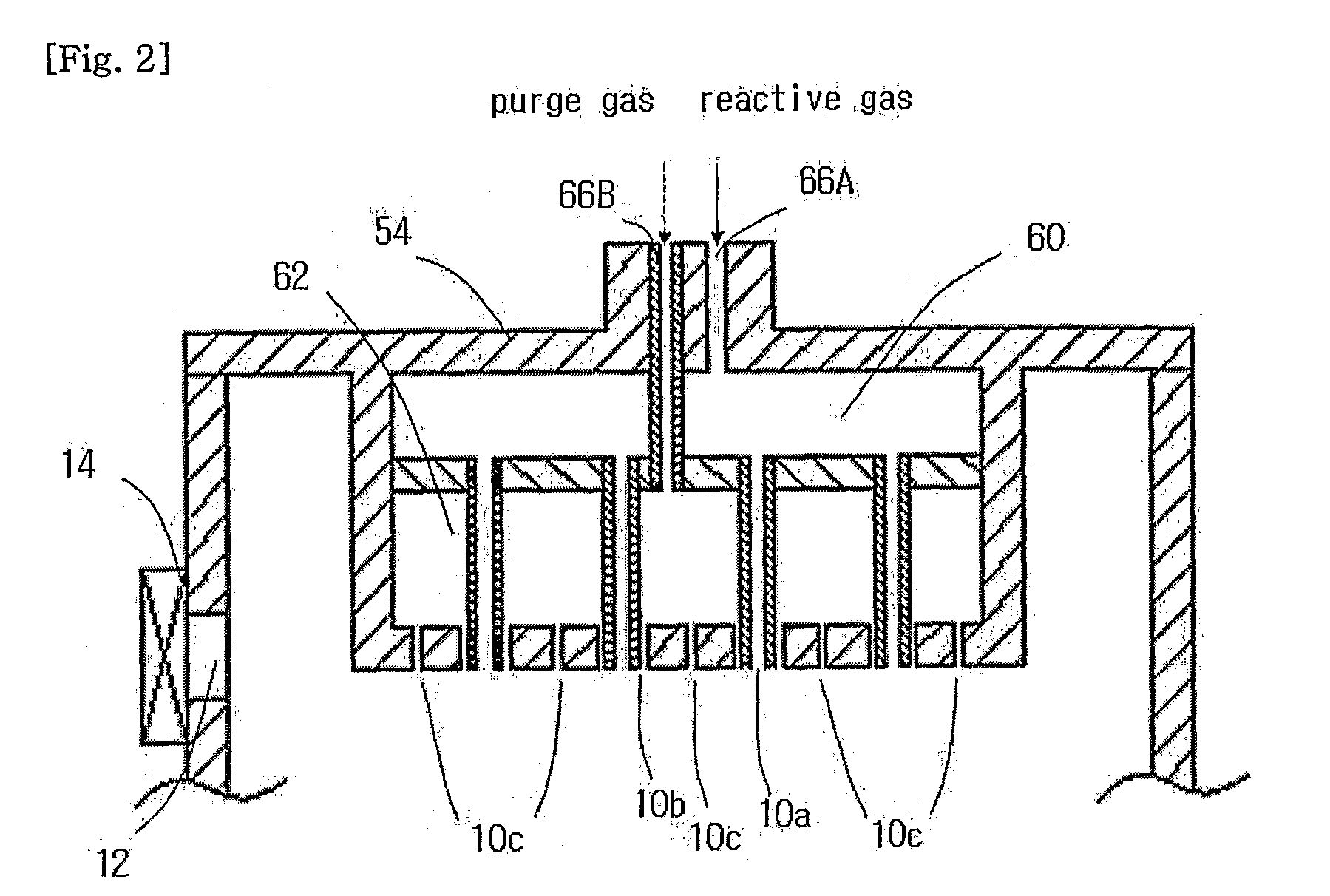

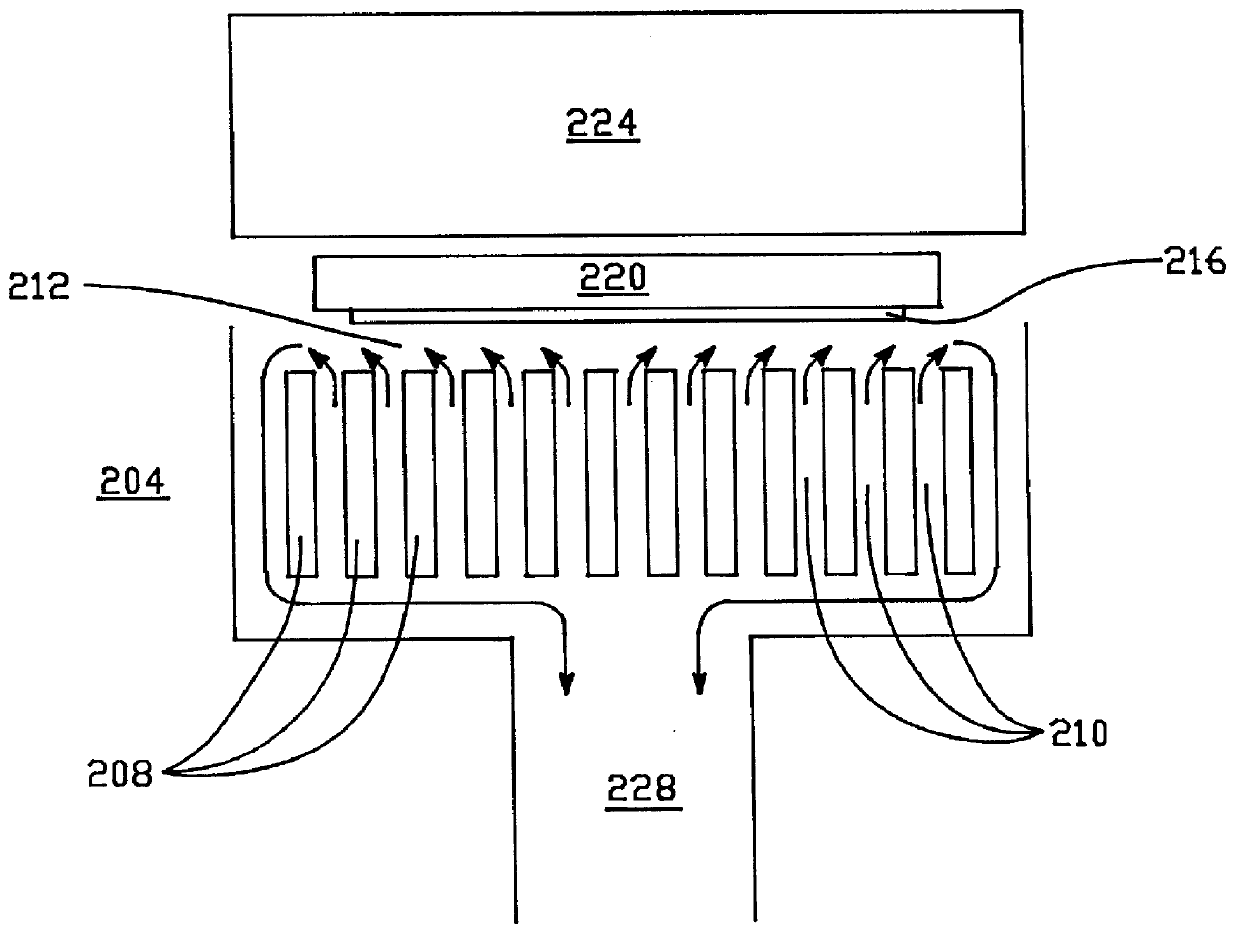

Apparatus of chemical vapor deposition with a showerhead regulating injection velocity of reactive gases postively and method thereof

ActiveUS20090169744A1Suppress DiffuseAvoid pollutionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingReactive gasGas phase

The present invention is related to an apparatus and a method for chemical vapor deposition (CVD) using a showerhead through which a reactive gas of at least one kind and a purge gas is injected over a substrate on which a film is growing. A plural number of reactive gas showerhead modules are laid on a purge gas showerhead module. Each reactive gas is injected from a bottom of the showerhead after flowing through the showerhead as separated, thereby preventing the reactive gases from causing homogeneous gas phase reactions and from generating unwanted particles at the inside of the showerhead. And purge gas is injected from the bottom surface of the showerhead by forming a protective curtain, thereby suppressing diffusion of the reactive gas injected backwardly. Each reactive gas is mixed with an injection support gas which is a kind of inert gas in a mixing zone at inside of the showerhead, where the injection velocity of each reactive gas is regulated positively by the amount of the injection support gas mixed. The present invention further includes an apparatus and a method, wherein the showerhead is cooled by a cooling jacket which keeps the temperature of the showerhead at proper levels to prevent both the condensation and the thermal decomposition of the reactive gas used.

Owner:KOREA INST OF IND TECH +1

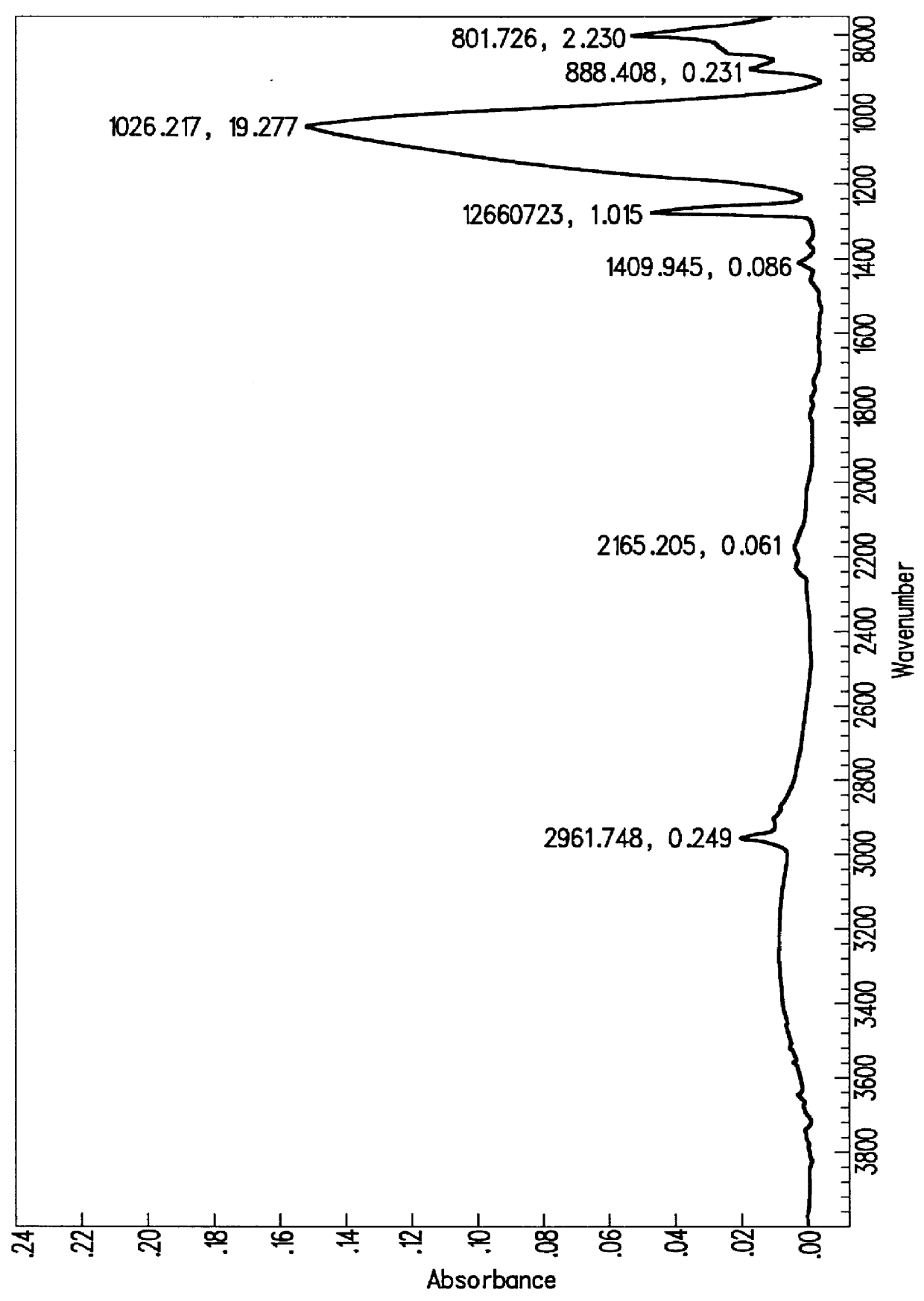

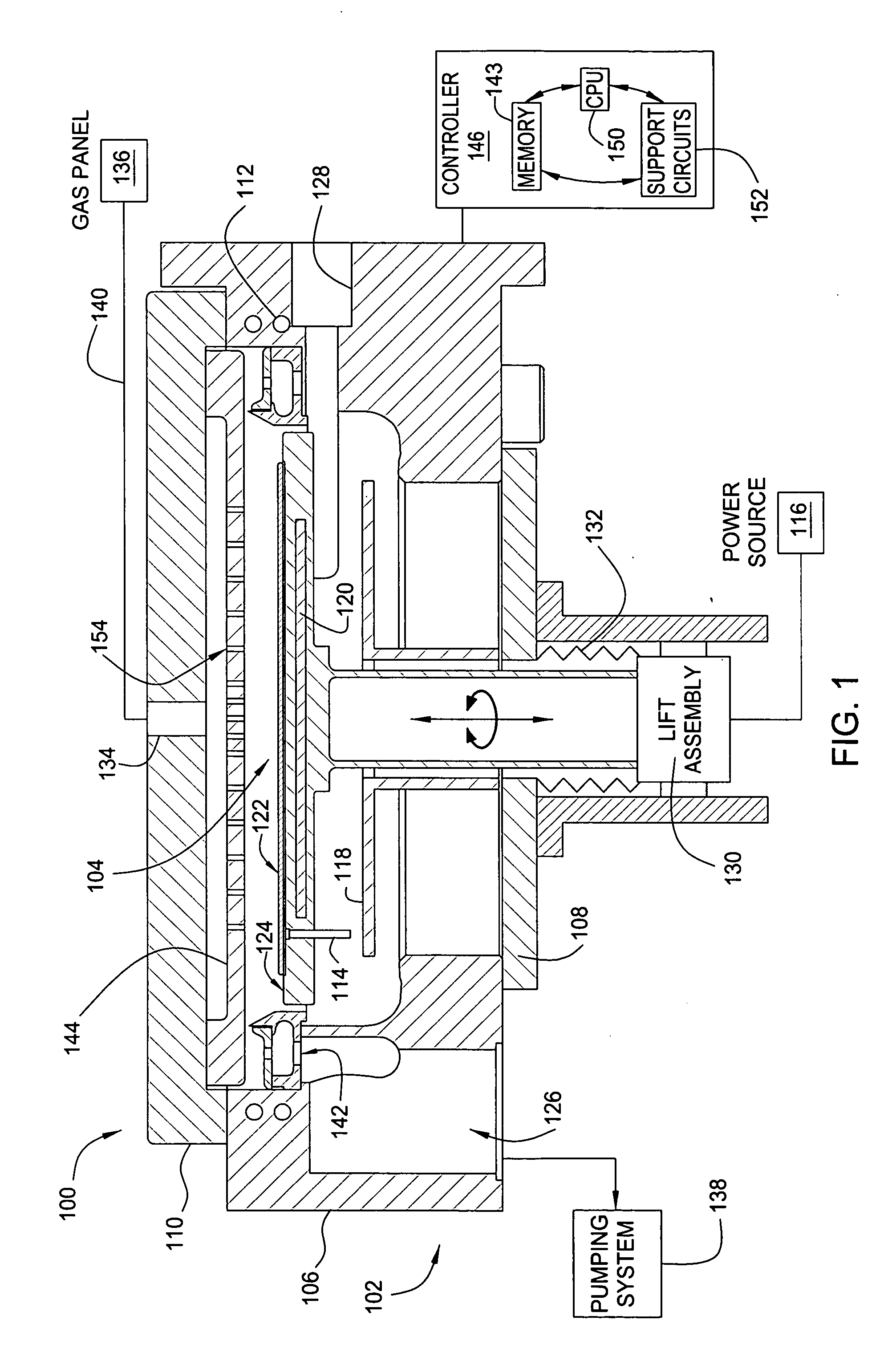

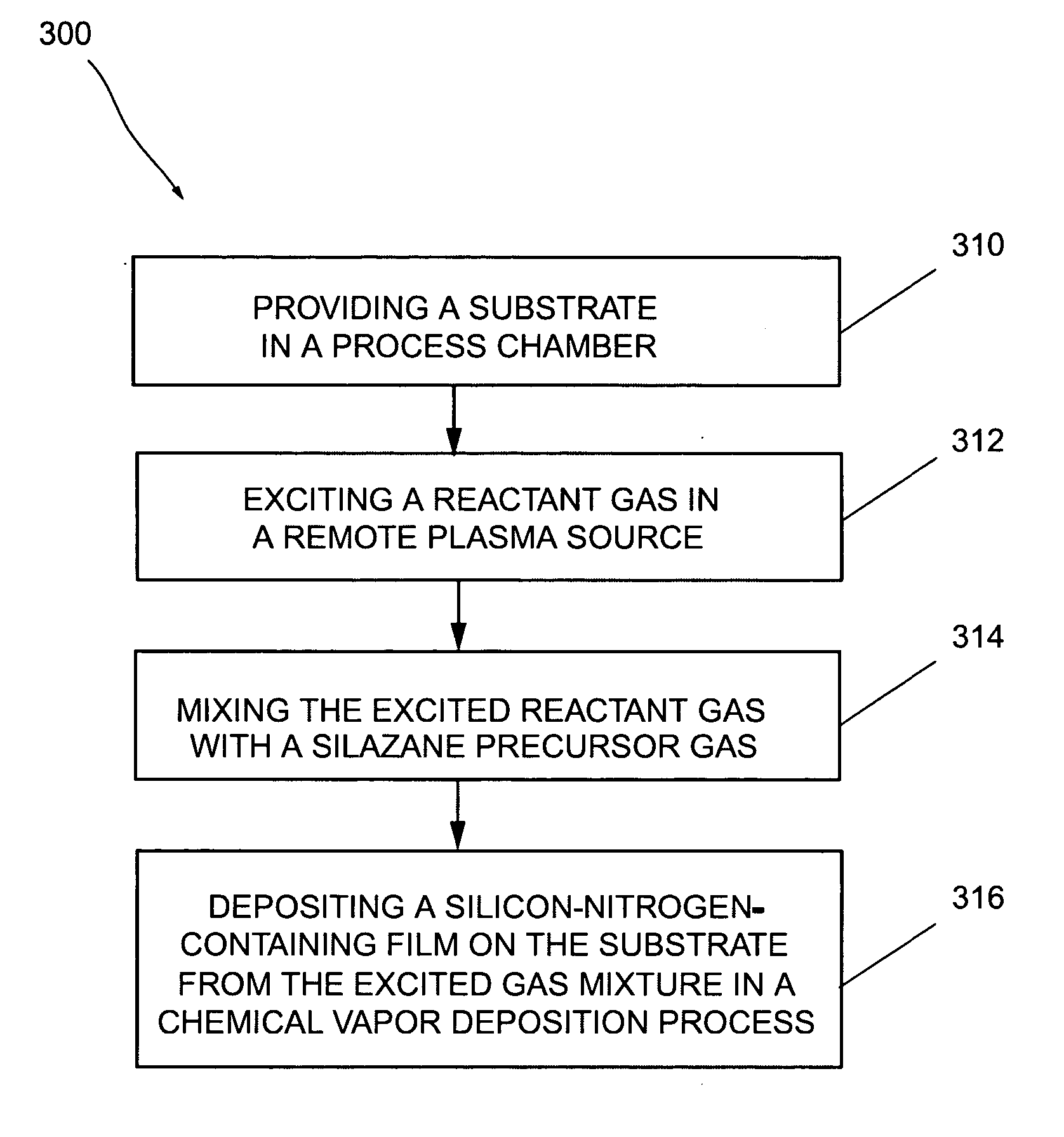

Low-temperature plasma-enhanced chemical vapor deposition of silicon-nitrogen-containing films

InactiveUS20060014399A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilazaneRemote plasma

A method for low-temperature plasma-enhanced chemical vapor deposition of a silicon-nitrogen-containing film on a substrate. The method includes providing a substrate in a process chamber, exciting a reactant gas in a remote plasma source, thereafter mixing the excited reactant gas with a silazane precursor gas, and depositing a silicon-nitrogen-containing film on the substrate from the excited gas mixture in a chemical vapor deposition process. In one embodiment of the invention, the reactant gas can contain a nitrogen-containing gas to deposit a SiCNH film. In another embodiment of the invention, the reactant gas can contain an oxygen-containing gas to deposit a SiCNOH film.

Owner:TOKYO ELECTRON LTD

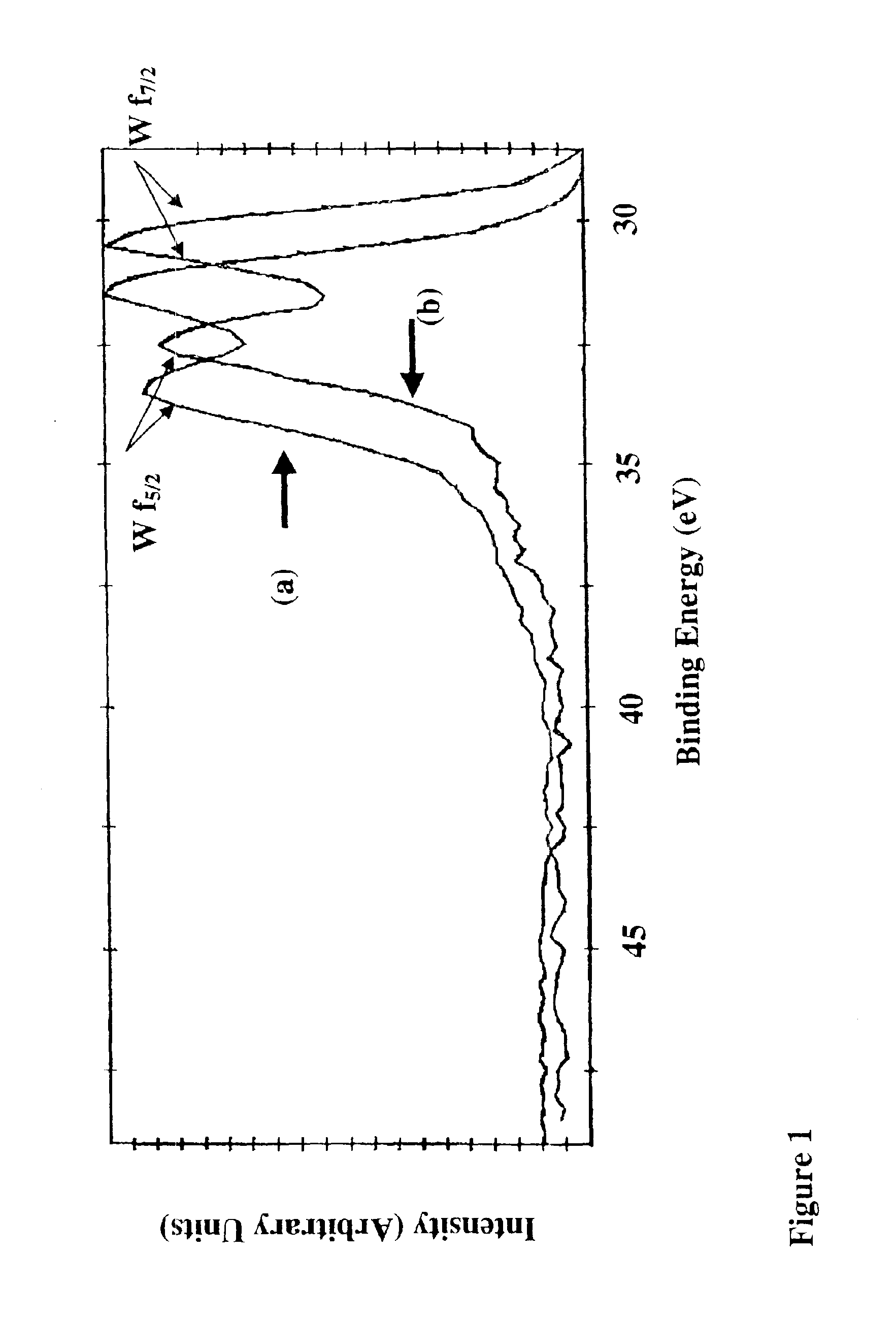

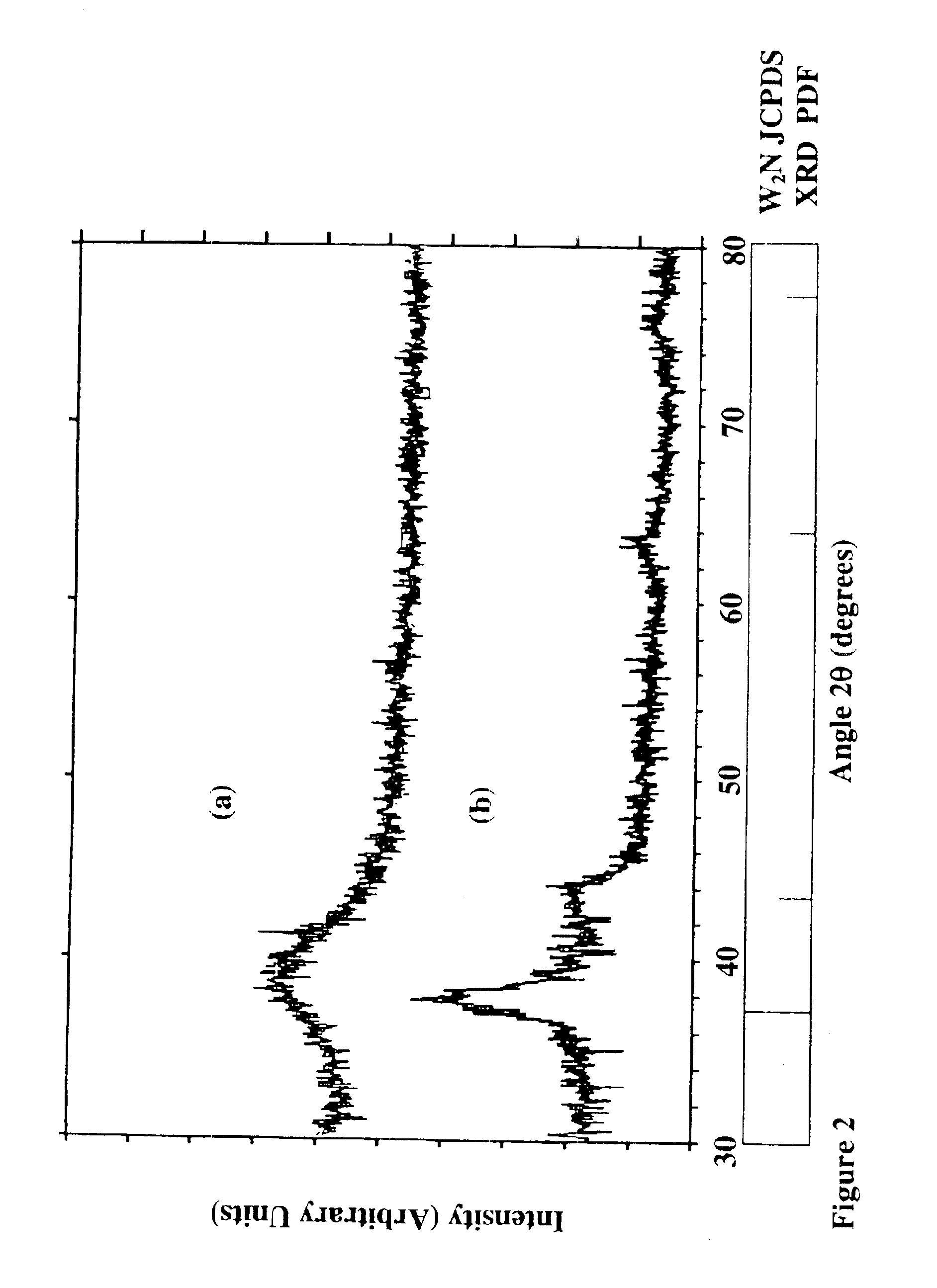

Process for low-temperature metal-organic chemical vapor deposition of tungsten nitride and tungsten nitride films

InactiveUS6884466B2Layered productsNitrogen-metal/silicon/boron binary compoundsTungsten nitrideNitrogen

Processes for producing tungsten nitride and tungsten nitride films are provided in which a tungsten carbonyl compound and a nitrogen-containing reactant gas are reacted at a temperature below about 600° C. Tungsten nitride precursors are also included which comprise a tungsten carbonyl compound capable of forming a tungsten nitride film in the presence of a nitrogen-containing reactant gas at a temperature of less than about 600° C. A process for forming a film by atomic layer deposition is also provided which includes introducing a substrate having a surface into a deposition chamber and heating the substrate to a temperature sufficient to allow adsorption of a tungsten source precursor or an intermediate thereof, and thereafter sequentially introducing by pulsing: a tungsten source precursor which is absorbed as a monolayer, a purging inert gas, a nitrogen-containing gas for reacting with the monolayer to form a first tungsten nitride layer on the substrate surface, and an inert purging gas, and repeating the sequence to form a film of desired thickness.

Owner:GELEST +1

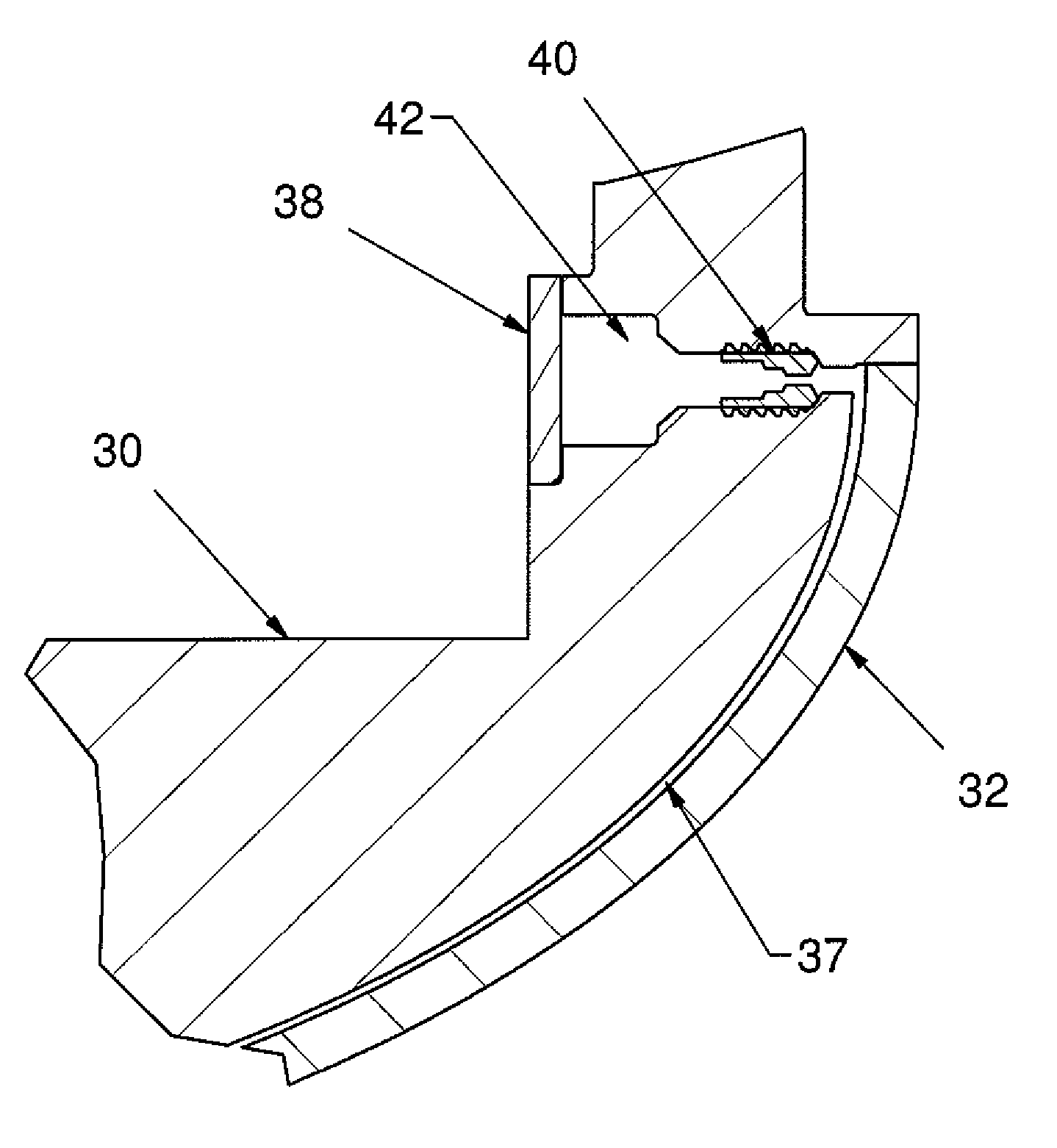

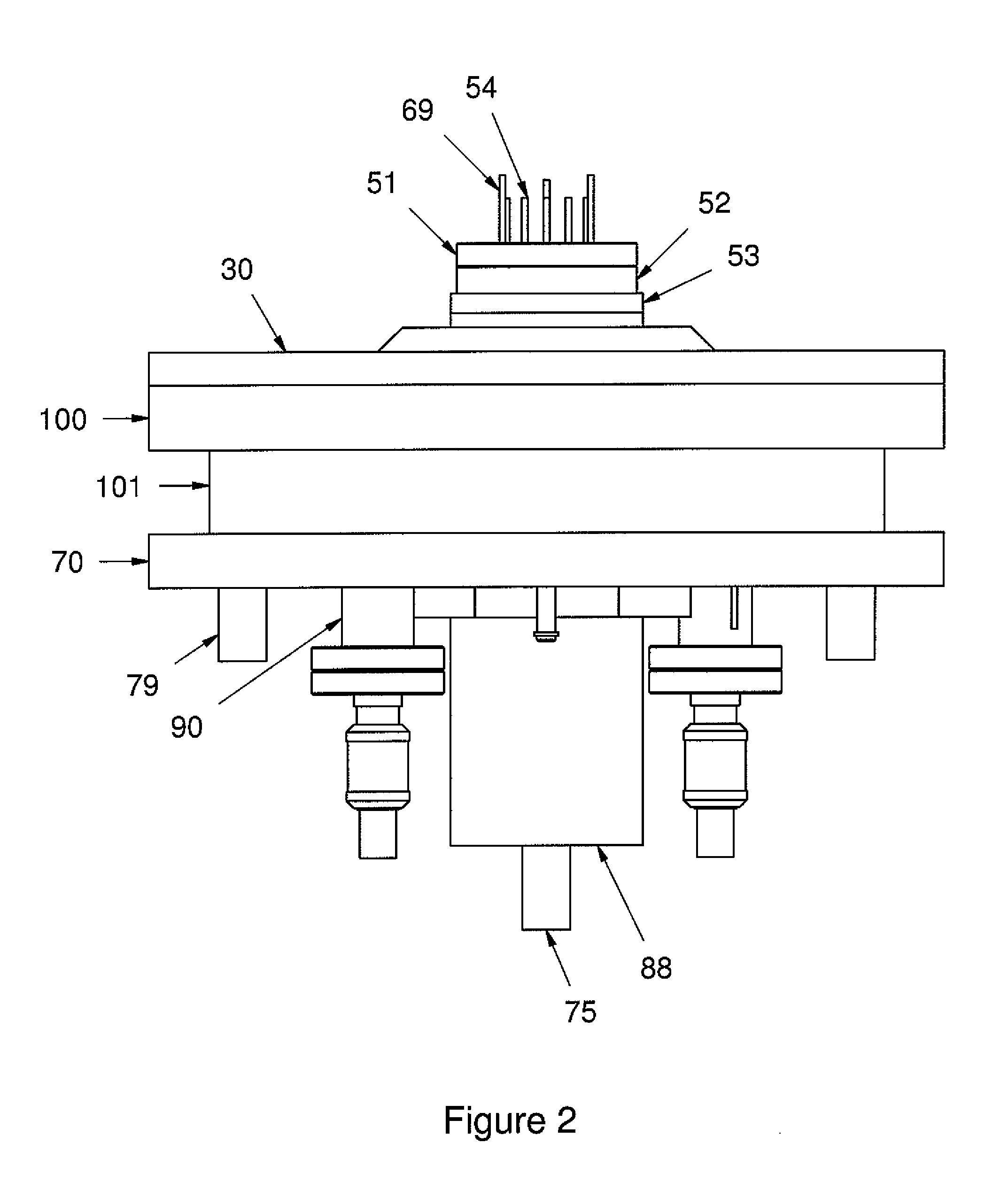

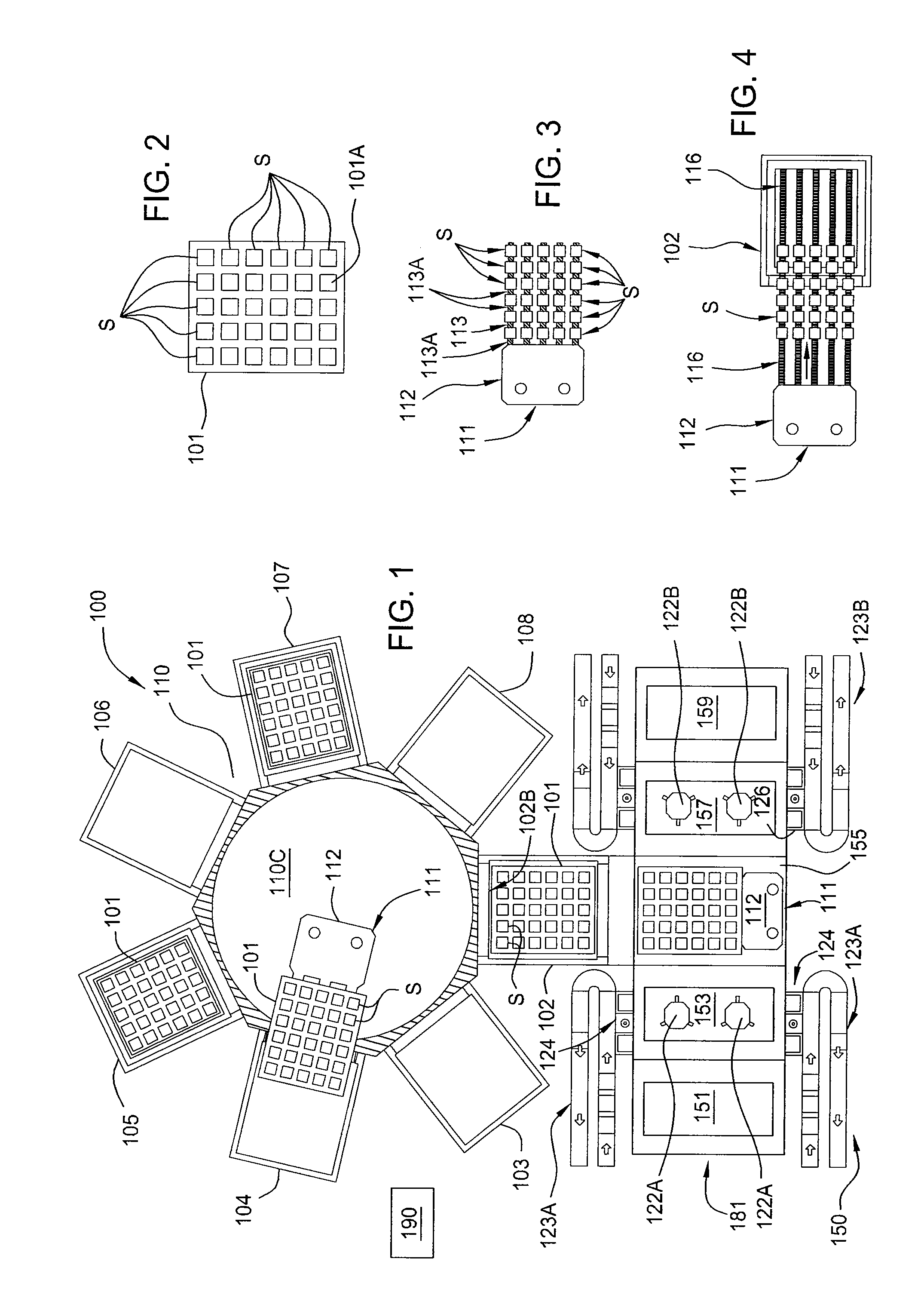

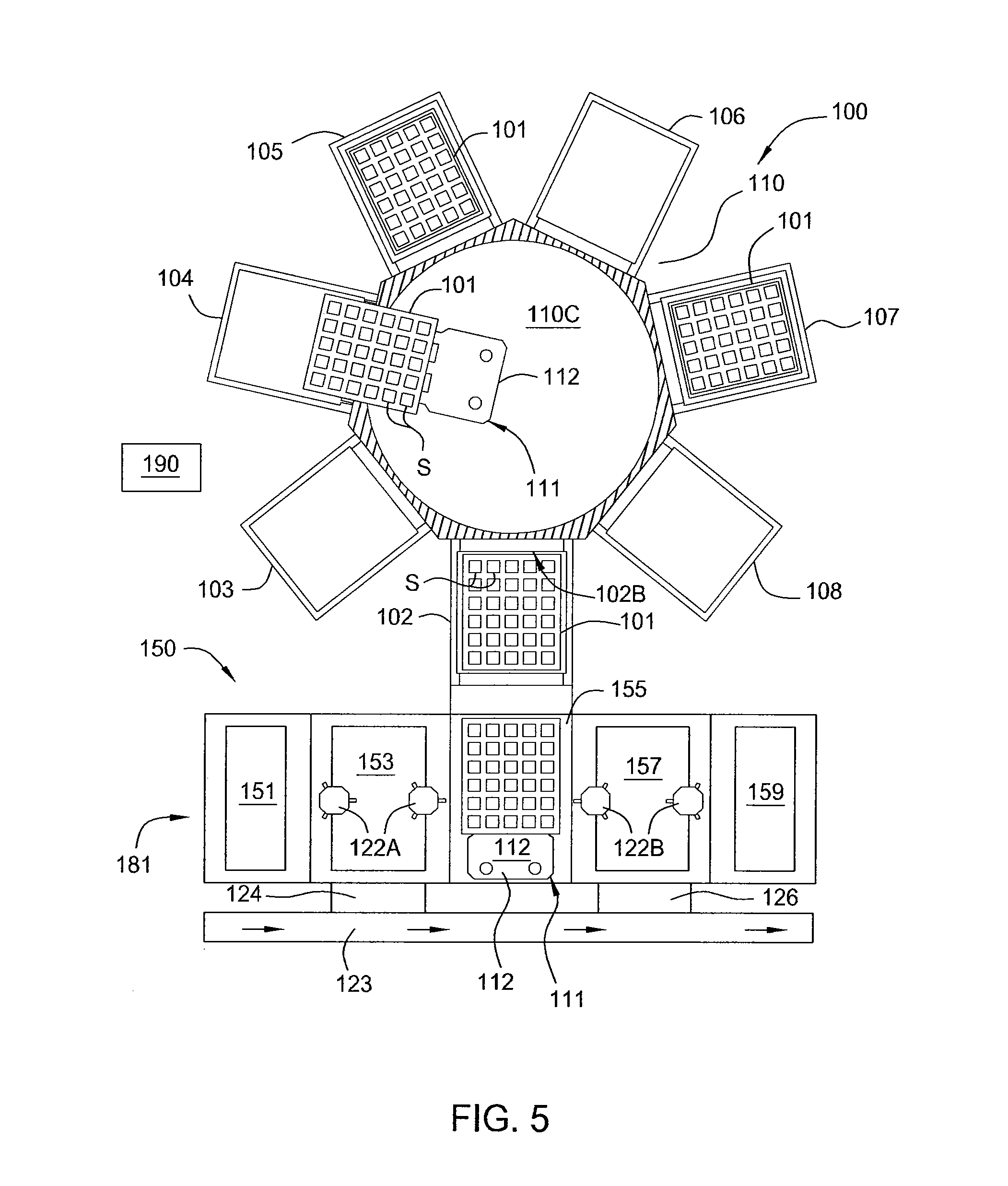

Advanced platform for processing crystalline silicon solar cells

InactiveUS20100087028A1Final product manufactureSemiconductor/solid-state device manufacturingGas phaseEngineering

The present invention generally provides a batch substrate processing system, or cluster tool, for in-situ processing of a film stack used to form regions of a solar cell device. In one configuration, the film stack formed on each of the substrates in the batch contains one or more silicon-containing layers and one or more metal layers that are deposited and further processed within the various chambers contained in the substrate processing system. The processing chambers may be, for example, physical vapor deposition (PVD) or sputtering chambers, plasma enhanced chemical vapor deposition (PECVD) chambers, low pressure chemical vapor deposition (LPCVD) chambers, hot wire chemical vapor deposition (HWCVD) chambers, plasma nitridation (DPN) chambers, ion implant / doping chambers, atomic layer deposition (ALD) chambers, plasma etching chambers, annealing chambers, rapid thermal oxidation (RTO) chambers, rapid thermal annealing (RTA) chambers, substrate reorientation chambers, laser annealing chambers, and / or plasma cleaning stations. In one embodiment, a batch of solar cell substrates is simultaneously transferred in a vacuum or inert environment to prevent contamination from affecting the solar cell formation process.

Owner:APPLIED MATERIALS INC

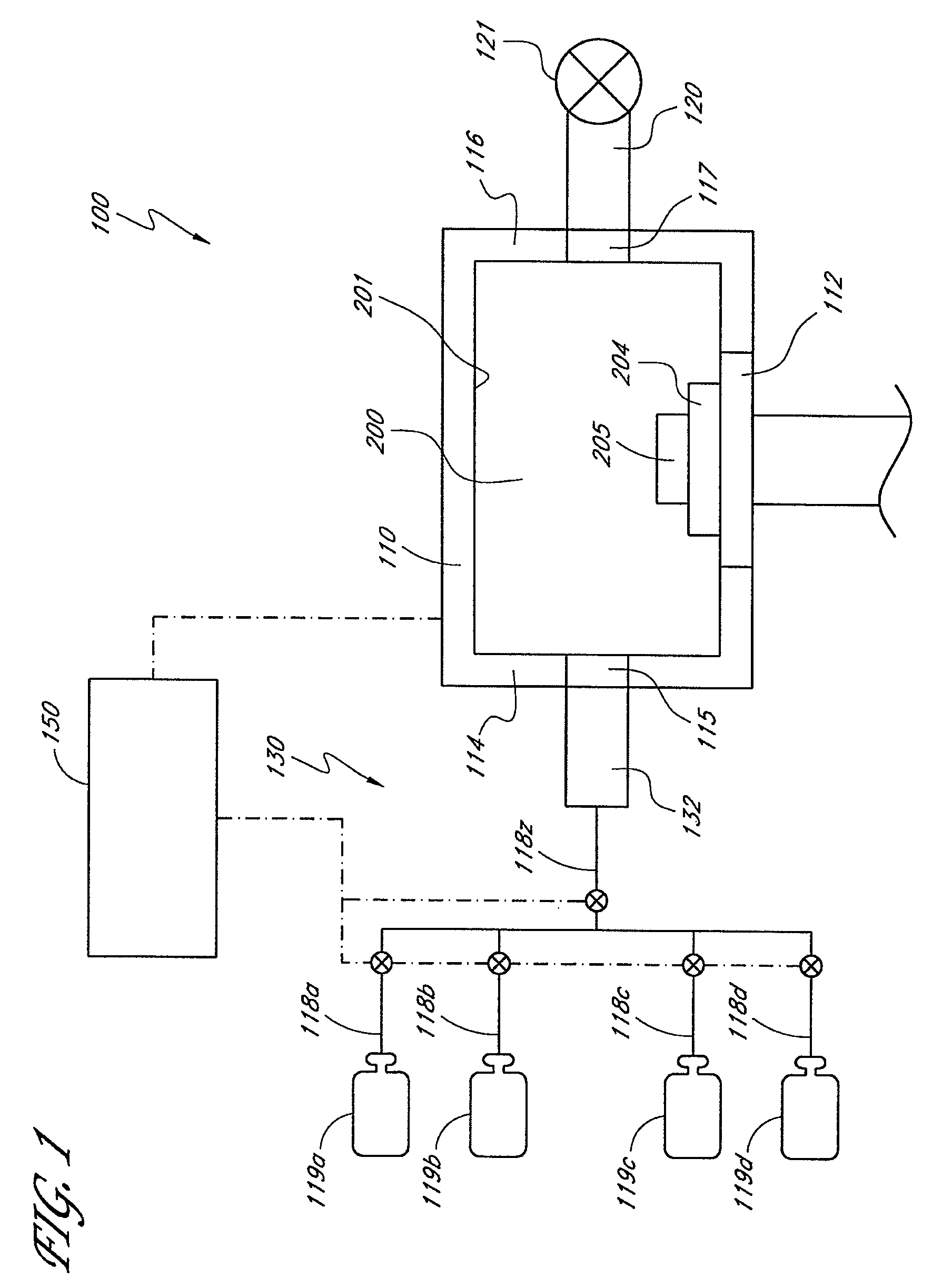

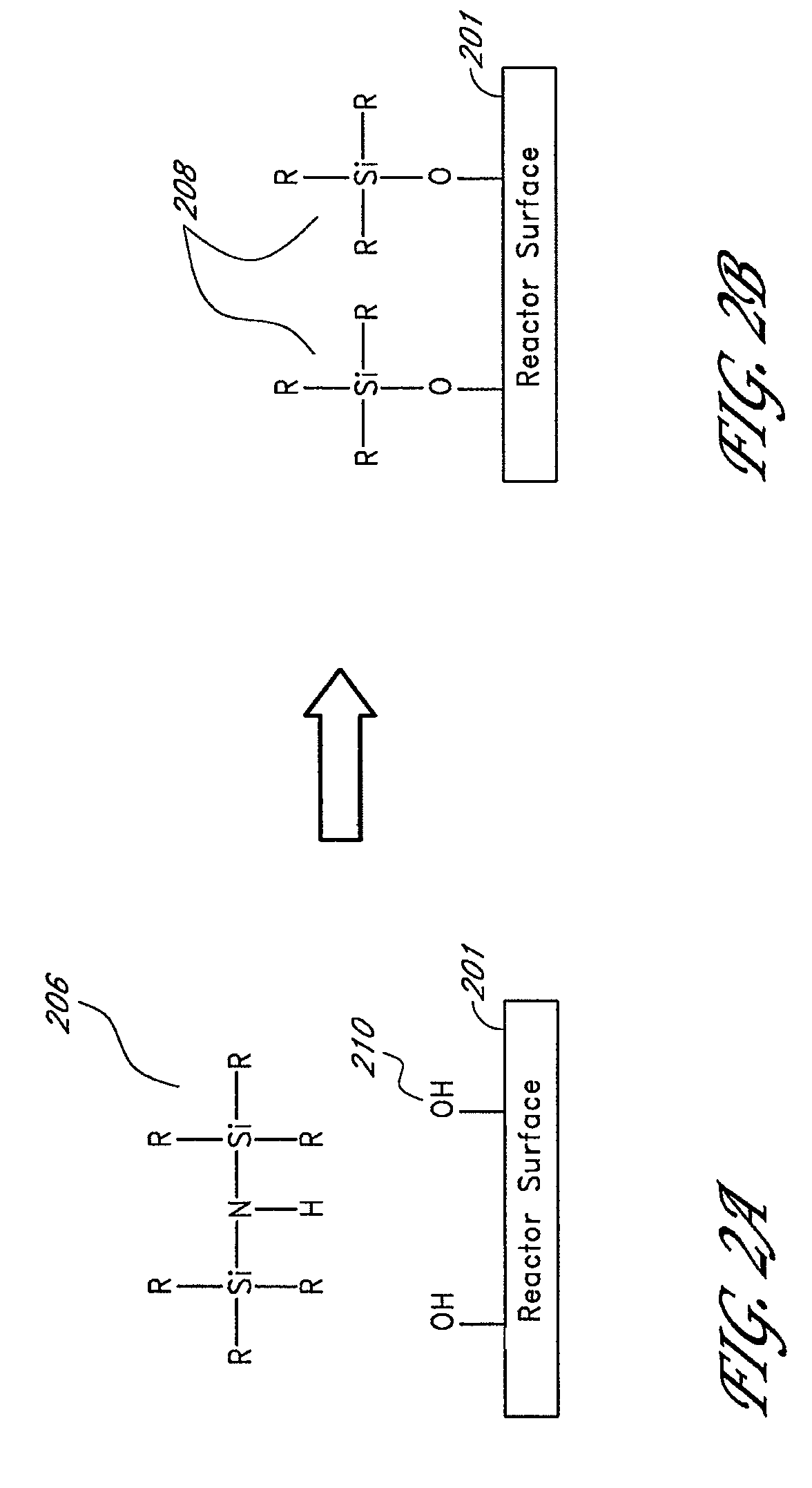

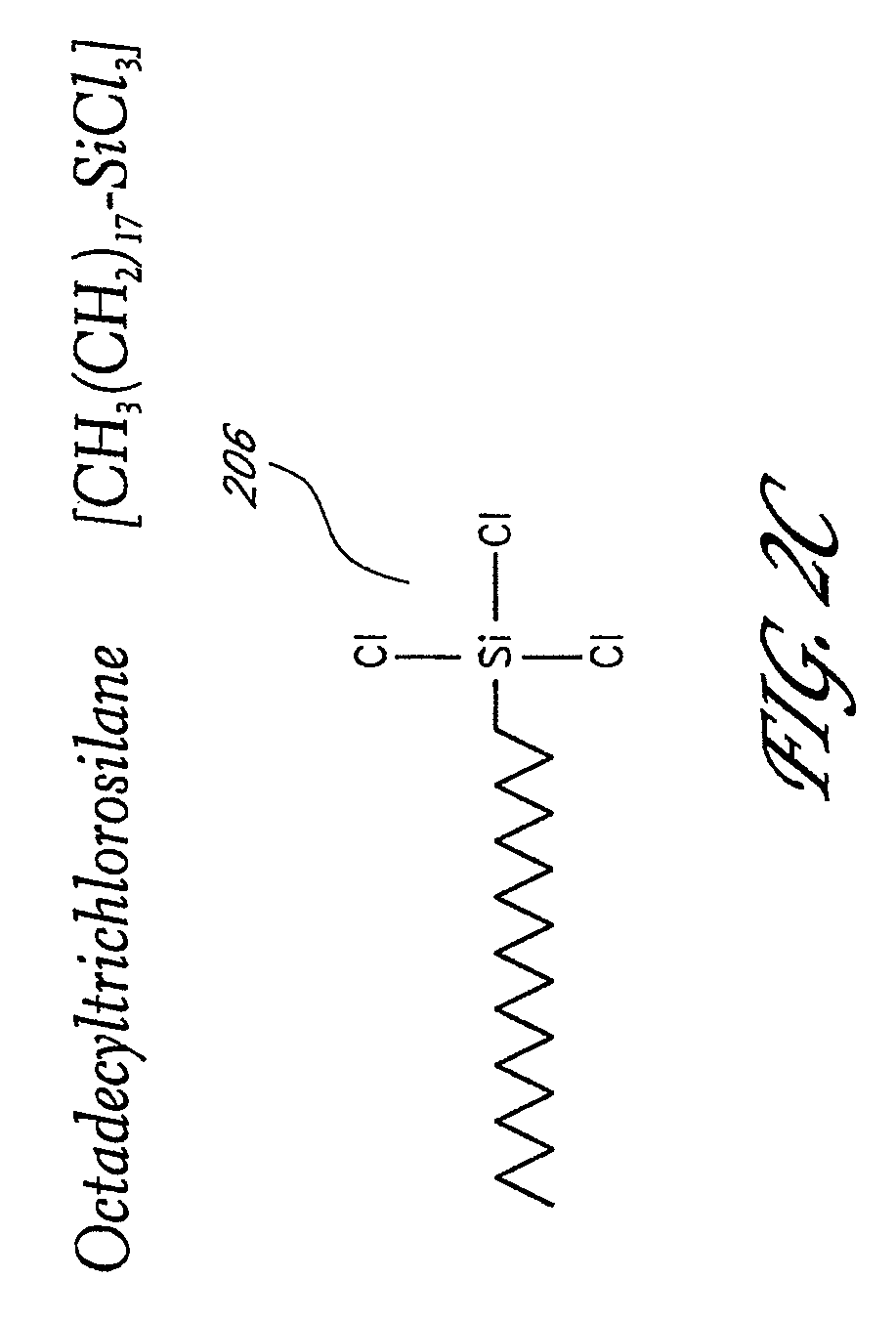

Reactor surface passivation through chemical deactivation

ActiveUS7914847B2Reduce the possibilityReduce buildMaterial nanotechnologyPolycrystalline material growthReactive sitePre treatment

Protective layers are formed on a surface of an atomic layer deposition (ALD) or chemical vapor deposition (CVD) reactor. Parts defining a reaction space for an ALD or CVD reactor can be treated, in situ or ex situ, with chemicals that deactivate reactive sites on the reaction space surface(s). A pre-treatment step can maximize the available reactive sites prior to the treatment step. With reactive sites deactivated by adsorbed treatment reactant, during subsequent processing the reactant gases have reduced reactivity or deposition upon these treated surfaces. Accordingly, purge steps can be greatly shortened and a greater number of runs can be conducted between cleaning steps to remove built-up deposition on the reactor walls.

Owner:ASM IP HLDG BV

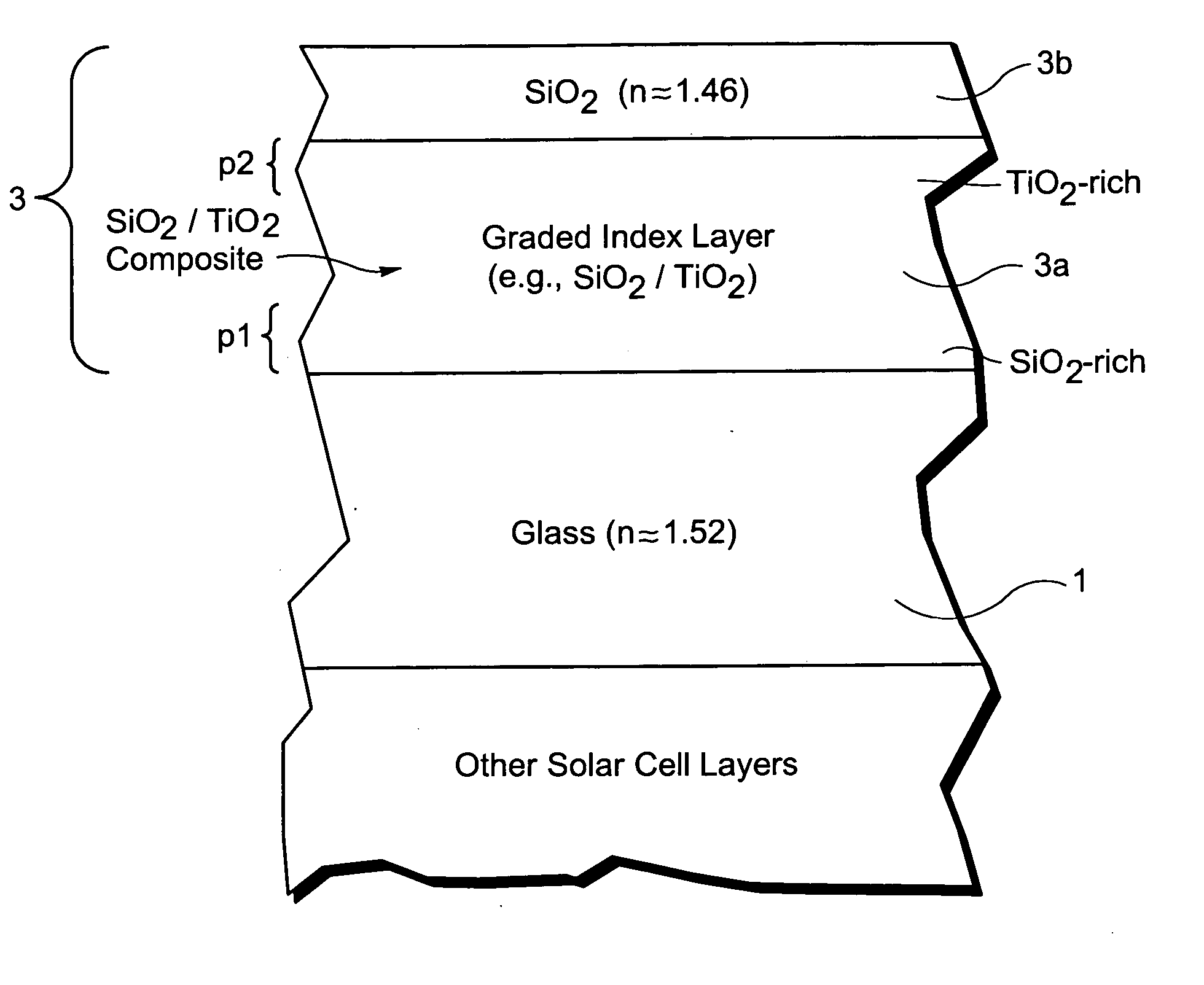

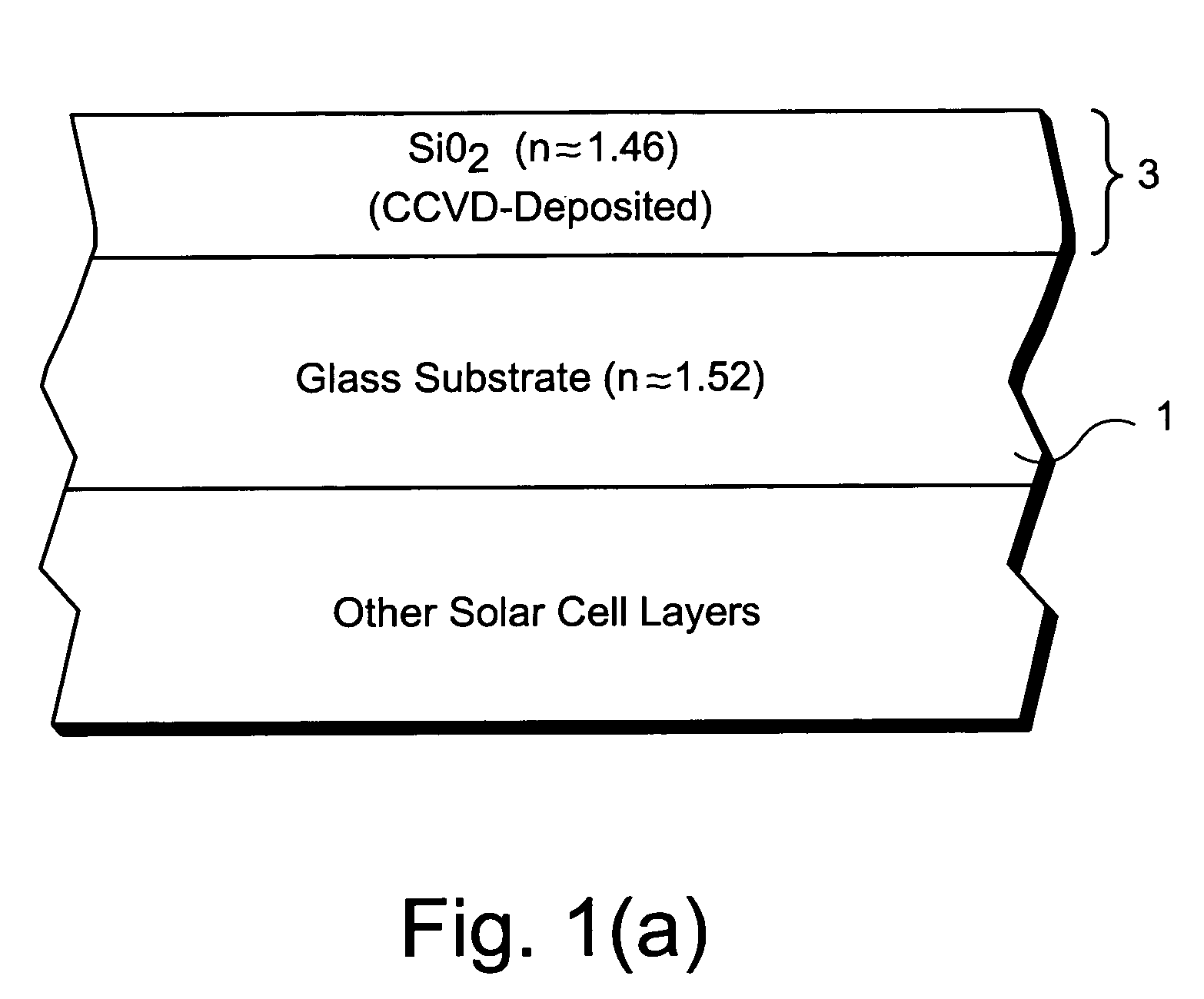

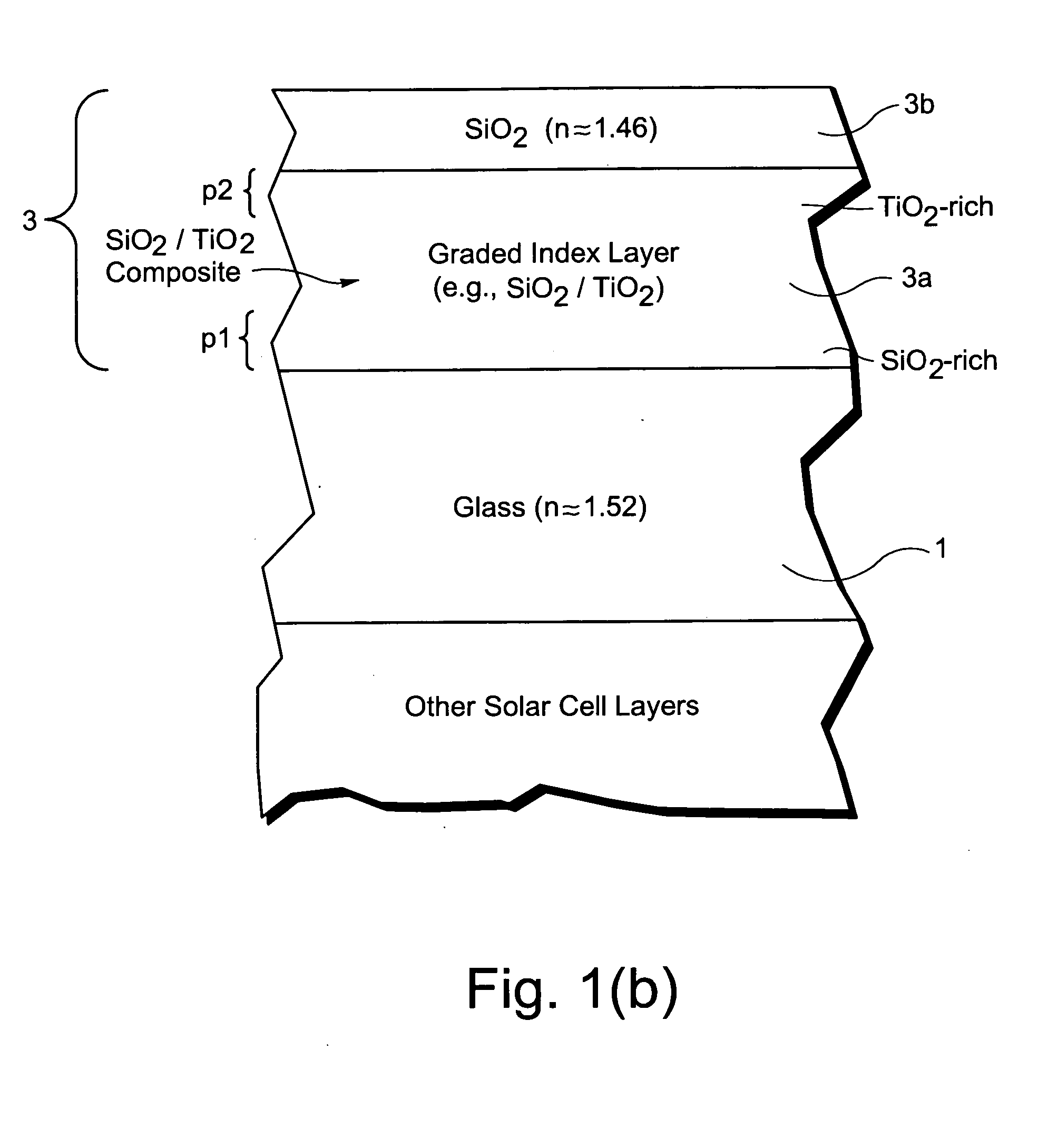

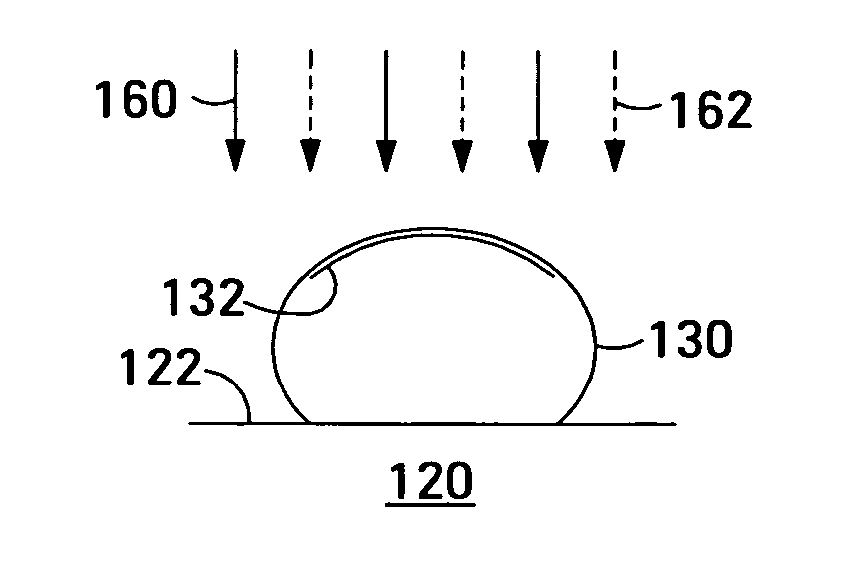

Method of making solar cell with antireflective coating using combustion chemical vapor deposition (CCVD) and corresponding product

InactiveUS20070113881A1Improved anti-reflection (AR) coatingReduce light reflectionPV power plantsSolid-state devicesAnti-reflective coatingSolar cell

There is provided a coated article (e.g., solar cell) that includes an improved anti-reflection (AR) coating. This AR coating functions to reduce reflection of light from a glass substrate, thereby allowing more light within the solar spectrum to pass through the incident glass substrate. In certain example embodiments, the AR coating is at least partially formed by flame pyrolysis.

Owner:GUARDIAN GLASS LLC

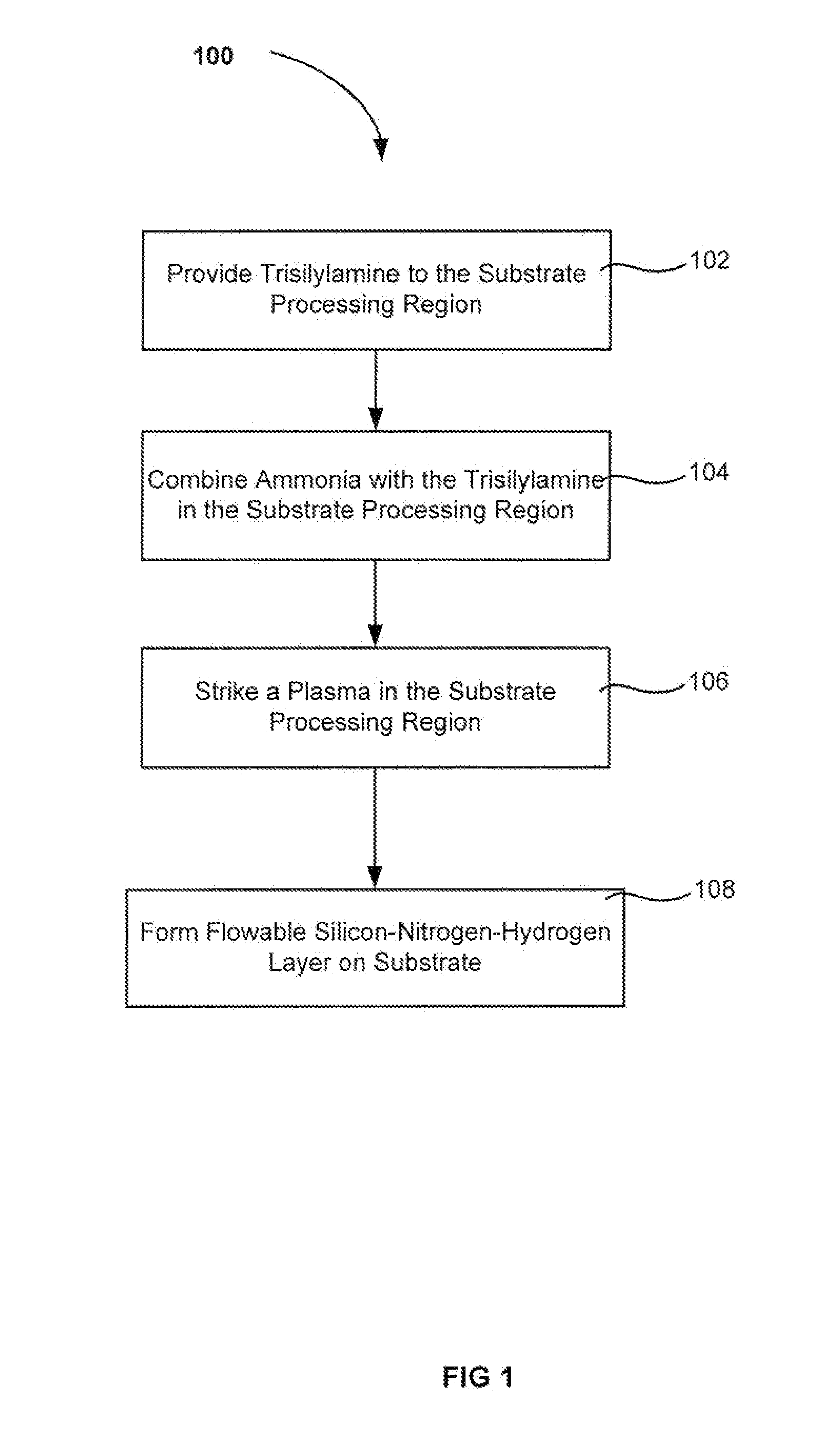

Low cost flowable dielectric films

ActiveUS20140073144A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilyleneSilanes

A method of forming a dielectric layer is described. The method deposits a silicon-containing film by chemical vapor deposition using a local plasma. The silicon-containing film is flowable during deposition at low substrate temperature. A silicon precursor (e.g. a silylamine, higher order silane or halogenated silane) is delivered to the substrate processing region and excited in a local plasma. A second plasma vapor or gas is combined with the silicon precursor in the substrate processing region and may include ammonia, nitrogen (N2), argon, hydrogen (H2) and / or oxygen (O2). The equipment configurations disclosed herein in combination with these vapor / gas combinations have been found to result in flowable deposition at substrate temperatures below or about 200° C. when a local plasma is excited using relatively low power.

Owner:APPLIED MATERIALS INC

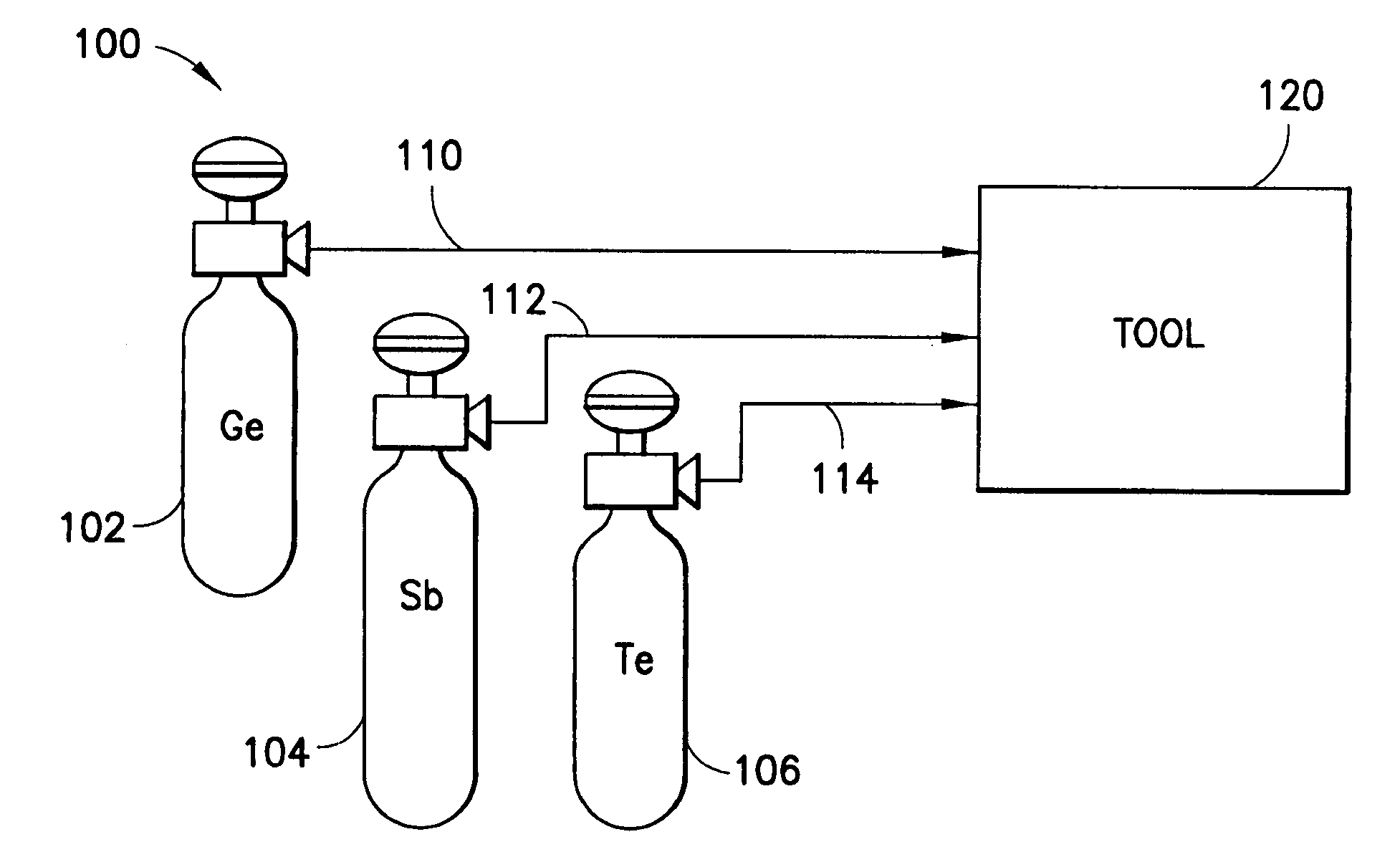

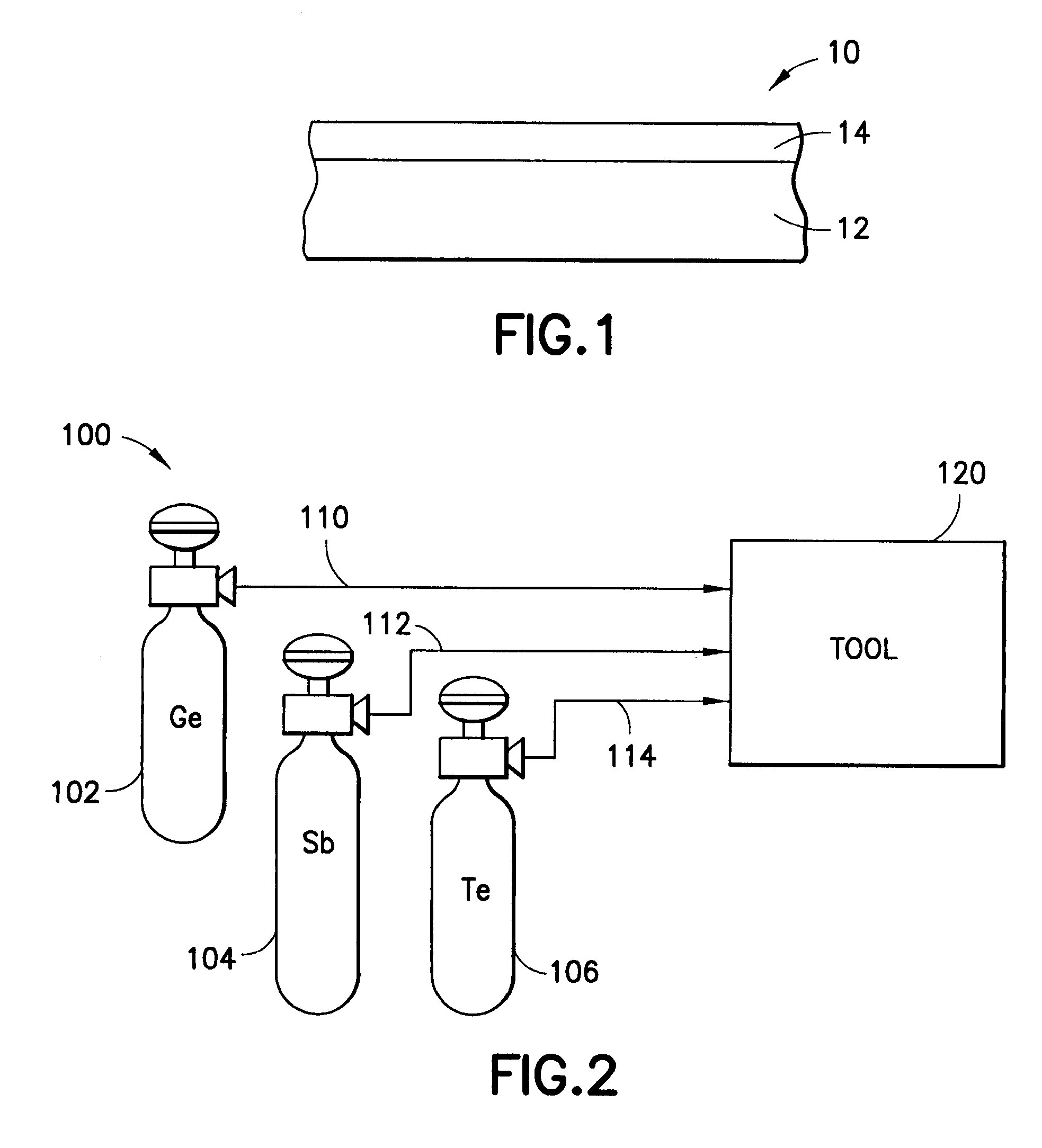

Low temperature deposition of phase change memory materials

InactiveUS20090124039A1Silicon organic compoundsGroup 8/9/10/18 element organic compoundsLow temperature depositionPhase-change memory

A system and method for forming a phase change memory material on a substrate, in which the substrate is contacted with precursors for a phase change memory chalcogenide alloy under conditions producing deposition of the chalcogenide alloy on the substrate, at temperature below 350° C. with the contacting being carried out via chemical vapor deposition or atomic layer deposition. Various tellurium, germanium and germanium-tellurium precursors are described, which are useful for forming GST phase change memory films on substrates.

Owner:ENTEGRIS INC

Fast luminescent silicon

There are provided mesoporous silica materials containing in their pores stabilized clusters of silicon atom, of size 2 nanometers or less, and capable of photoluminescence to emit fast photons. They are prepared by chemical vapor deposition of silicon or a silicon precursor such as disilane, under soft conditions such as temperature of 100-150 DEG C., into the mesopores of silicate films which have mesoporous channels prepared by growth of the films using a template to control their sizes, but without removing the template residues from the films prior to the chemical vapor deposition. The template residues serve to limit the size of the silicon clusters which conform. The use of the soft conditions on CVD retains the template residues in an intact, substantially unchanged form. The resultant films have clusters of silicon, of 2 nanometer size or less, anchored to the mesopores, and air stable, so that they can be used in optoelectronic devices in conjunction with standard silicon semiconductors.

Owner:THE GOVERNINIG COUNCIL OF THE UNIV OF TORANTO

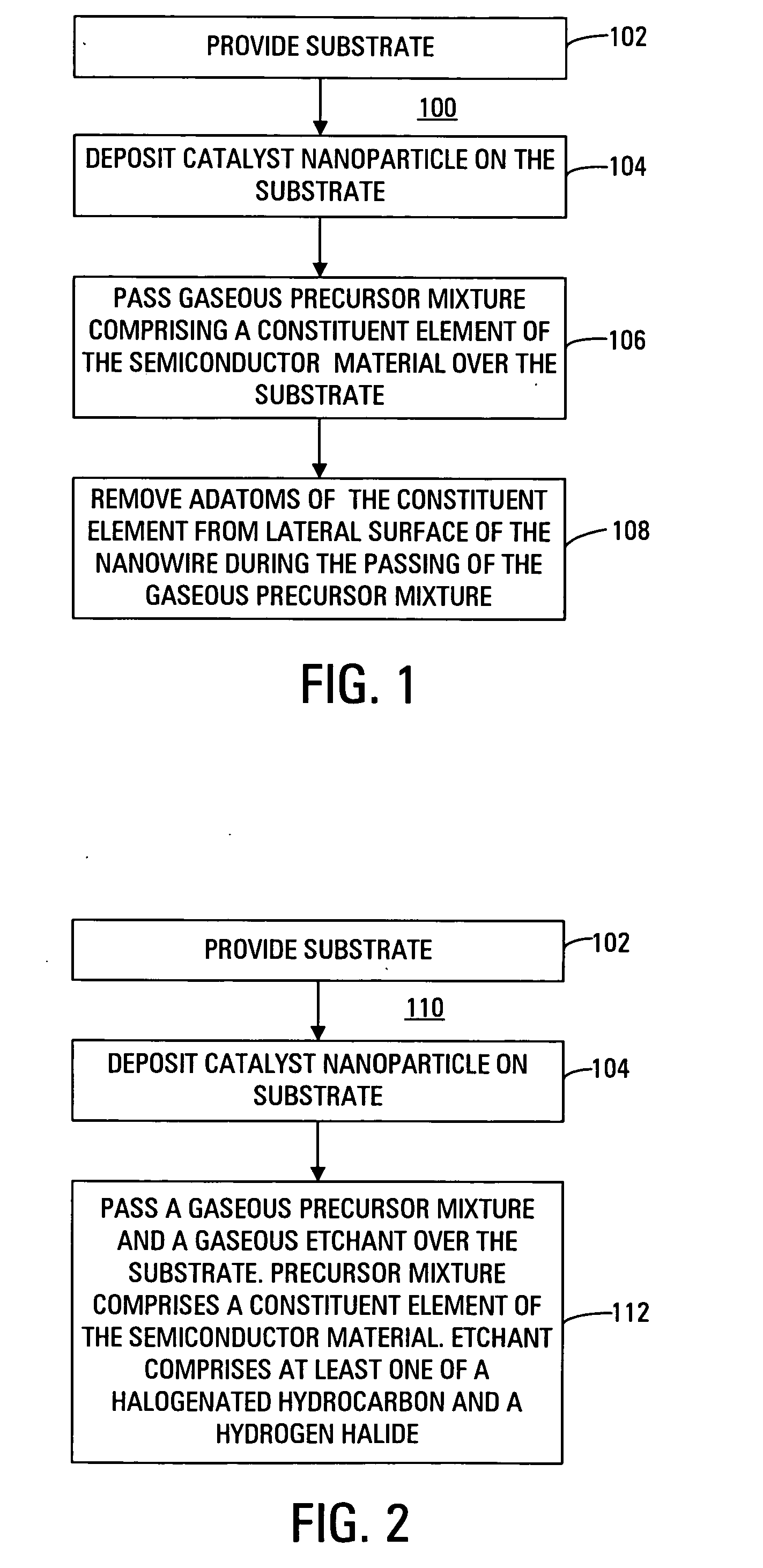

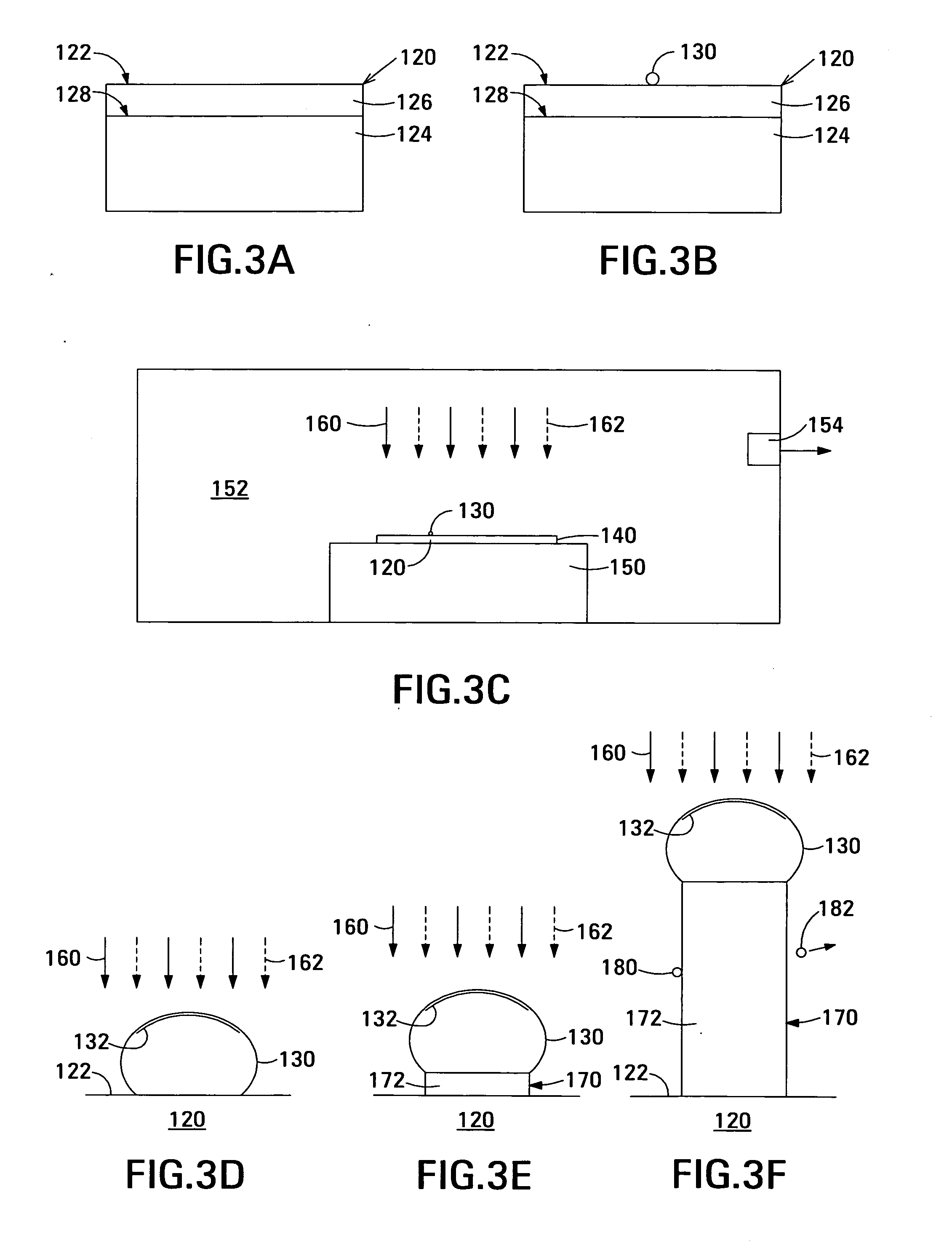

Method of growing semiconductor nanowires with uniform cross-sectional area using chemical vapor deposition

InactiveUS20050266662A1Uniform cross-sectional areaUniform areaMaterial nanotechnologyPolycrystalline material growthNanowireSemiconductor materials

A nanowire of a semiconductor material and having a uniform cross-sectional area along its length is grown using a chemical vapor deposition process. In the method, a substrate is provided, a catalyst nanoparticle is deposited on the substrate, a gaseous precursor mixture comprising a constituent element of the semiconductor material is passed over the substrate, and adatoms of the constituent element are removed from a lateral surface of the nanowire during the passing of the precursor mixture. Removing the adatoms of the constituent element before such adatoms are incorporated into the nanowire prevents such adatoms from accumulating on the lateral surface of the nanowire and allows the nanowire to grow with a uniform cross-sectional area along its length.

Owner:AGILENT TECH INC

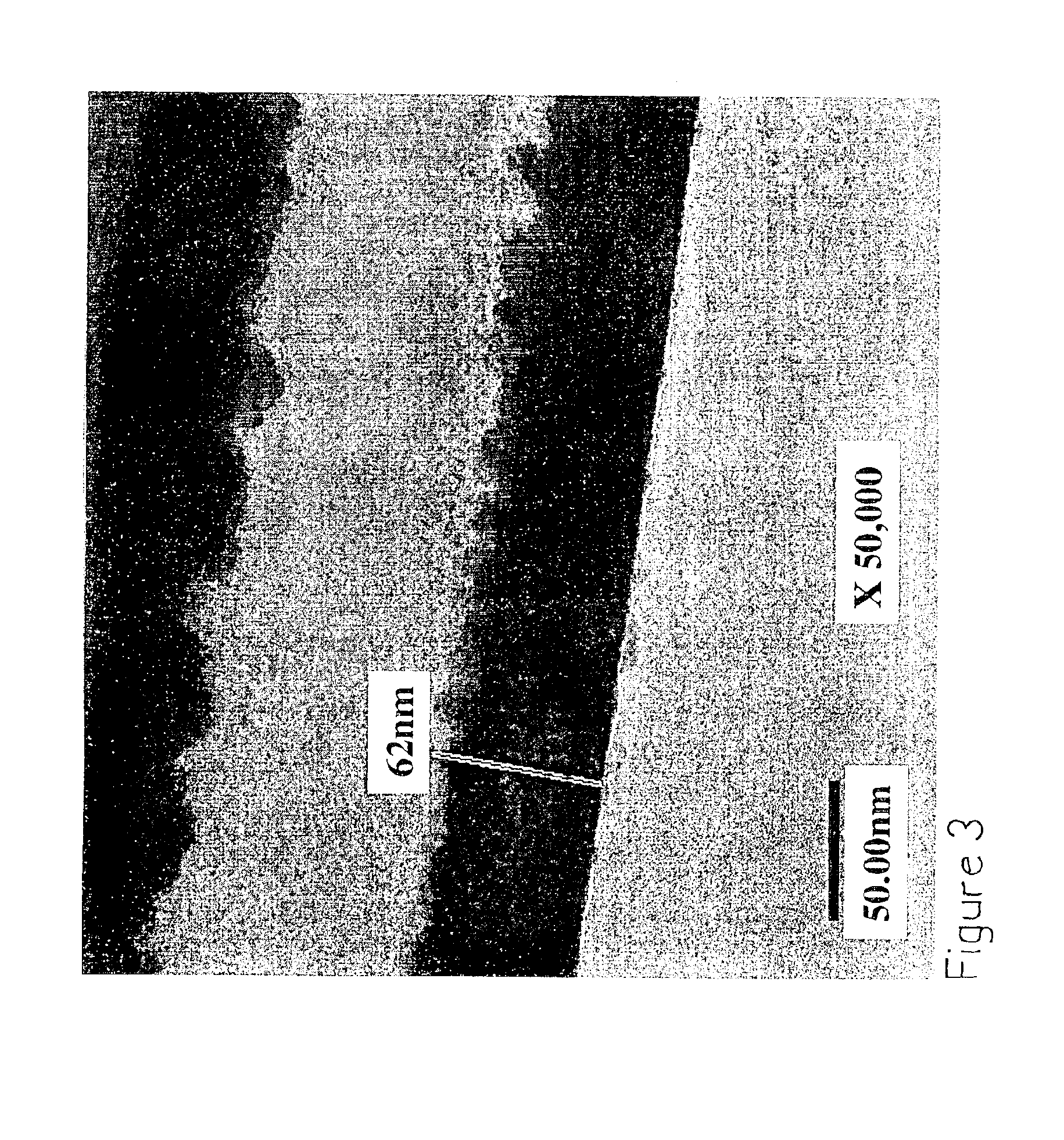

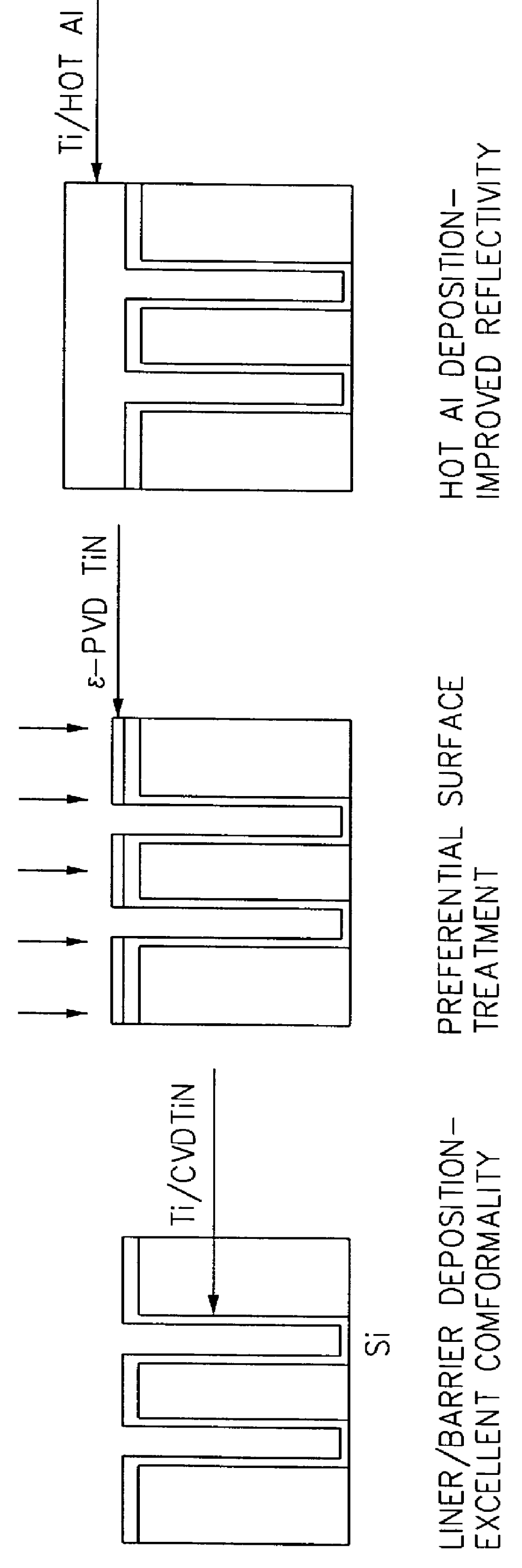

Blanket-selective chemical vapor deposition using an ultra-thin nucleation layer

The present invention relates generally to an improved apparatus and process for providing uniform step coverage on a substrate and planarization of conducting layers to form continuous, void-free interconnects in sub-half micron, high aspect ratio aperture width applications and highly oriented conducting layers. In one aspect of the invention, a dielectric layer is formed over a conducting or semiconducting layer and etched to form an aperture exposing the underlying conducting or semiconducting layer on the aperture floor. An ultra-thin nucleation layer is then deposited by physical vapor deposition onto the field of the dielectric layer. A CVD metal layer is then deposited onto the structure to achieve selective deposition on the floor of the aperture, while preferably also forming a highly oriented blanket layer on the field. The present apparatus and process reduce the number of steps necessary to fabricate CVD metal interconnects and layers that are substantially void-free and planarized. The metallization process is preferably carried out in an integrated processing system that includes both a PVD and CVD processing chamber so that once the substrate is introduced into a vacuum environment, the metallization of the apertures to form vias and contacts occurs without the formation of oxides between the layers.

Owner:APPLIED MATERIALS INC

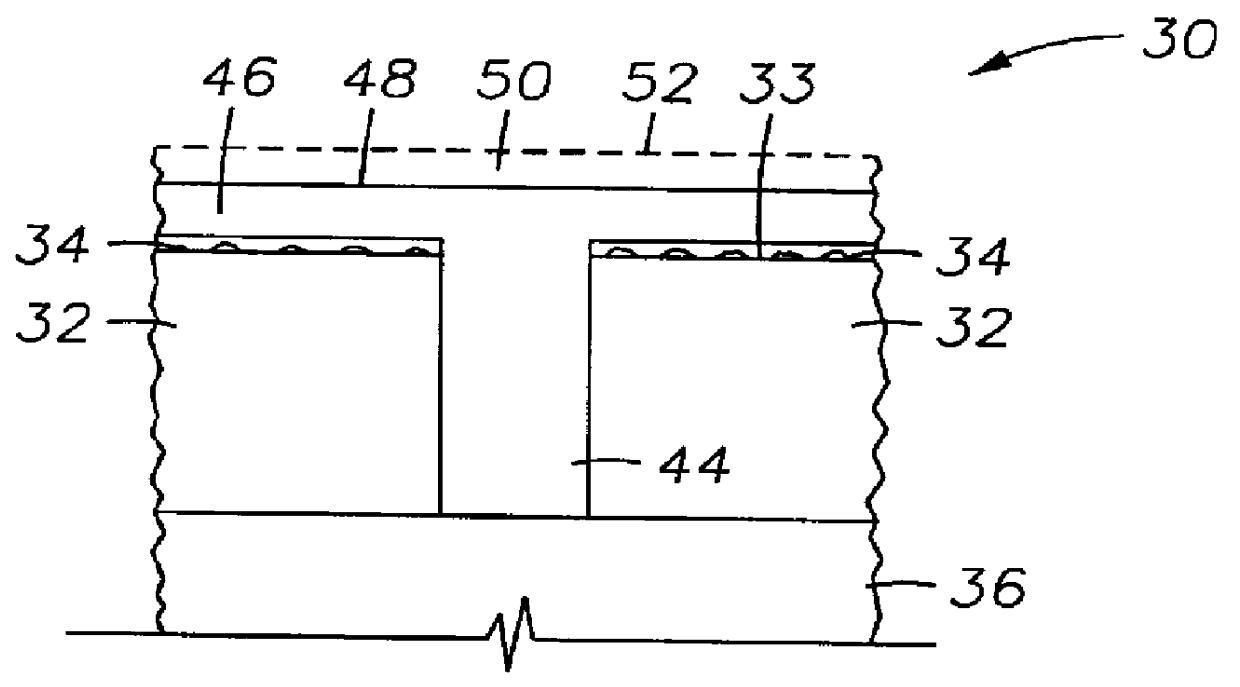

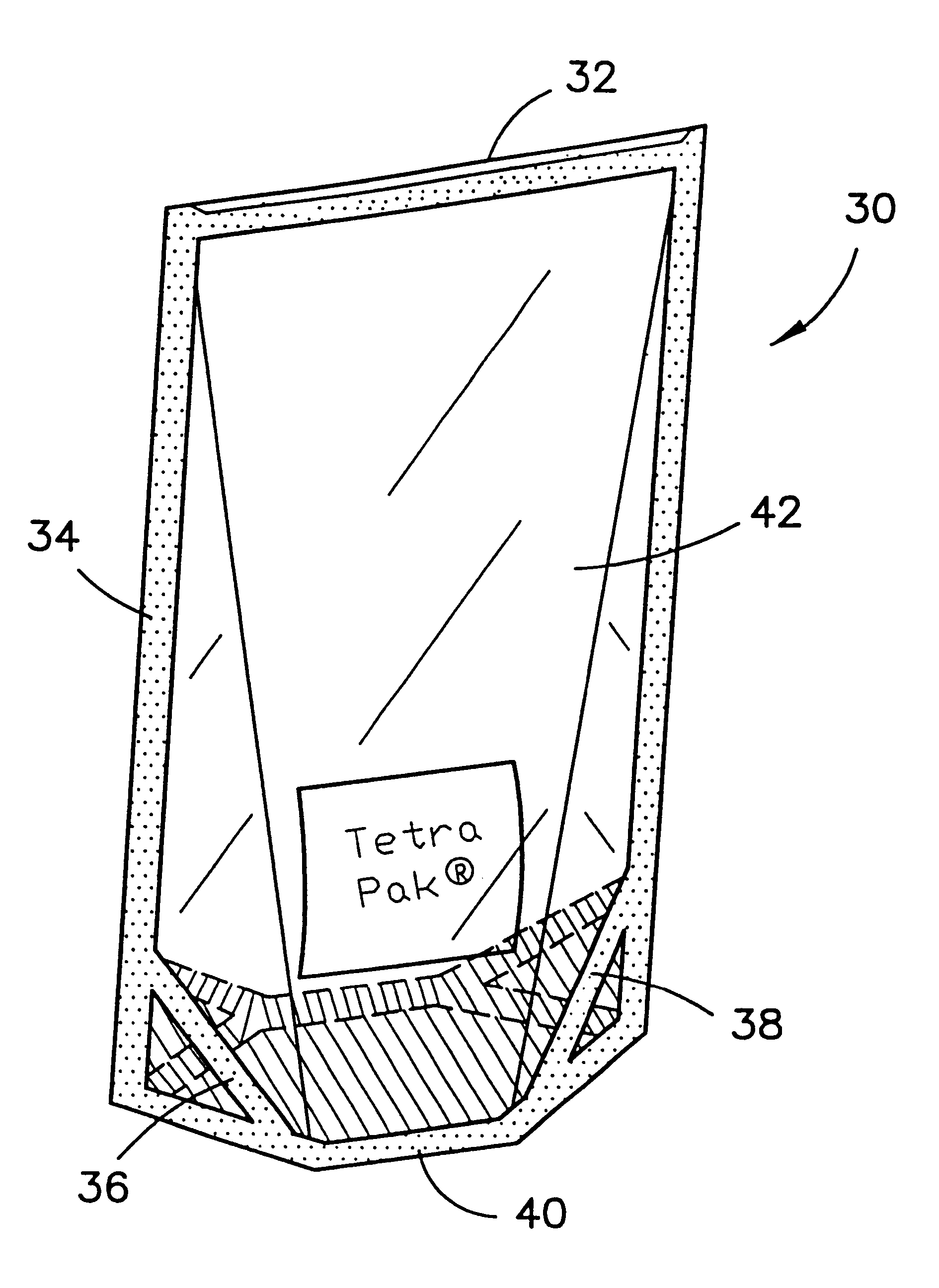

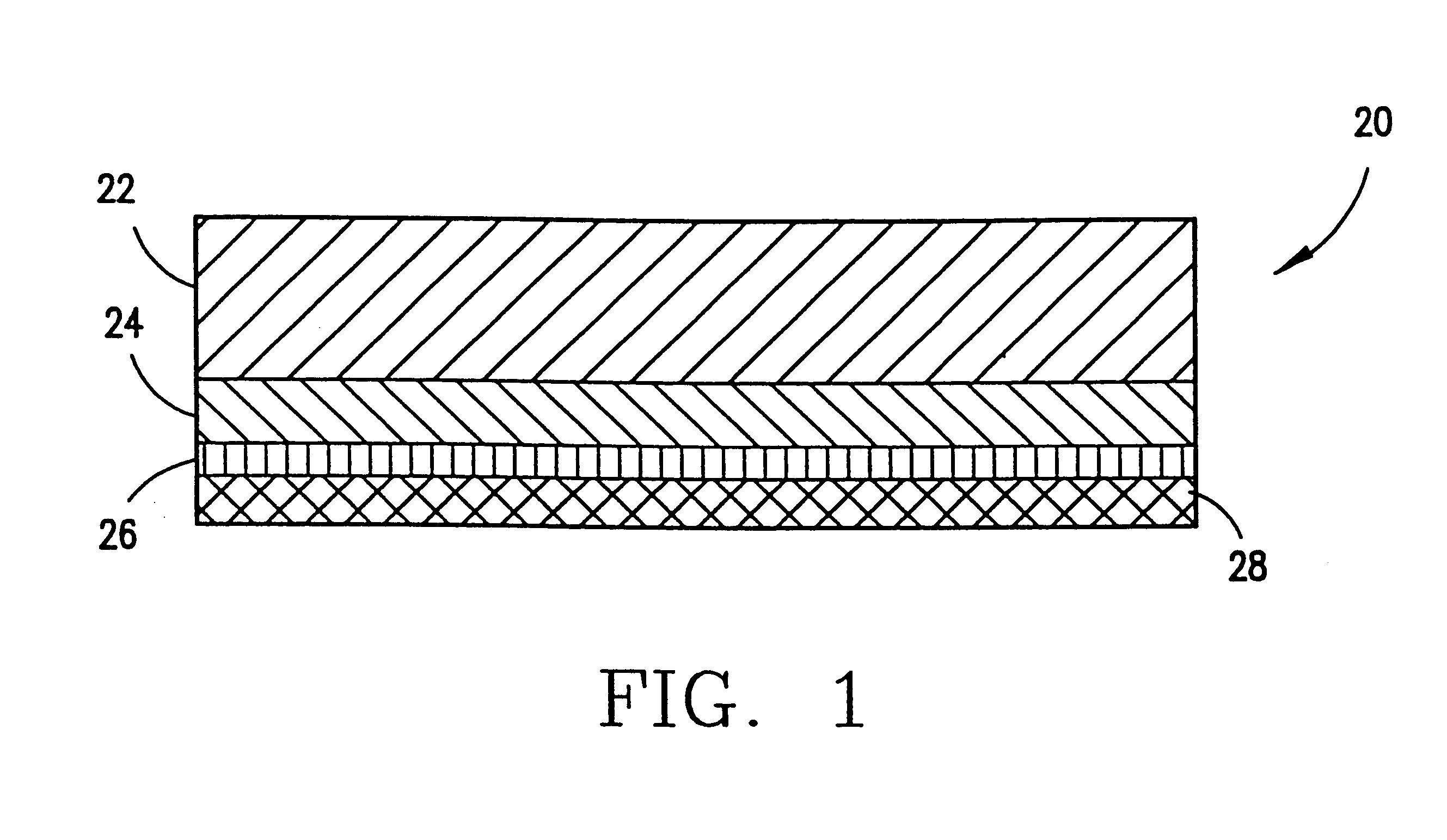

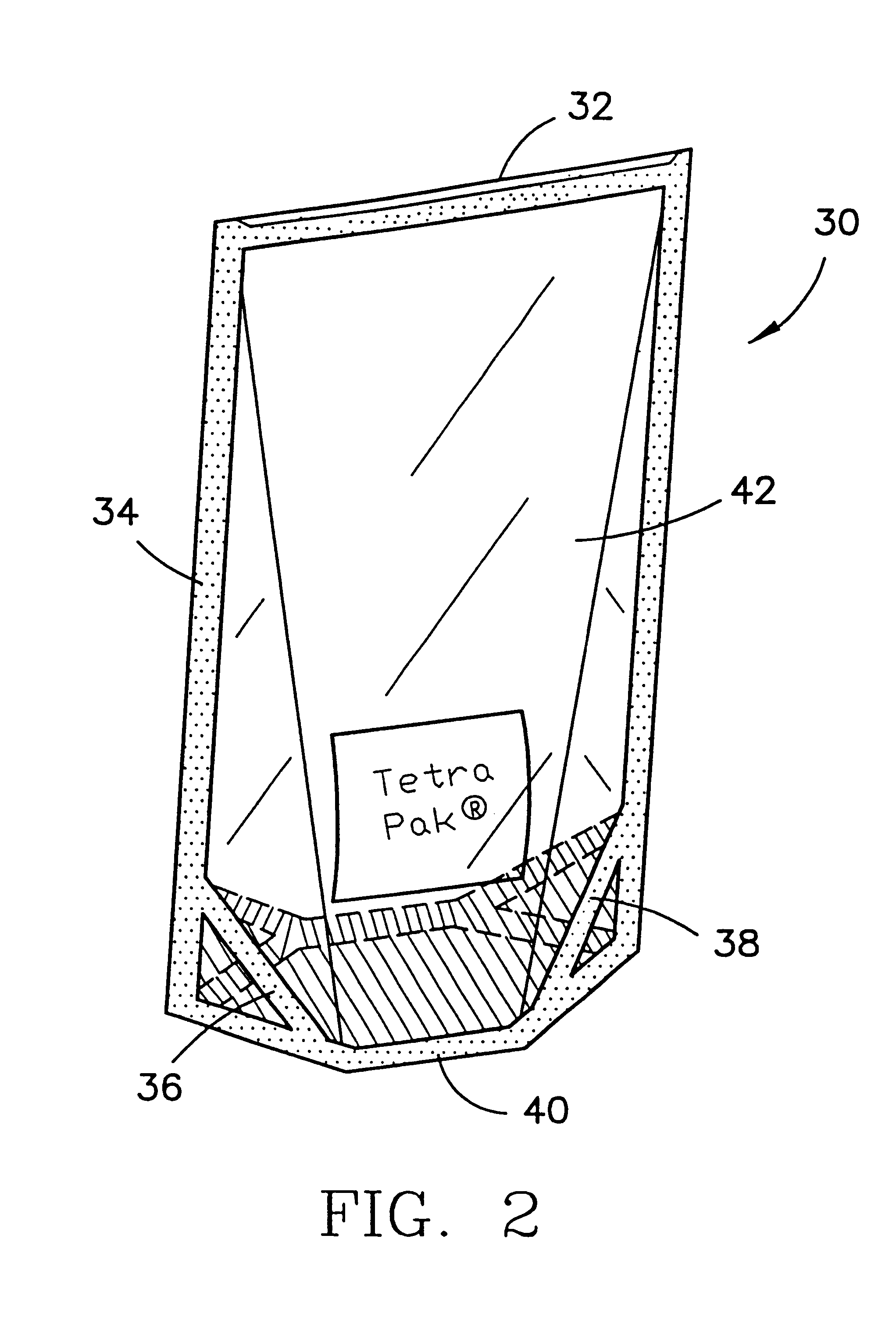

Transparent high barrier multilayer structure

A transparent multilayer structure is disclosed such as a flexible self-supporting container for a flowable food product such as fruit juice. The transparent multilayer structure possesses superior barrier properties to oxygen, water vapor and aromatic gases. The multilayer structure may include an exterior layer having a metal oxide deposition laminated to an interior layer through use of an adhesive. In one embodiment, the metal oxide is SiOx where x has a value between 1.5 and 2.2 thereby allowing for a transparent multilayer structure. The metal oxide may be deposited on the exterior layer through a number of various methods. An exemplary method is plasma-enhanced chemical vapor deposition. The exterior layer may be composed of a polymer material integrated with a clay mineral between 0.1% and 10% weight of the polymer material. The polymer material may be selected from the group consisting of polyamide, polyethylene terephthalate, copolymers of polyethylene terephthalate and mixtures thereof.

Owner:TETRA LAVAL HLDG & FINANCE SA

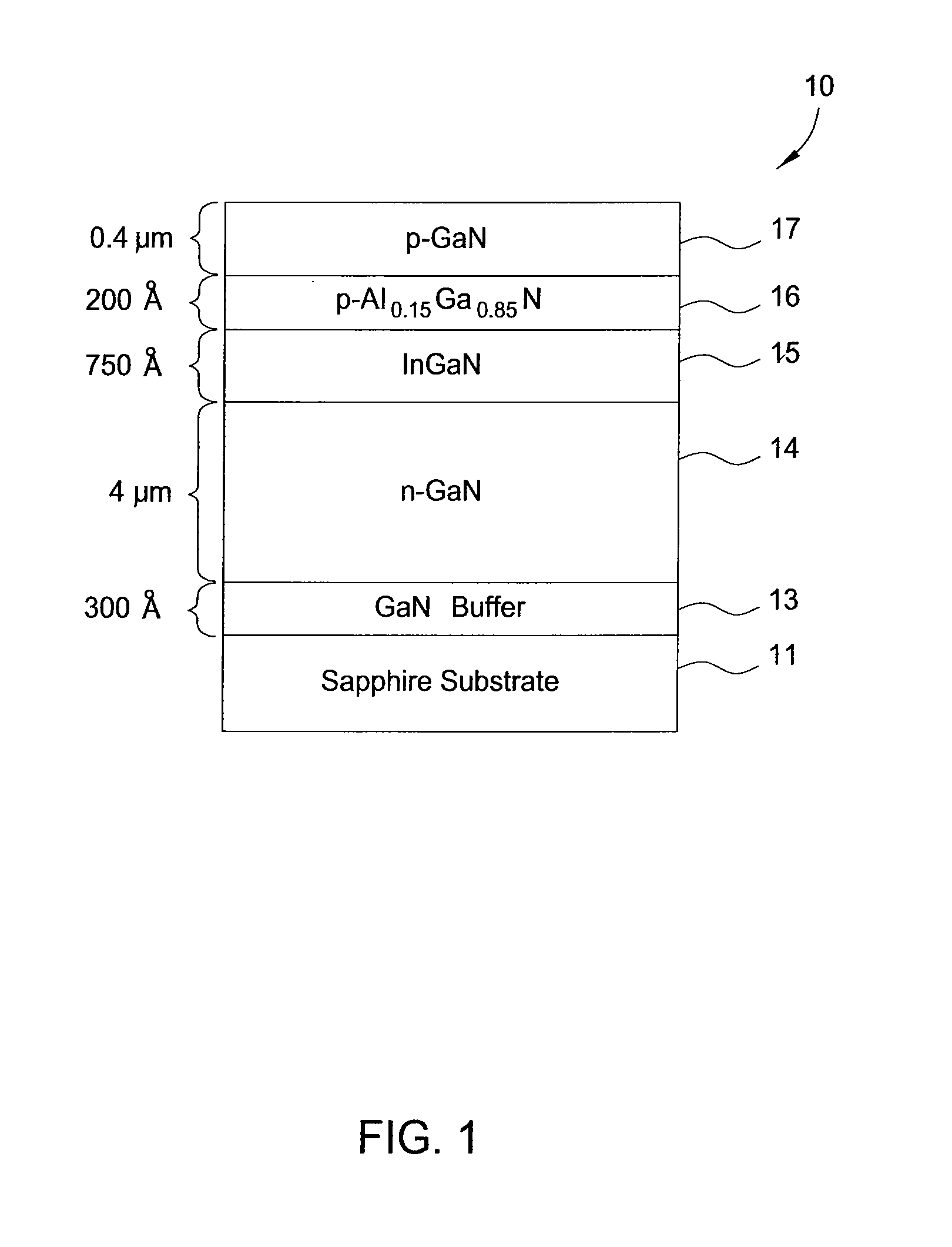

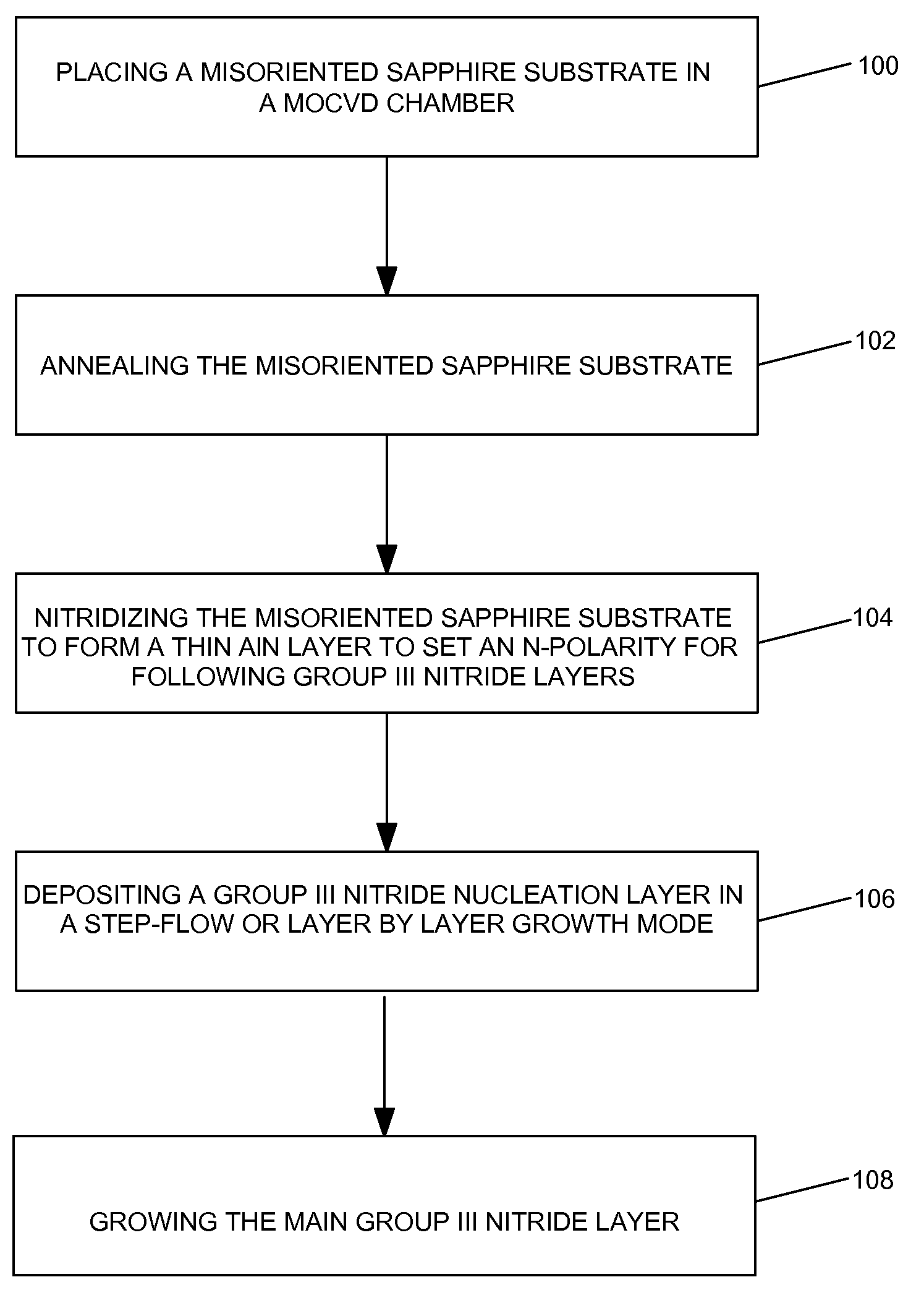

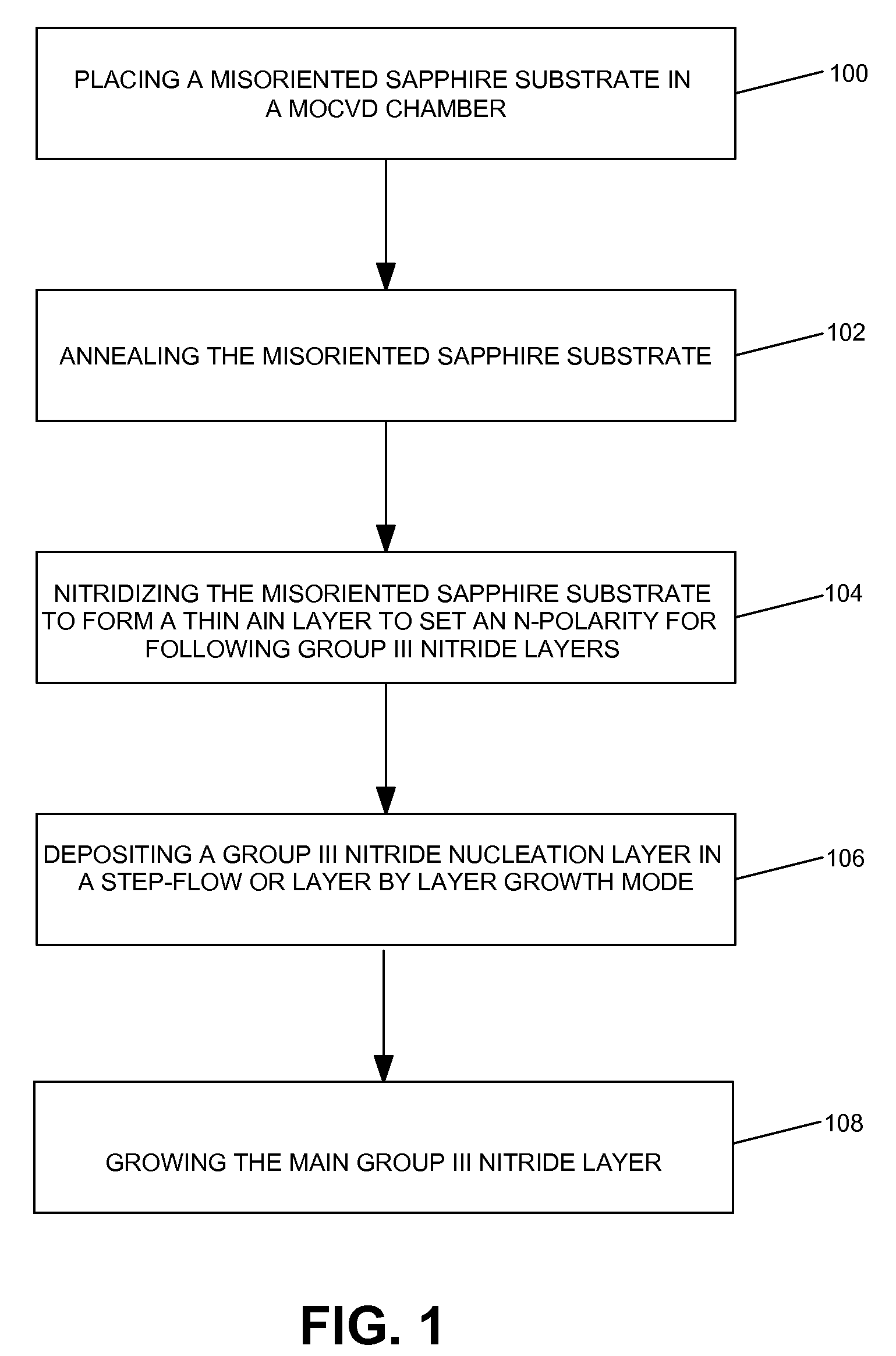

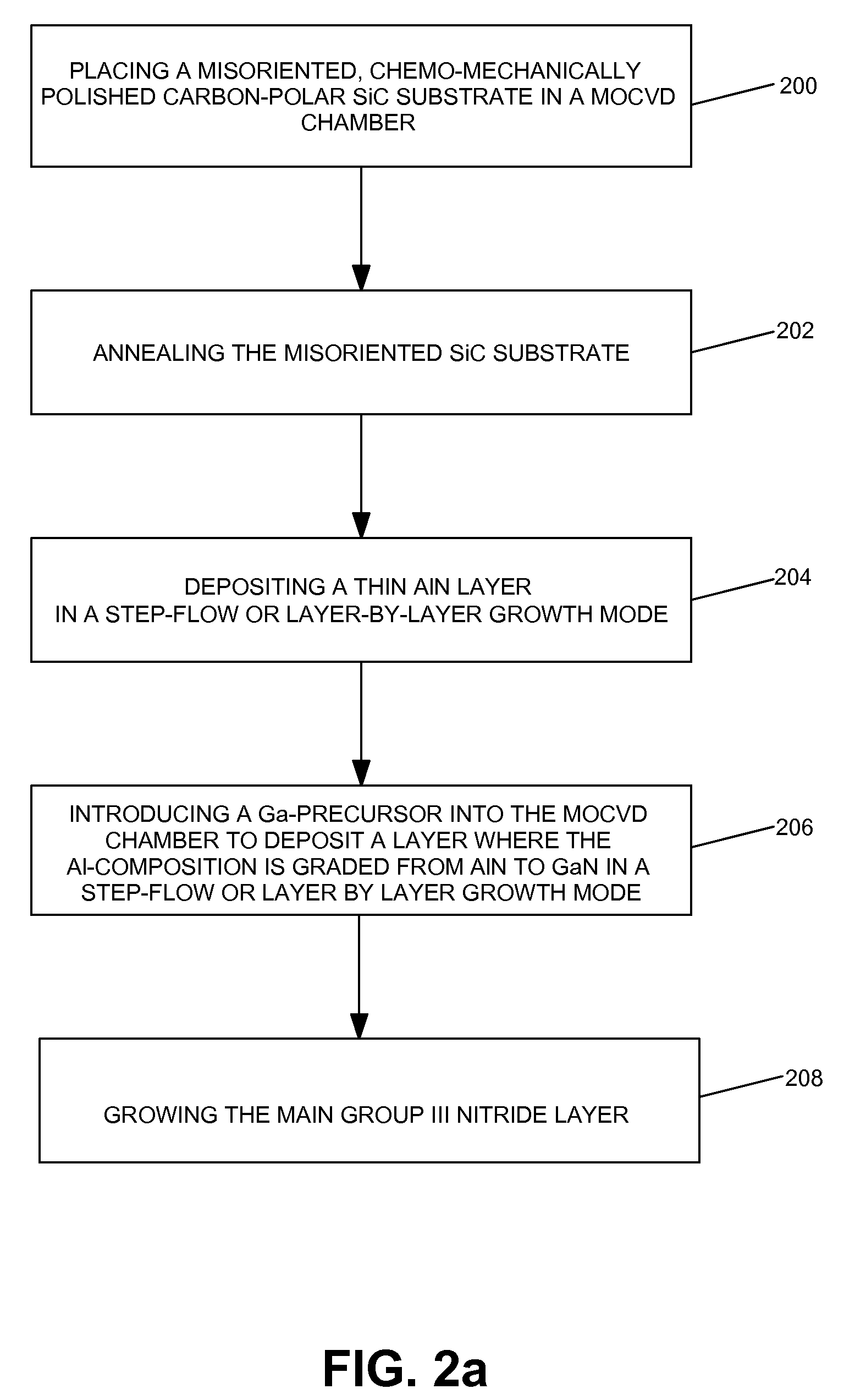

Method for heteroepitaxial growth of high-quality N-face GaN, InN, and AIN and their alloys by metal organic chemical vapor deposition

ActiveUS7566580B2Polycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseAlloy

Owner:RGT UNIV OF CALIFORNIA

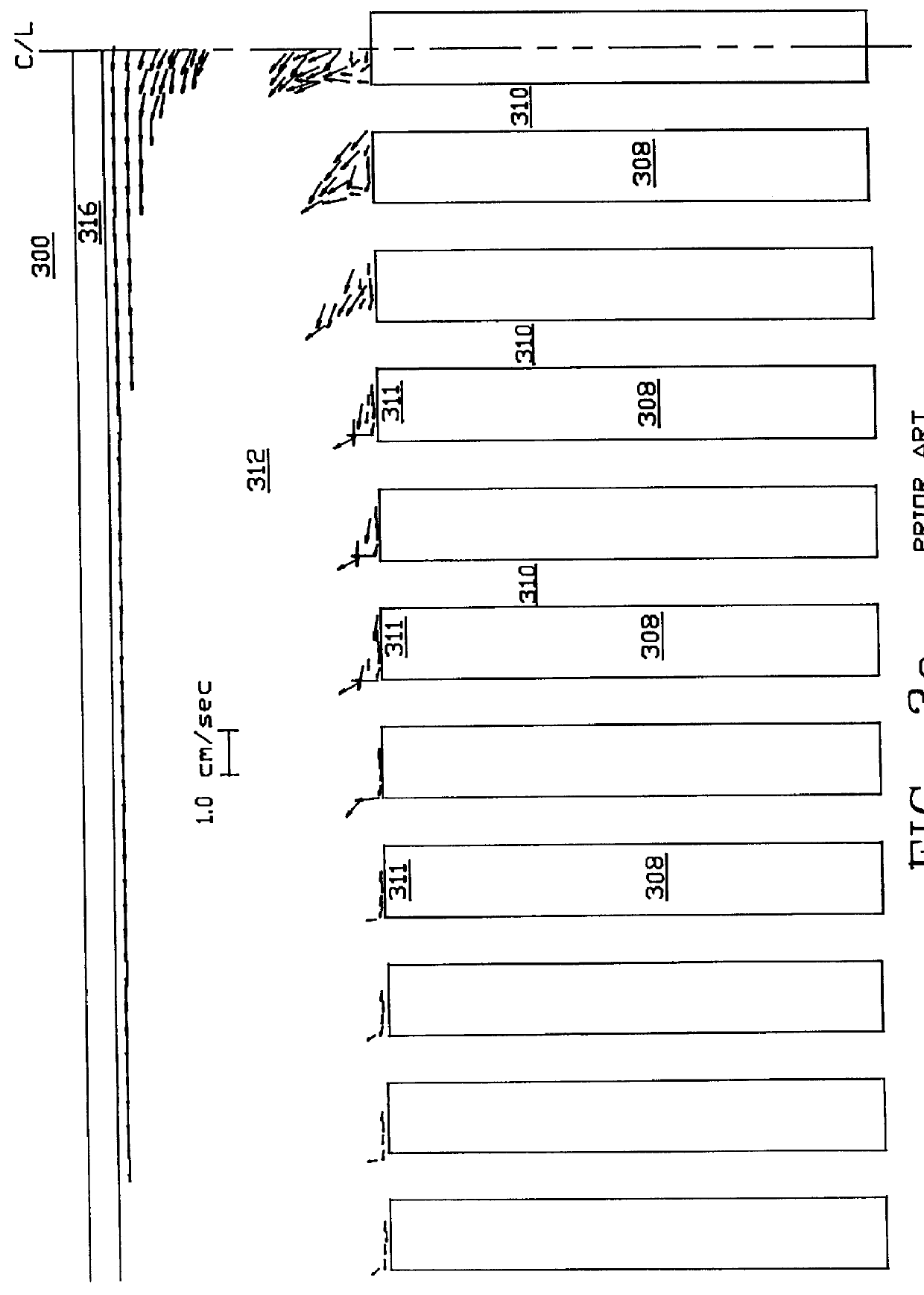

Chamber for reducing contamination during chemical vapor deposition

InactiveUS6079353AReduce the amount requiredExtension of timeSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseEngineering

This invention relates to the design of apparatus for processing electronic devices, including equipment for chemical vapor deposition. The new designs of gas separator plates, their configuration, and the regulation of gas flows through the system provides control over the pattern of precursor gas flow away from the separation plates, thereby decreasing the amount of byproducts that are deposited on the plates and throughout the reactor. New designs for shaping other surfaces of the dispersion head reduces contamination of those elements, and new designs for chamber panels decrease the deposition of byproducts on those surfaces, as well as other elements of the reactor. Decreasing deposition of byproducts increases the amount of thin film, and the quality of the film which can be deposited without requiring the system to be shut down. This increases the throughput of products in the deposition process, thereby increasing the efficiency of electronic device manufacture and lowering the cost.

Owner:CANON USA

Method for depositing silicon nitride films and silicon oxynitride films by chemical vapor deposition

InactiveUS6936548B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingChemical vapor depositionSilicon oxynitride

Owner:LAIR LIQUIDE SA POUR LETUDE & LEXPLOITATION DES PROCEDES GEORGES CLAUDE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com