Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3429 results about "Semiconductor device fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically the metal-oxide-semiconductor (MOS) devices used in the integrated circuit (IC) chips that are present in everyday electrical and electronic devices. It is a multiple-step sequence of photolithographic and chemical processing steps (such as surface passivation, thermal oxidation, planar diffusion and junction isolation) during which electronic circuits are gradually created on a wafer made of pure semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

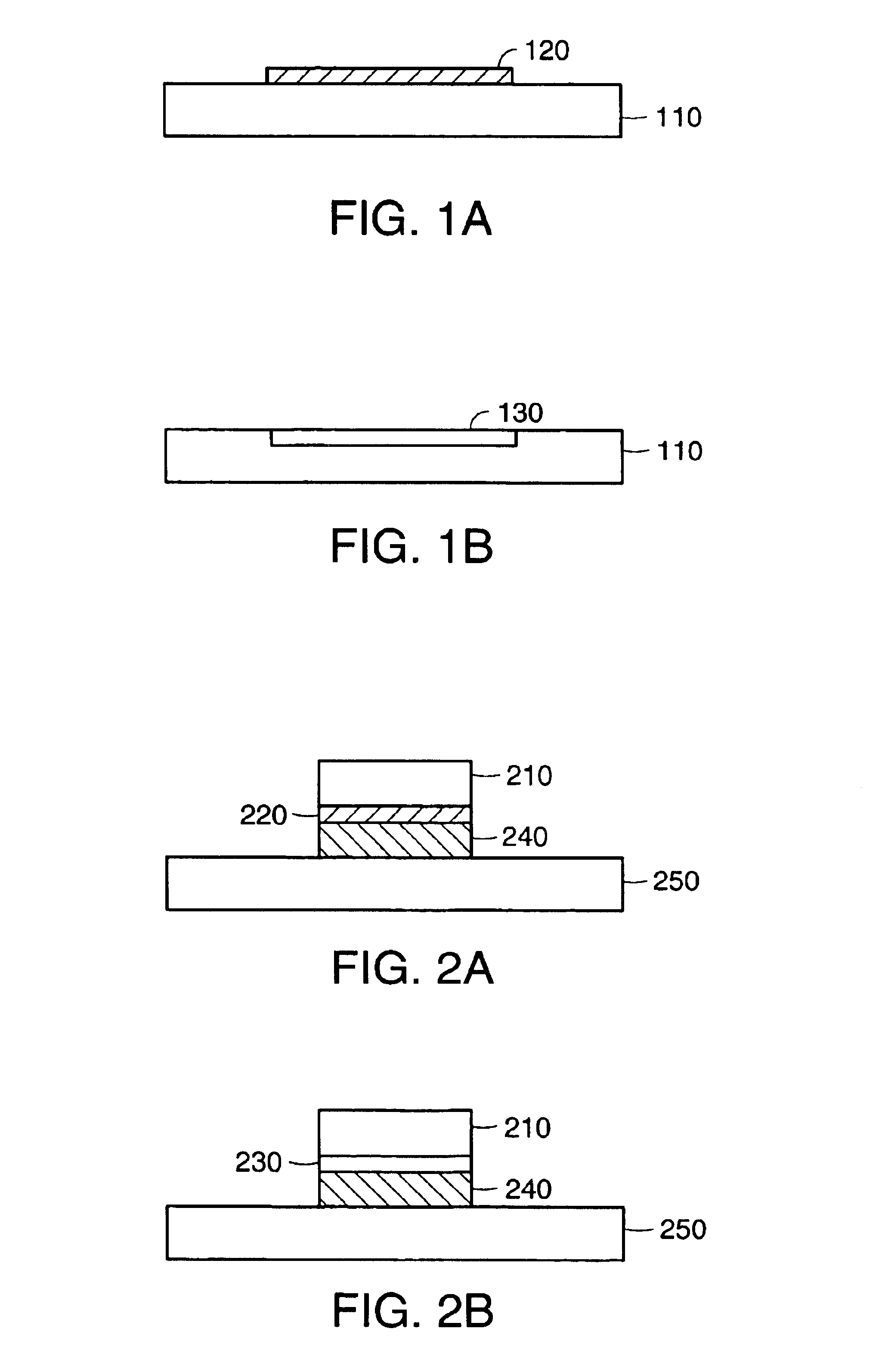

Reactive formation of dielectric layers and protection of organic layers in organic semiconductor device fabrication

InactiveUS6842657B1Use is harmfulDamage is causedSolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerOrganic semiconductor

In one embodiment of the invention, a method of manufacturing a semiconductor device comprises the steps of: a) providing an organic semiconductor layer; b) depositing a reactive species on a portion of the organic semiconductor layer; and c) reacting the reactive species with the portion of the organic layer to form a dielectric layer.

Owner:E INK CORPORATION

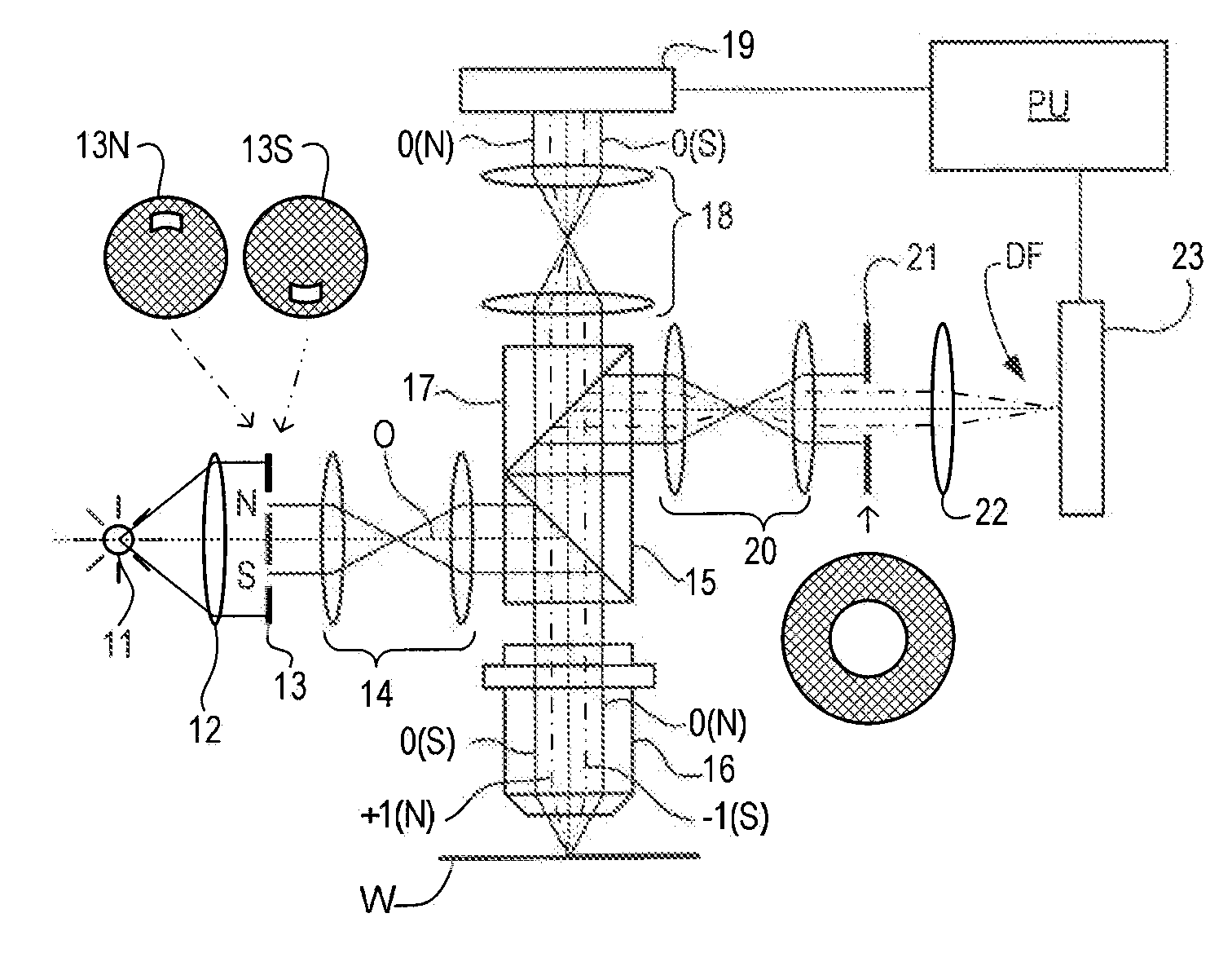

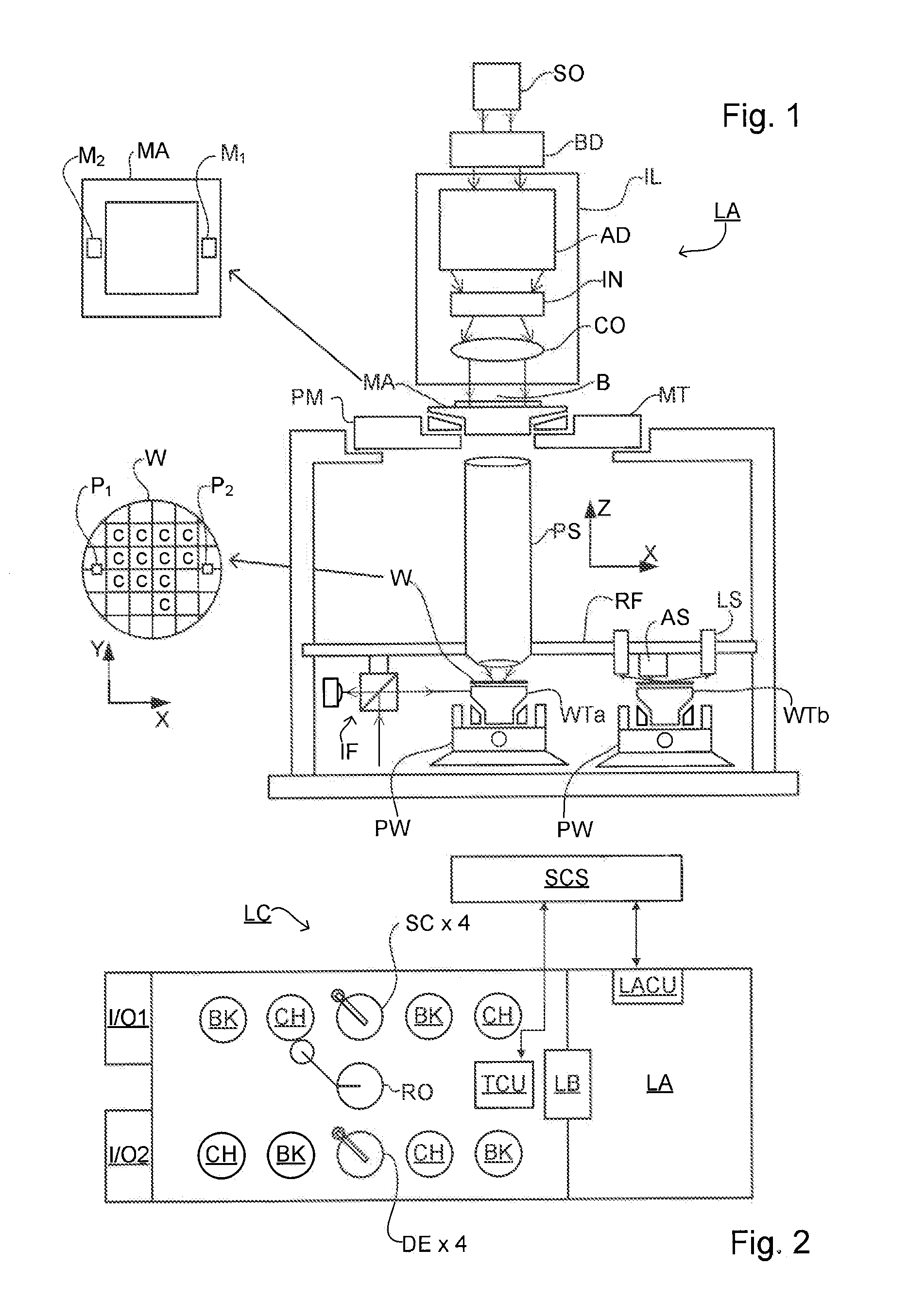

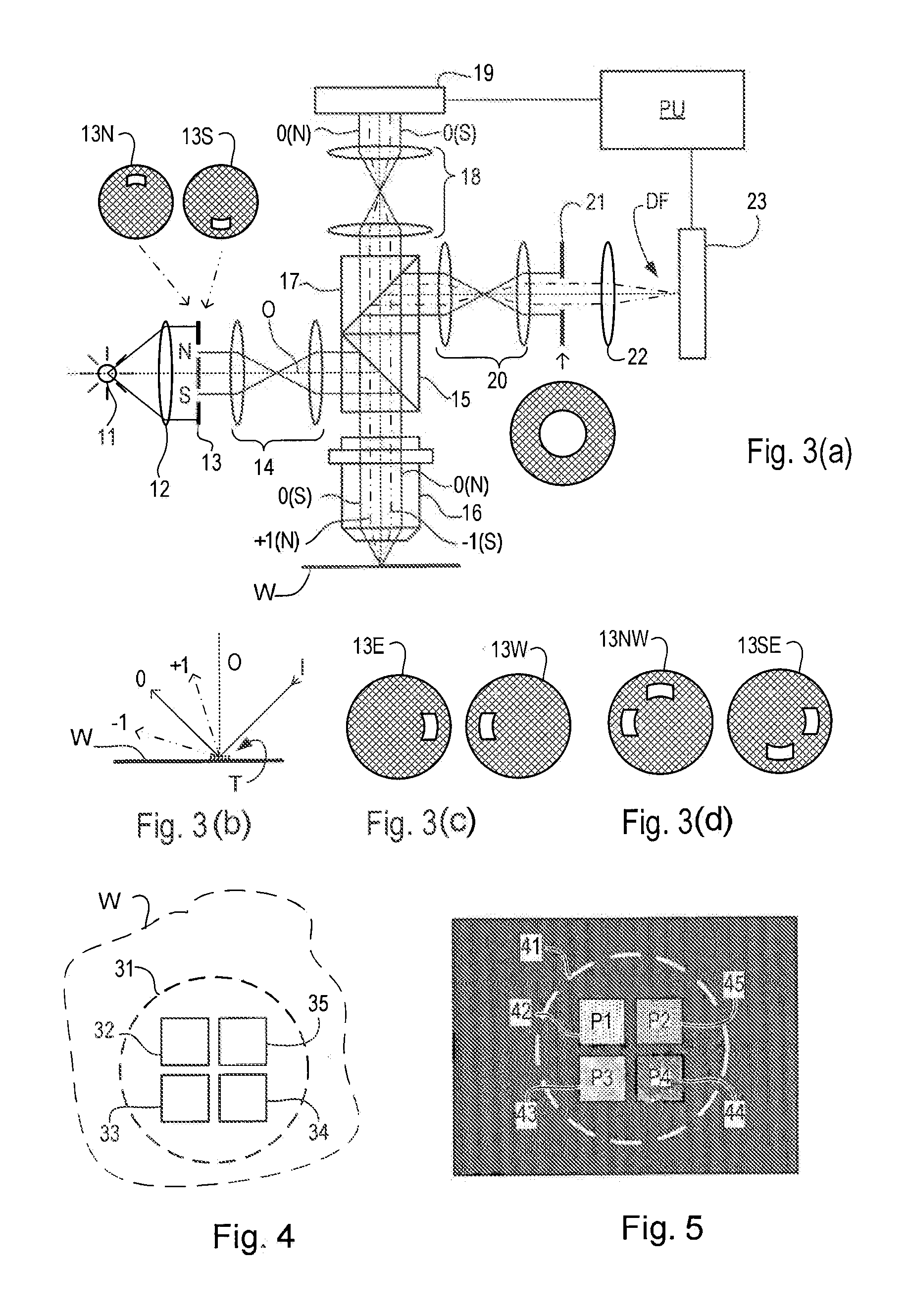

Metrology Method and Apparatus, and Device Manufacturing Method

ActiveUS20120242970A1Improve accuracyImprove throughputPhotomechanical apparatusOptically investigating flaws/contaminationMetrologyGrating

Methods are disclosed for measuring target structures formed by a lithographic process on a substrate. A grating or other structure within the target is smaller than an illumination spot and field of view of a measurement optical system. The position of an image of the component structure varies between measurements, and a first type of correction is applied to reduce the influence on the measured intensities, caused by differences in the optical path to and from different positions. A plurality of structures may be imaged simultaneously within the field of view of the optical system, and each corrected for its respective position. The measurements may comprise first and second images of the same target under different modes of illumination and / or imaging, for example in a dark field metrology application. A second type of correction may be applied to reduce the influence of asymmetry between the first and second modes of illumination or imaging, for example to permit a more accurate overly measurement in a semiconductor device manufacturing process.

Owner:ASML NETHERLANDS BV

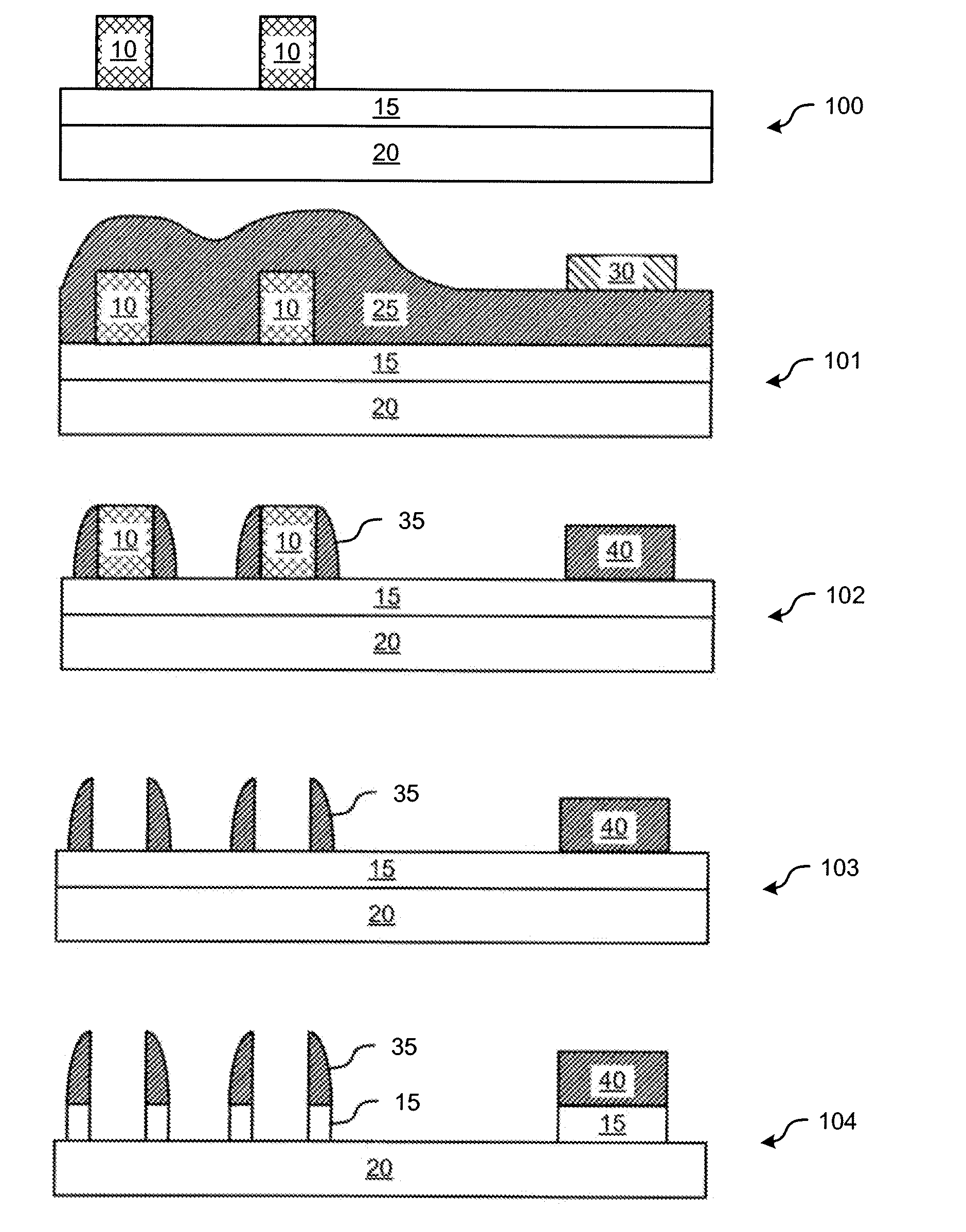

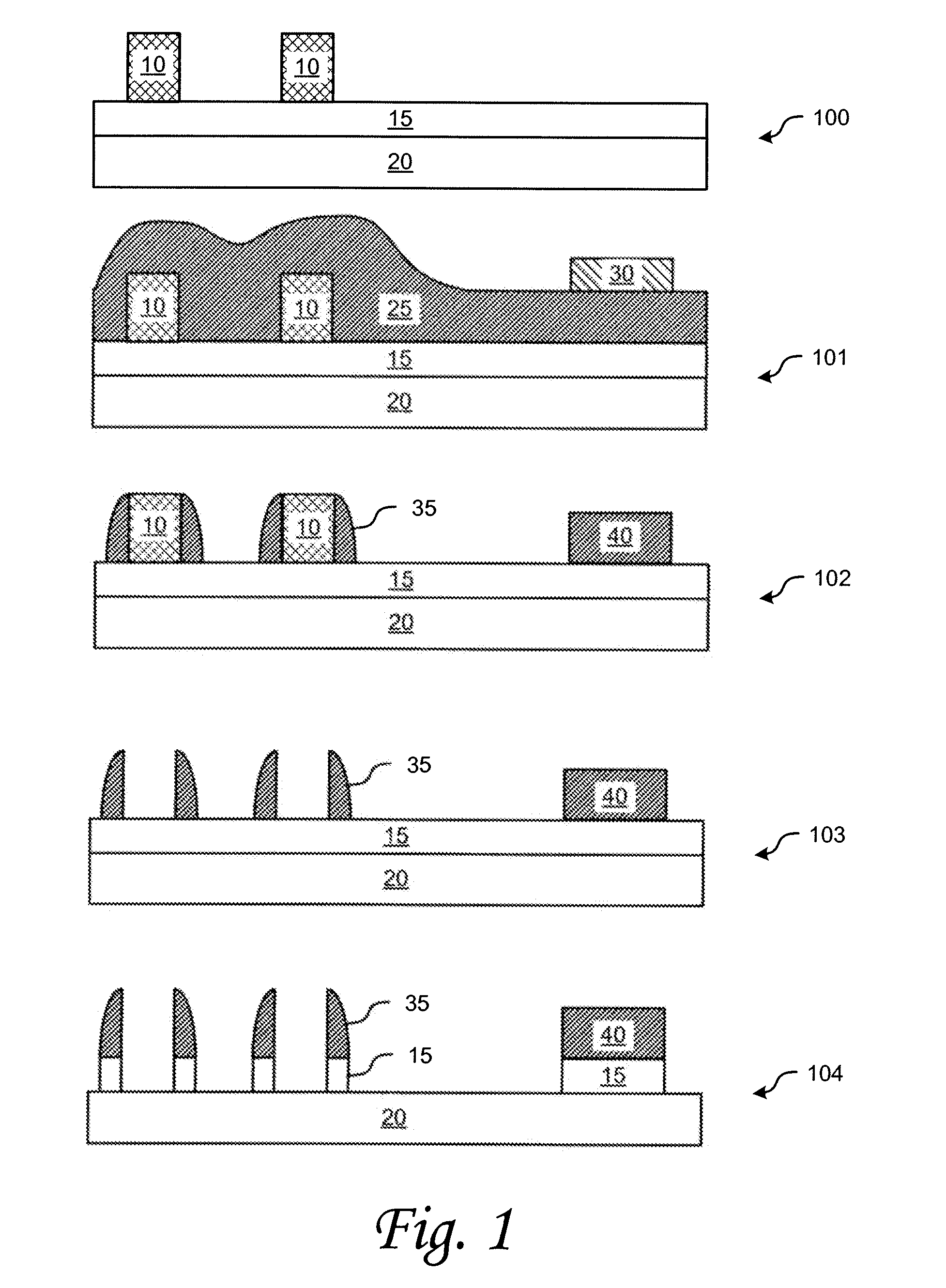

Method of eliminating a lithography operation

ActiveUS20090146322A1Semiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

Methods of semiconductor device fabrication are disclosed. An exemplary method includes processes of depositing a first pattern on a semiconductor substrate, wherein the first pattern defines wide and narrow spaces; depositing spacer material over the first pattern on the substrate; etching the spacer material such that the spacer material is removed from horizontal surfaces of the substrate and the first pattern but remains adjacent to vertical surfaces of a wide space defined by the first pattern and remains within narrow a space defined by the first pattern; and removing the first pattern from the substrate. In one embodiment, the first pattern can comprise sacrificial material, which can include, for example, polysilicon material. The deposition can comprise physical vapor deposition, chemical vapor deposition, electrochemical deposition, molecular beam epitaxy, atomic layer deposition or other deposition techniques. According to another embodiment, features for lines and logic device components having a width greater than that of the lines are formed in the spacer material in the same mask layer.

Owner:CADENCE DESIGN SYST INC

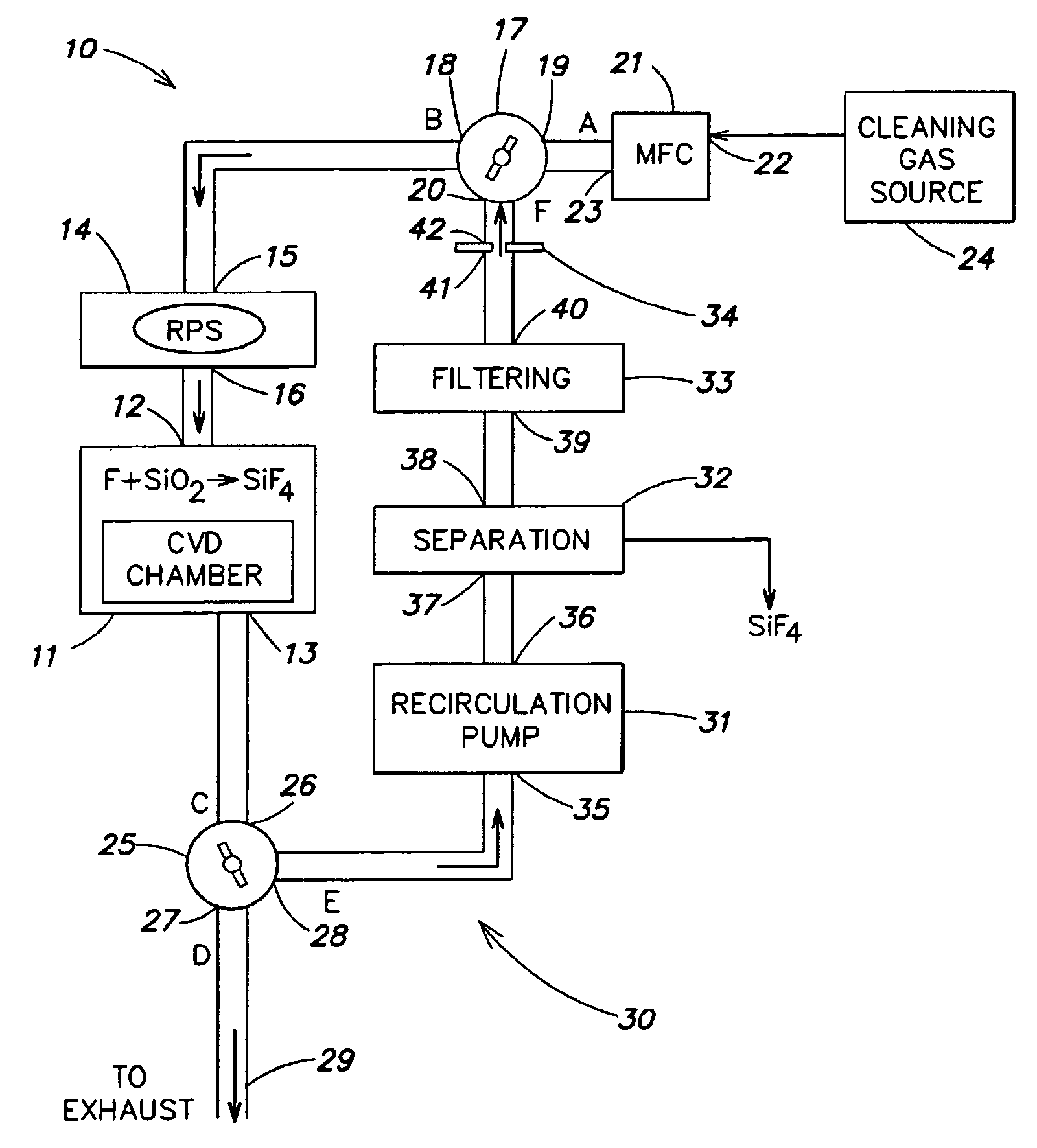

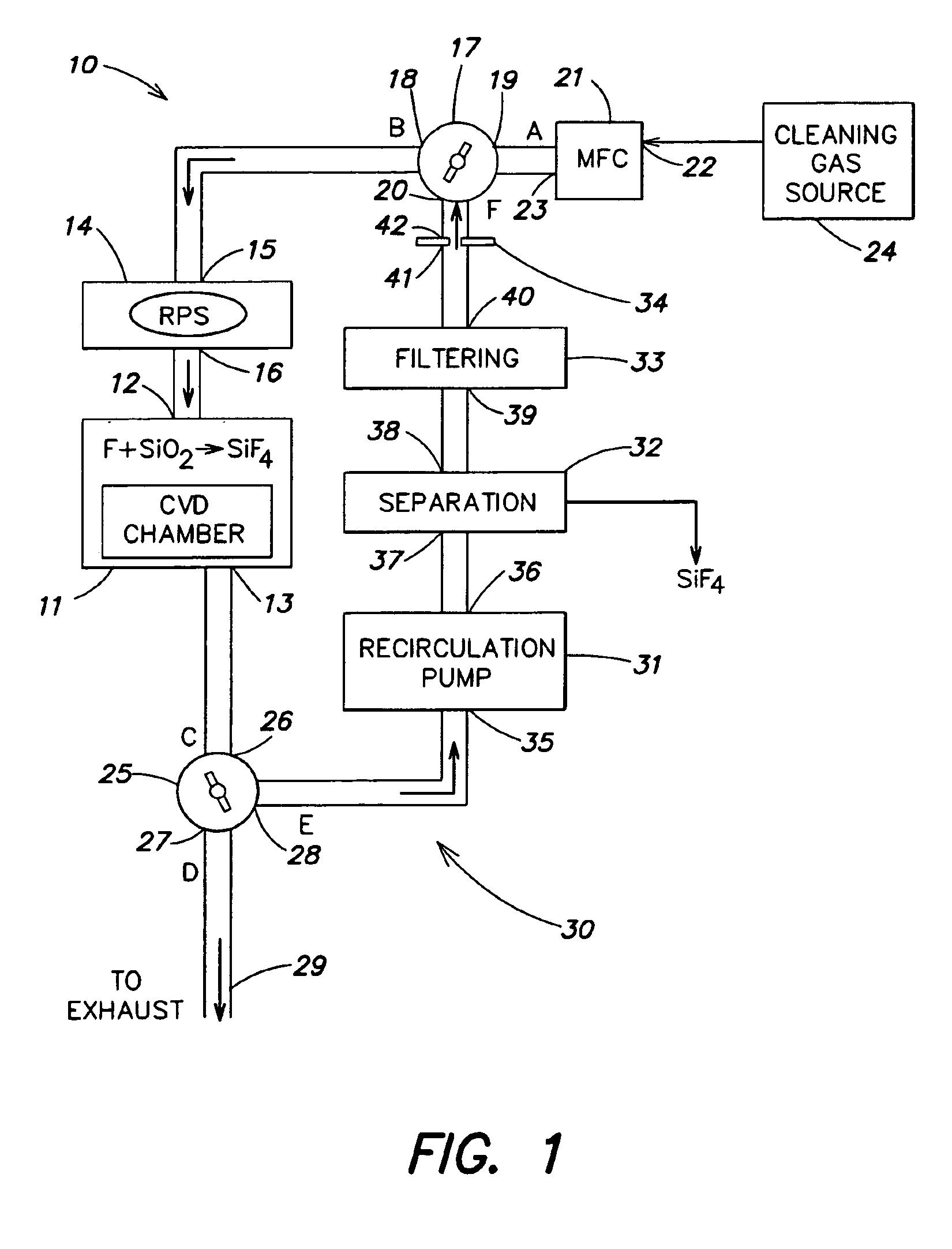

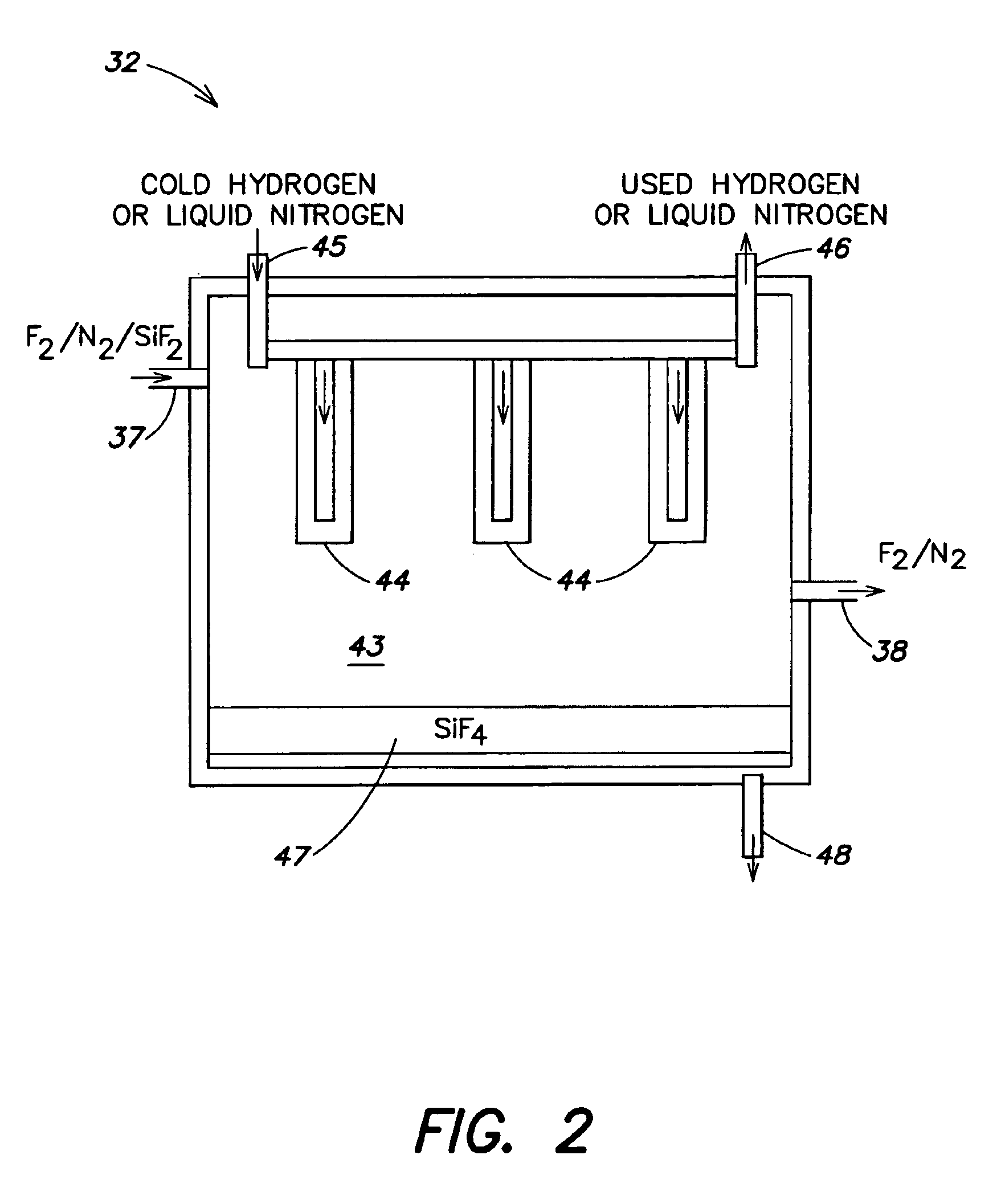

Semiconductor device fabrication chamber cleaning method and apparatus with recirculation of cleaning gas

InactiveUS6863019B2Low costReduce consumptionElectric discharge tubesElectrostatic cleaningNuclear engineeringProduct gas

A method of cleaning a semiconductor fabrication processing chamber involves recirculation of cleaning gas components. Consequently, input cleaning gas is utilized efficiently, and undesirable emissions are reduced. The method includes flowing a cleaning gas to an inlet of a processing chamber, and exposing surfaces of the processing chamber to the cleaning gas to clean the surfaces, thereby producing a reaction product. The method further includes removing an outlet gas including the reaction product from an outlet of the processing chamber, separating at least a portion of the reaction product from the outlet gas, and recirculating a portion of the outlet gas to the inlet of the processing chamber.

Owner:APPLIED MATERIALS INC

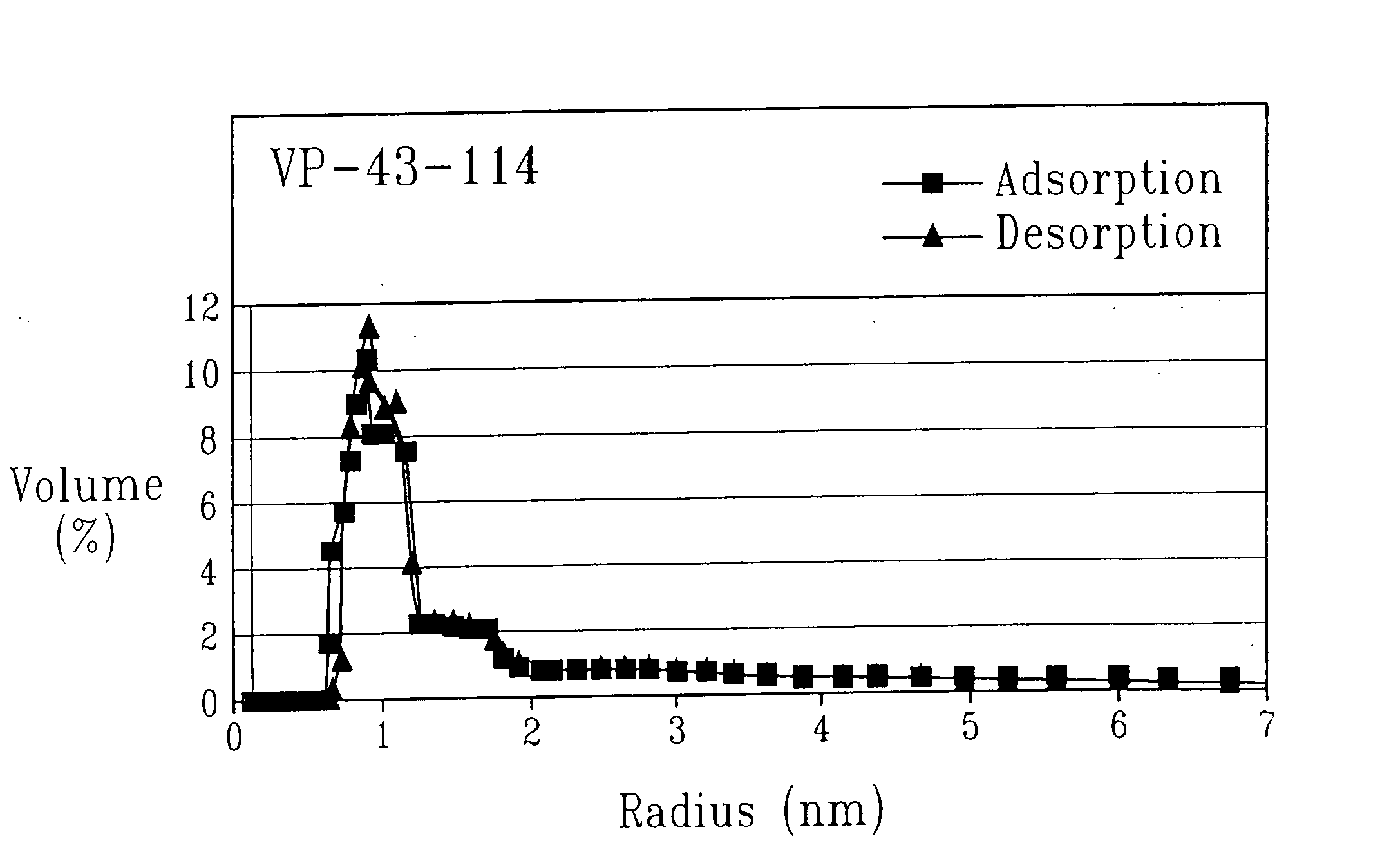

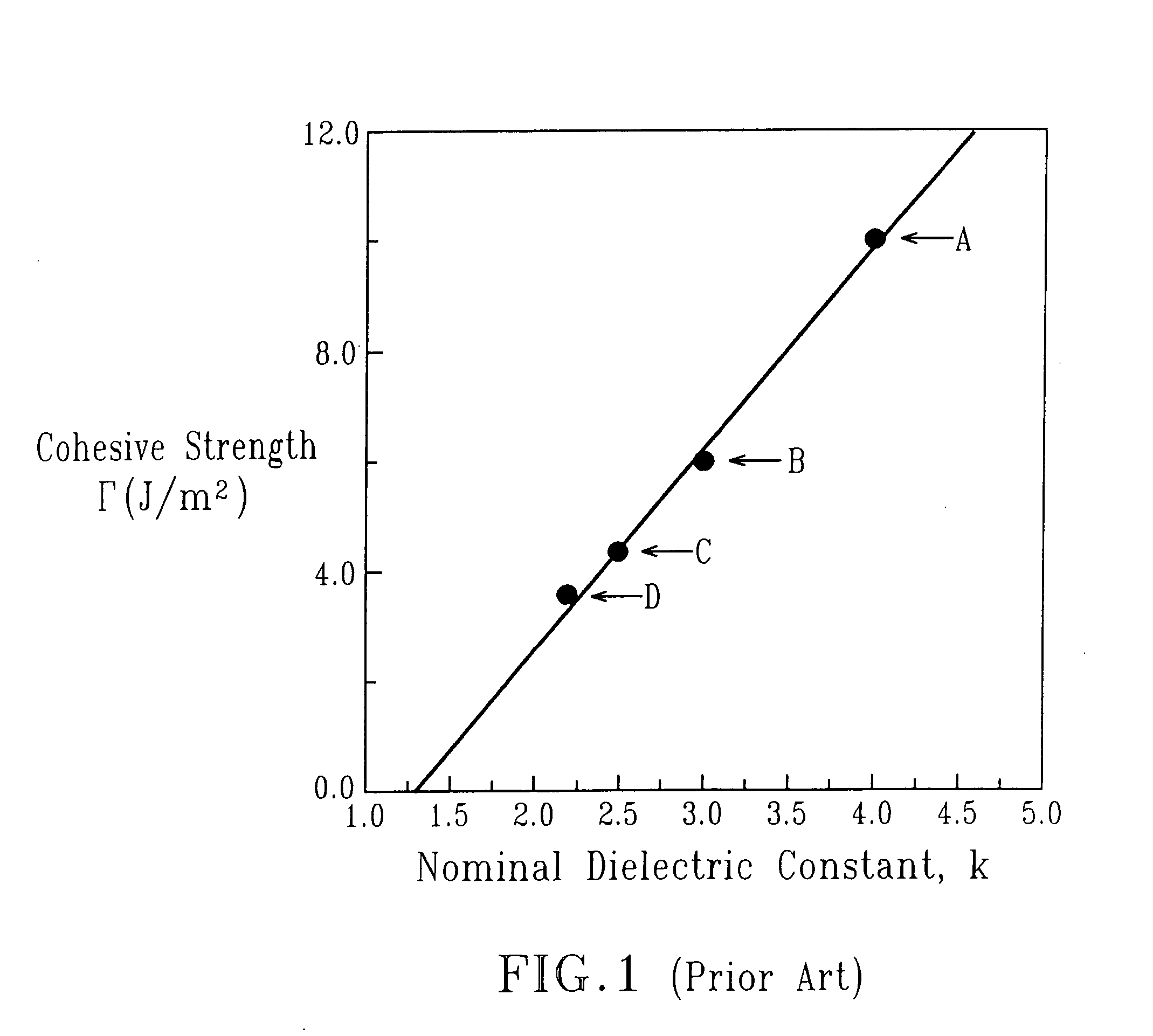

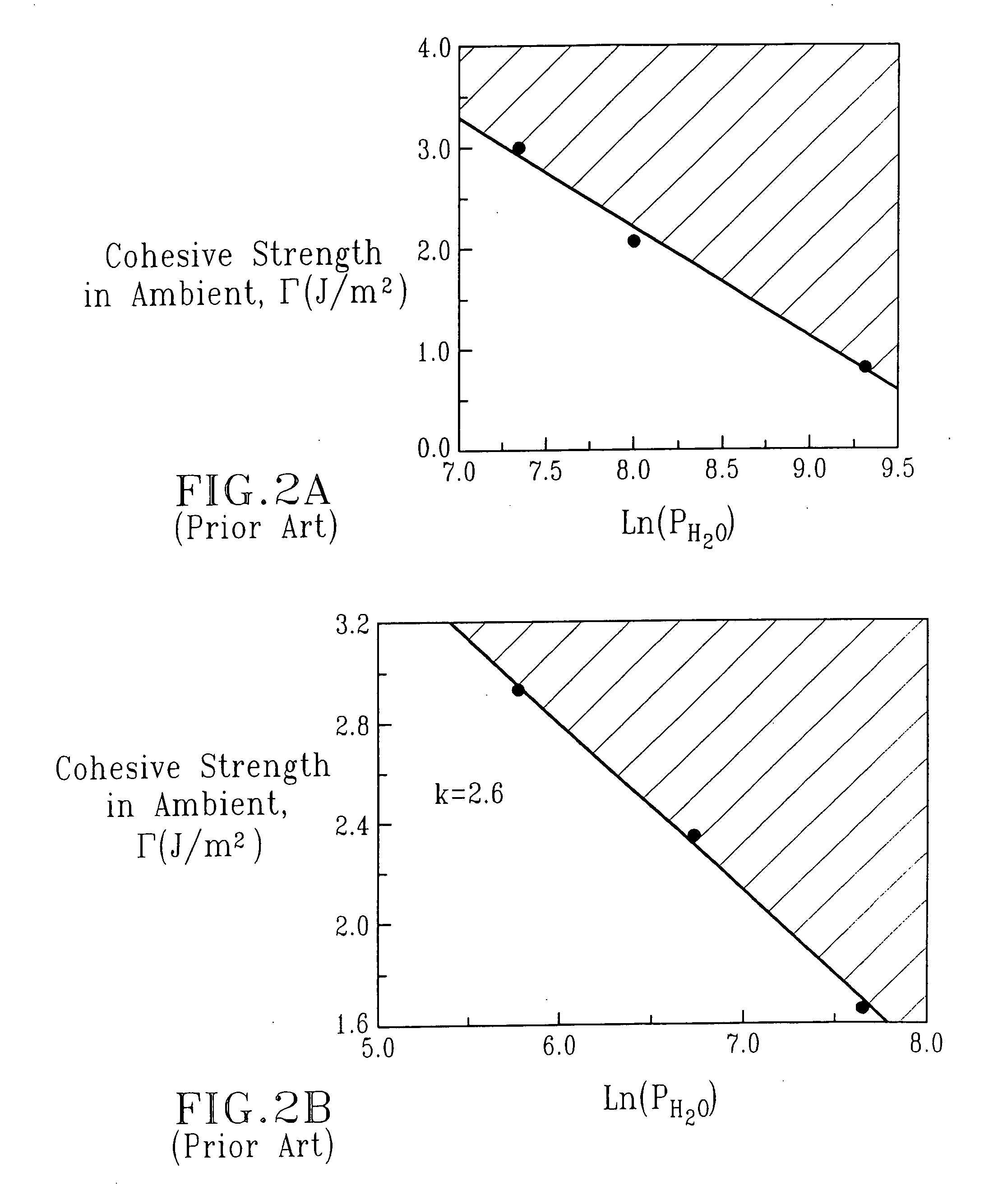

SiCOH dielectric

InactiveUS20070173071A1Improve cohesive strengthReduce brittlenessSemiconductor/solid-state device detailsSolid-state devicesDielectricDevice material

A porous composite material useful in semiconductor device manufacturing, in which the diameter (or characteristic dimension) of the pores and the pore size distribution (PSD) is controlled in a nanoscale manner and which exhibits improved cohesive strength (or equivalently, improved fracture toughness or reduced brittleness), and increased resistance to water degradation of properties such as stress-corrosion cracking, Cu ingress, and other critical properties is provided. The porous composite material is fabricating utilizing at least one bifunctional organic porogen as a precursor compound

Owner:INTEL CORP

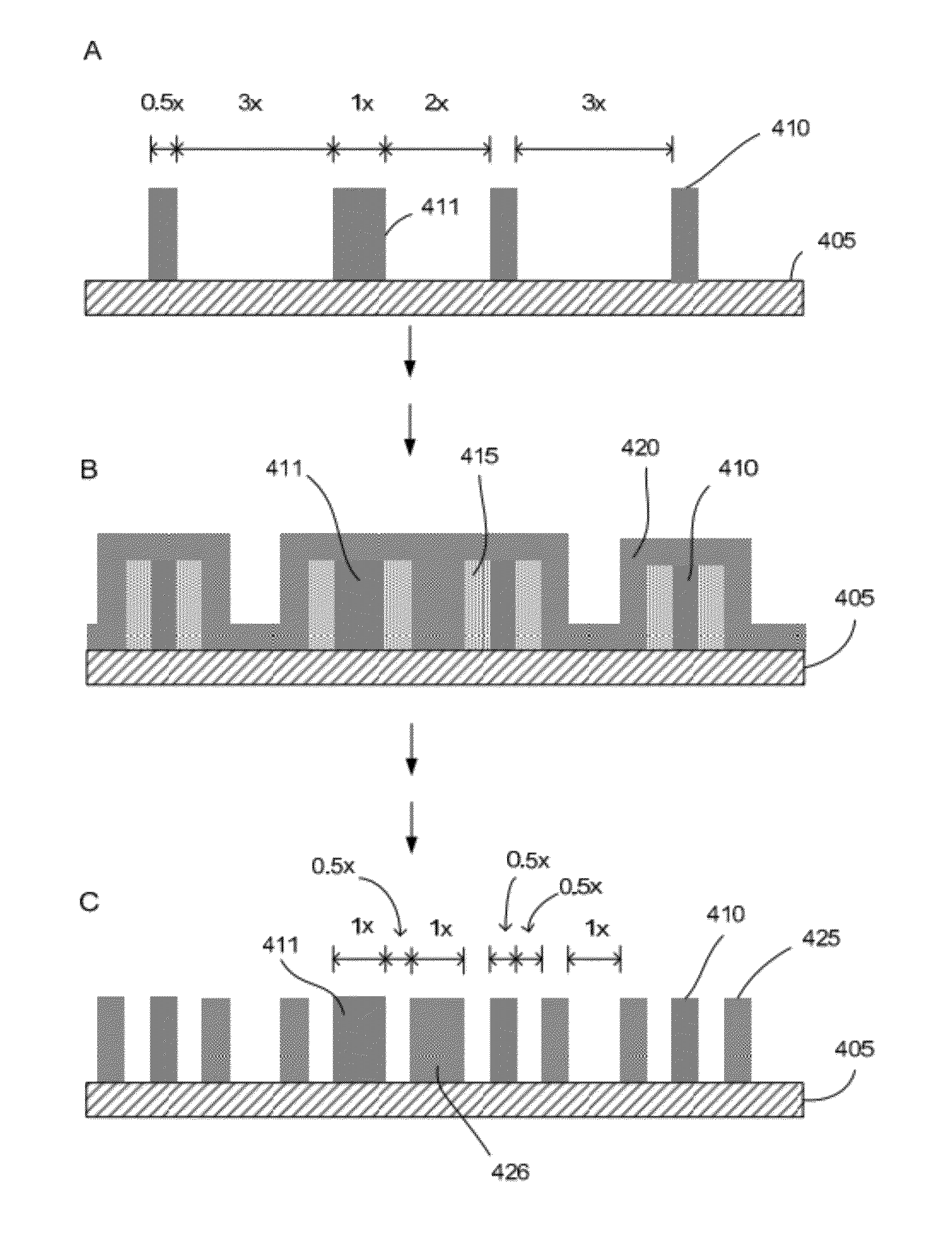

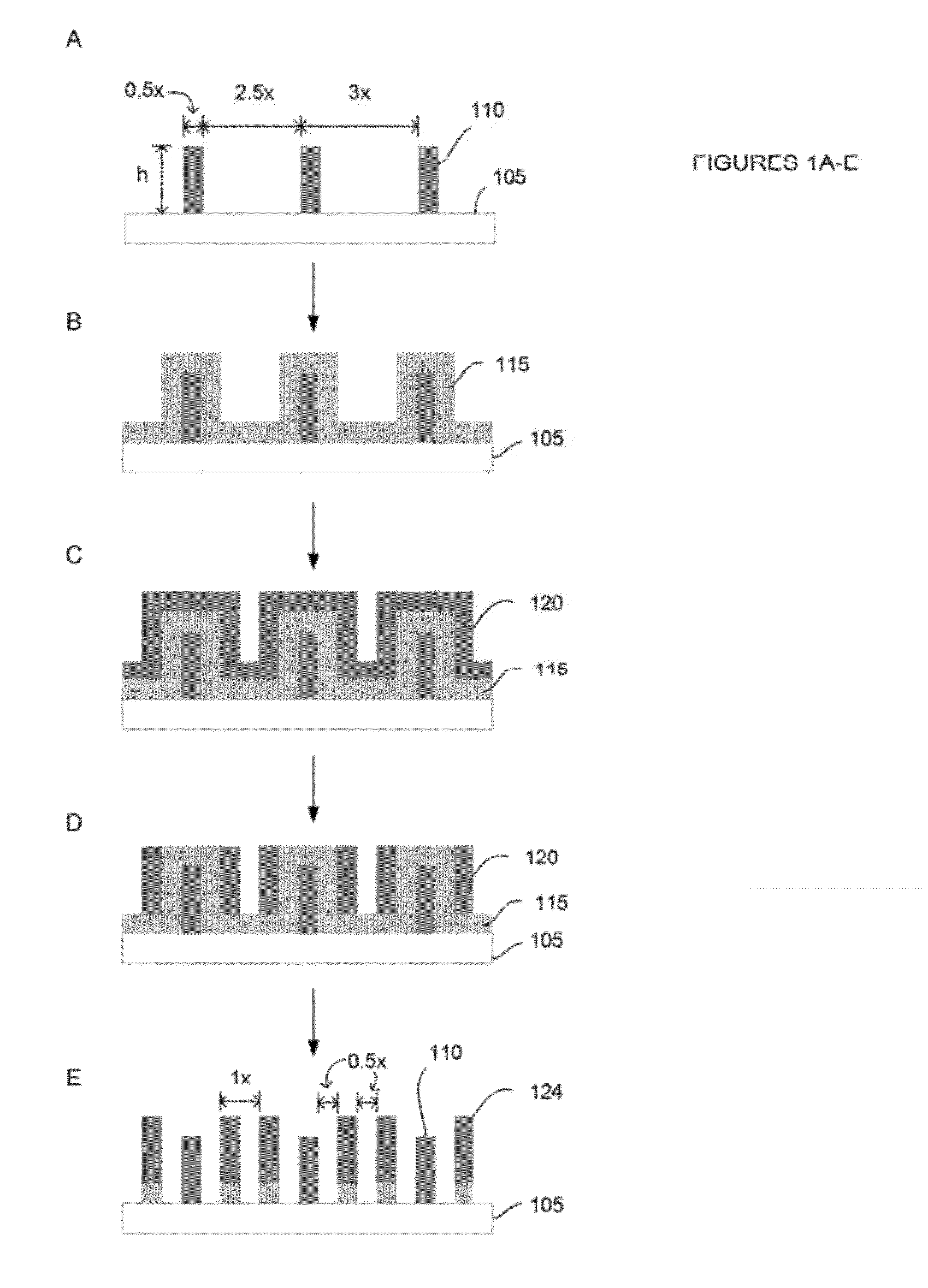

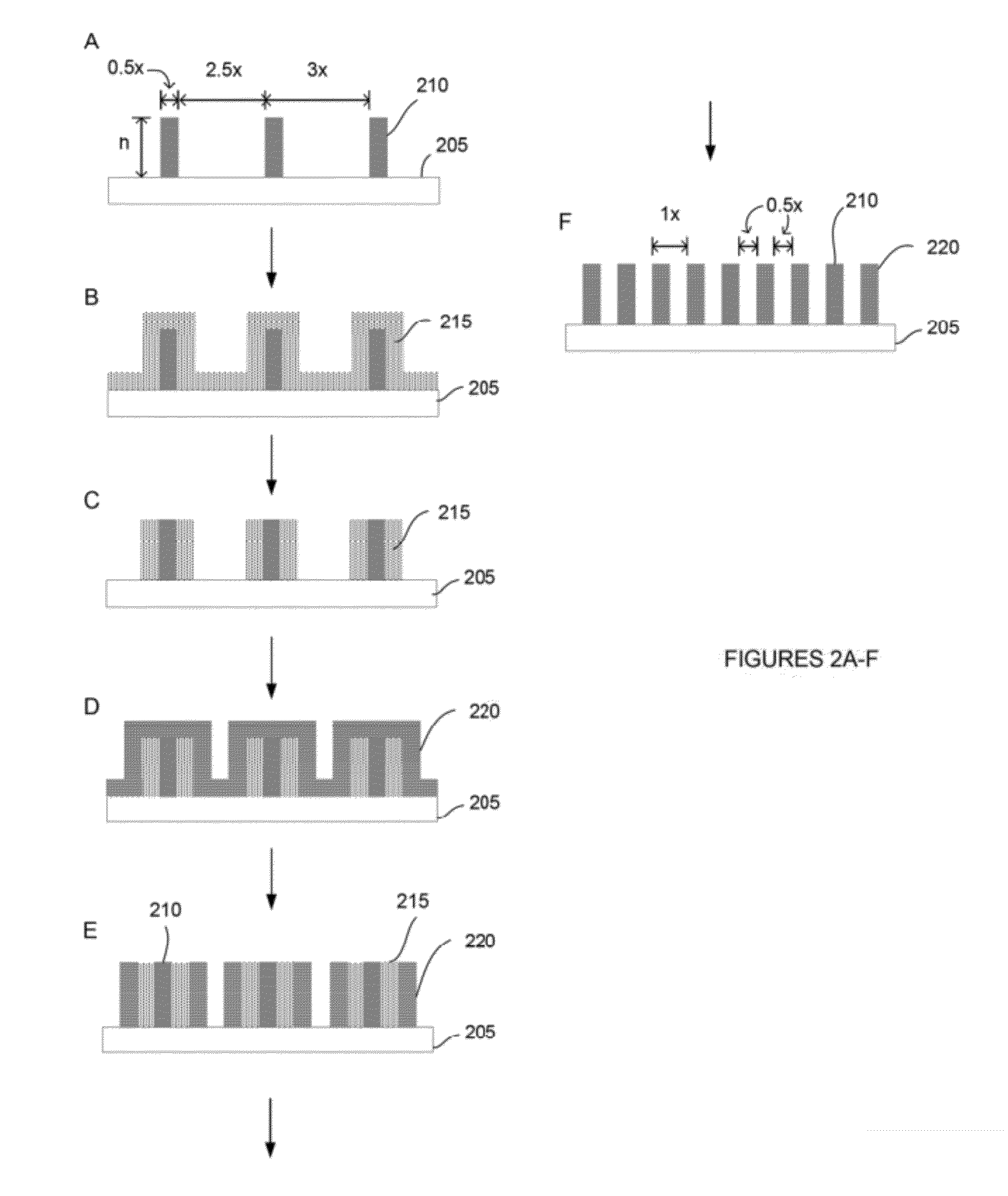

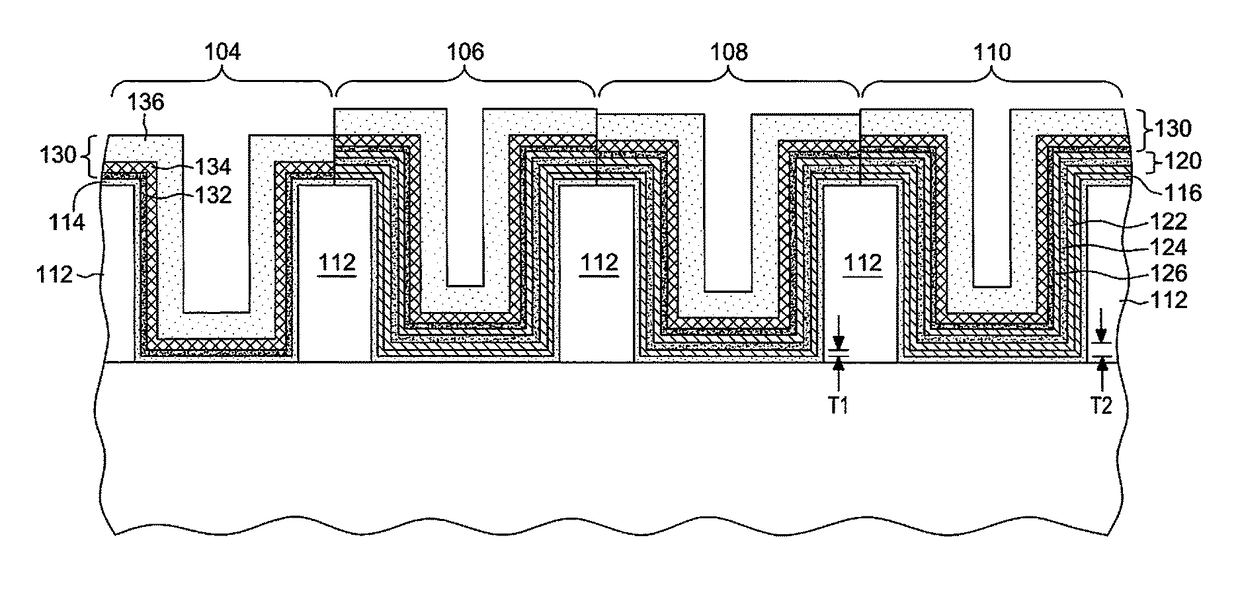

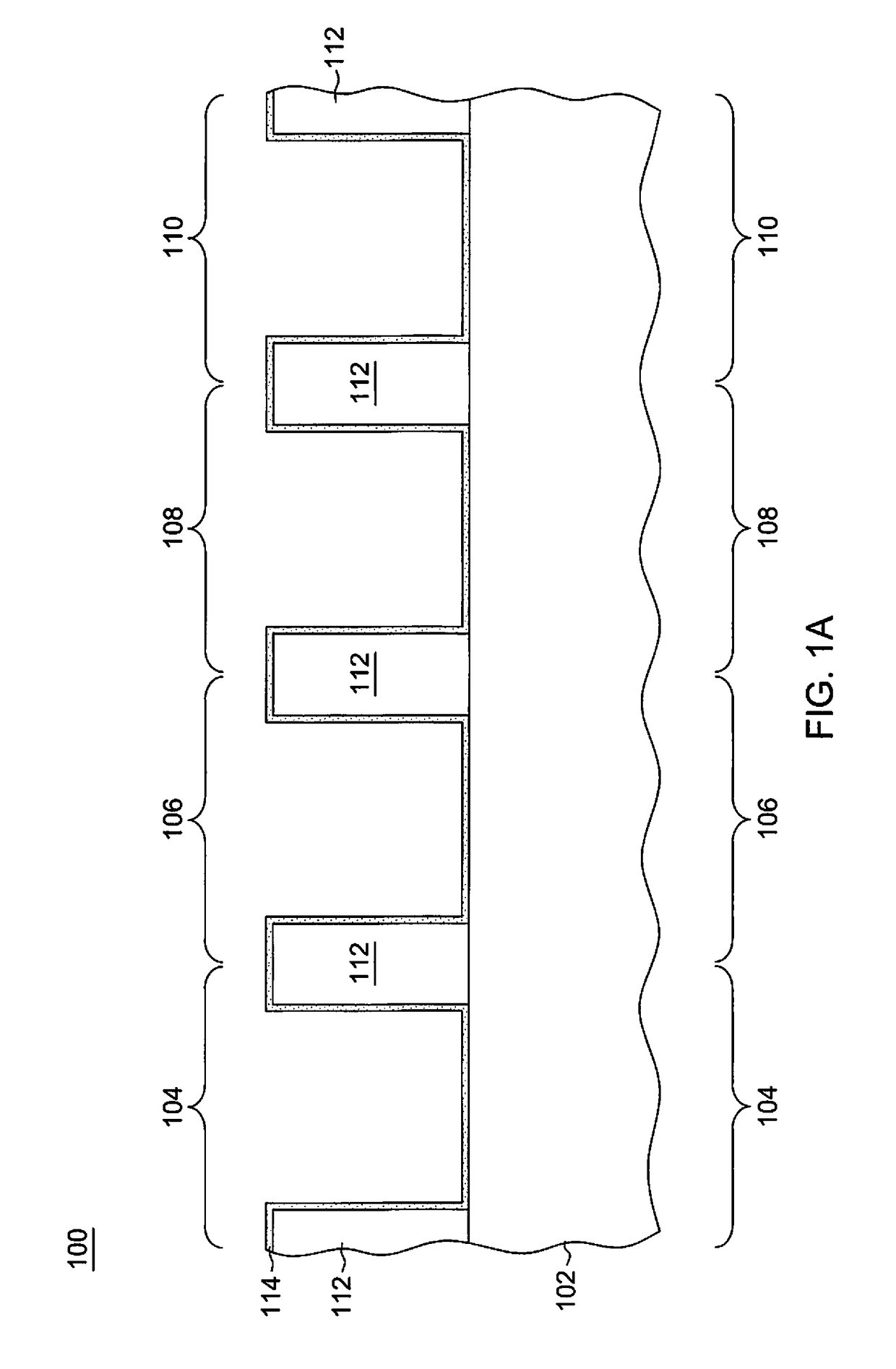

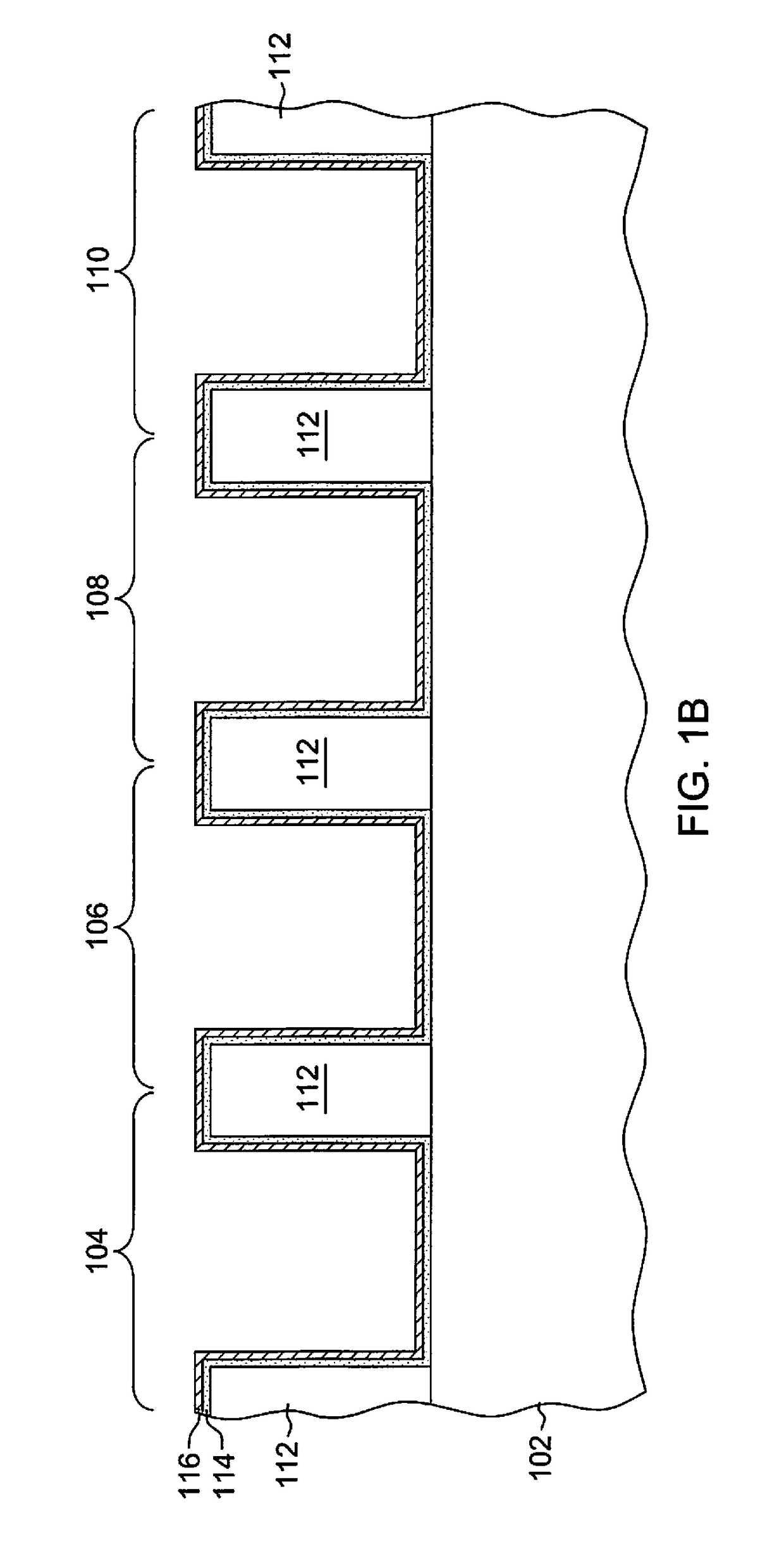

Feature size reduction

Methods for semiconductor device fabrication are provided. Features are created using spacers. Methods include creating a pattern comprised of at least two first features on the substrate surface, depositing a first conformal layer on the at least two first features, depositing a second conformal layer on the first conformal layer, partially removing the second conformal layer to partially expose the first conformal layer, and partially removing the first conformal layer from between the first features and the second conformal layer thereby creating at least two second features. Optionally the first conformal film is partially etched back before the second conformal film is deposited.

Owner:INTEL CORP

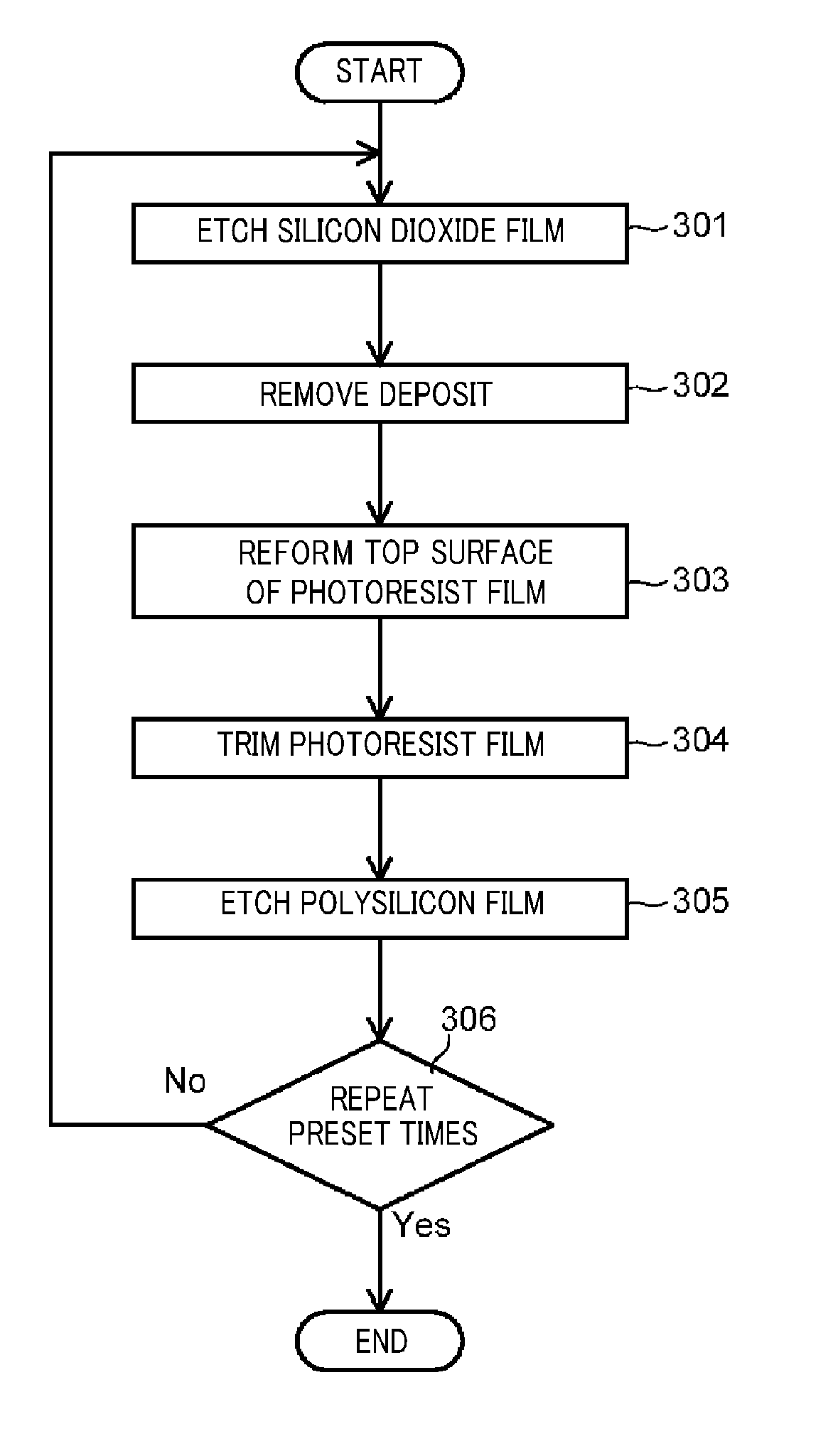

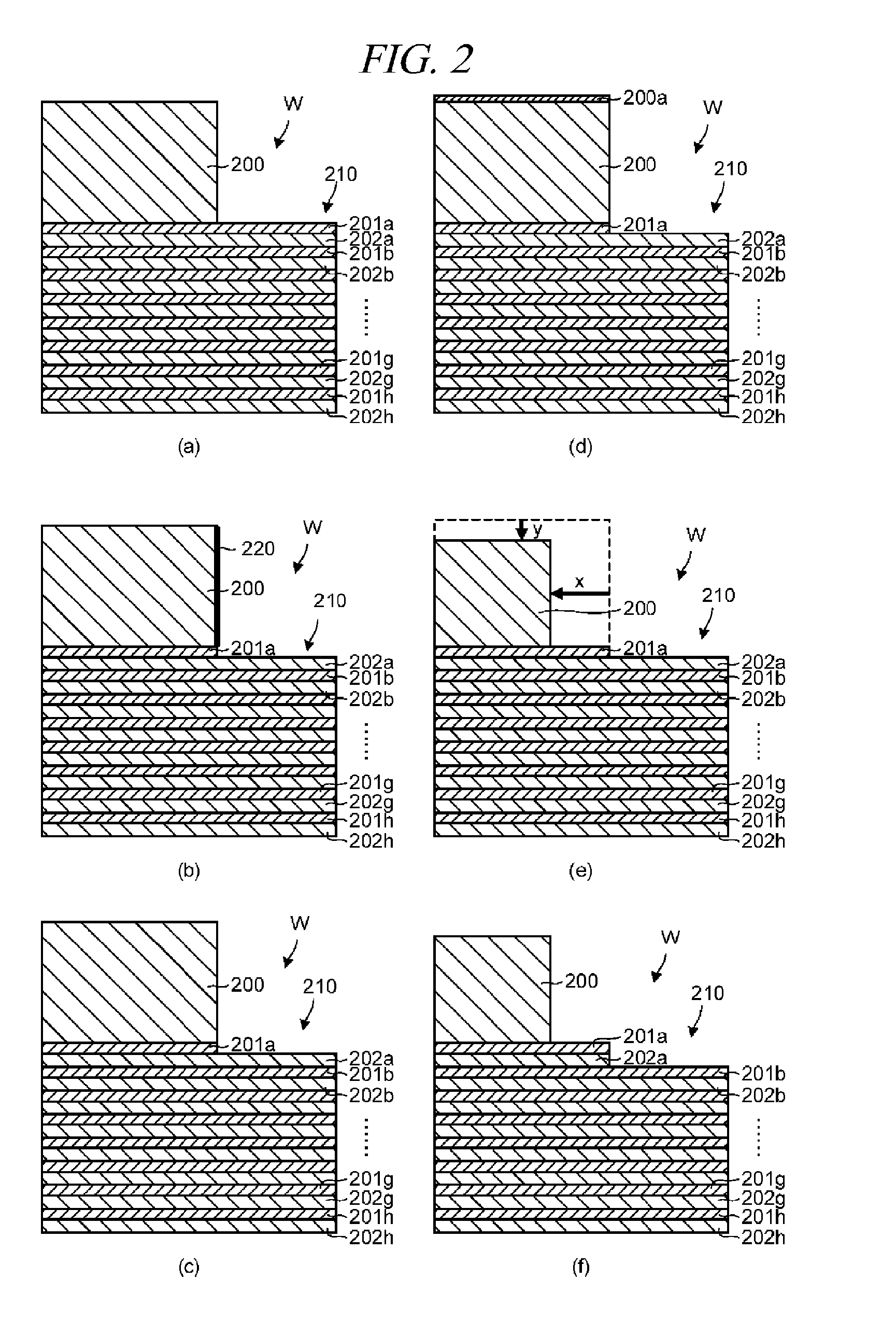

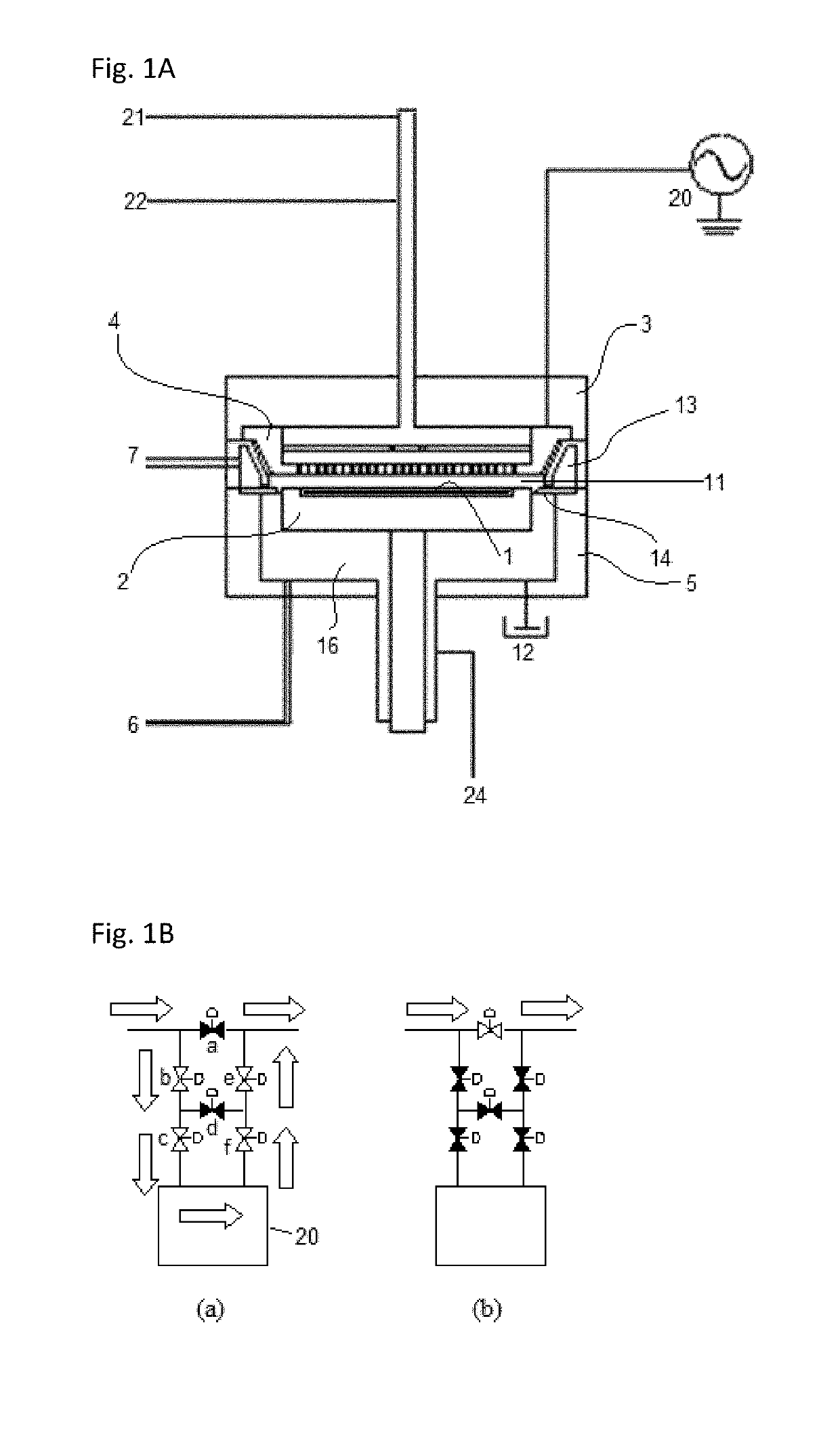

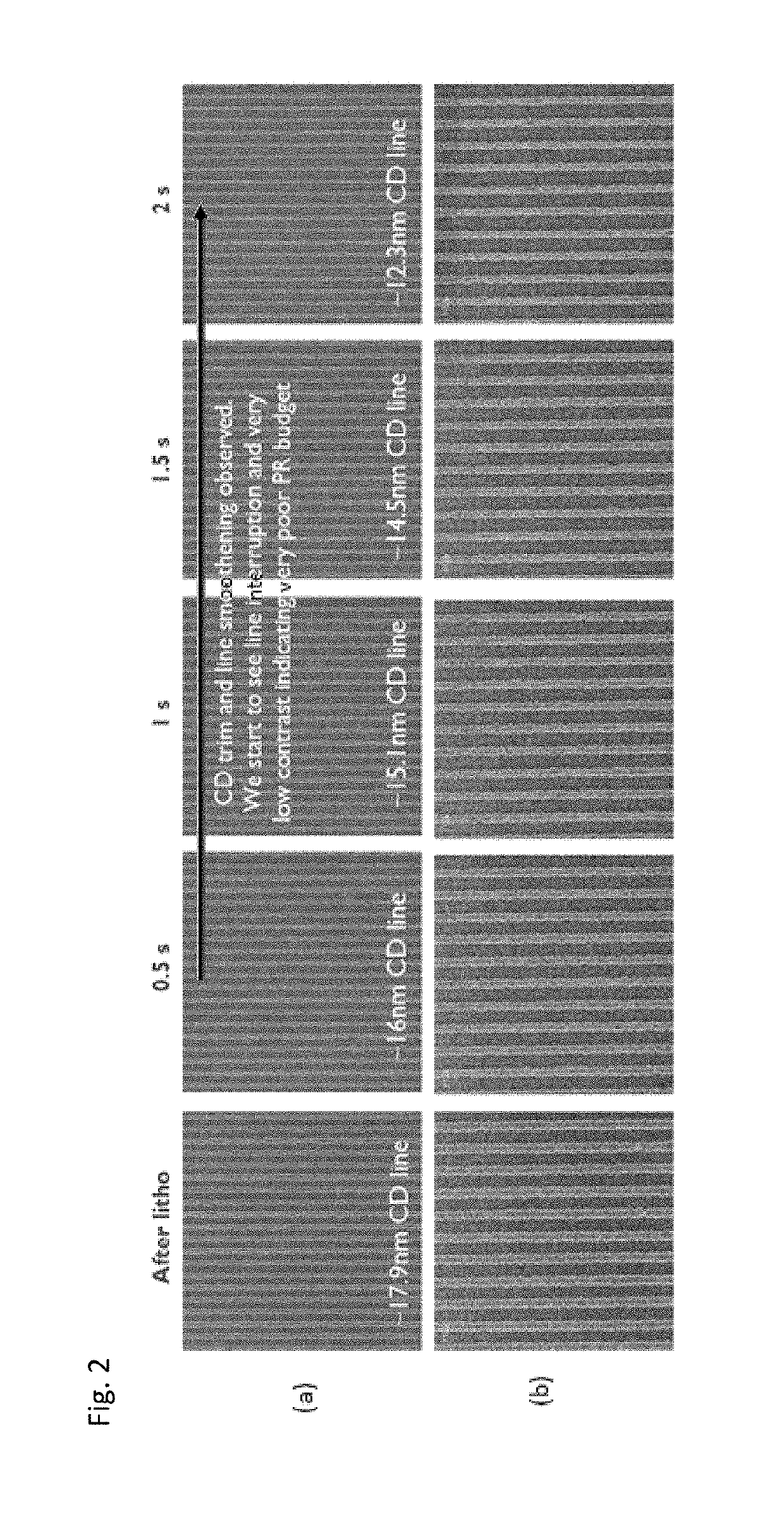

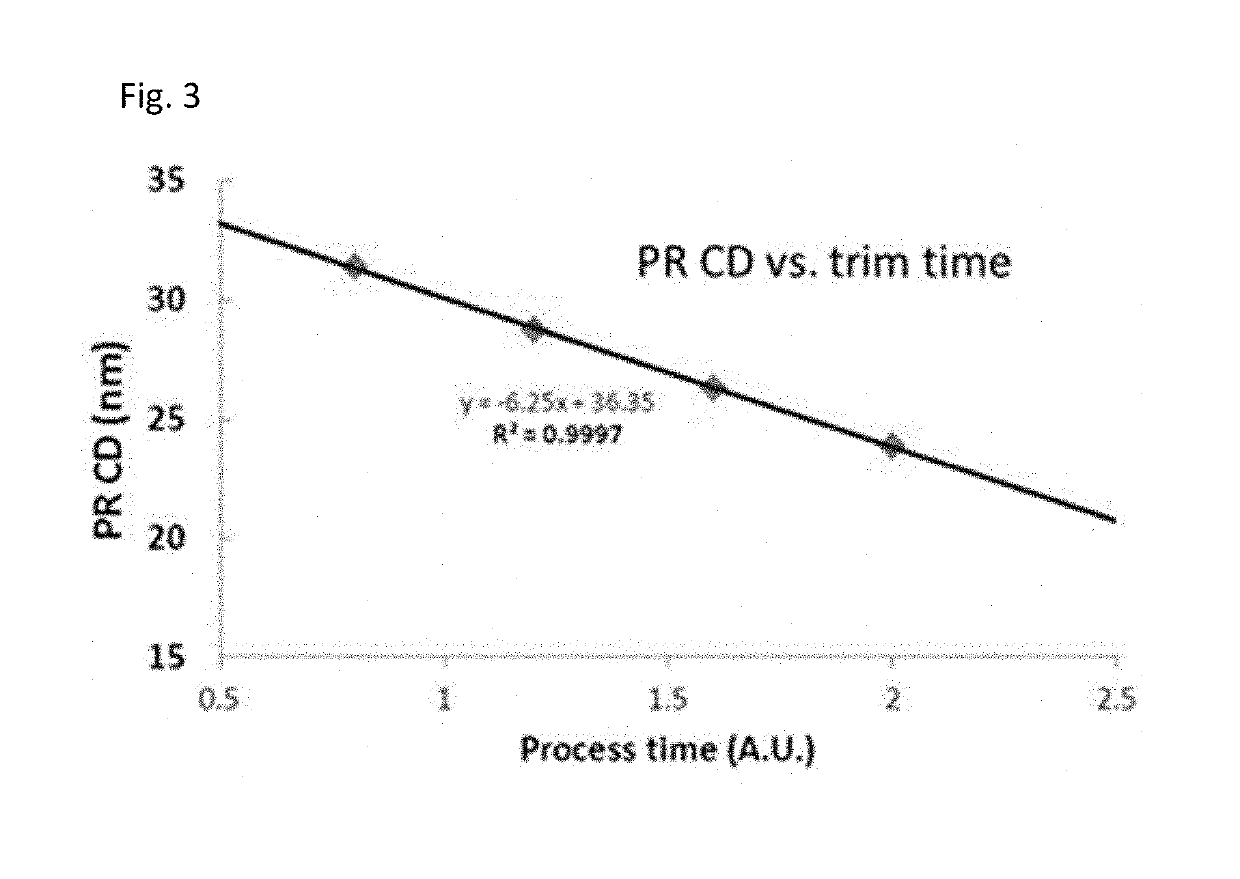

Semiconductor device manufacturing method and computer-readable storage medium

ActiveUS20120225561A1Efficiently formedLiquid surface applicatorsElectric discharge tubesResistHydrogen

There is provided a semiconductor device manufacturing method for forming a step-shaped structure in a substrate by etching the substrate having thereon a multilayer film and a photoresist film on the multilayer film and serving as an etching mask. The multilayer film is formed by alternately layering a first film having a first permittivity and a second film having a second permittivity different from the first permittivity. The method includes a first process for plasma-etching the first film by using the photoresist film as a mask; a second process for exposing the photoresist film to hydrogen-containing plasma; a third process for trimming the photoresist film; and a fourth process for etching the second film by using the trimmed photoresist film and the plasma-etched first film as a mask. The step-shaped structure is formed in the multilayer film by repeatedly performing the first process to the fourth process in this sequence.

Owner:TOKYO ELECTRON LTD

Thin film coated process kits for semiconductor manufacturing tools

InactiveUS20110207332A1Convenient coatingElectric discharge tubesElectrostatic cleaningQuartzSilicon

A plasma processing apparatus used in semiconductor device manufacturing includes a process kit formed of insulating materials such as quartz and coated with a Y2O3 coating. The Y2O3 coating is a thin film formed using suitable CVD or PVD operations. The Y2O3 coating is resistant to degradation in fluorine etching chemistries commonly used to etch silicon in semiconductor manufacturing. The plasma processing apparatus may be used in etching, stripping and cleaning operations. Also provided in another embodiment is a plasma processing apparatus having a quartz process kit coated with a sapphire-like film.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor devices with varying threshold voltage and fabrication methods thereof

ActiveUS9748145B1Overcomes shortcomingEnhanced advantageTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceDielectric layer

Semiconductor device fabrication methods are provided which include: providing a structure with at least one region and including a dielectric layer disposed over a substrate; forming a multilayer stack structure including a threshold-voltage adjusting layer over the dielectric layer, the multilayer stack structure including a first threshold-voltage adjusting layer in a first region of the at least one region, and a second threshold-voltage adjusting layer in a second region of the at least one region; and annealing the structure to define a varying threshold voltage of the at least one region, the annealing facilitating diffusion of at least one threshold voltage adjusting species from the first threshold-voltage adjusting layer and the second threshold-voltage adjusting layer into the dielectric layer, where a threshold voltage of the first region is independent of the threshold voltage of the second region.

Owner:GLOBALFOUNDRIES US INC

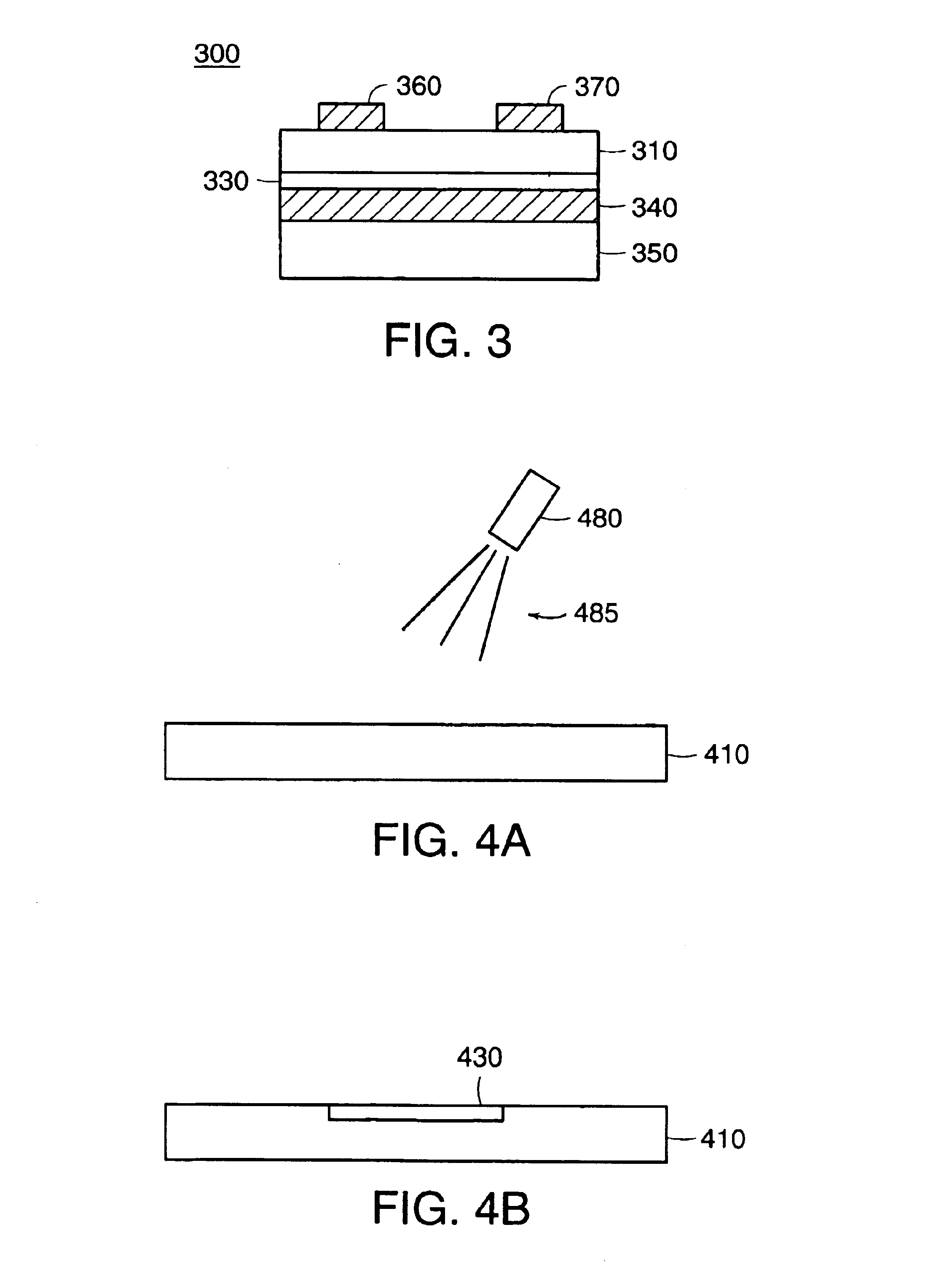

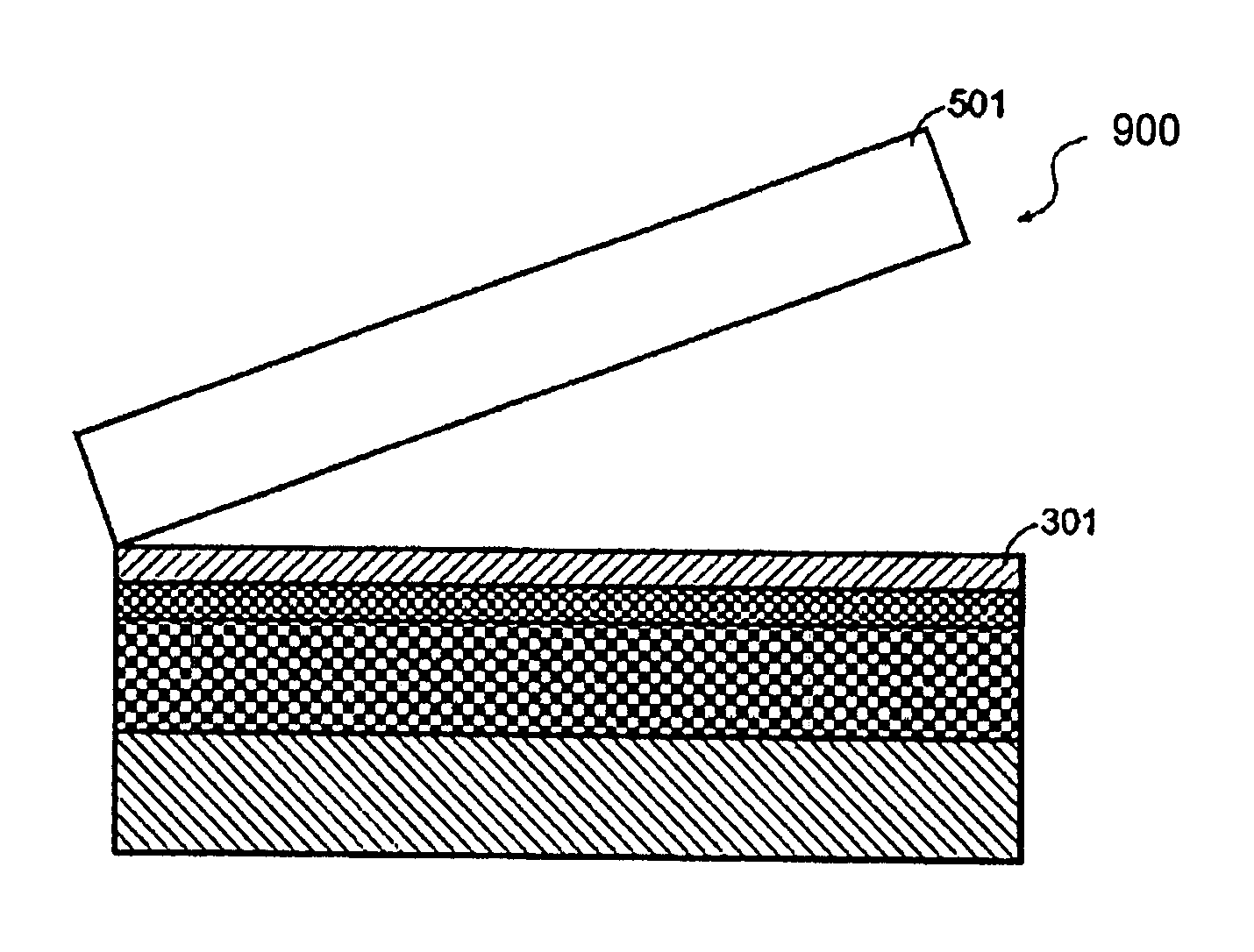

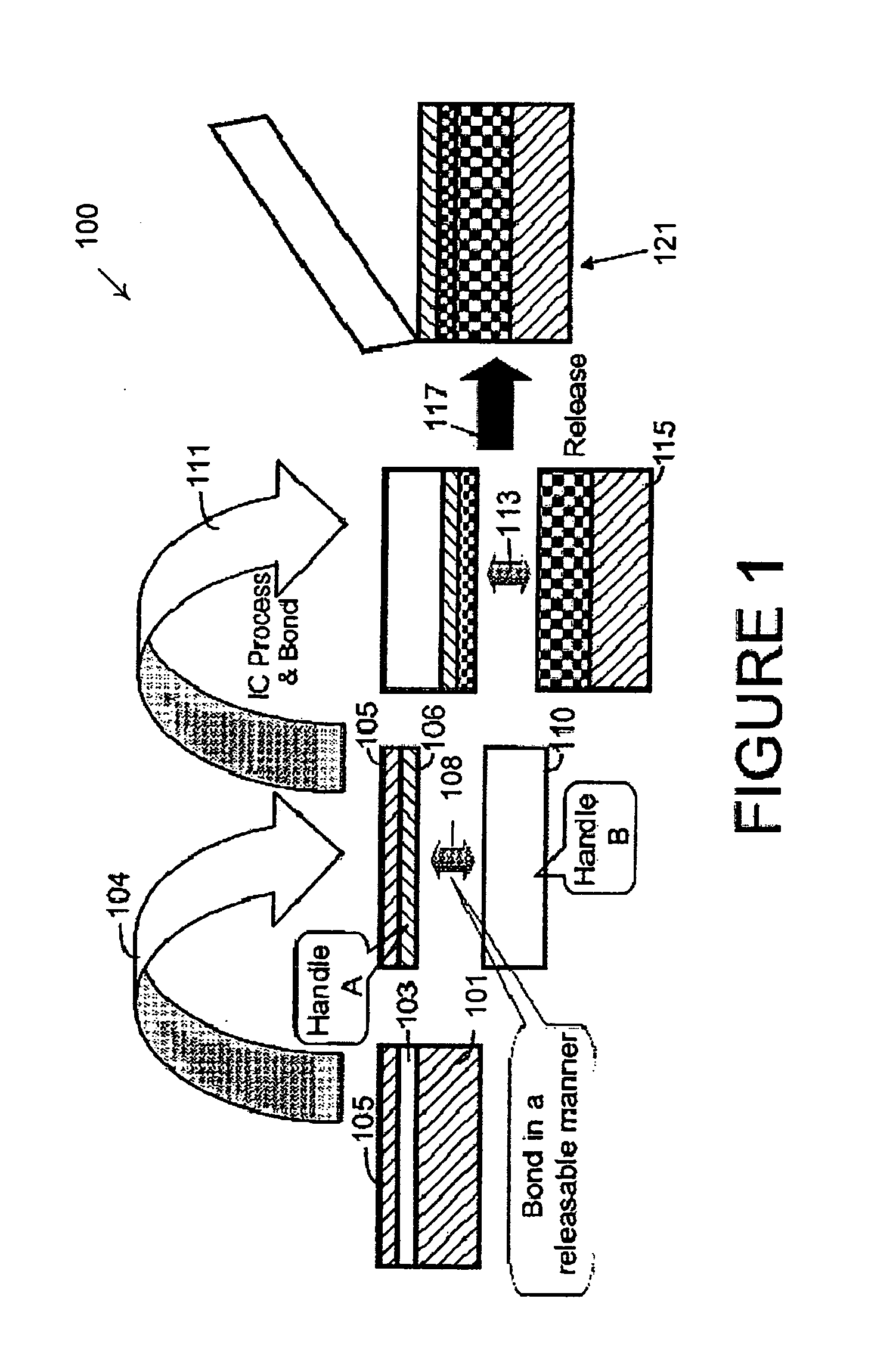

Thin handle substrate method and structure for fabricating devices using one or more films provided by a layer transfer process

ActiveUS7166520B1Avoid the possibility of damageEfficient processingSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

A method for fabricating one or more devices, e.g., integrated circuits. The method includes providing a substrate (e.g., silicon), which has a thickness of semiconductor material and a surface region. The substrate also has a cleave plane provided within the substrate to define the thickness of semiconductor material. The method includes joining the surface region of the substrate to a first handle substrate. In a preferred embodiment, the first handle substrate is termed a “thin” substrate, which provides suitable bonding characteristics, can withstand high temperature processing often desired during the manufacture of semiconductor devices, and has desirable de-bonding characteristics between it and a second handle substrate, which will be described in more detail below. In a preferred embodiment, the first handle substrate is also thick enough and rigid enough to allow for cleaving according to a specific embodiment.

Owner:SILICON GENERAL CORPORATION

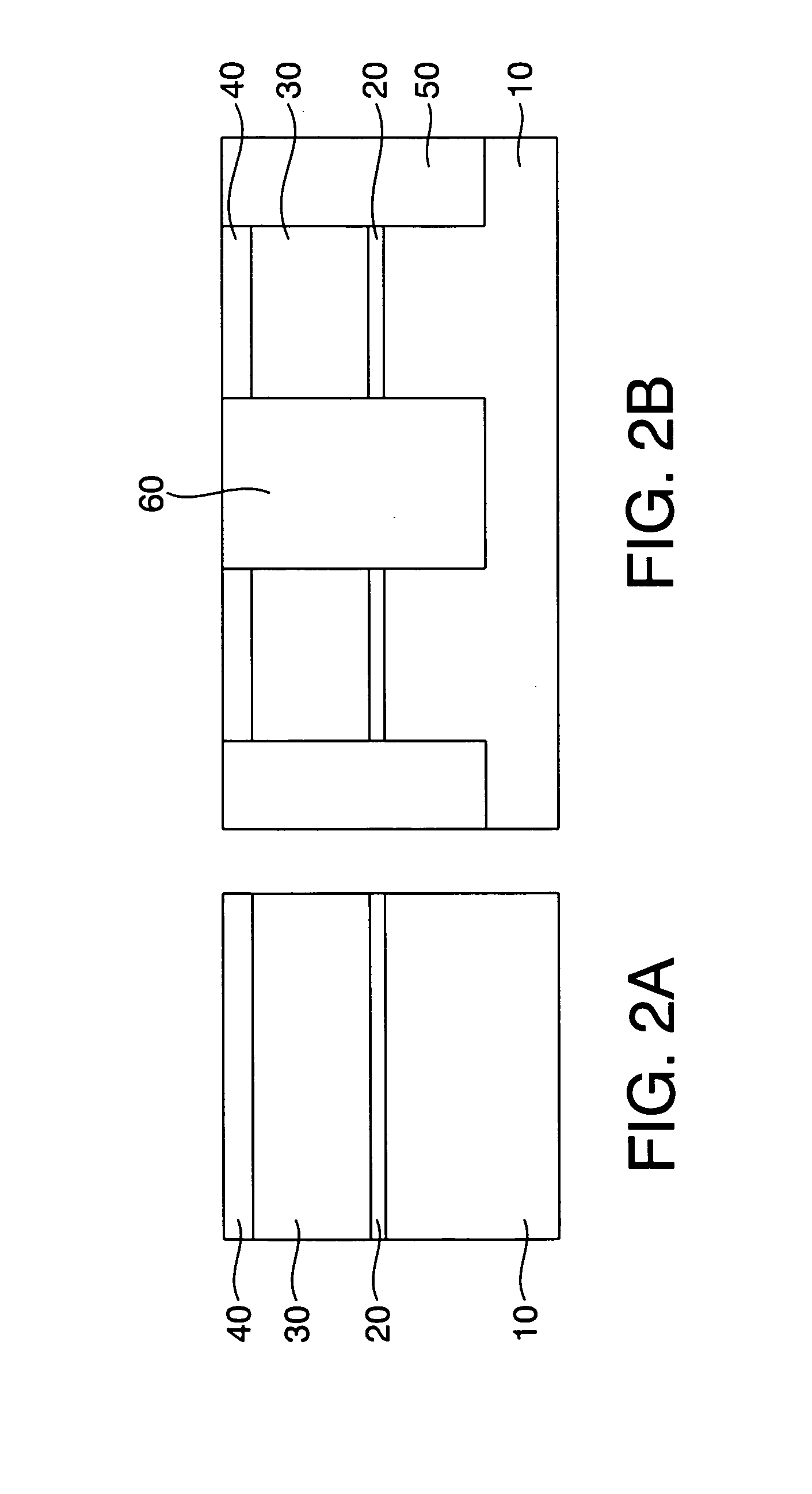

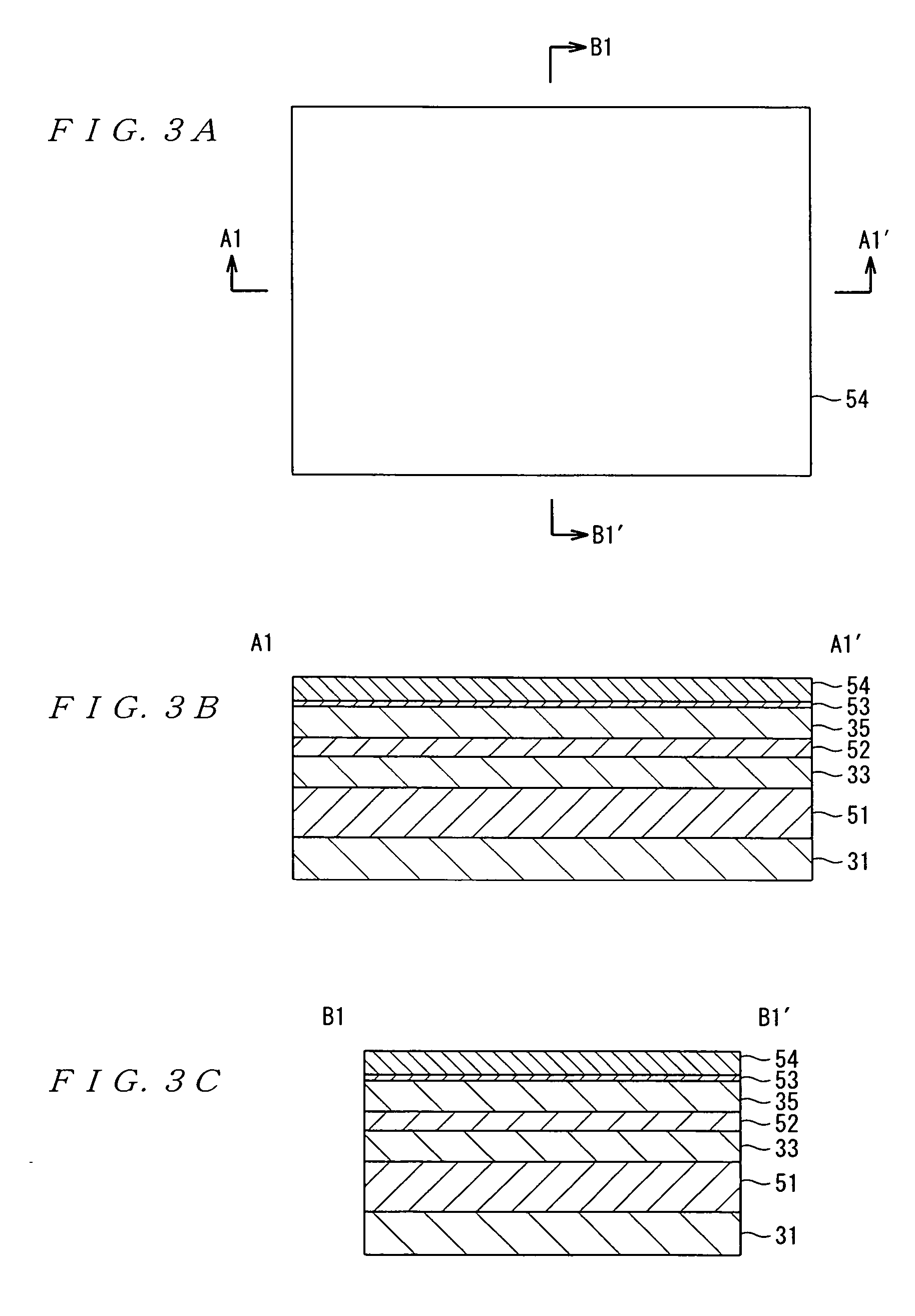

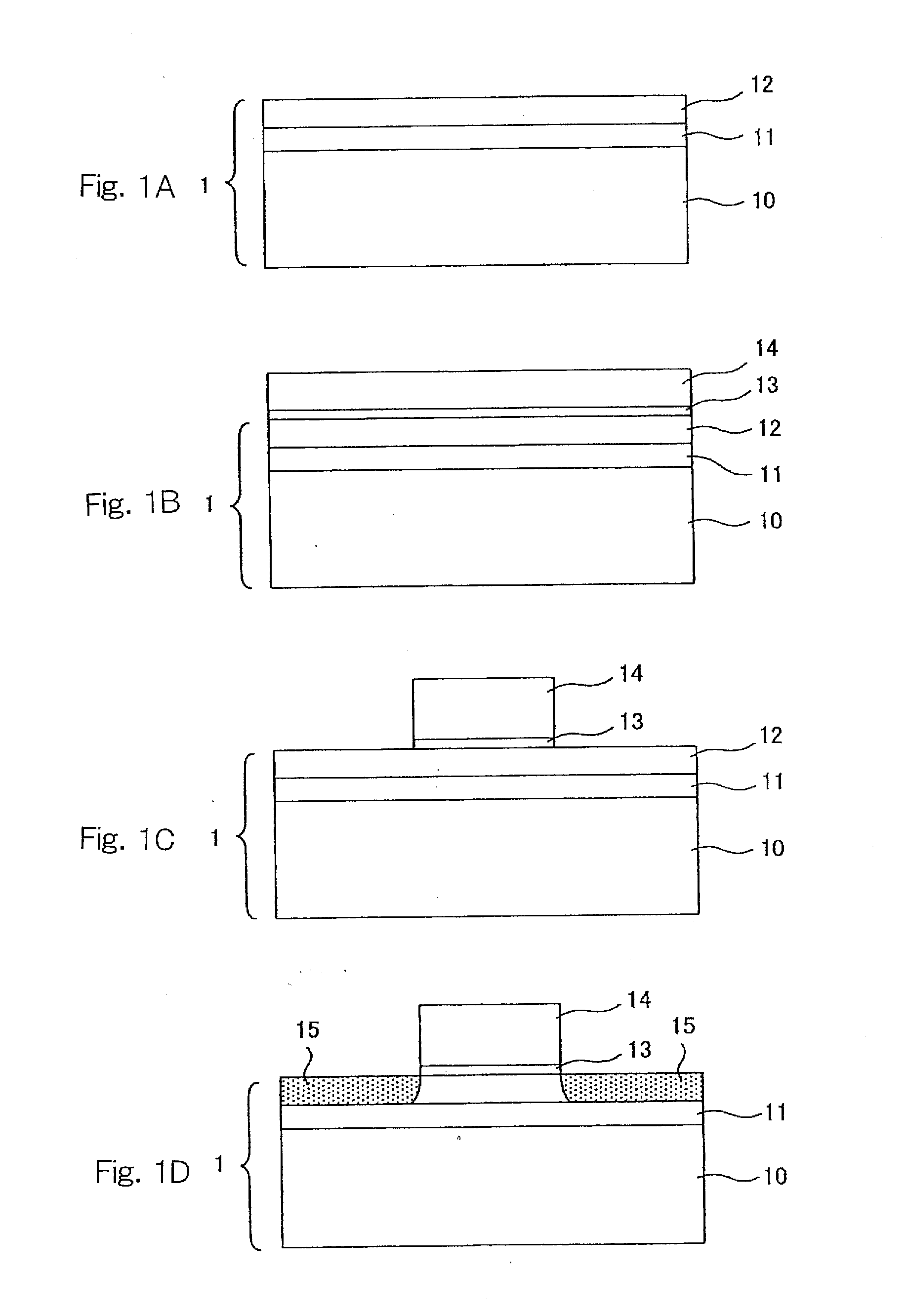

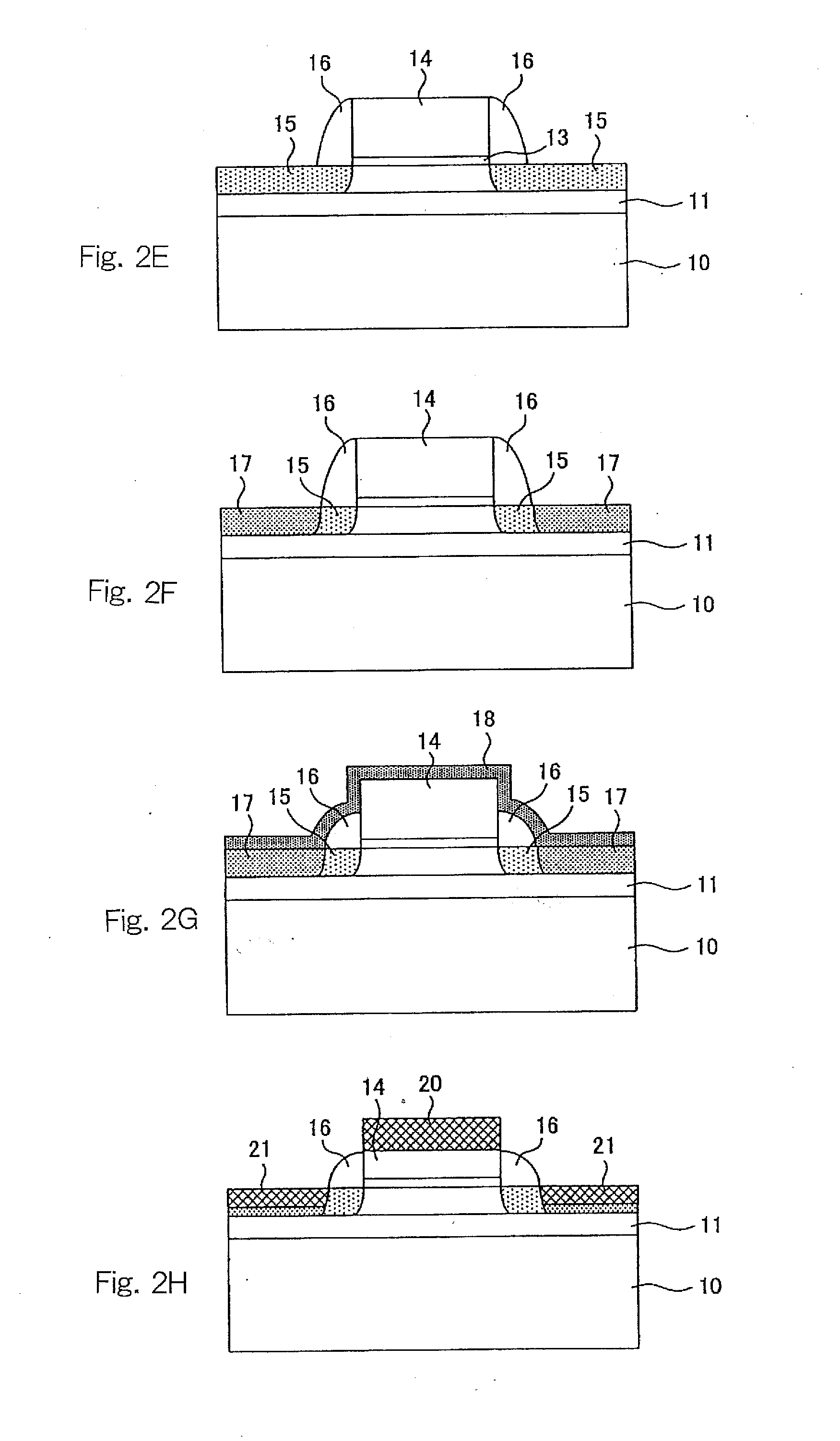

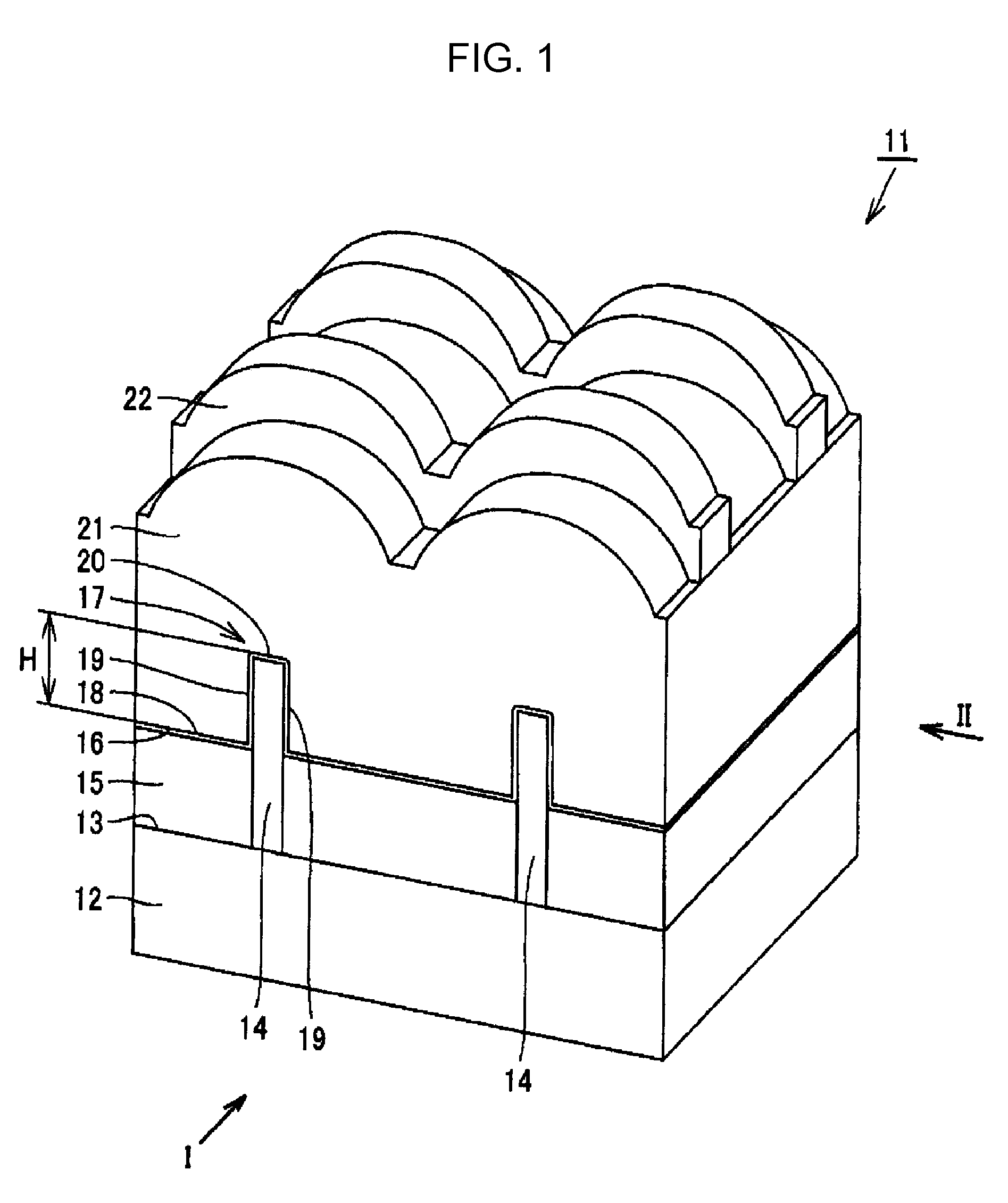

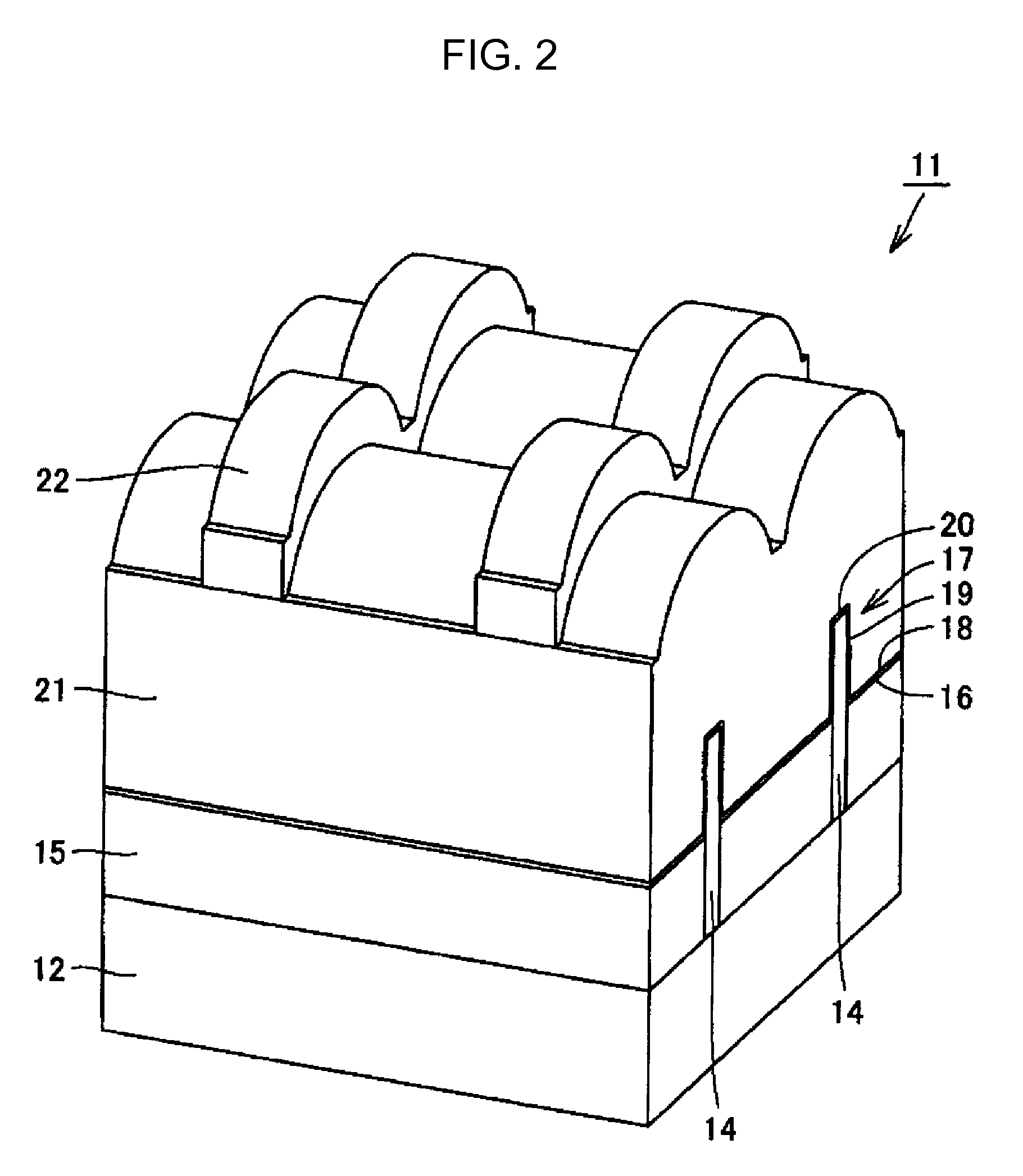

Semiconductor device and method of fabricating the same

InactiveUS20060166428A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

According to the present invention, there is provided a semiconductor device fabrication method comprising: forming a first insulating film on a semiconductor substrate; forming a first conductive layer on the first insulating film; forming a second insulating film on the first conductive layer in a first processing chamber isolated from an outside; performing a modification process on the second insulating film in the first processing chamber, and unloading the semiconductor substrate from the first processing chamber to the outside; annealing the second insulating film in a second processing chamber; and forming a second conductive layer on the second insulating film.

Owner:KK TOSHIBA

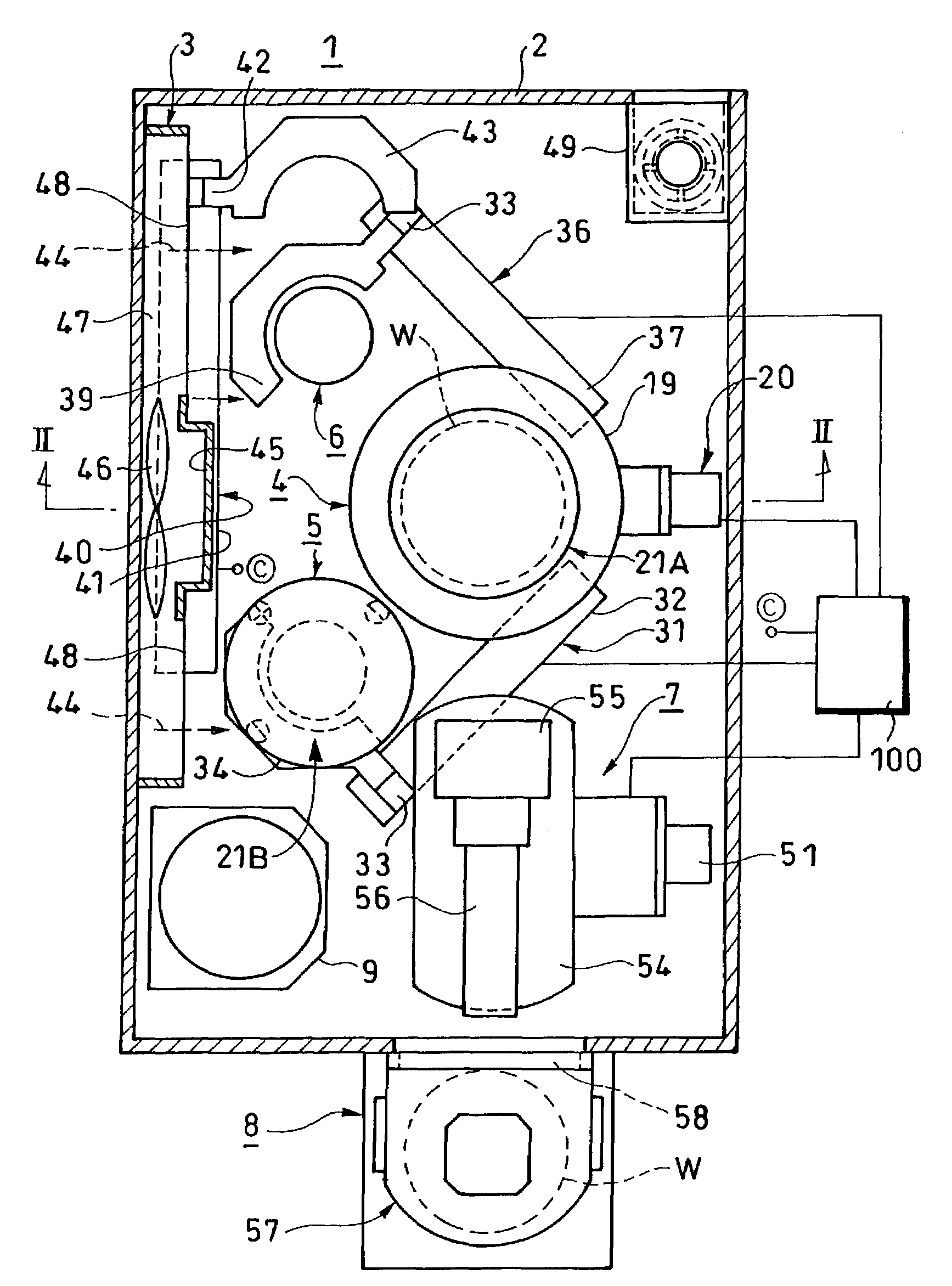

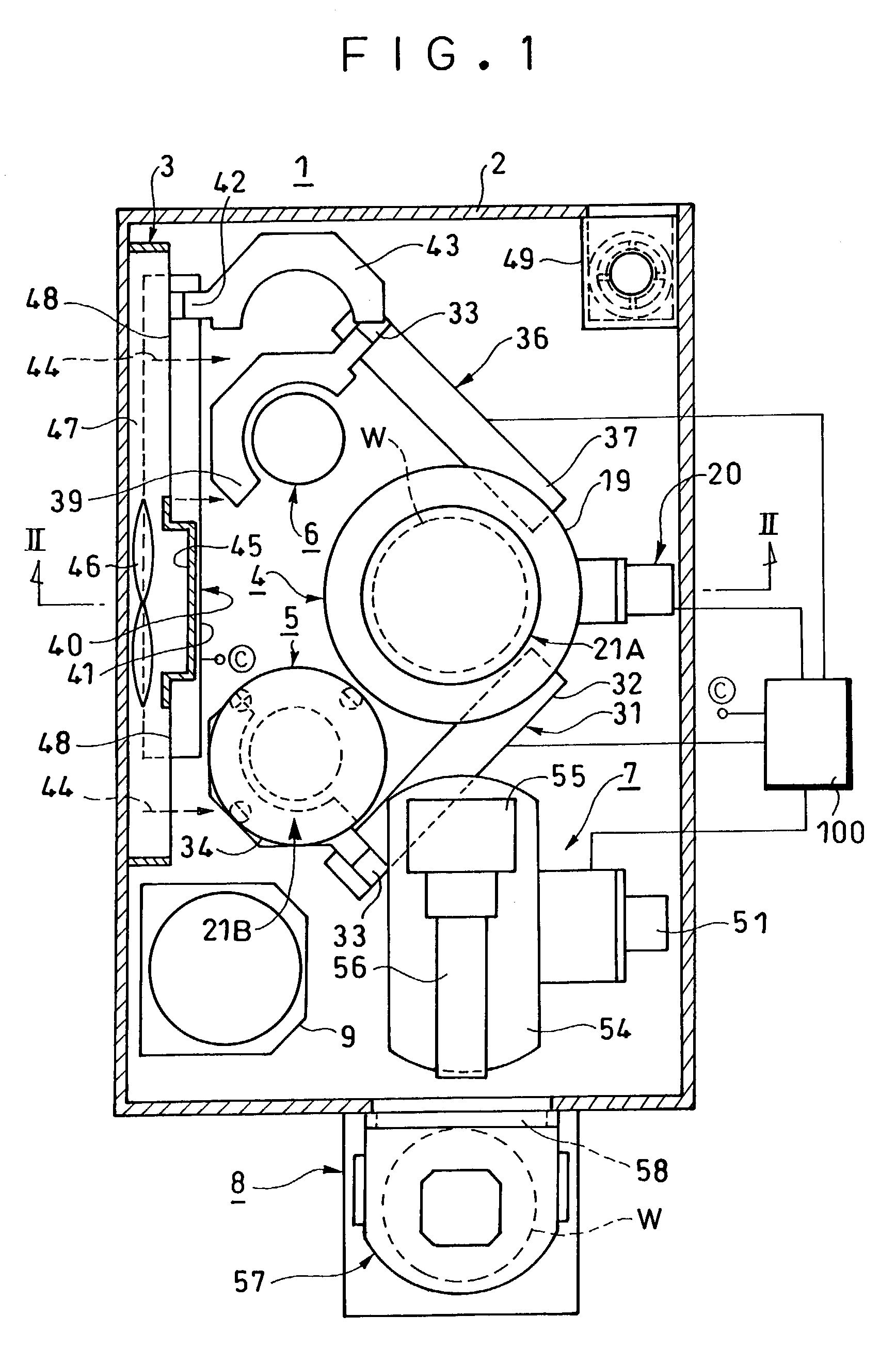

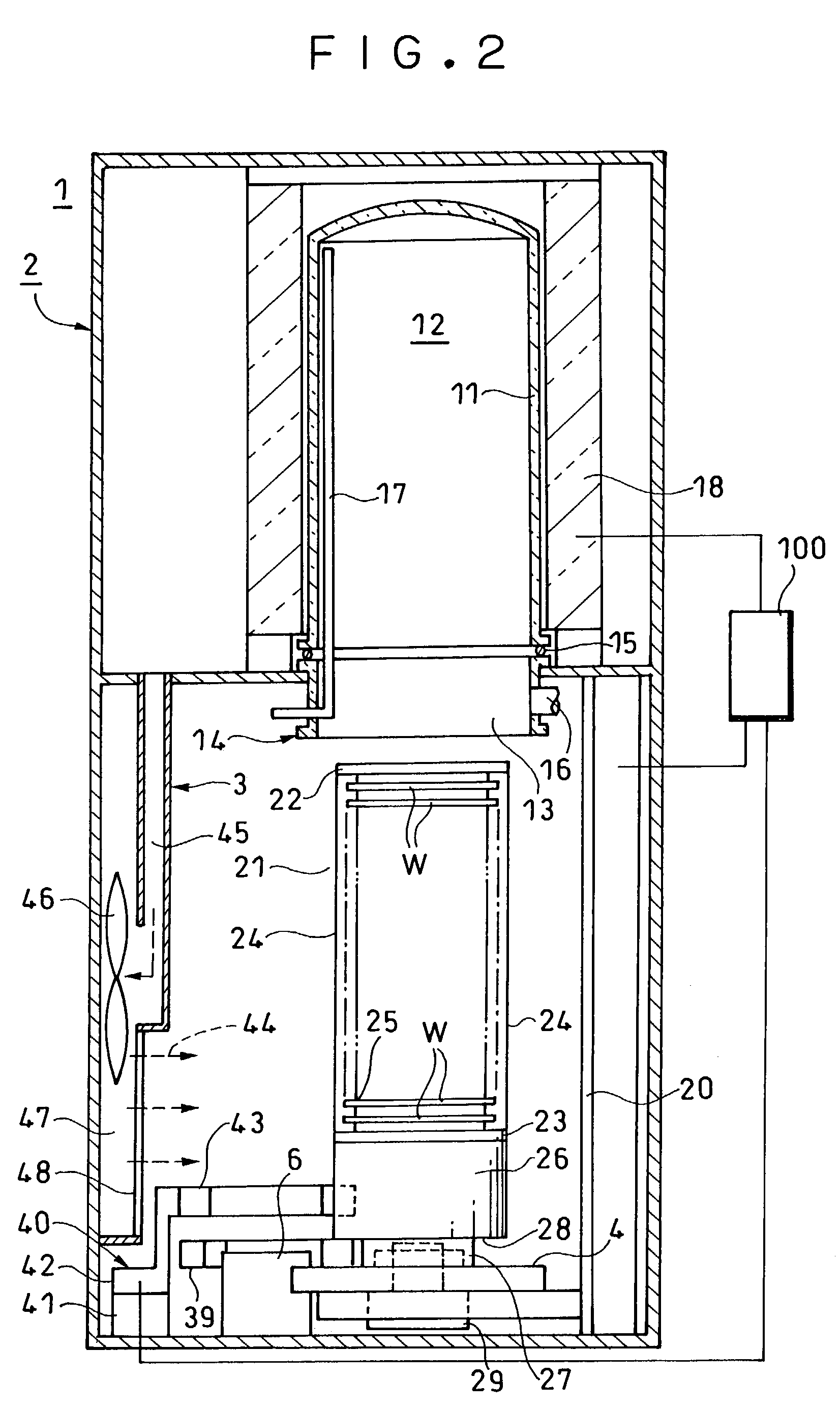

Semiconductor device producing apparatus and producing method of semiconductor device

InactiveUS7198447B2Reduce standby timeAvoid it happening againSemiconductor/solid-state device manufacturingArticle unpackingEngineeringTransfer mechanism

A semiconductor device producing apparatus is disclosed. The apparatus includes a carrier-holding stage for placing a carrier; first, second and third stages each for holding first and second boats one at a time, each boat holding one or more substrates; a boat transfer mechanism for transferring the boats among the first, second and third stages; and a substrate transfer mechanism for transferring the substrate(s) from the carrier to the boat held by the first stage. A controller controls the first stage, the boat transfer mechanism and the substrate transfer mechanism so that the boat transfer mechanism transfers one of the boats from the second stage to the first stage, the substrate transfer mechanism then transfers the substrate(s) from the carrier to the boat held by the first stage, and the first stage then moves the boat into the processing chamber for processing.

Owner:KOKUSA ELECTRIC CO LTD

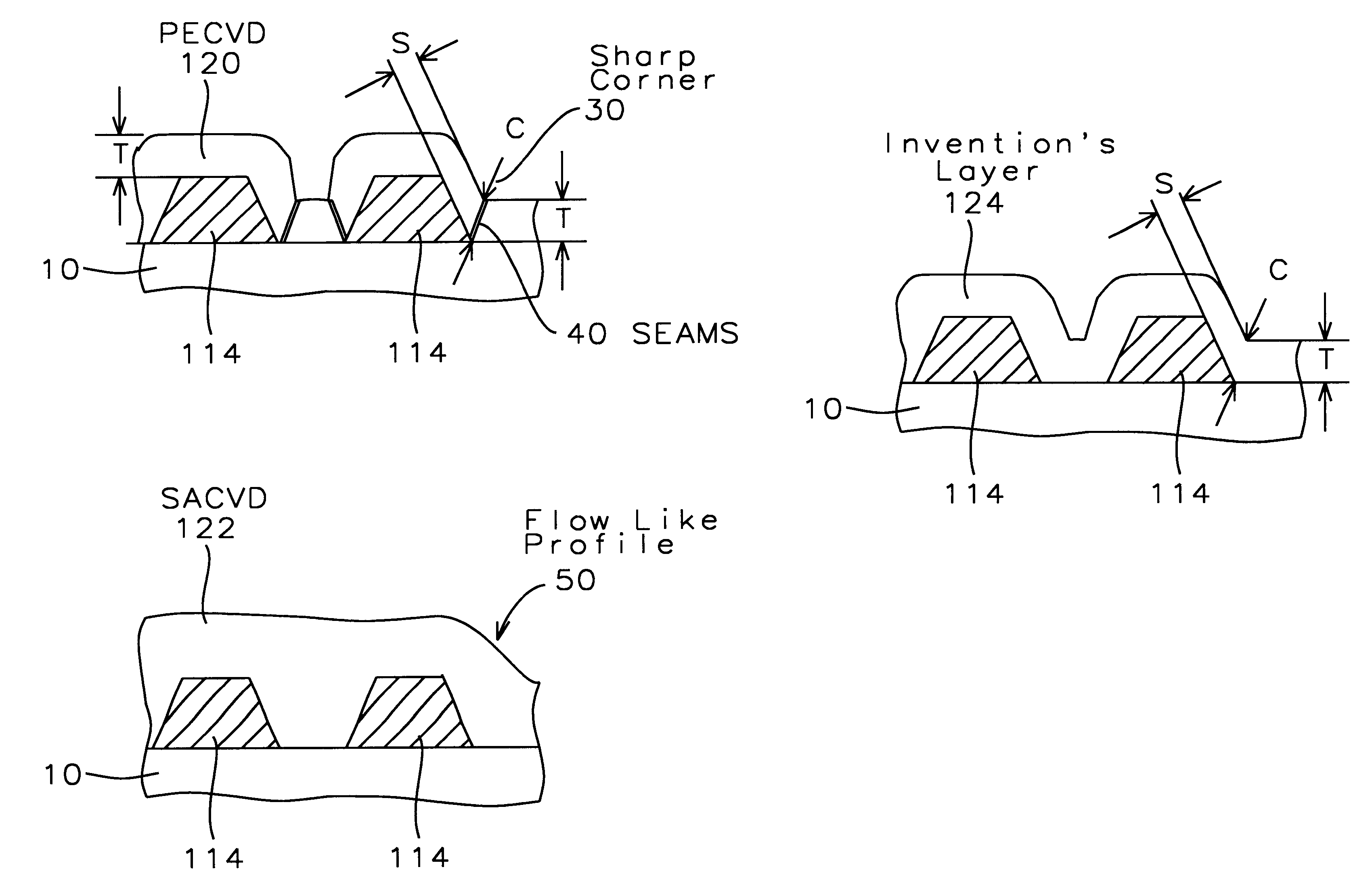

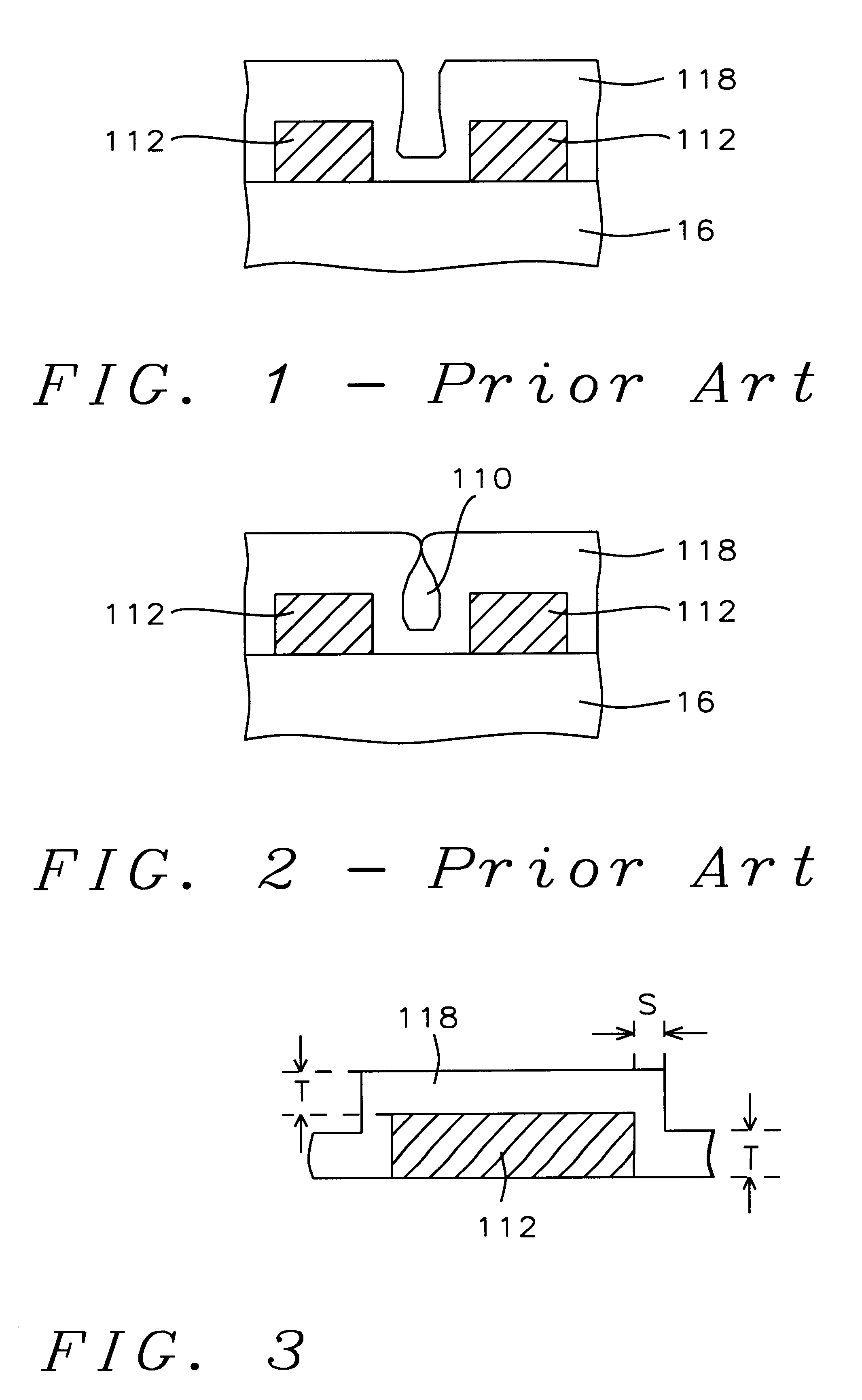

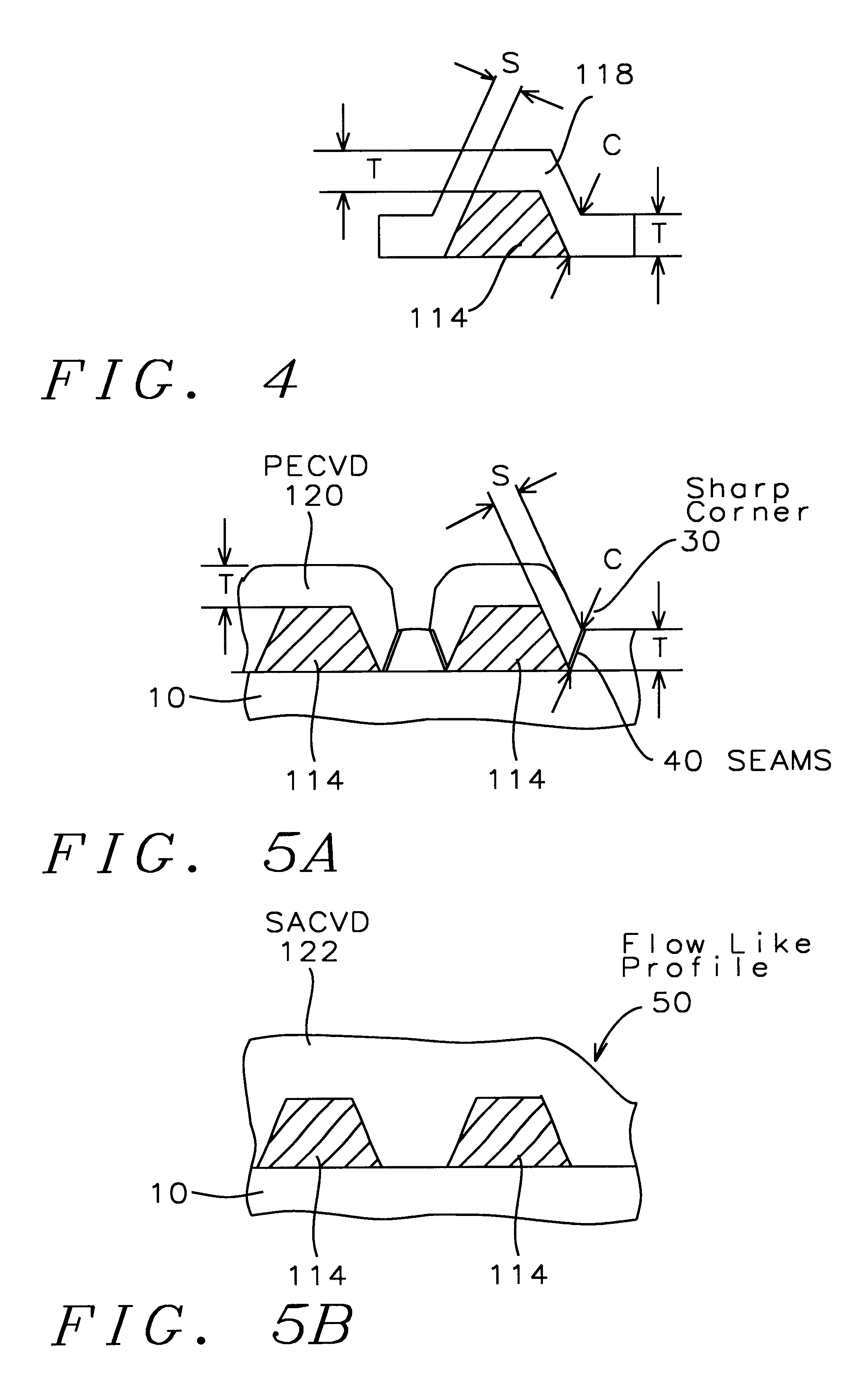

Method of silicon oxide and silicon glass films deposition

InactiveUS6197705B1Good step coverageImprove integrityPretreated surfacesSemiconductor/solid-state device manufacturingDielectricPlasma density

A method for fabricating a silicon oxide and silicon glass layers at low temperature using soft power-optimized Plasma-Activated CVD with a TEOS-ozone-oxygen reaction gas mixture (TEOS O3 / O2 PACVD) is described. It combines advantages of both low temperature Plasma-Enhanced Chemical Vapor Deposition (PECVD) and TEOS-ozone Sub-Atmospheric Chemical Vapor Deposition (SACVD) and yields a coating of silicon oxide with stable and high deposition rate, no surface sensitivity, good film properties, conformal step coverage and good gap-fill. Key features of the invention's O3 / O2 PACVD process are: a plasma is maintain throughout the entire deposition step in a parallel plate type reactor chamber, the precise RF plasma density, ozone concentration in oxygen and the deposition temperature. These features provide the reaction conditions for the proper O3 / O2 reaction mechanism that deposits a conformal silicon oxide layer. The process has significant implication for semiconductor device manufacturing involving the deposition of a dielectric over a conducting non-planar surface.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

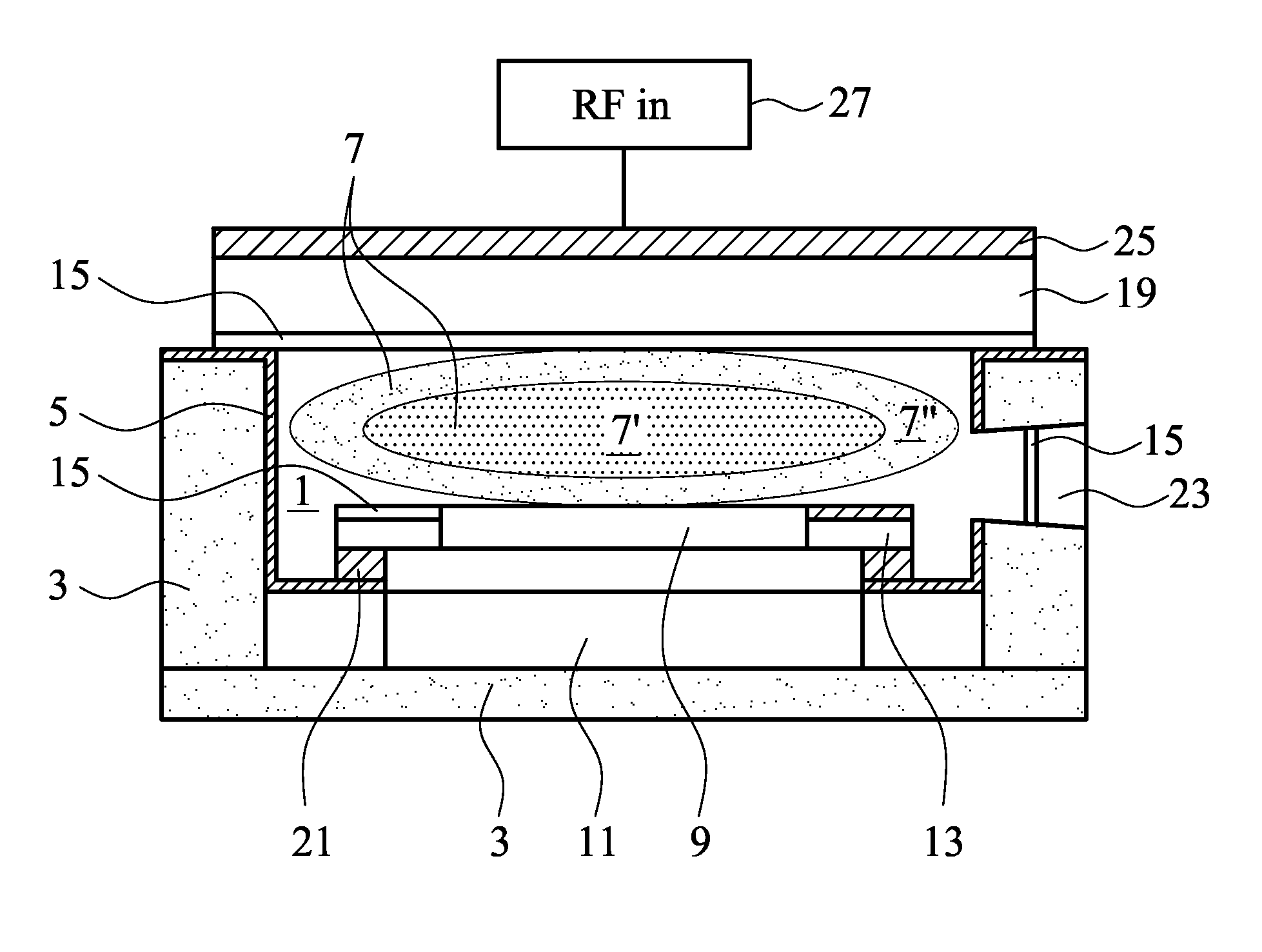

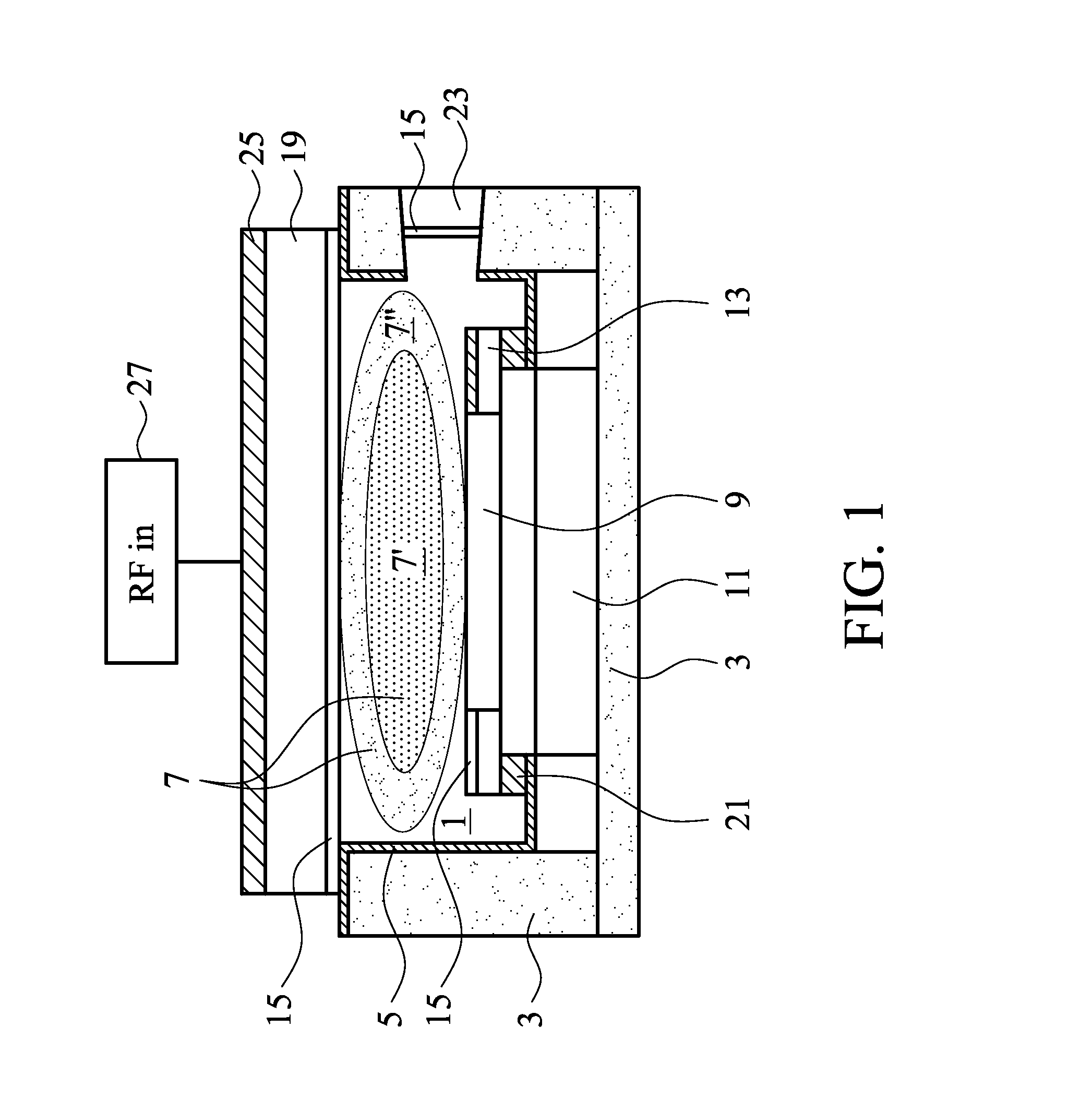

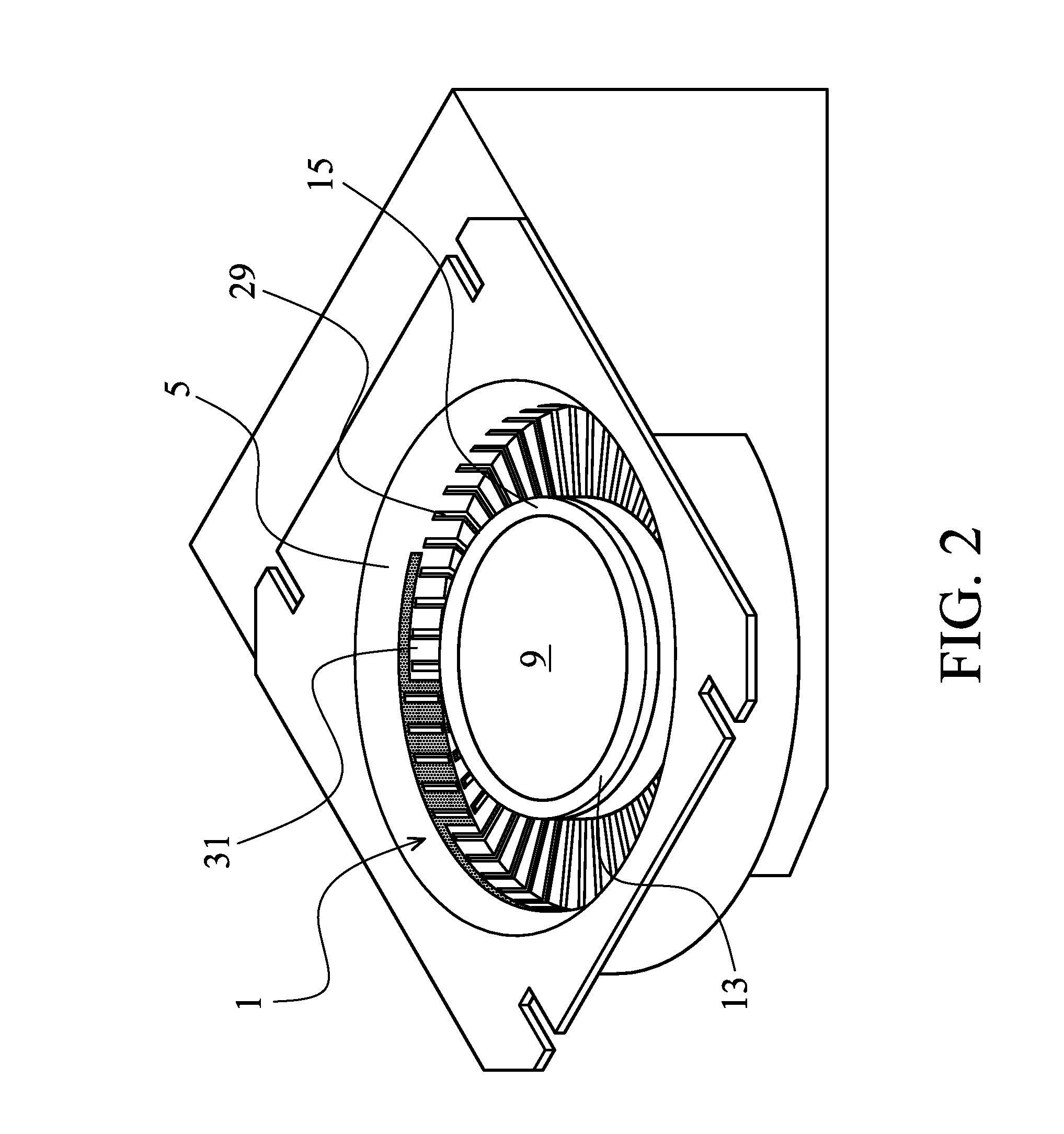

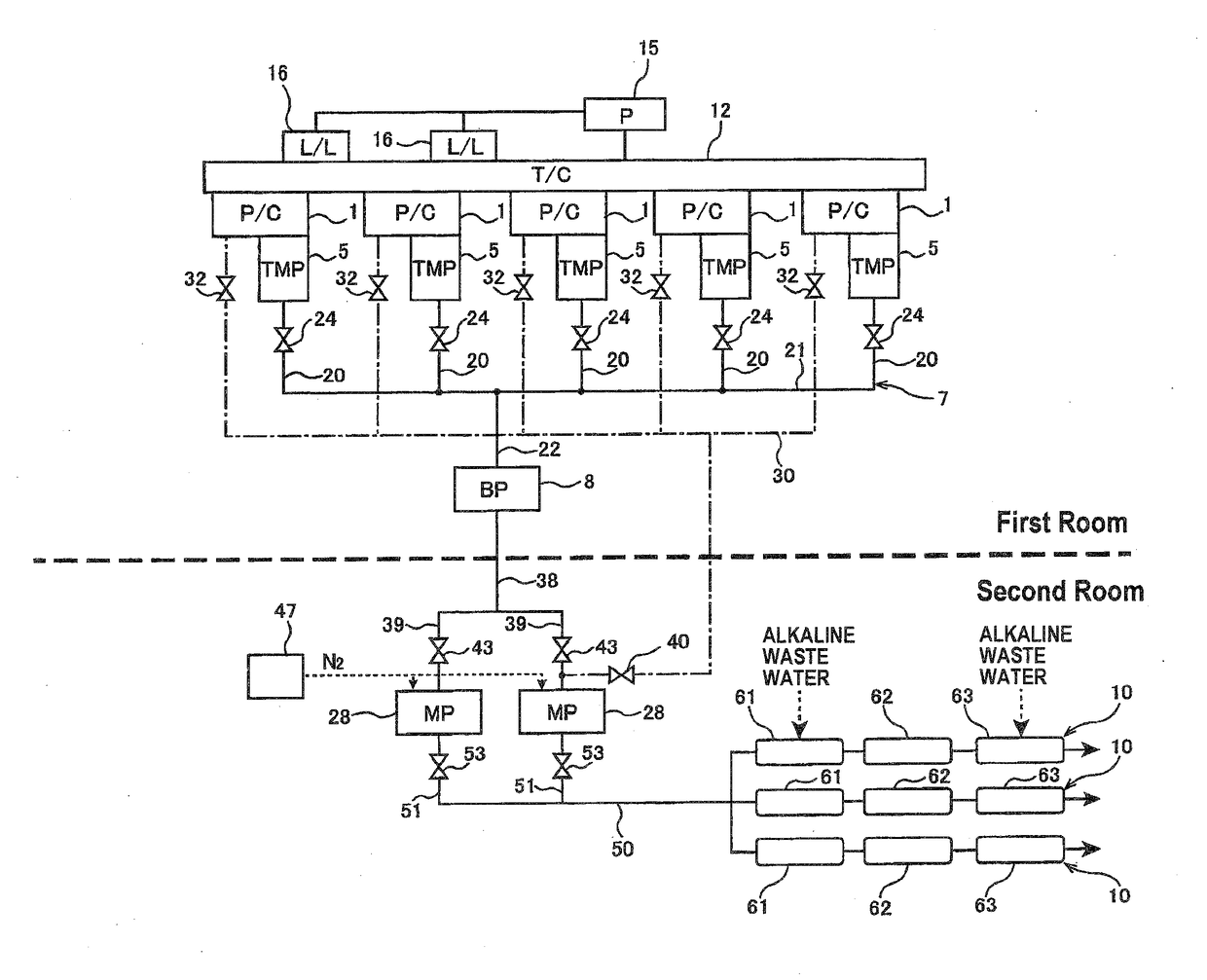

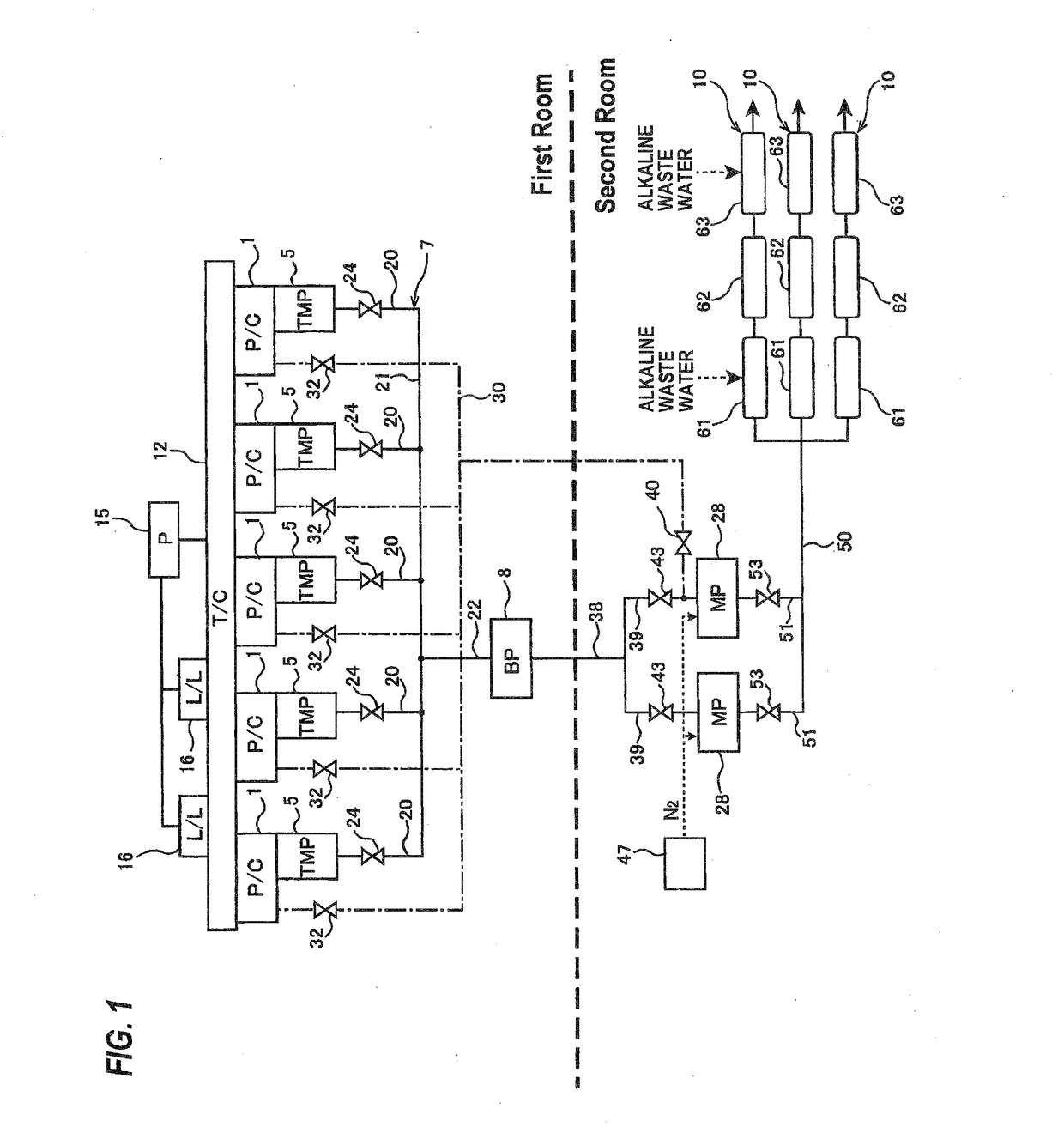

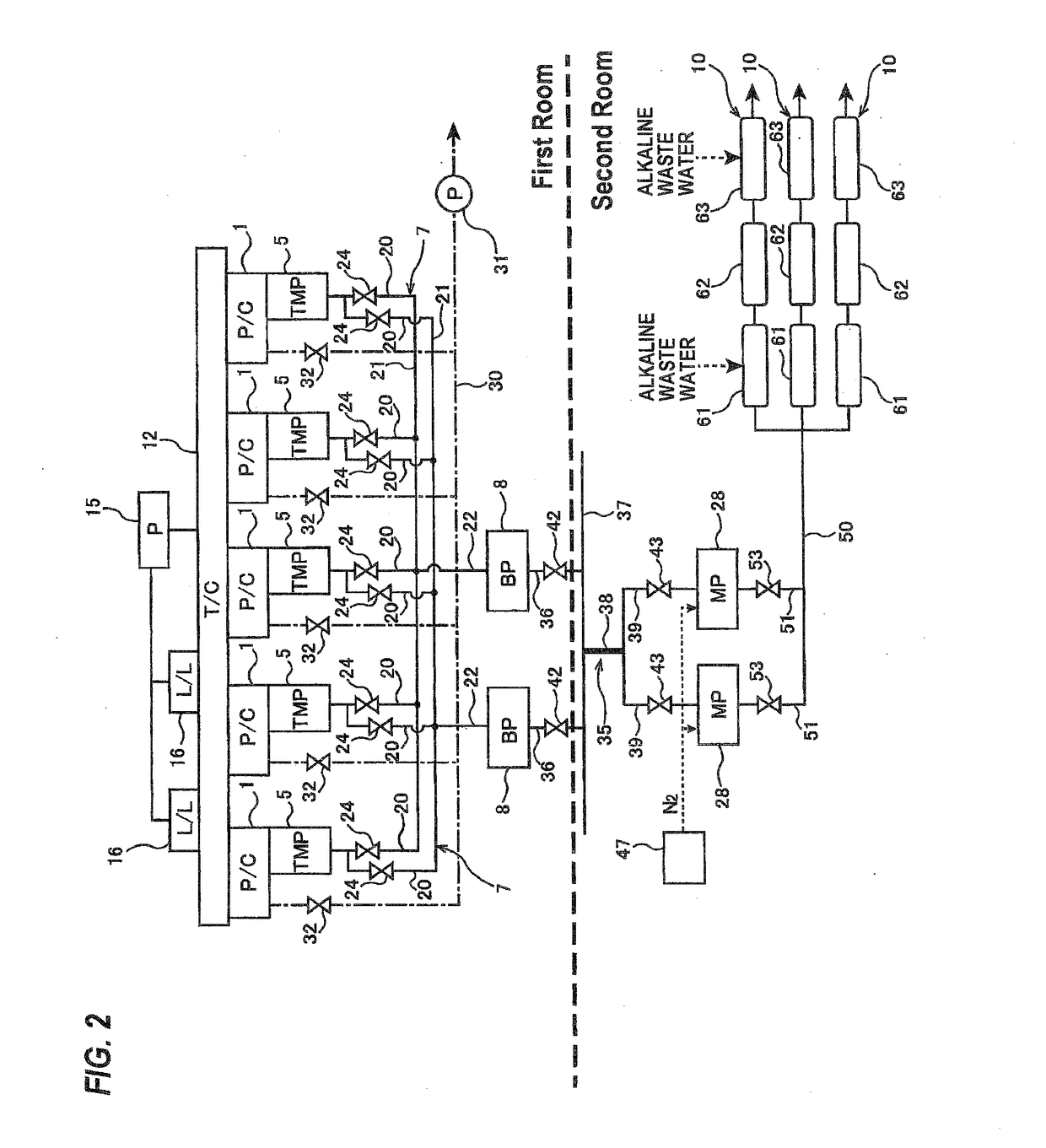

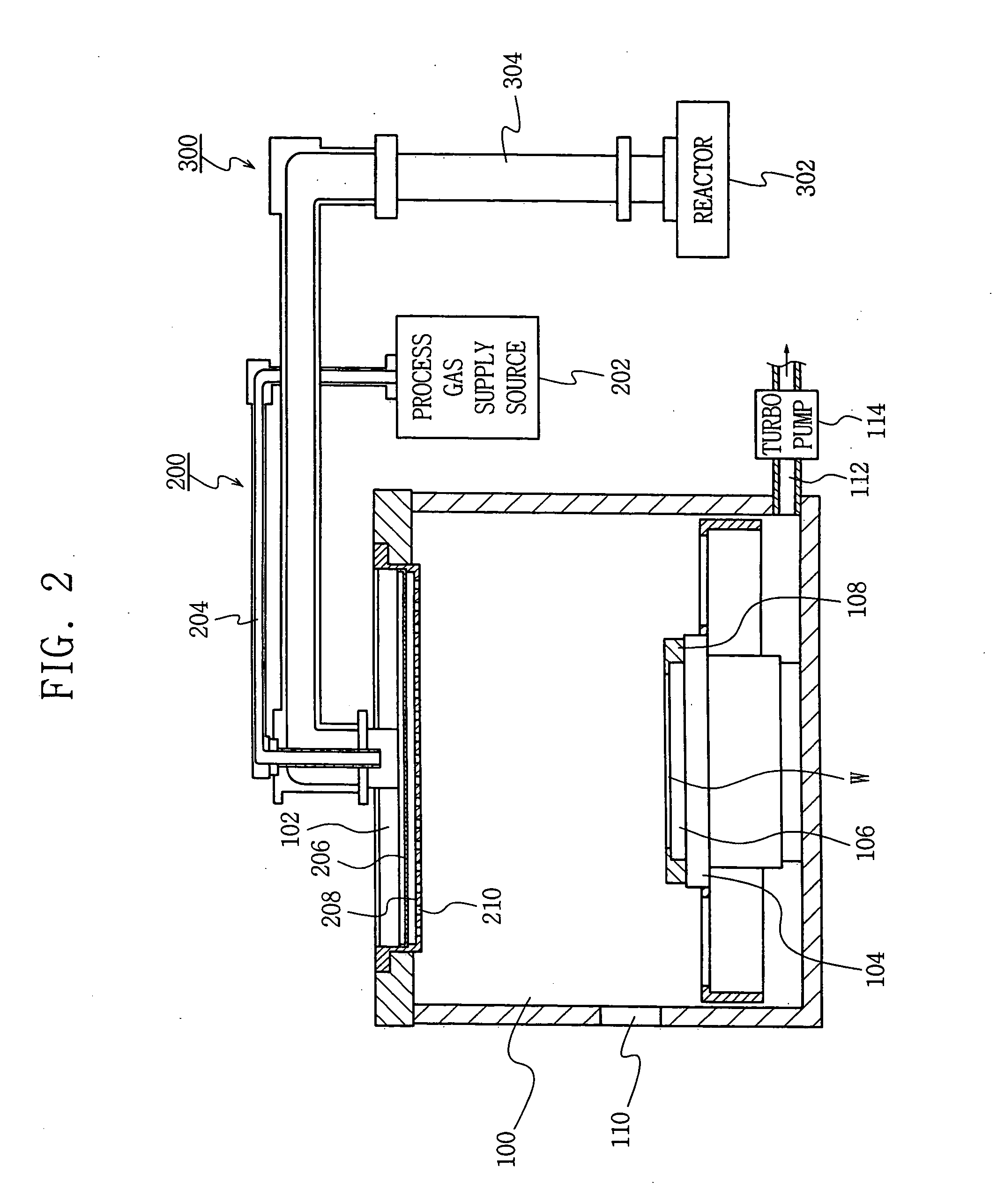

Vacuum evacuation system

ActiveUS20170200622A1Reduce installation costsIncrease pressureElectric discharge tubesFinal product manufactureProcess engineeringVacuum pump

The present invention relates to a vacuum evacuation system used to evacuate a processing gas from one or more process chambers for use in, for example, a semiconductor-device manufacturing apparatus. The vacuum evacuation system is a vacuum apparatus for evacuating a gas from a plurality of process chambers (1). The vacuum evacuation system includes a plurality of first vacuum pumps (5) coupled to the plurality of process chambers (1) respectively, a collecting pipe (7) coupled to the plurality of first vacuum pumps (5), and a second vacuum pump (8) coupled to the collecting pipe (7).

Owner:EBARA CORP

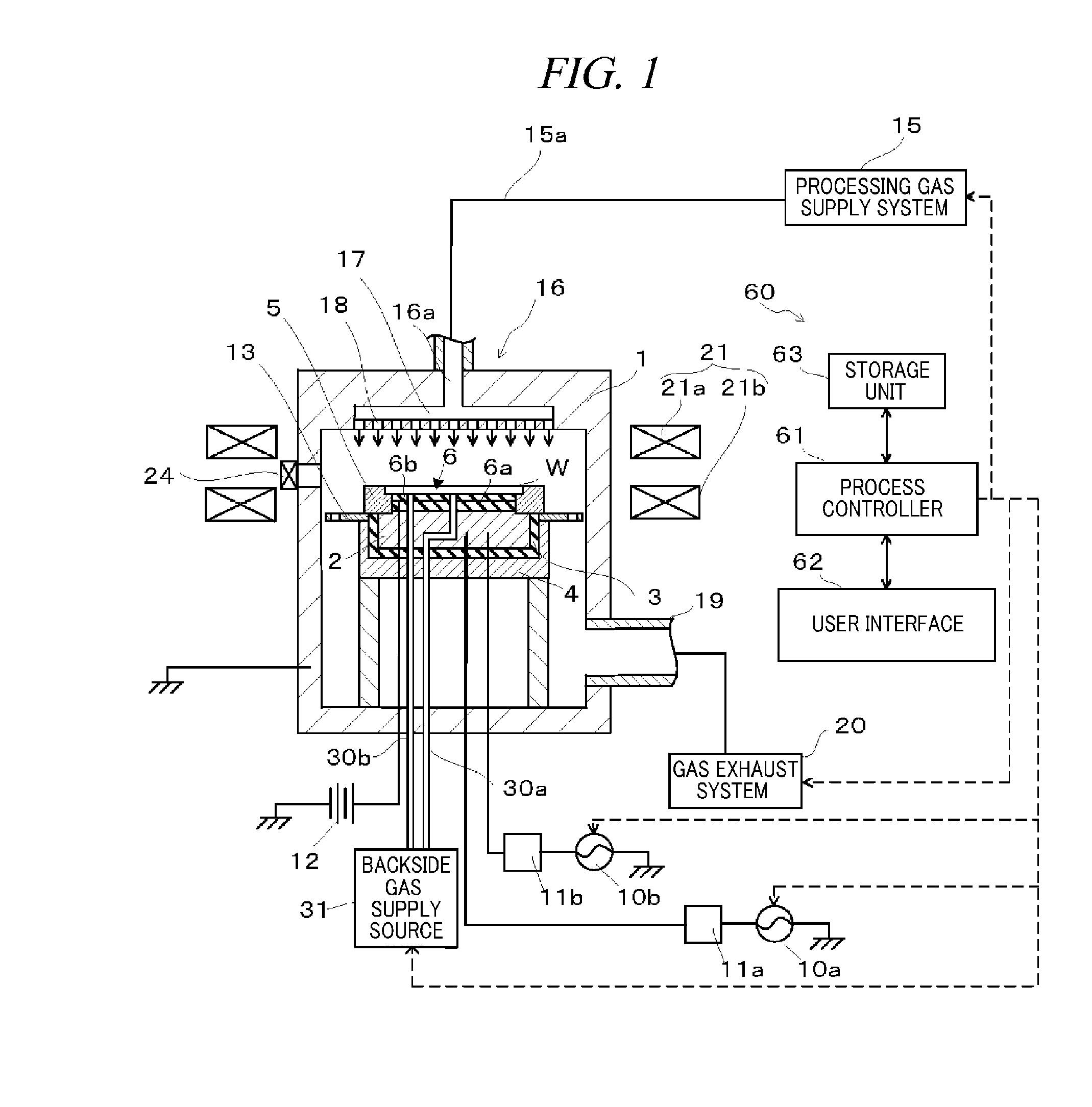

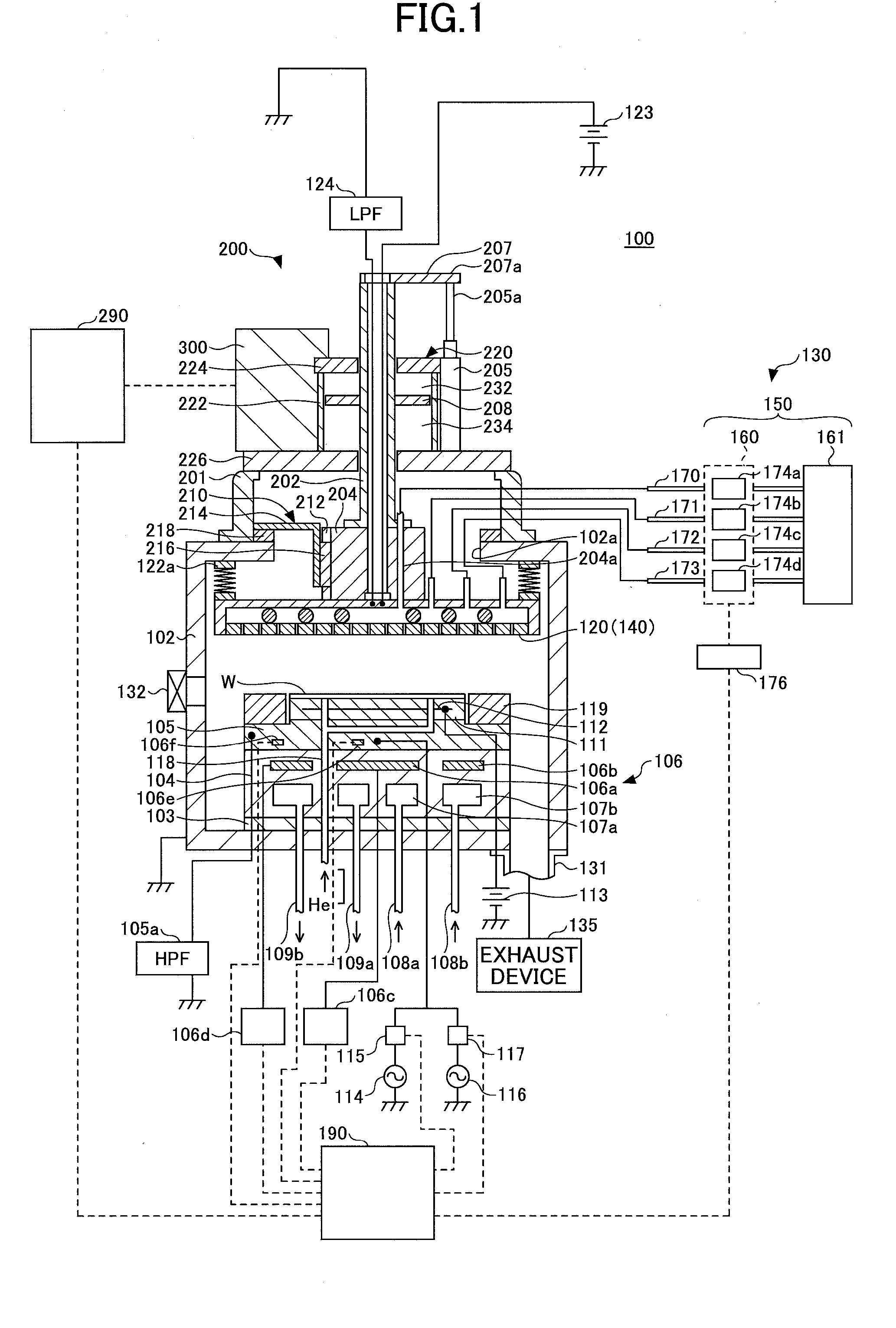

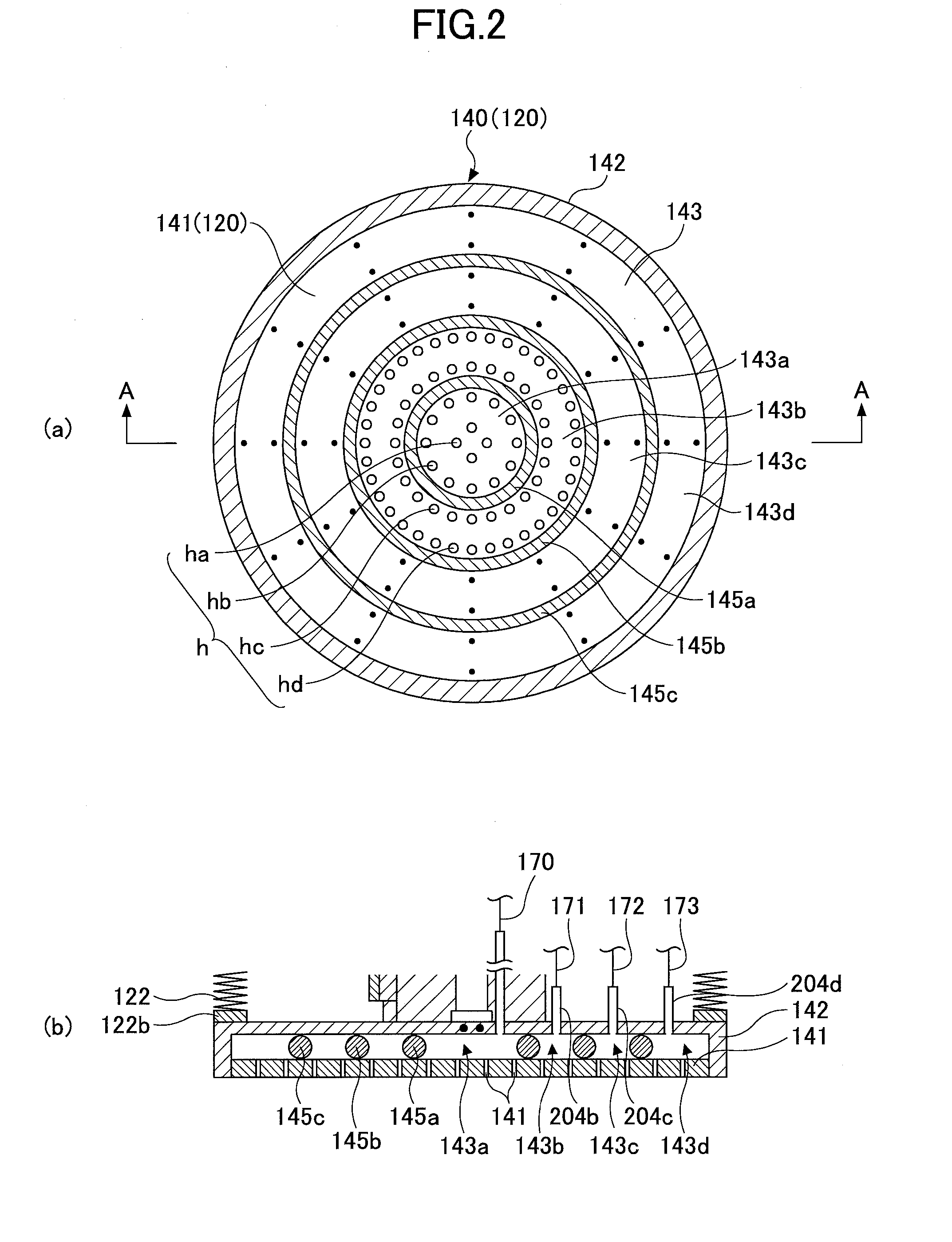

Plasma etching method and semiconductor device manufacturing method

ActiveUS20140234992A1Semiconductor/solid-state device testing/measurementElectric discharge tubesDevice materialPhysical chemistry

A plasma etching method is provided for etching a substrate corresponding to an etching object within an etching apparatus that includes a supply condition adjustment unit for adjusting a supply condition for supplying etching gas to the substrate, a temperature adjustment unit for adjusting a temperature of the substrate placed on a stage along a radial direction, and a plasma generating unit for generating plasma within a space between the supply condition adjustment unit and the stage. The plasma etching method includes a control step in which the temperature adjustment unit controls the temperature of the substrate to be uniform within a substrate plane of the substrate, and an adjustment step in which the supply condition adjustment unit adjusts a concentration distribution of active species contained in the plasma generated by the plasma generation unit within the space above the substrate.

Owner:TOKYO ELECTRON LTD

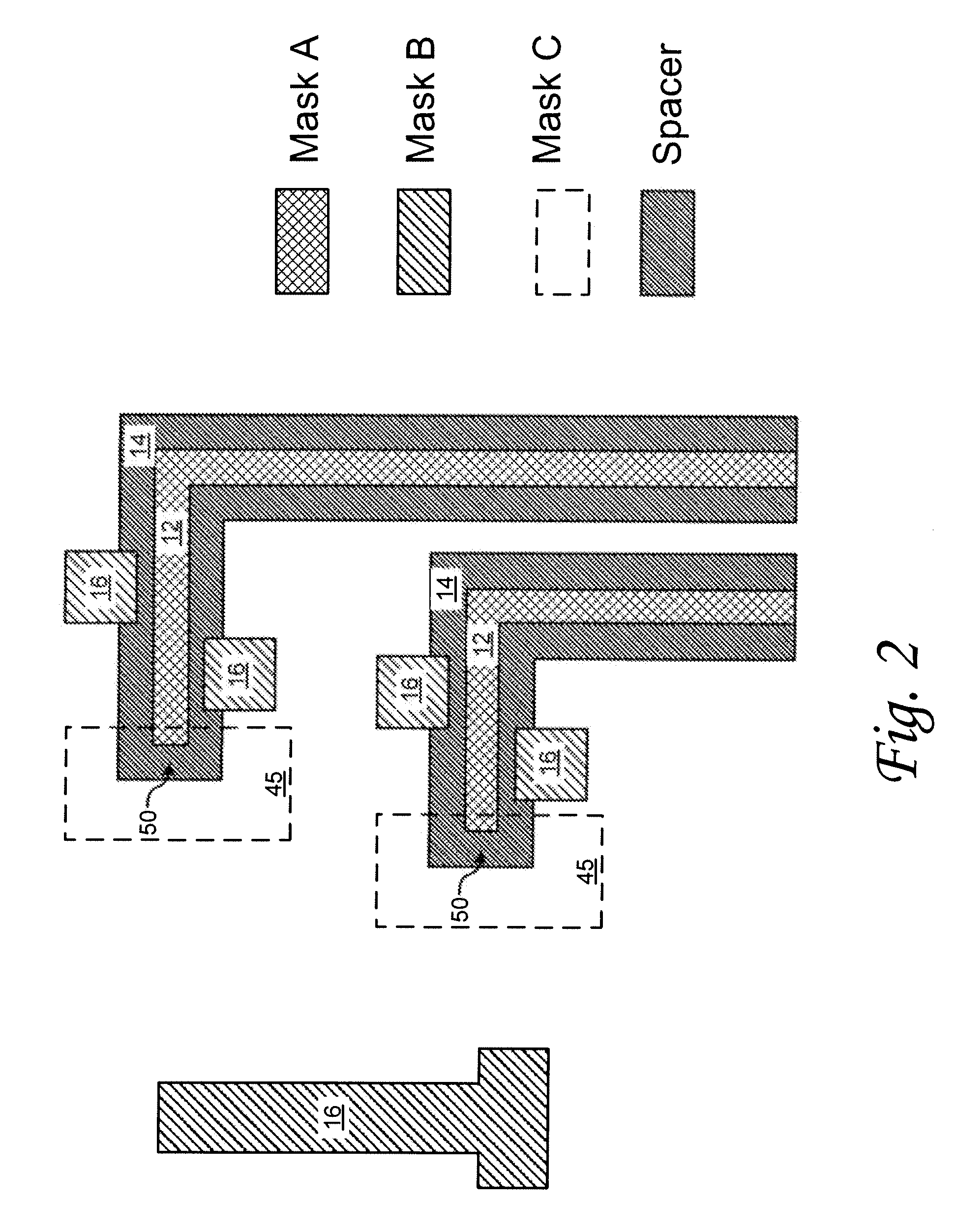

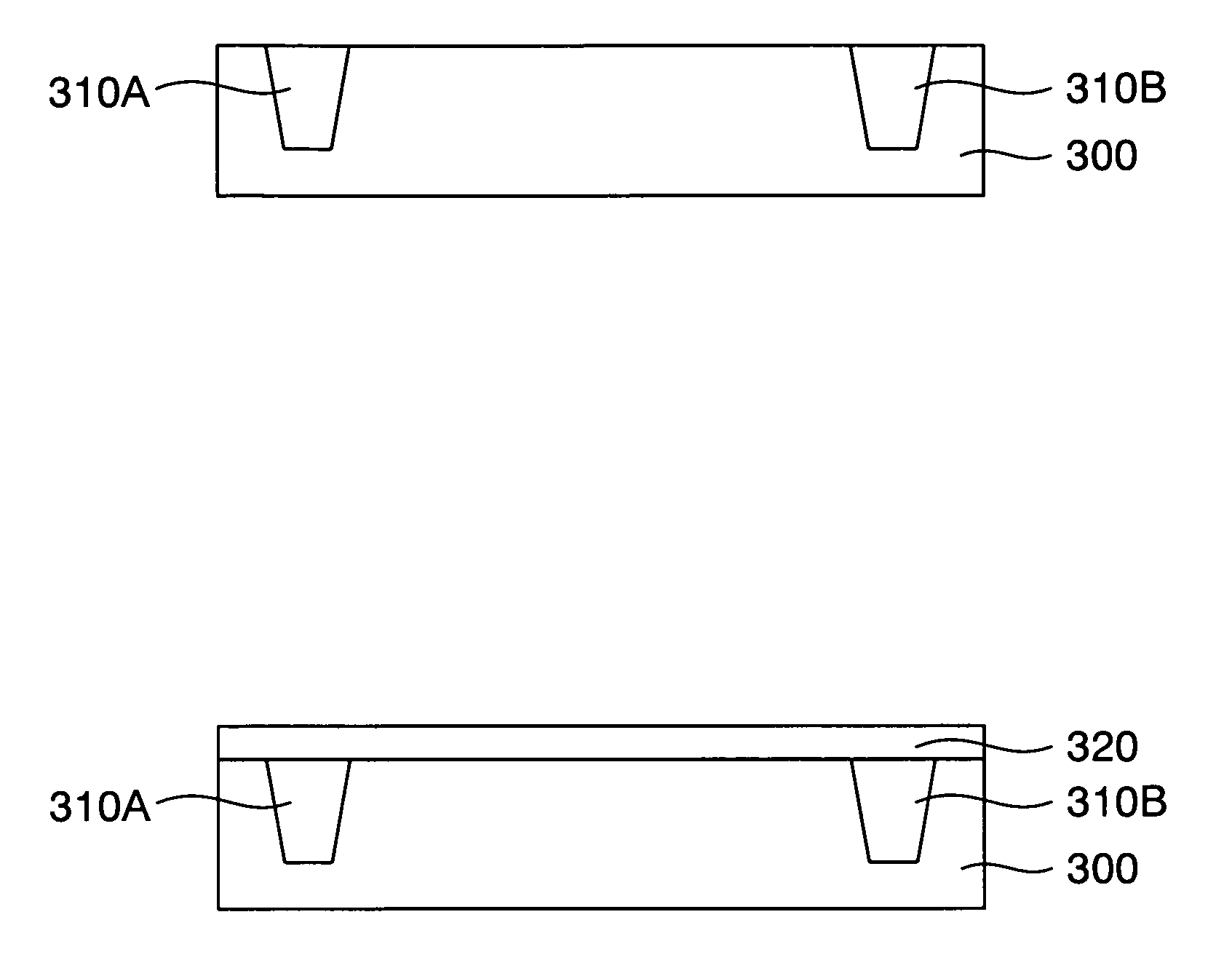

Method of spacer-defined direct patterning in semiconductor fabrication

ActiveUS20190259612A1Reduce variationPhotomechanical apparatusSemiconductor/solid-state device manufacturingResistEngineering

A method of spacer-defined direct patterning in semiconductor fabrication includes: providing a photoresist structure having a target width of lines; trimming the photoresist structures such that a width of each trimmed photoresist structure is smaller than the target width; depositing an oxide film on the template, thereby entirely covering with the oxide film an exposed top surface of the template and the trimmed photoresist structures; etching the oxide film-covered template to remove an unwanted portion of the oxide film without removing the trimmed photoresist structures so as to form vertical spacers isolated from each other, each spacer substantially maintaining the target width and being constituted by the trimmed photoresist structures and a vertical portion of the oxide film covering sidewalls of the trimmed photoresist structures; and etching the spacer-formed template to transfer a pattern constituted by the spacers to the template.

Owner:ASM IP HLDG BV

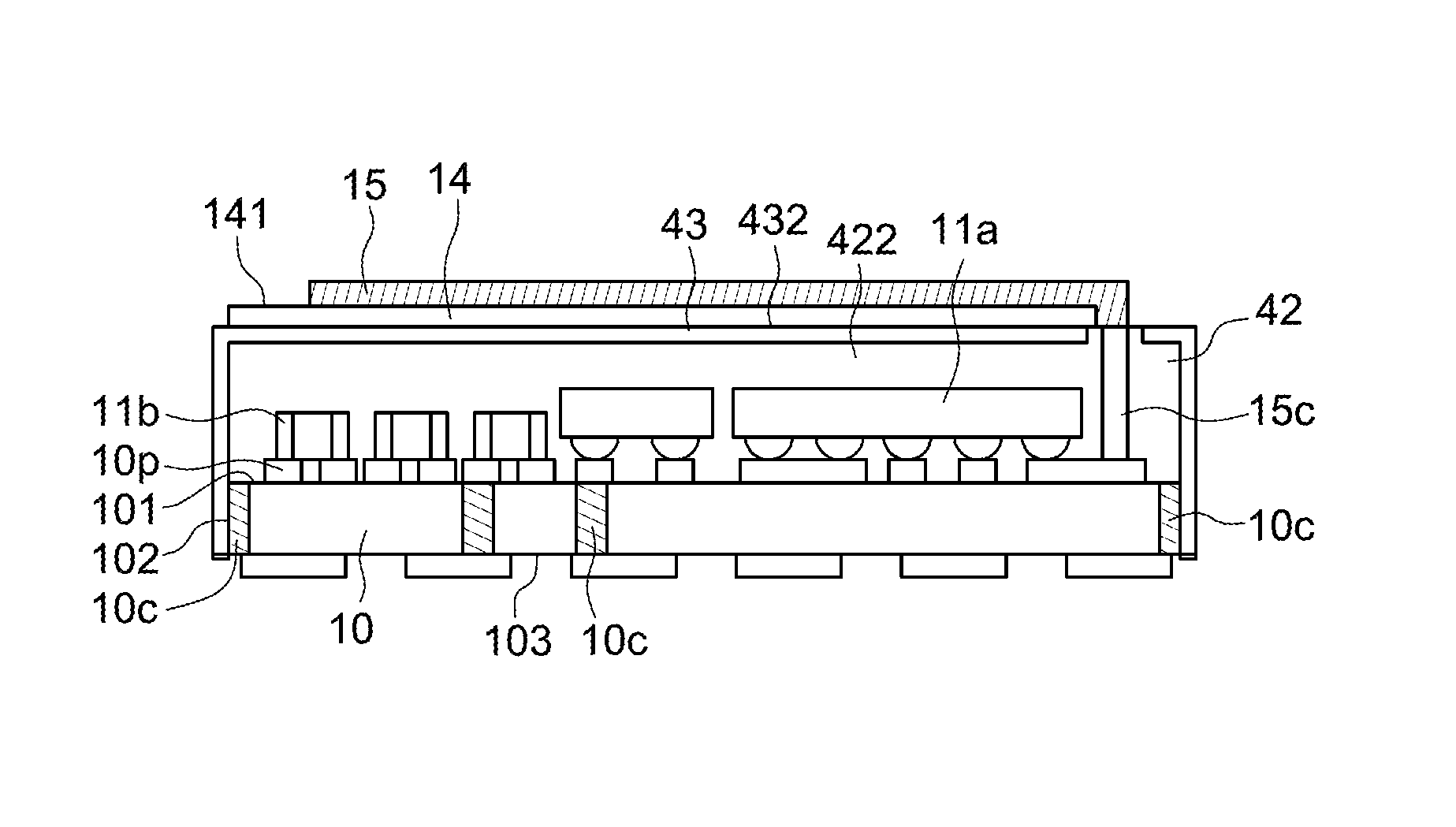

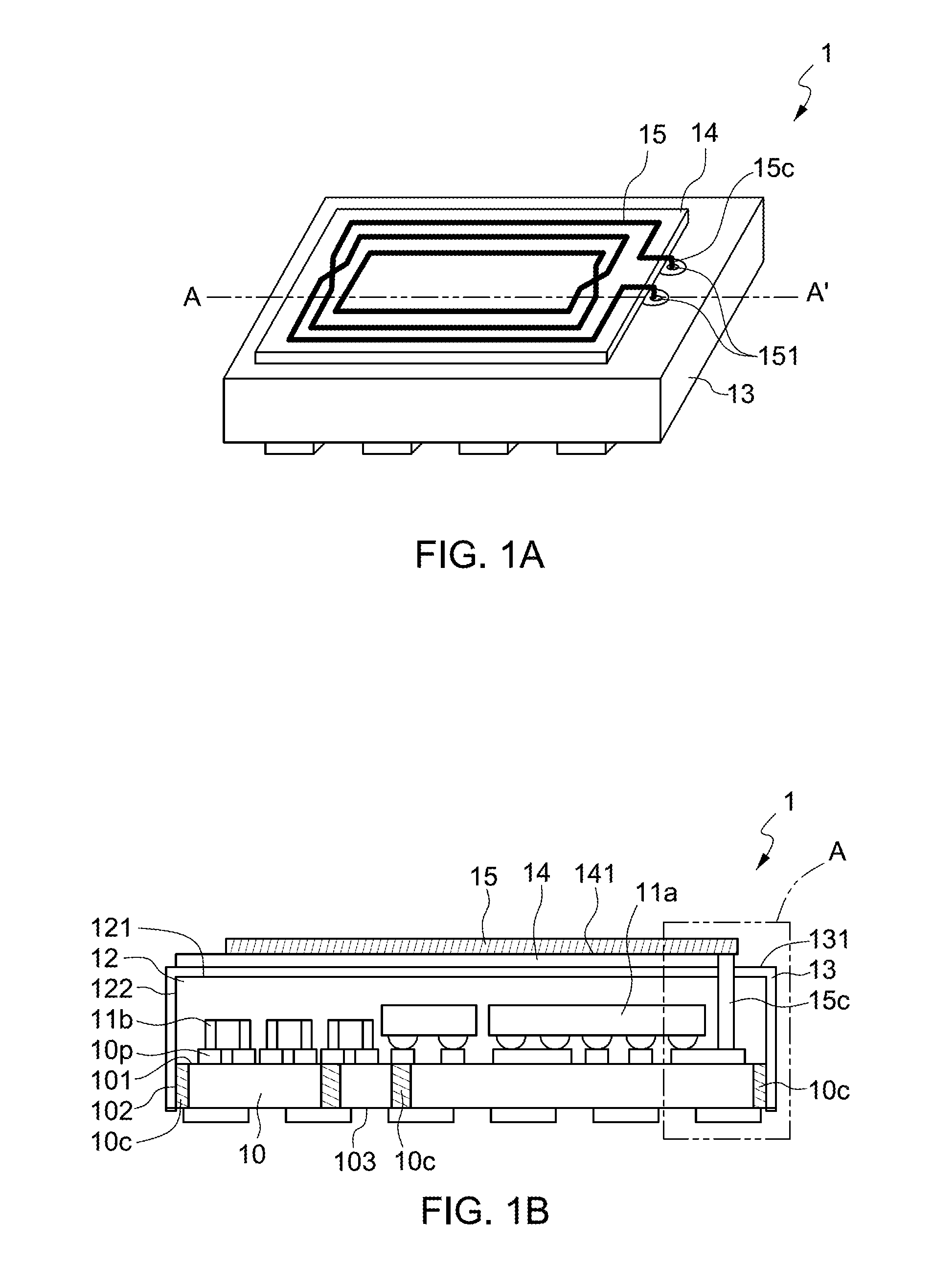

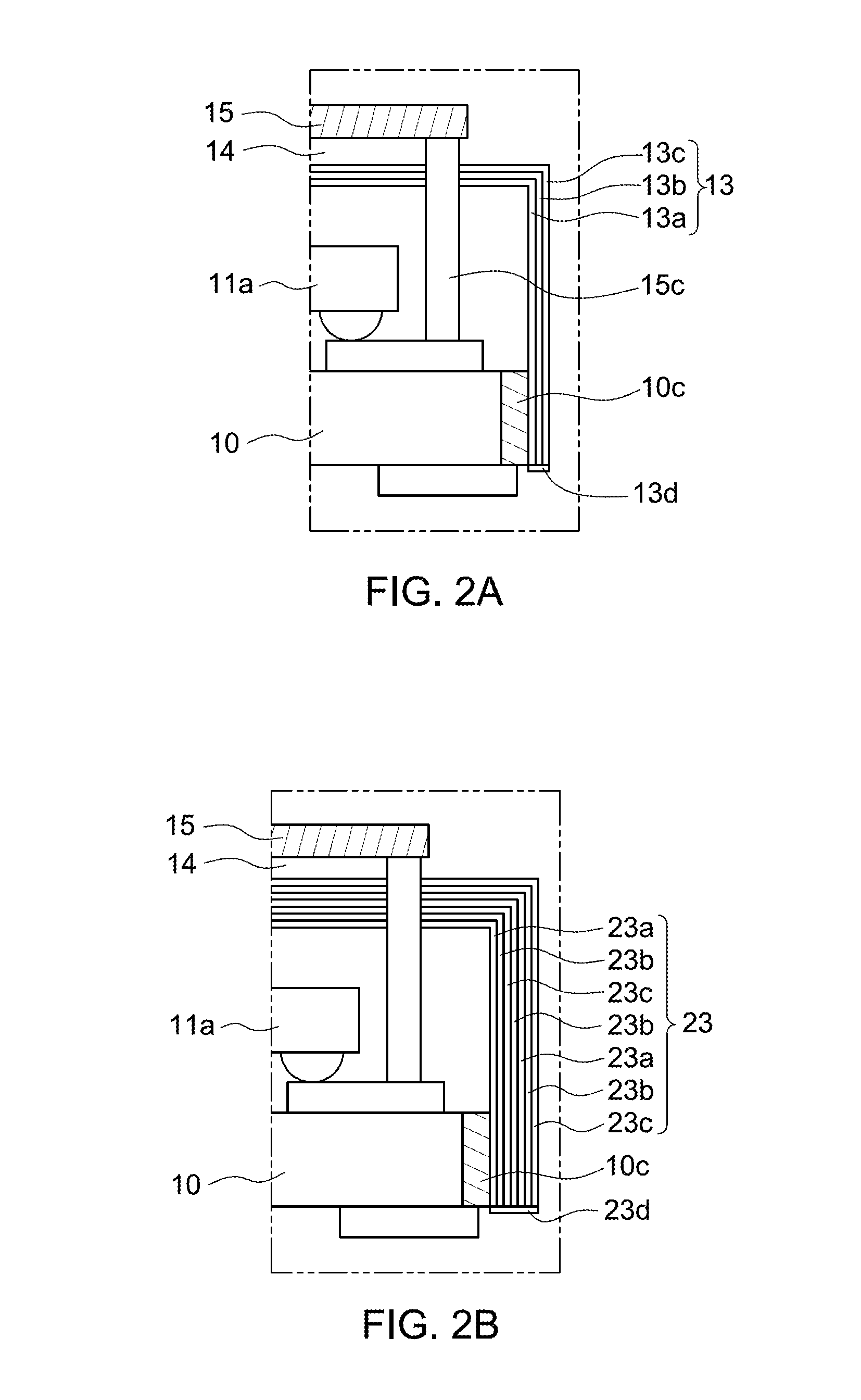

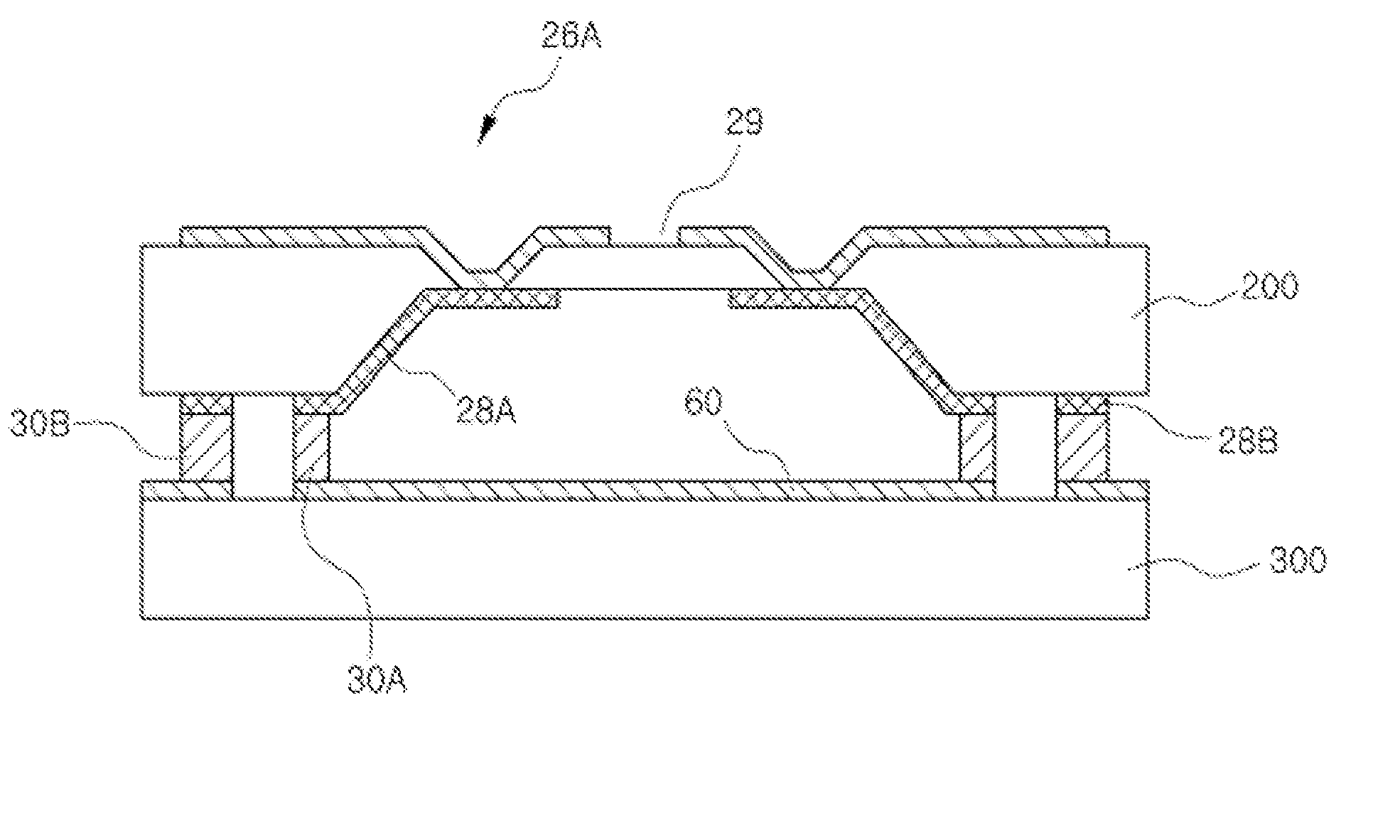

Semiconductor device package integrated with coil for wireless charging and electromagnetic interference shielding, and method of manufacturing the same

ActiveUS9461001B1Batteries circuit arrangementsSemiconductor/solid-state device detailsElectricityElectromagnetic interference

The present disclosure relates to a semiconductor device package which includes a carrier, an electronic component, conductive elements, a package body, a shield, a magnetic insulating layer, and a patterned conductive layer. The carrier has a top surface on which the electronic component is disposed. The conductive elements are disposed on the top surface of the carrier. The package body is disposed on the top surface of the carrier and encapsulates the electronic component and a portion of each of the conductive elements. The shield is disposed on the package body and covers an exterior of the package body. The magnetic insulating layer is disposed on a top surface of the shield. The patterned conductive layer is disposed on the magnetic insulating layer. Each of the conductive elements electrically connects the patterned conductive layer to the electronic component.

Owner:ADVANCED SEMICON ENG INC

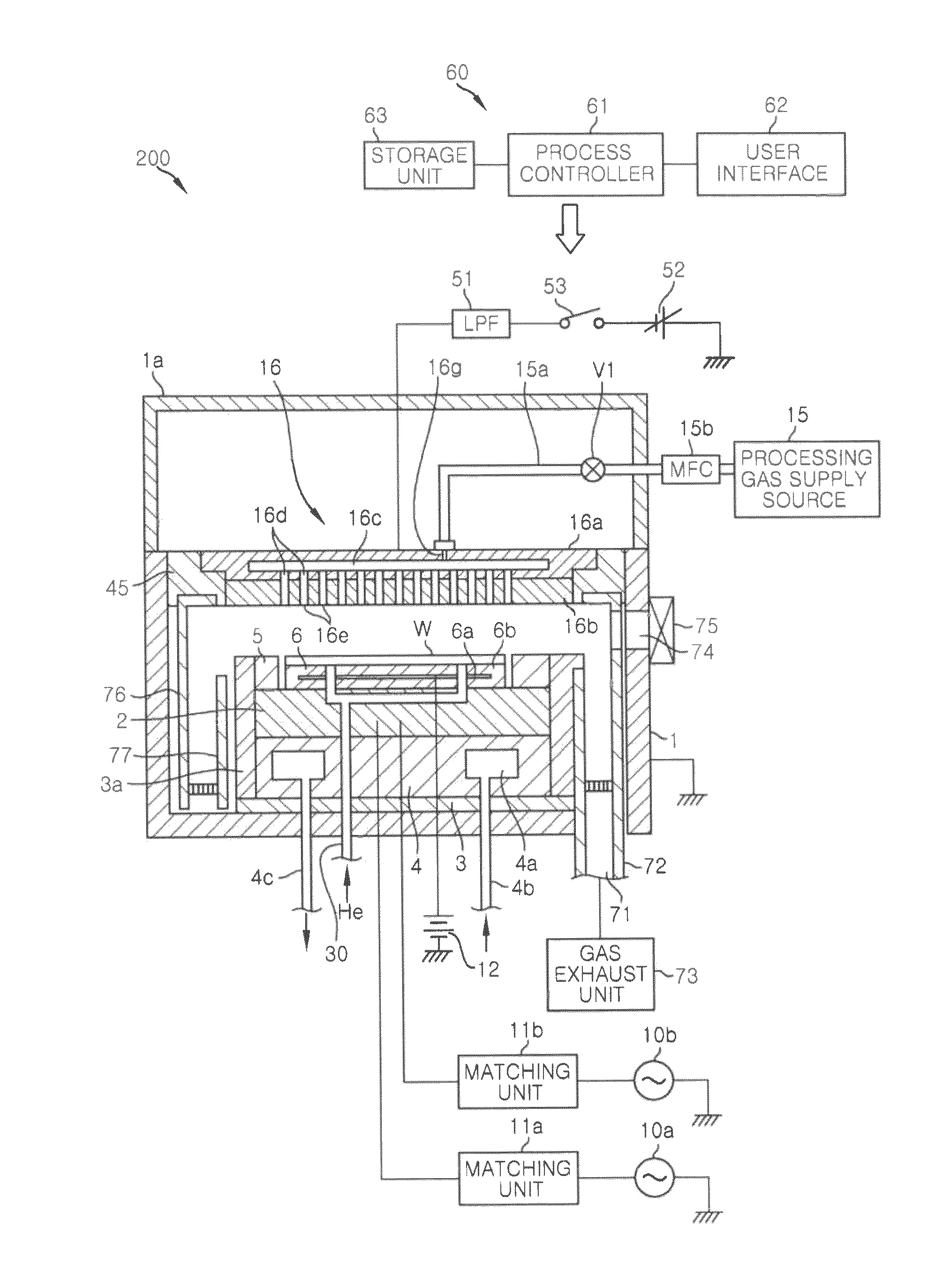

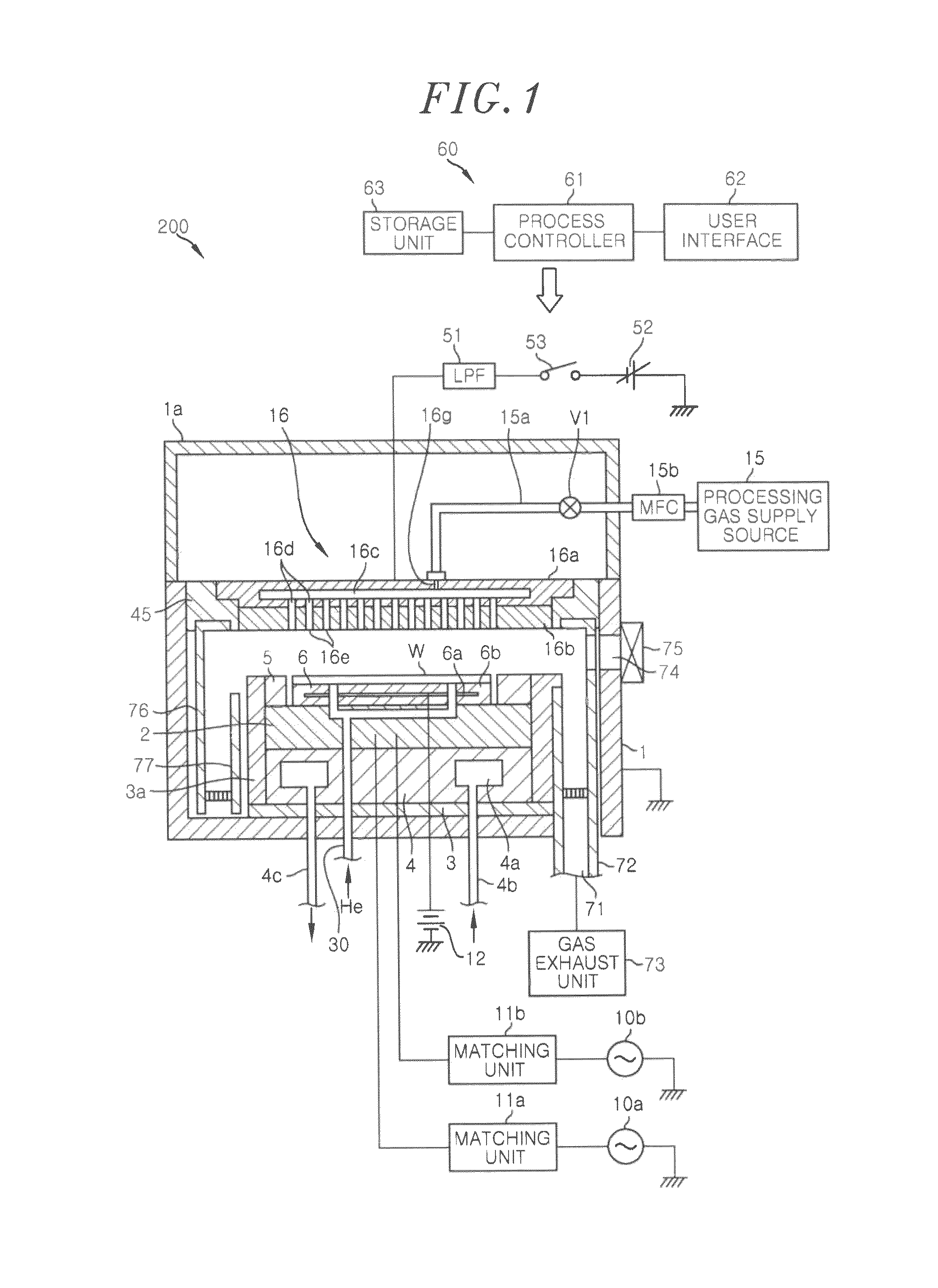

Semiconductor device manufacturing method and plasma etching apparatus

ActiveUS8491805B2Improve accuracyHigh selectivityElectric discharge tubesDecorative surface effectsEngineeringSemiconductor

Owner:TOKYO ELECTRON LTD

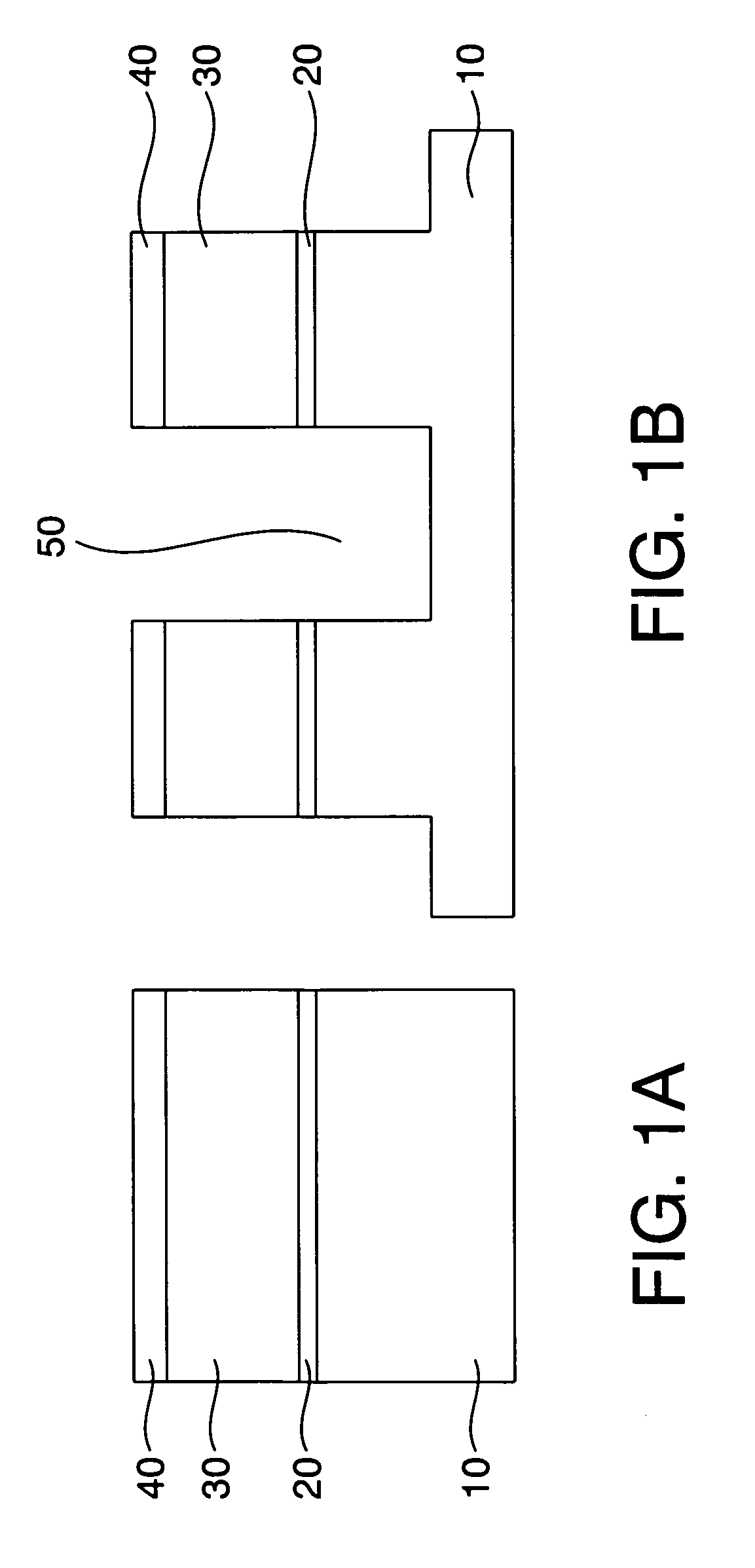

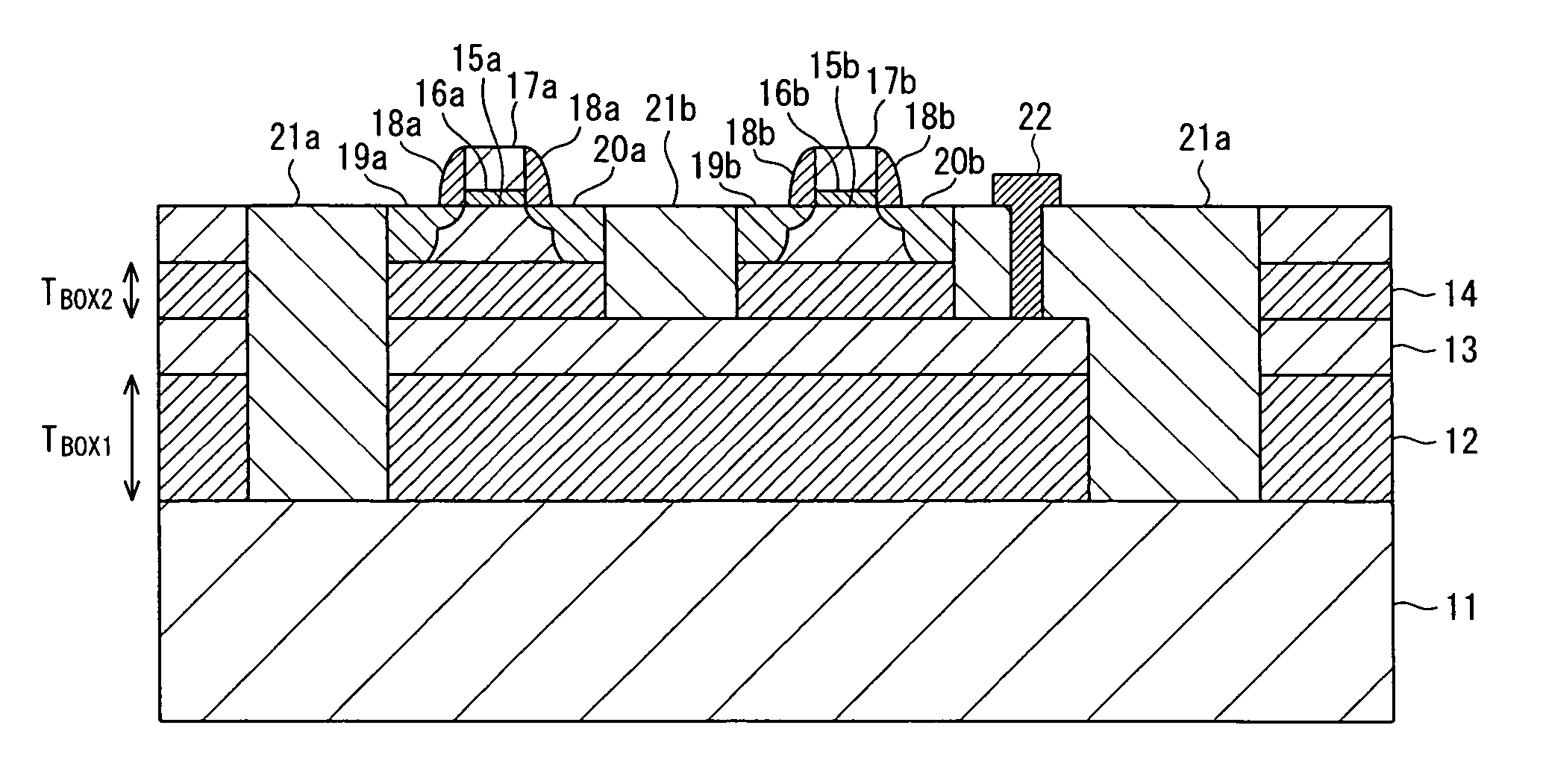

Semiconductor device and semiconductor device manufacturing method

InactiveUS20070075317A1Increase flexibilityImprove pressure resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device includes a back gate electrode composed of a first single-crystal semiconductor layer formed on a first insulating layer; a second insulating layer formed on the first single-crystal semiconductor layer and having a film thickness smaller than a film thickness of the first insulating layer; a second single-crystal semiconductor layer formed on the second insulating layer; a gate electrode formed on the second single-crystal semiconductor layer; and source and drain layers that are formed on the second single-crystal semiconductor layer and arranged on respective sides of the gate electrode.

Owner:SEIKO EPSON CORP +1

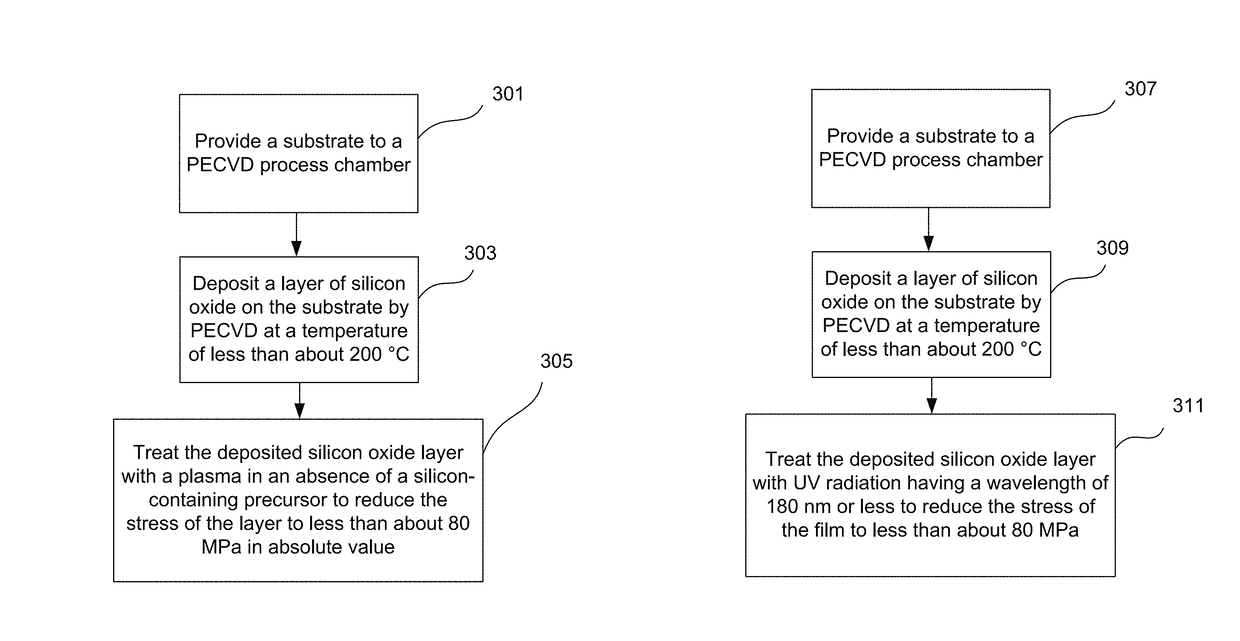

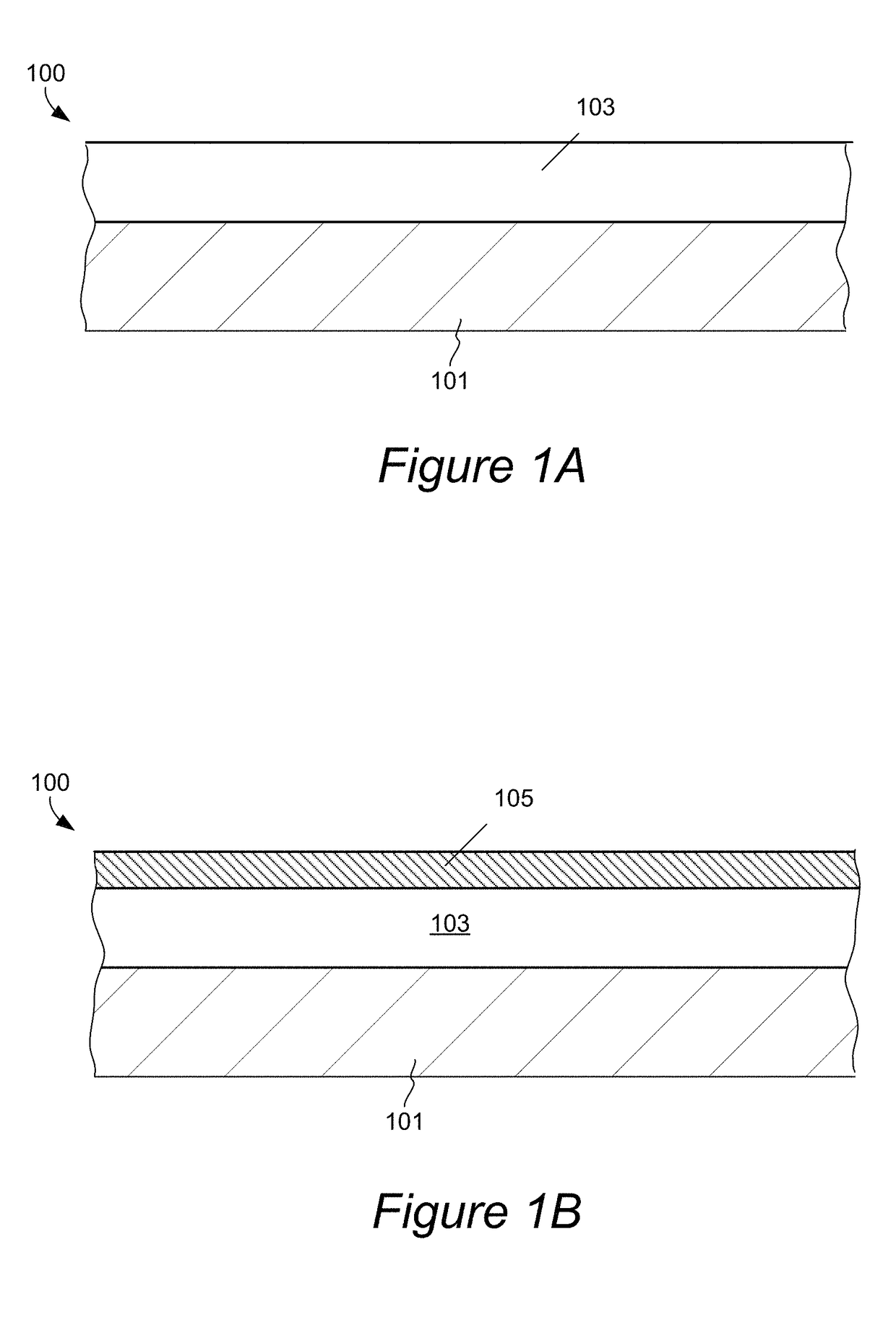

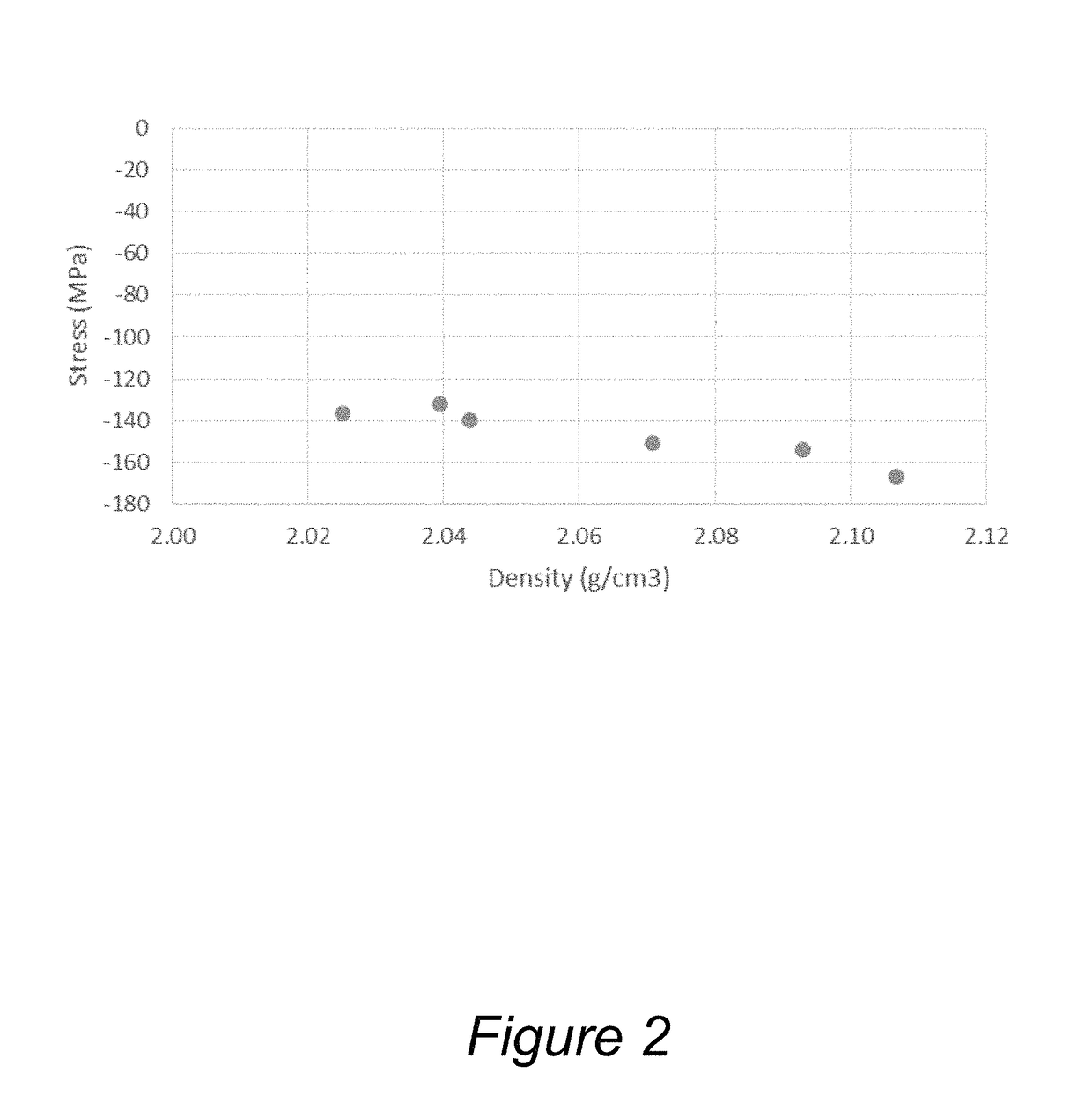

Low temperature formation of high quality silicon oxide films in semiconductor device manufacturing

ActiveUS9847221B1Relieve pressureReduce film stressSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricDevice material

Silicon oxide layer is deposited on a semiconductor substrate by PECVD at a temperature of less than about 200° C. and is treated with helium plasma to reduce stress of the deposited layer to an absolute value of less than about 80 MPa. Plasma treatment reduces hydrogen content in the silicon oxide layer, and leads to low stress films that can also have high density and low roughness. In some embodiments, the film is deposited on a semiconductor substrate that contains one or more temperature-sensitive layers, such as layers of organic material or spin-on dielectric that cannot withstand temperatures of greater than 250° C. In some embodiments the silicon oxide film is deposited to a thickness of between about 100-200 Å, and is used as a hardmask layer during etching of other layers on a semiconductor substrate.

Owner:LAM RES CORP

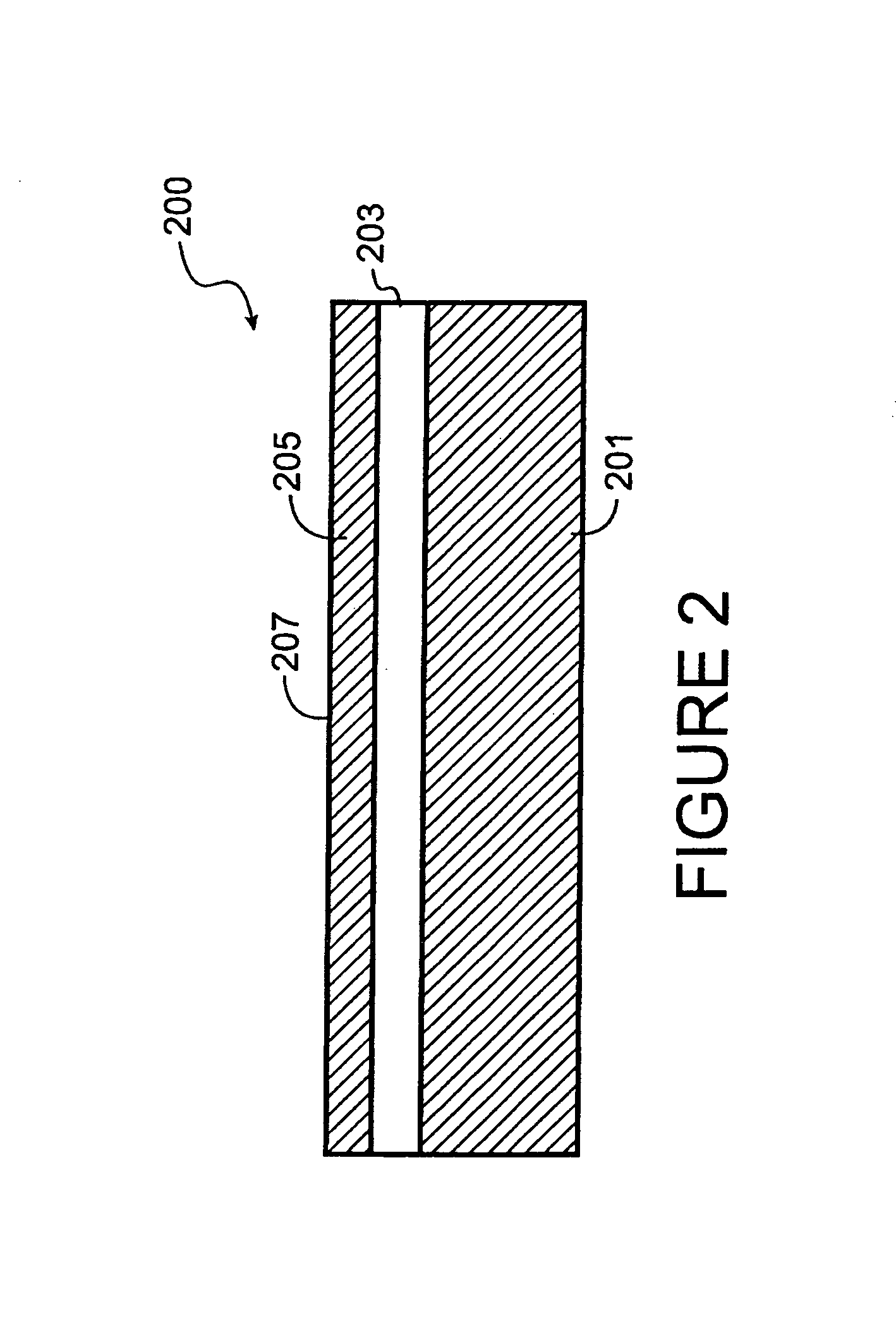

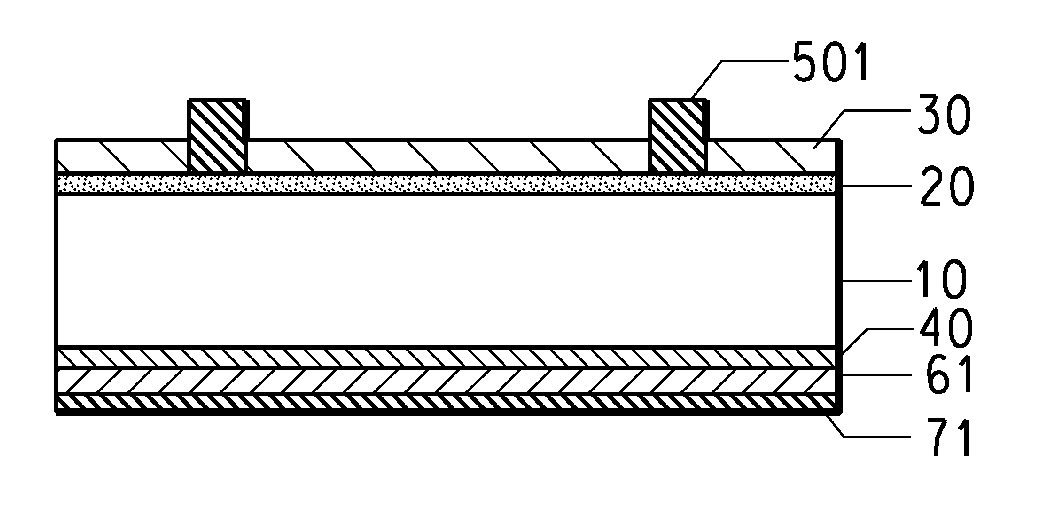

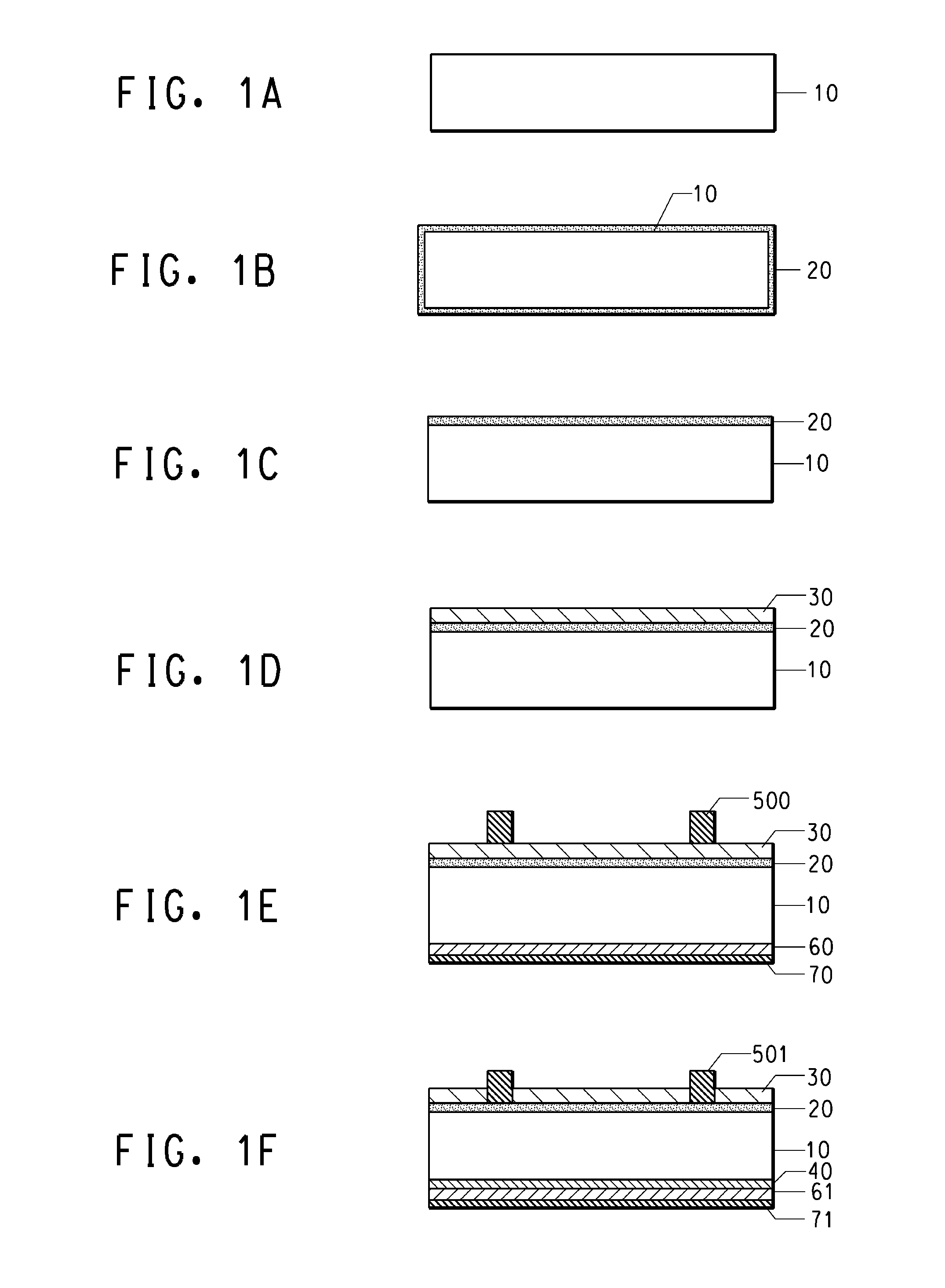

Substrate for semiconductor device and manufacturing method thereof

ActiveUS7902660B1Thin thicknessAvoid warpingSemiconductor/solid-state device detailsSolid-state devicesElectricitySolder ball

A substrate for a semiconductor device and a manufacturing thereof, and a semiconductor device using the same and a manufacturing method thereof are disclosed. For example, in the substrate according to the present invention, a core is eliminated, so that the substrate has a very thin thickness, as well, the length of electrically conductive patterns becomes shorter, whereby the electrical efficiency thereof is improved. Moreover, since a carrier having a stiffness of a predetermined strength is bonded on the substrate, it can prevent a warpage phenomenon during the manufacturing process of the semiconductor device. Furthermore, the carrier is removed from the substrate, whereby a solder ball fusing process or an electrical connecting process of the semiconductor die can be easily performed.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

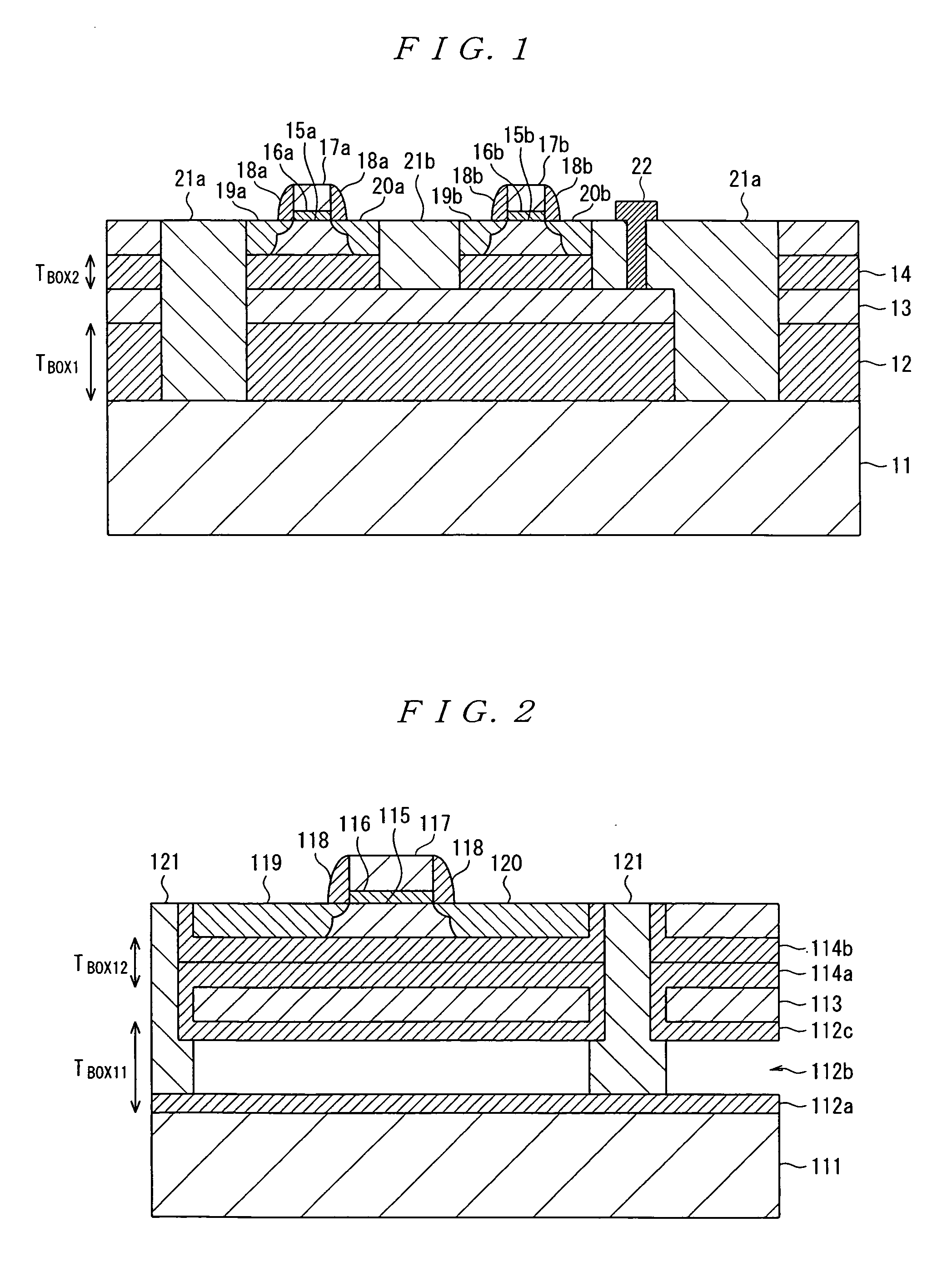

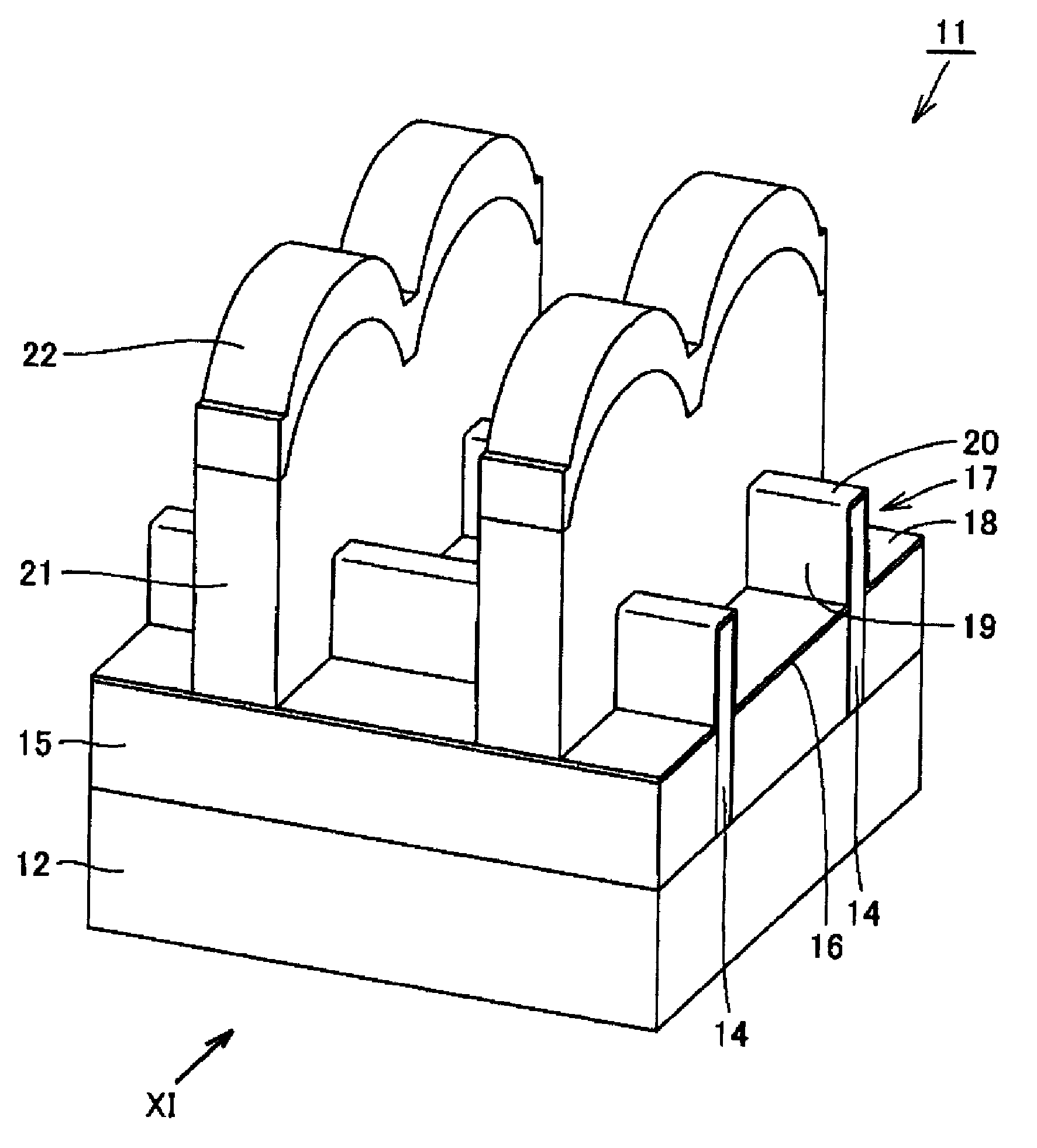

Method of manufacturing semiconductor device

InactiveUS20090317950A1Reduce parasitic resistanceImprove leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageSoi substrate

A semiconductor device manufacturing method which sequentially forms a gate oxide film and gate electrode material over a semiconductor layer of an SOI substrate and patterns the material into gate electrodes. The method further comprises the steps of forming sidewalls made of an insulator to cover side surfaces of the gate electrode; ion-implanting into the semiconductor layer on both sides of the gate electrode to form drain / source regions; partially etching the sidewalls to expose upper parts of the side surfaces of the gate electrode; depositing a metal film to cover the tops of the drain / source regions and of the gate electrode and the exposed upper parts of the side surfaces of the gate electrode; and performing heat treatment on the SOI substrate to form silicide layers respectively in the surfaces of the gate electrode and of the drain / source regions.

Owner:LAPIS SEMICON CO LTD

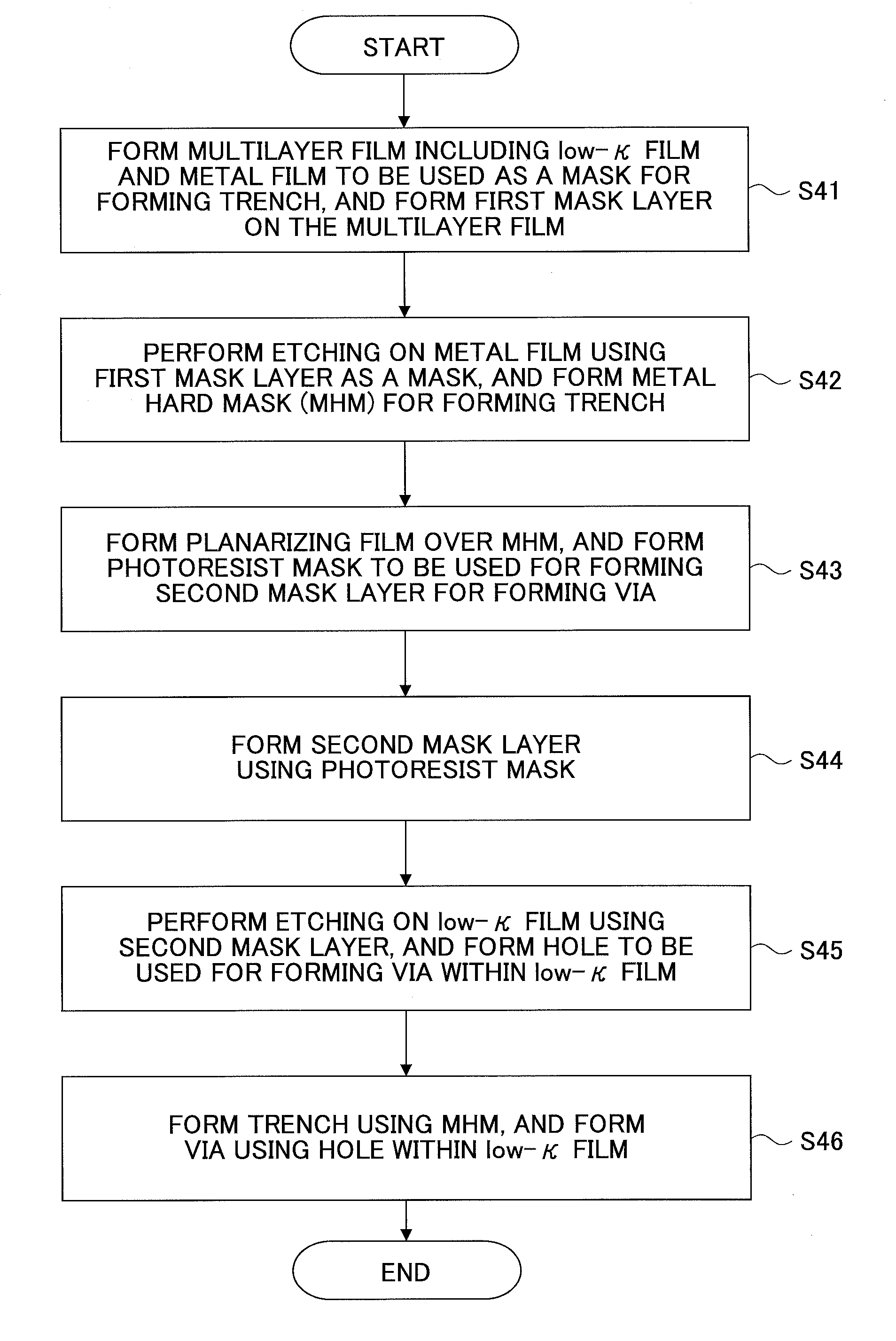

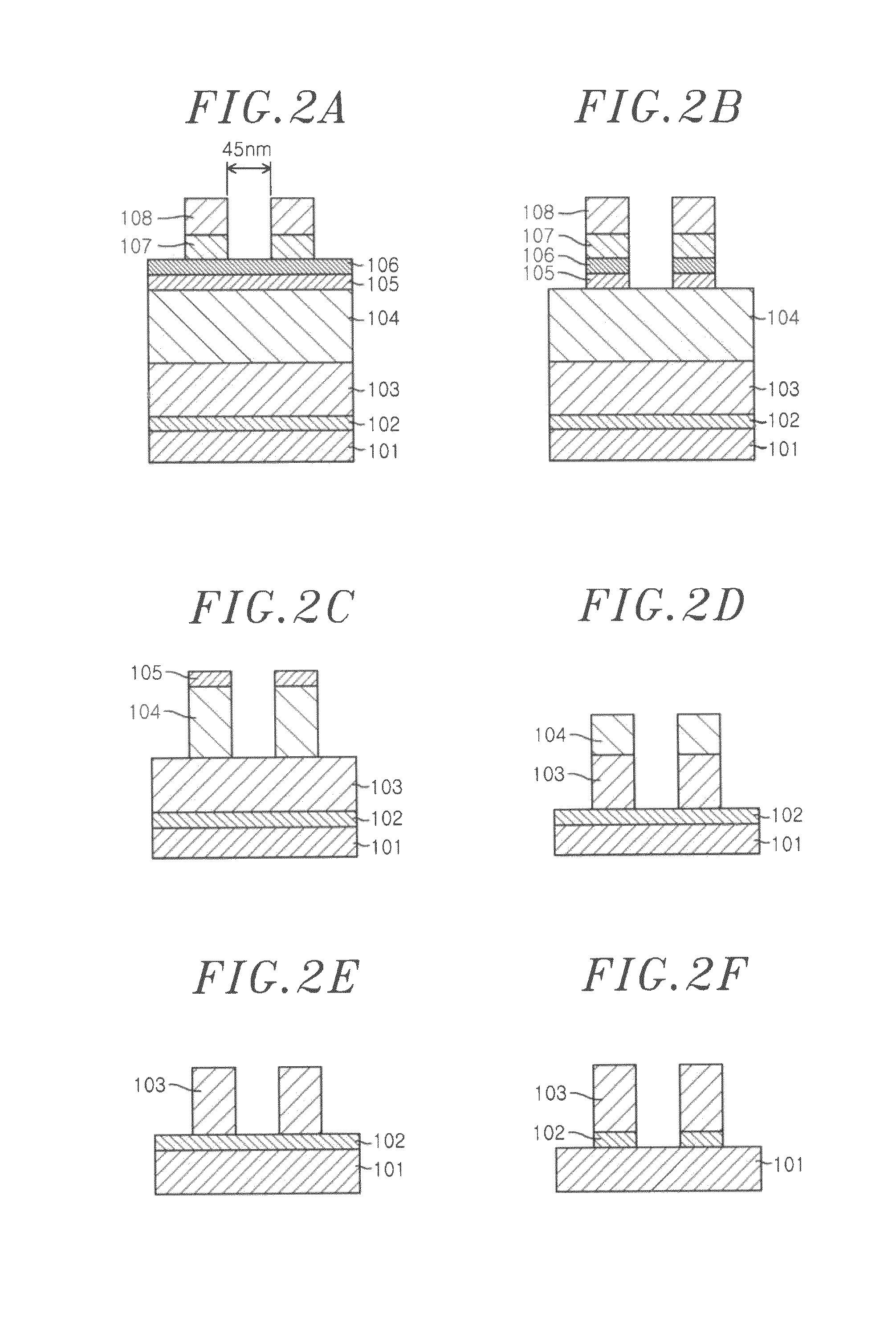

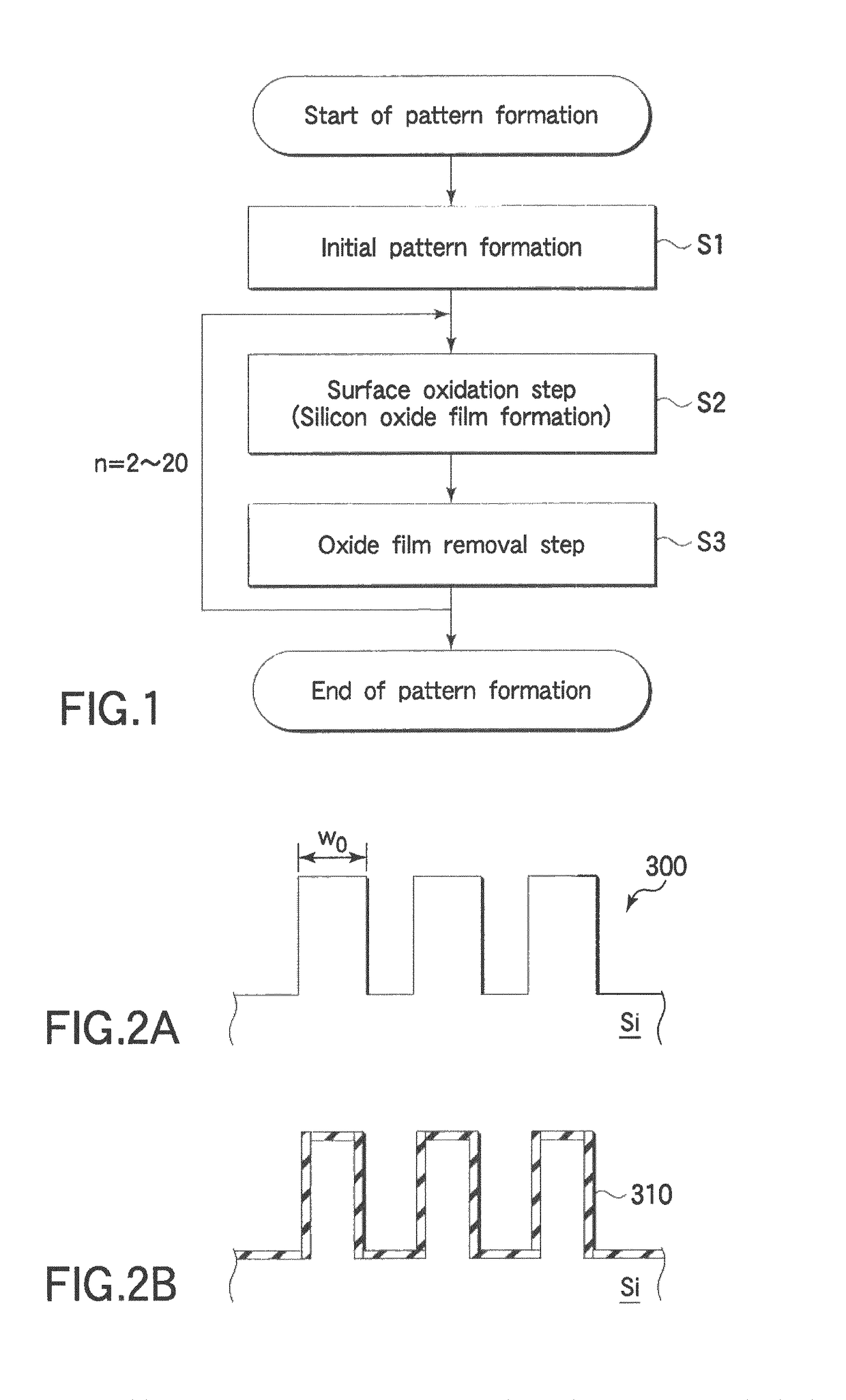

Pattern forming method and semiconductor device manufacturing method

ActiveUS8119530B2Not easy to damageImprove film qualitySemiconductor/solid-state device manufacturingSemiconductor devicesLine widthSilicon oxide

A pattern forming method includes preparing a target object including silicon with an initial pattern formed thereon and having a first line width; performing a plasma oxidation process on the silicon surface inside a process chamber of a plasma processing apparatus and thereby forming a silicon oxide film on a surface of the initial pattern; and removing the silicon oxide film. The pattern forming method is arranged to repeatedly perform formation of the silicon oxide film and removal of the silicon oxide film so as to form an objective pattern having a second line width finer than the first line width on the target object.

Owner:NAGOYA UNIVERSITY +1

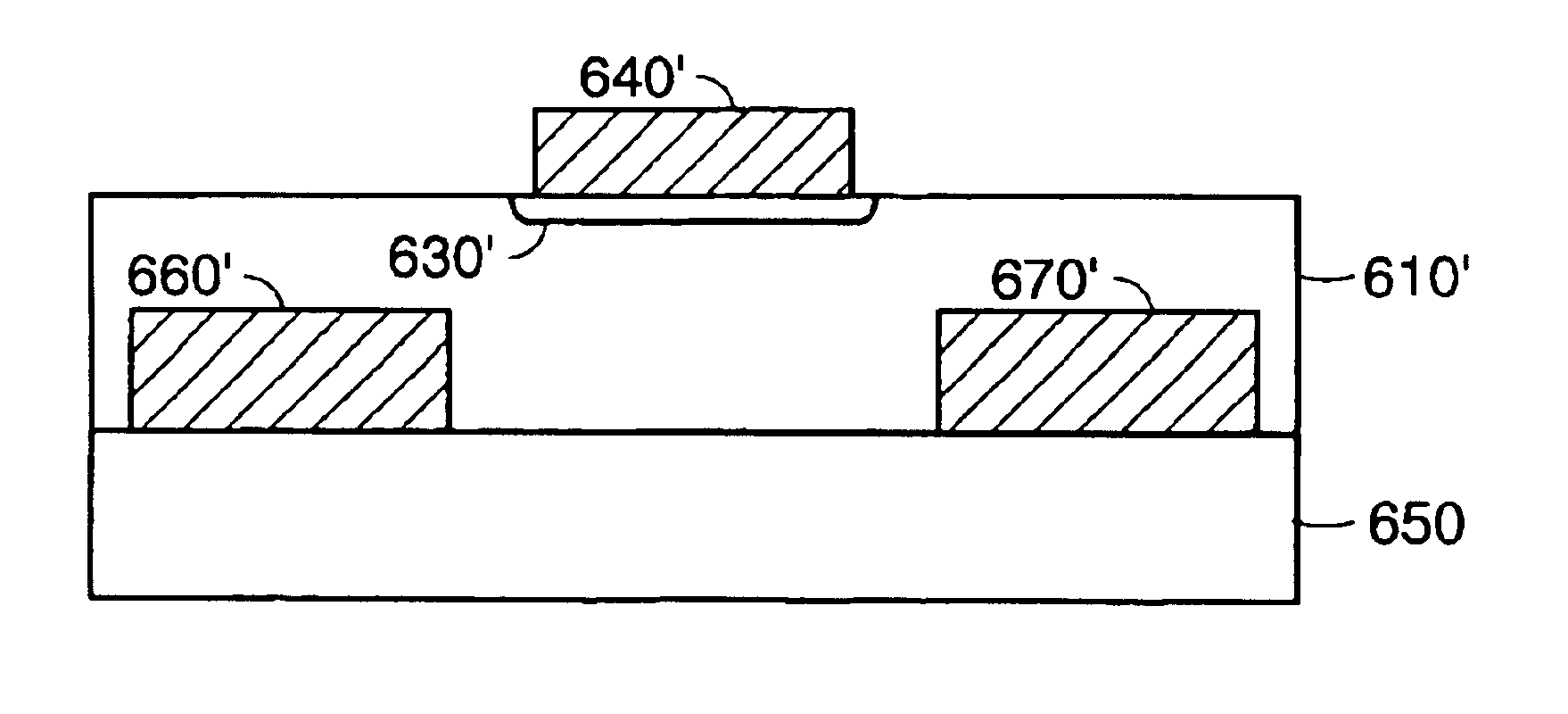

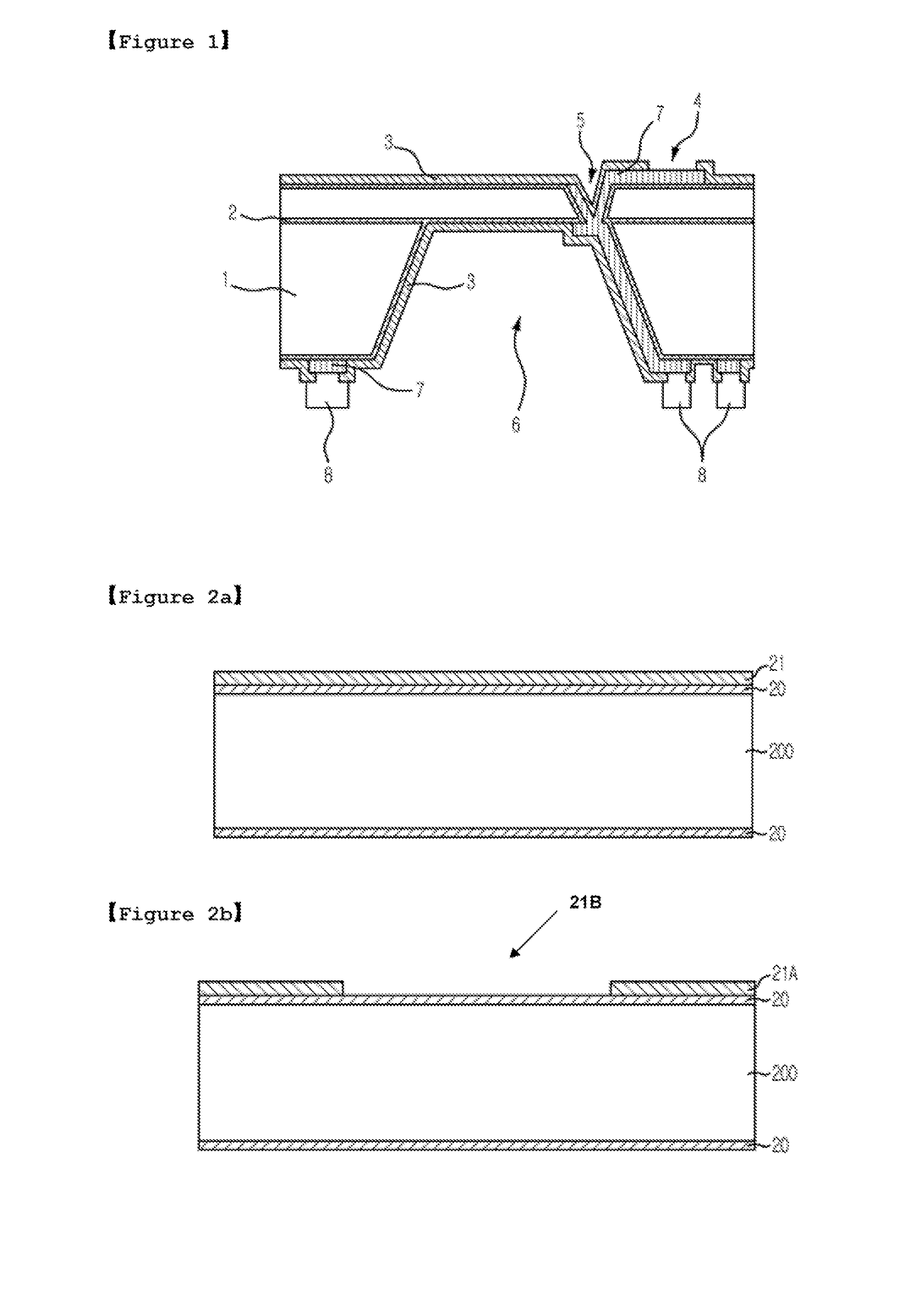

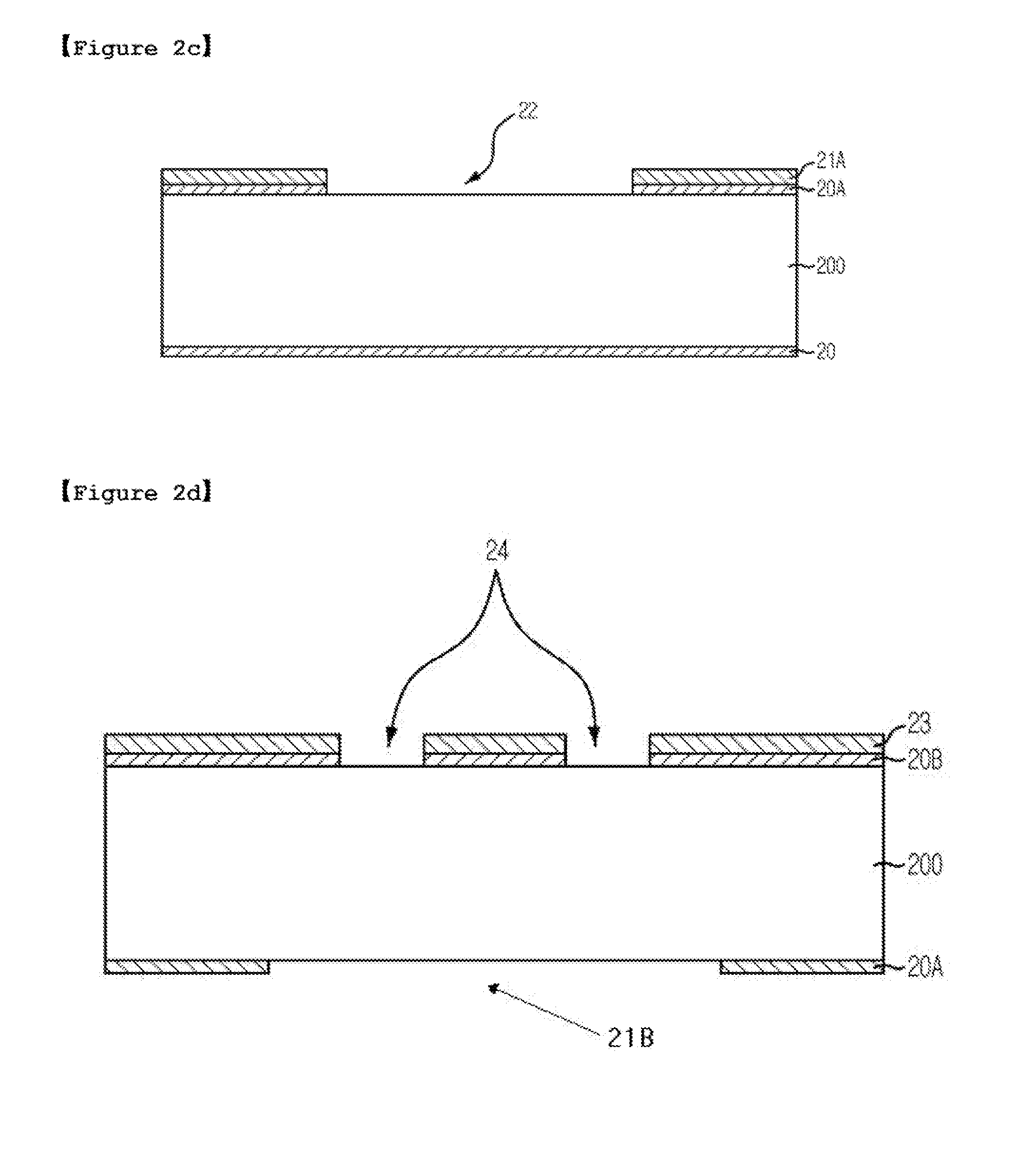

Cap Wafer for Wafer Bonded Packaging and Method for Manufacturing the Same

InactiveUS20080081398A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present invention relates to semiconductor device manufacturing techniques, and specifically to a field of device packaging techniques at wafer level. More specifically, it relates to a cap wafer for wafer bonding application that is bonded to top part of a device wafer. The method of the present invention excludes the use of deep reactive ion etching of silicon to form a through silicon via. The present invention provides a method for the preparation of cap wafer for wafer bonding application with a simple process of through silicon via interconnection and a wafer level packaging method using the same.

Owner:PHOCO

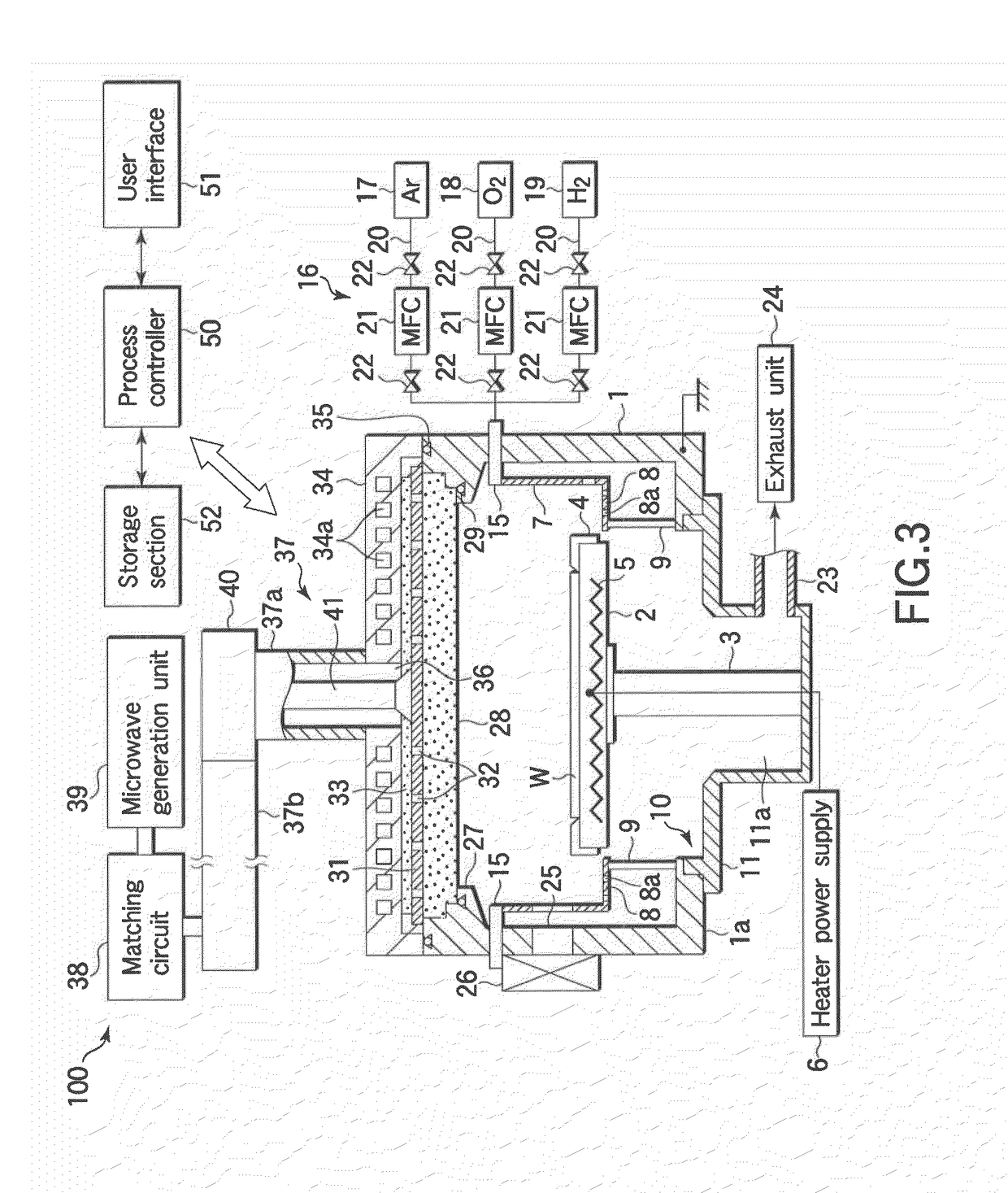

Semiconductor device manufacturing method

InactiveUS20110039407A1Appropriately and efficiently manufacturingAppropriatelySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerDevice material

A semiconductor device manufacturing method, the method including: forming an insulation layer having a protruding portion, the insulation layer having a surface and a rising surface that protrudes upward from the surface, on a semiconductor substrate; forming a conductive layer to cover the insulation layer having the protruding portion; and removing a predetermined region of the conductive layer by patterning the predetermined region according to an etching process using microwave plasma, which uses a microwave as a plasma source, while applying bias power of 70 mW / cm2 or above on the semiconductor substrate, under a high pressure condition of 85 mTorr or above.

Owner:TOKYO ELECTRON LTD

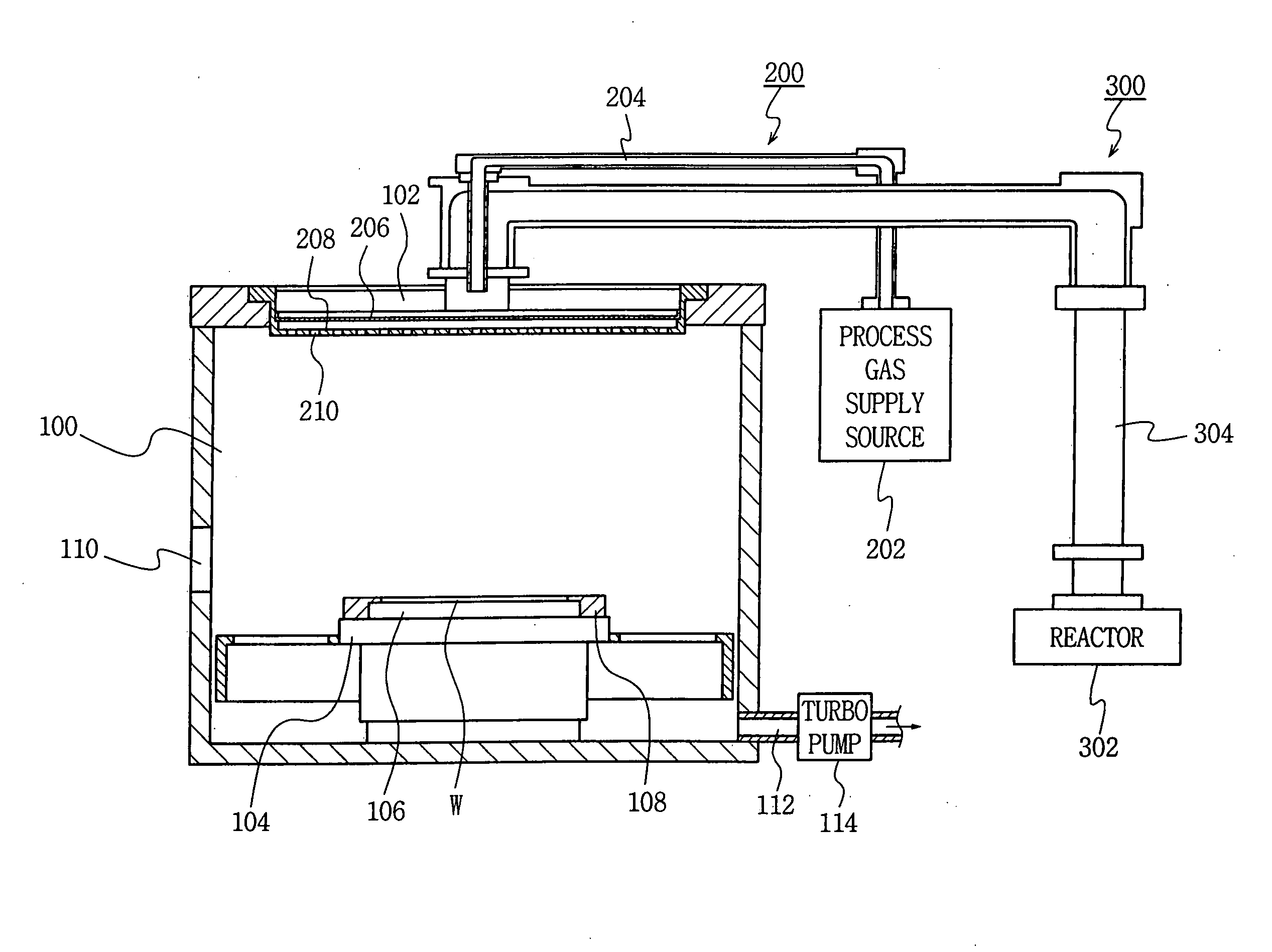

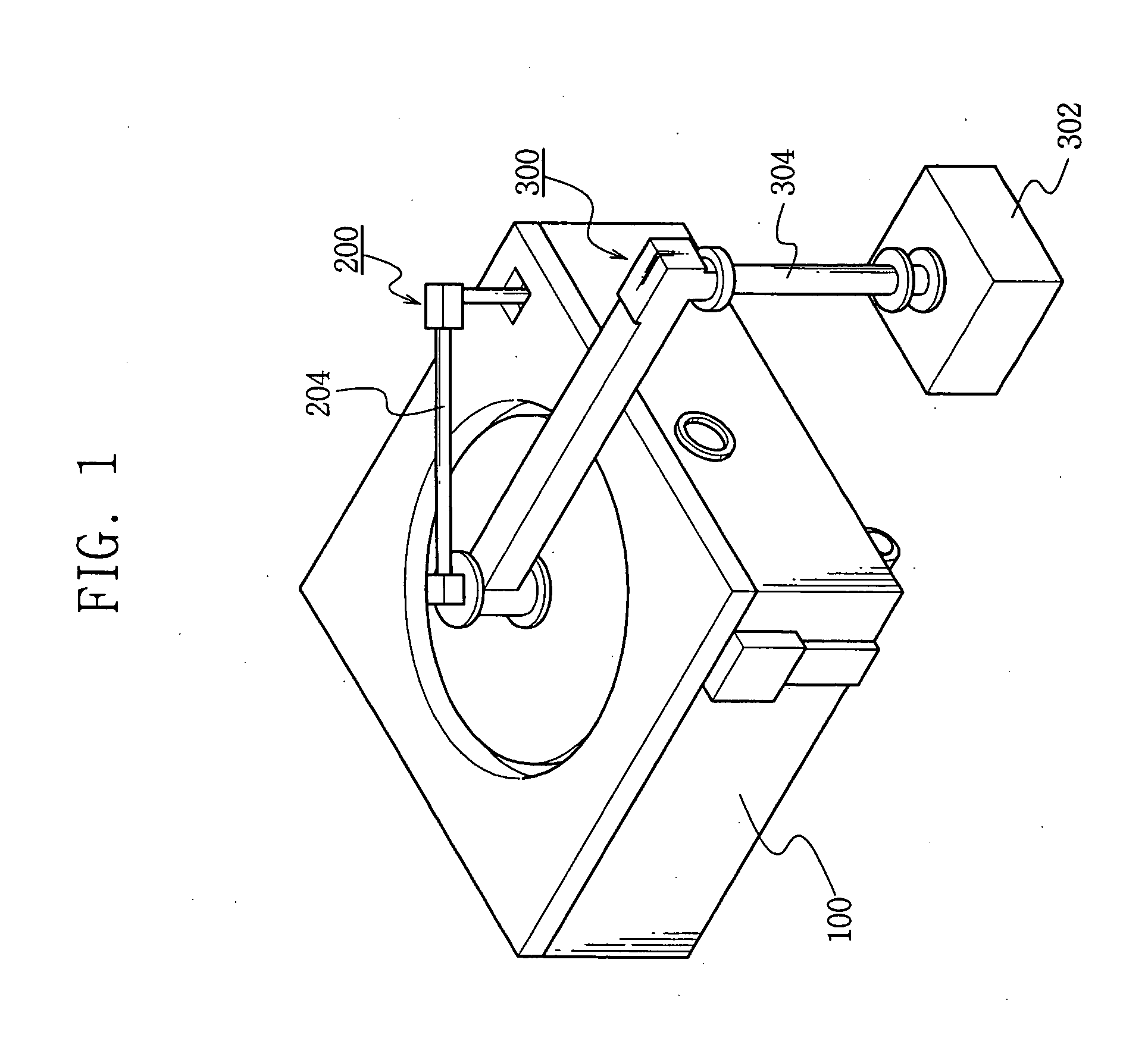

Semiconductor device manufacturing apparatus and method of using the same

InactiveUS20070266946A1Short amount of timeElectric discharge tubesChemical vapor deposition coatingPlasmonic waveguideRemote plasma

A semiconductor device manufacturing apparatus and a method for use in the manufacturing of such devices minimize the amount of particles which accumulate in the process chamber of the apparatus and clean the interior of the process chamber with a high degree of effectiveness. The semiconductor device manufacturing apparatus has a showerhead located at an upper portion of the process chamber, a plate-like gas diffuser disposed in the showerhead, and both a fluid supply line and a plasma waveguide connected to the showerhead. After a substrate is processed in the process chamber using process gas delivered to the showerhead through the fluid supply line, plasma is supplied into the upper portion of the process chamber from a remote plasma reactor via the plasma waveguide.

Owner:SAMSUNG ELECTRONICS CO LTD

Thick-film pastes containing lead-tellurium-boron-oxides, and their use in the manufacture of semiconductor devices

The present invention provides a thick-film paste for printing the front side of a solar cell device having one or more insulating layers. The thick-film paste comprises an electrically conductive metal and a lead-tellurium-boron-oxide dispersed in an organic medium.

Owner:SOLAR PASTE LLC

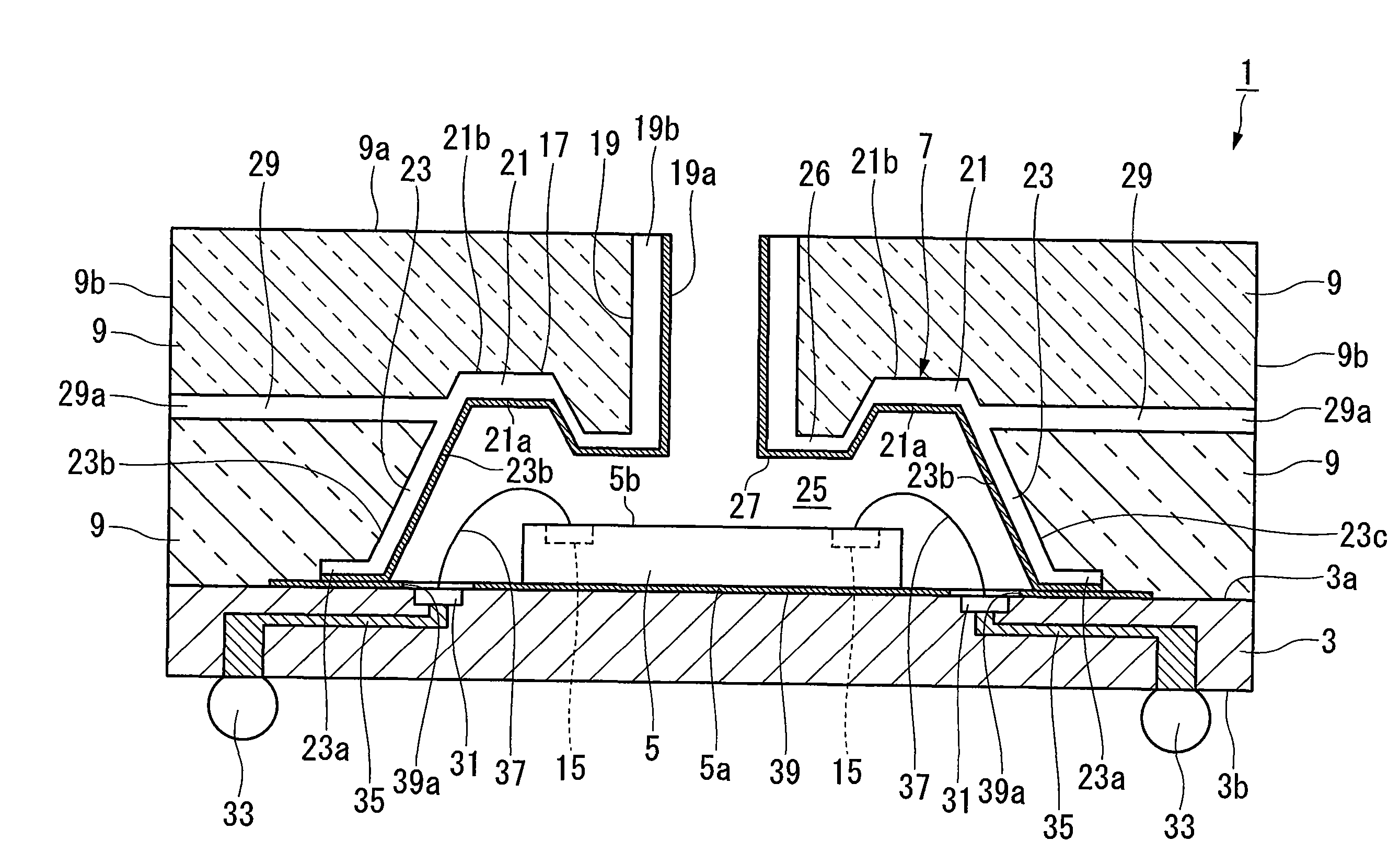

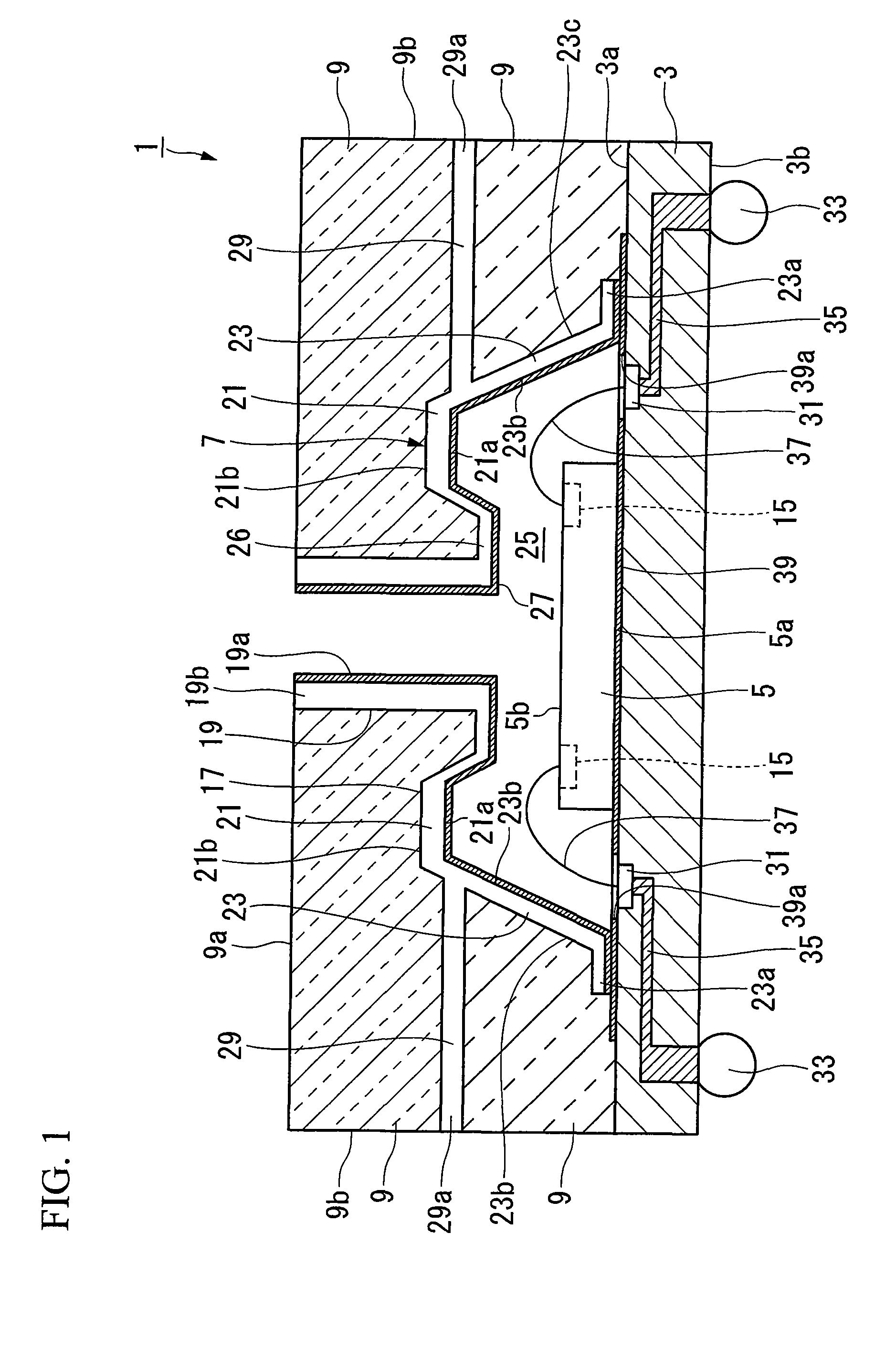

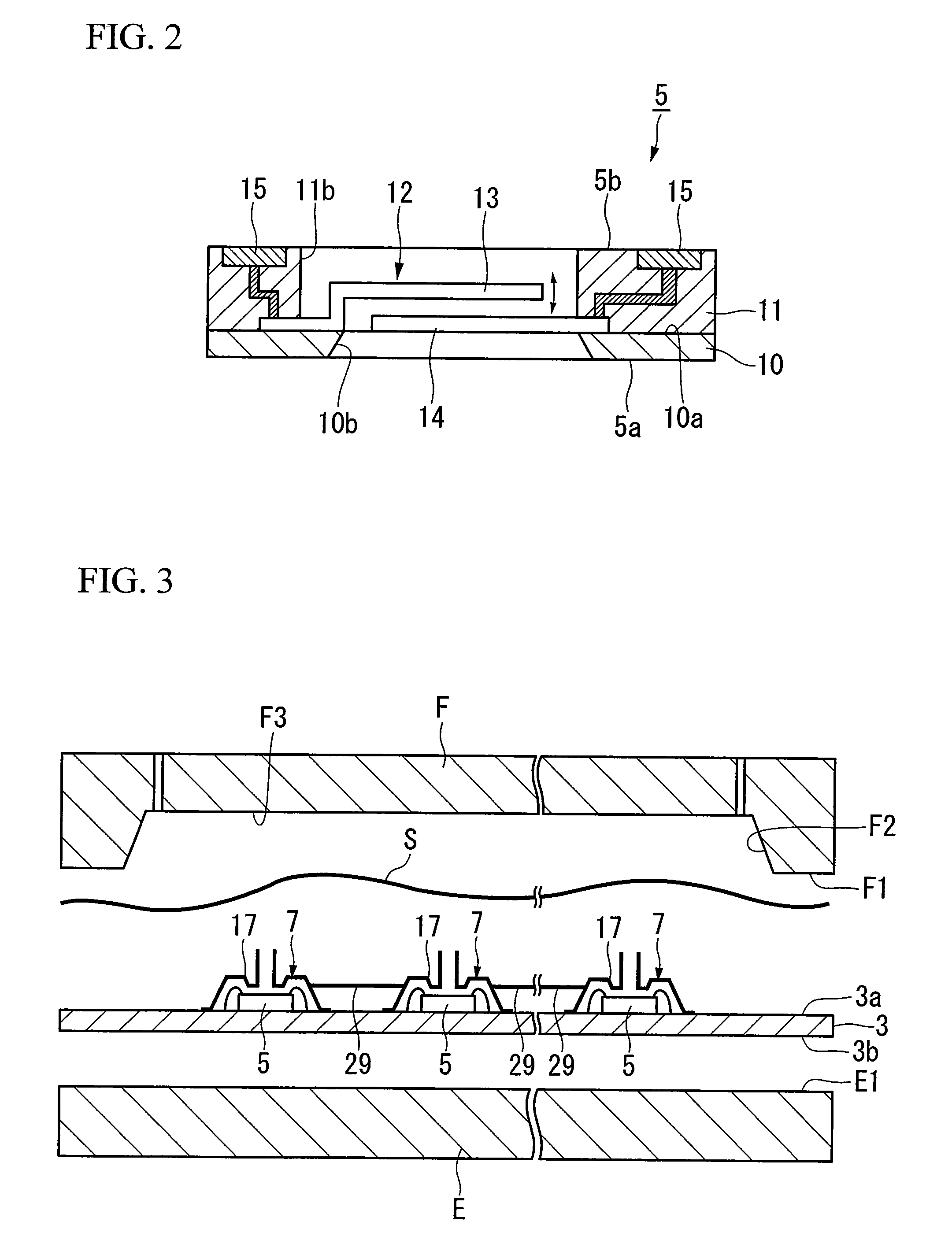

Semiconductor device, semiconductor device manufacturing method and lid frame

InactiveUS20090230487A1Low costImprove production efficiencySemiconductor/solid-state device detailsFluid pressure measurement by electric/magnetic elementsSemiconductor chipEngineering

A semiconductor device includes: a substrate; a semiconductor chip that is fixed to a first surface of the substrate; a chip covering lid body that is provided on the first surface of the substrate so as to cover the semiconductor chip and that forms a hollow first space portion that surrounds the semiconductor chip, and in which there is provided a substantially cylindrical aperture portion that extends to the outer side of the first space portion and has an aperture end at a distal end thereof and that is connected to the first space portion; and a first resin mold portion that forms the first space portion via the chip covering lid body and covers the substrate such that the aperture end is exposed, and that fixes the substrate integrally with the chip covering lid body.

Owner:YAMAHA CORP

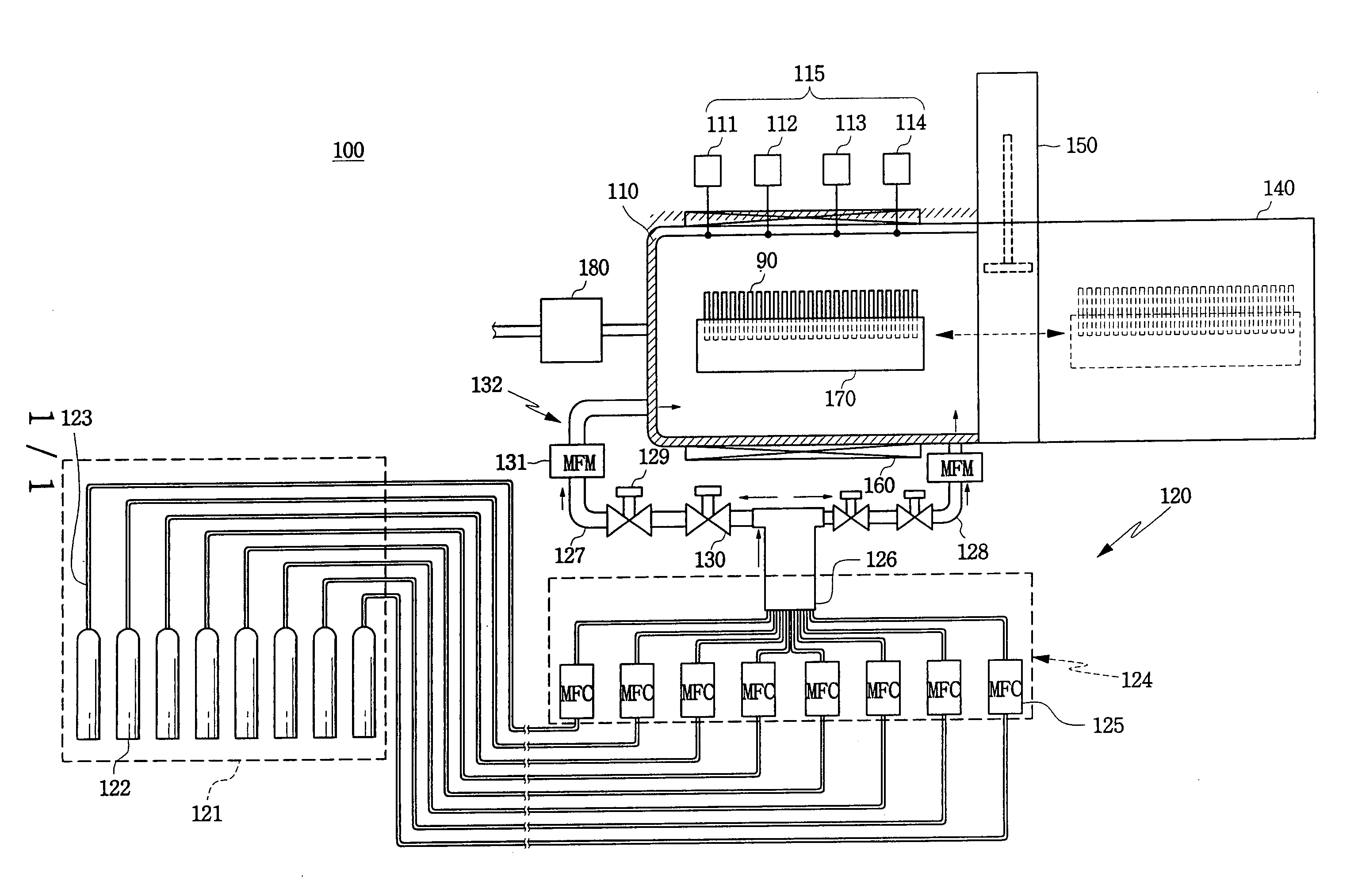

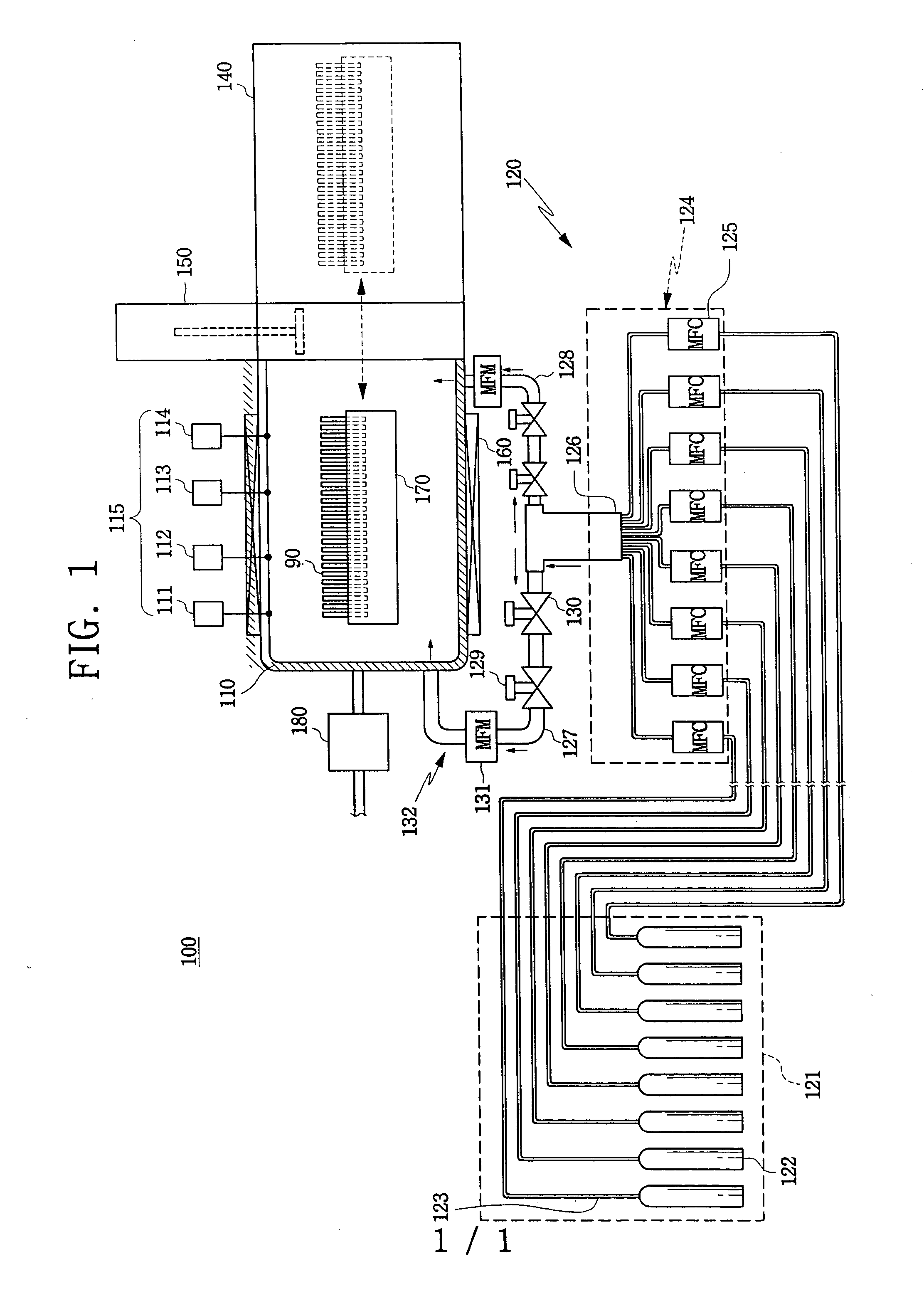

Gas supply unit and semiconductor device manufacturing apparatus using the same

InactiveUS20050016452A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialManufactured apparatus

A semiconductor device manufacturing apparatus is provided. The semiconductor device manufacturing apparatus comprises a furnace having a closed predetermined space for seating a wafer, a loading device located at one side of the furnace to load the wafer on which a prior process may have been performed, a gate valve interposed between the furnace and the loading device to selectively open / close a pathway between the furnace and the loading device, a heater for heating an interior of the furnace, a vacuum pump for maintaining the interior of the furnace with a suitable pressure necessary to the process, a gas reservoir for storing individually various kinds of reaction gases supplied from an exterior of the space, a gas mixing device connected to the gas reservoir to mix the various kinds of reaction gases supplied from the gas reservoir with an even mixing ratio, at least two mixed gases supply pipes connected to the gas mixing device to supply the reaction gases mixed in the gas mixing device to each direction of the furnace, and a mixed gases flow control unit installed at the mixed gases supply pipe to control the flow of the reaction gases supplied through the mixed gases supply pipe.

Owner:SAMSUNG ELECTRONICS CO LTD

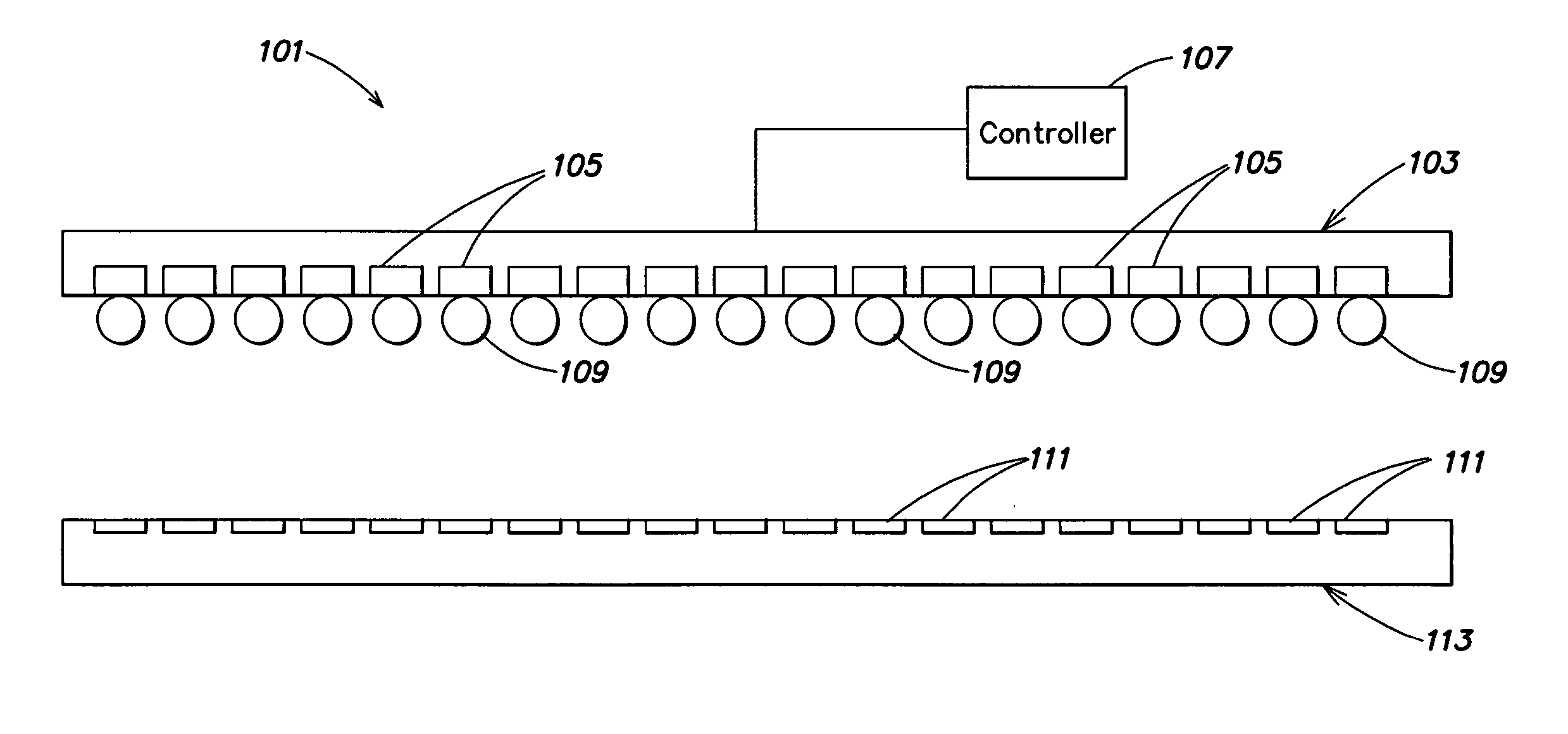

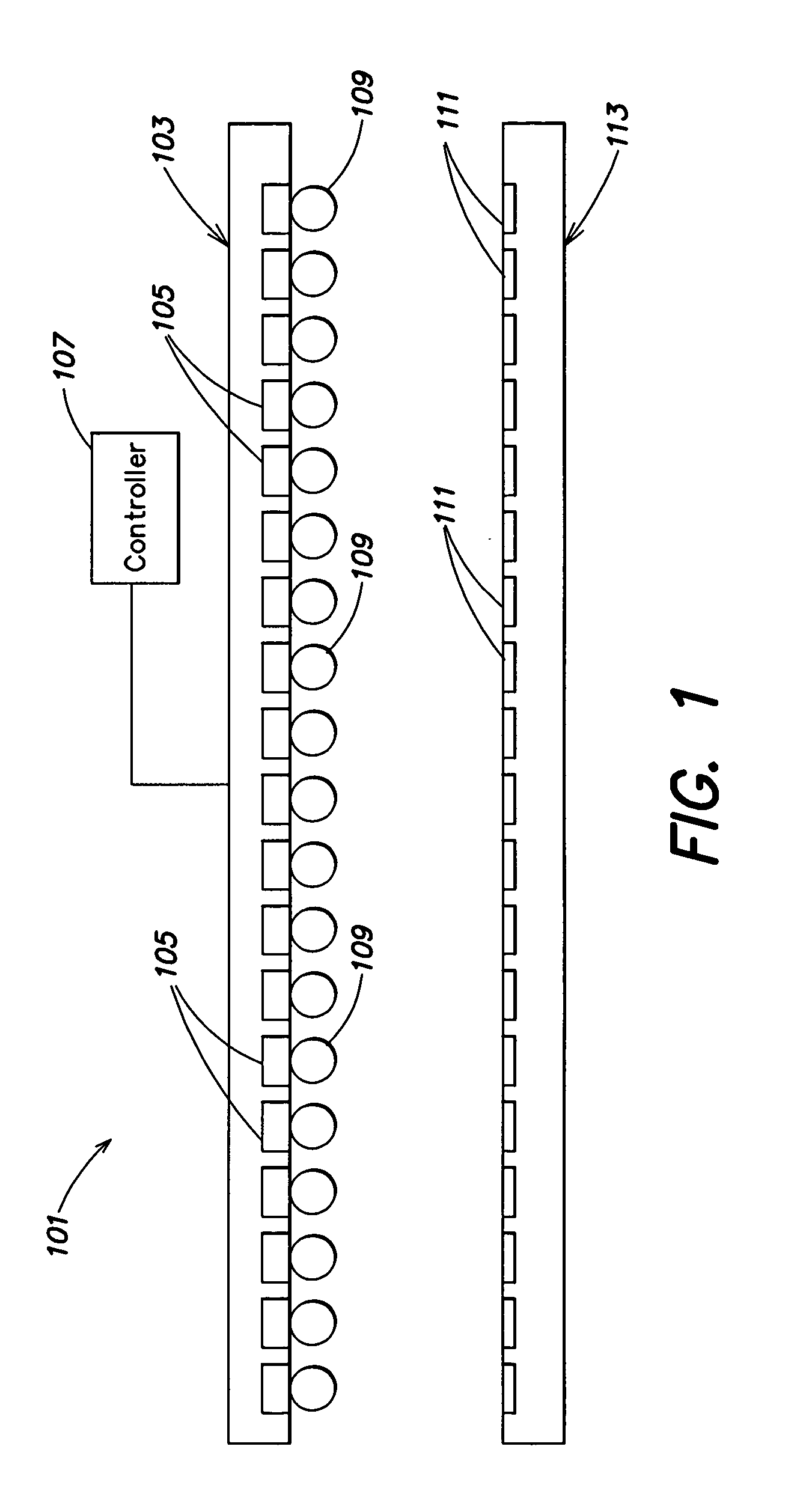

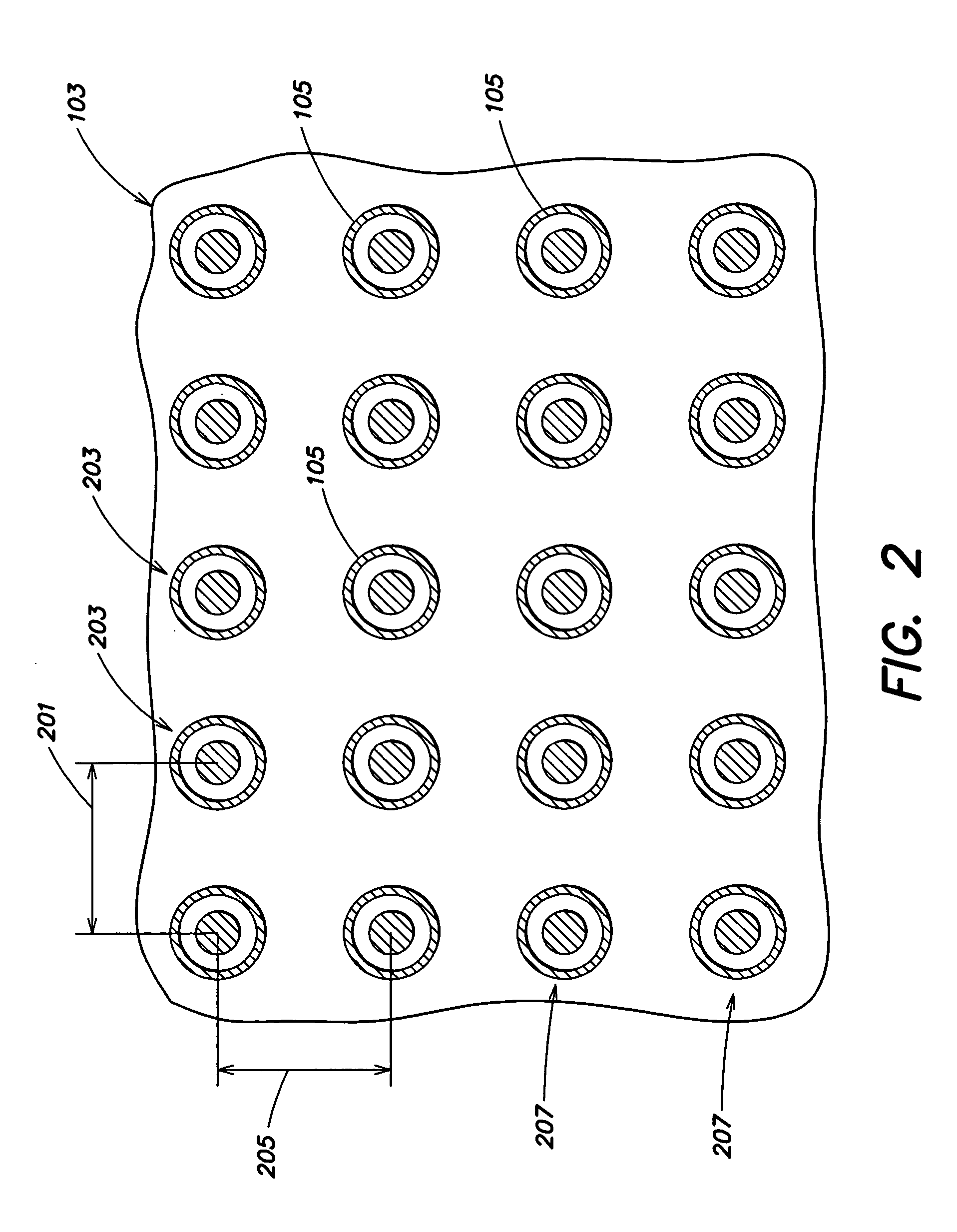

Methods and apparatus for transferring conductive pieces during semiconductor device fabrication

InactiveUS20050232728A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device fabrication

In a first aspect, a programmable transfer device is provided for transferring conductive pieces to electrode pads of a target substrate. The programmable transfer device includes (1) a transfer substrate; and (2) a plurality of individually addressable electrodes formed on the transfer substrate. Each electrode is adapted to selectively attract and hold a conductive piece during transfer of the conductive piece to an electrode pad of a target substrate. Numerous other aspects are provided.

Owner:APPLIED MATERIALS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com