Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3740 results about "Plasma etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Plasma etching is a form of plasma processing used to fabricate integrated circuits. It involves a high-speed stream of glow discharge (plasma) of an appropriate gas mixture being shot (in pulses) at a sample. The plasma source, known as etch species, can be either charged (ions) or neutral (atoms and radicals). During the process, the plasma generates volatile etch products at room temperature from the chemical reactions between the elements of the material etched and the reactive species generated by the plasma. Eventually the atoms of the shot element embed themselves at or just below the surface of the target, thus modifying the physical properties of the target.

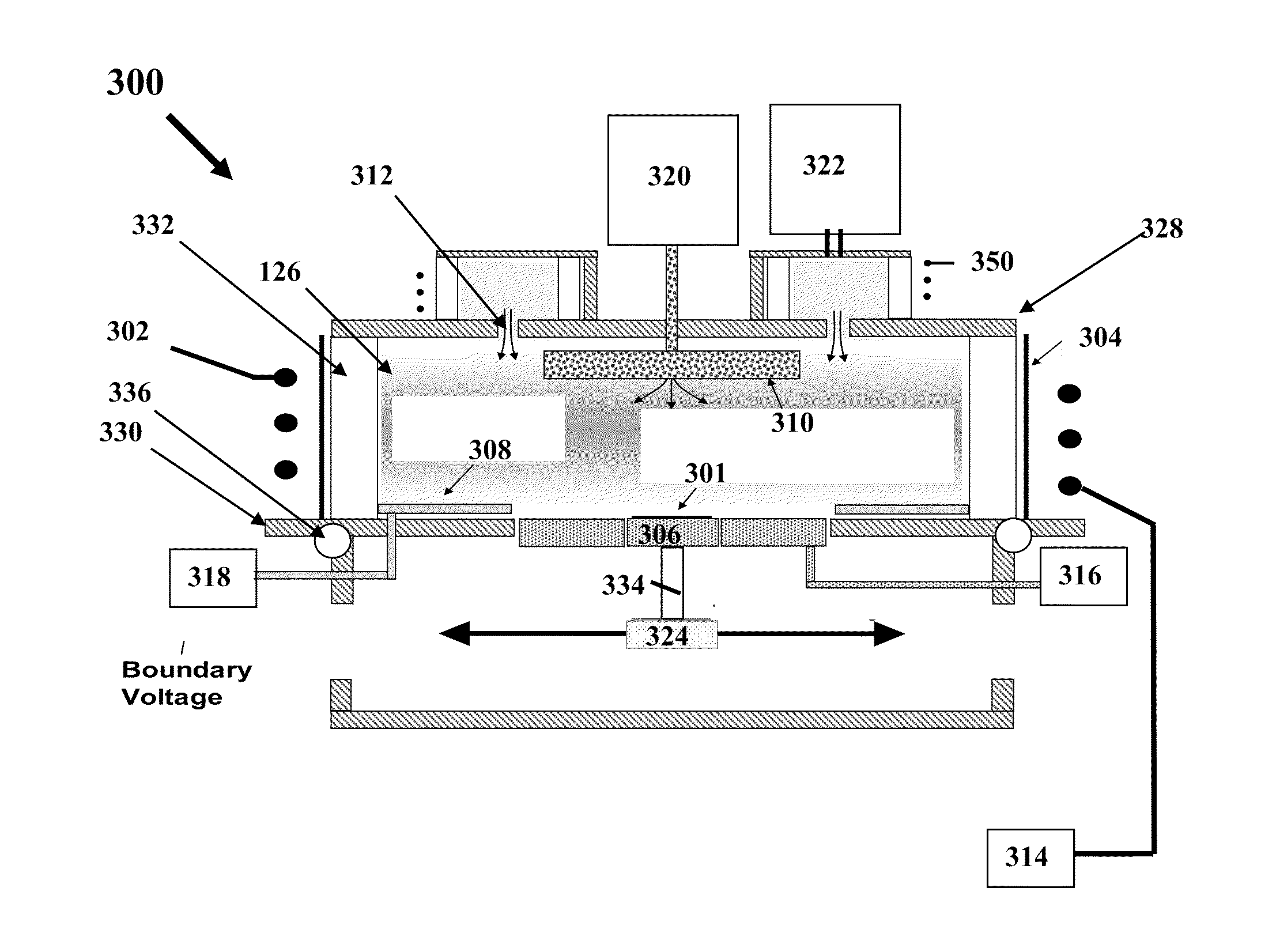

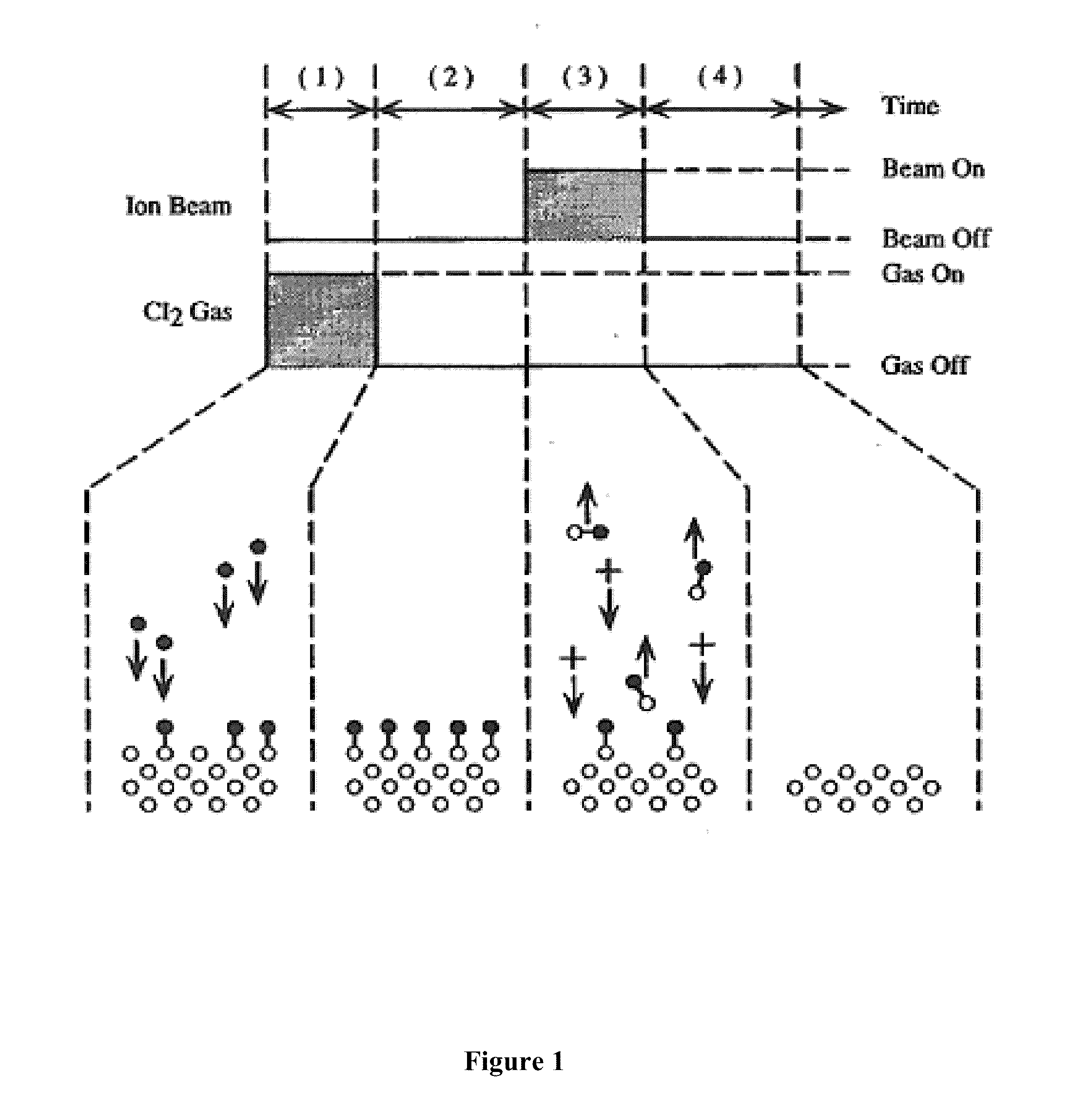

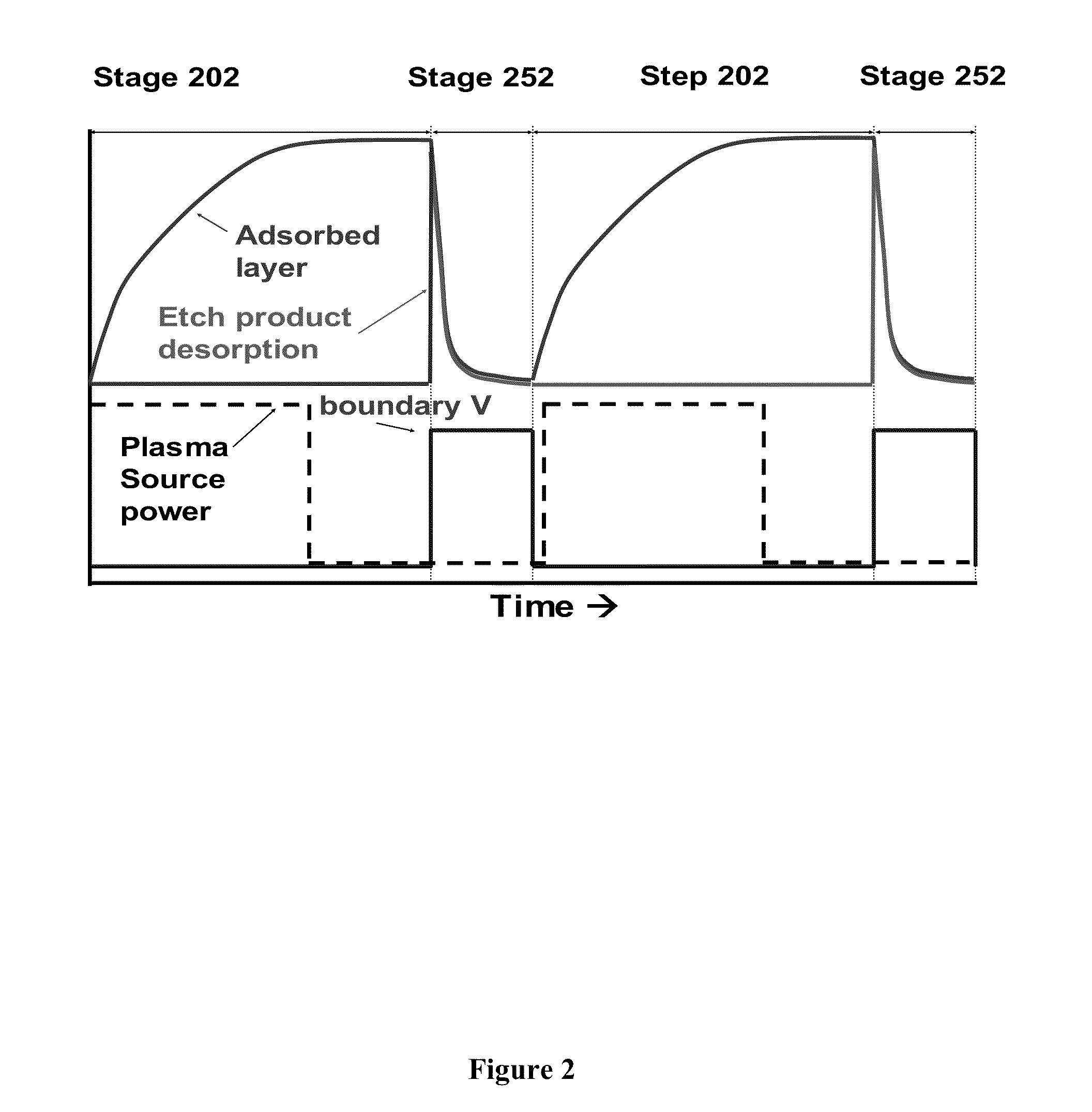

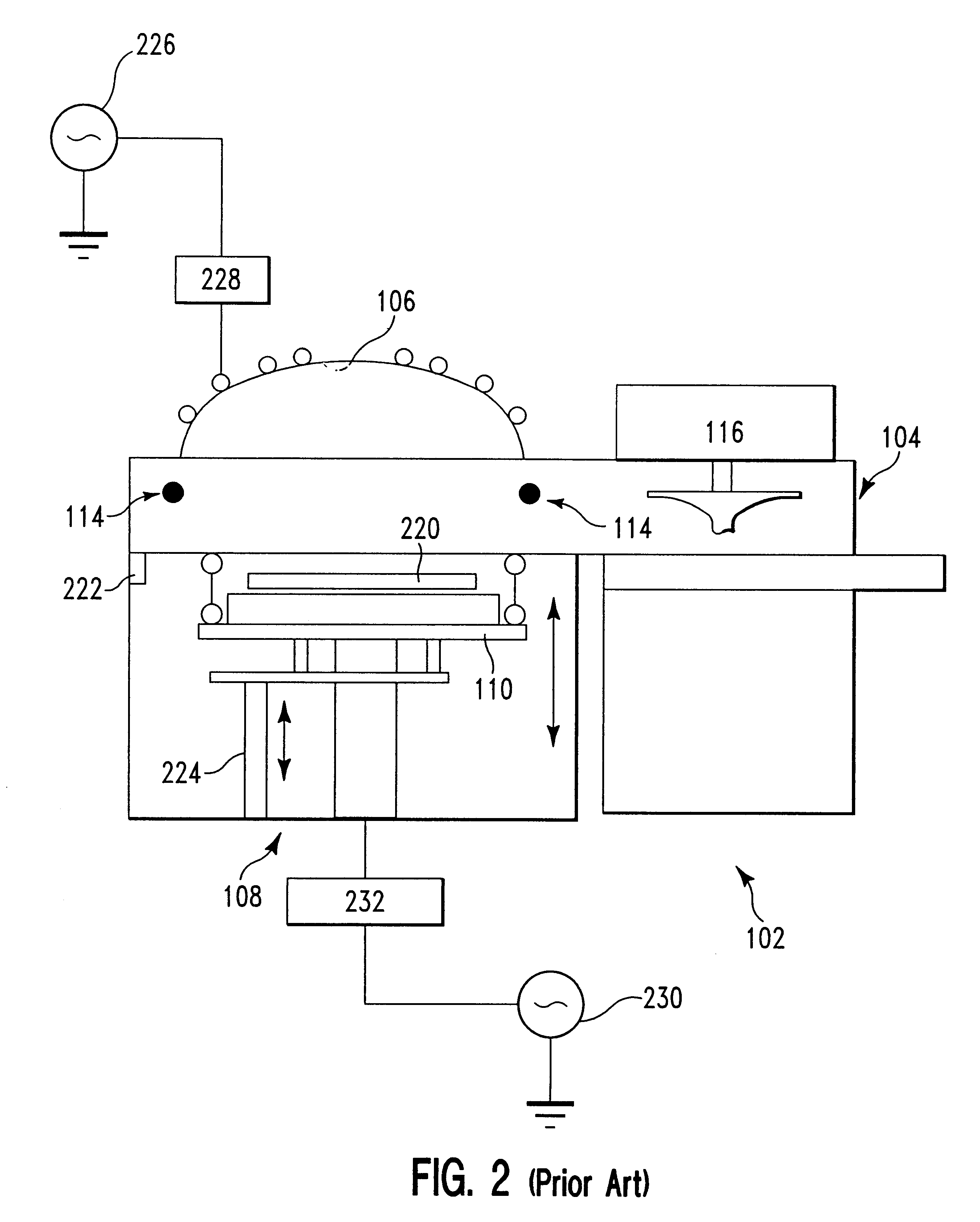

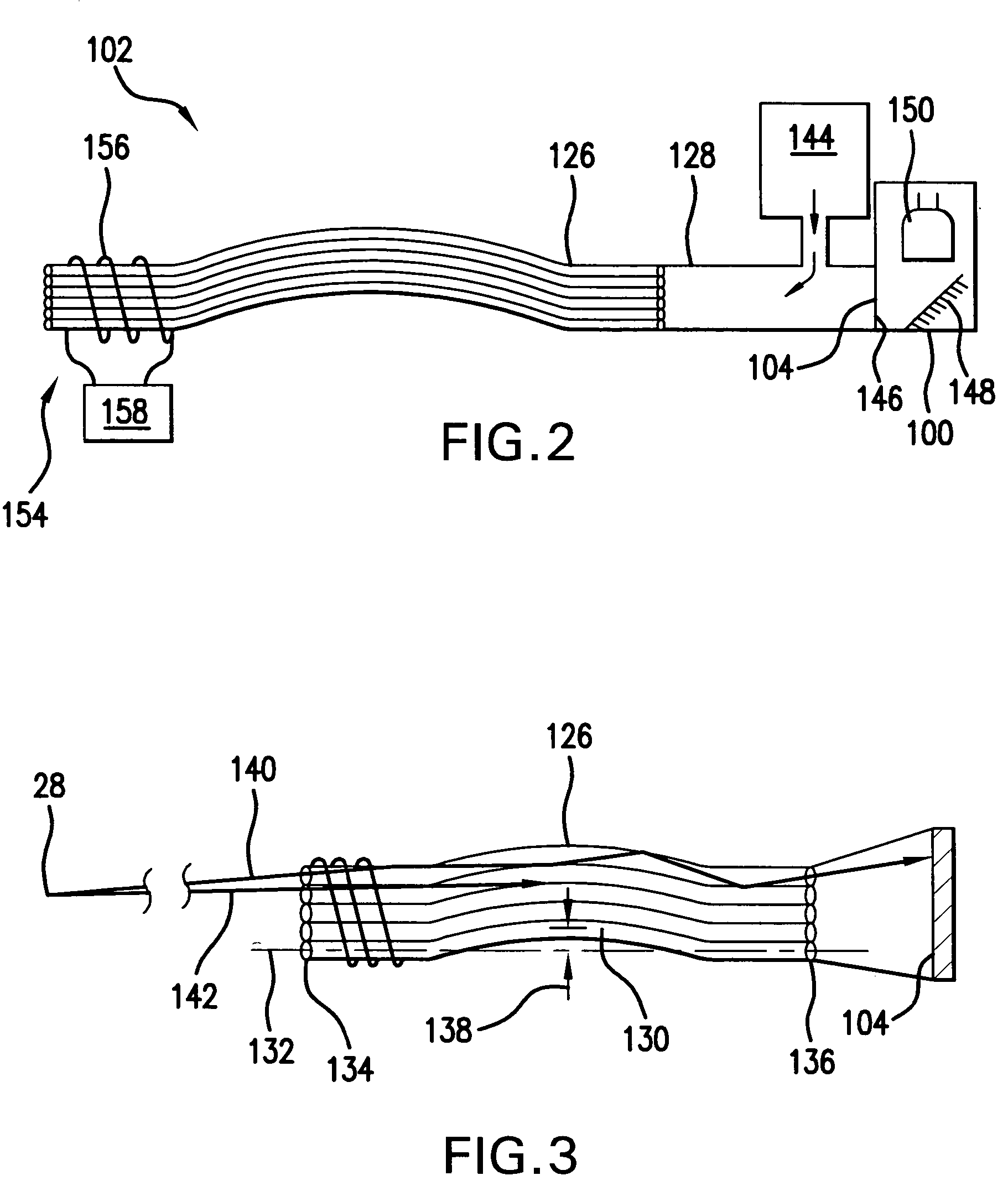

Atomic layer etching with pulsed plasmas

A system and method for rapid atomic layer etching (ALET) including a pulsed plasma source, with a spiral coil electrode, a cooled Faraday shield, a counter electrode disposed at the top of the tube, a gas inlet and a reaction chamber including a substrate support and a boundary electrode. The method includes positioning an etchable substrate in a plasma etching chamber, forming a product layer on the surface of the substrate, removing a portion of the product layer by pulsing a plasma source, then repeating the steps of forming a product layer and removing a portion of the product layer to form an etched substrate.

Owner:UNIV HOUSTON SYST

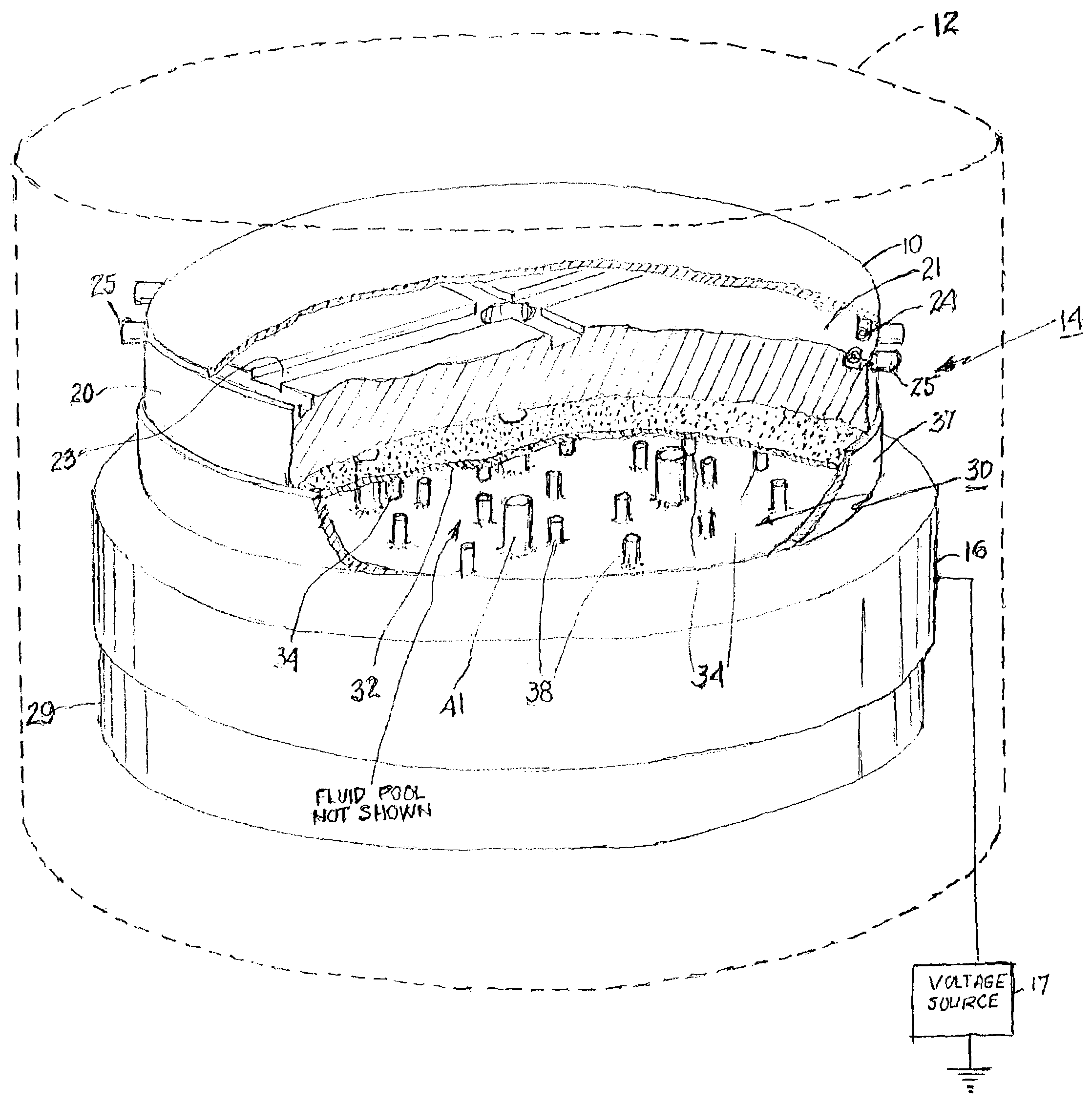

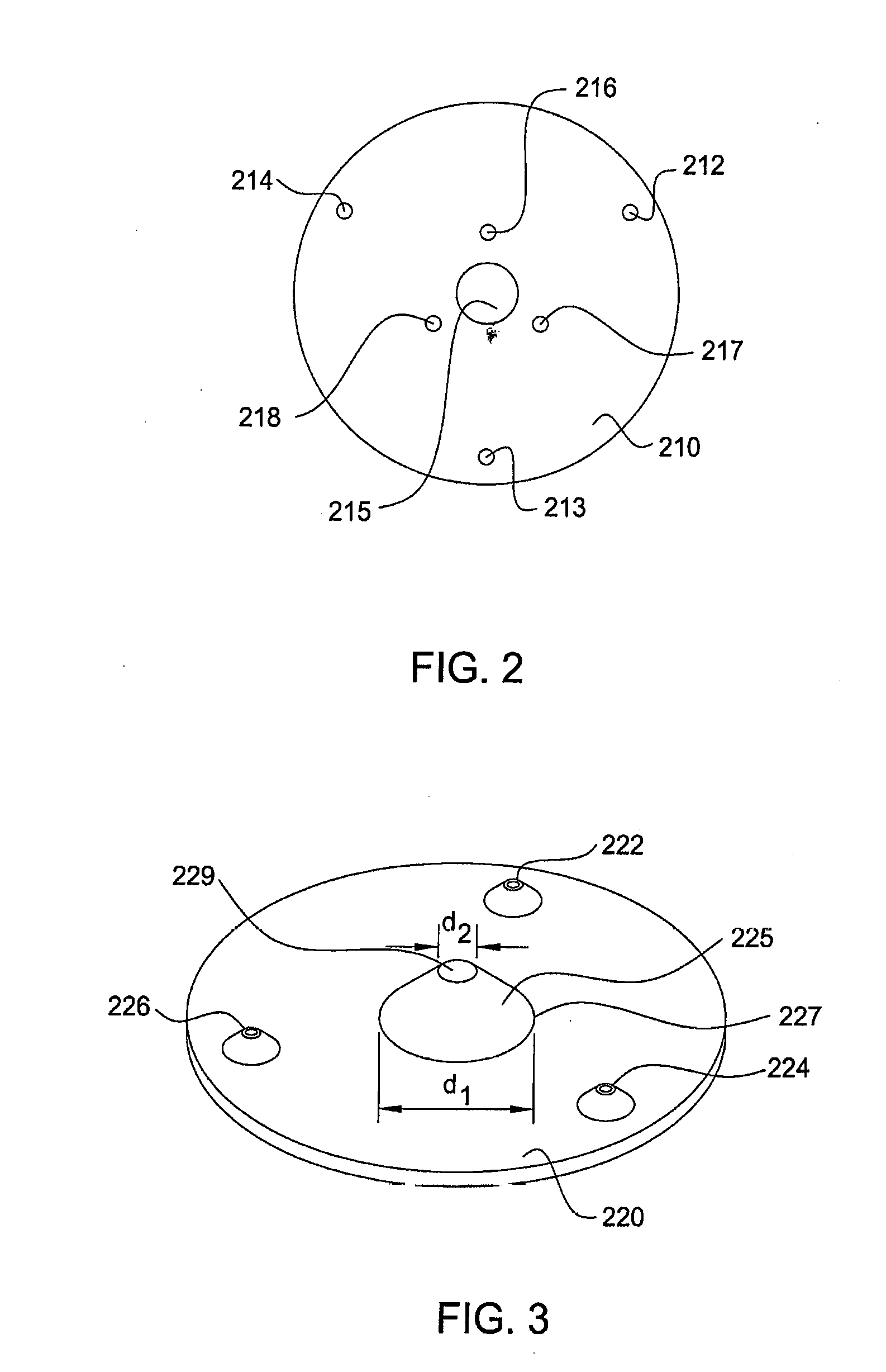

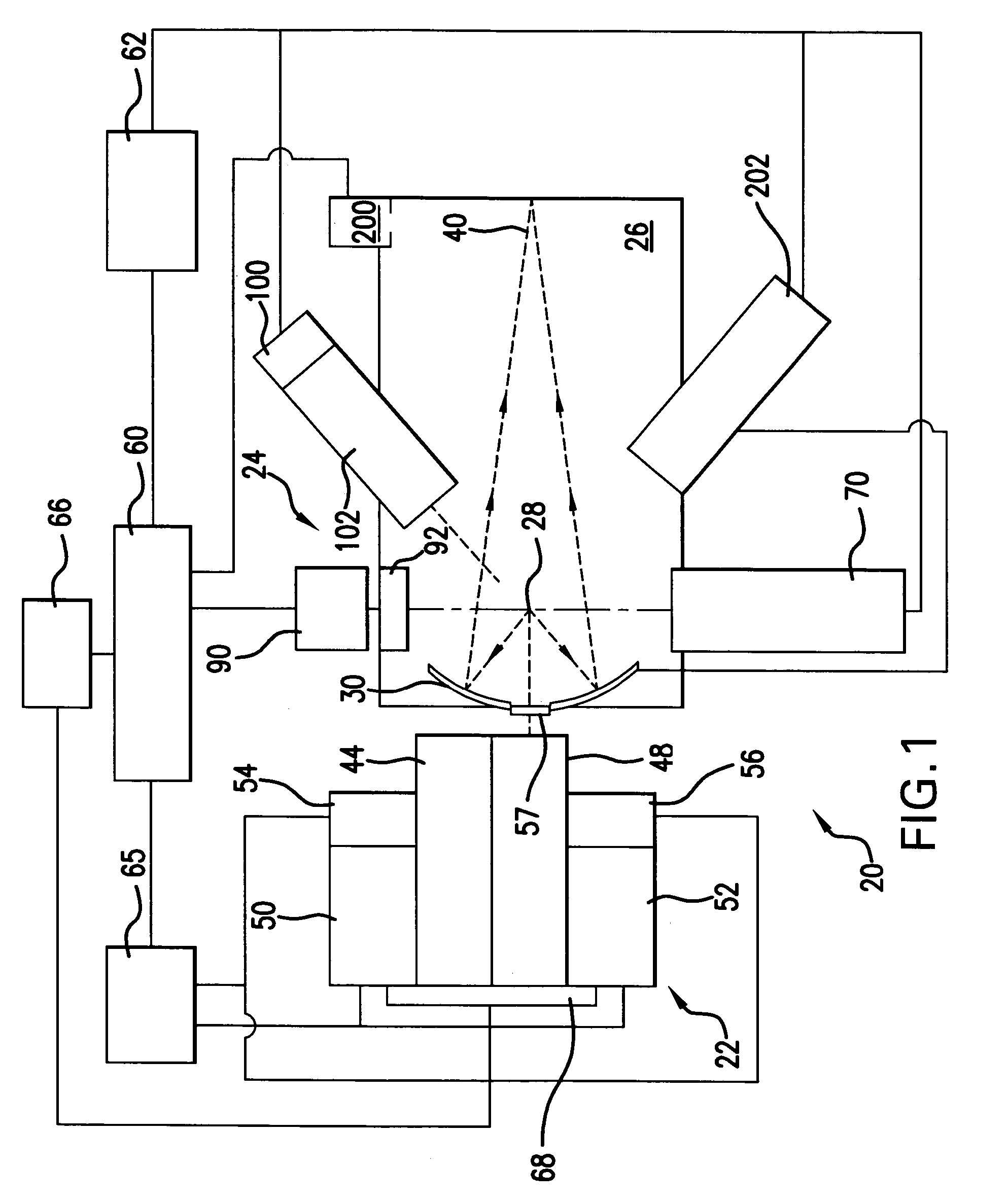

Lateral temperature equalizing system for large area surfaces during processing

ActiveUS7195693B2Rapid temperature stabilizationLittle changeElectric discharge tubesSemiconductor/solid-state device manufacturingHigh energyShortest distance

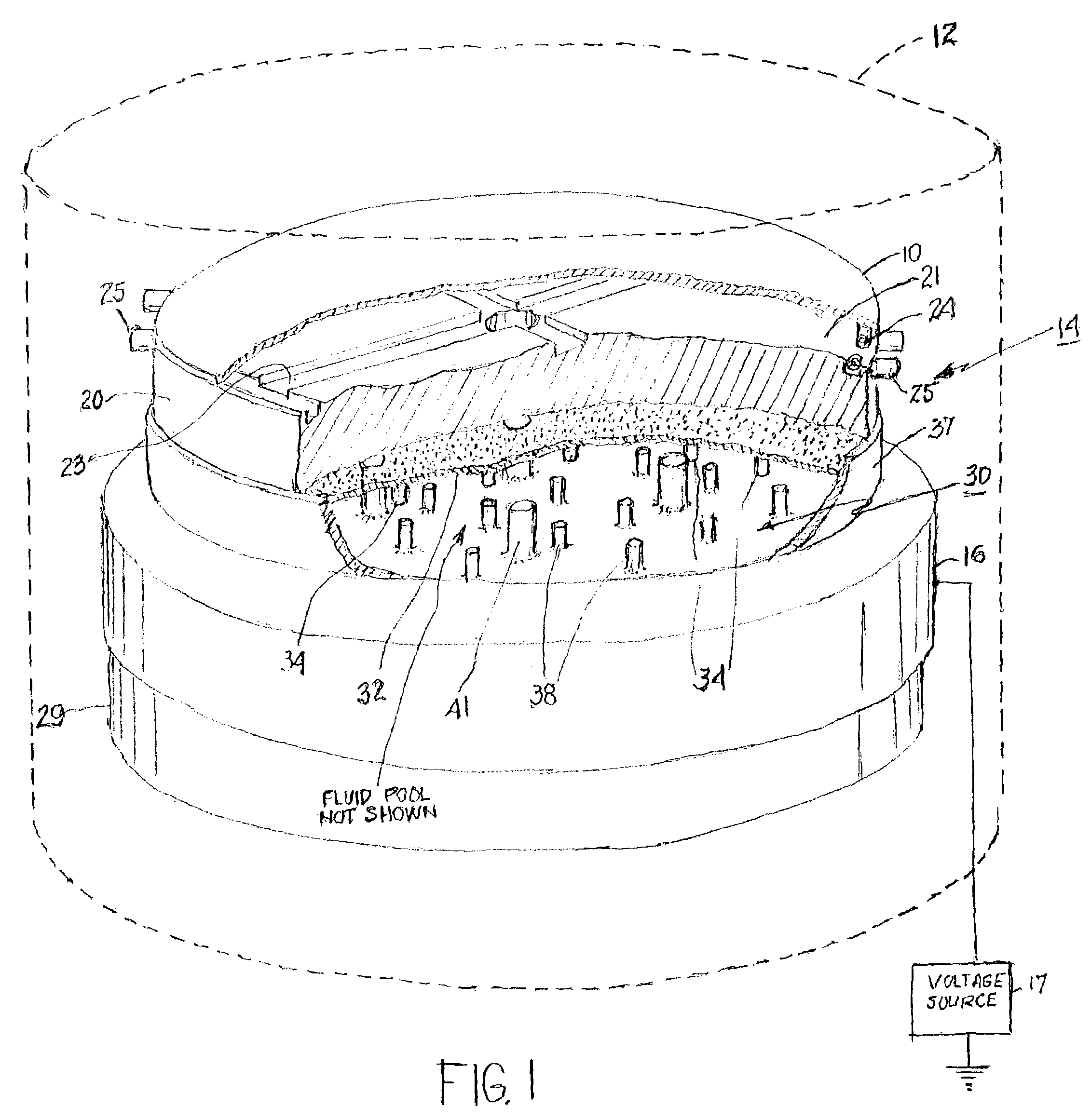

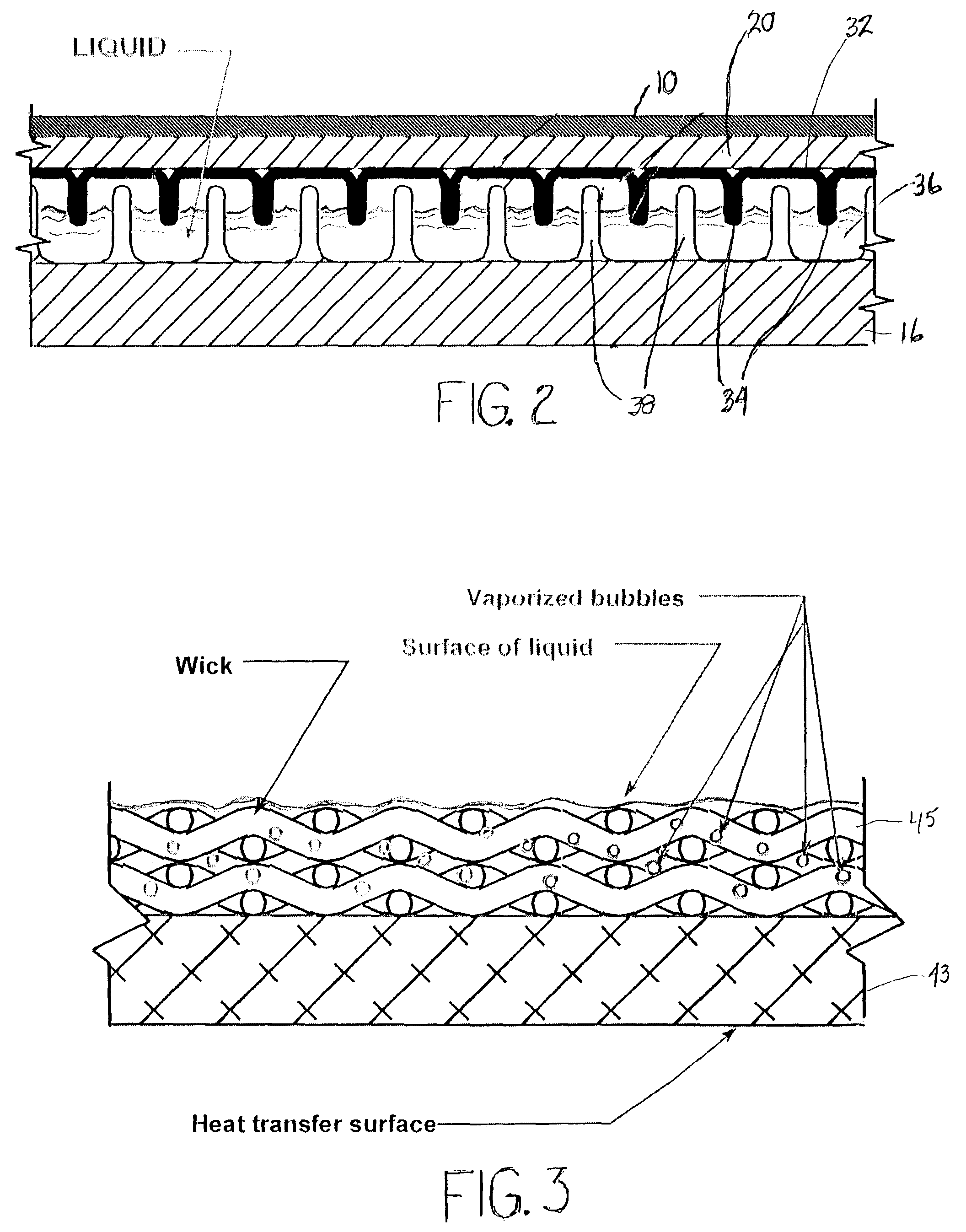

In many processes used in fabricating semiconductors the wafer is seated on the top surface of a pedestal and heated in a high energy process step, such as plasma etching. The pedestal, chuck or platen may be cooling but the wafer gradually heats until the process can no longer continue. Where large, e.g. 300 mm diameter, wafers are being processed the temperature level across the wafer is difficult to maintain substantially constant. In this system and method the lateral temperature distribution is equalized by a heat sink structure in a chamber immediately under the wafer support on top of the pedestal. A number of spatially distributed wicking posts extend downwardly from a layer of wicking material across the top of the chamber, into a pool of a vaporizable liquid. At hot spots, vaporized liquid is generated and transported to adjacent condensation posts extending up from the liquid. The system thus passively extracts heat to equalize temperatures while recirculating liquid and assuring adequate supply. The free volume above and within the liquid, and the short distances between posts, assure adequate heat transfer rates.

Owner:BE AEROSPACE INCORPORATED

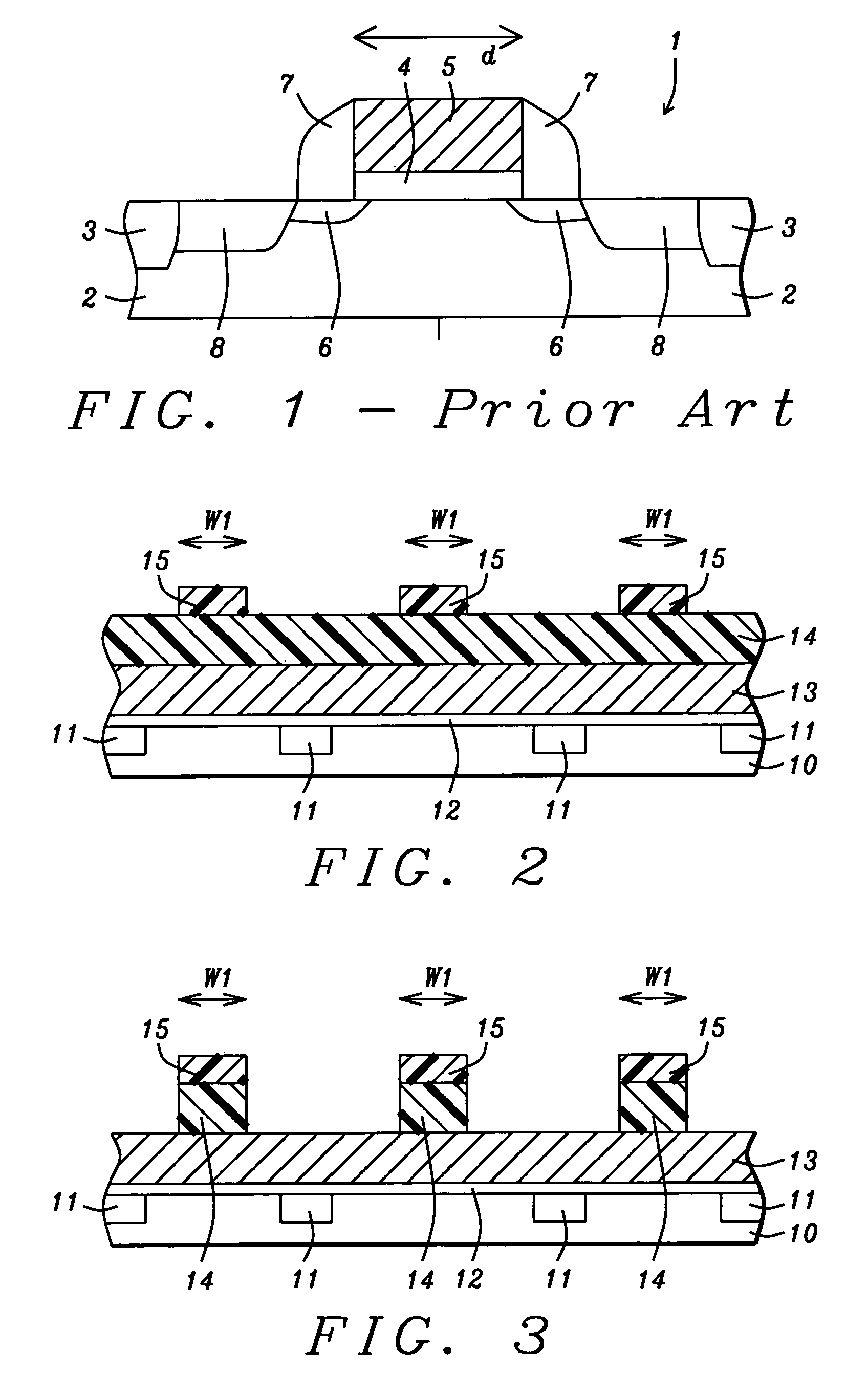

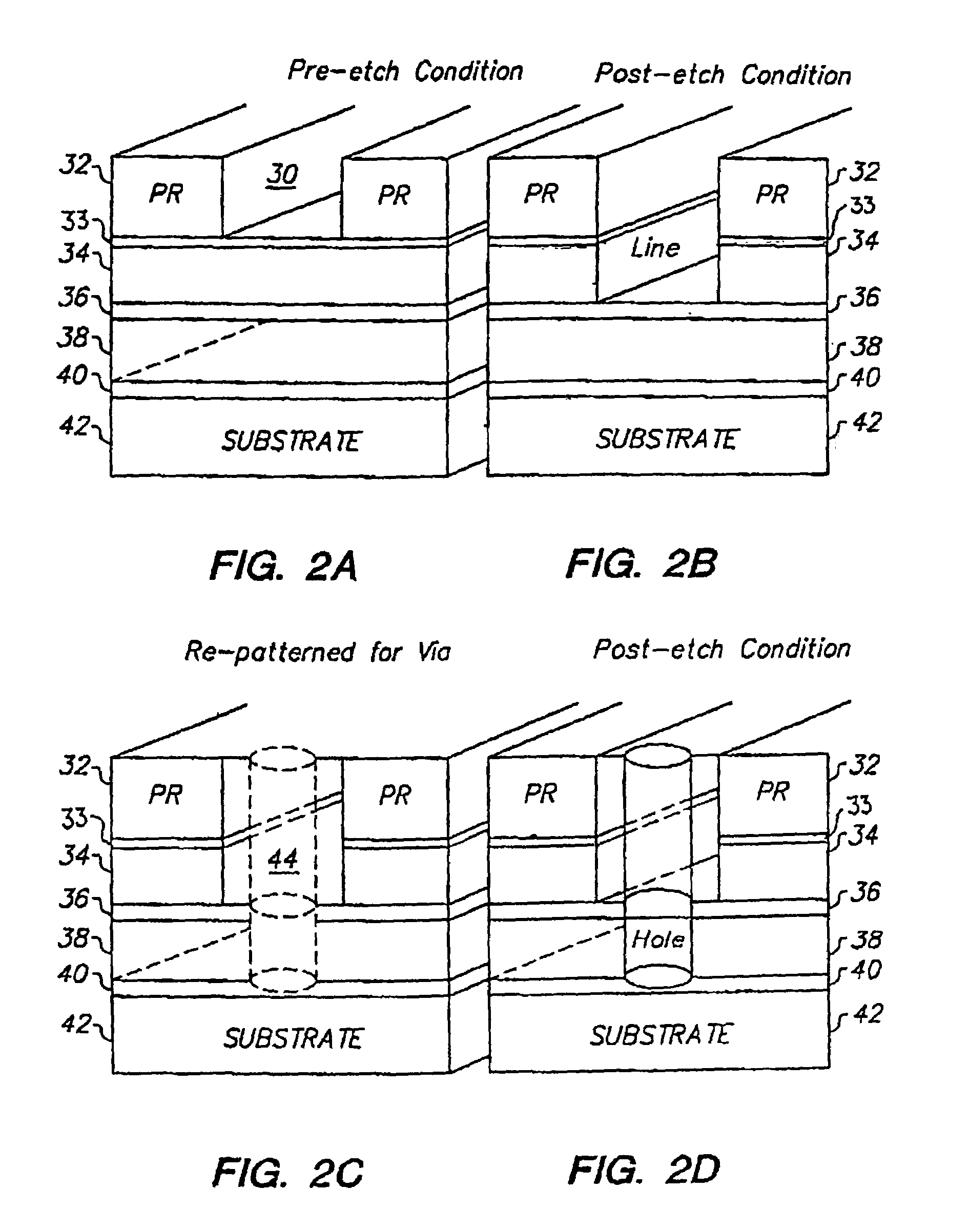

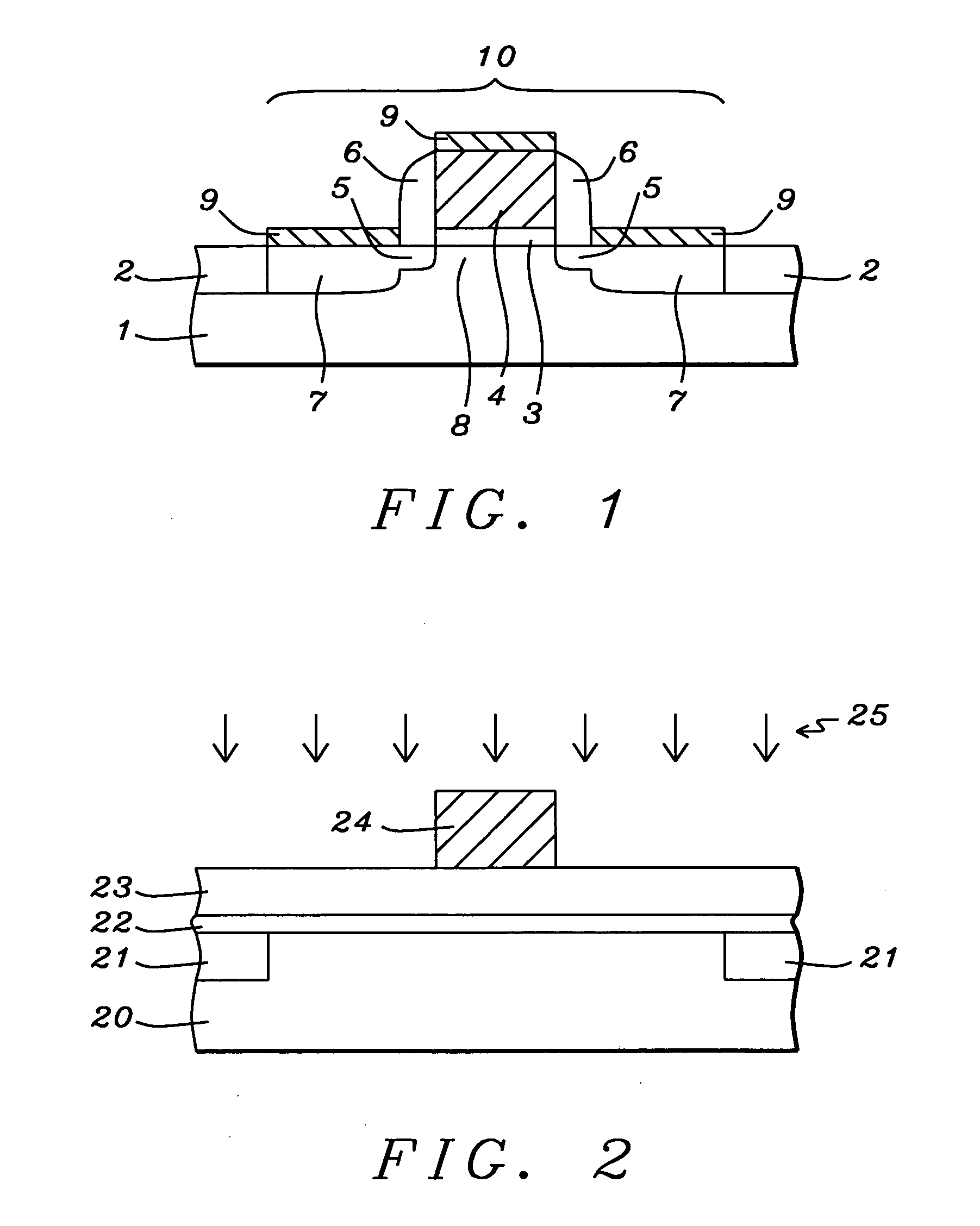

Gate linewidth tailoring and critical dimension control for sub-100 nm devices using plasma etching

InactiveUS6864041B2Tight tolerance variationMinimal variationVacuum gauge using ionisation effectsDecorative surface effectsImage resolutionLine width

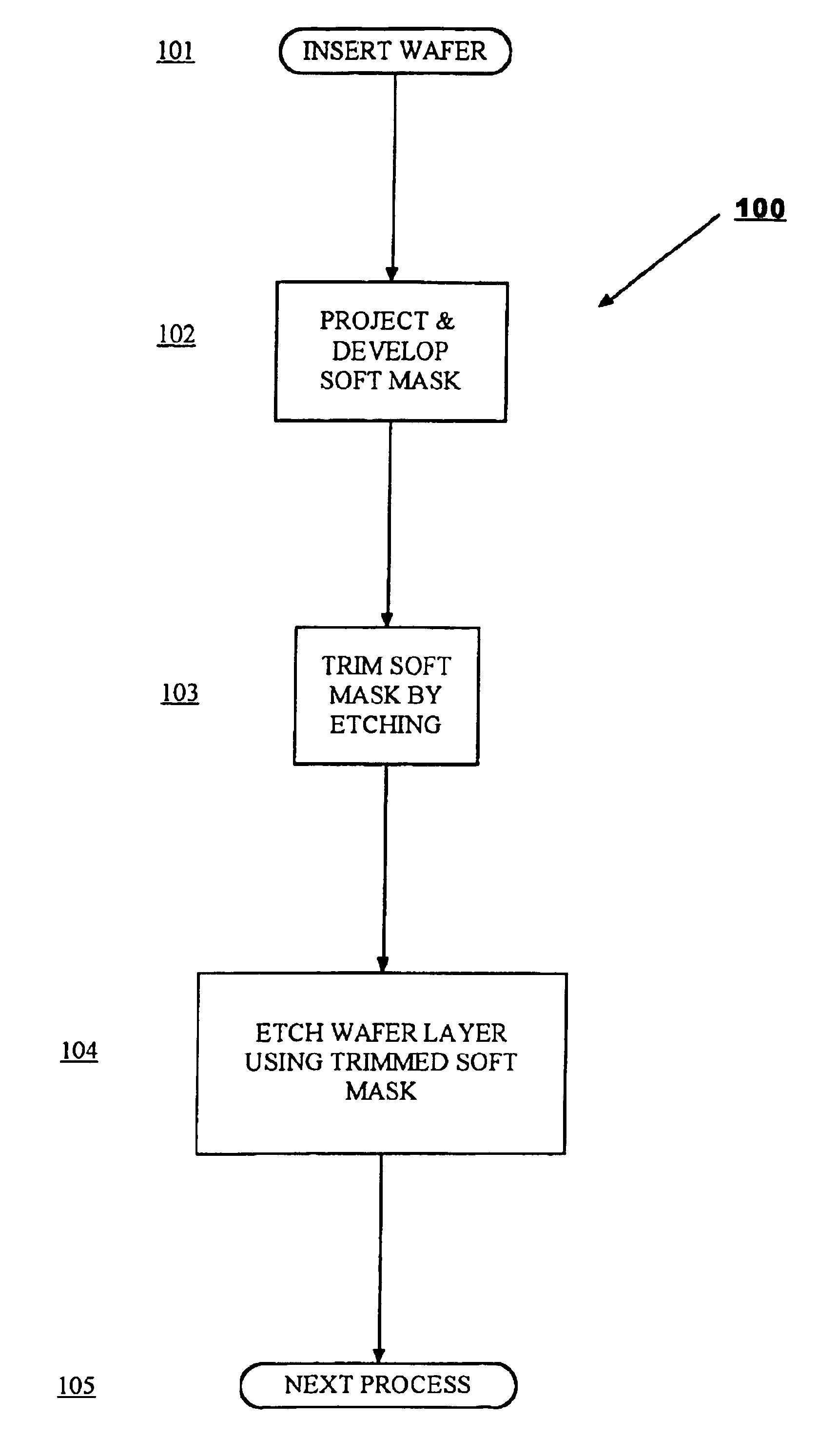

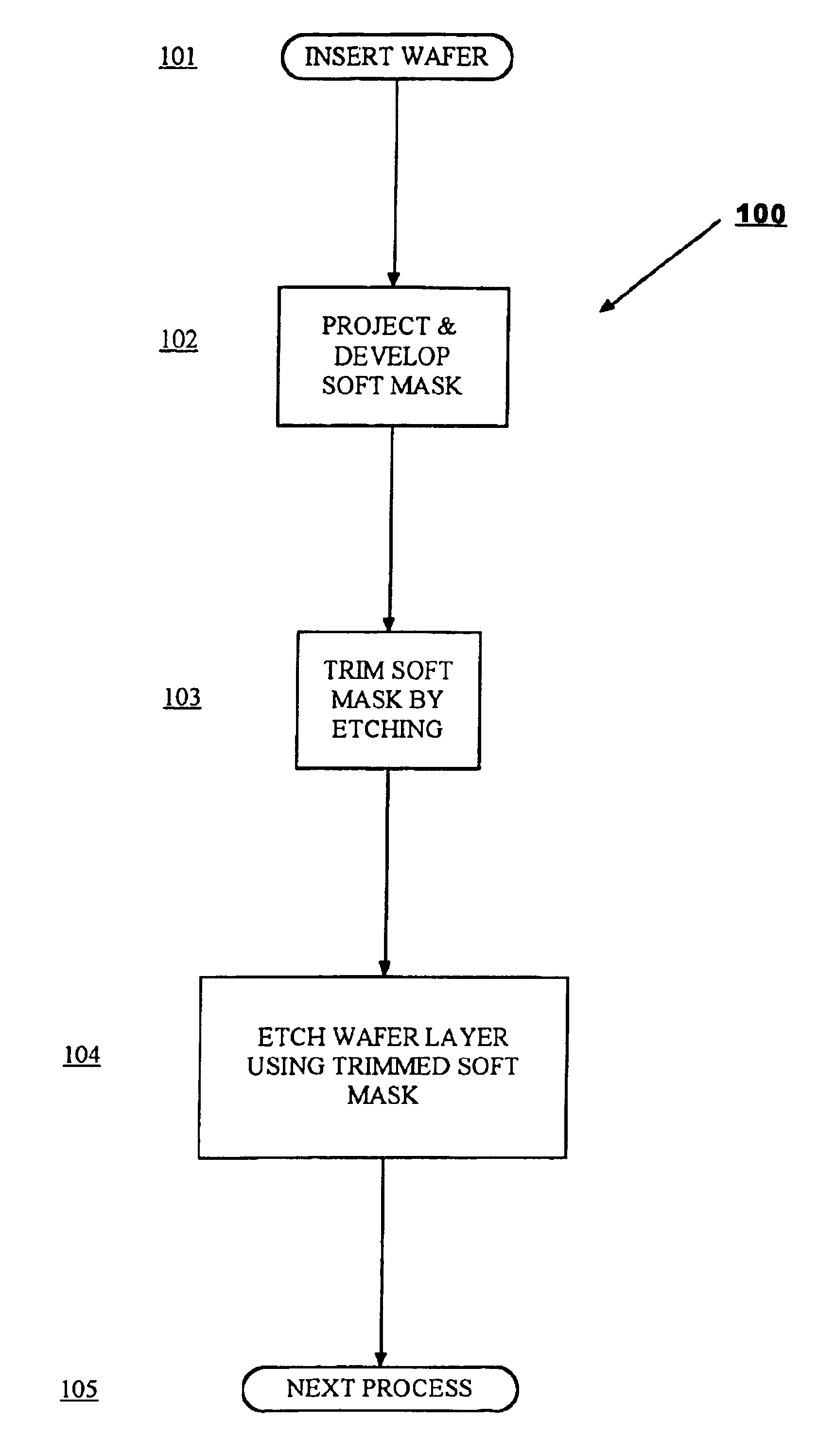

A method of fabricating an electronic chip on a wafer in which a first mask at a predetermined lower resolution is developed on the wafer and then etched under a first set of conditions for a predetermined period to achieve a mask that is below the resolution limit of current lithography. The etched mask is then used as a hard mask for etching material on a lower layer.

Owner:INT BUSINESS MASCH CORP

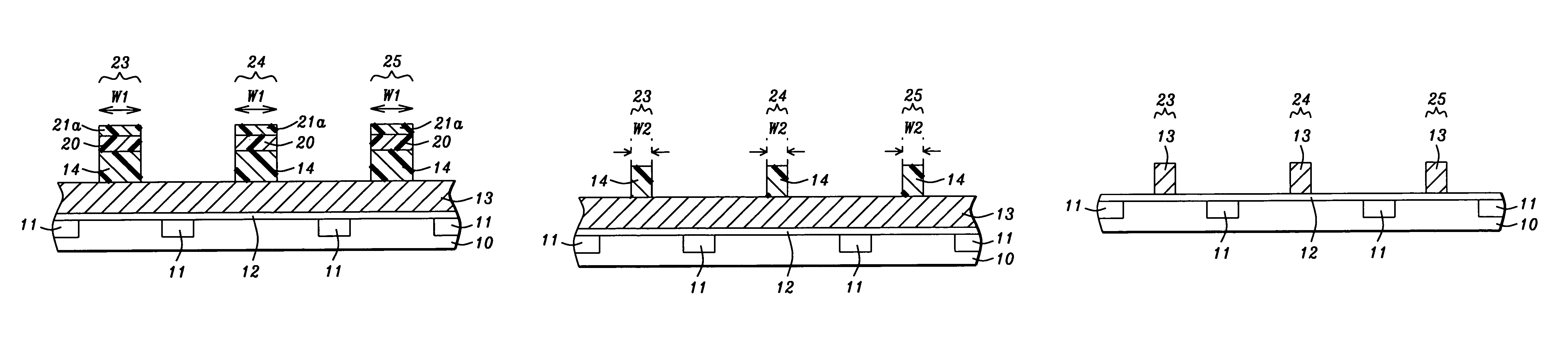

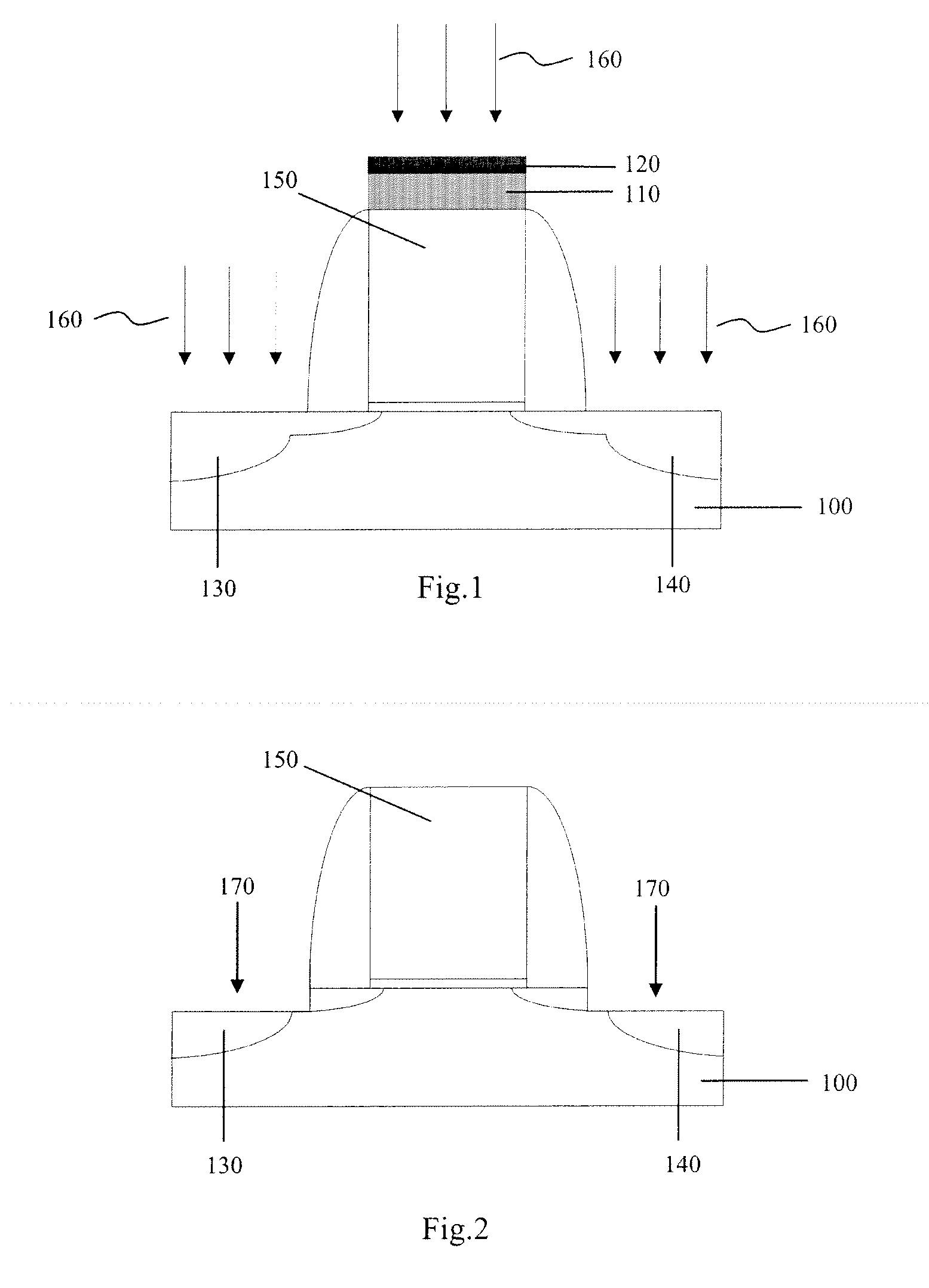

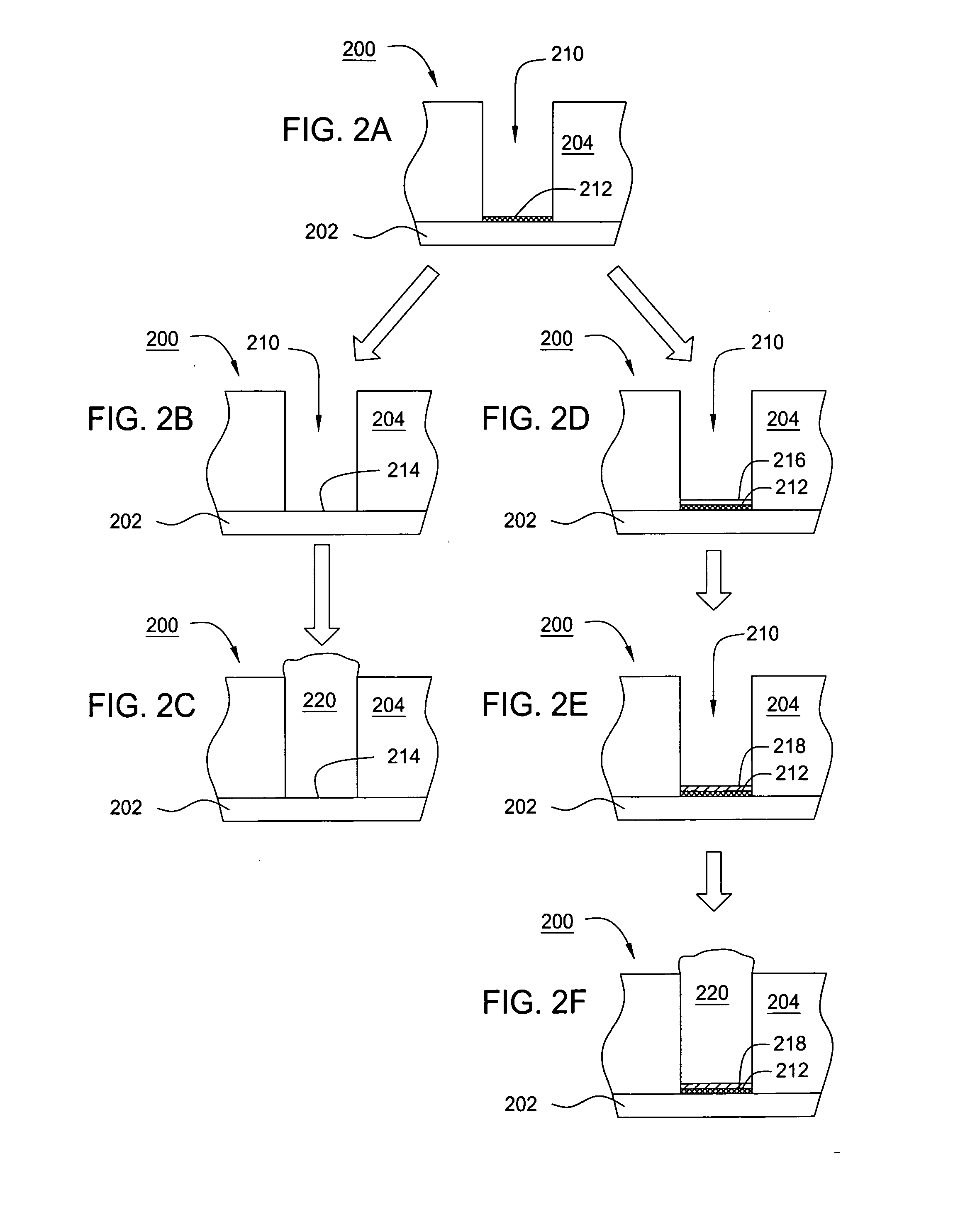

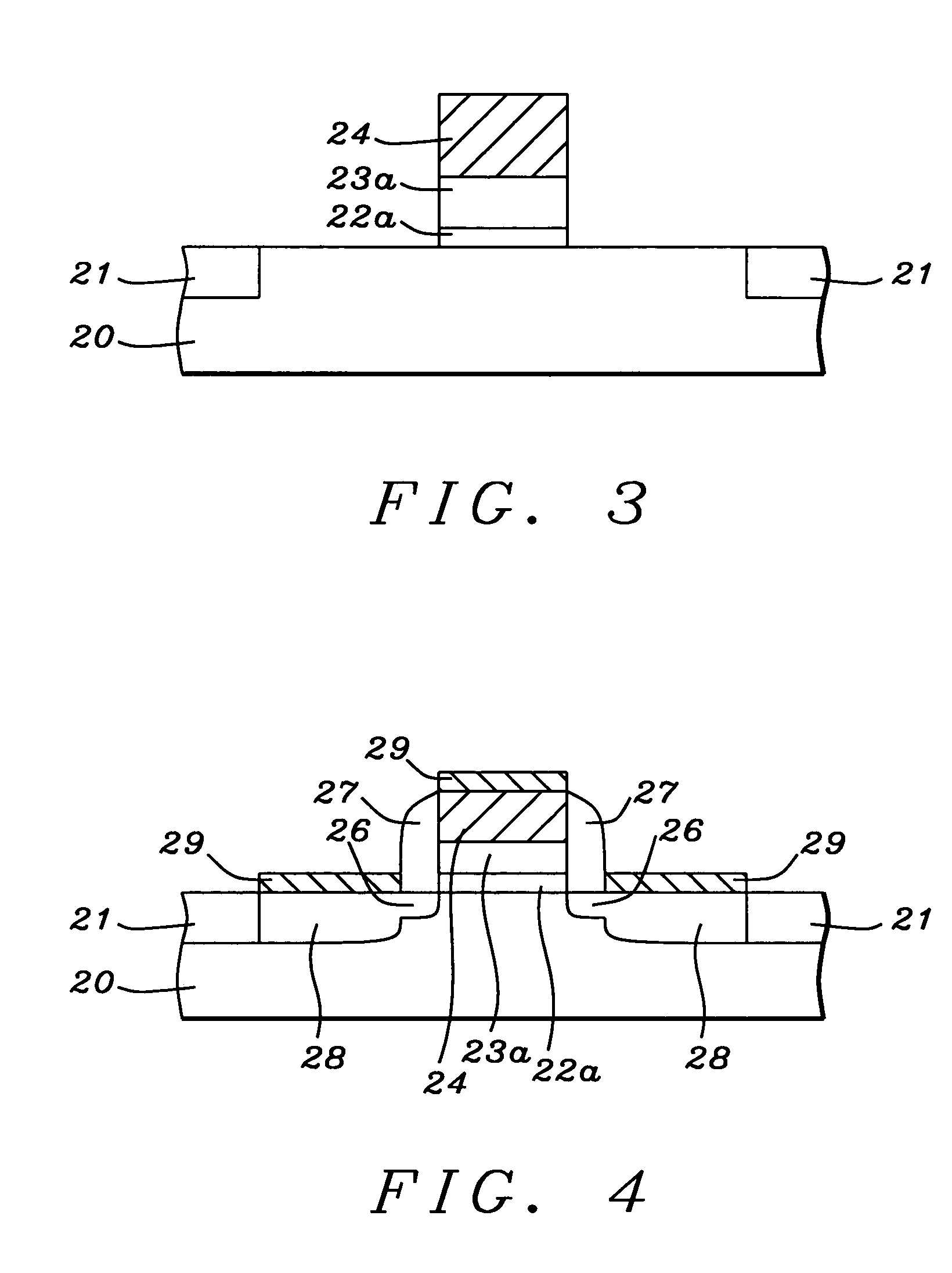

Method of trimming technology

ActiveUS7354847B2Easy to controlAvoid insufficient thicknessSolid-state devicesSemiconductor/solid-state device manufacturingResistMOSFET

A process for trimming a photoresist layer during the fabrication of a gate electrode in a MOSFET is described. A bilayer stack with a top photoresist layer on a thicker organic underlayer is patternwise exposed with 193 nm or 157 nm radiation to form a feature having a width w1 in the top layer. A pattern transfer through the underlayer is performed with an anisotropic etch based on H2 / N2 and SO2 chemistry. The feature formed in the bilayer stack is trimmed by 10 nm or more to a width w2 by a HBr / O2 / Cl2 plasma etch. The pattern transfer through an underlying gate layer is performed with a third etch based on HBr / O2 / Cl2 chemistry. The underlayer is stripped by an O2 ashing with no damage to the gate electrode. Excellent profile control of the gate electrode is achieved and a larger (w1−w2) is possible than in prior art methods.

Owner:TAIWAN SEMICON MFG CO LTD

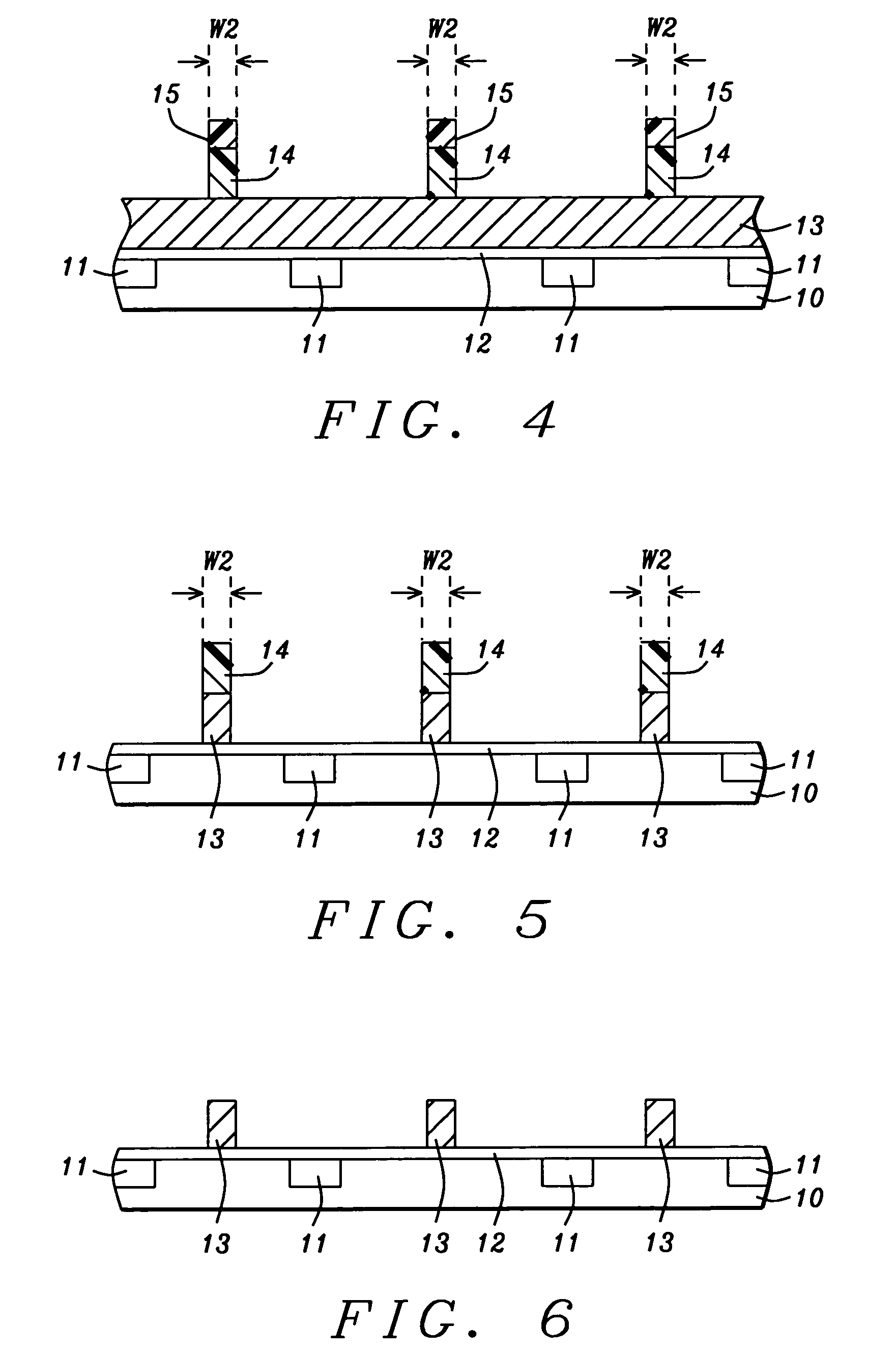

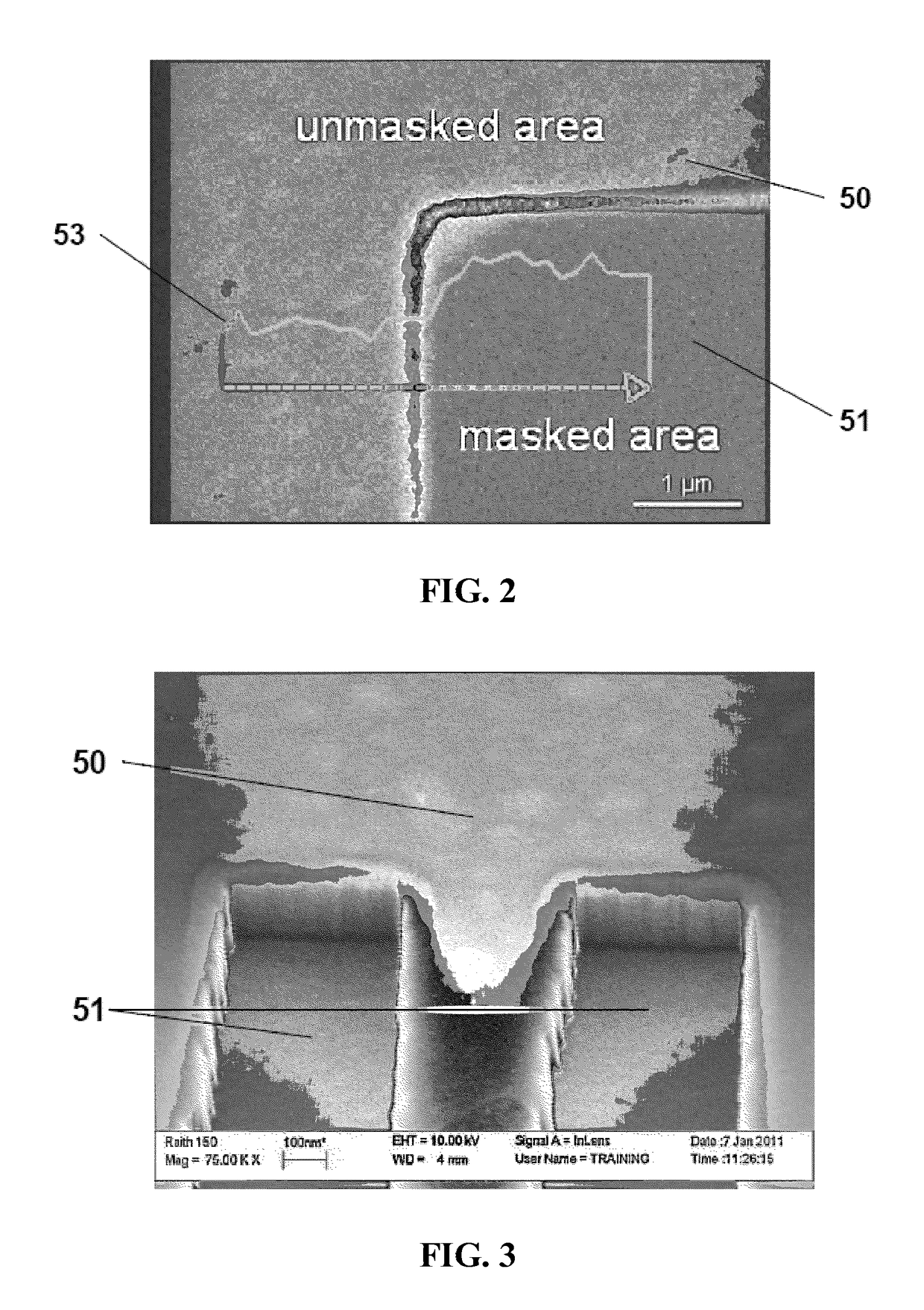

Sequential Infiltration Synthesis for Enhancing Multiple-Patterning Lithography

ActiveUS20130256265A1Reduce in quantityImprove throughputDecorative surface effectsPhotomechanical apparatusPhotoresistMultiple patterning lithography

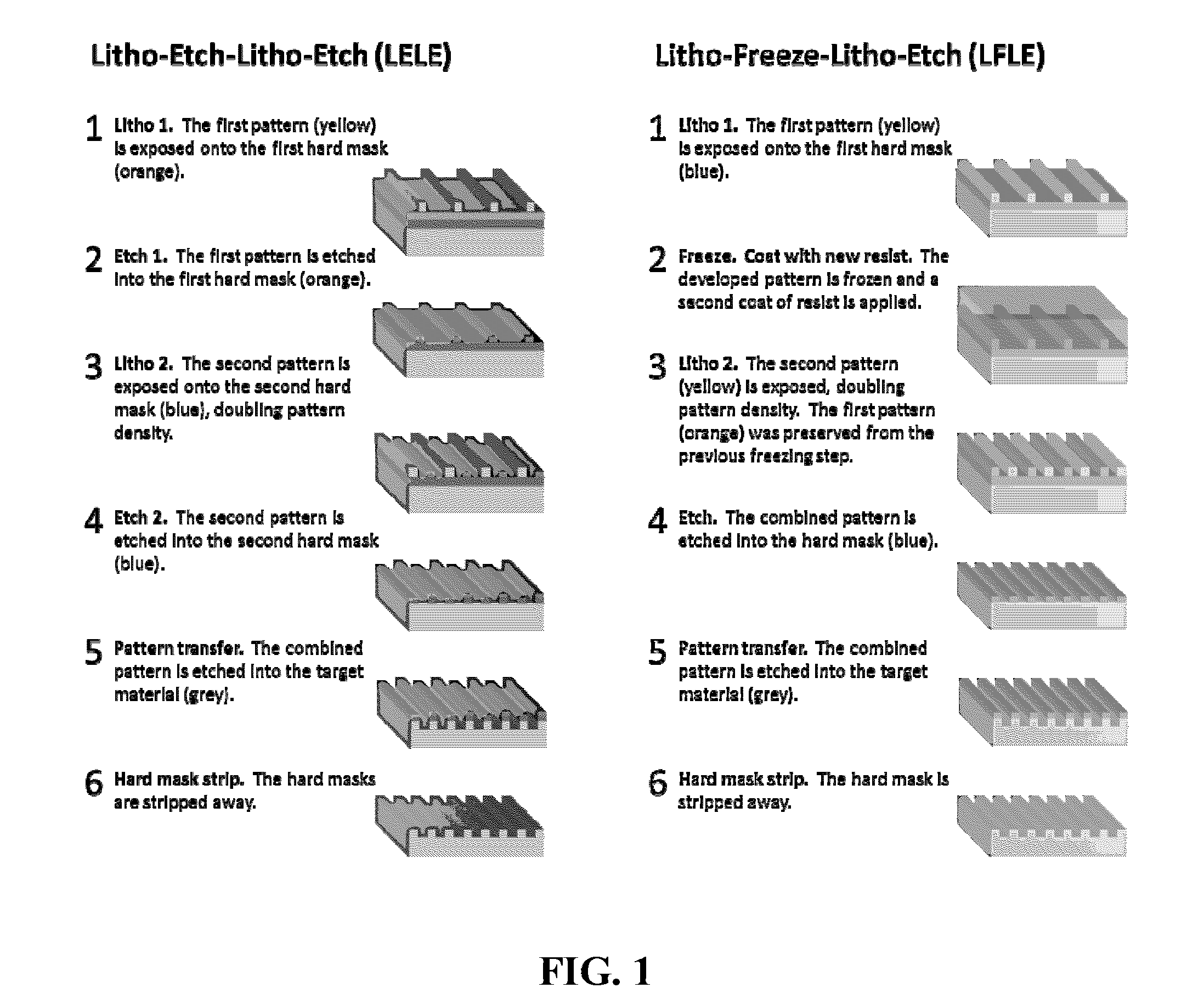

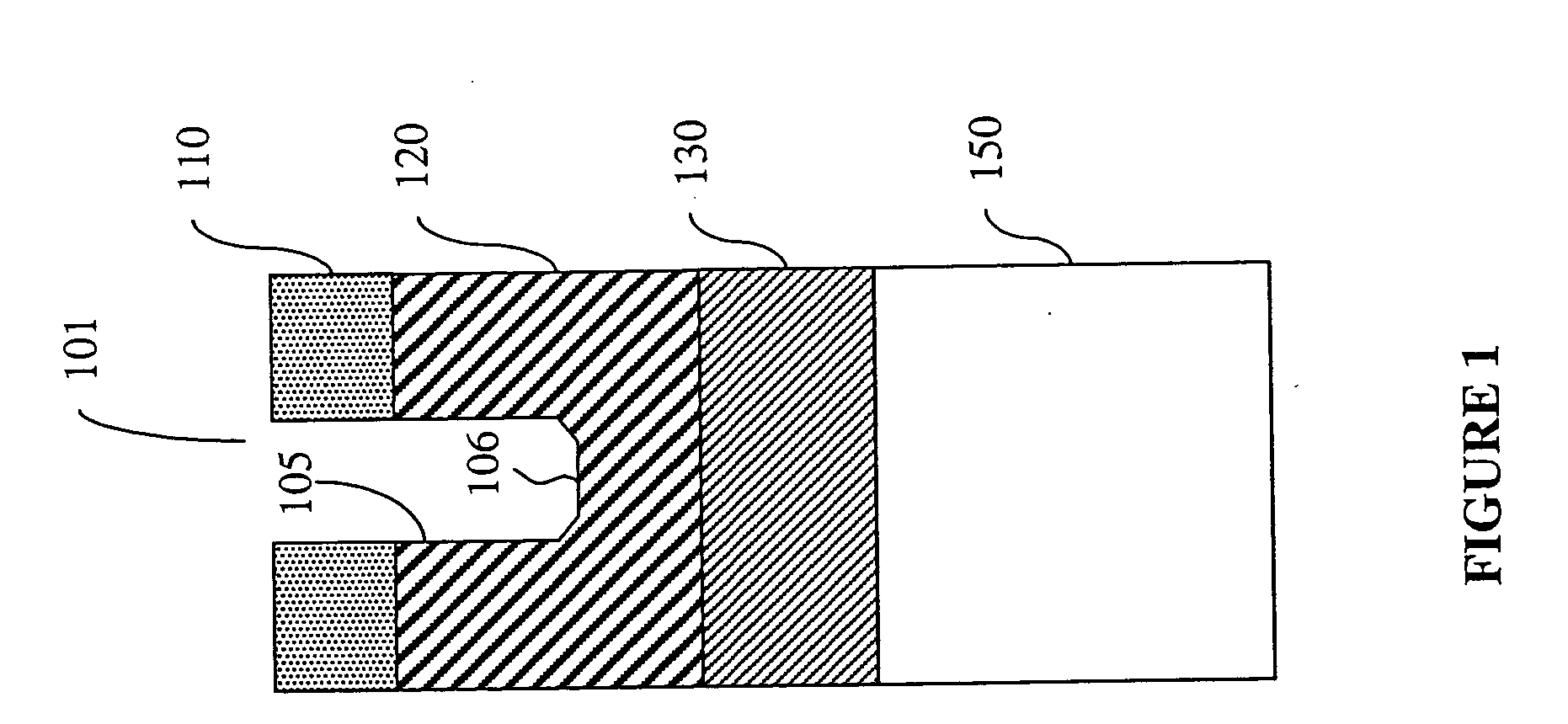

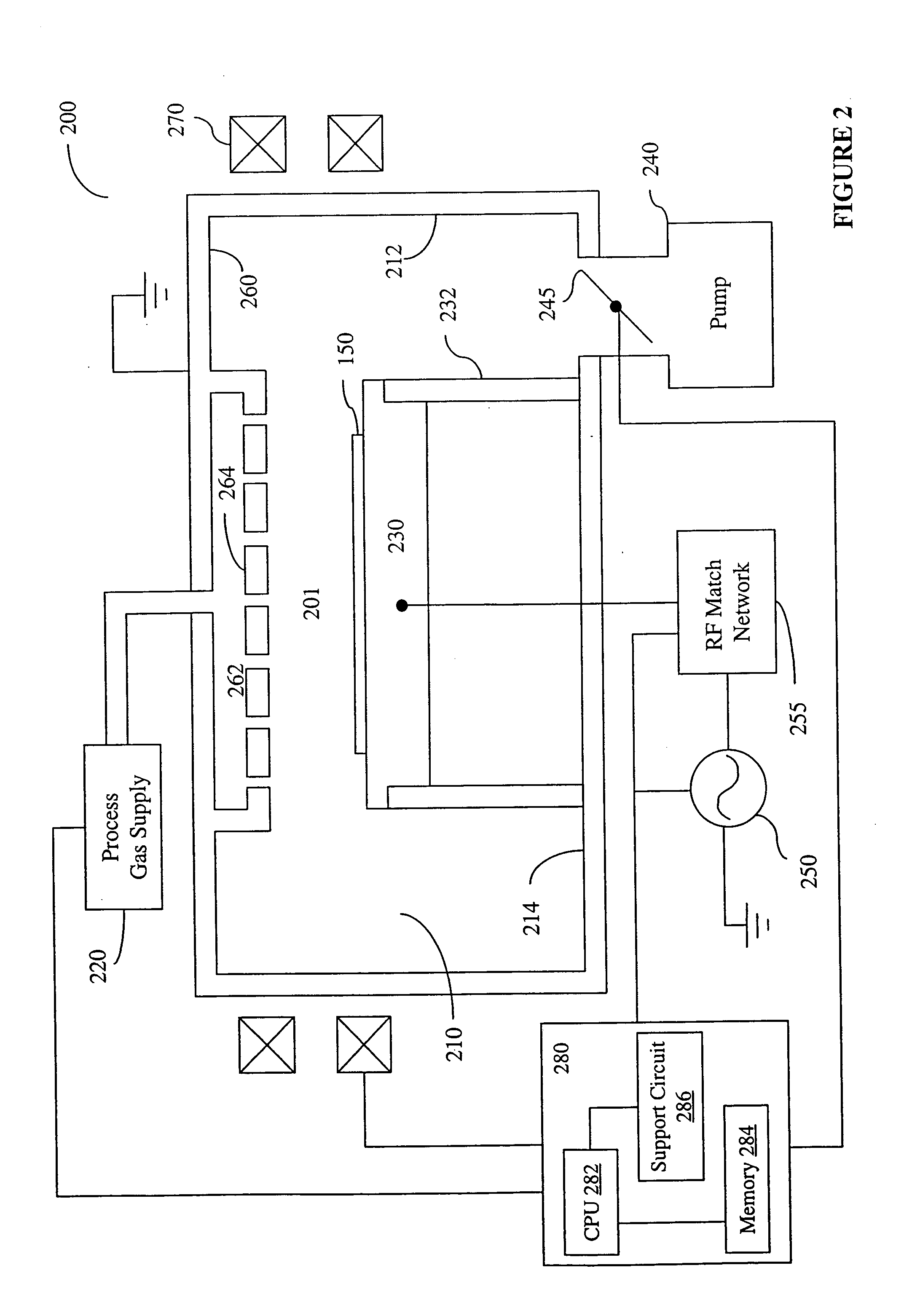

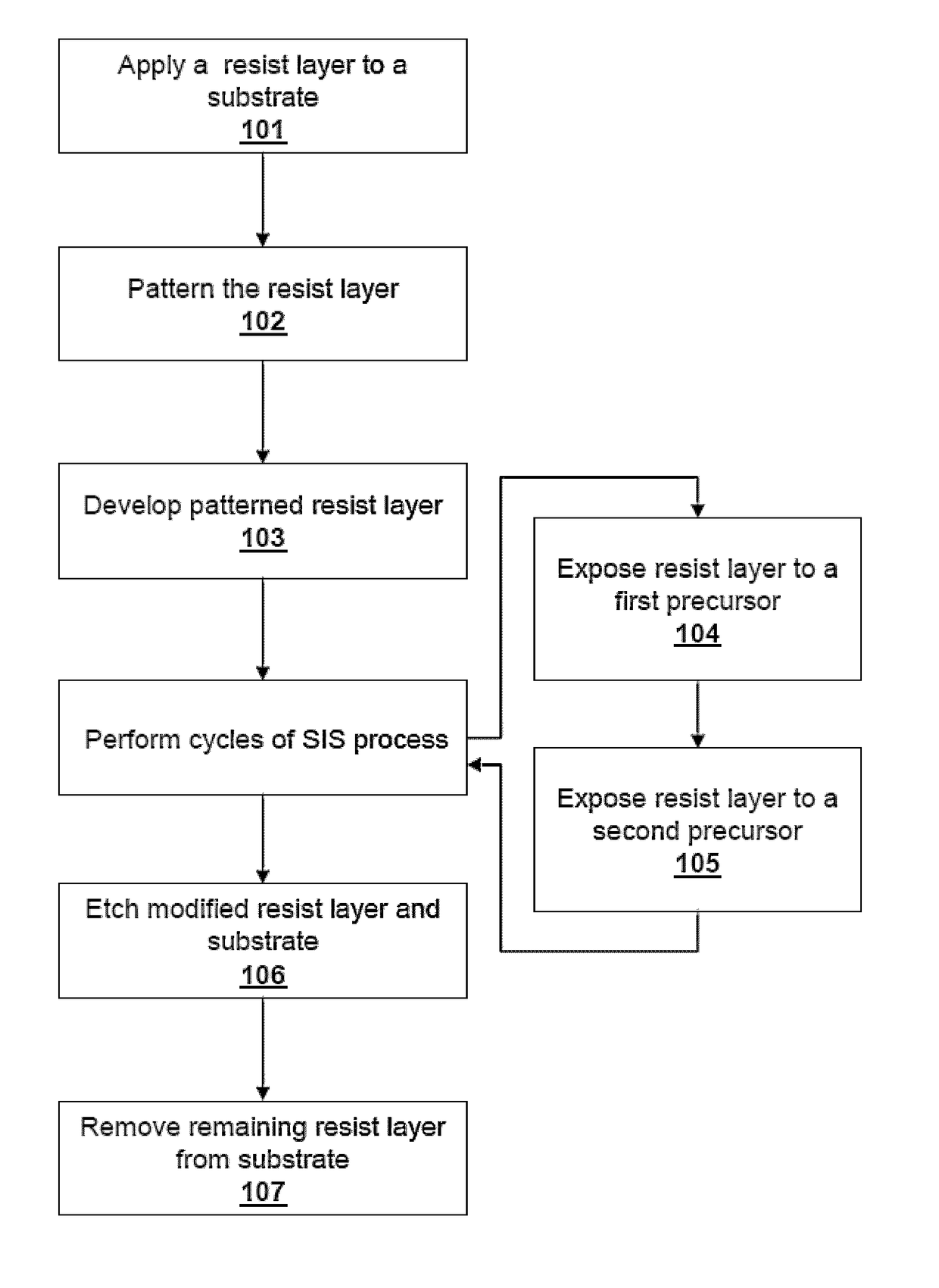

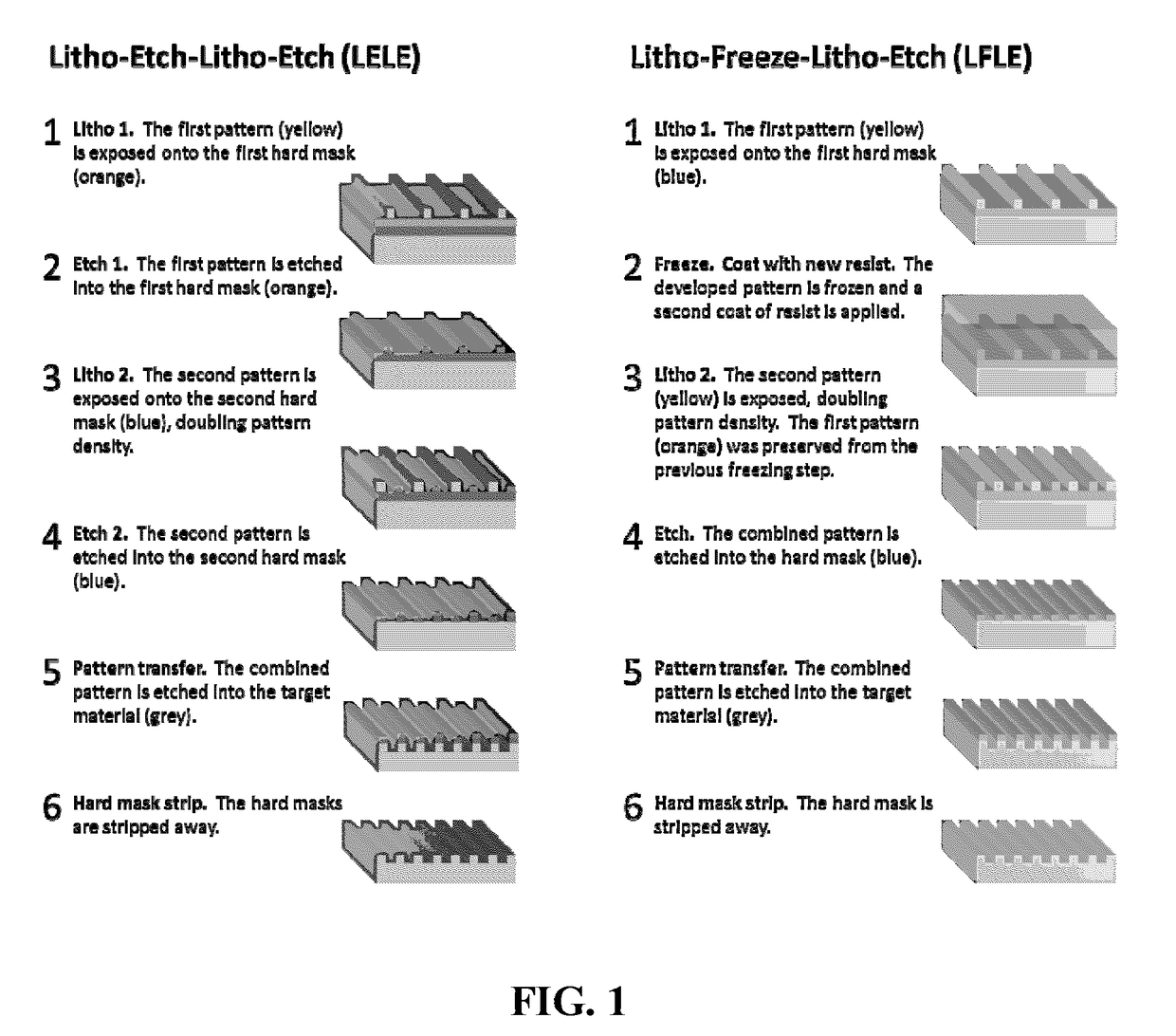

Simplified methods of multiple-patterning photolithography using sequential infiltration synthesis to modify the photoresist such that it withstands plasma etching better than unmodified resist and replaces one or more hard masks and / or a freezing step in MPL processes including litho-etch-litho-etch photolithography or litho-freeze-litho-etch photolithography.

Owner:UCHICAGO ARGONNE LLC

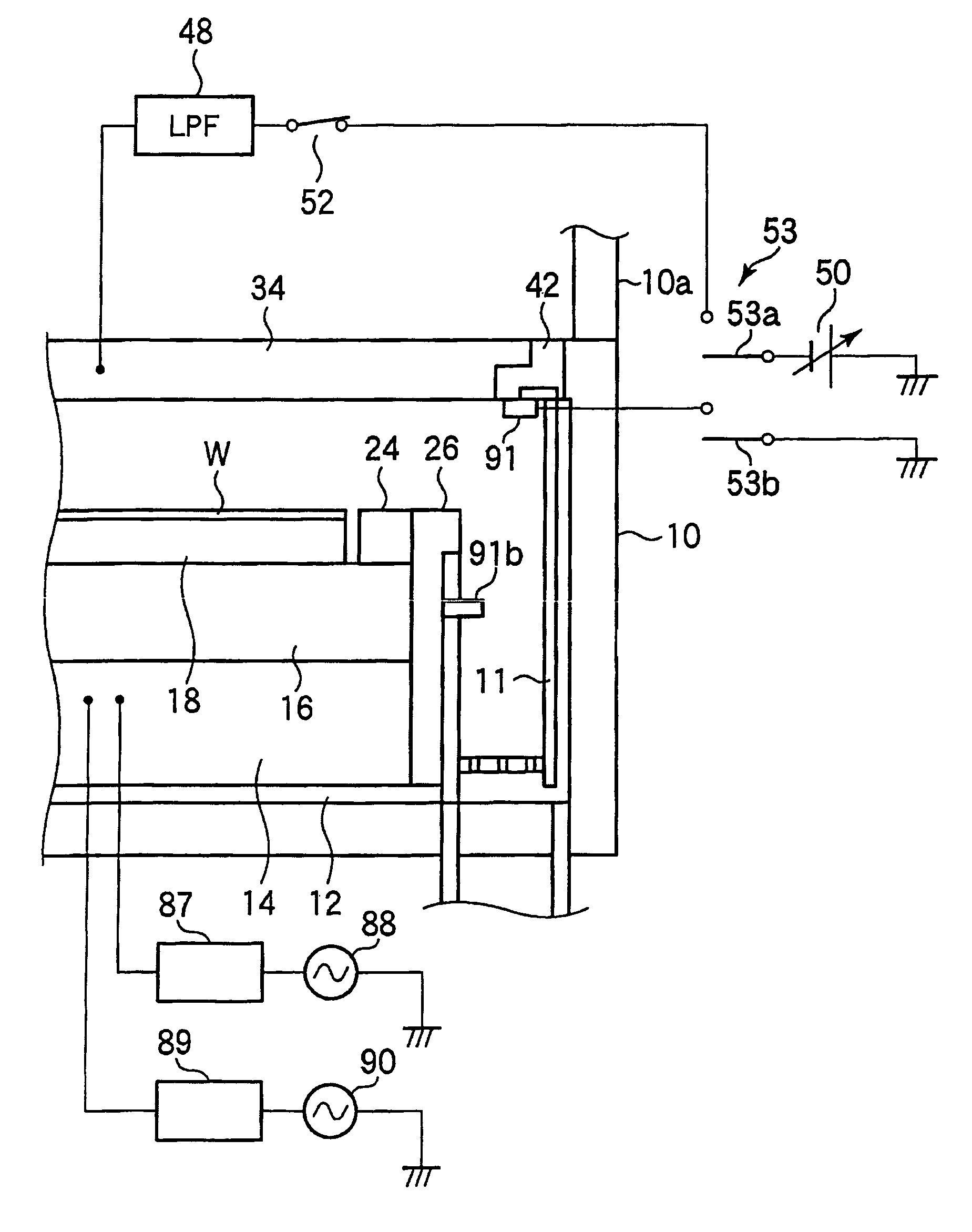

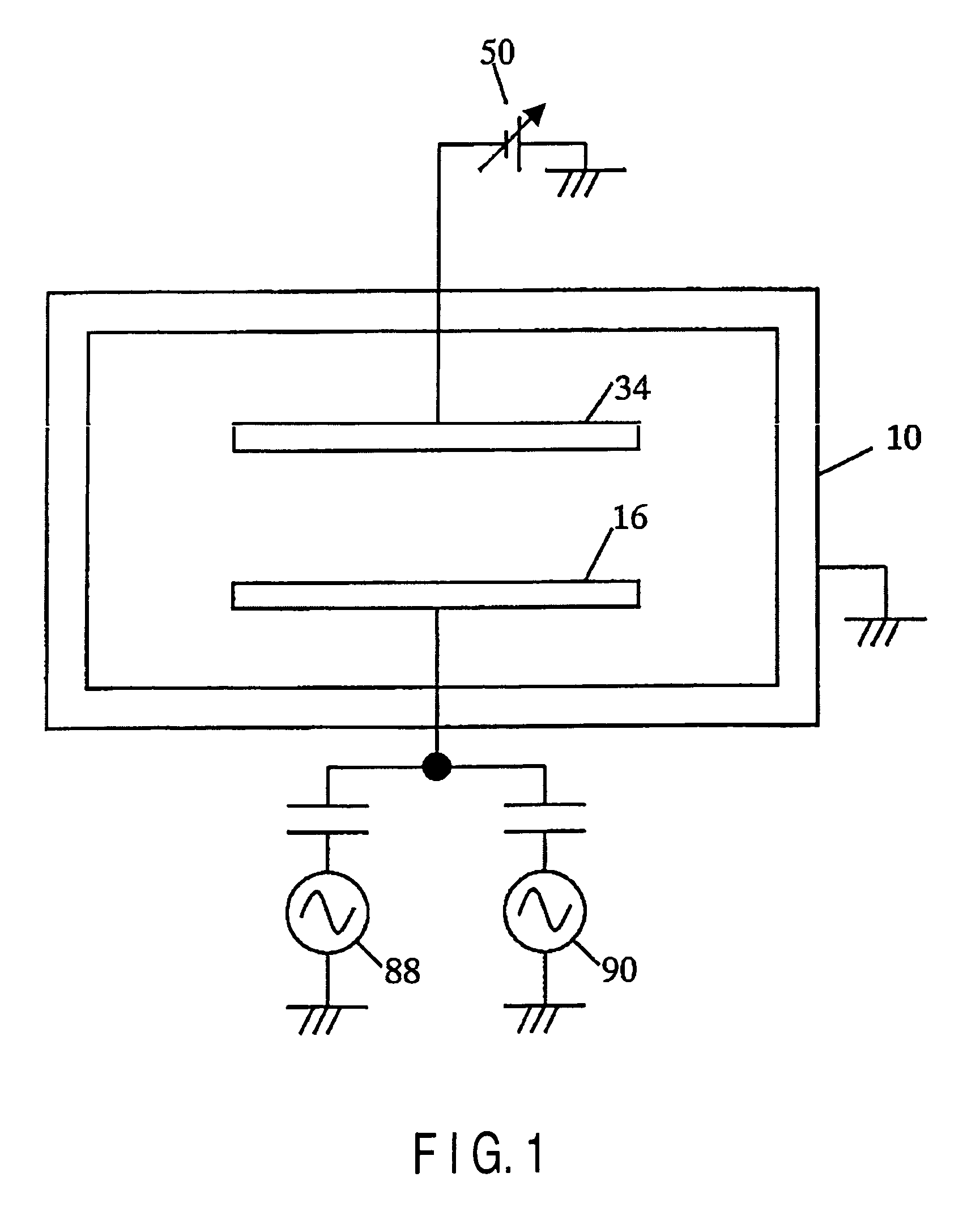

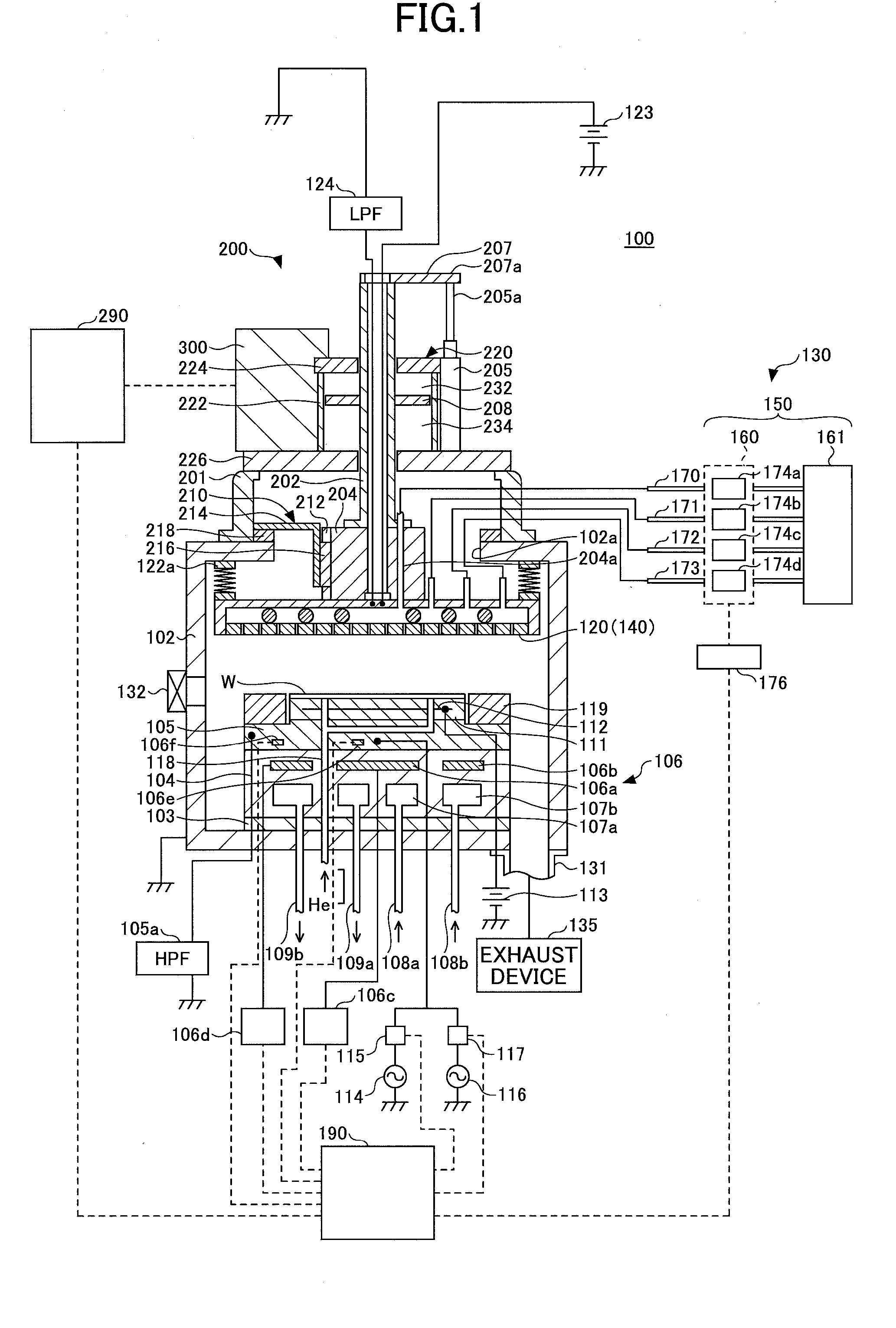

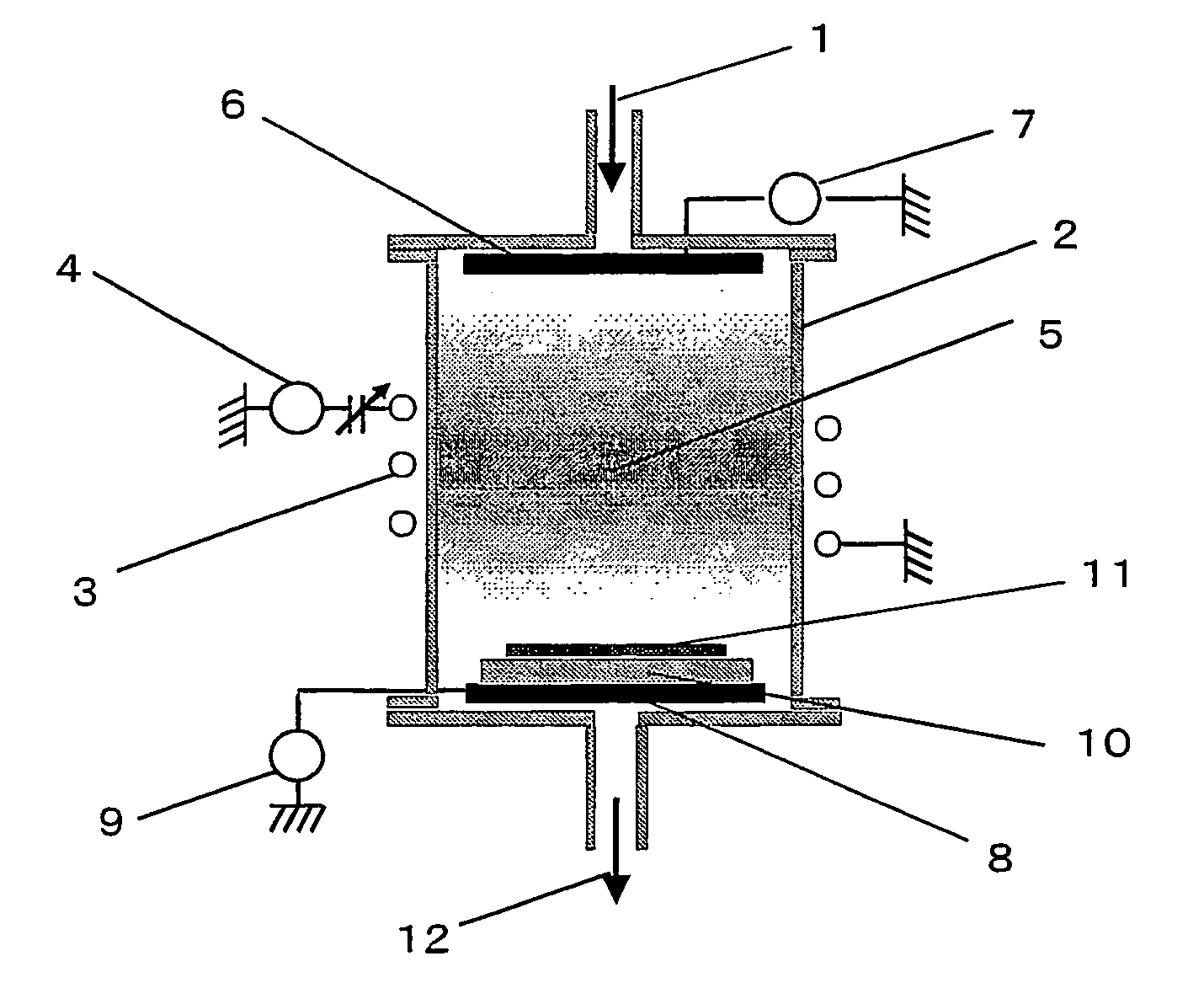

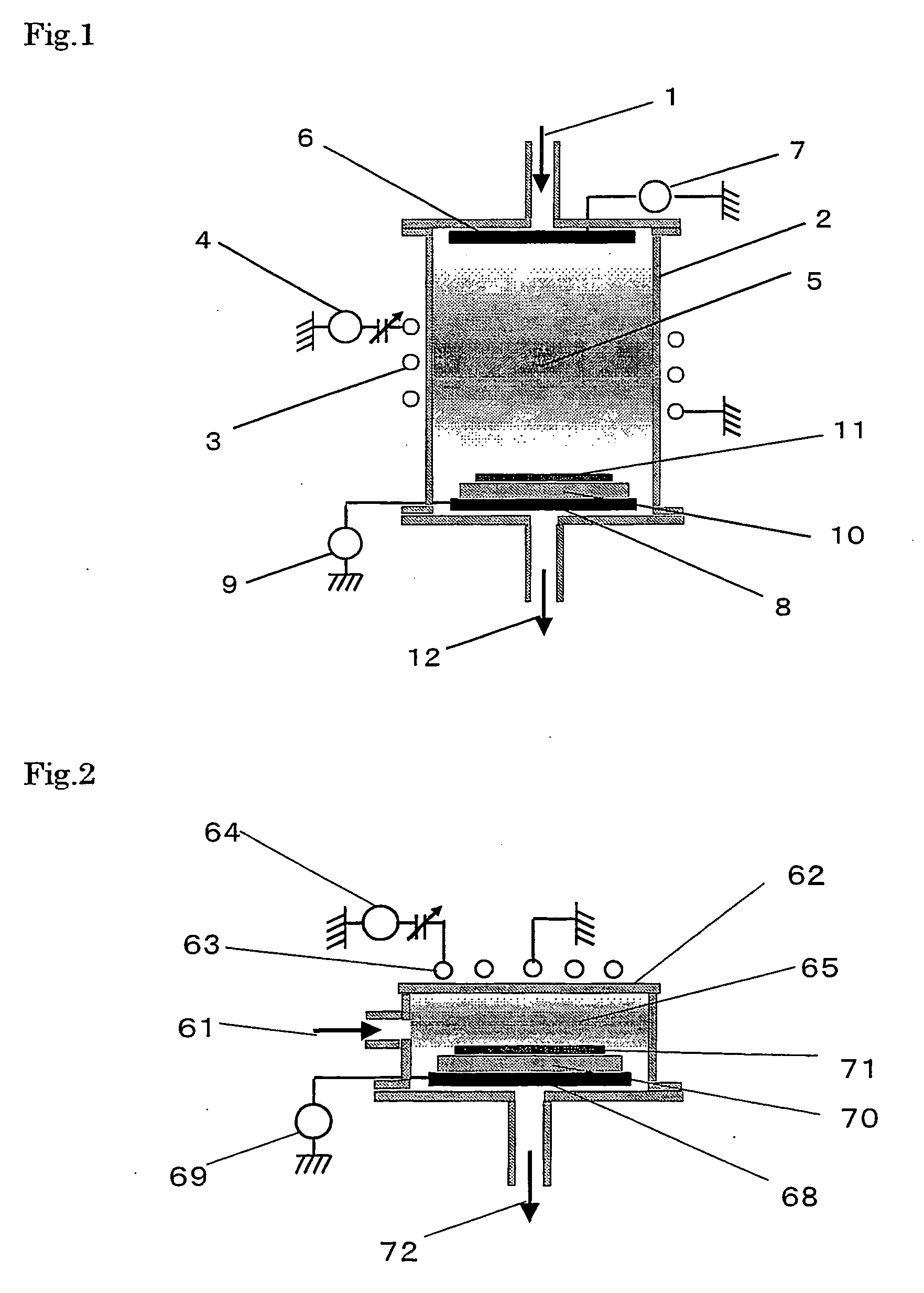

Plasma processing apparatus and method

ActiveUS7951262B2Improved resistance characteristicsIncrease chanceElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringPlasma processing

An apparatus includes an upper electrode and a lower electrode for supporting a wafer disposed opposite each other within a process chamber. A first RF power supply configured to apply a first RF power having a relatively higher frequency, and a second RF power supply configured to apply a second RF power having a relatively lower frequency is connected to the lower electrode. A variable DC power supply is connected to the upper electrode. A process gas is supplied into the process chamber to generate plasma of the process gas so as to perform plasma etching.

Owner:TOKYO ELECTRON LTD

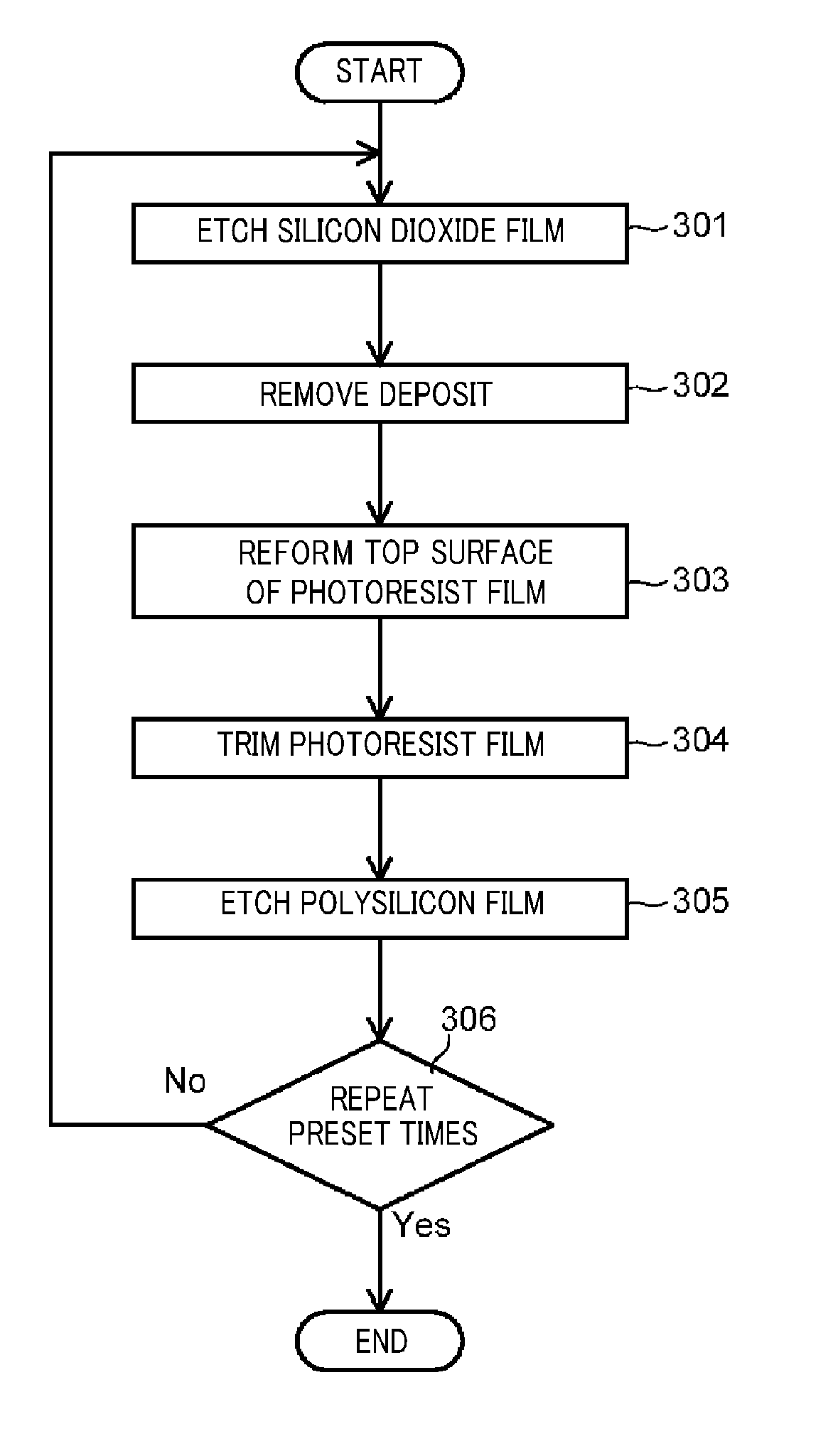

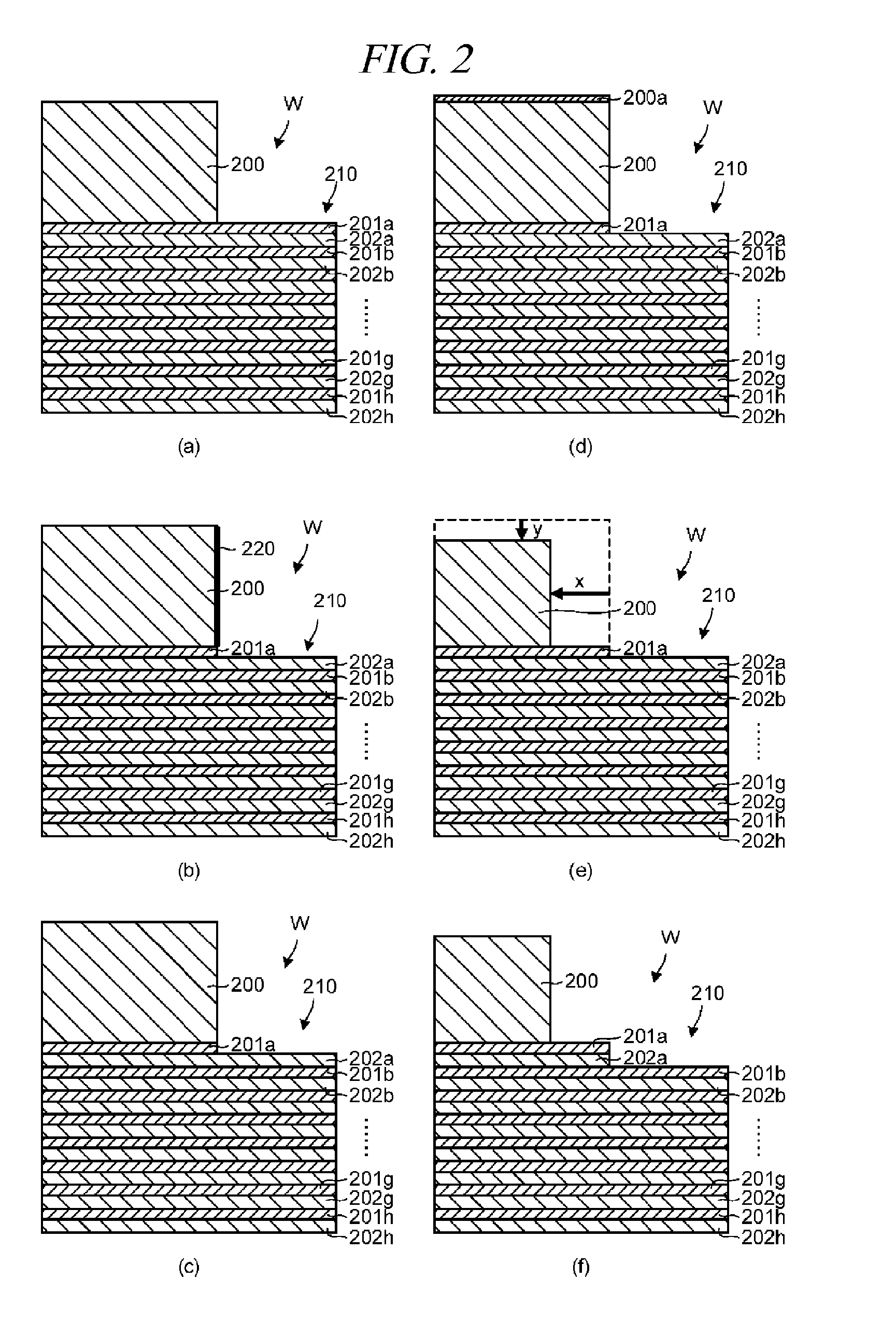

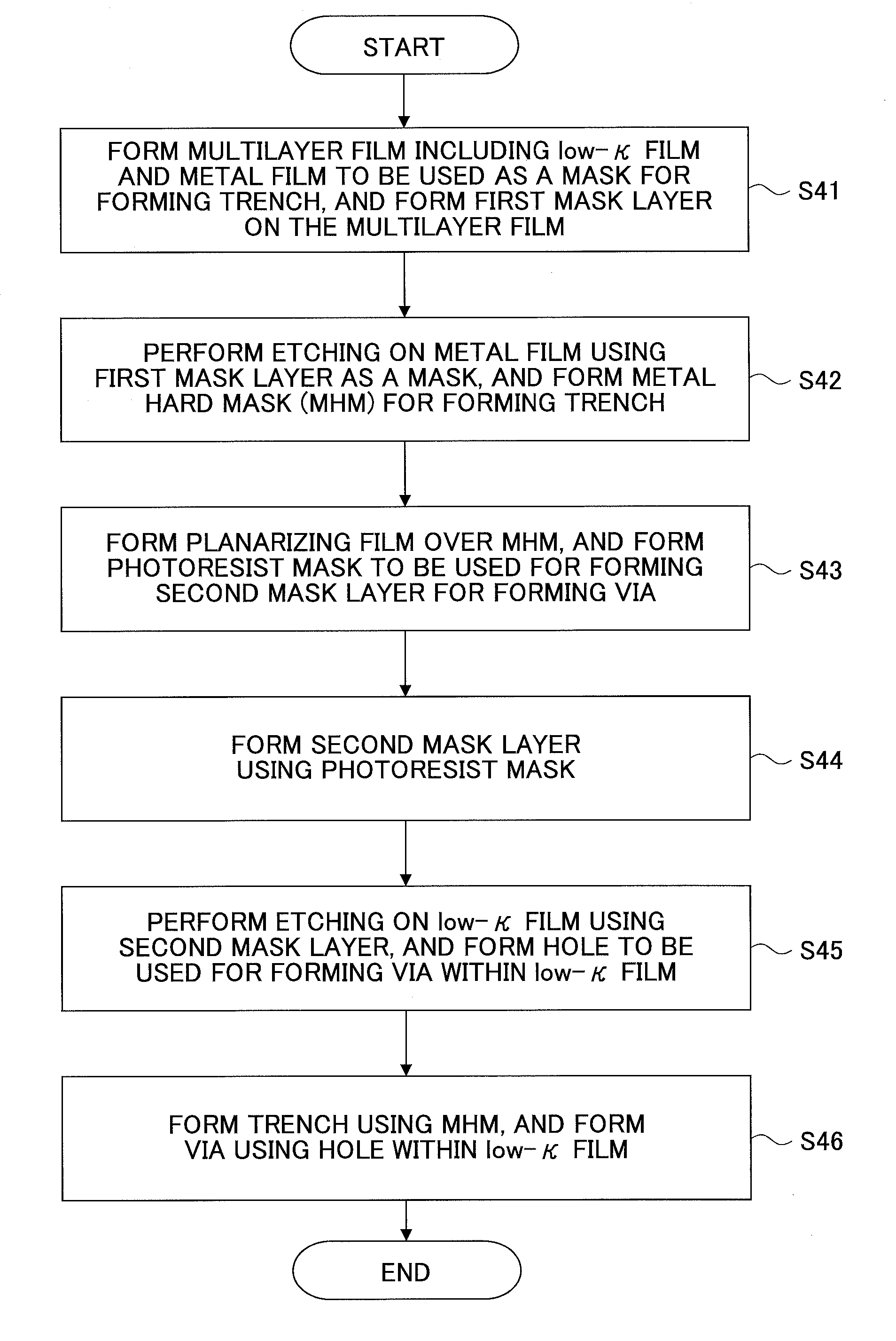

Semiconductor device manufacturing method and computer-readable storage medium

ActiveUS20120225561A1Efficiently formedLiquid surface applicatorsElectric discharge tubesResistHydrogen

There is provided a semiconductor device manufacturing method for forming a step-shaped structure in a substrate by etching the substrate having thereon a multilayer film and a photoresist film on the multilayer film and serving as an etching mask. The multilayer film is formed by alternately layering a first film having a first permittivity and a second film having a second permittivity different from the first permittivity. The method includes a first process for plasma-etching the first film by using the photoresist film as a mask; a second process for exposing the photoresist film to hydrogen-containing plasma; a third process for trimming the photoresist film; and a fourth process for etching the second film by using the trimmed photoresist film and the plasma-etched first film as a mask. The step-shaped structure is formed in the multilayer film by repeatedly performing the first process to the fourth process in this sequence.

Owner:TOKYO ELECTRON LTD

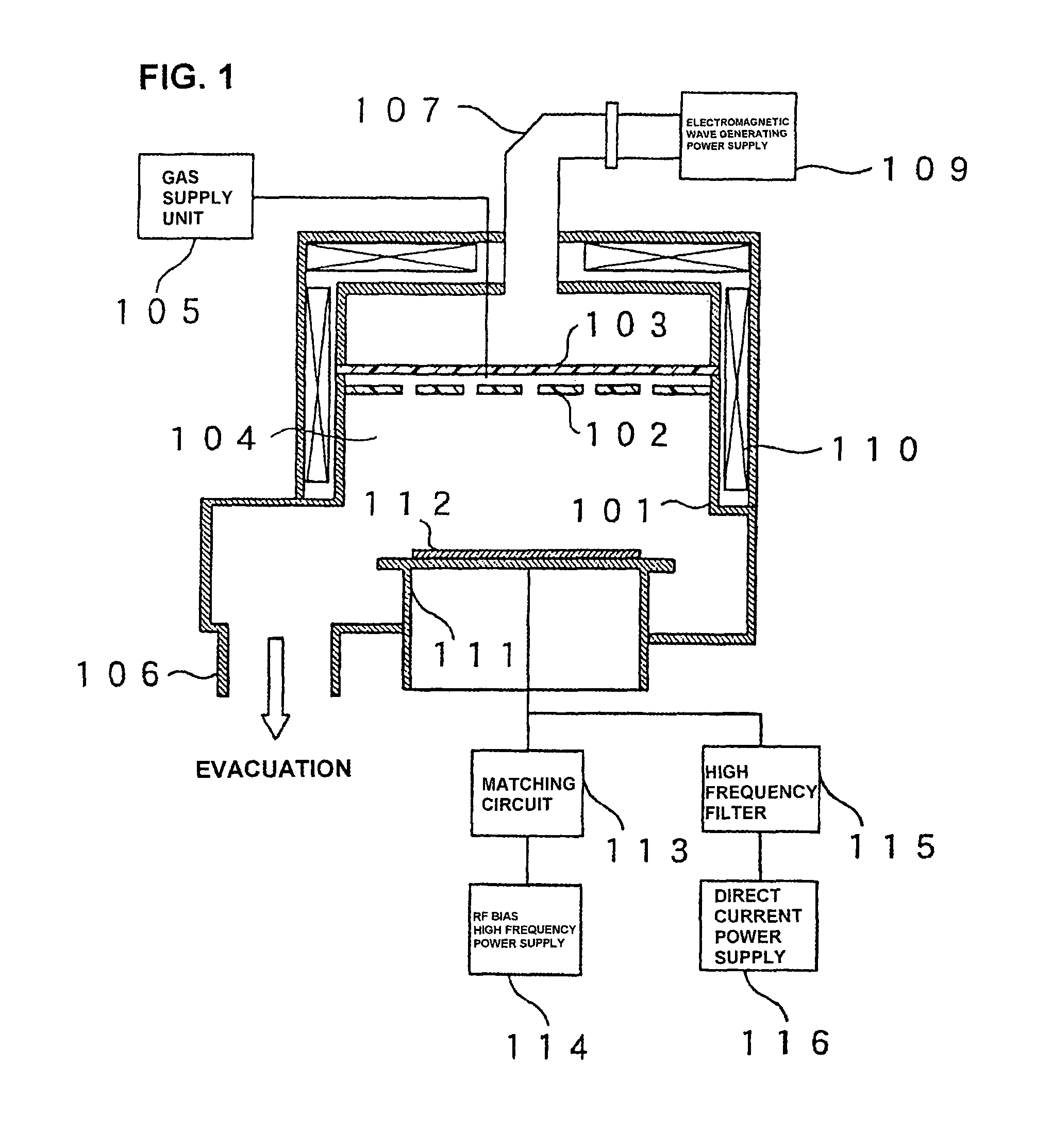

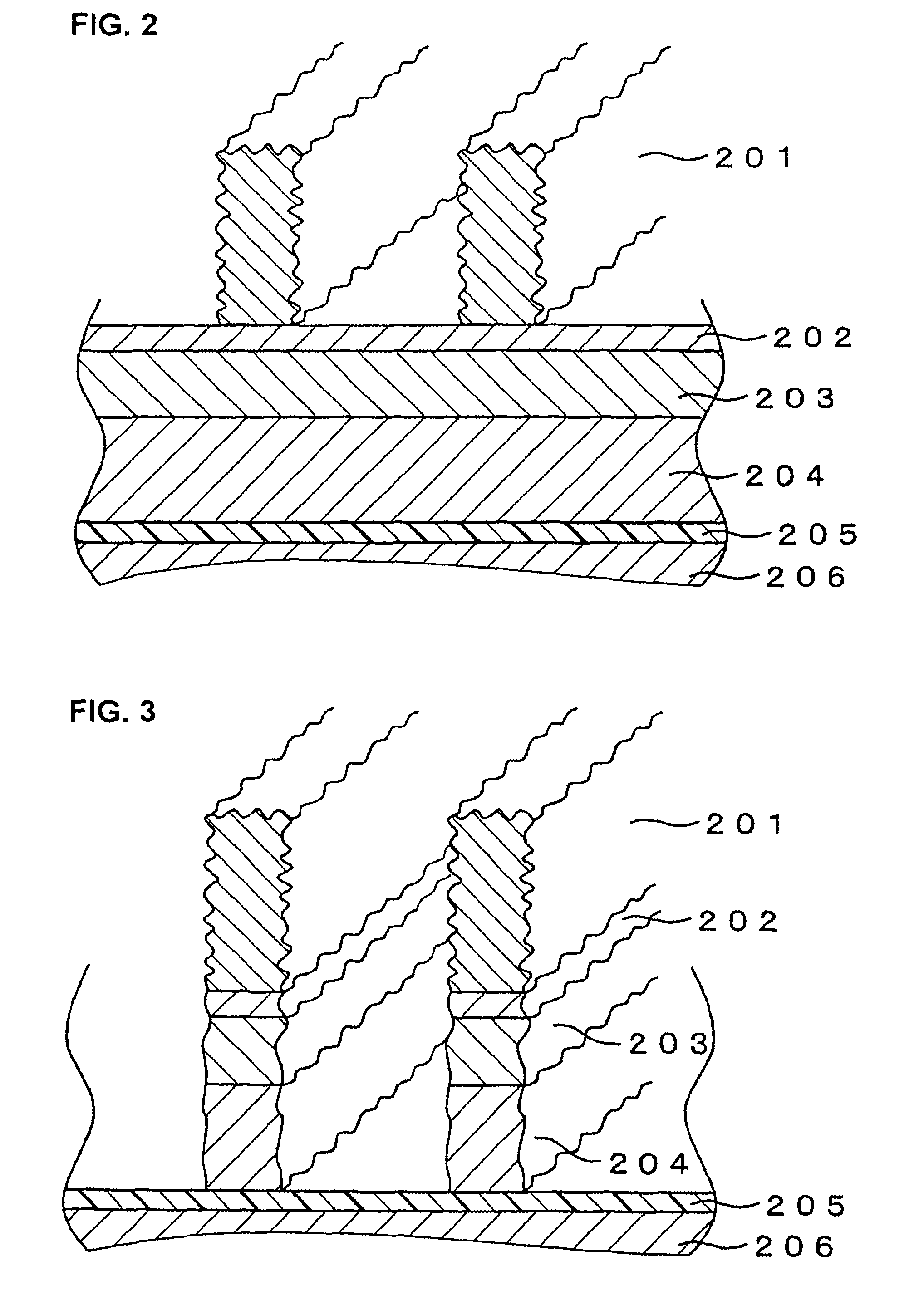

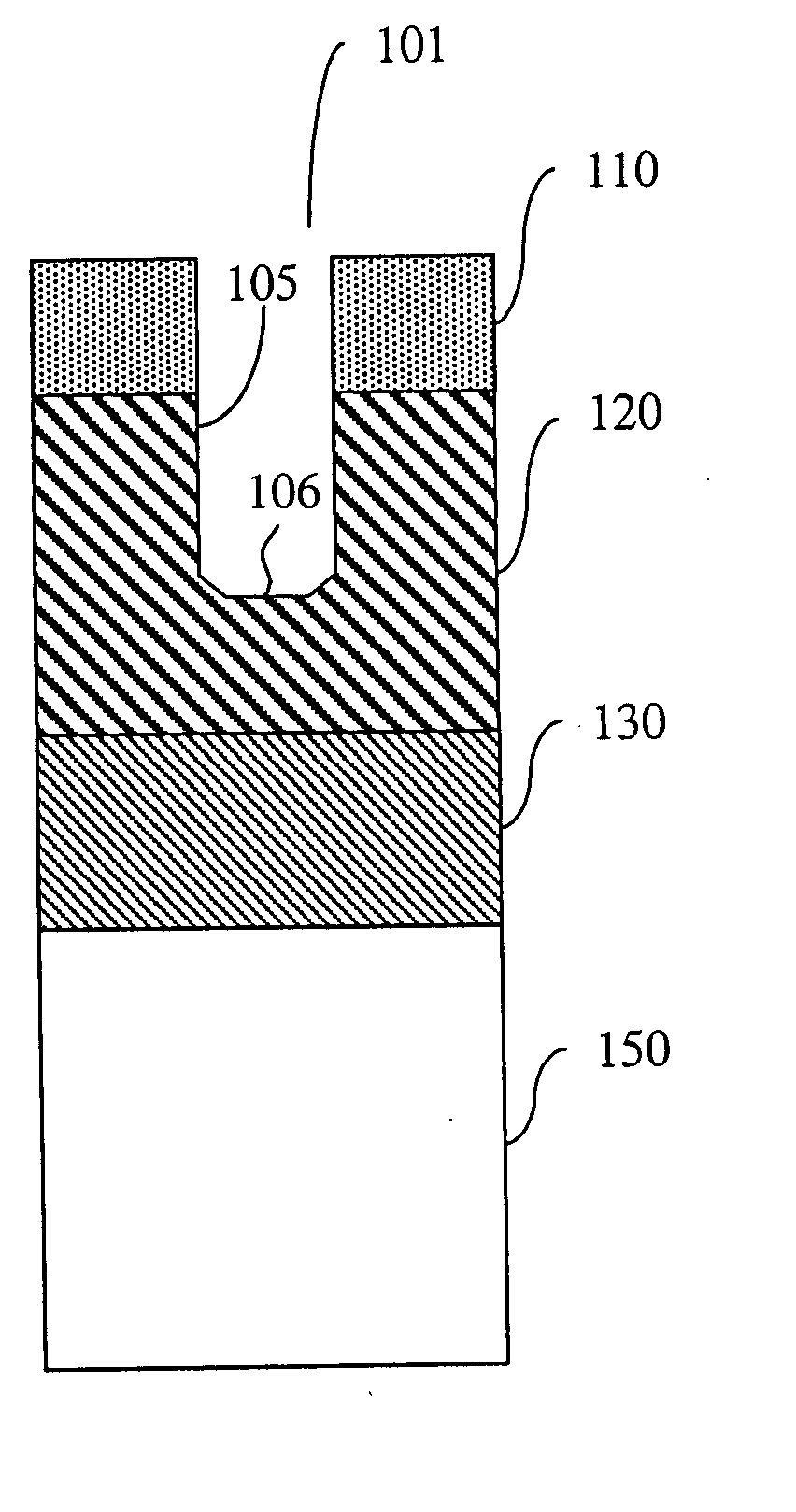

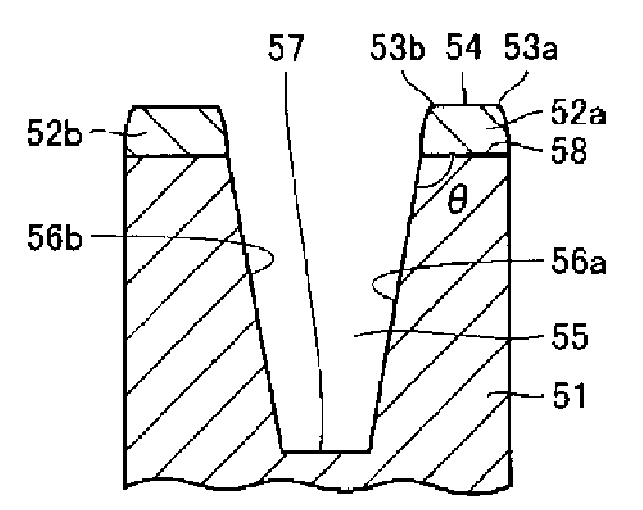

Plasma processing method

ActiveUS8497213B2Preventing deterioration of semiconductor device performanceReduce roughnessDecorative surface effectsSemiconductor/solid-state device manufacturingResistNitrogen gas

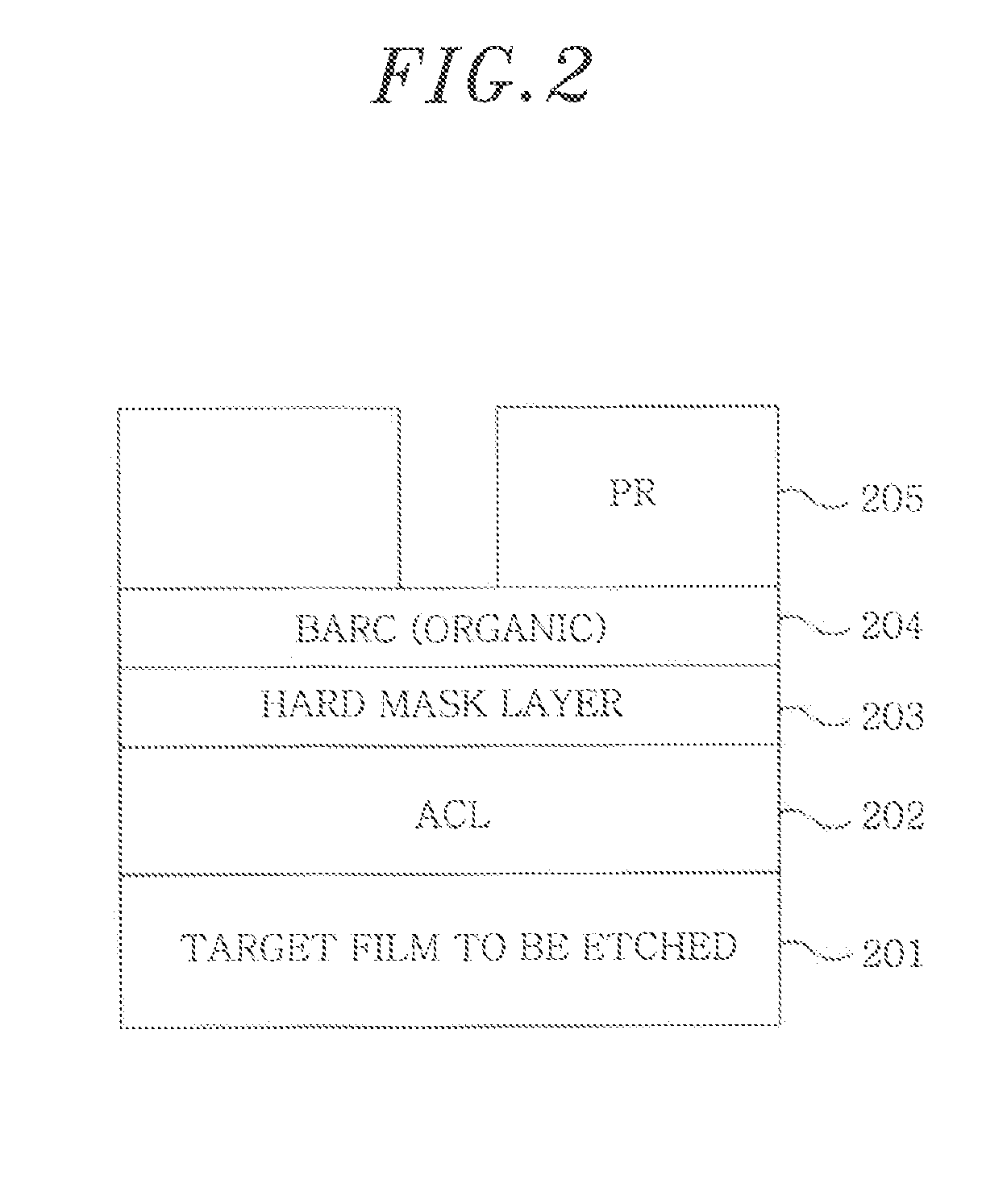

The invention provides a method for subjecting laminated thin films disposed below a photoresist mask pattern to plasma processing, wherein the roughness on the side walls of the formed pattern is reduced, and the LER and LWR are reduced. When etching a material to be processed to form a gate electrode including thin films such as a gate insulating film 205, a conducting layer 204, a mask layer 203 and an antireflection film 202 laminated on a semiconductor substrate 206 and a photoresist mask pattern 201 disposed on the antireflection film, prior to etching the mask pattern 201, plasma is generated from nitrogen gas or a mixed gas including nitrogen gas and deposition gas to subject the mask pattern 201 to a plasma curing process so as to reduce the roughness on the surface and side walls of the mask pattern 201, and then the laminated thin films 202, 203 and 204 disposed below the mask pattern 201 are subjected to a plasma etching process.

Owner:HITACHI HIGH-TECH CORP

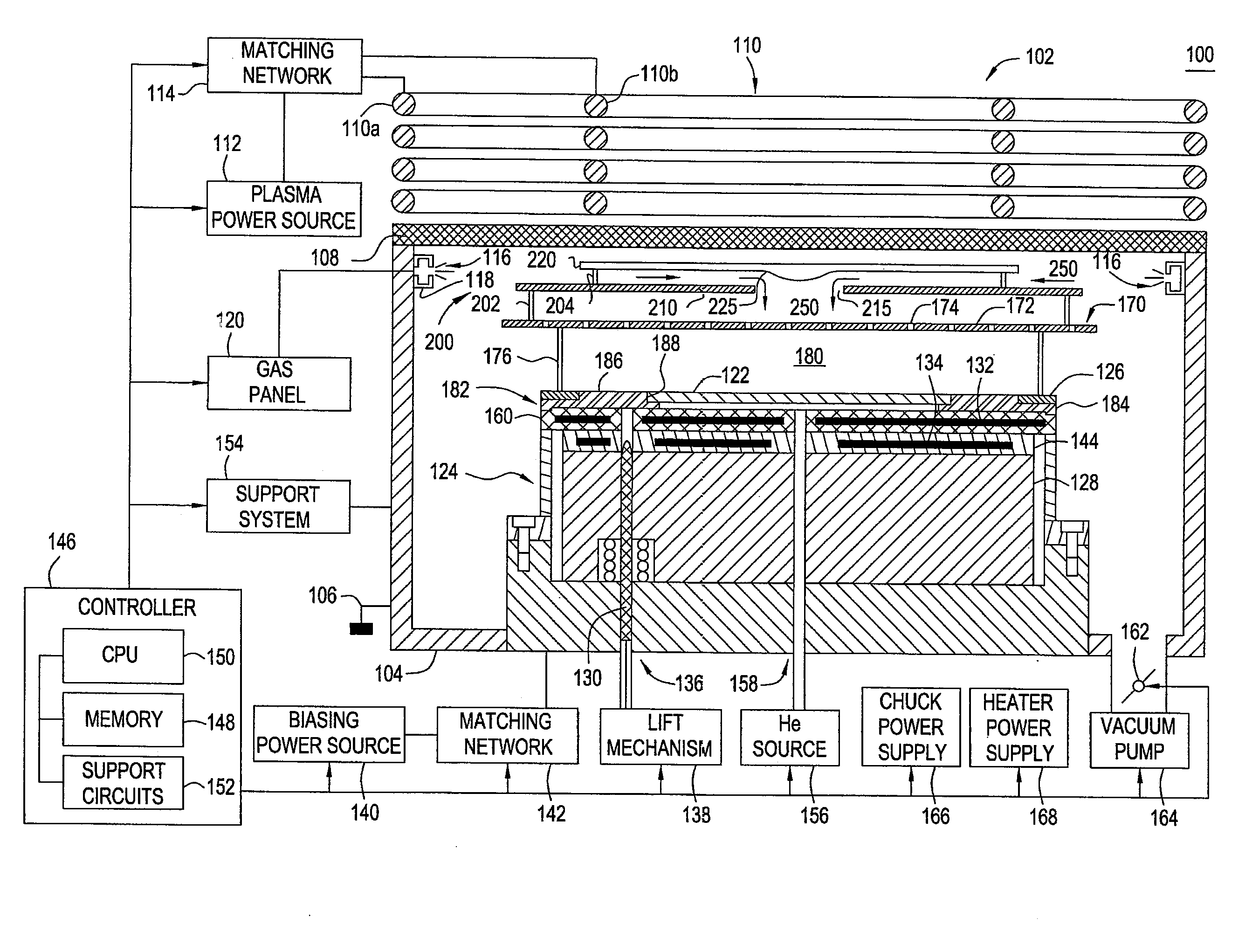

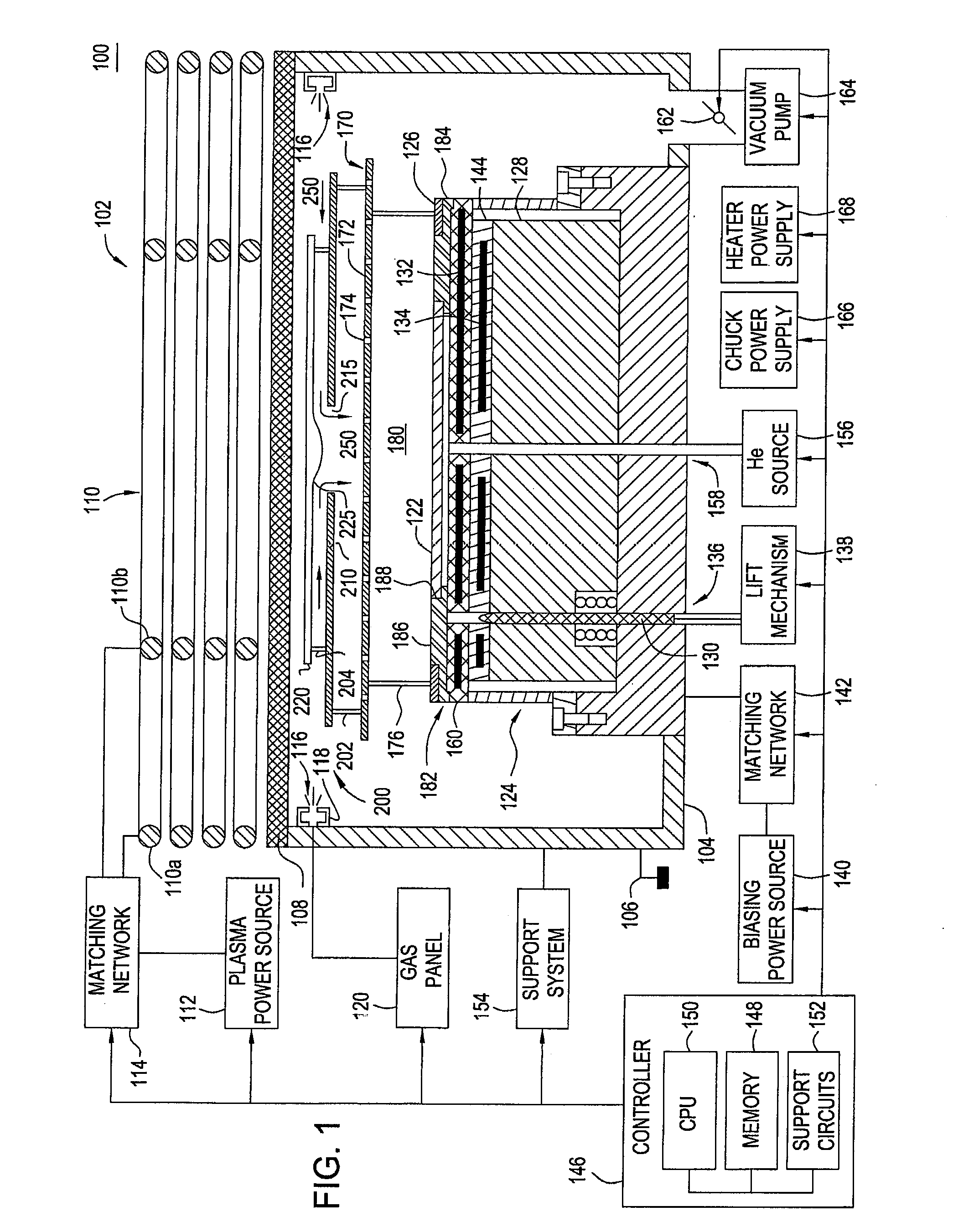

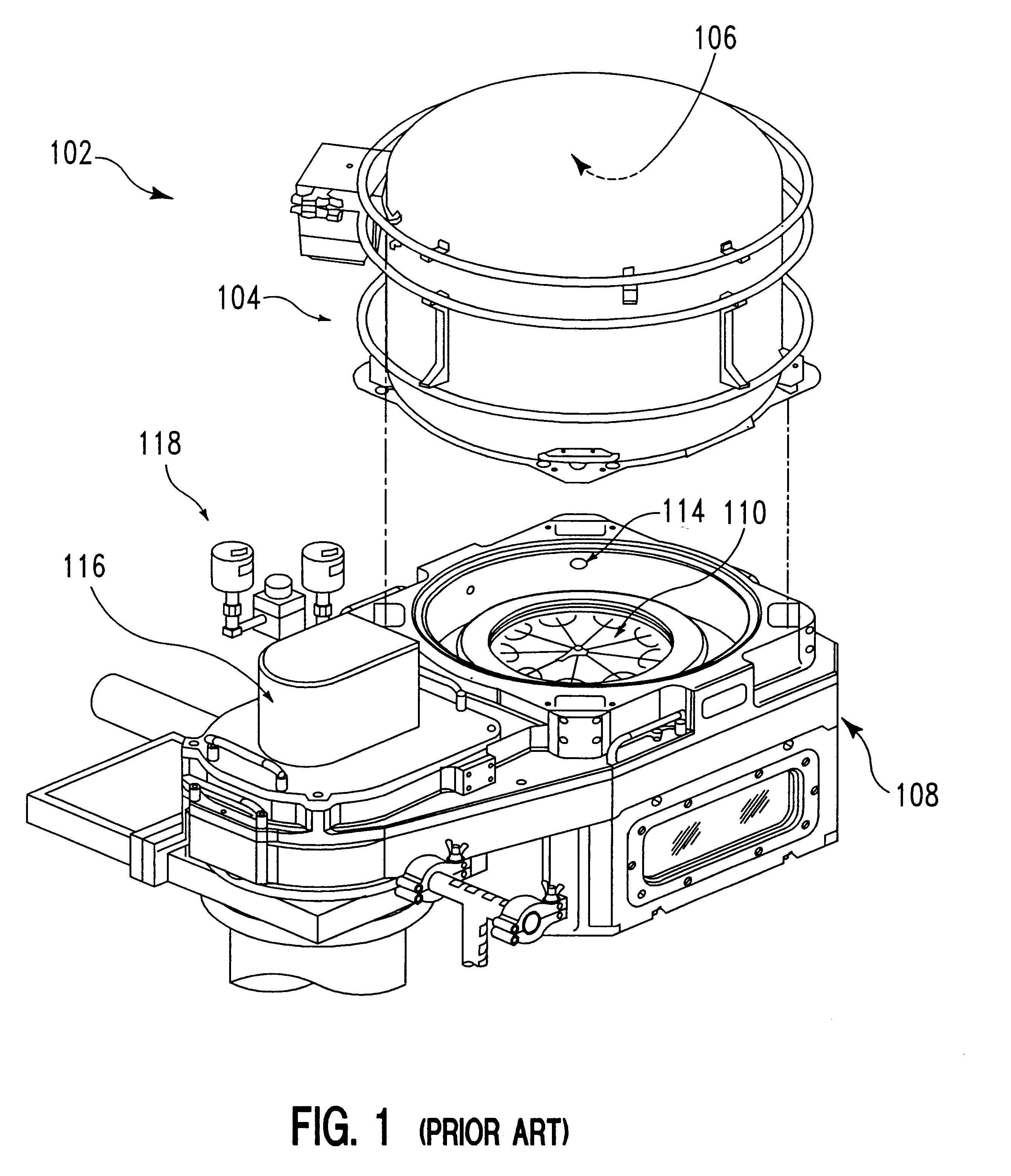

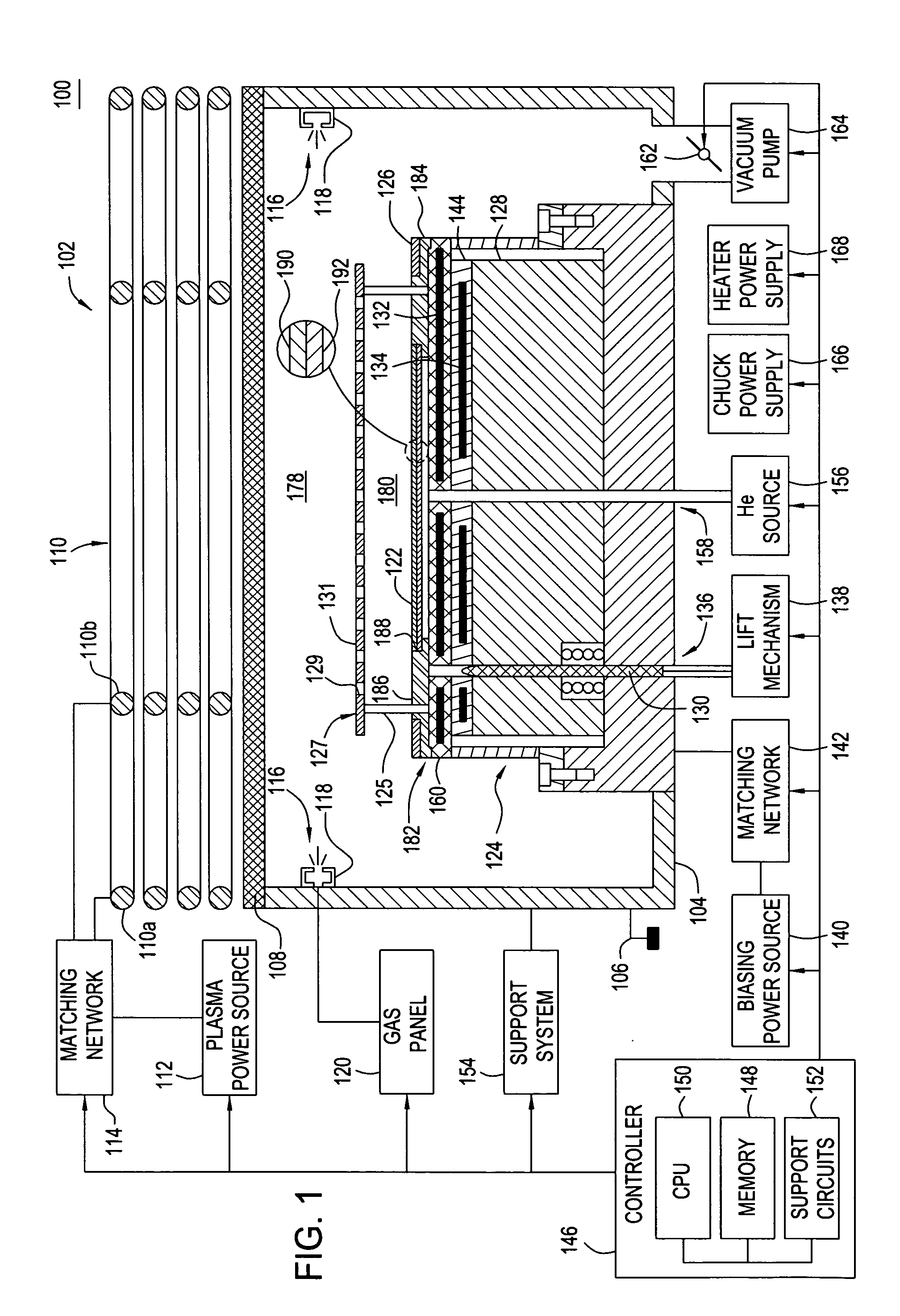

Method and apparatus for photomask plasma etching

A method and apparatus for etching photomasks is provided herein. In one embodiment, the apparatus comprises a process chamber having a support pedestal adapted for receiving a photomask. An ion-neutral shield is disposed above the pedestal and a deflector plate assembly is provided above the ion-neutral shield. The deflector plate assembly defines a gas flow direction for process gases towards the ion-neutral shield, while the ion-neutral shield is used to establish a desired distribution of ion and neutral species in a plasma for etching the photomask.

Owner:APPLIED MATERIALS INC

Plasma etching method

ActiveUS20140377960A1Electric discharge tubesSemiconductor/solid-state device manufacturingMetallurgyResidence time

In a plasma etching method of performing a plasma etching on an amorphous carbon layer of a substrate to be processed by using an inorganic film as a mask, the substrate being mounted in a processing chamber, the plasma etching on the amorphous carbon layer is performed by using O2 gas as a processing gas and the O2 gas to flow in the processing chamber such that a residence time of the O2 gas becomes 0.37 msec or less. The amorphous carbon layer is used as an etching mask of an etching target film formed on the substrate. The plasma etching is performed by using the O2 gas only.

Owner:TOKYO ELECTRON LTD

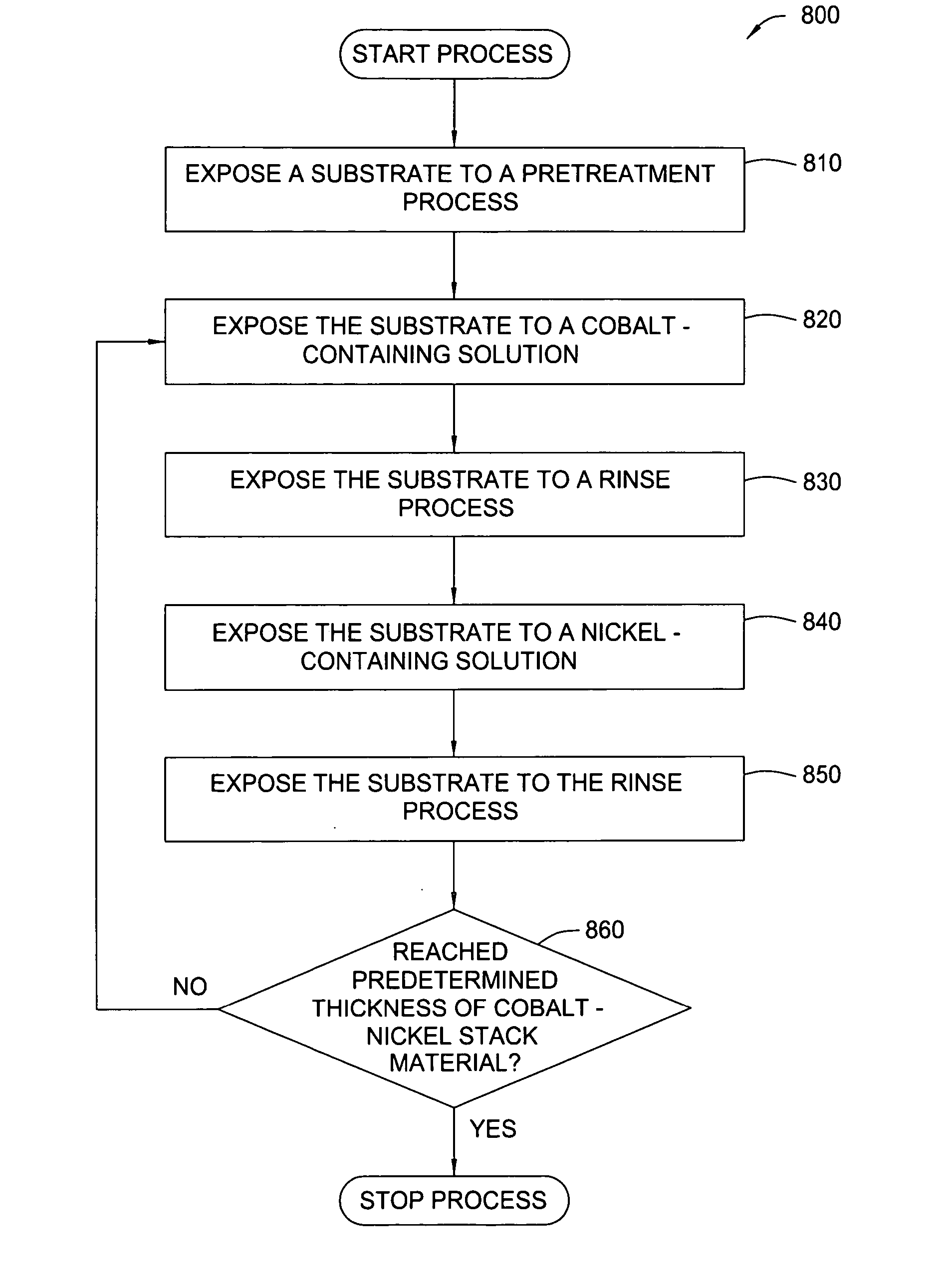

Electroless deposition process on a silicon contact

ActiveUS20060264043A1Material nanotechnologySemiconductor/solid-state device manufacturingSalicideAlloy

Embodiments as described herein provide methods for depositing a material on a substrate during electroless deposition processes, as well as compositions of the electroless deposition solutions. In one embodiment, the substrate contains a contact aperture having an exposed silicon contact surface. In another embodiment, the substrate contains a contact aperture having an exposed silicide contact surface. The apertures are filled with a metal contact material by exposing the substrate to an electroless deposition process. The metal contact material may contain a cobalt material, a nickel material, or alloys thereof. Prior to filling the apertures, the substrate may be exposed to a variety of pretreatment processes, such as preclean processes and activations processes. A preclean process may remove organic residues, native oxides, and other contaminants during a wet clean process or a plasma etch process. Embodiments of the process also provide the deposition of additional layers, such as a capping layer.

Owner:APPLIED MATERIALS INC

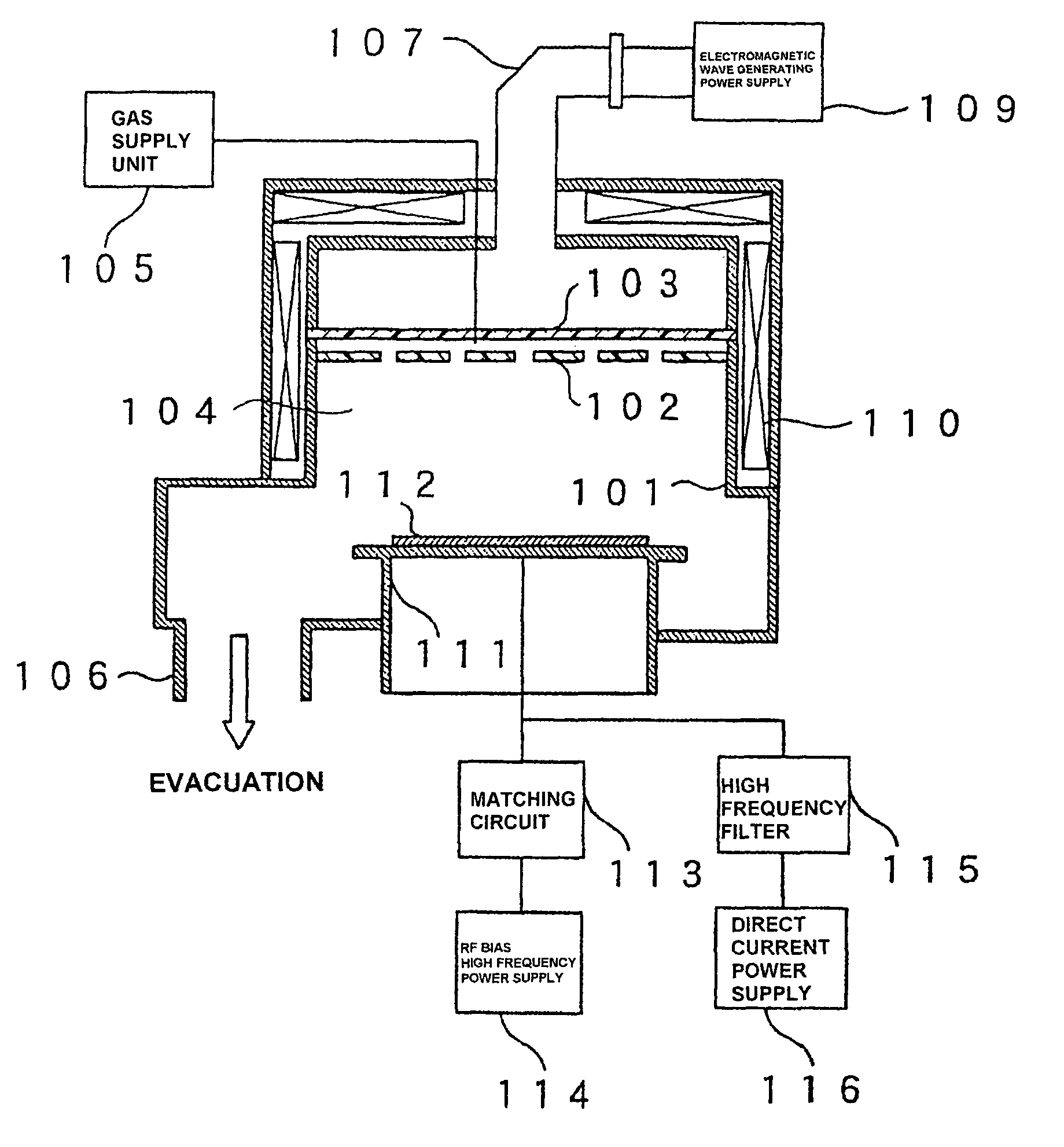

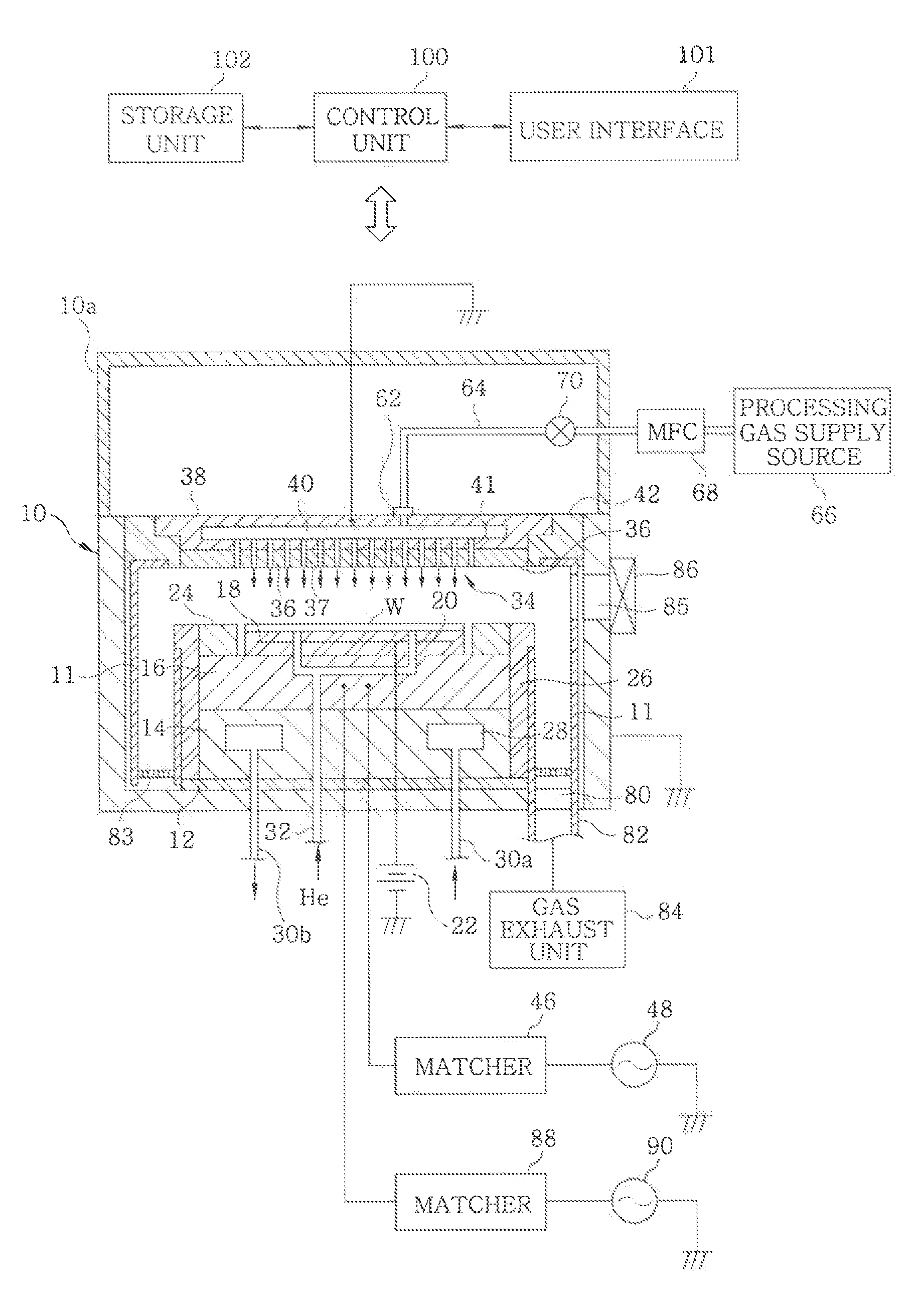

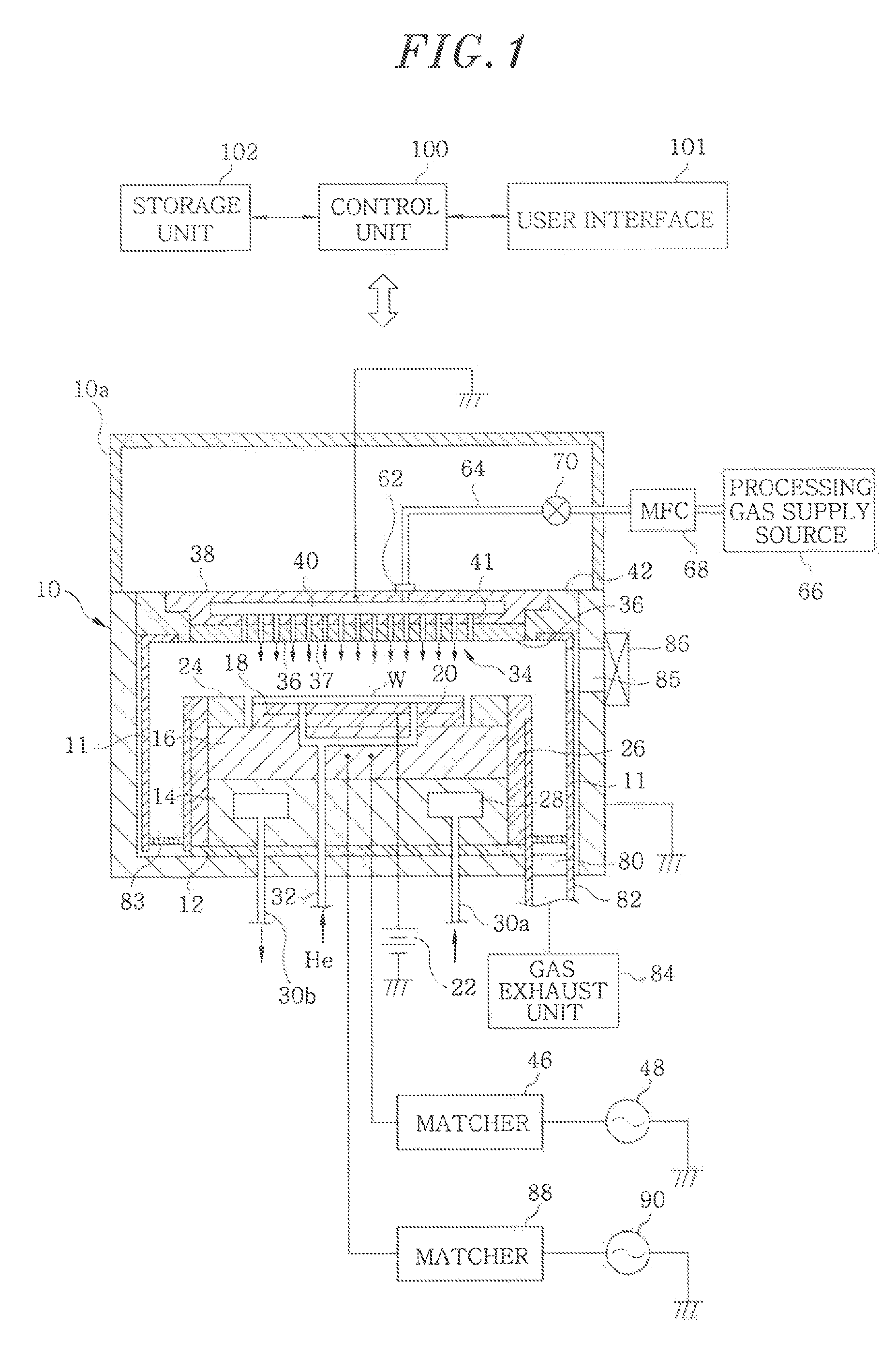

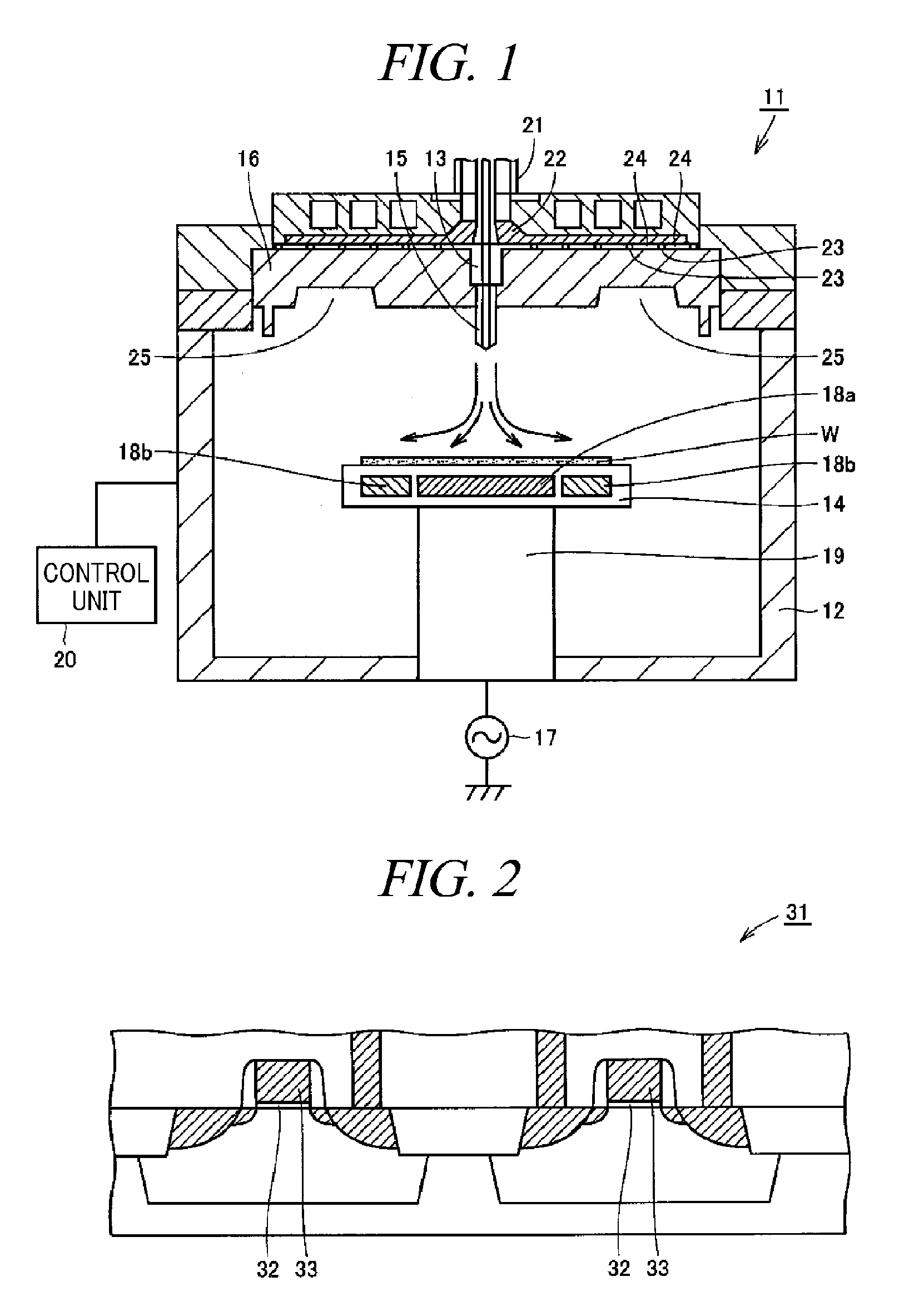

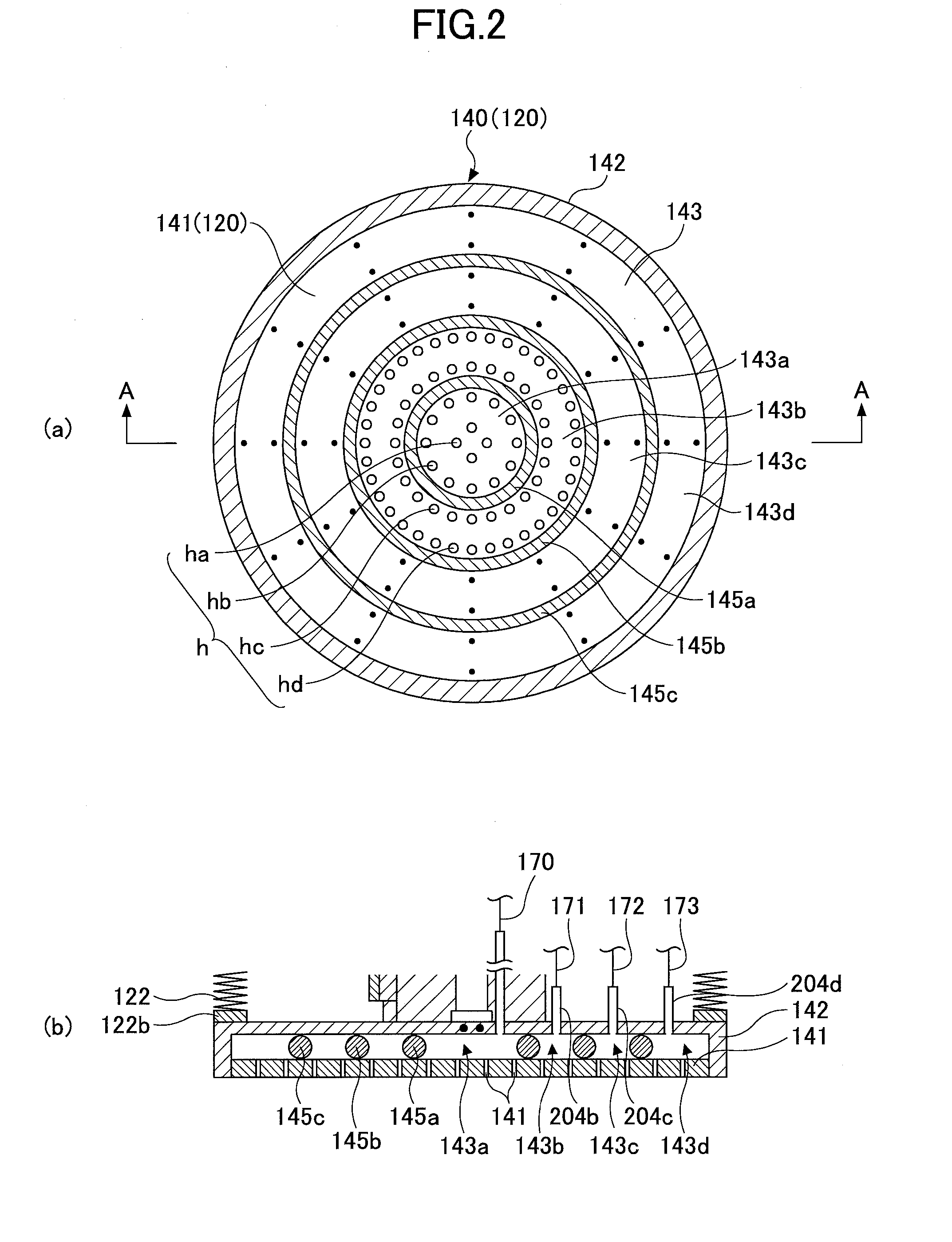

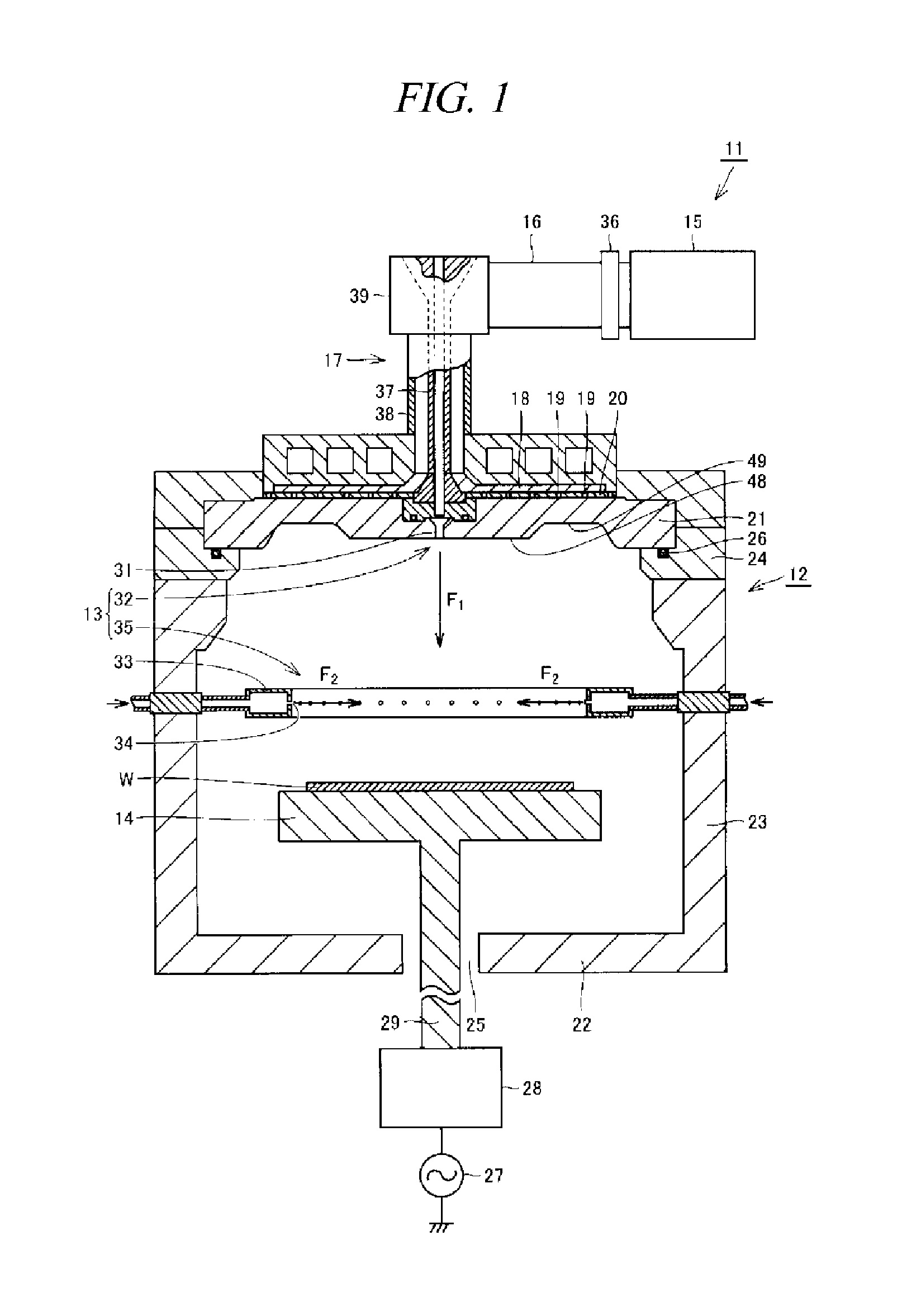

Plasma etching apparatus and plasma etching method

ActiveUS9263298B2Easy to controlUniform surfaceElectric discharge tubesDecorative surface effectsEngineeringGas supply

A plasma etching apparatus 11 includes a mounting table that holds a semiconductor substrate W thereon; a first heater 18a that heats a central region of the semiconductor substrate W held on the mounting table 14; a second heater 18b that heats an edge region around the central region of the semiconductor substrate W held on the mounting table 14; a reactant gas supply unit 13 that supplies a reactant gas for a plasma process toward the central region of the semiconductor substrate W held on the mounting table 14; and a control unit 20 that performs a plasma etching process on the semiconductor substrate W while controlling the first heater 18a and the second heater 18b to heat the central region and the edge region of the processing target substrate W held on the mounting table 14 to different temperatures.

Owner:TOKYO ELECTRON LTD

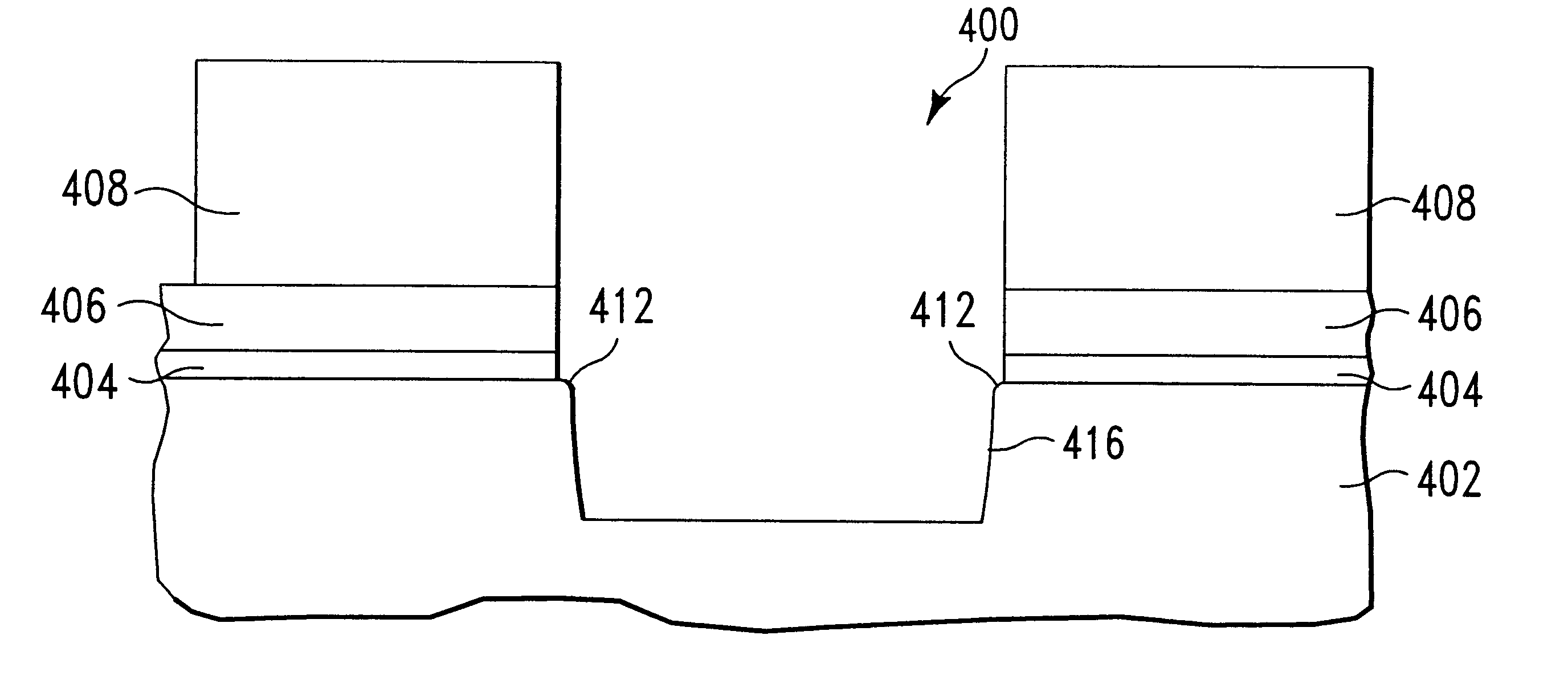

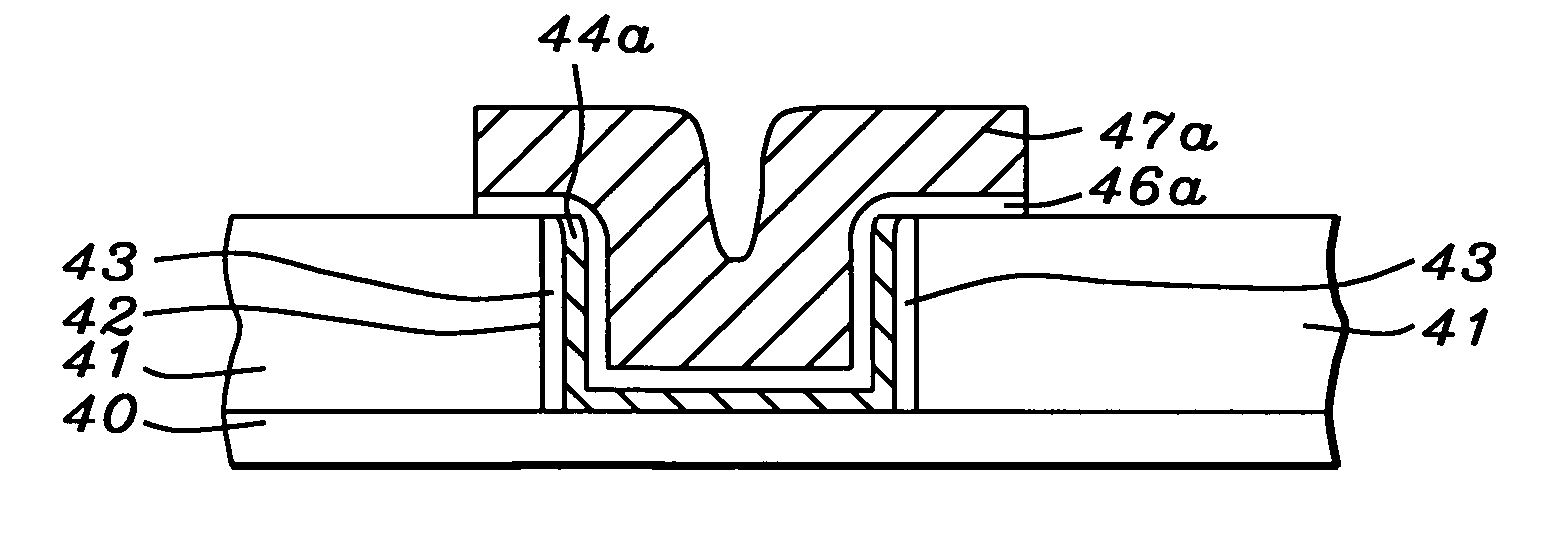

Method for etching a trench having rounded top and bottom corners in a silicon substrate

The present invention provides straight forward methods for plasma etching a trench having rounded top corners, or rounded bottom corners, or both in a silicon substrate. A first method for creating a rounded top corner on the etched silicon trench comprises etching both an overlying silicon oxide layer and an upper portion of the silicon substrate during a "break-through" step which immediately precedes the step in which the silicon trench is etched. The plasma feed gas for the break-through step comprises carbon and fluorine. In this method, the photoresist layer used to pattern the etch stack is preferably not removed prior to the break-through etching step. Subsequent to the break-through step, a trench is etched to a desired depth in the silicon substrate using a different plasma feed gas composition. A second method for creating a rounded top corner on the etched silicon trench comprises formation of a built-up extension on the sidewall of an overlying patterned silicon nitride hard mask during etch (break-through) of a silicon oxide adhesion layer which lies between the hard mask and a silicone substrate. The built-up extension upon the silicon nitride sidewall acts as a sacrificial masking material during etch of the silicon trench, delaying etching of the silicon at the outer edges of the top of the trench. This permits completion of trench etching with delayed etching of the top corner of the trench and provides a more gentle rounding (increased radius) at the top corners of the trench. During the etching of the silicon trench to its final dimensions, it is desirable to round the bottom corners of the finished silicon trench. We have discovered that a more rounded bottom trench corner is obtained using a two-step silicon etch process where the second step of the process is carried out at a higher process chamber pressure than the first step.

Owner:APPLIED MATERIALS INC

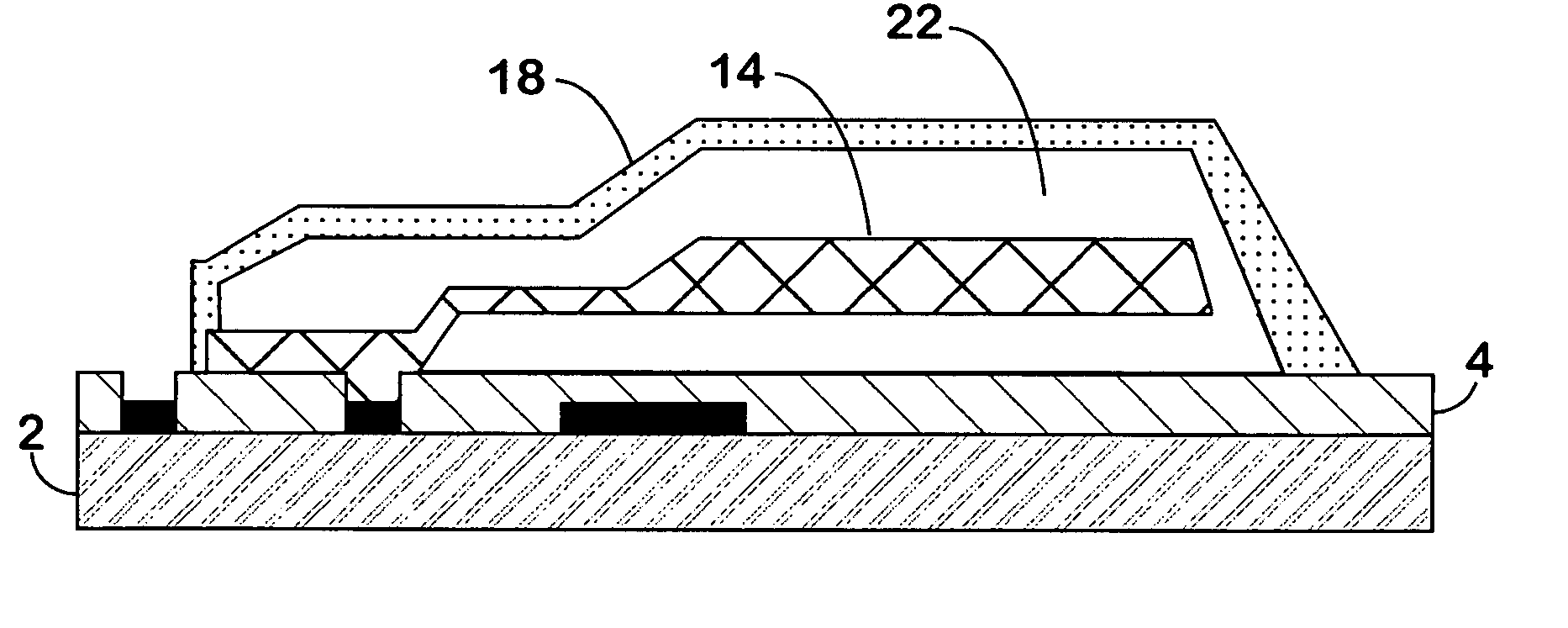

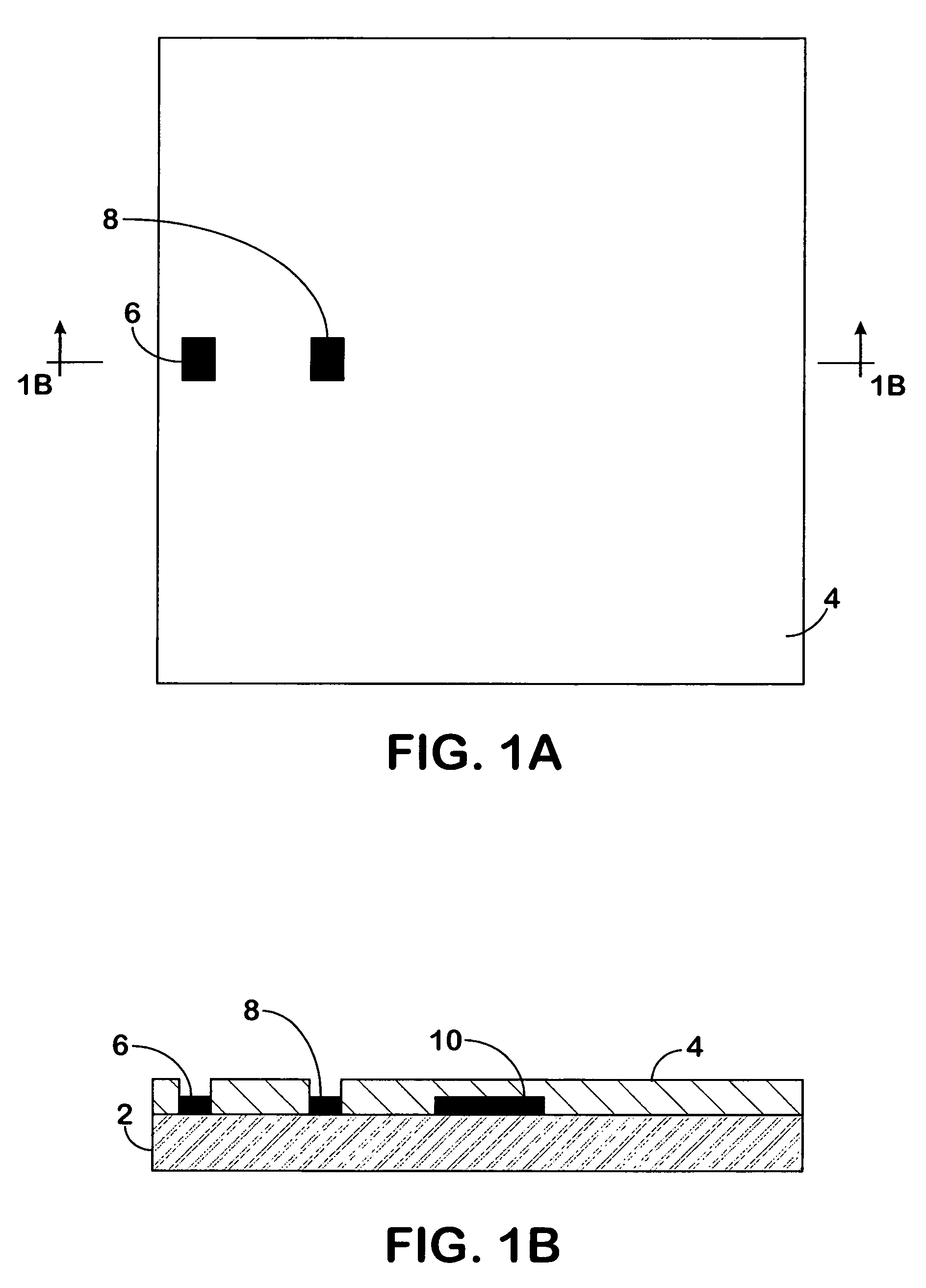

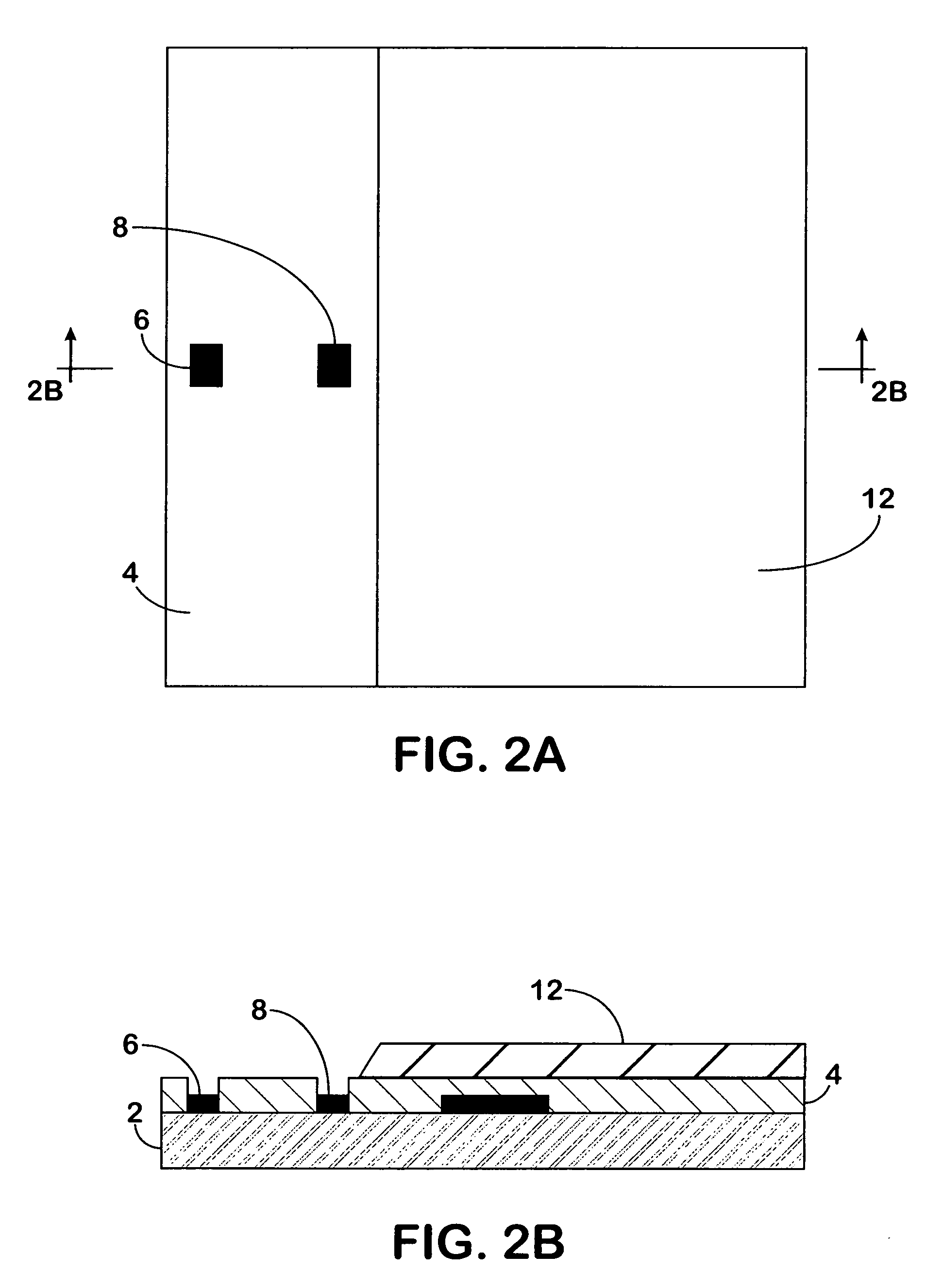

Manufacture of MEMS structures in sealed cavity using dry-release MEMS device encapsulation

InactiveUS7008812B1Eliminates undesirable liquid surface tensionIncrease etch rateAcceleration measurement using interia forcesSolid-state devicesMaterials sciencePlasma etching

The disclosed fabrication methodology addresses the problem of creating low-cost micro-electro-mechanical devices and systems, and, in particular, addresses the problem of delicate microstructures being damaged by the surface tension created as a wet etchant evaporates. This disclosure demonstrates a method for employing a dry plasma etch process to release encapsulated microelectromechanical components.

Owner:CYMATICS LAB CORP

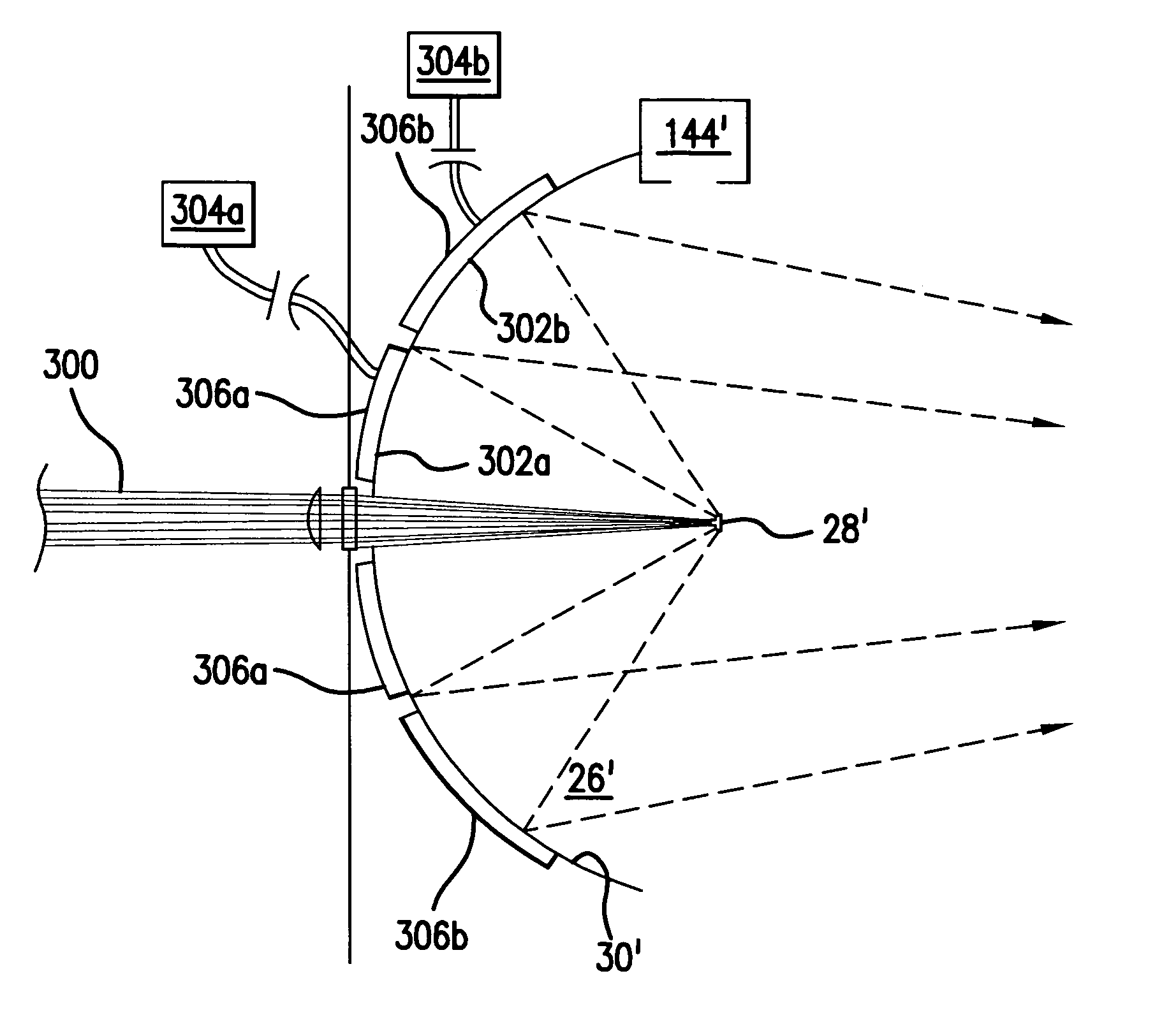

Systems and methods for reducing the influence of plasma-generated debris on the internal components of an EUV light source

ActiveUS7196342B2Prevented from reachingRadiation pyrometryLaser using scattering effectsSputteringHydrogen

Systems and methods are disclosed for reducing the influence of plasma generated debris on internal components of an EUV light source. In one aspect, an EUV meteorology monitor is provided which may have a heater to heat an internal multi-layer filtering mirror to a temperature sufficient to remove deposited debris from the mirror. In another aspect, a device is disclosed for removing plasma generated debris from an EUV light source collector mirror having a different debris deposition rate at different zones on the collector mirror. In a particular aspect, an EUV collector mirror system may comprise a source of hydrogen to combine with Li debris to create LiH on a collector surface; and a sputtering system to sputter LiH from the collector surface. In another aspect, an apparatus for etching debris from a surface of a EUV light source collector mirror with a controlled plasma etch rate is disclosed.

Owner:ASML NETHERLANDS BV

Selective etching of carbon-doped low-k dielectrics

InactiveUS20050026430A1High selectivityReducing micro-loadingDecorative surface effectsVacuum evaporation coatingPlasma etchingChemistry

The present invention includes a process for selectively etching a low-k dielectric material formed on a substrate using a plasma of a gas mixture in a plasma etch chamber. The gas mixture comprises a fluorine-rich fluorocarbon or hydrofluorocarbon gas, a nitrogen-containing gas, and one or more additive gases, such as a hydrogen-rich hydrofluorocarbon gas, an inert gas and / or a carbon-oxygen gas. The process provides a low-k dielectric to a photoresist mask etching selectivity ratio greater than about 5:1, a low-k dielectric to a barrier / liner layer etching selectivity ratio greater about 10:1, and a low-k dielectric etch rate higher than about 4000 Å / min.

Owner:APPLIED MATERIALS INC

Sequential infiltration synthesis for enhancing multiple-patterning lithography

ActiveUS9684234B2Reduce in quantityImprove throughputDecorative surface effectsSemiconductor/solid-state device manufacturingPhotoresistMultiple patterning lithography

Simplified methods of multiple-patterning photolithography using sequential infiltration synthesis to modify the photoresist such that it withstands plasma etching better than unmodified resist and replaces one or more hard masks and / or a freezing step in MPL processes including litho-etch-litho-etch photolithography or litho-freeze-litho-etch photolithography.

Owner:UCHICAGO ARGONNE LLC

Plasma etching method and semiconductor device manufacturing method

ActiveUS20140234992A1Semiconductor/solid-state device testing/measurementElectric discharge tubesDevice materialPhysical chemistry

A plasma etching method is provided for etching a substrate corresponding to an etching object within an etching apparatus that includes a supply condition adjustment unit for adjusting a supply condition for supplying etching gas to the substrate, a temperature adjustment unit for adjusting a temperature of the substrate placed on a stage along a radial direction, and a plasma generating unit for generating plasma within a space between the supply condition adjustment unit and the stage. The plasma etching method includes a control step in which the temperature adjustment unit controls the temperature of the substrate to be uniform within a substrate plane of the substrate, and an adjustment step in which the supply condition adjustment unit adjusts a concentration distribution of active species contained in the plasma generated by the plasma generation unit within the space above the substrate.

Owner:TOKYO ELECTRON LTD

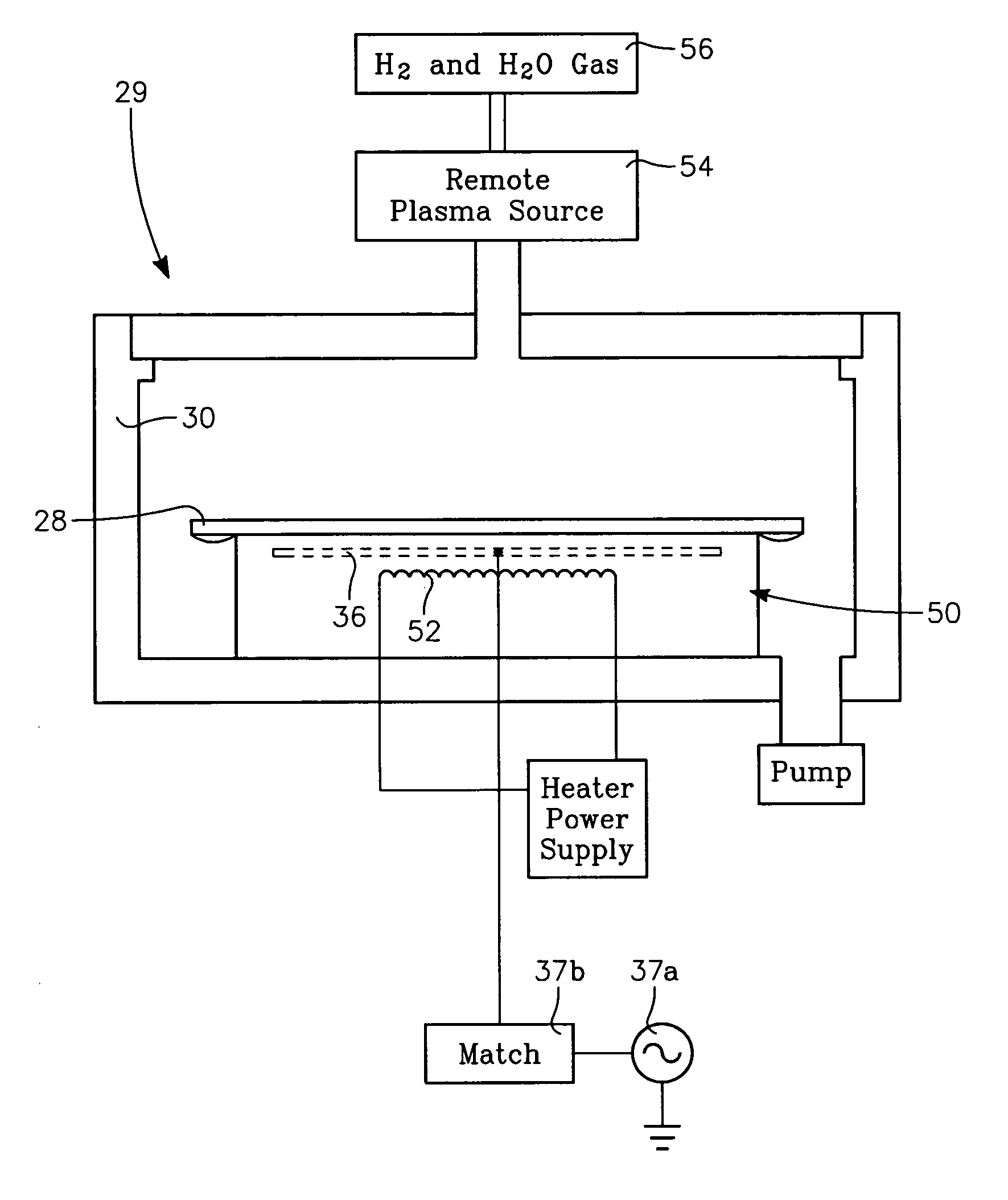

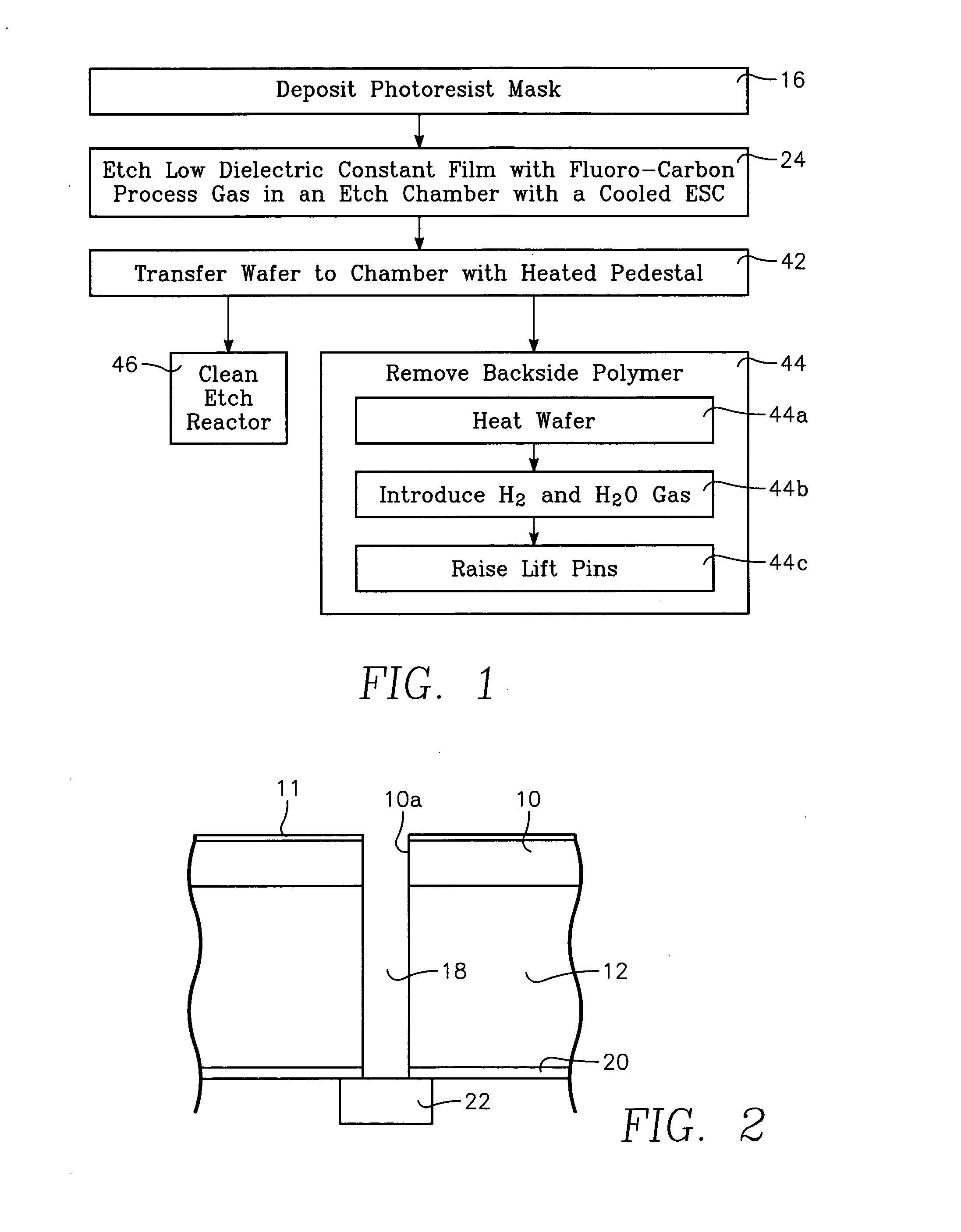

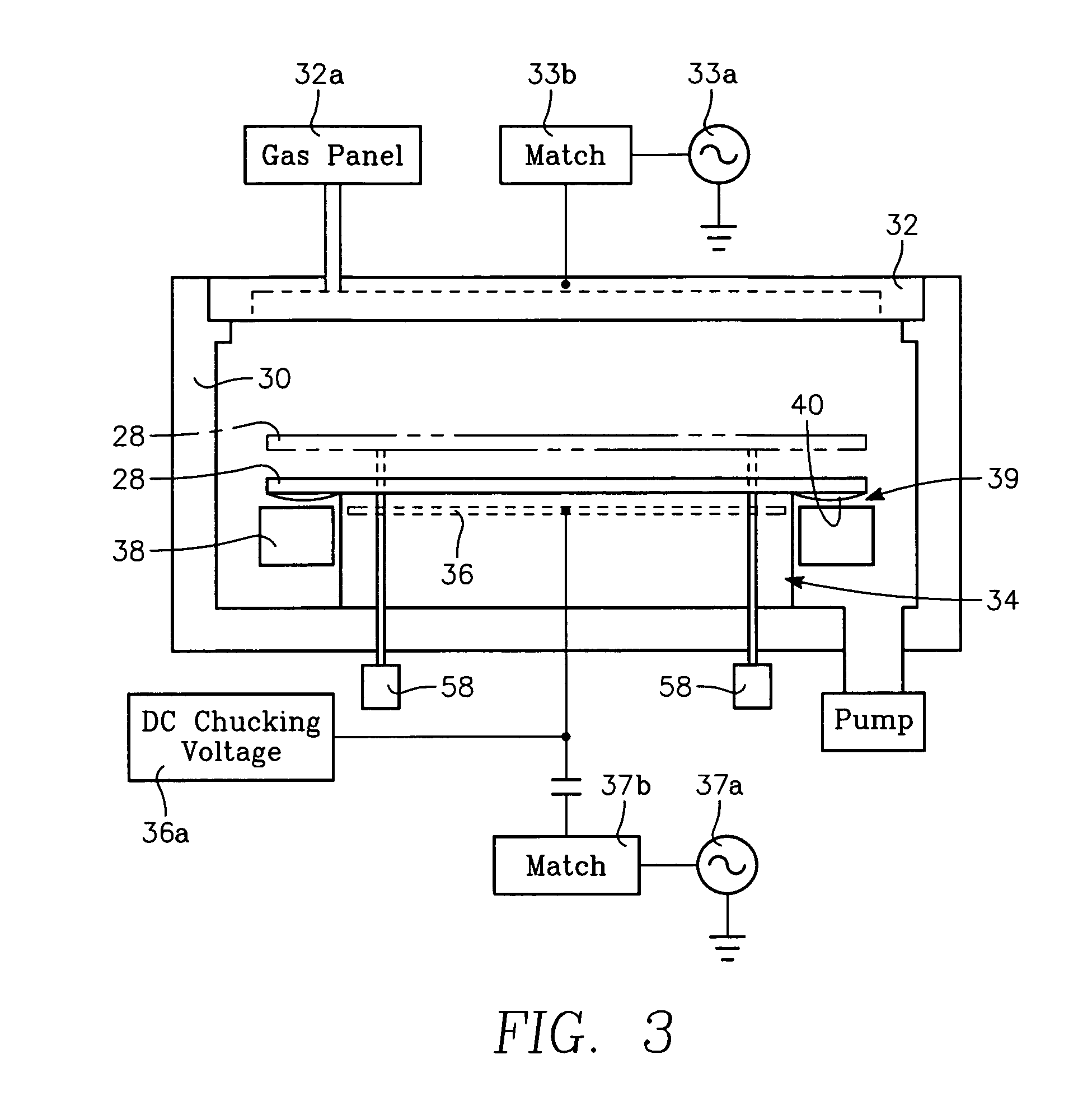

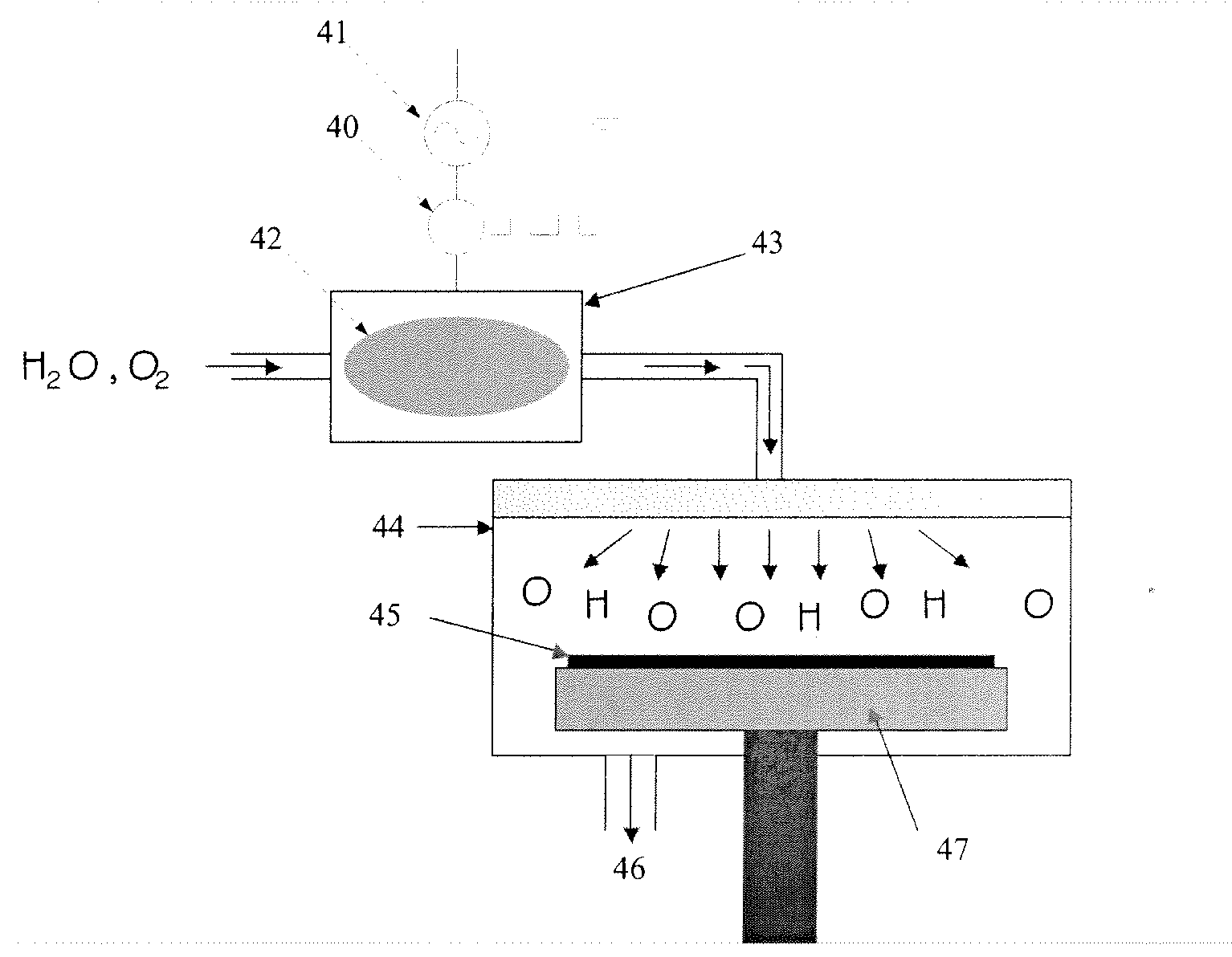

Plasma dielectric etch process including ex-situ backside polymer removal for low-dielectric constant material

A plasma etch process for etching a porous carbon-doped silicon oxide dielectric layer using a photoresist mask is carried out first in an etch reactor by performing a fluorocarbon based etch process on the workpiece to etch exposed portions of the dielectric layer while depositing protective fluorocarbon polymer on the photoresist mask. Then, in an ashing reactor, polymer and photoresist are removed by heating the workpiece to over 100 degrees C., exposing a peripheral portion of the backside of said workpiece, and providing products from a plasma of a hydrogen process gas to reduce carbon contained in polymer and photoresist on said workpiece until the polymer has been removed from a backside of said workpiece. The process gas preferably contains both hydrogen gas and water vapor, although the primary constituent is hydrogen gas. The wafer (workpiece) backside may be exposed by extending the wafer lift pins.

Owner:APPLIED MATERIALS INC

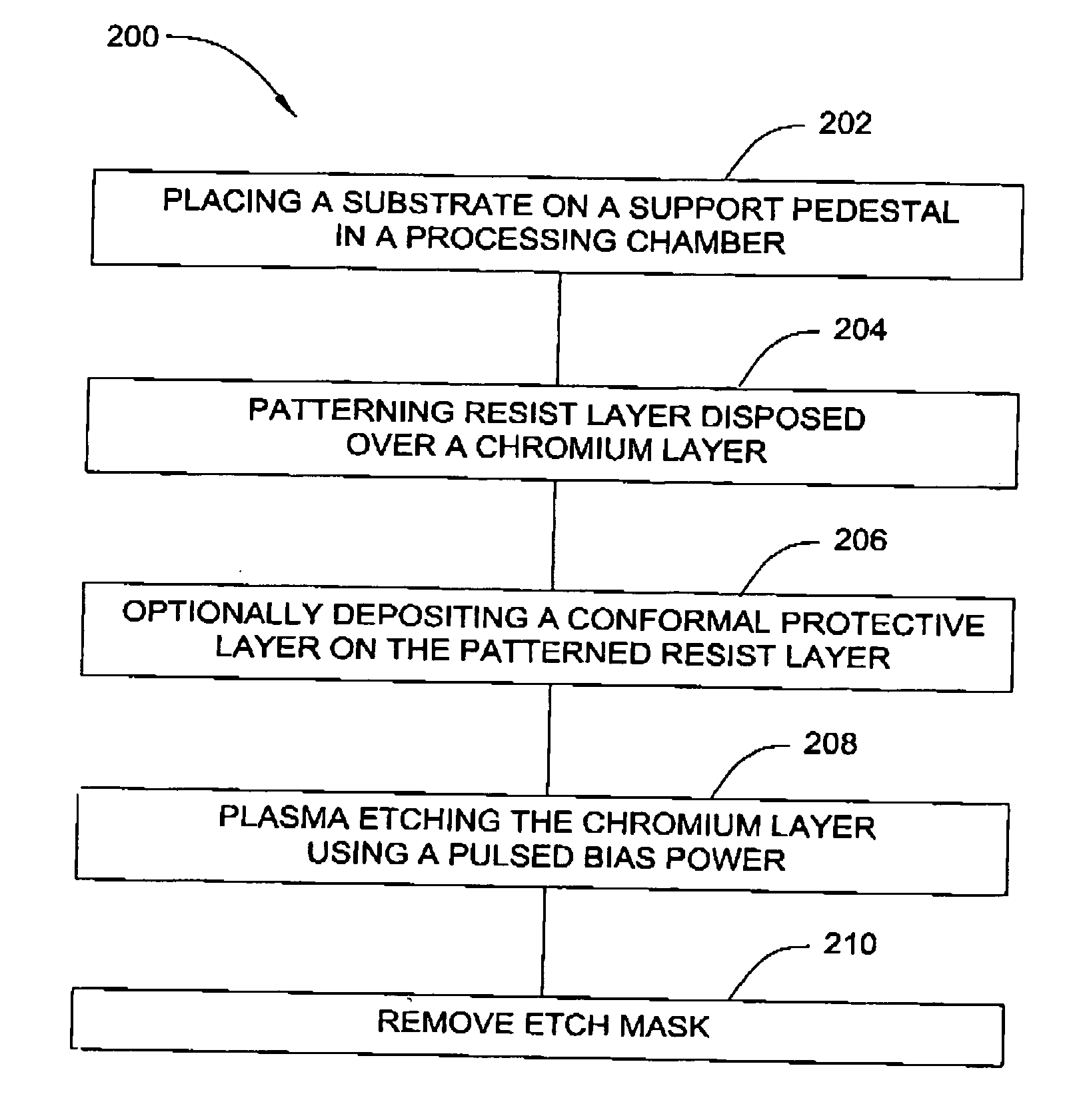

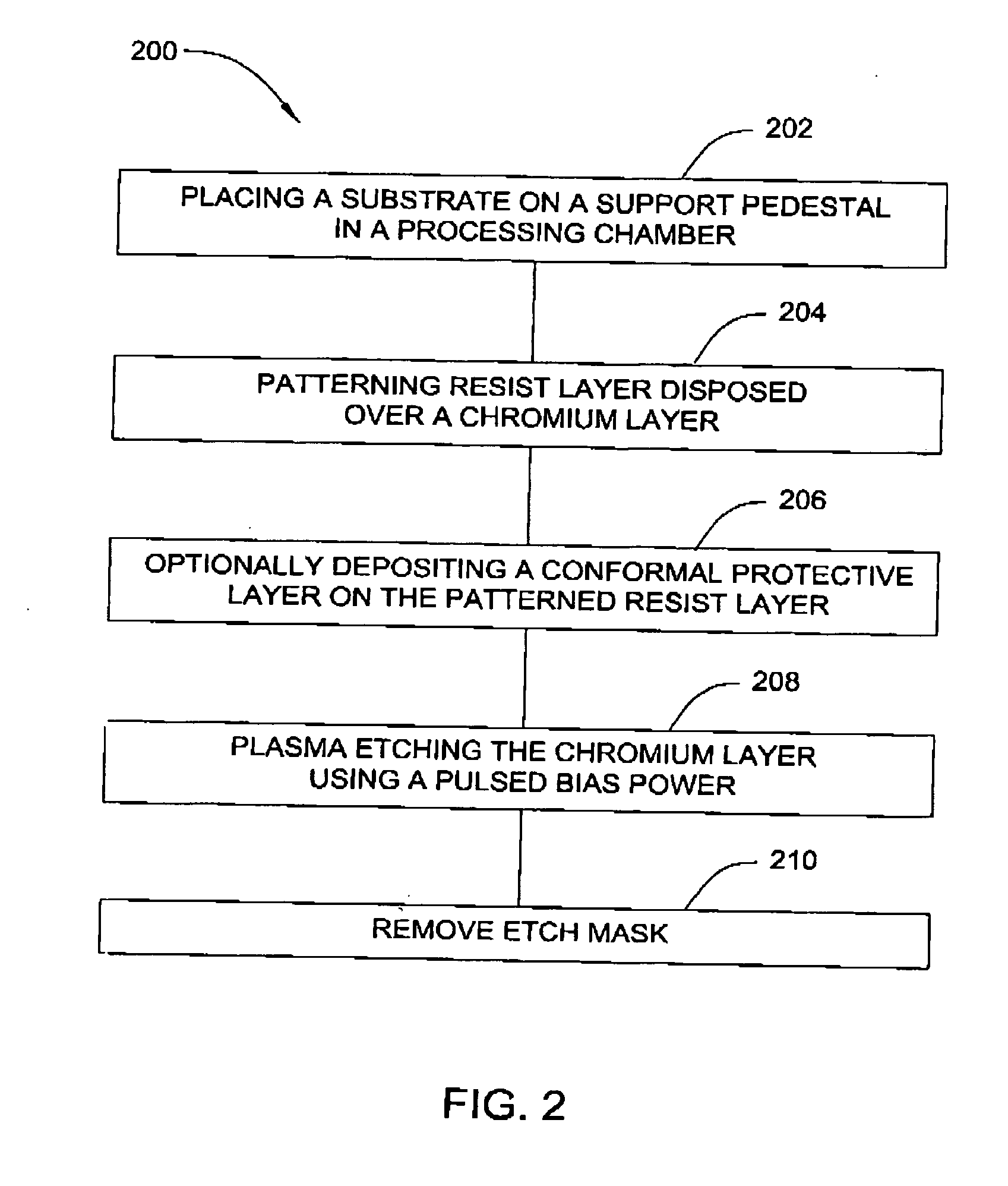

Method for plasma etching a chromium layer suitable for photomask fabrication

A method for etching a chromium layer is provided herein. In one embodiment, a method for etching a chromium layer includes providing a filmstack in an etching chamber, the filmstack having a chromium layer partially exposed through a patterned layer, providing at least one halogen containing process gas to a processing chamber, biasing the layer disposed on a substrate support in the processing chamber with a plurality of power pulses less than 600 Watts, and etching the chromium layer through a patterned mask. The method for plasma etching a chromium layer described herein is particularly suitable for fabricating photomasks.

Owner:APPLIED MATERIALS INC

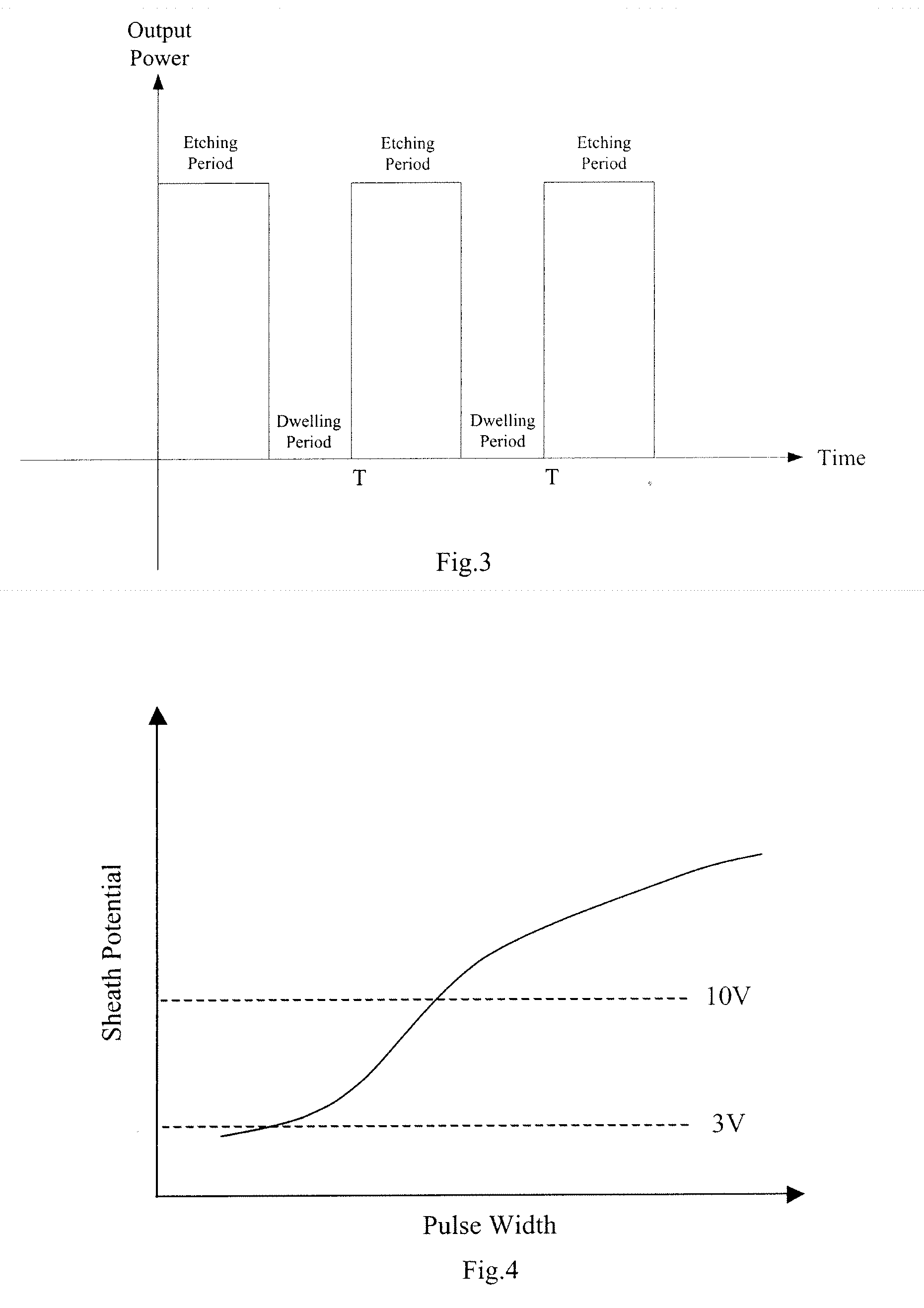

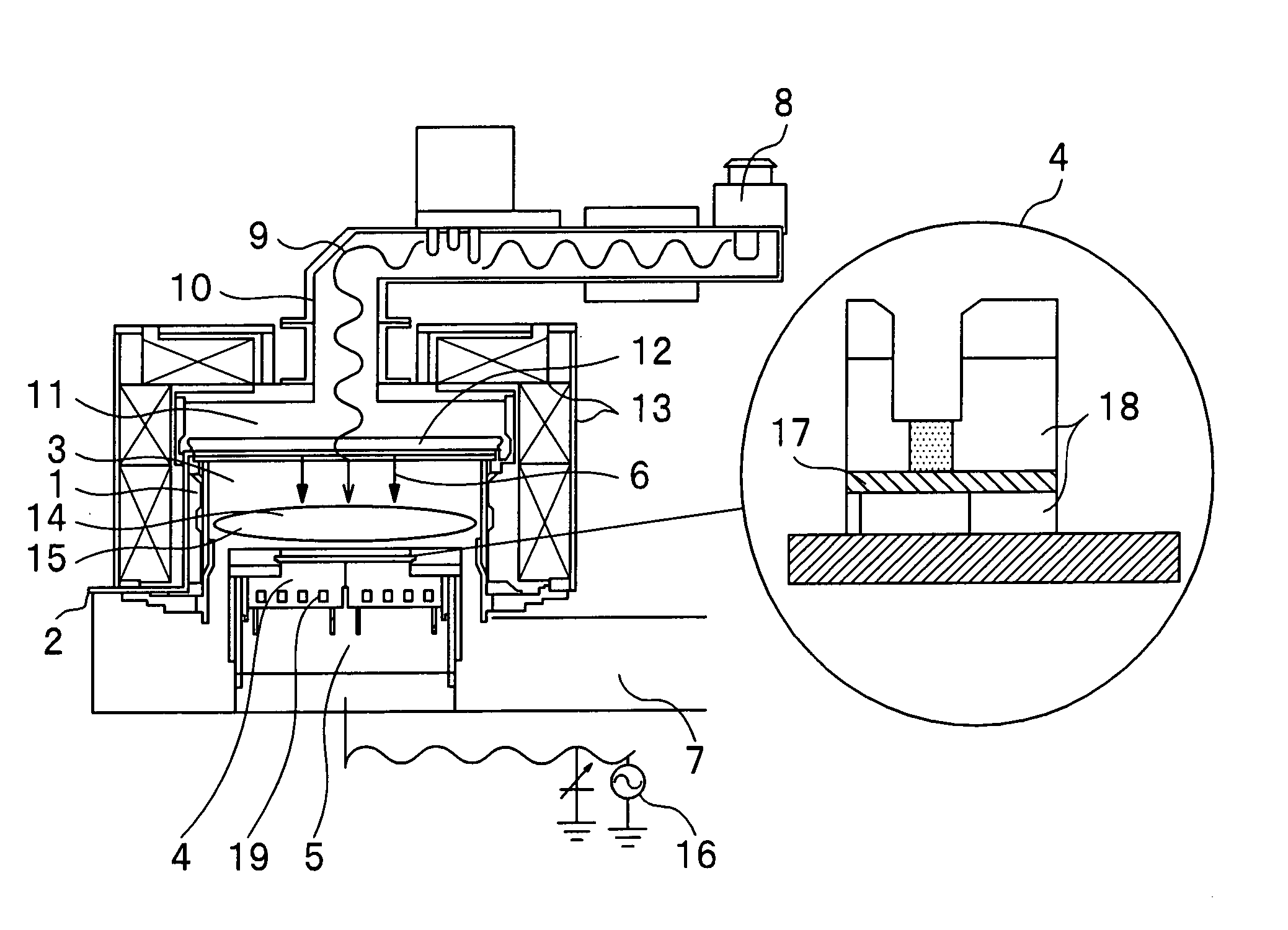

Pulsed plasma etching method and apparatus

InactiveUS20080081483A1High precisionEasy to controlElectric discharge tubesSemiconductor/solid-state device manufacturingPulse controlRadio frequency

A plasma etching method includes preparing in a reaction chamber a semiconductor substrate on which a material layer to be etched is provided; and injecting an etching gas into the reaction chamber, the etching gas being ionized through an RF (Radio Frequency) power source to generate a plasma, wherein the RF power source outputs RF power in a pulse output mode. The plasma etching apparatus includes a reaction chamber adapted to contain an etching gas; and an RF power source adapted to output RF power for excitation of the etching gas to generate plasma, wherein the apparatus further include a pulse control circuit adapted to control the RF power source to output RF power in a pulse output mode. With the invention, the plasma for etching can be generated in a pulse output mode, thus improving a precision of an endpoint where the etching can be disabled.

Owner:SEMICON MFG INT (SHANGHAI) CORP

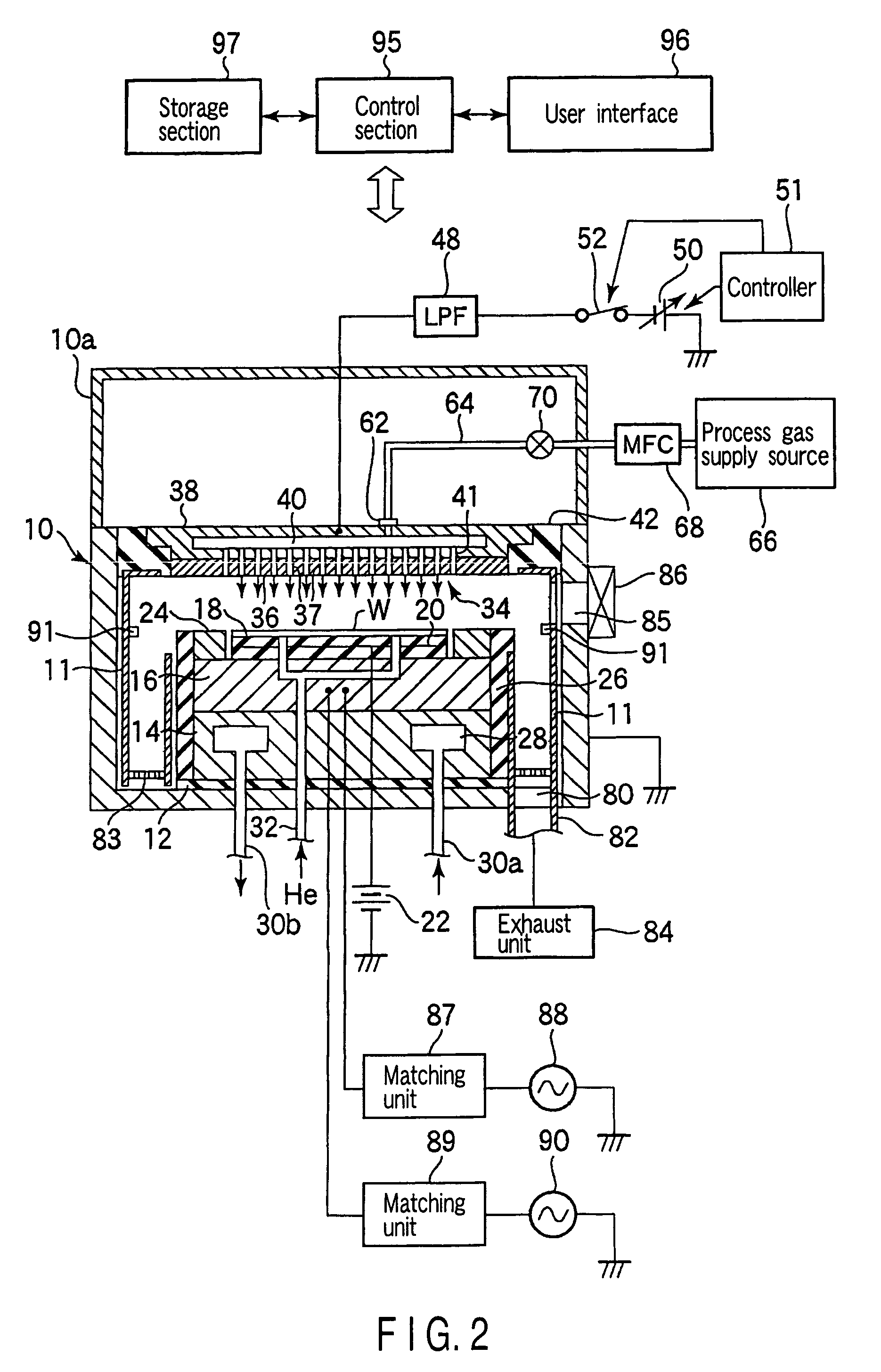

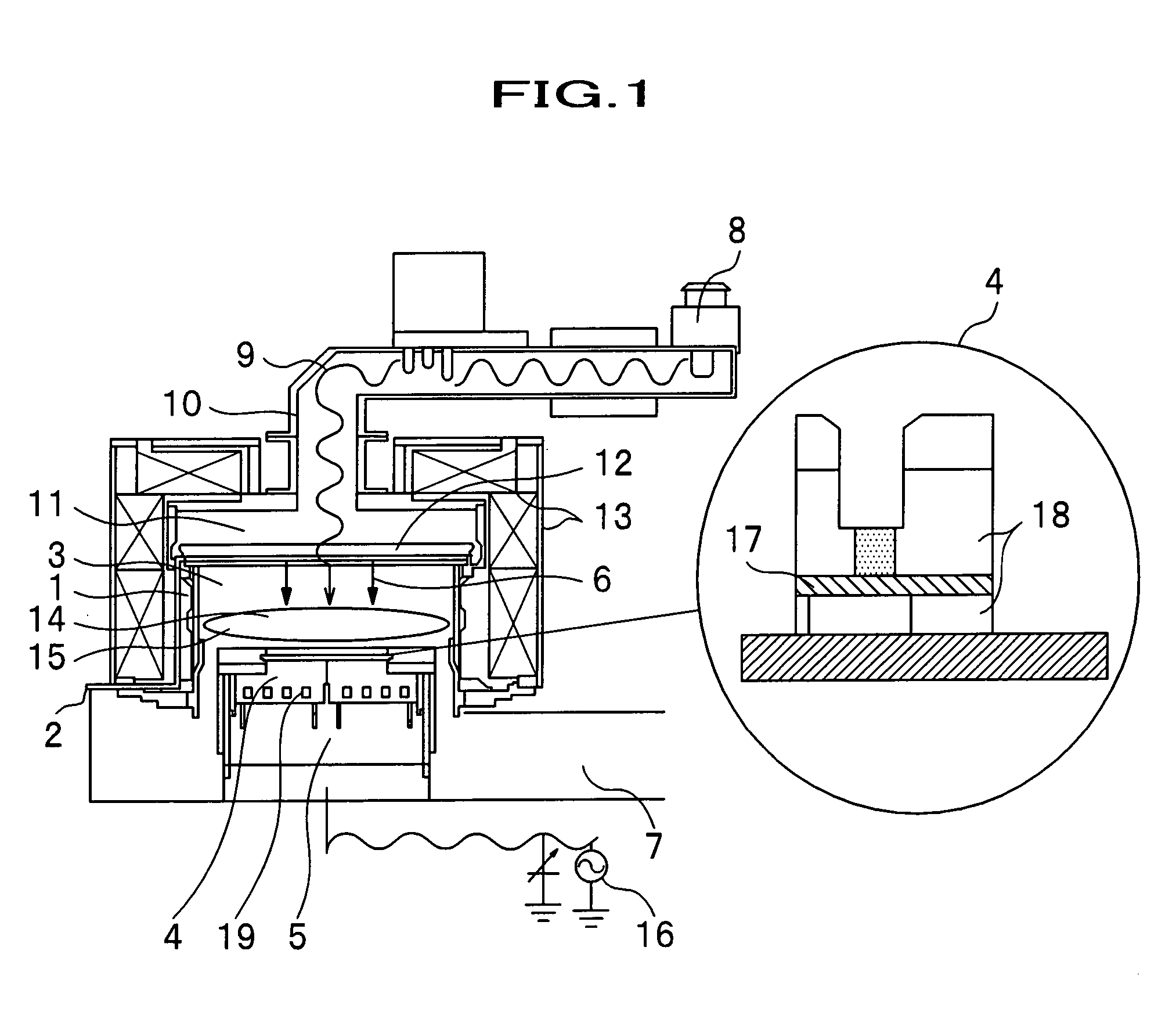

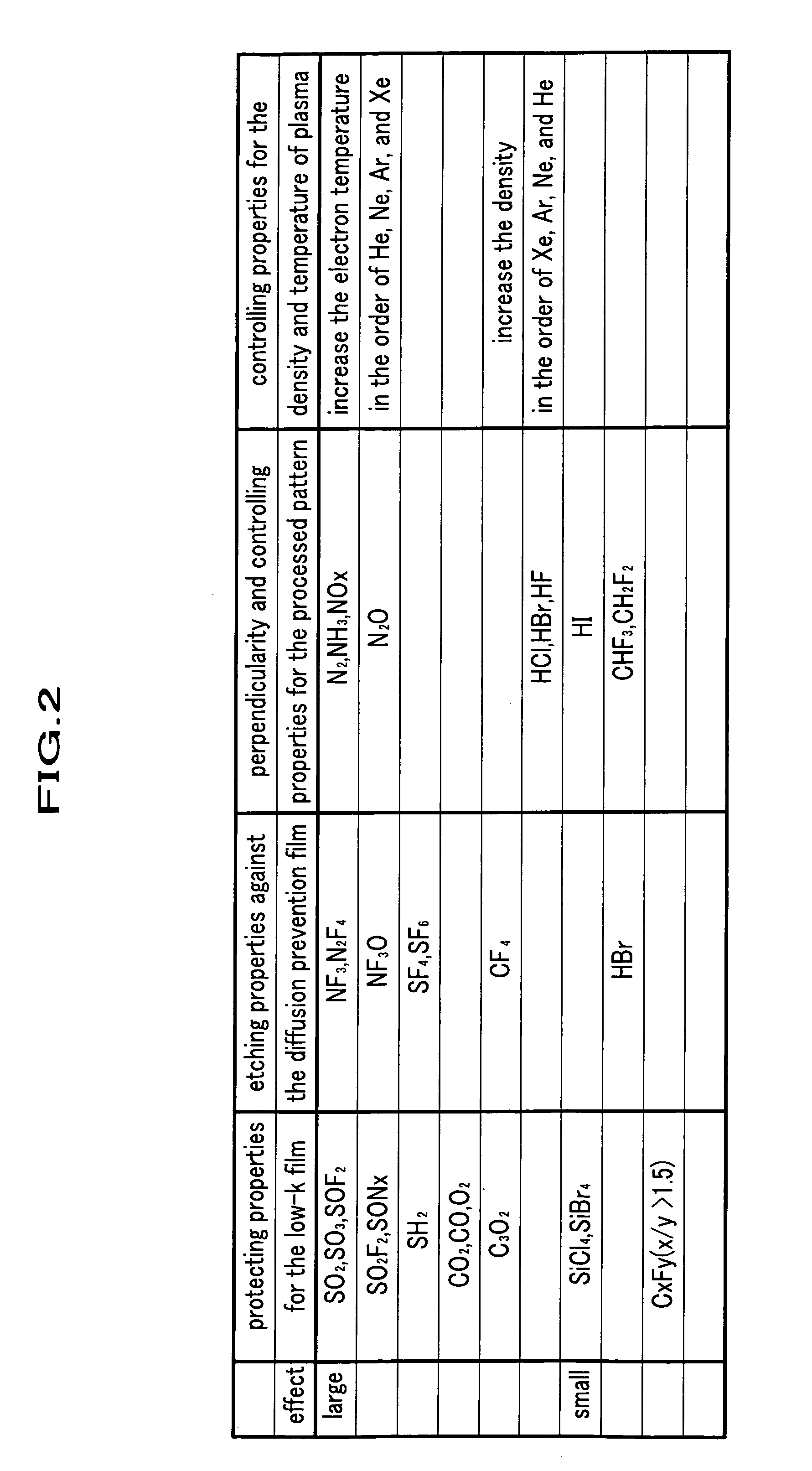

LSI device etching method and apparatus thereof

InactiveUS20050026431A1Realize processingImprove the protective effectSemiconductor/solid-state device manufacturingInterconnectionRadio frequency

An apparatus for performing a plasma-etching of a LSI device including a Cu interconnection, a low-k film, and a diffusion prevention film has a treatment chamber, into which an etching gas is introduced, and a support table which is equipped with electrodes and on which said LSI device is placed. In this apparatus, the etching gasses are turned into plasma by supplying radio frequency power to electrodes provided within the treatment chamber, so that the LSI device is etched with ions of the plasma. In this apparatus, a sulfur-containing gas and a fluorine-containing gas are mixed to the etching gasses, so that the diffusion prevention film is selectively etched against the low-k film.

Owner:HITACHI HIGH-TECH CORP

Plasma Treatment Method and Plasma Etching Method

InactiveUS20080085604A1Improve accuracySuitable for processingSemiconductor/solid-state device manufacturingGreenhouse effectElectric field

The present invention develops a process for plasma treatment using a gas having no greenhouse effect in order to realize global environmental preservation and sophistication of plasma process performance and provides a process for plasma etching with high accuracy which process can depress damage to devices. The process for plasma treatment according to the present invention comprises the steps of feeding a treatment gas containing fluorine gas (F2) into a plasma generating chamber, alternately repeating application of high frequency electric field and stop of the application thereof to generate plasma, and carrying out substrate treatment by irradiating the plasma to a substrate. Furthermore, the substrate treatment may be carried out by individually or alternately extracting negative ions or positive ions from the plasma, or selectively extracting only negative ions, neutralizing them, to generate a neutral beam and irradiating the neutral beam to the substrate.

Owner:SHOWA DENKO KK +1

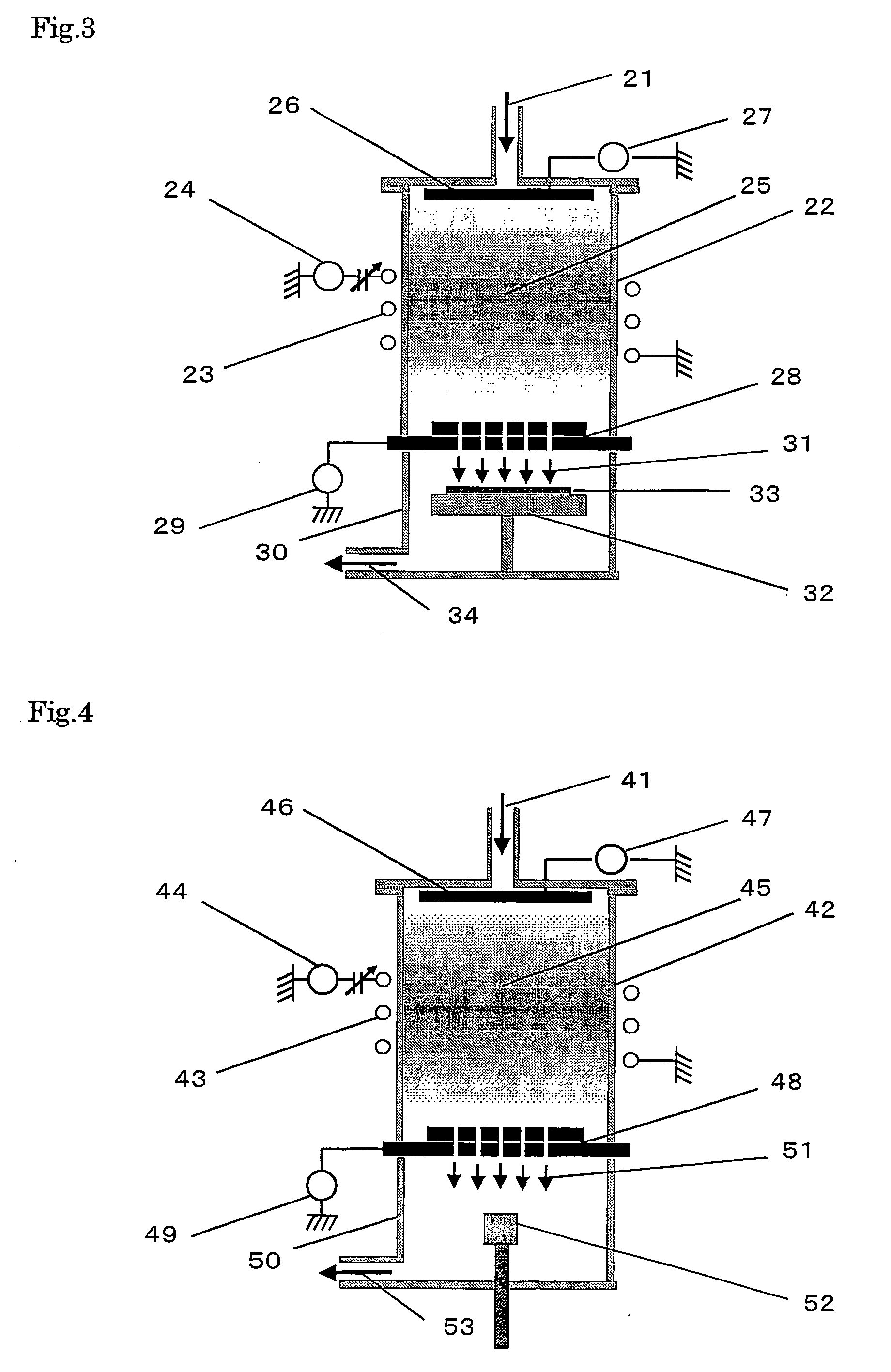

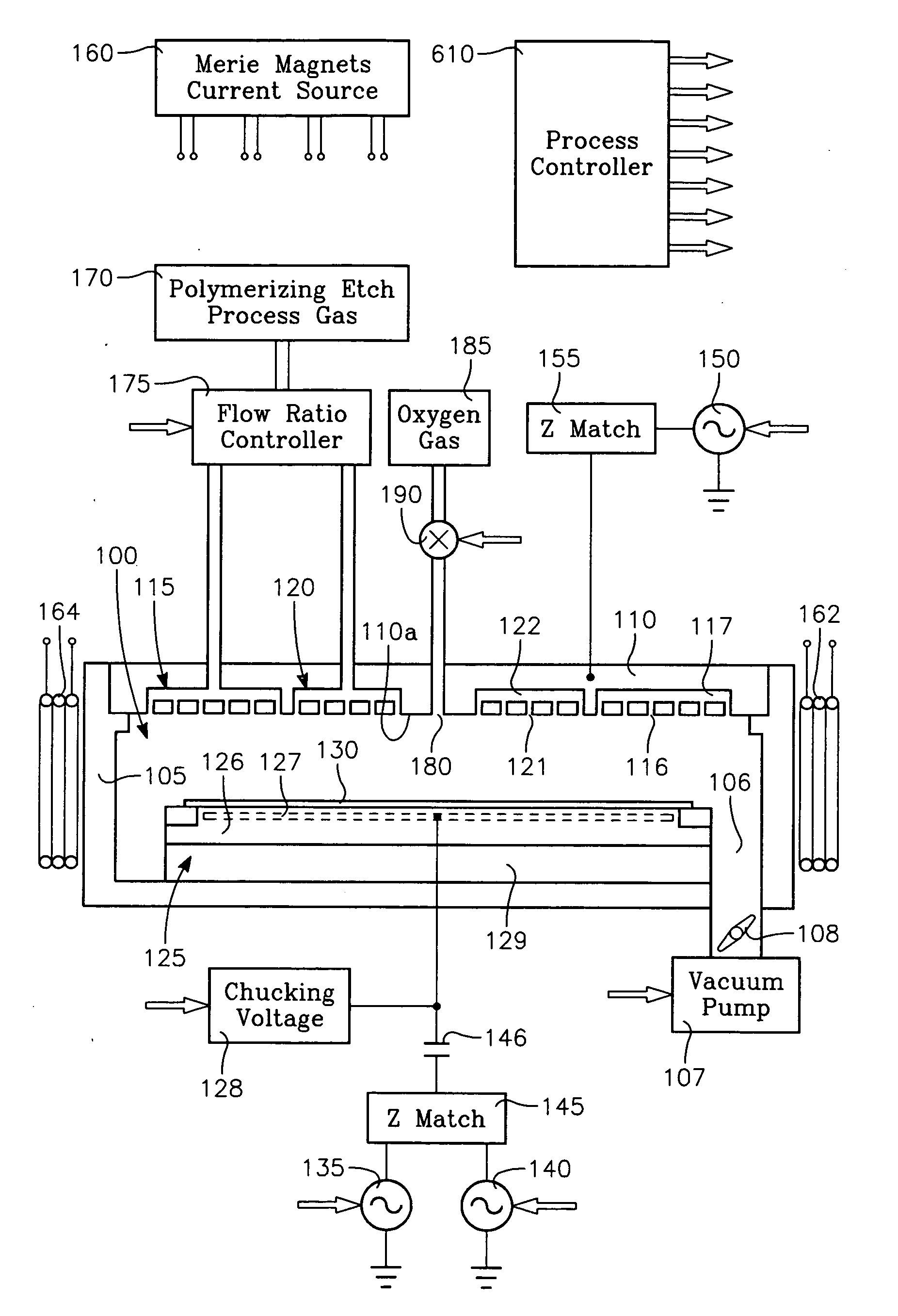

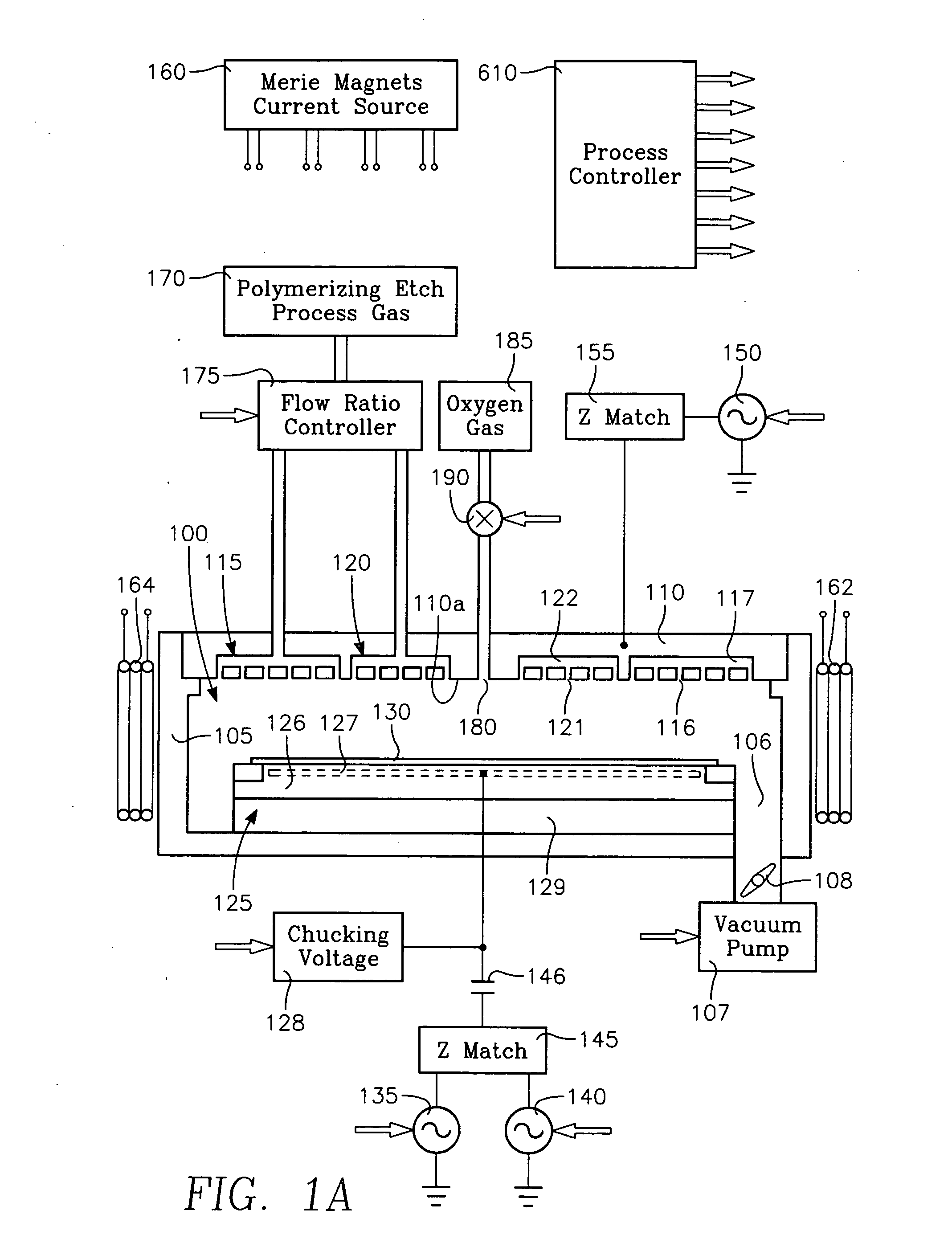

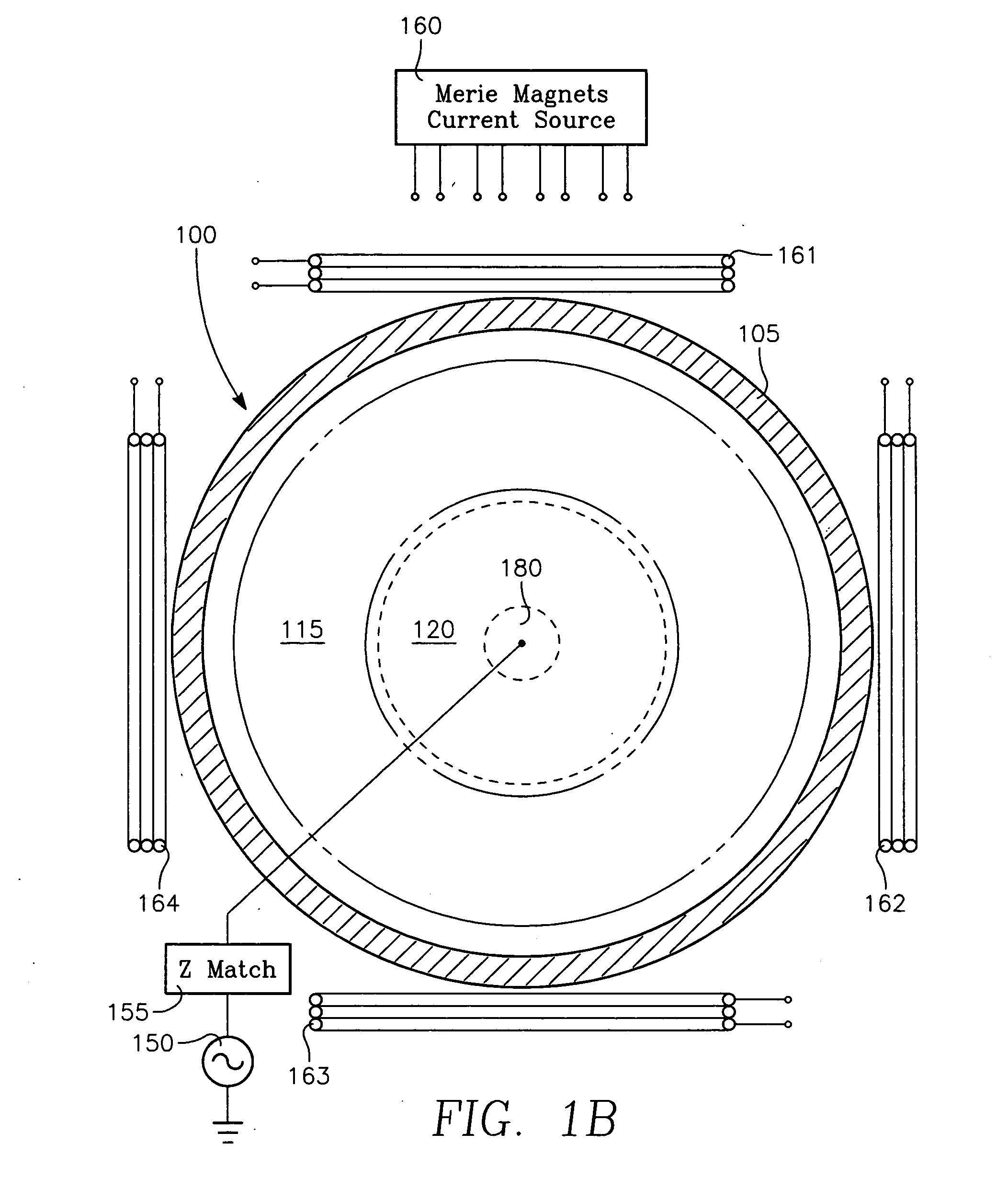

Plasma etch reactor with distribution of etch gases across a wafer surface and a polymer oxidizing gas in an independently fed center gas zone

A plasma etch reactor for plasma enhanced etching of a workpiece such as a semiconductor wafer includes a housing defining a process chamber, a workpiece support configured to support a workpiece within the chamber during processing and comprising a plasma bias power electrode. The reactor further includes a first process gas inlet coupled to receive predominantly or pure oxygen gas and a second process gas inlet coupled to receive a polymerizing etch process gas. The reactor has a ceiling plasma source power electrode including a center circular gas disperser configured to receive a process gas from the first process gas inlet and to distribute the process gas into the chamber over the workpiece, and an inner annular gas disperser centered around the center gas disperser configured to receive the process gas from the second process gas inlet and to distribute the process gas into the chamber over the workpiece through an inner plurality of injection ports.

Owner:APPLIED MATERIALS INC

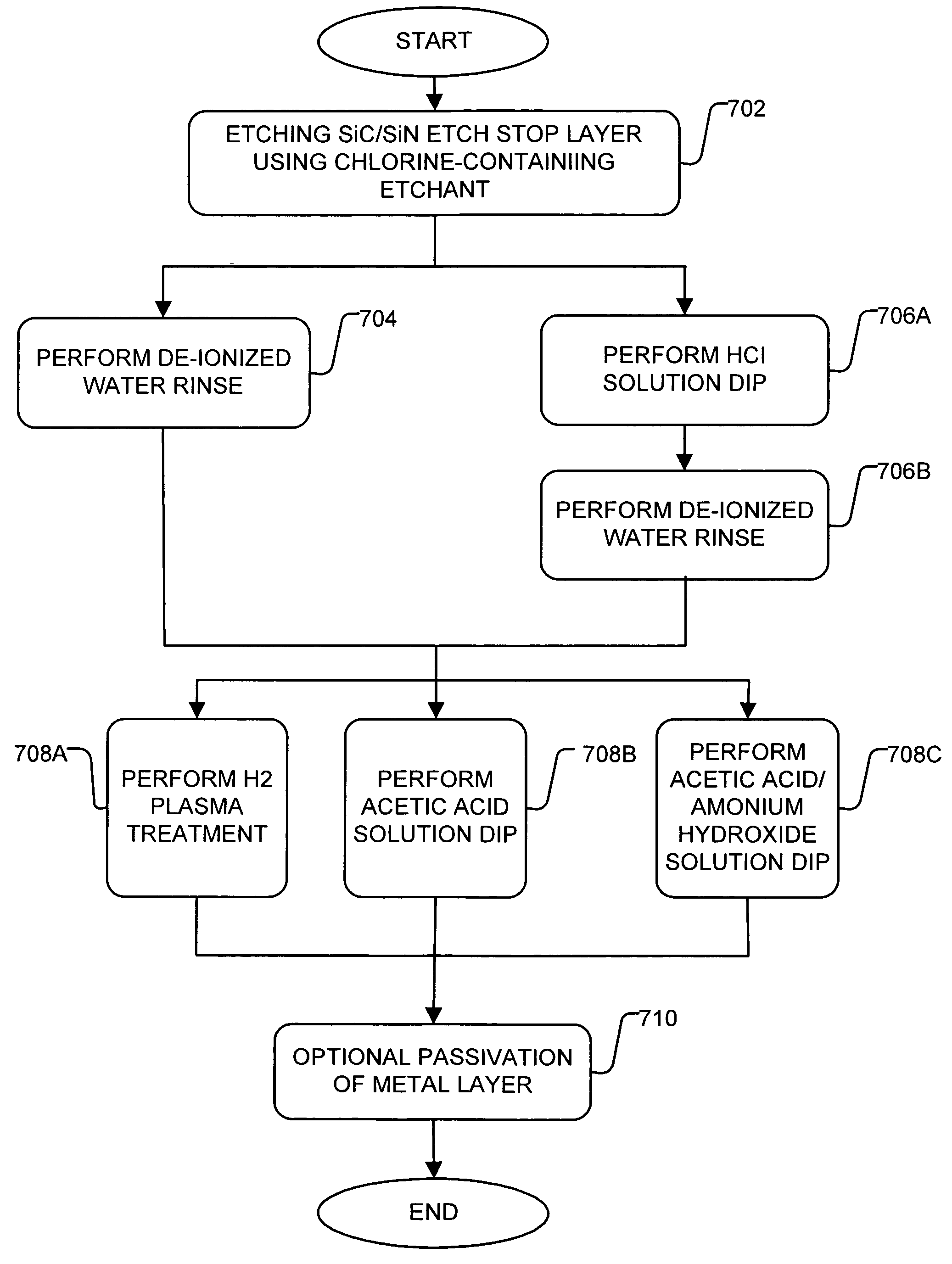

Treatment for corrosion in substrate processing

InactiveUS7084070B1Semiconductor/solid-state device manufacturingElectrostatic cleaningAcetic acidAmmonium hydroxide

A method for processing substrate to form a semiconductor device is disclosed. The substrate includes an etch stop layer disposed above a metal layer. The method includes etching through the etch stop layer down to the copper metal layer, using a plasma etch process that utilizes a chlorine-containing etchant source gas, thereby forming etch stop layer openings in the etch stop layer. The etch stop layer includes at least one of a SiN and SiC material. Thereafter, the method includes performing a wet treatment on the substrate using a solution that contains acetic acid (CH3COOH) or acetic acid / ammonium hydroxide (NH4OH) to remove at least some of the copper oxides. Alternatively, the copper oxides may be removed using a H2 plasma. BTA passivation may be optionally performed on the substrate.

Owner:LAM RES CORP

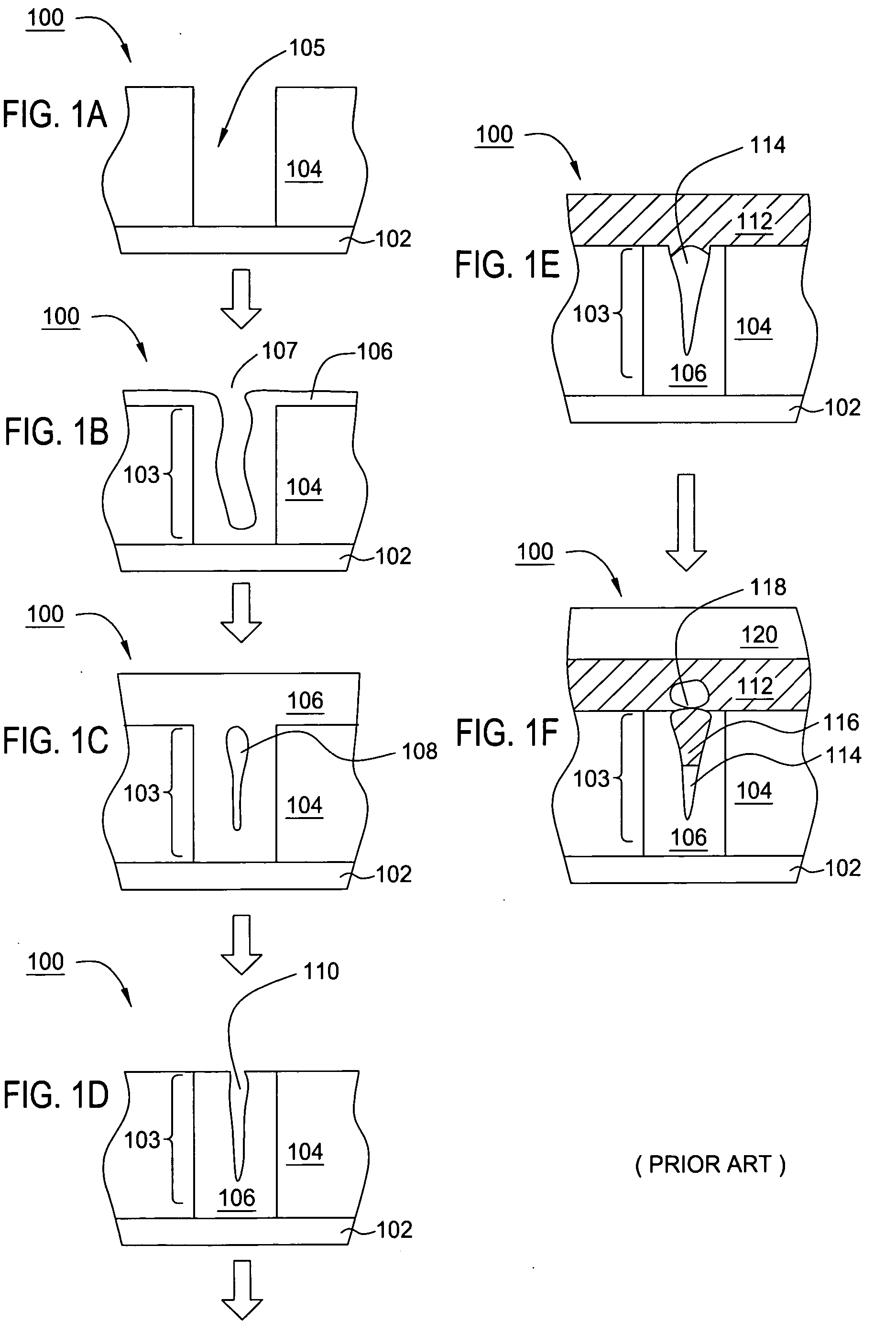

Electroless deposition process on a silicide contact

InactiveUS20060246217A1Material nanotechnologySemiconductor/solid-state device manufacturingSalicideElectroless deposition

Embodiments as described herein provide methods for depositing a material on a substrate during electroless deposition processes, as well as compositions of the electroless deposition solutions. In one embodiment, the substrate contains a contact aperture having an exposed silicon contact surface. In another embodiment, the substrate contains a contact aperture having an exposed silicide contact surface. The apertures are filled with a metal contact material by exposing the substrate to an electroless deposition process. The metal contact material may contain a cobalt material, a nickel material, or alloys thereof. Prior to filling the apertures, the substrate may be exposed to a variety of pretreatment processes, such as preclean processes and activations processes. A preclean process may remove organic residues, native oxides, and other contaminants during a wet clean process or a plasma etch process. Embodiments of the process also provide the deposition of additional layers, such as a capping layer.

Owner:APPLIED MATERIALS INC

Zirconium oxide and hafnium oxide etching using halogen containing chemicals

ActiveUS20050164479A1Effective meanSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHafnium

A method is described for selectively etching a high k dielectric layer that is preferably a hafnium or zirconium oxide, silicate, nitride, or oxynitride with a selectivity of greater than 2:1 relative to silicon oxide, polysilicon, or silicon. The plasma etch chemistry is comprised of one or more halogen containing gases such as CF4, CHF3, CH2F2, CH3F, C4F8, C4F6, C5F6, BCl3, Br2, HF, HCl, HBr, HI, and NF3 and leaves no etch residues. An inert gas or an inert gas and oxidant gas may be added to the halogen containing gas. In one embodiment, a high k gate dielectric layer is removed on portions of an active area in a MOS transistor. Alternatively, the high k dielectric layer is used in a capacitor between two conducting layers and is selectively removed from portions of an ILD layer.

Owner:TAIWAN SEMICON MFG CO LTD

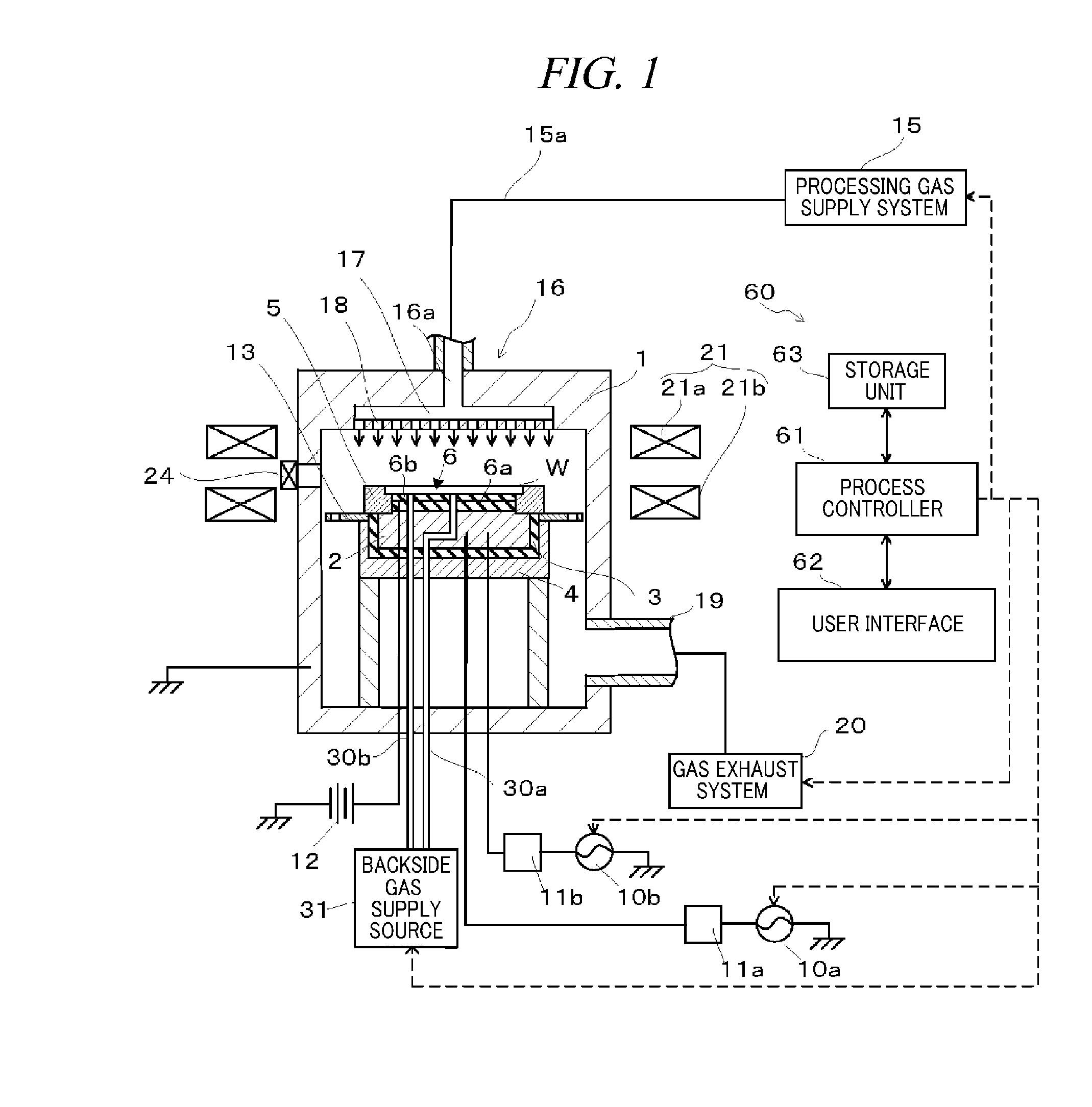

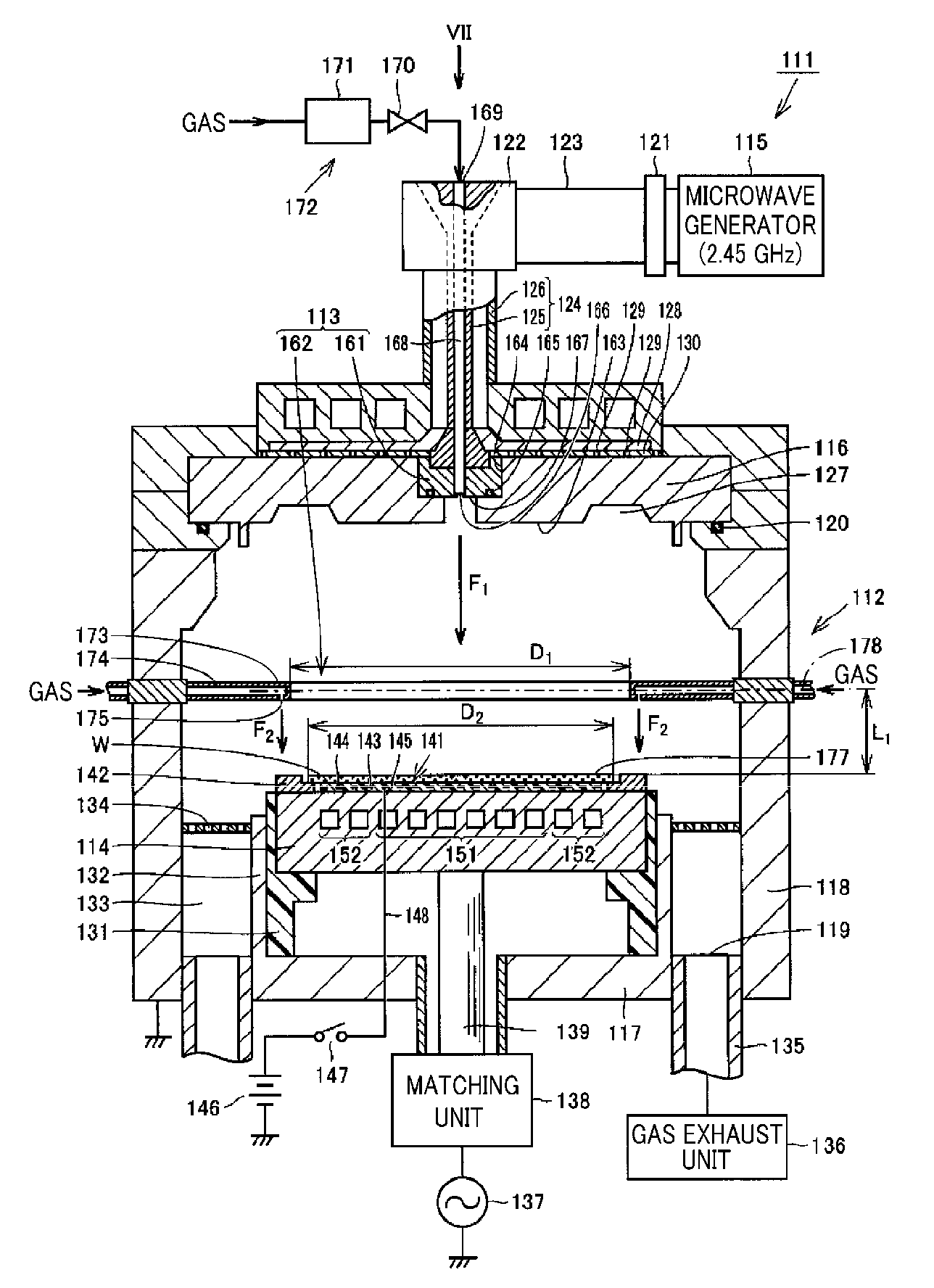

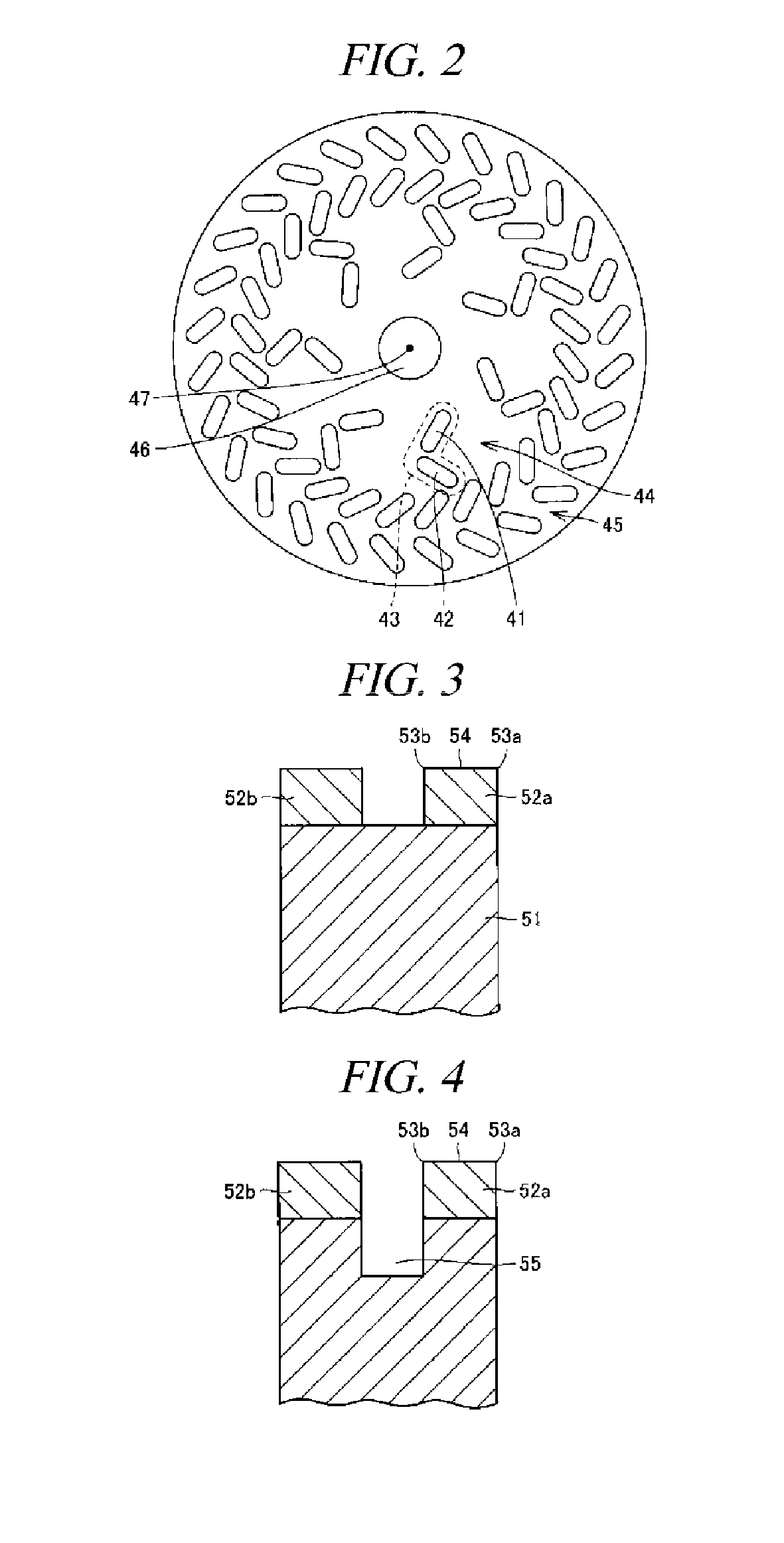

Plasma etching apparatus, plasma etching method, and semiconductor device manufacturing method

ActiveUS20120064726A1More accuracyDesirable shapeElectric discharge tubesSemiconductor/solid-state device manufacturingDevice materialControl cell

There is provided a plasma etching apparatus provided for performing an etching in a desirable shape. The plasma etching apparatus includes a processing chamber 12 for performing a plasma process on a target substrate W; a gas supply unit 13 for supplying a plasma processing gas into the processing chamber 12; a supporting table positioned within the processing chamber 12 and configured to support the target substrate thereon; a microwave generator 15 for generating a microwave for plasma excitation; a plasma generation unit for generating plasma within the processing chamber 12 by using the generated microwave; a pressure control unit for controlling a pressure within the processing chamber 12; a bias power supply unit for supplying AC bias power to the supporting table 14; and a control unit for controlling the AC bias power by alternately repeating supply and stop of the AC bias power.

Owner:TOKYO ELECTRON LTD

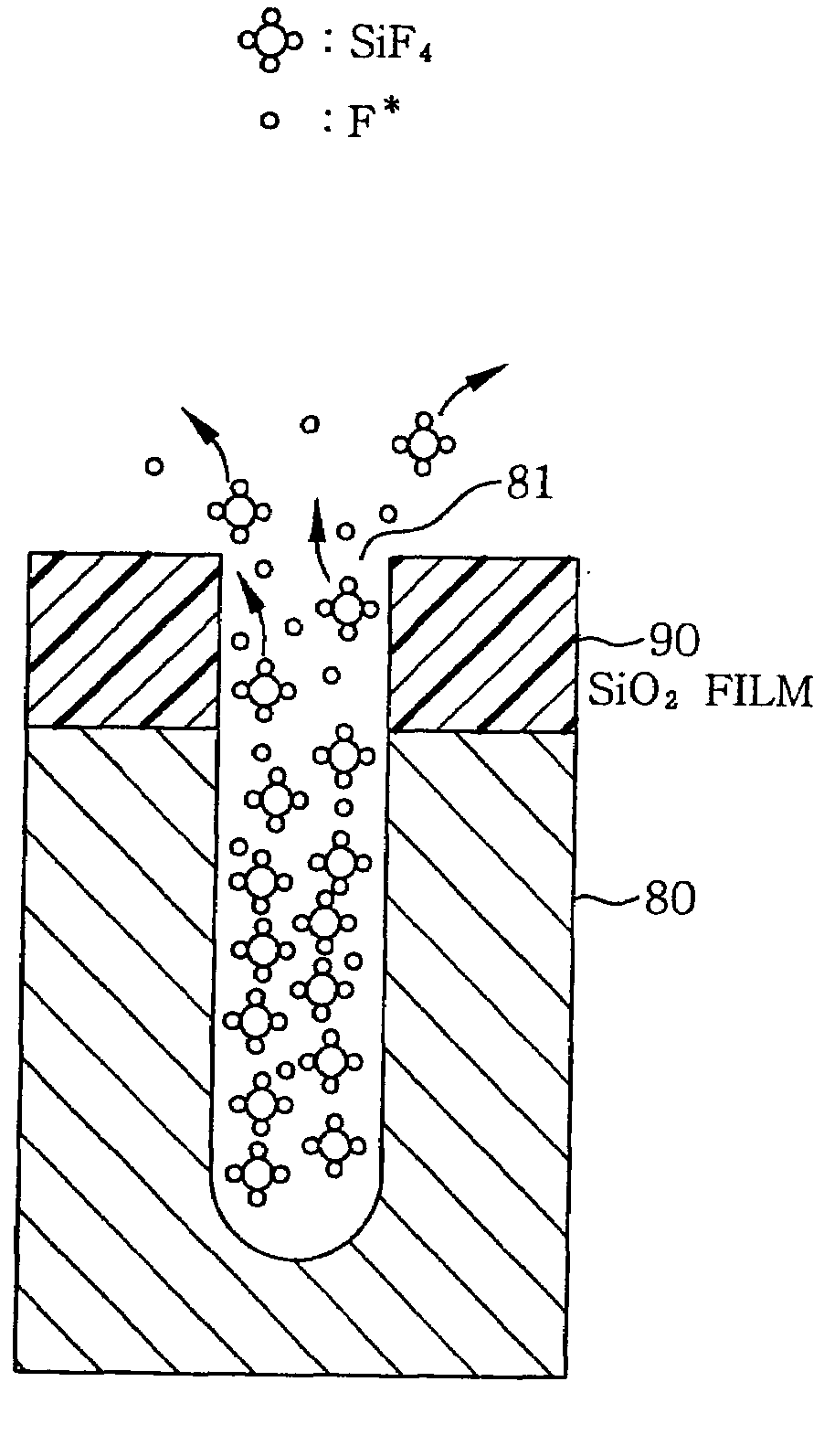

Plasma etching method and apparatus therefor

InactiveUS20090045167A1Increase chanceIncrease etch rateElectric discharge tubesVacuum gauge using ionisation effectsPeak intensityFluorine containing

A fluorine-containing compound gas, e.g., SF6 gas, is converted into a plasma and a silicon portion of an object to be processed is etched by the plasma. At the same time, using a light source having a peak intensity of light in a wavelength range of light absorption of a reaction product, e.g., SiF4, for which, to be more precise, ranges from 9 μm to 10 μm, the light is irradiated onto a surface of an object to be processed from the light source. The SiF4 molecules absorb the light, become activated and gain kinetic energy to be used in gaining an easy escape from a hole. As a consequence, an amount (a partial pressure) of fluorine radicals (F*) used as an etchant is increased and an etching rate of a silicon is increased.

Owner:TOKYO ELECTRON LTD

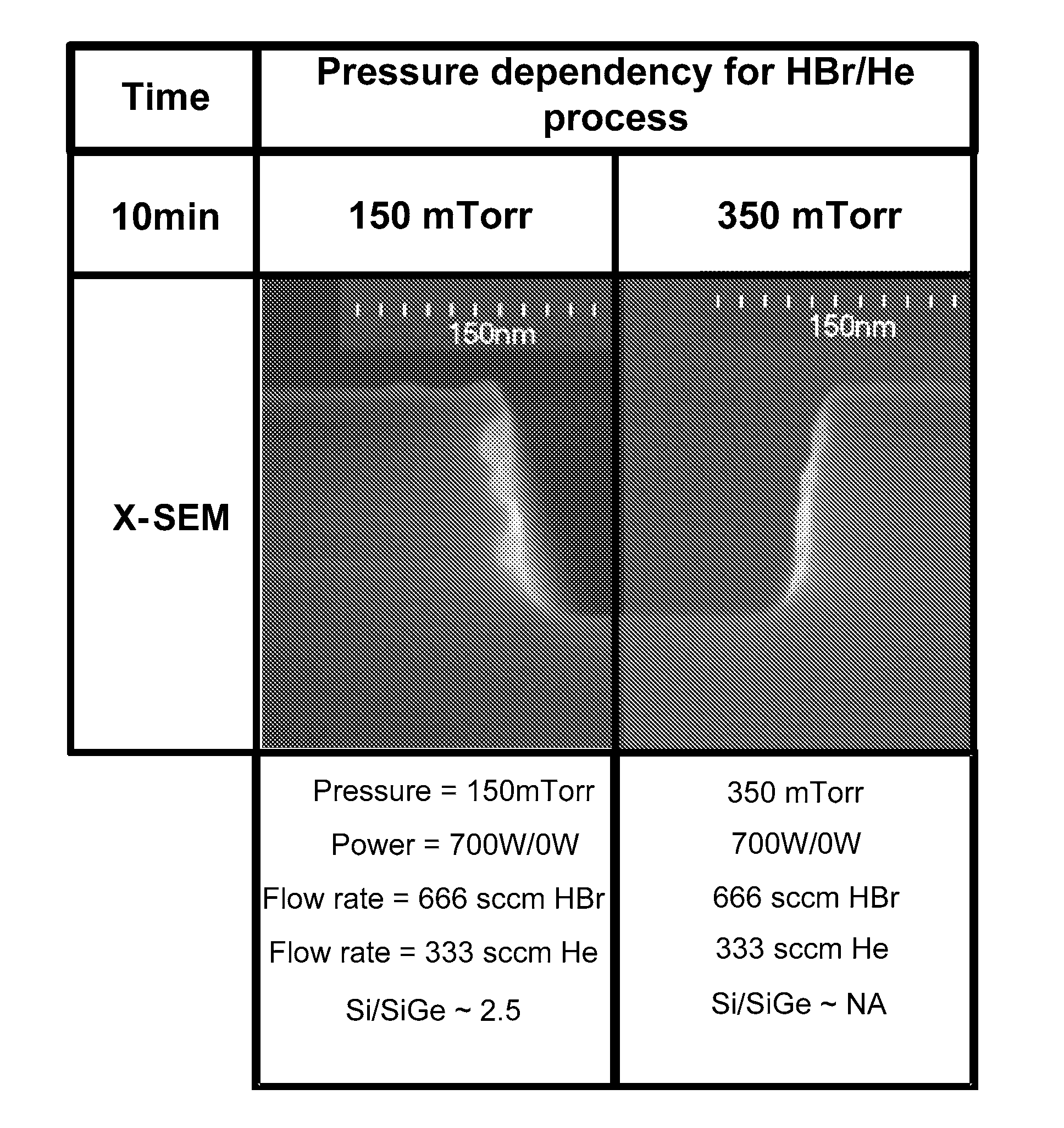

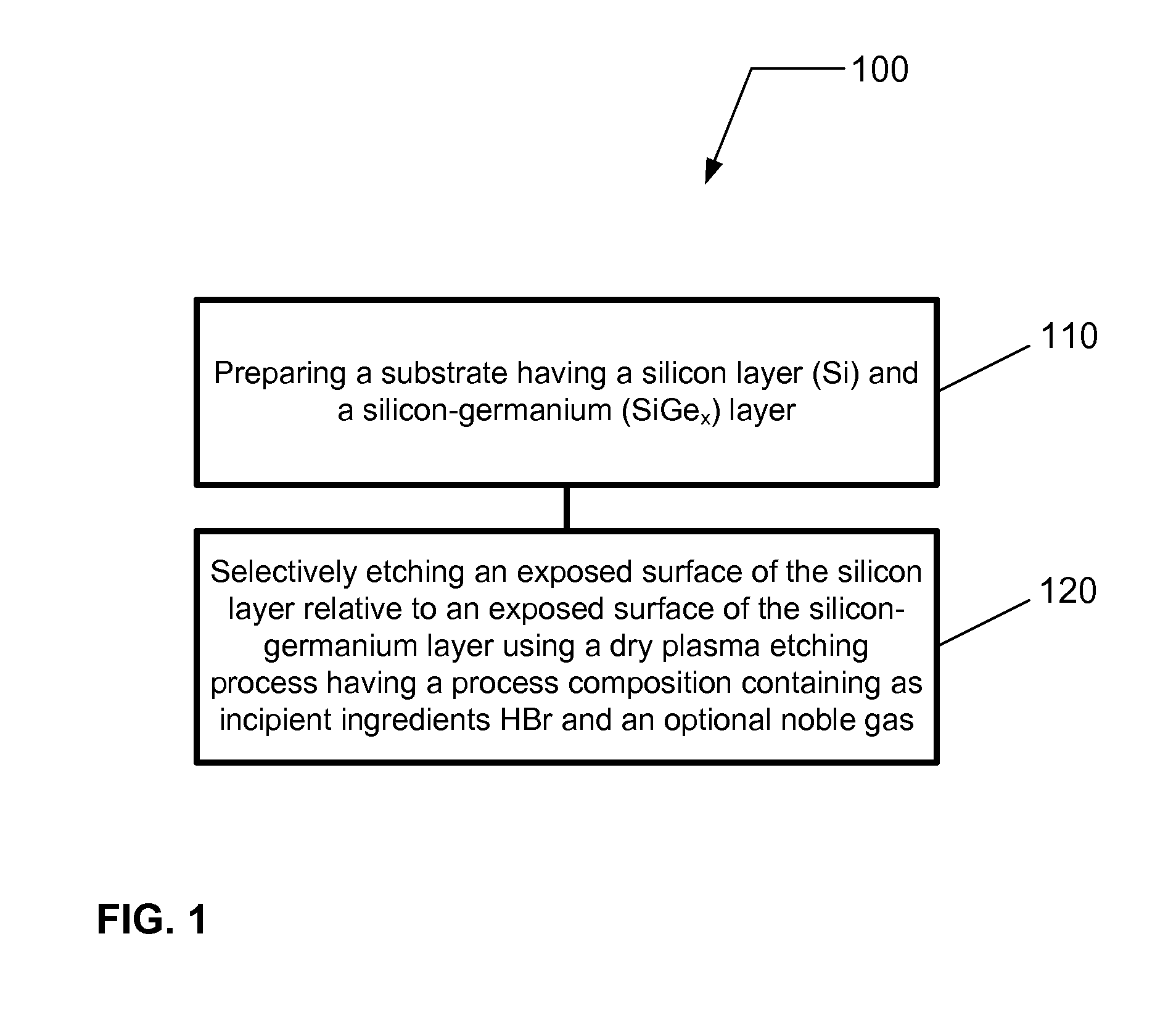

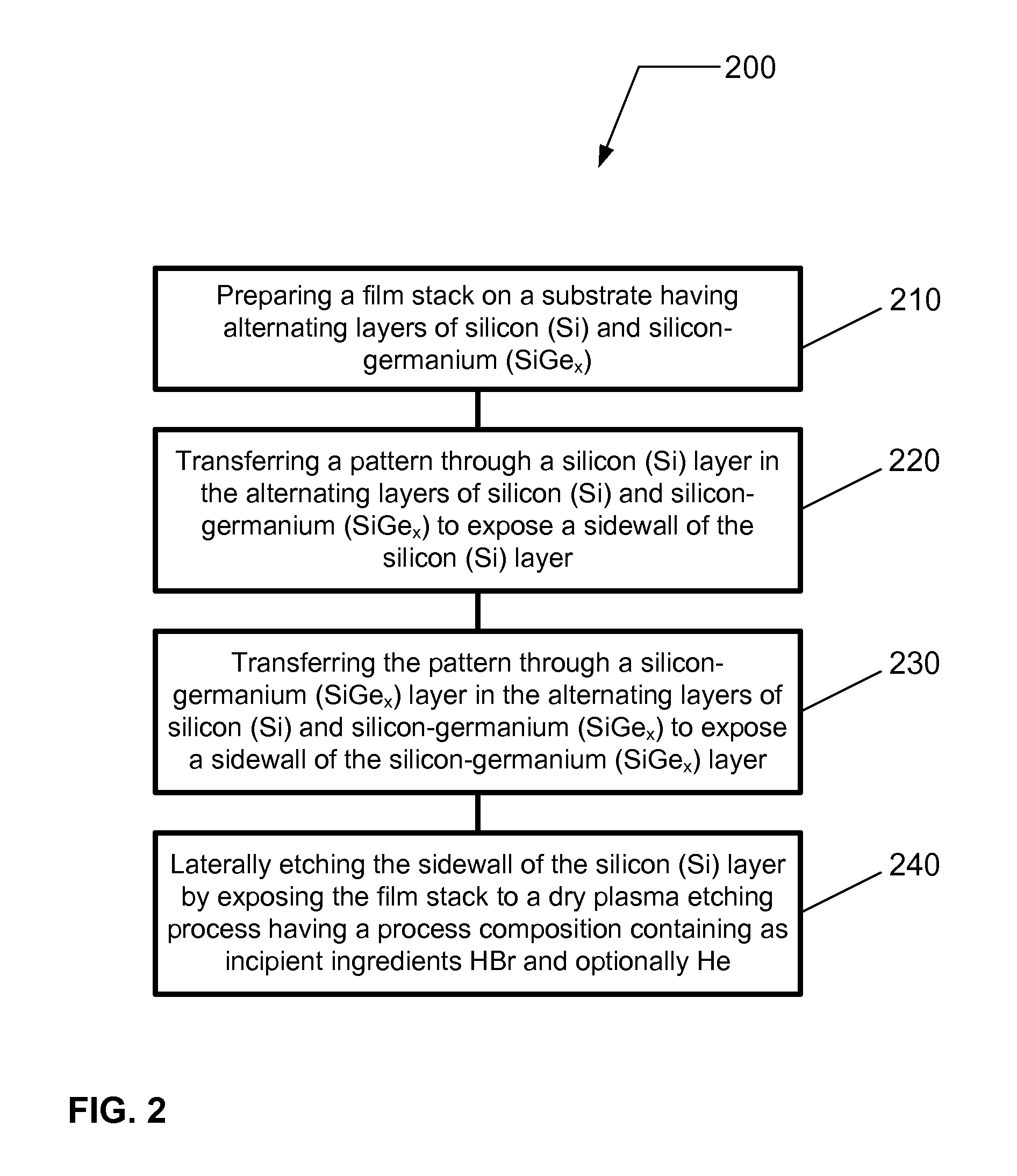

Process for etching silicon with selectivity to silicon-germanium

ActiveUS20120129354A1Electric discharge tubesSemiconductor/solid-state device manufacturingPlasma etchingSilicon-germanium

Owner:TOKYO ELECTRON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com