Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

128results about How to "Longer held" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

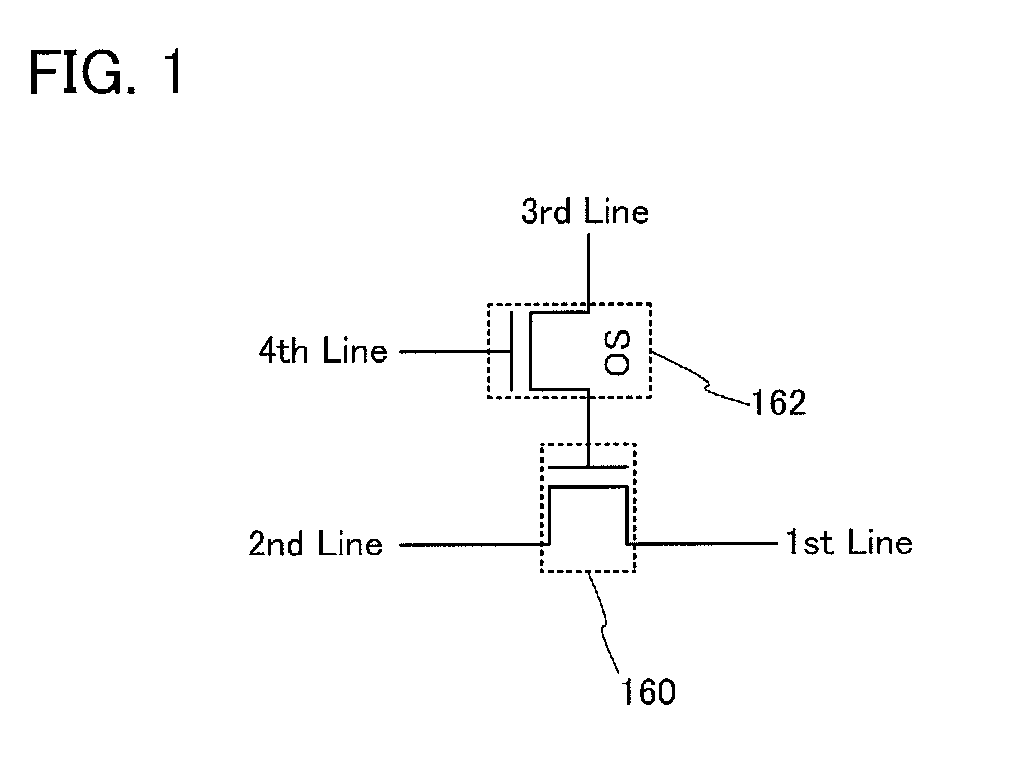

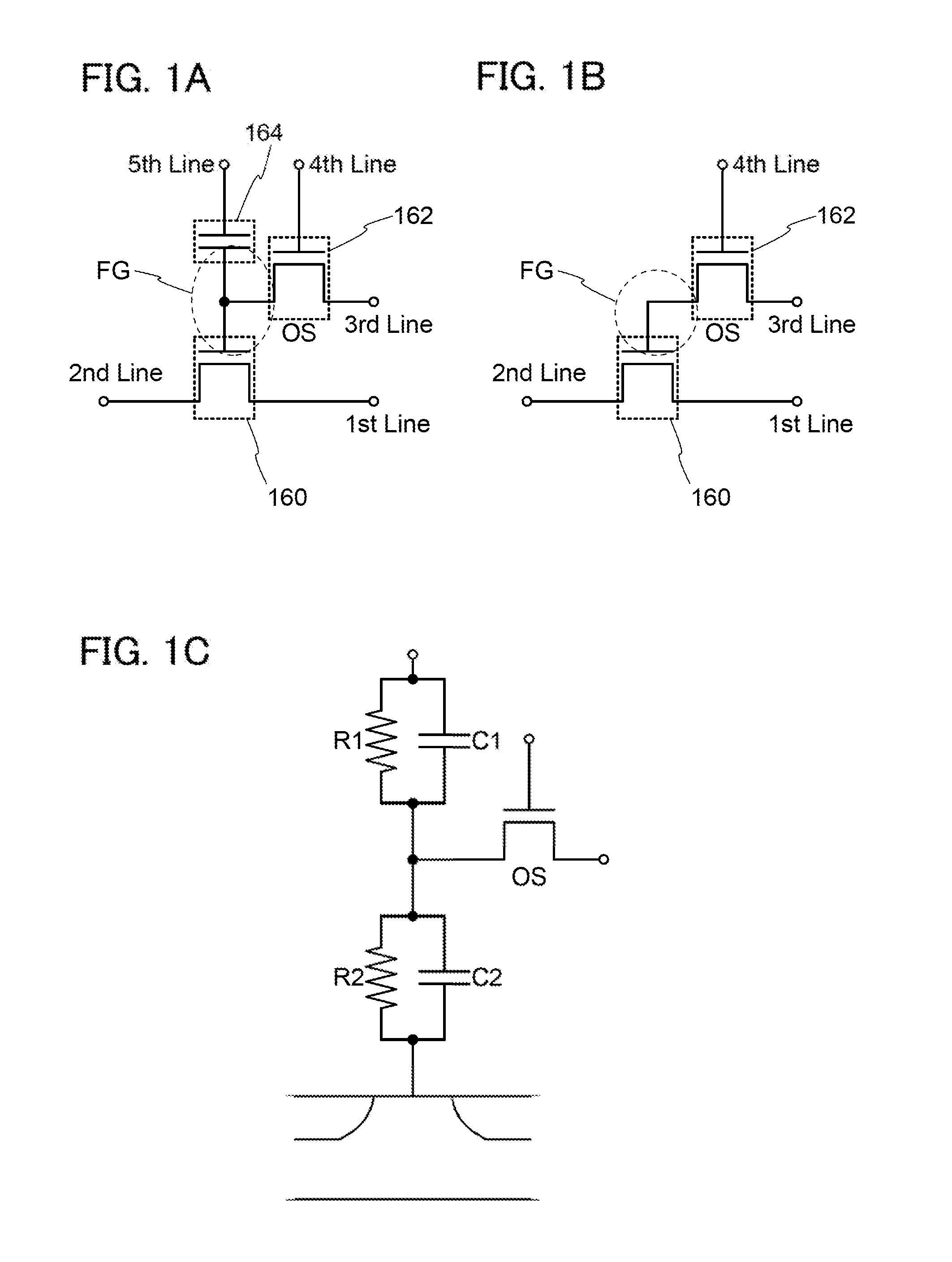

Semiconductor device

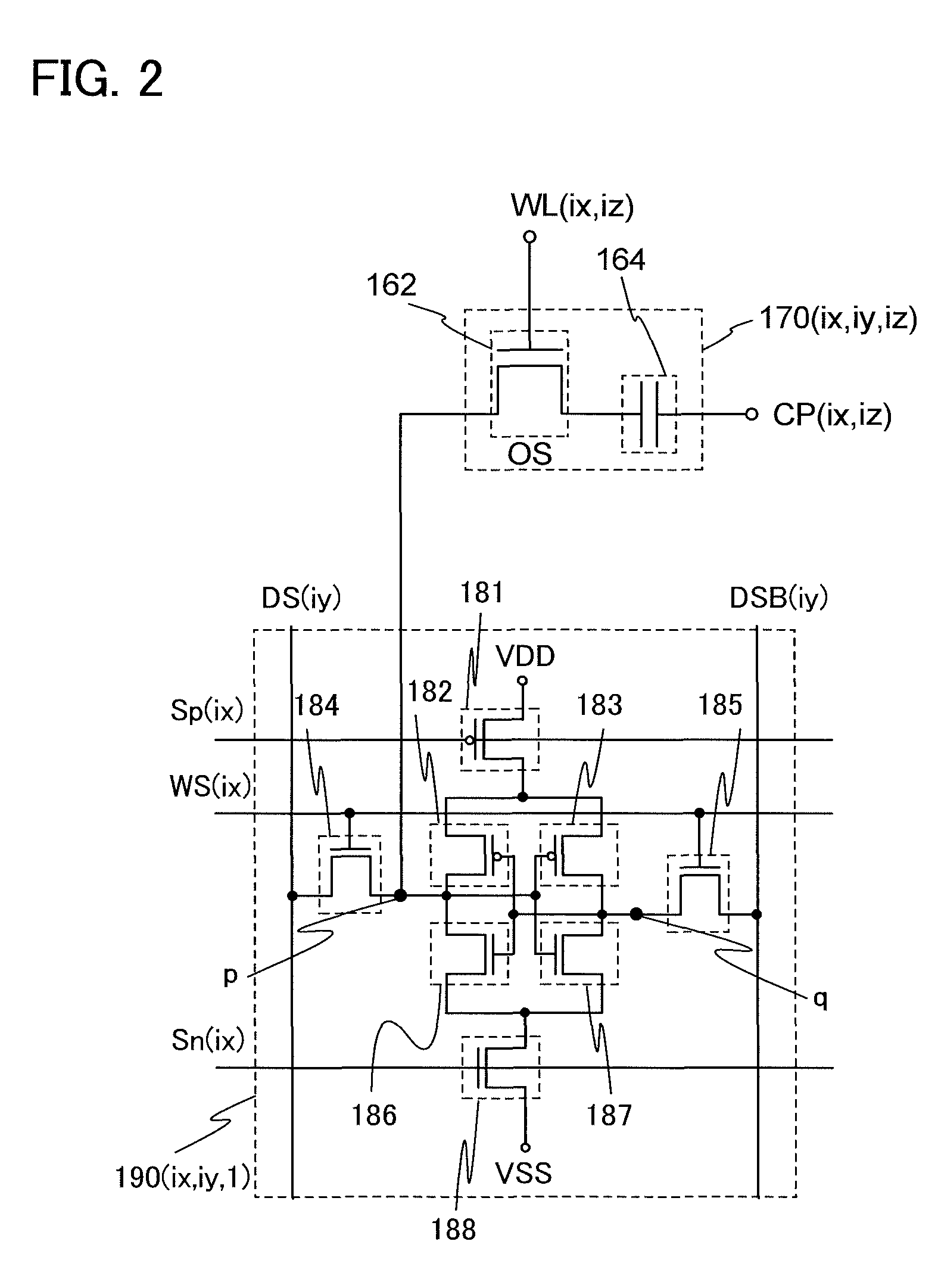

ActiveUS20110134683A1Easily multivaluedNovel structureTransistorSolid-state devicesPower semiconductor deviceDriver circuit

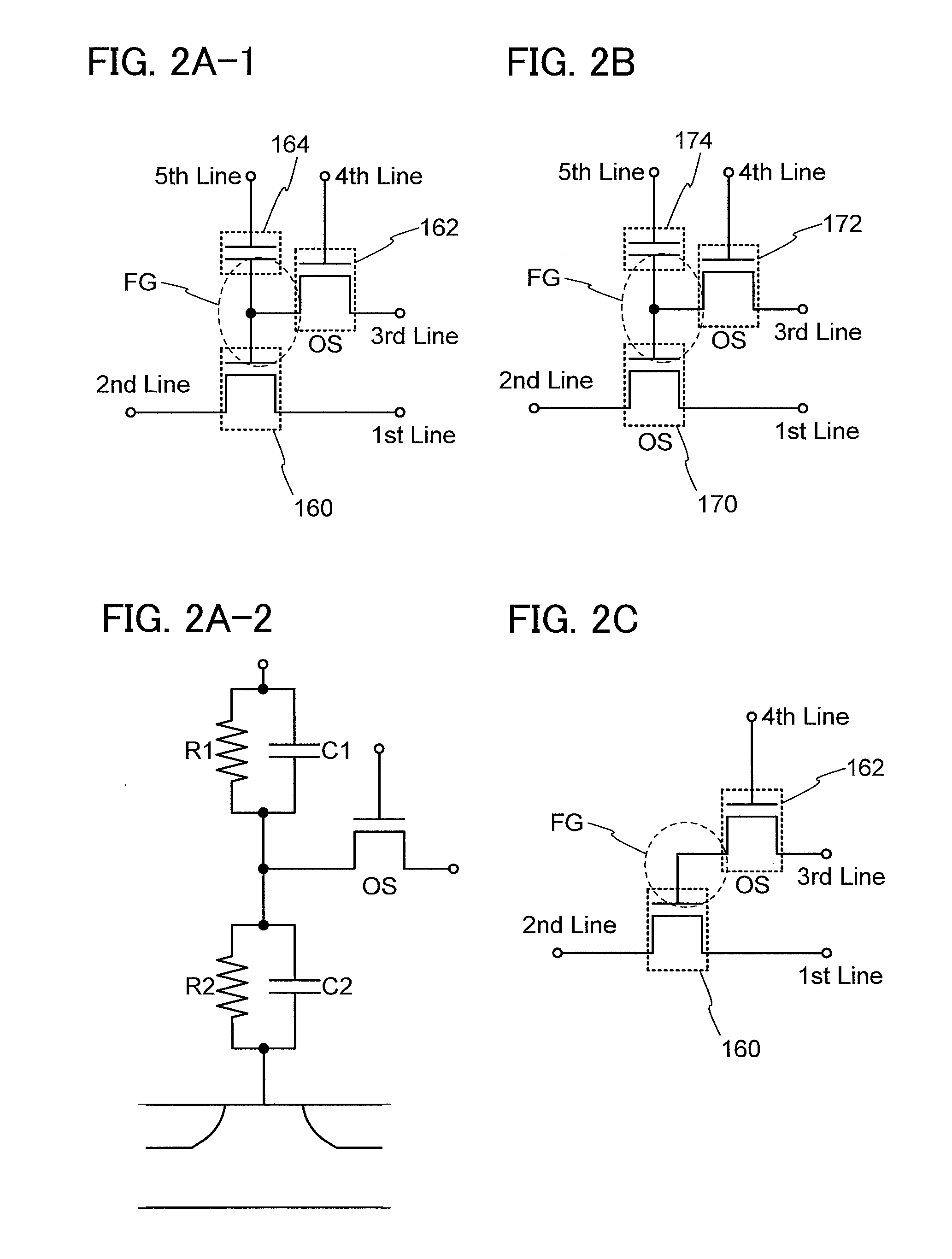

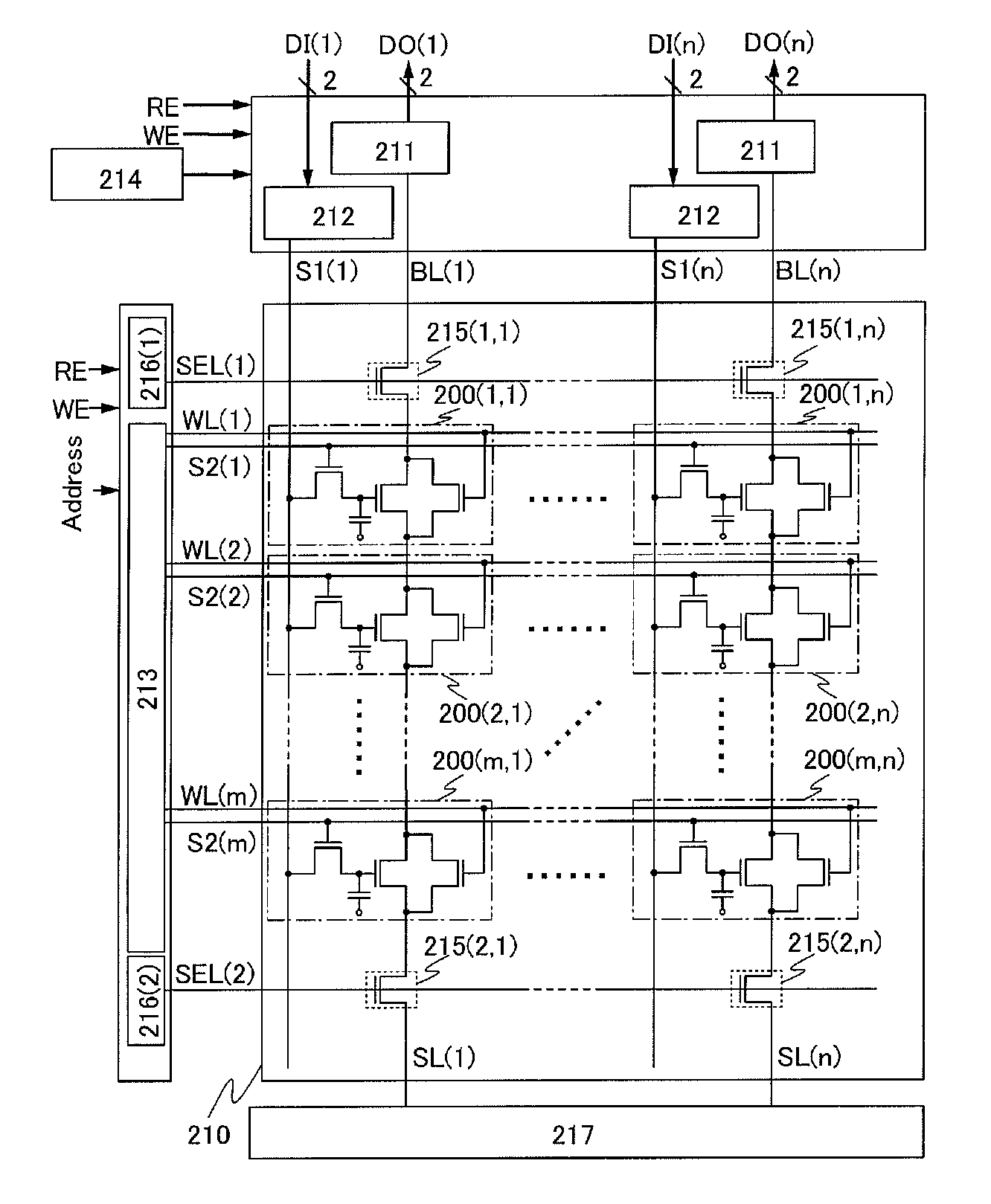

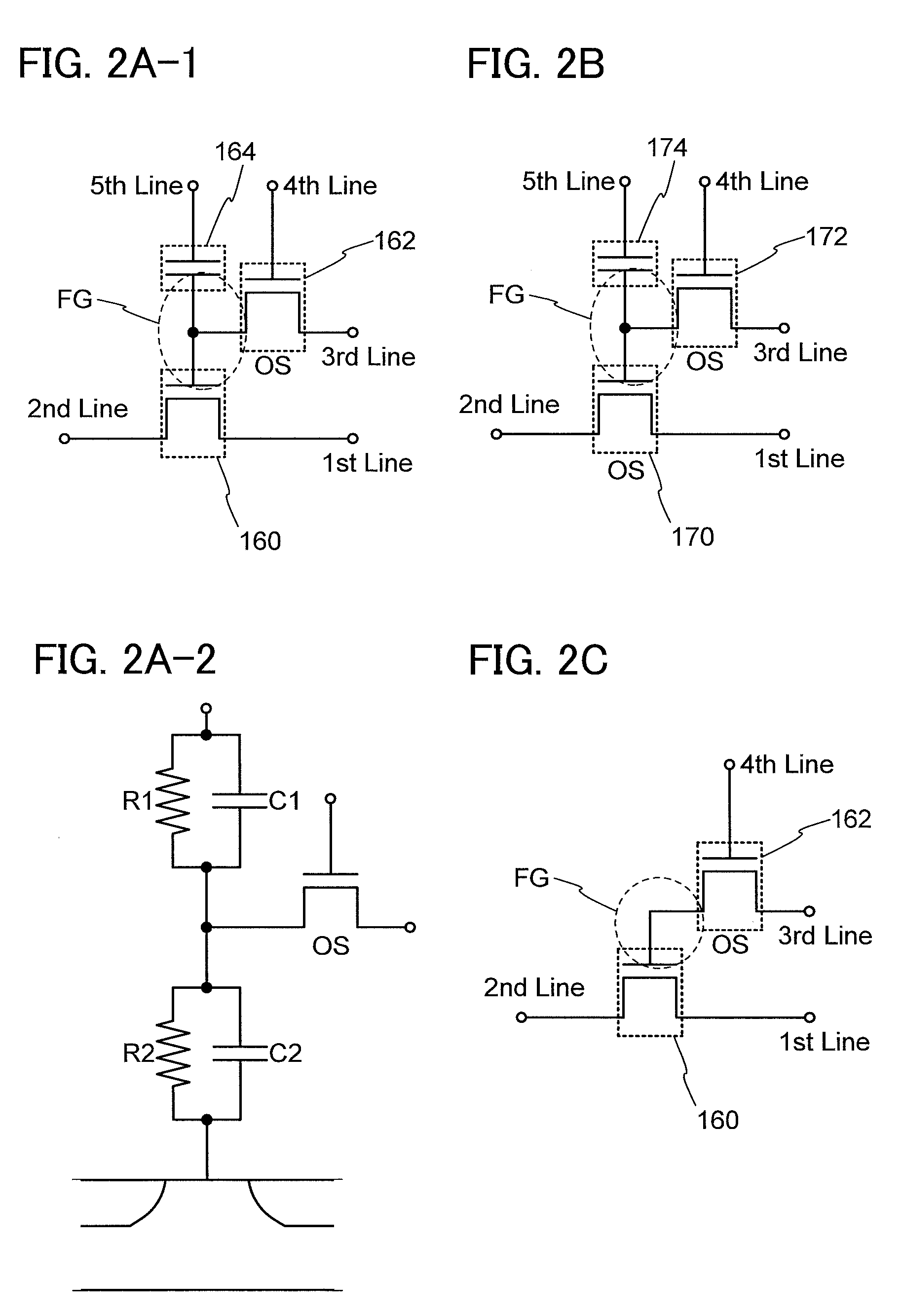

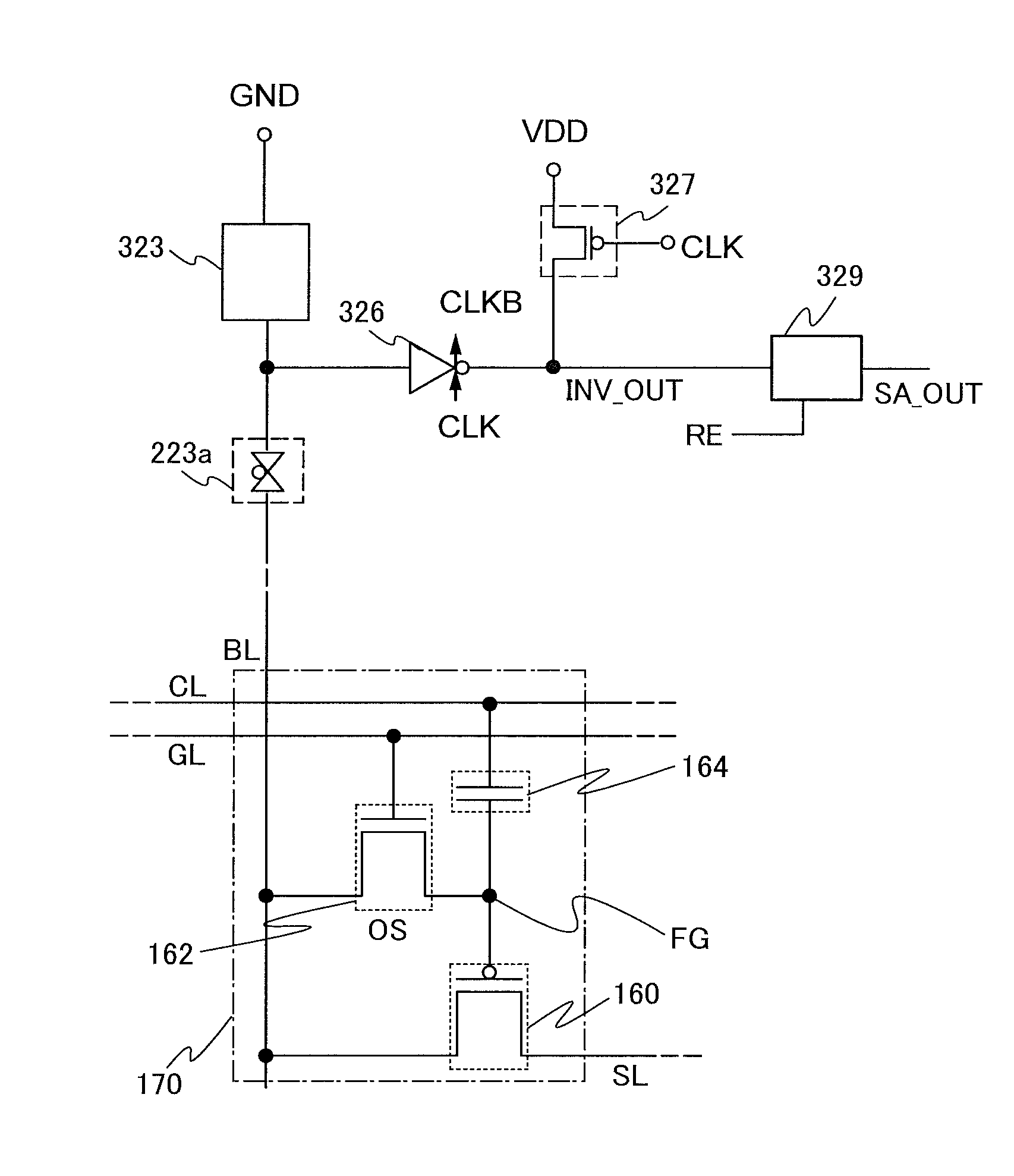

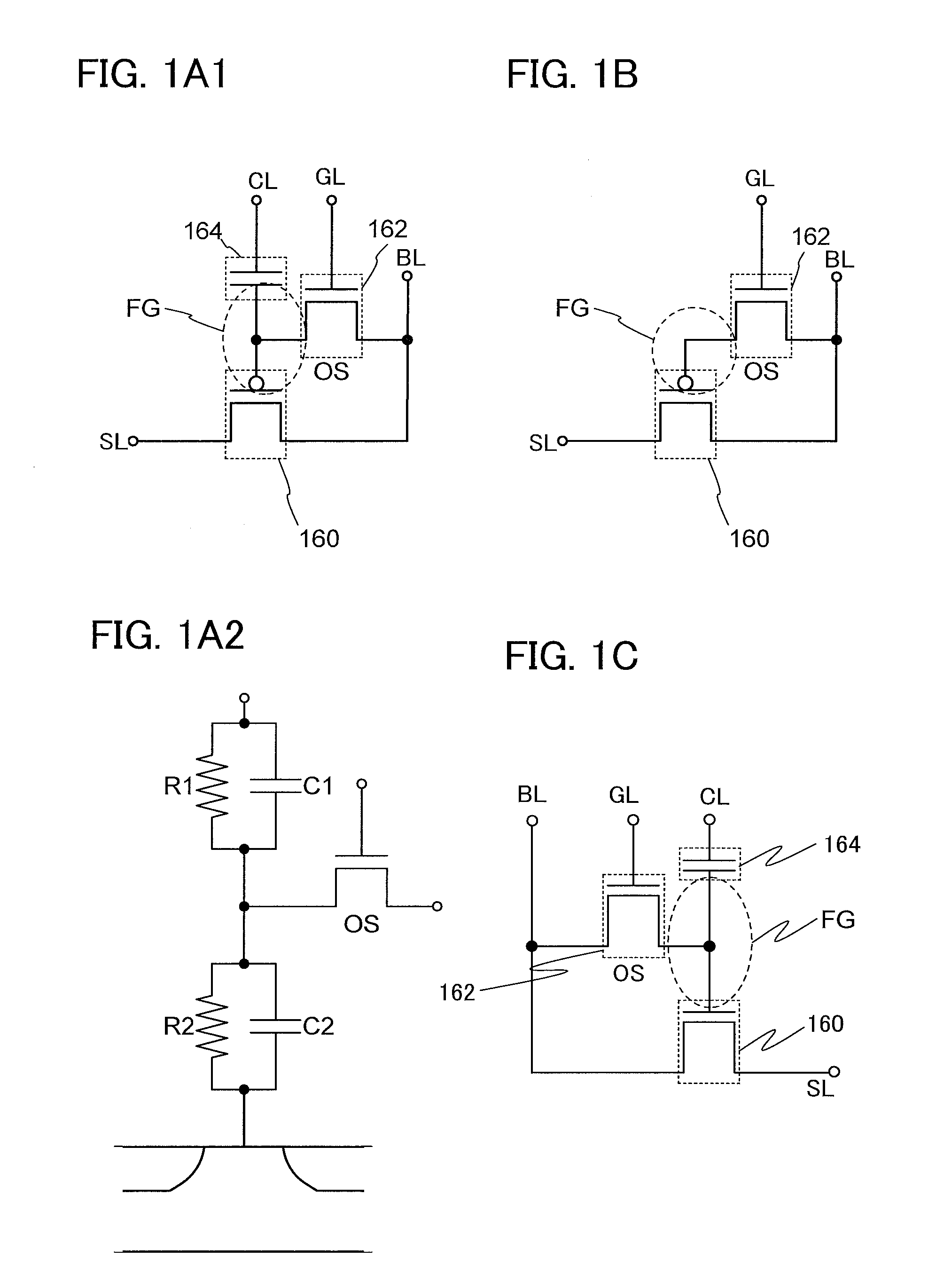

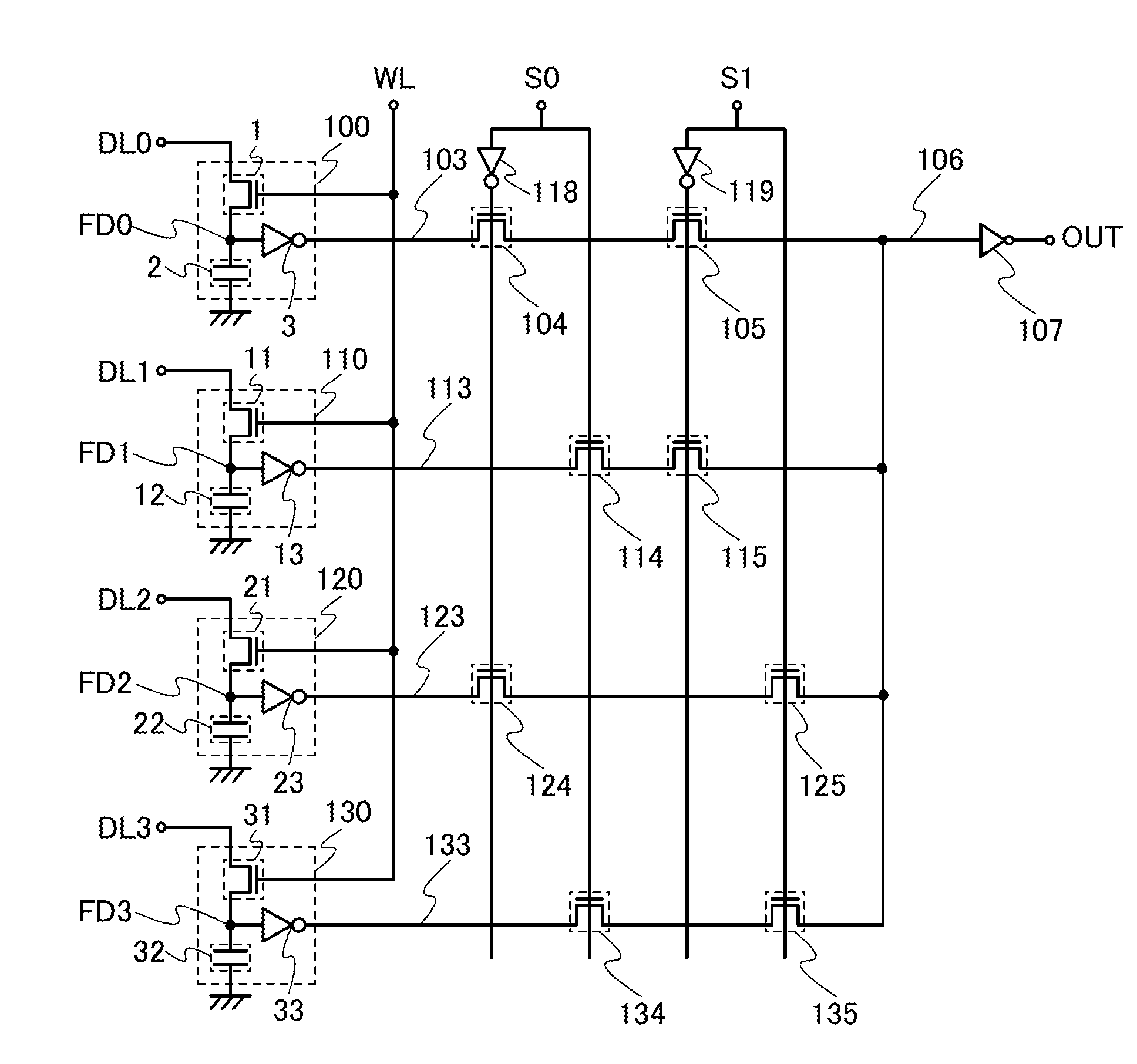

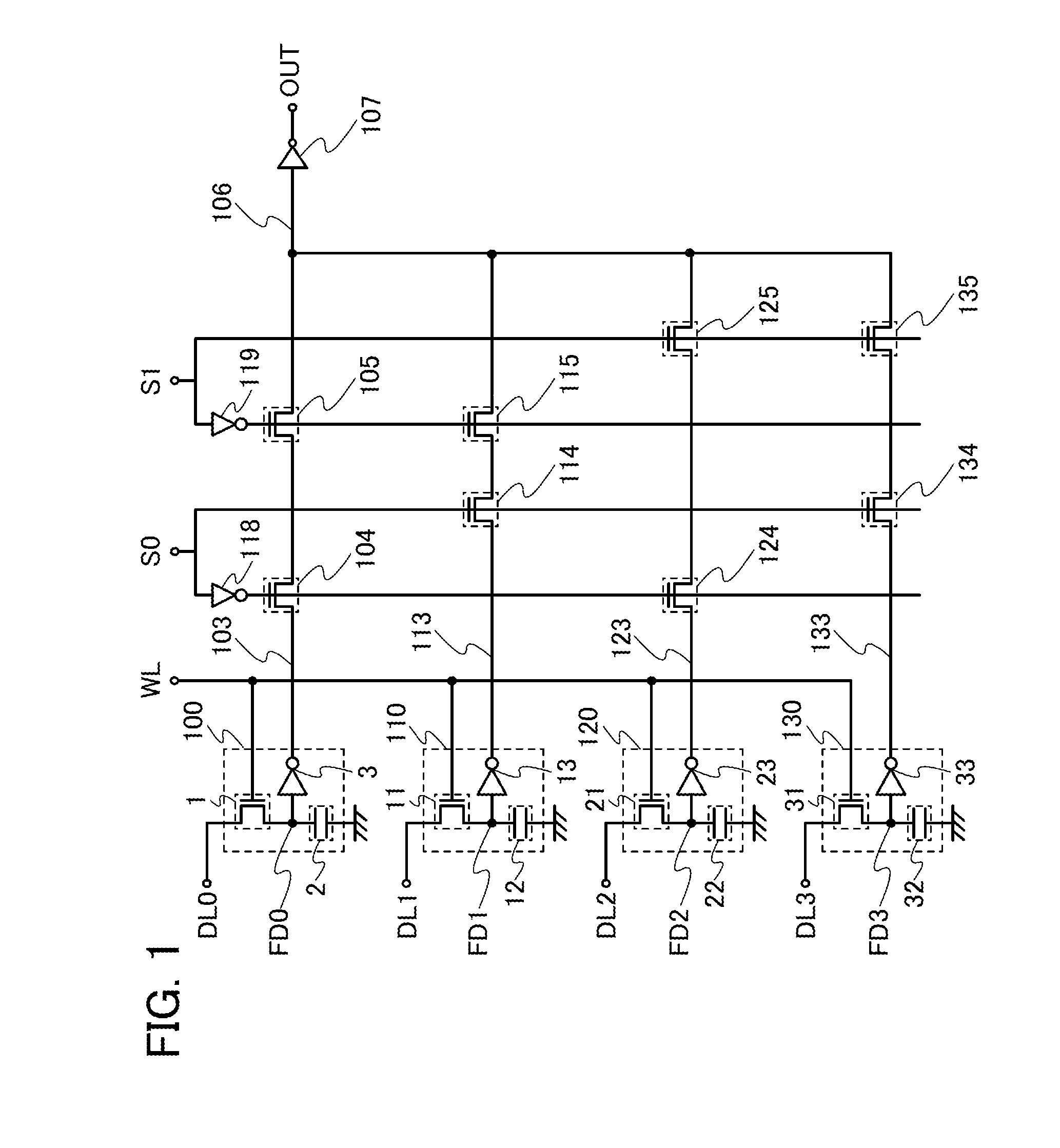

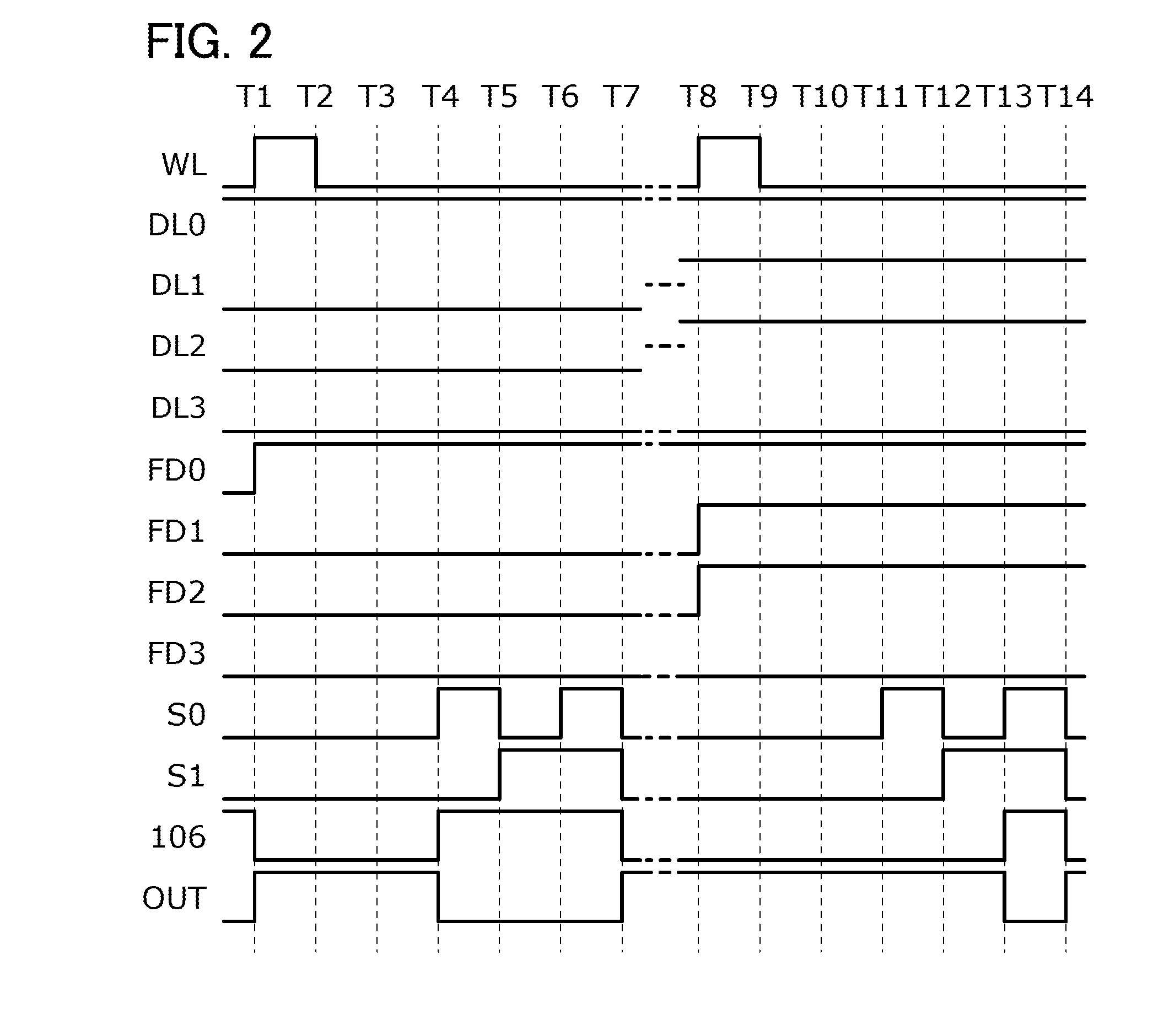

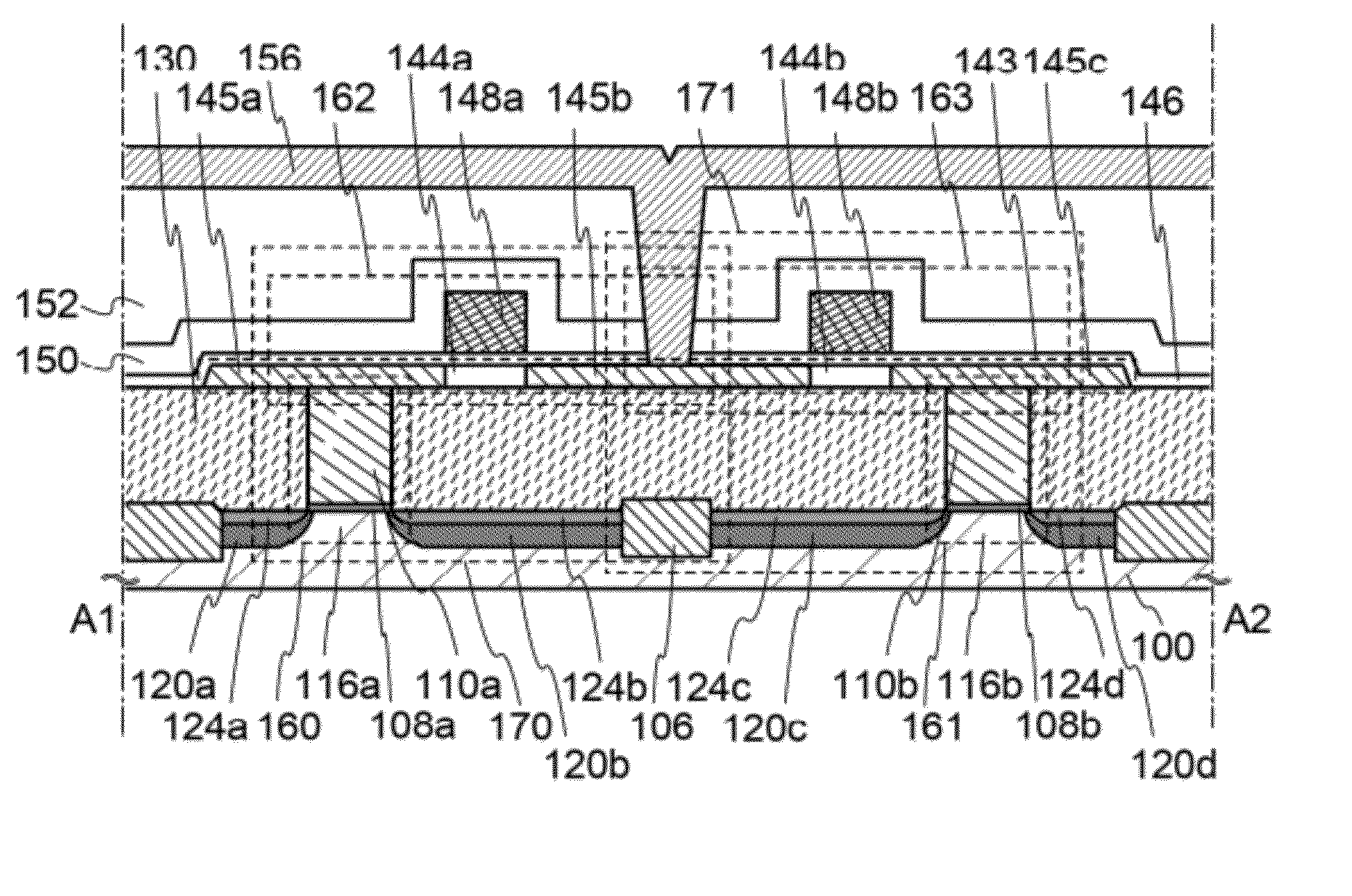

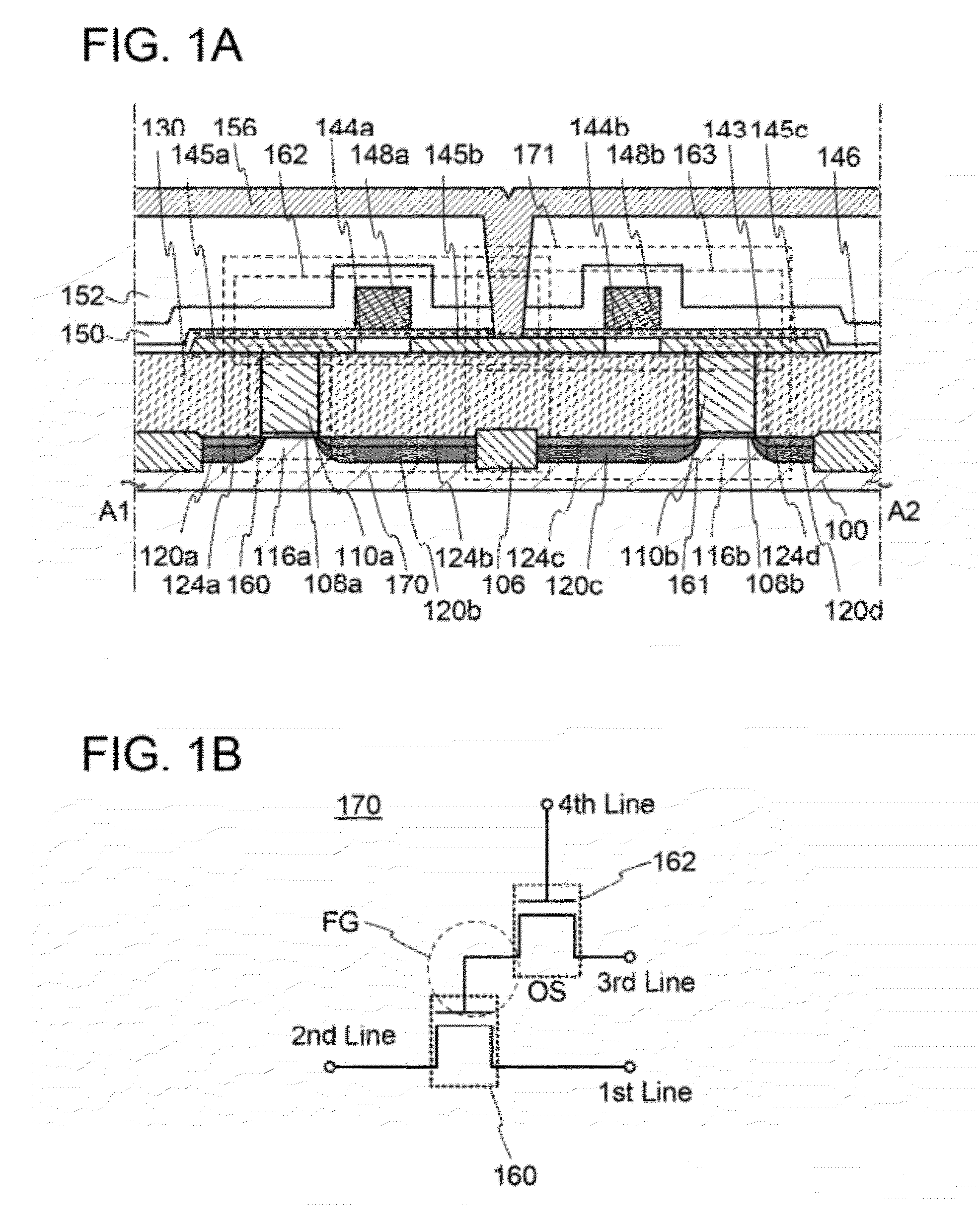

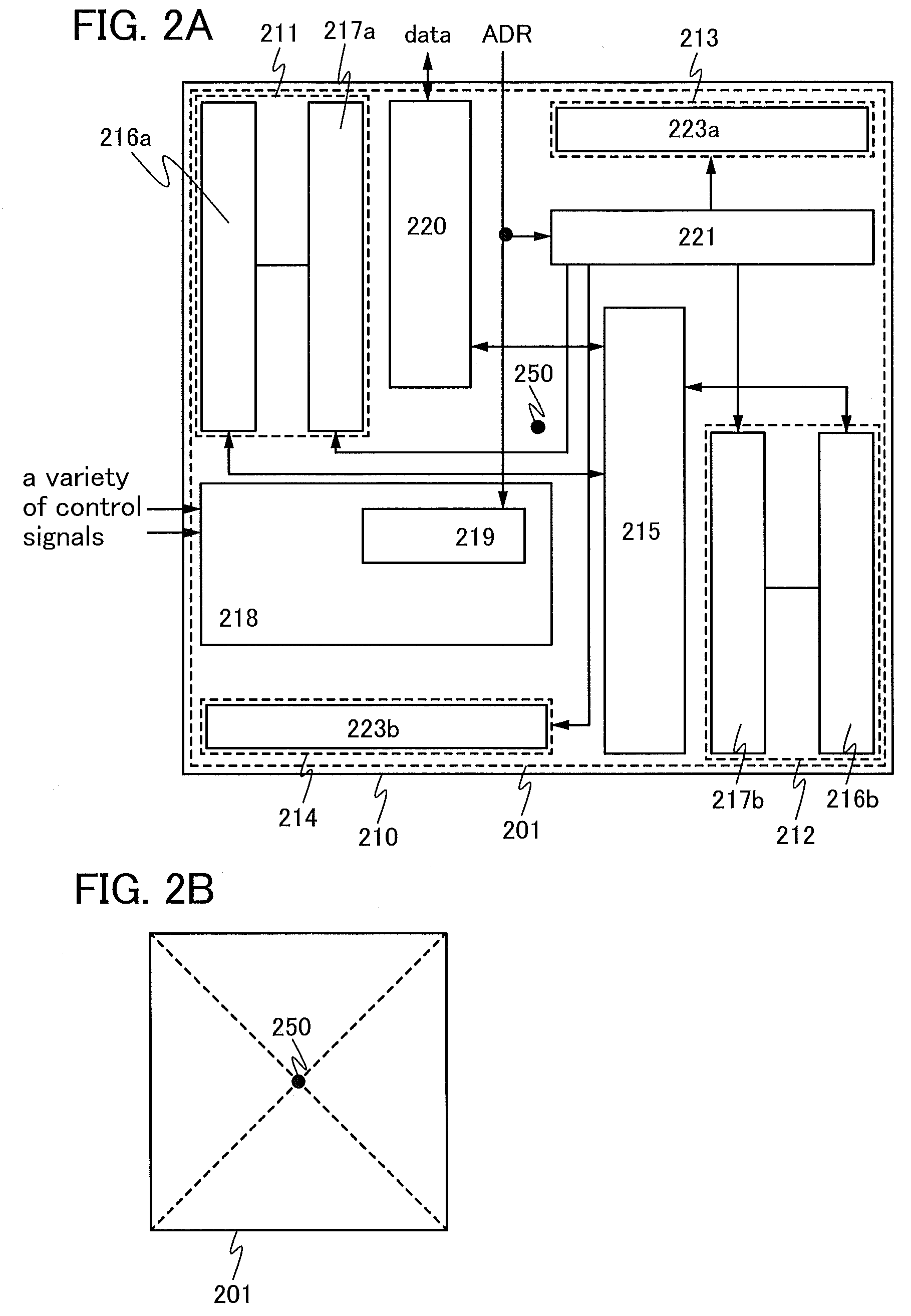

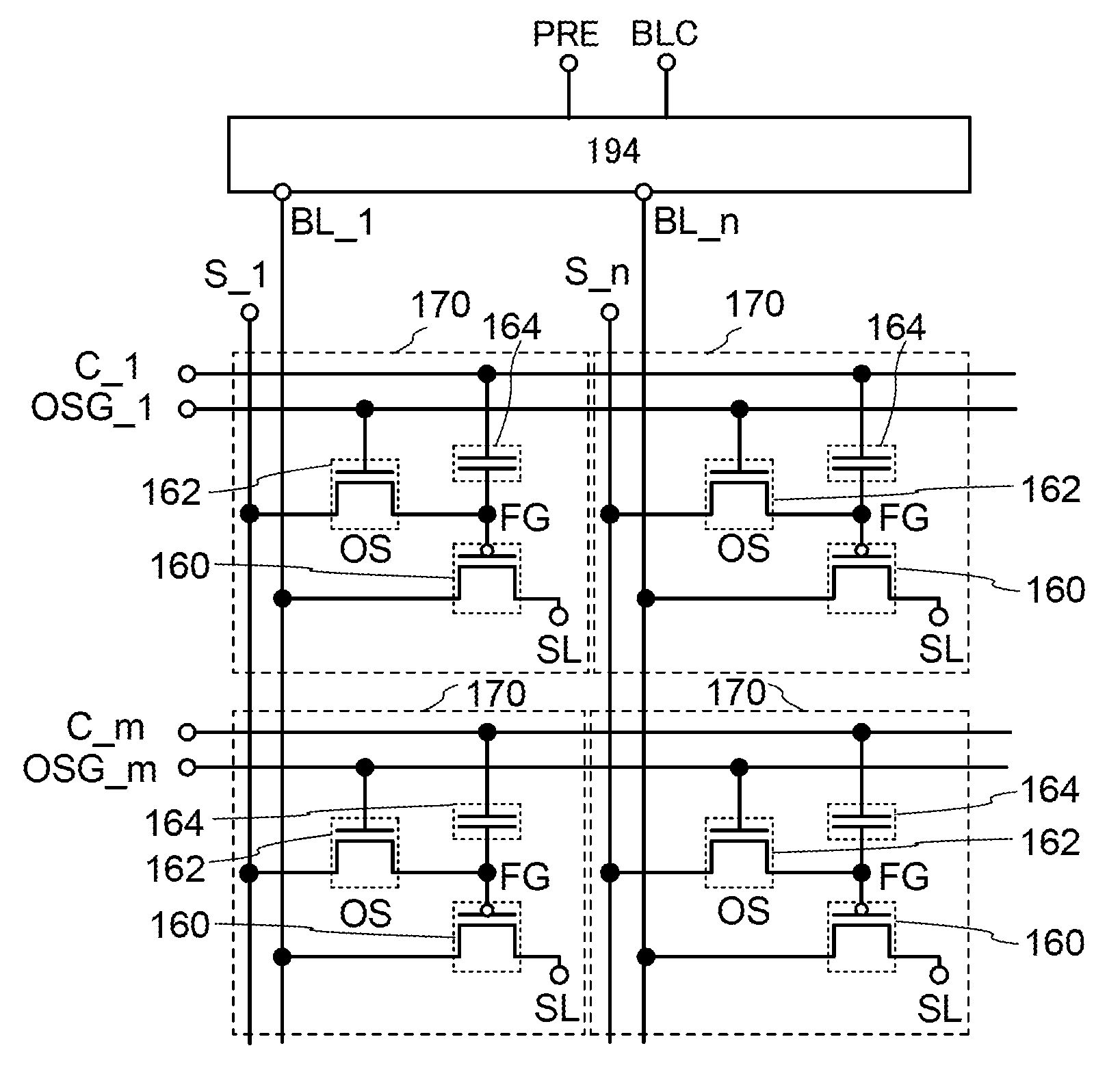

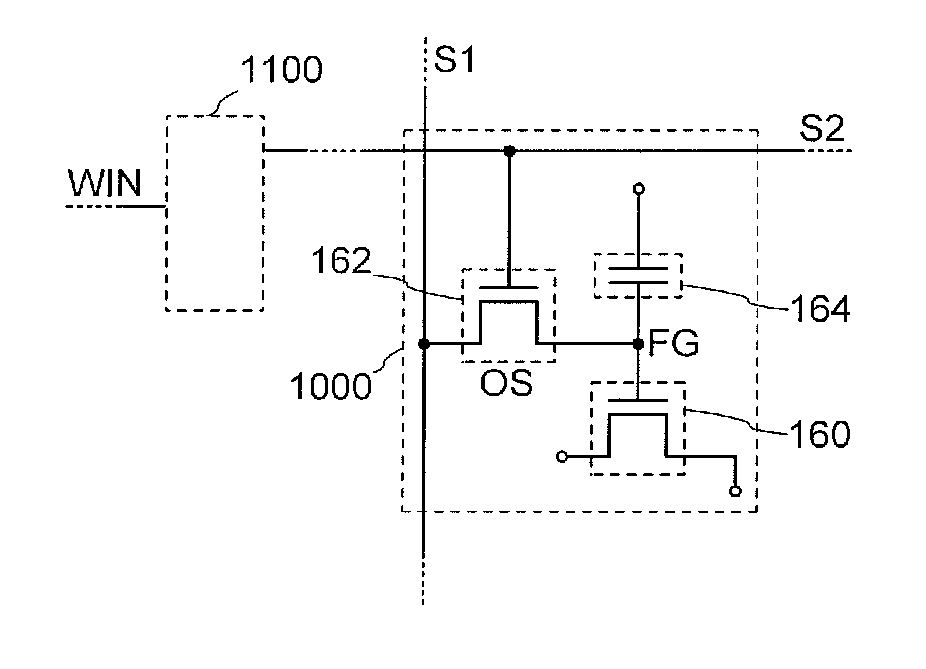

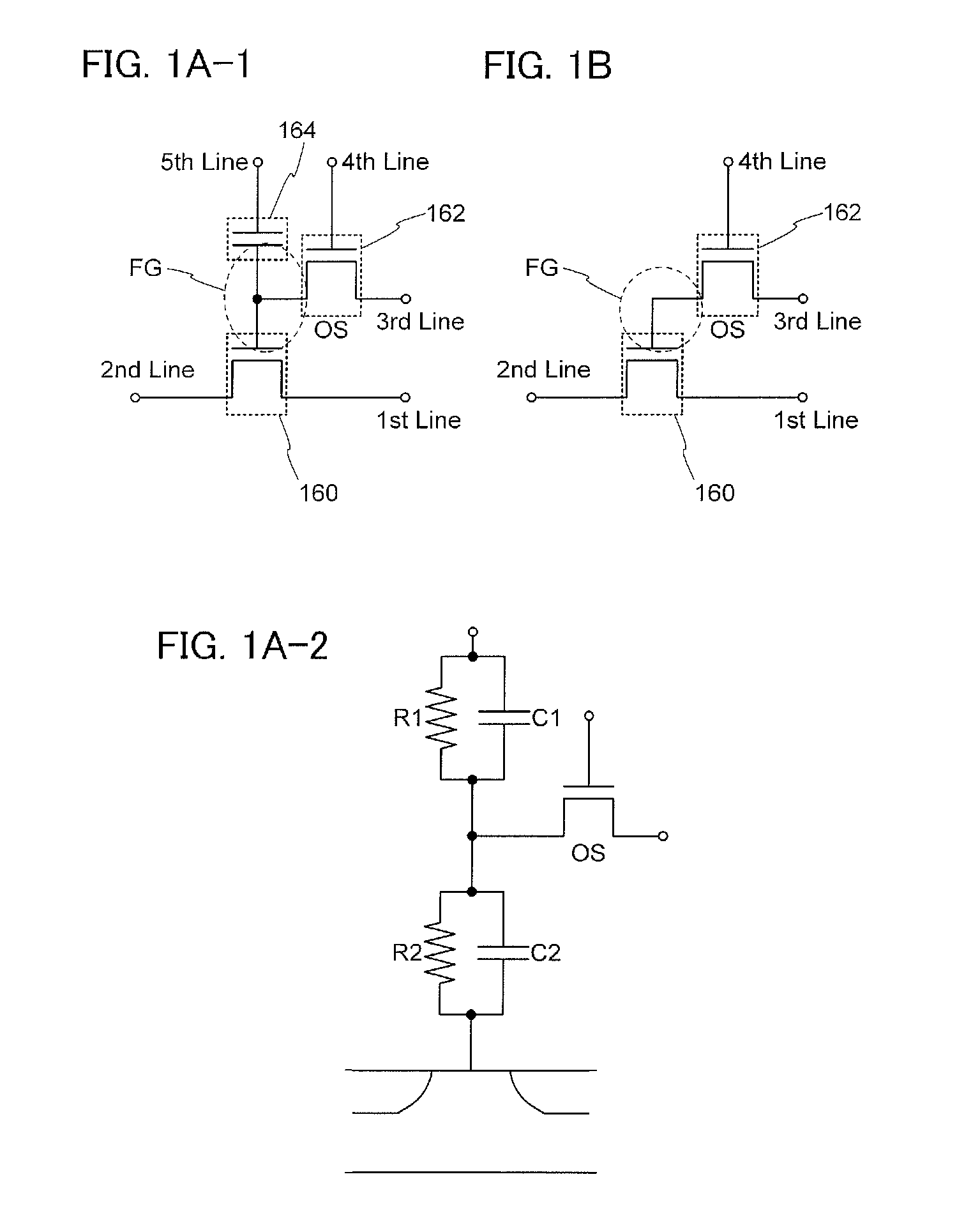

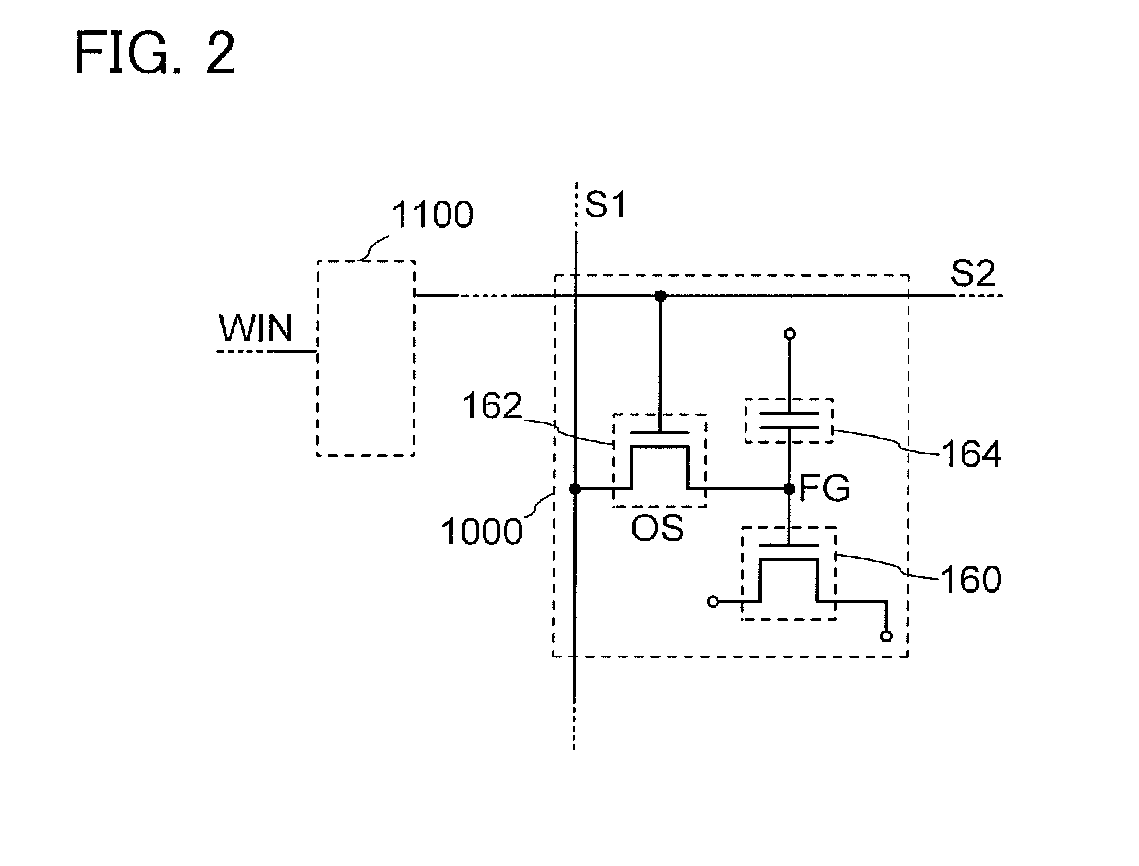

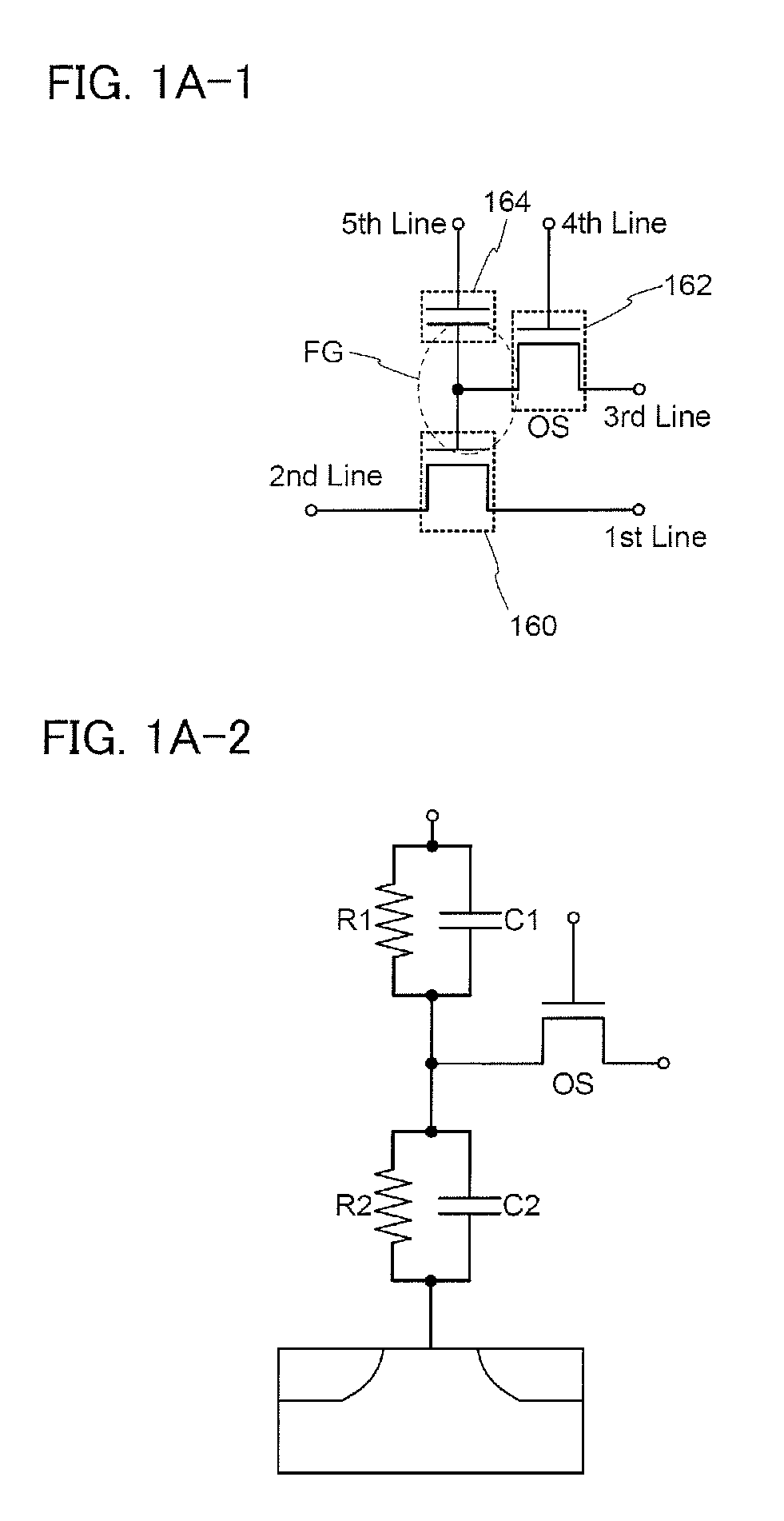

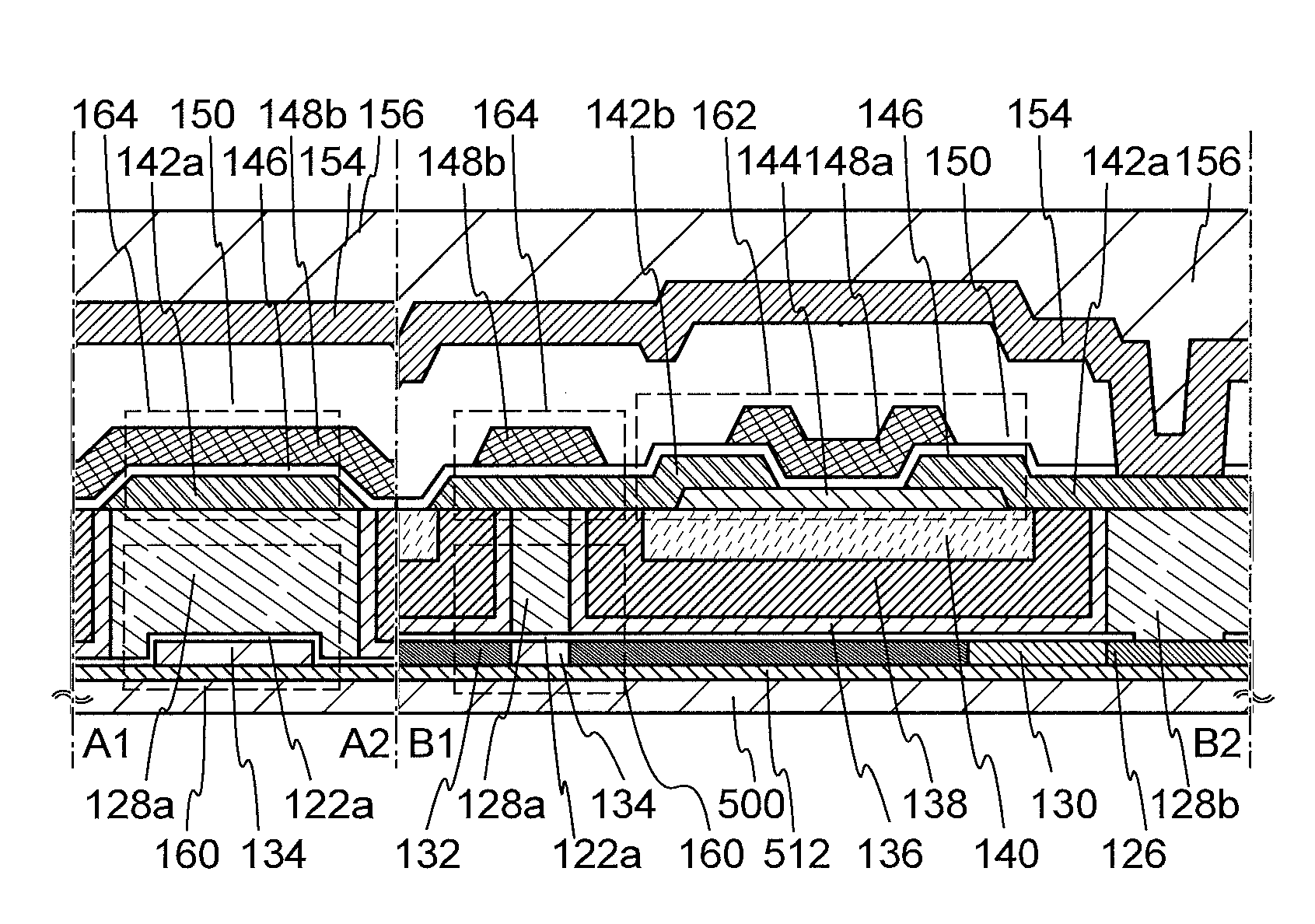

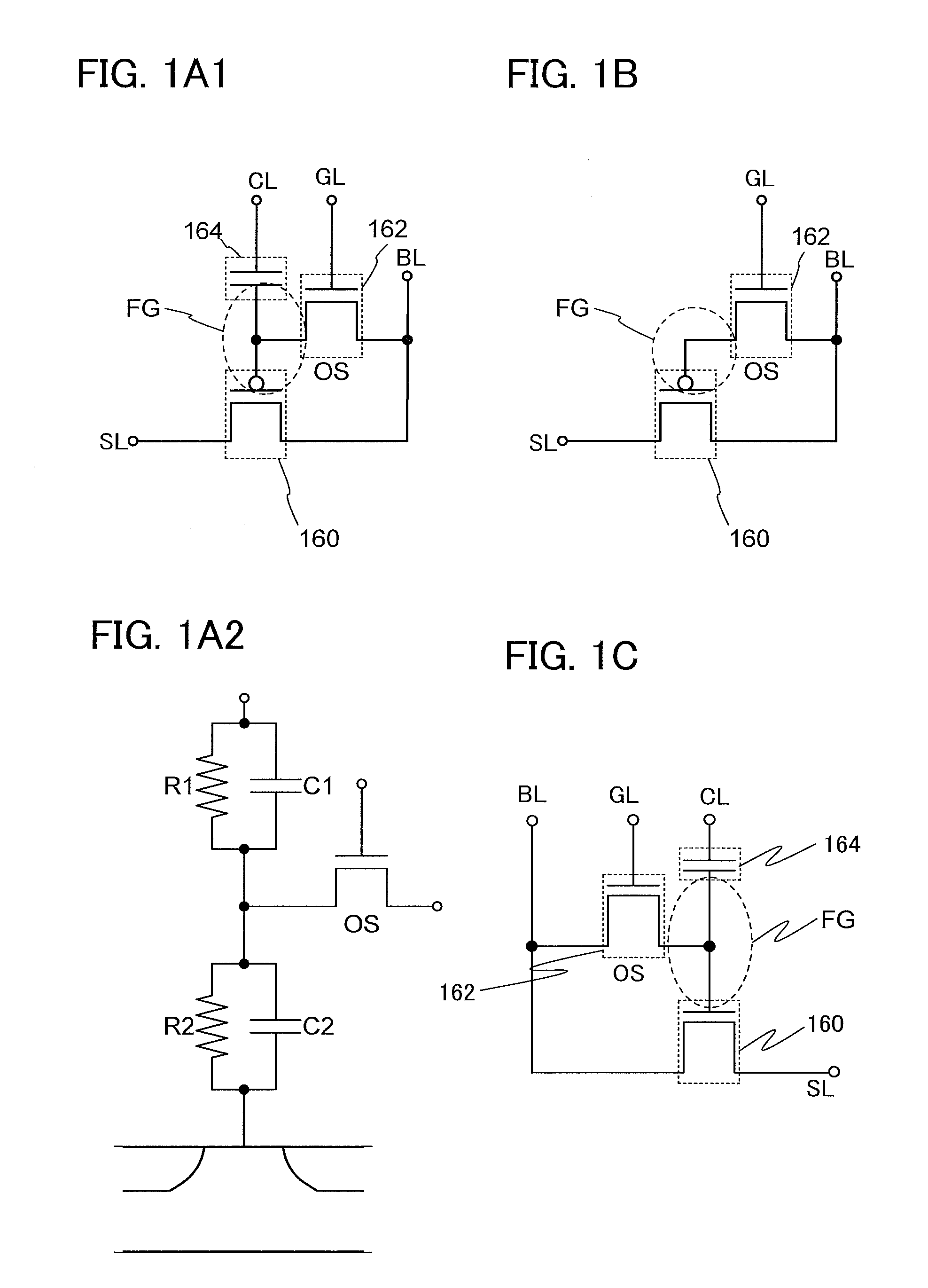

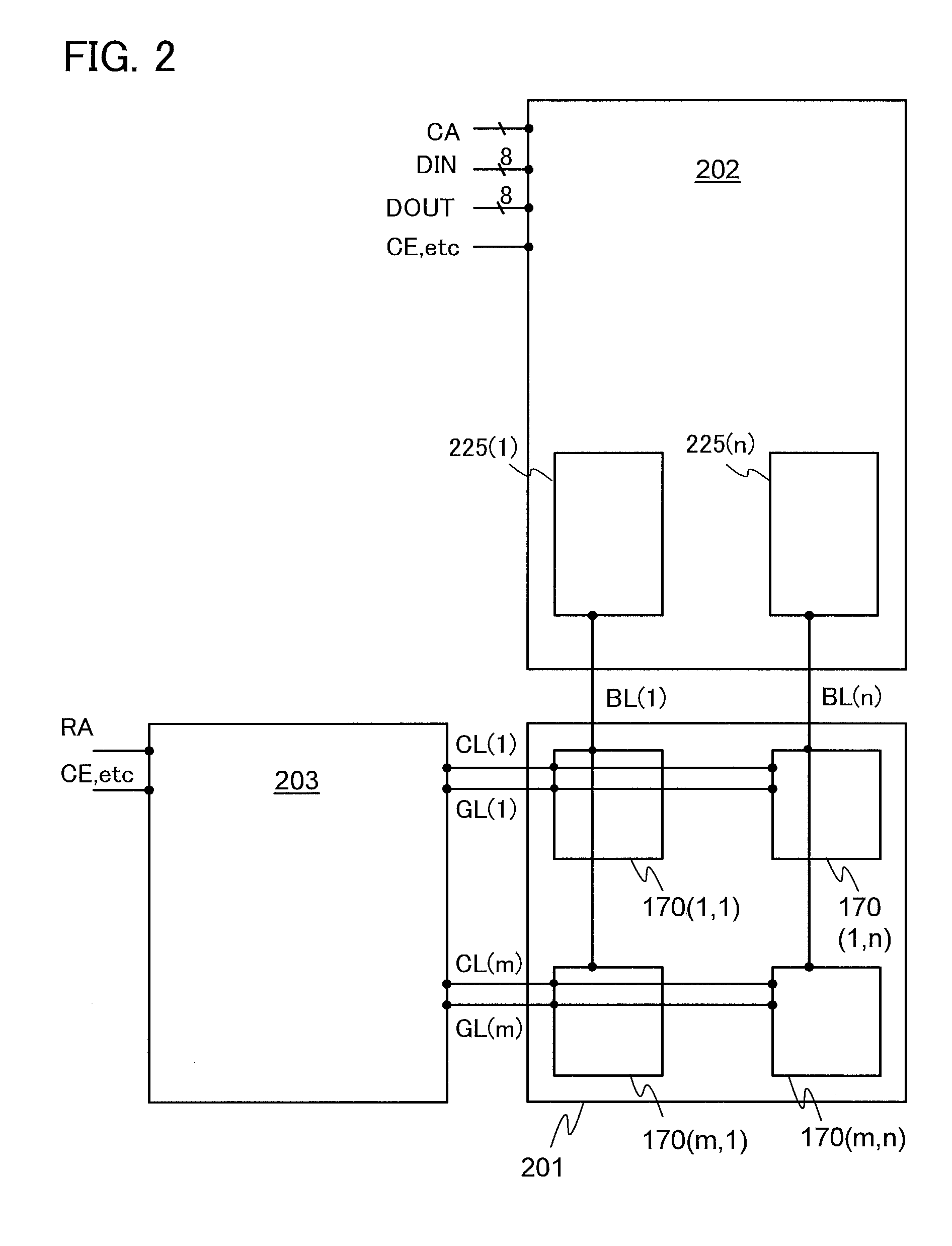

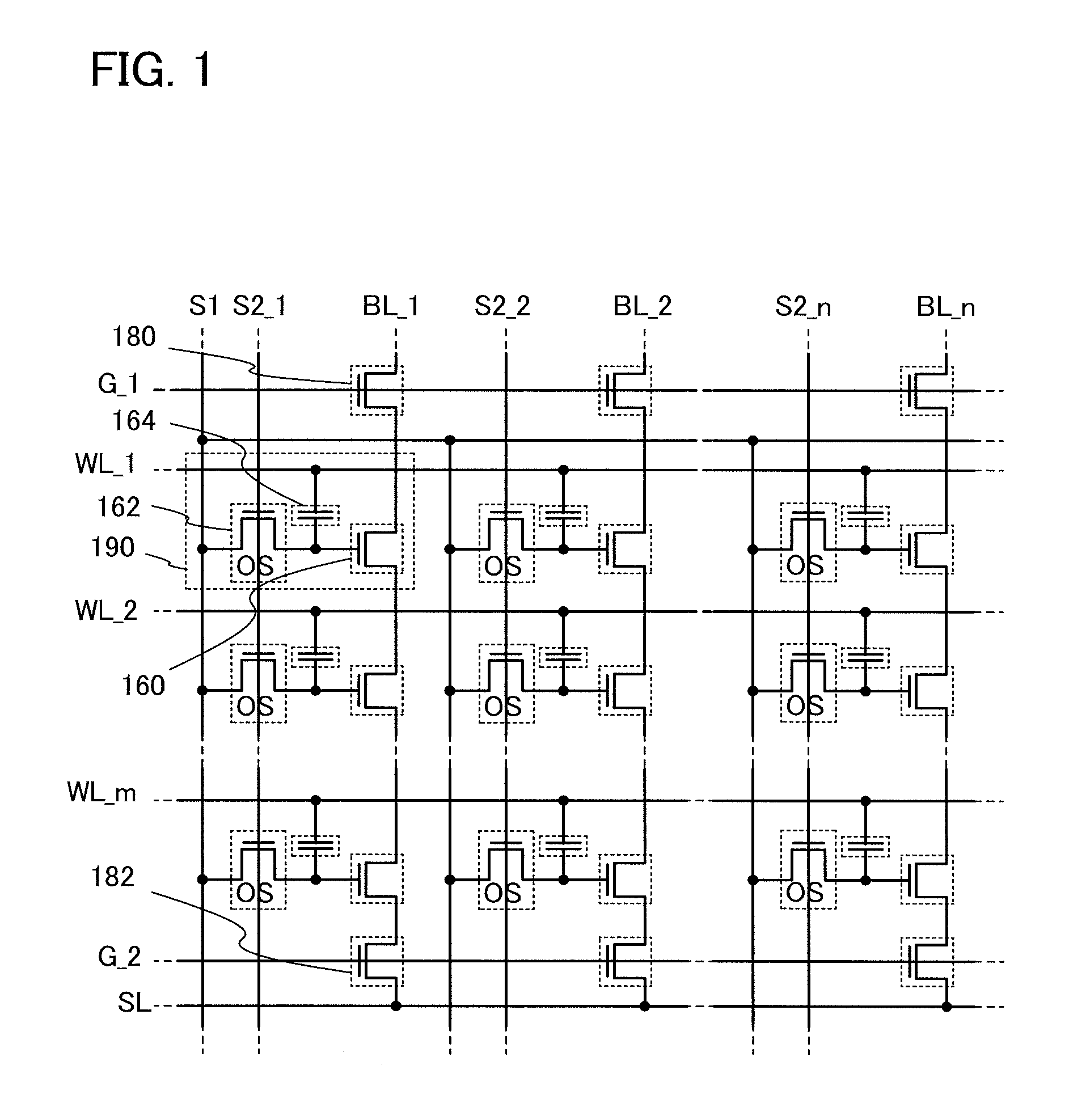

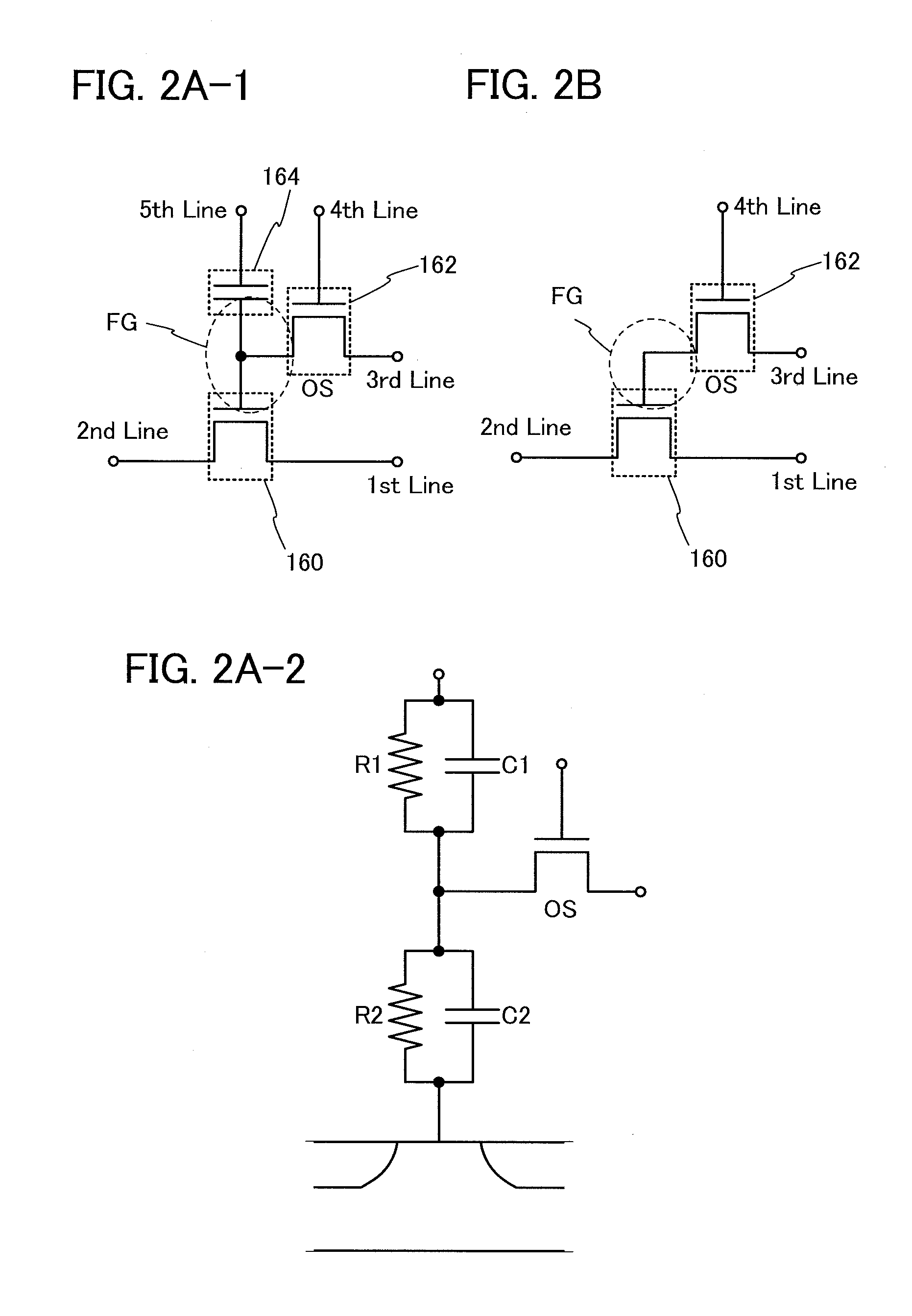

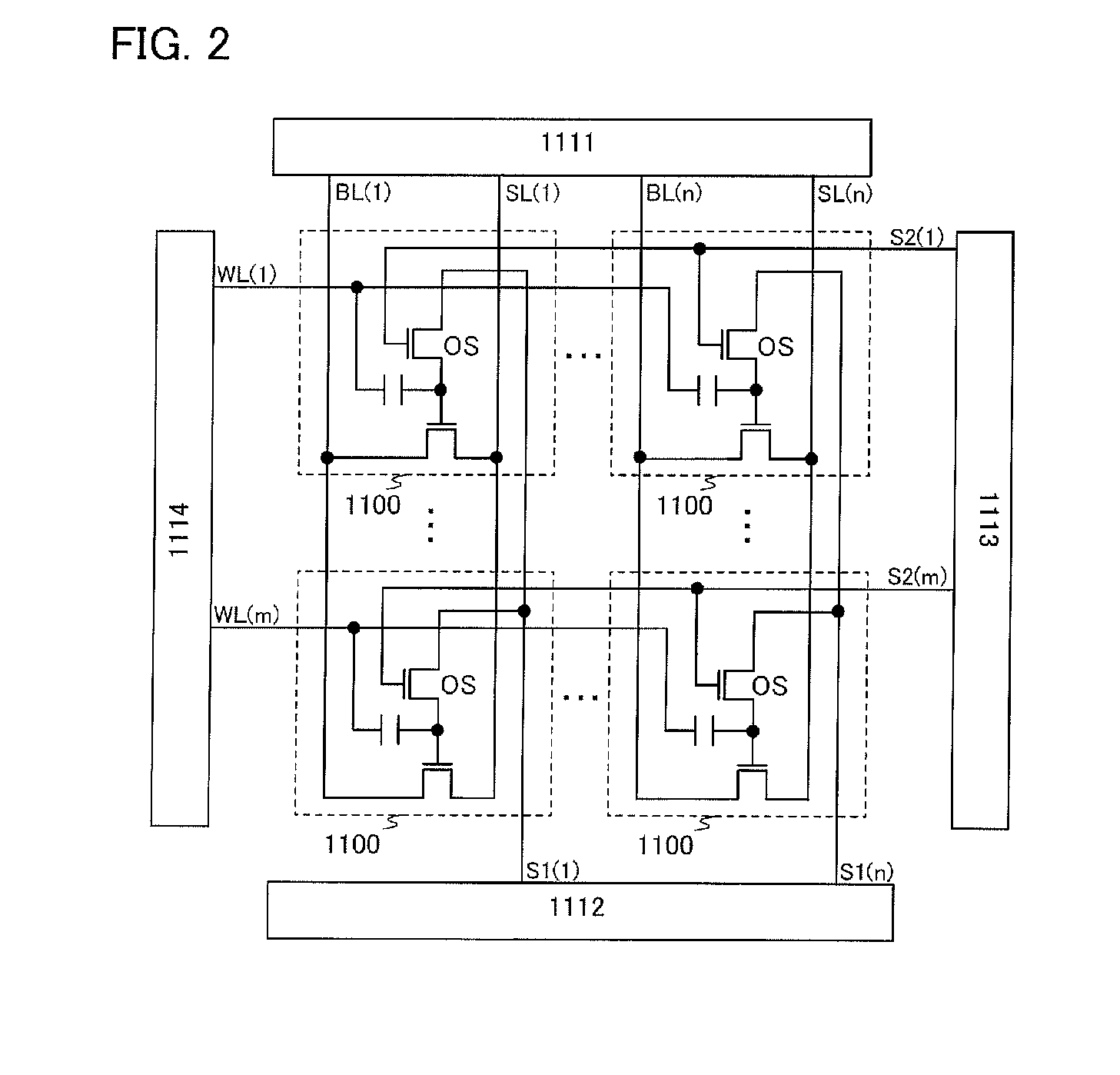

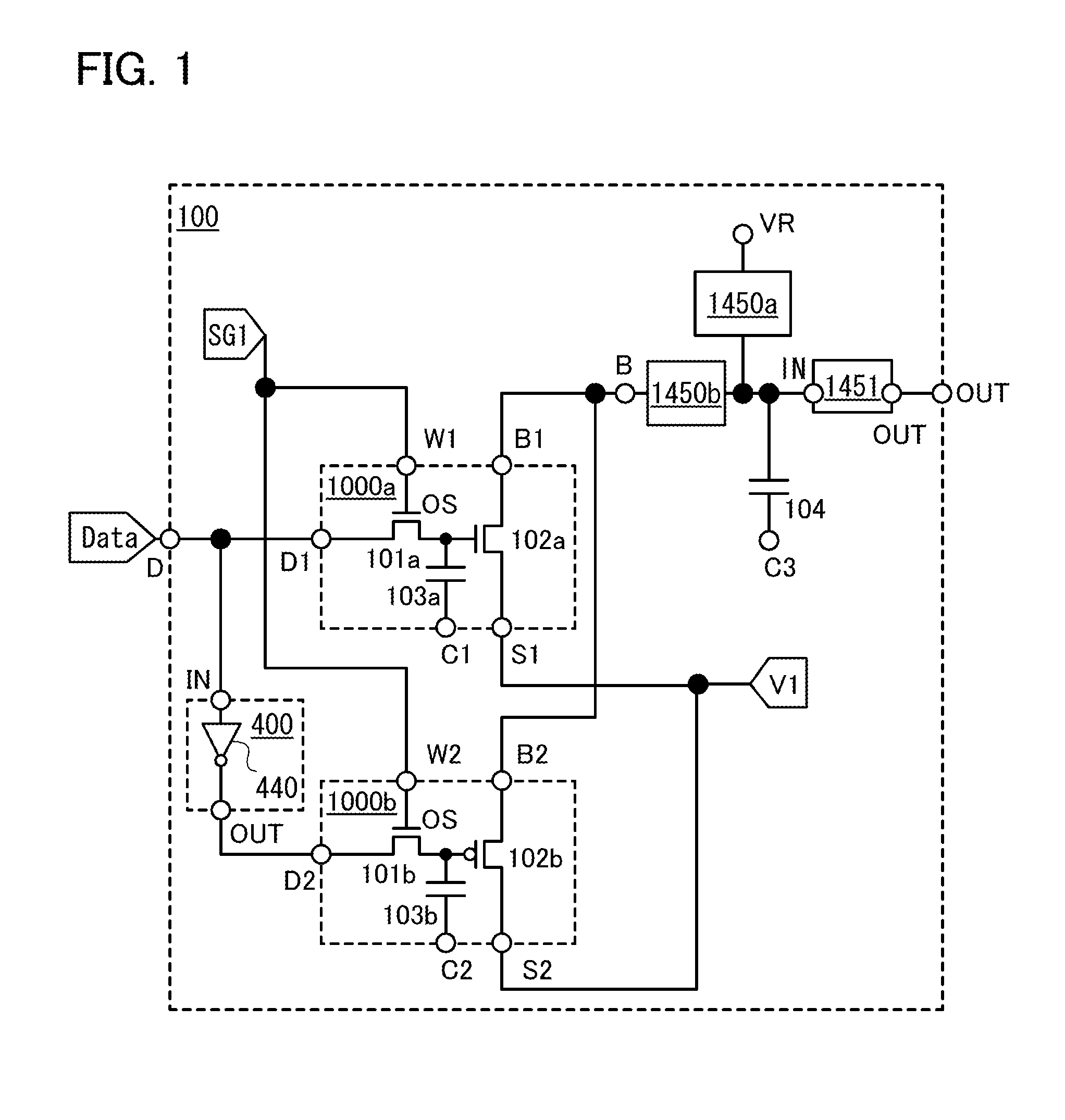

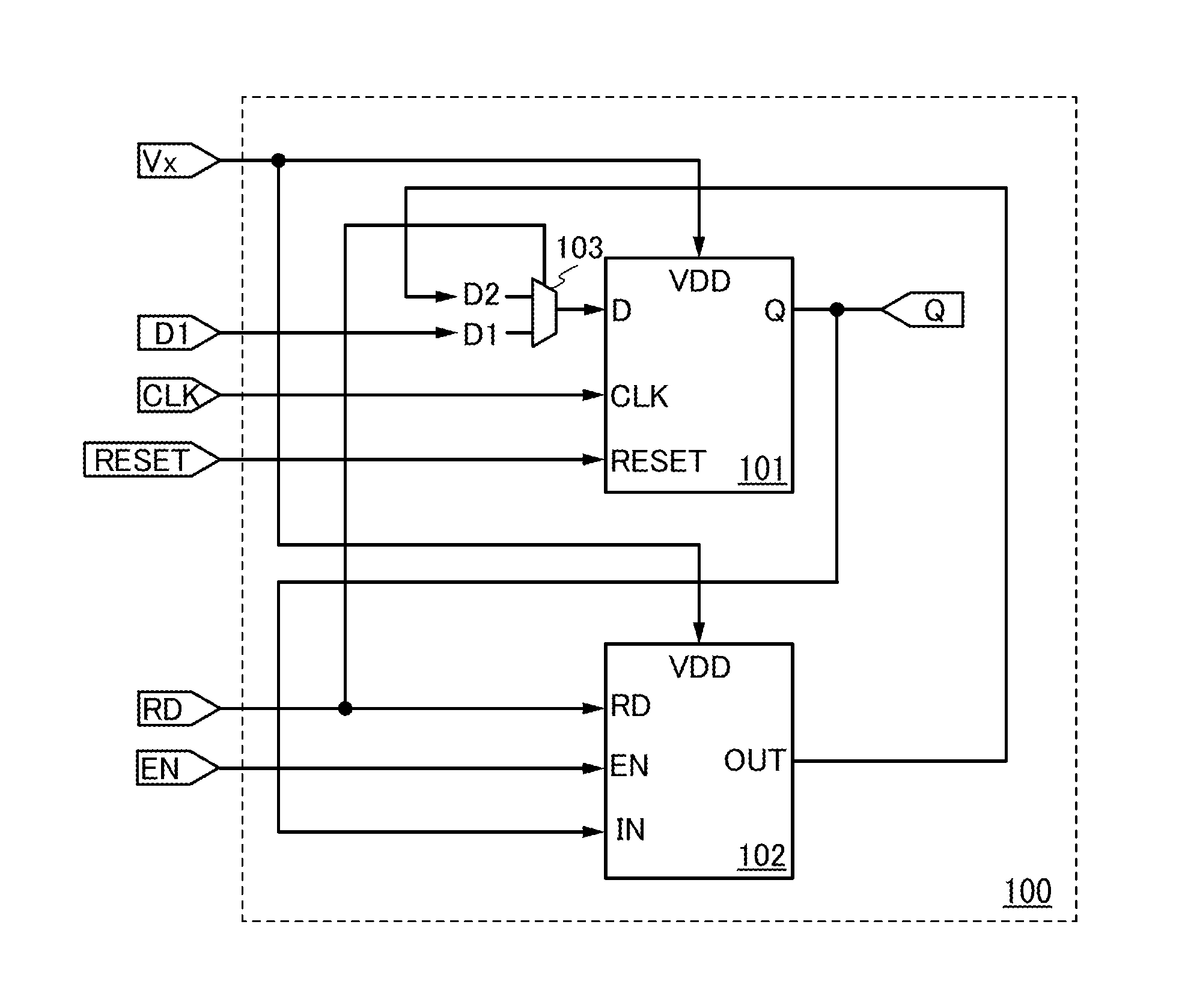

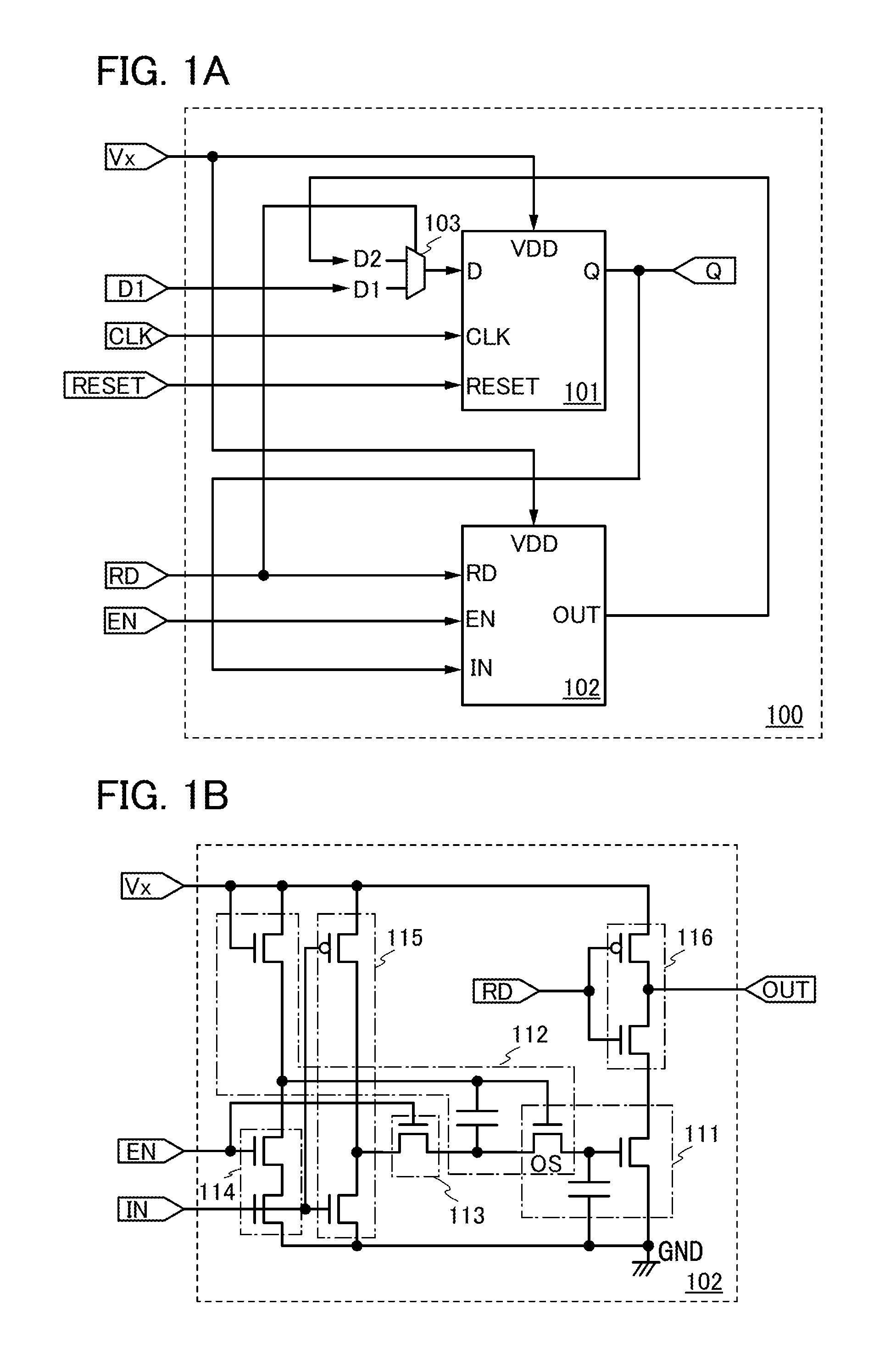

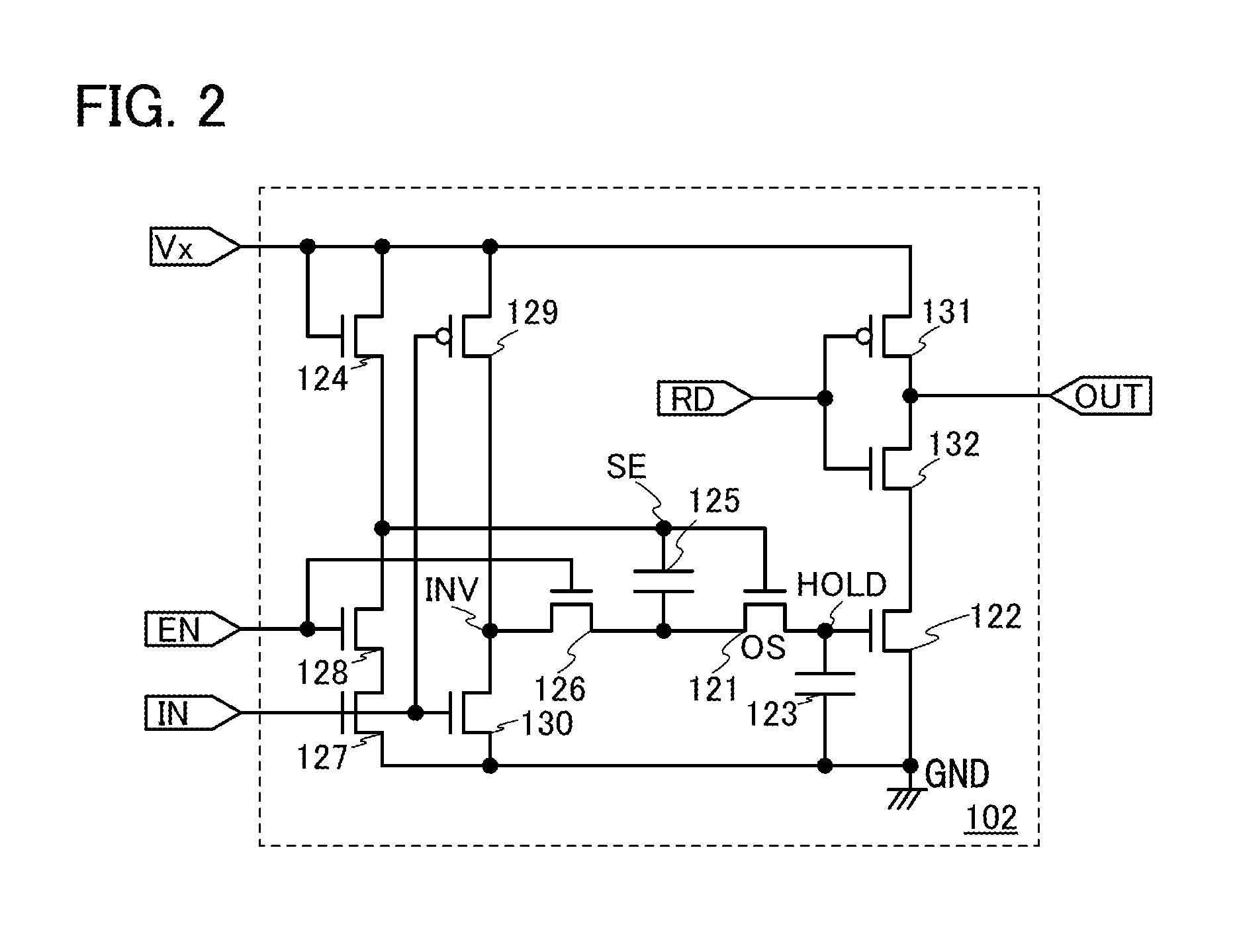

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

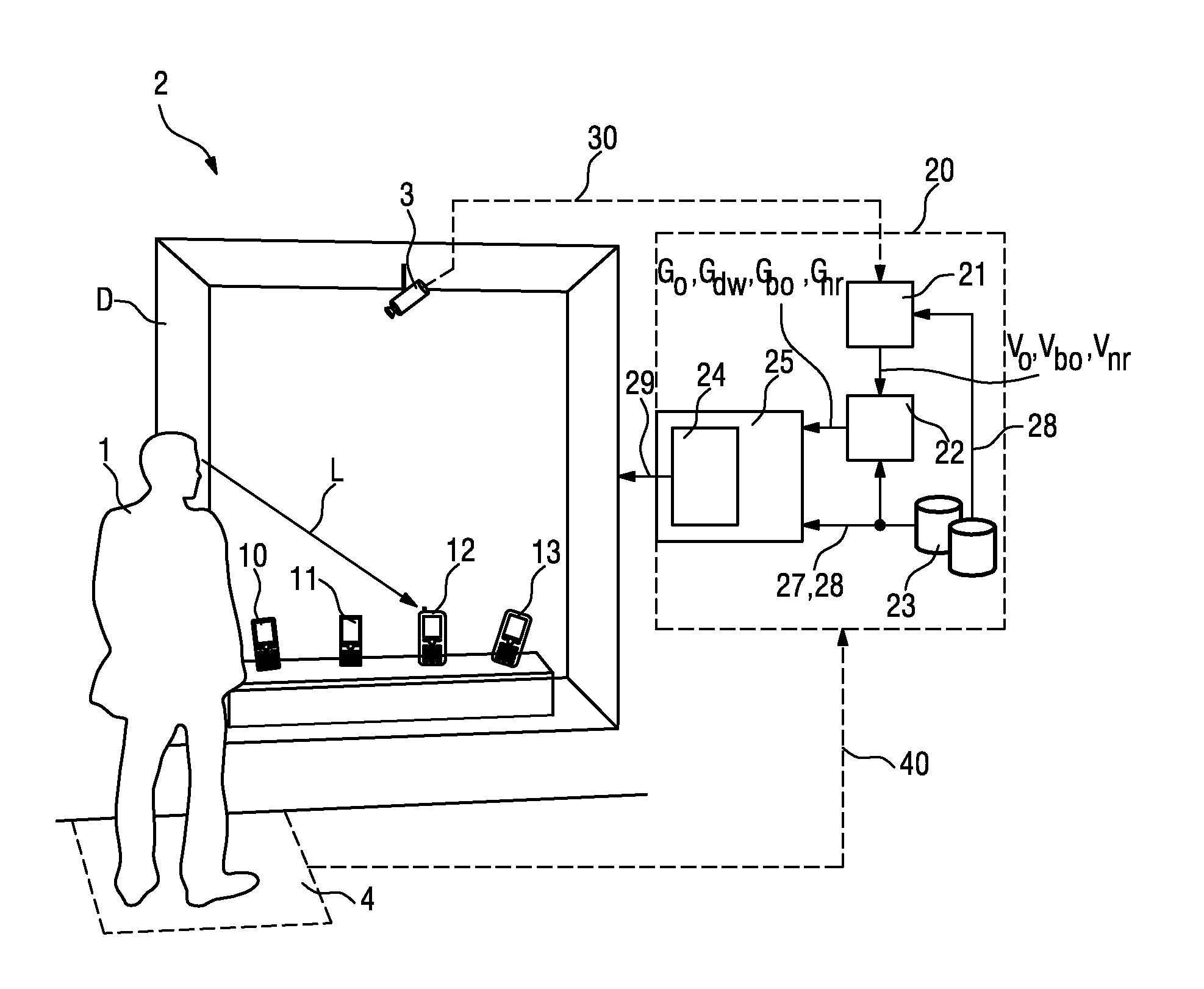

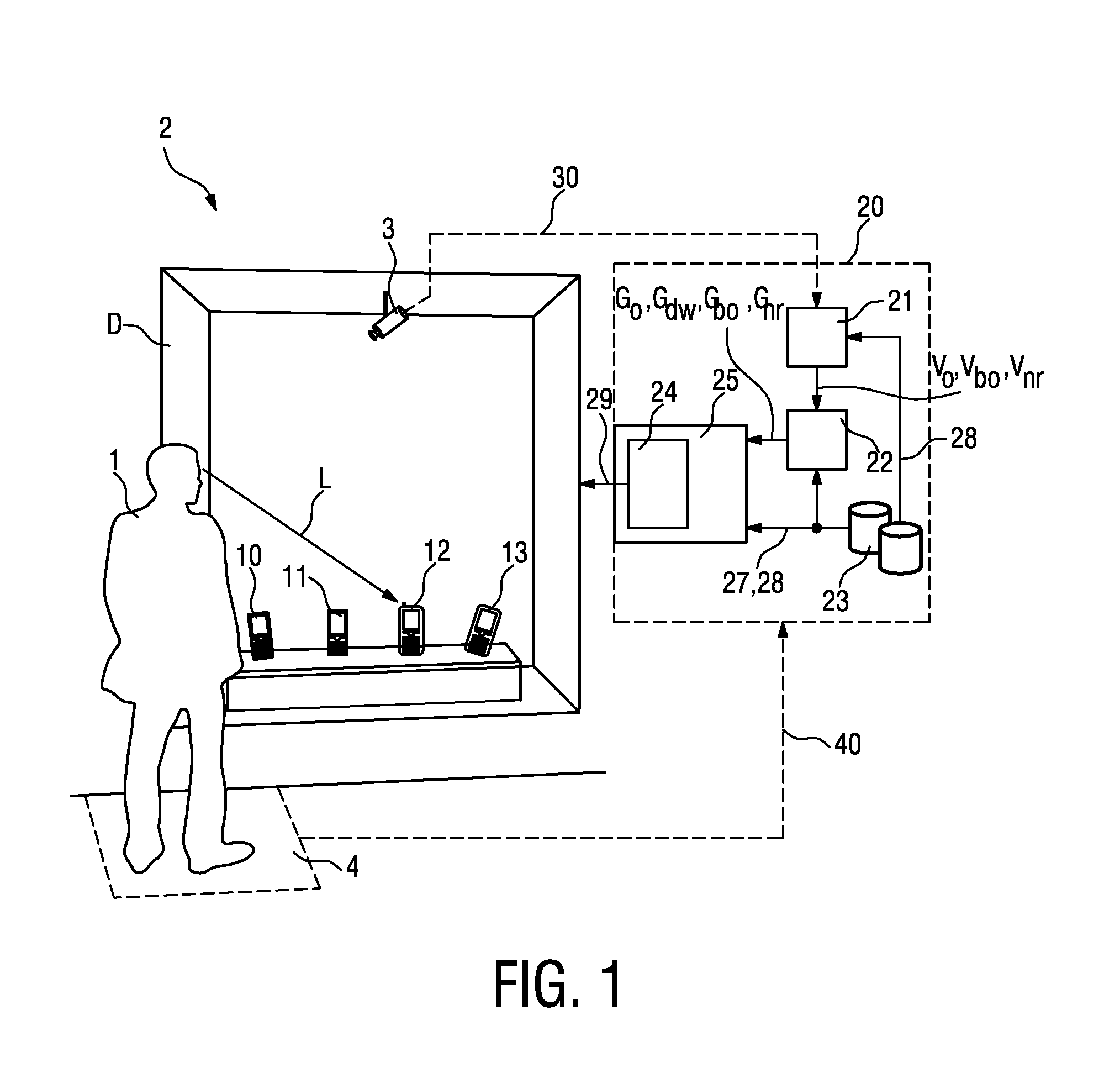

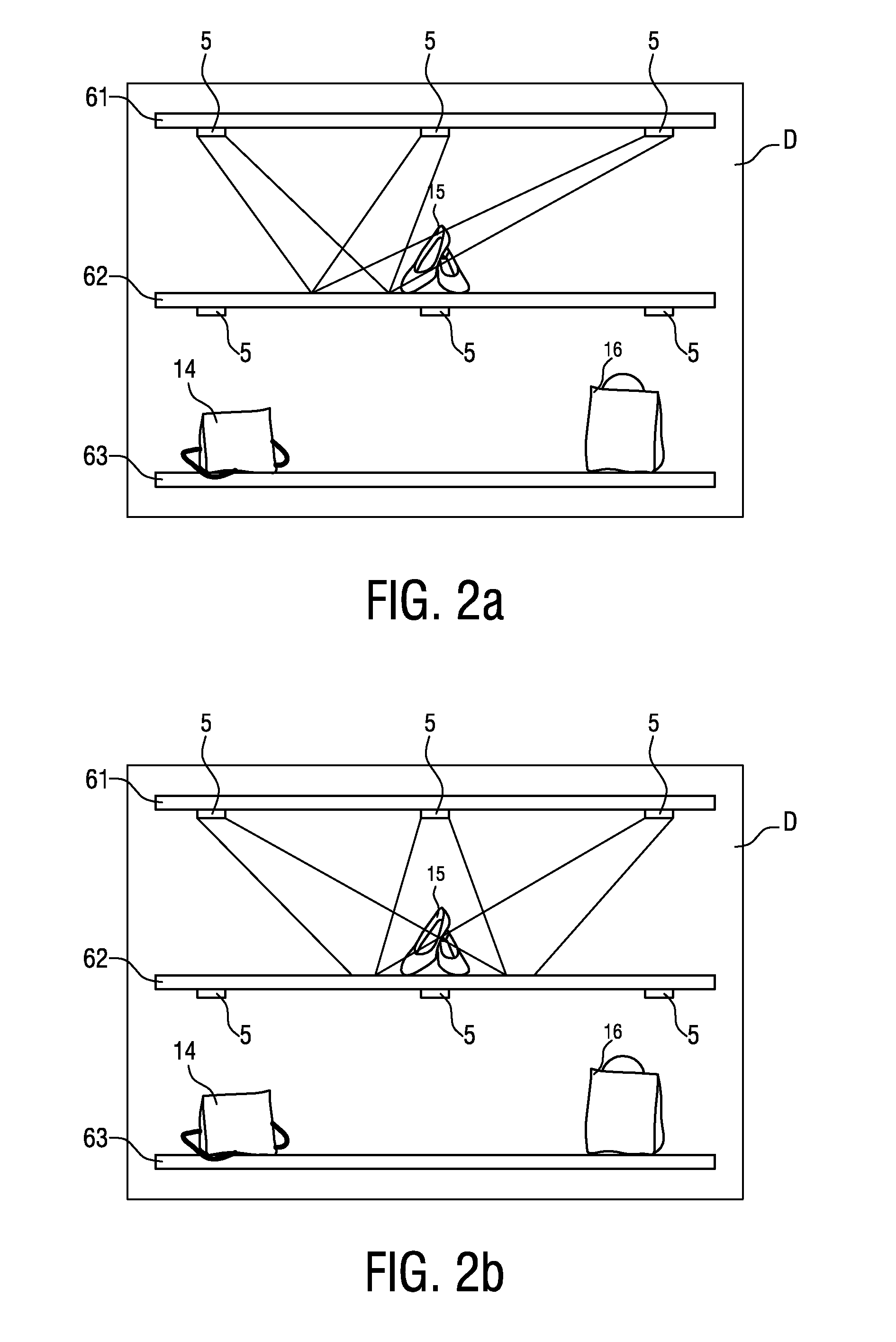

Method of performing a gaze-based interaction between a user and an interactive display system

InactiveUS20110141011A1Simple wayCheap to achieveInput/output for user-computer interactionCathode-ray tube indicatorsInteractive displaysHuman–computer interaction

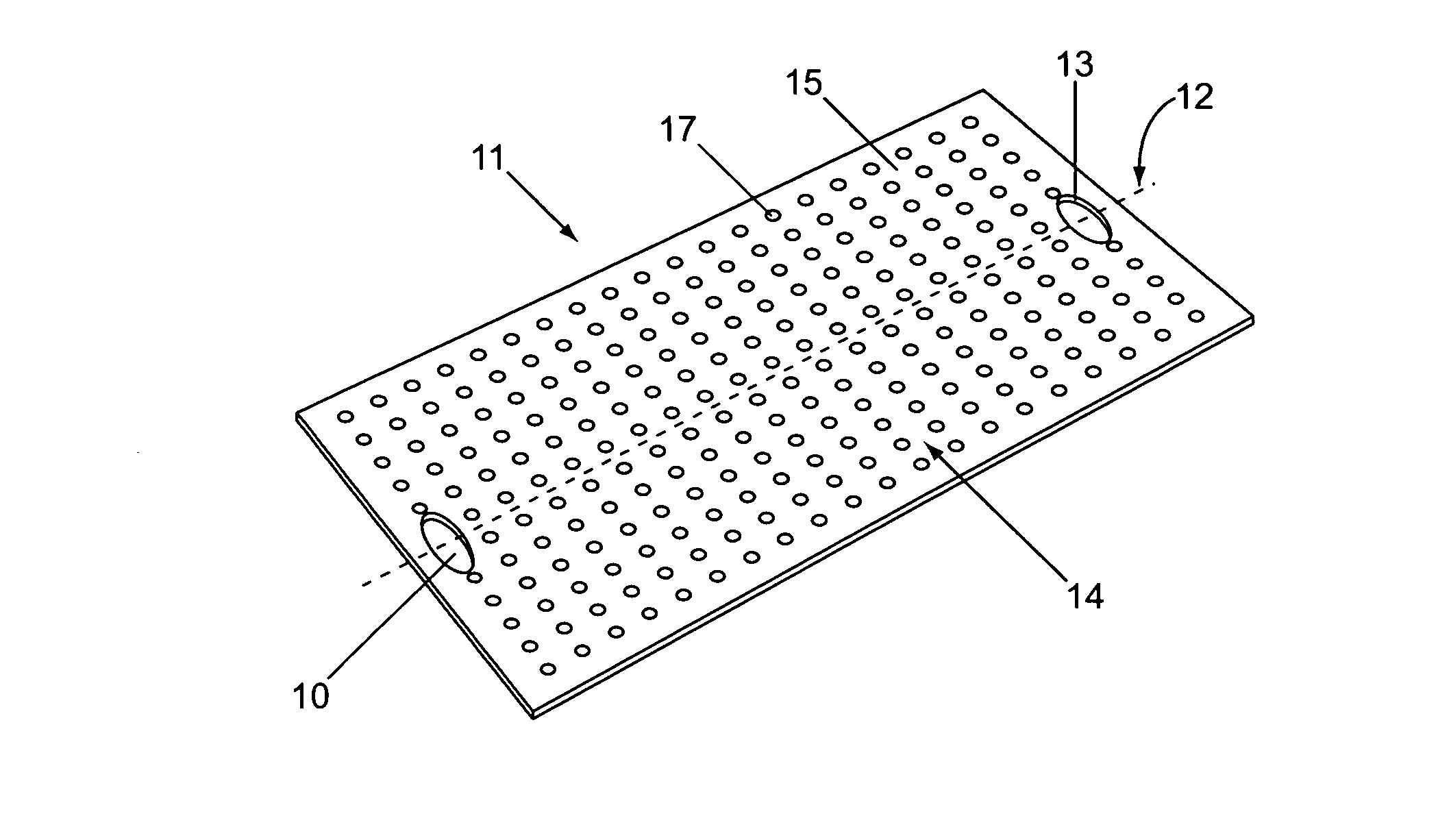

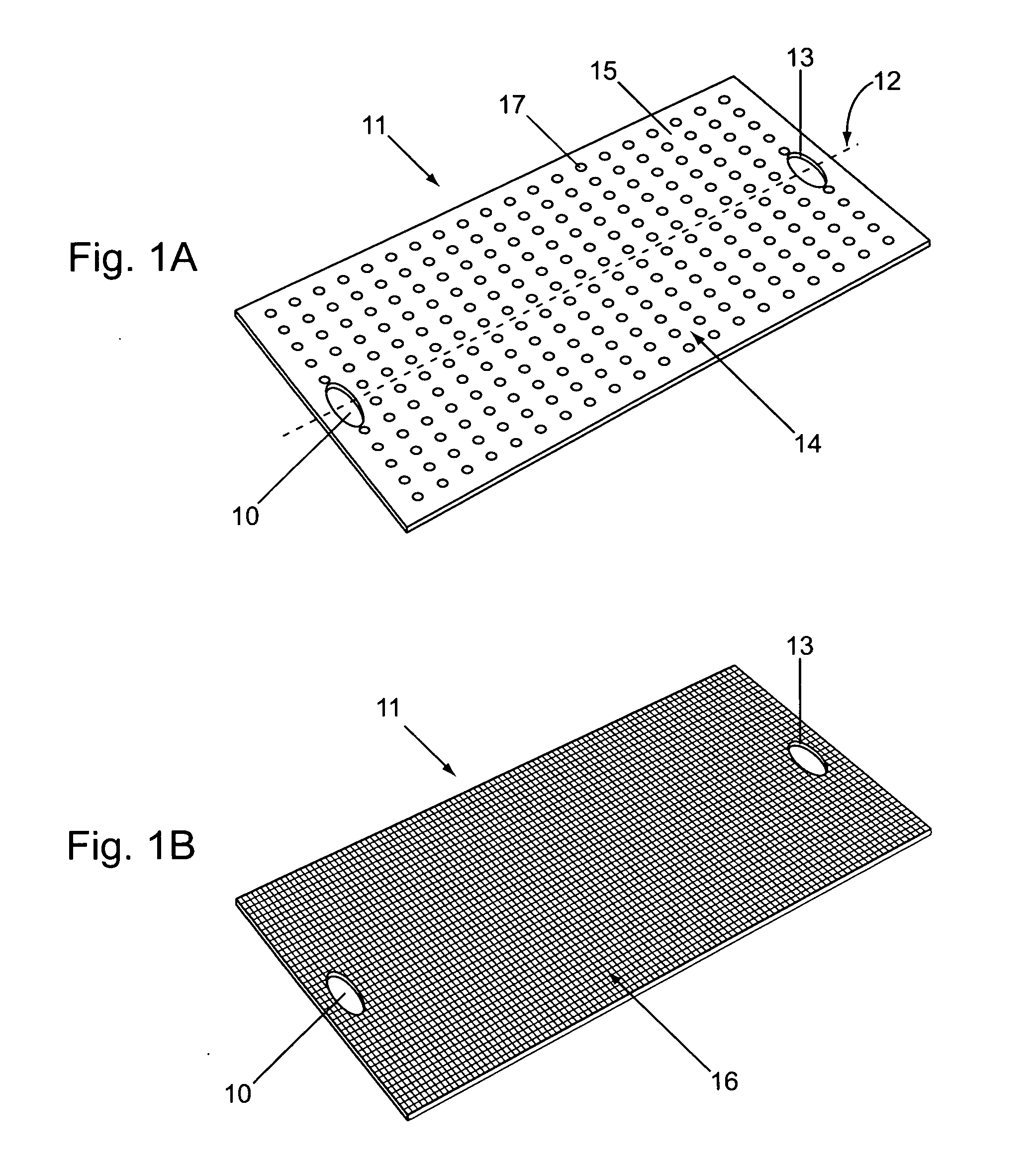

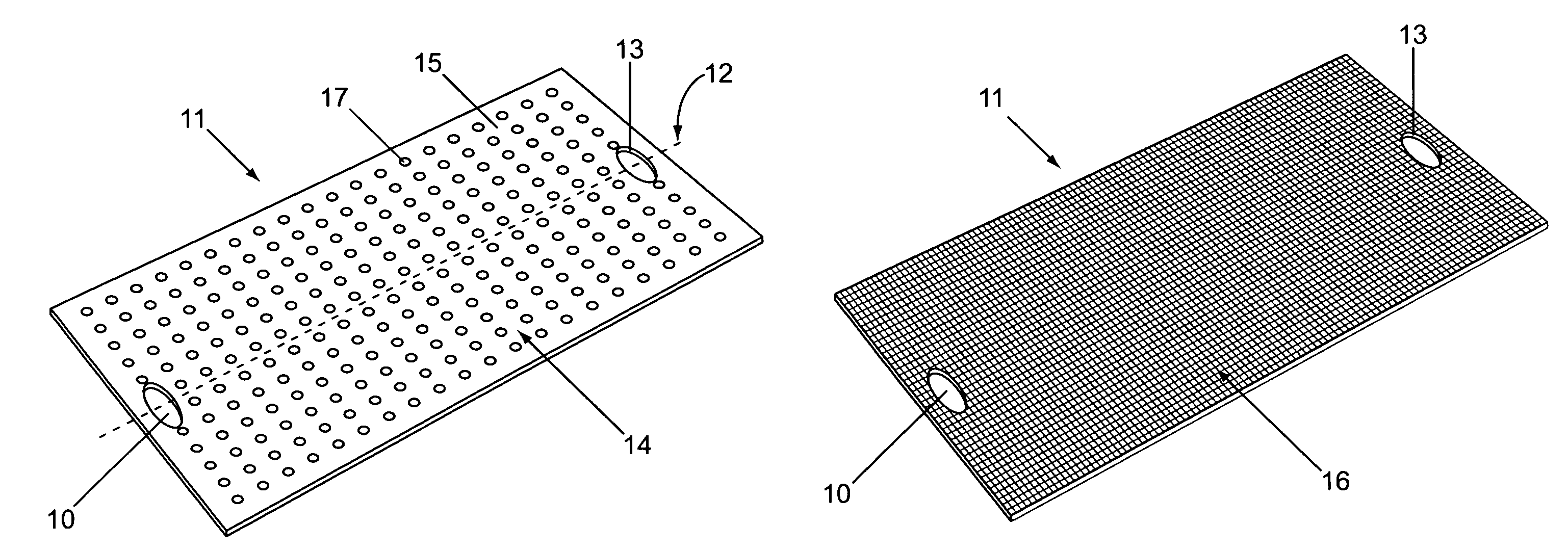

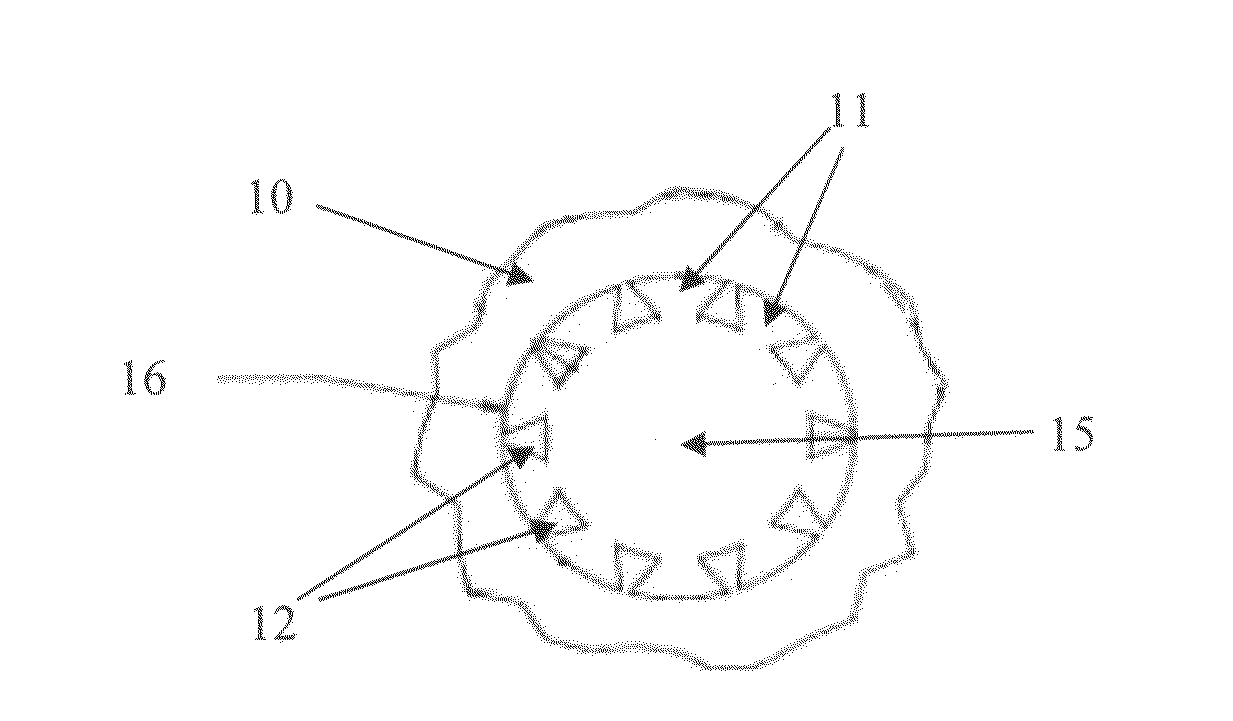

The invention describes a method of performing a gaze-based interaction between a user (1) and an interactive display system (2) comprising a three-dimensional display area (D) in which a number of physical objects (10, 11, 12, 13, 14, 15, 16) is arranged, and an observation means (3), which method comprises the steps of acquiring a gaze-related output (30) for the user (1) from the observation means (3), determining a momentary gaze category (Go, Gdw, Gbo, Gnr) from a plurality of gaze categories (Go, Gdw, Gbo, Gnr) on the basis of the gaze-related output (30); and continuously generating display area feedback according to the momentary determined gaze category (Go, Gdw, Gbo, Gnr). The invention further describes an interactive display system (2) comprising a three-dimensional display area (D) in which a number of physical objects (10, 11, 12, 13, 14, 15, 16) is arranged, an observation means (3) for acquiring a gaze-related output (30) for a user (1), a gaze category determination unit (22) for determining a momentary gaze category (Go, Gdw, Gbo, Gnr) from a plurality of gaze categories (Go, Gdw, Gbo, Gnr) on the basis of the gaze-related output (30); and a feedback generation unit (25) for continuously generating display area feedback (29) according to the momentary determined gaze category (Go, Gdw, Gbo, Gnr).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

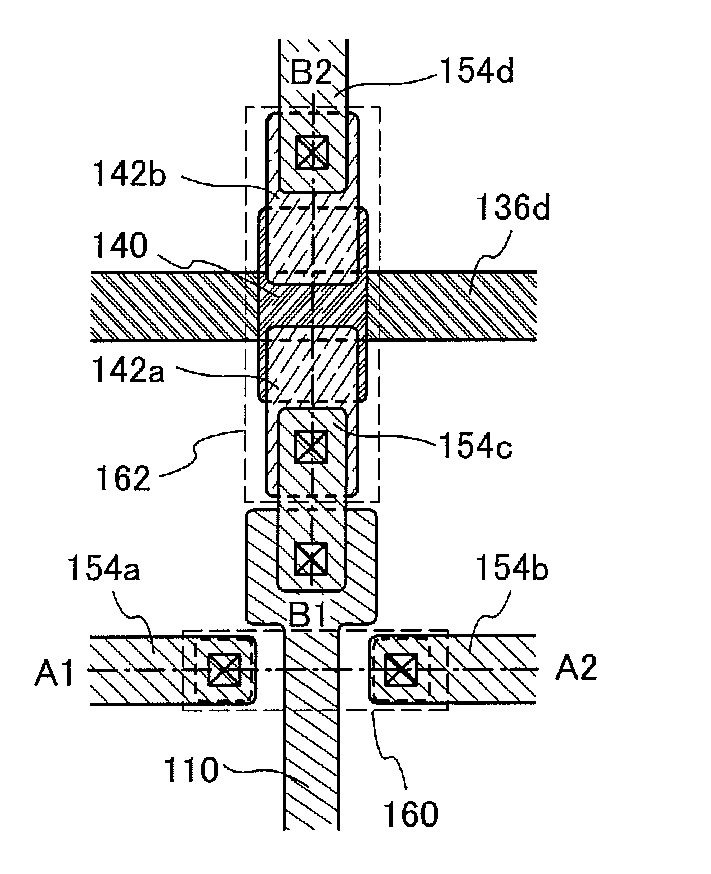

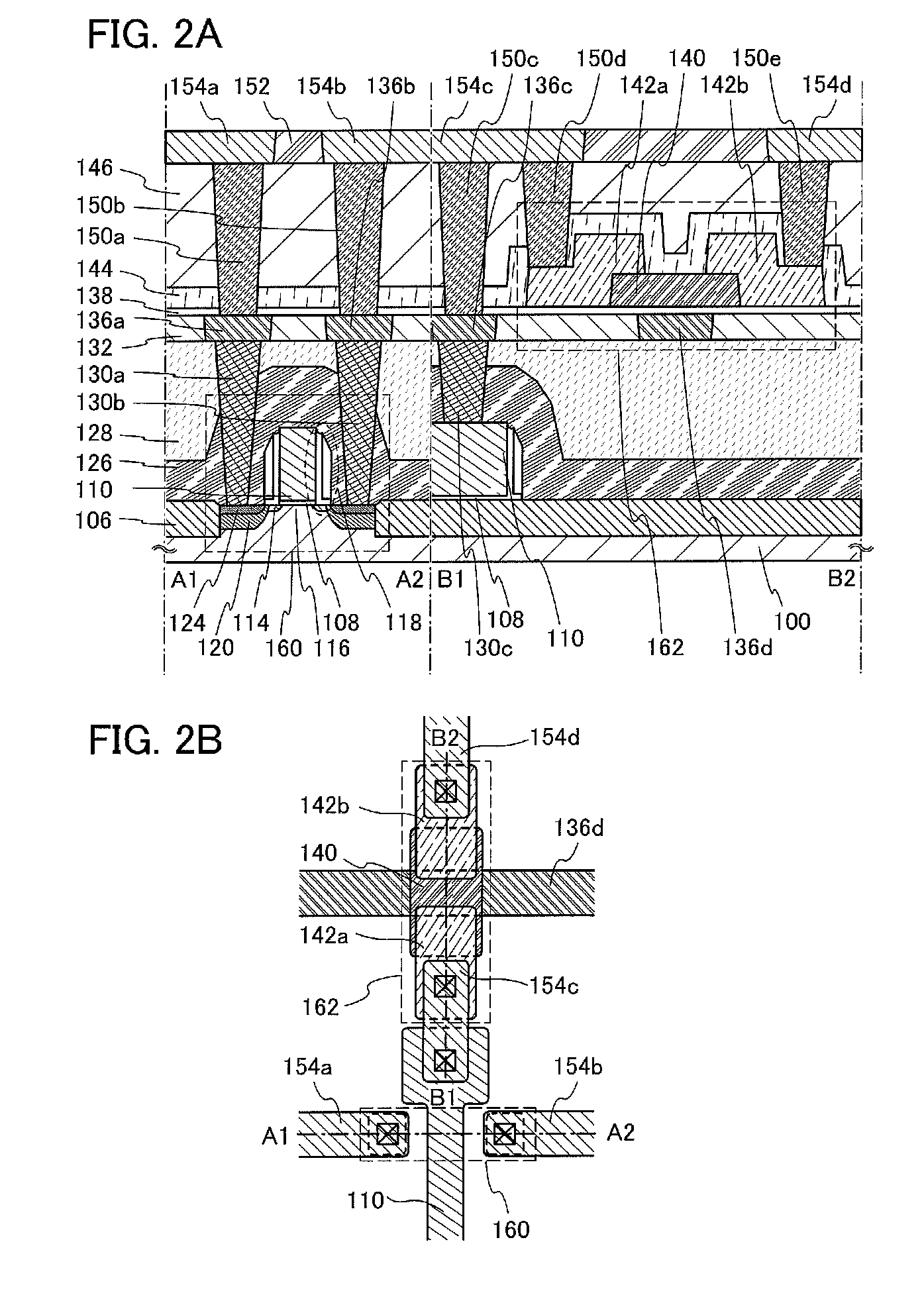

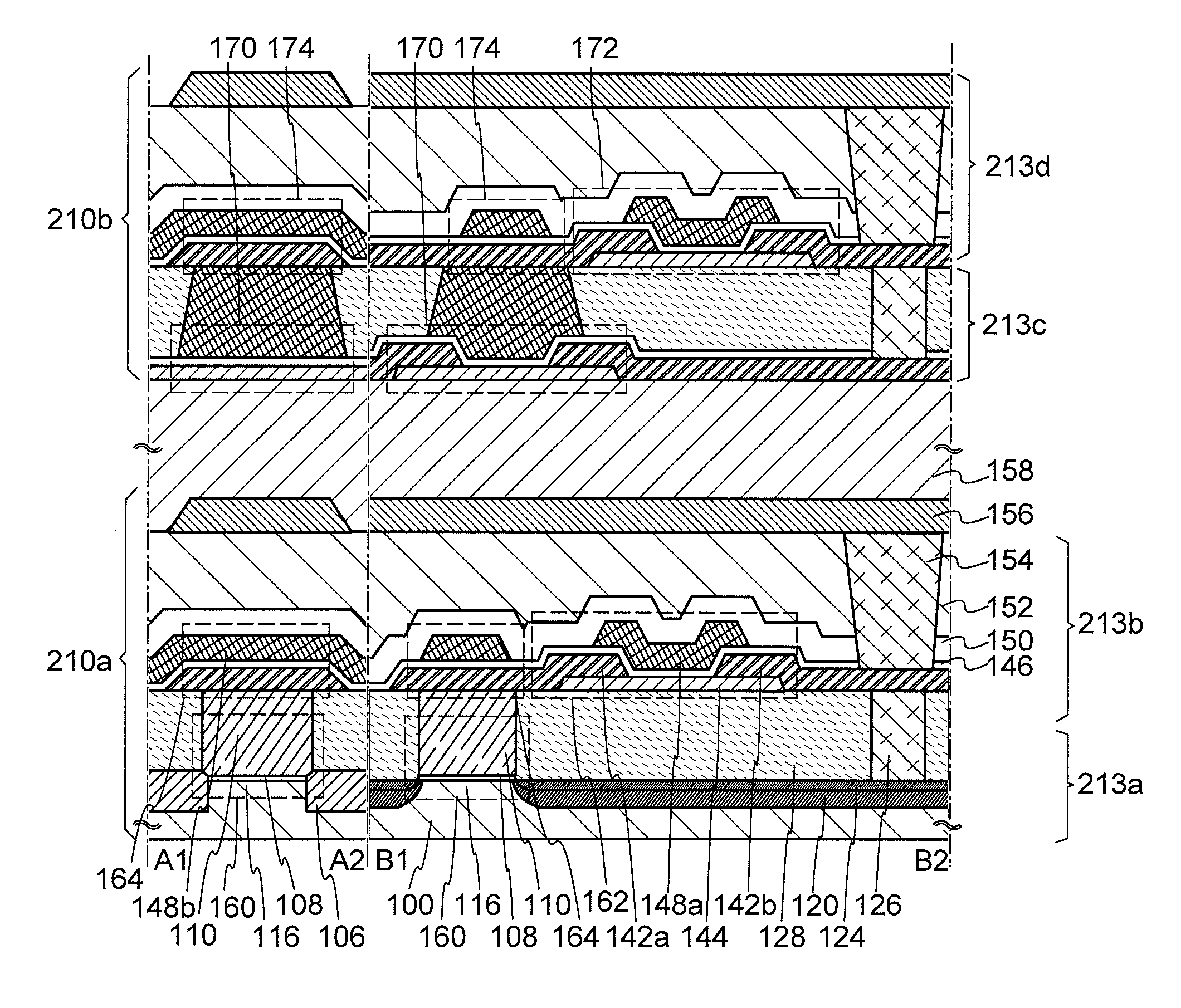

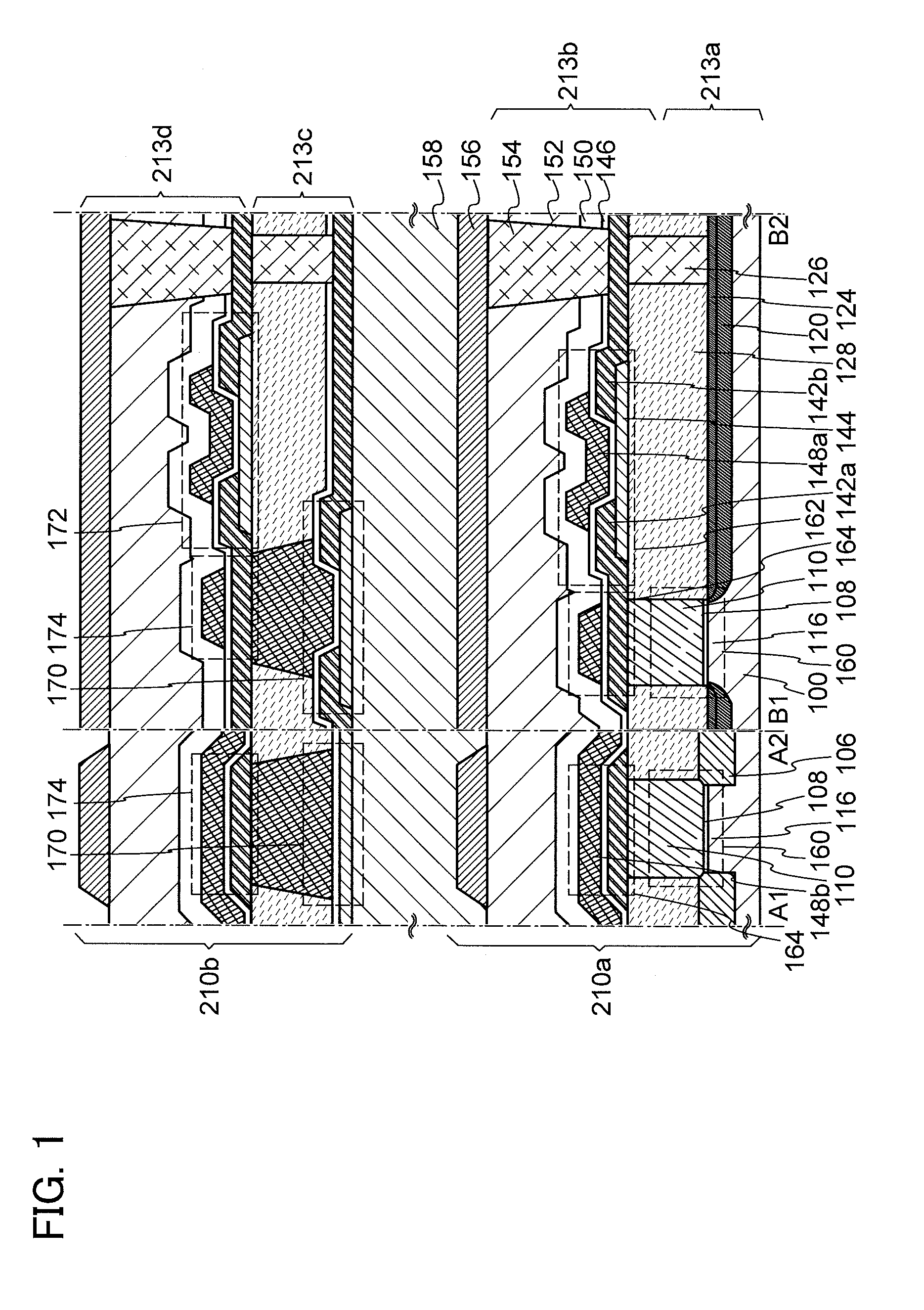

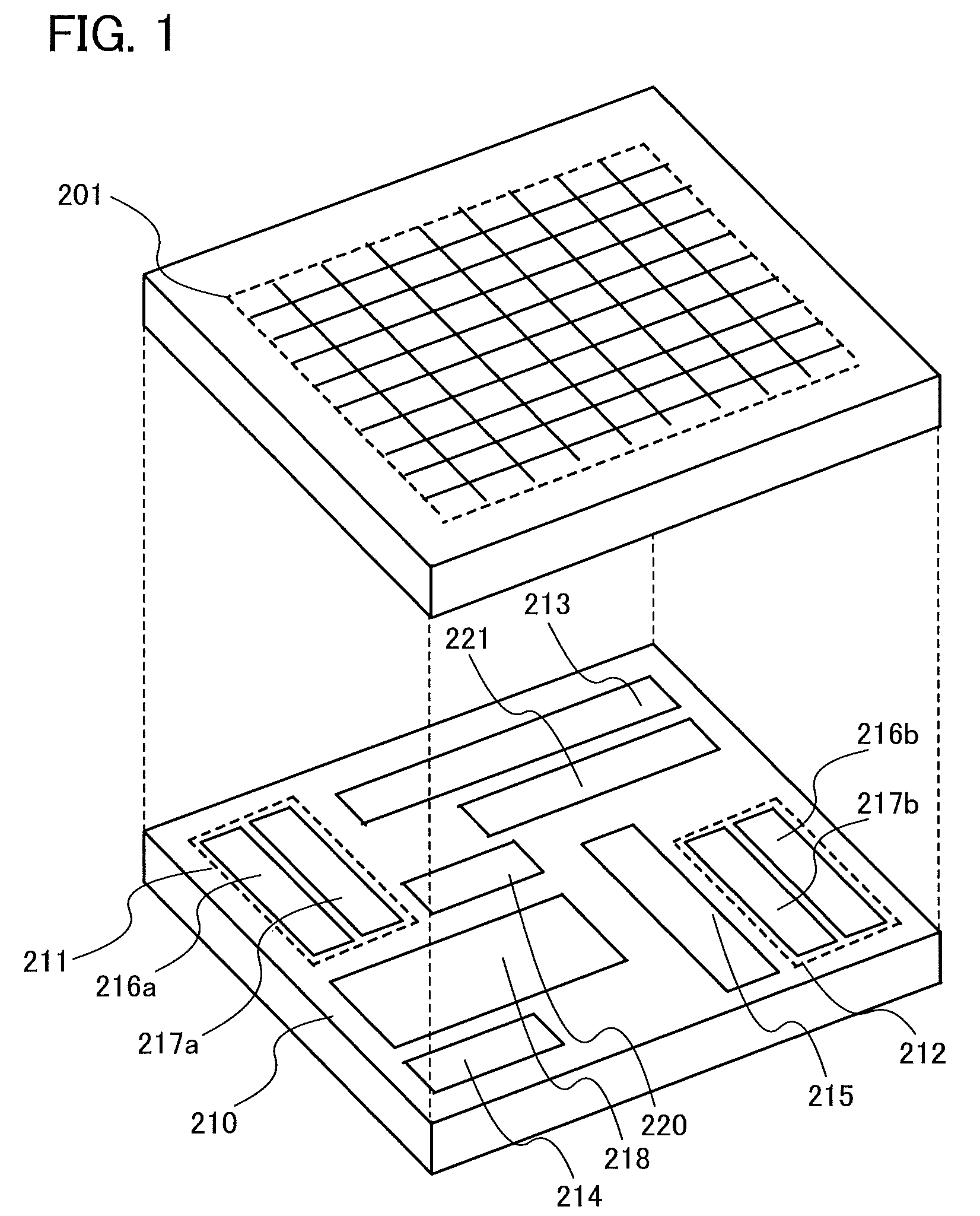

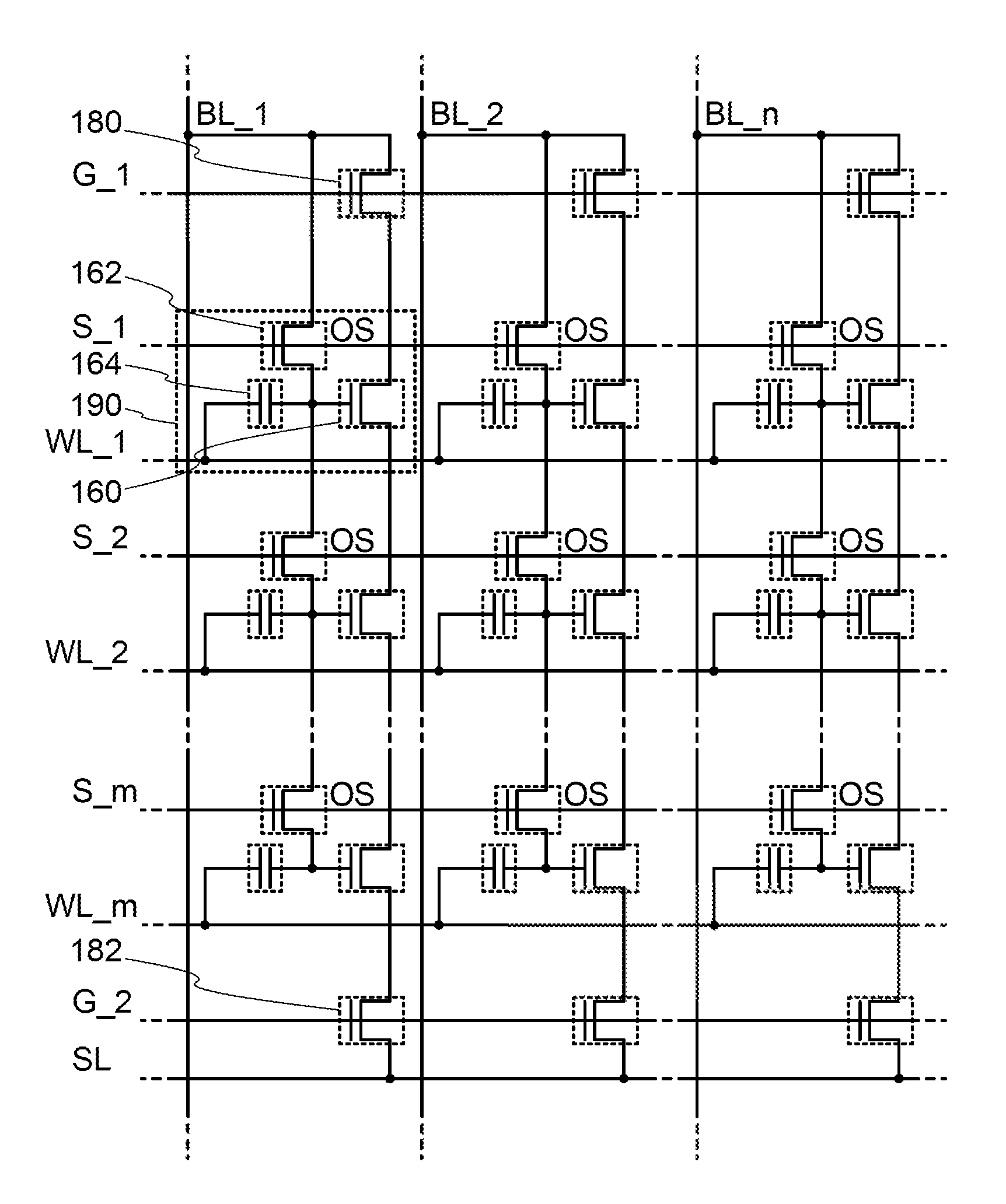

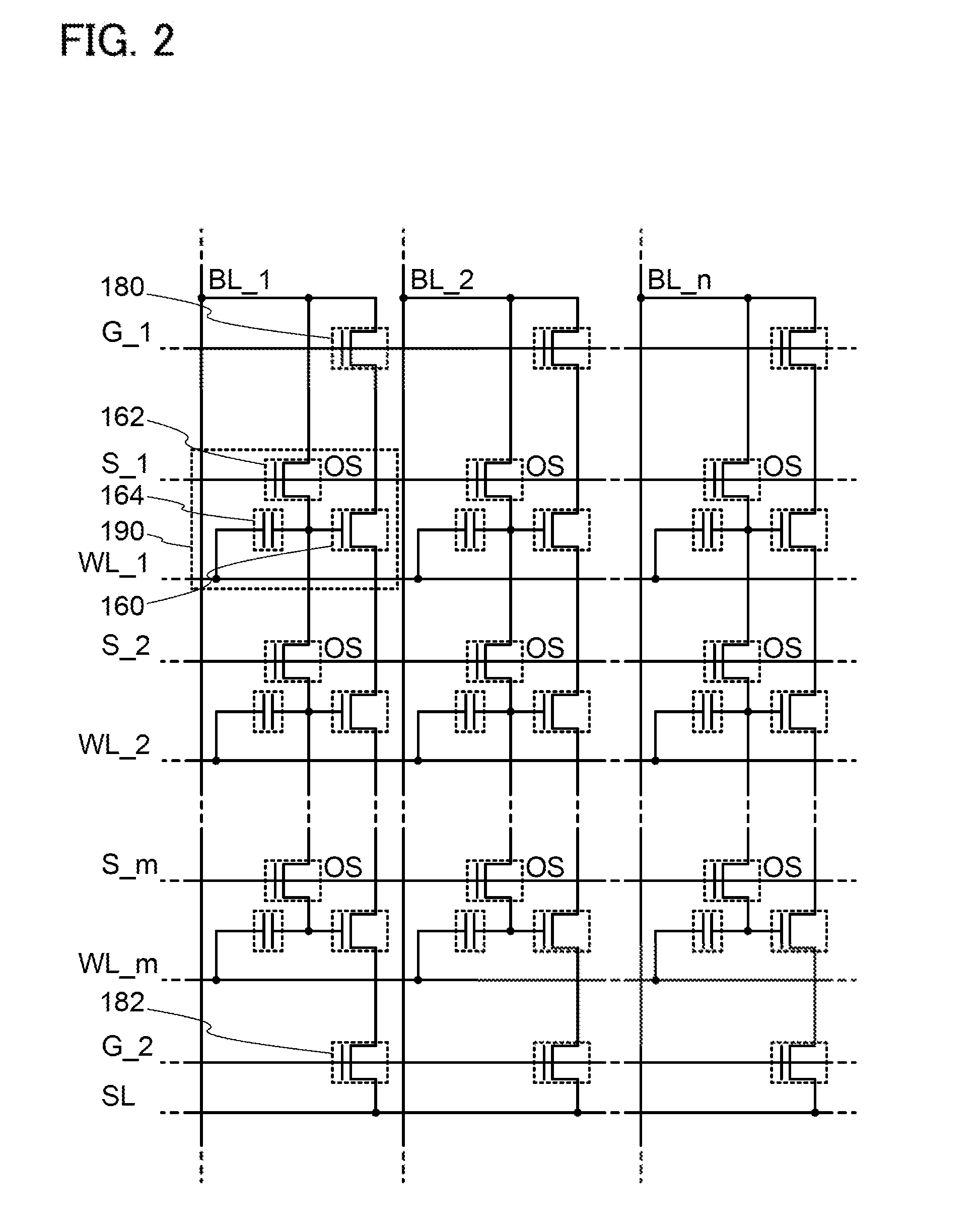

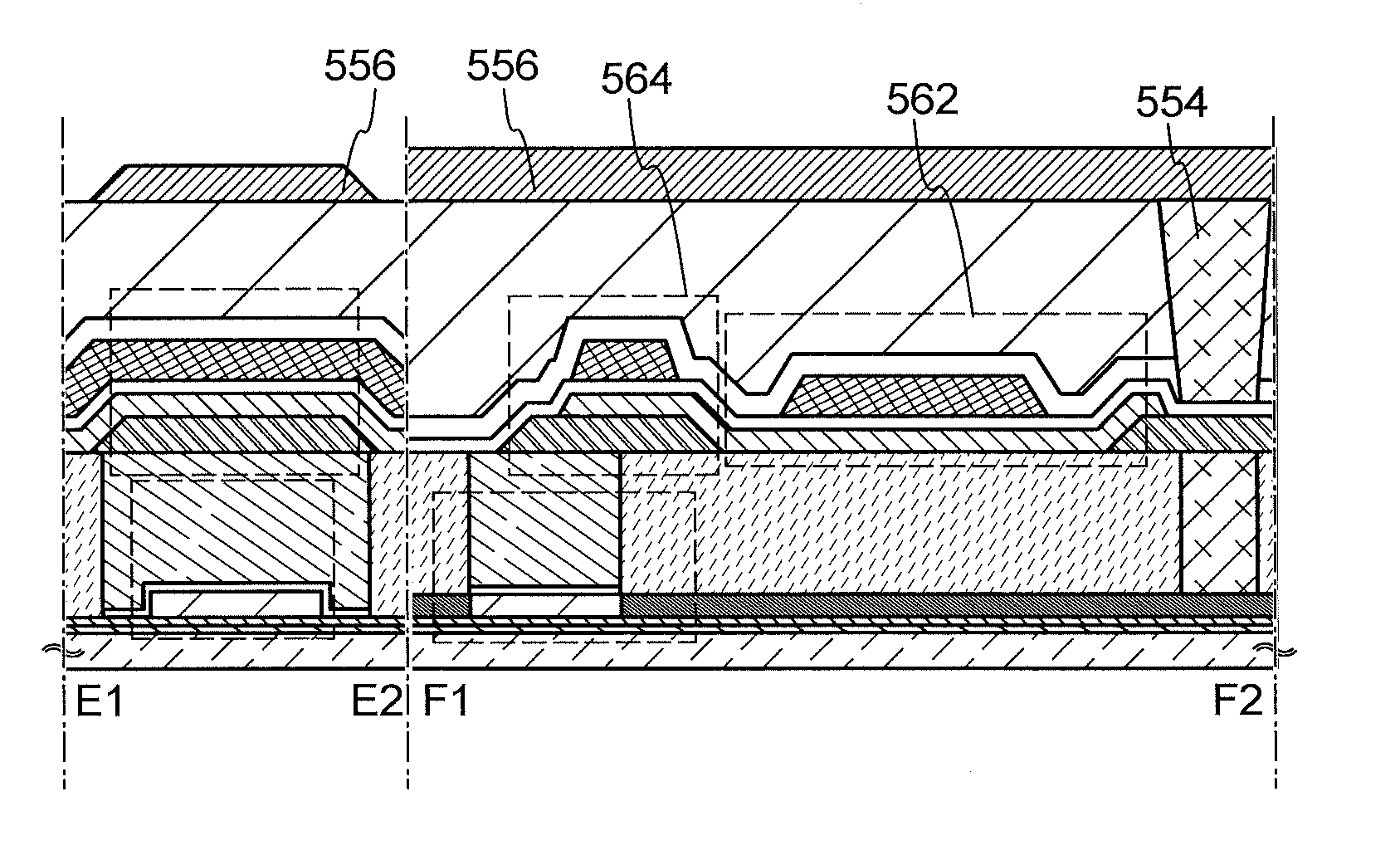

Semiconductor device

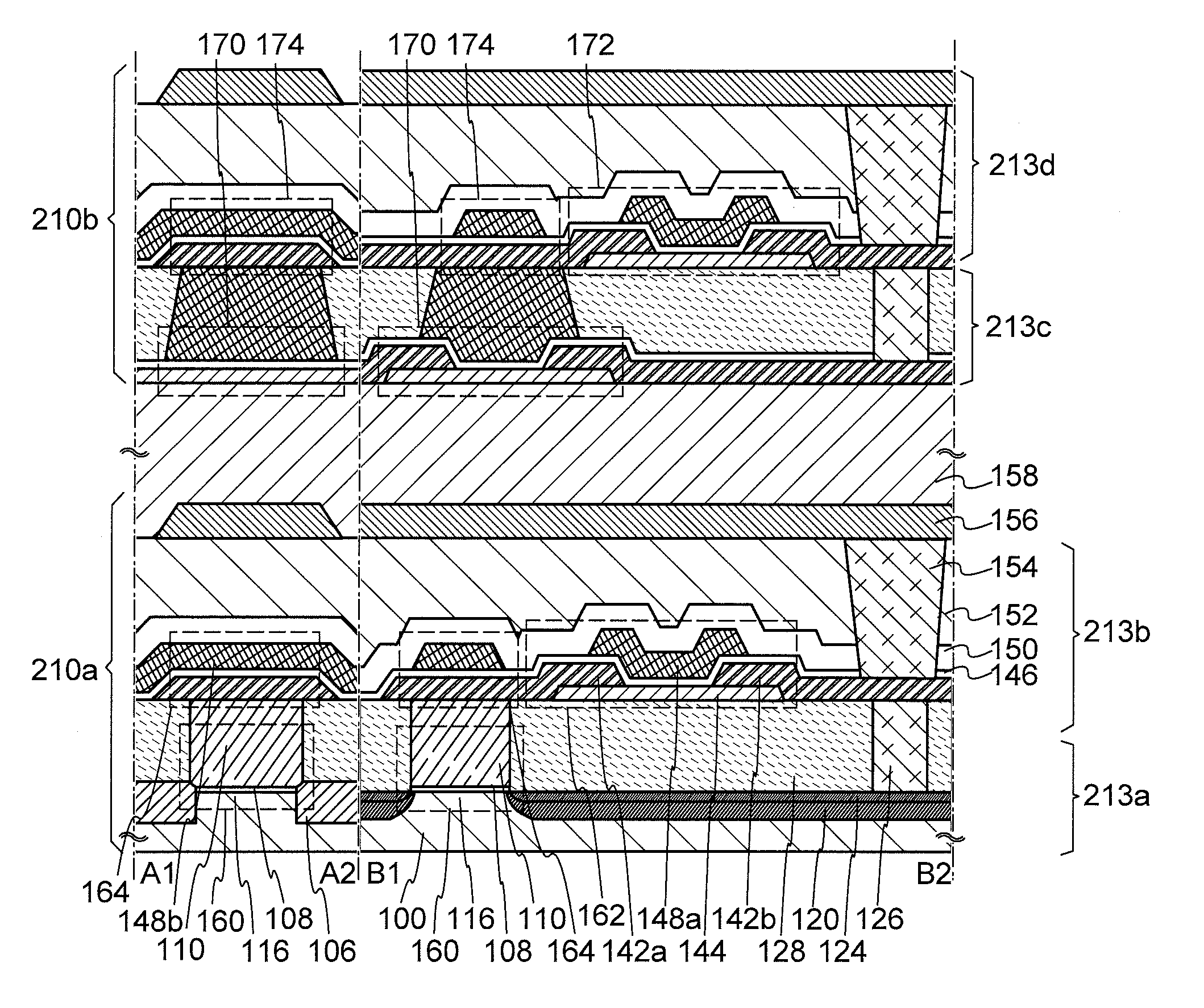

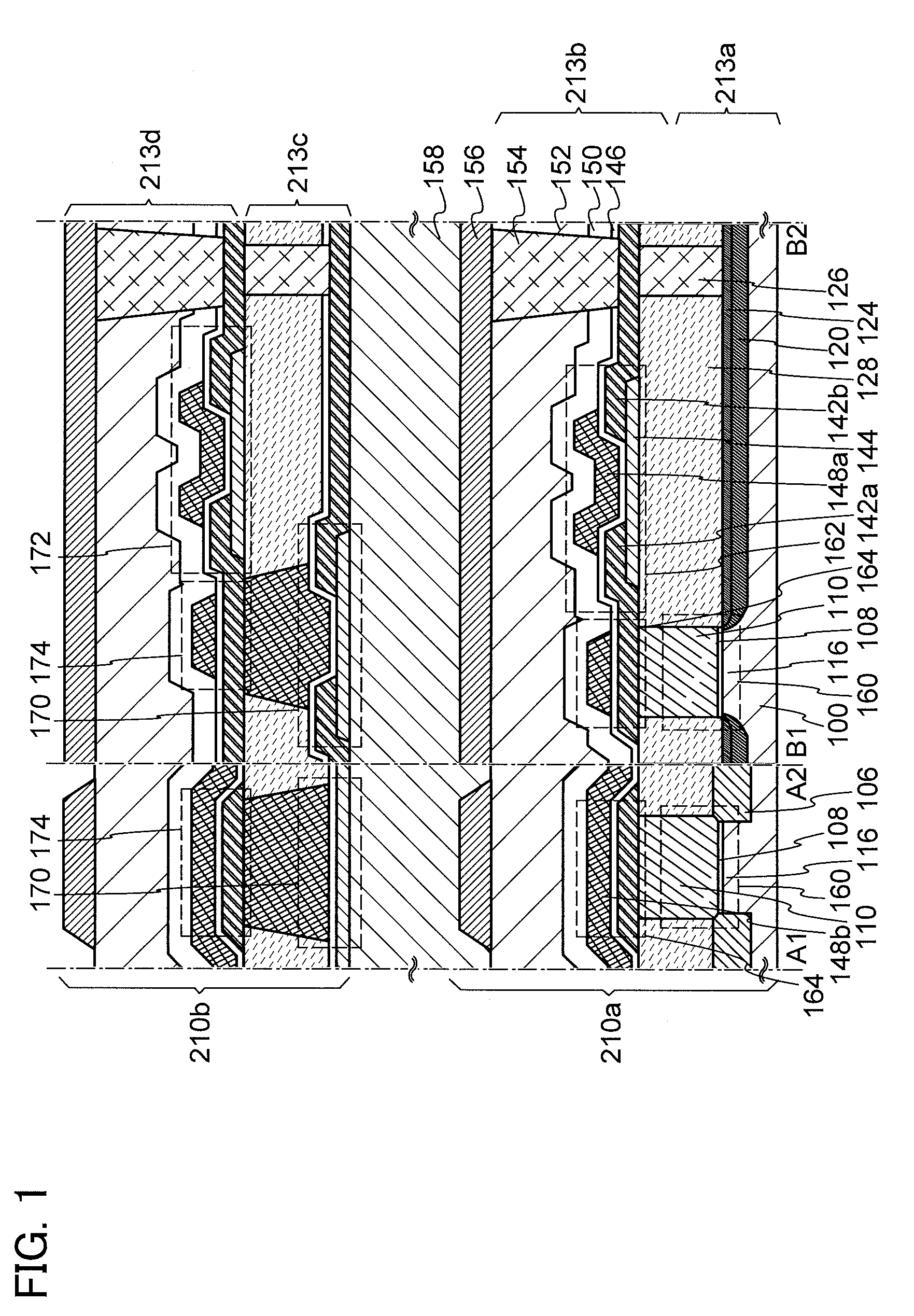

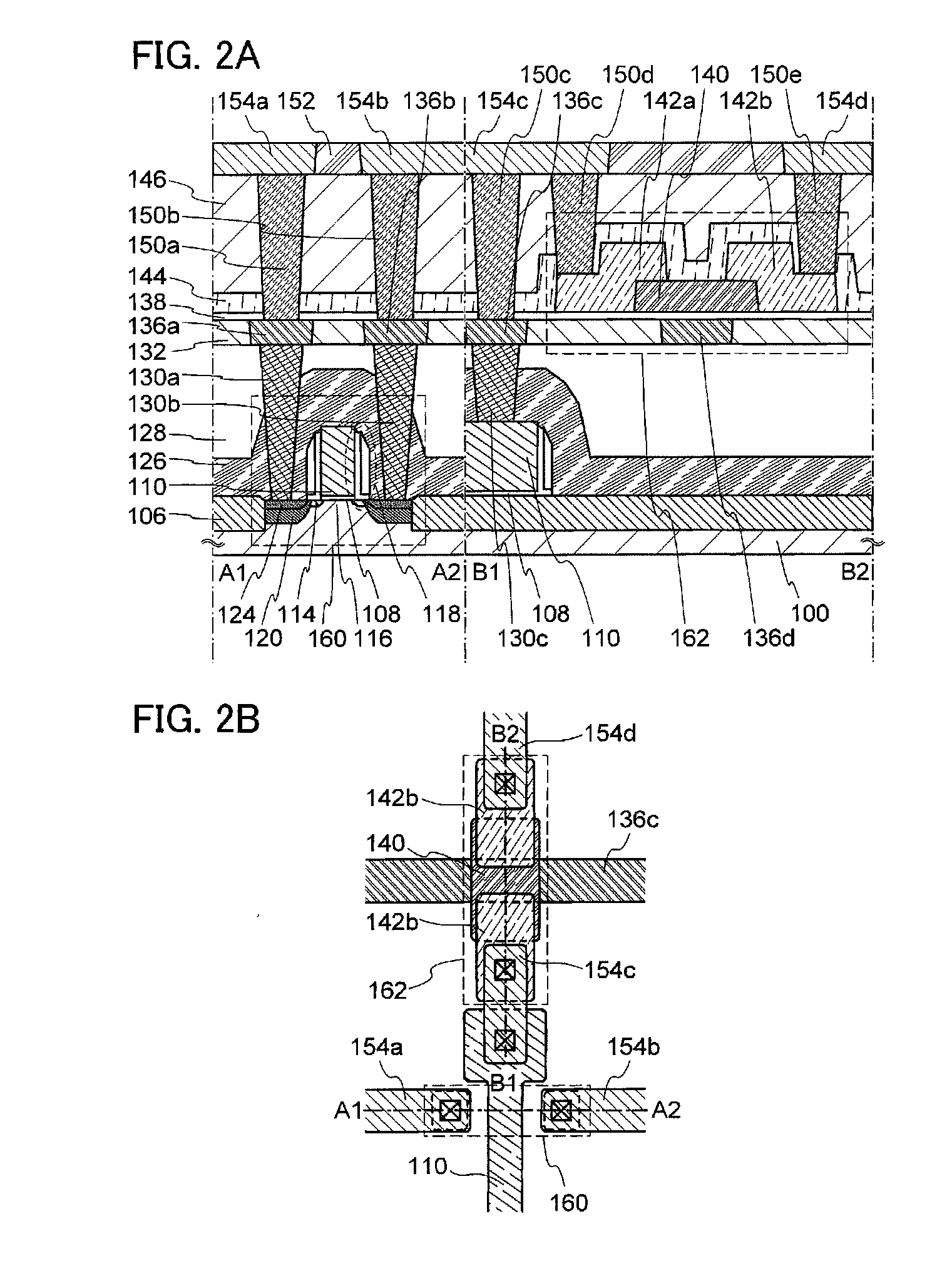

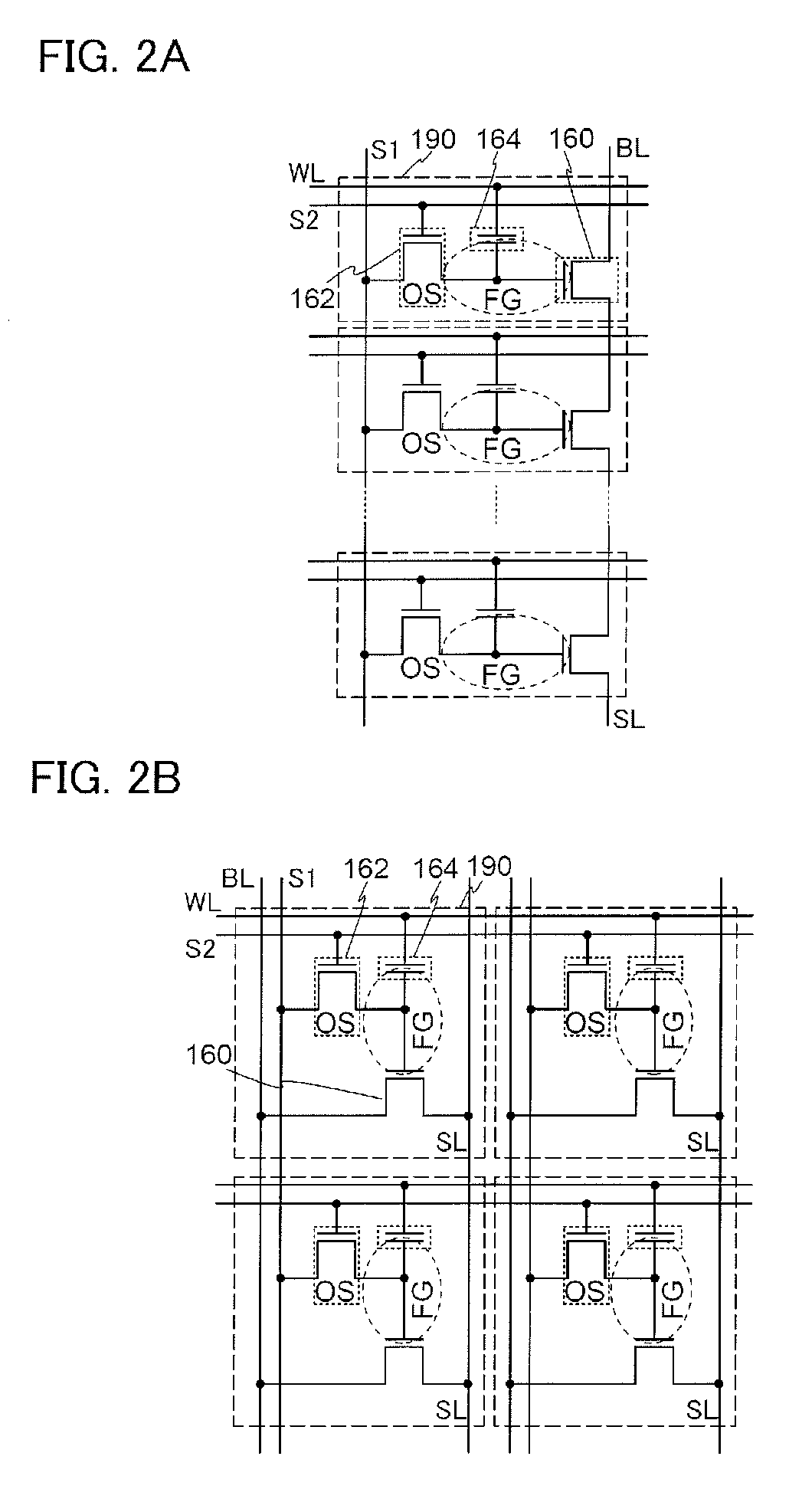

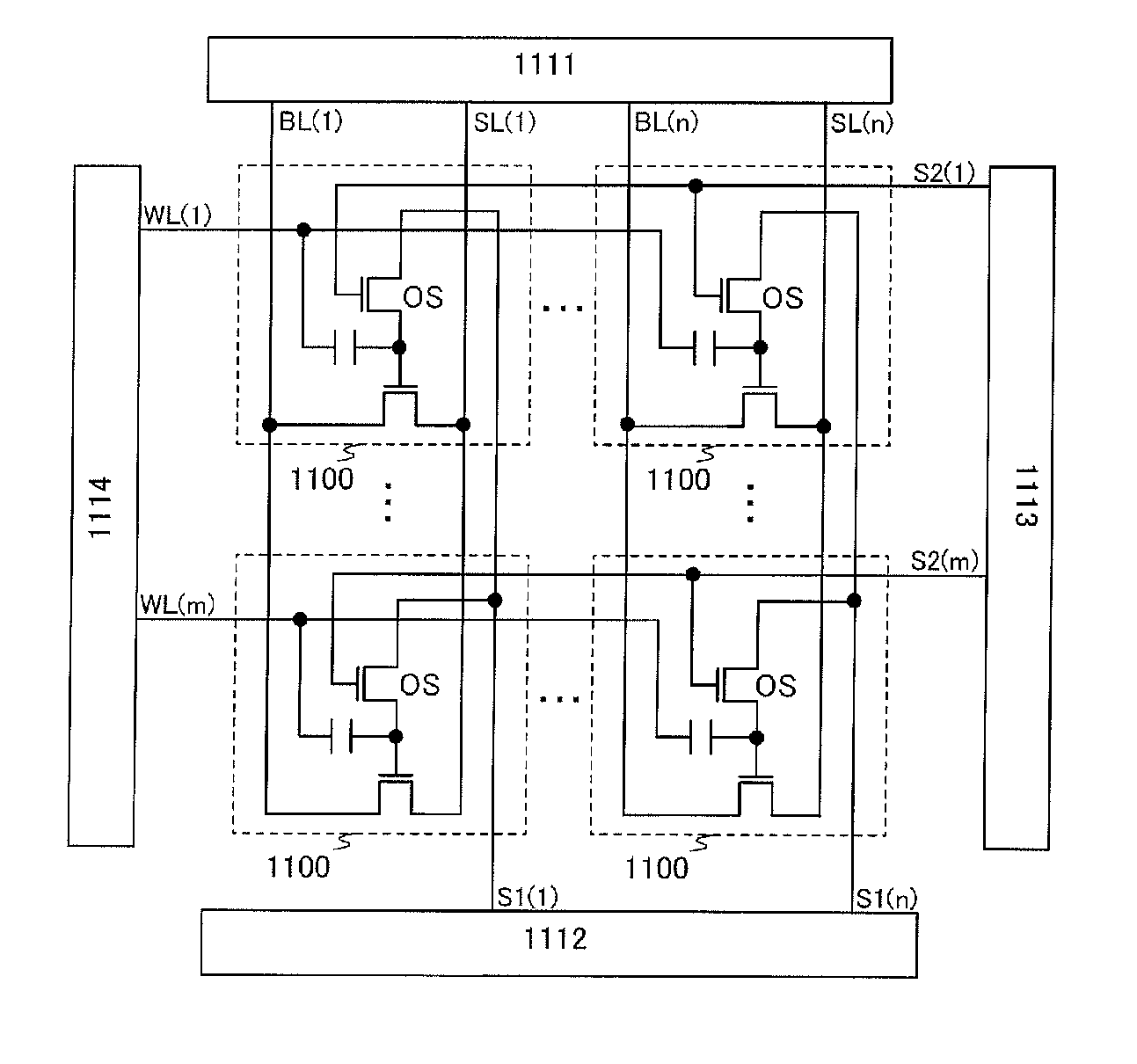

ActiveUS20120001243A1Increase degree of integrationHighly integratedTransistorSolid-state devicesPower semiconductor deviceSemiconductor device modeling

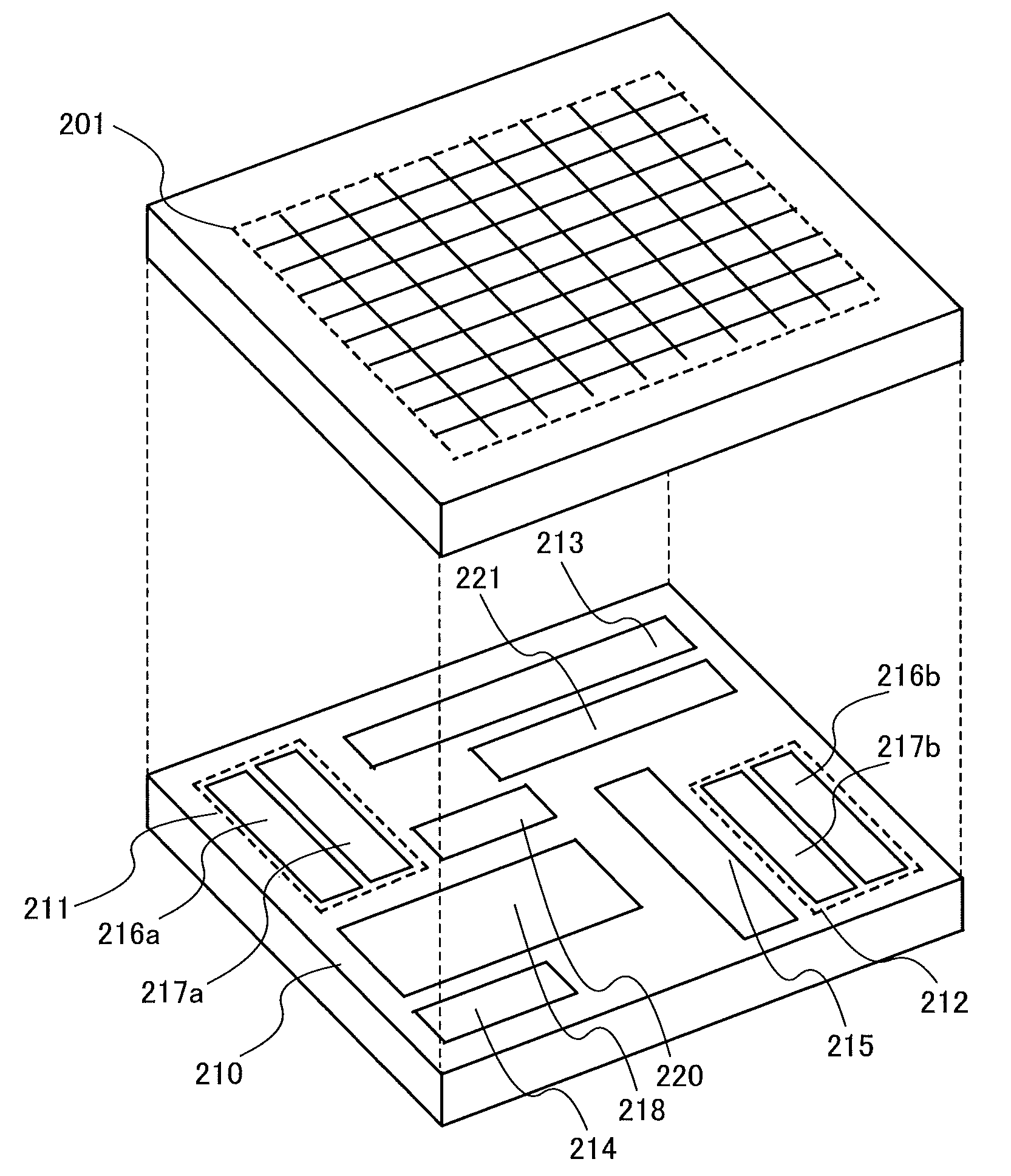

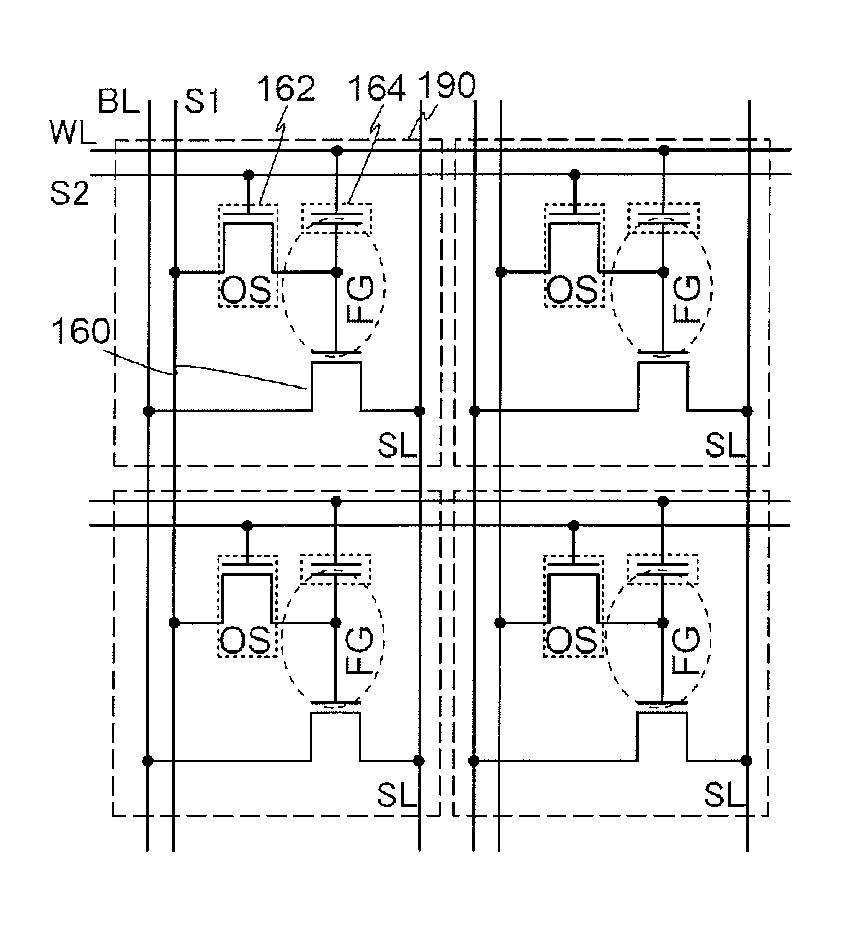

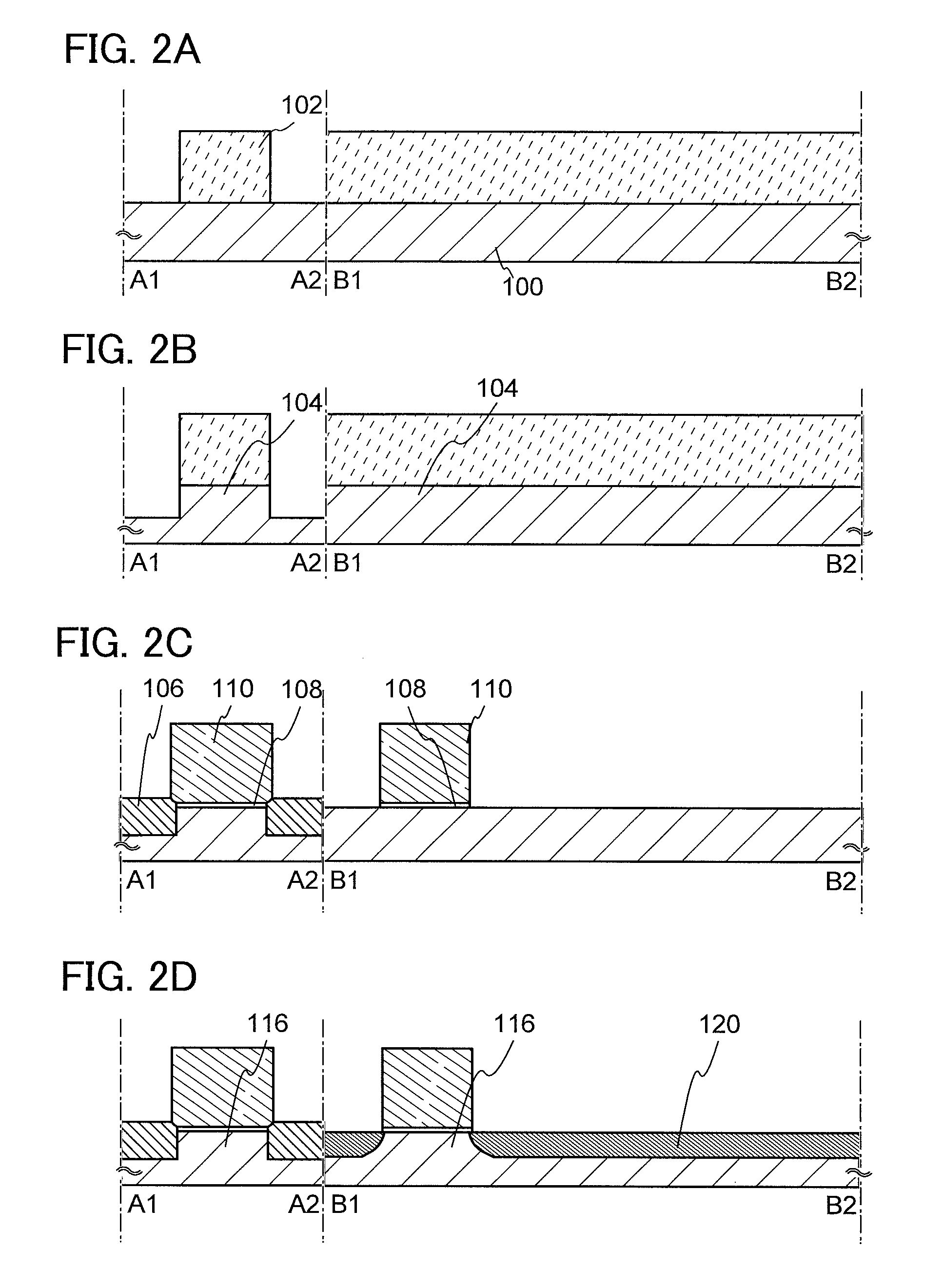

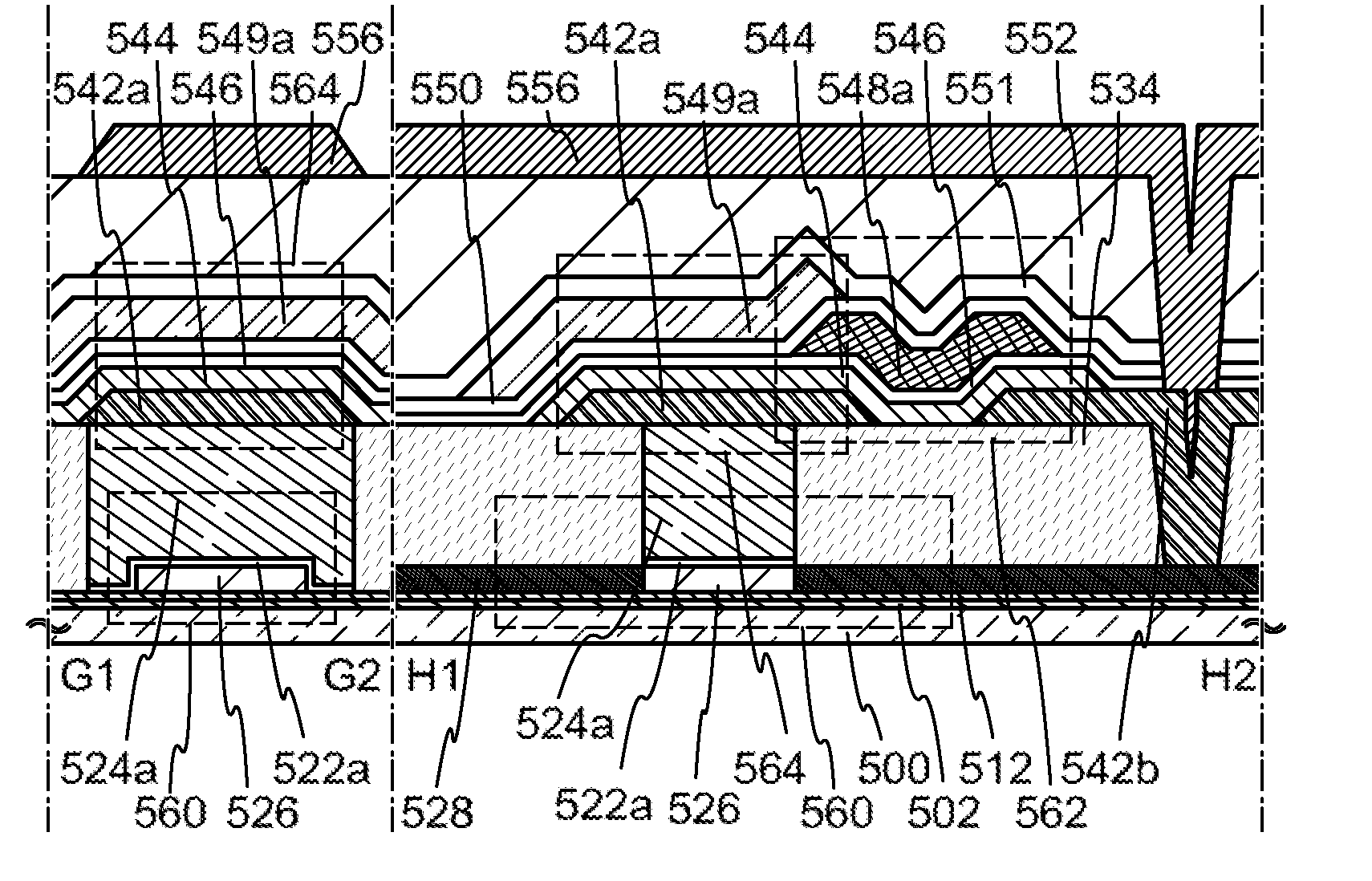

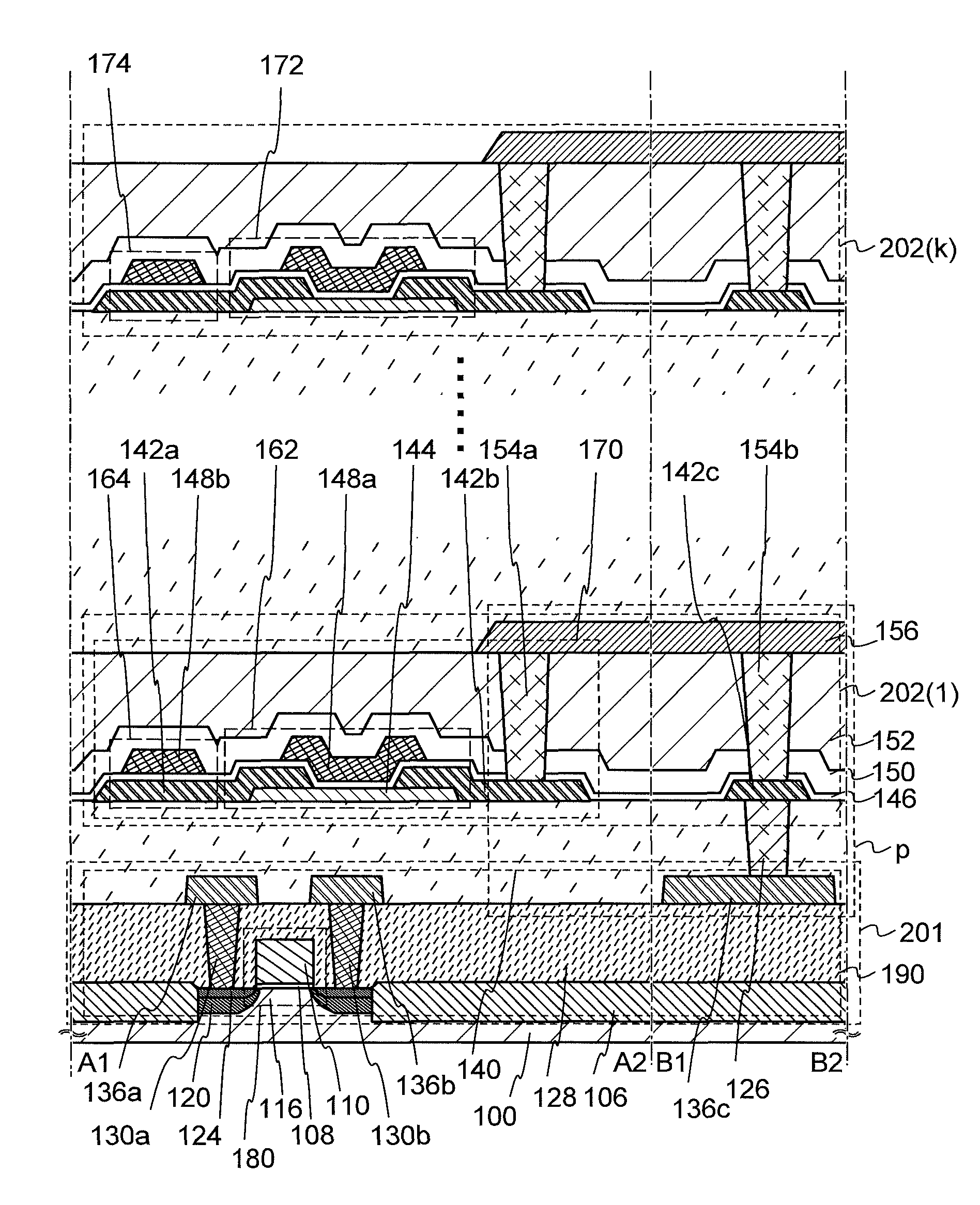

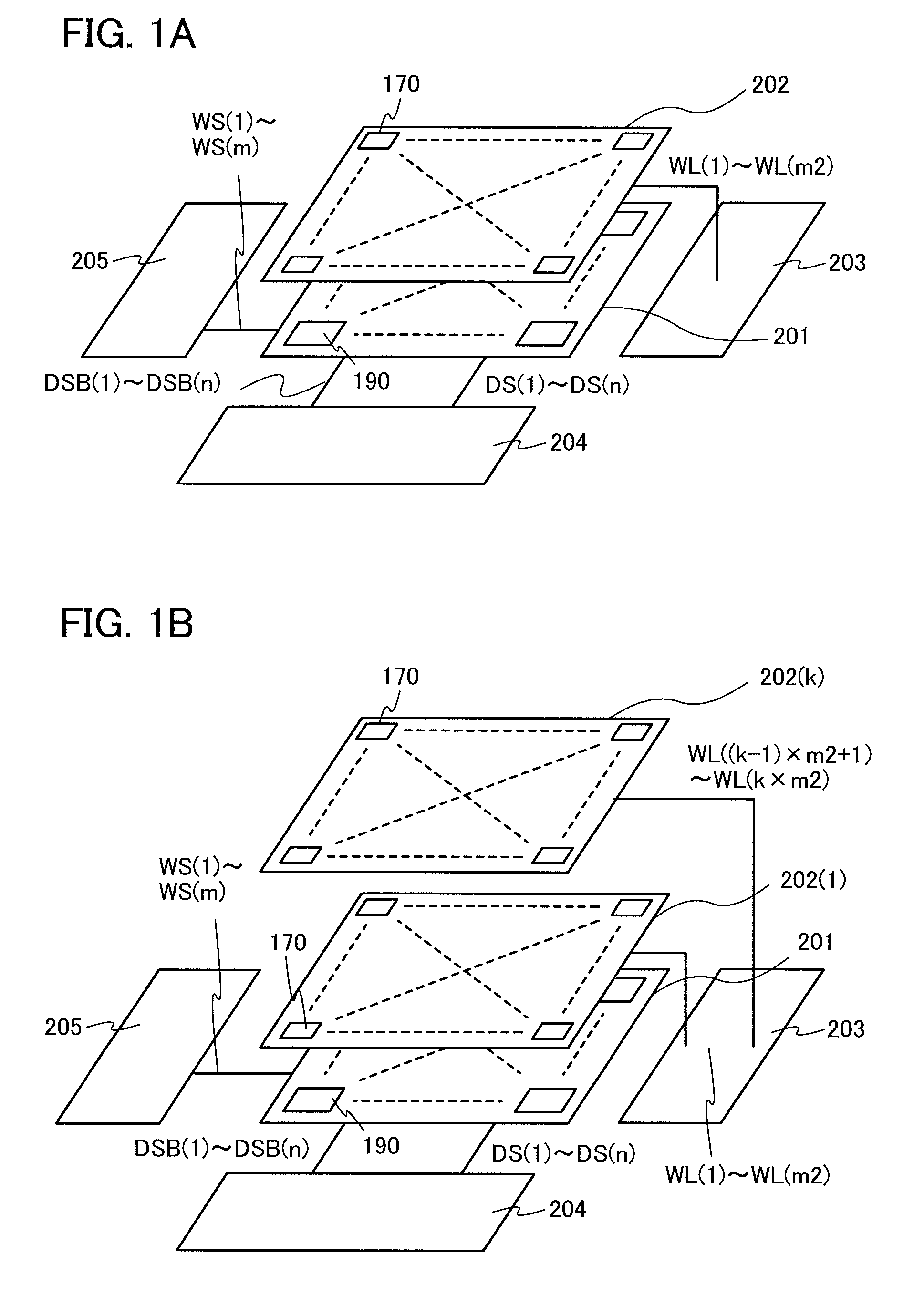

An object is to provide a semiconductor device with a novel structure in which stored data can be held even when power is not supplied and there is no limit on the number of write operations. The semiconductor device includes a first memory cell including a first transistor and a second transistor, a second memory cell including a third transistor and a fourth transistor, and a driver circuit. The first transistor and the second transistor overlap at least partly with each other. The third transistor and the fourth transistor overlap at least partly with each other. The second memory cell is provided over the first memory cell. The first transistor includes a first semiconductor material. The second transistor, the third transistor, and the fourth transistor include a second semiconductor material.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS8363452B2Easily multivaluedNovel structureTransistorSolid-state devicesBit lineDriver circuit

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS8378403B2Highly integratedReduce leakage currentTransistorSolid-state devicesDriver circuitSemiconductor materials

An object is to provide a semiconductor device with a novel structure in which stored data can be held even when power is not supplied and there is no limit on the number of write operations. The semiconductor device includes a first memory cell including a first transistor and a second transistor, a second memory cell including a third transistor and a fourth transistor, and a driver circuit. The first transistor and the second transistor overlap at least partly with each other. The third transistor and the fourth transistor overlap at least partly with each other. The second memory cell is provided over the first memory cell. The first transistor includes a first semiconductor material. The second transistor, the third transistor, and the fourth transistor include a second semiconductor material.

Owner:SEMICON ENERGY LAB CO LTD

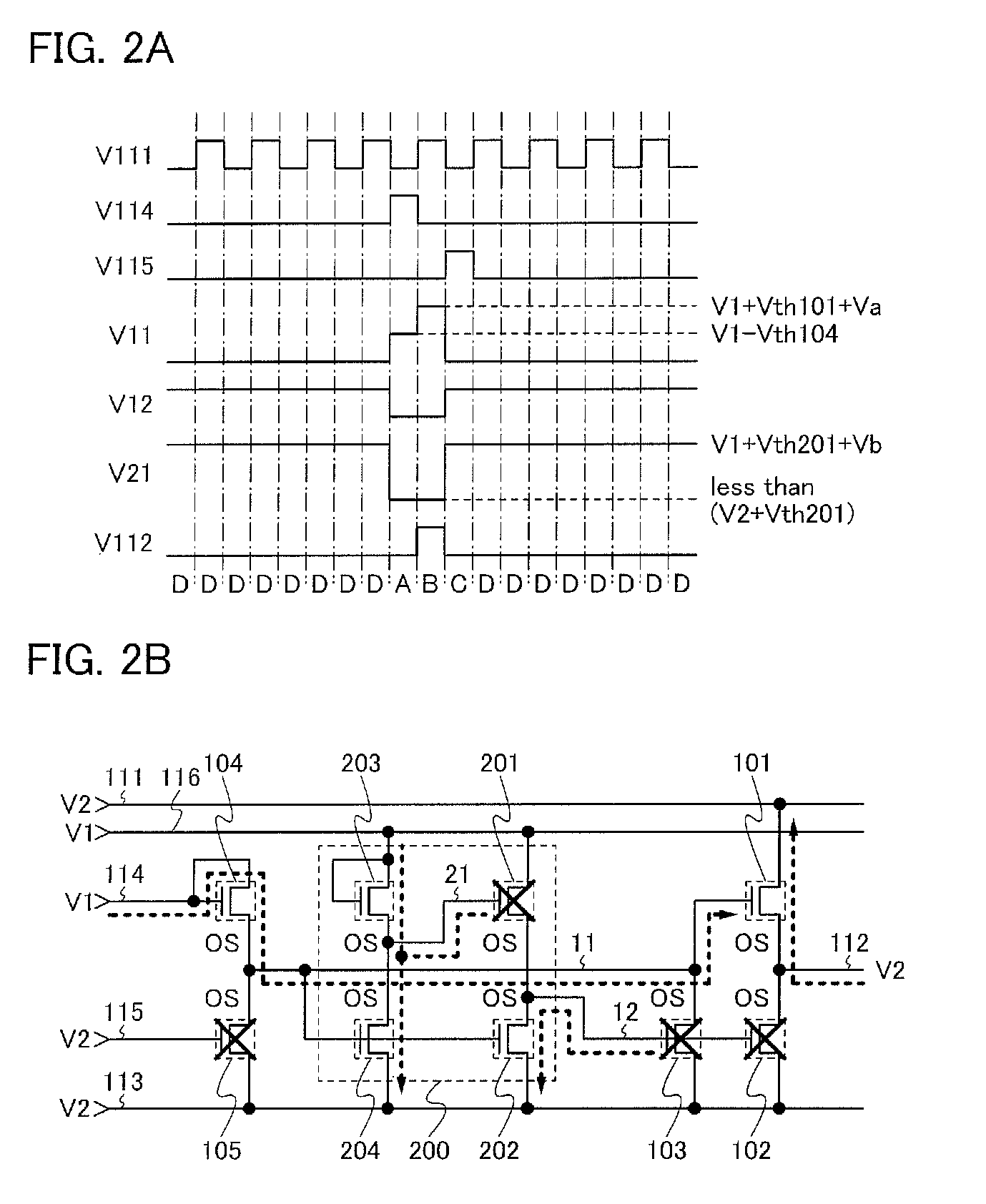

Semiconductor device and driving method thereof

InactiveUS8614916B2Reduce off-state currentLonger heldSolid-state devicesRead-only memoriesPotential changeHemt circuits

Owner:SEMICON ENERGY LAB CO LTD

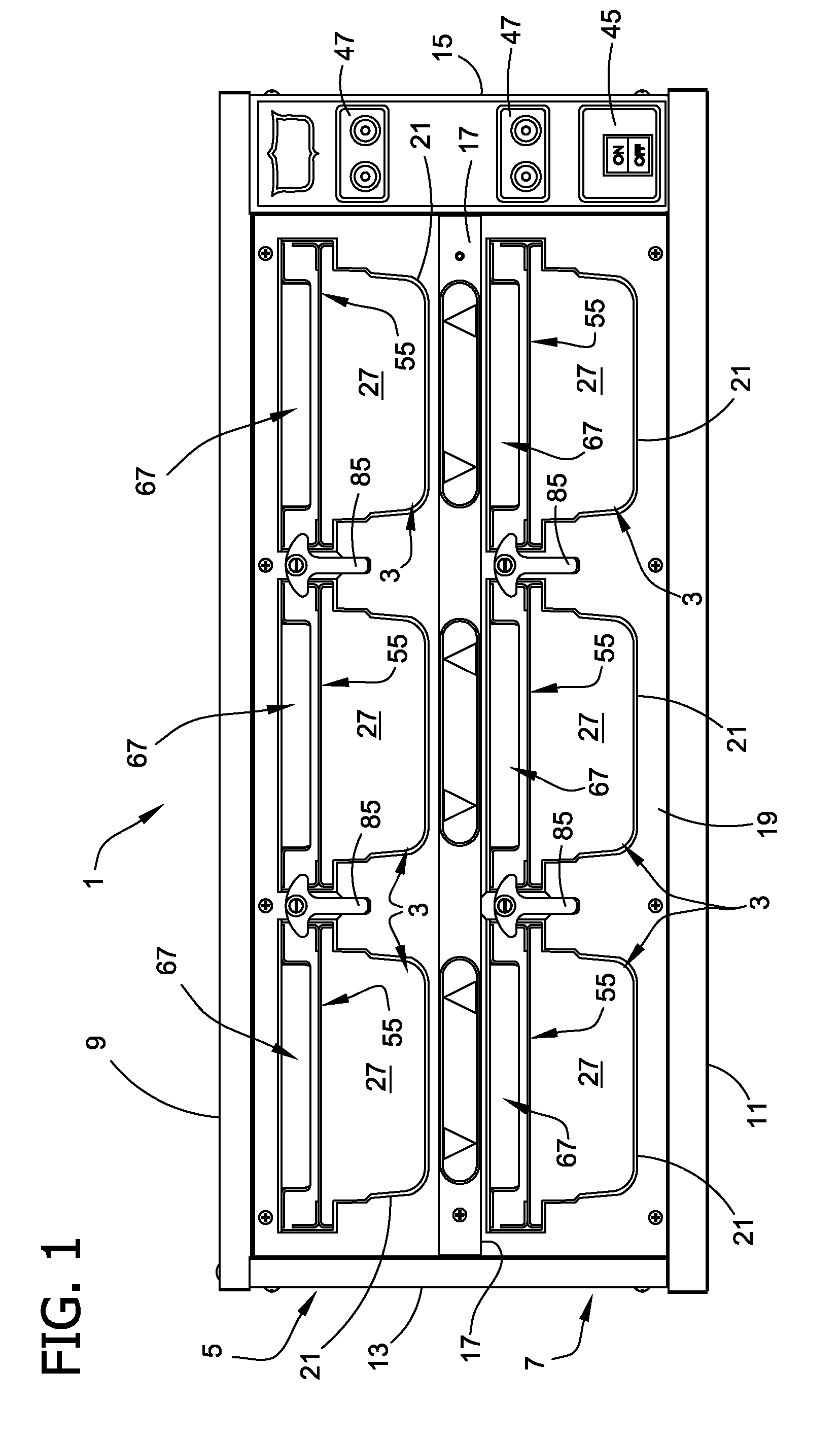

Food service apparatus and methods

InactiveUS7446282B2Avoid overall overheatingPrevent overheating of the foodAir-treating devicesDomestic stoves or rangesEngineeringFood products

Owner:DUKE MANUFACTURING COMPANY

Semiconductor device and driving method thereof

InactiveUS20110116310A1Distinguished clearly and easilyLower average currentSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceDriver circuit

A semiconductor device includes: a source line; a bit line; a word line; a memory cell connected to the bit line and the word line; a driver circuit which drives a plurality of second signal lines and a plurality of word lines so as to select the memory cell specified by an address signal; a potential generating circuit which generates a writing potential and a plurality of reading potentials to supply to a writing circuit and a reading circuit; and a control circuit which selects one of a plurality of voltages for correction on a basis of results of the reading circuit comparing a potential of the bit line with the plurality of reading potentials.

Owner:SEMICON ENERGY LAB CO LTD

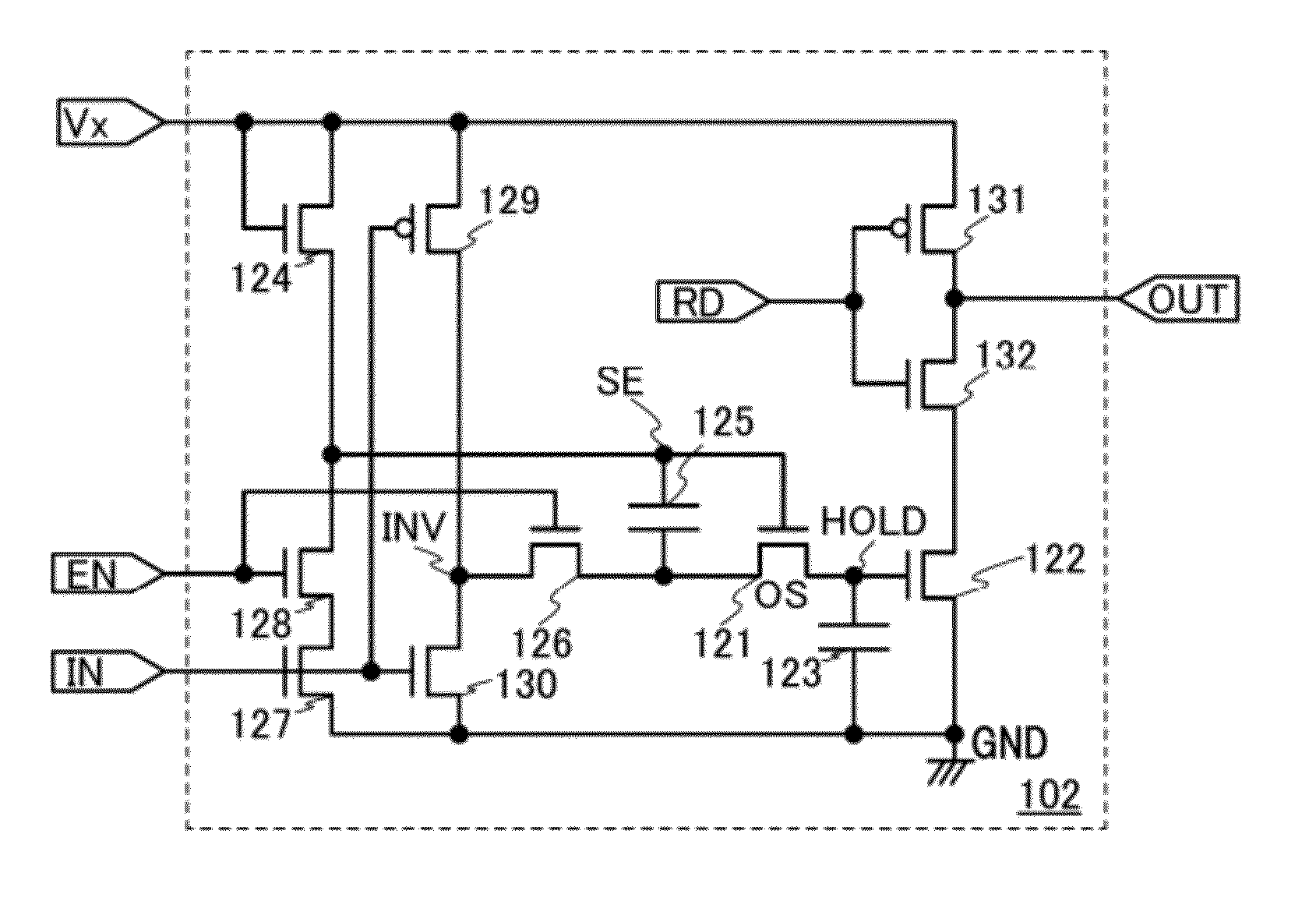

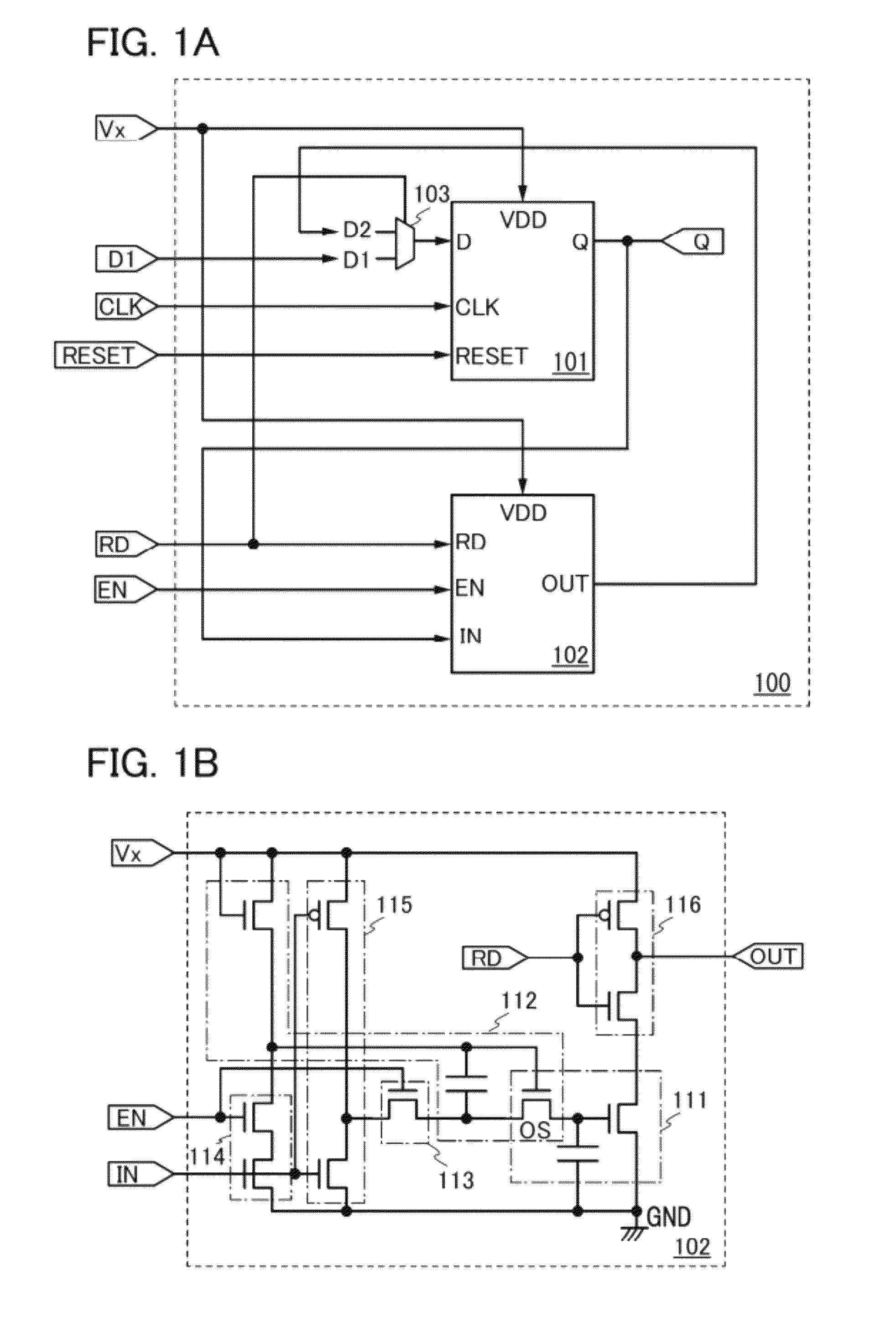

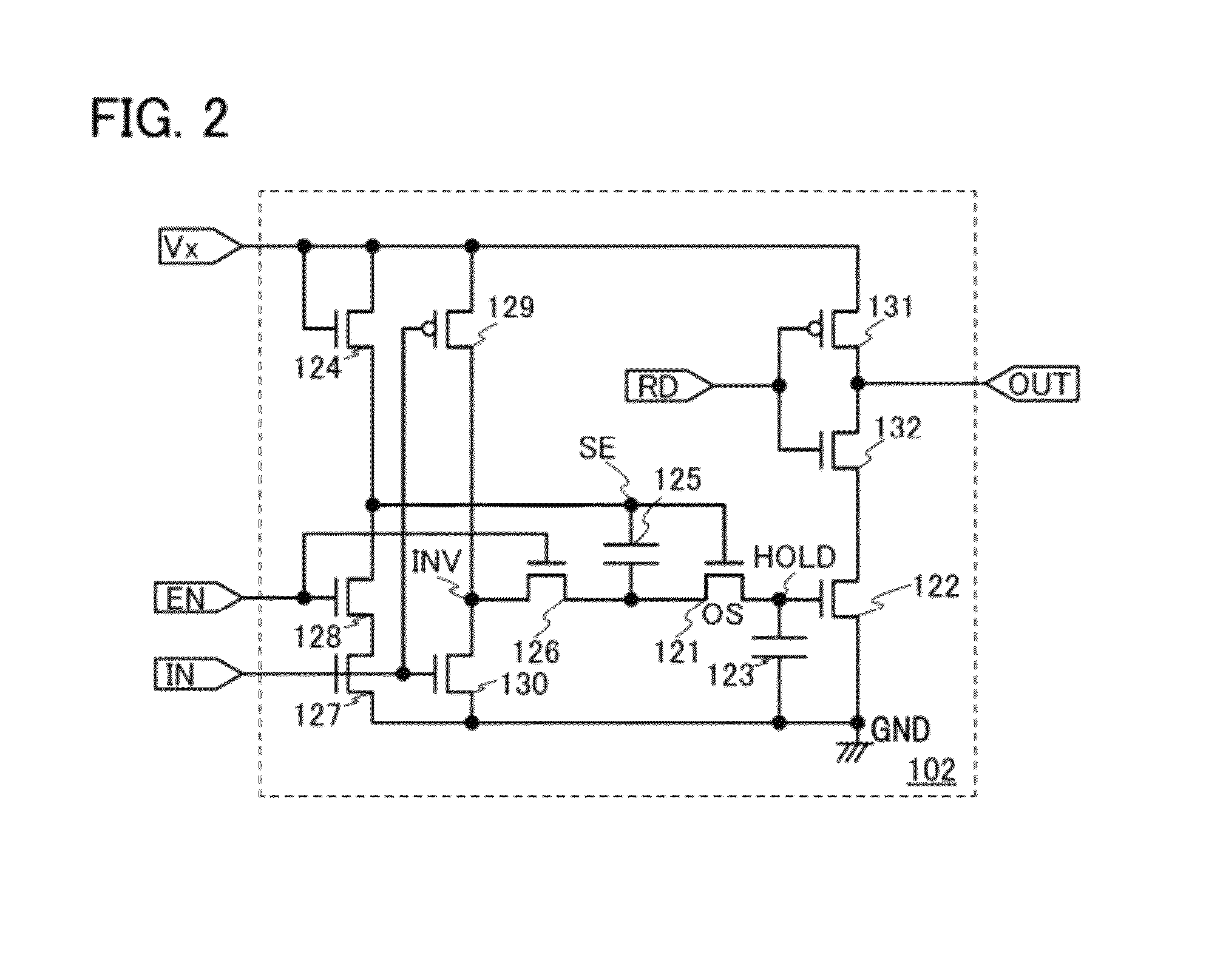

Programmable logic device

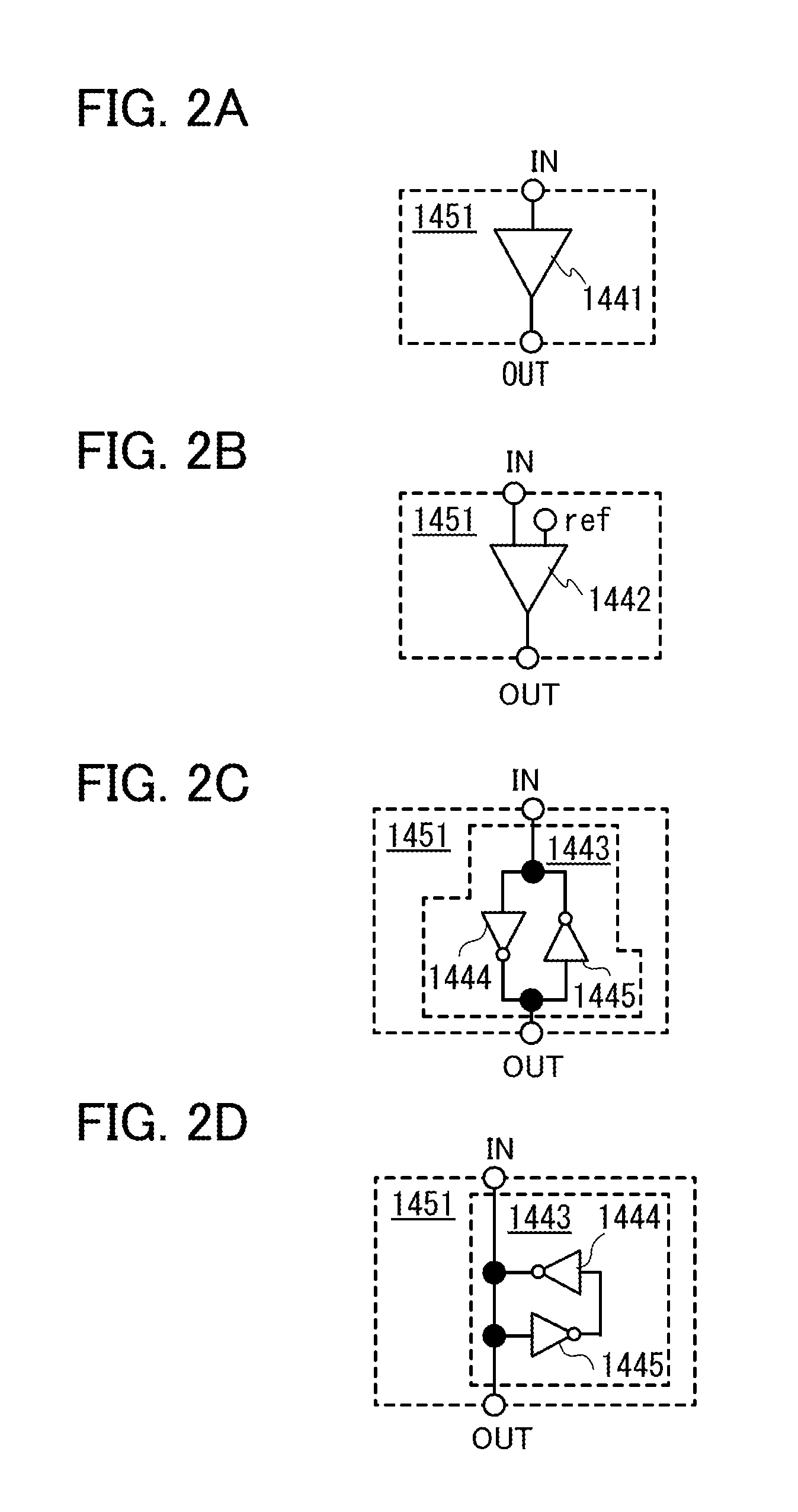

ActiveUS20130321025A1Short start-up timeReduced footprintSolid-state devicesLogic circuits using elementary logic circuit componentsOxide semiconductorProgrammable logic device

A PLD in which a configuration memory is formed using a nonvolatile memory with a small number of transistors and in which the area of a region where the configuration memory is disposed is reduced is provided. Further, a PLD that is easily capable of dynamic reconfiguration and has a short startup time is provided. A programmable logic device including a memory element, a selector, and an output portion is provided. The memory element includes a transistor in which a channel is formed in an oxide semiconductor film, and a storage capacitor and an inverter which are connected to one of a source and a drain of the transistor. The inverter is connected to the selector. The selector is connected to the output portion.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

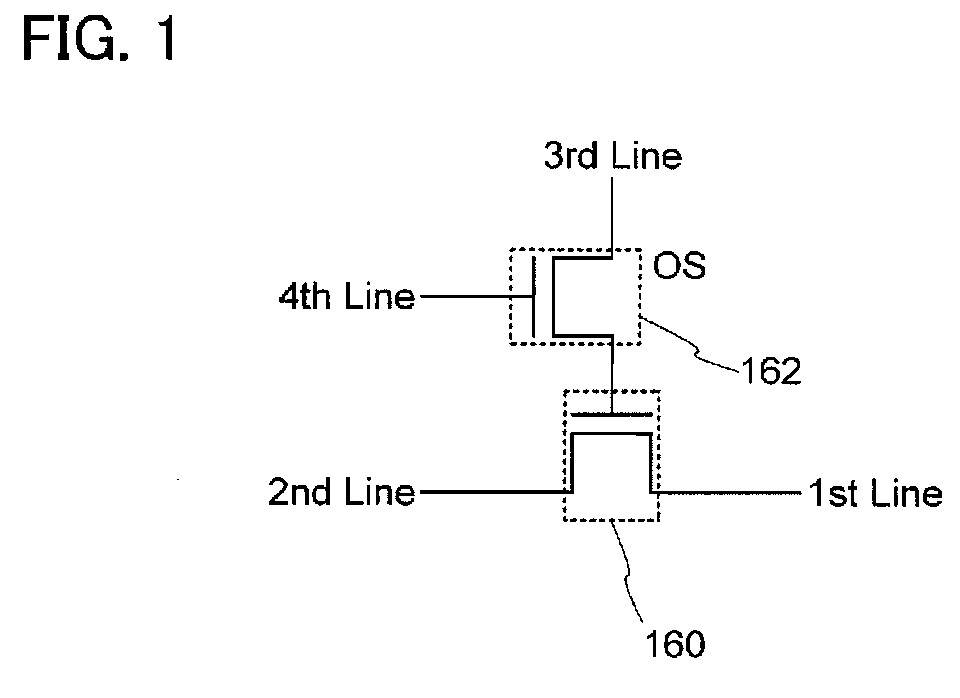

ActiveUS20120161220A1Reduced footprintHighly integratedTransistorSolid-state devicesPower semiconductor deviceEngineering

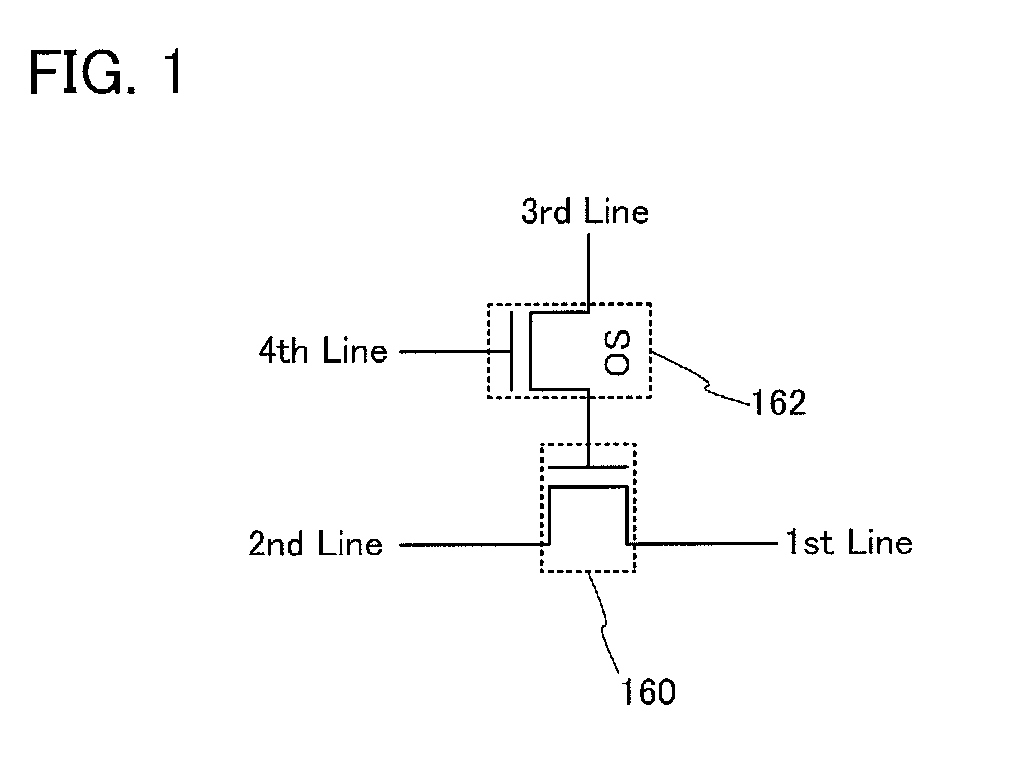

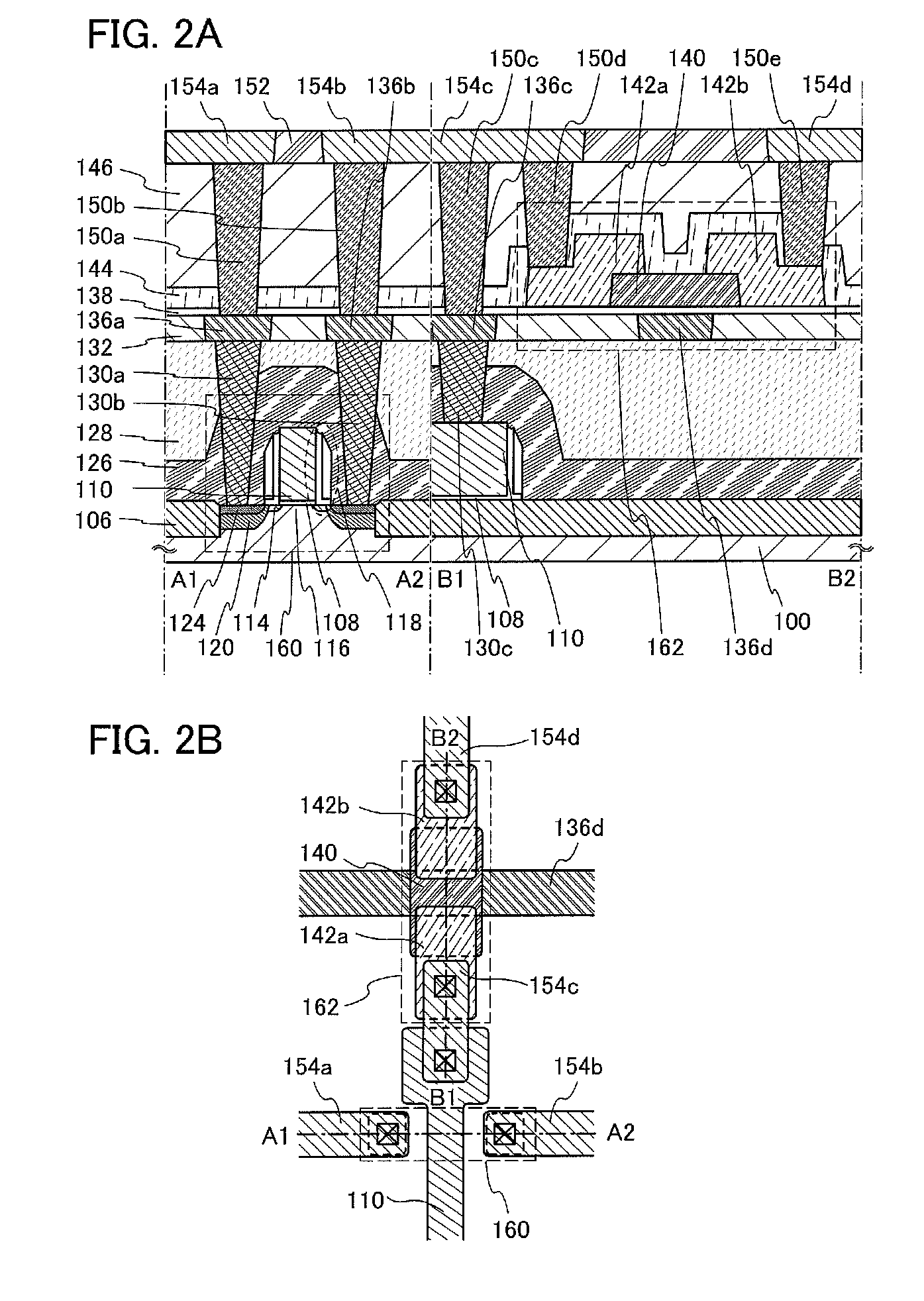

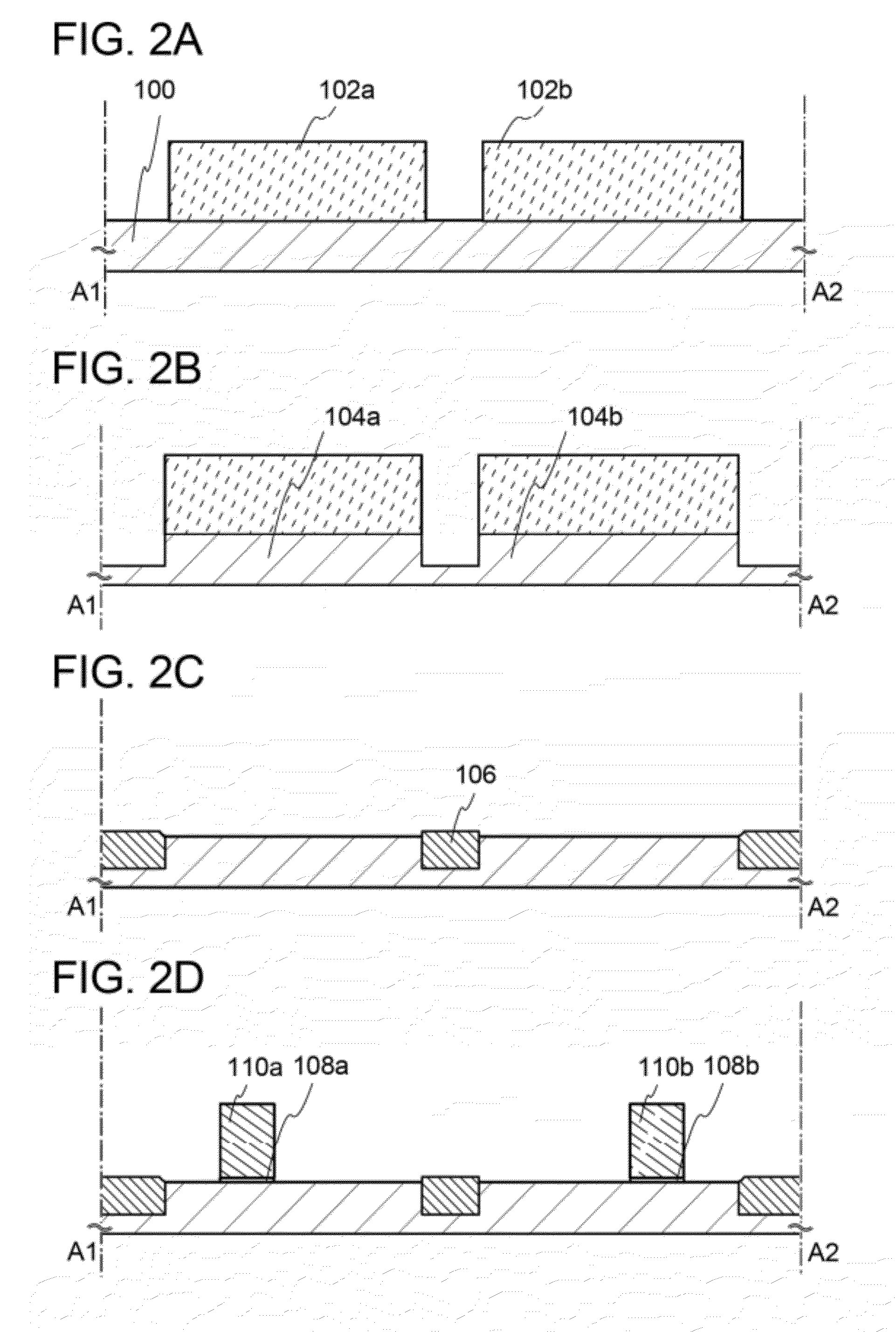

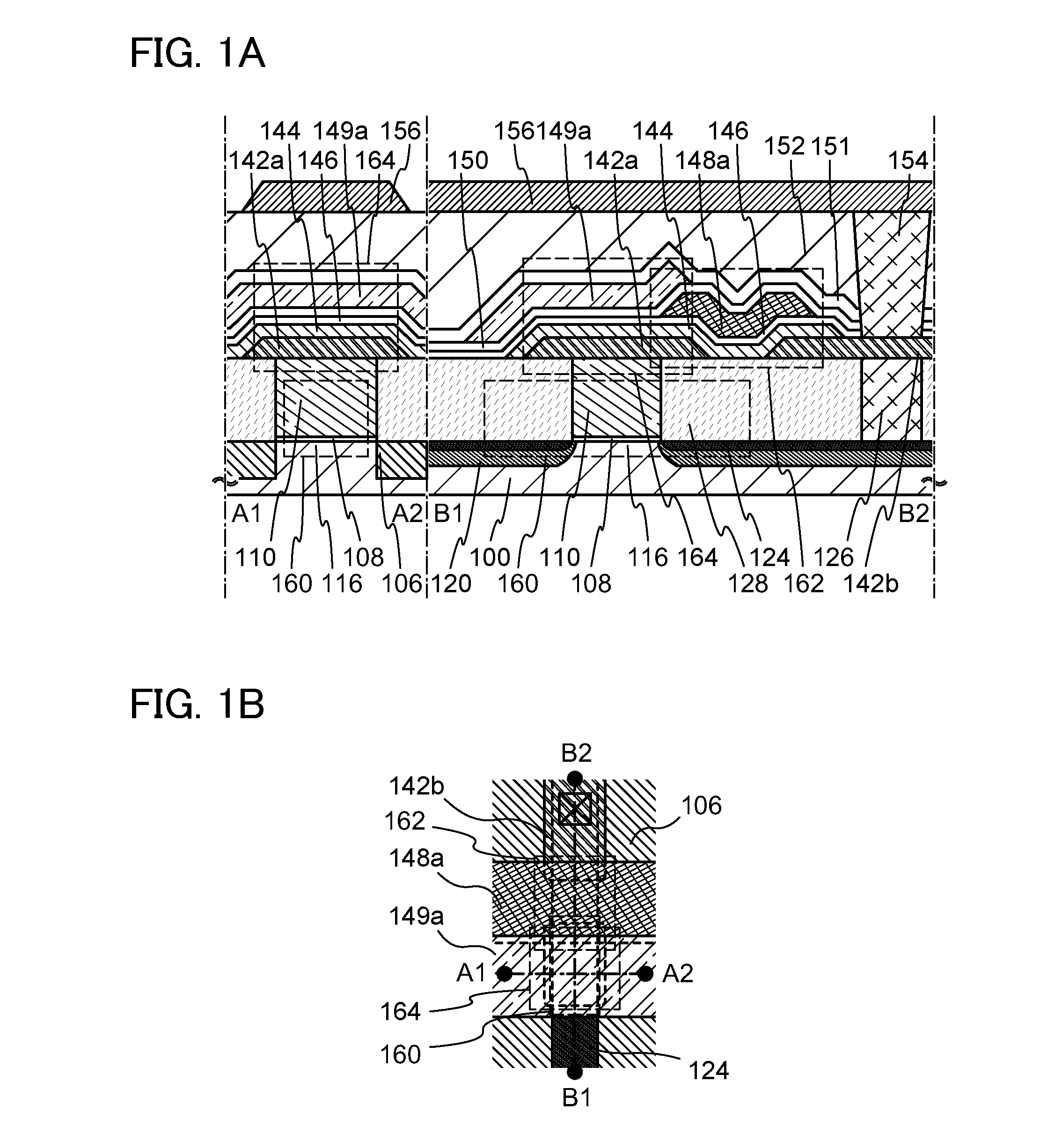

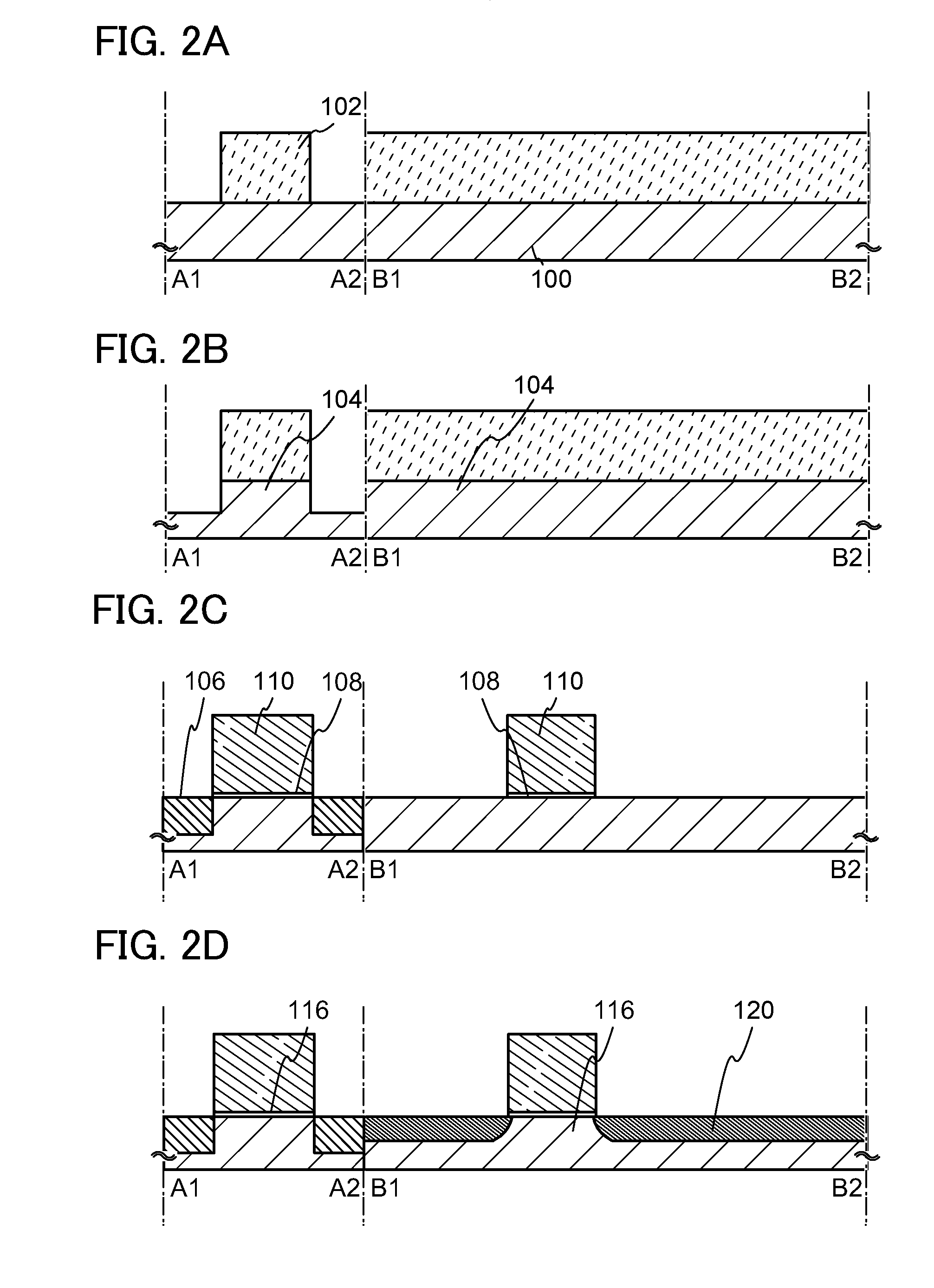

The degree of integration of a semiconductor device is enhanced and the storage capacity per unit area is increased. The semiconductor device includes a first transistor provided in a semiconductor substrate and a second transistor provided over the first transistor. In addition, an upper portion of a semiconductor layer of the second transistor is in contact with a wiring, and a lower portion thereof is in contact with a gate electrode of the first transistor. With such a structure, the wiring and the gate electrode of the first transistor can serve as a source electrode and a drain electrode of the second transistor, respectively. Accordingly, the area occupied by the semiconductor device can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

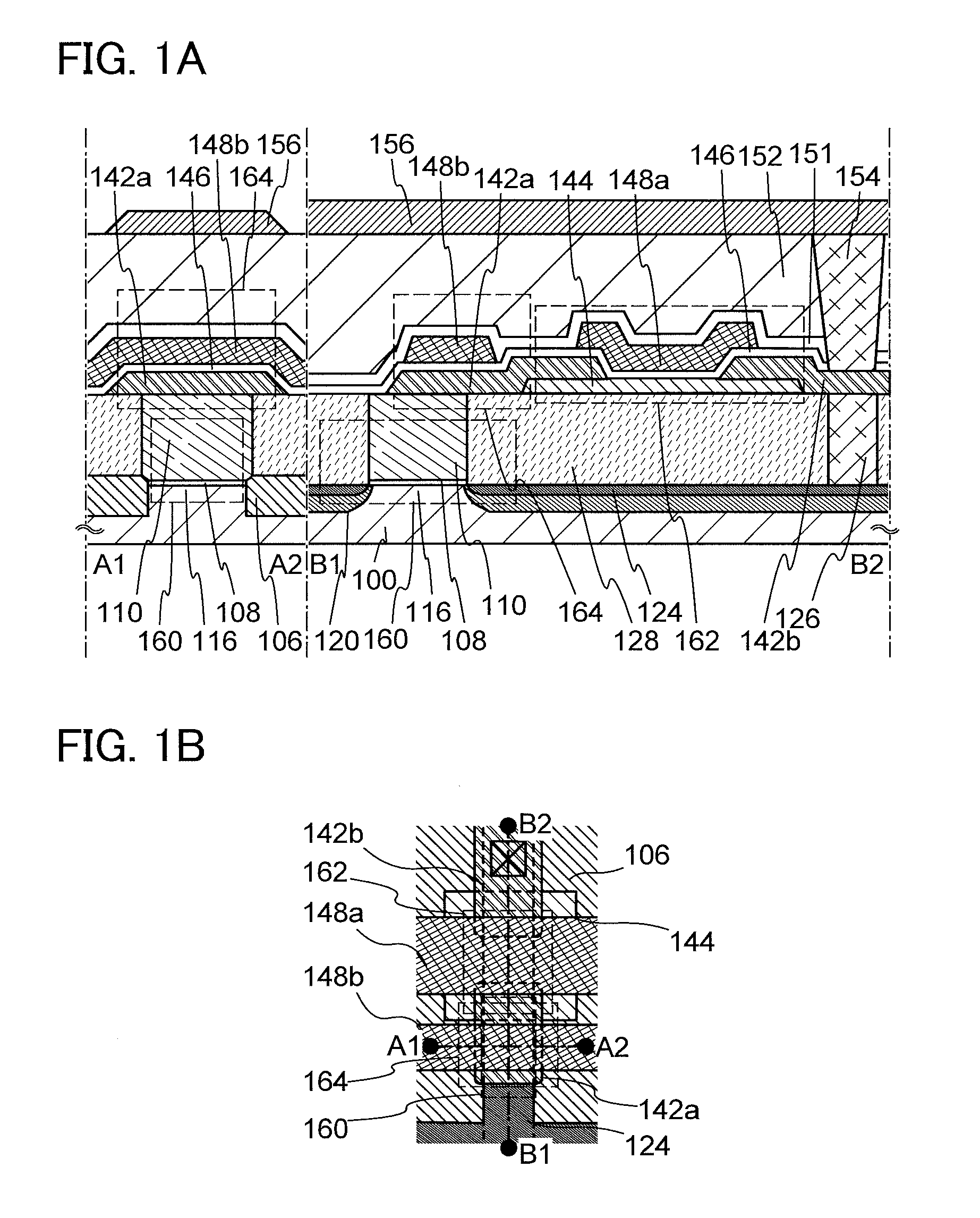

Semiconductor device and driving method of semiconductor device

ActiveUS8508967B2Total current dropReduce the refresh rateDigital storageDriver circuitPower semiconductor device

An object is to provide a semiconductor device having a novel structure, which can hold stored data even when not powered and which has an unlimited number of write cycles. A semiconductor device is provided with both a memory circuit including a transistor including an oxide semiconductor (in a broader sense, a transistor whose off-state current is sufficiently small) and a peripheral circuit such as a driver circuit including a transistor including a material other than an oxide semiconductor (in other words, a transistor capable of operating at sufficiently high speed). The peripheral circuit is provided in a lower portion and the memory circuit is provided in an upper portion; thus, the area and size of the semiconductor device can be decreased.

Owner:SEMICON ENERGY LAB CO LTD

Method for driving semiconductor device

InactiveUS20120294070A1Reduce power consumptionImprove reliabilitySolid-state devicesRead-only memoriesOxide semiconductorPower semiconductor device

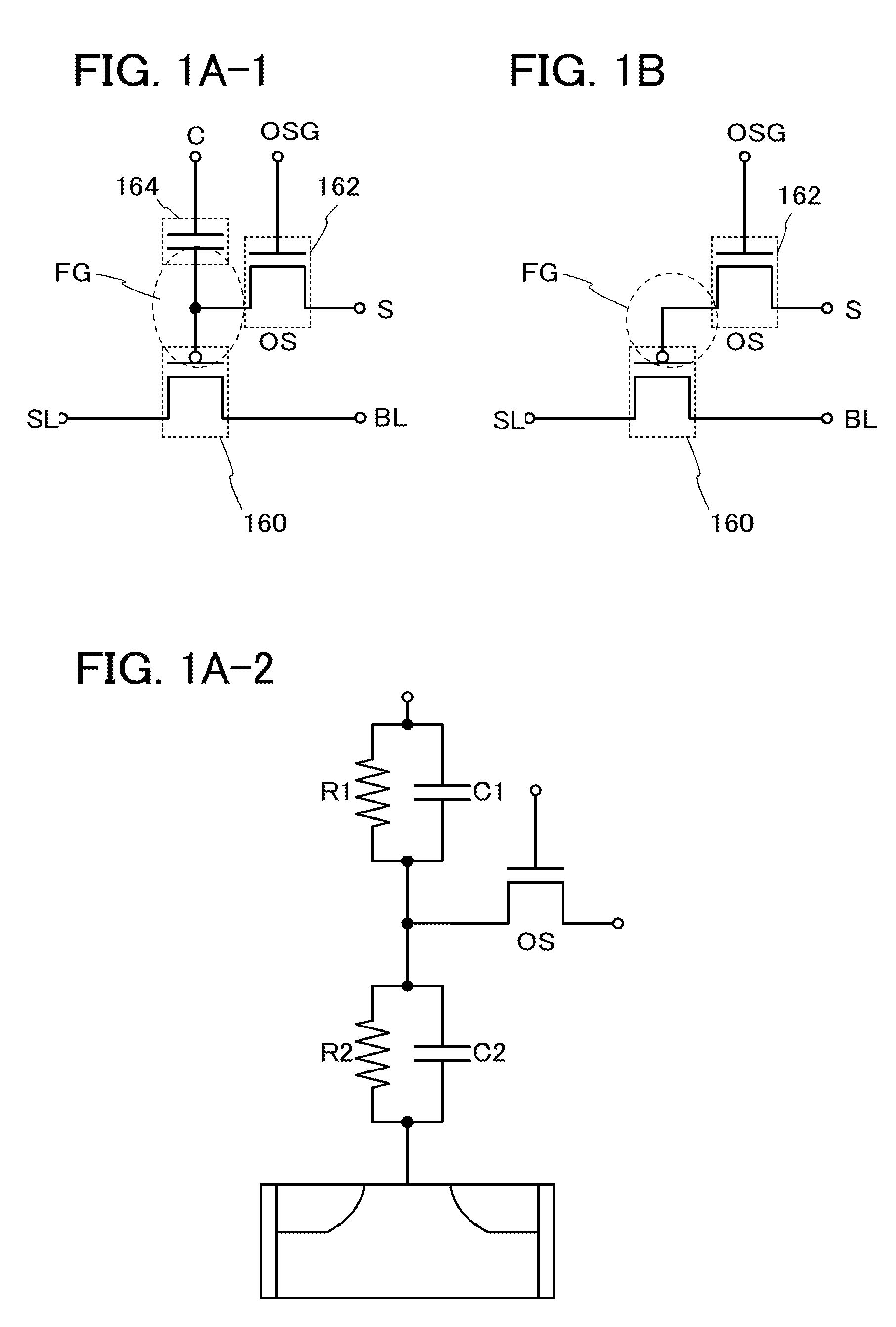

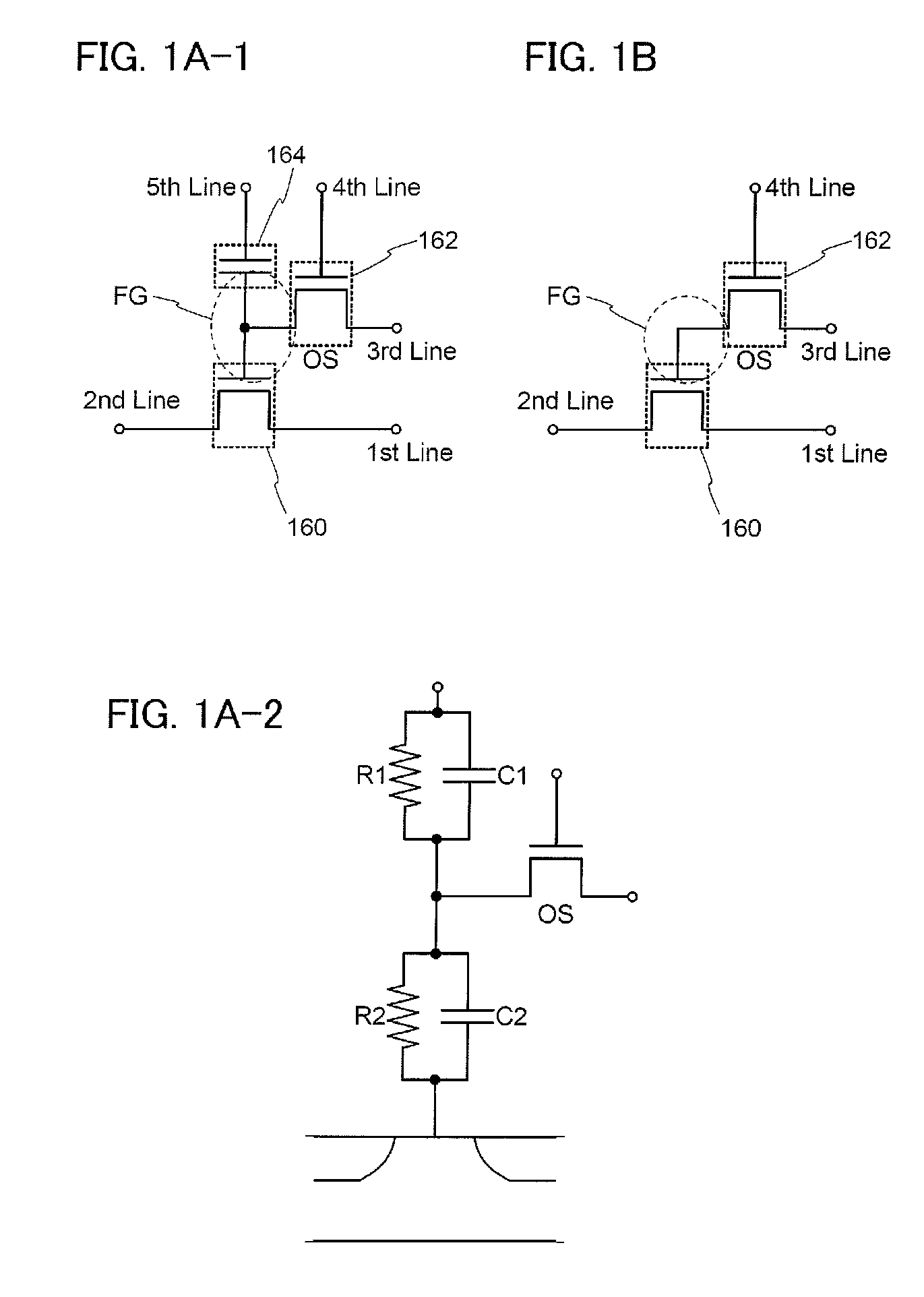

A semiconductor device includes a nonvolatile memory cell including a writing transistor including an oxide semiconductor, a reading transistor including a semiconductor material different from that of the writing transistor, and a capacitor. Data is written to the memory cell by turning on the writing transistor so that a potential is supplied to a node where a source electrode of the writing transistor, one electrode of the capacitor, and a gate electrode of the reading transistor are electrically connected, and then turning off the writing transistor so that a predetermined potential is held in the node. Data is read out from the memory cell by supplying a precharge potential to a bit line, stopping the supply of the potential to the bit line, and determining whether the potential of the bit line is kept at the precharge potential or decreased.

Owner:SEMICON ENERGY LAB CO LTD

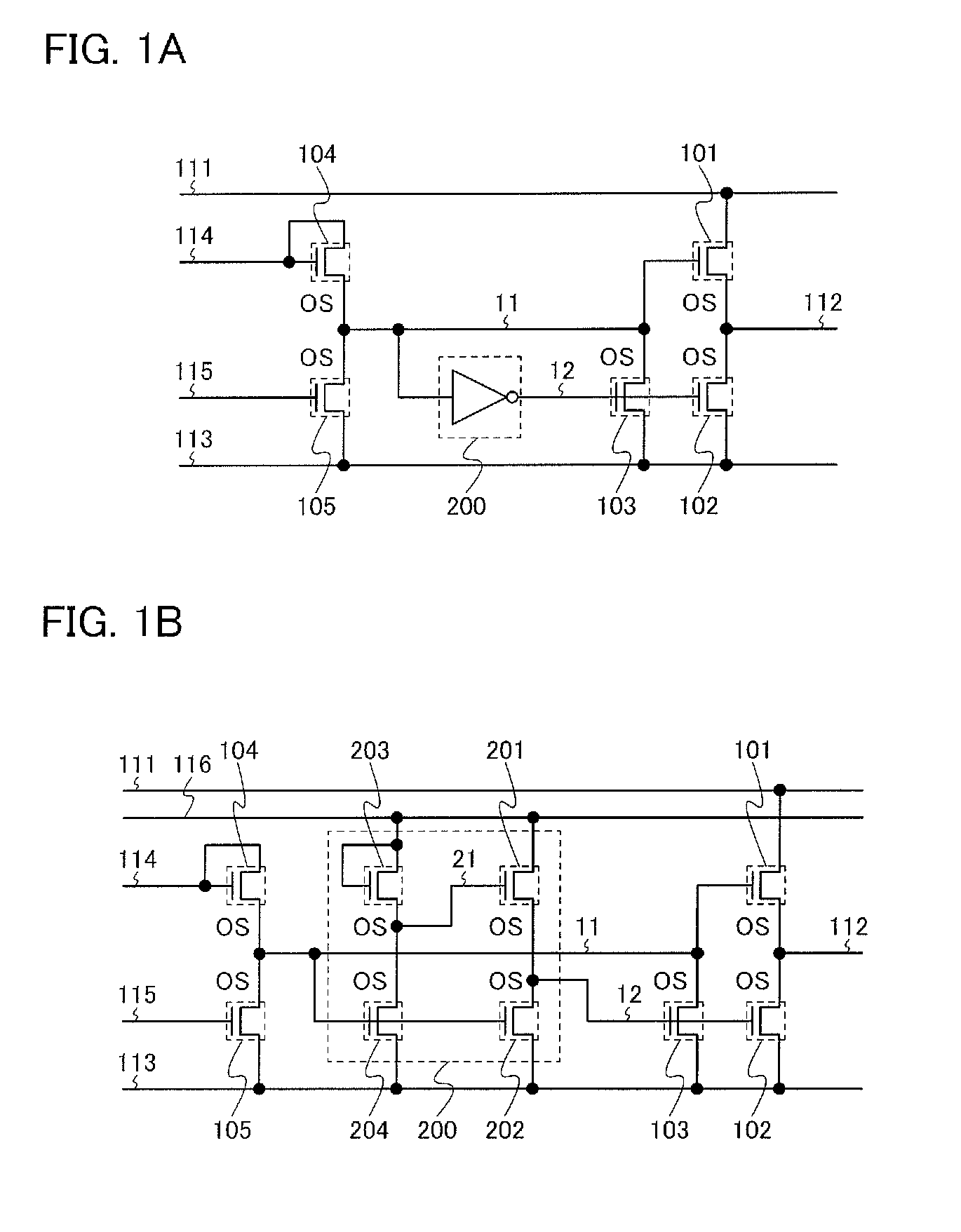

Semiconductor device and method for driving the same

InactiveUS20110199807A1Reduce frequencyReduce power consumptionSolid-state devicesDigital storageSemiconductor materialsEngineering

A semiconductor device includes a first signal line, a second signal line, a memory cell, and a potential converter circuit. The memory cell includes a first transistor including a first gate electrode, a first source electrode, a first drain electrode, and a first channel formation region; a second transistor including a second gate electrode, a second source electrode, a second drain electrode, and a second channel formation region; and a capacitor. The first channel formation region and the second channel formation region include different semiconductor materials. The second drain electrode, one electrode of the capacitor, and the first gate electrode are electrically connected to one another. The second gate electrode is electrically connected to the potential converter circuit through the second signal line.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and driving method thereof

ActiveUS20110176355A1Sufficient reduction in power consumptionReduce frequencySolid-state devicesRead-only memoriesCharge retentionSemiconductor materials

A semiconductor device has a non-volatile memory cell including a write transistor which includes an oxide semiconductor and has small leakage current in an off state between a source and a drain, a read transistor including a semiconductor material different from that of the write transistor, and a capacitor. Data is written or rewritten to the memory cell by turning on the write transistor and applying a potential to a node where one of a source electrode and drain electrode of the write transistor, one electrode of the capacitor, and a gate electrode of the read transistor are electrically connected to one another, and then turning off the write transistor so that the predetermined amount of charge is held in the node.

Owner:SEMICON ENERGY LAB CO LTD

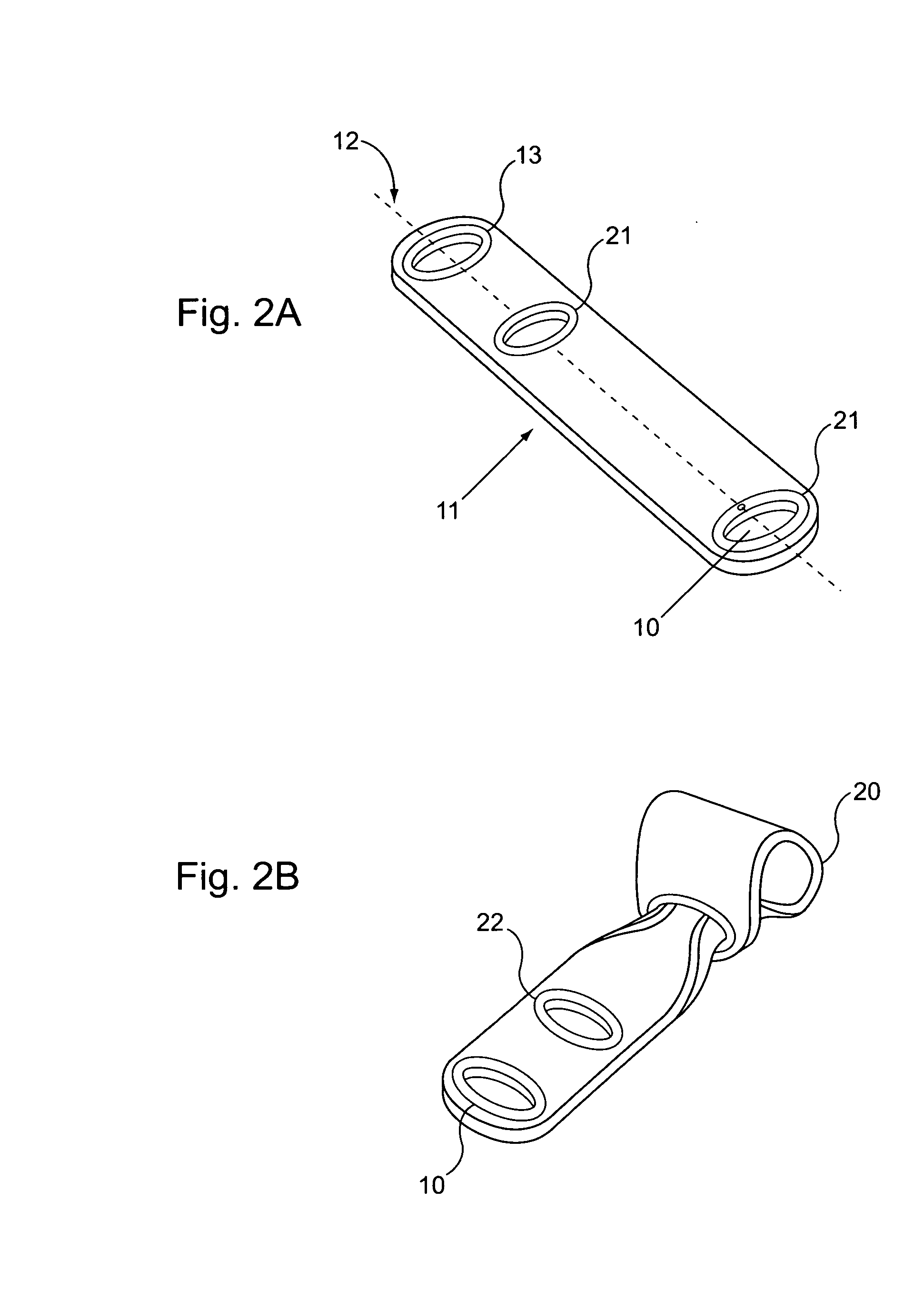

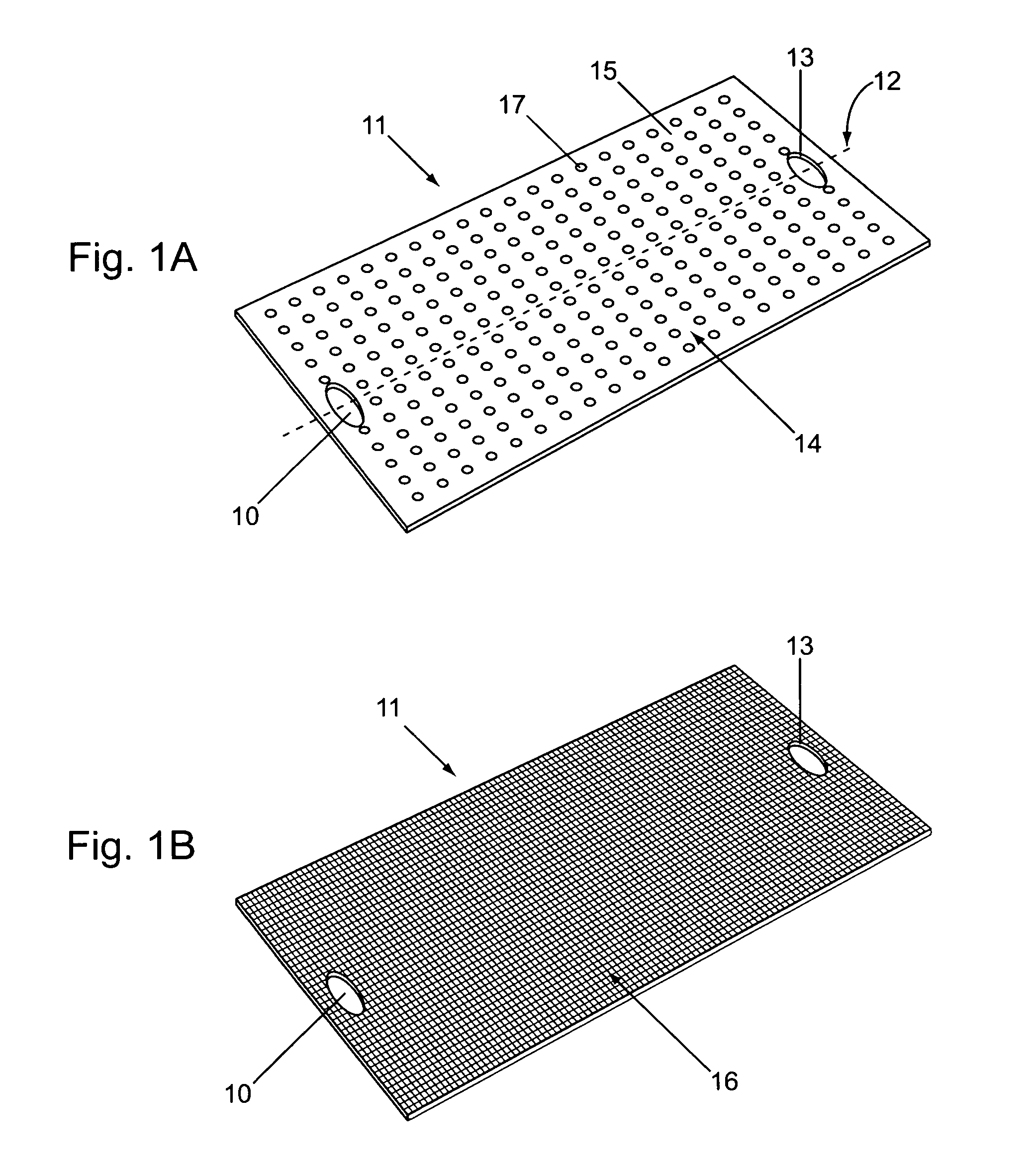

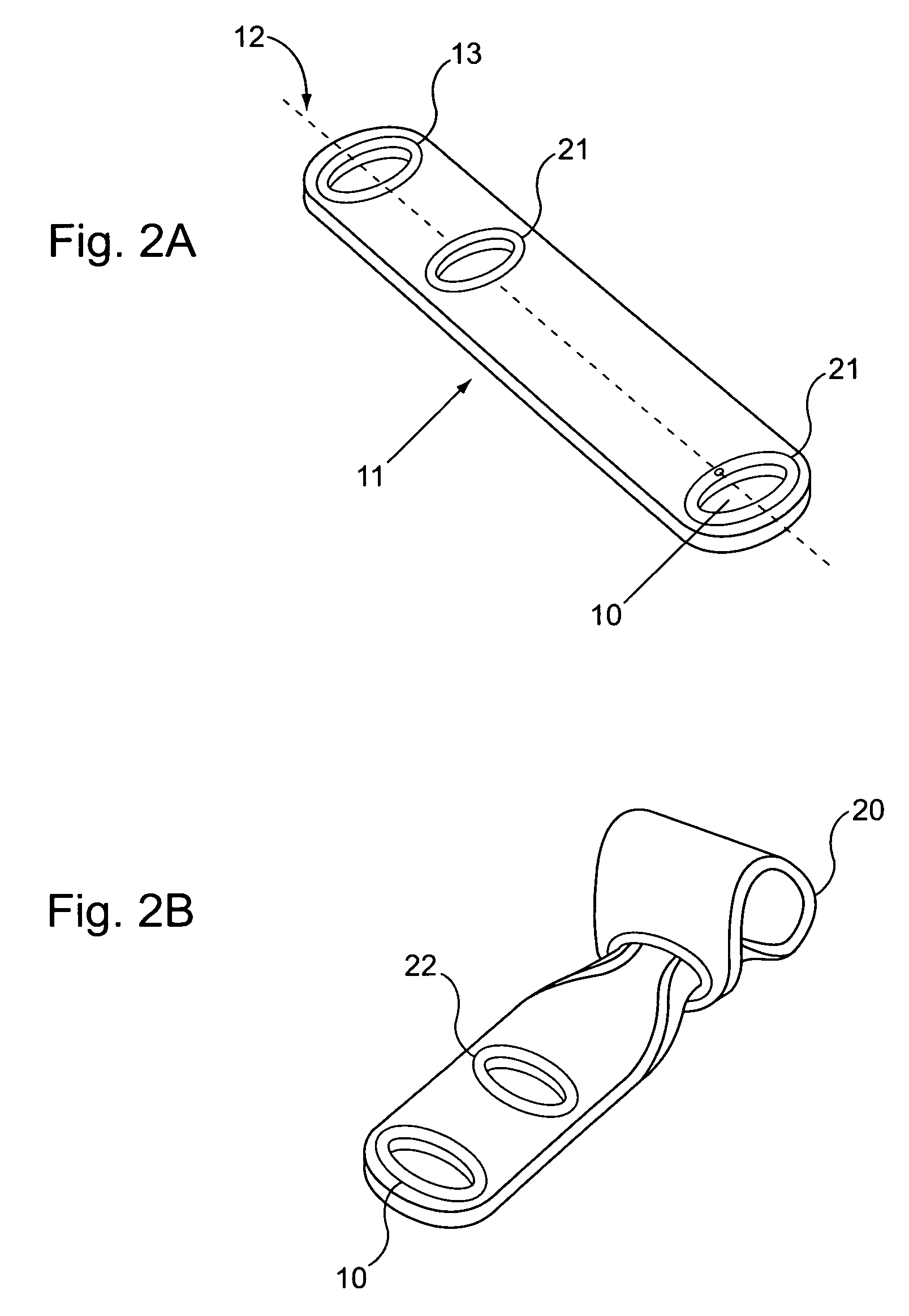

Fabric yoga straps

InactiveUS20070066467A1More sure gripMoisture absorptionSpace saving gamesTherapy exerciseEngineeringMoisture absorption

This invention provides composite yoga mats and straps comprising a fabric sheet and loop holes and / or filament loops functioning as hand grips or appendage supports useful in the practice of yoga positions. The yoga straps or mats can to provide support, a stable surface, and moisture absorption for the practice of yoga.

Owner:EDWARDS RICHARD

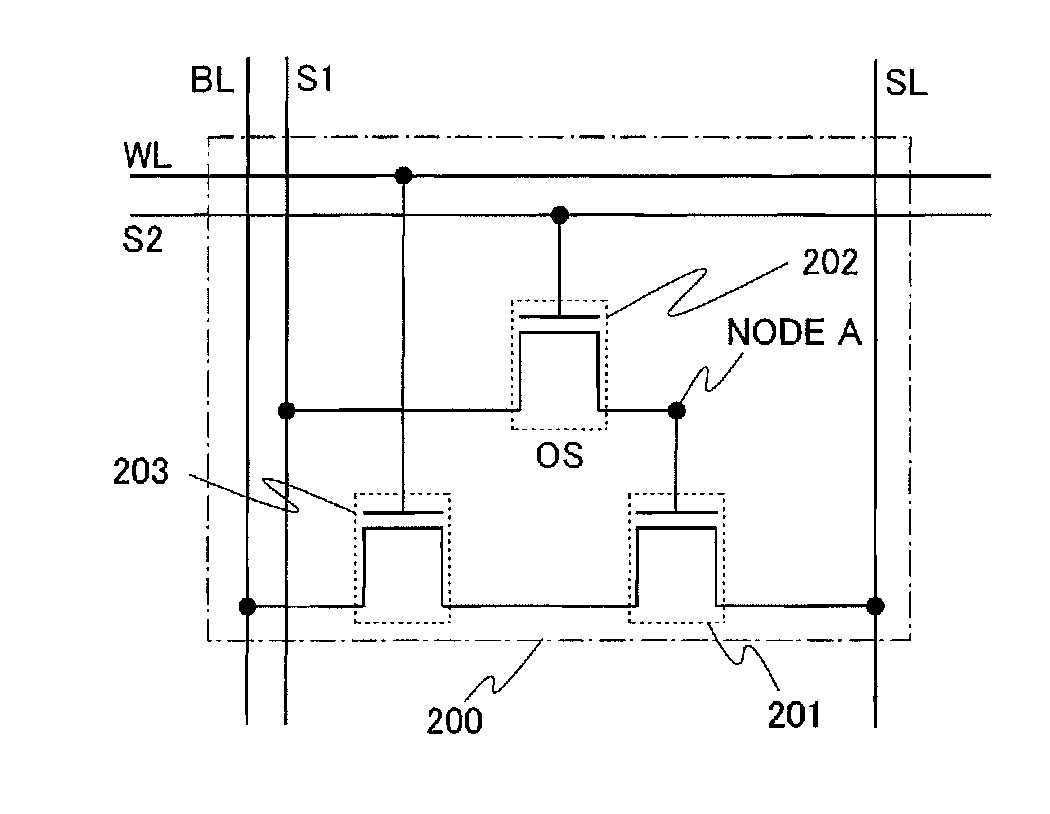

Semiconductor device and driving method of semiconductor device

InactiveUS20110227062A1Reduced footprintHighly integratedTransistorSolid-state devicesSemiconductor materialsMemory cell

A semiconductor device is formed using a material which allows a sufficient reduction in off-state current of a transistor; for example, an oxide semiconductor material, which is a wide-gap semiconductor, is used. When a semiconductor material which allows a sufficient reduction in off-state current of a transistor is used, the semiconductor device can hold data for a ions time. Transistors each including an oxide semiconductor in memory cells of the semiconductor device are connected in series; thus, a source electrode of the transistor including an oxide semiconductor in the memory cell and a drain electrode of the transistor including an oxide semiconductor in the adjacent memory cell can be connected to each other. Therefore, the area occupied by the memory cells can be reduced.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and driving method thereof

InactiveUS20120033488A1Reduce off-state currentLonger heldTransistorSolid-state devicesPotential changeEngineering

A semiconductor device including a memory cell formed using a wide bandgap semiconductor, for example, an oxide semiconductor is provided. The semiconductor device includes a potential change circuit having a function of outputting a potential lower than a reference potential for reading data from the memory cell. With the use of the wide bandgap semiconductor, an off-state current of a transistor included in the memory cell can be sufficiently reduced, and the semiconductor device which can hold data for a long period can be provided.

Owner:SEMICON ENERGY LAB CO LTD

Fabric yoga straps

InactiveUS7485071B2More sure gripMoisture absorptionSpace saving gamesTherapy exerciseMoisture absorptionEngineering

Owner:EDWARDS RICHARD

Semiconductor device

InactiveUS20110298027A1Highly integratedReduce layout areaTransistorSolid-state devicesPower semiconductor deviceCapacitor

It is an object to provide a semiconductor device with a novel structure in which stored data can be held even when power is not supplied and there is no limitation on the number of writings. A semiconductor device includes a second transistor and a capacitor provided over a first transistor. A source electrode of the second transistor which is in contact with a gate electrode of the first transistor is formed using a material having etching selectivity with respect to the gate electrode. By forming the source electrode of the second transistor using a material having etching selectivity with respect to the gate electrode of the first transistor, a margin in layout can be reduced, so that the degree of integration of the semiconductor device can be increased.

Owner:SEMICON ENERGY LAB CO LTD

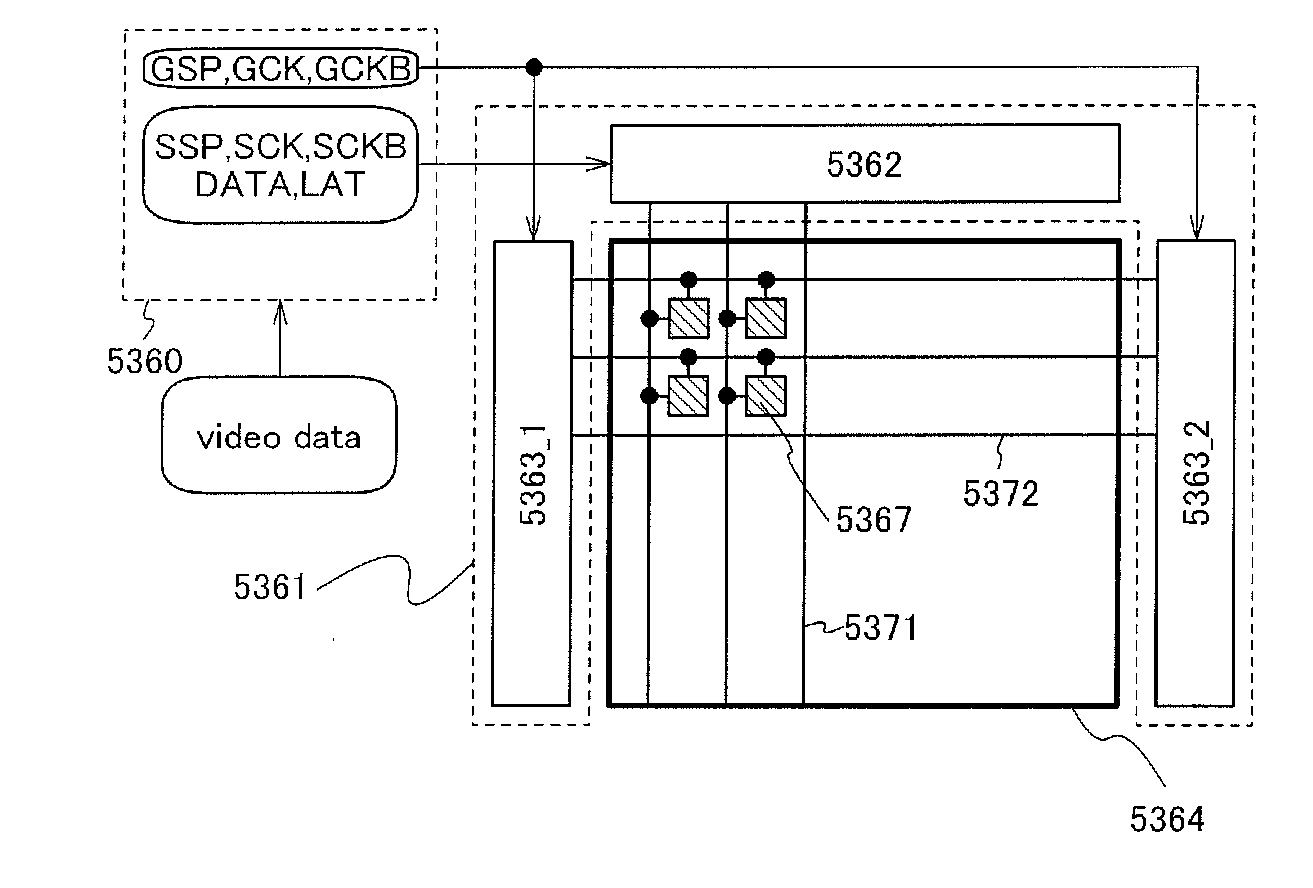

Pulse signal output circuit and shift register

ActiveUS20110199365A1Suppress degradationReduce numberTransistorSolid-state devicesOxide semiconductorEngineering

A transistor whose channel region includes an oxide semiconductor is used as a pull down transistor. The band gap of the oxide semiconductor is 2.0 eV or more, preferably 2.5 eV or more, more preferably 3.0 eV or more. Thus, hot carrier degradation in the transistor can be suppressed. Accordingly, the circuit size of the semiconductor device including the pull down transistor can be made small. Further, a gate of a pull up transistor is made to be in a floating state by switching of on / off of the transistor whose channel region includes an oxide semiconductor. Note that when the oxide semiconductor is highly purified, the off-state current of the transistor can be 1 aA / μm (1×10−18 A / μm) or less. Therefore, the drive capability of the semiconductor device can be improved.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20120032164A1Simple circuit configurationLonger heldSolid-state devicesRead-only memoriesPower semiconductor devicePower flow

In a semiconductor device which conducts multilevel writing operation and a driving method thereof, a signal line for controlling on / off of a writing transistor for conducting a writing operation on a memory cell using a transistor including an oxide semiconductor layer is disposed along a bit line, and a multilevel writing operation is conducted with use of, also in a writing operation, a voltage which is applied to a capacitor at a reading operation. Because an oxide semiconductor material that is a wide gap semiconductor capable of sufficiently reducing off-state current of a transistor is used, data can be held for a long period.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20110210339A1Longer heldReduce power consumptionTransistorSolid-state devicesPhysicsOxide semiconductor

A semiconductor device including a non-volatile memory cell including a writing transistor which includes an oxide semiconductor, a reading transistor which includes a semiconductor material different from that of the writing transistor, and a capacitor is provided. Data is written or rewritten to the memory cell by turning on the writing transistor and supplying a potential to a node where a source electrode (or a drain electrode) of the writing transistor, one electrode of the capacitor, and a gate electrode of the reading transistor are electrically connected to each other, and then turning off the writing transistor so that the predetermined amount of charge is held in the node. Further, when a transistor whose threshold voltage is controlled and set to a positive voltage is used as the reading transistor, a reading potential is a positive potential.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS20110227074A1Highly integratedDistanceTransistorSolid-state devicesDevice materialEngineering physics

A semiconductor device with a novel structure is provided in which stored data can be held even when power is not supplied and the number of writing is not limited. The semiconductor includes a second transistor and a capacitor over a first transistor. The capacitor includes a source or drain electrode and a gate insulating layer of the second transistor and a capacitor electrode over an insulating layer which covers the second transistor. The gate electrode of the second transistor and the capacitor electrode overlap at least partly with each other with the insulating layer interposed therebetween. By forming the gate electrode of the second transistor and the capacitor electrode using different layers, an integration degree of the semiconductor device can be improved.

Owner:SEMICON ENERGY LAB CO LTD

Memory circuit

InactiveUS8773906B2Reduce power consumptionSuppress power consumptionTransistorSolid-state devicesData signalMemory circuits

The present invention provides a memory circuit in which, while the power is not supplied, a data signal that has been held in a memory section corresponding to a volatile memory can be held in a capacitor in a memory section corresponding to a nonvolatile memory. In the nonvolatile memory section, a transistor whose channel is formed in an oxide semiconductor layer allows a signal to be held in the capacitor for a long period. Thus, the memory circuit can hold a logic state (data signal) even while the power supply is stopped. A potential applied to a gate of the transistor whose channel is formed in an oxide semiconductor layer is raised by a booster circuit provided between a wiring for carrying power supply potential and the gate of the transistor, allowing a data signal to be held even by one power supply potential without malfunction.

Owner:SEMICON ENERGY LAB CO LTD

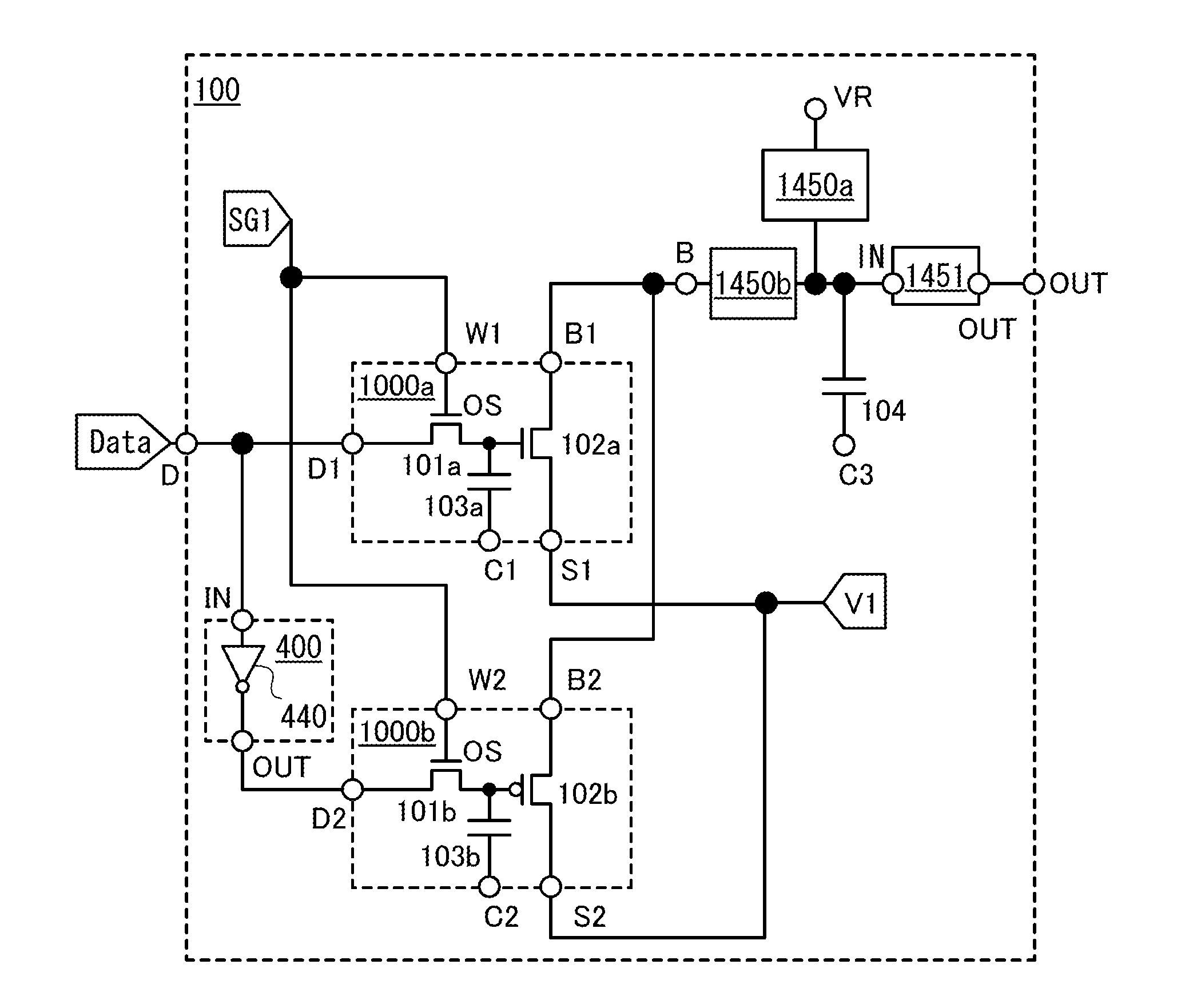

Memory element and signal processing circuit

ActiveUS20120230138A1Reduce the refresh rateIncrease number of rewritable timeDigital data processing detailsRead-only memoriesSignal processing circuitsHemt circuits

A memory element having a novel structure and a signal processing circuit including the memory element are provided. A first circuit, including a first transistor and a second transistor, and a second circuit, including a third transistor and a fourth transistor, are included. A first signal potential and a second signal potential, each corresponding to an input signal, are respectively input to a gate of the second transistor via the first transistor in an on state and to a gate of the fourth transistor via the third transistor in an on state. After that, the first transistor and the third transistor are turned off. The input signal is read out using both the states of the second transistor and the fourth transistor. A transistor including an oxide semiconductor in which a channel is formed can be used for the first transistor and the third transistor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS8896046B2Guaranteed high speed operationRun at high speedTransistorSolid-state devicesDriver circuitEngineering

Provided is a semiconductor device with a novel structure in which stored data can be retained even when power is not supplied, and which does not have a limitation on the number of writing. The semiconductor device includes both a memory circuit including a transistor including an oxide semiconductor (in a broader sense, a transistor whose off-state current is sufficiently small), and a peripheral circuit such as a driver circuit including a transistor including a material other than an oxide semiconductor (that is, a transistor capable of operating at sufficiently high speed). Further, the peripheral circuit is provided in a lower portion and the memory circuit is provided in an upper portion, so that the area and size of the semiconductor device can be decreased.

Owner:SEMICON ENERGY LAB CO LTD

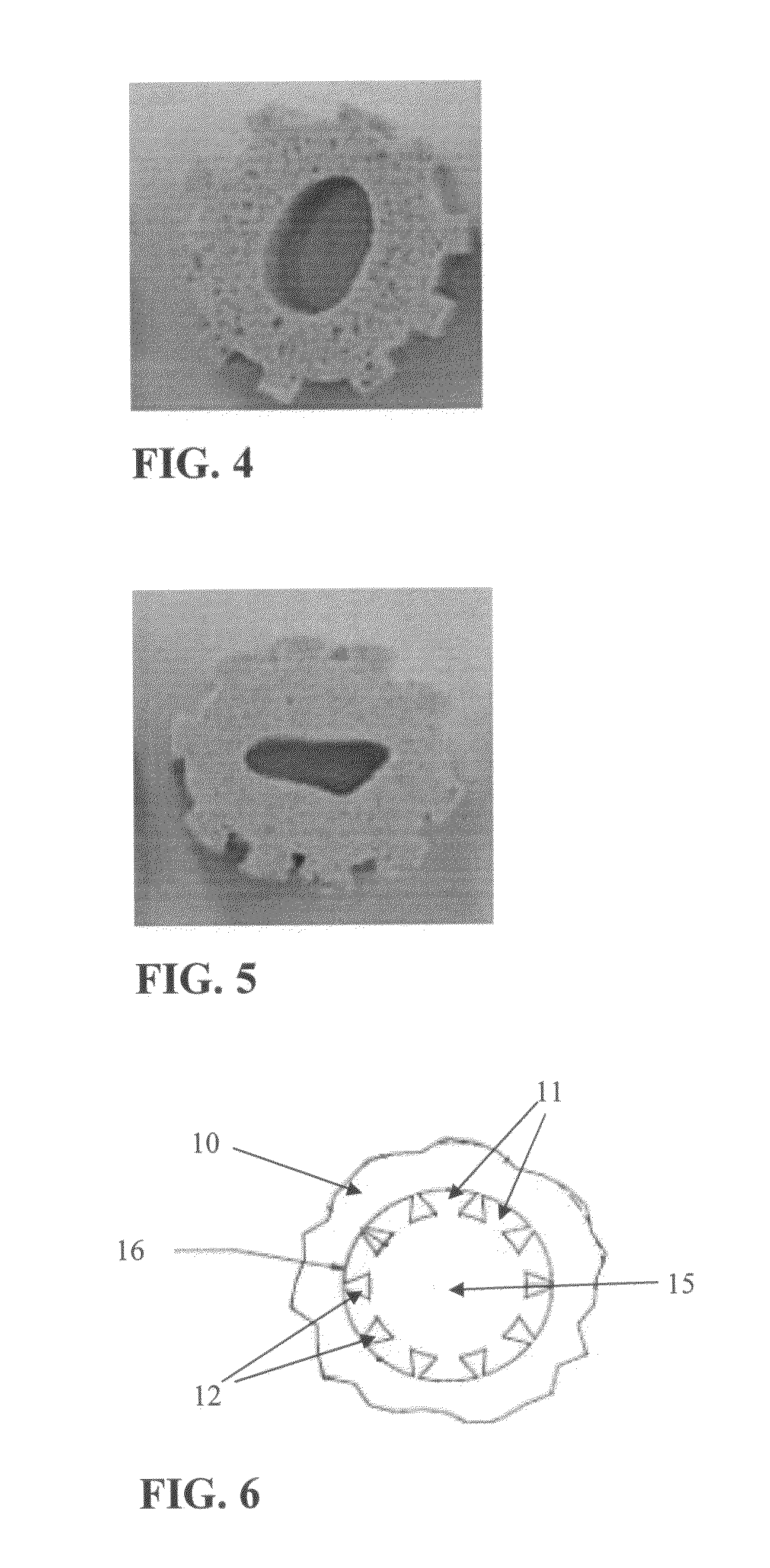

Low density edible animal chews and methods of making same

InactiveUS20160143320A1Low densitySmoother exterior surfaceBaking mixturesAnimal feeding stuffDental ProductLow density

Edible chews for pets have a low density (e.g. about 1.0 Kg / L or less) and a smooth exterior surface. One method by which the low density and the smooth exterior surface can be achieved uses a modified extrusion die to increase shear and restrict surface bubbles. Another method by which the low density and the smooth exterior surface can be achieved uses an extruder screw with a modified profile that holds a dough longer therein to create a whipping effect resulting in more bubble nucleation sites and hence a more uniform cellular matrix. The puffed (expanded) product was experimentally tested and provided better dental cleaning scores than a current unexpanded similarly formulated commercial dental product.

Owner:SOC DES PROD NESTLE SA

Memory circuit

InactiveUS20120195122A1Raise the potentialSuppress power consumptionTransistorSolid-state devicesOxide semiconductorEngineering

The present invention provides a memory circuit in which, while the power is not supplied, a data signal that has been held in a memory section corresponding to a volatile memory can be held in a capacitor in a memory section corresponding to a nonvolatile memory. In the nonvolatile memory section, a transistor whose channel is formed in an oxide semiconductor layer allows a signal to be held in the capacitor for a long period. Thus, the memory circuit can hold a logic state (data signal) even while the power supply is stopped. A potential applied to a gate of the transistor whose channel is formed in an oxide semiconductor layer is raised by a booster circuit provided between a wiring for carrying power supply potential and the gate of the transistor, allowing a data signal to be held even by one power supply potential without malfunction.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for driving semiconductor device

InactiveUS8542528B2Reduce variationLow working voltageRead-only memoriesDigital storageDriver circuitHemt circuits

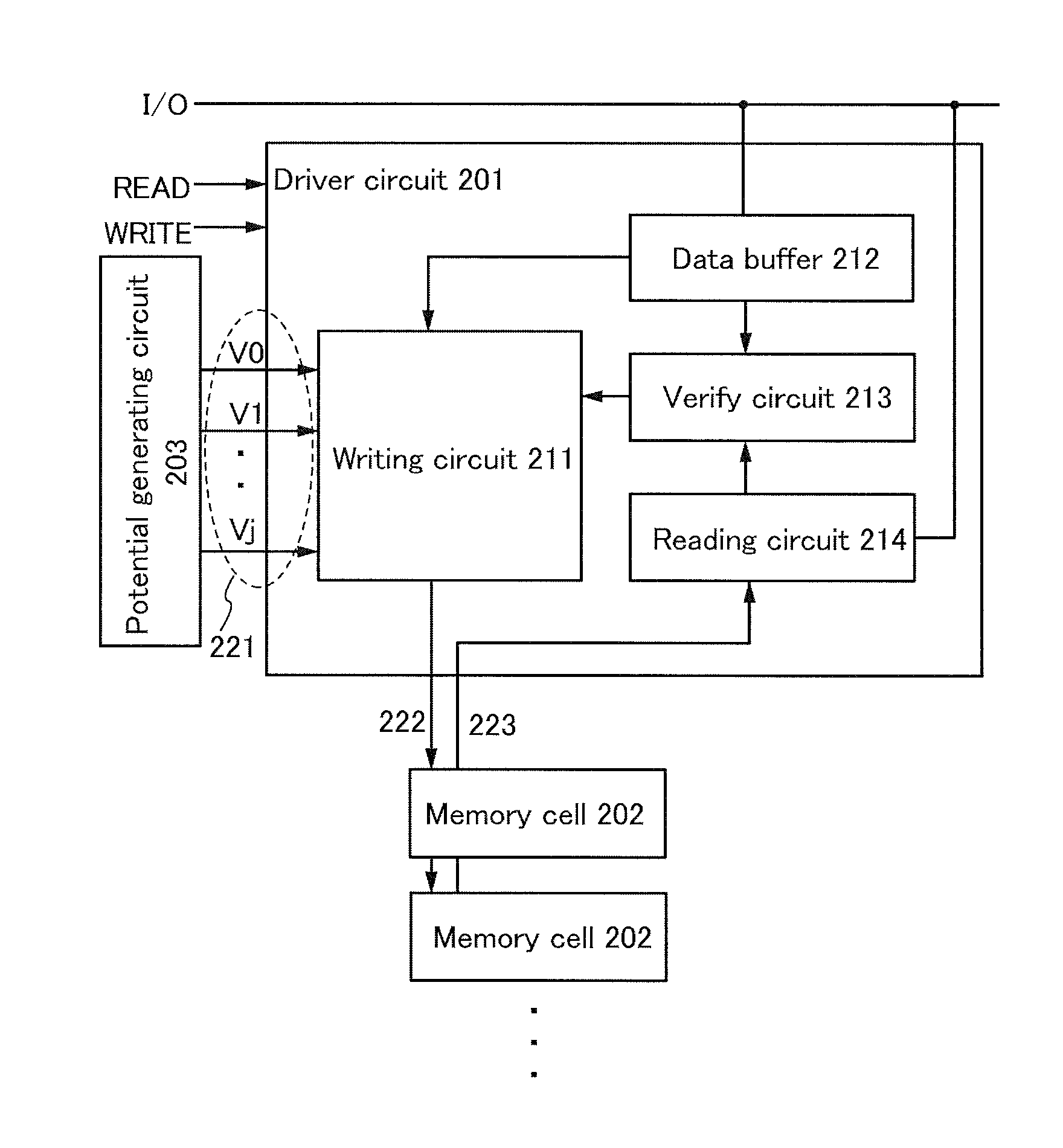

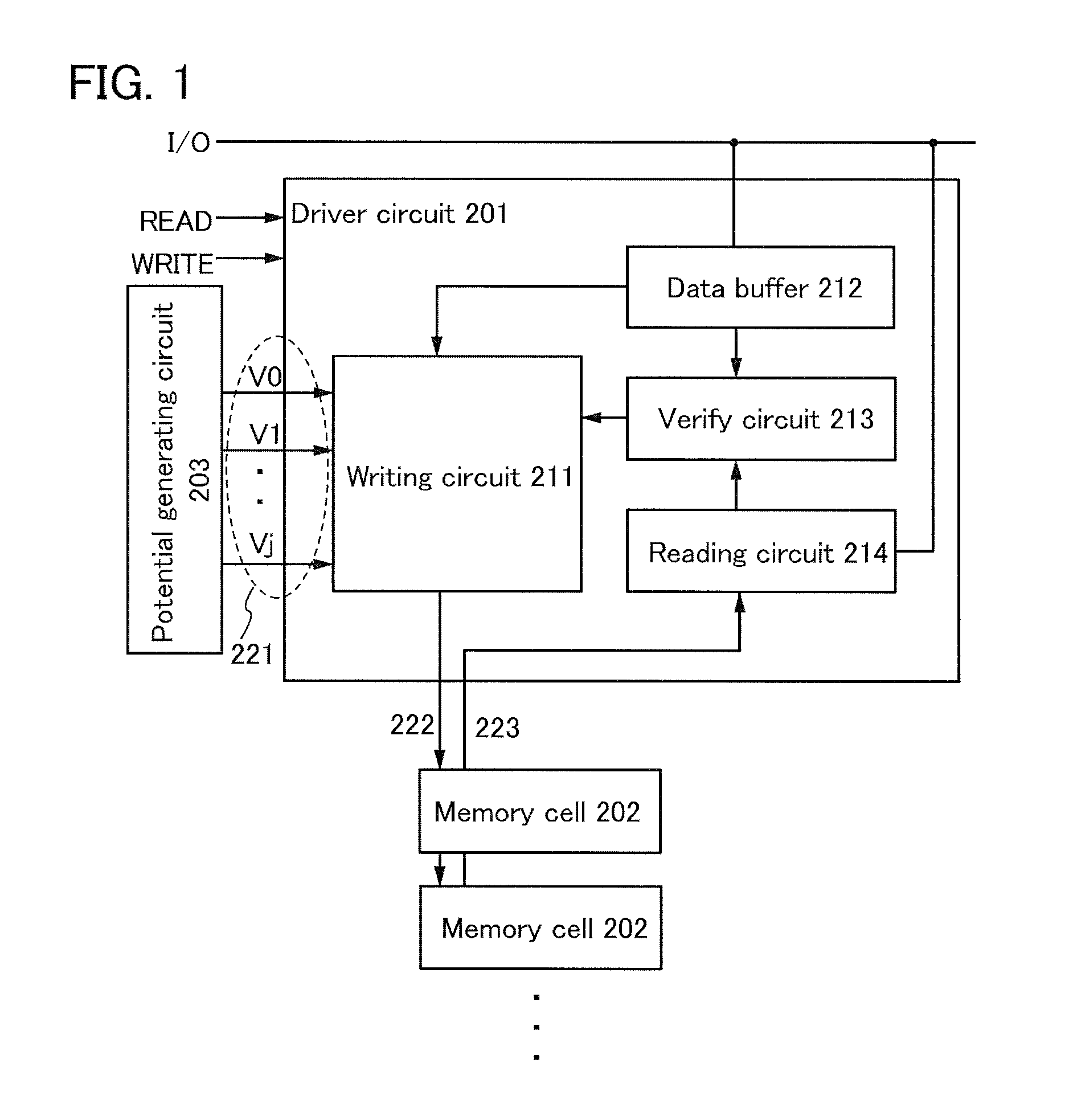

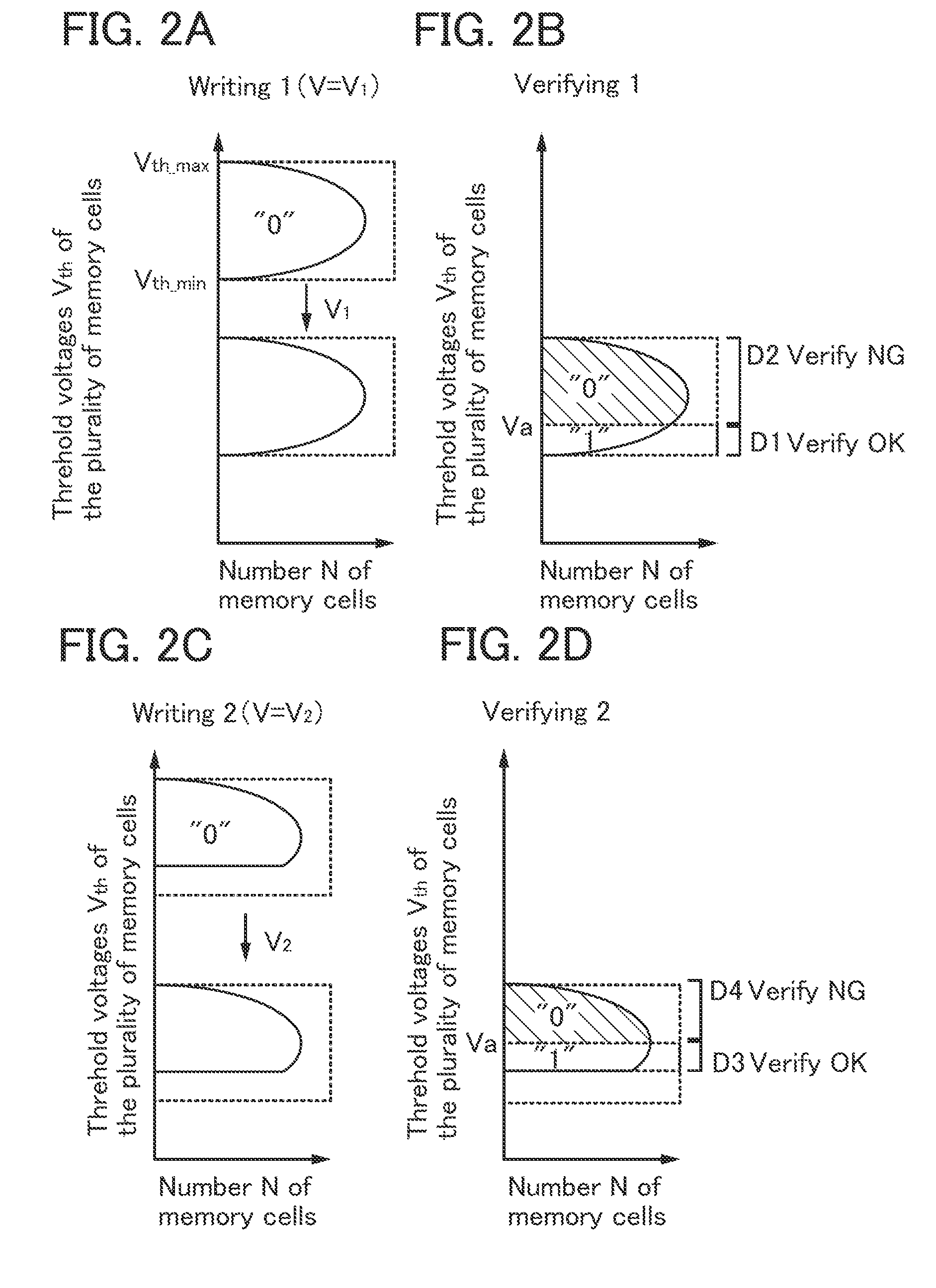

A semiconductor device with a novel structure is provided, in which the operation voltage is reduced or the storage capacity is increased by reducing variation in the threshold voltages of memory cells after writing. The semiconductor device includes a plurality of memory cells each including a transistor including an oxide semiconductor and a transistor including a material other than an oxide semiconductor, a driver circuit that drives the plurality of memory cells, and a potential generating circuit that generates a plurality of potentials supplied to the driver circuit. The driver circuit includes a data buffer, a writing circuit that writes one potential of the plurality of potentials into each of the plurality of memory cells as data, a reading circuit that reads the data written into the memory cells, and a verifying circuit that verifies whether the read data agrees with data held in the data buffer or not.

Owner:SEMICON ENERGY LAB CO LTD

Delayed gelling starch compositions

ActiveUS20130236624A1Flexibility to manufacturer's processingLonger heldMilk preparationBakery productsAlant starchChemistry

The present application is related to starches that exhibit delayed gelling. In one embodiment, the application is related to compositions of a degraded gelling starch having a stabilizing group. A delayed gelling starch comprises a starch base material and a stabilization agent. Food products may comprise the delayed gelling starch.

Owner:CORN PROD DEV INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com