Thin film transistor device and preparation method therefor

A thin-film transistor and device technology, applied in the field of thin-film transistor devices and their preparation, can solve the problem of large off-state current, achieve the effects of reducing off-state current, simple process, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

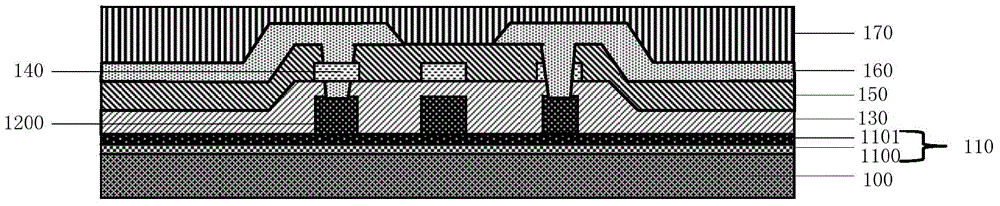

[0027] Please refer to figure 1 , which is a schematic cross-sectional view of the thin film transistor device provided in Embodiment 1 of the present invention. Such as figure 1 As shown, the thin film transistor device sequentially includes: a substrate 100, a buffer layer 110, a channel layer 120, a gate insulating layer 130, a gate 140, an interlayer insulating layer 150, and a source and drain 160; the channel layer 120 is curved in shape.

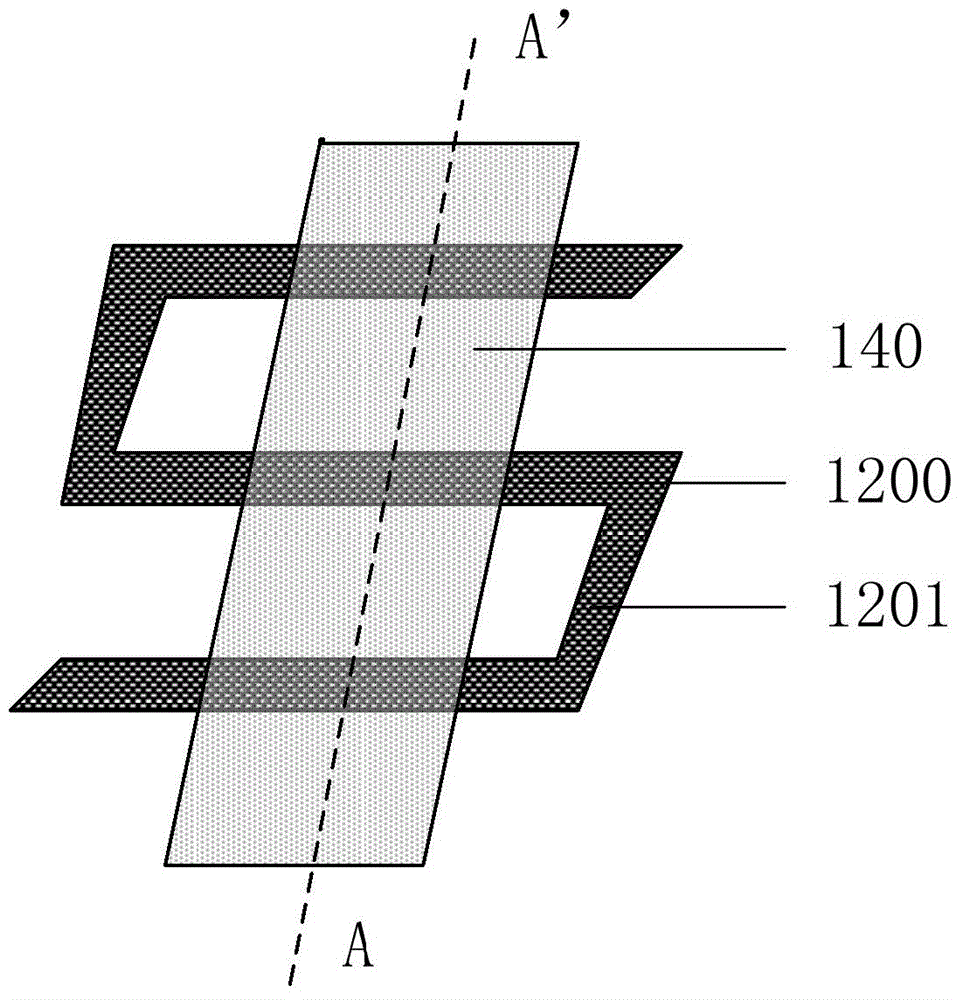

[0028] Please refer to figure 2 , which is a schematic structural view of the channel layer in the thin film transistor device provided in Embodiment 1 of the present invention, as shown in figure 2 As shown, in this embodiment, the shape of the channel layer 120 is S-type, and the channel layer 120 includes a channel layer 1200 in an undoped region and a channel layer 1201 in a doped region. The projection of the channel layer 1200 on the substrate 100 is located in the projection area of the gate 140 on the substrate 100, th...

Embodiment 2

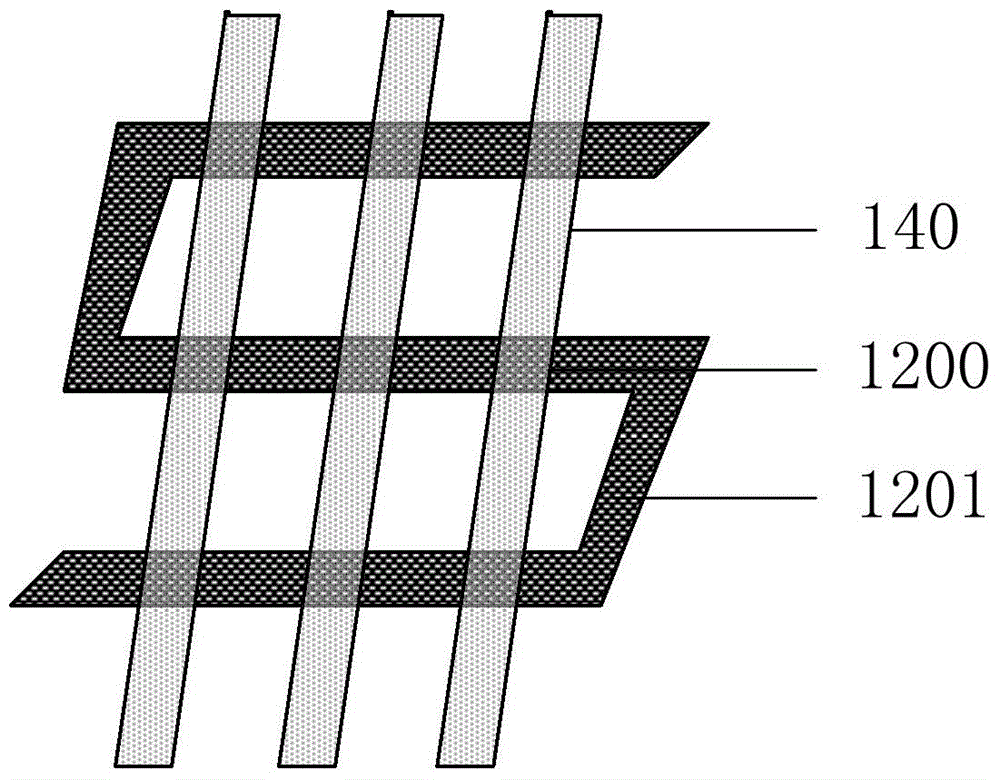

[0039] On the basis of Embodiment 1, the thin film transistor device is a multi-gate S-channel, such as image 3 As shown, since its cross-sectional view and preparation method are consistent with Embodiment 1, it is not repeated here.

[0040] The multi-gate S-channel can adjust the length and width of the thin film transistor device, so as to obtain a thin film transistor device with better matching process and design.

[0041] To sum up, the thin film transistor device and its preparation method provided by the present invention, by setting the channel layer of the thin film transistor device in a curved shape, avoids the impact on the device pixels due to the length of the channel being too long, and the channel layer The length and width can be adjusted according to the needs, which solves the problem that the channel layer is long in one direction; the present invention arranges the channel layer in the non-doped region in the area covered by the gate, and the channel la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com