Thin film transistor liquid crystal display (TFT-LCD) array substrate and manufacturing method thereof

An array substrate and substrate technology, applied in semiconductor/solid-state device manufacturing, instruments, semiconductor devices, etc., can solve the problems of excessive TFT off-state current, shortened pixel electrode charge retention time, and affecting TFT performance, etc., to reduce The effects of off-state current, prolonging the charge retention time of the pixel electrode, and improving TFT performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

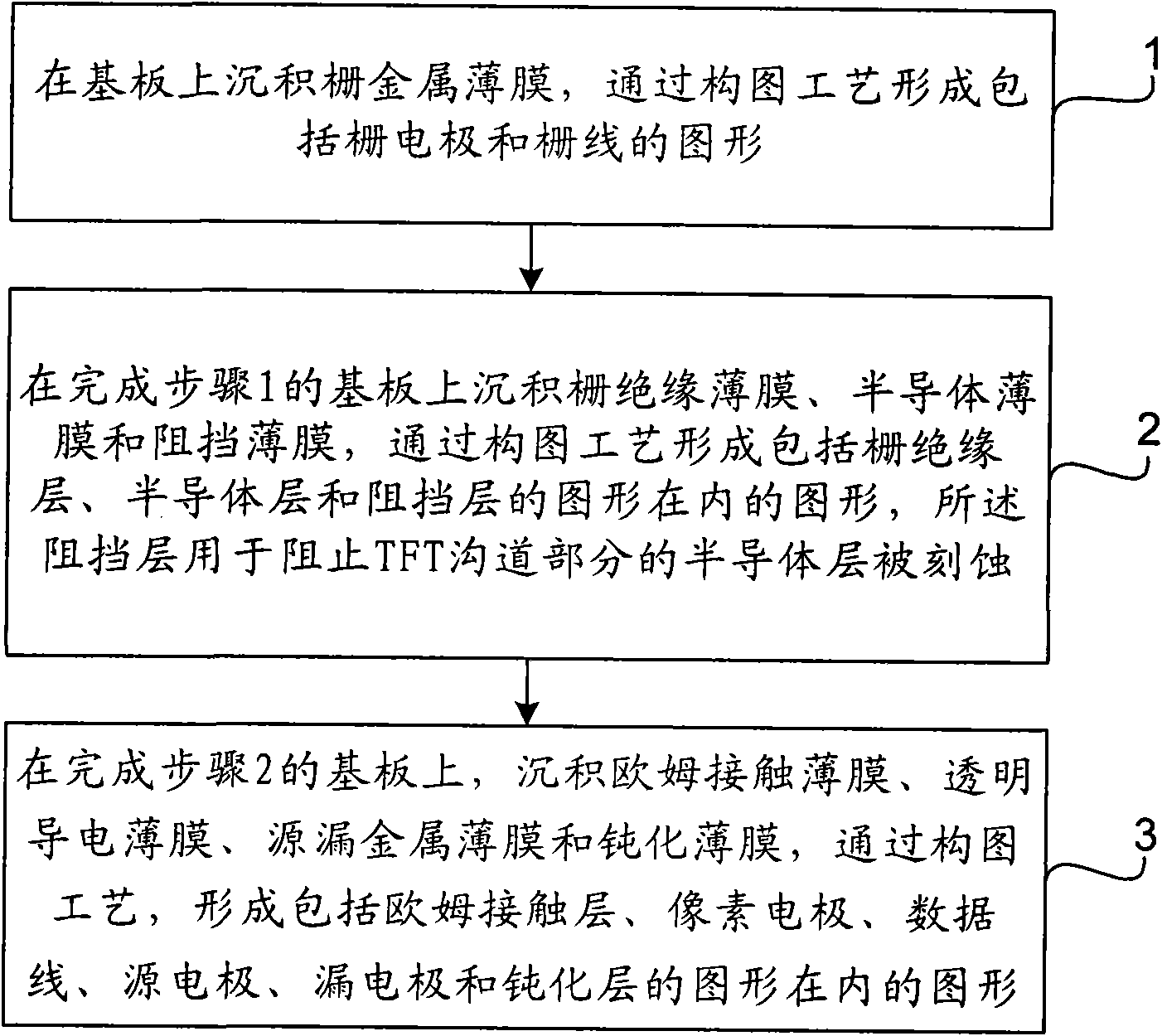

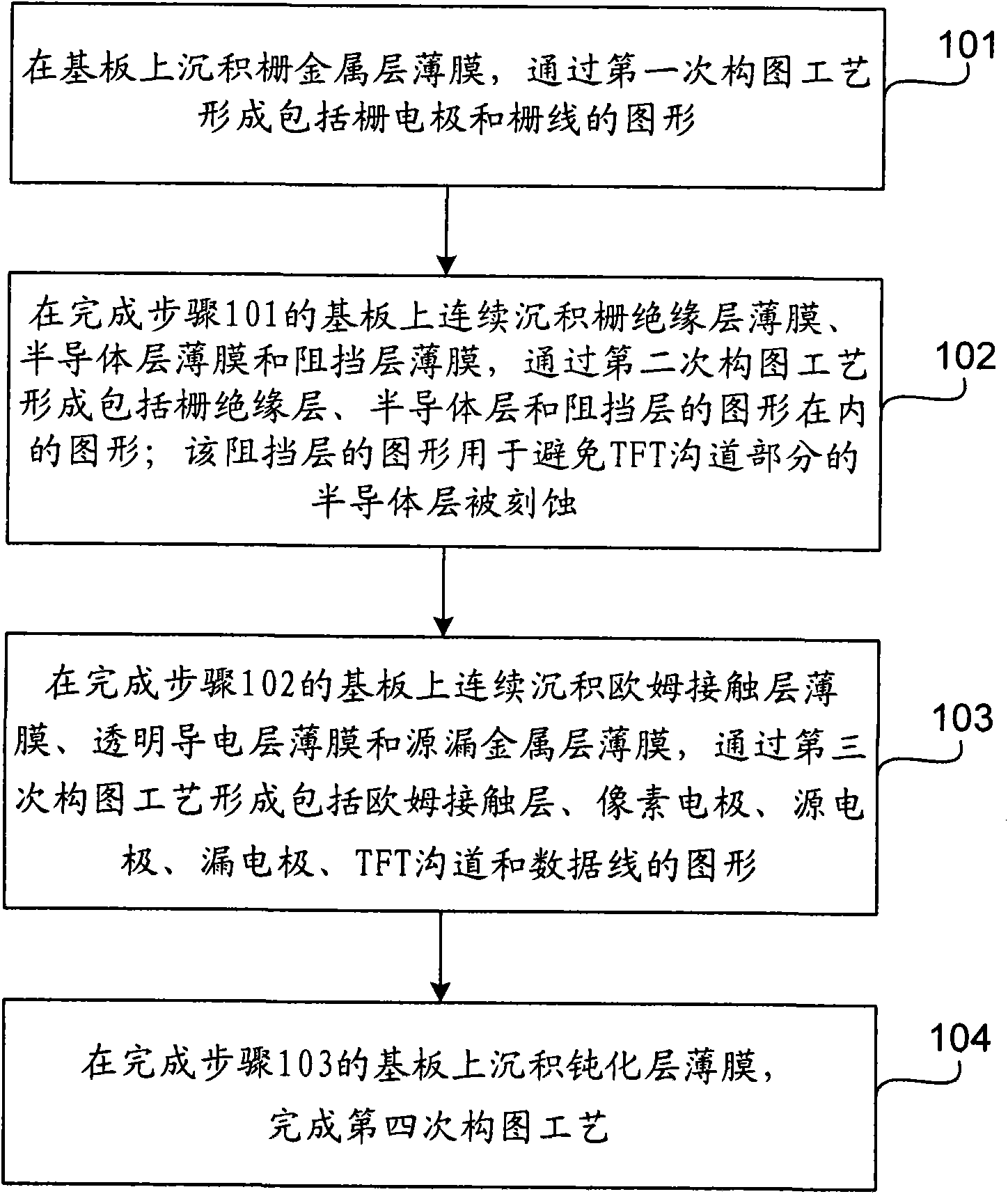

[0041] Such as figure 2 The flow chart of the first embodiment of the manufacturing method of the TFT-LCD array substrate of the present invention is shown, including:

[0042] Step 101: Deposit a gate metal layer film on a substrate, and form a pattern including gate electrodes and gate lines through a first patterning process;

[0043] Step 102: successively deposit a gate insulating layer film, a semiconductor layer film, and a barrier layer film on the substrate after step 101, and form patterns including patterns of the gate insulating layer, the semiconductor layer and the barrier layer through the second patterning process; The pattern of the barrier layer is used to prevent the semiconductor layer of the TFT channel part from being etched;

[0044] Step 103: Continuously deposit an ohmic contact layer film, a transparent conductive layer film, and a source-drain metal layer film on the substrate after step 102, and form an ohmic contact layer, pixel electrode, source electro...

no. 2 example

[0058] Such as Figure 7 Shown is a flowchart of a second embodiment of a method for manufacturing a TFT-LCD array substrate of the present invention, and the method includes:

[0059] Step 201: Deposit a gate metal layer film on a substrate, and form a pattern including gate electrodes and gate lines through the first patterning process;

[0060] Step 202: successively deposit a gate insulating layer film, a semiconductor layer film, and a barrier layer film on the substrate after step 201, and form patterns including patterns of the gate insulating layer, the semiconductor layer, and the barrier layer through the second patterning process; The pattern of the barrier layer is used to prevent the semiconductor layer of the TFT channel part from being etched;

[0061] Step 203: Continuously deposit an ohmic contact layer film, a transparent conductive layer film, and a source / drain metal layer film on the substrate after step 202, and form an ohmic contact layer, a pixel electrode, a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com