Method for reducing parasitic resistance of graphene top gate FET device

A parasitic resistance and graphene technology is applied in the field of graphene top-gate FET device preparation to achieve the effects of increasing on-state current, improving transconductance and cut-off frequency, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

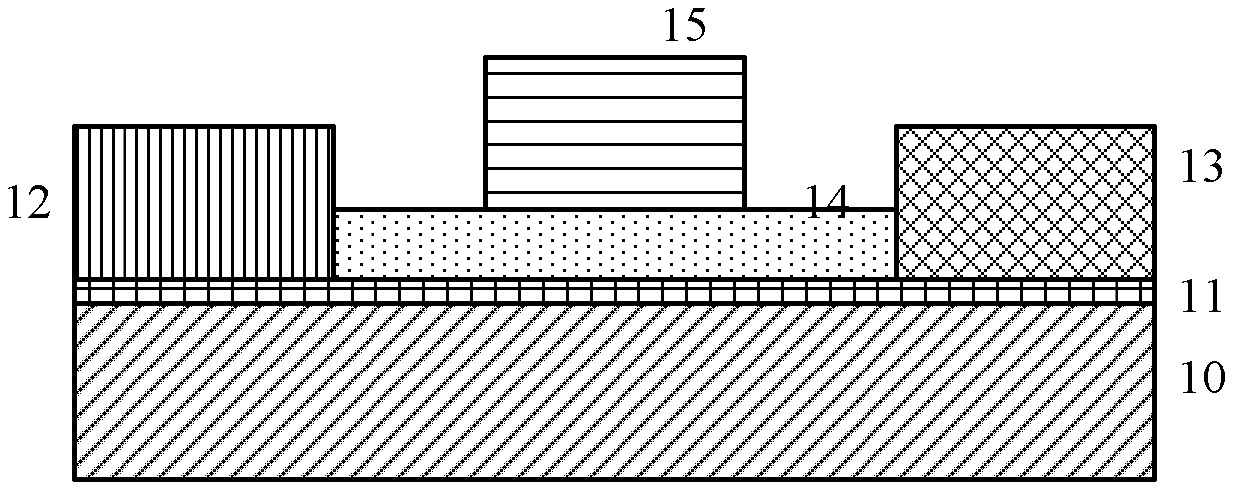

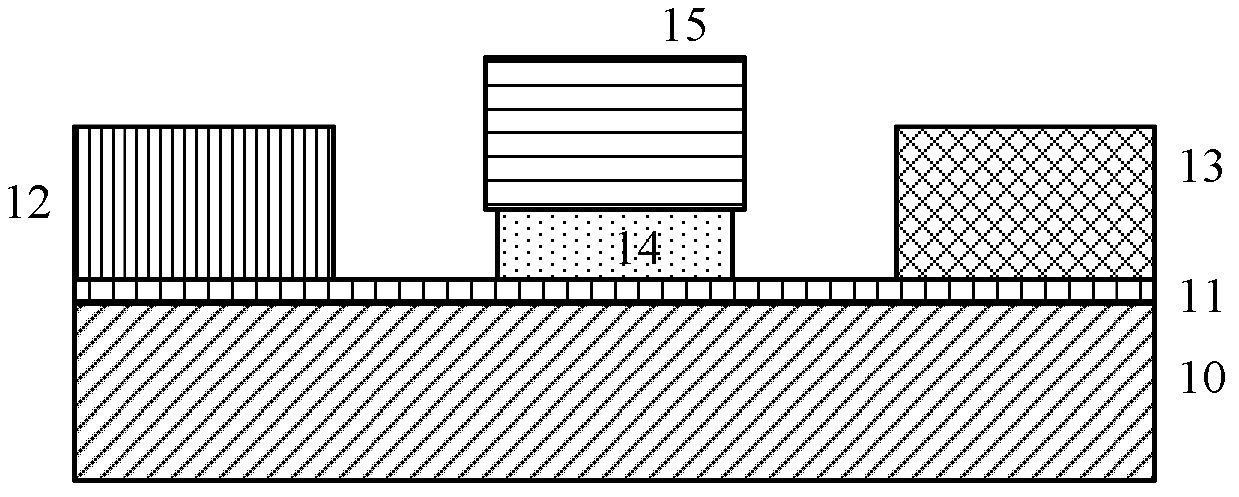

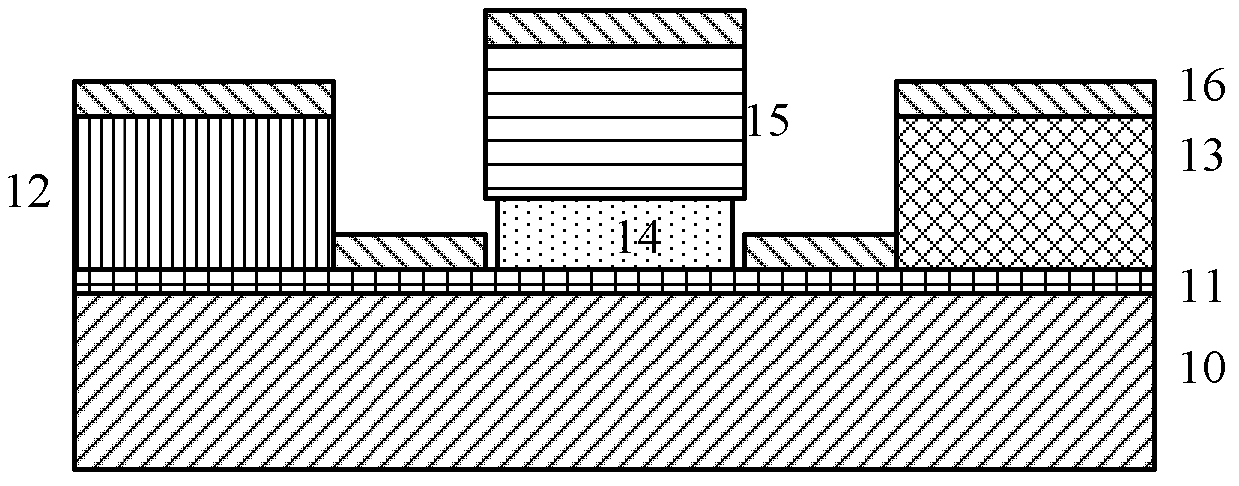

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0021] The invention provides a method for reducing the parasitic resistance of a graphene top-gate FET device. The method is to use the top-gate metal as a mask to protect the top-gate metal lower gate medium, corrode the graphene top-gate FET device, and remove the gate source , the gate dielectric covered on the graphene channel region between the gate and drain, and then vapor-deposit a layer of metal covering the graphene material between the gate source and the gate drain to form a metal graphene contact, eliminating the gap introduced by the distance between the gate source and the gate drain channel resistance. The present invention uses a self-alignment method to vapor-deposit metal to reduce the distance between...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com