Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

65results about How to "Increase reverse voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

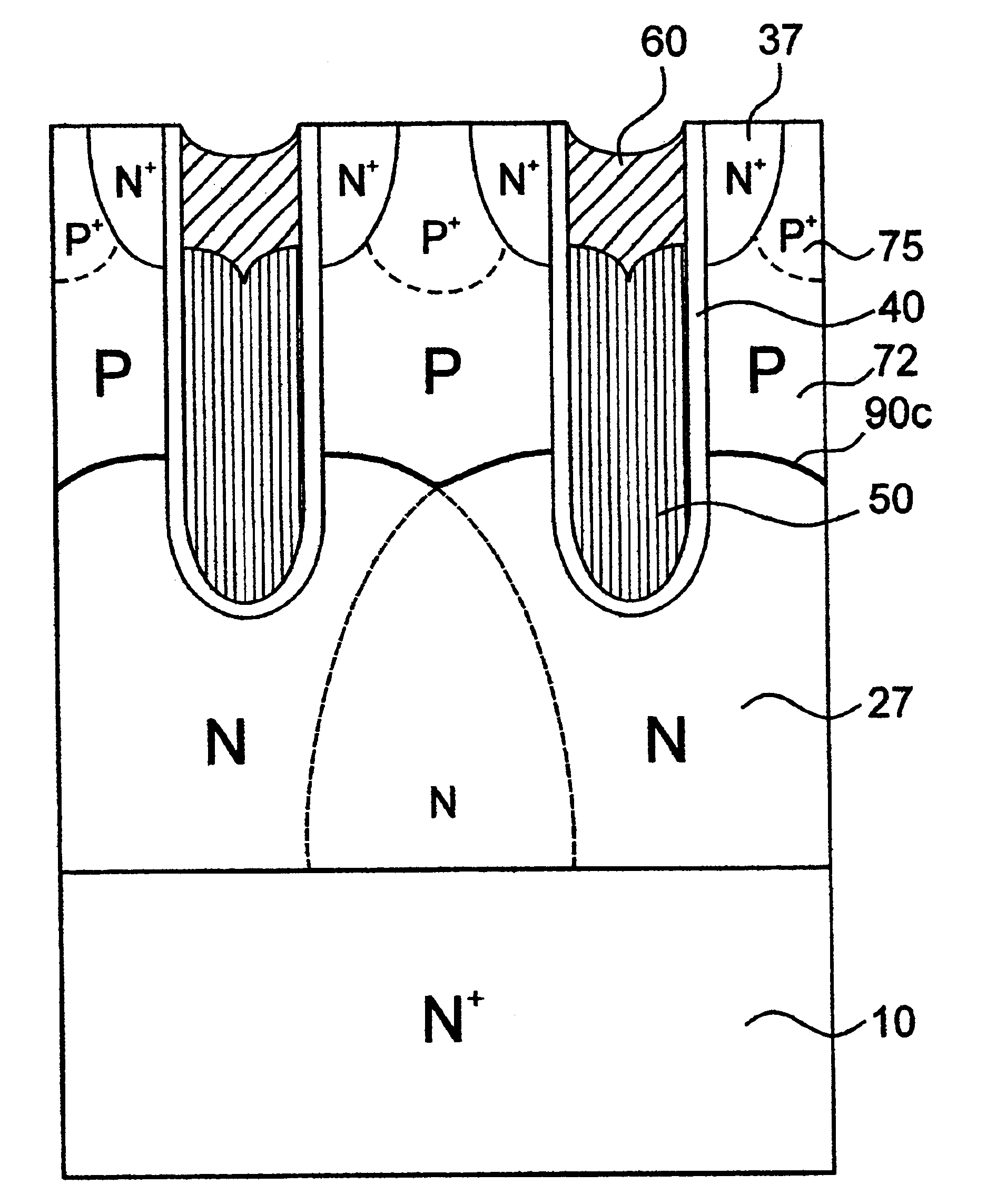

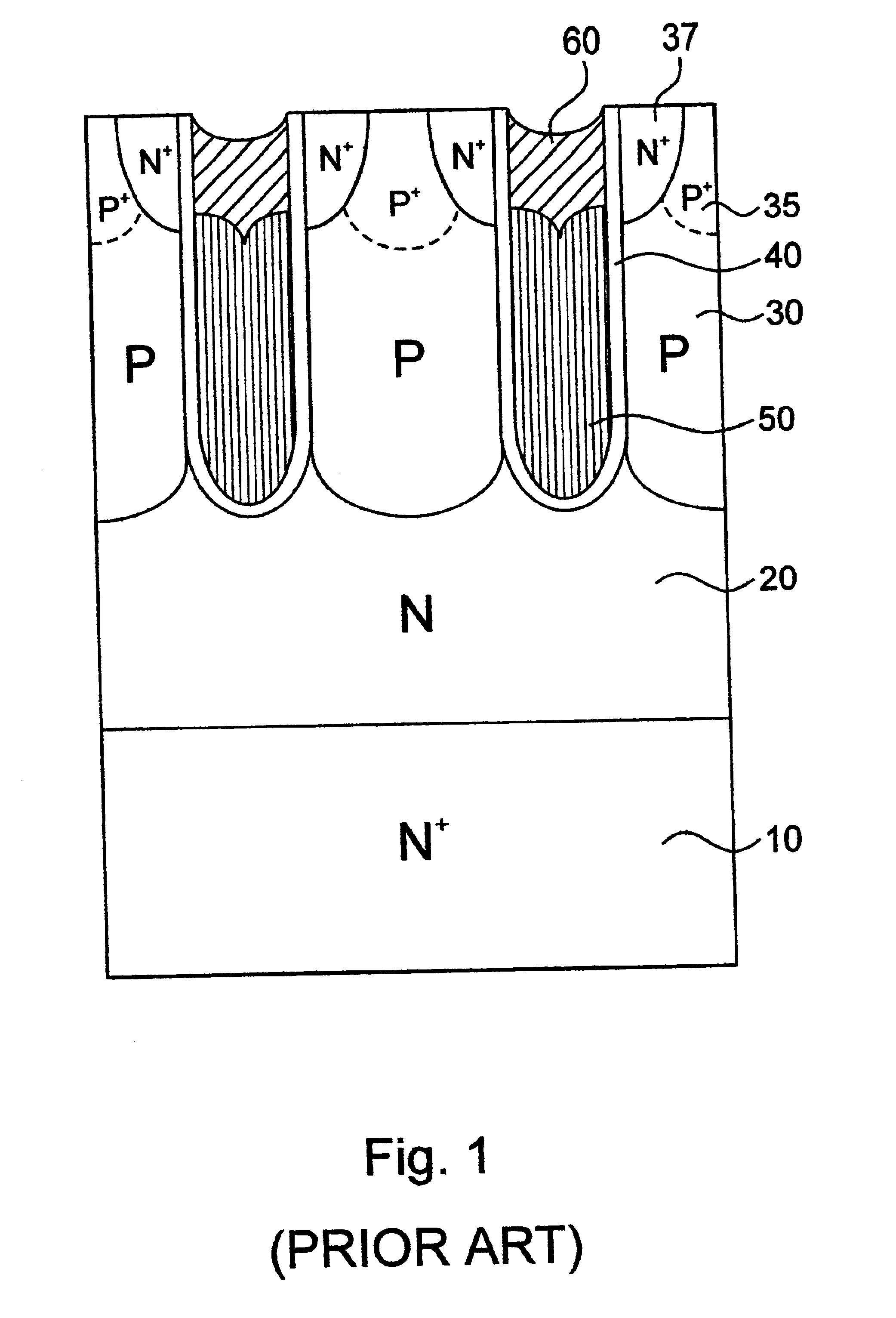

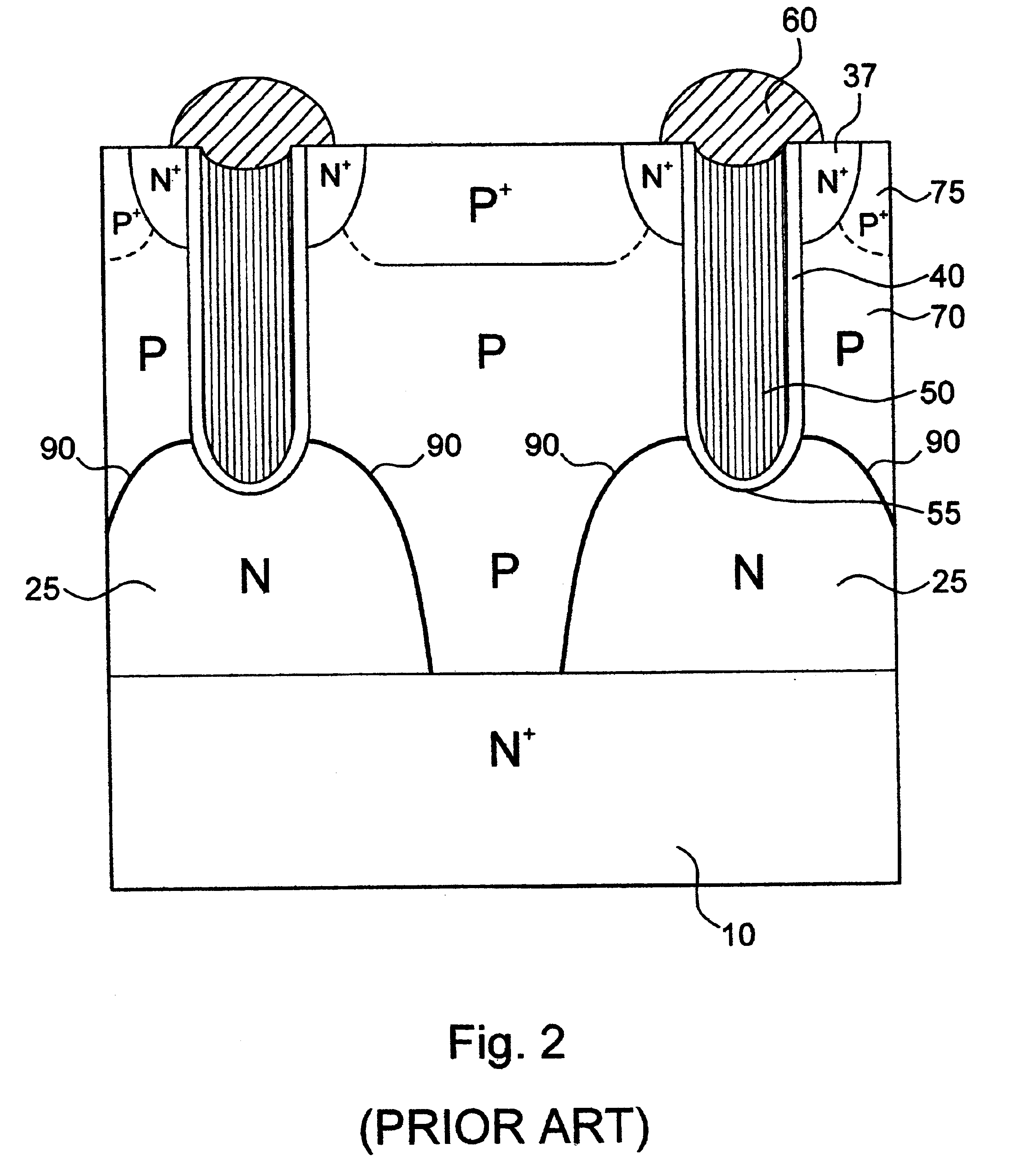

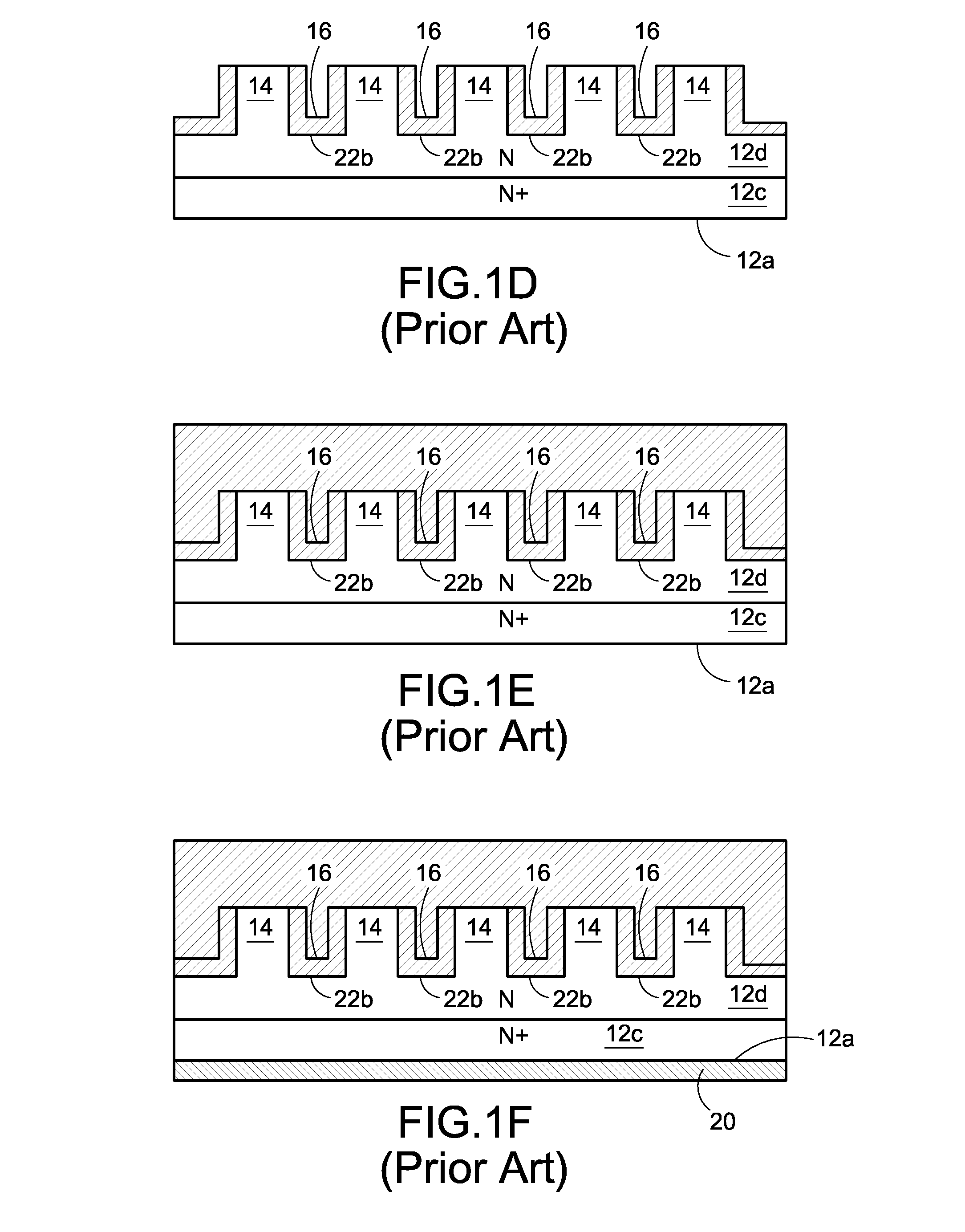

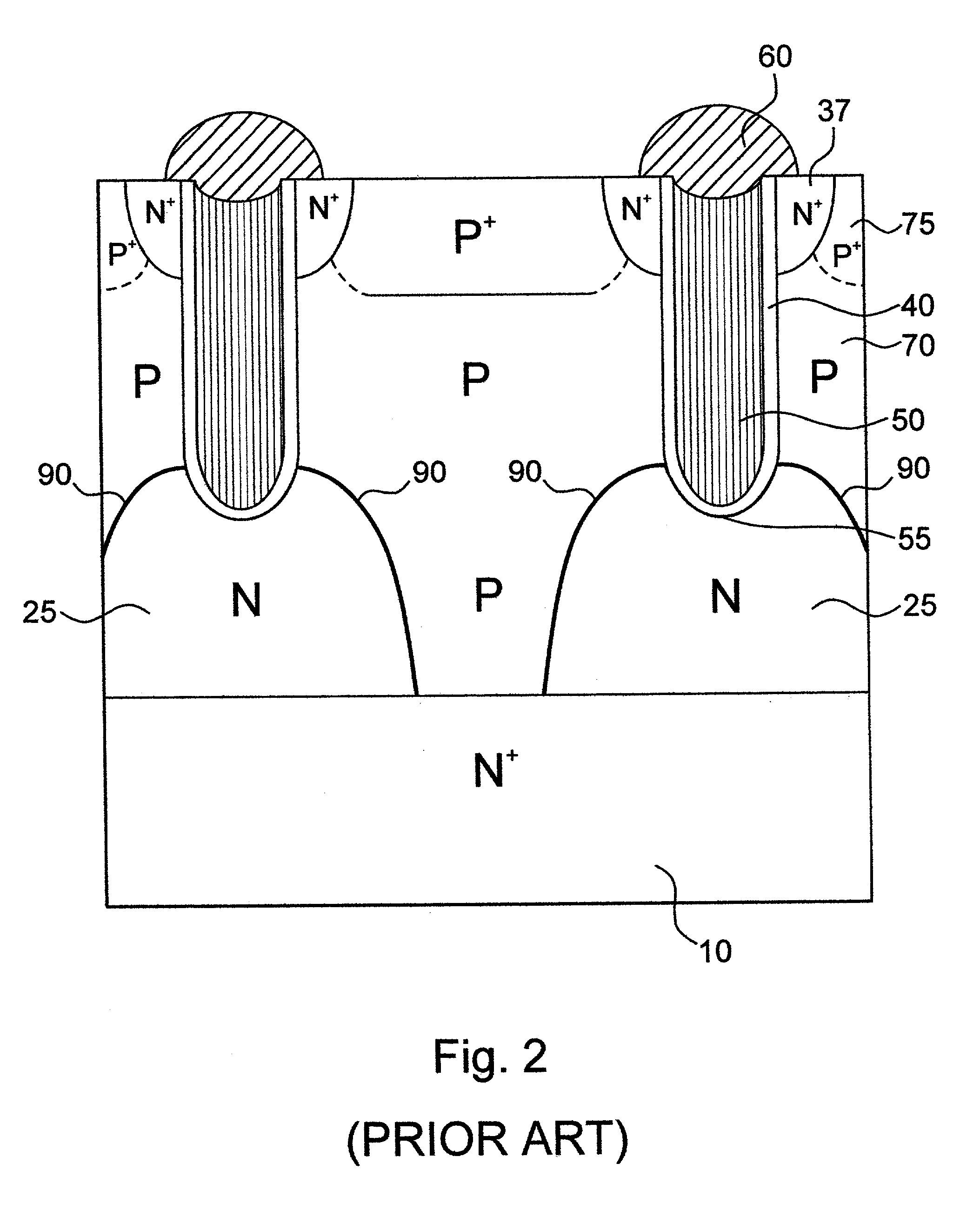

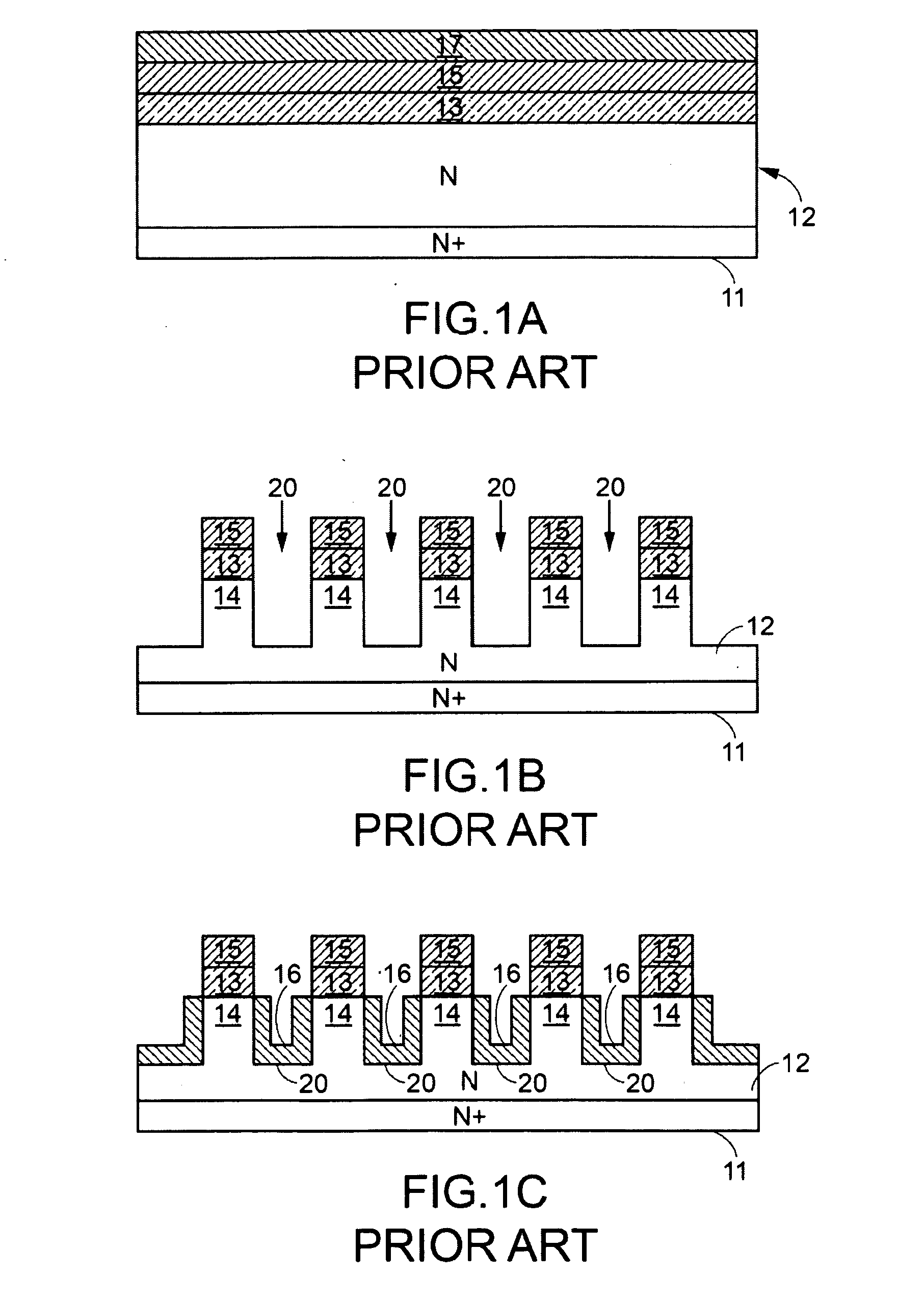

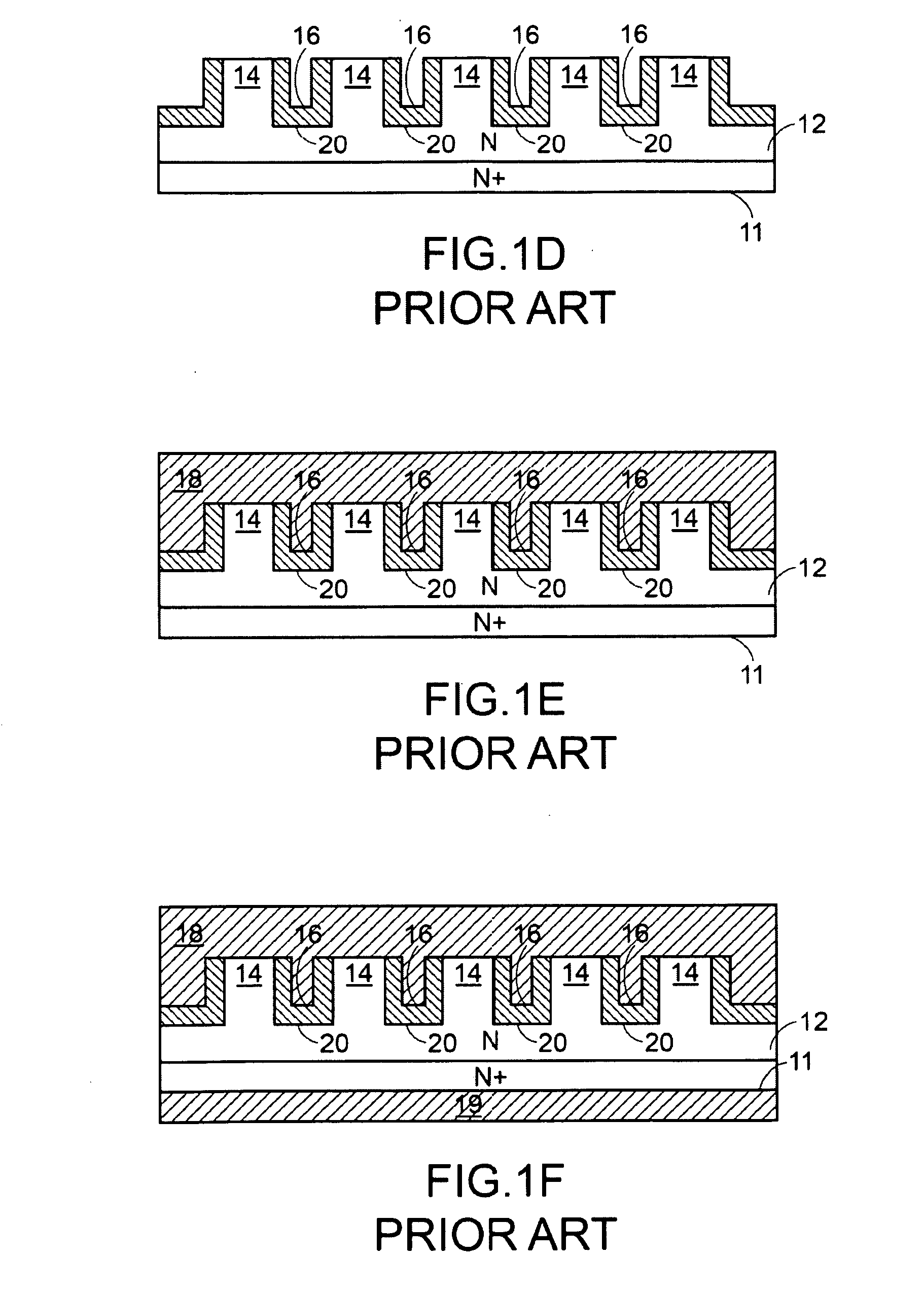

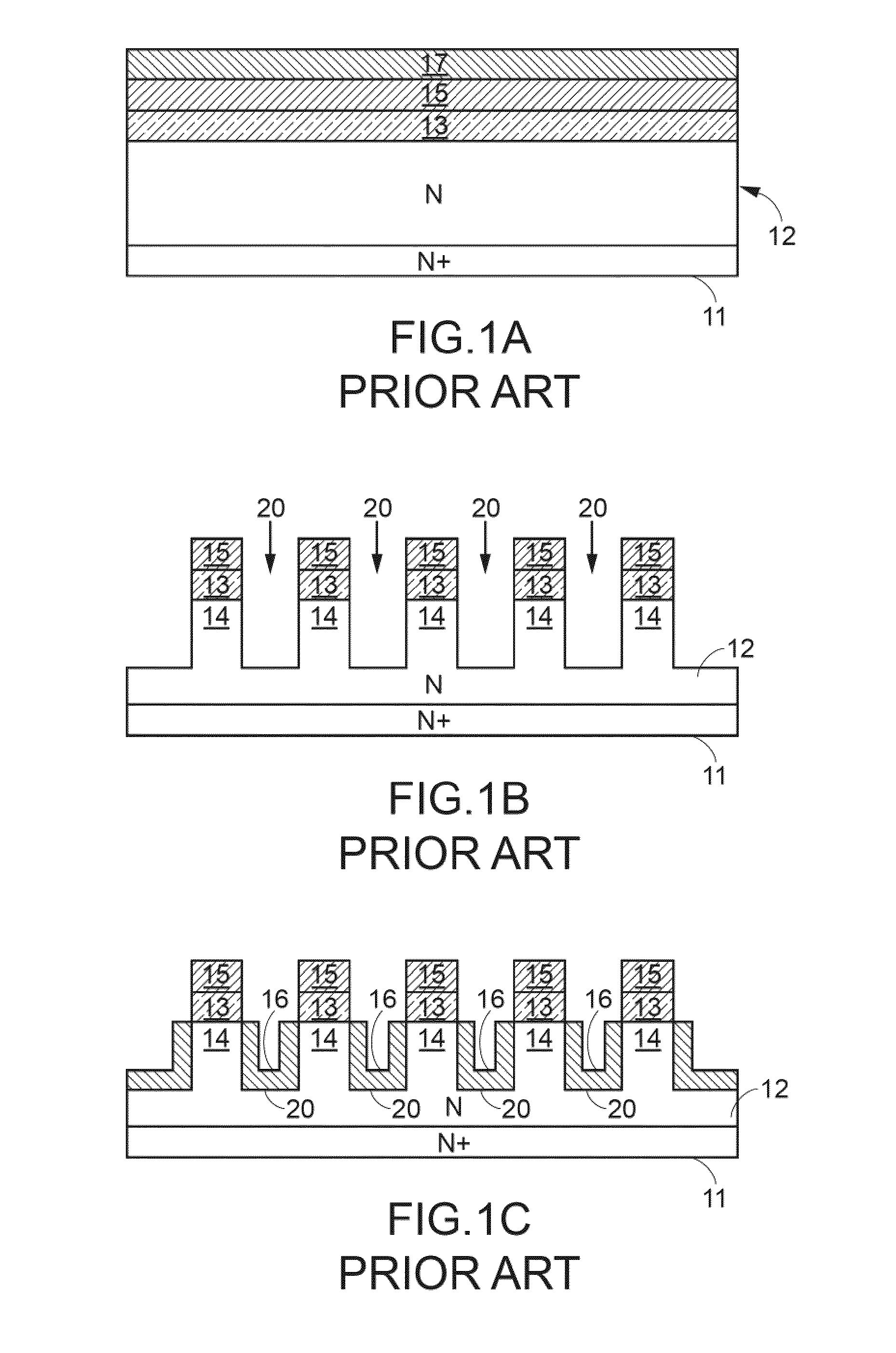

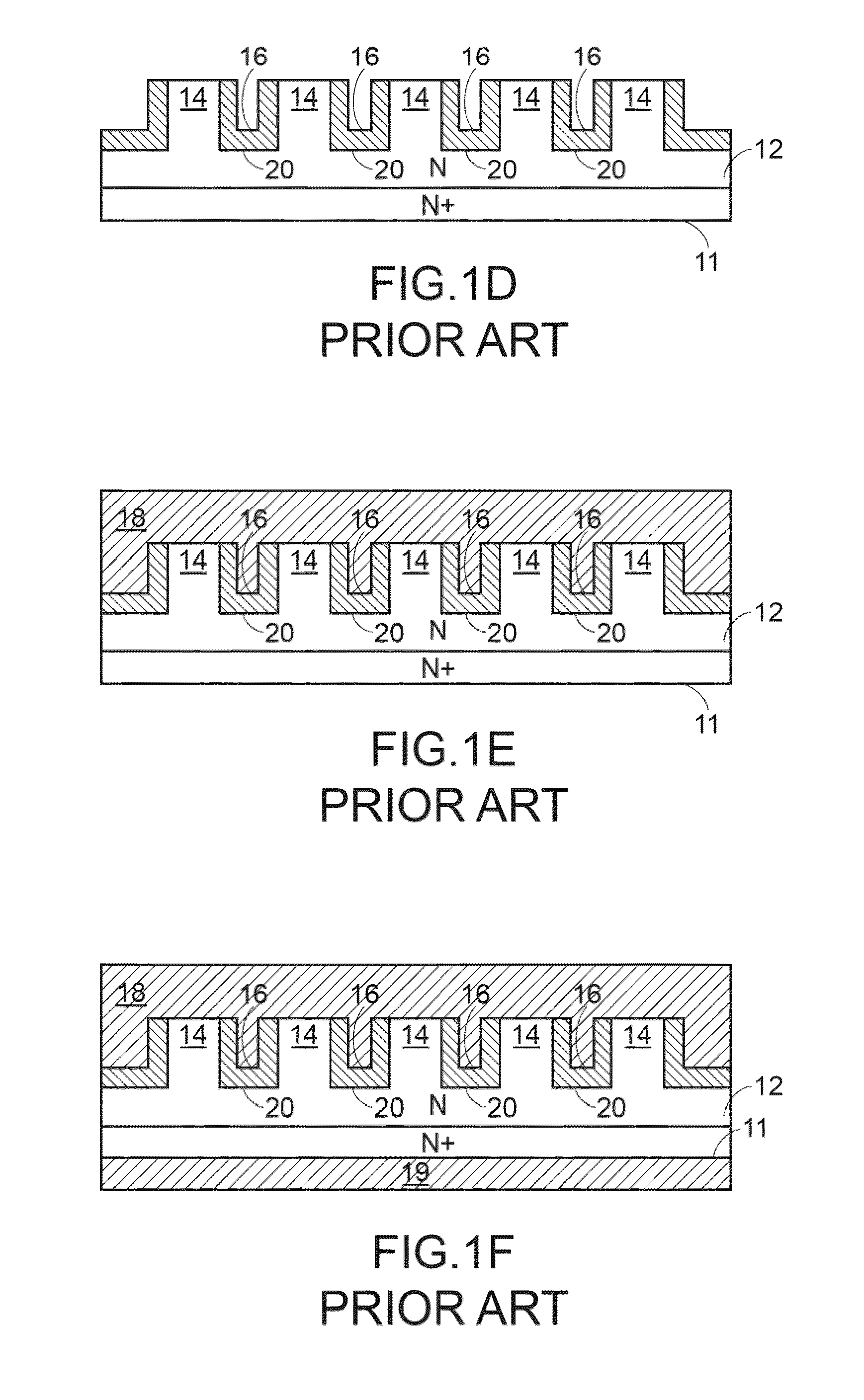

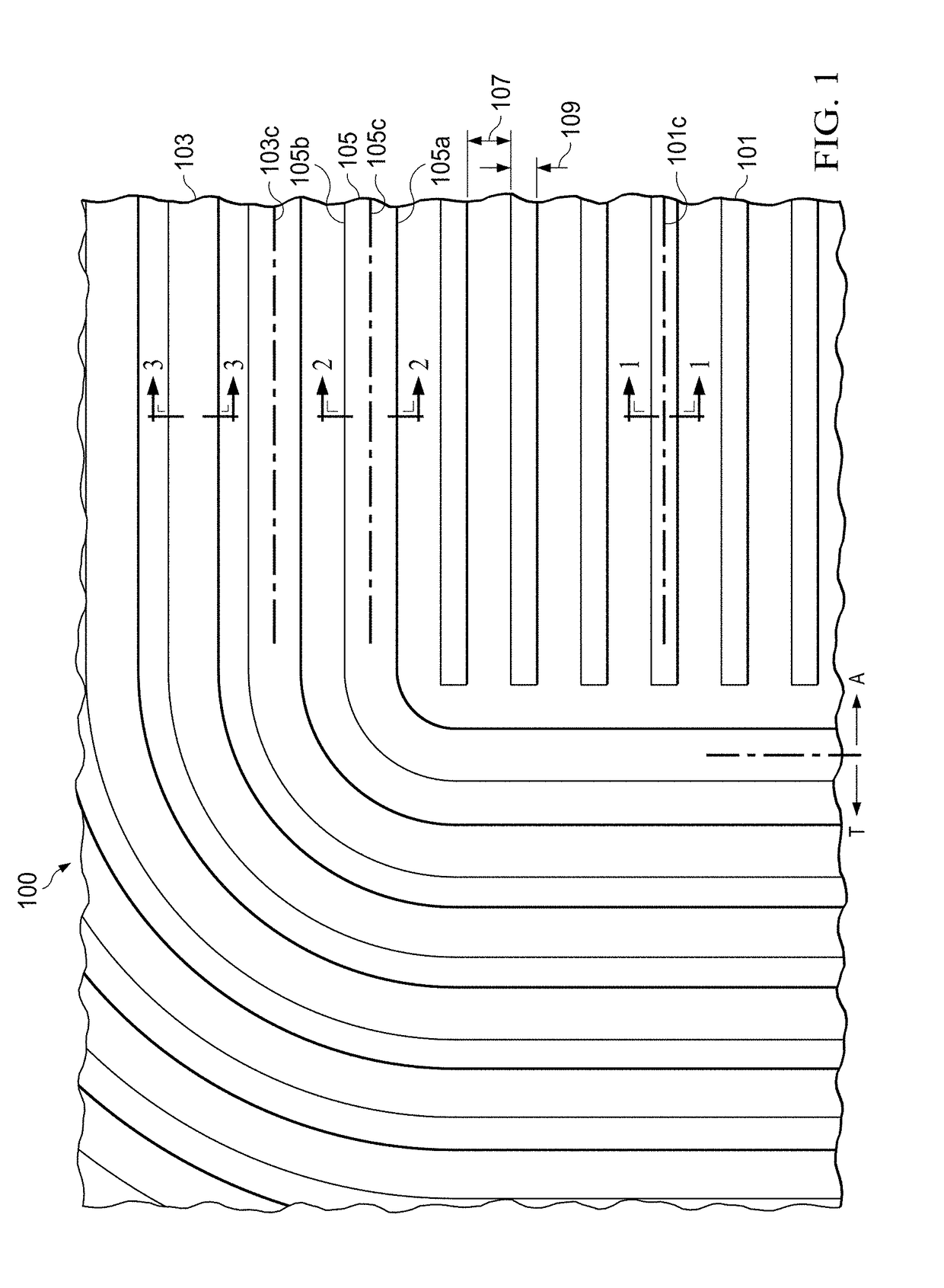

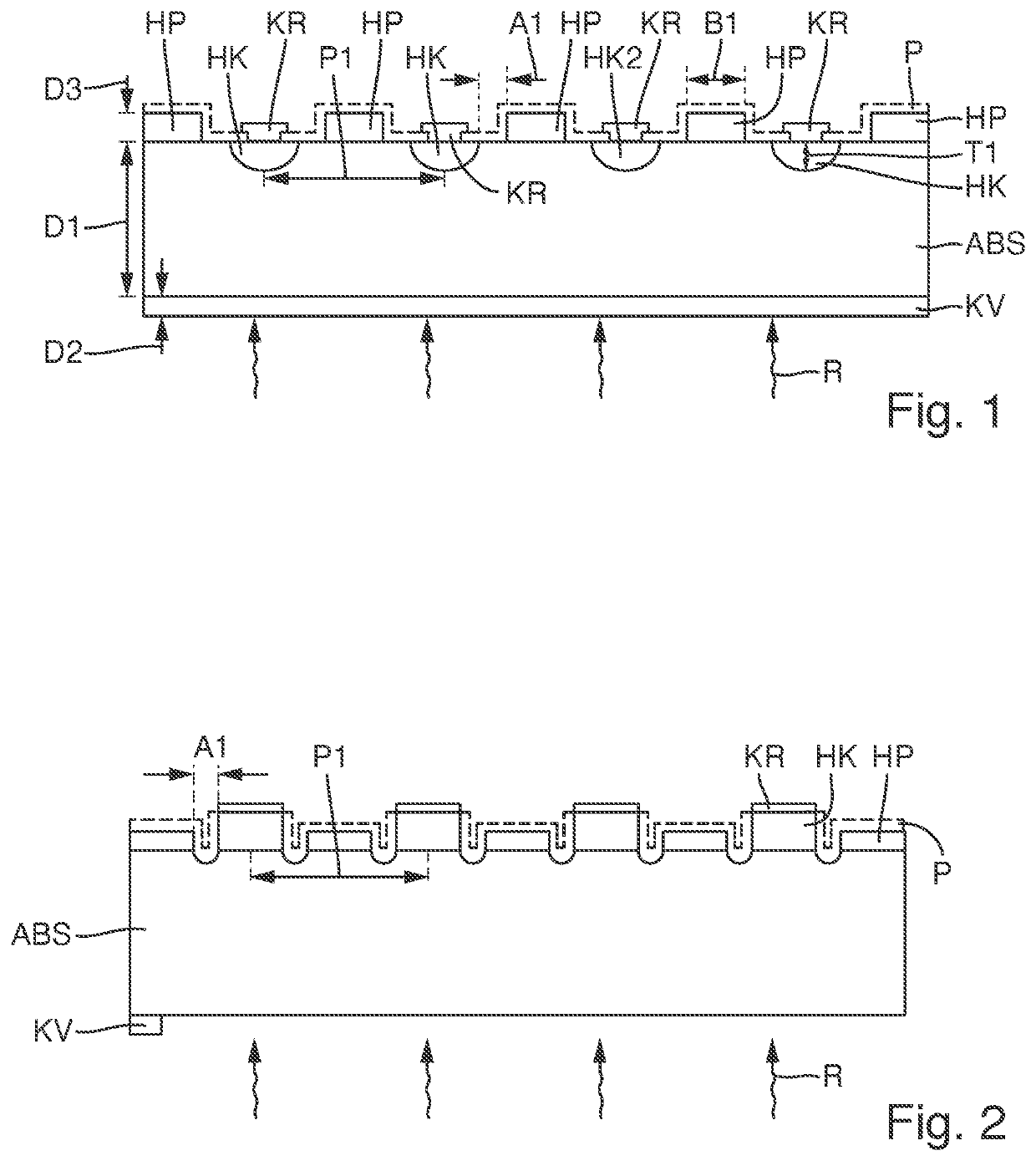

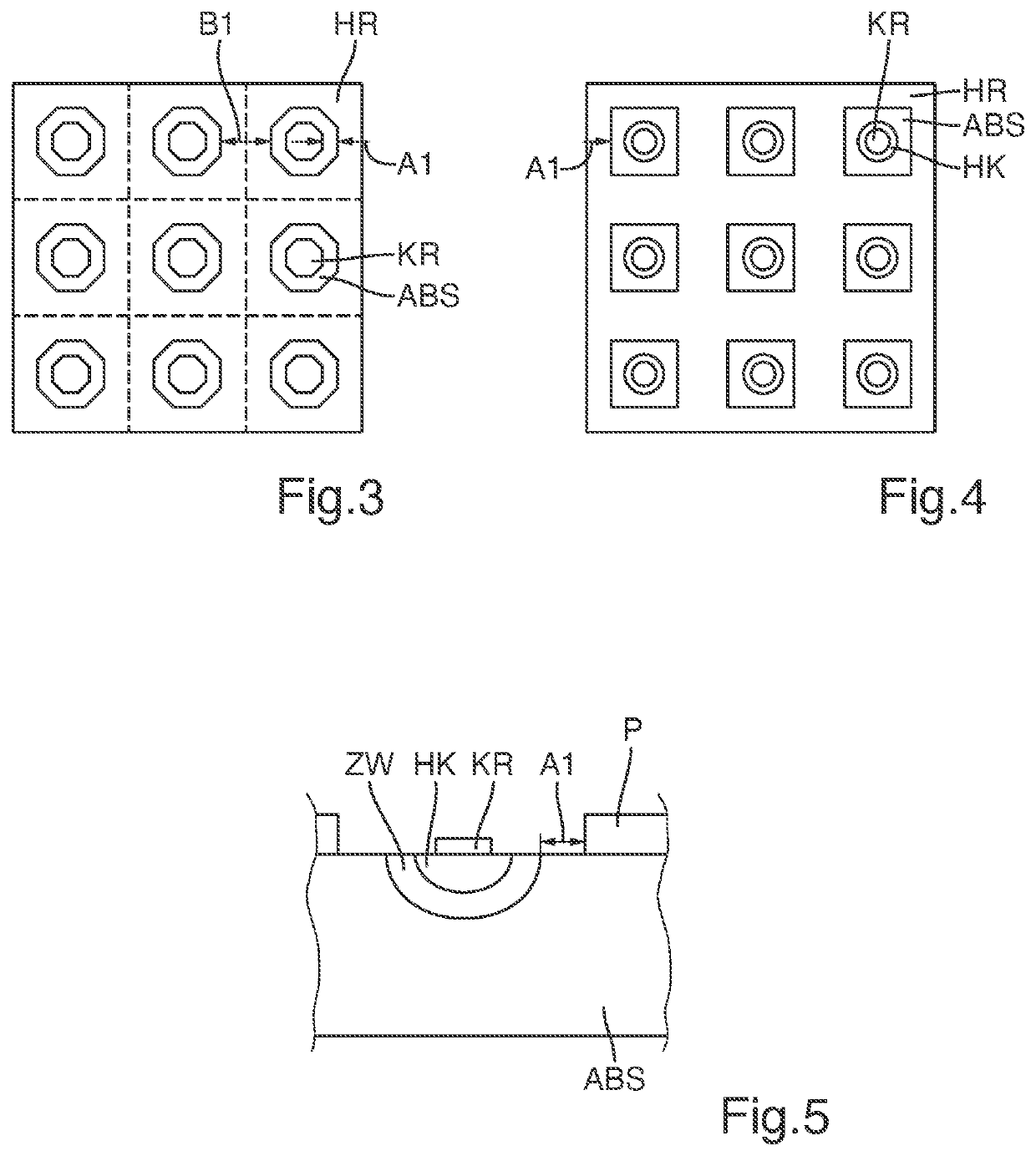

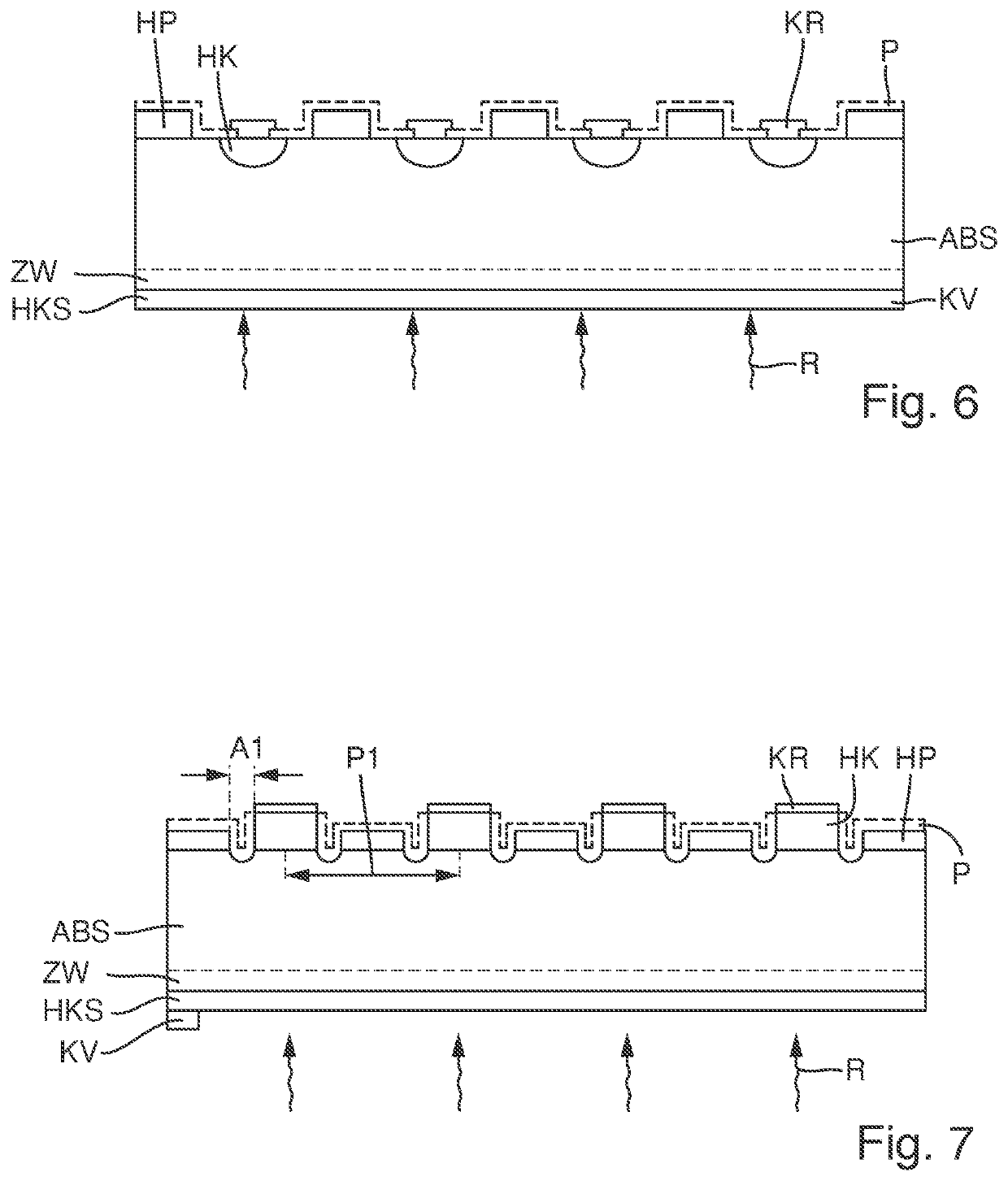

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS6784505B2Increase reverse voltageLow densityTransistorSolid-state devicesDopantChannel density

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

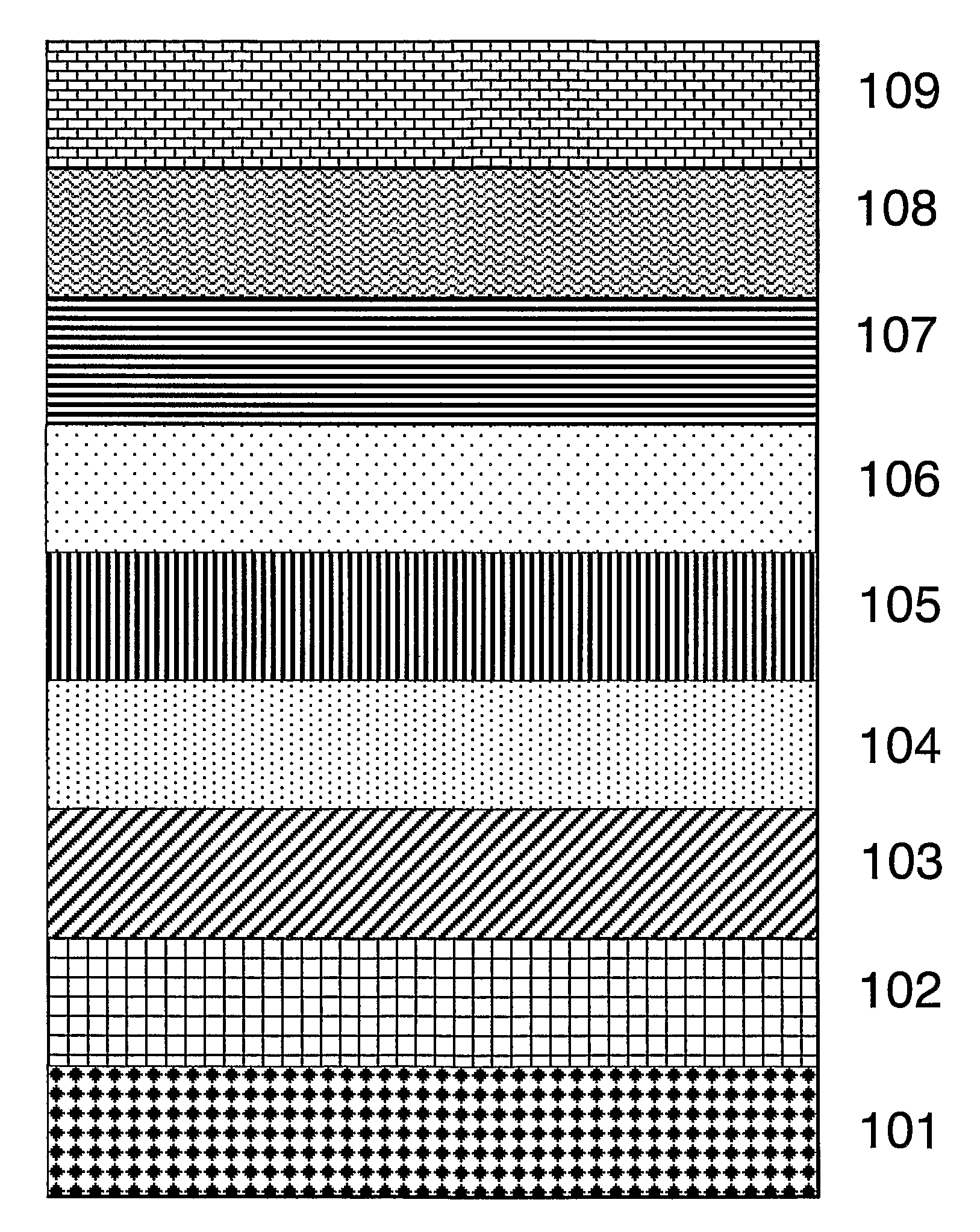

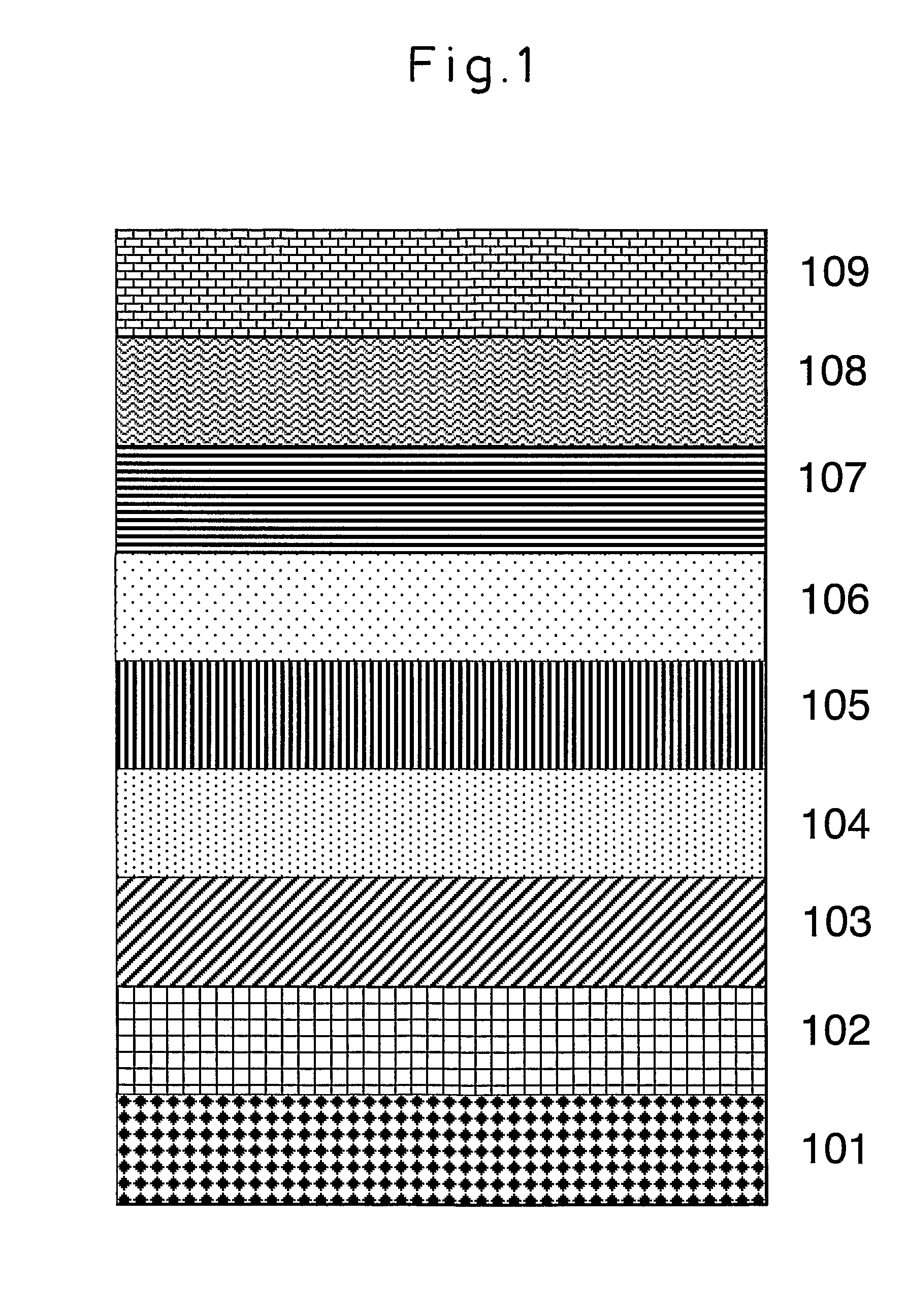

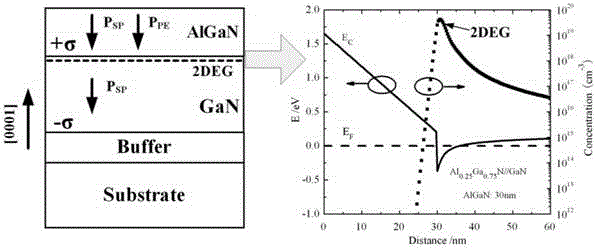

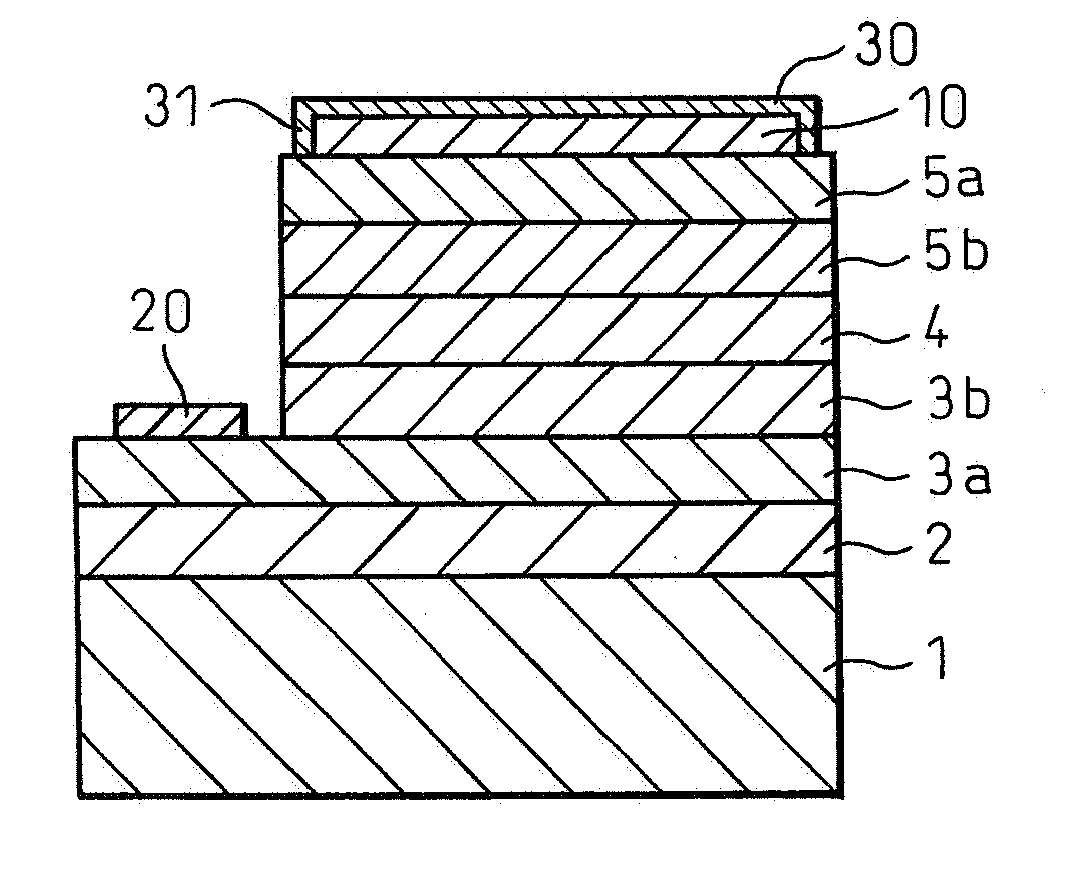

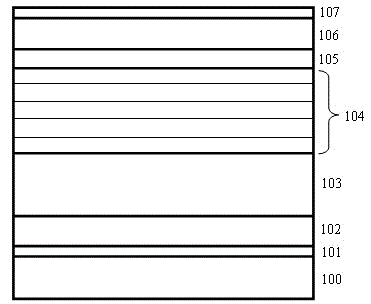

N-type group III nitride semiconductor stacked layer structure

ActiveUS7612363B2Lower resistanceImprove flatnessSolid-state devicesNanoopticsHigh concentrationOptoelectronics

An n-type Group III nitride semiconductor stacked layer structure including a first n-type layer which includes a layer containing n-type impurity atoms at a high concentration and a layer containing n-type impurity atoms at a low concentration, a second n-type layer containing n-type impurity atoms at an average concentration smaller than that of the first n-type layer, the second n-type layer neighboring the layer containing n-type impurity atoms at a low concentration in the first n-type layer.

Owner:TOYODA GOSEI CO LTD

N-Type Group III Nitride Semiconductor Layer Stacked Structure

ActiveUS20080093621A1Good flatnessLow resistanceSolid-state devicesNanoopticsHigh concentrationNitride semiconductors

An object of the present invention provides an n-type Group III nitride semiconductor stacked layer structure of a low resistance having excellent flatness generating few cracks and pits in the uppermost surface. The inventive n-type Group III nitride semiconductor stacked layer structure comprises a first n-type layer which includes a layer containing n-type impurity atoms at a high concentration and a layer containing n-type impurity atoms at a low concentration, a second n-type layer containing n-type impurity atoms at an average concentration smaller than that of the first n-type layer, the second n-type layer neighboring the layer containing n-type impurity atoms at a low concentration in the first n-type layer.

Owner:TOYODA GOSEI CO LTD

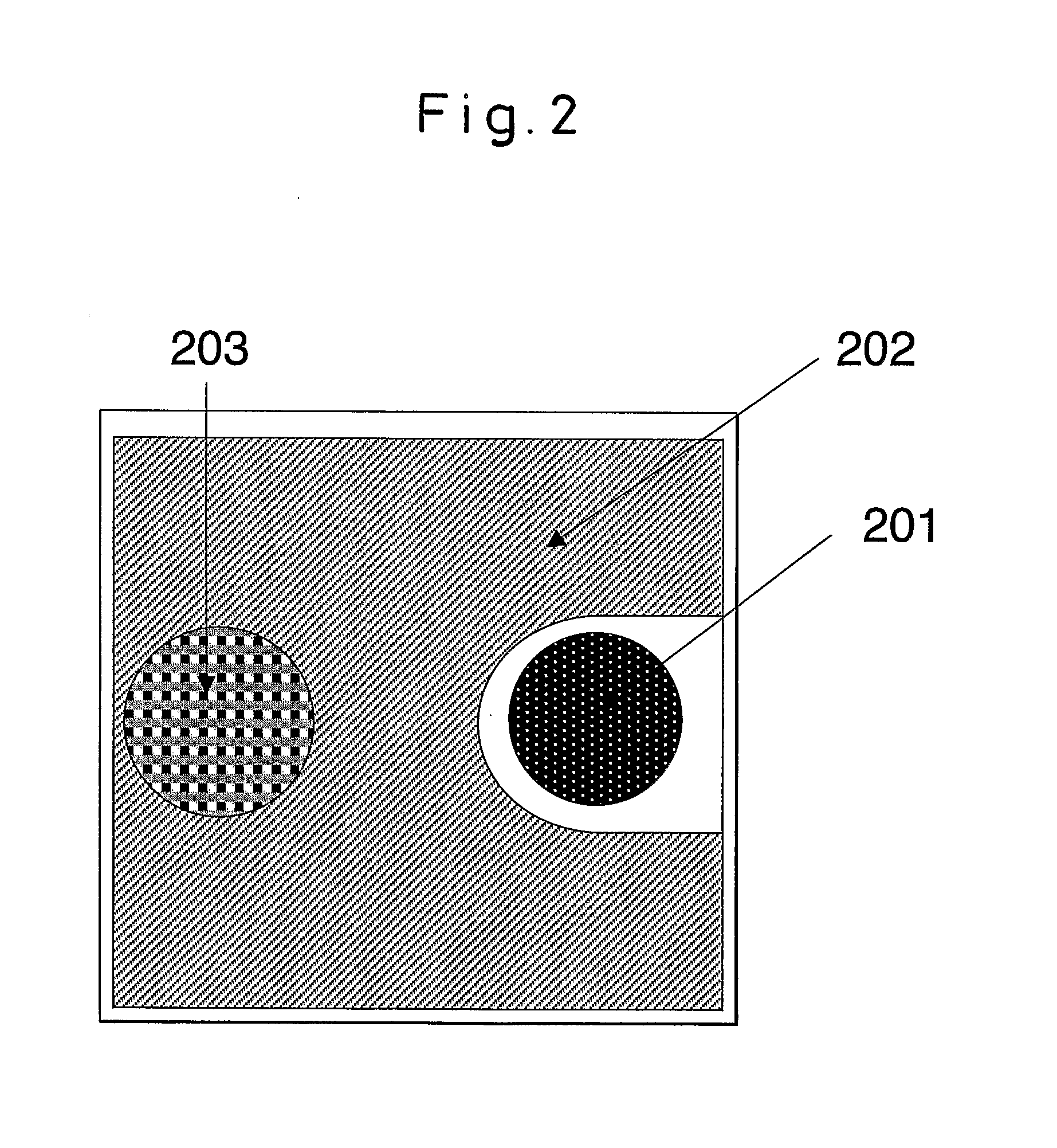

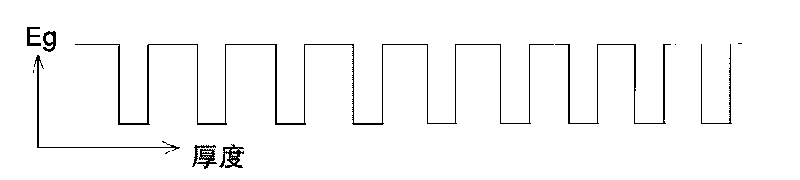

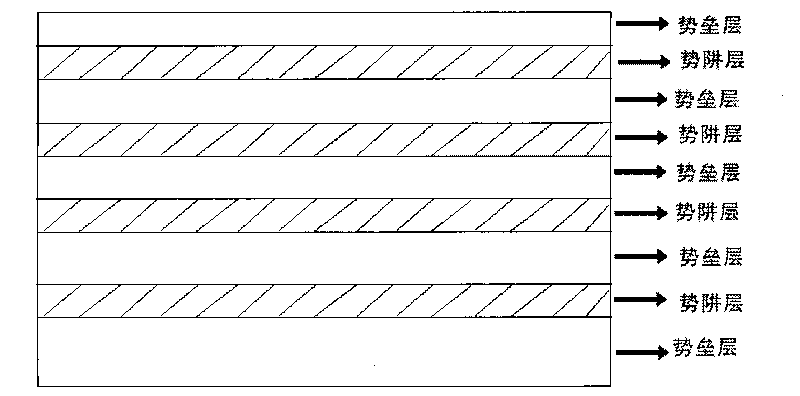

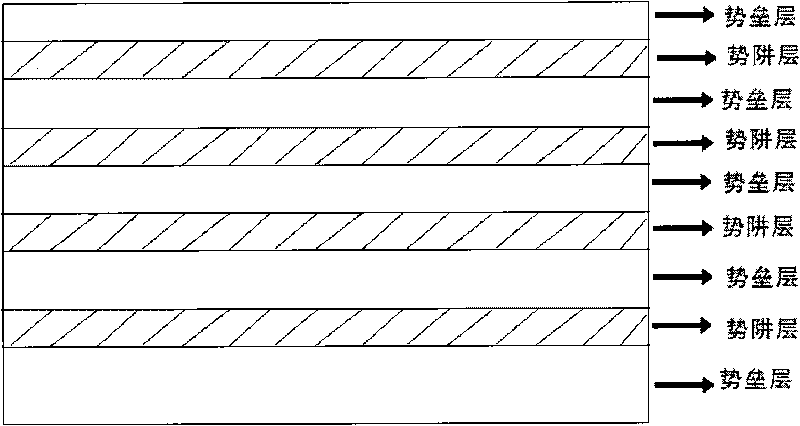

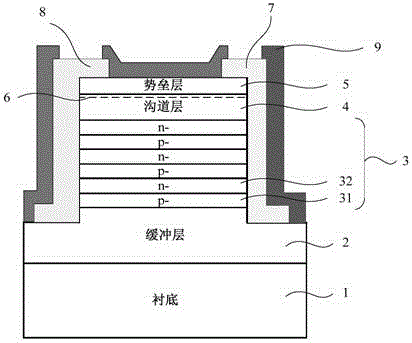

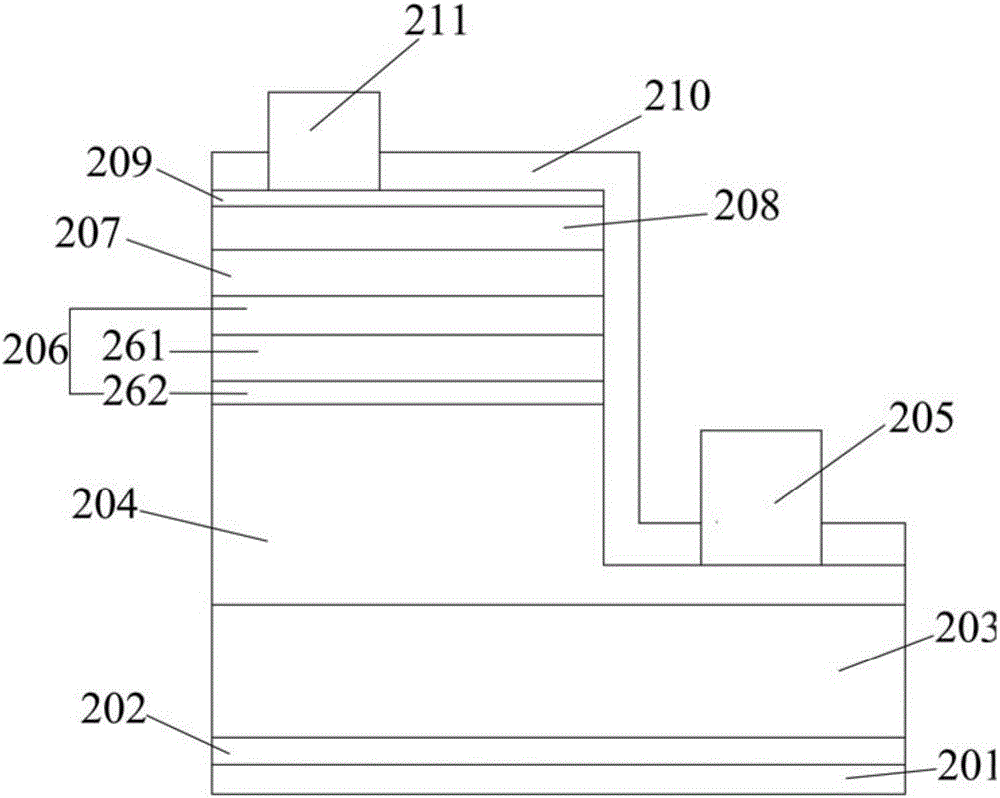

Multiple quantum well structure for photoelectric device

InactiveCN101714602AImprove luminous efficiencyIncrease the number ofSemiconductor devicesQuantum efficiencyQuantum

The invention discloses a multiple quantum well structure for a photoelectric device, which comprises n quantum well structures overlapped sequentially. The photoelectric device comprises an N-type semiconductor layer and a P-type semiconductor layer, and is characterized in that the thickness of the barrier layer close to the N-type semiconductor layer is larger than the thickness of the barrier layer close to the P-type semiconductor layer; and n is an integer which is larger than 2 and less than 20. The invention can improve the internal quantum efficiency, and because the barrier layer close to the N layer is wider, the invention can compel holes to move near to the N layer, thereby increasing the number of luminous quantum wells and improving the luminous efficiency of the quantum wells and the brightness. The invention can increase the backward voltage and improve the antistatic property, and because the barrier layer close to the N layer is thicker than the barrier layer close to the P layer, a PN junction is widened when the backward voltage is applied.

Owner:EPILIGHT TECH +1

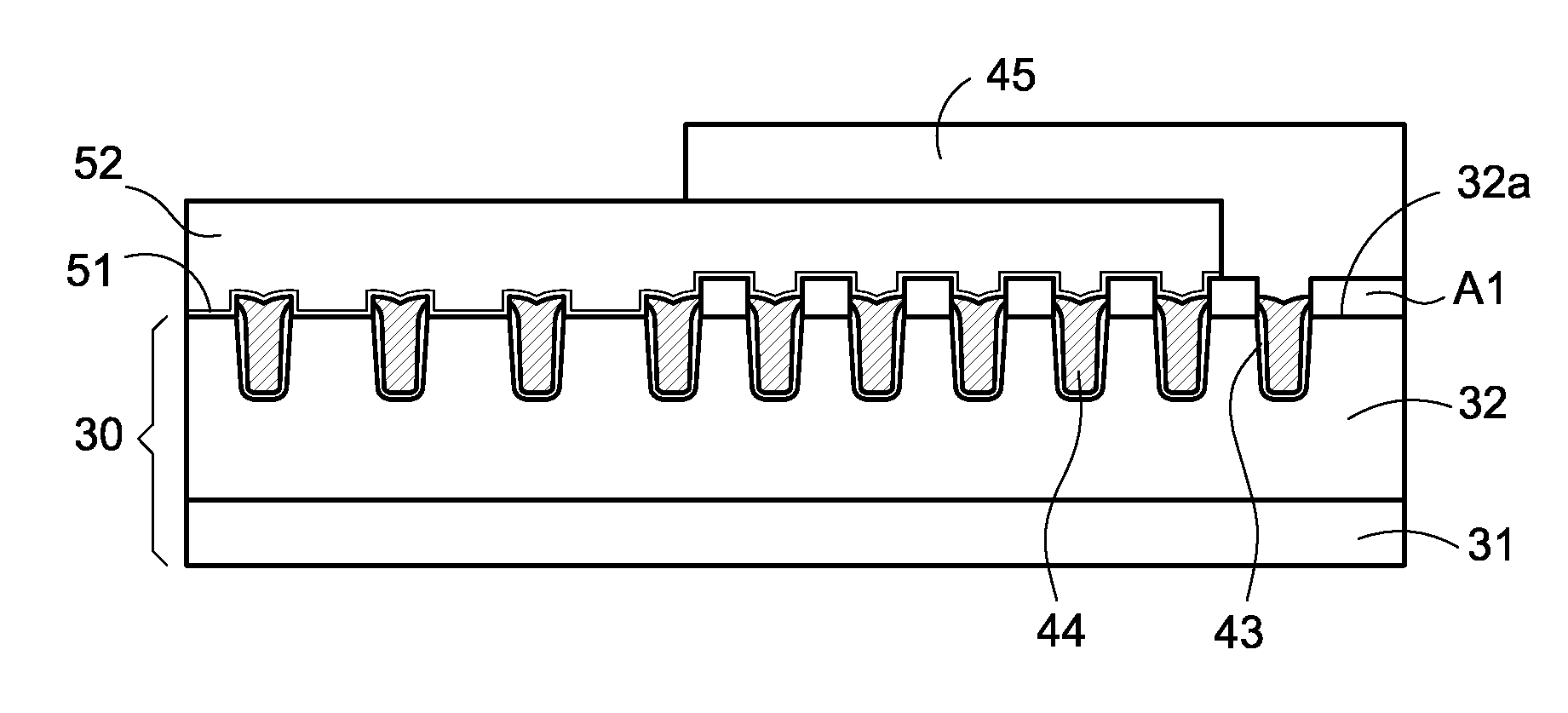

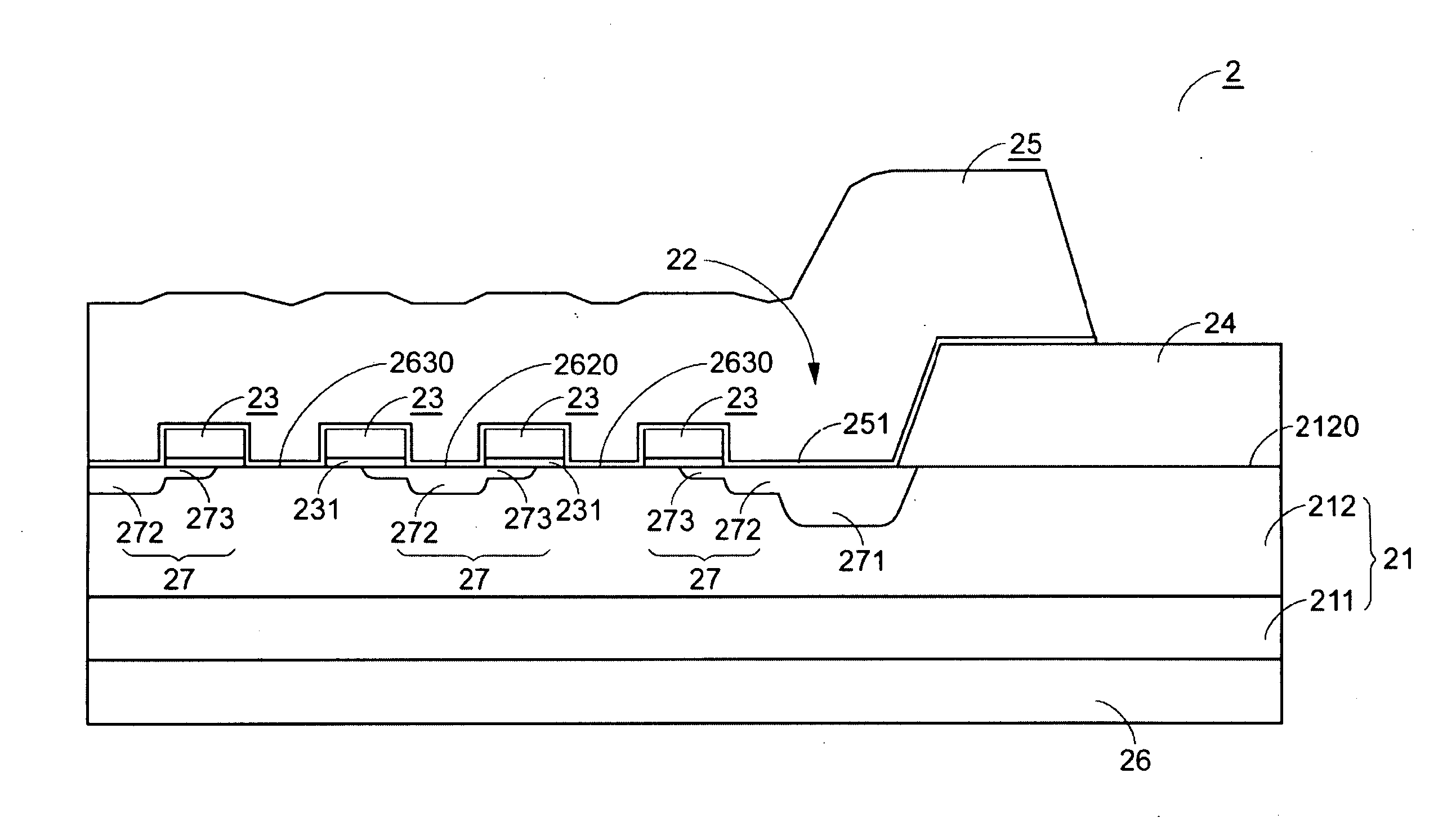

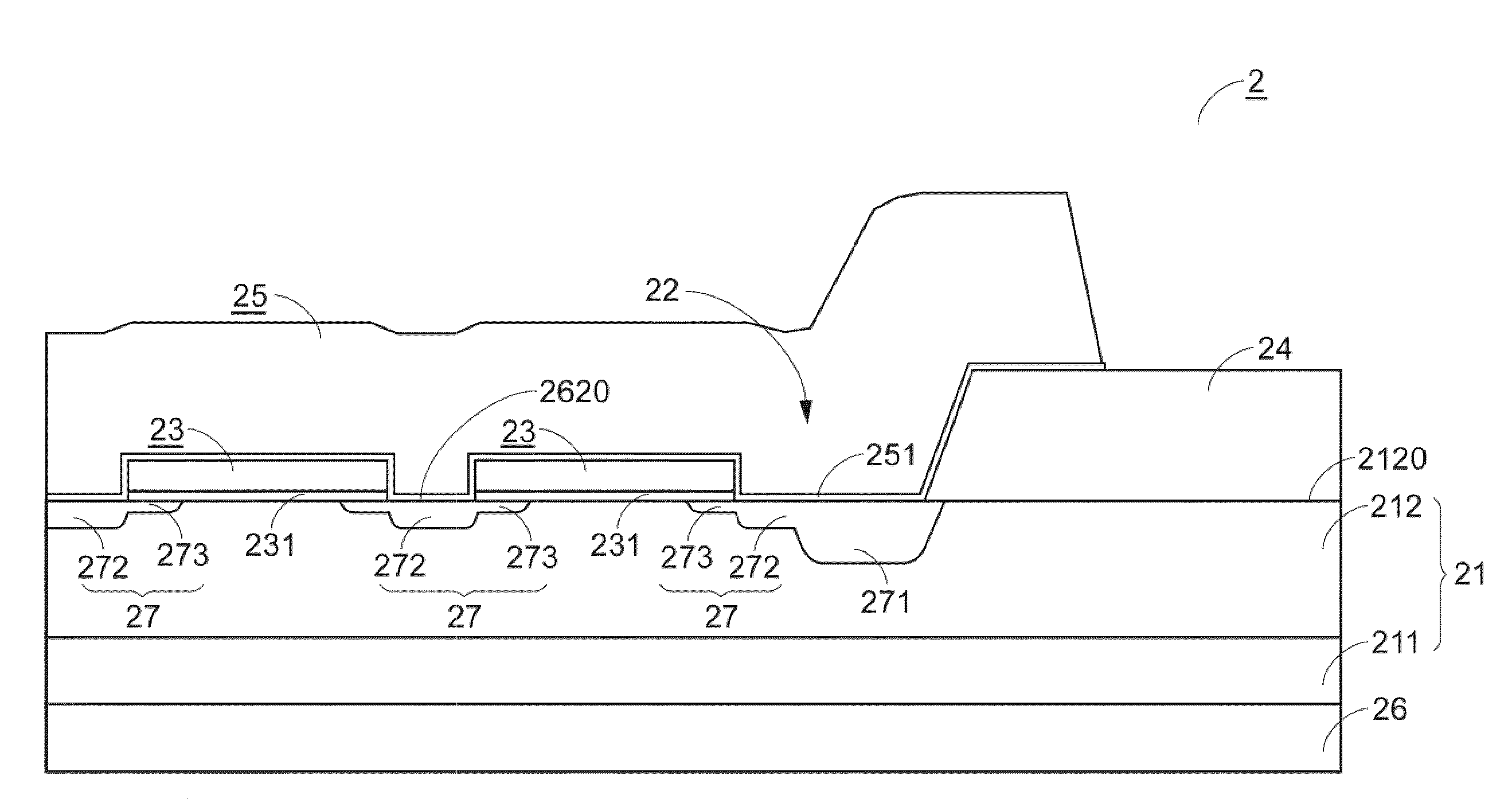

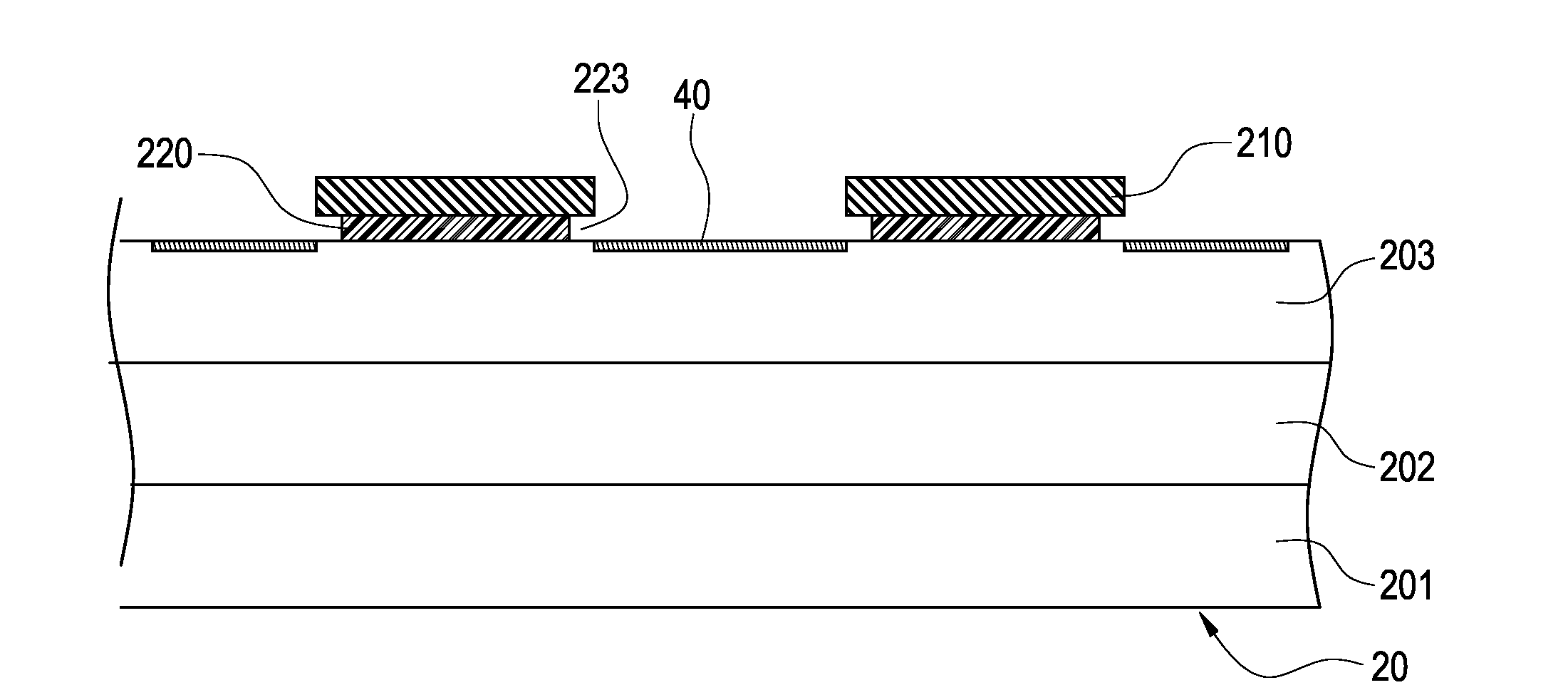

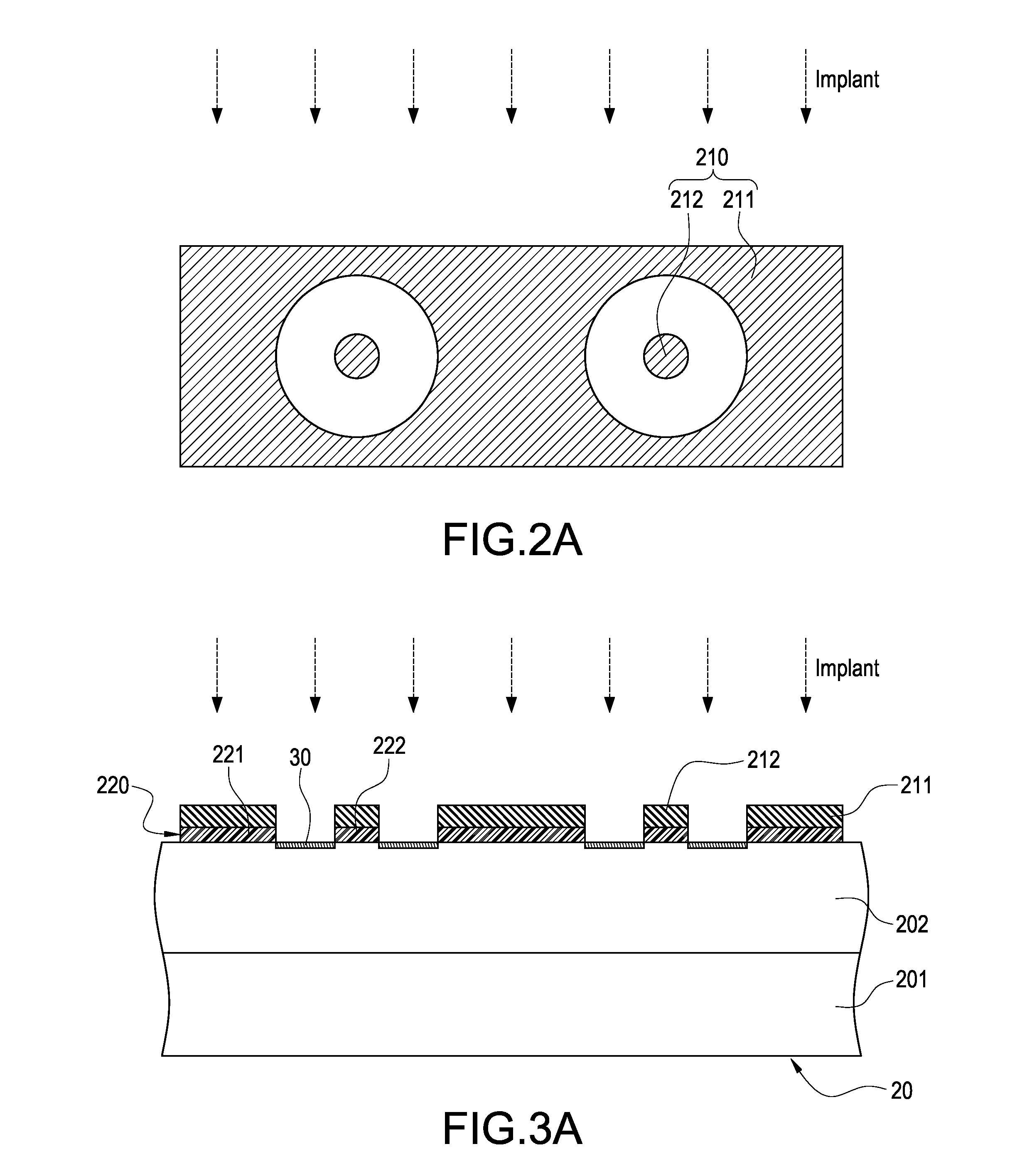

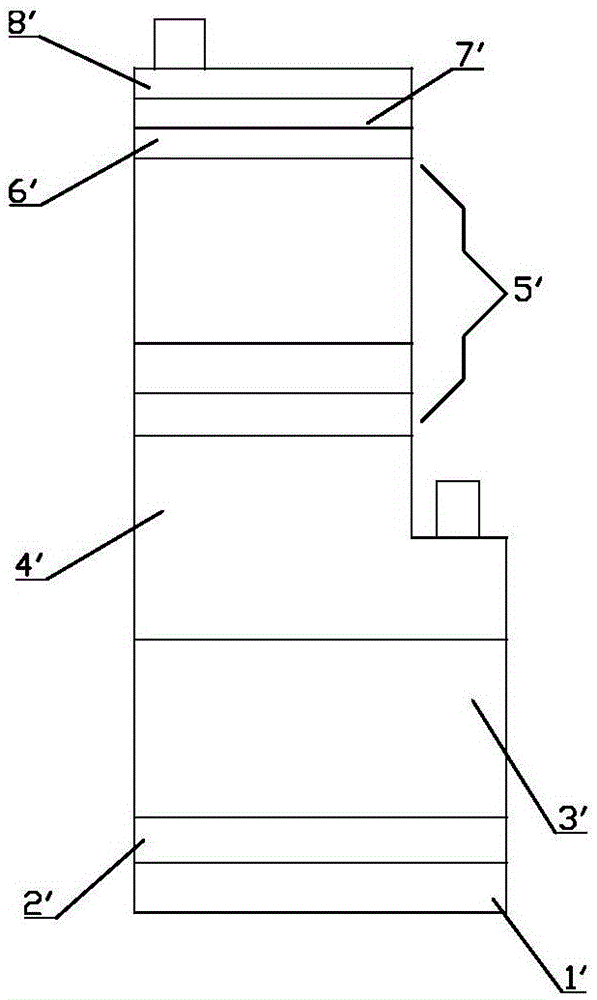

Multi-trench termination structure for semiconductor device and manufacturing mehtod thereof

ActiveUS20130228891A1Enhance toleranceHigh reverse voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor device modelingActive structure

A multi-trench termination structure for semiconductor device is disclosed, where the semiconductor device includes a semiconductor substrate and an active structure region. The multi-trench termination structure includes multiple trenches defined on an exposed face of the semiconductor substrate, a first mask layer formed on a partial exposed surface of the semiconductor substrate and corresponding to a termination structure region of the semiconductor device, a gate insulation layer formed in the trenches, a conductive layer formed on the gate insulation layer and protruding out of the exposed surface of the semiconductor substrate, and a metal layer formed over the first mask layer and conductive layer on the termination structure region of the semiconductor device.

Owner:PFC DEVICE HLDG

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS20030205758A1Increase reverse voltageLow densityTransistorSolid-state devicesChannel densityLow voltage

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

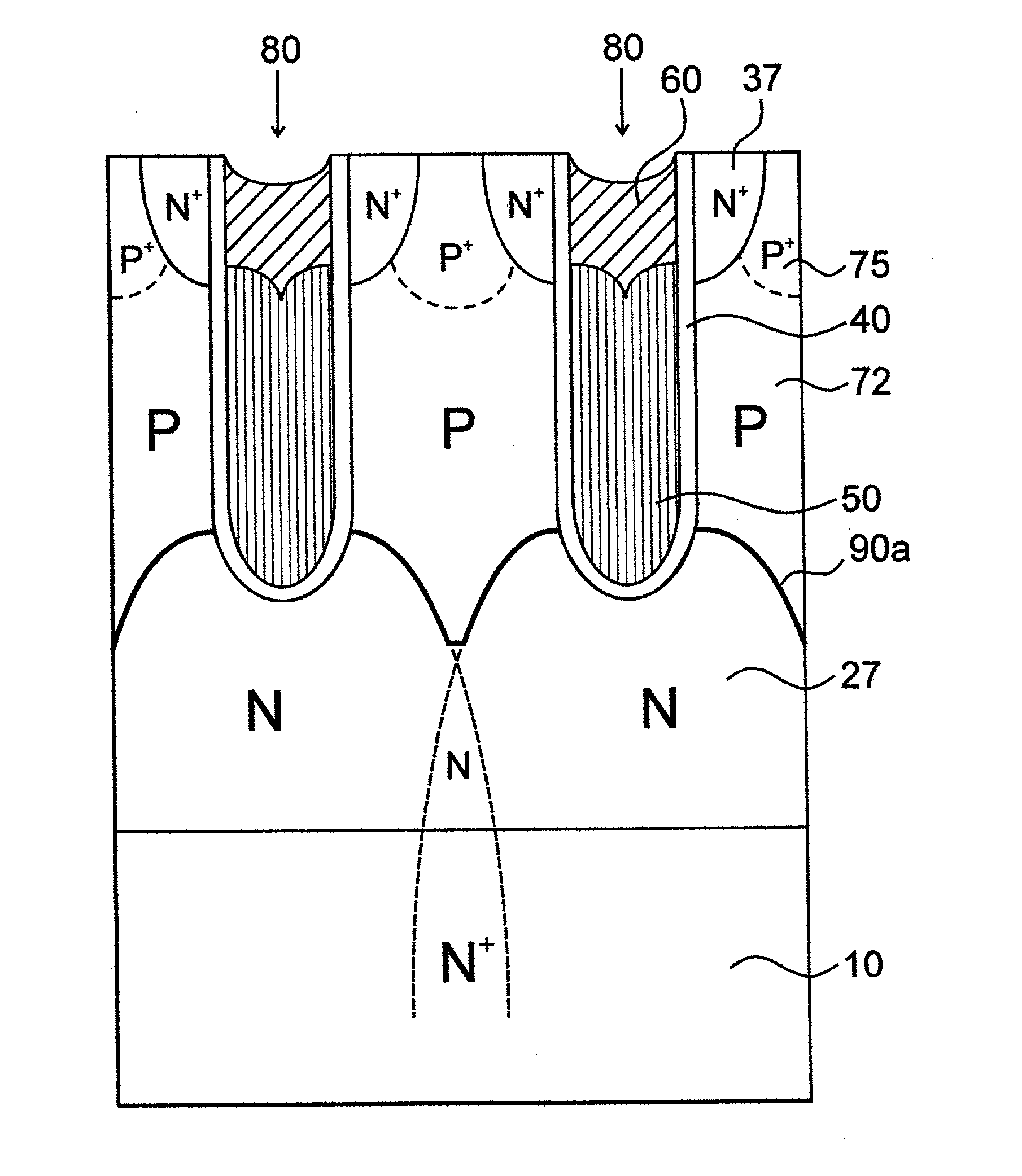

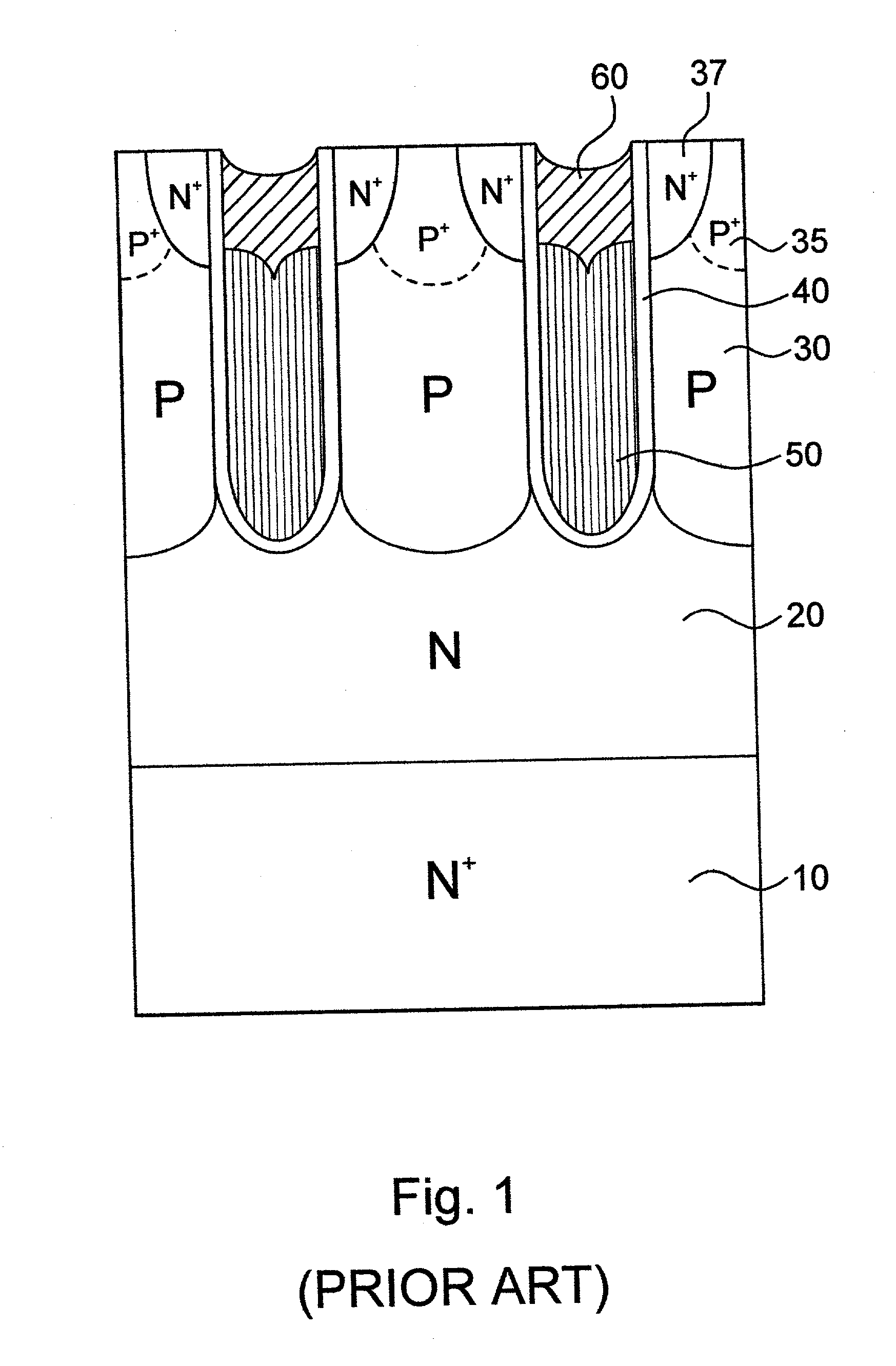

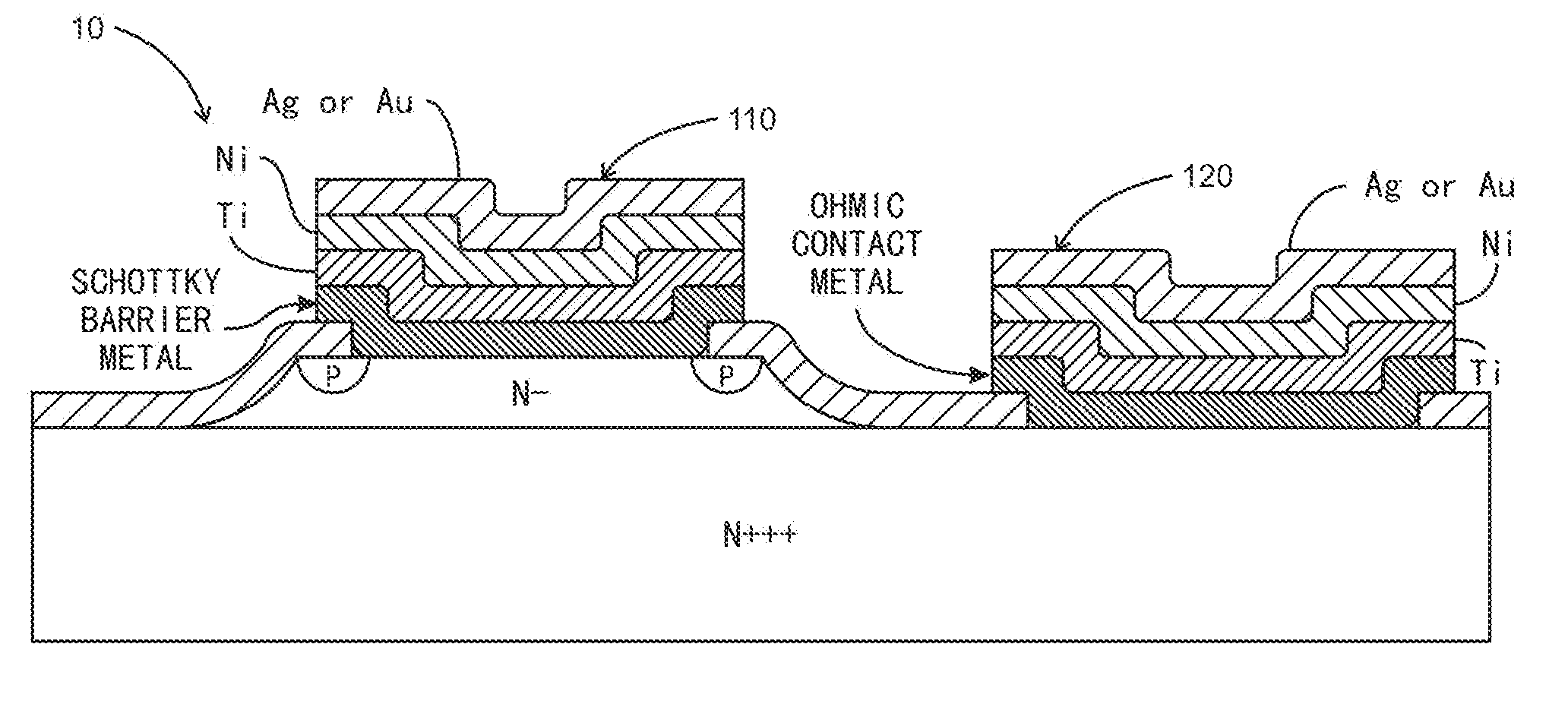

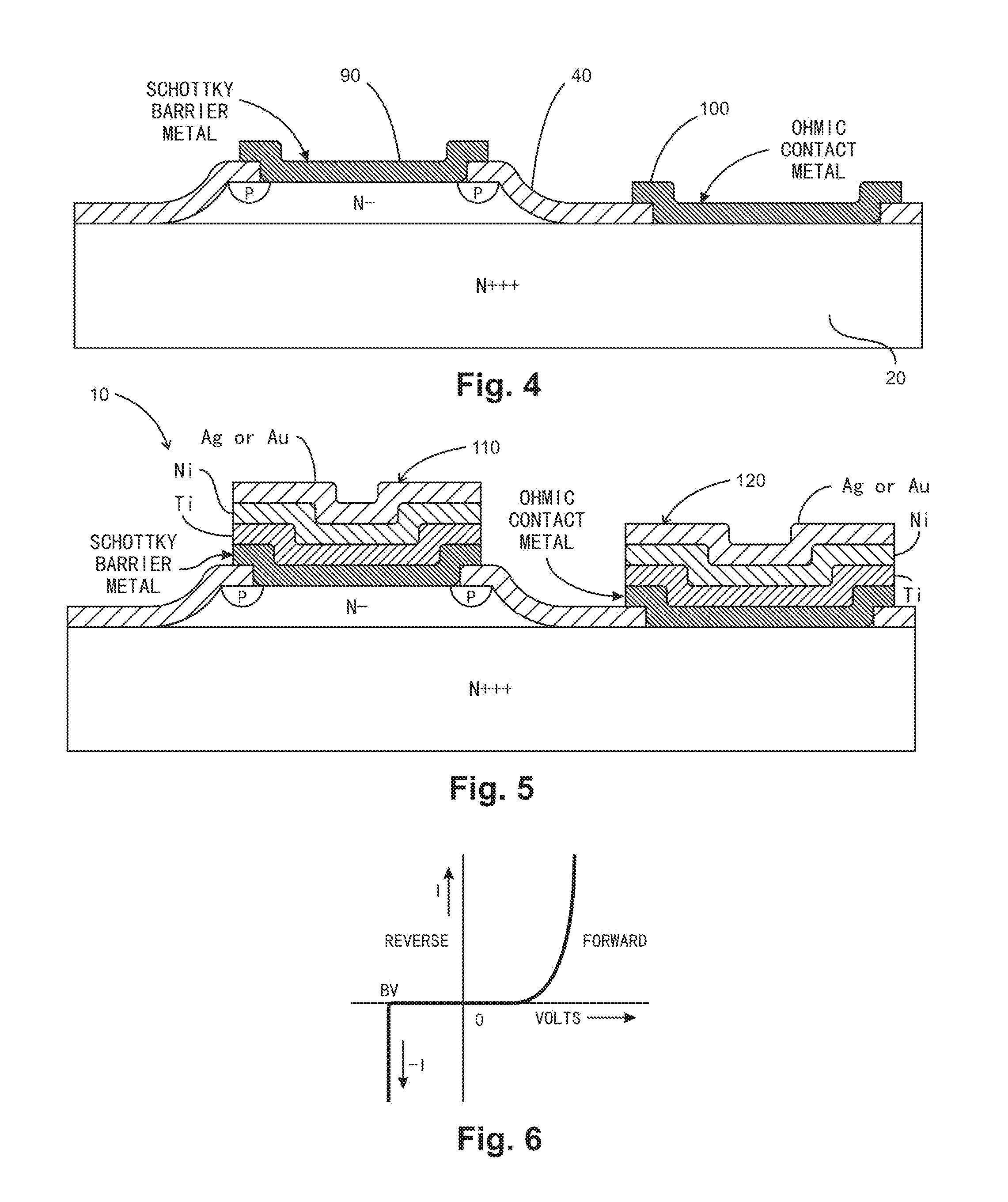

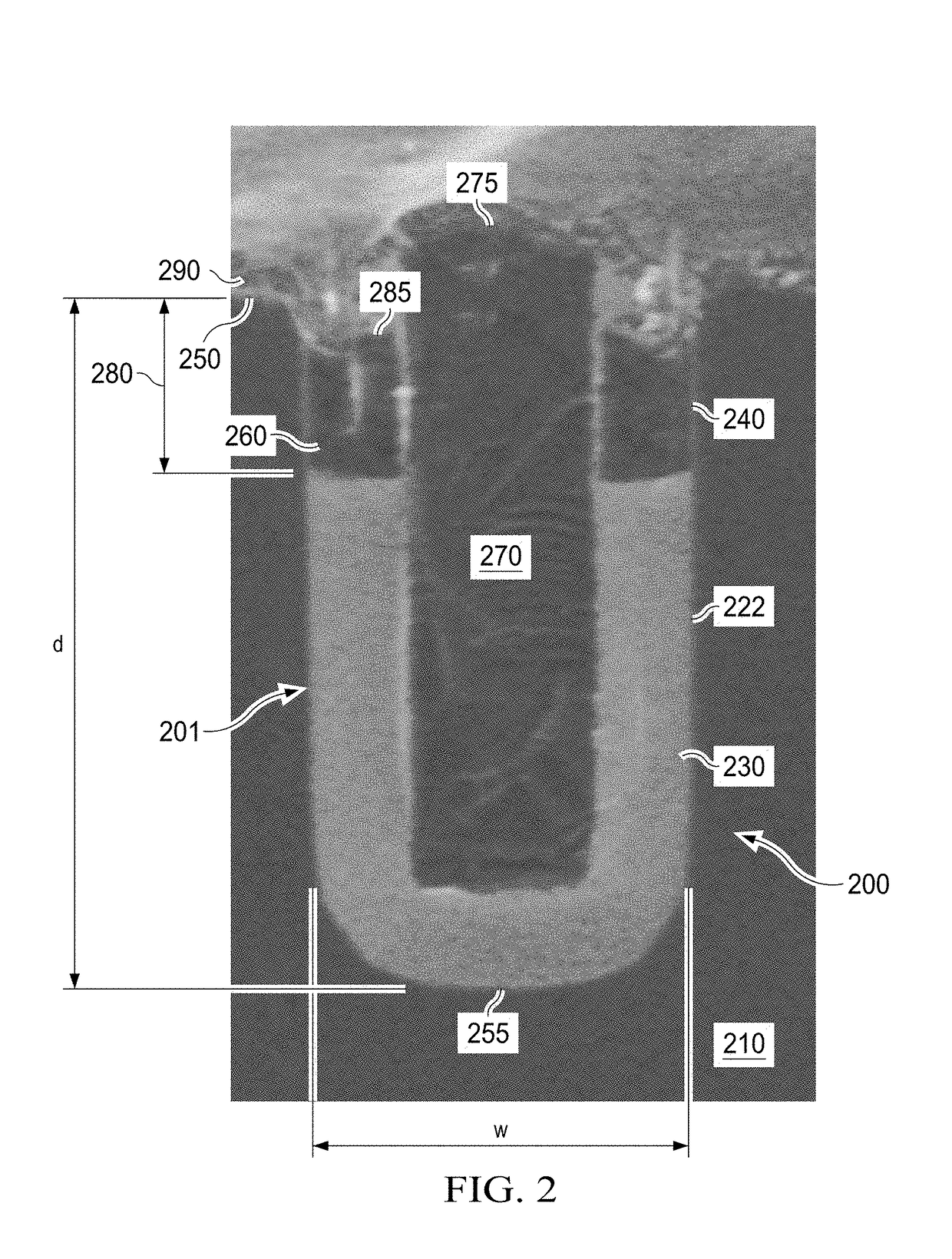

Mos p-n junction schottky diode device and method for manufacturing the same

ActiveUS20090261428A1Improve performanceReduce leakage currentSemiconductor/solid-state device manufacturingDiodeOhmic contactReverse recovery

A MOS P-N junction Schottky diode device includes a substrate having a first conductivity type, a field oxide structure defining a trench structure, a gate structure formed in the trench structure and a doped region having a second conductivity type adjacent to the gate structure in the substrate. An ohmic contact and a Schottky contact are formed at different sides of the gate structure. The method for manufacturing such diode device includes several ion-implanting steps to form several doped sub-regions with different implantation depths to constitute the doped regions. The formed MOS P-N junction Schottky diode device has low forward voltage drop, low reverse leakage current, fast reverse recovery time and high reverse voltage tolerance.

Owner:PFC DEVICE HLDG

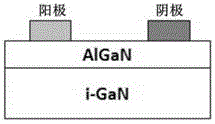

Schottky diode and manufacturing method thereof

ActiveCN104617160AIncrease concentrationImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowOhmic contact

The invention discloses a Schottky diode and a manufacturing method thereof. The Schottky diode comprises a substrate, a buffer layer, an extension structure, a Schottky contact metal and an Ohmic contact metal, wherein the substrate the buffer layer and the extension structure are sequentially arranged in an overlapped structure; the extension structure comprises a super bonding layer, a GaN channel layer and a barrier layer which are sequentially stacked, and the super bonding layer is composed of a plurality of p-type GaN layer and a plurality of n-type GaN layer which are alternately stacked each other; the Schottky contact metal and the Ohmic contact metal are symmetrically arranged on the opposite two side surfaces of the extension structure, one ends of the Schottky contact metal and the Ohmic contact metal extend to the upper surface of the extension structure, and the other ends of the Schottky contact metal and the Ohmic contact metal extend to the buffer layer. The Schottky diode has relatively high pressure resistance, ensures current transmission capacity and stability and avoids a traditional field plate structure or protecting ring structure, thereby simplifying the manufacturing process and reducing the cost.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

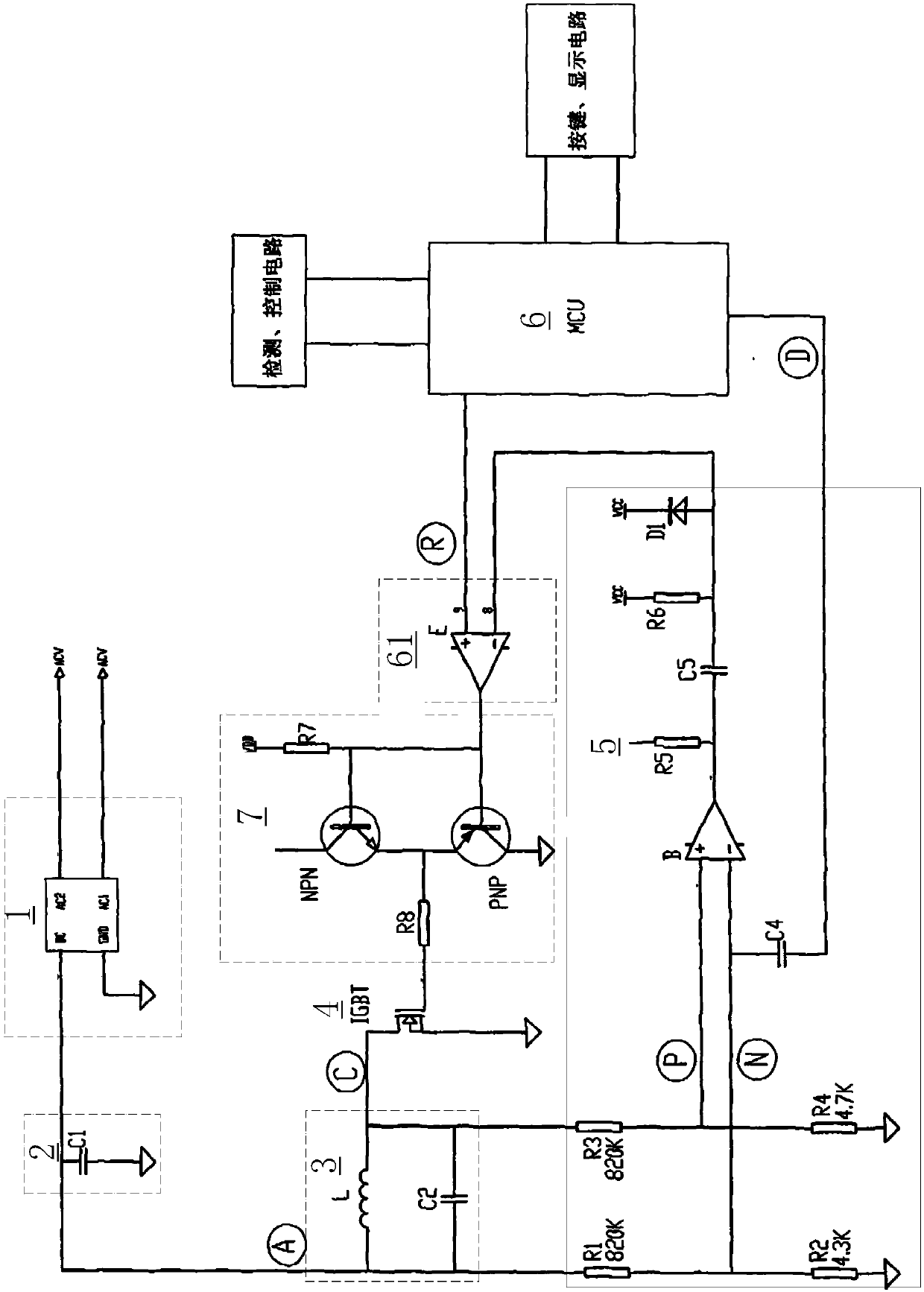

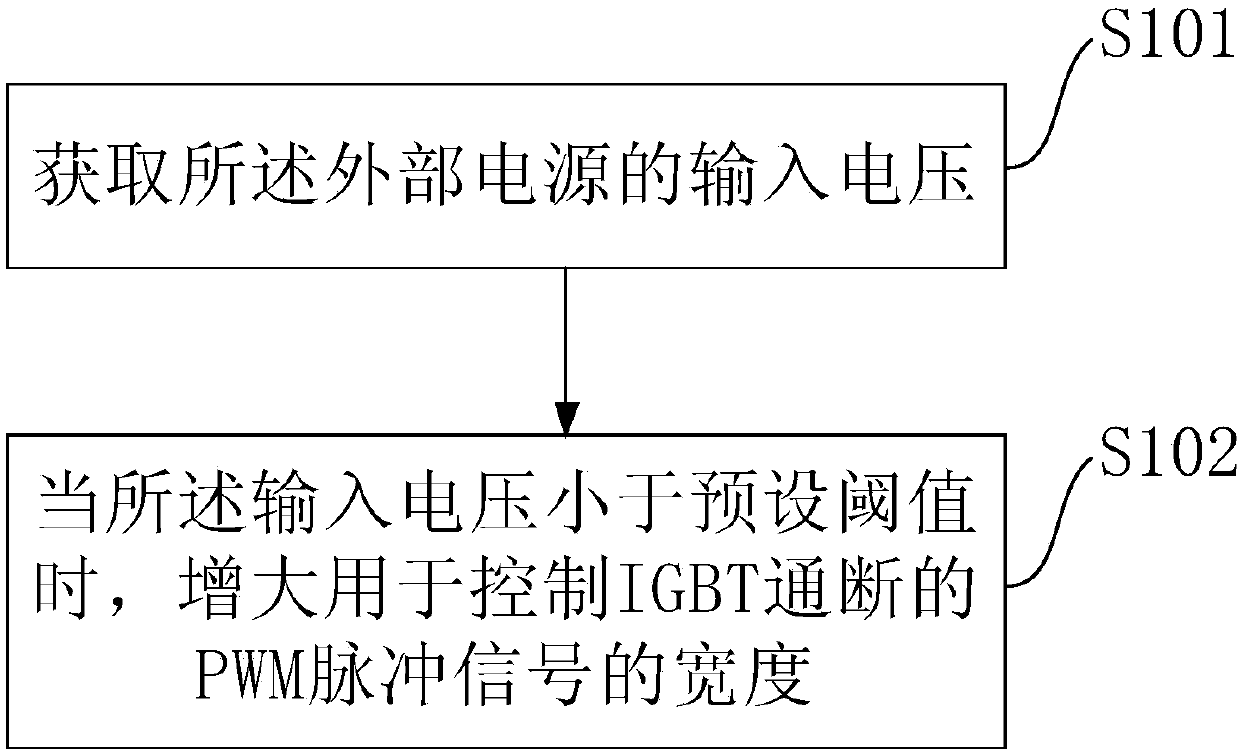

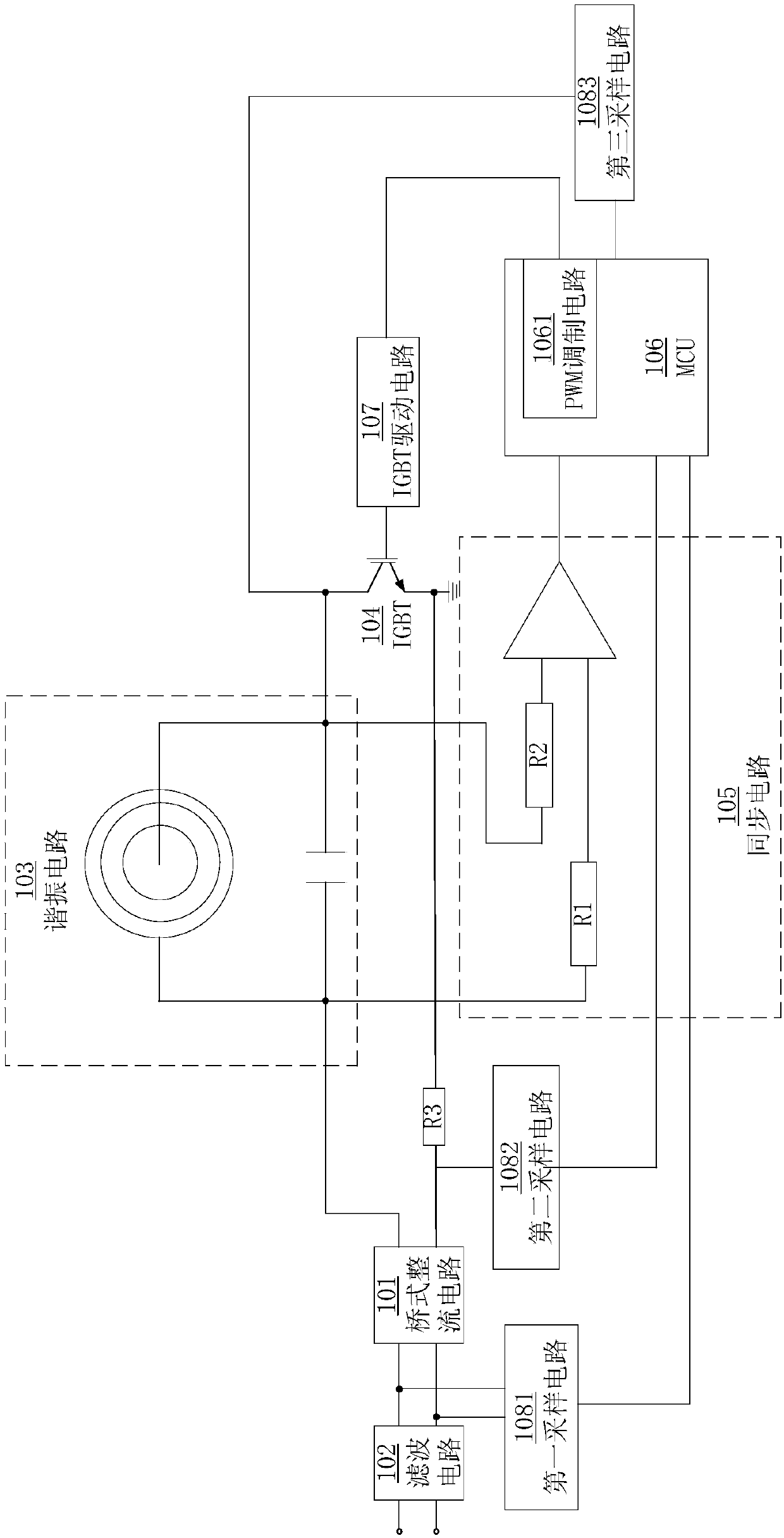

Electromagnetic heating cooker and control method and control apparatus therefor

ActiveCN107708243AAvoid vibration stopControl on timeInduction heating controlInduction heating apparatusResonanceCoupling

The invention provides an electromagnetic heating cooker and a control method and a control apparatus therefor. The electromagnetic heating cooker comprises a resonance circuit and an IGTB; the resonance circuit, the IGBT and an external power supply form an electromagnetic oscillation circuit; the control method comprises the steps of obtaining the input voltage of the external power supply; andwhen the input voltage is less than a preset threshold value, increasing the width of a PWM pulse signal for controlling on-off of the IGBT. By virtue of the electromagnetic heating cooker and the control method and the control apparatus therefor, oscillation stop of the resonance circuit of the electromagnetic heating cooker can be prevented without needing a timing circuit or a coupling circuit,so that the electromagnetic heating cooker is simple and easy to use, and low in cost.

Owner:ZHEJIANG SHAOXING SUPOR DOMESTIC ELECTRICAL APPLIANCE CO LTD

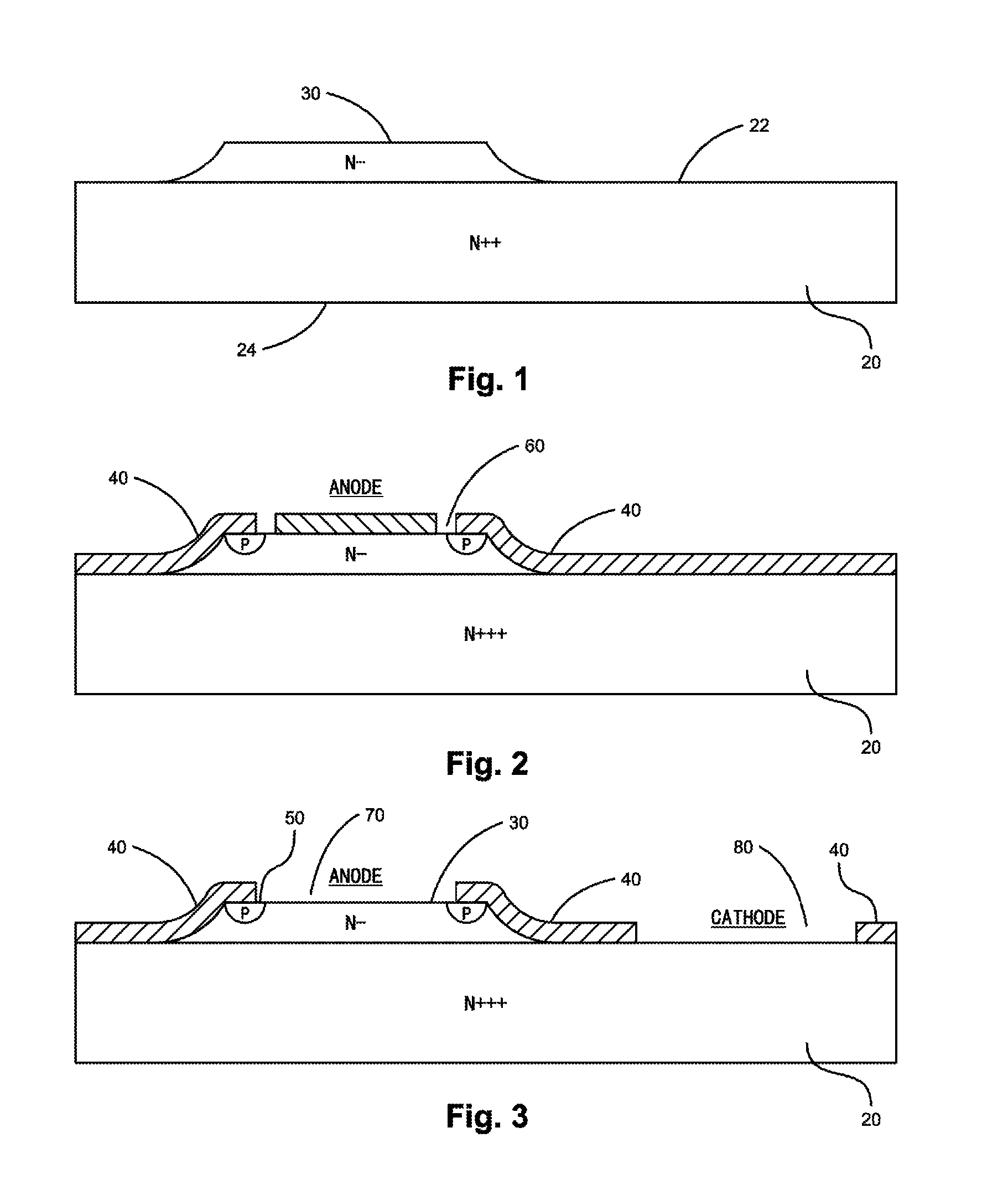

Low profile Schottky barrier diode for solar cells and solar panels and method of fabrication thereof

InactiveUS8164154B1Increase reverse voltageTighter manufacturing tolerance for the series resistance of a Schottky barrier diodeSemiconductor/solid-state device detailsSolid-state devicesDopantSchottky barrier

A low profile high power Schottky barrier bypass diode for solar cells and panels with the cathode and anode electrodes on the same side of the diode and a method of fabrication thereof are disclosed for generating a thin chip with both electrodes being on the same side of the chip. In an embodiment, a mesa isolation with a Zener diode over the annular region surrounding the central region of the mesa anode in the Epi of the substrate is formed. In an embodiment, a P-type Boron dopant layer is ion implanted in the annular region for the Zener Diode. This controls recovery from high voltage spikes from the diode rated voltage. A Schottky barrier contact for the anode and a contact for the cathode are simultaneously created on the same side of the chip.

Owner:TANIELIAN ARAM +1

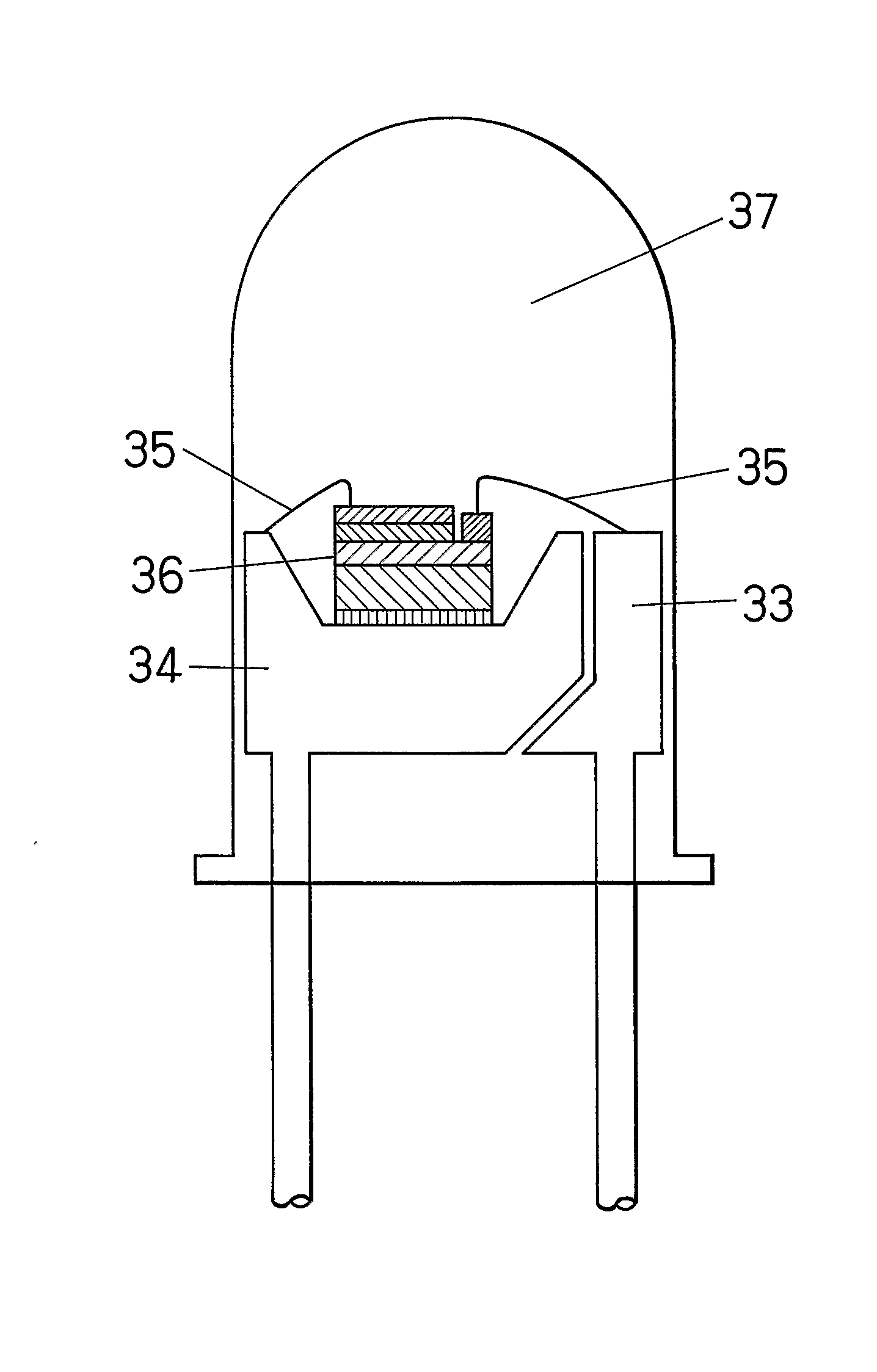

Reflective Positive Electrode And Gallium Nitride-Based Compound Semiconductor Light-Emitting Device Using The Same

InactiveUS20090263922A1Increase reverse voltageImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesAlloyGallium nitride

A gallium nitride-based compound semiconductor light-emitting device which has a highly reflective positive electrode that has high reverse voltage and excellent reliability with low contact resistance to the p-type gallium nitride-based compound semiconductor layer. The reflective positive electrode for a semiconductor light-emitting device comprises a contact metal layer adjoining a p-type semiconductor layer, and a reflective layer on the contact metal layer, wherein the contact metal layer is formed of a platinum group metal or an alloy containing a platinum group metal, and the reflective layer is formed of at least one metal selected from the group consisting of Ag, Al, and alloys containing at least one of Ag and Al. Also disclosed is a production method of the reflective positive electrode.

Owner:RESONAC HOLDINGS CORPORATION

Method for substrate epitaxial growth of luminous diode based on AlN template

ActiveCN106328780AEpitaxy SimplifiedIncrease productivitySemiconductor devicesDiodeLight-emitting diode

The invention discloses a method for substrate epitaxial growth of luminous diode based on AlN template, including processing substrate, growing AlxGa(1-x)N layer, AlyGa(1-y)N layer, SivAlzGa(1-z-v)N layer, N type GaN layer mixed with Si, Inx1Ga(1-x1)N / GaN luminous layer (wherein, x1=0.20-0.25), P type AlGaN layer and P type GaN layer mixed with Mg and cooling. The method enables the simplification of epitaxial growth and improves the production efficiency of LED.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

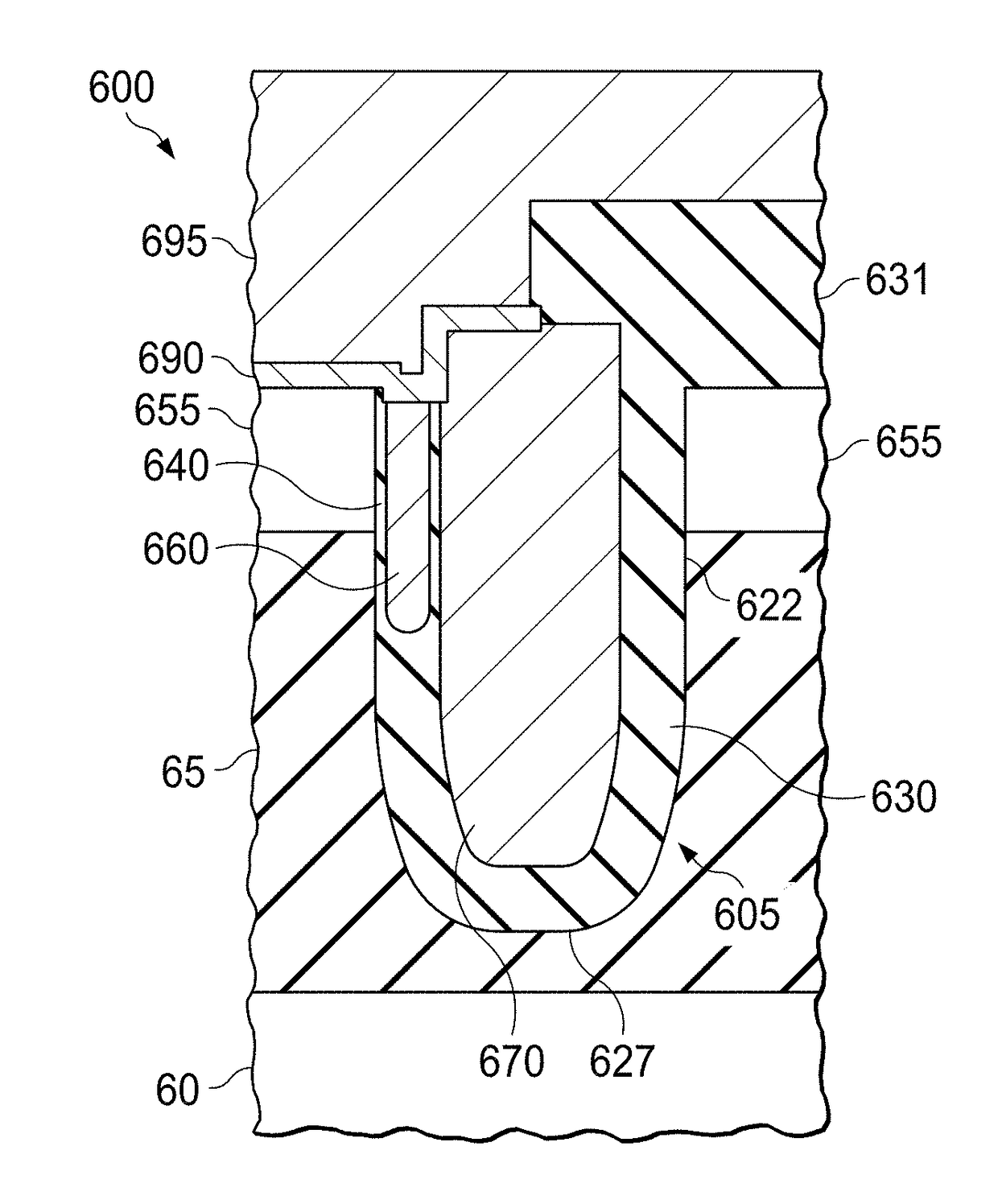

Mos p-n junction diode device and method for manufacturing the same

ActiveUS20090261427A1Improve performanceReduce leakage currentSemiconductor/solid-state device manufacturingDiodeResistReverse recovery

A MOS P-N junction diode device includes a substrate having a first conductivity type, a field oxide structure defining a trench structure, a gate structure formed in the trench structure and a doped region having a second conductivity type adjacent to the gate structure in the substrate. The method for manufacturing such diode device includes several ion-implanting steps. After the gate structure is formed by isotropic etching using a patterned photo-resist layer as a mask, an ion-implanting step is performed using the patterned photo-resist layer as a mask to form a deeper doped sub-region. Then, another ion-implanting step is performed using the gate structure as a mask to form a shallower doped sub-region between the gate structure and the deeper doped sub-region. The formed MOS P-N junction diode device has low forward voltage drop, low reverse leakage current, fast reverse recovery time and high reverse voltage tolerance.

Owner:PFC DEVICE

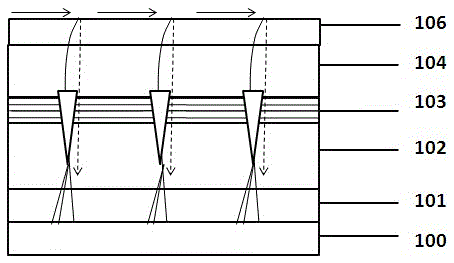

Nitride light emitting diode with AIN quantum dots and manufacturing method thereof

ActiveCN105633230APrevents current from flowing through the dislocation line regionIncrease reverse voltageSemiconductor devicesDislocationMultiple quantum

The present invention discloses a nitride light emitting diode with AIN quantum dots and a manufacturing method thereof. The nitride light emitting diode comprises a substrate, a buffer layer, an N-type nitride, multiple quantum wells with V-pits, P-type nitride, AIN quantum dots without Mg doping and P-type nitride and P-type contact layer with high Mg doping, an AIN quantum dot layer is inserted between the P-type nitride and the P-type nitride with high Mg doping, and the quantum dots uniformly block the terminal of a dislocation line through a multistep relaxation deposition method with high-resistance AIN quantum dots. The nitride light emitting diode with AIN quantum dots and the manufacturing method thereof are able to prevent current from flowing the dislocation line area, improve the backward voltage, reduce the electric leakage and improve the current lateral extension and ESD.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

Super junction for semiconductor device and method for manufacturing the same

A super junction for semiconductor device includes a silicon substrate with a first conductive type epitaxial layer, a plurality of highly-doped second conductive type columns formed in the first conductive type epitaxial layer, and a plurality of lightly-doped (first conductive type or second conductive type) side walls formed on outer surfaces of the highly-doped second conductive type. The semiconductor device is super-junction MOSFET, super junction MOSFET, super junction Schottky rectifier, super junction IGBT, thyristor or super junction diode.

Owner:PFC DEVICE HLDG

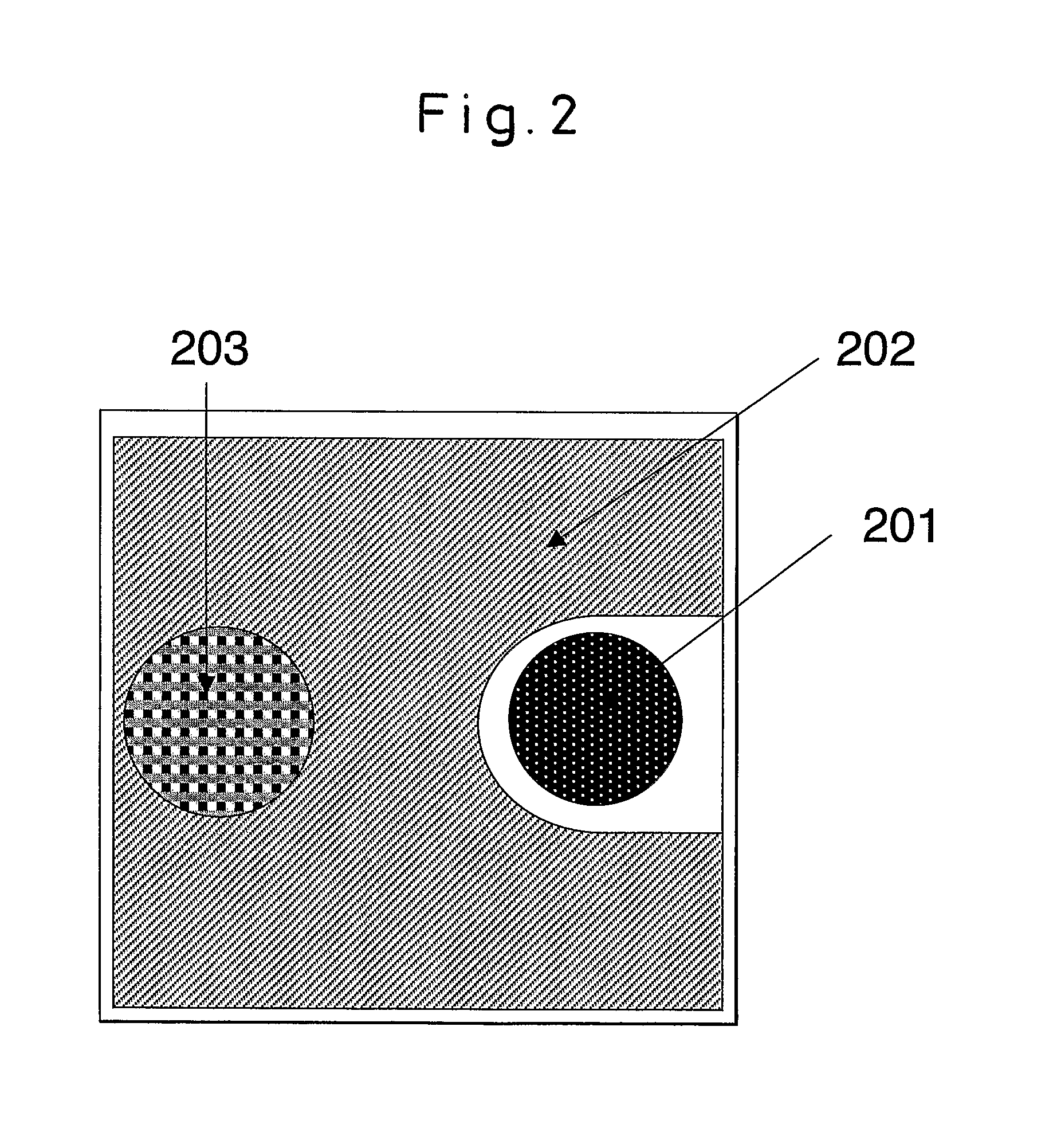

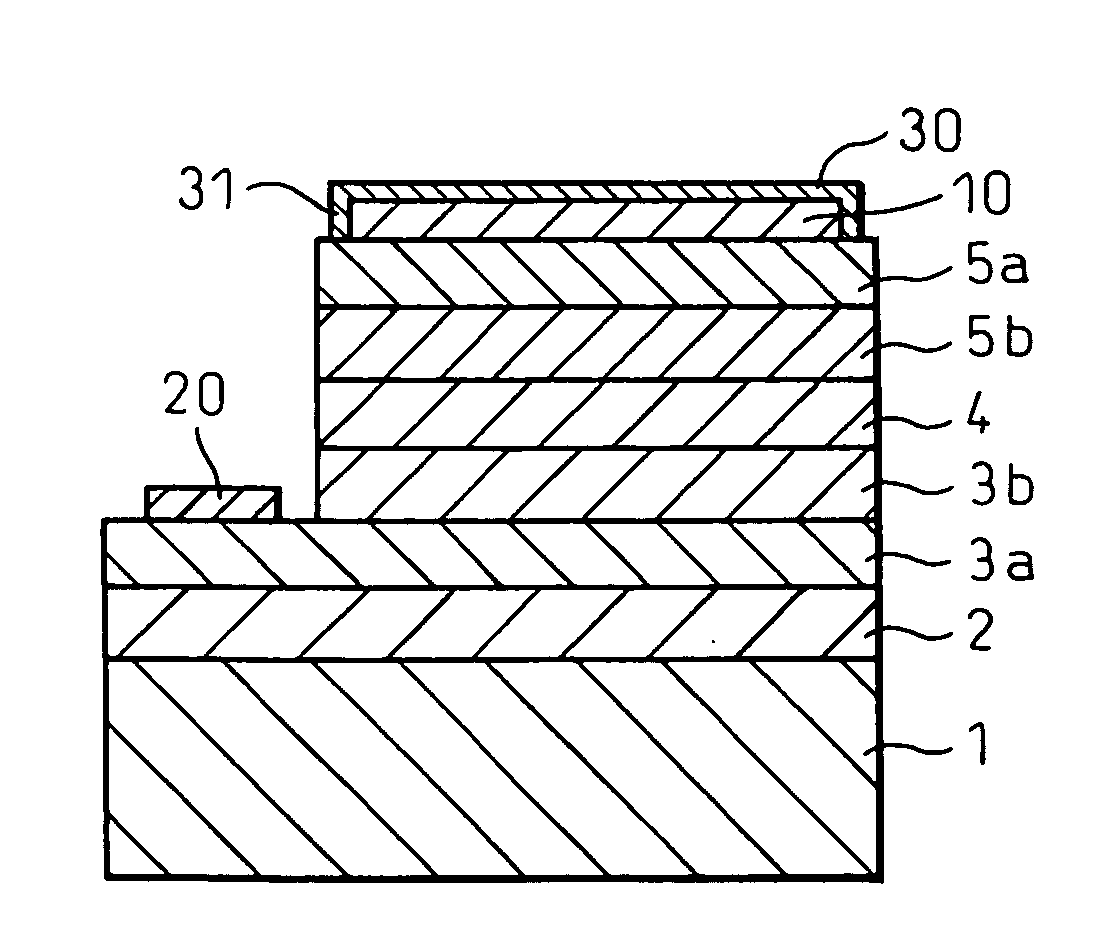

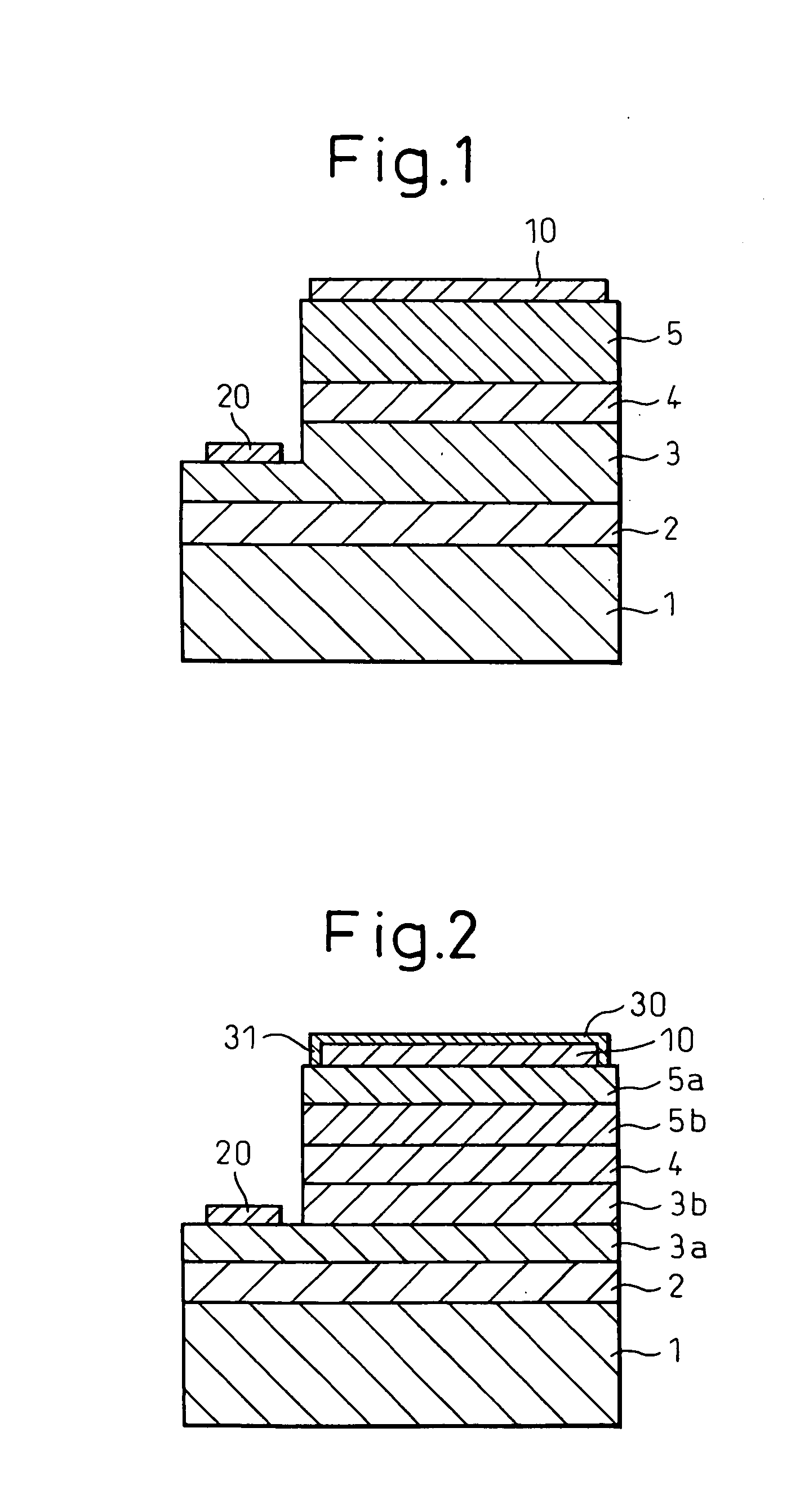

Overvoltage-protected light-emitting semiconductor device, and method of fabrication

InactiveUS7897497B2More compact constructionEasy and economical to manufactureSemiconductor/solid-state device detailsSolid-state devicesOvervoltagePower semiconductor device

A light-generating semiconductor region is grown by epitaxy on a silicon substrate. The light-generating semiconductor region is a lamination of layers of semiconducting nitrides containing a Group III element or elements. The silicon substrate has a p-type impurity-diffused layer formed therein by thermal diffusion of the Group III element or elements from the light-generating semiconductor region as a secondary product of the epitaxial growth of this region on the substrate. The p-type impurity-diffused layer is utilized as a part of overvoltage protector diodes which are serially interconnected with each other and in parallel with the LED section of the device between a pair of electrodes.

Owner:SANKEN ELECTRIC CO LTD

Reflective Positive Electrode and Gallium Nitride-Based Compound Semiconductor Light-Emitting Device Using the Same

InactiveUS20080283850A1Good electrical characteristicHigh reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideVoltage

It is an object of the present invention to provide a gallium nitride-based compound semiconductor light-emitting device which has a highly reflective positive electrode that has high reverse voltage and excellent reliability with low contact resistance to the p-type gallium nitride-based compound semiconductor layer.The inventive reflective positive electrode for a semiconductor light-emitting device comprises a contact metal layer adjoining a p-type semiconductor layer, and a reflective layer on the contact metal layer, wherein the contact metal layer is formed of a platinum group metal or an alloy containing a platinum group metal, and the reflective layer is formed of at least one metal selected from the group consisting of Ag, Al, and alloys containing at least one of Ag and Al.

Owner:SHOWA DENKO KK

Production technology of controllable silicon

ActiveCN101901763AShorten the timeIncrease reverse voltageSemiconductor/solid-state device manufacturingSilicon chipBoron diffusion

The invention relates to a production technology of controllable silicon, which comprises the following steps of oxidizing, photoetching and penetrating a ring, penetrating and diffusing, diffusing a short base region, and photoetching a cathode. The production technology is characterized in that the step of evaporating aluminum and alloy and retaining an alloy layer is added between the step of photoetching and penetrating the ring and the step of penetrating and diffusing. The production technology has the advantages that 1, as the diffusion rate of the aluminum in the silicon is far greater than that of the boron in the silicon, the production technology takes the aluminum as the penetrating and diffusing impurity source, so that the penetrating and diffusing time of the 4-inch silicon wafer (250-260um) is less than 180h; 2, as the impurity concentration of the aluminum diffusion is lower, the production technology further can effectively improve the backward voltage; and 3, as the transverse diffusion distance is 65-70% and the normal boron diffusion is 80%, the diffusion method can effectively improve the effective use ratio of the area of the chip and reduce the area of the chip.

Owner:江苏吉莱微电子股份有限公司

LED epitaxial growth method based on sapphire graphical substrate

InactiveCN106374021ASolve the problem of extreme warpageResolve transitionPolycrystalline material growthSemiconductor/solid-state device manufacturingLength waveBiology

The invention discloses an LED epitaxial growth method based on a sapphire graphical substrate. The method comprises processing the substrate, growing an AlGaN layer, growing an InAlN layer, growing a MgAlGaN layer, growing a Si-doped N type GaN layer, growing an InxGa(1-x)N / GaN layer, growing a P type AlGaN layer, growing a Mg-doped P type GaN layer, and cooling; and x equals 0.20 to 0.25. According to the growth method, the wavelength hit rate of an epitaxial wafer is improved, the crystal quality of the epitaxial wafer is improved, and the photoelectric performance of an LED is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

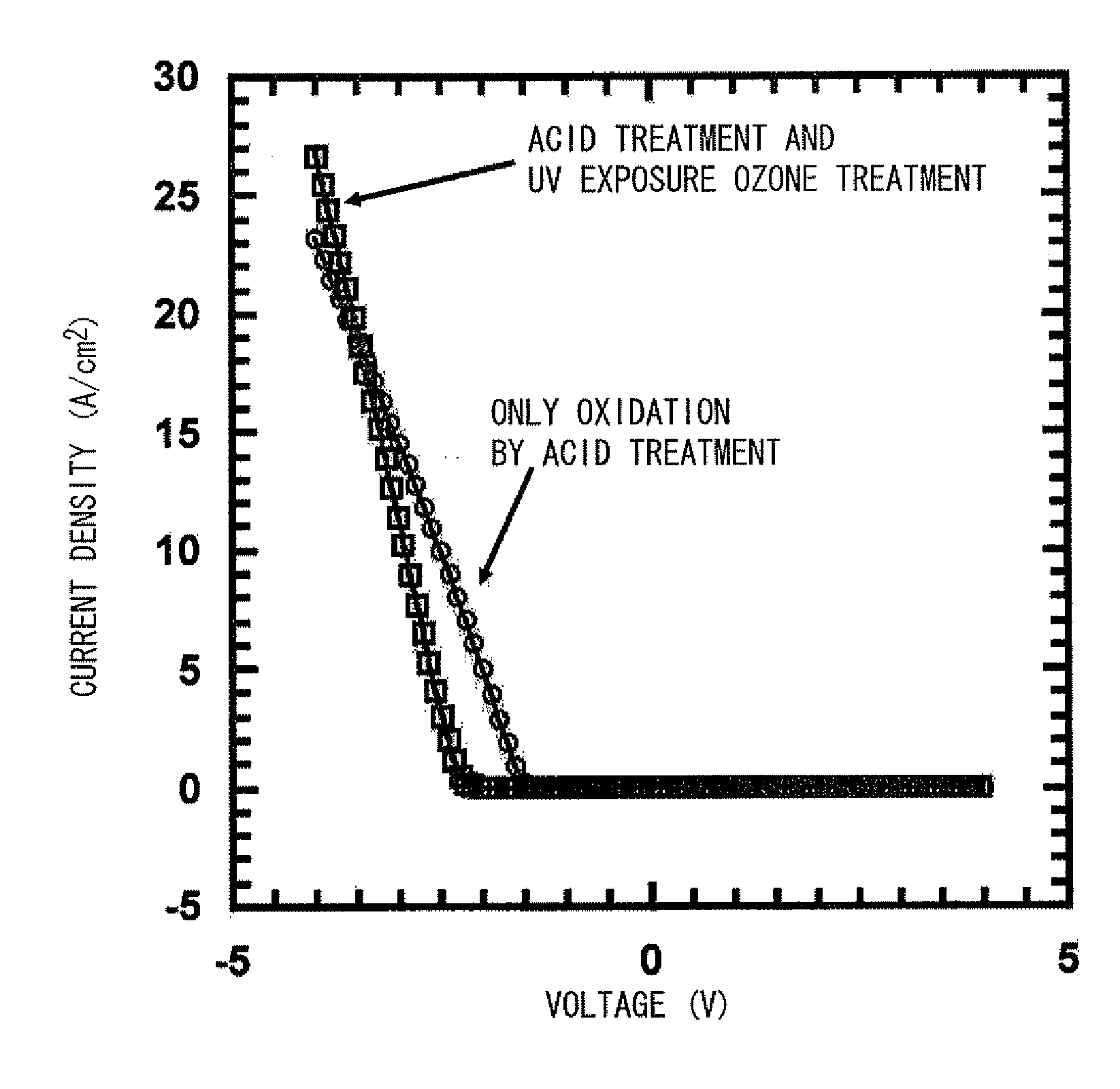

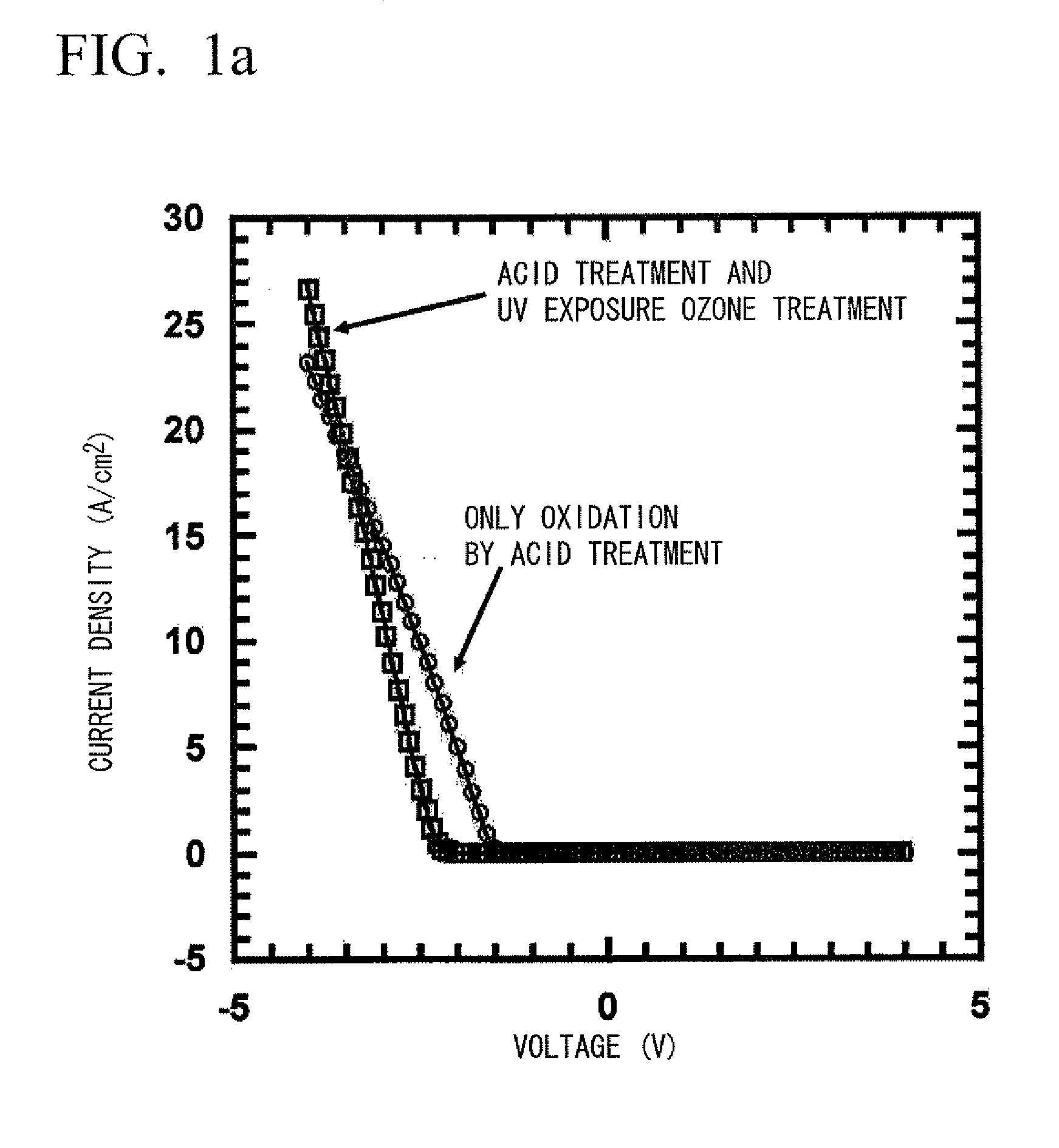

Method for diamond surface treatment and device using diamond thin film

InactiveUS20090140263A1Suppresses reverse leakage currentStabilize diode characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesOxygenLength wave

A method for surface treatment of diamond comprising exposing the surface of diamond to UV light containing wavelengths of 172 nm to 184.9 nm and 253.7 nm at an integrated exposure of 10 to 5,000 J / cm2 in an environment of an atmosphere having an oxygen concentration of 20 to 100% and an ozone concentration of 10 to 500,000 ppm to adsorb oxygen on the surface of diamond.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Trenched MOS Gate Controlled Rectifier

ActiveUS20170288065A1Efficient switchingAlleviate premature breakdownSemiconductor/solid-state device manufacturingSemiconductor devicesReverse biasGate control

A trenched MOS gate controlled rectifier has an asymmetric trench structure between the active area of active trenches and the termination area of termination trenches. The asymmetric trench structure has a gate electrode on one side of the trench to turn on and off the channel of the MOS structure effectively and a field plate structure on the other side with field dielectric sufficiently thick in order to sustain the high electric field during the reverse bias condition.

Owner:DIODES INC

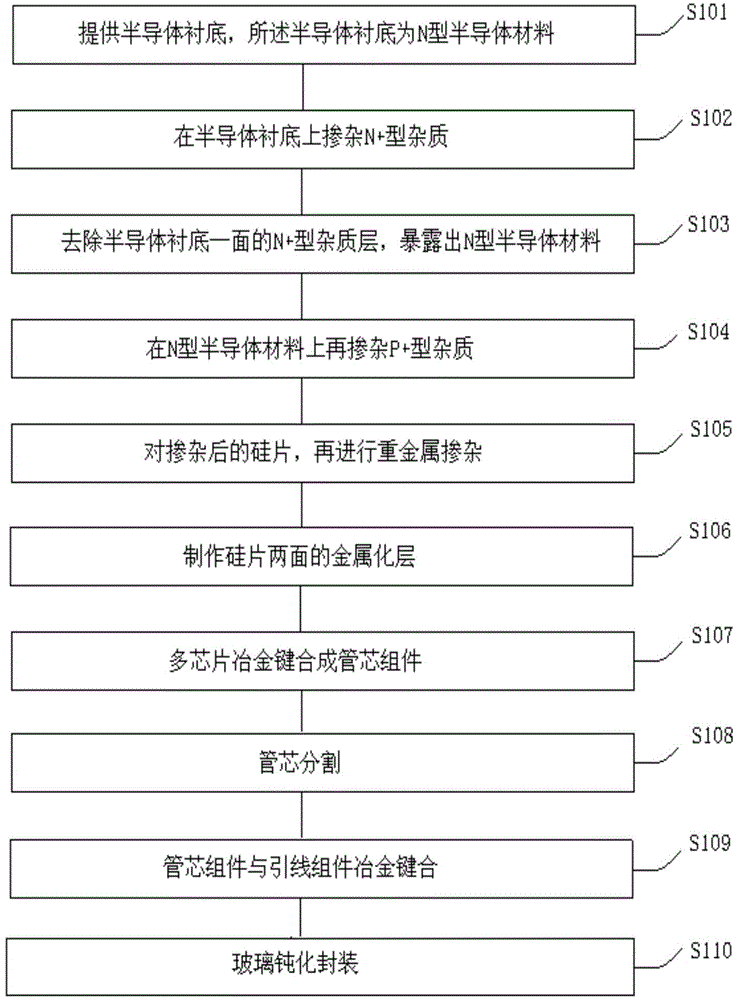

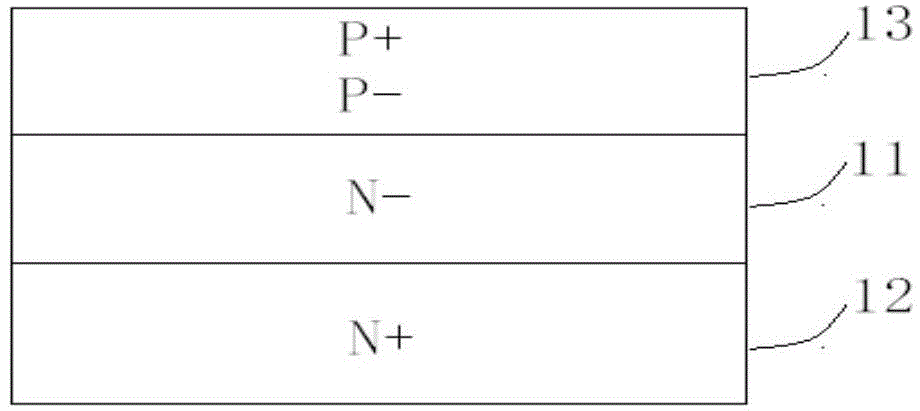

Method for manufacturing fast-recovery glass package diode with ultra-high voltage above 13,000 V

ActiveCN104377129AReduce package sizeLower forward voltage dropSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsUltra high voltage

The invention discloses a method for manufacturing a fast-recovery glass package diode with an ultra-high voltage above 13,000 V. The method comprises the steps that N type semiconductor silicon materials are adopted as a semiconductor substrate, N+ type impurities are doped on the N type semiconductor substrate, an N+ type impurity layer on one face of the semiconductor substrate is removed, P+ type impurities are dually doped on exposed N- type semiconductor materials, then heavy metal platinum doping is carried out, metallization layers on the two faces of a silicon wafer are manufactured through a vacuum coating technology, a plurality of chips are bonded to a pipe core assembly in a metallurgy mode, the silicon wafer is divided into pipe cores of the needed size, the divided pipe core assembly and a lead assembly are bonded through high-temperature sintering and metallurgy, glass passivation and packaging are carried out, adjusted glass powder paste coats the twelve pipe cores connected in series, and manufacturing of the glass package diode is completed. The method has the advantages of being high in voltage, small in forward direction, fast in reverse restoration, good in high-temperature work stability, high in long-term work stability and the like, and is widely applied to the field of aviation, aerospace, electronics, weapons, ships and the like.

Owner:西安卫光科技有限公司

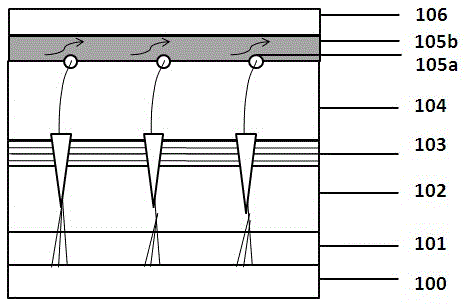

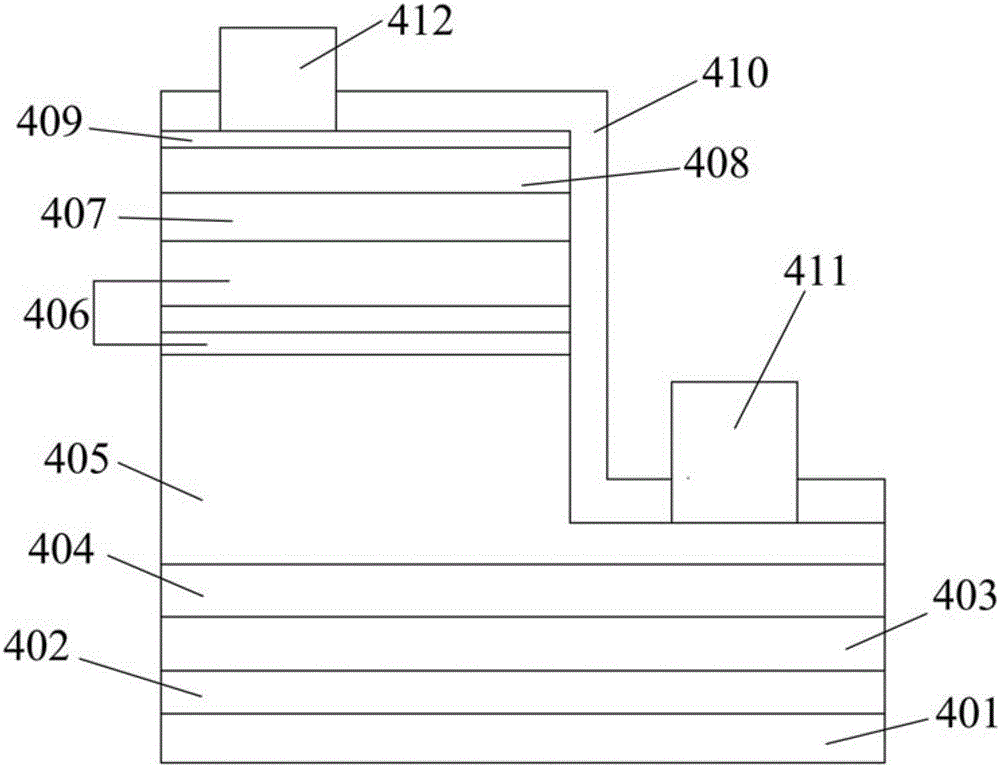

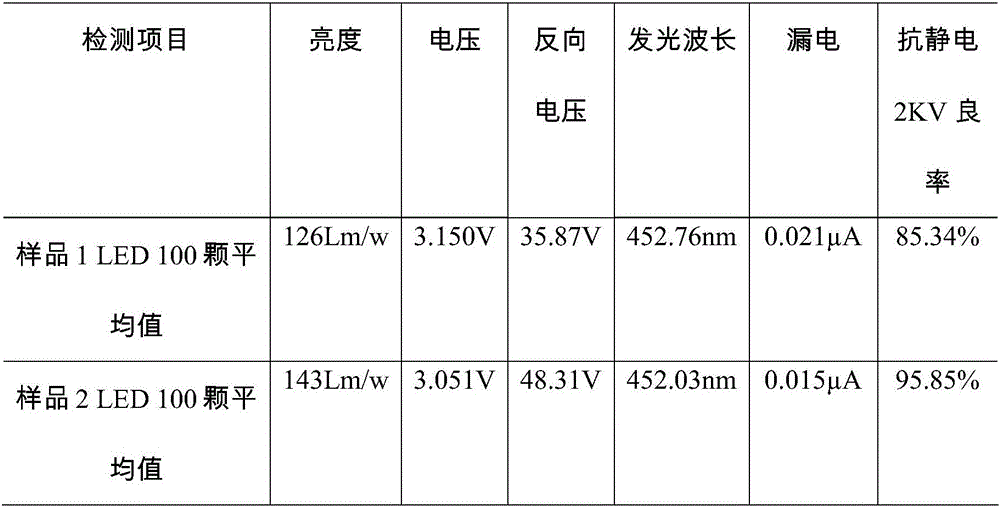

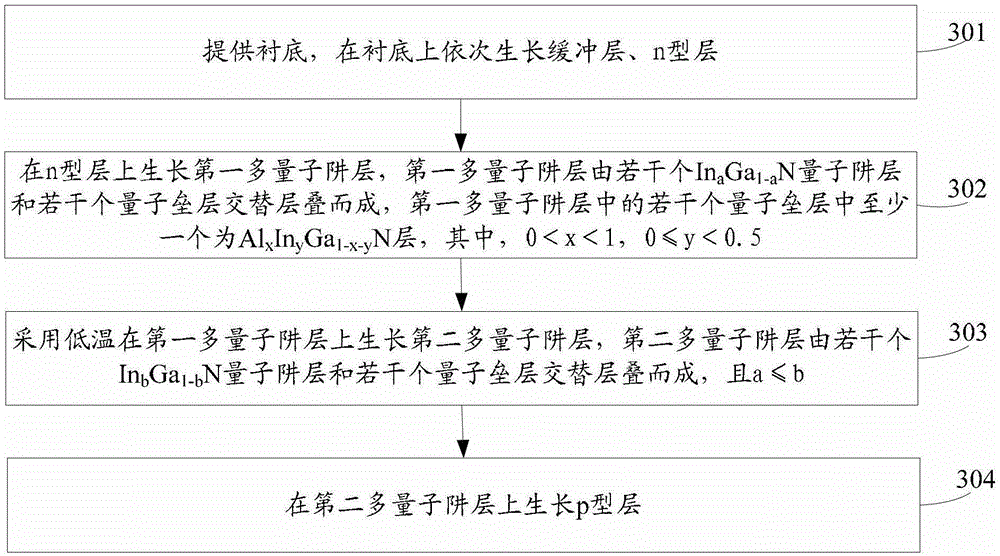

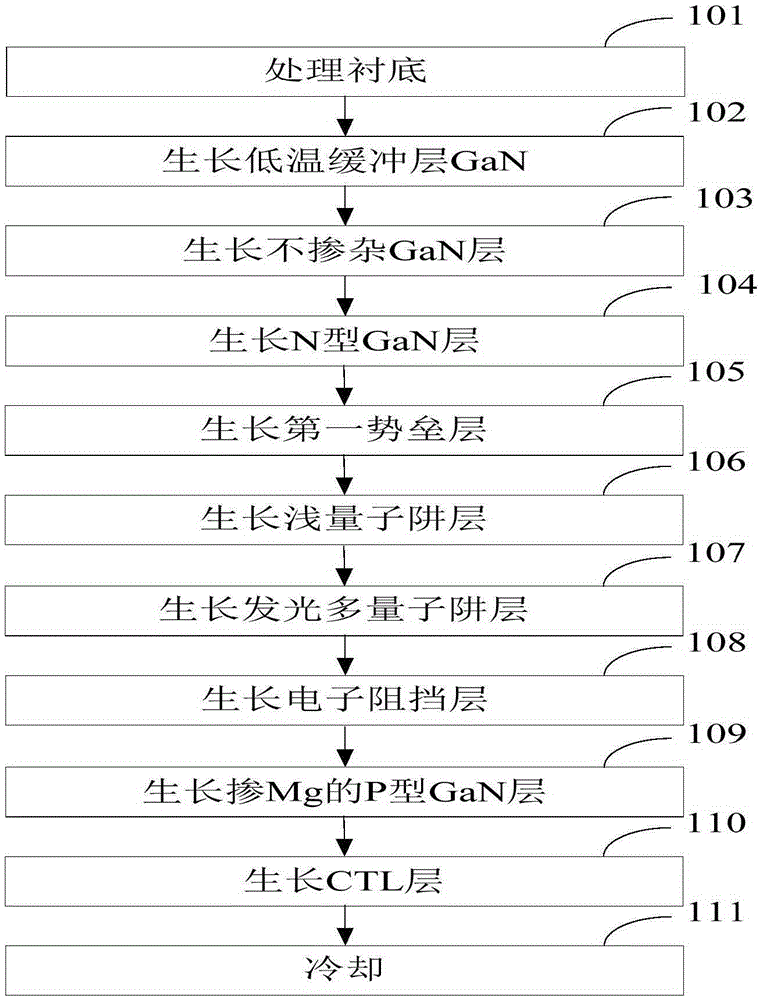

Manufacturing method of LED epitaxial wafer

ActiveCN106653959AImprove growth qualityImprove luminous efficiencySemiconductor devicesQuantum wellLuminescence

The invention discloses a manufacturing method of an LED epitaxial wafer. By using the method, luminescence area losses can be further reduced, a supplementation layer is increased and growing quality of a quantum well is improved; and a backward voltage is increased, internal electric leakage of a device is reduced, and simultaneously, an In-component gradual-change inclined well layer is used to change a forbidden band width of the well so as to capture more electrons and cavities. Contact areas of the electrons and the cavities are increased. A luminescence area is increased too. Operation speeds of the electrons are reduced and a number of effective electrons which are contacted with the cavities is increased.

Owner:GUANGDONG HONGRUI TECH CO LTD

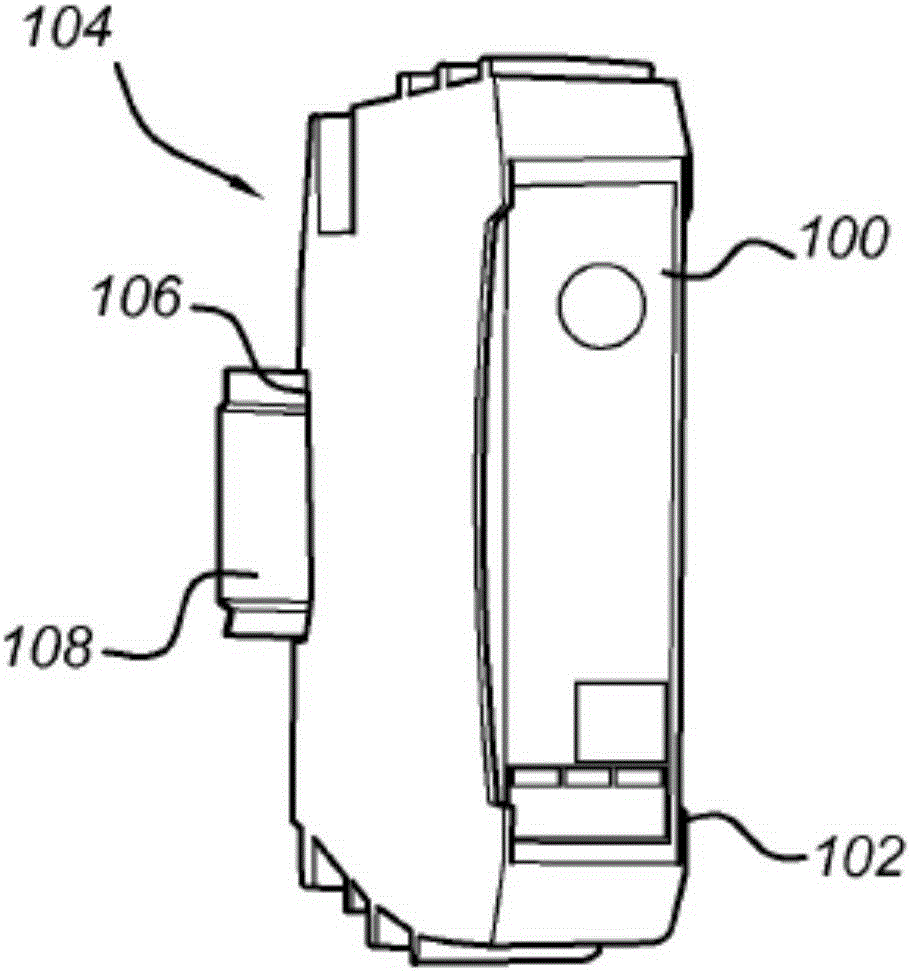

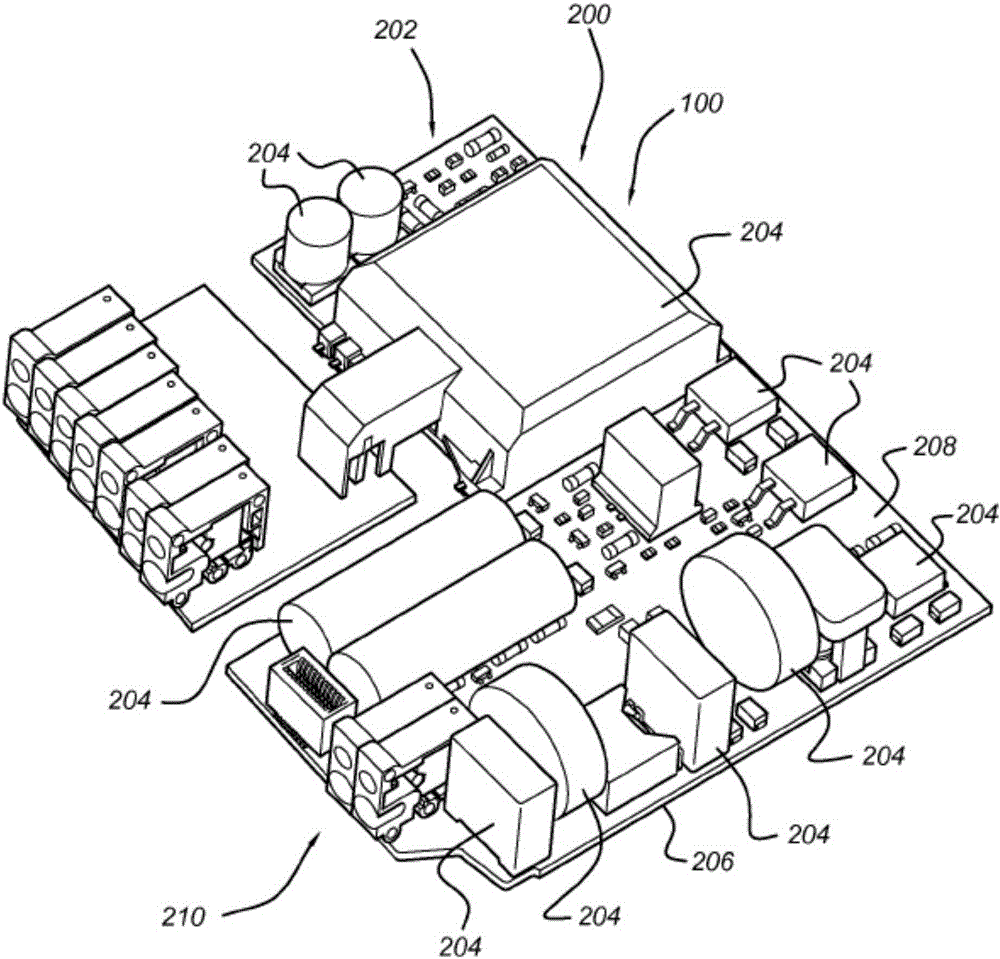

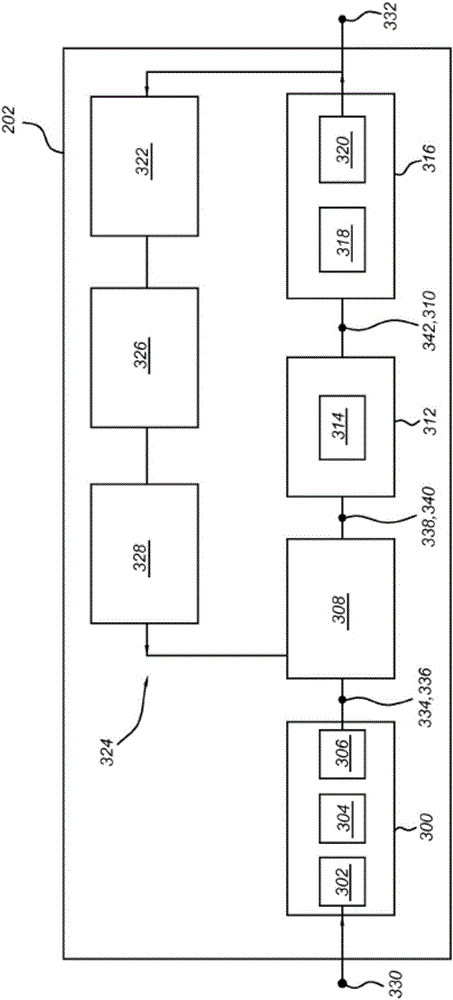

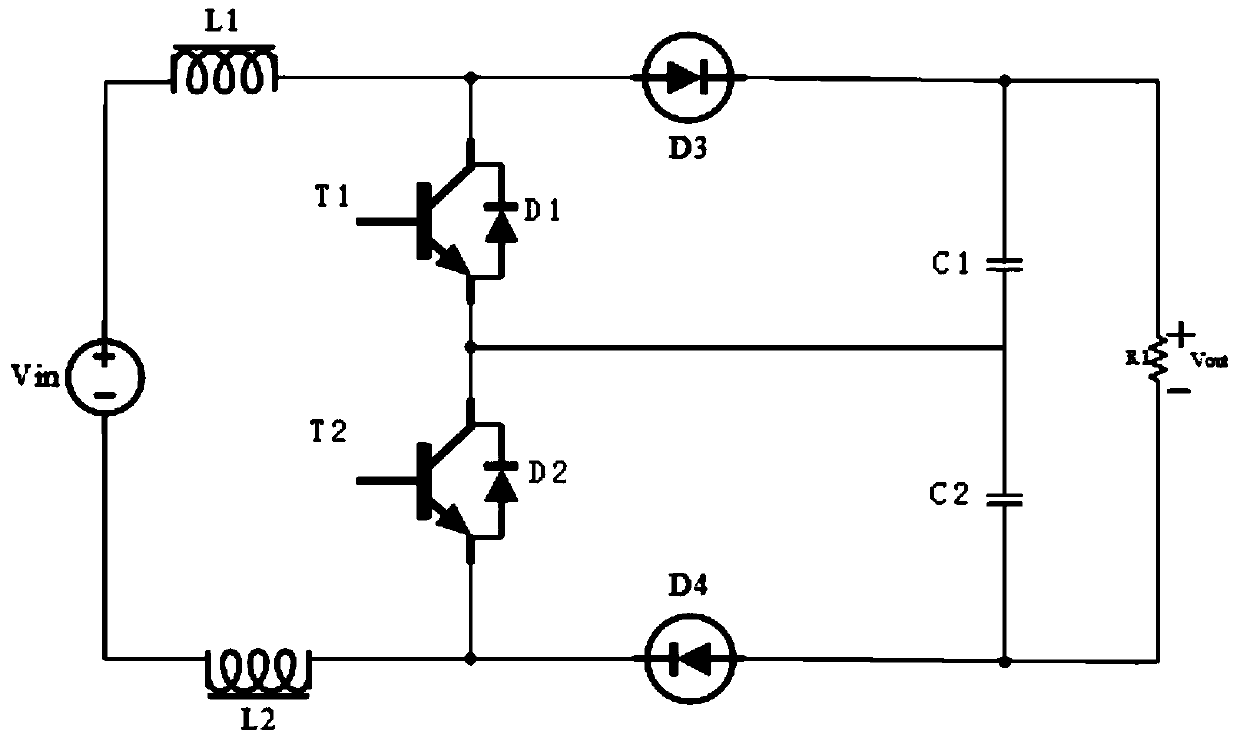

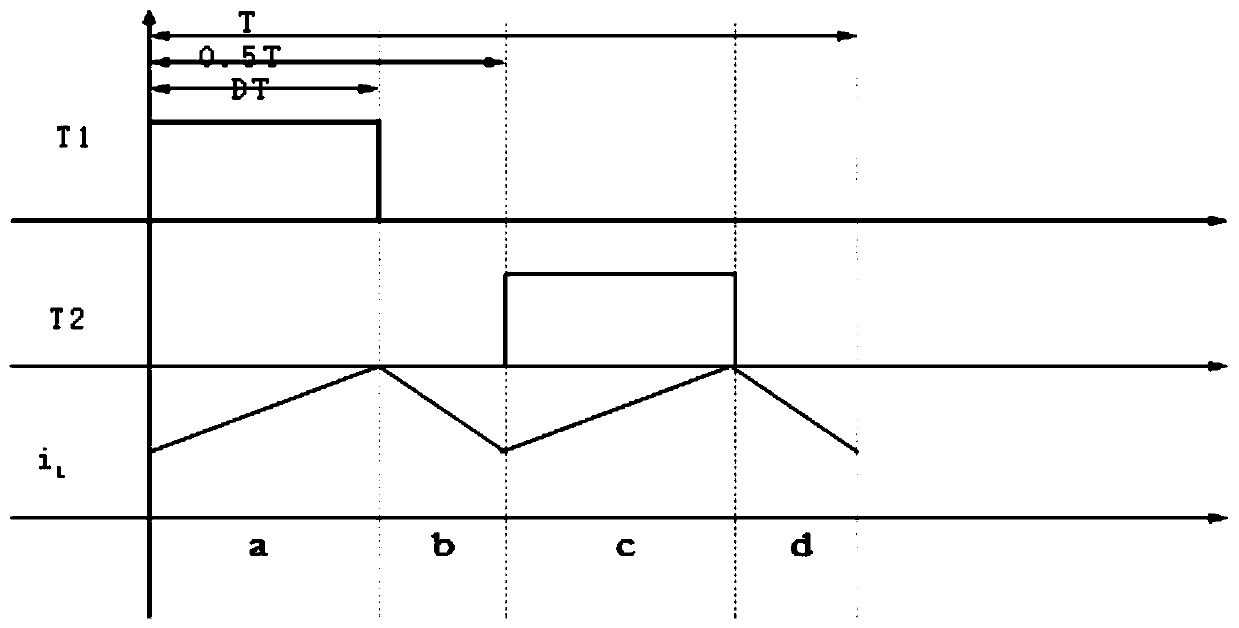

Switch mode power supply with a cascode circuit

InactiveCN105229926ALoss minimizationFast switching speedEfficient power electronics conversionDc-dc conversionTransformerCascode

The invention relates to a switch mode power supply (202) comprising a switch element (308) comprising an NPN-bipolar transistor (402) and a self-conductive field effect transistor (404). Said bipolar transistor (402) and the field effect transistor (404) are connected to form a cascode (400). A bipolar transistor (402) is electrically connected to a winding (502) of a transformer (504), and an additional winding (508) of the transformer (504) is electrically connected to a base connection (408) of the bipolar transistor (402).

Owner:PHOENIX CONTACT GMBH & CO KG +1

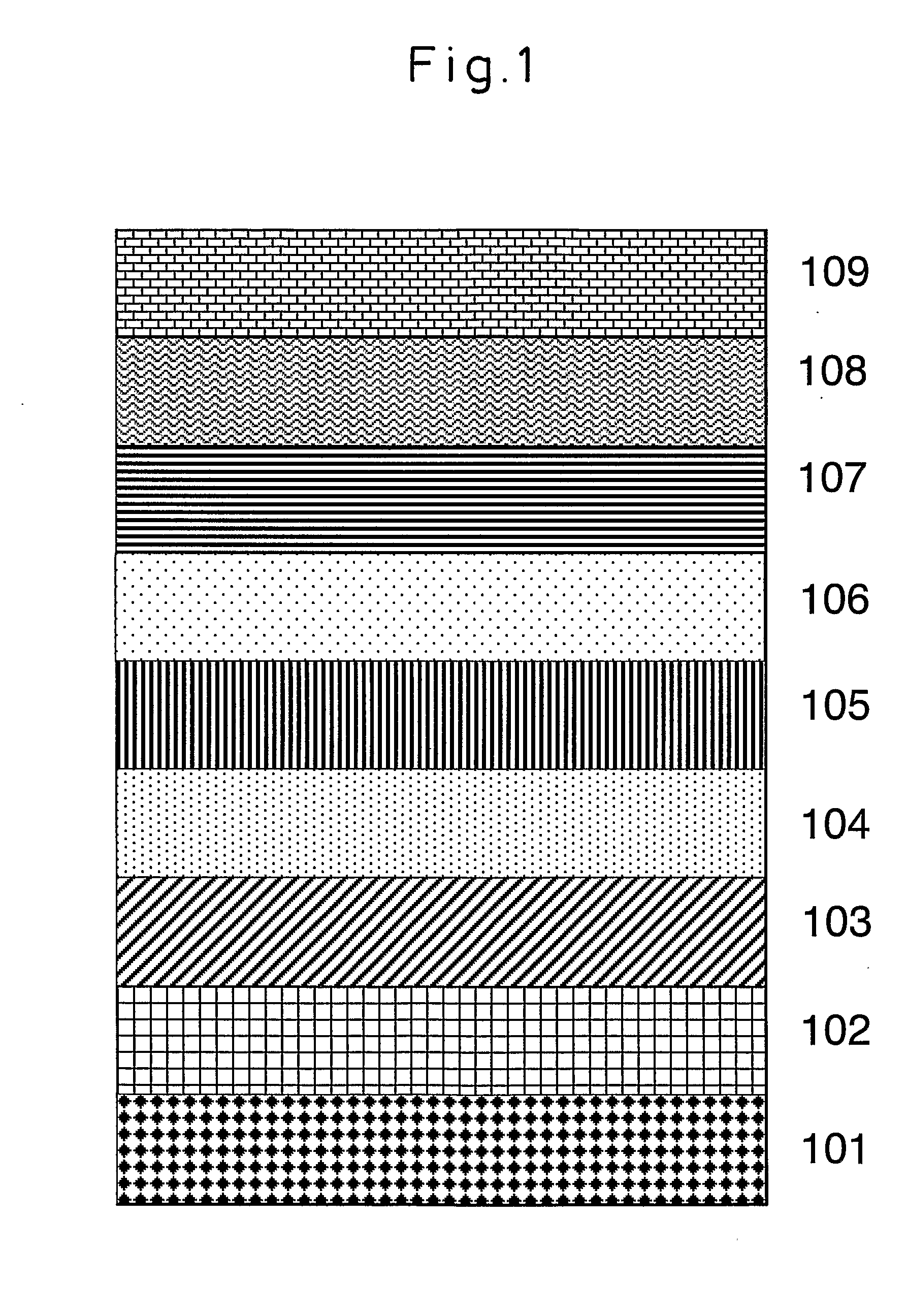

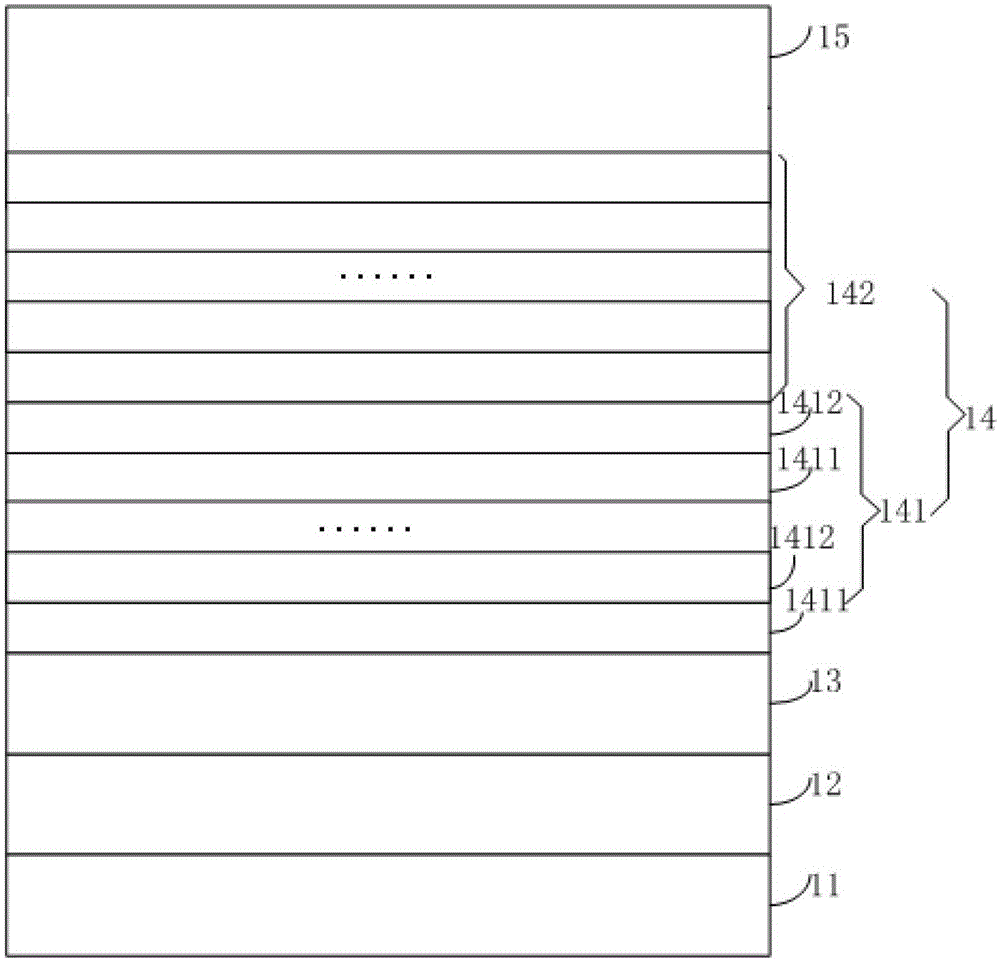

A kind of epitaxial wafer of light-emitting diode and its manufacturing method

ActiveCN103035791BImprove buffering effectImprove interception effectSemiconductor devicesBand bendingLattice mismatch

The invention discloses a light emitting diode epitaxial wafer and a manufacturing method of the light emitting diode epitaxial wafer and belongs to the technical field of semiconductors. The epitaxial wafer comprises a substrate, a buffer layer, an n-type layer, a multi-quantum well layer and a p-type layer, the buffer layer, the n-type layer, the multi-quantum well layer and the p-type layer are stacked on the substrate in sequence, the p-type layer is directly arranged on the multi-quantum well layer which comprises a first multi-quantum well layer and a second multi-quantum well layer, a plurality of InaGa1-aN quantum well layers and a plurality of quantum barrier layers are stacked alternately to form the first multi-quantum well layer, at least one of the quantum barrier layers is the AlxInyGa1-x-yN layer, wherein 0 <x <1, 0<= y <0.5. A plurality of InbGa1-bN quantum well layers and a plurality of quantum barrier layers are stacked alternately to form the second multi-quantum well layer, and a <=b. Due to the scheme, the defect concentration of the second multi-quantum well layer is reduced, barrier height is increased, buffering and intercepting abilities are improved, luminous efficiency of devices is increased, and the problems of lattice mismatch and band bending caused by an electron blocking layer are solved.

Owner:HC SEMITEK CORP

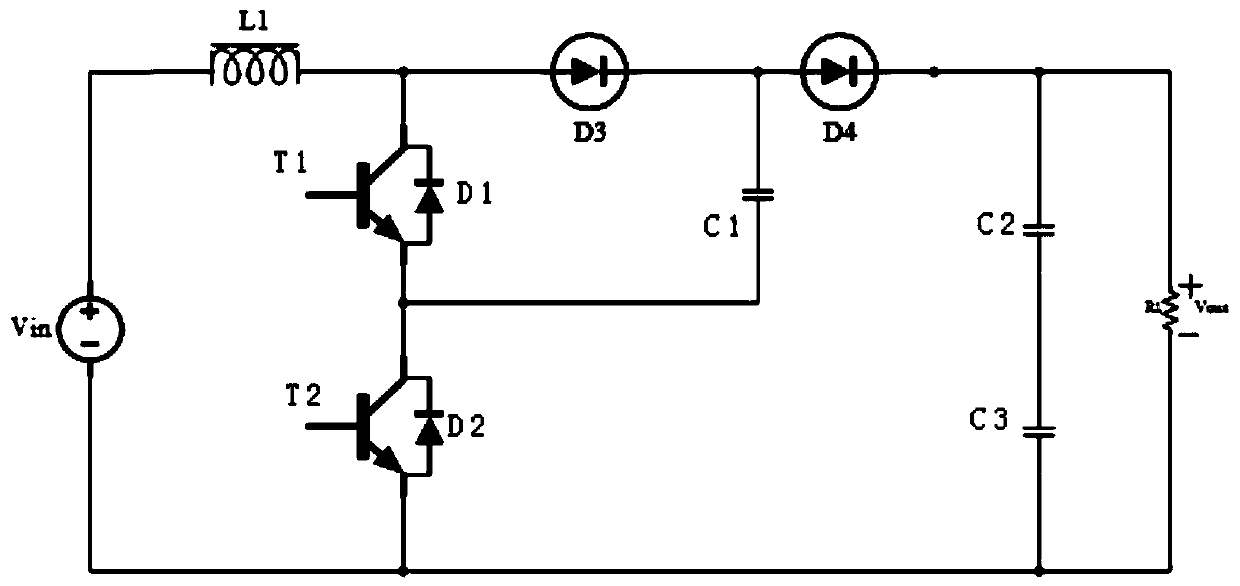

BOOST power conversion circuit and control method thereof

PendingCN111371323AIncrease reverse voltageReduce reverse withstand voltageDc-dc conversionSingle network parallel feeding arrangementsCapacitanceHemt circuits

The invention discloses a BOOST power conversion circuit and a control method thereof. According to the conversion circuit, an initial voltage establishing circuit of a flying capacitor C1 is added onthe basis of an input and output common-ground type three-level Boost converter. The initial voltage establishing circuit is composed of a first resistor R1, a second resistor R2 and a third resistorR3. Initial voltage is established for a first capacitor C1 when the voltage of the input end of the voltage-boosting power conversion circuit is lower than starting threshold voltage Vstart of the voltage-boosting power conversion circuit, and the BOOST power conversion circuit has the effects that firstly, forward voltage of a second switching tube T2 is reduced; and secondly, the reverse voltage borne by the fourth diode D4 is reduced, the second switching tube T2 is further protected, and the fourth diode D4 with smaller reverse voltage stress can be selected.

Owner:NINGBO GINLONG TECH

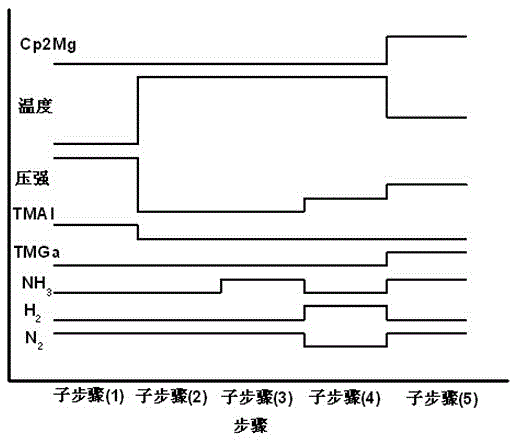

Growth method for GaN-based LED epitaxial wafer

InactiveCN105118900AInhibition of cluster effectLower reverse voltagePolycrystalline material growthFrom chemically reactive gasesForward voltageMaterials science

The invention discloses a growth method for a GaN-based LED epitaxial wafer. During the growing of InGaN / GaN multiple quantum wells, a proper amount of hydrogen is let in at a proper time under the conventional growth conditions, thereby effectively inhibiting a cluster effect of In, improving the flatness of an InGaN / GaN interface, improving the light-emitting efficiency, improving a reverse voltage of a device, and reducing a forwarding voltage. The method is simple and feasible, has no special requirements for the growing technology. A 300 microns* 300 microns chip is manufactured according to a standard chip technology, thereby improving the brightness by 10%-20%, improving the reverse voltage by 5V, and reducing the forwarding voltage by more than 0.05V.

Owner:DALIAN MEIMING EPITAXIAL WAFER TECH

An LED epitaxial layer growth method and an epitaxial layer structure and an LED chip obtained through the method

ActiveCN105118904AIncrease reverse voltageEnhanced Spillover CapabilitiesSemiconductor devicesQuantum wellDislocation

The invention provides an LED epitaxial layer growth method and an epitaxial layer structure and an LED chip obtained through the method. The growth method for the epitaxial layer growth comprises the following steps of growing a P-type AlGaN layer and a first P-Type GaN layer arranged on the top surface of the P-type AlGaN layer; and growing a shield layer between the P-type AlGaN layer and the first P-Type GaN layer, of which the shield layer is a P-type AlGaN / InGaN superlattice structure. In the growing of the P-type AlGaN layer, the growth temperature is 750-800 DEG C; the Al dosage concentration is 1.8E+20-2.2E+20atom / cm<3>;and the Mg dosage concentration is 1E+20-2E+20atom / cm<3>. In the growing of the P-type AlGaN / InGaN superlattice structure, the growth temperature is 850-900 DEG C; the Al dosage concentration is 2E+20-3E+20atom / cm<3>;and the Mg dosage concentration is 1E+20-2E+20atom / cm<3>.In the LED epitaxial layer structure provided by the invention, the P-type AlGaN / InGaN superlattice structure is inserted between the P-type AlGaN layer and the P-Type GaN layer, so that on one hand, deects of large quantities of dislocation of quantum well areas are overcome to prevent leakage passages to form between the dislocation defects and the P-Type GaN layer, and meanwhile, capability of obstructing quantum from overflowing from the multi-quantum well areas are improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Light-emitting diode epitaxial wafer and preparation method thereof

ActiveCN105261680AIncrease reverse voltageNanotechnologySemiconductor devicesQuantum wellElectron blocking layer

The invention discloses a light-emitting diode epitaxial wafer and a preparation method thereof. The light-emitting diode epitaxial wafer is characterized by comprising a low-temperature buffer layer GaN, an undoped GaN layer, a uAl superlattice layer, an N-type GaN layer, a first barrier layer, a shallow quantum well layer, a multi-quantum well layer, an electronic barrier layer, an Mg-doped P-type GaN layer and a CTL layer, wherein the undoped GaN layer is located on the low-temperature buffer layer GaN; the uAl superlattice layer is located on the undoped GaN layer; the N-type GaN layer is located on the uAl superlattice layer; the first barrier layer is located on the N-type GaN layer; the shallow quantum well layer is located on the first barrier layer; the multi-quantum well layer is located on the shallow quantum well layer; the electronic barrier layer is located on the multi-quantum well layer; the Mg-doped P-type GaN layer is located on the electronic barrier layer; and the CTL layer is located on the Mg-doped P-type GaN layer. According to the light-emitting diode epitaxial wafer and the preparation method thereof disclosed by the invention, the backward voltage can be significantly improved by adding the uAl superlattice layer structure.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Iii-v semiconductor pixel x-ray detector

ActiveUS20210296391A1Low blocking currentImprove breakdown voltageSolid-state devicesRadiation controlled devicesEngineeringContact layer

A III-V semiconductor pixel X-ray detector, including an absorption region of a first or a second conductivity type, at least nine semiconductor contact regions of the second conductivity type arranged in a matrix along the upper side of the absorption region, and optionally a semiconductor contact layer of the first conductivity type, a metallic front side connecting contact being arranged beneath the absorption region, and a metallic rear side connecting contact being arranged above each semiconductor contact region, and a semiconductor passivation layer of the first or the second conductivity type. The semiconductor passivation layer and the absorption region being lattice-matched to each other. The semiconductor passivation layer being arranged in regions on the upper side of the absorption region. The semiconductor passivation layer having a minimum distance of at least 2 μm or at least 20 μm with respect to each highly doped semiconductor contact region.

Owner:AZUR SPACE SOLAR POWER

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com