Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

457results about How to "Increase cell density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

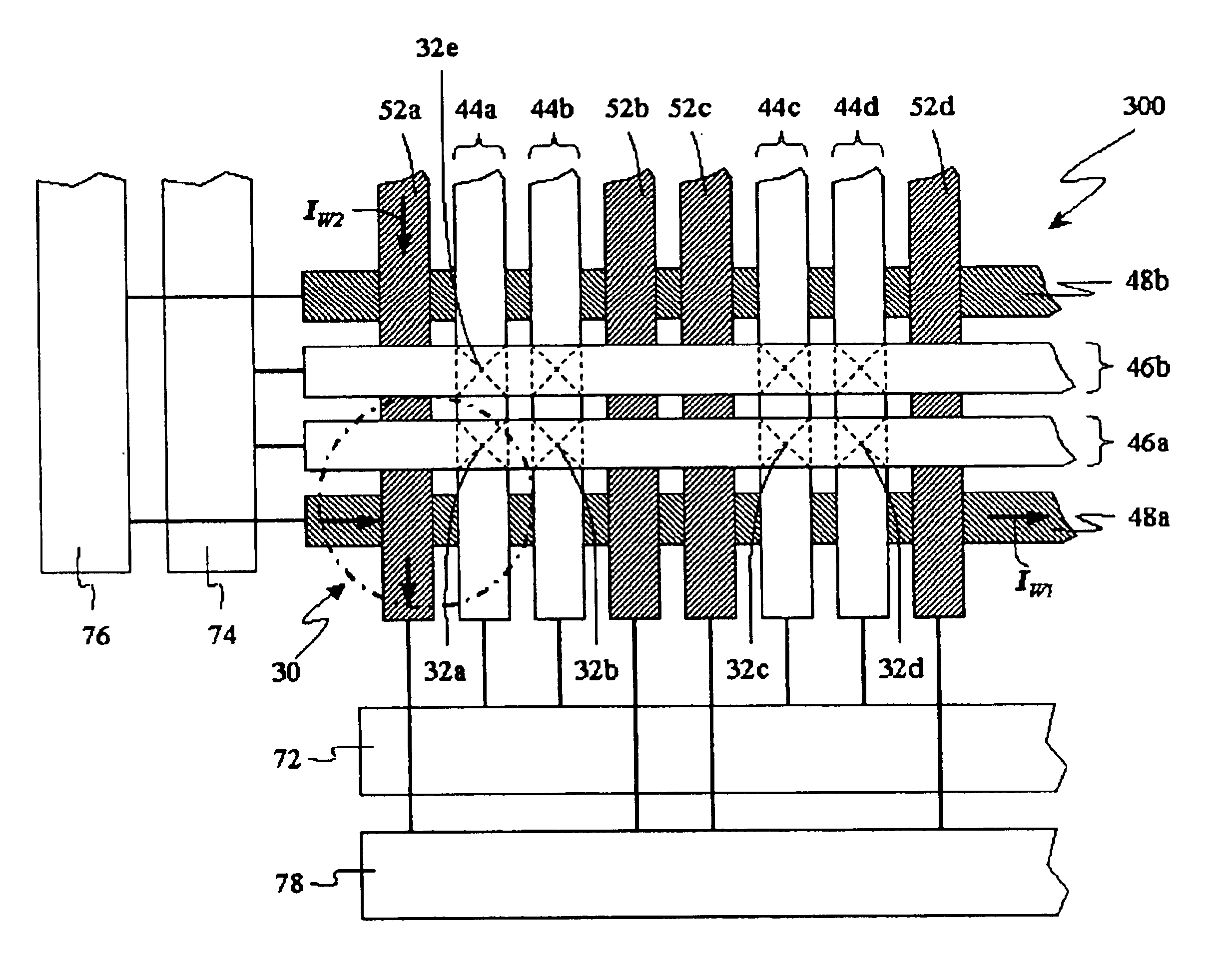

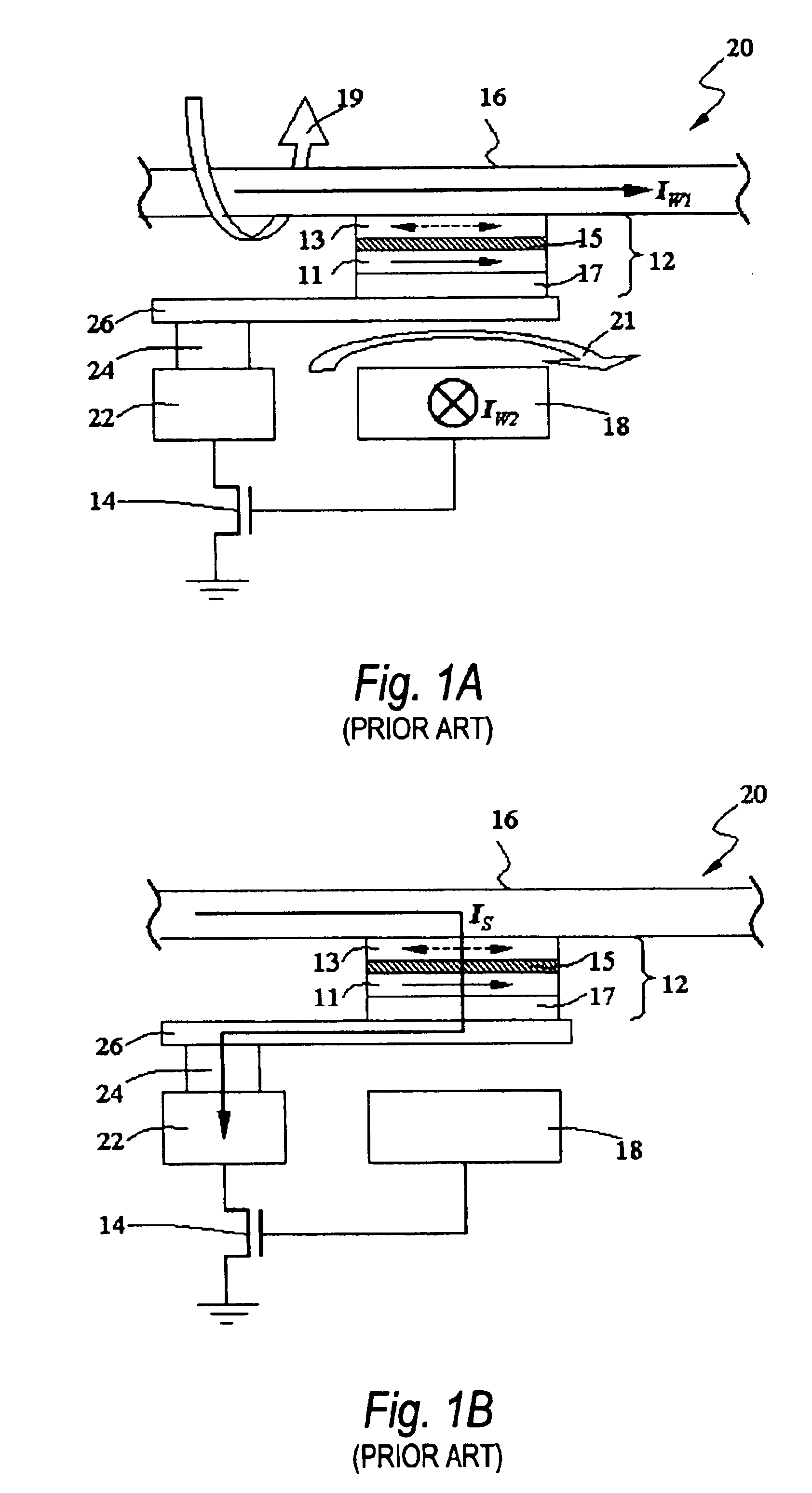

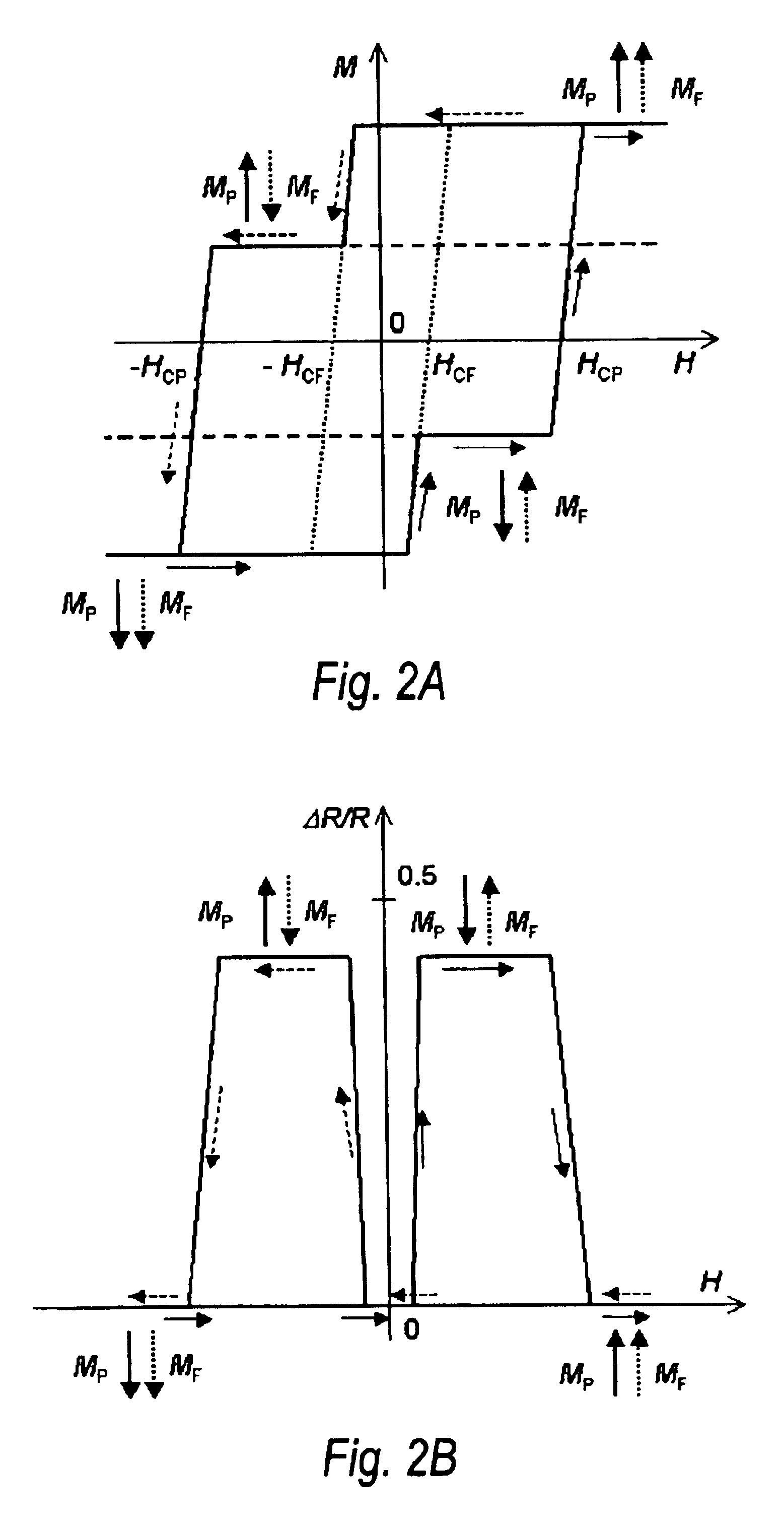

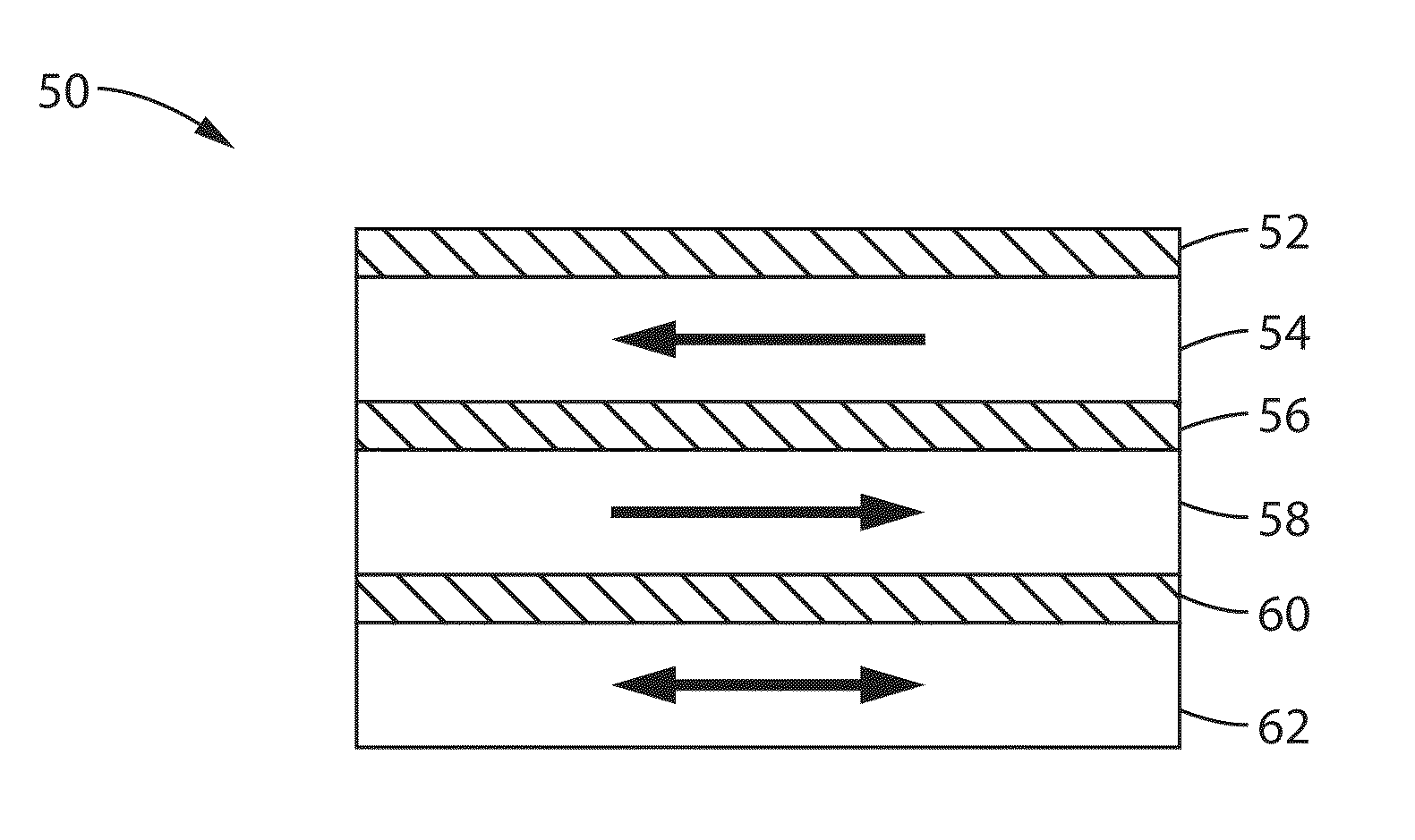

Magnetic tunnel junction memory device

InactiveUS6845038B1Improve permeabilityLow resistivityDigital storageBit linePerpendicular magnetization

A memory cell for magnetic random access memory devices based on a magnetic tunnel junction (MTJ) memory element with a perpendicular orientation of magnetization in pinned and free magnetic layers, and a tunnel barrier layer sandwiched between the pinned and free layers. The memory cell can include the MTJ memory element, a magnetic flux guide in series with selection devices, such as a bit line, a word line, and a transistor. The magnetic flux guide can have two electrically conductive magnetic portions with the MTJ memory element positioned between the magnetic portions. The MTJ memory element is magnetically isolated from the magnetic flux guide by thin non-magnetic conductive spacers. The MTJ memory element is arranged in a vertical space between the intersecting bit and word lines at their intersection region. The memory cell also includes write and excitation lines. The write line is parallel to the bit line and the excitation line is parallel to the word line. The write and excitation lines also intersect each other and define a corner. The MTJ memory element is positioned in the corner of the intercepting write and excitation lines.

Owner:SHUKH ALLA MIKHAILOVNA

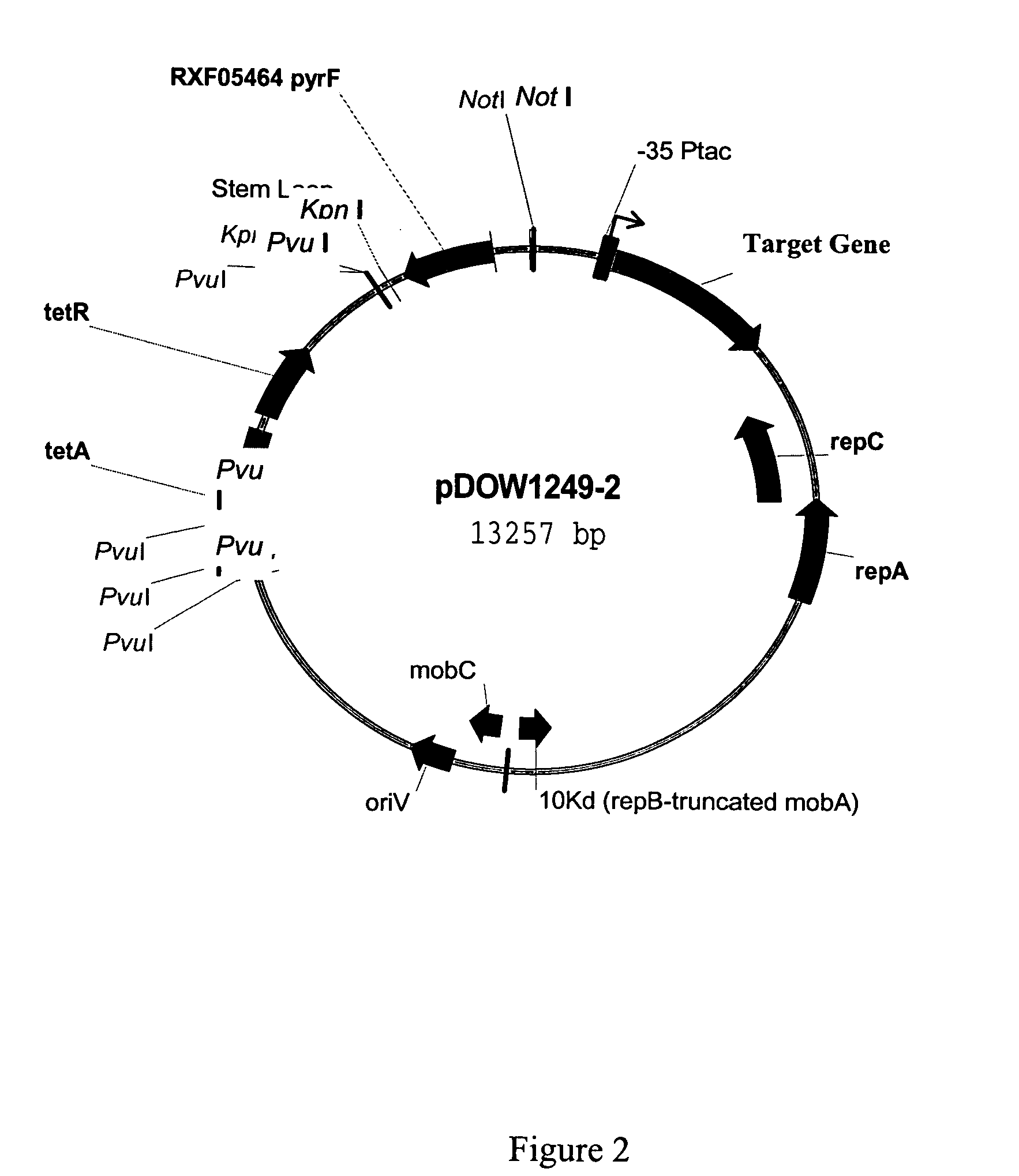

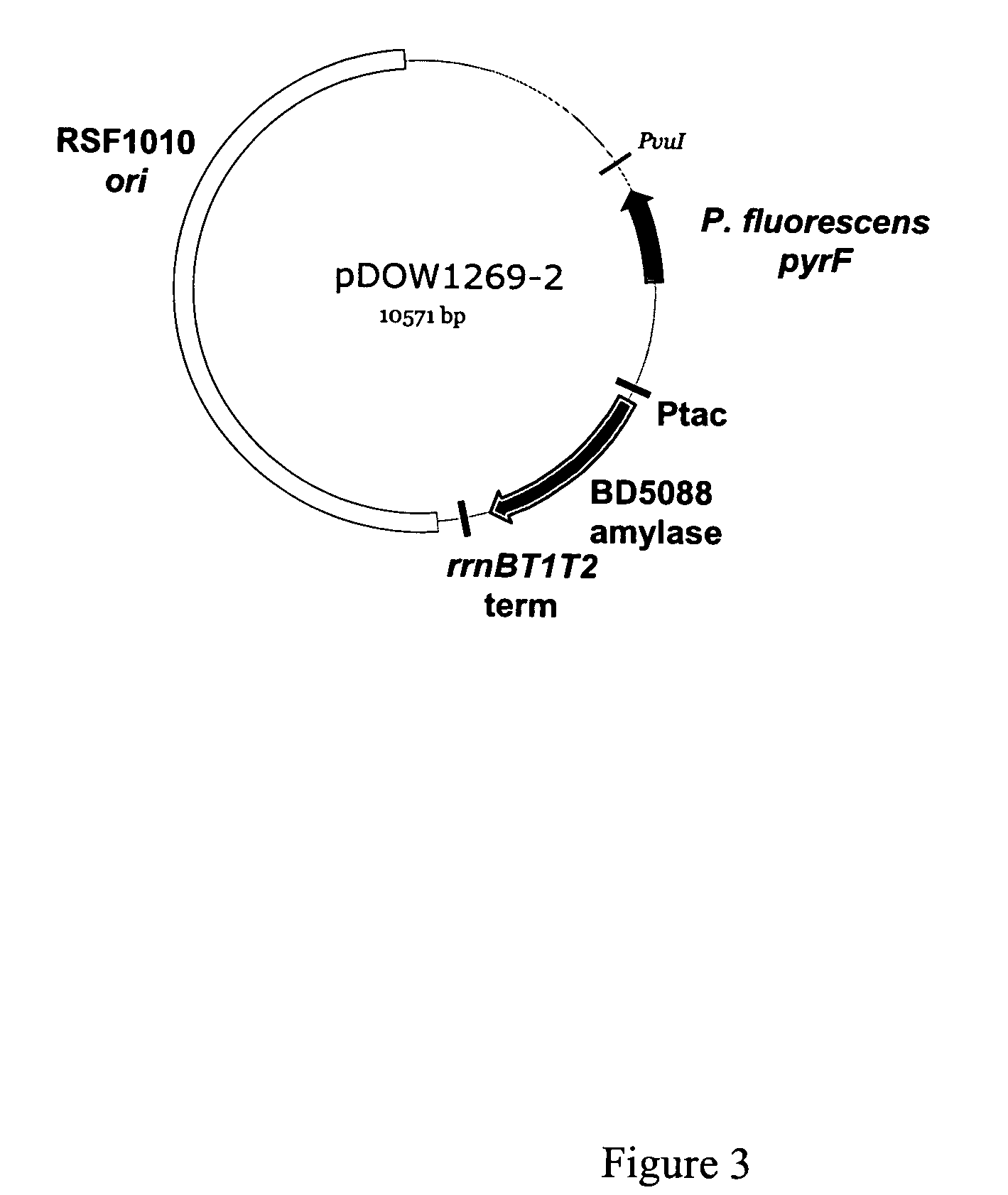

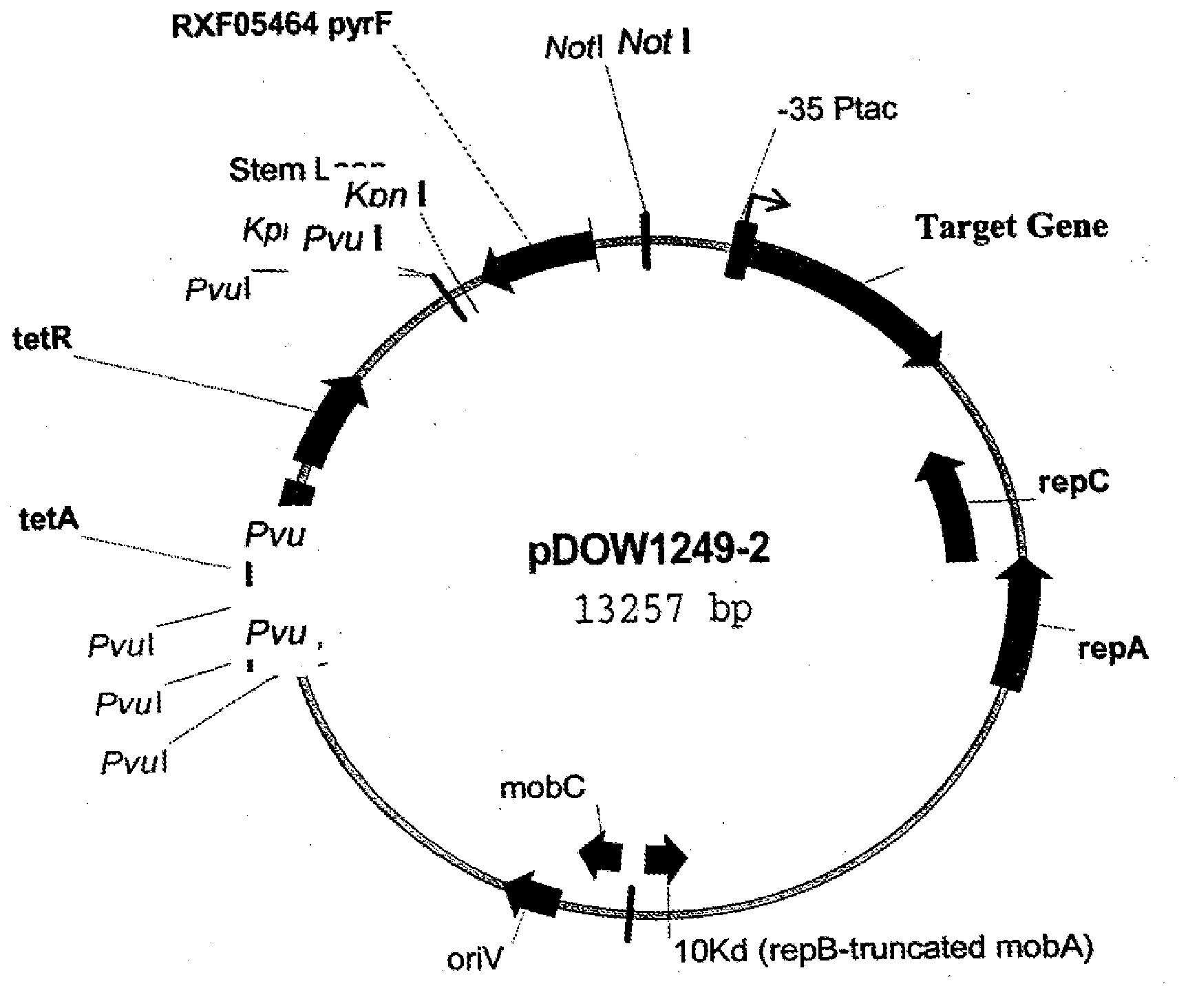

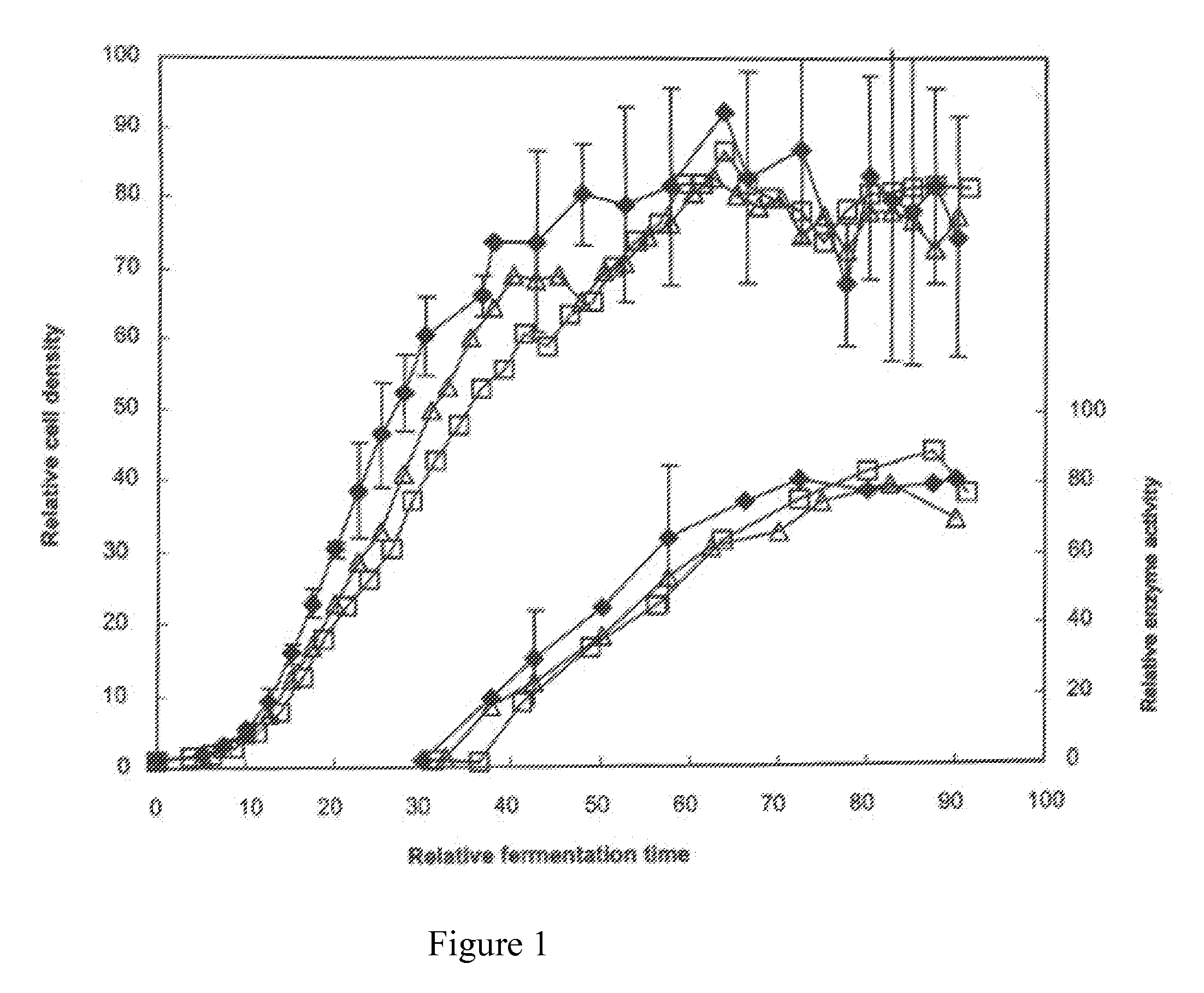

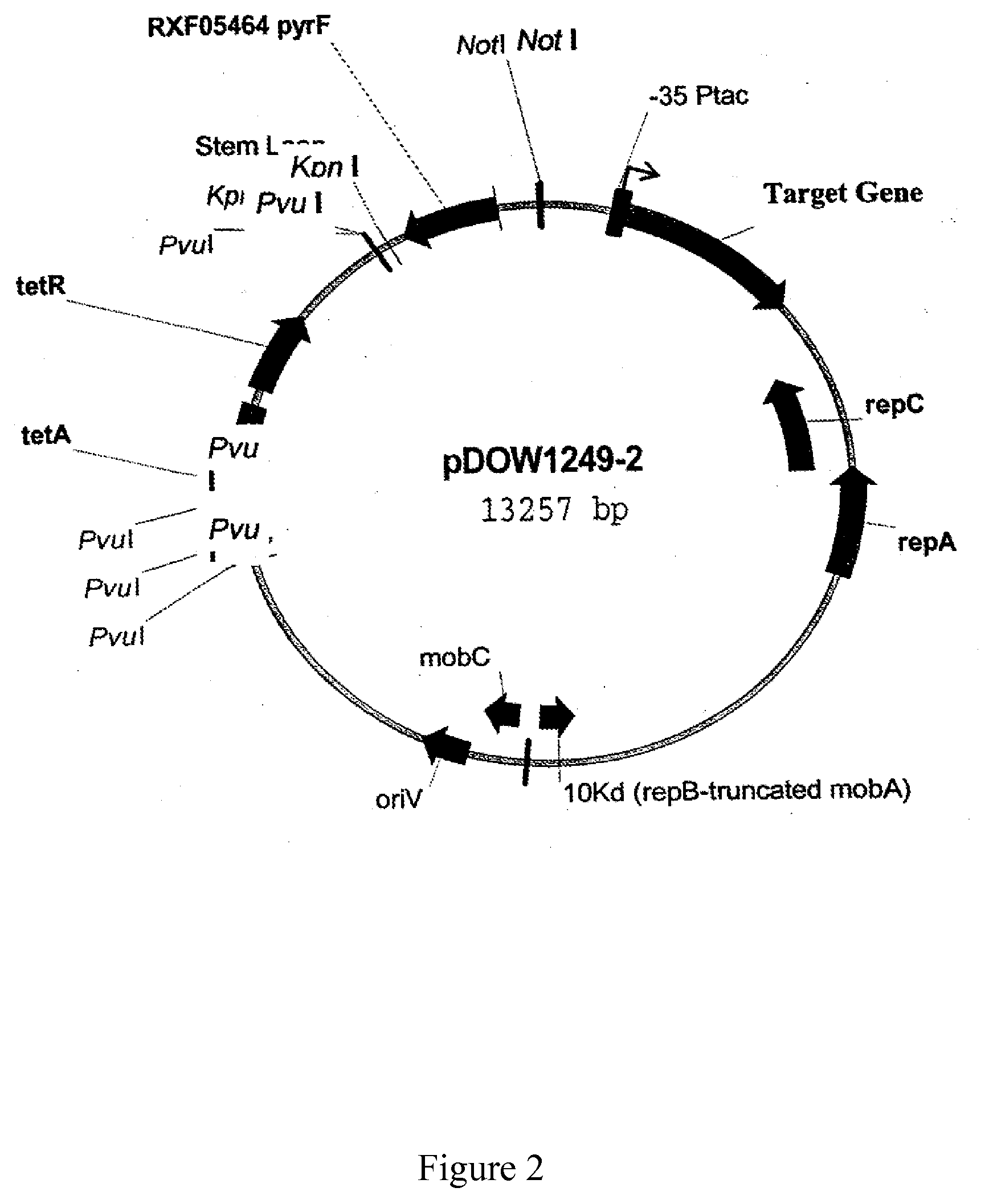

Protein expression systems

InactiveUS20050186666A1High protein yieldEfficient productionBacteriaHydrolasesBiotechnologyRecombinant protein production

The present invention provides an improved expression system for the production of recombinant polypeptides utilizing auxotrophic selectable markers. In addition, the present invention provides improved recombinant protein production in host cells through the improved regulation of expression.

Owner:PFENEX

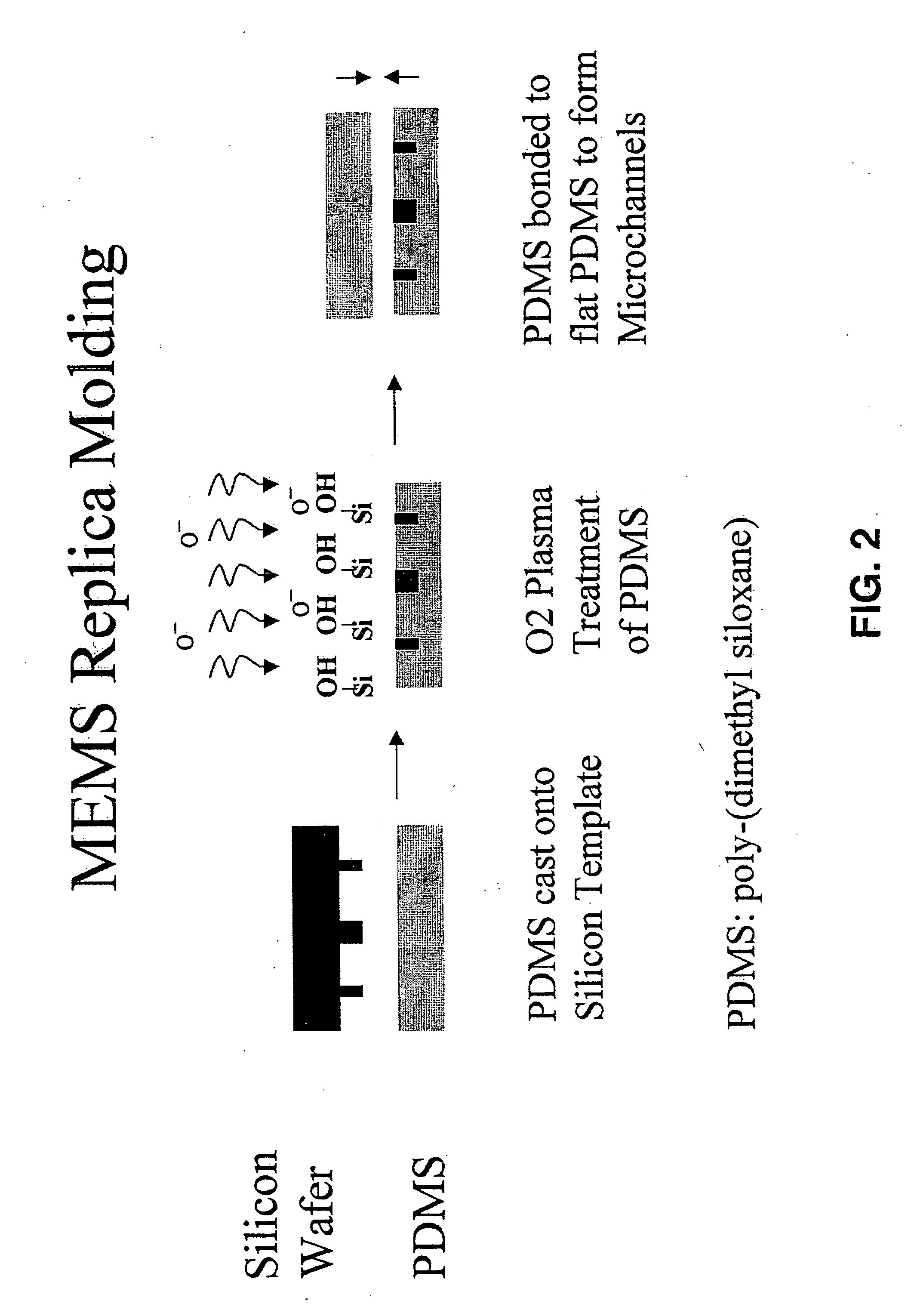

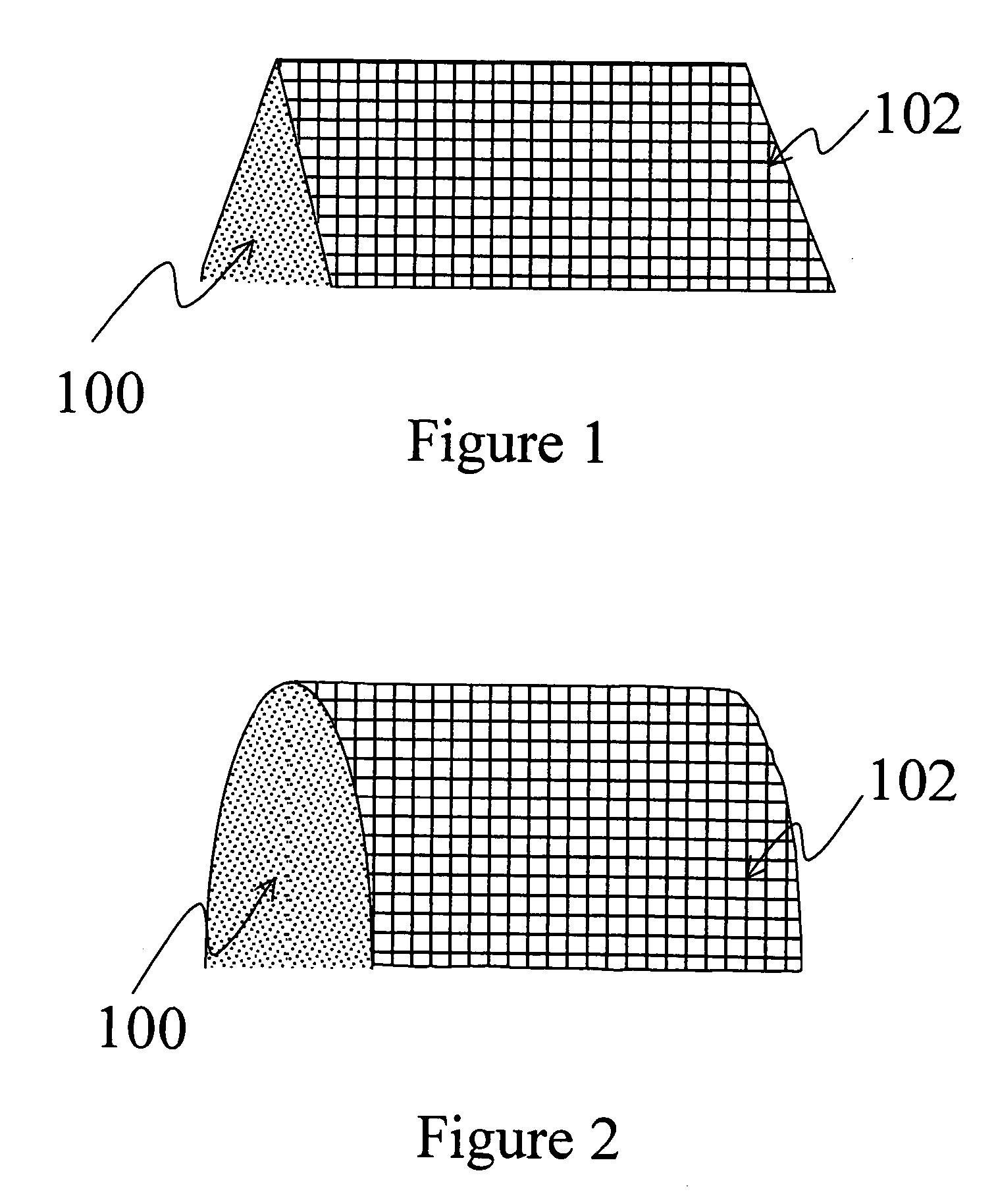

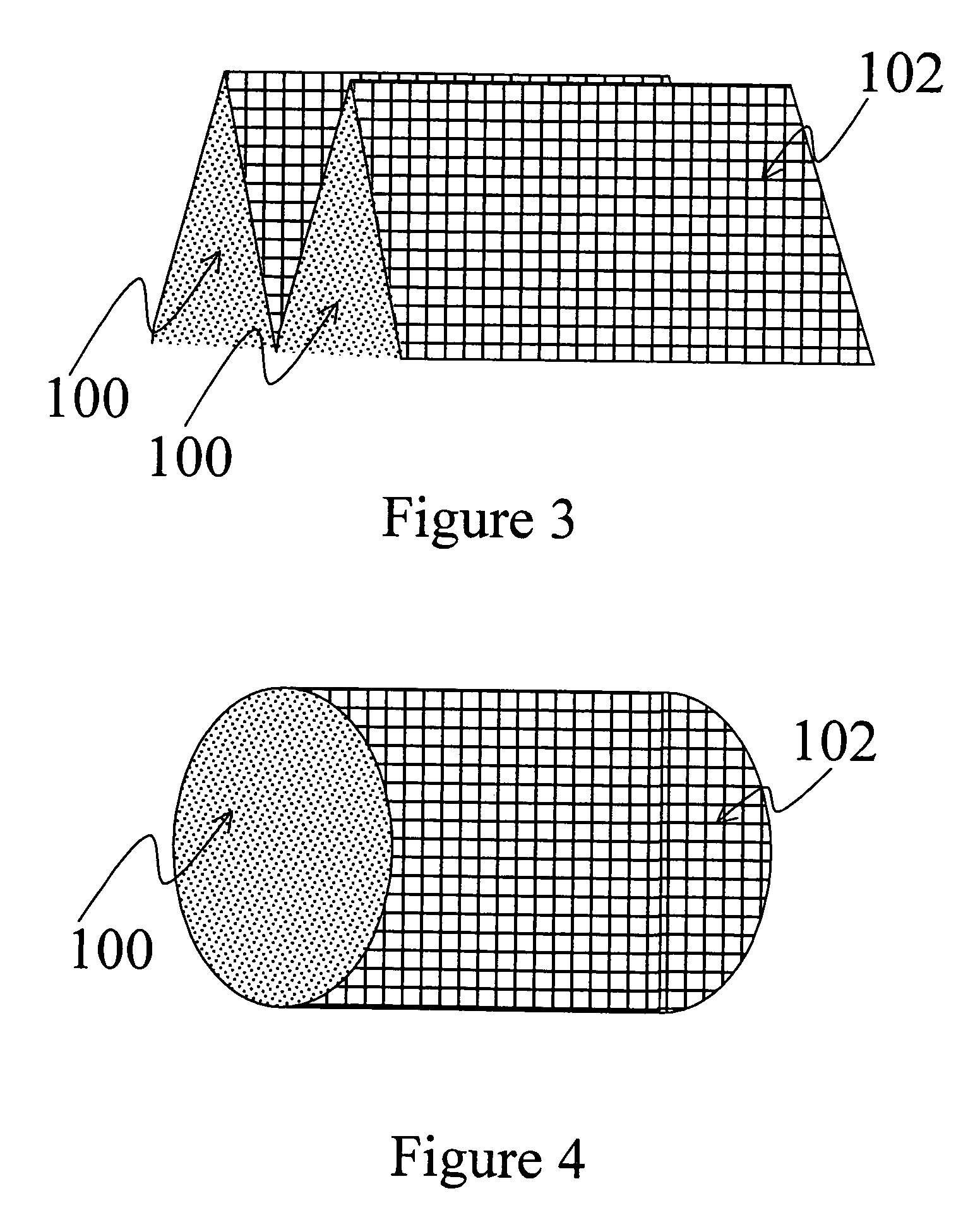

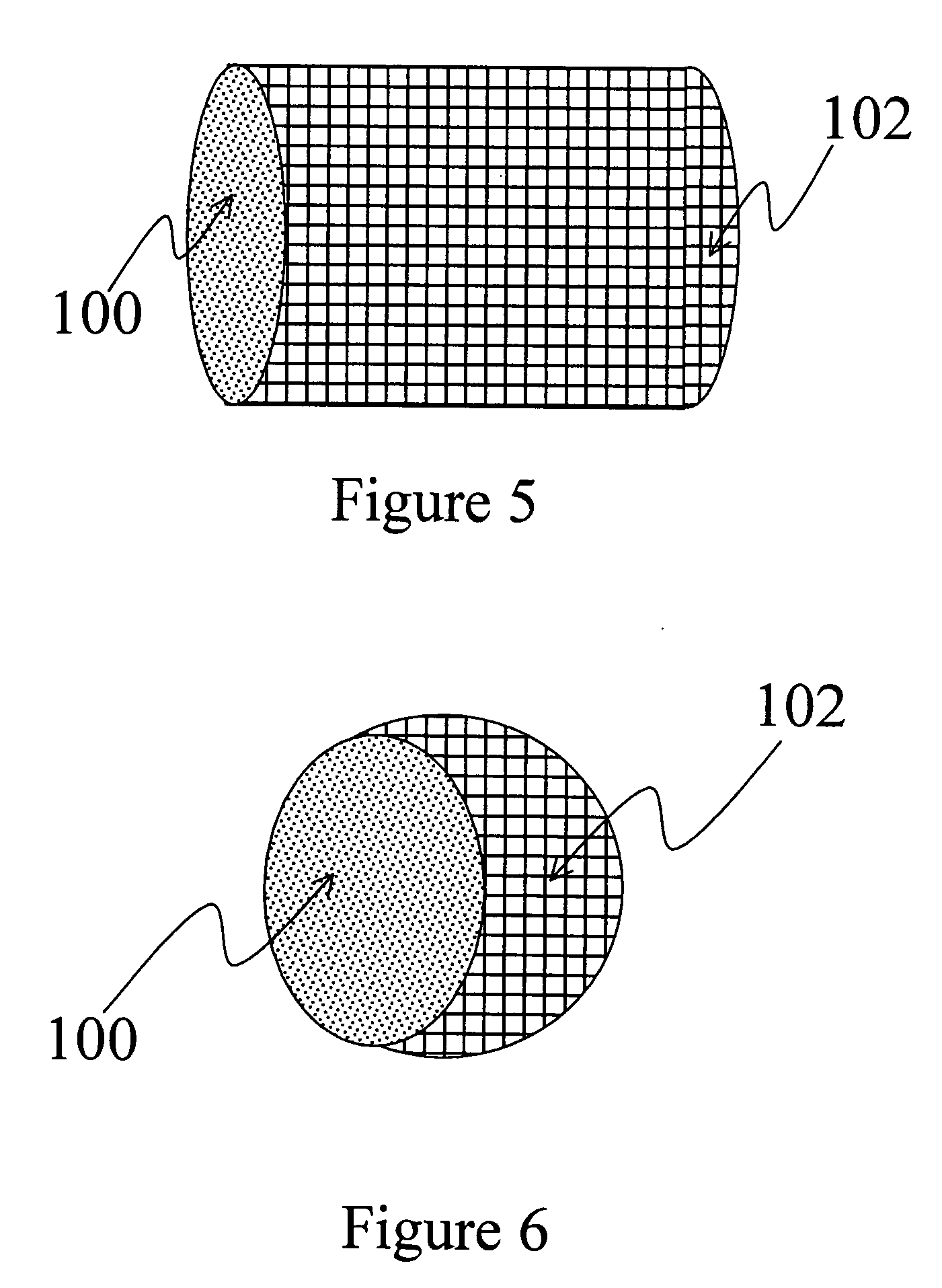

Three dimensional construct for the design and fabrication of physiological fluidic networks

ActiveUS20060136182A1Increase cell densityIncrease the number ofMedical simulationAdditive manufacturing apparatusEngineeringSmall vessel

Owner:MASSACHUSETTS INST OF TECH +2

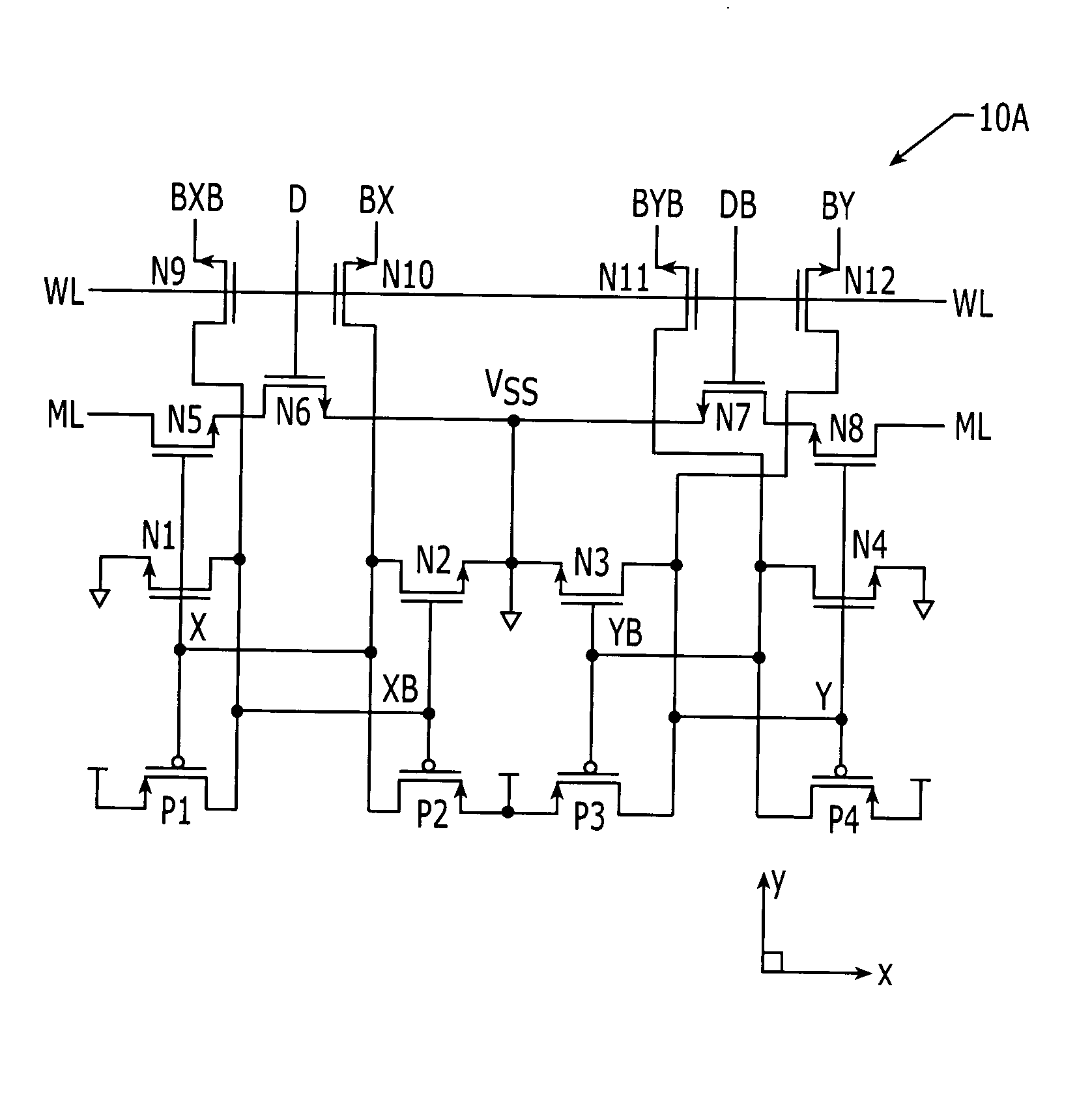

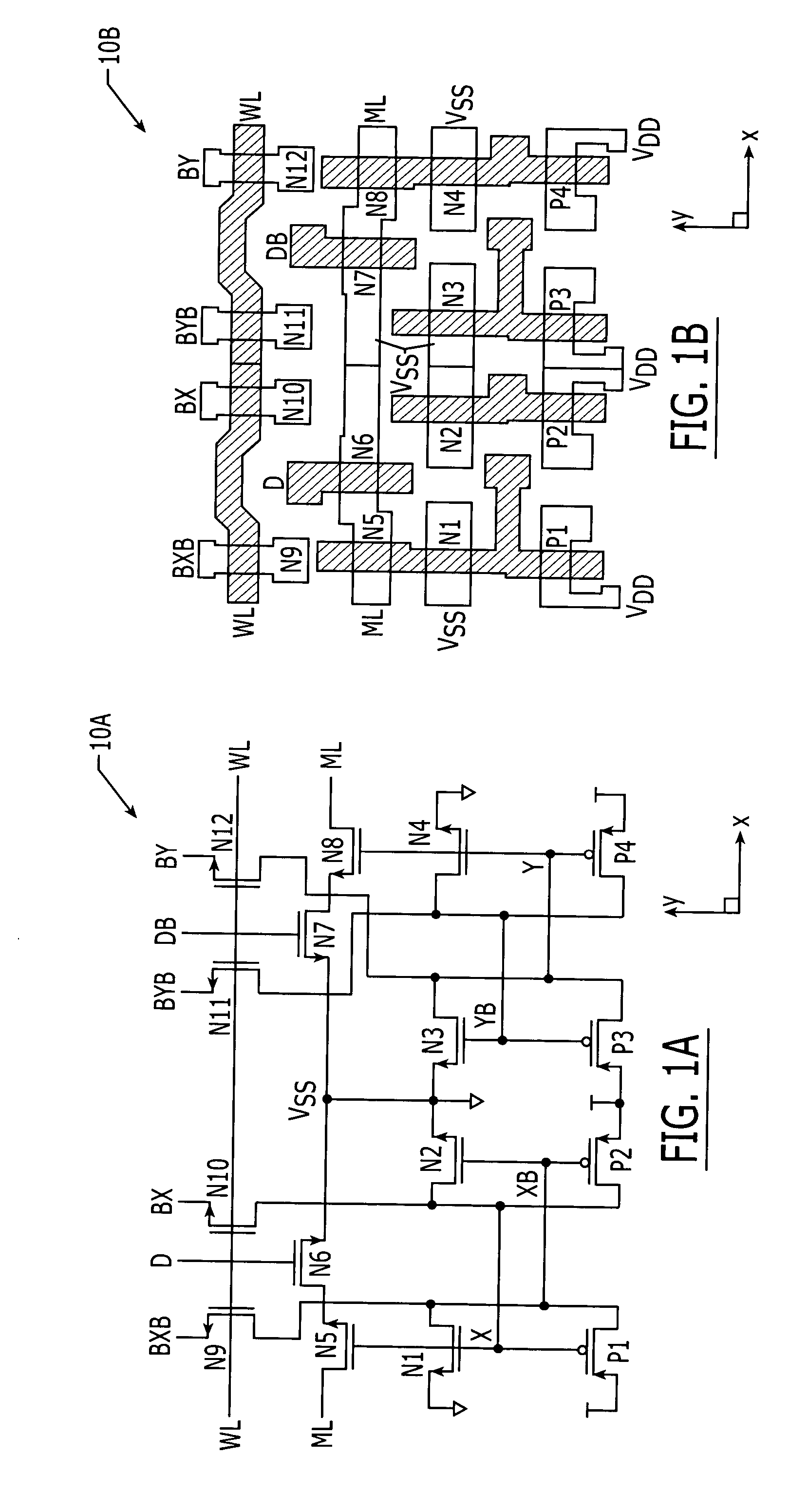

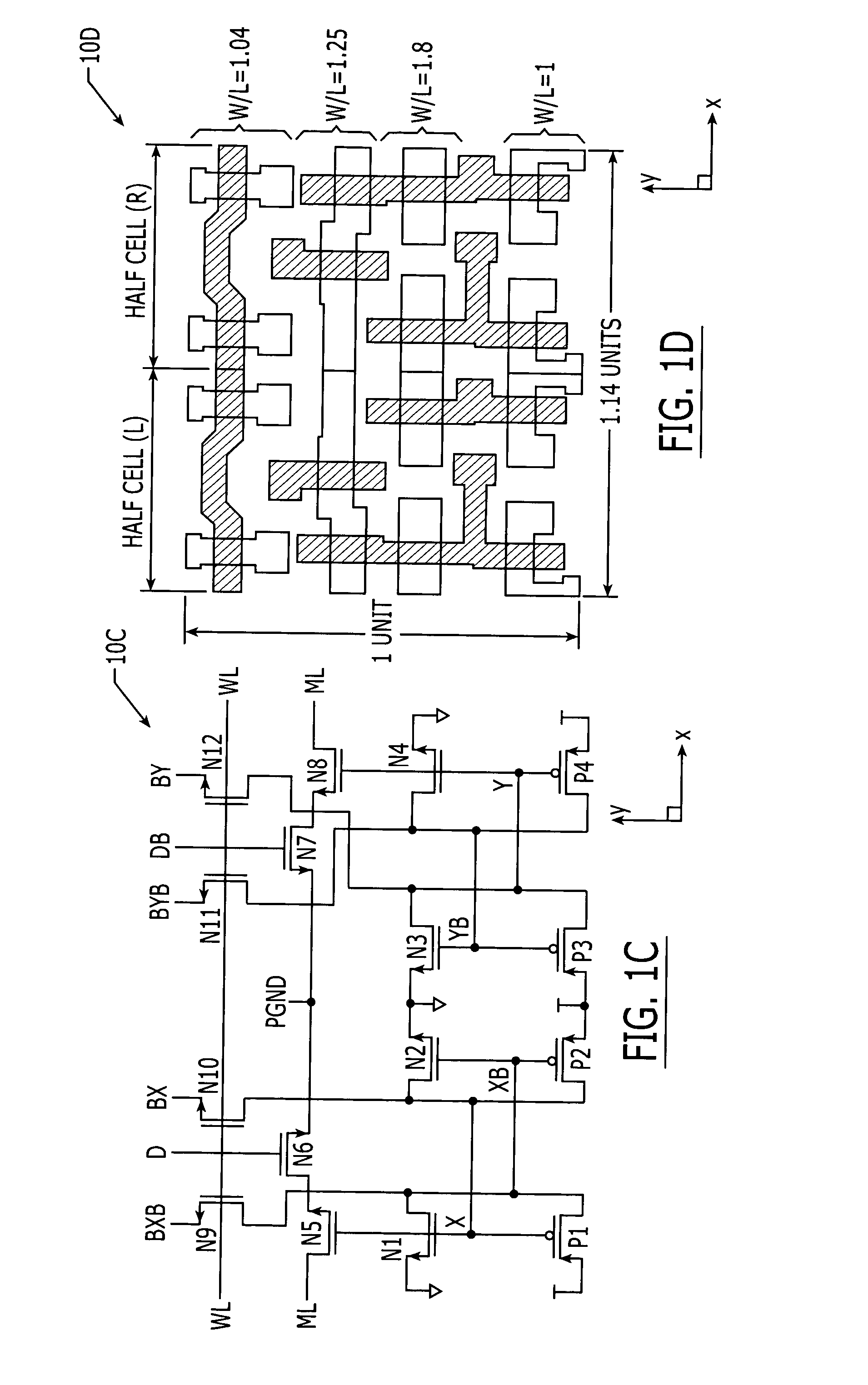

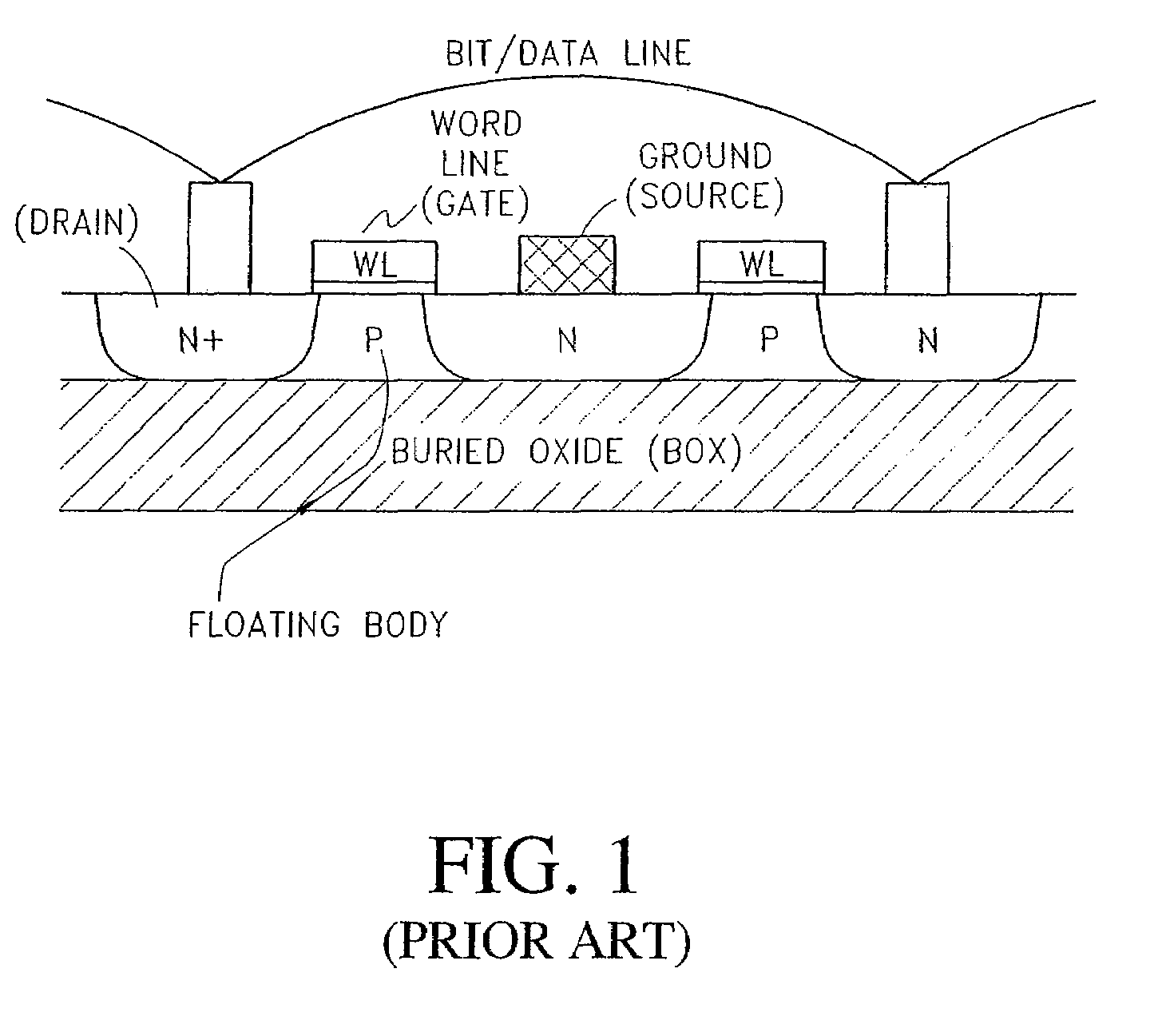

Ternary content addressable memory (TCAM) cells with small footprint size and efficient layout aspect ratio

InactiveUS20050135134A1Small layout footprint sizeEnhance scalability and uniformityDigital storageExtensibilityEngineering

Ternary CAM cells are provided that have extremely small layout footprint size and efficient layout aspect ratios that enhance scalability. The cells also have high degrees of symmetry that facilitate high yield interconnections to bit, data and match lines. A 16T ternary CAM cell includes first and second pairs of access transistors that extend adjacent a first side of the cell, and first and second pairs of cross-coupled inverters that extend adjacent a second side of the cell. First and second halves of a 4T compare circuit are also provided. The first half of the 4T compare circuit is positioned so that is extends between the first pair of access transistors and the first pair of cross-coupled inverters. Similarly, the second half of the 4T compare circuit is positioned so that it extends between the second pair of access transistors and the second pair of cross-coupled inverters.

Owner:AVAGO TECH INT SALES PTE LTD

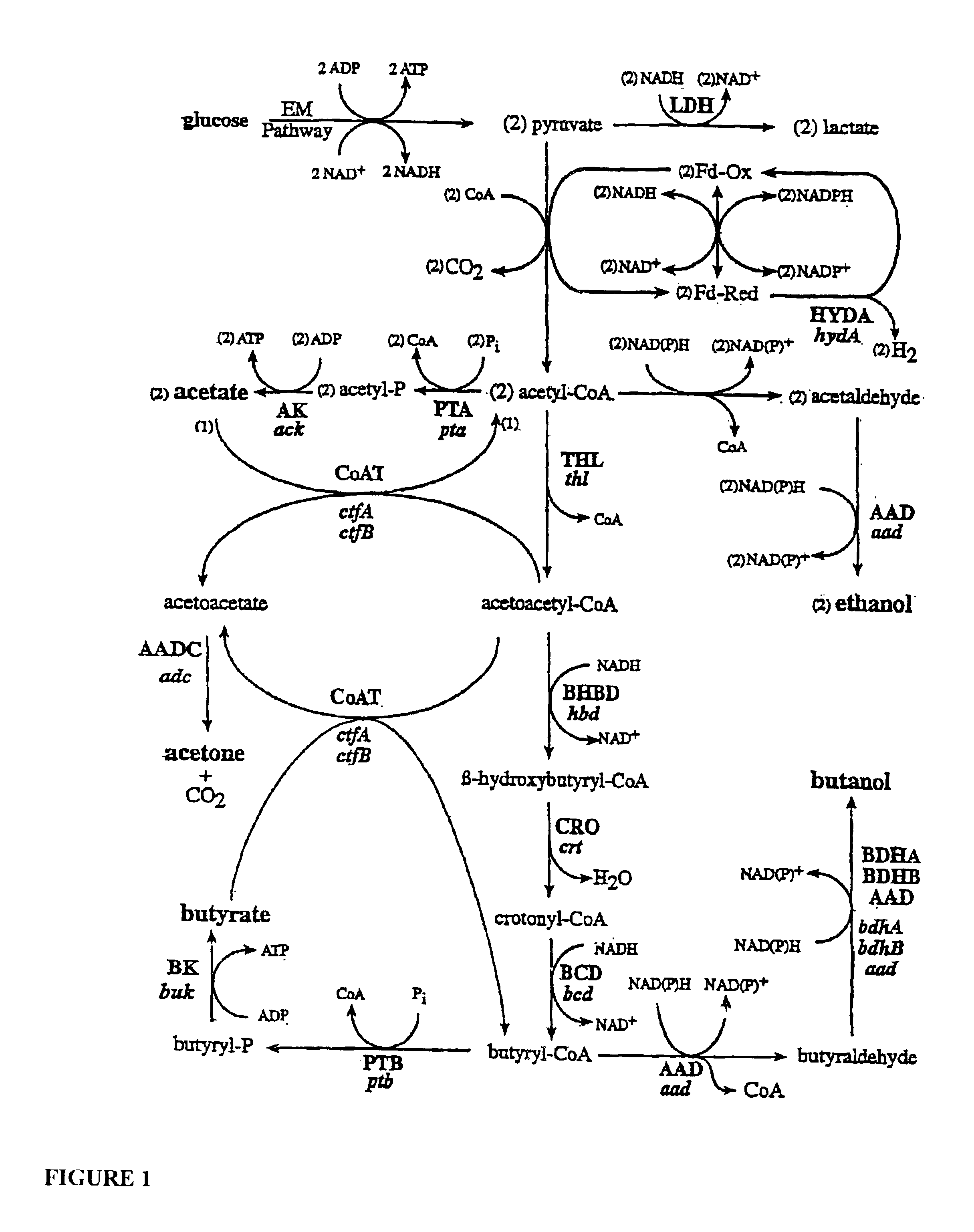

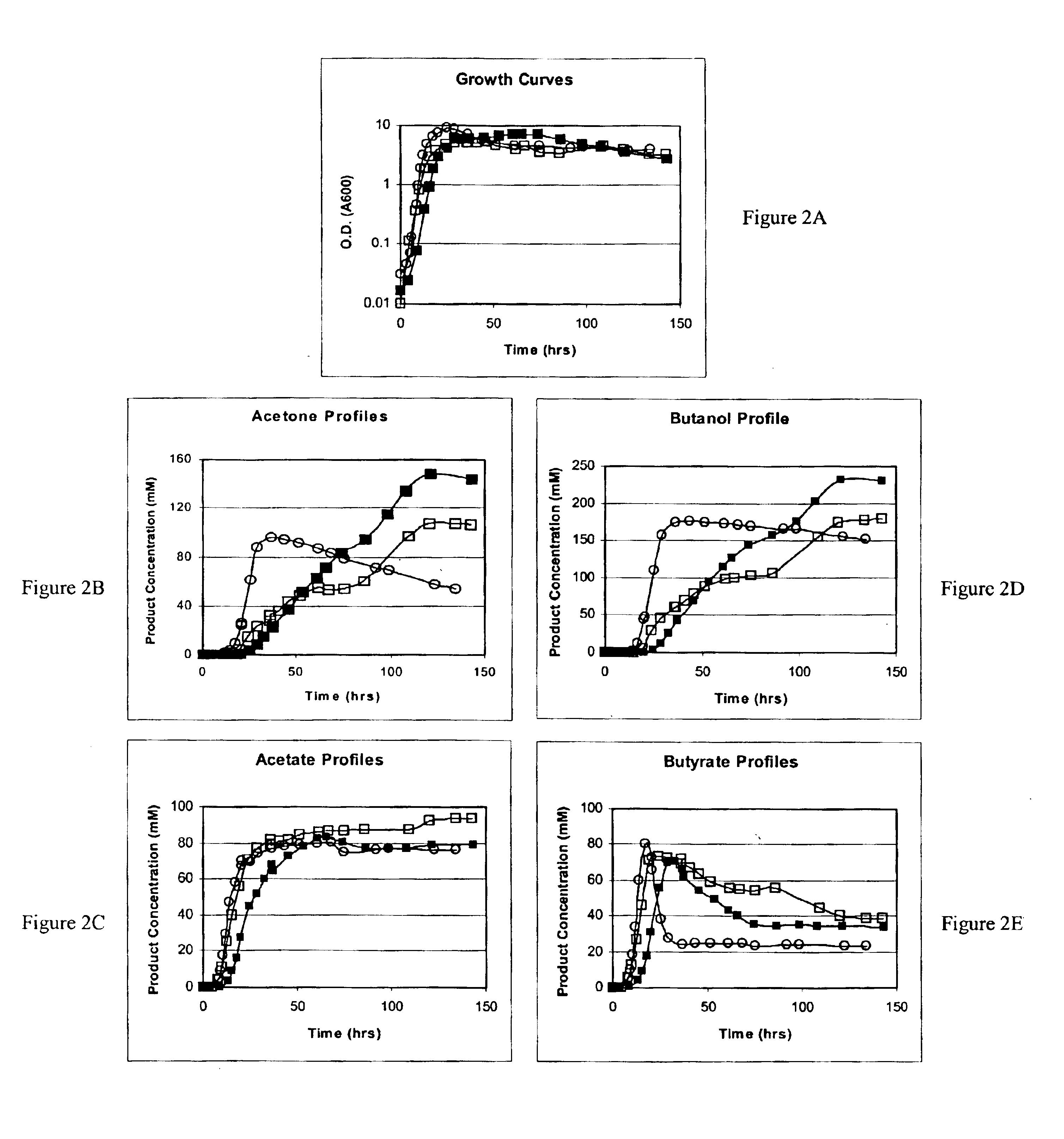

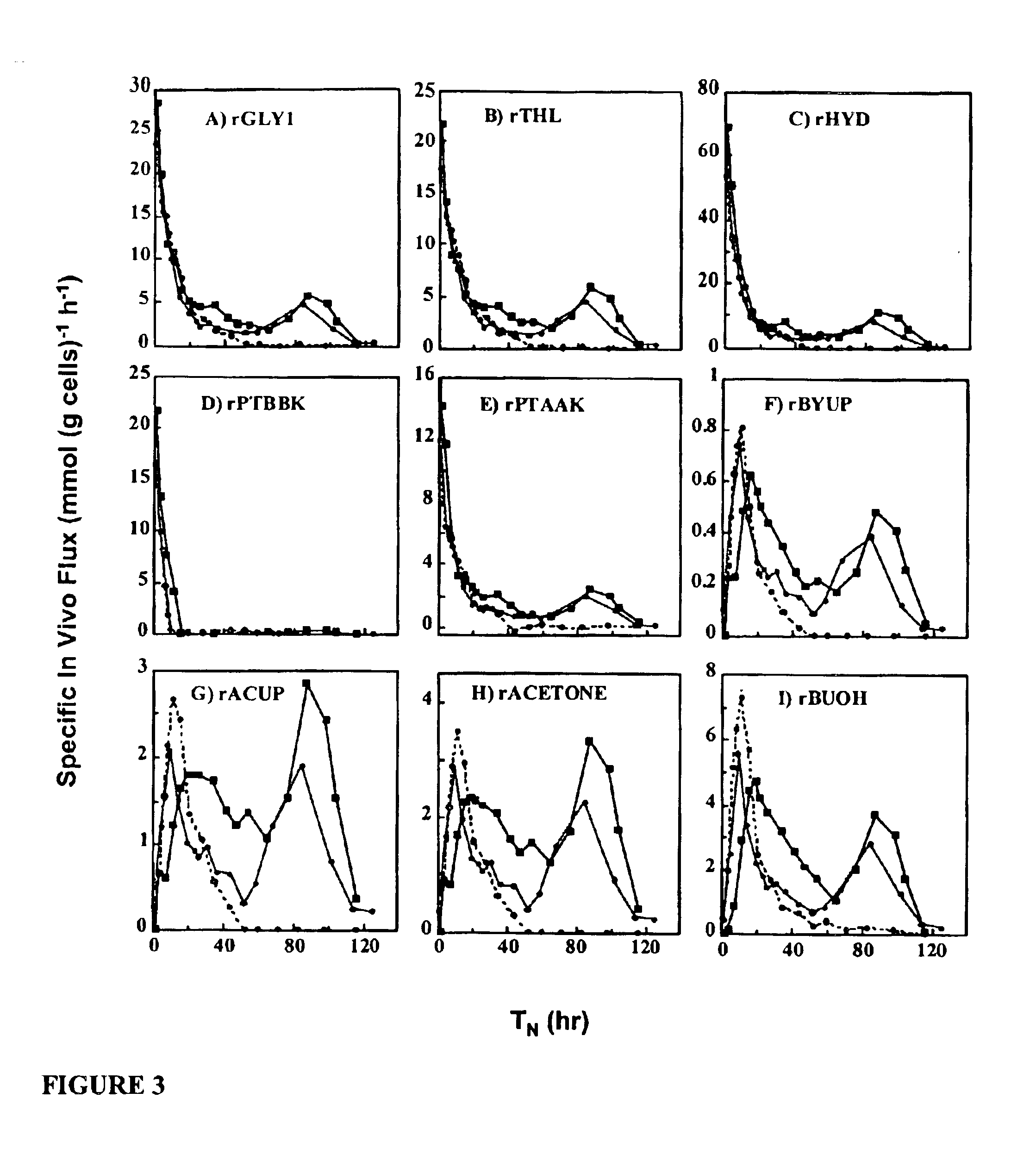

Increased cell resistance to toxic organic substances

Recombinant microorganisms and related methods of use to enhance tolerance to toxic substances. In particular, such microorganisms and methods can be used to increase solvent production.

Owner:NORTHWESTERN UNIV

Polypropylene foaming material and production method thereof

The invention discloses a polypropylene foaming material. The polypropylene foaming material comprises the following components according to proportioning by weight: 60-99 parts of polypropylene resin; 0.1-10 parts of nucleating agent; 0.1-5 parts of antioxidant; 0-5 parts of colorant; 0-5 parts of lubricant; and 0-20 parts of filling material; and the melt index of the polypropylene resin is 0.1-20 g / 10 min, and the foaming process adopts supercritical fluid as the foaming agent, i.e. 0.1-20 parts of supercritical fluid (proportioning by weight). The invention also discloses a production method of the foaming material. Compared with the prior art, the invention has the advantages that the universal polypropylene can be adopted as a base material, no polymer is provided, the cross-linking reaction does not occur, the foaming process is free from environmental pollution, and the production method is safe; the quality of the obtained foaming material is stable, the foaming percentage and the cell density are high, the distribution is uniform, and the invention is suitable for the industrial production at a large scale; and meanwhile, the overall production method is simple, the operation is easy, and the production cost is relatively lower.

Owner:合肥朗润中科材料有限公司

Methods for growing mammalian cells in vitro

InactiveUS7390660B2Increase cell densityEnhance cell viabilityCulture processCell culture mediaMammalGlucose polymers

Owner:F HOFFMANN LA ROCHE & CO AG

Method of making cell growth surface

InactiveUS20060292690A1Cell density be limitedReduced viabilityCell culture supports/coatingTissue/virus culture apparatusCell adhesionCell growth

The present invention discloses a three-dimensional porous growth surface made from polysaccharide material, especially the alginic acid, to enhance cell growth surface, promote cell adherence, immobilization and propagation, maintain surface structure integrity, enable programmable degradation, and thus increase cellular production. The present invention teaches several methods: a method to enhance the integrity of the growth surface by protecting the growth surface in a rigid solid support; a method of use for enhancing the performance of the surface; and a method of modifying a growth surface for eukaryotic and / or prokaryotic cells comprising the steps of increasing surface area by creating porous and 3-D structure, treating a surface to encourage cell attachment, promoting cell growth and proliferation, and disposing the growth surface in any conventional cell cultivating device. The growth surface is able to program degradation and release the cell / tissue mass after the culture is completed.

Owner:CESCO BIOENGINEERING CO LTD

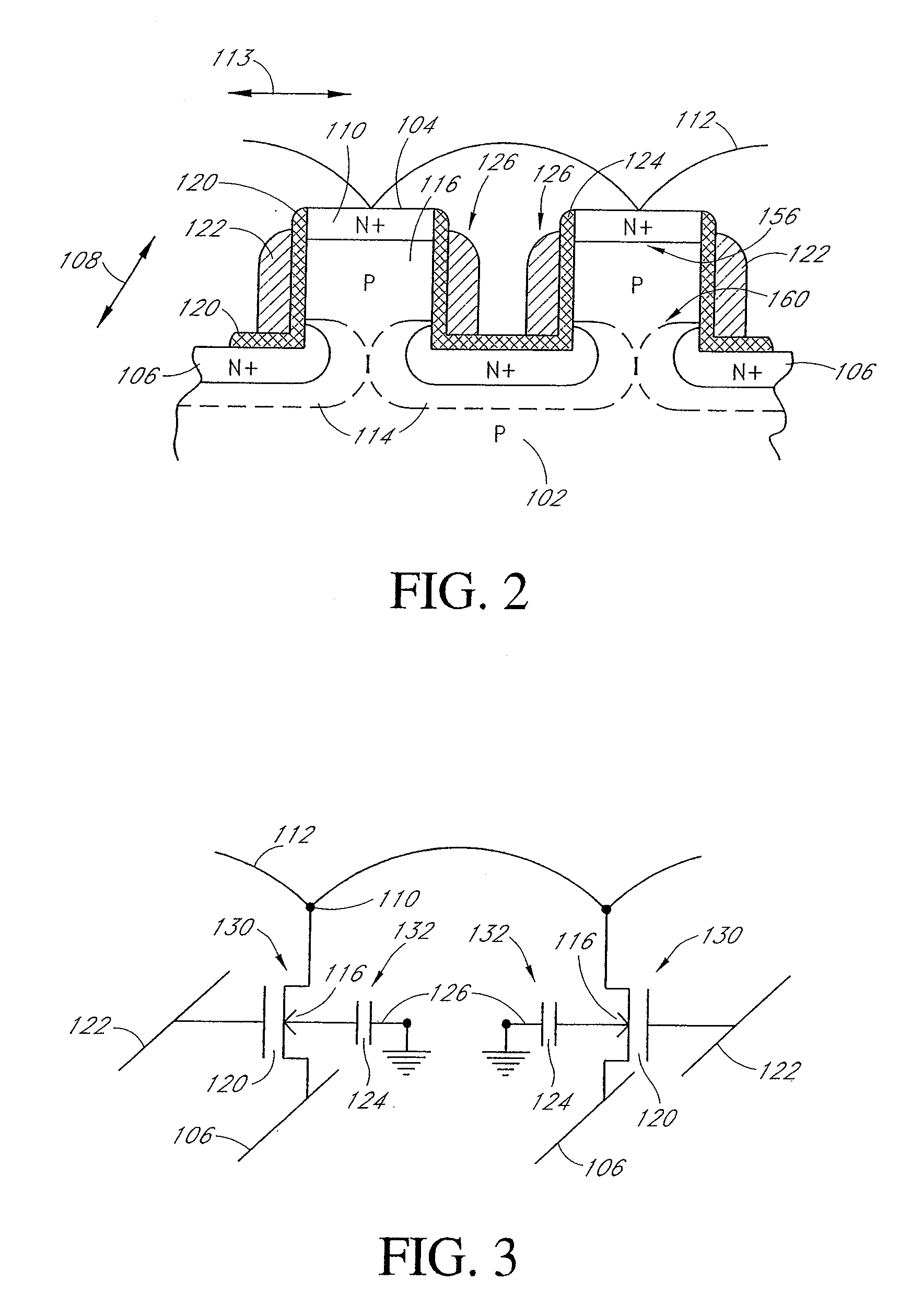

Long retention time single transistor vertical memory gain cell

ActiveUS7271052B1High band gap energyAvoid excessive leakage currentTransistorSolid-state devicesHigh cellRetention time

A single transistor vertical memory gain cell with long data retention times. The memory cell is formed from a silicon carbide substrate to take advantage of the higher band gap energy of silicon carbide as compared to silicon. The silicon carbide provides much lower thermally dependent leakage currents which enables significantly longer refresh intervals. In certain applications, the cell is effectively non-volatile provided appropriate gate bias is maintained. N-type source and drain regions are provided along with a pillar vertically extending from a substrate, which are both p-type doped. A floating body region is defined in the pillar which serves as the body of an access transistor as well as a body storage capacitor. The cell provides high volumetric efficiency with corresponding high cell density as well as relatively fast read times.

Owner:MICRON TECH INC

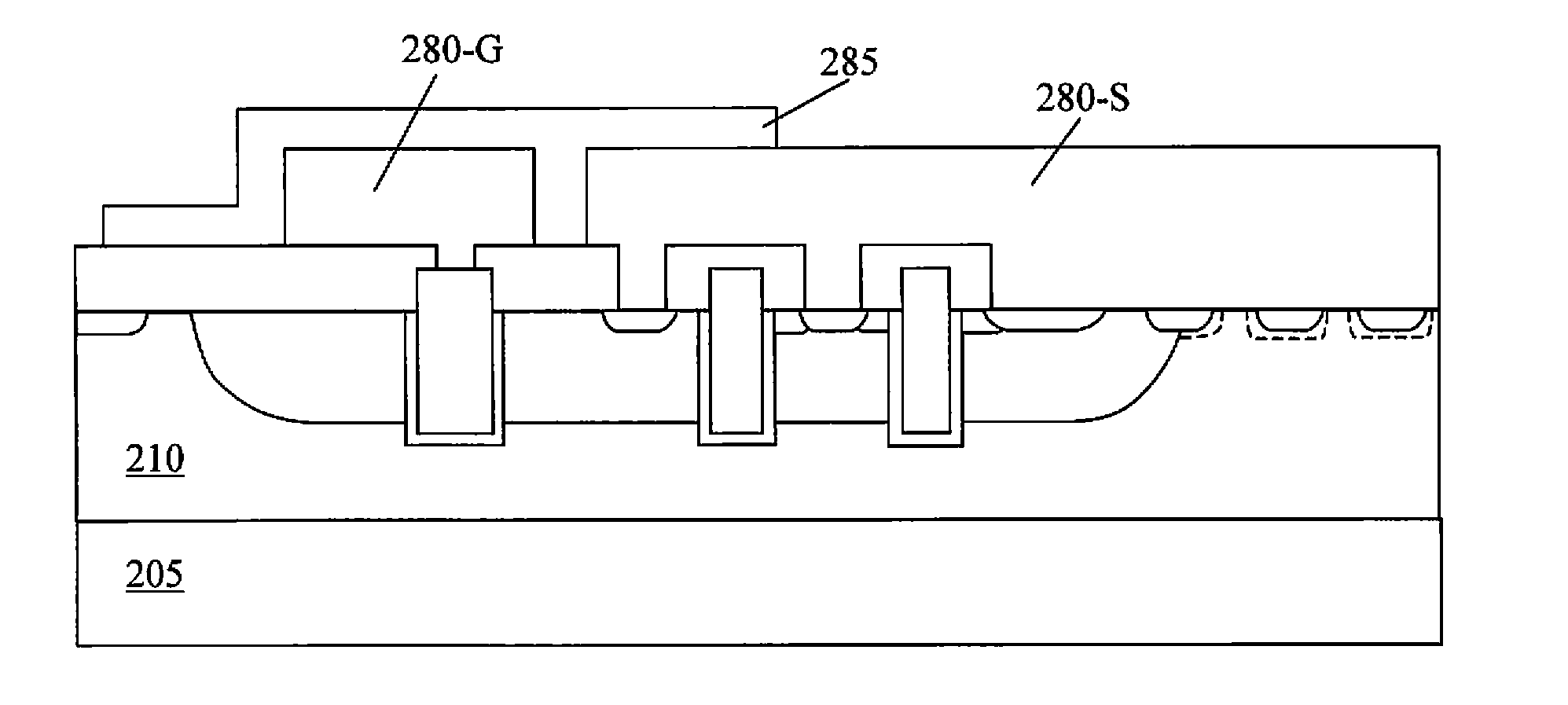

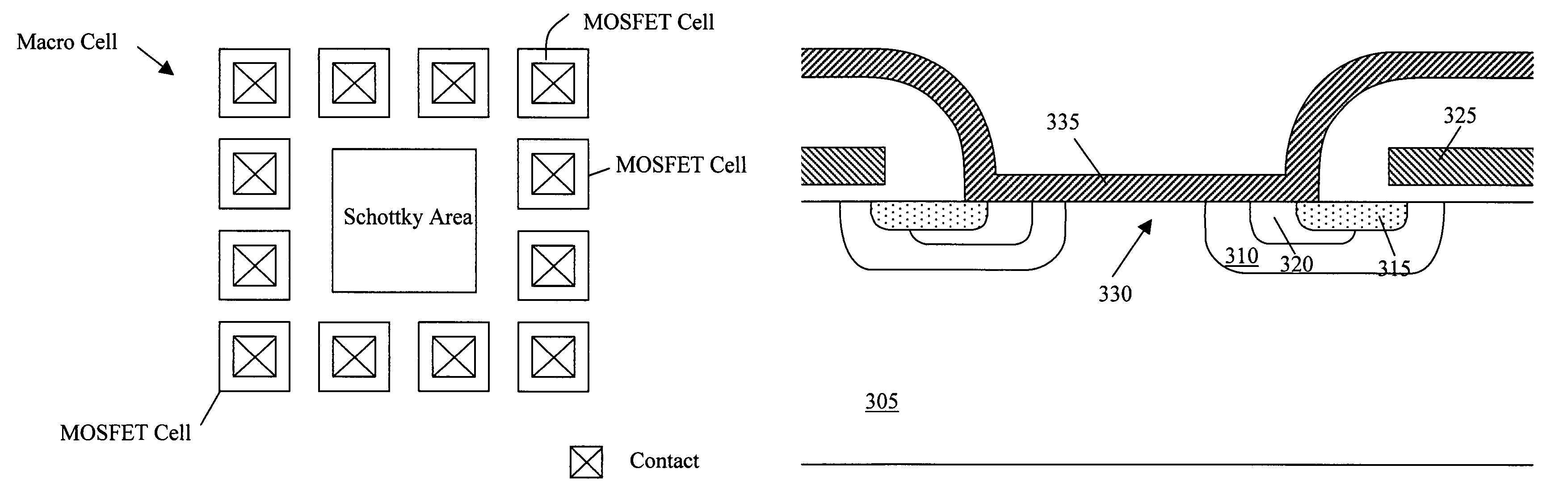

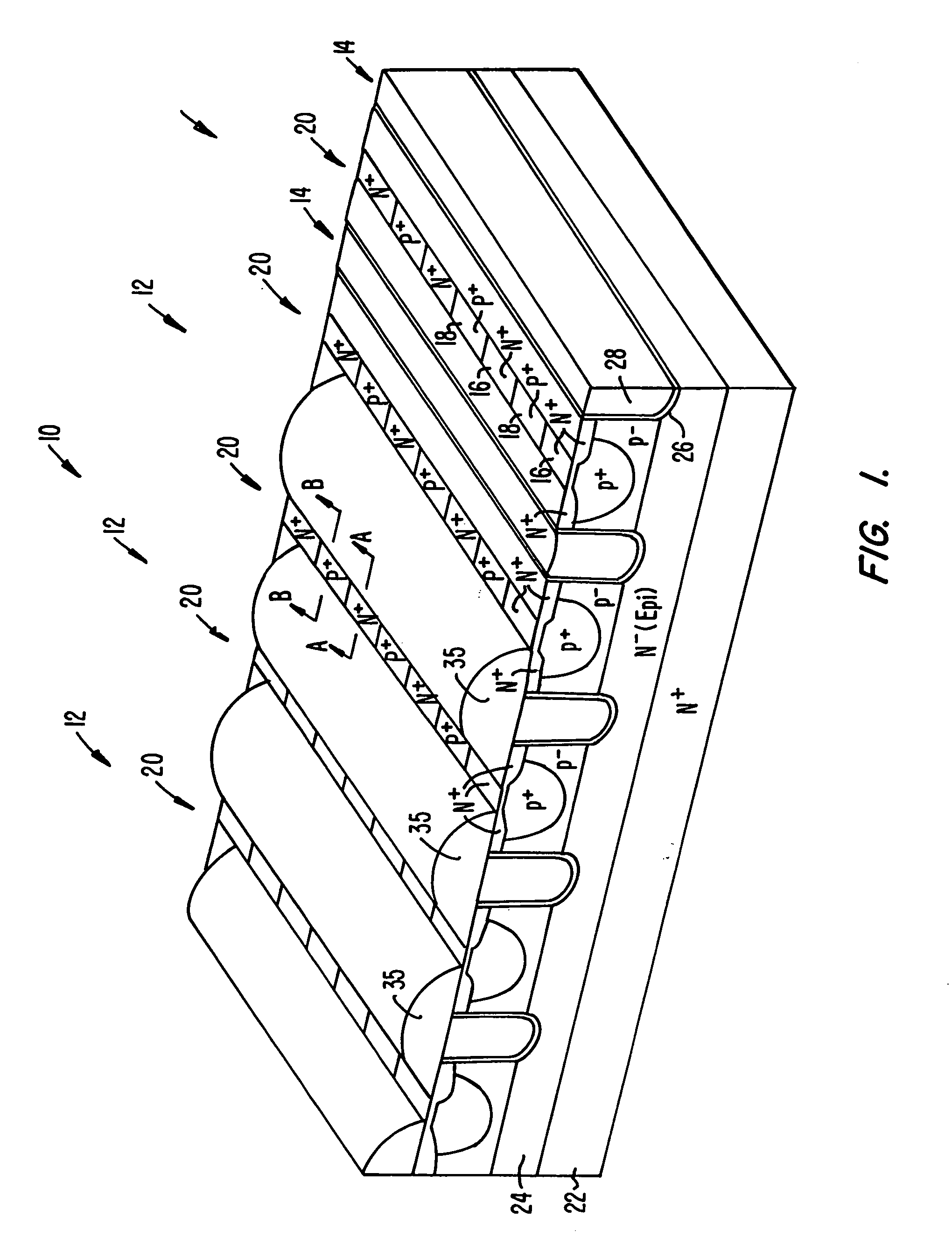

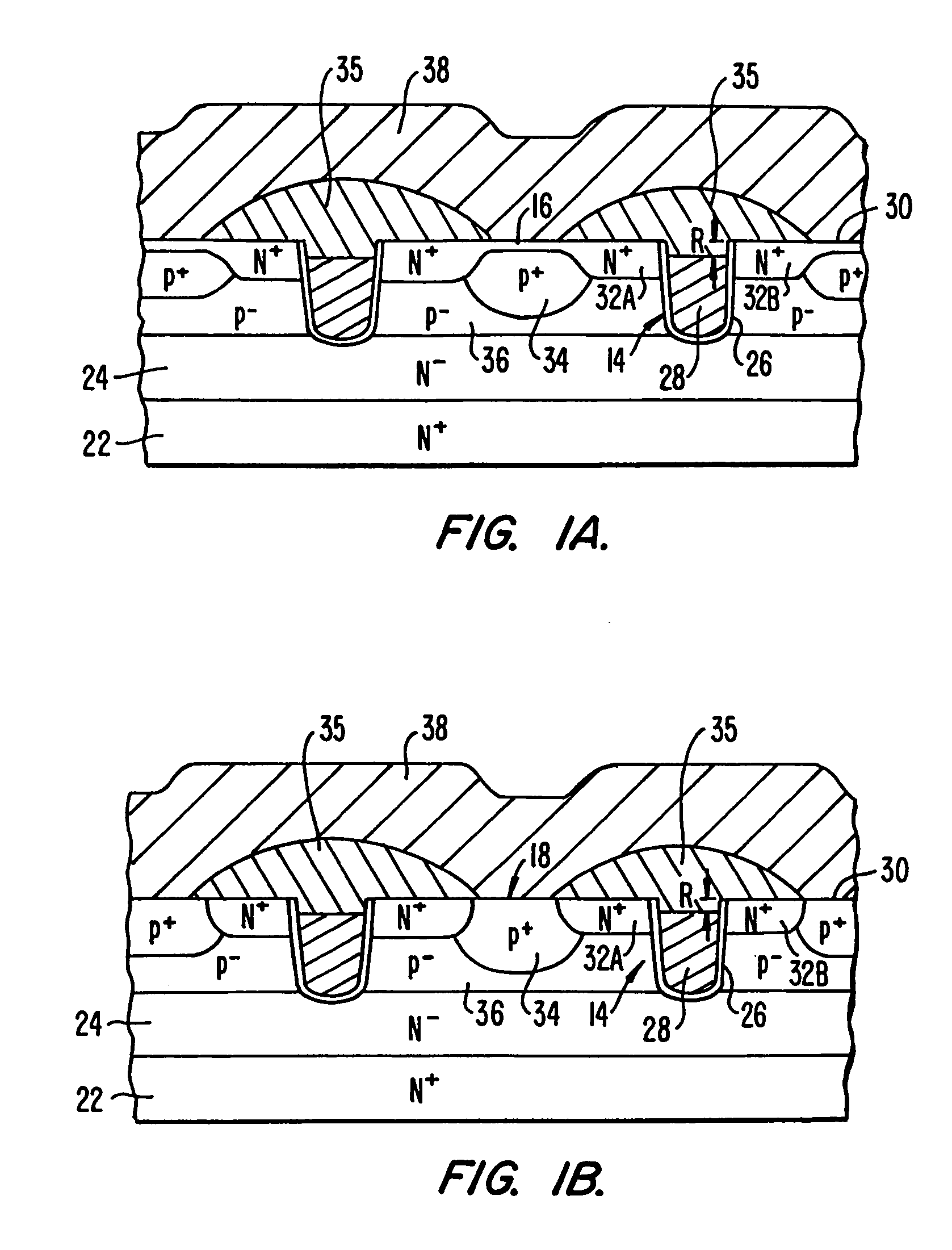

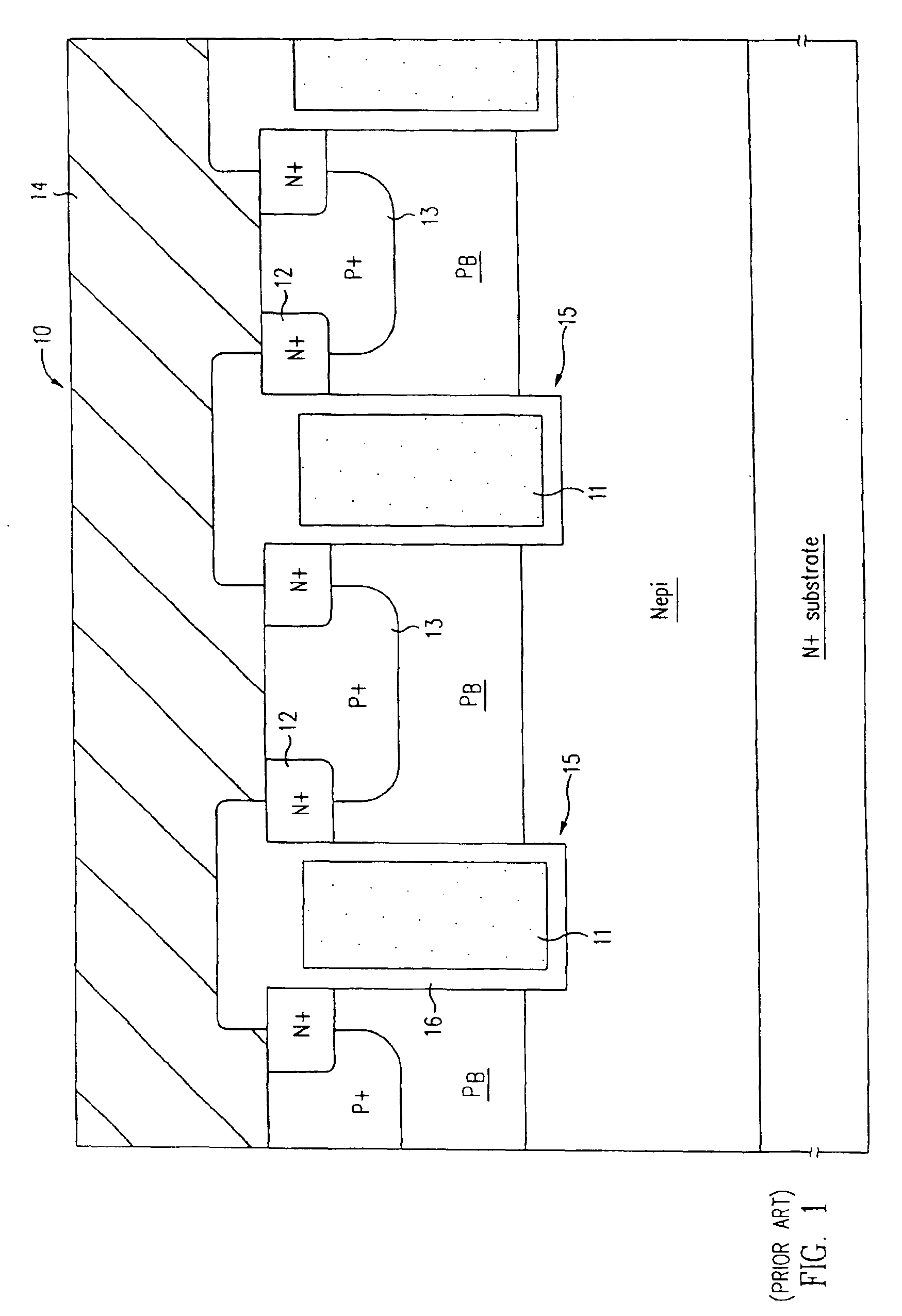

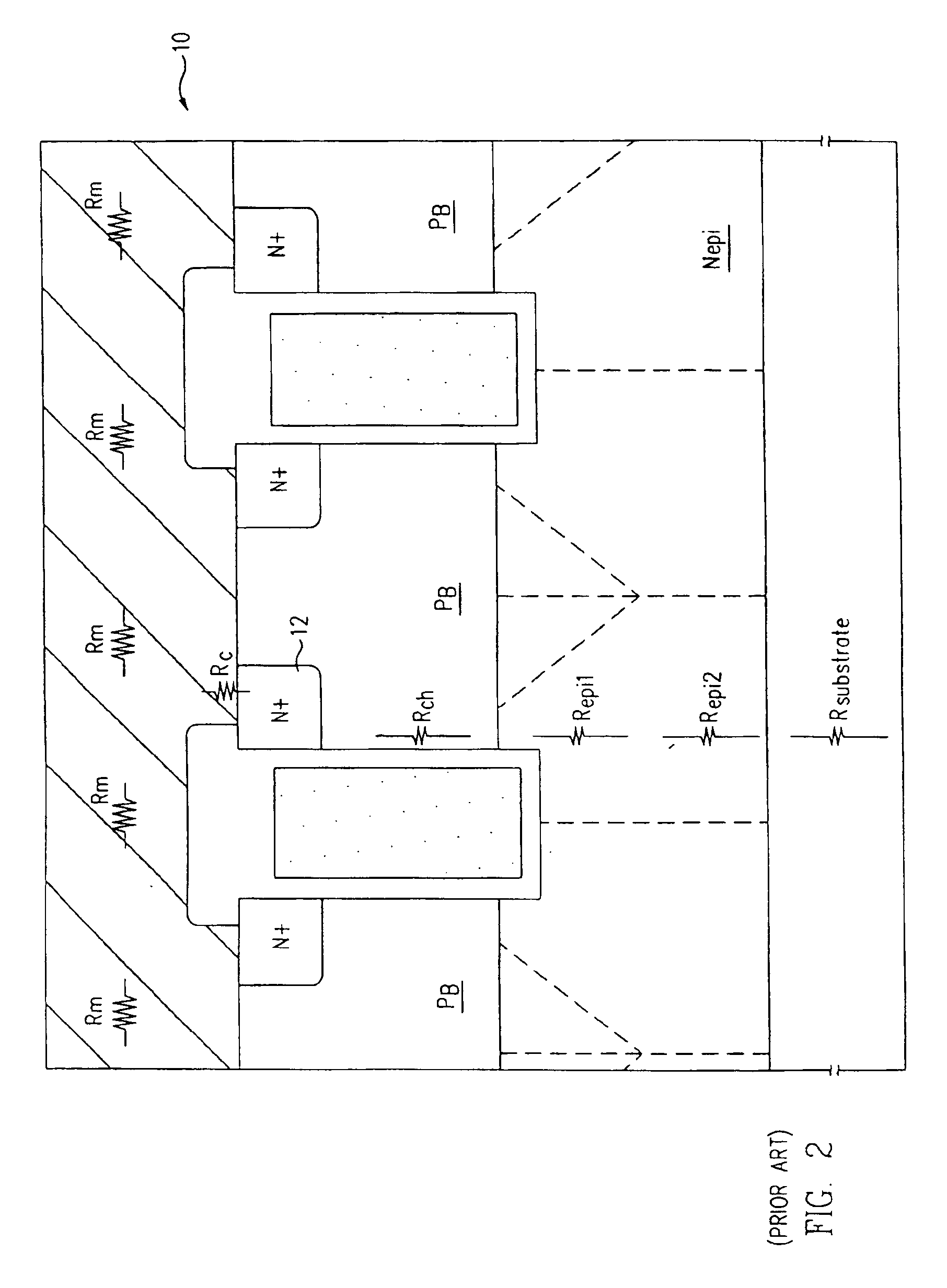

Planar SRFET using no additional masks and layout method

A semiconductor power device supported on a semiconductor substrate of a first conductivity type with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer with a same conductivity type as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region of a second conductivity type extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region of second conductivity type. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON LTD

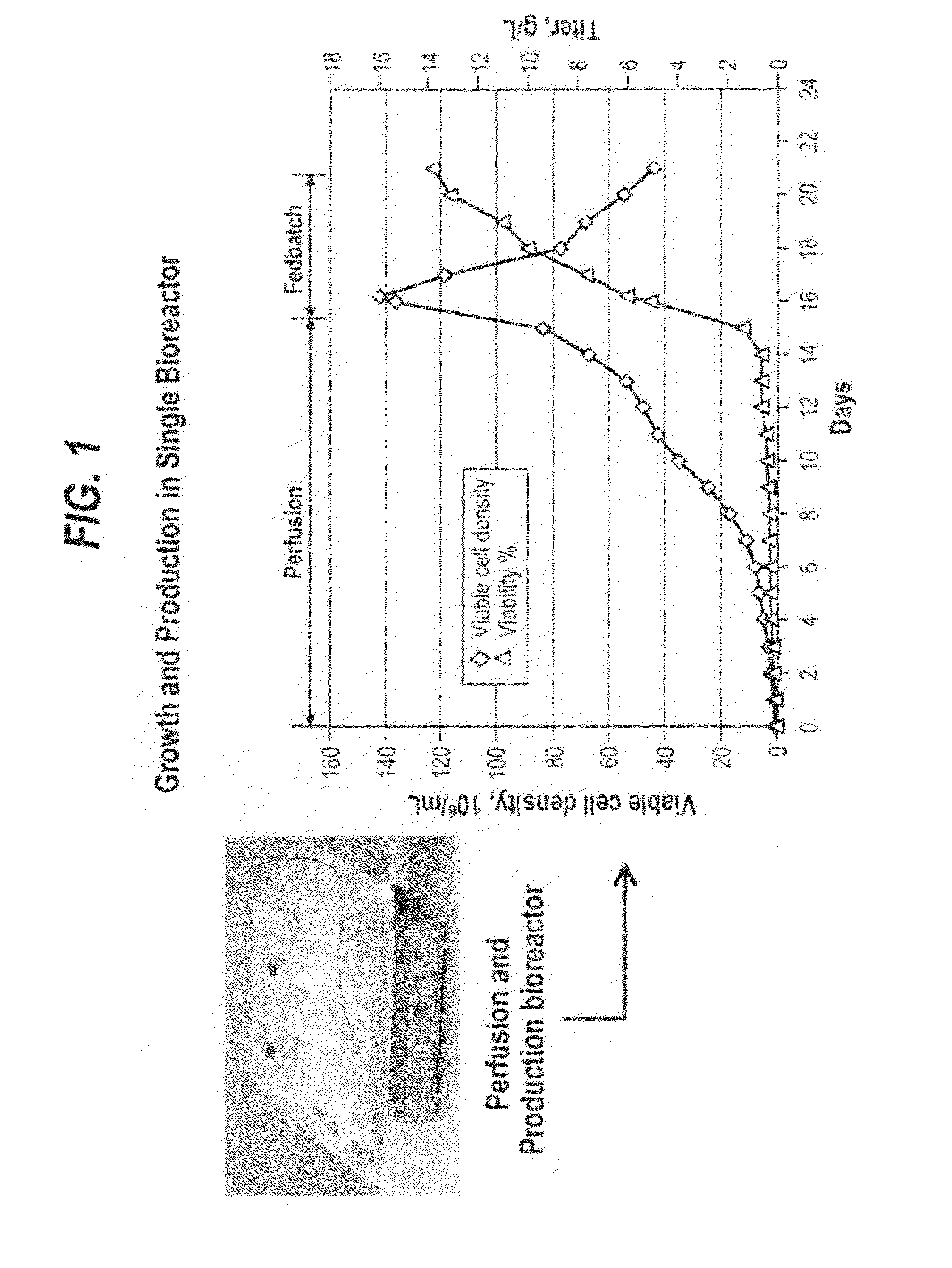

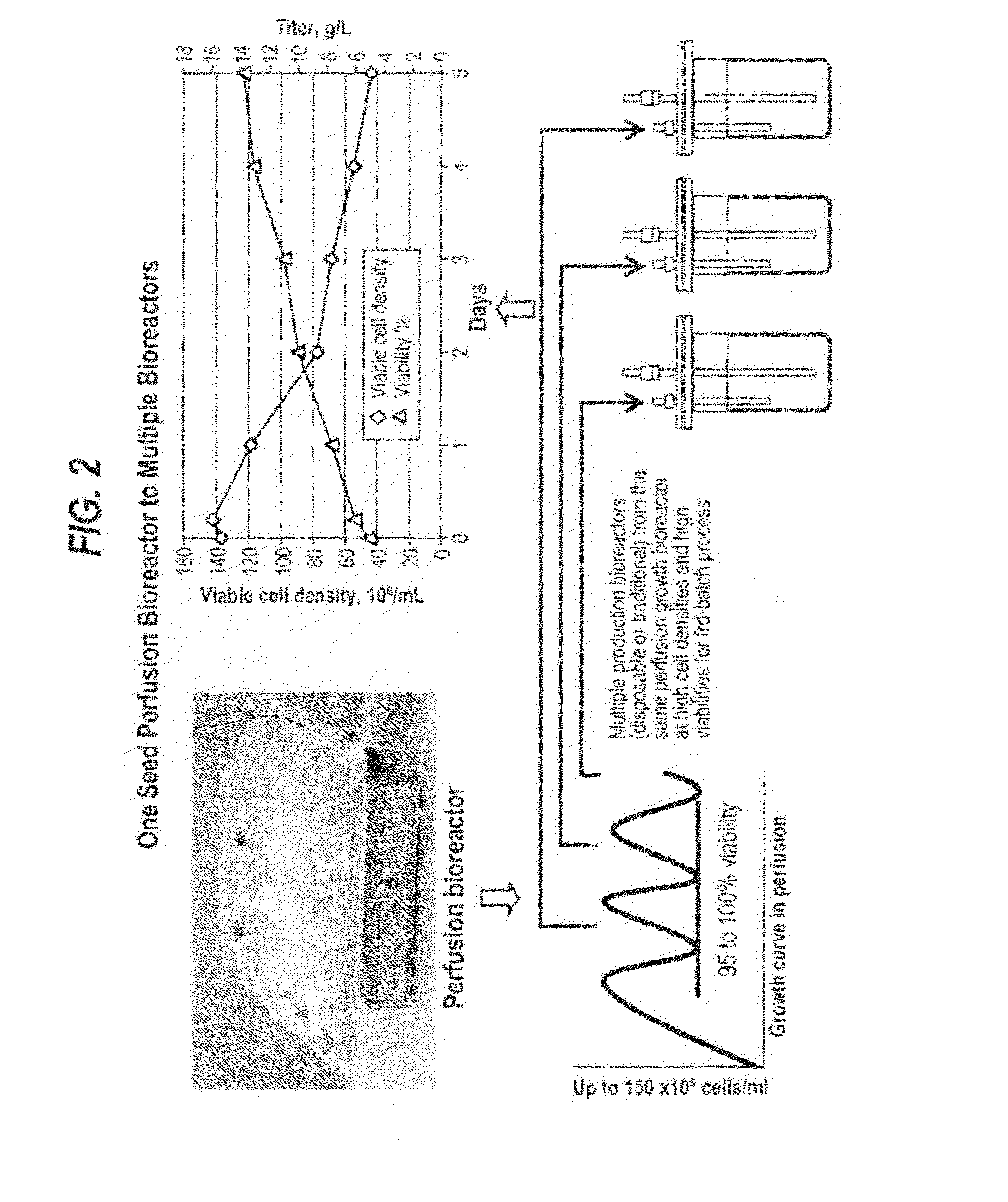

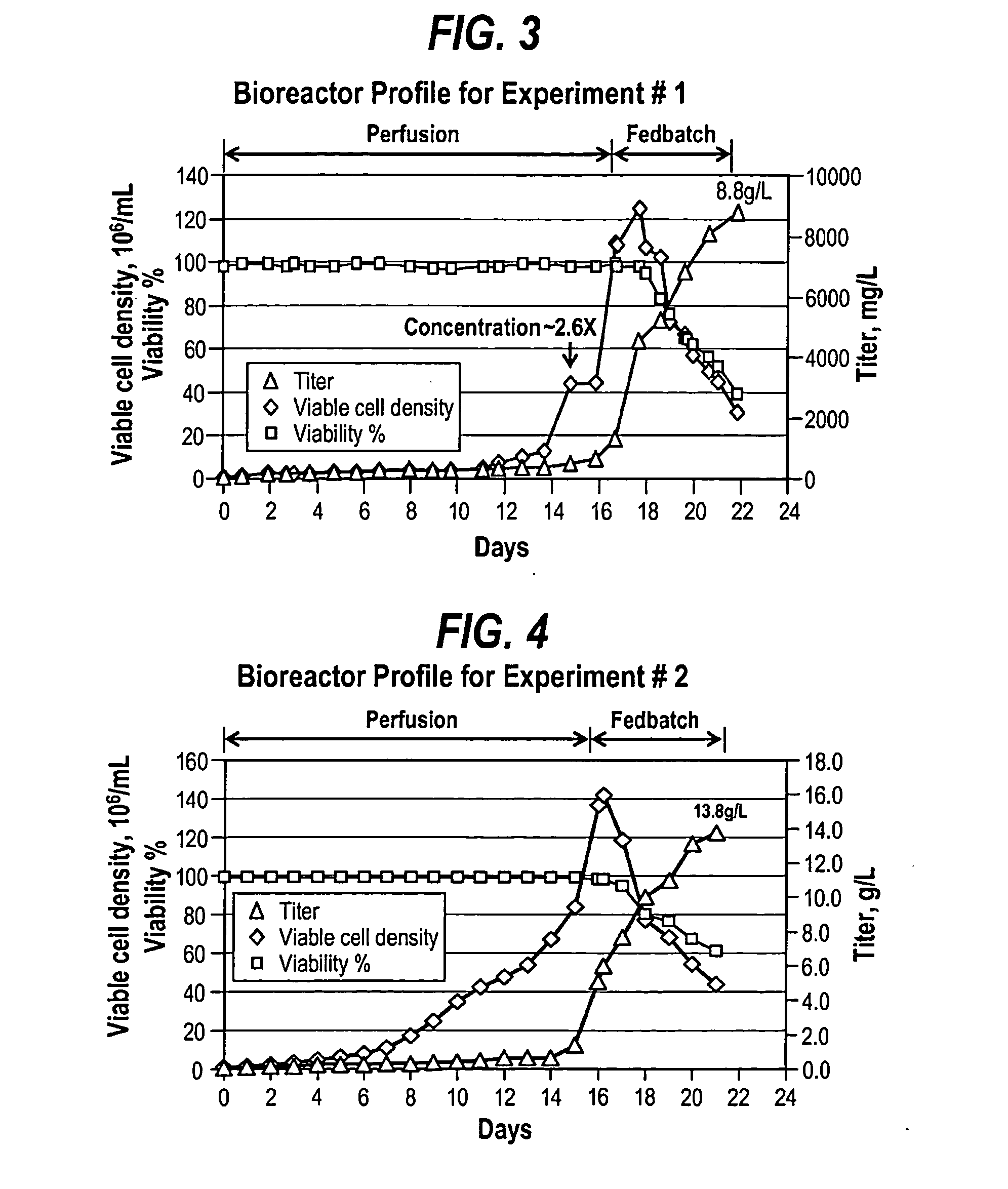

Methods for enhanced protein production

ActiveUS20130017577A1Increase cell densityA large amountAnimal cellsMicroorganism separationHigh cellLiquid layer

The present invention provides a method of increasing protein production in a cell culture by growing cells that produce the protein (e.g., the growth phase) in a perfusion cell culture to a high cell density (i.e., at least above about 40×106 cells / N mL) and then switching to a protein production phase, wherein the cells are cultured in a fed-batch cell culture. The present invention further provides a method for clarifying a protein from a cell culture by adjusting the pH of the cell culture to below neutral pH (i.e., below a pH of 7) and settling the cell culture, such that the cell culture separates to form a supernatant layer and a cell-bed layer, wherein the protein is in the supernatant layer.

Owner:ER SQUIBB & SONS INC

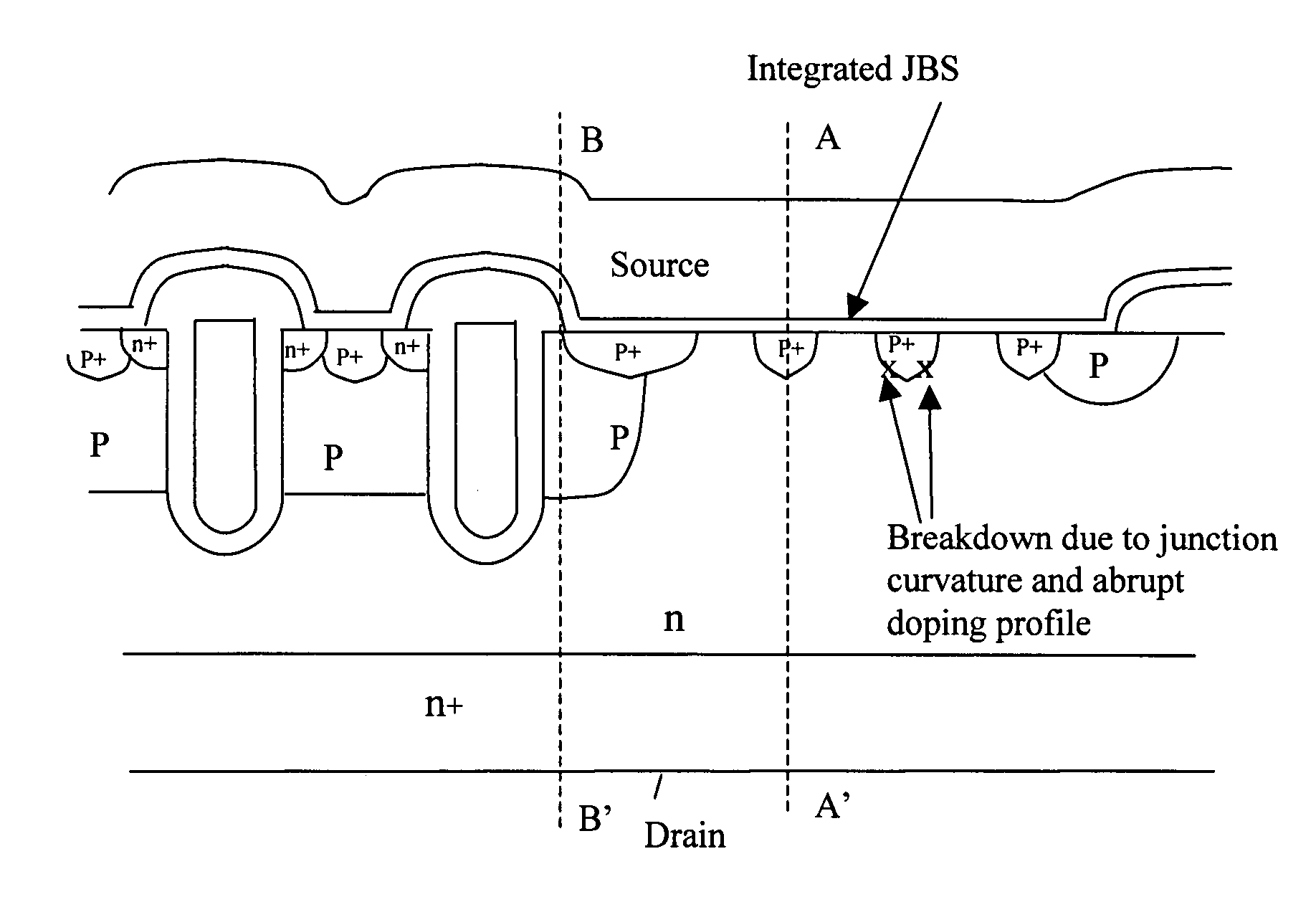

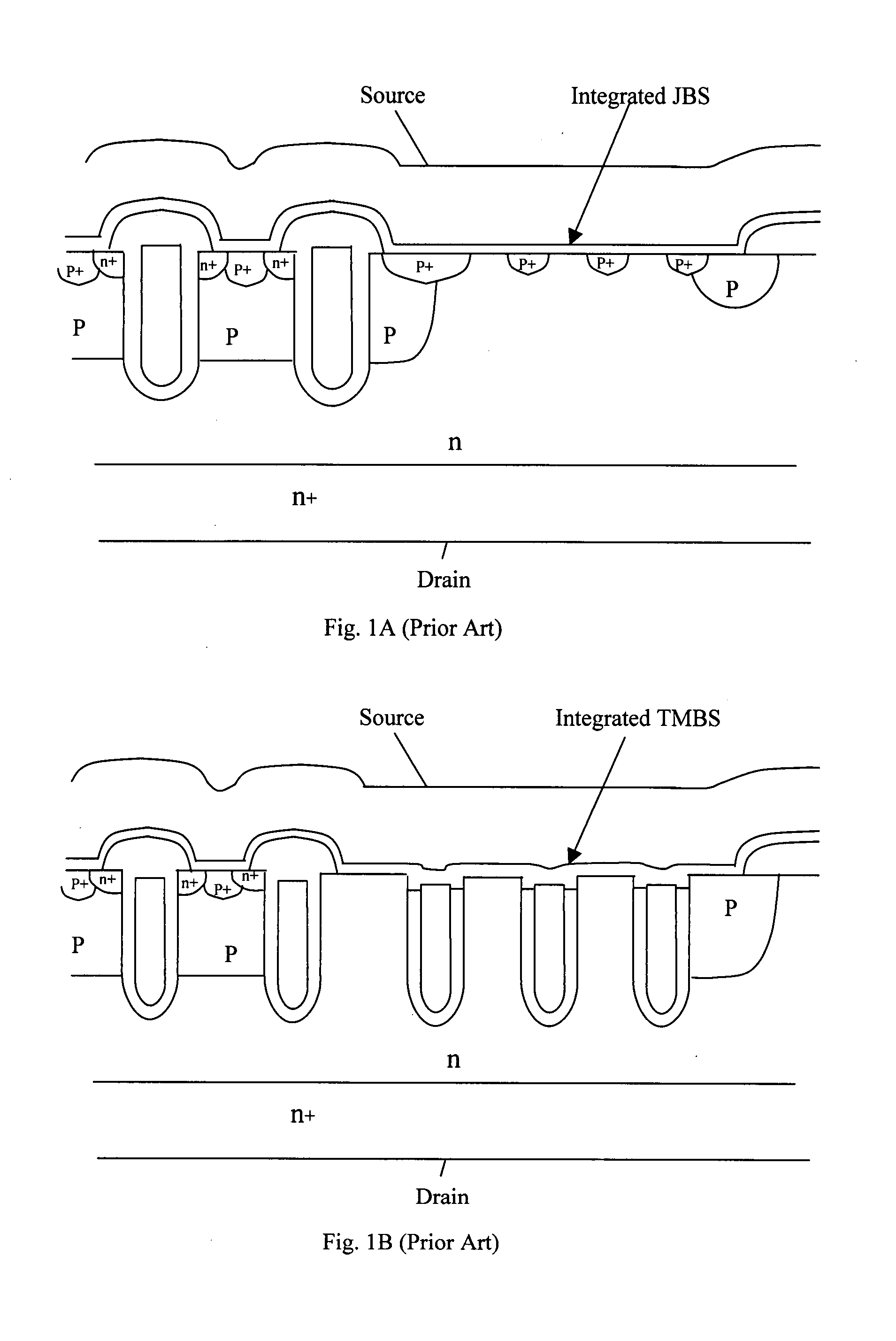

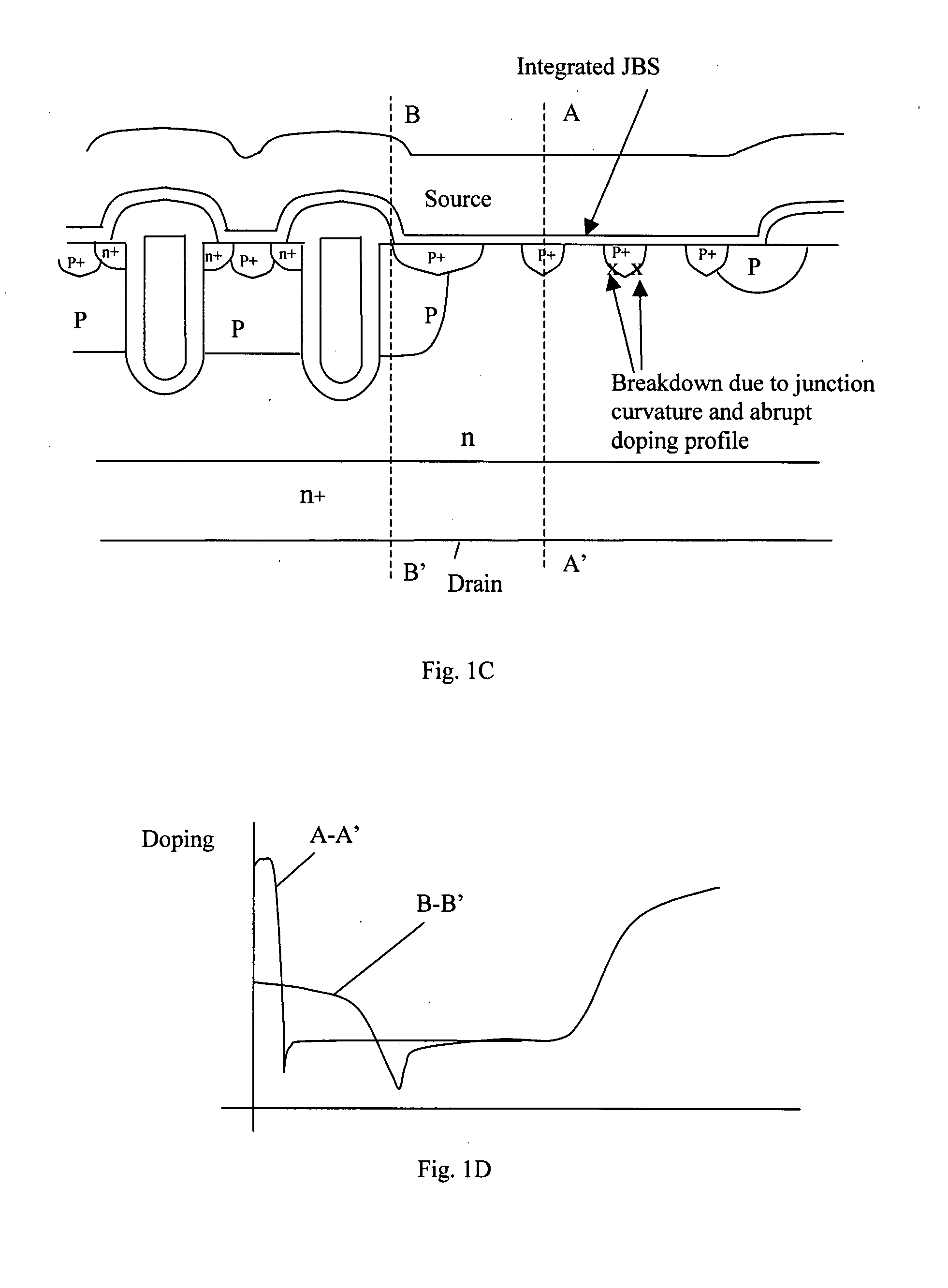

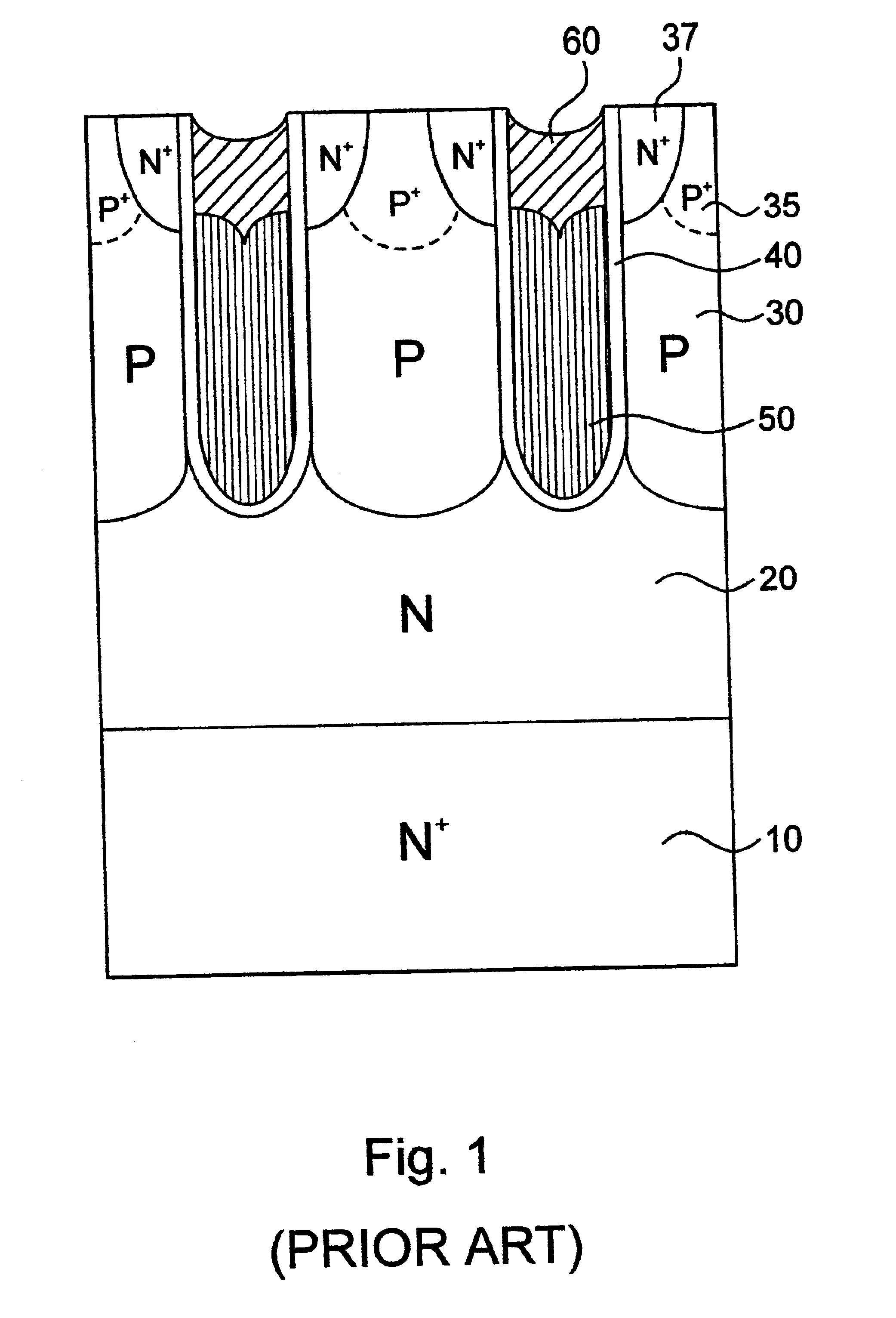

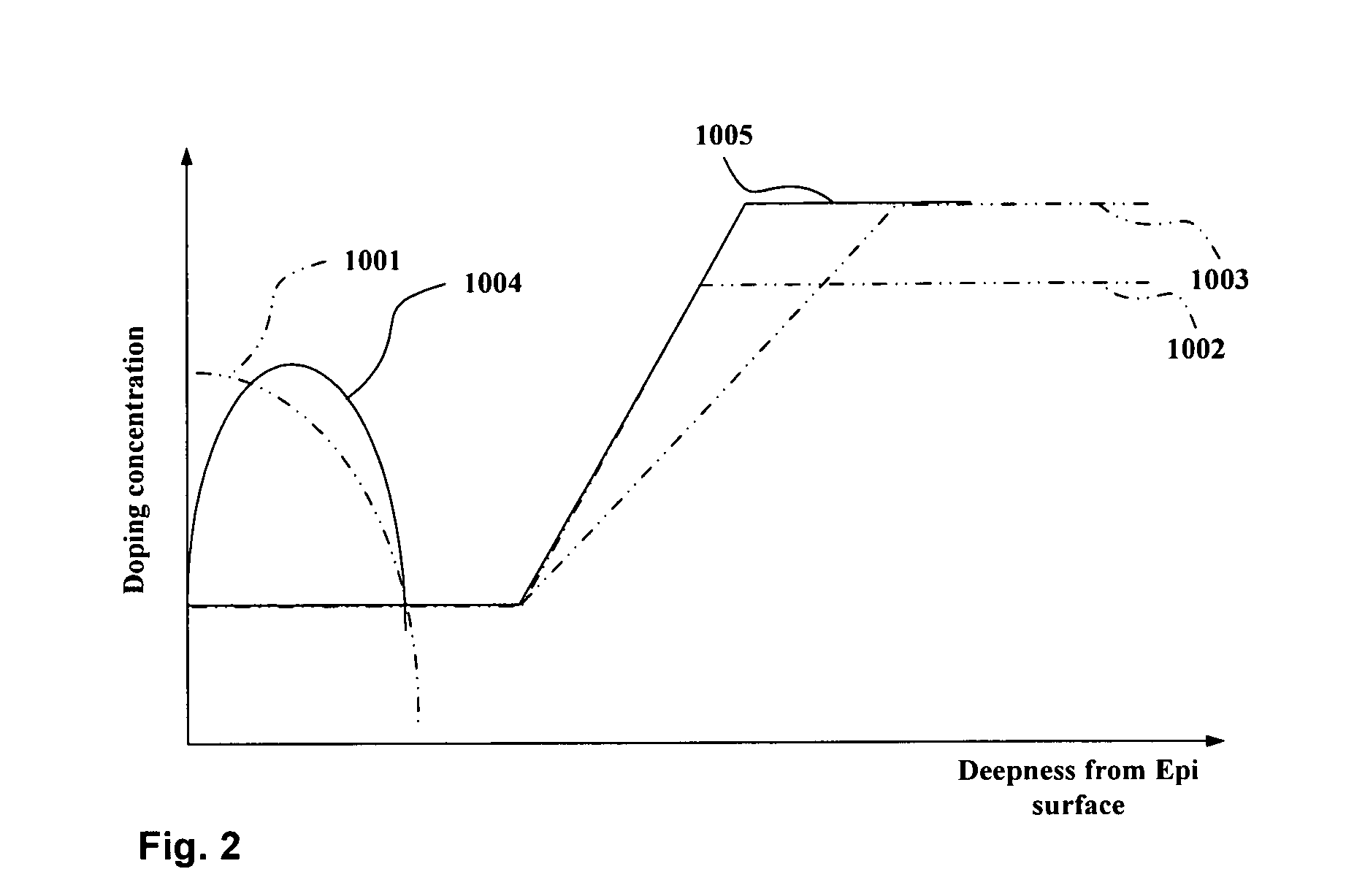

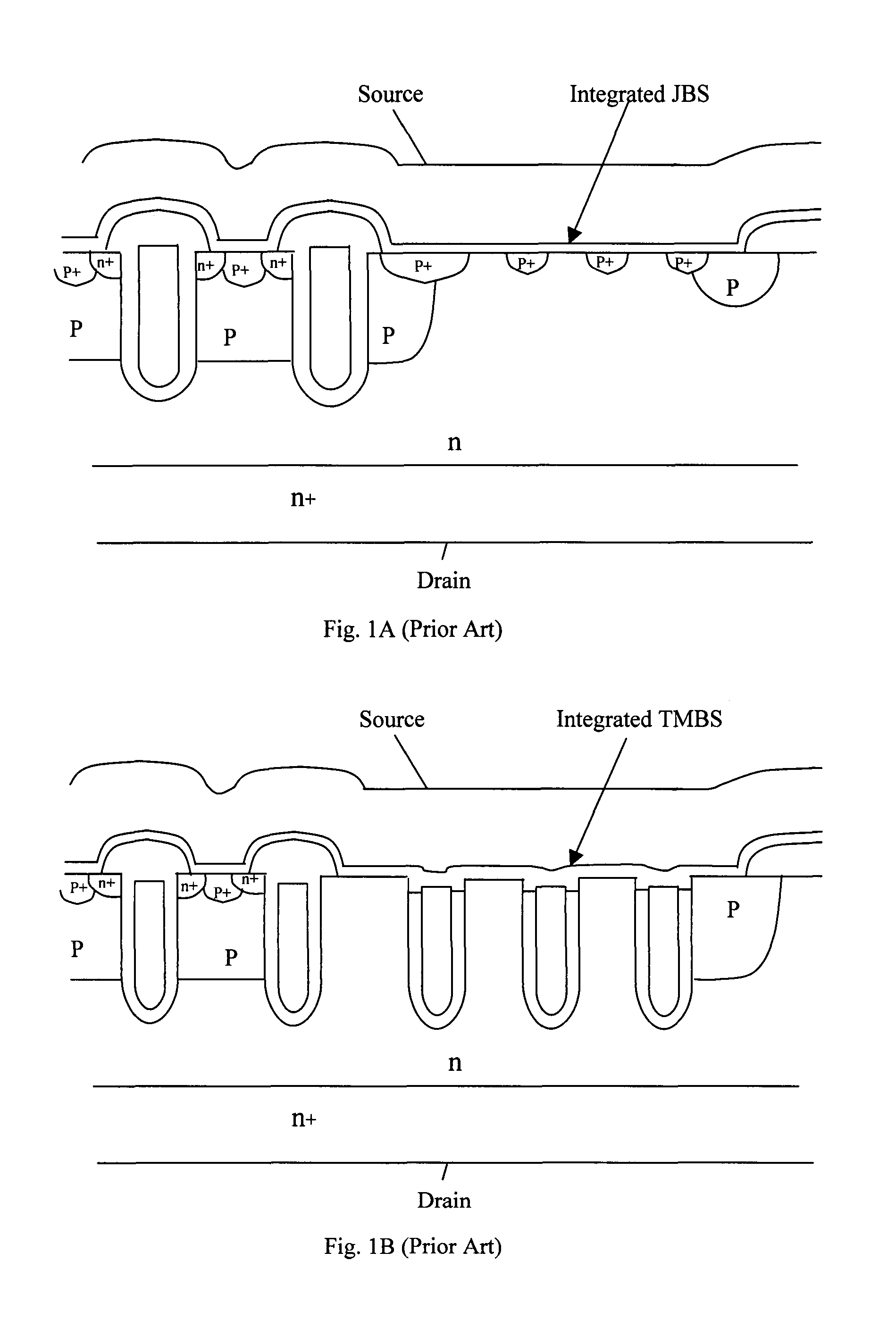

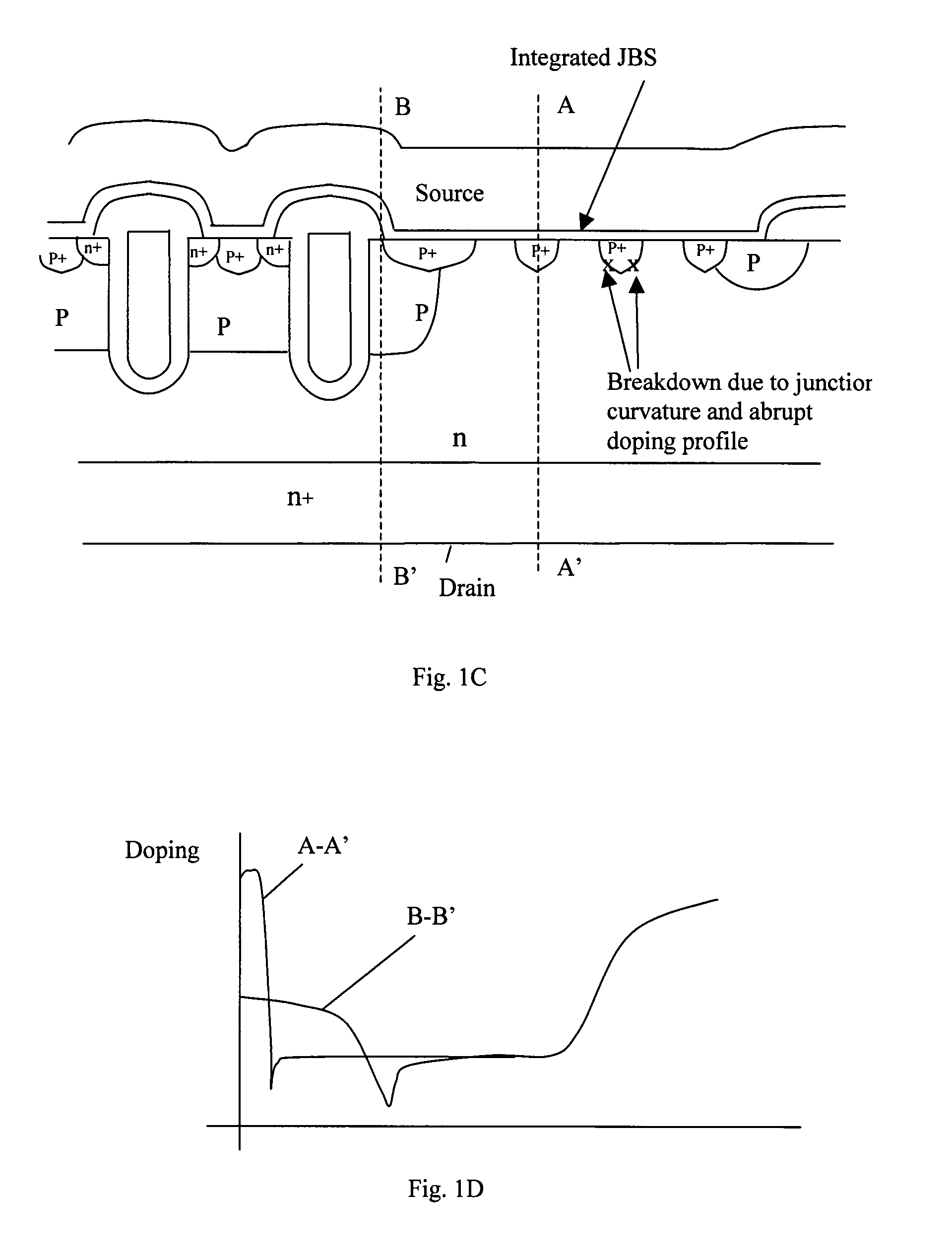

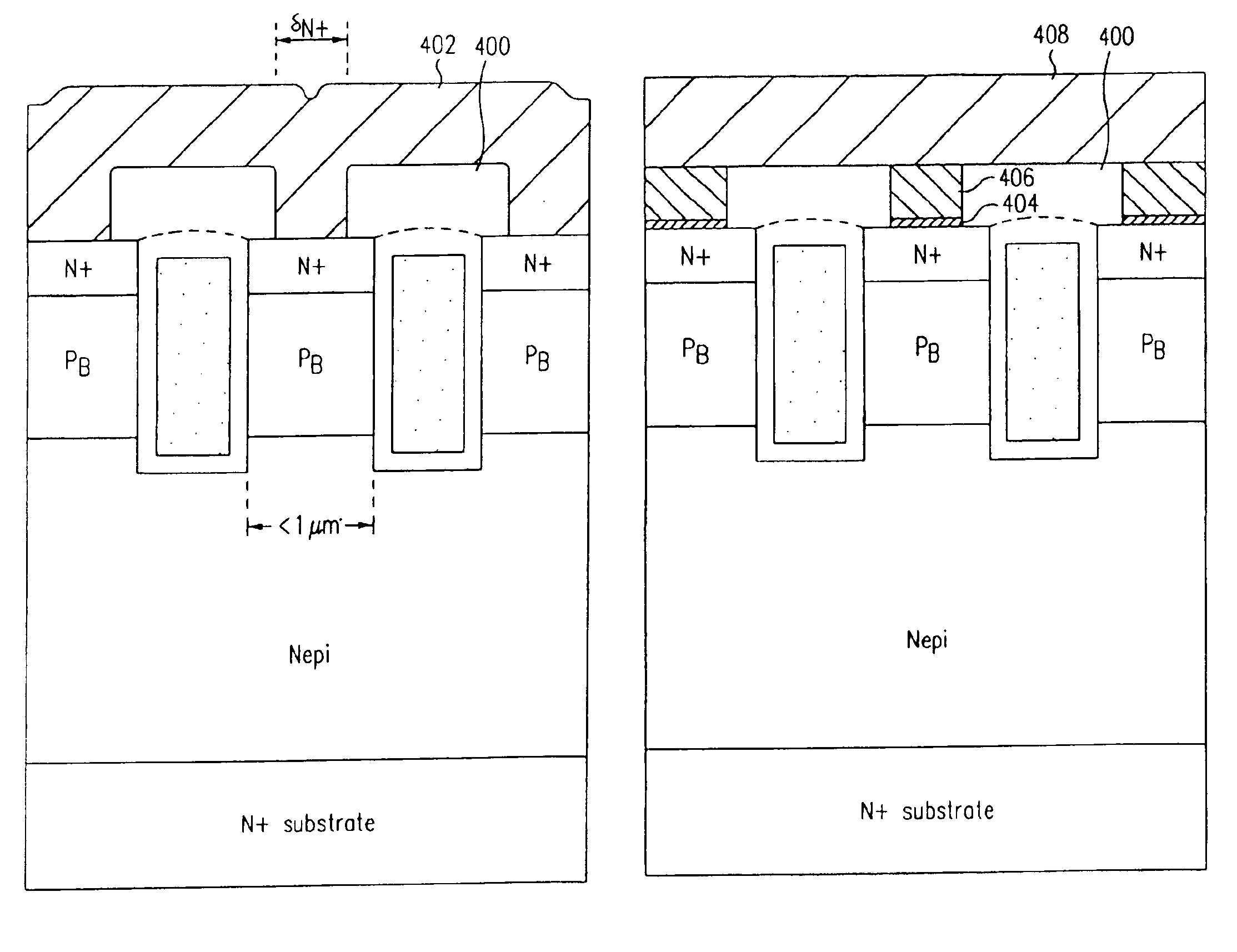

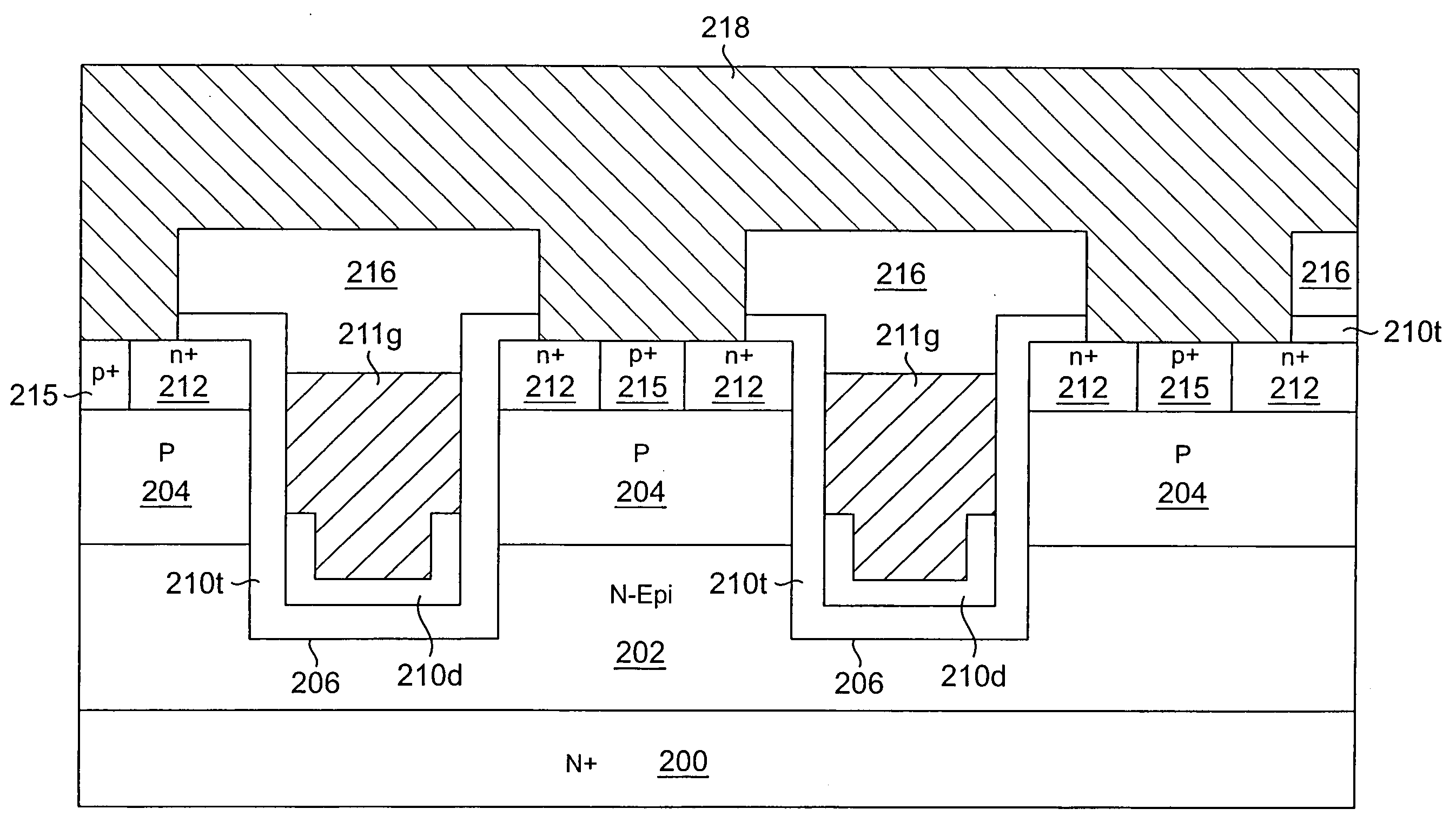

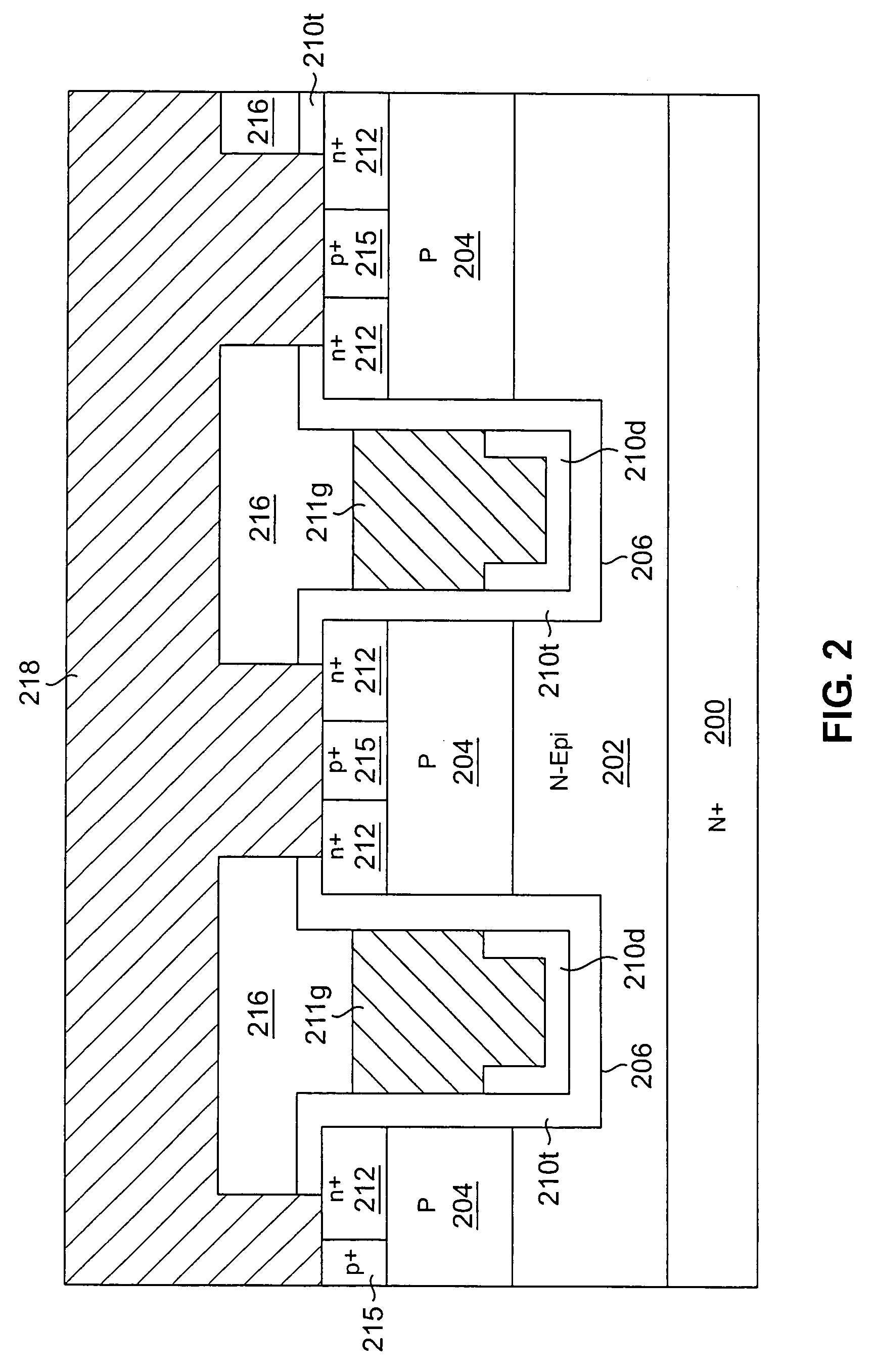

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS6784505B2Increase reverse voltageLow densityTransistorSolid-state devicesDopantChannel density

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

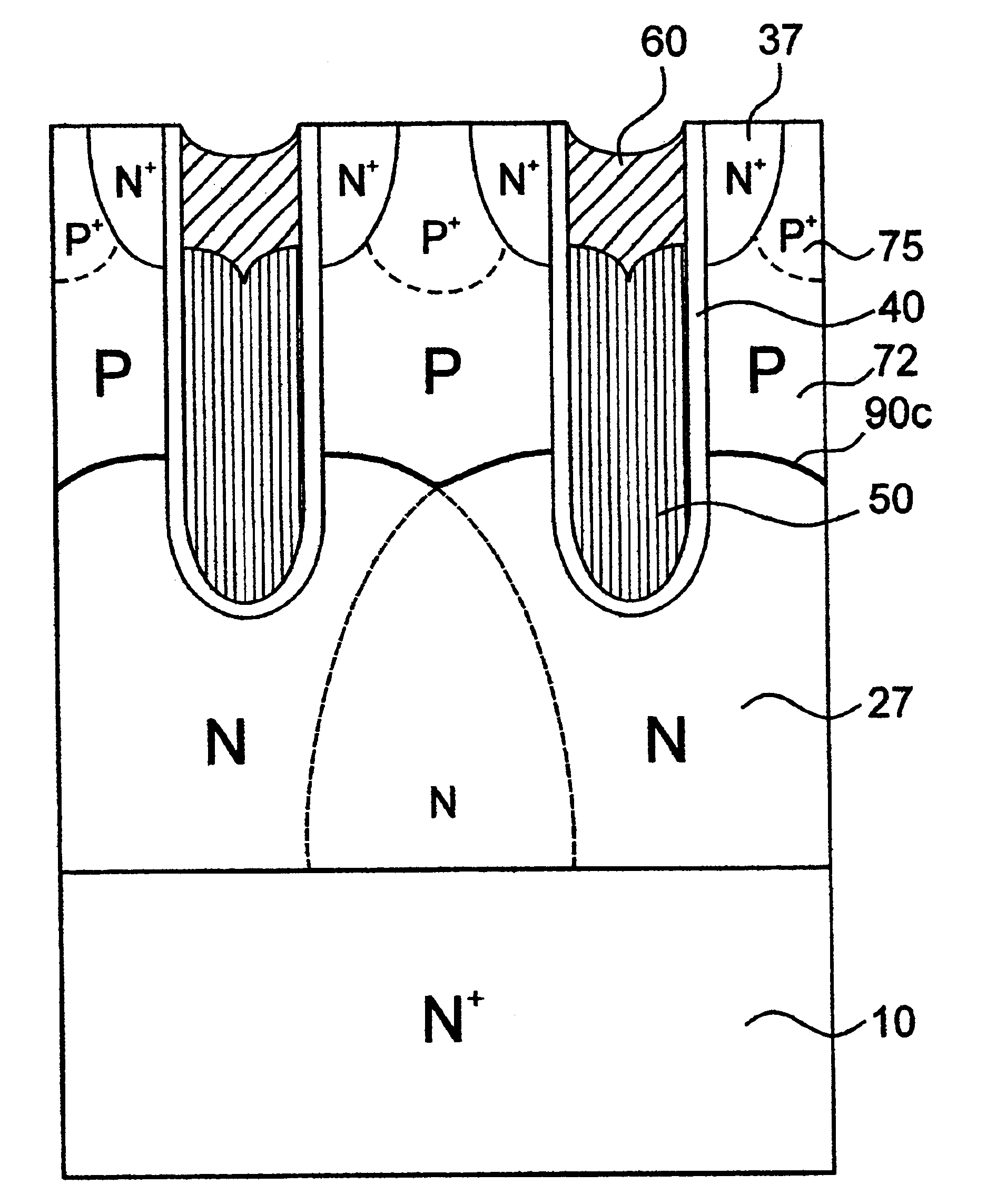

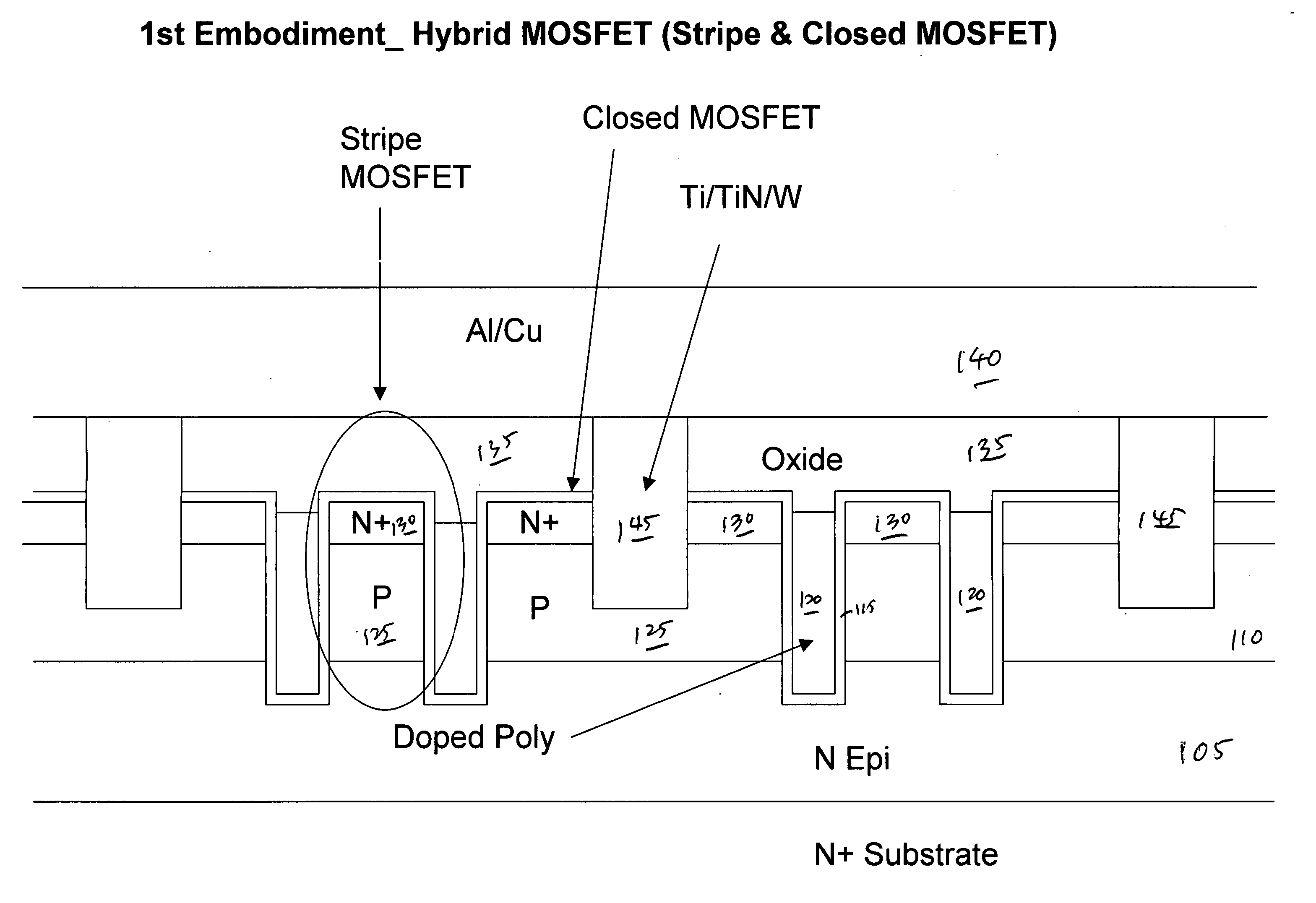

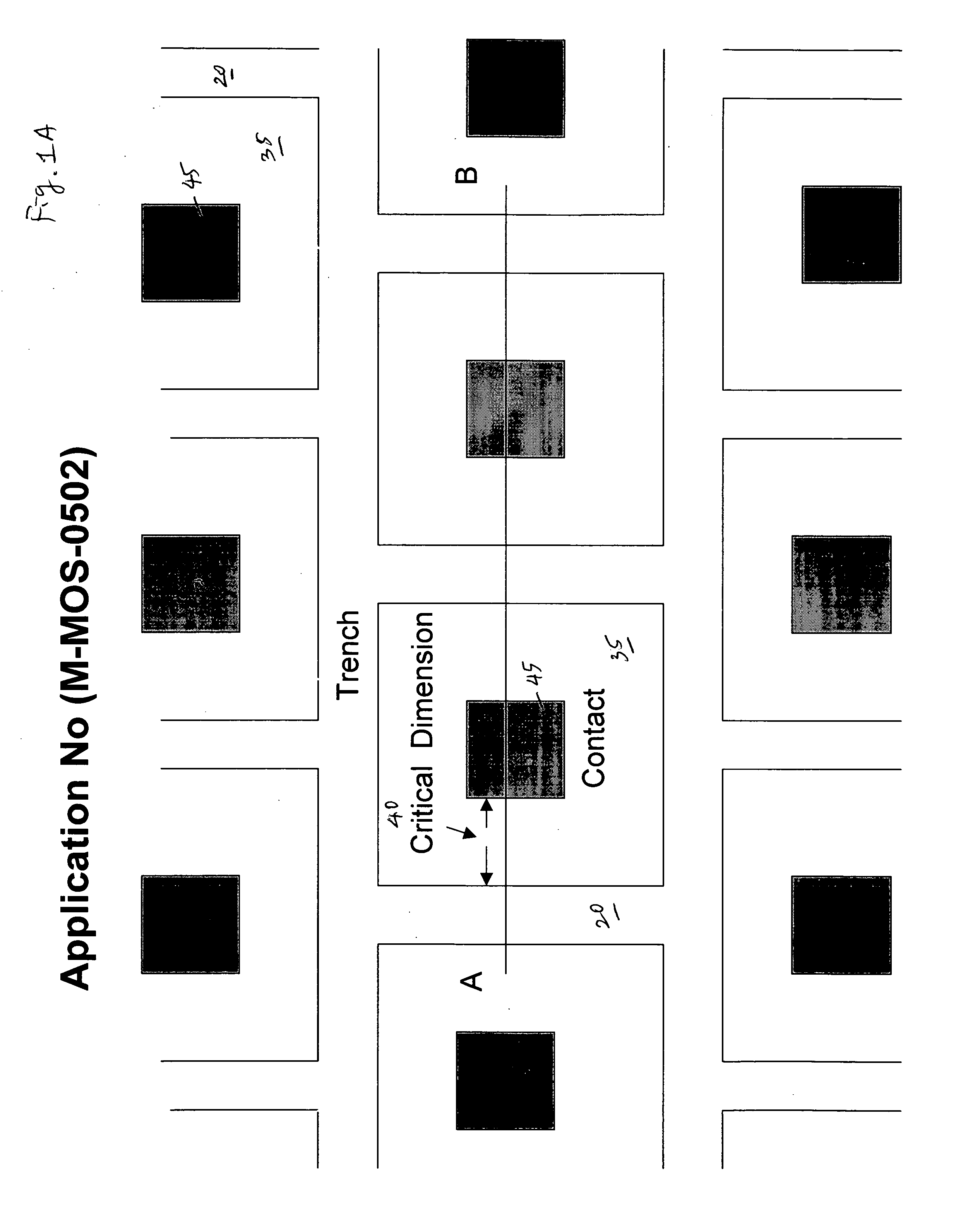

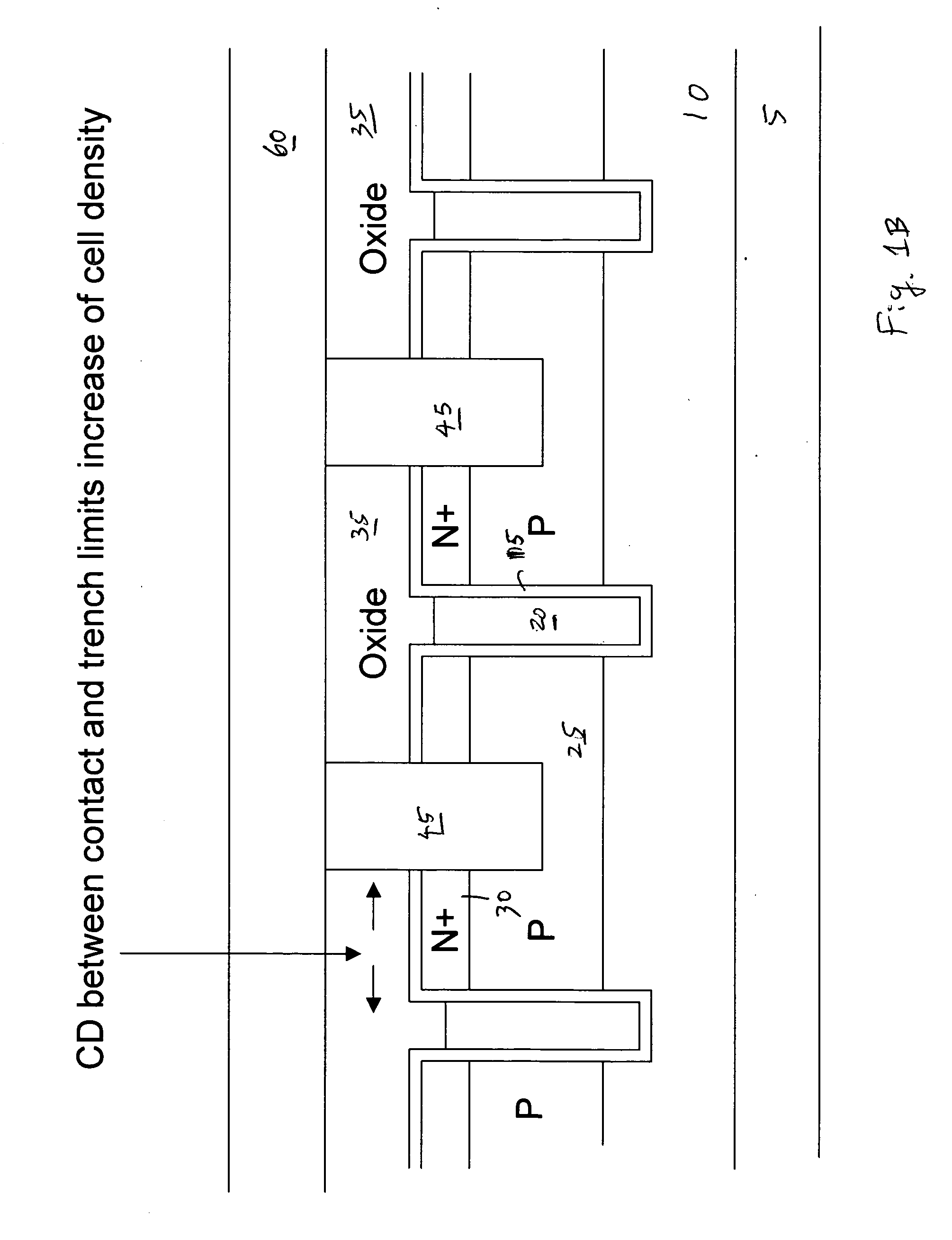

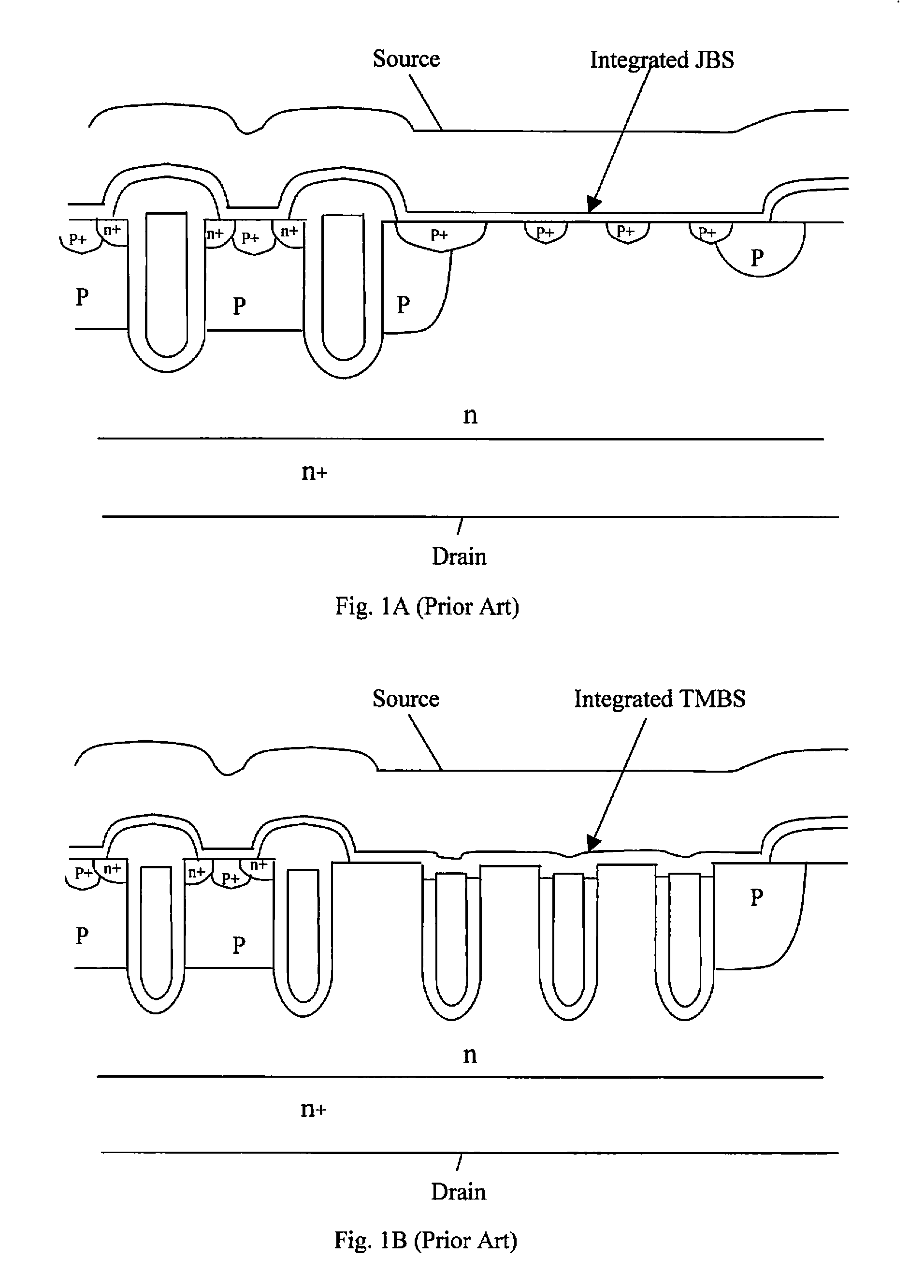

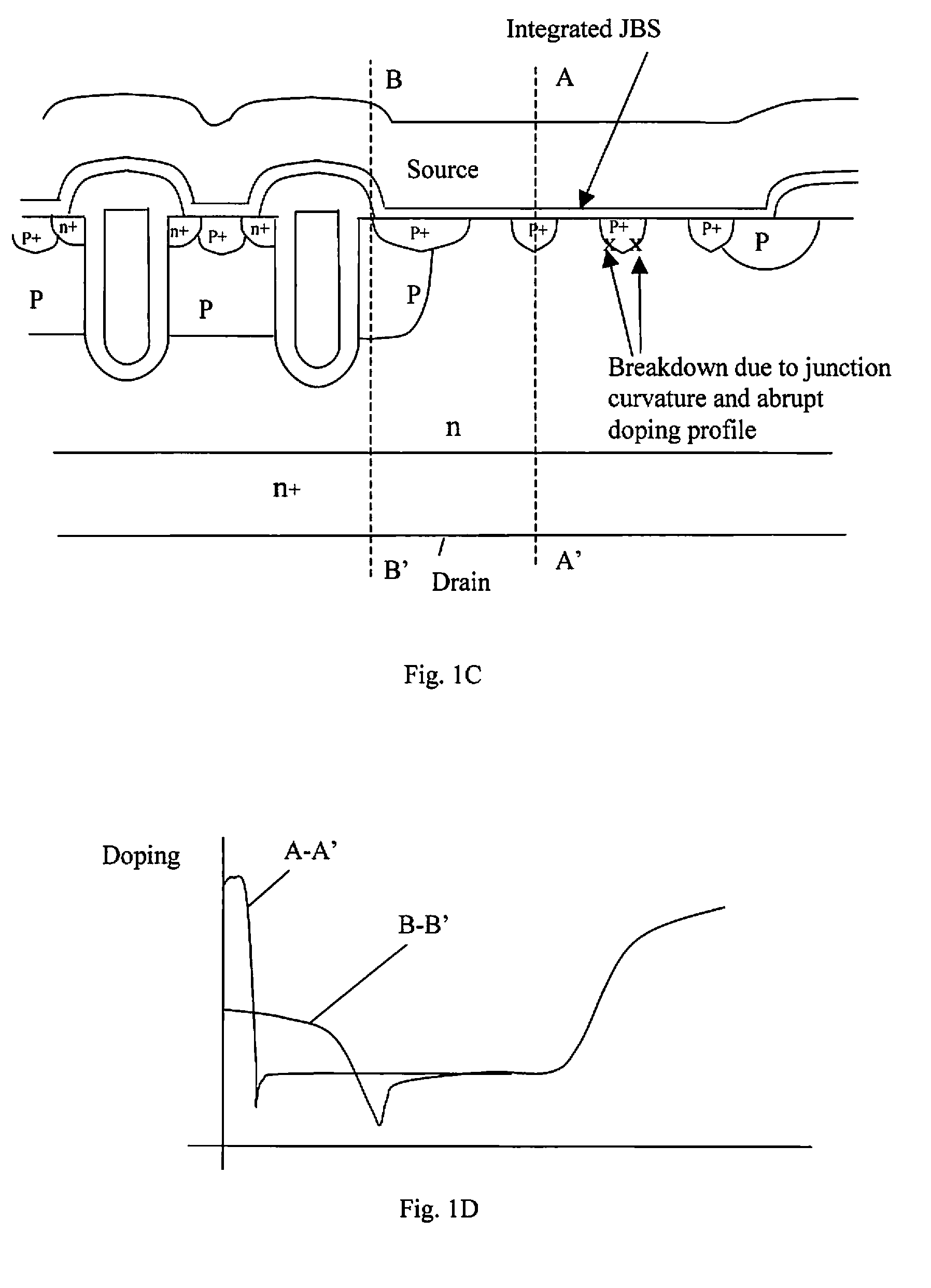

High density hybrid MOSFET device

InactiveUS20060273383A1Increase cell densityLower source-drain resistanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEngineering

A hybrid semiconductor power device that includes a plurality of closed power transistor cells each surrounded by a first and second trenched gates constituting substantially a closed cell and a plurality of stripe cells comprising two substantially parallel trenched gates constituting substantially an elongated stripe cell wherein the closed cells and stripe cells constituting neighboring cells sharing trenched gates disposed thereinbetween as common boundary trenched gates. The closed MOSFET cell further includes a source contact disposed substantially at a center portion of the closed cell wherein the trenched gates are maintained a critical distance (CD) away from the source contact.

Owner:M MOS SEMICON

Trench MOSFET with on-resistance reduction

InactiveUS20110006362A1Reducing drain-source resistanceLowering substrate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetInsulation layer

A trench MOSFET with on-resistance reduction comprises a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate, wherein the said MOSFET further comprises a plurality of source-body contact trenches opened relative to a top surface into said source and body regions and each of the source-body contact trenches is filled with a contact metal plug as a source-body contact; a insulation layer covered over the top of the trenched gate, the body region and the source region; a front metal layer formed on a top surface of the MOSFET; wherein a low-resistivity phosphorus substrate and retrograded P-body formed by medium or high energy Ion Implantation to reduce Rds contribution from substrate and drift region.

Owner:FORCE MOS TECH CO LTD

Planar srfet using no additional masks and layout method

ActiveUS20130026568A1Maximized Schottky areaImprove performanceTransistorSemiconductor/solid-state device manufacturingDopantControl layer

A semiconductor power device is supported on a semiconductor substrate with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON INC

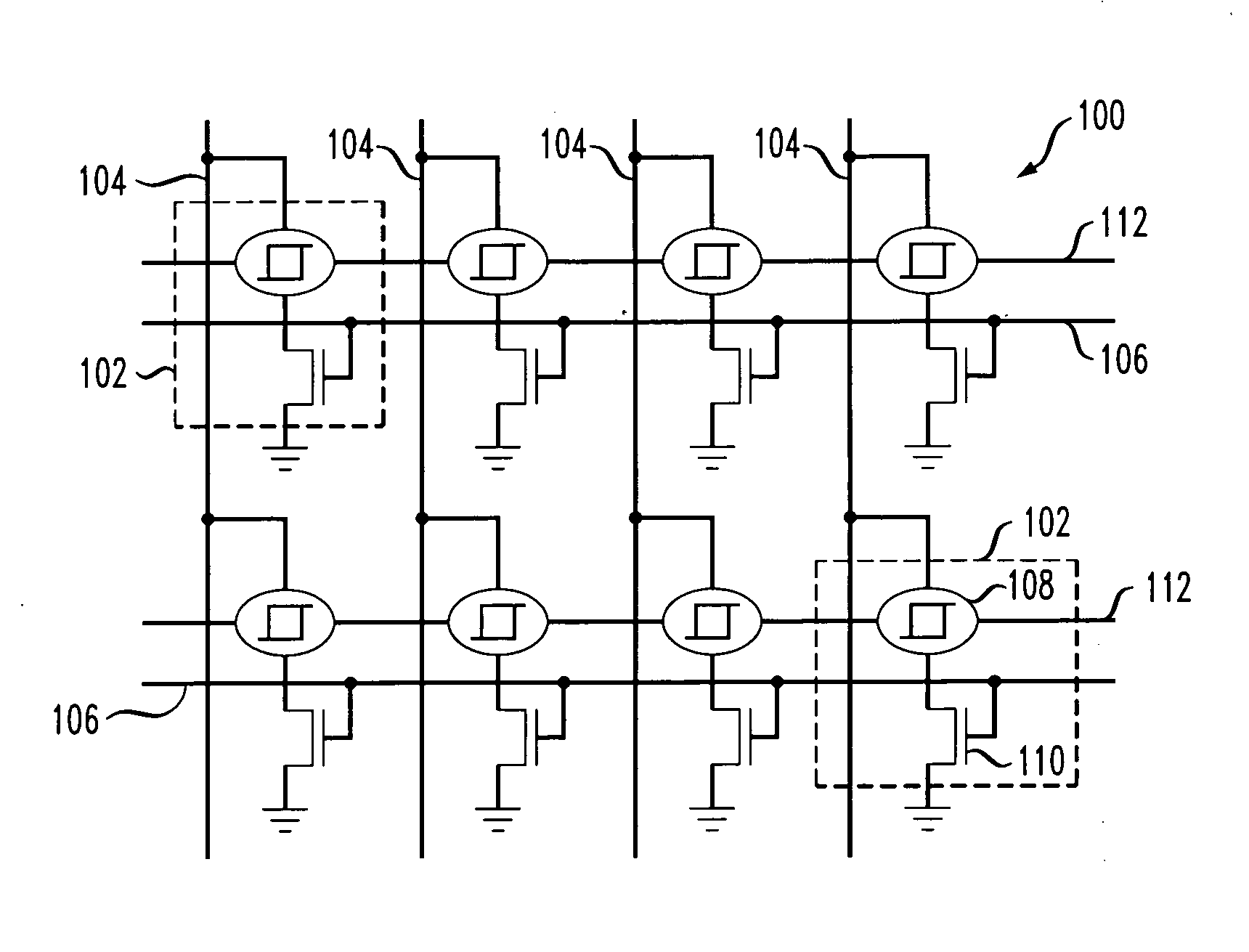

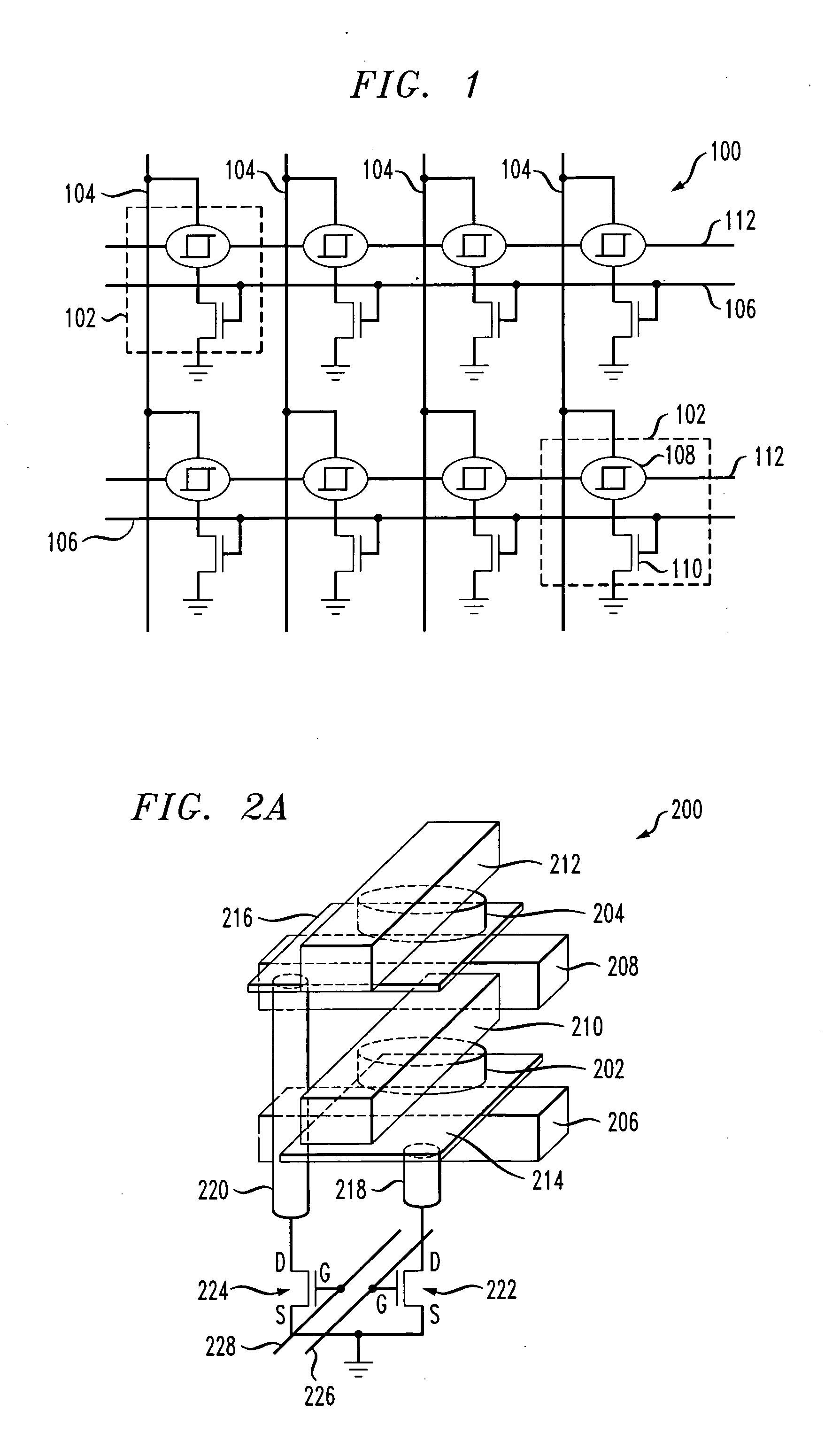

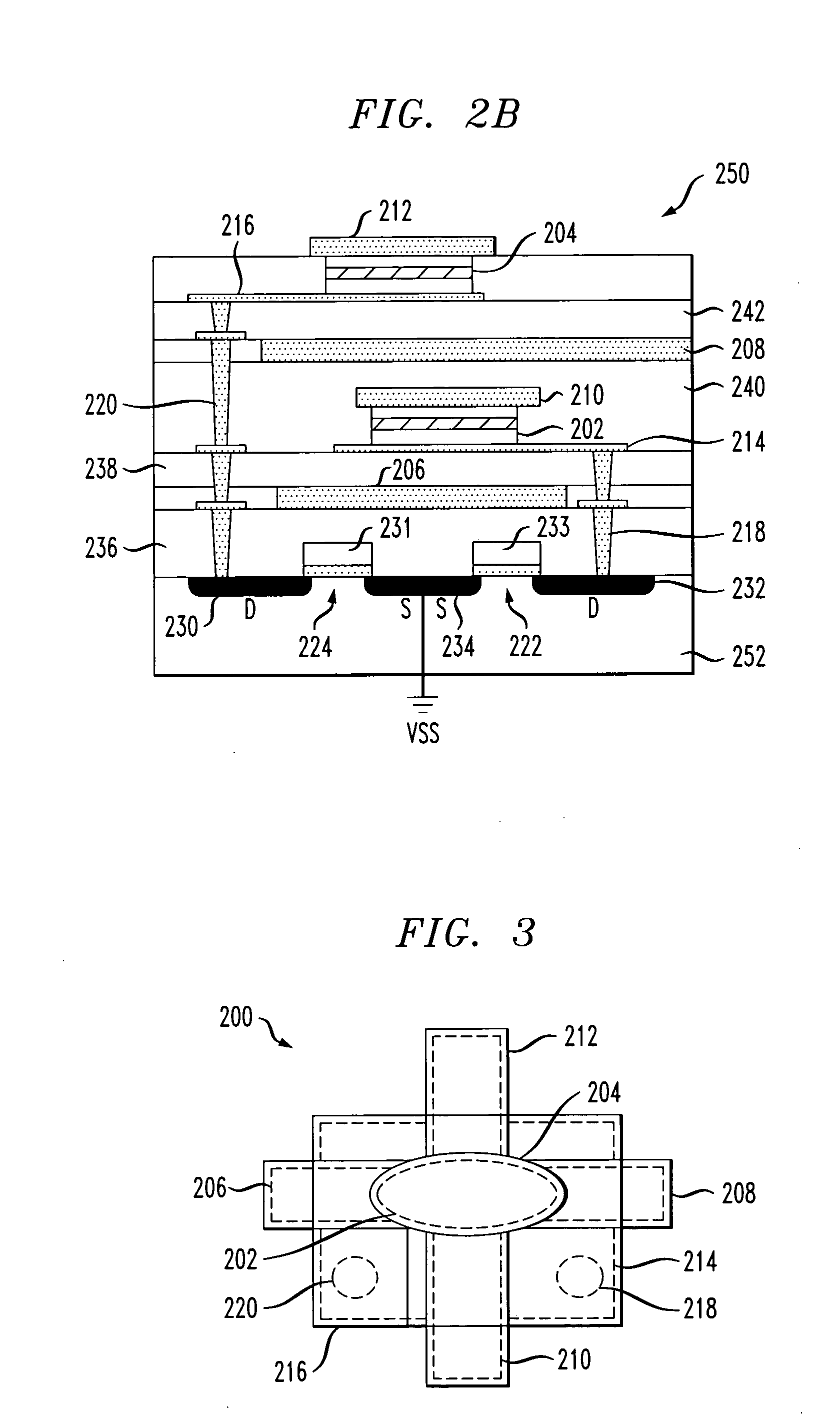

Magnetic random access memory cell

ActiveUS20050087785A1Increase cell densityReduce horizontal sizeNanoinformaticsSolid-state devicesMagnetic storageRandom access memory

A memory cell for use in a magnetic random access memory (MRAM) circuit includes at least first and second transistors formed in a semiconductor layer. A first insulating layer is formed on at least a portion of the first and second transistors. The memory cell further includes a first magnetic storage element formed on at least a portion of the first insulating layer, at least a second insulating layer formed on at least a portion of the first magnetic storage element, and at least a second magnetic storage element formed on at least a portion of the second insulating layer. The first and second magnetic storage elements are electrically connected to the first and second transistors, respectively.

Owner:IBM CORP

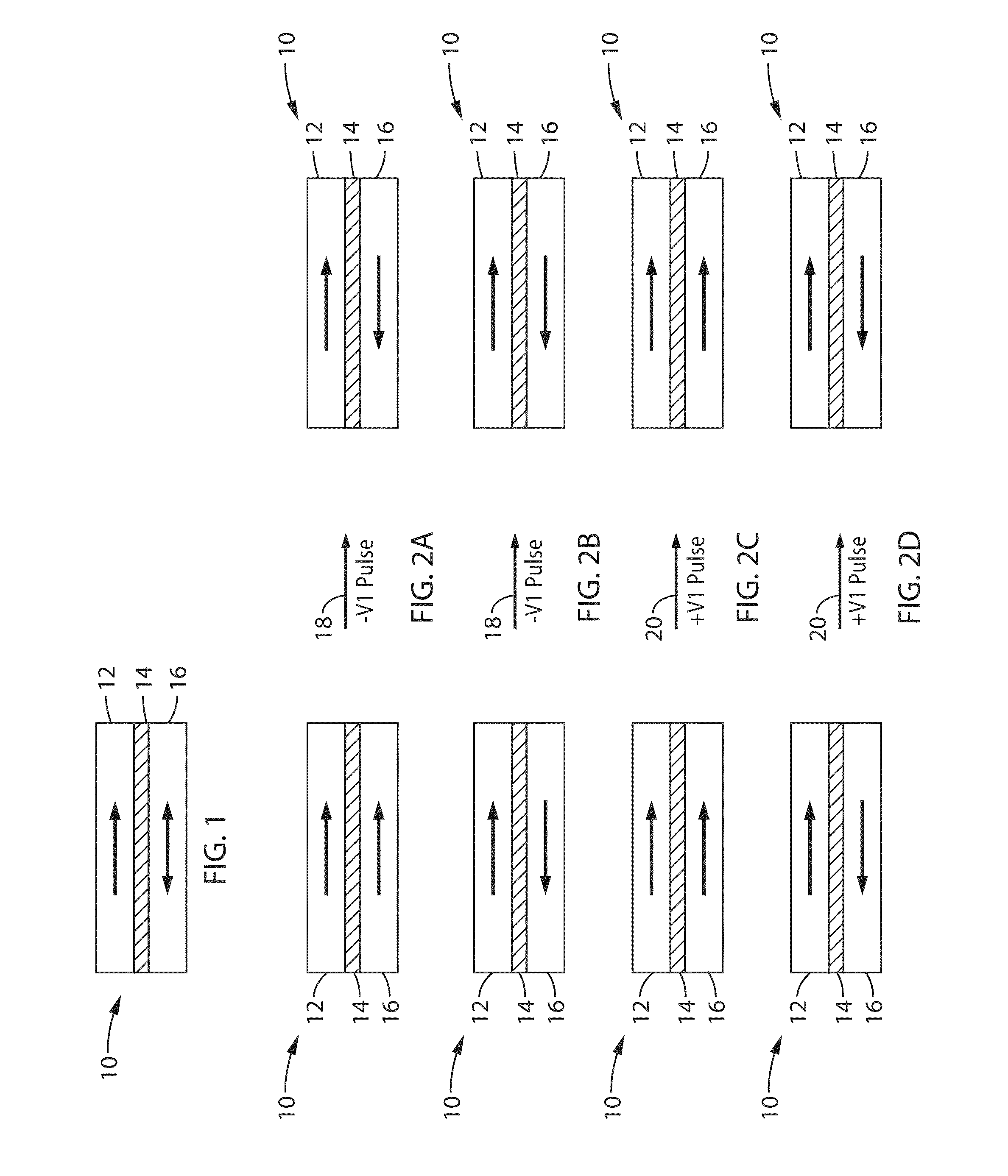

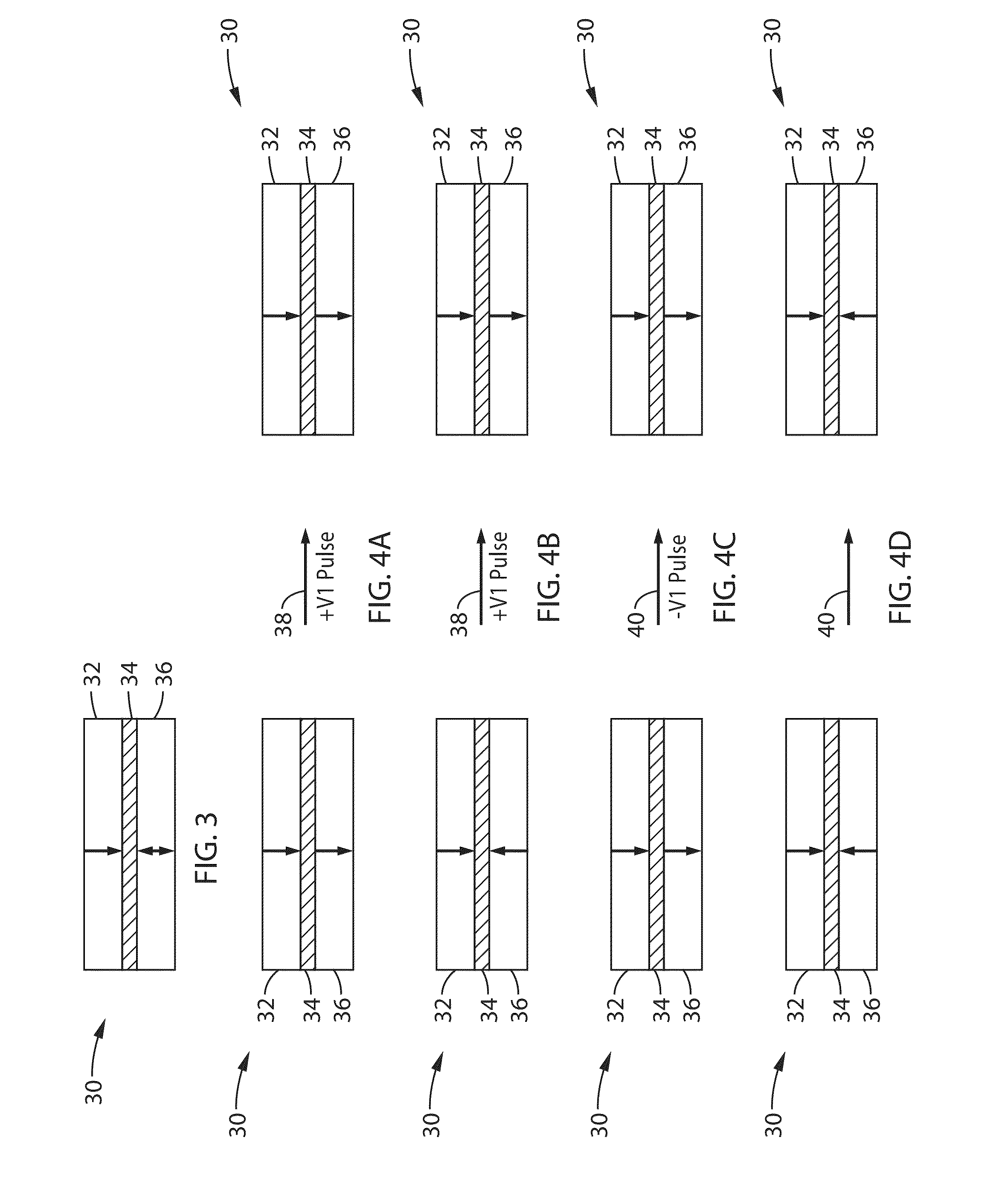

Voltage-controlled magnetic anisotropy (VCMA) switch and magneto-electric memory (MERAM)

ActiveUS20140177327A1High cell densityGood scalabilityGalvano-magnetic device detailsDigital storageMagnetoDomain wall dynamics

Voltage controlled magnetic tunnel junctions and memory devices are described which provide efficient high speed switching of non-volatile magnetic devices at high cell densities. Implementations are described which provide a wide range of voltage control alternatives with in-plane and perpendicular magnetization, bidirectionally switched magnetization, and control of domain wall dynamics.

Owner:RGT UNIV OF CALIFORNIA

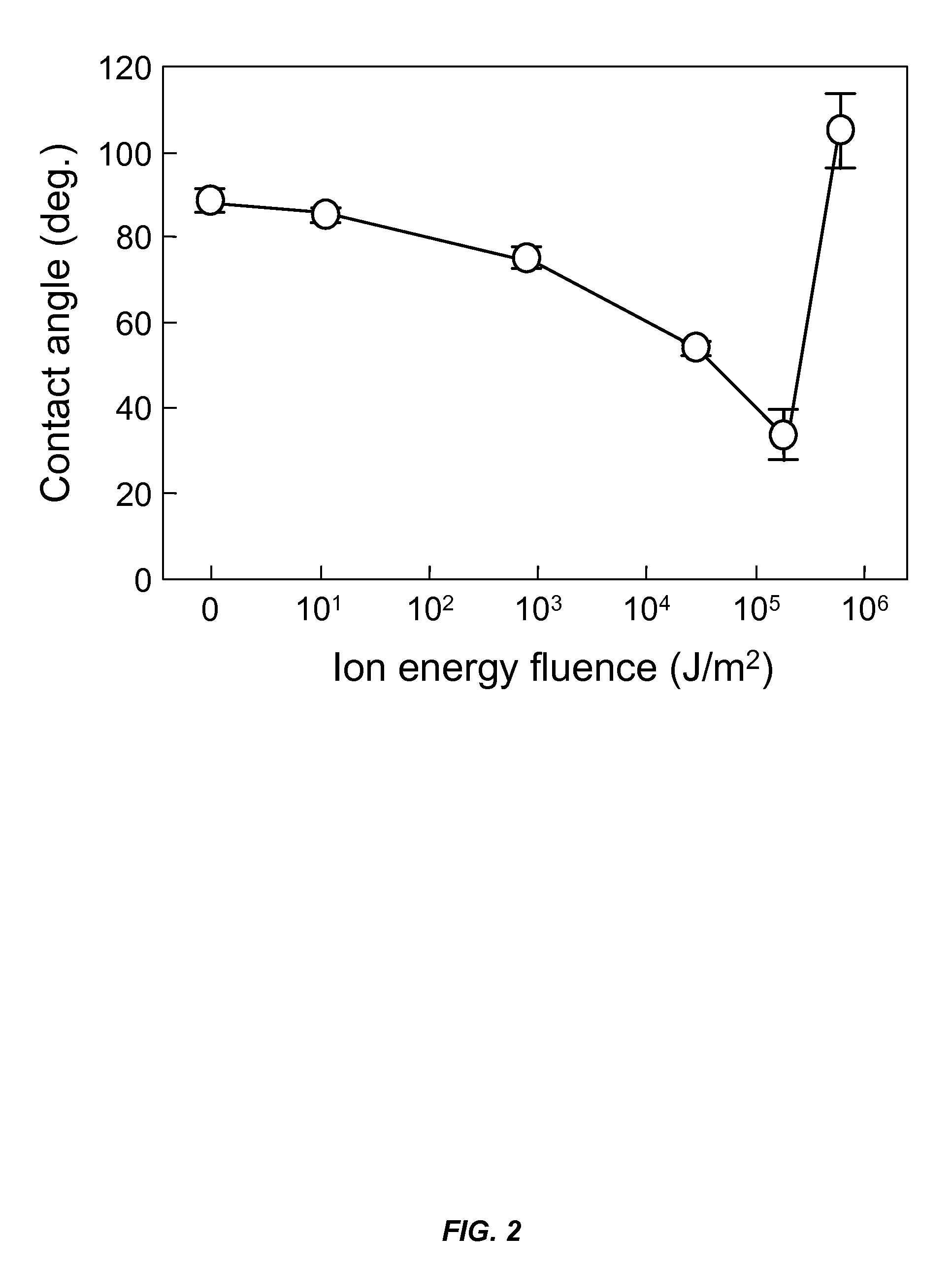

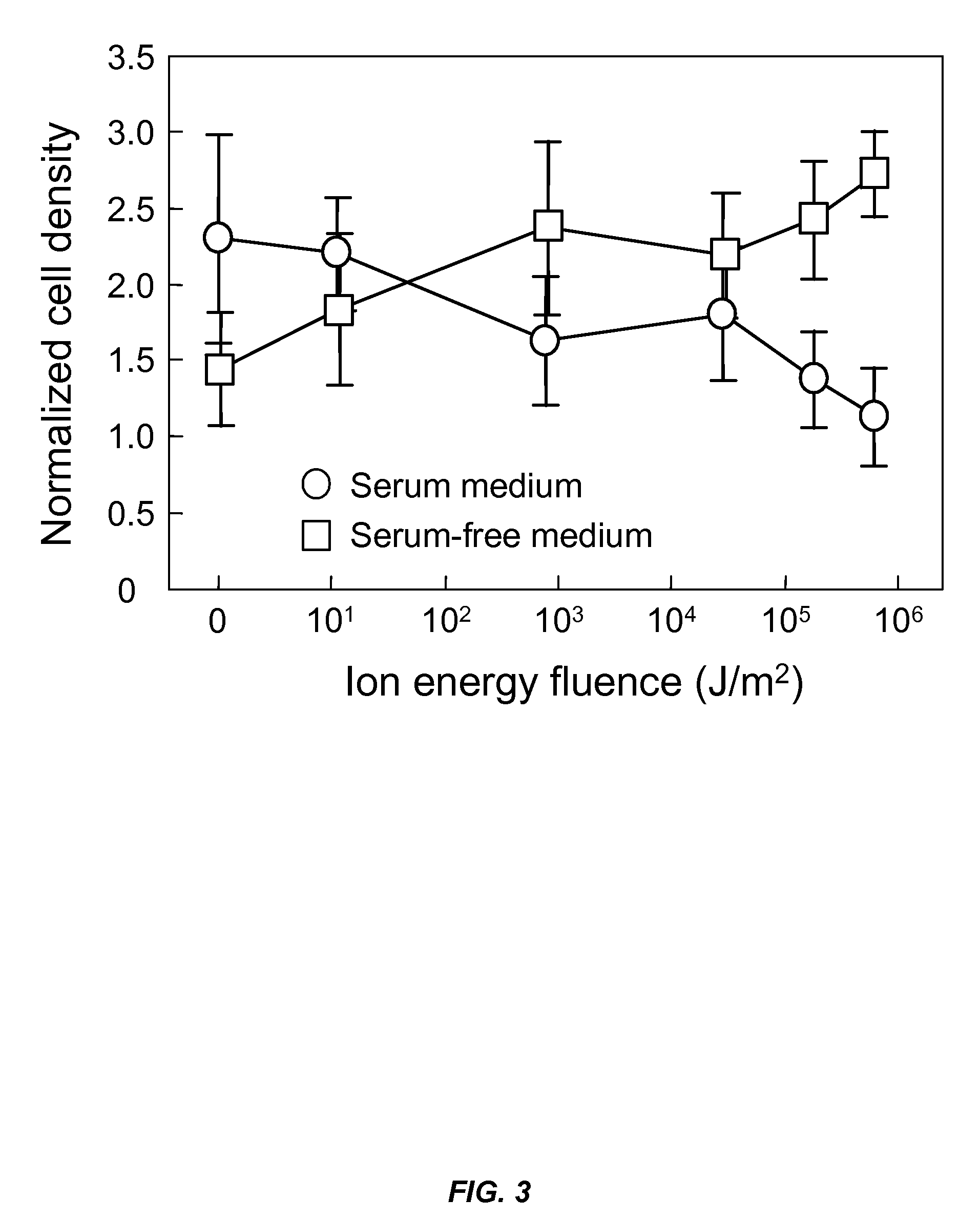

Method to control cell adhesion and growth on biopolymer surfaces

Methods for treating surfaces of polymeric substrates (as used in medical implants) with inert plasmas to promote the growth of bioentities (such as cells) on these surfaces is disclosed. The treated surfaces are subsequently exposed to an environment to form functionalities associated with enhanced growth of the bioentity on the surface. For example, the substrate may be exposed to the ambient environment. The bioentity may then be deposited on the modified surface. This inert plasma treatment and exposure to a suitable environment does not degrade the implants, and thus improved implants are created. Also, due to the specific functional groups at the modified surface, high cell densities are achieved.

Owner:RGT UNIV OF CALIFORNIA

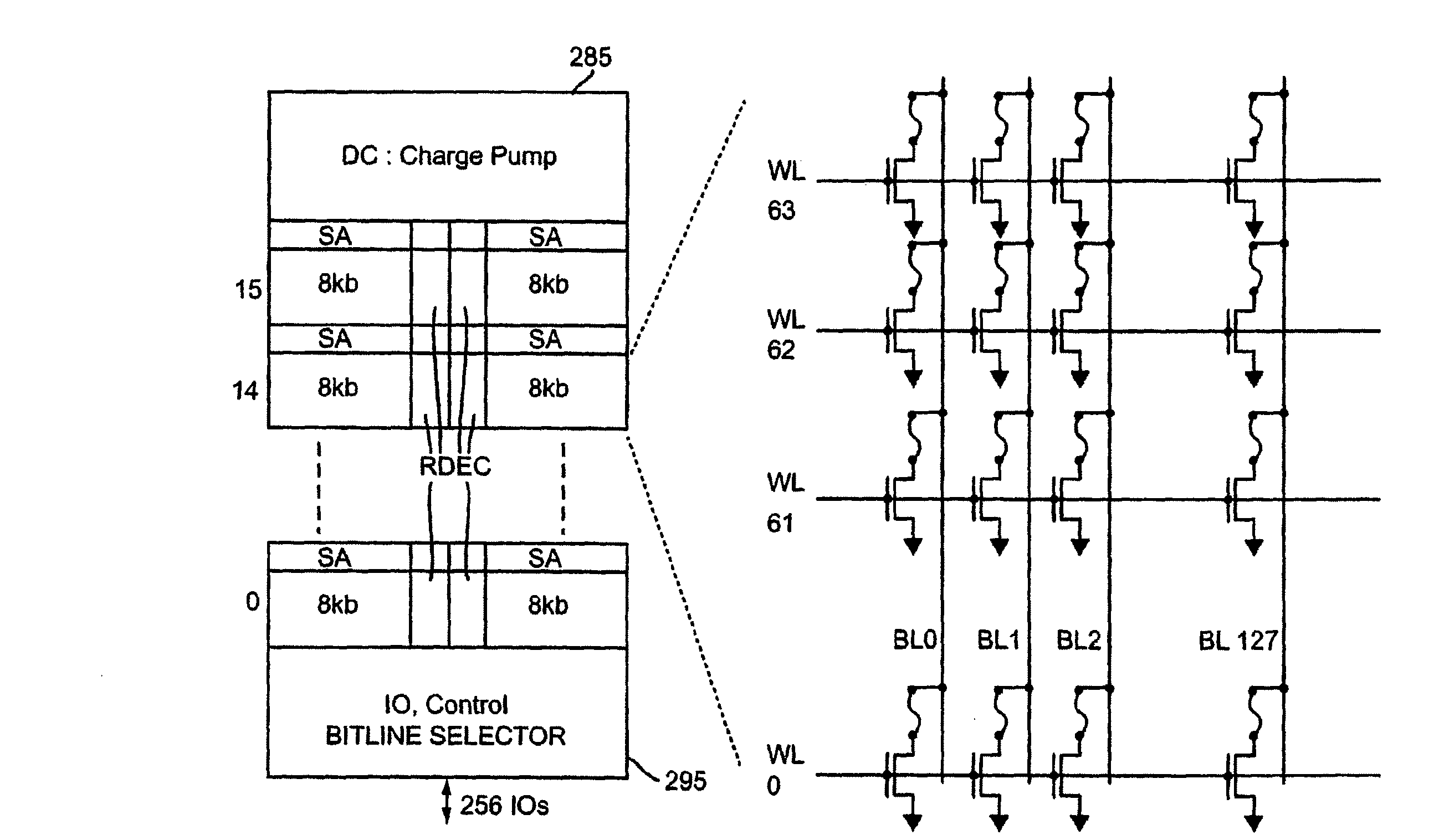

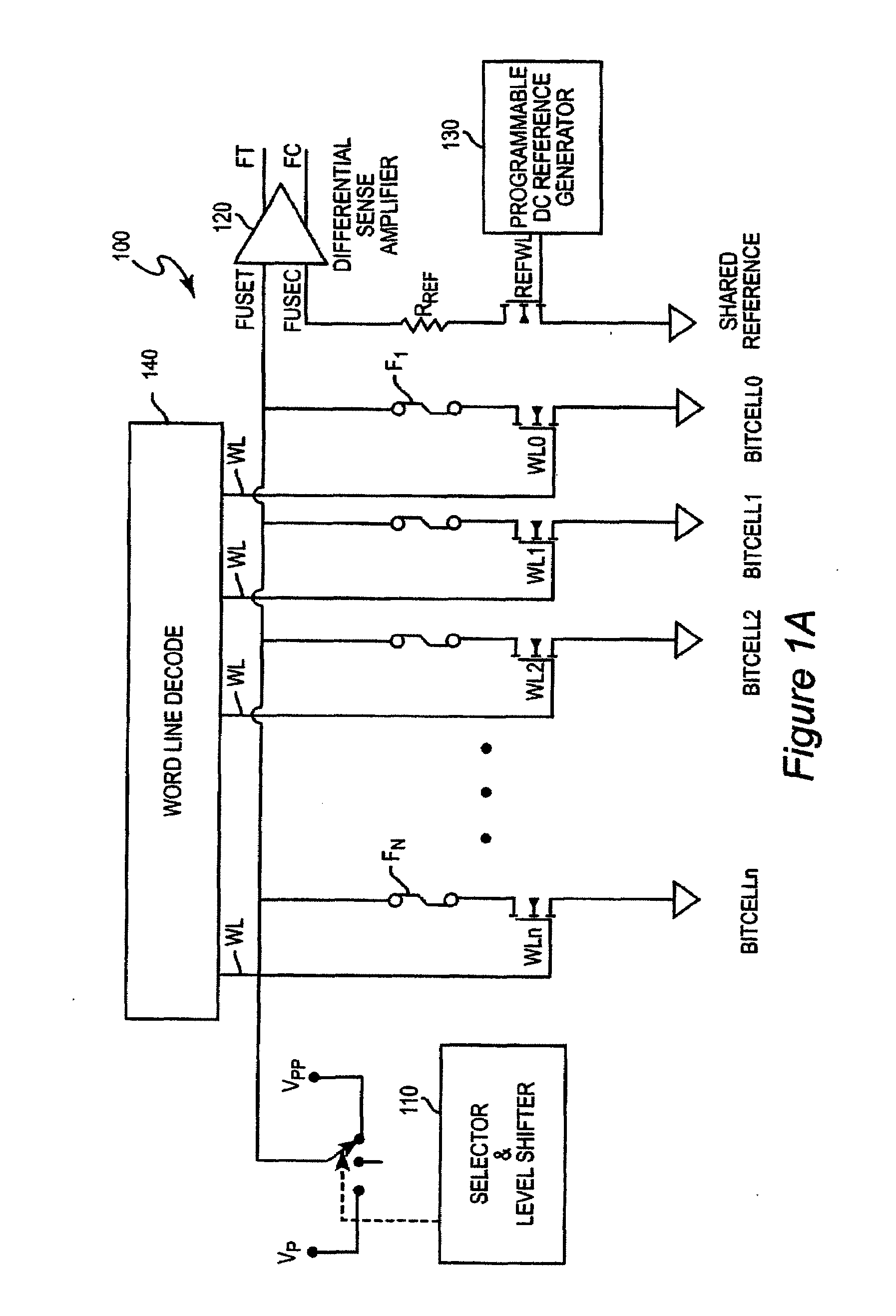

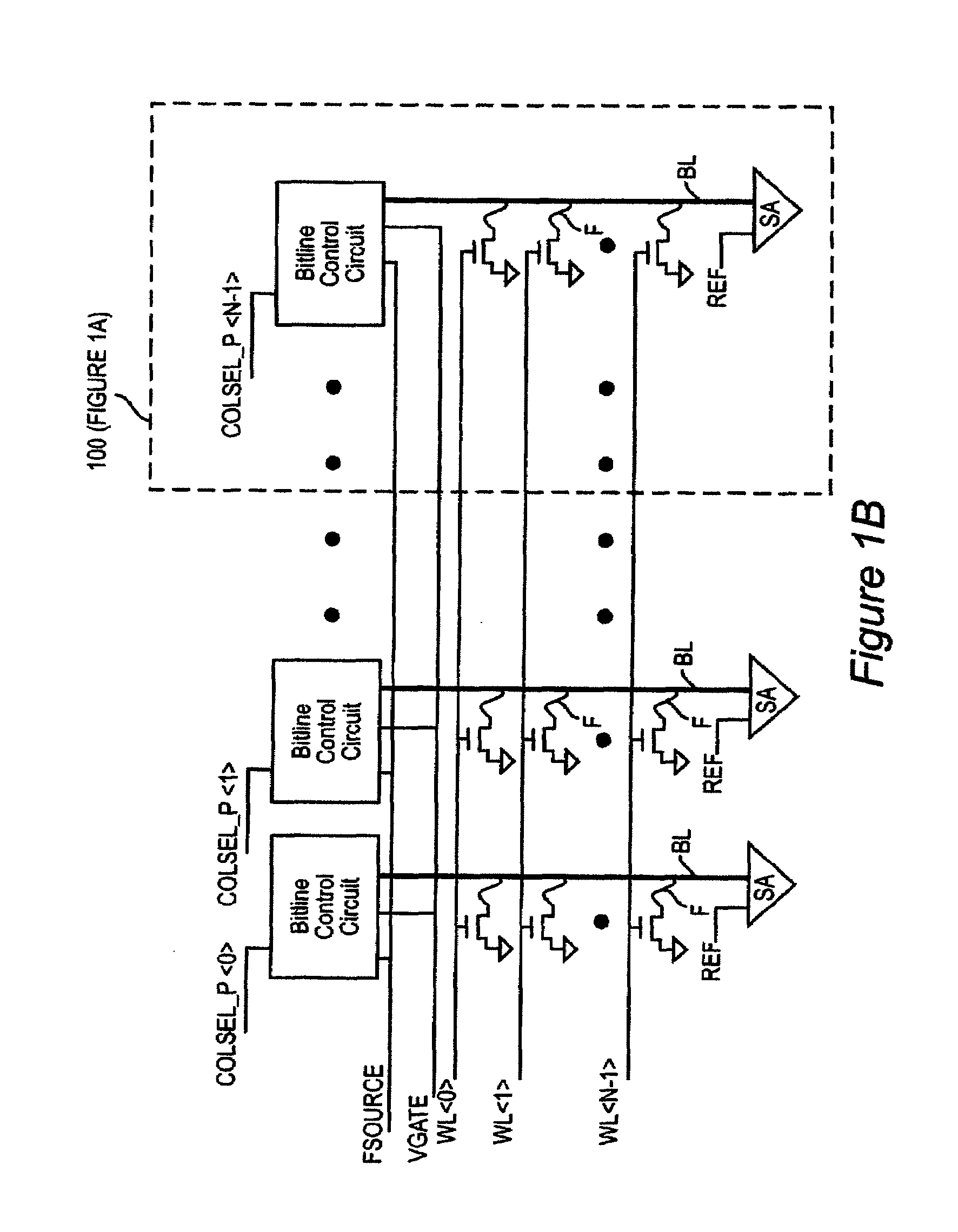

Random Access Electrically Programmable E-Fuse Rom

ActiveUS20080316789A1Reduce resistanceShorten the timeRead-only memoriesDigital storageBit lineProgrammable read-only memory

A one-time-programmable-read-only-memory (OTPROM) is implemented in a two-dimensional array of aggressively scaled suicide migratable e-fuses. Word line selection is performed by decoding logic operating at VDD while the bit line drive is switched between VDD and a higher voltage, Vp for programming. The OTPROM is thus compatible with and can be integrated with other technologies without a cost adder and supports optimization of the high current path for minimal voltage drop during fuse programming. A differential sense amplifier with a programmable reference is used for improved sense margins and can support an entire bit line rather than sense amplifiers being provided for individual fuses.

Owner:IBM CORP

Planar SRFET using no additional masks and layout method

ActiveUS8110869B2Improved body diode recovery behaviorLess voltage oscillationDiodeDopantControl layer

A semiconductor power device supported on a semiconductor substrate of a first conductivity type with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer with a same conductivity type as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region of a second conductivity type extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region of second conductivity type. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON LTD

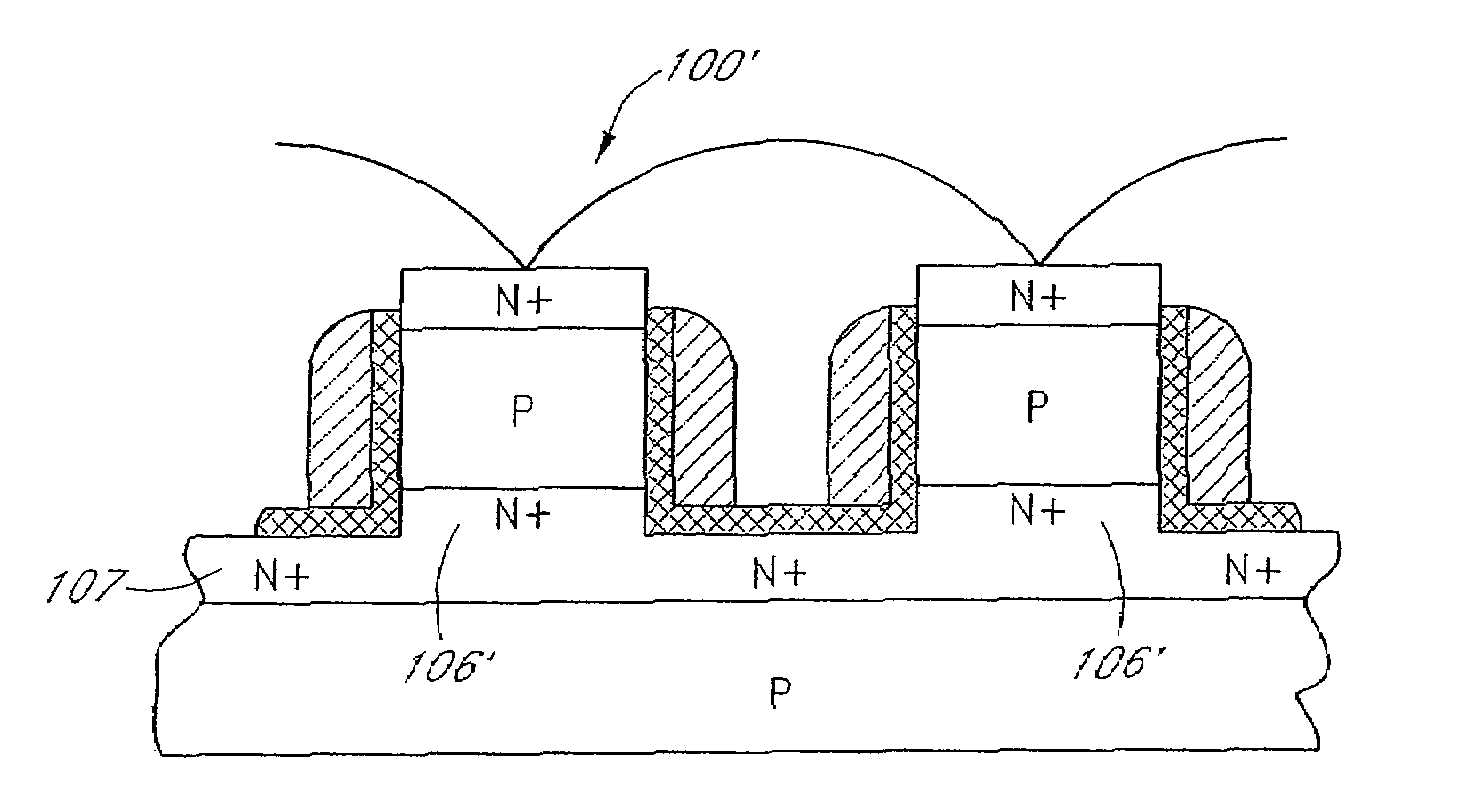

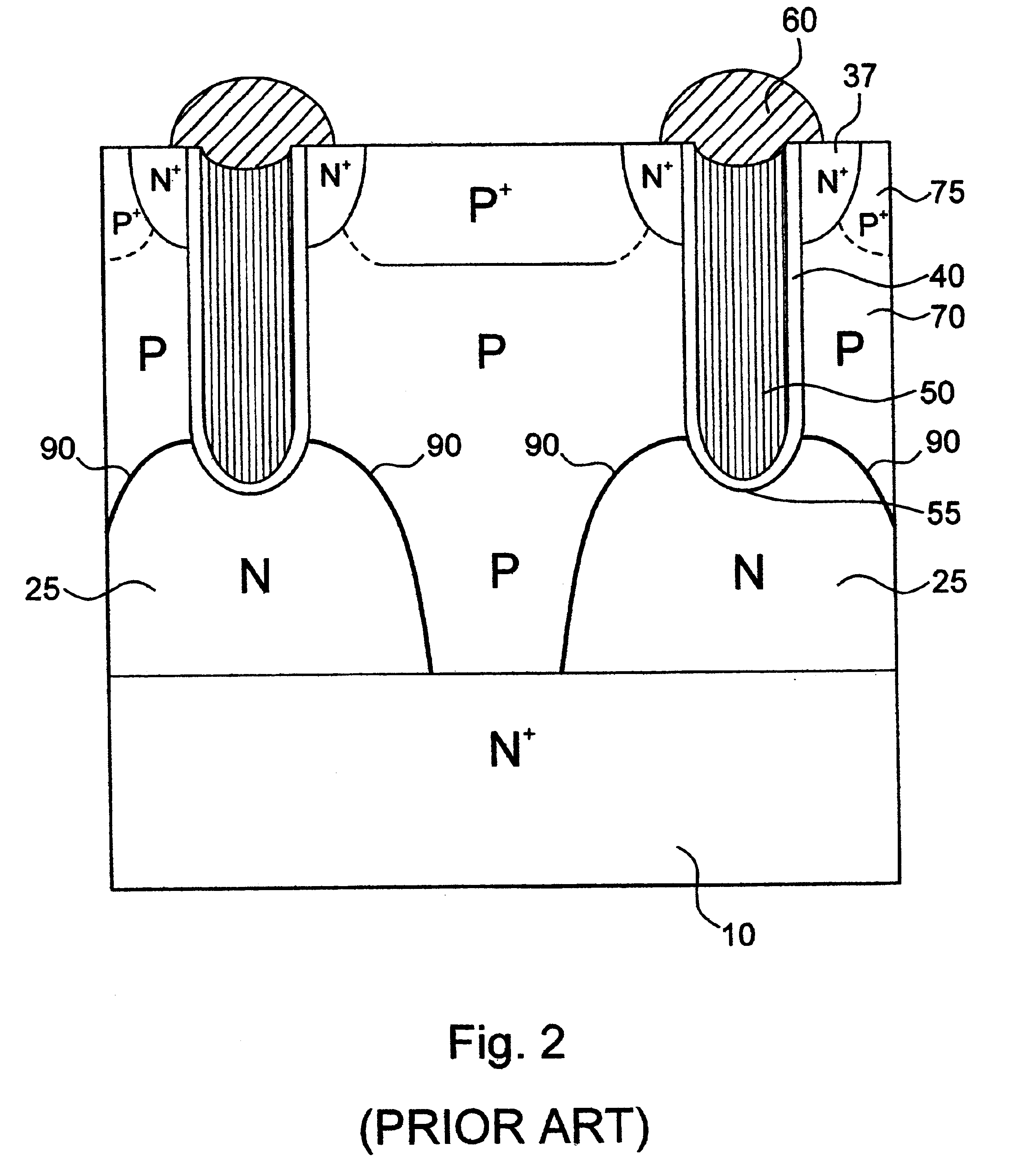

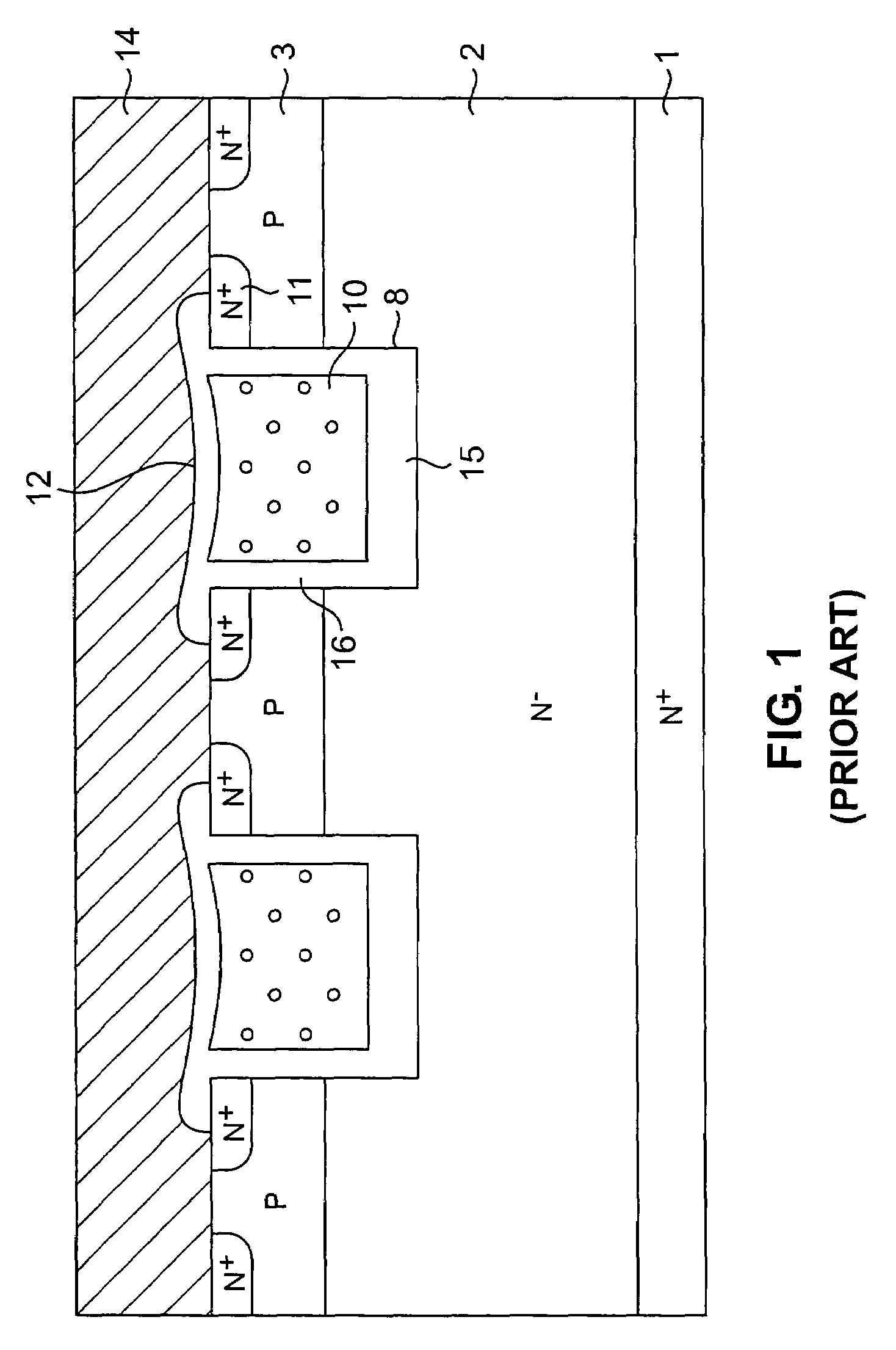

Method of manufacturing a trench transistor having a heavy body region

InactiveUS20050079676A1Increase cell densityImprove scalabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBody positionsField-effect transistor

A trenched field effect transistor is provided that includes (a) a semiconductor substrate, (b) a trench extending a predetermined depth into the semiconductor substrate, (c) a pair of doped source junctions, positioned on opposite sides of the trench, (d) a doped heavy body positioned adjacent each source junction on the opposite side of the source junction from the trench, the deepest portion of the heavy body extending less deeply into said semiconductor substrate than the predetermined depth of the trench, and (e) a doped well surrounding the heavy body beneath the heavy body.

Owner:SEMICON COMPONENTS IND LLC

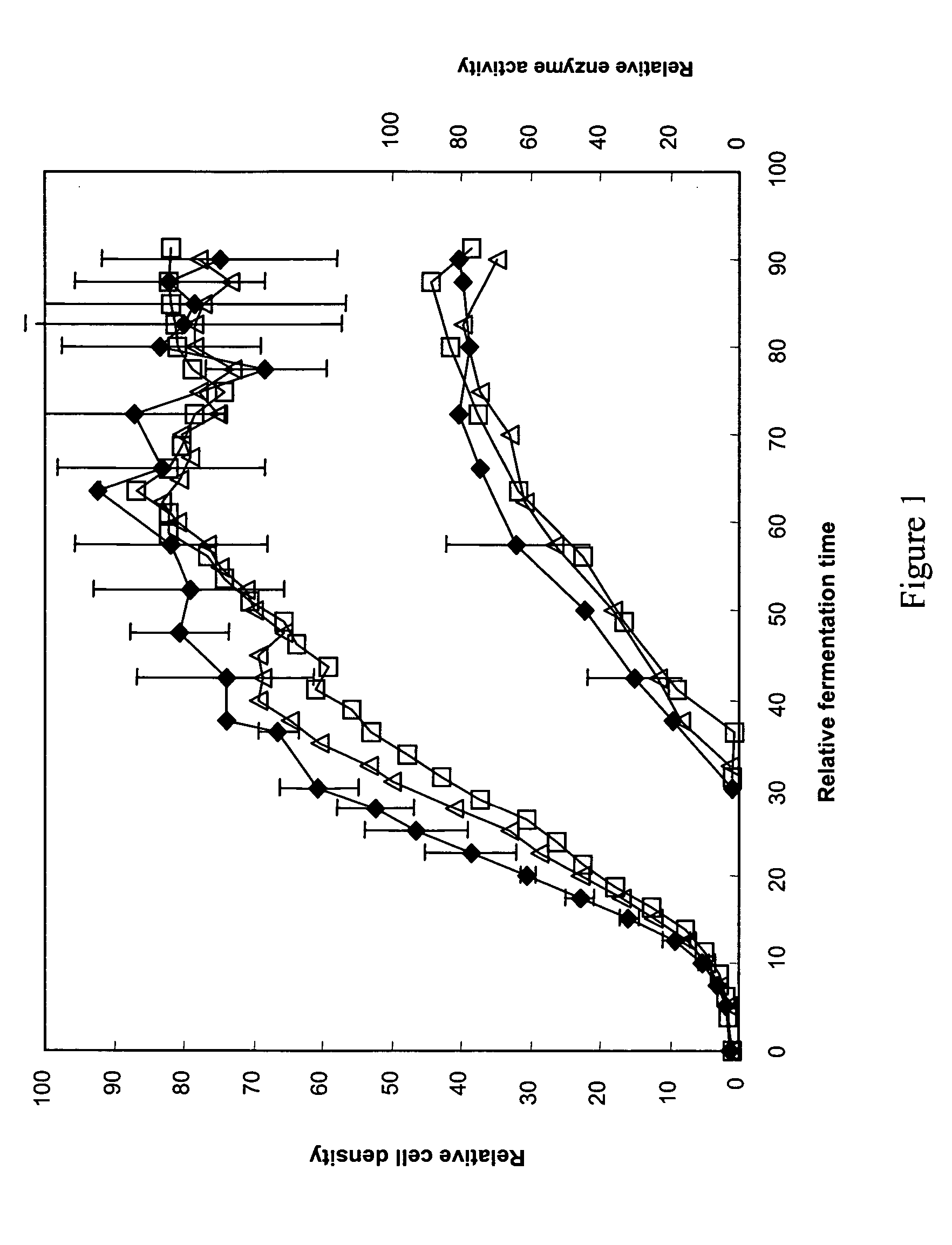

Protein expression systems

ActiveUS20090325230A1High protein yieldEfficient productionBacteriaSugar derivativesBiotechnologyRecombinant protein production

The present invention provides an improved expression system for the production of recombinant polypeptides utilizing auxotrophic selectable markers. In addition, the present invention provides improved recombinant protein production in host cells through the improved regulation of expression.

Owner:PELICAN TECH HLDG INC

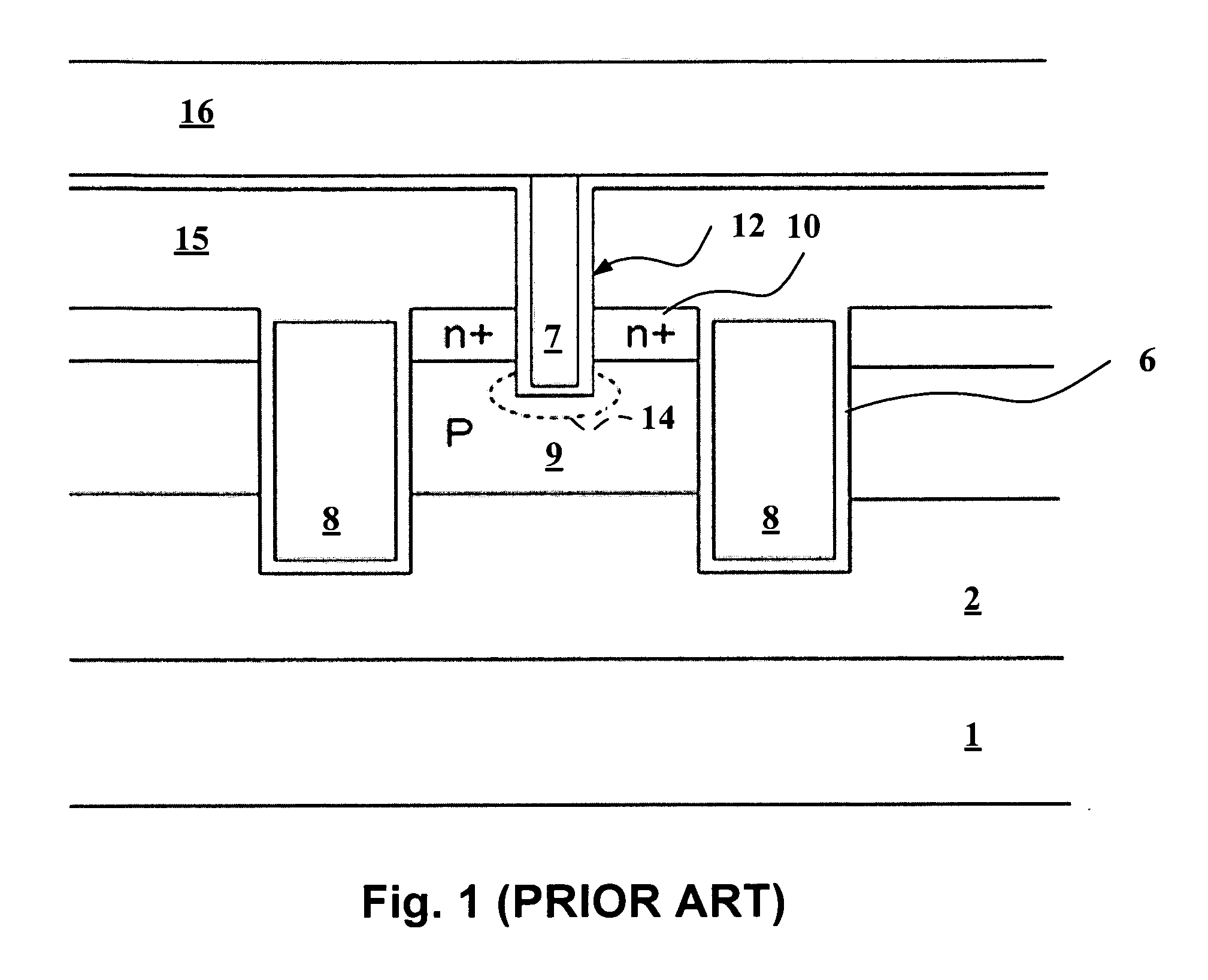

Self-aligned trench transistor using etched contact

InactiveUS6924198B2Avoid problemsAvoid shortingSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceMOSFET

A trench-gated MOSFET formed using a super self aligned (SSA) process employs an insulating layer such as a glass layer and a contact mask to define contact openings for electrical connections to source regions of the MOSFET. Use a contact mask and an intervening glass in otherwise self-aligned process reduces the coupling capacitance between source metal and the top of the embedded trench gate. A metal layer deposited to make electrical contact to source regions can be planarized, for example, ground flat using chemical-mechanical polishing to provide a flat surface to avoid formation of conductive traces that extend over the steps that the glass layer forms.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

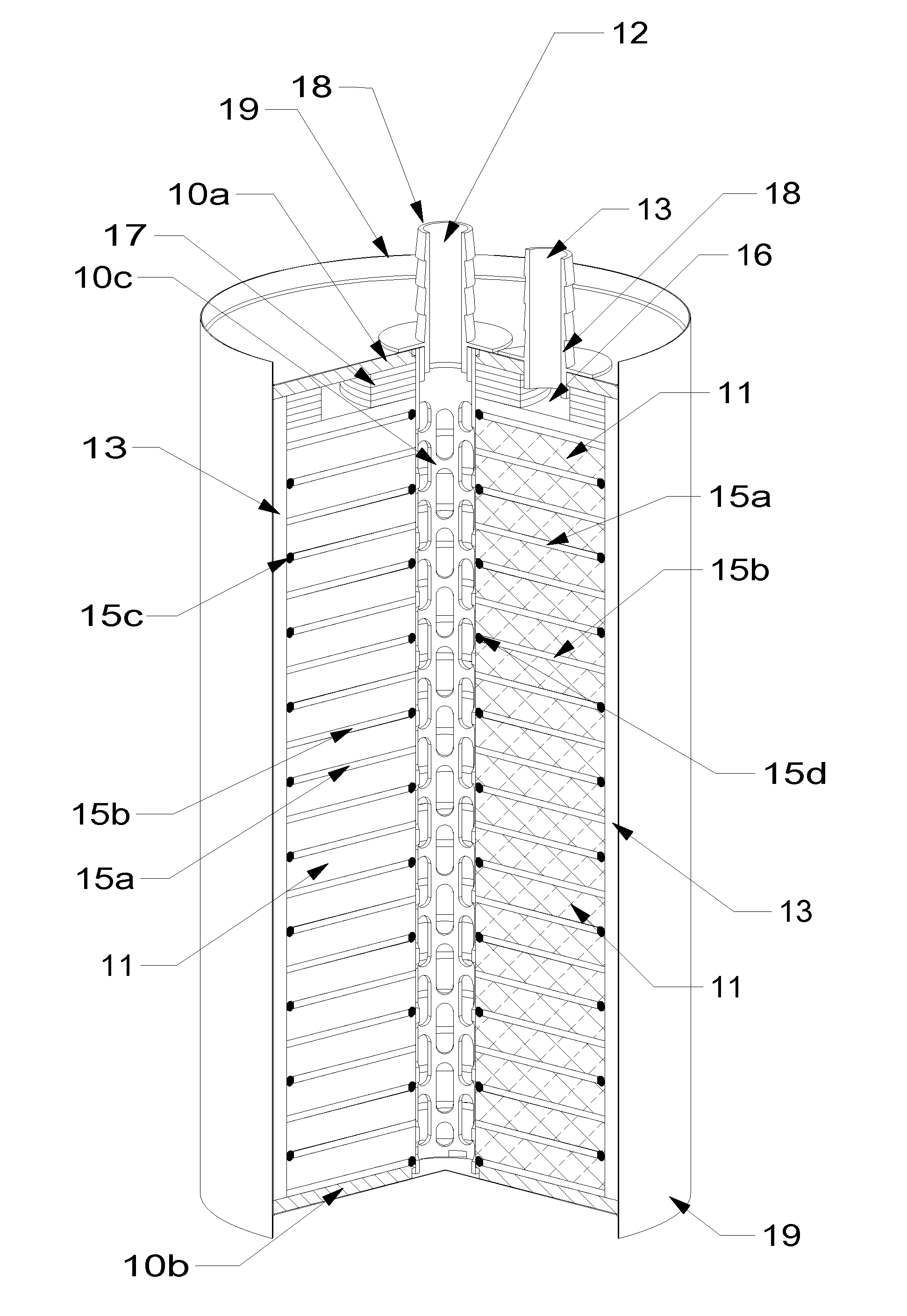

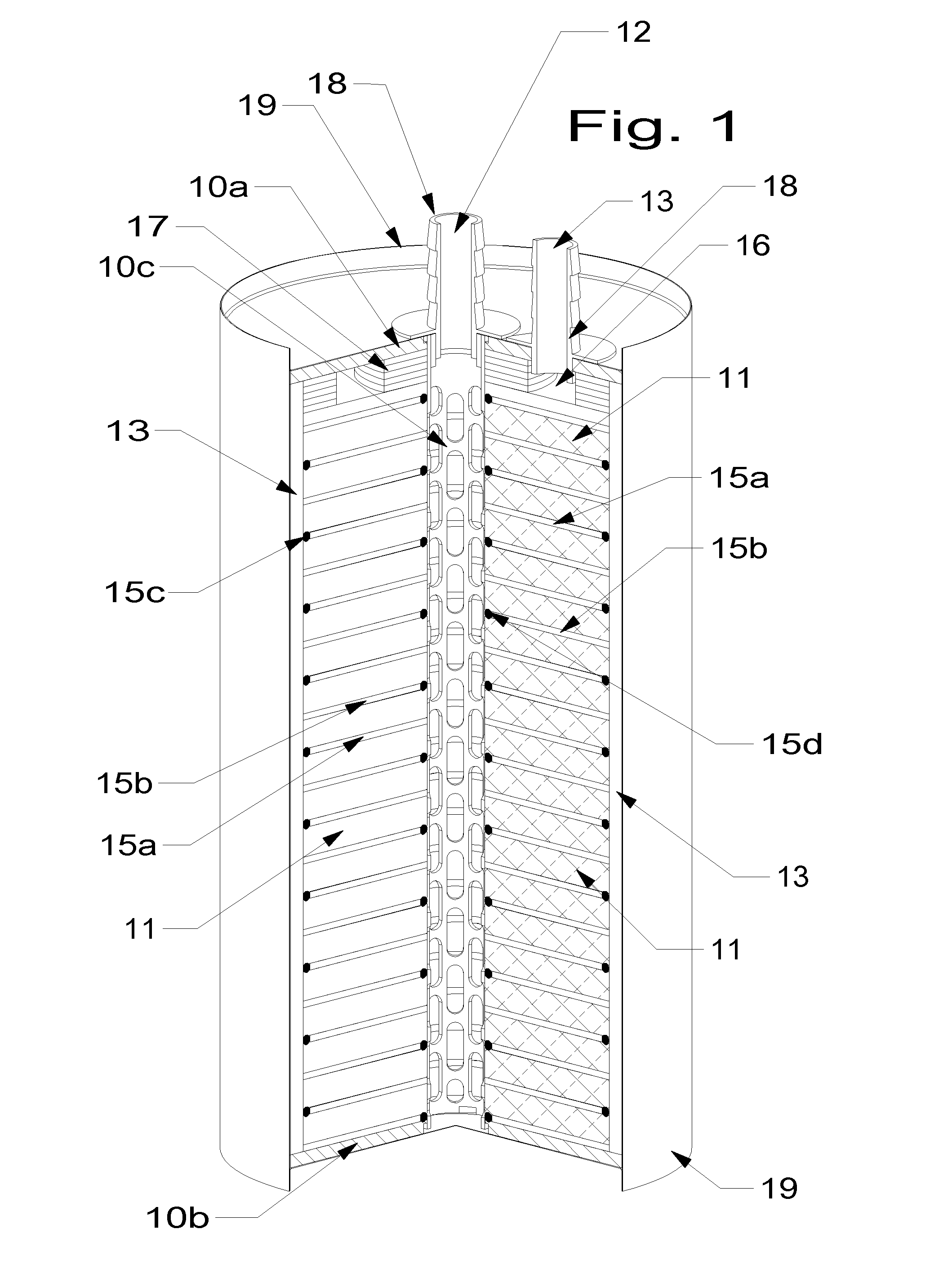

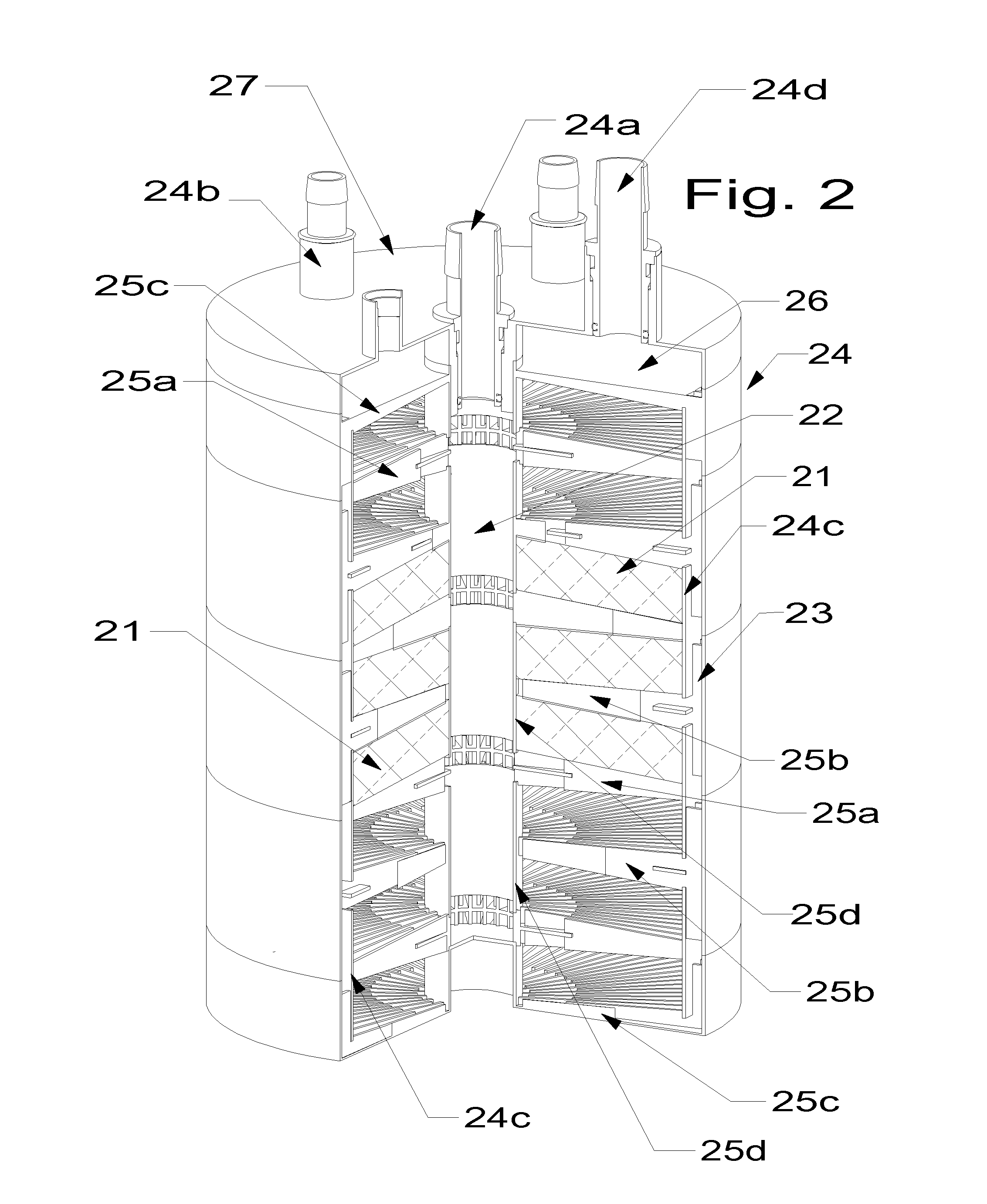

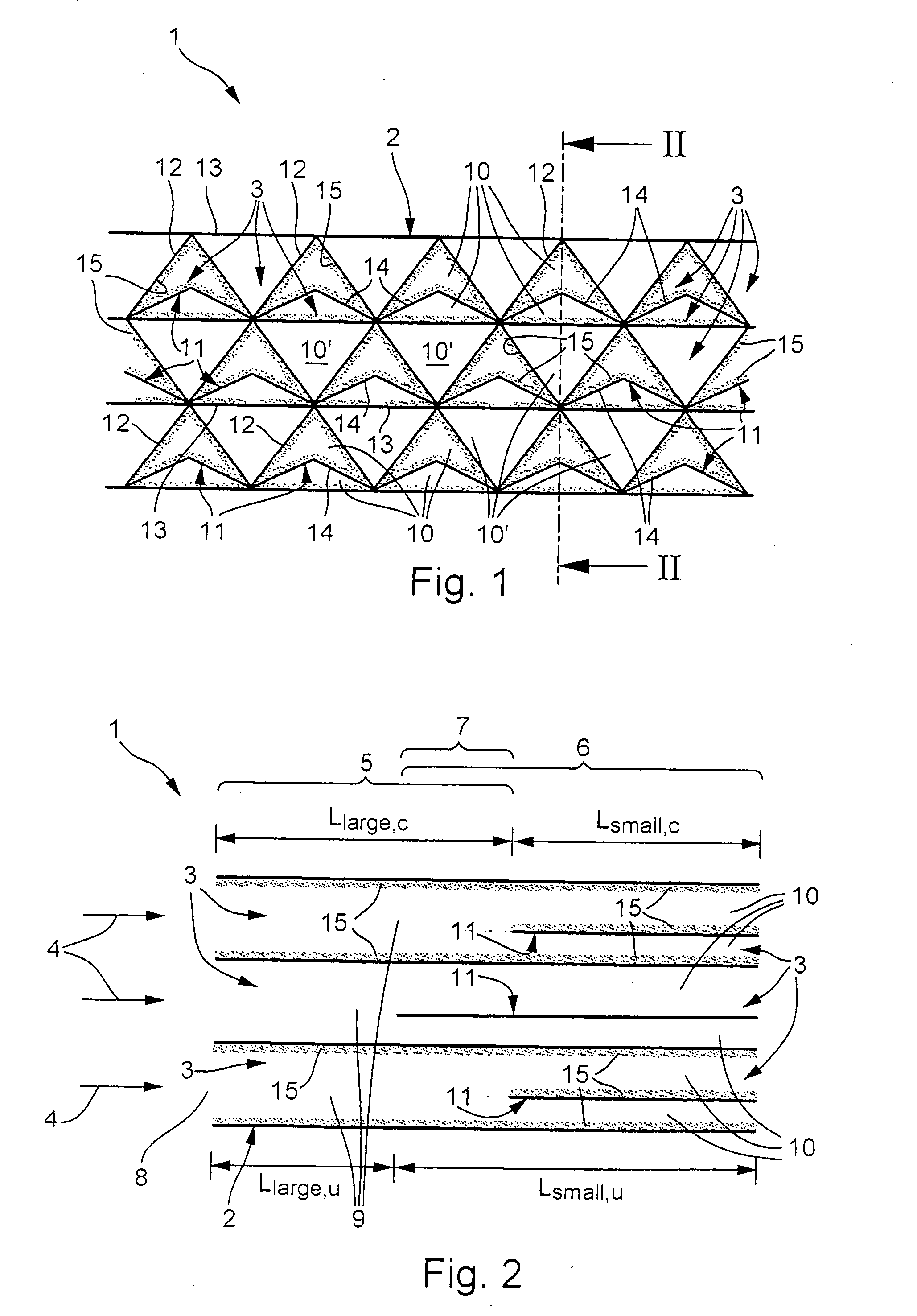

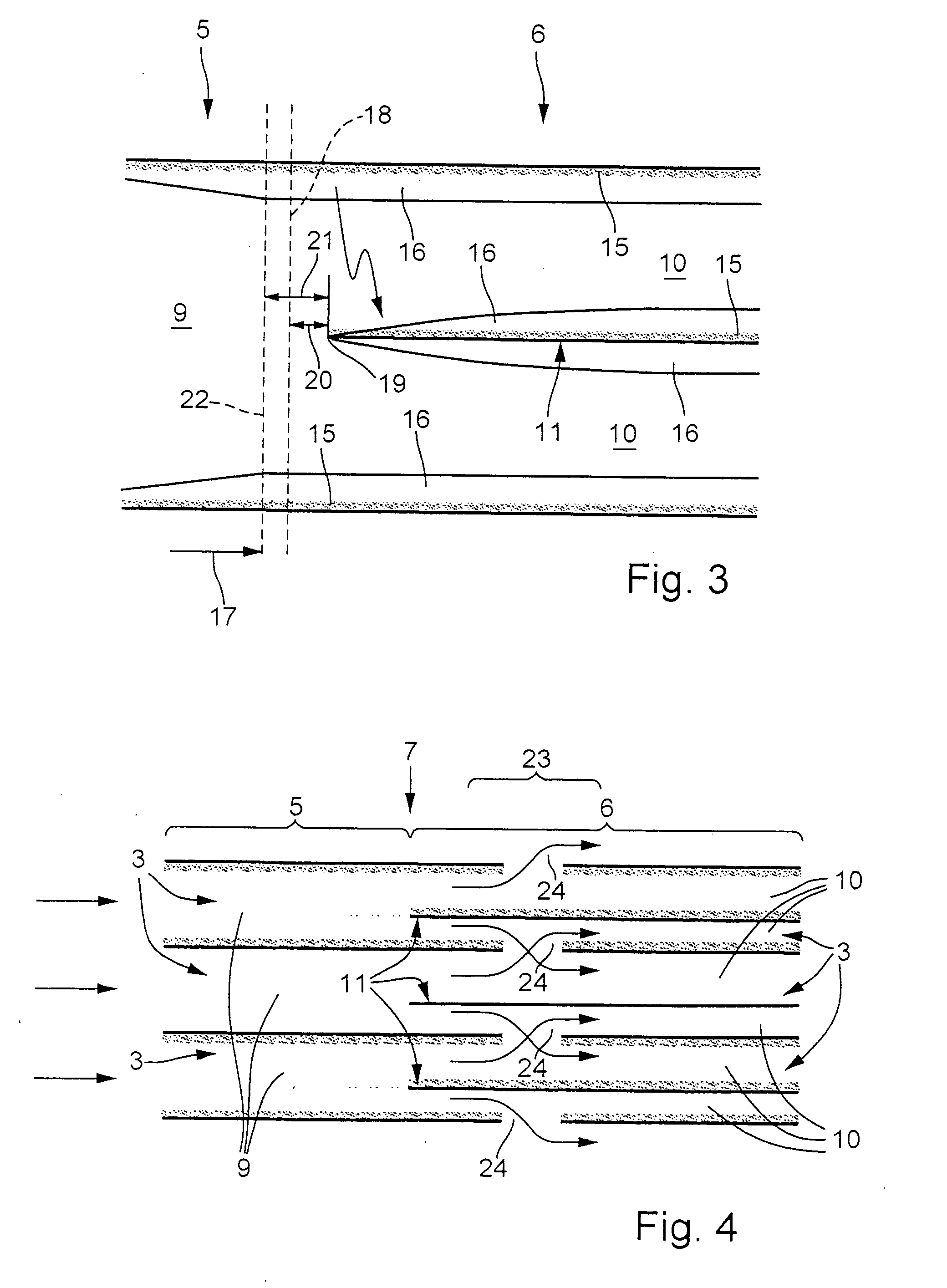

Device and method for industrial cultivation of cells

ActiveUS20140227769A1Effectively scaledLower the volumeBioreactor/fermenter combinationsBiological substance pretreatmentsBiotechnologyBiochemical engineering

Owner:STOBBE GMBH

Trench MOSFET having low gate charge

InactiveUS6979621B2High cell densityLow gate chargeSolid-state devicesSemiconductor/solid-state device manufacturingBody regionTrench mosfet

A trench MOSFET device comprising: (a) a silicon substrate of a first conductivity type (preferably N-type conductivity); (b) a silicon epitaxial layer of the first conductivity type over the substrate, the epitaxial layer having a lower majority carrier concentration than the substrate; (c) a body region of a second conductivity type (preferably P-type conductivity) within an upper portion of the epitaxial layer; (d) a trench having trench sidewalls and a trench bottom, which extends into the epitaxial layer from an upper surface of the epitaxial layer and through the body region of the device; (f) an oxide region lining the trench, which comprises a lower segment covering at least the trench bottom and upper segments covering at least upper regions of the trench sidewalls; (g) a conductive region within the trench adjacent the oxide region; and (h) a source region of the first conductivity type within an upper portion of the body region and adjacent the trench. The lower segment of the oxide region is thicker than the upper segments of the oxide region in this embodiment.

Owner:GEN SEMICON

Manufacturing foams by stress-induced nucleation

InactiveUS6080798AShort induction timeThe implementation process is simpleCoatingsVitrificationStress induced

The invention disclosed provides a method for inducing nucleation in a polymer by subjecting the polymer containing dissolved gas to an external stress generated, for example, by applying hydrostatic or mechanical pressure. The applied stress restricts the bubble growth so that the foamed materials have small cells and high cell density. Such microcellular foams can be produced over a wide low temperature range, i.e. from the temperature at which the polymer is conditioned with the blowing agent up to about the glass transition temperature of the polymer-blowing agent system. Stress induced nucleation can also be conducted at higher temperatures i.e. up to about the Tg of the neat polymer, leading to foams with larger cells. A variety of homogeneous and heterogeneous foams can be produced by this technique.

Owner:NAT RES COUNCIL OF CANADA

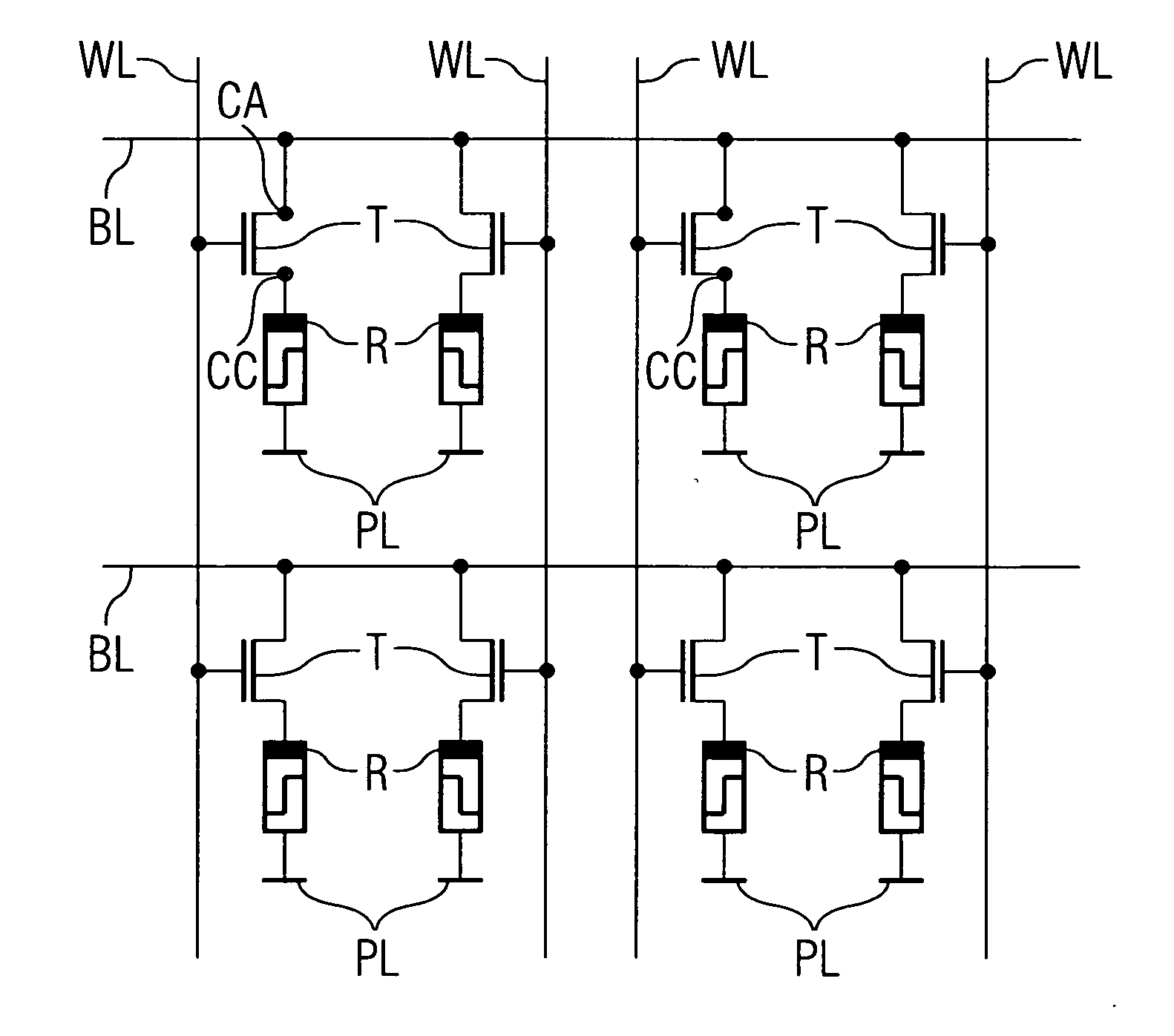

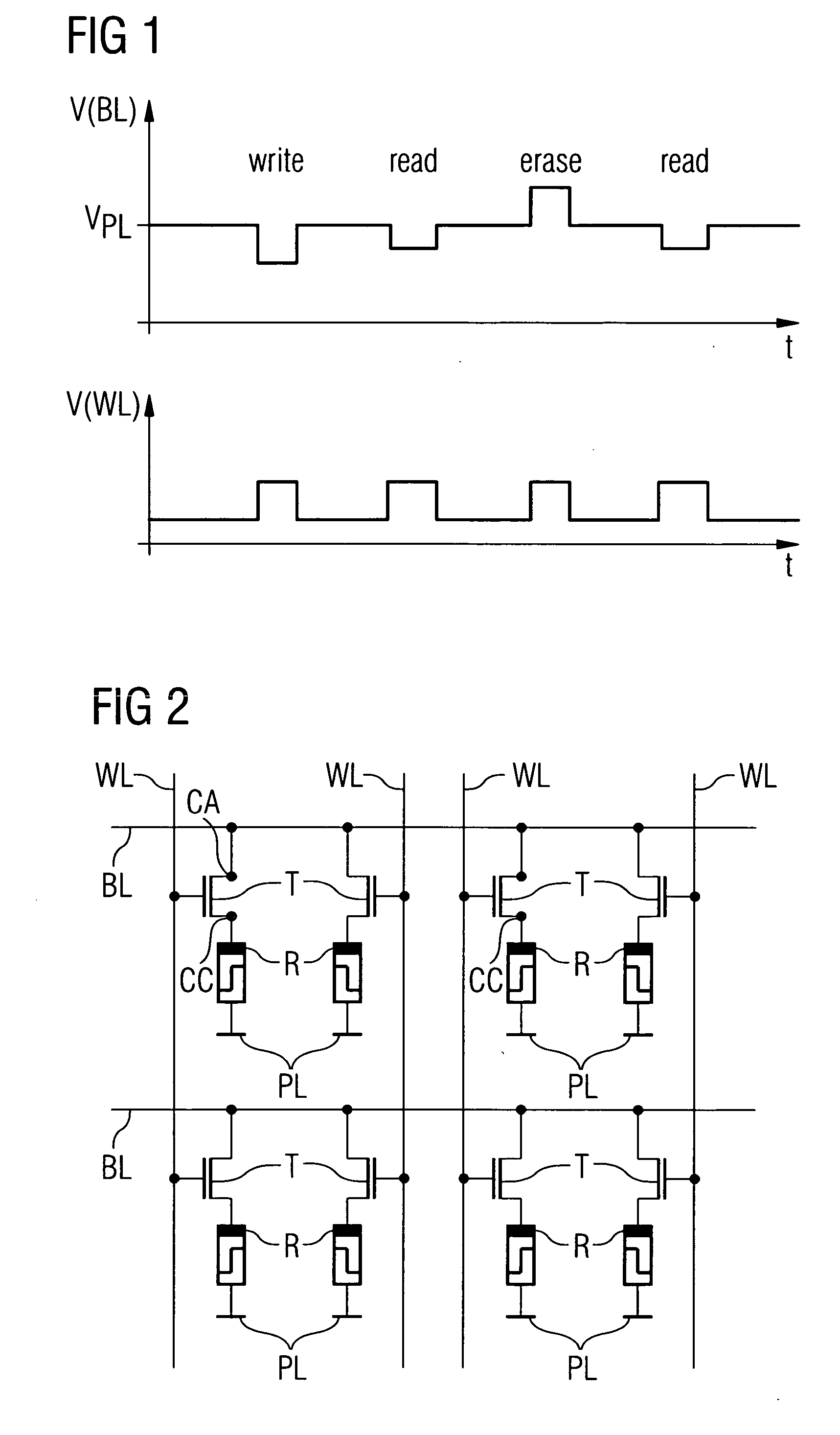

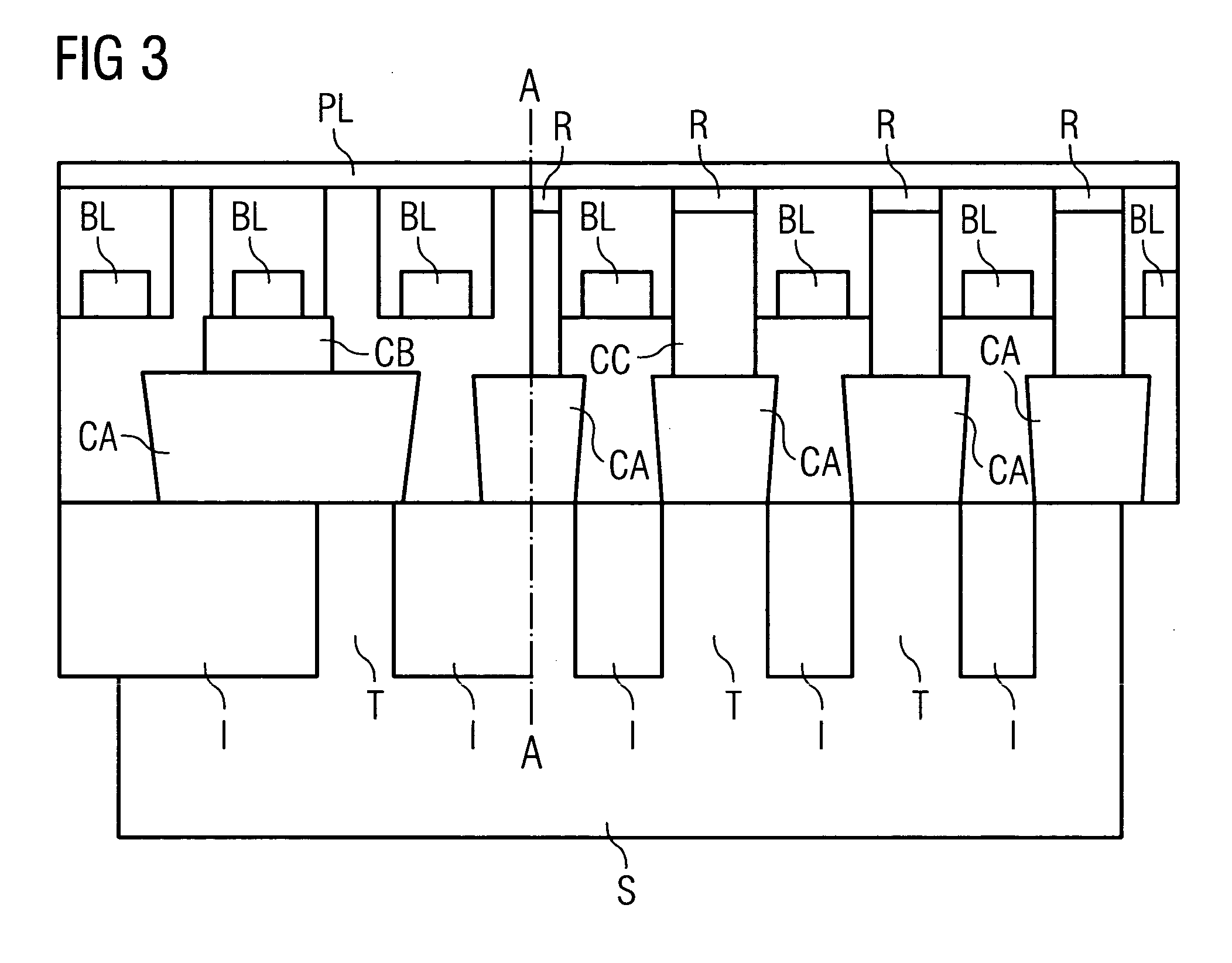

Integration of 1T1R CBRAM memory cells

InactiveUS20060139989A1Limited spaceLimit diffusion regionSolid-state devicesDigital storageBit lineSolid state electrolyte

A memory cell field with an integrated arrangement of solid body electrolyte memory cells, and in particular of CBRAM solid body electrolyte memory cells with 1T1R architecture, wherein the solid body electrolyte memory cells each comprise a layer stack that comprises at least a bottom and a top electroconductive, in particular metal layer and a layer of solid body electrolyte material or ion conductor material, respectively, positioned therebetween, and wherein each solid body electrolyte memory cell can be controlled via a word line, a bit line, and a plate line by means of a selection transistor, wherein at least a number of solid body electrolyte memory cells in the memory cell field have a common plate electrode or are connected to a common plate line, respectively.

Owner:INFINEON TECH AG

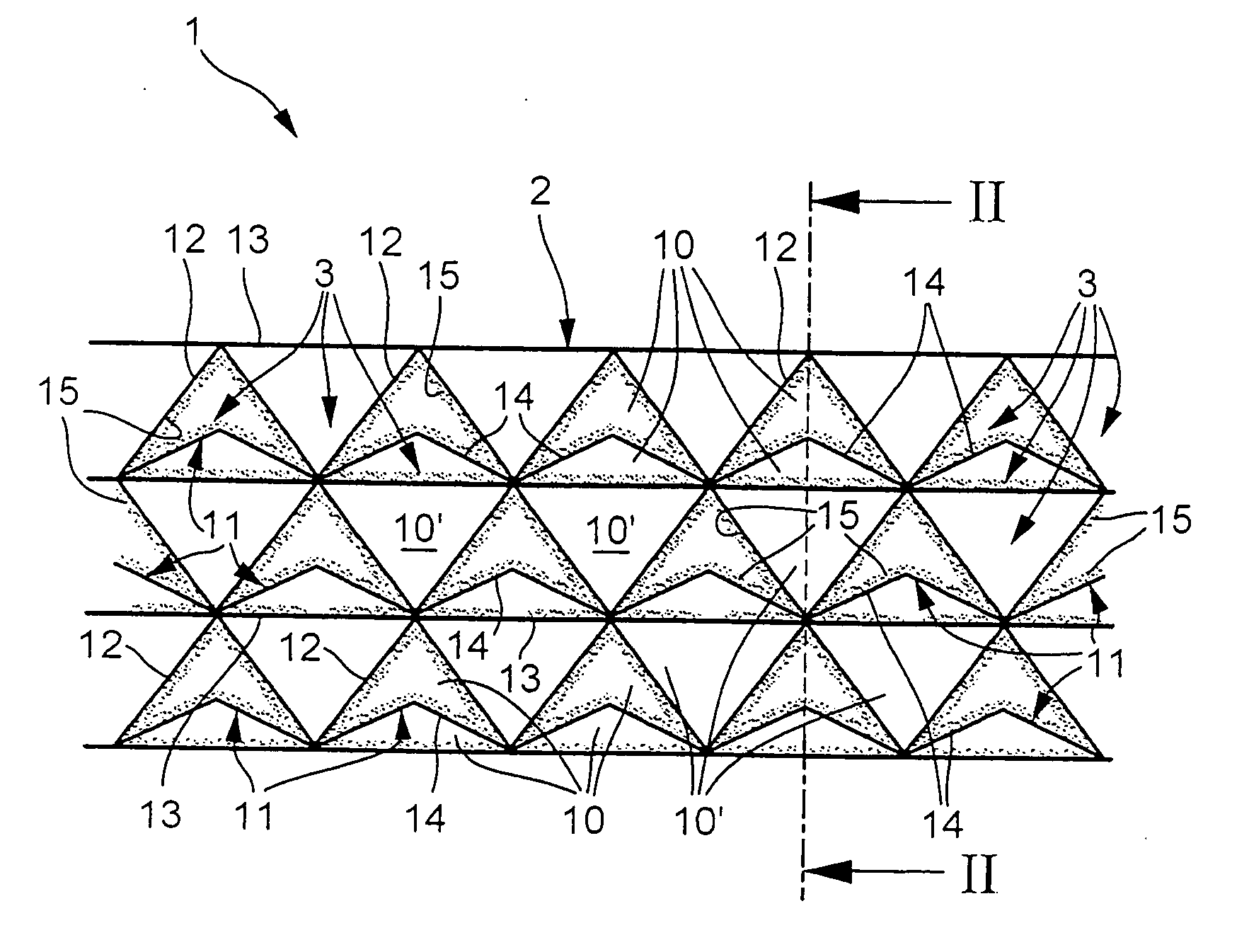

Catalyst

InactiveUS20050201909A1Reduced dimensionIncrease cell densityPhysical/chemical process catalystsCombustion using catalytic materialCombustionInlet channel

The present invention relates to a catalyst (1) for combustion of at least a portion of a gaseous fuel-oxidant mixture flowing through the catalyst (1), in particular for a burner of a power plant. An inlet sector (5) comprises inlet channels (9). A succeeding sector (6) comprises succeeding channels (10). The succeeding channels (10) have smaller internal cross-sectional areas than the inlet channels (9). To improve the production of the catalyst (1), the invention proposes channels (3) which extend through the inlet sector (5) and through the succeeding sector (6) and have the internal cross-sectional area of the inlet channels (9). The inlet channels (9) are formed by portions of the channels (3) lying in the inlet sector (5). The succeeding channels (10) are provided by arranging separation walls (11) within portions of the channels (3) lying in the succeeding sector (6), the separation walls (11) dividing each of the respective channel portions in the succeeding sector (6) into two succeeding channels (10).

Owner:ALSTOM TECH LTD

Three dimensional construct for the design and fabrication of physiological fluidic networks

ActiveUS8147562B2Increase cell densityIncrease the number ofMedical simulationAdditive manufacturing apparatusEngineeringSmall vessel

Owner:MASSACHUSETTS INST OF TECH +2

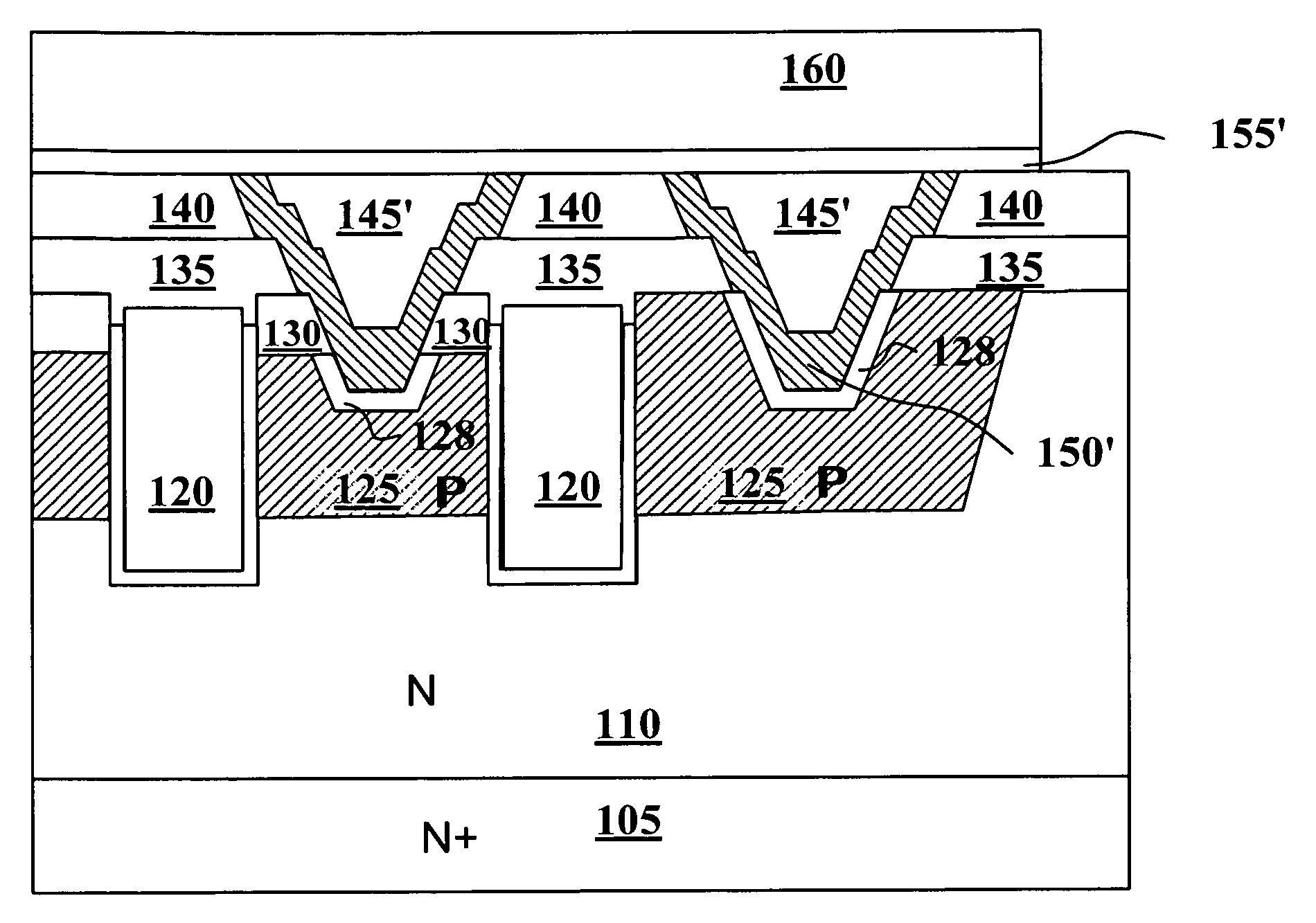

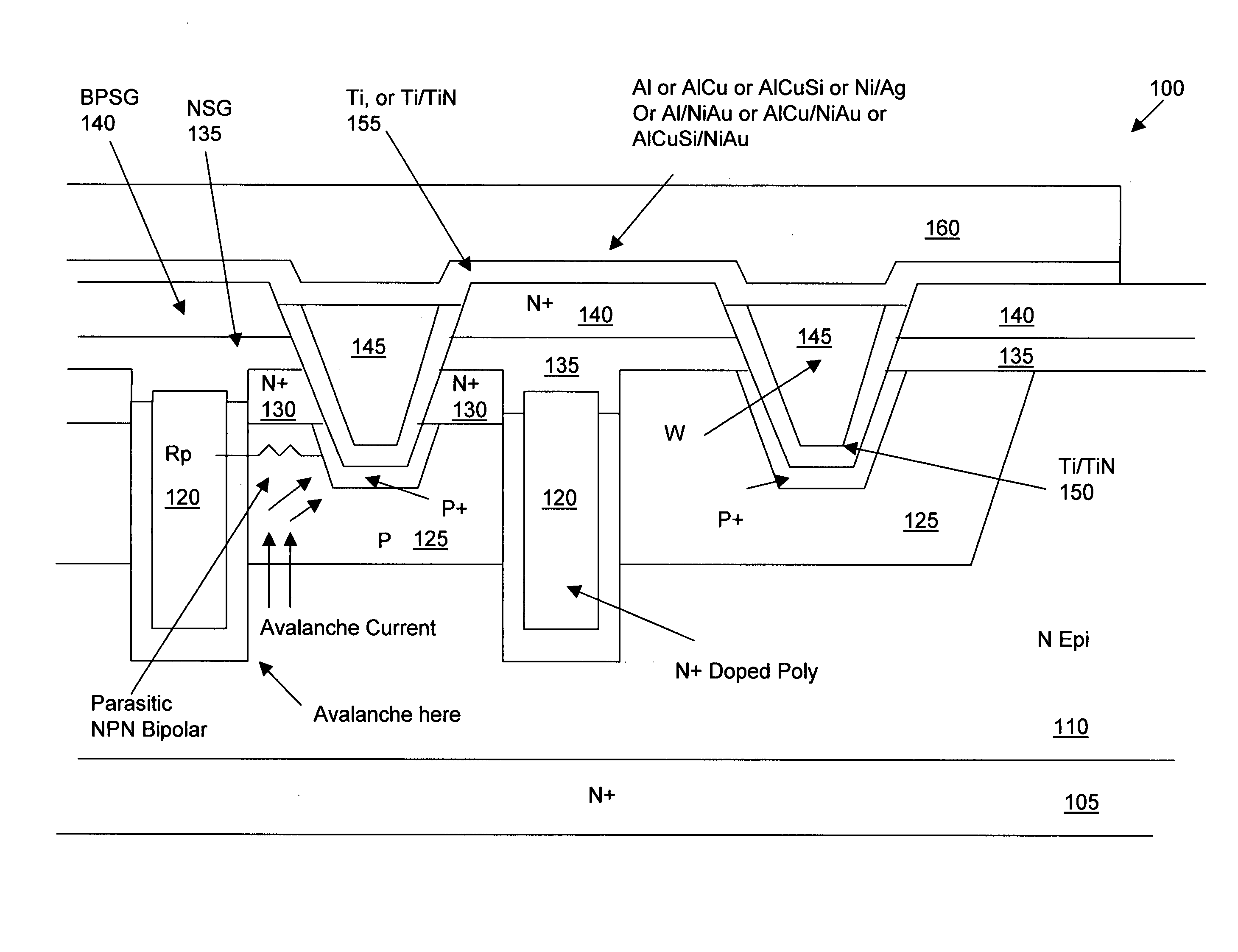

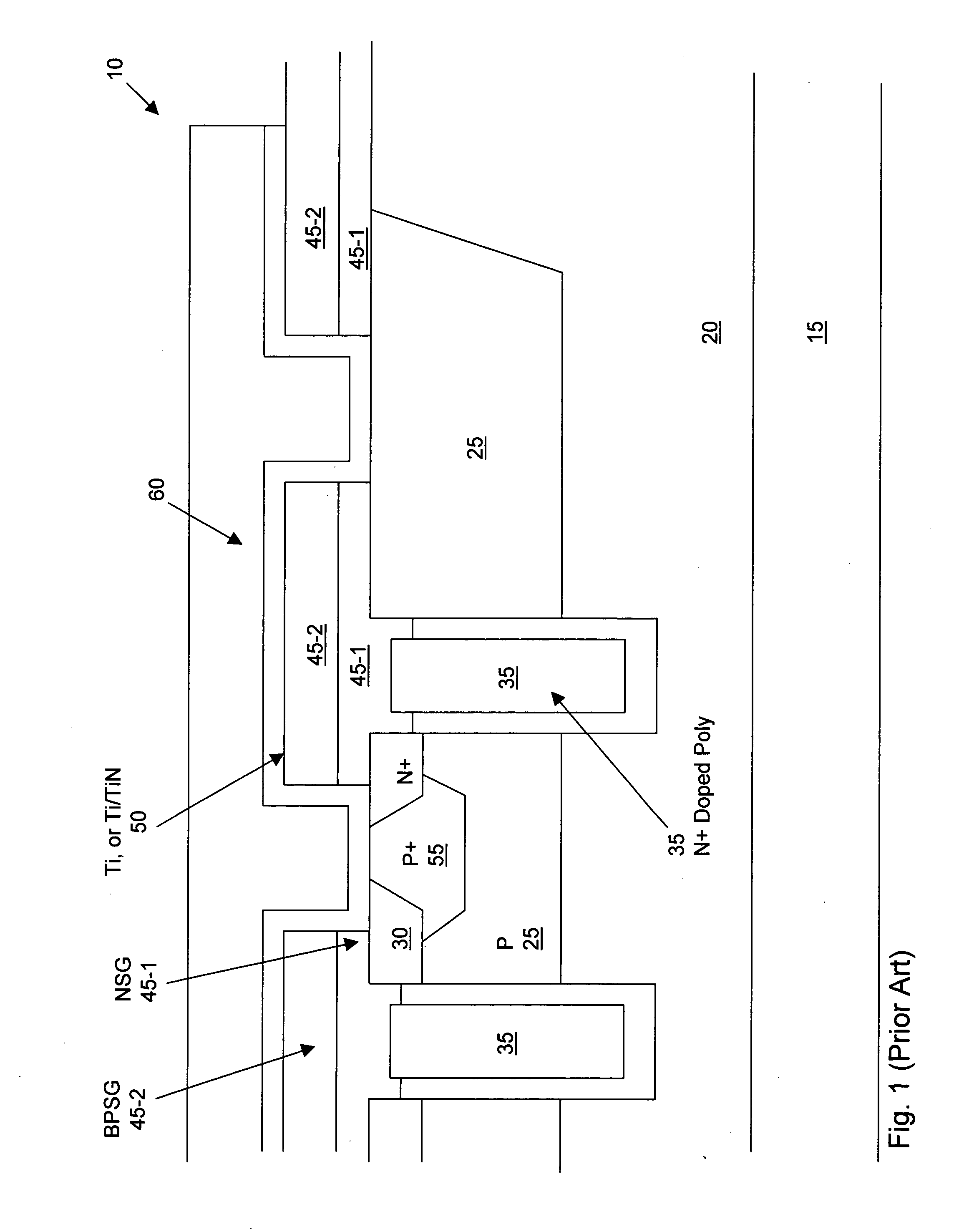

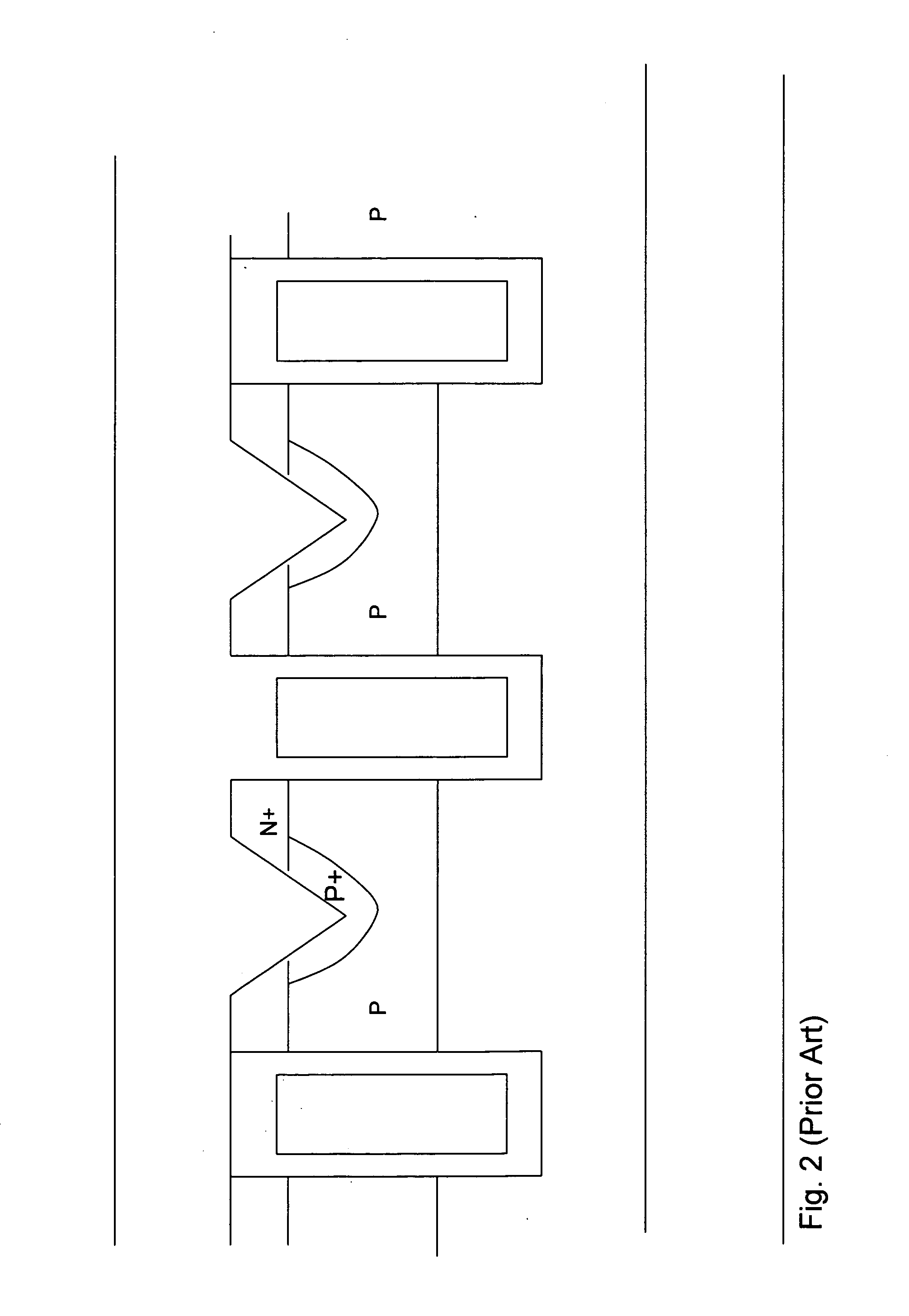

Structure for avalanche improvement of ultra high density trench MOSFET

InactiveUS20060273384A1Increase cell densityLower body resistanceSolid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetBody contact

A trenched metal oxide semiconductor field effect transistor (MOSFET) cell that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a source-body contact trench opened with sidewalls substantially extend vertically relative to a top surface into the source and body regions and filled with contact metal plug. A body-resistance reduction region doped with body-doped is formed to surround the source-body contact trench to reduce a body-region resistance between the source-body contact metal and the trenched gate to improve an avalanche capability.

Owner:M MOS SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com