Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1659 results about "Photonic integrated circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A photonic integrated circuit (PIC) or integrated optical circuit is a device that integrates multiple (at least two) photonic functions and as such is similar to an electronic integrated circuit. The major difference between the two is that a photonic integrated circuit provides functions for information signals imposed on optical wavelengths typically in the visible spectrum or near infrared 850 nm-1650 nm.

Integrated circuits with varying gate structures and fabrication methods

ActiveUS20150243658A1Overcomes shortcomingEnhanced advantageTransistorSolid-state devicesGate stackField-effect transistor

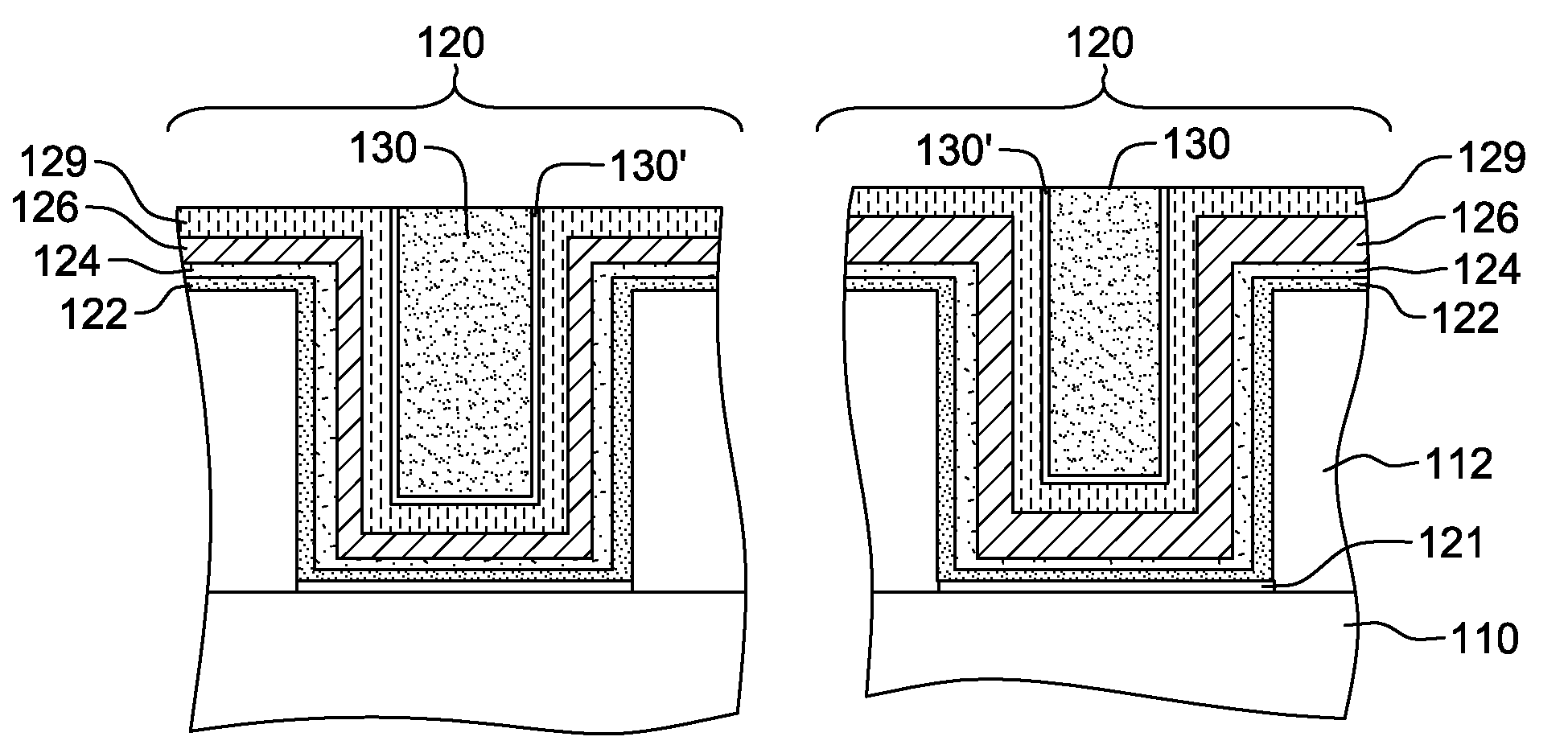

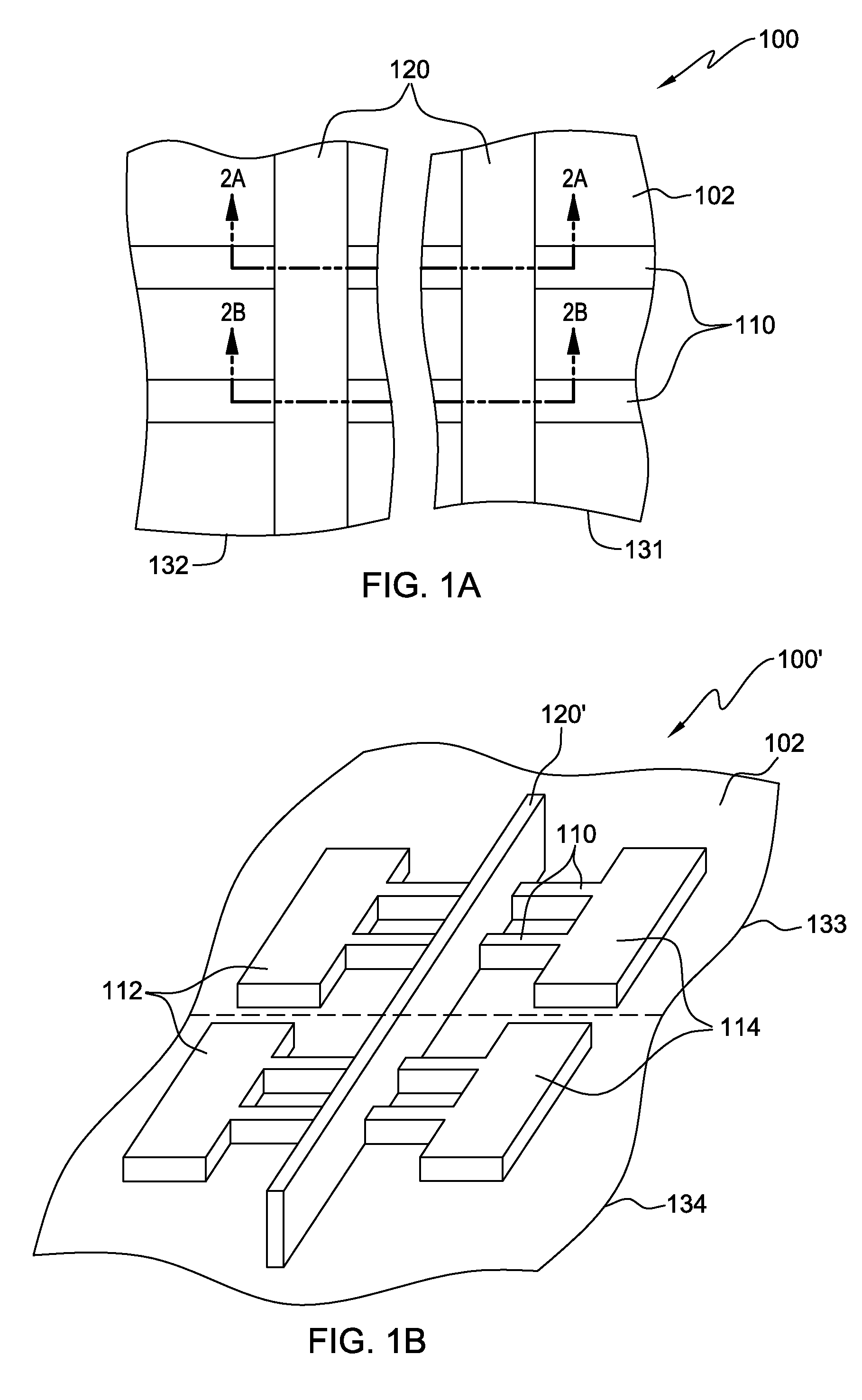

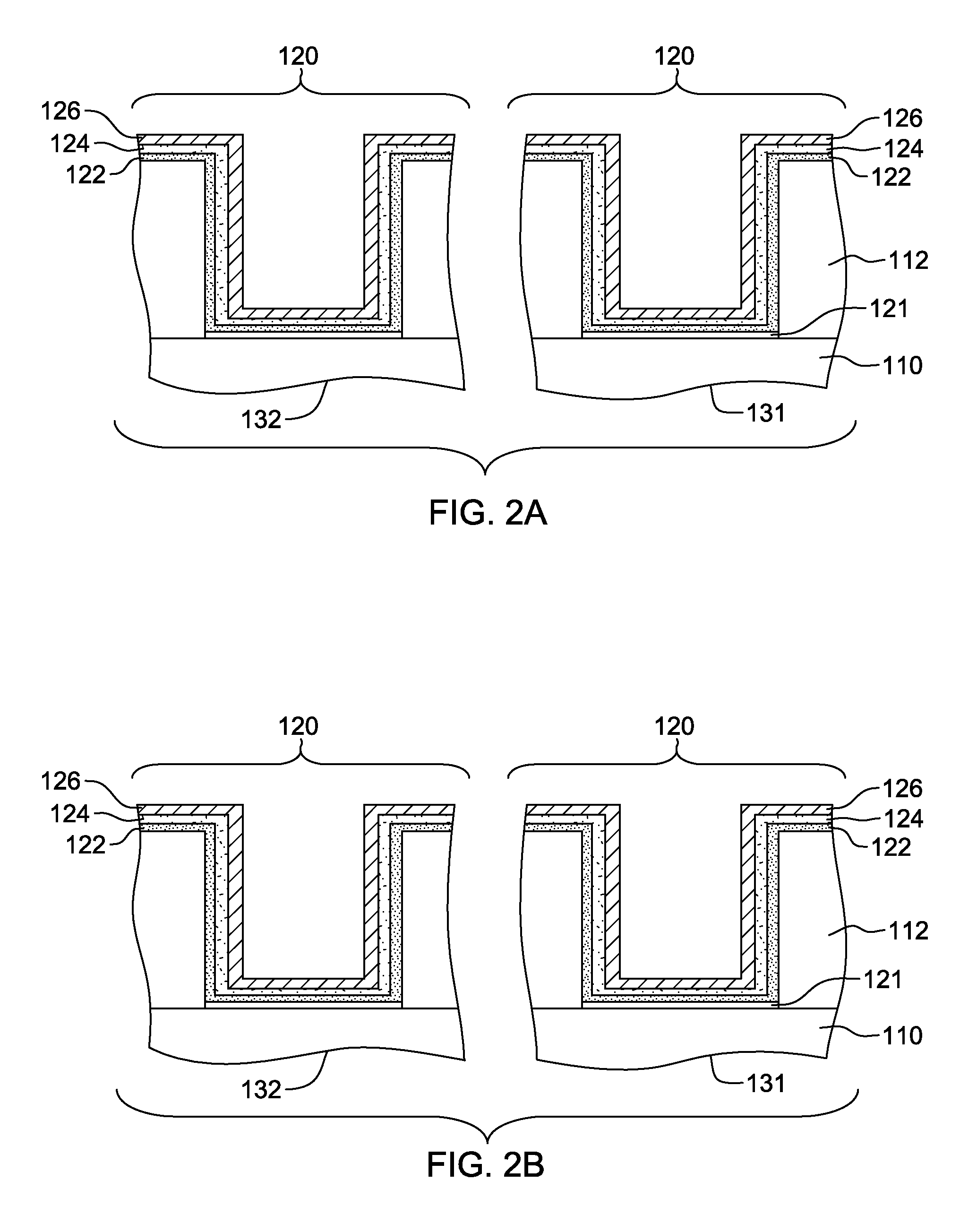

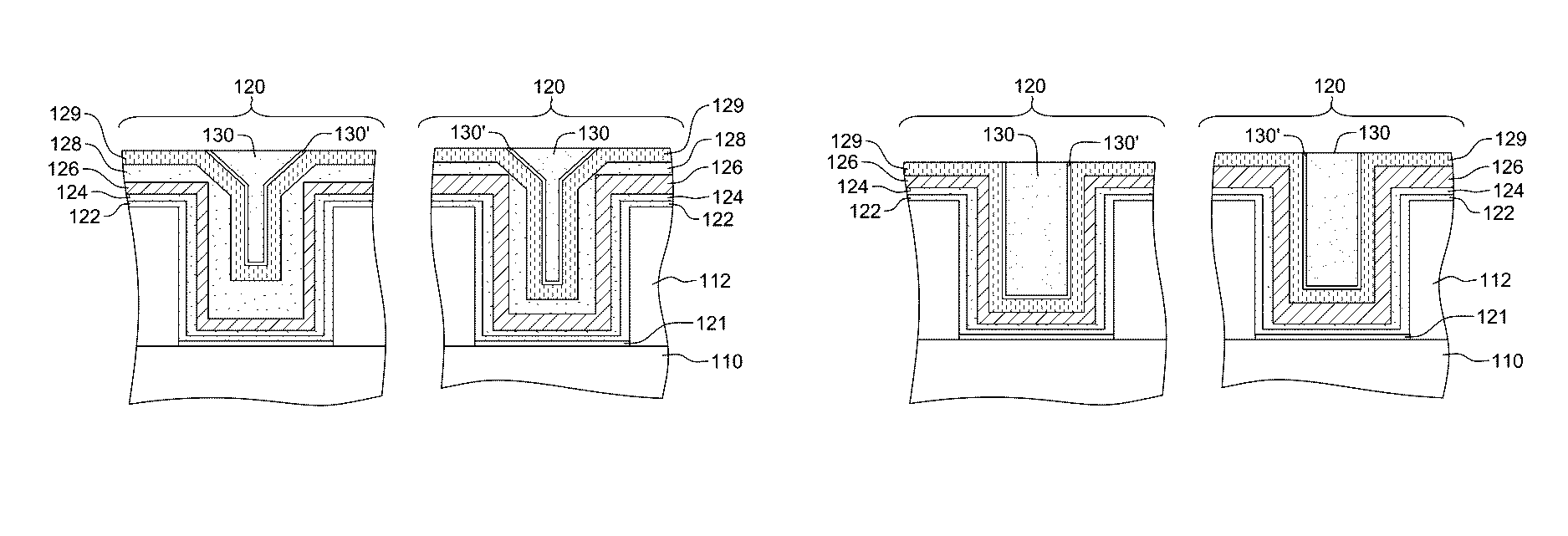

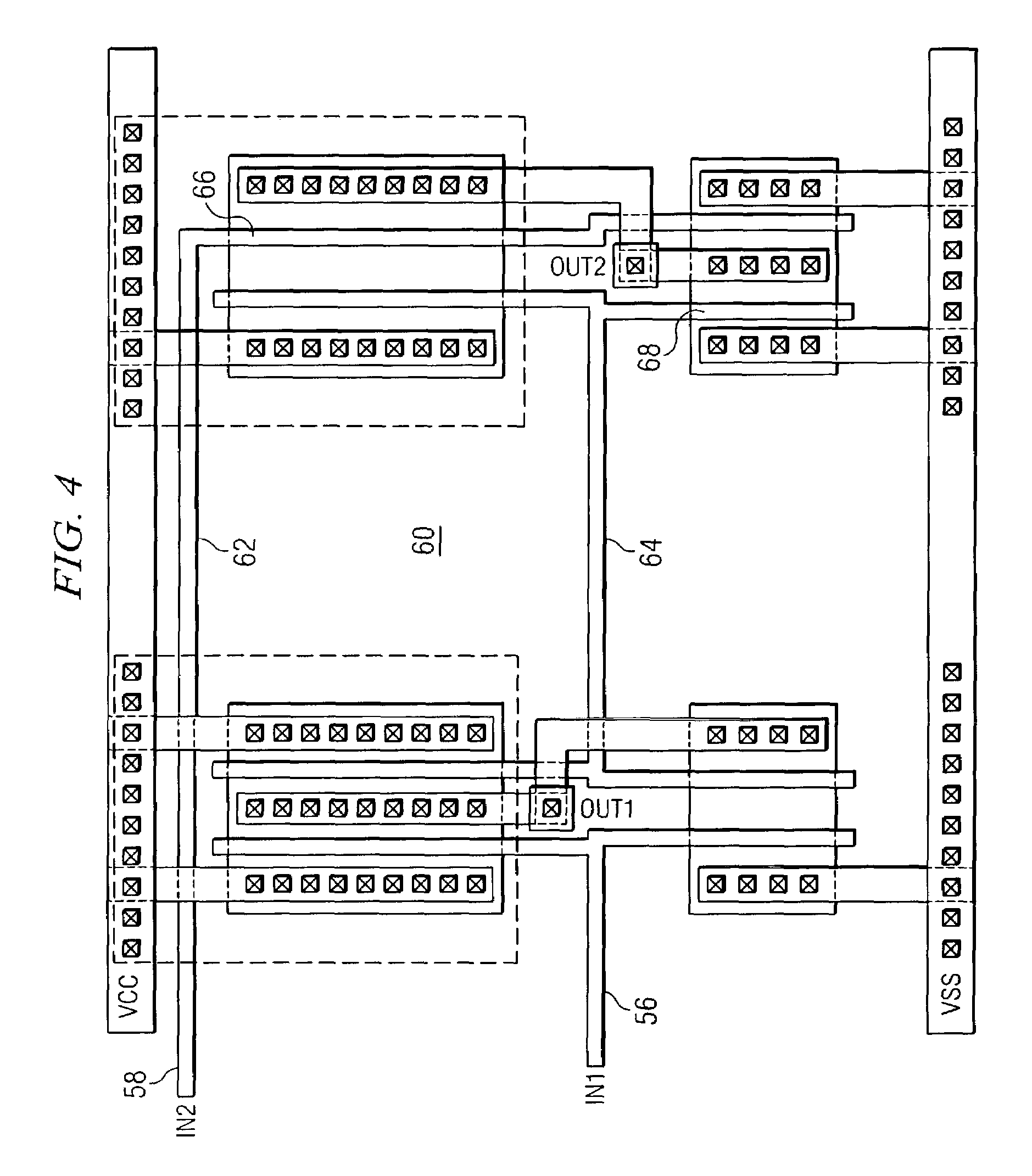

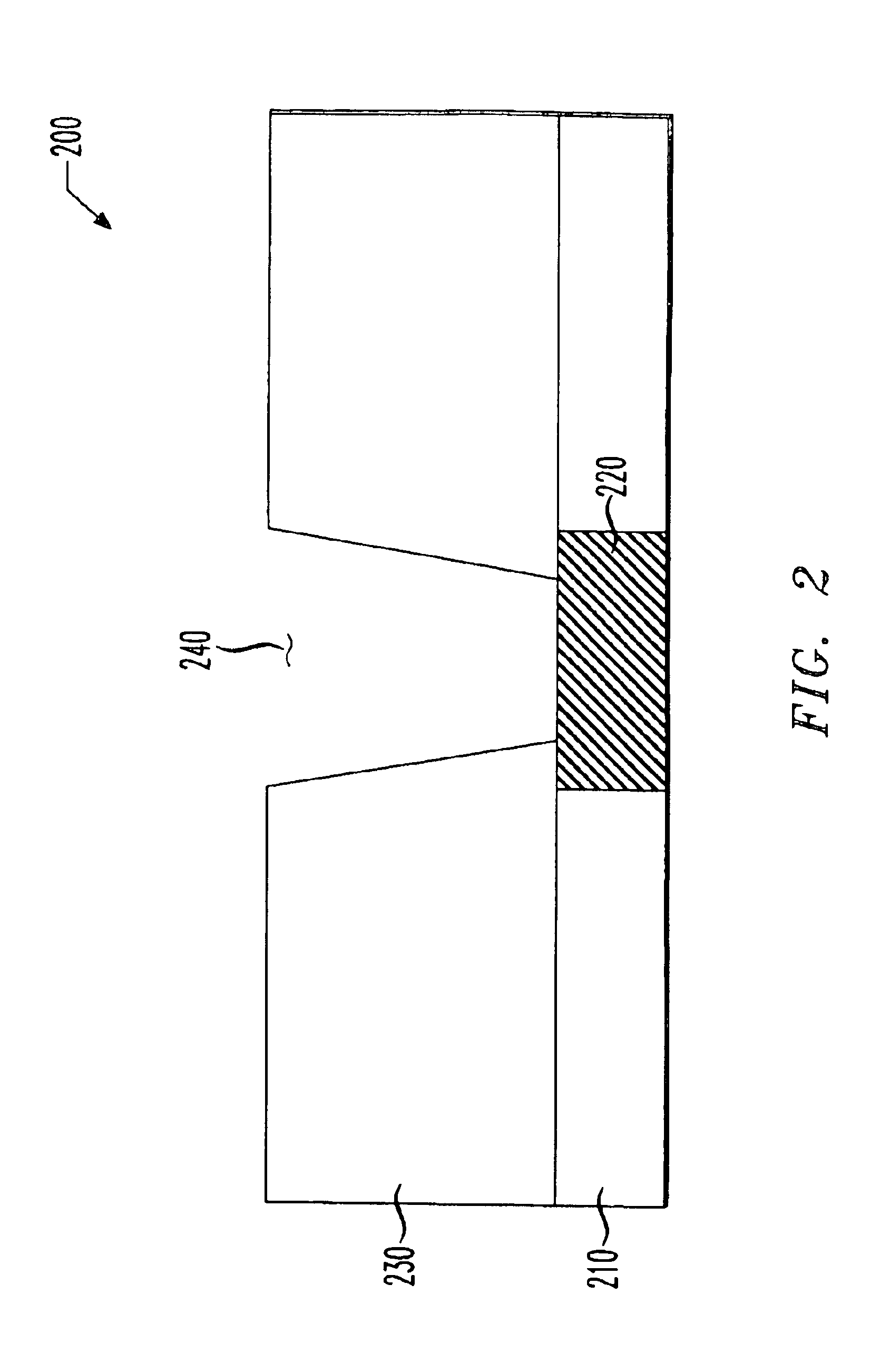

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES US INC

Integrated circuits with varying gate structures and fabrication methods

Integrated circuits and fabrication methods are provided. The integrated circuit includes: a varying gate structure disposed over a substrate structure, the varying gate structure including a first gate stack in a first region of the substrate structure, and a second gate stack in a second region of the substrate structure; a first field-effect transistor in the first region, the first field-effect transistor including the first gate stack and having a first threshold voltage; and a second field-effect transistor in the second region, the second field-effect transistor including the second gate stack and having a second threshold voltage, where the first threshold voltage is different from the second threshold voltage. The methods include providing the varying gate structure, the providing including: sizing layer(s) of the varying gate structure with different thickness(es) in different region(s).

Owner:GLOBALFOUNDRIES U S INC

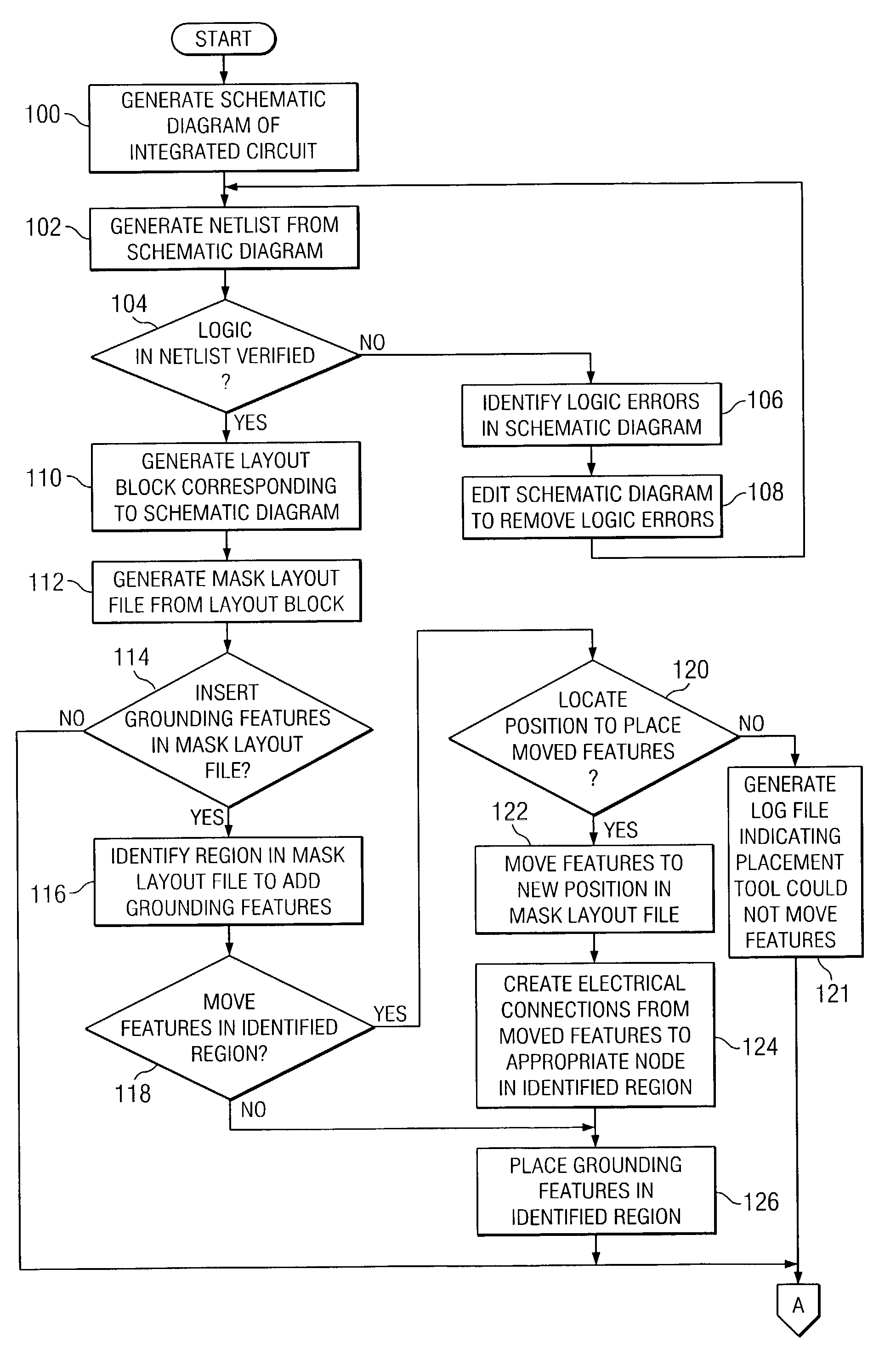

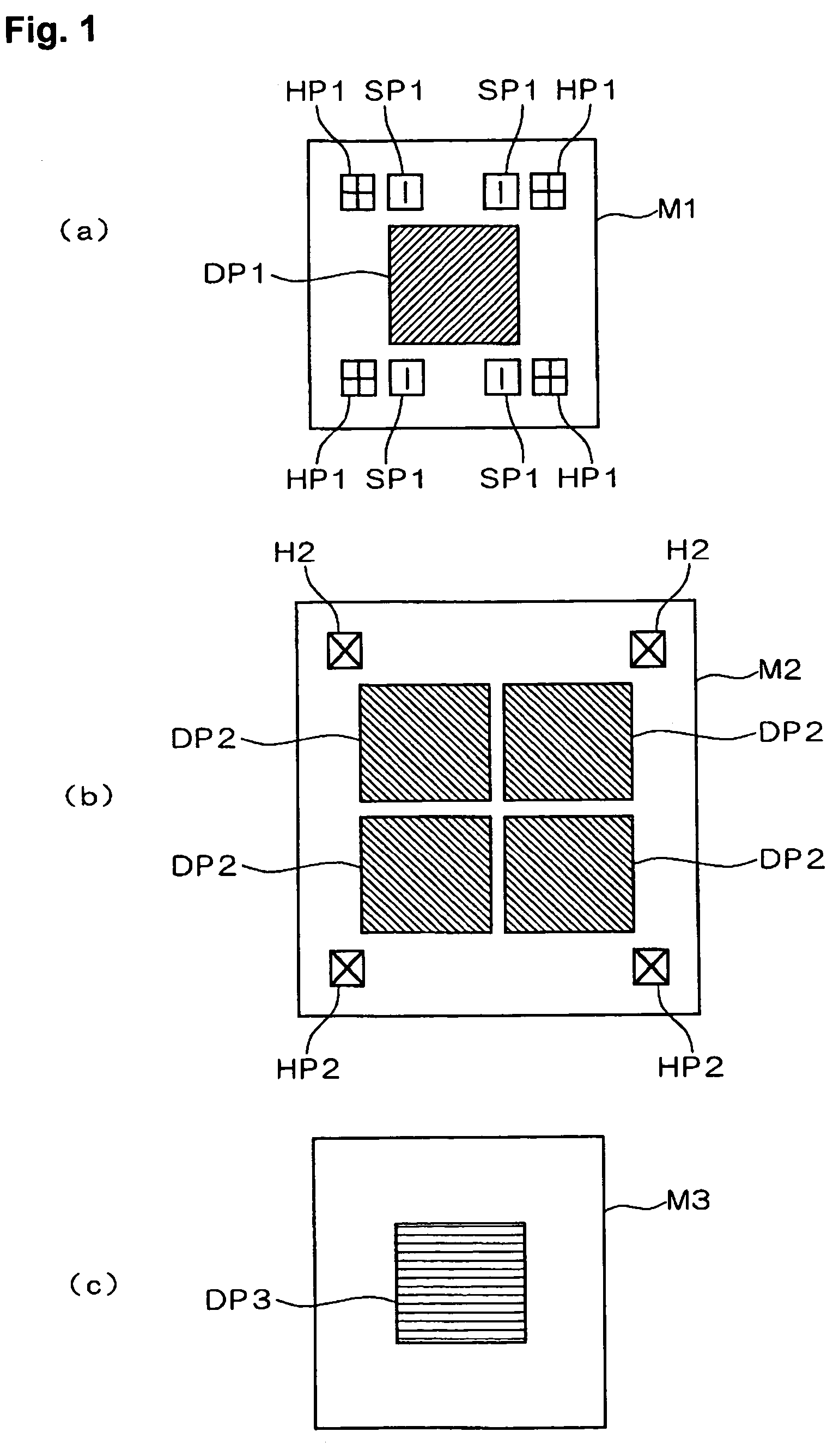

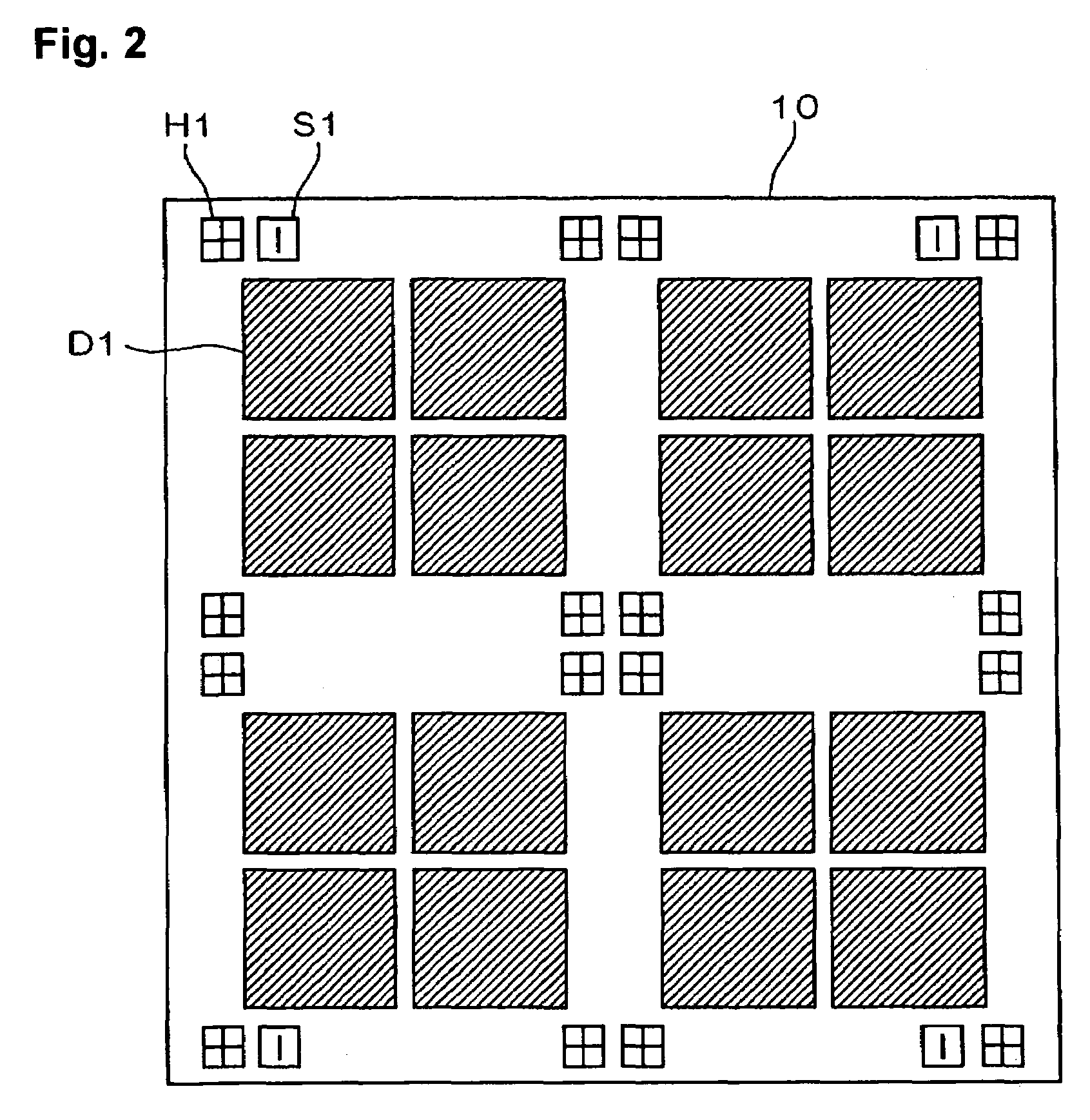

Photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufacture with same

InactiveUS6978437B1Increase antenna ratioRaise the ratioSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

A photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufactured with the photomask are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region including an antenna ratio less than a first design rule. A feature located in the identified region is moved based on a second design rule from a first position to a second position in the mask layout file to create a space in the identified region. A grounding feature is placed in the space and automatically connected to a gate feature in the mask layout file such that the antenna ratio is increased to greater than or approximately equal to the first design rule.

Owner:CELERICS TECH

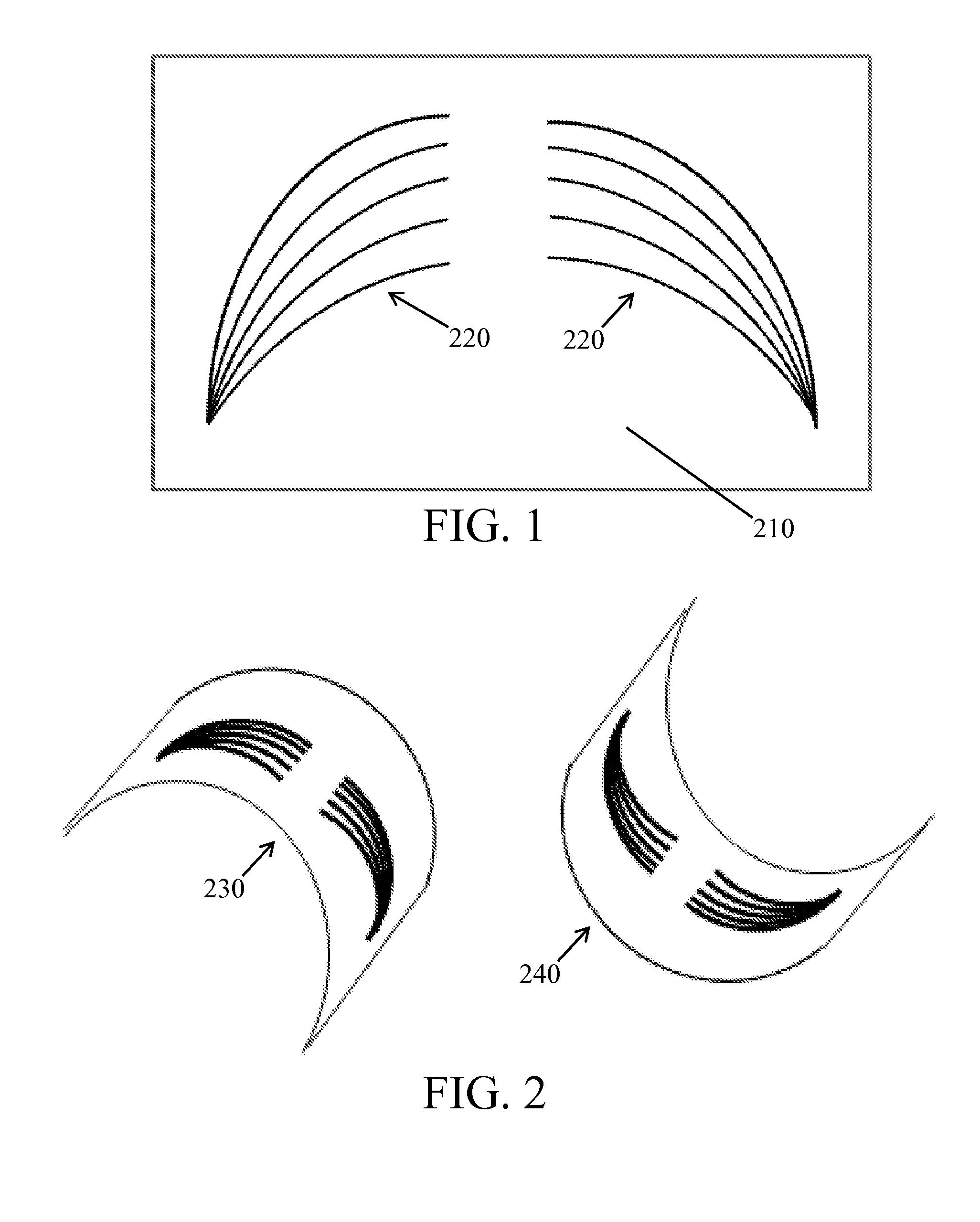

Optical phased array lidar system and method of using same

A lidar-based system and method are used for the solid state beamforming and steering of laser beams using optical phased array (OPA) photonic integrated circuits (PICs) and the detection of laser beams using photodetectors. Transmitter and receiver electronics, power management electronics, control electronics, data conversion electronics and processing electronics are also included in the system and used in the method.Laser pulses beamformed by the OPA PIC reflect from objects in the field of view (FOV) of said OPA, and are detected by a detector or a set of detectors.A lidar system includes at least one lidar, and any subset and any number of complementary sensors, data processing / communication / storage modules, and a balance of system for supplying power, protecting, connecting, and mounting the components of said system.Direct correlation between the 3D point cloud generated by the lidar and the color images captured by an RGB (Red, Green, Blue) video camera can be achieved by using an optical beam splitter that sends optical signals simultaneously to both sensors.A lidar system may contain a plurality of lidar sensors, a lidar sensor may contain a plurality of optical transmitters, and an optical transmitter may contain a plurality of OPA PICs.

Owner:QUANERGY SOLUTIONS INC

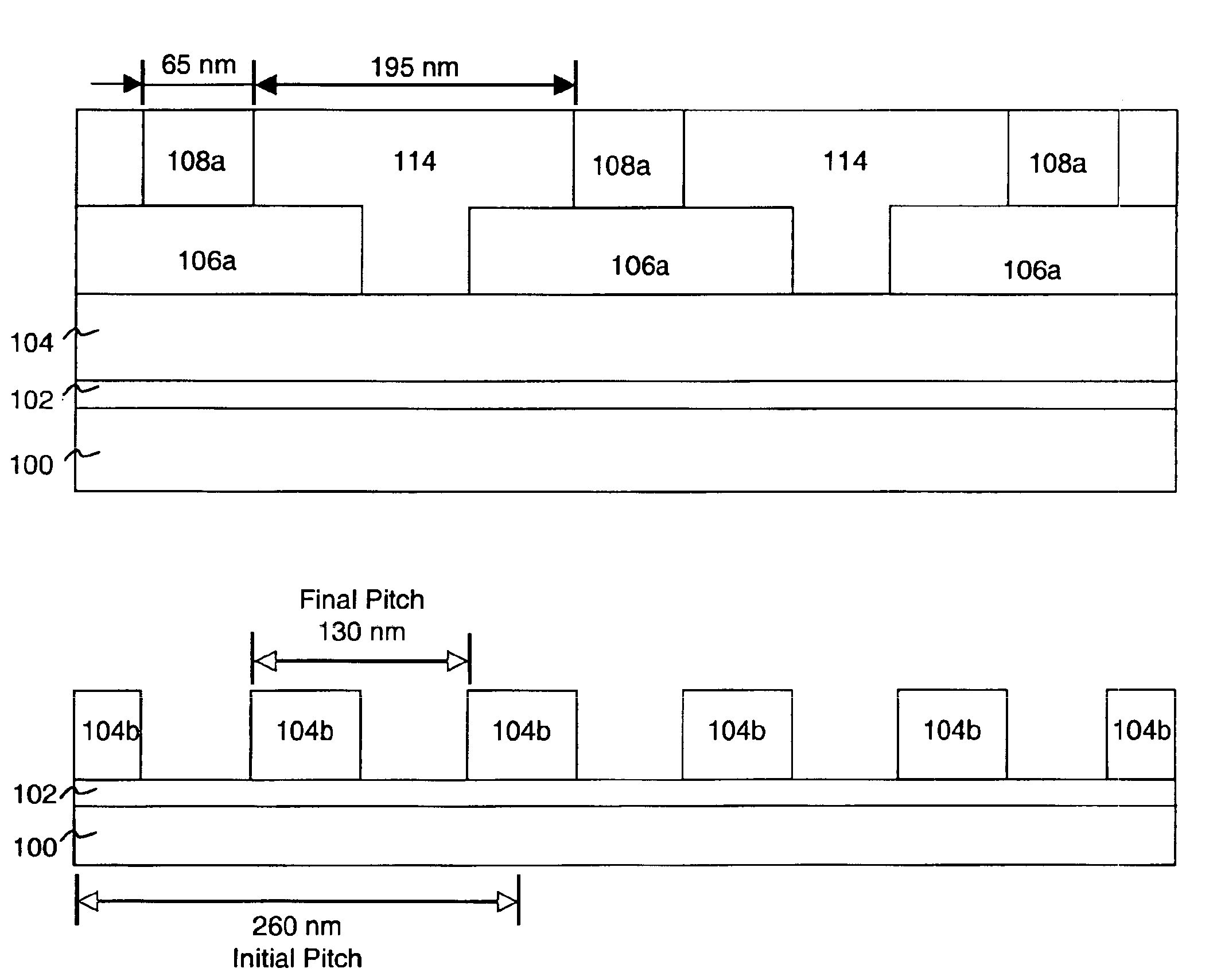

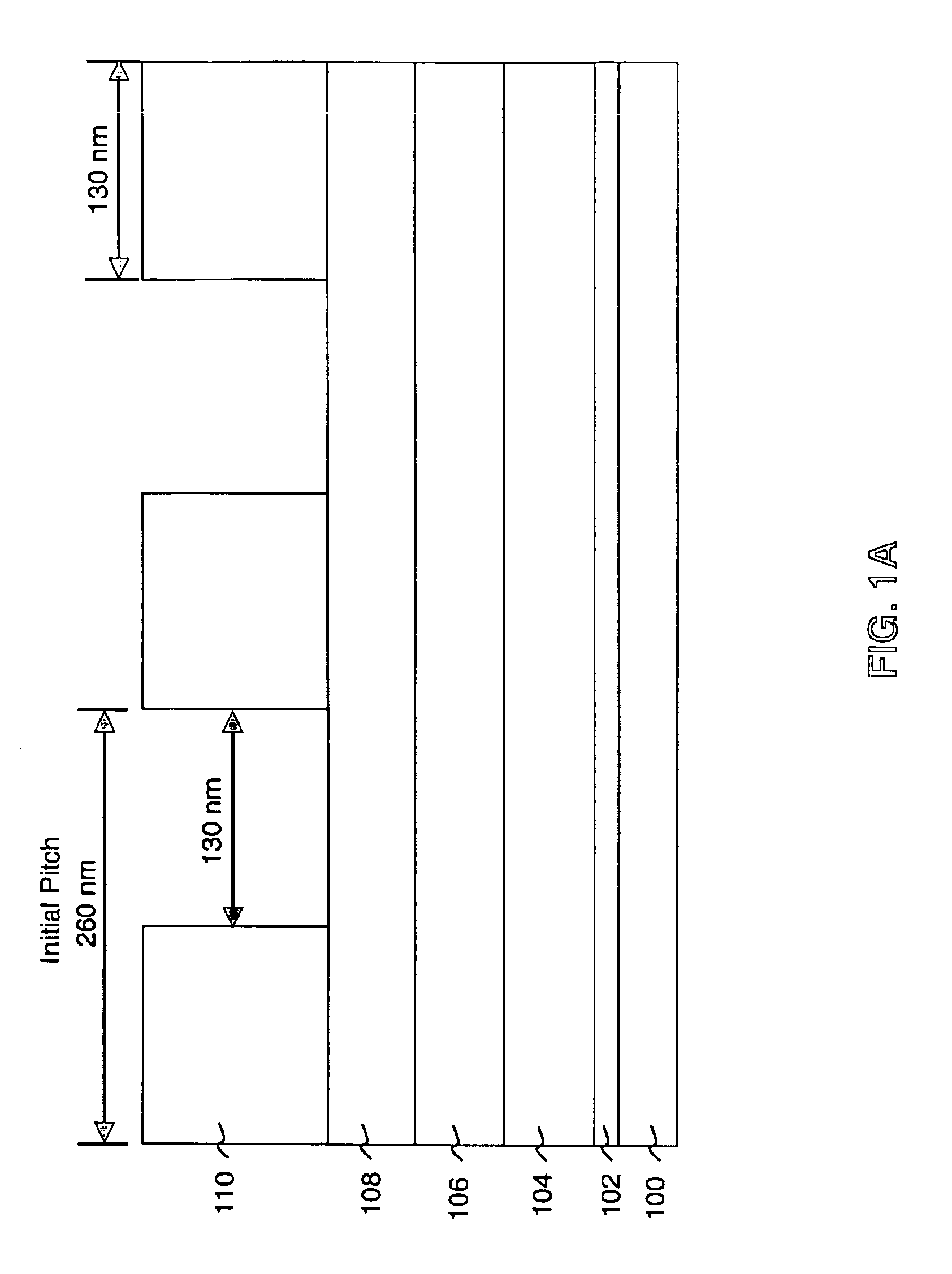

Fabrication method of sub-resolution pitch for integrated circuits

ActiveUS6867116B1Reduce spacingCost-effectiveSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotonic integrated circuit

A method of manufacturing a semiconductor device using a scanner, wherein the scanner is capable of realizing a minimum pitch, wherein the minimum pitch is the smallest possible pitch for the scanner, the method including providing a semiconductor substrate, forming a first layer over the semiconductor substrate, forming a second layer over the first layer, patterning the second layer to form a plurality of second layer patterns, patterning the first layer to form a plurality of first layer patterns, performing a tone reversal to form a reversed tone for the second layer patterns, and etching the first layer patterns using the reversed tone as a mask, wherein the etched first layer patterns have a final pitch size, and wherein the final pitch is smaller than the minimum pitch.

Owner:MACRONIX INT CO LTD

Method for fabricating semiconductor device, and electro-optical device, integrated circuit and electronic apparatus including the semiconductor device

InactiveUS7547589B2High resolutionDecrease productivityTransistorOther printing matterProduction rateEngineering

The invention provides a technique that enables formation of minute patterns on an uneven substrate in volume production without reducing productivity. The method for fabricating a semiconductor device includes: first patterning a semiconductor film on a substrate to form element regions, each of which will be provided with a source / drain region and a channel region, second forming a gate insulating film covering segments of the patterned semiconductor film in the respective element regions, third forming gate electrodes on the gate insulating film at predetermined positions, and fourth forming the source / drain region and the channel region in each element region. At least the gate electrodes are formed by a process including an exposure step through a holographic exposure mask in the third step, and by a process including an exposure step through a projection exposure mask, the element regions are formed in the first step, and the source / drain regions and the channel regions are formed in the fourth step.

Owner:SEIKO EPSON CORP

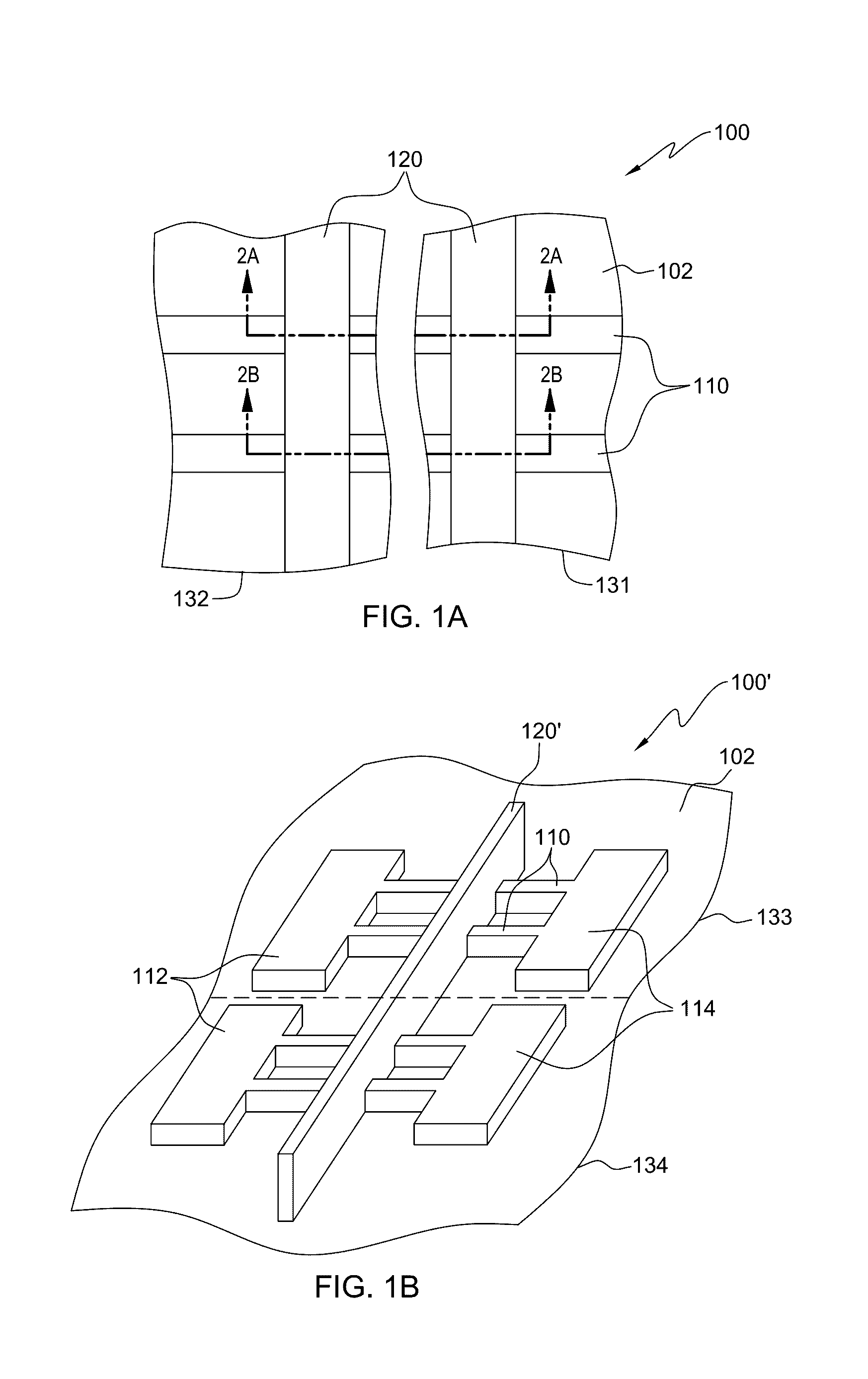

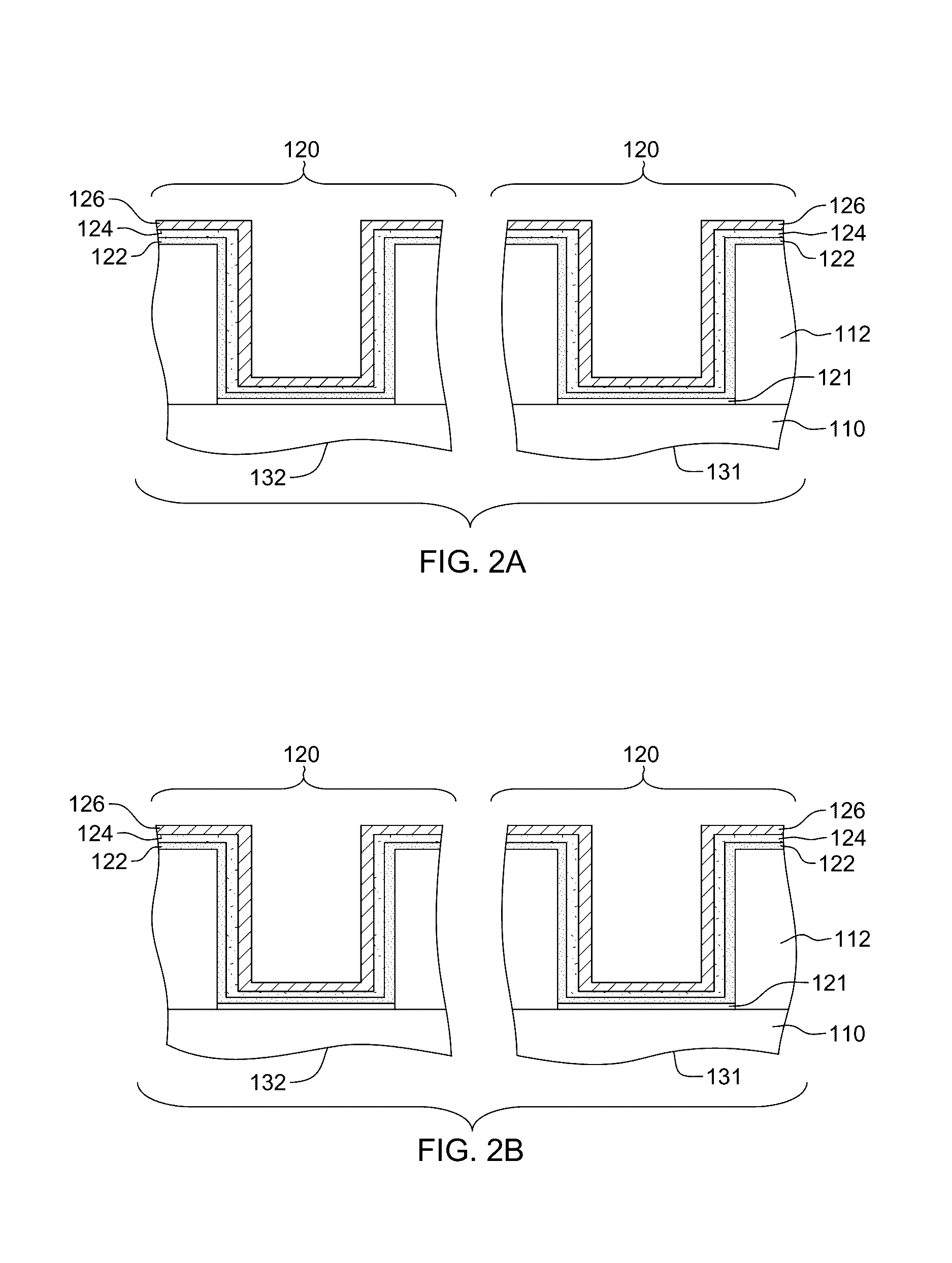

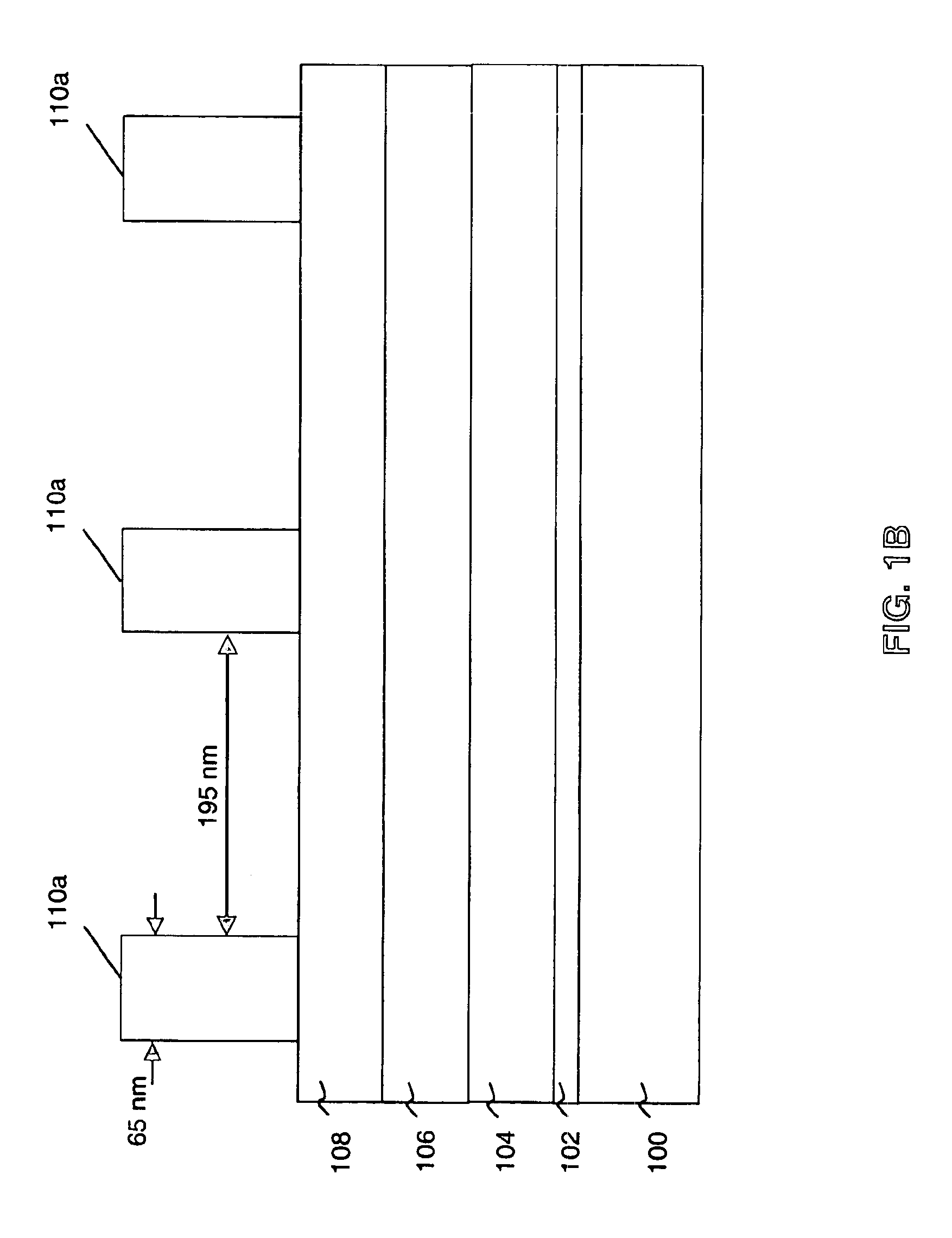

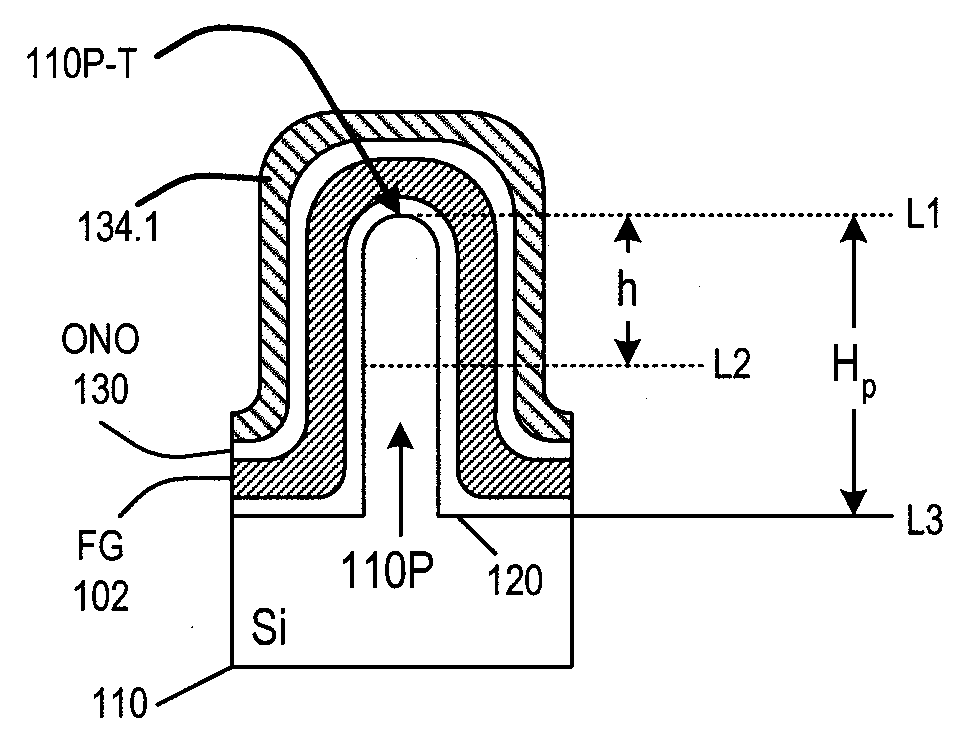

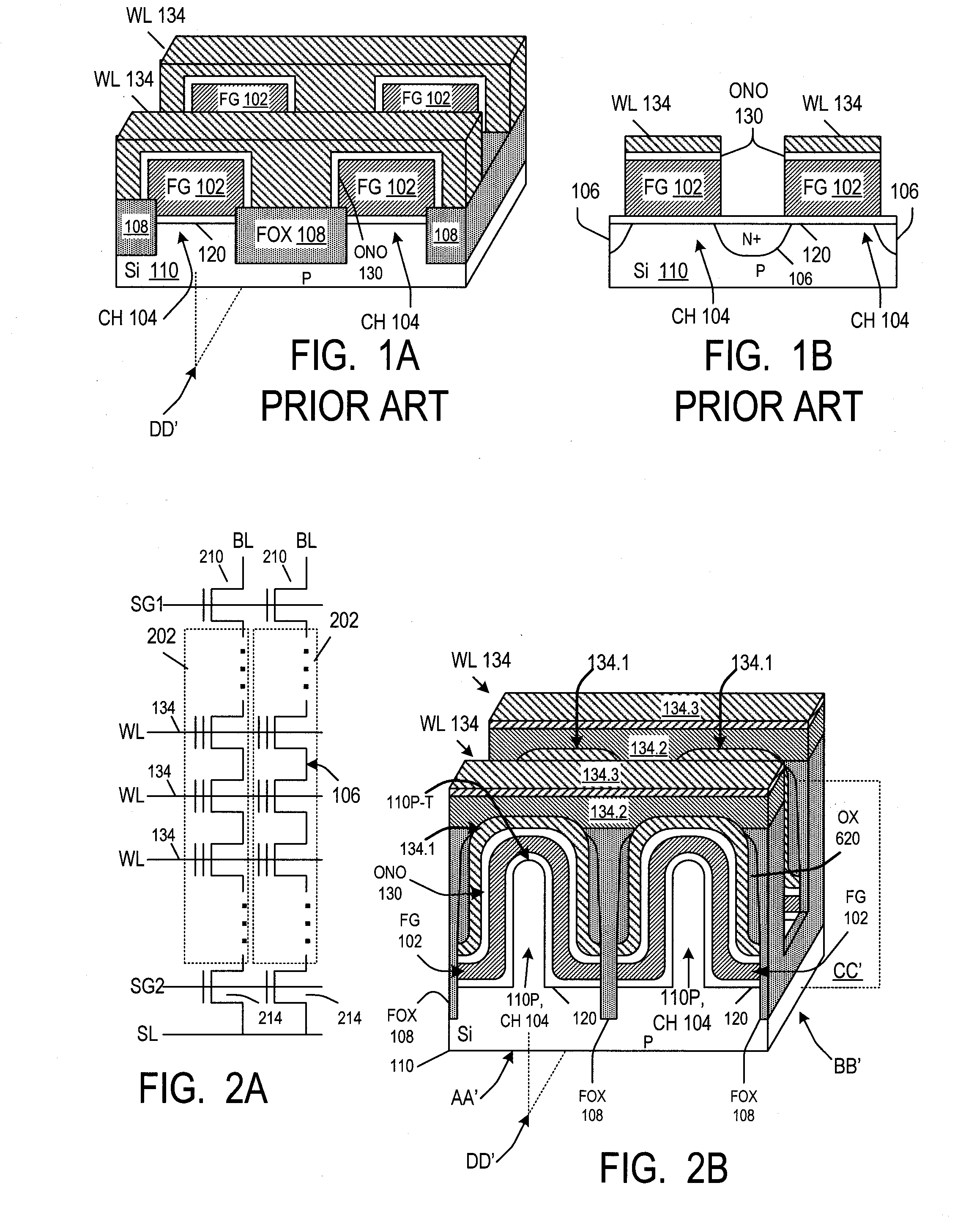

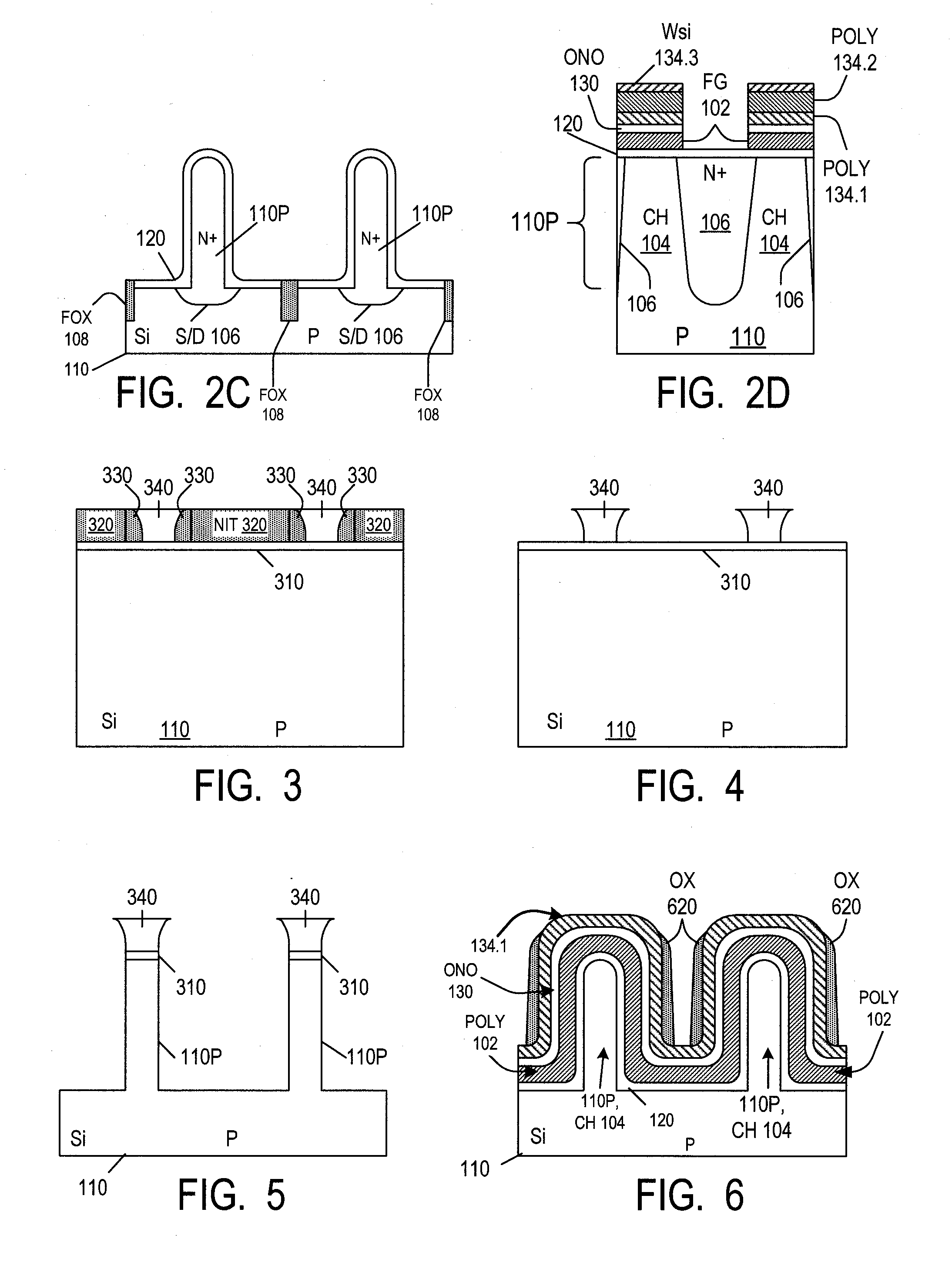

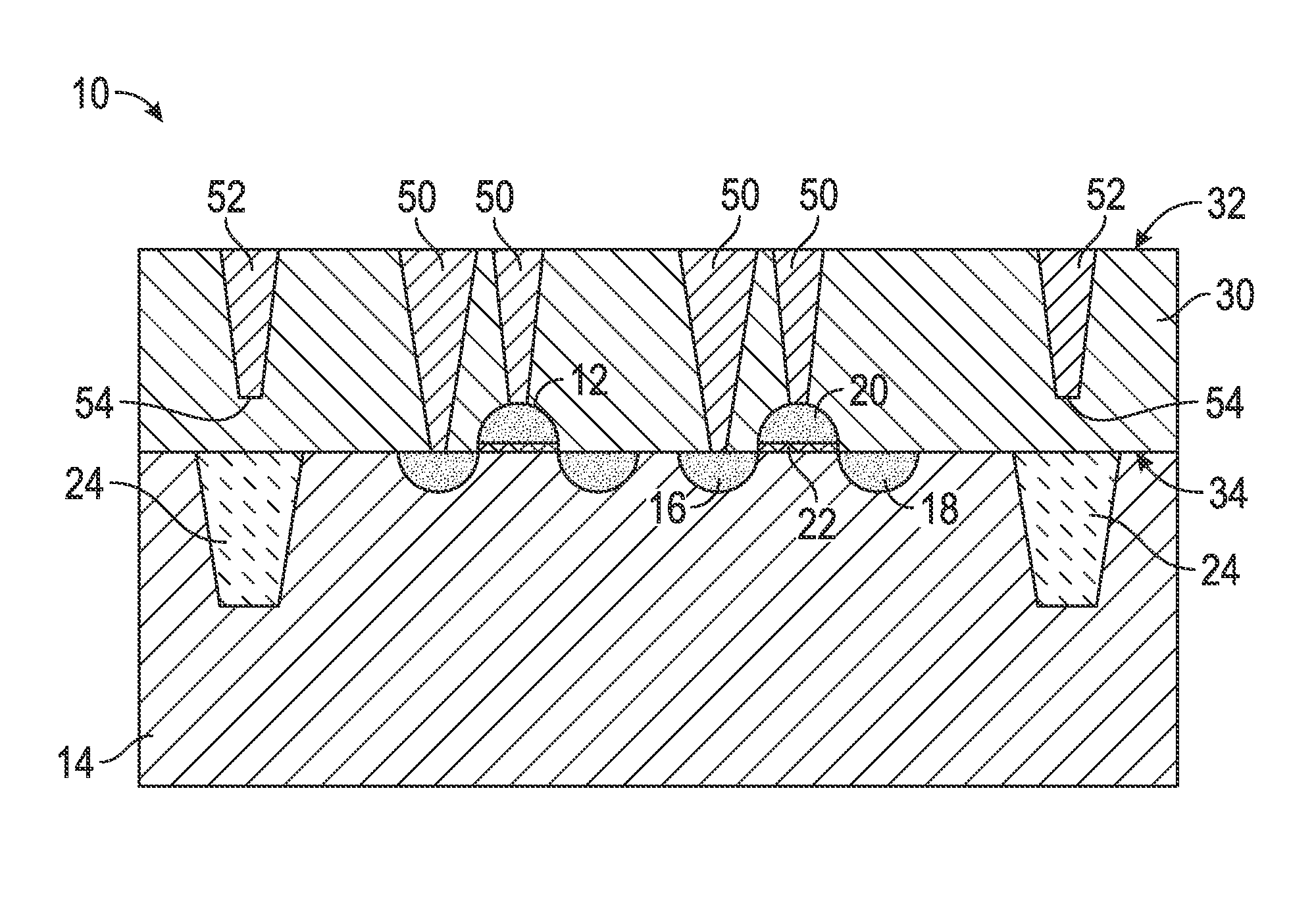

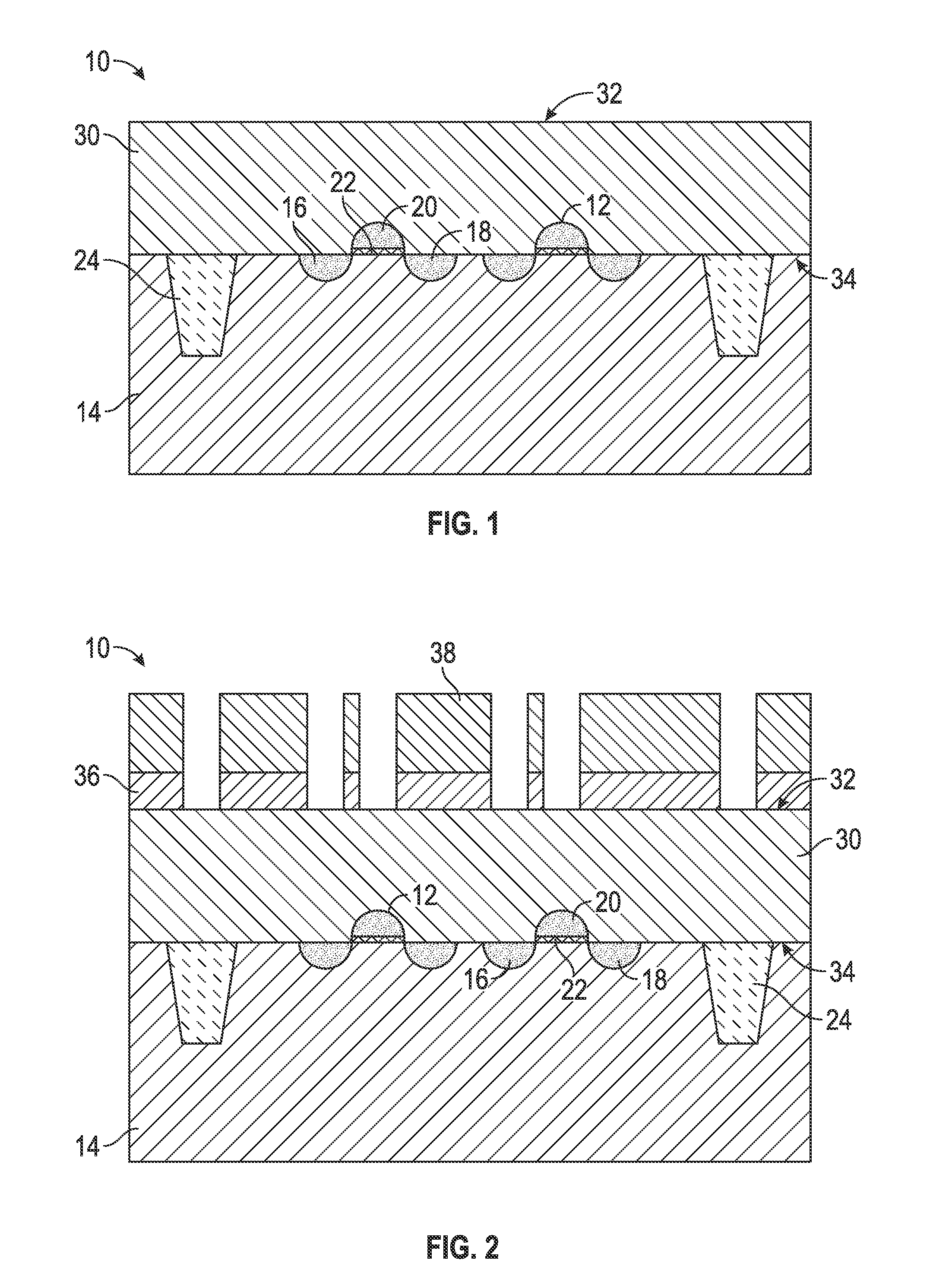

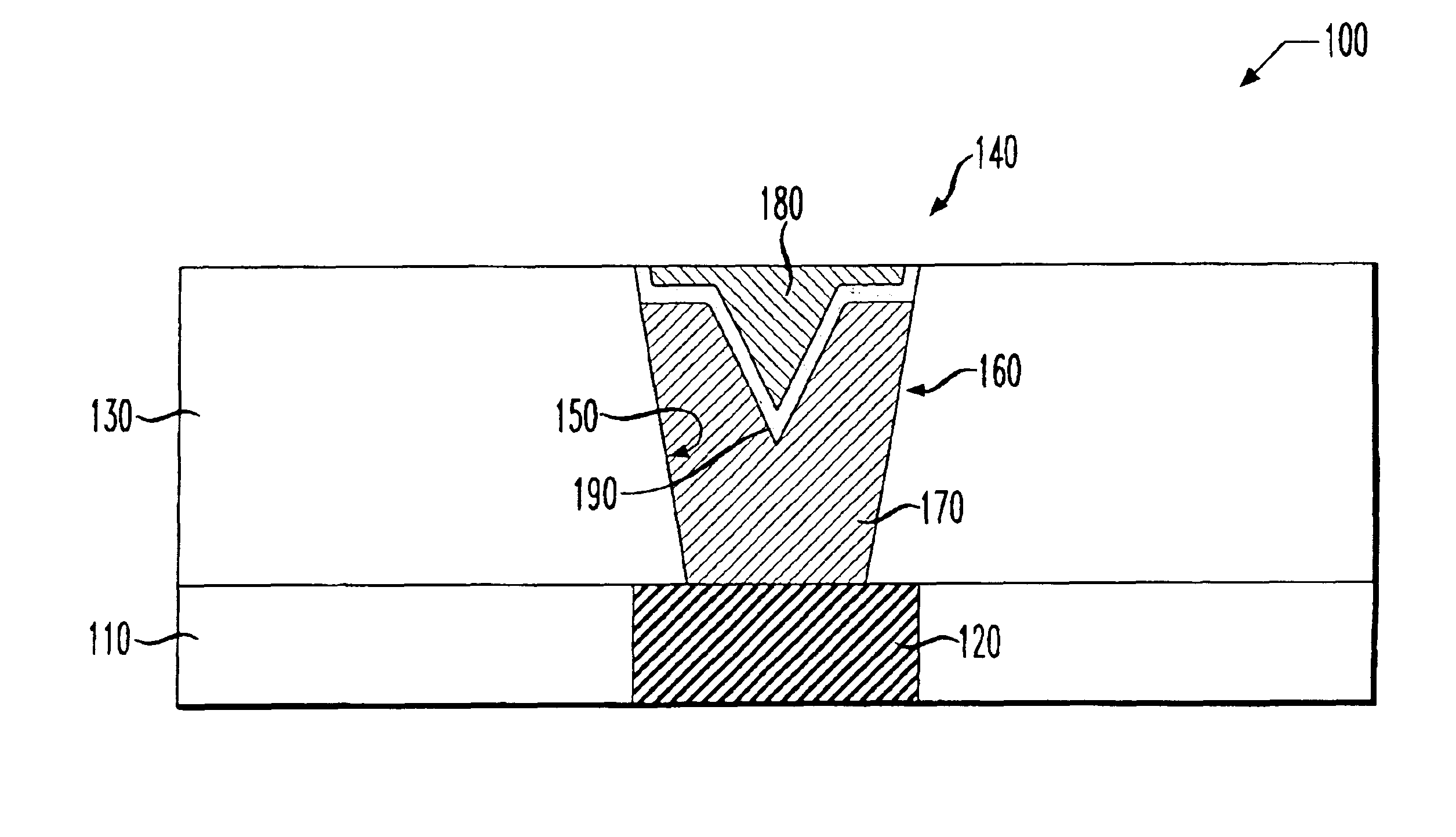

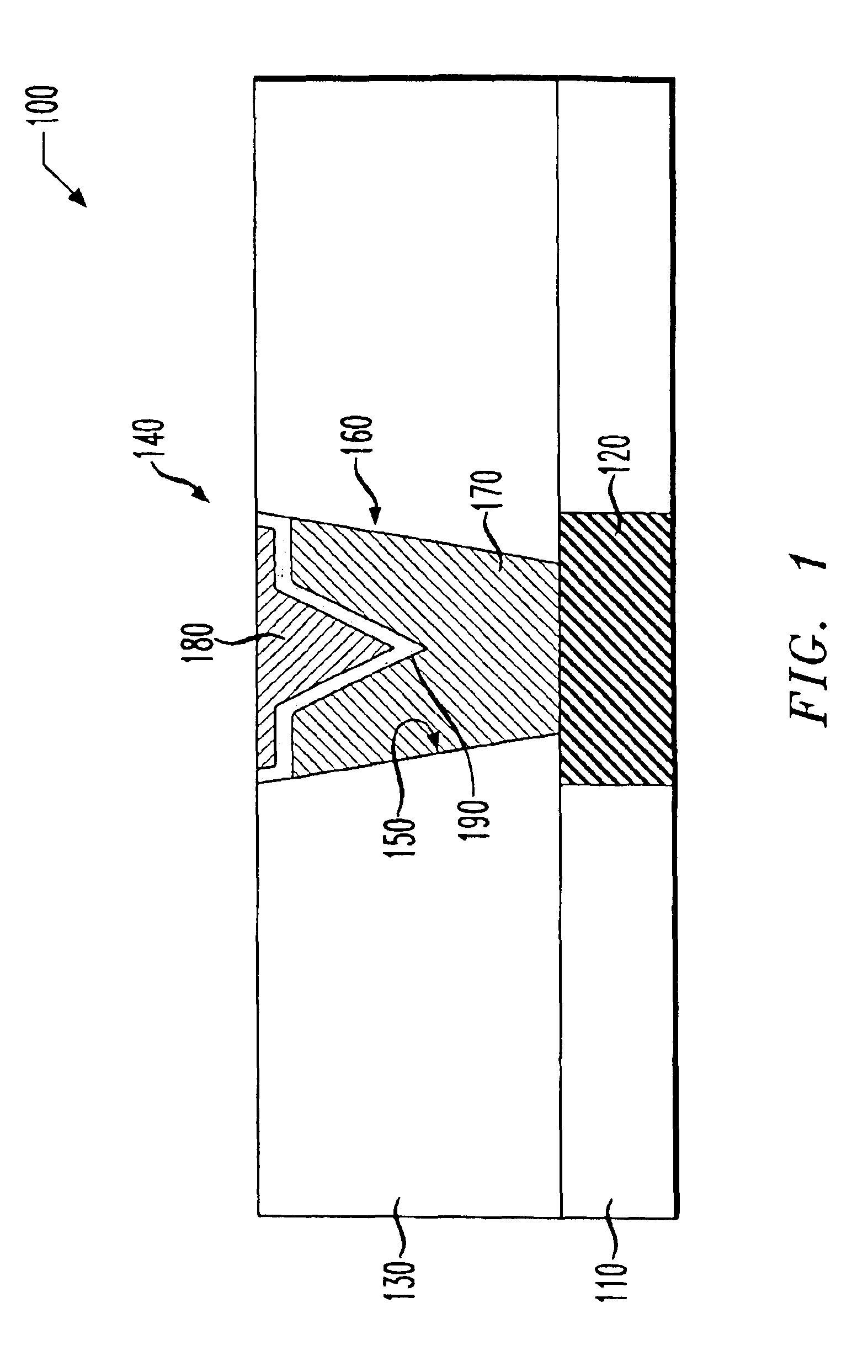

Integrated circuits with substrate protrusions, including (but not limited to) floating gate memories

ActiveUS20080265305A1Enhanced couplingIncrease currentTransistorSolid-state devicesDielectricPhotonic integrated circuit

A floating gate memory cell's channel region (104) is at least partially located in a fin-like protrusion (110P) of a semiconductor substrate. The floating gate's top surface may come down along at least two sides of the protrusion to a level below the top (110P-T) of the protrusion. The control gate's bottom surface may also comes down to a level below the top of the protrusion. The floating gate's bottom surface may comes down to a level below the top of the protrusion by at least 50% of the protrusion's height. The dielectric (120) separating the floating gate from the protrusion can be at least as thick at the top of the protrusion as at a level (L2) which is below the top of the protrusion by at least 50% of the protrusion's height. A very narrow fin or other narrow feature in memory and non-memory integrated circuits can be formed by providing a first layer (320) and then forming spacers (330) from a second layer without photolithography on sidewalls of features made from the first layer. The narrow fin or other feature are then formed without further photolithography in areas between the adjacent spacers. More particularly, a third layer (340) is formed in these areas, and the first layer and the spacers are removed selectively to the third layer. The third layer is used as a mask to form the narrow features.

Owner:PROMOS TECH INC

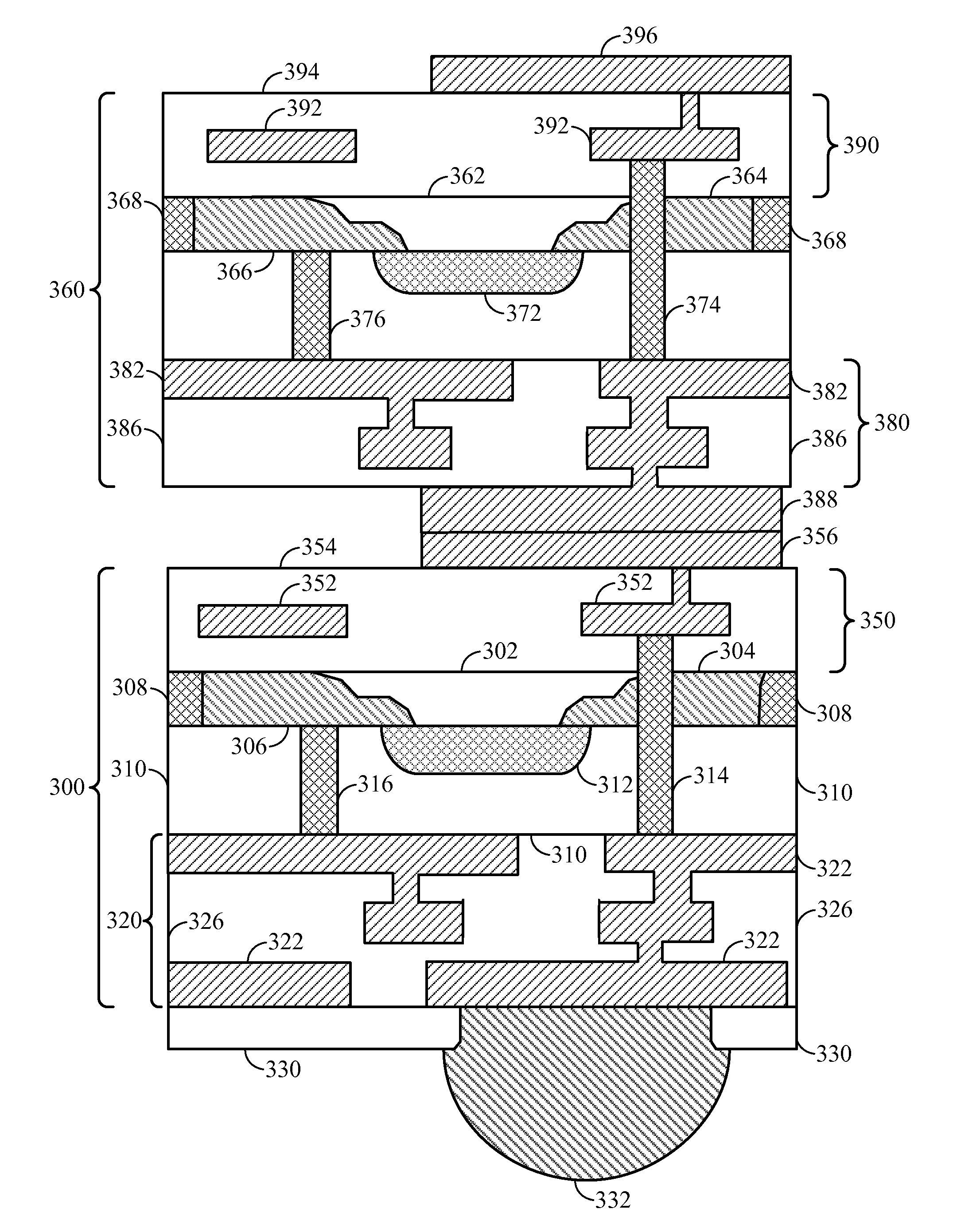

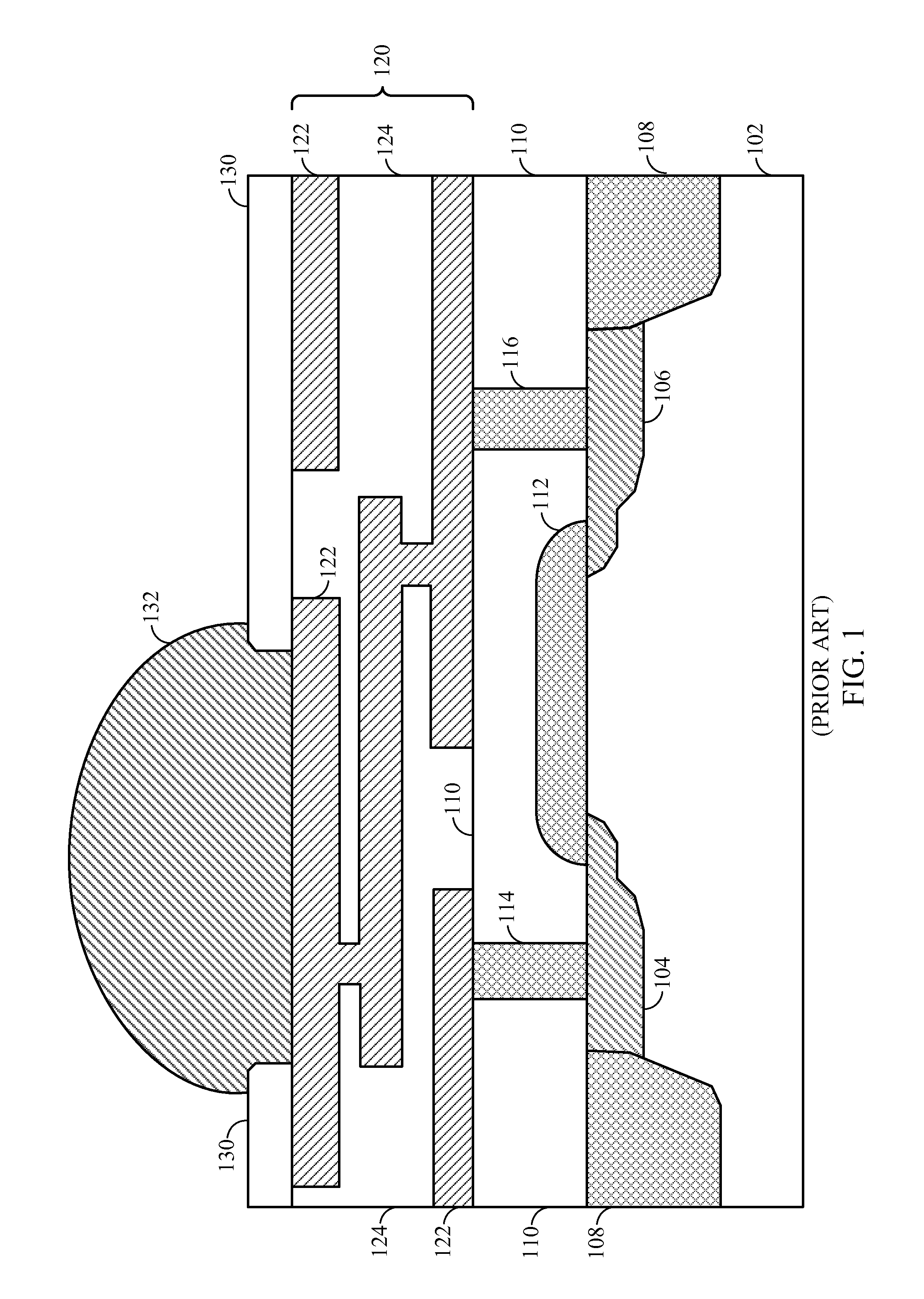

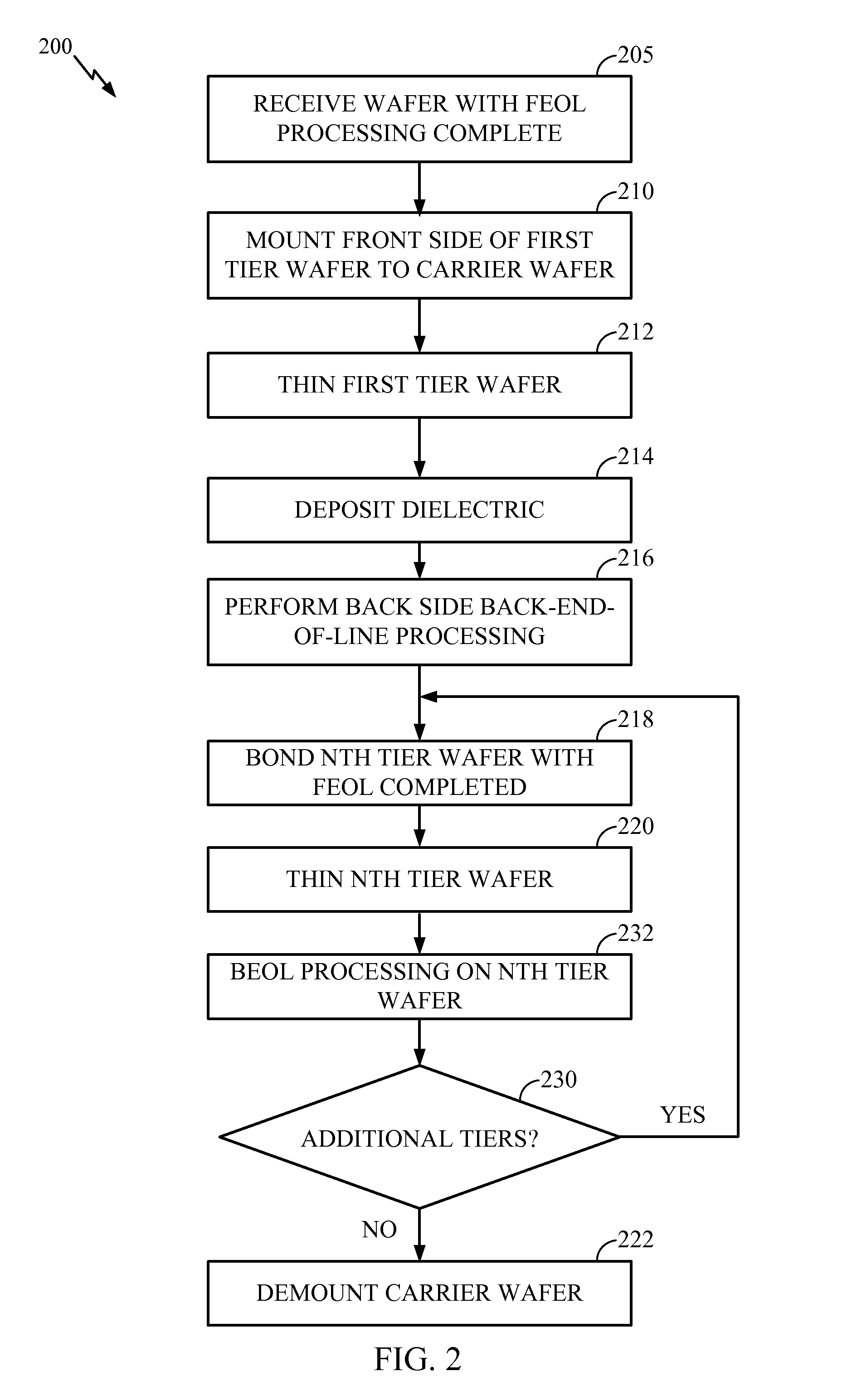

Dual-side interconnected CMOS for stacked integrated circuits

Owner:QUALCOMM INC

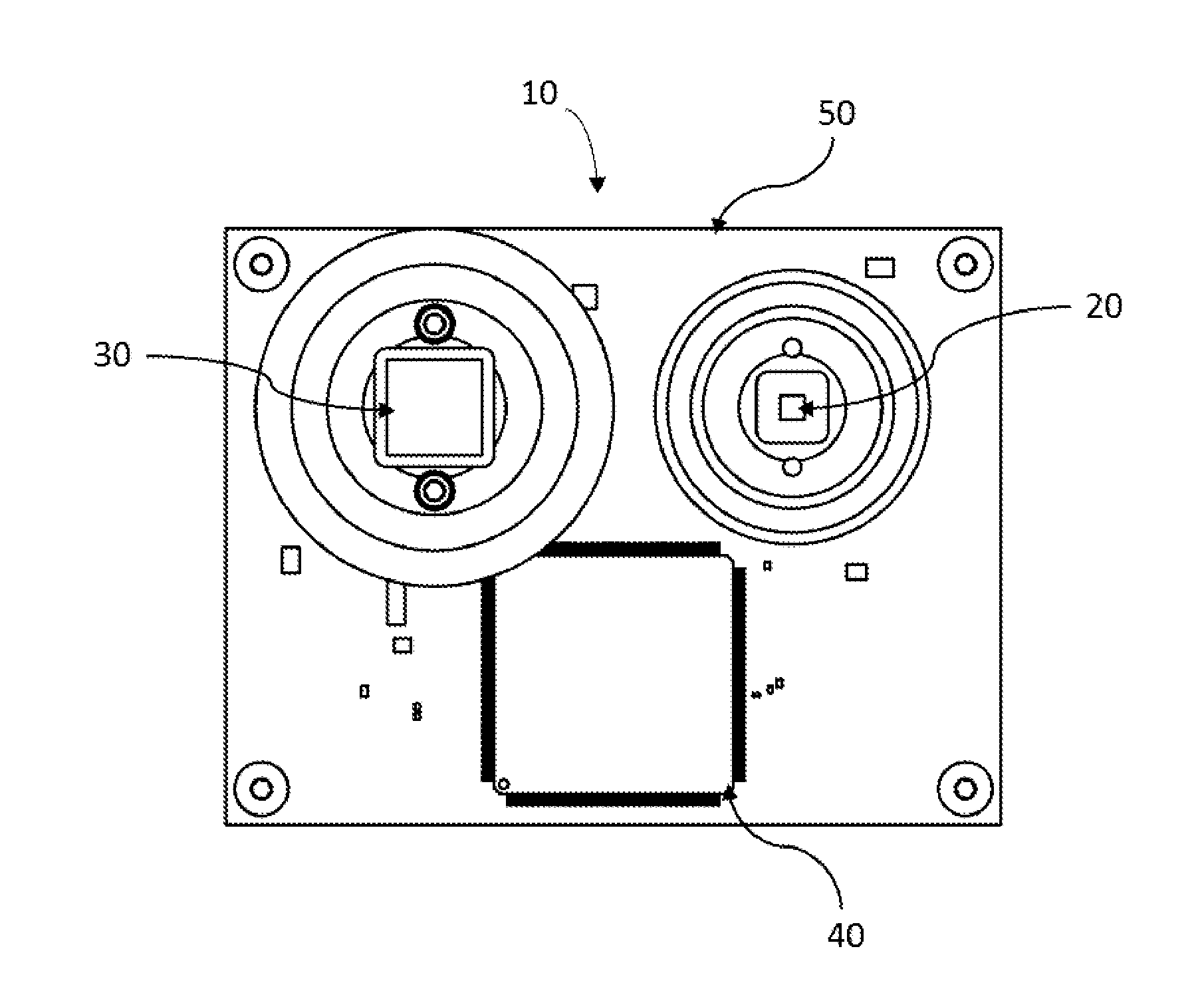

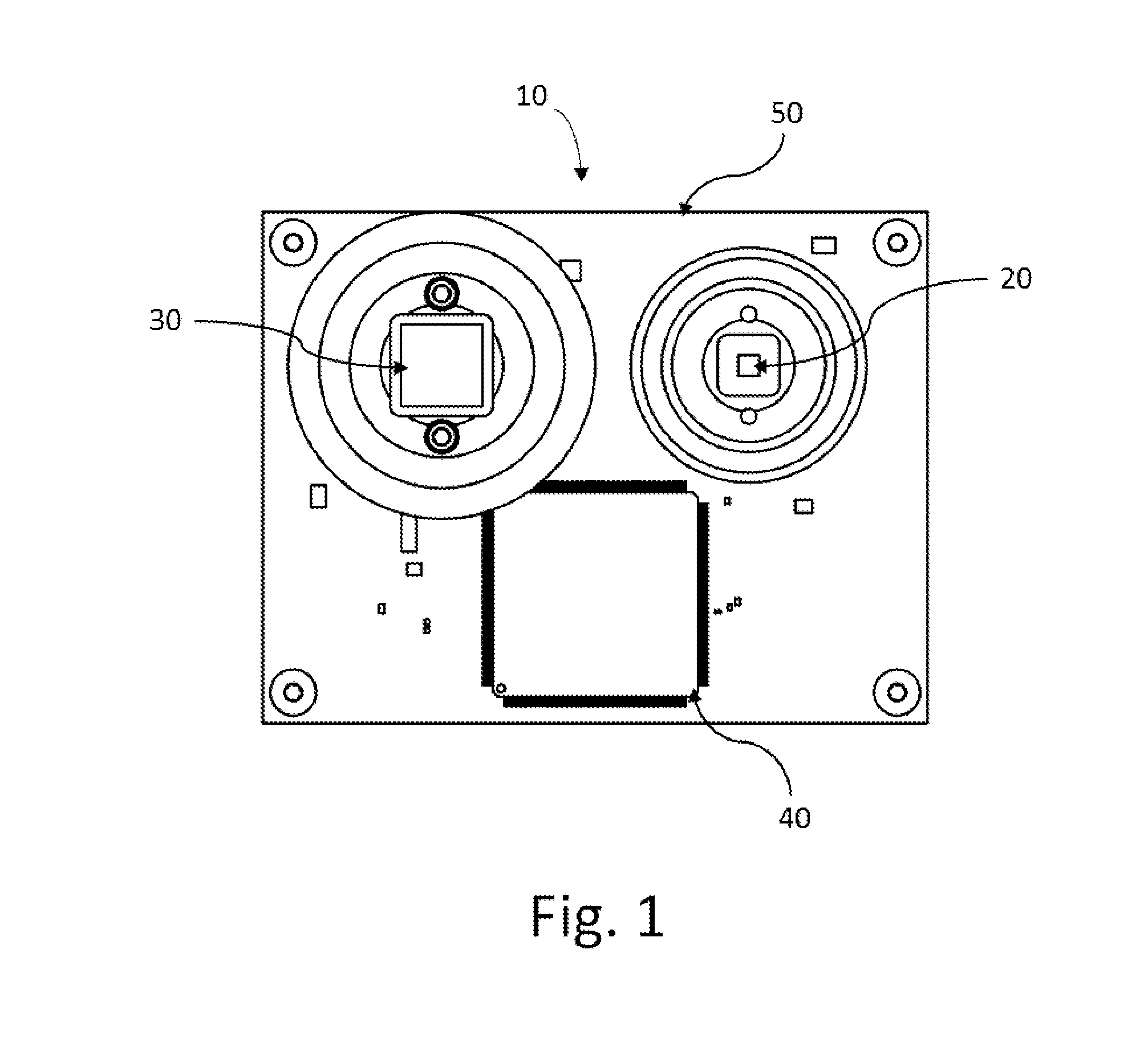

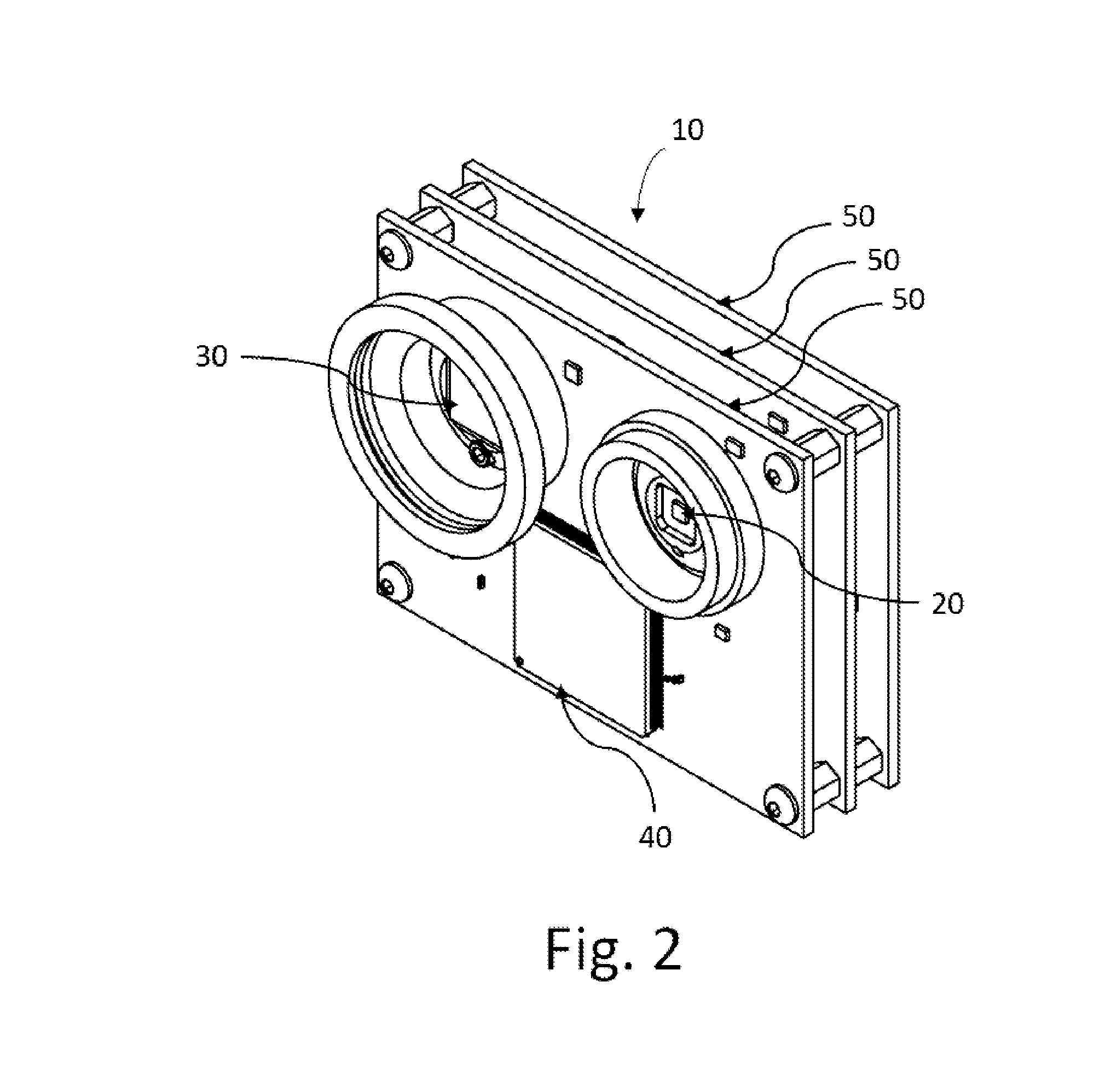

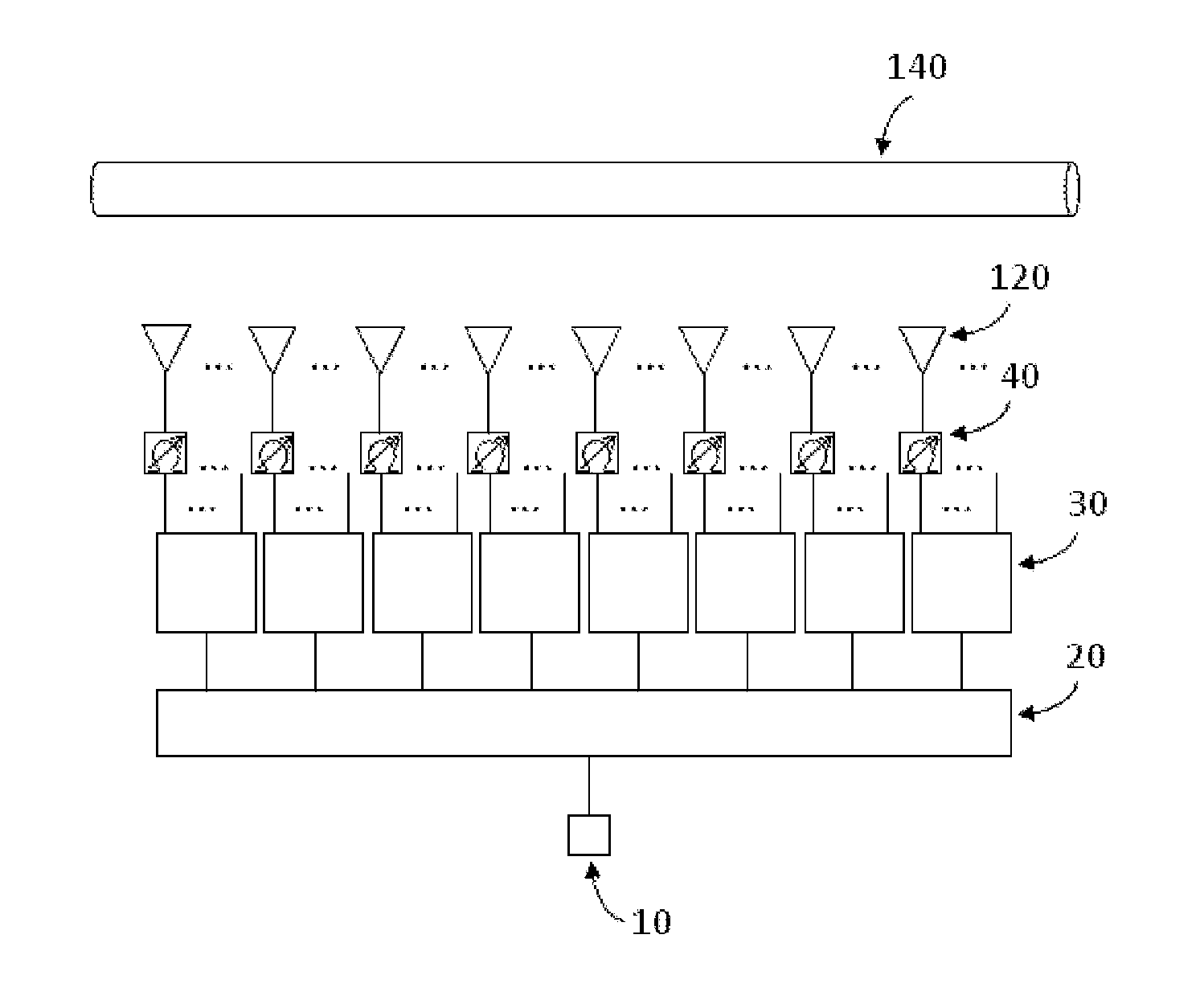

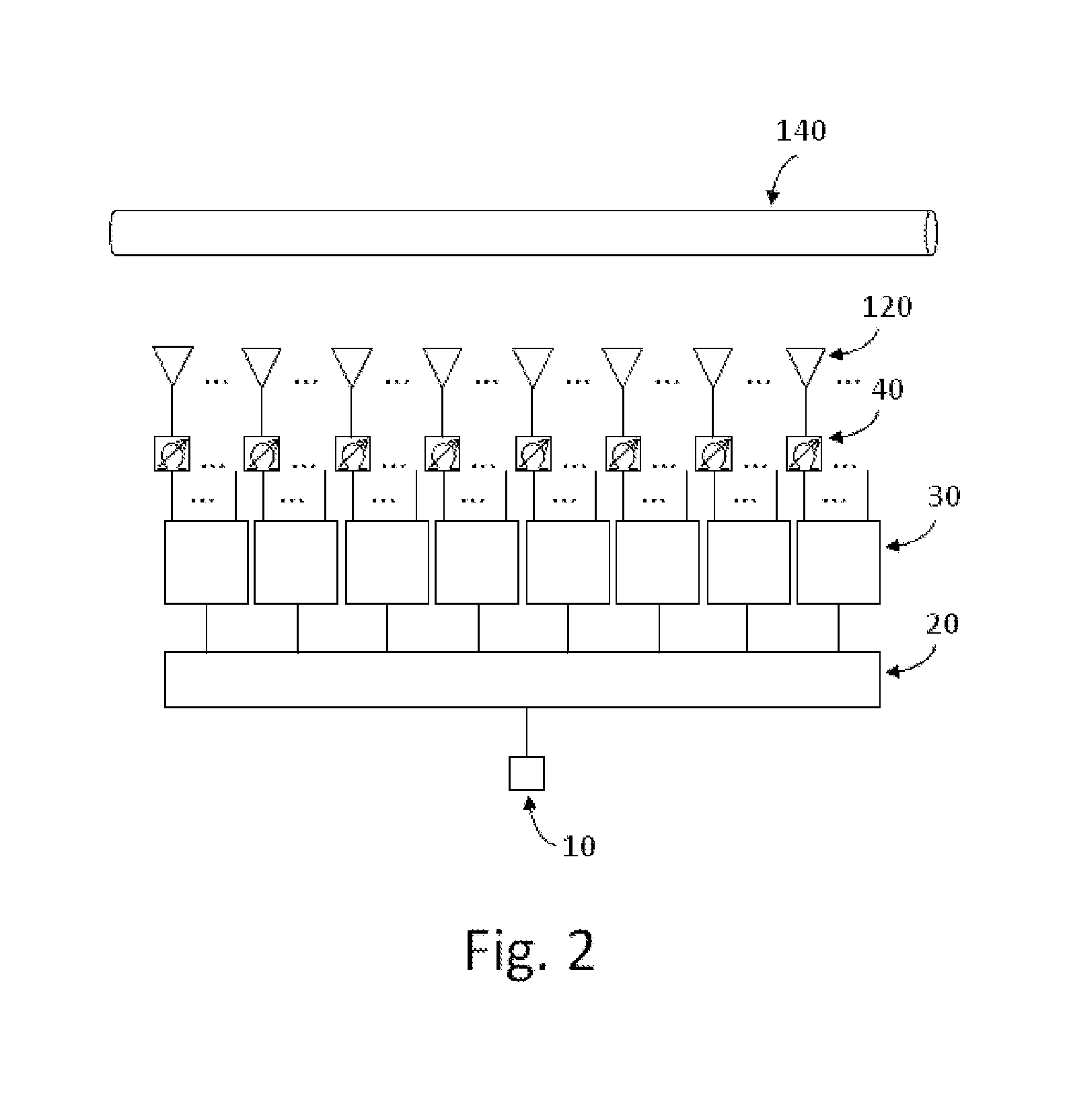

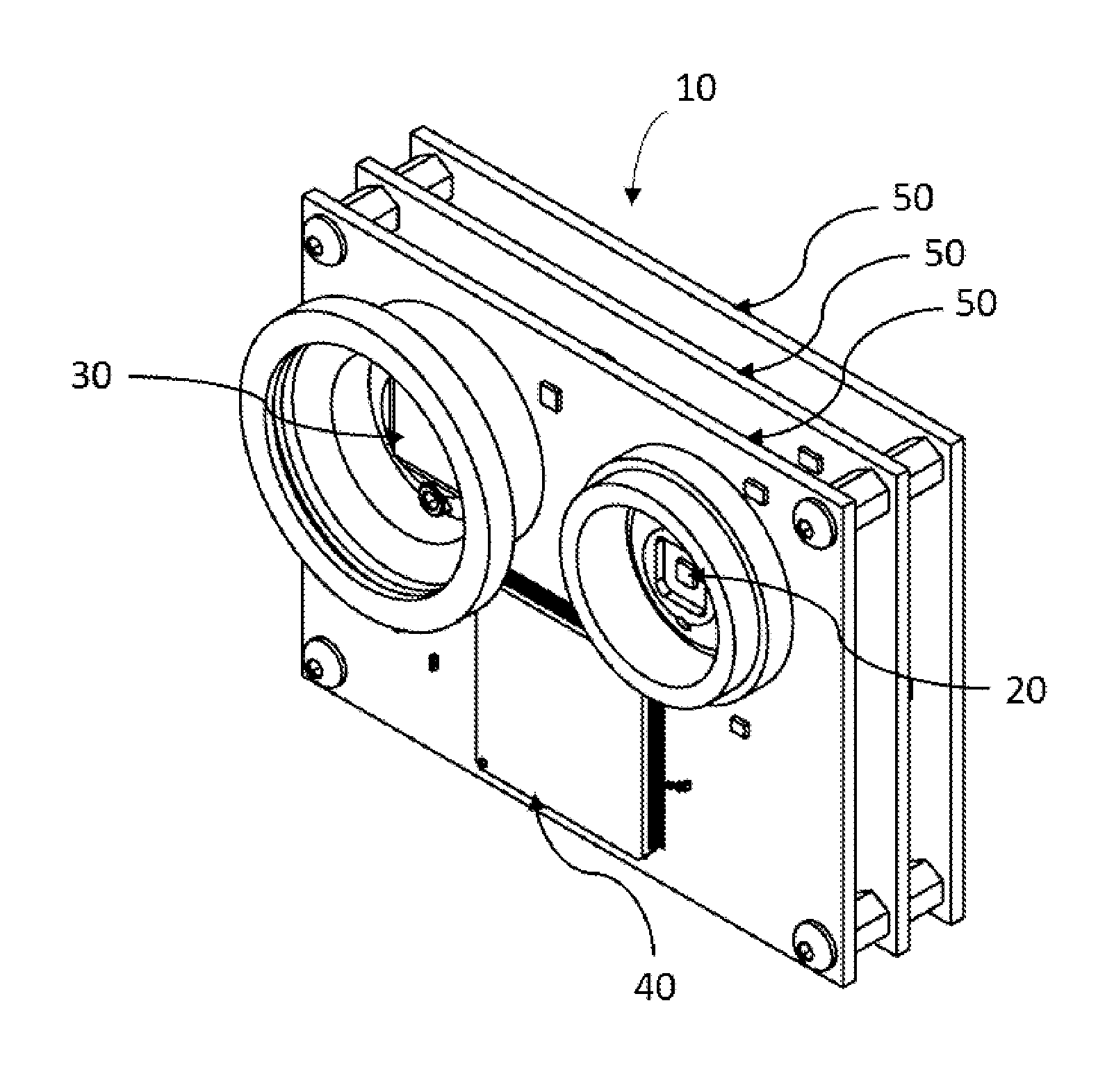

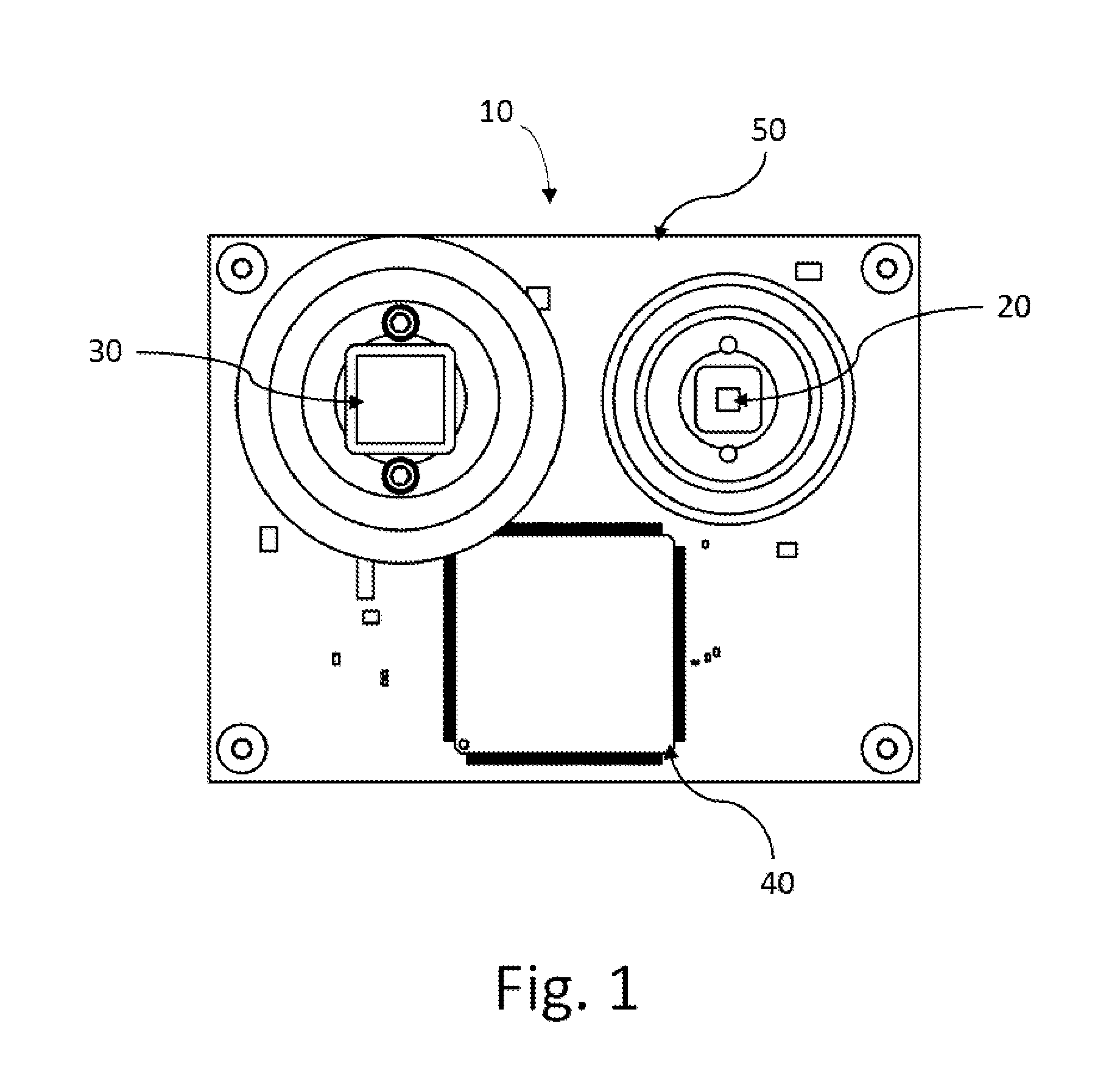

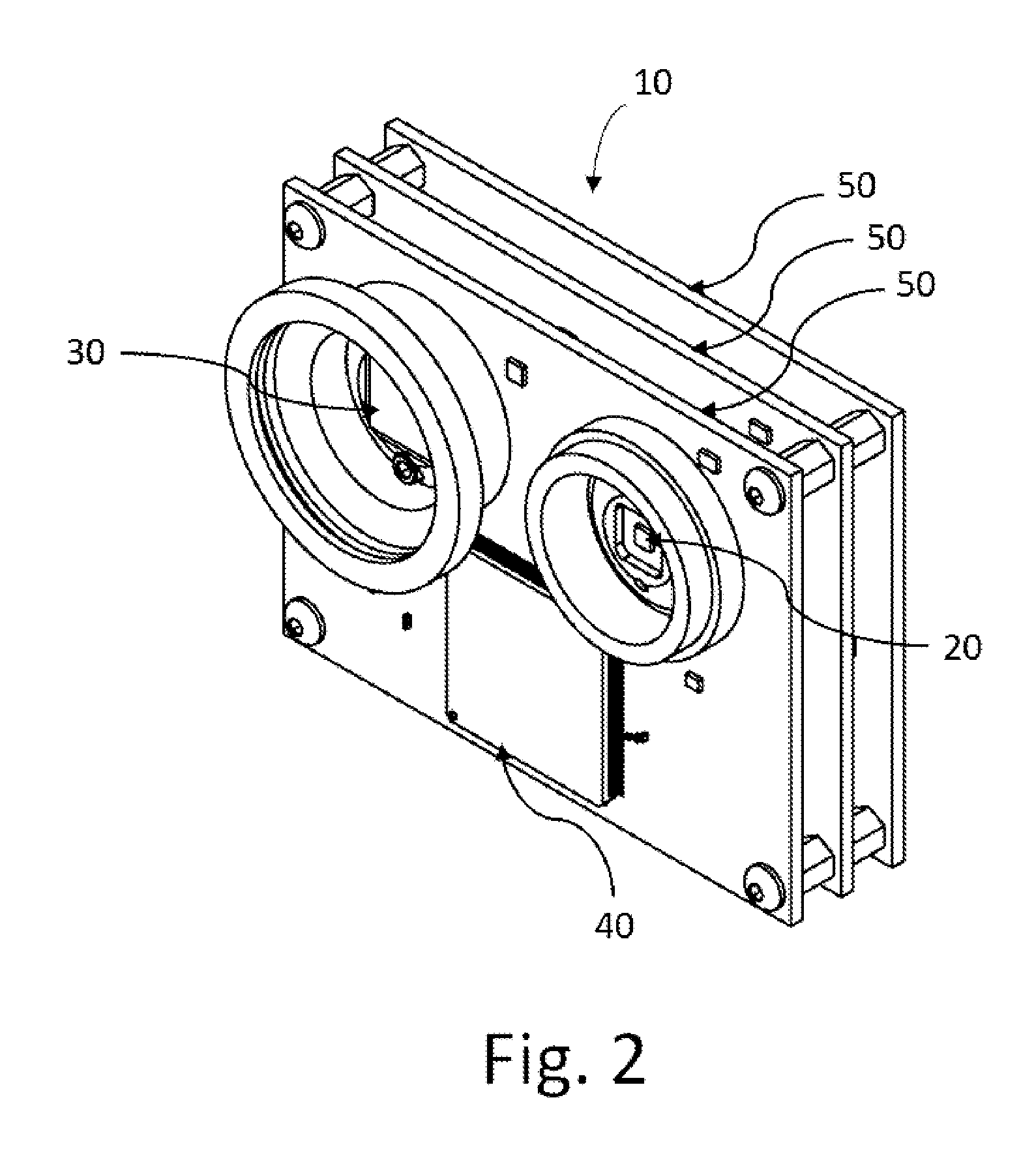

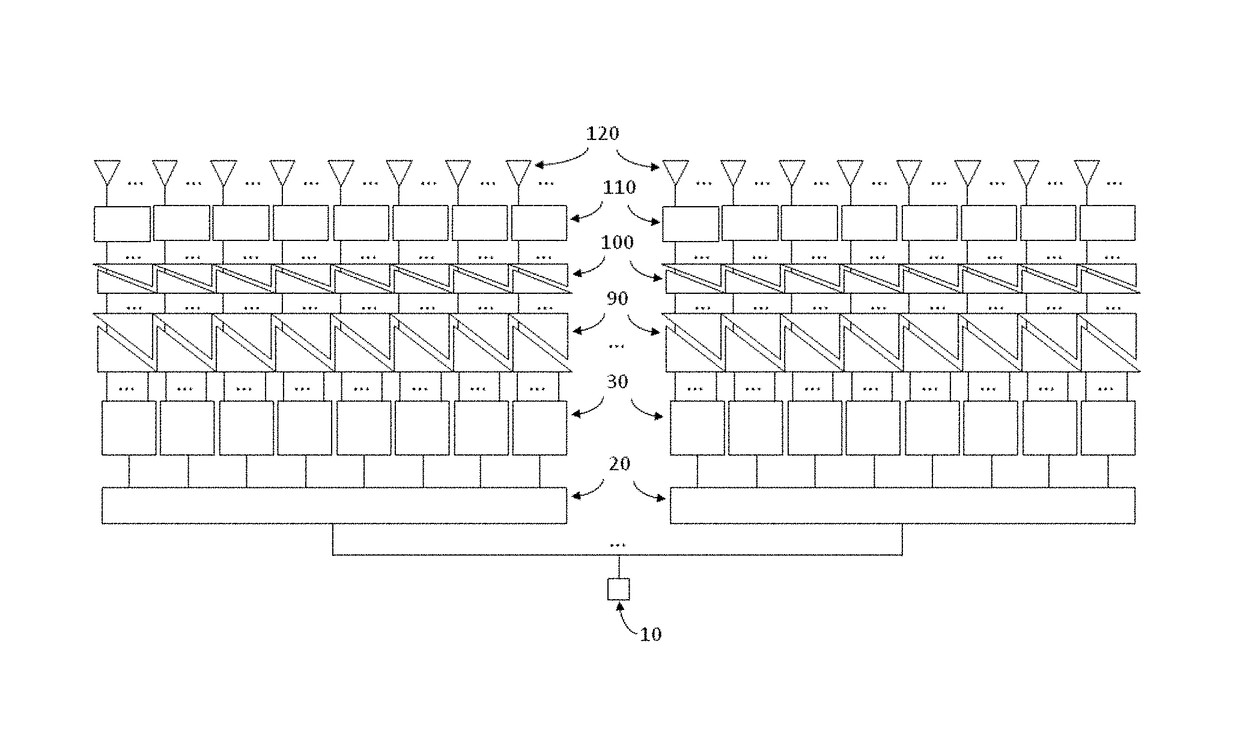

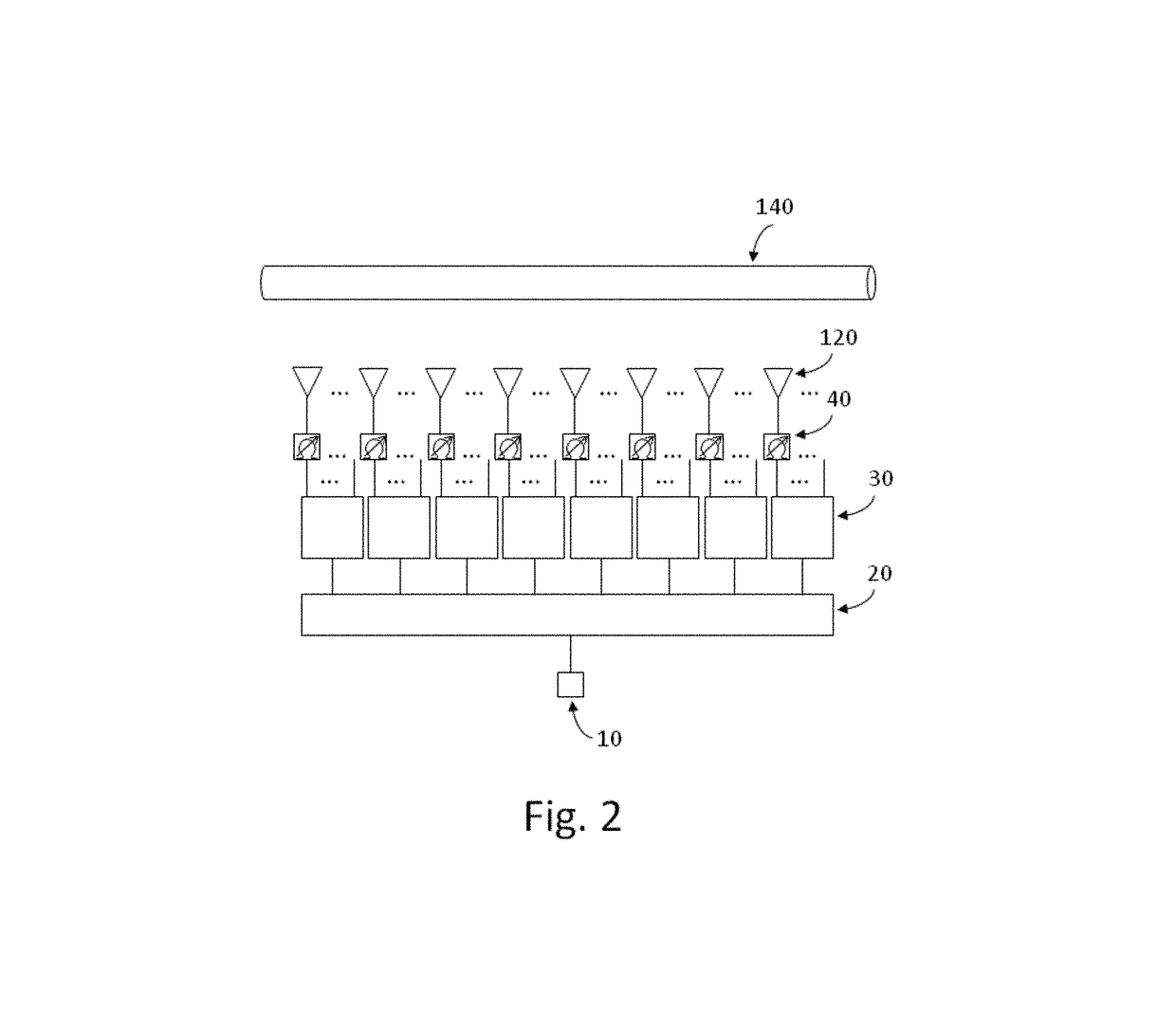

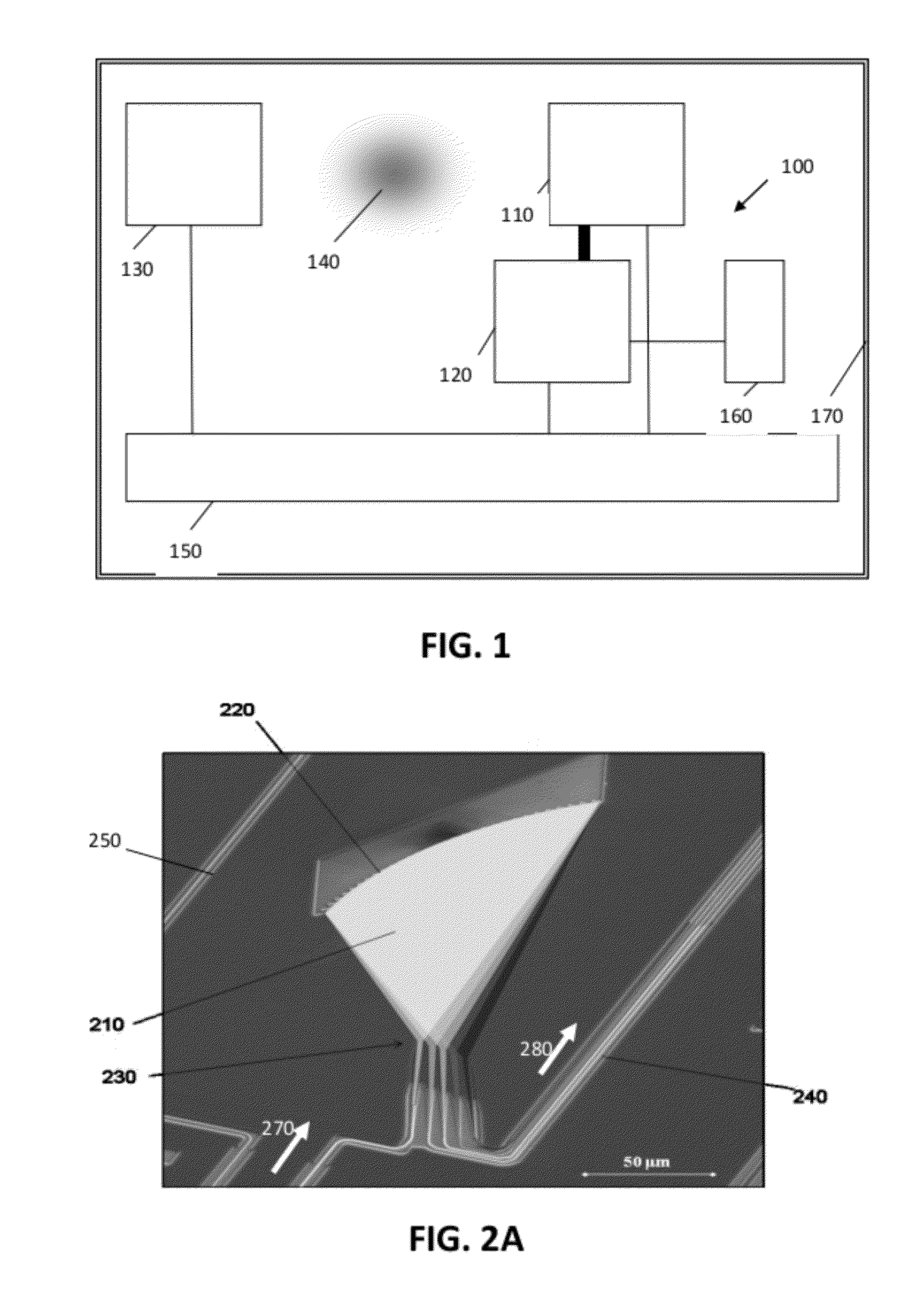

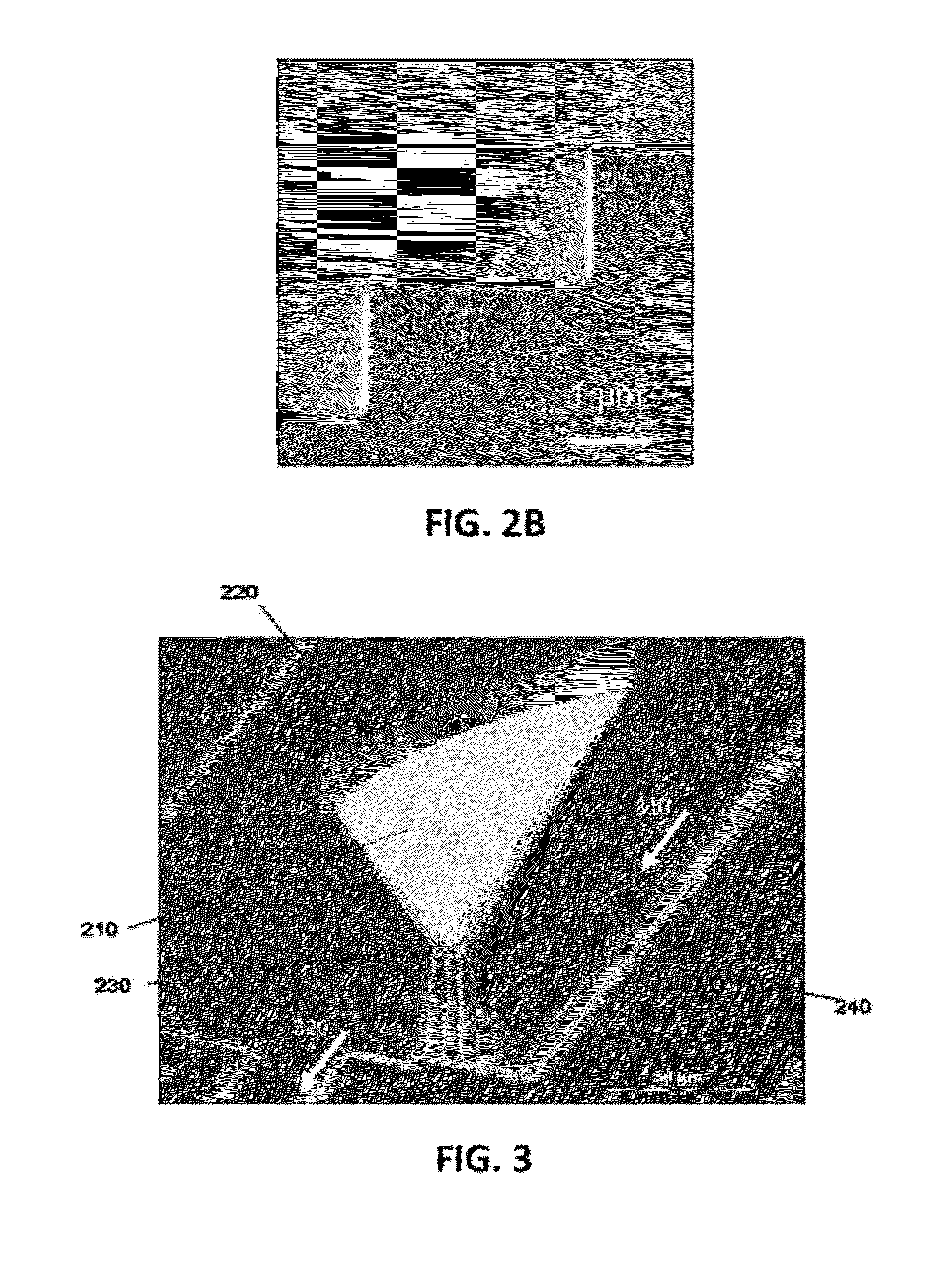

Planar beam forming and steering optical phased array chip and method of using same

ActiveUS20150378241A1High yieldLow costWave based measurement systemsNon-linear opticsRadarChip architecture

A one-dimensional planar beam forming and steering optical phased array chip is a simple building block of a two-dimensional beam forming and steering solid-state lidar, enabling manufacturing of said lidars at high yield and low cost through the use of a plurality of said chips. Innovative photonic integrated circuit chip architectures that follow design for manufacturing rules enable said building blocks.

Owner:QUANERGY SOLUTIONS INC

Integrated circuits with dummy contacts and methods for producing such integrated circuits

InactiveUS20150171008A1Reducing density variationReduce variationSemiconductor/solid-state device detailsSolid-state devicesDielectricElectrical connection

Integrated circuits with dummy contacts and methods for fabricating such integrated circuits are provided. The method includes forming an interlayer dielectric overlying an electronic component and a substrate, wherein the interlayer dielectric has an interlayer dielectric top surface. An active contact is formed through the interlayer dielectric and forms an electrical connection with the electronic component. A dummy contact is formed within the interlayer dielectric where the dummy contact extends to a dummy contact termination point between the interlayer dielectric top surface and the substrate such that an insulator is positioned between the dummy contact termination point and the electronic component.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

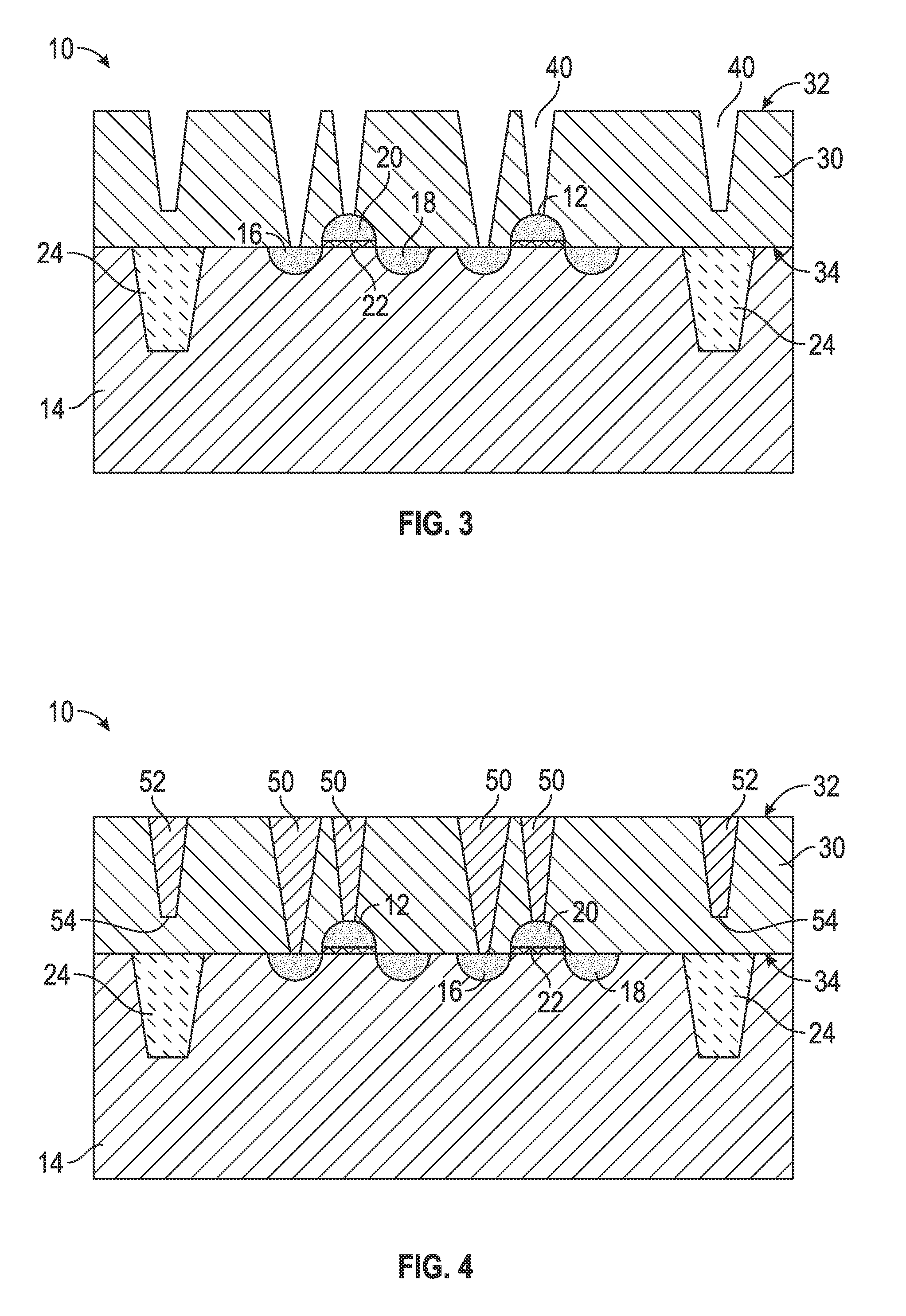

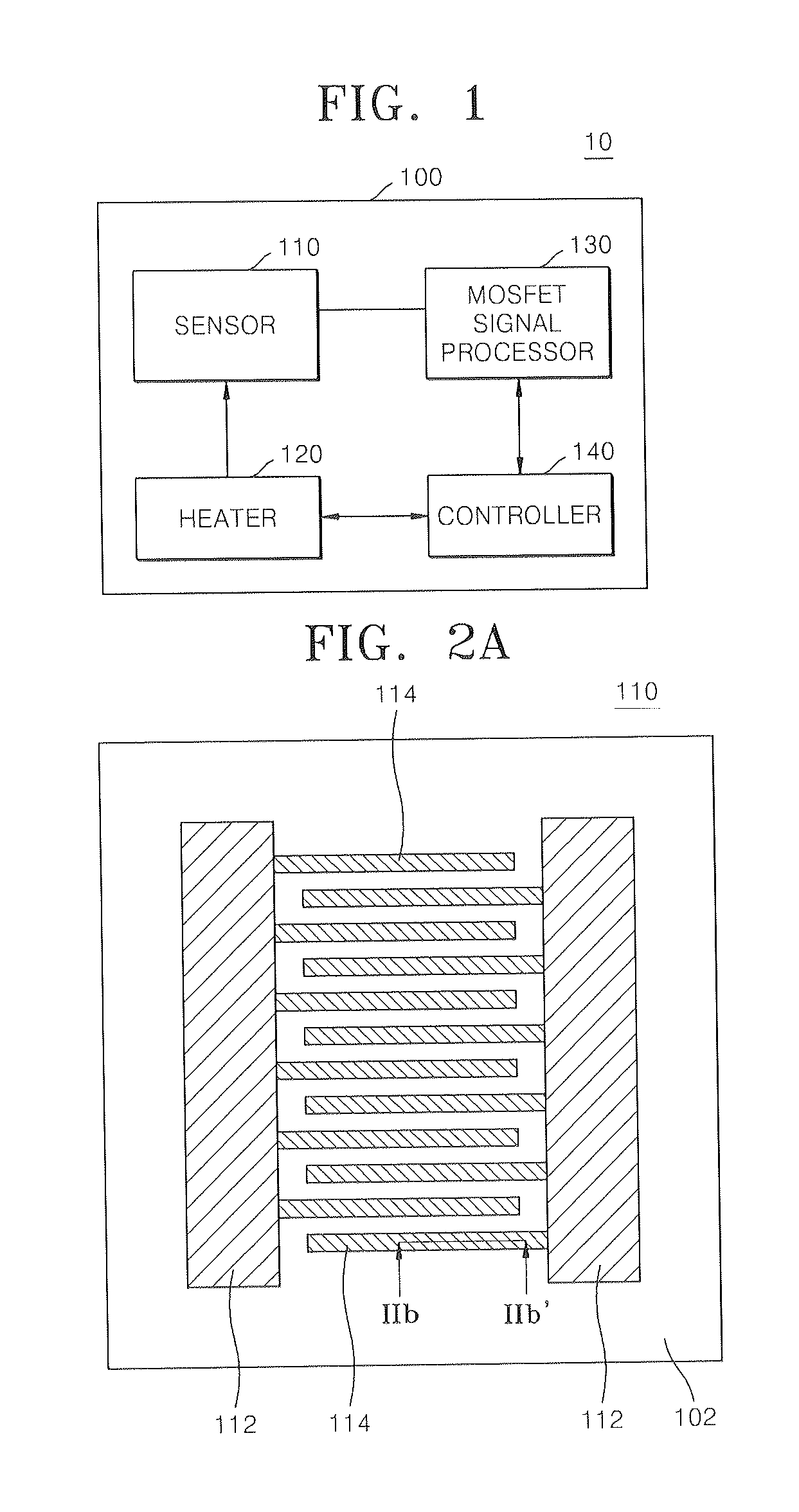

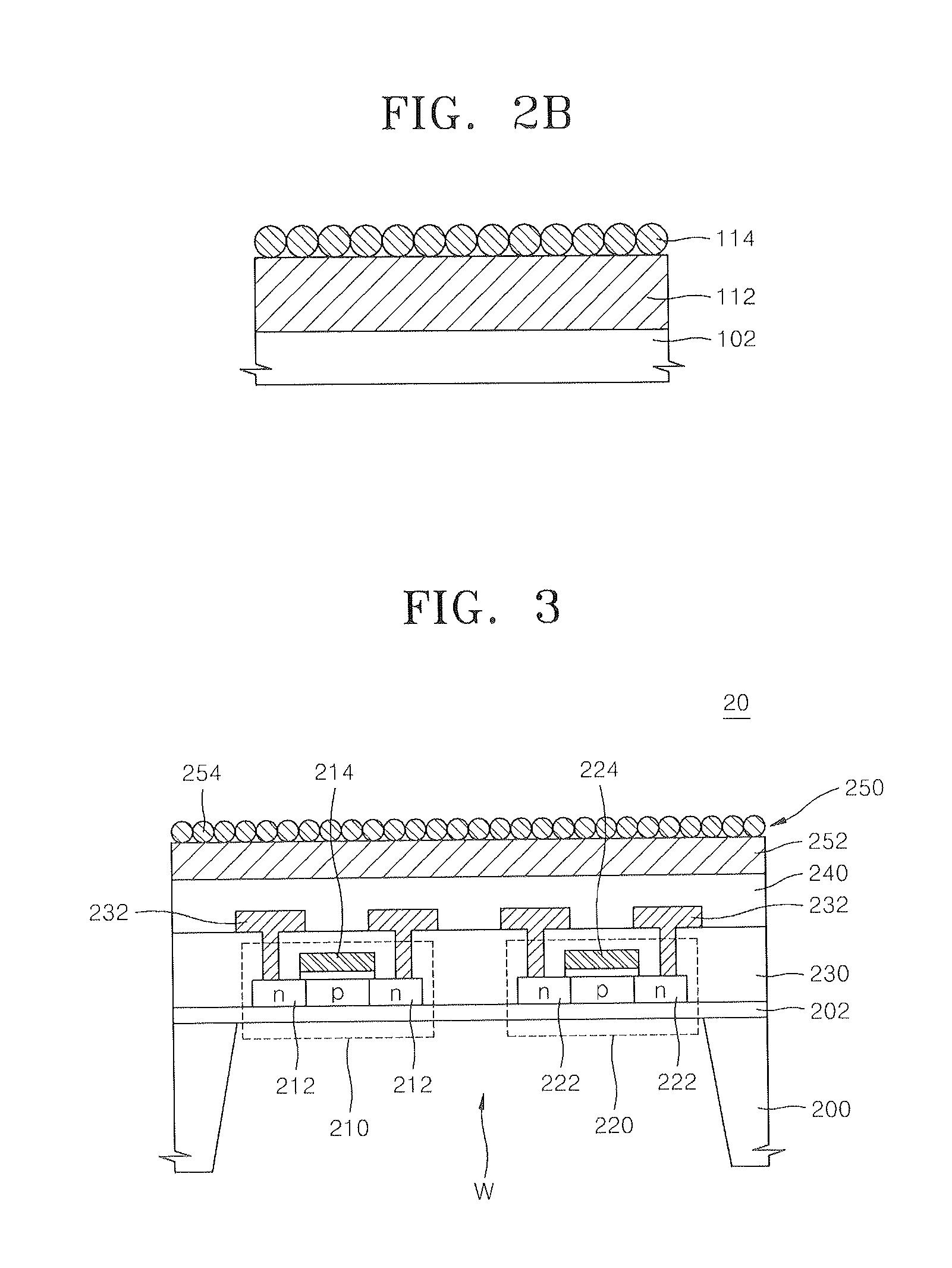

Method of forming sensor for detecting gases and biochemical materials, integrated circuit having the sensor, and method of manufacturing the integrated circuit

InactiveUS20080121946A1Characteristics degradation of an integrated circuit caused by heating the unit devices when forming the sensor can be preventedSemiconductor/solid-state device manufacturingNanosensorsMOSFETNano structuring

A method of forming a sensor for detecting gases and biochemical materials that can be fabricated at a temperature in a range from room temperature to 400° C., a metal oxide semiconductor field effect transistor (MOSFET)-based integrated circuit including the sensor, and a method of manufacturing the integrated circuit are provided. The integrated circuit includes a semiconductor substrate. The sensor for detecting gases and biochemical materials includes a pair of electrodes formed on a first region of the semiconductor substrate, and a metal oxide nano structure layer formed on surfaces of the pair electrodes. A heater is formed to perform thermal treatment to re-use the material detected in the metal oxide nano structure layer. Also, a signal processor is formed by a MOSFET to process a predetermined signal obtained from a quantity change of a current flowing through the pair of electrodes of the sensor. To form the sensor, the metal oxide nano structure layer is formed on surfaces of the pair of electrodes at a temperature in a range from room temperature to 400° C.

Owner:ELECTRONICS & TELECOMM RES INST

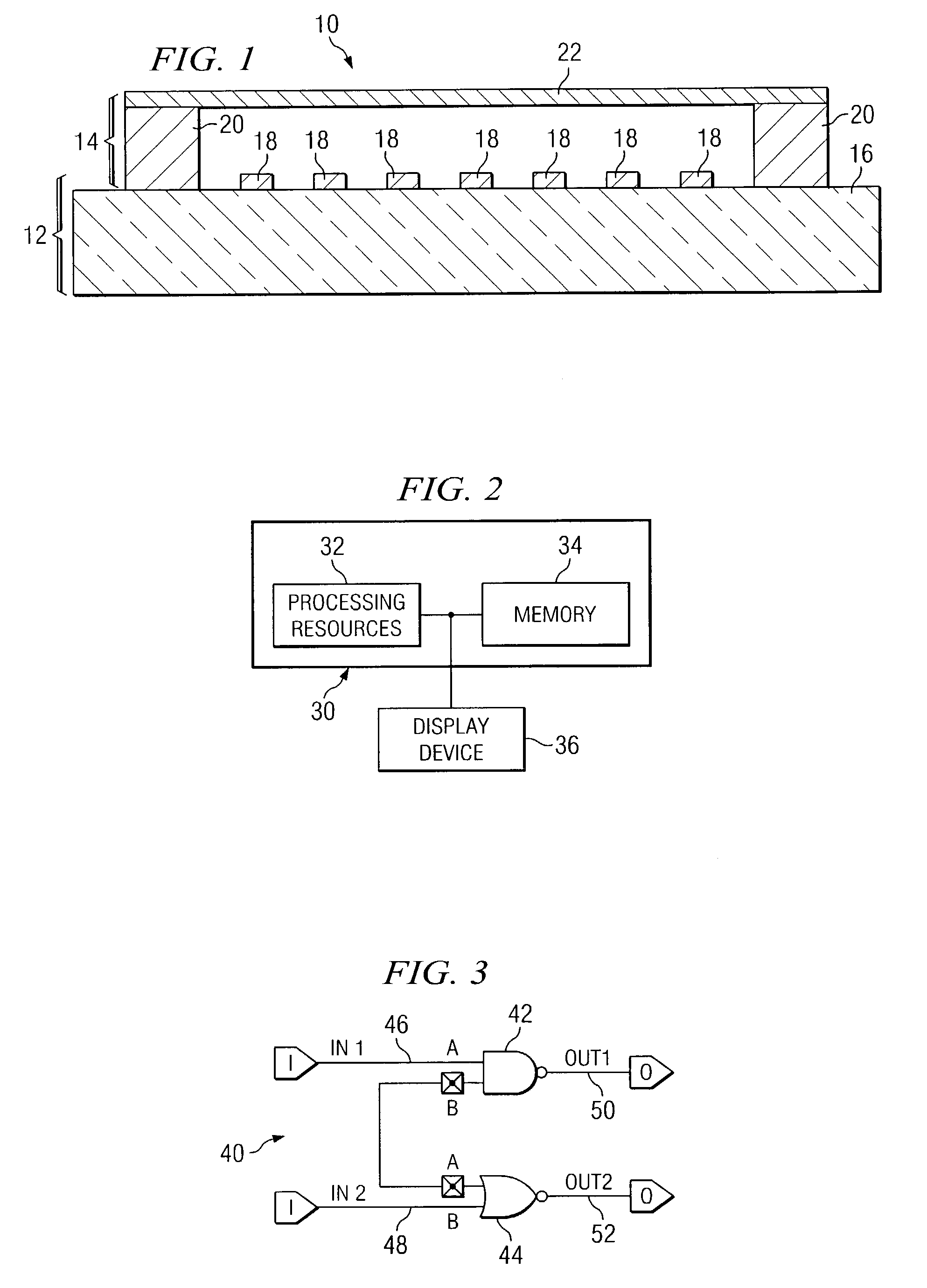

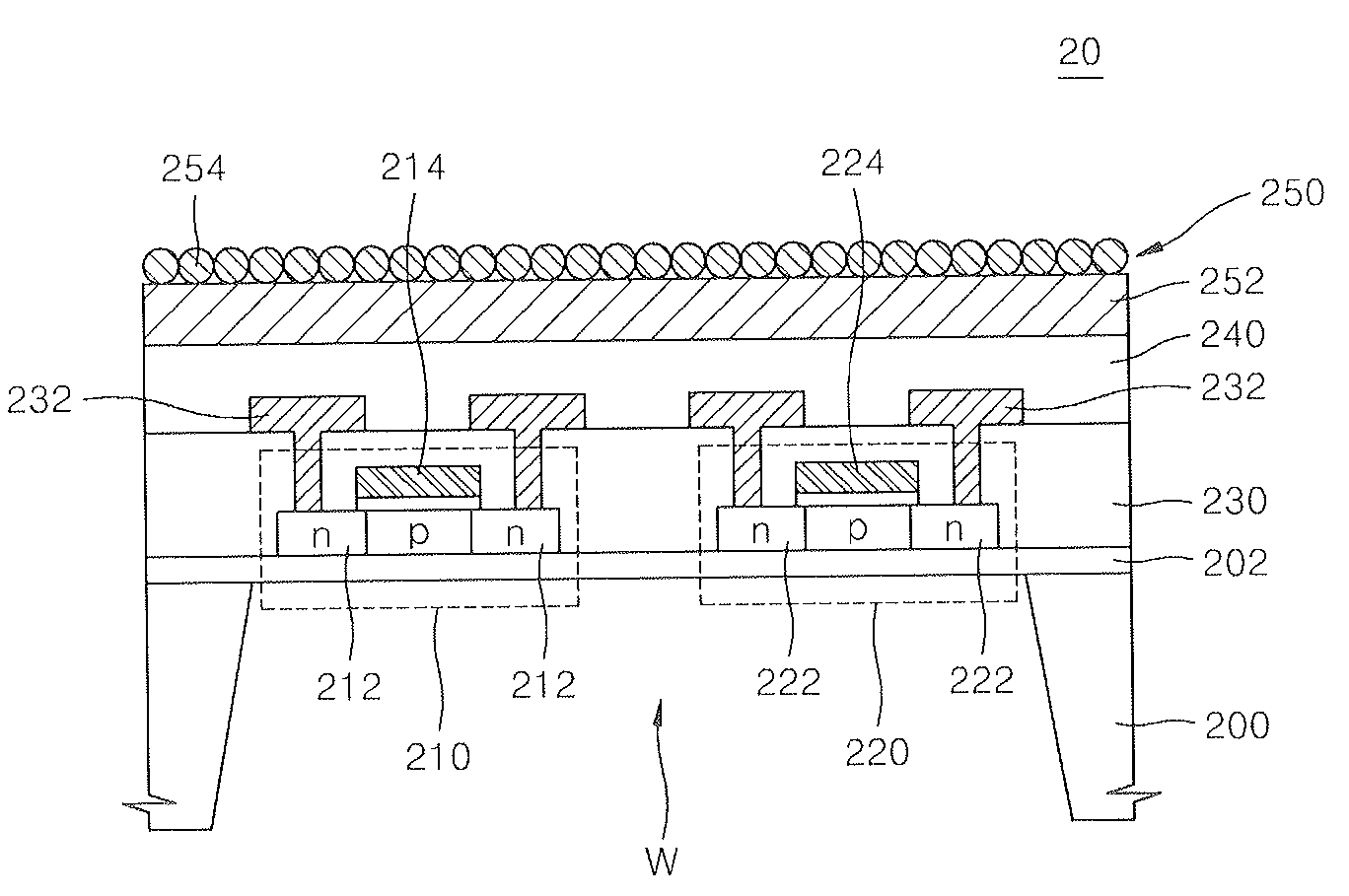

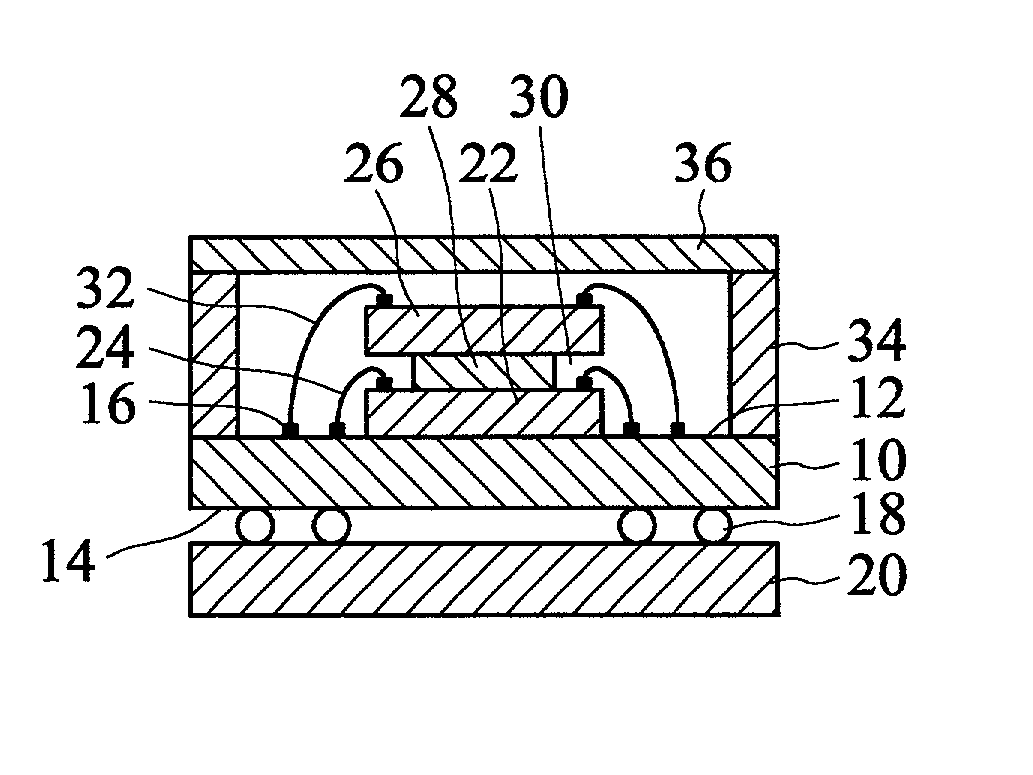

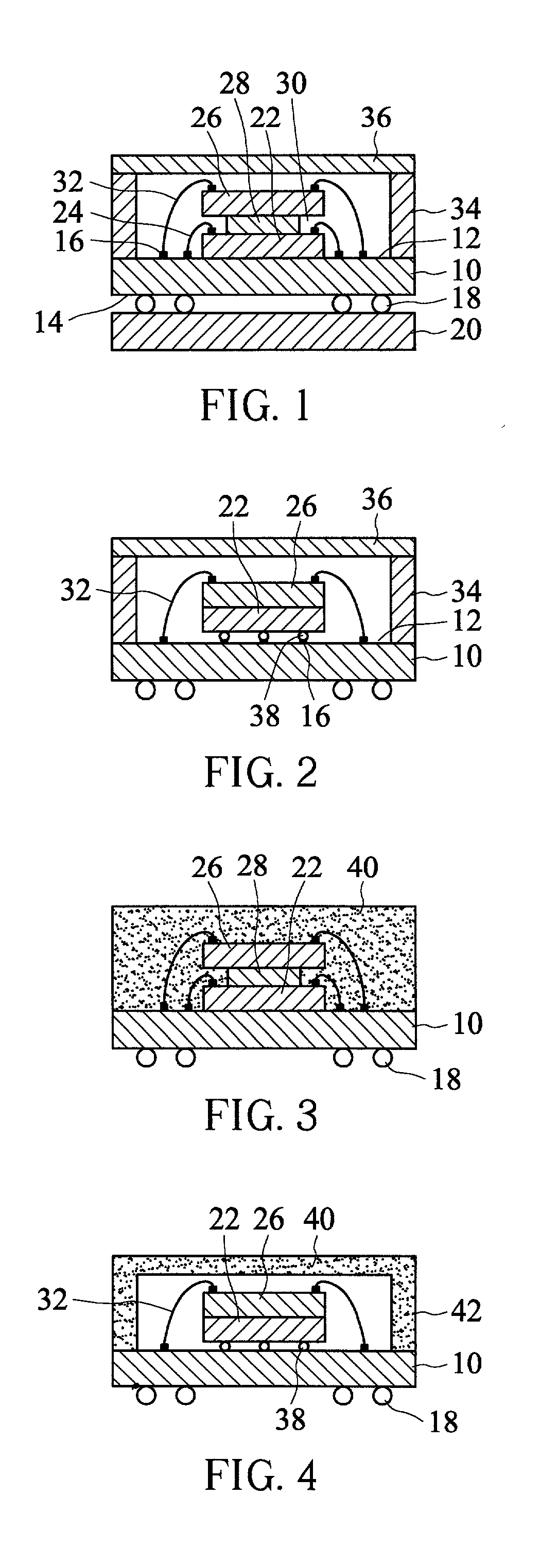

Stacked package structure of image sensor

InactiveUS20020096729A1Solid-state devicesSemiconductor/solid-state device manufacturingImage signalPrinted circuit board

A stacked package structure of an image sensor for electrically connecting to a printed circuit board includes a substrate, an integrated circuit, an image sensing chip, and a transparent layer. The substrate has a first surface and a second surface opposite to the first surface. The first surface is formed with signal input terminals. The second surface is formed with signal output terminals for electrically connecting the substrate to the printed circuit board. The integrated circuit is mounted on the first surface of the substrate and electrically connected to the signal input terminals of the substrate. The image sensing chip is located above the integrated circuit to form a stacked structure with the integrated circuit for electrically connecting to the signal input terminals of the substrate. The transparent layer covers the image sensing chip. The image sensing chip receives image signals via the transparent layer and converts the image signals into electrical signals that are to be transmitted to the substrate. Thus, the image sensing chip of the image sensing product and the integrated circuit can be integrally packaged.

Owner:KINGPAK TECH INC

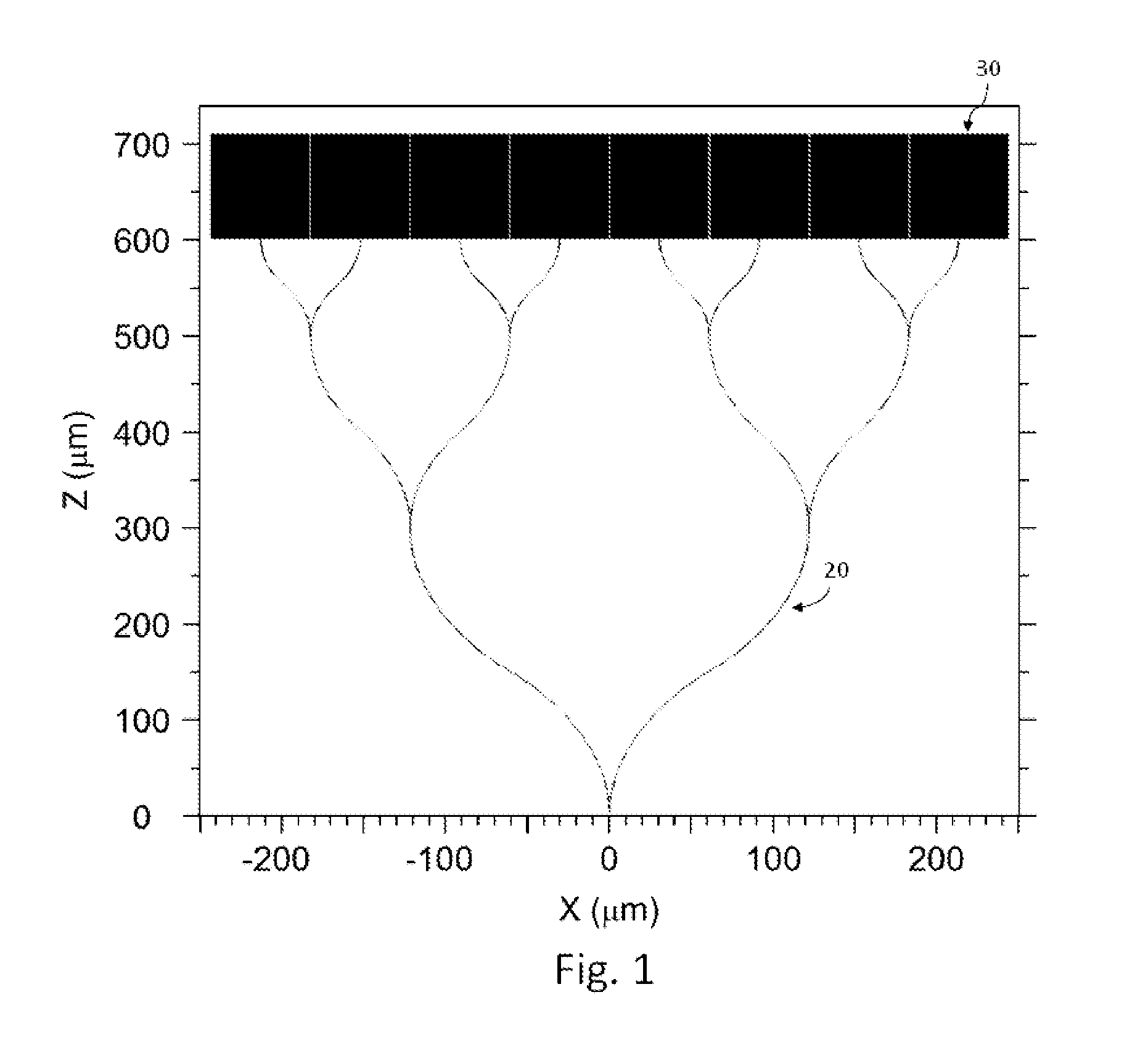

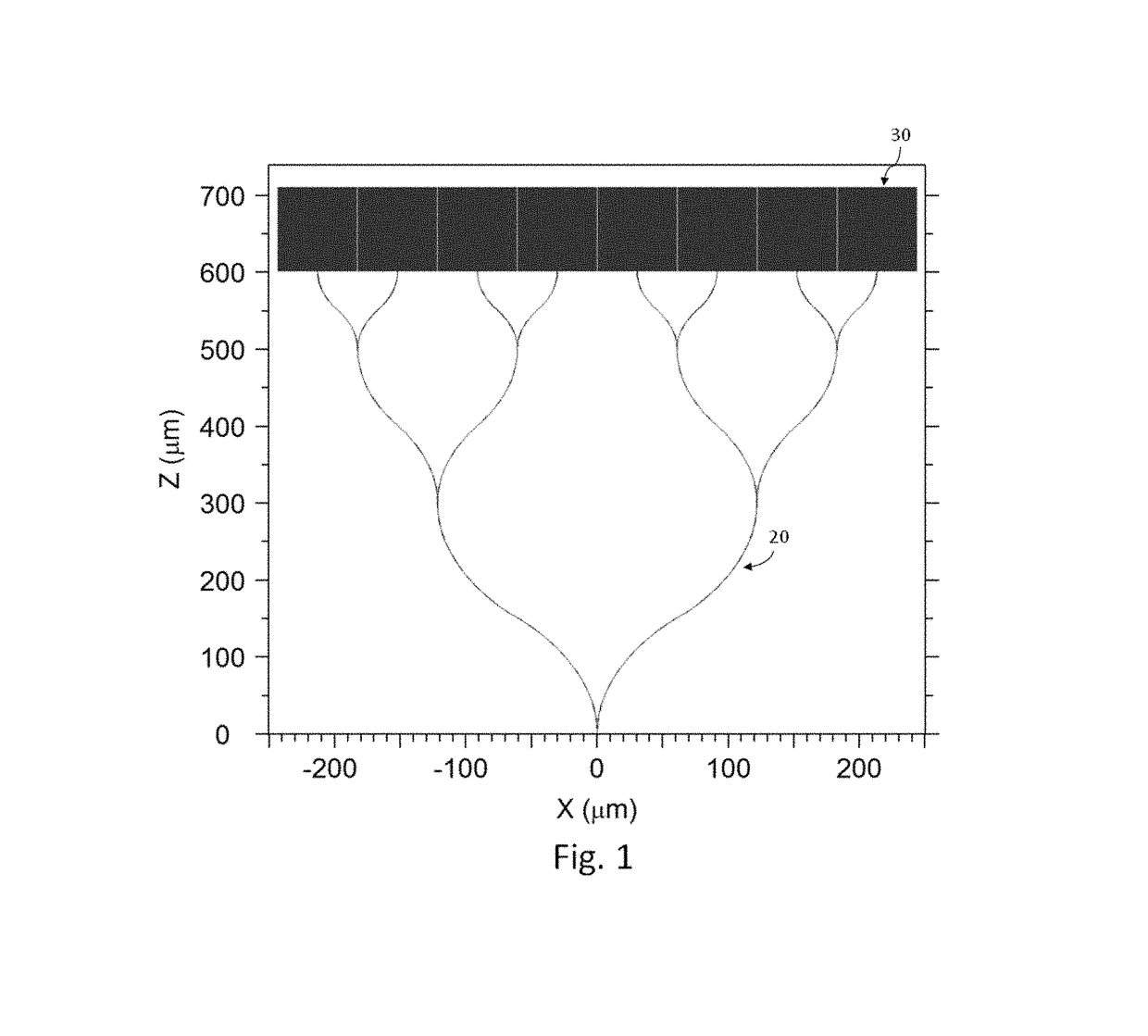

Solid state optical phased array lidar and method of using same

ActiveUS20150293224A1Instruments for comonautical navigationMaterial analysis by optical meansOptical delay lineRadiation pattern

A lidar-based apparatus and method are used for the solid state steering of laser beams using Photonic Integrated Circuits. Integrated optic design and fabrication micro- and nanotechnologies are used for the production of chip-scale optical splitters that distribute an optical signal from a laser essentially uniformly to an array of pixels, said pixels comprising tunable optical delay lines and optical antennas. Said antennas achieve out-of-plane coupling of light.As the delay lines of said antenna-containing pixels in said array are tuned, each antenna emits light of a specific phase to form a desired far-field radiation pattern through interference of these emissions. Said array serves the function of solid state optical phased array.By incorporating a large number of antennas, high-resolution far-field patterns can be achieved by an optical phased array, supporting the radiation pattern beam forming and steering needed in solid state lidar, as well as the generation of arbitrary radiation patterns as needed in three-dimensional holography, optical memory, mode matching for optical space-division multiplexing, free space communications, and biomedical sciences. Whereas imaging from an array is conventionally transmitted through the intensity of the pixels, the optical phased array allows imaging through the control of the optical phase of pixels that receive coherent light waves from a single source.

Owner:QUANERGY SOLUTIONS INC

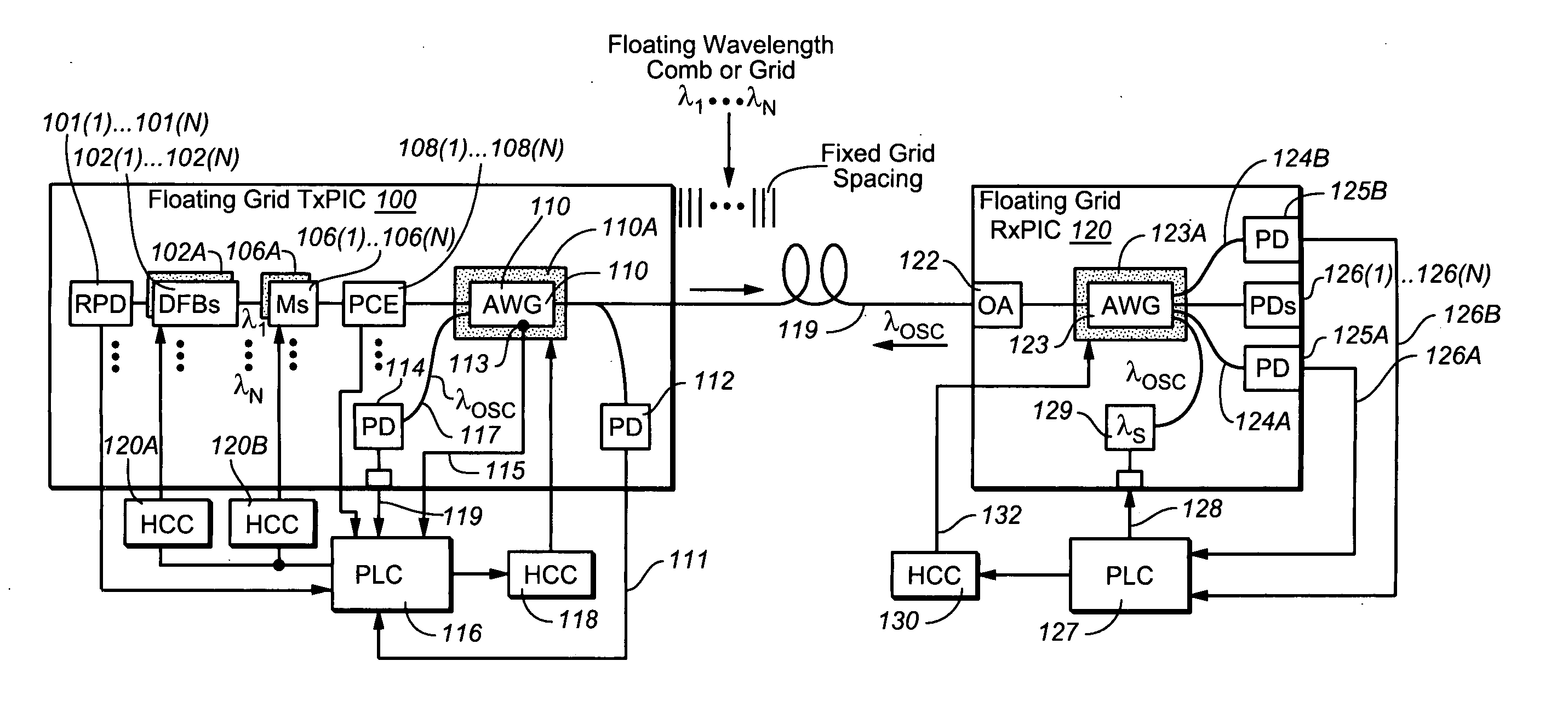

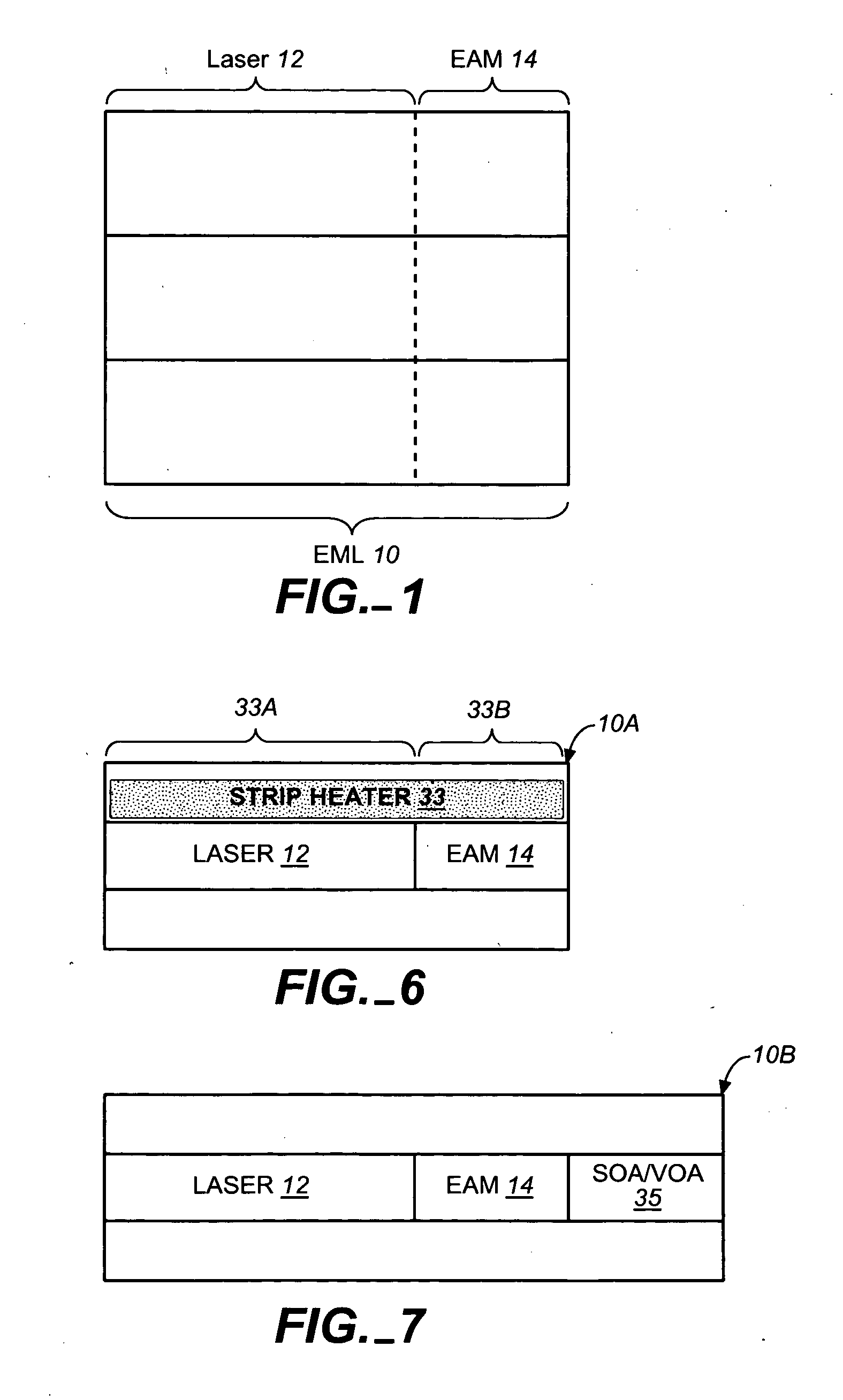

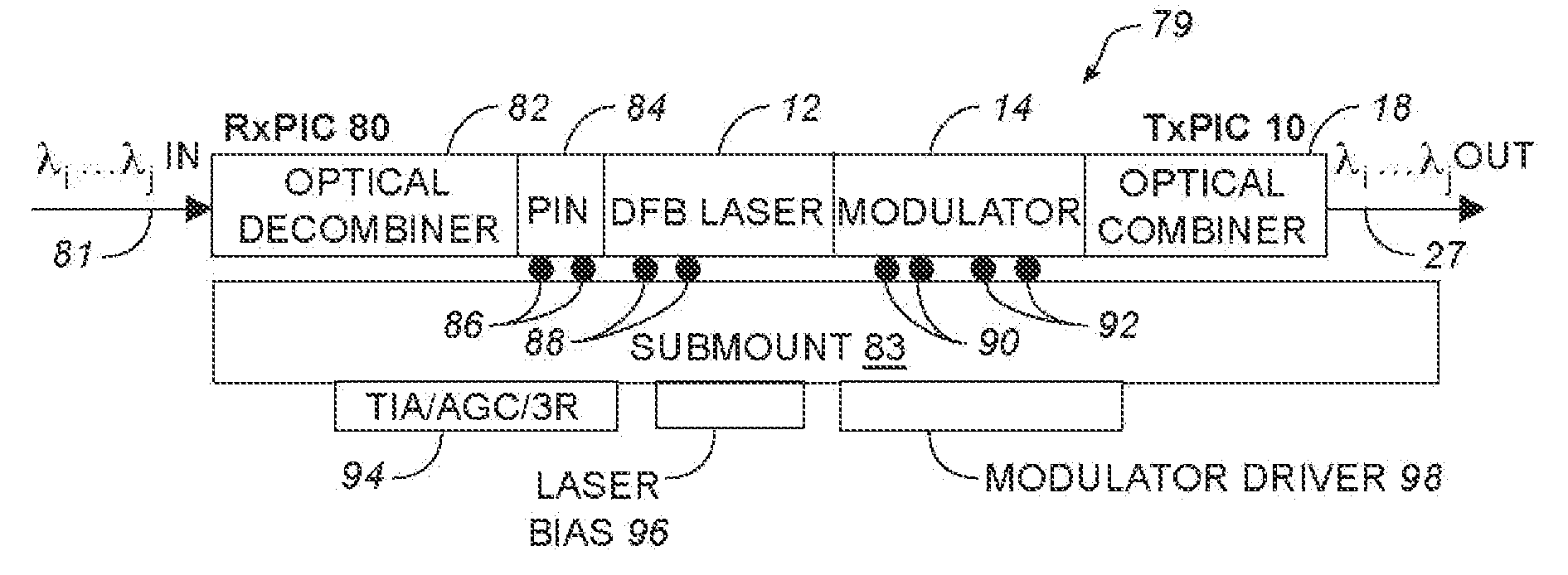

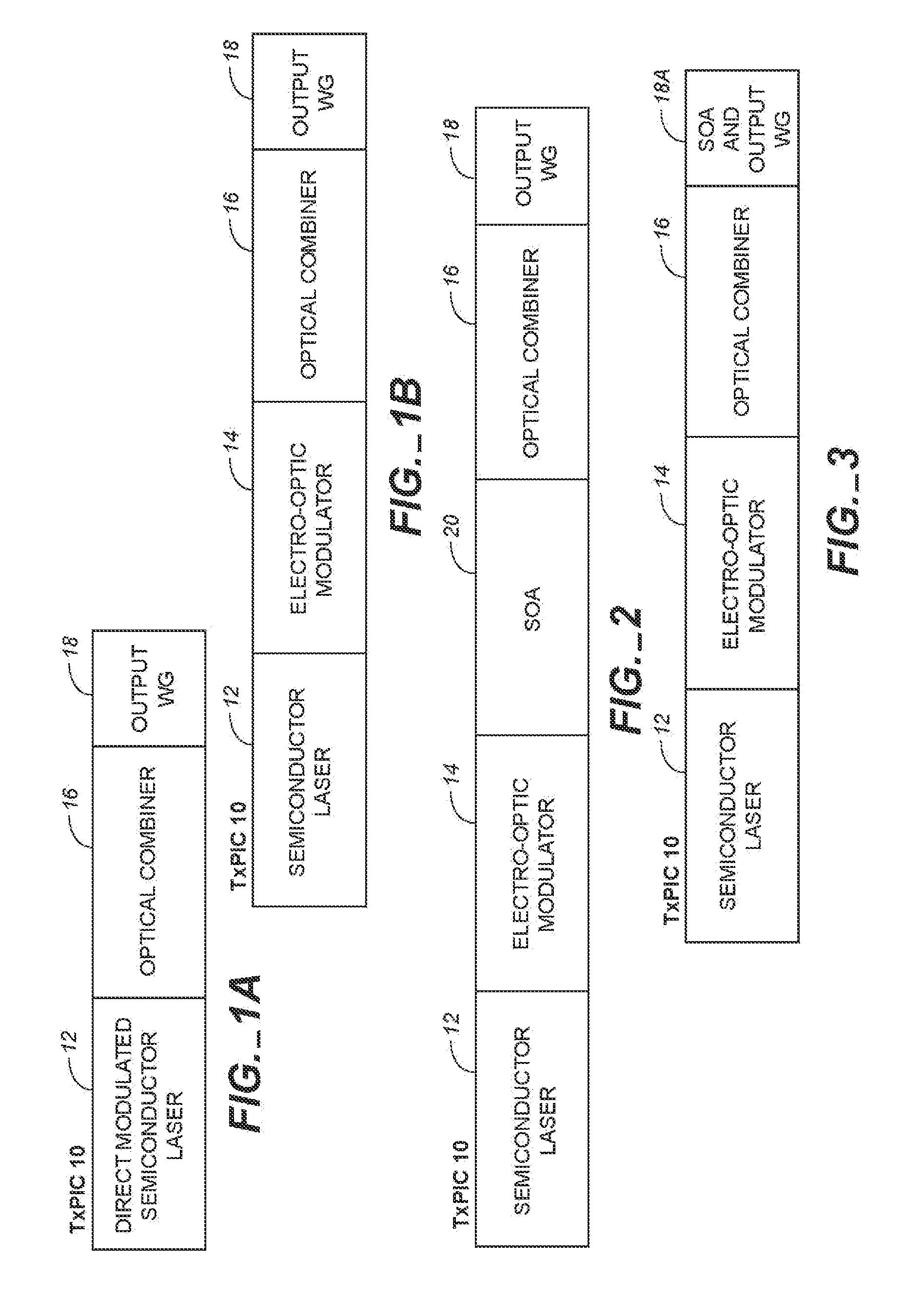

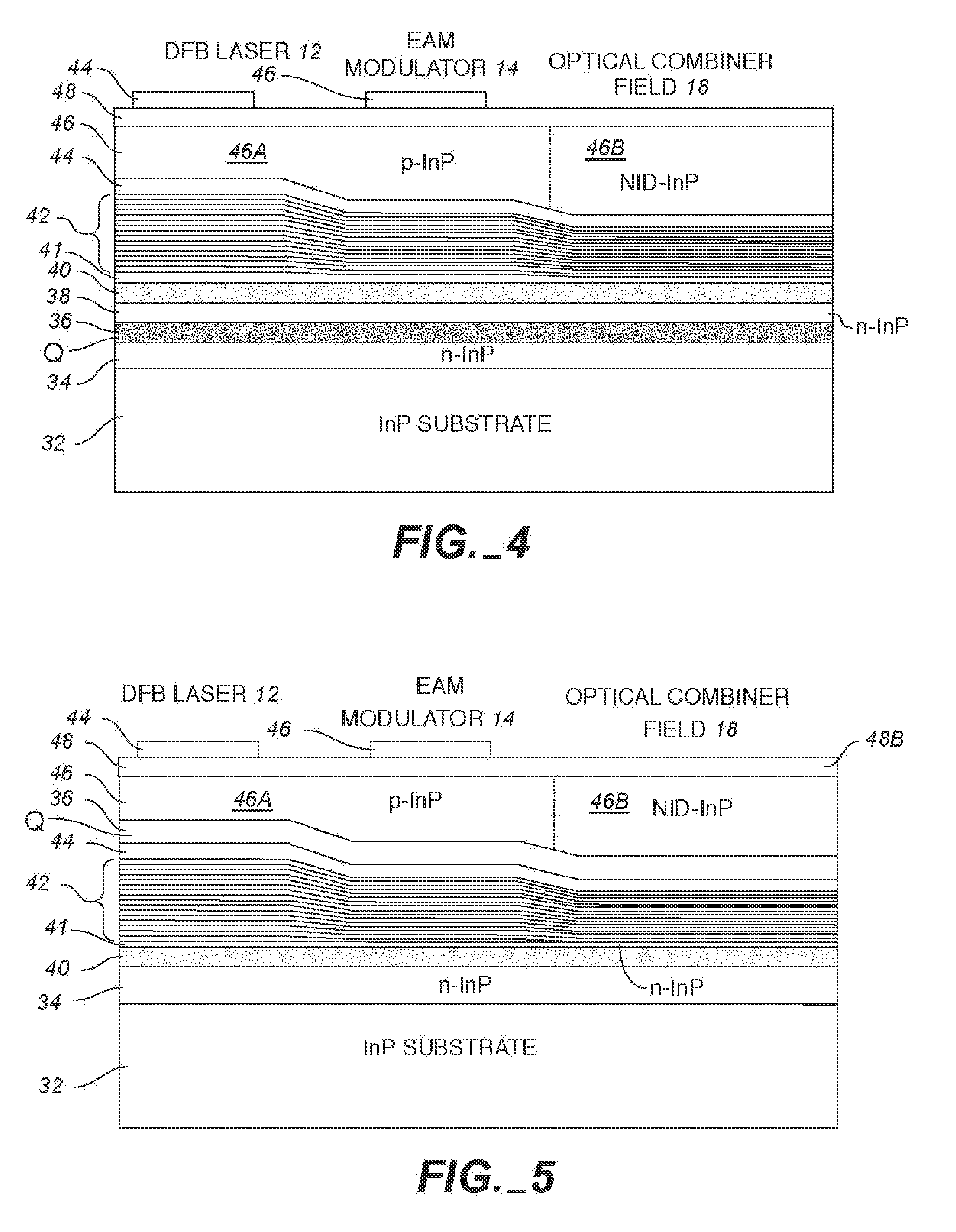

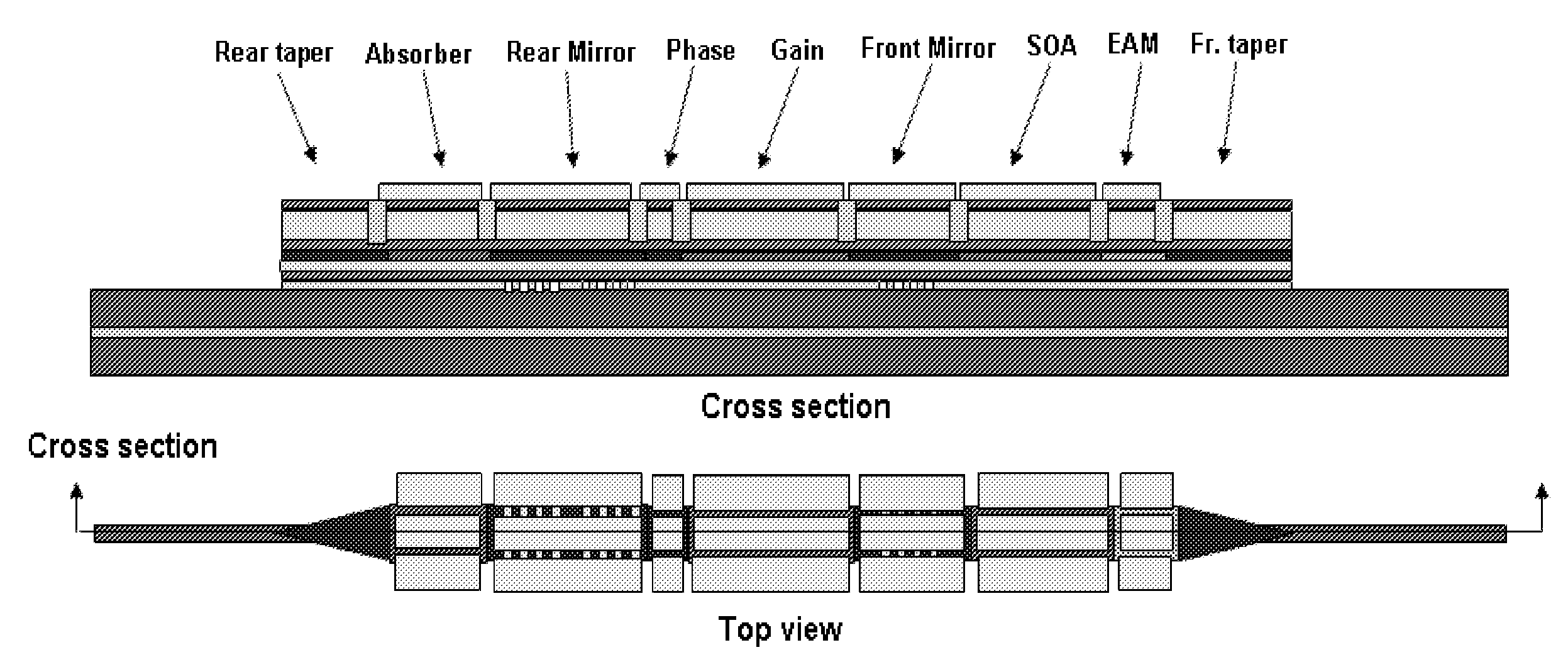

Coolerless photonic integrated circuits (PICs) for WDM transmission networks and PICs operable with a floating signal channel grid changing with temperature but with fixed channel spacing in the floating grid

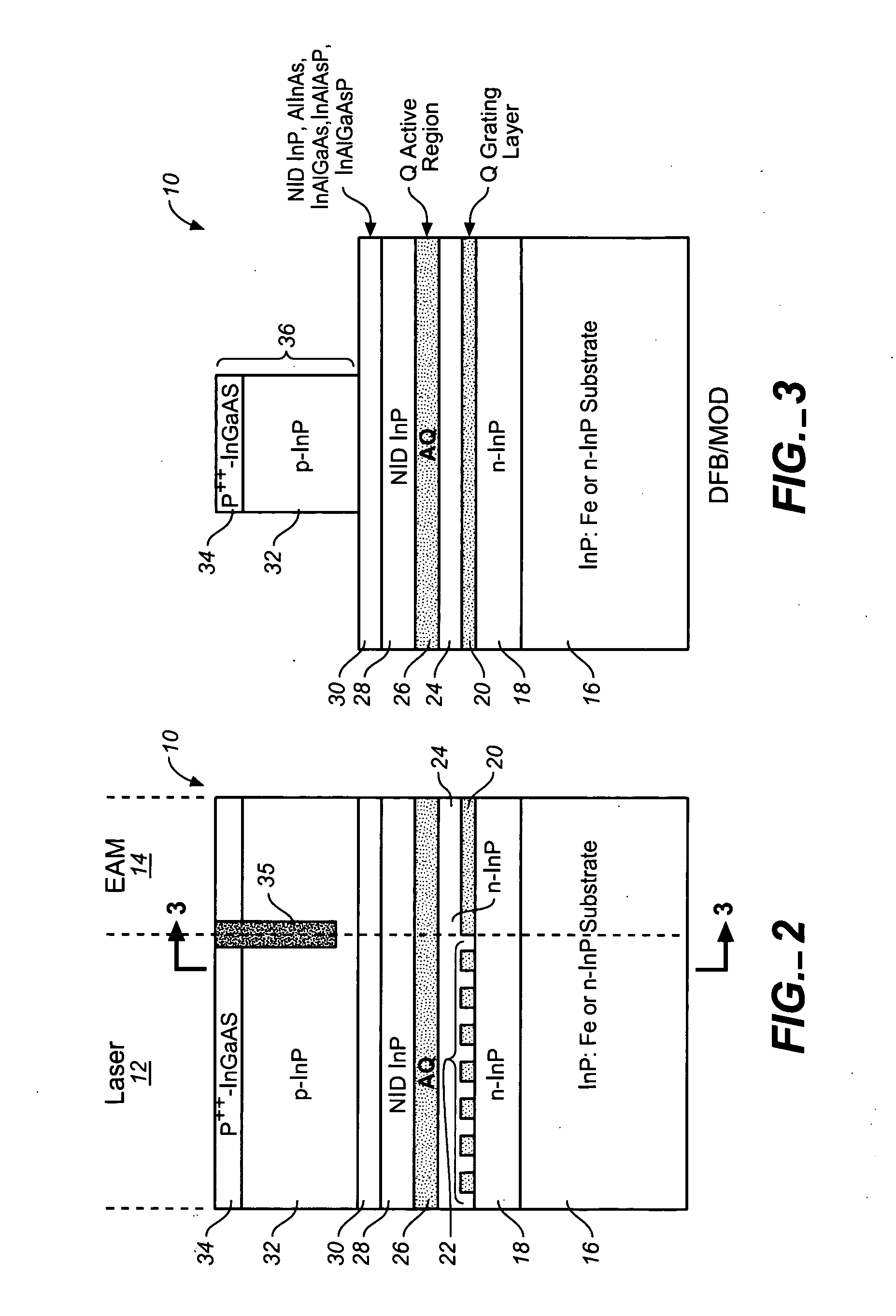

ActiveUS20050249509A1Requirements for a hermetically sealed package are substantially relievedEasy to controlLaser optical resonator constructionSemiconductor laser arrangementsElectro-absorption modulatorHermetic packaging

A coolerless photonic integrated circuit (PIC), such as a semiconductor electro-absorption modulator / laser (EML) or a coolerless optical transmitter photonic integrated circuit (TxPIC), may be operated over a wide temperature range at temperatures higher then room temperature without the need for ambient cooling or hermetic packaging. Since there is large scale integration of N optical transmission signal WDM channels on a TxPIC chip, a new DWDM system approach with novel sensing schemes and adaptive algorithms provides intelligent control of the PIC to optimize its performance and to allow optical transmitter and receiver modules in DWDM systems to operate uncooled. Moreover, the wavelength grid of the on-chip channel laser sources may thermally float within a WDM wavelength band where the individual emission wavelengths of the laser sources are not fixed to wavelength peaks along a standardized wavelength grid but rather may move about with changes in ambient temperature. However, control is maintained such that the channel spectral spacing between channels across multiple signal channels, whether such spacing is periodic or aperiodic, between adjacent laser sources in the thermally floating wavelength grid are maintained in a fixed relationship. Means are then provided at an optical receiver to discover and lock onto floating wavelength grid of transmitted WDM signals and thereafter demultiplex the transmitted WDM signals for OE conversion.

Owner:INFINERA CORP

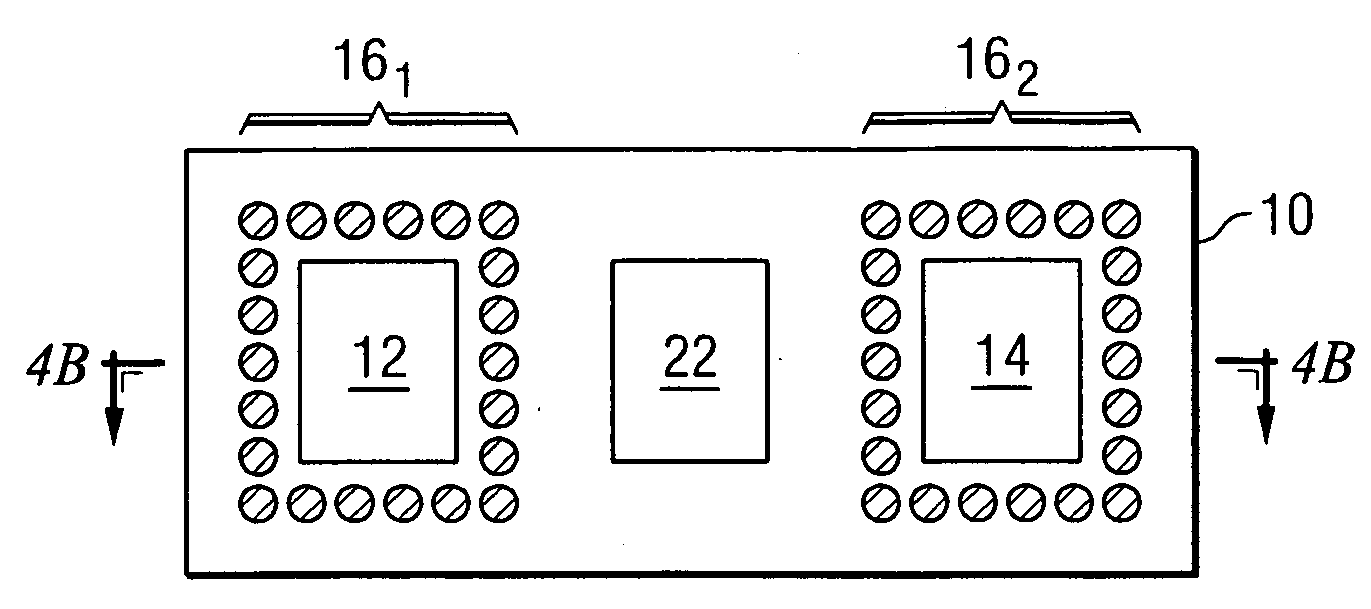

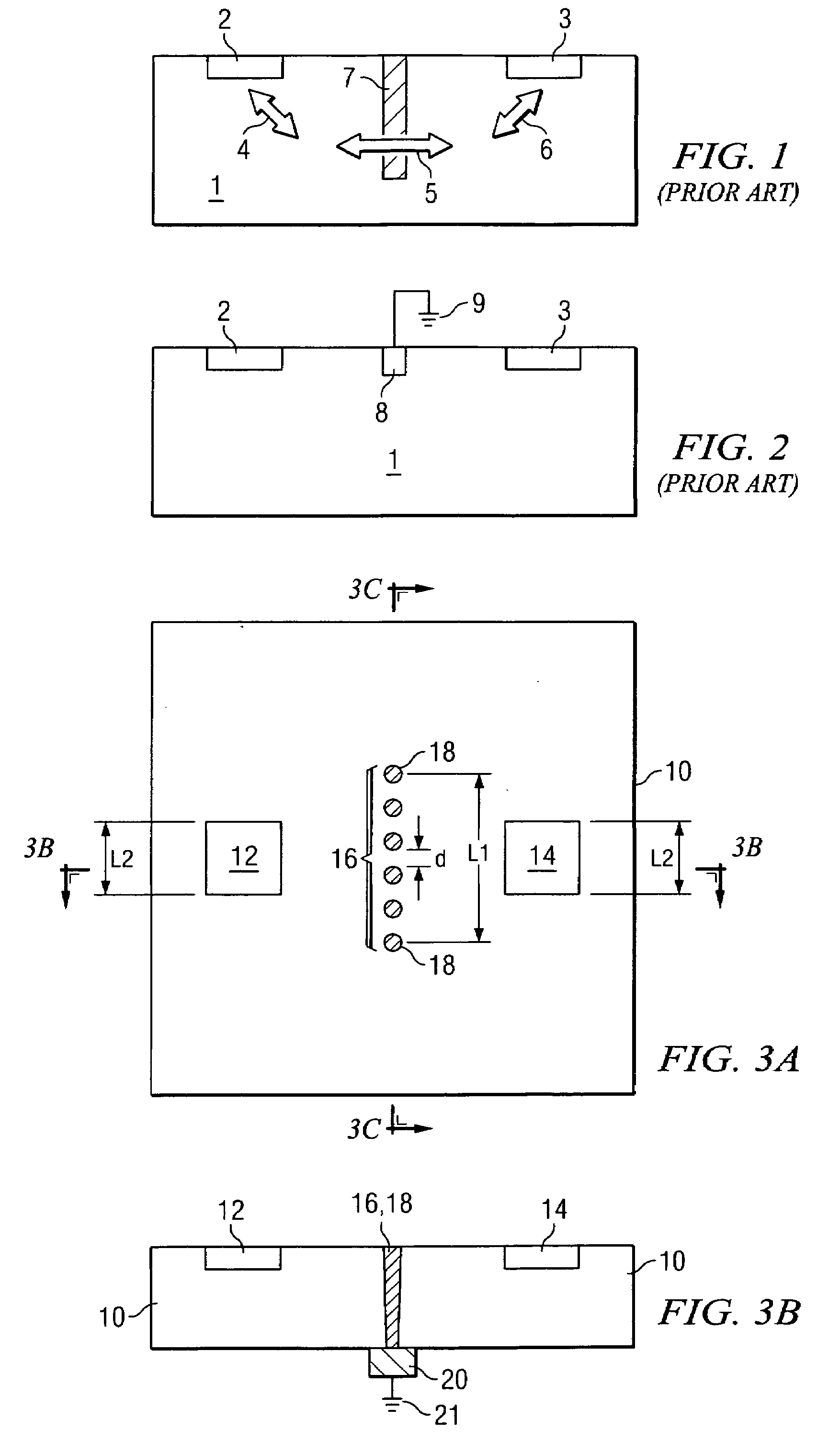

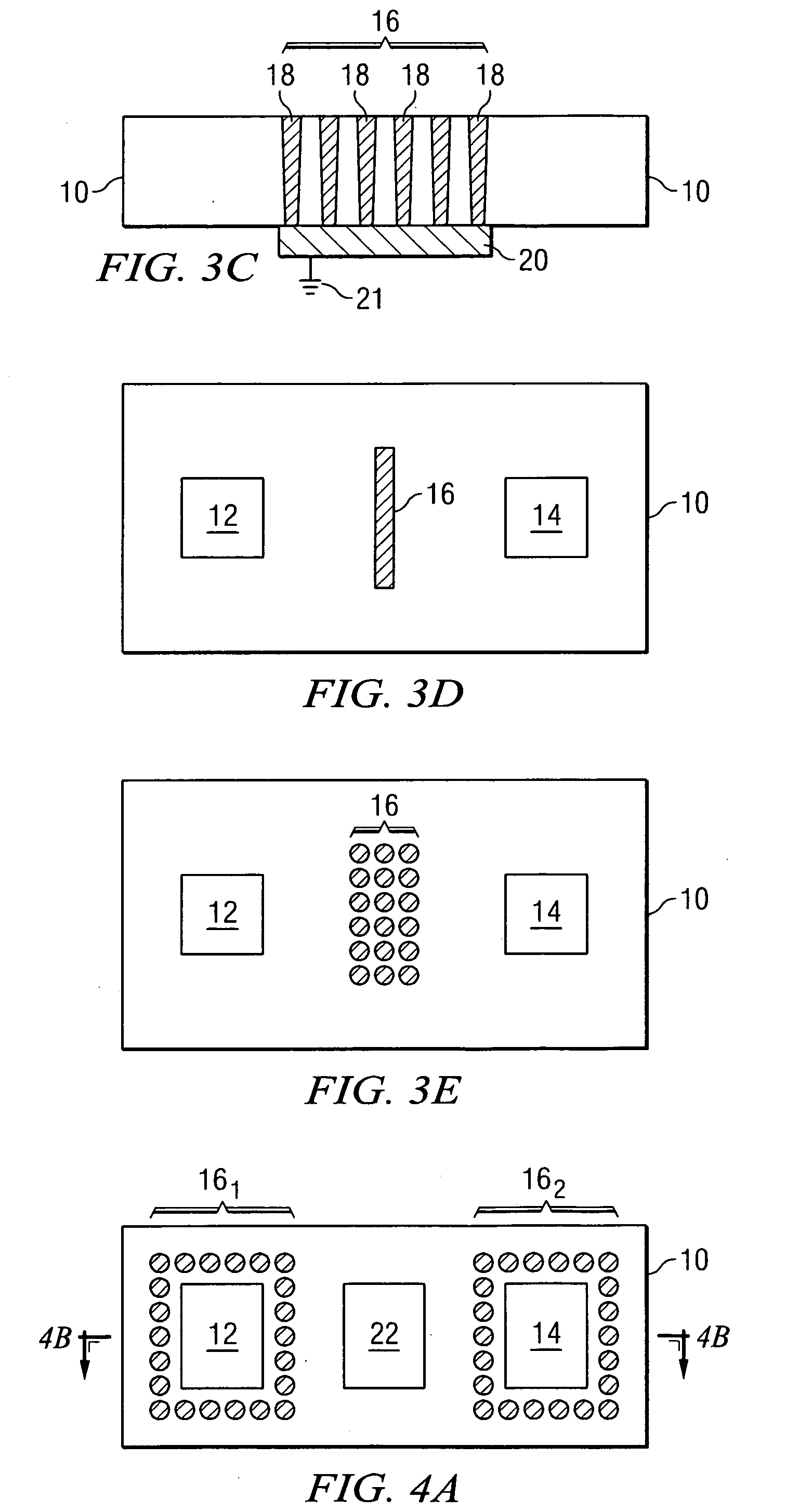

Electromagnetic shielding using through-silicon vias

ActiveUS20080073747A1Good electromagnetic isolationImprove isolationSemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceDirect path

An isolation structure for electromagnetic interference includes a semiconductor substrate, a first integrated circuit in the semiconductor substrate, a second integrated circuit in the semiconductor substrate, and an isolation structure in a direct path between the first and the second integrated circuits, wherein the isolation structure comprises a through-silicon via.

Owner:TAIWAN SEMICON MFG CO LTD

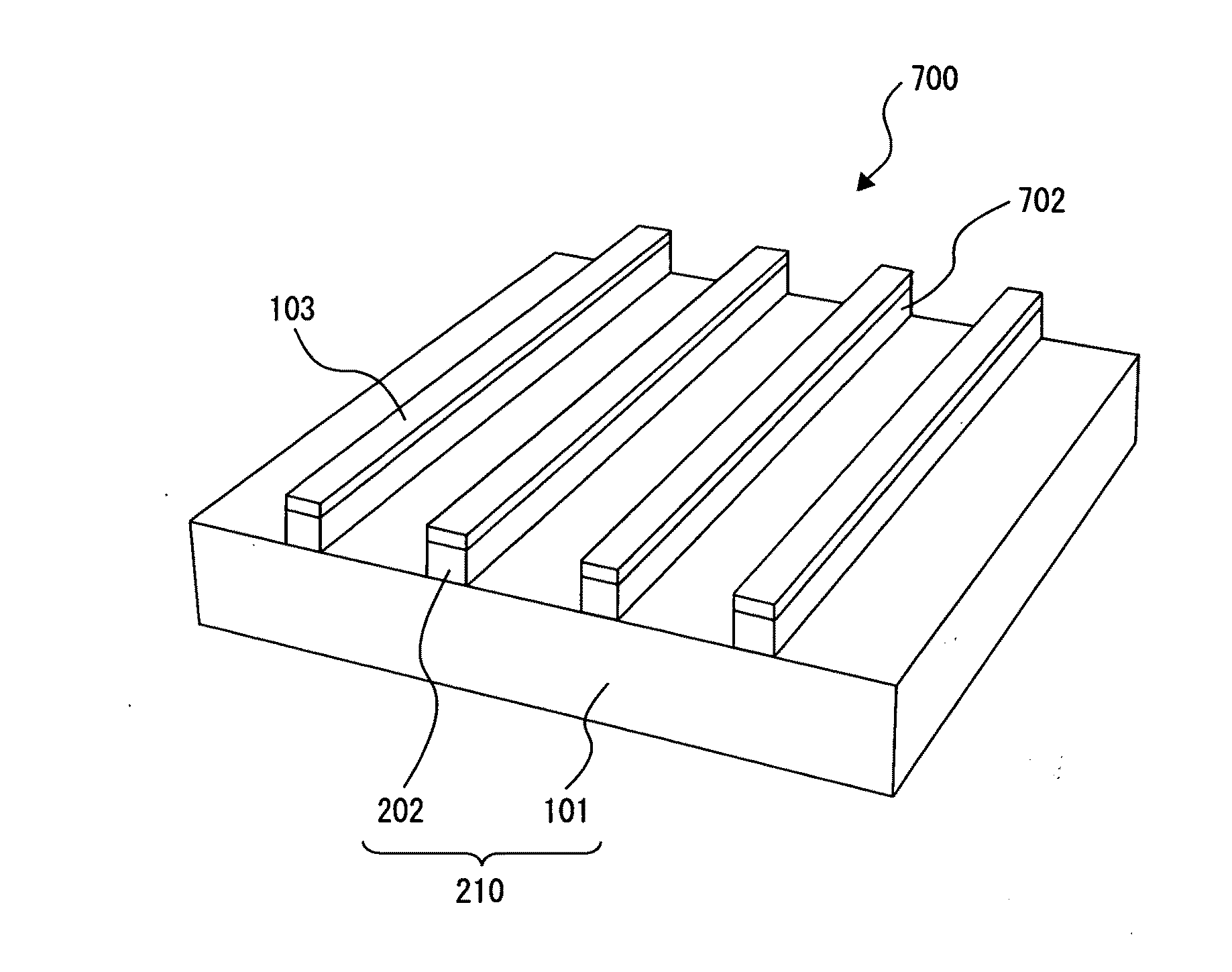

Flexible 3-D Photonic Device

ActiveUS20140219604A1Function increaseSemiconductor/solid-state device manufacturingOptical waveguide light guidePolymerPhoton

Three-dimensional flexible photonic integrated circuits on silicon are fabricated in semiconductor wafer form and then transferred to Silicon-on-Polymer (SOP) substrates. SOP provides flexibility for conformal mounting with devices capable of maintaining performance when dynamically deformed to allow routing of light in x, y and z directions. Bonding a wafer or individual die of III-V semiconductor, such as Gallium Arsenide or similar photonic material, to the flexible silicon creates an active region for lasers, amplifiers, modulators, and other photonic devices using standard processing. Mounting additional photonic devices to the opposite side of a flexible photonic waveguide produces a stack for three-dimensional devices. Multiple flexible photonic waveguides may be stacked to increase functionality by transferring light between stacked waveguides. The flexible photonic circuit allows for integration of photonic devices such as low threshold lasers, tunable lasers, and other photonic integrated circuits with flexible Complementary Metal Oxide Semiconductor (CMOS) integrated circuits.

Owner:AMERICAN SEMICON

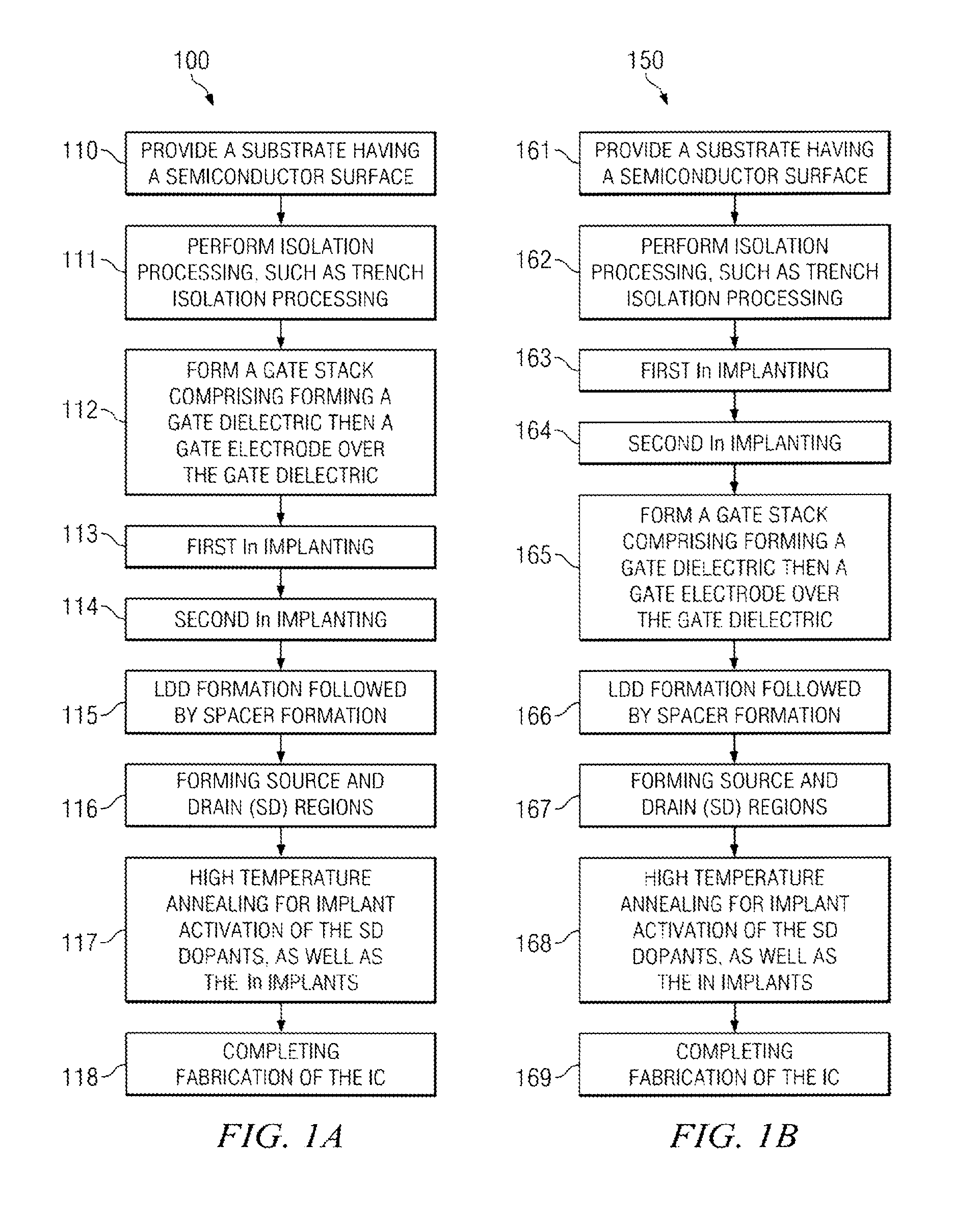

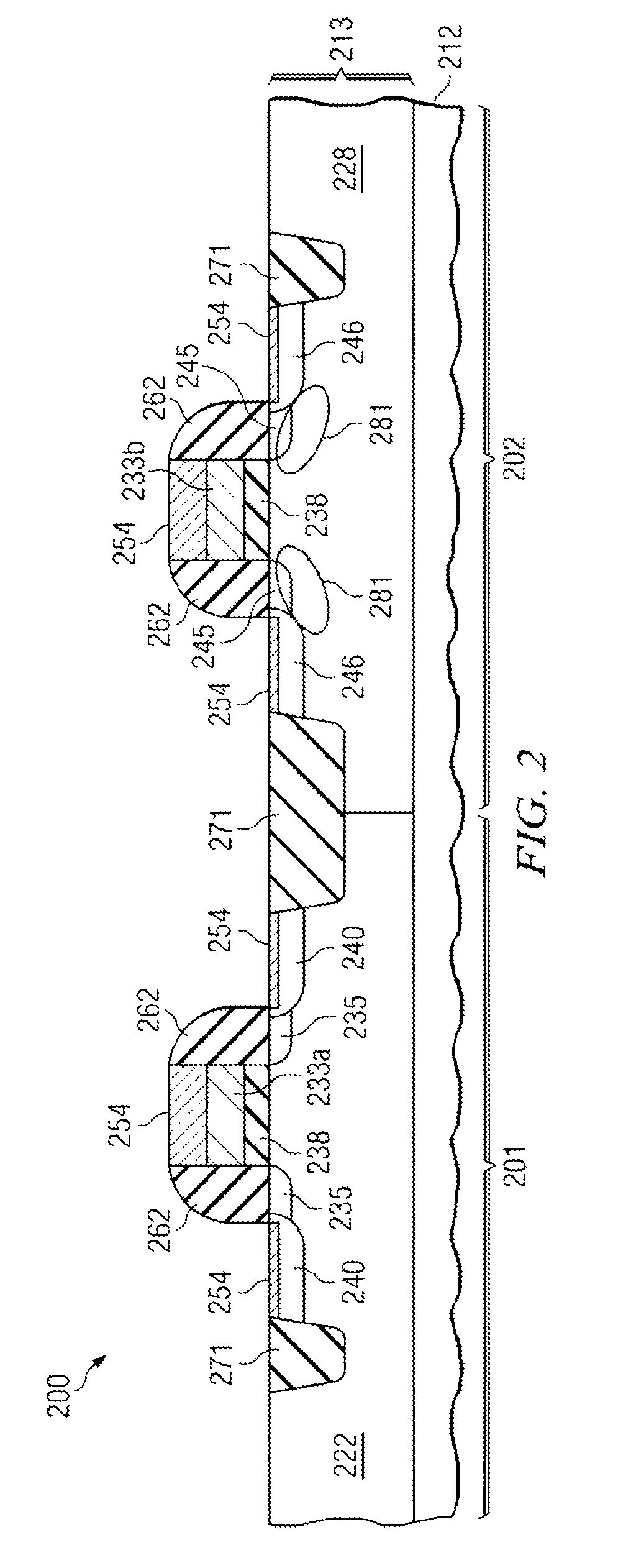

Multiple indium implant methods and devices and integrated circuits therefrom

An integrated circuit (IC) includes at least one NMOS transistor, wherein the NMOS transistor includes a substrate having a semiconductor surface, and a gate stack formed in or on the surface including a gate electrode on a gate dielectric, wherein a channel region is located in the semiconductor surface below the gate dielectric. A source and a drain region are on opposing sides of the gate stack. An In region having a retrograde profile is under at least a portion of the channel region. The retrograde profile includes (i) a surface In concentration at a semiconductor surface interface with the gate dielectric of less than 5×1016 cm−3, (ii) a peak In concentration at least 20 nm from the semiconductor surface below the gate dielectric, and wherein (iii) the peak In concentration is at least two (2) orders of magnitude higher than the In concentration at the semiconductor surface interface. A method to form an IC including at least one NMOS transistor includes implanting a first In implant at a first energy and a second In implant at a second energy, wherein the first In implant together with the second In implant form an In region having a retrograde profile under at least a portion of the channel region, and wherein the second energy is at least 5 keV more than the first energy.

Owner:TEXAS INSTR INC

Contact for use in an integrated circuit and a method of manufacture therefor

InactiveUS6910907B2Semiconductor/solid-state device manufacturingCoupling contact membersMechanical engineeringPhotonic integrated circuit

The present invention provides a contact for use in an integrated circuit, a method of manufacture therefor, and an integrated circuit including the aforementioned contact. The contact, in accordance with the principles of the present invention, may include a via located in a substrate, and a contact plug located in the via, wherein the contact plug has a first portion having a notch removed therefrom and a second portion filling the notch.

Owner:BELL SEMICON LLC

Compact inductor with stacked via magnetic cores for integrated circuits

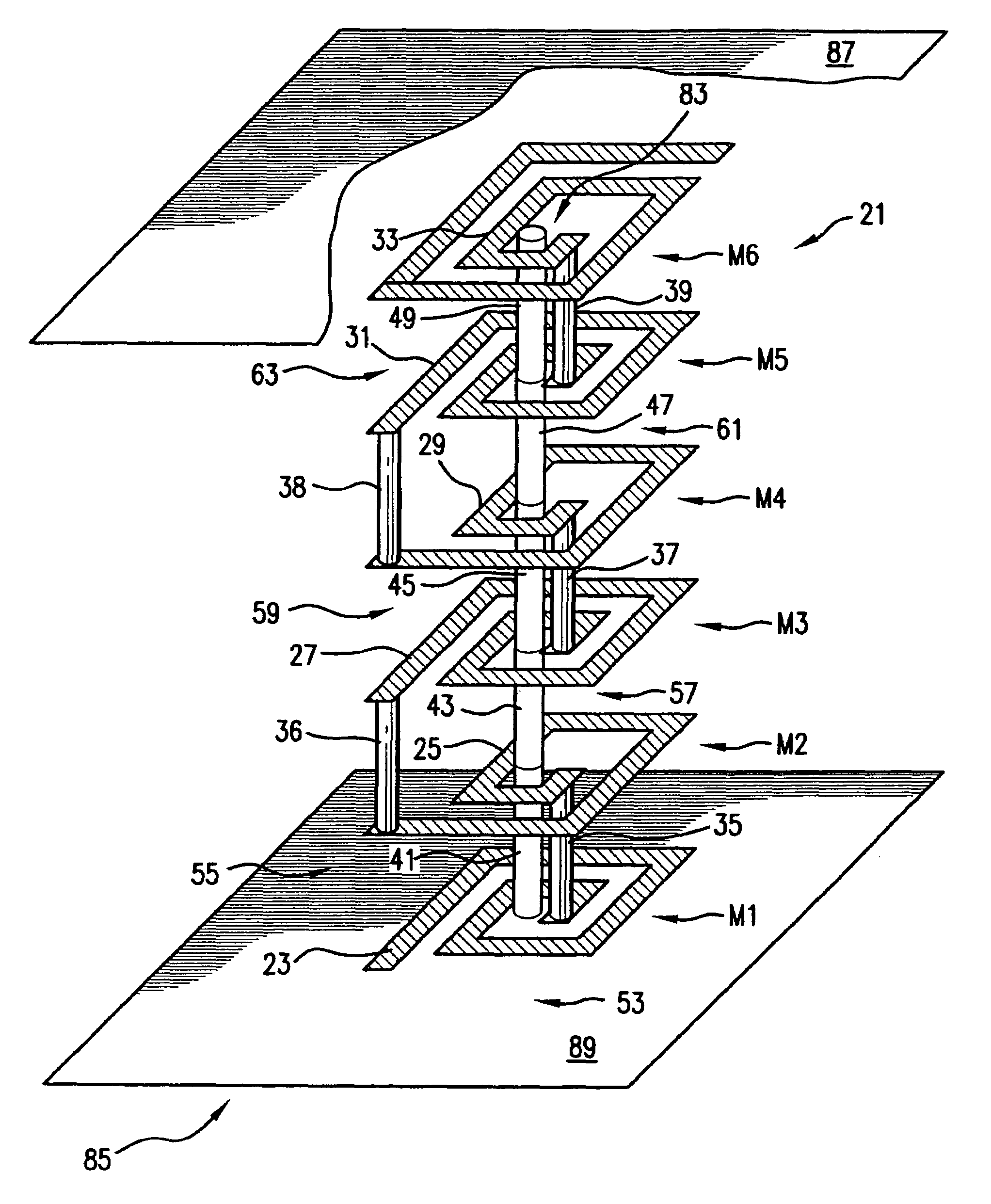

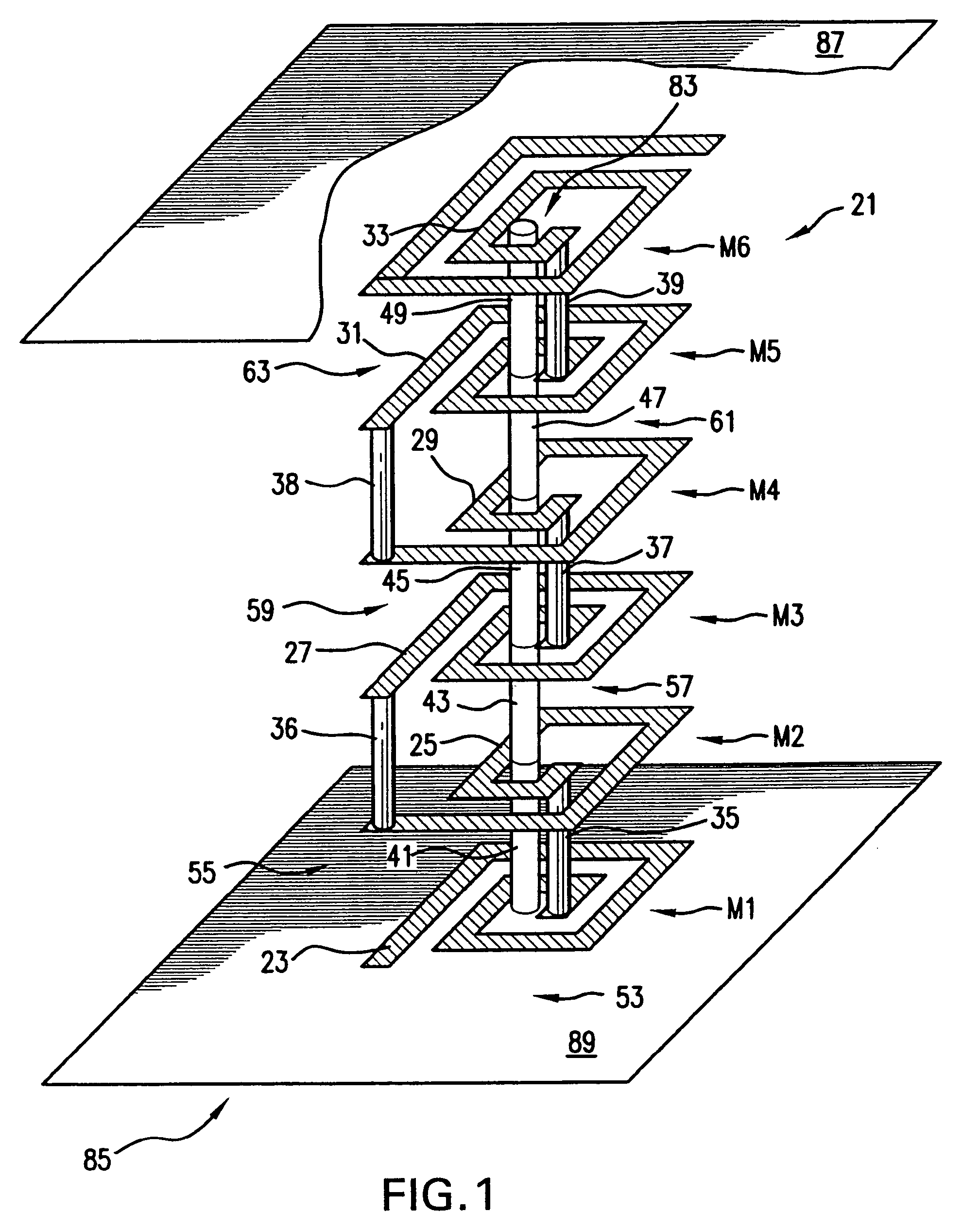

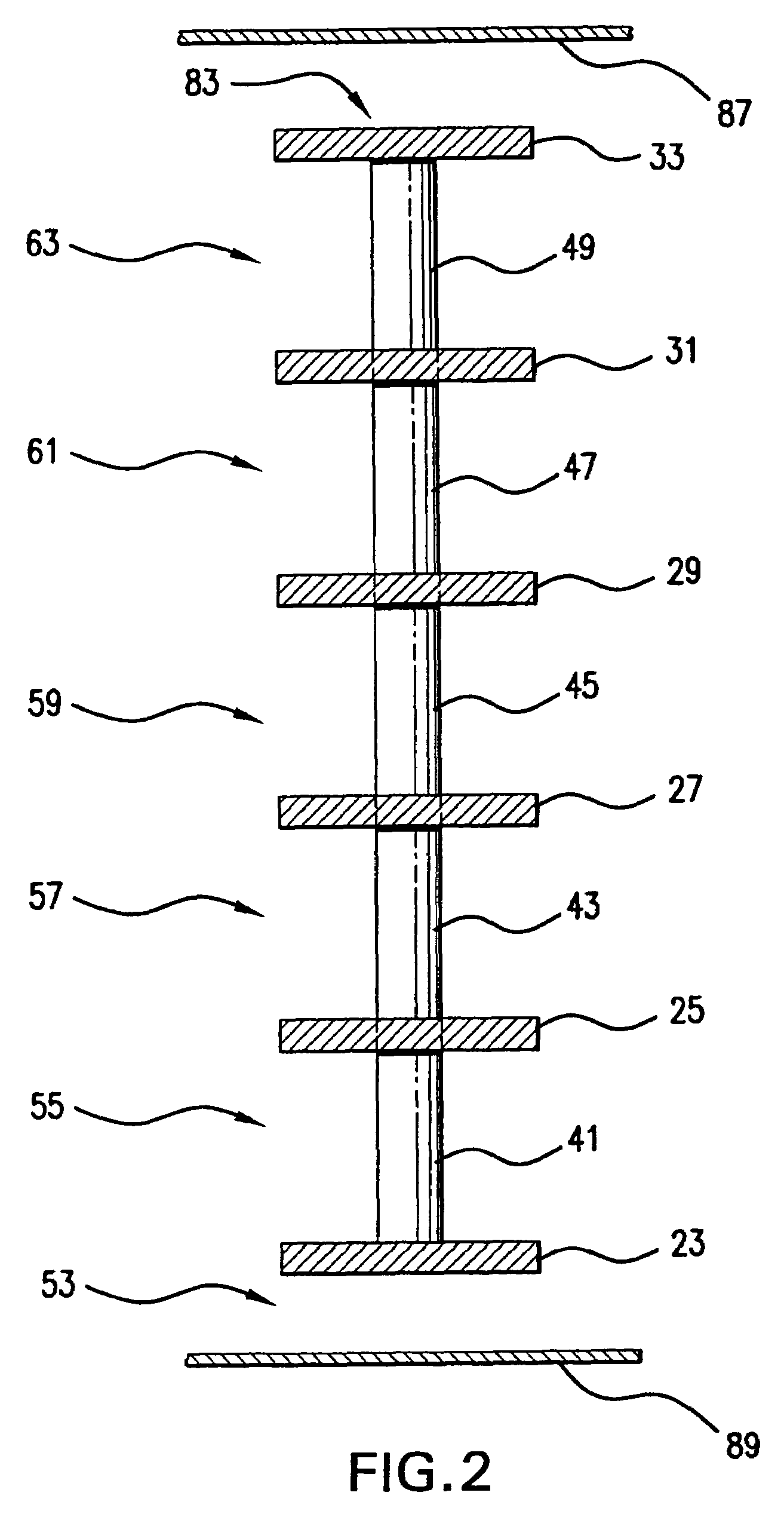

InactiveUS7262680B2Small sizeReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit designIntegrated circuit

An on-chip inductor device for Integrated Circuits utilizes coils on a plurality of metal layers of the IC with electrical connectors between the coils and a magnetic core for the inductor of stacked vias running between the coils. The magnetic core is made from a series of stacked vias which are deposited between each metal layer of the IC having a coil. The magnetic core desirably includes an array of magnetic bars comprising the magnetic core. The via material of the magnetic core may be both magnetic and electrically conductive. The magnetic and electrically conductive via material may also be used for the planar coil electrical connectors or other electrically conductive parts of the IC, or both, thereby lessening fabrication steps. Films of magnetic material may be formed at the ends of the inductor to provide a closed magnetic circuit for the inductor. A high Q factor inductor of small (e.g., transistor) size is thus obtained. The materials and processes which enable the on-chip inductor device are compatible with ordinary IC fabrication methods.

Owner:ILLINOIS INSTITUTE OF TECHNOLOGY

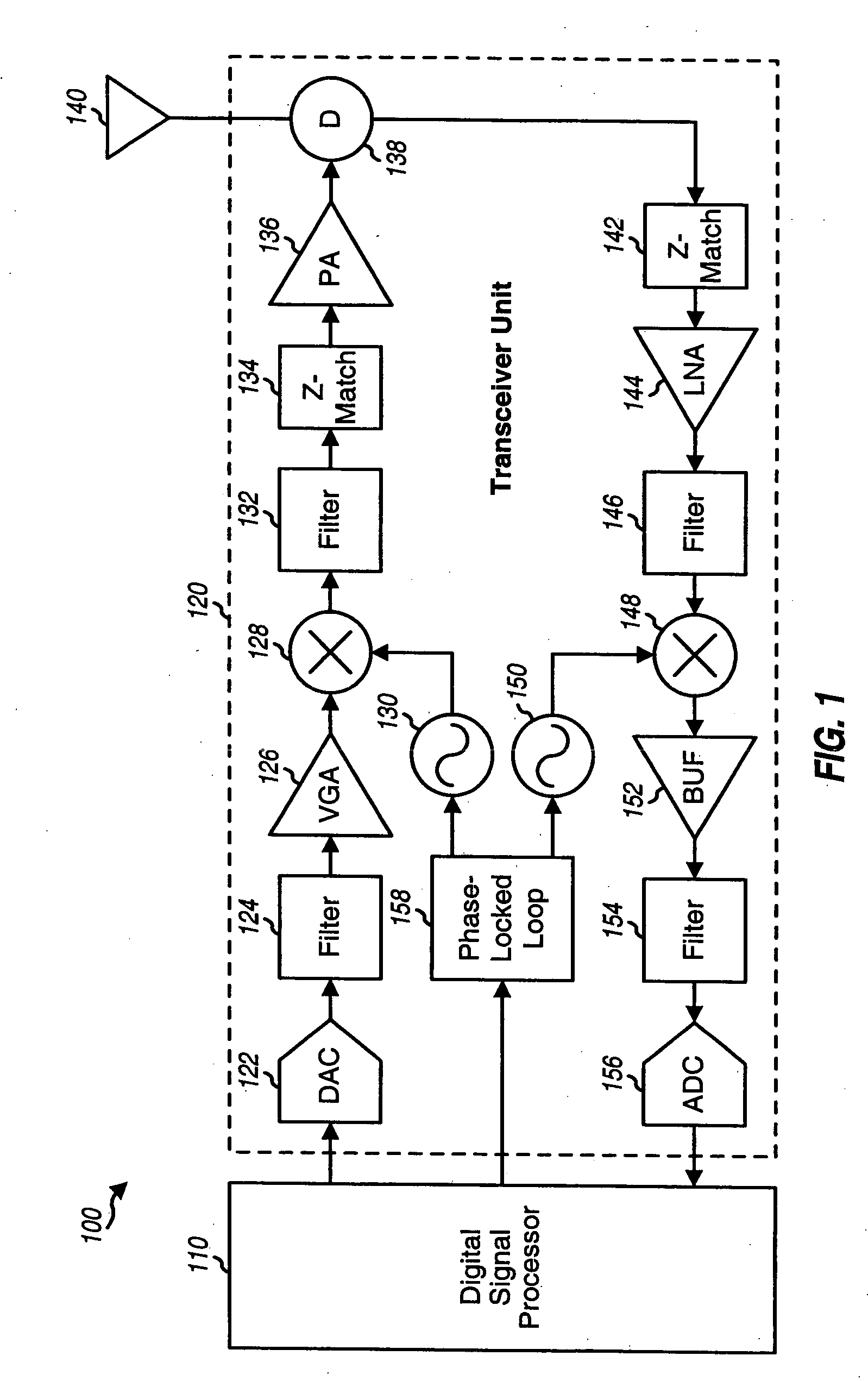

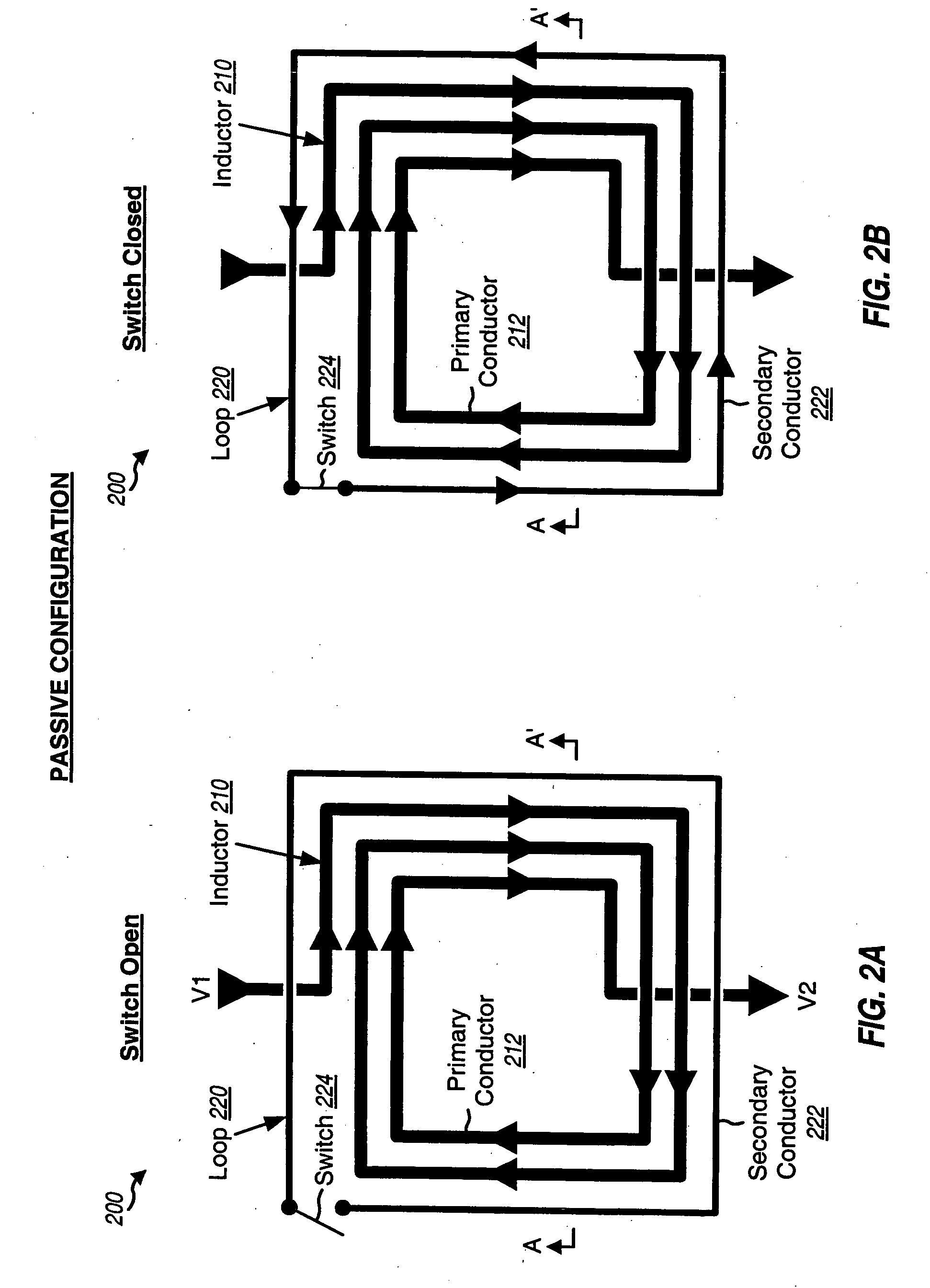

Variable inductor for integrated circuit and printed circuit board

InactiveUS20050068146A1Conveniently fabricatedImprove RF performanceResonant circuit tuningSemiconductor/solid-state device detailsElectrical conductorImpedance matching

A variable inductor can be formed on an integrated circuit with a primary conductor, a secondary conductor, and a switch. The primary conductor implements an inductor and may be formed in various patterns (e.g., a spiral). The secondary conductor forms a loop in proximity to (e.g., on the outside of) the primary conductor. The switch couples in series with the secondary conductor and opens or closes the loop. The inductance of the inductor is varied by closing and opening the loop with the switch. A current source may also be coupled in series with the secondary conductor and used to control the current flow in the secondary conductor to either increase or decrease the inductance. Multiple loops may be formed to change the inductance in more than two discrete steps. The variable inductor may be used for various applications such as filters, VCOs, and impedance matching networks.

Owner:QUALCOMM INC

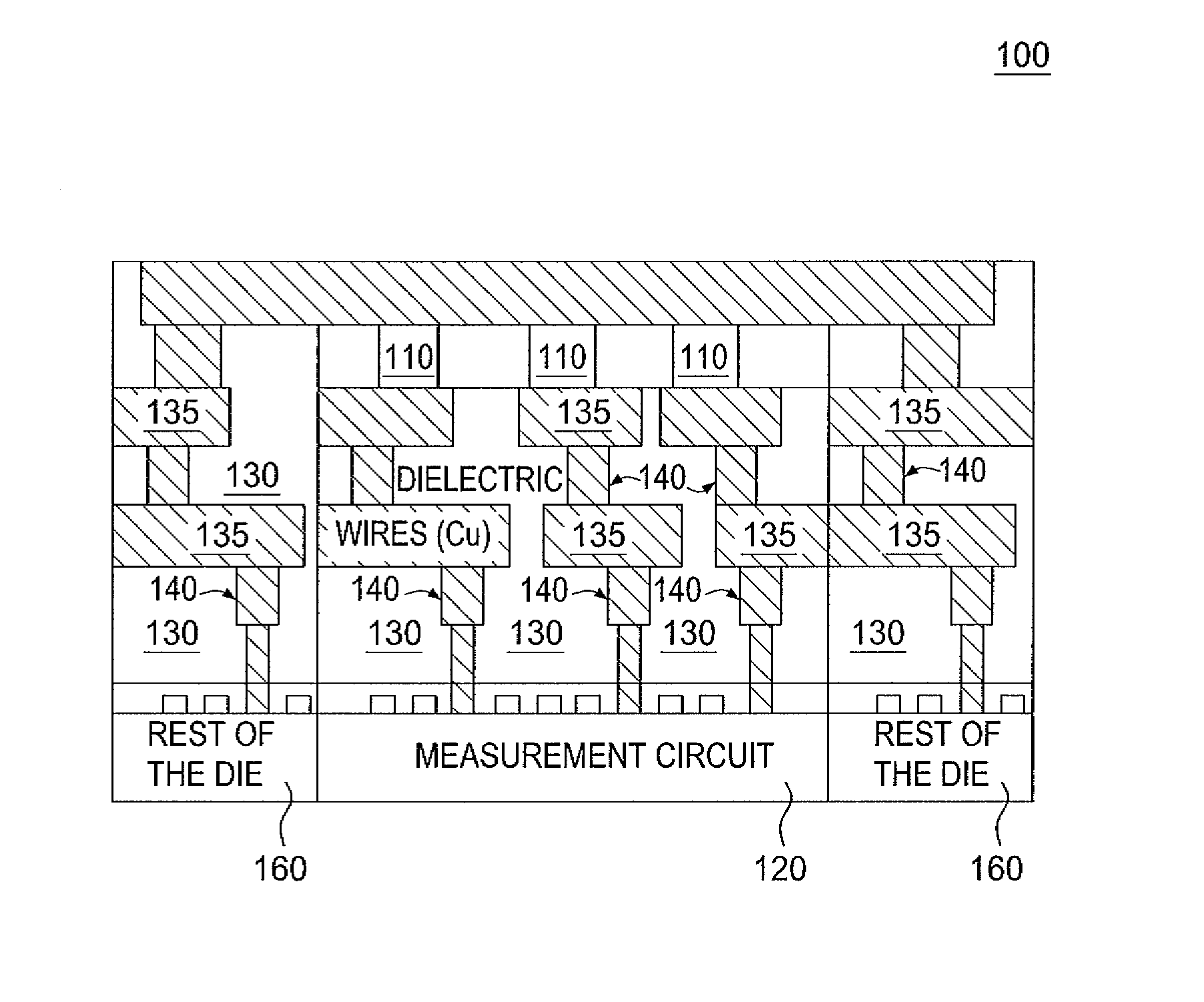

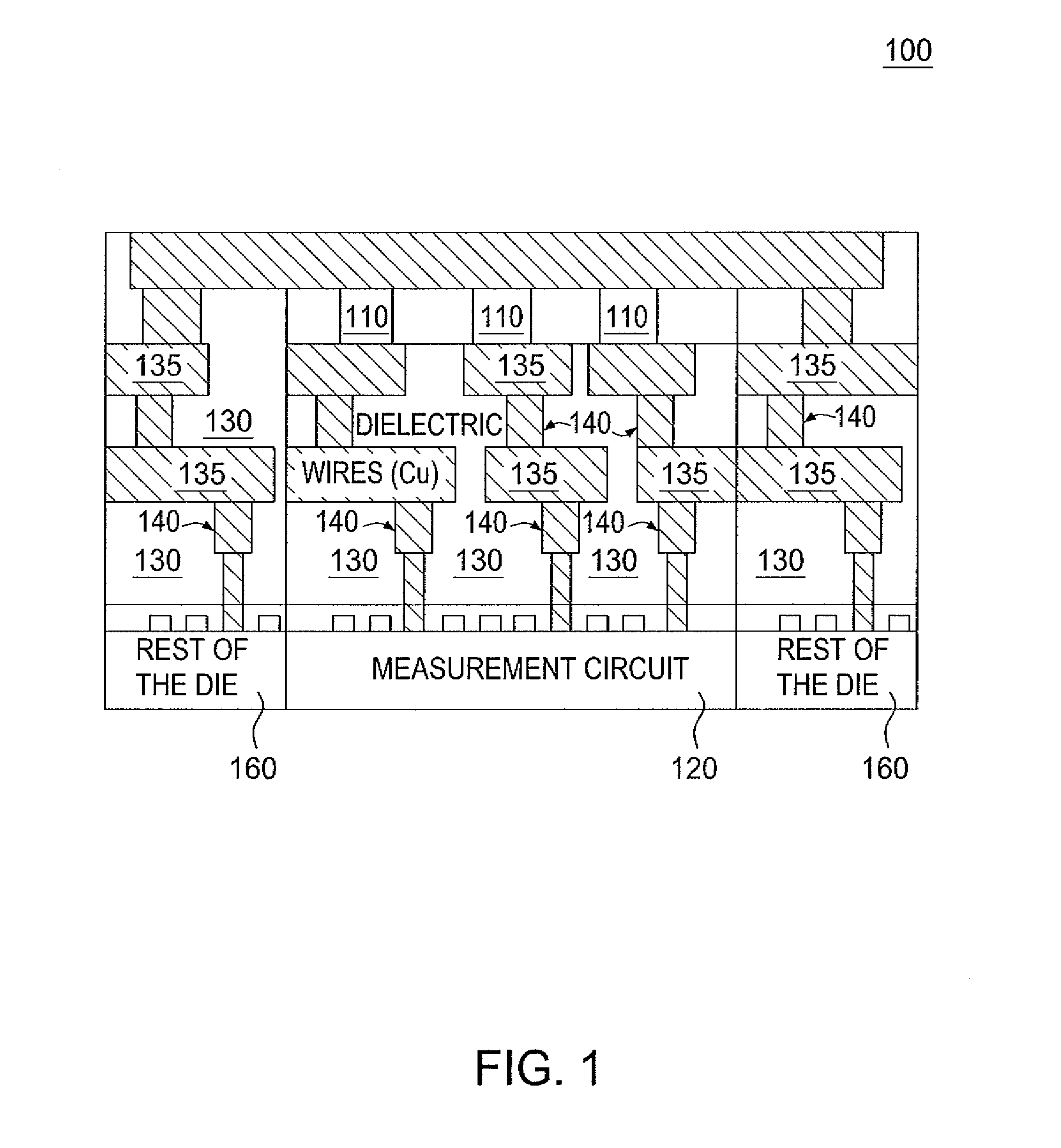

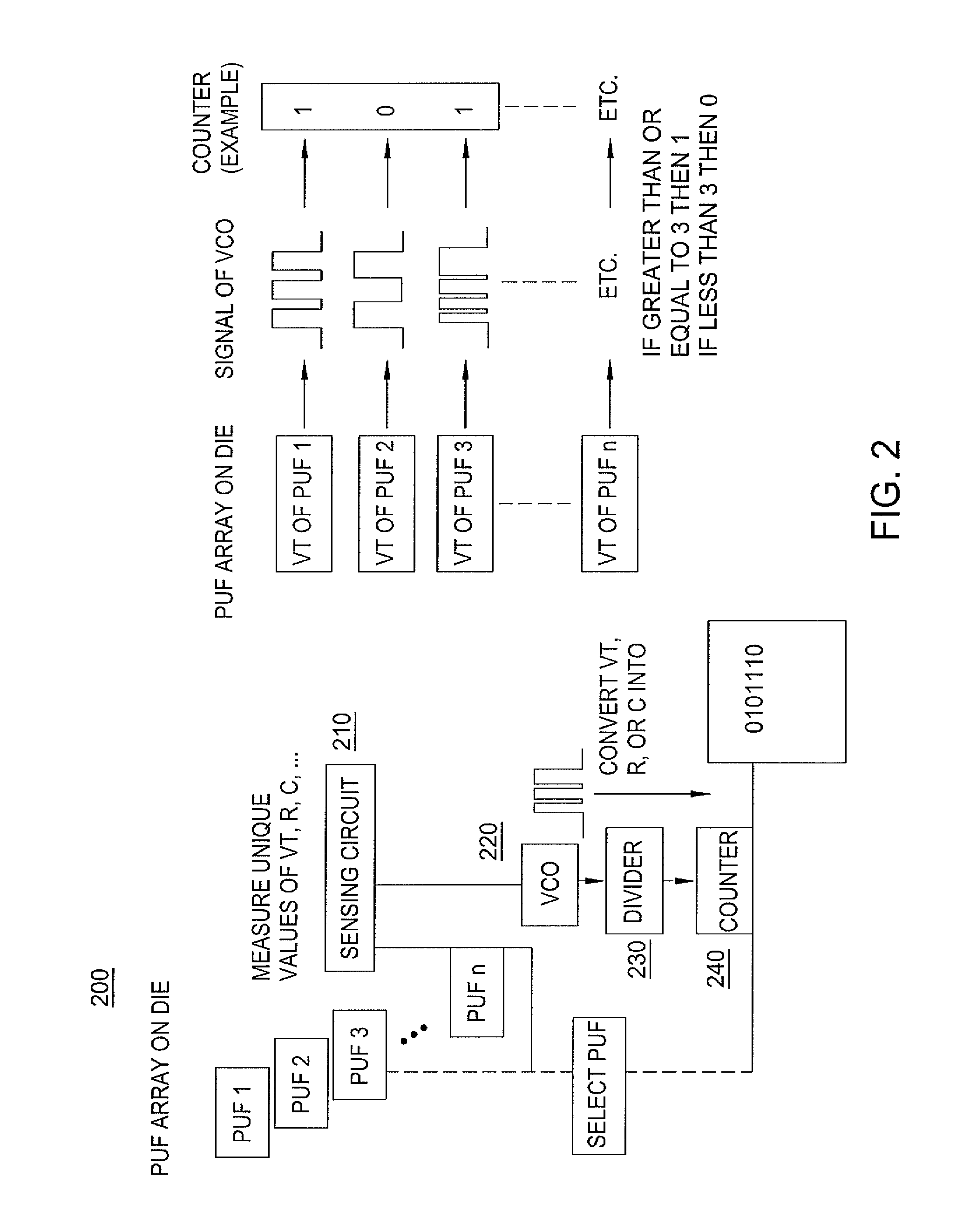

Reliable physical unclonable function for device authentication

ActiveUS8525169B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsComputer hardwareSemiconductor materials

The present disclosure relates to a secure device having a physical unclonable function. The device includes an integrated circuit having a semiconducting material in at least one via in a backend of the integrated circuit. The present disclosure also relates to a method for manufacturing a secure device having a physical unclonable function. The method includes providing an integrated circuit and adding a semiconducting material to at least one via in a backend of the integrated circuit. In some instances a property of the semiconducting material in the at least one via is measured to derive a signature.

Owner:GLOBALFOUNDRIES US INC

Monolithic transmitter photonic integrated circuit (TXPIC) having tunable modulated sources with feedback system for source power level or wavelength tuning

InactiveUS20080138088A1Reduce in quantityImprove chip yieldLaser optical resonator constructionElectromagnetic transmittersSignal onWavelength

A photonic integrated circuit (PIC) chip comprising an array of modulated sources, each providing a modulated signal output at a channel wavelength different from the channel wavelength of other modulated sources and a wavelength selective combiner having an input optically coupled to received all the signal outputs from the modulated sources and provide a combined output signal on an output waveguide from the chip. The modulated sources, combiner and output waveguide are all integrated on the same chip.

Owner:INFINERA CORP

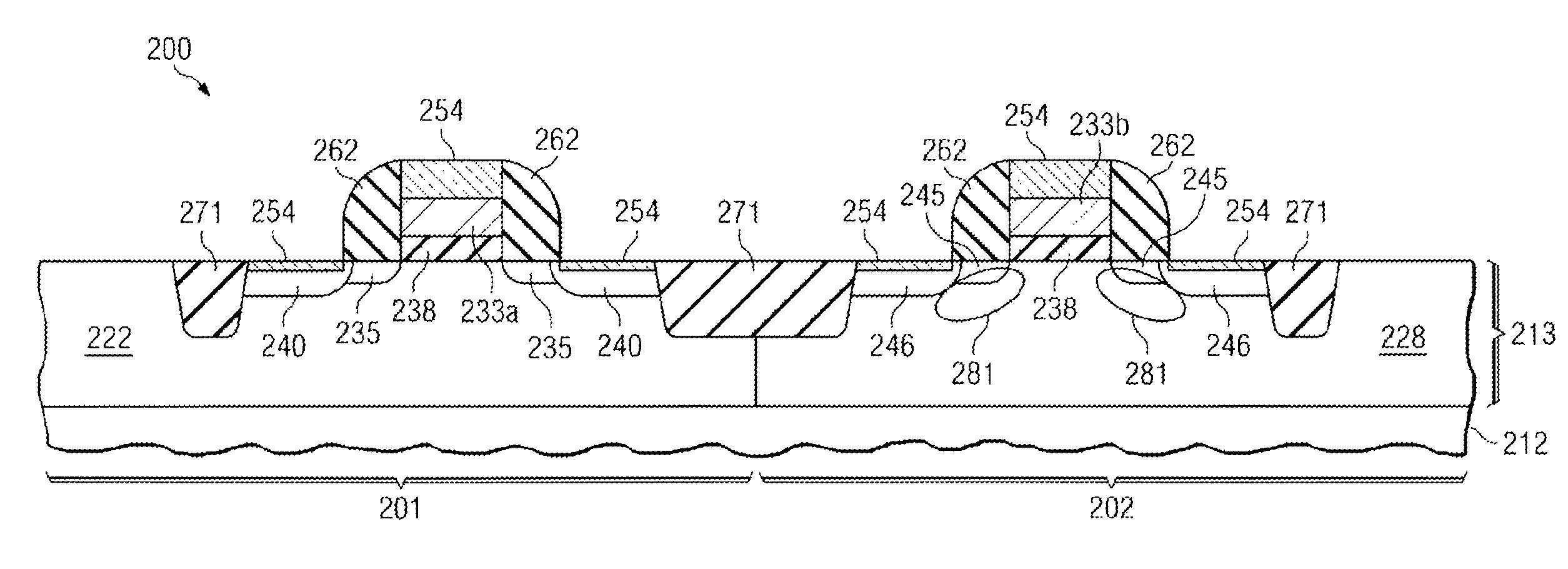

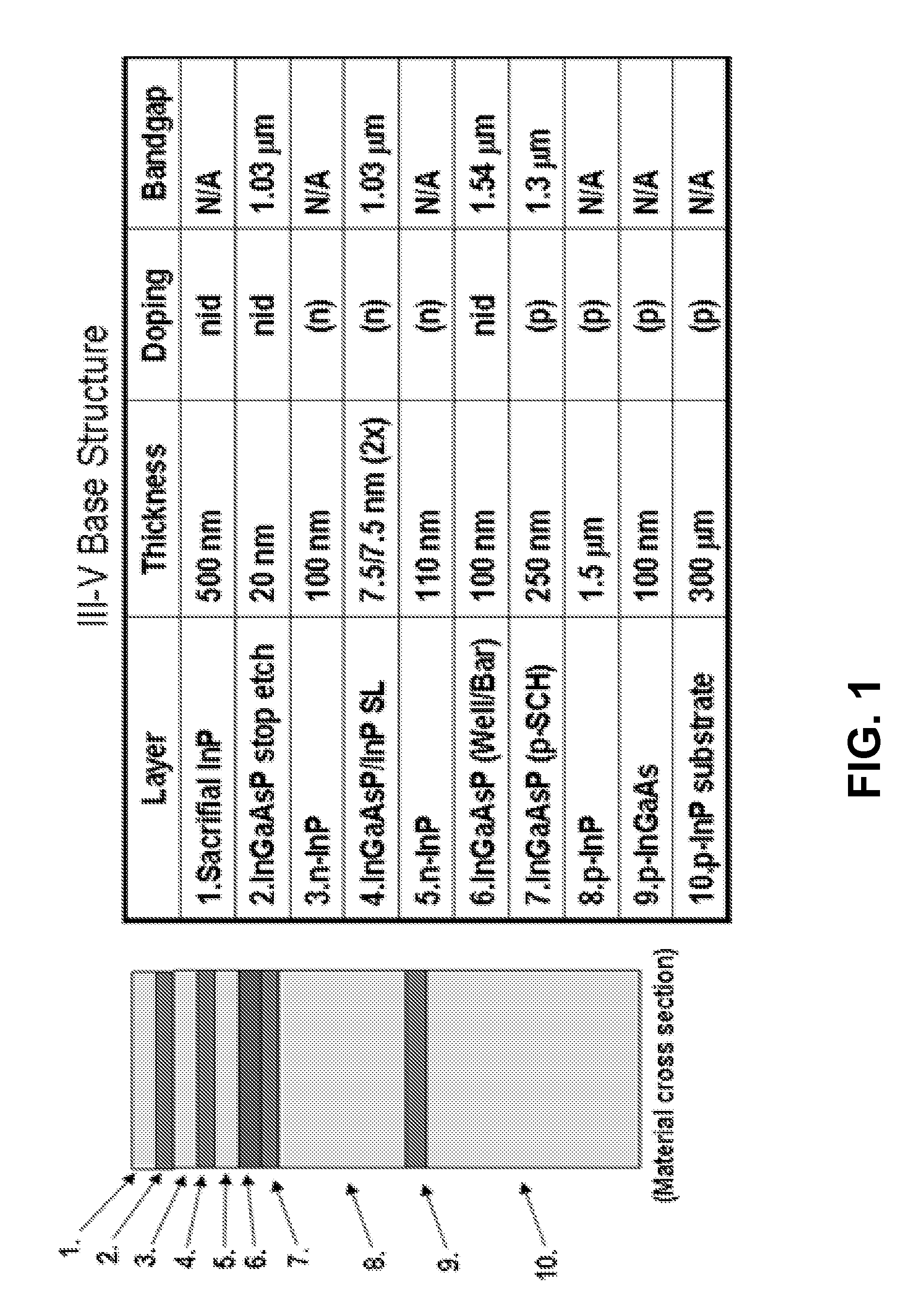

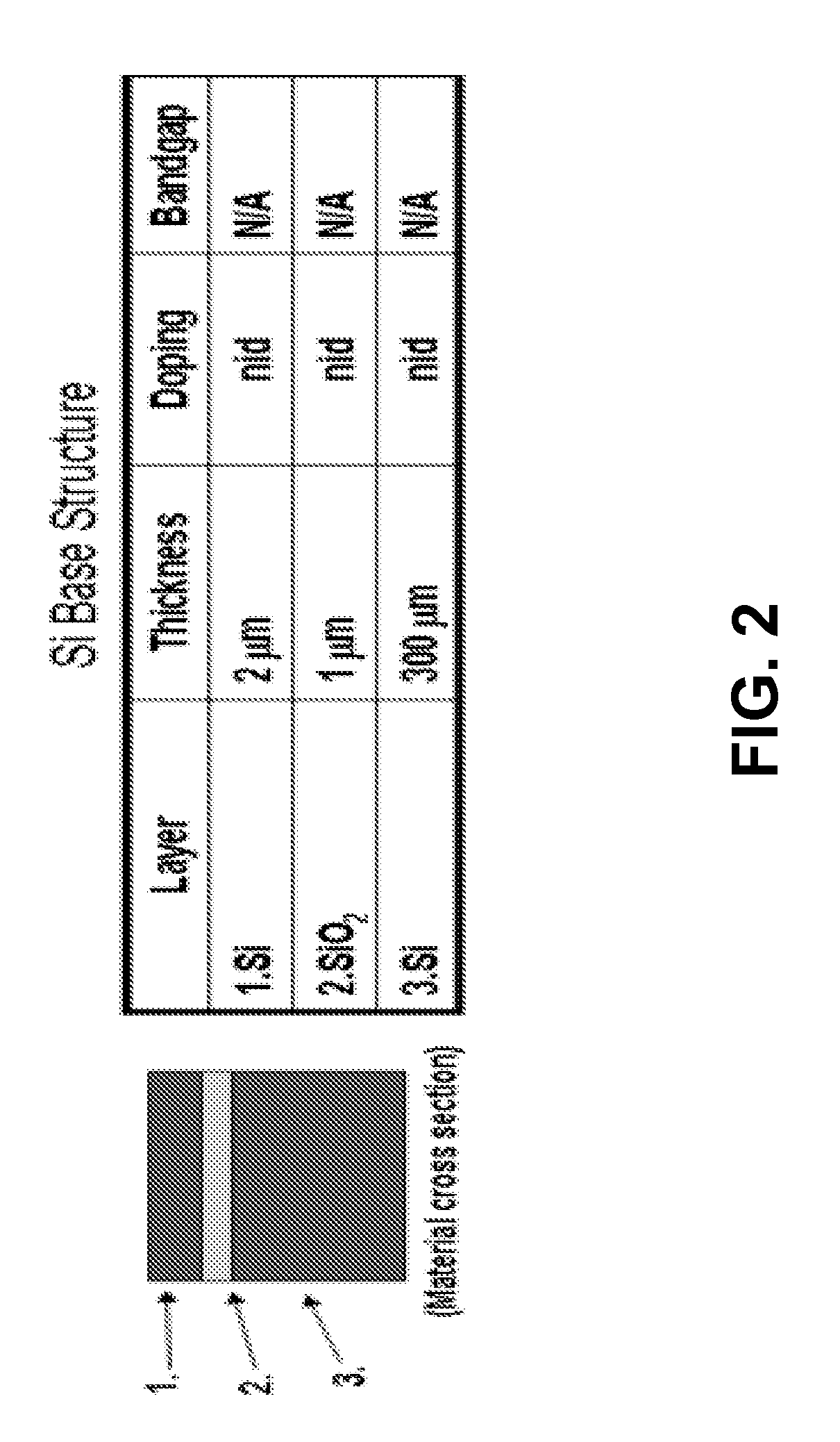

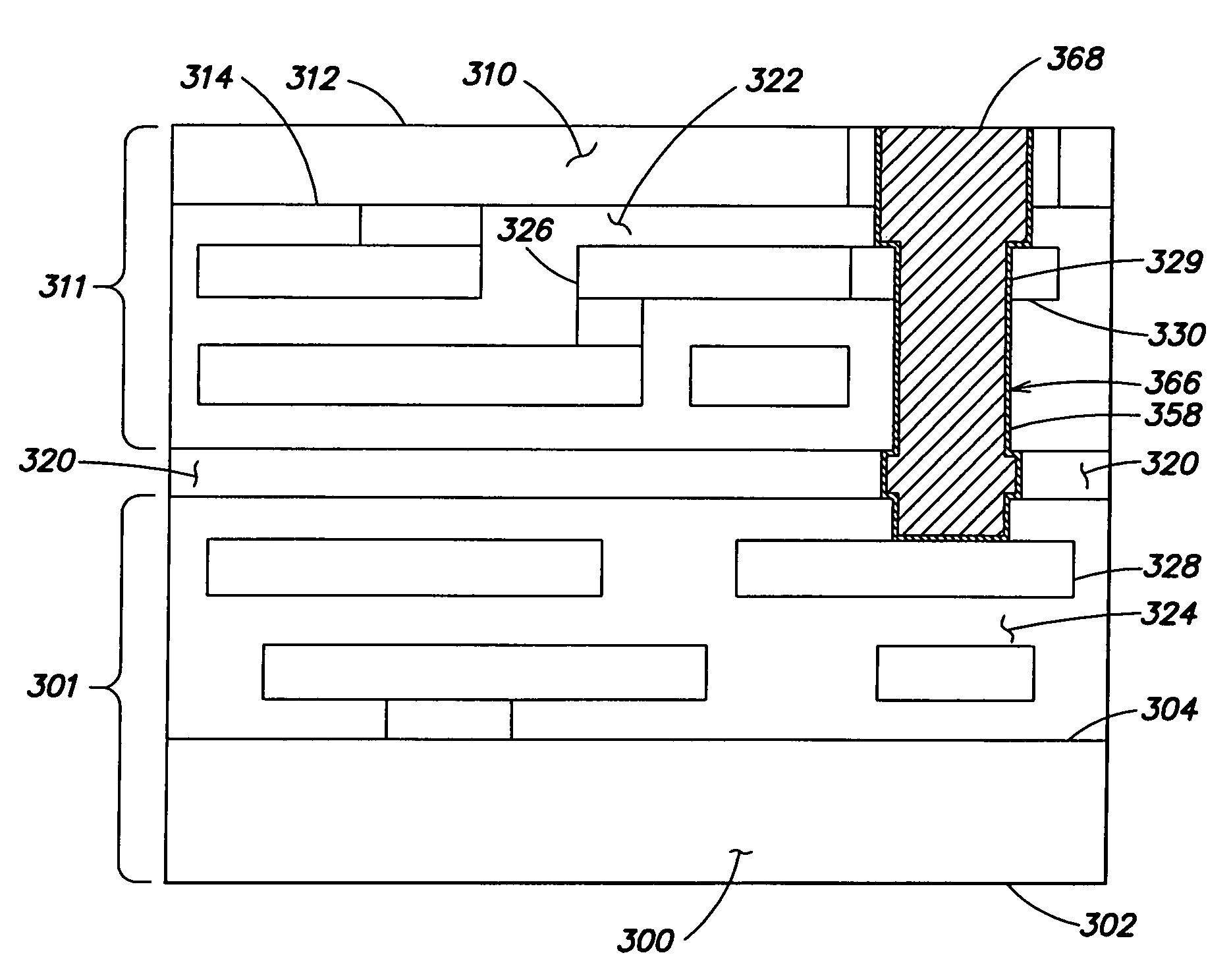

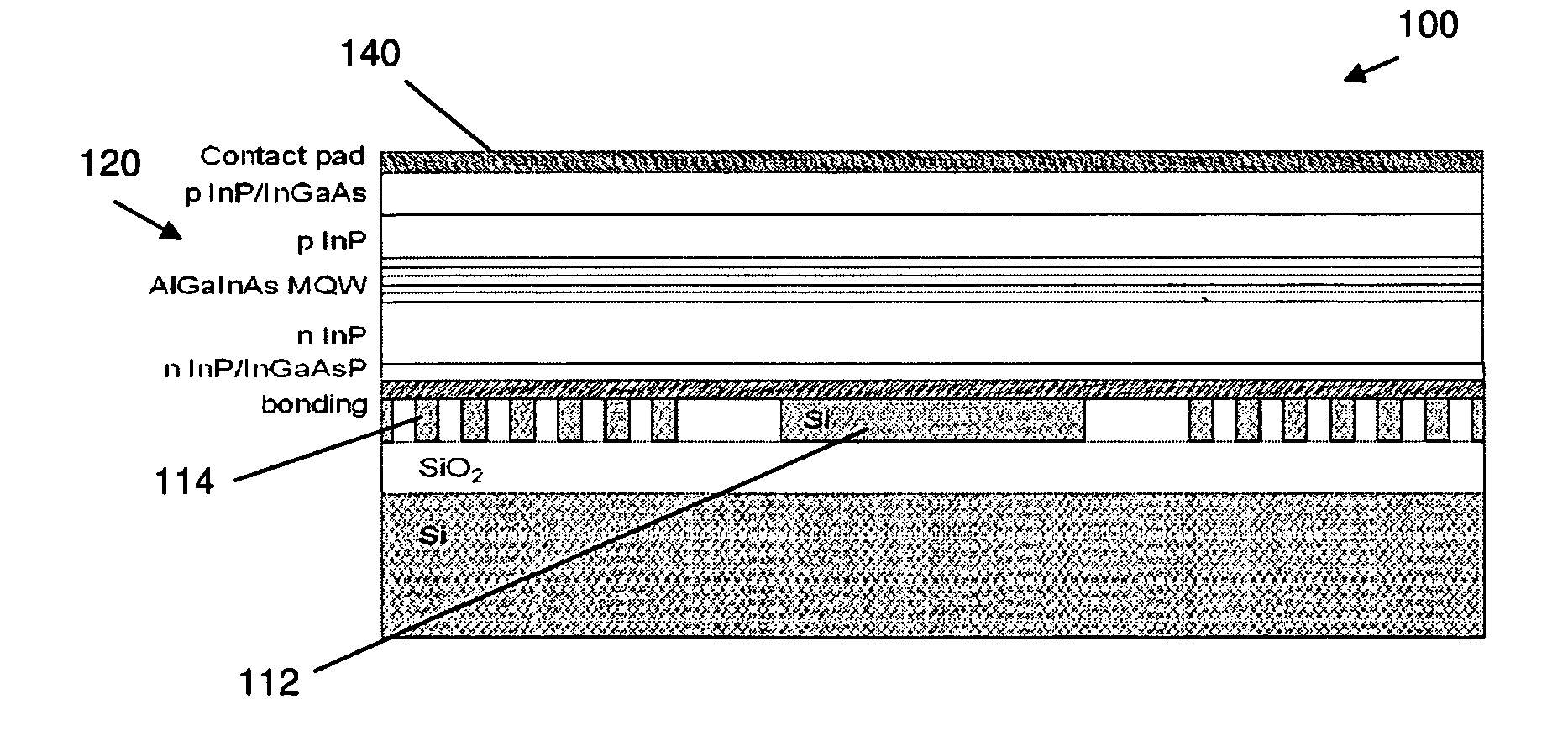

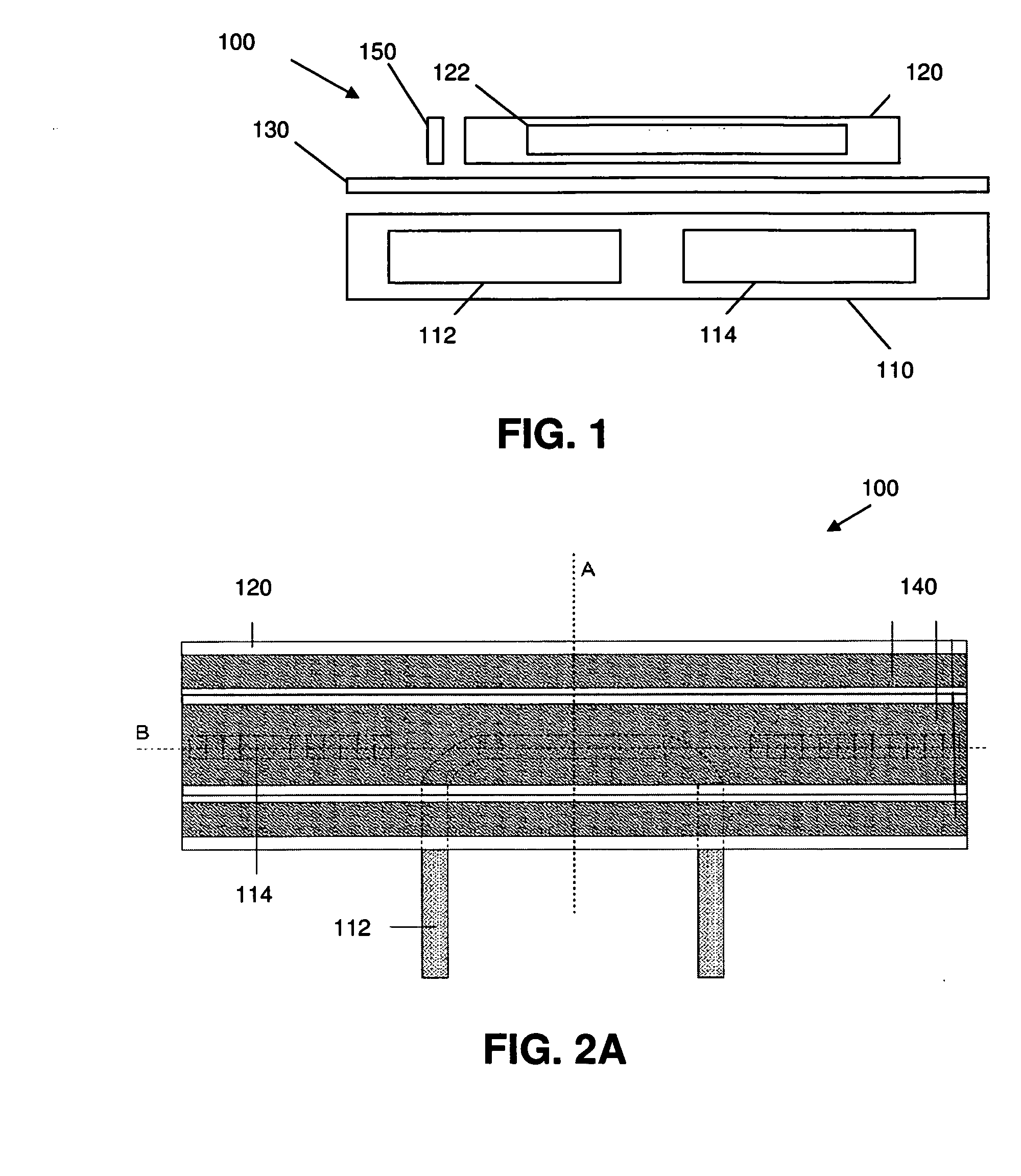

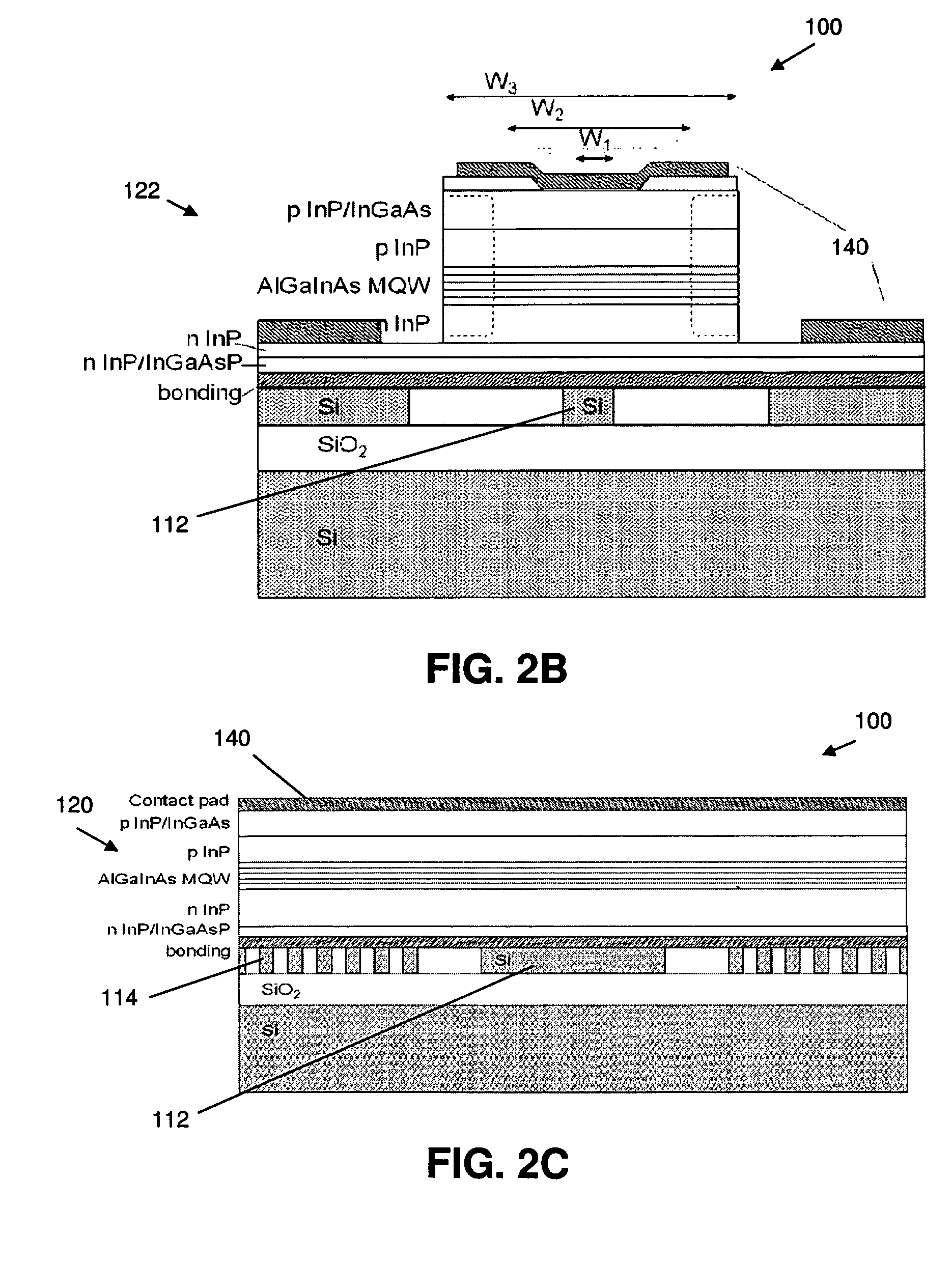

Hybrid silicon laser-quantum well intermixing wafer bonded integration platform for advanced photonic circuits with electroabsorption modulators

ActiveUS20090245298A1Semiconductor/solid-state device manufacturingOptical resonator shape and constructionElectro-absorption modulatorWafer bonding

Photonic integrated circuits on silicon are disclosed. By bonding a wafer of compound semiconductor material as an active region to silicon and removing the substrate, the lasers, amplifiers, modulators, and other devices can be processed using standard photolithographic techniques on the silicon substrate. A silicon laser intermixed integrated device in accordance with one or more embodiments of the present invention comprises a silicon-on-insulator substrate, comprising at least one waveguide in a top surface, and a compound semiconductor substrate comprising a gain layer, the compound semiconductor substrate being subjected to a quantum well intermixing process, wherein the upper surface of the compound semiconductor substrate is bonded to the top surface of the silicon-on-insulator substrate.

Owner:RGT UNIV OF CALIFORNIA

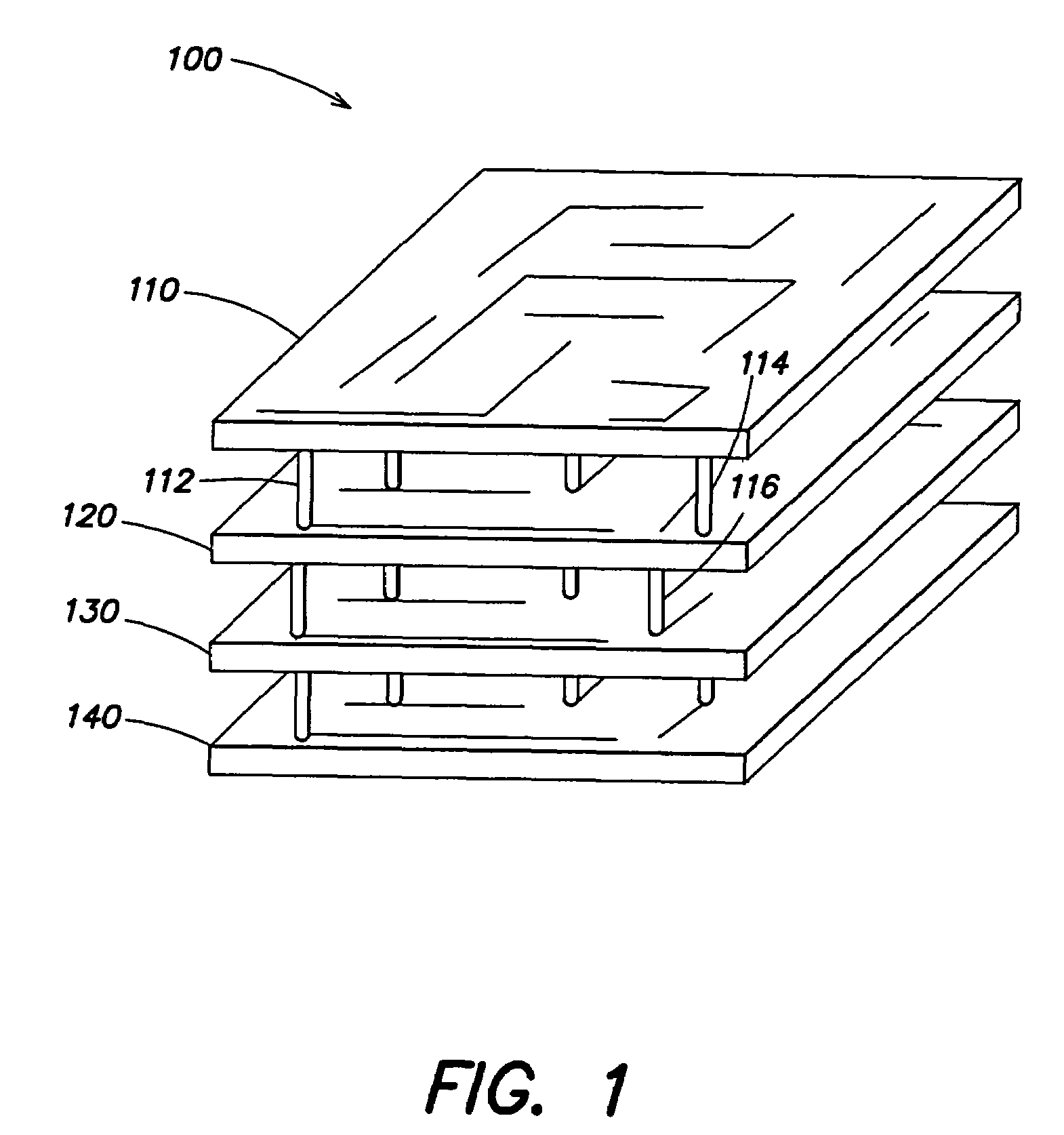

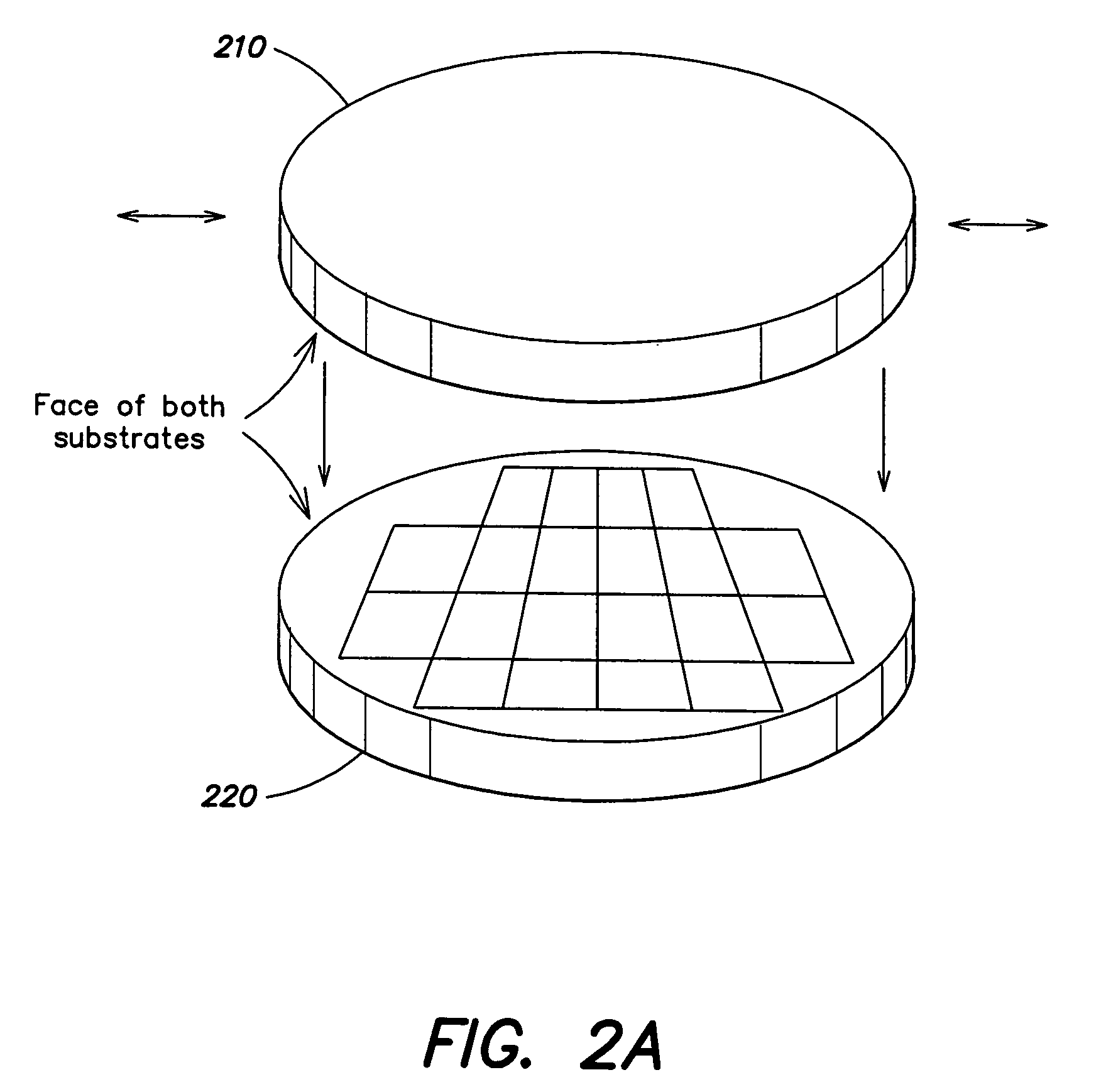

Three-dimensional face-to-face integration assembly

ActiveUS7453150B1Semiconductor/solid-state device detailsSolid-state devicesHigh densityInterconnection

A via for connecting metallization layers of chips bonded in a face-to-face configuration is provided, as well as methods of fabricating the via. The via may function as an interconnection of metallization layers in three-dimensional, stacked, integrated circuits, and may enable high density, low-resistance interconnection formation.

Owner:RENESSELAER POLYTECHNIC INST

Graphene grown substrate and electronic/photonic integrated circuits using same

InactiveUS20100200839A1Polycrystalline material growthSemiconductor/solid-state device detailsSurface roughnessPhotonic integrated circuit

A graphene-on-oxide substrate according to the present invention includes: a substrate having a metal oxide layer formed on its surface; and, formed on the metal oxide layer, a graphene layer including at least one atomic layer of the graphene. The graphene layer is grown generally parallel to the surface of the metal oxide layer, and the inter-atomic-layer distance between the graphene atomic layer adjacent to the surface of the metal oxide layer and the surface atomic layer of the metal oxide layer is 0.34 nm or less. Preferably, the arithmetic mean surface roughness Ra of the metal oxide layer is 1 nm or less.

Owner:HITACHI LTD

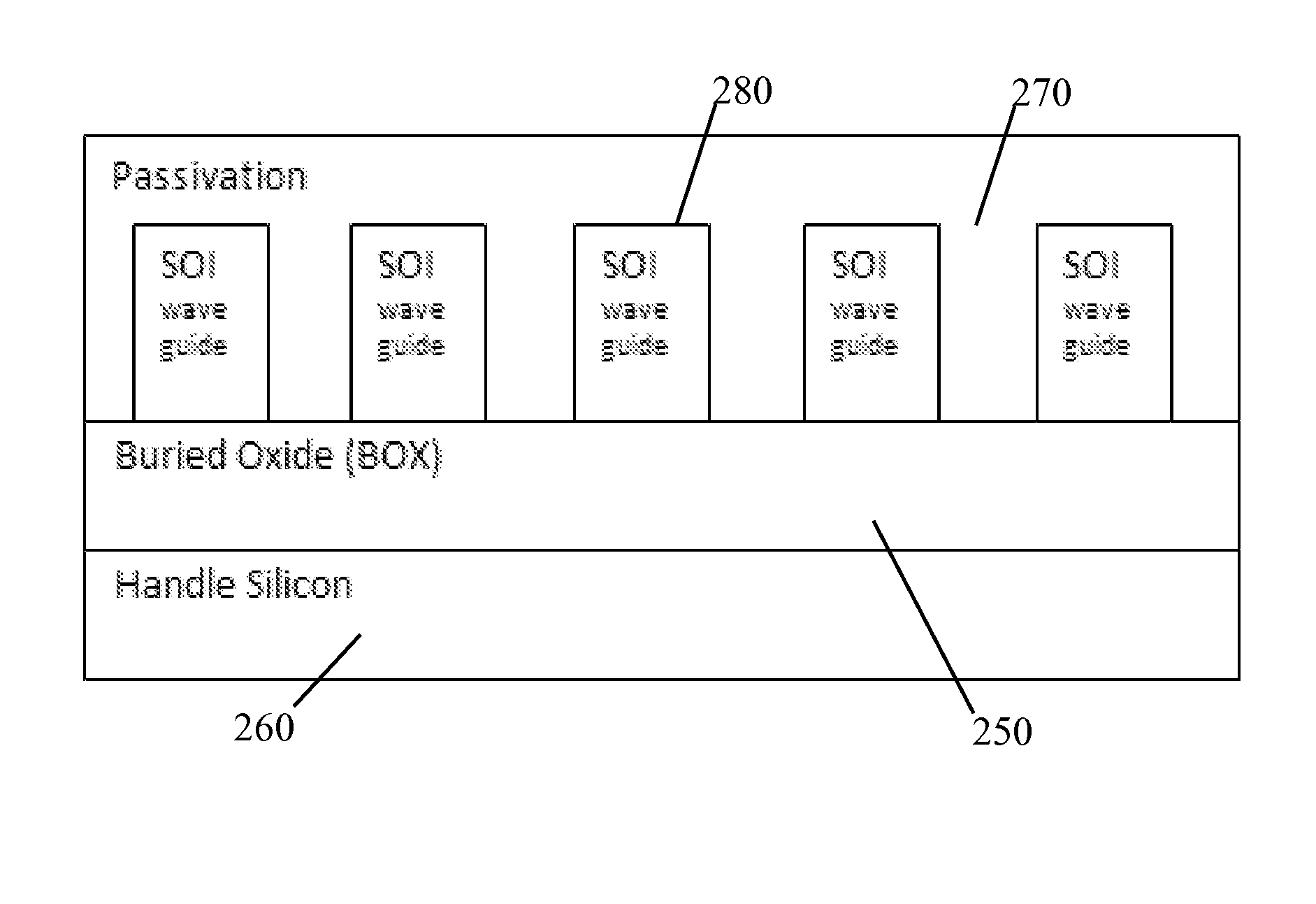

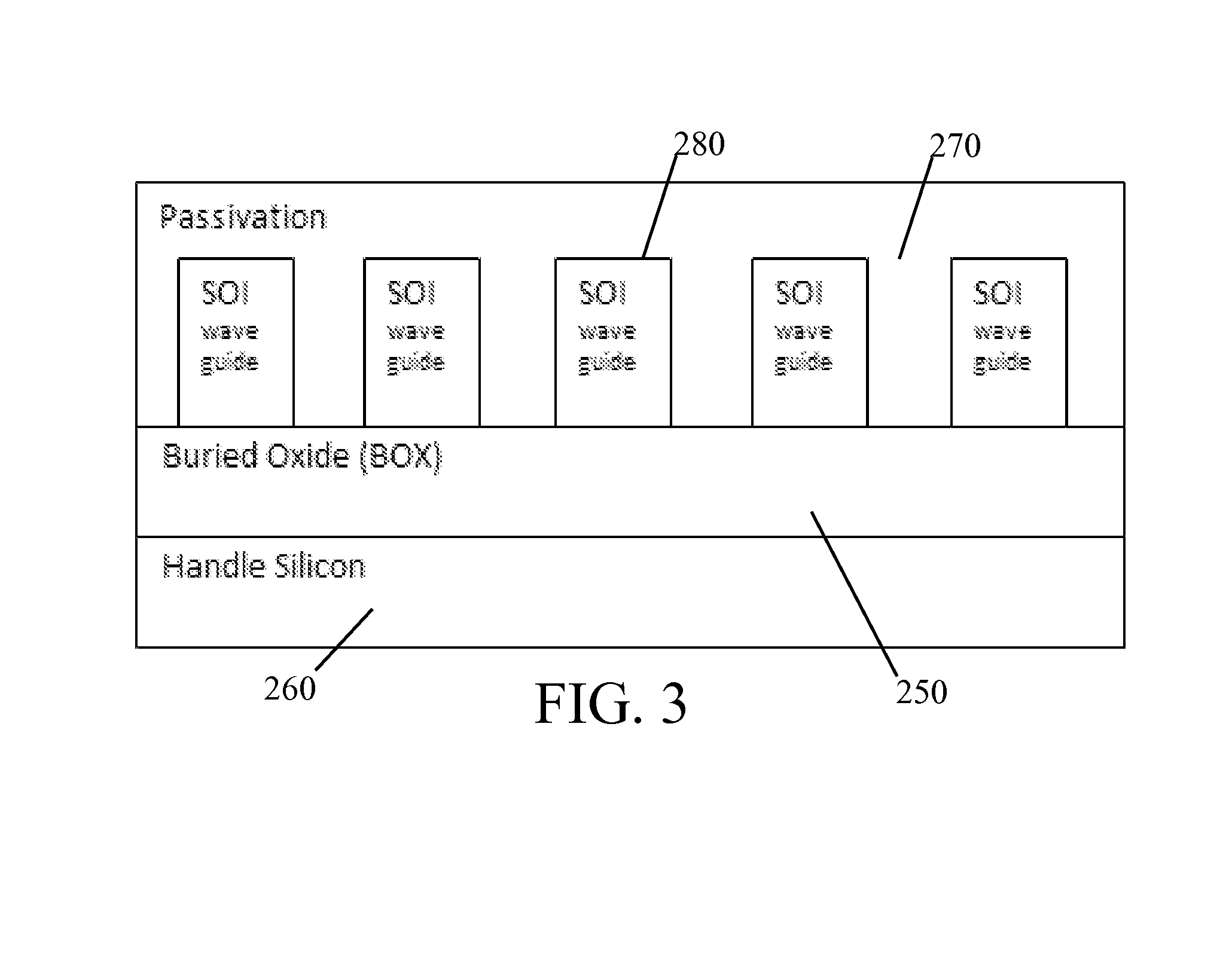

Laser light coupling into soi CMOS photonic integrated circuit

ActiveUS20120320939A1Less complexSmall sizeLaser detailsSemiconductor laser structural detailsSoi cmosCoupling

A hybrid laser for generating radiation includes an optical passive material and an optical active material. The laser includes a first optical waveguide and optical laser components with reflectors in the optical passive material. The first optical waveguide is adapted for coupling out radiation from the hybrid laser. The laser also includes a second optical waveguide defined in the optical active material. The optical laser components include reflectors defining a cavity and furthermore are adapted for providing laser cavity confinement in the first optical waveguide and the second optical waveguide. The second optical waveguide thereby is positioned at least partly over the first optical waveguide so that an evanescent coupling interface is defined between the second optical waveguide and the first optical waveguide and the evanescent coupling interface is positioned within the laser cavity.

Owner:UNIV GENT +1

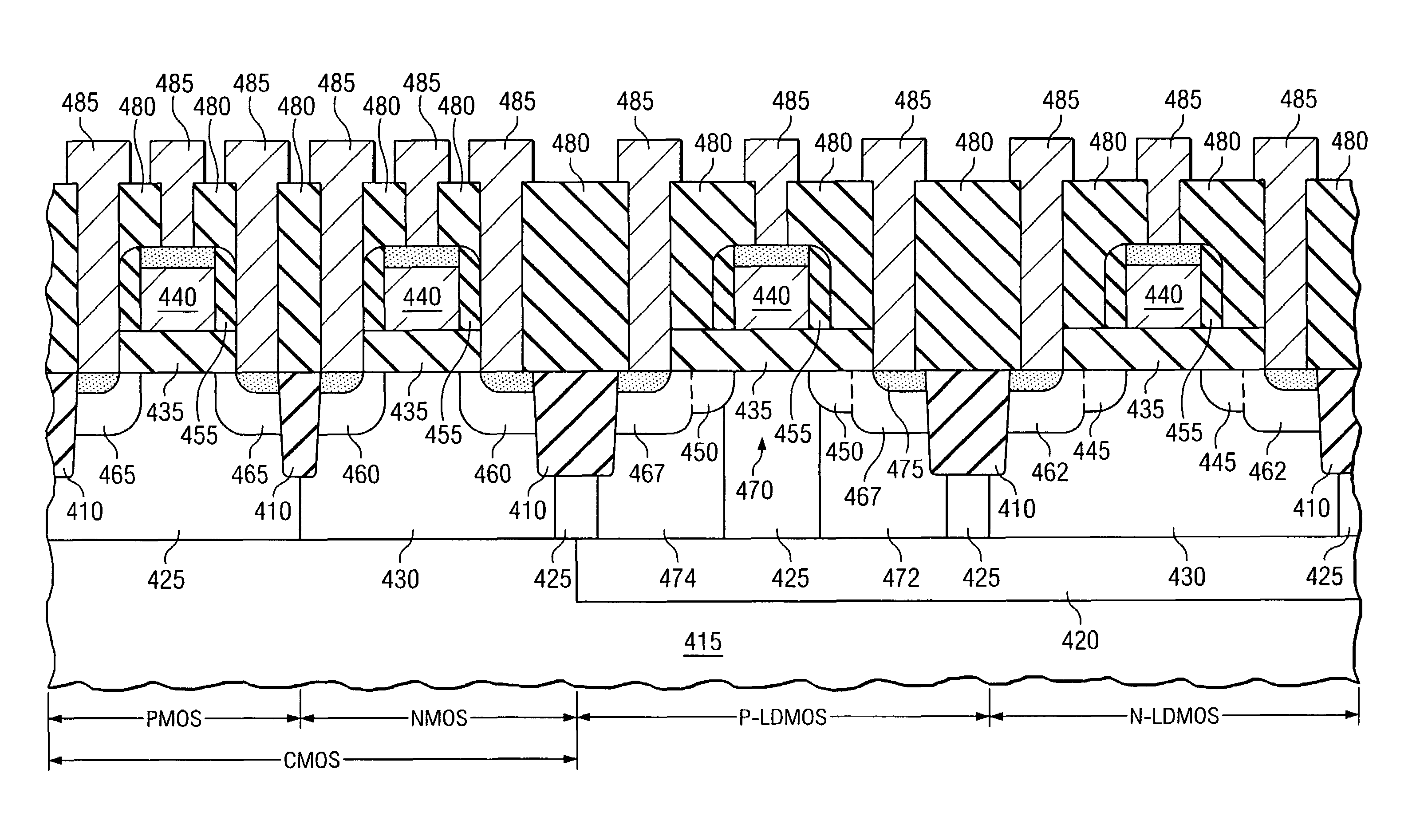

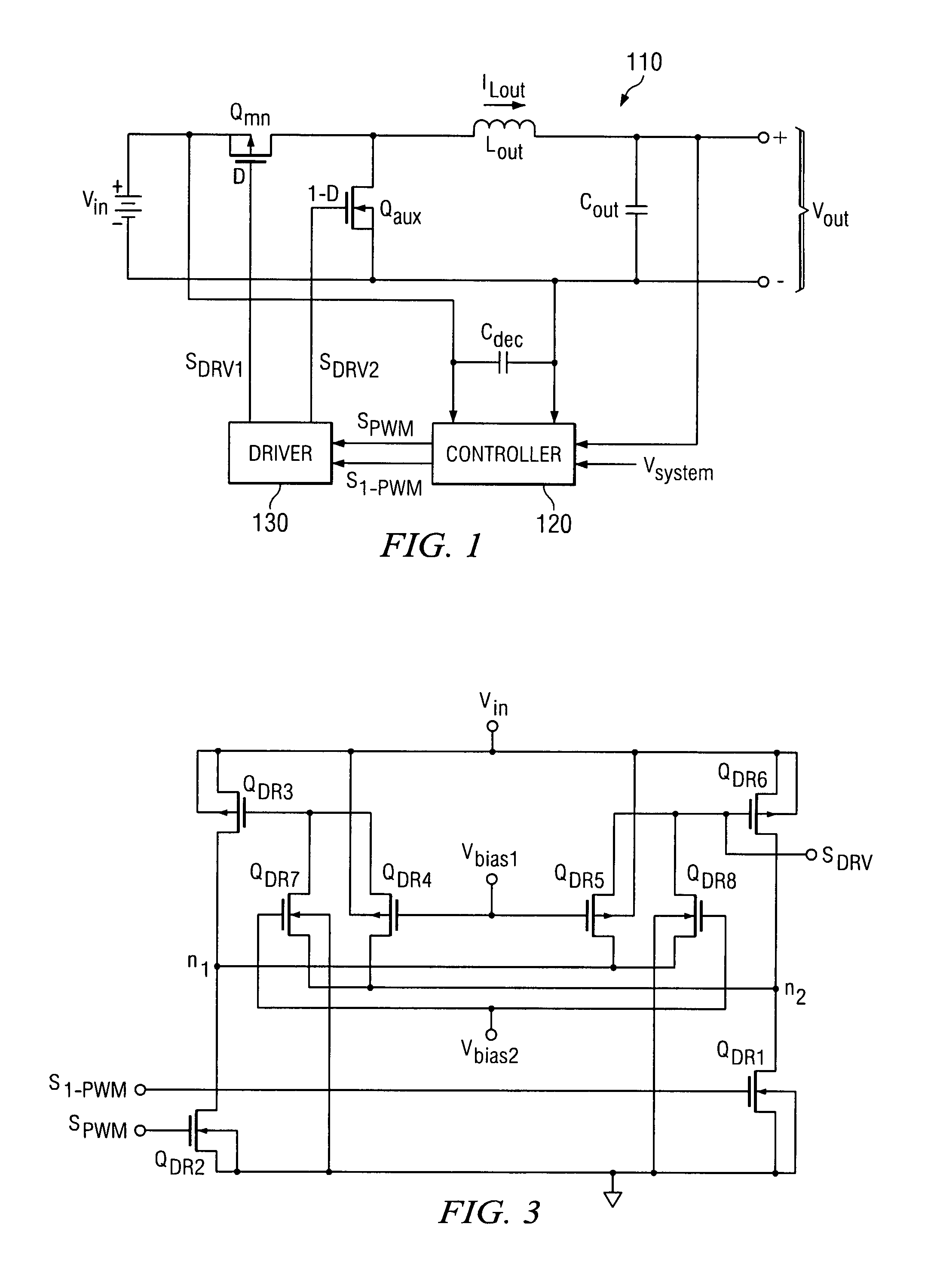

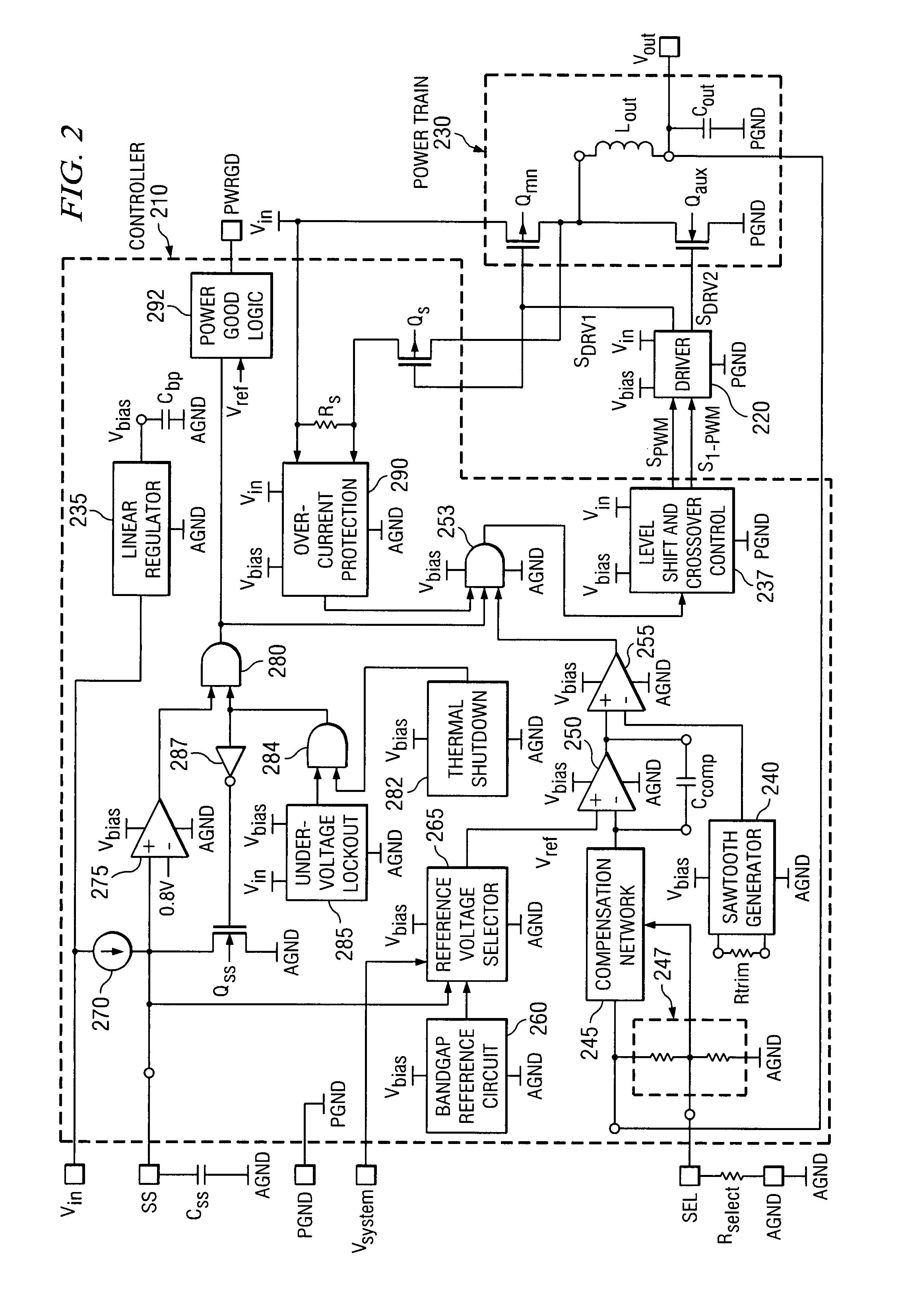

Method of forming an integrated circuit incorporating higher voltage devices and low voltage devices therein

A method of forming an integrated circuit configured to accommodate higher voltage and low voltage devices. In one embodiment, the method of forming the integrated circuit includes forming a transistor by forming a gate over a semiconductor substrate. The method of forming the transistor also includes forming a source / drain by forming a lightly doped region adjacent a channel region recessed into the semiconductor substrate and forming a heavily doped region adjacent the lightly doped region. The method of forming the transistor further includes forming an oppositely doped well under and within the channel region, and forming a doped region between the heavily doped region and the oppositely doped well. The doped region has a doping concentration profile less than a doping concentration profile of the heavily doped region. The method of forming the integrated circuit also includes forming a driver switch of a driver on the semiconductor substrate.

Owner:TAHOE RES LTD

Planar beam forming and steering optical phased array chip and method of using same

ActiveUS9753351B2High yieldLow costWave based measurement systemsNon-linear opticsRadarChip architecture

A one-dimensional planar beam forming and steering optical phased array chip is a simple building block of a two-dimensional beam forming and steering solid-state lidar, enabling manufacturing of said lidars at high yield and low cost through the use of a plurality of said chips. Innovative photonic integrated circuit chip architectures that follow design for manufacturing rules enable said building blocks.

Owner:QUANERGY SOLUTIONS INC

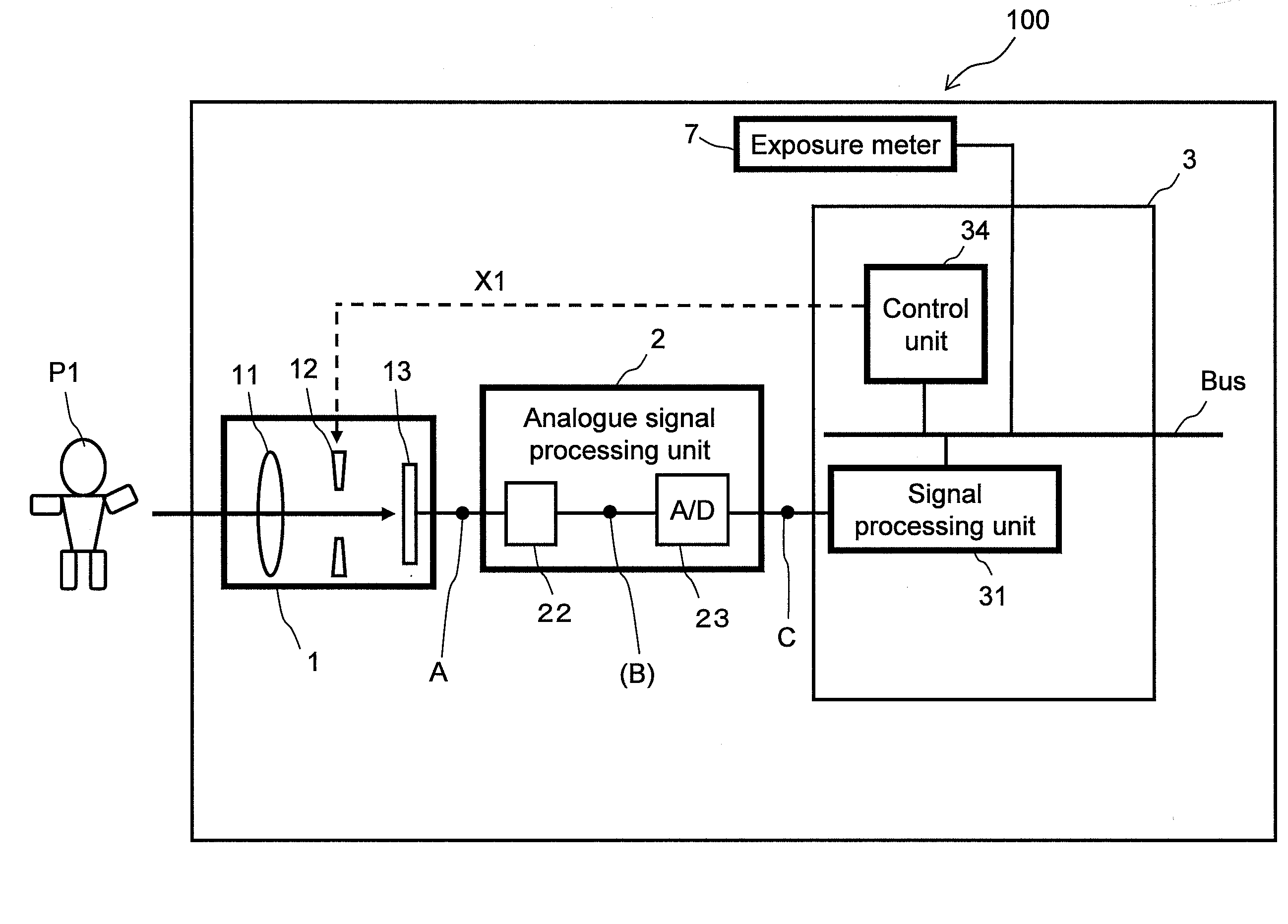

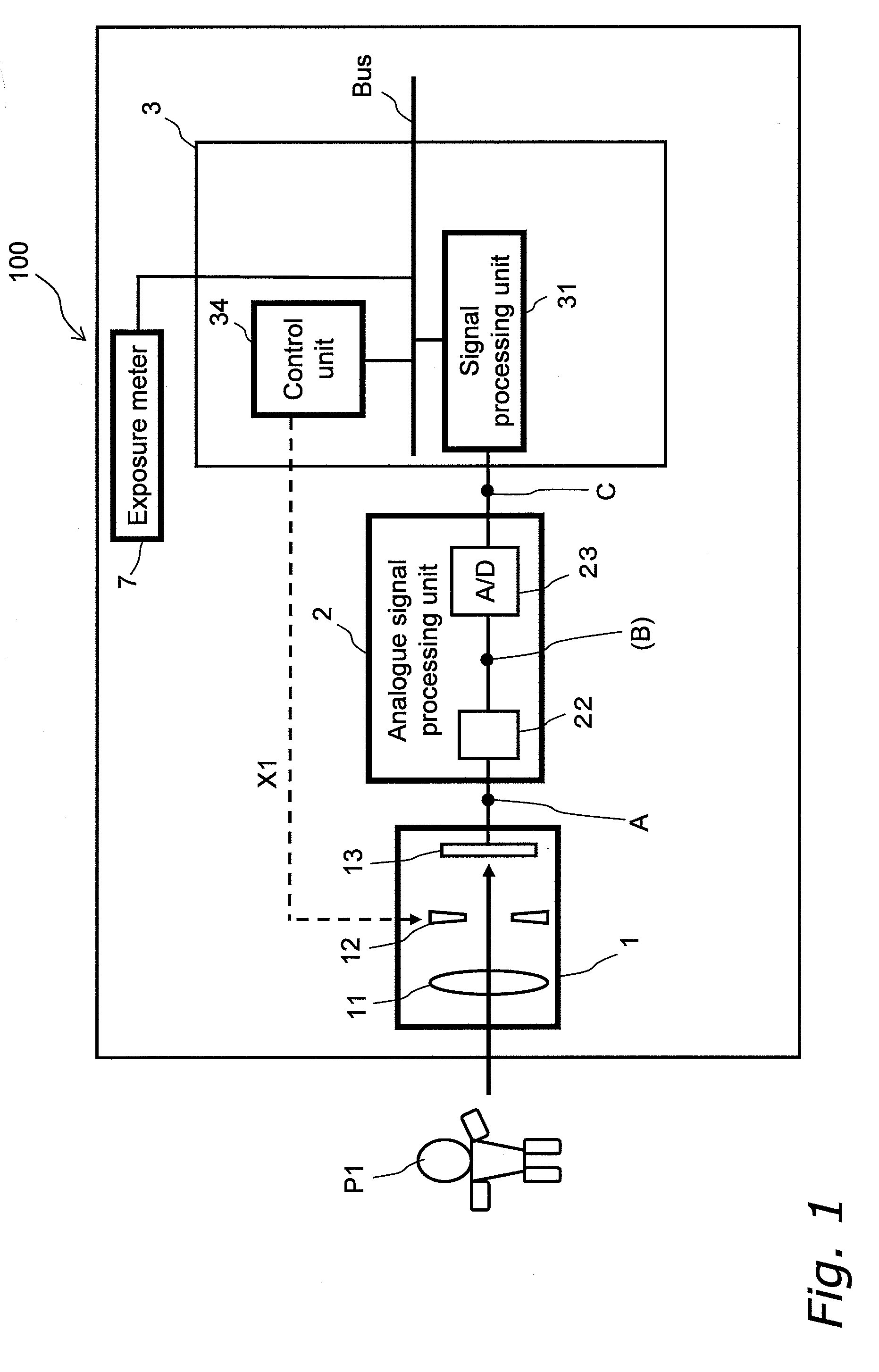

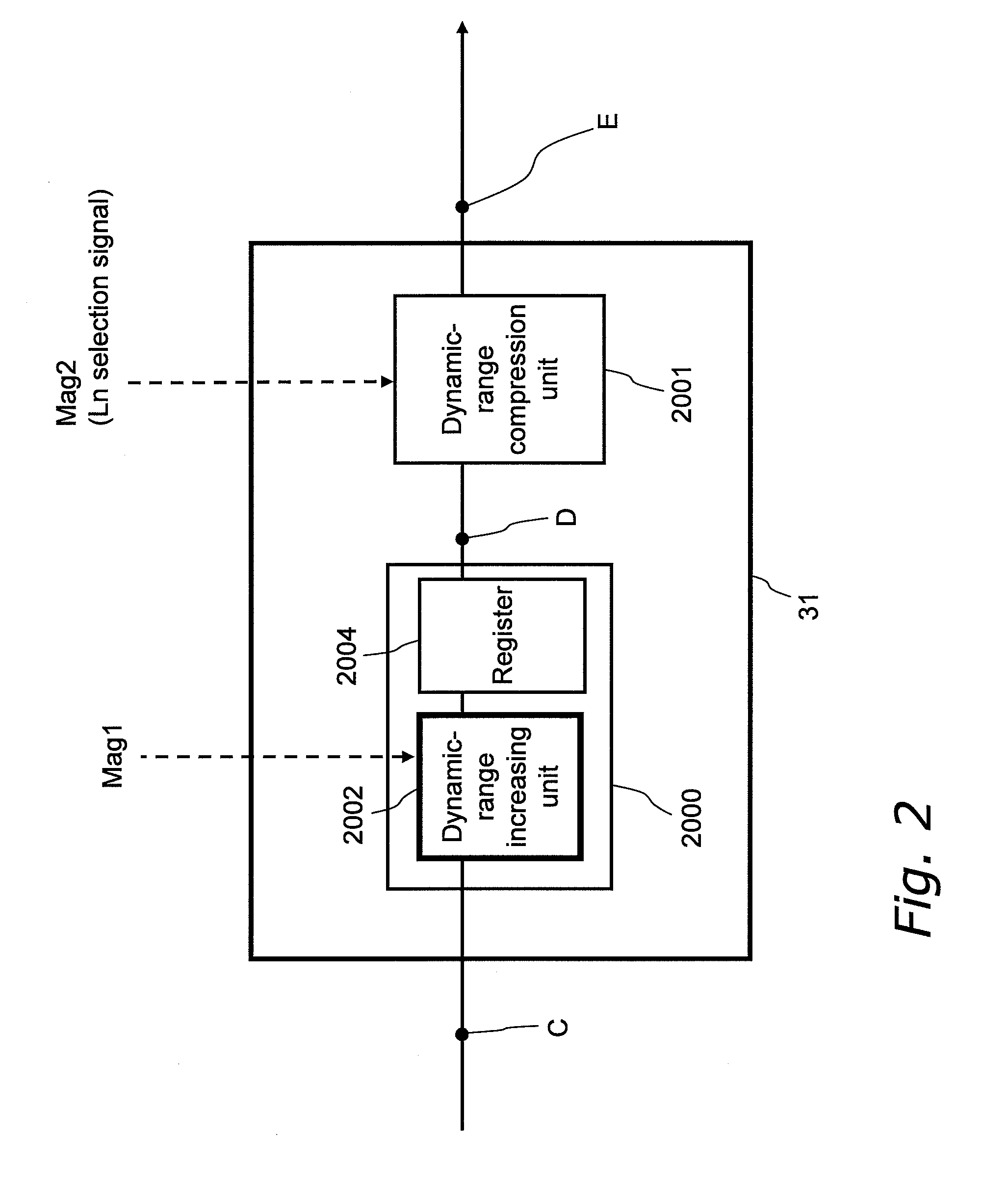

Imaging apparatus, imaging method, integrated circuit, and storage medium

ActiveUS20080259181A1Increase brightnessAppropriately capturedTelevision system detailsColor television detailsNon linear dynamicExposure control

An imaging apparatus appropriately captures a large dynamic range image of even a scene including a backlit person with a blue sky background in a manner that the person's face has an appropriate luminance level without saturating the background sky. In the imaging apparatus, an imaging unit obtains analogue image signals through exposure control that prevents a highlight from being saturated, an A / D converter converts the analogue image signals to digital image signals, and a signal processing unit linearly increases the dynamic range of the digital image signals. The image signals with the increased dynamic range are nonlinearly compressed to have a dynamic range of 100% or less through nonlinear dynamic range compression that intensively compresses a highlight portion. The imaging apparatus with this structure first increases the dynamic range of an image and efficiently compresses the increased large dynamic range of the image.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

Implantable sensor

ActiveUS20120226118A1Increase the number ofMade smallCatheterDiagnostic recording/measuringSilicon photonicsPhotonic integrated circuit

A sensor is described for sensing a substance such as for example glucose. The sensor is implantable in the body of a living creature. The sensor comprises a photonic integrated circuit, e.g. silicon-photonics, based radiation processor for spectrally processing radiation interacting with the sample. A continuous monitoring system also is described using such a sensor.

Owner:INDIGO DIABETES NV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com