Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

177 results about "Boundary scan testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

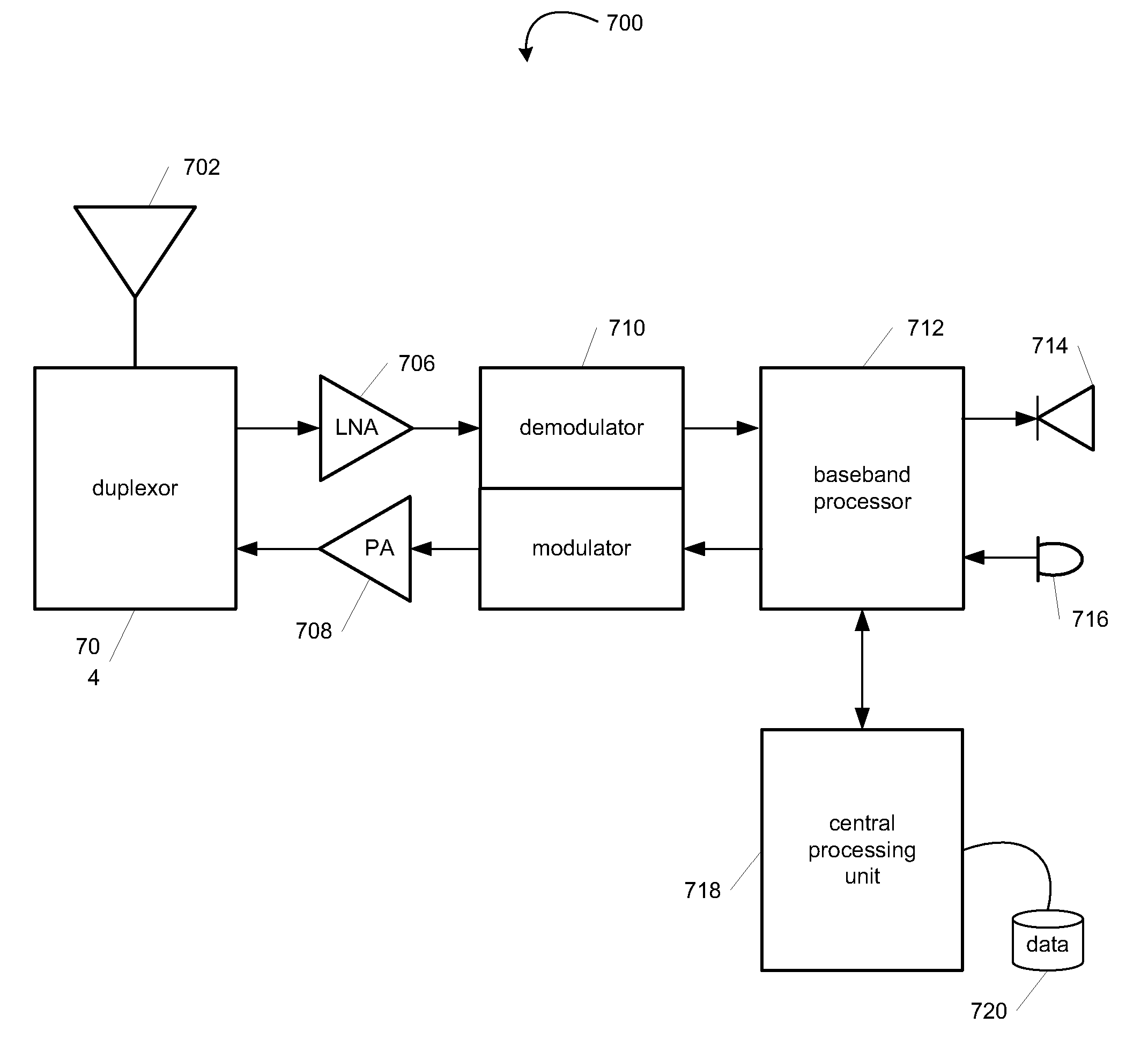

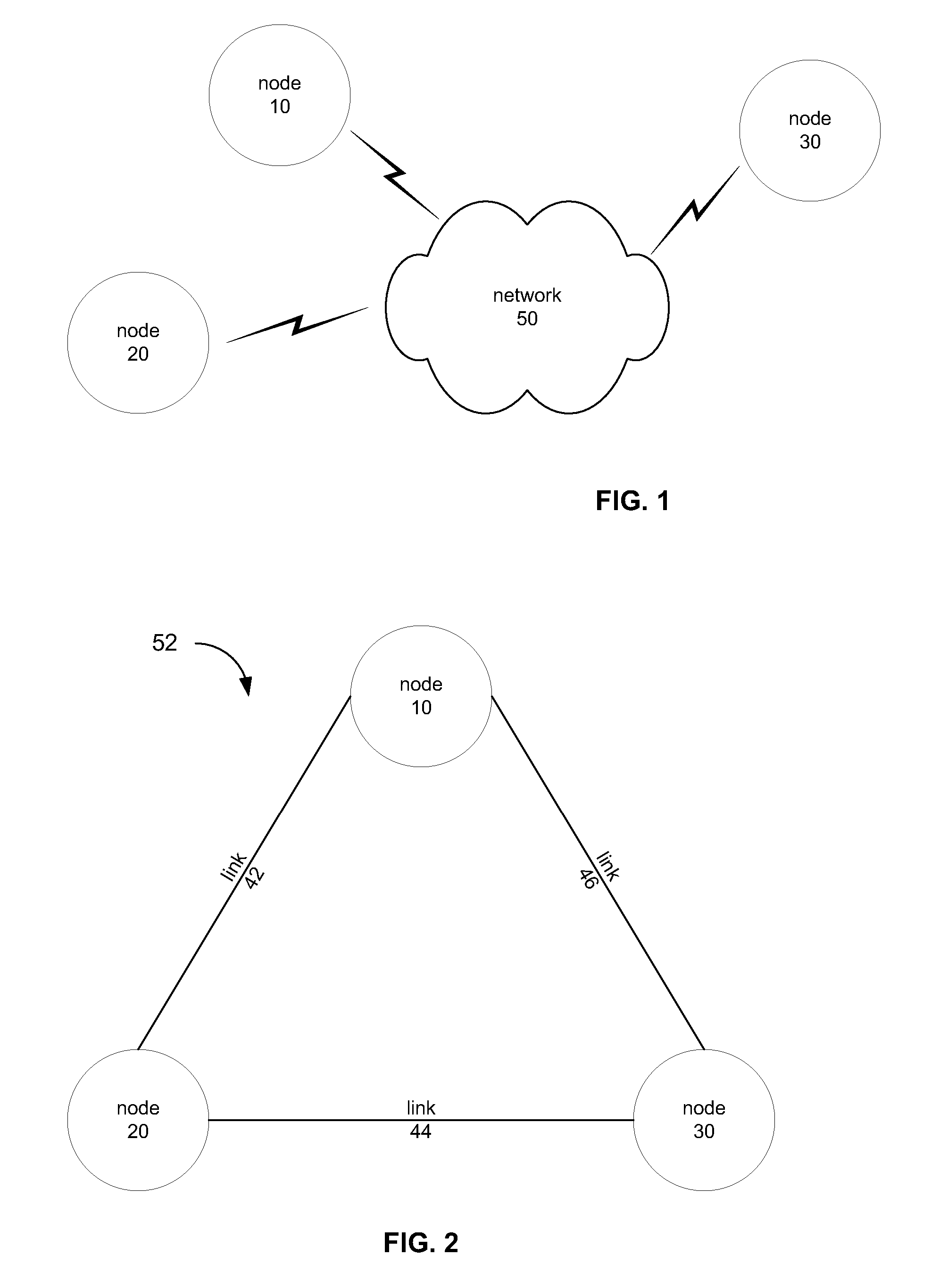

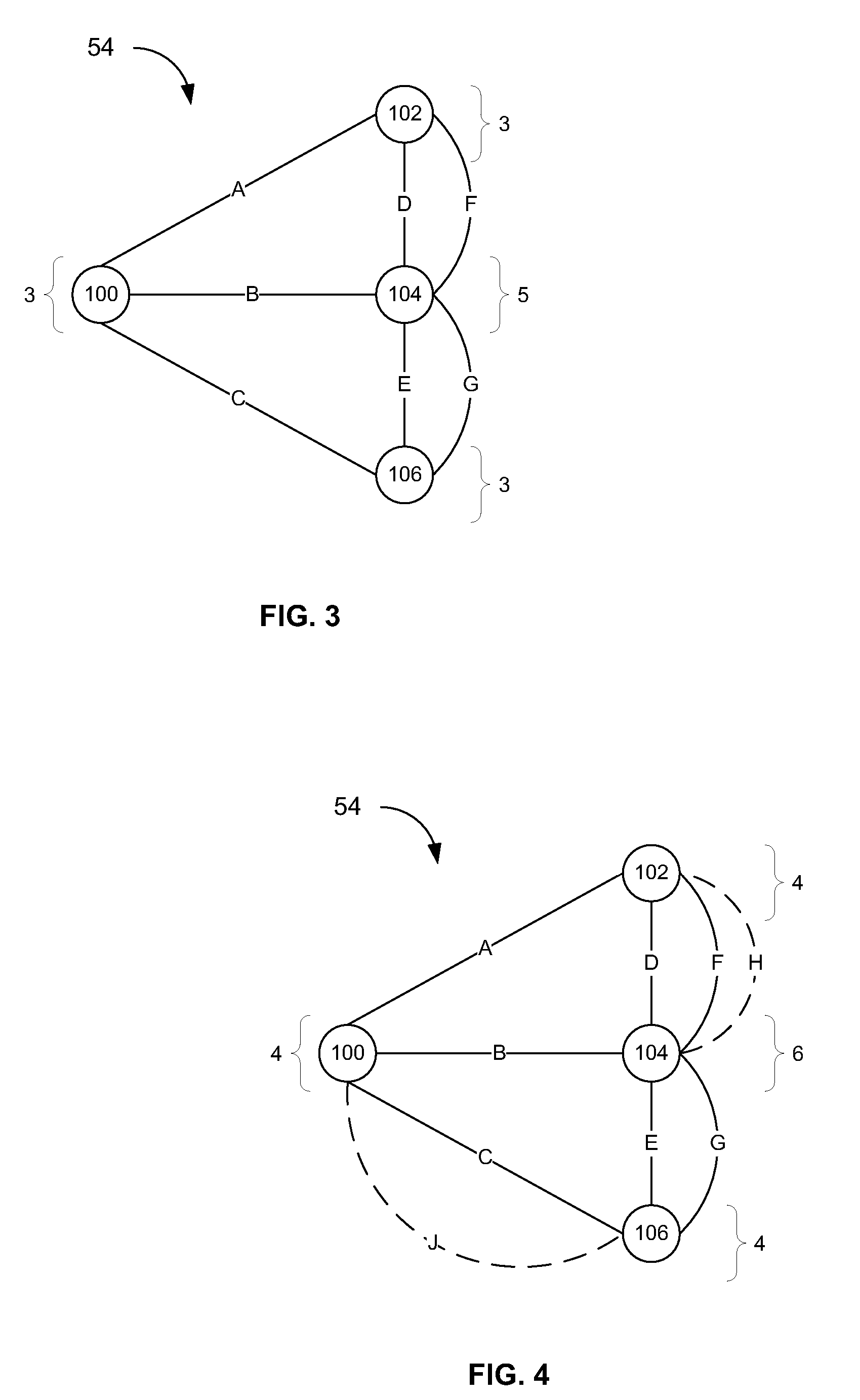

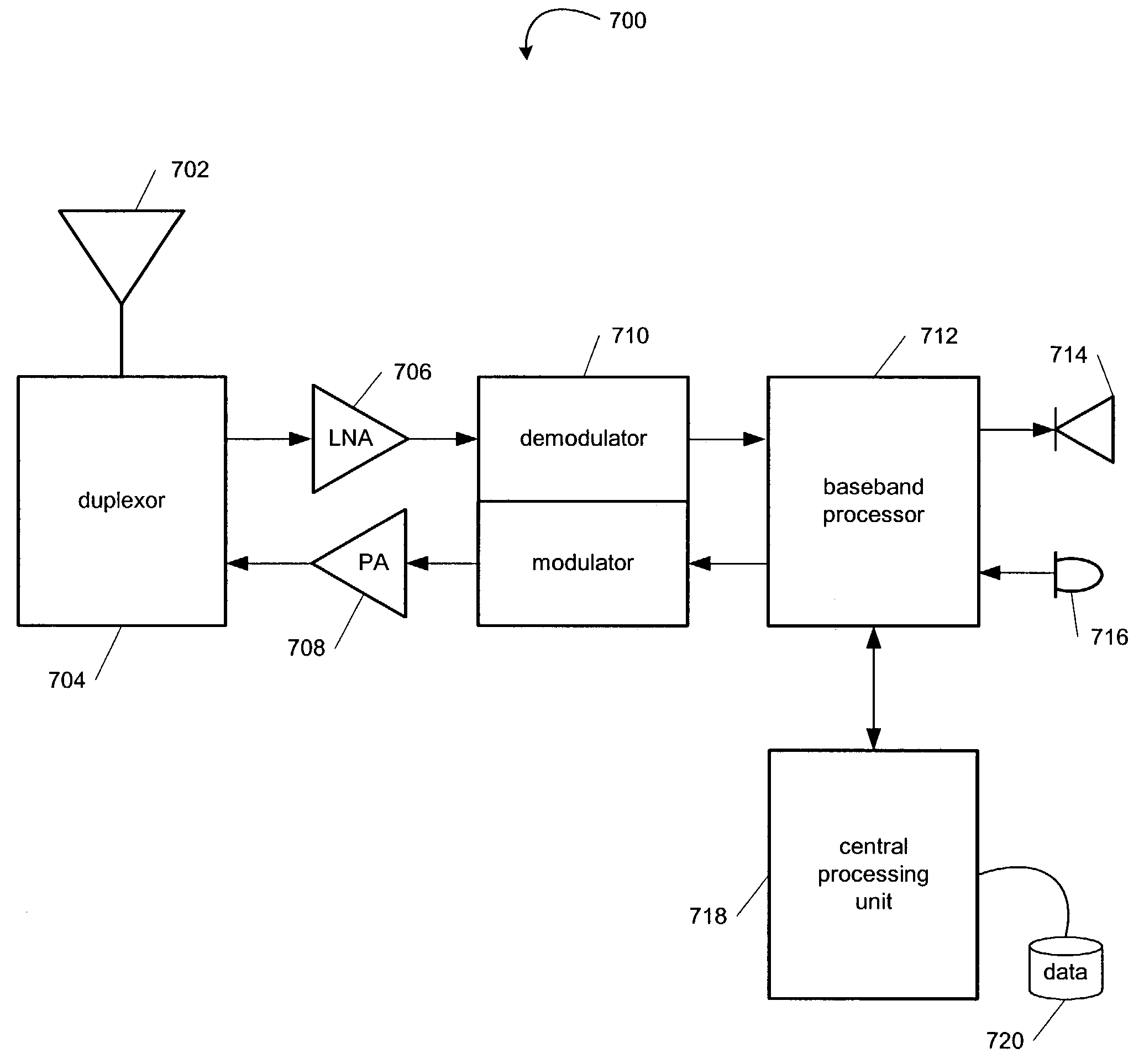

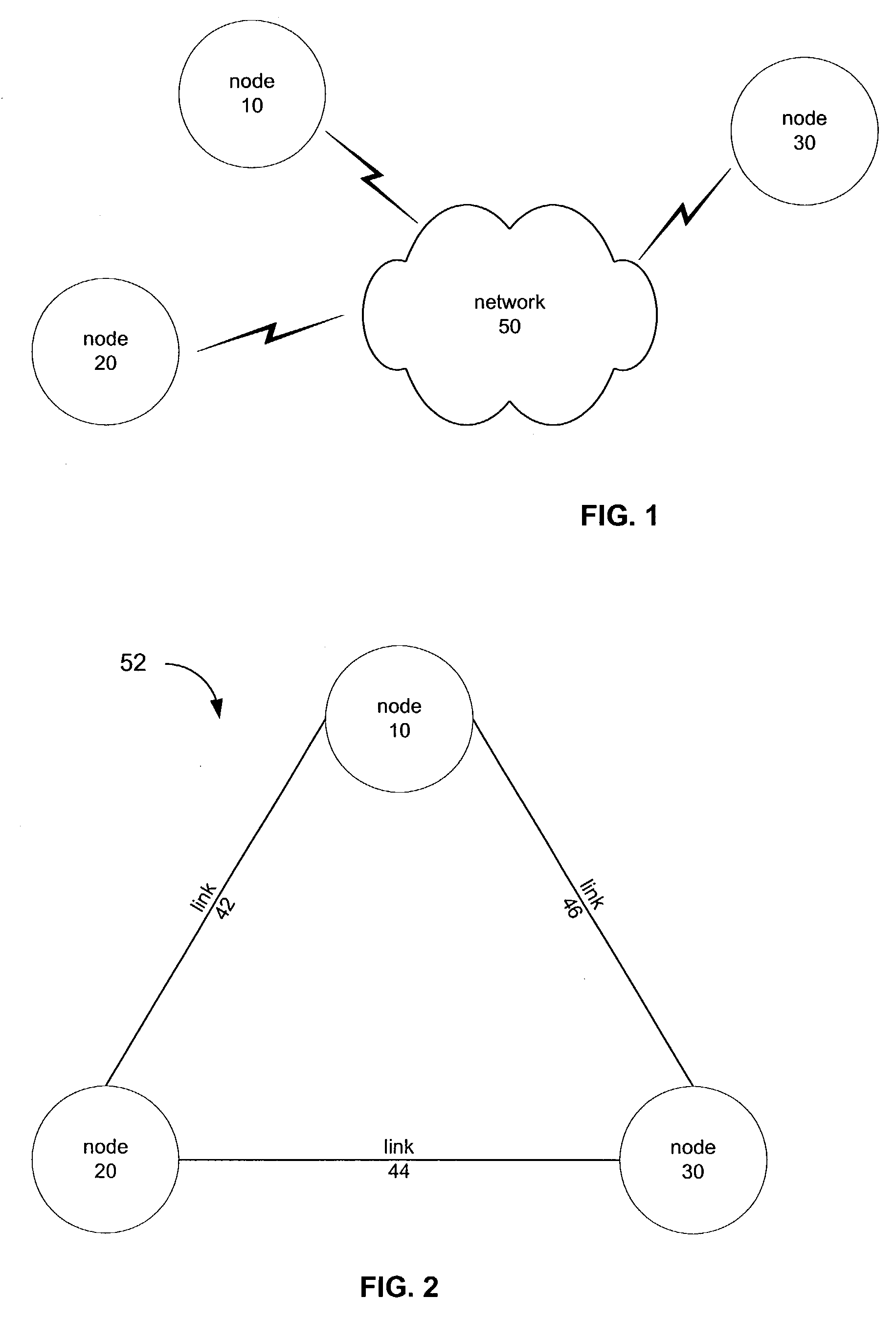

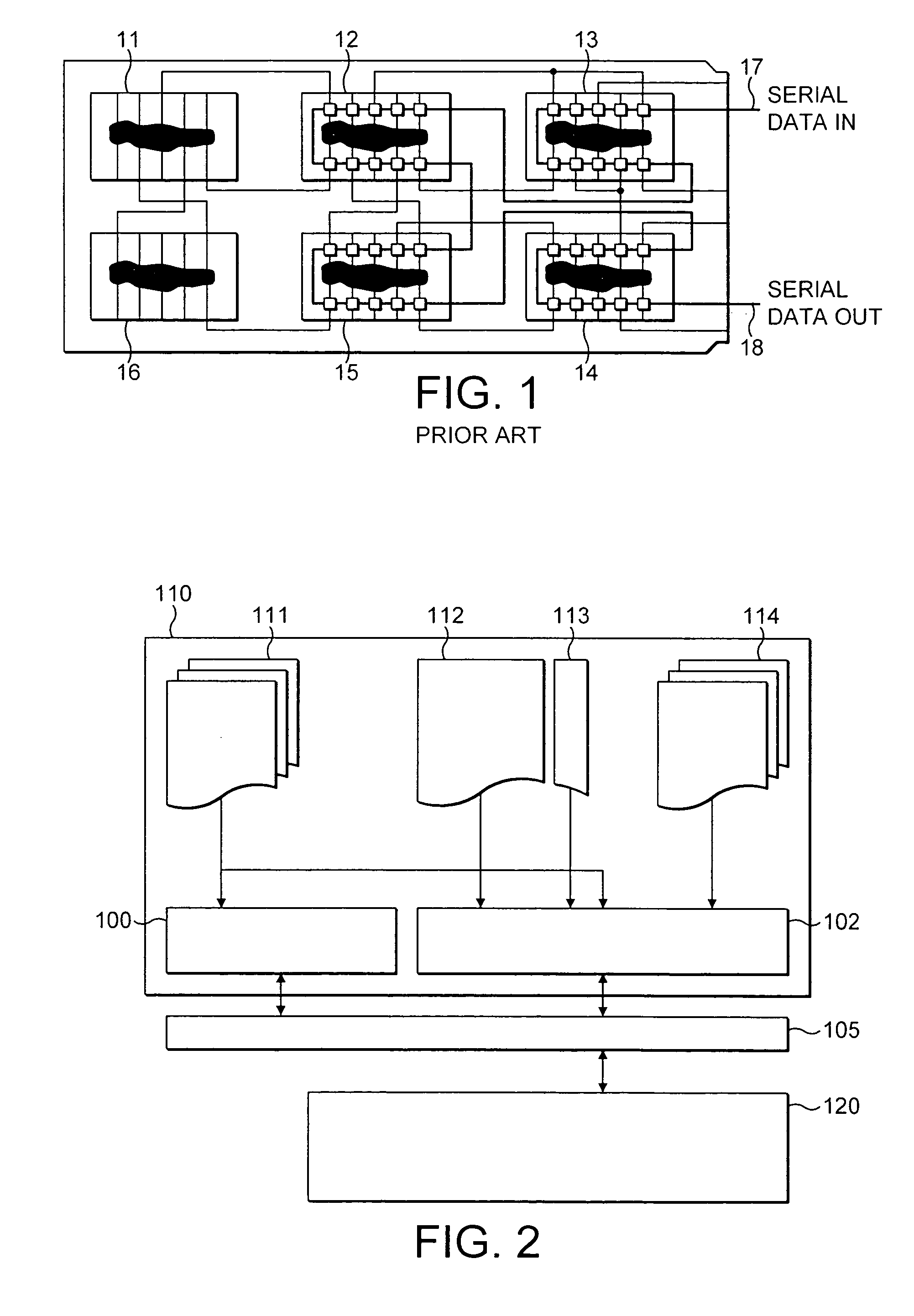

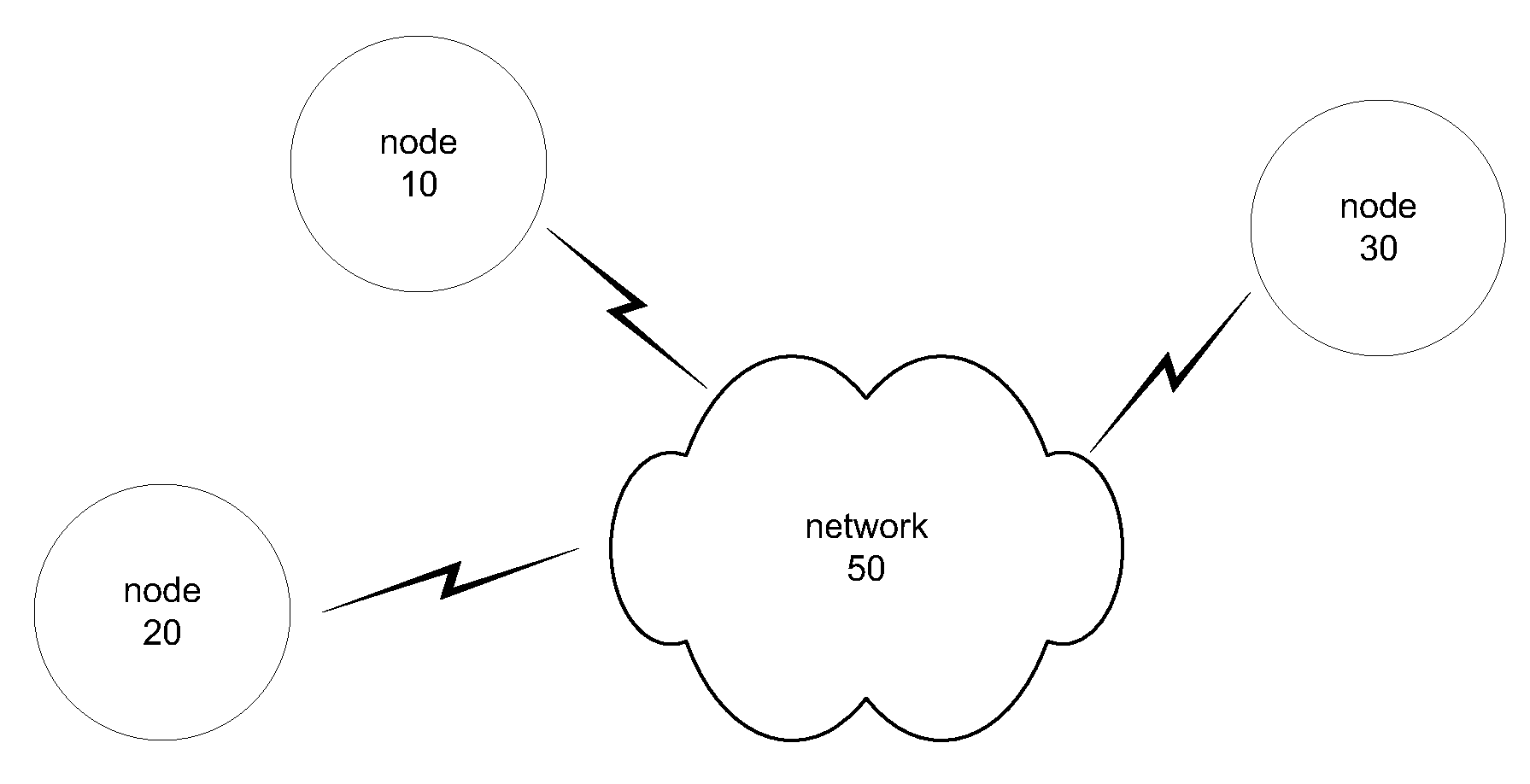

System and method for identifying nodes in a wireless network

InactiveUS7451365B2Blocking in networkAvoids a circular dependency on routing tablesElectronic circuit testingNetwork topologiesComputer hardwareWireless mesh network

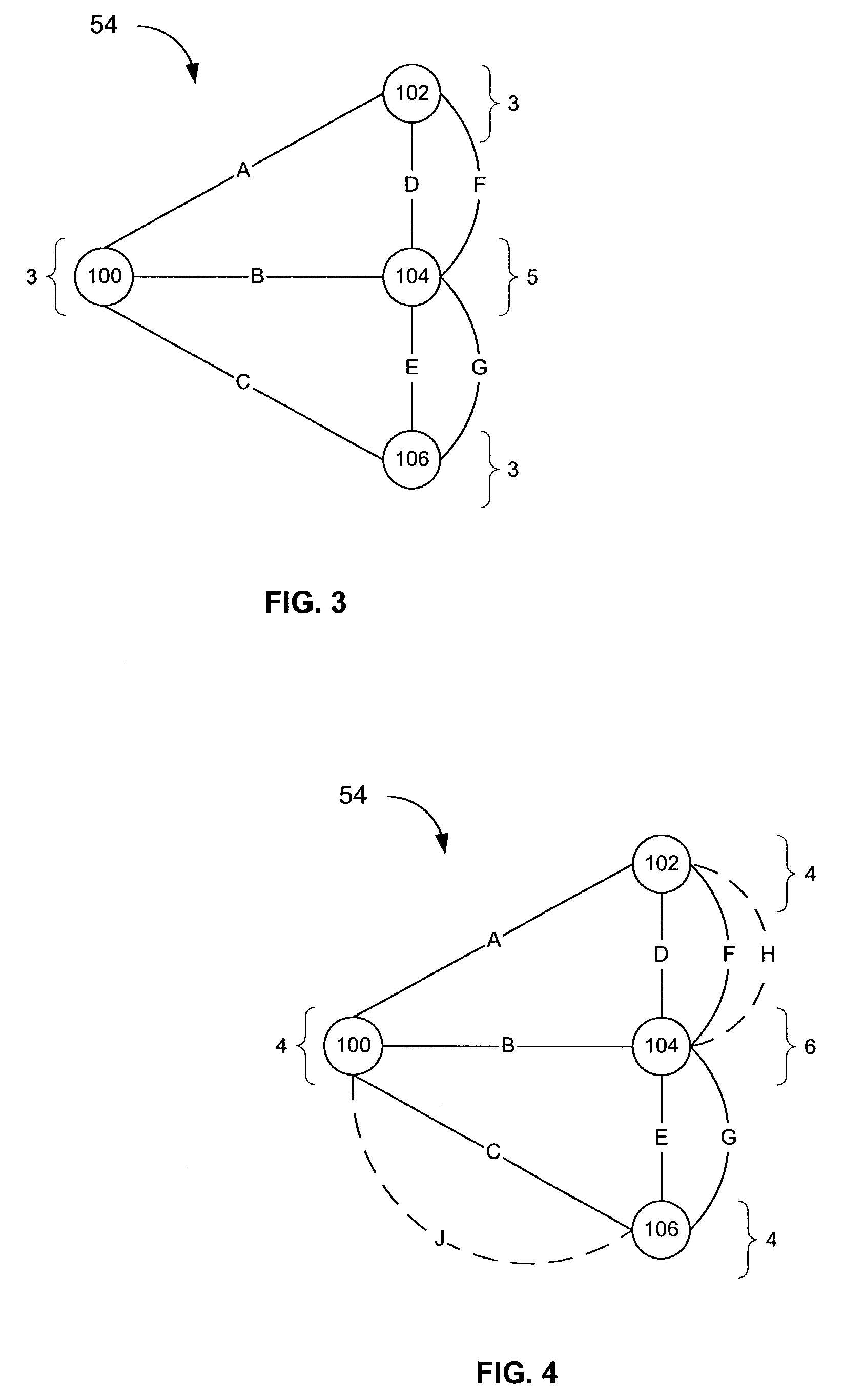

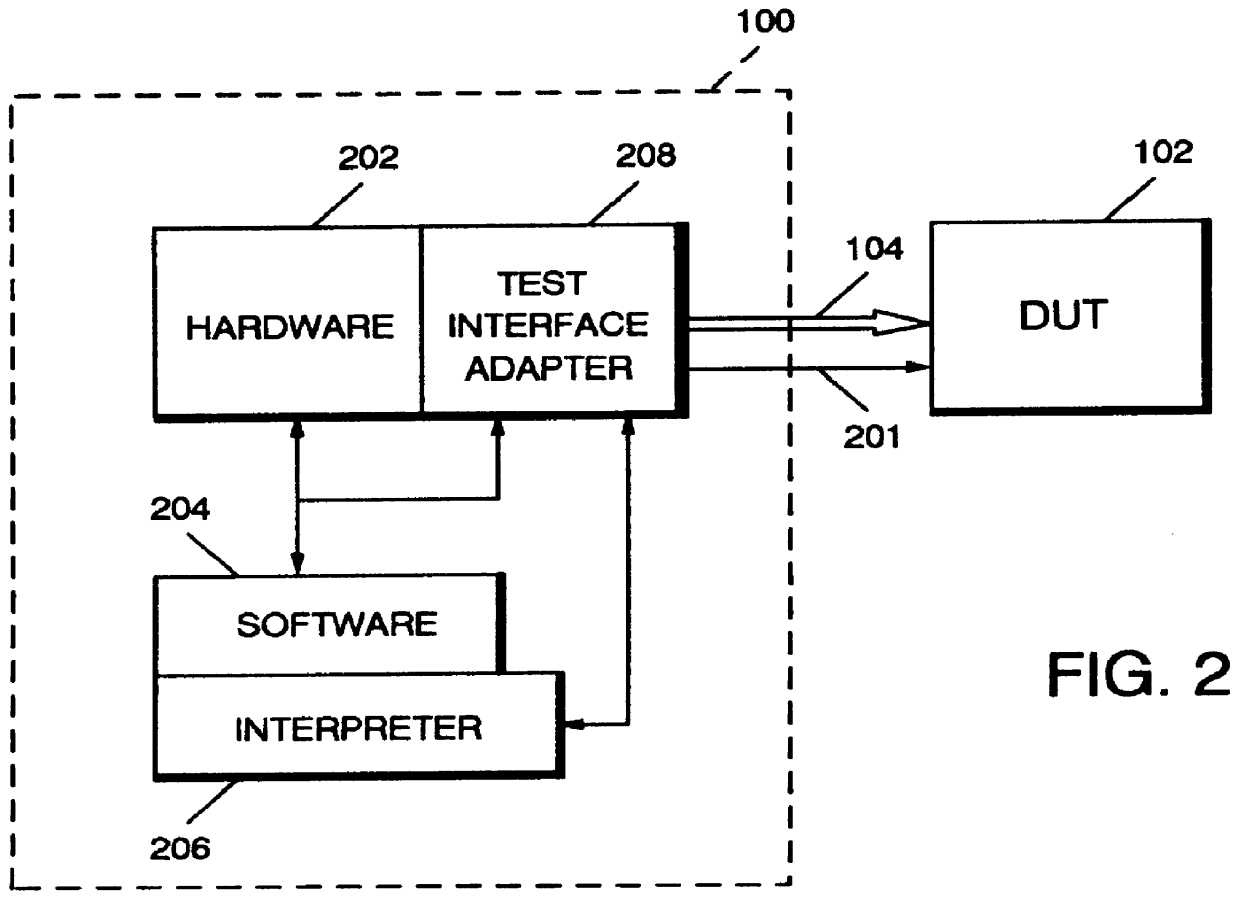

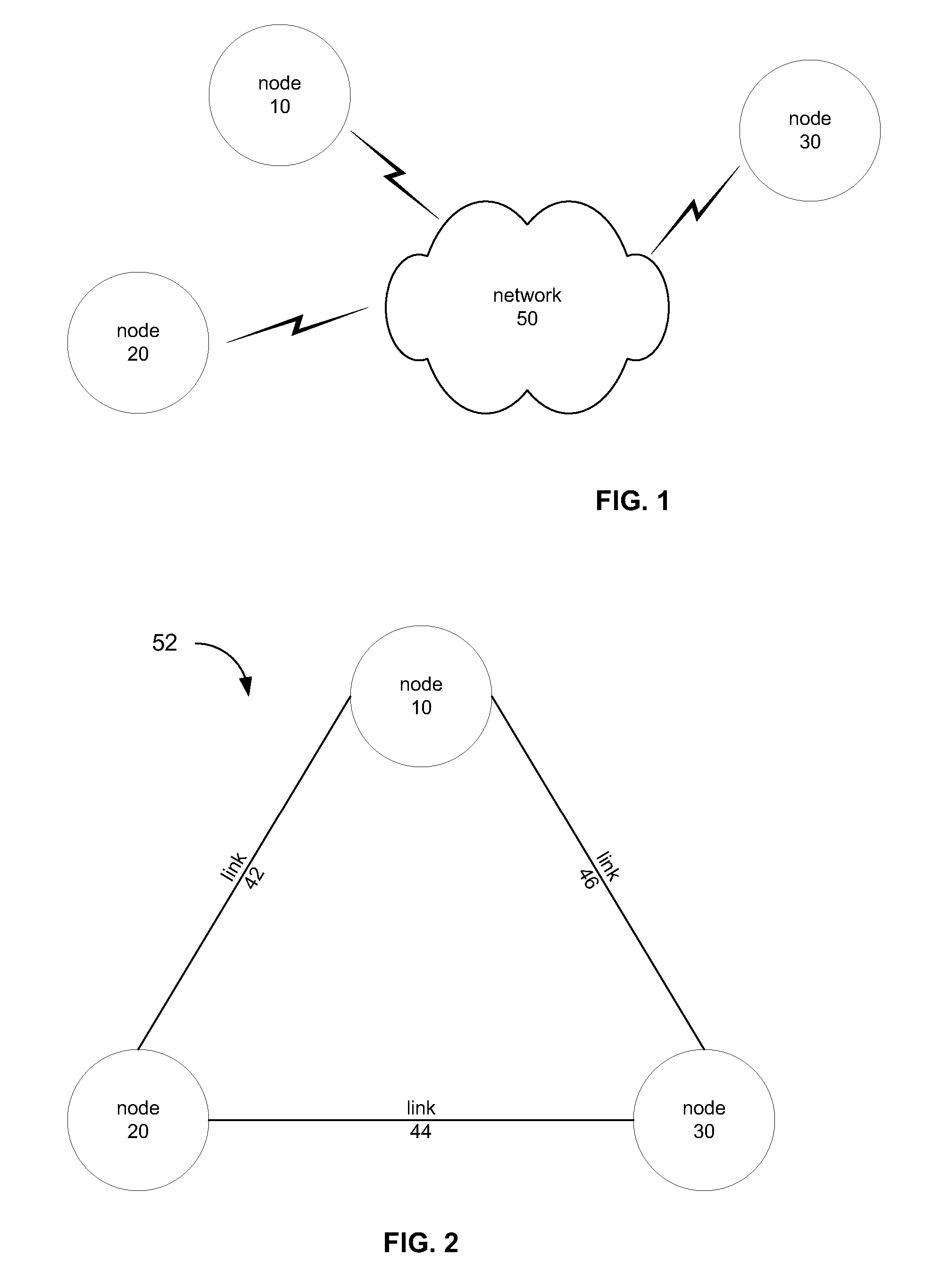

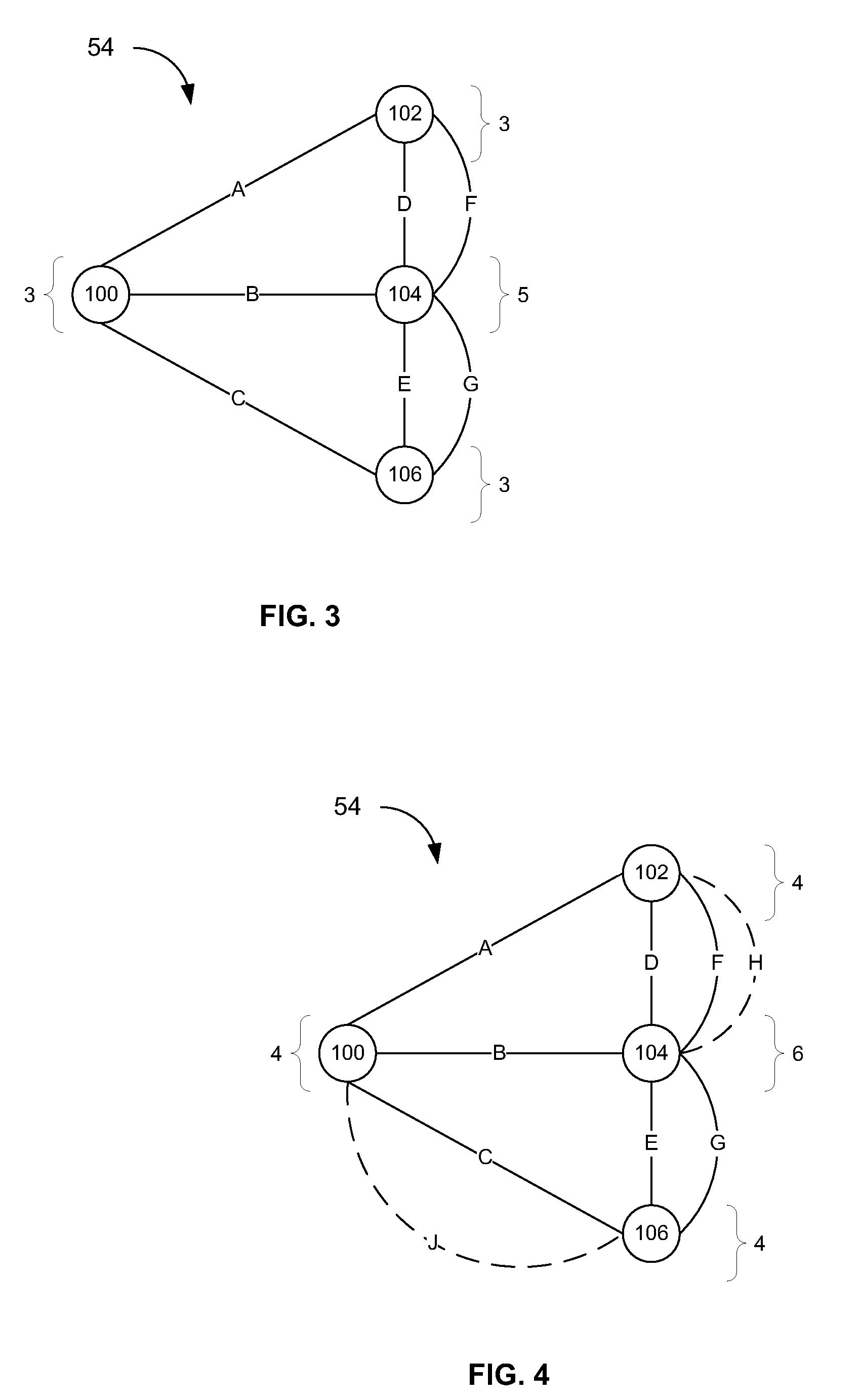

Systems and methods for providing a boundary scan test of a wired or wireless network having a plurality of network nodes are presented. The system includes a test station communicatively coupled with the network. The test station creates a MAC layer scan test route sequence that includes each link in the network and is independent of the routing mechanism and protocol used for the network. The test station also creates a test agent that is configured to traverse each link in the scan test route sequence. The test agent is then deployed on the network and information about a link is reported back to the test station after the test agent examines the link. The scan test route sequence can be created by sending out a series of broadcast messages from one or more nodes in the network, sequentially applying a network tour to cover the entire network, or performing a depth first search on the entire network.

Owner:UNWIRED BROADBAND INC

System and method for identifying nodes in a wireless mesh network

InactiveUS7069483B2Robust and simplifiedFind quicklyElectronic circuit testingNetwork topologiesComputer hardwareDepth-first search

Systems and methods for providing a boundary scan test of a wired or wireless network having a plurality of network nodes are presented. The system includes a test station communicatively coupled with the network. The test station creates a MAC layer scan test route sequence that includes each link in the network and is independent of the routing mechanism and protocol used for the network. The test station also creates a test agent that is configured to traverse each link in the scan test route sequence. The test agent is then deployed on the network and information about a link is reported back to the test station after the test agent examines the link. The scan test route sequence can be created by sending out a series of broadcast messages from one or more nodes in the network, sequentially applying a network tour to cover the entire network, or performing a depth first search on the entire network.

Owner:UNWIRED BROADBAND INC

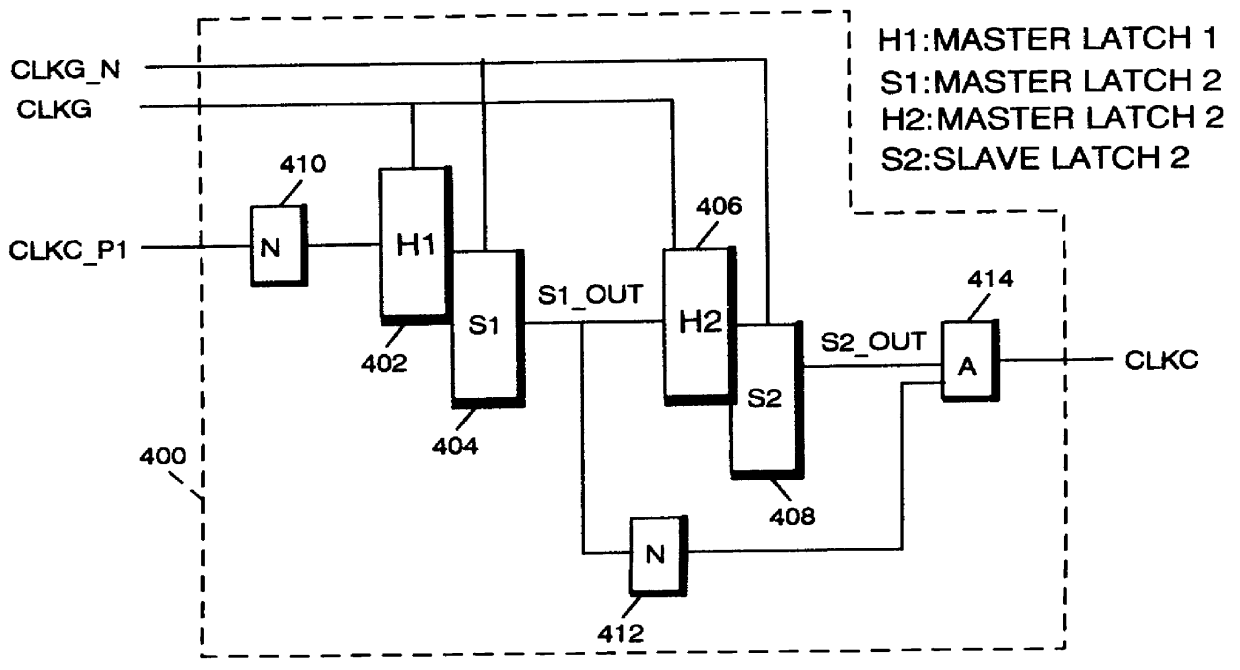

Apparatus and method for testing high speed components using low speed test apparatus

A system for testing a high speed integrated circuit includes a test device having a test clock with a first maximum frequency for performing level sensitive scan design (LSSD) testing of the integrated circuit device under test, a frequency multiplier circuit for multiplying the test clock signal to a higher second frequency capable of operating the device under test, and a finite state machine for generating a first internal clock for testing the device under test. In a practical embodiment, the internal clock speed may be running at a frequency many multiples of the test clock. Alternatively, a method of testing a device under test (DUT) at design speed includes running a predetermined group of tests with a test device operating at a lower speed than the design speed; incorporating LSSD or boundary scan test techniques in the device under test, together with a frequency multiplying device; generating a global clock for the device under test from the frequency multiplying circuit and using a finite state machine as a synchronizer and pulse generator to control a capture clock with respect to the global clock.

Owner:IBM CORP

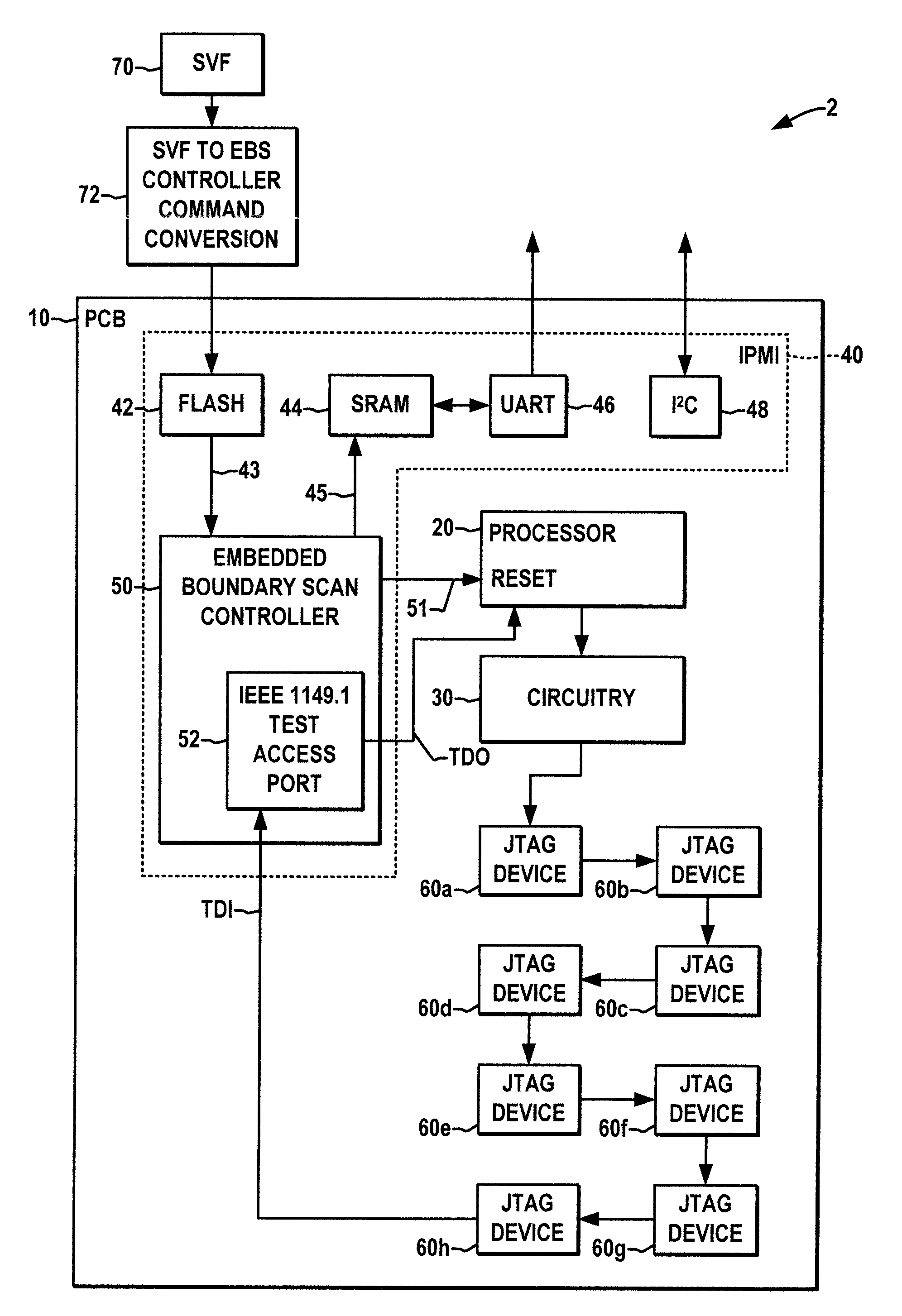

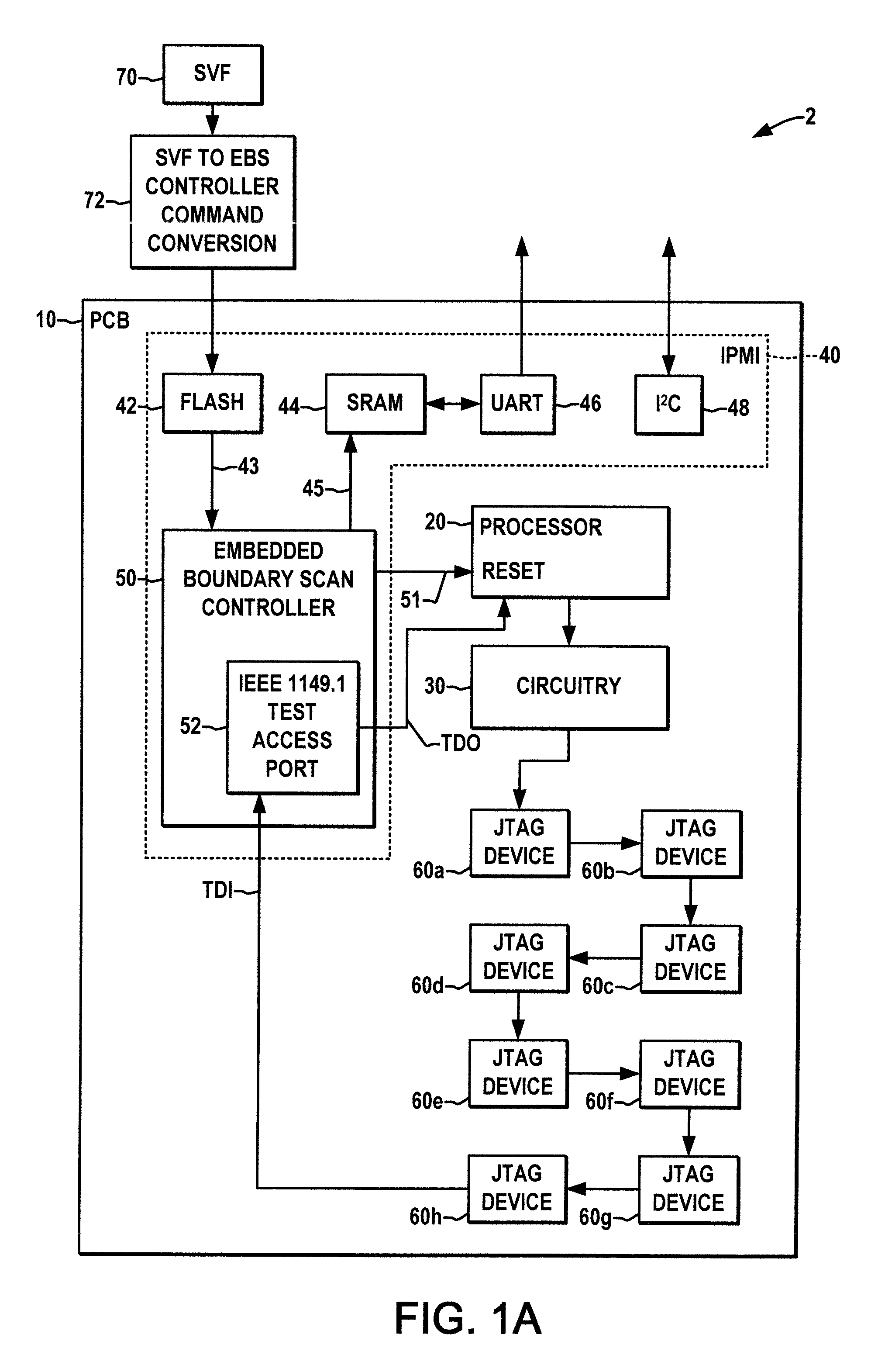

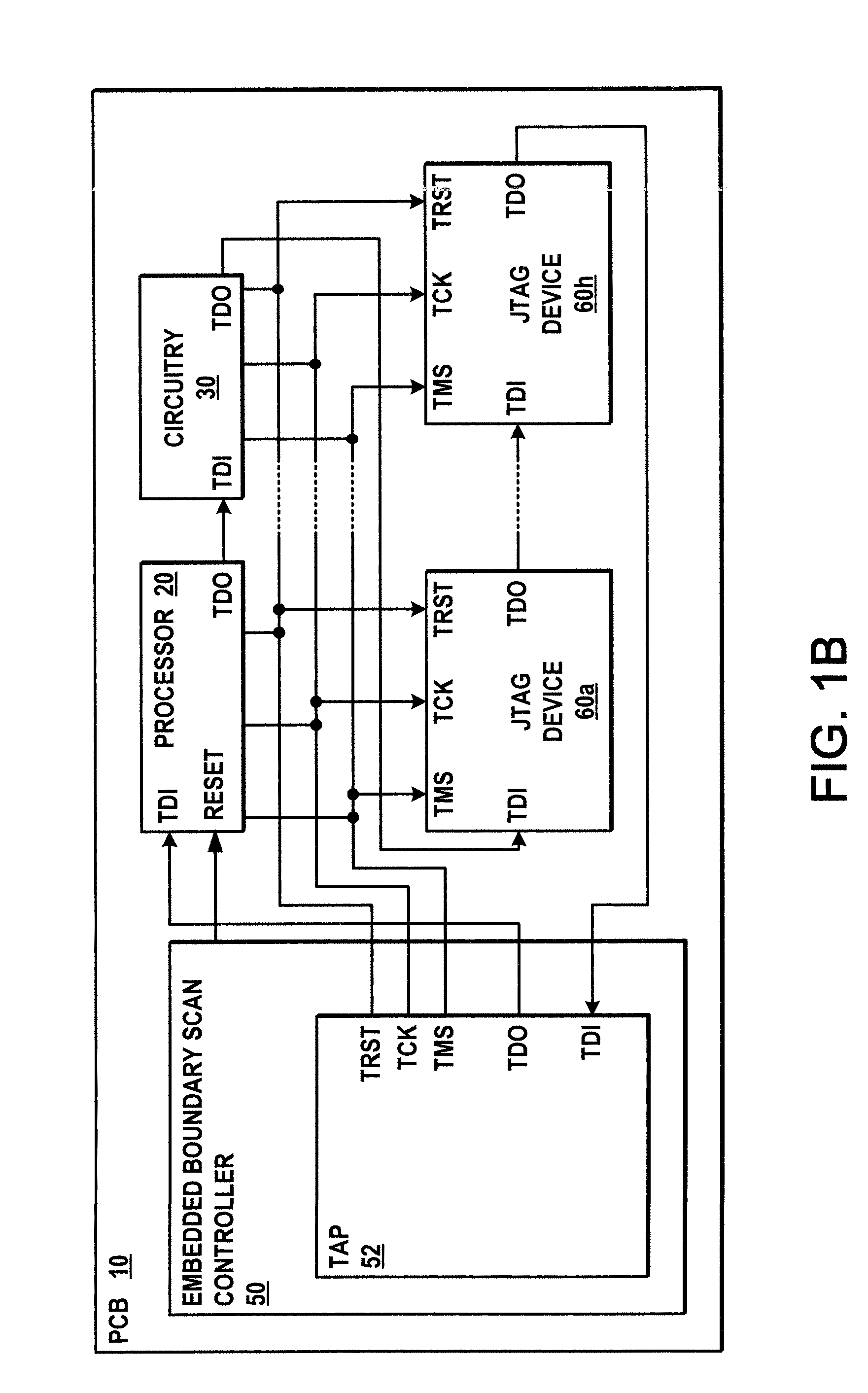

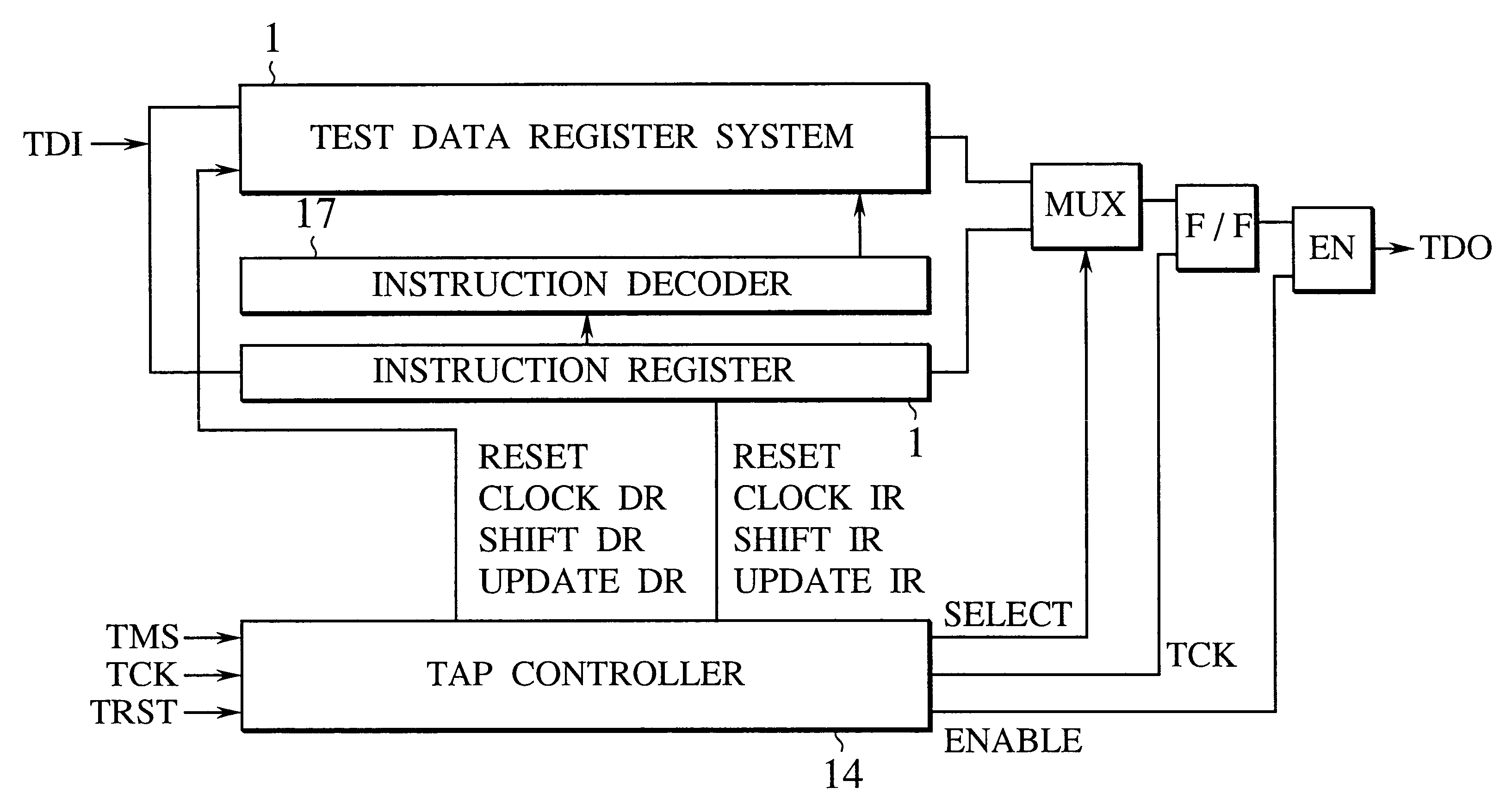

Apparatus and method for embedded boundary scan testing

ActiveUS20090006915A1Small sizeElectronic circuit testingLogical operation testingOn boardJoint Test Action Group

Embedded boundary scan testing apparatus and methodologies are disclosed for testing processor-based circuit boards without processor intervention. A boundary scan controller is embedded in a circuit board along with a boundary scan chain having JTAG devices connected with an electrical circuit of the board. Upon power up, the boundary scan controller holds an on-board processor system in reset, loads boundary scan test vectors and commands from an on-board non-volatile memory, and runs boundary scan testing while holding the processor system in the reset state. The boundary scan controller preferably includes a test access port controller that implements only a subset of the JTAG standard 16 machine states to optimize performance and minimize controller hardware. The test results may be stored in an externally accessible on-board memory for subsequent retrieval in order to facilitate board troubleshooting and / or repair, where the provision of on-board boundary scan testing allows testing of boards while installed in the field, and the embedded scan controller allows field testing of on-board processor systems and related circuitry to enhance the test coverage over processor-driven boundary scan testing.

Owner:ALCATEL-LUCENT USA INC

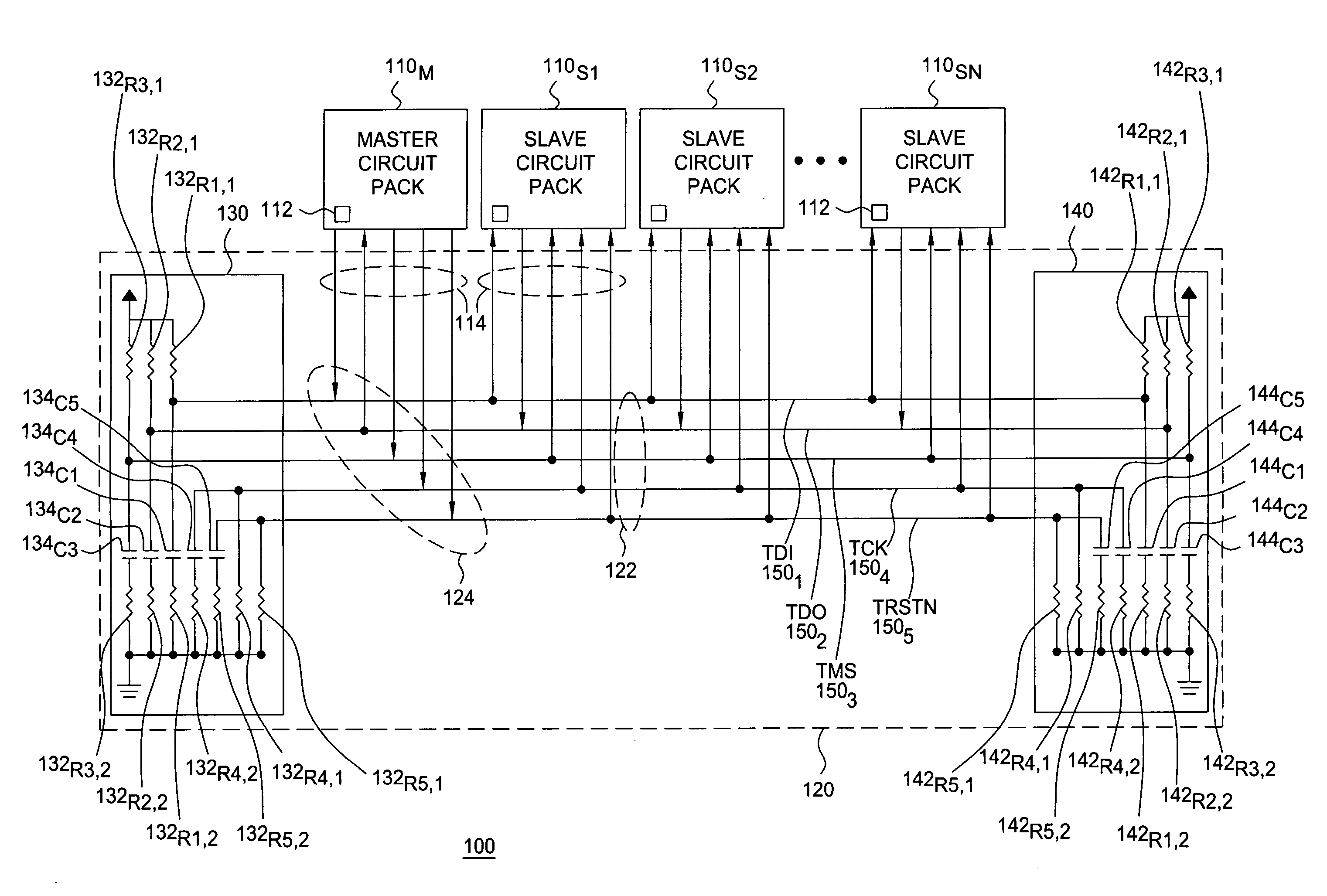

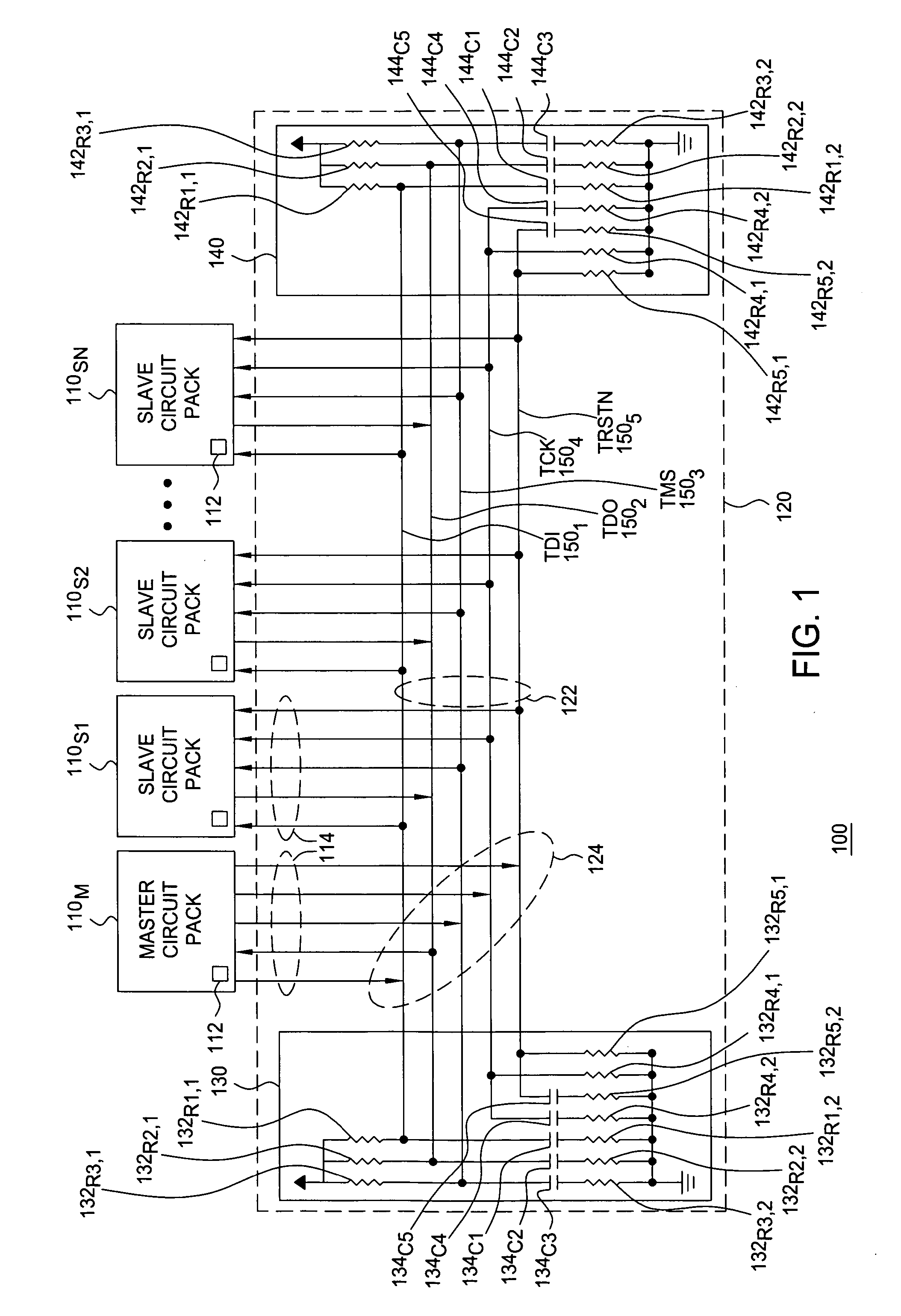

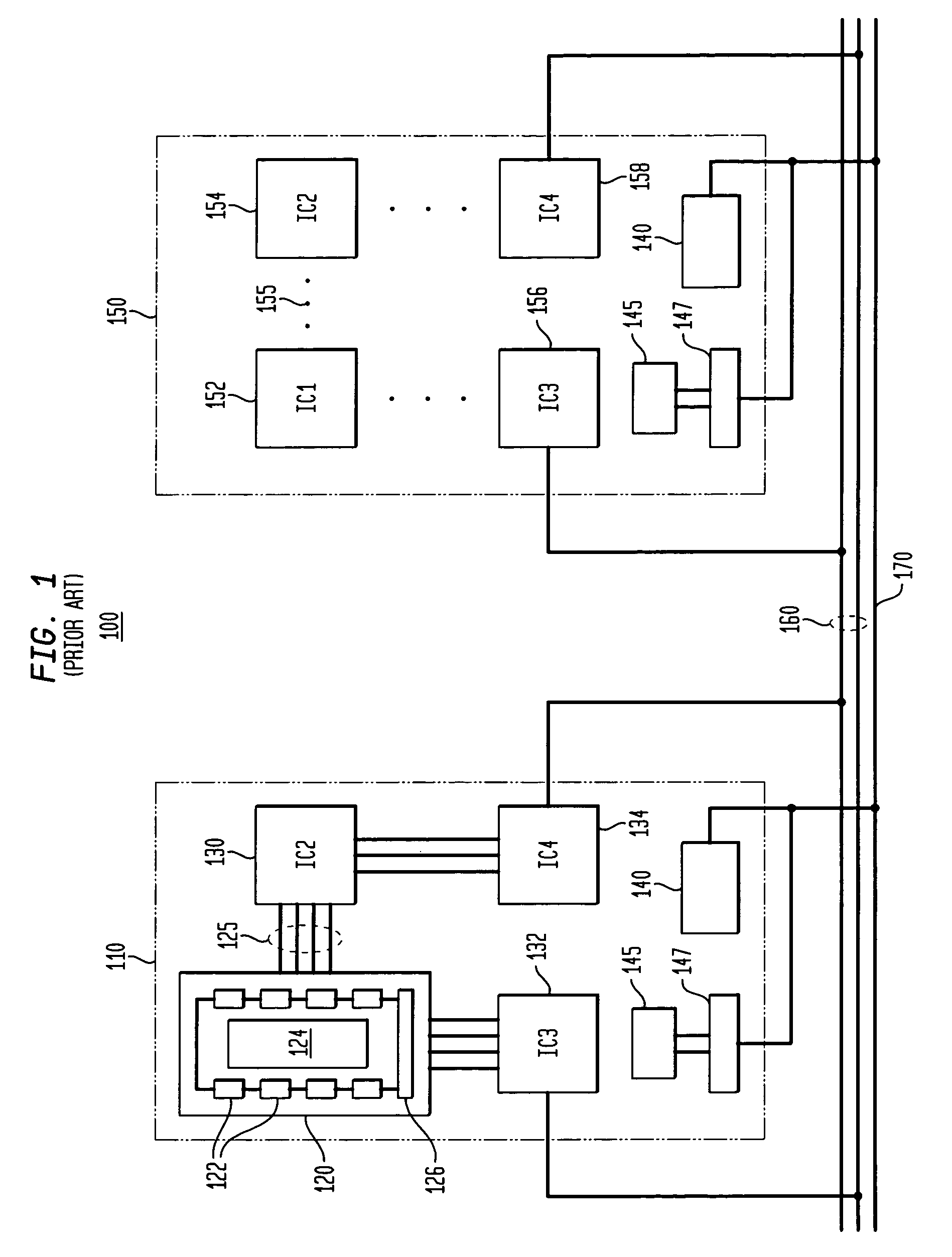

Method and apparatus for enabling multipoint bus access

The invention includes a method and apparatus for enabling multipoint bus access. In one example, the open ring-architecture bus includes a boundary scan bus including a plurality of bus access points adapted for interfacing with a plurality of circuit packs, a first termination circuit coupled to a first end of the bus, and a second termination circuit coupled to a second end of the bus. The first termination circuit and second termination circuit are adapted for terminating signaling on the boundary scan bus. The open-ring architecture bus provides a master circuit pack a multipoint access capability such that the master circuit pack may be disposed at any of the plurality of bus access points. In one example, signaling includes signaling operable for performing hierarchical system testing, including boundary scan testing. In another example, signaling includes upgrade signaling operable for performing firmware upgrades, software upgrades, and like circuit pack upgrades.

Owner:LUCENT TECH INC

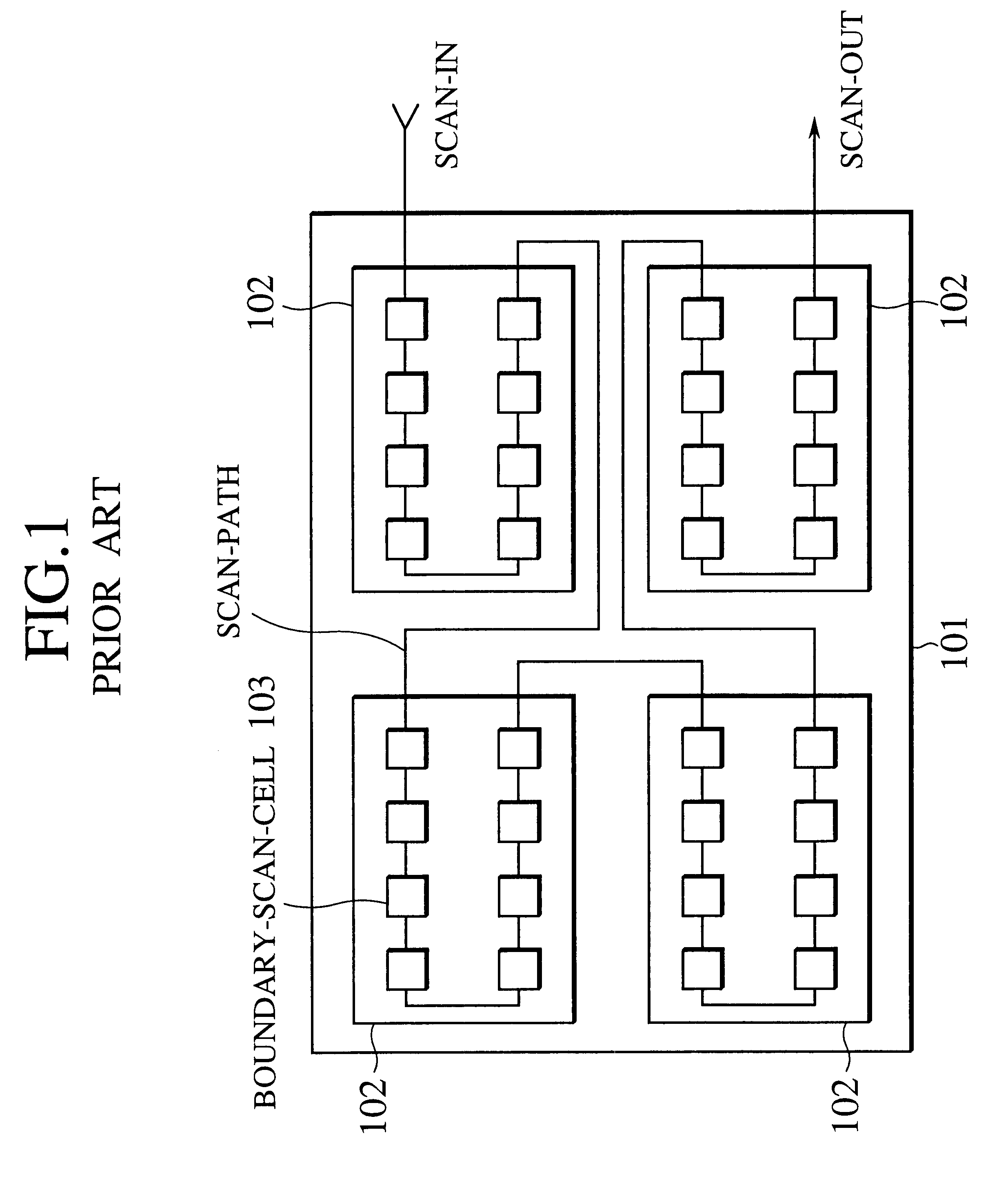

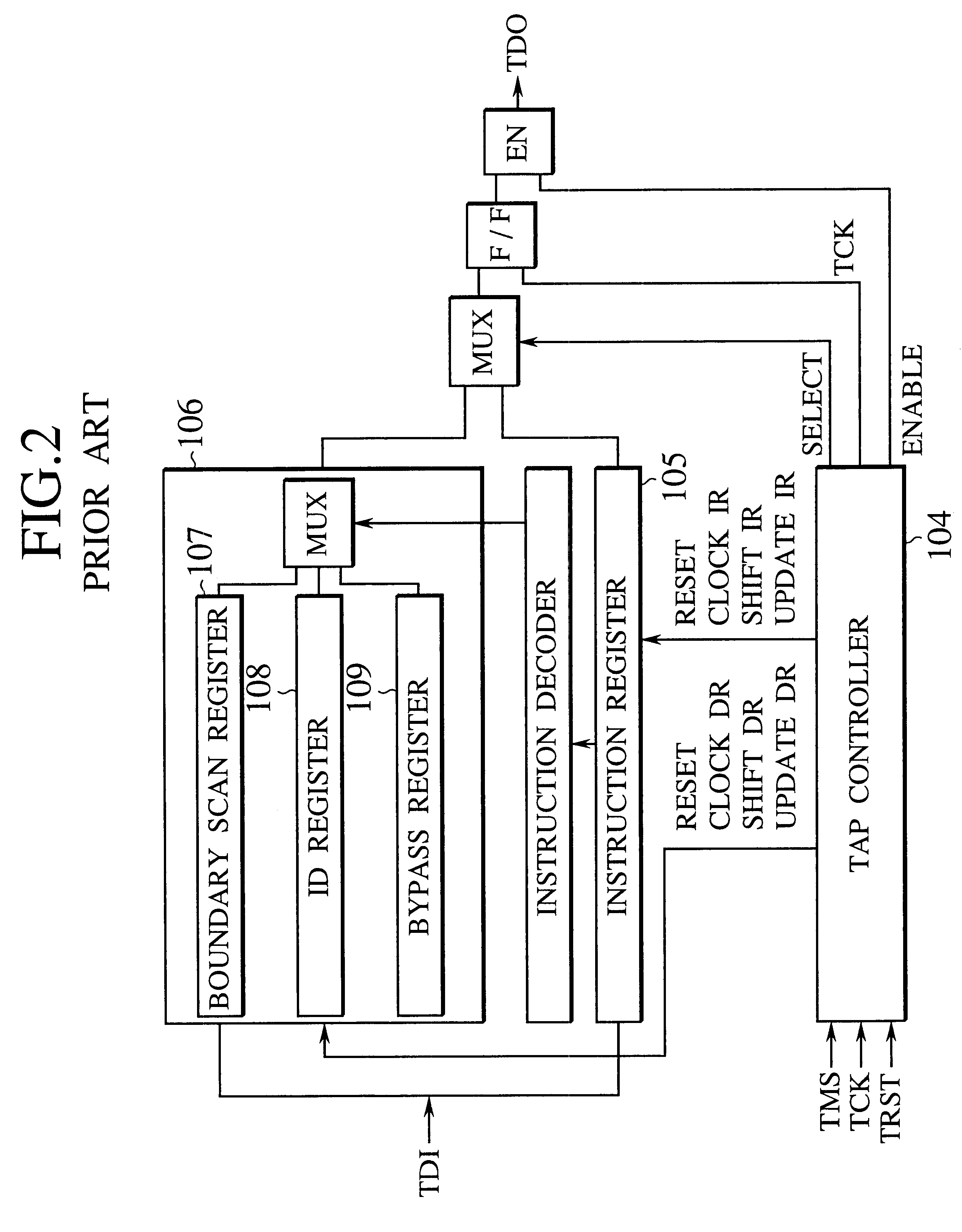

Semiconductor device provided with a boundary-scan test circuit

A semiconductor device provided with a compact Boundary-Scan test circuit is shown. The Boundary-Scan test circuit comprises a Boundary-Scan test register which is composed of bit elements serially connected to each other in the form of a scan path and each of which is connected respectively to one of pads of the semiconductor device, wherein part of the bit elements of said Boundary-Scan test register functions also as an ID-Code register while an initial bit element of said Boundary-Scan test register functions also as a bypass register for bypassing the subsequent bit elements of said Boundary-Scan test register.

Owner:KK TOSHIBA

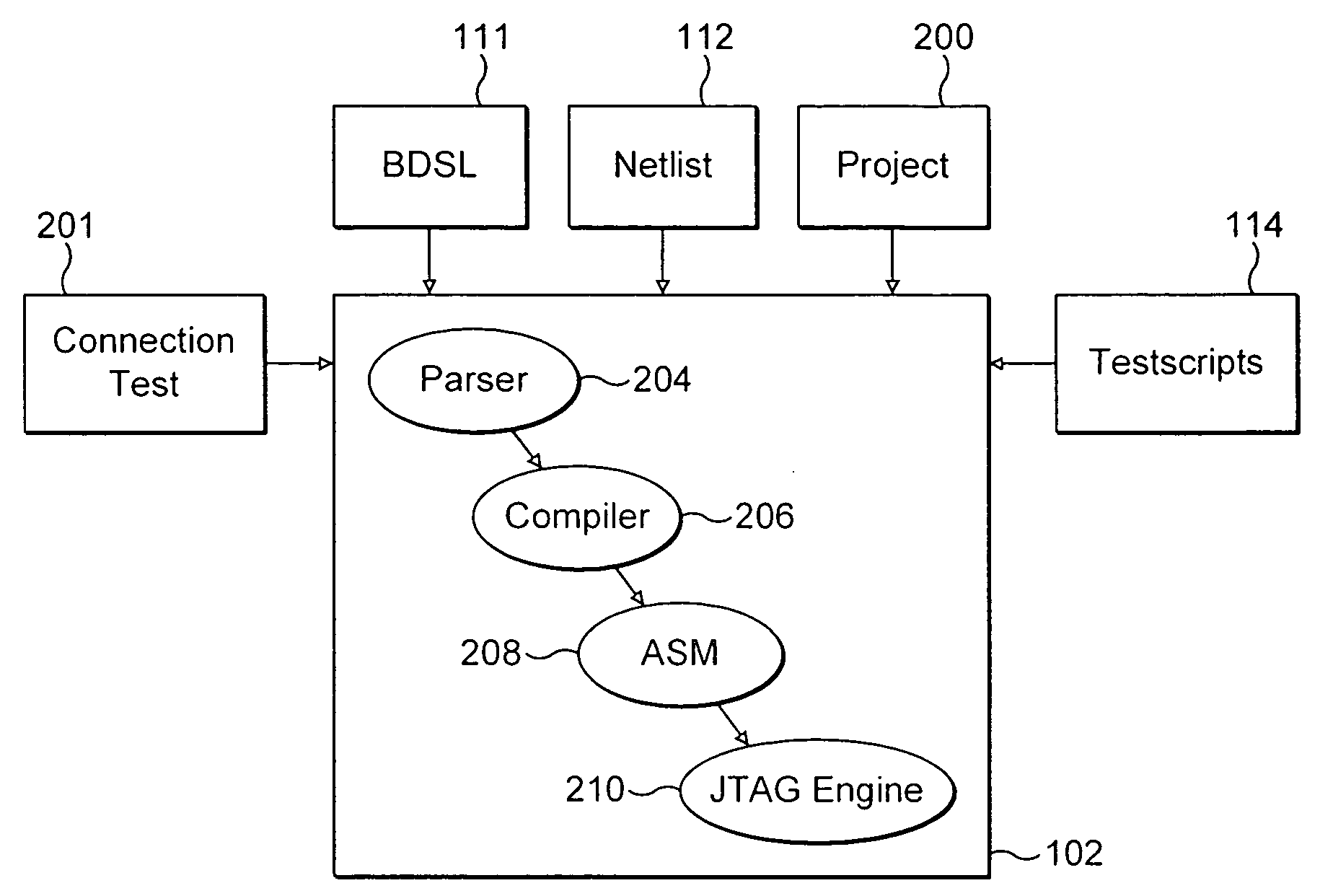

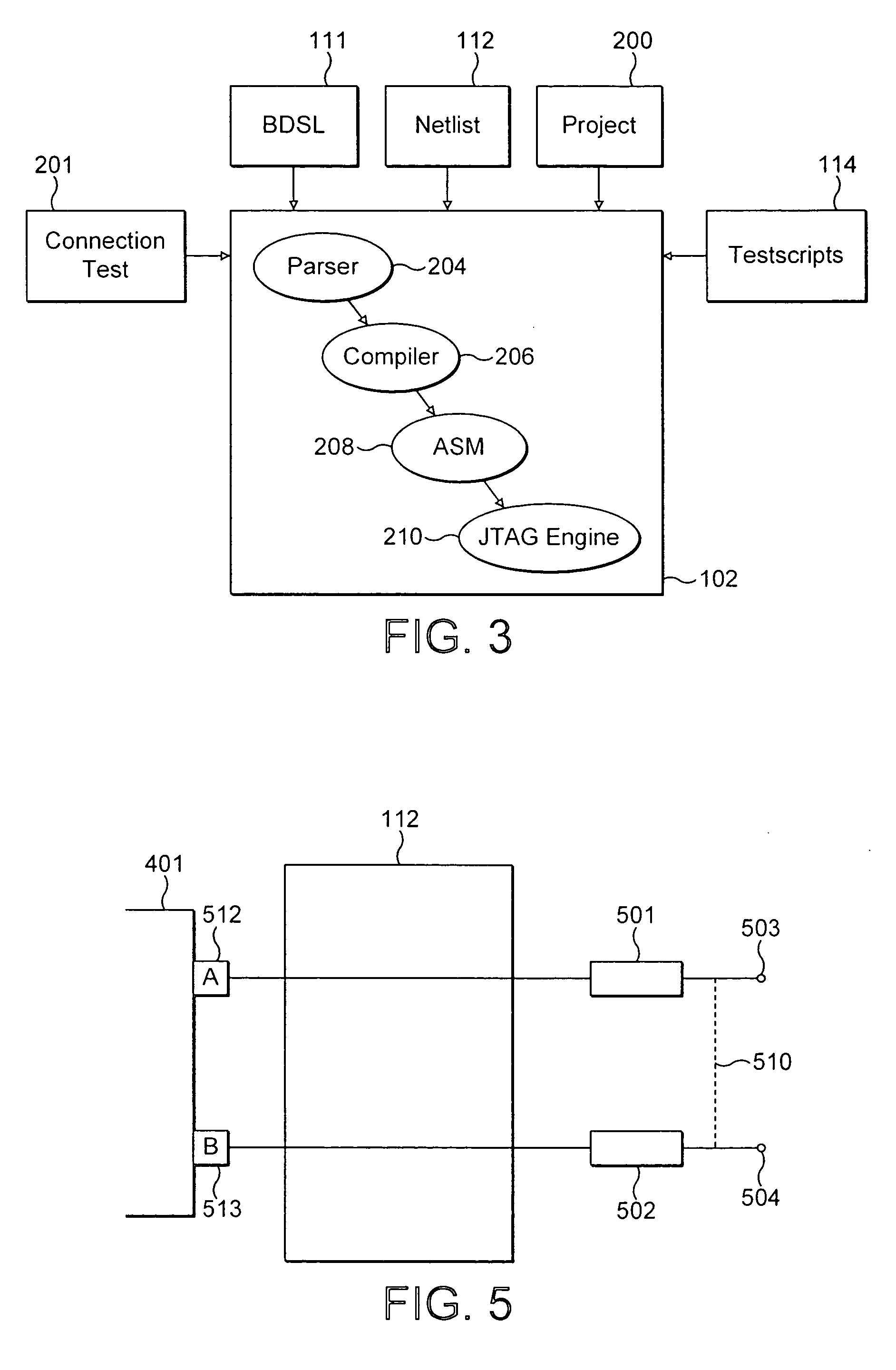

Testing of integrated circuits using boundary scan

Circuit testing equipment comprising a computer (110) having stored thereon a boundary scan description language (BSDL) file (111), a netlist (112) and a connections list (113). An adapter (105) connects the computer to a boundary scan bus of a circuit (120) to be tested. The computer is arranged to parse and compile the BSDL file, the netlist and the connections list to generate a data structure which, when combined with a test script (114), permits execution of the test script from the computer through the boundary scan bus. The test script can be IC-specific such that it is valid for a particular IC independent of the circuit in which the IC is located.

Owner:MIDAS YELLOW

System and Method for Identifying Nodes in a Wireless Network

InactiveUS20060253747A1Blocking in networkAvoids a circular dependency on routing tablesElectronic circuit testingNetwork topologiesComputer hardwareDepth-first search

Systems and methods for providing a boundary scan test of a wired or wireless network having a plurality of network nodes are presented. The system includes a test station communicatively coupled with the network. The test station creates a MAC layer scan test route sequence that includes each link in the network and is independent of the routing mechanism and protocol used for the network. The test station also creates a test agent that is configured to traverse each link in the scan test route sequence. The test agent is then deployed on the network and information about a link is reported back to the test station after the test agent examines the link. The scan test route sequence can be created by sending out a series of broadcast messages from one or more nodes in the network, sequentially applying a network tour to cover the entire network, or performing a depth first search on the entire network.

Owner:UNWIRED BROADBAND INC

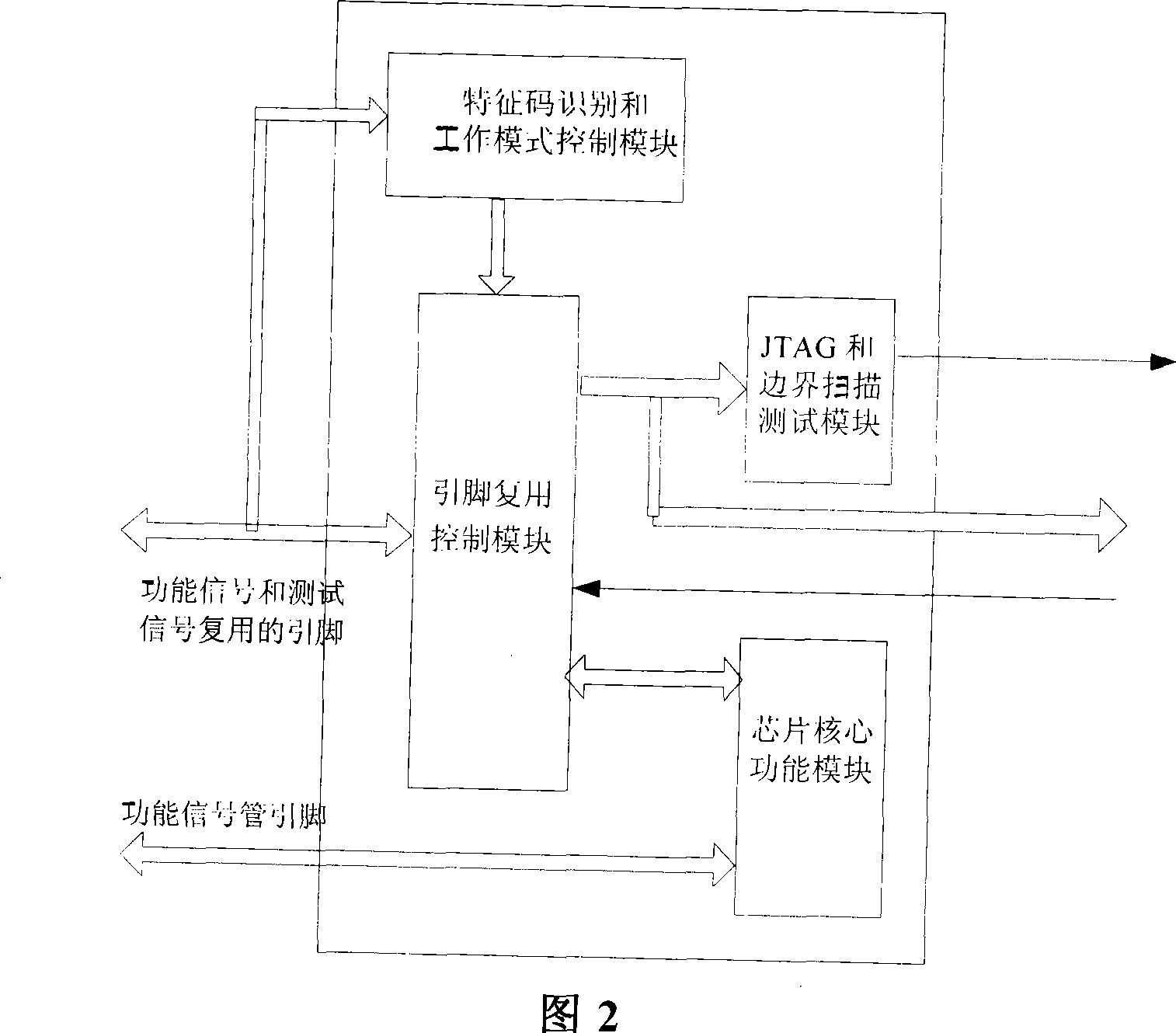

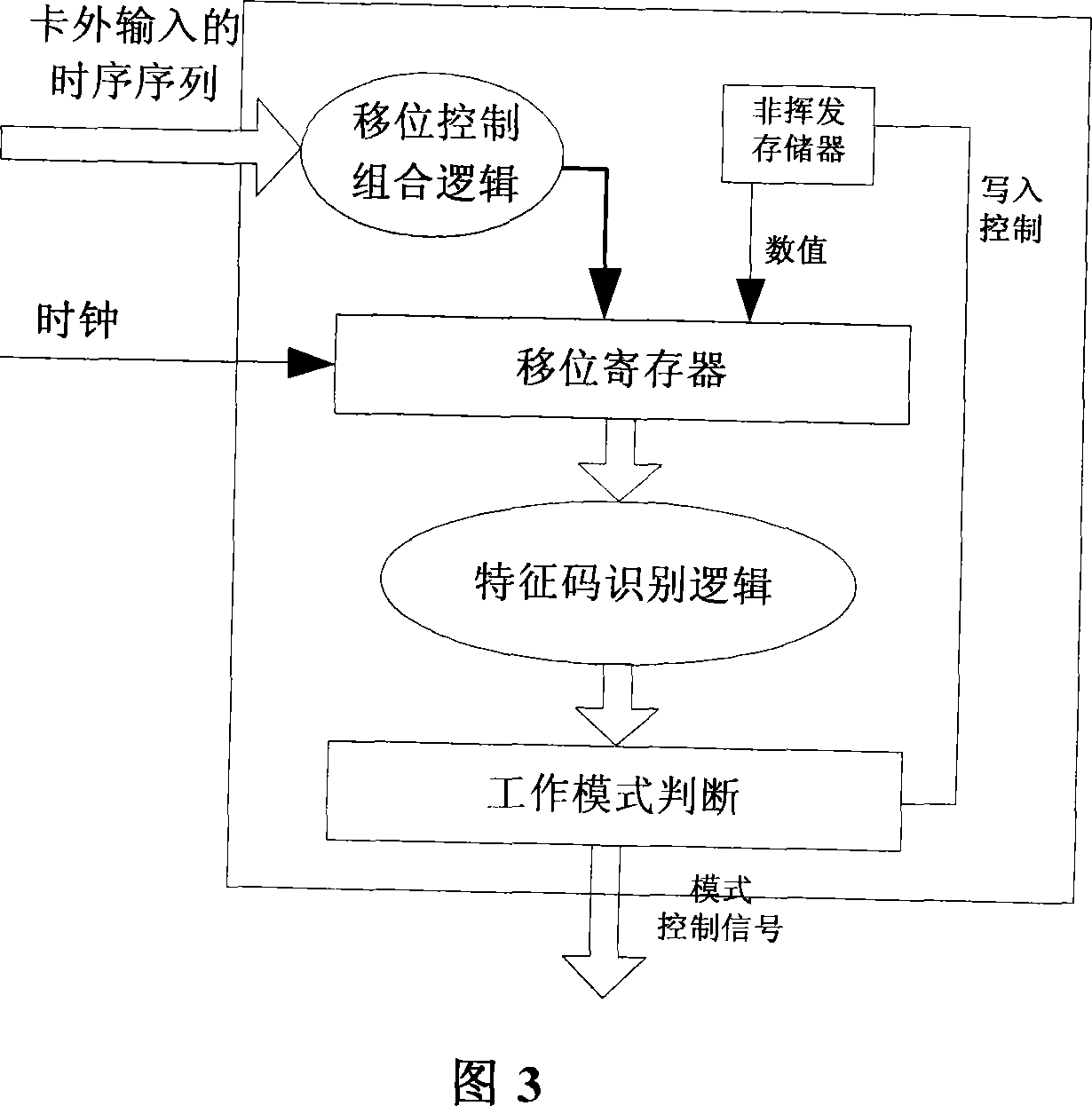

Border scanning test structure of multiple chip package internal connection and test method

ActiveCN101078746AConnected testingAvoid situations that mislead the chip into test modeSemiconductor/solid-state device testing/measurementIndividual semiconductor device testingElectricityEngineering

The invention relates to a boundary scanning testing structure connected with multiple-chip packaging body with finite pins in it and the testing method, belonging to IC chip design, chip testability design and chip packaging fields. A typical application is the modern new SIM card with large capacity constituted by multiple chips. The invention sets finite functional pins of packaging body as pins with boundary scanning function by a special logic sequence relationship when multiple-chip packaging body is tested and then by these pins boundary scanning test in packaging body can be carried out so as to achieve the test to inner connection relationship of packaging body. After test is done, by a special operation, the function of testing circuit is closed to avoid chip error action, which is not necessary in future. The invention realizes special power-on flow of chip, realization of a special circuit and corresponding structure adjustment of chip.

Owner:RDA MICROELECTRONICS SHANGHAICO LTD

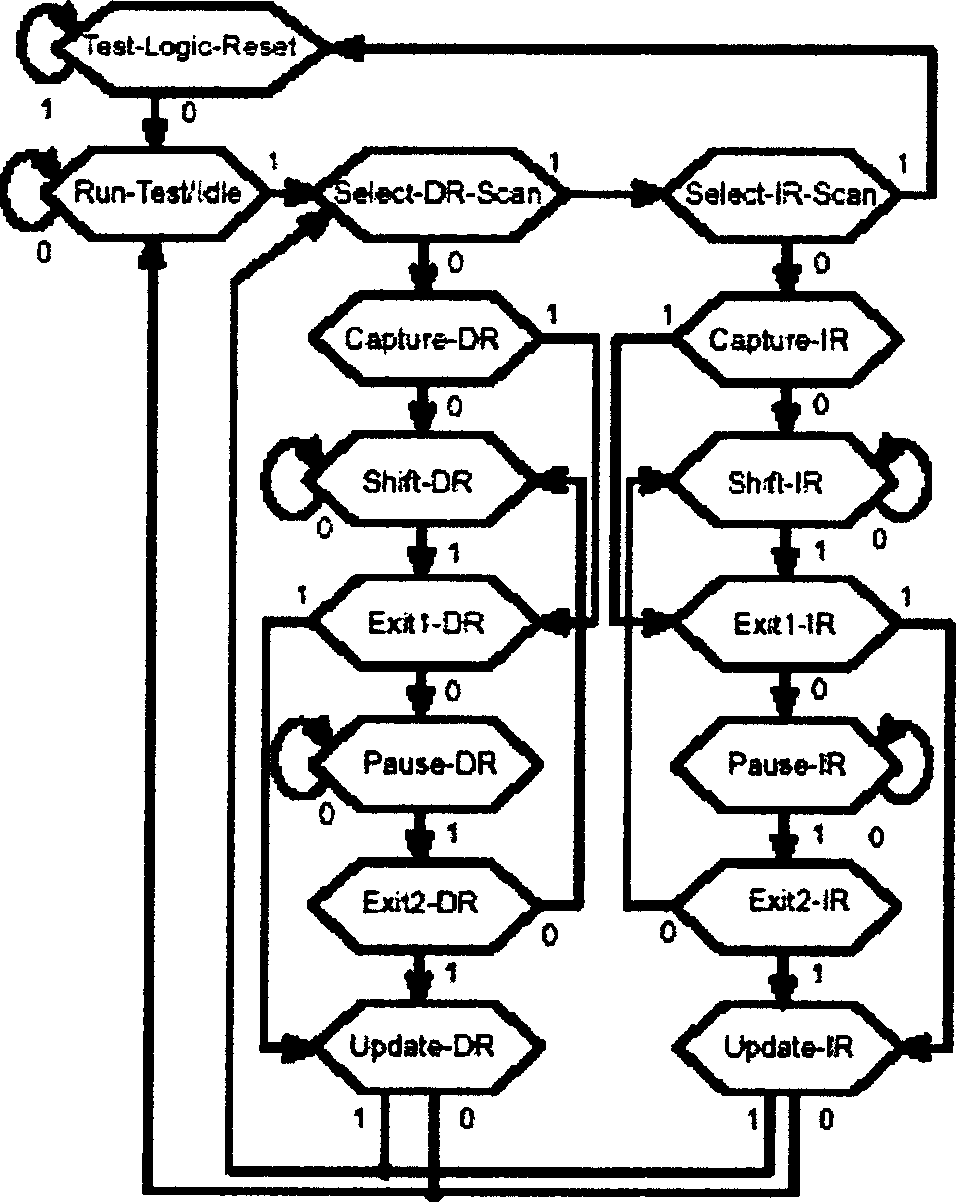

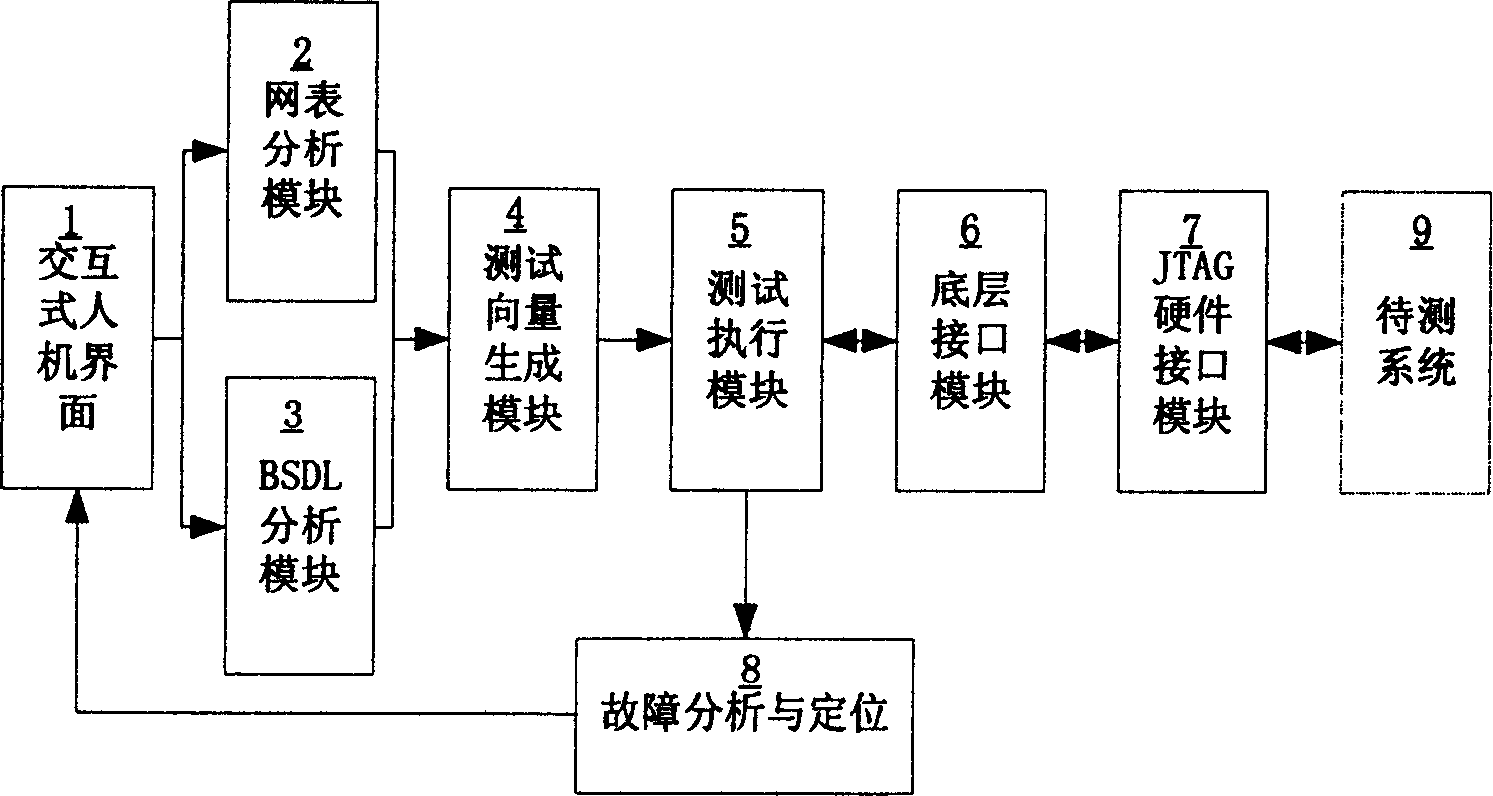

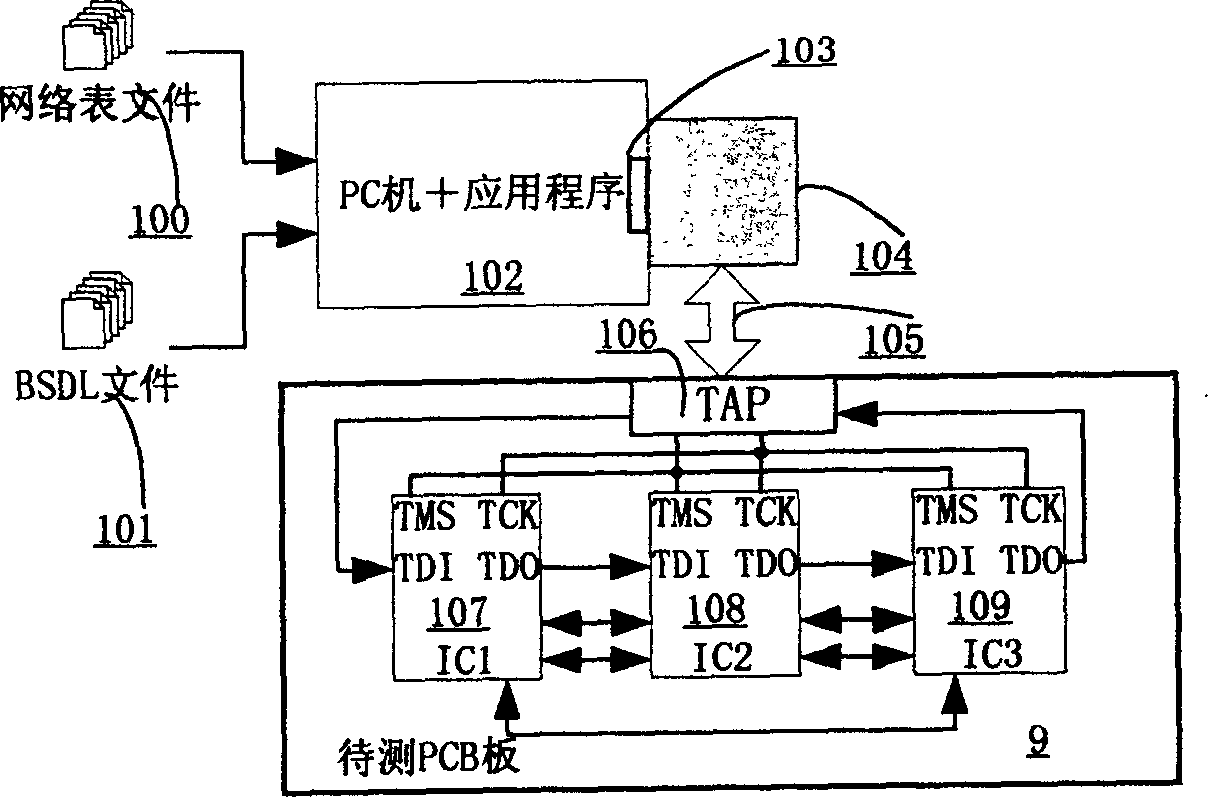

Boundary scan testing device for integrated circuit

InactiveCN1542459AImprove pass rateImprove production testabilityElectrical testingCommunications-electronicsBoundary scan testing

The integrated circuit boundary scanning measurement device is used in measuring integrated circuit on printed circuit board in communication electronic technology. The boundary scanning measurement device utilizing the parallel port of computer includes bottom interface module, initializing module, measurement vector producing module, measurement module, fault analyzing and locating module, and boundary scanning describing language file analysis module. Boundary scanning measurement is completed via making full use of the PC resource, i. e., compiling PC boundary scanning application program, utilizing the parallel port in PC and assisting with the JTAG interface hardware unit. The present invention can complete the boundary scanning measurement of devices in printed circuit board and the whole printed circuit board. The present invention can raise the measurement capacity of printed circuit boards.

Owner:徐州铁手五金工具制造有限公司

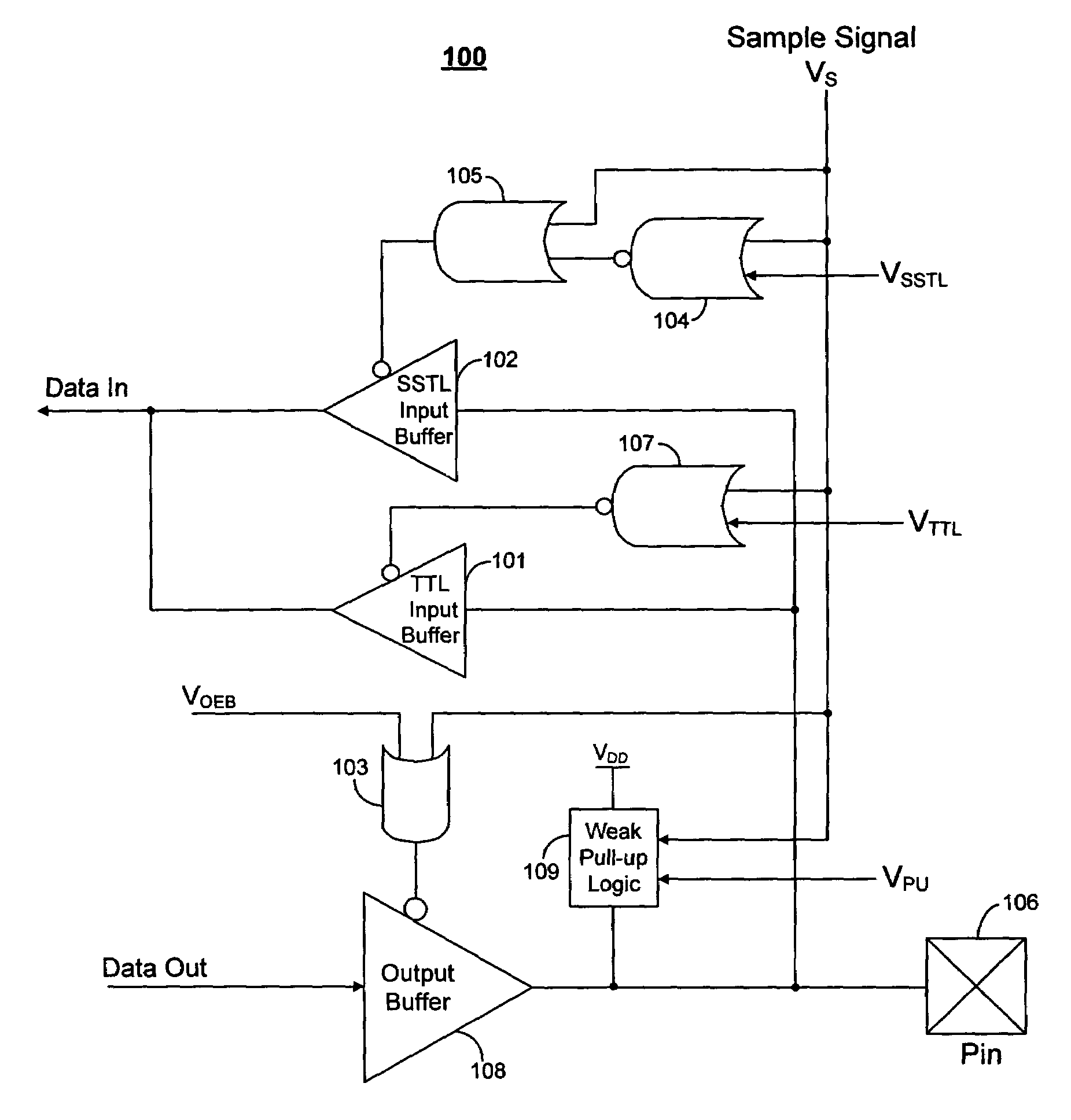

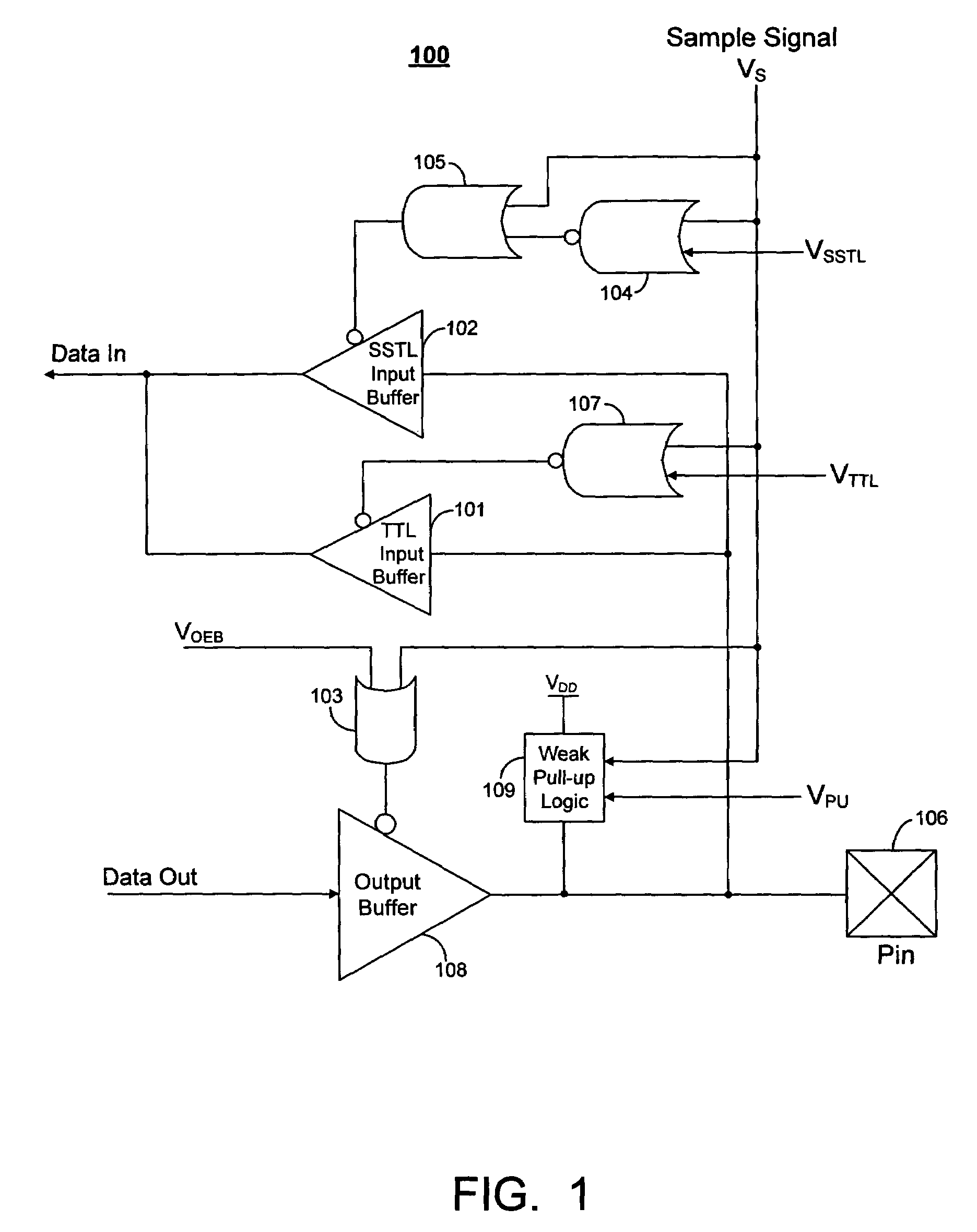

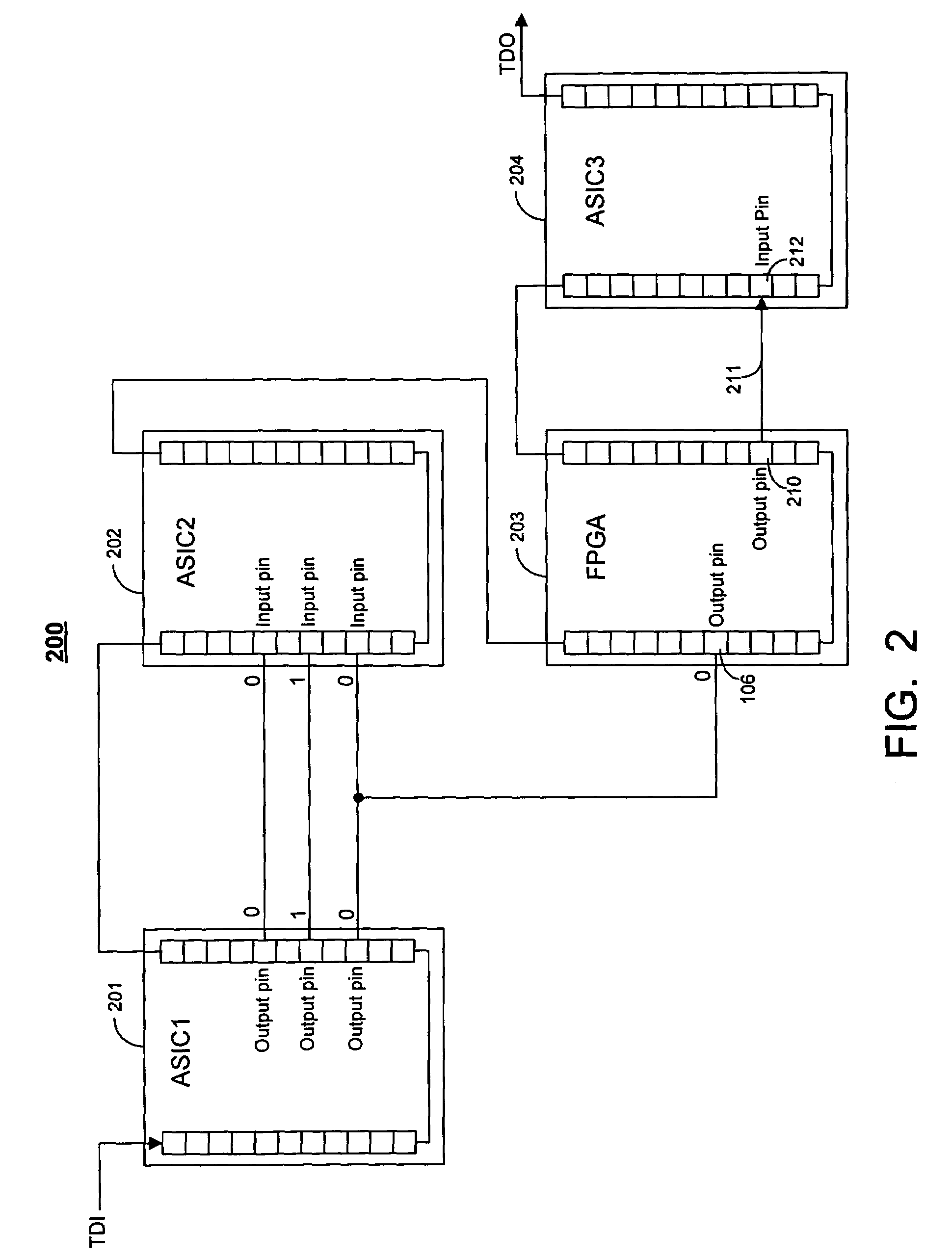

Techniques for capturing signals at output pins in a programmable logic integrated circuit

InactiveUS7406642B1Easy to implementLess timeElectronic circuit testingTransmission line coupling arrangementsProgrammable logic deviceSignal on

Techniques are provided for capturing external signals at output pins on a programmable logic integrated circuit (IC) during a boundary scan test. A JTAG sample signal is routed to an input / output block on a chip and active during a JTAG sampling phase. An input buffer coupled to an output pin is turned on during the JTAG sample phase. Logic gates enable the input buffer in response to the JTAG sample signal so that the input buffer can capture a signal on the pin. The input buffer is turned off after the JTAG sampling phase to conserve power. The output buffer coupled to the pin that receives the test signal is tristated to prevent contention during the JTAG sampling phase. The techniques of the present invention can be used to test board level interconnects in less time and are easy to implement.

Owner:ALTERA CORP

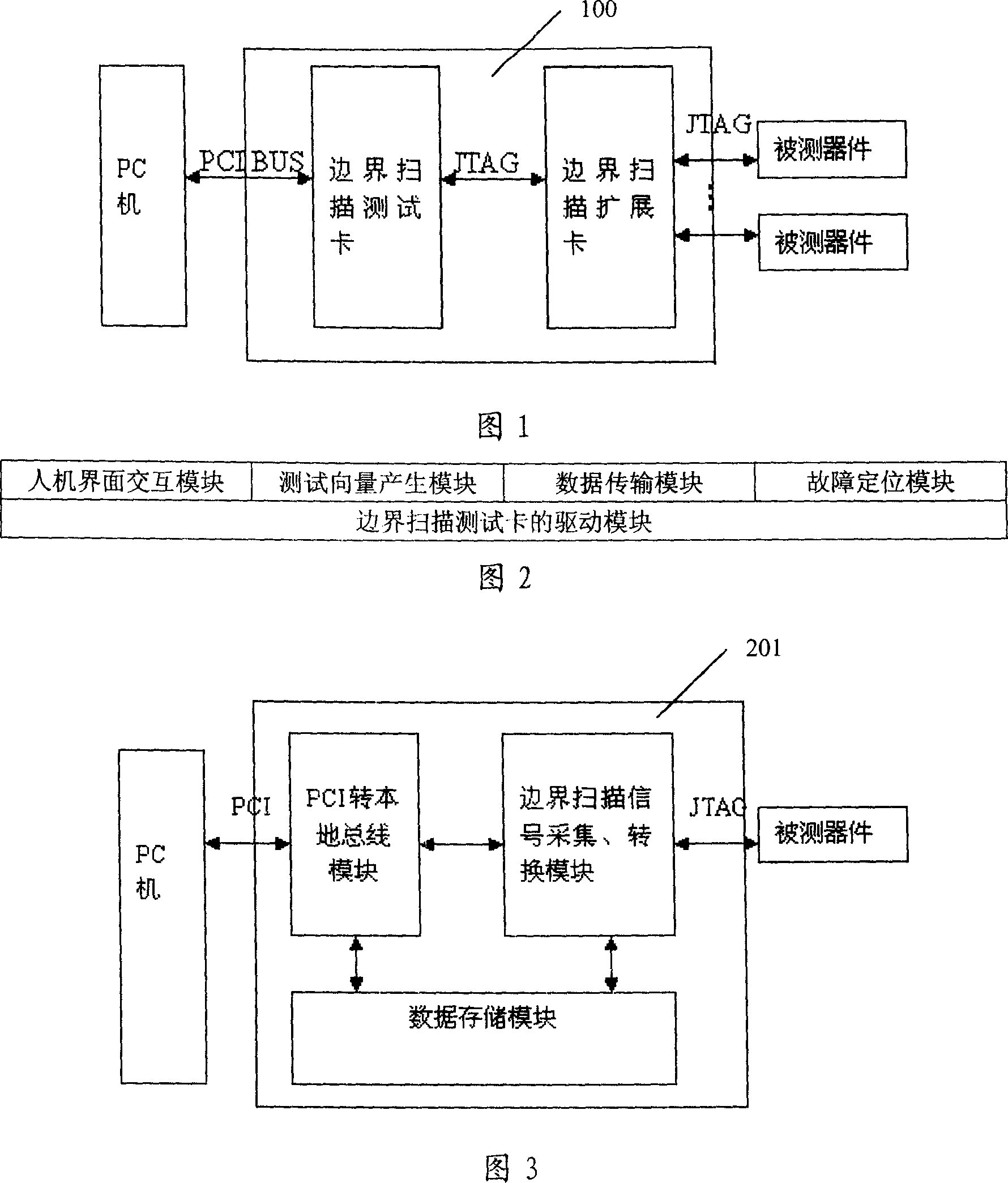

Device and method for realizing border-scanning multi-link test

InactiveCN101071155AExpansion is simple, convenient and flexibleReduce the number of times to replace the scan linkDigital circuit testingExpansion cardTest card

This invention discloses multi-link testing devices and methods which can realize boundary scan. Including: PC module, boundary-scan test card and boundary scan card expansion card; described boundary-scan extended card composed by boundary scan expansion modules , used in a number of boundary-scan test link, through analytical sent from the PC port choice test configuration, boundary scan port expansion card on the number of boundary scan link together into a new boundary scan link , for testing. The invention through the boundary-scan test device provide to PC users easy-to-use interface, test vector generation and the analysis of test data, through PC hardware and procedures rapidly with good boundary-scan test and link extension, chains expansion is easy and convenient flexible scanning, reduced the frequency of chains replacement and increase test coverage and achieve program simple, economical and practical.

Owner:ZTE CORP

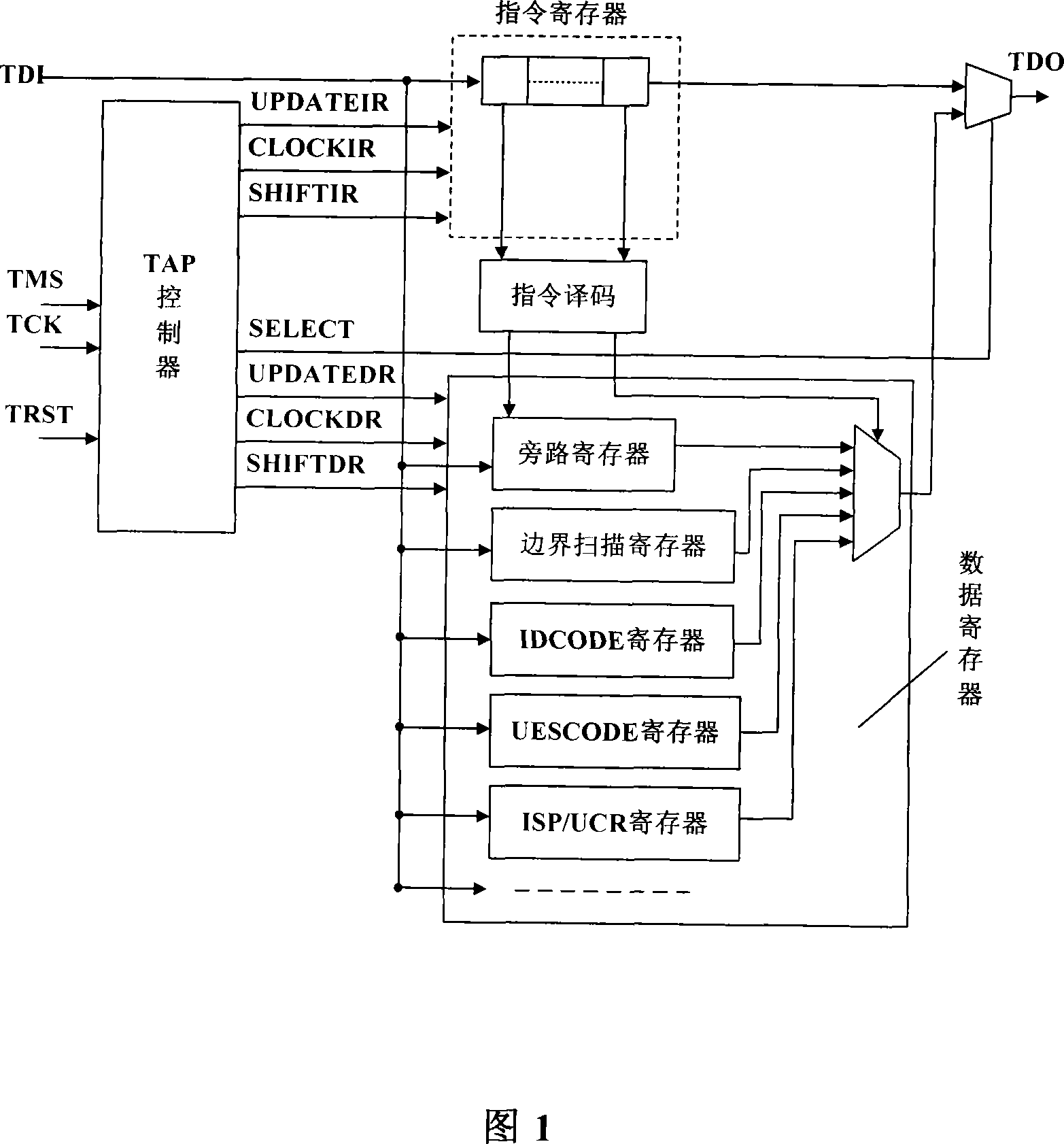

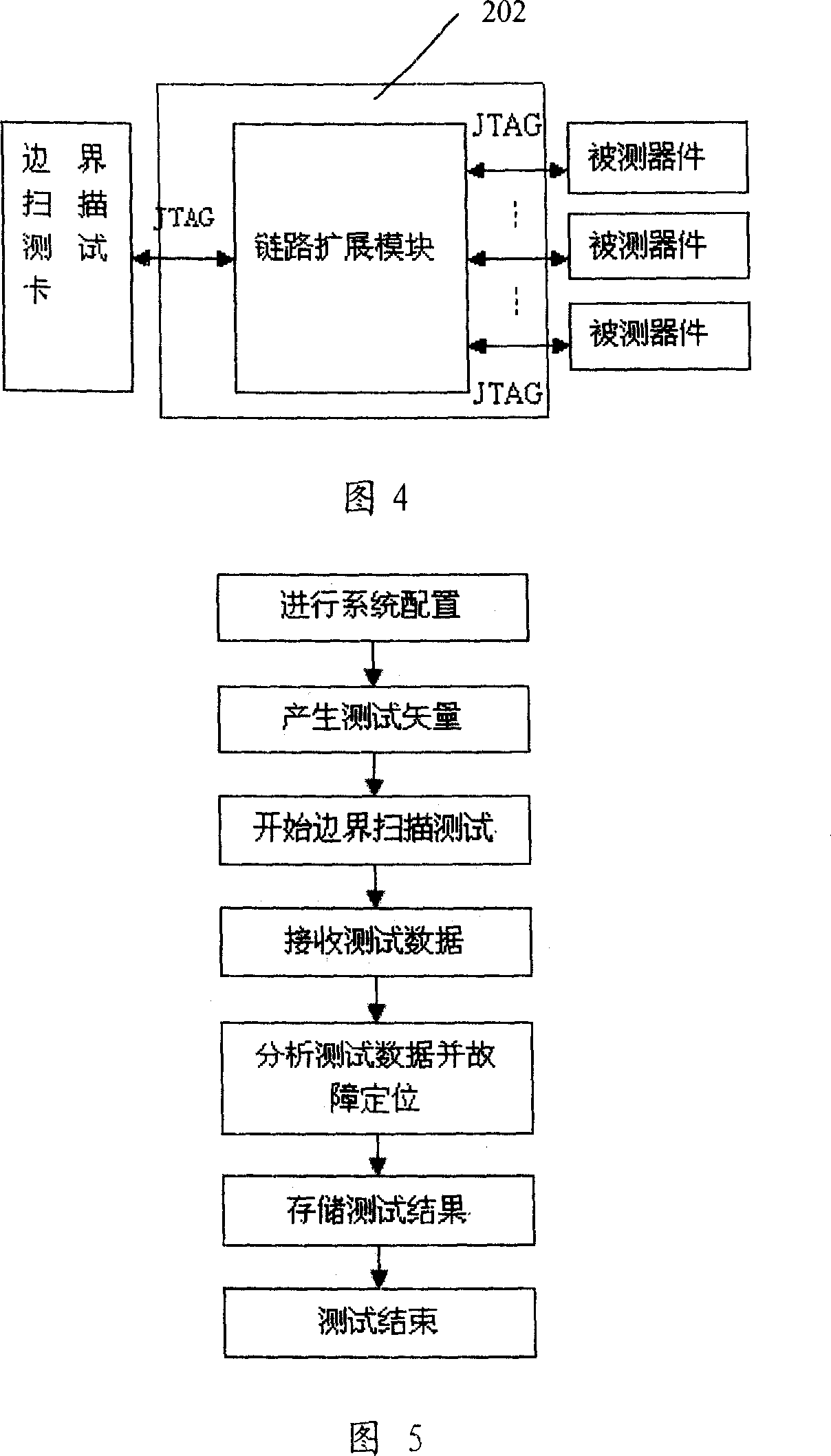

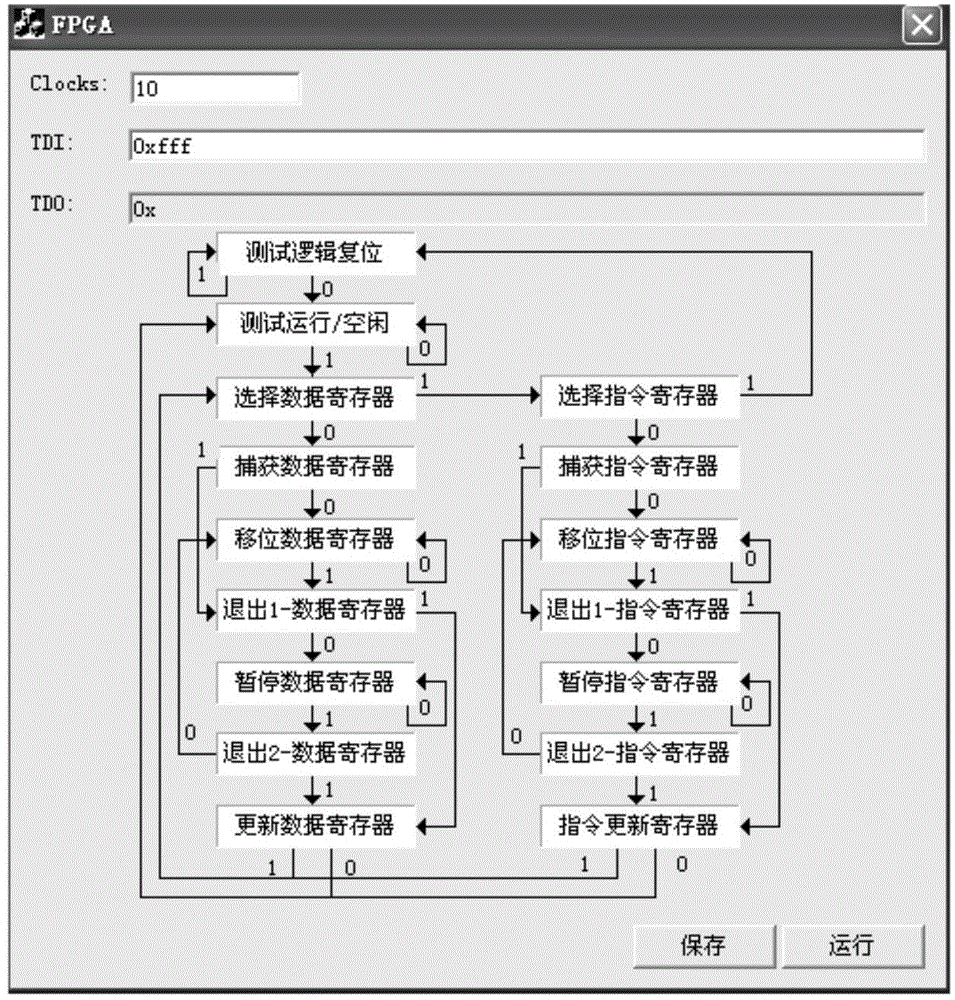

Boundary scan testing controller and testing method thereof

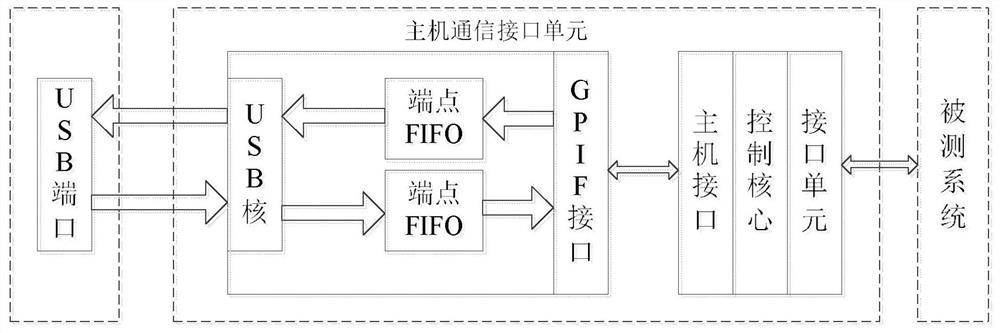

ActiveCN101097242AImplement storageBoundary Scan Test ImplementationElectronic circuit testingElectric digital data processingTransducing UnitTest response

The invention discloses a controller and testing method of boundary scanning, said controller includes PC unit, USB interface unit, two-end memory unit, control and transforming unit; said PC unit can set test, generate test vector, send and receive test data, analyze test data, store test result and USB drive of controller; said USB interface unit realizes communication between boundary scanning test controller and computer; said two-end memory unit realizes memory of test vector and stores test response; said control and transforming unit generates boundary scanning test clock to realize transforming test data to JTAC signal, and realizes reading and writing of data from two-end memory unit. The invention adopts USB interface, memory of two-end memory unit and FPGA design, plug and play, data transmission and boundary scanning test can be preceded at the same time, test speed is increased.

Owner:ZTE CORP

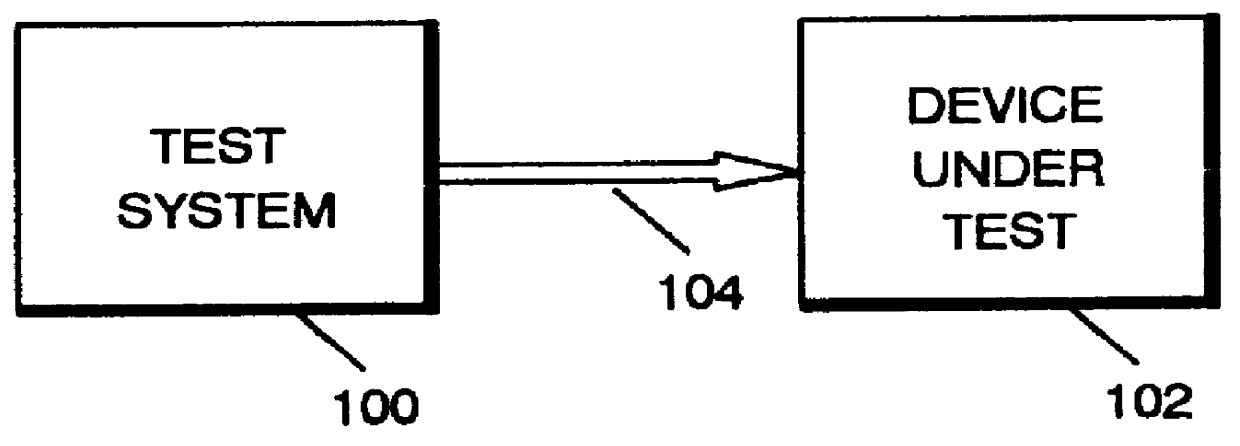

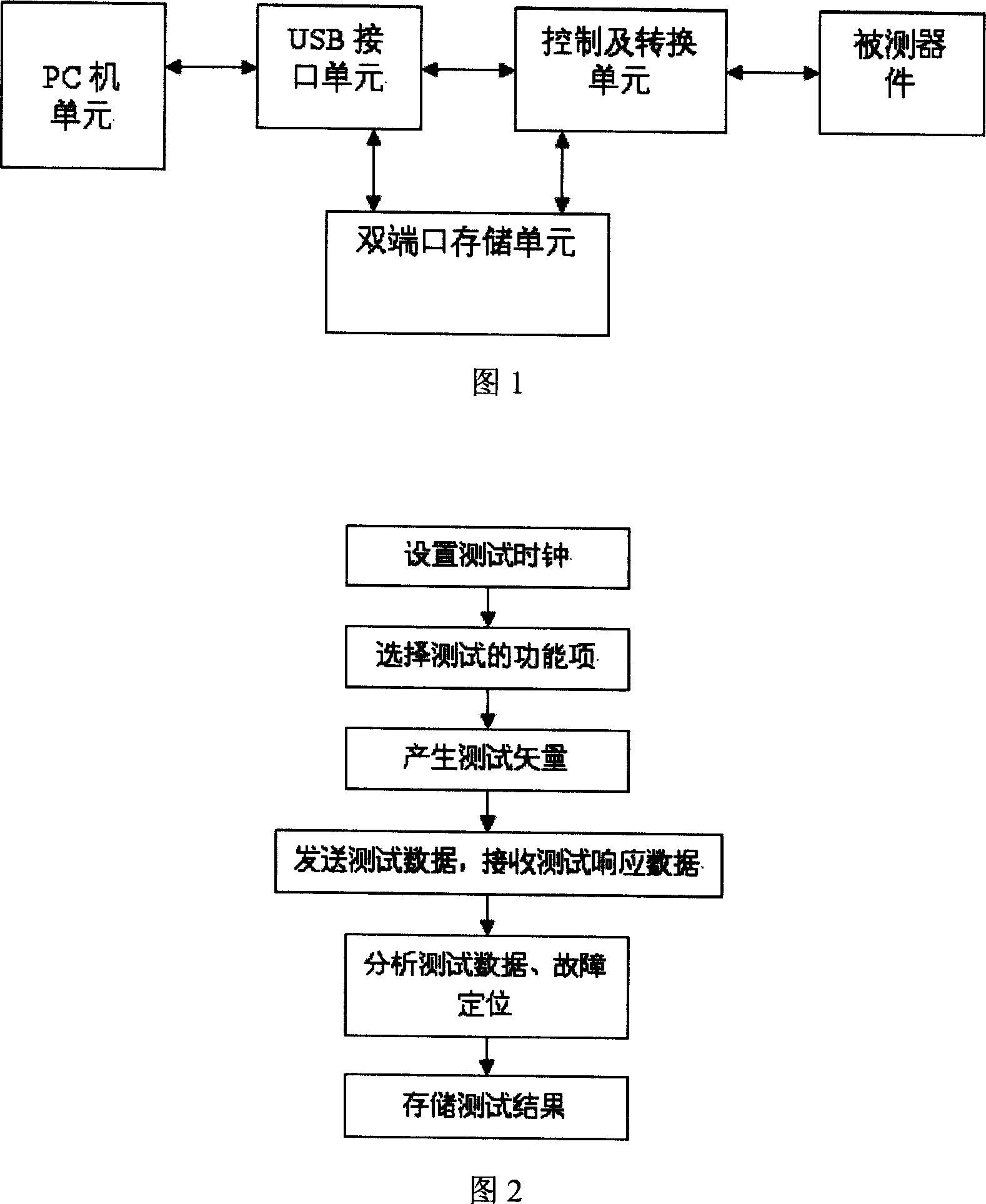

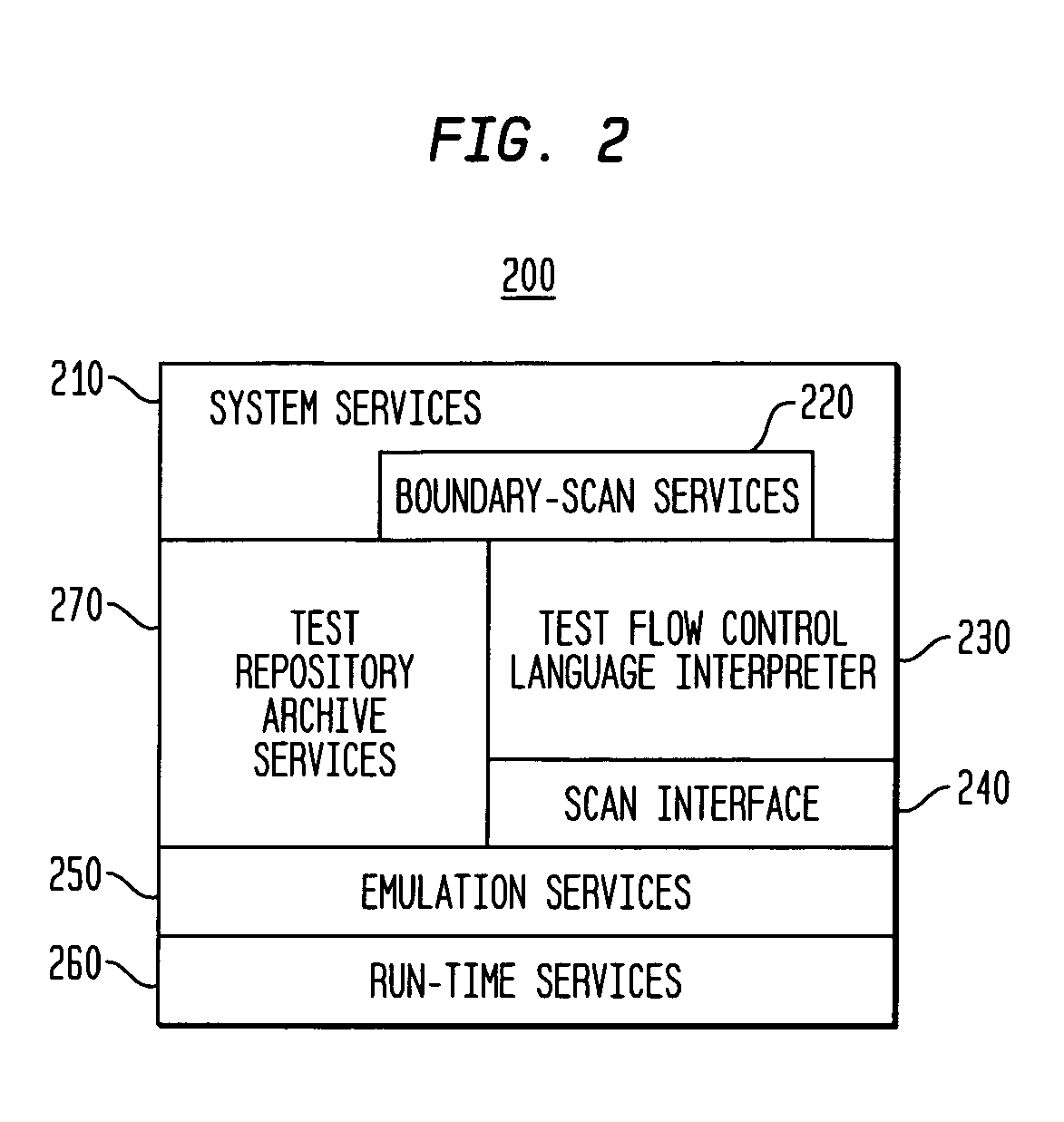

System for flexible embedded Boundary Scan testing

ActiveUS7149943B2Electronic circuit testingSpecial data processing applicationsData informationParallel computing

A flexible Boundary Scan test system is disclosed. The system includes an interpreter module operable to execute a program element selected from a plurality of program elements that include at least one instruction type having an interface to identify and execute selected functions wherein each of the selected functions has associated therewith at least one data information item. In one aspect of the invention, selected ones of the functions are composed of a plurality of functions. In another aspect of the invention, the instruction includes parameters and adornments for determining the selected function execution.

Owner:LUCENT TECH INC

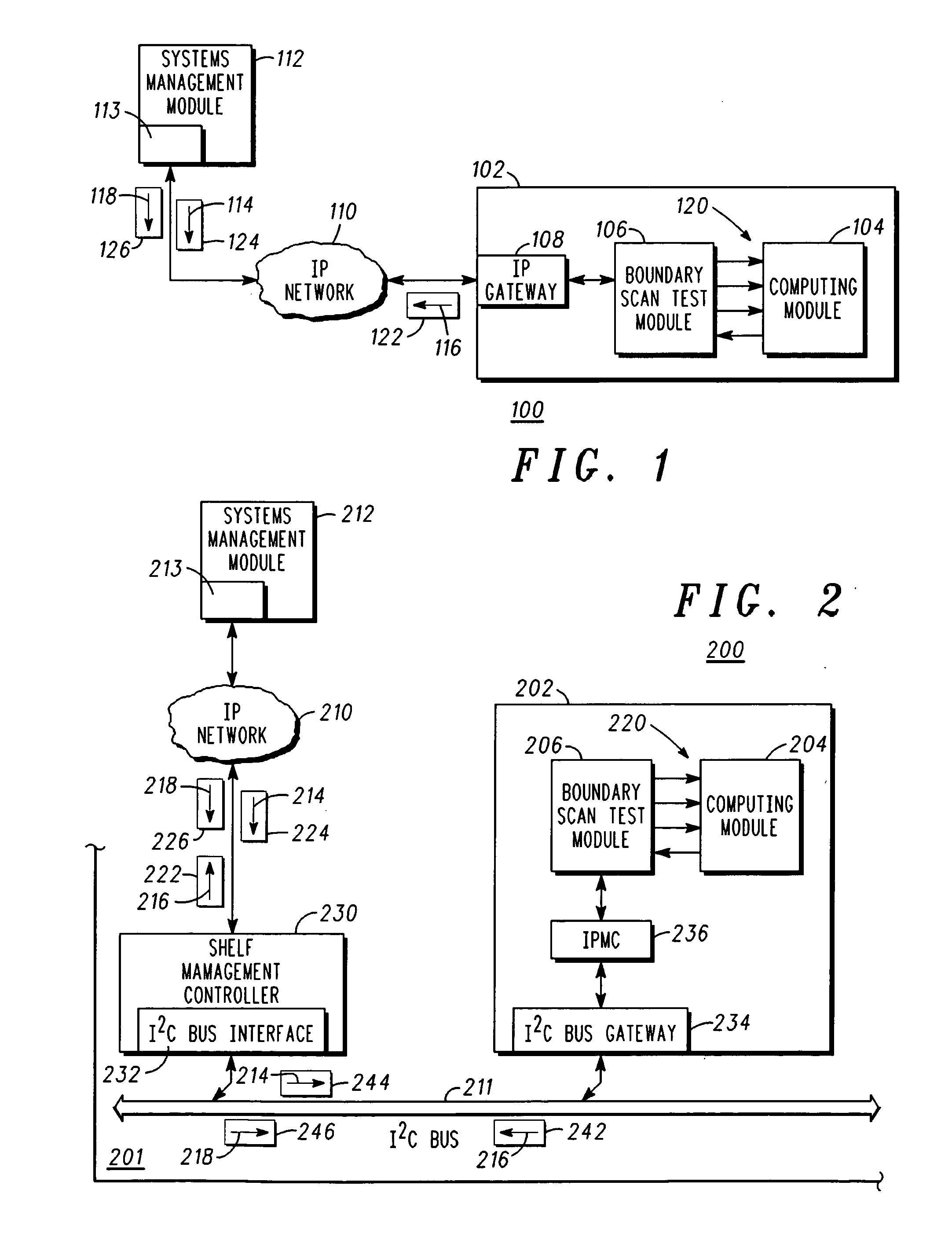

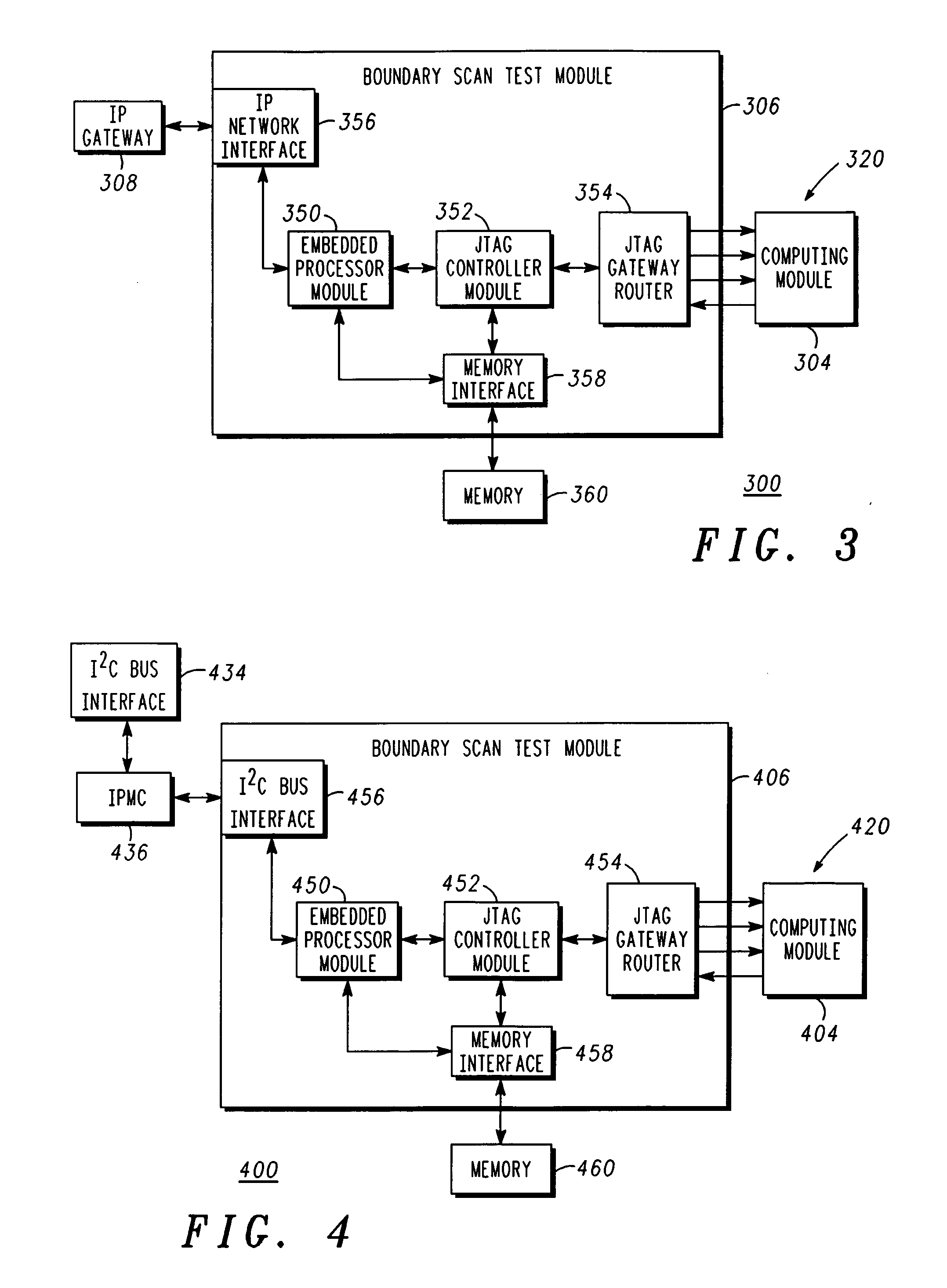

Boundary scan testing system

InactiveUS20060200718A1Printed circuit testingElectric digital data processingComputer hardwareBoundary scan testing

A boundary scan testing system may include a baseboard (102, 202), a computing module (104, 204) coupled to the baseboard, and a boundary scan test module (106, 206, 306, 406) coupled to the computing module, where the boundary scan test module is coupled to execute a boundary scan test (120, 220, 320, 420) on the computing module via a set of boundary scan instructions (114, 214) received remotely over at least one of an IP network (110, 210) and an I2C bus (211).

Owner:SMART EMBEDDED COMPUTING INC

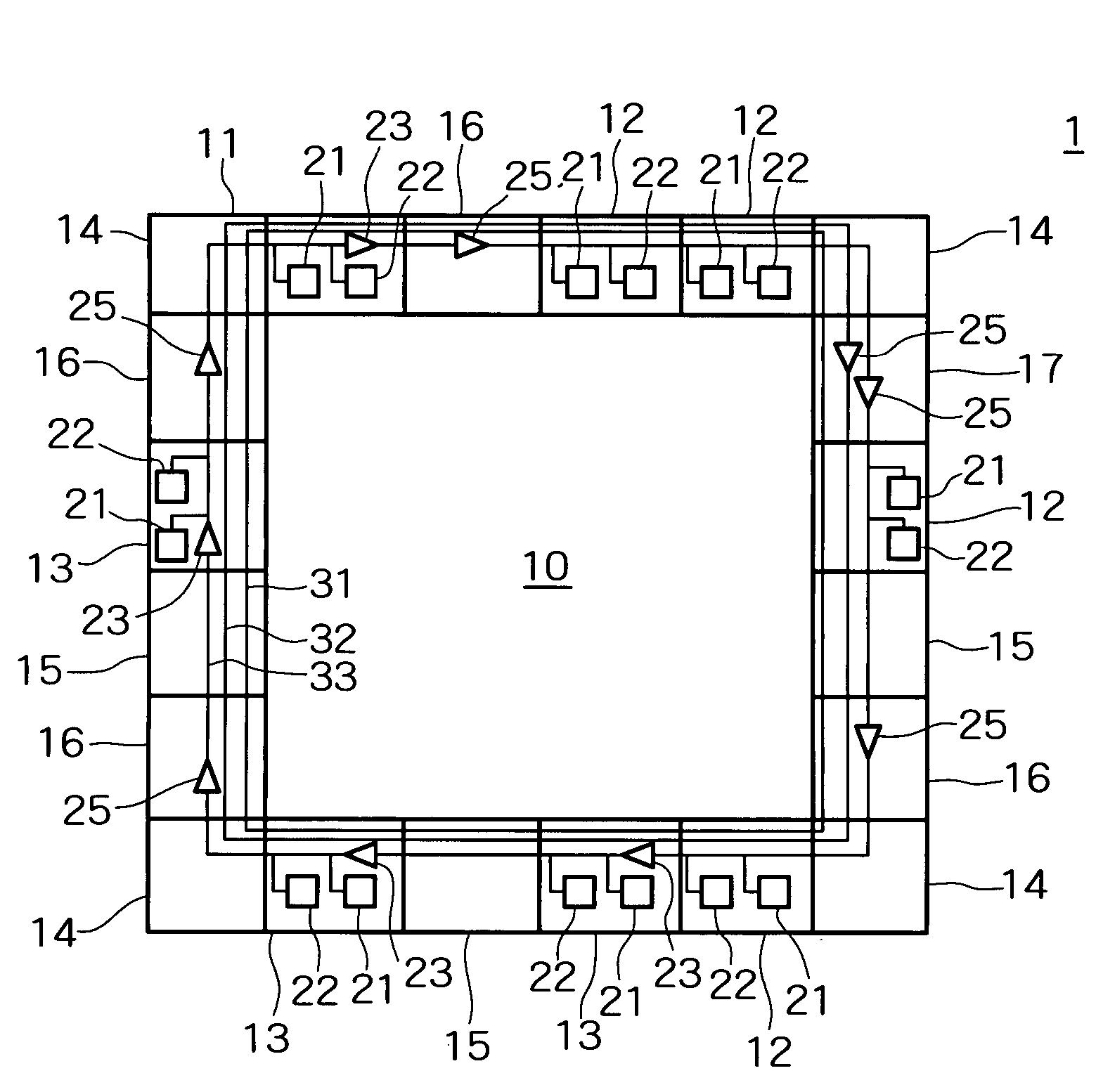

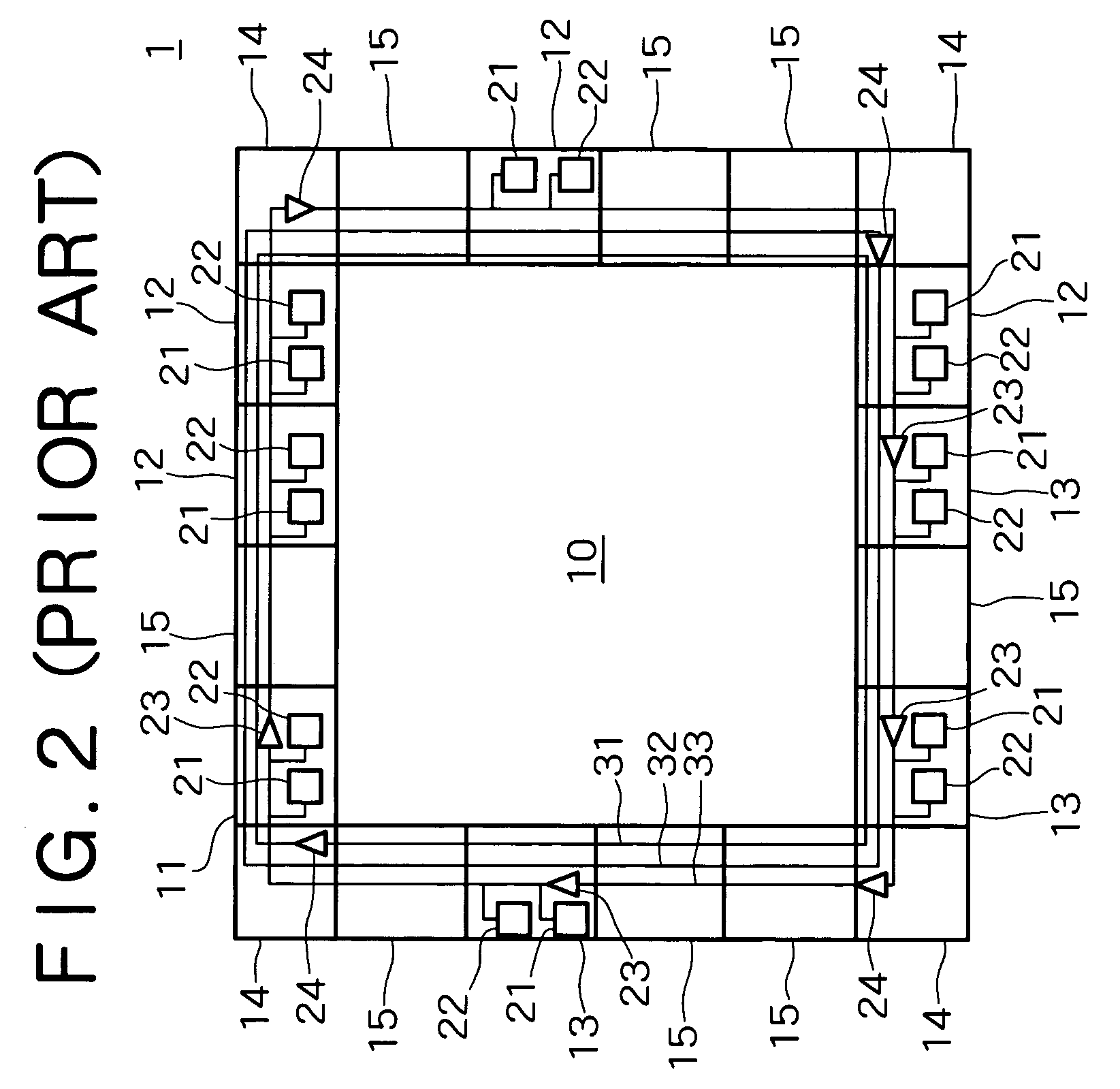

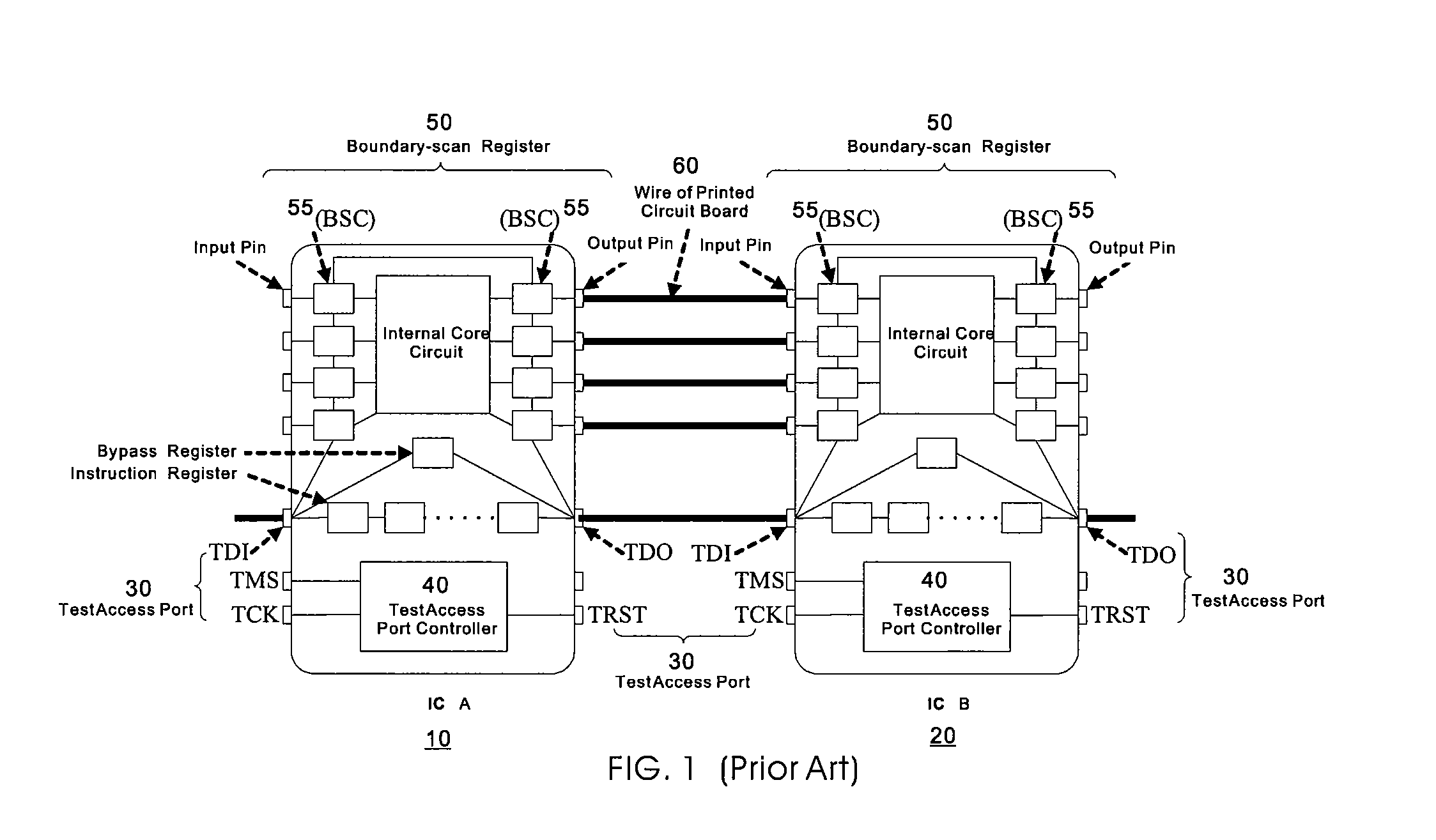

Semiconductor integrated circuit device with boundary scan test and design automation apparatus, boundary scan test method and program

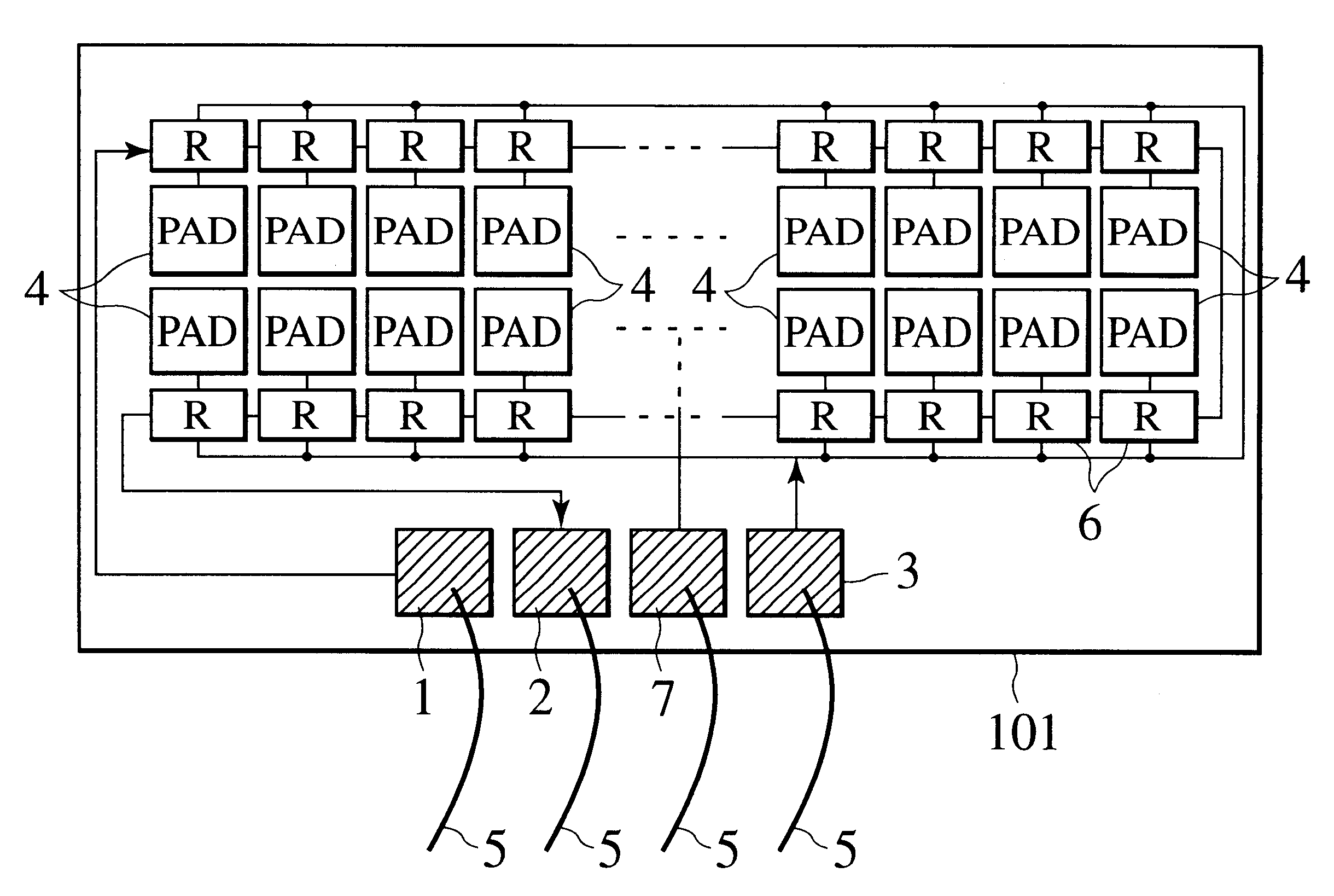

InactiveUS7263679B2Improve reliabilityImprove precisionElectronic circuit testingDetecting faulty computer hardwareBoundary knot methodEngineering

An area for layout of a plurality of I / O cells (called an “I / O area”) is provided in the peripheral portion of a chip and signal wirings for transferring test signals to the I / O cells are provided in the layout direction of the I / O cells. At least one empty cell provided in the I / O area at a position where I / O cells are not provided has a repeater circuit which constitutes a transfer path for the test signal. The repeater circuit receives the test signal and outputs the test signal. This structure provides a suitable semiconductor integrated circuit device adaptable for an ASIC or the like, which can adjust the delay of a test signal to be transferred along the chip's peripheral portion by suppressing an increase in the delay and degradation in waveform depression.

Owner:RENESAS ELECTRONICS CORP

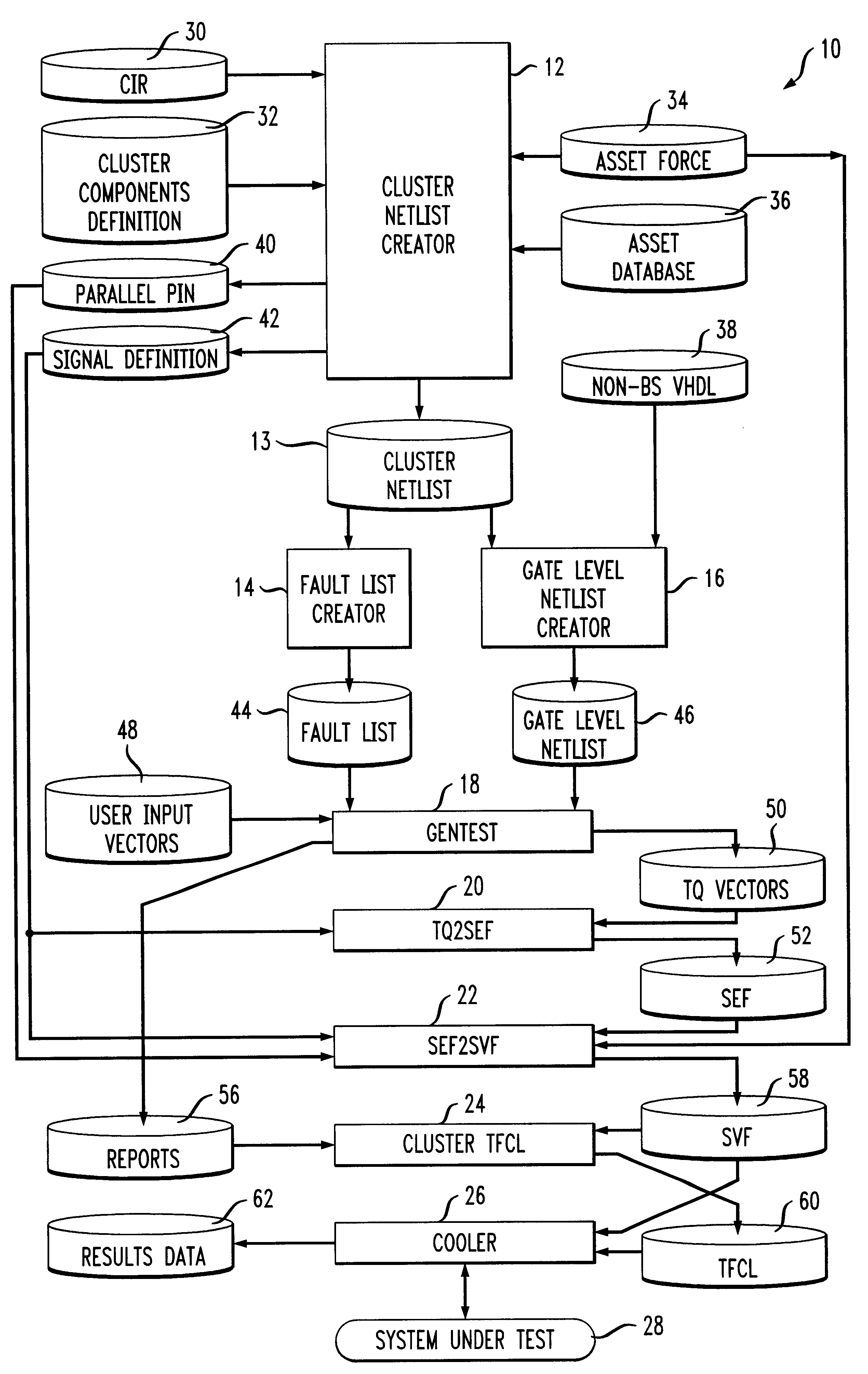

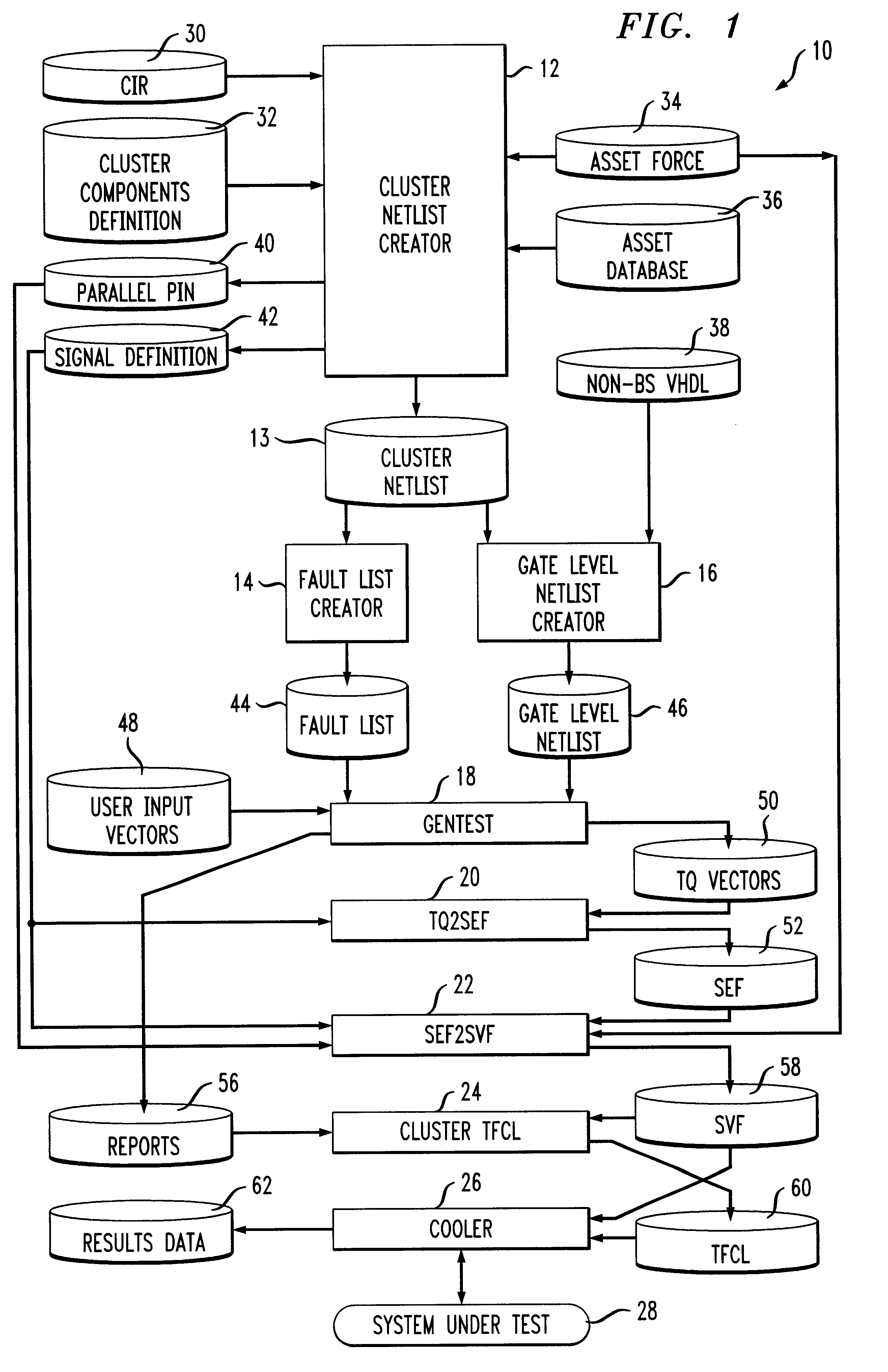

Method and system for testing cluster circuits in a boundary scan environment

InactiveUS6378094B1Electronic circuit testingError detection/correctionSystem identificationComputer science

A method and system for testing circuit clusters in a boundary scan environment identifies the circuit clusters and corresponding neighboring boundary scan elements, and generates one or more test vectors to be applied to the cluster under test. The generated test vectors are serialized and input into an identified boundary scan element connected to the cluster being tested in the form of a boundary scan test chain. The output of the applied test vectors is observed from an output of another correspondingly identified boundary scan element connected to the cluster under test. During generation of test vectors a list of faults for detecting by each generated vector is maintained such that the observed output can be used to diagnose faults at the component level within the identified cluster.

Owner:LUCENT TECH INC

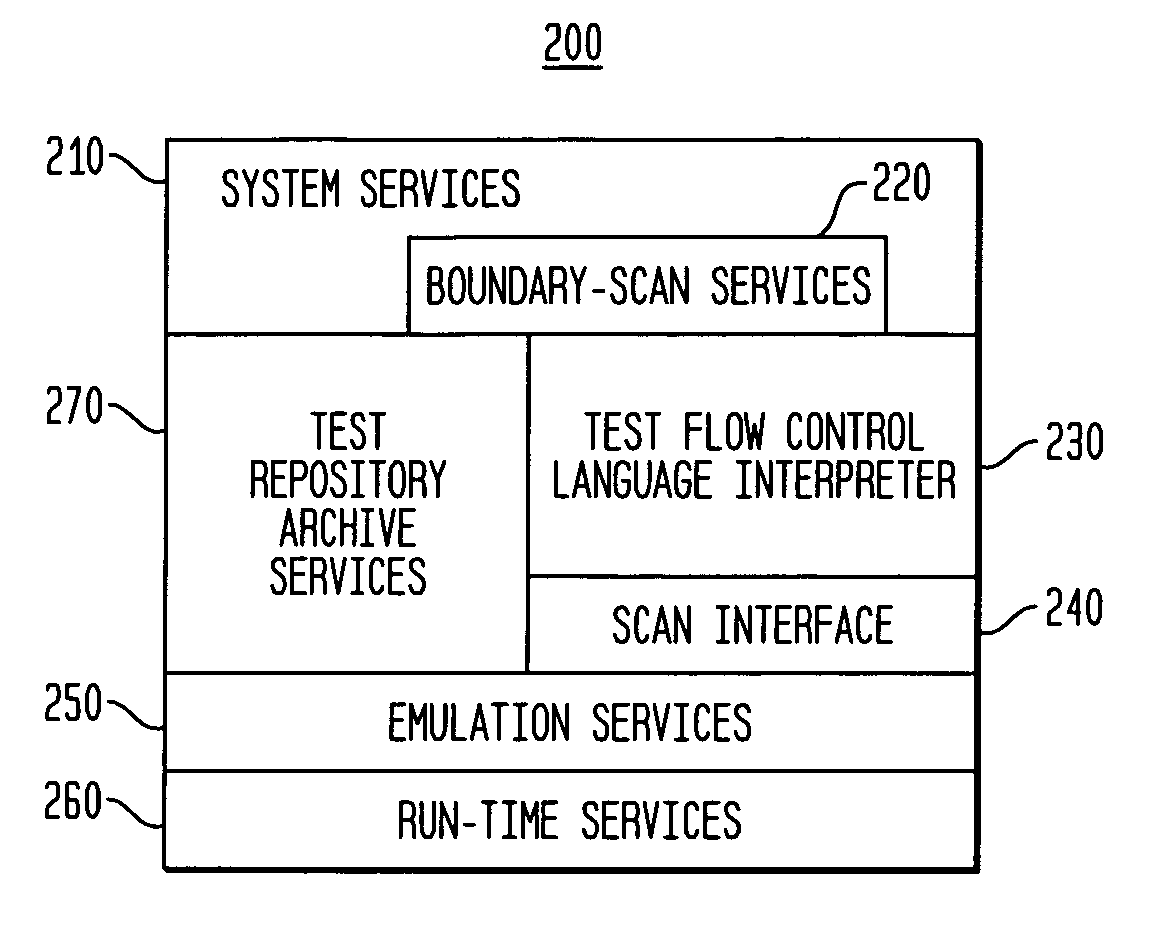

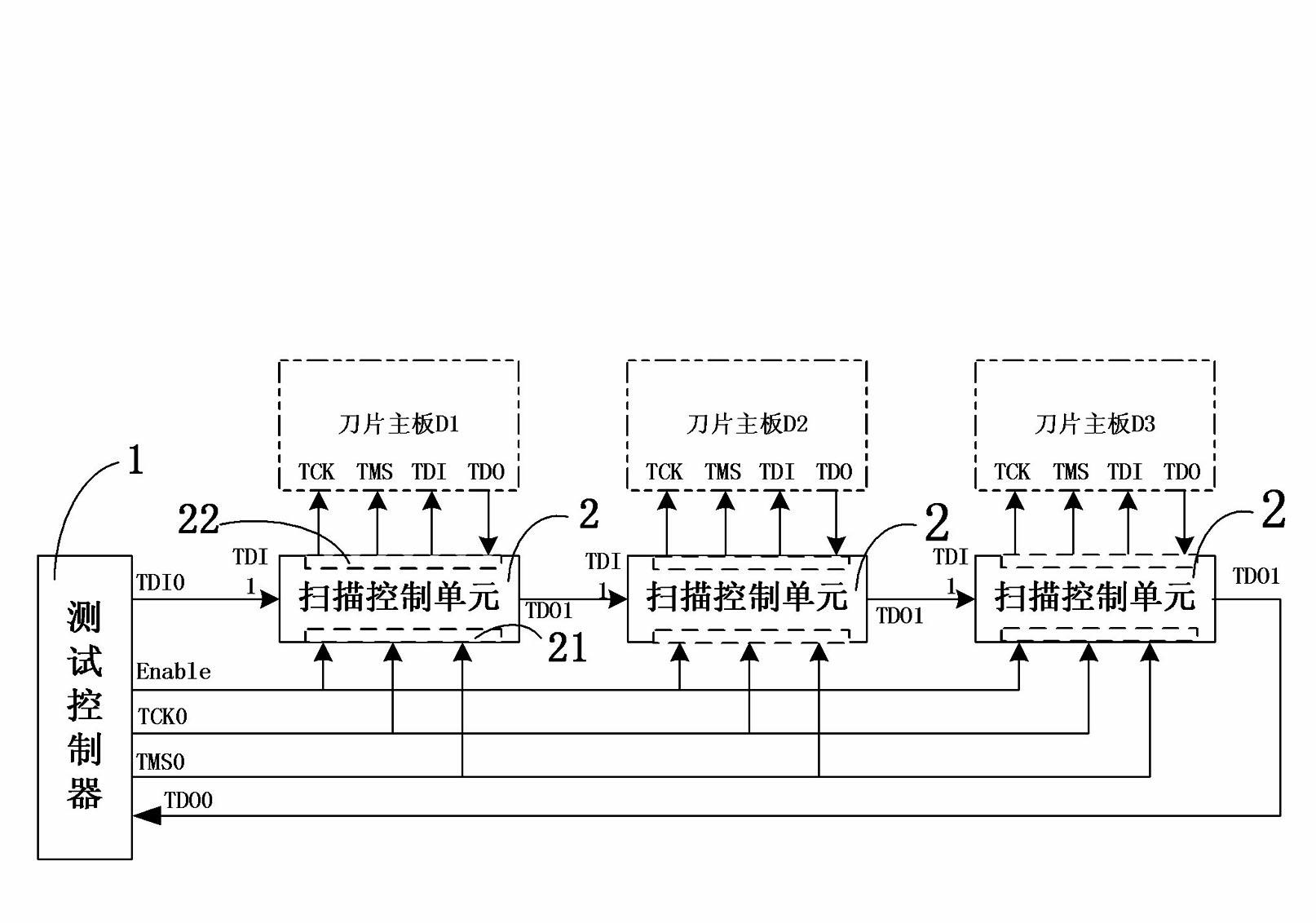

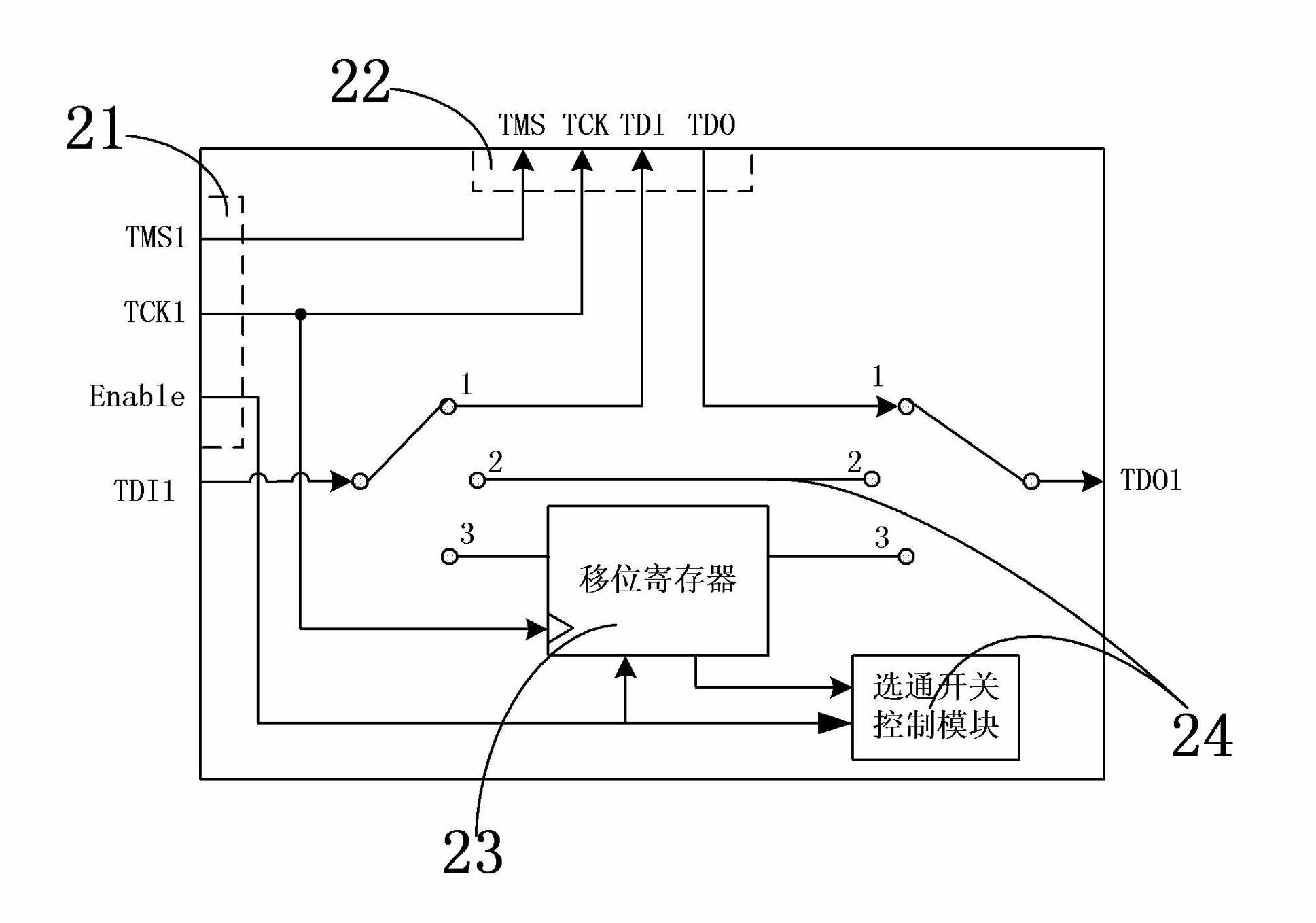

Multi-link parallel boundary scanning testing device and method

ActiveCN102621483ASolve the problem that the increase and decrease configuration of multiple boundary scan links cannot be automatically completedSolve test problemsElectrical testingTest efficiencyMulti link

The invention discloses a multi-link parallel boundary scanning testing device and method. The device comprises a testing controller and scanning control units which correspond to boundary scanning chains to be tested one by one, wherein each scanning control unit comprises a multi-link control logic and test data input port, a test result output port, a controller interface and a boundary scanning chain interface. The method comprise the following steps: (1) the testing controller transmits an invalid signal, and detects the quantity of all boundary scanning chains to be tested which are arranged in parallel; (2) the testing controller sets a scanning selection code, and transmits the scanning selection code to each scanning control unit; (3) the testing controller outputs a valid signal, and the scanning control units control the selection and switch-off of the boundary scanning chains to be tested according to the scanning selection codes; and (4) the test controller outputs boundary scanning test data, and the scanning control units test the selected boundary scanning chains to be tested and transmit a final test result to the testing controller. The device and the method have the advantages of high testing efficiency, and easiness and convenience for using.

Owner:湖南长城银河科技有限公司

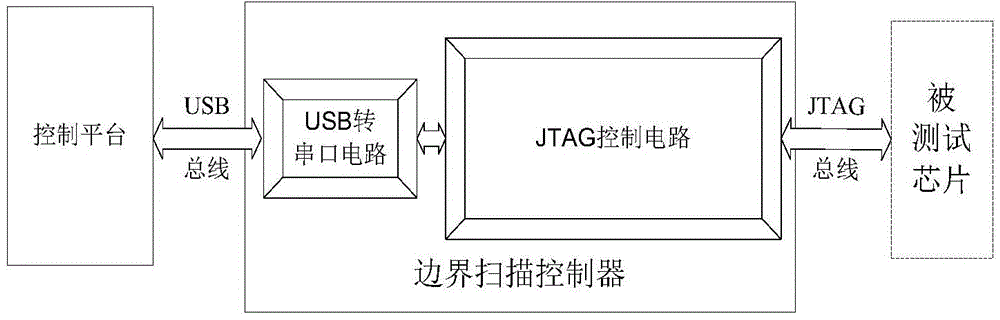

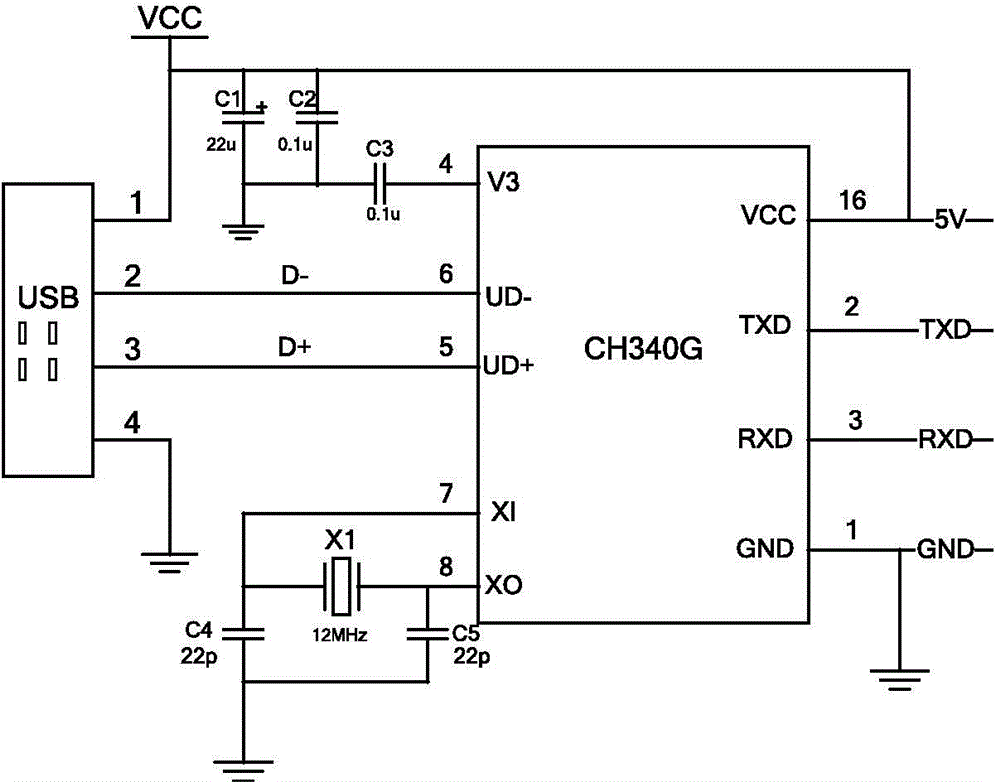

Simple boundary scan test system and method based on single-chip microcomputer

The invention discloses a simple boundary scan test system based on a single-chip microcomputer. The simple boundary scan test system comprises a control platform, a USB-to-serial port conversion circuit and a JTAG control circuit, wherein the control platform is used for transmitting TMS signals and TCK signals to a tested chip, controlling the tested chip to enter the corresponding working state, and receiving TDO signals output by the tested chip; the USB-to-serial-port conversion circuit is used for receiving USB bus signals output by the control platform, converting the USB bus signals into TMS signals and TCK signals in the serial data format and outputting the TMS signals and the TCK signals to the JTAG control circuit and also used for receiving TDO signals in the serial data format output by the JTAG control circuit, converting the TDO signals into the USB bus signals and outputting the USB bus signals to the control platform; the JTAG control circuit is used for receiving TDO signals output by the tested chip and outputting the TDO signals to the USB-to-serial port conversion circuit. The boundary scan test system is simple in structure and low in cost; the control platform of the system is independently developed, and thus the system is good in safety, and function extension is convenient to perform; the system is good in universality.

Owner:AIR FORCE EARLY WARNING ACADEMY

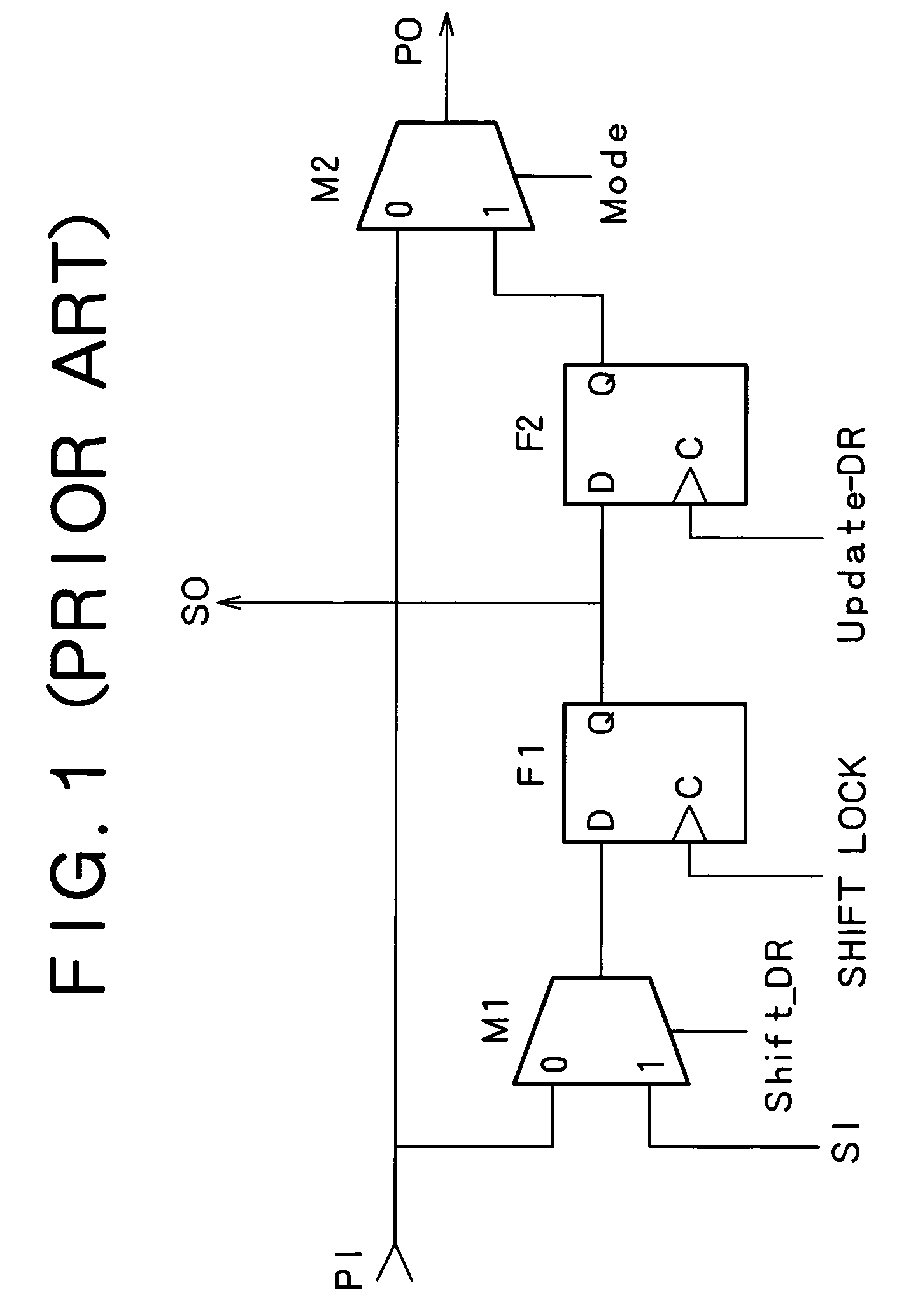

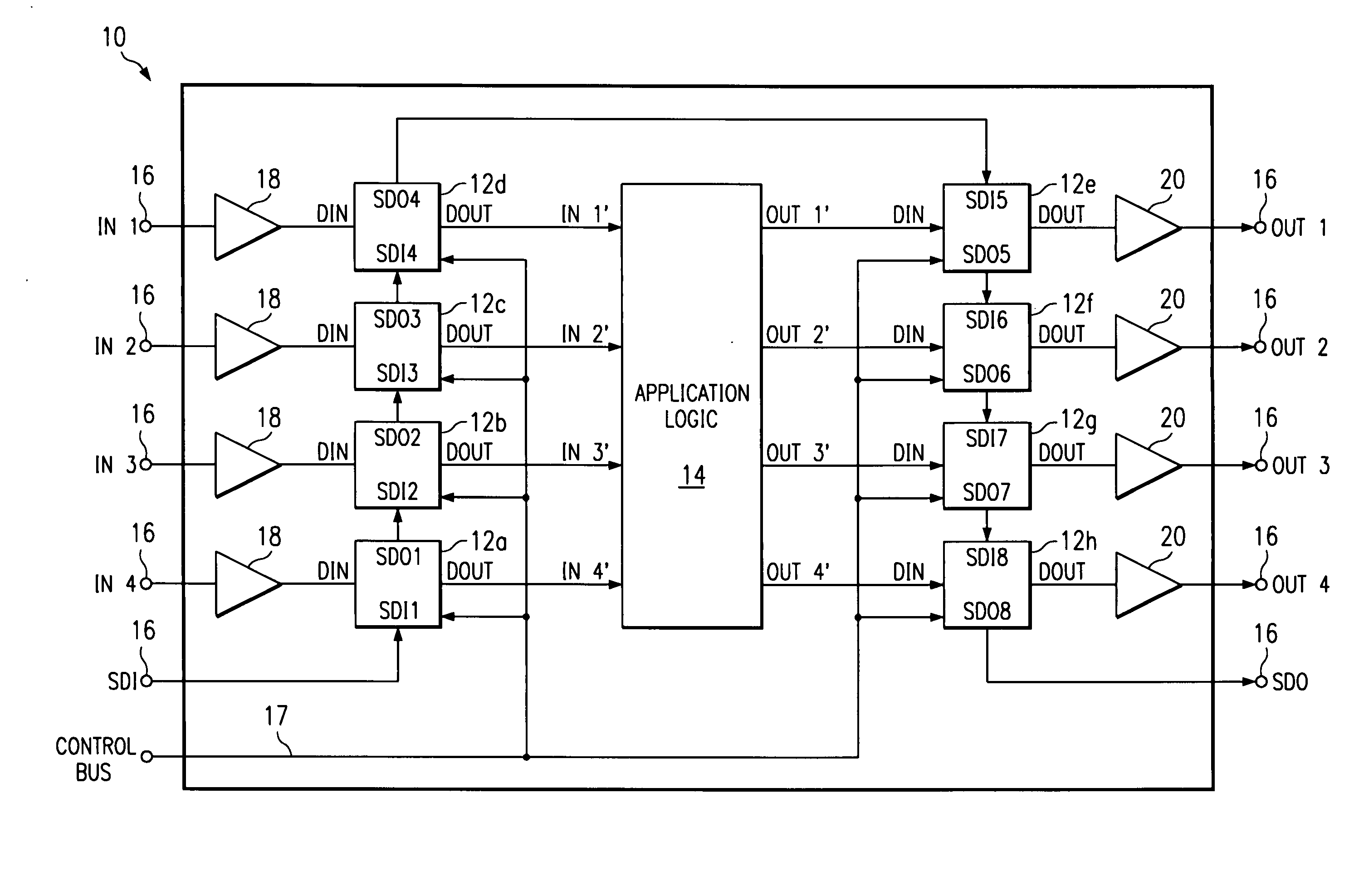

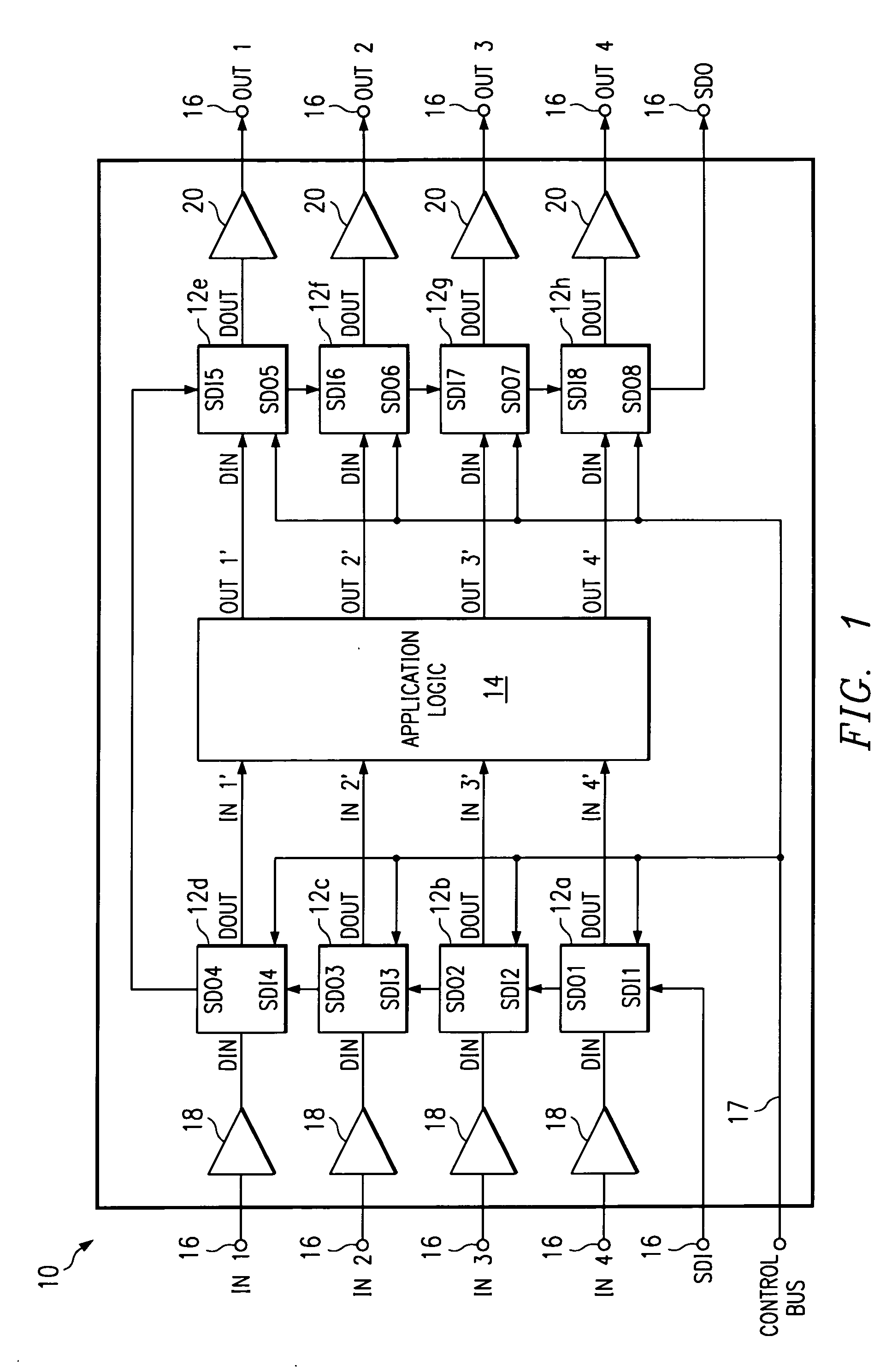

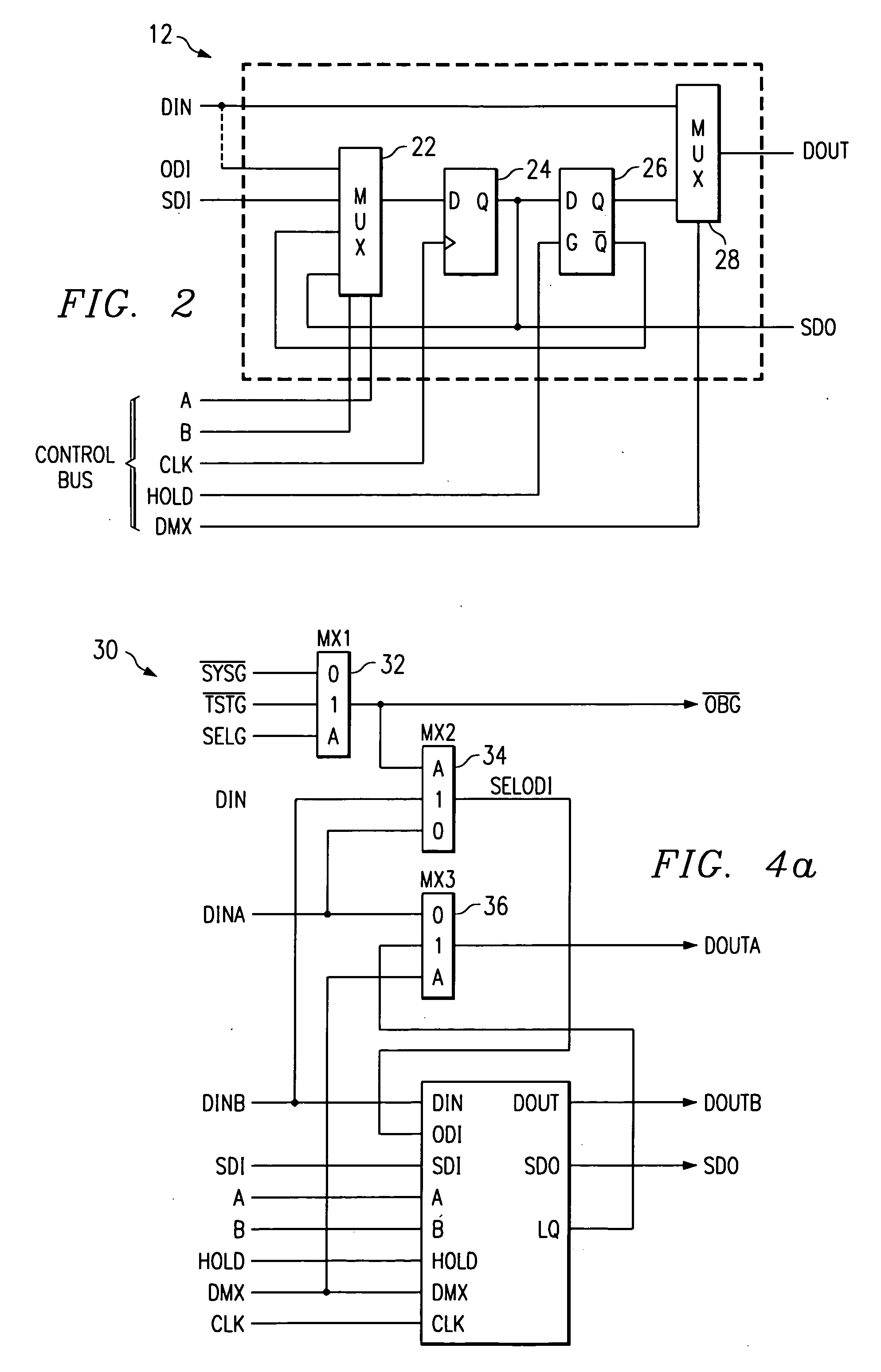

Changing scan cell output signal states with a clock signal

InactiveUS20040199839A1Shorten test timeFacilitate boundary testElectronic circuit testingSpecial data processing applicationsMultiplexingMultiplexer

A test cell (12) provides boundary scan testing in an integrated circuit (10) The test cell (12) comprises two memories, a flip-flop (24) and a latch (26), for storing test data. A first multiplexer (22) selectively connects one of a plurality of inputs to the flip-flop (24). The input of the latch (26) is connected to output of the flip-flop (24). The output of the latch (26) is connected to one input of a multiplexer (28), the second input to the multiplexer (28) being a data input (DIN) signal. A control bus (17) is provided for controlling the multiplexers (22, 28), flip-flop (24) and latch (26). The test cell allows input data to be observed and output data to be controlled simultaneously.

Owner:WHETSEL LEE D JR

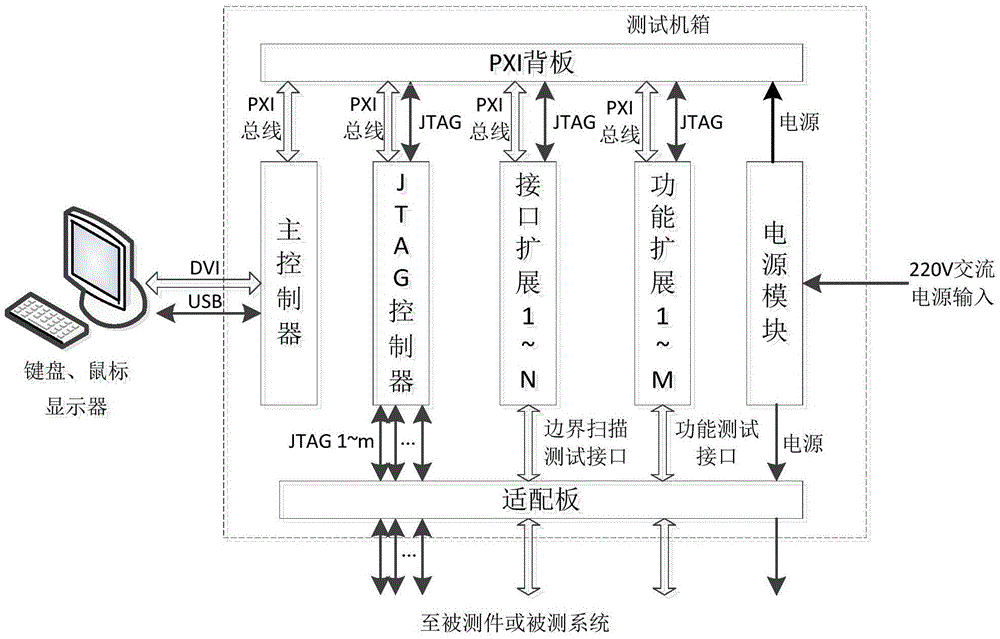

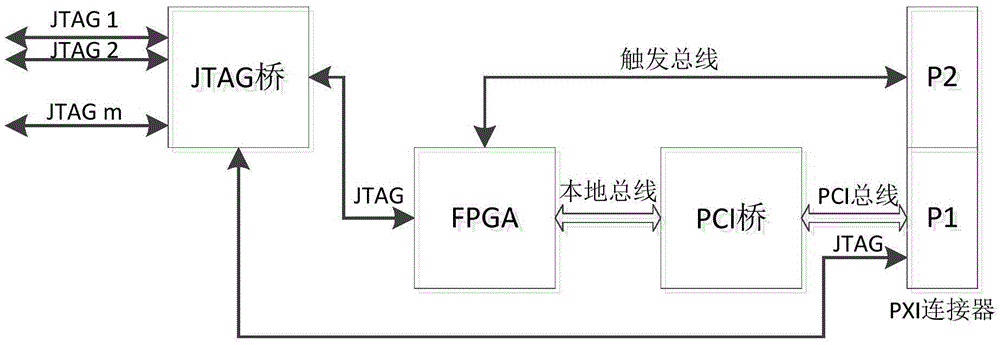

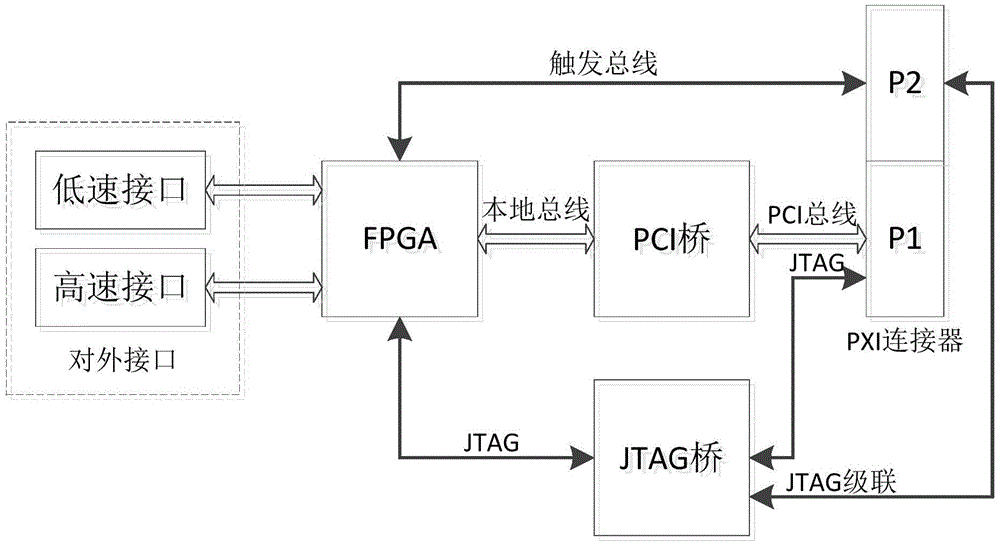

Boundary scan digital circuit test system and test method thereof based on PXI bus

InactiveCN105486999AImprove scalabilityAdvanced and reasonable structureElectrical testingFunctional testingDisplay device

The invention discloses a boundary scan digital circuit test system and a test method thereof based on a PXI bus. The test system comprises a PXI backboard, a main controller, a JTAG controller, 1-N interface expansion modules, 1-M function expansion modules and an adapter board. The PXI backboard is connected with the main controller, the JTAG controller, the interface expansion modules and the function expansion modules; the adapter board is connected with the main controller, the JTAG controller, the interface expansion modules and the function expansion modules; and the main controller is connected with a keyboard and a mouse of a computer through a USB interface, and is connected with a displayer of the computer through a DVI. The boundary scan digital circuit test system has an advanced framework and high expandability, can solve the problem that since the existing test equipment is highly targeted, boundary scan test and function test are incompatible, and system test cannot be realized, and can be served as a general development platform. The invention also discloses the test method of the boundary scan digital circuit test method based on the PXI bus.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

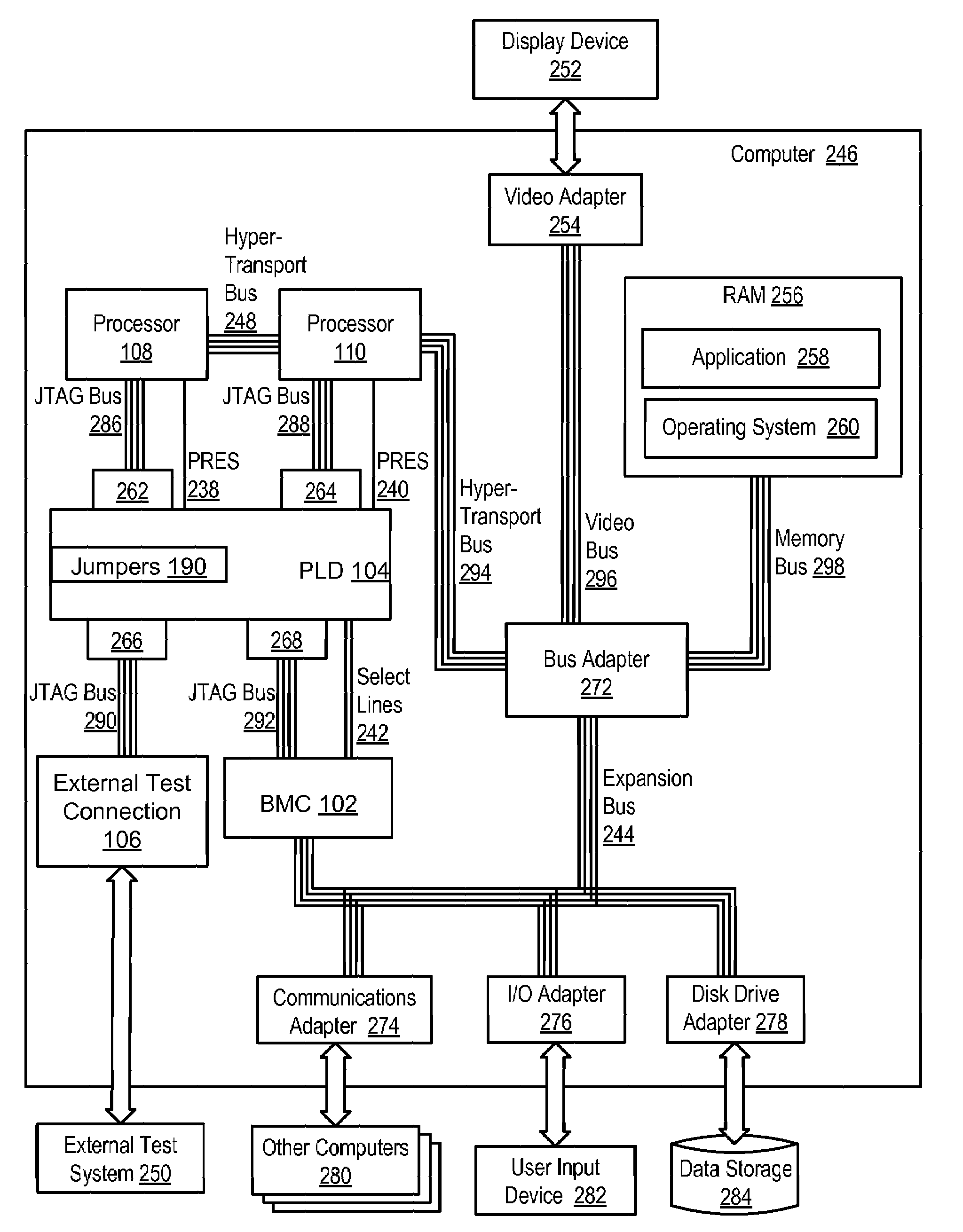

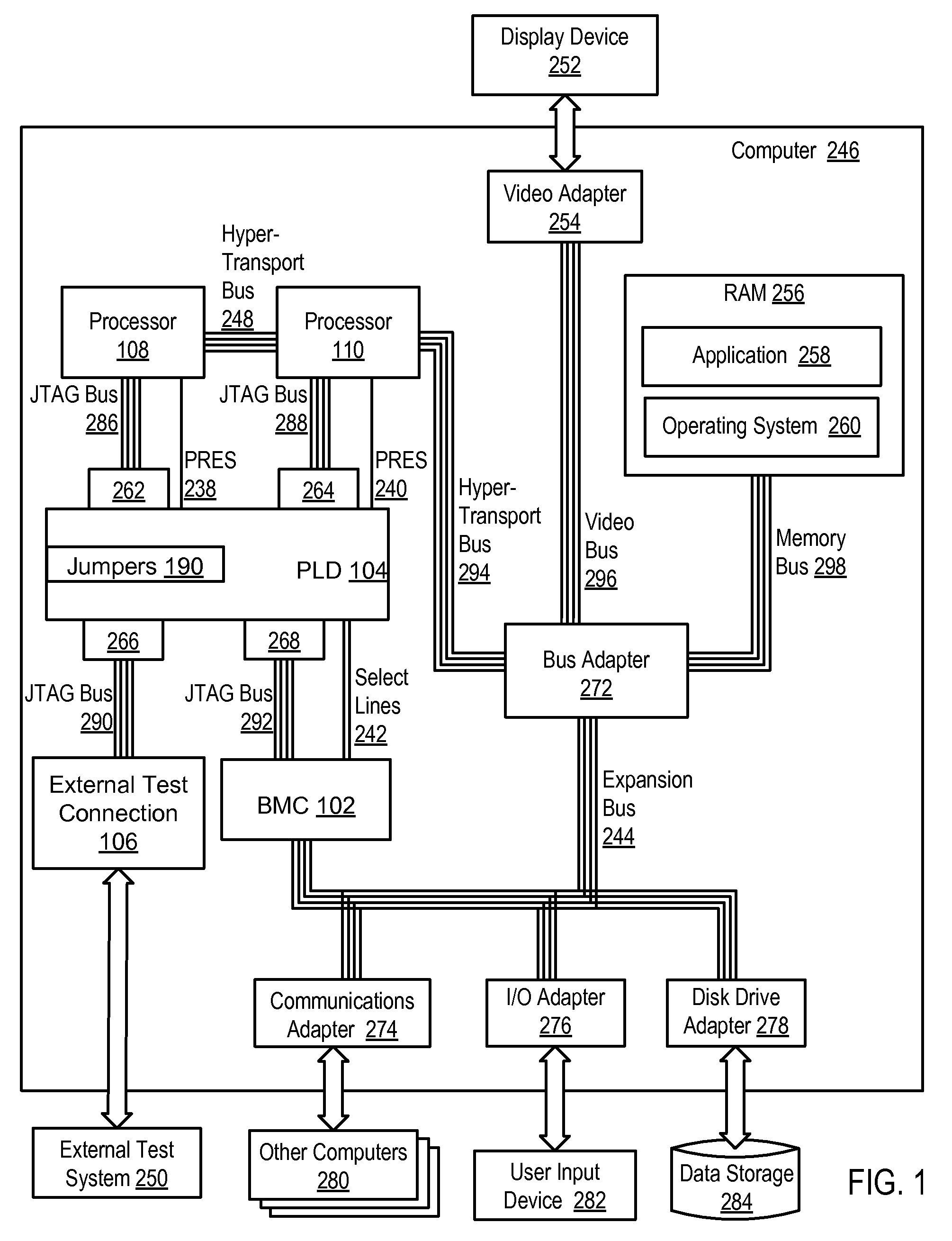

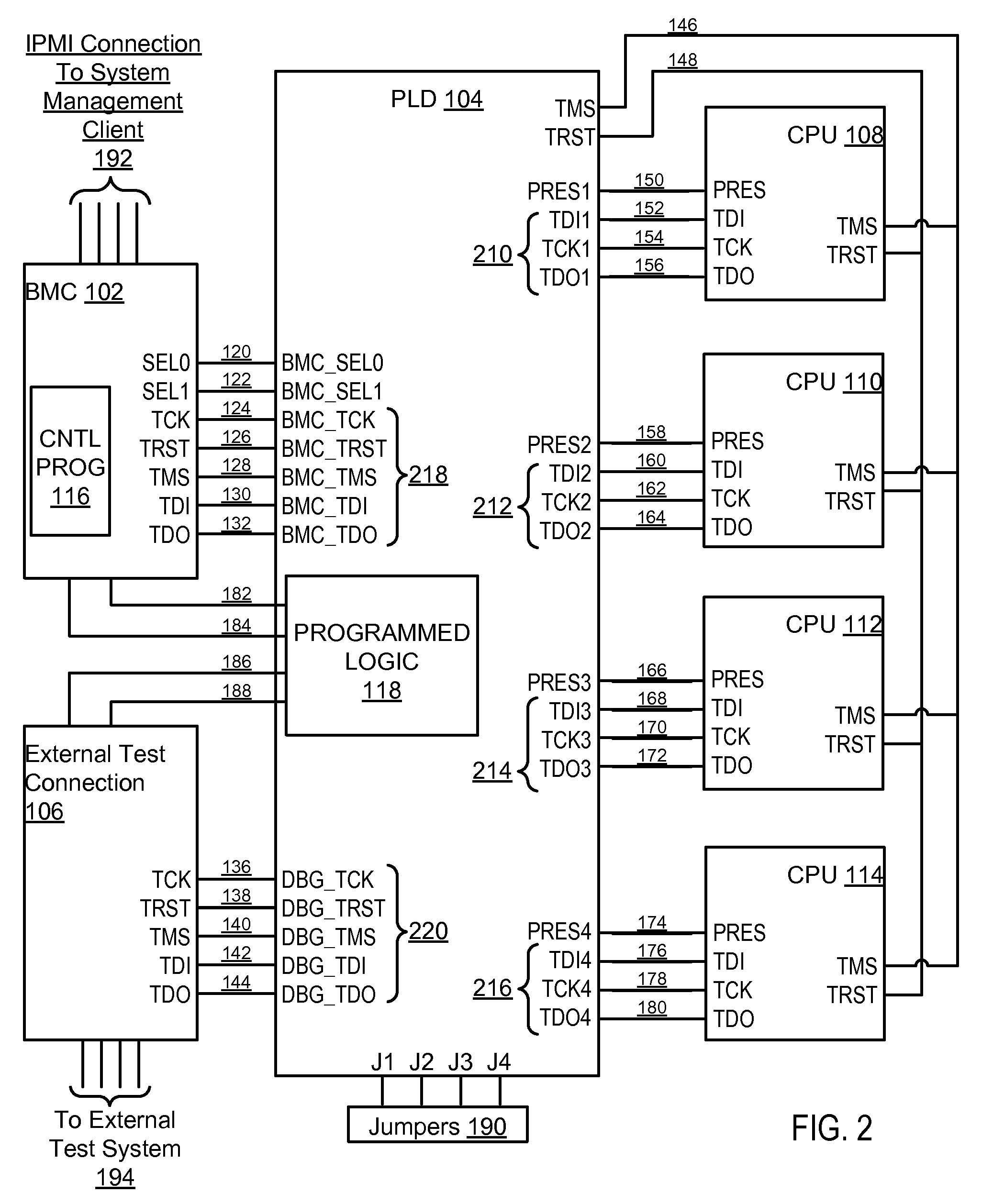

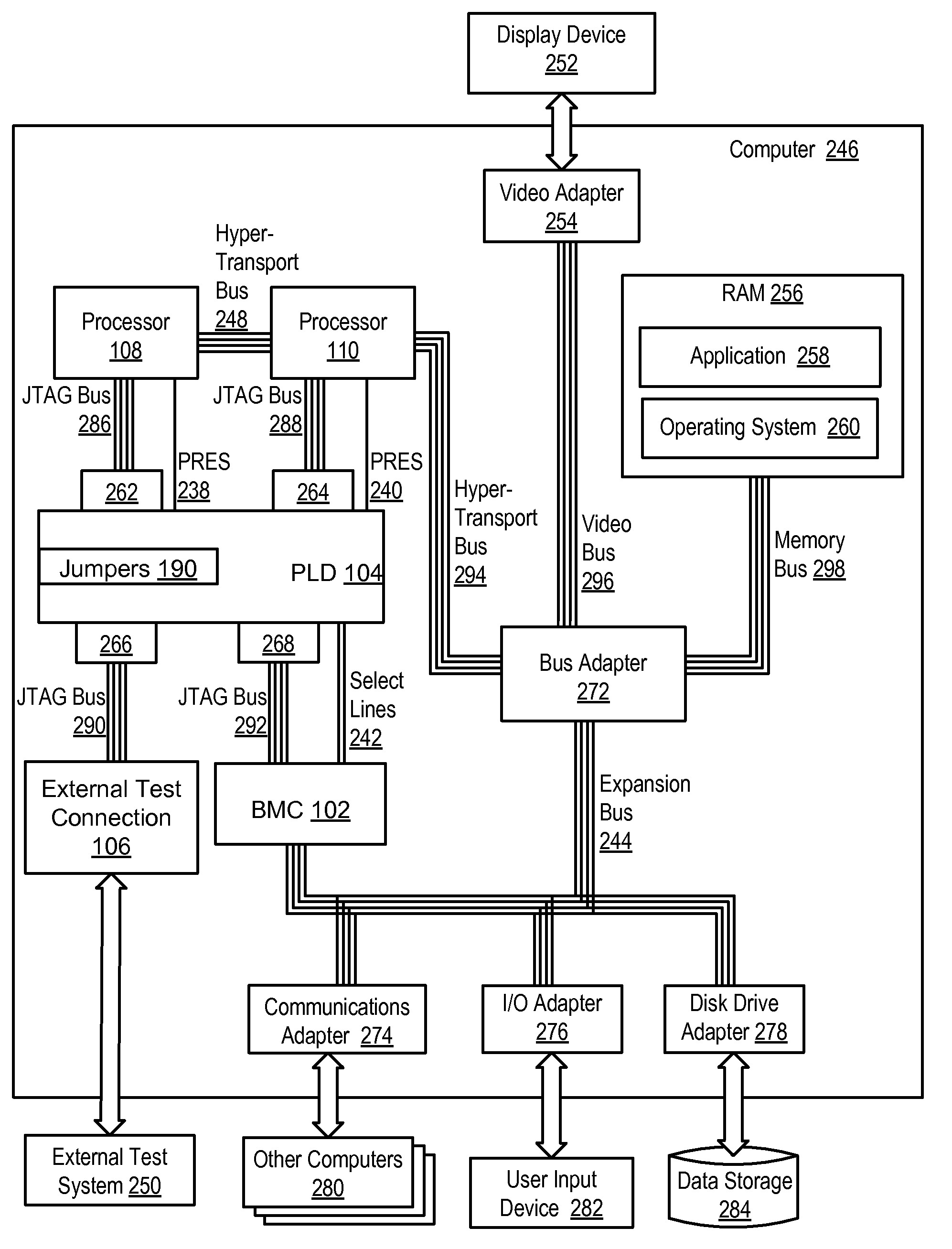

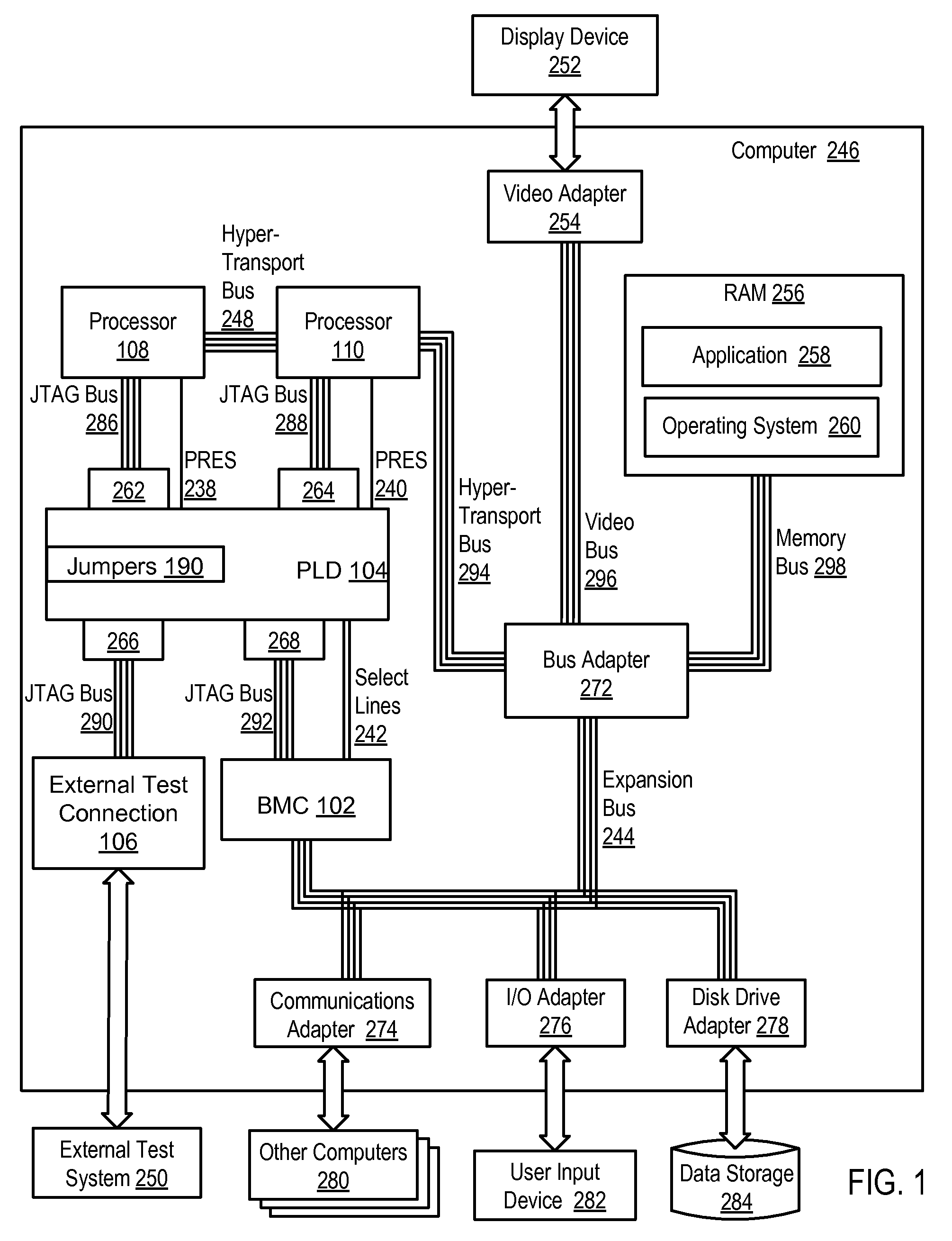

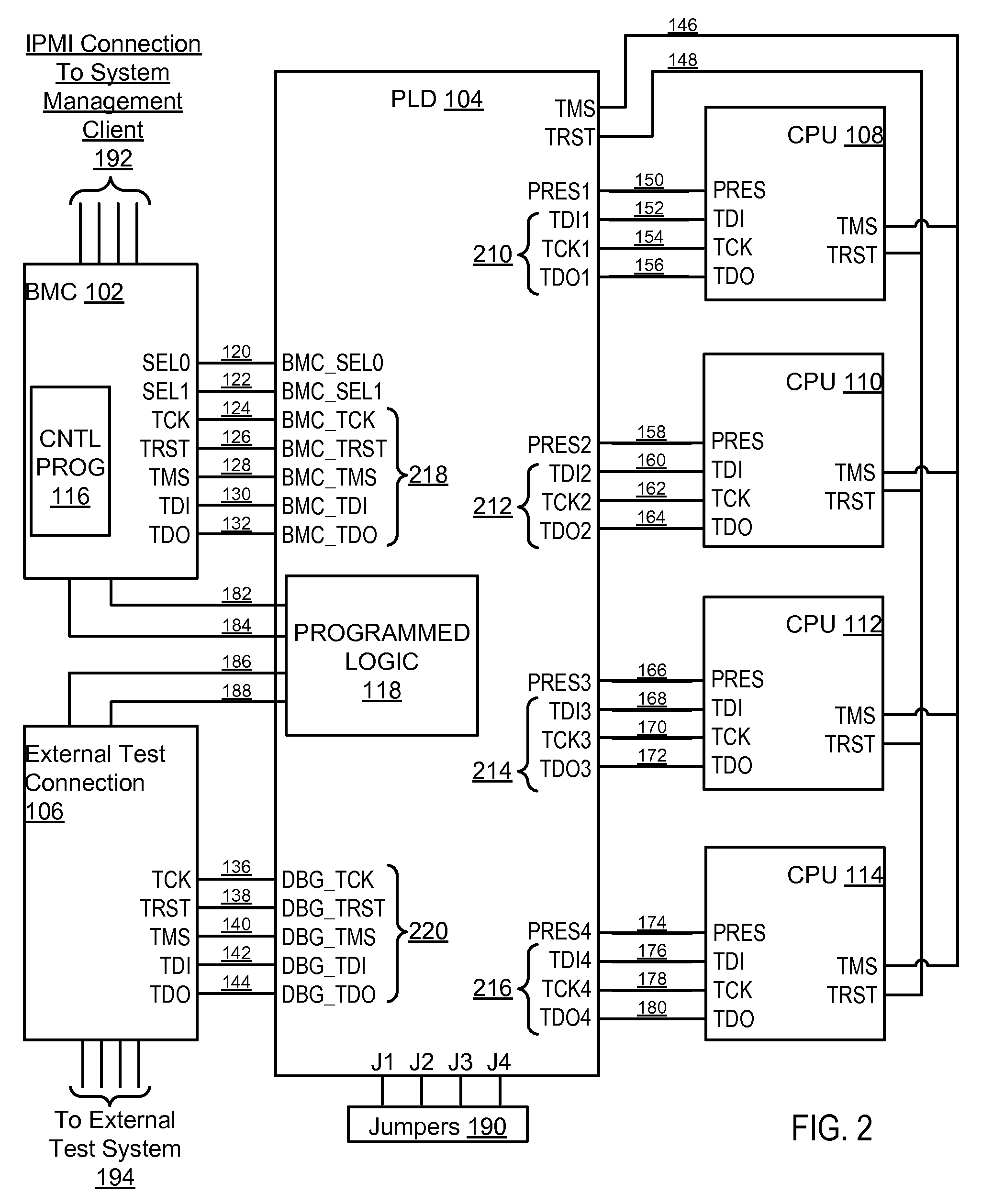

Processor Fault Isolation

ActiveUS20080052576A1Electronic circuit testingError detection/correctionMultiplexingMicrocontroller

Methods, apparatus, and products for processor fault isolation are disclosed that include sending, by an embedded system microcontroller to a programmable logic device (‘PLD’) a selection signal identifying one processor for boundary scan operations; sending boundary scan input signals to be sent to the identified processor; multiplexing by the PLD the boundary scan input signals to the identified processor; and sending boundary scan output signals returned from the identified processor. Methods, apparatus, and products for processor fault isolation are also disclosed that include connecting two or more processors in a boundary scan test chain, the connecting carried out by a PLD of a computer, the PLD further connected to sense lines carrying presence signals indicating whether processors are present in the computer; and including in the chain all processors indicated present according to presence signals.

Owner:LENOVO GLOBAL TECH INT LTD

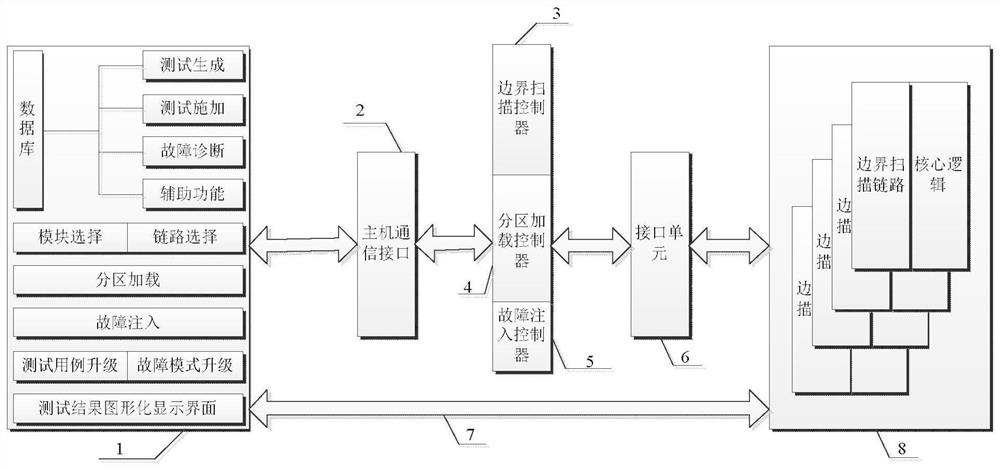

Test system for intelligently diagnosing faults of high-integration digital signal processing system

InactiveCN111624477AOvercoming Individual Measurement FlawsShorten test timeElectrical testingDigital signal processingTestware

The invention discloses a test system for intelligently diagnosing faults of a high-integration digital signal processing system, and aims to solve the problem of low fault diagnosis capability of anexisting boundary scanning test system. According to the technical scheme, an intelligent test platform management unit operates control software, collects data of multichannel signals, generates a test sequence, allocates physical addresses to all modules, lists all the modules connected to a system backboard on a software interface, processes the multichannel data and diagnoses faults; the control software calls boundary scanning test software to generate a test vector for the tested module, applies the test vector to the chip core logic input end to form a circuit fault criterion, and sendsthe circuit fault criterion to the boundary scanning controller; the test vectors of different regions are loaded to a tested module to generate a fault injection vector, and the fault injection vector is transmitted to a fault injection controller; and the fault injection vector is loaded to the tested module to complete the fault diagnosis of the multichannel signal processing subrack platformmodule-level digital chip.

Owner:10TH RES INST OF CETC

Semiconductor device with test circuit

InactiveUS6429454B2Electronic circuit testingSemiconductor/solid-state device detailsProcessor registerEngineering

A semiconductor device has pads that are arranged in such a manner as to easily accept manual needles to carry out a test. This technique is applicable to carry out a test with use of a boundary scan test circuit in synchronization with a cycle time defined by a normal operation clock signal. The semiconductor device has a first pad connected to a first one of registers that form a serial scan chain, to supply test data to the registers, a second pad connected to a last one of the registers, and a third pad to supply a test clock signal to the registers. The registers are arranged in a central part of the semiconductor device, and the first to third pads are arranged at the periphery of the semiconductor device.

Owner:KK TOSHIBA

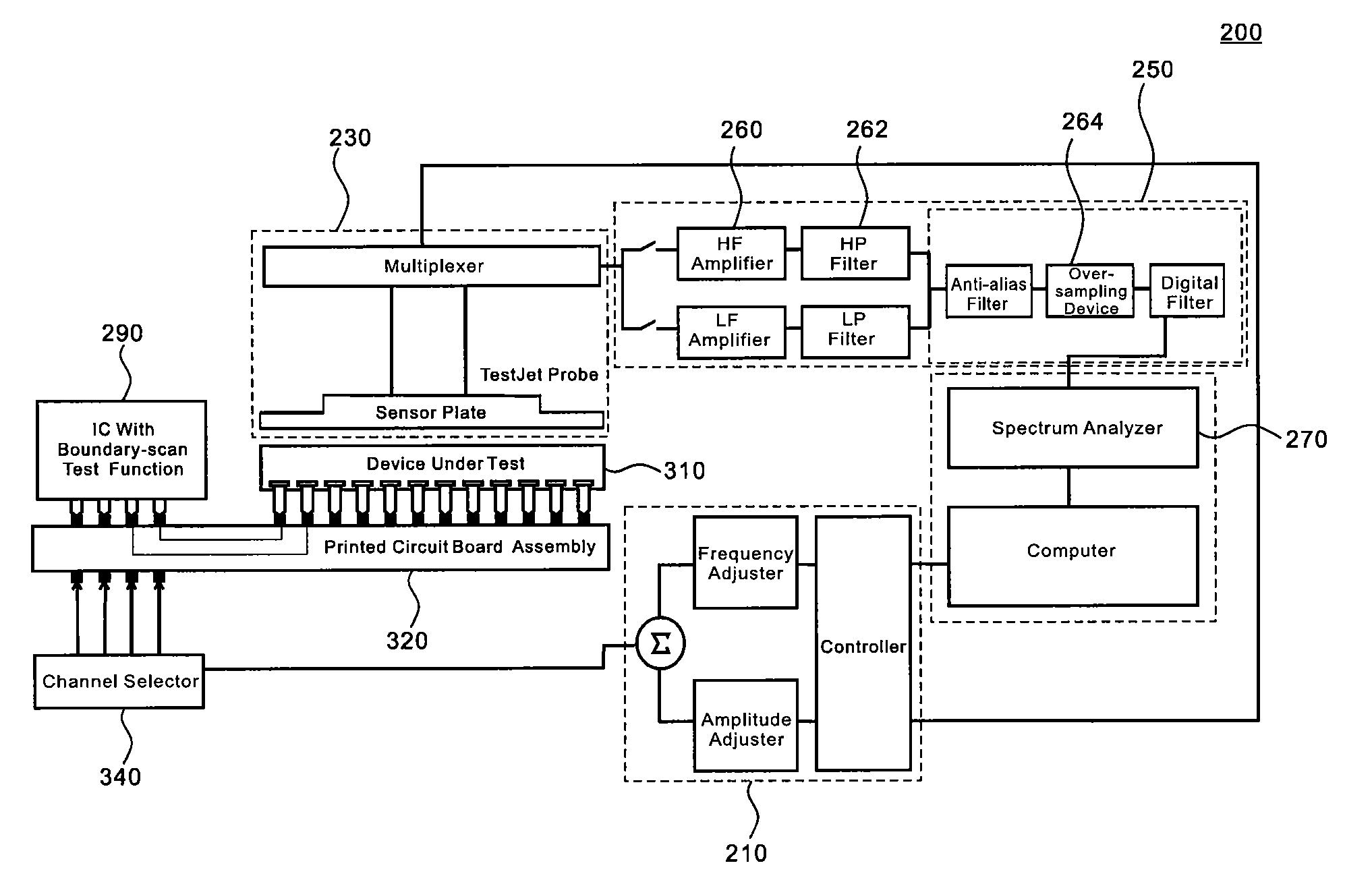

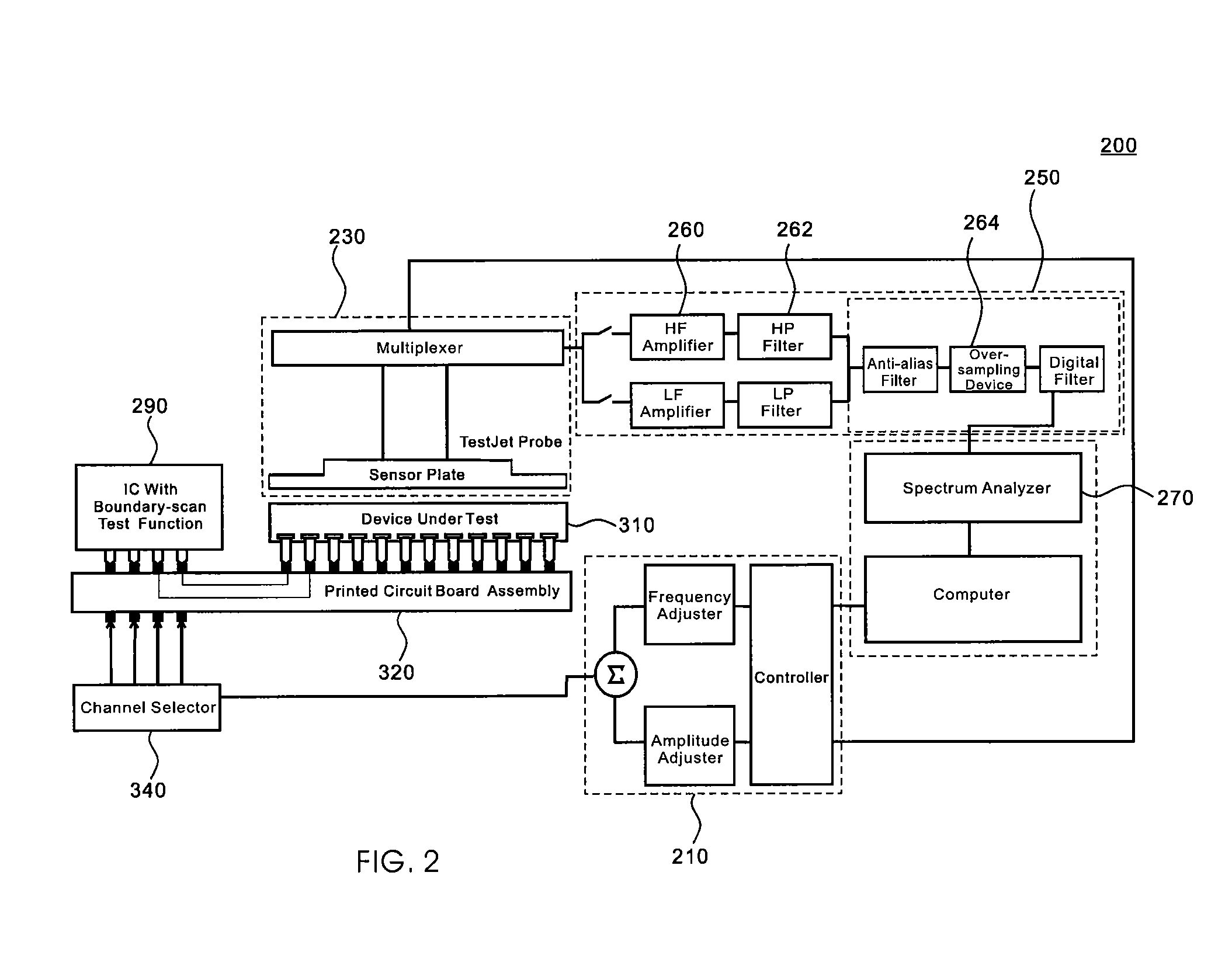

Electronic Device Testing System and Method

ActiveUS20090089635A1Accurate connectionElectronic circuit testingElectric connection testingEngineeringSignal detector

The invention provides a testing system and method suitable for determining whether a pin-out of an electrical component is properly connected to a PCB. The testing system includes a testing signal source, a signal detector, a signal processor, an analysis unit and an integrated circuit having boundary-scan test function to provide testing signals to the device under test (DUT) whose signal traces are passing through inner layer of PCB in order to detect whether the sensed signal is an error signal.

Owner:TEST RES INC

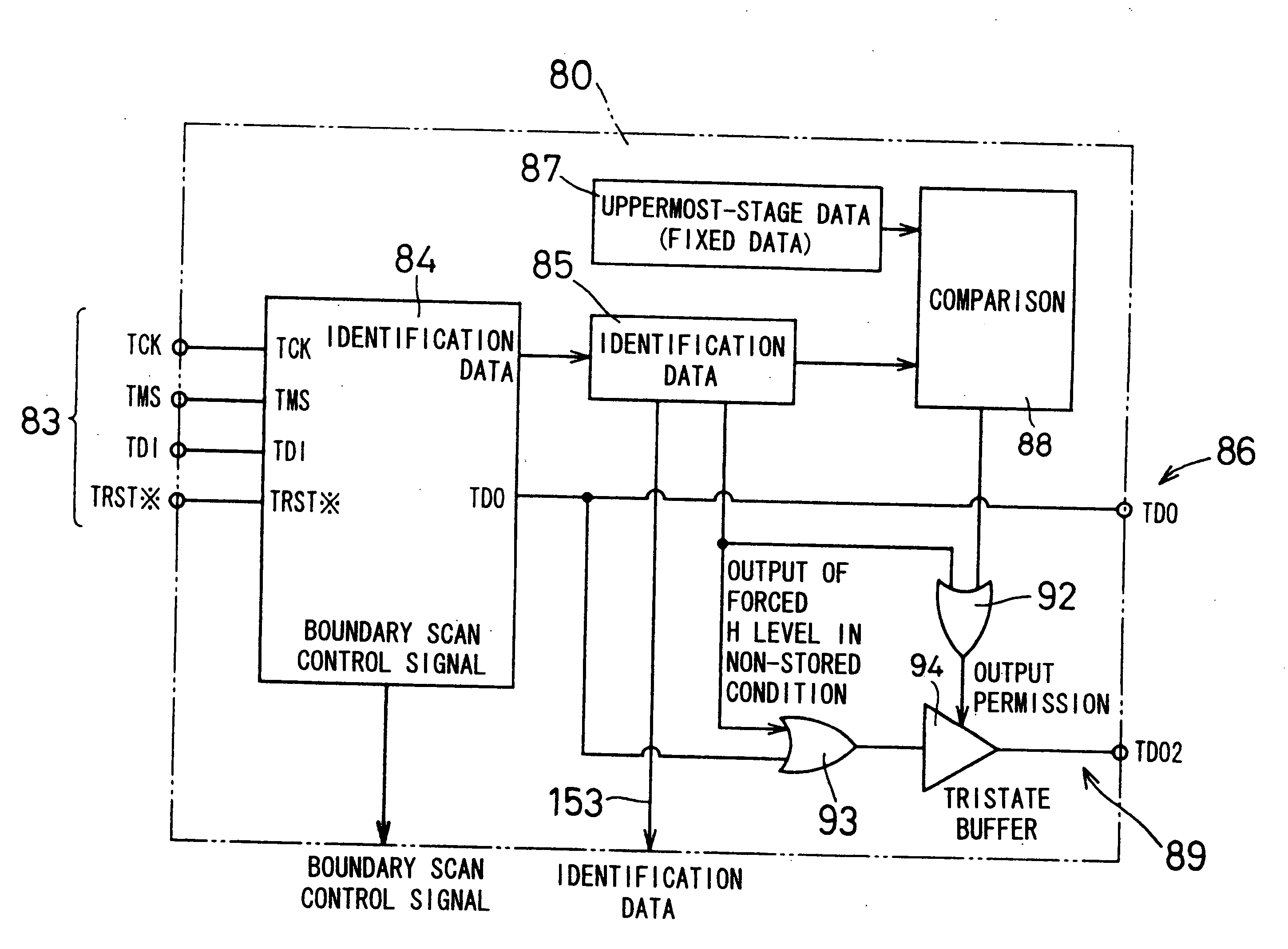

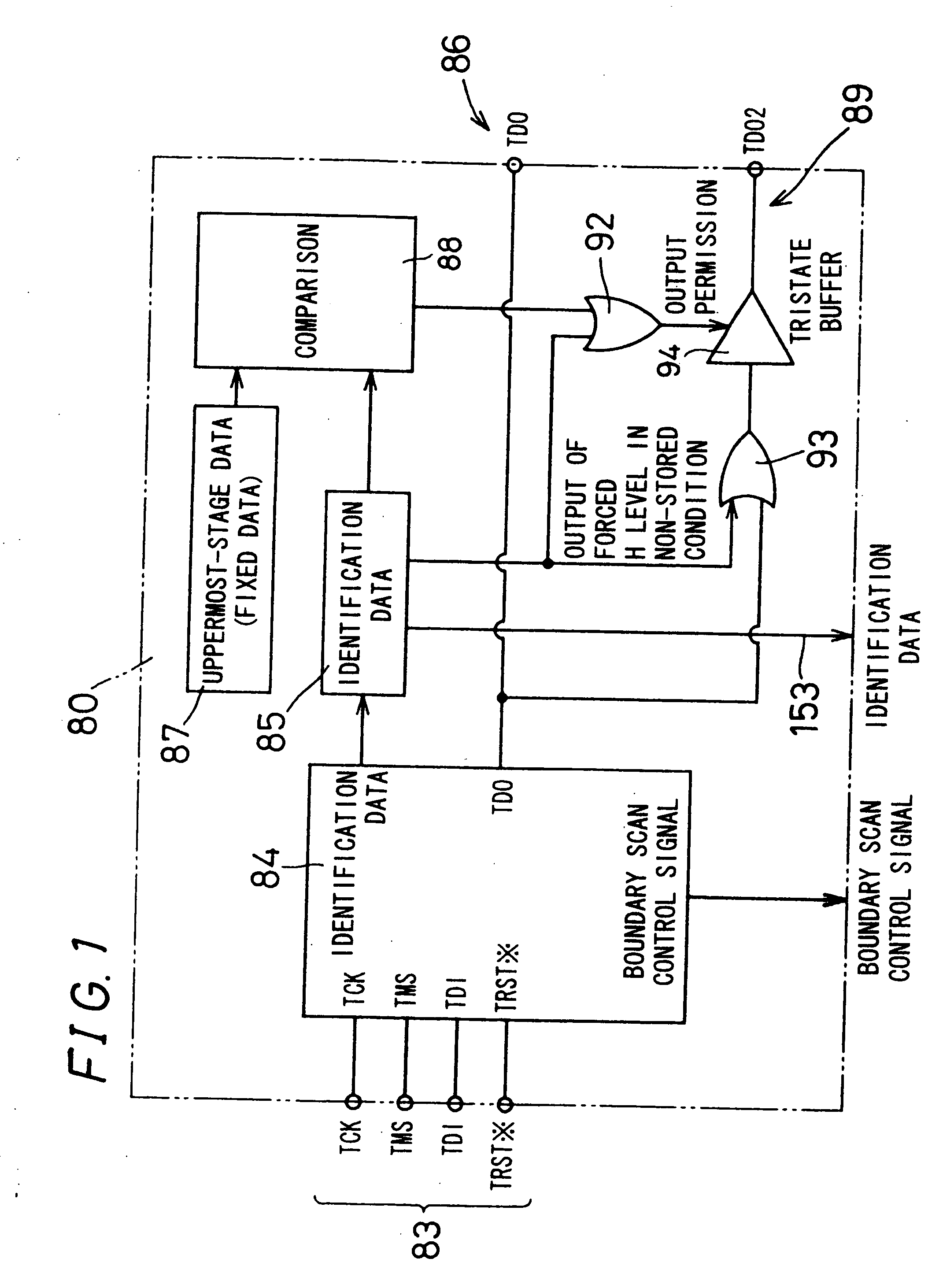

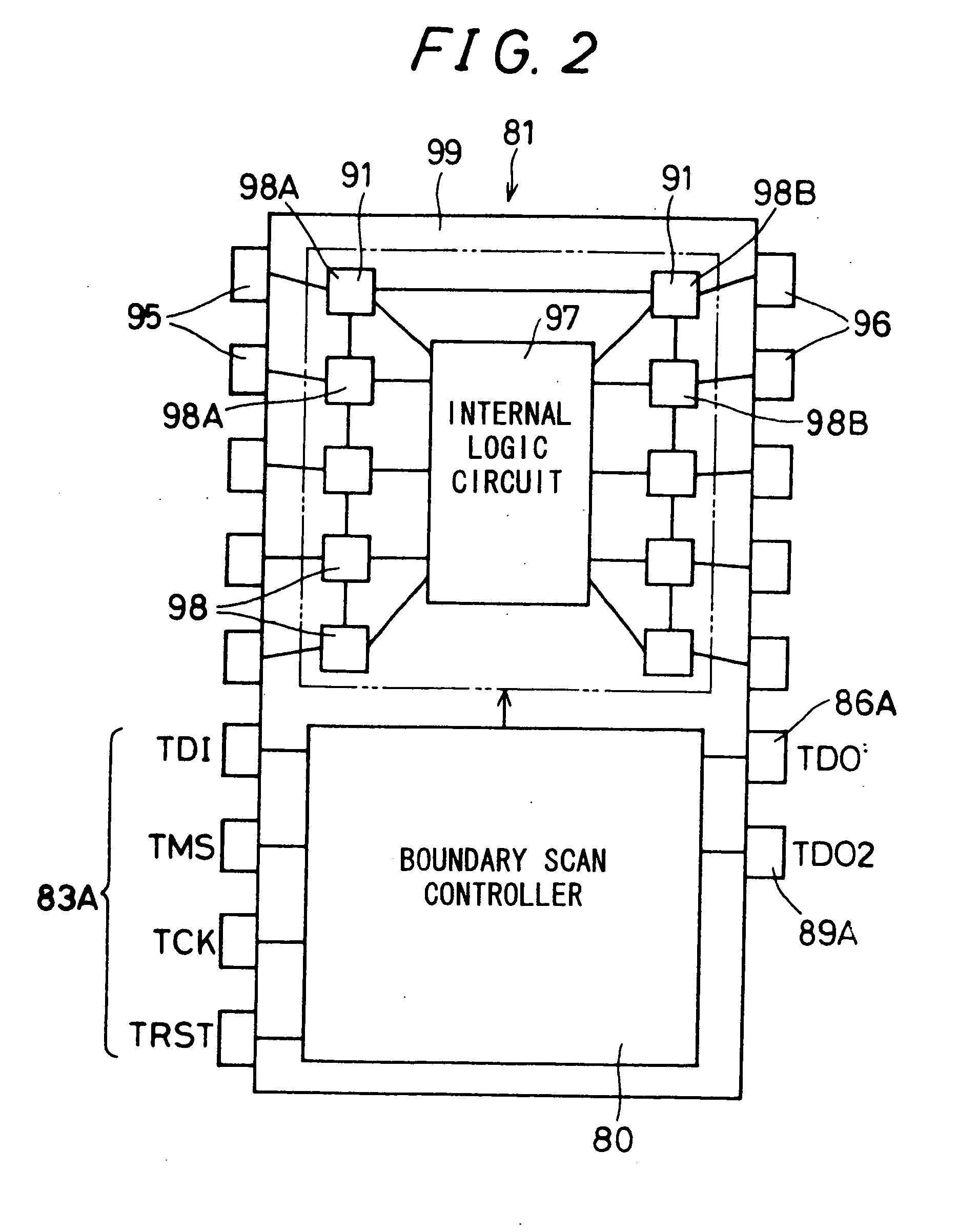

Boundary scan controller, semiconductor device, method for identifying semiconductor circuit chip of semiconductor device, and method for controlling semiconductor circuit chip of semiconductor device

InactiveUS20060220672A1Easy to operateReduce laborElectronic circuit testingSolid-state devicesDevice materialData storing

An object of the invention is to provide a boundary scan controller that allows a boundary scan to be executed and also allows a semiconductor apparatus to be manufactured in such a manner that the same type of semiconductor circuit chips are stacked. When identification data stored in memory means (85) is compared with fixed data held in fixed-data holding means (87) by comparison means (88) and the identification data is coincident with the fixed data, a data derivation section (89) outputs the same data as data which is outputted from an output section (86). In a boundary scan test, a data derivation section (89) of a boundary controller (80) provided for each semiconductor circuit chip is connected to the same bus line. When the identification data is not coincident with the fixed data, the data derivation section (89) can be substantially disconnected from the bus line. In this way, the same type of semiconductor circuit chips for which the boundary controller (80) is provided can be stacked, thereby manufacturing the semiconductor apparatus.

Owner:SHARP KK

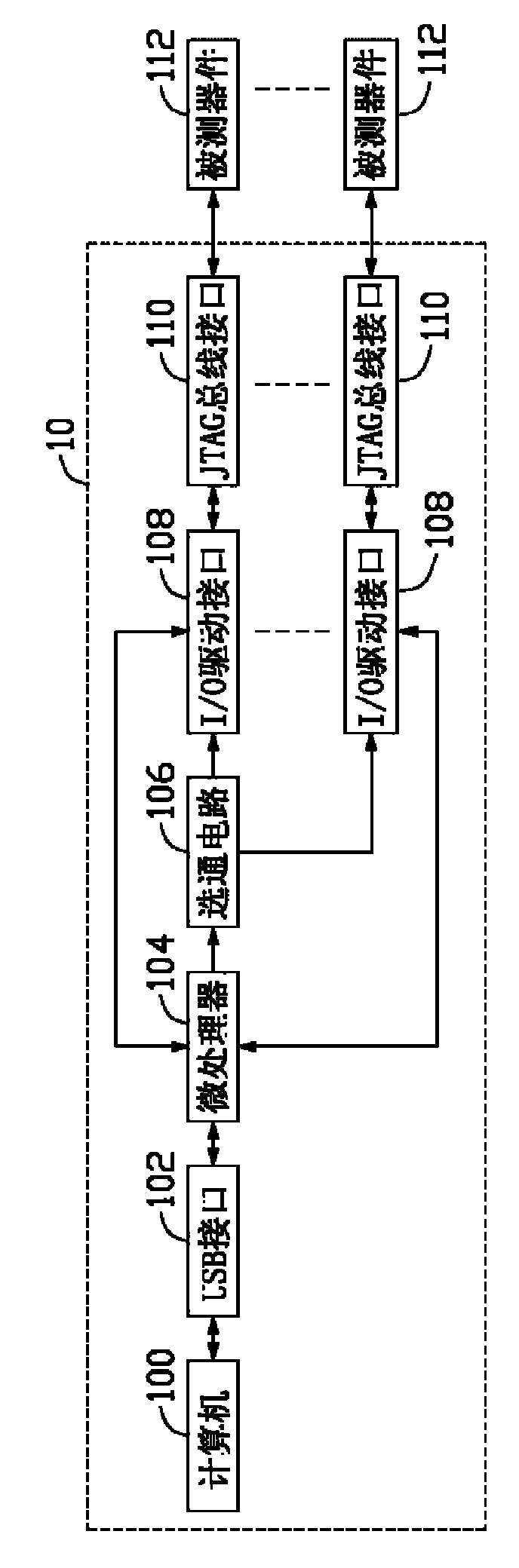

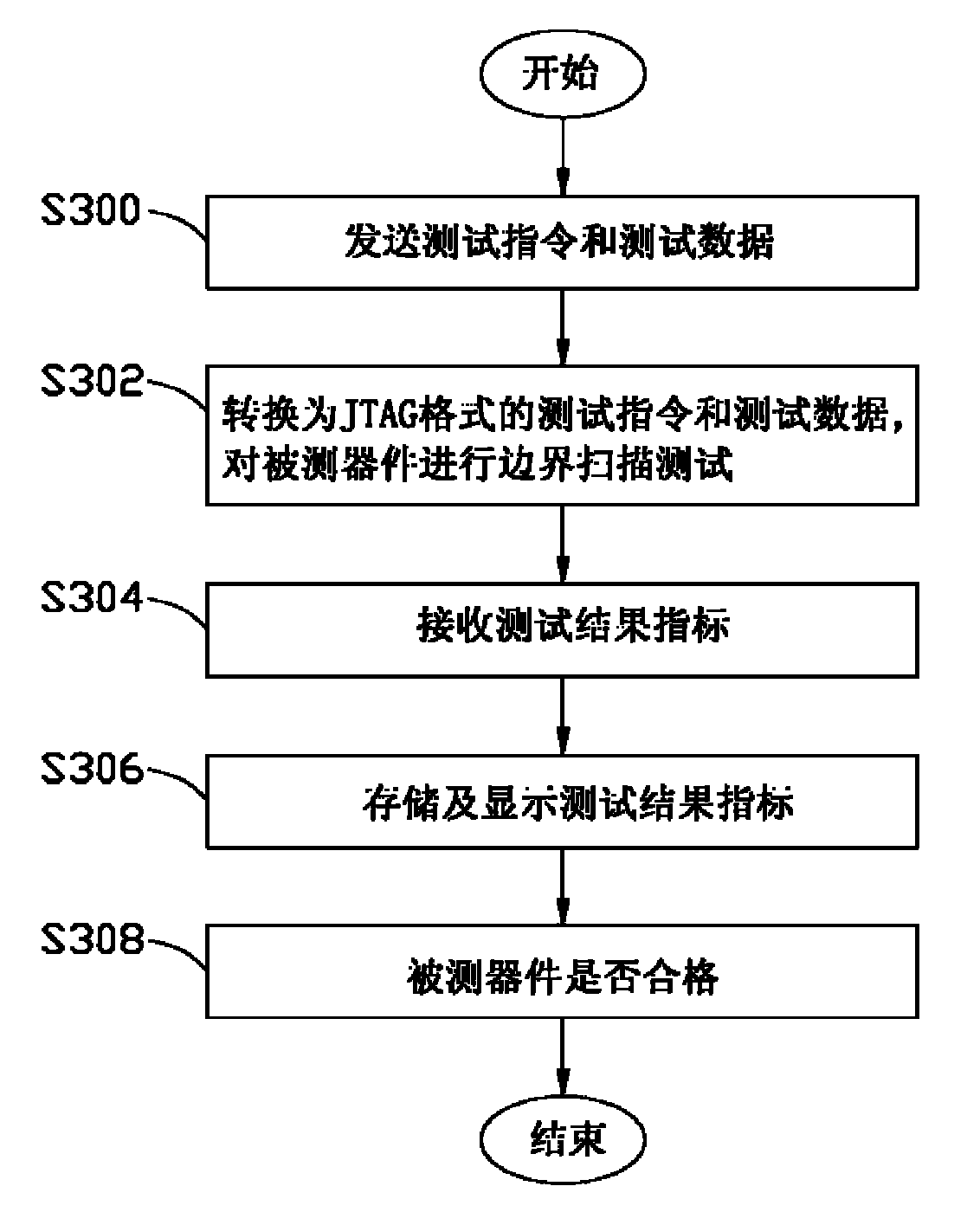

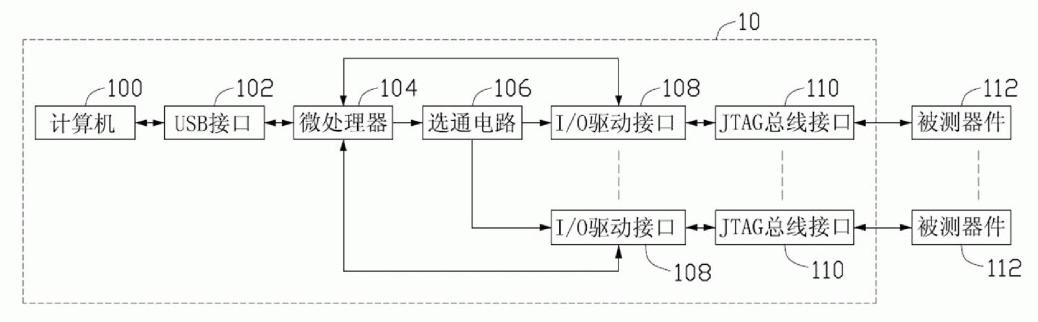

Boundary scanning test system and test method

InactiveCN101865976AImprove test efficiencyShorten the timeElectrical testingTest efficiencyBus interface

The invention discloses a boundary scanning test system, which comprises test equipment, an external interface, a microprocessor, a gating circuit, a plurality of I / O (Input / Output) driving interfaces and a plurality of JTAG (Joint Test Action Group) bus interfaces used for connecting devices to be tested. The test equipment is connected with the microprocessor through the external interface, the microprocessor is connected with the plurality of I / O driving interfaces through the gating circuit, each I / O driving interface is correspondingly connected with one JTAG bus interface, and the microprocessor is connected with the plurality of I / O driving interfaces. The invention also provides a boundary scanning test method. The boundary scanning test system and the boundary scanning test method can simultaneously test a plurality of devices to be tested so as to improve the test efficiency.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

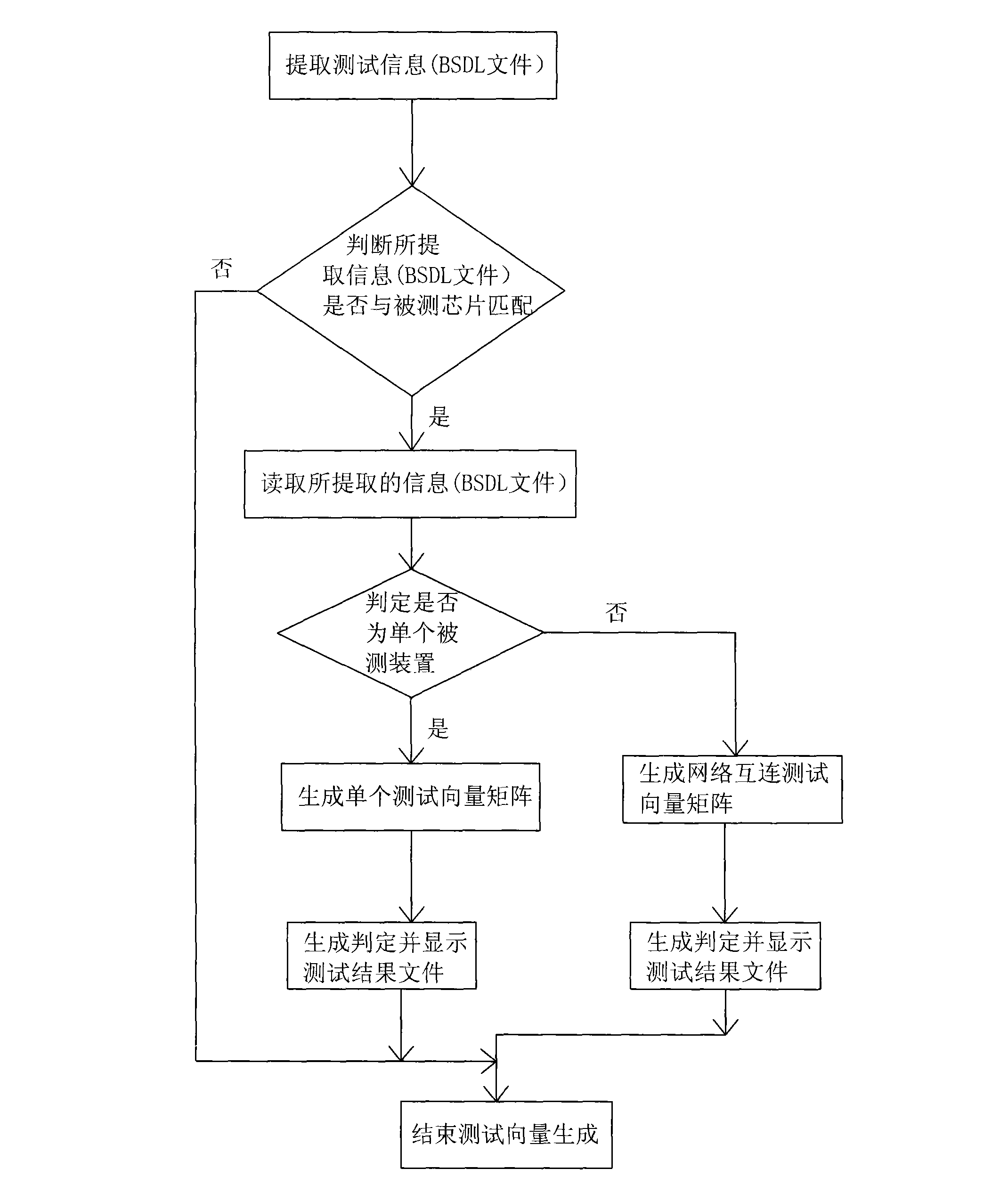

Test vector generating method for boundary scanning

InactiveCN101526582APromote generationComplete detectionElectronic circuit testingThe InternetTest vector generator

The invention discloses a test vector generating method for boundary scanning, which generates a test vector by integrating test information of a tested device. The method comprises the following specific steps: a, extracting the test information; and b, analyzing the test information, and generating a test vector matrix, wherein the vector matrix can be a single test vector matrix and a network interconnecting test vector matrix, and can perform self test and internet test of a single device respectively. The method generates the test vector by integrating the test information of the tested device; the method can conveniently generate the test vector and extract the information required by diagnosis; and simultaneously, the generated test vector is favorable for complete detection and more convenient operation.

Owner:MITAC COMP (SHUN DE) LTD

Processor fault isolation

Methods, apparatus, and products for processor fault isolation are disclosed that include sending, by an embedded system microcontroller to a programmable logic device (‘PLD’) a selection signal identifying one processor for boundary scan operations; sending boundary scan input signals to be sent to the identified processor; multiplexing by the PLD the boundary scan input signals to the identified processor; and sending boundary scan output signals returned from the identified processor. Methods, apparatus, and products for processor fault isolation are also disclosed that include connecting two or more processors in a boundary scan test chain, the connecting carried out by a PLD of a computer, the PLD further connected to sense lines carrying presence signals indicating whether processors are present in the computer; and including in the chain all processors indicated present according to presence signals.

Owner:LENOVO GLOBAL TECH INT LTD

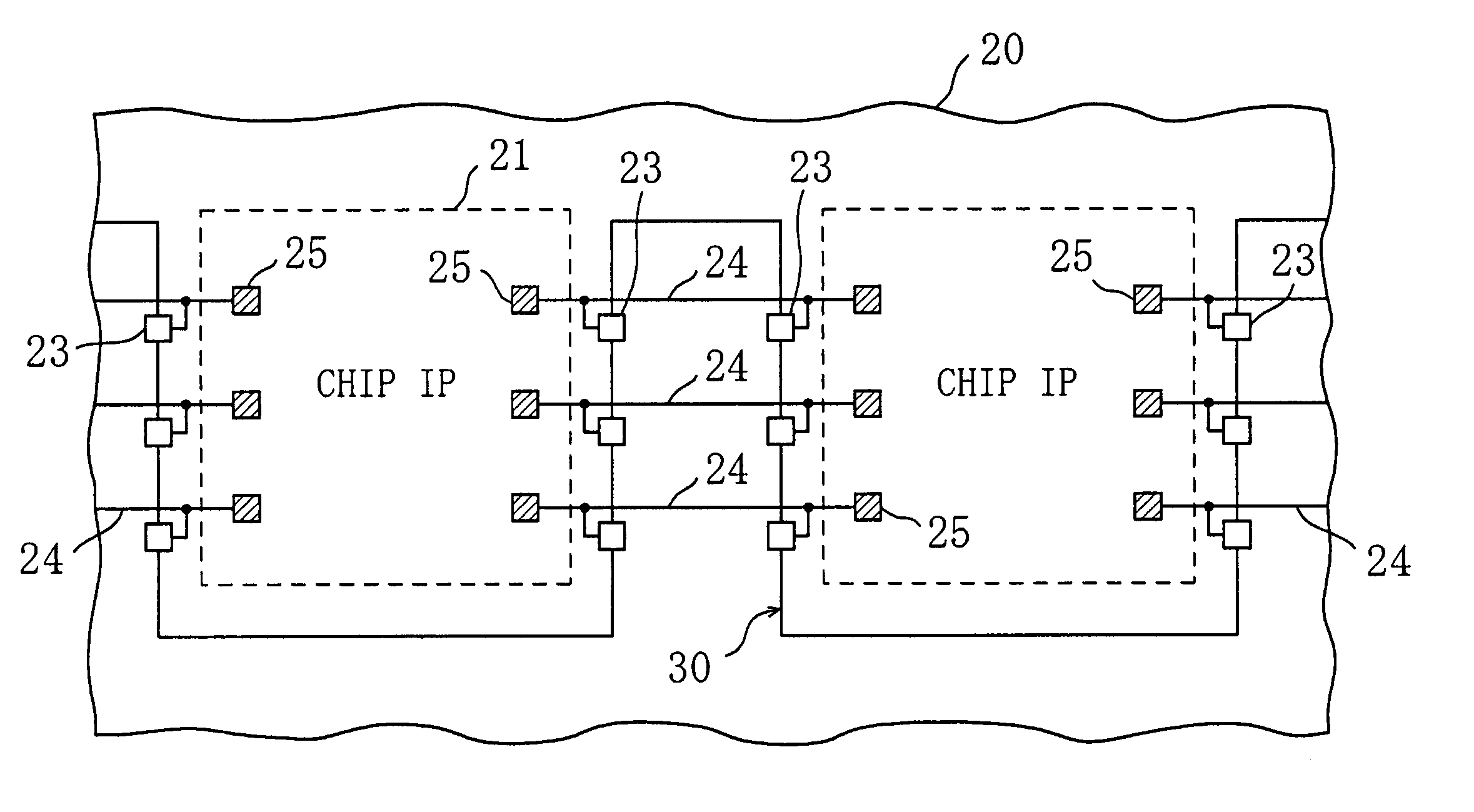

Semiconductor wiring substrate, semiconductor device, method for testing semiconductor device, and method for mounting semiconductor device

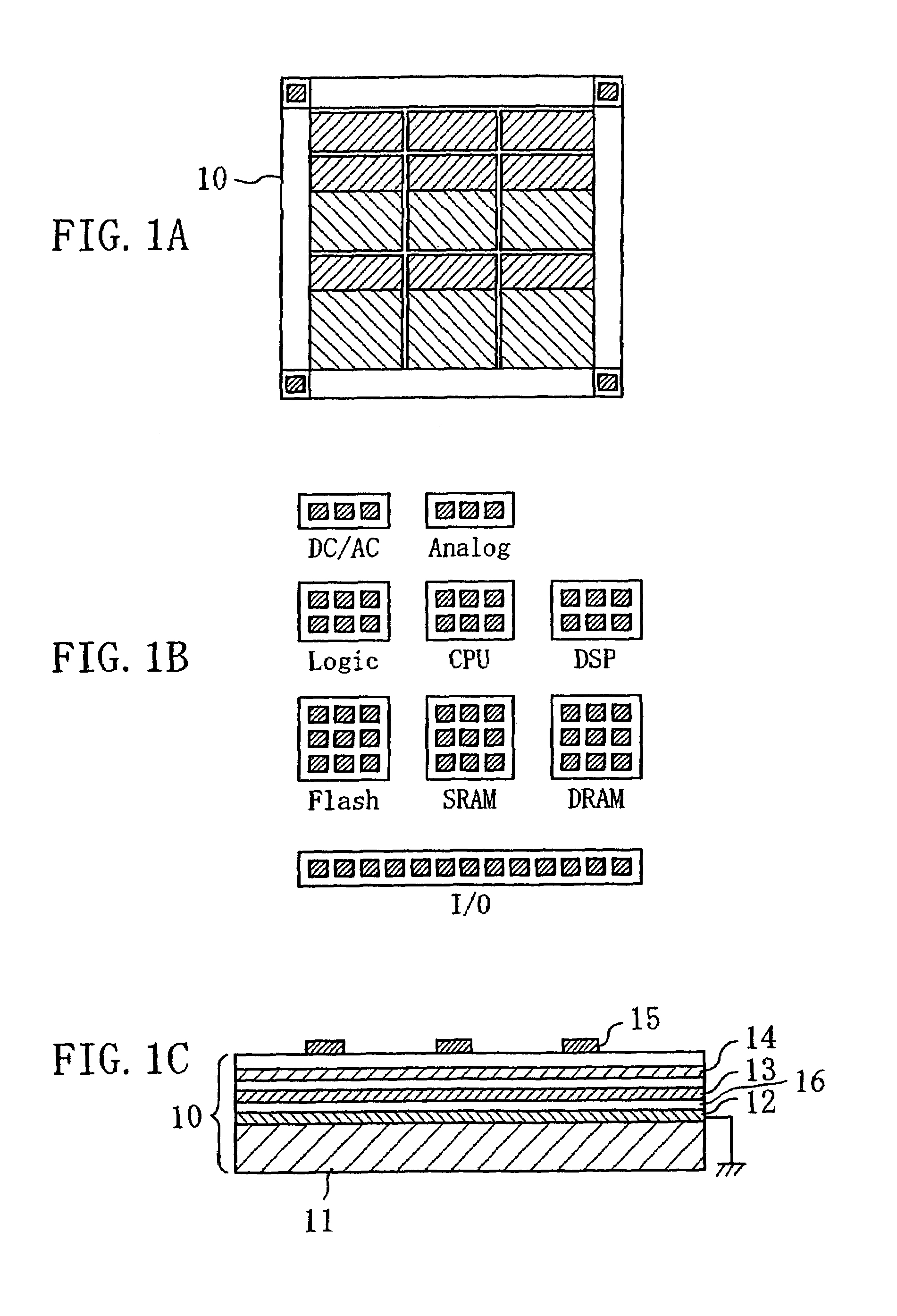

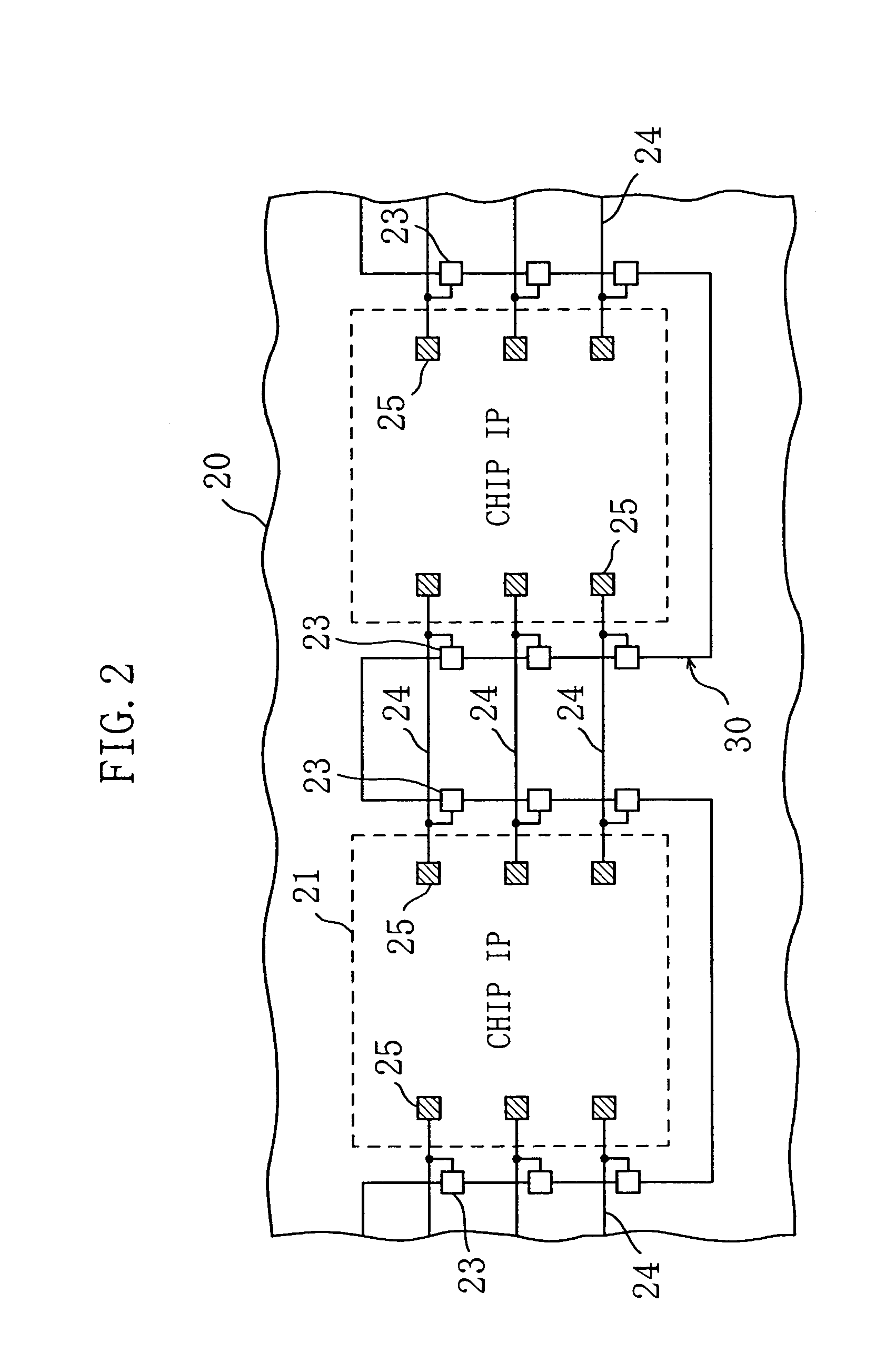

InactiveUS7032196B2Improve reliabilityEasy to installDigital circuit testingSemiconductor/solid-state device testing/measurementIntellectual propertySilicon

A semiconductor device constructed by mounting a plurality of chip intellectual properties (IPs) on a common semiconductor wiring substrate, a method for testing the device and a method for mounting the chip IPs. A silicon wiring substrate on which chip IPs can be mounted is provided. A circuit for a boundary scan test is formed on the silicon wiring substrate by connecting flip flops. The flip flops are connected to wiring and are arranged to test connections in the wiring. The entire IP On Super-Sub (IPOS) device or each chip IP may be arranged to facilitate a scan test, a built-in self-test (BIST), etc., on the internal circuit of the chip IP.

Owner:SOCIONEXT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com