Changing scan cell output signal states with a clock signal

a clock signal and scan cell technology, applied in the field of integrated circuits, can solve the problems of increasing the complexity of the board level testability, the difficulty of in-circuit testing of the board, and the difficulty of the traditional method of probing the board, so as to facilitate boundary test and reduce the overall test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The preferred embodiment of the present invention is best understood by referring to FIGS. 1-5 of the drawings, like numerals being used for like and corresponding parts of the various drawings.

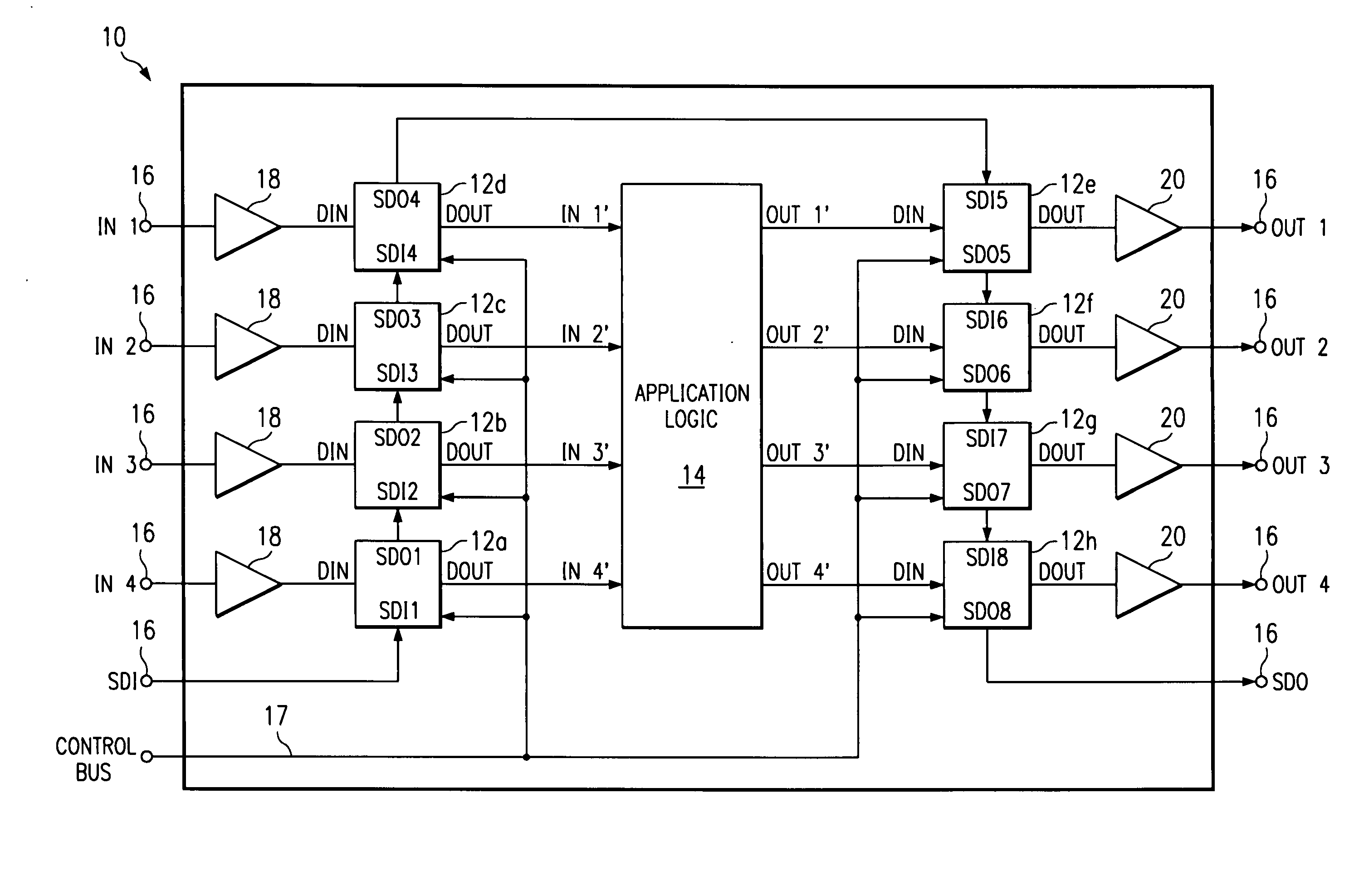

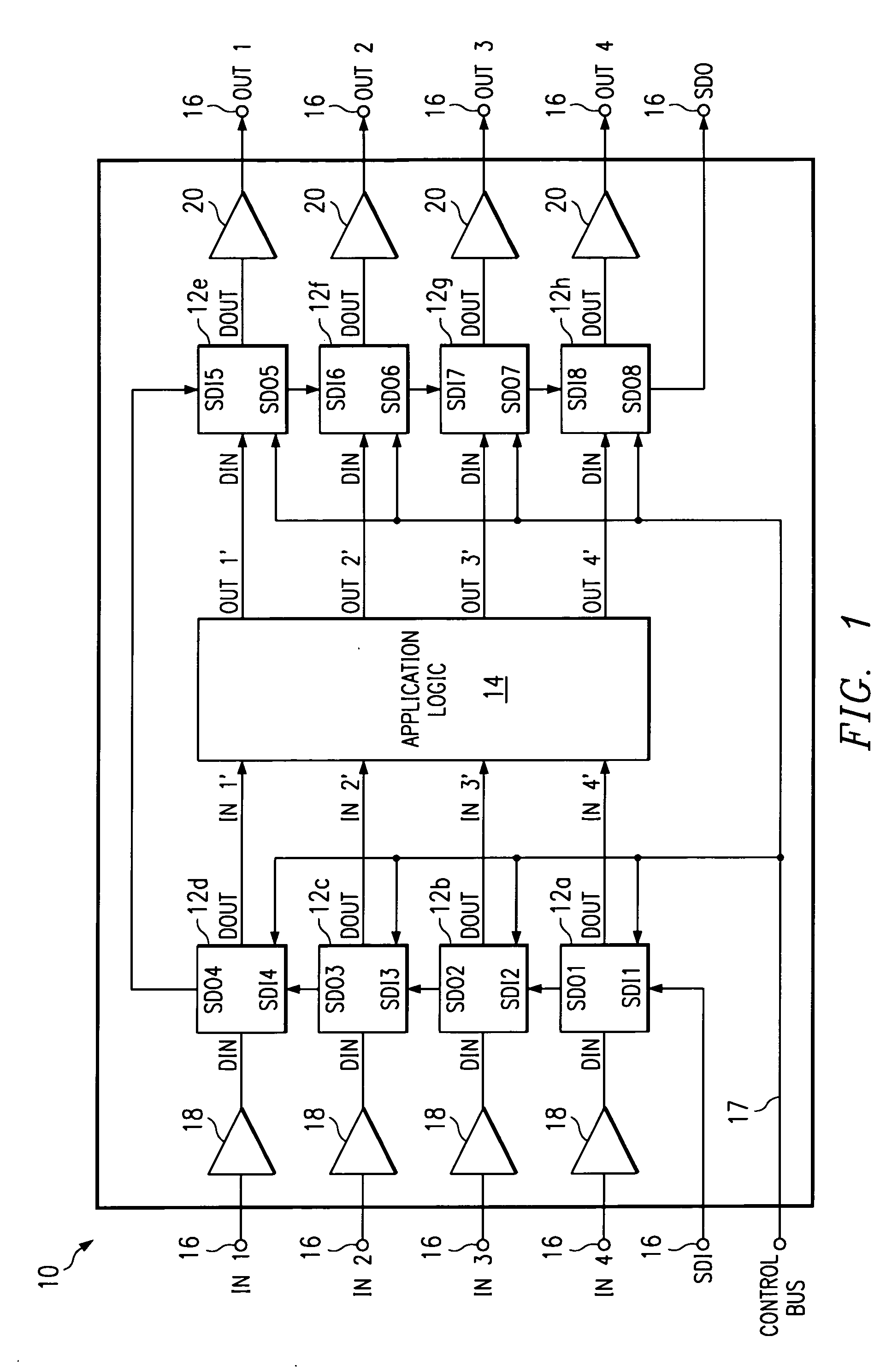

[0030] FIG. 1 illustrates a block diagram of an integrated circuit (IC) 10 having test cells 12a-h disposed about its boundary to control and observe data flow through the application logic 14 of the IC 10. The integrated circuit 10 comprises a plurality of pins 16 which provide an electrical connection between the integrated circuit 10 and other integrated circuits. For purposes of illustration, the integrated circuit 10 is shown with four pins receiving input signals, IN1, IN2, IN3 and IN4, and four pins providing output signals, OUT1, OUT2, OUT3 and OUT4. Other signals to the chip include a serial data input (SDI), a control bus 17, and a serial data output (SDO). The input signals IN1-IN4 are connected to input buffers 18 which output to respective test cells 12a-d. Each test cell ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com