Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "Reduce test power consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

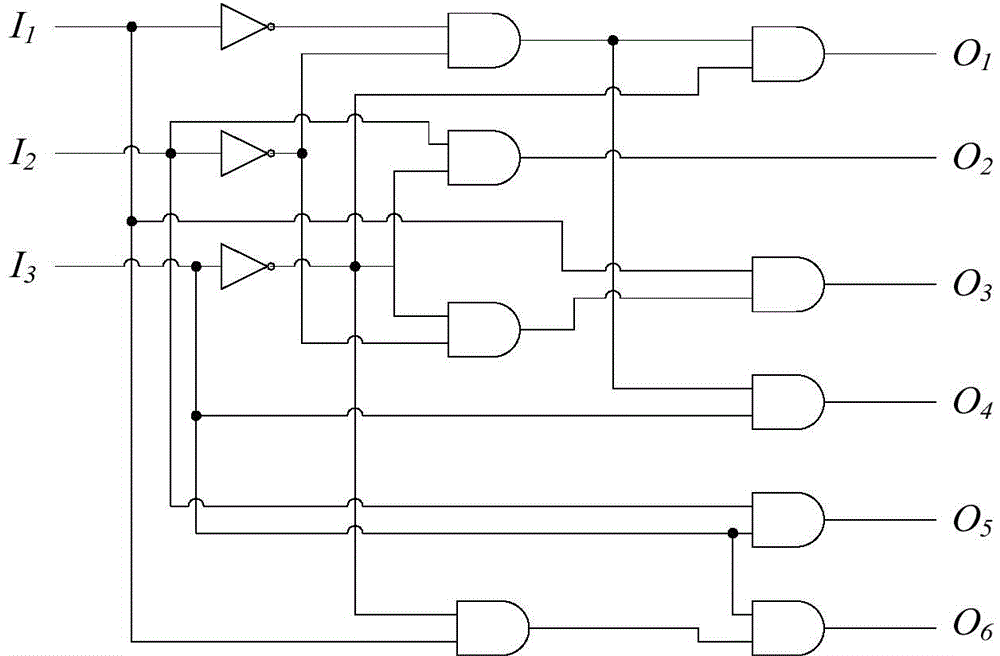

Test graphic generator of integrated circuit and test method thereof

InactiveCN101776730AReduce overheadReduce the number of test pattern transitionsElectrical testingFault coverageTest power

The invention relates to the field of an integrated circuit test, and discloses a test graphic generator of an integrated circuit and a test method thereof. The test graphic generator comprises a reconfigurable linear feedback shift register of cyclic code with single bit change, a liner feedback shift register based on a primitive polynomial and a two-dimensional exclusive or gate array; compared with the traditional test graphic generator, the test graphic generator has less hardware overhead, few quantity of repeated test graphics, short test time, uniform distribution of generated test graphics, and can obtain higher fault coverage rate; and the generated single jump test sequence reduces the conversion times of a tested circuit input end, thus greatly reducing the test power consumption of the tested integrated circuit.

Owner:XI AN JIAOTONG UNIV

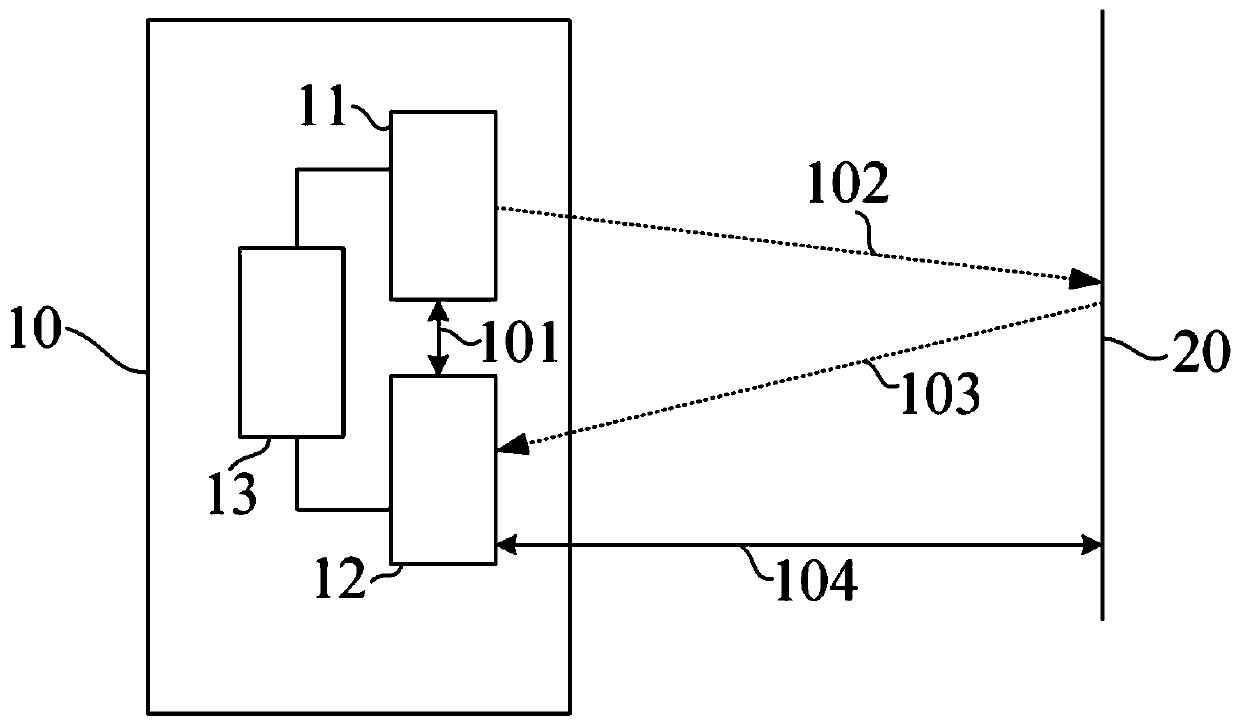

Distance measuring method and depth camera

ActiveCN110187355AReduce test power consumptionIncrease test distanceOptical rangefindersWater resource assessmentTest powerSingle exposure

The invention is applied to the technical field of optics, and provides a distance measuring method and a depth camera. The distance measuring method comprises the following steps: transmitting an optical signal to an object to be measured; receiving the optical signal reflected by the object to be measure through a receiving module, wherein the receiving module comprises a plurality of signal collecting units, the timing sequences of the plurality of signal collecting units are different, and each signal collecting unit has at least two sets of collection signals with different frequencies inone exposure time; and calculating the flight time of the optical signal. By setting a plurality of taps in the depth camera, and controlling the collecting timing sequences of the plurality of collecting units through the control module, each tap has at least two sets of collection signals with different frequencies in one exposure time; therefore, the contradiction of in test scheme in the prior art that the pulse width is proportional to the test distance and power consumption and is negatively correlated with the test accuracy is got rid of, and the measurement distance is no longer limited by the pulse width; therefore, lower test power consumption and higher test accuracy is maintained while achieving a farther test distance.

Owner:SHENZHEN ORBBEC CO LTD

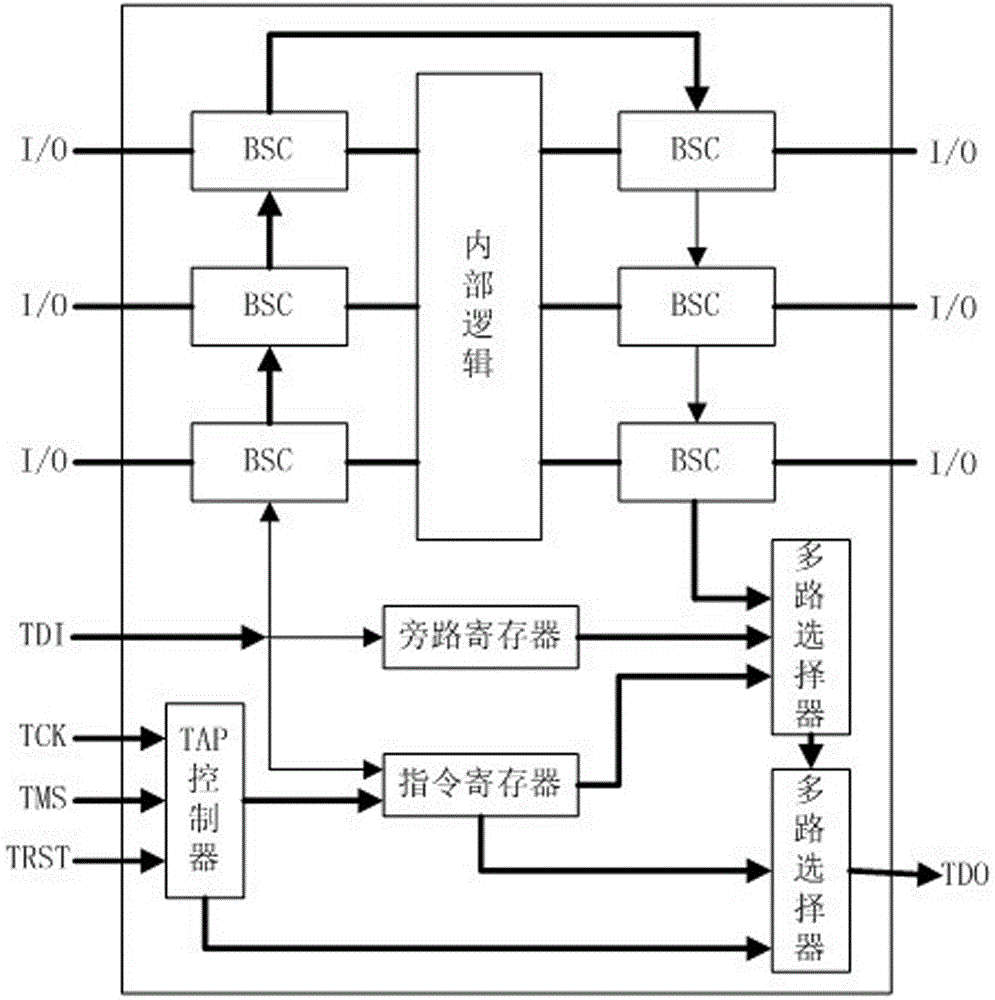

Scanning subchain type test structure and method capable of conforming to boundary scan standards

ActiveCN103487747ALower bit pass rateFew test parametersElectrical testingComputer moduleTest response

The invention discloses a scanning subchain type test structure capable of conforming to boundary scan standards. The scanning subchain type test structure comprises a vector configuration module and a response aggregation module, wherein the vector configuration module is used for conducting reconfiguration to divide a test signal into a plurality of parallel boundary scanning subchains to be connected with the response aggregation module, all data output ends of the vector configuration module are connected with the data input ends of all the boundary scanning subchains respectively, and a test response output by the output end of the response aggregation module is connected with a TDI port of a boundary scan test controller. The invention further discloses a scanning subchain type test method capable of conforming to the boundary scan standards and application of the scanning subchain type test structure and method in diagnosis of faults of a tested circuit board. According to the scanning subchain type test structure and method, the scanning subchain type test structure and method can conform to the standards, the requirements of the scanning subchain type test structure can be met, the position passing rate in the shifting process of a boundary scan test is lowered, and therefore the power consumption of the boundary scanning test is lowered.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Test data compression method based on dichotomy symmetric folding technology

The invention discloses a test data compression method based on a dichotomy symmetric folding technology. Vectors in a test set are arranged according to the degressive sequence of the number of determined bits. The first vector in the sequenced test set is selected as a seed, and a folding set is generated. The vectors in the test set are compared with vectors in the folding set, if Cj is the bit of the determined bit, the value of the bit, corresponding to Cj in position, in Vi is the unrelated bit or the same determined bit, or if the value in Cj is the bit of the unrelated bit, the value of the bit, corresponding to Cj in position, in Vi is the unrelated bit; the vector VI is deleted from the test set. The process is repeatedly carried out till the test set is null, and the obtained seed set S is the corresponding result of the test data T through compression. Compared with the prior art, the test data compression method has the following advantages that the non-invasive type test data compression method is adopted, a tested circuit structure is not changed, the structure of a scan chain in the circuit is not changed, the seed set is used for covering the whole test set, the compression rate is increased, the testing power consumption is reduced, and the test application time is shortened.

Owner:SHANGHAI TAIYU INFORMATION TECH

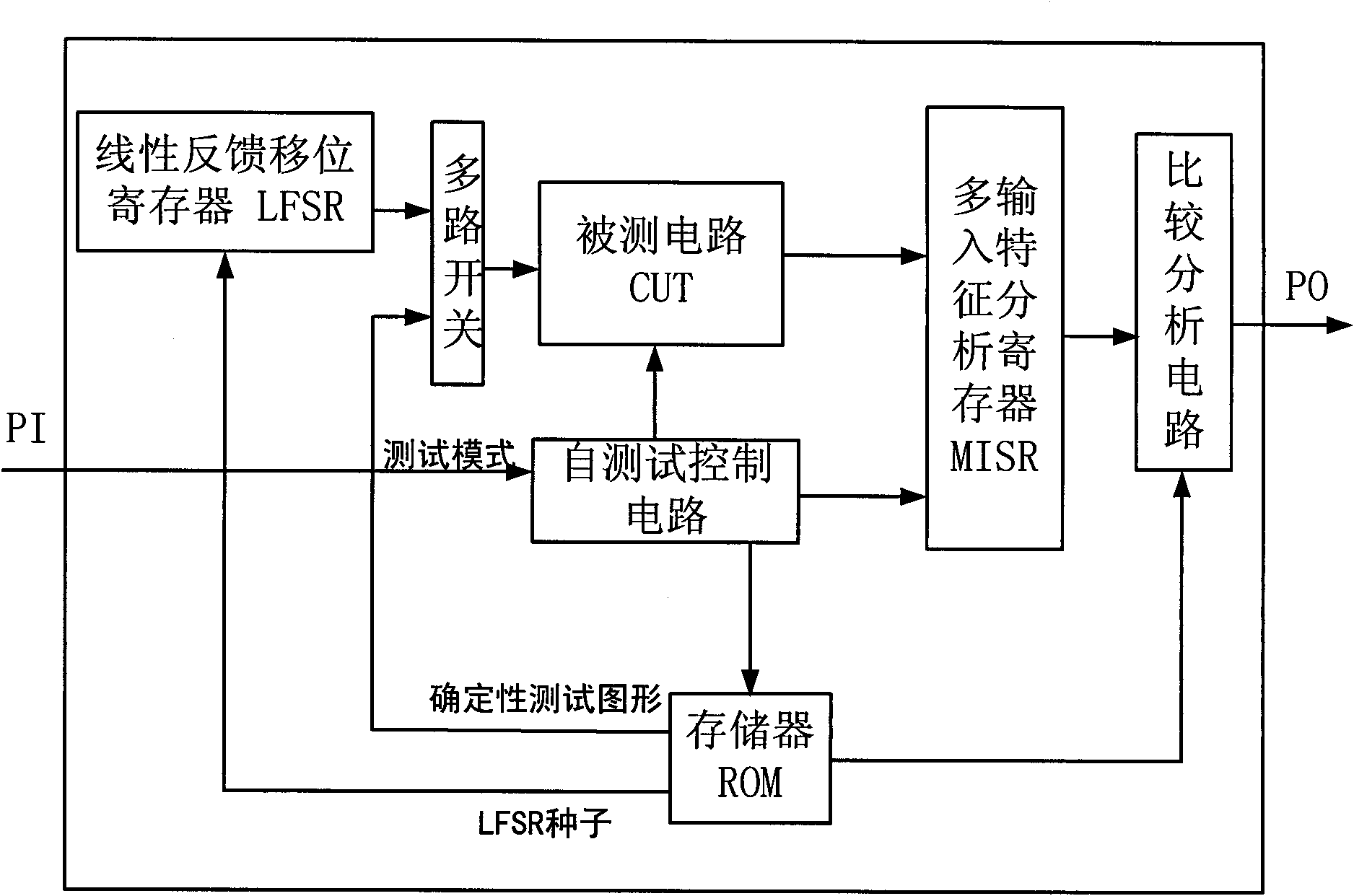

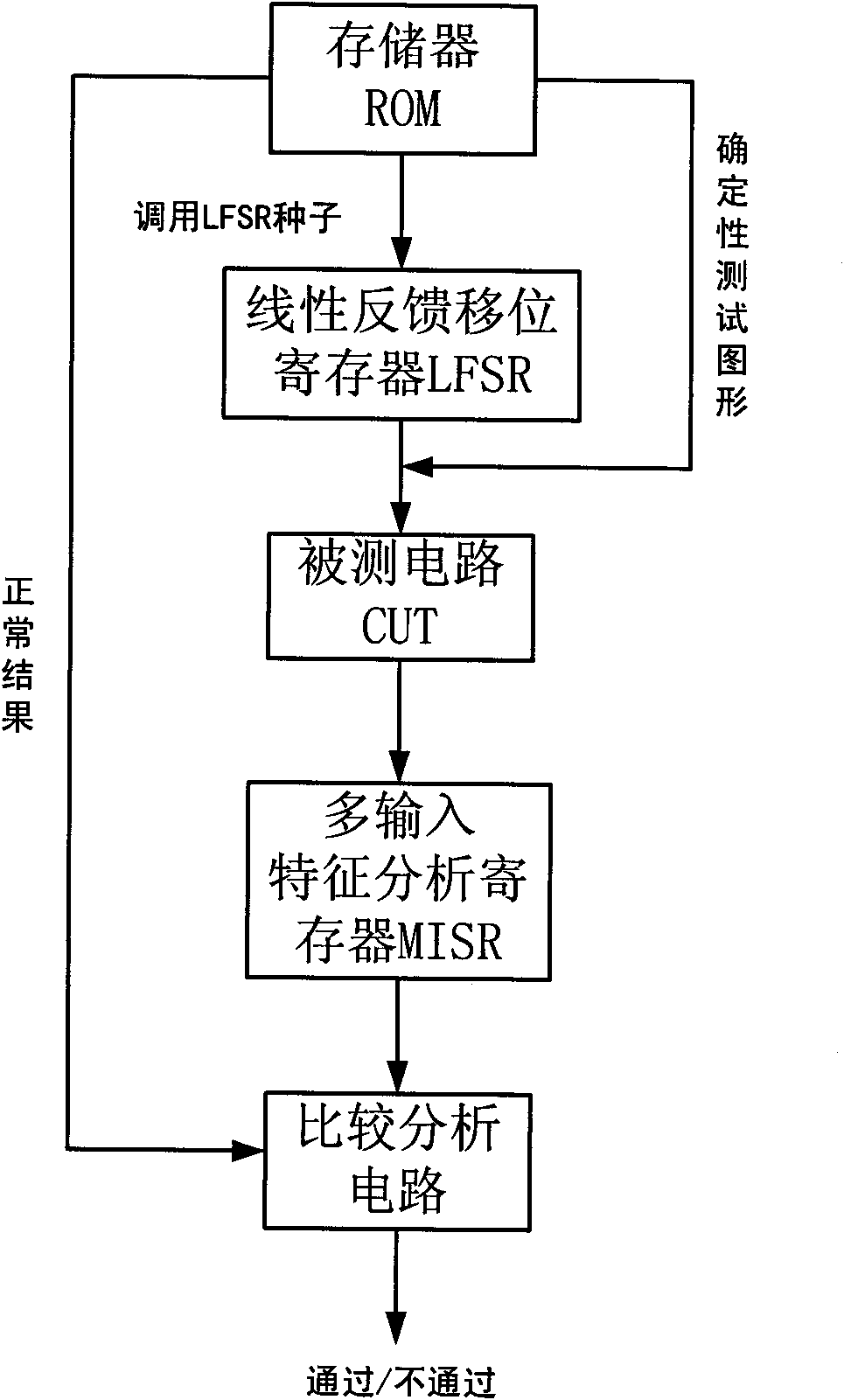

Built-in self-testing system and method thereof with mixed mode

InactiveCN101881812AImprove fault coverageReduce test power consumptionElectrical testingMulti inputFault coverage

The invention relates to a built-in self-testing system and a method thereof with a mixed mode. The testing system comprises a circuit (CUT) to be tested, a self-testing control circuit, a multi-input feature analysis register (MISR), a memory (ROM) and a comparative analysis circuit. The invention has the improvement that the built-in self-testing system also comprises a linear feedback shift register (LFSR) which is used for generating a pseudo-random testing figure and a multi-way switch; the input end of the linear feedback shift register (LFSR) is connected with the memory (ROM), one input end of the multi-way switch is connected with the output end of the linear feedback shift register (LFSR), the other input end of the multi-way switch is connected with the memory (ROM), and the output end of the multi-way switch is connected to the input end of the circuit (CUT) to be tested; and the testing method of the built-in self-testing system is a built-in self-testing method which is based on a pseudo-random method and a determinacy generation method and has a mixed mode. The invention has the advantage that the self-testing system and the method thereof have high fault-coverage rate, short testing time, low testing power consumption and simple structure.

Owner:NO 63908 TROOPS PLA

Low-power consumption boundary scanning test method

ActiveCN110007217AReduce test power consumptionReduce dynamic power consumptionElectronic circuit testingTest responseScan chain

The invention discloses a low-power consumption boundary scanning test method, belongs to the field of SOC boundary scanning test, and aims at solving the problem that the existing low-power consumption boundary scanning test methods are at the cost of sacrificing the fault coverage rate so that the test results are influenced. According to the method, the output end of each chip on an SOC is connected with a BSLC scanning unit; the SI ends and SO ends of every two adjacent boundary scanning units in n BSLC scanning units are sequentially connected in series to form an input boundary scanningchain which is used for sending test excitations to a function path; the input end of each chip is connected with a BSCC scanning unit; the SI ends and SO ends of every two adjacent boundary scanningunits in m BSCC scanning units are sequentially connected in series to form an output boundary scanning chain which is used for capturing and moving test responses; and when each bit of test data is moved in, the state of a trigger on the whole scanning chain is switched for less than twice, so that the test power consumption is greatly decreased.

Owner:HARBIN INST OF TECH AT WEIHAI

Means scanning scan path parts sequentially and capturing response simultaneously

InactiveUS7131044B2Less operational powerReduce test power consumptionDigital circuit testingResistance/reactance/impedenceTest powerEngineering

Scan architectures are commonly used to test digital circuitry in integrated circuits. The present invention describes a method of adapting conventional scan architectures into a low power scan architecture. The low power scan architecture maintains the test time of conventional scan architectures, while requiring significantly less operational power than conventional scan architectures. The low power scan architecture is advantageous to IC / die manufacturers since it allows a larger number of circuits (such as DSP or CPU core circuits) embedded in an IC / die to be tested in parallel without consuming too much power within the IC / die. Since the low power scan architecture reduces test power consumption, it is possible to simultaneously test more die on a wafer than previously possible using conventional scan architectures. This allows wafer test times to be reduced which reduces the manufacturing cost of each die on the wafer.

Owner:TEXAS INSTR INC

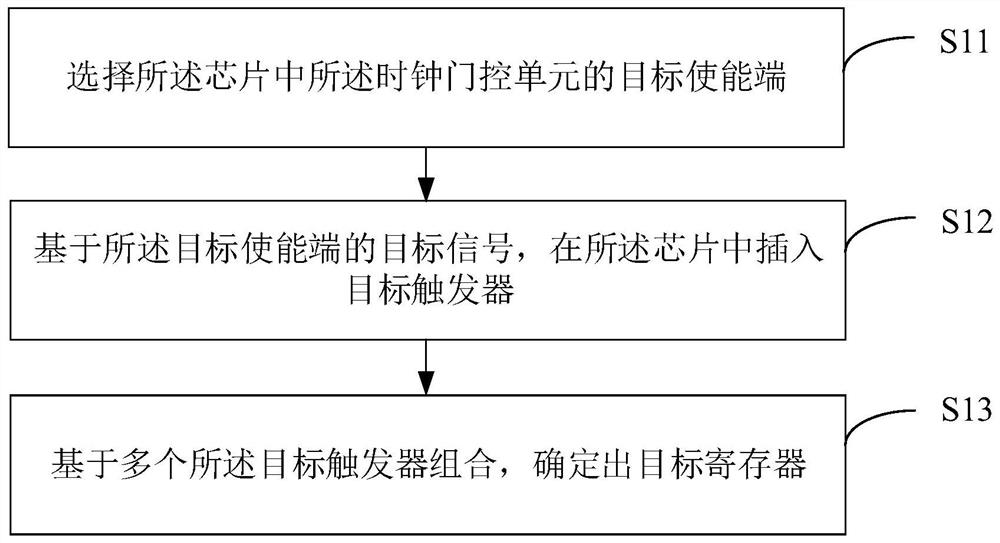

Chip testing method and device, chip testing machine and storage medium

PendingCN114280454AControlled Scan TestObservable scan testElectronic circuit testingEnergy efficient computingTest powerControl register

The invention provides a chip testing method and device, a chip testing machine and a storage medium, and relates to the technical field of chip testing, and the method comprises the steps: determining a target register of a target enabling end of a clock gating unit in a chip; obtaining a target scan chain based on a plurality of target register combinations; generating a target enable signal through the set values of a plurality of target registers on the target scan chain; and controlling a target clock gating unit corresponding to a target enabling end in the clock gating units to be opened or closed through the target enabling signal. On the basis of generating the target scan chain, the clock gating unit can be controlled to be opened and closed in the chip scan test mode by controlling the value of the register, so that the control difficulty of the clock gating unit is reduced, the opening proportion of the clock gating unit is effectively controlled, the number of test vectors is reduced, the test coverage rate is improved, and the test efficiency is improved. Therefore, the test power consumption during the chip scanning test is reduced, and the test cost is reduced.

Owner:西安爱芯元智科技有限公司

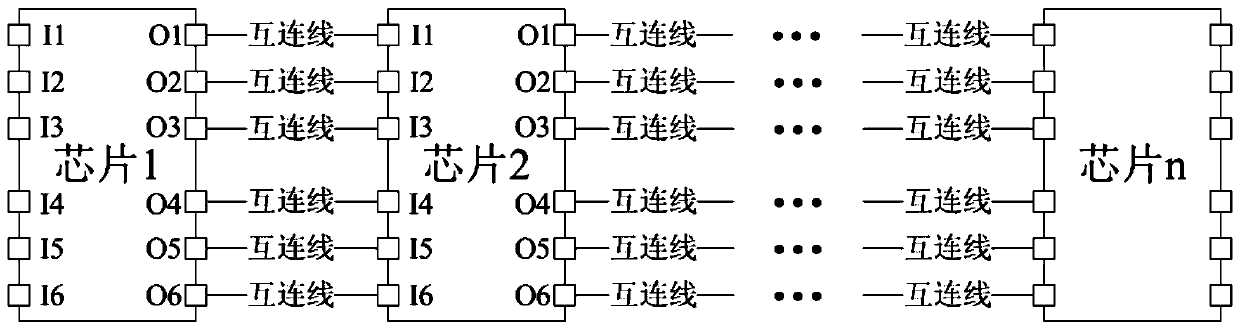

Controllable Chiplet serial test circuit

ActiveCN114578217AReduce the numberGuaranteed shift operationElectronic circuit testingTest inputControl signal

The invention discloses a controllable Chiplet serial test circuit, and belongs to the technical field of testing or measuring of semiconductor devices in the manufacturing or processing process. The test circuit comprises a master control test module, a slave control test module, a clock control module and an output module, the master control test module is composed of a test access port module, a segment insertion bit module and a test data register module, and a test control signal is generated through the master control test module; the slave control test modules respectively control test input signals of the slave control core particles after receiving the test control signals. Meanwhile, the test control signal is input to the clock control module to obtain a clock signal of the slave control core particle. The output signal of the test output module is determined by the test control signal. According to the test circuit, an external test port is used for directly controlling an internal test signal of the multi-core-particle integrated circuit, core particle test selection and final test output are realized, and effectiveness and independence of each core particle test are ensured.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

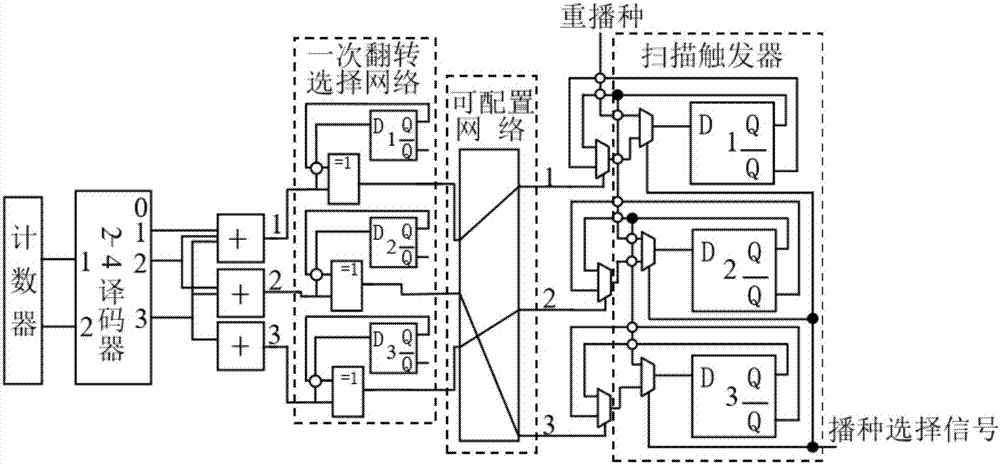

Primary overturn selection network, overturn sequence decompression structure thereof and decompression method

ActiveCN106124962ADecompression time shortenedReduce test power consumptionElectronic circuit testingTest powerTested time

The present invention discloses a primary overturn selection network, an overturn sequence decompression structure thereof and a decompression method. The primary overturn selection network comprises a plurality of combined units of same structures, and each combined unit comprises a D trigger and an XOR gate corresponding to the D trigger. The in-phase input ends of the XOR gates are the input ends of the corresponding combined units, the inverted input ends of the XOR gates are connected with the in-phase input ends, the input ends of the D triggers and the in-phase output ends of the D triggers, and the output ends of the XOR gates are used as the output ends of the corresponding combined units. According to the present invention, the overturn times of the corresponding primary overturn sequence decompression structure is reduced by half, namely the test time is reduced to a half of the original time. In addition, the overturn power consumption of the circuits connected with the triggers is reduced, namely, the test power consumption is also reduced. The present invention also discloses the primary overturn sequence decompression structure having the primary overturn selection network, and the decompression method of the overturn sequence decompression structure.

Owner:池州华宇电子科技股份有限公司

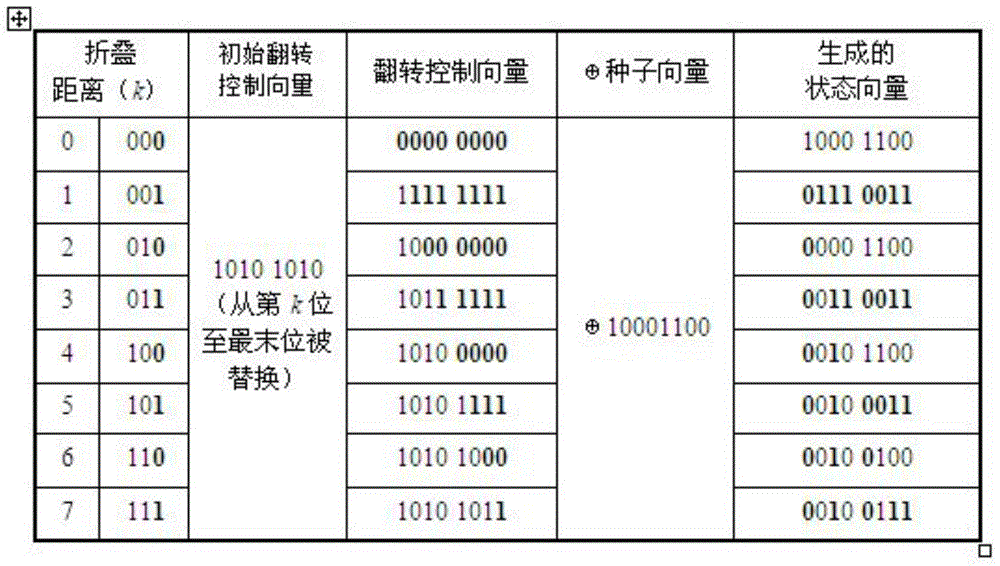

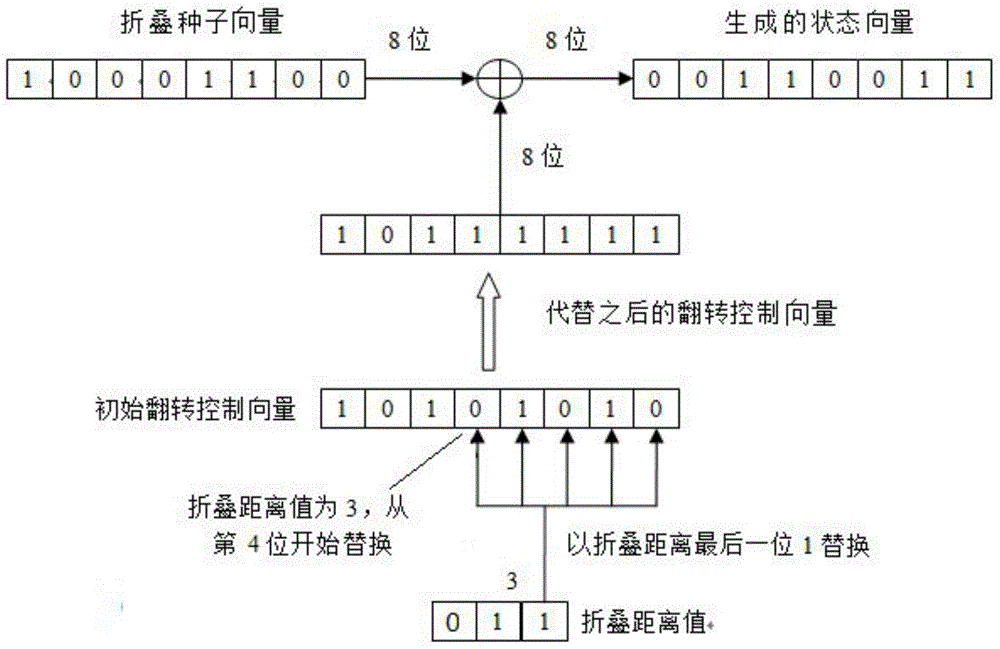

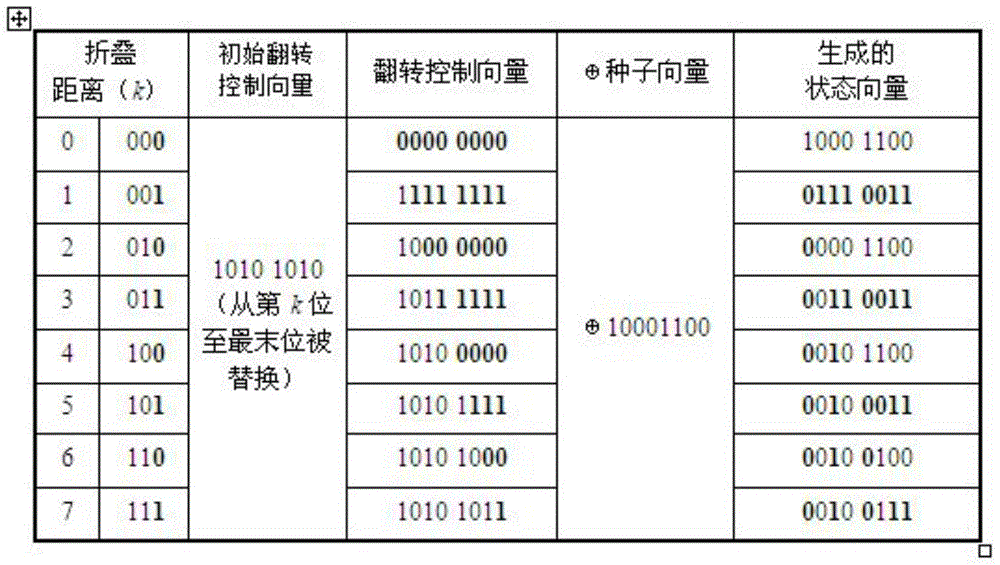

Selective generation method for state vectors of parallel folding counter and hardware circuit for selective generation method

InactiveCN104635148AShorten test timeReduce test power consumptionDigital circuit testingTest powerControl vector

The invention relates to a selective generation method for state vectors of a parallel folding counter and a hardware circuit for the selective generation method. The selective generation method is characterized by comprising the following steps of establishing a logical relation among an initial inversion control vector, a folding distance and a corresponding inversion control vector; realizing selective bit replacement on the initial inversion control vector through the decoded output of the folding distance to generate the inversion control vector corresponding to the folding distance; then, performing bitwise exclusive-or operation on the generated inversion control vector and folding seeding vectors in sequence, therefore realizing the selective generation of the state vectors of the folding counter. According to the selective generation method disclosed by the invention, for the given folding seeding vectors and a given folding distance value, the state vector corresponding to the folding distance can be directly generated, and therefore the generation efficiency of deterministic BIST (build-in self-test) test vectors is obviously increased, the generation of redundant state vectors is avoided, and the test time and the test power dissipation of the circuit are reduced.

Owner:HEFEI UNIV OF TECH

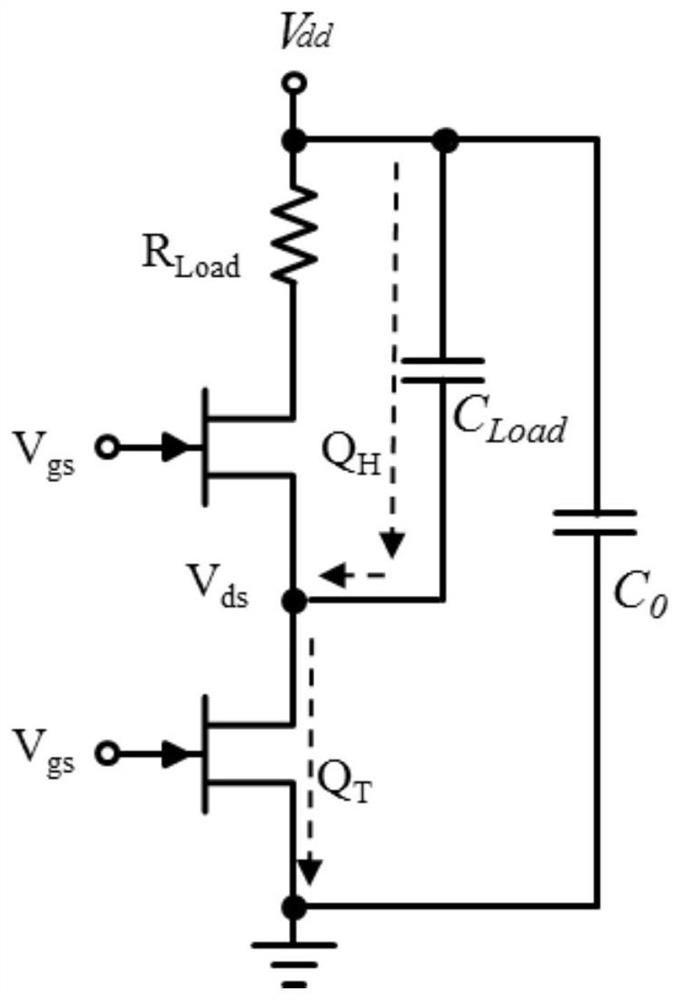

Gallium nitride device reliability testing device and testing method

ActiveCN112986779AReduce system test power consumptionIncrease flexibilityEfficient power electronics conversionSemiconductor operation lifetime testingLoad resistanceCapacitance

The invention discloses a gallium nitride device reliability testing device and a testing method. The device comprises a load resistor, a load capacitor and a first semiconductor switching device, wherein one end of the load resistor is connected to a direct current power supply, and the other end of the load resistor is connected to a drain electrode of the first semiconductor switching device; the source electrode of the first semiconductor switching device is respectively connected to the drain electrode of the gallium nitride device to be tested and one end of the load capacitor, the other end of the load capacitor is connected to the direct current power supply, and the source electrode of the gallium nitride device to be tested is grounded; the grid electrode of the first semiconductor switching device is connected to the first pulse generator, and the grid electrode of the gallium nitride device to be tested is connected to the second pulse generator. By adopting the device and the testing method provided by the invention, the system testing power consumption is greatly reduced, the test can be accelerated in a single wide range, and the requirements of low power consumption, high flexibility, multi-dimension and large-batch test of the gallium nitride device are met.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

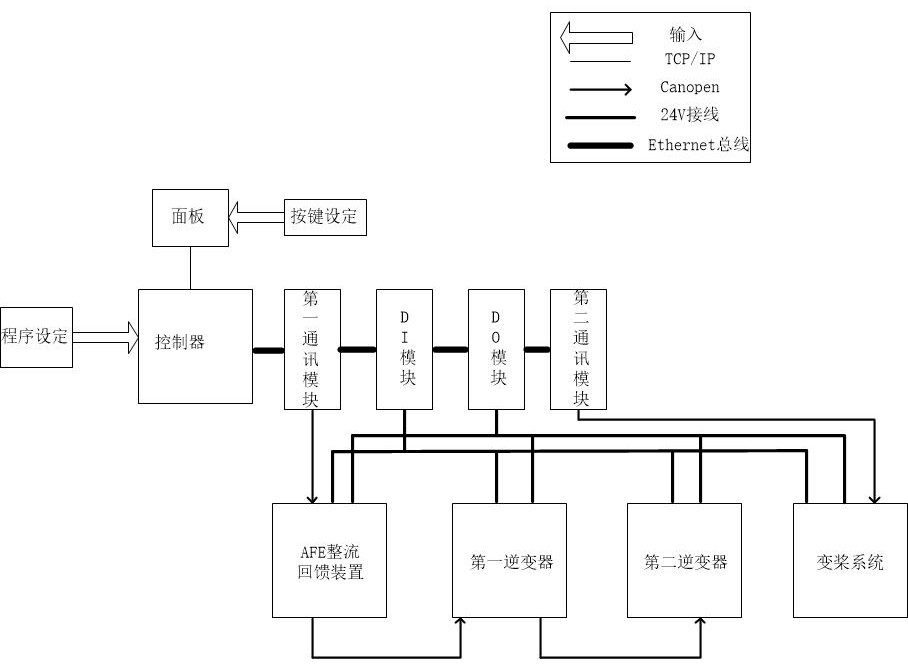

Pitch loading cabinet and control system

ActiveCN114326578BSave powerReduce test power consumptionWind energy generationProgramme control in sequence/logic controllersBusbarControl system

The invention discloses a variable pitch loading cabinet and a control system, belonging to the field of wind power variable pitch testing, comprising a controller, an AFE rectification feedback device, an inverter, a loading motor and an electrical main circuit; The structure of one incoming line + two power supplies + busbar in parallel, the power supply of the pitch system and the loading system are connected in parallel, and the loading system is supplied by the electric power from the tow motor to the pitch system for use; the controller is connected with the AFE rectifier feedback device, The AFE rectifier feedback device is connected to the inverter, and the inverter is connected to the loading motor. The invention realizes energy feedback, and has the advantages of energy saving, simple structure, low cost, mobility, small size, and the ability to realize torque command programming simulation and the like.

Owner:东方电气风电股份有限公司

Test graphic generator of integrated circuit and test method thereof

InactiveCN101776730BReduce overheadReduce the number of test pattern transitionsElectrical testingTest powerFault coverage

The invention relates to the field of an integrated circuit test, and discloses a test graphic generator of an integrated circuit and a test method thereof. The test graphic generator comprises a reconfigurable linear feedback shift register of cyclic code with single bit change, a liner feedback shift register based on a primitive polynomial and a two-dimensional exclusive or gate array; compared with the traditional test graphic generator, the test graphic generator has less hardware overhead, few quantity of repeated test graphics, short test time, uniform distribution of generated test graphics, and can obtain higher fault coverage rate; and the generated single jump test sequence reduces the conversion times of a tested circuit input end, thus greatly reducing the test power consumption of the tested integrated circuit.

Owner:XI AN JIAOTONG UNIV

A controllable Chiclet serial test circuit

ActiveCN114578217BReduce the numberGuaranteed shift operationElectronic circuit testingTest inputControl signal

The invention discloses a controllable Chiplet serial test circuit, which belongs to the technical field of testing or measurement of semiconductor devices in the process of manufacturing or processing. The test circuit includes a master control test module, a slave control test module, a clock control module, and an output module. The master control test module is composed of a test access port module, a segment insertion bit module, and a test data register module. The test control module is generated through the master control test module. After receiving the test control signal, the slave control test module respectively controls the test input signal of the slave control core particles. At the same time, the test control signal is input to the clock control module to obtain the clock signal of the slave chip. The output signal of the test output module is determined by the test control signal. The test circuit uses the external test port to directly control the internal test signal of the multi-chip integrated circuit, realizes the selection of the chip test and the final test output, and ensures the validity and independence of each chip test.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

A method for selecting and generating the state vector of a parallel folding counter and its hardware circuit

InactiveCN104635148BShorten test timeReduce test power consumptionDigital circuit testingTest powerControl vector

The invention relates to a selective generation method for state vectors of a parallel folding counter and a hardware circuit for the selective generation method. The selective generation method is characterized by comprising the following steps of establishing a logical relation among an initial inversion control vector, a folding distance and a corresponding inversion control vector; realizing selective bit replacement on the initial inversion control vector through the decoded output of the folding distance to generate the inversion control vector corresponding to the folding distance; then, performing bitwise exclusive-or operation on the generated inversion control vector and folding seeding vectors in sequence, therefore realizing the selective generation of the state vectors of the folding counter. According to the selective generation method disclosed by the invention, for the given folding seeding vectors and a given folding distance value, the state vector corresponding to the folding distance can be directly generated, and therefore the generation efficiency of deterministic BIST (build-in self-test) test vectors is obviously increased, the generation of redundant state vectors is avoided, and the test time and the test power dissipation of the circuit are reduced.

Owner:HEFEI UNIV OF TECH

A test system and test method for a power distribution cabinet

ActiveCN111060759BShorten test timeReduce test power consumptionElectrical testingMeasurement instrument housingTest powerElectrical testing

The application discloses a test system and a test method for a power distribution cabinet, which relate to the field of electrical test. The power distribution cabinet test system includes an AC power supply, a tested AC power distribution cabinet, a rectifier, a tested DC power distribution cabinet and a load; the AC power supply, a tested AC power distribution cabinet, a rectifier, a tested DC The cabinet and the load are connected in series in sequence; the output voltage level of the rectifier device matches the DC power distribution cabinet under test; the load is adjusted to control the AC power distribution cabinet under test and the DC power distribution cabinet under test carry out testing. The application can save test time and reduce test power consumption.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

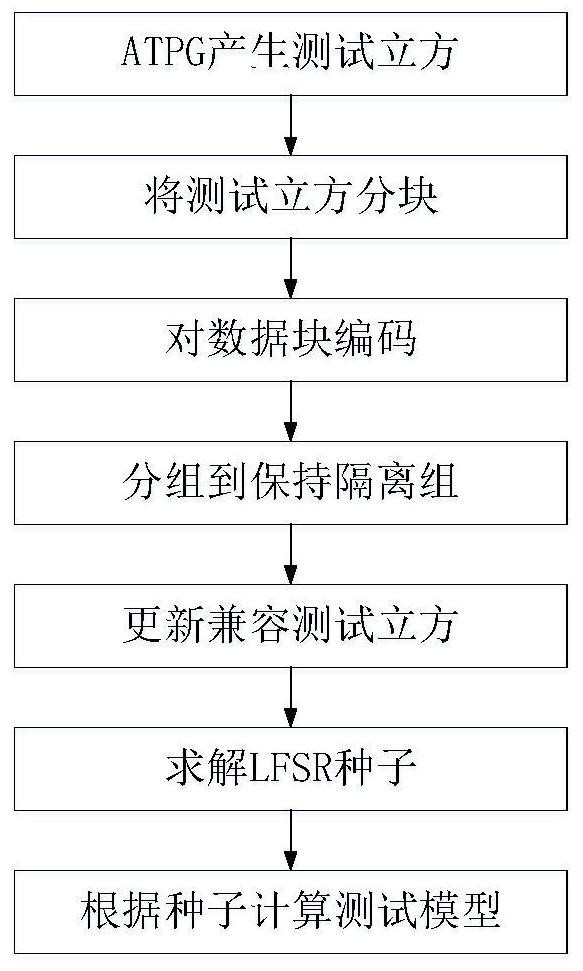

A low power lfsr reseeding test compression method for scan design

ActiveCN109444727BReduce the number of certain bitsReduce the numberElectrical testingTest powerLogisim

The invention discloses a low power consumption LFSR reseeding test compression method facing scanning design structures. Thus, problems of excessive high test power consumption brought by a traditional LFSR reseeding technology can be solved. Based on an optimized coding algorithm of a test cube, the method can combine with any LFSR reseeding scheme, and be applied to industrial grade super-large-scale integrated circuits and the built-in self-testing of system on chips and functional verification thereof. The basic thinking of the method is as follows: random filling can be performed on don't care bits in the test cube during a LFSR reseeding process, which can trigger excessive high switch switching rates and test power consumption. The method can enhance the logic consistency between adjacent bits in the test cube by optimizing codes, so that test power consumption can be effectively reduced; and seed vector solving difficulty can be reduced by reducing the number of determined bits in the test cube and the number of state equations, so that test data compression rates can be effectively enhanced, and the challenges of testing storage resources can be alleviated.

Owner:BEIJING UNIV OF TECH

Scan sub-chain type test structure and test method in compliance with boundary scan standard

ActiveCN103487747BLower bit pass rateFew test parametersElectrical testingControl engineeringCircuit under test

The invention discloses a scan sub-chain type test structure conforming to the boundary scan standard, including a vector configuration module and a response aggregation module. The vector configuration module reconfigures the test signal into multiple parallel boundary scan sub-chains and is connected to the response aggregation module. Each data output end of the vector configuration module is connected to the data input end of each boundary scan sub-chain, the data output end of each boundary scan sub-chain is connected to the data input end of the response aggregation module, and the test response output by the output end of the response aggregation module Connects to the TDI port of the boundary scan test controller. The invention simultaneously discloses a scan sub-chain type test method conforming to the boundary scan standard, and the application of the scan sub-chain type test structure and the test method in diagnosing the fault of the tested circuit board. The invention can not only meet the standard but also satisfy the requirement of the scan sub-chain test structure, reduce the bit passing rate in the shifting process of the boundary scan test, and further reduce the power consumption of the boundary scan test.

Owner:GUILIN UNIV OF ELECTRONIC TECH

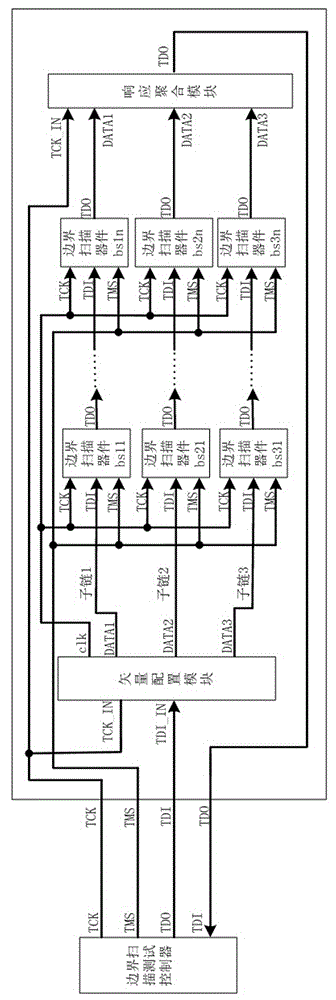

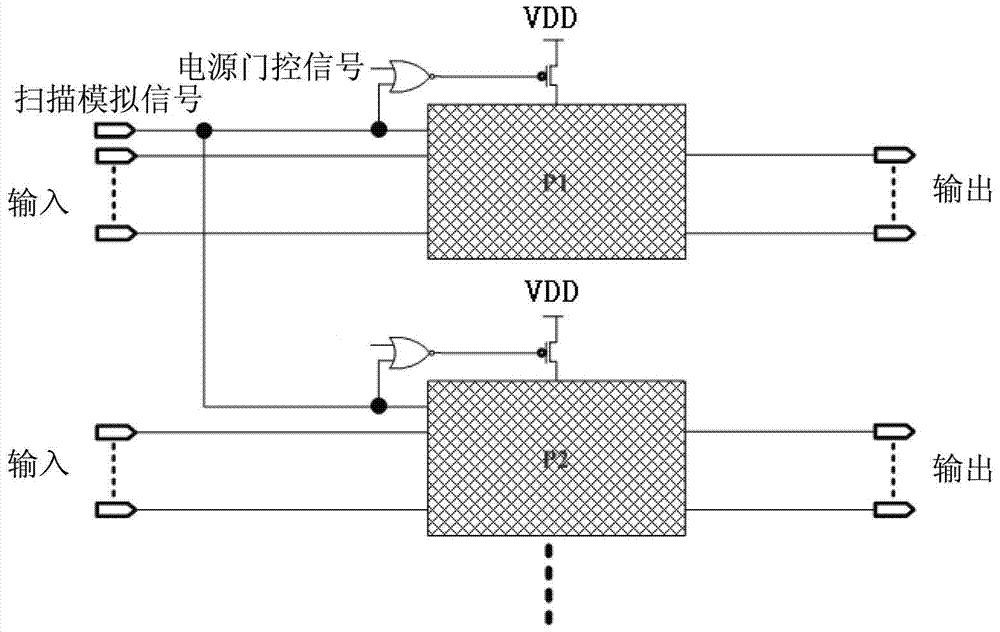

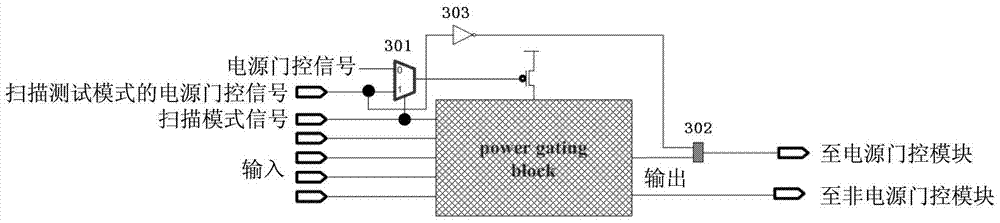

Scan Test Control Circuit for SoC

ActiveCN103983912BReduce flipReduce test power consumptionElectronic circuit testingControl circuitPower gating

Owner:SAMSUNG SEMICON CHINA RES & DEV +1

Compressing and encoding method of low energy consumption SOC (System On a Chip) test data

InactiveCN101807926BImprove compression efficiencyShorten test timeCode conversionData compressionTest power

The invention relates to a compressing and encoding method of low energy consumption SOC (System On a Chip) test data. Original test data is divided into a 1 string with continuous data 1 and an ending of 0 or a 0 string with continuous data 0 and an ending of 1 based on test data types, and the 0 string and the 1 string are alternatively encoded; only when the continuous 0 string or 1 string occurs, an additional separation code 10 is inserted in the 0 string or the 1 string which continuously occurs, and each string of data is compressed and encoded; and each code word after encoding is less than a code word generated by FDR coding or other encoding method improved based on FDR coding by a bit, thereby greatly enhancing the compression efficiency of the test data and having importance significance to reduce the test time and lower the test power consumption.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

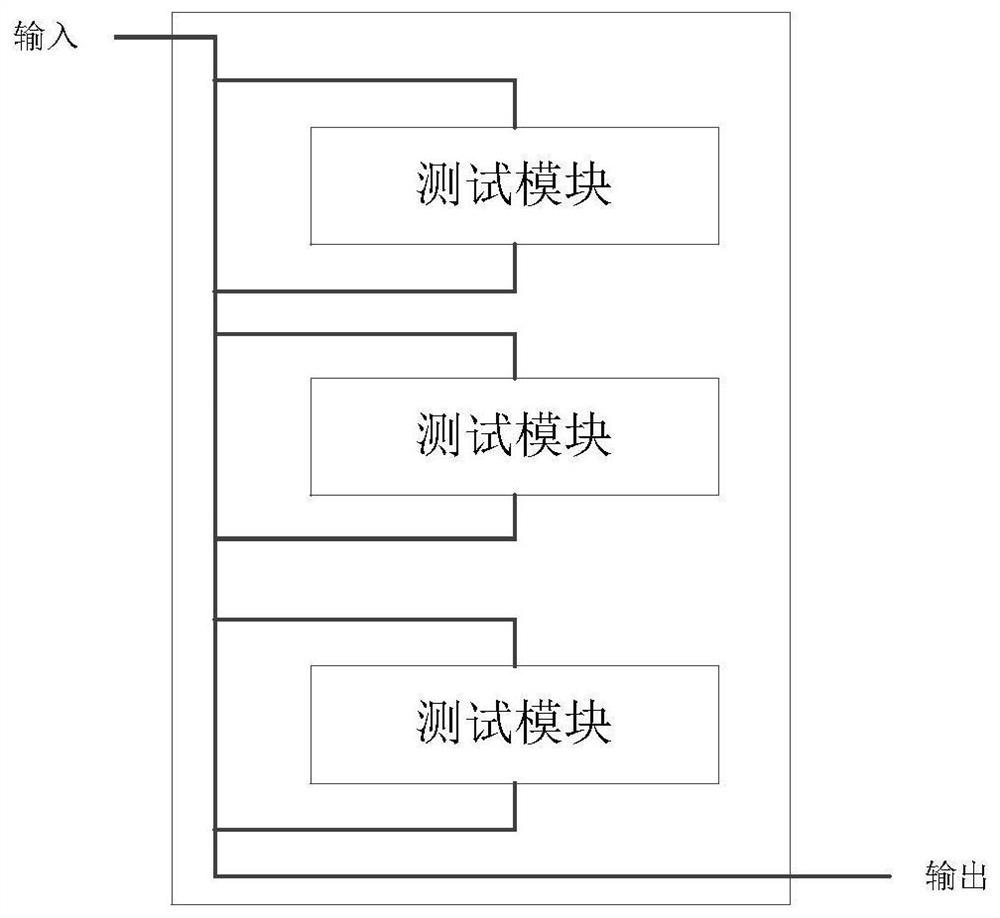

Test access architecture and test access method of digital chip

PendingCN114280449AReduced Quantity RequirementsShorten test timeElectronic circuit testingComputer architectureDistributed testing

The embodiment of the invention provides a test access architecture and a test access method of a digital chip, and belongs to the technical field of integrated circuit testing. The architecture comprises N test groups divided by all modules in a digital chip; wherein each test group in the N test groups comprises a plurality of test modules, and the plurality of test modules in each test group are configured to be tested by adopting a distributed test access mechanism; the N test groups are configured to adopt a multi-path selection test access mechanism for testing. The embodiment of the invention is suitable for architecture division in the test process of large-scale digital chips.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +3

Test method and device of integrated circuit chip and storage medium

The invention aims to provide the test method and device of the integrated circuit chip and the storage medium, so that the test power consumption of the integrated circuit chip can be effectively reduced; in order to achieve the purpose, the testing method and device of the integrated circuit chip and the storage medium are provided, in the testing process, the testing device uses data of all registers as testing signals to be provided for all circuit modules of the integrated circuit chip through the initial shifting action, and therefore the testing accuracy of the integrated circuit chip is improved. And then obtaining output data of each logic circuit in each register through a capture action. Then, the shift operation and the capture operation are repeated, and the test of each logic circuit is performed by comparing the obtained output data of each circuit module with an expected value thereof.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

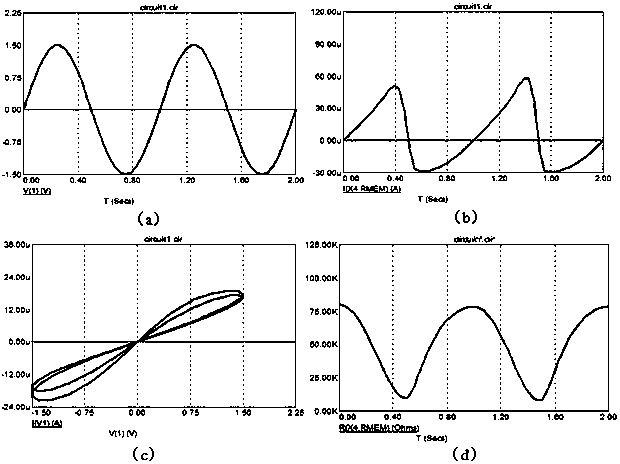

A scanning flip-flop circuit based on HP memristor and its design method

InactiveCN104980129BSupport power-off working modeReduce test power consumptionElectric pulse generator circuitsMultiplexerComputer module

The invention relates to an HP memristor-based scan flip-flop circuit and a design method thereof. The scan flip-flop circuit comprises a master-slave flip-flop, an either-or data selector, a memory control module, a return control module and a memristor, wherein the master-slave flip-flop is respectively connected with the either-or data selector, the memory control module and the return control module; the memory control module and the return control module are also connected onto the memristor; the memory control module is used for controlling data of the master-slave flip-flop to be transmitted to the memristor; and the return control module is used for controlling data in the memristor to be returned to the master-slave flip-flop. Before the entire flip-flop is power-off, data stored in the master-slave flip-flop are stored in the memristor via the memory control module; and when the flip-flop is power-on again, the data stored in the memristor can be returned to the master-slave flip-flop via the return control circuit.

Owner:FUZHOU UNIV

A flipping selection network and its flipping sequence decompression structure and decompression method

ActiveCN106124962BDecompression time shortenedReduce test power consumptionElectronic circuit testingTest powerTested time

The present invention discloses a primary overturn selection network, an overturn sequence decompression structure thereof and a decompression method. The primary overturn selection network comprises a plurality of combined units of same structures, and each combined unit comprises a D trigger and an XOR gate corresponding to the D trigger. The in-phase input ends of the XOR gates are the input ends of the corresponding combined units, the inverted input ends of the XOR gates are connected with the in-phase input ends, the input ends of the D triggers and the in-phase output ends of the D triggers, and the output ends of the XOR gates are used as the output ends of the corresponding combined units. According to the present invention, the overturn times of the corresponding primary overturn sequence decompression structure is reduced by half, namely the test time is reduced to a half of the original time. In addition, the overturn power consumption of the circuits connected with the triggers is reduced, namely, the test power consumption is also reduced. The present invention also discloses the primary overturn sequence decompression structure having the primary overturn selection network, and the decompression method of the overturn sequence decompression structure.

Owner:池州华宇电子科技股份有限公司

A Test Data Compression Method for Bipartite Flipping and Folding Technology

The invention discloses a test data compression method of bipartite symmetric folding technology, which sorts the vectors in the test set in the descending order of the determined number of bits. The first vector in the sorted test set is selected as a seed to generate a folded set. Compare the vectors in the test set with the vectors in the folded set, if Cj is a definite bit, the value of the bit corresponding to it in Vi is an irrelevant bit or the same definite bit or if the value in Cj is an unrelated bit, Vi The value of the bit corresponding to it in is also an irrelevant bit; then the vector Vi is deleted from the test set. Repeat the above process until the test set is empty, then the obtained seed set S is the result corresponding to the compressed test data T. Compared with the prior art, the present invention has the following advantages: the present invention adopts a non-invasive test data compression method, does not change the structure of the circuit to be tested, does not change the structure of the scan chain in the circuit, uses a seed set to cover the entire test set, and improves Compression ratio reduces test power consumption and shortens test application time.

Owner:SHANGHAI TAIYU INFORMATION TECH

Low-power deterministic bist and seed compression method based on single and double jumps

ActiveCN105738800BReduce test power consumptionShorten test timeElectrical testingFunctional testingTest powerTest performance

The invention relates to the technical field of large-scale digital integrated circuits, and provides a low-power-consumption certainty BIST based on single and double jump and a seed compression method thereof. In order to reduce test power consumption, a novel single and double jump unit and an ROM control signal are applied to generate a certainty seed through single and double hybrid jump, and then certainty test vectors are generated by utilizing a single jump reseeding technology. Meanwhile, the generation number of the certainty test vectors in the reseeding process is constrained by additional arrangement of a 2-bit subtracting counter so as to reduce the number of redundant vectors and reduce test time. Besides, the corresponding seed compression method is also put forward so as to compress area overhead and generate the control signal. The experiment result proves that the test performance, such as test time, the area overhead and test power consumption, of the BIST and the seed compression method can be reduced to a large extent.

Owner:厦门润积集成电路技术有限公司

Fault injection method based on dual-port SRAM (system random access memory)

InactiveCN102446559AImplement fault injection testingReduce test power consumptionStatic storageTest powerStatic random-access memory

The invention discloses a fault injection method based on dual-port SRAM (system random access memory), which comprises the following steps:A arranging a first code selector behind a coder of a first port of the SRAM; arranging a second code selector behind a coder of a second port; and globally applying an external control signal TEST to the first code selector and the second code selector of the SRAM. The in-chip fault injection method disclosed by the invention can implement control by one control signal outside the chip without introducing any other external injection signal, only occupies small internal chip area, and can quickly implement the fault injection test. Meanwhile, since the method is only logically equivalent fault injection instead of direct error injection, thereby lowering the test power consumption. Besides, the test operation is simple and quick, and the method has the advantages of low cost and high test coverage rate.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Large scale integrated circuit test data and method for testing power consumption cooperate optimization

InactiveCN100557454CReduce test power consumptionGuaranteed reliabilityElectronic circuit testingTest powerData compression

A method for cooperative optimization of test data and test power consumption of large-scale integrated circuits. It involves the technical field of large-scale integrated circuits, and it is proposed for the current SOC test technology that can effectively reduce the amount of test data and test power consumption at the same time. Its method steps are: analyze the compatibility of scanning units in the circuit, and divide them into three categories; connect the scanning units in each category separately to construct a scanning chain with a "copy" mechanism; adjust the structure according to the new scanning chain A test vector set; the test set is compressed using a method based on repetitive data compression to obtain a compressed test set TE. When testing, the compressed data is completely restored by the decompression circuit for testing. The invention is a design method for testability of integrated circuits; it can reduce the power consumption of the circuit during testing, thereby ensuring its reliability and testability; it can effectively reduce the amount of test data, test time, and the number of ATE channels .

Owner:HARBIN INST OF TECH

Low power consumption LFSR reseeding test compression method facing scanning design

ActiveCN109444727AReduce the number of certain bitsReduce the numberElectrical testingTest powerFace scanning

The invention discloses a low power consumption LFSR reseeding test compression method facing scanning design structures. Thus, problems of excessive high test power consumption brought by a traditional LFSR reseeding technology can be solved. Based on an optimized coding algorithm of a test cube, the method can combine with any LFSR reseeding scheme, and be applied to industrial grade super-large-scale integrated circuits and the built-in self-testing of system on chips and functional verification thereof. The basic thinking of the method is as follows: random filling can be performed on don't care bits in the test cube during a LFSR reseeding process, which can trigger excessive high switch switching rates and test power consumption. The method can enhance the logic consistency between adjacent bits in the test cube by optimizing codes, so that test power consumption can be effectively reduced; and seed vector solving difficulty can be reduced by reducing the number of determined bits in the test cube and the number of state equations, so that test data compression rates can be effectively enhanced, and the challenges of testing storage resources can be alleviated.

Owner:BEIJING UNIV OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com