A method for selecting and generating the state vector of a parallel folding counter and its hardware circuit

A technology of state vector and selection generation, applied in digital circuit testing, measuring electricity, measuring electrical variables, etc., can solve the problems of increased circuit test time and test power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

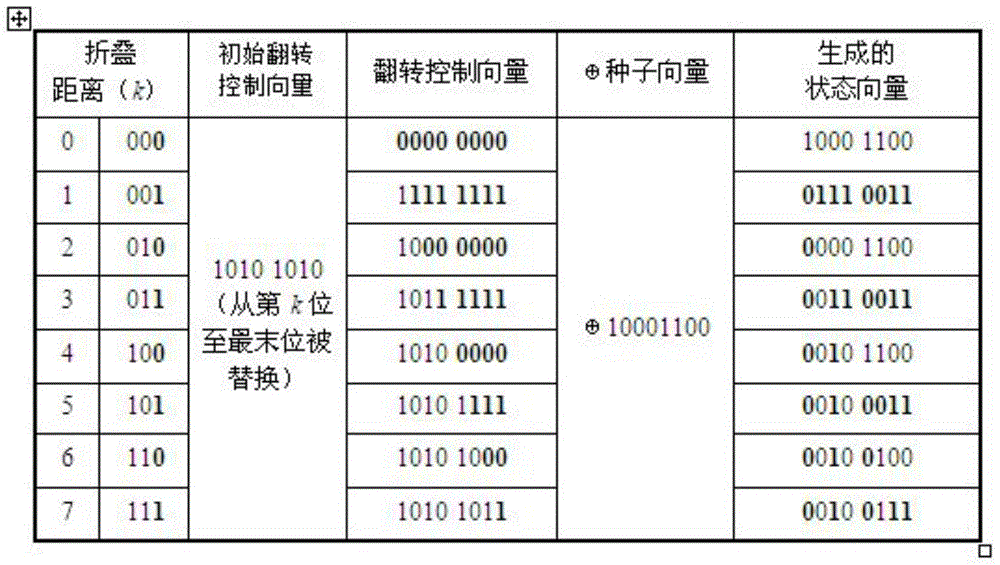

[0048] For an n-bit parallel folding counter, there are a folding seed vector of an n-bit binary number and n state vectors corresponding to the folding seed vector; the folding seed vector of an n-bit binary number is s=[s 1 s 2 …S j …S n ];S j Represents the jth binary bit in the folded seed vector s; s 1 Represents the first binary bit, the highest binary bit; s n Represents the nth binary bit, that is, the lowest binary bit; 1≤j≤n; record the n state vectors corresponding to the folded seed vector s as X={x 1 ,x 2 ,...,X i ,...,X n }; x i Represents the i-th state vector corresponding to the folding seed vector s; 1≤i≤n; remember that the folding distance value corresponding to each of the n state vectors X in turn is {0,1,...,i-1 ,...,N-1}; i-1 means the same as the i-th state vector x i The corresponding folding distance value;

[0049] In this embodiment, as figure 1 As shown, for an n-bit parallel folding counter, an initial flip control vector 10101010 with a length of n b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com