Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

859 results about "Electrical testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

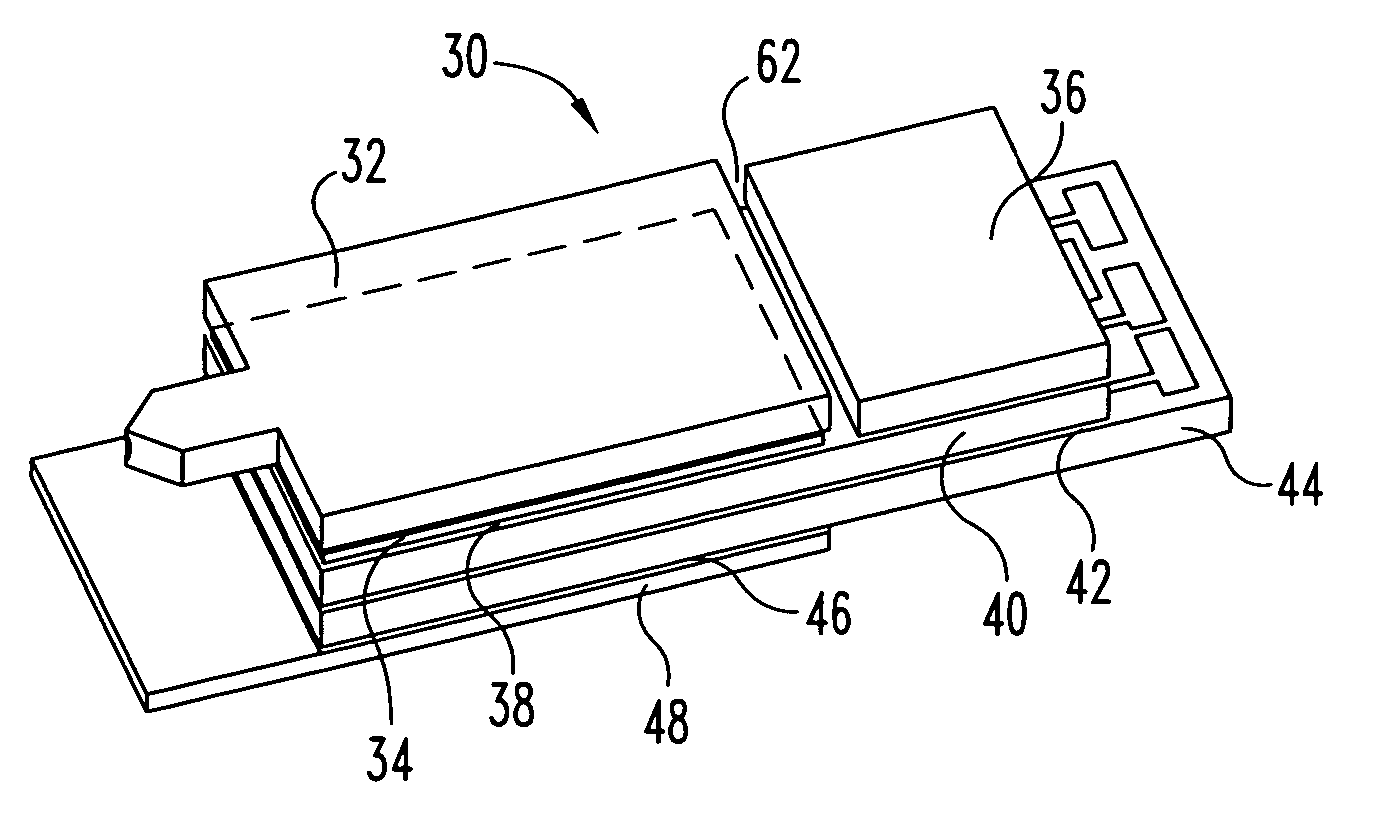

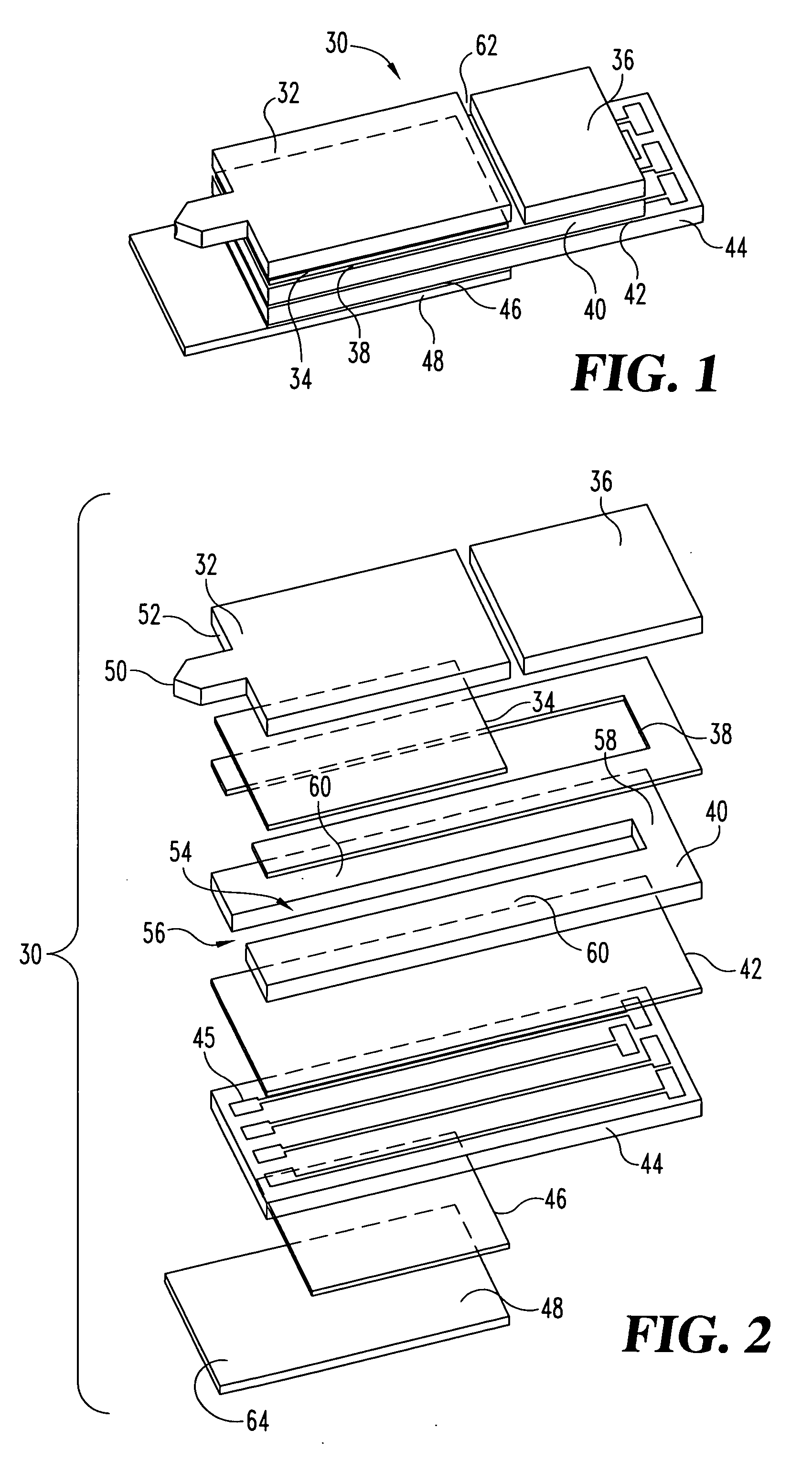

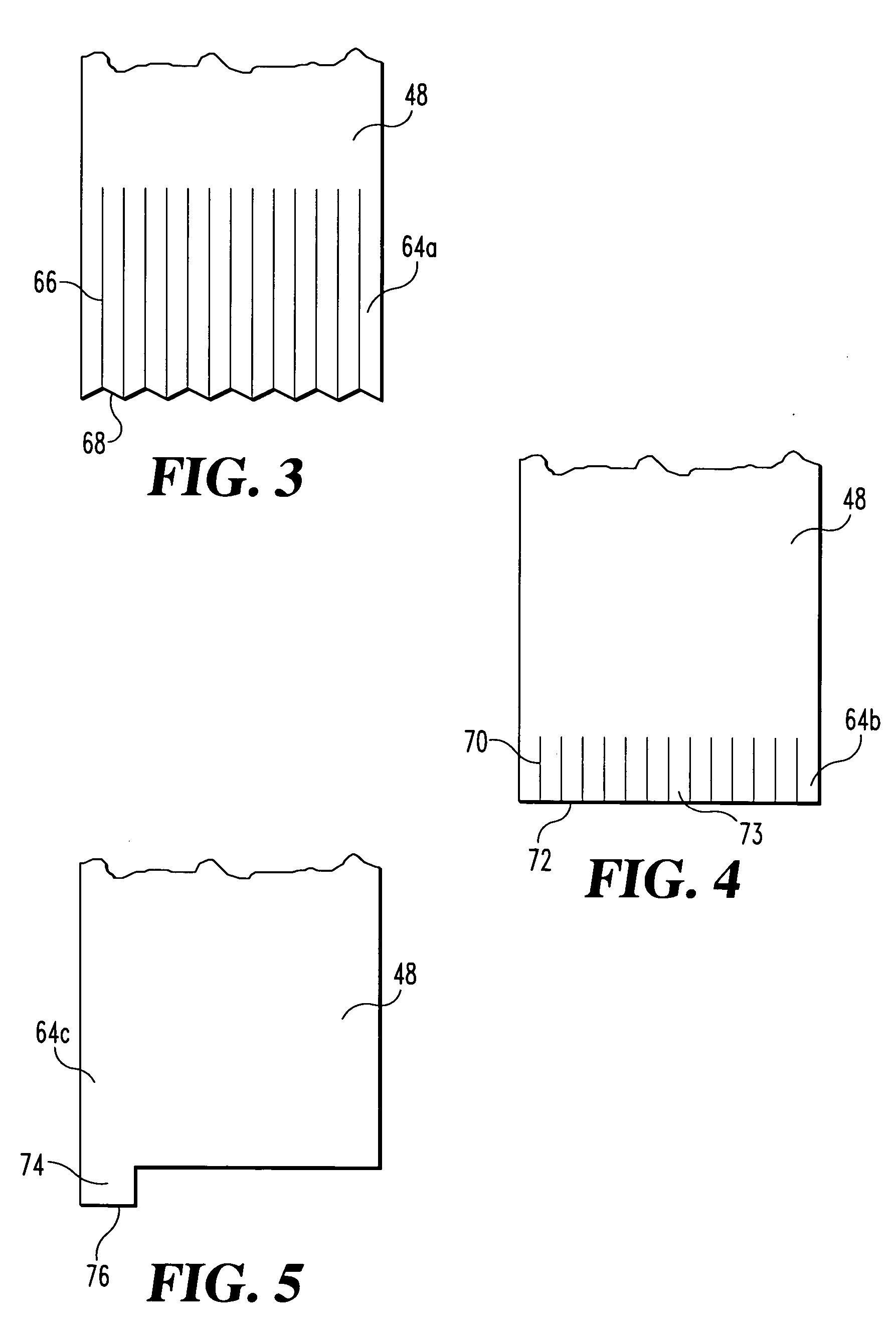

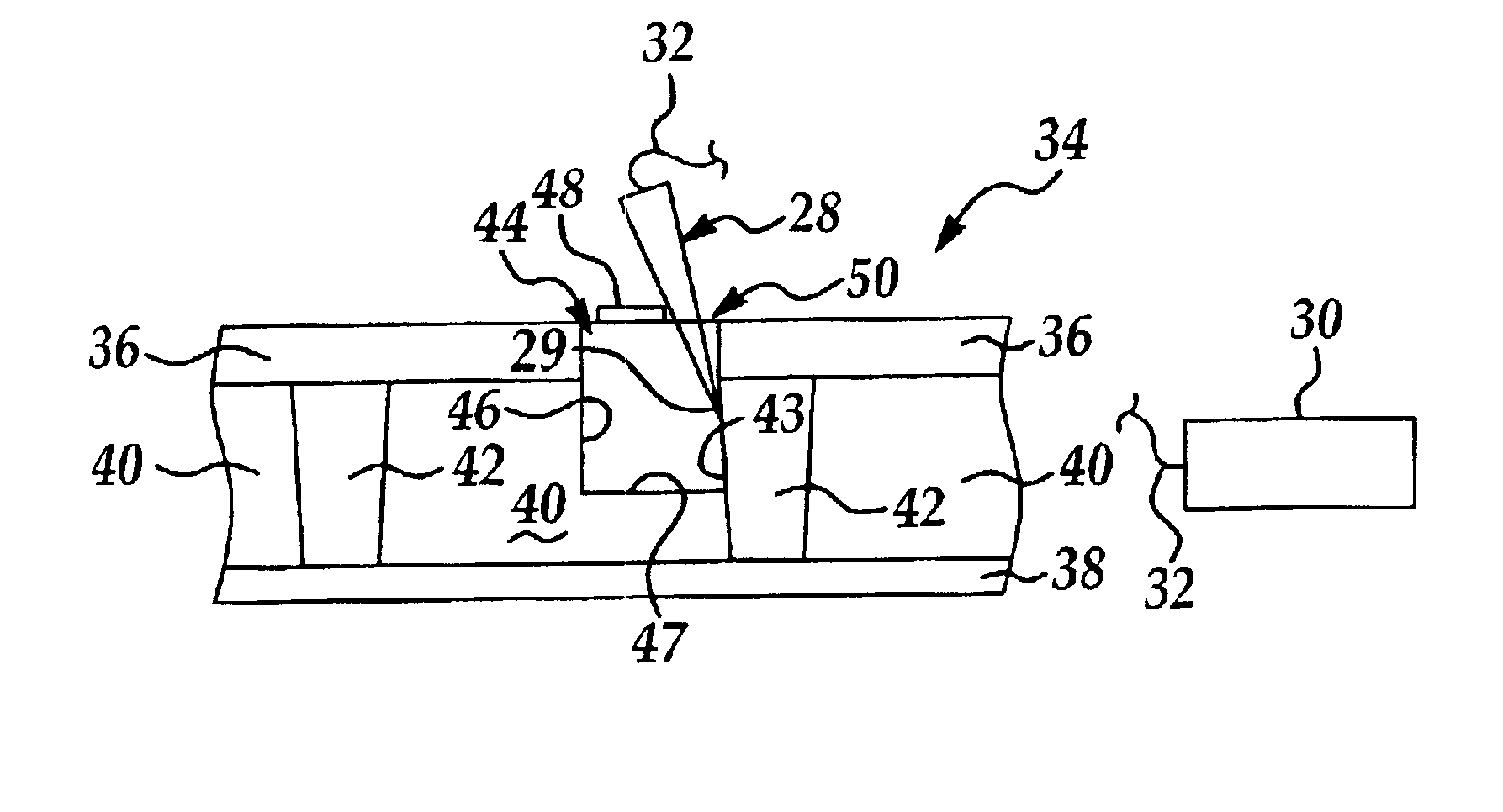

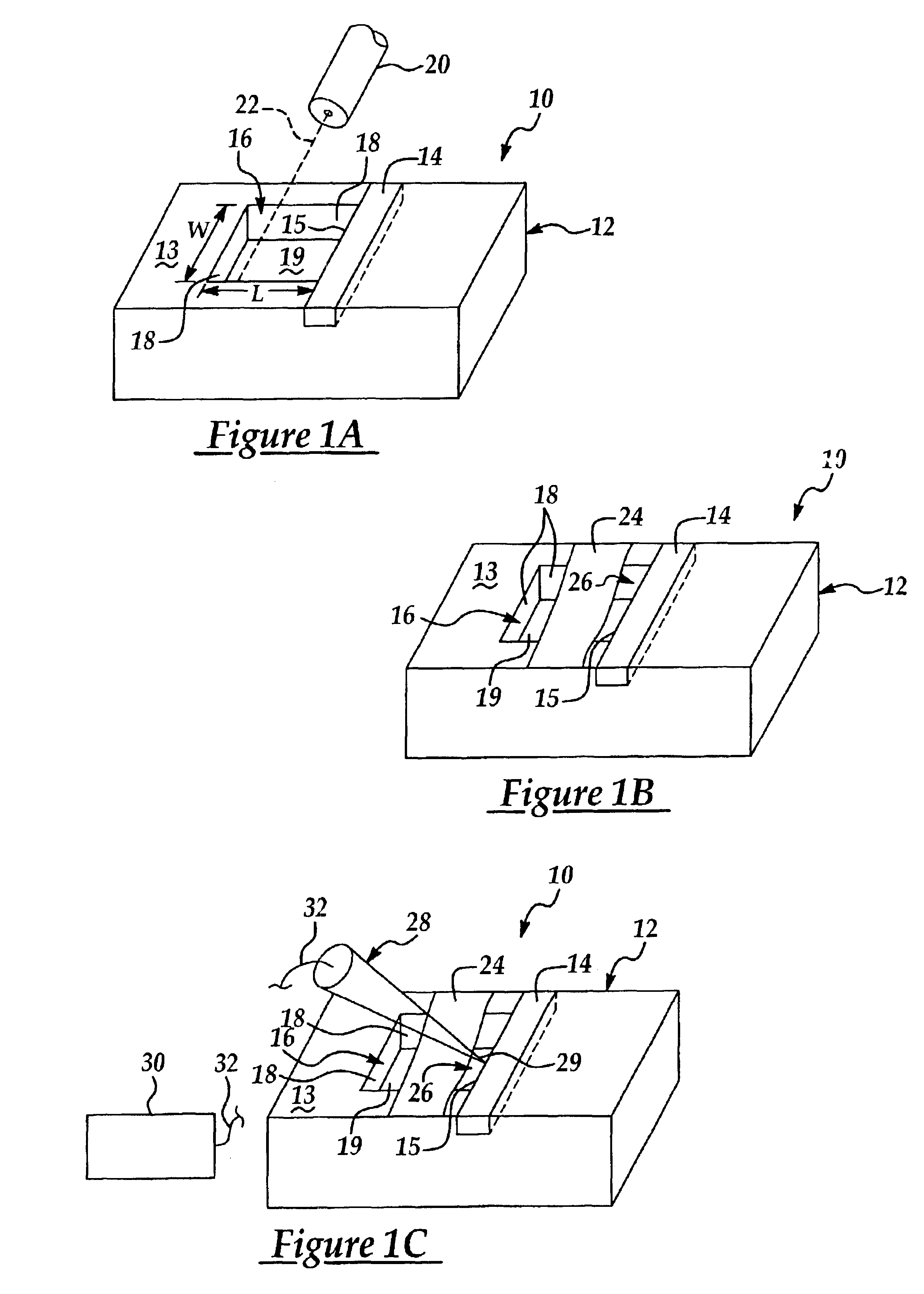

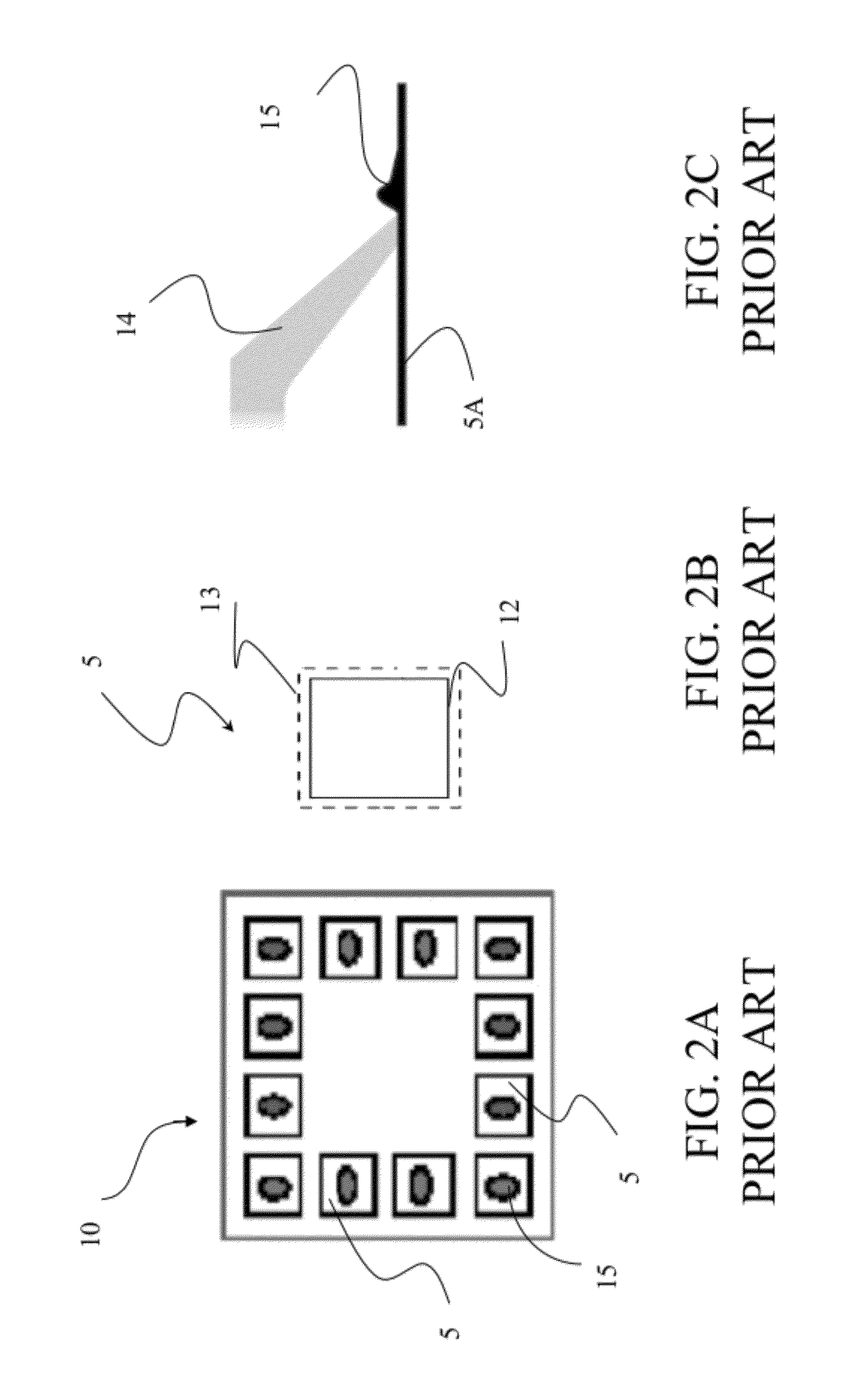

Integrated lancing test strip with capillary transfer sheet

InactiveUS20060079810A1Minimize lateral wickingAvoid electrical interferenceDiagnostic recording/measuringSensorsElectrical testingEngineering

An integrated bodily fluid sampling device includes a lancet, a test strip attached to the lancet, and a flexible sheet extending from the test strip. The lancet and the flexible sheet form a gap sized to draw bodily fluid onto the test strip via capillary action. Further, a sampling end portion of the flexible sheet is shaped to enhance capillary action of the sheet. In one form, a removable film covers the lancet and forms a seal with the flexible sheet such that the seal surrounds a lancet tip. In another form, an insulating layer covers a portion of the lancet to prevent electrical interference between the lancet and an electrical testing system on the test strip and ensure an accurate analysis of the bodily fluid.

Owner:ROCHE DIABETES CARE INC

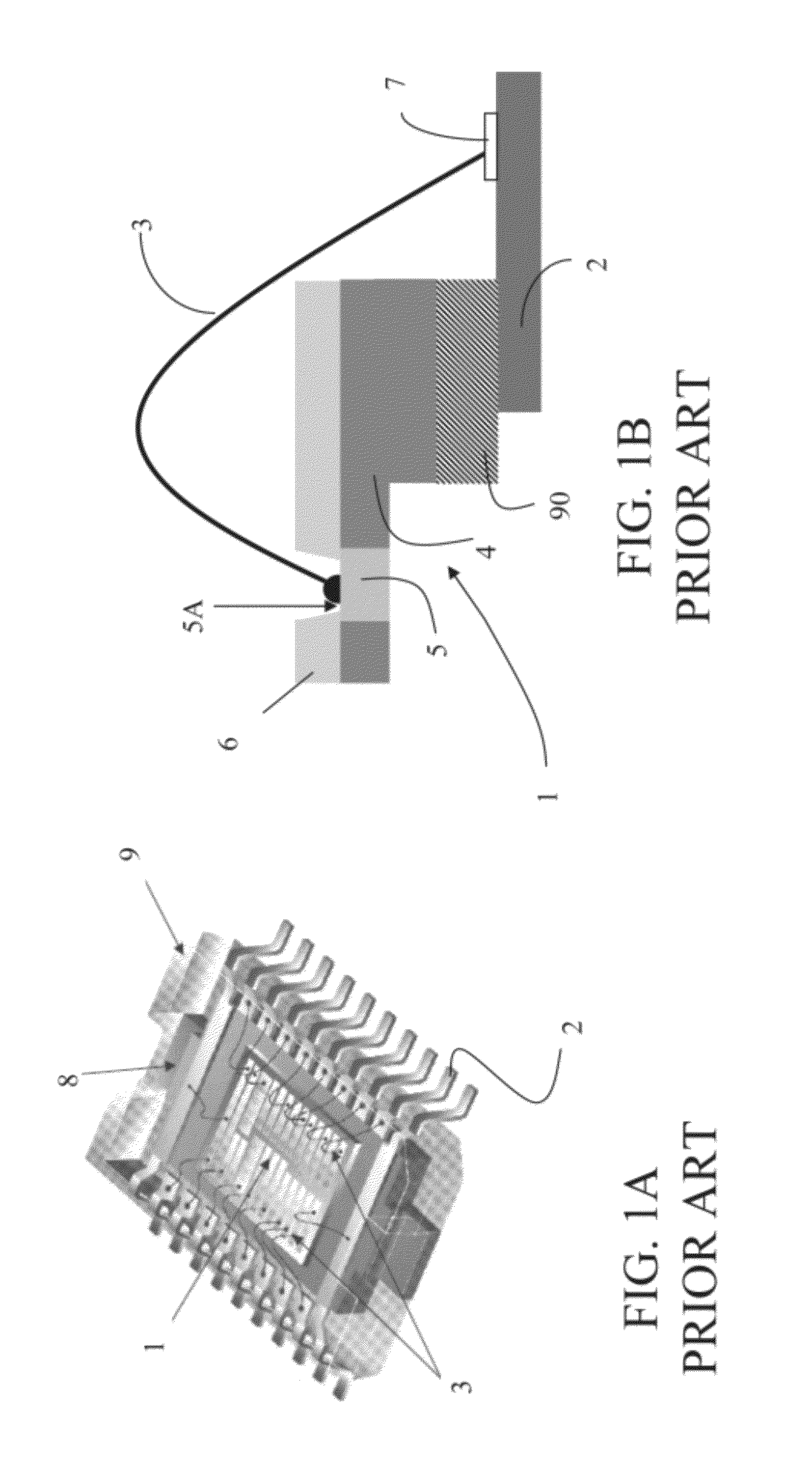

Probing of device elements

InactiveUS6902941B2Reduce contact resistanceAvoid Particle ContaminationSemiconductor/solid-state device testing/measurementElectronic circuit testingDielectricElectricity

A new and improved method for the probing of integrated circuits (ICs) and is particularly suitable for probing various elements of an IC for failure analysis or other electrical testing and / or measurement of the IC. The method includes providing a probe access trench in the IMD (intermetal dielectric) or other substrate adjacent to the circuit element to be tested and then providing direct electrical contact between the test probe and the sidewall of the element through the trench, during the testing process. Such direct electrical contact between the test probe and the sidewall of the element prevents excessively high contact resistance which may otherwise occur in the use of a probing pad between the test probe and the element.

Owner:TAIWAN SEMICON MFG CO LTD

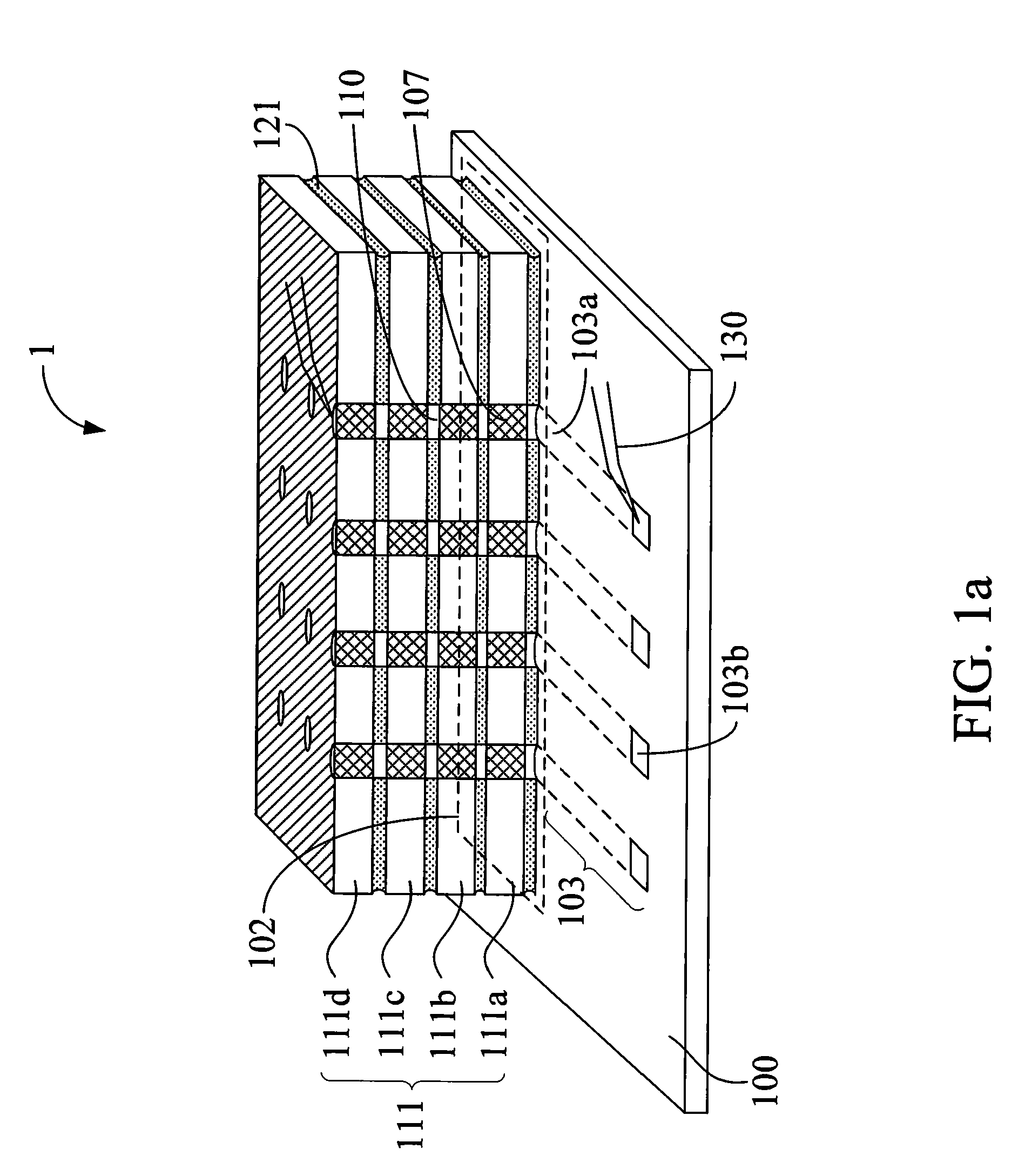

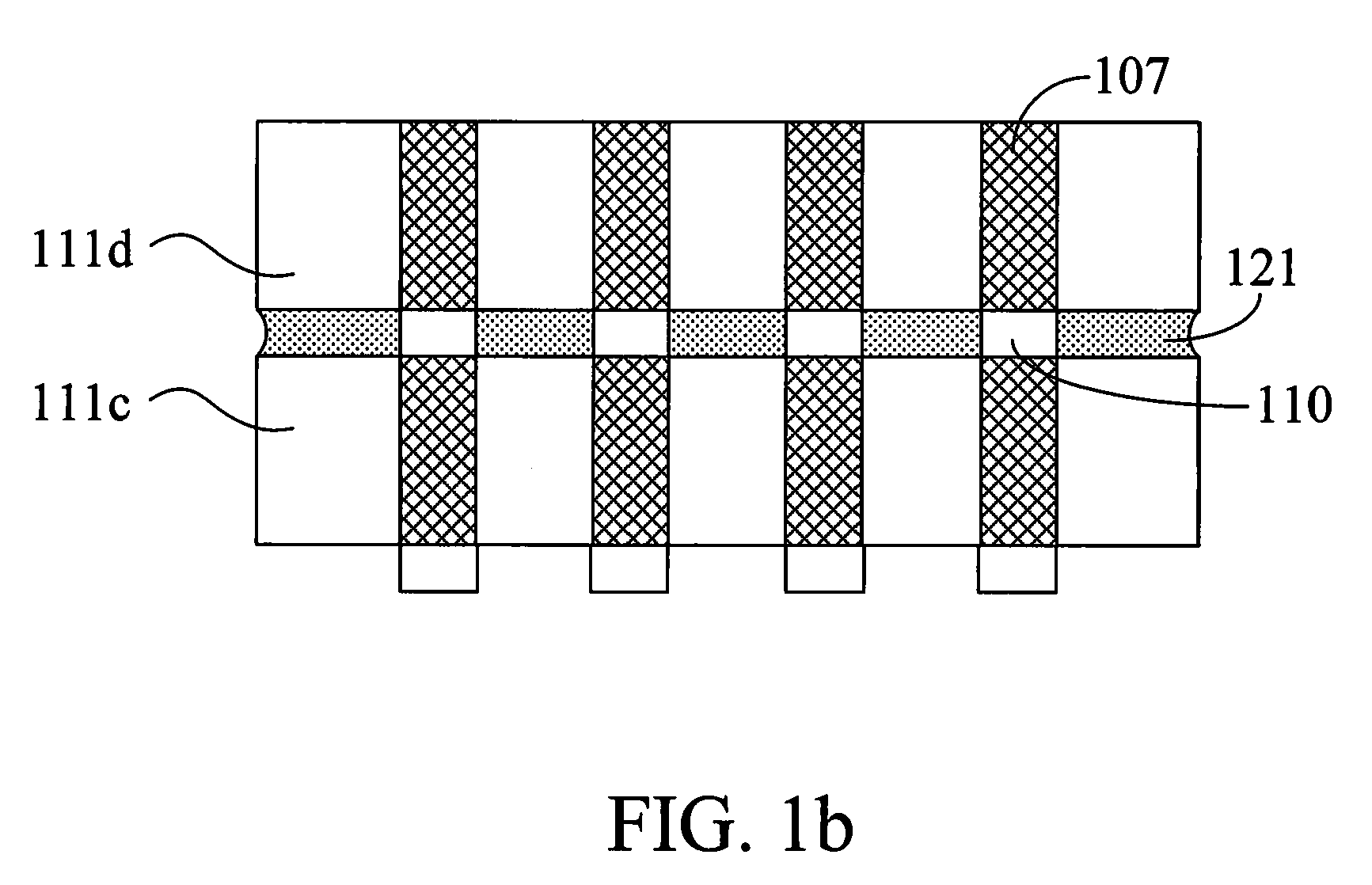

Semiconductor package structure and method for manufacturing the same

ActiveUS20100007001A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipSemiconductor package

Semiconductor package structures and methods for manufacturing the same are provided. The semiconductor package structure comprises a substrate unit and a first chip stack structure. The substrate unit comprises a circuit structure having test pads. The first chip stack structure comprises chips, and each of the chips has a plurality of through silicon plugs. The through silicon plugs of two adjacent chips are electrically connected and further electrically connected to the test pads of the substrate unit for electrical testing. Another semiconductor package structure provided by the present invention comprises a first semiconductor chip and a second semiconductor chip. Each of the semiconductor chips has test pads for electrical testing and a plurality of through silicon plugs connecting to the test pads. The second semiconductor chip is mounted on the first semiconductor chip, and a portion of the through silicon plugs of two semiconductor chips are electrically connected with each other.

Owner:ZAWASHIRO DIGITAL INNOVATIONS

Self-calibrating electrical test probe

InactiveUS6870359B1Easy to understandElectronic circuit testingElectrical measurement instrument detailsEngineeringCalibration test

A self-calibrating test probe system of the present invention does not require probing head removal and replacement. Using the system of the present invention, the test probe and / or the entire system (including a testing instrument) may be calibrated or may self-calibrate while the probing head remains connected to an electrical component under test. The self-calibrating electrical testing probe system includes calibration circuitry including at least one input resistor, at least one relay, and at least one known calibration reference signal. If the test probe is an active test probe, the calibration circuitry may also include at least one amplifier. Each relay has a first position that provides signal access to a testing signal from an electrical component under test and a second position that provides signal access to the known calibration reference signal. Using the present invention, the error of the test probe and / or system is determined and compensated. Exemplary methods by which error compensation may be provided includes, for example, amplifying the testing signal, creating a correction table of correction values and adding an appropriate value from the correction table, or mathematically compensating.

Owner:TELEDYNE LECROY

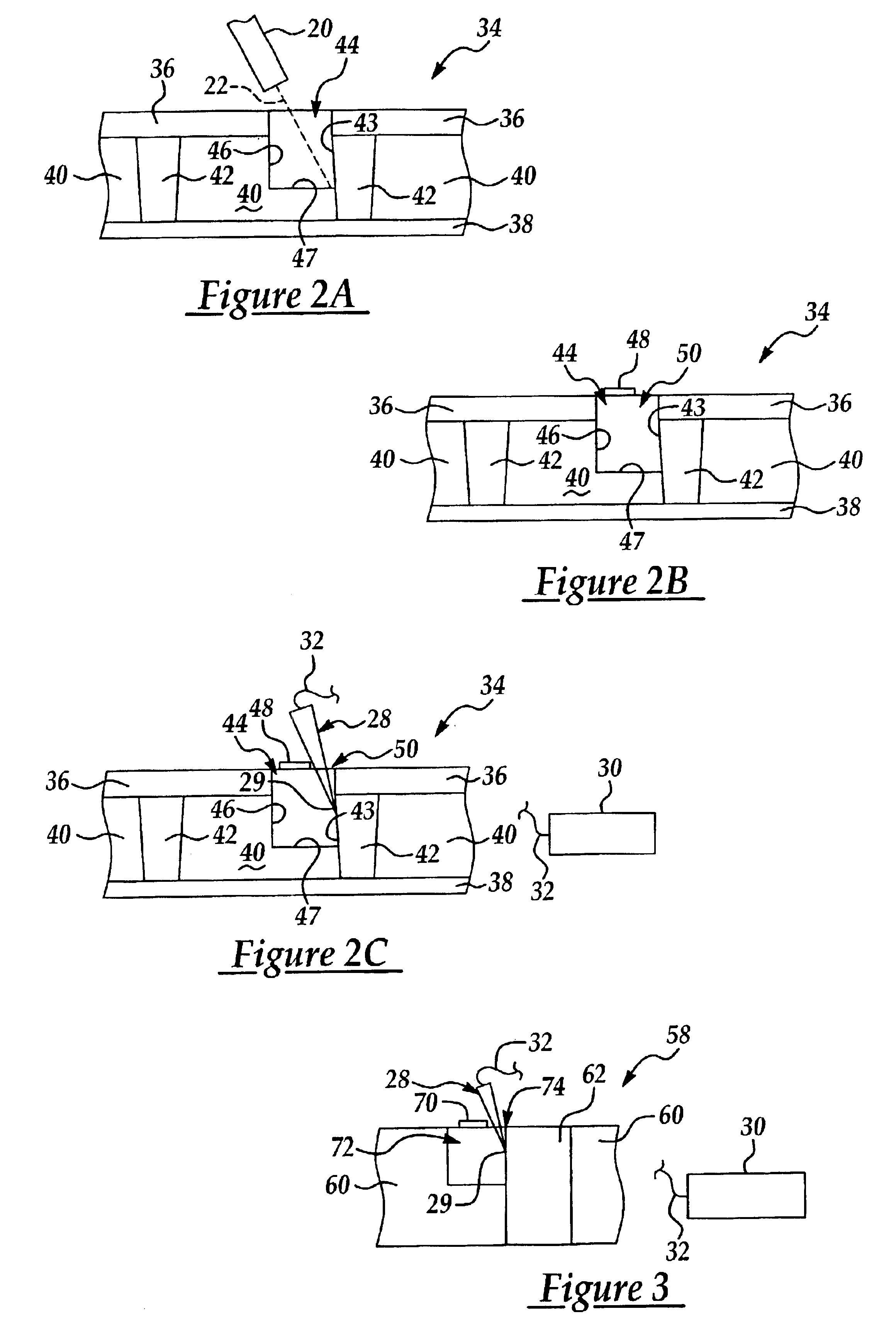

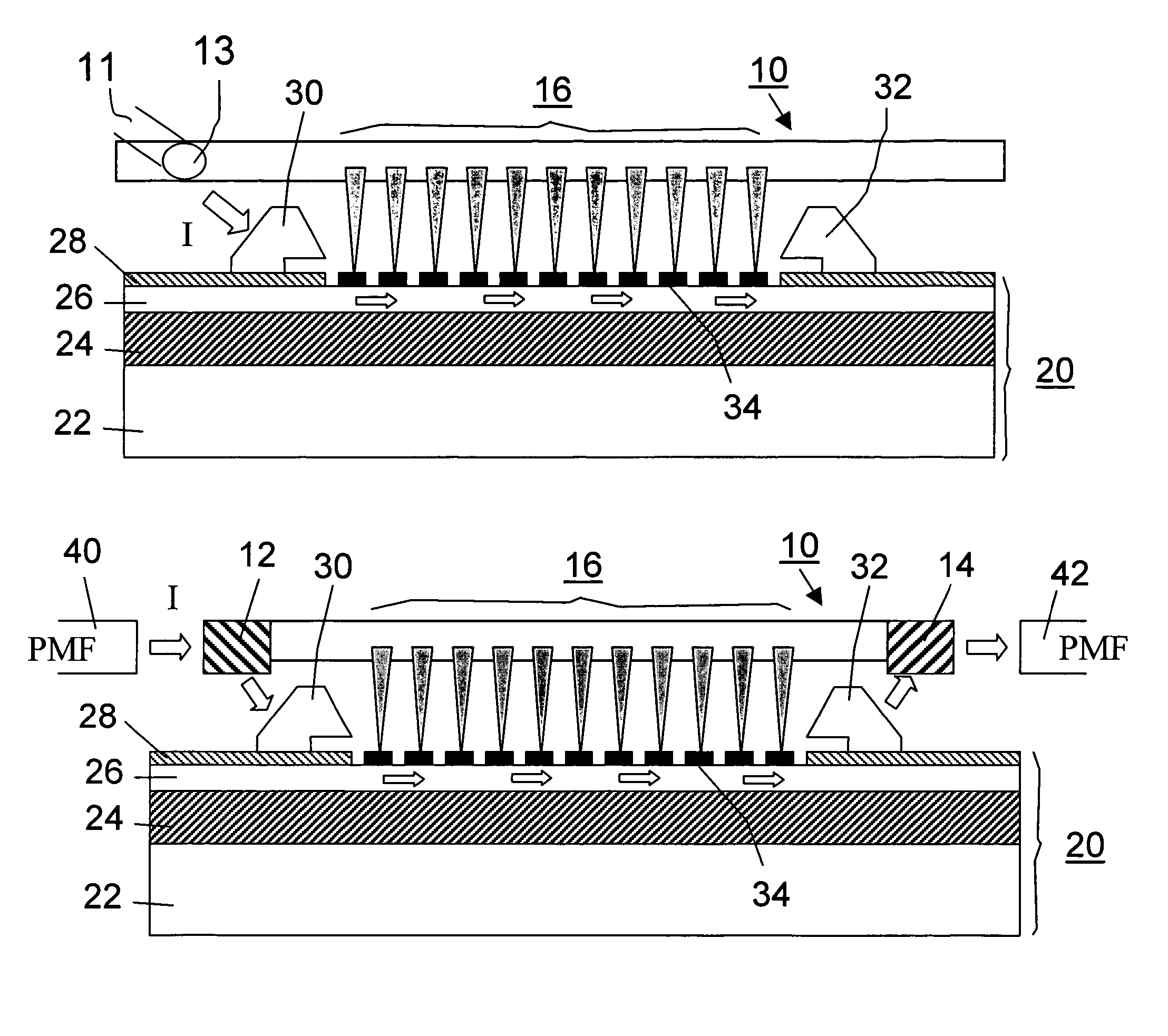

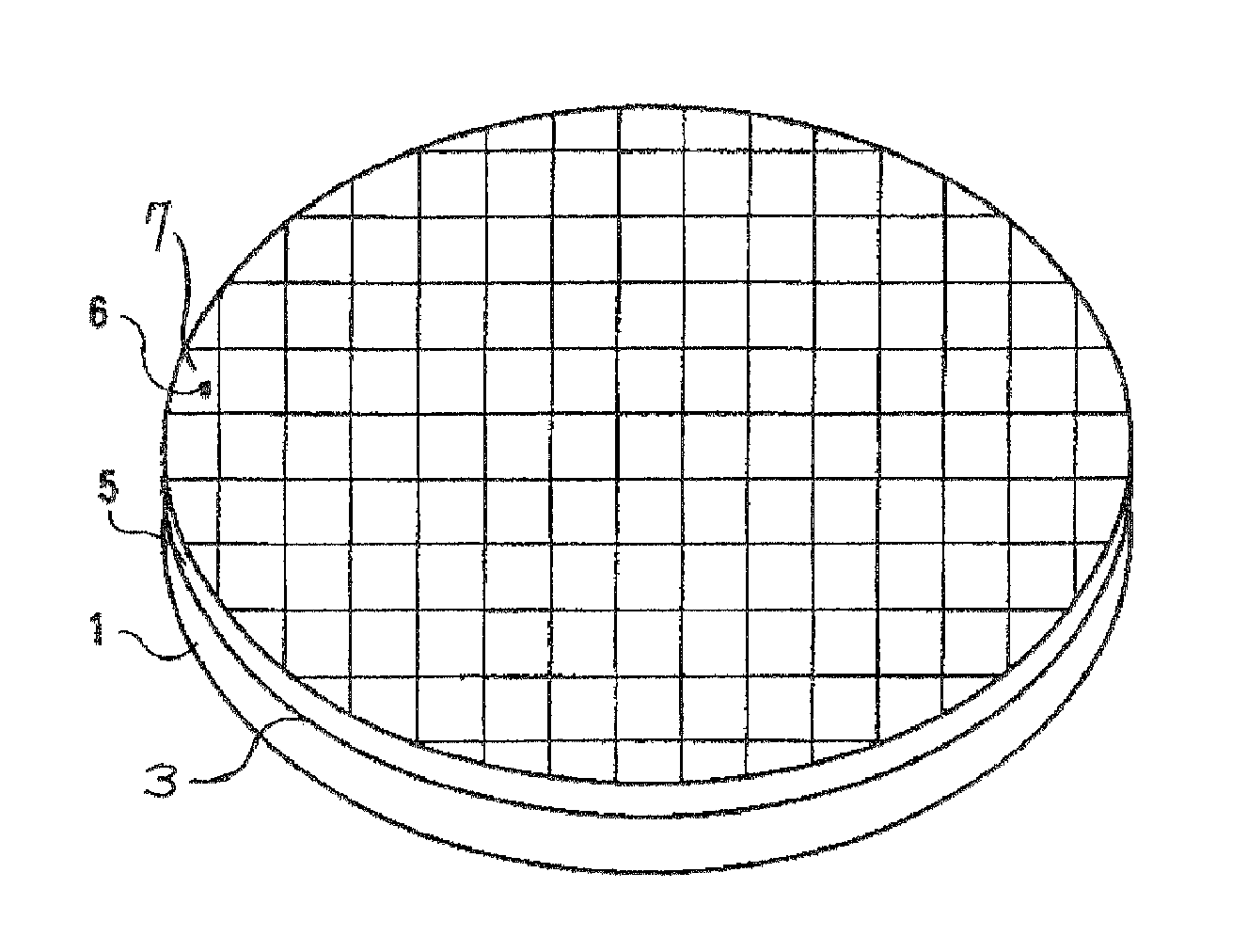

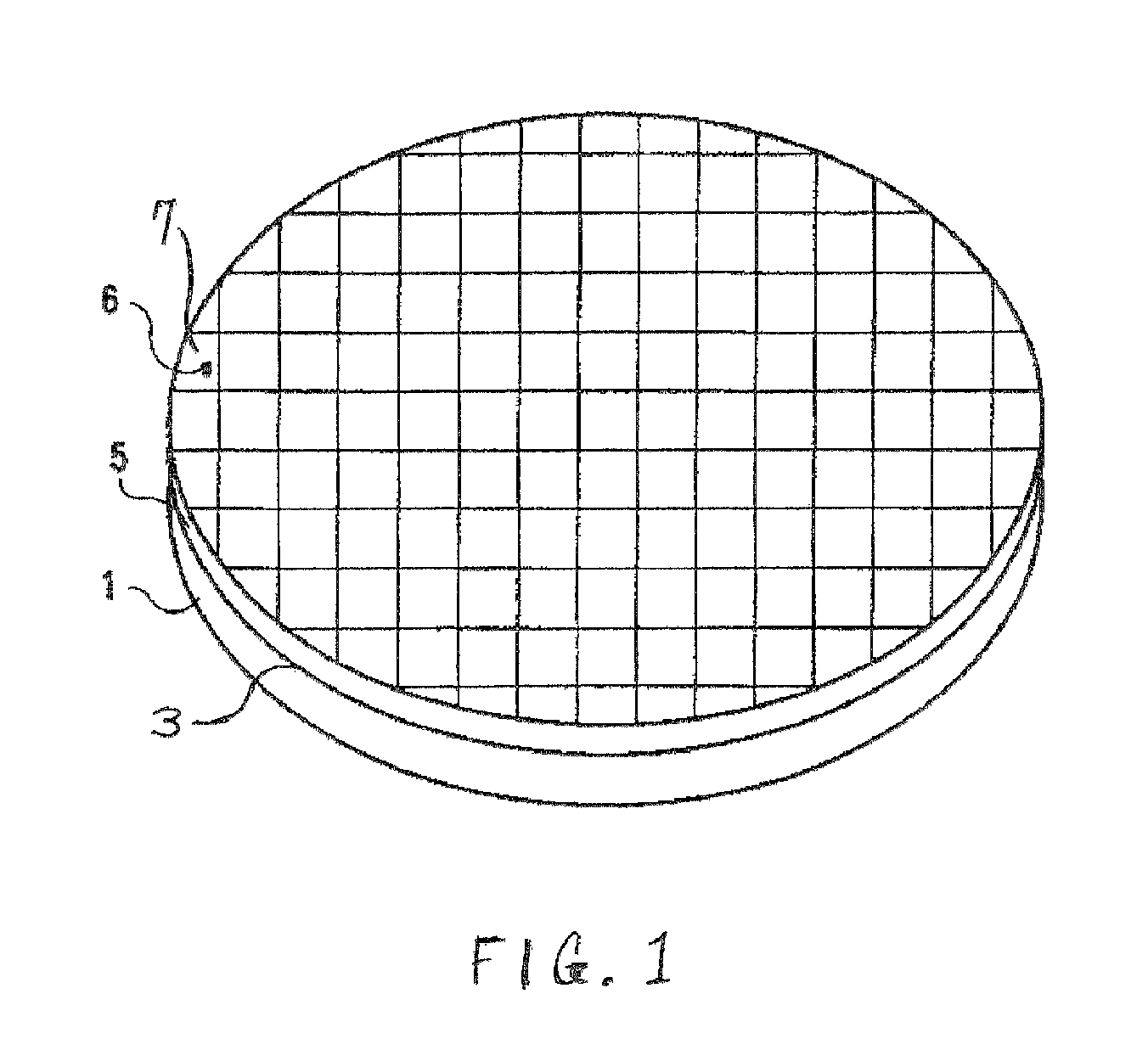

Wafer-level opto-electronic testing apparatus and method

ActiveUS20050194990A1Optical coupling efficiency improvementEnhanced couplingSemiconductor/solid-state device testing/measurementCoupling light guidesGratingDevice form

A wafer-level testing arrangement for opto-electronic devices formed in a silicon-on-insulator (SOI) wafer structure utilizes a single opto-electronic testing element to perform both optical and electrical testing. Beam steering optics may be formed on the testing element and used to facilitate the coupling between optical probe signals and optical coupling elements (e.g., prism couplers, gratings) formed on the top surface of the SOI structure. The optical test signals are thereafter directed into optical waveguides formed in the top layer of the SOI structure. The opto-electronic testing element also comprises a plurality of electrical test pins that are positioned to contact a plurality of bondpad test sites on the opto-electronic device and perform electrical testing operations. The optical test signal results may be converted into electrical representations within the SOI structure and thus returned to the testing element as electrical signals.

Owner:CISCO TECH INC

Semiconductor chip

ActiveUS20070164279A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipElectrical testing

A semiconductor chip comprises a metal pad exposed by an opening in a passivation layer, wherein the metal pad has a testing area and a bond area. During a step of testing, a testing probe contacts with the testing area for electrical testing. After the step of testing, a polymer layer is formed on the testing area with a probe mark created by the testing probe. Alternatively, a semiconductor chip comprises a testing pad and a bond pad respectively exposed by two openings in a passivation layer, wherein the testing pad is connected to the bond pad. During a step of testing, a testing probe contacts with the testing pad for electrical testing. After the step of testing, a polymer layer is formed on the testing pad with a probe mark created by the testing probe.

Owner:QUALCOMM INC

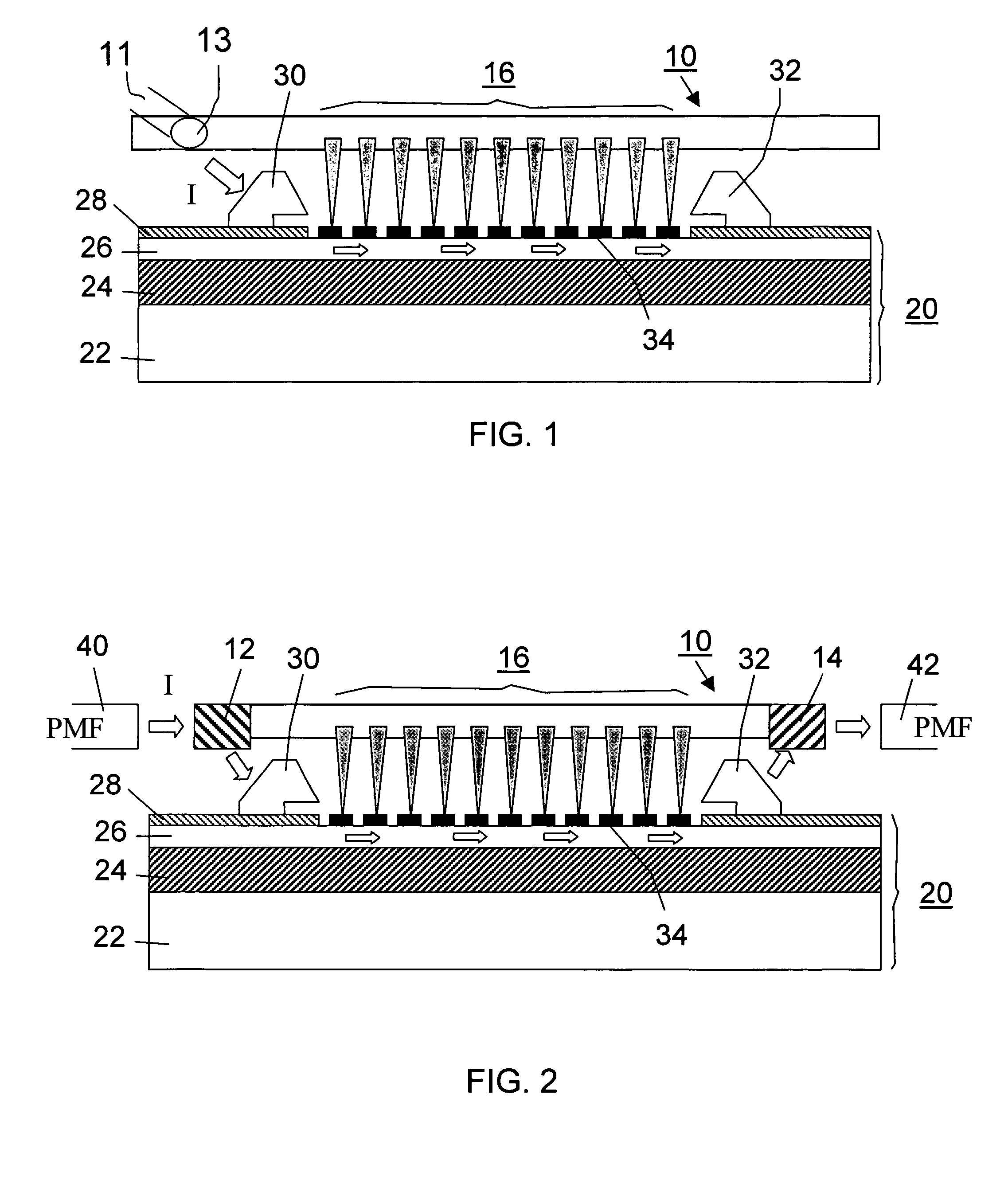

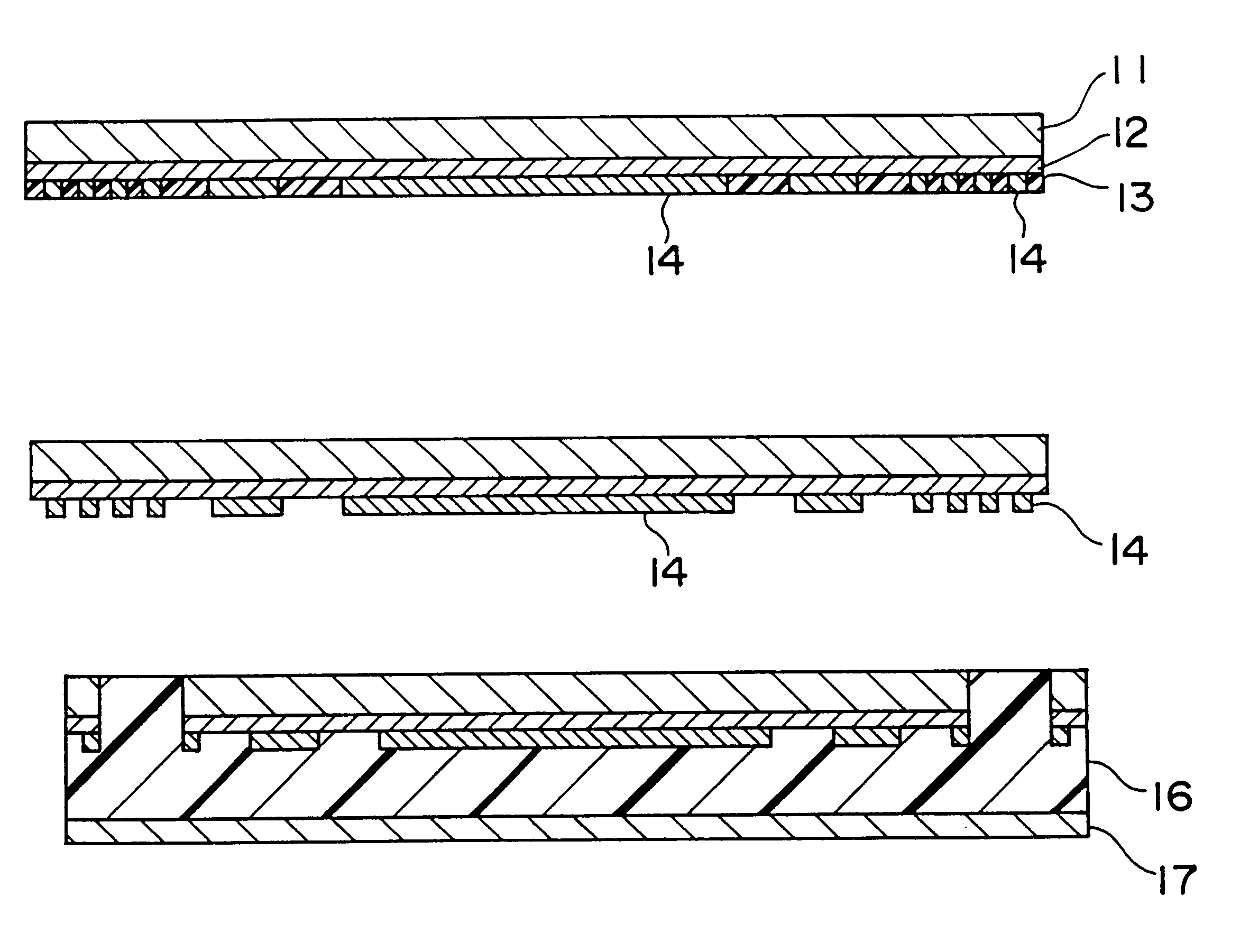

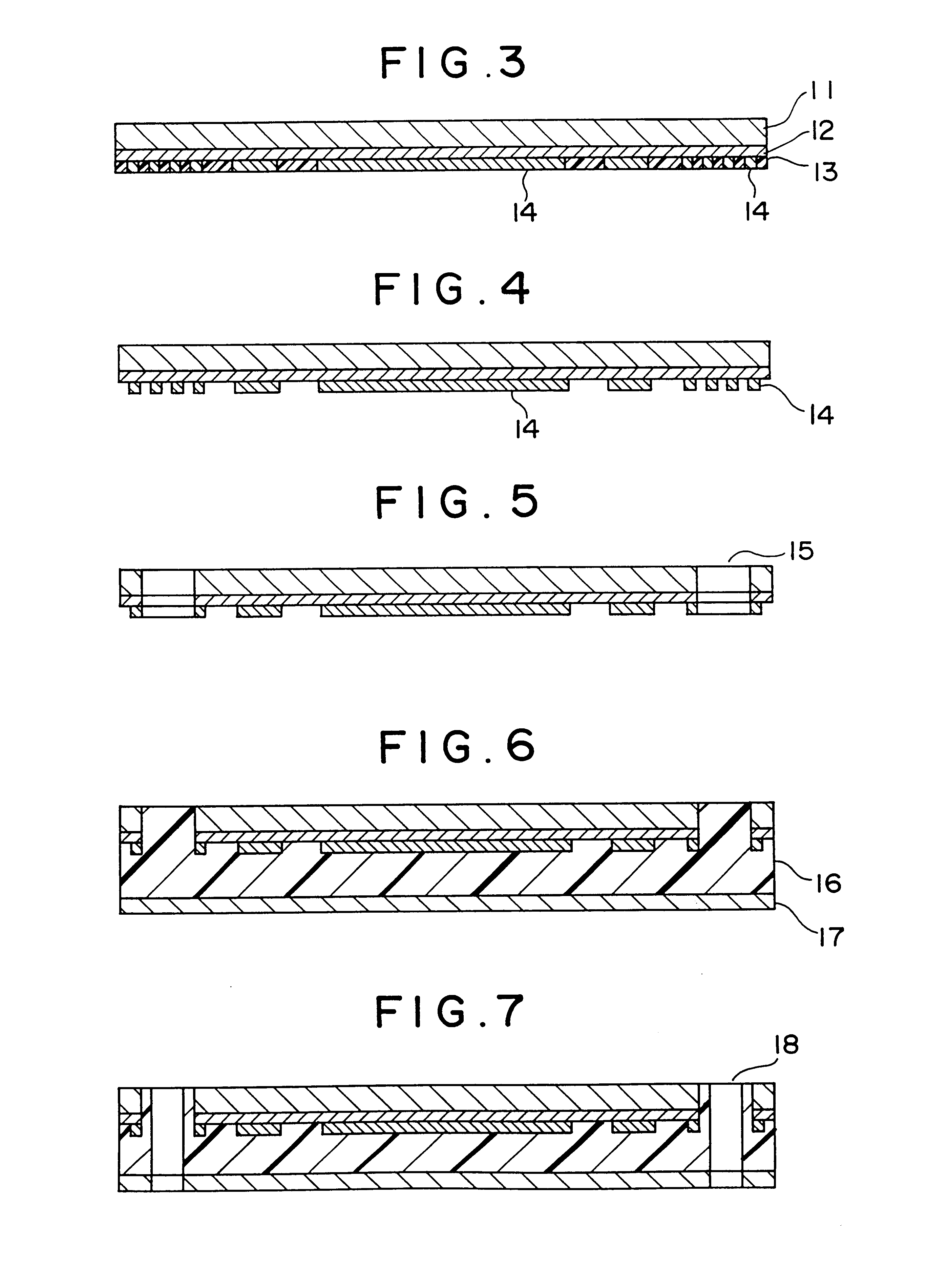

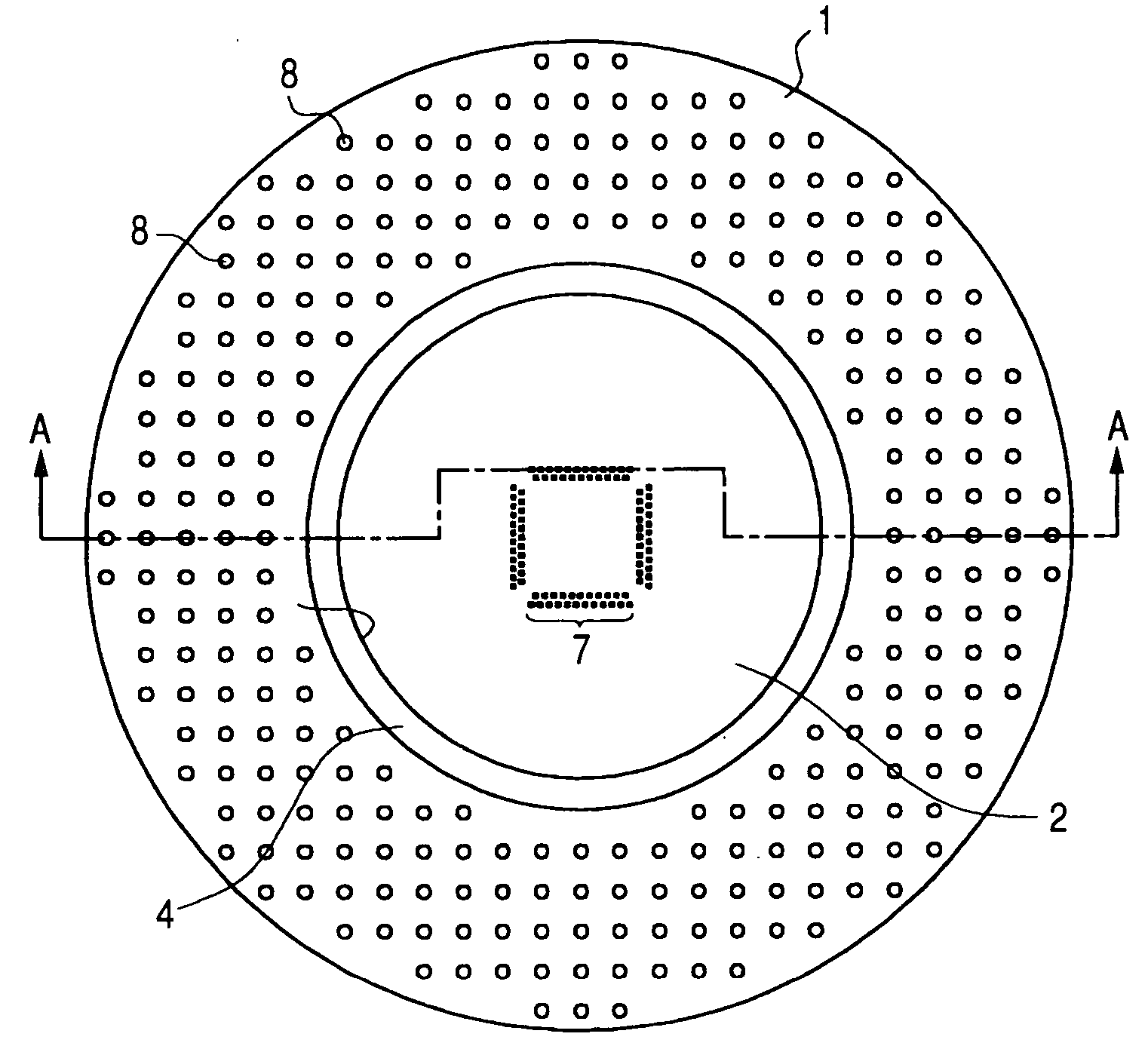

Wiring board for electrical tests with bumps having polymeric coating

InactiveUS6133534AElectrical measurement instrument detailsPrinted electric component incorporationElectrical testingEngineering

A wiring board for electrical tests; having an insulating substrate, wiring of predetermined pattern which is embedded in the insulating substrate, and bump electrodes which are formed on the wiring and which are respectively brought into contact with corresponding electrodes of an article to-be-tested. Thus, even when the electrode pitch of the article to-be-tested such as a semiconductor device has become smaller(for example, less than 0.1 [mm]), the electrodes can be formed so as to cope with the electrical tests of the article.

Owner:HITACHI CHEM CO LTD

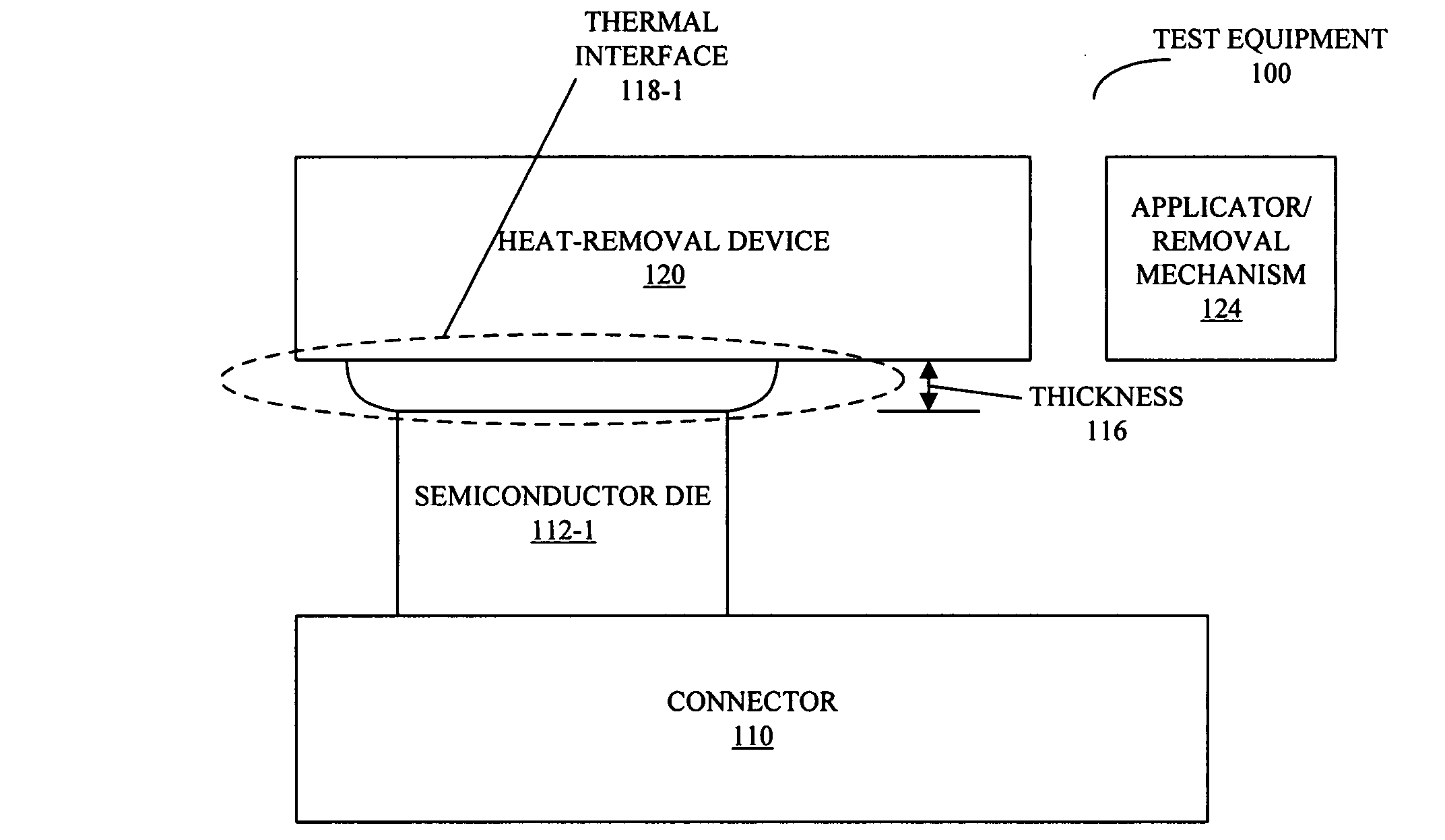

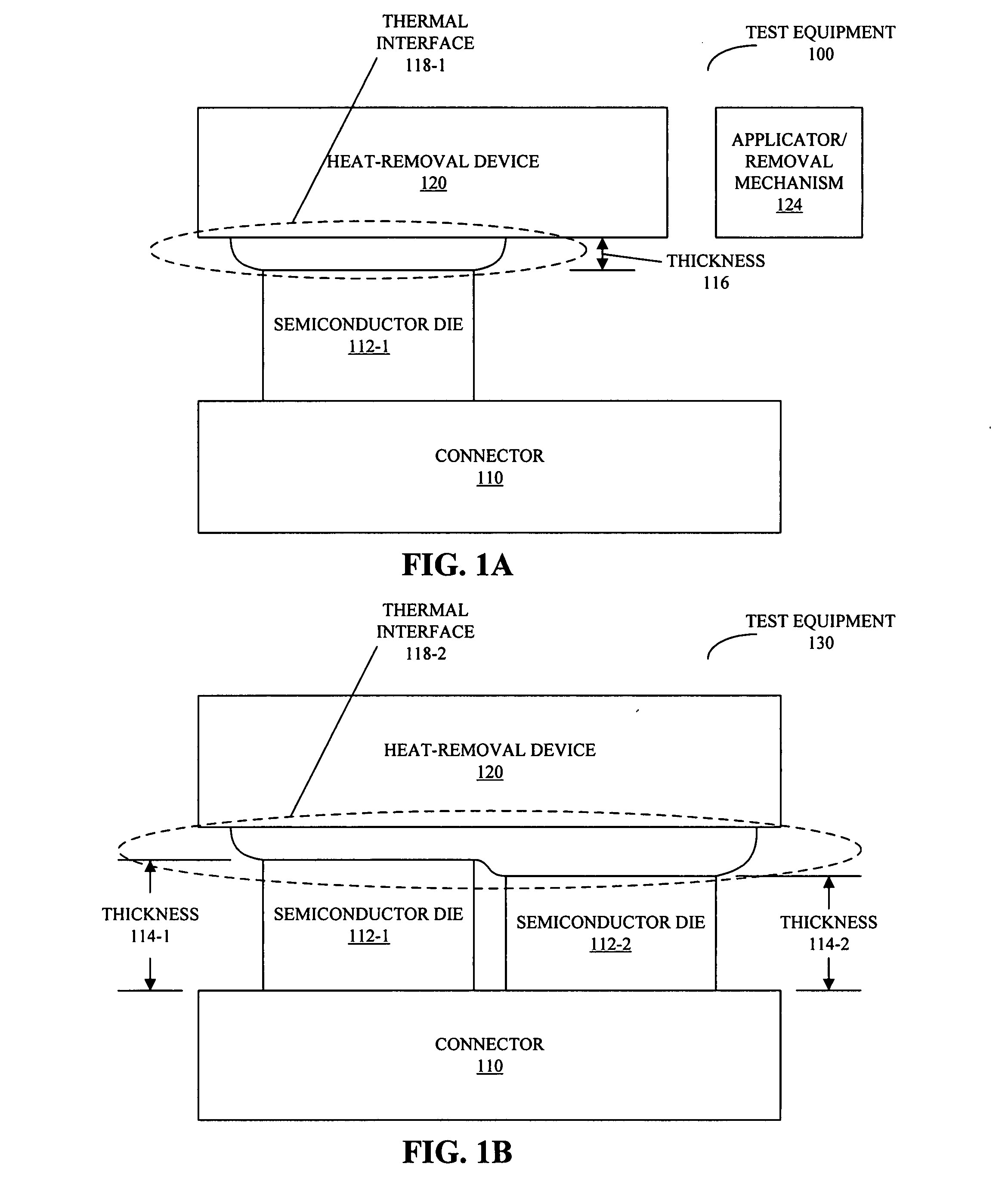

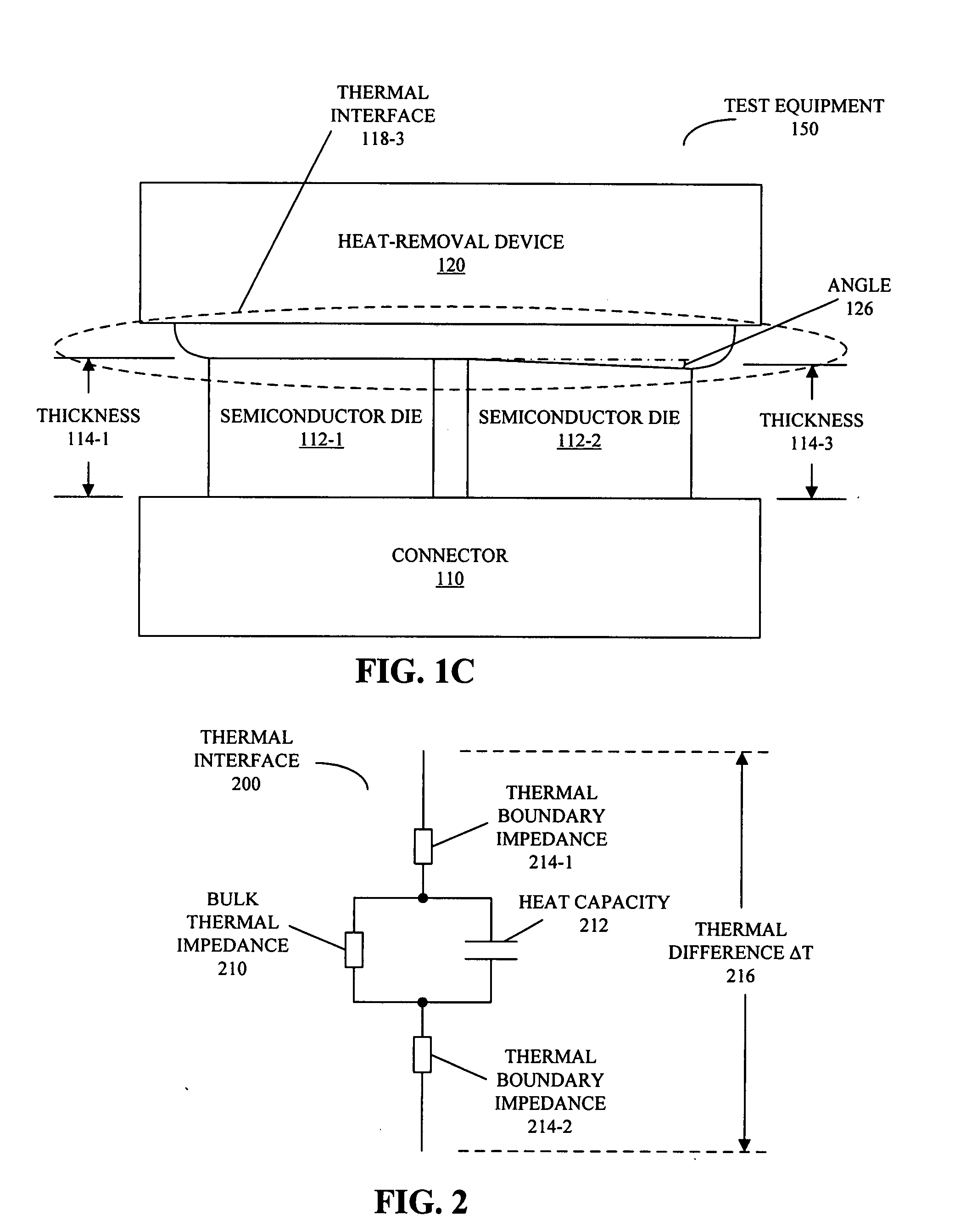

Thermal interface for electronic chip testing

InactiveUS20080191729A1Promote wettingEasy to testSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingElectricityLiquid state

An apparatus that performs electrical testing is described. This apparatus includes a first semiconductor die that is to be tested, and a connector configured to be coupled to a first surface of the first semiconductor die. Furthermore, a thermal interface in the apparatus is between a second surface of the first semiconductor die and a heat-removal device. This thermal interface includes a metal which is in a liquid state at an operating temperature of the semiconductor die during the testing.

Owner:APPLE INC

Method and apparatus for head gimbal assembly testing

InactiveUS20050209797A1Avoid timeLower cost of capitalRecord information storageStructural/machines measurementElectrical testingEngineering

A method for dynamic electrical testing of head gimbal assemblies may include initiating an automated continuous process that includes selecting an unmounted head gimbal assembly; aligning the unmounted head gimbal assembly; loading the unmounted head gimbal assembly to a disc; and testing the unmounted head gimbal assembly.

Owner:SEAGATE TECH LLC

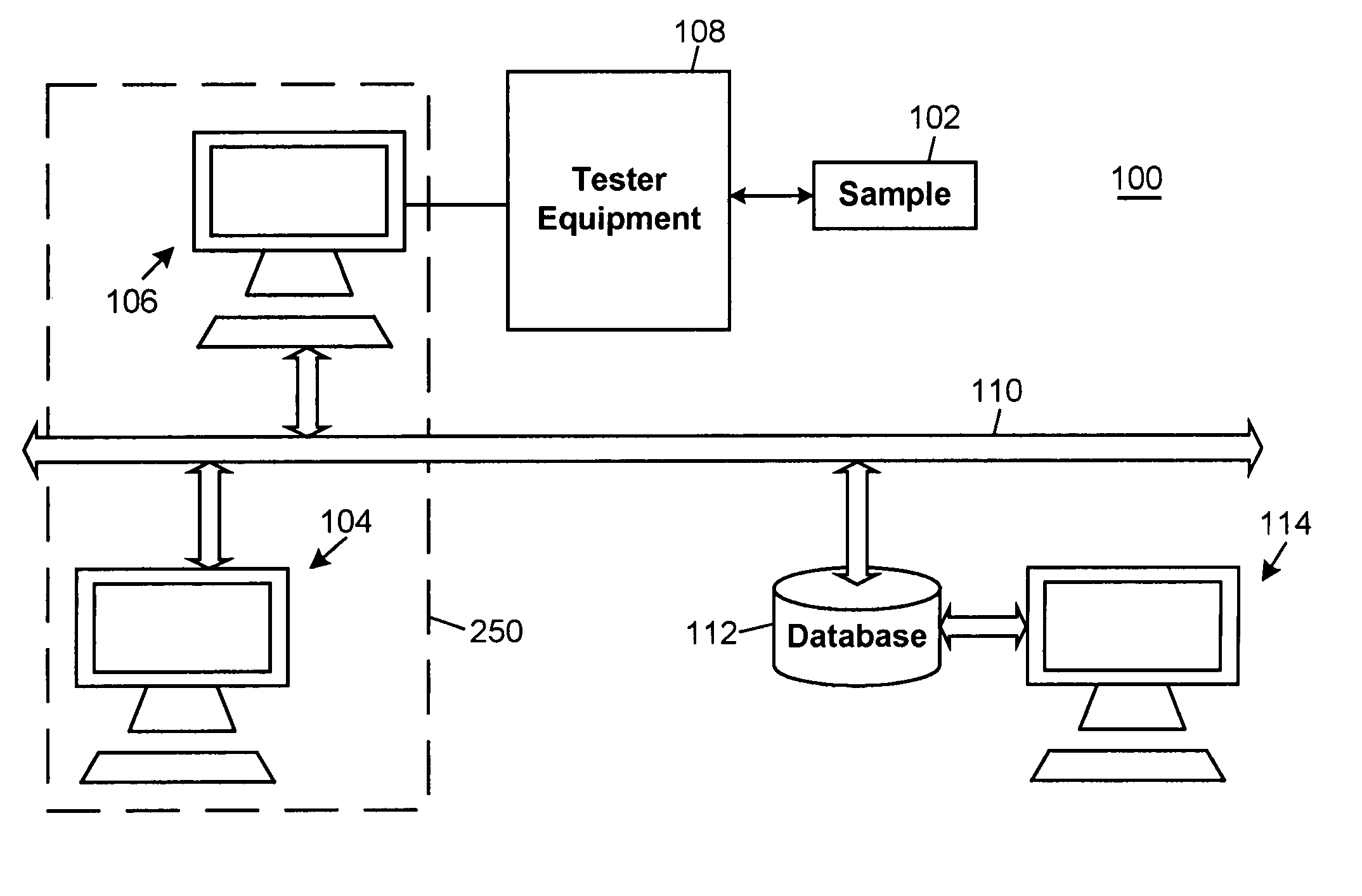

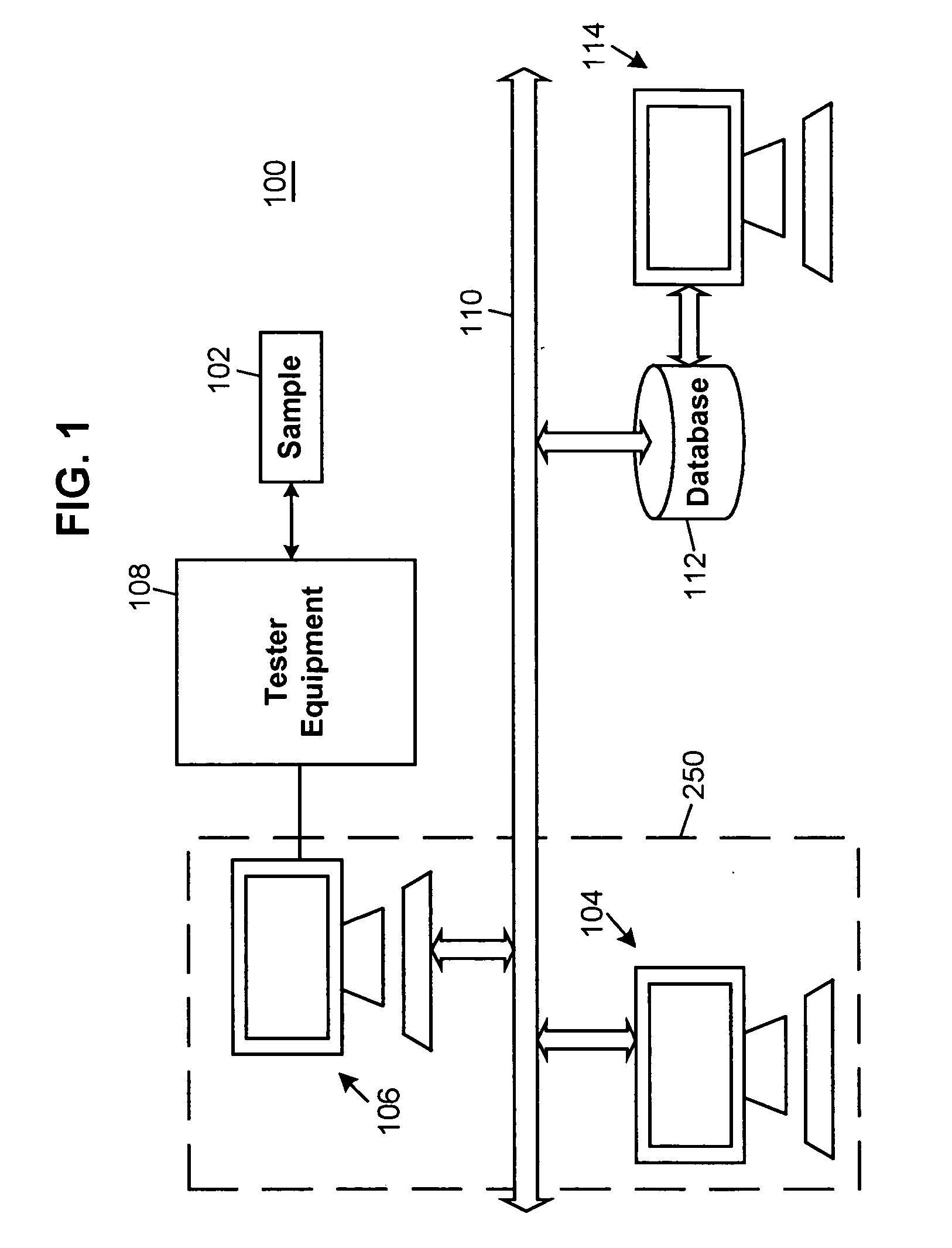

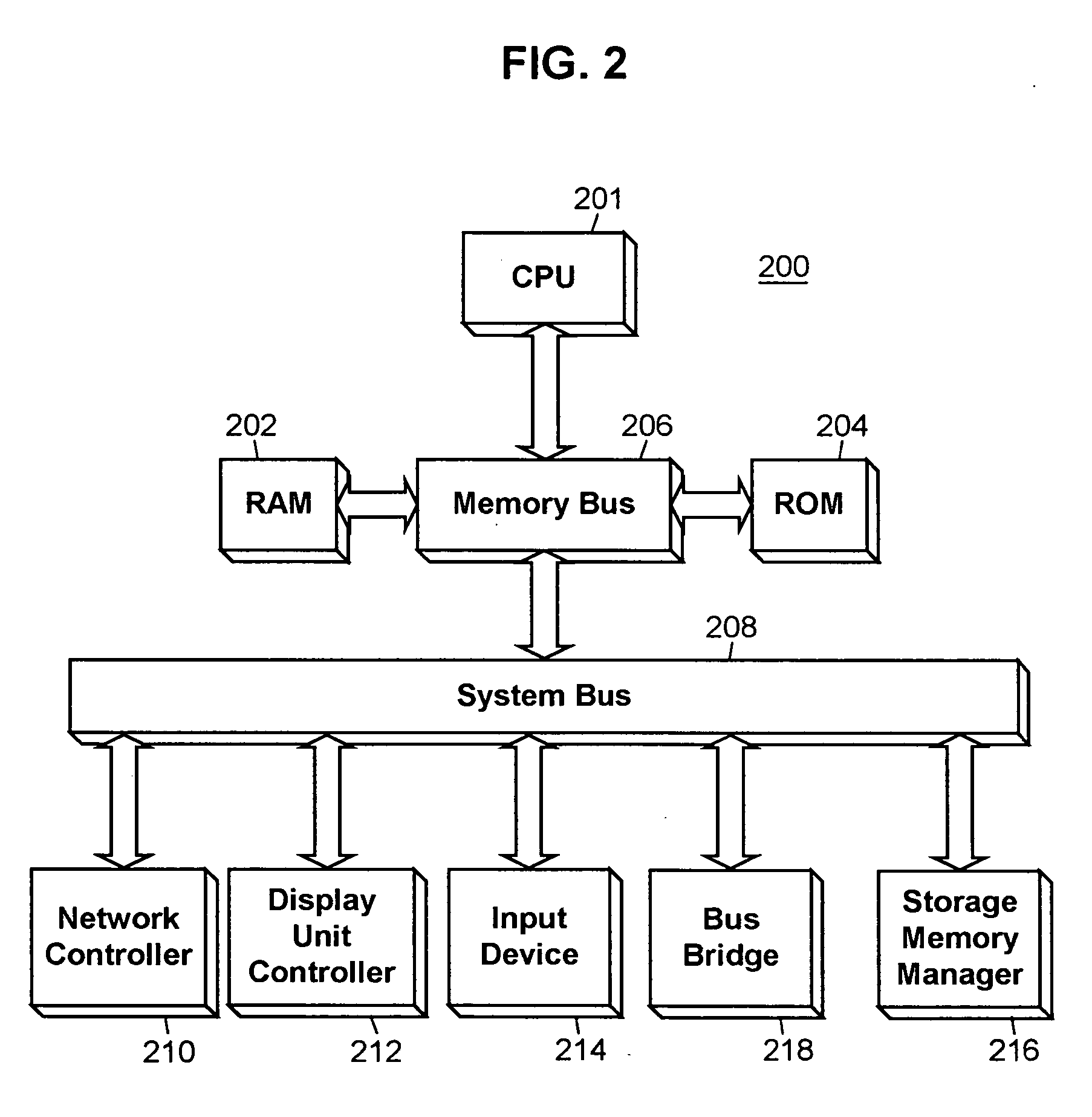

Automated and customizable generation of efficient test programs for multiple electrical test equipment platforms

InactiveUS20050273685A1Electronic circuit testingError detection/correctionDevice materialTest algorithm

Automating techniques provide a way to create efficient test programs for characterizing semiconductor devices, such as those on a silicon die sample. Typically, test program creation is a drawn out process involving data entry for every test to be run as part of the test program. The described techniques improve test algorithm selection and automatically populate the test algorithm data in creating the test program. The automatic population may occur by accessing test structure, header, and test algorithm catalogs. The test structure catalog contains physical data for the test program, while the header catalog contains global parameter values. The test algorithm catalog has all of the various test algorithms that may be run in a given test, where these test algorithms may be in a template form and specific to any number of different test language abstractions. After test program creation, a validation process is executed to determine if the test program data is valid. Invalid data may be flagged, in an example. Once validated, techniques are described for converting the validated test program into an executable form, by formatting the various test algorithm data in the test program into a form compatible with the applicable test language abstraction selected by the user or the tester.

Owner:INTEL CORP

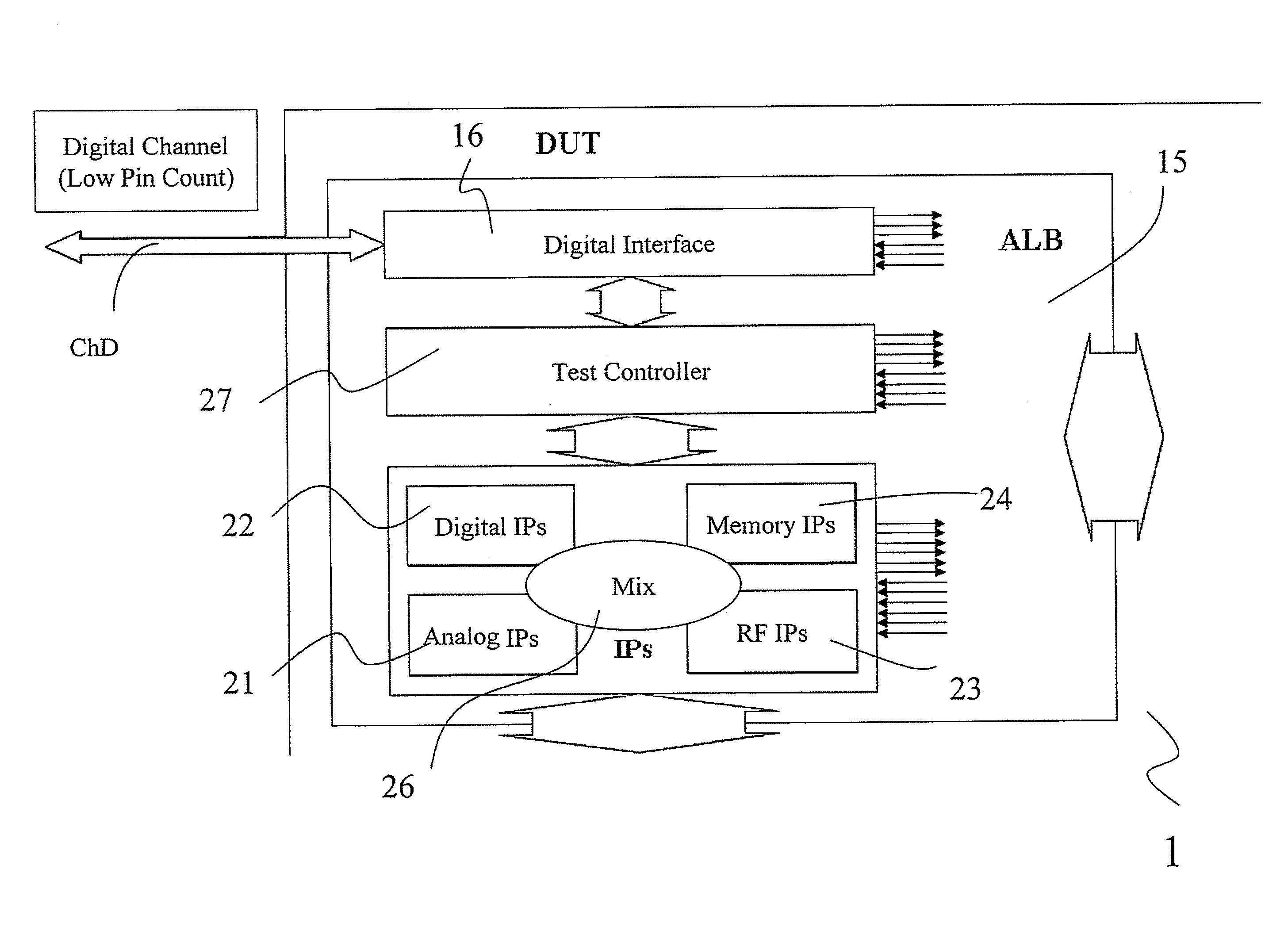

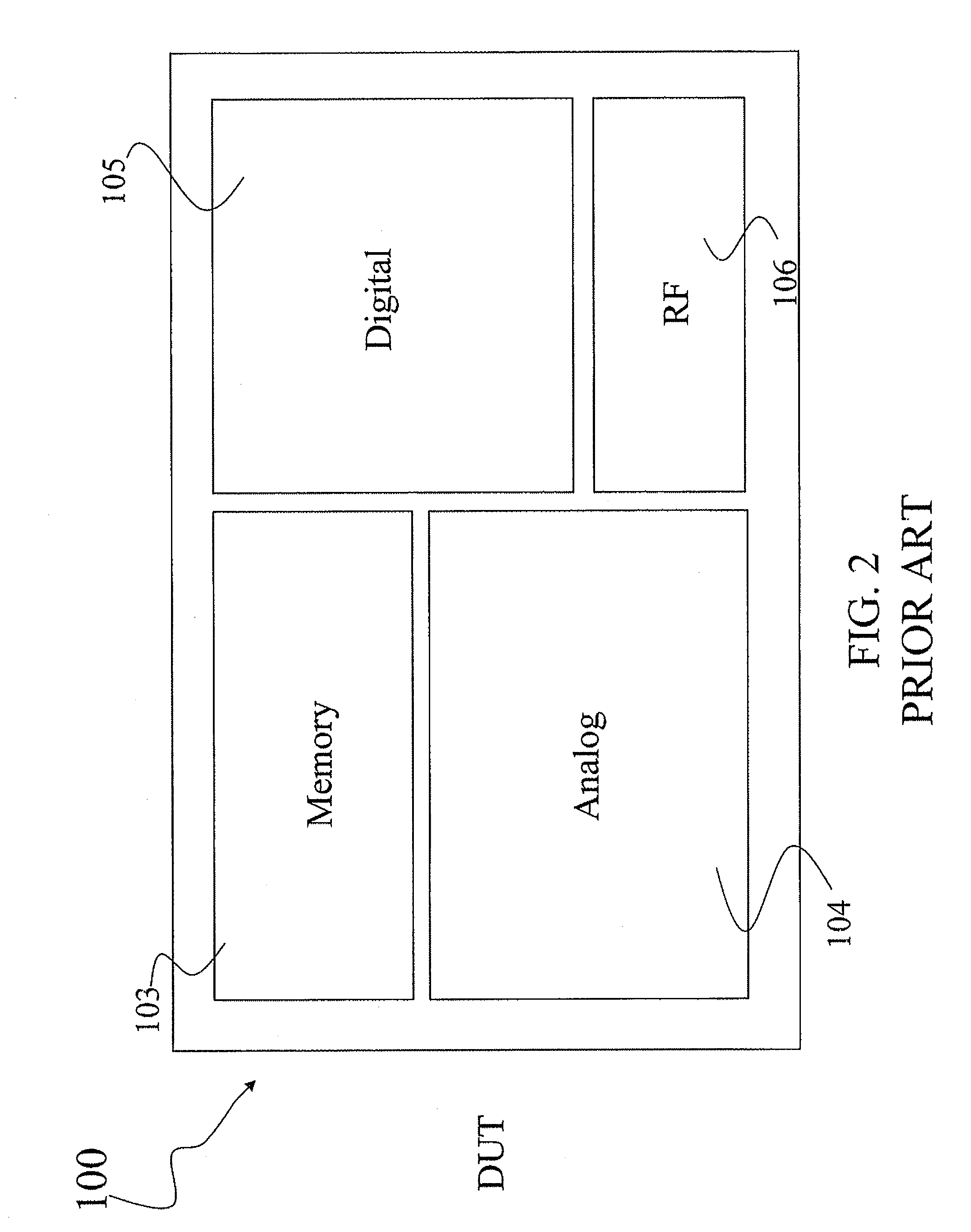

Method for performing an electrical testing of electronic devices

A method of electrical testing electronic devices DUT, comprising: connecting at least an electronic device DUT to an automatic testing apparatus suitable for performing the testing of digital circuits or memories or of digital circuits and memories; sending electrical testing command signals to the electronic device DUT by means of the ATE apparatus; performing electrical testing of the electronic device DUT by means of at least one advanced supervised self testing system “Advanced Low Pin Count BIST” ALB which is built in the electronic device DUT, the ALB system being digitally interfaced with the ATE through a dedicated digital communication channel; and sending reply messages, if any, which comprise measures, failure information and reply data to the command signals from the electronic device DUT toward the ATE apparatus by means of the digital communication channel.

Owner:STMICROELECTRONICS SRL

Electronic devices with extended metallization layer on a passivation layer

ActiveUS8362620B2Reduce harmSimple and low-cost processSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectricityElectrical testing

A method performs electrical testing and assembly of an electronic device on a wafer and comprising a pad made in an oxide layer covered by a passivation layer. The method includes connecting the electronic device to a testing apparatus; providing said electronic device with a metallization layer extending on the passivation layer from the pad to a non-active area of said wafer. The method comprises-performing the electrical testing on wafer of the electronic device by placing a probe of on a portion of the extended metallization layer; performing the cut of said wafer, reducing the extension of the metallization layer to the edge of the electronic device; embedding the device inside a package, forming on the metallization layer an electrical connection configured to connect the metallization layer to a circuit in said package.

Owner:STMICROELECTRONICS SRL

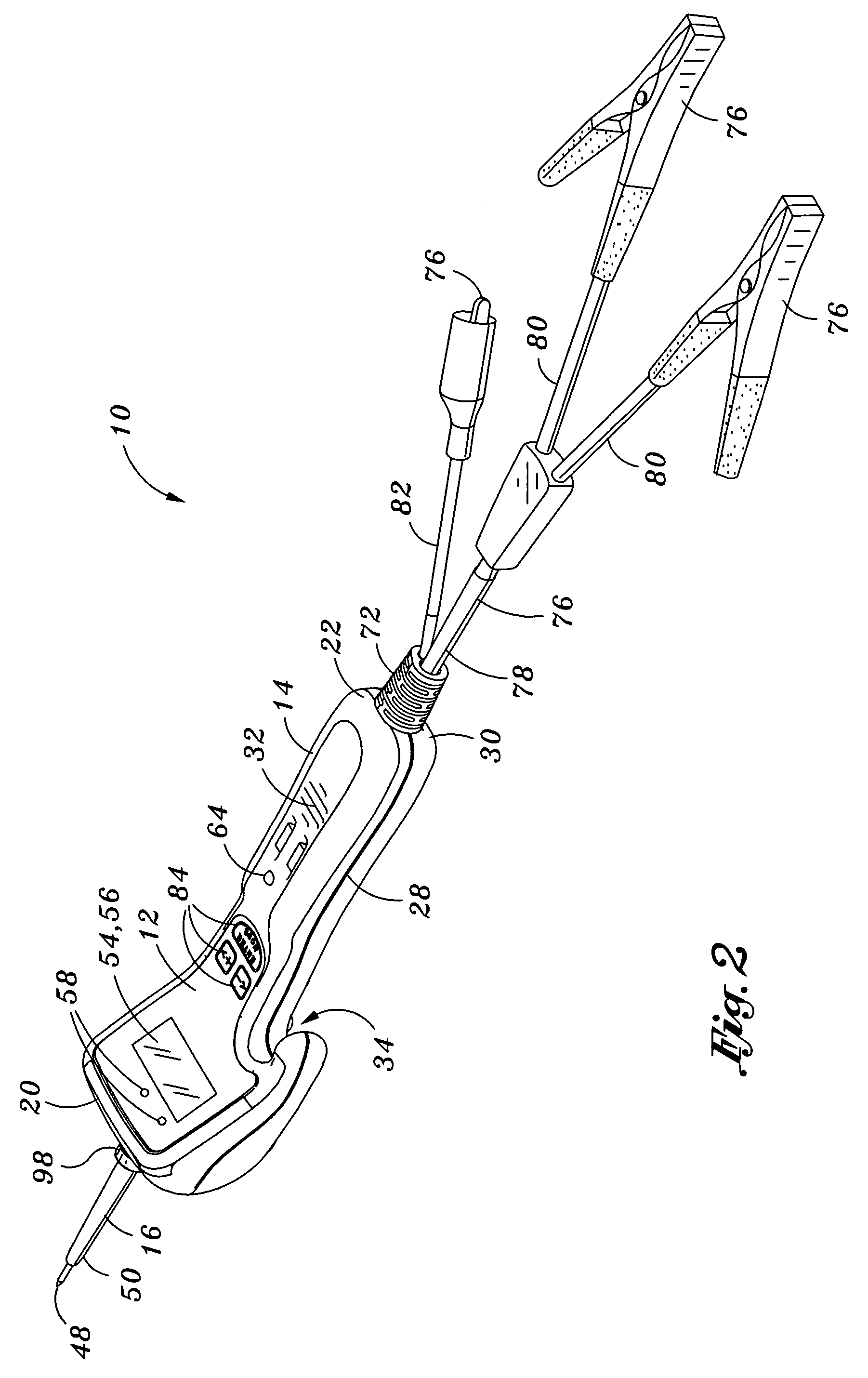

Handheld low voltage testing device

InactiveUS6866639B2Effective auditory screening deviceElectroencephalographyCurrent/voltage measurementCapacitive couplingLow voltage

A portable hand-held electrical testing device including a processor housed within an enclosure. The processor is configured to operate on commands by a user to process sub-microvolt electrical signals received through an input / output interface. The input / output interface includes a capacitive coupled amplifier with adjustable gain settings. Onboard memory linked to the processor stores processing data and instructions. A display device is mounted to said enclosure and is operatively connected to the processor to display processing results in real time.

Owner:BRAINSCOPE SPV LLC +1

Process for the fabrication of wiring board for electrical tests

InactiveUS6568073B1Decorative surface effectsElectrical measurement instrument detailsMetal foilElectrical testing

Owner:HITACHI CHEM CO LTD

Conductive adhesive for thinned silicon wafers with through silicon vias

ActiveUS7541203B1Prevent electrostatic dischargeSemiconductor/solid-state device testing/measurementSolid-state devicesConductive polymerElectrical testing

The present invention relates to a process for preparing a thinned silicon wafer for electrical testing, the thinned silicon wafer comprising at least one circuit design and at least one through-silicon via or hole; the process comprising temporarily attaching the thinned silicon wafer to a mechanical handler by means of an electrically conductive polymeric adhesive material.

Owner:IBM CORP

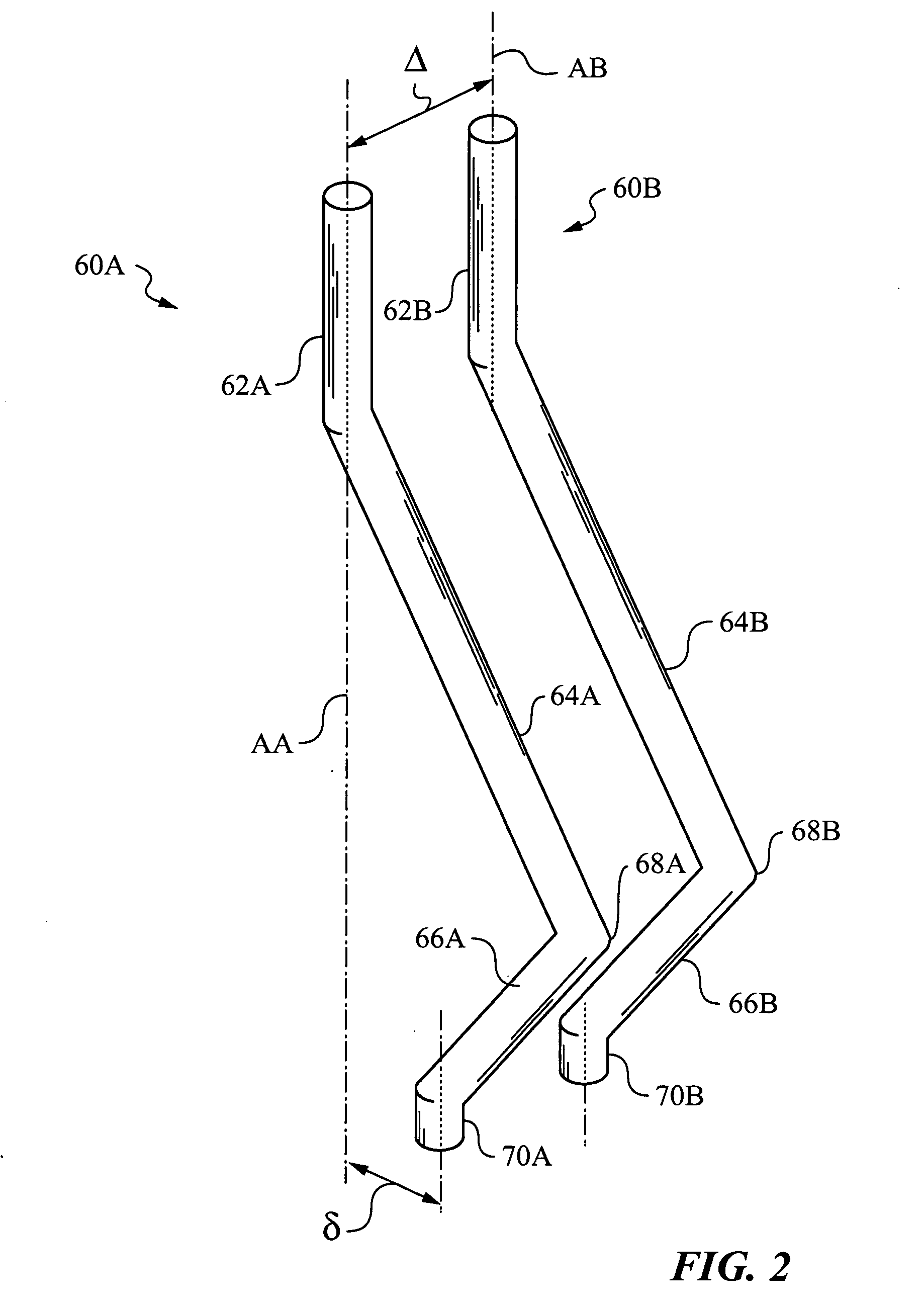

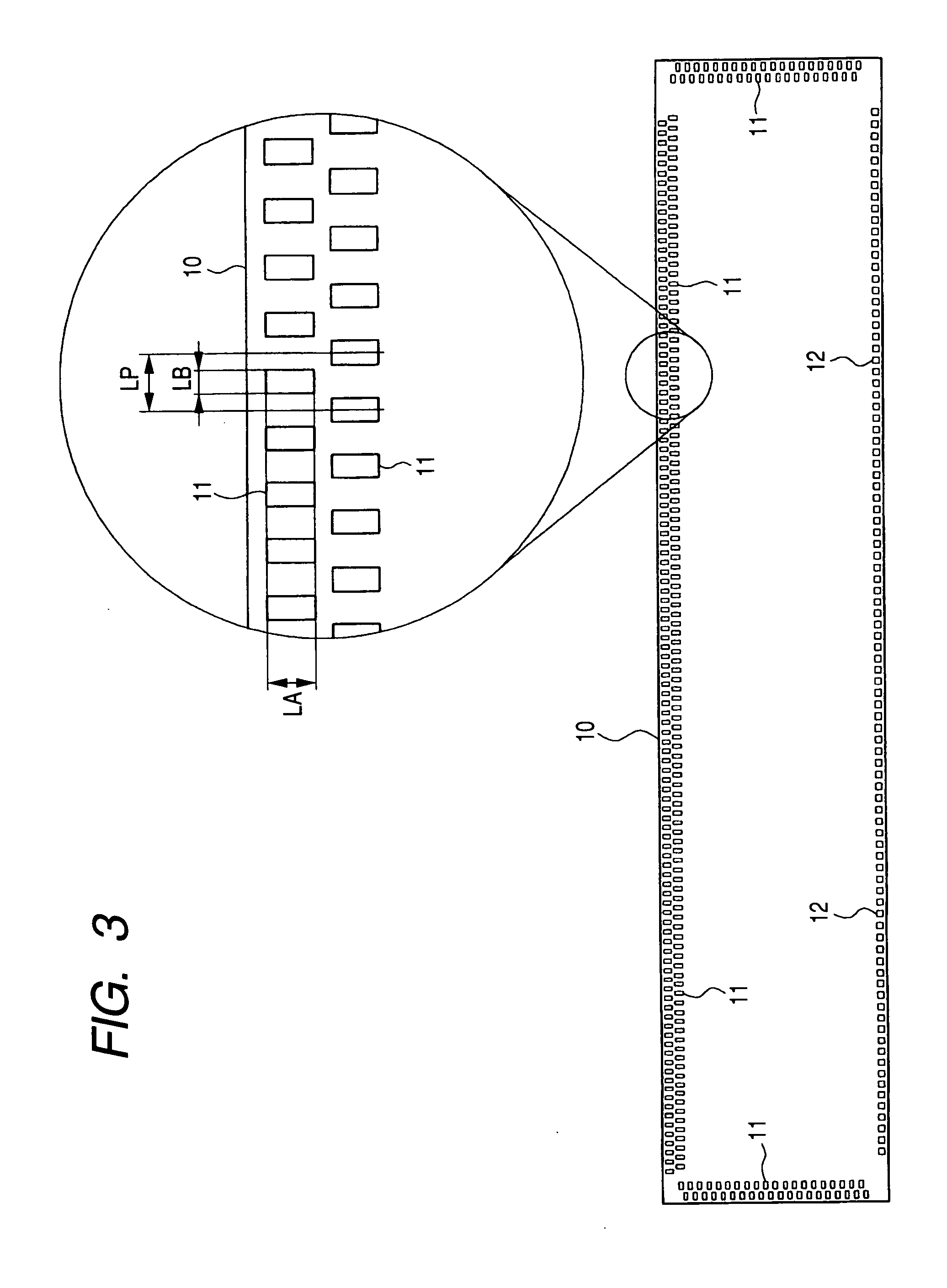

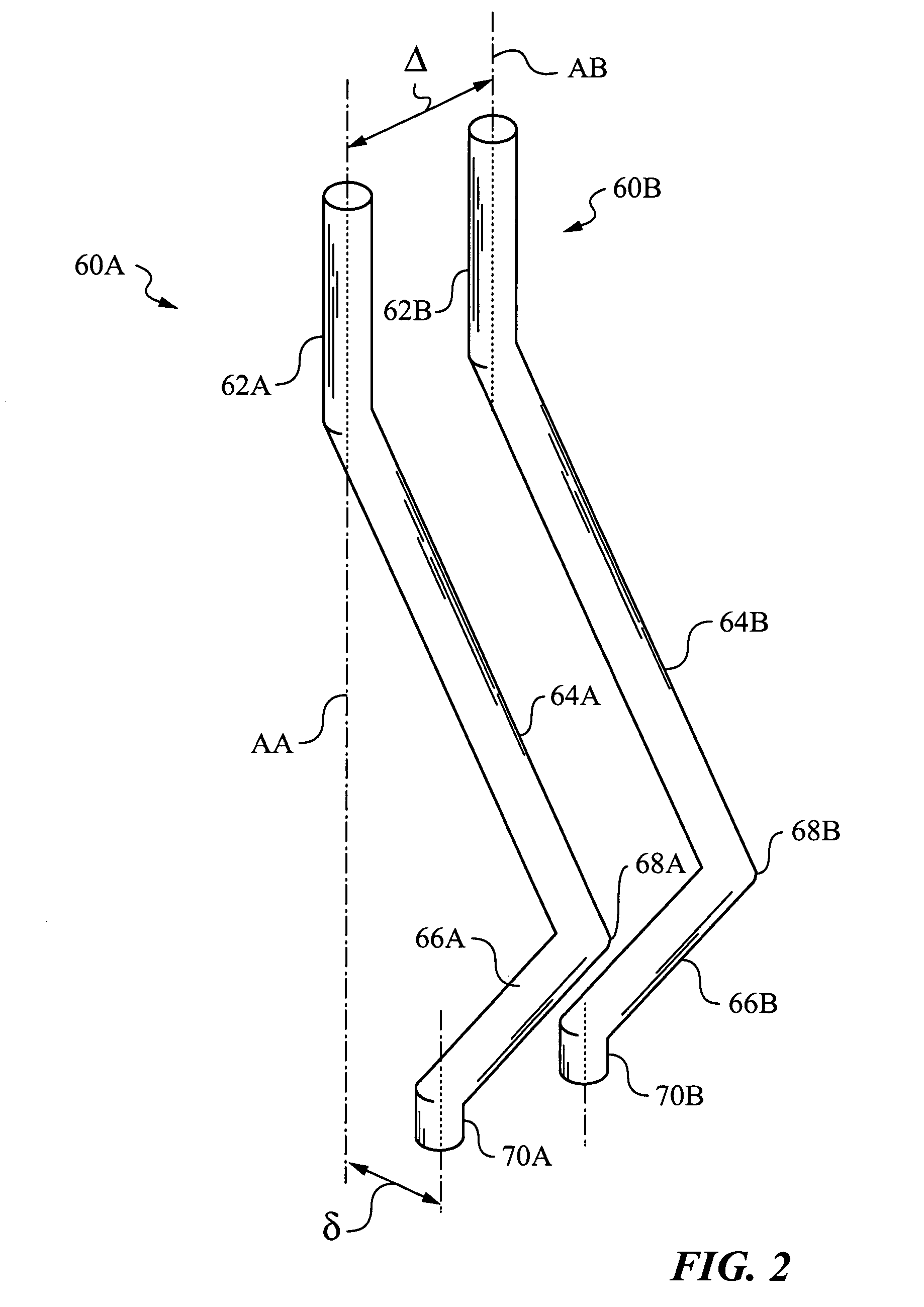

Probe cards employing probes having retaining portions for potting in a potting region

ActiveUS20080088327A1Electrical measurement instrument detailsContactless circuit testingProbe cardTransformer

Method and apparatus using a retention arrangement for probes used for electrical testing of a device under test (DUT). The apparatus has a number of probes each of which has a connect end for applying a test signal, a retaining portion, at least one arm portion and a contact tip for making an electrical contact with the DUT. A retention arrangement has a tip holder for holding each of the probes by its contacting tip and a plate with openings for holding each of the probes below the retaining portion. The retaining portion of each of the probes is potted in a potting region defined above the plate with the aid of a potting agent. The apparatus can be used with space transformers, a variety of probes of different geometries and scrub motion characteristics and is well-suited for use in probe card apparatus under tight pitch and small tolerance requirements.

Owner:MICRO PROBE

Multilayer ceramic capacitor with internal current cancellation and bottom terminals

ActiveUS20090002921A1Minimizes loop areaSimple designFixed capacitor electrodesCross-talk/noise/interference reductionCapacitanceCeramic capacitor

Low inductance capacitors include electrodes that are arranged among dielectric layers and oriented such that the electrodes are substantially perpendicular to a mounting surface. Vertical electrodes are exposed along a device periphery to determine where termination lands are formed, defining a narrow and controlled spacing between the lands that is intended to reduce the current loop area, thus reducing the component inductance. Further reduction in current loop area and thus component equivalent series inductance (ESL) may be provided by interdigitated terminations. Terminations may be formed by various electroless plating techniques, and may be directly soldered to circuit board pads. Terminations may also be located on “ends” of the capacitors to enable electrical testing or to control solder fillet size and shape. Two-terminal devices may be formed as well as devices with multiple terminations on a given bottom (mounting) surface of the device. Terminations may also be formed on the top surface (opposite a designated mounting surface) and may be a mirror image, reverse-mirror image, or different shape relative to the bottom surface.

Owner:KYOCERA AVX COMPONENTS CORP

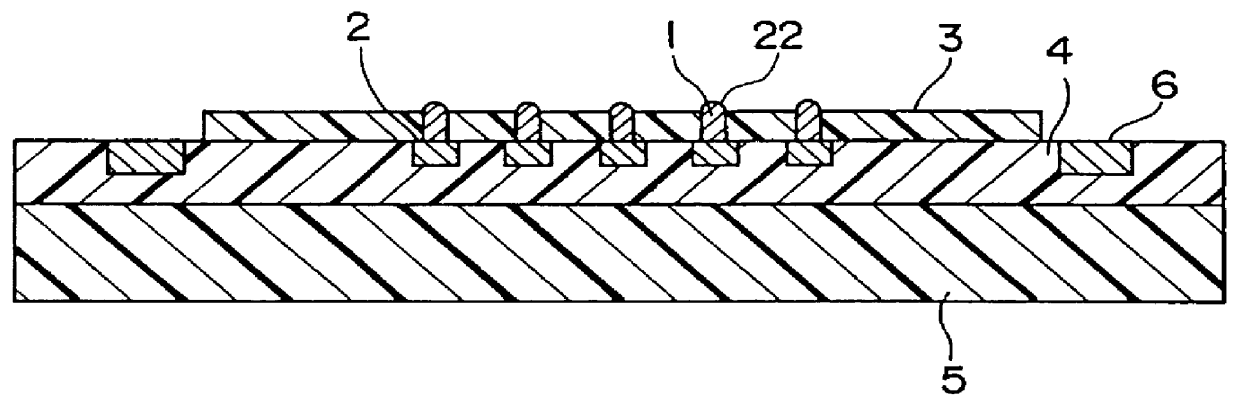

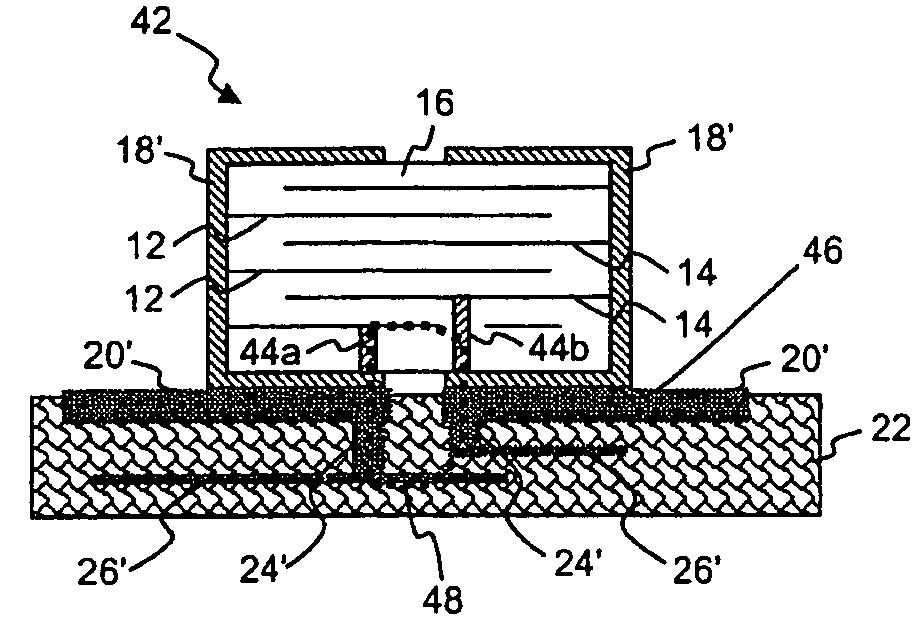

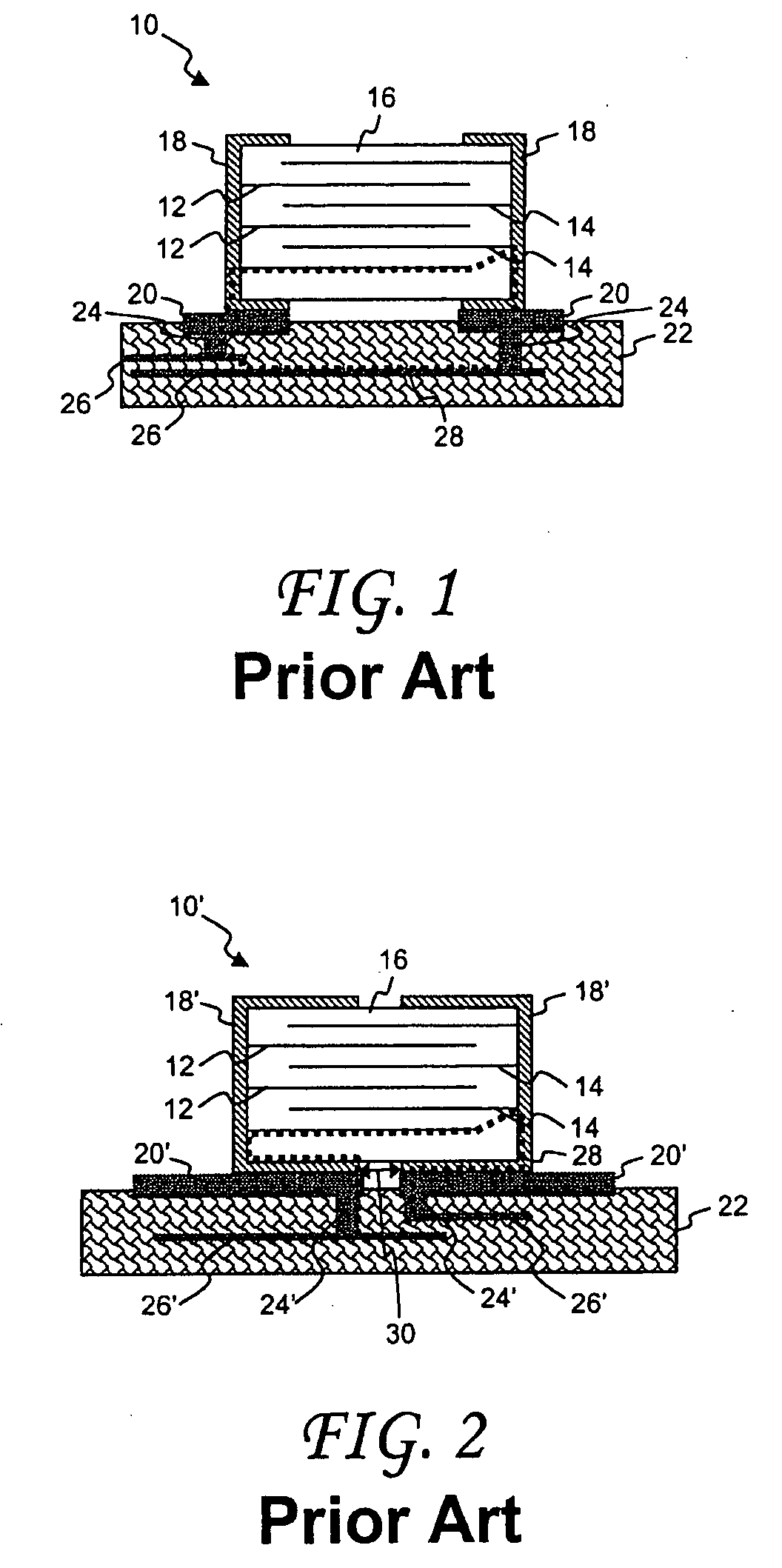

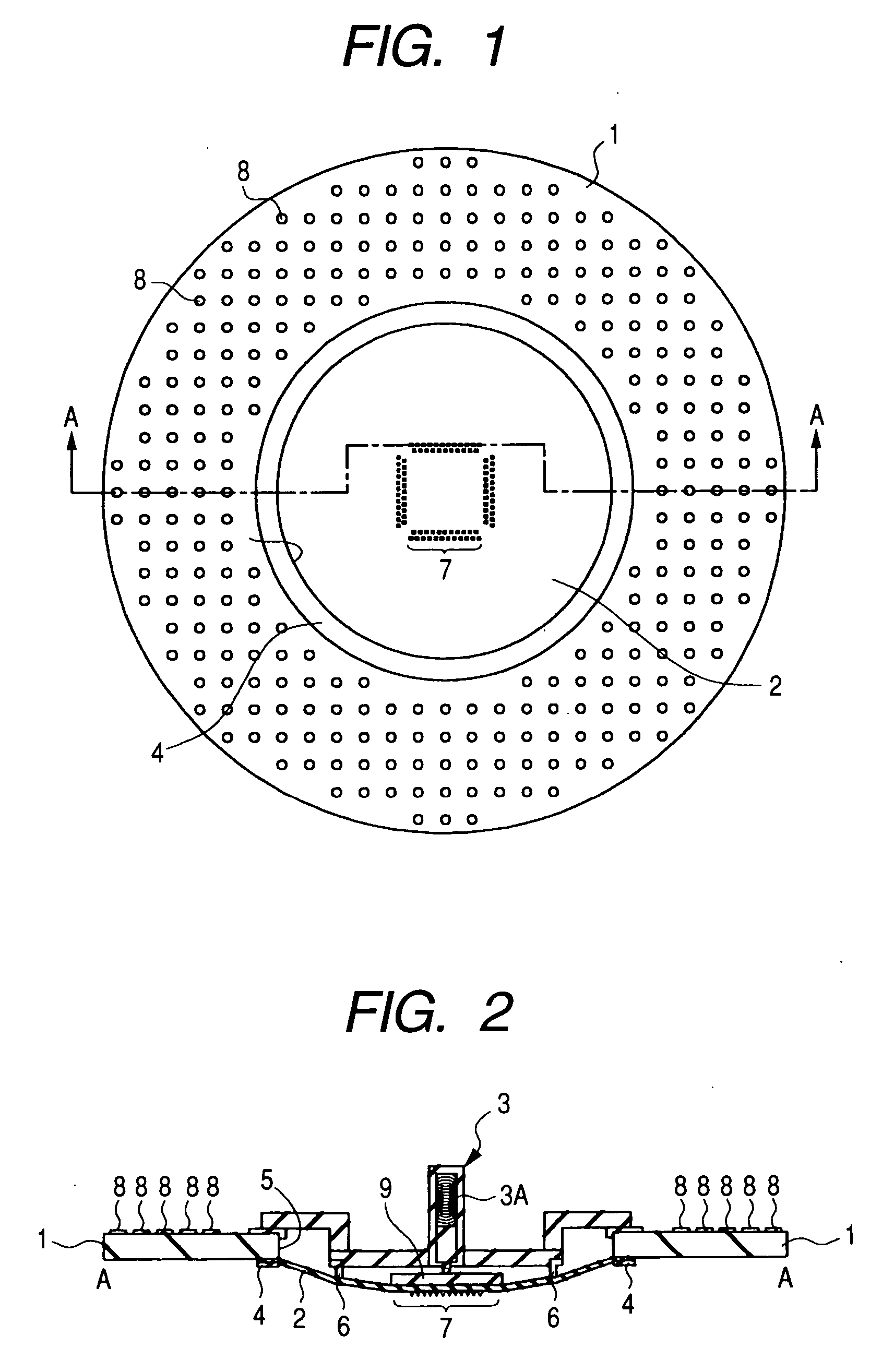

Fabrication method of semiconductor integrated circuit device

InactiveUS20050093565A1Reduce manufacturing costIncrease the number ofSemiconductor/solid-state device testing/measurementElectronic circuit testingElectrical testingEngineering

To permit electrical testing of a semiconductor integrated circuit device having test pads disposed at narrow pitches probes in a pyramid or trapezoidal pyramid form are formed from metal films formed by stacking a rhodium film and a nickel film successively. Via through-holes are formed in a polyimide film between interconnects and the metal films, and the interconnects are electrically connected to the metal films. A plane pattern of one of the metal films equipped with one probe and through-hole is obtained by turning a plane pattern of the other metal film equipped with the other probe and through-hole through a predetermined angle.

Owner:RENESAS TECH CORP

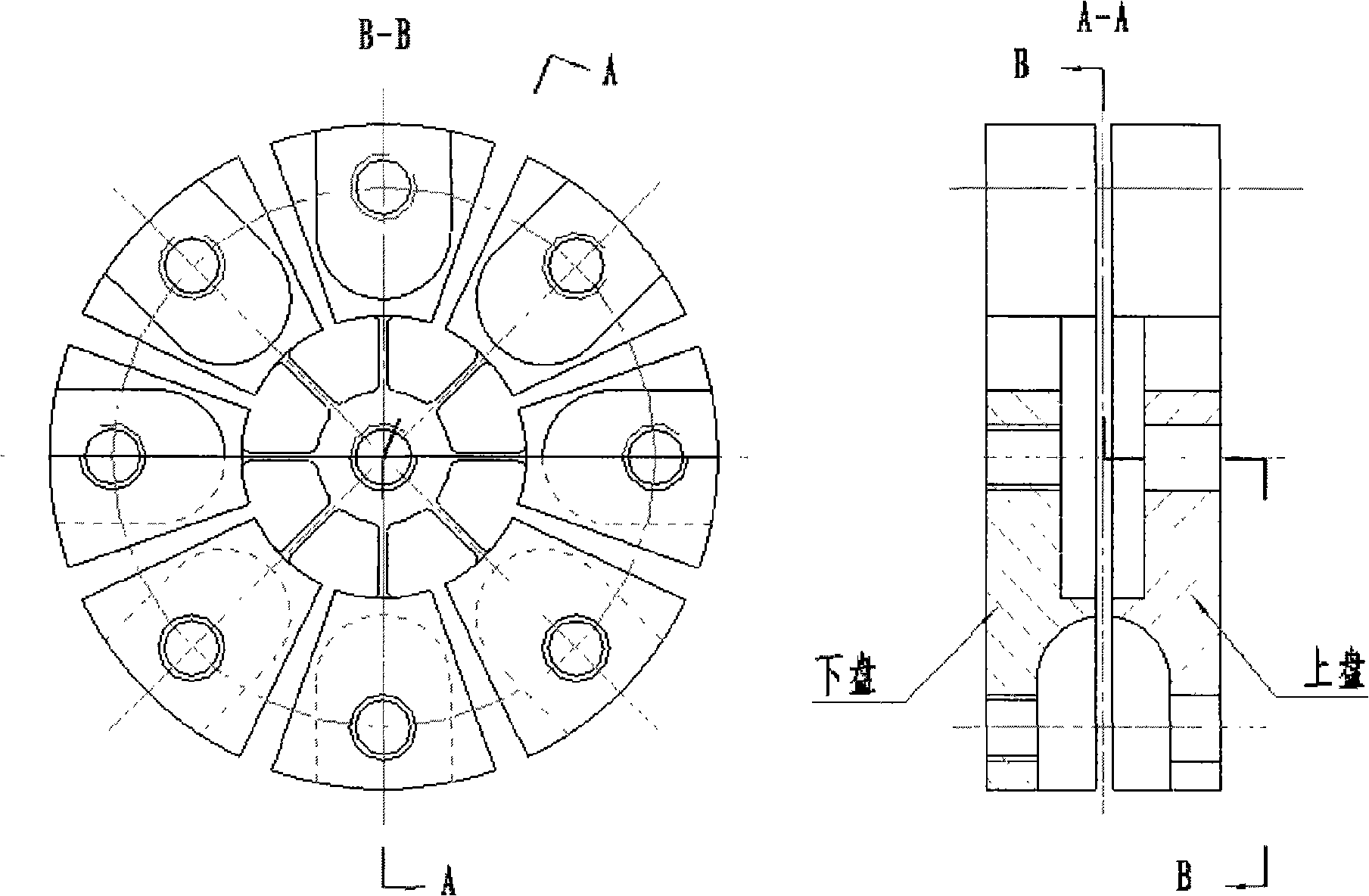

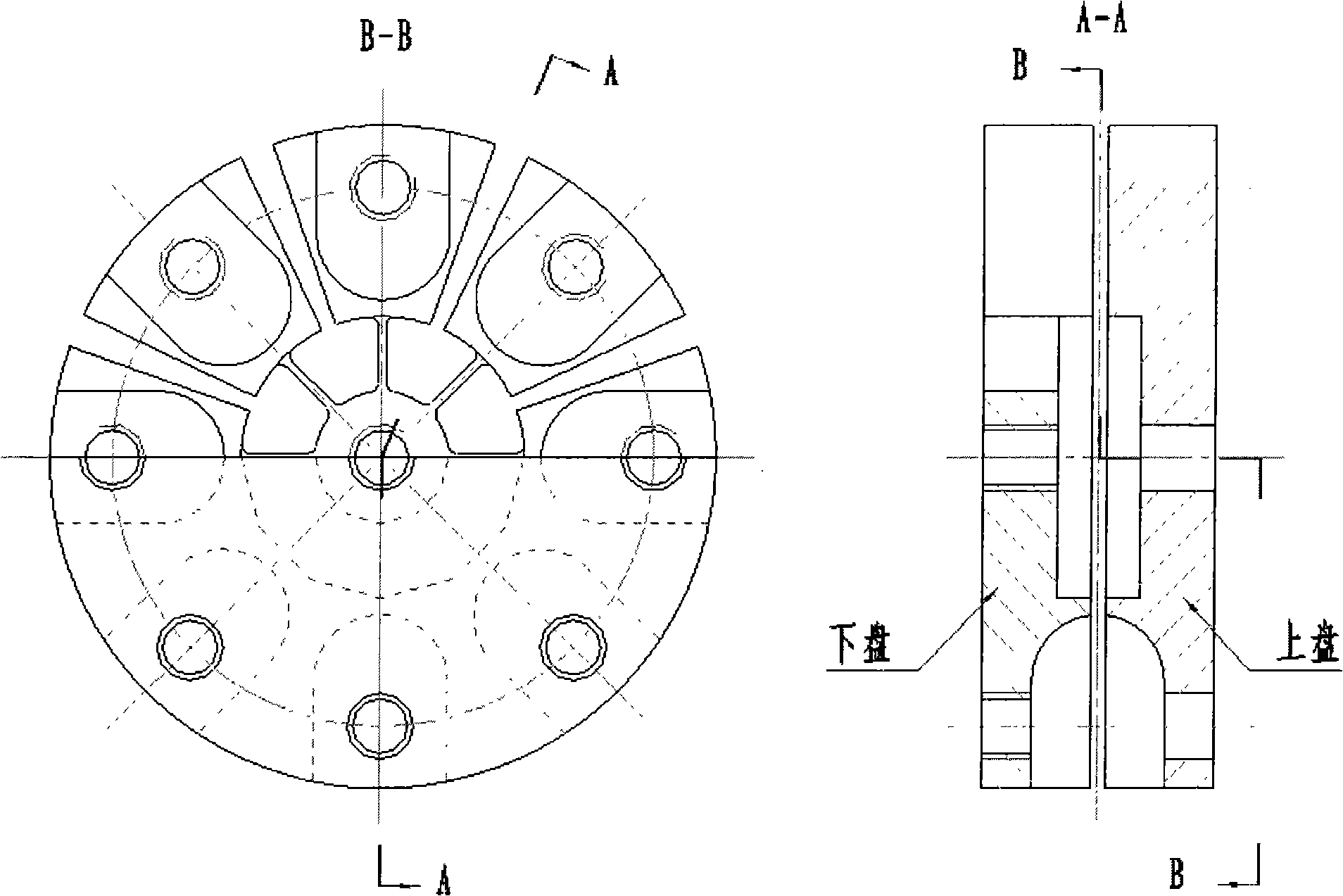

Structure mechanics combined experimental device

The invention relates to the field of experiment-teaching equipment of 'Structural Mechanics' in colleges and universities; the products of the invention are mainly applied to the experiment teaching of rigid frames, trusses and combined structures in beam structures; the invention is characterized in that: a node plate adopts a split structure, the trusses are arranged between two node plates, a weak connection with a particular shape is arranged on an articulated node plate, and a relatively ideal articulating node can be obtained by utilizing the mechanical property that the weak connection can transmit a relatively large axial force but only can transmit a very small bending moment. By choosing a reasonable connecting way between a rigid node plate and the trusses, the influences on the testing result made by the size effect of the rigid node plate is reduced and a relatively ideal rigid node can be obtained. The node property and the support property can be transferred conveniently. All the tests can realize electrical testing by using the computer data collecting and analyzing. The application of the computer data collecting and analyzing system not only facilitate data collection, but also enriches the experiment-teaching means, which is beneficial for carrying out open experiment-teaching.

Owner:YANTAI UNIV +1

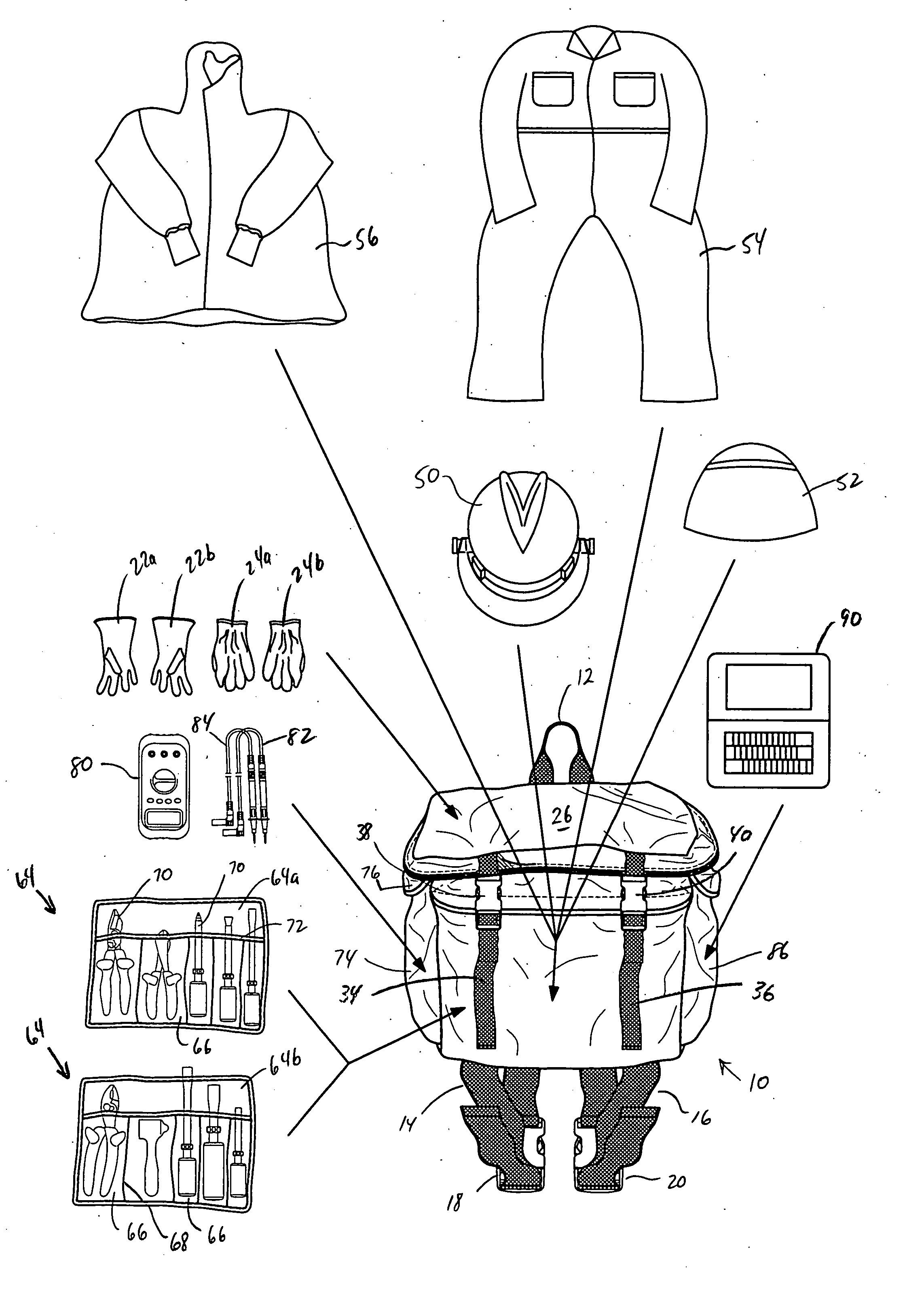

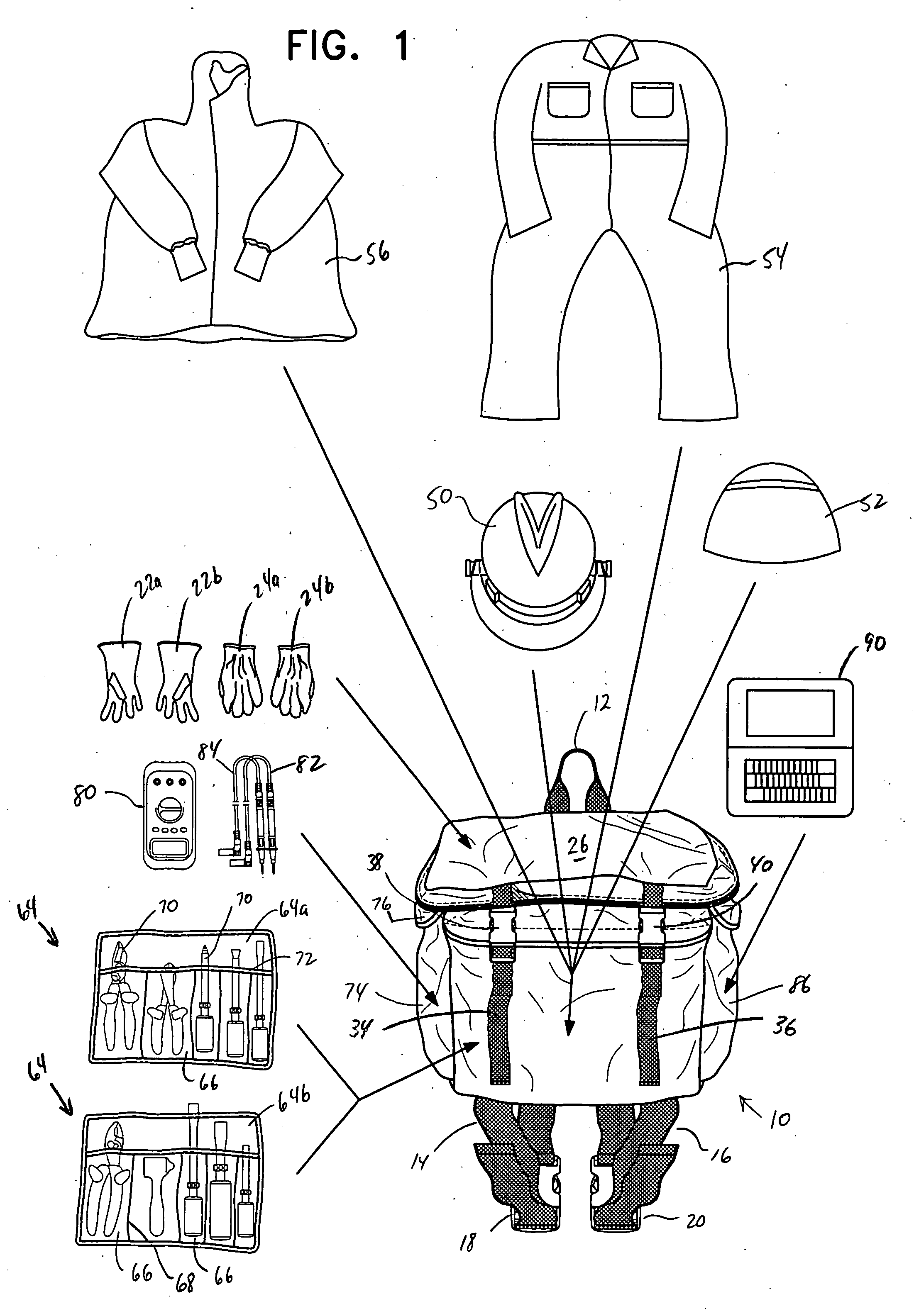

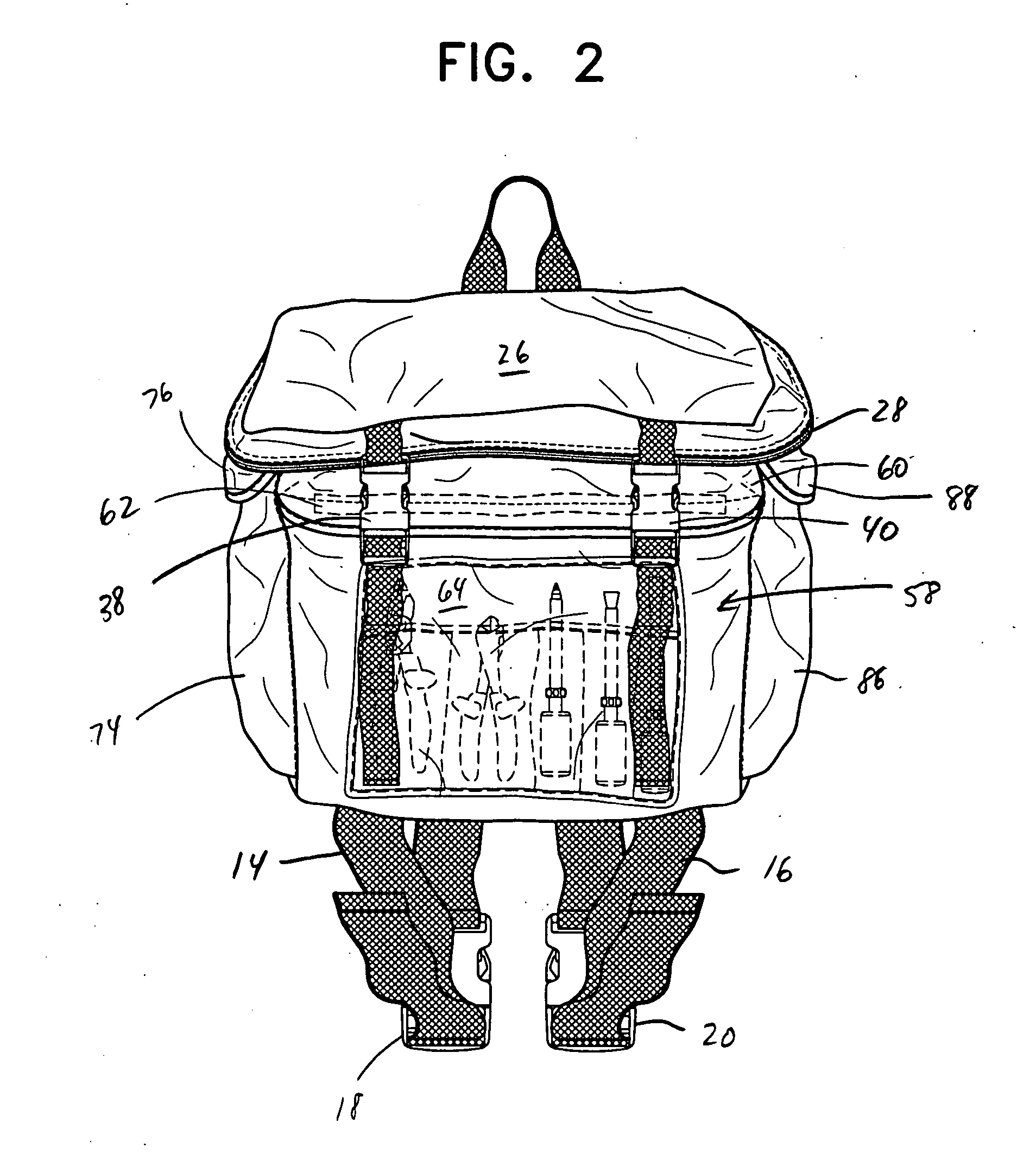

Electrical safety backpack

InactiveUS20050236449A1Easy accessTravelling sacksTravelling carriersPersonal protective equipmentElectrical testing

An electrical safety backpack contains all of the products needed for working near or on energized circuits in a single transportable container which can be carried from various vantage points and which provides easy, immediate access to insulated tools, electrical test equipment and personal protective equipment (PPE) and clothing. This collection of disparate tools puts all the necessary items that are needed to work on energized equipment in one portable container.

Owner:CERTIFIED INSULATED PRODS CORP

Probe cards employing probes having retaining portions for potting in a potting region

ActiveUS7786740B2Electrical measurement instrument detailsContactless circuit testingProbe cardTransformer

Method and apparatus using a retention arrangement for probes used for electrical testing of a device under test (DUT). The apparatus has a number of probes each of which has a connect end for applying a test signal, a retaining portion, at least one arm portion and a contact tip for making an electrical contact with the DUT. A retention arrangement has a tip holder for holding each of the probes by its contacting tip and a plate with openings for holding each of the probes below the retaining portion. The retaining portion of each of the probes is potted in a potting region defined above the plate with the aid of a potting agent. The apparatus can be used with space transformers, a variety of probes of different geometries and scrub motion characteristics and is well-suited for use in probe card apparatus under tight pitch and small tolerance requirements.

Owner:MICRO PROBE

Semiconductor package structure and method for manufacturing the same

ActiveUS7973310B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical testingSemiconductor chip

Owner:ZAWASHIRO DIGITAL INNOVATIONS

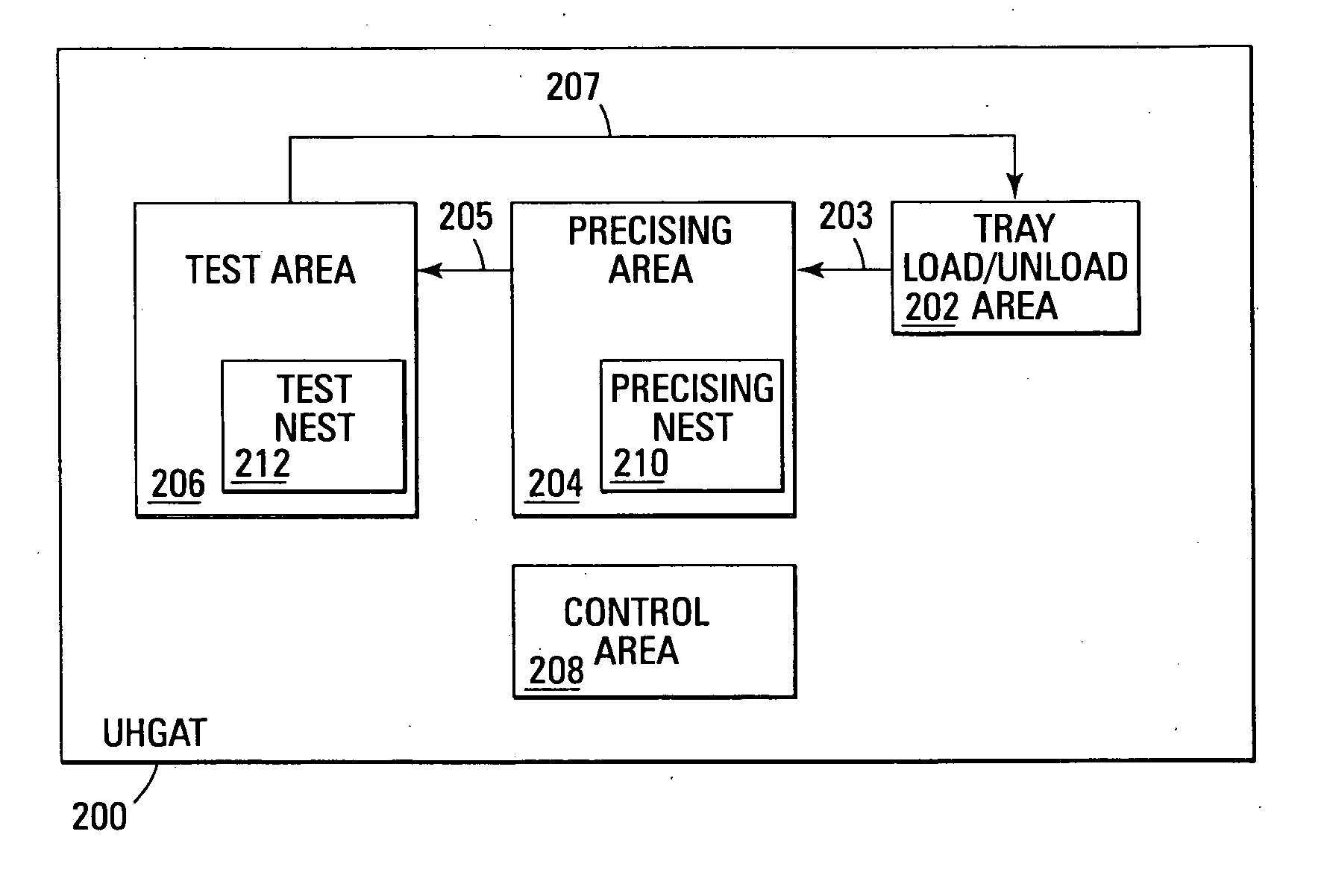

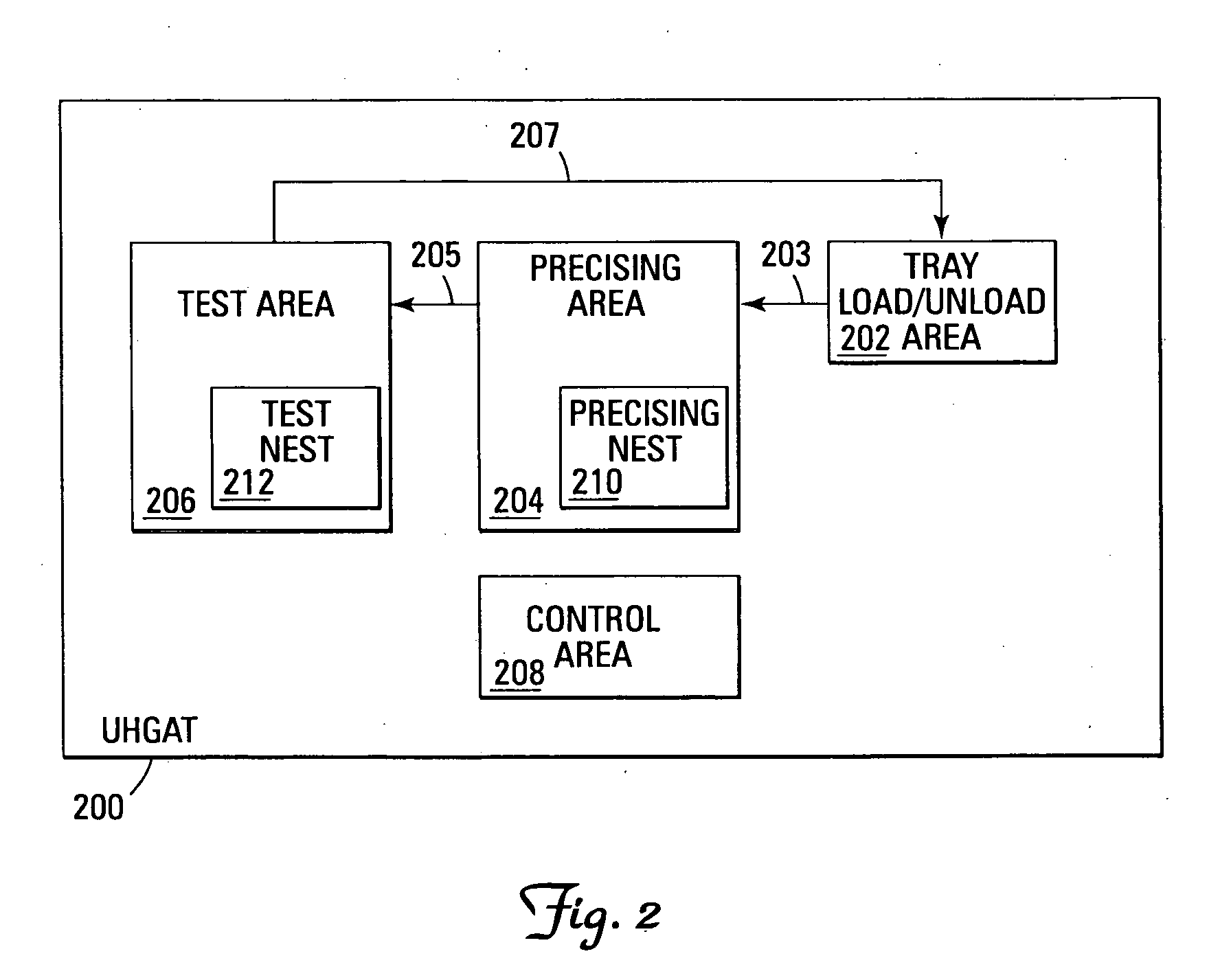

Device transfer mechanism for a test handler

ActiveUS6967475B2Reduce in quantitySimple structureElectronic circuit testingElectrical measurement instrument detailsElectricityElectrical testing

The invention provides a mechanism for a test handler using for electrical testing of electronic devices. The devices are placed on a platform configured to move semiconductor devices from an onloading position to an offloading position along a predetermined path. A transfer arm with a plurality of transfer heads connected to it is located adjacent the path. The transfer heads are configured to pick up and transfer semiconductor devices from the platform to a testing position for testing, and thereafter to transfer the semiconductor devices from the testing position to the platform for offloading.

Owner:ASM ASSEMBLY AUTOMATION LTD

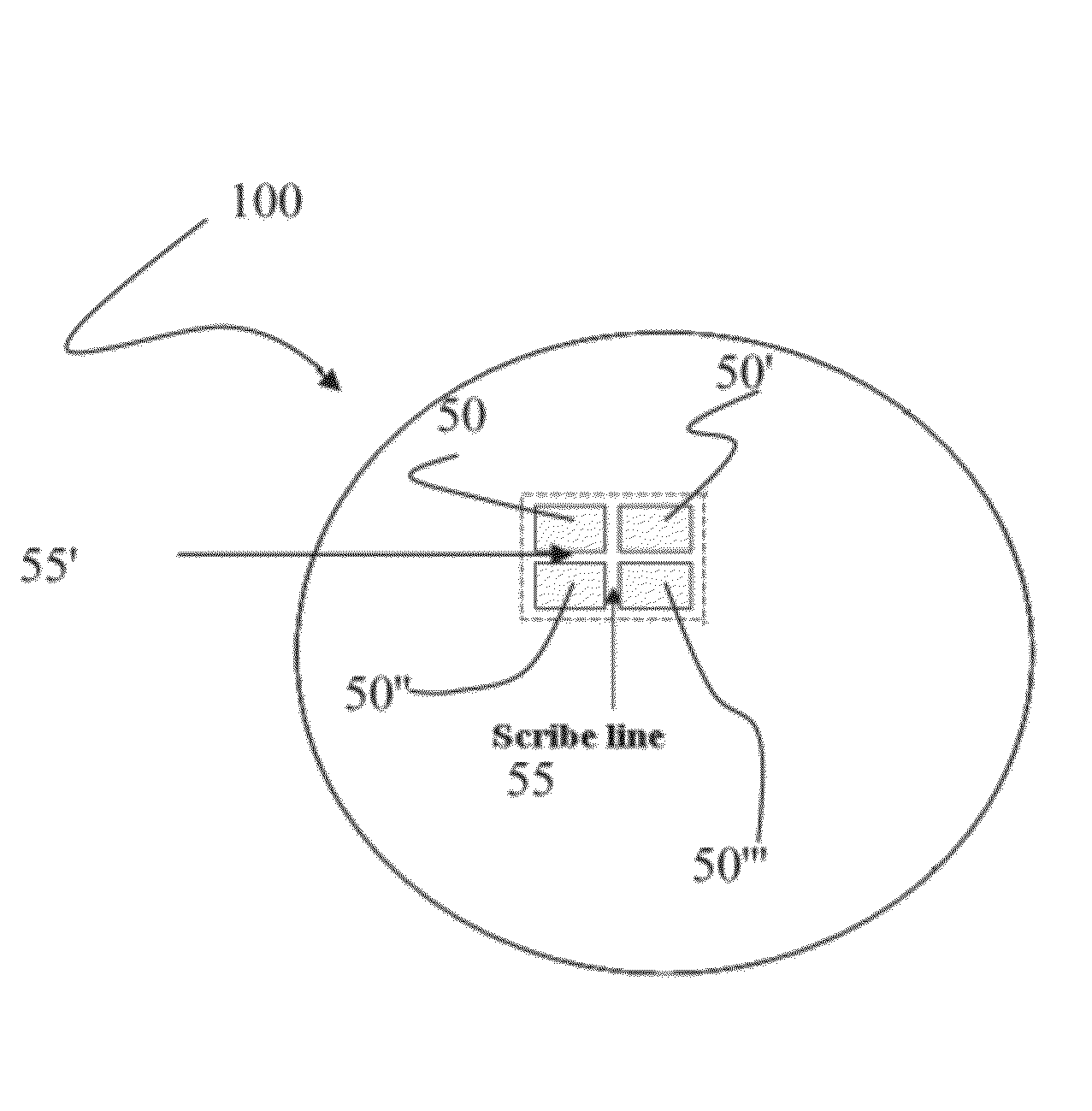

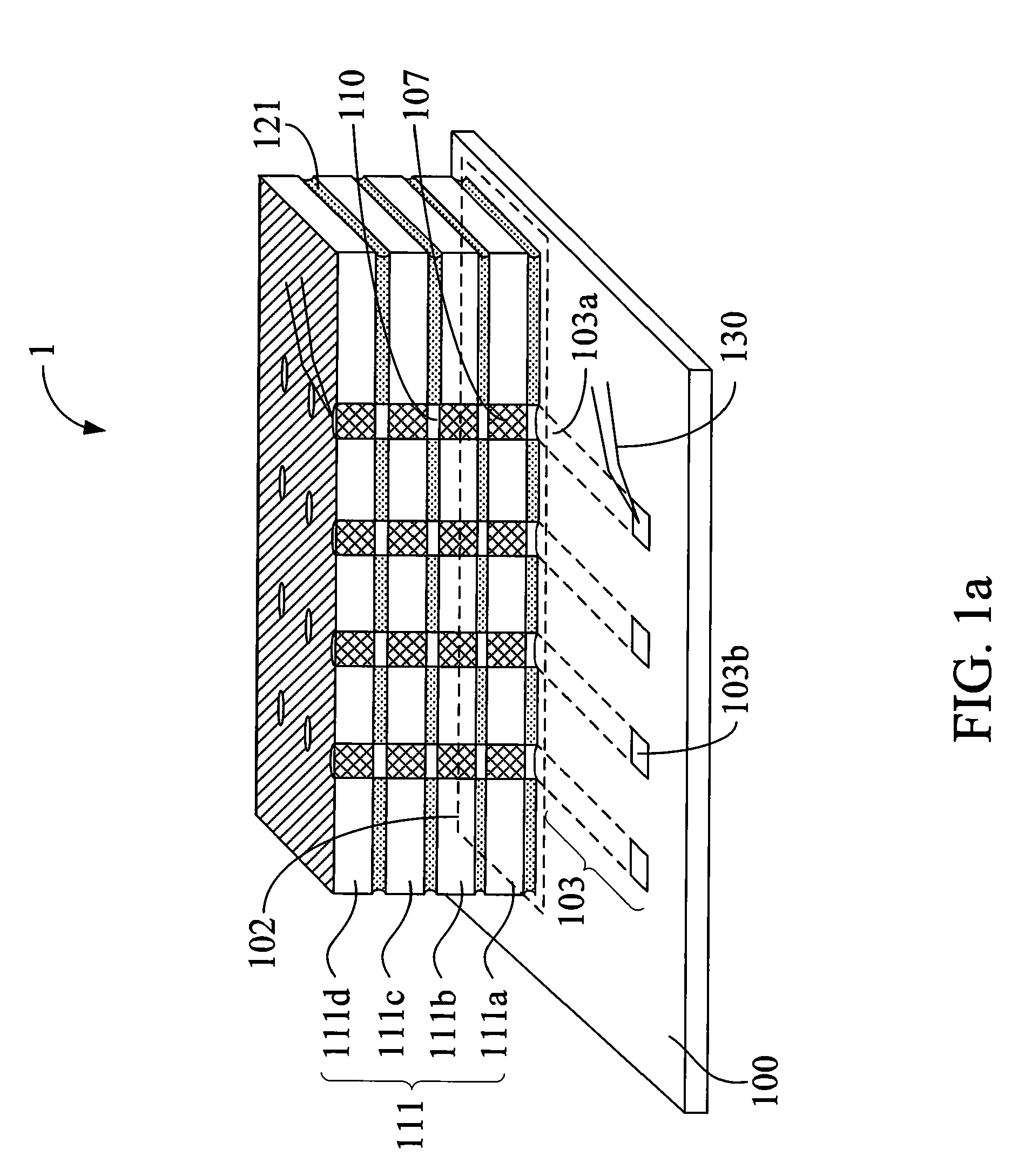

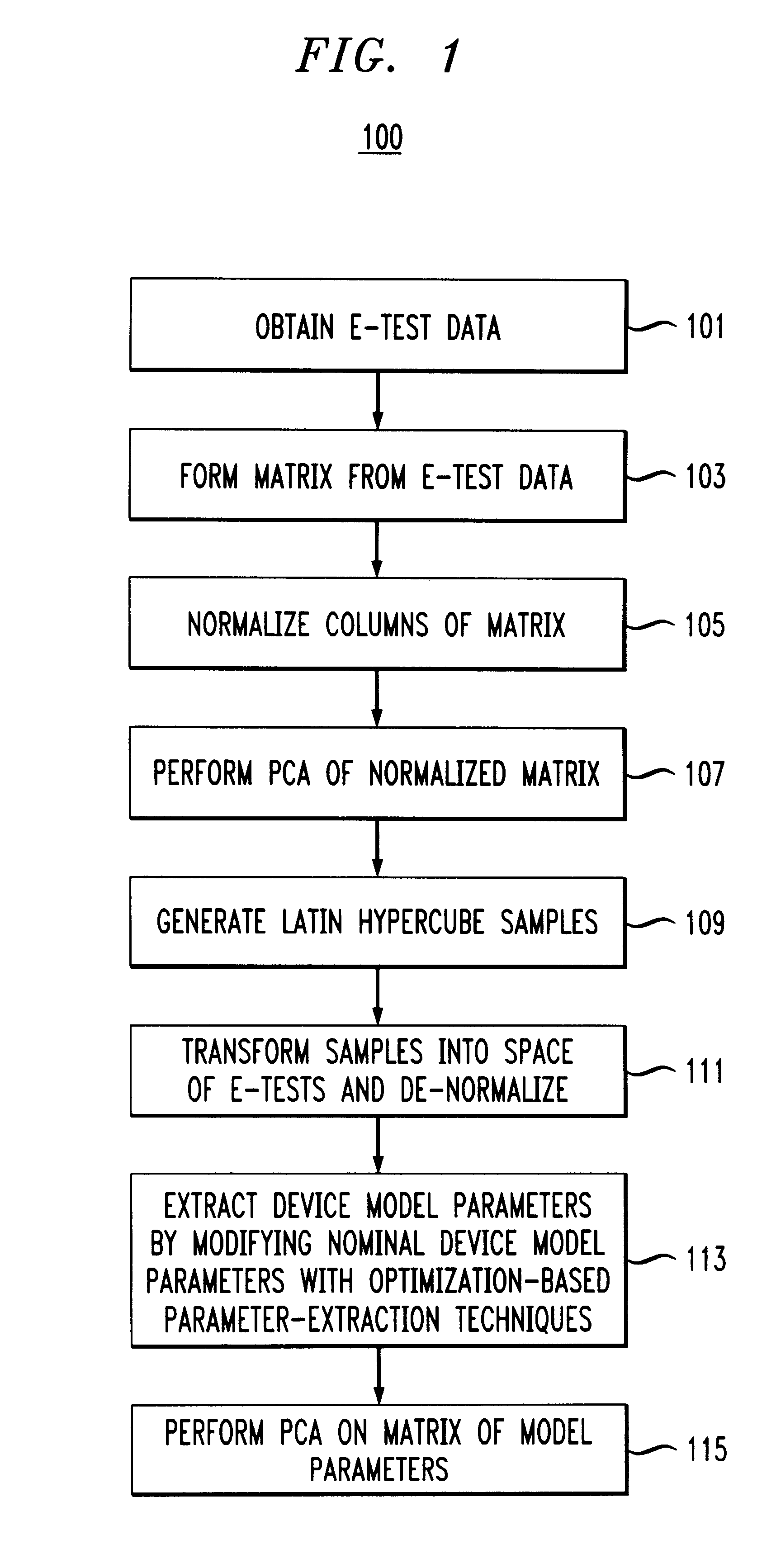

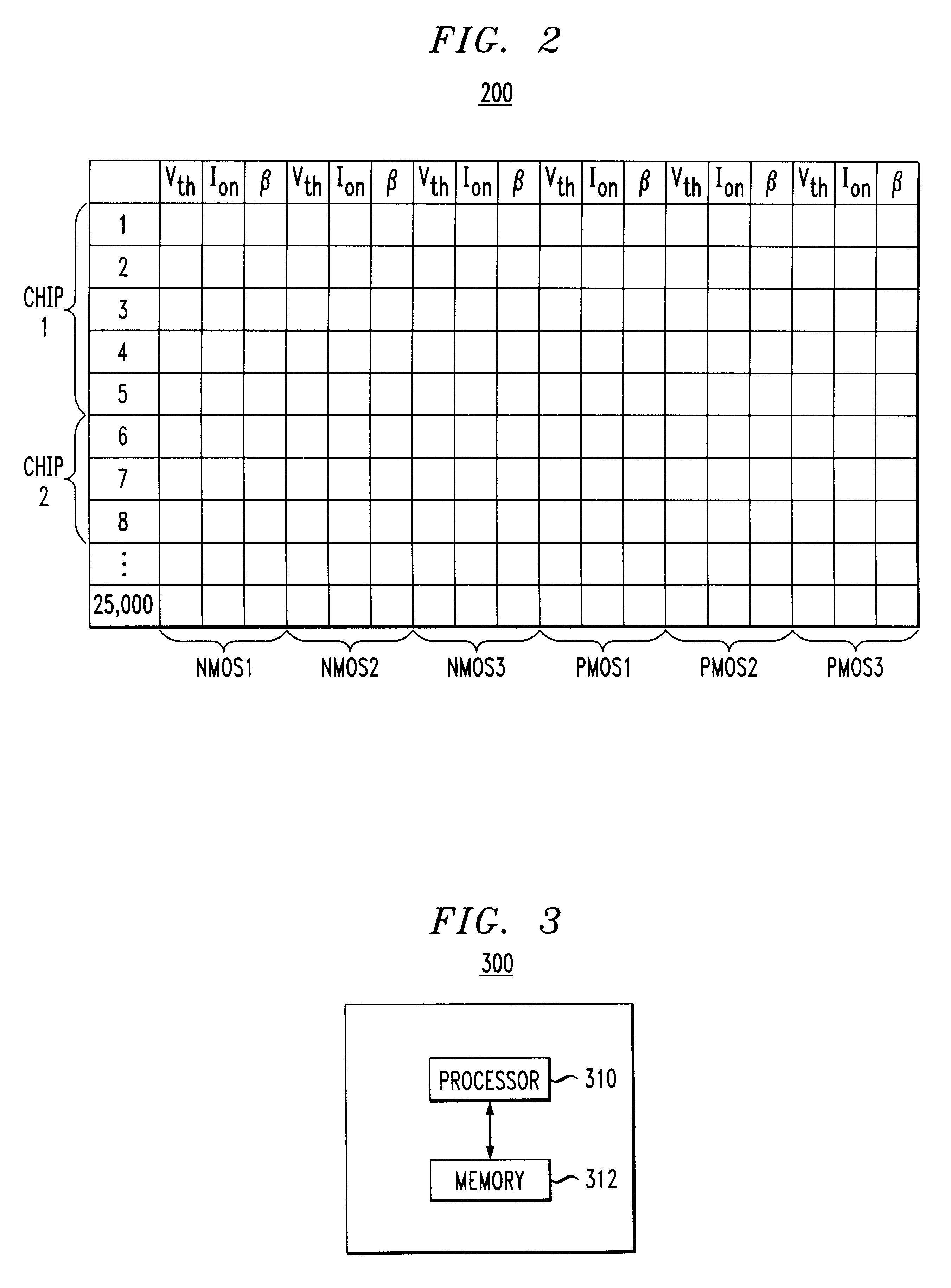

Deriving statistical device models from electrical test data

InactiveUS6560568B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingElectrical testingIntegrated circuit layout

A production process is used to mass-produce chips, each chip being formed in a substrate of a wafer and having an integrated circuit, each integrated circuit having a plurality of primitive device model types. The integrated circuits are produced using a statistical device model for the production process, which is derived from the sets of e-test data.

Owner:LUCENT TECH INC +1

Wafer-level opto-electronic testing apparatus and method

ActiveUS7109739B2Enhanced couplingSemiconductor/solid-state device testing/measurementCoupling light guidesGratingDevice form

A wafer-level testing arrangement for opto-electronic devices formed in a silicon-on-insulator (SOI) wafer structure utilizes a single opto-electronic testing element to perform both optical and electrical testing. Beam steering optics may be formed on the testing element and used to facilitate the coupling between optical probe signals and optical coupling elements (e.g., prism couplers, gratings) formed on the top surface of the SOI structure. The optical test signals are thereafter directed into optical waveguides formed in the top layer of the SOI structure. The opto-electronic testing element also comprises a plurality of electrical test pins that are positioned to contact a plurality of bondpad test sites on the opto-electronic device and perform electrical testing operations. The optical test signal results may be converted into electrical representations within the SOI structure and thus returned to the testing element as electrical signals.

Owner:CISCO TECH INC

Multilayer ceramic capacitor with internal current cancellation and bottom terminals

ActiveUS7697262B2Simple designLow costFixed capacitor electrodesFixed capacitor dielectricCapacitanceCeramic capacitor

Low inductance capacitors include electrodes that are arranged among dielectric layers and oriented such that the electrodes are substantially perpendicular to a mounting surface. Vertical electrodes are exposed along a device periphery to determine where termination lands are formed, defining a narrow and controlled spacing between the lands that is intended to reduce the current loop area, thus reducing the component inductance. Further reduction in current loop area and thus component equivalent series inductance (ESL) may be provided by interdigitated terminations. Terminations may be formed by various electroless plating techniques, and may be directly soldered to circuit board pads. Terminations may also be located on “ends” of the capacitors to enable electrical testing or to control solder fillet size and shape. Two-terminal devices may be formed as well as devices with multiple terminations on a given bottom (mounting) surface of the device. Terminations may also be formed on the top surface (opposite a designated mounting surface) and may be a mirror image, reverse-mirror image, or different shape relative to the bottom surface.

Owner:KYOCERA AVX COMPONENTS CORP

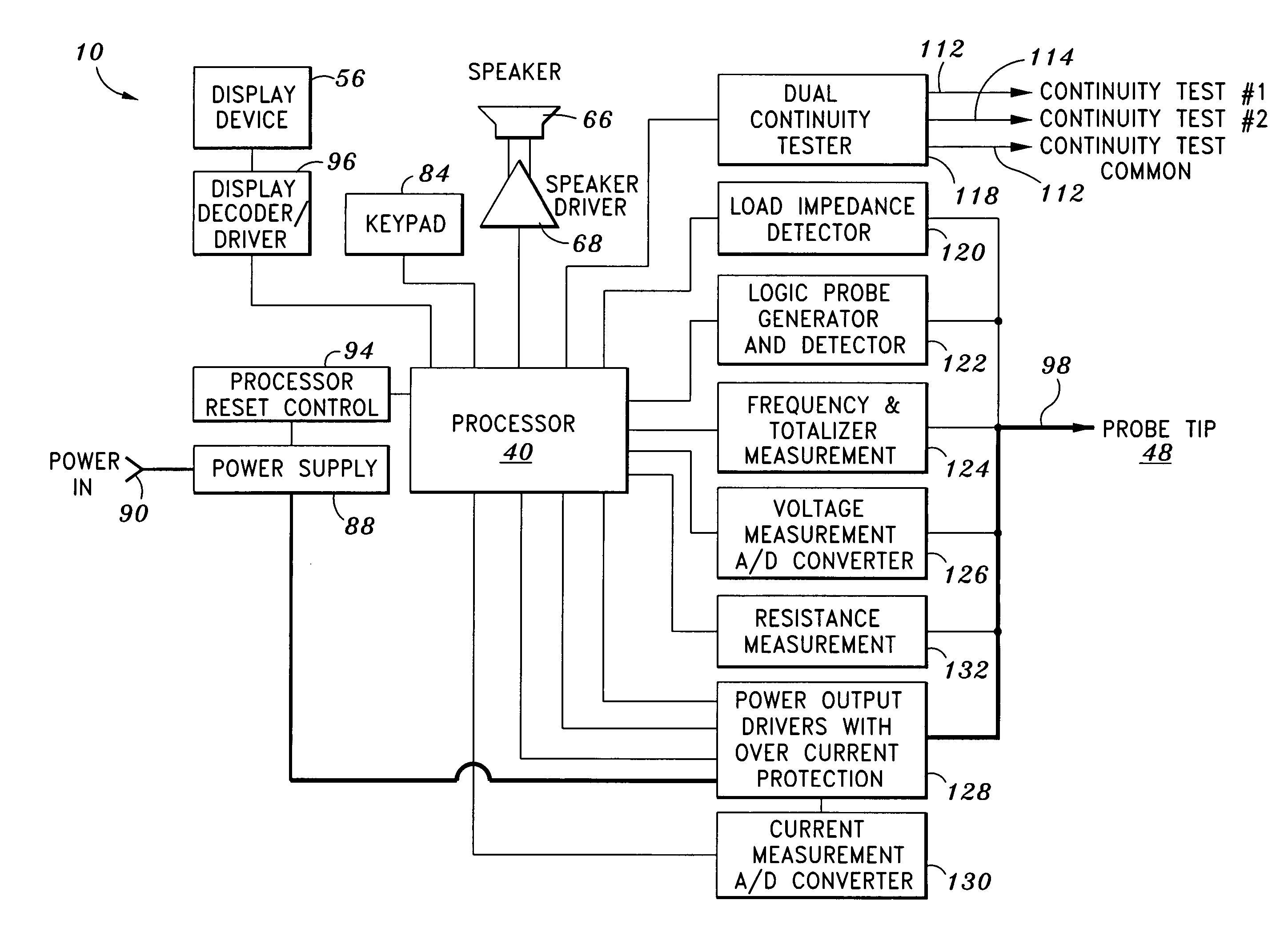

Energizable electrical test device for measuring current and resistance of an electrical circuit

ActiveUS7184899B2Eliminate needInput/output for user-computer interactionElectric devicesElectricityElectrical resistance and conductance

Owner:POWER PROBE

Semiconductor chip with bond area

ActiveUS7947978B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical testingSemiconductor chip

A semiconductor chip comprises a metal pad exposed by an opening in a passivation layer, wherein the metal pad has a testing area and a bond area. During a step of testing, a testing probe contacts with the testing area for electrical testing. After the step of testing, a polymer layer is formed on the testing area with a probe mark created by the testing probe. Alternatively, a semiconductor chip comprises a testing pad and a bond pad respectively exposed by two openings in a passivation layer, wherein the testing pad is connected to the bond pad. During a step of testing, a testing probe contacts with the testing pad for electrical testing. After the step of testing, a polymer layer is formed on the testing pad with a probe mark created by the testing probe.

Owner:QUALCOMM INC

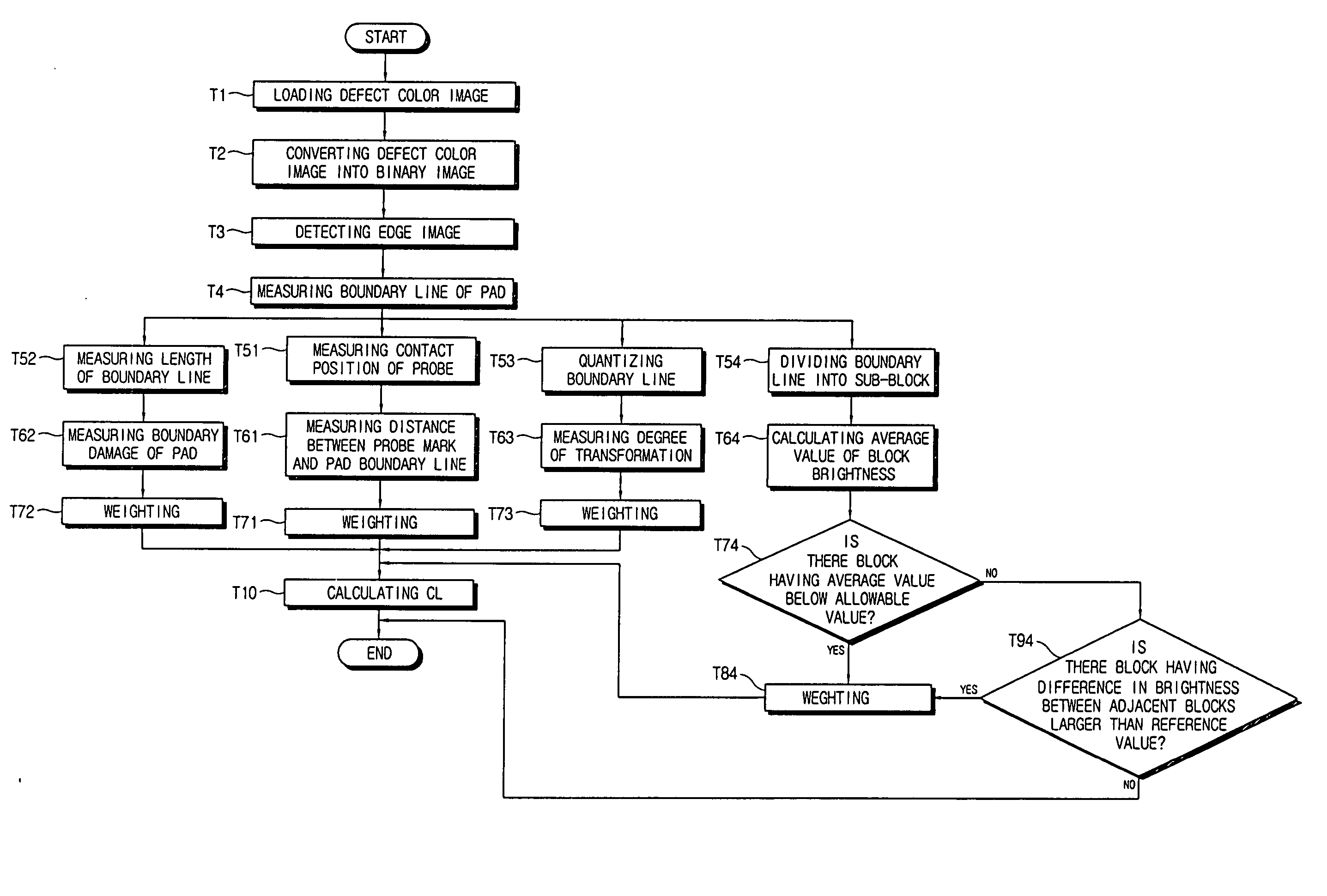

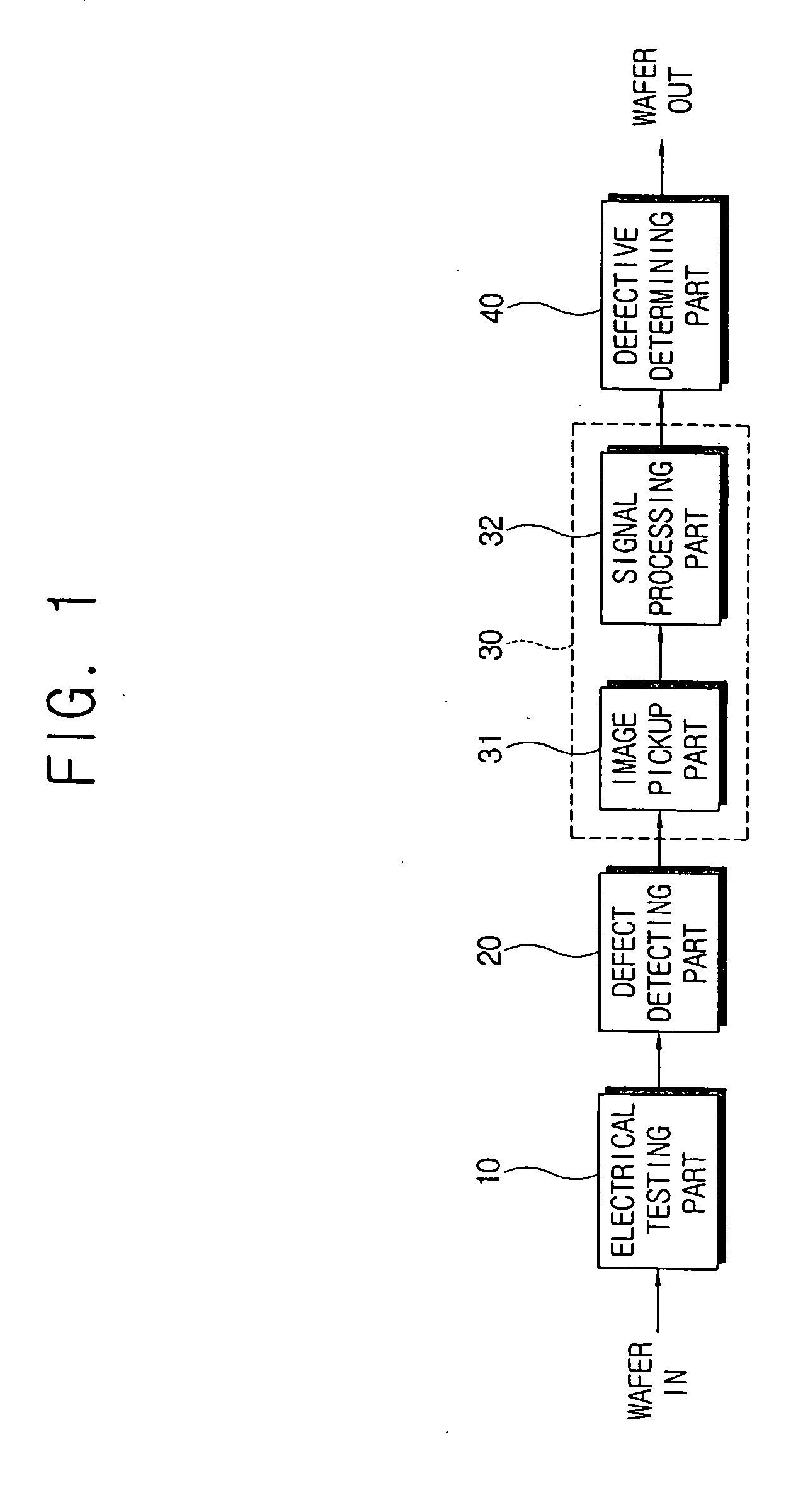

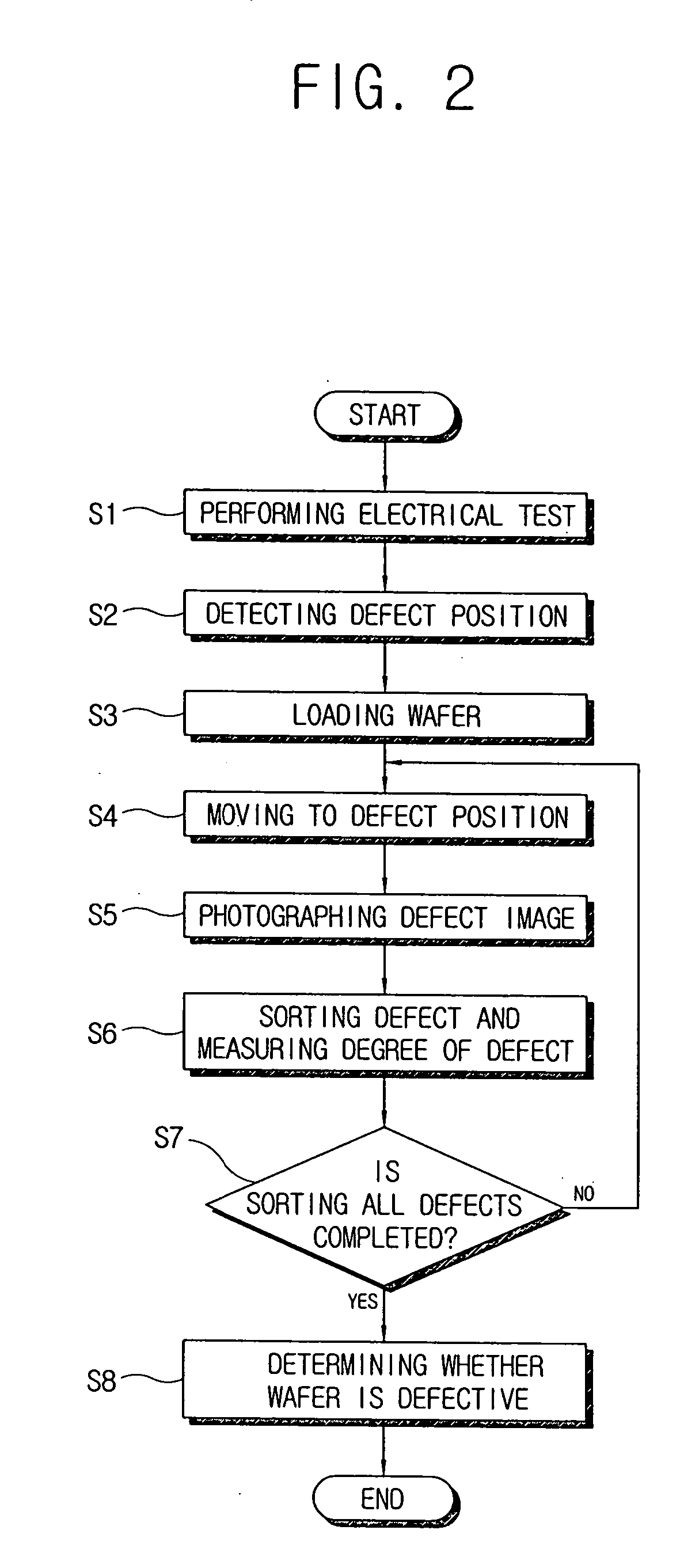

Wafer inspection system and method thereof

ActiveUS20050282299A1Cancel noiseDifference in brightnessImage enhancementImage analysisElectrical testing

A wafer inspection system includes an electrical testing part to control a probe to be in contact with a pad of a wafer to perform a predetermined electrical test, a defect detecting part to detect a defect in the wafer passing through the electrical test, a defect sorting part to sort the defect detected in the defect detecting part by an in-line method, and a defective determining part to determine whether the wafer is a defective according to a sorting result of the defect sorting part. The wafer inspection system and a method thereof can determine the kinds of the defect in the wafer during a fabricating procedure, so that it is possible to instantly and correctly determine whether the die on the wafer is a defective.

Owner:SAMSUNG ELECTRONICS CO LTD

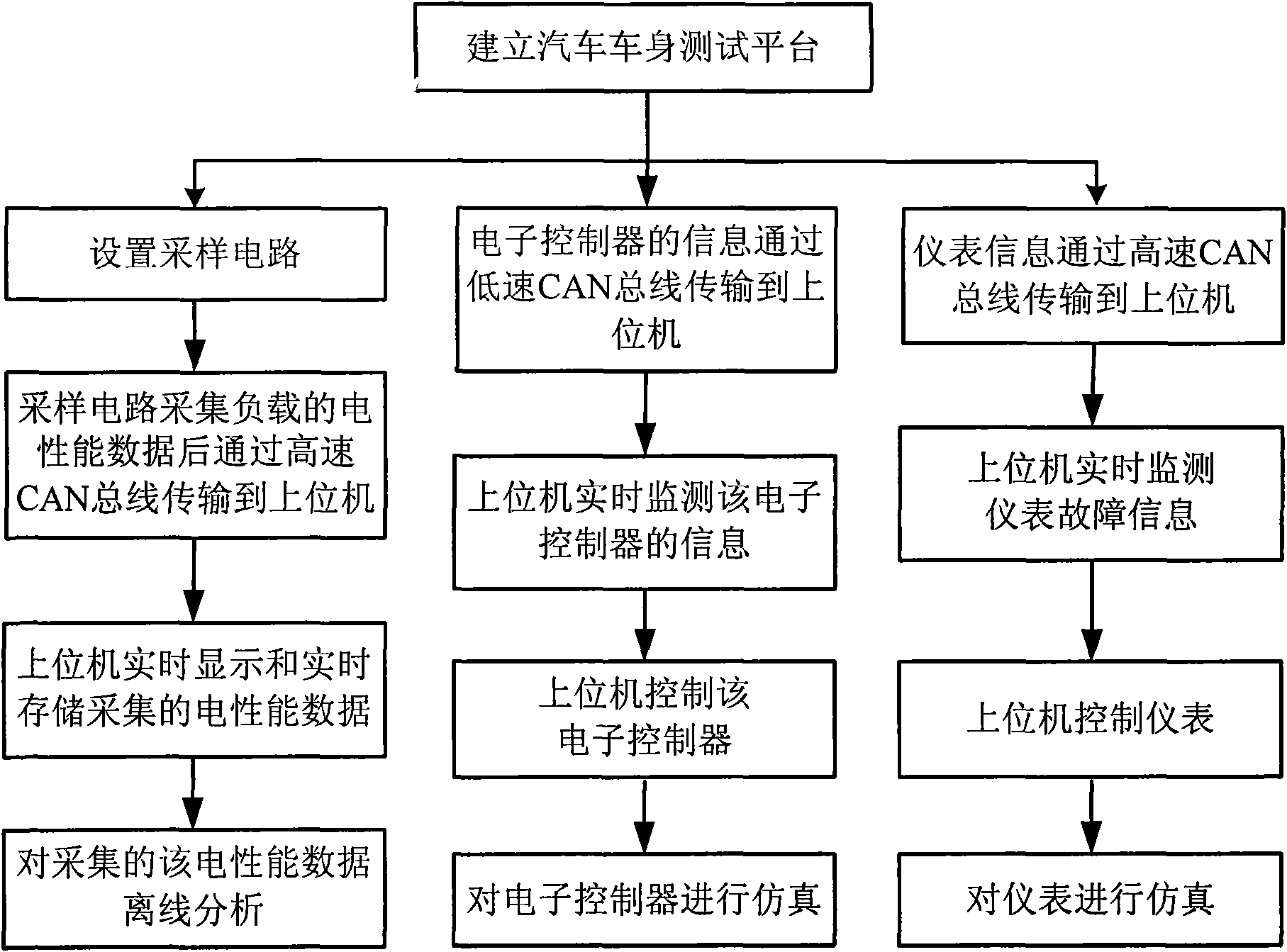

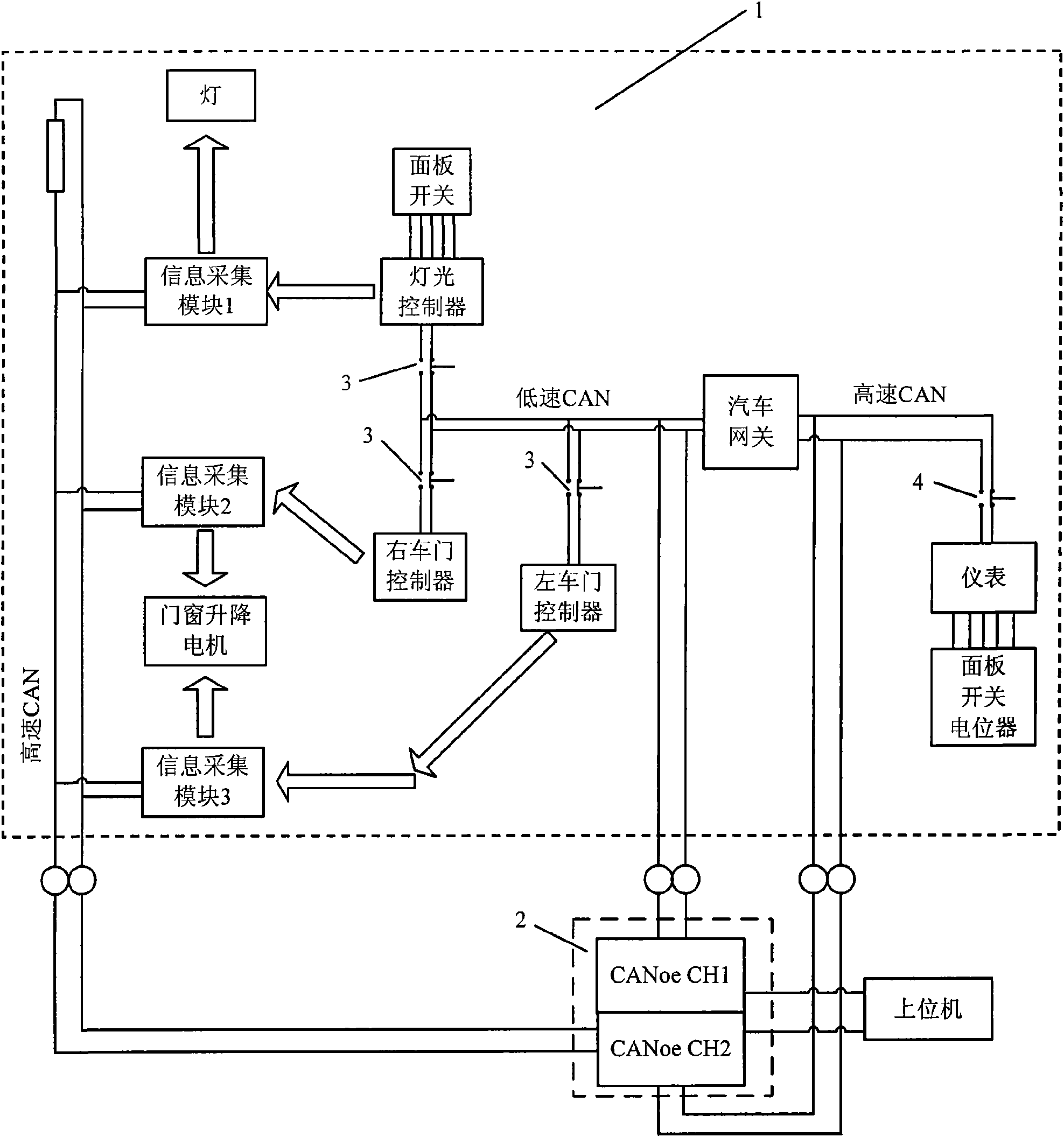

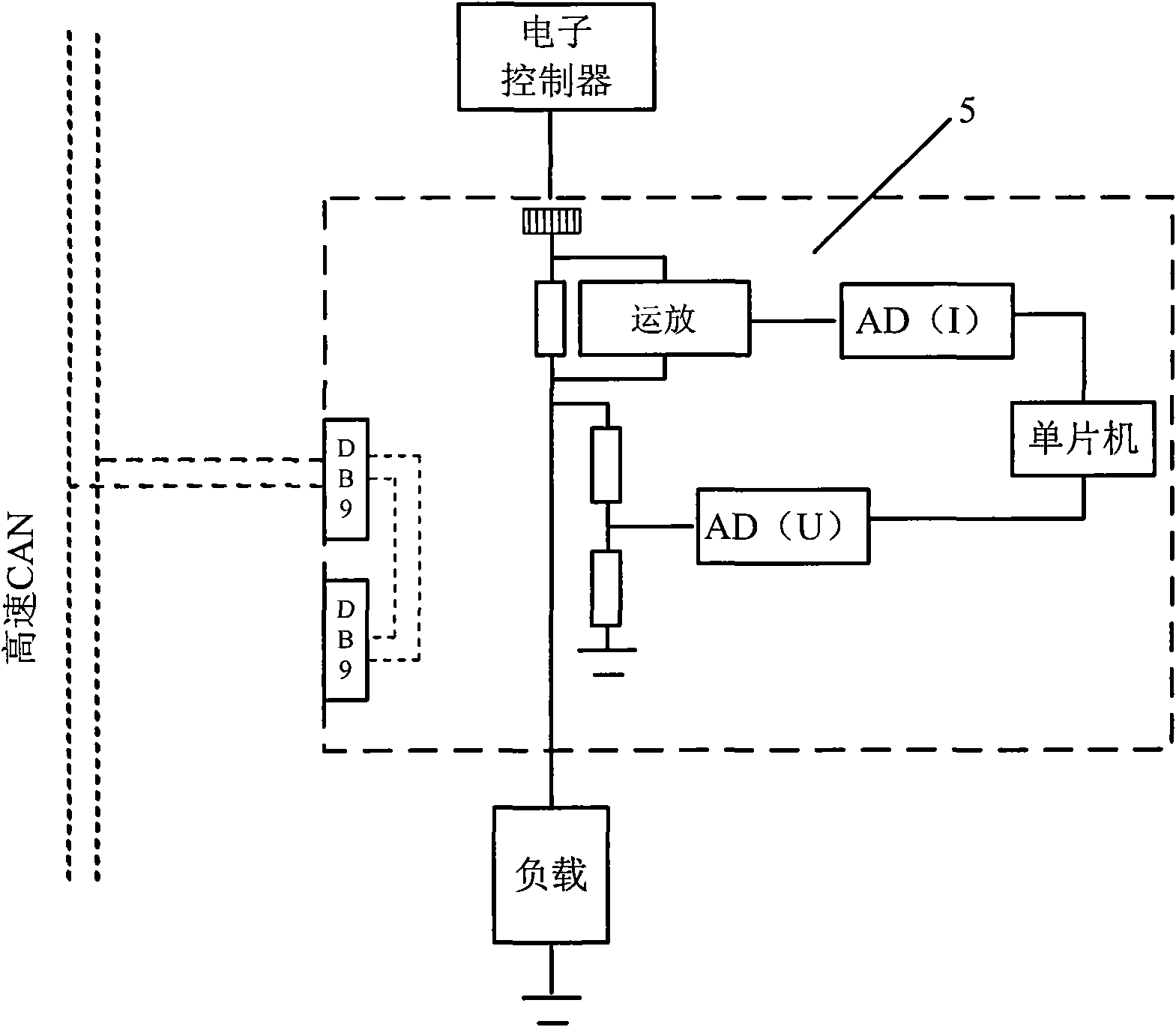

Electrical test system and method of automotive body based on CAN bus

ActiveCN101639698AShorten development timeImprove development efficiencyElectric testing/monitoringTime informationTest efficiency

The invention relates to an electrical test system and a method of an automotive body based on a CAN bus, the method establishes a test platform of the automotive body with one or a plurality of electronic controllers and loads and is provided with a sampling circuit between each electronic controller and the corresponding load, the sampling circuits collect electrical performance data of the loads, then the electrical performance data is transmitted to an upper computer located by a CANoe card through the high-speed CAN bus for carrying out electrical function test, and information of the electronic controllers is transmitted to the upper computer located by the CANoe card through a low-speed CAN bus for carrying out real-time information monitoring. The method is convenient to operation,can complete signal collection and realize the real-time information monitoring of the electronic controllers and has the advantages of improving test efficiency, shortening ECU development time andreducing development cost.

Owner:EON CHINA (BEIJING) TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com