Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

48results about How to "Avoid Particle Contamination" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

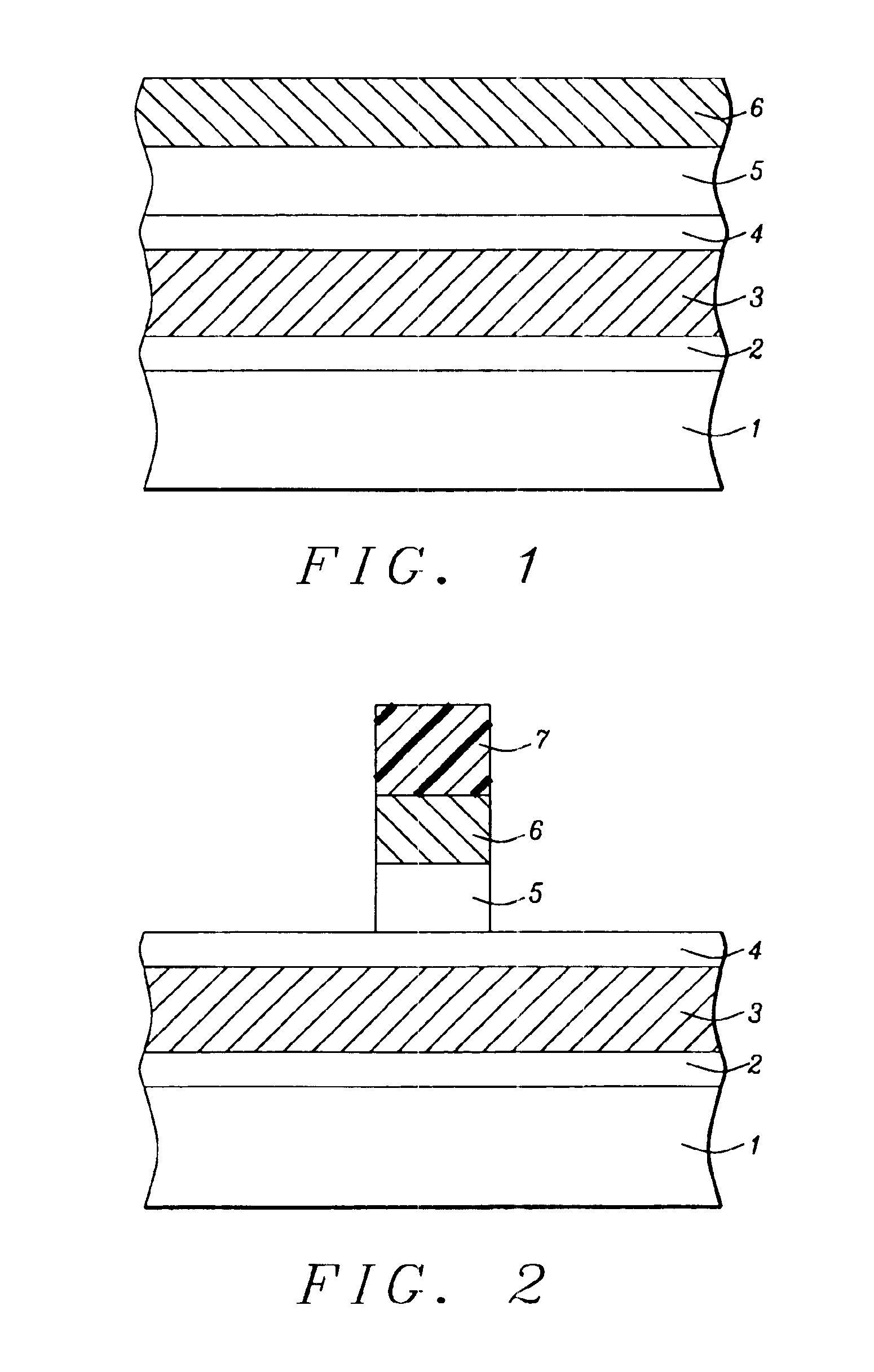

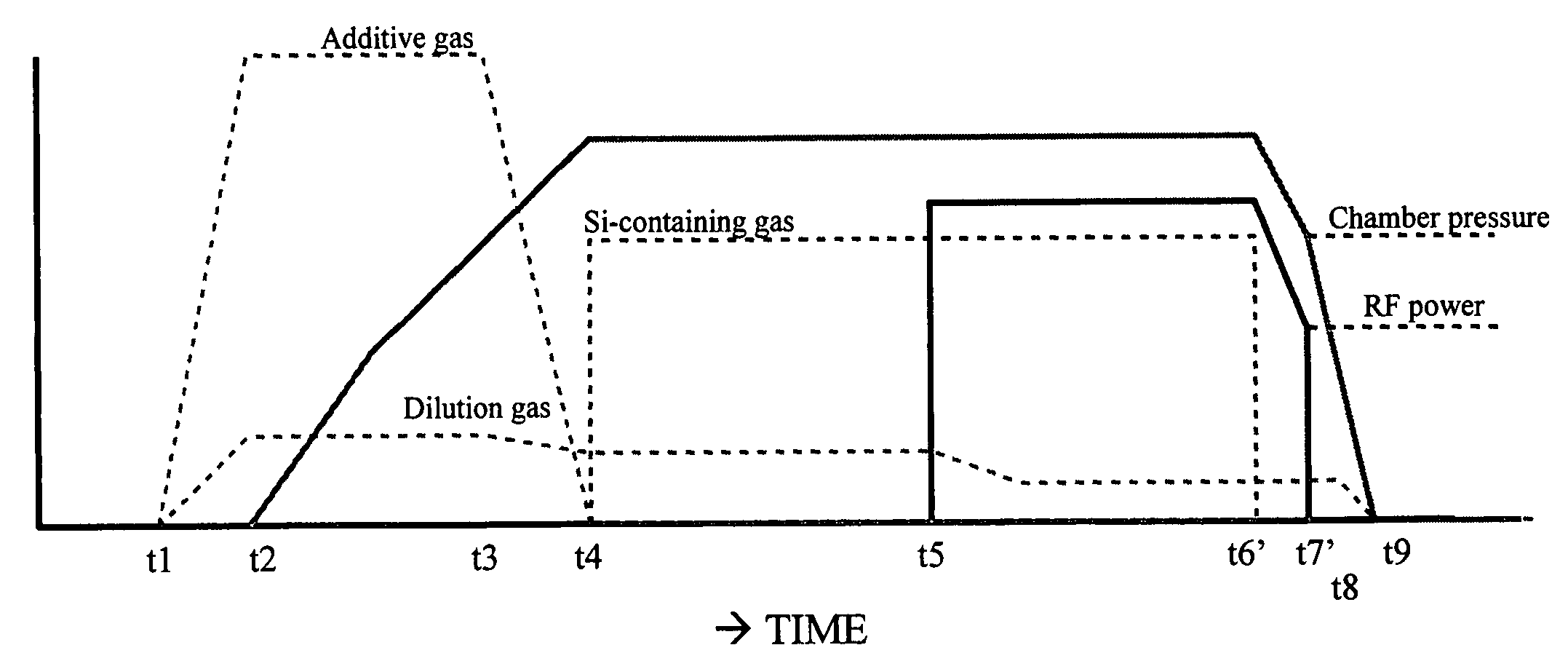

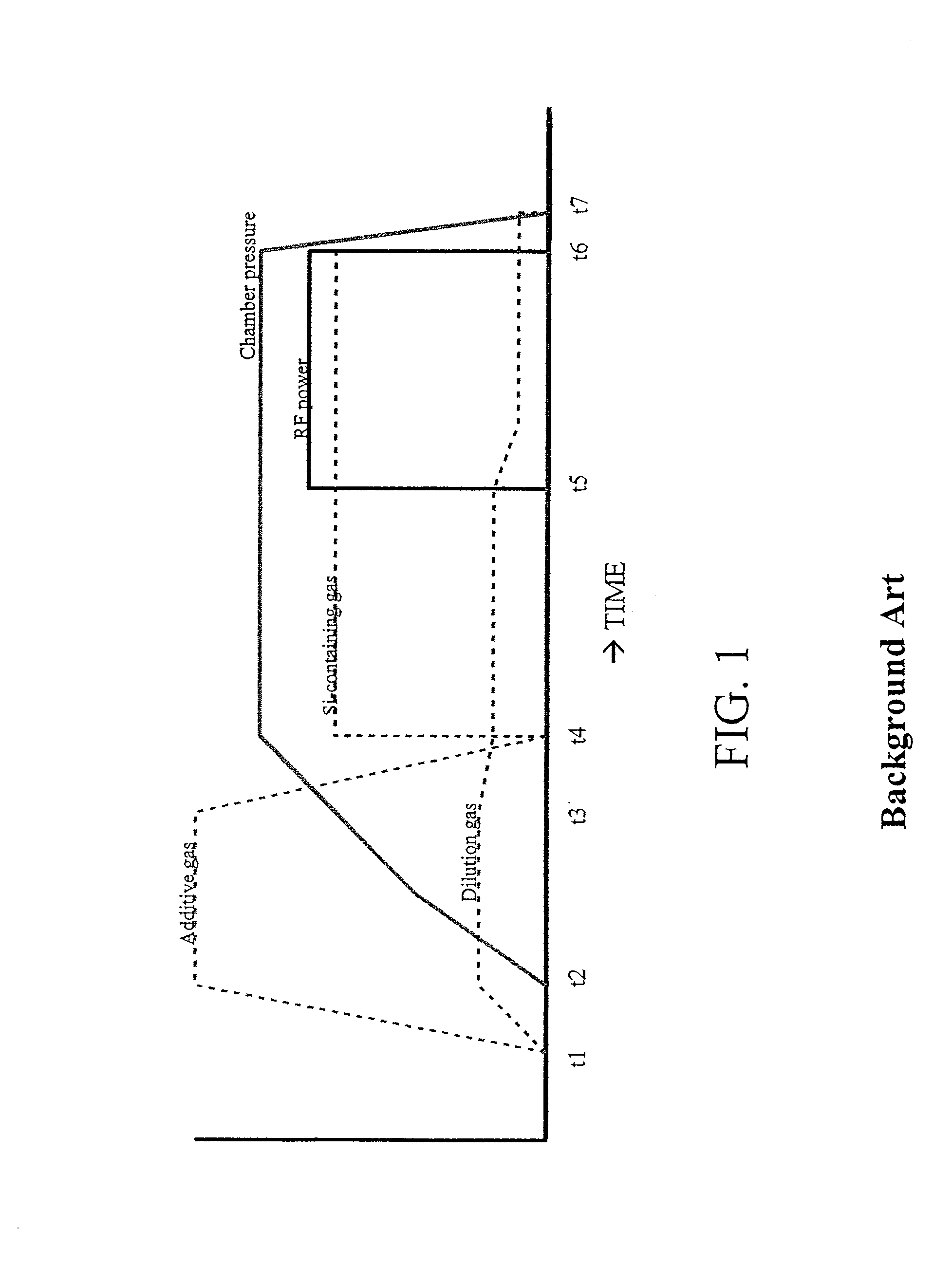

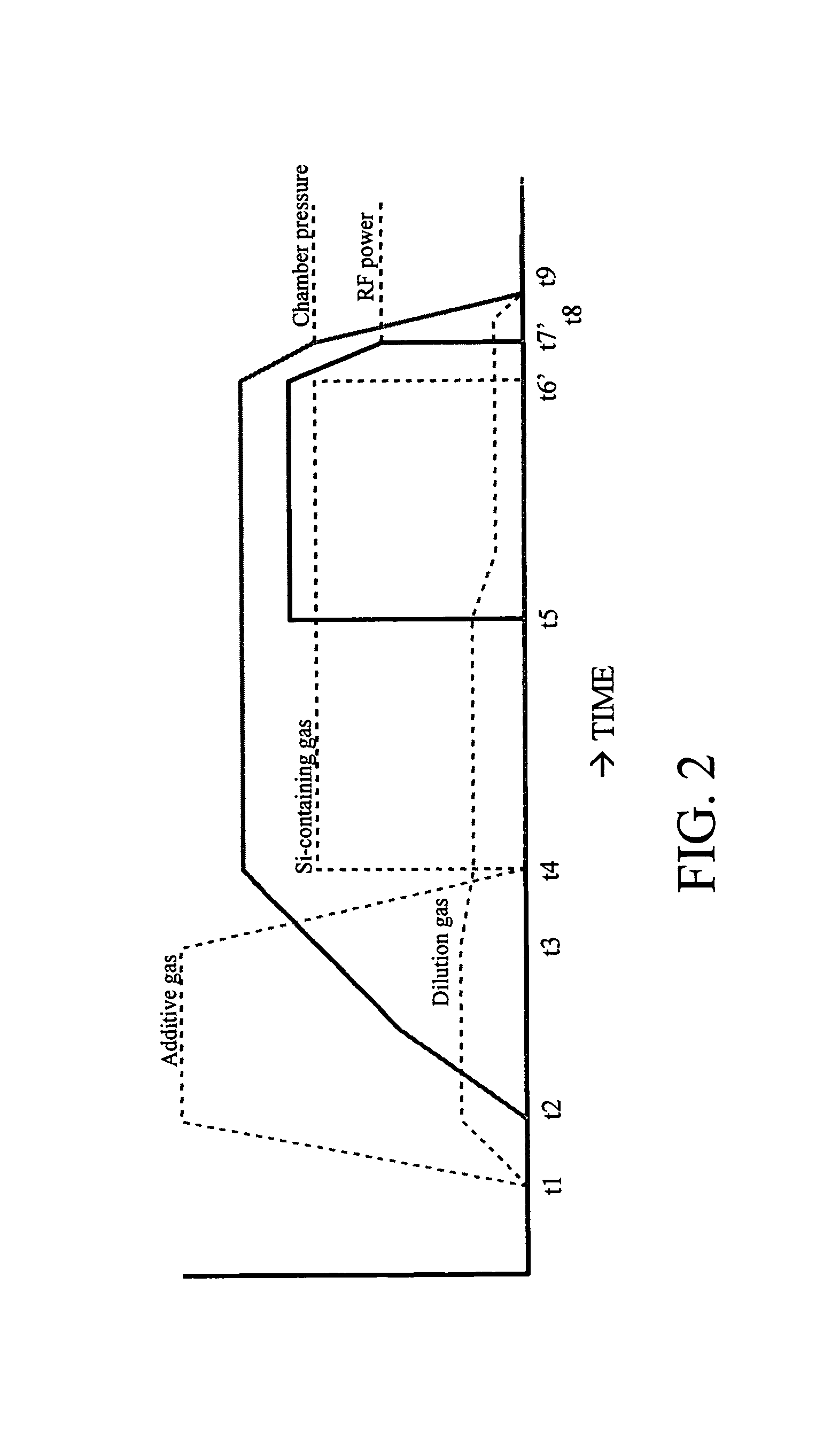

Method of forming thin film

ActiveUS20050048797A1Reduce plasma damageImprove adhesionSemiconductor/solid-state device manufacturingSolid state diffusion coatingRadio frequencyMechanics

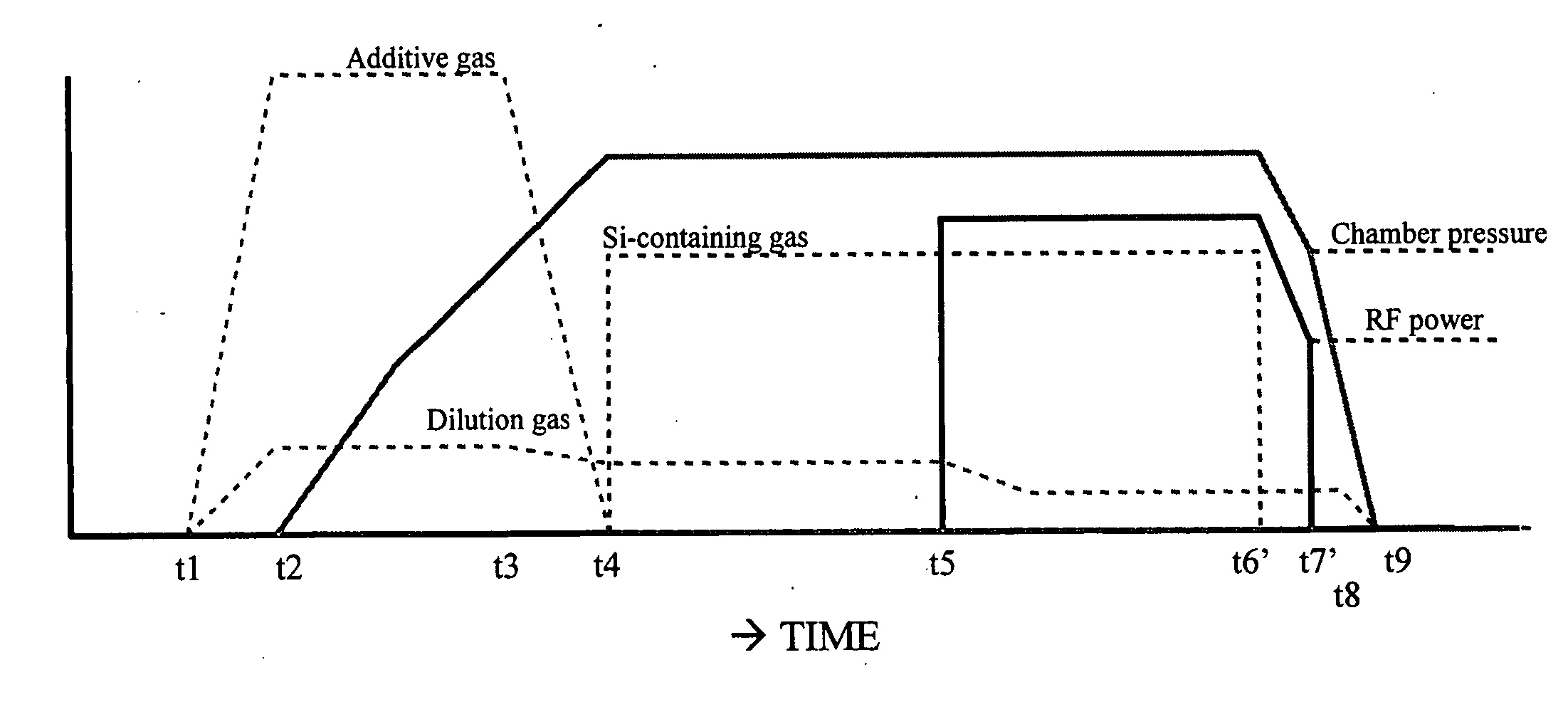

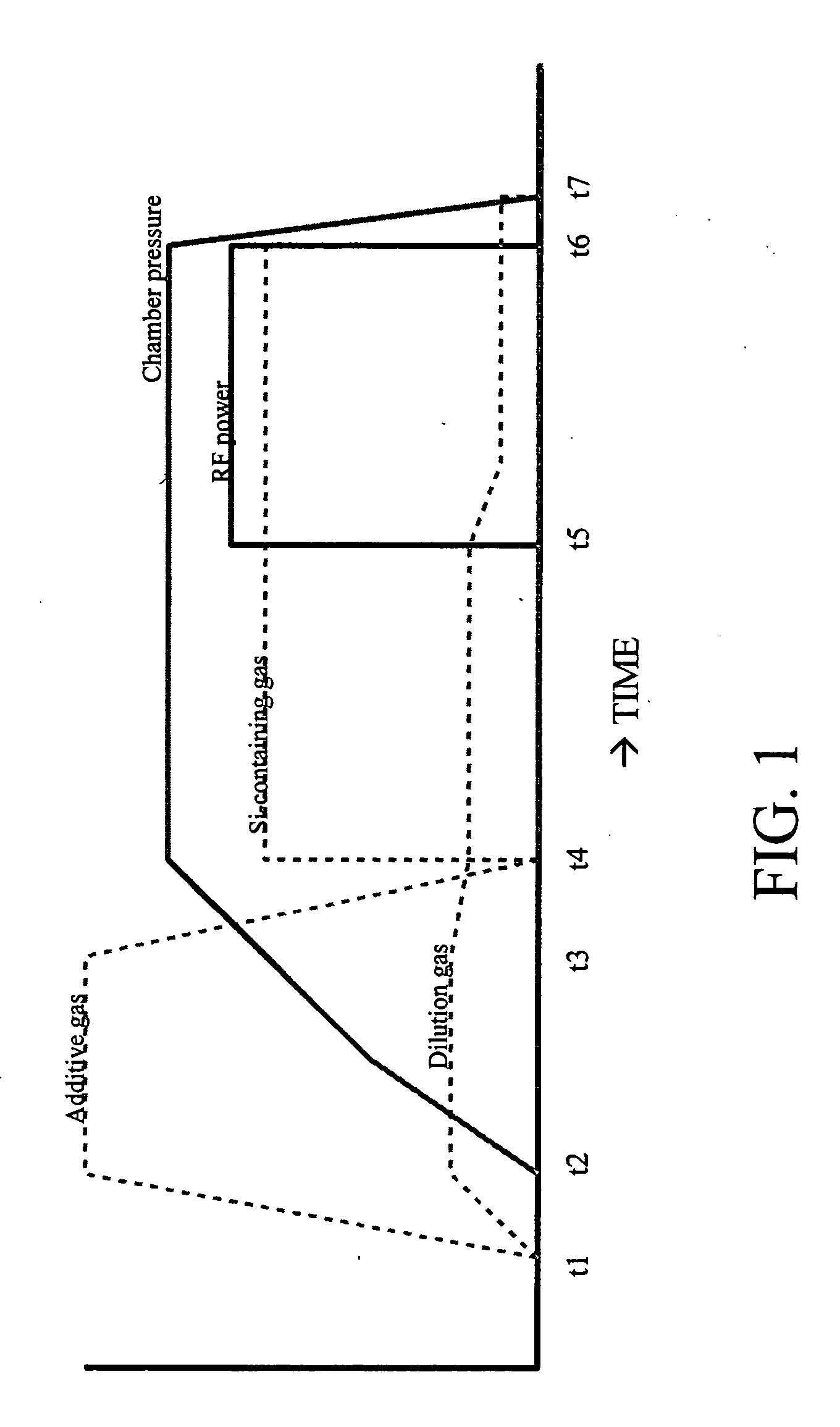

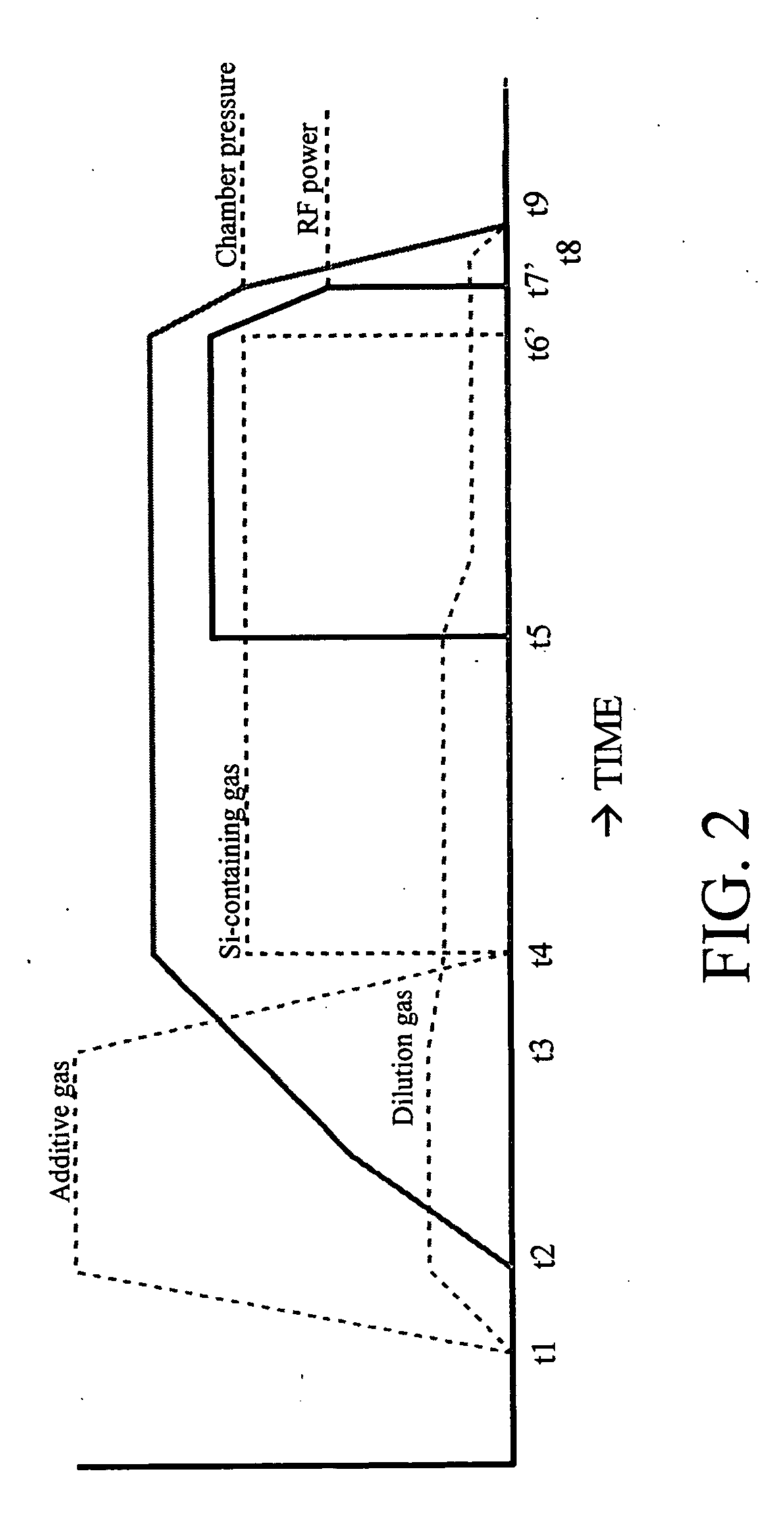

A method for forming a thin film includes: supplying an additive gas, a dilution gas, and a silicon-containing source gas into a reaction chamber wherein a substrate is placed; forming a thin film on the substrate by plasma CVD under a given pressure with a given intensity of radio-frequency (RF) power from a first point in time to a second point in time; at the second point in time, stopping the supply of the silicon-containing source gas; and at the second point in time, beginning reducing but not stopping the RF power, and beginning reducing the pressure, wherein the reduction of the RF power and the reduction of the pressure are synchronized up to a third point in time.

Owner:ASM JAPAN

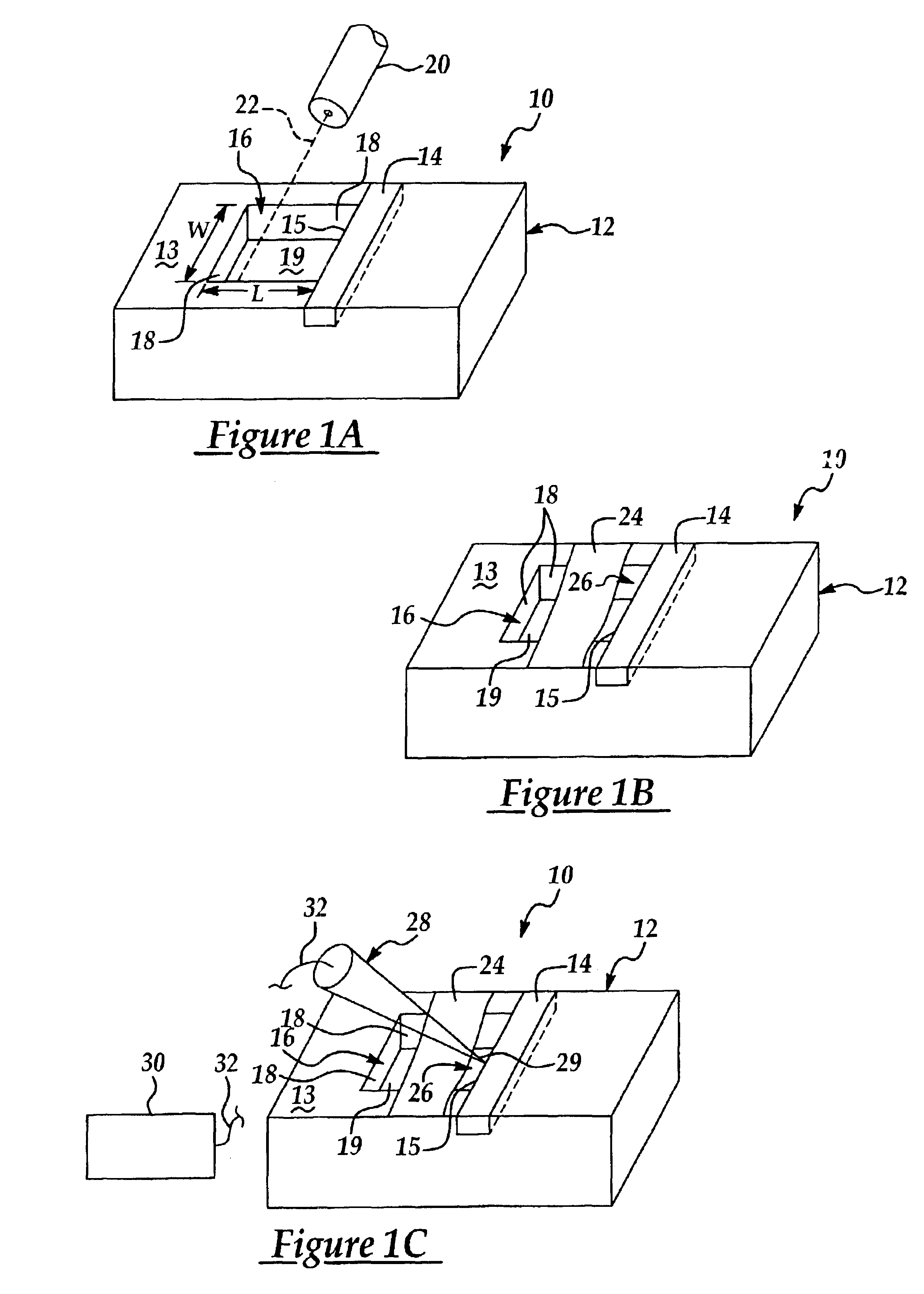

Probing of device elements

InactiveUS6902941B2Reduce contact resistanceAvoid Particle ContaminationSemiconductor/solid-state device testing/measurementElectronic circuit testingDielectricElectricity

A new and improved method for the probing of integrated circuits (ICs) and is particularly suitable for probing various elements of an IC for failure analysis or other electrical testing and / or measurement of the IC. The method includes providing a probe access trench in the IMD (intermetal dielectric) or other substrate adjacent to the circuit element to be tested and then providing direct electrical contact between the test probe and the sidewall of the element through the trench, during the testing process. Such direct electrical contact between the test probe and the sidewall of the element prevents excessively high contact resistance which may otherwise occur in the use of a probing pad between the test probe and the element.

Owner:TAIWAN SEMICON MFG CO LTD

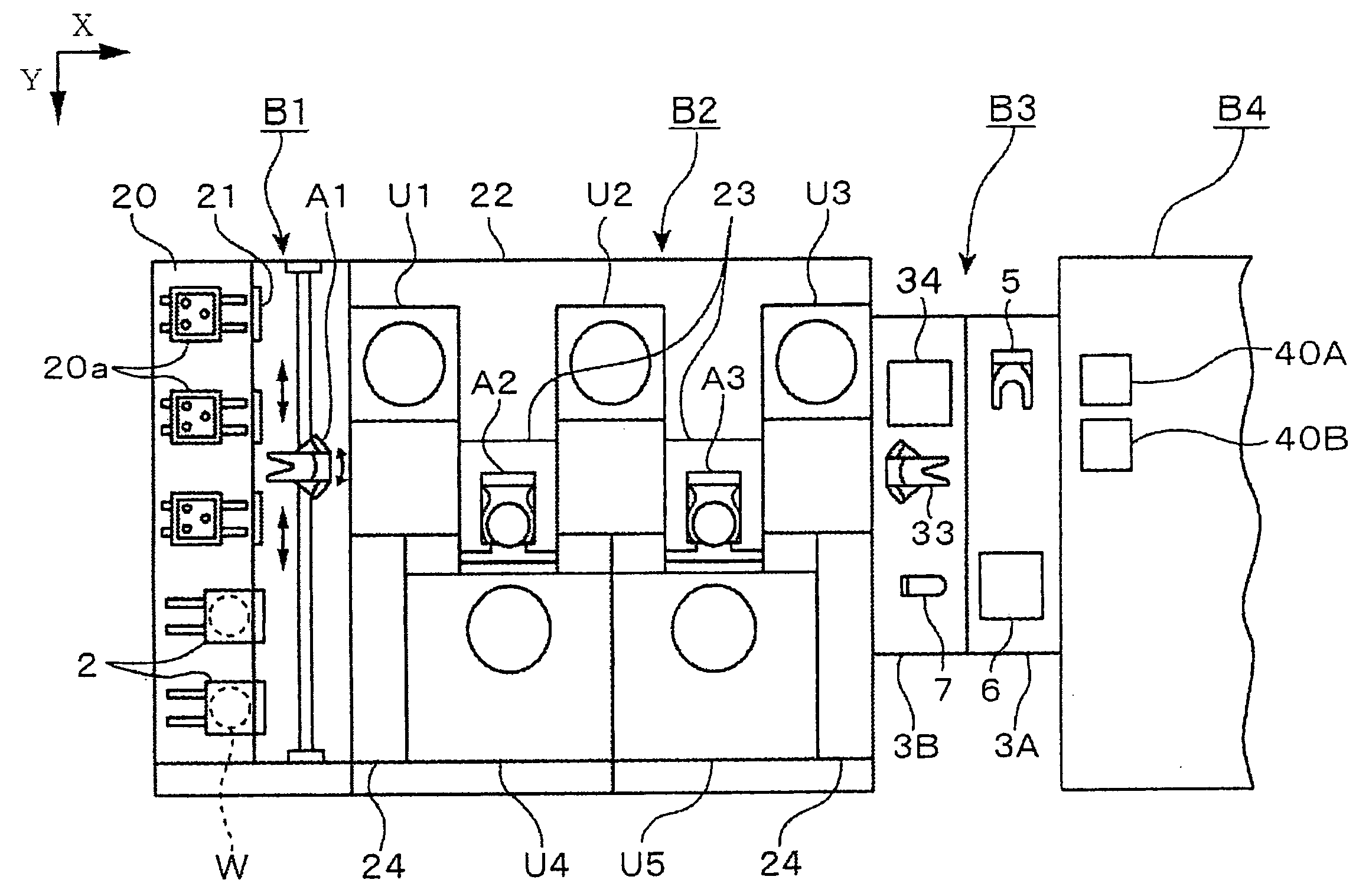

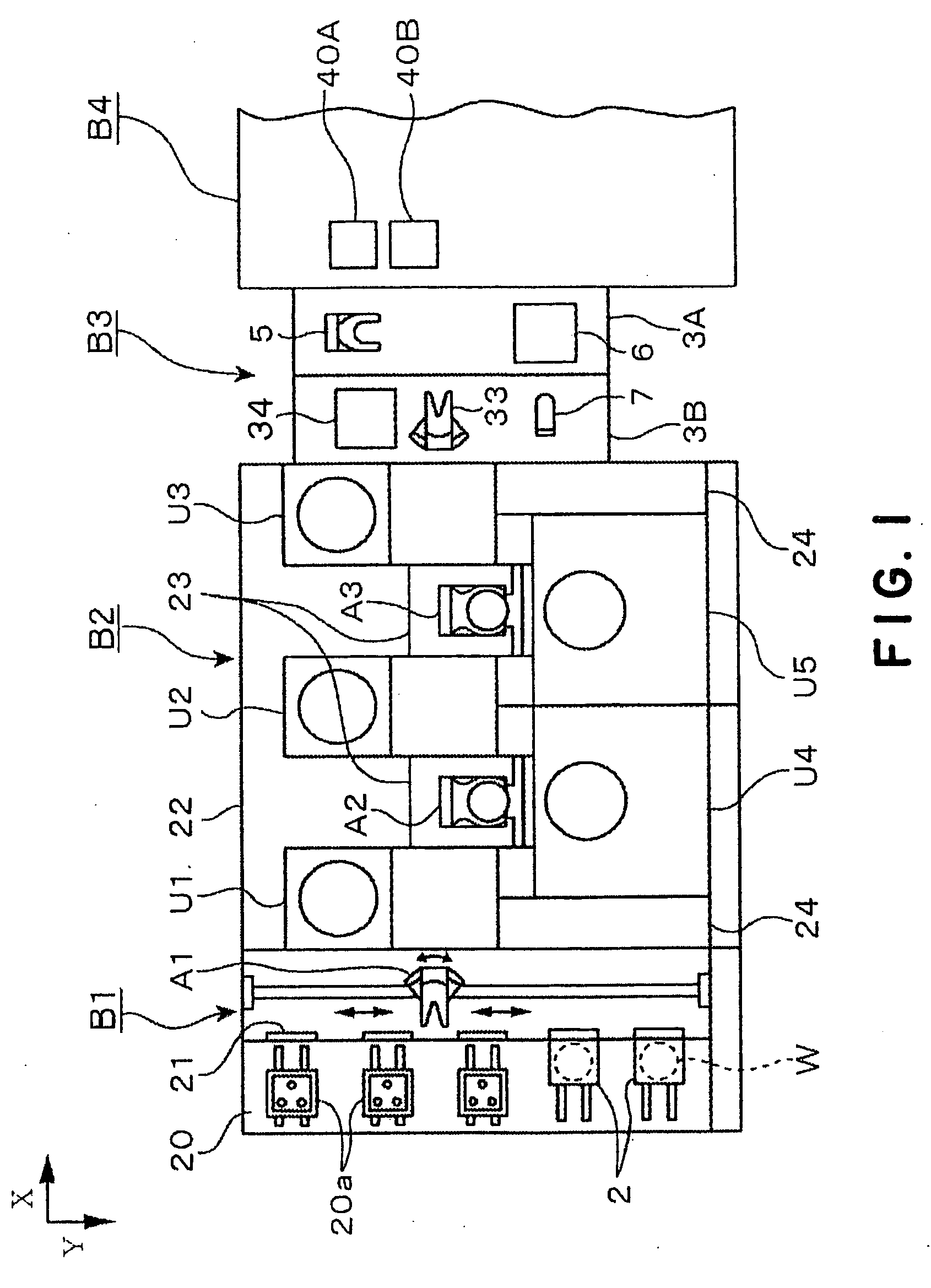

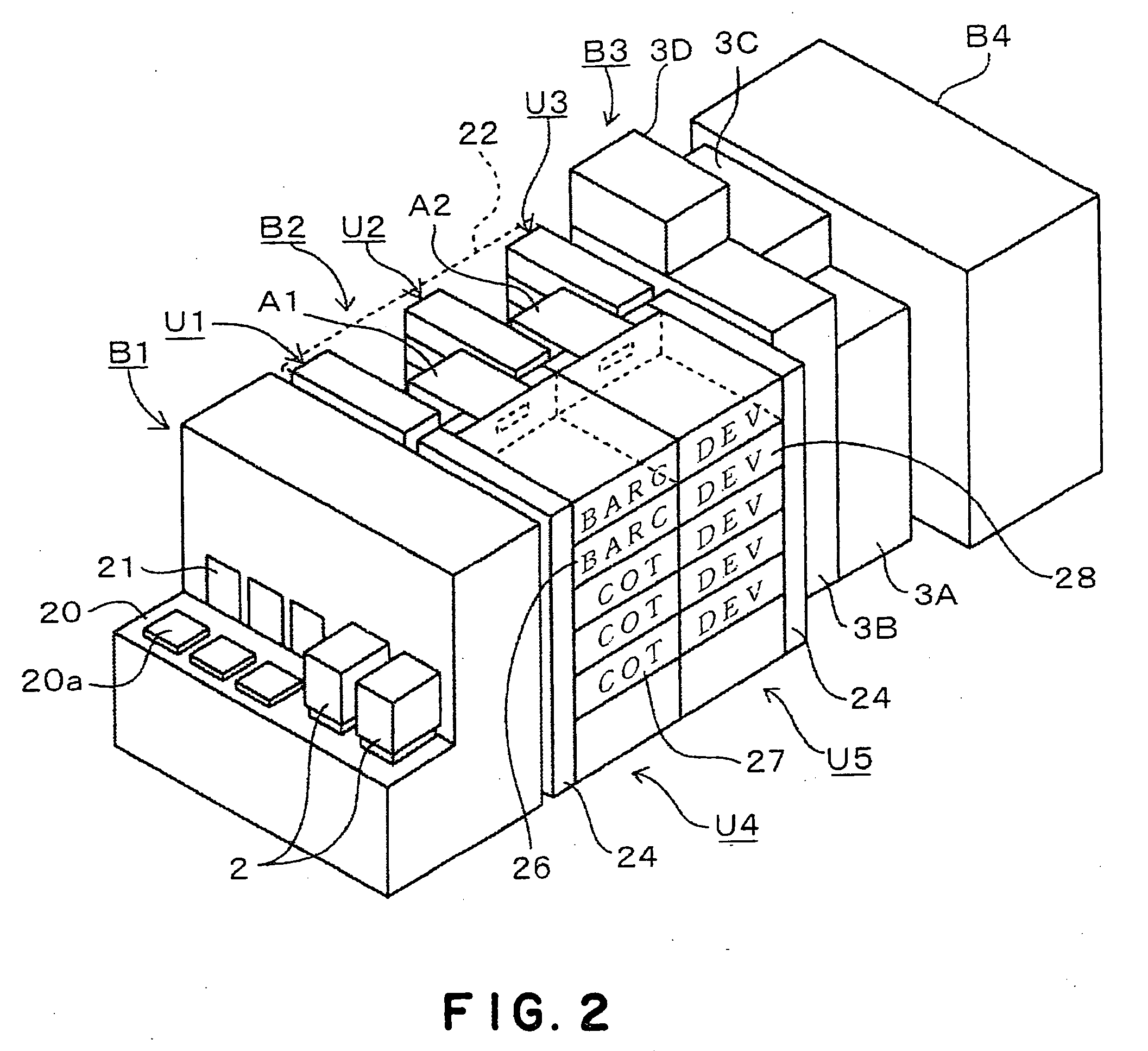

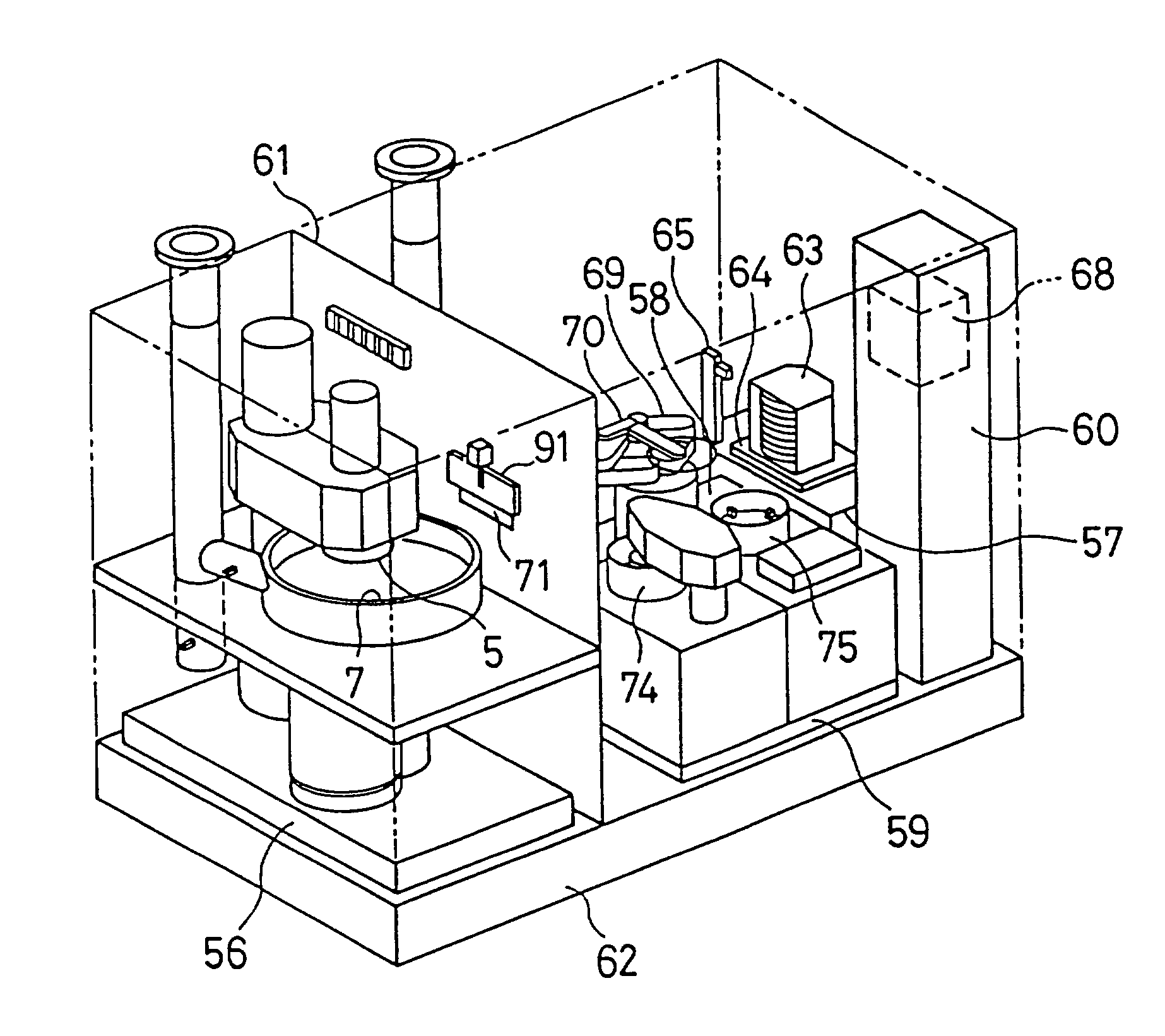

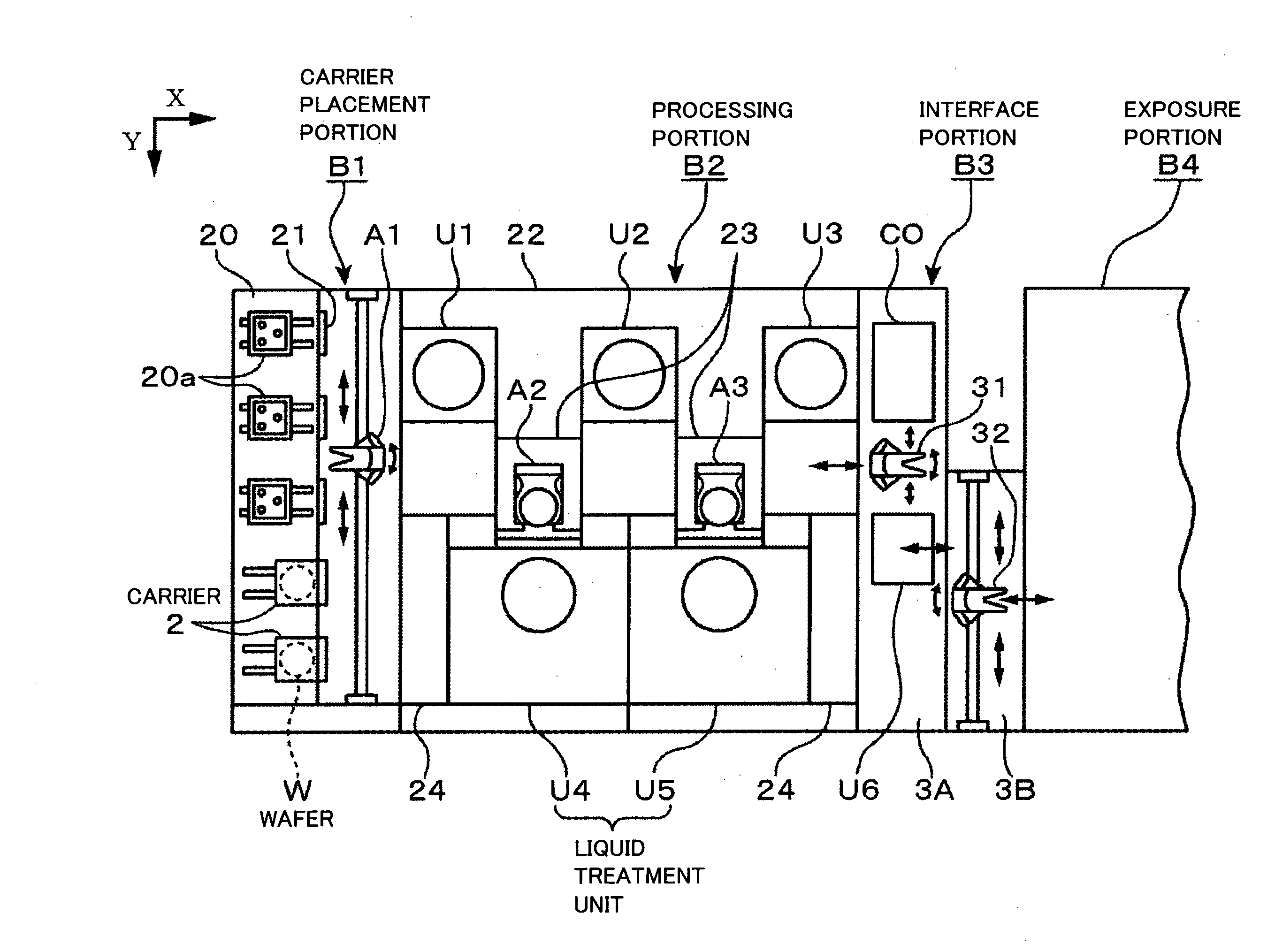

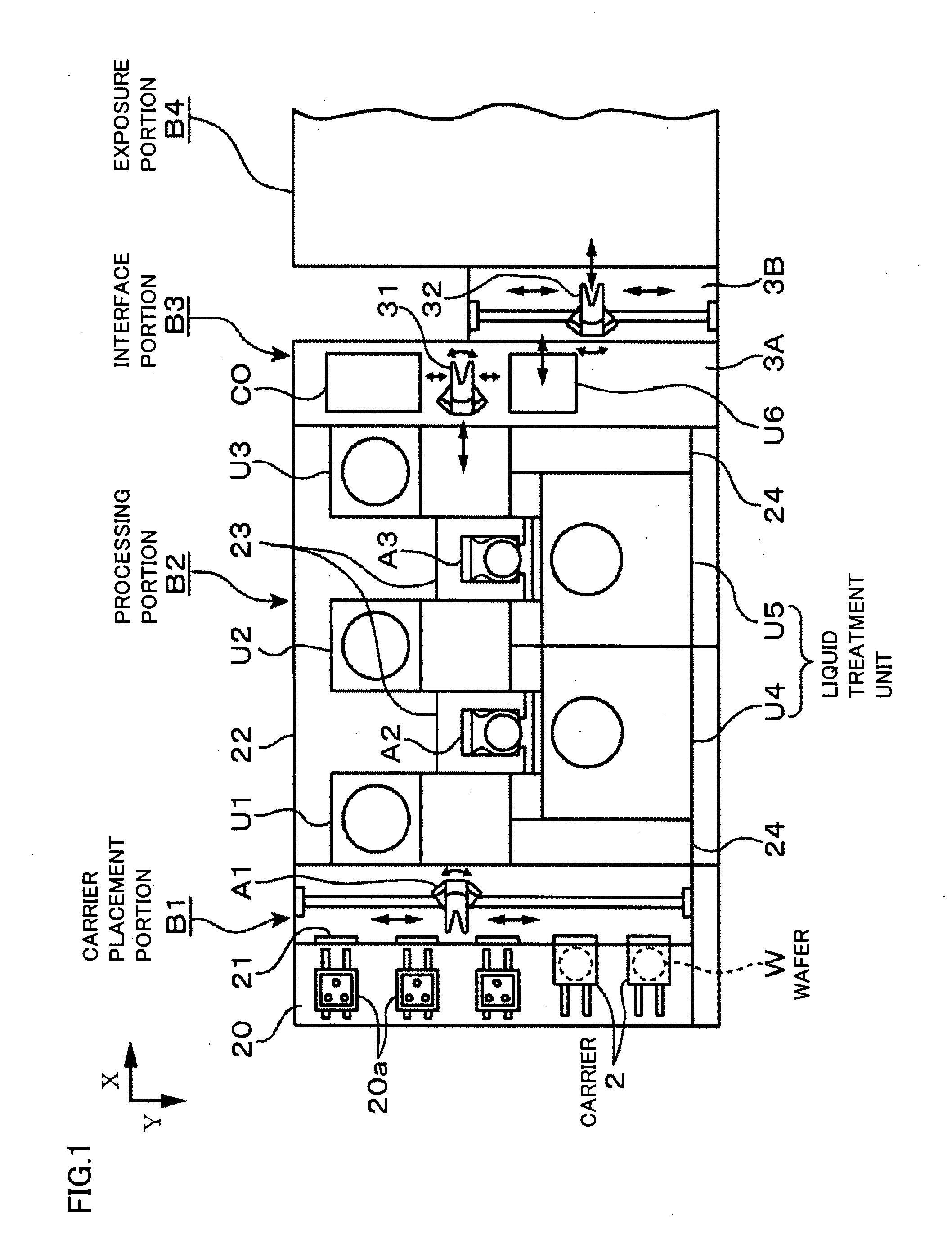

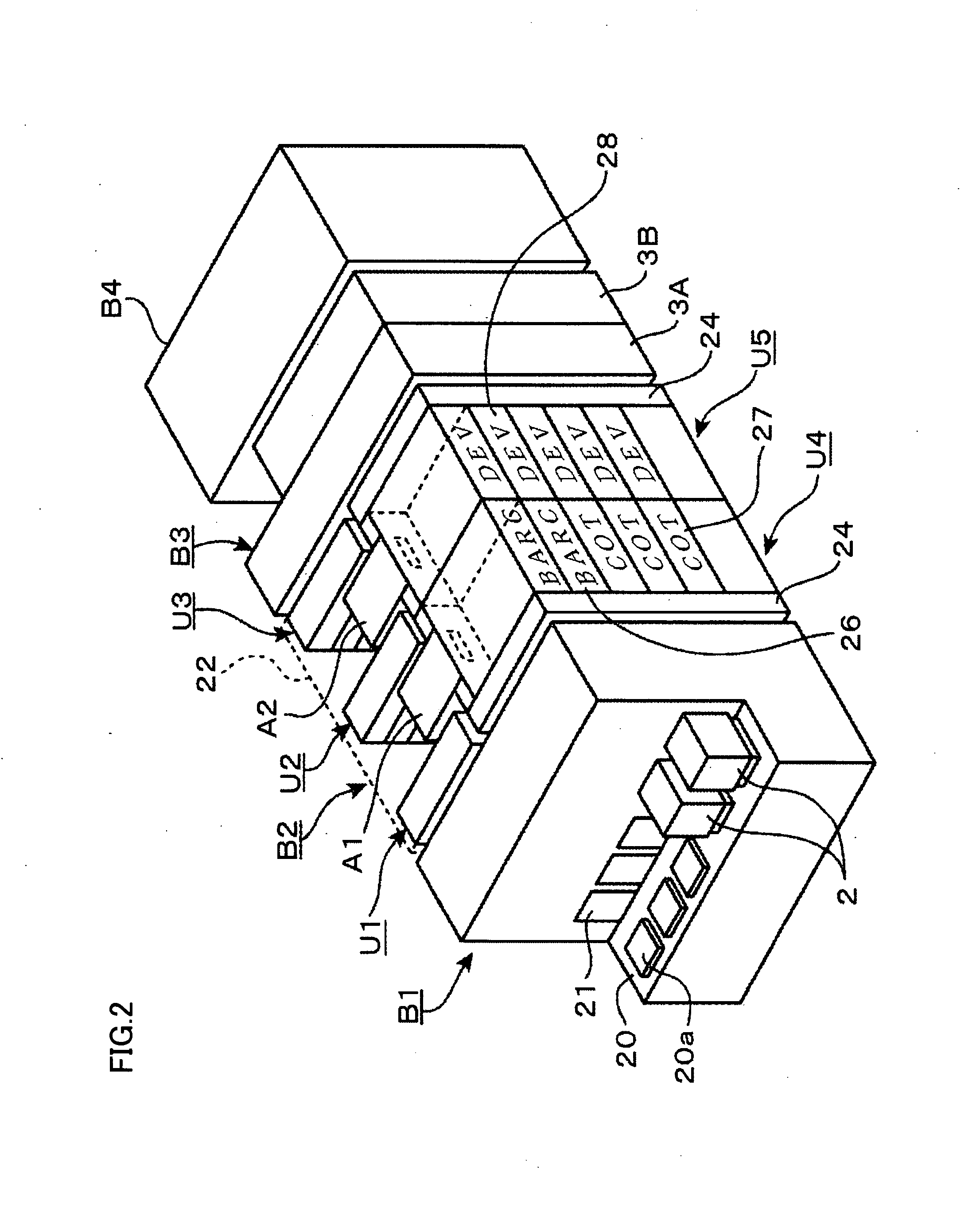

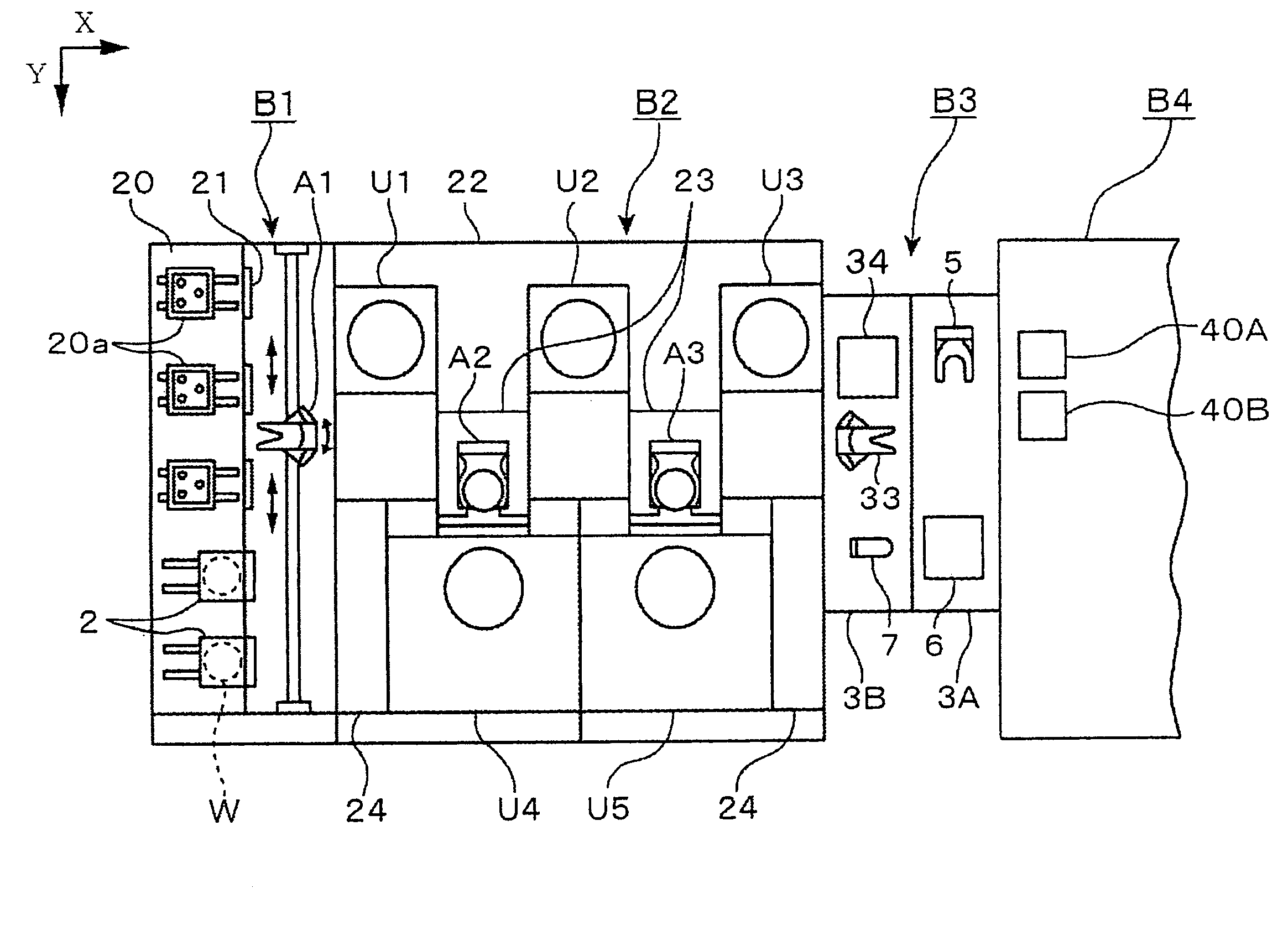

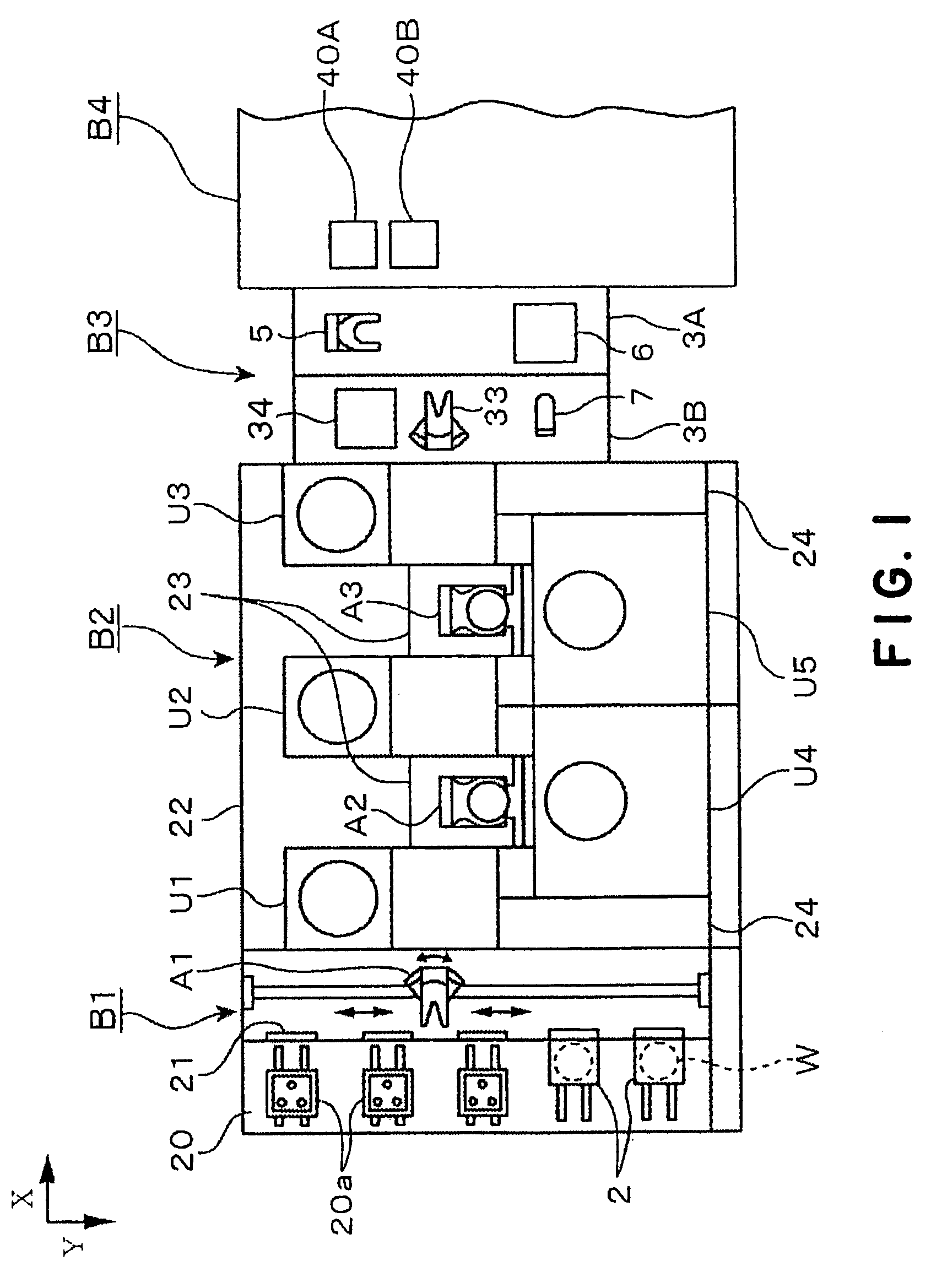

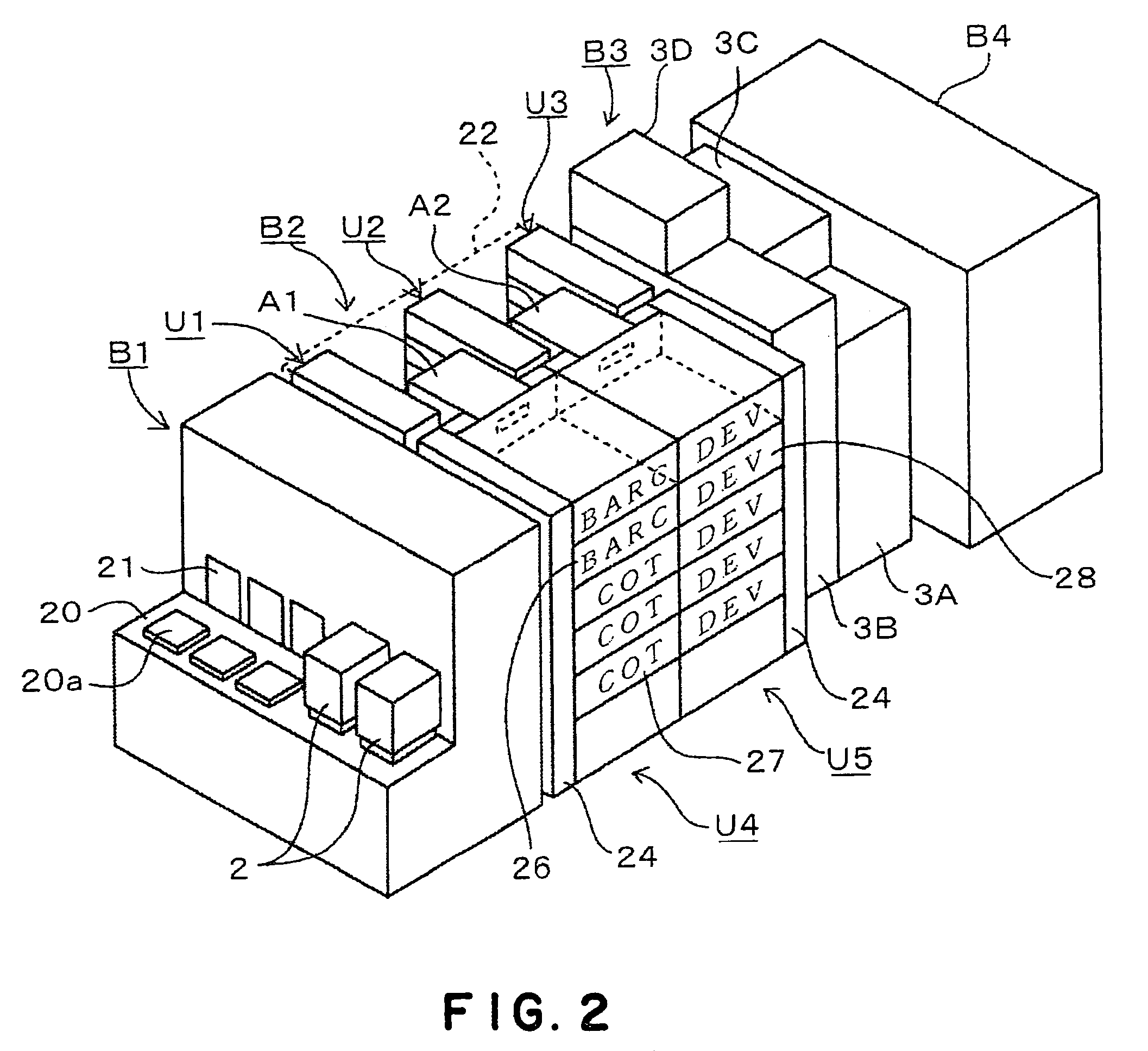

Coating and developing system and coating and developing method

ActiveUS20060177586A1Accurate resist patternAvoid obstructionLiquid processingDoors/windowsResistEngineering

A coating and developing system is capable of preventing the contamination of a substrate with particles while the same coats a surface of a substrate with a resist film and develops the resist film after the substrate has been processed by immersion exposure. The coating and developing system includes: a processing block including coating units for forming a resist film on a surface of a substrate and developing units for processing the resist film formed on the substrate with a developer, and an interface block connected to the processing block and an exposure system for carrying out an immersion exposure process. The interface block includes: substrate cleaning units for cleaning the substrate processed by the immersion exposure process, a first carrying mechanism and a second carrying mechanism. The first carrying mechanism carries a substrate processed by immersion exposure to the substrate cleaning unit. The second carrying mechanism carries the substrate cleaned by the substrate cleaning unit. Thus the contamination of the substrate with external particles can be prevented and hence the spread of contamination with particles over the processing units of the processing block and substrates processed by the processing units can be prevented.

Owner:TOKYO ELECTRON LTD

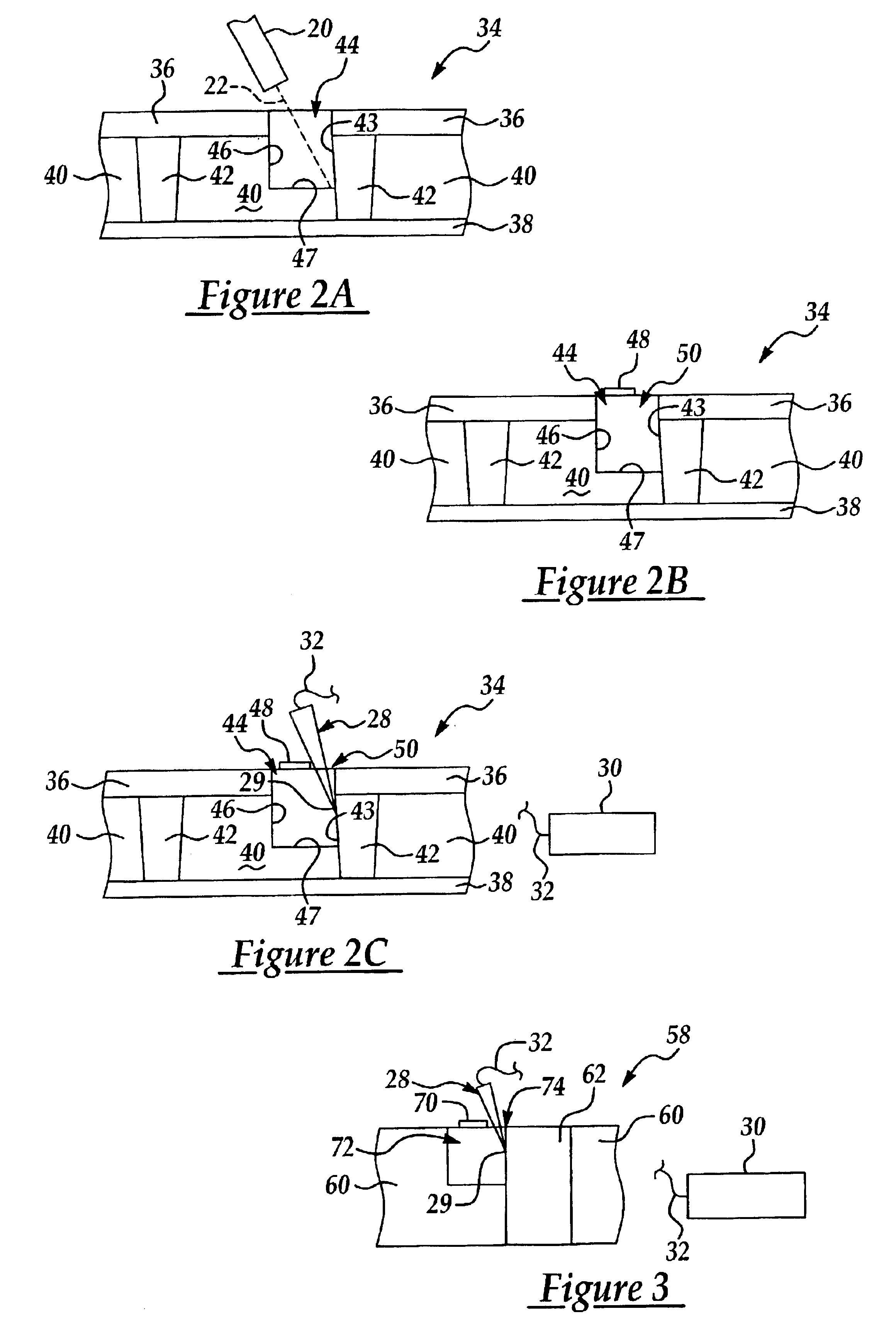

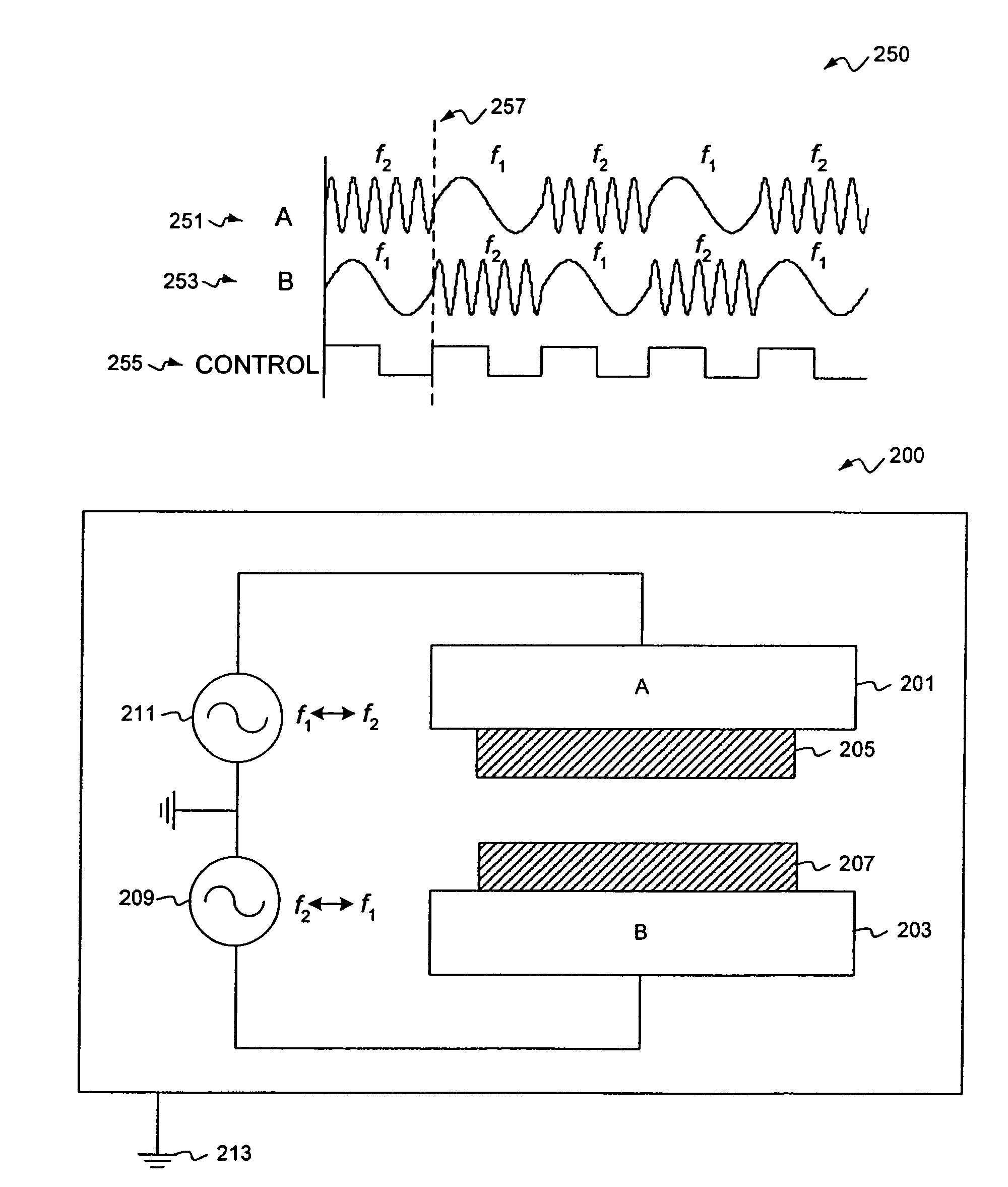

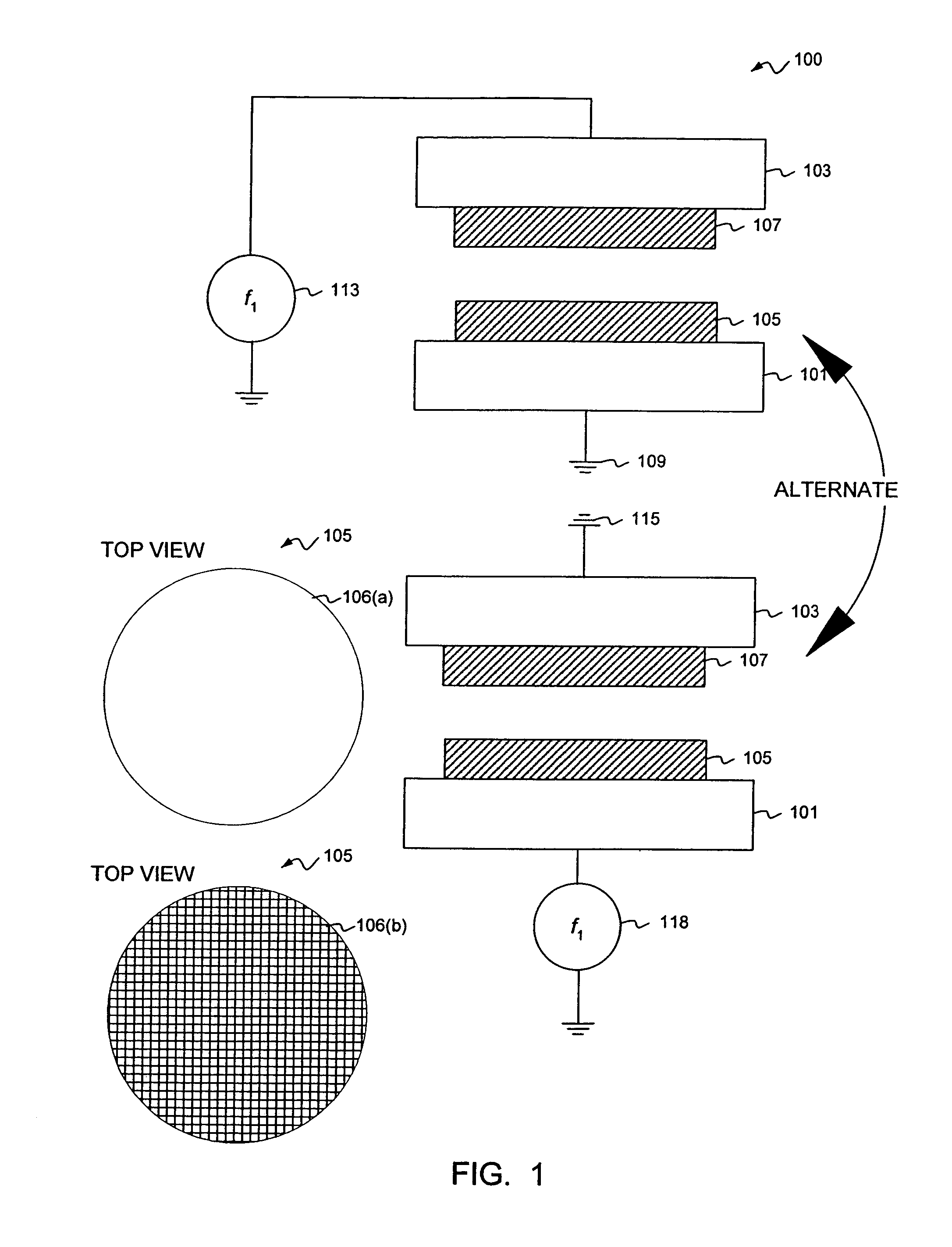

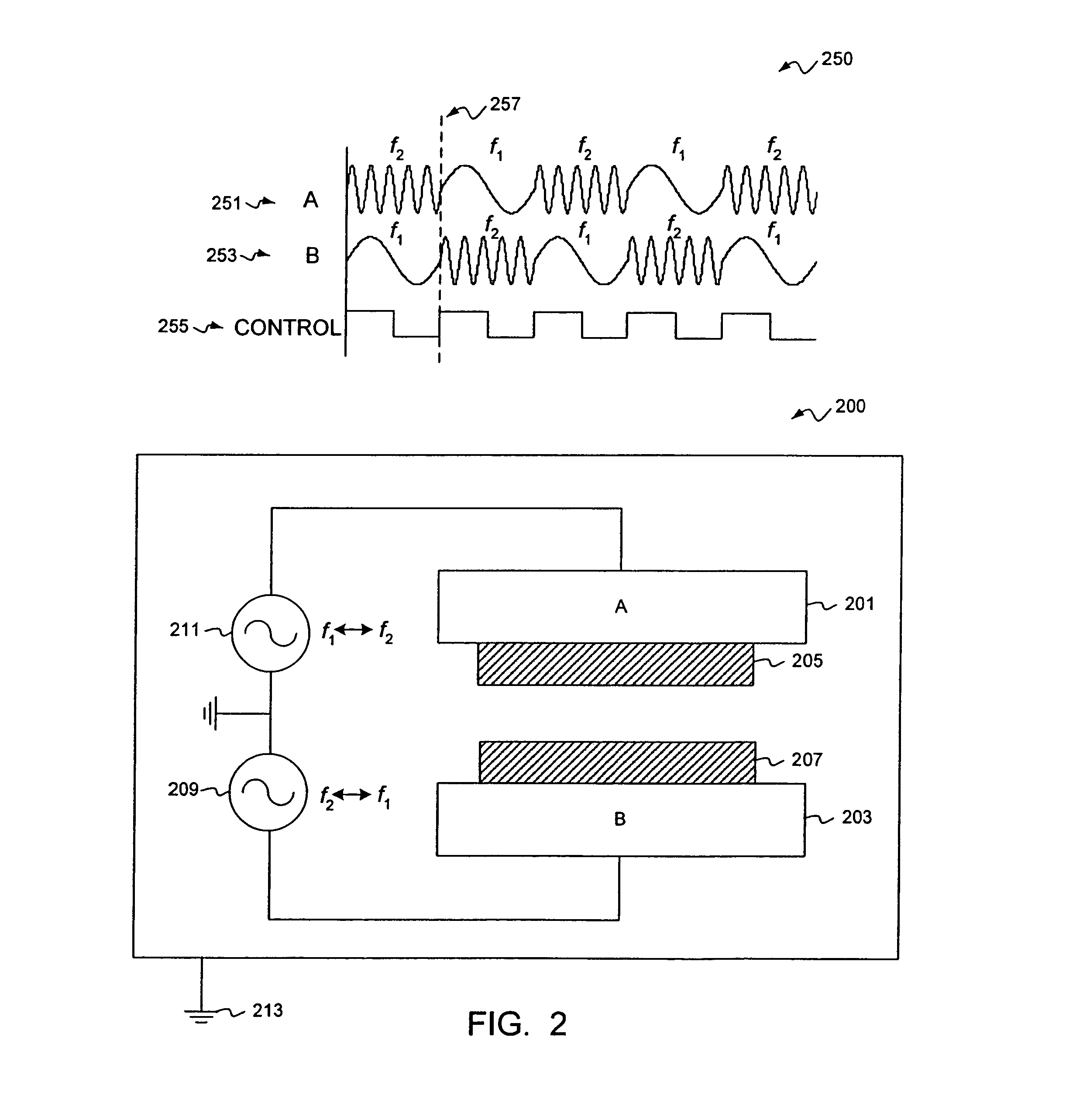

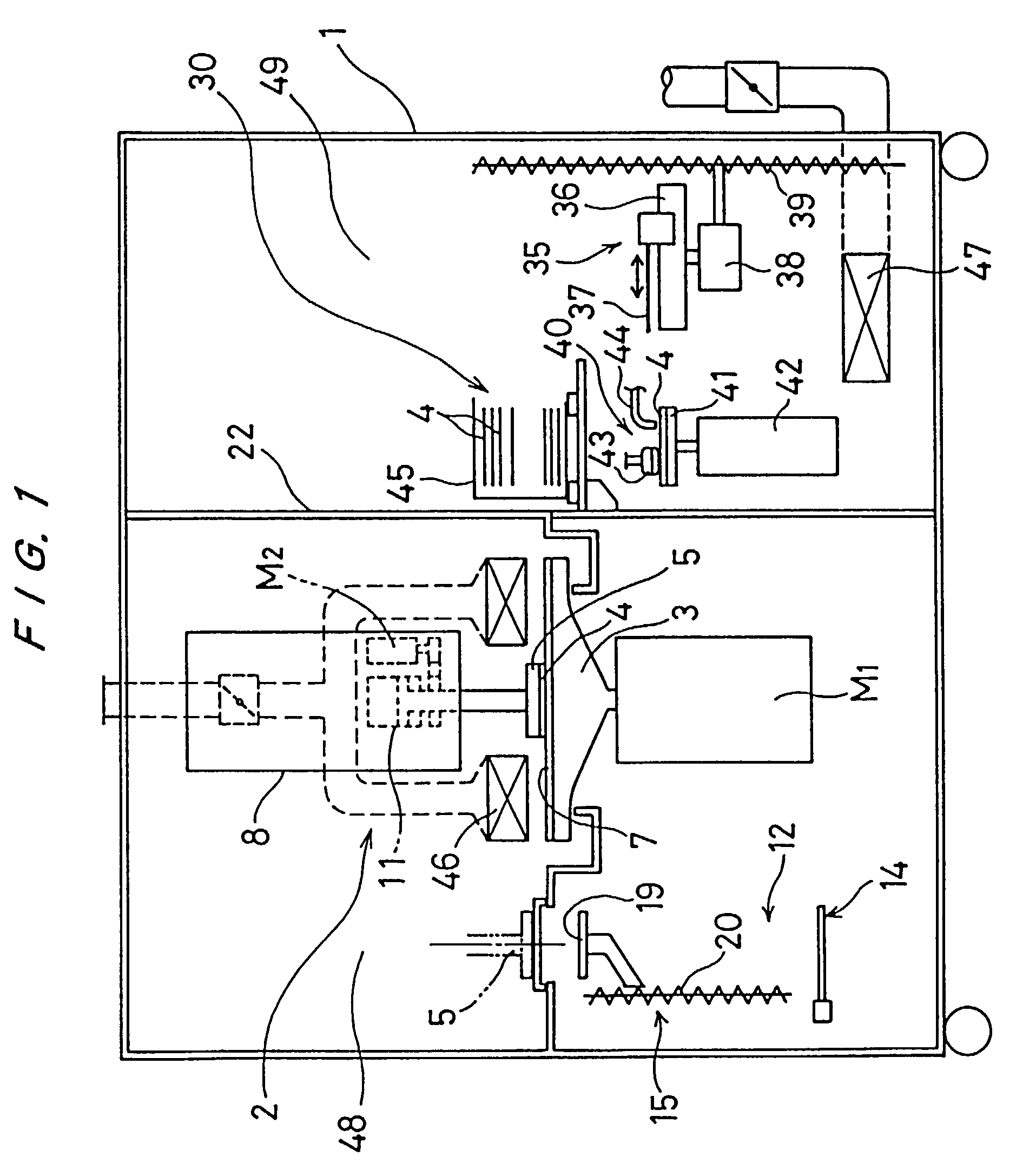

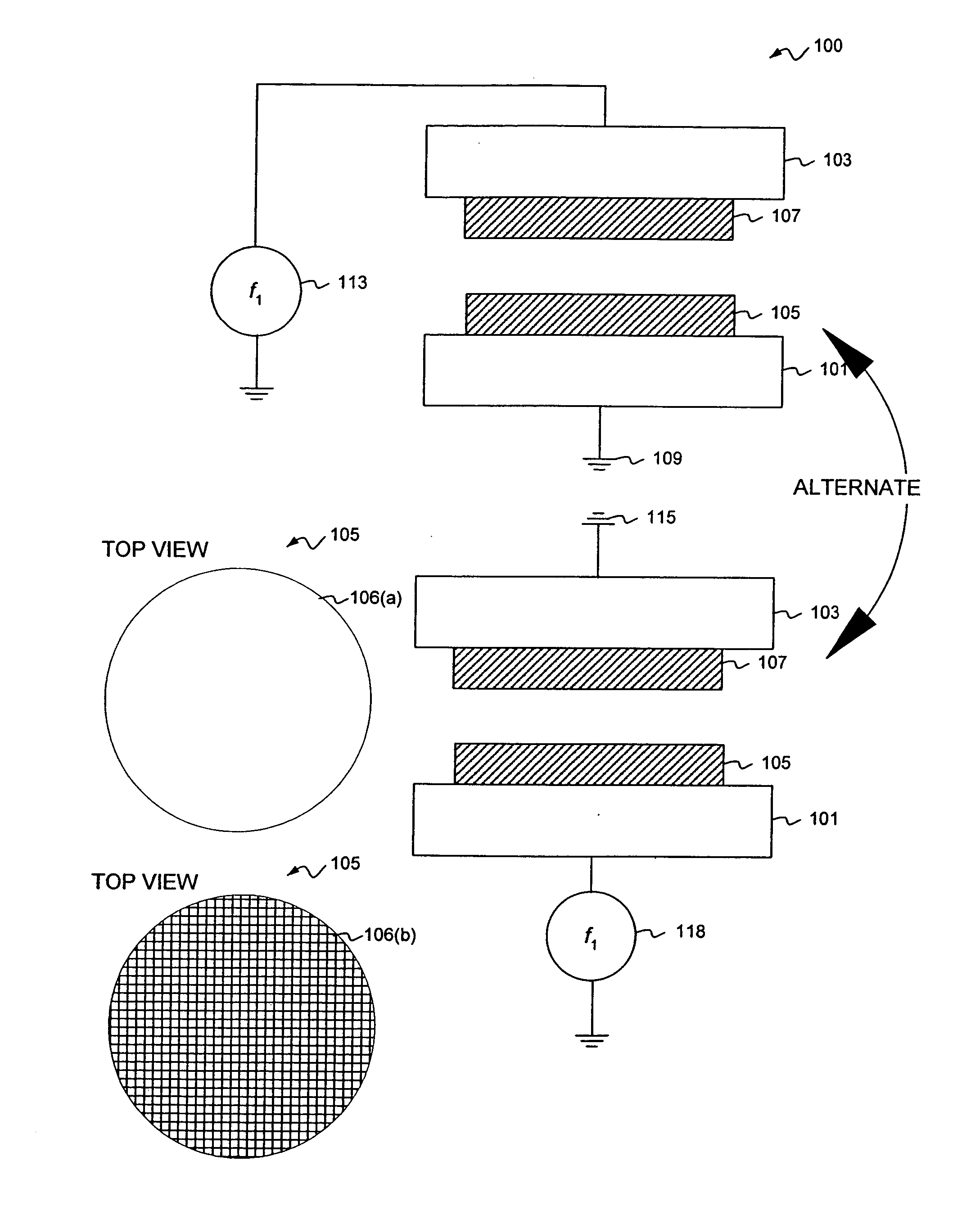

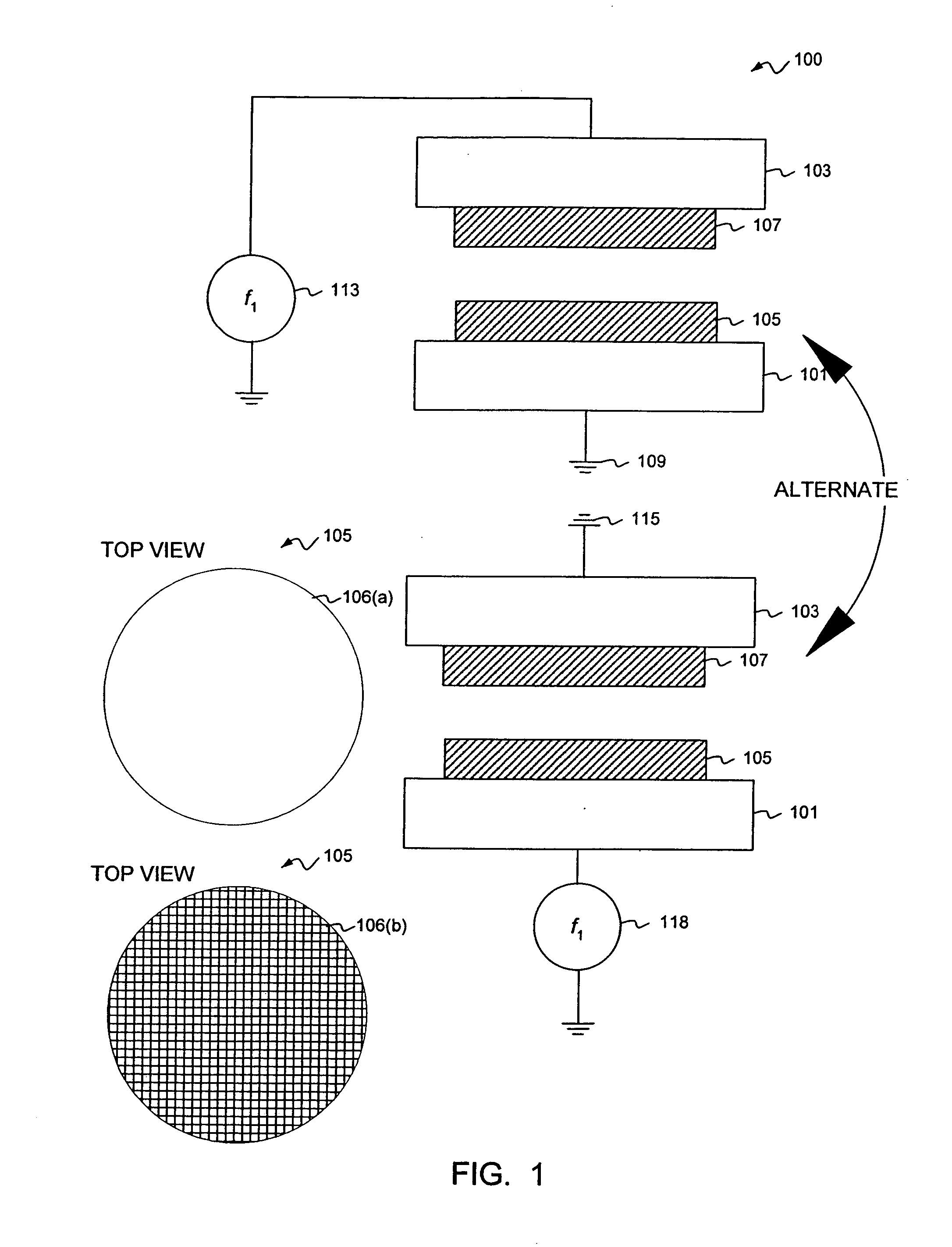

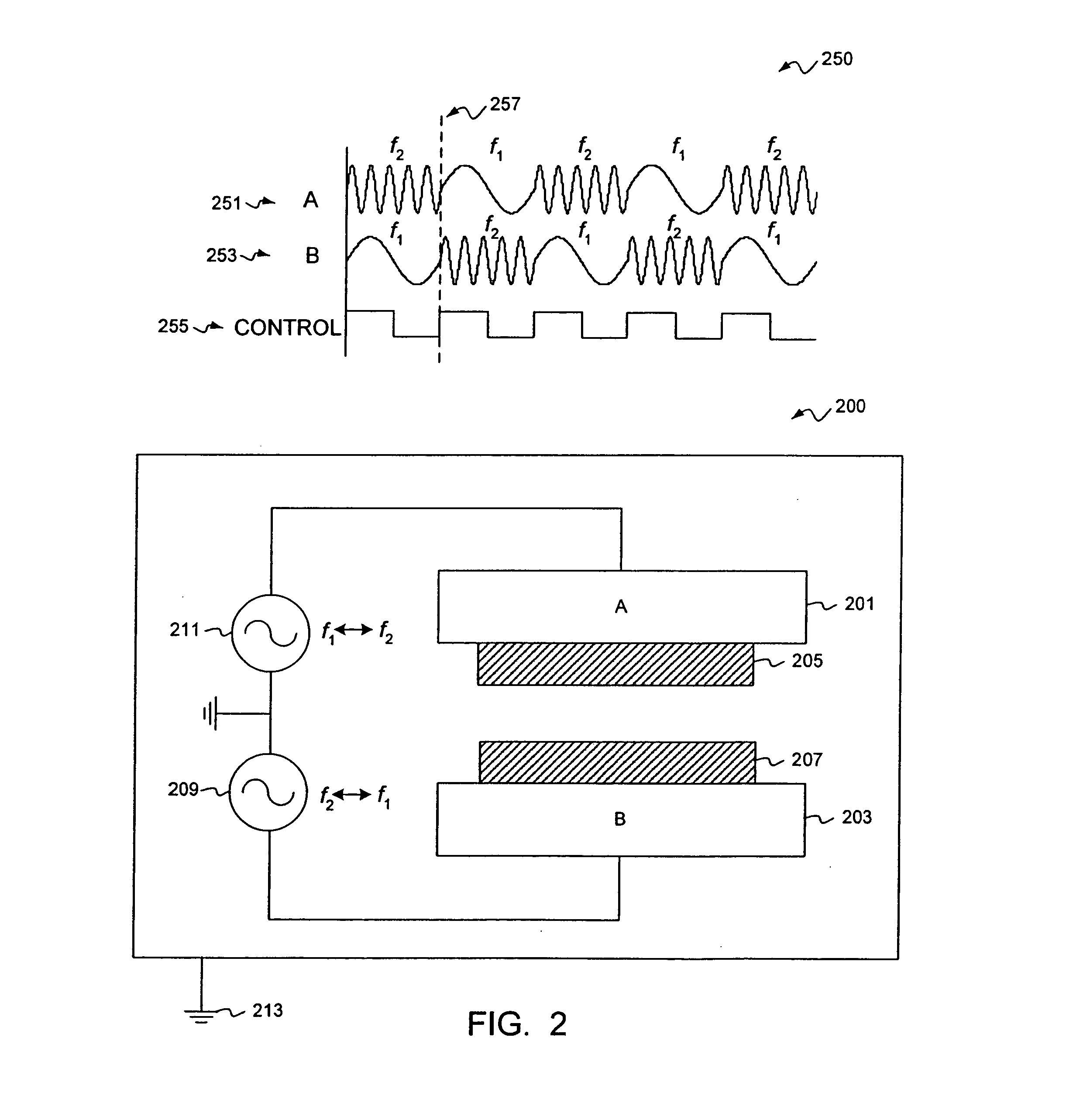

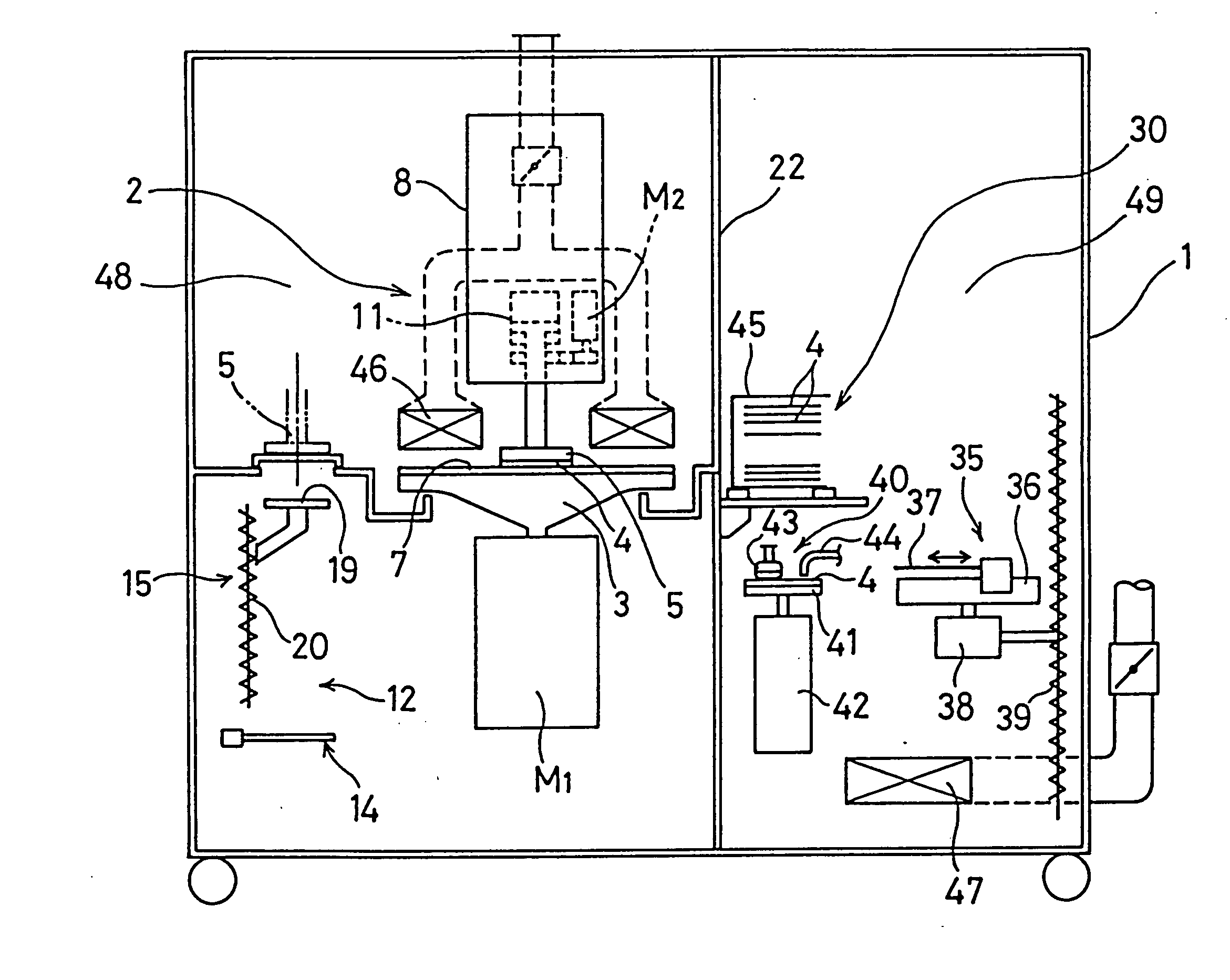

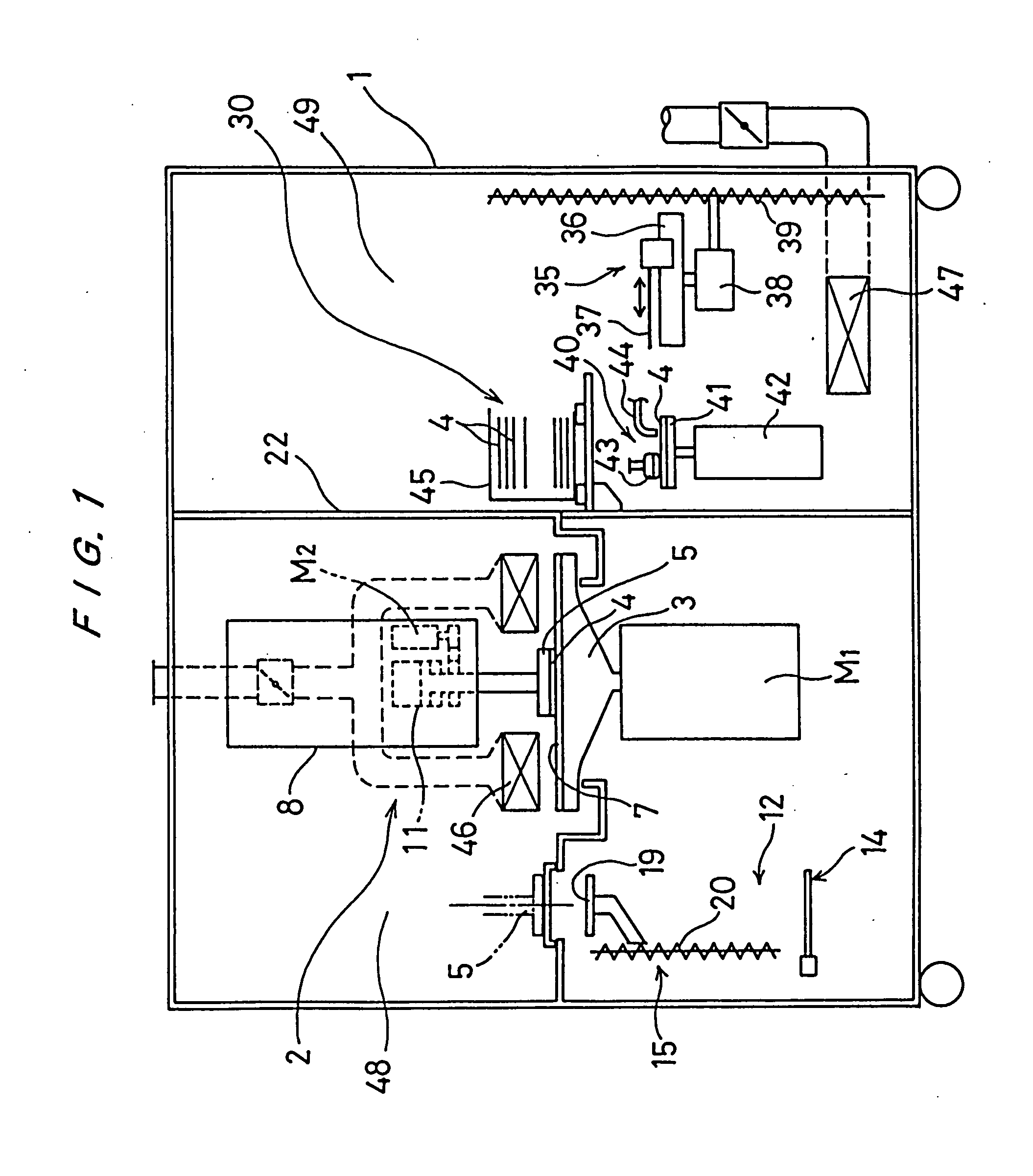

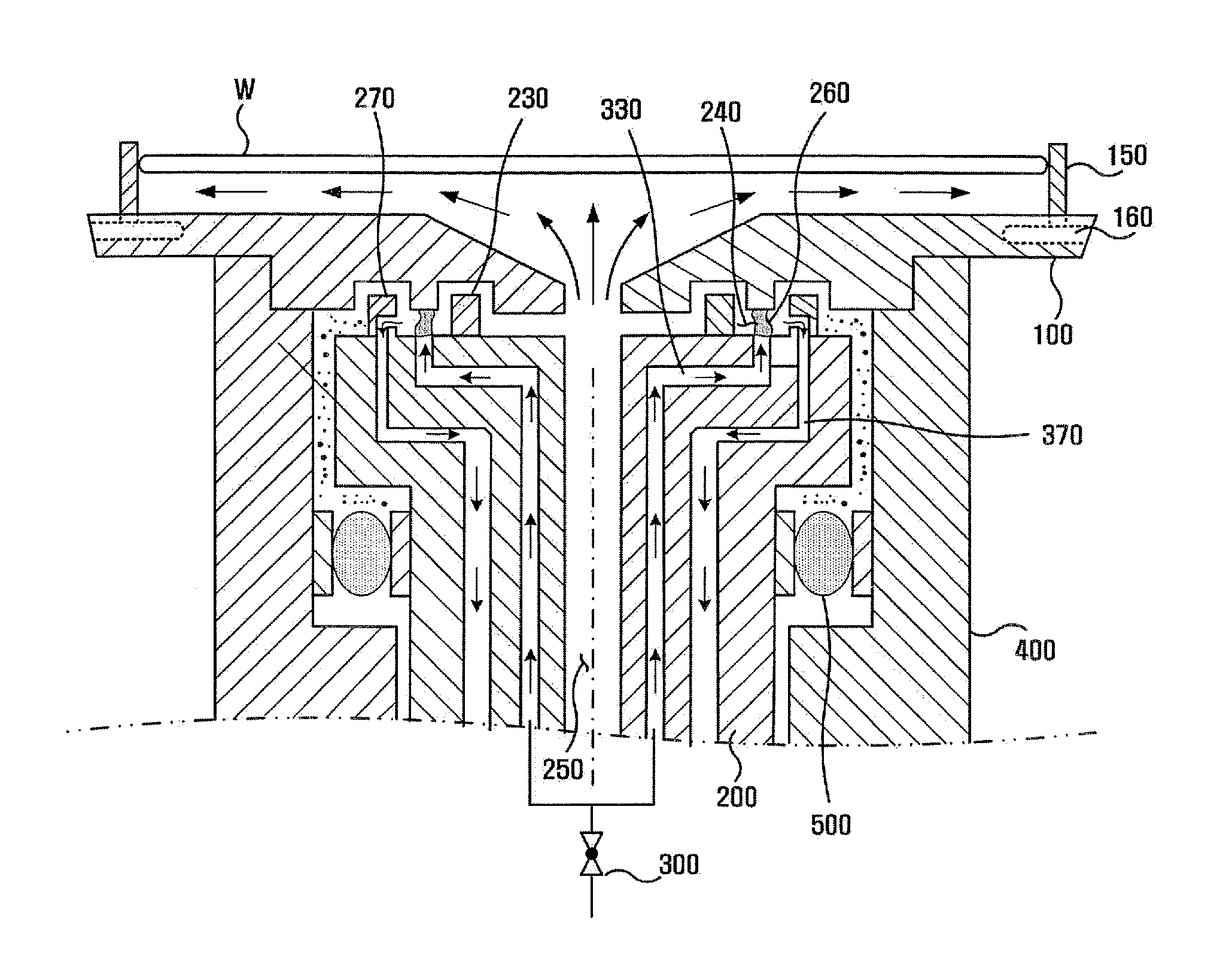

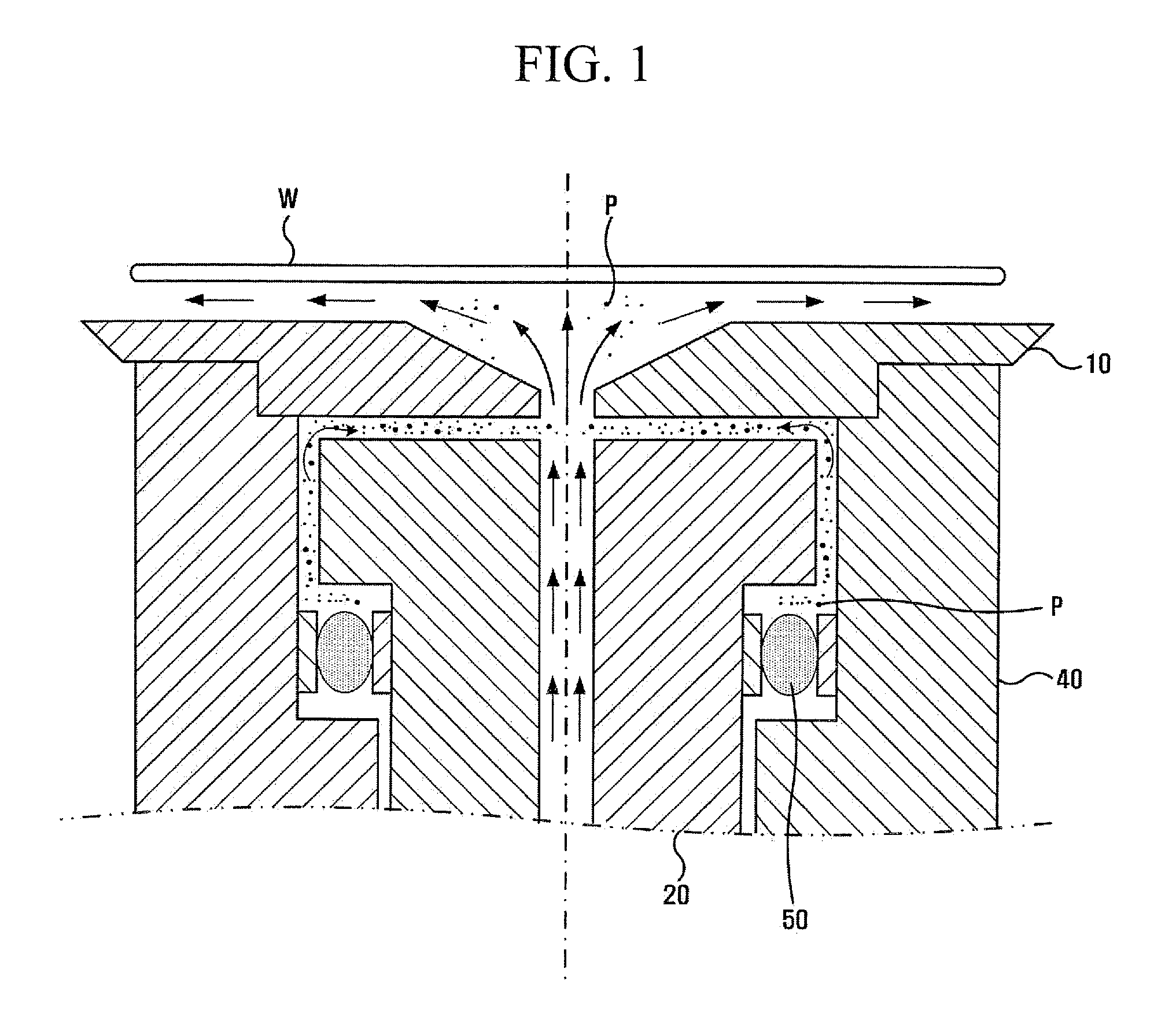

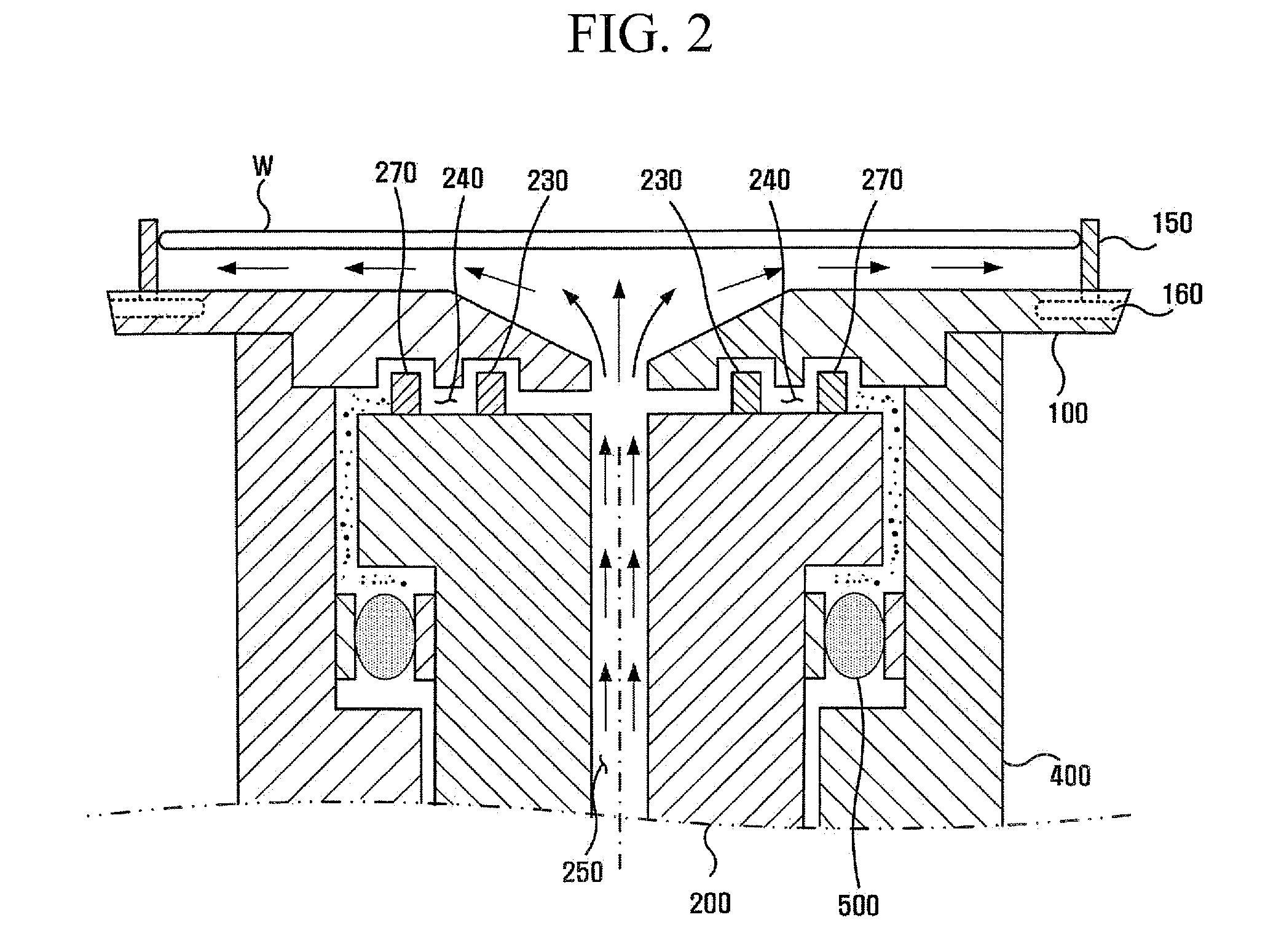

Method and system for source switching and in-situ plasma bonding

ActiveUS7078317B2Quality improvementHigh yieldElectric discharge tubesSemiconductor/solid-state device manufacturingSusceptorEngineering

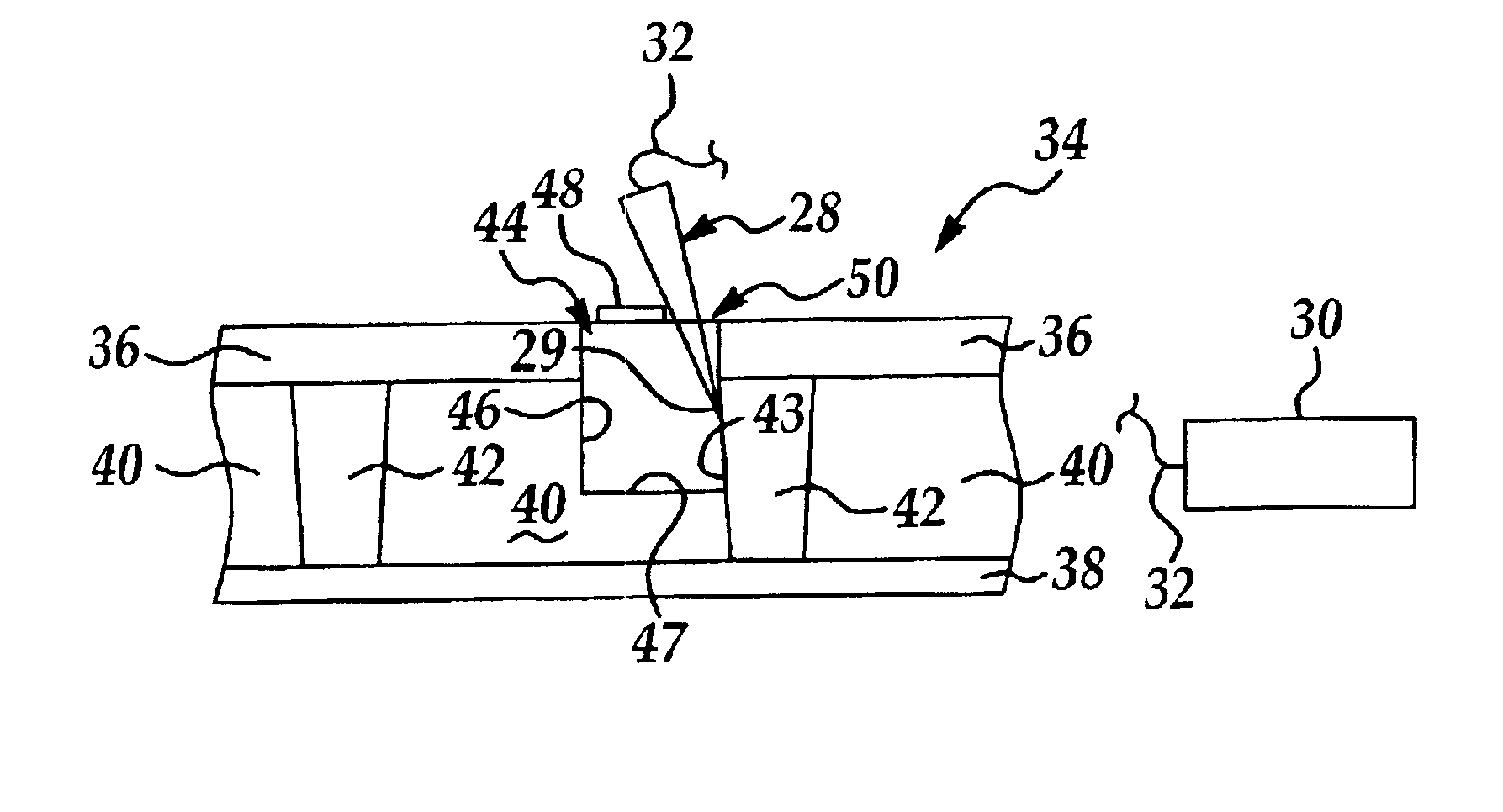

A system for in-situ plasma treatment. The system has a processing chamber, e.g., plasma chamber. The system has a first susceptor coupled within the chamber and a second susceptor facing the first susceptor and being within the chamber. The system has one or more power sources. Preferably, a first power source is characterized by a first frequency. The first power source is coupled to the first susceptor and the second susceptor. A second power source is characterized by a second frequency. The second power source is coupled to the first susceptor and the second susceptor. A switching device is coupled to the first power source and is coupled the second power source. The switching device is configured to selectively apply the first frequency to the first susceptor while the second frequency is applied to the second susceptor and is alternatively configured to selectively apply the first frequency to the second susceptor while the second frequency is applied to the first susceptor.

Owner:SILICON GENERAL CORPORATION

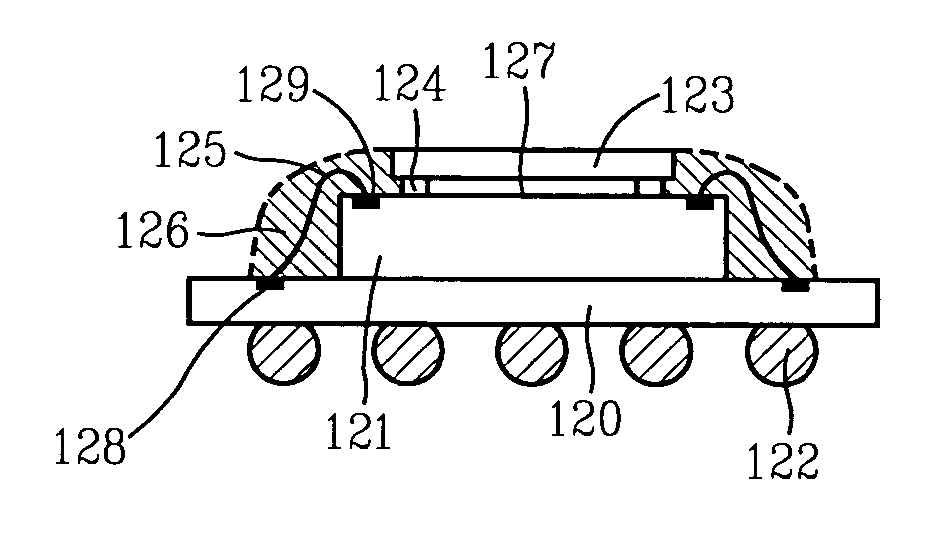

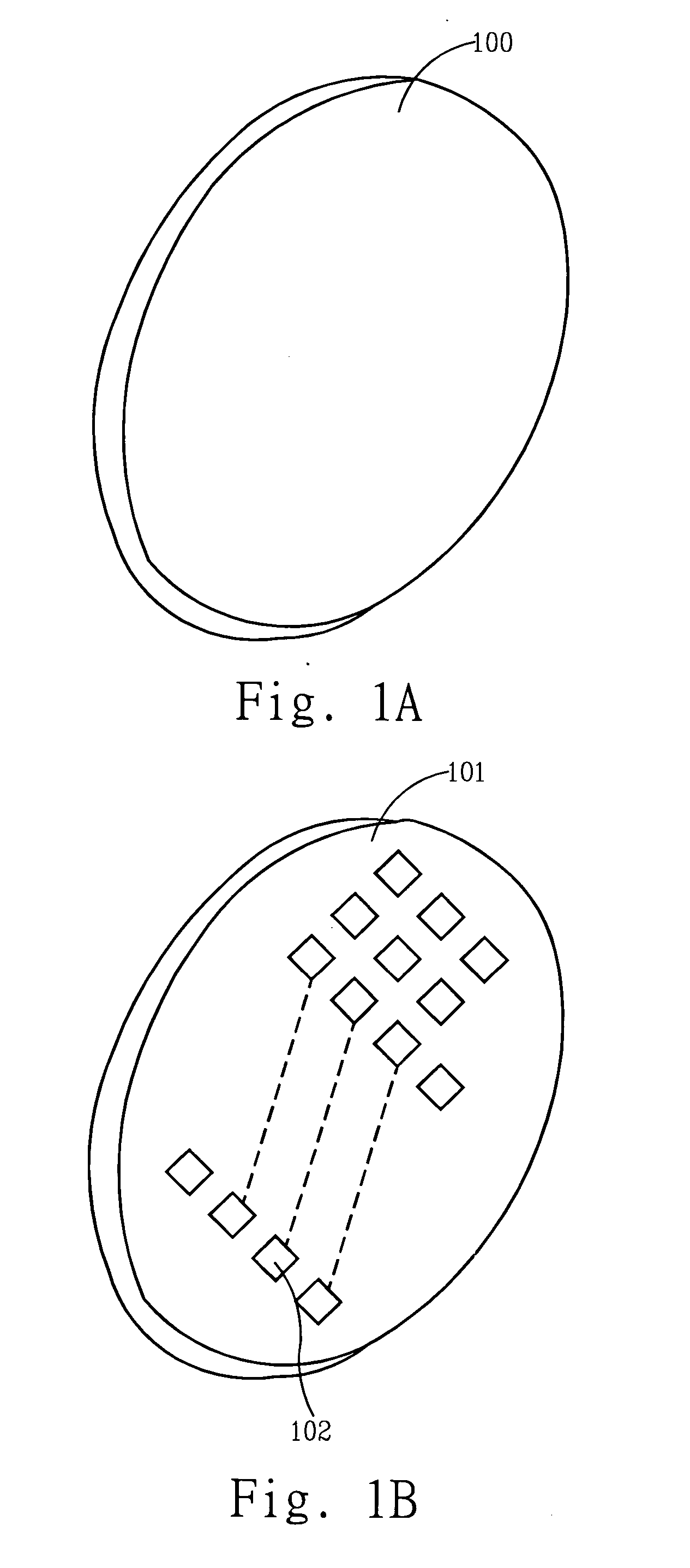

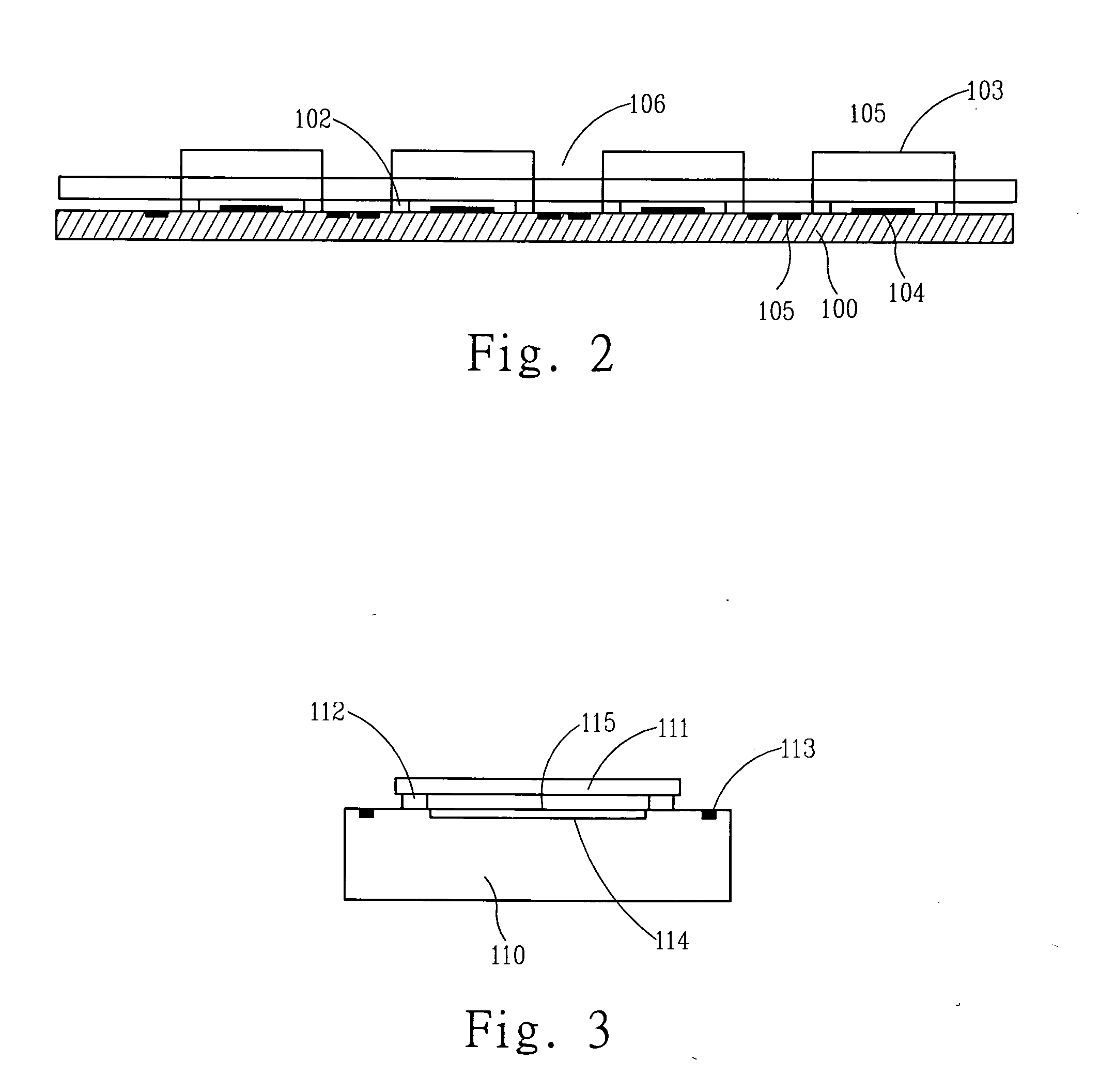

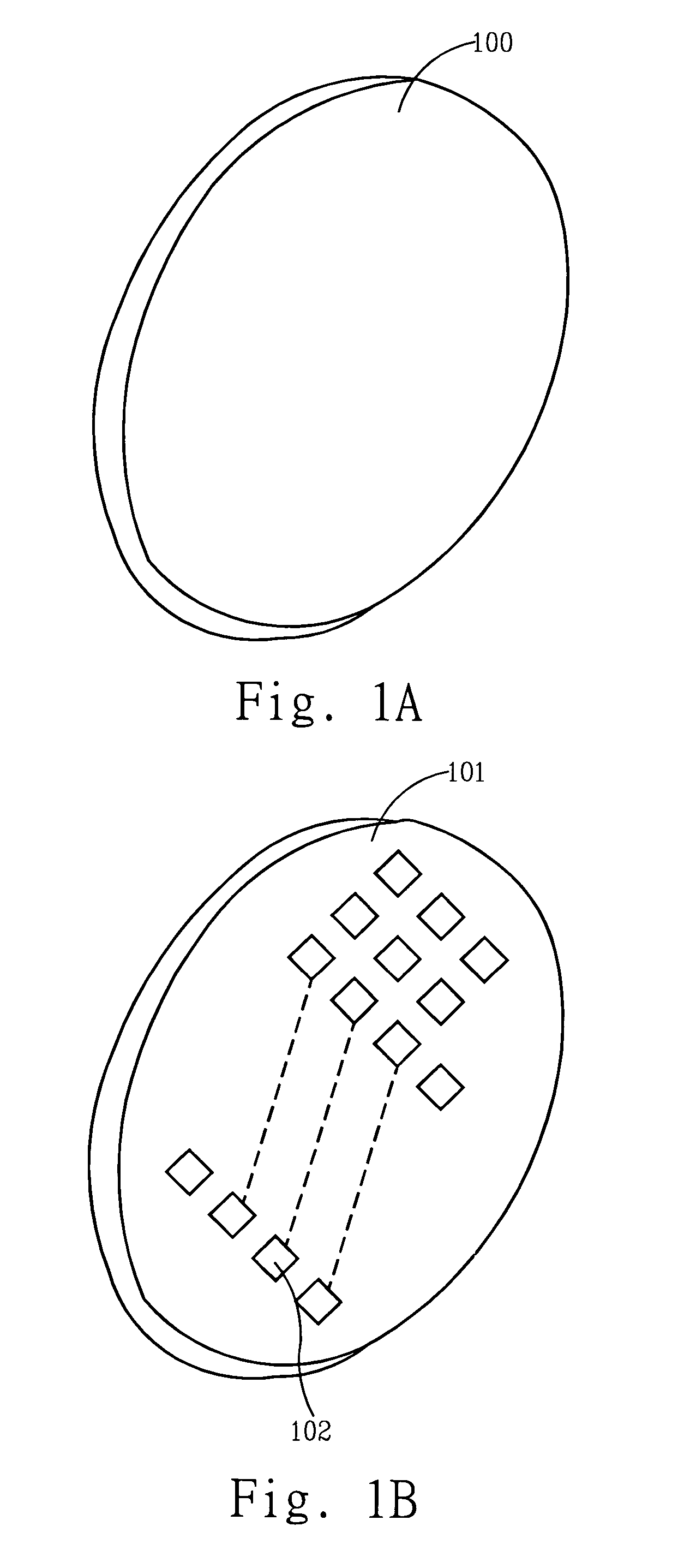

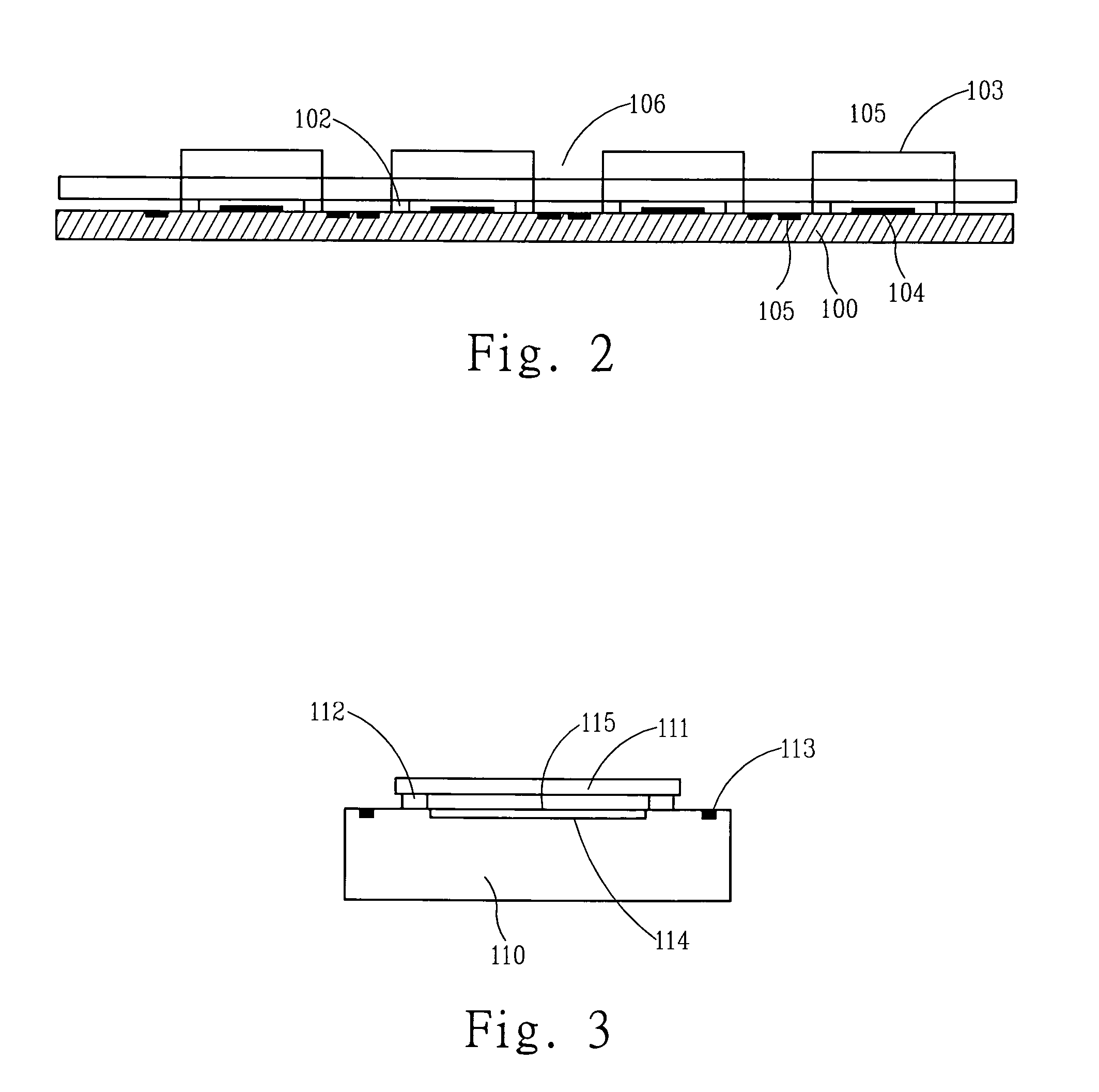

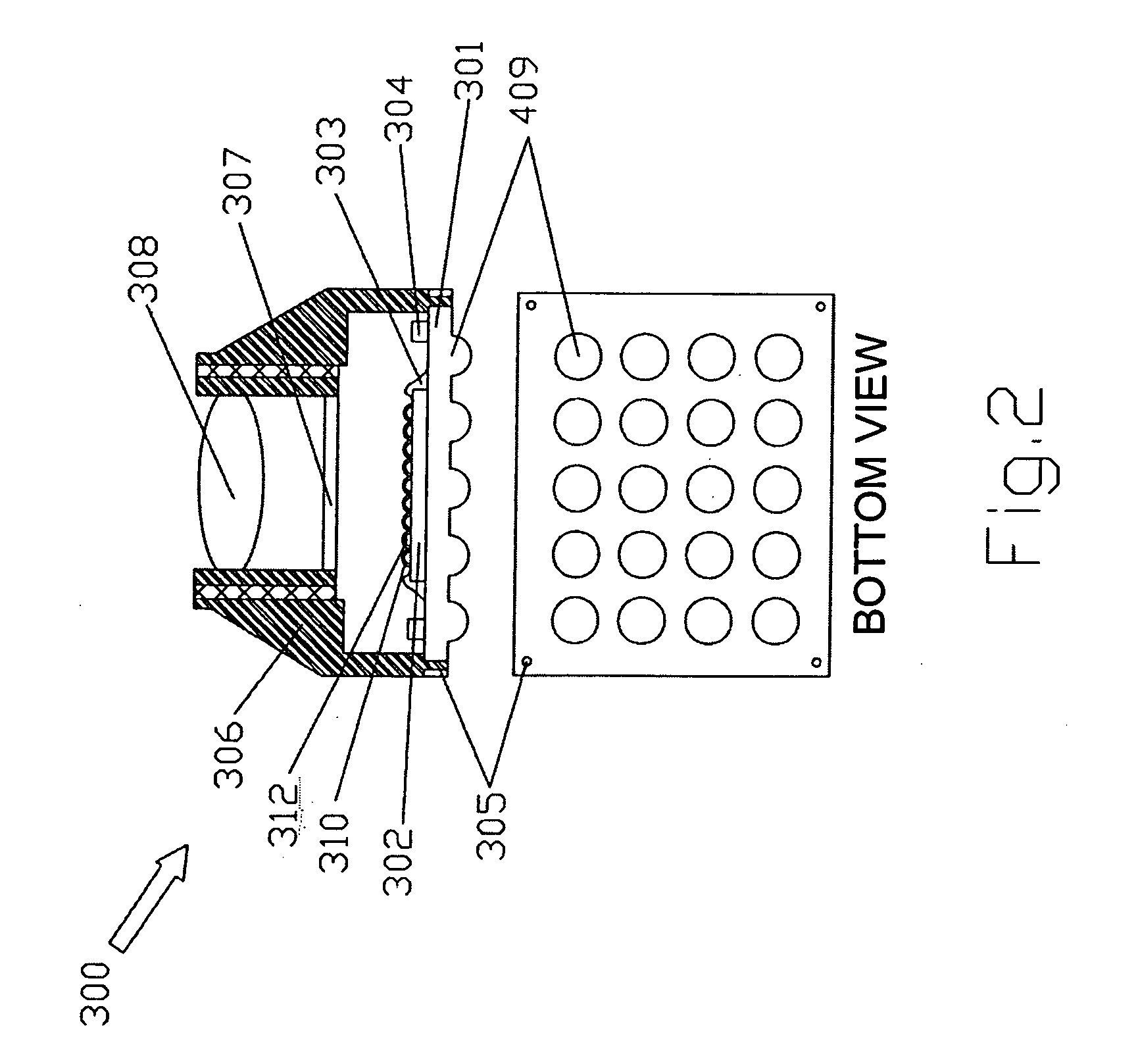

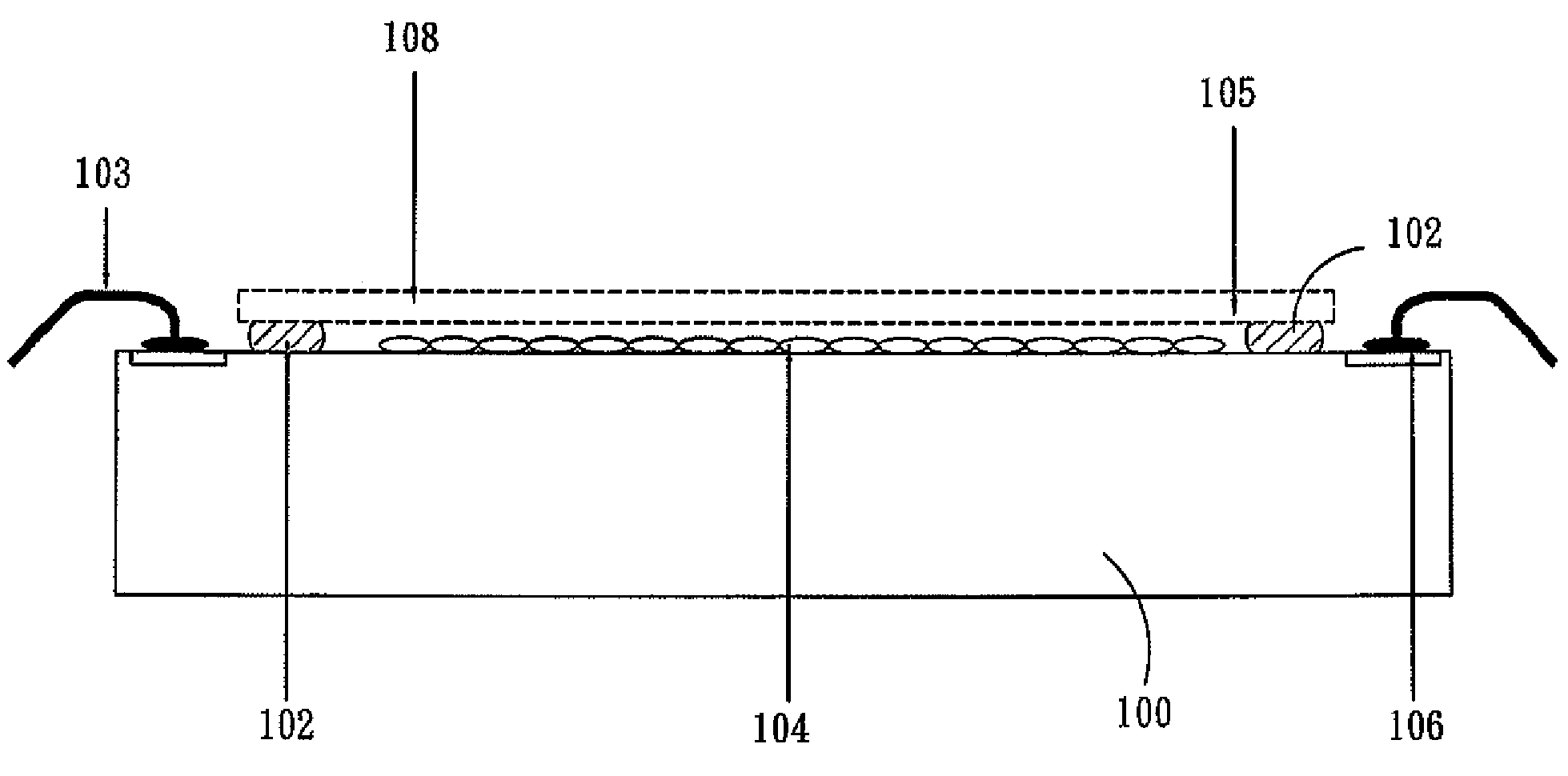

FBGA and COB package structure for image sensor

ActiveUS20060145325A1Avoid Particle ContaminationSemiconductor/solid-state device detailsSolid-state devicesEngineeringPrinted circuit board

A structure of package comprises a die placed on printed circuit board. A glass substrate is adhered on an adhesive film pattern to form an air gap area between the glass substrate and the chip. Micro lens are disposed on the chip. A lens holder is fixed on printed circuit board. The glass substrate can prevent the micro lens from particle contamination.

Owner:ADVANCED CHIP ENG TECH

FBGA and COB package structure for image sensor

ActiveUS7279782B2Avoid Particle ContaminationSemiconductor/solid-state device detailsSolid-state devicesEngineeringPrinted circuit board

Owner:ADL ENERGY CORP

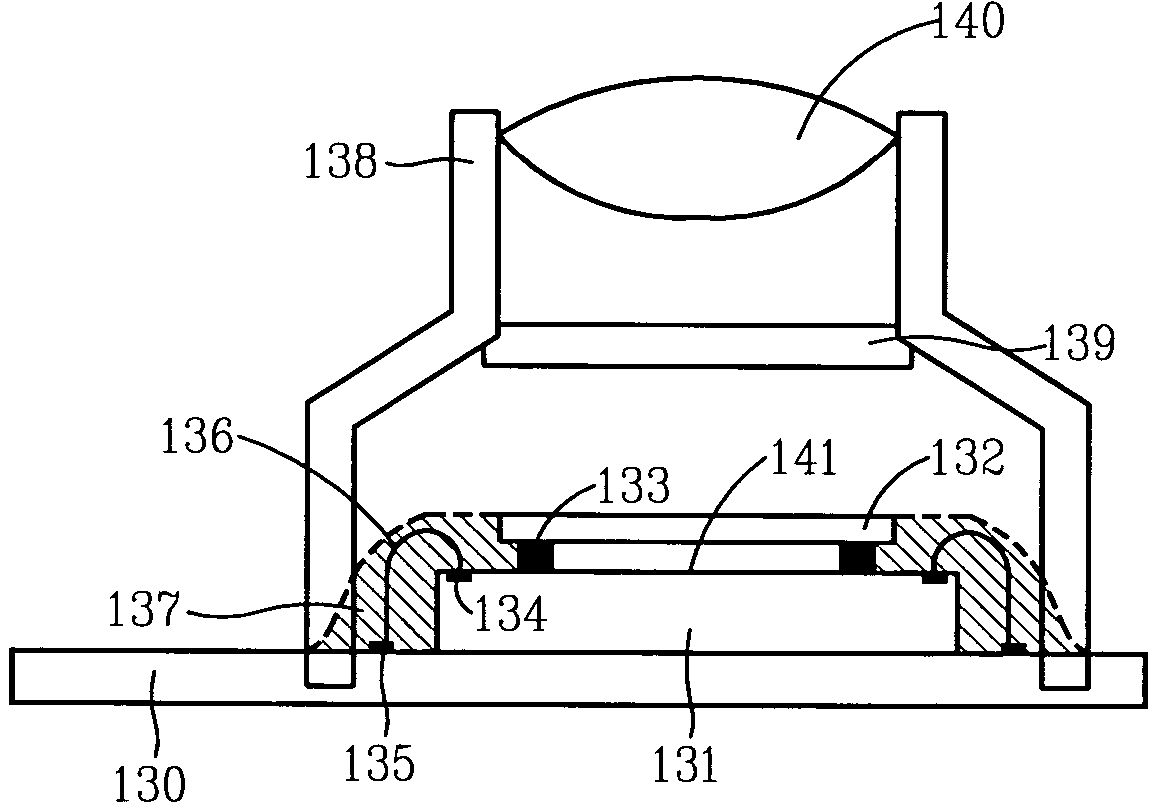

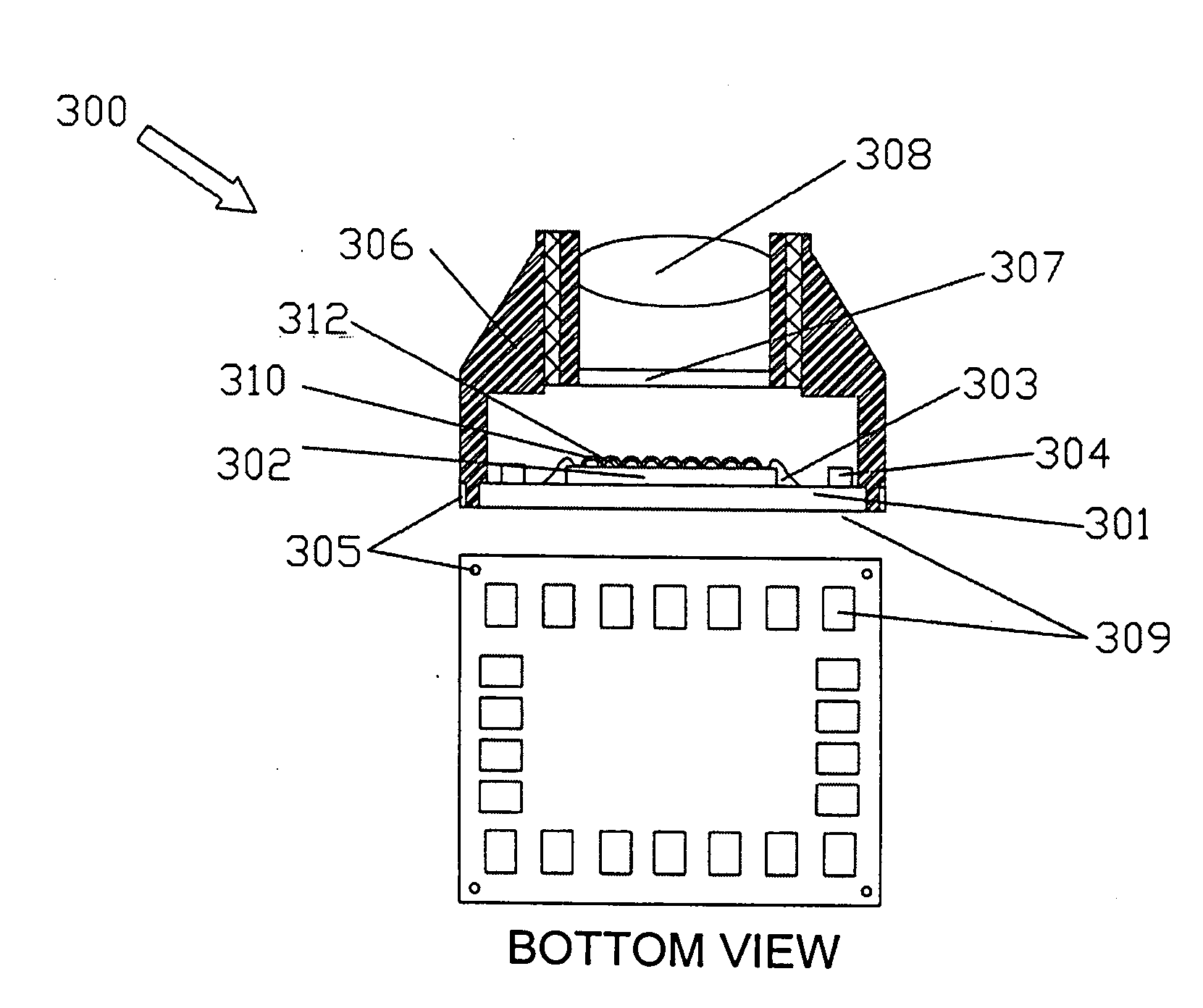

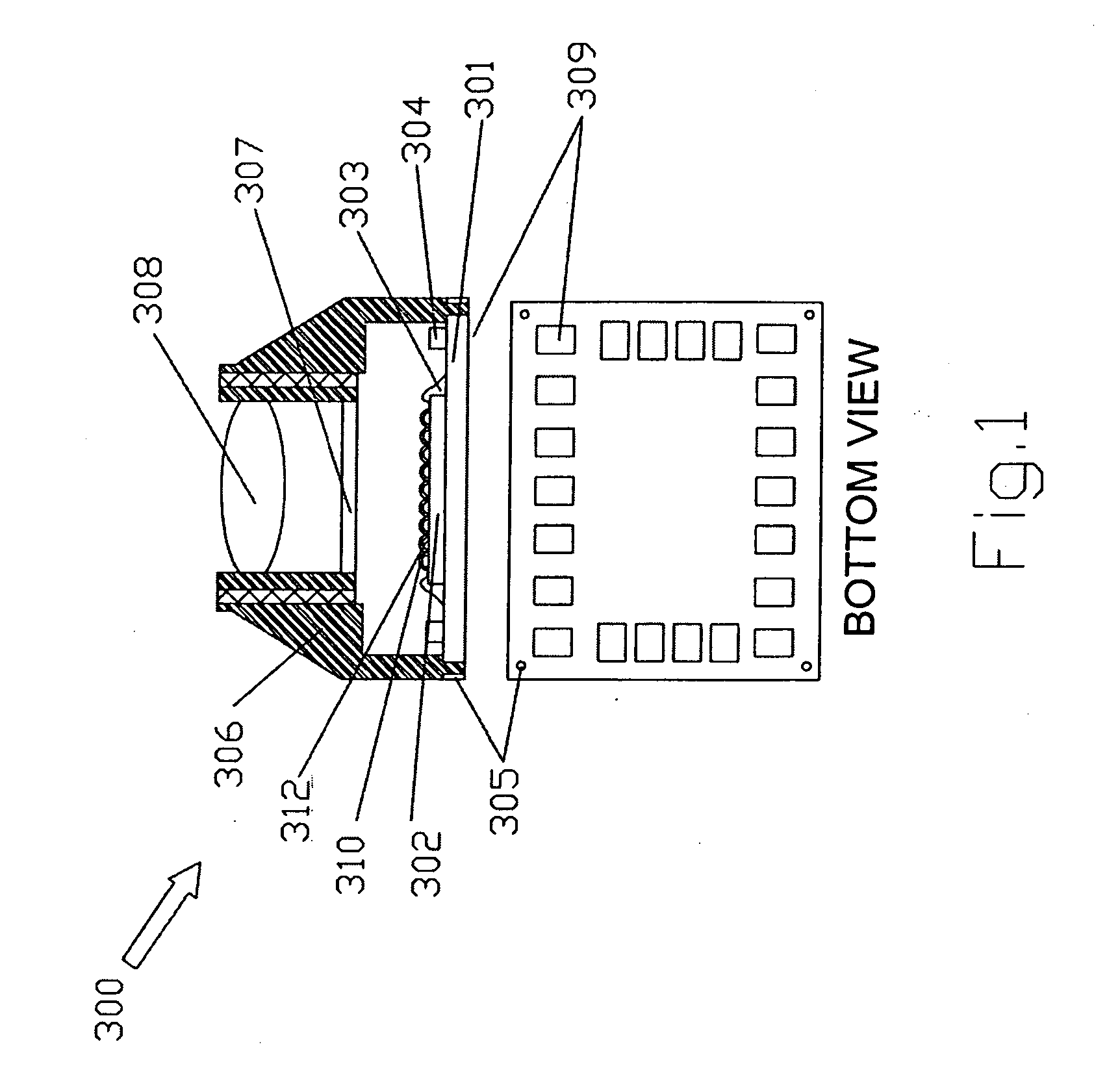

Image sensor module

ActiveUS20080135728A1Small foot printReduce device sizeTelevision system detailsBeam/ray focussing/reflecting arrangementsDevice formMicrolens

The present invention provides an image sensor module. The image sensor module has a die formed on a substrate, the die having a micro lens area, a lens holder formed on the substrate and over the die, a lens formed in the lens holder. A filter is formed within the lens holder and between the lens and the die, and at least one passive device formed on the substrate and covered within the lens holder. Conductive bumps or LGA (leadless grid array) are formed on the bottom surface of the substrate.

Owner:ADVANCED CHIP ENG TECH

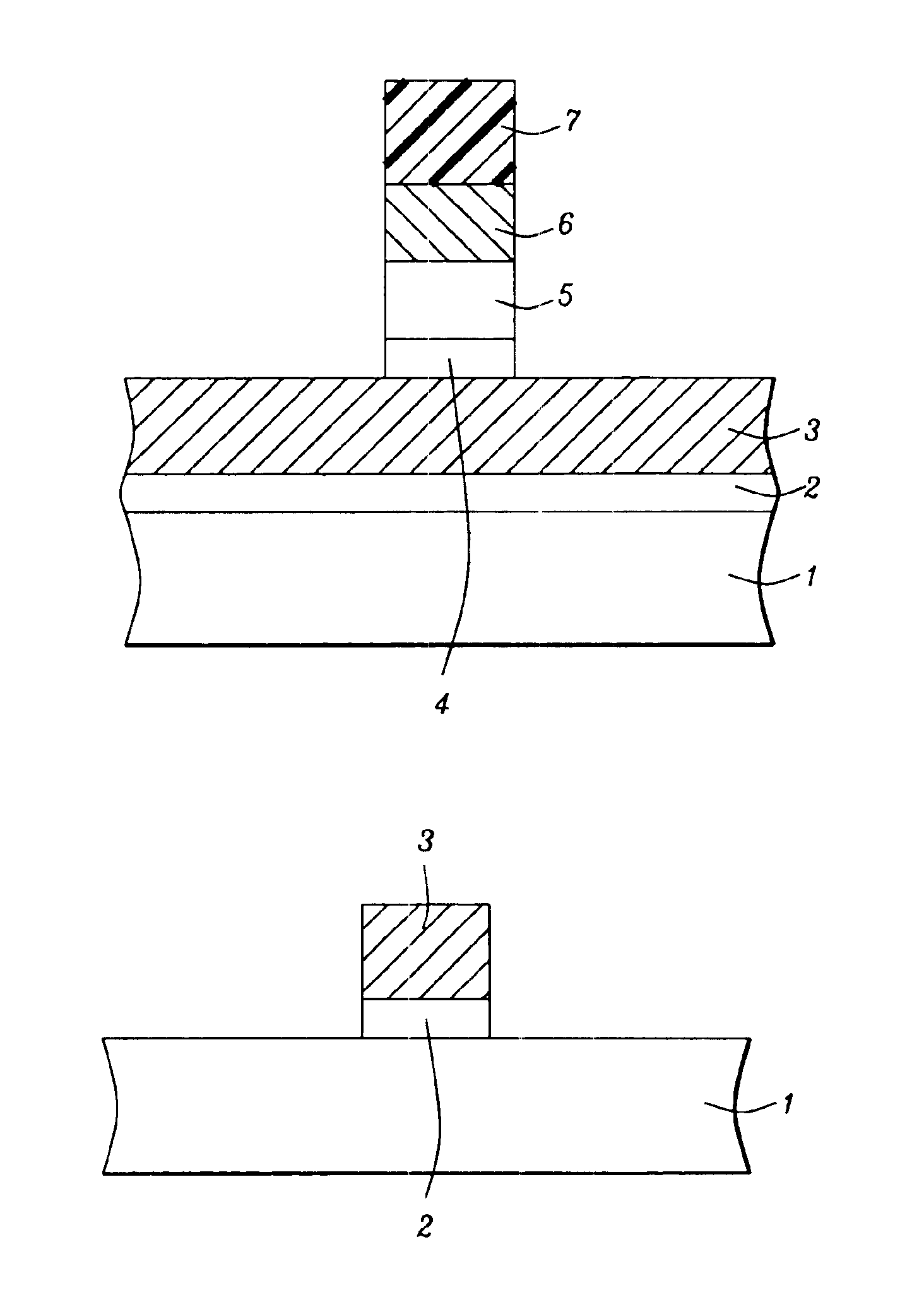

Phosphoric acid free process for polysilicon gate definition

InactiveUS6849531B1Easy to controlAvoid Particle ContaminationSemiconductor/solid-state device manufacturingSemiconductor devicesHydrofluoric acidMOSFET

A method of defining a gate structure for a MOSFET device featuring the employment of dual anti-reflective coating (ARC) layers to enhance gate structure resolution, and featuring a dry procedure for removal of all ARC layers avoiding the use of hot phosphoric acid, has been developed. After formation of a polysilicon layer on an underlying silicon dioxide gate insulator layer, a capping silicon oxide, a dielectric ARC layer, and an overlying organic ARC layer are deposited. A photoresist shape is formed and used as an etch mask to allow a first anisotropic RIE procedure to define the desired gate structure shape in the dual ARC layers and in the capping silicon oxide layer. After removal of the photoresist shape and the overlying organic ARC layer a second anisotropic RIE procedure is used to define a desired polysilicon gate structure, with the second anisotropic RIE procedure also resulting in the removal of the dielectric ARC shape. A final hydrofluoric acid type solution is then used to remove the capping silicon oxide shape as well as to remove the portions of the silicon dioxide gate insulator layer not covered by the polysilicon gate structure.

Owner:TAIWAN SEMICON MFG CO LTD

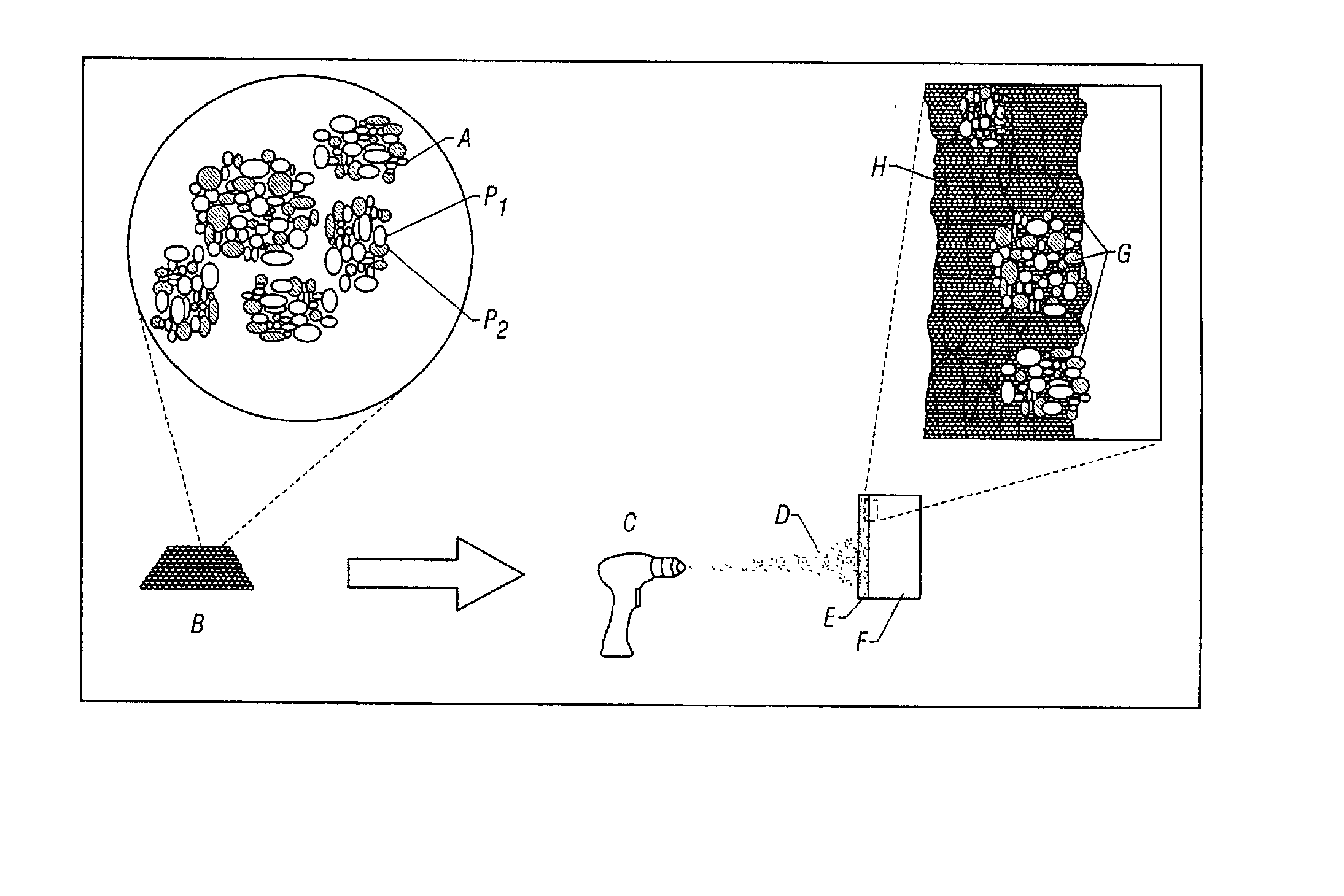

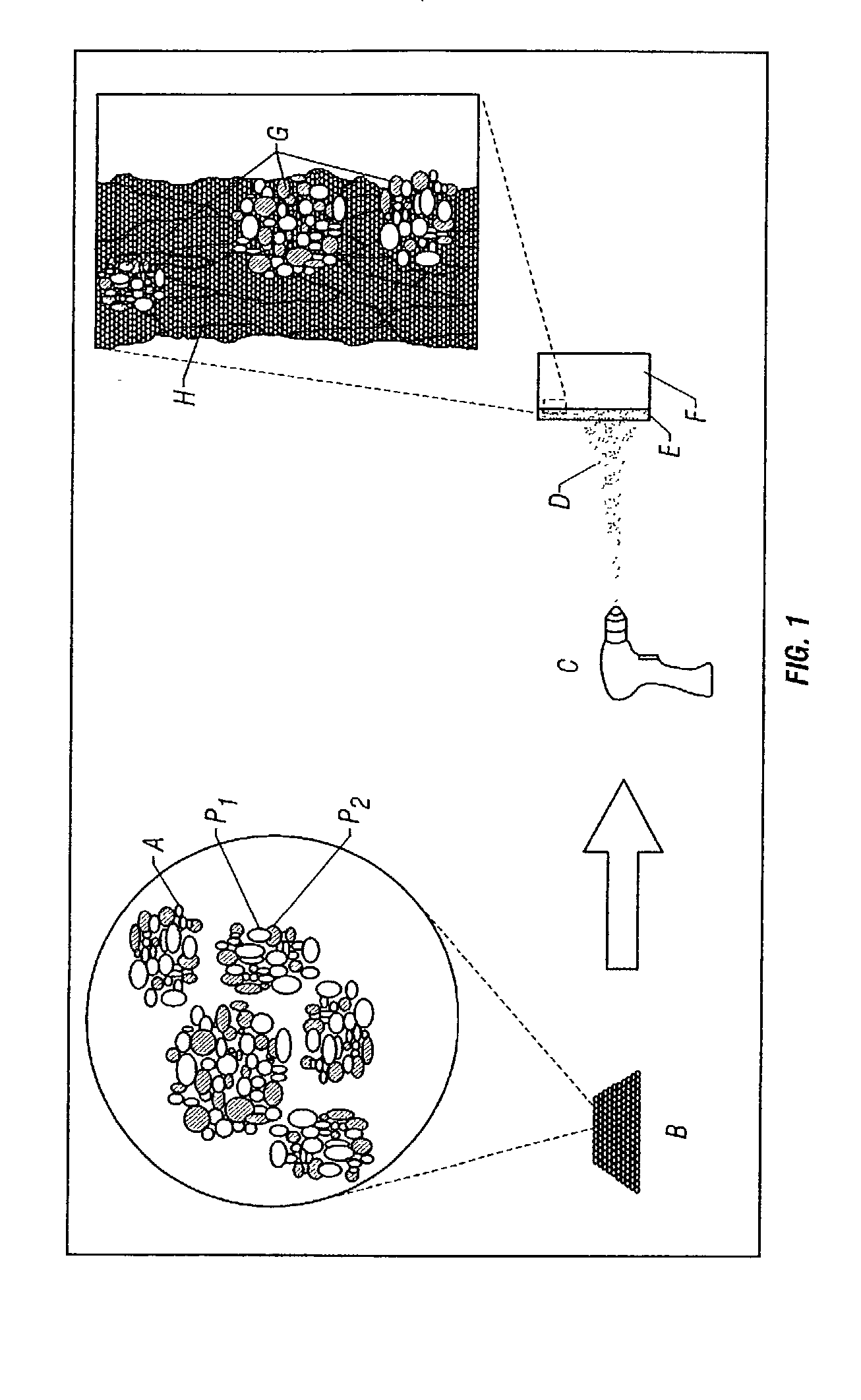

Nanostructured titania coated titanium

InactiveUS6835449B2Enhance reliability and lifeConvenient coatingMaterial nanotechnologyPigmenting treatmentTitaniumNanostructure

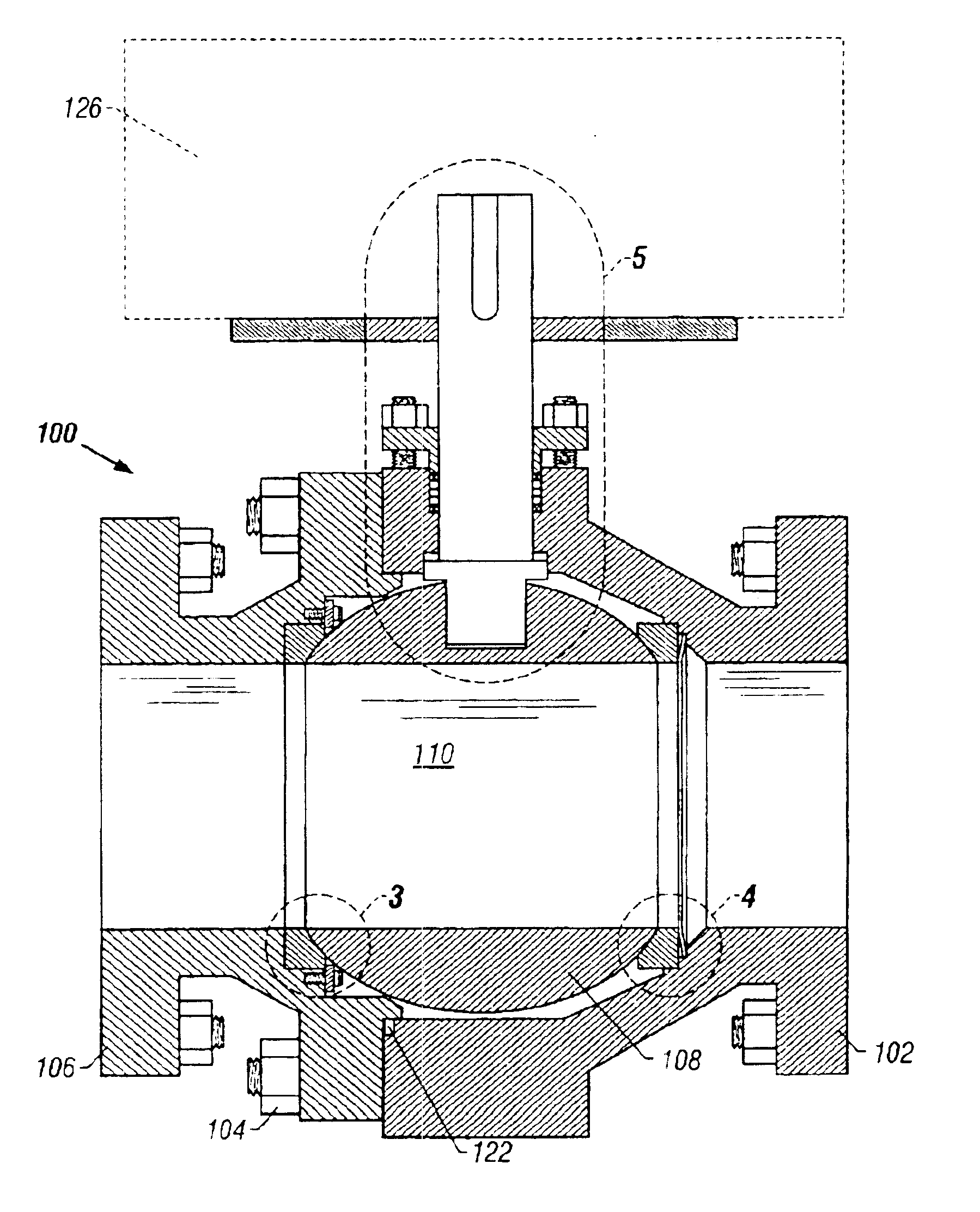

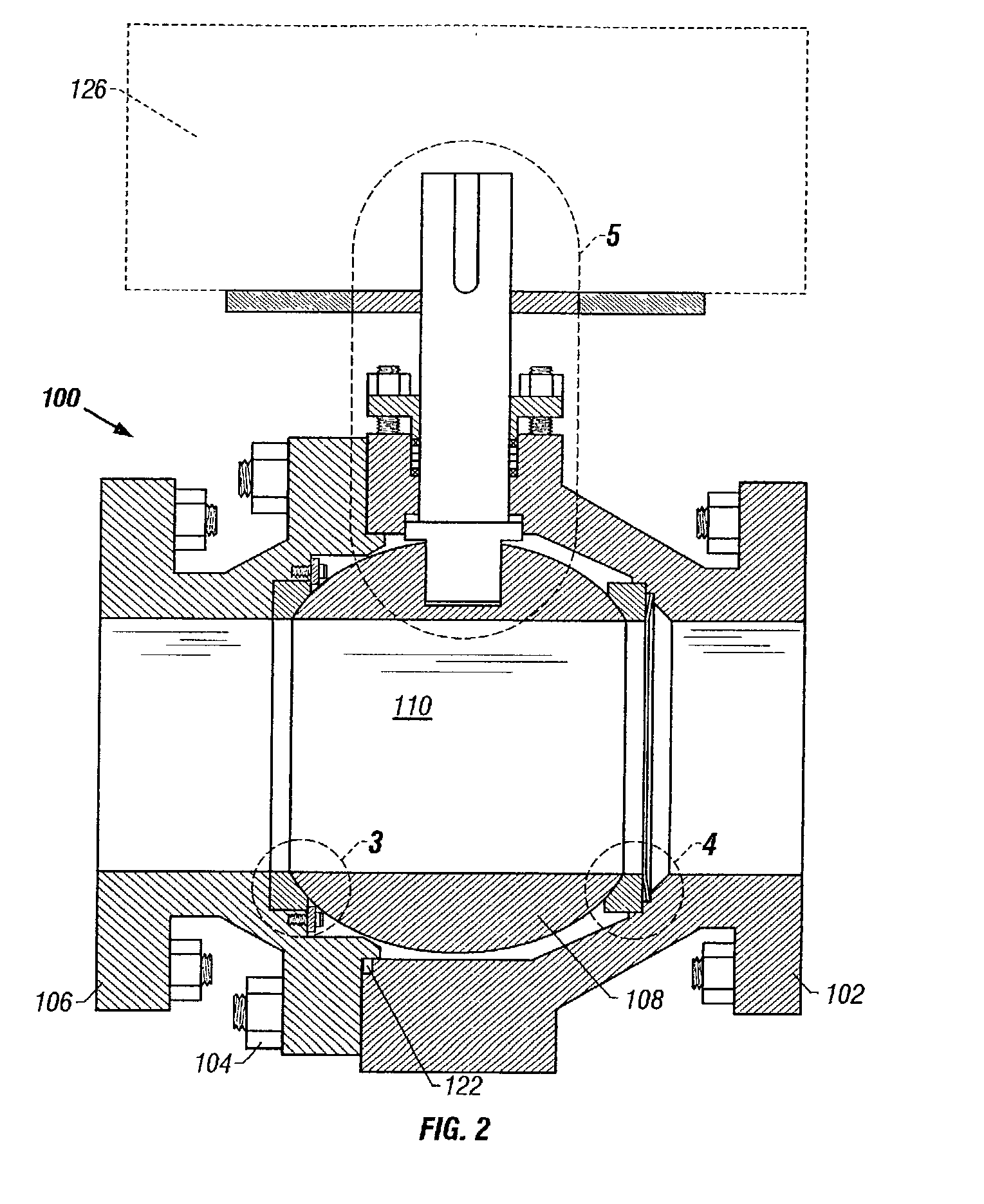

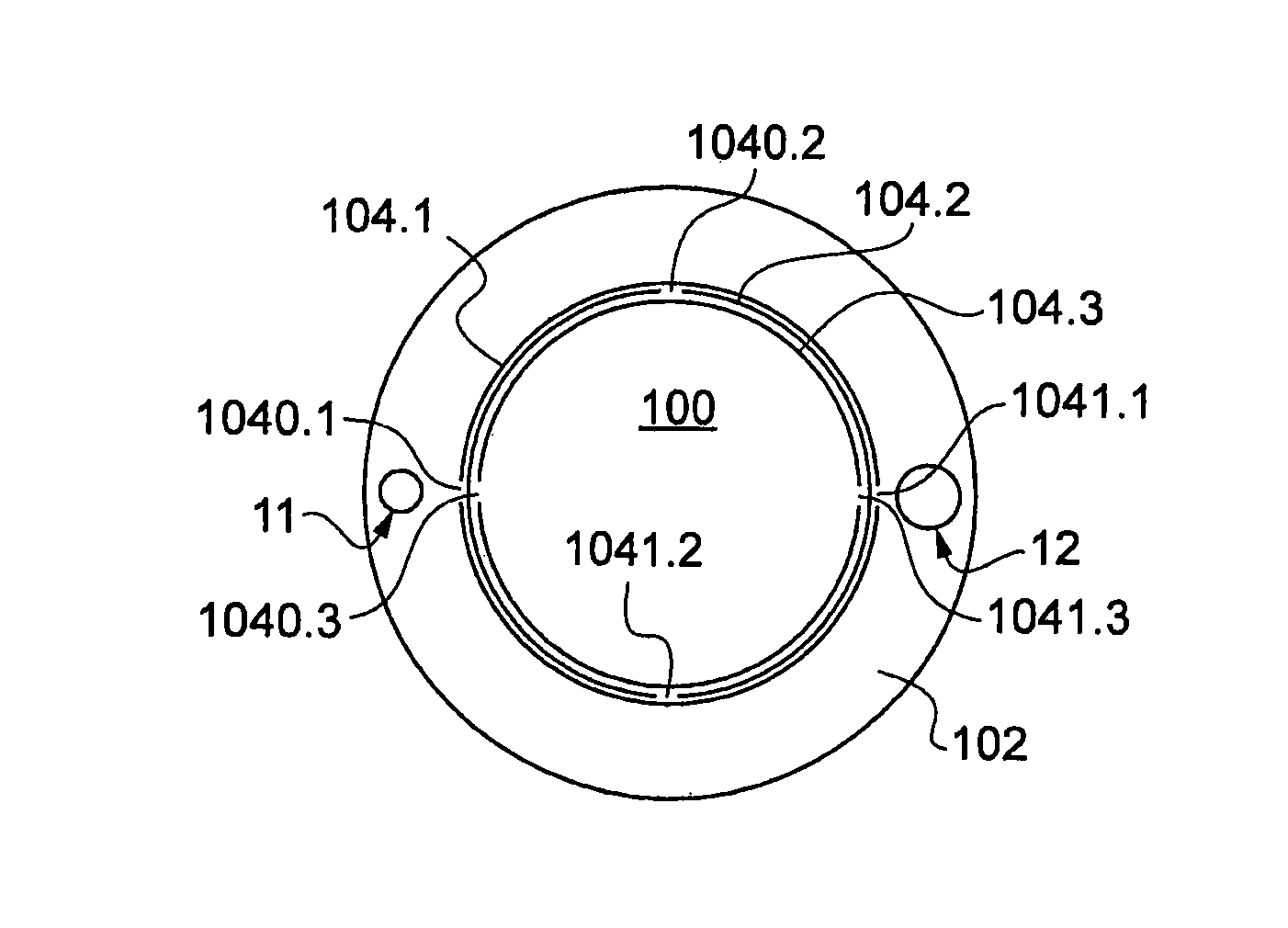

A ball valve for use in the pressure acid leaching of nickel ores is disclosed. The valve has a valve body and a ball centrally positioned in the valve body, which has a central passage rotatable in the valve body between open and closed positions. At least one seat is disposed between the ball and the valve body. The ball and seat each comprise a titanium substrate and an ultrafine or nanostructured titania coating. The titania can include from 5 to 45 volume percent of a second phase material that is immiscible with the titania and exhibits corrosion resistance.

Owner:MOGAS IND +1

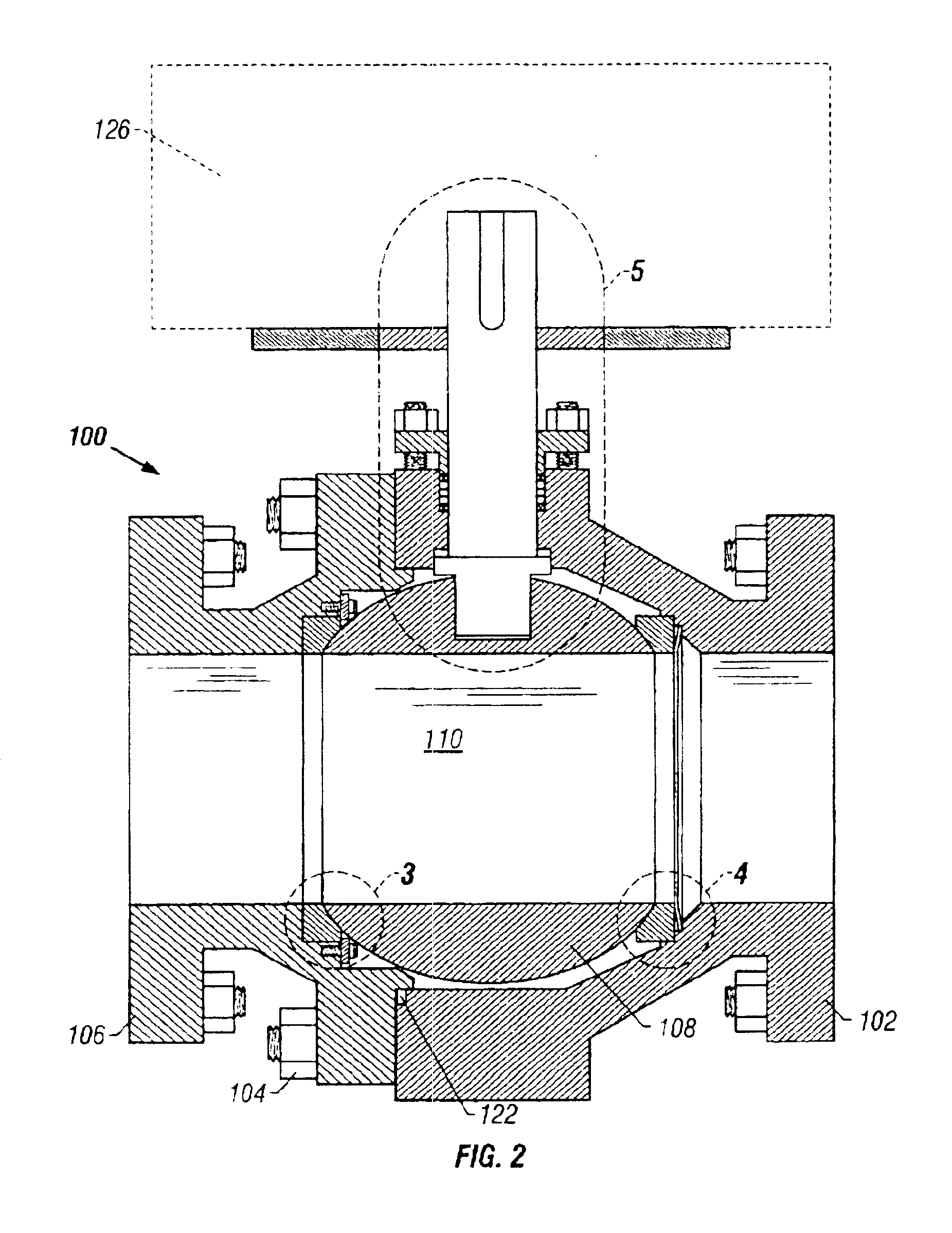

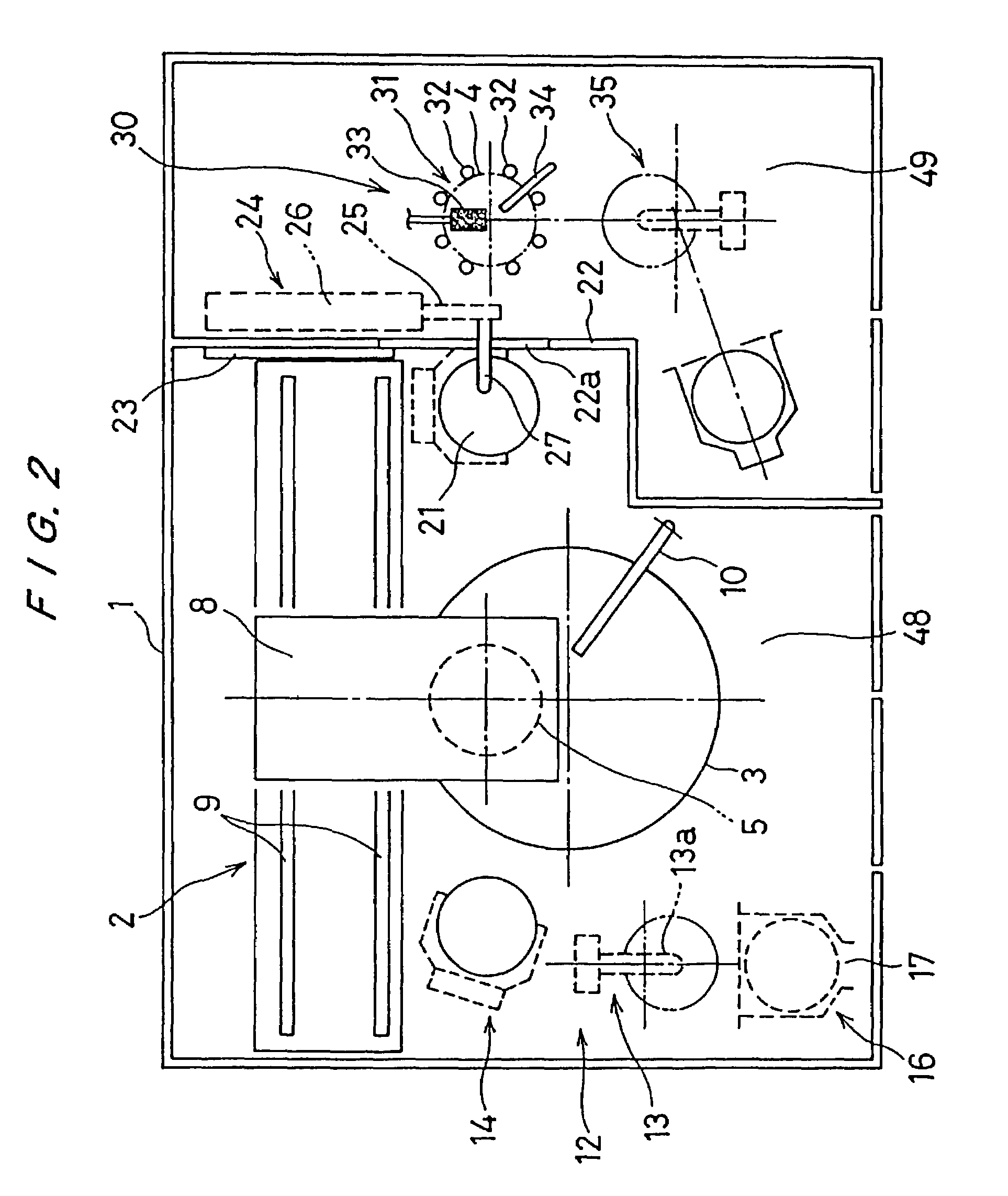

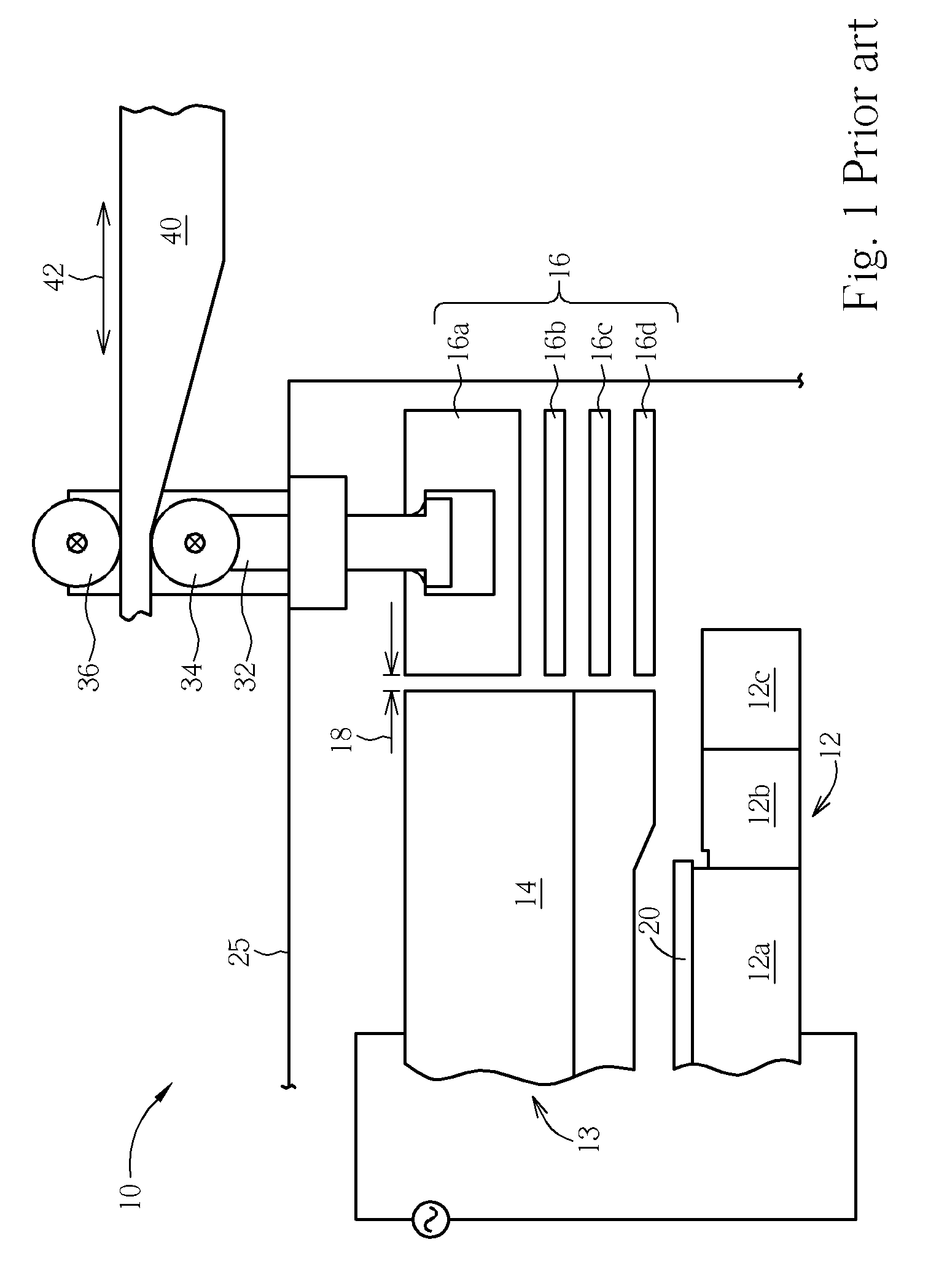

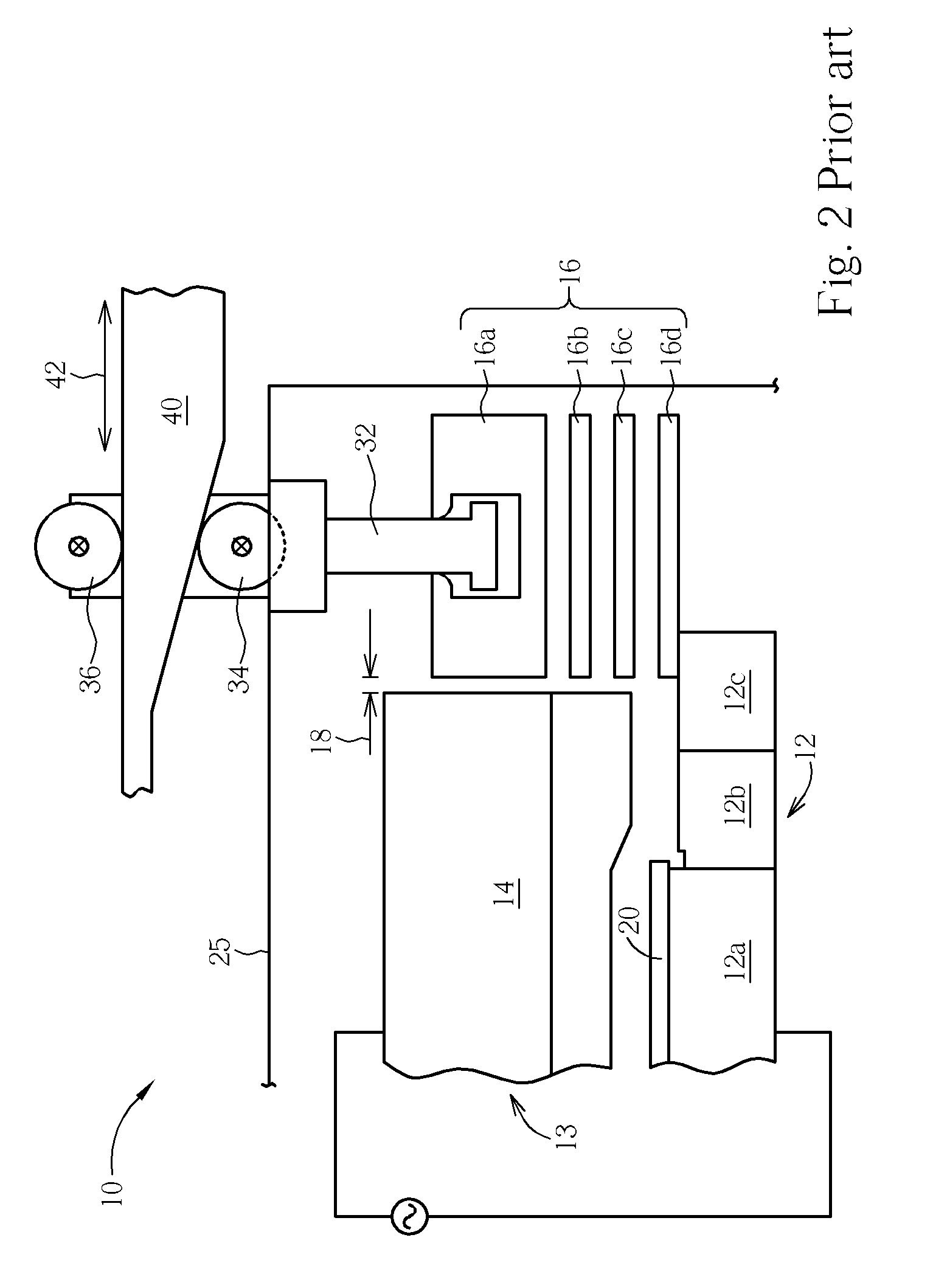

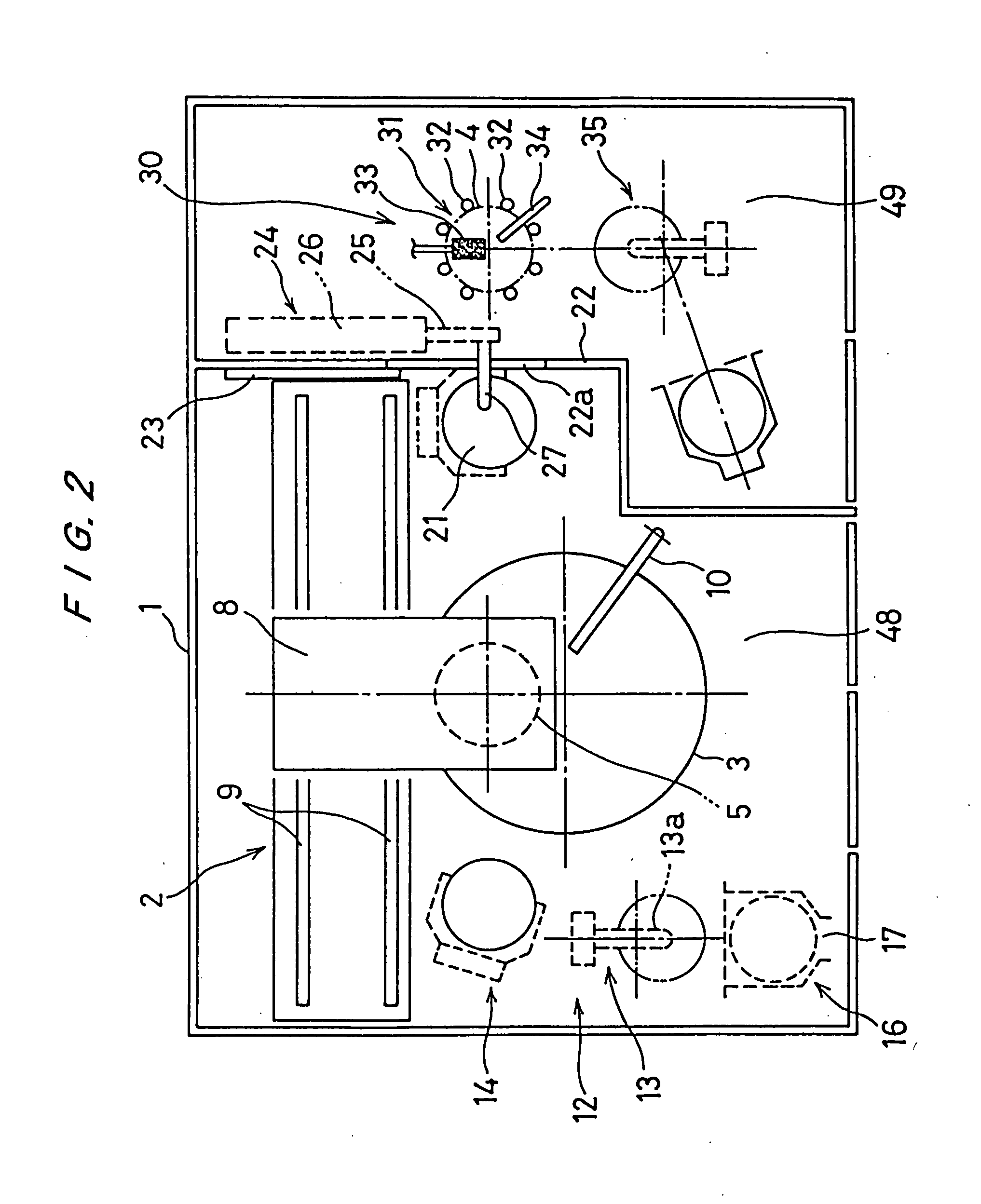

Polishing apparatus and a method of polishing and cleaning and drying a wafer

InactiveUS6997782B2Avoid Particle ContaminationWithout contaminating the clean room atmosphereEdge grinding machinesMechanical apparatusEngineeringAmbient air

A polishing apparatus for polishing a surface of a workpiece includes a housing unit, a partition wall partitioning an interior of the housing unit into a first chamber and a second chamber, a polishing section disposed in the first chamber and having a turntable with an abrasive cloth mounted on an upper surface thereof and a top ring positioned above the turntable for supporting the workpiece to be polished and pressing the workpiece against the abrasive cloth, and a cleaning section disposed in the second chamber and cleaning the workpiece which has been polished. The polishing apparatus further includes a transferring device for transferring the workpiece which has been polished from the polishing section to the cleaning section through an opening and an exhaust system for exhausting ambient air from each of the polishing section and cleaning section separately and independently.

Owner:EBARA CORP +1

Method and system for source switching and in-situ plasma bonding

ActiveUS20060030167A1Enhanced yieldEnhances process quality and device yieldElectric discharge tubesSemiconductor/solid-state device manufacturingPlasma treatmentEngineering

A system for in-situ plasma treatment. The system has a processing chamber, e.g., plasma chamber. The system has a first susceptor coupled within the chamber and a second susceptor facing the first susceptor and being within the chamber. The system has one or more power sources. Preferably, a first power source is characterized by a first frequency. The first power source is coupled to the first susceptor and the second susceptor. A second power source is characterized by a second frequency. The second power source is coupled to the first susceptor and the second susceptor. A switching device is coupled to the first power source and is coupled the second power source. The switching device is configured to selectively apply the first frequency to the first susceptor while the second frequency is applied to the second susceptor and is alternatively configured to selectively apply the first frequency to the second susceptor while the second frequency is applied to the first susceptor.

Owner:SILICON GENERAL CORPORATION

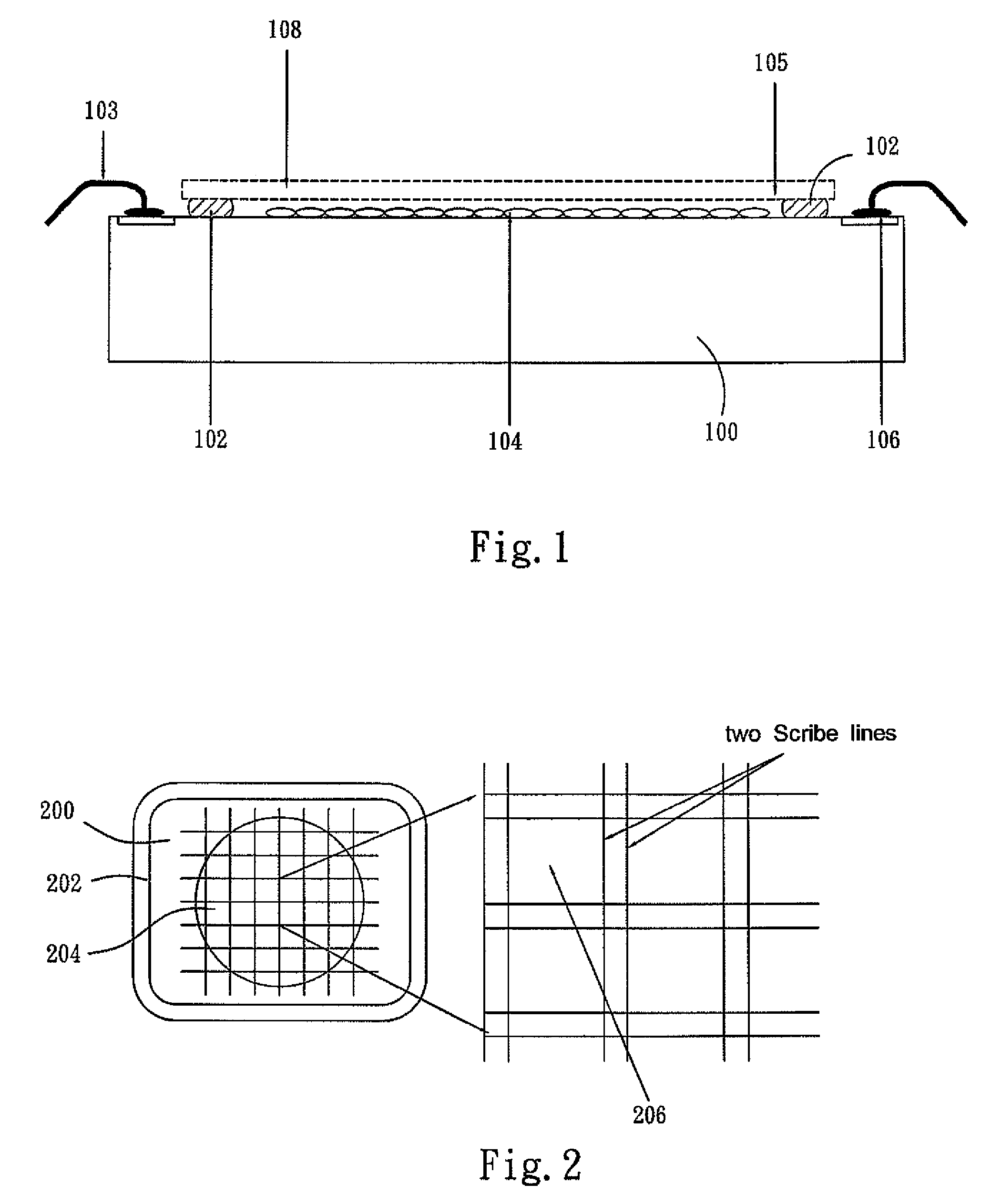

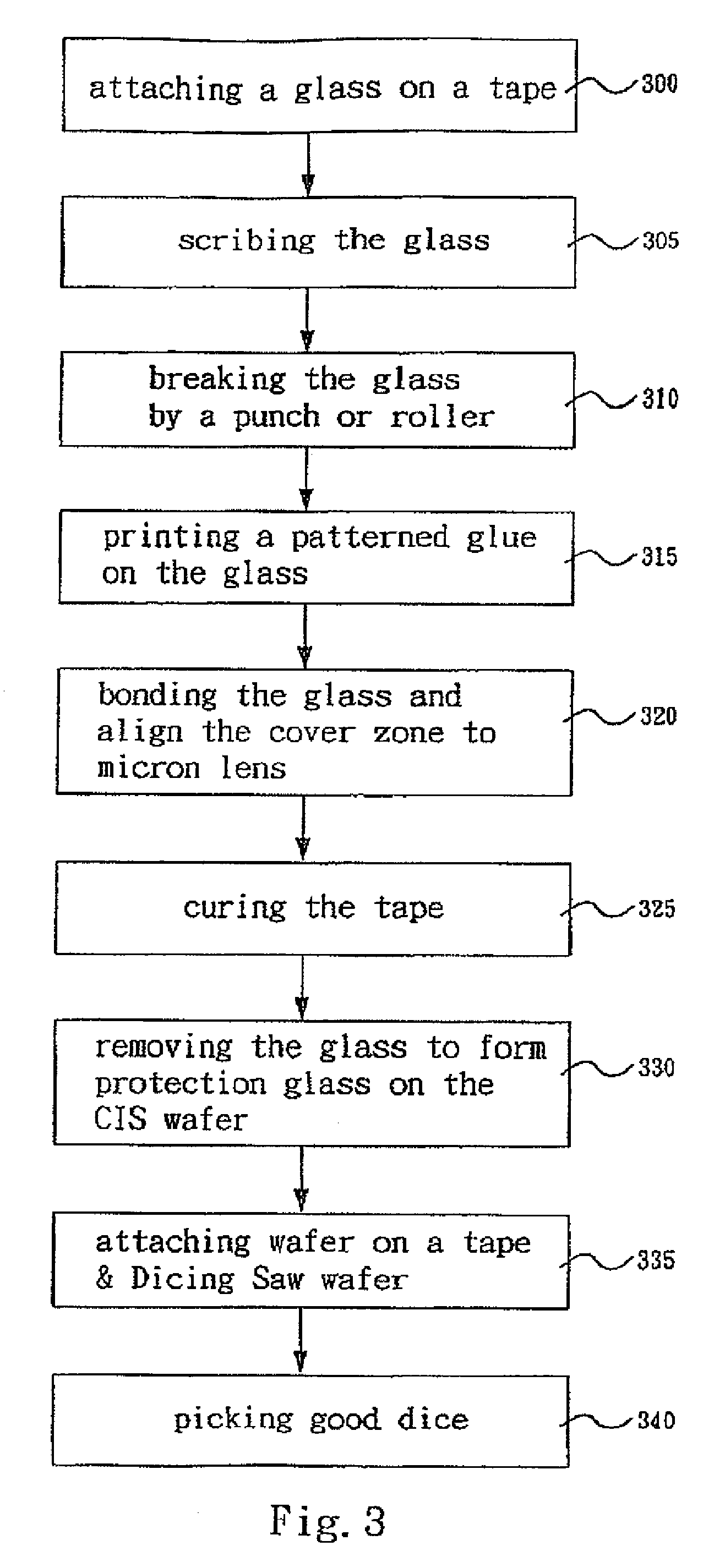

Method for image sensor protection

InactiveUS7335870B1Avoid Particle ContaminationSolid-state devicesSemiconductor/solid-state device manufacturingImage sensorEngineering

The method of forming image sensor protection comprises attaching a glass on a tape and scribing the glass with lines to define cover zones on the glass, the glass is then break by a rubber puncher followed by forming glue on the edge of the cover zones. The glass is bonded on a wafer with an image sensor to align the cover zones to a micron lens area of the image sensor, and then the tape is removed from the wafer, thereby forming glass with cover zones on the image sensor.

Owner:ADVANCED CHIP ENG TECH

Rare earth metal member and making method

InactiveUS20070003790A1Improve corrosion resistanceImprove plasma resistanceWashersElectric discharge tubesOrganic acidHalogen

By using a rare earth metal having a minimal content of impurity metal element, machining it into a member and cleaning with an organic acid-base capping agent, there is obtained a rare earth metal member composed entirely of a rare earth metal and containing not more than 100 ppm of impurity metal element in a sub-surface zone, which member is characterized by a high surface purity, a large grain size, minimized grain boundaries, and improved halogen resistance or corrosion resistance.

Owner:SHIN ETSU CHEM IND CO LTD

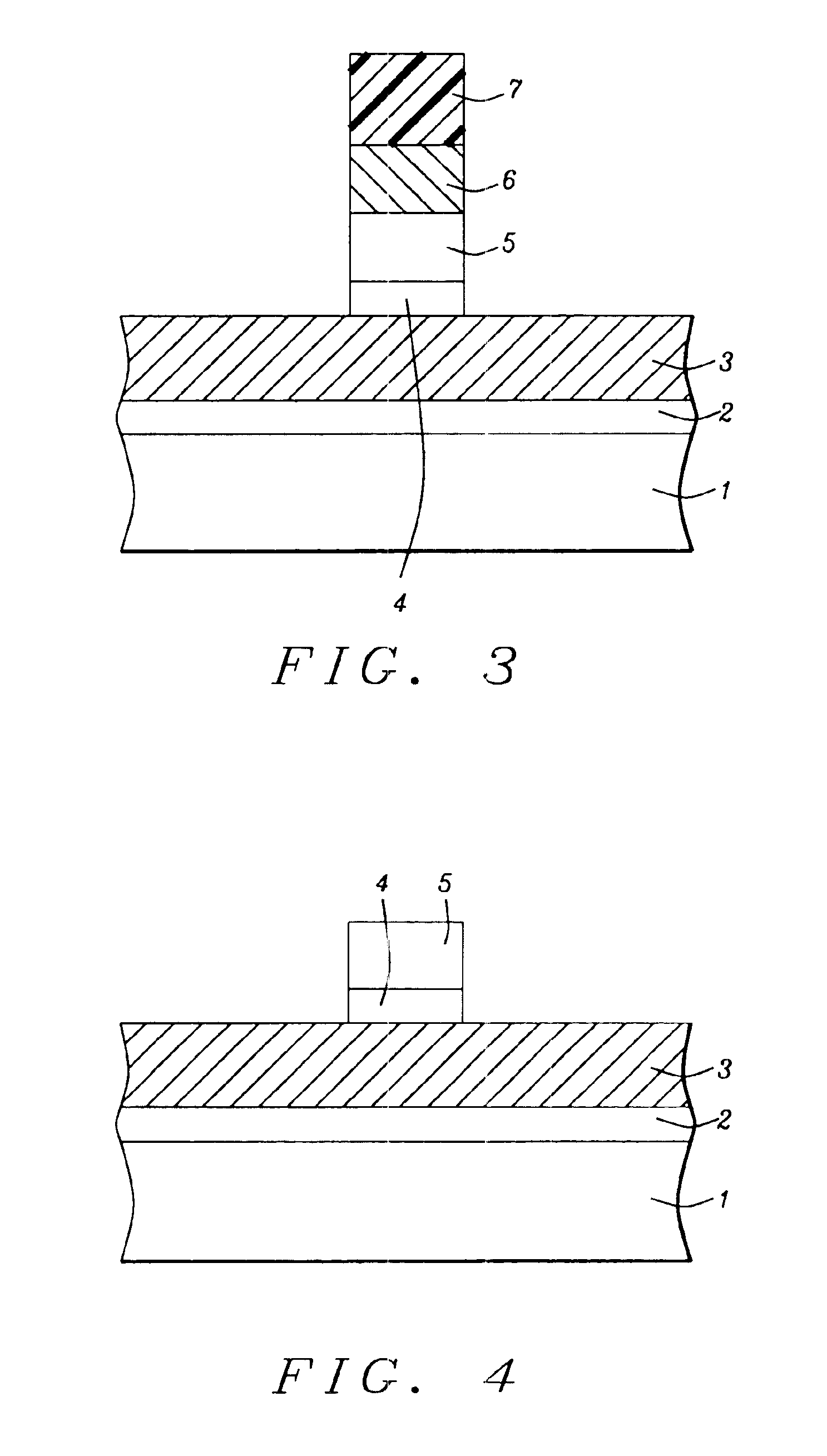

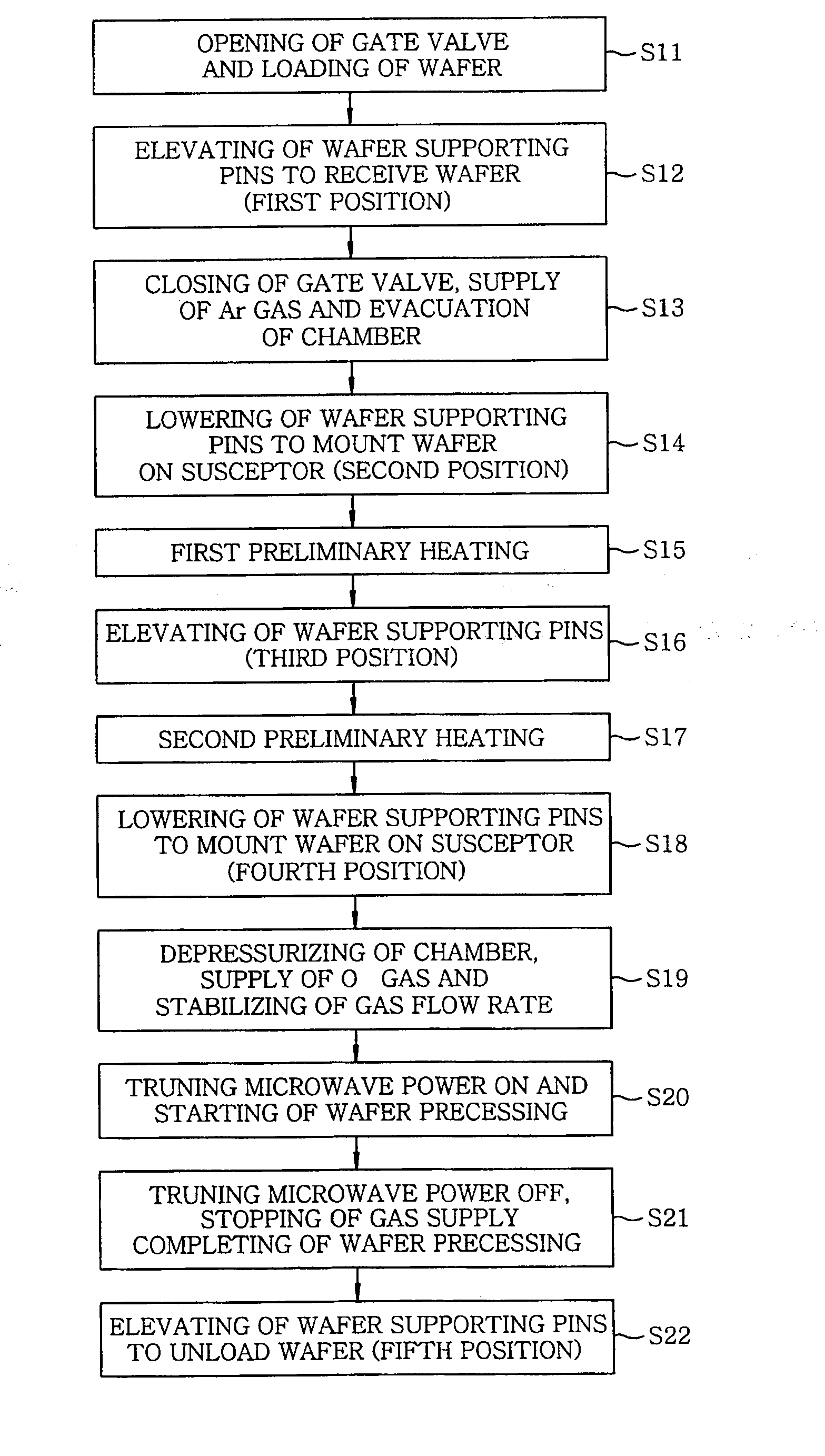

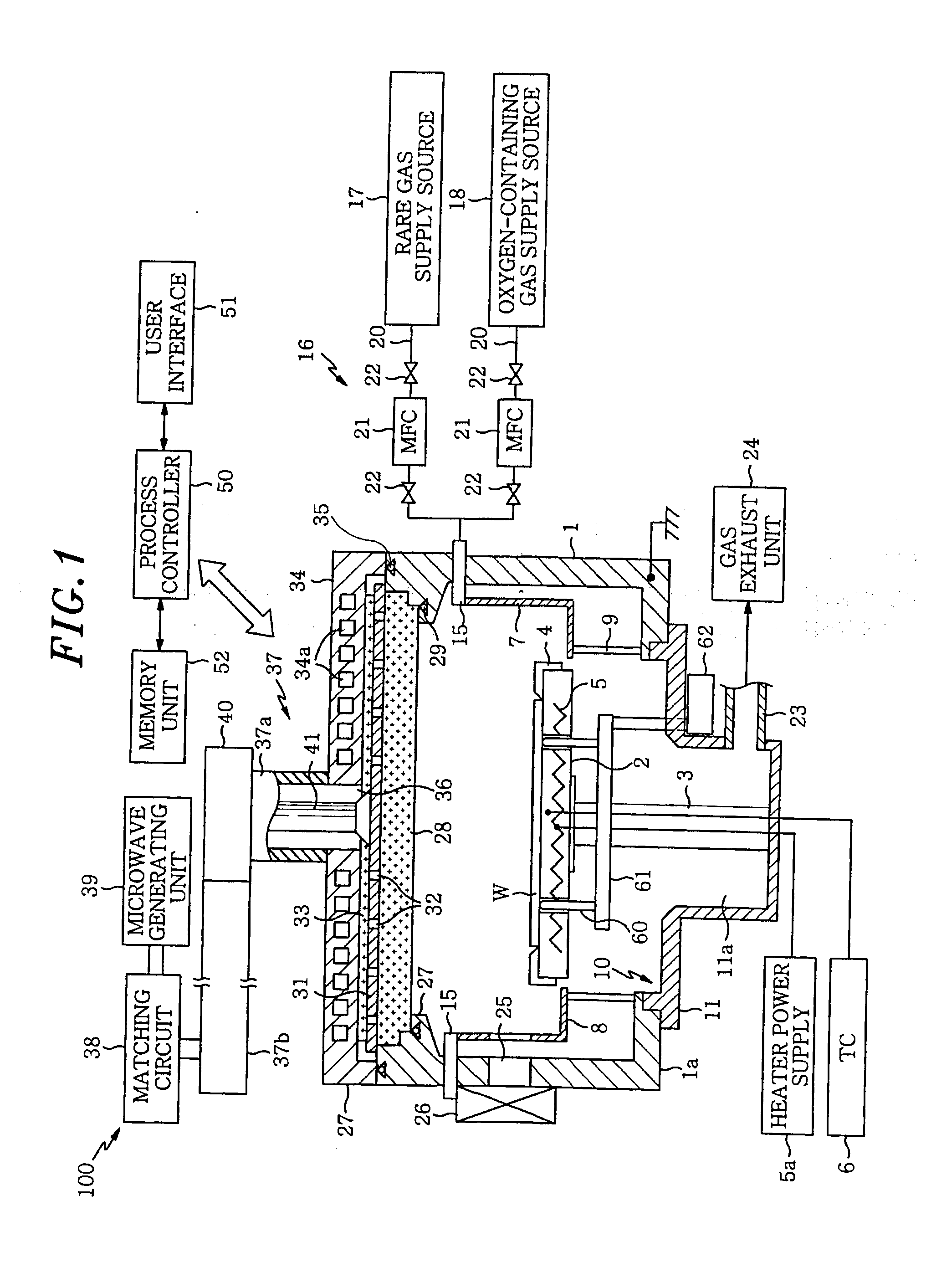

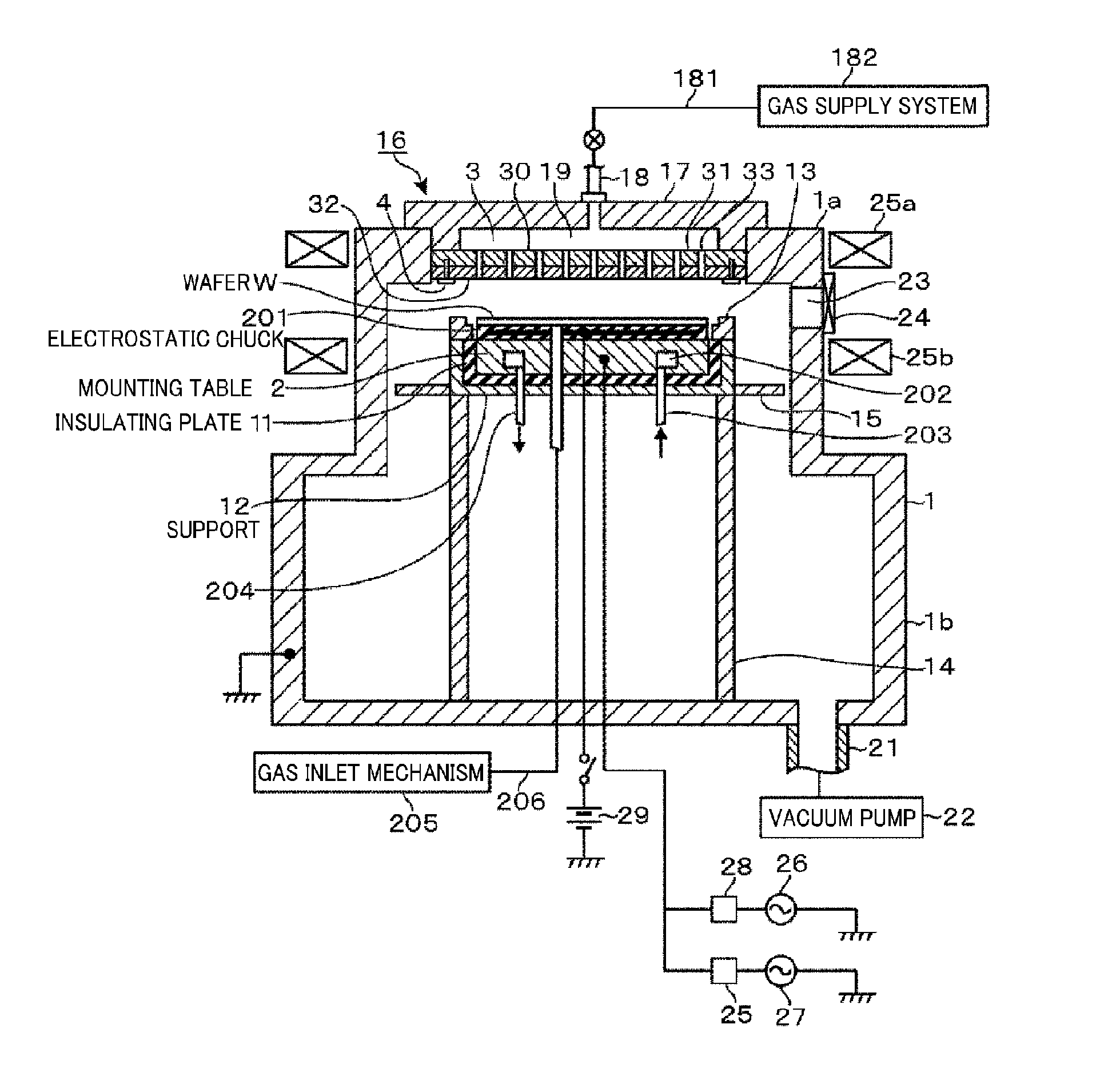

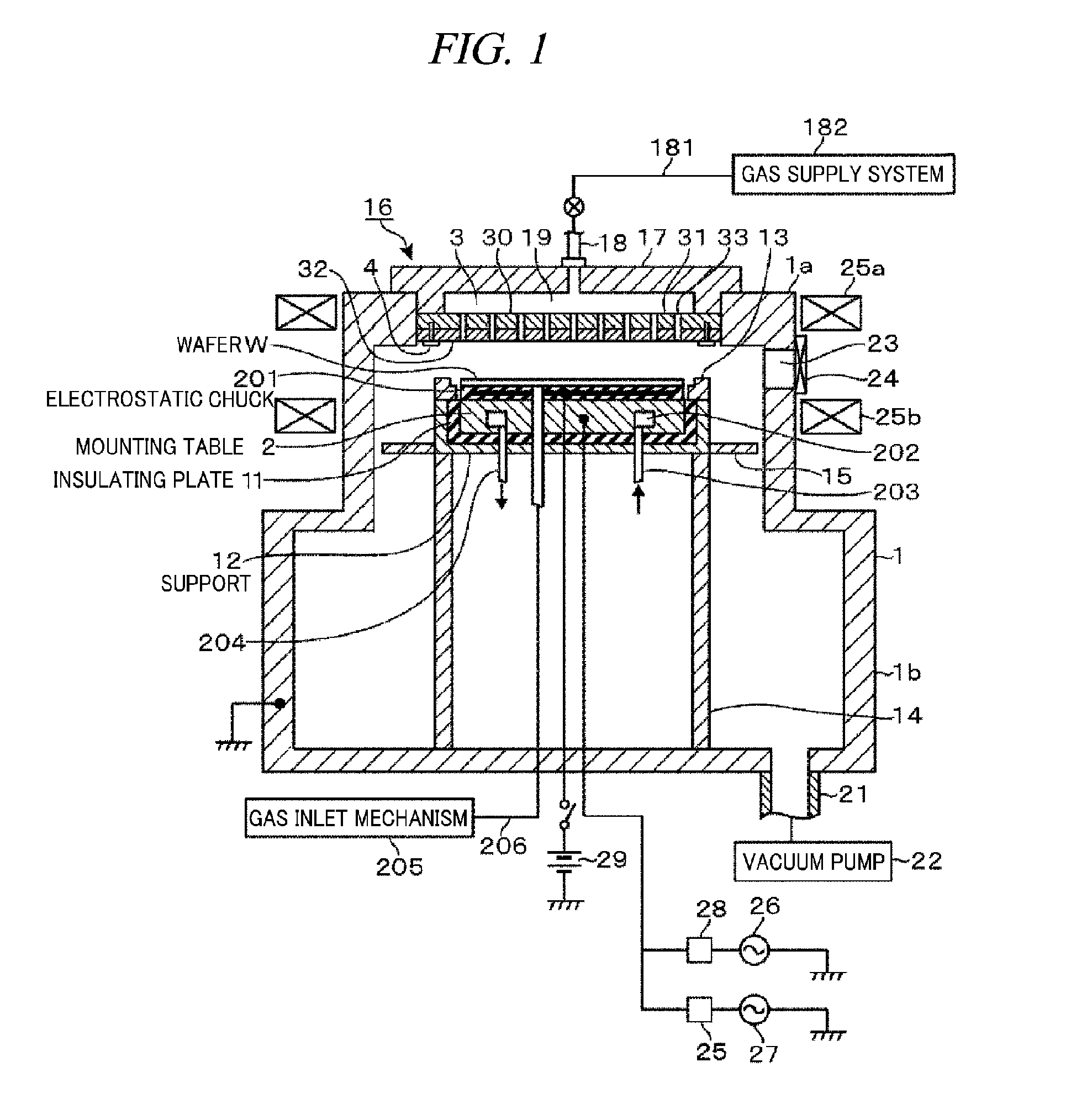

Substrate processing method and substrate processing apparatus

InactiveUS20100144159A1Avoid damageAvoid Particle ContaminationLiquid surface applicatorsElectric discharge tubesEngineering

In a substrate processing method, a substrate to be processed is mounted on a mounting table in a processing chamber of a substrate processing apparatus, and while heating the substrate by a heating unit through the mounting table to a processing temperature of 700° C. or higher, the substrate is processed. The substrate to be processed is loaded into the processing chamber, a first preliminary heating is performed until the substrate reaches a prescribed temperature while being mounted on the mounting table. Then, substrate supporting pins of the mounting table are elevated, and a second preliminary heating is performed in a state where the substrate is held on the substrate supporting pins. Then, the substrate supporting pins are moved down to mount the substrate on the mounting table and a process such as plasma oxidation is performed thereon.

Owner:TOKYO ELECTRON LTD

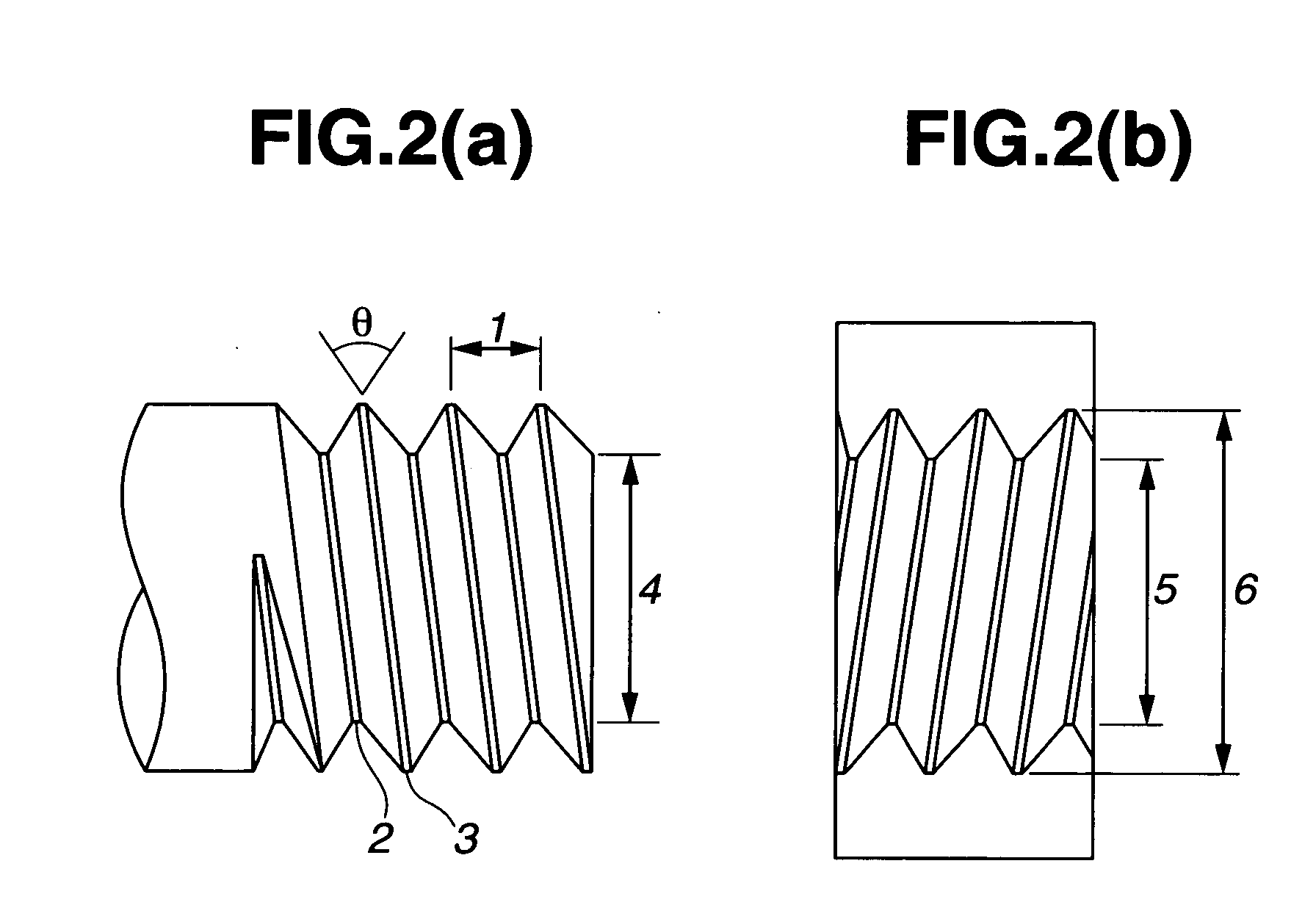

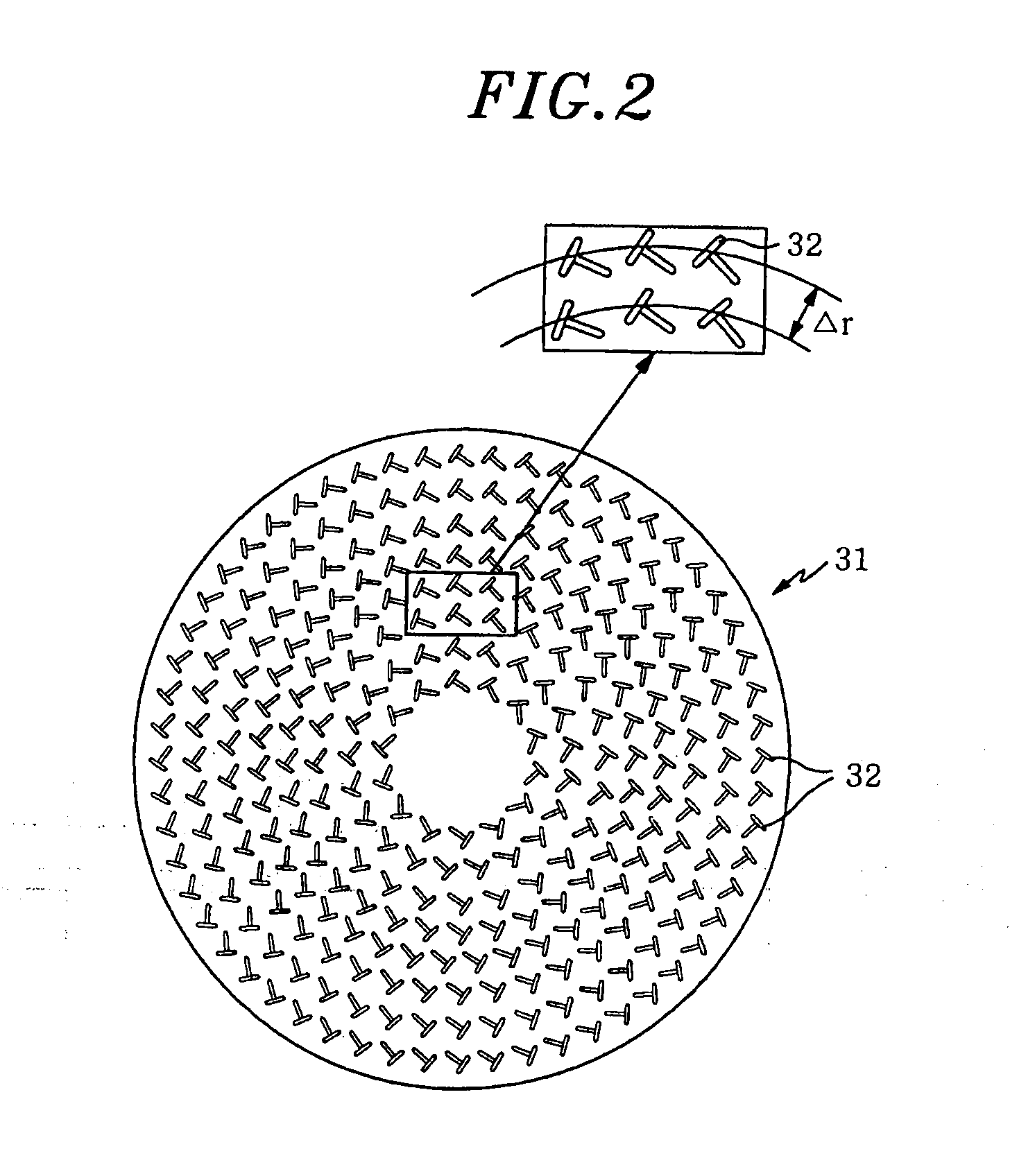

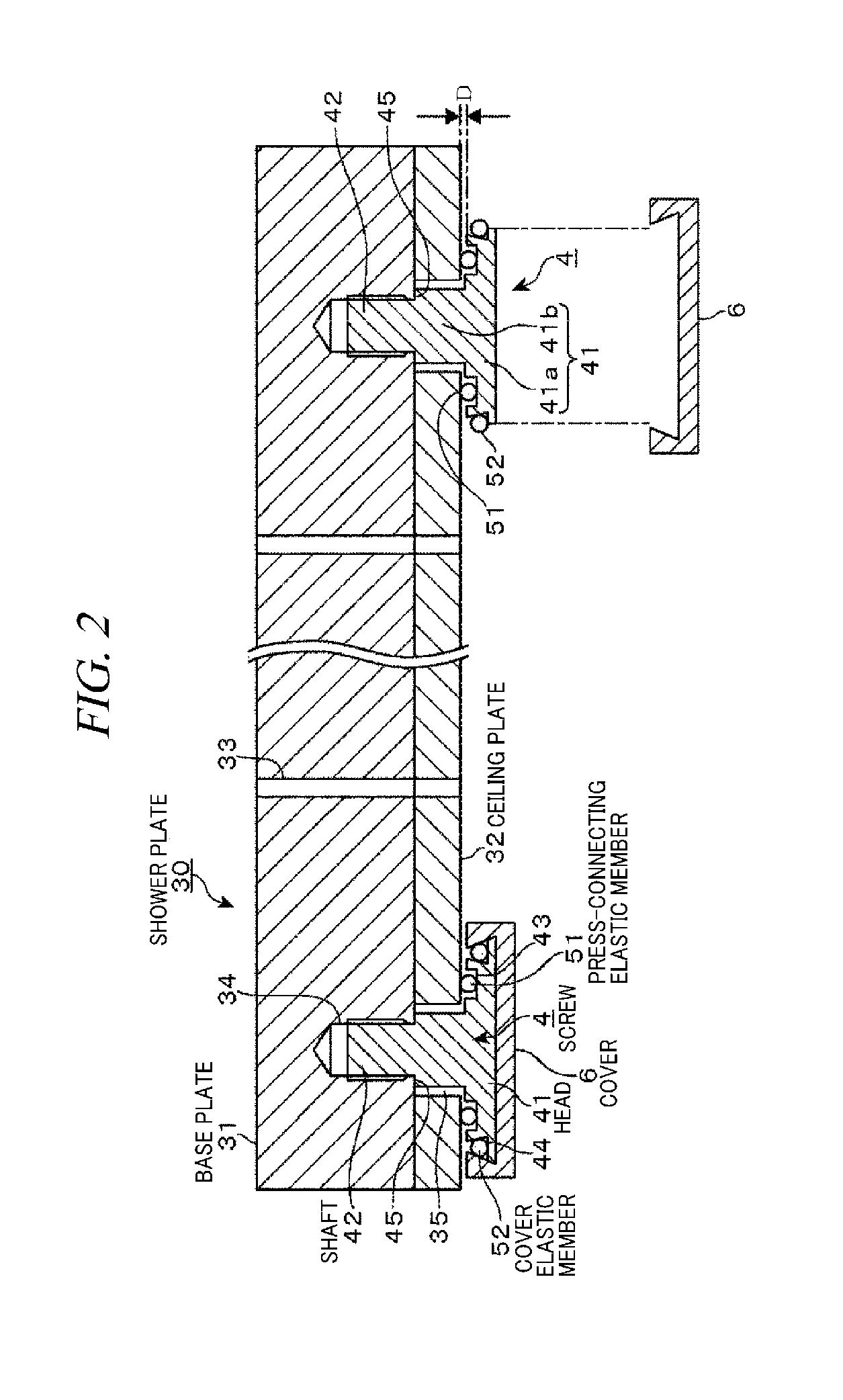

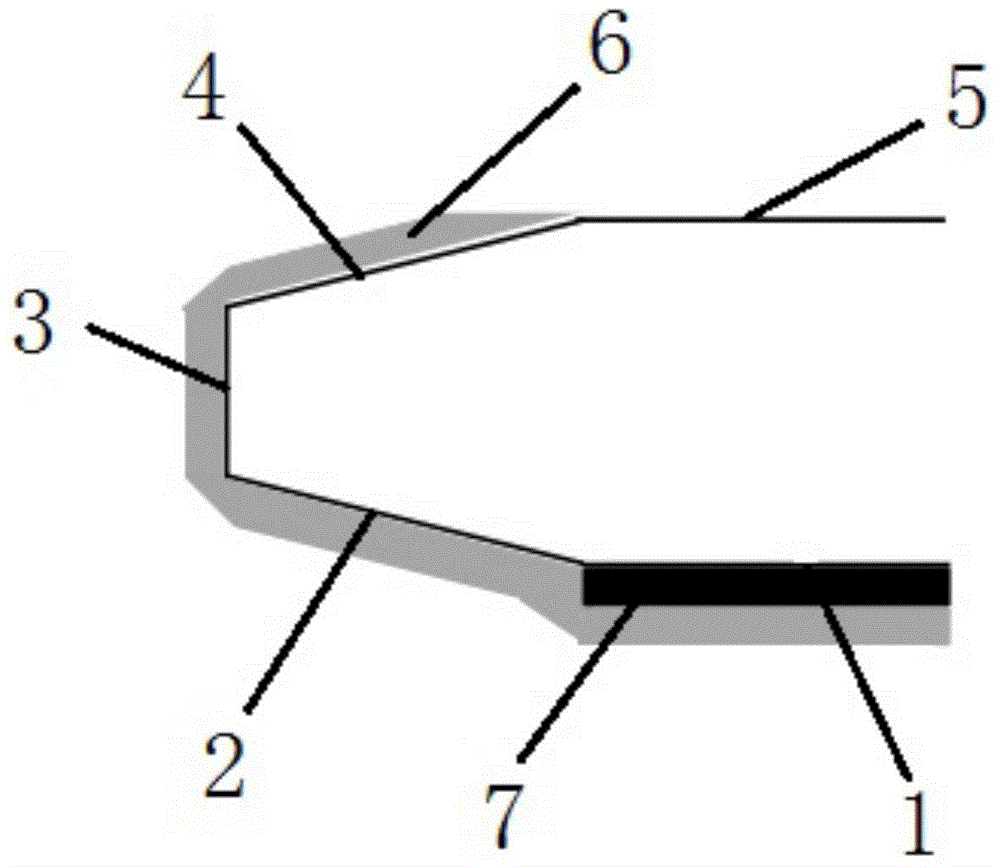

Gas shower structure and substrate processing apparatus

ActiveUS20110186229A1Avoid Particle ContaminationElectric discharge tubesDust removalEngineeringMechanical engineering

Screws 4 are inserted from a bottom surface of a ceiling plate 32 and screwed to a base plate 31, and the ceiling plate 32 and the base plate 31 are press-connected to each other by an elastic restoring force of an elastic member 51 interposed between a head of the screw 4 and the ceiling plate 32. A gap is formed between the head and the ceiling plate 32. Further, a periphery of the head is covered with a cover via a ring-shaped elastic member 52. In another embodiment, a periphery of a base plate 31 is protruded from a periphery of a ceiling plate 32, and the protruded portion of the base plate 31 and a ring-shaped clamp positioned at an outer side of the ceiling plate 32 are joined by screws. Here, an elastic member is interposed between the clamp and the ceiling plate 32.

Owner:TOKYO ELECTRON LTD

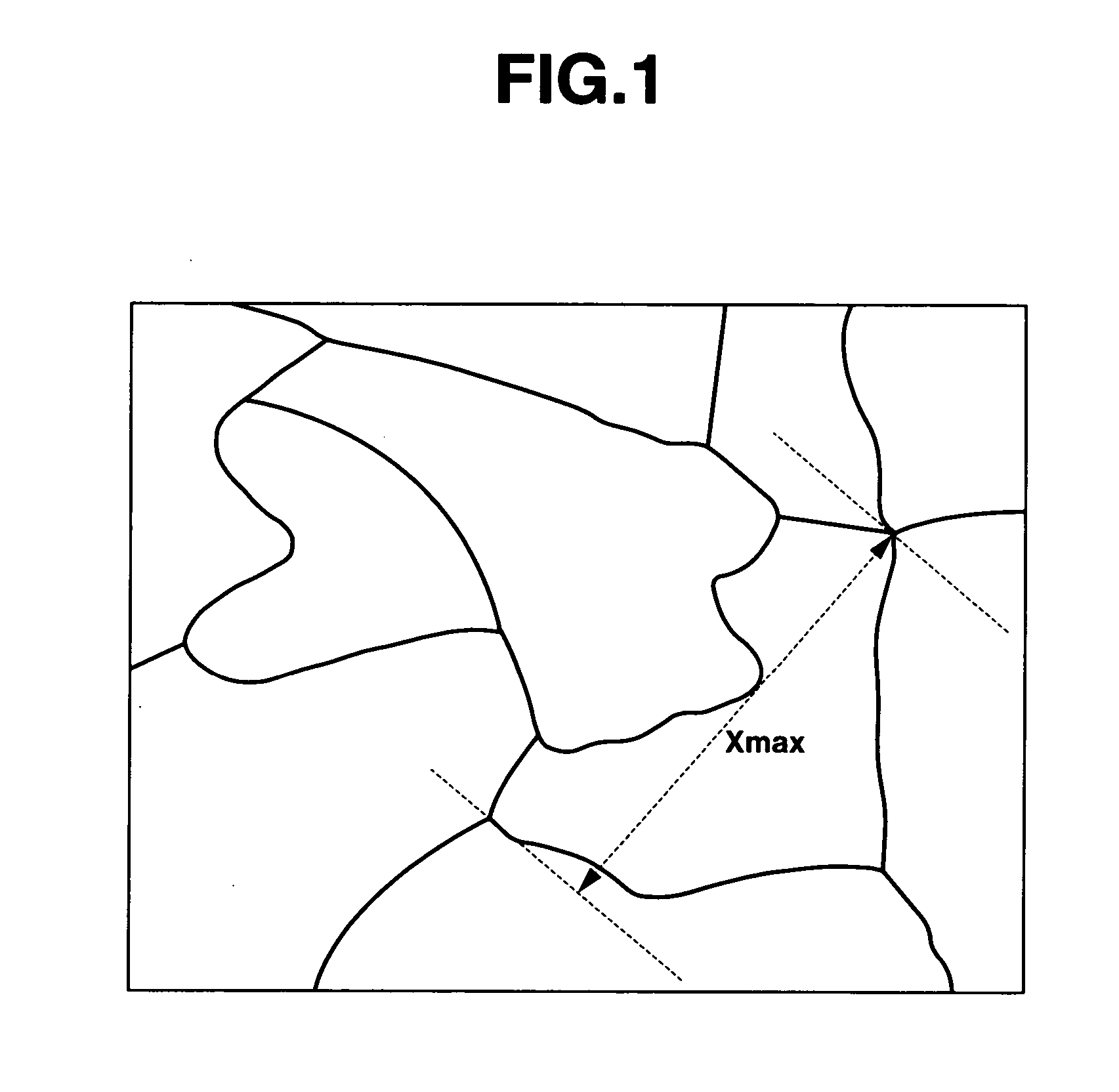

Edge exposure apparatus, coating and developing apparatus, edge exposure method and coating and developing method, and storage medium

InactiveUS20080088809A1High accuracy of shapeHigh accuracy of widthLiquid surface applicatorsLiquid processingResistEngineering

An edge exposure apparatus performing an exposure process on an edge portion of a wafer having a coating film (resist film) formed thereon includes position detection means for detecting positional data of an outer edge of a wafer held by a spin chuck, an exposure portion for performing an exposure process on the edge portion of the wafer, a development nozzle supplying a developer to the exposed region, and alignment means for horizontally moving the spin chuck. An exposure process is performed by the exposure portion on the edge portion of the wafer held by the spin chuck while the alignment means is controlled, based on the positional data of the outer edge of the wafer which is detected by the position detection means, such that the positional relation between the outer edge of the wafer and the exposure portion is kept constant.

Owner:TOKYO ELECTRON LTD

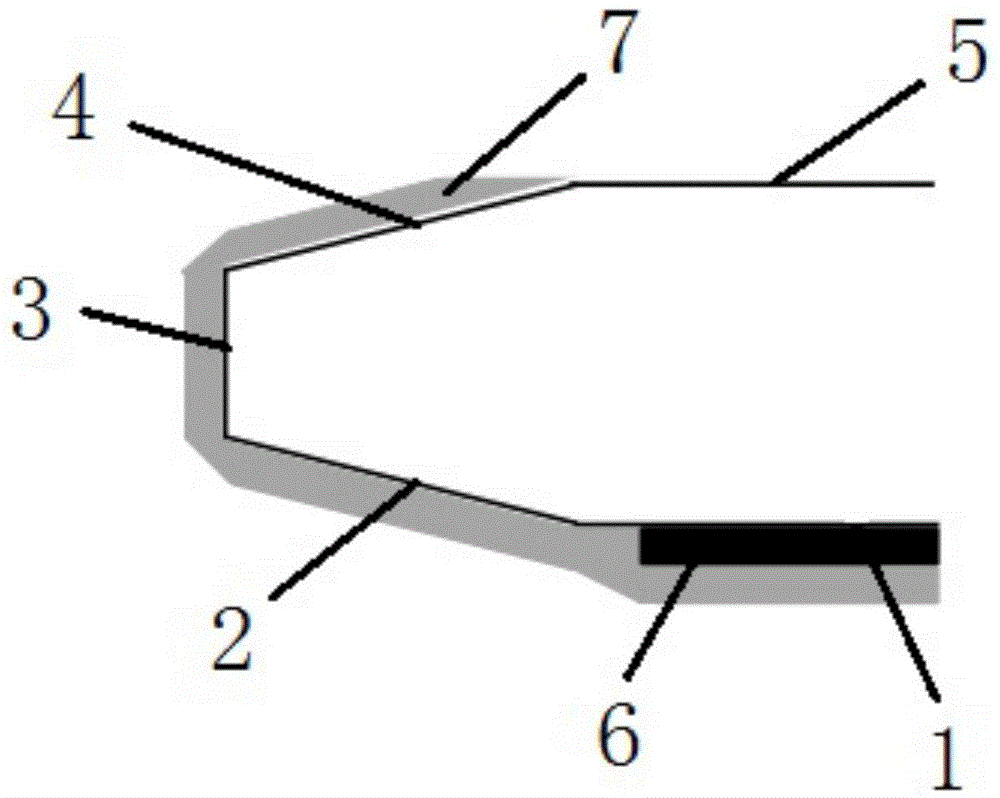

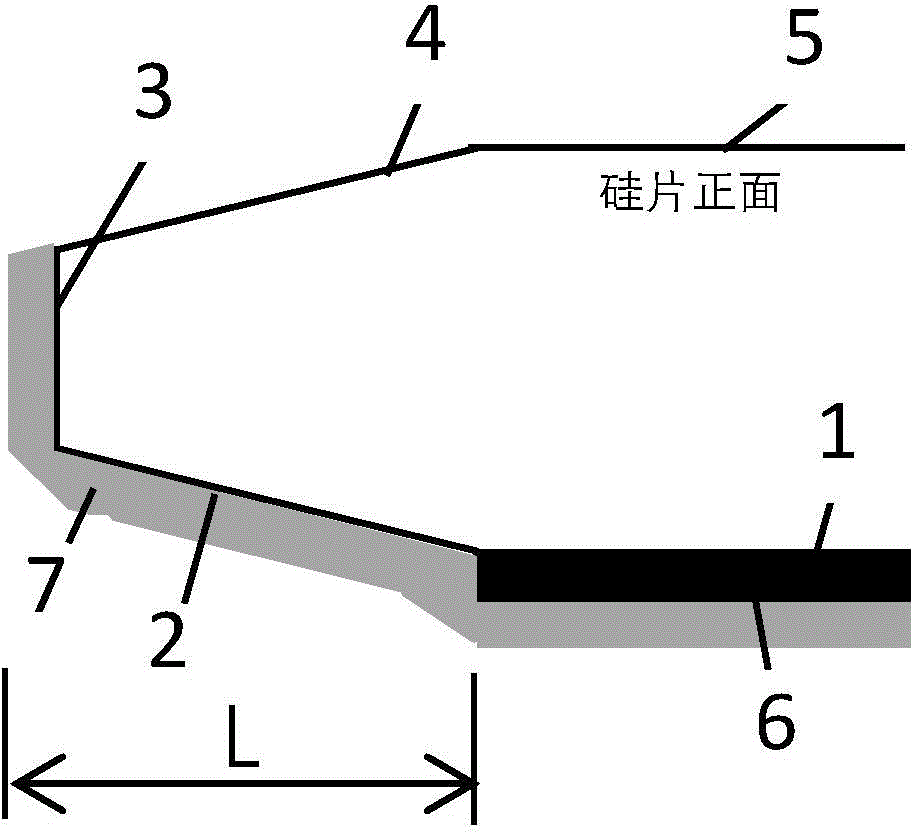

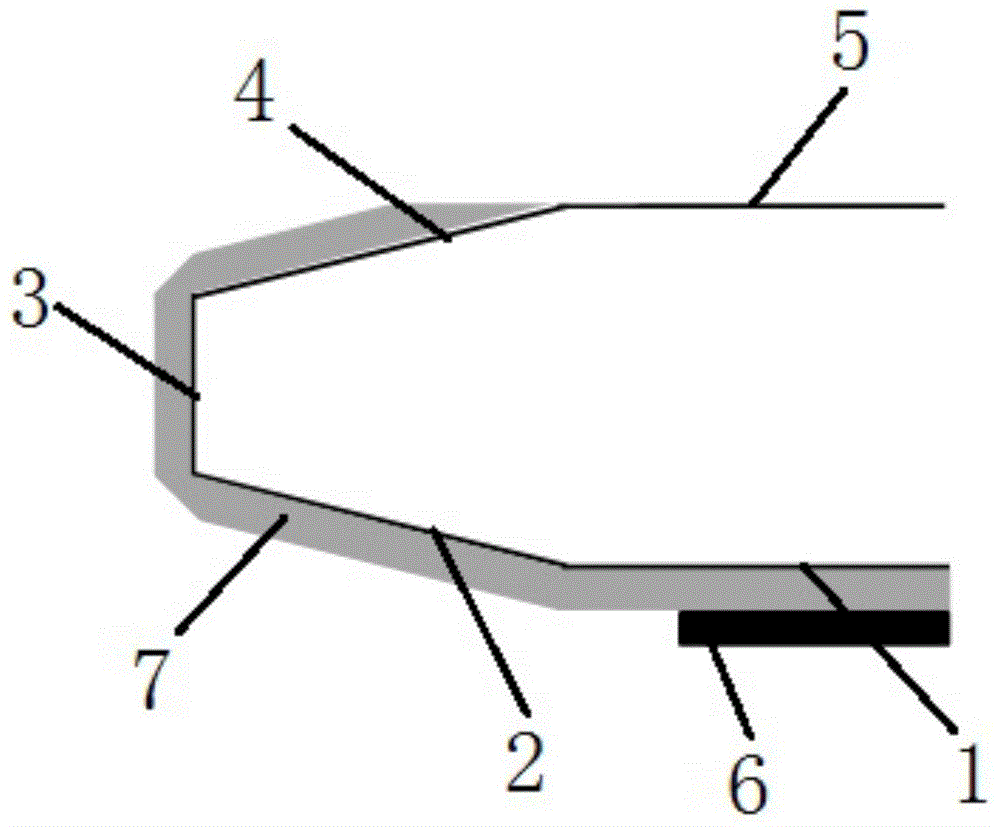

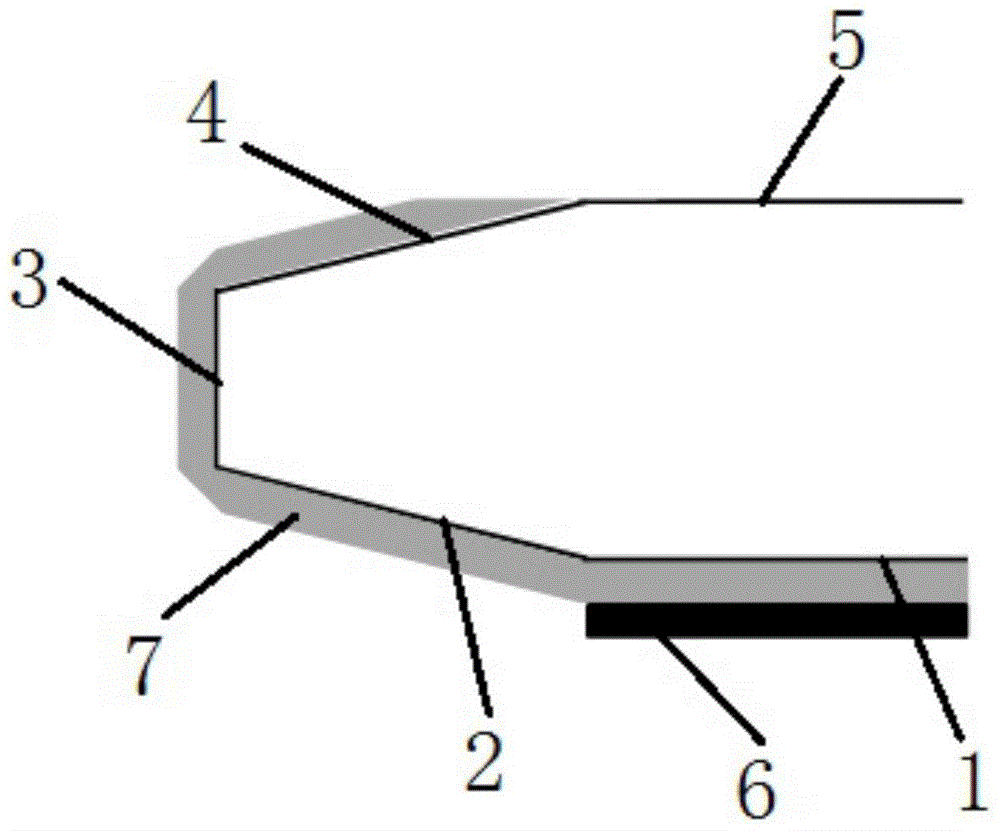

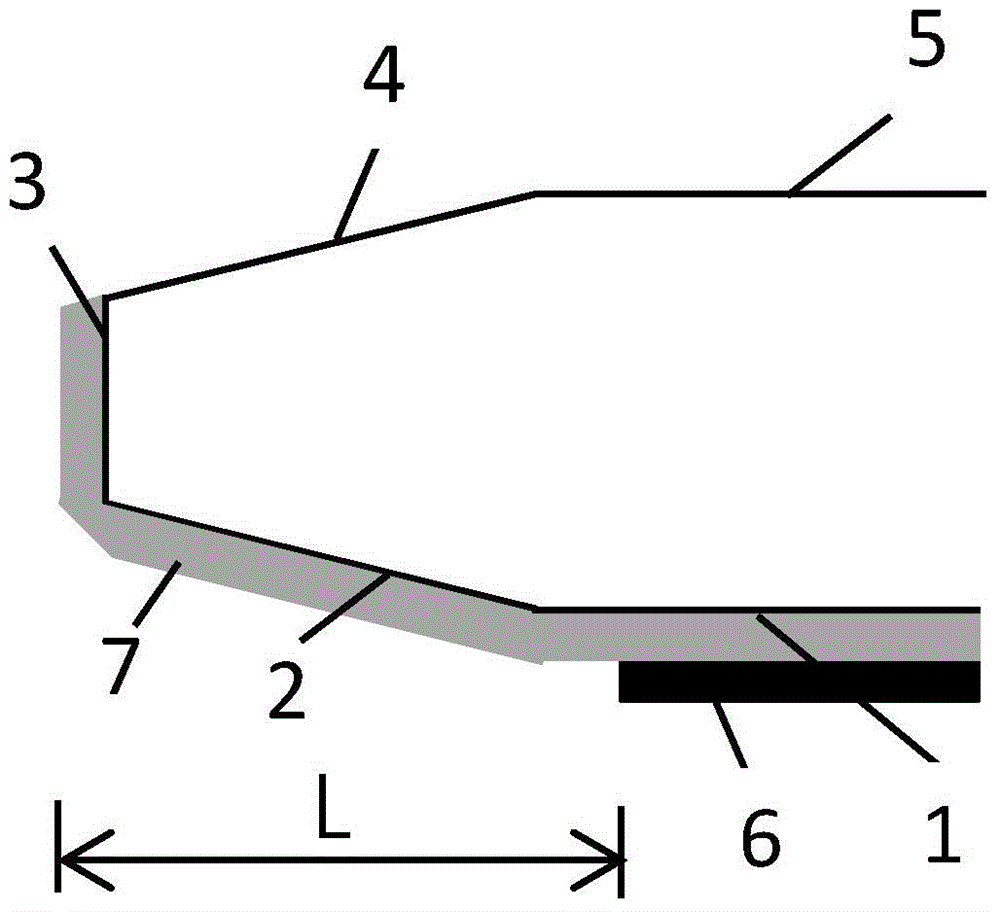

De-edged super back seal layer structure for silicon wafer and manufacturing method thereof

ActiveCN106158771AAchieve seamless connectionNo stratificationSemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon dioxide

The invention provides a de-edged super back seal layer structure for a silicon wafer. The structure comprises a silicon dioxide back seal layer, wherein the silicon dioxide back seal layer is covered on the back surface of the silicon wafer; and a polycrystalline silicon back seal layer, wherein the polycrystalline silicon back seal layer is covered on the outer side of the silicon dioxide back seal layer and covers the back surface of the silicon wafer, a back surface slope edge area and an edge area. According to the de-edged super back seal layer structure for the silicon wafer, the positive surface slope edge of the silicon wafer only has monocrystalline silicon serving as a body material, and has a high-quality smooth surface, which hardly has no difference with a polished surface. The monocrystalline silicon layer is grown on the positive surface slope edge and the polished surface of the silicon wafer during epitaxy, so that seamless connection can be realized, stratification phenomenon does not occur, the problems of particle pollution, edge dislocation and pyramid in epitaxy are also solved, and process yield rate is improved.

Owner:上海中欣晶圆半导体科技有限公司

Nanostructured titania coated titanium

InactiveUS20030049449A1Low operating torqueHigh resistanceMaterial nanotechnologyPigmenting treatmentNanometreBall valve

A ball valve for use in the pressure acid leaching of nickel ores is disclosed. The valve has a valve body and a ball centrally positioned in the valve body, which has a central passage rotatable in the valve body between open and closed positions. At least one seat is disposed between the ball and the valve body. The ball and seat each comprise a titanium substrate and an ultrafine or nanostructured titania coating. The titania can include from 5 to 45 volume percent of a second phase material that is immiscible with the titania and exhibits corrosion resistance.

Owner:MOGAS IND +1

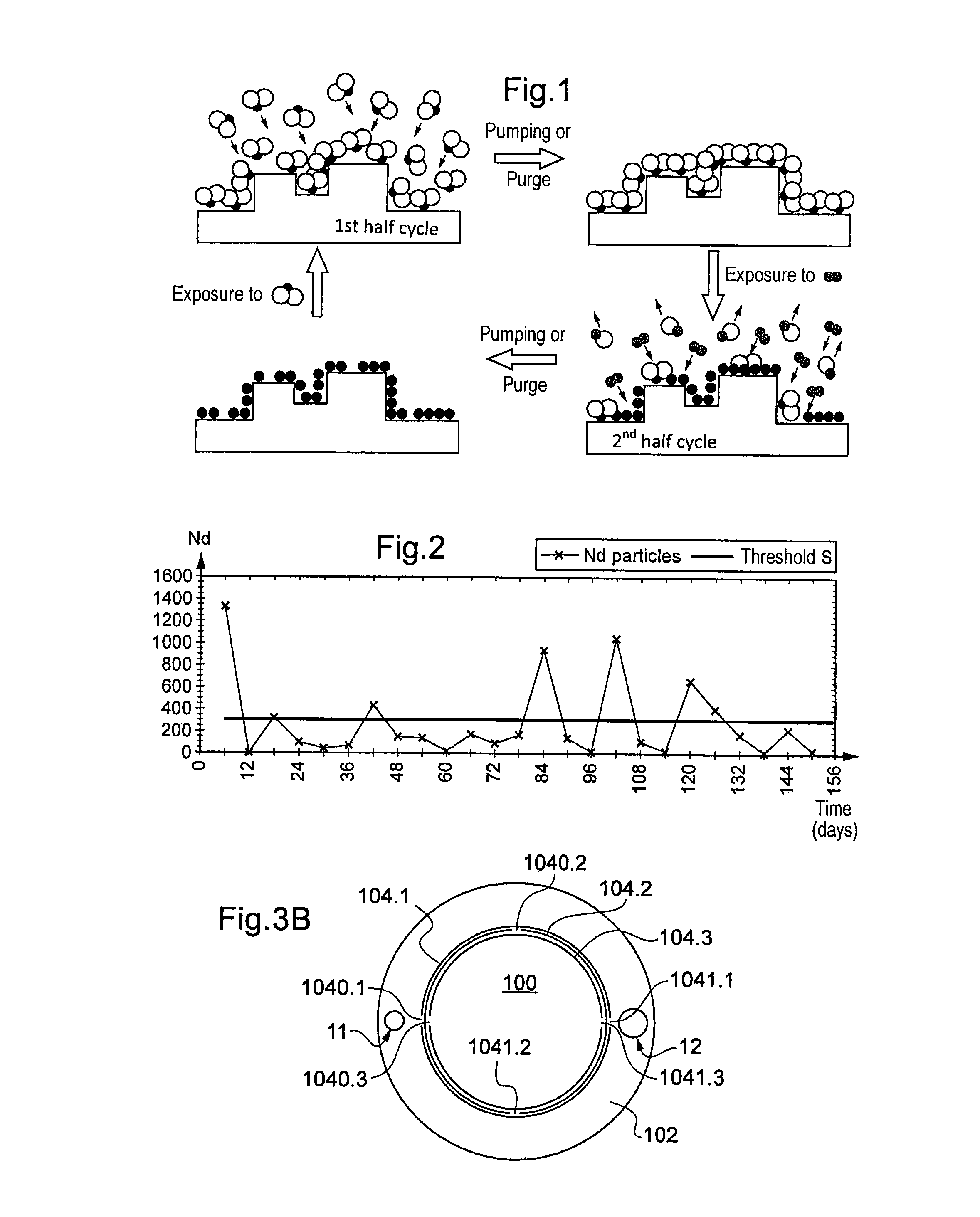

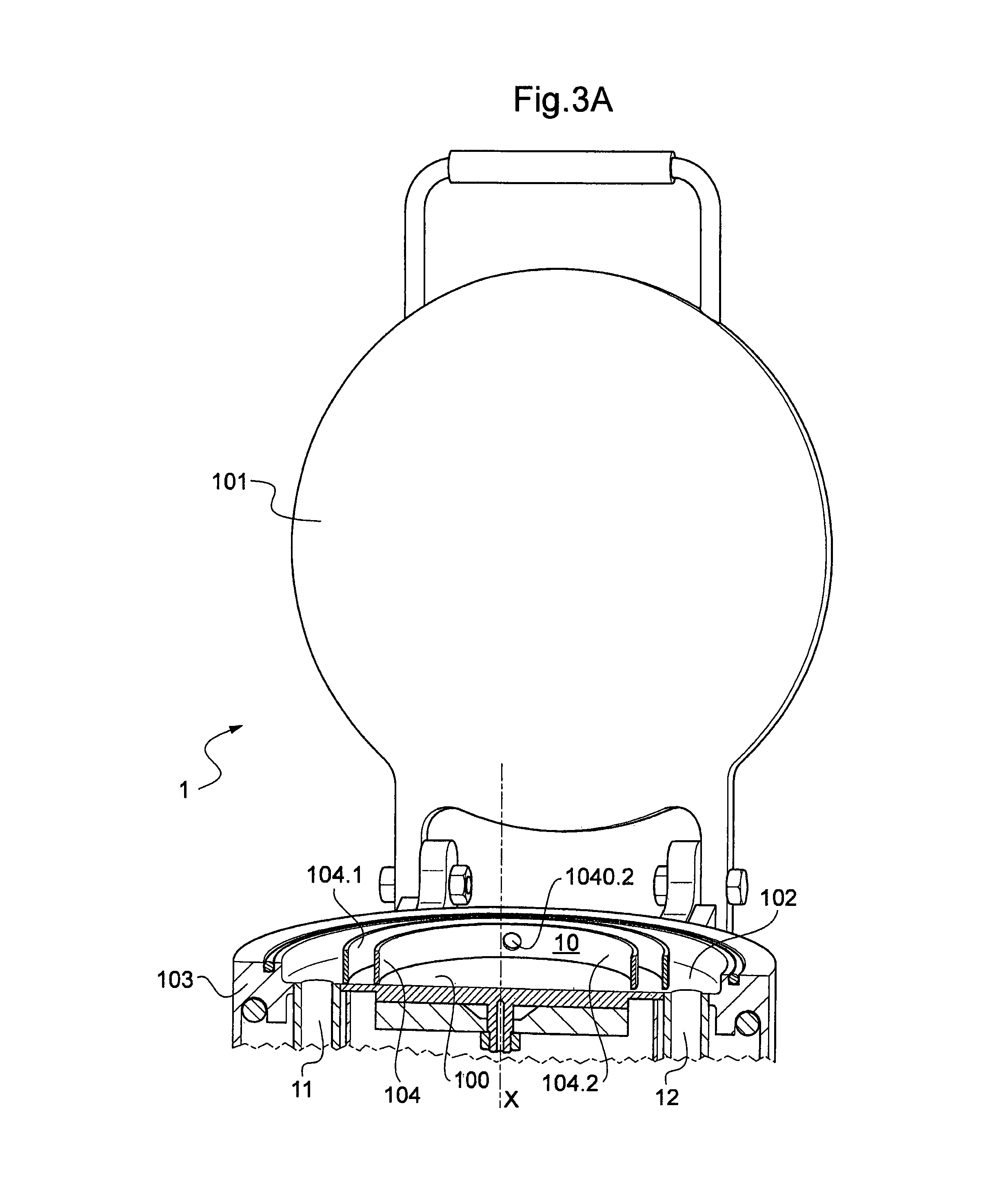

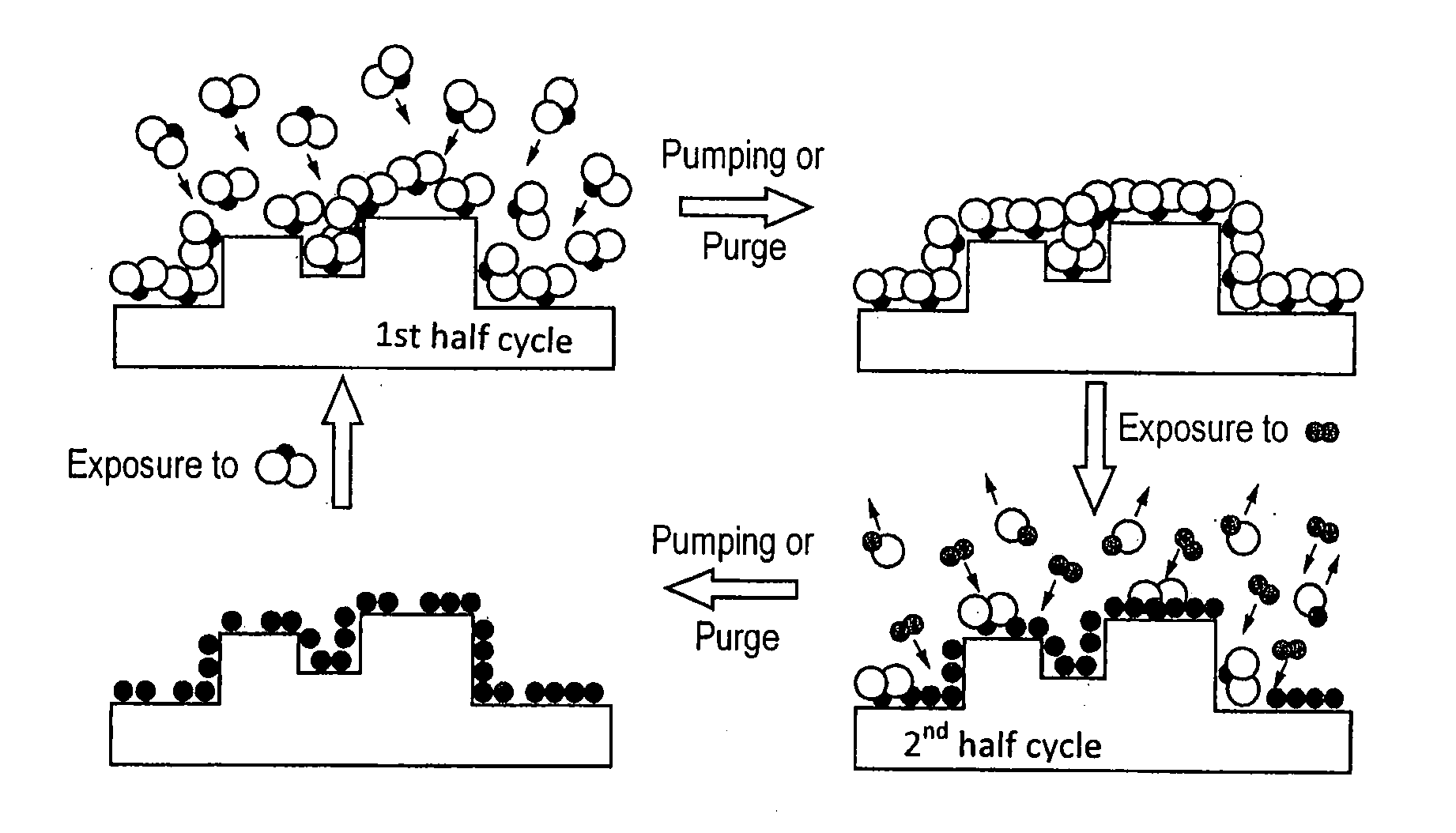

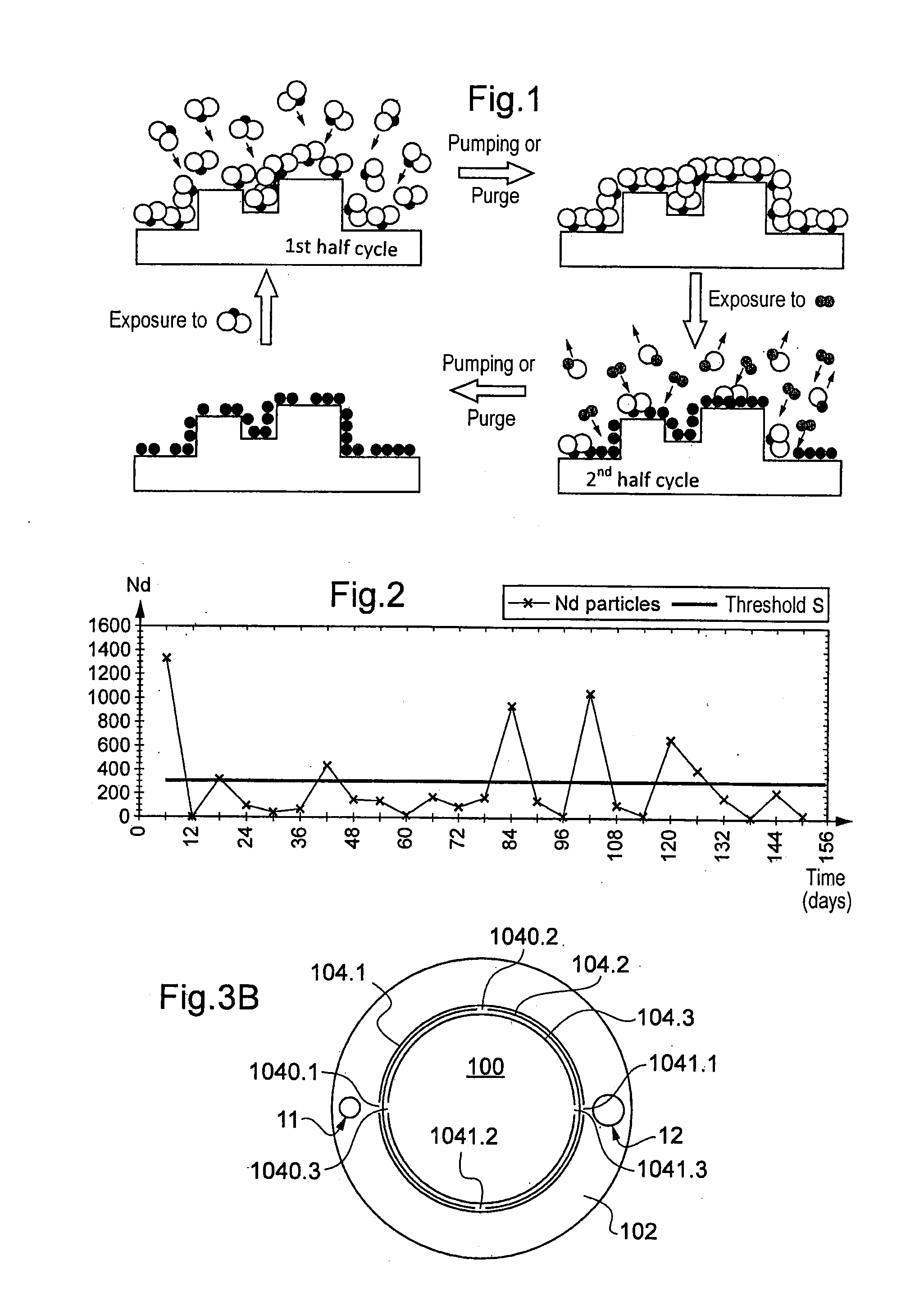

Reactor for atomic layer deposition (ALD), application to encapsulation of an OLED device by deposition of a transparent AI2O3 film

InactiveUS9083005B2Reduce in quantityAvoid Particle ContaminationElectroluminescent light sourcesSolid-state devicesEngineeringChicane

The present invention relates to a reactor for atomic layer deposition (ALD), comprising a reaction chamber comprising a platen and bounded internally by surfaces; at least one inlet orifice and at least one outlet orifice, each emerging from one of the surfaces bounding the chamber. The reactor furthermore comprises, within it, at least one wall apertured with at least one orifice, the apertured wall extending around the platen and over at least most of the height between the lower surface and the upper surface, at least one orifice in at least one of the apertured walls not facing the inlet orifice so as to form chicanes in the flow of gaseous precursor from each inlet orifice to the platen.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

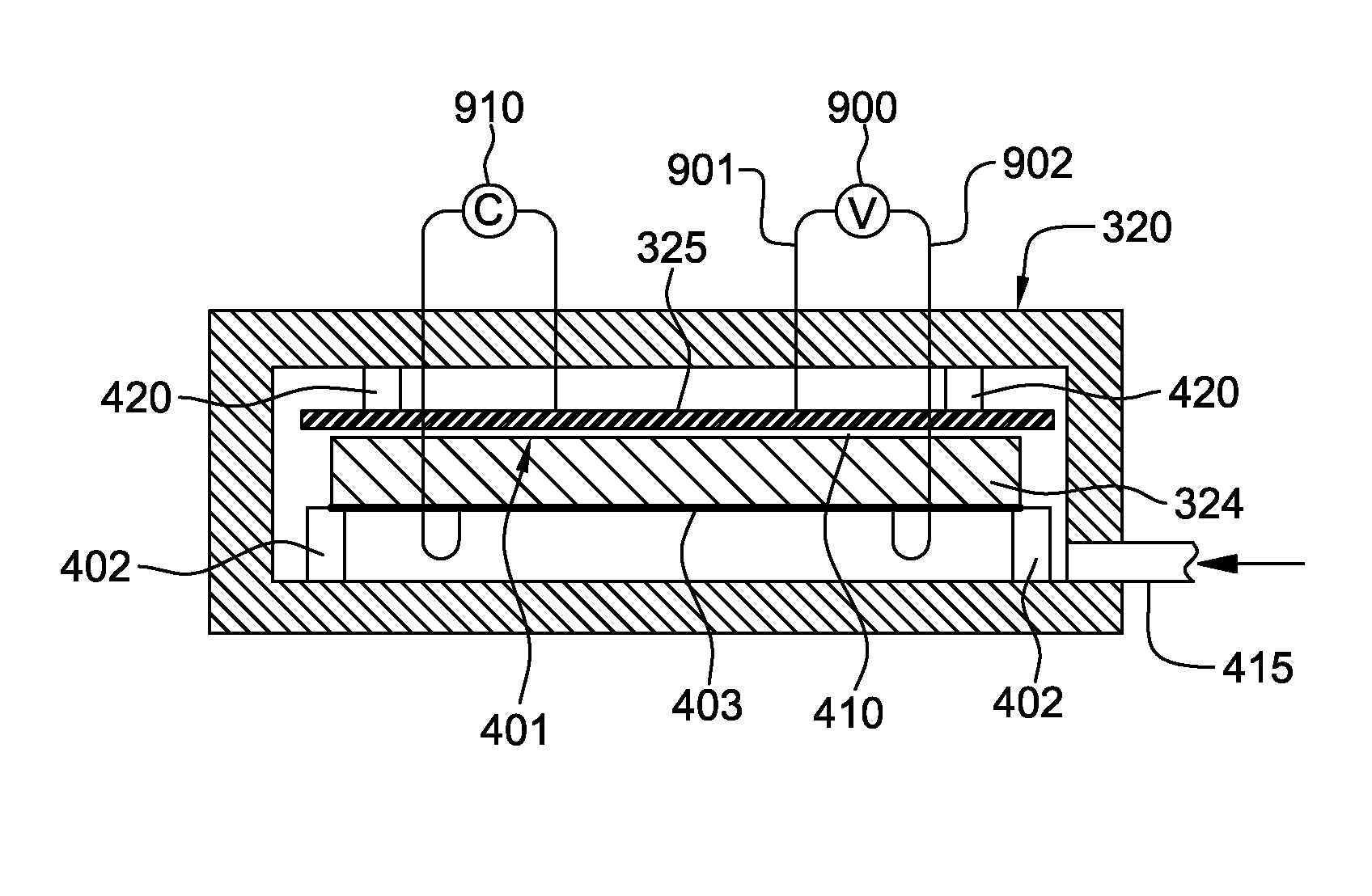

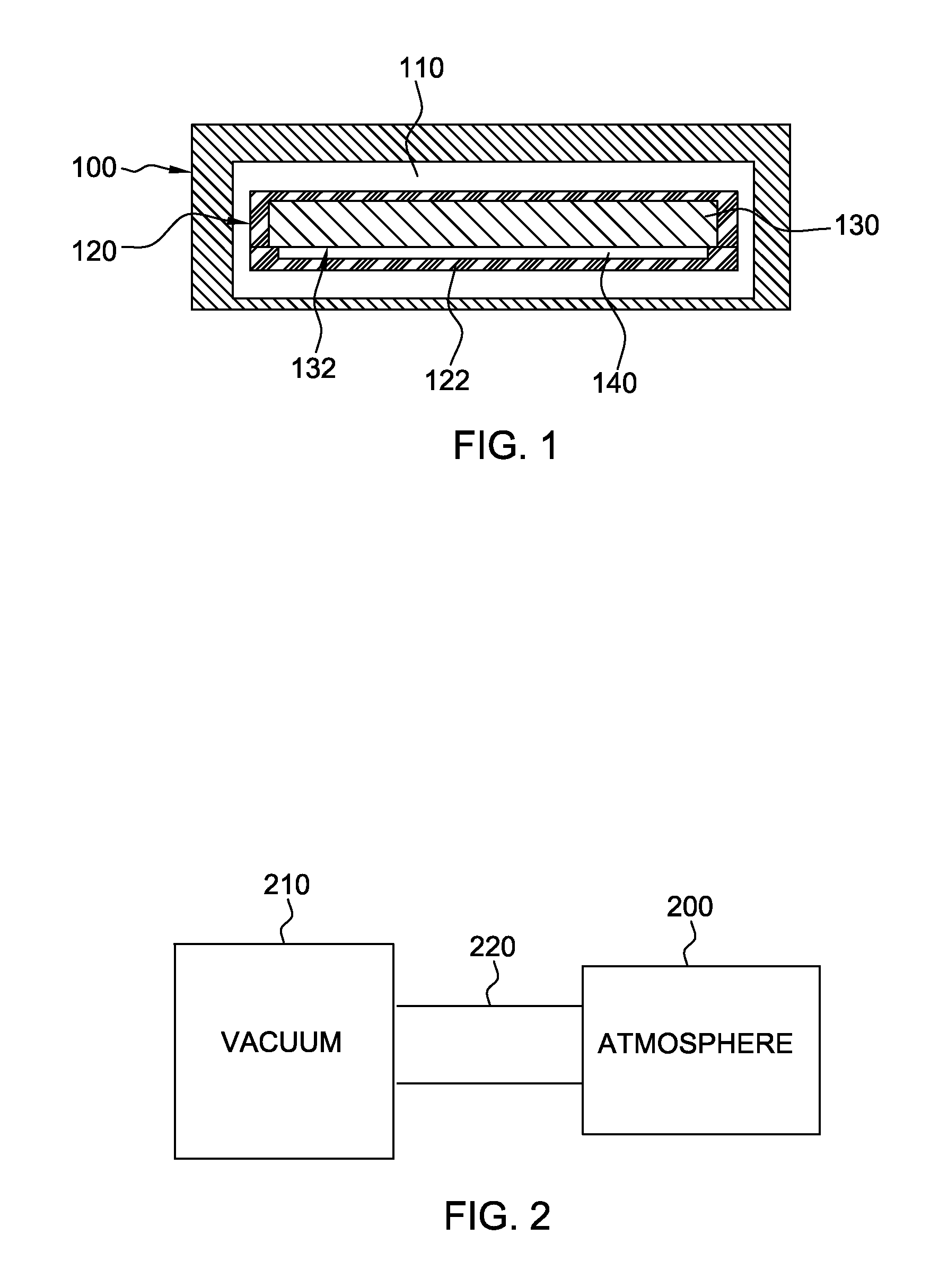

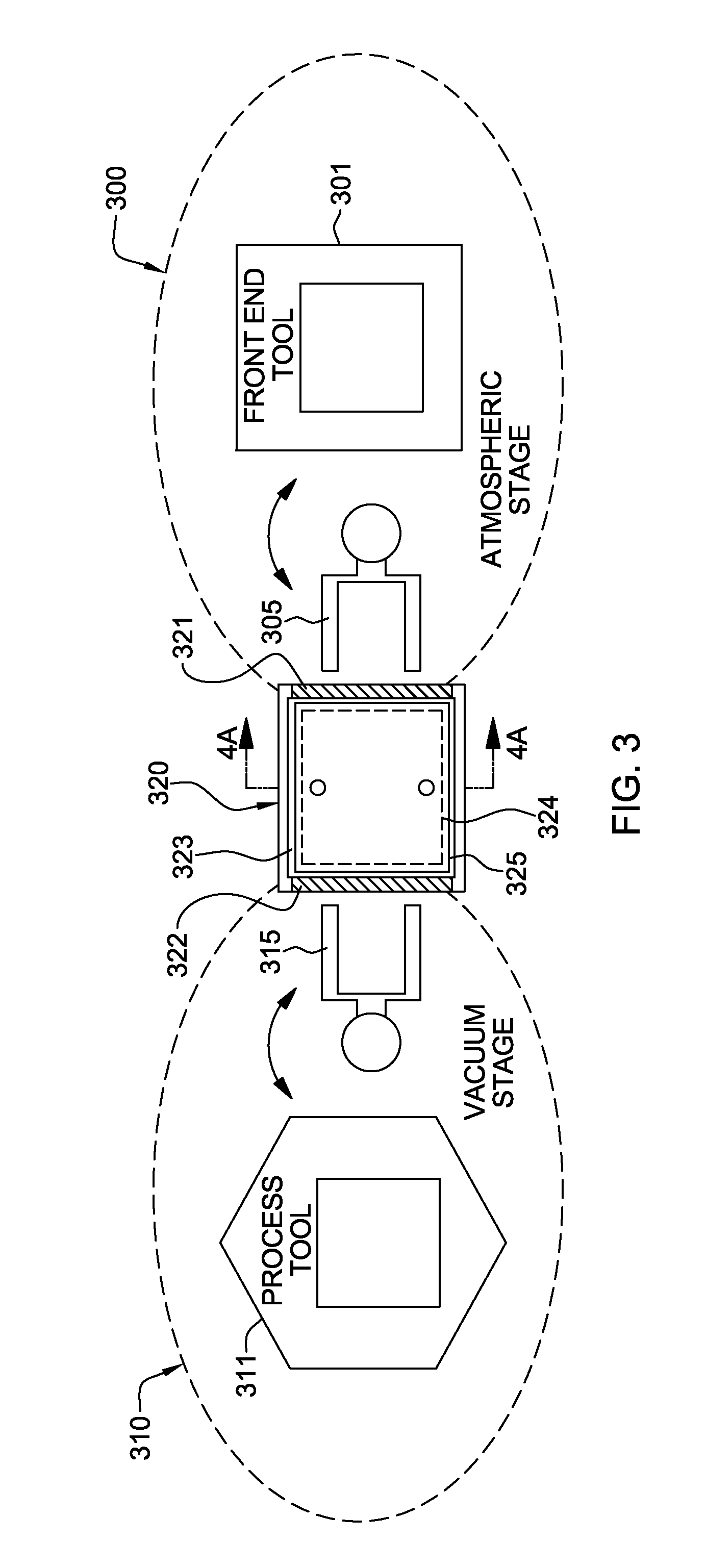

Apparatus with surface protector to inhibit contamination

InactiveUS8888086B2Avoid Particle ContaminationOvercomes shortcomingWorkpiece holdersSemiconductor/solid-state device manufacturingEngineeringDiffusion barrier

An apparatus is provided for protecting a surface of interest from particle contamination, and particularly, during transitioning of the surface between atmospheric pressure and vacuum. The apparatus includes a chamber configured to receive the surface, and a protector plate configured to reside within the chamber with the surface, and inhibit particle contamination of the surface. A support mechanism is also provided suspending the protector plate away from an inner surface of the chamber. The support mechanism holds the protector plate within the chamber in spaced, opposing relation to the surface to provide a gap between the protector plate and the surface which presents a diffusion barrier to particle migration into the gap and onto the surface, thereby inhibiting particle contamination of the surface.

Owner:SEMATECH

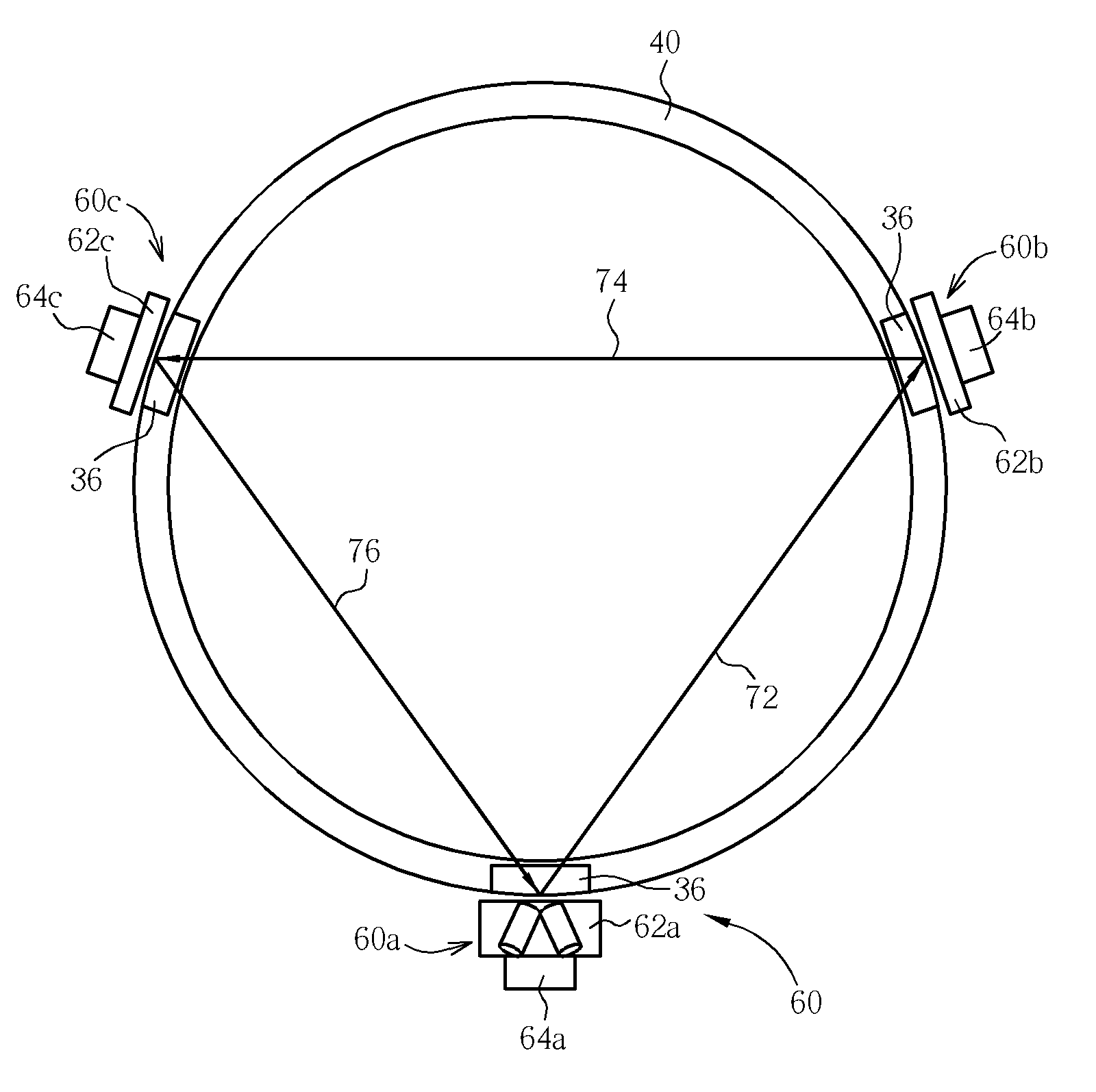

Dry etching apparatus capable of monitoring motion of WAP ring thereof

ActiveUS7632377B2Avoid Particle ContaminationElectric discharge tubesSemiconductor/solid-state device manufacturingOptical reflectionTransceiver

An optical monitoring system includes a ring-shaped object suspended by and engaged with a plurality of vertical plunger shafts. Normally, the vertical plunger shafts move upward and downward reciprocally and coherently, but independently, such that the ring-shaped object ascends or descends horizontally. A light transceiver device is affixed to one vertical plunger shaft. A plurality optical reflector elements are affixed to respective other plunger shafts. A light beam emanated from said light transceiver is reflected by the optical reflector elements and is eventually re-directed back to the light transceiver device.

Owner:UNITED MICROELECTRONICS CORP

Polishing apparatus

InactiveUS20060084369A1Avoid Particle ContaminationWithout contaminating the clean room atmosphereMechanical apparatusPolishing machinesMechanical engineeringAmbient air

A polishing apparatus for polishing a surface of a workpiece includes a housing unit, a partition wall partitioning an interior of the housing unit into a first chamber and a second chamber, a polishing section disposed in the first chamber and having a turntable with an abrasive cloth mounted on an upper surface thereof and a top ring positioned above the turntable for supporting the workpiece to be polished and pressing the workpiece against the abrasive cloth, and a cleaning section disposed in the second chamber and cleaning the workpiece which has been polished. The polishing apparatus further includes a transferring device for transferring the workpiece which has been polished from the polishing section to the cleaning section through an opening and an exhaust system for exhausting ambient air from each of the polishing section and cleaning section separately and independently.

Owner:EBARA CORP +1

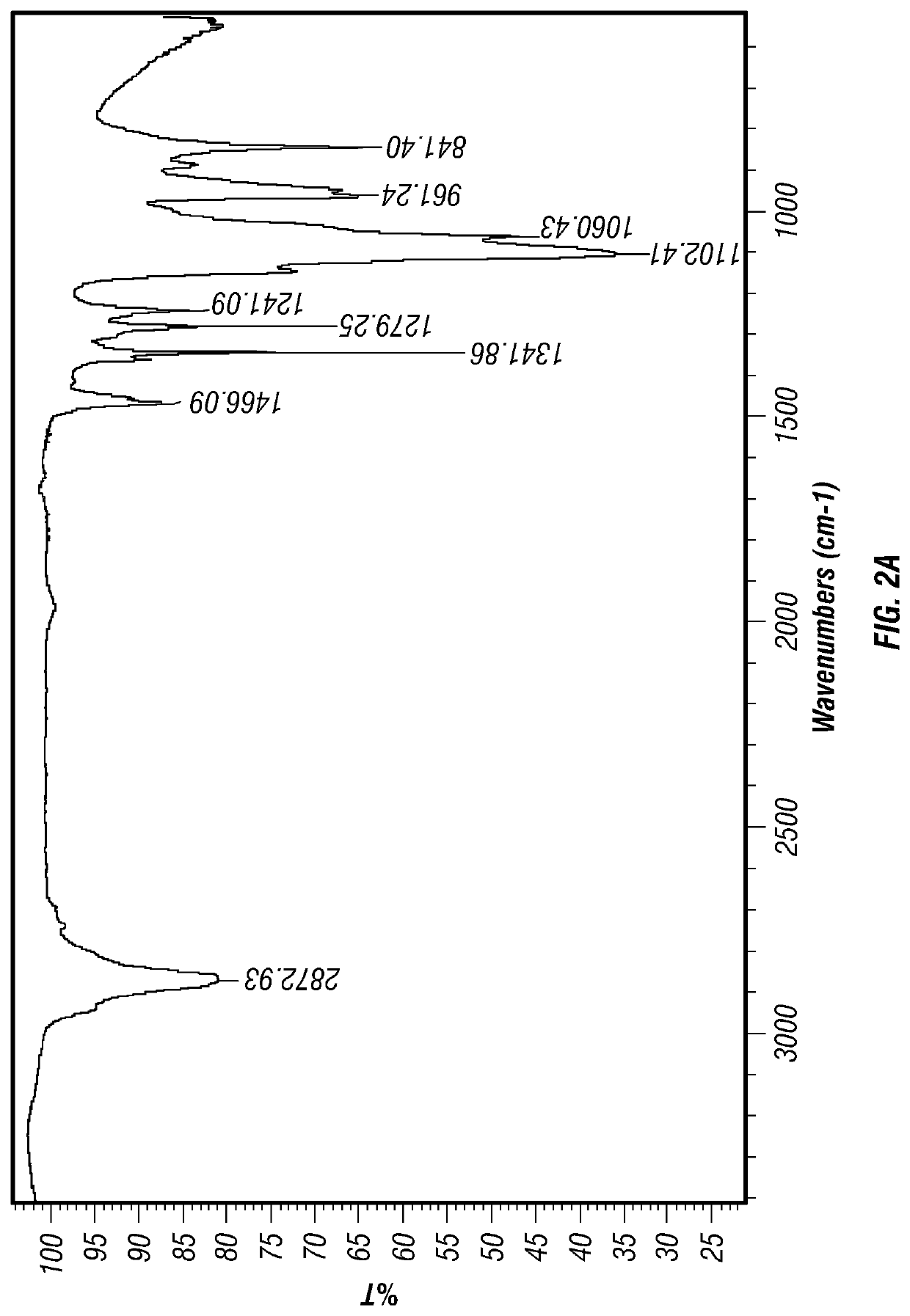

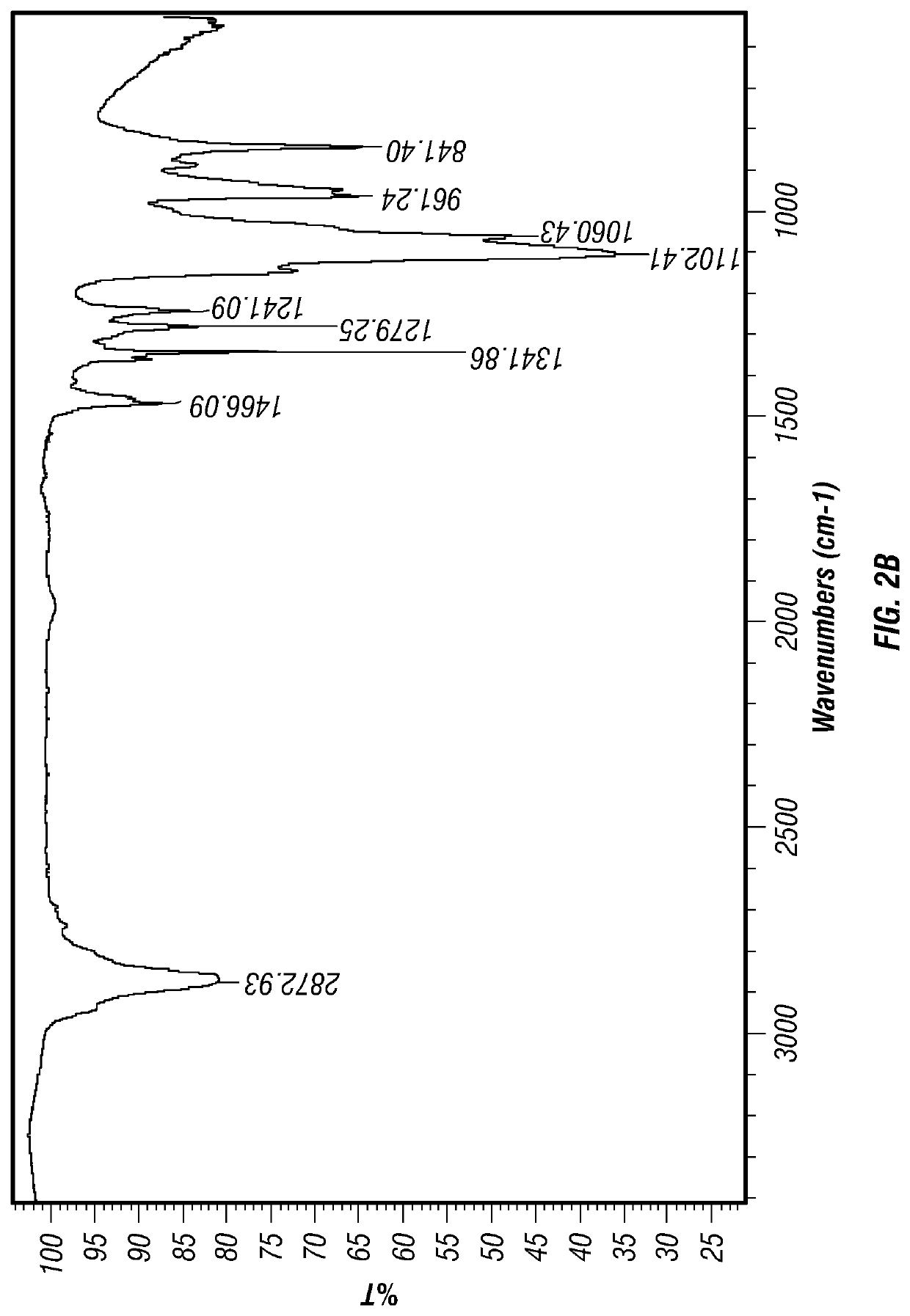

Method of forming a thin film by plasma CVD of a silicon-containing source gas

ActiveUS7229935B2Reduce plasma damageImprove adhesionSemiconductor/solid-state device manufacturingSolid state diffusion coatingProduct gasRadio frequency

A method for forming a thin film includes: supplying an additive gas, a dilution gas, and a silicon-containing source gas into a reaction chamber wherein a substrate is placed; forming a thin film on the substrate by plasma CVD under a given pressure with a given intensity of radio-frequency (RF) power from a first point in time to a second point in time; at the second point in time, stopping the supply of the silicon-containing source gas; and at the second point in time, beginning reducing but not stopping the RF power, and beginning reducing the pressure, wherein the reduction of the RF power and the reduction of the pressure are synchronized up to a third point in time.

Owner:ASM JAPAN

Edge-trimmed composite back sealing layer structure used for silicon wafer, and manufacturing method thereof

InactiveCN106158768AAchieve seamless connectionNo stratificationSemiconductor/solid-state device detailsSolid-state devicesStacking faultEngineering

The invention discloses an edge-trimmed composite back sealing layer structure used for a silicon wafer. The edge-trimmed composite back sealing layer structure comprises a polysilicon back sealing layer and a silicon dioxide back sealing layer, wherein the polysilicon back sealing layer covers the back surface, back surface bevel edge regions and fringe regions of the silicon wafer; the silicon dioxide back sealing layer covers the polysilicon back sealing layer and is positioned on the back surface of the silicon wafer. According to the edge-trimmed composite back sealing layer structure used for the silicon wafer, only monocrystal silicon serving as a body material is left on the front surface bevel edge of the silicon wafer, and the front surface bevel edge has a smooth surface with high quality, which makes almost no difference from a polished surface. Only the monocrystal silicon layers are grown on the front surface bevel edge of the silicon wafer and the polished surface in epitaxial processing, seamless connection can be achieved, the layered phenomenon cannot occur, and the problems of particle contaminant, edge stacking fault and pyramid in epitaxial processing can be solved, thereby increasing the yield in manufacturing process.

Owner:SHANGHAI SHENHE THERMO MAGNETICS ELECTRONICS CO LTD

Coating and developing system and coating and developing method

ActiveUS7284917B2Reduce processing stepsAvoid Particle ContaminationLiquid processingDoors/windowsResistEngineering

A coating and developing system is capable of preventing the contamination of a substrate with particles while the same coats a surface of a substrate with a resist film and develops the resist film after the substrate has been processed by immersion exposure. The coating and developing system includes: a processing block including coating units for forming a resist film on a surface of a substrate and developing units for processing the resist film formed on the substrate with a developer, and an interface block connected to the processing block and an exposure system for carrying out an immersion exposure process. The interface block includes: substrate cleaning units for cleaning the substrate processed by the immersion exposure process, a first carrying mechanism and a second carrying mechanism. The first carrying mechanism carries a substrate processed by immersion exposure to the substrate cleaning unit. The second carrying mechanism carries the substrate cleaned by the substrate cleaning unit. Thus the contamination of the substrate with external particles can be prevented and hence the spread of contamination with particles over the processing units of the processing block and substrates processed by the processing units can be prevented.

Owner:TOKYO ELECTRON LTD

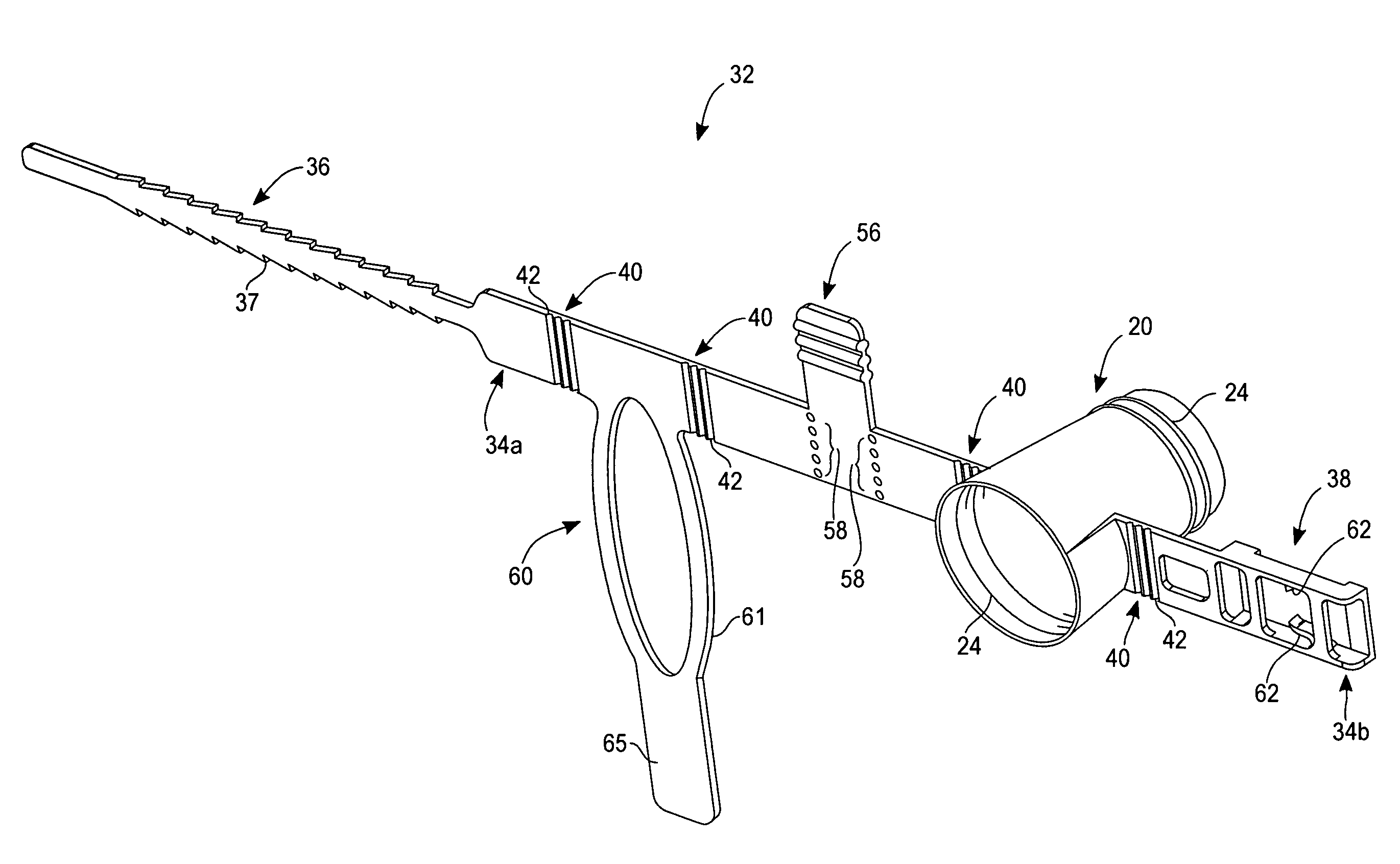

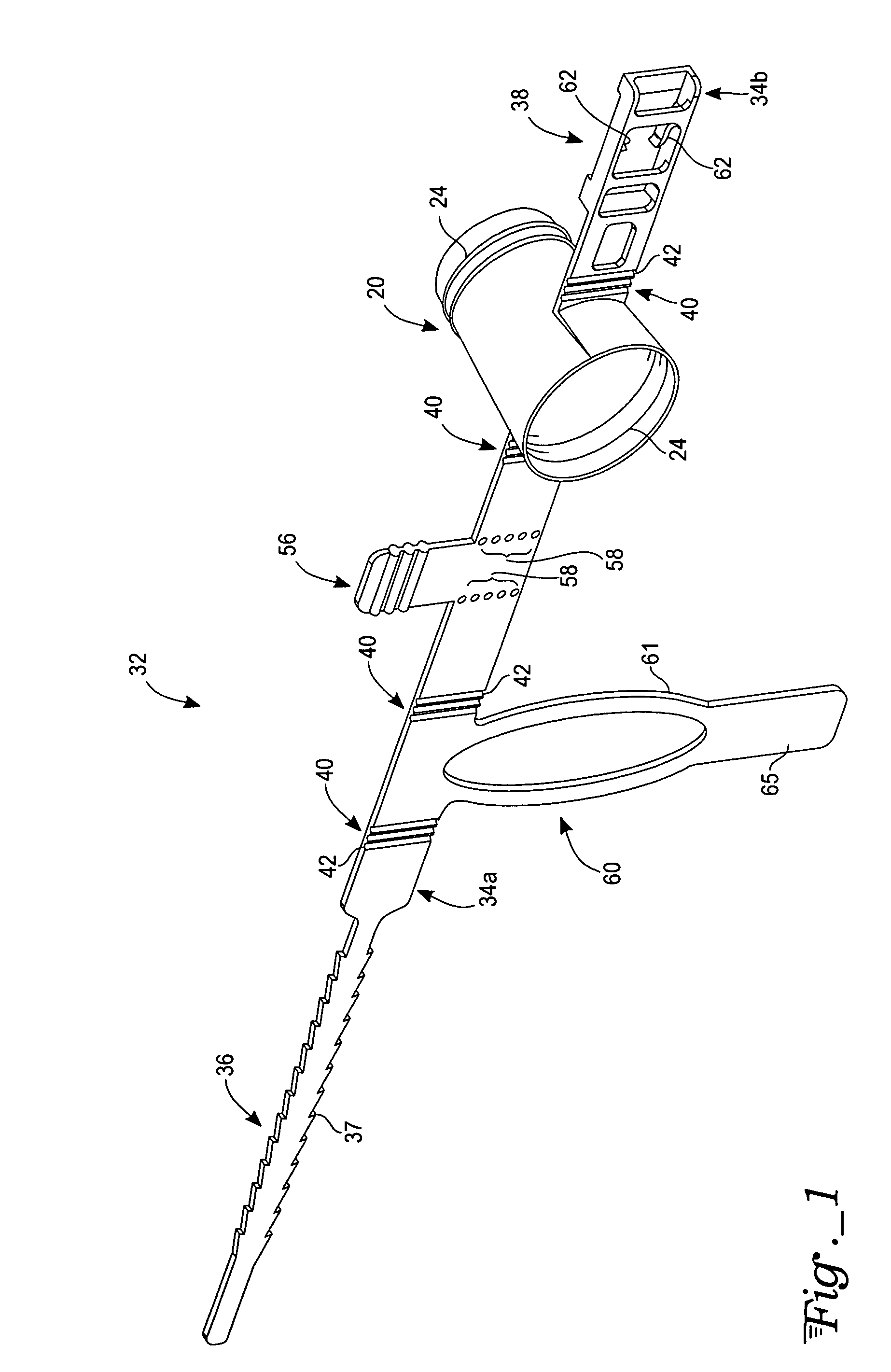

Protection and tamper notification device for use with a valve

InactiveUS7438085B2Avoid Particle ContaminationCapsEngineering safety devicesEngineeringParticulate contamination

A device for prevention of particulate contamination of a valve fitting and for notification of whether actual access or tampering or potential access or tampering of a fluid from a fluid tank connected to the valve and / or the valve has occurred, featuring a fitting block which is insertable within the fitting or capable of receiving the fitting, and first and second straps bendable about the valve and fastenable to each other. One of the straps may include a ring through which a valve burst disk is insertable when the strap is bent about the valve. If the device was compromised and the cylinder was removed for access to the valve fitting, the ring of one of the straps would remain on the burst disk even though the cylinder was removed from the fitting. Thus, the compromised device would remain on the valve indicating that access to the valve or fluid had been attempted or achieved.

Owner:RATERMANN GEORGE W

Wafer spin chuck and an etcher using the same

ActiveUS8007634B2Avoid Particle ContaminationPrevents a spin chunk from corrosionSemiconductor/solid-state device manufacturingCleaning using liquidsSpinsPhysics

A wafer spin chuck and an etcher using the same are provided. According to an aspect of the present invention, there is provide a wafer spin chuck device comprising: a spin body which spins a wafer; and a stationary body which holds the spin body and is under the spin body with a space between the spin body and the stationary body, wherein the stationary body includes a blocking unit which blocks the space with a fluid.

Owner:SEMES CO LTD

Reactor for Atomic Layer Deposition (ALD), Application to Encapsulation of an OLED Device by Deposition of a Transparent Al2O3 Film

InactiveUS20130280833A1Reduce in quantityAvoid Particle ContaminationElectroluminescent light sourcesSolid-state devicesEngineeringChicane

The present invention relates to a reactor for atomic layer deposition (ALD), comprising a reaction chamber comprising a platen and bounded internally by surfaces; at least one inlet orifice and at least one outlet orifice, each emerging from one of the surfaces bounding the chamber. The reactor furthermore comprises, within it, at least one wall apertured with at least one orifice, the apertured wall extending around the platen and over at least most of the height between the lower surface and the upper surface, at least one orifice in at least one of the apertured walls not facing the inlet orifice so as to form chicanes in the flow of gaseous precursor from each inlet orifice to the platen.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

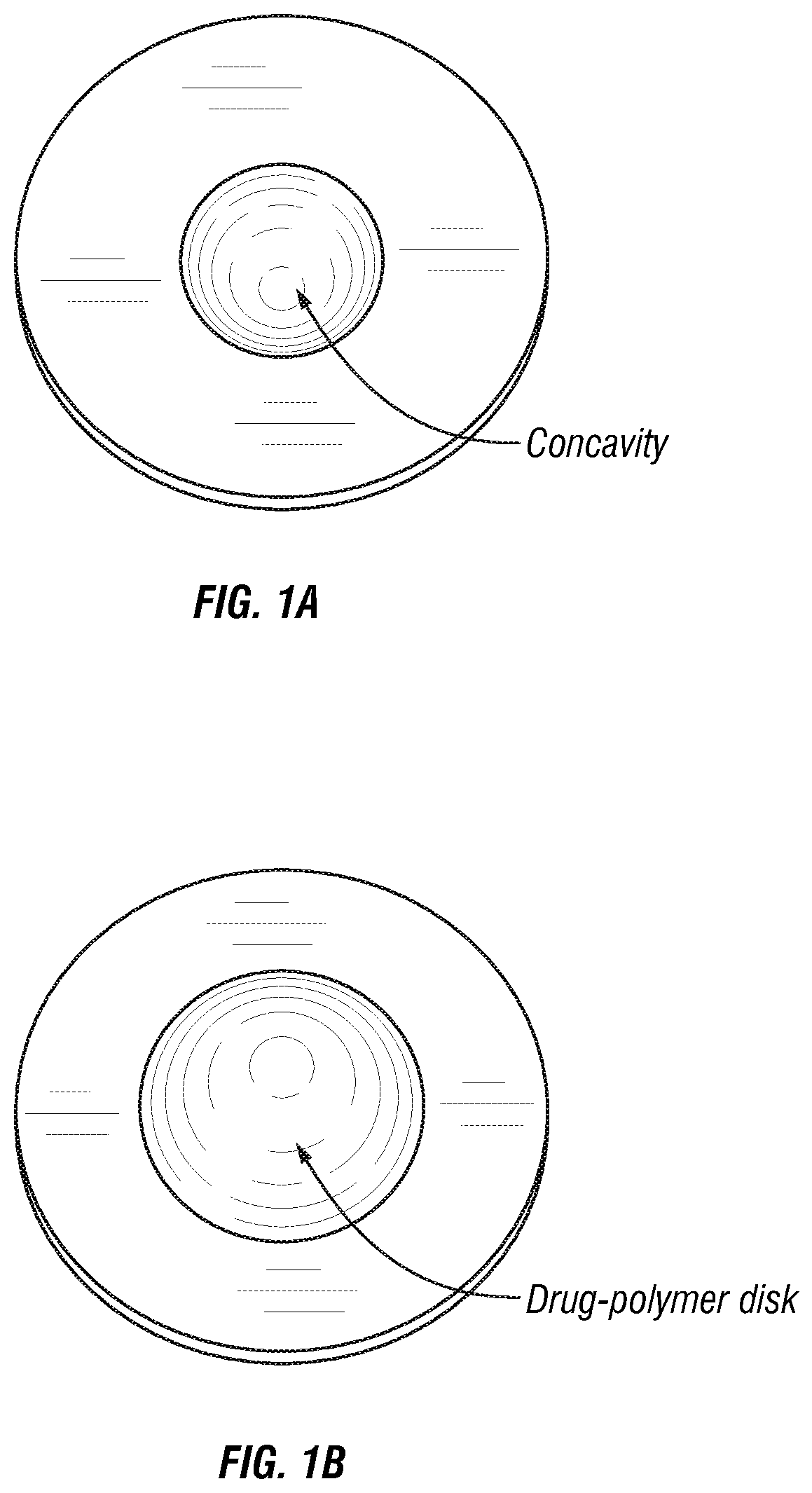

Drug delivery systems and methods for preparation thereof

InactiveUS20200054567A1Avoid polluting the environmentAvoid Particle ContaminationOrganic active ingredientsCoatingsPlaceboPharmaceutical Substances

The invention provides a drug delivery system in which a drug or another active substance is delivered from the surface of an inactive, placebo carrier. The system uses a placebo tablet carrier having a concavity or multiple concavities in the top surface for receiving a drug. After manufacture of the placebo tablet carrier, a dosage of the drug in liquid or semisolid form is deposited in the concavity and solidifies as a dot or disk on the tablet surface. Thus, the drug is carried on the surface of the tablet and is not part of the tablet bulk. The drug delivery system is particularly useful for delivery of low dose (i.e. potent) drugs, for delivery of multiple doses of a drug, or for delivery of multiple types of drugs. Additionally, the invention provides methods for preparation of the inventive drug delivery systems.

Owner:NOVA SOUTHEASTERN UNIVERSITY

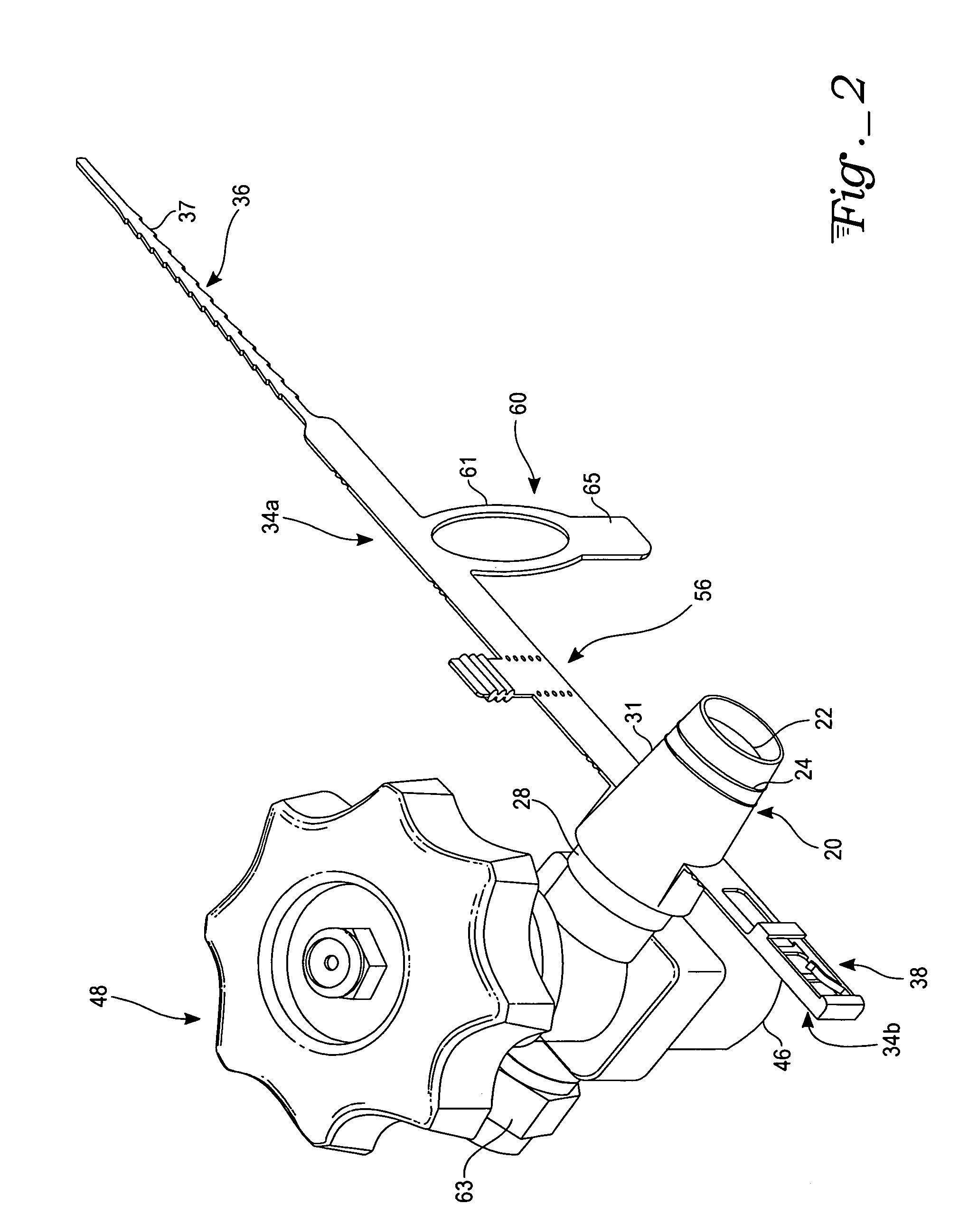

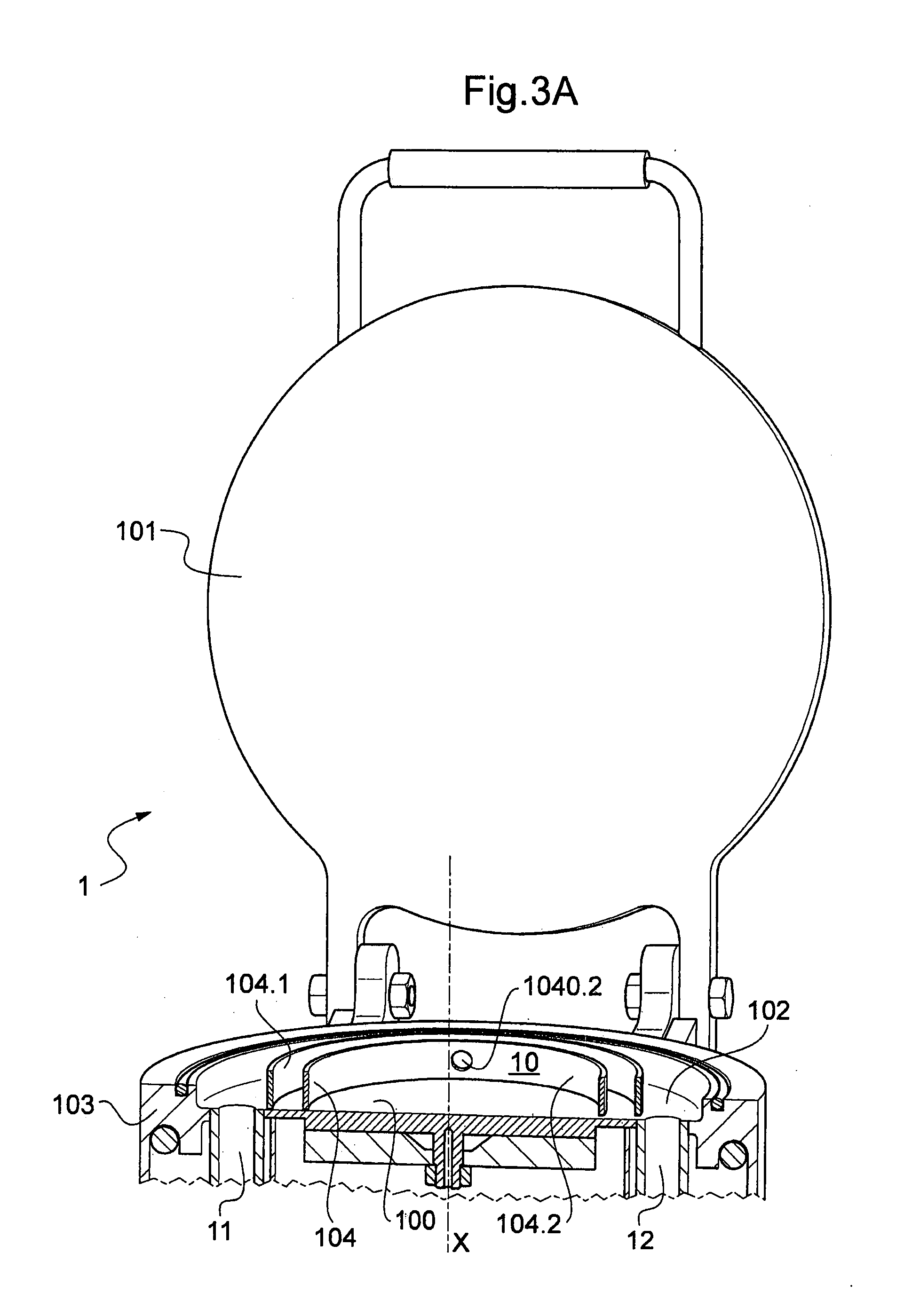

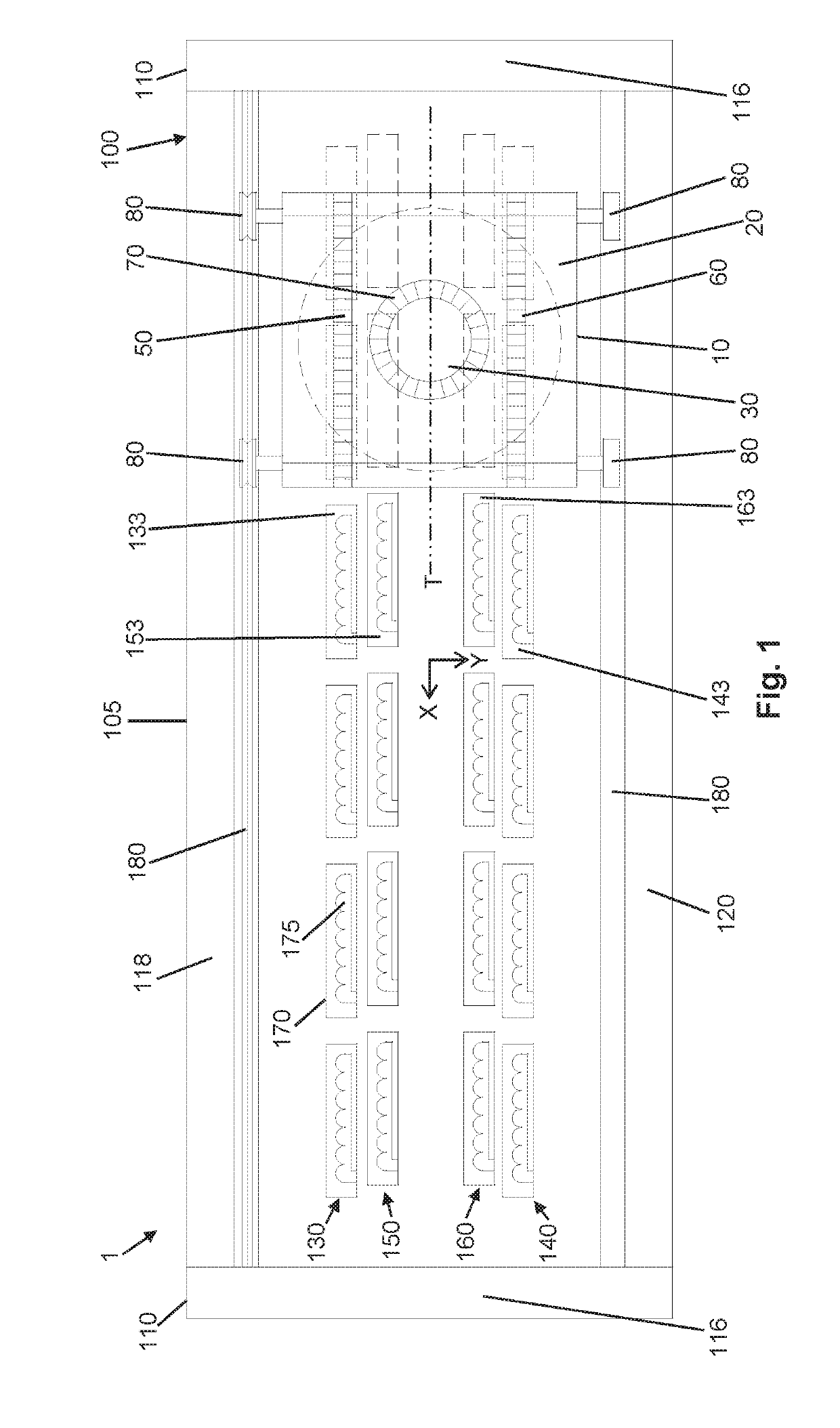

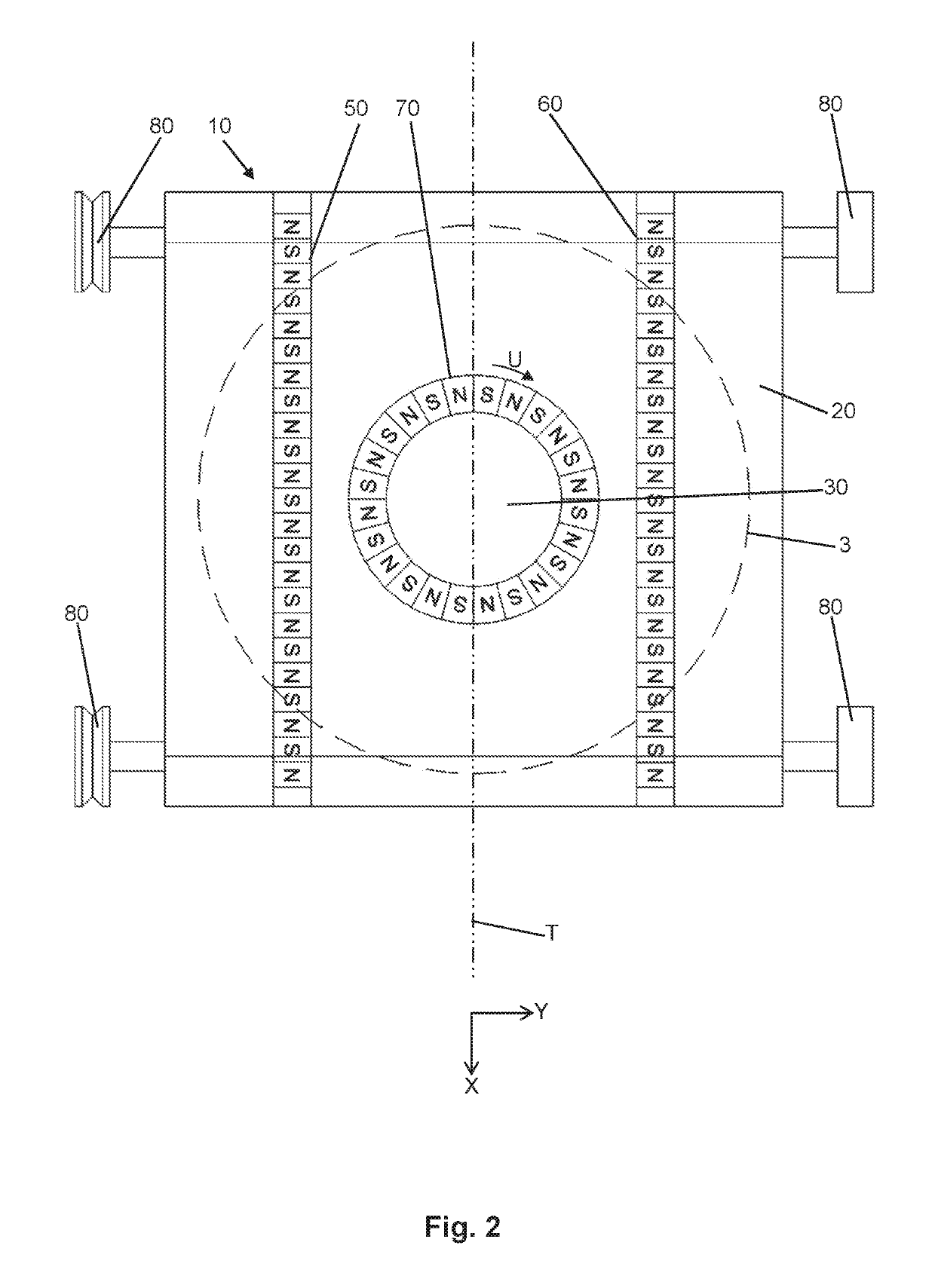

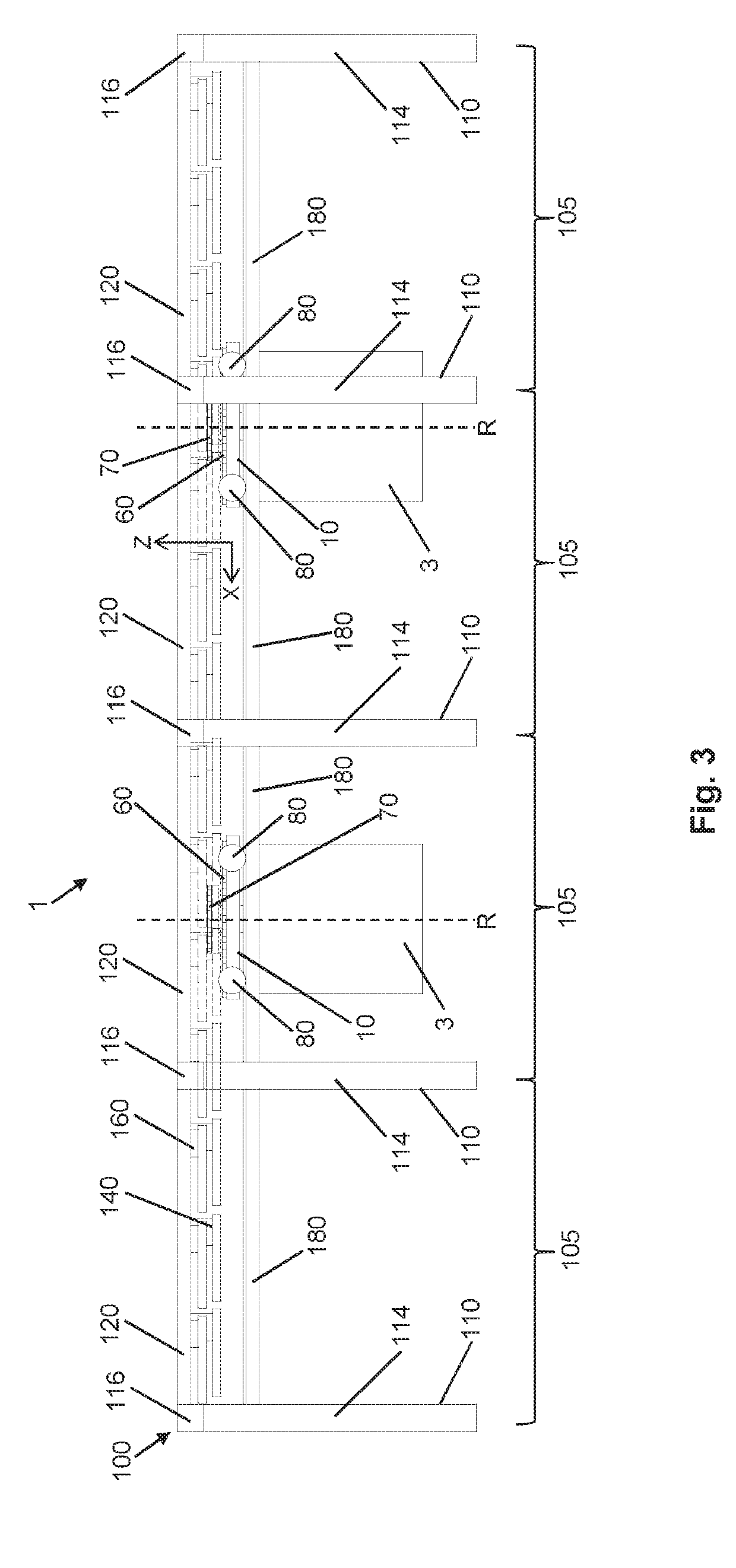

Device for processing a component, carriage for the device, and method for operating the device

ActiveUS20190329279A1Reduce disadvantagesAvoid Particle ContaminationElectric discharge tubesMagnetic circuitBogieControl theory

The present invention relates to a device for processing a component, comprising: a travel carriage having a frame which defines an axis of translation along which the travel carriage is translationally movable, a bogie which is relatively rotatably connected to the frame and to which the component is attachable, a first translation-permanent magnet device which is mounted on the frame and having permanent magnets, a rotation-permanent magnet device attached to the bogie and having permanent magnets, and a carriage-side longitudinal guide means mounted on the frame, a stationary travel carriage guide device having a guide-side longitudinal guide means, a first electromagnet translation device with electromagnets which magnetically interact with the permanent magnets of the first translation-permanent magnet device, a first rotation-electromagnet device having electromagnets which magnetically interact with the permanent magnets of the rotation-permanent magnet device, and a controller connected to the first translating electromagnet device and to the first rotation-electromagnet device to control its electromagnets to control the translational movement of the travel carriage and the rotational movement of the bogie.

Owner:SCIA SYST GMBH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com