Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

208 results about "Low Pin Count" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Low Pin Count bus, or LPC bus, is a computer bus used on IBM-compatible personal computers to connect low-bandwidth devices to the CPU, such as the boot ROM, "legacy" I/O devices (integrated into a super I/O chip), and Trusted Platform Module (TPM). "Legacy" I/O devices usually include serial and parallel ports, PS/2 keyboard, PS/2 mouse, and floppy disk controller.

Low pin count (LPC) I/O bridge

InactiveUS6990549B2Reduce the possibilityEliminates compatibility concernDigital data processing detailsElectrical apparatus contructional detailsDocking stationSerialization

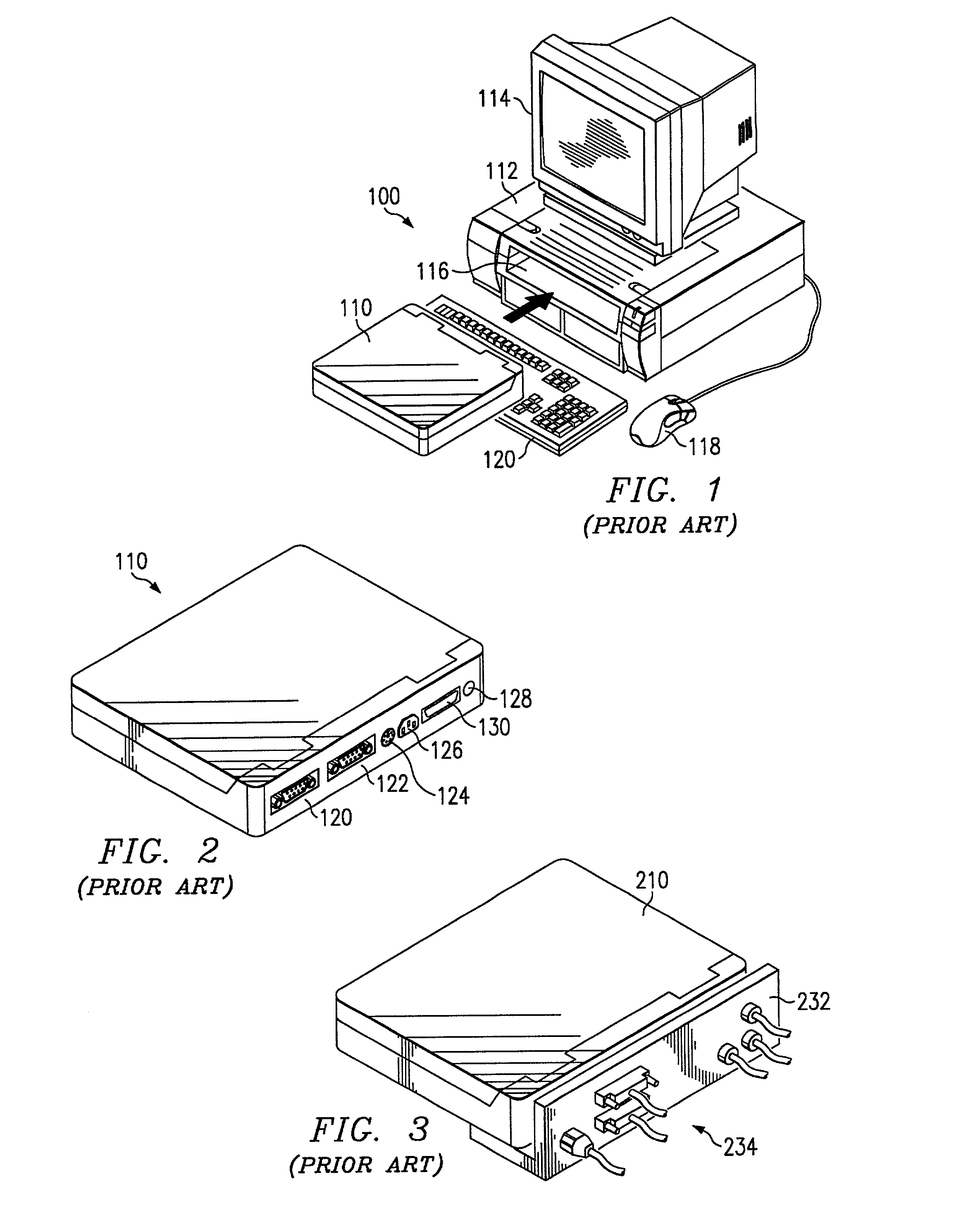

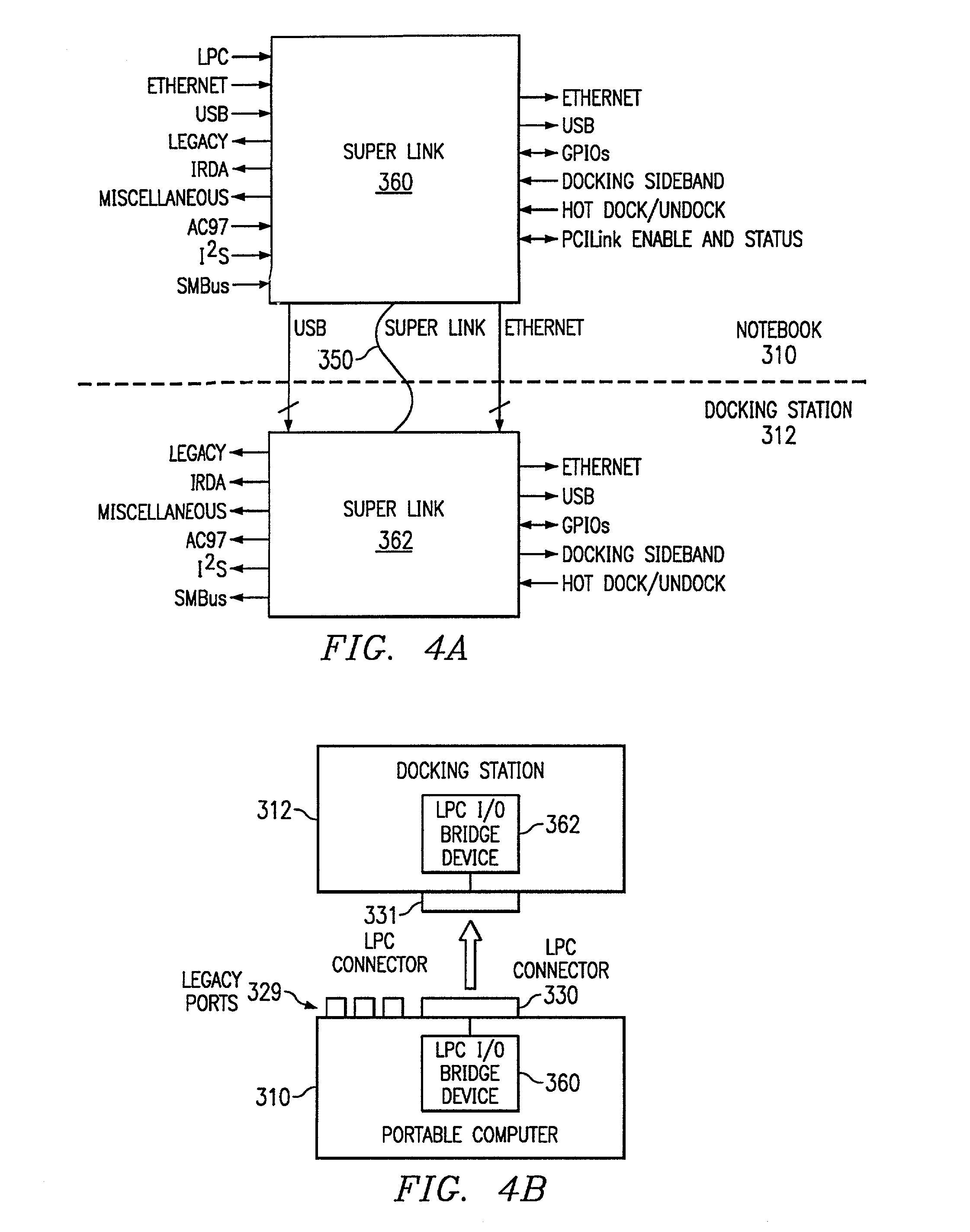

A low pin count (LPC) input / output (I / O) bridge device and method for a portable computer having a plurality of legacy ports and a docking connector. The LPC I / O bridge device includes an LPC controller coupled to the legacy ports and docking connector. The LPC controller is adapted to detect whether the portable computer is coupled to a docking station via the docking connector and route data transmissions to the legacy ports, docking connector, or both, based on information received from an LPC interface. Serialization logic coupled to the LPC controller serializes data transmissions routed to the docking connector.

Owner:TEXAS INSTR INC

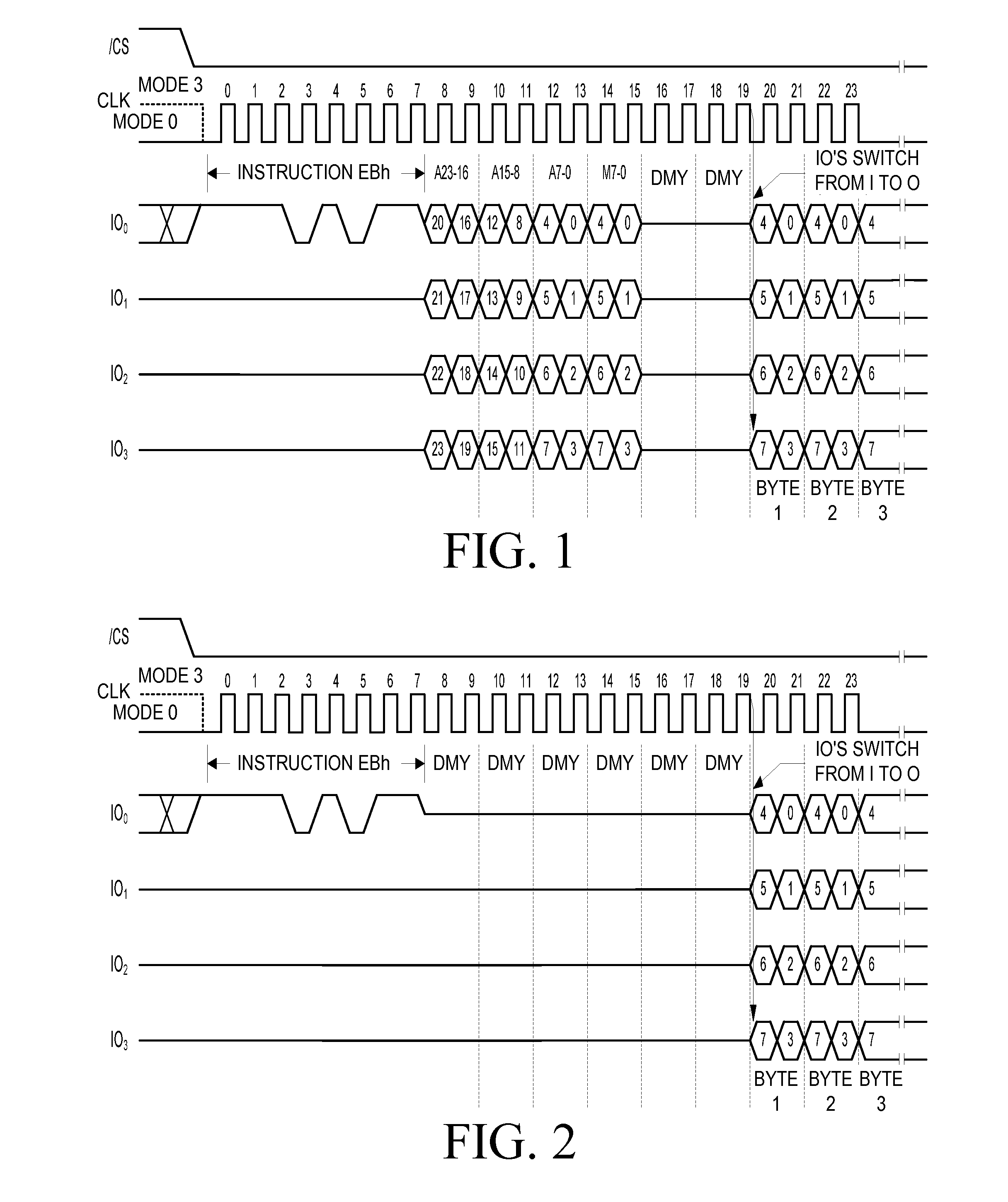

Serial flash semiconductor memory

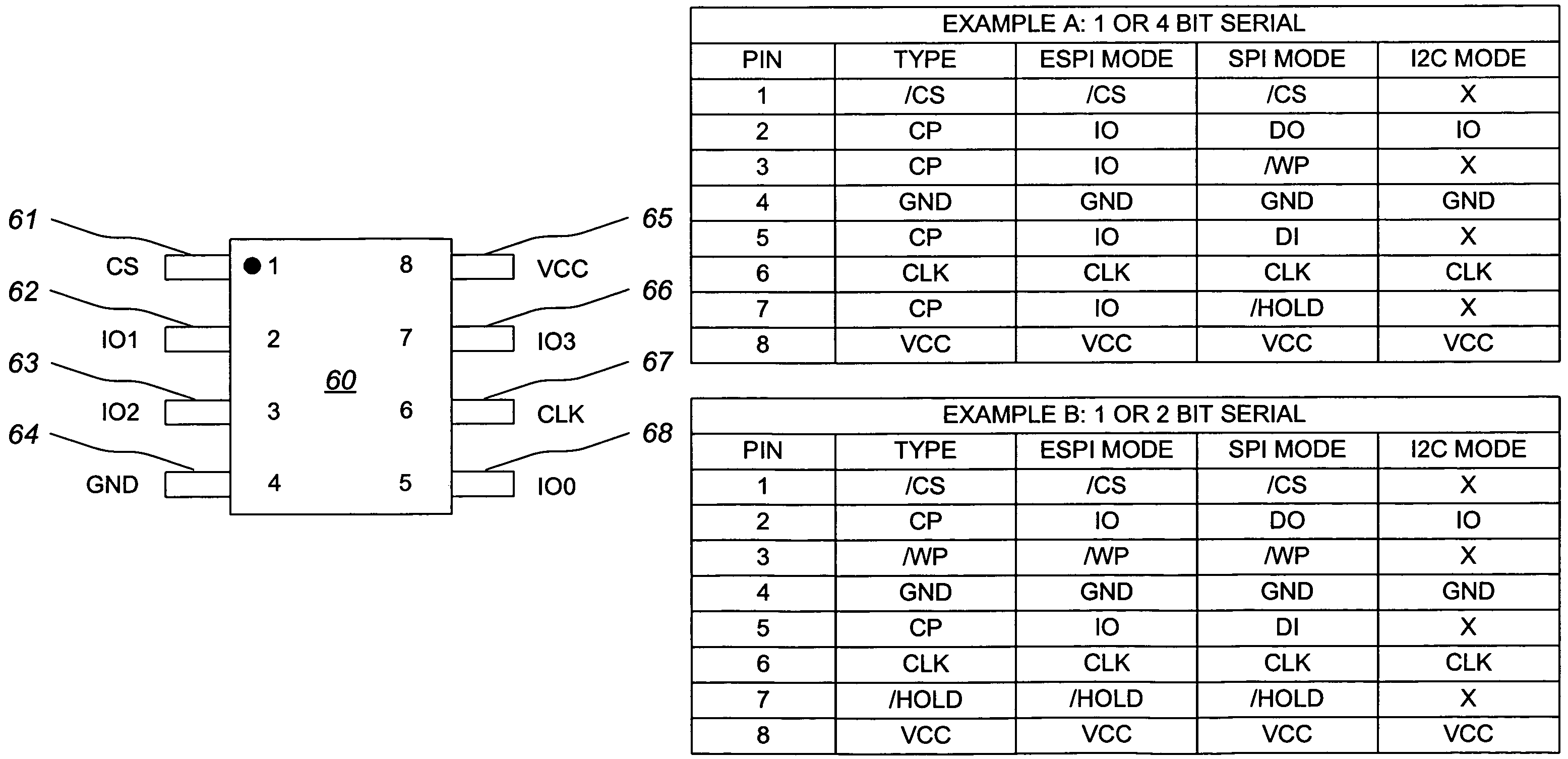

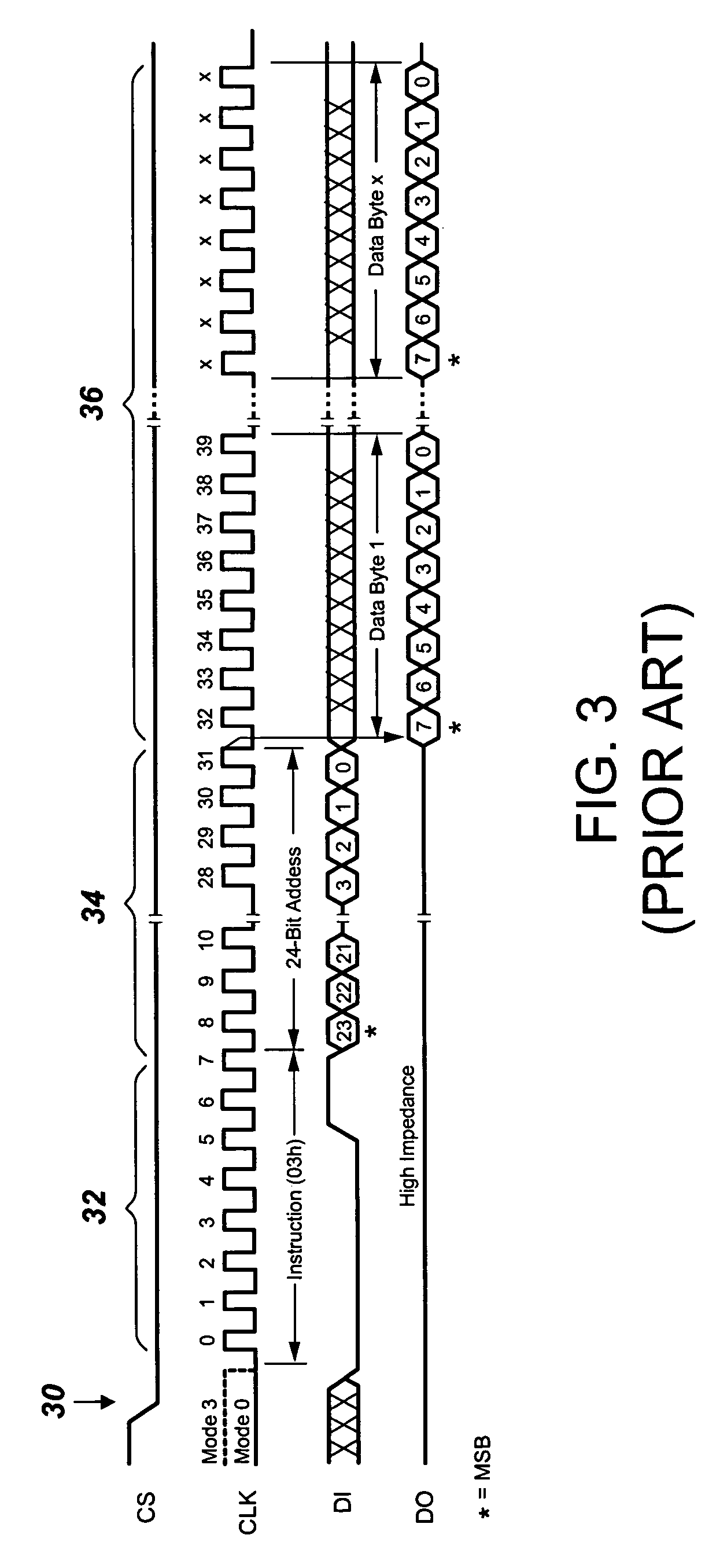

ActiveUS7558900B2Reduced pin countImprove rendering capabilitiesRead-only memoriesDigital storageData transmissionLow Pin Count

A serial flash memory is provided with multiple configurable pins, at least one of which is selectively configurable for use in either single-bit serial data transfers or multiple-bit serial data transfers. In single-bit serial mode, data transfer is bit-by-bit through a pin. In multiple-bit serial mode, a number of sequential bits are transferred at a time through respective pins. The serial flash memory may have 16 or fewer pins, and even 8 or fewer pins, so that low pin count packaging such as the 8-pin or 16-pin SOIC package and the 8-contact MLP / QFN / SON package may be used. The availability of the single-bit serial type protocol enables compatibility with a number of existing systems, while the availability of the multiple-bit serial type protocol enables the serial flash memory to provide data transfer rates, in systems that can support them, that are significantly faster than available with standard serial flash memories.

Owner:WINBOND ELECTRONICS CORP

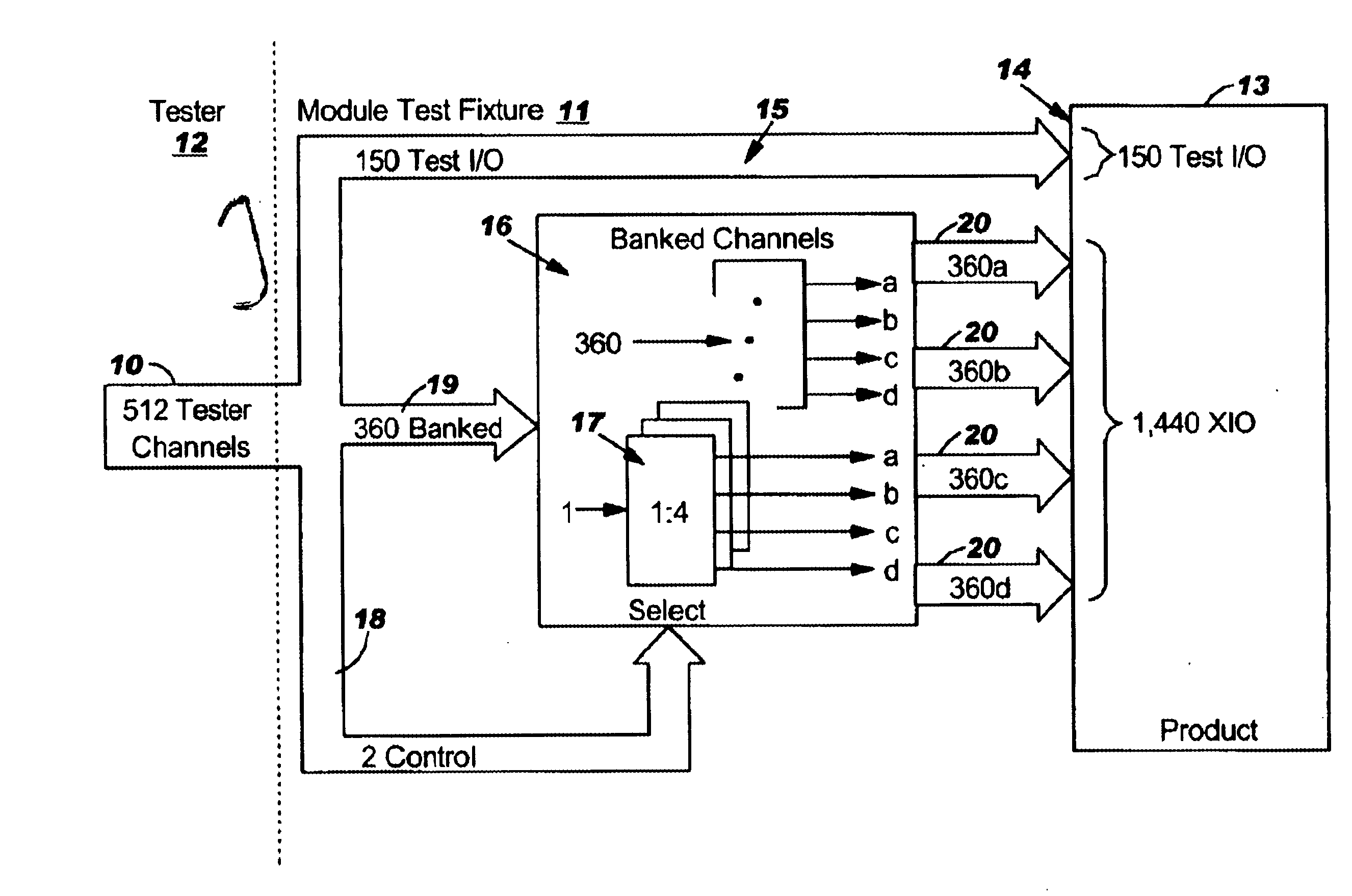

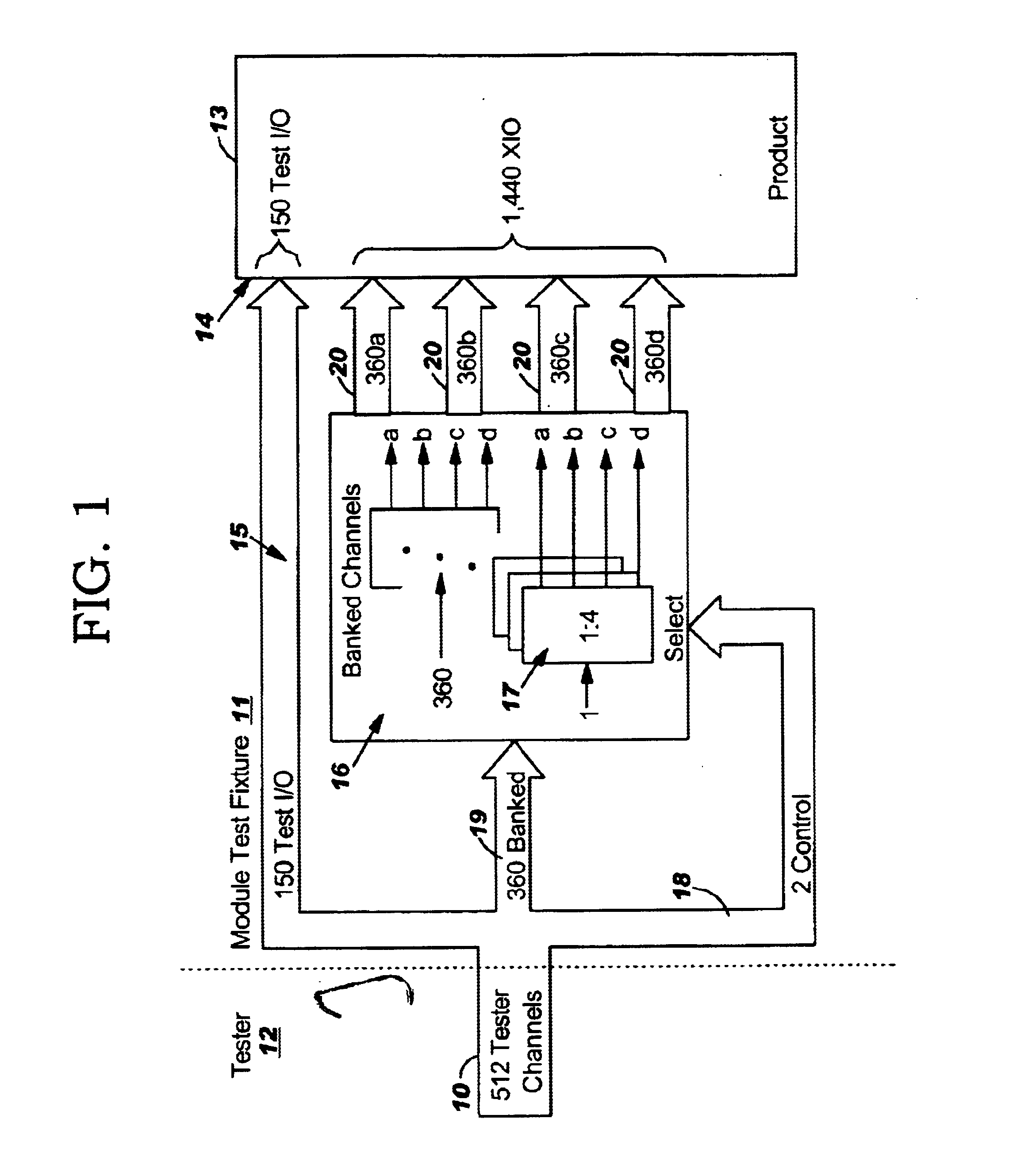

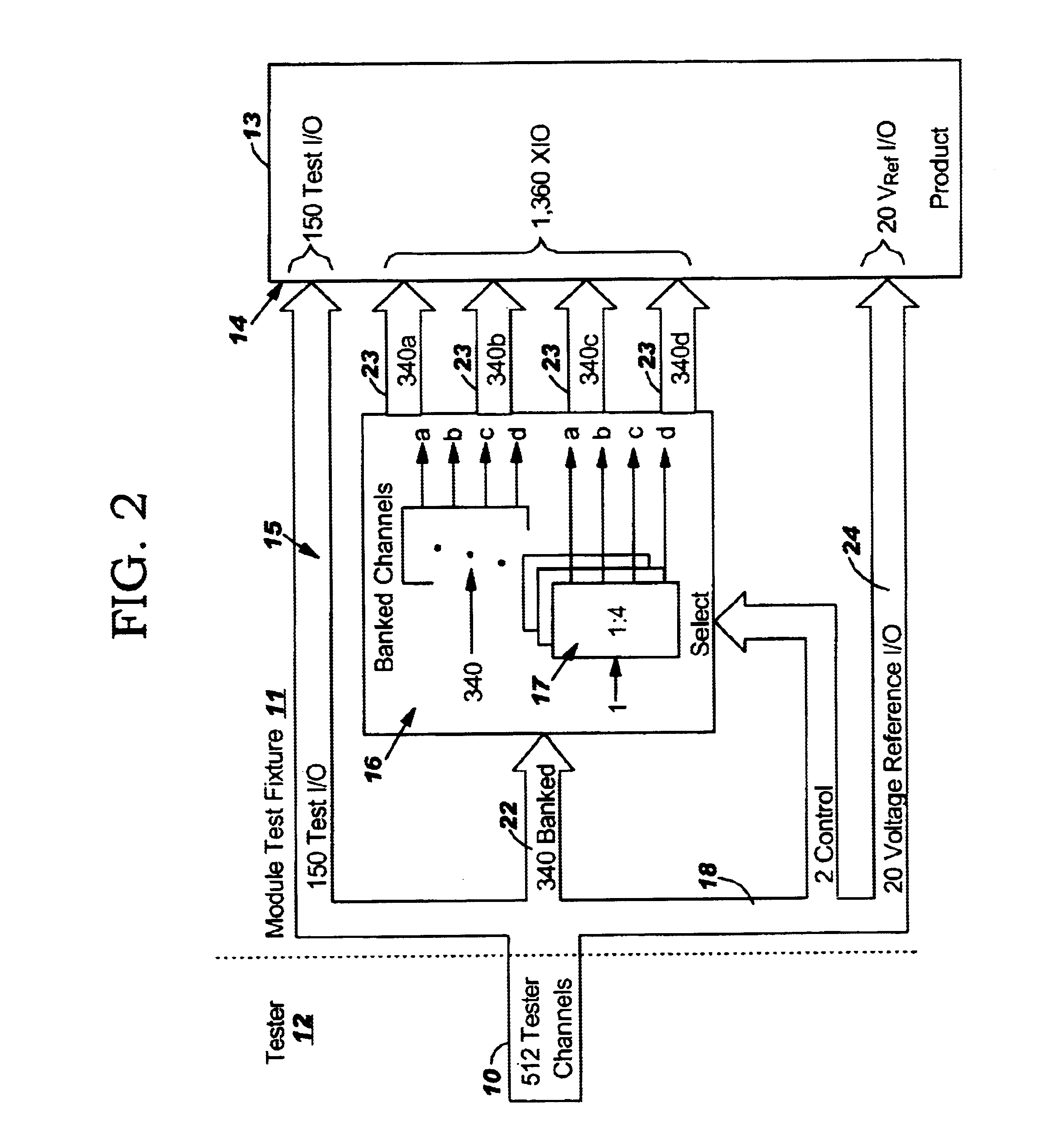

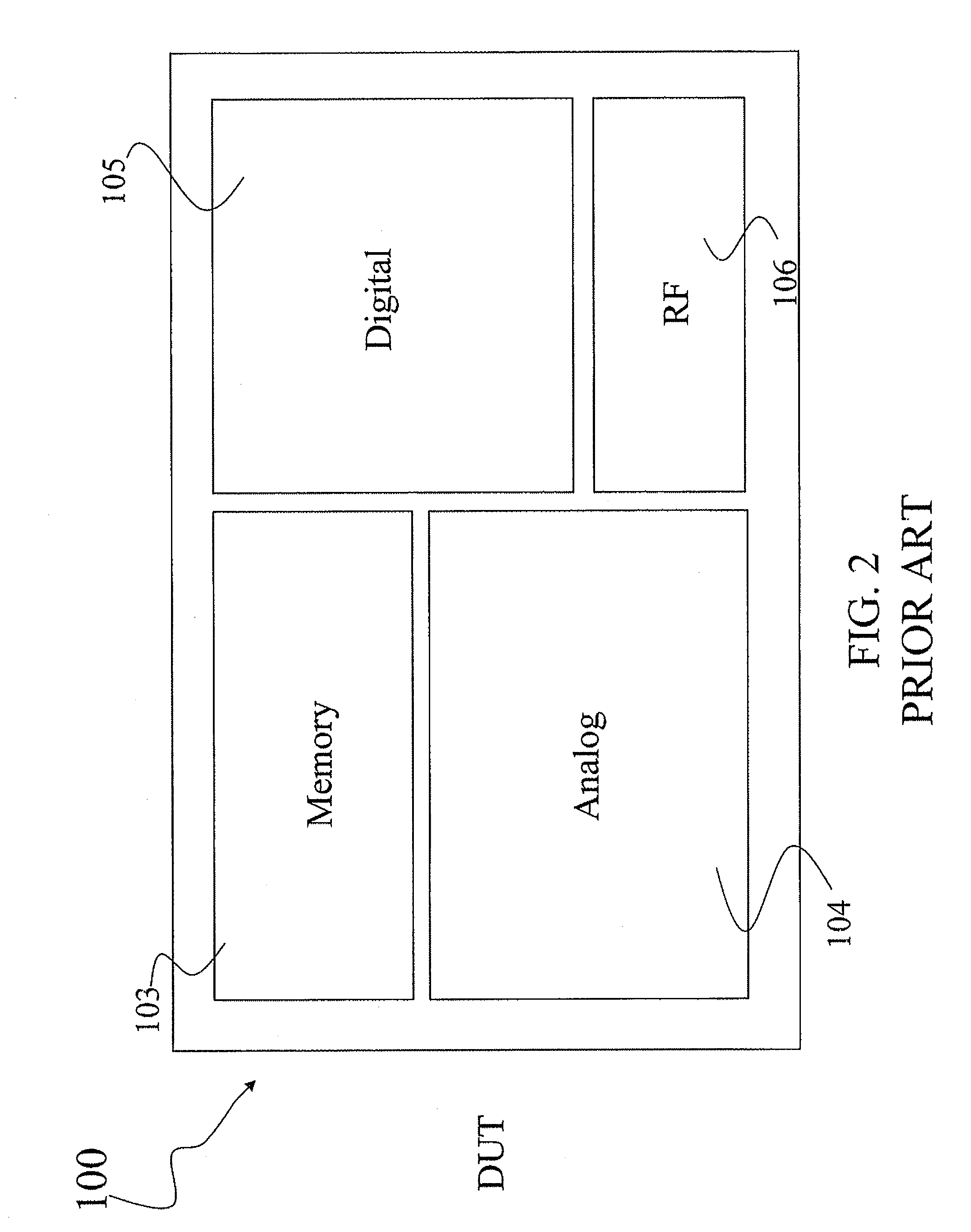

Applying parametric test patterns for high pin count ASICs on low pin count testers

InactiveUS6847203B1Digital circuit testingElectrical measurement instrument detailsContact padComputer module

Disclosed is an integrated circuit chip test apparatus that has a module test fixture having contact pads that are adapted to make contact with signal input / output pins on an integrated circuit chip being tested. An intermediate banking box is connected to the module text fixture and a tester is connected to the intermediate banking box. The tester includes at least one bank of channels there are more pins on the integrated circuit chip than there are channels in the tester. The intermediate banking box includes switches that are connected between the contact pads and the channels. The switches are adapted to selectively connect a subset of the contact pads to the channels to connect the tester to a subset of pins, thereby allowing the tester to test a portion of the integrated circuit that corresponds to the subset of pins.

Owner:IBM CORP

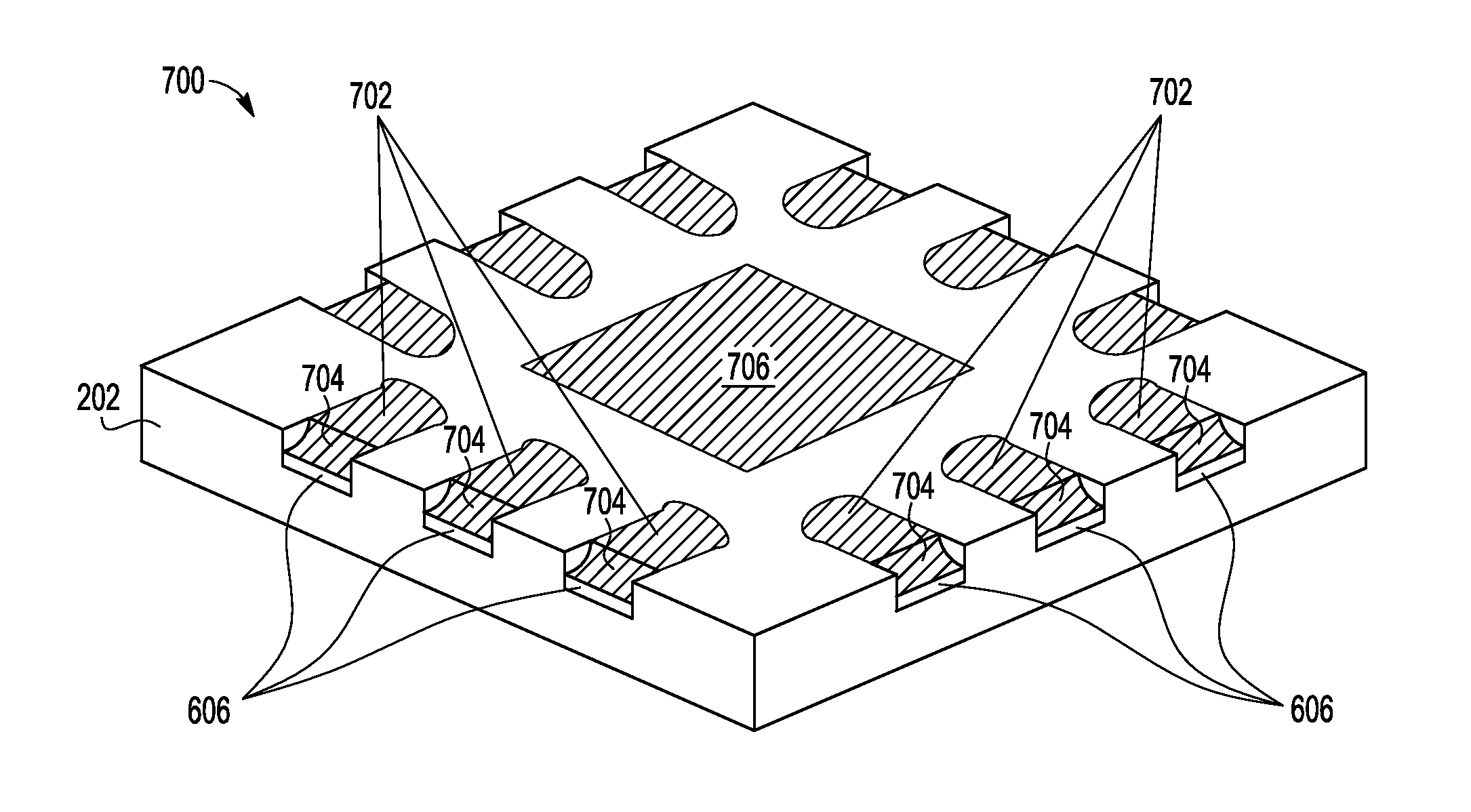

Packaging Process to Create Wettable Lead Flank During Board Assembly

ActiveUS20110244629A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

A method and apparatus are described for fabricating a low-pin-count chip package (701) including a die pad (706) for receiving an integrated circuit device and a plurality of connection leads (702) having recessed lead ends (704) at the outer peripheral region of each contact lead. After forming the package body (202) over the integrated circuit device, unplated portions (104) of the exposed bottom surface of the selectively plated lead frame are partially etched to form recessed lead ends (302) at the outer peripheral region of each contact lead, and the recessed lead ends are subsequently re-plated (402) to provide wettable recessed lead ends at the outer peripheral region of each contact lead.

Owner:NXP USA INC

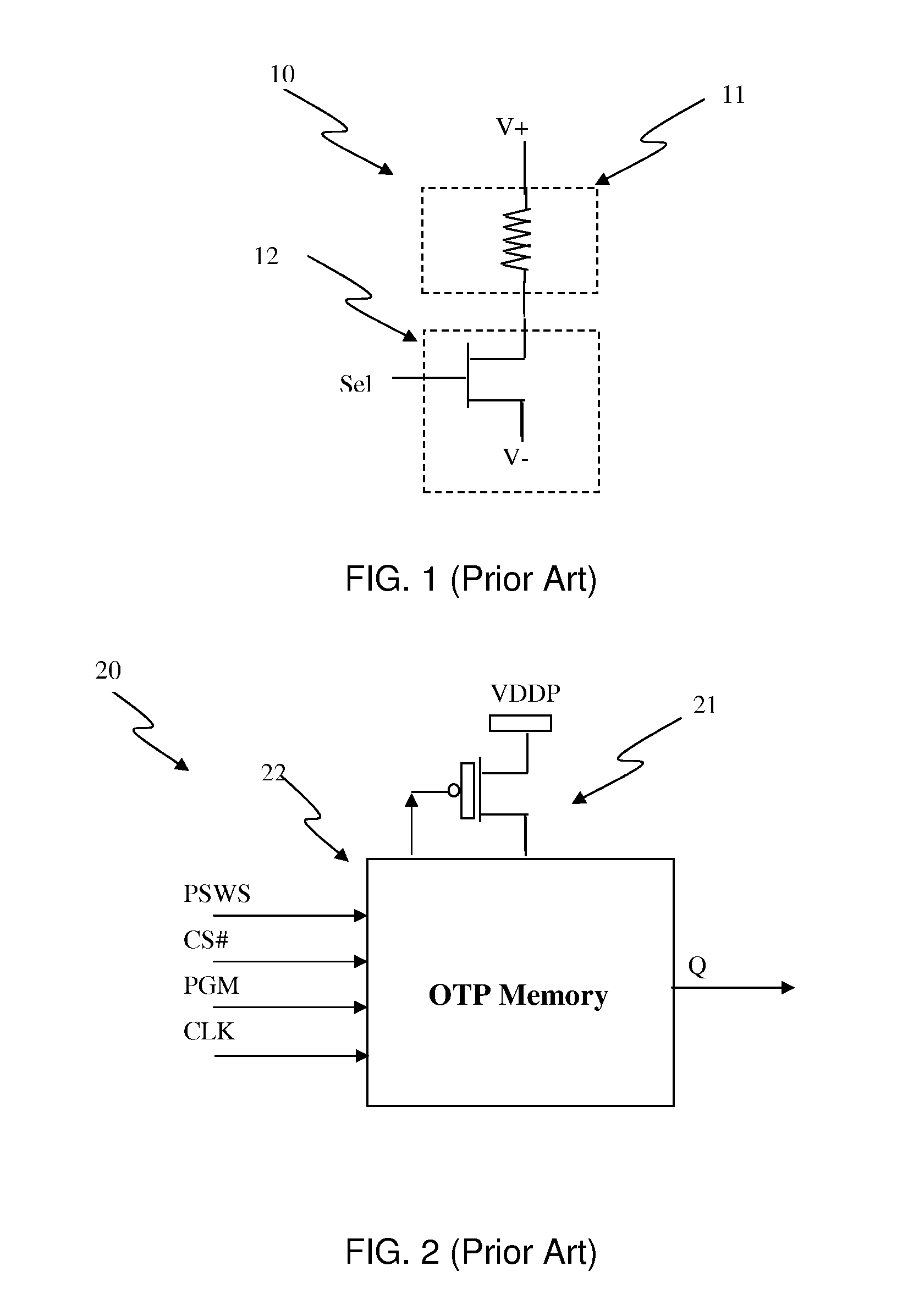

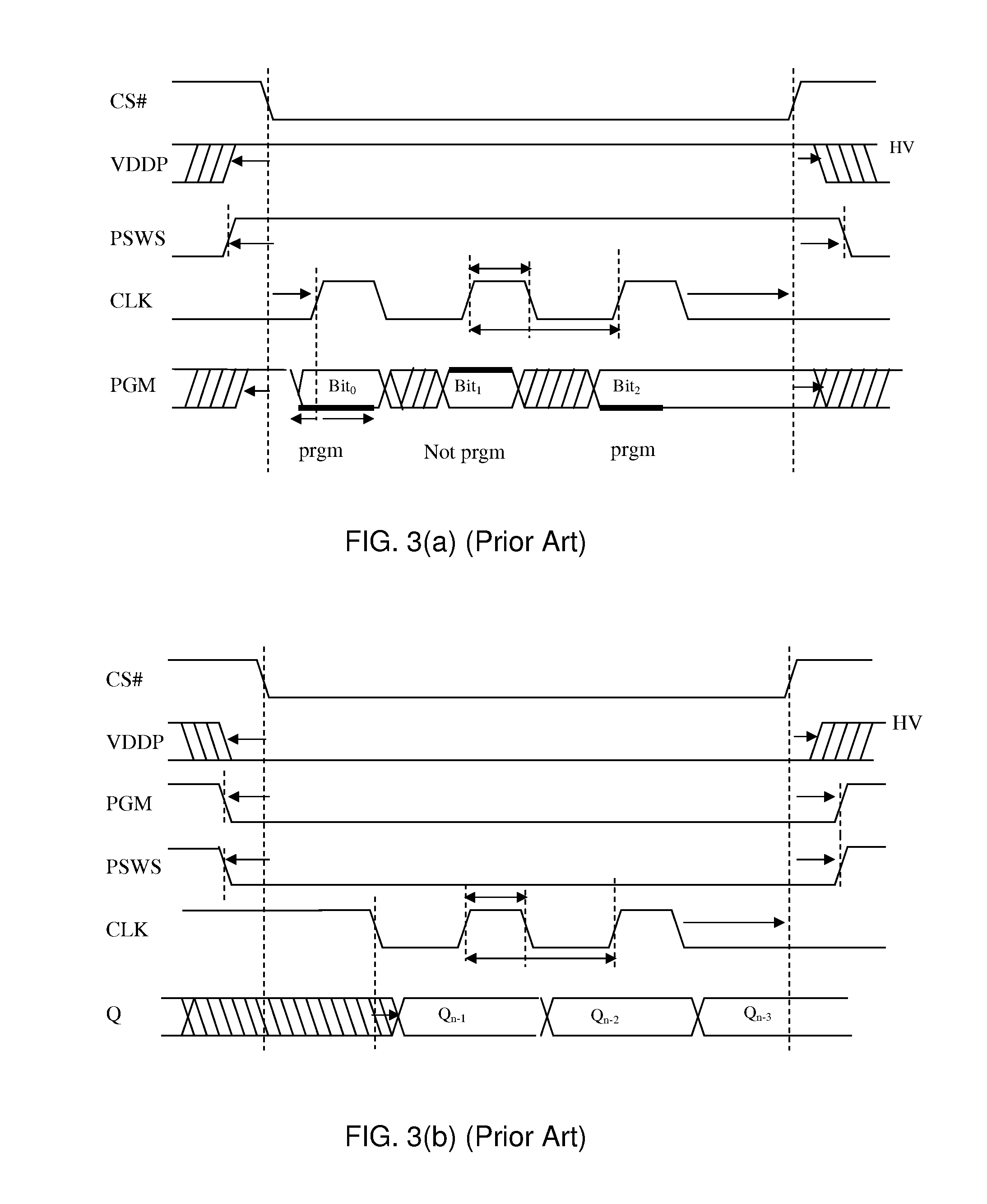

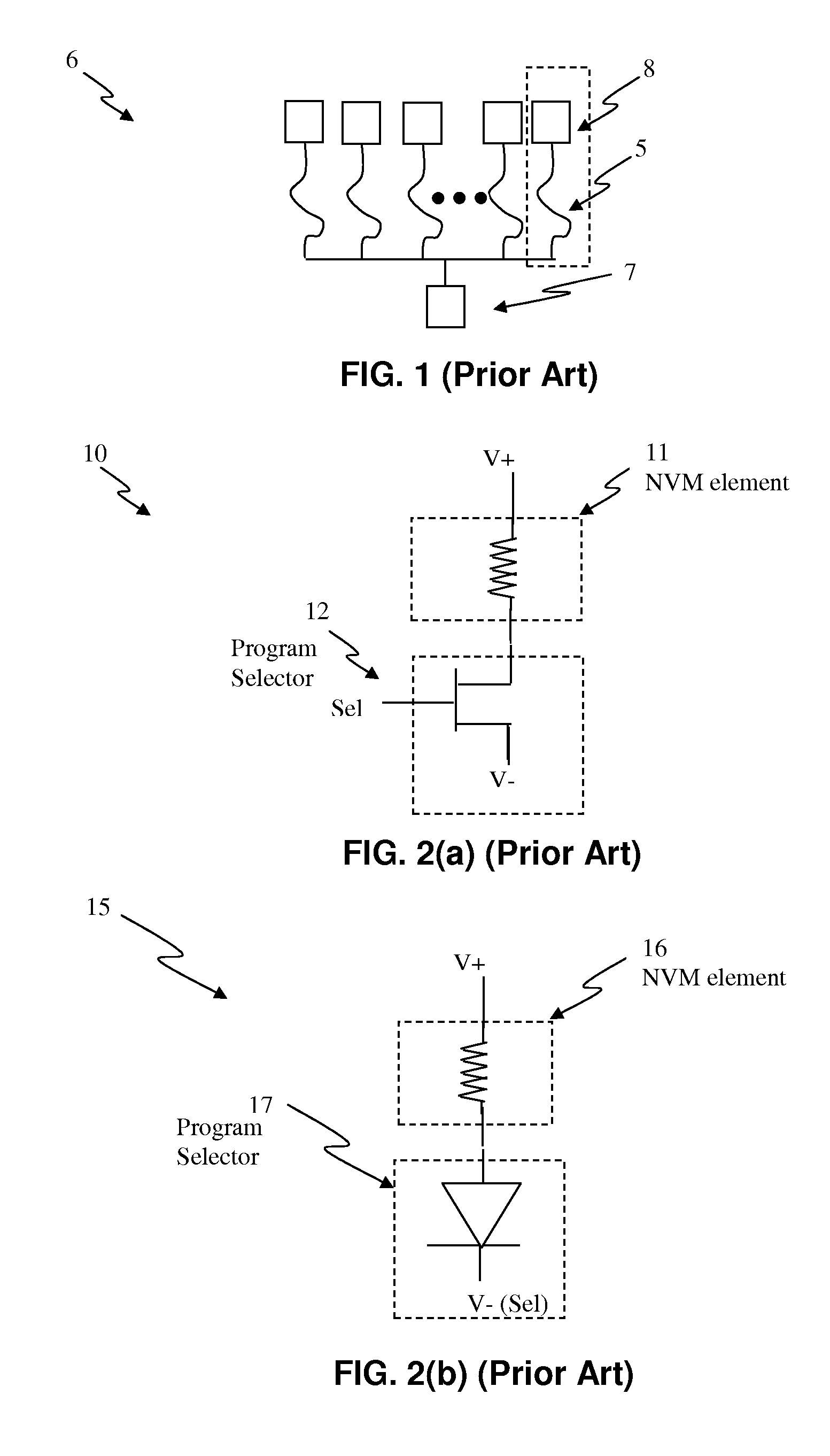

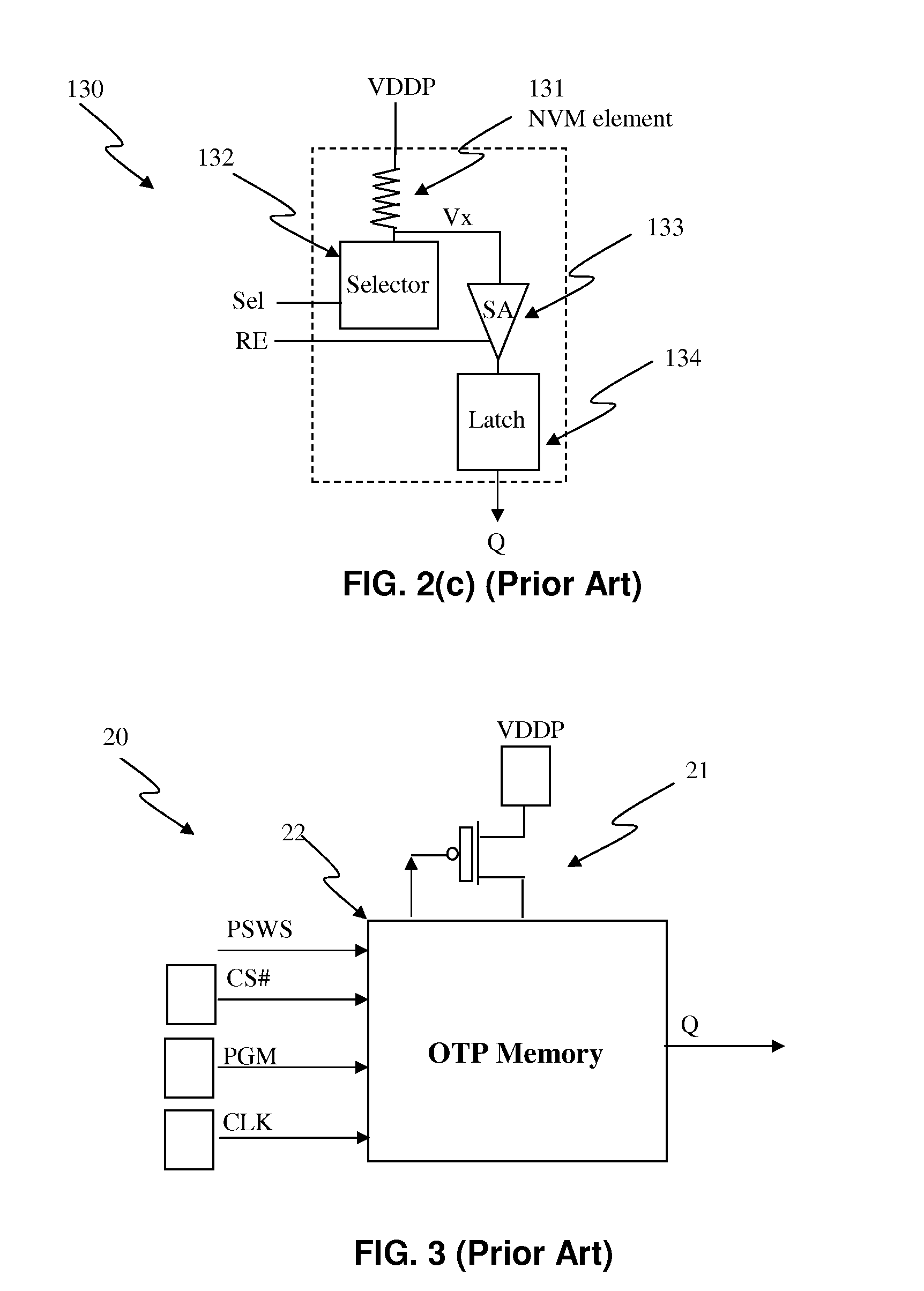

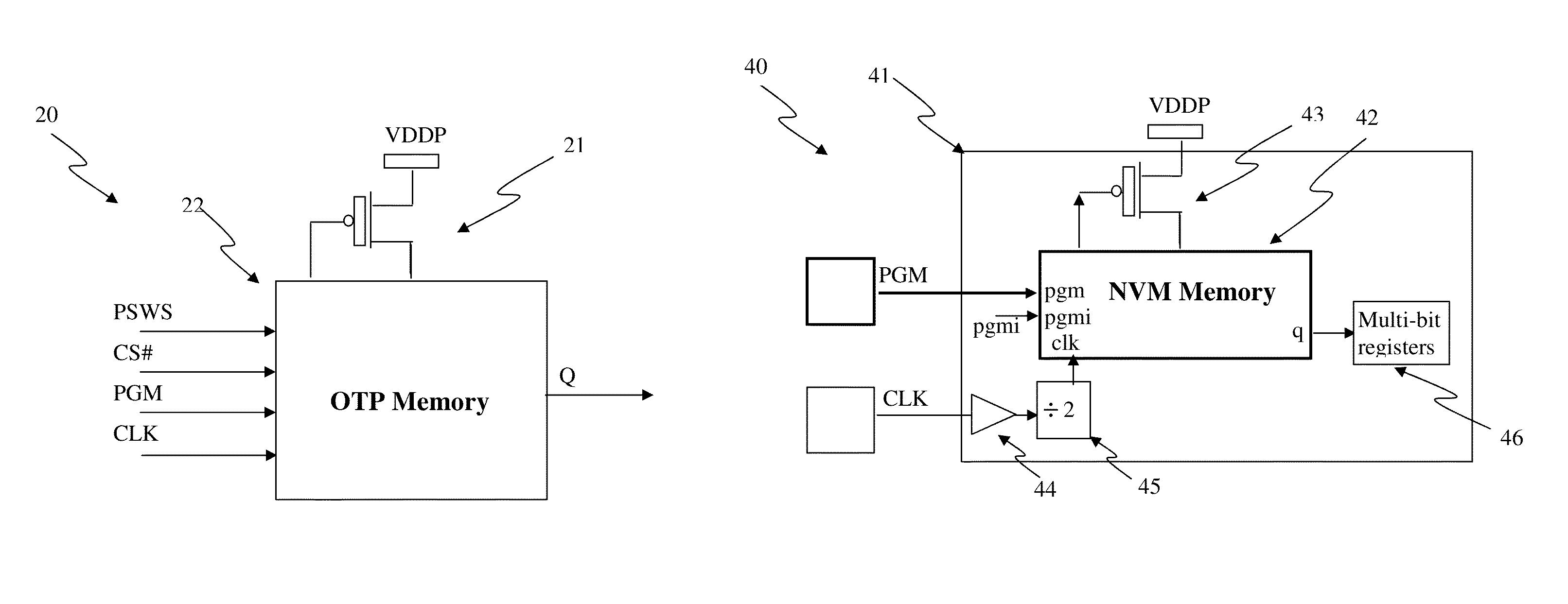

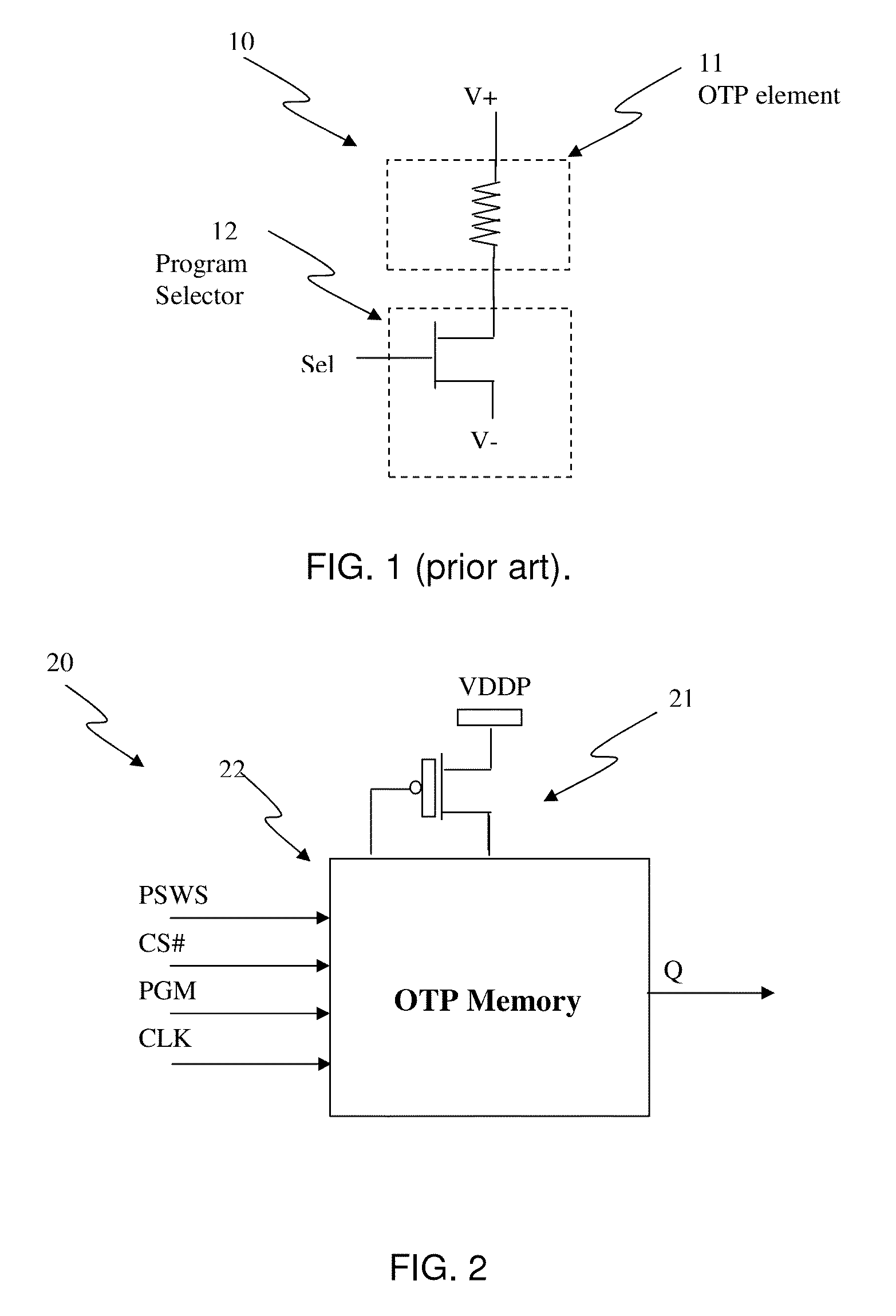

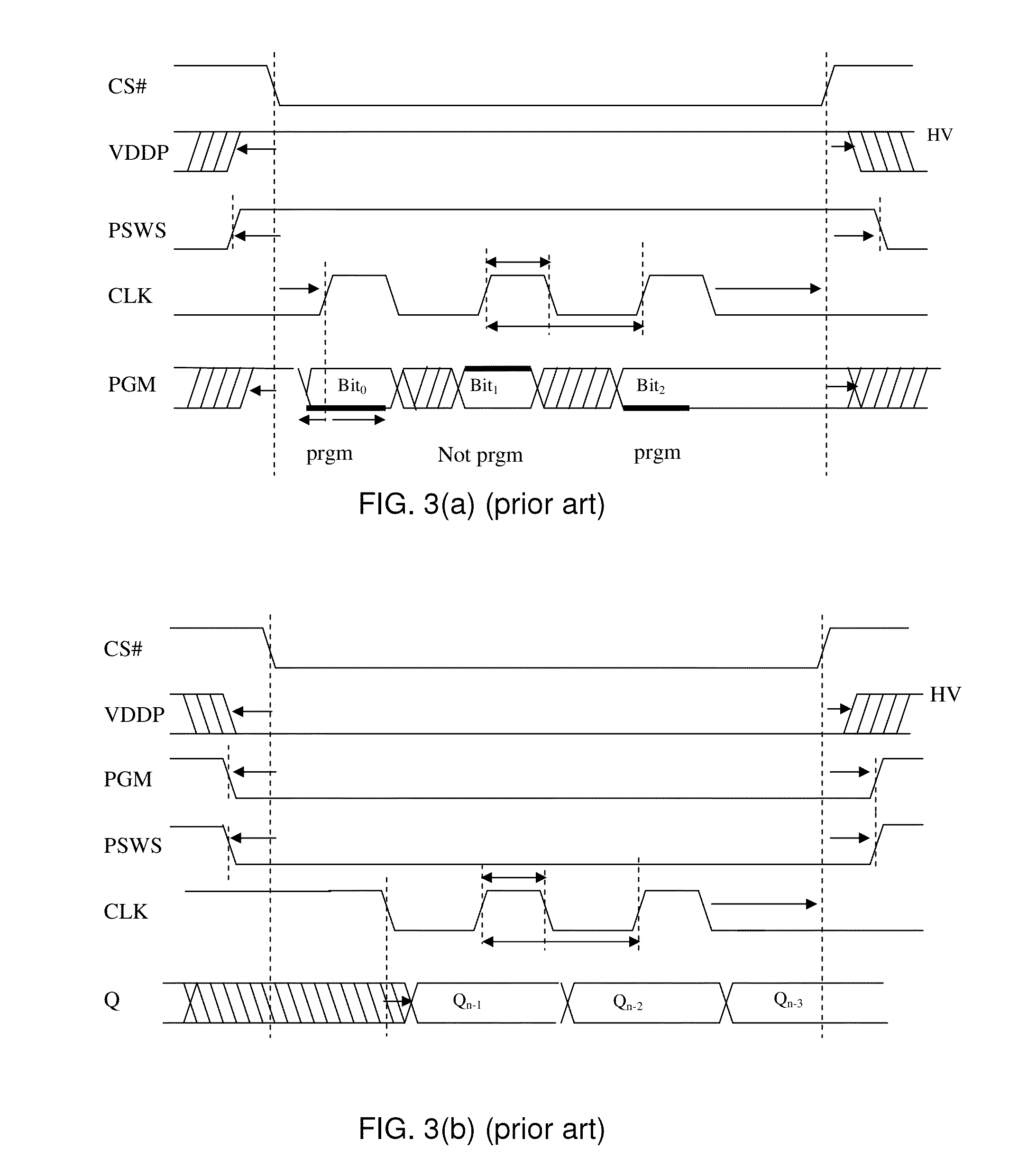

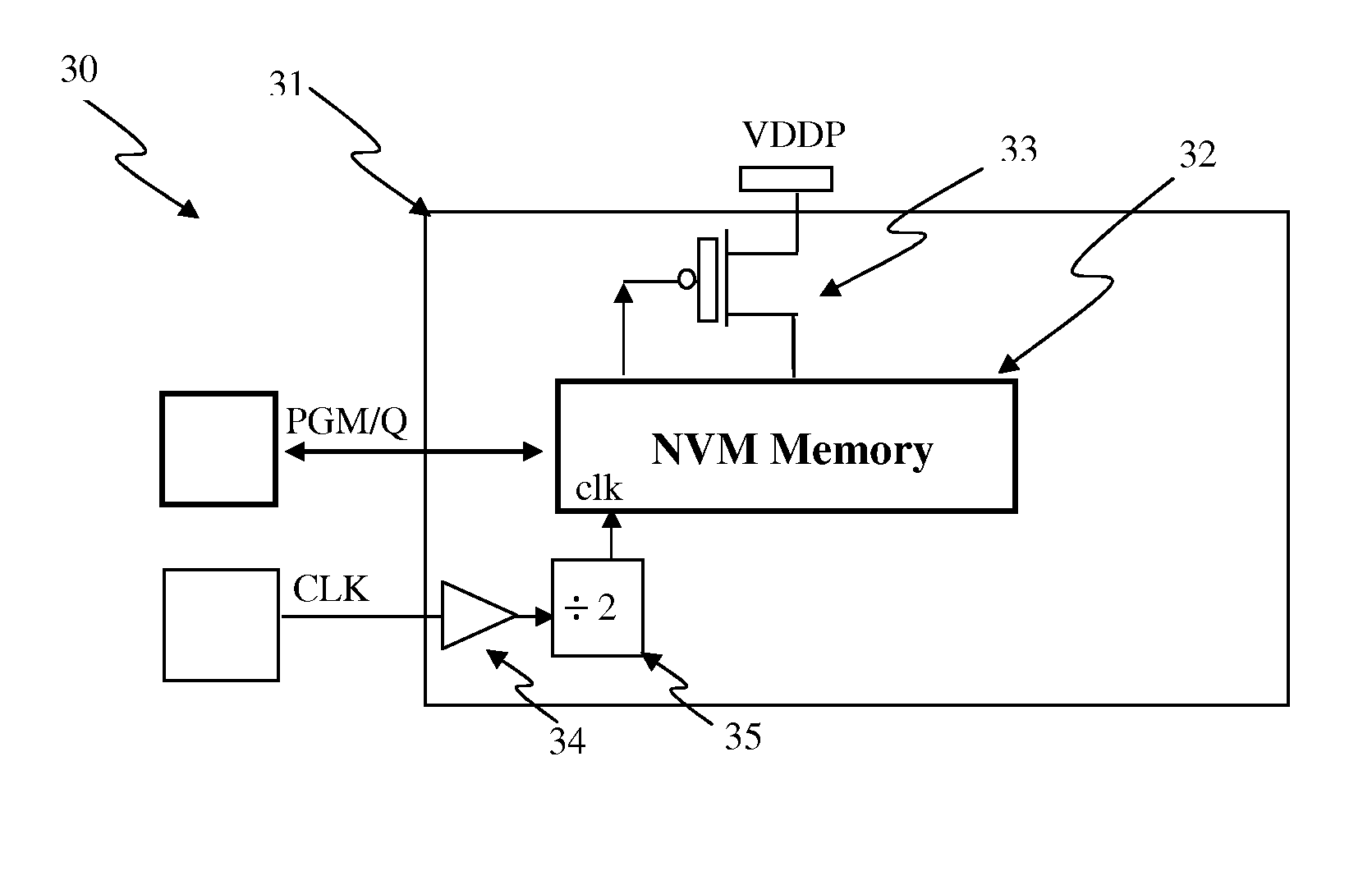

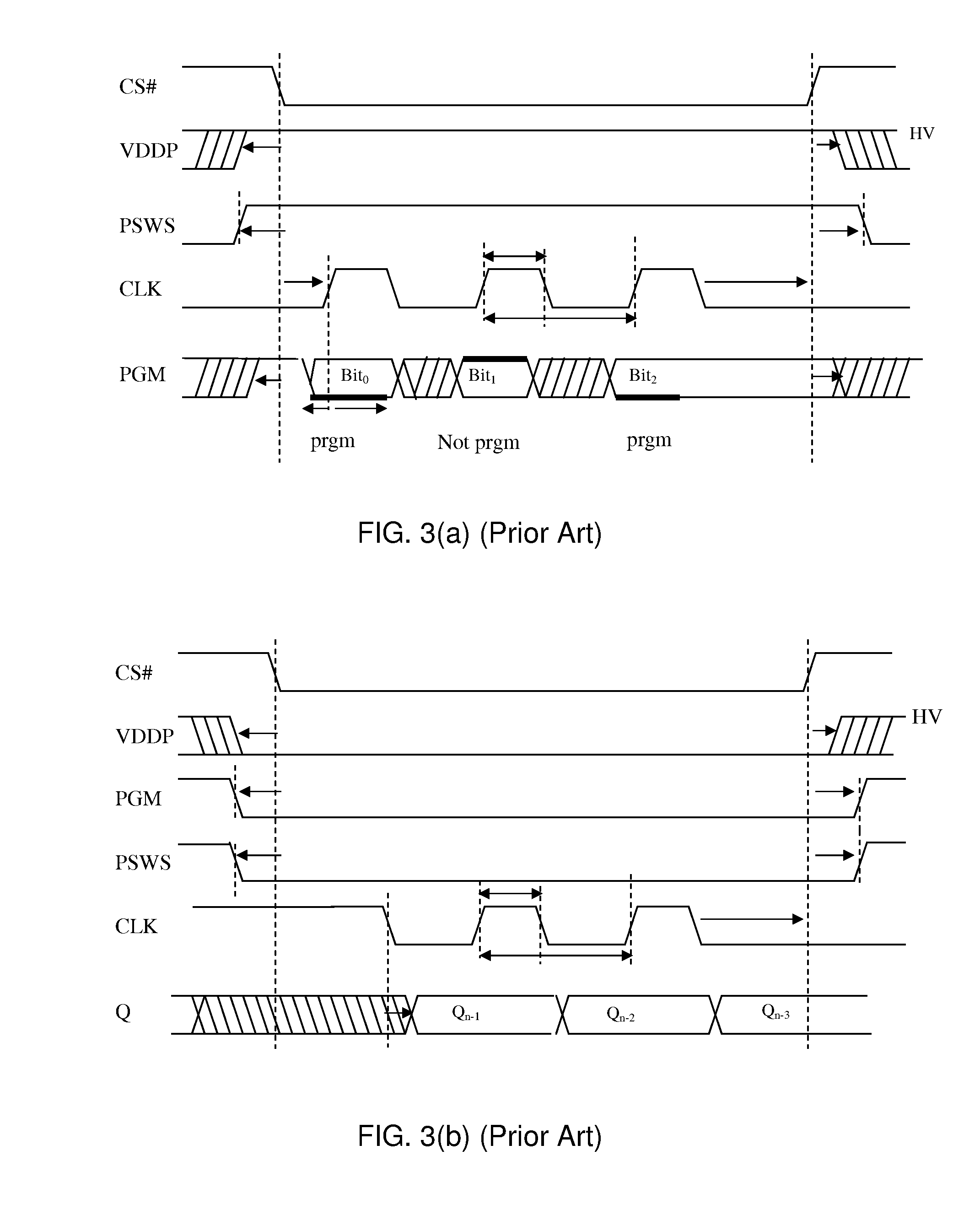

Low-pin-count non-volatile memory interface

ActiveUS20120106231A1Easily integrated into integrated circuitReduce areaRead-only memoriesDigital storageControl signalLow Pin Count

A low-pin-count non-volatile (NVM) memory to be provided in an integrated circuit. In one embodiment, the low-pin-count non-volatile (NVM) memory can use only one external control signal and one internal clock signal to generate start, stop, device ID, read / program / erase pattern, starting address, and actual read / program / erase cycles. When programming or erasing begins, toggling of the control signal increments / decrements a program or erase address and a pulse width of the control signal determines the actual program or erase time. A data out of the low-pin-count non-volatile (NVM) memory can be multiplexed with the control signal. Since the clock signal can be derived and shared from the system clock of the integrated circuit, the NVM memory need only have one external control pin for I / O transactions to realize a low-pin-count interface.

Owner:ATTOPSEMI TECH CO LTD

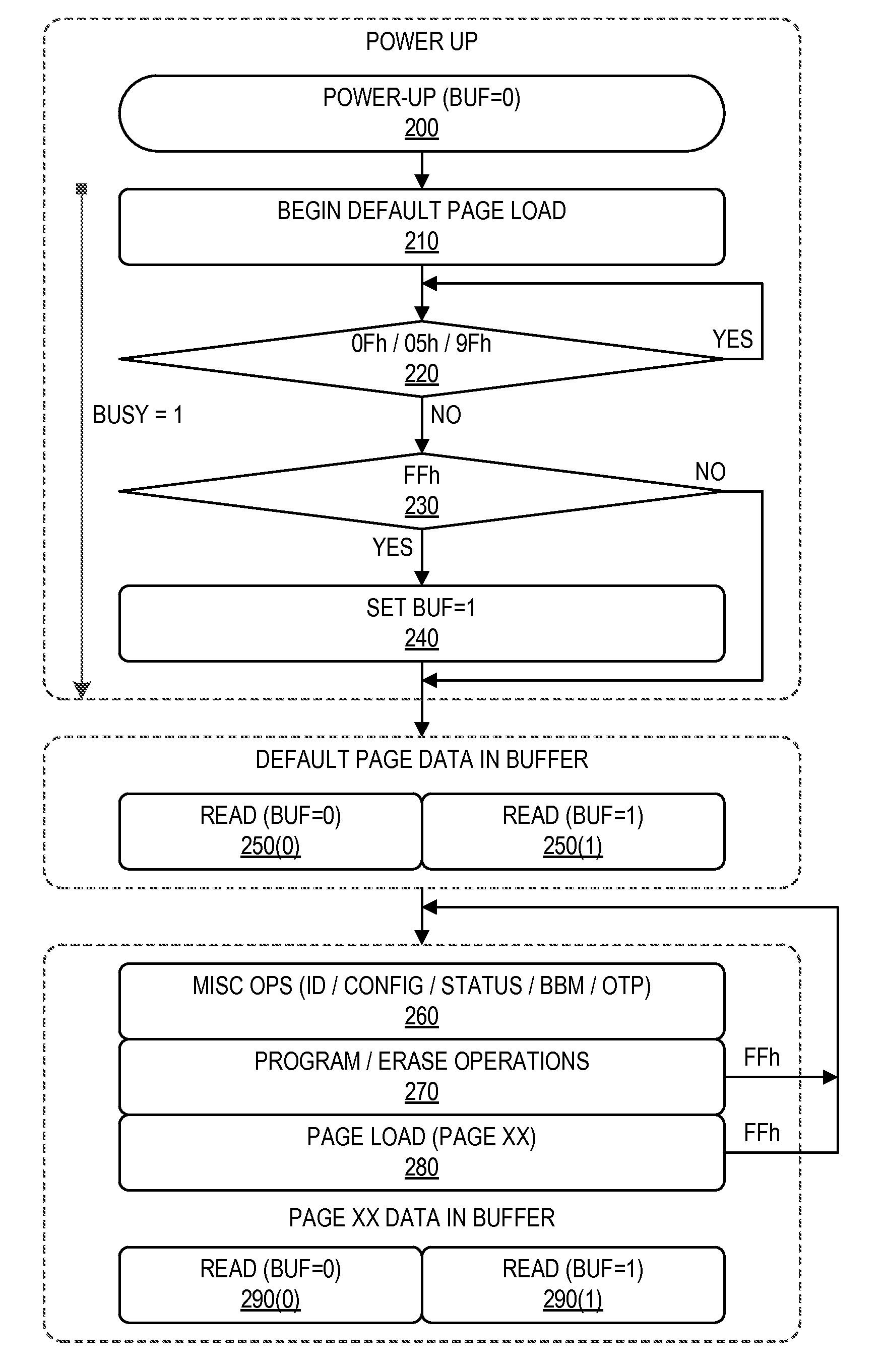

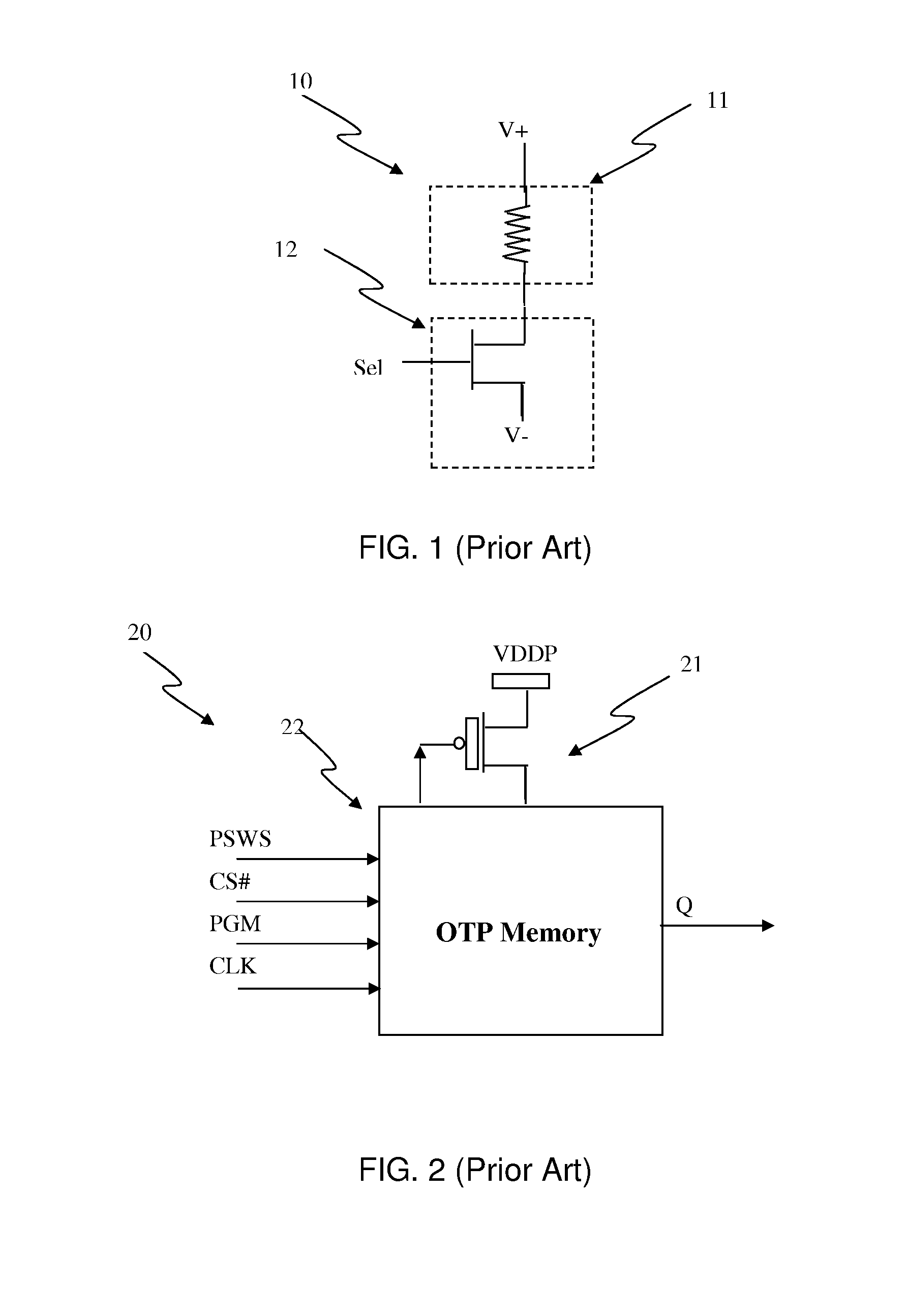

Low-Pin-Count Non-Volatile Memory Embedded in a Integrated Circuit without any Additional Pins for Access

ActiveUS20140211567A1Easily integrated into integrated circuitReduce areaRead-only memoriesDigital storageLow Pin CountNon-volatile memory

A low-pin-count non-volatile memory (NVM) embedded an integrated circuit can be accessed without any additional pins. The NVM has one or more memory cells and at least one of the NVM cells can have at least one NVM element coupled to at least one selector and to a first supply voltage line. The selector can be coupled to a second supply voltage line and has a selecting signal. The integrated circuit can include at least one test mode detection circuit to activate a test mode upon detecting an abnormal (or out of normal) operation condition(s). Once a test mode is activated, at least one I / O or supply voltage of the integrated circuit can be used as the I / O or supply voltage of the NVM to select at least one NVM cell for read, program into nonvolatile, or volatile state. At least one NVM cell can be read during ramping of at least one supply voltage line.

Owner:ATTOPSEMI TECH CO LTD

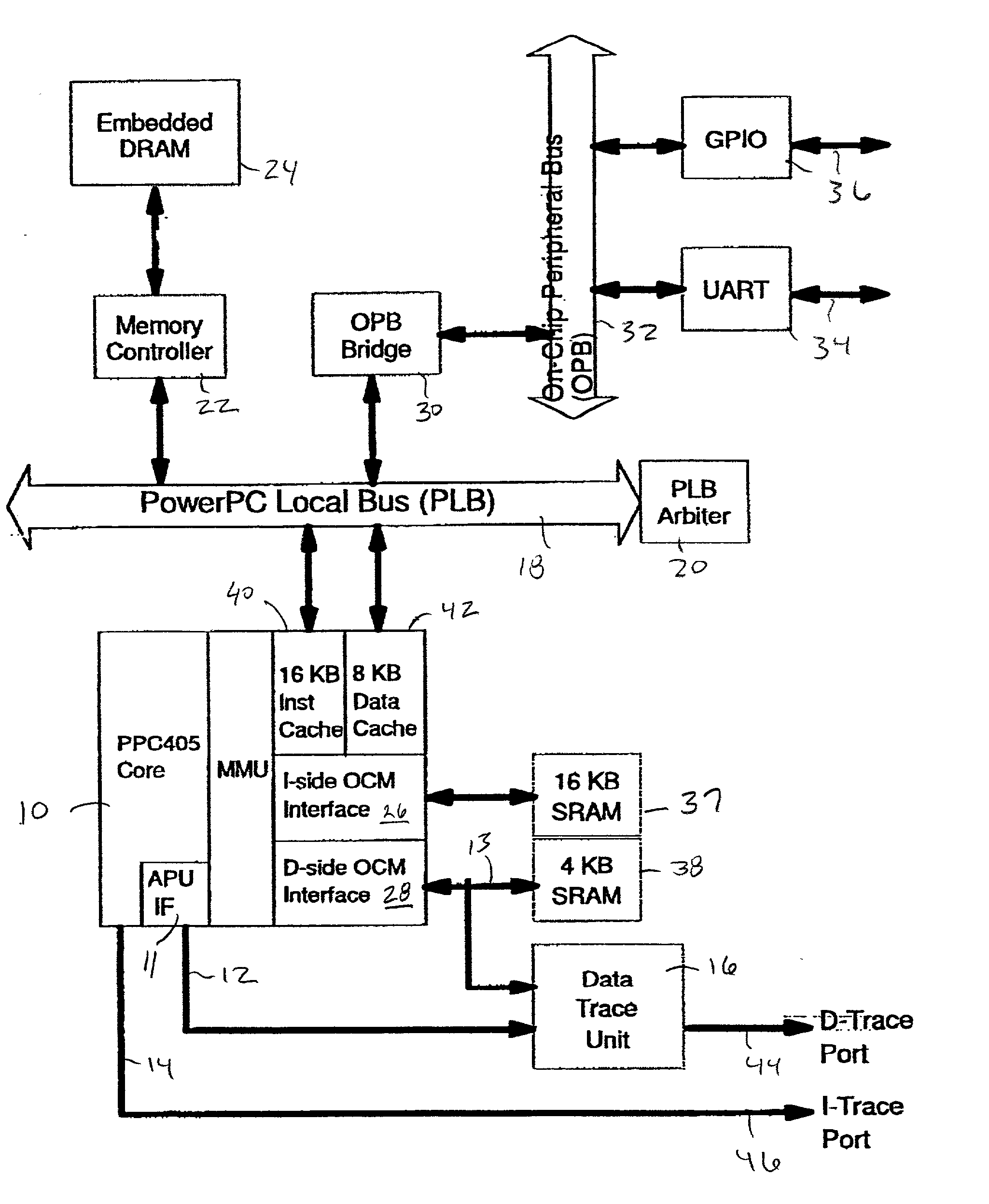

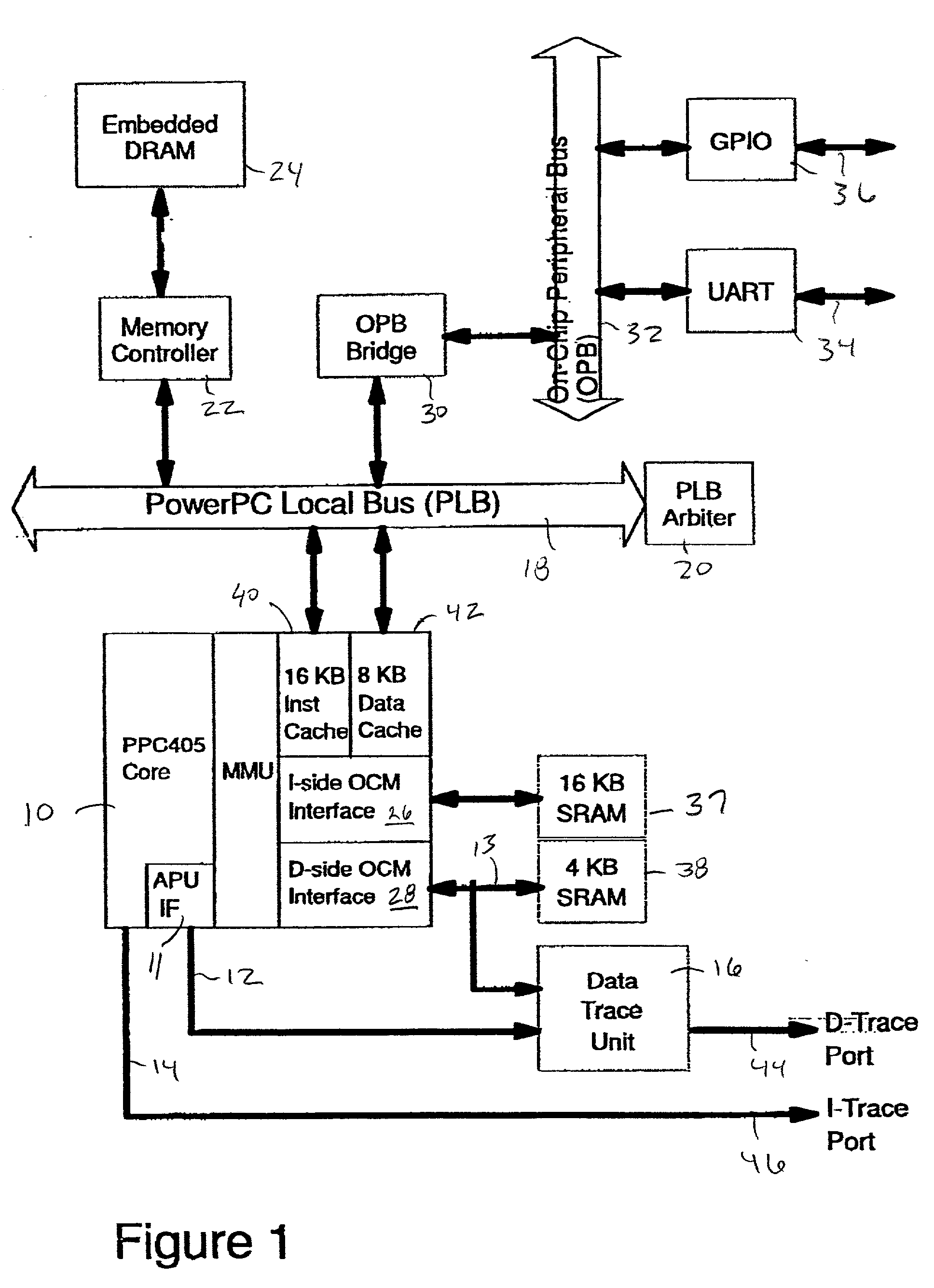

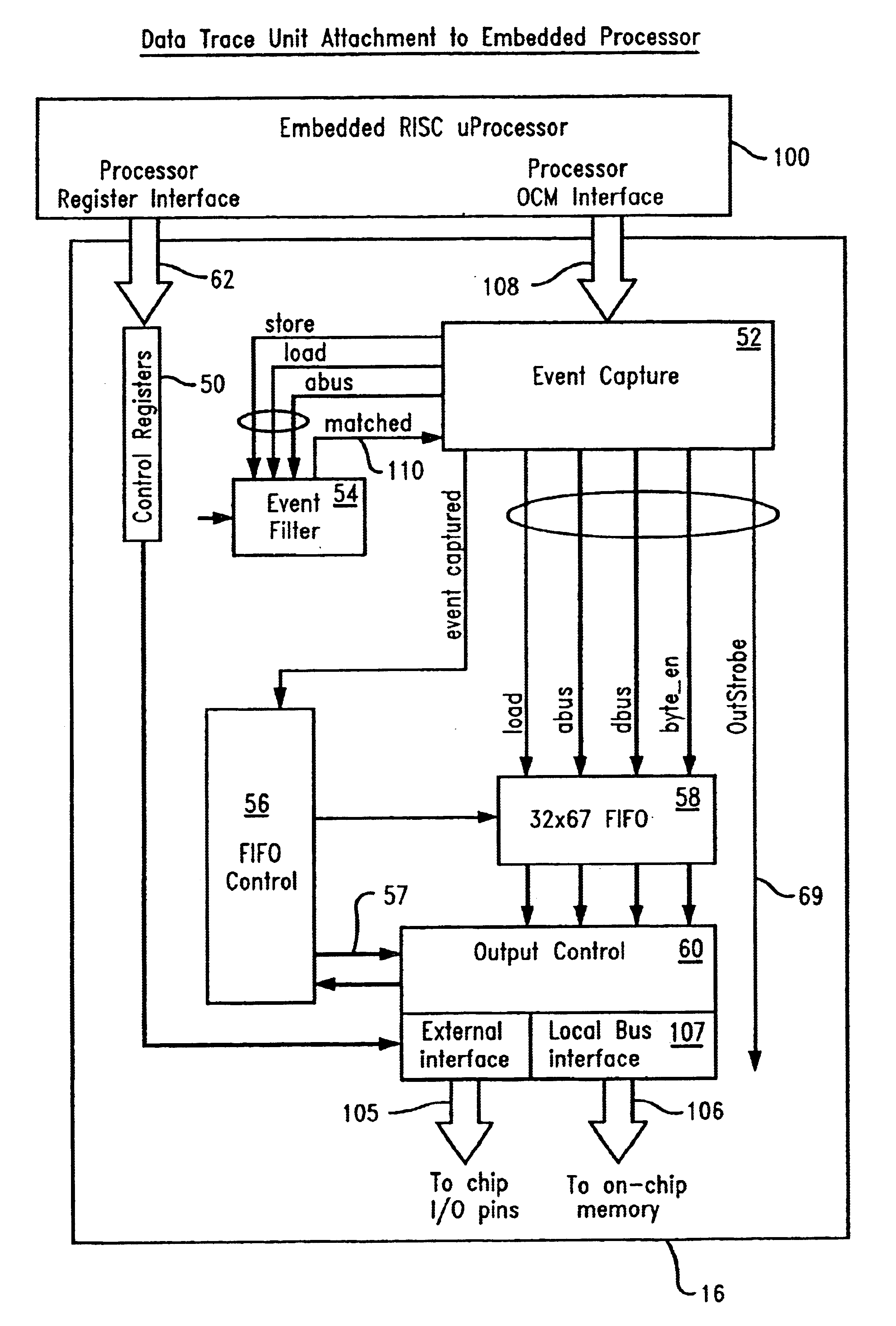

Integrated real-time data tracing with low pin count output

InactiveUS20030018929A1Low bandwidthAccurately indicatedHardware monitoringSoftware testing/debuggingReal-time dataData signal

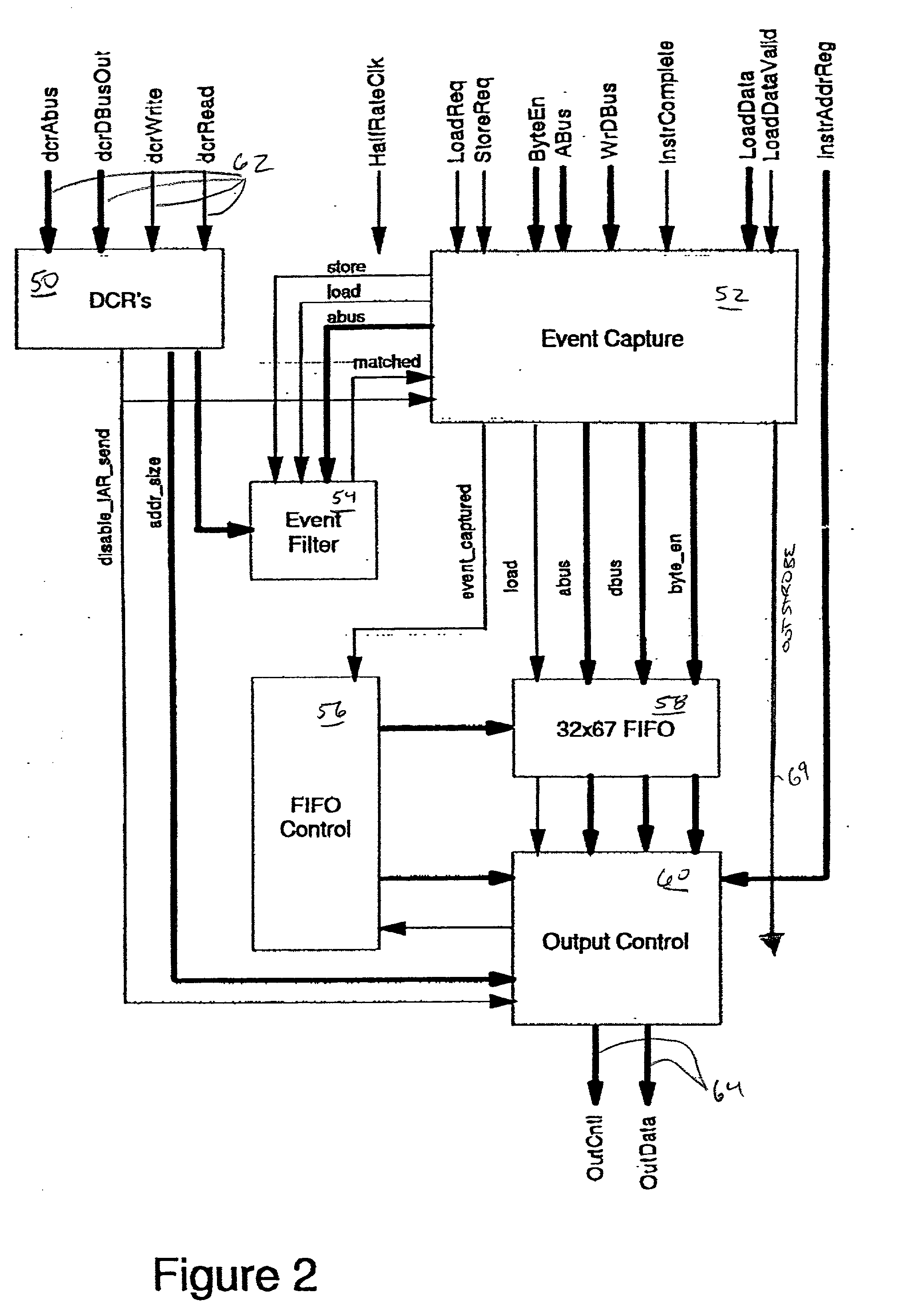

An integrated circuit real-time data tracing apparatus for analyzing microprocessor based computer systems for monitoring, in real-time, parameters sufficient to define the load and store operations information that the embedded core controller may assert, and process information during events. Integral on this single chip apparatus is a data trace unit designed to access control, address, and data signal lines required to monitor the embedded core controller's activities; perform data tracing independent of instruction tracing; synchronize with an instruction trace stream; allow for selection of multiple ranges for data tracing; report lost events to a FIFO array; and, output strobe signals to give a cycle accurate indication of when an event has been captured.

Owner:MARVELL ASIA PTE LTD

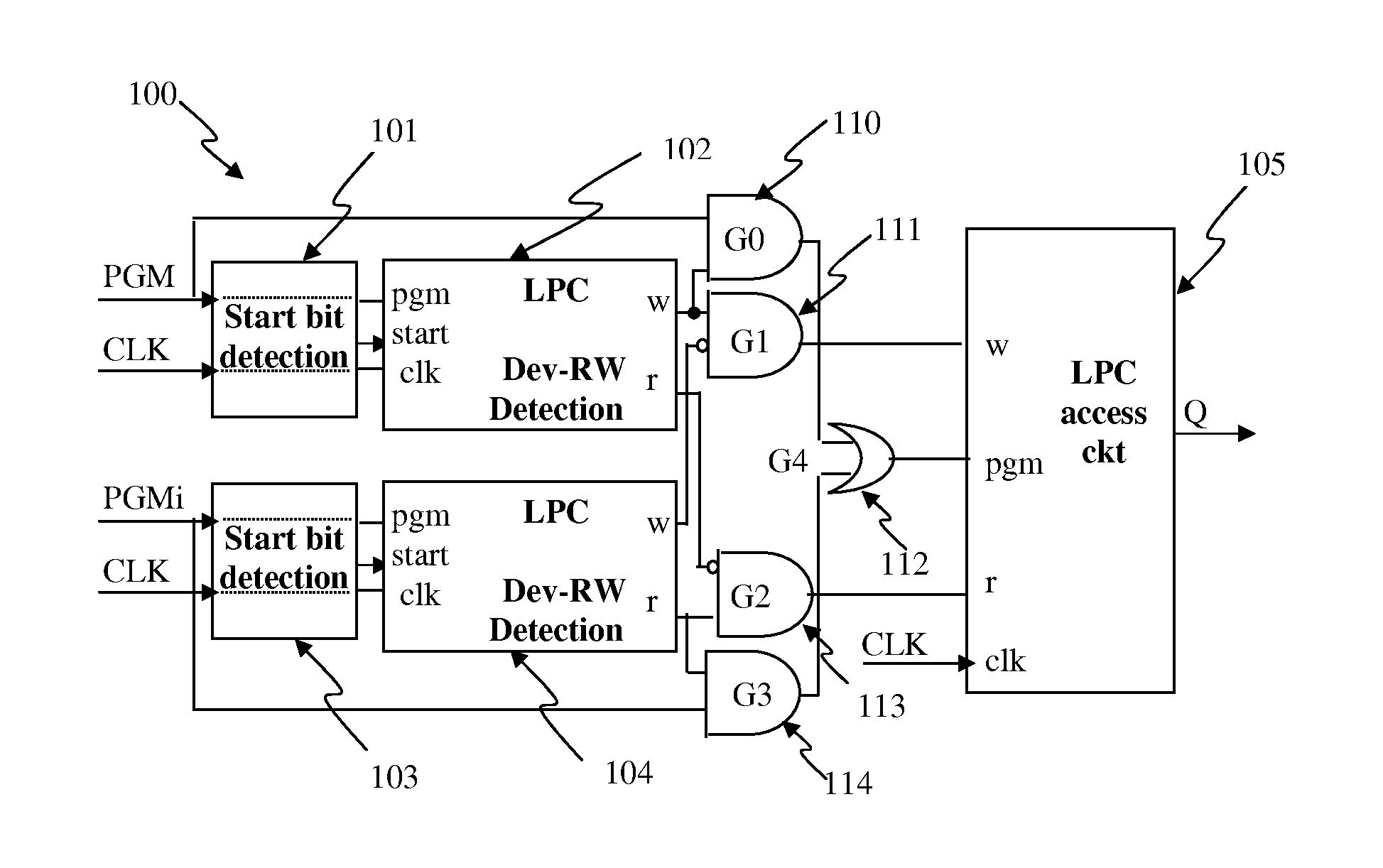

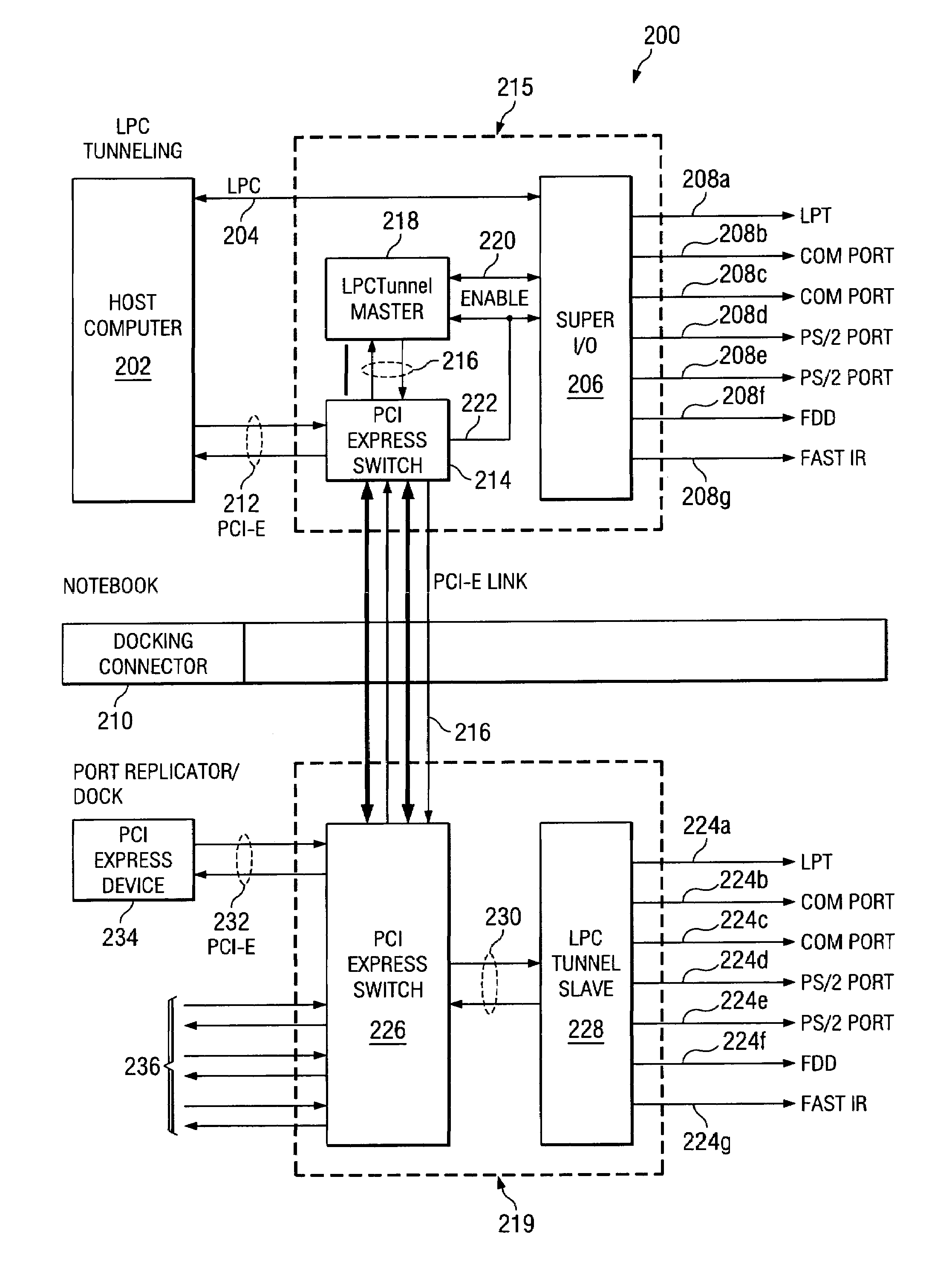

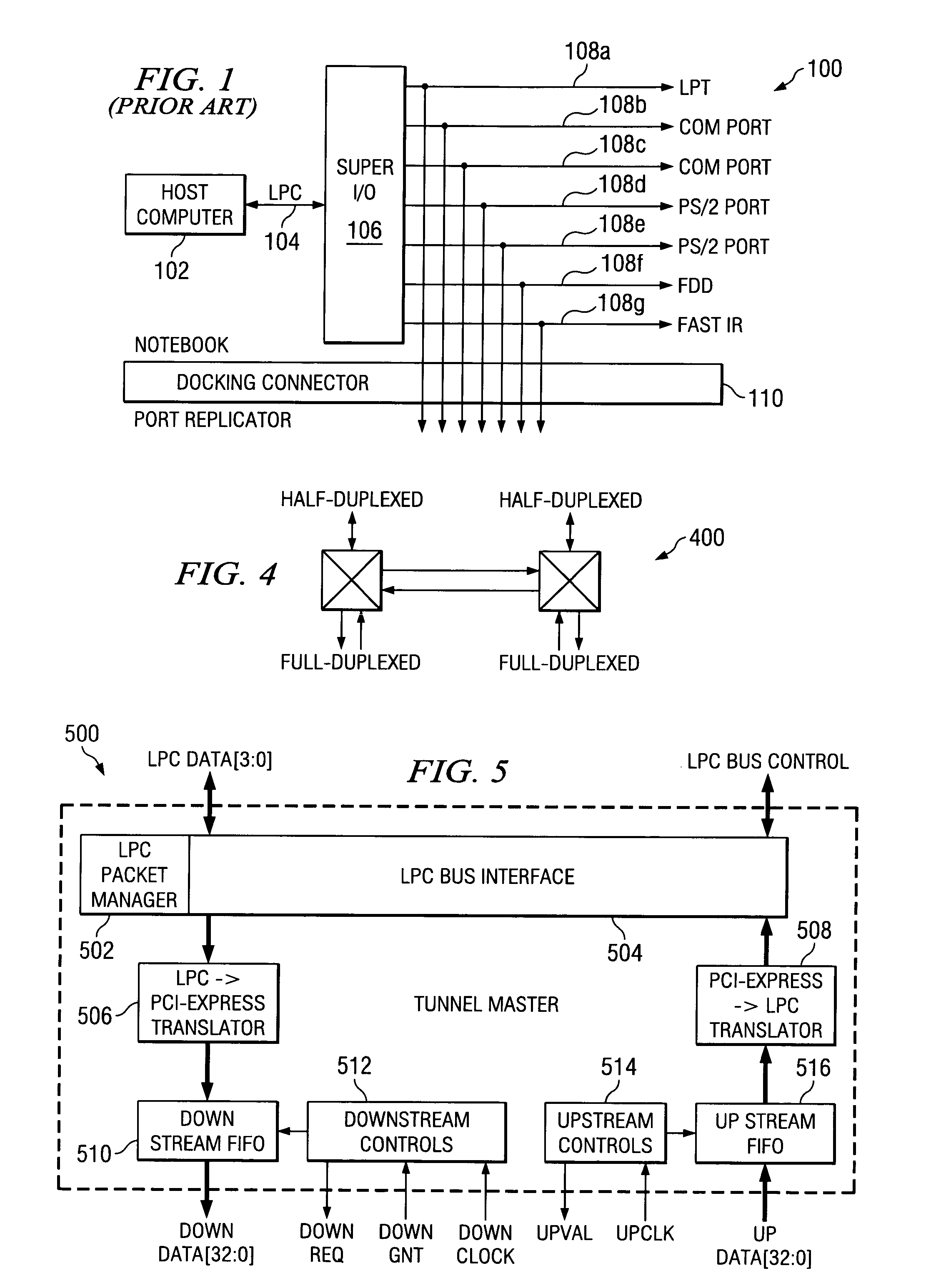

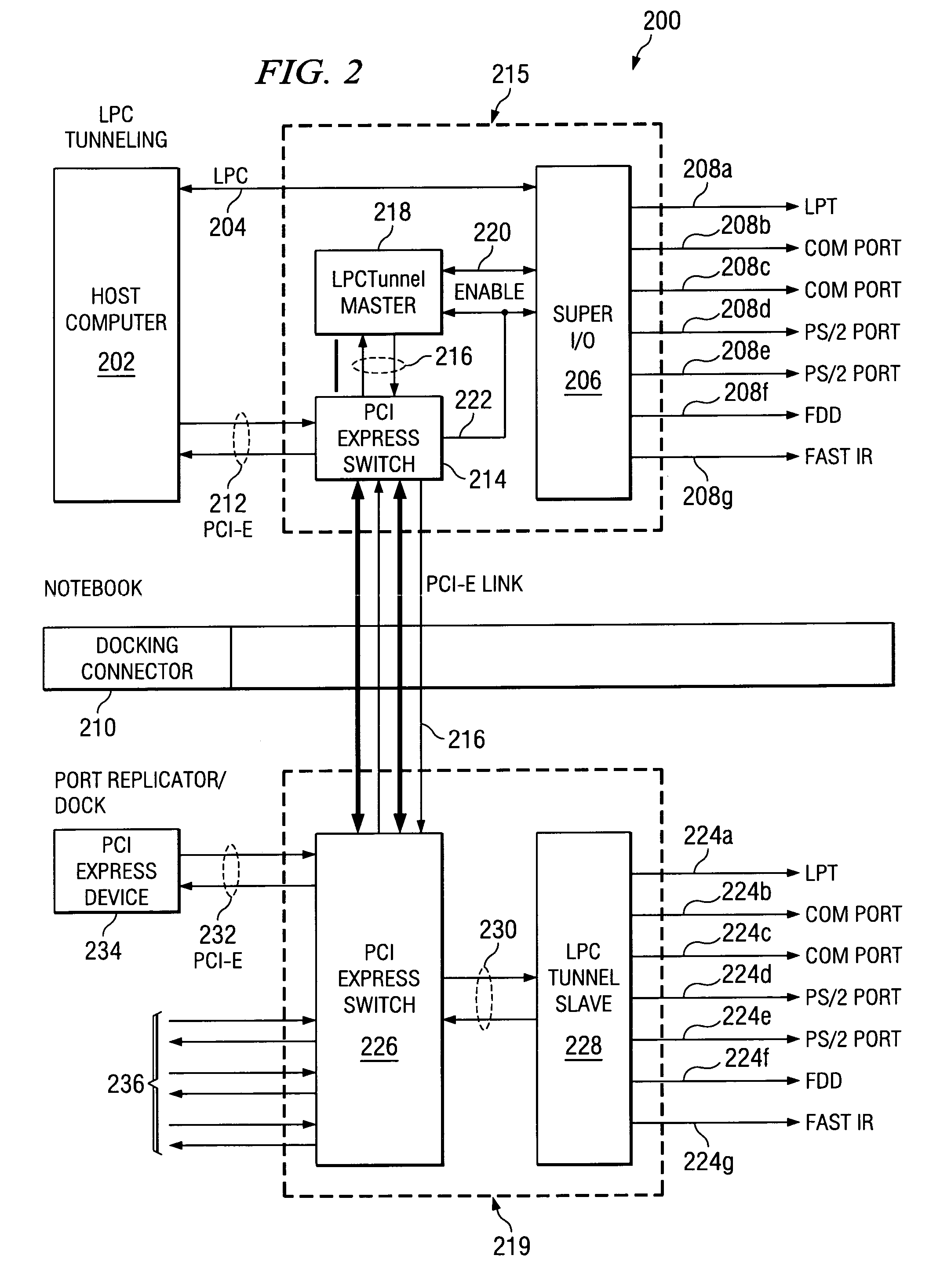

LPC transaction bridging across a PCI-express docking connection

A hybrid PCI_Express fabric system allows LPC bus commands and data to be sent across the PCI_Express fabric from a portable computer to its docking station. This permits the portable computer to be coupled to peripheral devices connected to the docking station without additional connectors on the portable computer and the docking station.

Owner:TEXAS INSTR INC

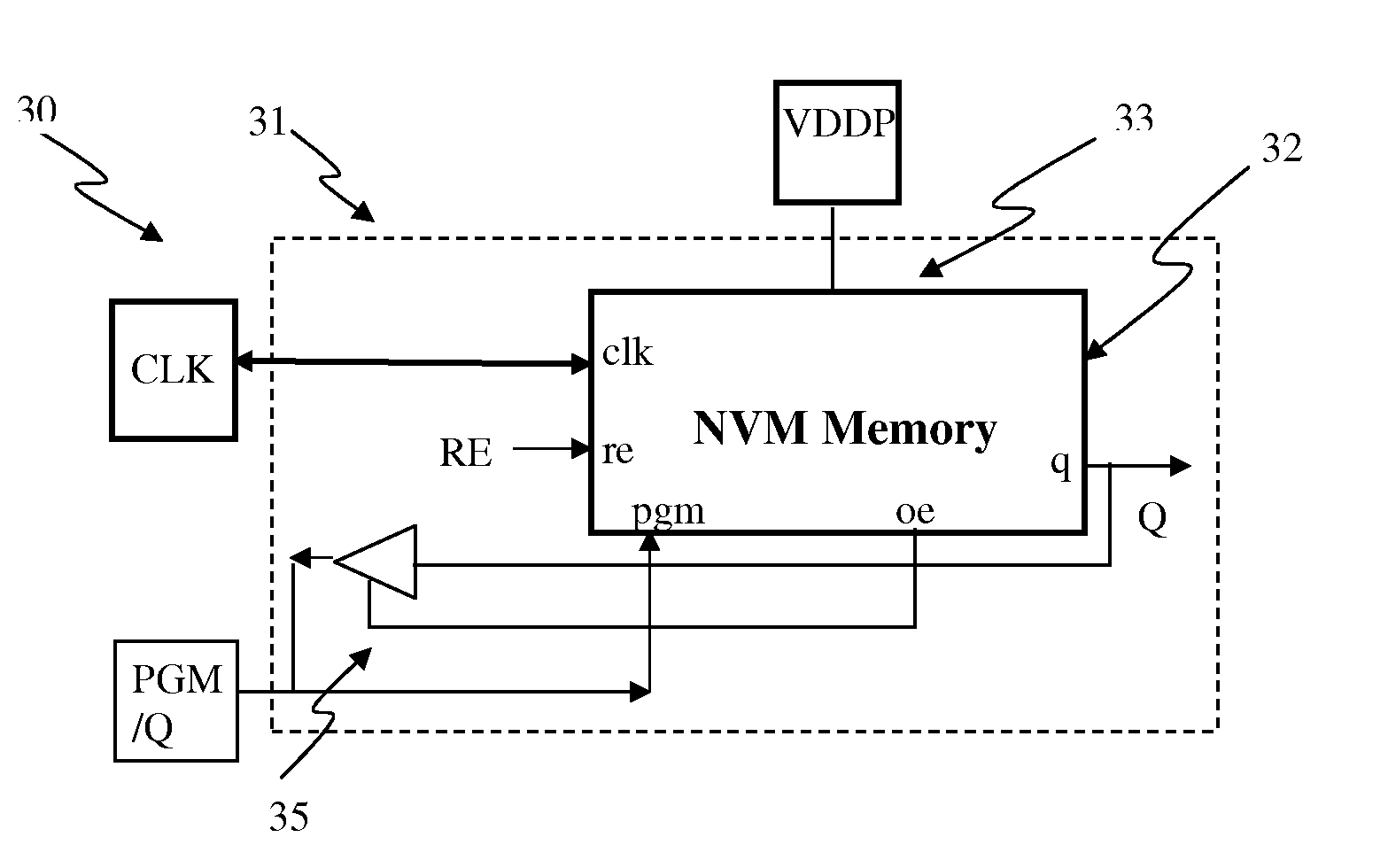

Low-pin-count non-volatile memory interface for 3D IC

ActiveUS9019791B2Easily integrated into integrated circuitReduce areaRead-only memoriesDigital storageLow Pin CountNon-volatile memory

A low-pin-count non-volatile (NVM) memory to be provided in an integrated circuit for a 3D IC to repair defects, trim devices, or adjust parameters is presented here. At least one die in a 3D IC can be built with at least one low-pin-count OTP memory. The low-pin-count OTP memory can be built with a serial interface such as I2C-like or SPI-like of interface. The pins of the low-pin-count OTP in at least one dies can be coupled together to have only one set of low-pin-count bus for external access. With proper device ID, each dies in a 3D IC can be accessed individually for soft programming, programming, erasing, or reading. This technique can improve the manufacture yield, device, circuit, or logic performance or to store configuration parameters for customization after 3D IC are built.

Owner:ATTOPSEMI TECH CO LTD

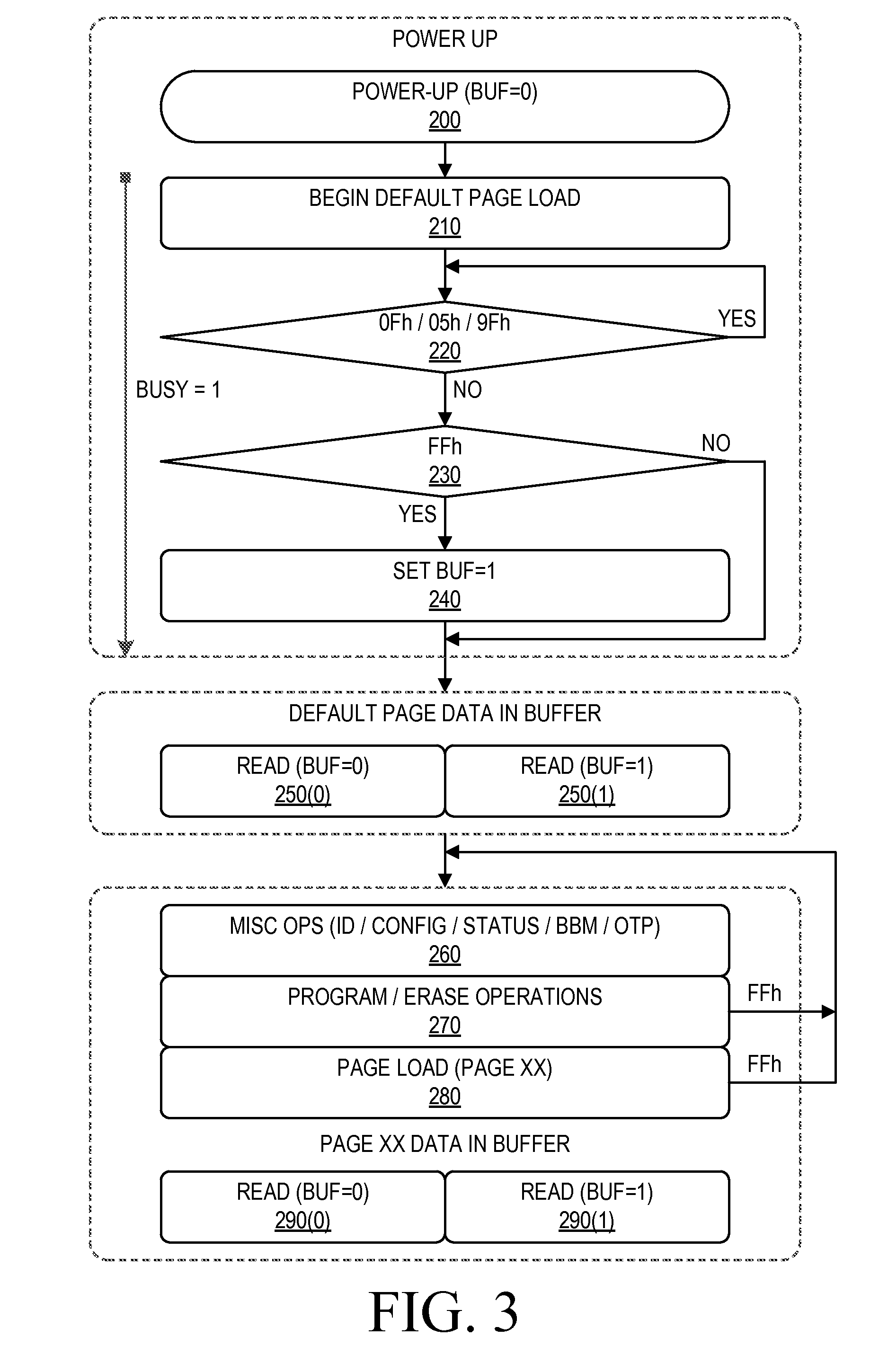

NAND Flash Memory

Serial NAND flash memory may be provided with the characteristics of continuous read of the memory across page boundaries and from logically contiguous memory locations without wait intervals, while also being clock-compatible with the high performance serial flash NOR (“HPSF-NOR”) memory read commands so that the serial NAND flash memory may be used with controllers designed for HPSF-NOR memory. Serial NAND flash memory having these compatibilities is referred to herein as high-performance serial flash NAND (“SPSF-NAND”) memory. Since devices and systems which use HPSF-NOR memories and controllers often have extreme space limitations, HPSF-NAND may also be provided with the same physical attributes of low pin count and small package size of HPSF-NOR memory for further compatibility. HPSF-NAND memory is particularly suitable for code shadow applications, even while enjoying the low “cost per bit” and low per bit power consumption of a NAND memory array at higher densities.

Owner:WINBOND ELECTRONICS CORP

Low-Pin-Count Non-Volatile Memory Interface

ActiveUS20150078060A1Easily integrated into integrated circuitReduce areaRead-only memoriesDigital storageControl signalLow Pin Count

A low-pin-count non-volatile (NVM) memory to be provided in an integrated circuit. The low-pin-count non-volatile (NVM) memory can use only one external control signal and one internal clock signal to generate start, stop, device ID, read / program / erase pattern, starting address, and actual read / program / erase cycles. When programming or erasing begins, toggling of the control signal increments / decrements a program or erase address and a pulse width of the control signal determines the actual program or erase time. A data out of the low-pin-count non-volatile (NVM) memory can be multiplexed with the control signal. In some applications where only the integrated circuit can read the data, a second control signal internal to the integrated circuit generates start, stop, device ID, read pattern, starting address, and actual read cycles, while the first control signal external to the integrated circuit can do the same for the program or erase path. Since the clock signal can be derived and shared from the system clock of the integrated circuit, the NVM memory need only have one external control pin for I / O transactions to realize a low-pin-count interface.

Owner:ATTOPSEMI TECH CO LTD

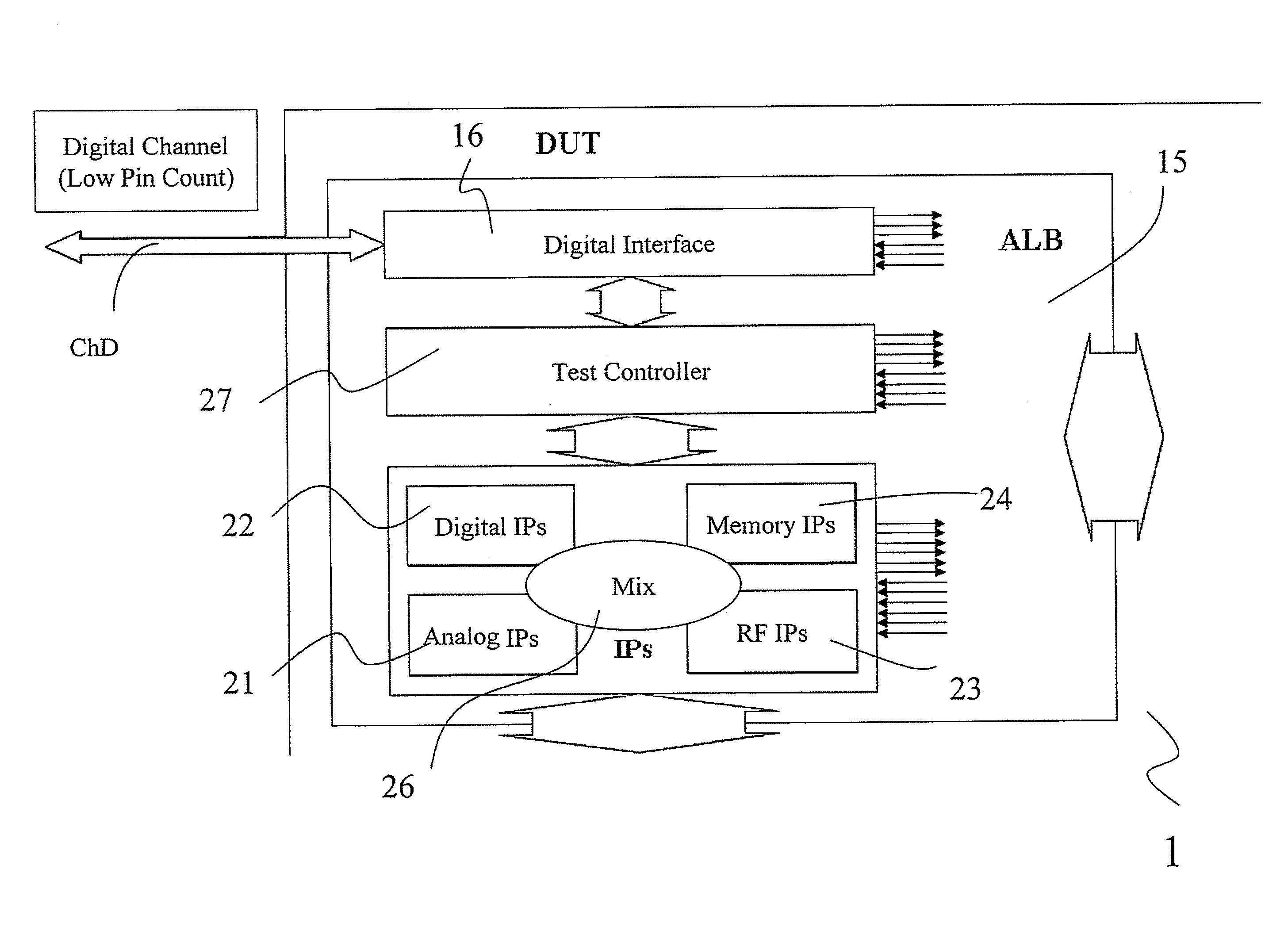

Method for performing an electrical testing of electronic devices

A method of electrical testing electronic devices DUT, comprising: connecting at least an electronic device DUT to an automatic testing apparatus suitable for performing the testing of digital circuits or memories or of digital circuits and memories; sending electrical testing command signals to the electronic device DUT by means of the ATE apparatus; performing electrical testing of the electronic device DUT by means of at least one advanced supervised self testing system “Advanced Low Pin Count BIST” ALB which is built in the electronic device DUT, the ALB system being digitally interfaced with the ATE through a dedicated digital communication channel; and sending reply messages, if any, which comprise measures, failure information and reply data to the command signals from the electronic device DUT toward the ATE apparatus by means of the digital communication channel.

Owner:STMICROELECTRONICS SRL

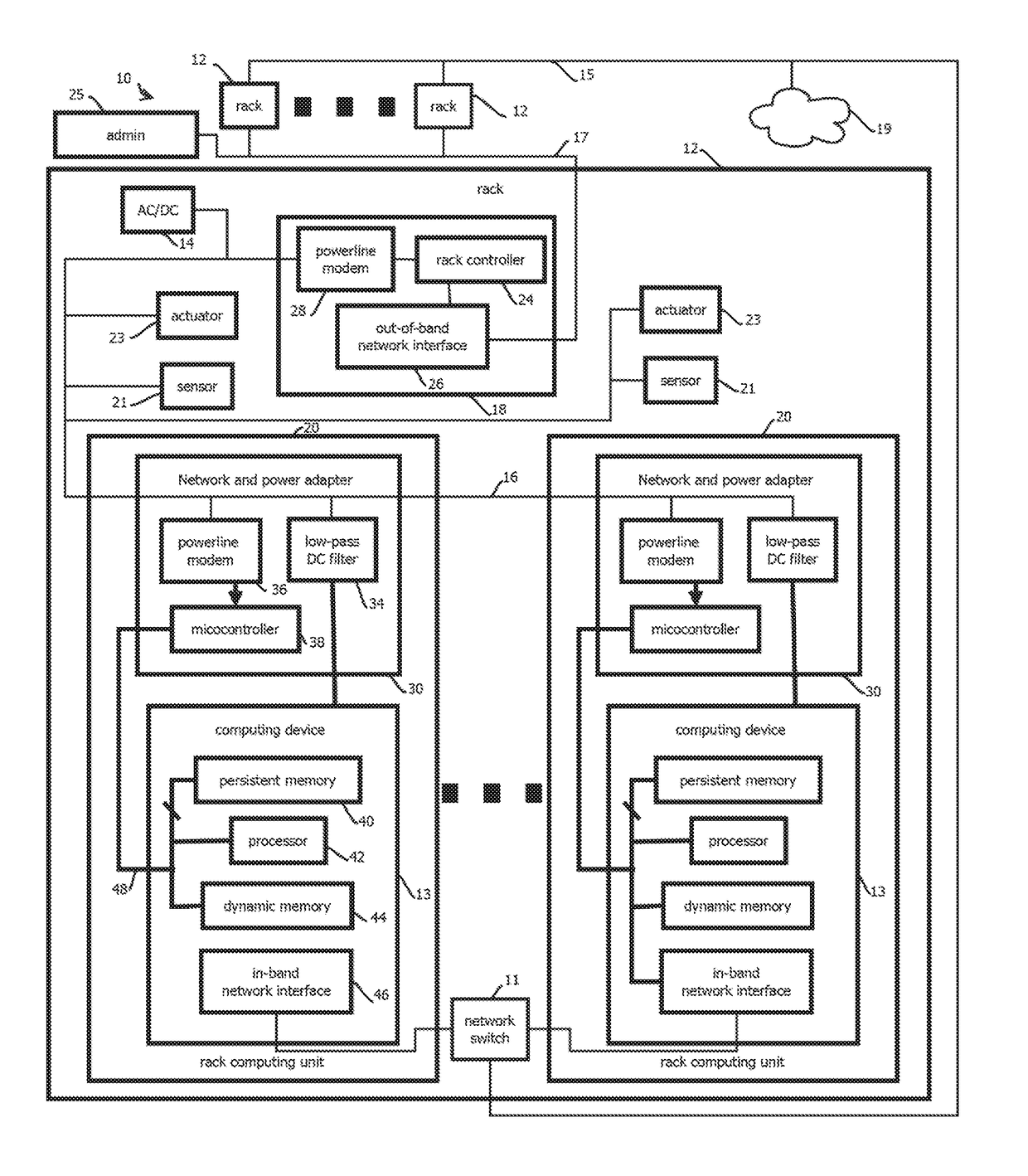

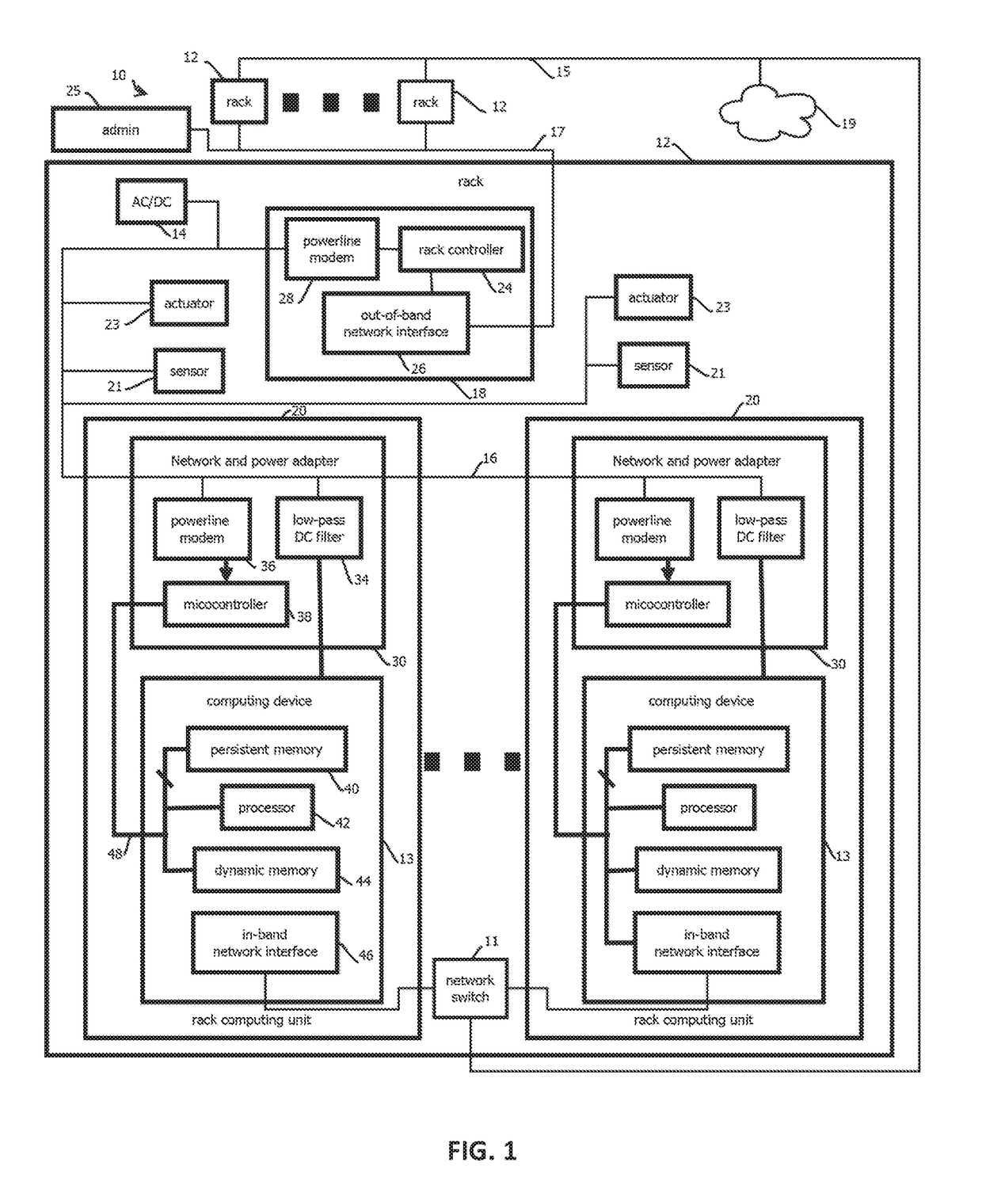

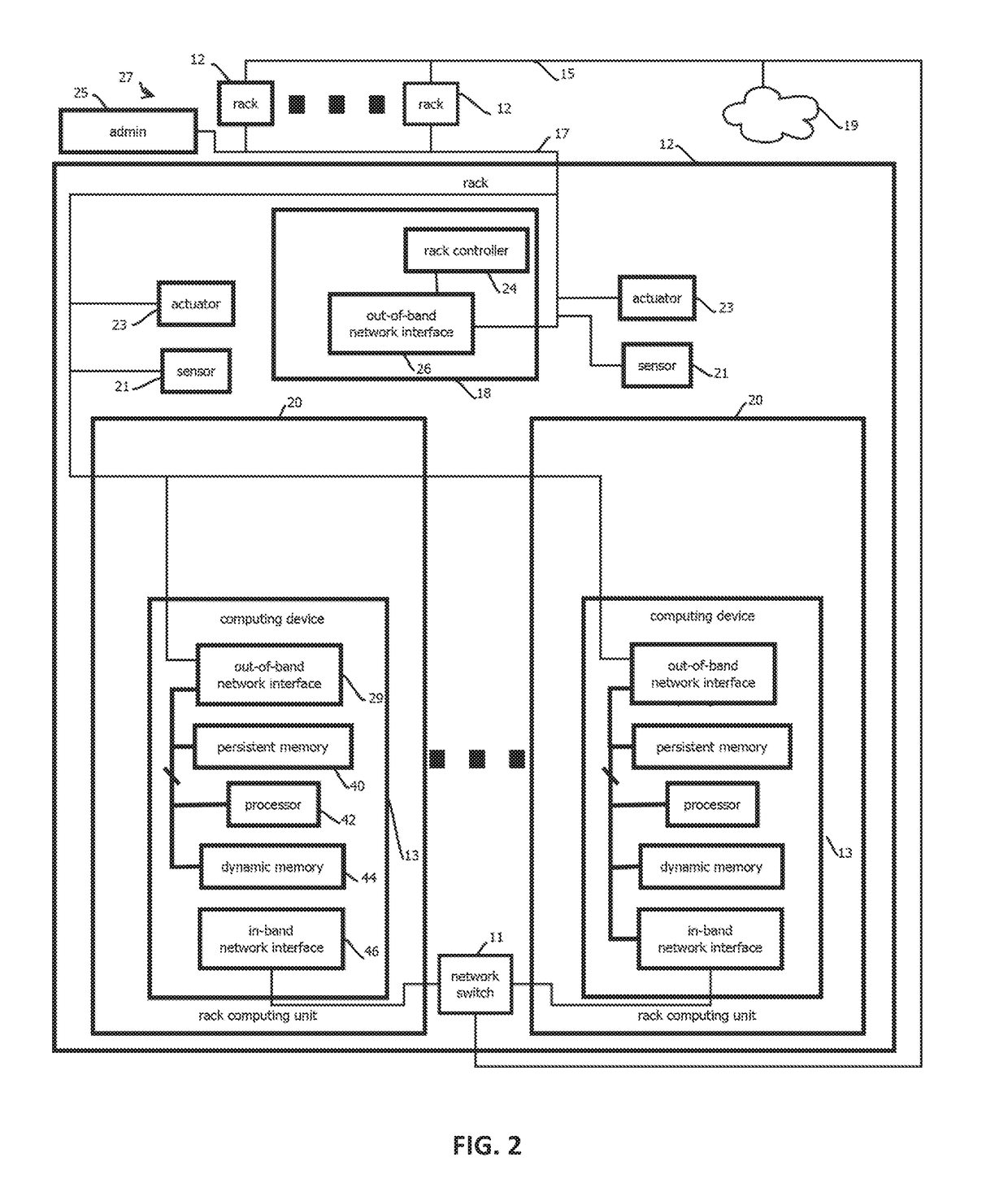

Data center management via out-of-band, low-pin count, external access to local motherboard monitoring and control

Provided is an external secondary computing device configured to monitor or control a rack-mounted computing device independently of whether the rack-mounted computing device is operating or is turned off via a low-pin-count motherboard bus independently of a baseboard management controller.

Owner:VAPOR IO INC

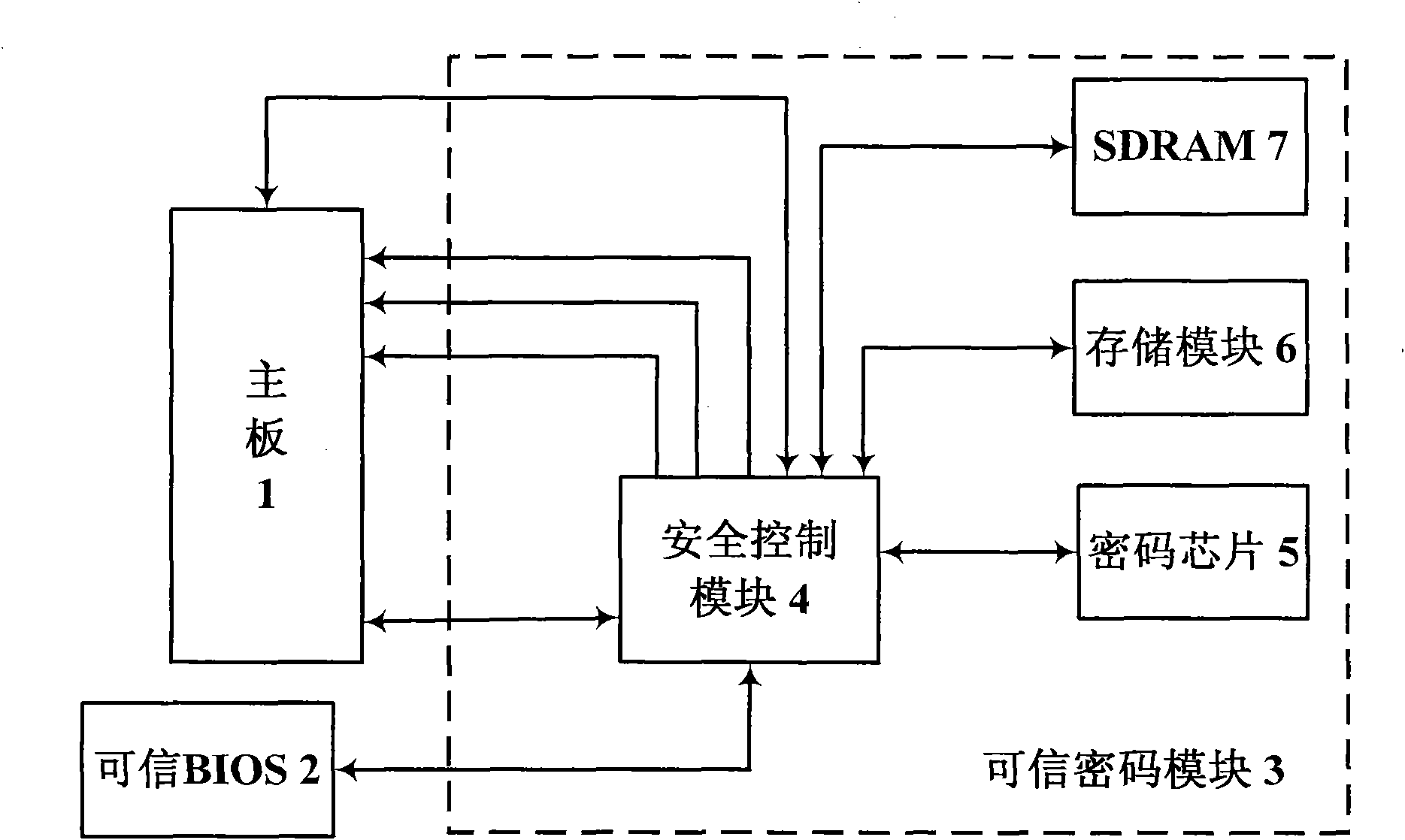

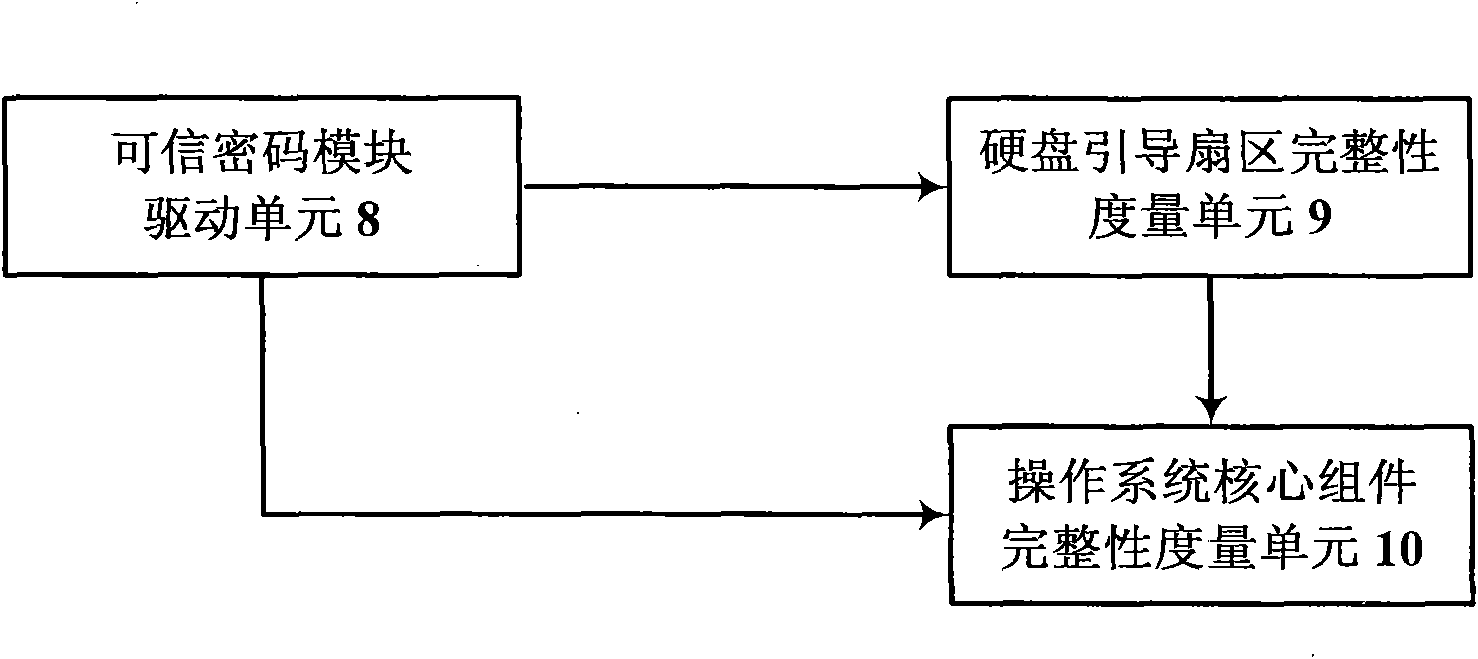

High-reliability computing platform

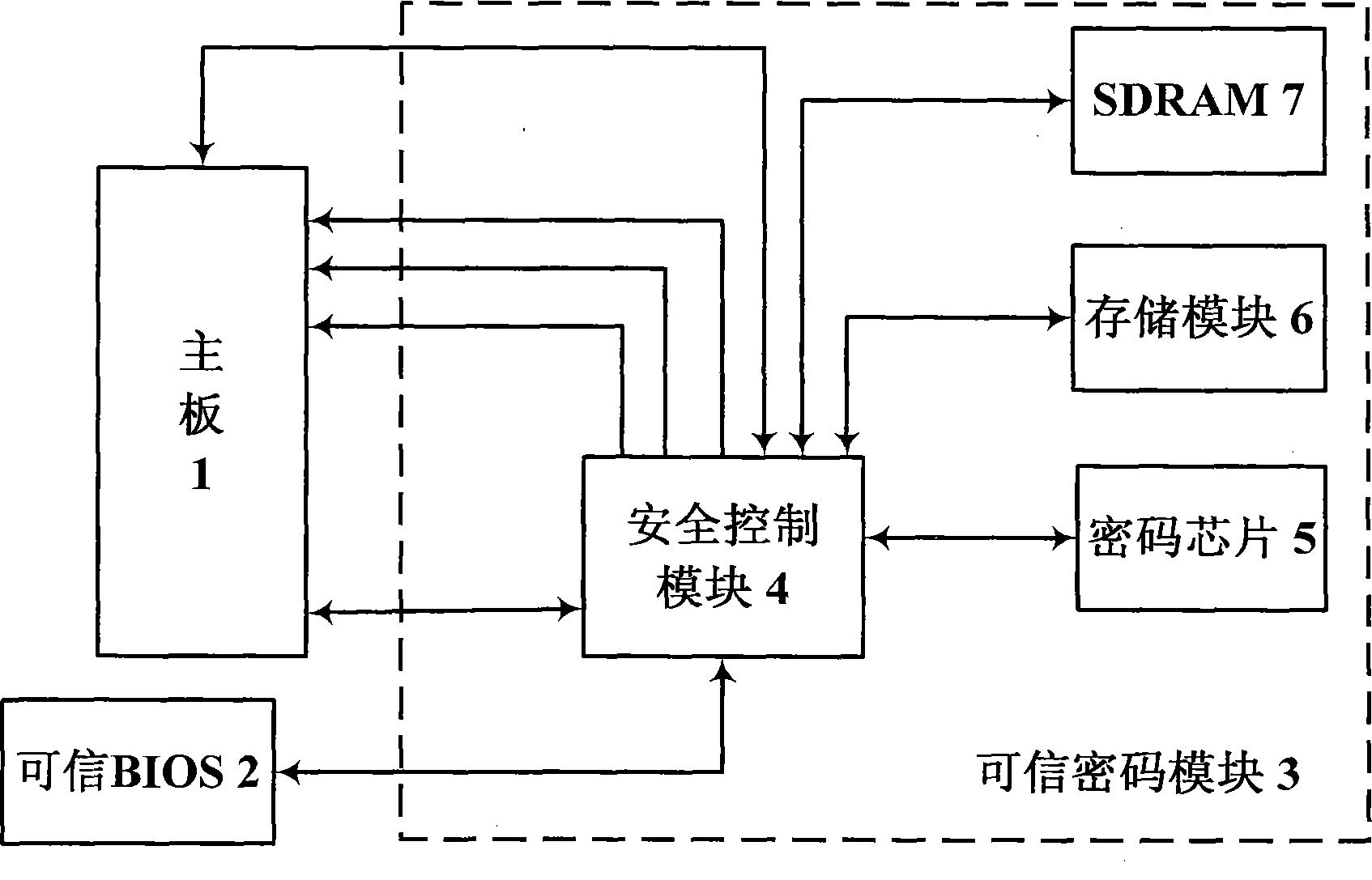

InactiveCN101877040AEnsure crediblePrevent potential safety hazardsInternal/peripheral component protectionOperational systemPassword

The invention discloses a high-reliability computing platform, which comprises a mainboard (1), a reliable BIOS (3) and a reliable password module (2) connected through a bus. A computer is electrified, and then the reliable password module (2) is electrified at first; the mainboard (1) is kept at a reset state by controlling a power, a clock and reset signal line, meanwhile a safety control module (4) starts a BIOS integrity measuring mechanism to ensure the reliability of the BIOS and then releases the power, the clock and the reset signal; the mainboard (1) directly accesses the BIOS chip through an LPC bus and loads the reliable BIOS (3) for normal start; the reliable BIOS (3) sequentially loads a hard disk boot sector integrity measuring unit (9) and an operating system core component integrity measuring unit (10) therein to finish the software integrity measurement; and after the measurement is successful, the operating system is normally loaded and operated. The invention ensures the safety and reliability during the computer starting process.

Owner:706 INST SECOND RES INST OF CHINAAEROSPACE SCI & IND

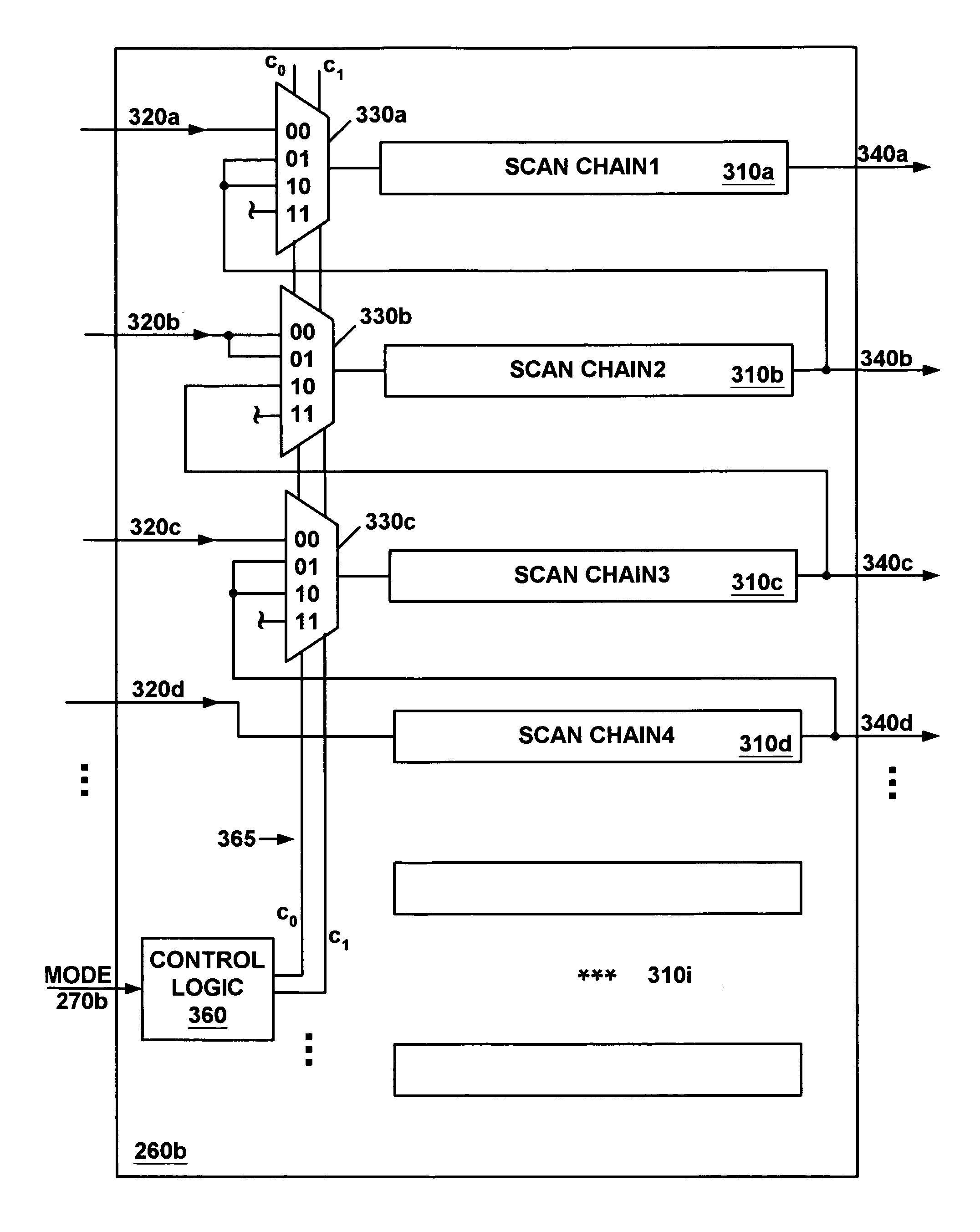

System and method for automatically retargeting test vectors between different tester types

Owner:SYNOPSYS INC

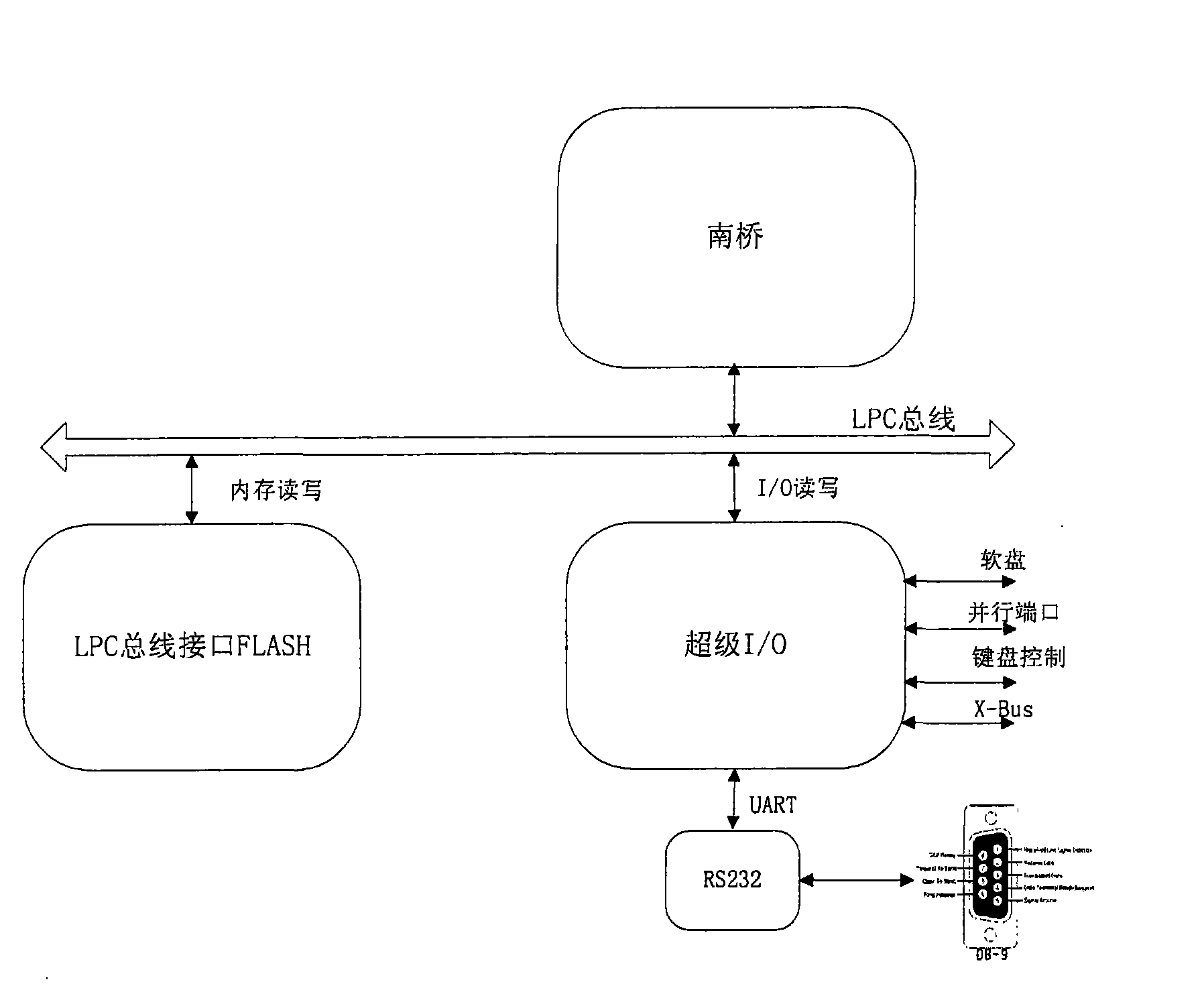

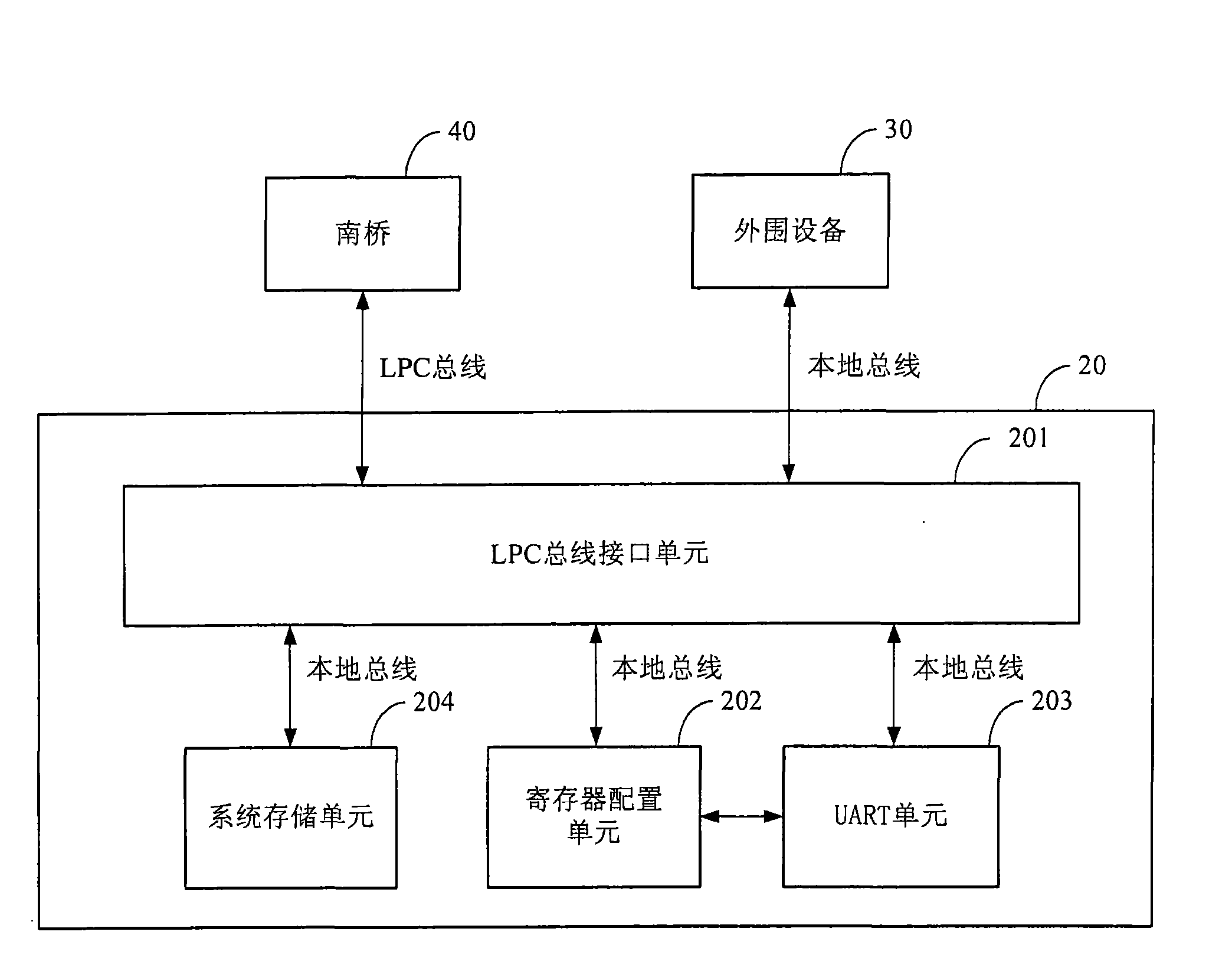

Signal conversion device and method as well as communication equipment

ActiveCN101989244AReduce complexityReduce usageElectric digital data processingRegister allocationMemory address

The embodiment of the invention provides a signal conversion device and method as well as communication equipment. The signal conversion device comprises an LPC (Low Pin Count) bus interface unit, a register configuration unit and a UART (Universal Asynchronous Receiver Transmitter) unit, wherein the LPC bus interface unit is used for performing protocol analysis on signals from an LPC bus and outputting local signals through a local bus, and the local signals comprise a control signal, an address signal and a data signal; the register configuration unit is used for configuring registers of the UART unit according to the local signals; the registers of the UART unit are allocated in a memory address space and an I / O address space; and the UART unit is used for converting data from the LPCbus into serial data according to the local signals and the values of configured registers of the UART unit and then outputting the serial data through a UART interface or outputting the serial data received by the UART interface to the LPC bus through the local signals. The embodiment of the invention can simplify the configuration process of the registers of the USRT unit.

Owner:HUAWEI TECH CO LTD

Method for diagnosing fault of server in real time

InactiveCN105677500AGuaranteed return to workReduce the impactRedundant data error correctionReal time servicesBIOS

The invention discloses a real-time server fault diagnosis method. The method is interconnected by BMC and BIOS through LPC bus, BMC and CPU are interconnected through PECI bus, BIOS and memory and PCIE devices are interconnected through SMBus and PCIE bus; BMC is interconnected through LPC bus Read the fault status of CPU, memory and PCIE devices in real time; when the BMC detects a device fault, it will trigger an interrupt in real time, and the interrupt processing process reads some specific fault status registers of the CPU through the PECI bus, and records them in the BMC storage space. The invention realizes the purpose of real-time diagnosis of server faults at the fault site, improves the hit rate of fault diagnosis, reduces the time for fault location, and effectively reduces the impact on customer services.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

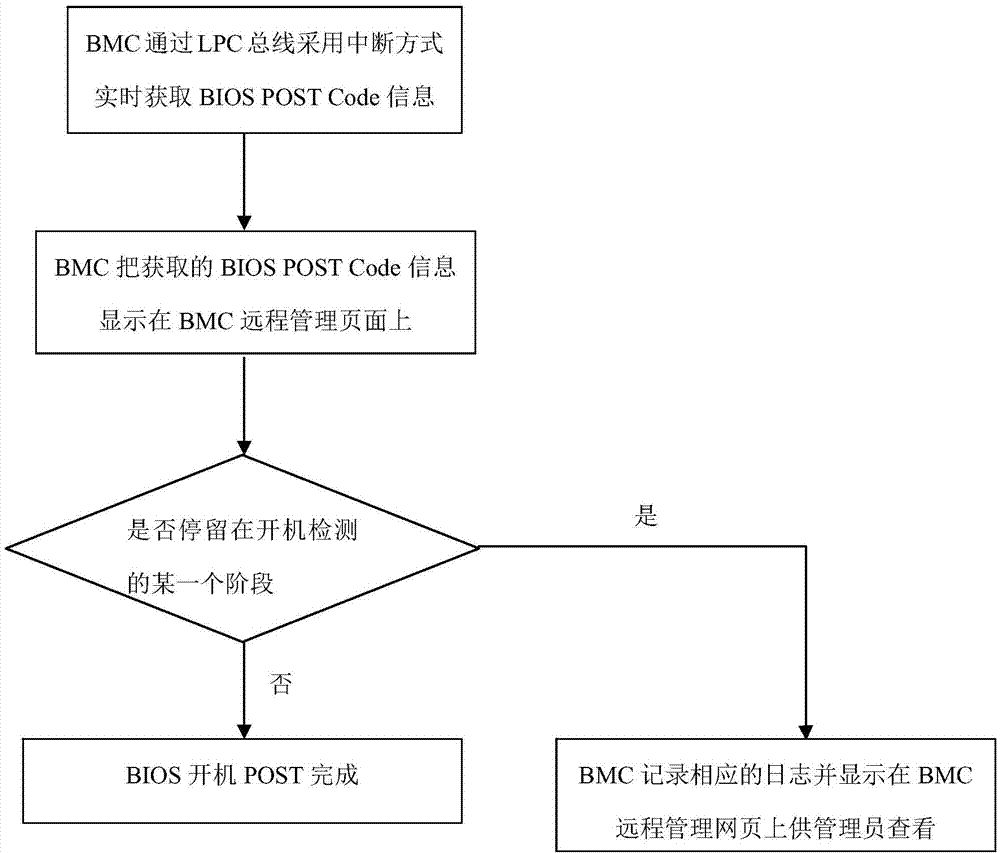

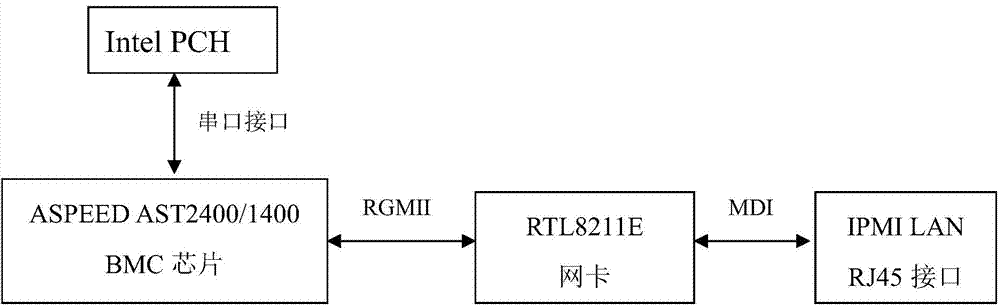

BMC based method and system for remote diagnosis of server startup failure

InactiveCN104850485AImprove maintenance work efficiencyConvenient remote real-time monitoringHardware monitoringElectricityBaseboard

The present invention provides a BMC based method and system for remote diagnosis of a server startup failure. The BMC based method for remote diagnosis of a server startup failur comprises: creating a BMC detection module on a BMC by adding code, wherein the BMC detection module acquires BIOS POST Code information in real time in an interrupting manner by using an LPC bus; and the BMC detection module displaying the acquired BIOS POST Code information on a BMC remote management webpage. According to the technical scheme provided by the invention, an initialization process of each hardware device in a power-on and start-up process of a server baseboard is monitored remotely in real time, and a problem that occurs during start-up of a system can be rapidly located without the need to use a debug card, thus increasing server maintenance efficiency. Moreover, an administrator may locate the failures without going to a computer room, thereby reducing server maintenance costs and improving server maintenance efficiency.

Owner:SHENZHEN TONGTAIYI INFORMATION TECH CO LTD

Integrated real-time data tracing with low pin count output

InactiveUS6834365B2Low bandwidthAccurately indicatedHardware monitoringSoftware testing/debuggingLow Pin CountProcess information

Owner:MARVELL ASIA PTE LTD

Secure authentication using a low pin count based smart card reader

ActiveUS20060112423A1Shorten the counting processDigital data processing detailsUser identity/authority verificationPasswordService provision

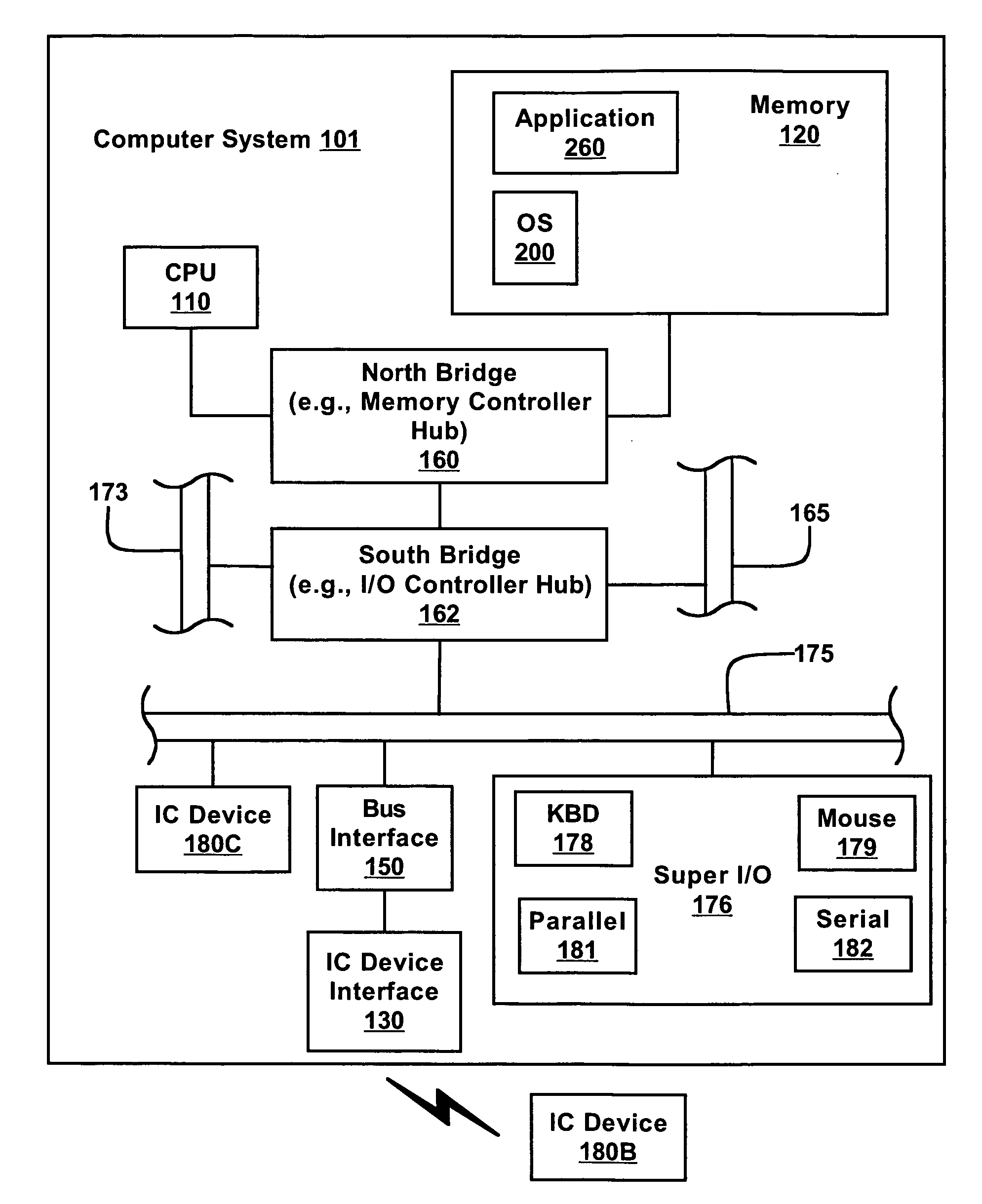

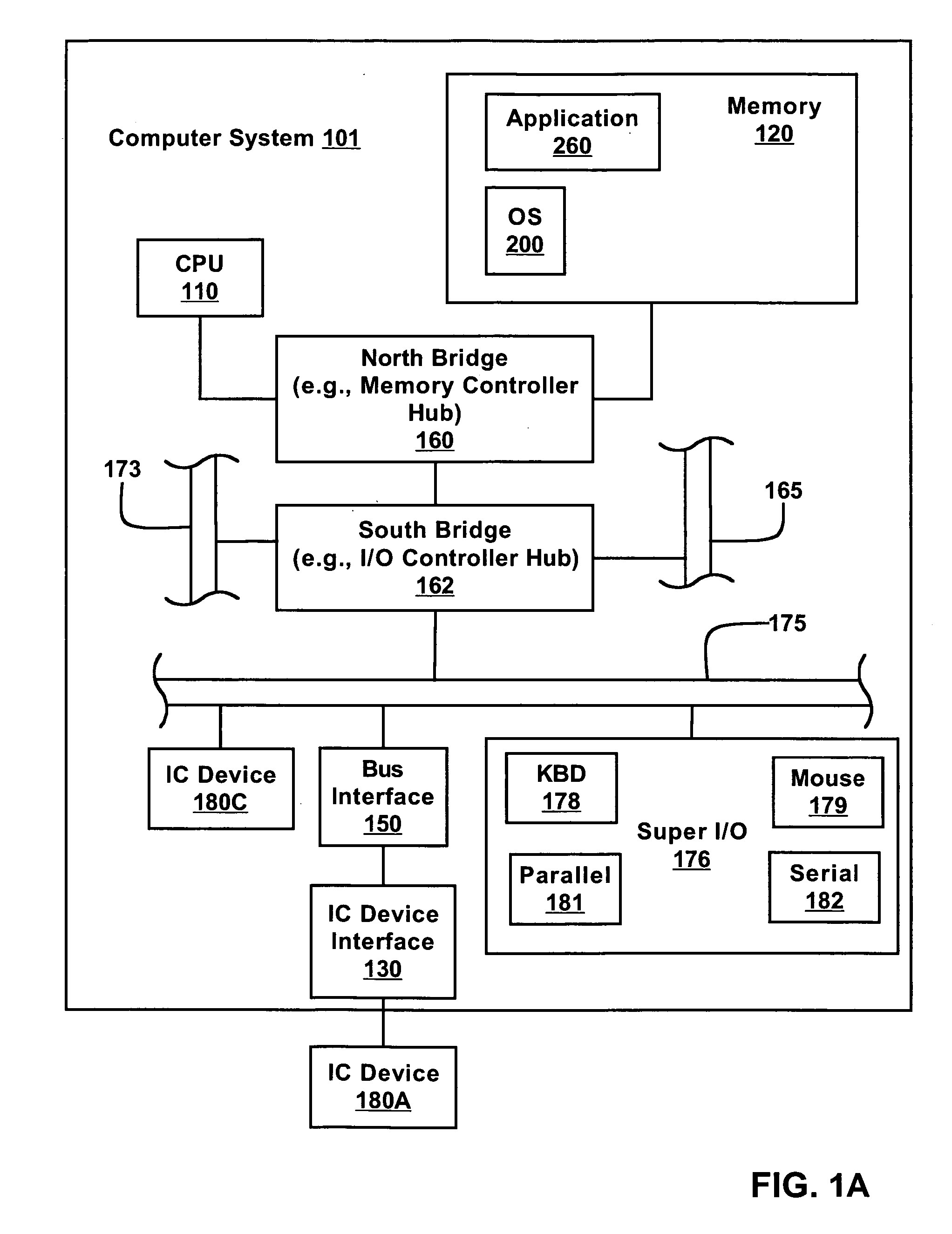

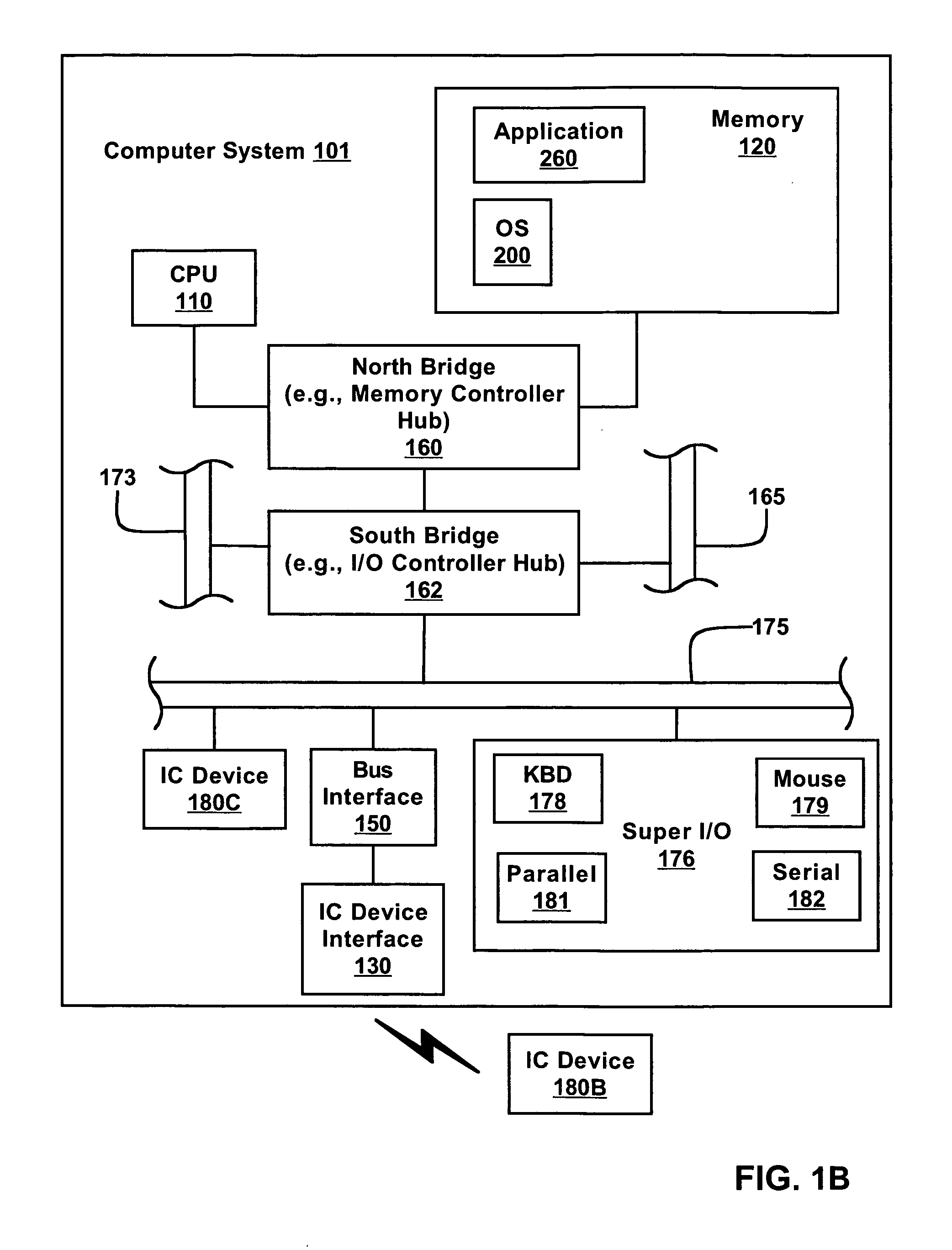

A computer system may receive one or more credentials of a user (e.g., username, password, etc.) from an integrated circuit (IC) device carried by the user. The computer system may include an IC device interface to receive the user credential(s) from the IC device. The IC device interface may be coupled to a CPU of the computer system through a low pin count (LPC) bus. The user credential(s) may be used to grant access to software and / or to grant access to information. Access may be granted to information stored on the computer system. In some embodiments, the computer system may be coupled to a network and transmit the user credential(s) from the IC device and a request for access of information to a service provider coupled to the network. The service provider may grant or deny the request for access of information based on user credential(s).

Owner:MICROCHIP TECH INC

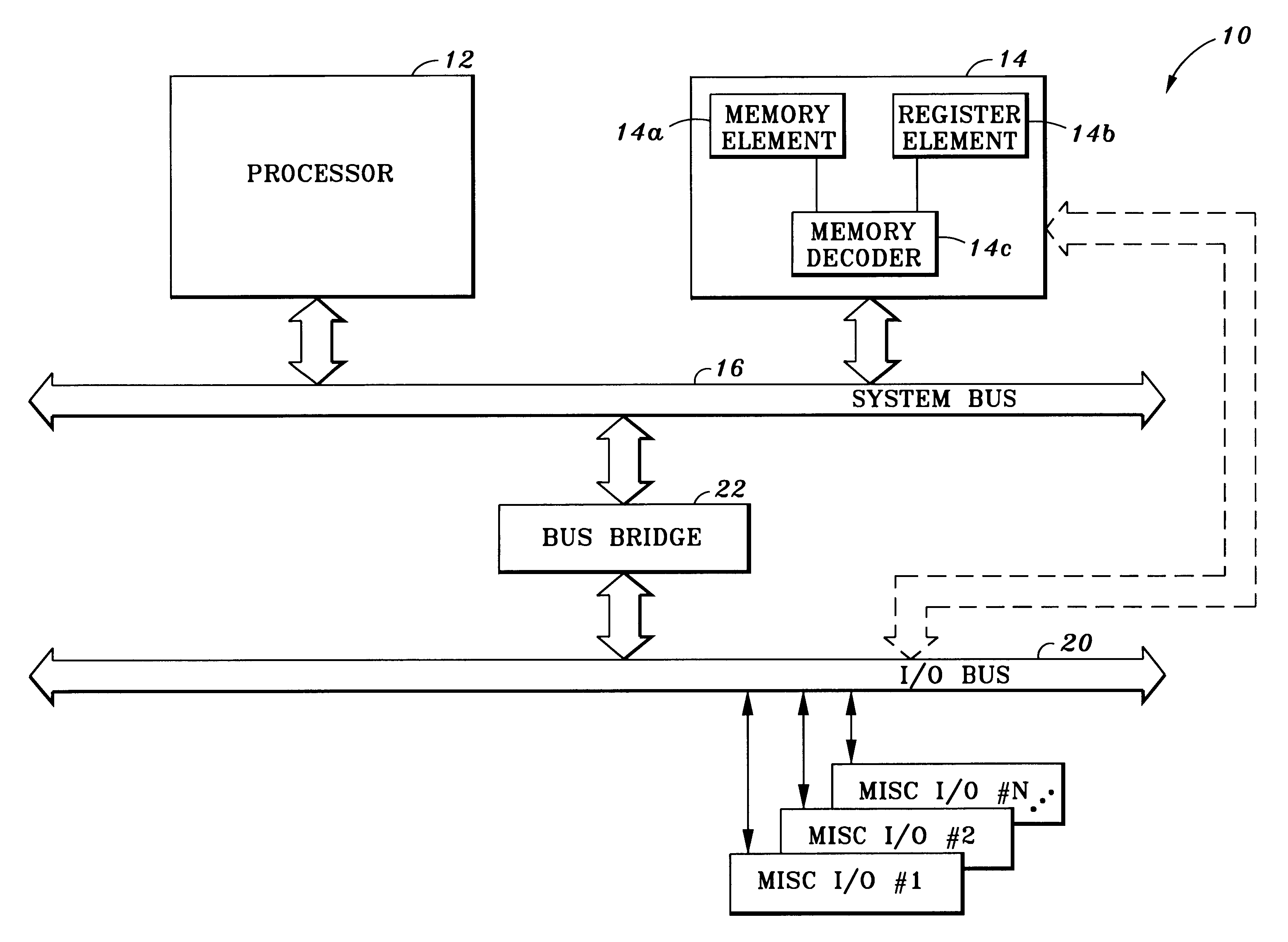

Method and apparatus for selecting functional space in a low pin count memory device

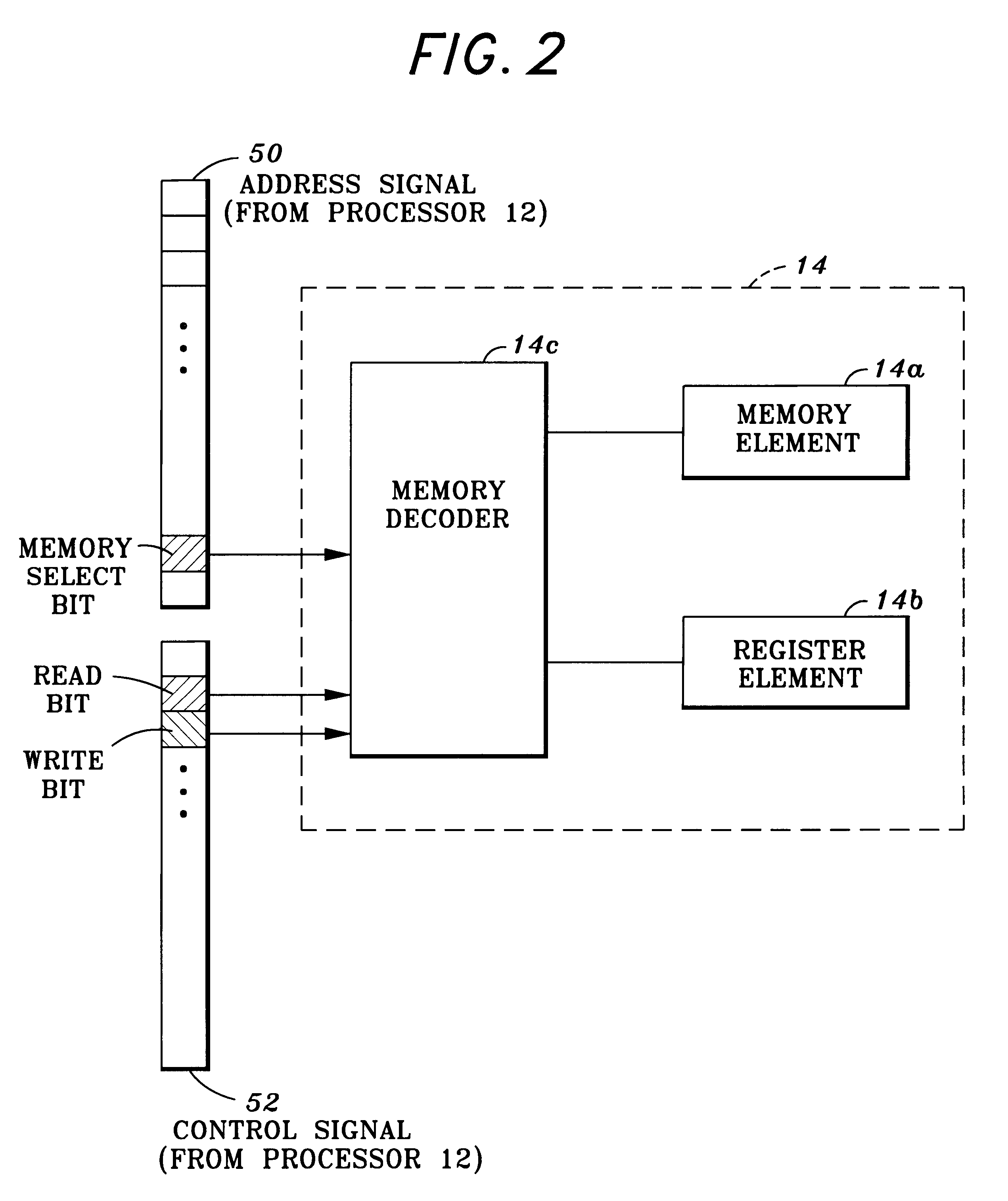

InactiveUS6421765B1Memory adressing/allocation/relocationMicro-instruction address formationControl signalLow Pin Count

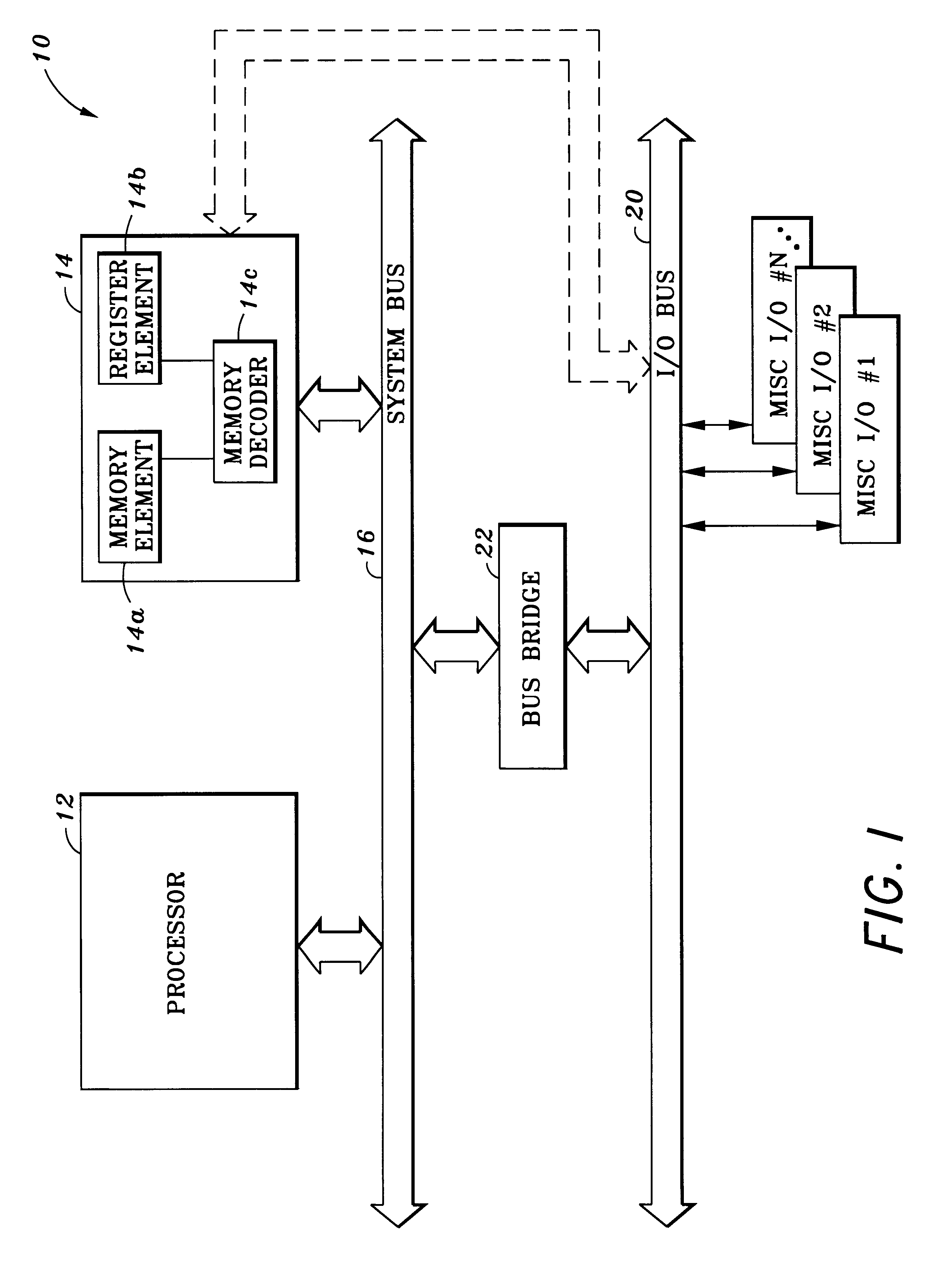

The present invention is an apparatus and method for selecting one of a first and a second storage element in response to a control signal issued by a processor in a low pin count device. The apparatus comprises a decoder to receive the control signal and an address signal having a select bit indicative of one of the first and the second storage elements. The decoder generates a select signal to access one of the first and the second storage elements based on the select bit.

Owner:INTEL CORP

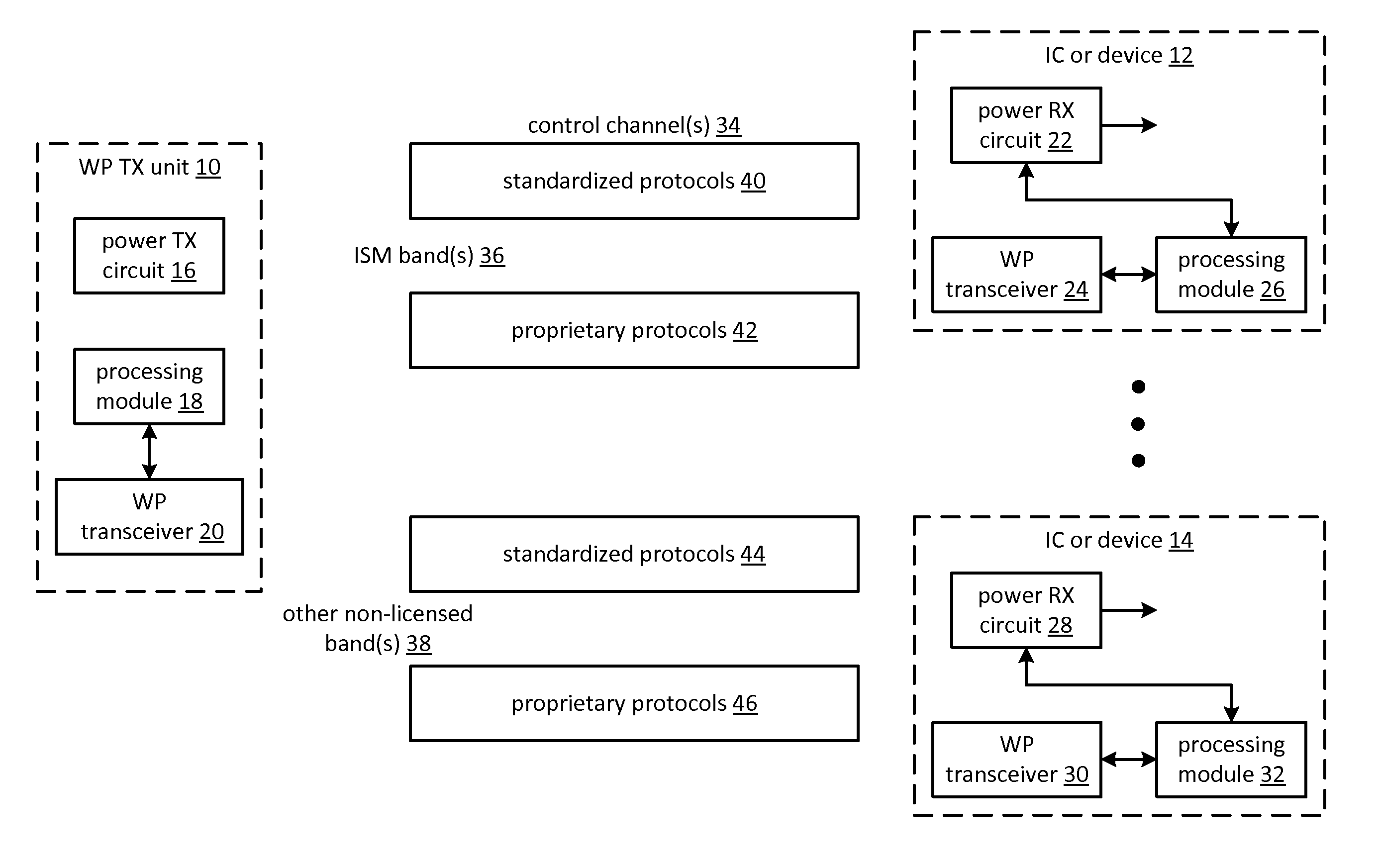

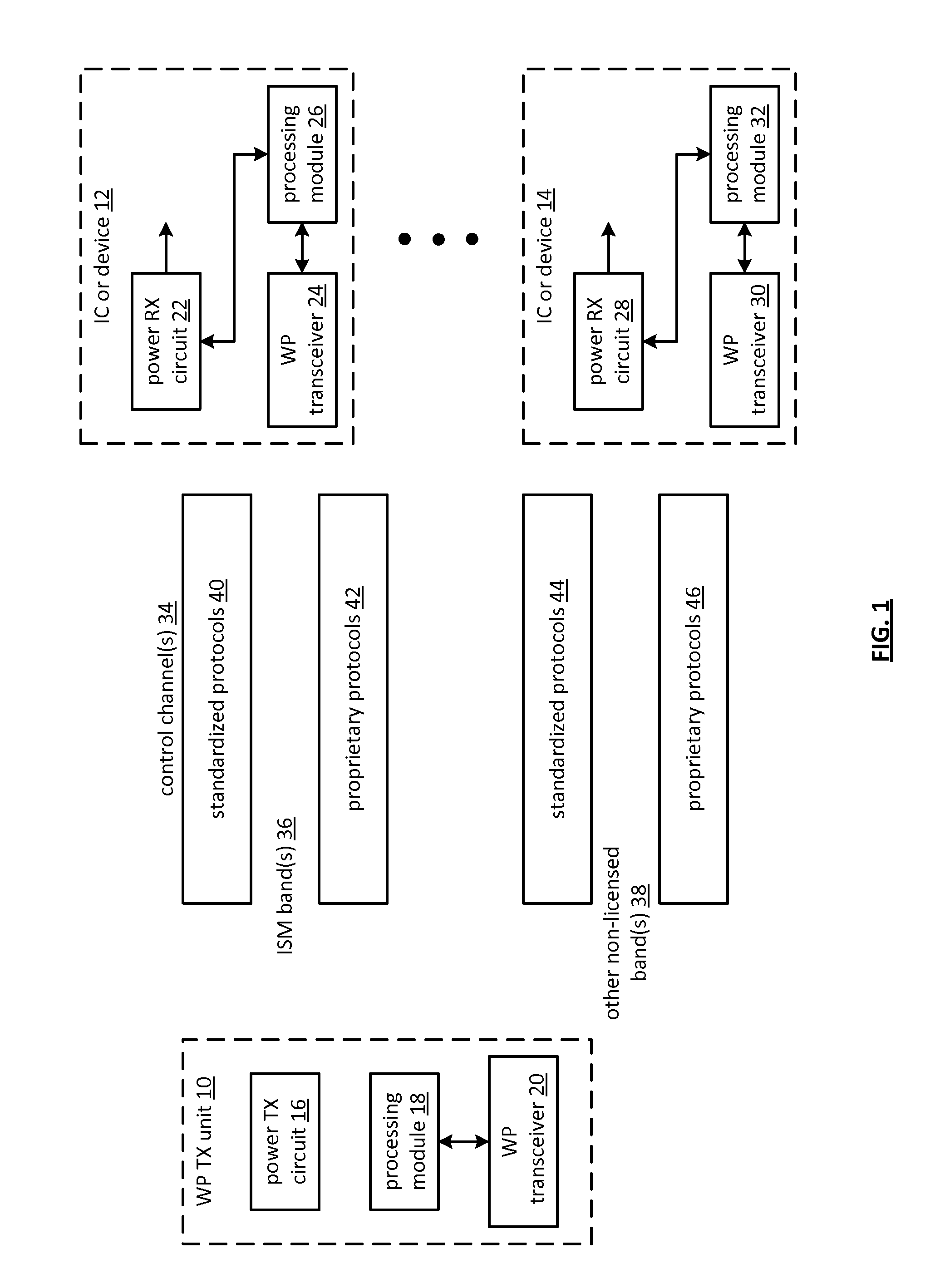

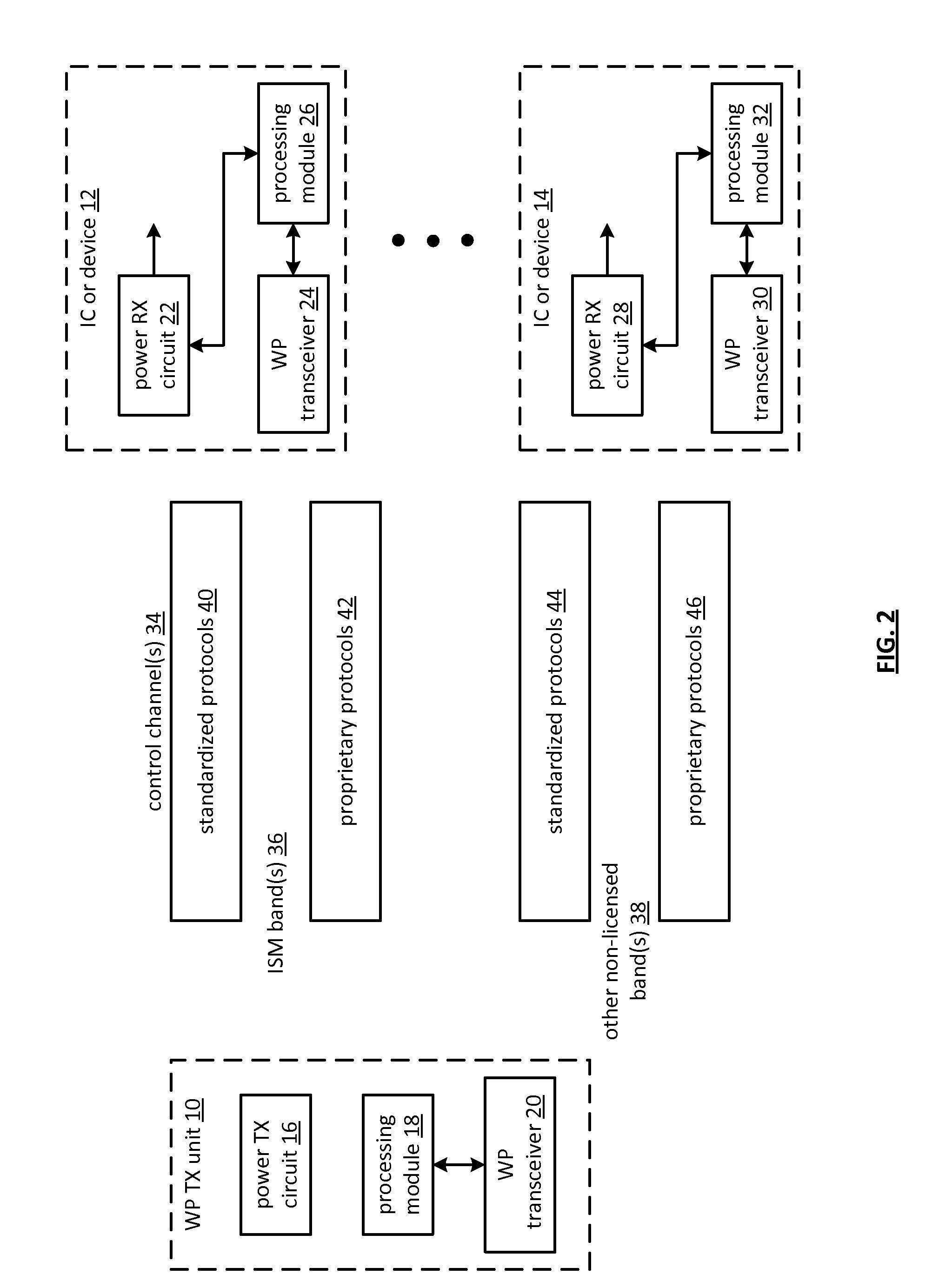

Low pin count wireless power IC

ActiveUS20110127844A1Near-field transmissionBatteries circuit arrangementsComputer modulePower Management Unit

A low pin count IC includes a wireless power receive coil, a rectifying circuit, an output circuit, circuit modules, a power management unit (PMU), a die, and a package substrate. The wireless power receive coil generates an AC voltage from a wireless power electromagnetic signal and the rectifying circuit generates a rectified voltage from the AC voltage. The output circuit generates a DC voltage from the rectified voltage. The PMU manages distribution of the DC voltage to the circuit modules. The die supports the circuit modules and the PMU, wherein the die includes return pads for coupling to circuit return nodes and a PMU return node. The package substrate supports the die and includes return pins for coupling to the return pads, wherein at least one of the die and the package substrate support the wireless power receive coil, the rectifying circuit, and the output circuit.

Owner:KONINKLJIJKE PHILIPS NV

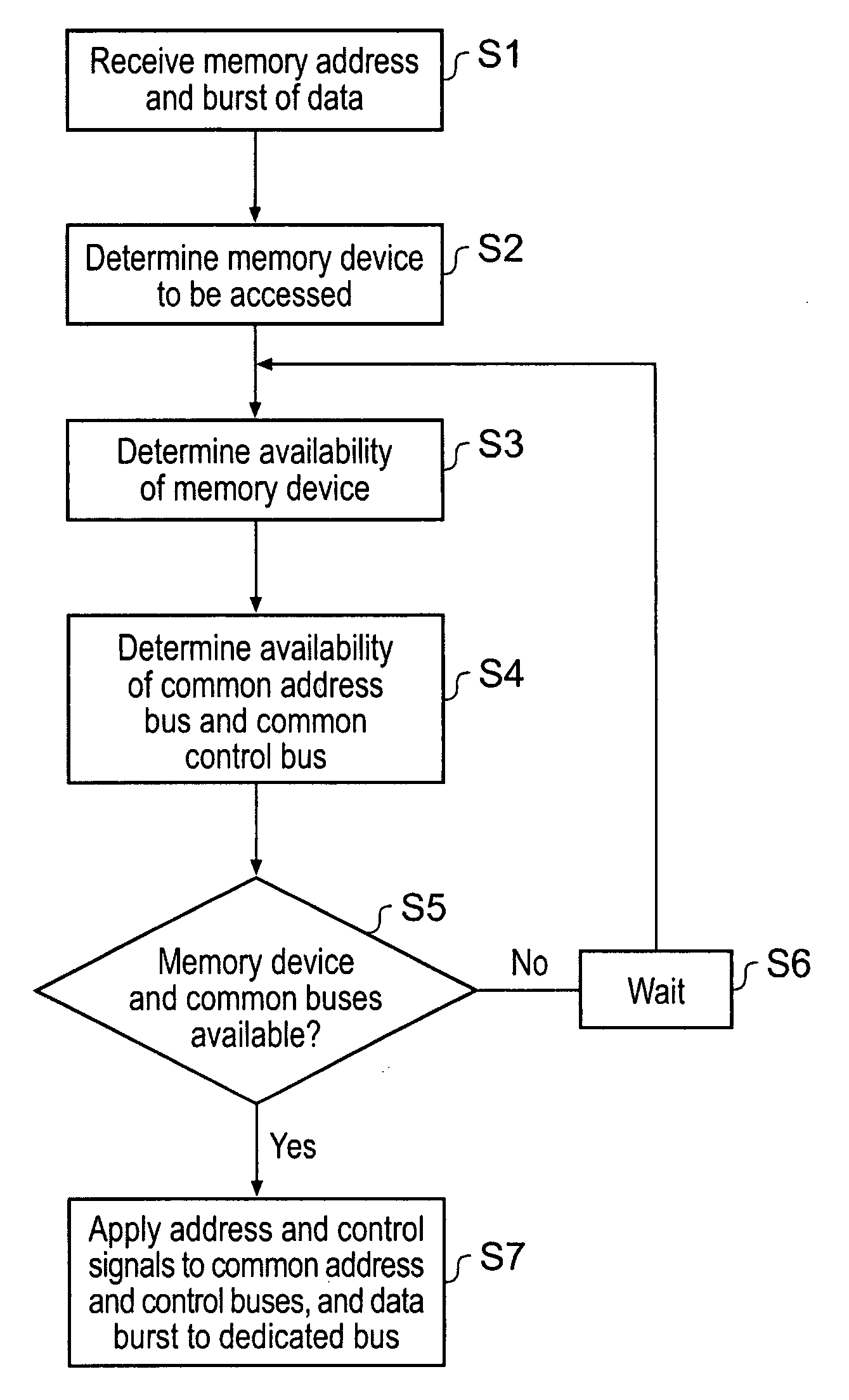

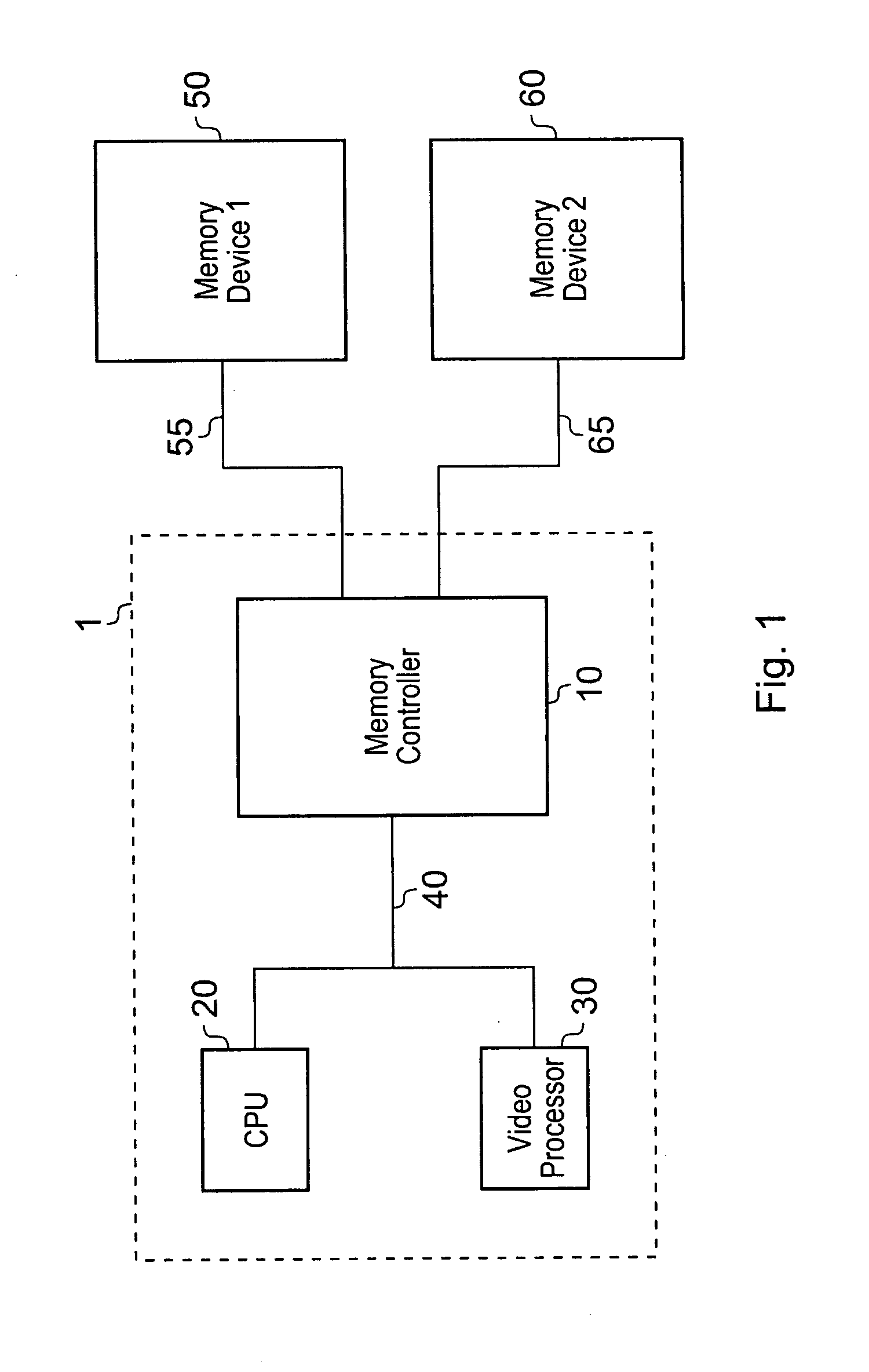

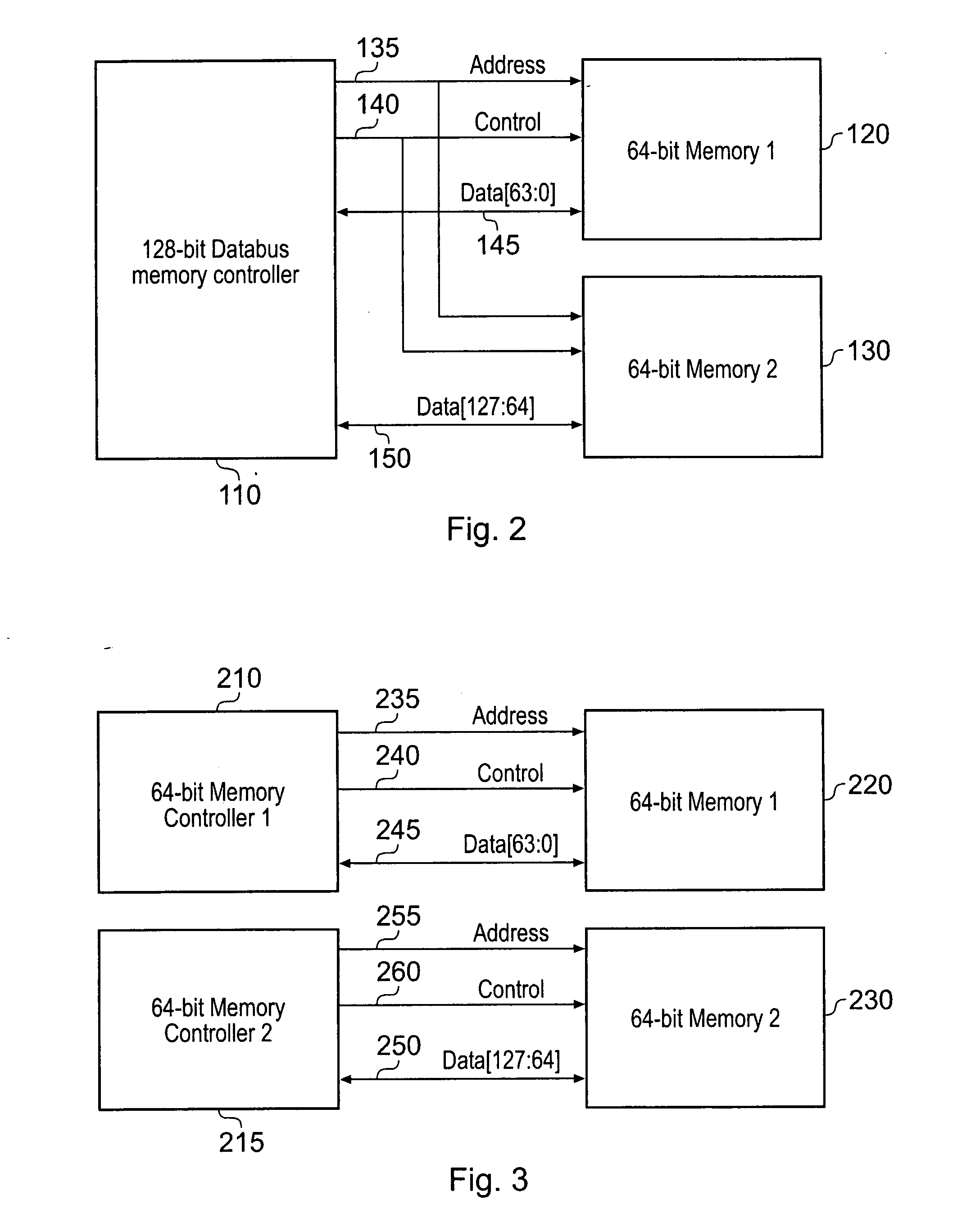

Memory controller connectivity

ActiveUS20080172515A1Increase heightReduced pin countMemory adressing/allocation/relocationData signalAddress bus

A memory controller with an interface for providing a connection to a plurality of memory devices at least one of said plurality of memory devices supporting burst mode data transfers comprises data interface circuitry for connecting to a plurality of separate data buses for communicating data signals between said memory controller and a respective one of said memory devices, each of said data buses providing a dedicated data signal path to a different one of said memory devices, address interface circuitry for connecting to a common address bus for communicating address signals to each of said memory devices on a shared address signal path, address signals which are directed to different ones of said memory devices being time division multiplexed together on said common address bus, and device selecting circuitry for generating one or more device selecting signals synchronised with said time division multiplexing of said common address bus to select that memory device to which address signals currently asserted on said common address bus are directed. In this way, an increased bandwidth memory controller can be provided which is efficient for both short, narrow and long and wide burst lengths and which has interface circuitry with a relatively low pin count.

Owner:ARM LTD

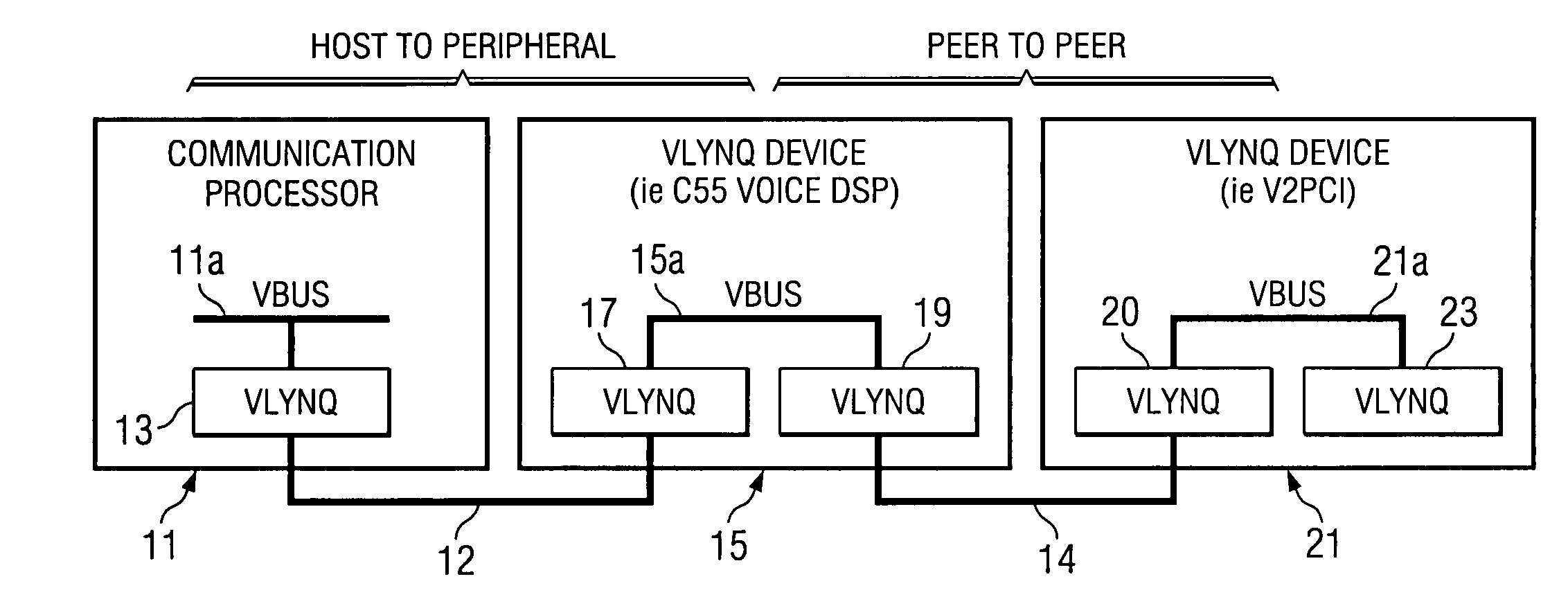

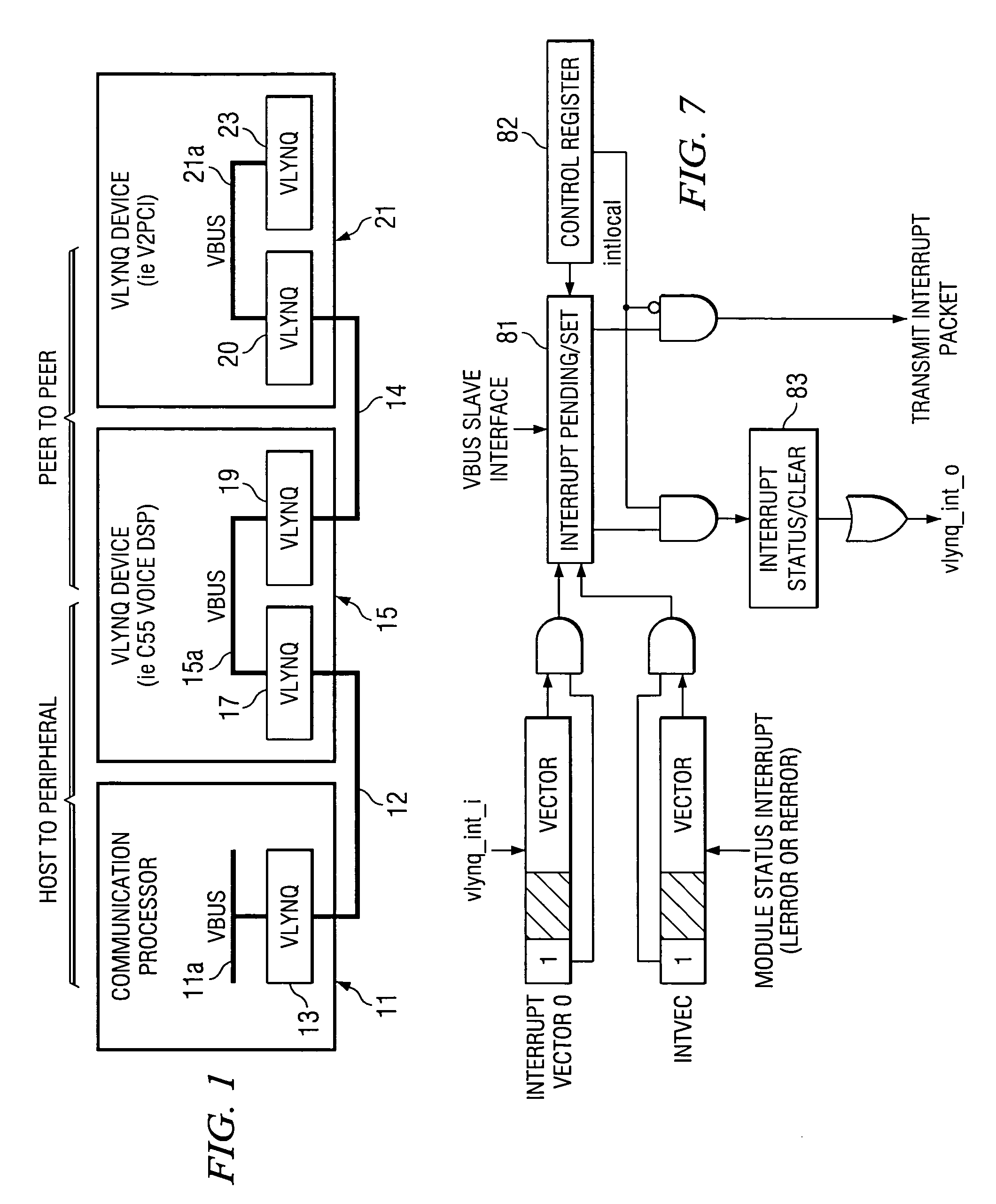

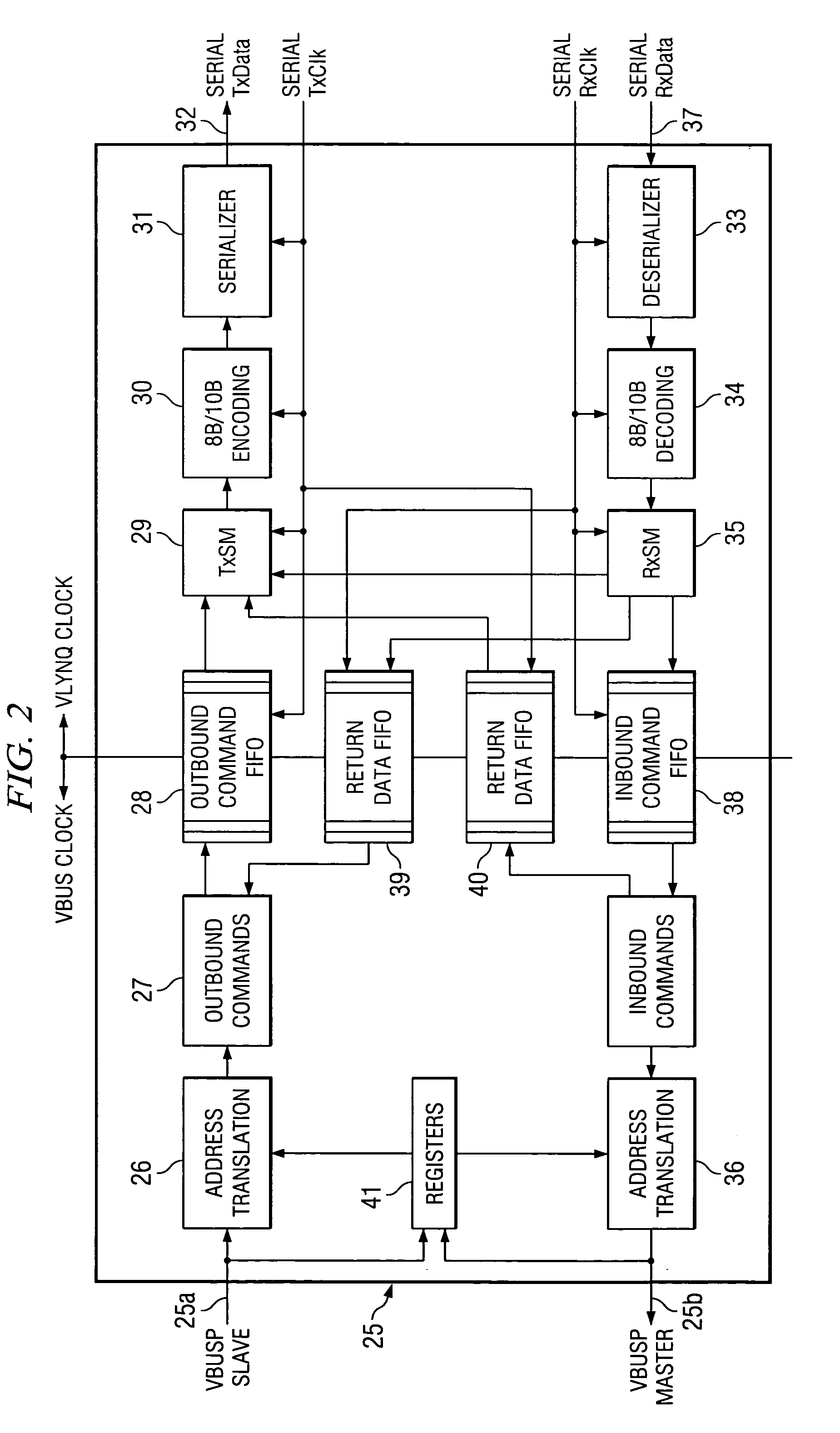

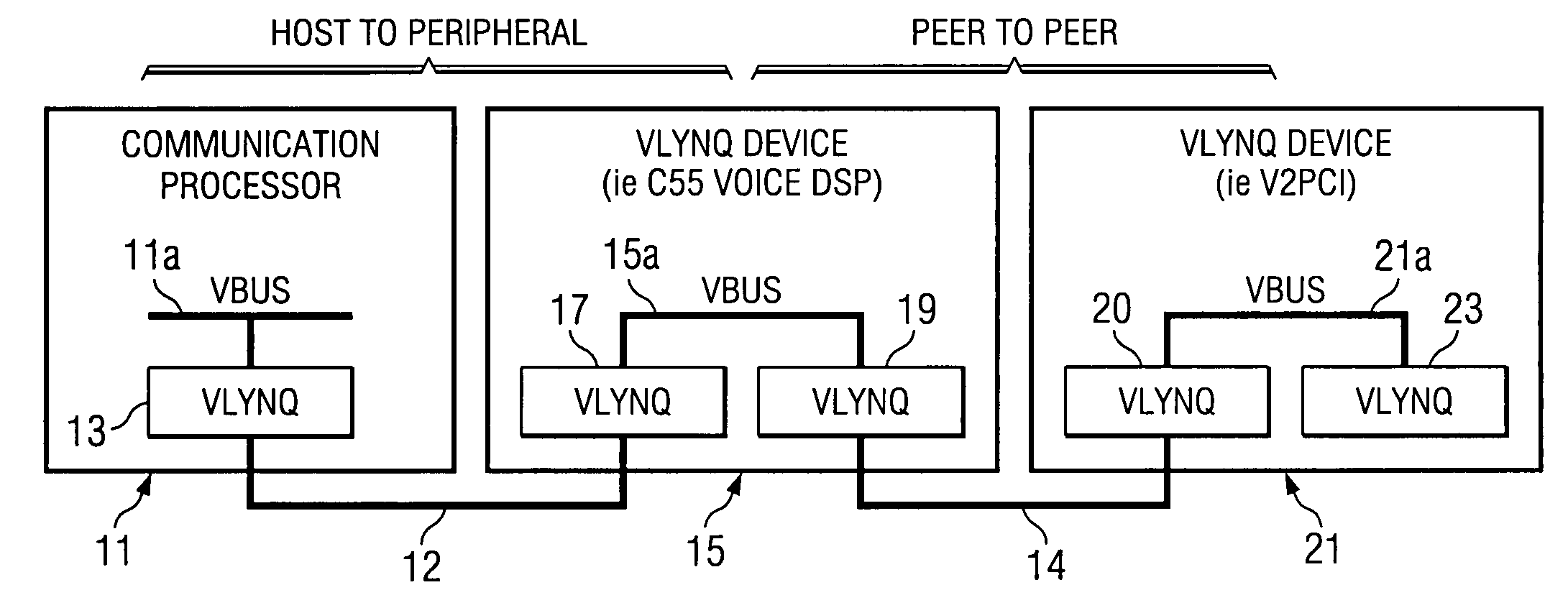

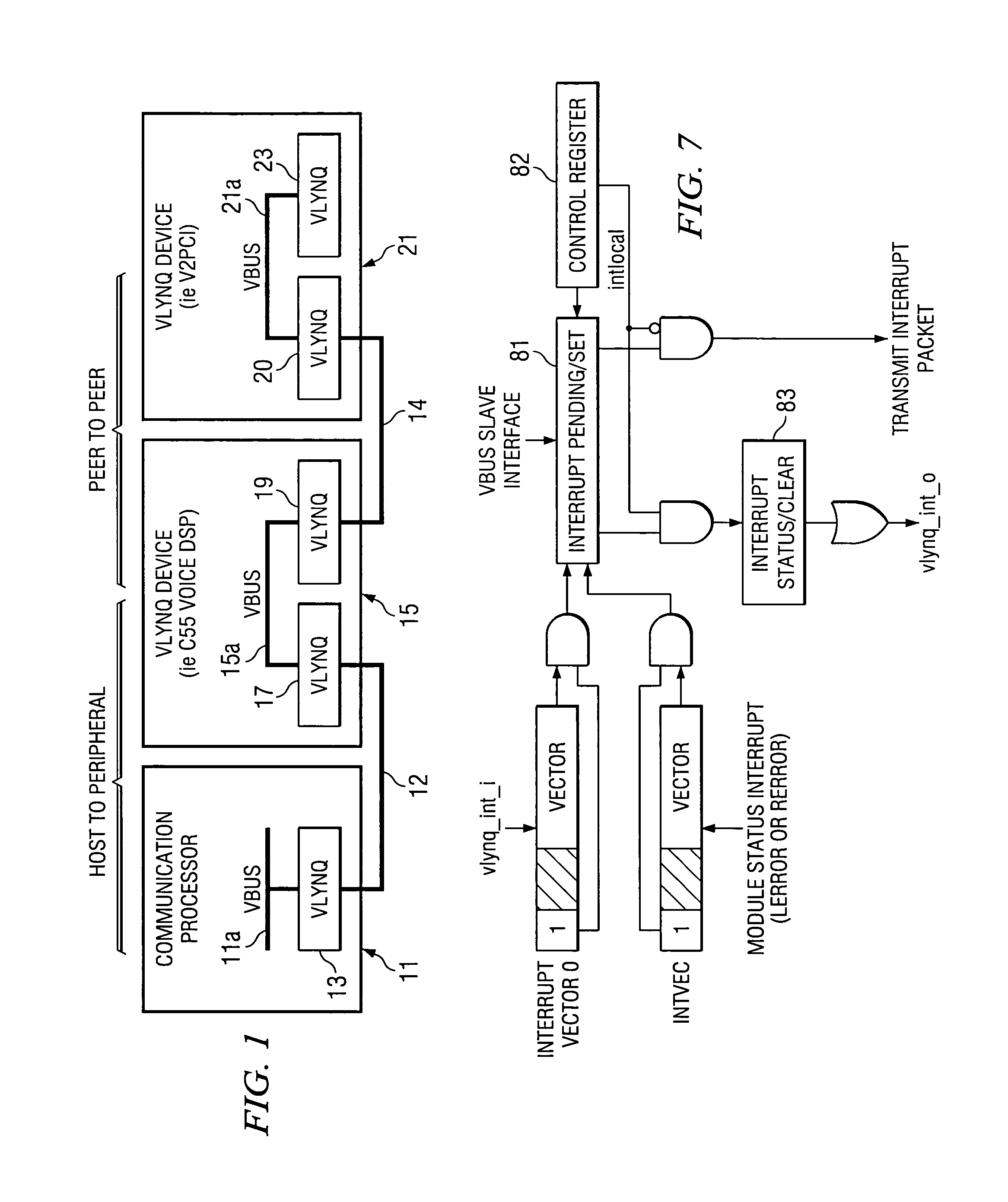

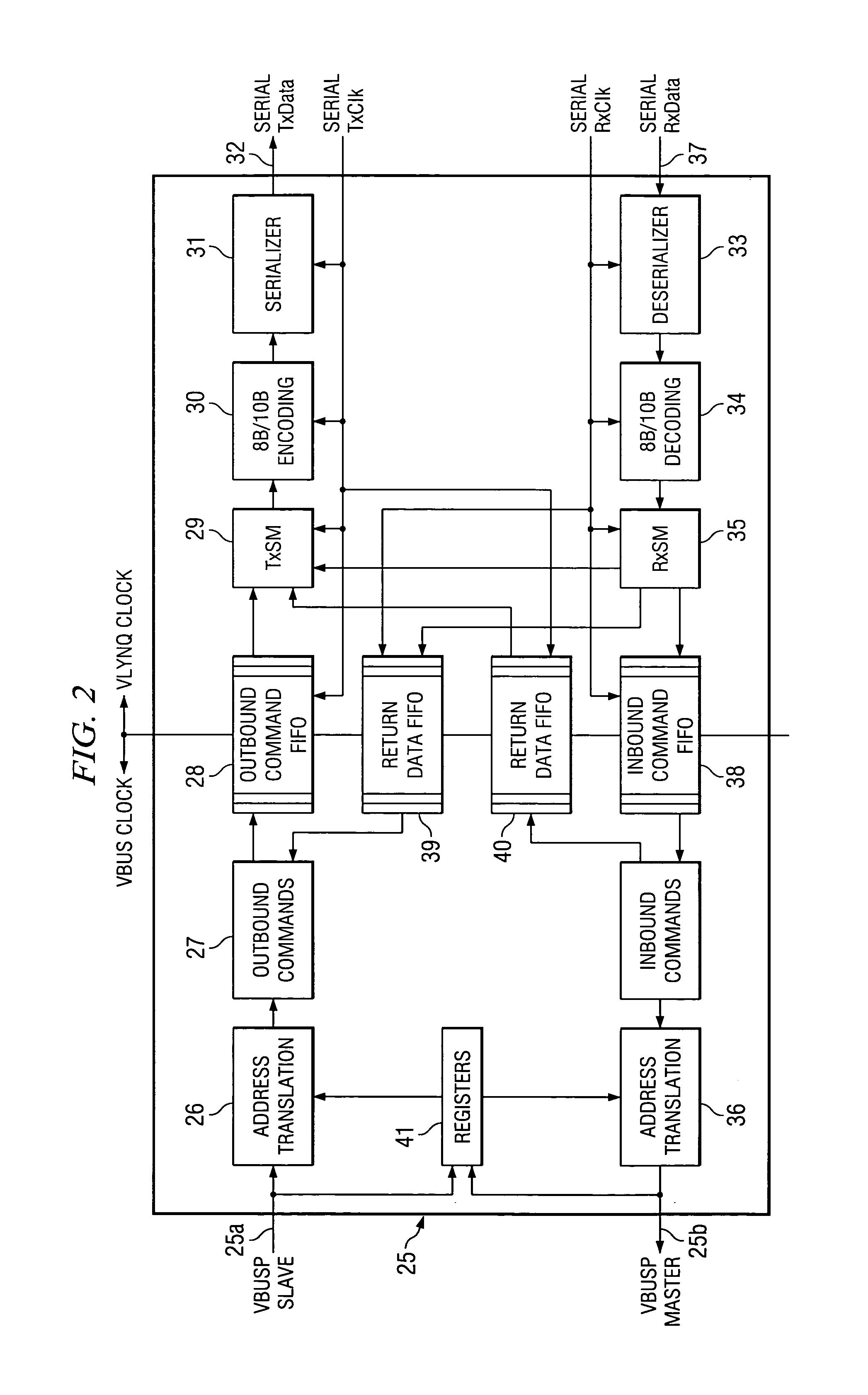

Communications interface

A serial communications interface is described that enables the extension of an internal Communications Bus Achitecture (CBA) bus segment to one or more external devices. The interface accomplishes this function by serializing bus transactions in one device, transferring the serial transaction between devices via one interface port, and de-serializing the transaction in the external device. The general features include low pin count (as few as three signals), simple packet based transfer protocol for memory mapped access, symmetric operation, simple block code formatting, supports both host to peripheral and peer to peer transactions, and support multiple outstanding transactions.

Owner:TEXAS INSTR INC

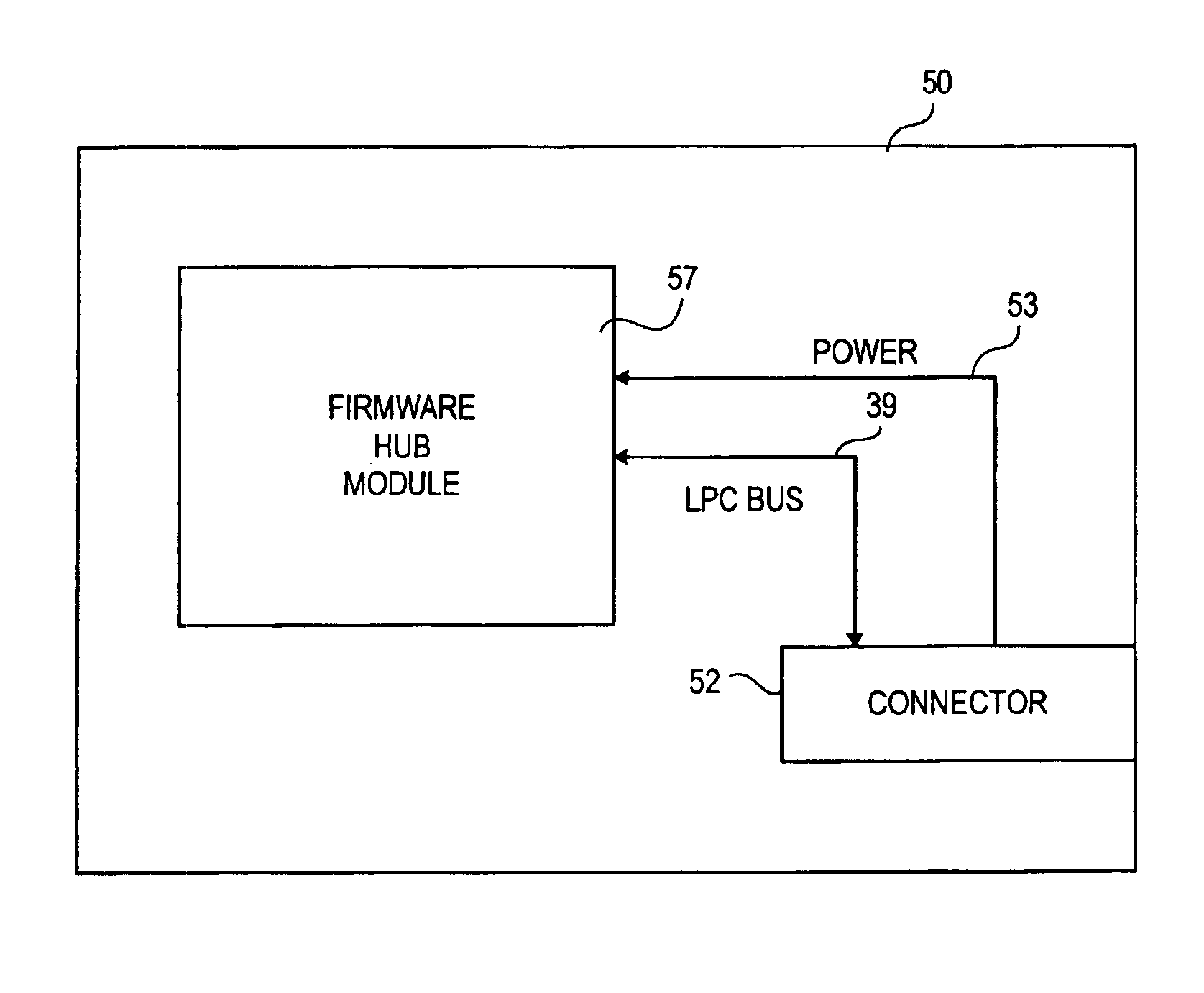

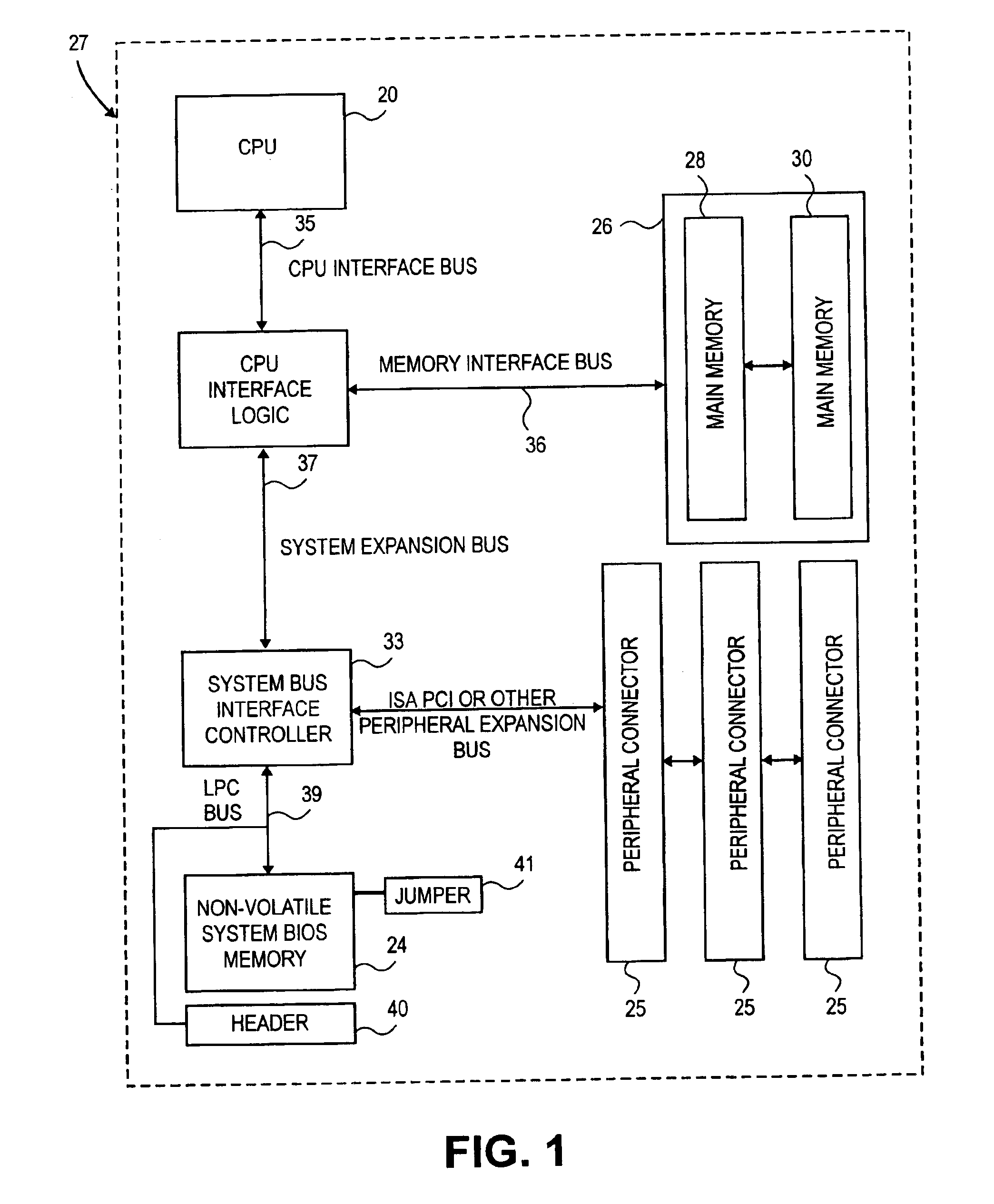

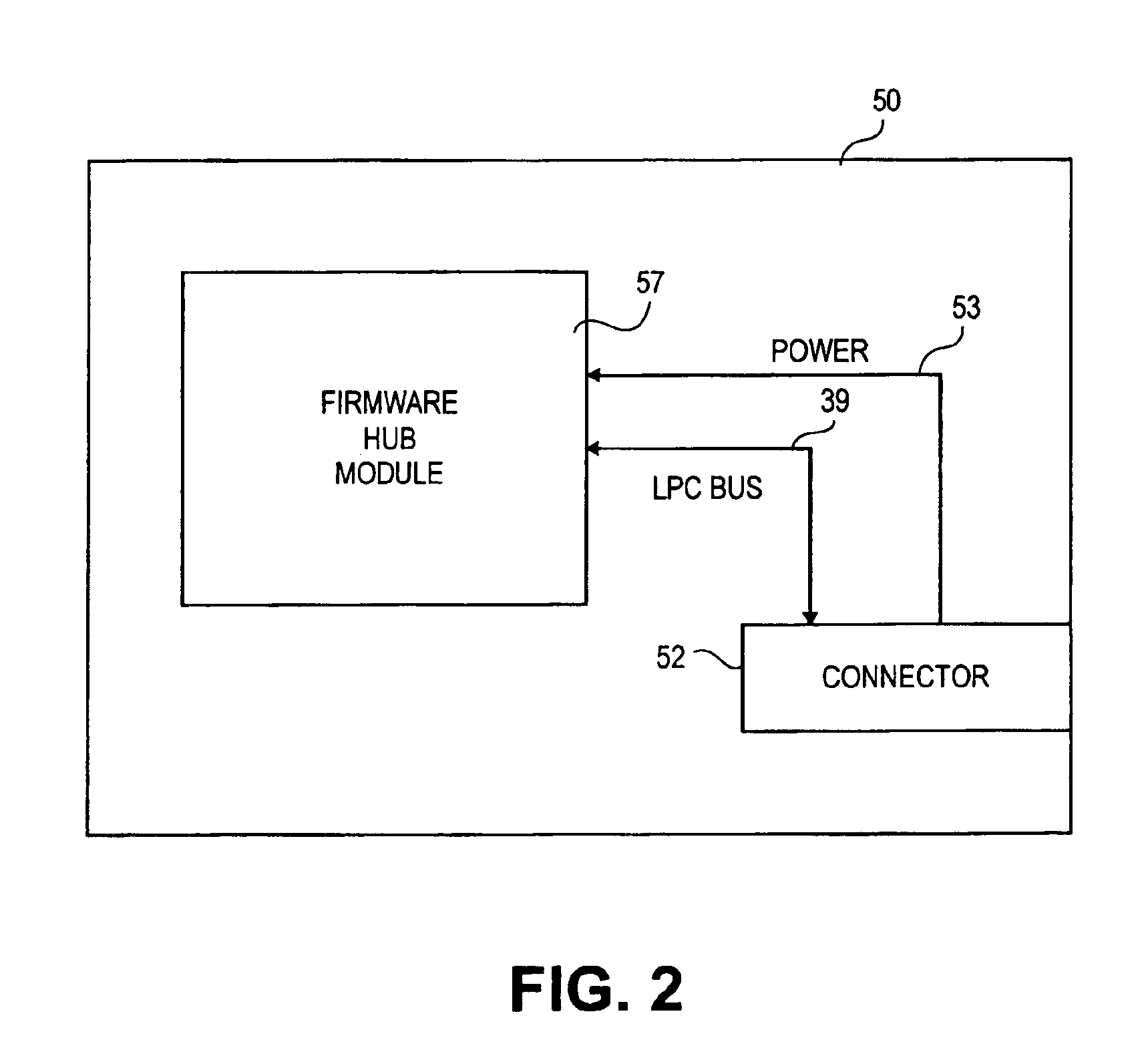

Low pin count (LPC) firmware hub recovery

A method and apparatus for low pin count firmware hub recovery on a circuit board having a firmware hub includes coupling a firmware hub recovery module having a firmware program onto the circuit board, establishing communication between a central processing unit (CPU) and the firmware hub recovery module, and reprogramming the firmware hub by the firmware program.

Owner:INTEL CORP

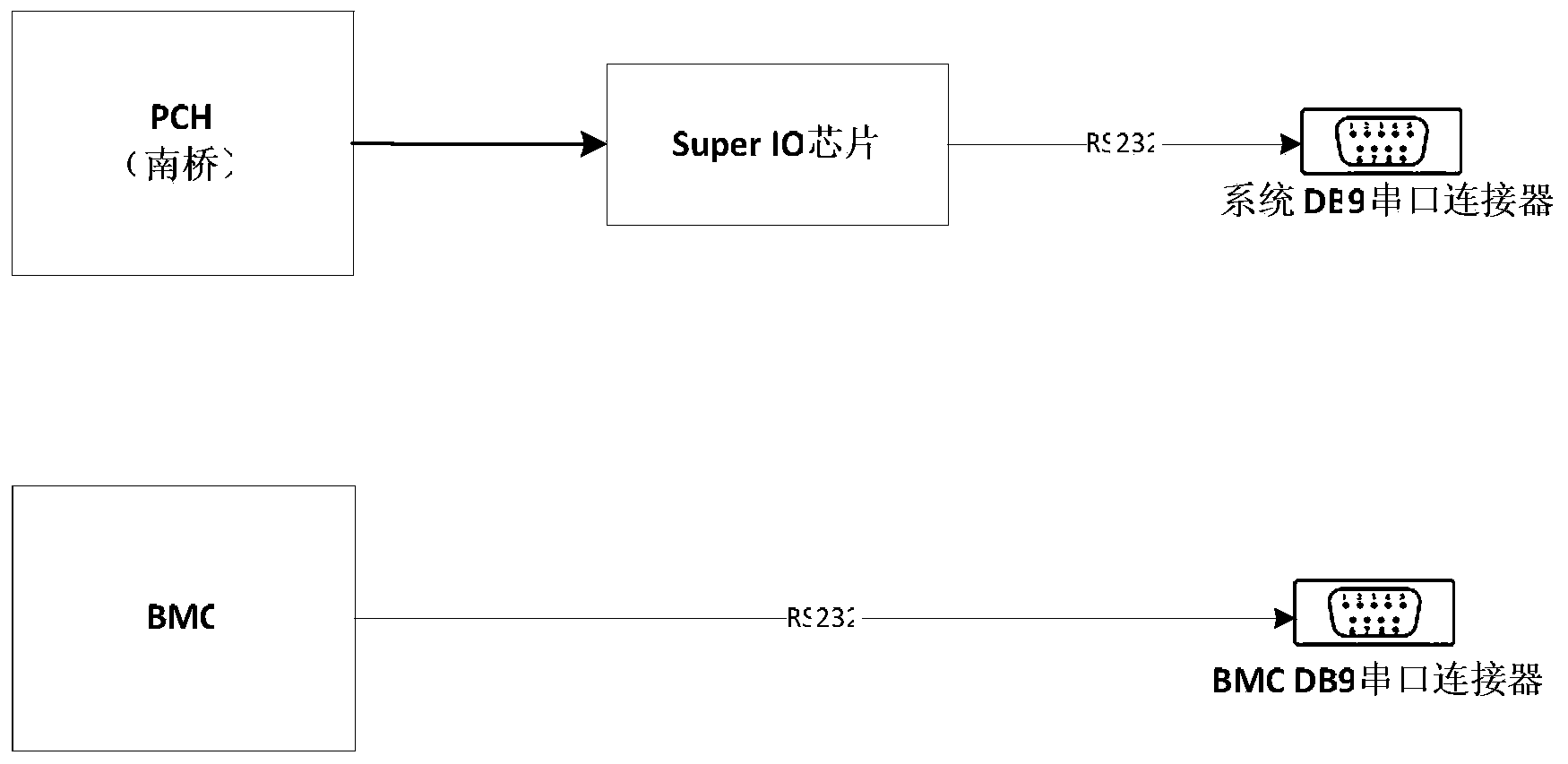

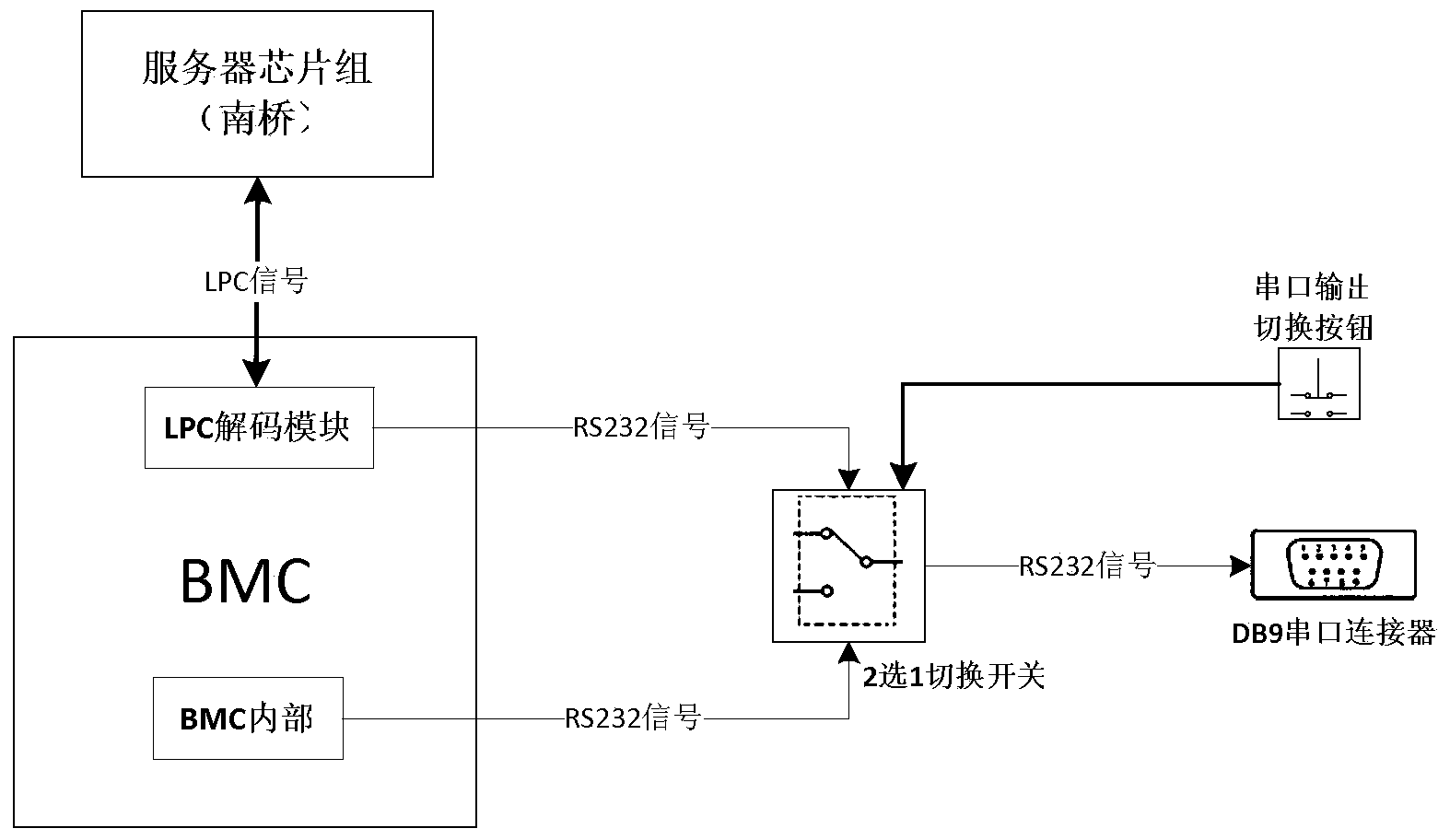

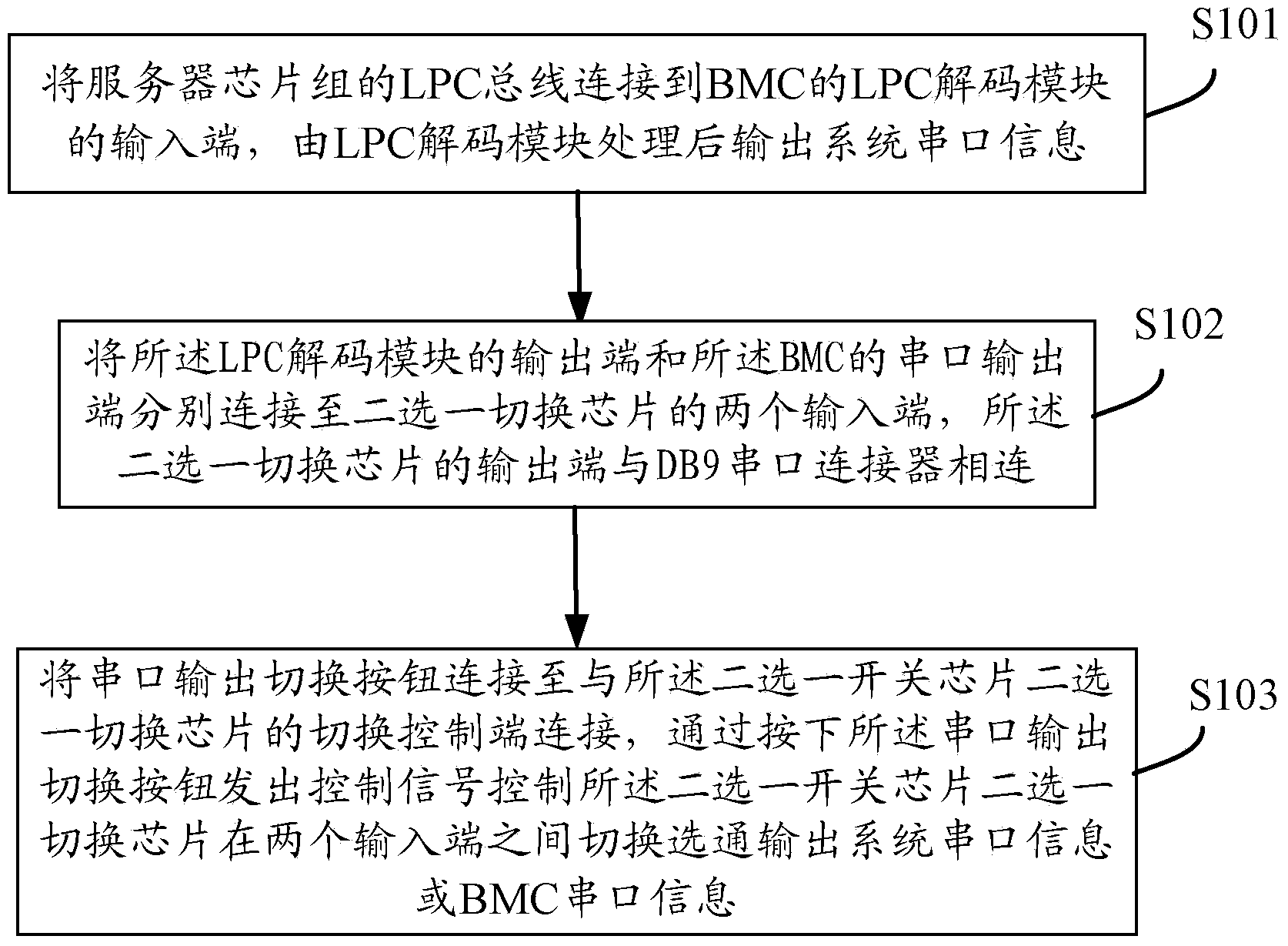

Server serial port output method and server serial port output device

InactiveCN104102614ASimple designMeet needsElectric digital data processingControl signalComputer module

The invention discloses a server serial port output method and a server serial port output device. The device comprises a BMC (Baseboard Management Controller), an either-or switching chip, a serial port output switching press button and a DB9 serial port connector, wherein the input end of an LPC (Low Pin Count) decoding module of the BMC is connected with an LPC bus of a server chip group; the output end of the LPC decoding module outputs system serial port information; the output end of the LPC decoding module and the serial port output end of the BMC are respectively connected to two input ends of the either-or switching chip; the output end of the either-or switching chip is connected with the DB9 serial port connector; the serial port output switching press button is connected to the switching control end of the either-or switching chip; and the either-or switching chip is controlled to be switched between the two input ends through control signals. The server serial port output method and the server serial port output device have the advantages that the free switching between a system serial port and a BMC serial port for output can be realized only through the DB9 serial port connector; the requirements of development personnel on the system serial port and BMC serial port information are met; and the mainboard design is also simplified.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

Communications interface for enabling extension of an internal common bus architecture (CBA)

A serial communications interface is described that enables the extension of an internal Communications Bus Architecture (CBA) bus segment to one or more external devices. The interface accomplishes this function by serializing bus transactions in one device, transferring the serial transaction between devices via one interface port, and de-serializing the transaction in the external device. The general features include low pin count (as few as three signals), simple packet based transfer protocol for memory mapped access, symmetric operation, simple block code formatting, supports both host to peripheral and peer to peer transactions, and support multiple outstanding transactions.

Owner:TEXAS INSTR INC

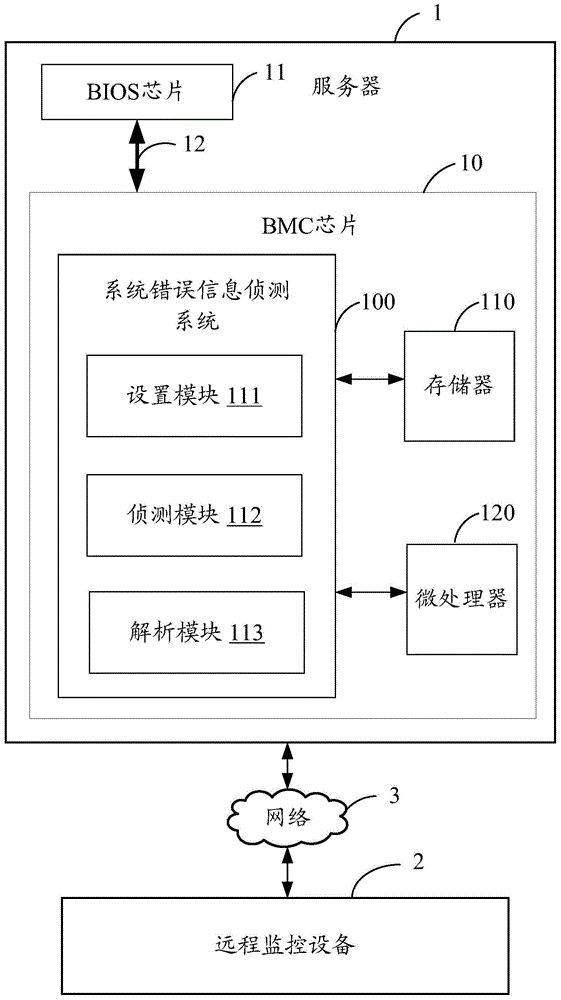

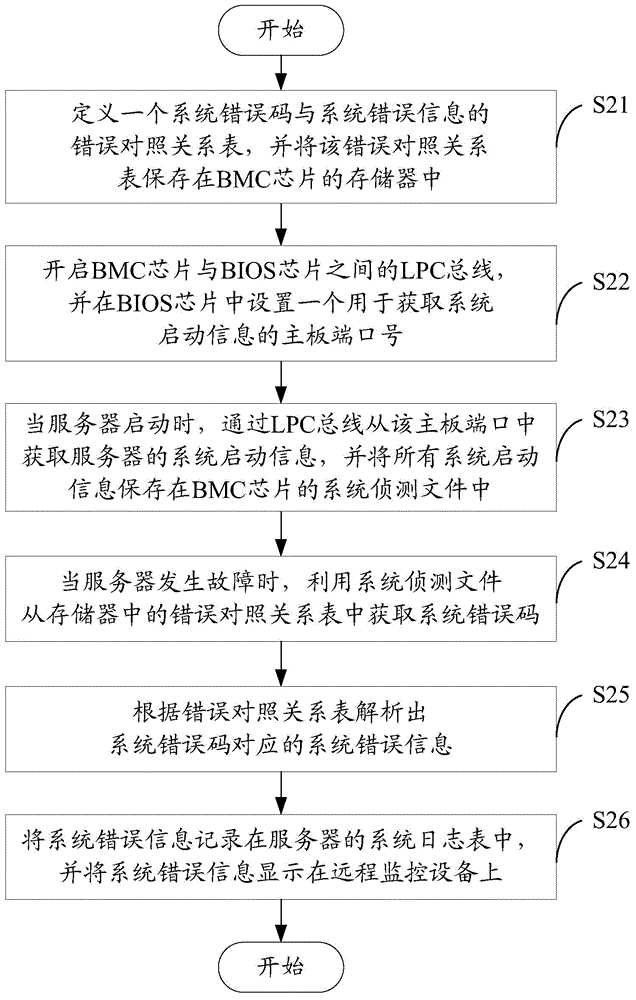

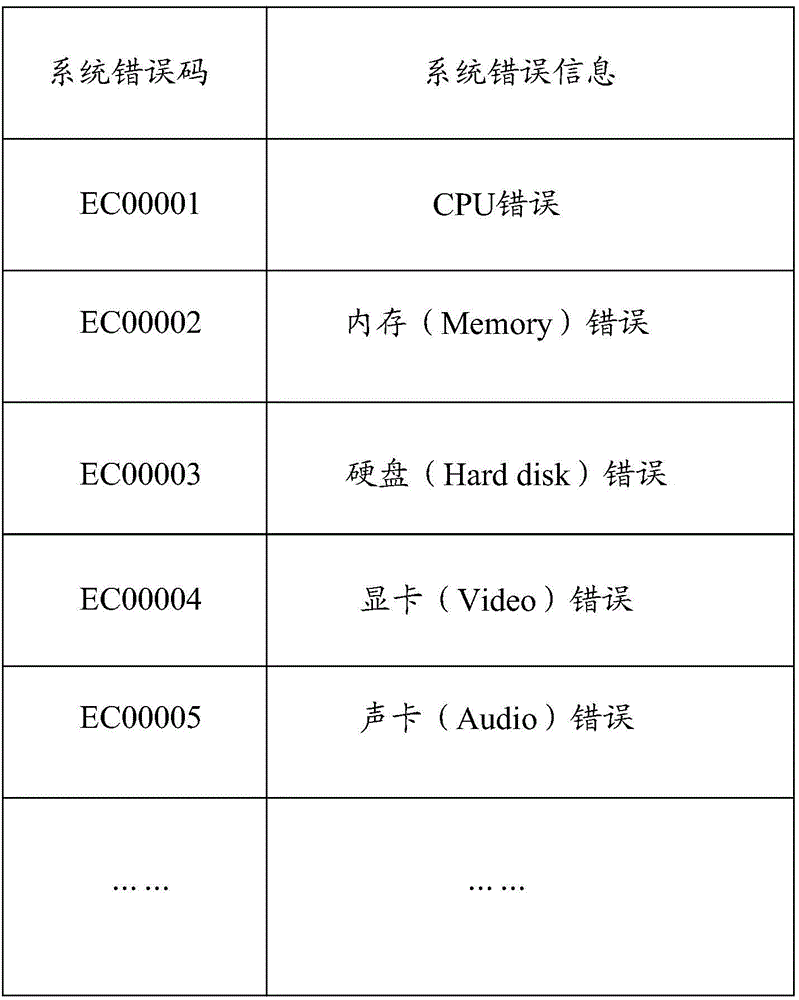

System error information detection system and method for server

InactiveCN104424084AEnhanced troubleshooting capabilitiesSimple and efficient operationDetecting faulty computer hardwareHardware monitoringSystem failureFault correction

The invention discloses a system error information detection system and method for a server. The server comprises a BMC (Baseboard Management Controller) chip and a BIOS (Basic Input Output System) chip. The system error information detection method comprises the following steps of defining an error contrast relationship table between system error codes and system error information in the BMC chip; starting an LPC (Low Pin Count) bus between the BMC chip and the BIOS chip and setting a mainboard port which is used for obtaining server system starting information in the BIOS chip; obtaining system starting information of a server from a mainboard port and storing the system starting information in a system detection file through the LPC bus when the server is normally started; obtaining a system error code from the error contrast relationship table through the system detection file when the server breaks down; analyzing system error information which is corresponding to the system error code according to the error contrast relationship table in the BMC chip. The system error information detection system and method for the server can accurately, rapidly and simply obtain system fault reasons of the server to achieve system fault correction of the server as soon as possible.

Owner:WARECONN TECH SERVICE (TIANJIN) CO LTD +1

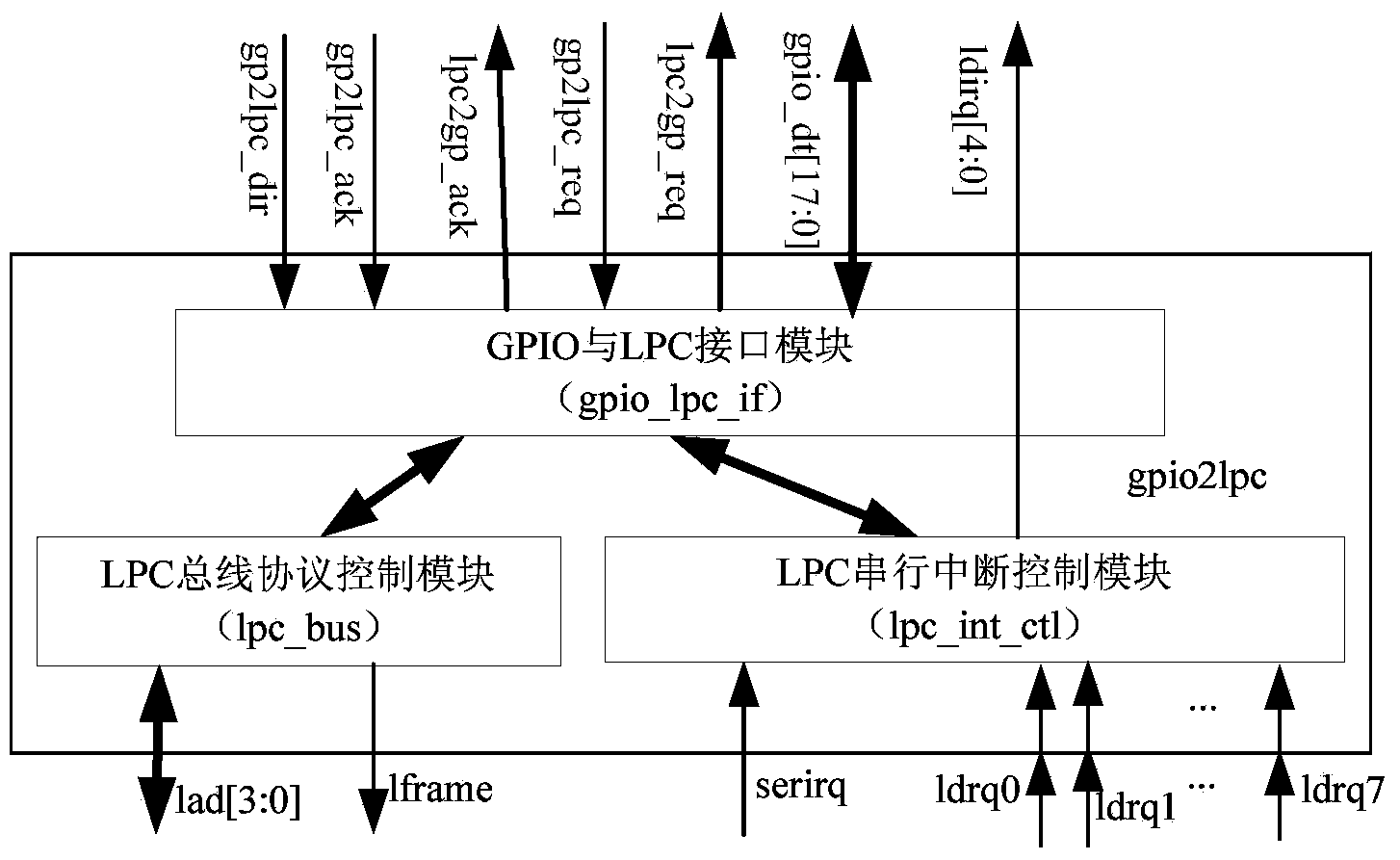

Method and device for expanding LPC (linear predictive coding) peripheral on basis of GPIO (general purpose input/output) interface

ActiveCN103914424ASolve the problem of communication infeasibilityMeet flexibilityElectric digital data processingProcessor registerComputer module

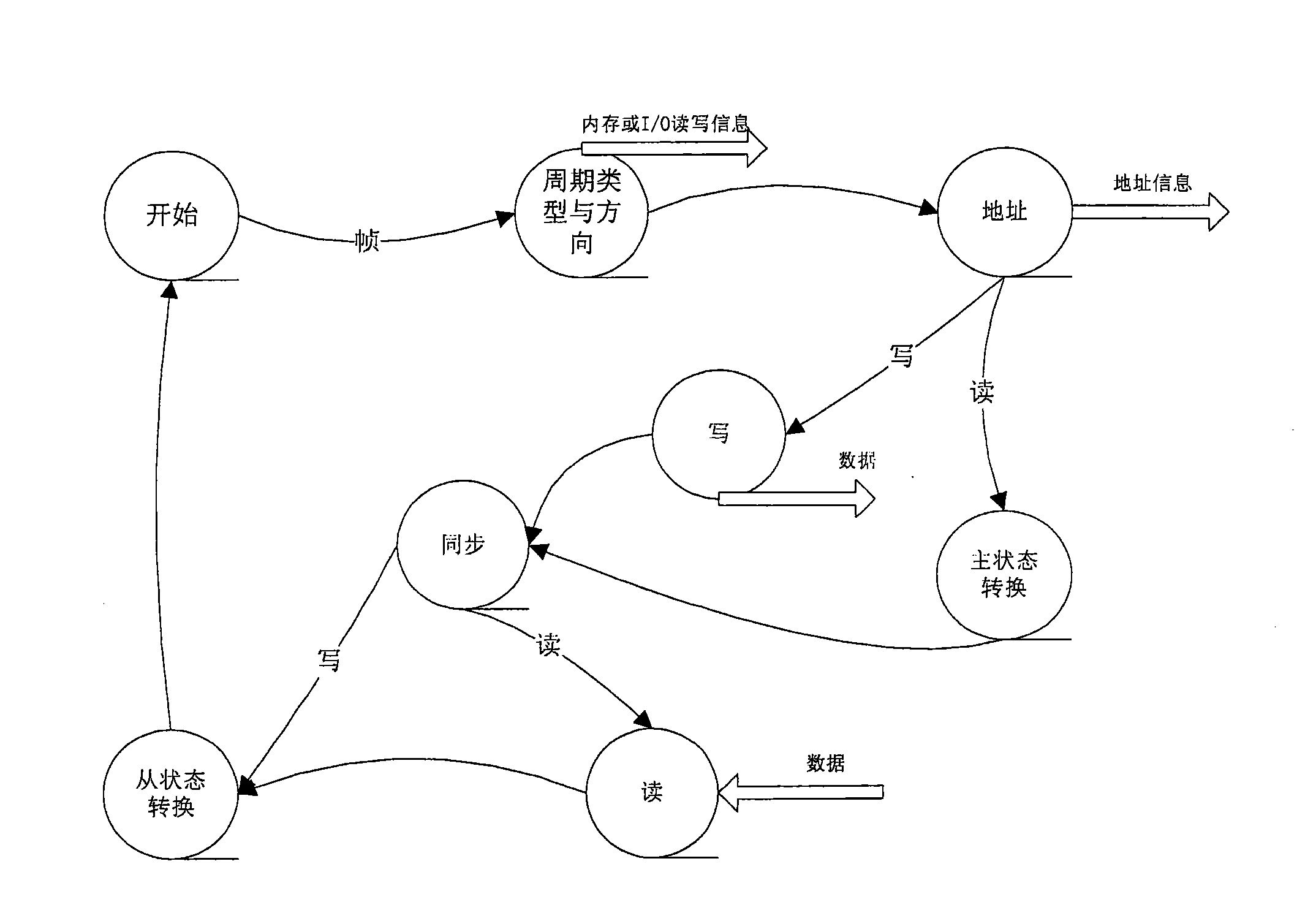

The invention discloses a method and a device for expanding an LPC (linear predictive coding) peripheral on the basis of a GPIO (general purpose input / output) interface. The method includes primarily communicating the LPC peripheral with the GPIO interface of a CPU (central processing unit) on the basis of a two-way asynchronous request-acknowledge handshake protocol; forwarding received messages to the lower-level LPC peripheral by the aid of a secondary synchronous handshake protocol or interrupting operation on an internal register; reversely initiating interrupt requests to the GPIO interface of the CPU if serial interrupt requests or internal interrupt requests of the LPC peripheral are received. The device comprises a GPIO and LPC interface module, an LPC bus protocol control module and an LPC serial interrupt control module. The GPIO and LPC interface module is connected with the CPU. The method and the device have the advantages that the LPC peripheral can be expanded easily and flexibly, a system can be expanded conveniently, communication is irrelevant to particular clocks, special requirements on a clock of the GPIO interface can be omitted, communication data are reliable, hardware resources can be saved, and the method and the device are transparent for upper-layer users.

Owner:NAT UNIV OF DEFENSE TECH

Management system compatible with different GPUs and design method thereof

The invention provides a management system compatible with different GPUs and a design method thereof. The management system comprises a CPU chip, a south bridge chip, a BMC chip, a PCIE slot, pins, an error indication lamp and a handheld terminal, wherein the CPU chip is connected with the BMC chip through the south bridge chip, the BMC chip is connected with the handheld terminal through an Ethernet or a serial port, the PCIE slot is connected with the BMC chip through an SMB bus, the BMC chip is connected with the pins at the same time, and the error indication lamp is connected with the BMC chip through an error indication signal line. The BMC chip in the management system can intelligently identify types of GPU board cards inserted into the PCIE slot and automatically call relevant programs to establish communication protocols matched with the GPUs, and therefore, the BMC chip can manage the GPU board cards effectively. The BMC can read information on the GPU board cards from a BIOS through an LPC bus and through the SMB bus, and functions of performing monitoring management, fault alarming and the like on the GPU board cards can be achieved by comparing information obtained by the BMC chip respectively through the LPC bus and through the SMB bus.

Owner:DAWNING INFORMATION IND BEIJING +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com