Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

357 results about "Local bus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, a local bus is a computer bus that connects directly, or almost directly, from the CPU to one or more slots on the expansion bus. The significance of direct connection to the CPU is avoiding the bottleneck created by the expansion bus, thus providing fast throughput. There are several local buses built into various types of computers to increase the speed of data transfer. Local buses for expanded memory and video boards are the most common.

Integrating sensors over a digital link

ActiveUS20060163227A1Well formedReduce deficiencyElectric discharge heatingArc welding apparatusLocal busEmbedded system

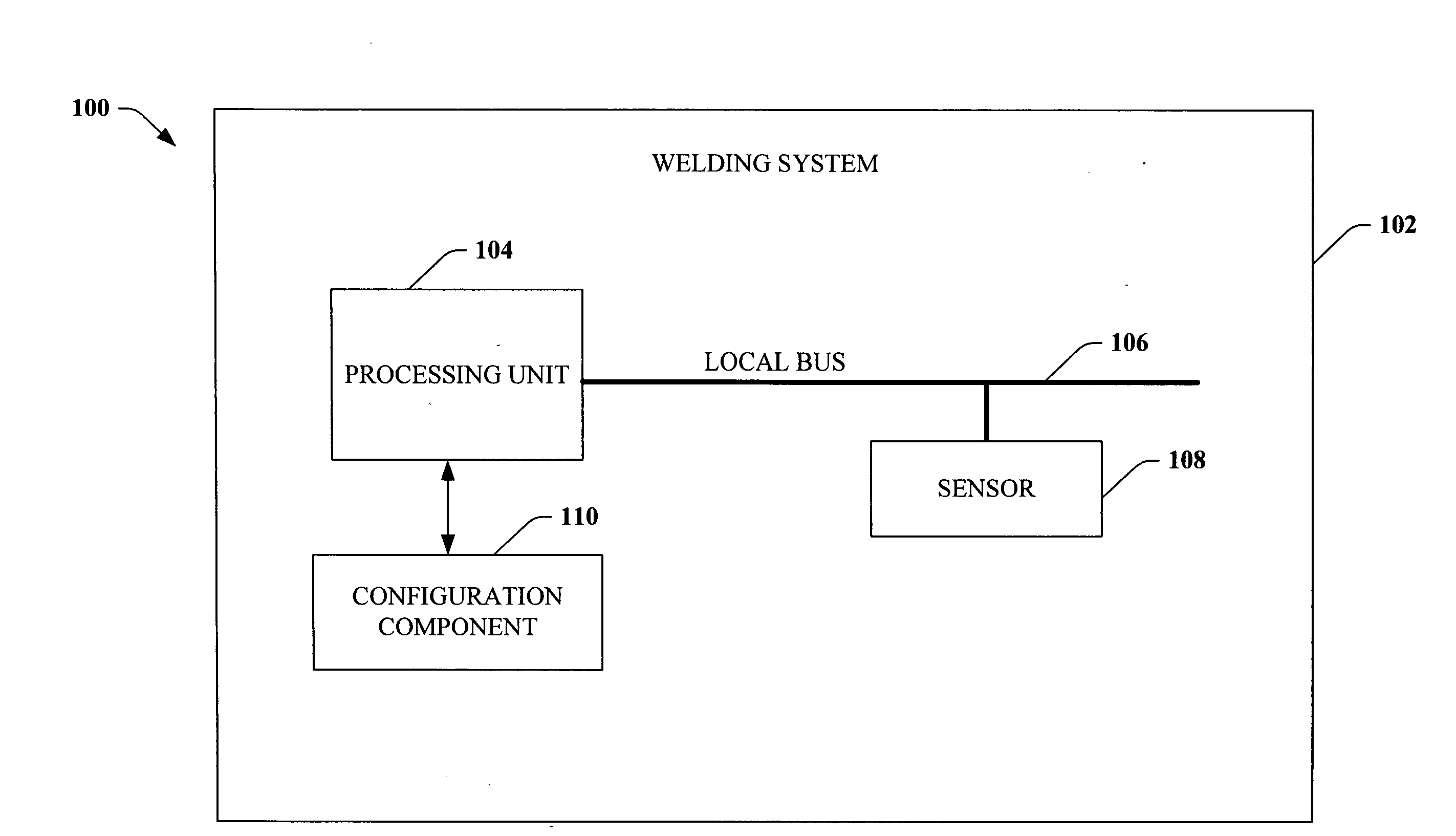

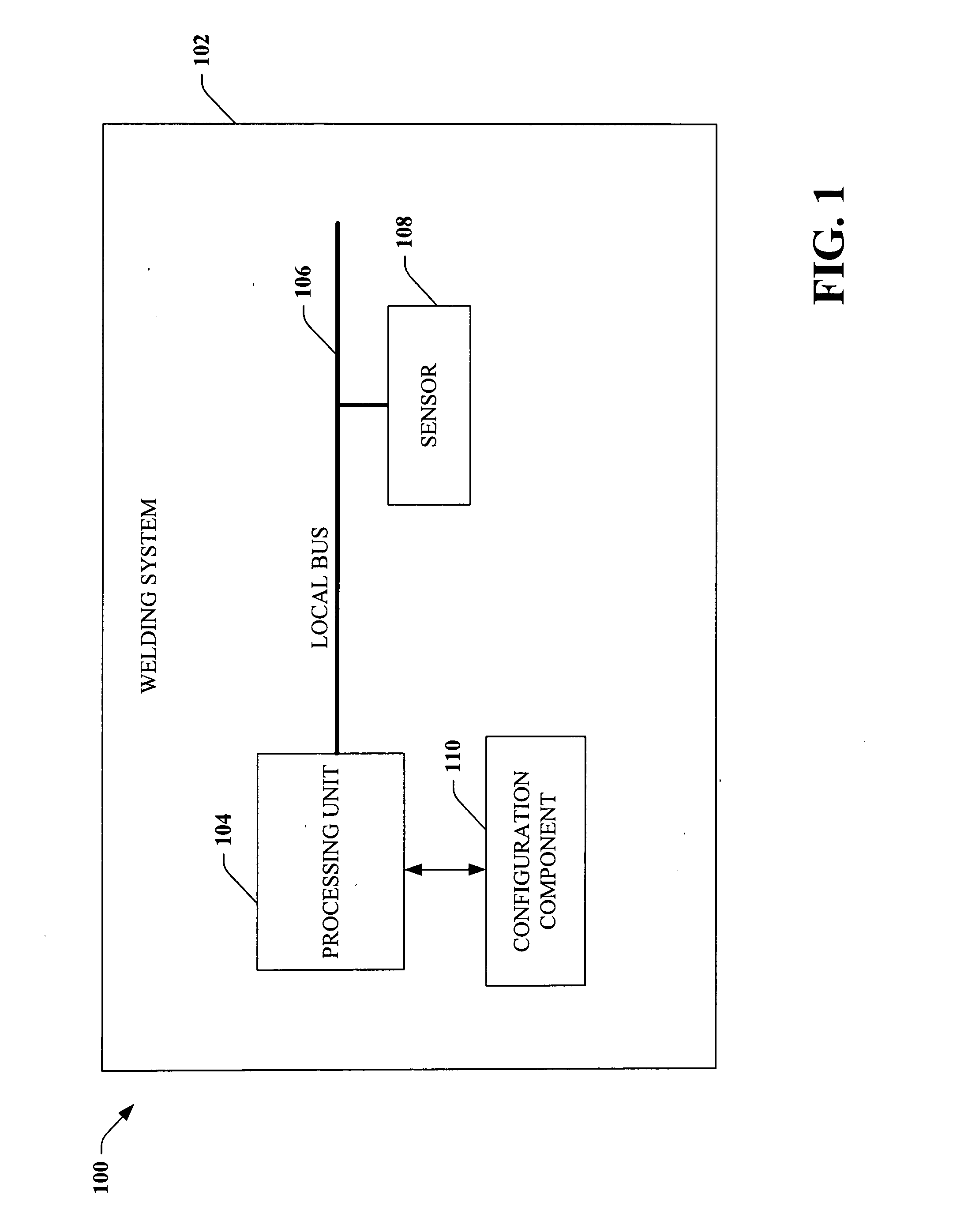

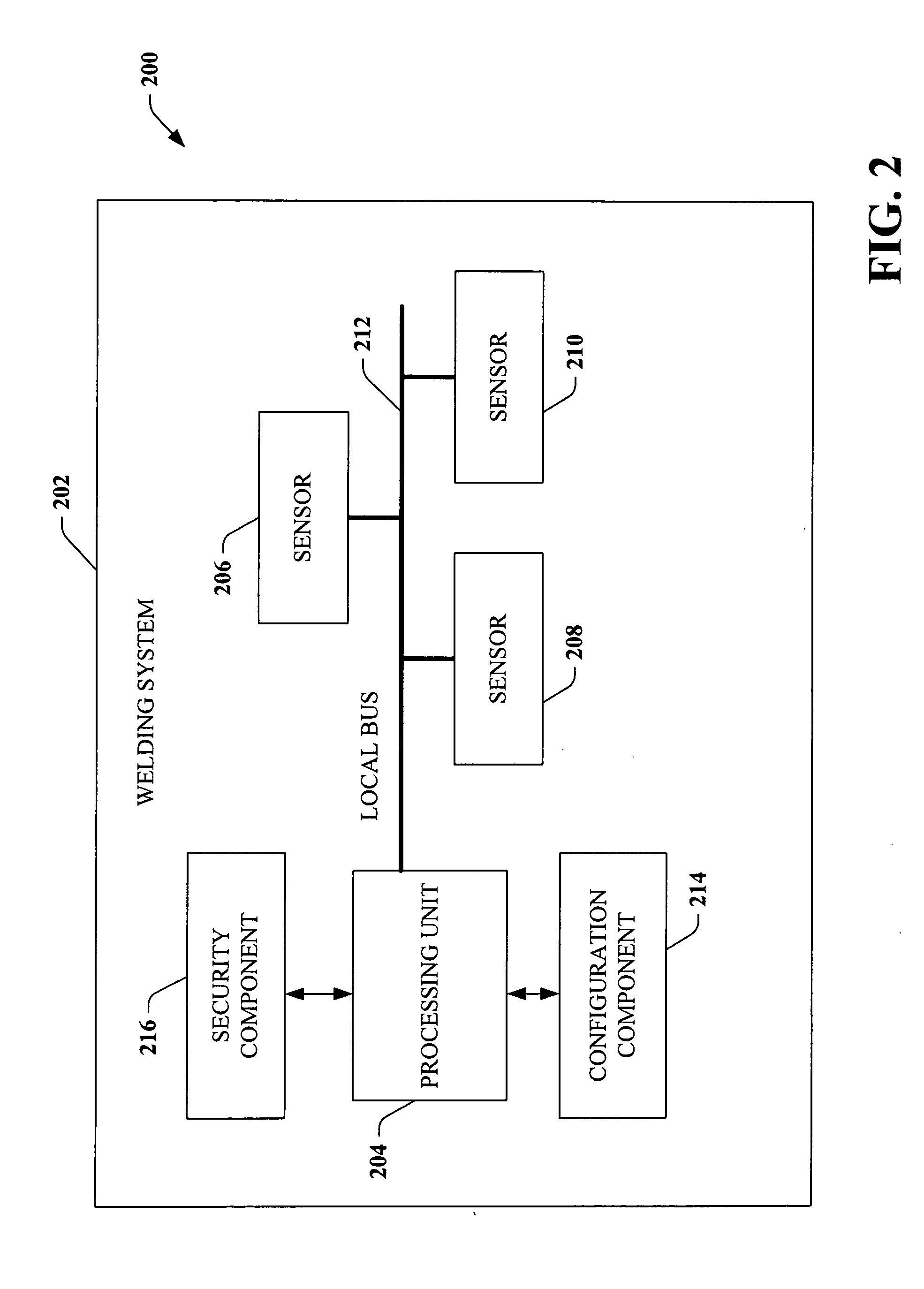

A system that facilitates dynamic configuration of a welding system with respect to a sensor comprises a processing unit associated with the welding system. A configuration component facilitates configuring the welding system with respect to the sensor upon determining that the sensor is coupled to a local bus associated with the processing unit. A remote access component can facilitate remotely accessing the welding system, the configuration of the welding system alterable by way of the remote access component.

Owner:LINCOLN GLOBAL INC

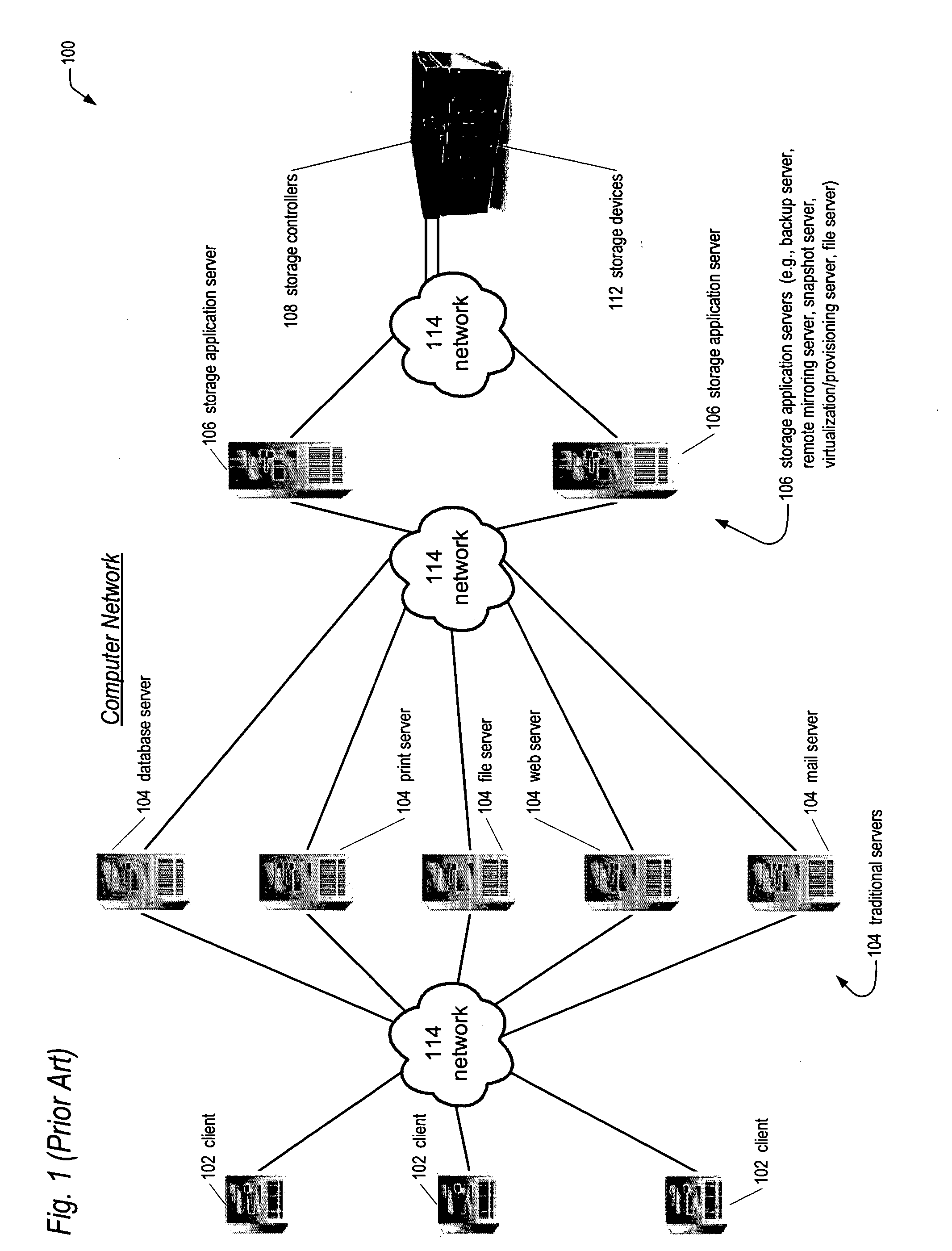

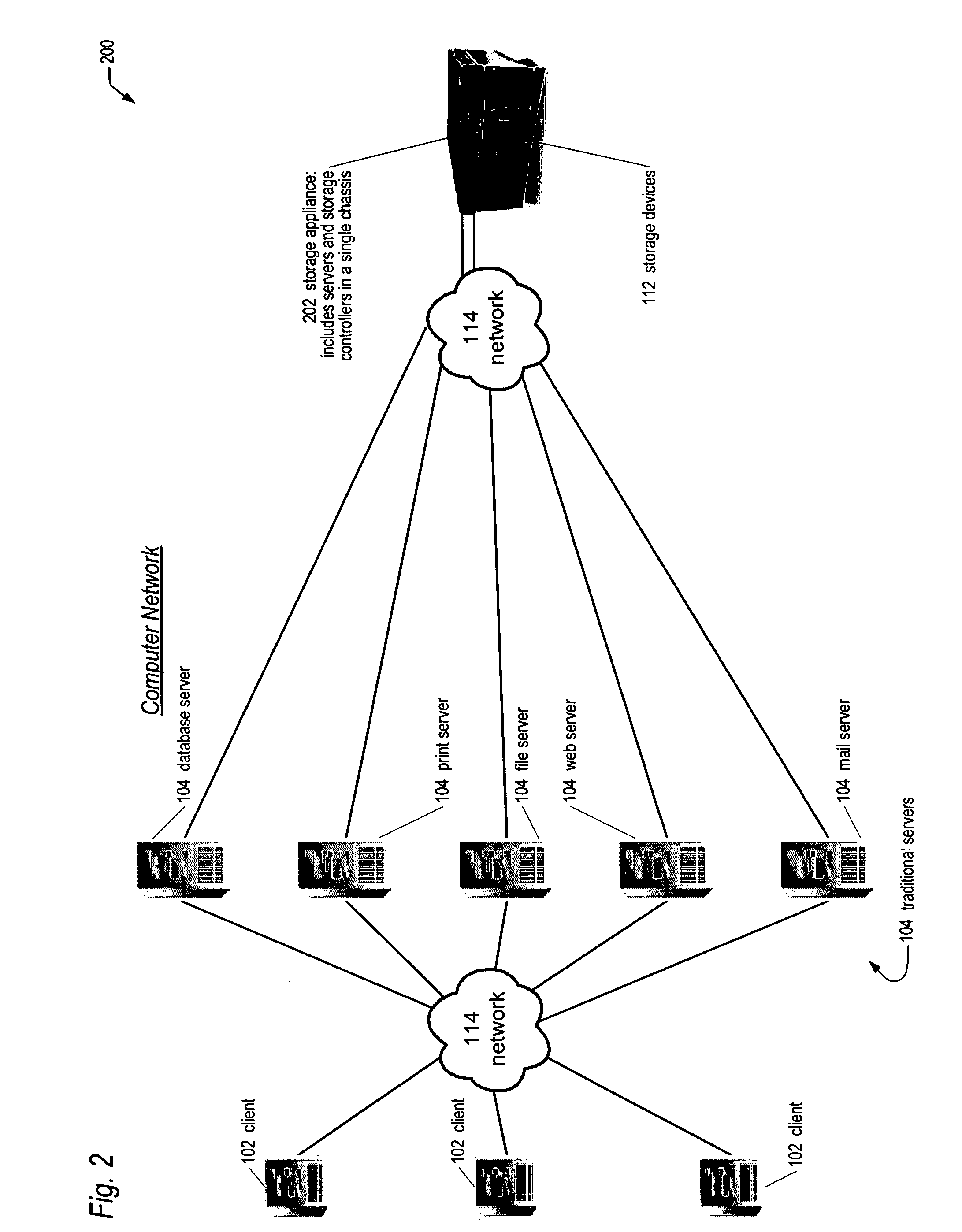

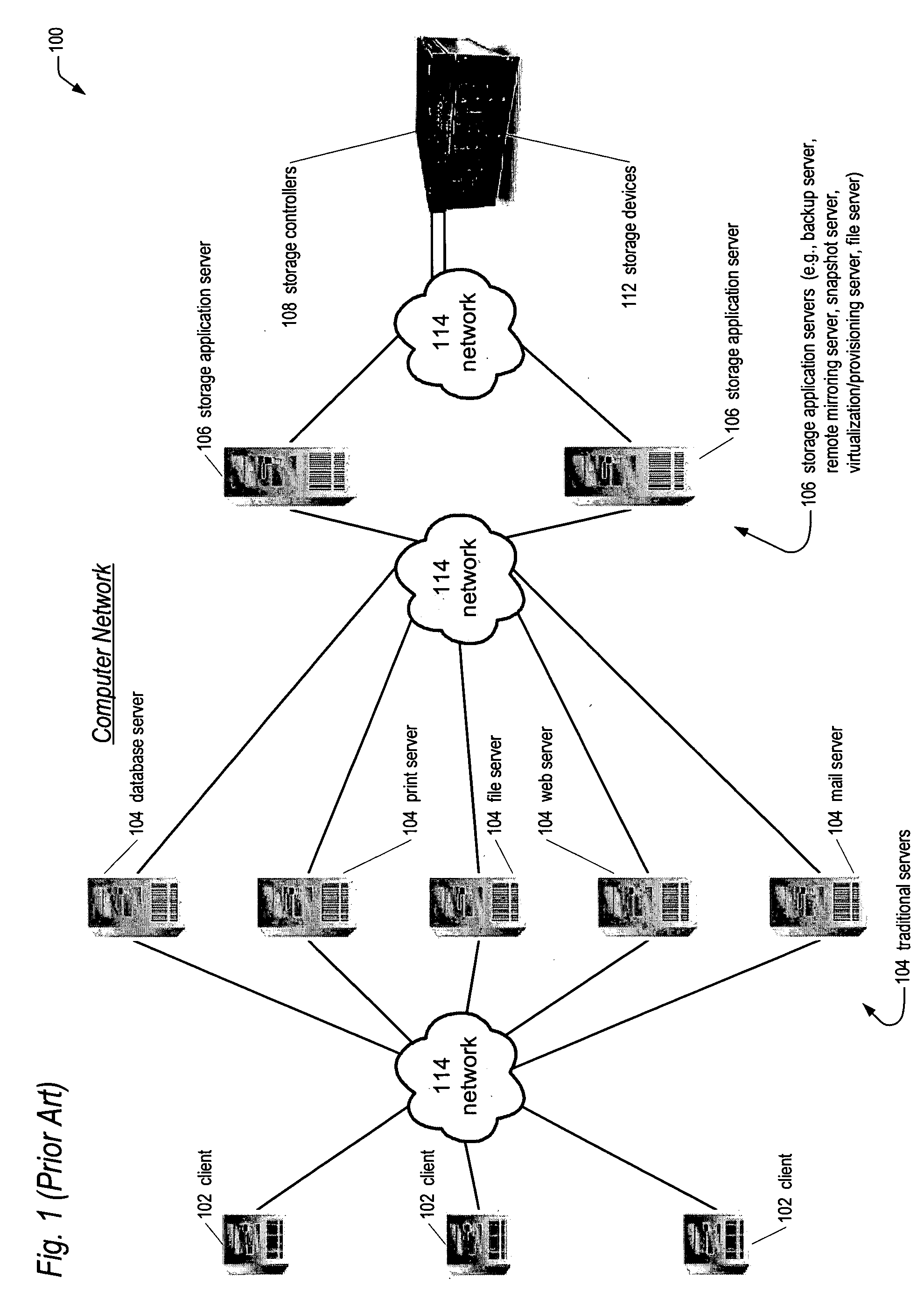

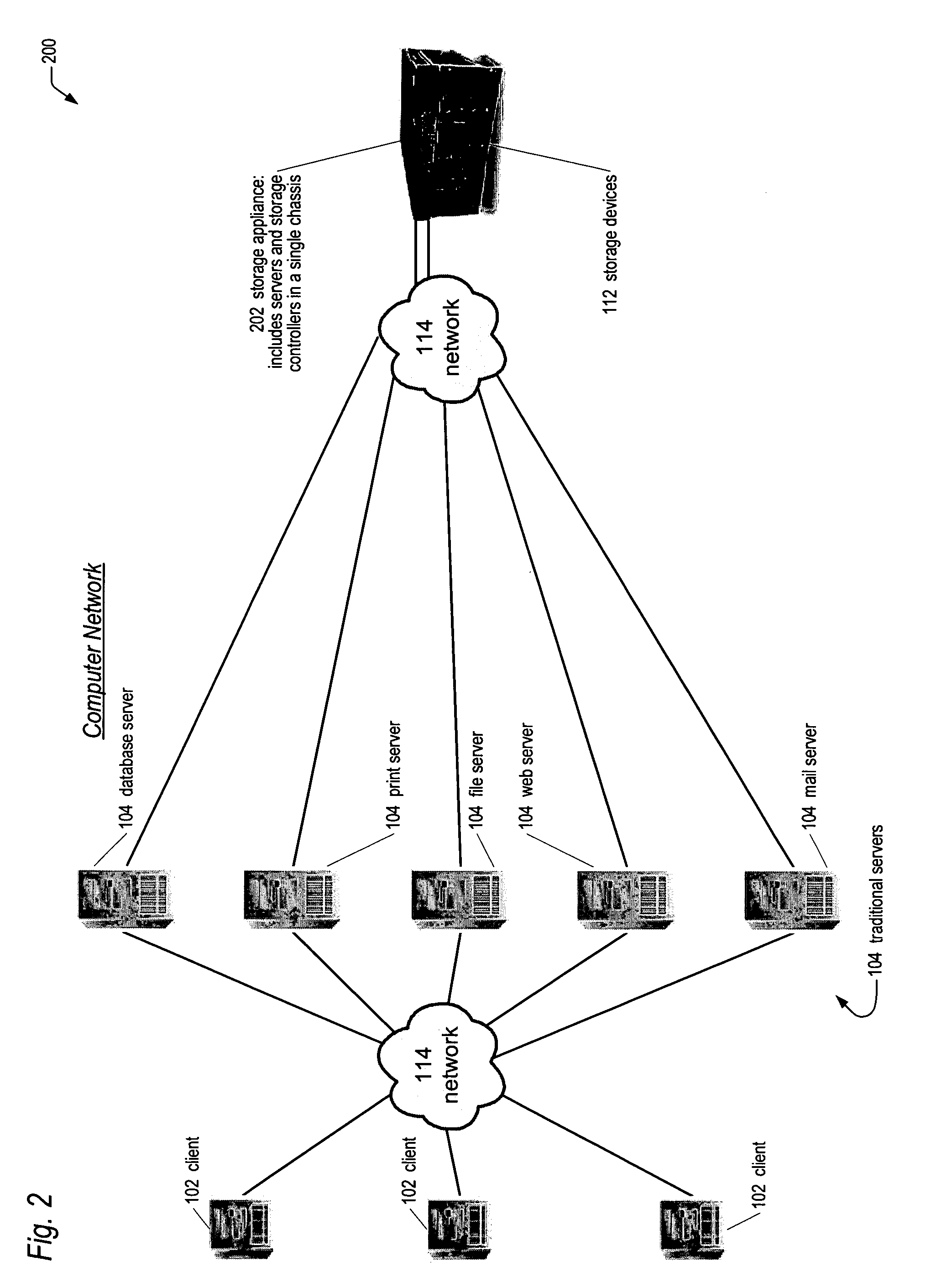

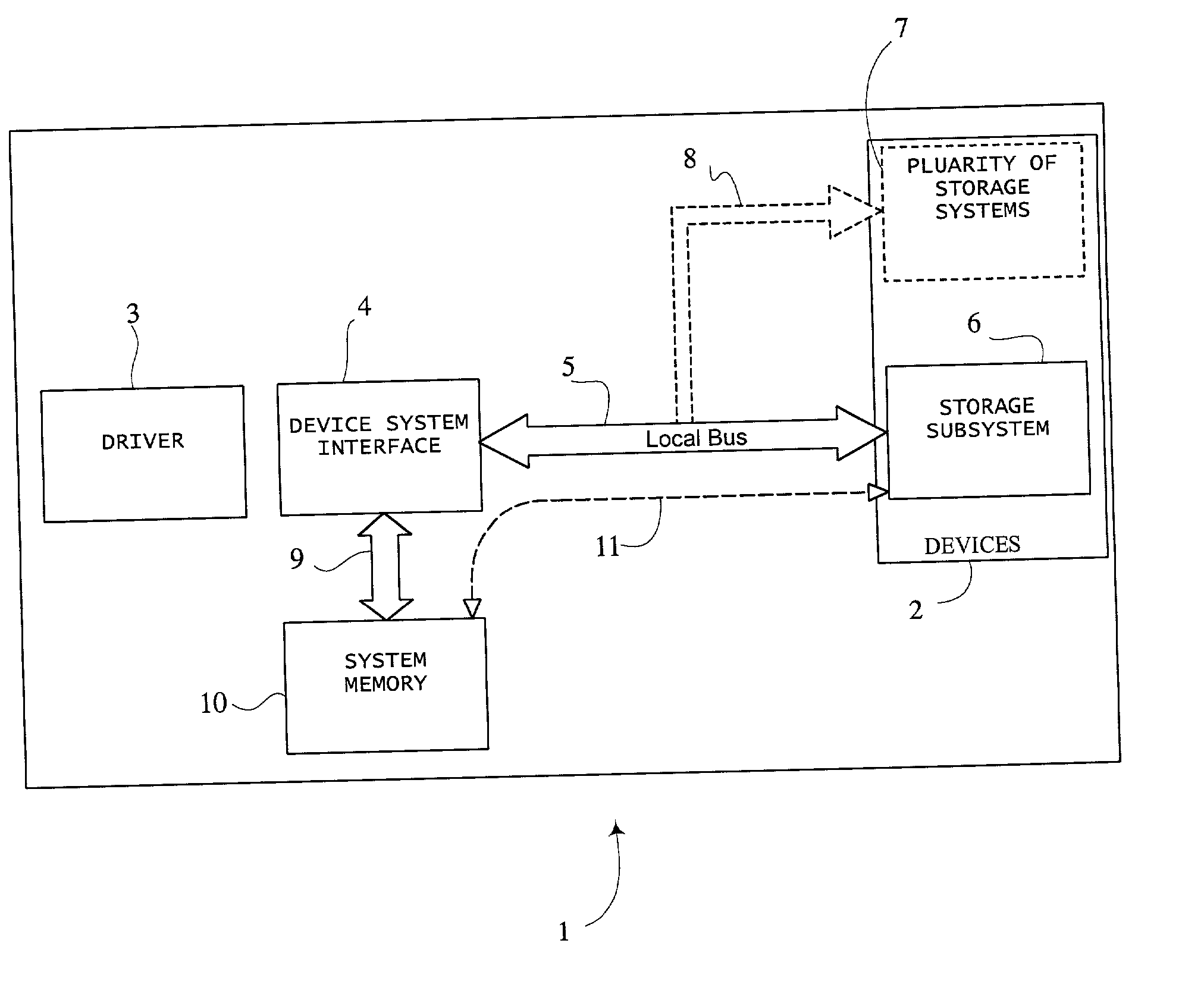

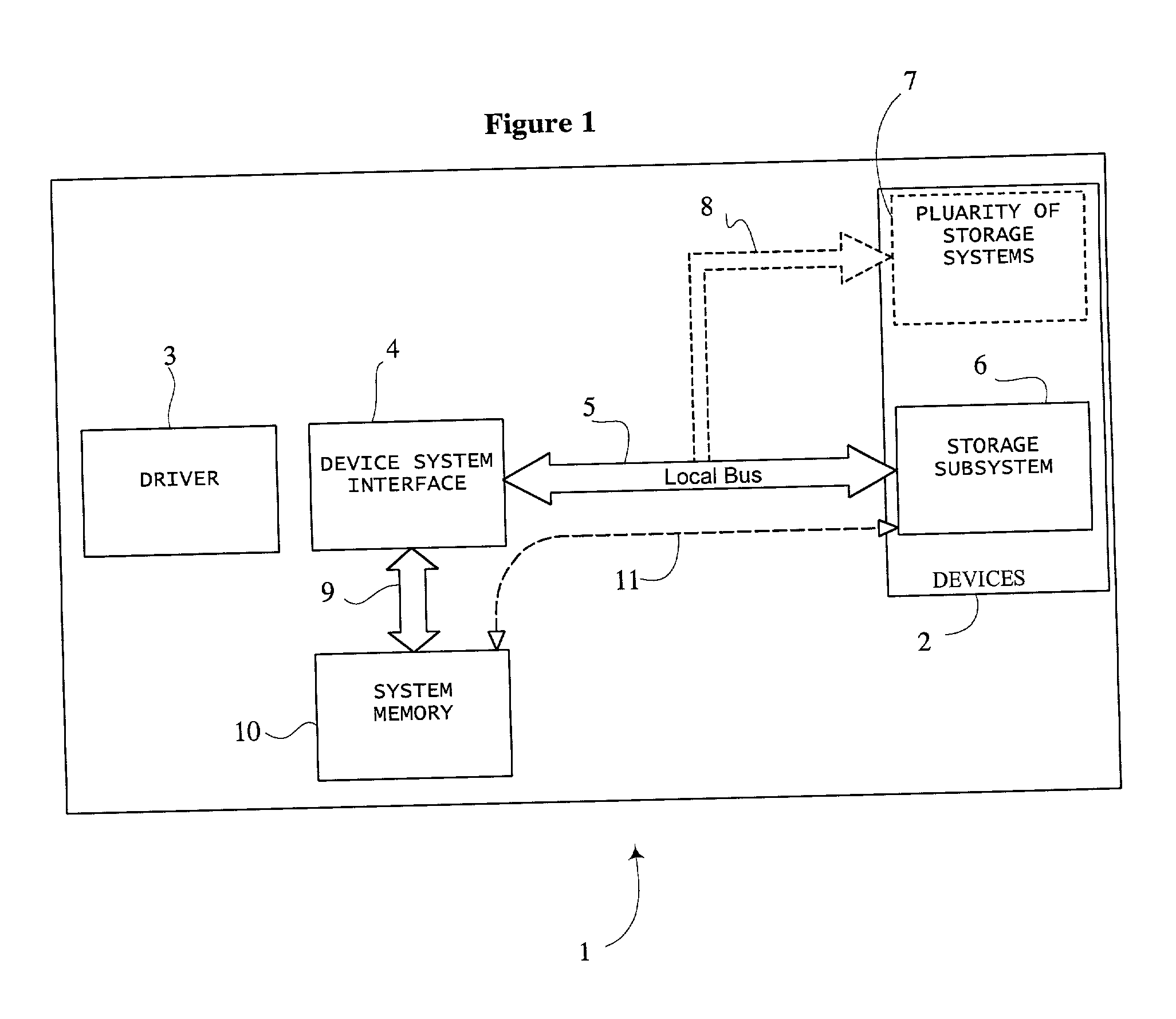

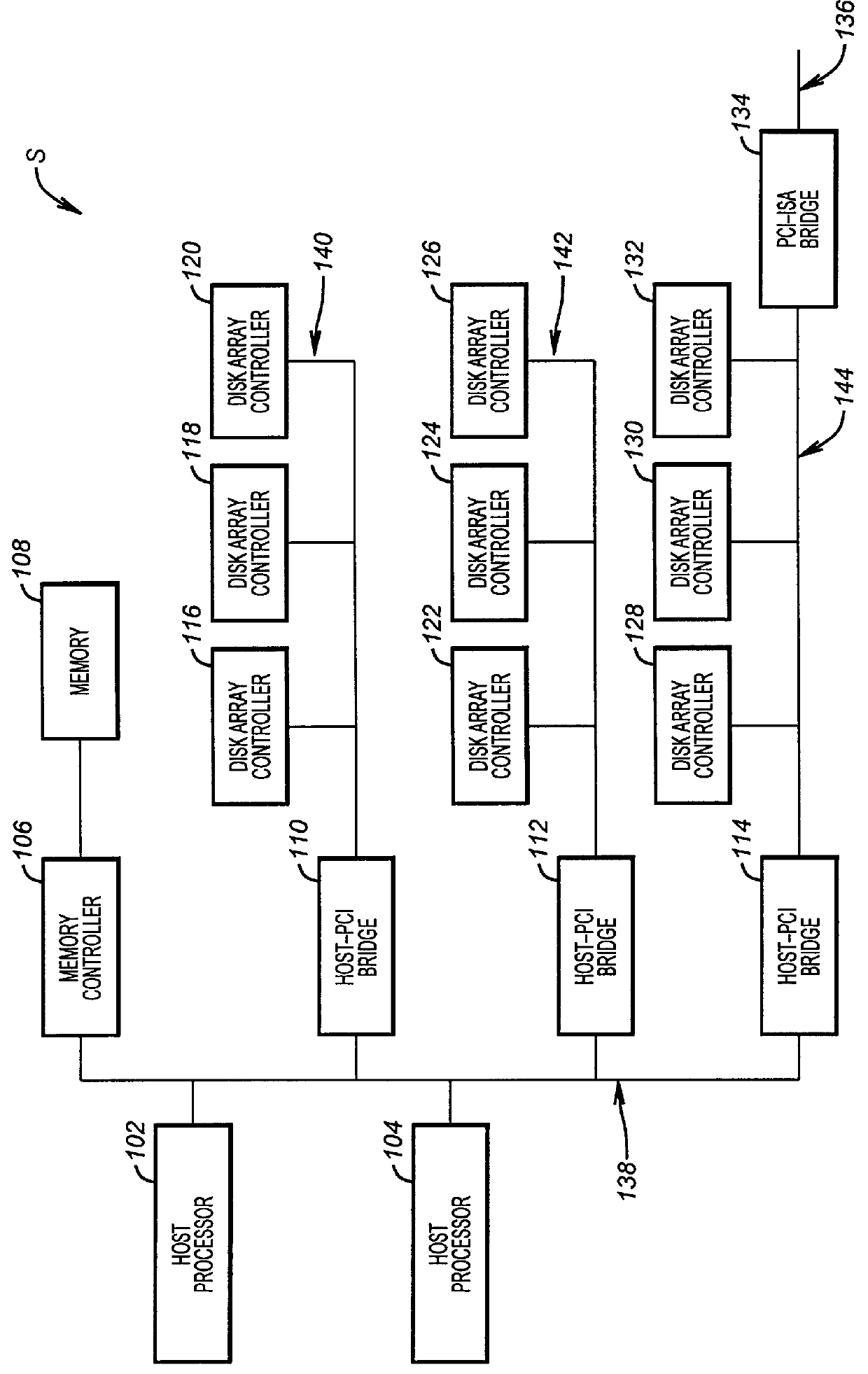

Network storage appliance with integrated redundant servers and storage controllers

ActiveUS20050021606A1Reduce needLow costInput/output to record carriersDigital data processing detailsHard disc driveOff the shelf

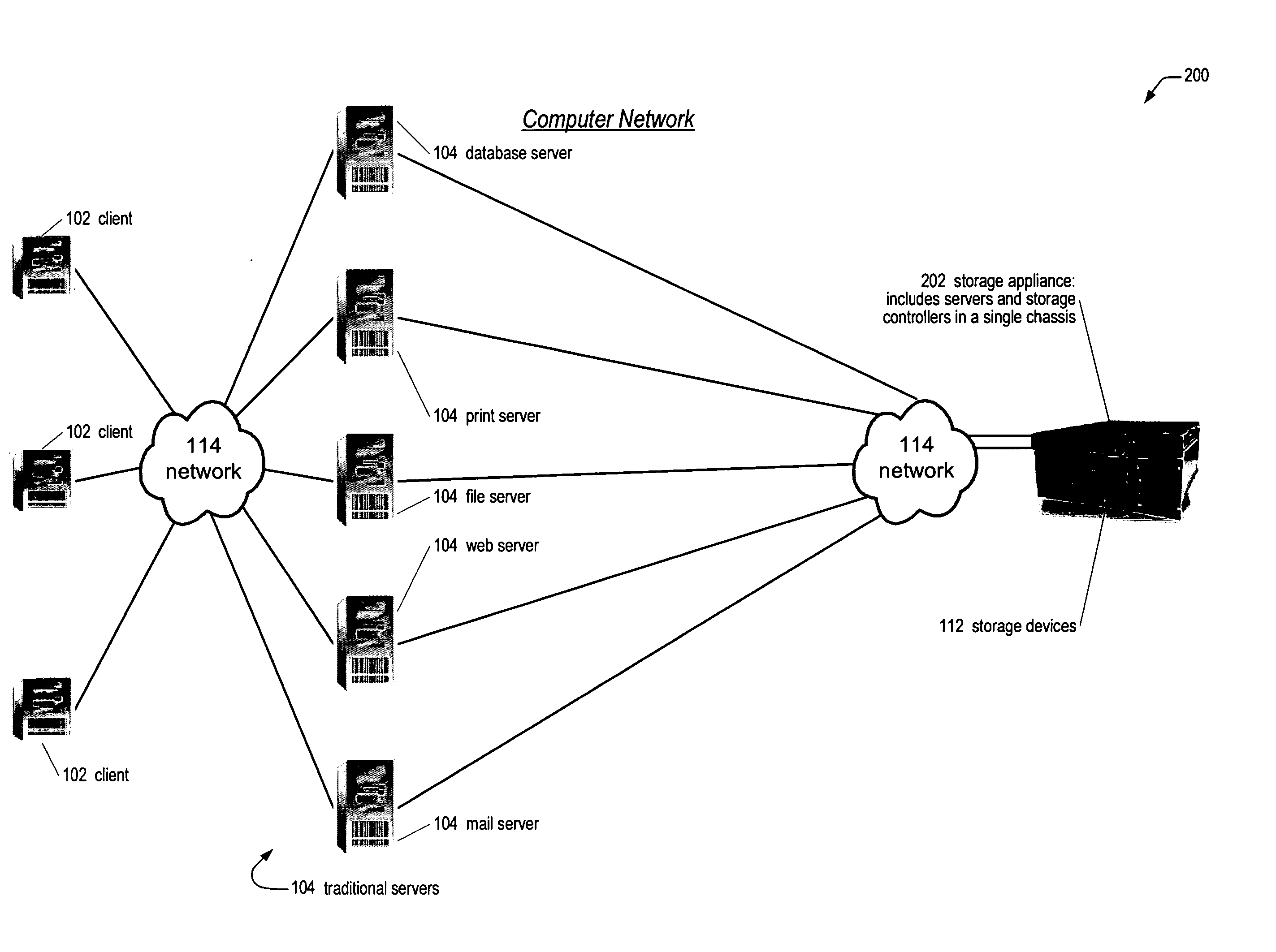

A network storage appliance is disclosed. The appliance includes a single chassis that encloses a plurality of servers and a plurality of storage controllers coupled together via a chassis backplane. The storage controllers control the transfer of data between the plurality of servers and a plurality of storage devices coupled to the storage controllers. The servers and storage controllers include a plurality of field replaceable unit (FRUs) hot-pluggable into the backplane such that any one of the FRUs may fail without loss of availability to the storage devices' data. In various embodiments, the chassis fits in a 19″ wide rack; is 1U high; the servers are standard PCs configured to execute off-the-shelf server applications and to facilitate porting of popular operating systems with little modification; the servers include disk-on-chip memory rather than a hard drive; local buses (e.g., PCIX) on the backplane interface the various FRUs.

Owner:DOT HILL SYST

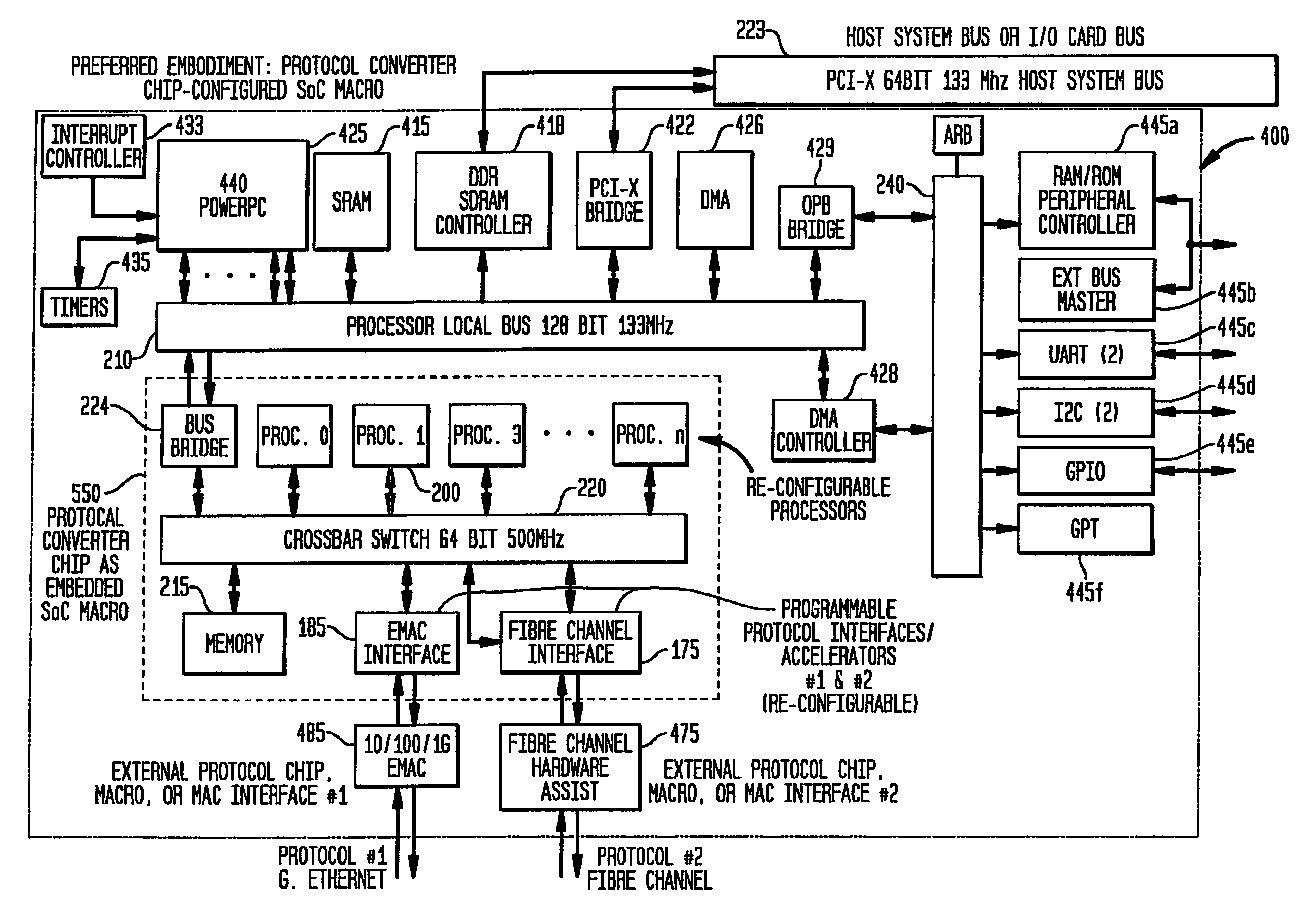

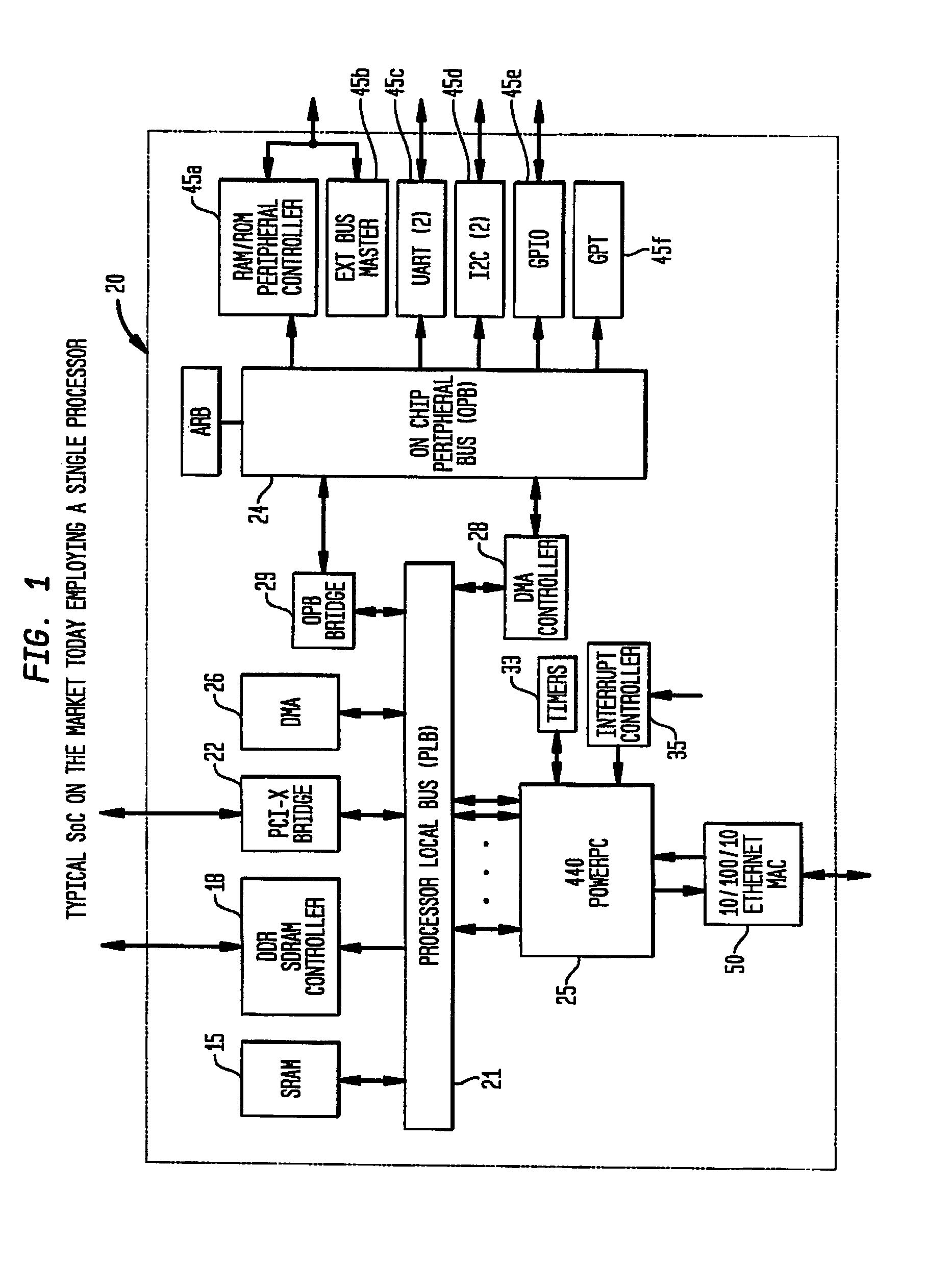

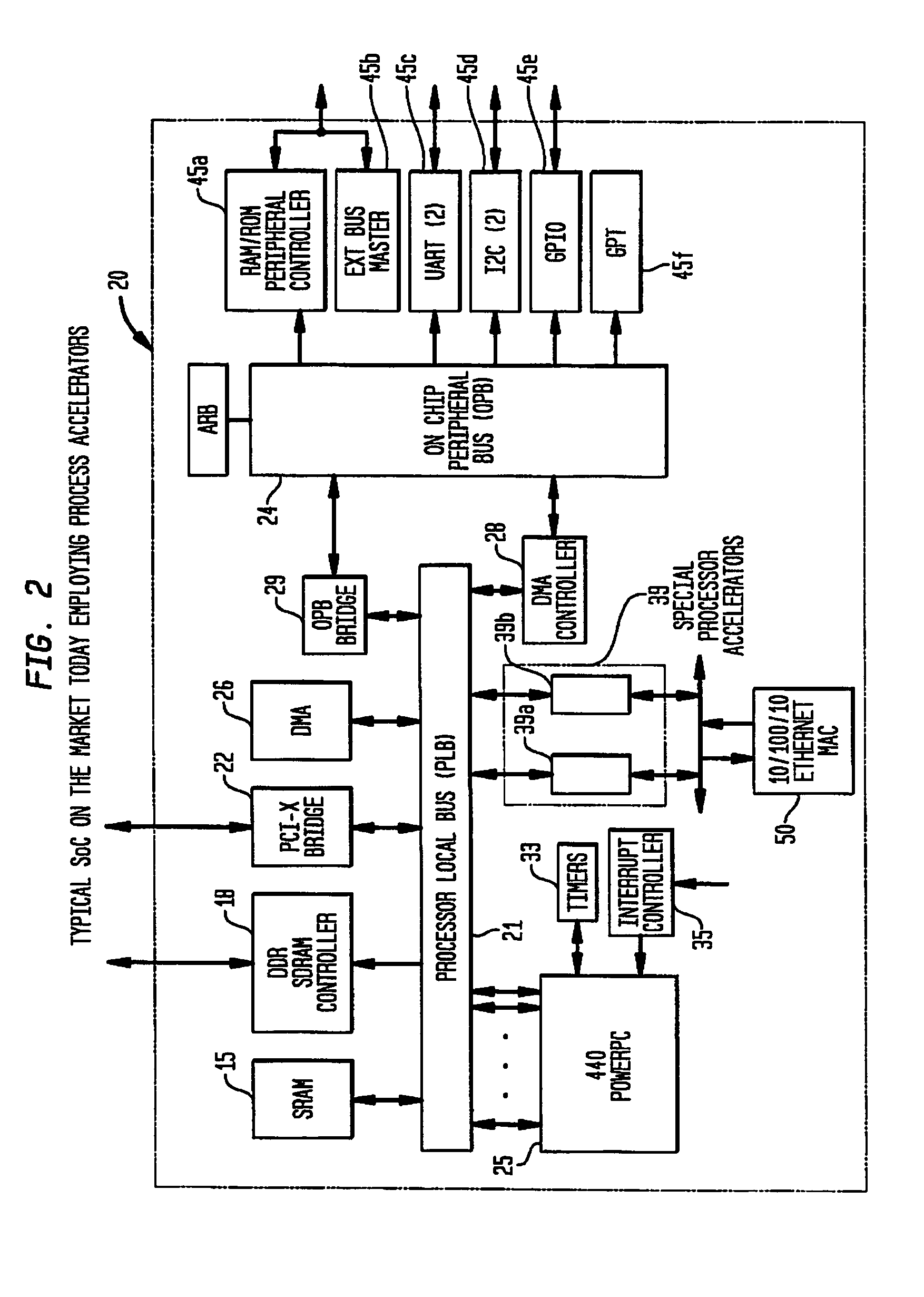

Network processor system on chip with bridge coupling protocol converting multiprocessor macro core local bus to peripheral interfaces coupled system bus

ActiveUS7412588B2Increase the number ofHigh bandwidthMultiple digital computer combinationsConcurrent instruction executionMulti processorCoupling system

A network processor includes a system-onchip (SoC) macro core and functions as a single chip protocol converter that receives packets generating according to a first protocol type and processes the packets to implement protocol conversion and generates converted packets of a second protocol type for output thereof, the process of protocol conversion being performed entirely within the SoC macro core. The process of protocol conversion contained within the SoC macro core does not require the processing resources of a host system. The system-on chip macro core includes a bridge device for coupling a local bus in the protocol converting multiprocessor SoC macro core local bus to peripheral interfaces coupled to a system bus.

Owner:MICROSOFT TECH LICENSING LLC

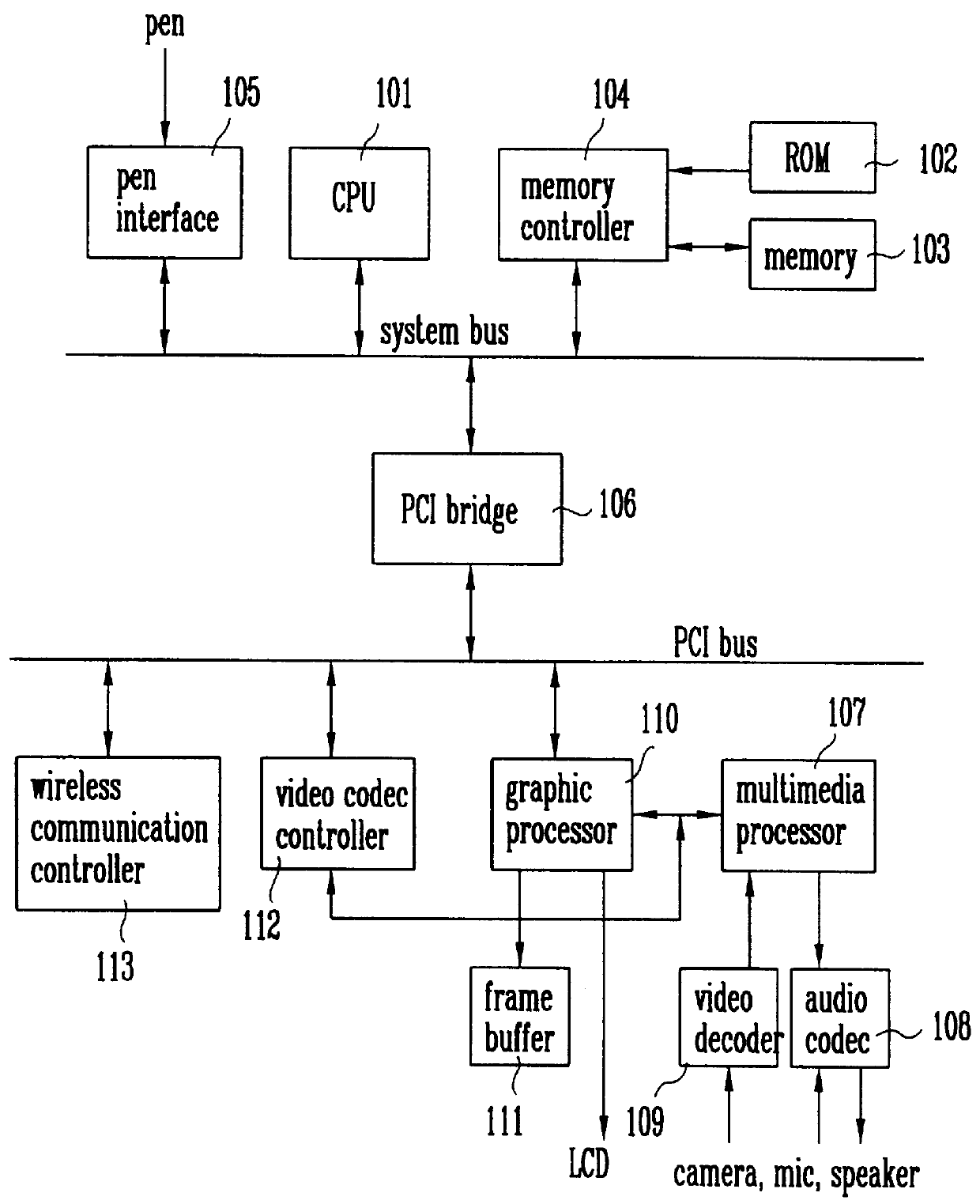

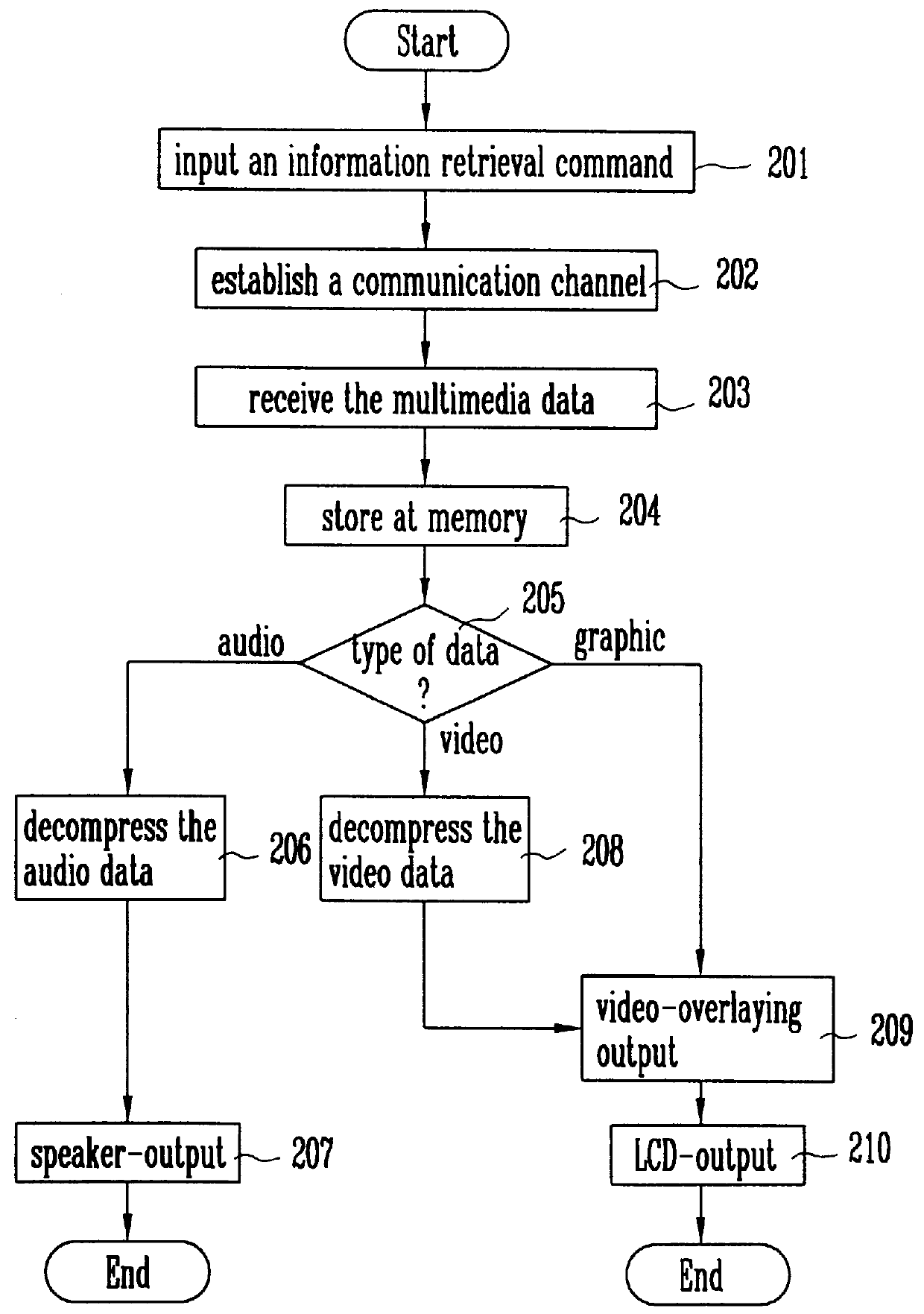

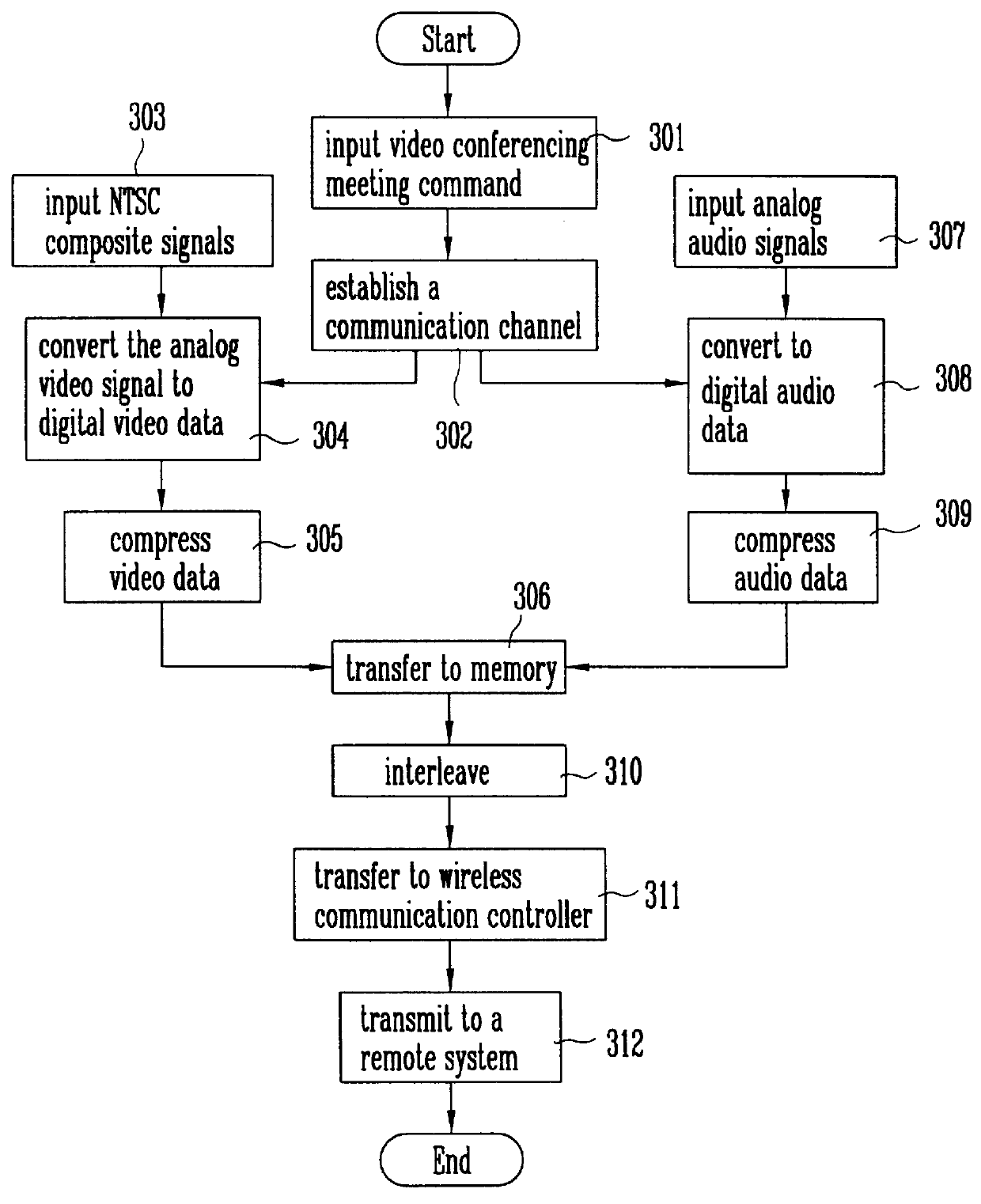

Structure of portable multimedia data input/output processor and method for driving the same

InactiveUS6035349AIncrease speedHigh speed machiningEnergy efficient ICTMultiple digital computer combinationsRemote systemOutput device

Potable multimedia terminal which is small and consumes low power, can process a large quantity of multimedia data such as video and audio data. Portable multimedia data input / output processor can be made smaller by using a pen as an input device and can also process a large quantity of multimedia data at a high speed by adopting a PCI bus as a local bus of a system. To retrieve, compress, and decompress multimedia data, main components of this portable multimedia data input / output processor are comprised of audio codec for compressing and decompressing audio data, video codec controller for compressing and decompressing video data, and multimedia processor for transmitting audio data to wireless communication controller and video data to video codec controller and to graphic processor. The method for retrieving multimedia data includes steps of receiving data, de-interleaving received data into audio, video, and graphic data, decompressing the data, and outputting the data to output device. The method for compressing data includes steps of inputting video data to video codec controller, compressing video and audio data at video codec controller and audio codec, interleaving the compressed data, and transmitting them to a remote system. The steps to decompress data are in reverse to the steps to compress data.

Owner:UNILOC 2017 LLC

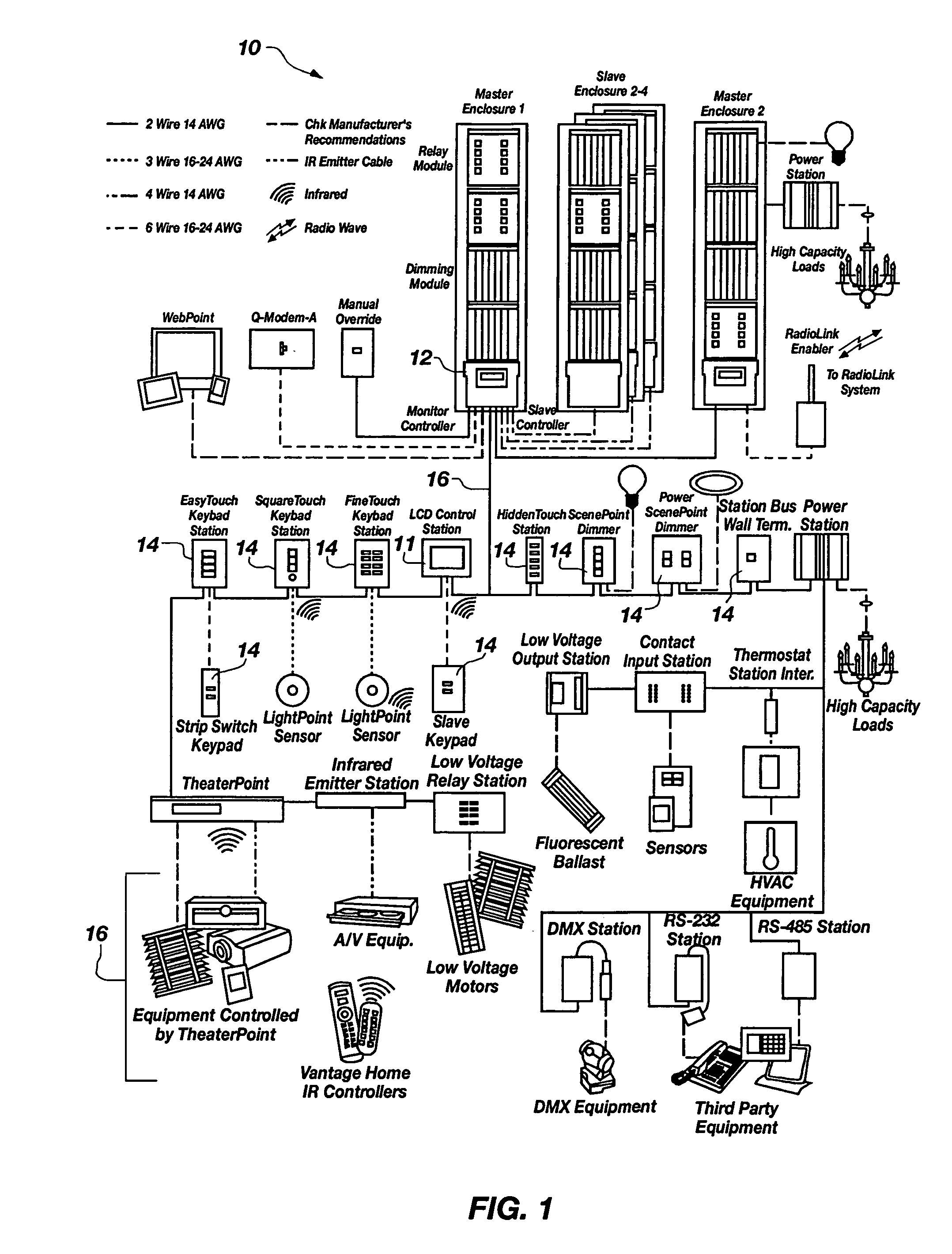

Backlit display with motion sensor

ActiveUS7394451B1Energy efficient ICTSubstation/switching arrangement detailsGraphicsGraphical user interface

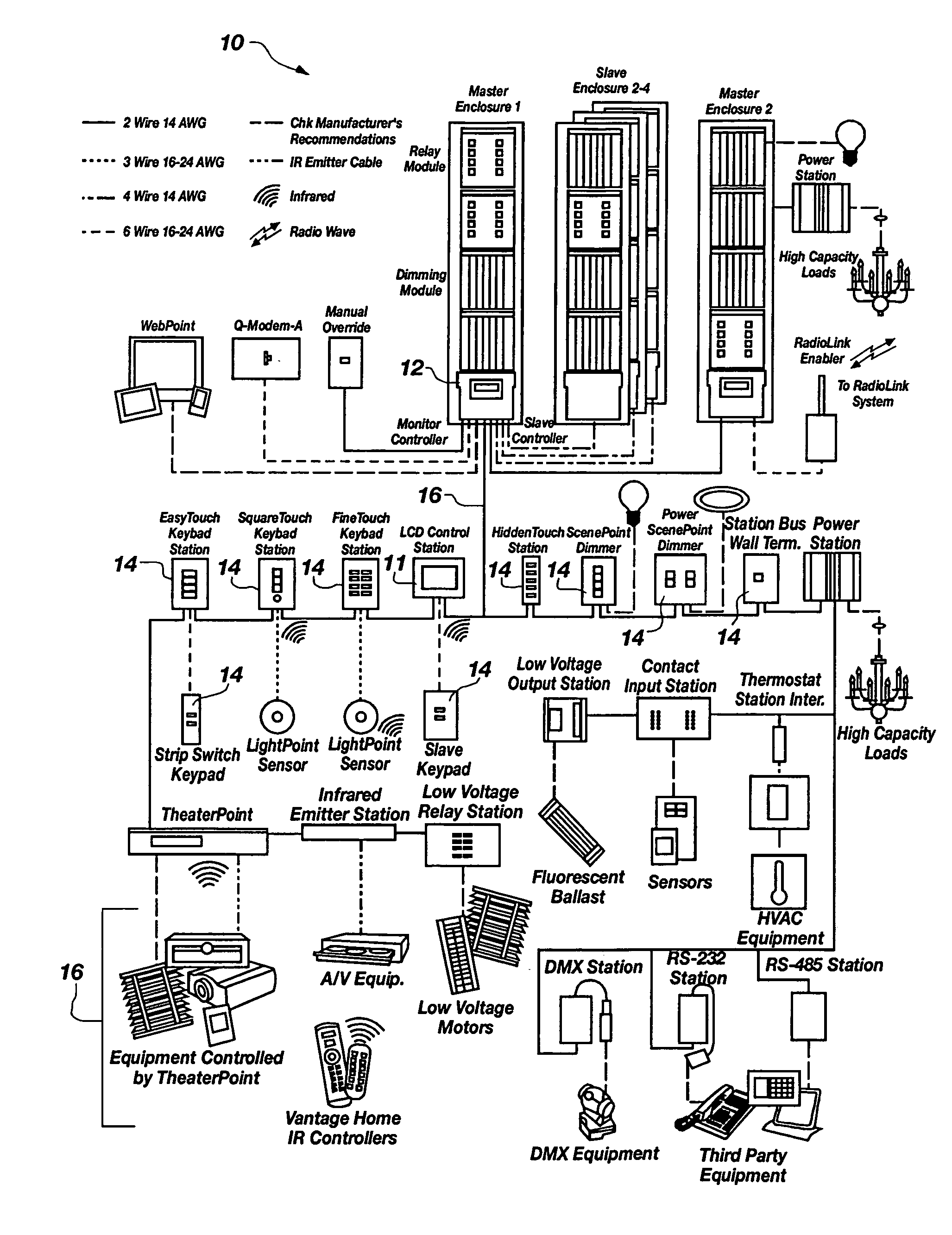

An apparatus for interfacing with a control system, and in particular a home automation system. In one embodiment, the apparatus comprises an integrated LCD touch screen and motion sensor. The motion sensor is used to illuminate a backlight to the touch screen when a person approaches the apparatus. The sensitivity of the motion sensor may be adjusted through a graphical user interface displayed on the touch screen. In addition, the backlighting may be adjusted so that the illumination is at a specific level with the screen is on, i.e., when the motion sensor has been tripped, and a specific level when the screen is off. The apparatus may further comprise an IR receiver for receiving commands via a remote. In addition, the apparatus may be powered from a local bus or an external power supply. The apparatus may comprise a communications port for receiving customized pages from a computer.

Owner:LEGRAND HOME SYST

System and method for providing state capture and restoration to an I/O system

InactiveUS6175932B1Easy to determineElectrically conductive connectionsError detection/correctionLocal busBase station

A modular distributed I / O system includes a computer coupled to module banks through a network bus. A module bank includes a communication module, terminal bases, and I / O modules. The adjoined terminal bases form a local bus mastered by the communication module. The I / O modules connect to the local bus through terminal bases. I / O modules are pluriform and programmable. The communication module maintains a memory image of the configuration state of each I / O module resident in the module bank. A memory image persists when an I / O module is removed from its terminal base. The memory image is used to configure a new I / O module which is inserted into the same terminal base. The communication module monitors for communication failure on the network bus, and is configured to capture the state of the module bank and automatically restore this captured state after a power-loss event. The terminal bases realize a local bus which includes a parallel bus, a serial bus, and an address assignment bus. Each terminal base receives a value from a preceding terminal base, increments this value, and asserts the increment value to a succeeding terminal base. Each terminal base is automatically assigned an physical proximity address. An I / O module controls read / write access to its register space by a semaphore mechanism which supports multi-threaded processing. The I / O module latches an ungranted semaphore request and assumes a self-exclusion state upon releasing the semaphore wherein the semaphore is reserved for the communication module.

Owner:NATIONAL INSTRUMENTS

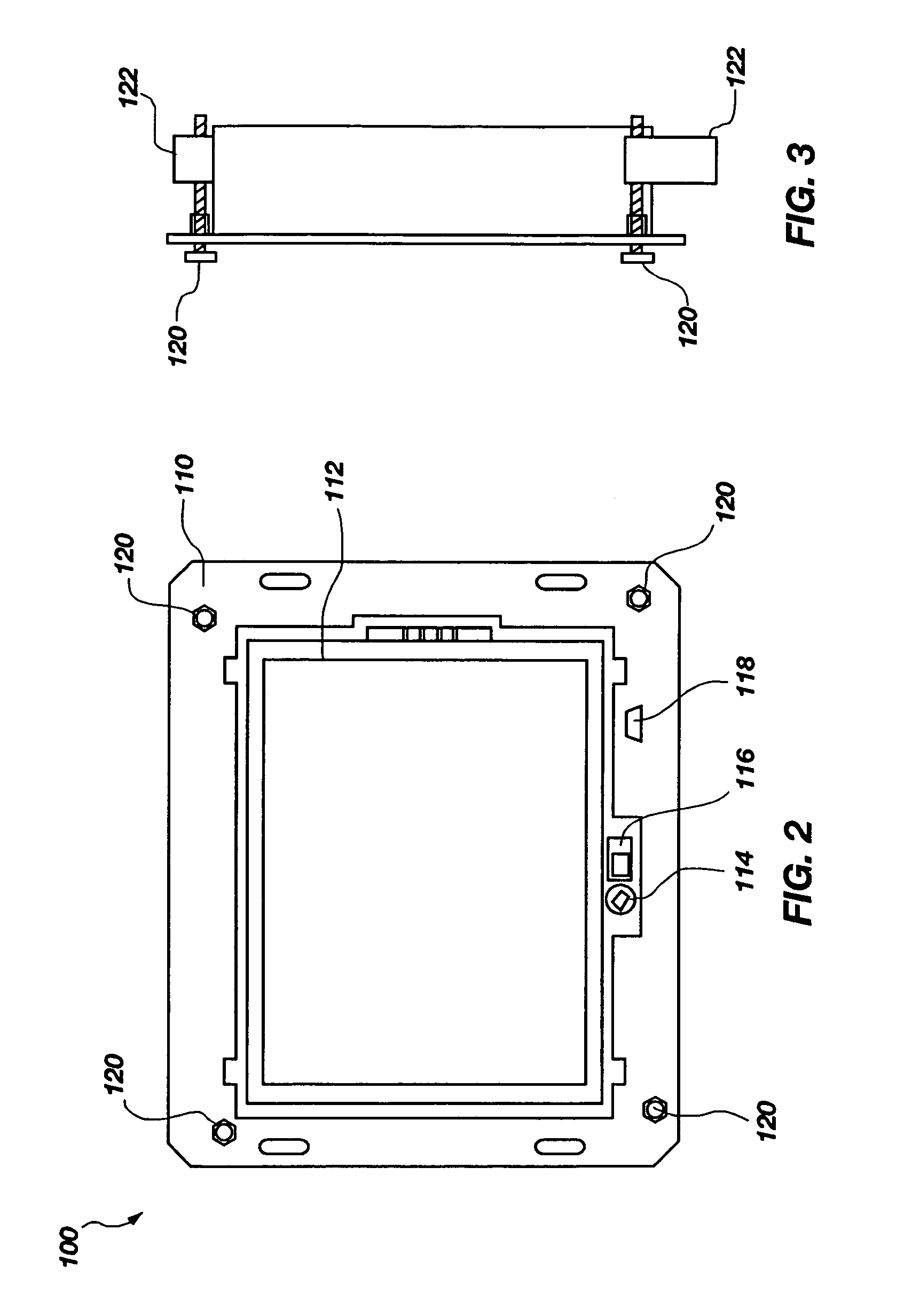

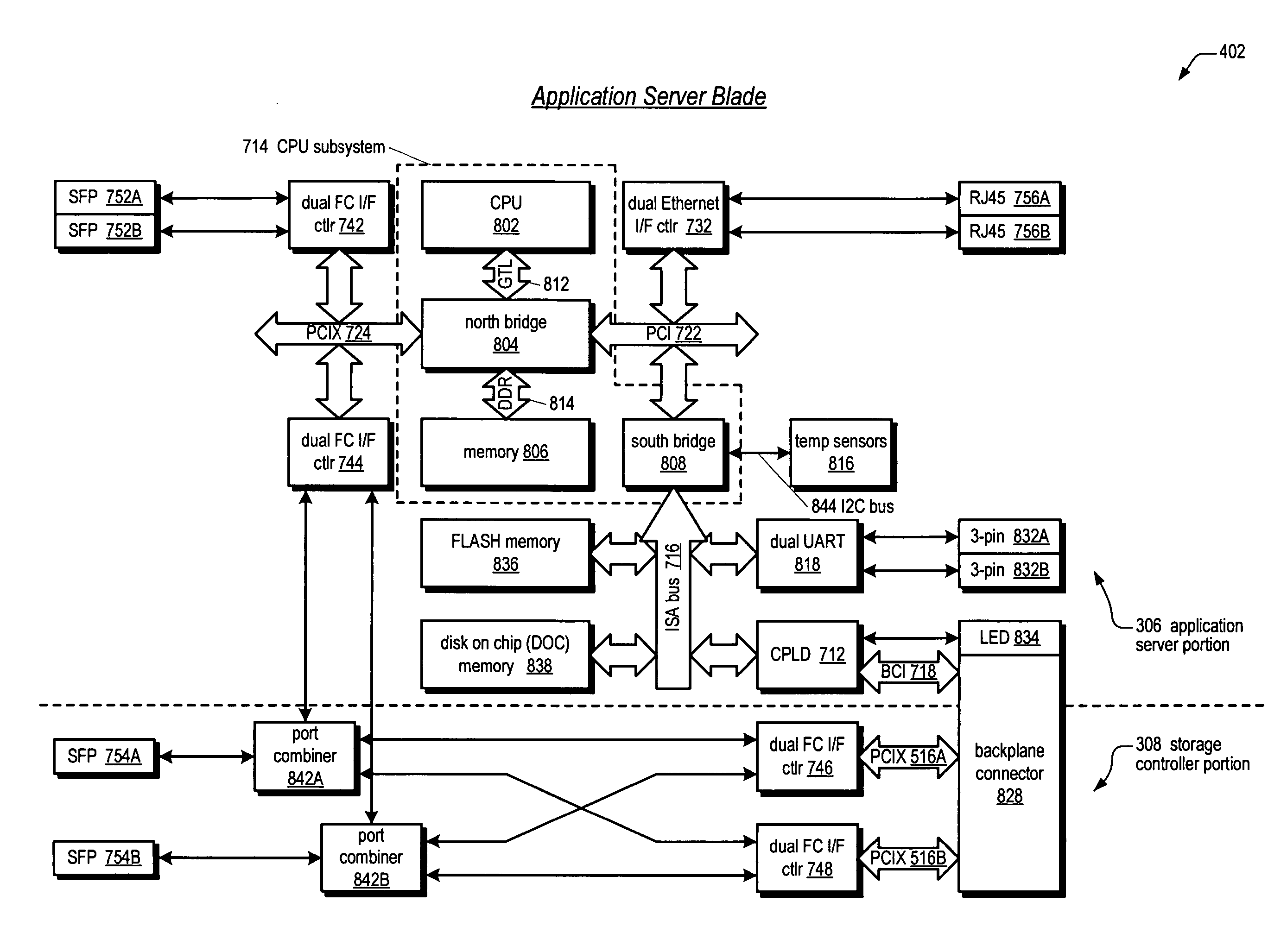

Application server blade for embedded storage appliance

ActiveUS20050010709A1Little and no software developmentEasy to reuseInput/output to record carriersDigital data processing detailsData packApplication server

An application server blade for an embedded storage appliance is disclosed. The blade includes a printed circuit board (PCB) with a connector for connecting to a chassis backplane including a local bus. Affixed on the PCB is a server, a portion of a storage controller, and an I / O link coupling the server and storage controller portion. The server transmits packets on the I / O link to the storage controller portion. The packets include commands to transfer data to a storage device controlled by the storage controller. The storage controller portion receives the packets from the server on the I / O link and forwards the commands on the backplane local bus to another portion of the storage controller affixed on a separate PCB also enclosed in the chassis. The blade also includes a removal mechanism for hot-replacement of the blade in the chassis. The blade architecture facilitates software reuse.

Owner:DOT HILL SYST

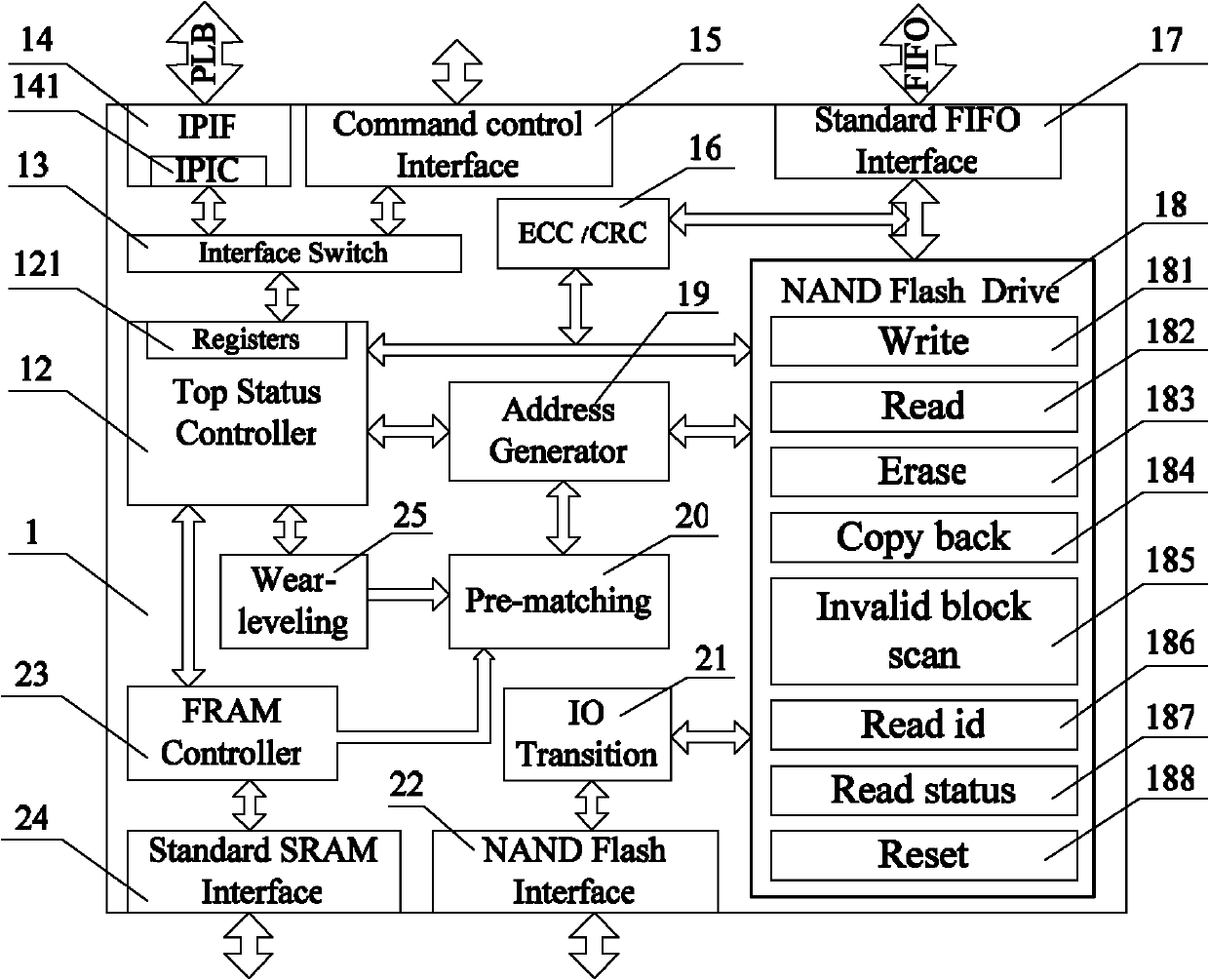

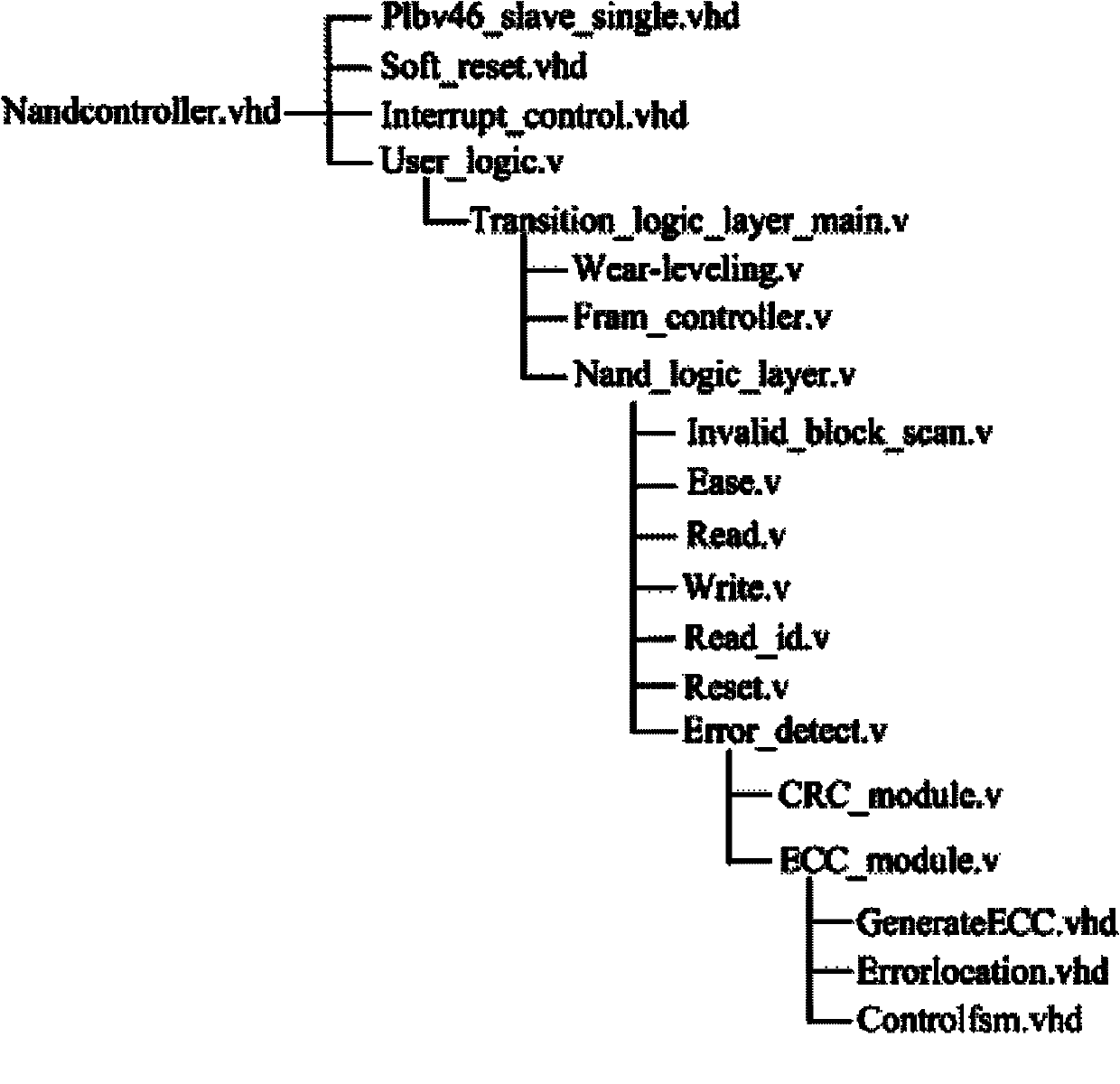

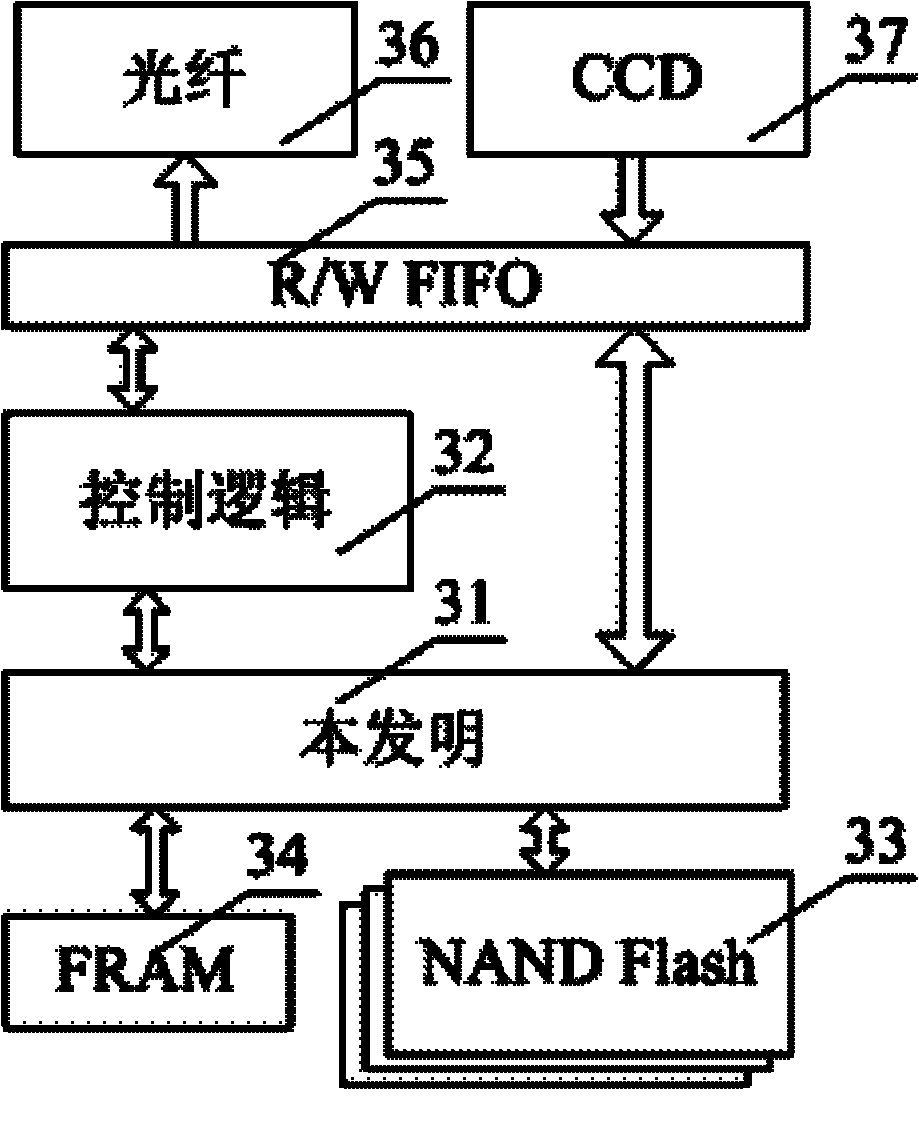

NAND Flash-based data recording method and recording controller

InactiveCN102169462AReduce usageImprove acceleration performanceInput/output to record carriersMemory adressing/allocation/relocationStatic random-access memoryControl signal

The invention discloses an NAND Flash-based data recording method and an NAND Flash-based data recording controller. The method comprises the following methods: a hardware bad block management method comprising the following steps of: when a sudden bad block appears, jumping to a next matched valid block without time delay to continuously record, and finally writing the data lag of a page before the bad block appears back to the jumped valid block; a hardware balance method comprising the following step of: starting the erasing-writing operation in succession to the last erasing-writing address so that the erasing-writing times of each block of the NAND Flash is approximately equal; and an input output (IO) expansion method comprising the following steps of: converting data bit width and switching control signals so that a single NAND Flash driver can control multiple chips and multiple groups of NAND Flashes. The controller comprises a ferroelectric random access memory (FRAM) controller, a top state controller, a loss equalizer, an interface switching module, a pre-matching module, an address generating module, a register set, a data verification module, a standard first in first out (FIFO) interface, a standard static random access memory (SRAM) interface, a command control interface and the NAND Flash driver. The whole controller can be mounted on a processor local bus (PLB) of an embedded processor, and data conversion between a control signal and a state signal can be performed through the command control interface and an external module.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

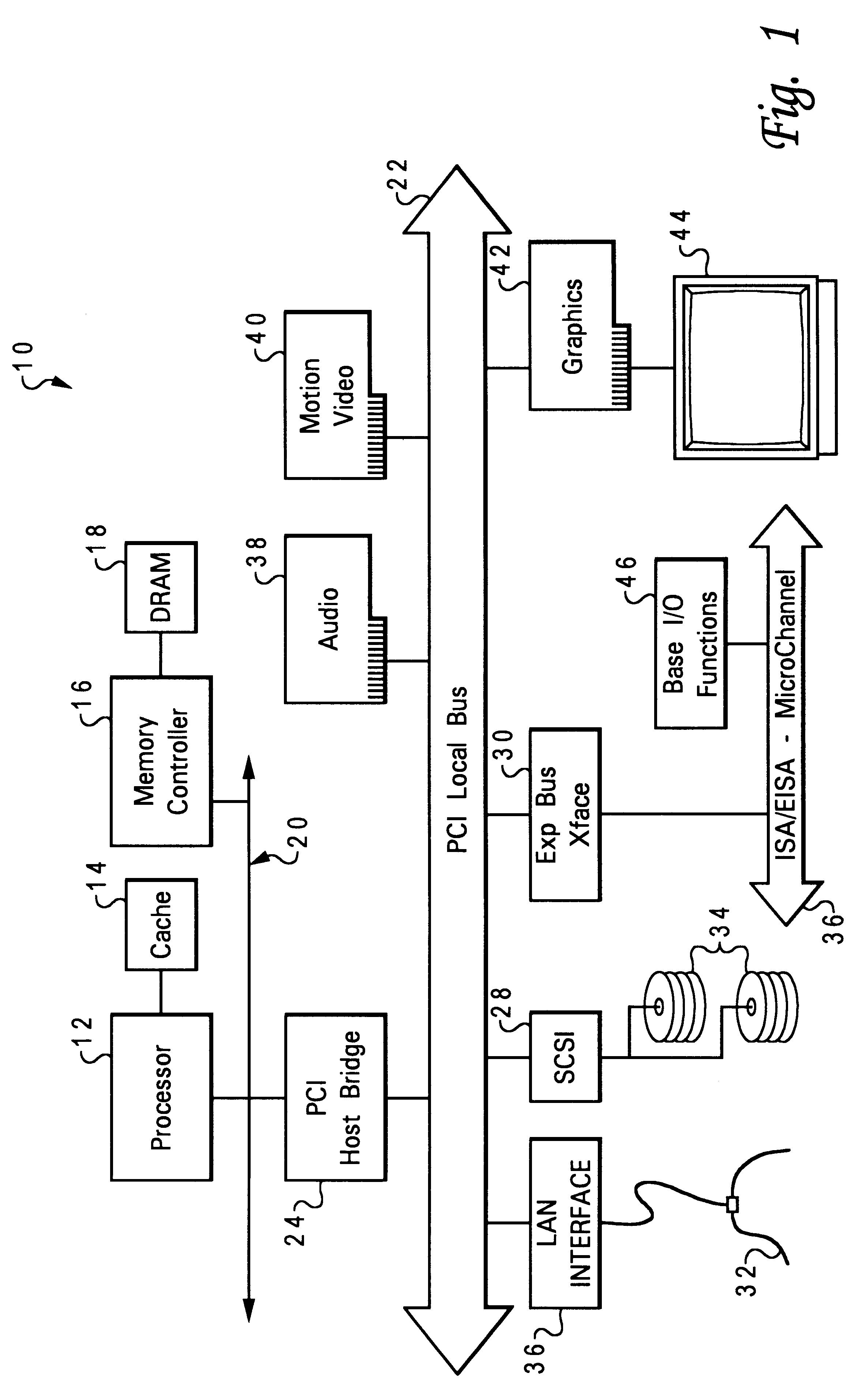

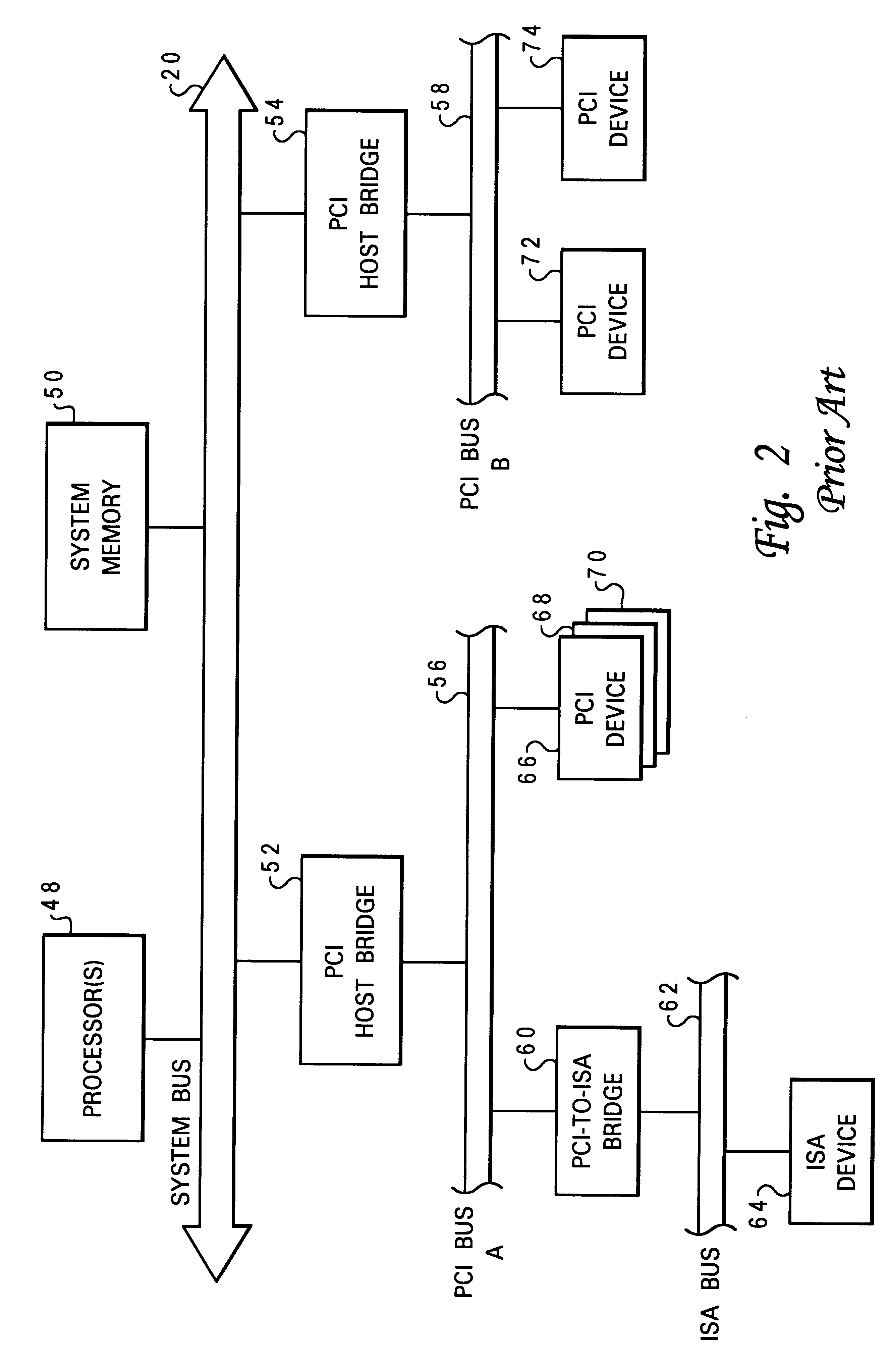

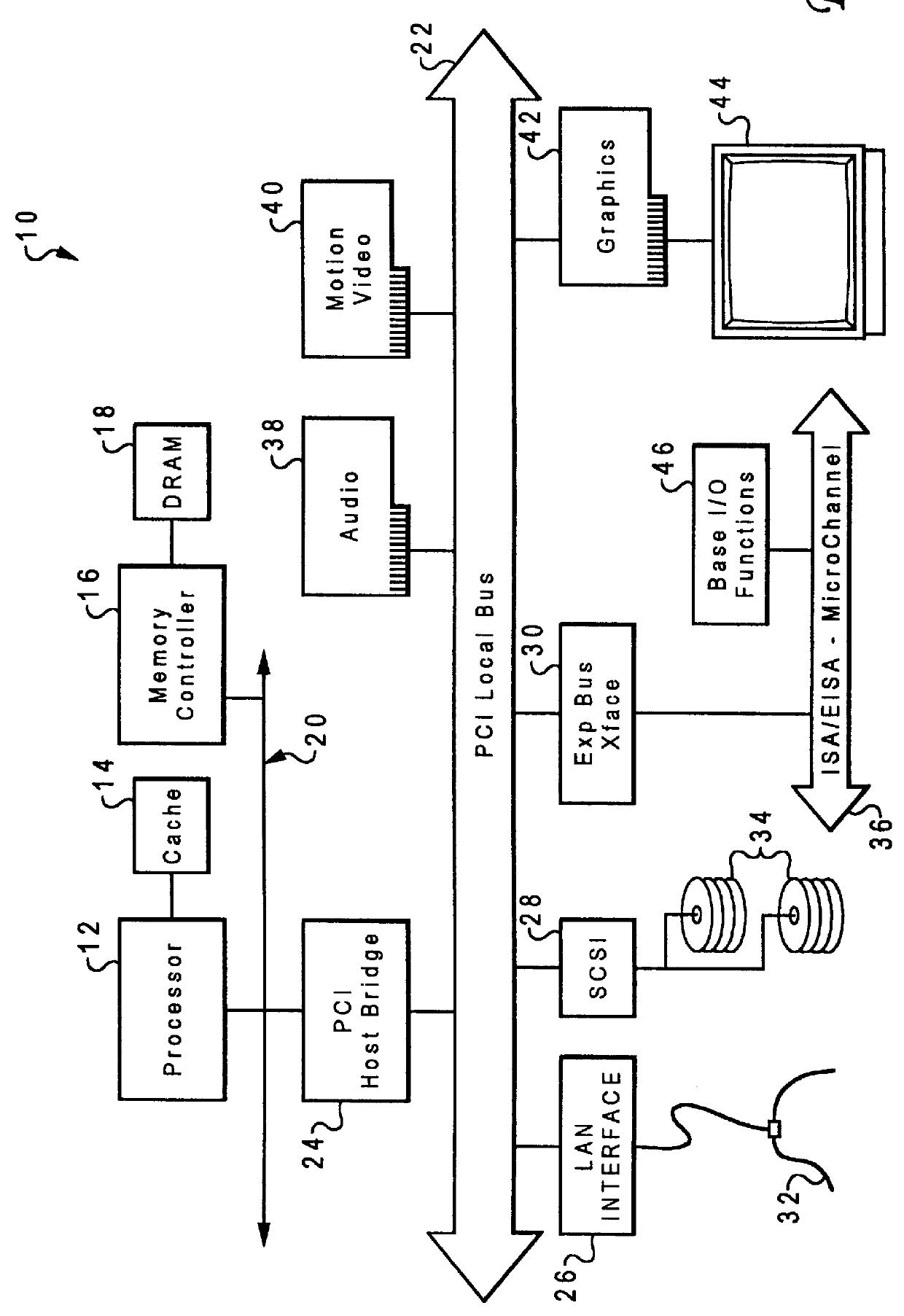

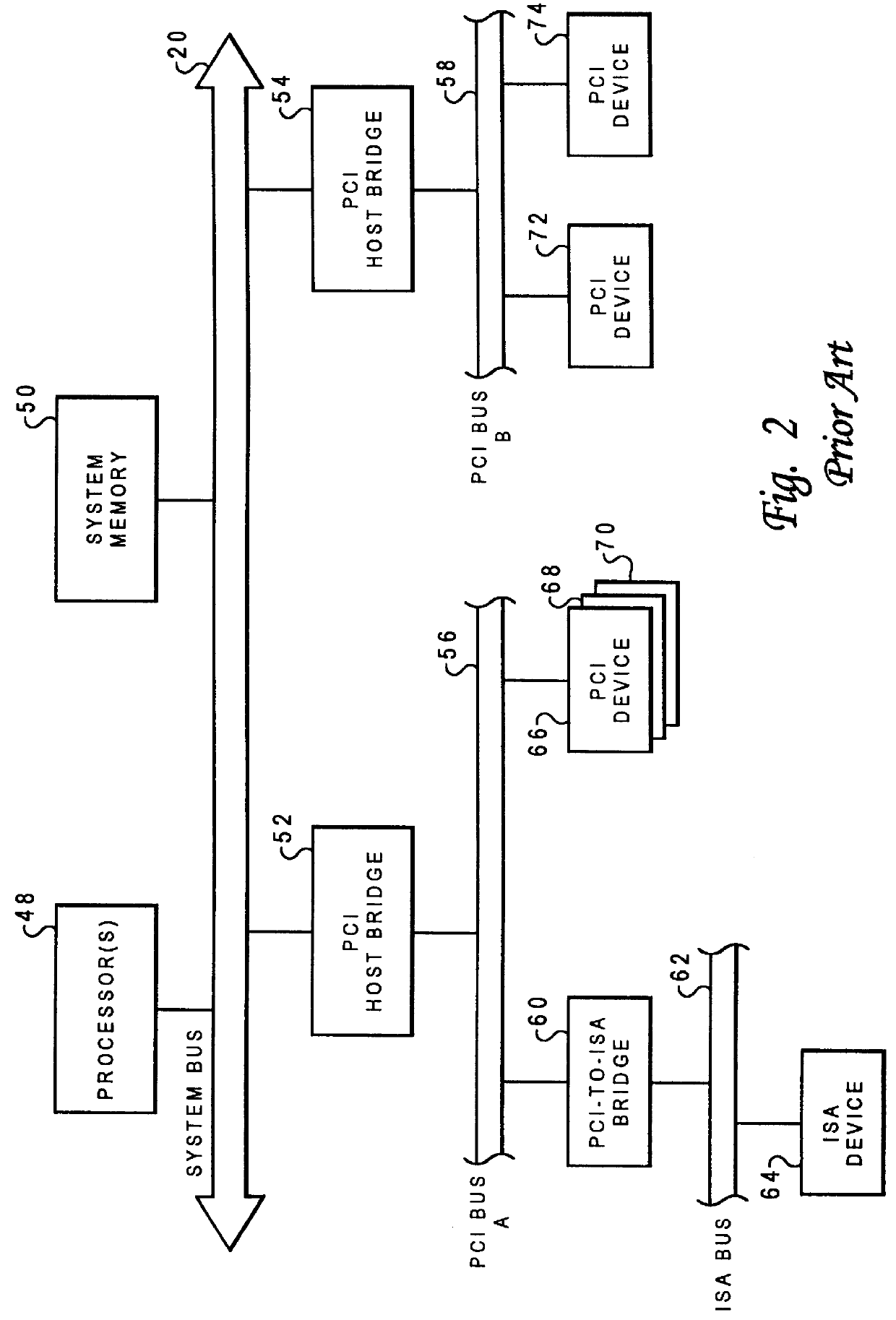

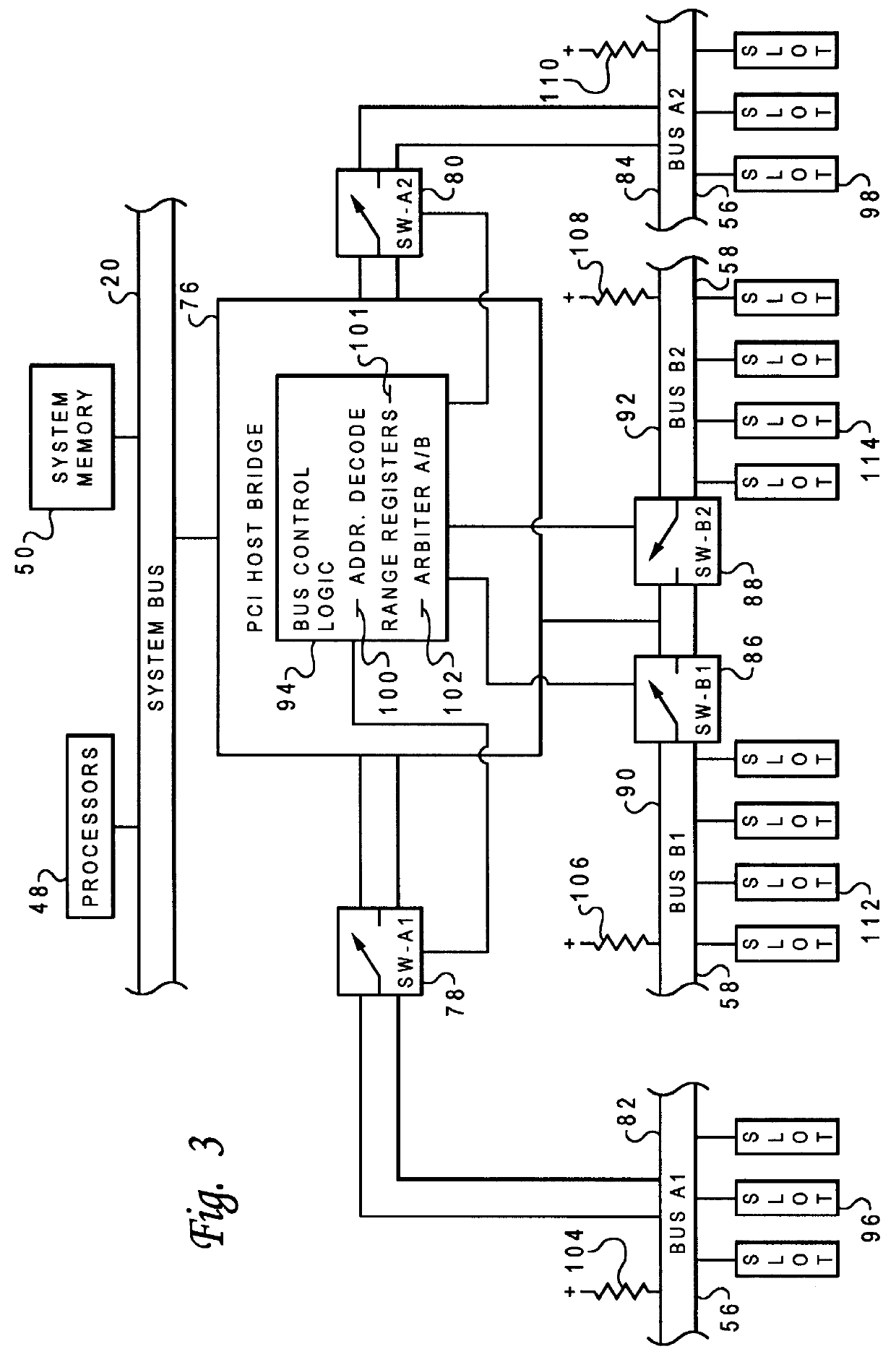

Method and system for supporting peripheral component interconnect (PCI) peer-to-peer access across a PCI host bridge supporting multiple PCI buses

A method and system for supporting multiple Peripheral Component Interconnect (PCI) local buses through a single PCI host bridge having multiple PCI interfaces within a data-processing system are disclosed. In accordance with the method and system of the present invention, a processor and a system memory are connected to a system bus. First and second PCI local buses are connected to the system bus through a PCI host bridge. The first and second PCI local buses have sets of in-line electronic switches, dividing the PCI local buses into PCI local bus segments supporting a plurality of PCI peripheral component slots for connecting PCI devices. The sets of in-line electronic switches are open and closed in accordance with bus control logic within the PCI host bridge allowing up to fourteen or more PCI peripheral component slots for connecting up to fourteen PCI devices to have access through a single PCI host bridge to the system bus. An internal PCI-to-PCI bridge is provided to allow a PCI device to share data with another PCI device as peer-to-peer devices across the first and second PCI local bus segments.

Owner:IBM CORP

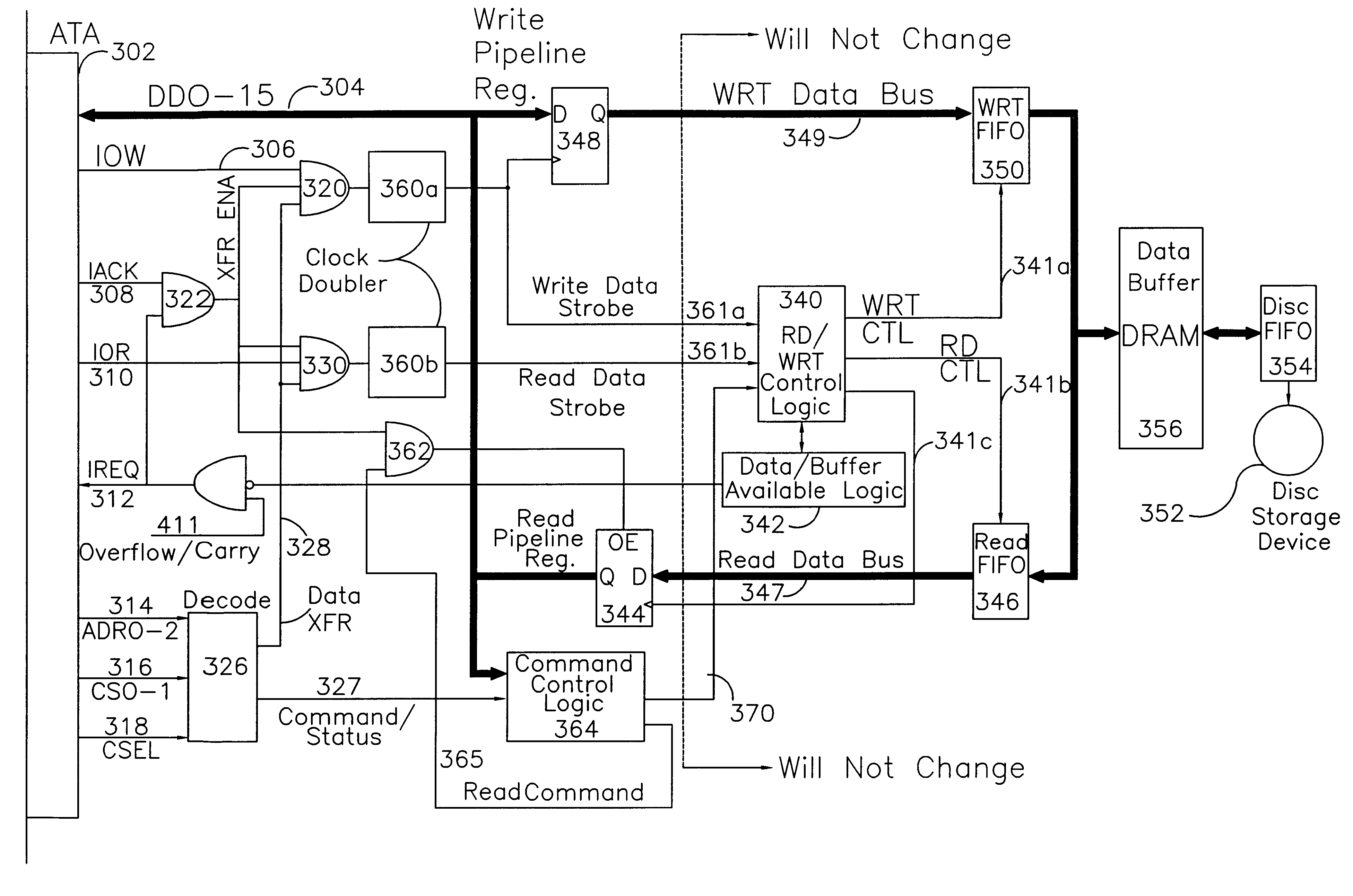

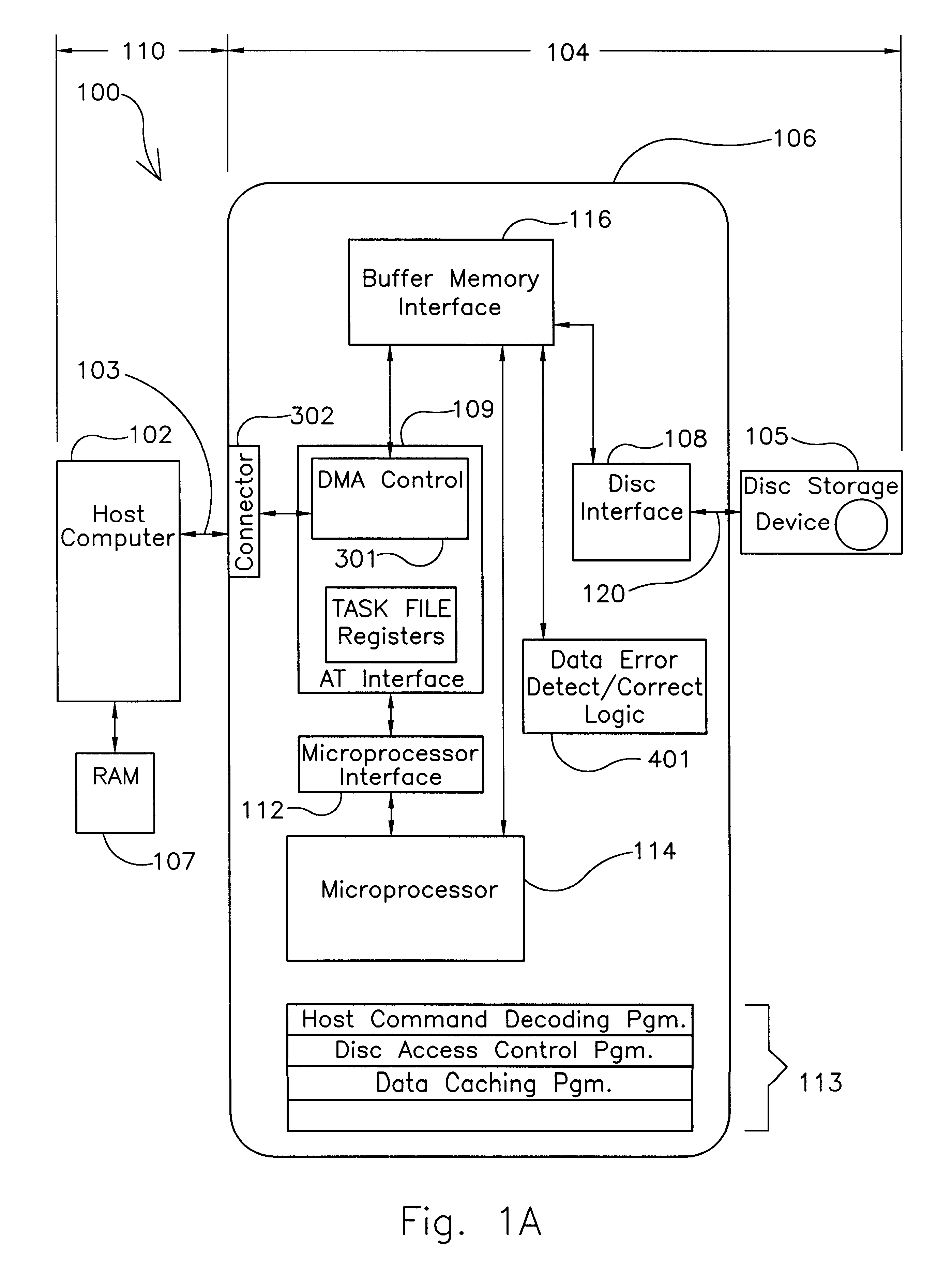

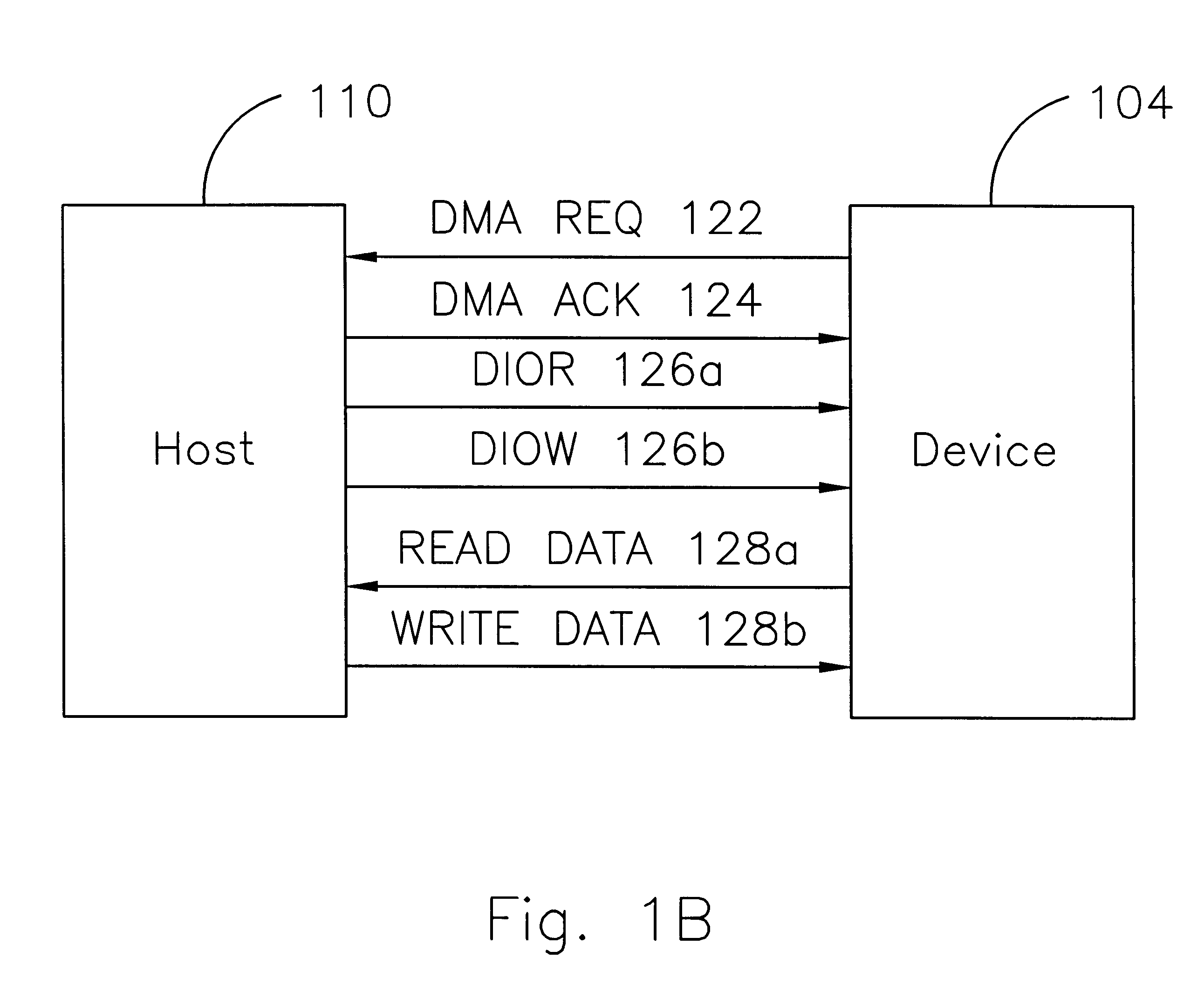

Fast ATA-compatible drive interface with error detection and/or error correction

InactiveUS6192492B1Emergency protective arrangements for automatic disconnectionStatic storageHard disc driveData integrity

An ATA-compatible drive interface with error correction and detection capabilities is disclosed. Being fully ATA backward compatible, this interface functions with the same physical cable and connectors as current ATA systems, employs bus drivers that are the same as or backward compatible with those provided by earlier versions of the ATA standard and uses signals with cable signal transitions no faster than those presently seen by current ATA devices. The error detection feature indicates when a data block is erroneously transferred between the device and host; the error correction feature identifies the words transmitted in error and corrects those words on the receiving side of the interface. So that ATA backward compatibility is maintained, the data integrity checking feature does not require additional words in a data transfer, and the data correction feature does not require new data transfer protocols or additional data transfer overhead. Also disclosed are interface circuitry and a new ATA-compatible transfer mode capable of transferring data at 40 MB / sec, the rate supported by local bus adapters for disk drives. Given the physical limits of the ATA cables and connectors, the error correction and detection features are especially useful for correcting data words corrupted during high-speed transmission; however, error correction and detection can also operate independently of the fast transfer mode. Consistent with full backward compatibility, a hard drive configured with the new, fast, error-correcting interface is transparently functional when plugged into a current ATA adapter provided by a legacy computer system.

Owner:SEAGATE TECH LLC

Combined local and network storage interface

ActiveUS20070028138A1Error detection/correctionMultiple digital computer combinationsOperational systemSCSI

A method, system and computer program product for a generic data storage interface for local and remote networked storage is provided. It comprises providing a data storage interface accessible by an operating system, transmitting data from an application running on the operating system to the data storage interface and selectively storing the data using the same data storage interface in either a local or a remote networked storage location. Firmware for the common data storage interface assigns a unique identifier that classifies an I / O request as a local or remote networked I / O request and adds the I / O request to a common stack for local and remote networked data storage elements. When an I / O request is removed from the stack, the unique identifier is used to identify the I / O request as a local or remote networked I / O request. Local I / O requests are executed via a local bus such as PCI, or SCSI. Remote networked I / O requests require a connection to one or more remote networked storage elements via a network. Memory space in a cache may be allocated for both local or remote networked I / O requests. DMA transfer may be employed for both local and remote networked I / O requests. Both local and remote networked I / O requests are executed using the same firmware and the same data interface.

Owner:AVAGO TECH INT SALES PTE LTD

Multi-master computer system with overlapped read and write operations and scalable address pipelining

InactiveUS6772254B2Lower latencyElectric digital data processingComputer hardwareComputerized system

Owner:INTEL CORP

Method and system for internal cache management of solid state disk based on novel memory

ActiveCN103049397AOvercome read and write imbalanceEasy to operateMemory architecture accessing/allocationMemory adressing/allocation/relocationFlash memory controllerCache management

The invention provides a method and a system for internal cache management of a solid state disk based on a novel memory. The system for internal cache management of the solid state disk comprises an SATA (serial advanced technology attachment) interface controller, a microprocessor, a DRAM (dynamic random access memory), a local bus, a flash controller, an NAND flash and a PCRAM (phase change random access memory) cache. The PCRAM cache comprises a data block displacement area and a mapping table storage area, wherein the data block replacement area is used for storing data blocks displaced to the PCRAM cache from the DRAM, and the mapping table storage area is used for storing mapping tables among logic addresses and physical addresses of data pages. By the method for internal cache management of the SSD (solid state disk) based on the PCRAM, write cache for the solid state disk is realized to overcome read-write imbalance of the solid state disk, write performances are effectively improved, random write operation and wiping operation of the solid state disk are decreased, accordingly, the service life of the solid state disk is prolonged, and the integral I / O (input / output) performance of the solid state disk is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

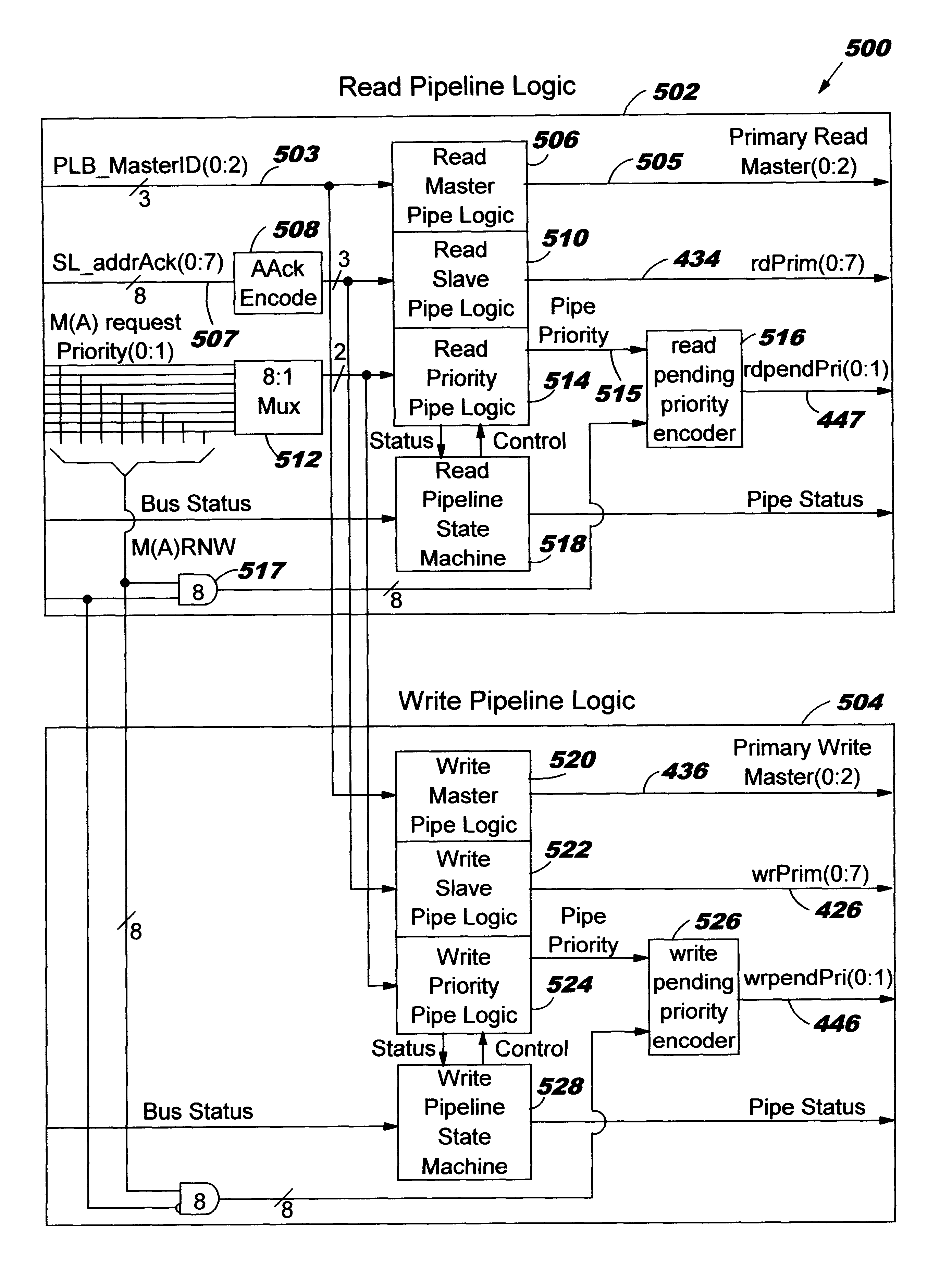

Multi-master computer system with overlapped read and write operations and scalable address pipelining

InactiveUS20020062414A1Reduce system latencyLower latencyMemory systemsComputer hardwareComputerized system

A multi-master computer system having overlapped read and write signal with scalable address pipelining programmable increases the depth of address pipelining independently on two overlapped read and write data busses up to "N" deep requests. The system includes a local bus having an address bus, a read bus, and a write bus. Master devices are coupled to separate address, read data and write data buses. Slave devices are attached to the data busses through shared, but decoupled address, read and write data buses. An arbiter is coupled to the data bus and allows masters to compete for bus ownership. The arbiter includes read and write pipeline logic for processing and priortizing master and slave read and write data transfers across the data bus. Programming apparatus alters the read and write pipeline logic for address pipelining

Owner:INTEL CORP

Apparatus and method for adopting an orphan I/O port in a redundant storage controller

InactiveUS20050102557A1Transparent failoverEliminate needError detection/correctionComponent plug-in assemblagesControl storeField replaceable unit

A storage controller configured to adopt orphaned I / O ports is disclosed. The controller includes multiple field-replaceable units (FRUs) that plug into a backplane having local buses. At least two of the FRUs have microprocessors and memory for processing I / O requests received from host computers for accessing storage devices controlled by the controller. Other of the FRUs include I / O ports for receiving the requests from the hosts and bus bridges for bridging the I / O ports to the backplane local buses in such a manner that if one of the processing FRUs fails, the surviving processing FRU detects the failure and responsively adopts the I / O ports previously serviced by the failed FRU to service the subsequently received I / O requests on the adopted I / O ports. The I / O port FRUs also include I / O ports for transferring data with the storage devices that are also adopted by the surviving processing FRU.

Owner:DOT HILL SYST

Expandable slave device system

A bus system for use with addressable memory has a global bus of uni-directional signal lines. The global bus has a first end and a second end. A master device transmits data to and receives data from the global bus. First and second global bus terminators are coupled to the first and second ends of the global bus, respectively. One or more subsystems are connected in parallel to each other and to the master device via the global bus. Each subsystem includes a local bus, one or more slave devices coupled to the local bus, a write buffer that receives incoming signals from the master device via the global bus and transmits the incoming signals to the one or more slave devices via the local bus, and a read buffer that receives outgoing signals from the one or more slave devices via the local bus and transmits the outgoing signals to the master device via the global bus.

Owner:RAMBUS INC

Method and system for supporting multiple peripheral component interconnect PCI buses by a single PCI host bridge within a computer system

A method and system for supporting multiple Peripheral Component Interconnect (PCI) local buses through a single PCI host bridge having multiple PCI interfaces within a data-processing system are disclosed. In accordance with the method and system of the present invention, a processor and a system memory are connected to a system bus. First and second PCI local buses are connected to the system bus through a PCI host bridge. The first and second PCI local buses have sets of in-line electronic switches, dividing the PCI local buses into PCI local bus segments supporting a plurality of PCI peripheral component slots. The sets of in-line electronic switches are open and closed in accordance with bus control logic within the PCI host bridge allowing up to fourteen PCI peripheral component slots to have access through a single PCI host bridge to the system bus.

Owner:GOOGLE LLC

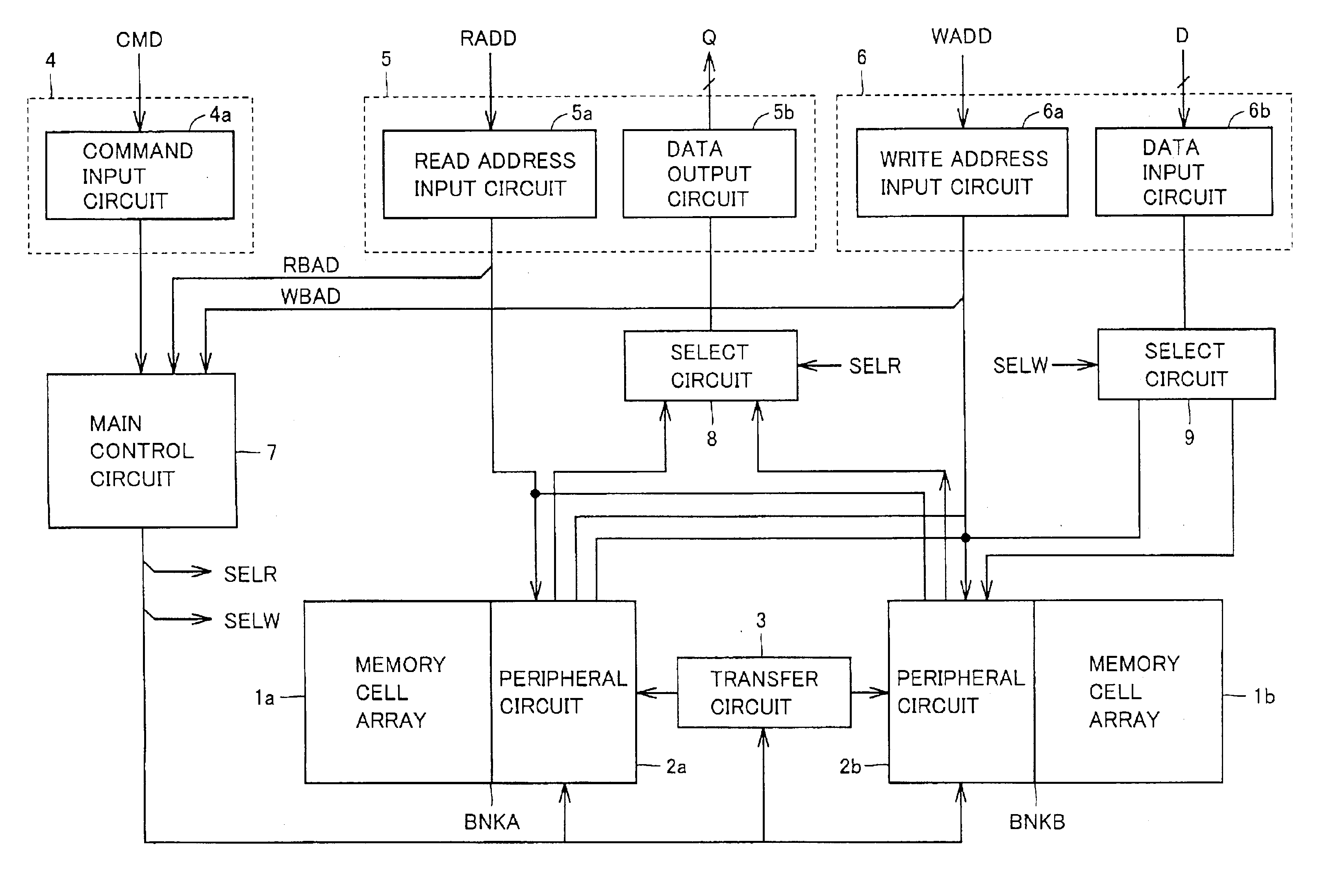

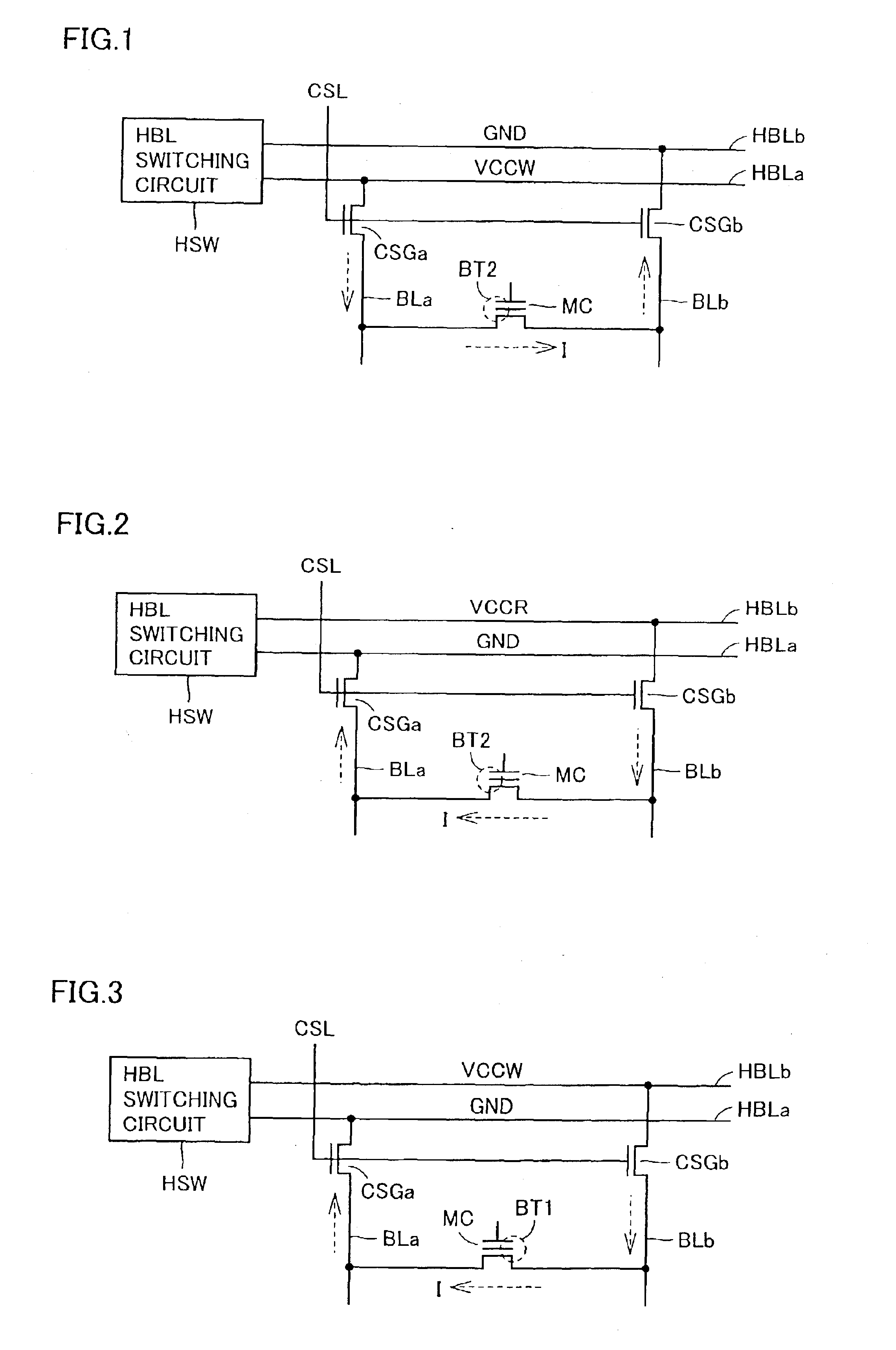

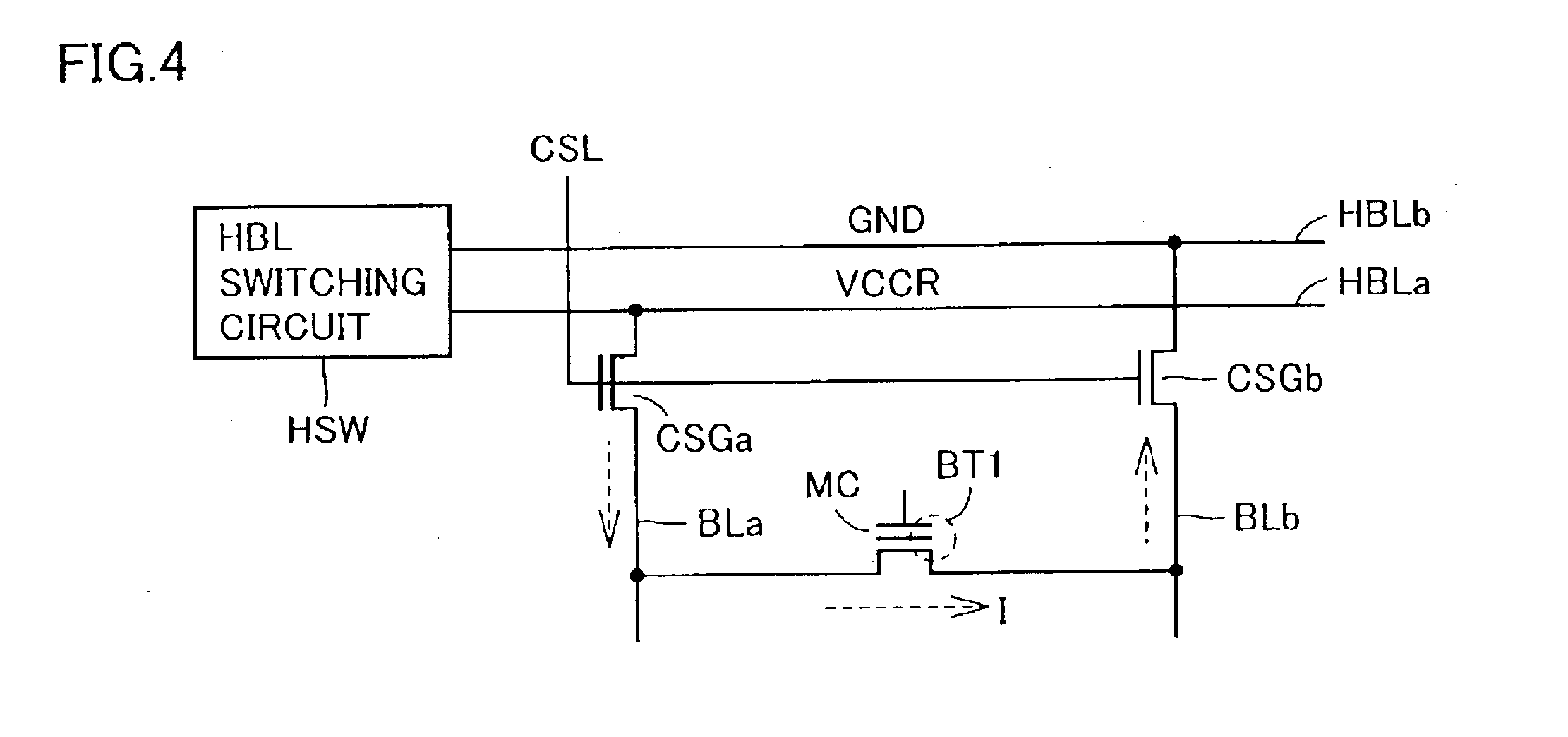

Nonvolatile semiconductor memory device allowing high speed data transfer

ActiveUS6922359B2Efficiently performing writing and reading of dataImprove data transfer efficiencyRead-only memoriesDigital storageParallel computingTransfer switch

Local buses for performing writing / reading of data are provided in correspondence to memory blocks each having a plurality of nonvolatile memory cells, and also circuits for performing writing / reading of data are provided in correspondence to the memory blocks. In addition, data transfer lines for bidirectionally transferring data are provided commonly to the memory blocks, and transfer switch gates for performing data transfer between the memory blocks are provided commonly to the memory blocks. The memory blocks are divided into banks, writing / reading of data on individual memory blocks are performed in units of banks, and parallel execution of writing and reading or of writing / reading and internal transfer is performed. Thus, it is possible to improve data transfer processing efficiency in a nonvolatile semiconductor device.

Owner:RENESAS ELECTRONICS CORP

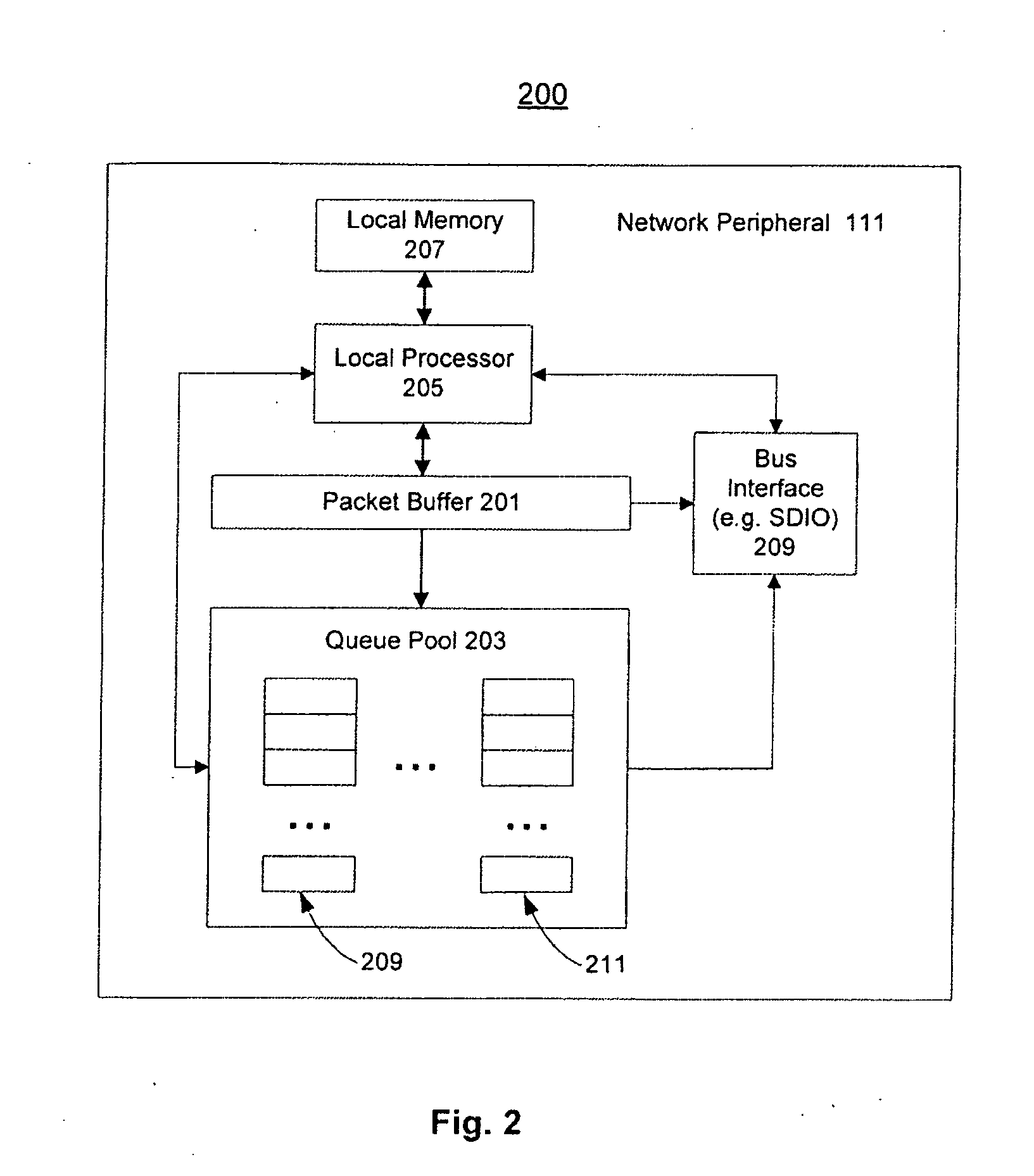

High speed communications device/system

InactiveUS20020199040A1Easy data transferEasy to moveEnergy efficient ICTEnergy efficient computingComputer hardwareLocal bus

A system and device are disclosed for the high-speed direct movement of data between remote blocks of memory and between blocks of memory and storage devices. The high speed movement of data is facilitated by a high-speed local bus, and in preferred embodiments, the data undergoes only a single DMA transfer.

Owner:PLATYPUS TECH HLDG +1

Packet Filter Optimization For Network Interfaces

A method and apparatus to reduce the transaction overhead involved with packet I / O on a host bus without sacrificing the latency of packets of important traffic types is described. This involves determining whether a packet is to be aggregated in response to receiving the packet in a receive buffer. If it is determined that the packet should not be aggregated, a host system may be interrupted to indicate availability of the received packet. Subsequently, the packet may be forwarded to an interrupted system via a local bus directly from a receiving buffer without being stored in a local storage. If it is determined that a packet is to be aggregated, it may be stored in a queue in local storage. Subsequently, it may be sent to a host system with a group of other frames using a single bus transaction to eliminate overhead.

Owner:APPLE INC

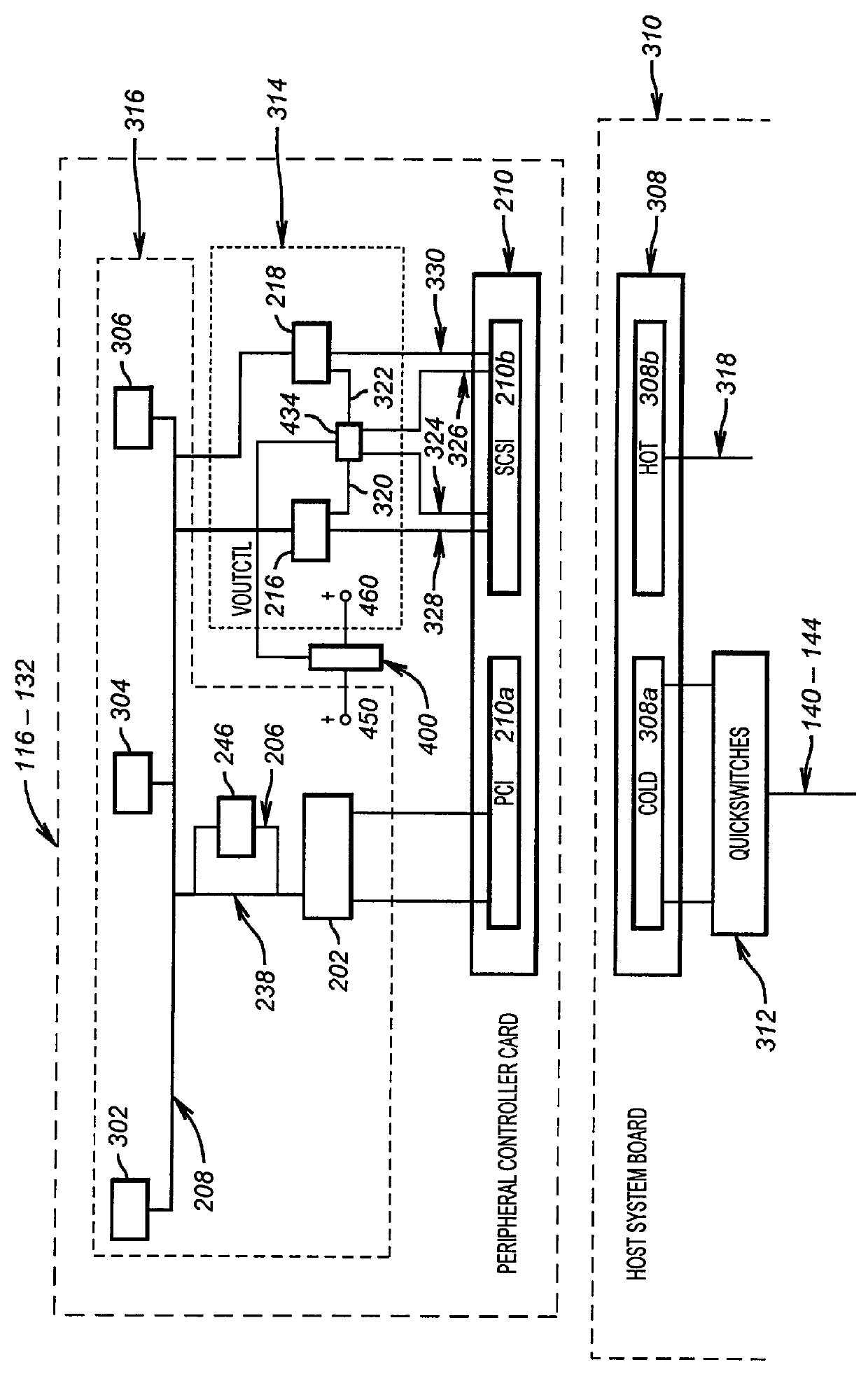

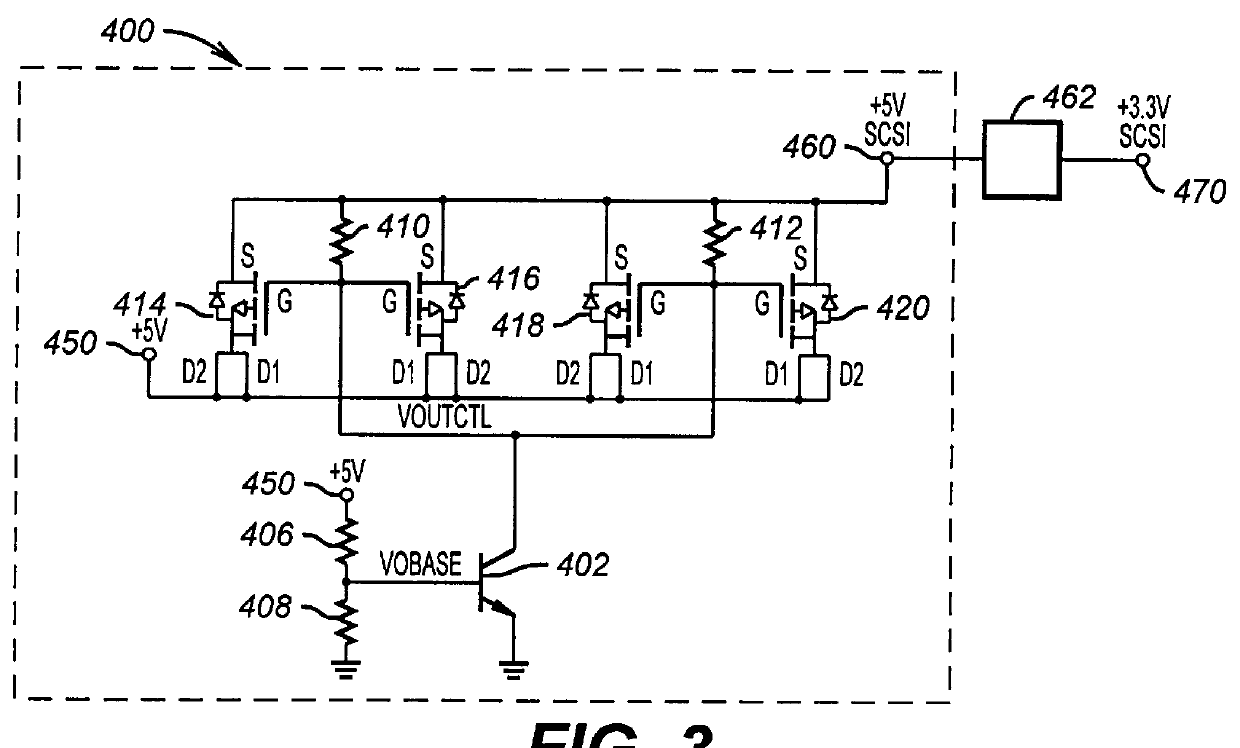

Technique for hot plugging a peripheral controller card containing PCI and SCSI buses on a single connector into a host system board

InactiveUS6061752AComponent plug-in assemblagesDigital processing power distributionMass storageOperational system

An embodiment of the present invention discloses a technique that allows hot plugging a peripheral controller card, containing both a local bus and a peripheral bus on a single connector, into a host system board containing a host system bus and a host I / O bus. When mating the peripheral controller card to the host system board a local device power supply (LDPS) is inactive, a peripheral device power bus (PDPB) is powered, and signal lines of a peripheral device are maintained in a high impedance state. Following a delay after the mating, the LDPS is activated by the host operating system (OS). Following the activation of the LDPS, the host system bus is coupled to the single connector through switches that are under OS control. In response to the activation of the LDPS, the signal lines of the peripheral device are enabled. In a disclosed embodiment the peripheral controller card is a disk array controller card, the local bus is a PCI bus, and the peripheral bus is a SCSI bus. In one embodiment the disk array controller card is coupled to a mass storage peripheral and in another embodiment is programmed for RAID. An advantage of an embodiment of the present invention is that a PCI bus and a SCSI bus are carried on a single peripheral connector which provides cable management and readily allows hot plugging a redundant peripheral controller card into the host system board.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

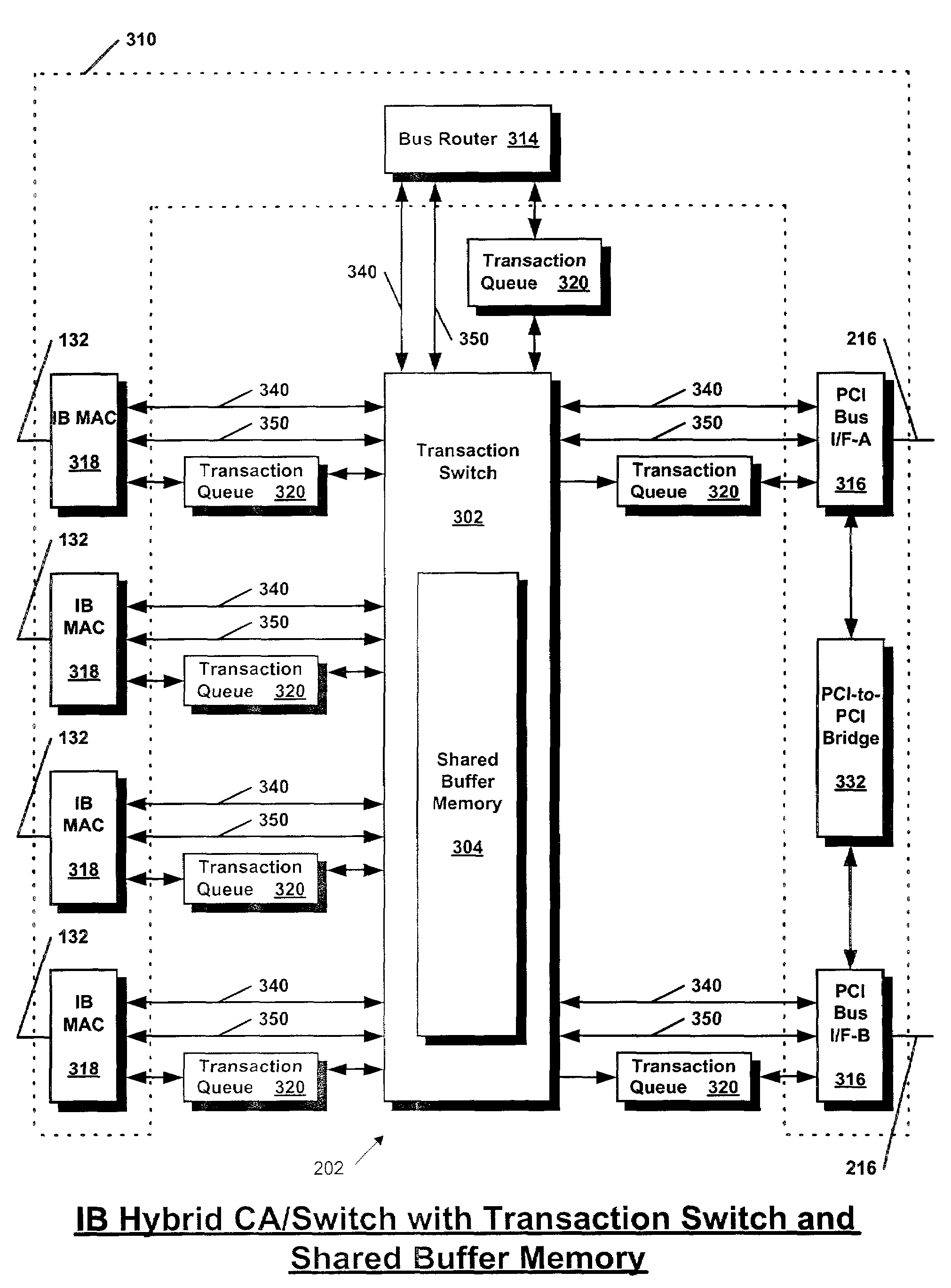

Transaction switch and network interface adapter incorporating same

InactiveUS7401126B2Easy to useFacilitates manufacturableMultiplex system selection arrangementsData switching by path configurationNetwork packetData interface

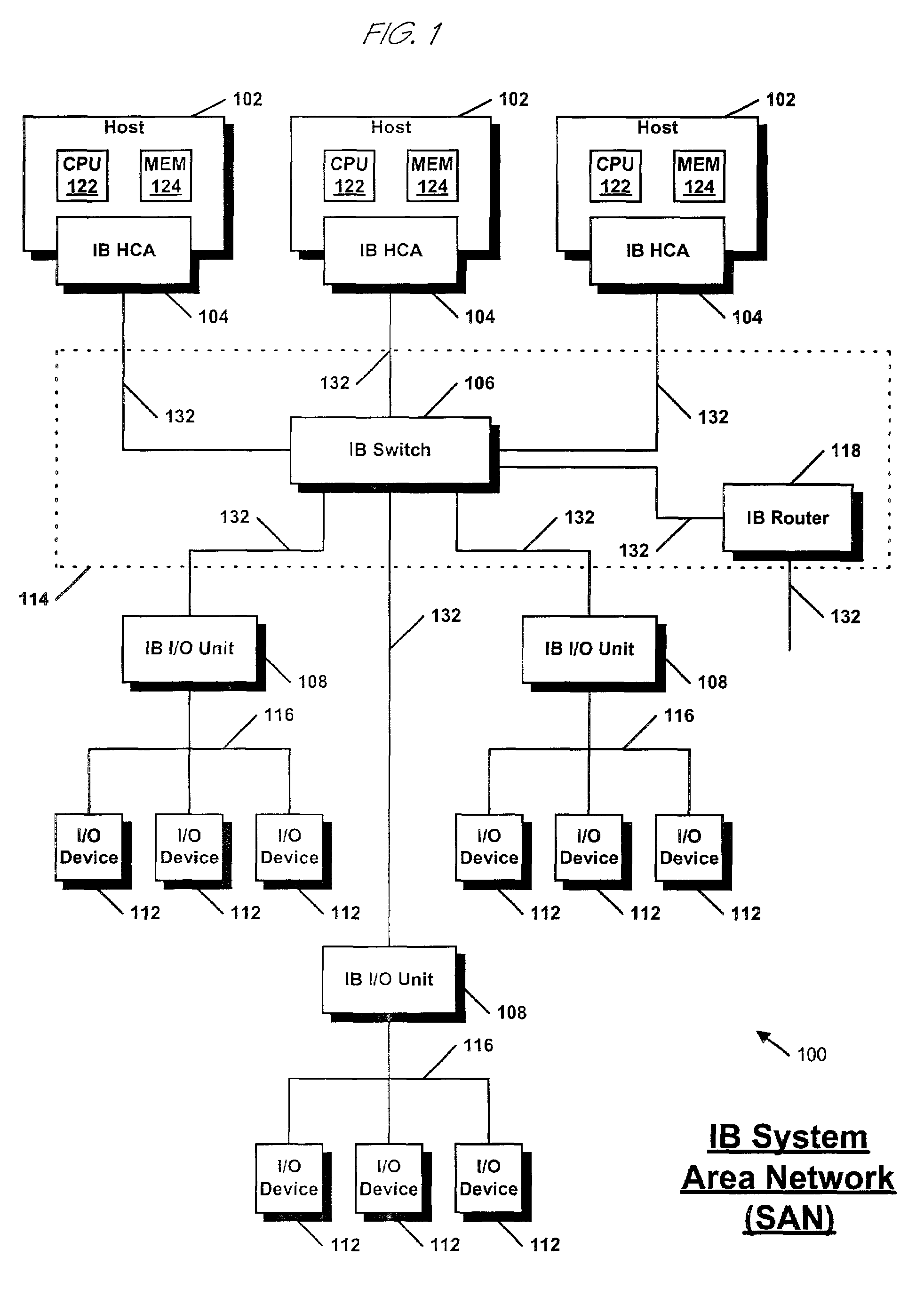

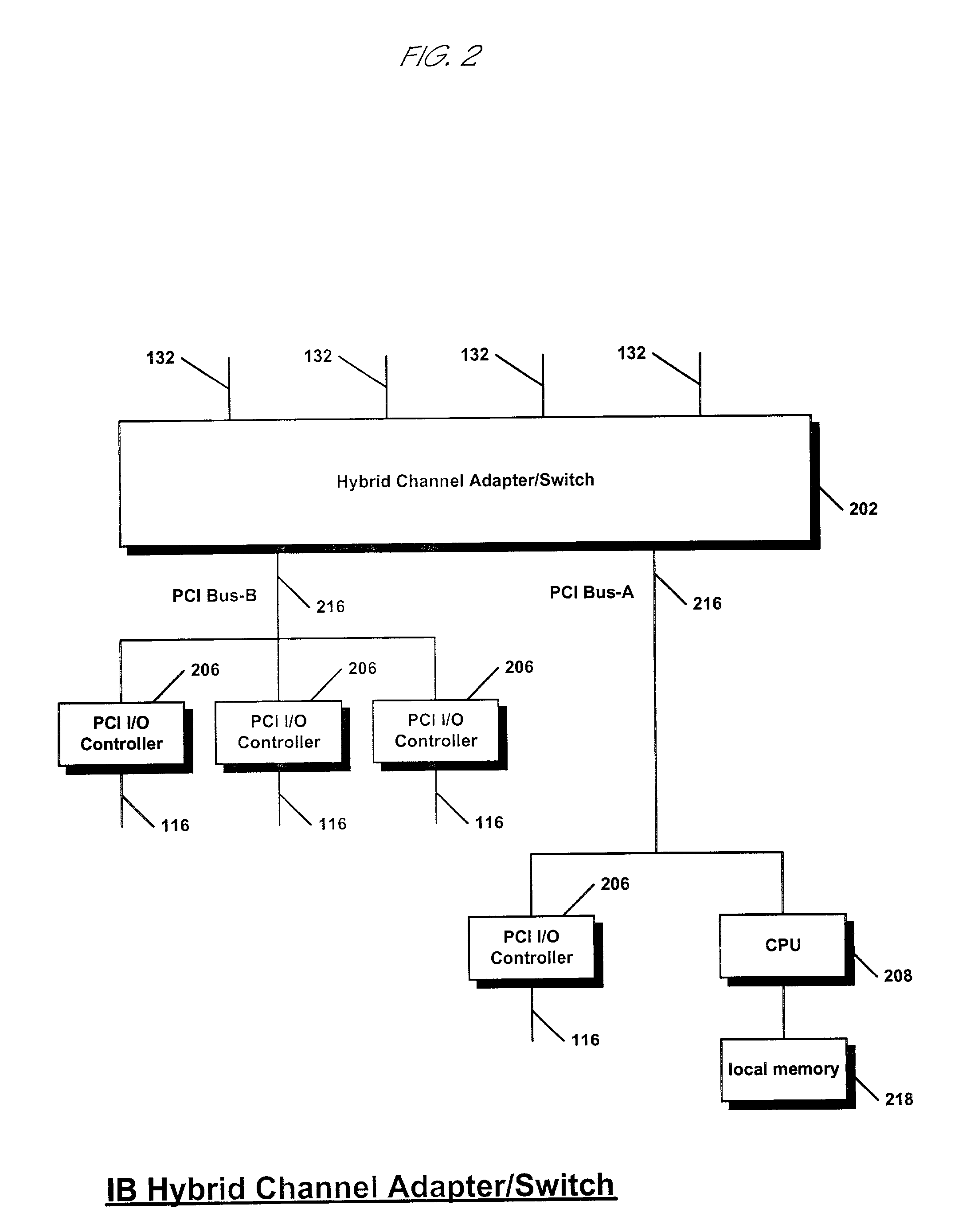

A transaction switch and integrated circuit incorporating said for switching data through a shared memory between a plurality of data interfaces that support different data protocols, namely packetized interfaces like InfiniBand and addressed data interfaces like PCI. The transaction switch also switches transactions commanding data transfers between the disparate protocol data interfaces and between those of the data interfaces having like protocols. For example, the transaction switch enables a hybrid InfiniBand channel adapter / switch to perform both InfiniBand packet to local bus protocol data transfers through the shared memory as well as InfiniBand packet switching between the multiple InfiniBand interfaces. The transactions are tailored for each interface type to include information needed by the particular interface type to perform a data transfer. The shared buffer memory, dynamically allocated by the transaction switch on a first-come-first serve basis, results in more efficient use of precious buffering resources than in a statically allocated scheme.

Owner:INTEL CORP

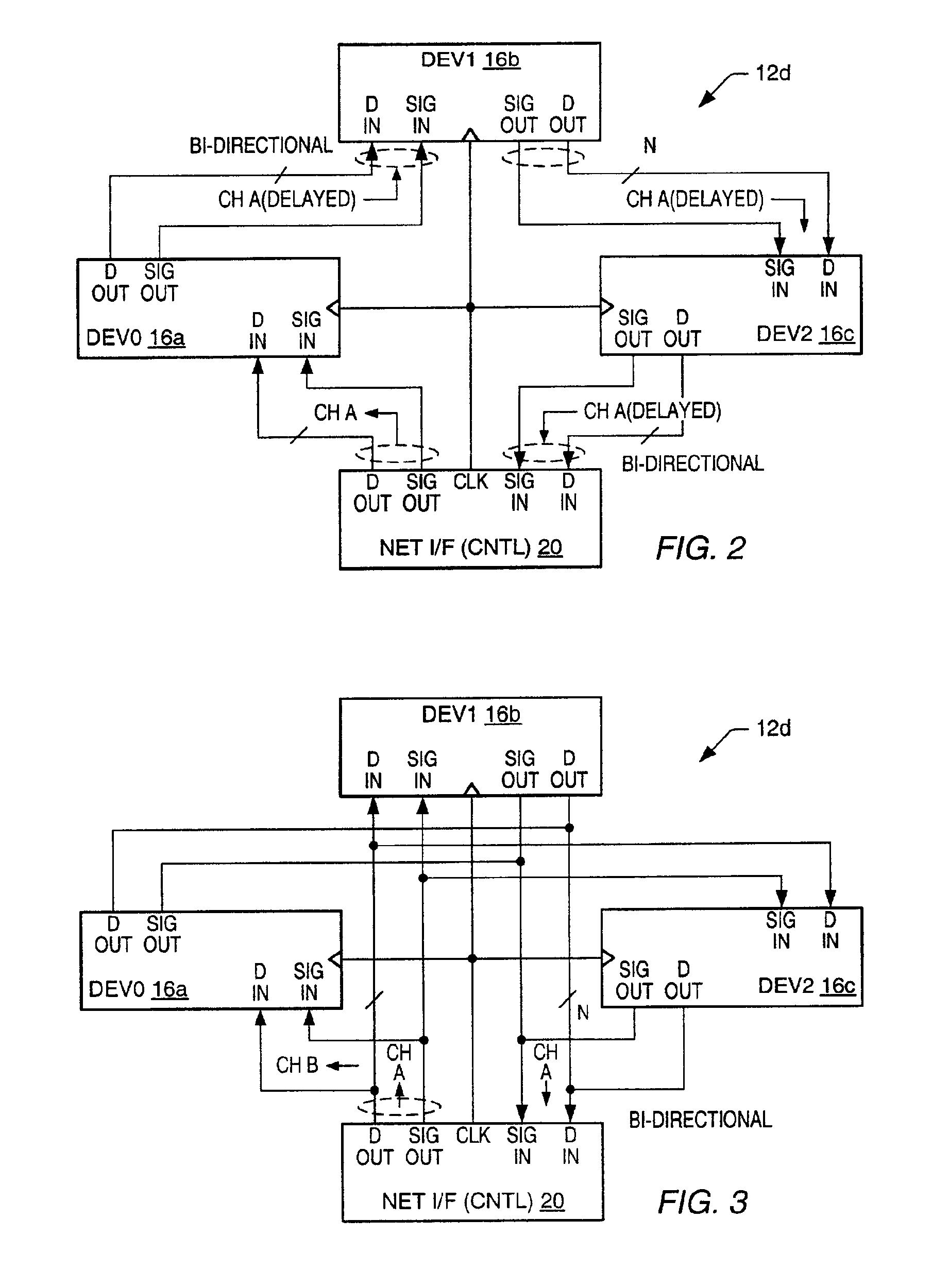

Communication system and methodology for sending a designator for at least one of a set of time-division multiplexed channels forwarded across a locally synchronized bus

ActiveUS6874048B2Easy to decodeFast decodingHybrid switching systemsTime-division multiplexCommunications systemControl data

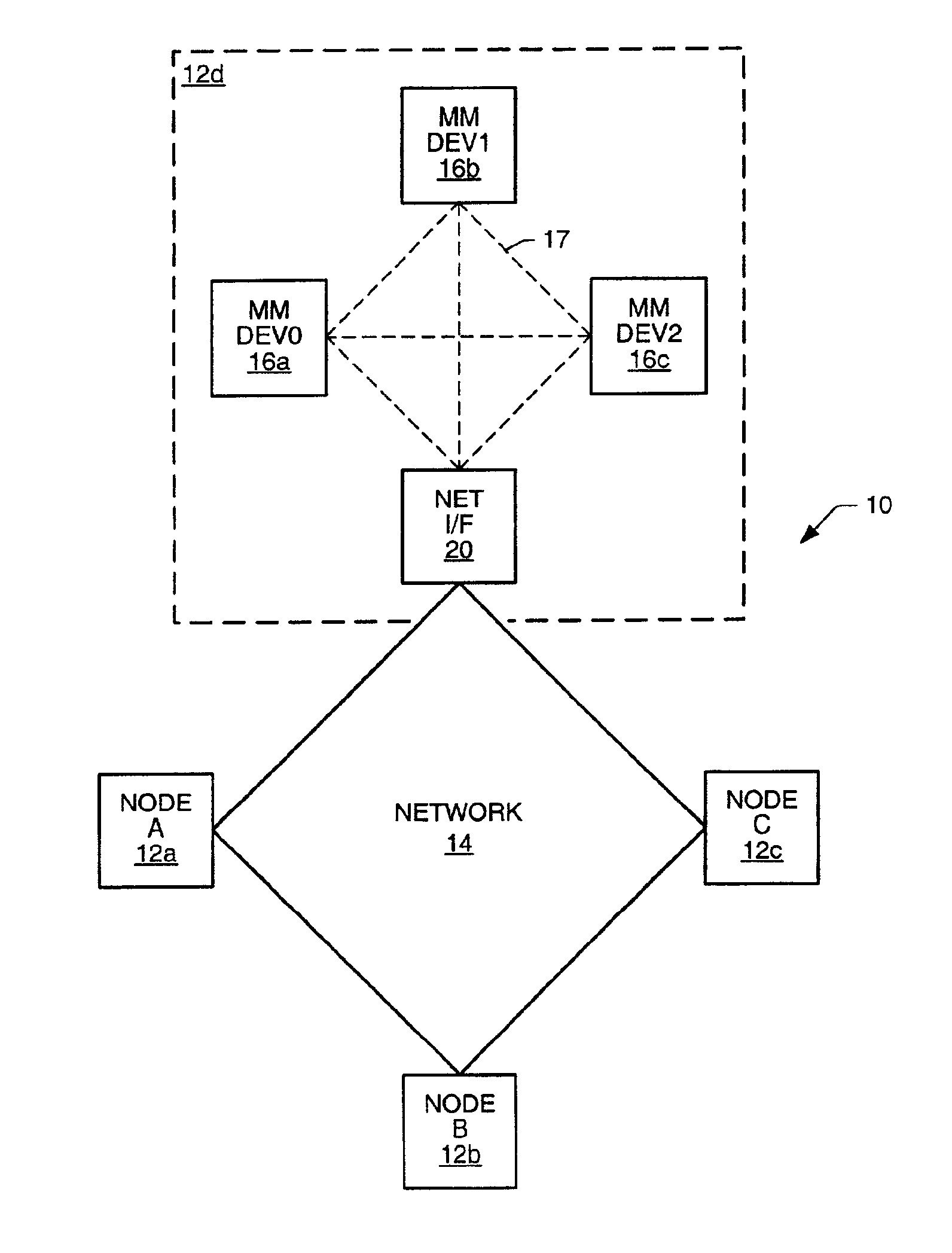

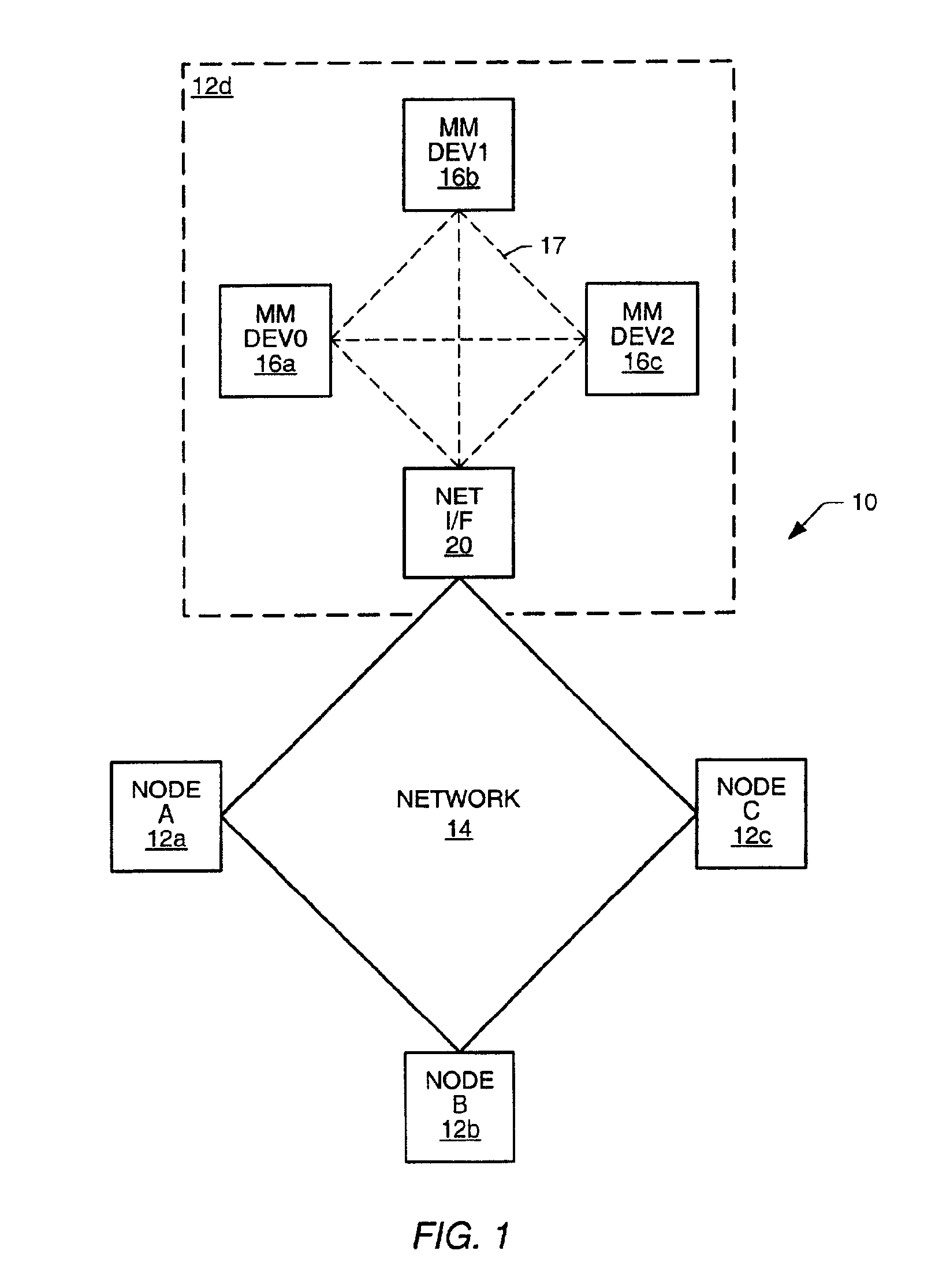

A communication system, network interface and communication port is provided that includes a media local bus. The local bus is connected between a controller and one or more multimedia devices located within a node of the communication system. The controller periodically broadcasts sync signals to the source device, or devices, to synchronize data transmission partitioned into time slots. Each time slot represents is dedicated to a particular data type. Thus, time slot 1 can accommodate packetized data, time slot 2 can accommodate synchronous data, time slot 3 can accommodate control data, and time slot 4 can accommodate isochronous data. Various combinations and variations of those time slots can occur where fewer than four data types can be present within a frame or all four data types can be present. The local bus includes a signal line and one or more data lines.

Owner:MICROCHIP TECH INC

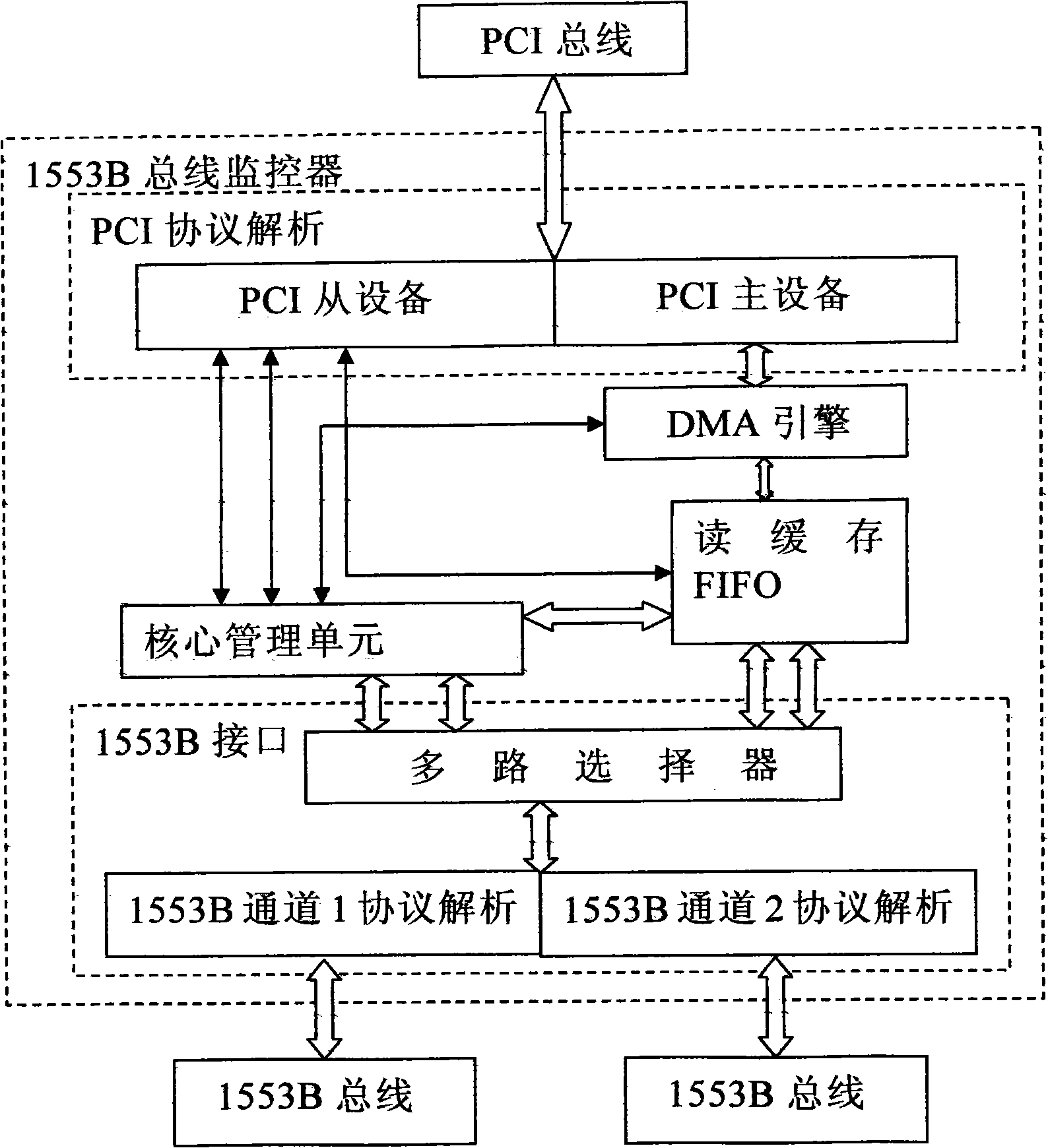

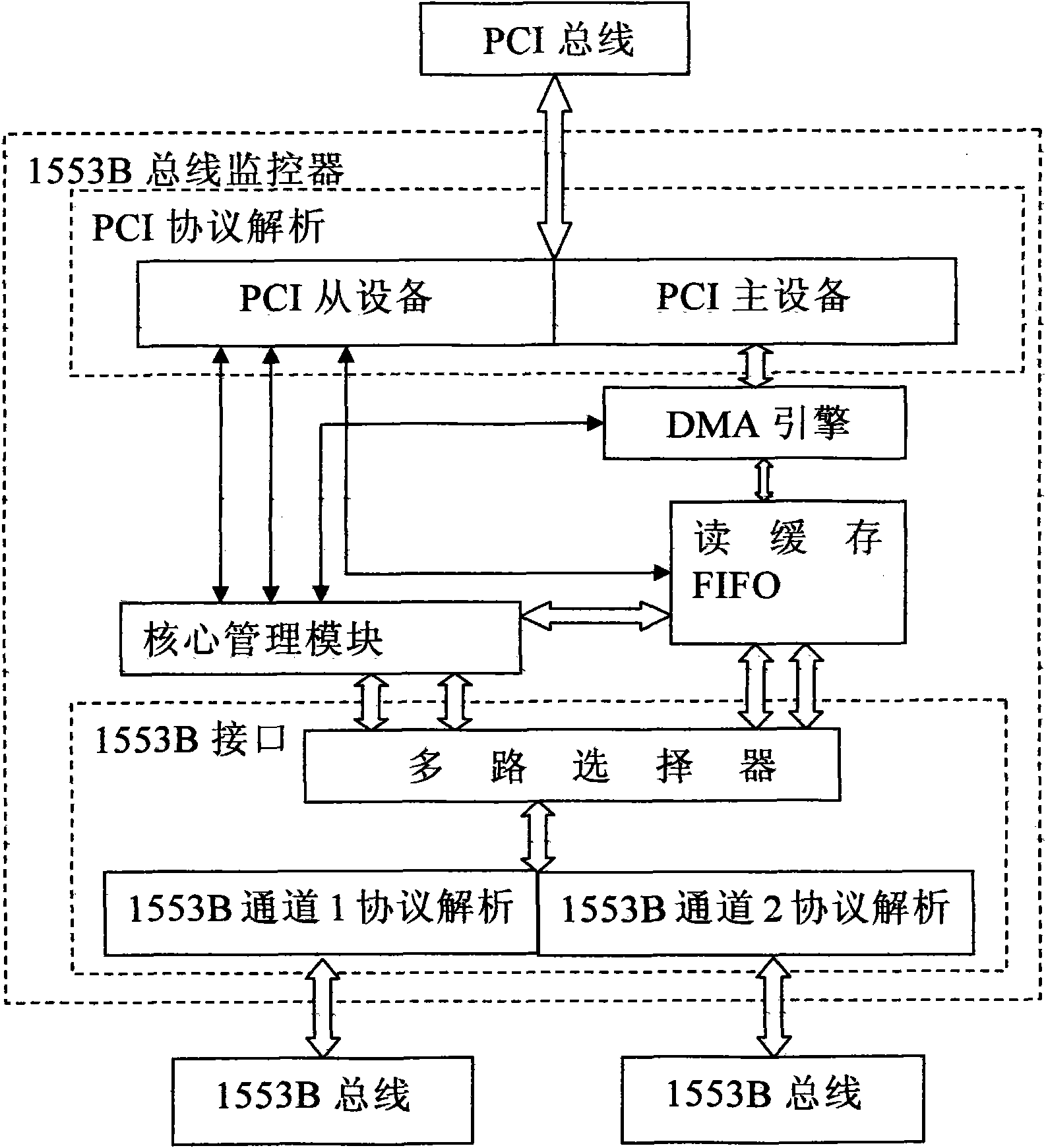

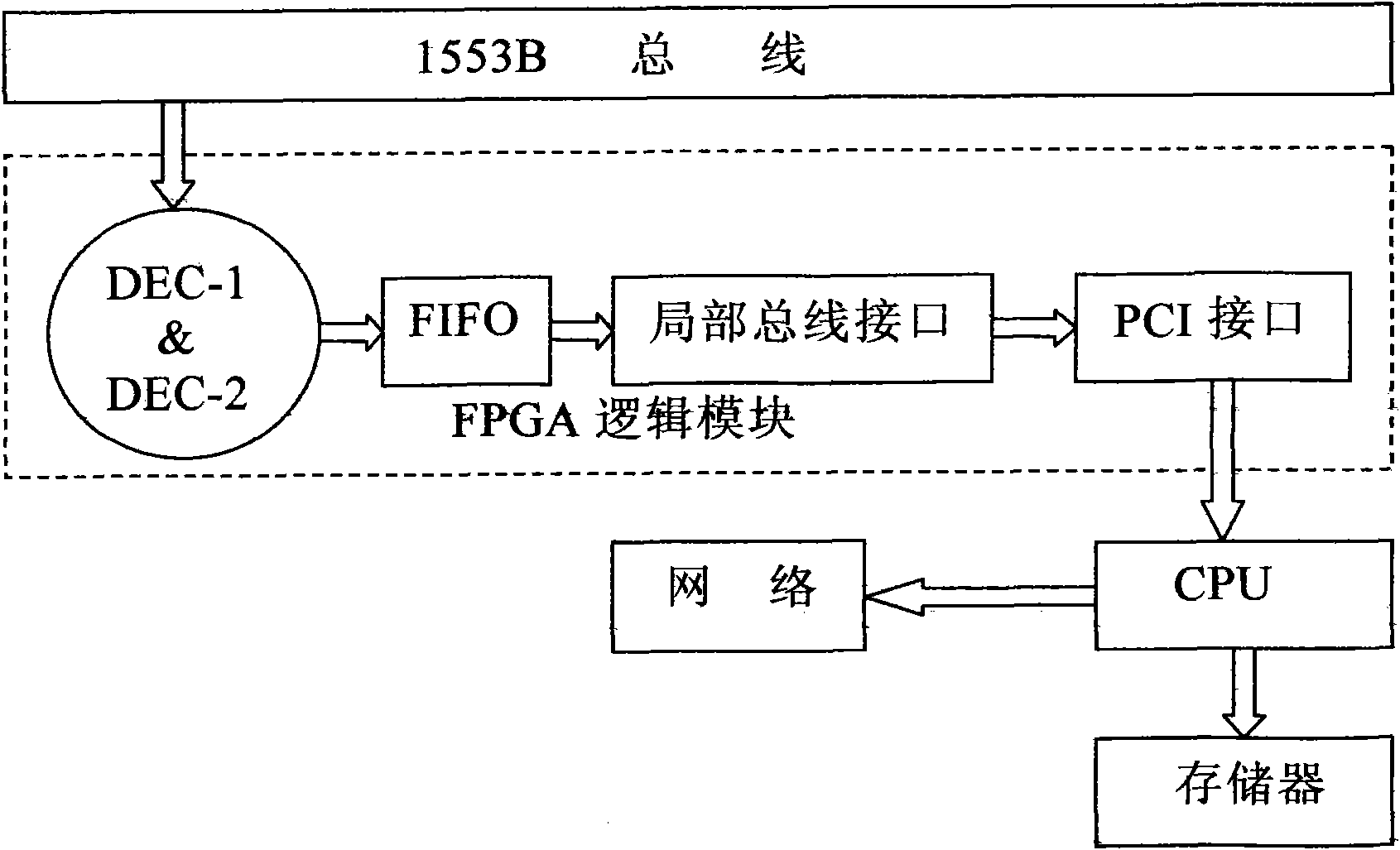

1553B bus monitor and bus system with same

ActiveCN101799795AEasy to mountImprove data transfer efficiencyElectric digital data processingBurst transmissionPci interface

The invention discloses a 1553B bus monitor. A local bus module of the 1553B bus monitor connected with a PCI bus comprises a PCI master equipment unit and a PCI slave equipment unit, wherein the PCI master equipment unit and the PCI slave equipment unit provide a 32-bit PCI interface together; the PCI slave equipment unit supports passive access; and the PCI master equipment unit realizes direct memory transmission and actively transmits data to memory space pre-allocated by a central processing unit (CPU). This invention also discloses a 1553B bus system with the 1553B bus monitor. The 32-bit 1553B bus monitor adopting PCI interface design can be conveniently hung to the PCI bus outside a microprocessor, has processing bandwidth of 32 bits, integrates DMA modules, can automatically initiate data transmission after CPU configuration, supports a BURST transmission mode, and greatly improves the efficiency of data transmission.

Owner:LOONGSON TECH CORP

System for storing and updating configuration information about I/O card and using stored configuration information to configure newly installed I/O card when compatible with old card

InactiveUS6065068AEasy to determineInput/output processes for data processingData conversionComputer hardwareModularity

A modular distributed I / O system includes a computer coupled to module banks through a network bus. A module bank includes a communication module, terminal bases, and I / O modules. The adjoined terminal bases form a local bus mastered by the communication module. The I / O modules connect to the local bus through terminal bases. I / O modules are pluriform and programmable. The communication module maintains a memory image of the configuration state of each I / O module resident in the module bank. A memory image persists when an I / O module is removed from its terminal base. The memory image is used to configure a new I / O module which is inserted into the same terminal base. The communication module monitors for communication failure on the network bus, and is configured to capture the state of the module bank and automatically restore this captured state after a power-loss event. The terminal bases realize a local bus which includes a parallel bus, a serial bus, and an address assignment bus. Each terminal base receives a value from a preceding terminal base, increments this value, and asserts the increment value to a succeeding terminal base. Each terminal base is automatically assigned an physical proximity address. An I / O module controls read / write access to its register space by a semaphore mechanism which supports multi-threaded processing. The I / O module latches an ungranted semaphore request and assumes a self-exclusion state upon releasing the semaphore wherein the semaphore is reserved for the communication module.

Owner:NATIONAL INSTRUMENTS

Control unit with PCI and SCSI buses and computing system with electronic semiconductor disk

Use of a control unit with PCI bus and SCSI bus with program equipment for the electronic semiconductor disk of a computing system. The electronic semiconductor disk includes a processor and semiconductor memory, selected from a group comprising dynamic memory, synchronous dynamic memory, static memory and flash type memory. A computing system with electronic semiconductor disk with processor, where this processor is connected by a PCI bus to a PCI adapter, which is linked through the PCI bus to a semiconductor memory, connected by the local bus to a processor. The PCI adapter comprises a unit of the programmable SCSI control unit, connected both to the interface of the PCI bus for communicating with the electronic semiconductor disk, and to the interface of the SCSI bus for communicating with the external computing system with the SCSI control unit.

Owner:SOLID ACCESS TECH L L C

Computer system and method of setting an interface card therein

InactiveUS20040260853A1BootstrappingProgram loading/initiatingEnvironmental SettingOperational system

A computer system and a method of setting an interface card therein that can be directly used without any separate setting of the interface card. In a computer system having a display device, an input device, a storage medium, a processor, an operating system, and a local bus capable of performing data transmission with the processor for a predetermined timing, the computer system includes at least one extension slot, provided in the computer system, for connecting with the local bus, and at least one interface card, detachably mounted in the extension slot, for loading built-in driver programs and environmental setting values to the operating system when the computer system is booted in a state that the interface card connects with the extension slot.

Owner:SAMSUNG ELECTRONICS CO LTD

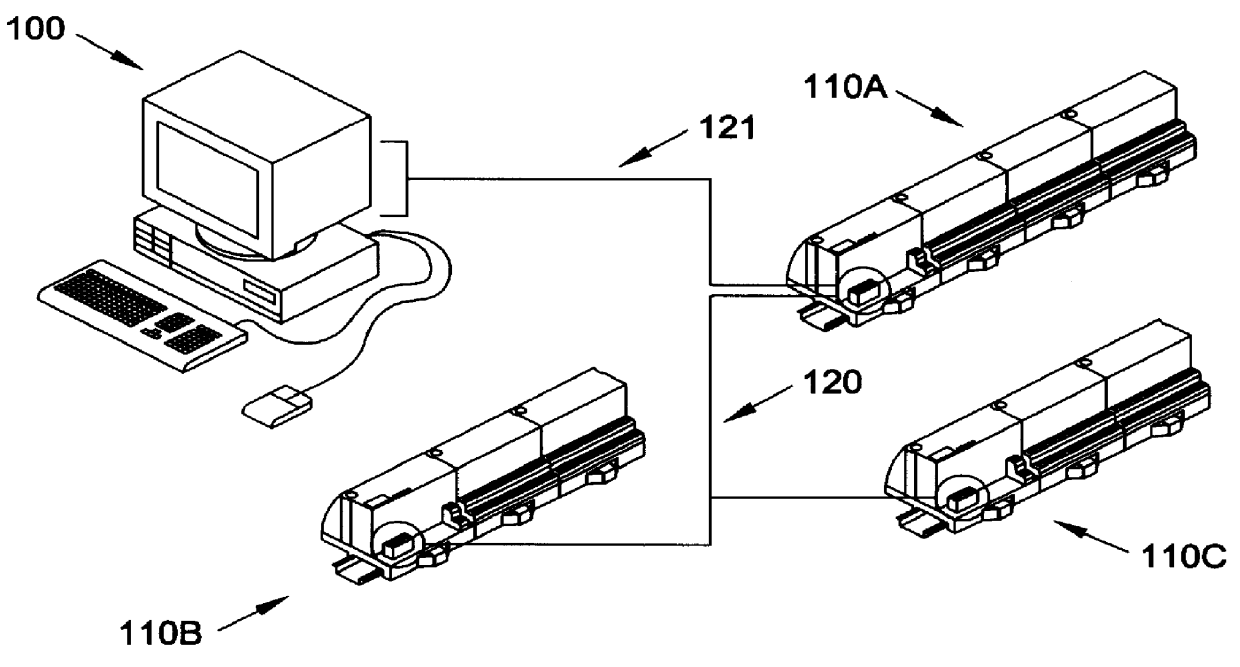

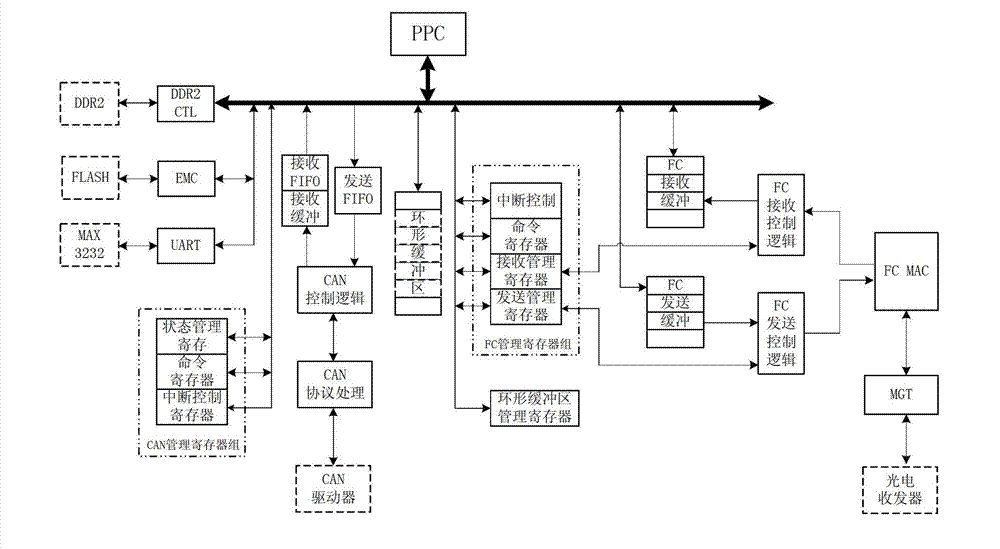

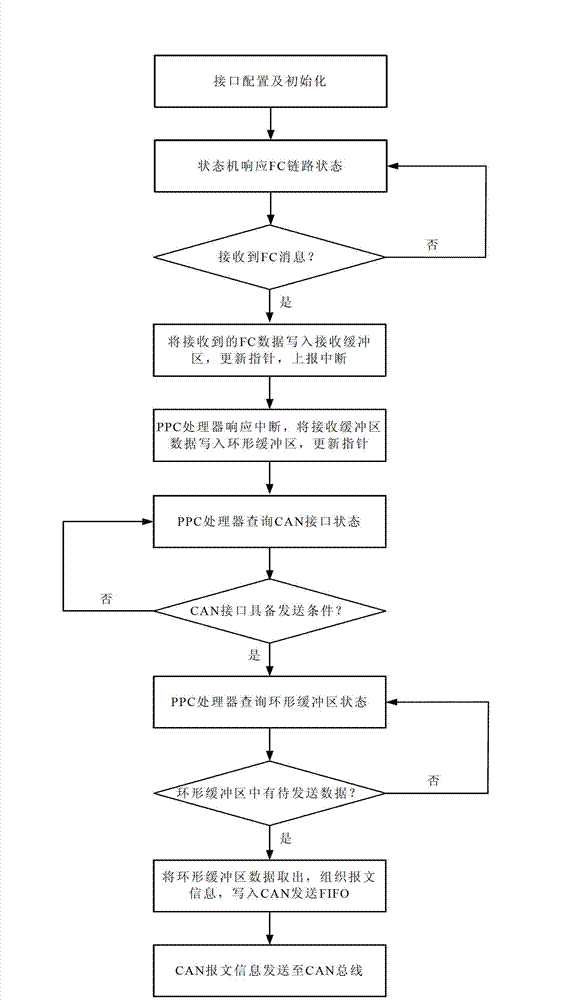

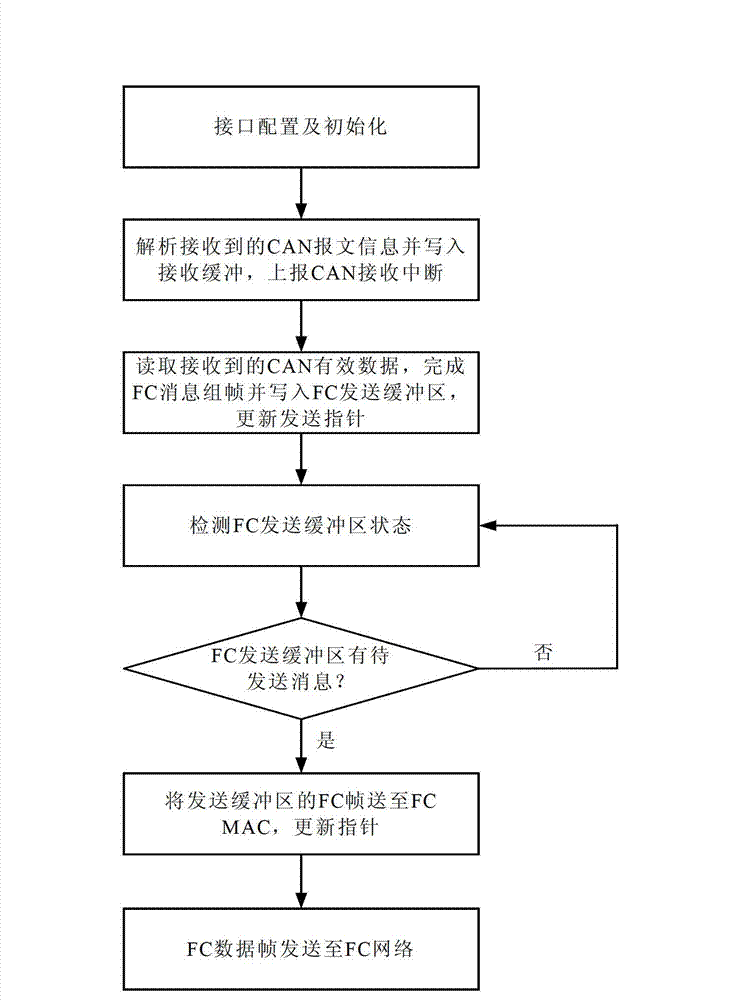

Method for converting and transmitting data between FC (fiber channel) bus and CAN (controller area network) bus

The invention provides a method for converting and transmitting data between an FC (fiber channel) bus and a CAN (controller area network) bus and solves the problem about data communication between a subsystem utilizing the CAN bus as a local bus and the FC backbone network. The method includes subjecting interfaces of the FC bus and the CAN bus to initializing, transceiving control, data management, interrupt processing and the like by a PPC (performance optimization with enhanced RISC-performance computing) processor in an FPGA (field programmable gate array), completing analysis and frame format conversion of FC data frame information and CAN message information under an FC-AE-ASM (fiber channel-avionics environment-anonymous subscriber messaging) protocol. Meanwhile, an annular buffer area is designed in the FPGA, and the problem about unmatched speed during bandwidth data transfer of the two different FC and CAN buses.

Owner:AVIC NO 631 RES INST

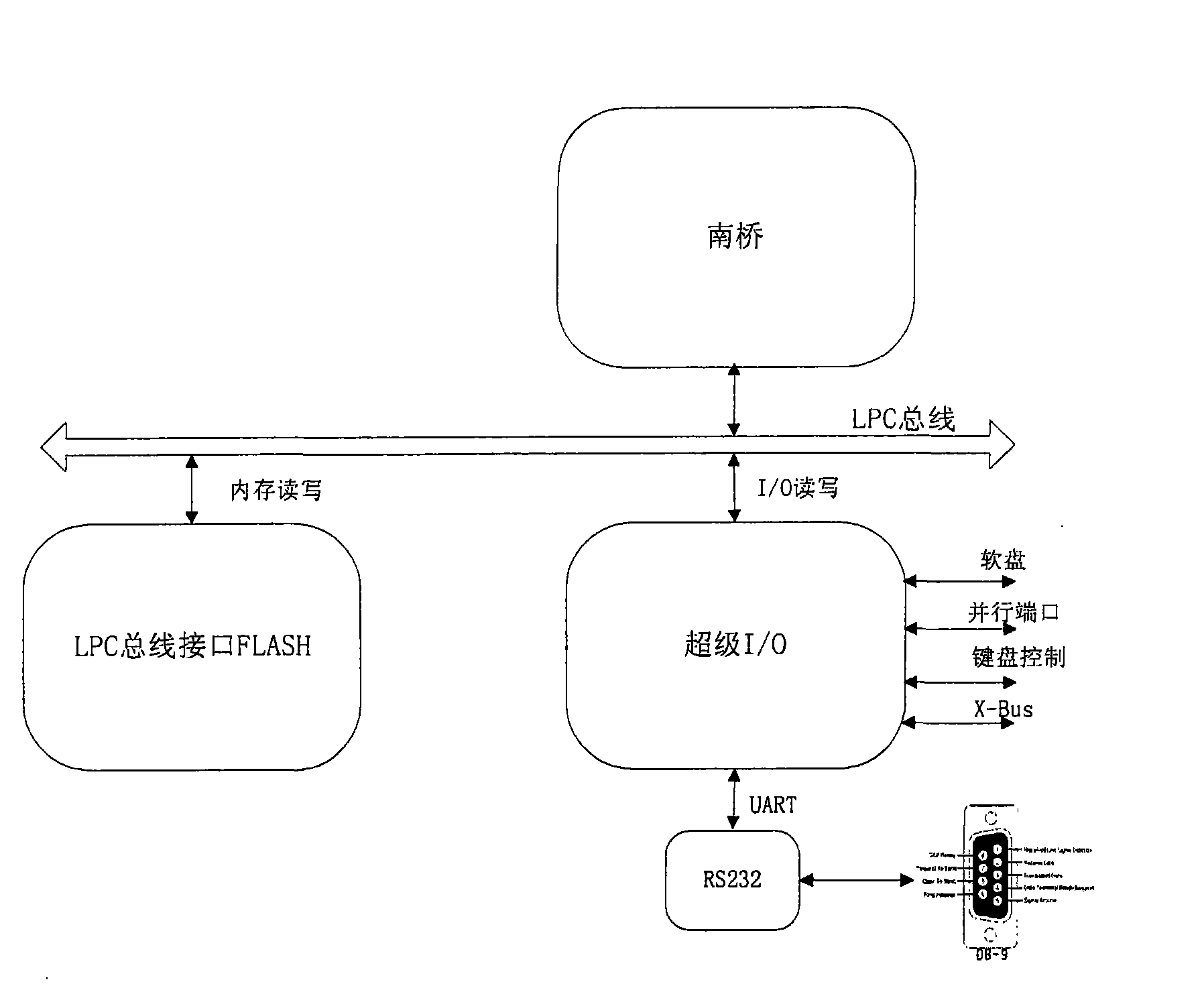

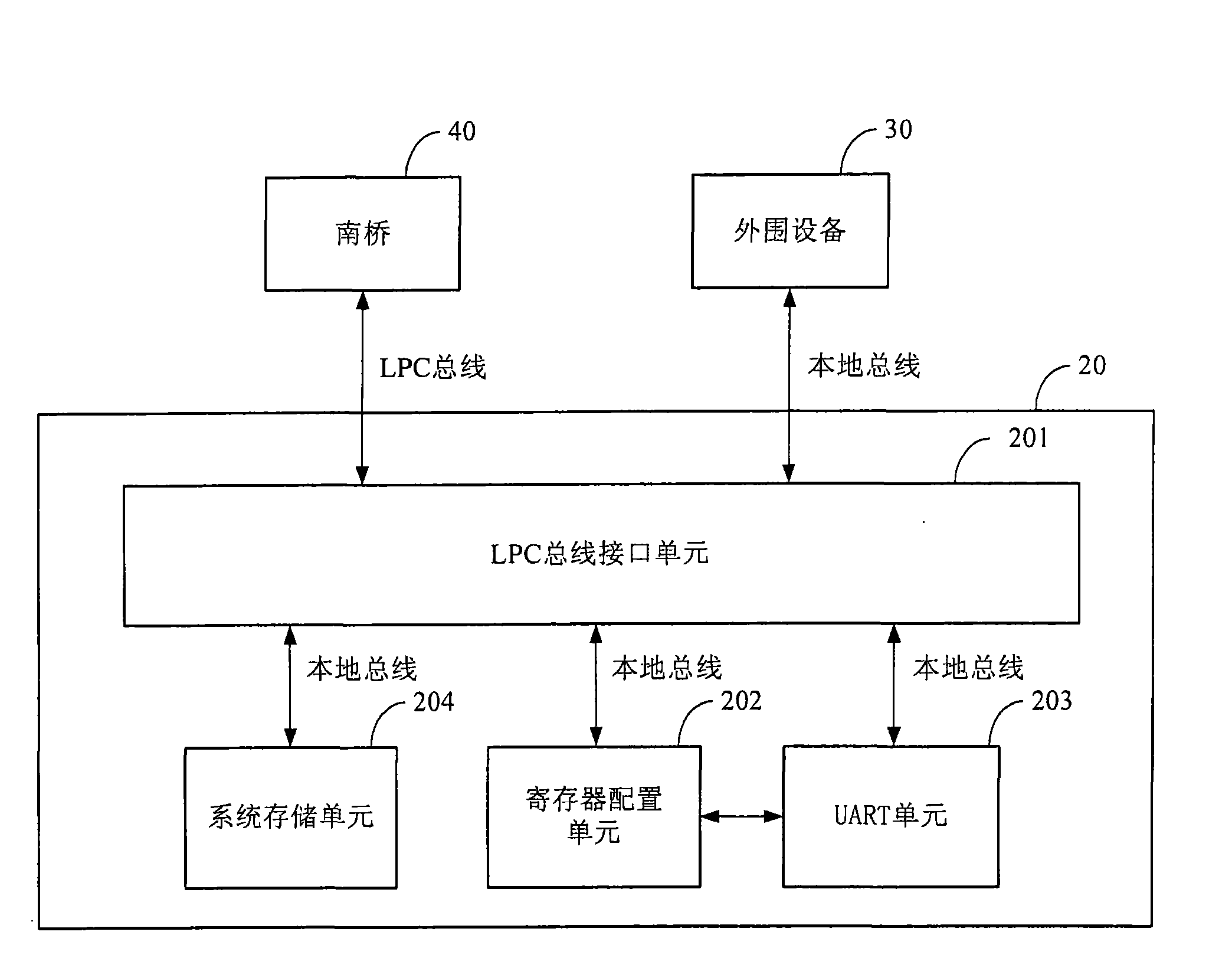

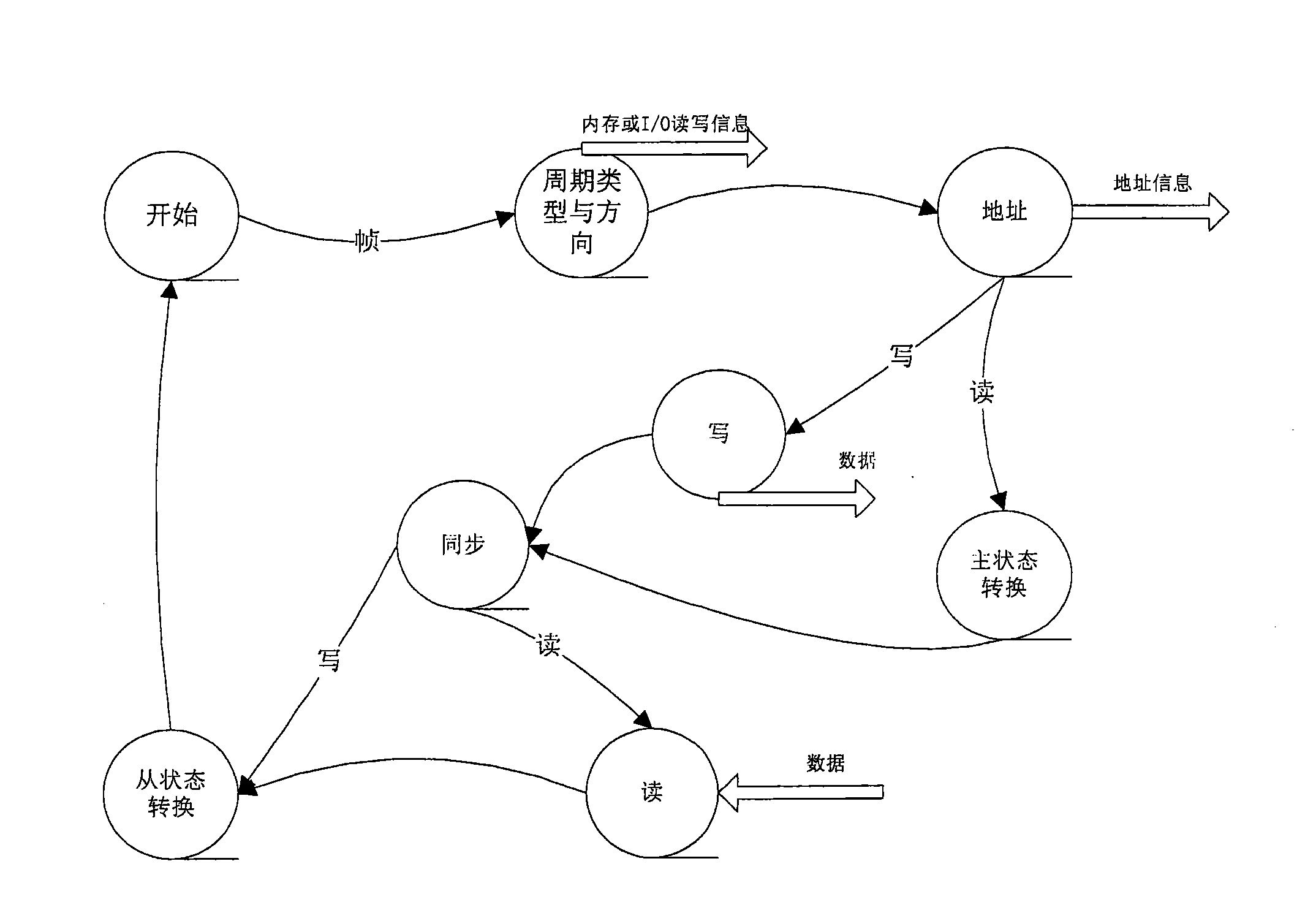

Signal conversion device and method as well as communication equipment

ActiveCN101989244AReduce complexityReduce usageElectric digital data processingRegister allocationMemory address

The embodiment of the invention provides a signal conversion device and method as well as communication equipment. The signal conversion device comprises an LPC (Low Pin Count) bus interface unit, a register configuration unit and a UART (Universal Asynchronous Receiver Transmitter) unit, wherein the LPC bus interface unit is used for performing protocol analysis on signals from an LPC bus and outputting local signals through a local bus, and the local signals comprise a control signal, an address signal and a data signal; the register configuration unit is used for configuring registers of the UART unit according to the local signals; the registers of the UART unit are allocated in a memory address space and an I / O address space; and the UART unit is used for converting data from the LPCbus into serial data according to the local signals and the values of configured registers of the UART unit and then outputting the serial data through a UART interface or outputting the serial data received by the UART interface to the LPC bus through the local signals. The embodiment of the invention can simplify the configuration process of the registers of the USRT unit.

Owner:HUAWEI TECH CO LTD

Data processing system and method for dynamically setting bus clock frequency in response to a number of loads

A data processing system includes a bus, one or more loads coupled to the bus, and a clock generator. The clock generator generates a bus clock signal that is coupled to at least one of the loads. While the clock generator is generating a bus clock signal having a first frequency, the number of loads connected to the bus is determined. In response to this determination, the frequency of the bus clock signal is automatically changed from the first frequency to a second frequency. In one embodiment in which the bus is a PCI local bus having a plurality of slots, the determination of the number of loads is made by examining at least one storage location associated with each of a plurality of slots.

Owner:LENOVO (SINGAPORE) PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com