Test access architecture and test access method of digital chip

A digital chip and access method technology, applied in the direction of electronic circuit testing, etc., can solve the problems of large test power consumption, increased wiring overhead, and long test time, and achieve the goal of reducing layout and wiring overhead, reducing test time, and reducing test power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The specific implementation manners of the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific implementation manners described here are only used to illustrate and explain the embodiments of the present invention, and are not intended to limit the embodiments of the present invention.

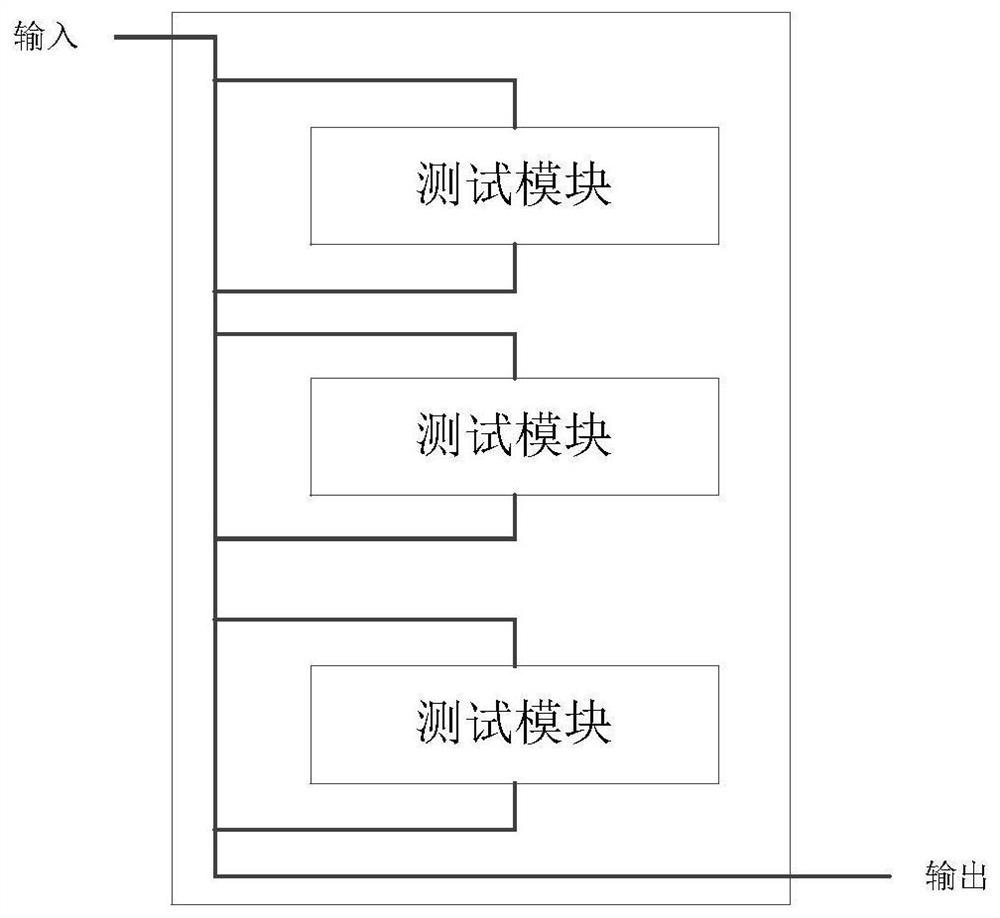

[0031] In the prior art, the multiplex-based test access mechanism belongs to a time-division multiplexing structure, and all modules to be tested are tested serially. by figure 1 The example shown includes the test access structure of three modules to be tested. In order to minimize the test cost, the designer should use the test bandwidth as much as possible to achieve the purpose of reducing the length of the scan chain. Another common test access mechanism is the daisy chain structure, such as figure 2 As shown, in this structure, the scan chain of each module under test i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com