Built-in self-testing system and method thereof with mixed mode

A built-in self-test and mixed-mode technology, which is applied in the field of electronic equipment testing, can solve problems such as circuit thermal effects, increased test power consumption, and complex generation processes, achieving low test power consumption, reduced test power consumption, and high fault coverage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0024] Embodiment 1 (the embodiment of the built-in self-test system of the present invention):

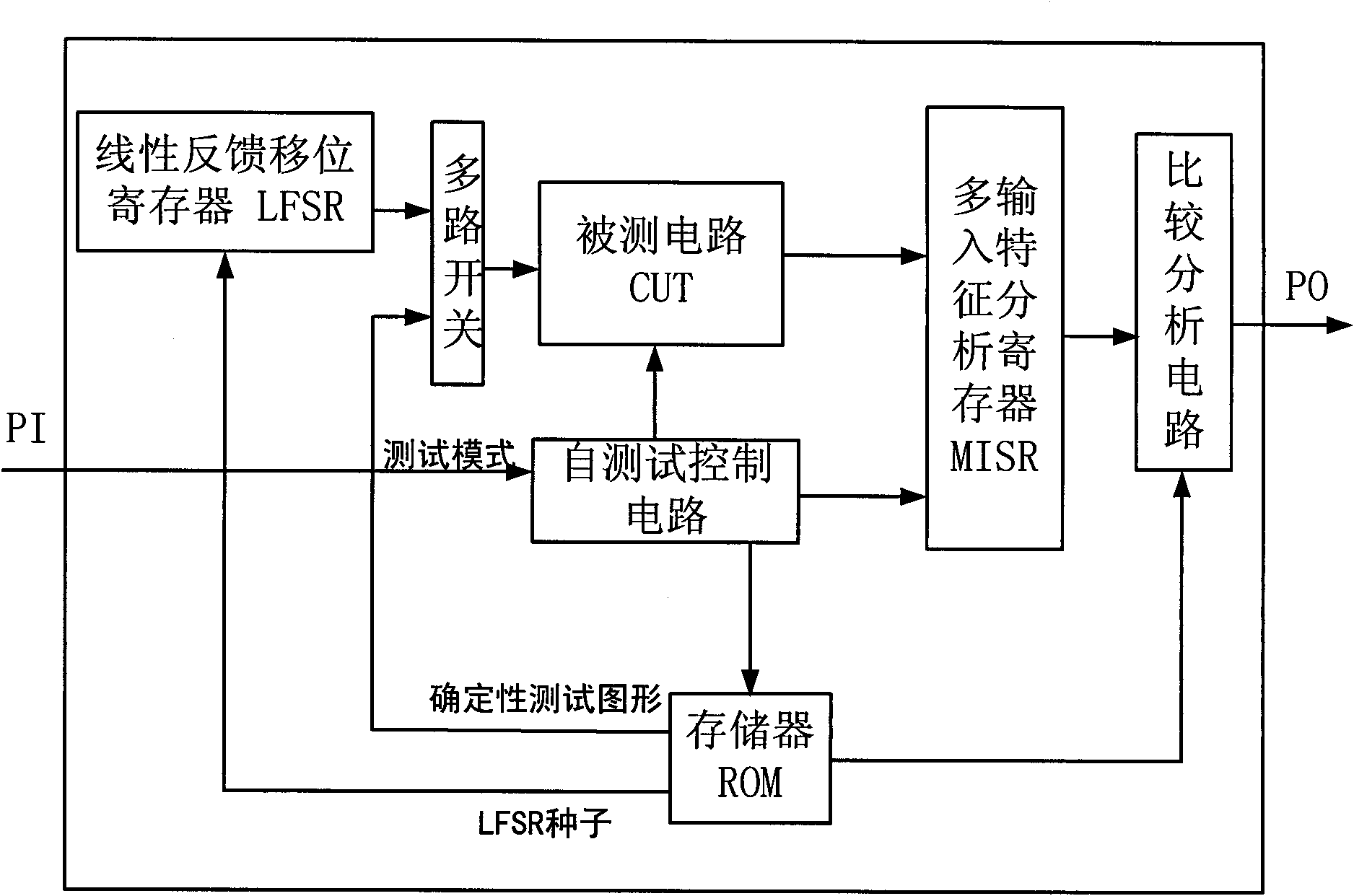

[0025] see figure 1 , a built-in self-test system of a mixed mode, comprising a circuit under test CUT, a self-test control circuit, a multi-input characteristic analysis register MISR, a memory ROM and a comparative analysis circuit; the self-test control circuit is respectively connected to the circuit under test CUT, The control terminal of the multi-input characteristic analysis register MISR and the memory ROM, the output terminal of the circuit under test CUT is connected to the input end of the multi-input characteristic analysis register MISR, and the input end of the comparison analysis circuit is respectively connected to the multi-input characteristic analysis register MISR Output terminal and the output terminal of memory ROM, PI is the signal input terminal of described self-test control circuit, PO is the signal output terminal of described comparative analysis circ...

Embodiment 2

[0026] Embodiment 2 (the embodiment of the built-in self-test method of the present invention):

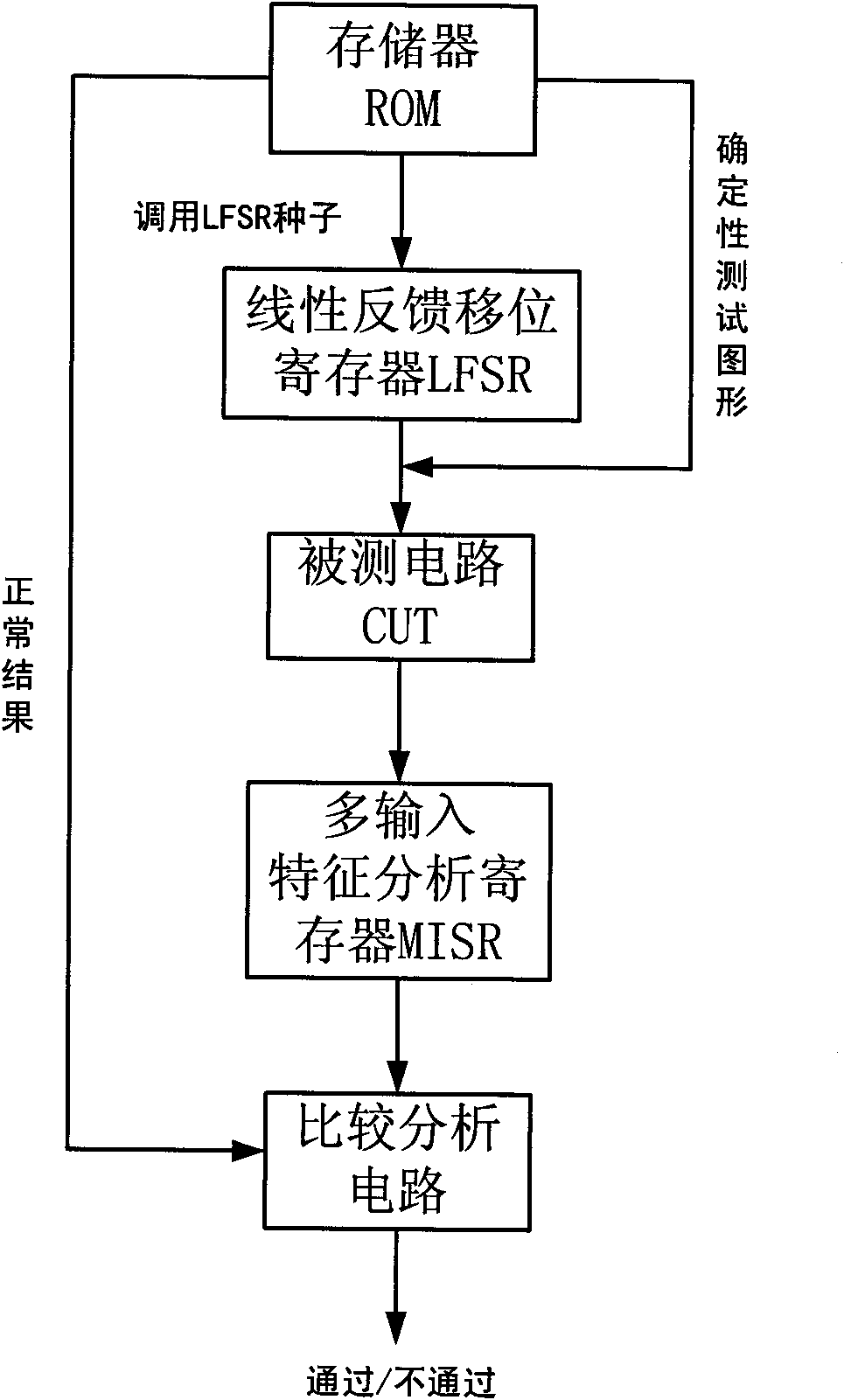

[0027] see figure 2 , a mixed-mode built-in self-test method. In the first step, the linear feedback shift register LFSR is selected as the test pattern generation circuit through a multi-way switch, and the required test pattern is generated after calling the seed stored in the memory ROM and then applied To the circuit under test CUT, its output response is analyzed by the multi-input characteristic analysis register MISR, and then compared with the characteristic response pre-stored in the memory ROM by the comparison analysis circuit, and a pass / fail result is given;

[0028] In the second step, the deterministic test pattern stored in the memory ROM is selected by a multi-way switch as the test pattern of the circuit under test CUT, and the output response of the circuit under test CUT is analyzed by the multi-input characteristic analysis register MISR and then analyzed by ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com