Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

249 results about "Fault coverage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fault coverage refers to the percentage of some type of fault that can be detected during the test of any engineered system. High fault coverage is particularly valuable during manufacturing test, and techniques such as Design For Test (DFT) and automatic test pattern generation are used to increase it.

System and method for testing high speed VLSI devices using slower testers

InactiveUS6345373B1Shorten application timeLow fault coverageDigital circuit testingError detection/correctionGeneration processFault coverage

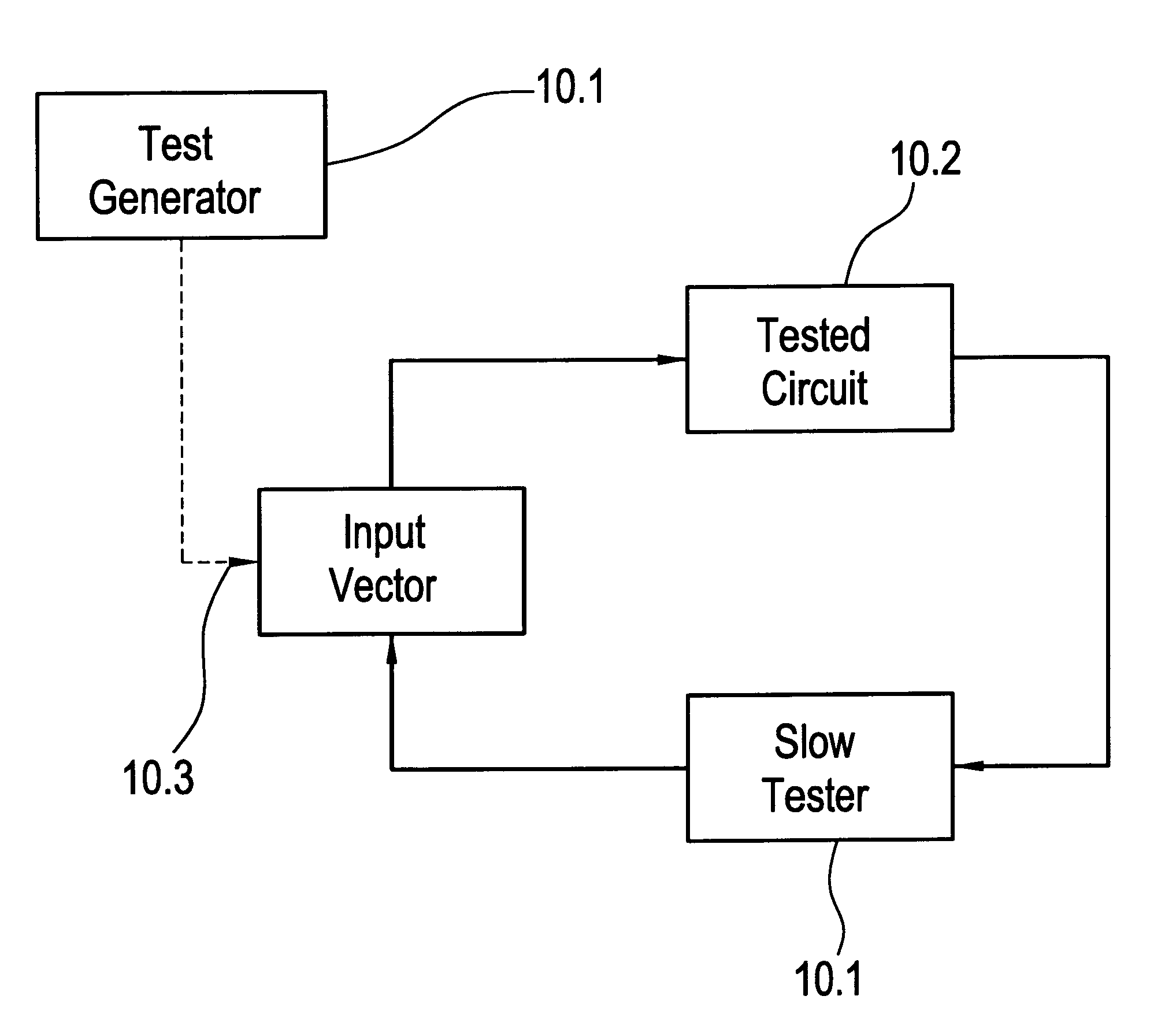

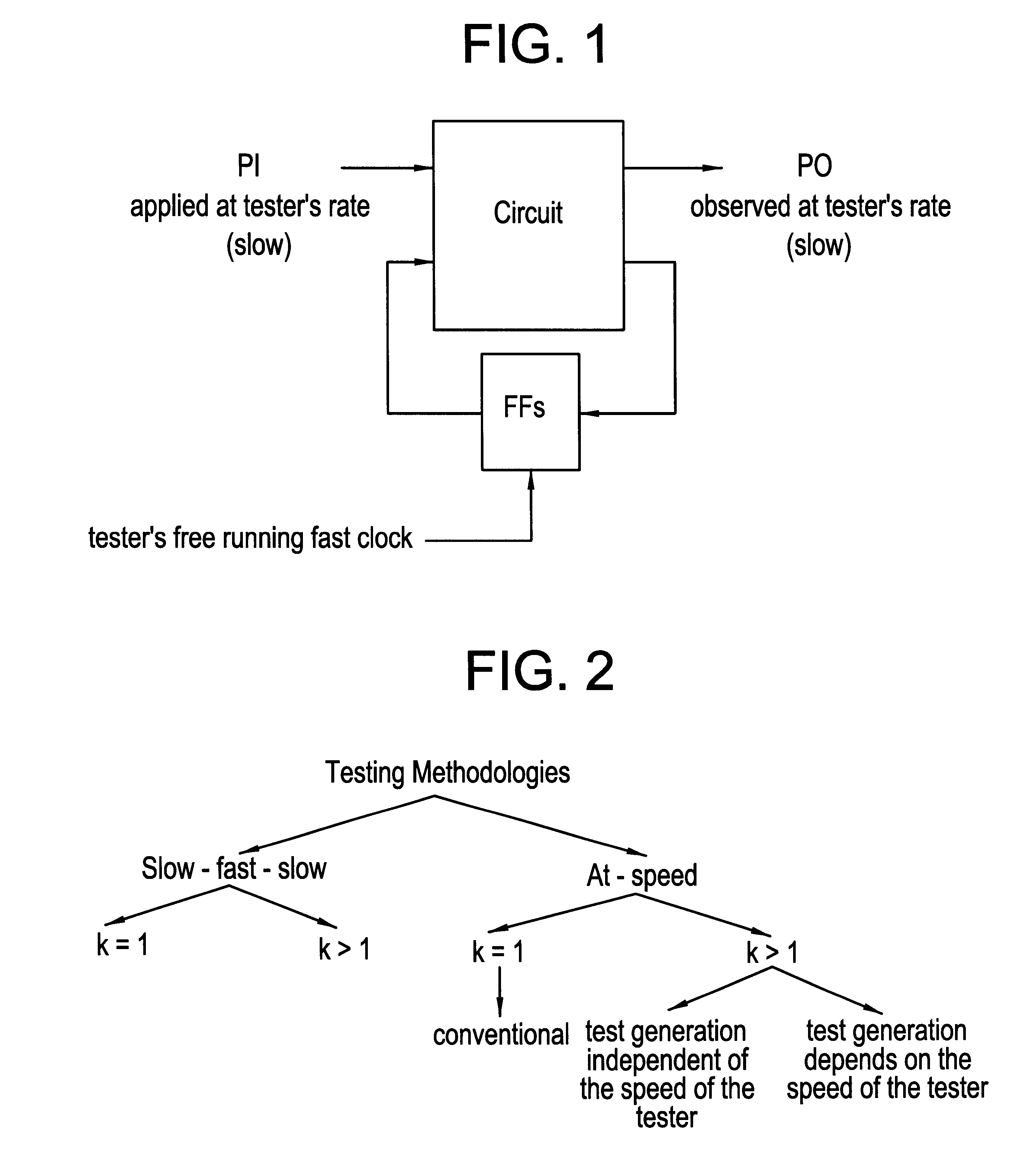

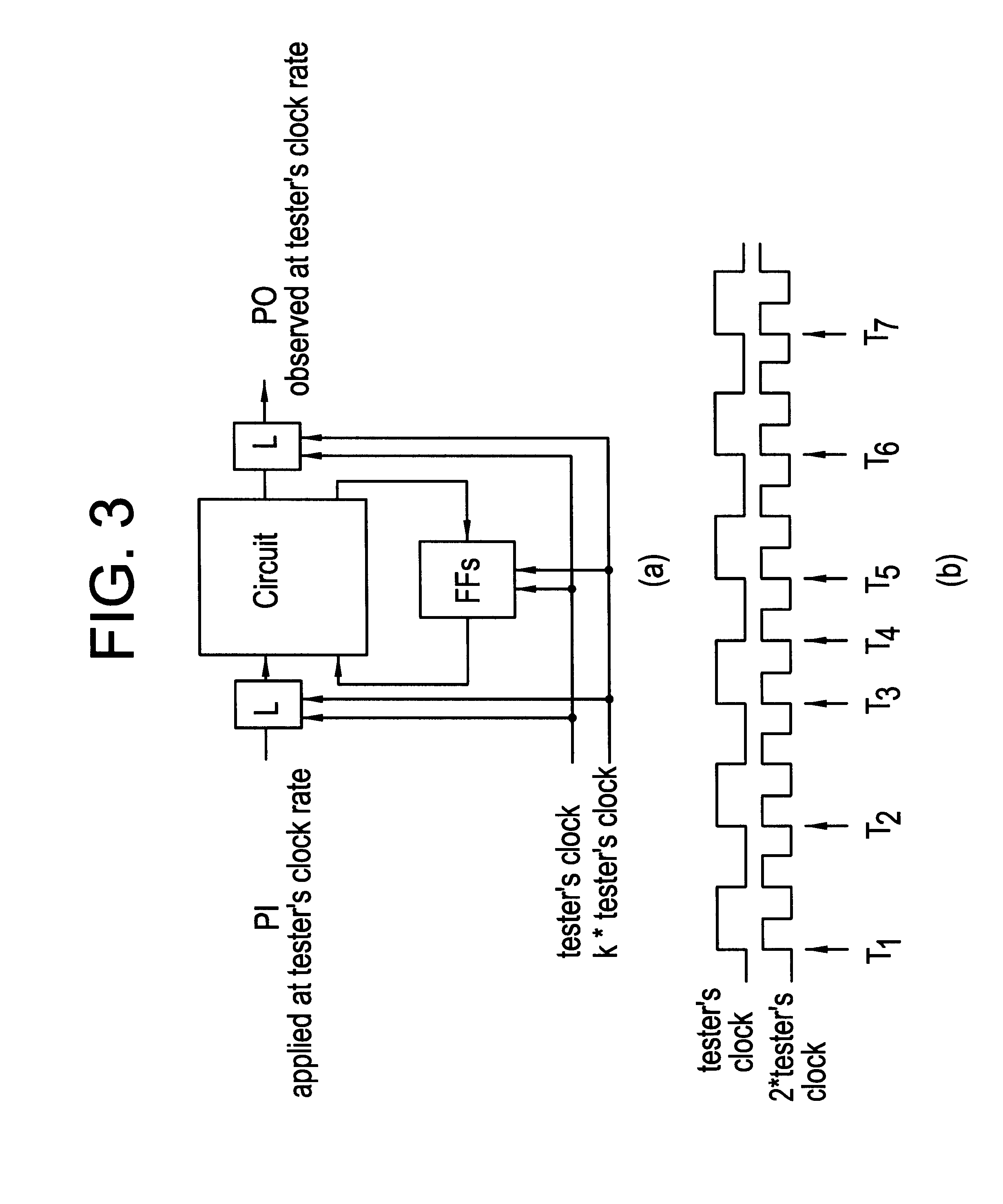

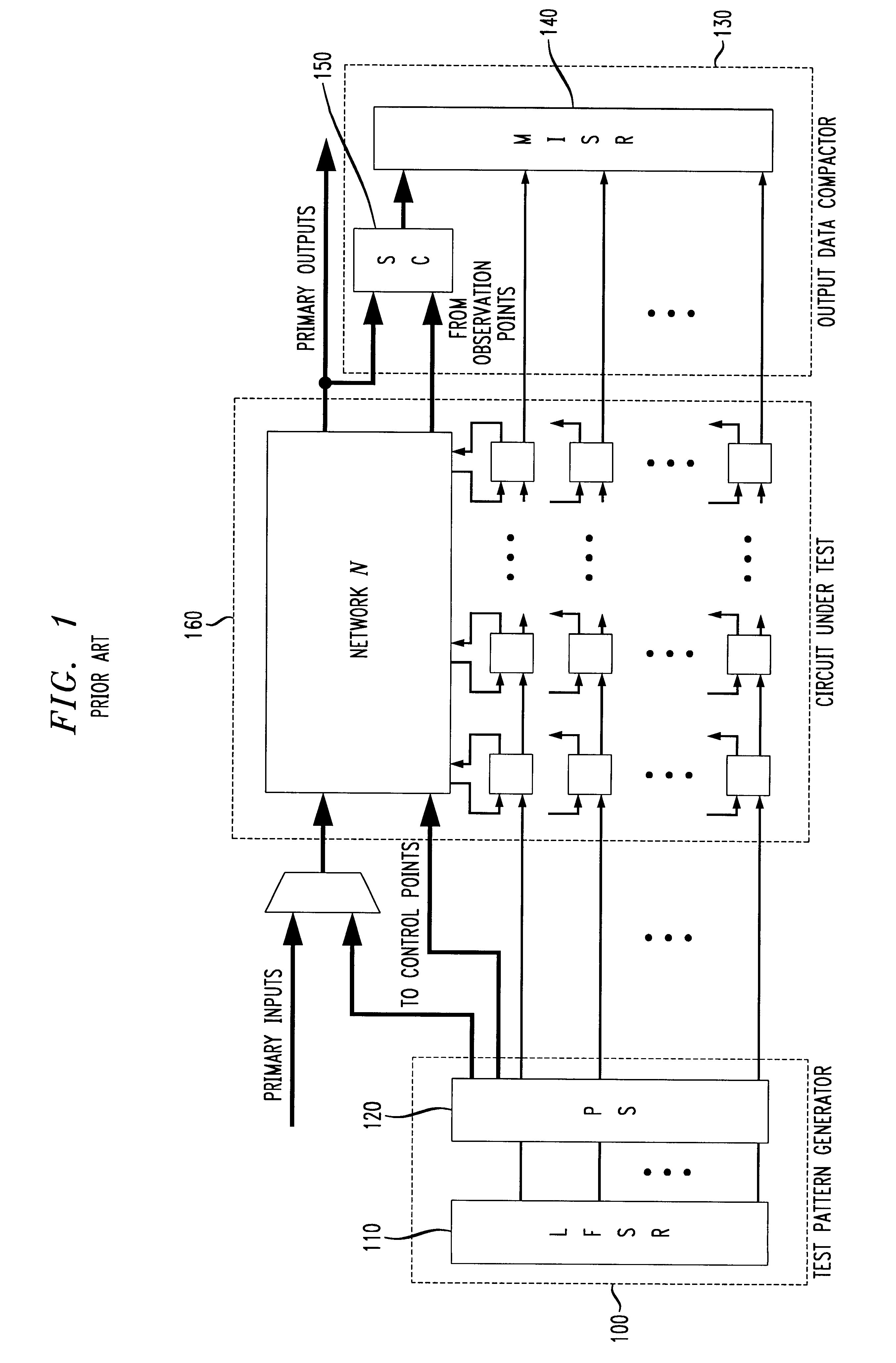

At-speed strategies for testing high speed designs on slower testers. At-speed testing schemes is provided that integrates the tester's speed limitations with the test generation process. Due to constraints placed at the test generation process, these schemes might result in a reduced fault coverage. To increase the fault coverage and reduce the test application time, the slow-fast-slow and at-speed strategies can be combined for testing high speed designs on slower testers. A slow tester that uses test vectors that are generated while taking into account the speed of the tester.

Owner:NEC CORP +1

Bist architecture for detecting path-delay faults in a sequential circuit

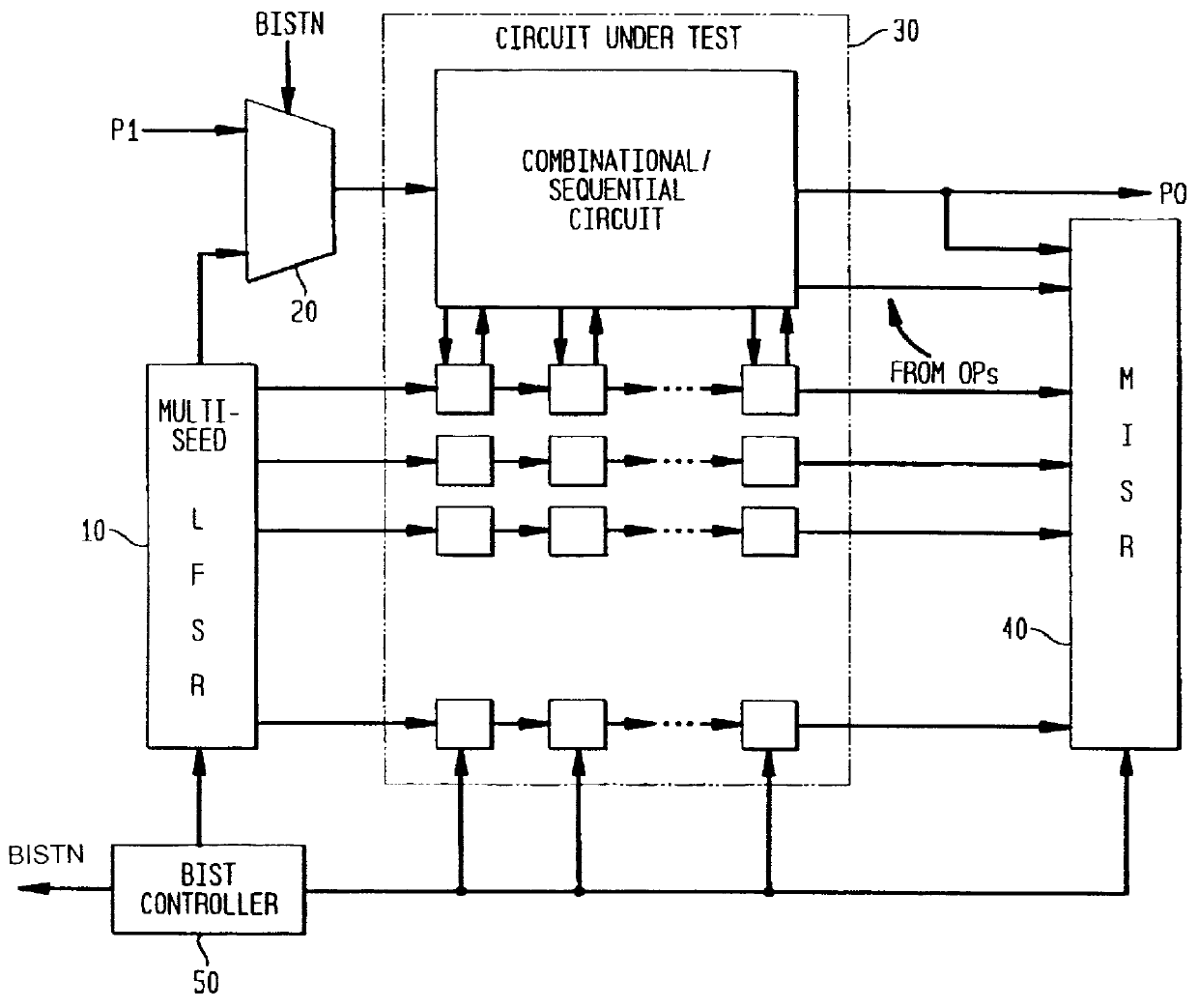

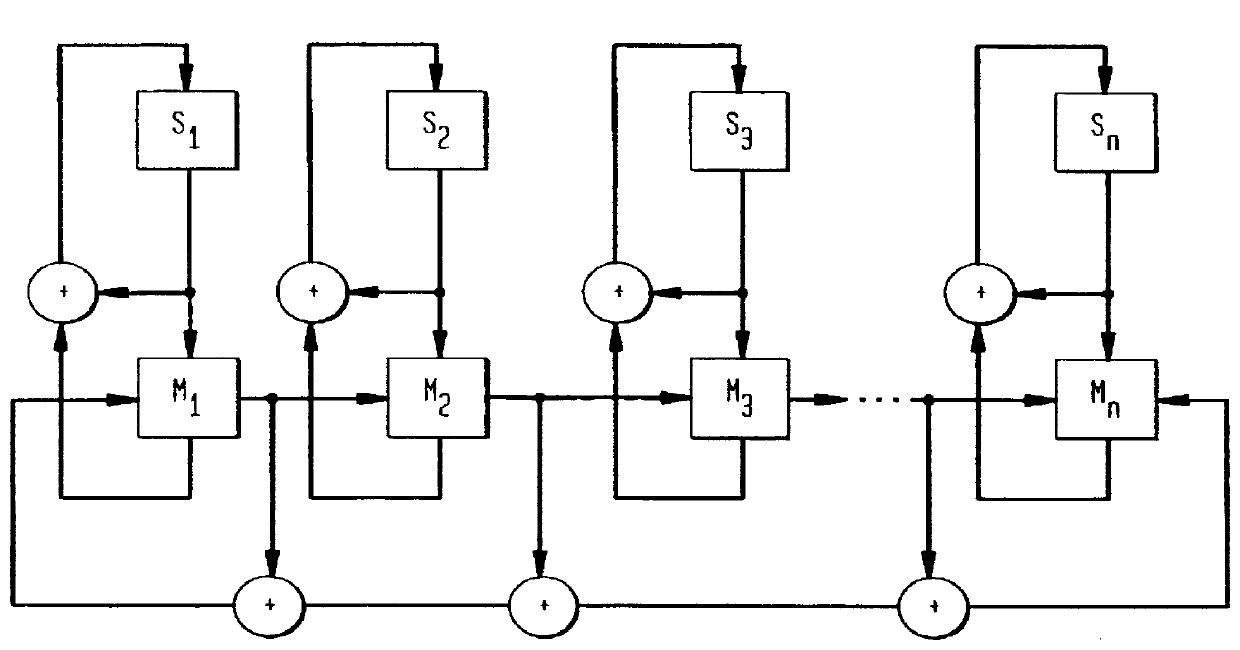

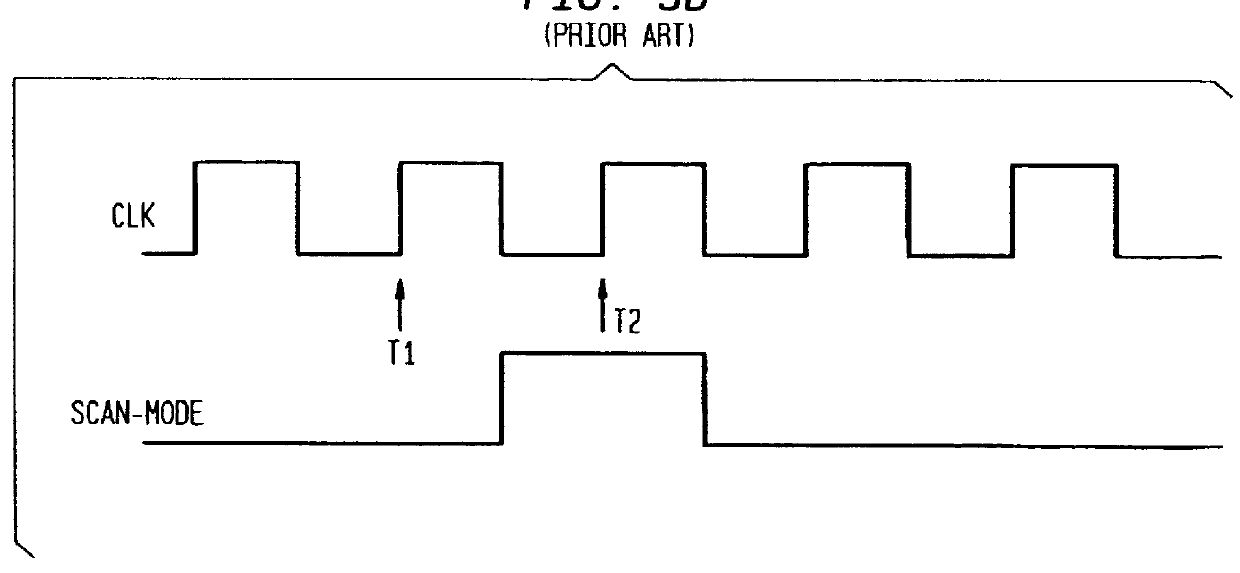

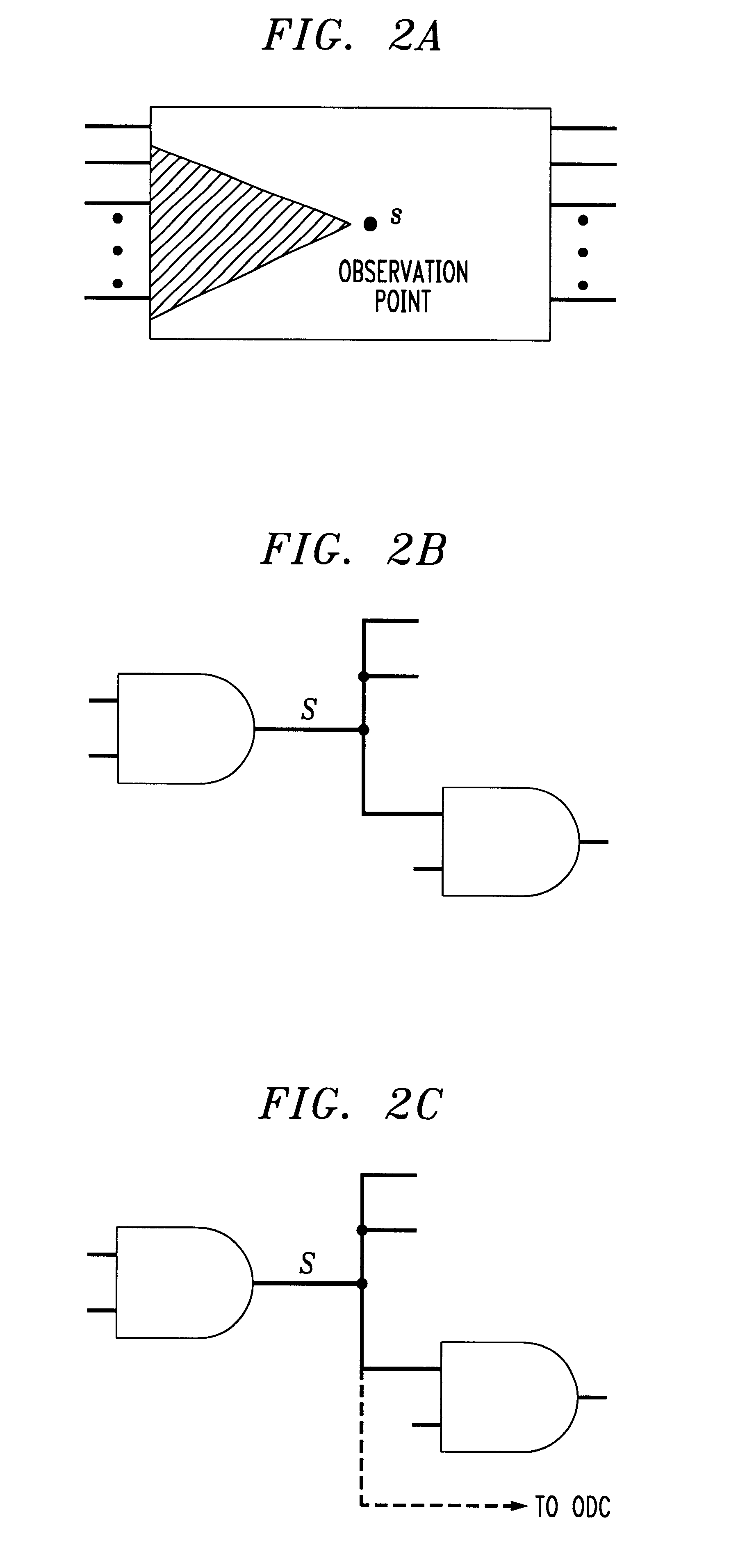

A scan-based BIST architecture for detecting path-delay faults in a sequential circuit converted to a combinational circuit or a less complex sequential circuit including a combinational portion and a plurality of scan flip-flops. The BIST structure includes a test pattern generator for generating two test patterns and a controller for generating a clock signal and an extended scan mode signal which is held high for two clock cycles while the output response of the combinational portion to the first and second test vectors is latched into the scan flip-flops in order to detect a signal transition. The invention is further directed to a method for detection of path-delay faults using this scan-based BIST architecture. To improve the fault coverage for path-delay faults, observation points may be inserted at the inputs of selected scan flip-flops. A predetermined number of scan flip-flops having the highest activation frequency are selected as the observation points.

Owner:LUCENT TECH INC +1

Hybrid algorithm for test point selection for scan-based BIST

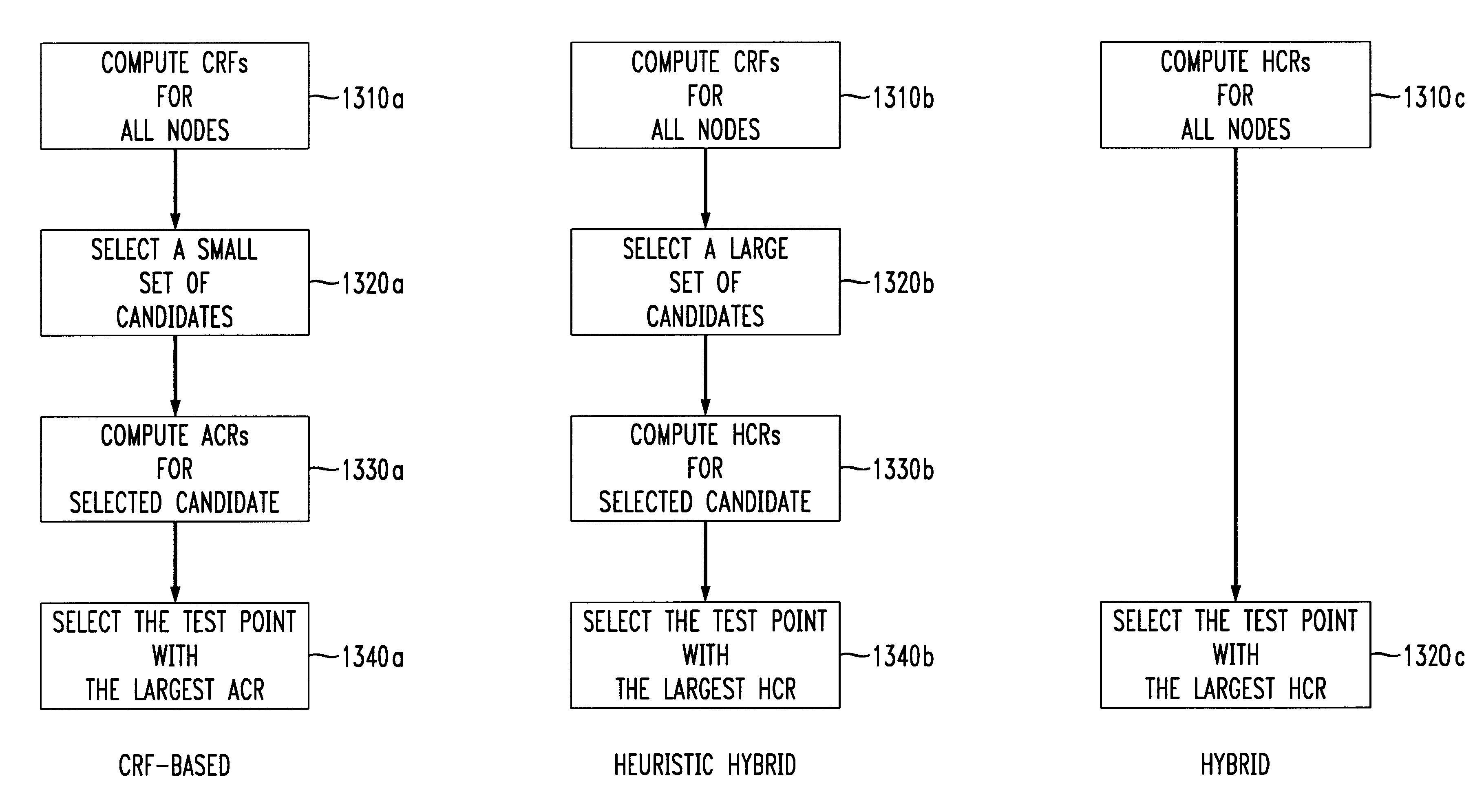

A test point selection method for scan-based built-in self-test (BIST). The method calculates a hybrid cost reduction (HCR) value as an estimated value of the corresponding actual cost reduction for all nodes in a circuit under test. A test point is then selected having a largest HCR. This iterative process continues until the fault coverage of the circuit under test reaches a desired value or the number of test points selected is equal to a maximum number of test points. In an alternative embodiment, the cost reduction factor is calculated for all nodes in the circuit under test, the HCR is calculated for only a selected set of candidates, and the candidate having the largest HCR is selected as the test point. The test point selection method achieves higher fault coverage results and reduces computational processing relative to conventional selection methods.

Owner:LUCENT TECH INC +1

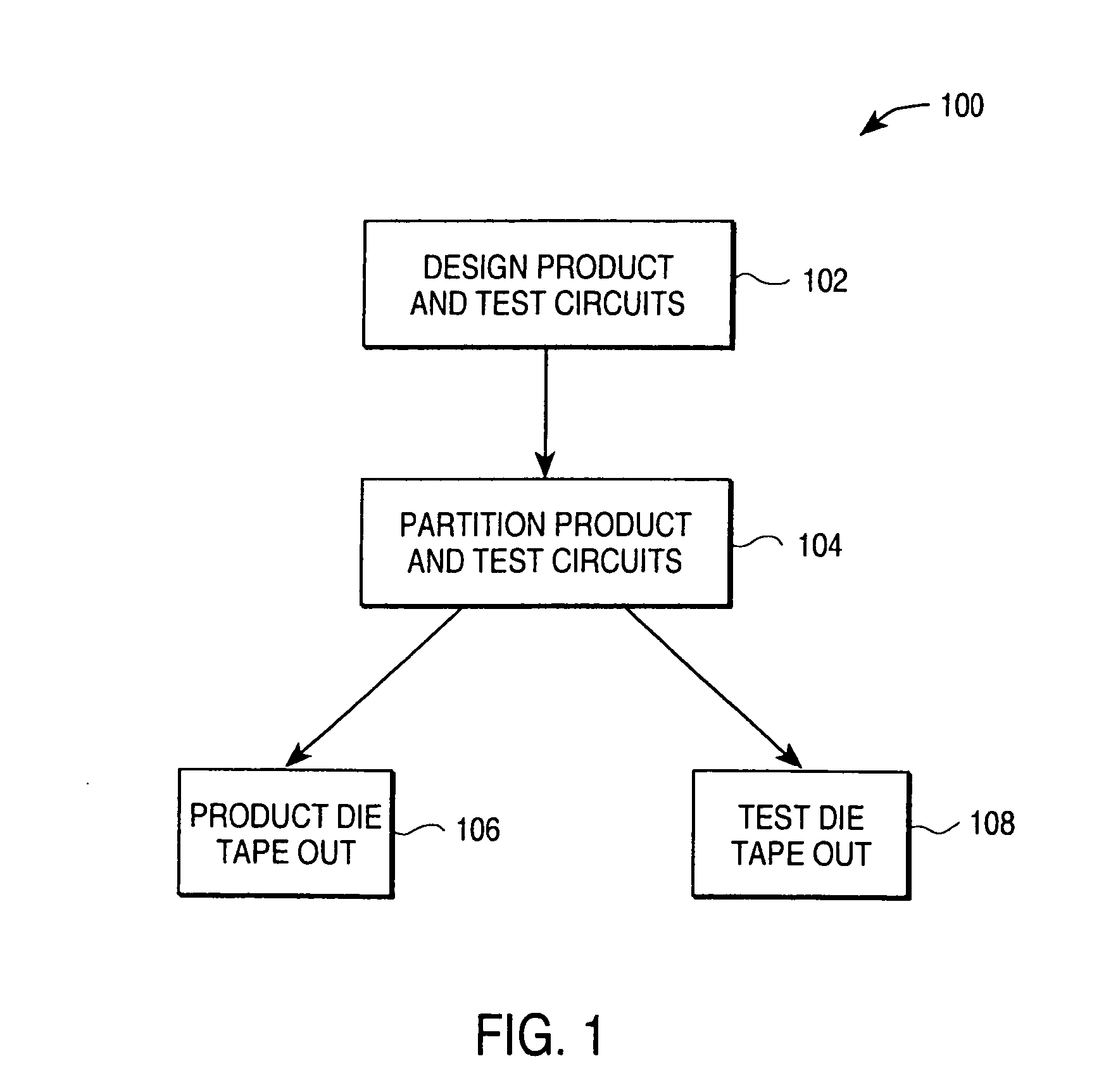

Test assembly including a test die for testing a semiconductor product die

InactiveUS20050156165A1High degreeSmall sizePrinted circuit assemblingSemiconductor/solid-state device testing/measurementFault coverageUniform design

One embodiment of the present invention concerns a test assembly for testing product circuitry of a product die. In one embodiment, the test assembly includes at test die and an interconnection substrate for electrically coupling the test die to a host controller that communicates with the test die. The test die may be designed according to a design methodology that includes the step of concurrently designing test circuitry and a product circuitry in a unified design. The test circuitry can be designed to provide a high degree of fault coverage for the corresponding product circuitry generally without regard to the amount of silicon area that will be required by the test circuitry. The design methodology then partitions the unified design into the test die and the product die. The test die includes the test circuitry and the product die includes the product circuitry. The product and test die may then be fabricated on separate semiconductor wafers. By partitioning the product circuitry and test circuitry into separate die, embedded test circuitry can be either eliminated or minimized on the product die. This will tend to decrease the size of the product die and decrease the cost of manufacturing the product die while maintaining a high degree of test coverage of the product circuits within the product die. The test die can be used to test multiple product die on one or more wafers.

Owner:FORMFACTOR INC

Graphical user interface for testability operation

InactiveUS6341361B1Accurate analysisQuickly and efficiently and accurately testabilityElectronic circuit testingFunctional testingFault coverageGraphics

A graphical user interface (GUI) provides a design engineer the capability of automatically inserting scan logic and test logic into a design. The graphical user interface includes a scan insertion option for a design engineer to invoke a scan insertion tool to check the design for testability. The graphical user interface also permits the design engineer to invoke a test generation tool such as an automatic test pattern generator (ATPG) tool to check the design for fault coverage. The graphical user interface, which can serve as a front end for a design framework, enables a design engineer to efficiently increase testability while still in a design phase.

Owner:ADVANCED MICRO DEVICES INC

Calculation system of fault coverage and calculation method of the same

A calculation system of fault coverage includes a data acquiring module acquiring layout information and gate net data, a layout analysis and fault link module extracting a layout element information and generating a undetected fault list, a fault detecting module generating a detected and undetected fault list, and a weight calculating module adding layout element information as weight, based on a link file between faults and layout element information to be generated based on the layout information, the gate net data, and the detected and undetected fault list.

Owner:KK TOSHIBA

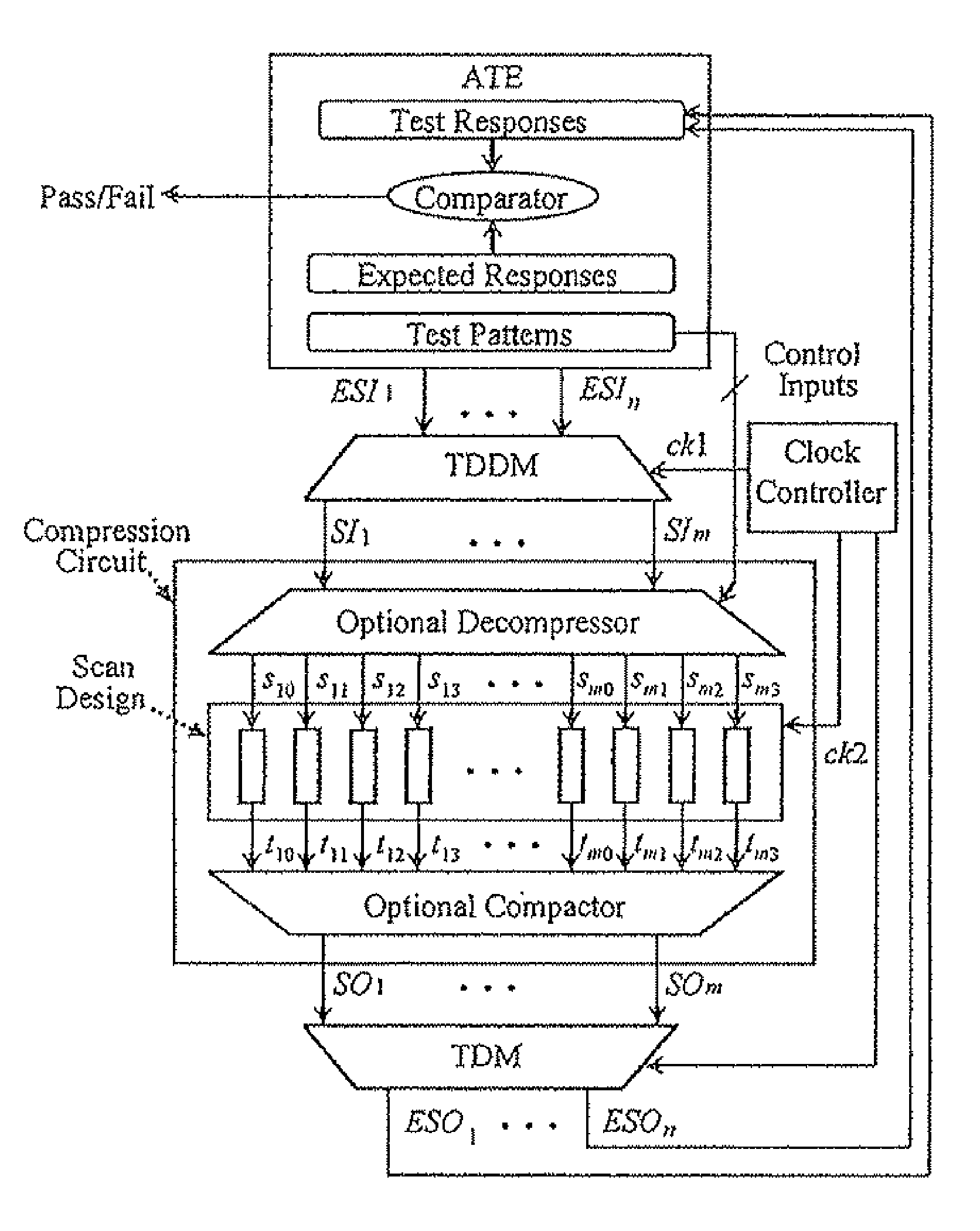

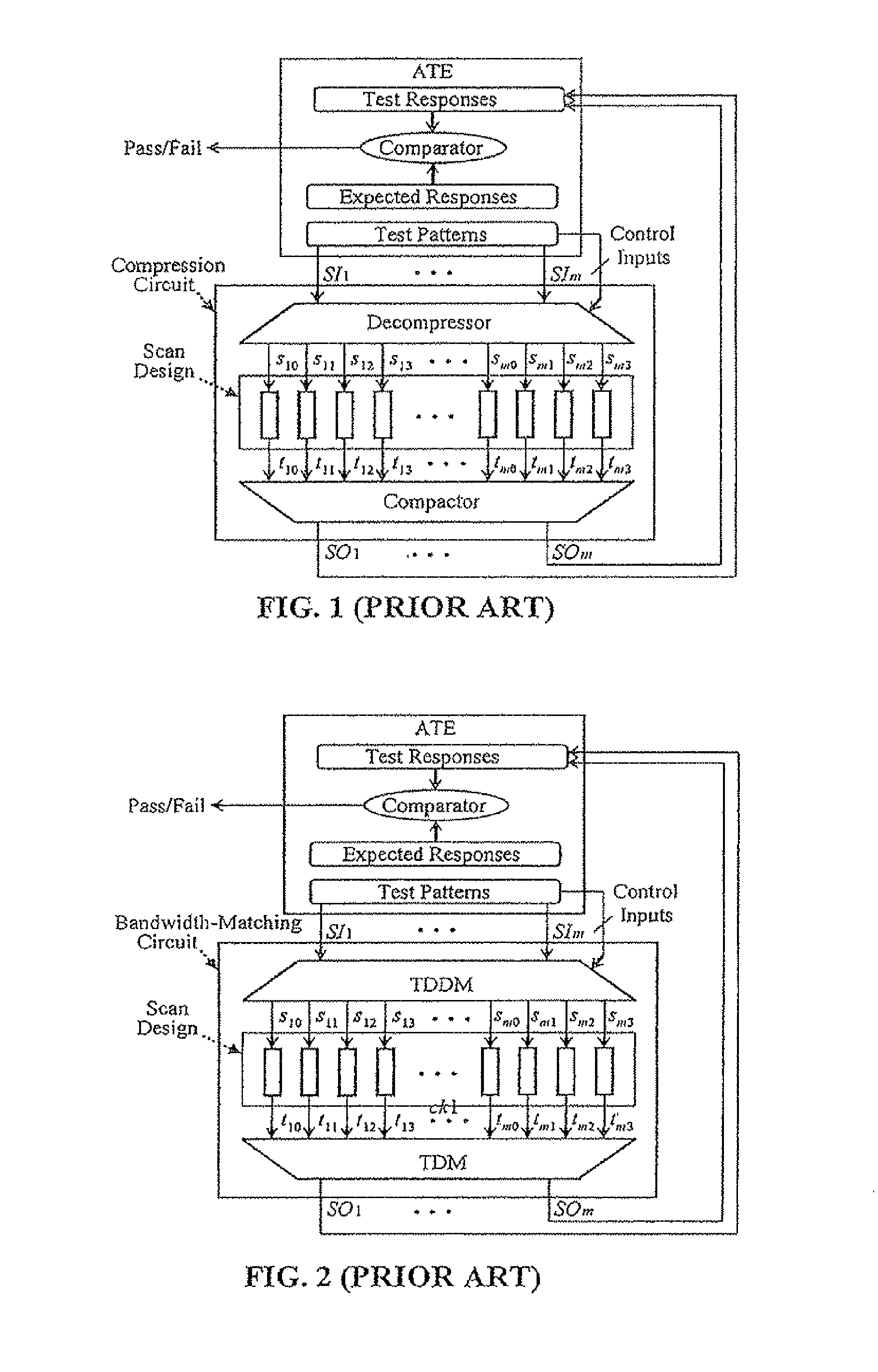

Method and apparatus for testing 3D integrated circuits

InactiveUS8522096B2Reduce testing costsIncrease data rateElectronic circuit testingFault coverageEngineering

A method and apparatus for testing a scan-based 3D integrated circuit (3DIC) using time-division demultiplexing / multiplexing allowing for high-data-rate scan patterns applied at input / output pads converting into low-data-rate scan patterns applied to each embeddded module in the 3DIC. A set of 3D design guidelines is proposed to reduce the number of test times and the number of through-silicon vias (TSVs) required for both pre-bond testing and post-bond testing. The technique allows reuse of scan patterns developed for pre-bond testing of each die (layer) for post-bond testing of the whole 3DIC. It further reduces test application time without concerns for I / O pad count limit and risks for fault coverage loss.

Owner:SYNTEST TECH

Automated fault diagnosis in a programmable device

ActiveUS7219287B1Simplify and reduce time requiredReduce settingsData processing applicationsElectronic circuit testingFault coverageProgrammable logic device

A method and apparatus are disclosed that simplify and reduce the time required for detecting faults in a programmable device such as a programmable logic device (PLD) by utilizing fault coverage information corresponding to a plurality of test patterns for the PLD to reduce the set of potential faults. For one embodiment, each test pattern is designated as either passing or failing, the faults that are detectable by at least two failing test patterns and the faults that are not detectable by any passing test patterns are eliminated, and the remaining faults are diagnosed. For another embodiment, the faults detectable by each failing test pattern are diagnosed to generate corresponding fault sets, and the faults not common to the fault sets and not detectable by one or more of the failing test patterns are eliminated.

Owner:XILINX INC

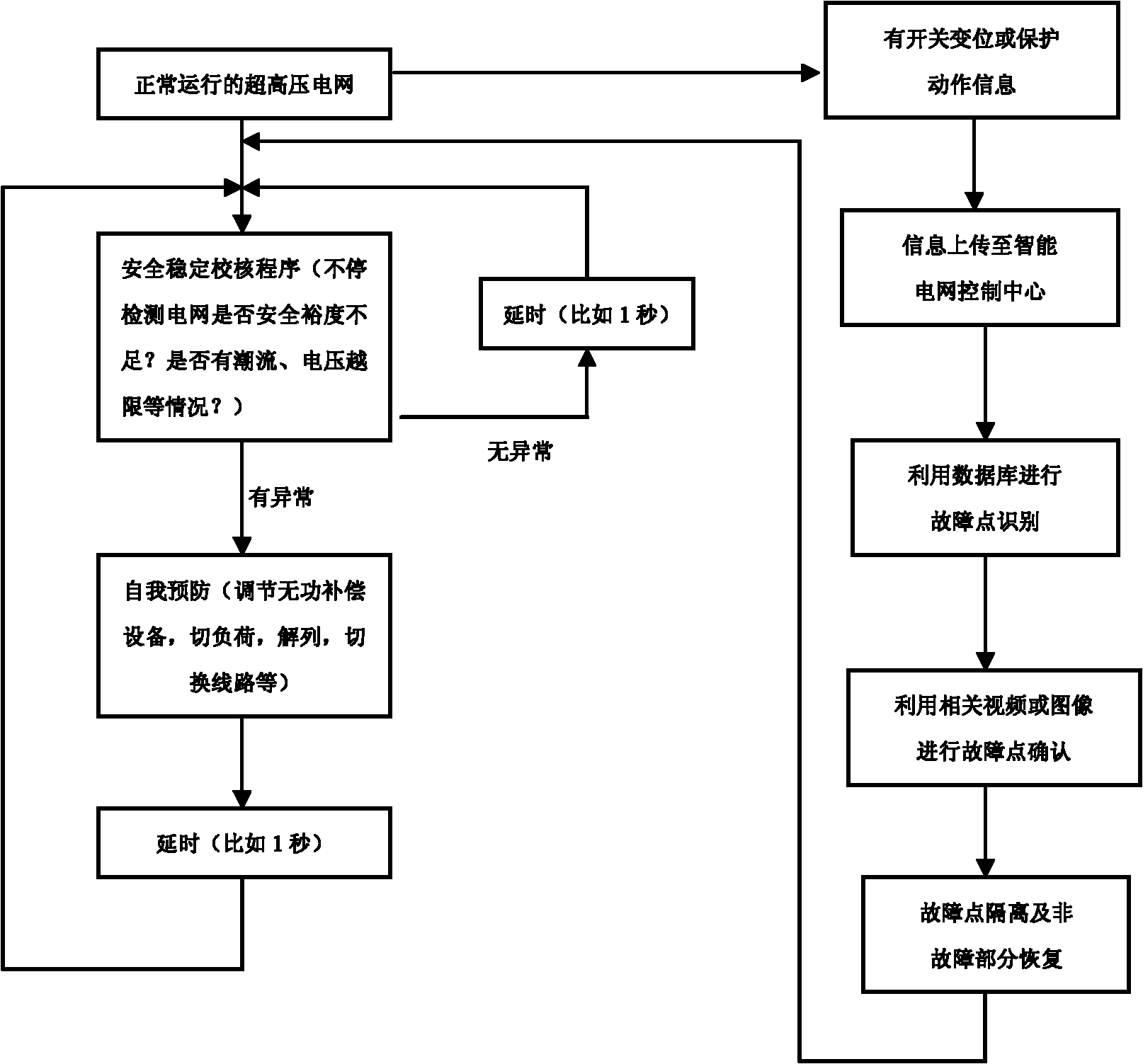

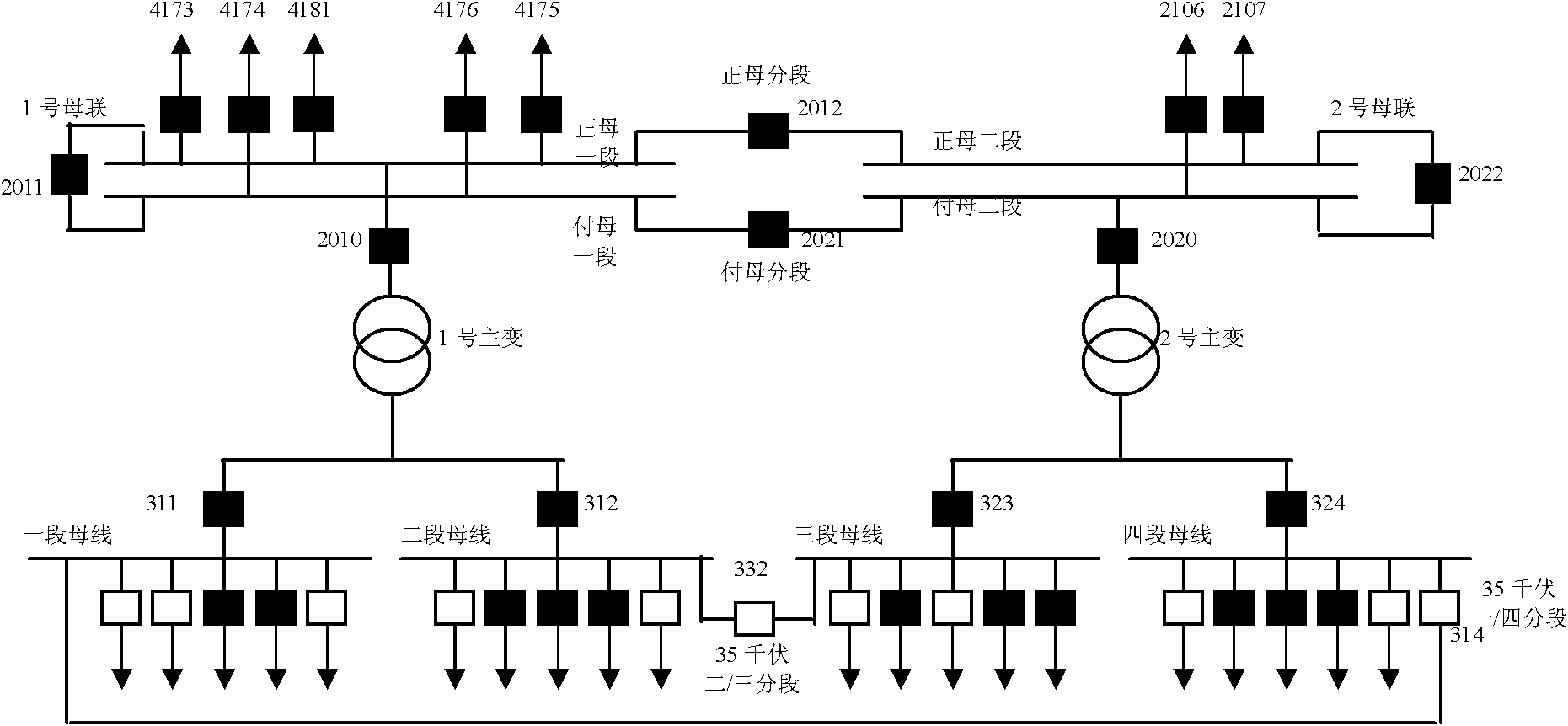

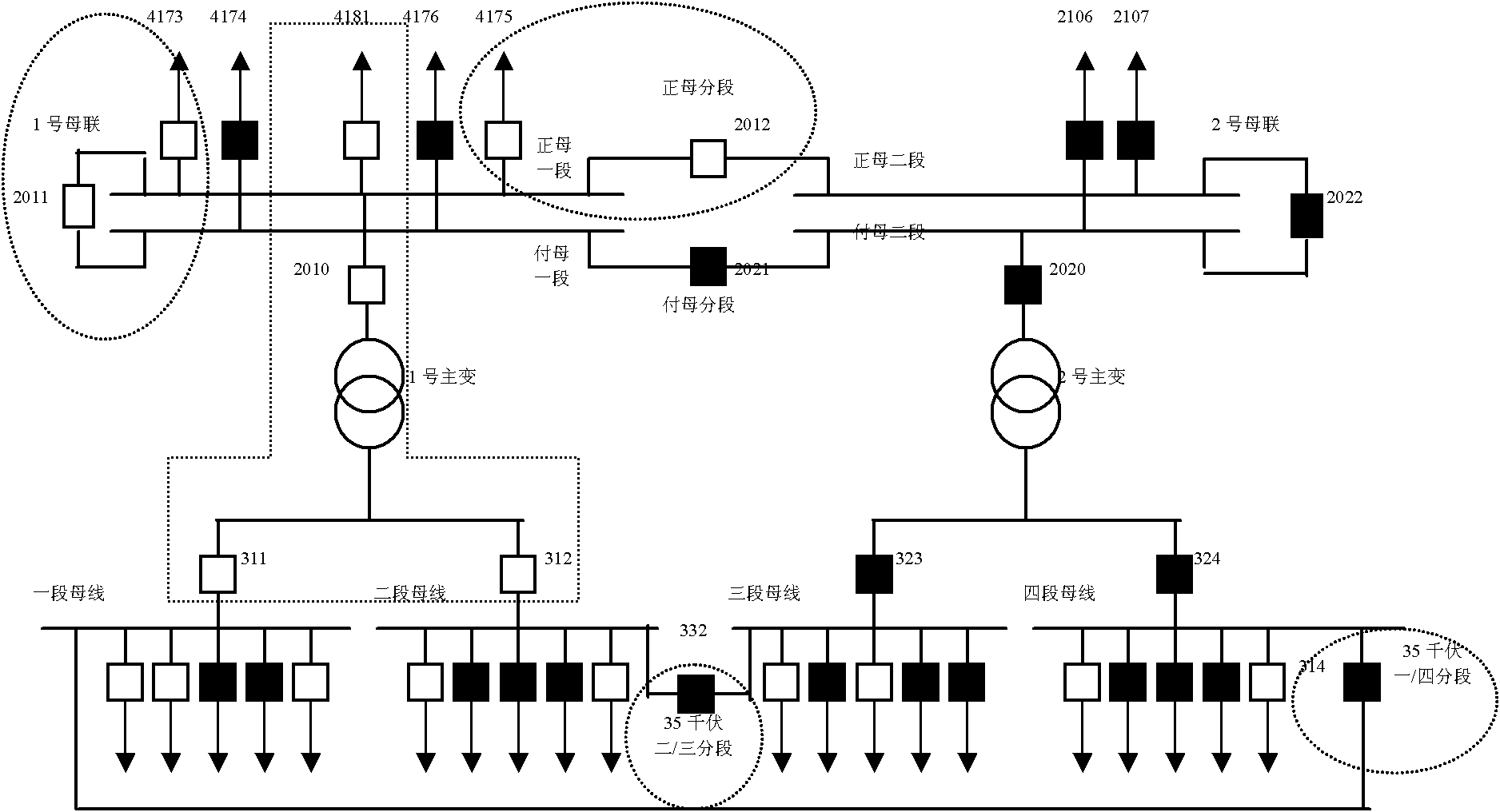

Intelligent self-healing monitoring method of extra high voltage power network

ActiveCN101944777ASecurity and Stability Additional ControlSolve self-healing problemsCircuit arrangementsSelf-healingFault coverage

The invention discloses an intelligent self-healing monitoring method of extra high voltage power network, belonging to the field of electric transformer and distribution. The invention uses the self-healing monitoring method that the power network control center collects the fault information, estimates the fault point according to the action information, judges the fault point according to the visualization technology, and starts the automatic recovery project. The method solves the self-healing problem of extra high voltage power network, performs the prevention and correction control, andmakes the dispose strategy based on the information quickly, thereby avoiding the cascade trip caused by load transfer, realizing the safe and stable addition control of the power network from the entire network perspective, and replenishing the disadvantages of area and in situ emergency control measure. Aiming at the specific characteristics in the aspects of running, dispatching and managing of the extra high voltage power network, the method can collect and use the information more comprehensive, and make the dispose strategy quickly to earn the time for the avoiding of cascade trip caused by load transfer, thereby avoiding the further enlargement of fault coverage due to wrong dispose, and solving the self-healing problem of the extra high voltage power network.

Owner:SHANGHAI MUNICIPAL ELECTRIC POWER CO +1

Method for implementing testability analysis and diagnosis decision system for electronic products

InactiveCN101980225AChange the situation of lack of testable auxiliary software designStrong scalabilitySpecial data processing applicationsFault coverageDecision system

The invention relates to a method for implementing a testability analysis and diagnosis decision system for electronic products and is applied to the field of electronic product design. The method comprises the following steps of: (1) arranging a testability design modeling module which comprises a graphical testability model of equipment, testability design information integration and description, and testability information acquisition and testability information storage; (2) arranging an inherent testability analysis module which comprises fault coverage analysis, fault ambiguity group discrimination, and redundancy testing analysis; and (3) arranging an actual testability analysis module which comprises diagnosis strategy generation and testability design result analysis. The invention has the advantages that: (1) the situation of deficiency of testability assisted software in China is changed, and the method is used for performing testability verification and analysis on complex electronic products; (2) each functional unit of the system can be independently used, and the system has good expandability; and (3) inherent testability analysis function and actual testability analysis function can be provided for the electronic products.

Owner:NO 63908 TROOPS PLA

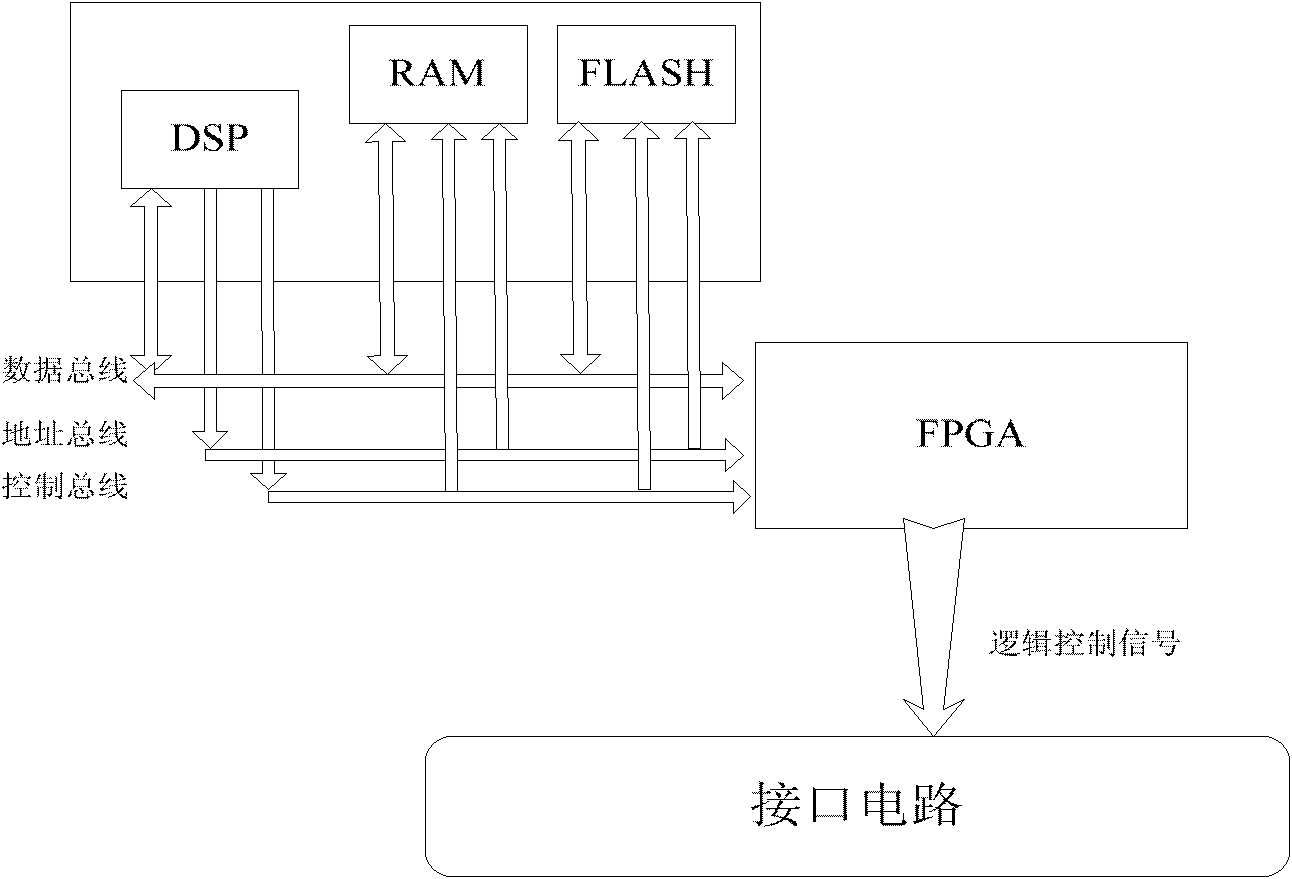

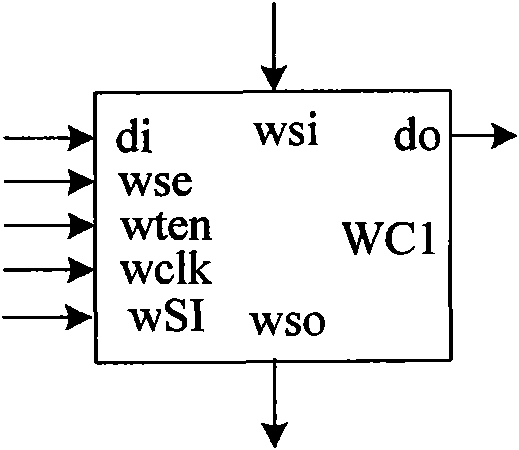

Fault injection system for embedded spaceborne computer and injection method thereof

ActiveCN102135920AAddress reliabilitySolve fault tolerance evaluationError detection/correctionFault coverageOperational system

The invention discloses a fault injection system for an embedded spaceborne computer and an injection method thereof, which are mainly used for software evaluation of the operation system of the spaceborne computer. The fault injection system for the embedded spaceborne computer comprises a Digital Signal Processor (DSP), a Random Access Memory (RAM), a FLASH, a Joint Test Action Group (JTAG) controller, and one or more Field Programmable Gate Arrays (FPGAs) (one of which is a fault injection FPGA) and an interface circuit, wherein the DSP processor and the fault injection FPGA are provided with boundary scanning units; the Test Compatibility Kit (TCK) and the Time-Multiplexed Switching (TMS) signal terminals of a chip are connected in parallel; the Total Domestic Output (TDO) signal terminal of a front-stage apparatus and the Transport Driver Interface (TDI) signal terminal of a rear-stage apparatus are connected in series to form a daisy chain. The device is simple and is capable ofshortening evaluation time and reducing evaluation cost; a signal level is directly controlled in the computer without special external instruments; signals needing to control influence can be flexibly selected to have a relatively large fault coverage rate; therefore, the reliability and the fault-tolerant capability of the embedded spaceborne computer can be more comprehensively verified.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

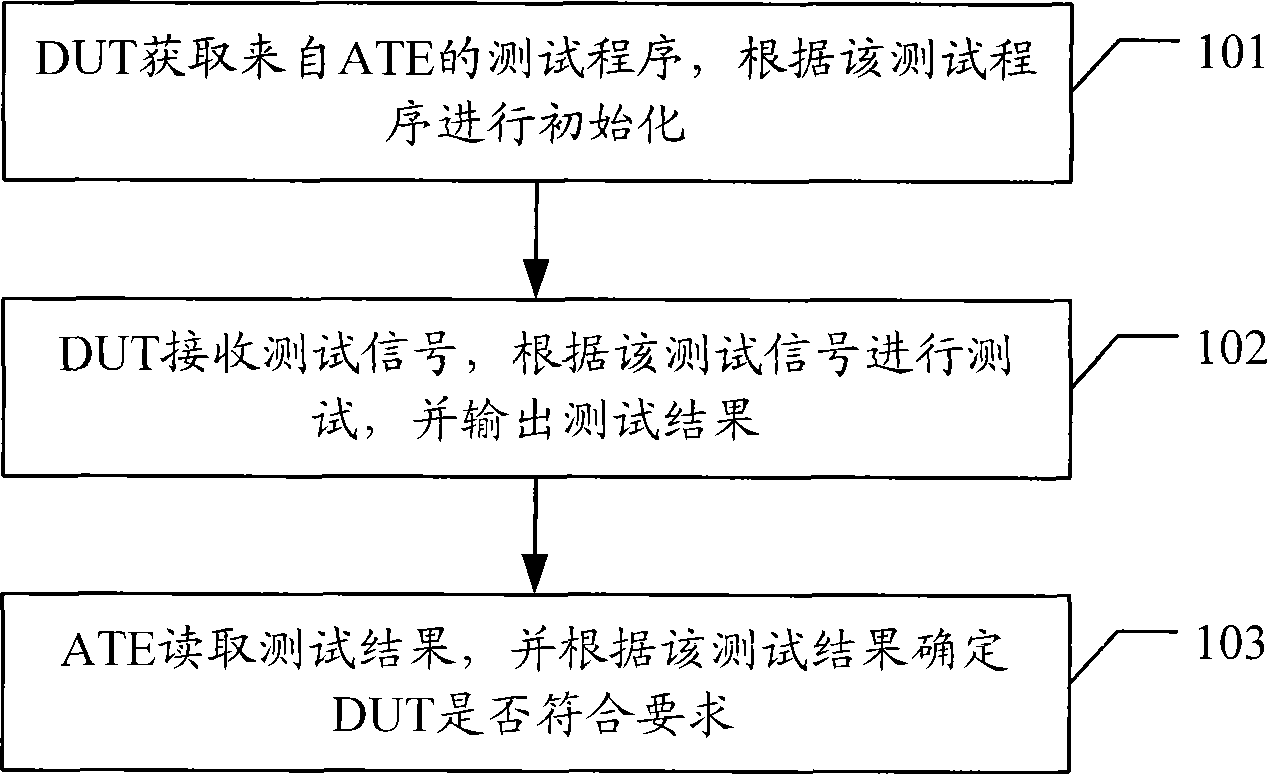

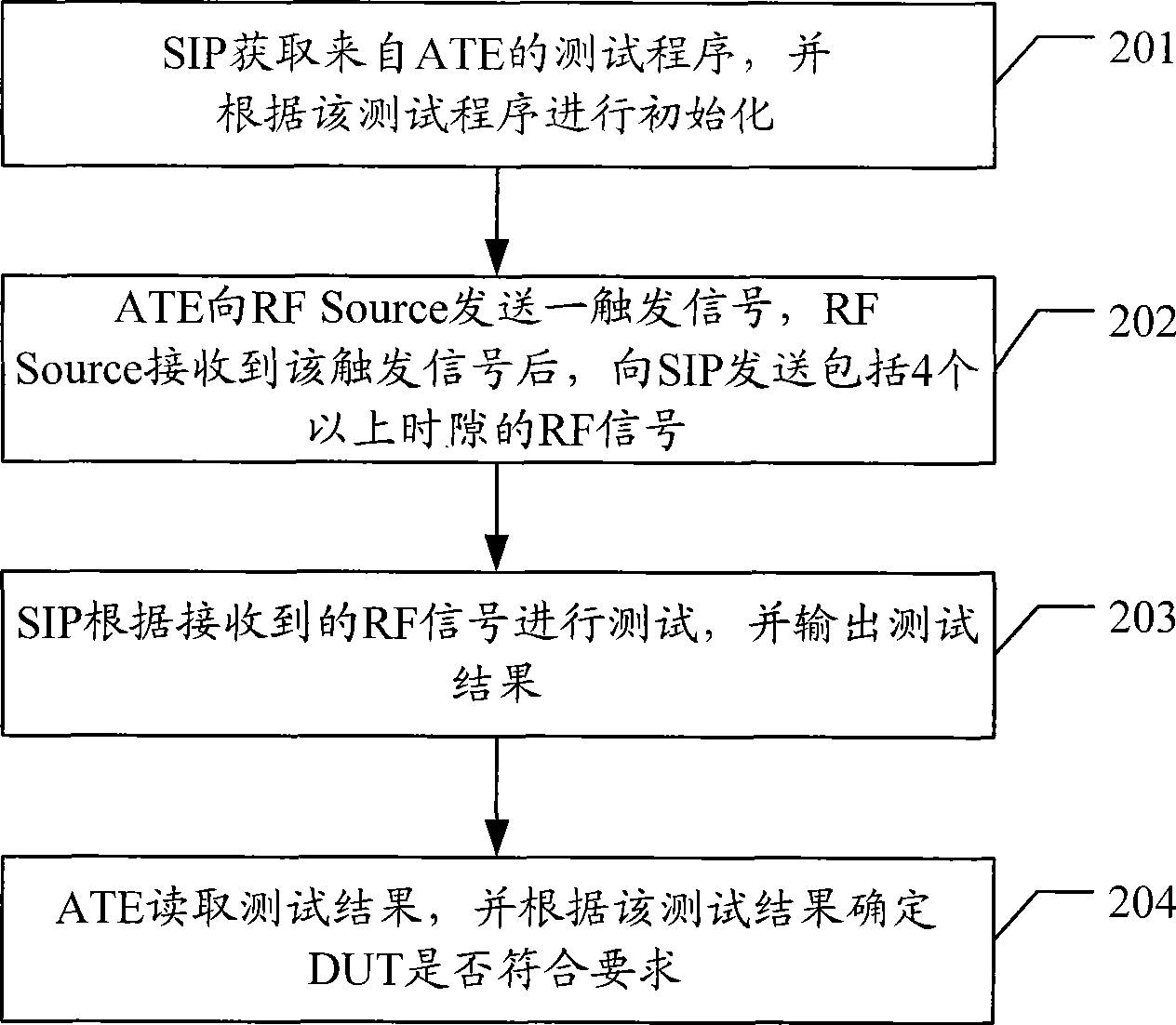

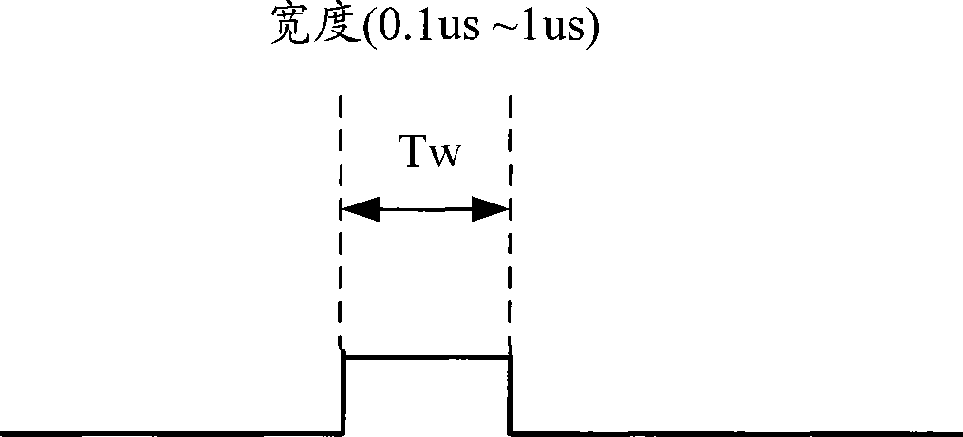

Test method and system

InactiveCN101464491AEasy to implementReduced pin countElectronic circuit testingFault coverageAutomatic test equipment

The invention discloses a testing method which comprises the following steps: acquiring the testing procedure from automatic test equipment (ATE) by using a device under test (DUT) and initializing according to the testing procedure; receiving test signals by using the DUT, and testing according the test signals, and outputting test results; and reading the test results by using the ATE and determining whether the DUT conforms to the requirements according to the test results. The invention simultaneously discloses a testing system. By applying the method and the system, the test cost can be reduced, the fault coverage can be improved, and the invention can be implemented easily.

Owner:新奇点智能科技集团有限公司

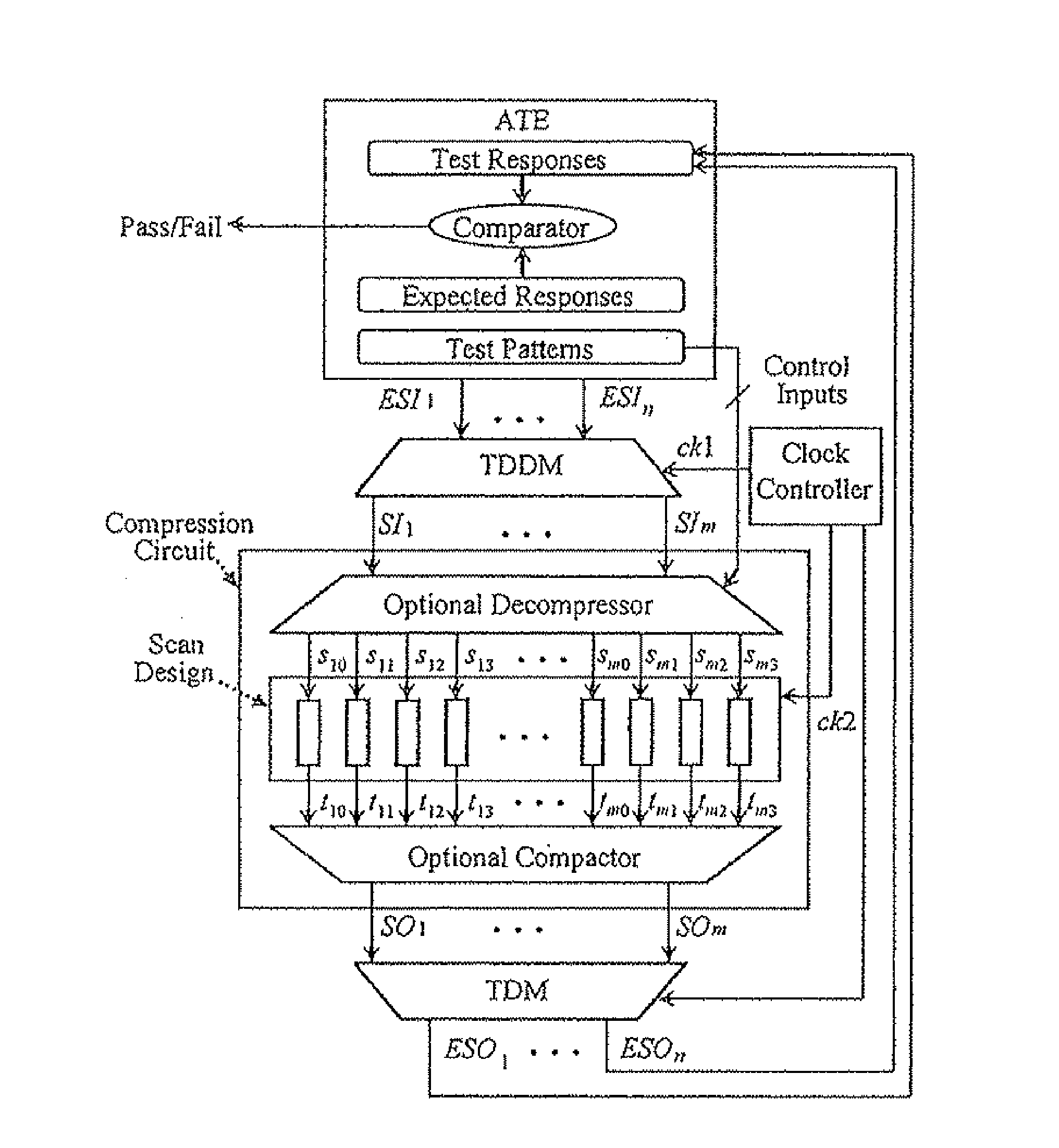

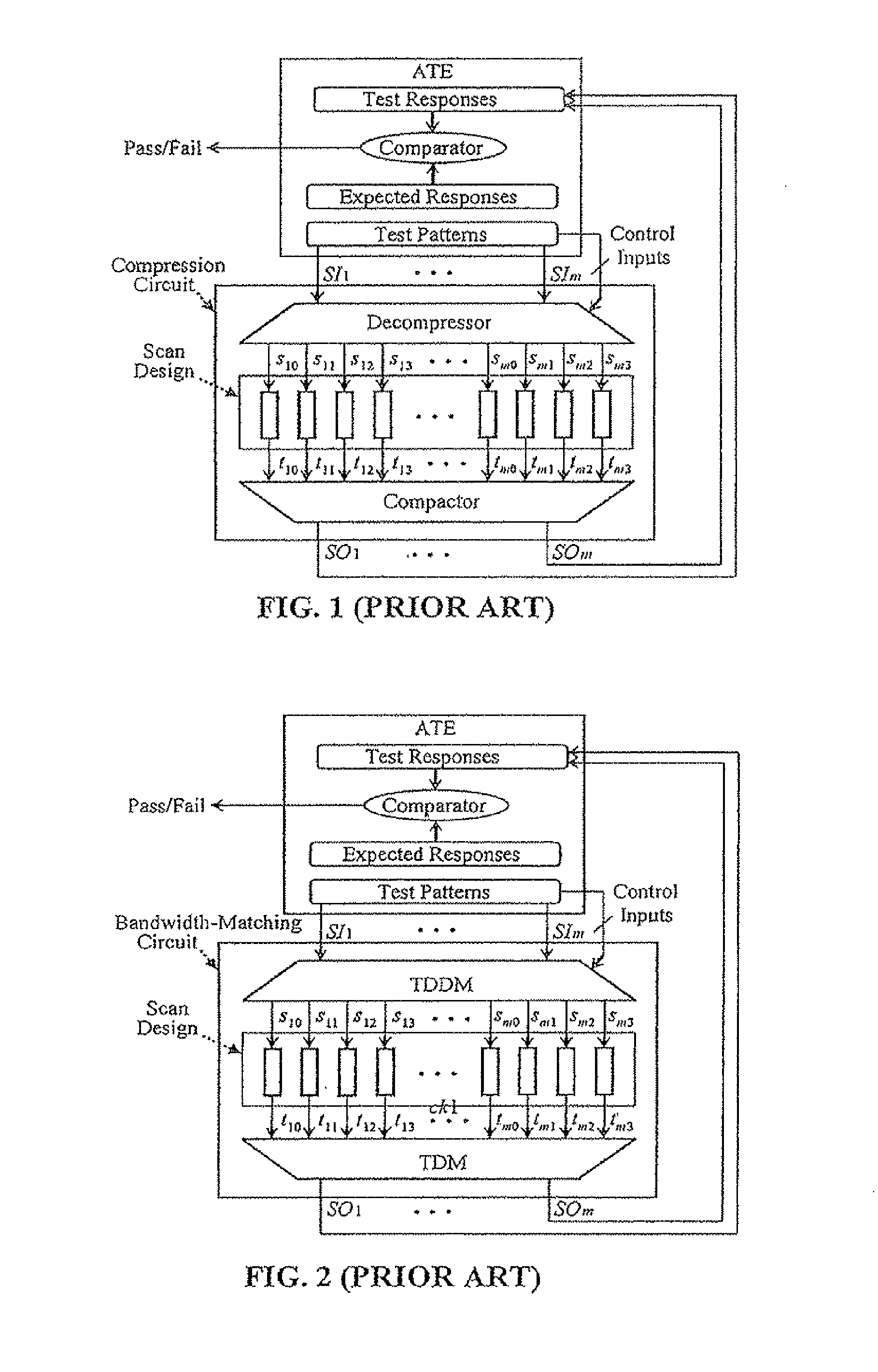

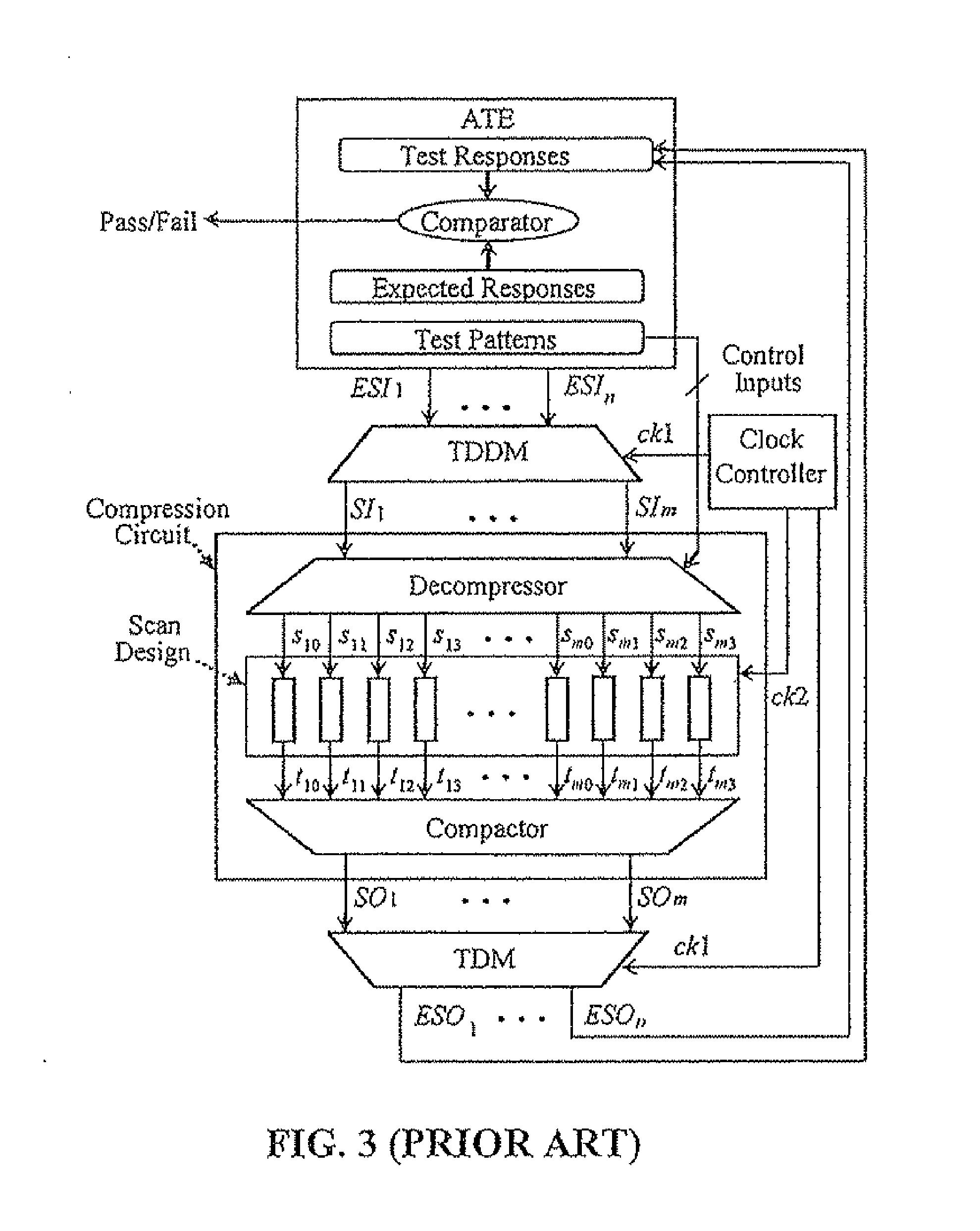

Method and apparatus for testing 3D integrated circuits

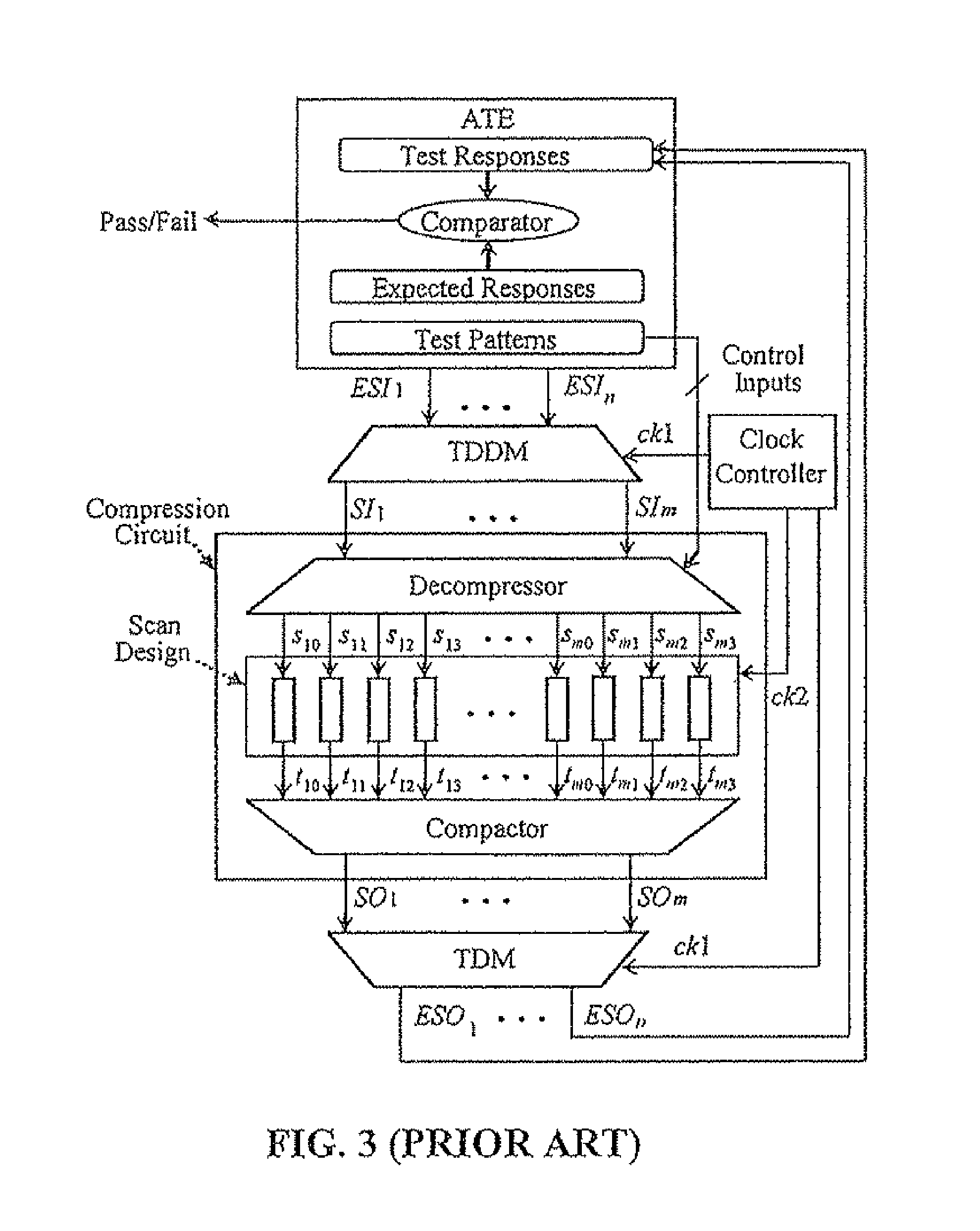

InactiveUS20120110402A1Reduce testing costsIncrease data rateElectronic circuit testingLogical operation testingFault coverageEngineering

A method and apparatus for testing a scan-based 3D integrated circuit (3DIC) using time-division demultiplexing / multiplexing allowing for high-data-rate scan patterns applied at input / output pads converting into low-data-rate scan patterns applied to each embeddded module in the 3DIC. A set of 3D design guidelines is proposed to reduce the number of test times and the number of through-silicon vias (TSVs) required for both pre-bond testing and post-bond testing. The technique allows reuse of scan patterns developed for pre-bond testing of each die (layer) for post-bond testing of the whole 3DIC. It further reduces test application time without concerns for I / O pad count limit and risks for fault coverage loss.

Owner:SYNTEST TECH

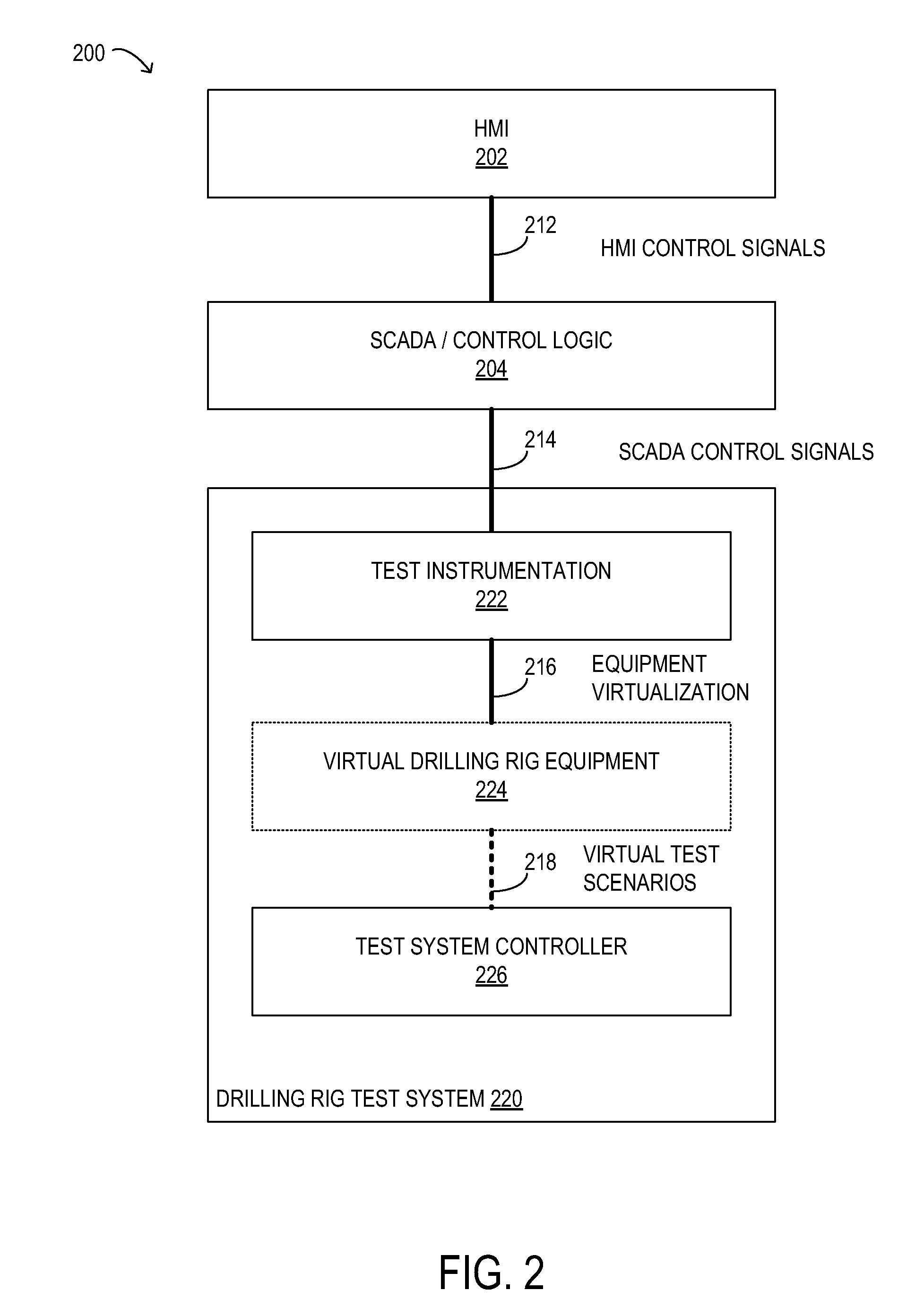

Method and system for drilling rig testing using virtualized components

A method and system dynamically generates virtualized configurations of sensors and signals used in drilling system equipment. The virtualized configurations may be used for novel operational testing of automation systems on drilling rigs. The methods and systems may be configured to virtualize actual drill floor equipment in order to have enhanced fault coverage of the automation systems. A control network that is a component of the automation systems may implement a testing loop that accommodates virtualized equipment in a manner substantially similar to actual equipment. In this manner, the testing loop may be configured to control elements specific to the equipment under control, and generate testing results for those specific control elements.

Owner:ATHENS GRP SERVICES INC

Circuits, architectures, apparatuses, systems, methods, algorithms, software and firmware for using reserved cells to indicate defect positions

ActiveUS7836364B1Less voltage levelEasy to correctError correction/detection using convolutional codesError detection/correctionFault coverageComputer architecture

Circuits, architectures, systems, methods, algorithms, software and firmware for indicating positions of defective data storage cells using reserved (e.g., “pilot”) cells. The circuit generally includes a memory having multiple subunits, each subunit containing multiple data storage cells and at least one reserved cell. The reserved cells store information identifying whether one or more data storage cells in a subunit are defective. The method of identifying defective memory positions generally includes determining the status of data storage cells in a multi-subunit memory; storing such status information in a reserved cell; and reading the reserved cell. In various embodiments, the reserved cells differentiate between fewer voltage levels and / or store a lower density of information than the data storage cells. The present invention improves error correction capabilities using cells that are typically already available in many conventional nonvolatile memories. In some cases, marking data from defective cells as erasures effectively doubles the error correction capability of the system. When the reserved cells contain more than one level, the overhead for a given level of fault coverage decreases as a function of memory size.

Owner:MARVELL ASIA PTE LTD

System for testing system internuclear wiring fault on integrated circuit chip and method thereof

InactiveCN101923133AShorten test timeImprove fault coverageElectrical testingFault coverageMultiplexing

The invention relates to a system for testing a system internuclear wiring fault on an integrated circuit chip and a method thereof. The system comprises a circuit structure which is added for perfecting the IP internuclear wiring fault test and the IP intranuclear fault test in a system on the integrated circuit chip and a test inquiring mechanism which runs on the basis of the circuit structure. The invention can test the IP internuclear wiring of the system on the integrated circuit chip. The fault types of the test comprises the solid-zero fault, the solid-solid fault, the open circuit fault, the short circuit fault, the delaying fault and the noise fault. By adding a hardware structure, the invention decomposes a scanning chain of edge packing units, thereby making the best of a test buss and shortening the test time; with the output type edge packing unit, the invention automatically generates a test vector; with the input type edge packing unit, the invention further shortens the test time. The structure is compatible with the intranuclear test structure, thereby realizing the higher flexibility, making the best of the test resource, and further improving the fault coverage rate of the system of the whole integrated circuit chip. The invention is simple in circuit structure, convenient in test inquiring mechanism, and suitable for the various systems on the integrated circuit chips which are designed and built with the IP multiplexing technology.

Owner:SHANGHAI UNIV

Test method of semiconductor intergrated circuit and test pattern generator

InactiveUS6922803B2Avoid problemsEliminate overheadElectronic circuit testingDetecting faulty computer hardwareFault coverageGraphics

A semiconductor integrated circuit test method which reduces the required data volume for testing and efficiently detects faults in a circuit to be tested, the method comprising means 110 to generate identical pattern sequences repeatedly and means 120 to control flipped bits in pattern sequences, in order to generate neighborhood pattern sequences and use the neighborhood patterns to test the circuit under test 130. The neighborhood patterns include, in whole or in part, such pattern sequences as ones without flipped bits, ones with all or some flipped bits in one pattern and ones with all or some flipped bits in consecutive patterns or patterns at regular intervals, the interval being equivalent to a given number of patterns. Because a test pattern generator is provided independently of the circuit to be tested, the problem of a prolonged design period can be eliminated, a loss in the operating speed of the circuit under test is minimized and a high fault coverage can be achieved with less hardware overhead and a smaller volume of test data.

Owner:HITACHI LTD

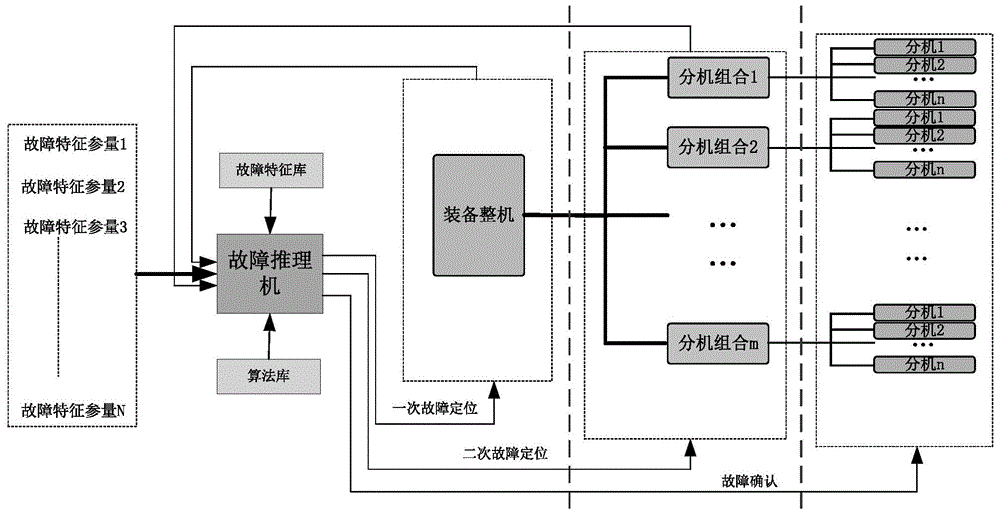

Hierarchical fault diagnosis method for electronic information equipment

The invention provides a hierarchical fault diagnosis method for electronic information equipment, and solves the problems that existing equipment fault diagnosis technology is low in fault detection rate and fault coverage rate, poor in fault isolation capacity and the like. The hierarchical fault diagnosis method includes the steps: firstly, analyzing an equipment fault mode: building an equipment fault model, extracting fault characteristics, and simulating, verifying and evaluating faults; secondly, building a hierarchical fault model: optimizing equipment fault mode analysis results and further reversely guiding system fault model hierarchical optimization; thirdly, building a fault diagnosis system: selecting software and hardware resources according to the fault mode analysis results and the hierarchical fault model obtained by the first step and the second step; fourthly, verifying equipment system-level fault diagnosis: finishing system-level diagnosis testing of the equipment.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

Test assembly including a test die for testing a semiconductor product die

InactiveUS7557596B2Small sizeImprove test coveragePrinted circuit assemblingSemiconductor/solid-state device testing/measurementElectricityFault coverage

One embodiment of the present invention concerns a test assembly for testing product circuitry of a product die. In one embodiment, the test assembly includes at test die and an interconnection substrate for electrically coupling the test die to a host controller that communicates with the test die. The test die may be designed according to a design methodology that includes the step of concurrently designing test circuitry and a product circuitry in a unified design. The test circuitry can be designed to provide a high degree of fault coverage for the corresponding product circuitry generally without regard to the amount of silicon area that will be required by the test circuitry. The design methodology then partitions the unified design into the test die and the product die. The test die includes the test circuitry and the product die includes the product circuitry. The product and test die may then be fabricated on separate semiconductor wafers. By partitioning the product circuitry and test circuitry into separate die, embedded test circuitry can be either eliminated or minimized on the product die. This will tend to decrease the size of the product die and decrease the cost of manufacturing the product die while maintaining a high degree of test coverage of the product circuits within the product die. The test die can be used to test multiple product die on one or more wafers.

Owner:FORMFACTOR INC

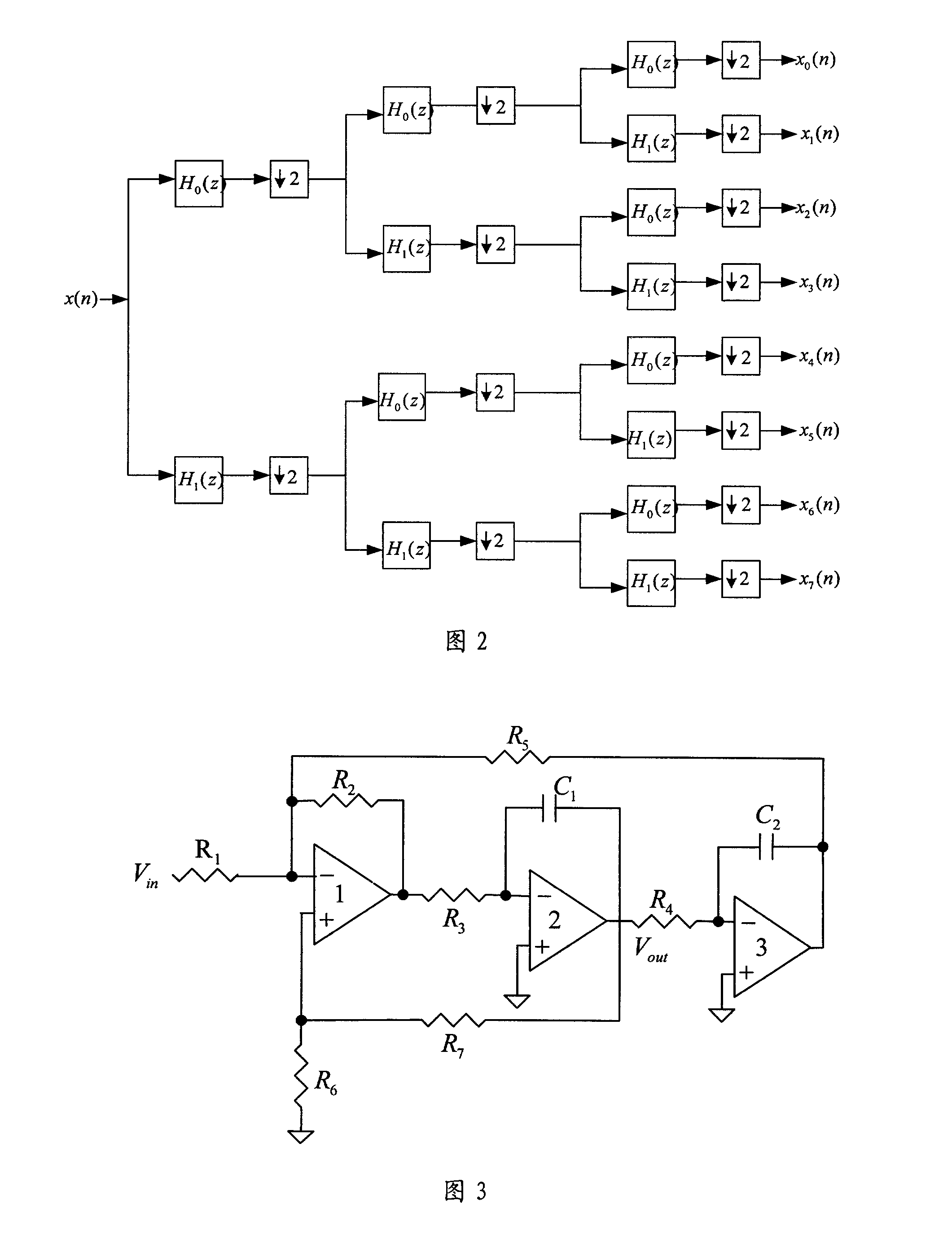

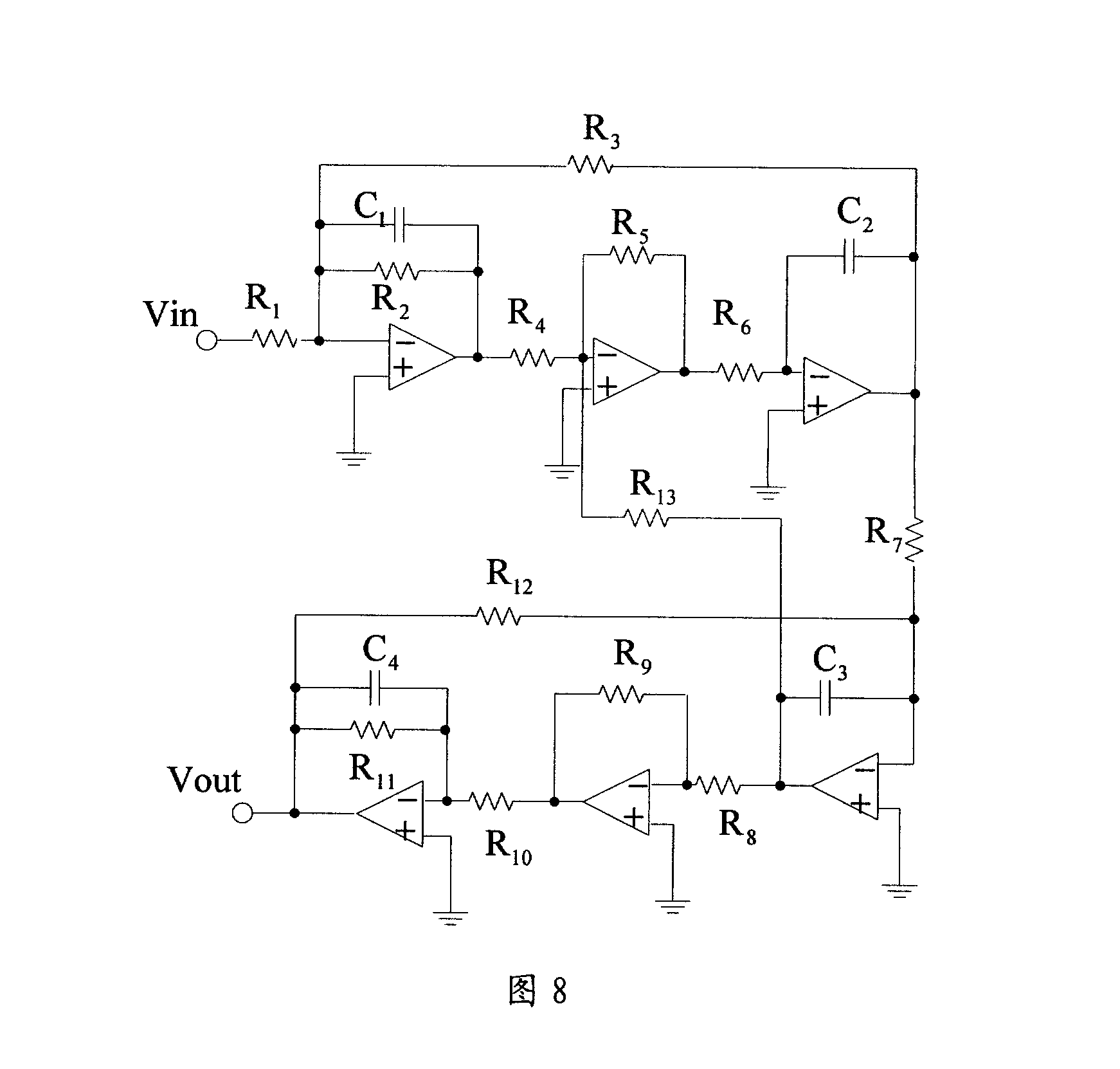

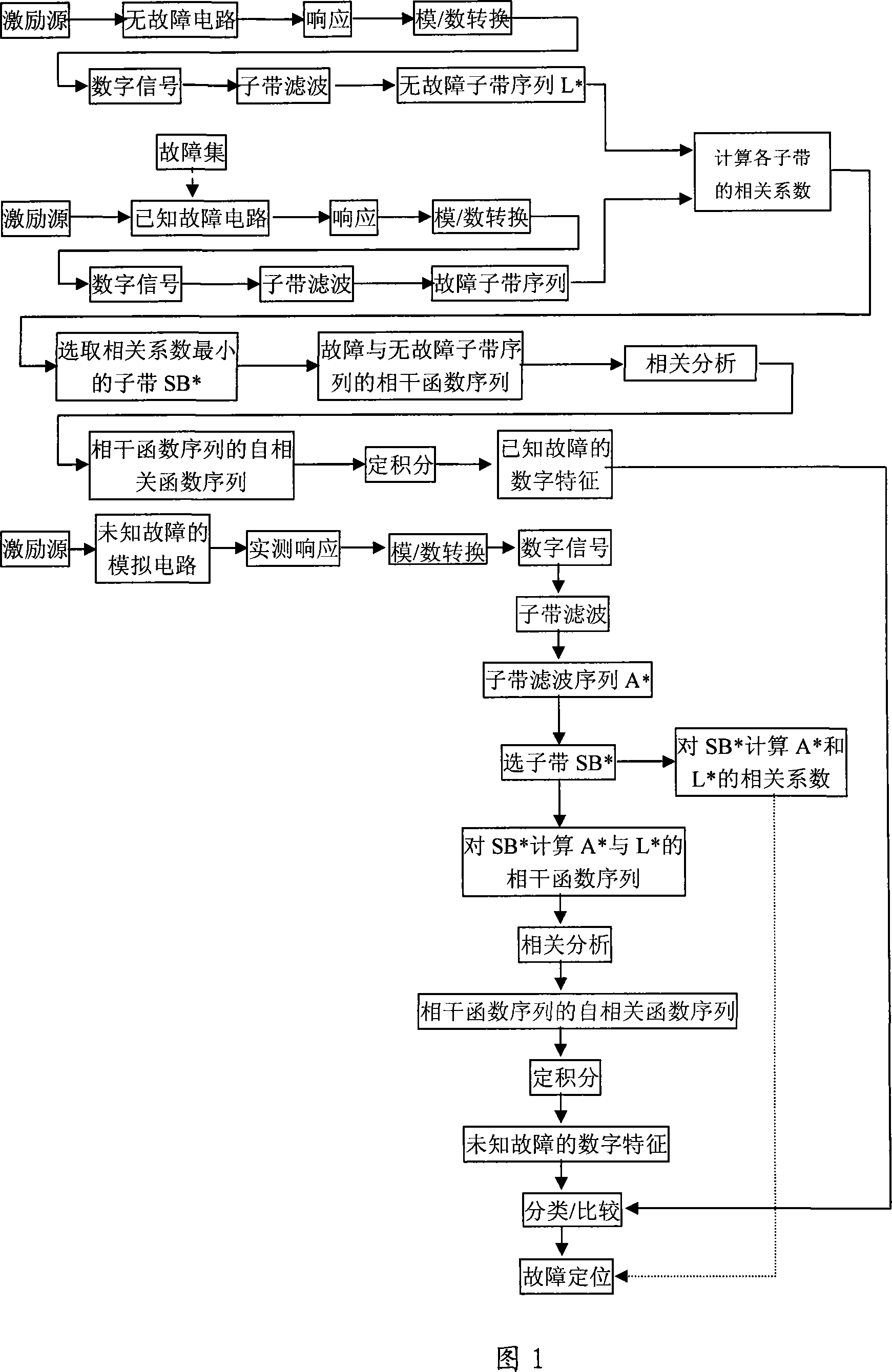

Method for locating parameter type fault of analogue integrated circuit

InactiveCN101201386AImprove the accuracy of fault diagnosisHigh fault resolutionAnalog circuit testingFault coverageImage resolution

The invention discloses a location method of the parameter type fault of the analog integrated circuit. The invention carries out the polyphase filter bank for the measured analog integrated circuit, then calculates the cohere function sequence which corresponds to the faultless sub band sequence for the fault polyphase filter bank sequence in the sub band of the highest fault resolution, and obtains the autocorrelation function sequence of the cohere function sequence, and takes the definite integral answers of the autocorrelation function sequence of the cohere function as the digital characteristic of the fault to realize the fault location. By comparing to the exist technology, the invention can realize the location of the parameter type fault of the analog integrated circuit, reach high accuracy of fault diagnosis, high fault resolution and high fault coverage, realize the multi-parameter type fault location, and easily realize the automation of the fault diagnosis by the digitized fault characteristic with the obvious difference.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Cold rolling process for 304 stainless steel 2B base material for decorative panel

ActiveCN106807751AReduce depthReduce surface roughnessRoll force/gap control deviceBelt grinding machinesFault coverageSolution treatment

The invention discloses a cold rolling process for a 304 stainless steel 2B base material for a decorative panel. The cold rolling process specifically comprises the following steps of: solution treatment, online pickling, pickling, coping, cold rolling, cold rolling and annealing, pickling after cold rolling and annealing, leveling, shearing and packaging by means of a transverse shear. The cold rolling process disclosed by the invention has the advantages that by combining optimization of a cold rolling step in three aspects, the surface roughness of the final 2B base material is low, the fault coverage is extremely small, the surface of strip steel is uniform and smooth, and the 304 stainless 2B which is excellent in grinding and polishing properties can directly replace a 304 stainless BA plate to be used as the base material of the decorative panel which is relatively high in surface requirement. The production process is simpler than a step of the 304 stainless steel BA plate, so that the production cost is lowered, and the processing efficiency is increased.

Owner:GANSU JIU STEEL GRP HONGXING IRON & STEEL CO LTD

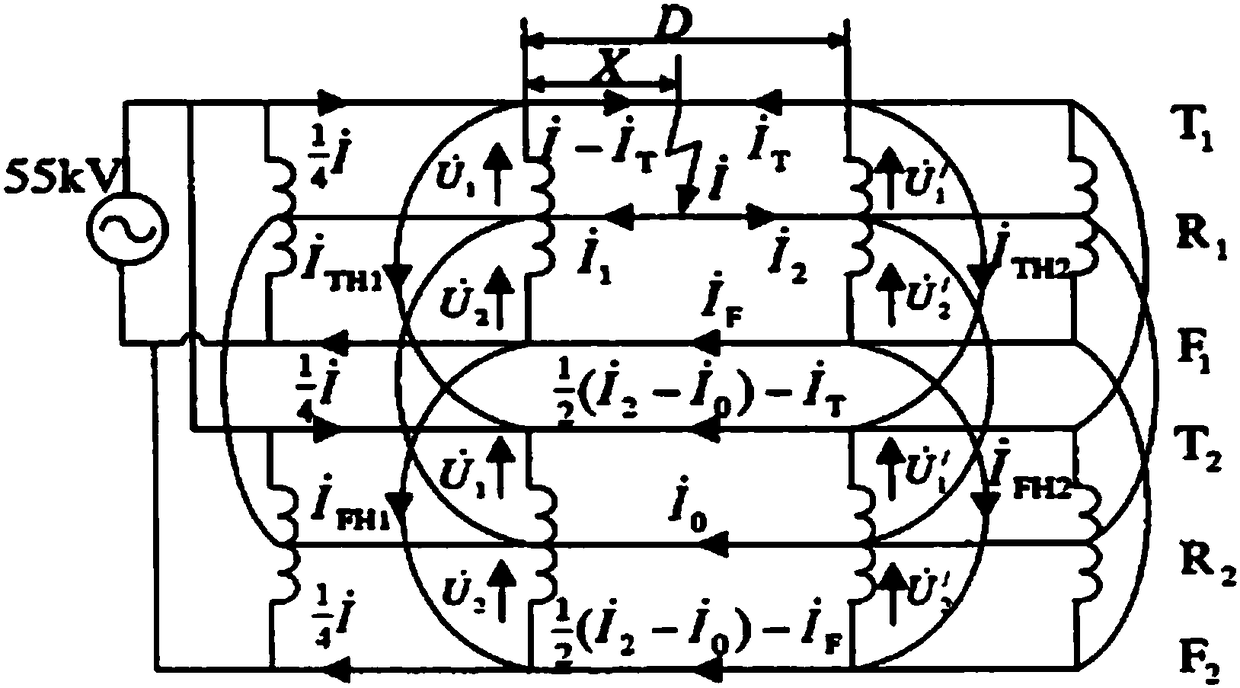

Method for improving fault range finding precision of CRH (China Railway High-speed) maintenance and management traction substation

ActiveCN108152669AImprove accuracyImprove fault location accuracyFault locationFault coverageShort-circuit test

Owner:CHINA RAILWAY ELECTRIFICATION BUREAU GRP5TH ENG

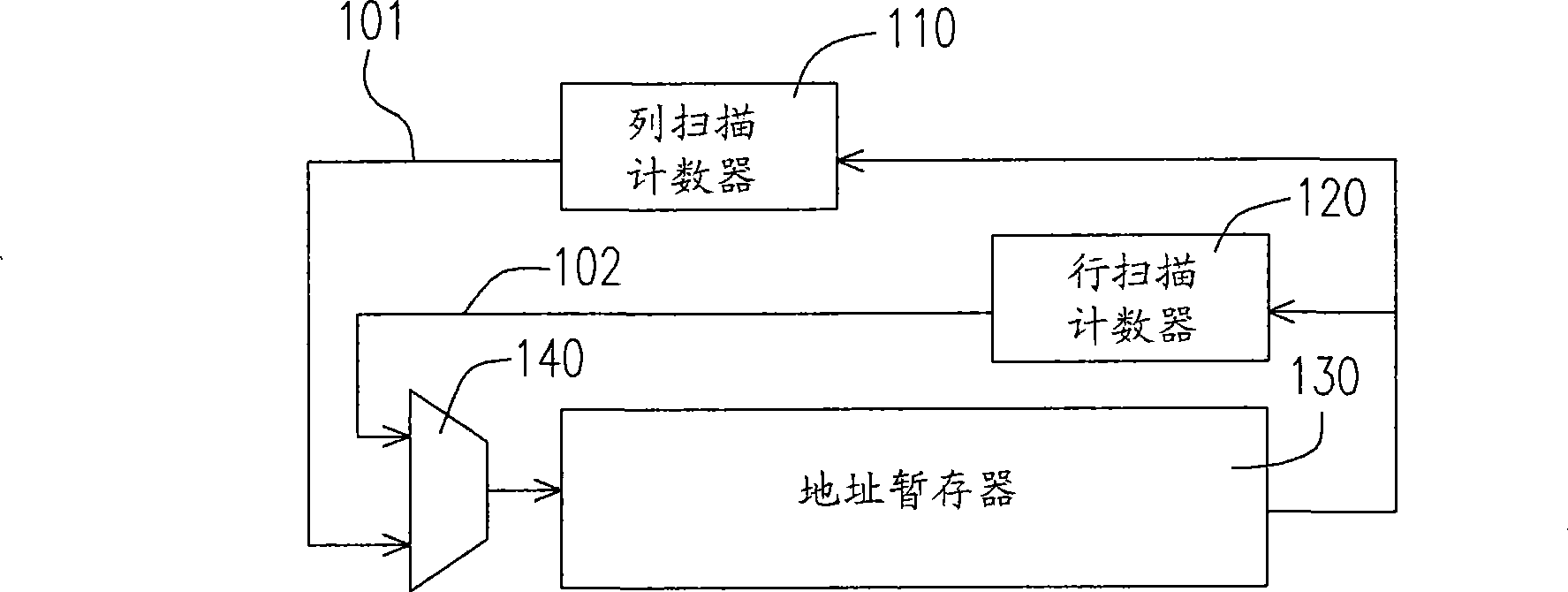

Built-in self-testing circuit and clock switching circuit of programmable memory

InactiveCN101399087AMeet the testing needs of different applicationsQuality improvementStatic storageFault coverageHemt circuits

The invention provides a programmable memory build-in self-test circuit and a clock switching circuit. Through an instruction decoder and a built-in test controller, more self-test functions can be set by users, abundant circuits in the traditional technology are simplified, and the area of a chip is lowered to reduce the cost. Control circuits around the memory are also provided. Less area is occupied. The position of the memory can be tested more flexibly. The clock switching circuit is also provided. The chip can be correctly tested at clocks of different speeds. The testability and the analyzability of the memory in the chip can be improved. And the error covering rate is improved.

Owner:FARADAY TECH CORP

Systems and Methods for Improved Fault Coverage of LBIST Testing

InactiveUS20070273401A1Improve fault coverageReduce in quantityElectronic circuit testingError detection/correctionFault coverageEngineering

Systems and methods for improved fault coverage of logic built-in-self-tests (LBISTs) in integrated circuits (ICs) by determining weighting and / or seed values to be used in generating pseudorandom test bit patterns for each channel to optimize fault coverage. In one embodiment, a method includes generating a pseudorandom sequence of bits, applying a weighting value to the sequence, propagating the weighted sequence through one or more levels of logic, and capturing the resulting data. Metrics are then applied to the captured data to determine the suitability or optimality of the weighting value, and an optimal weighting value is selected. This may be performed for a plurality of trial values for each of a number of channels to obtain a set of weighting values for the different LBIST channels. The method may also include determining a seed value for the pseudorandom bit pattern generator.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

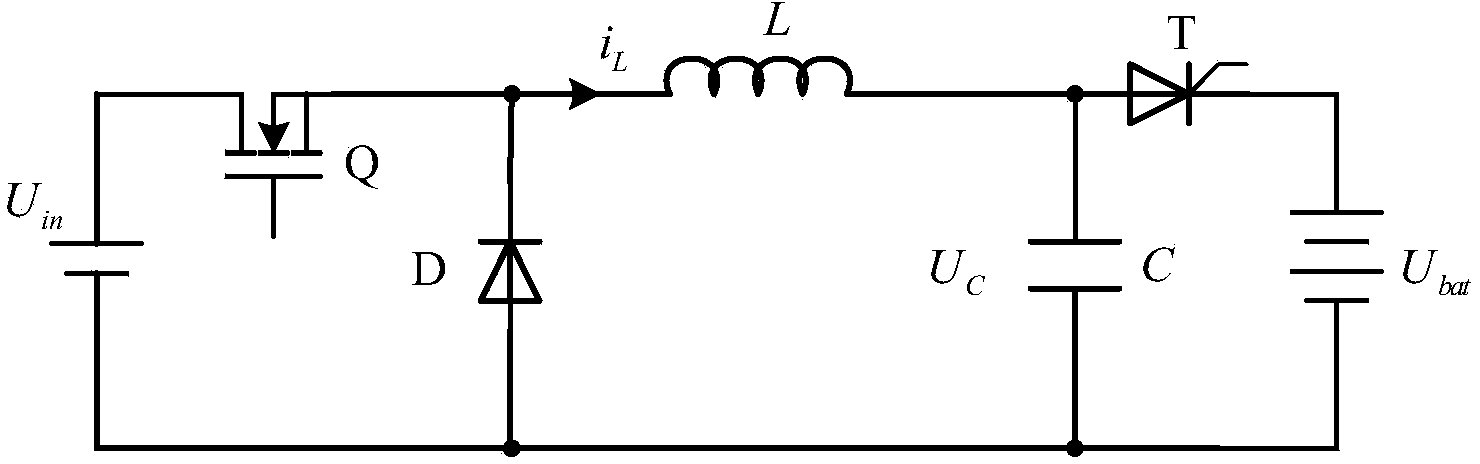

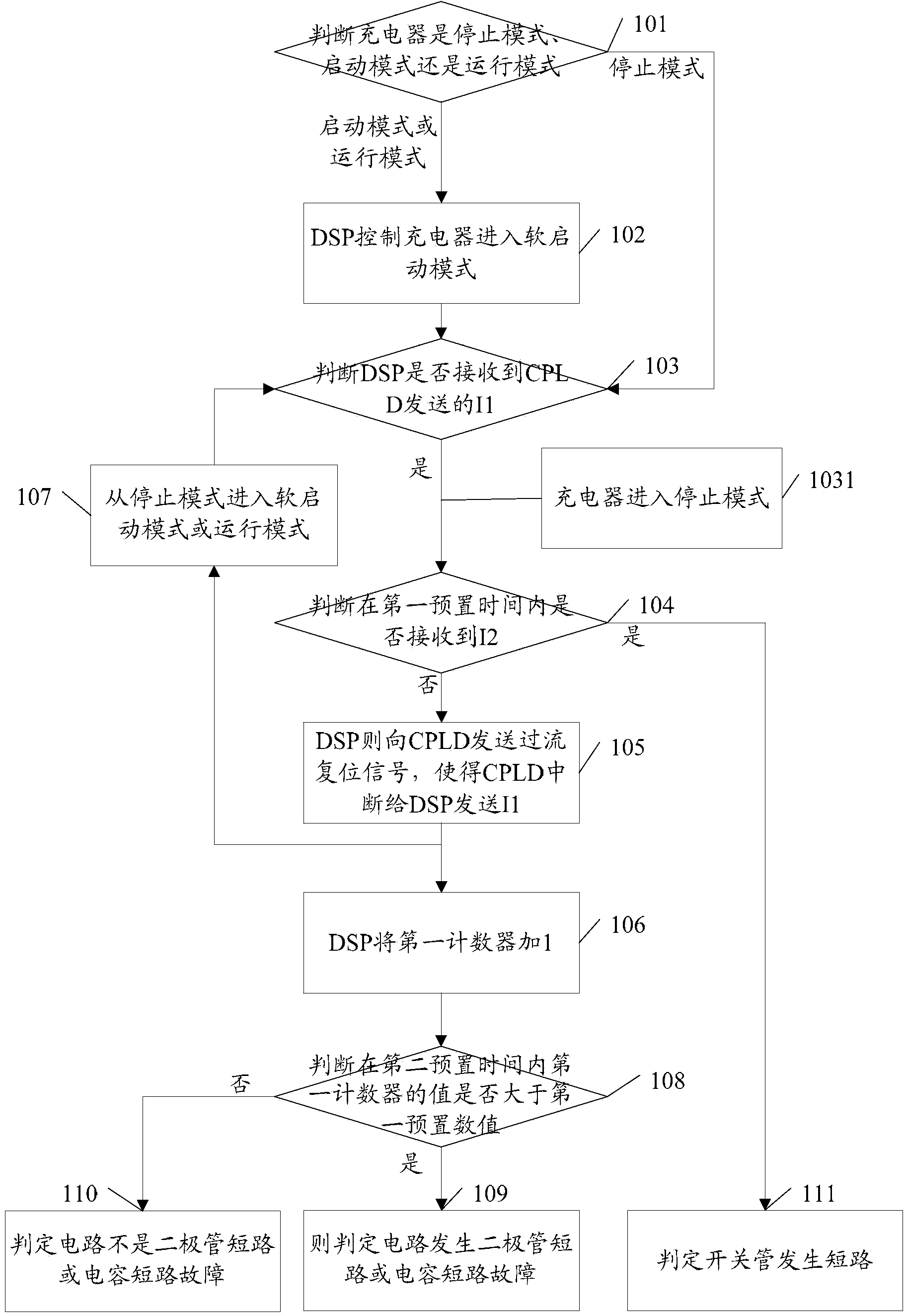

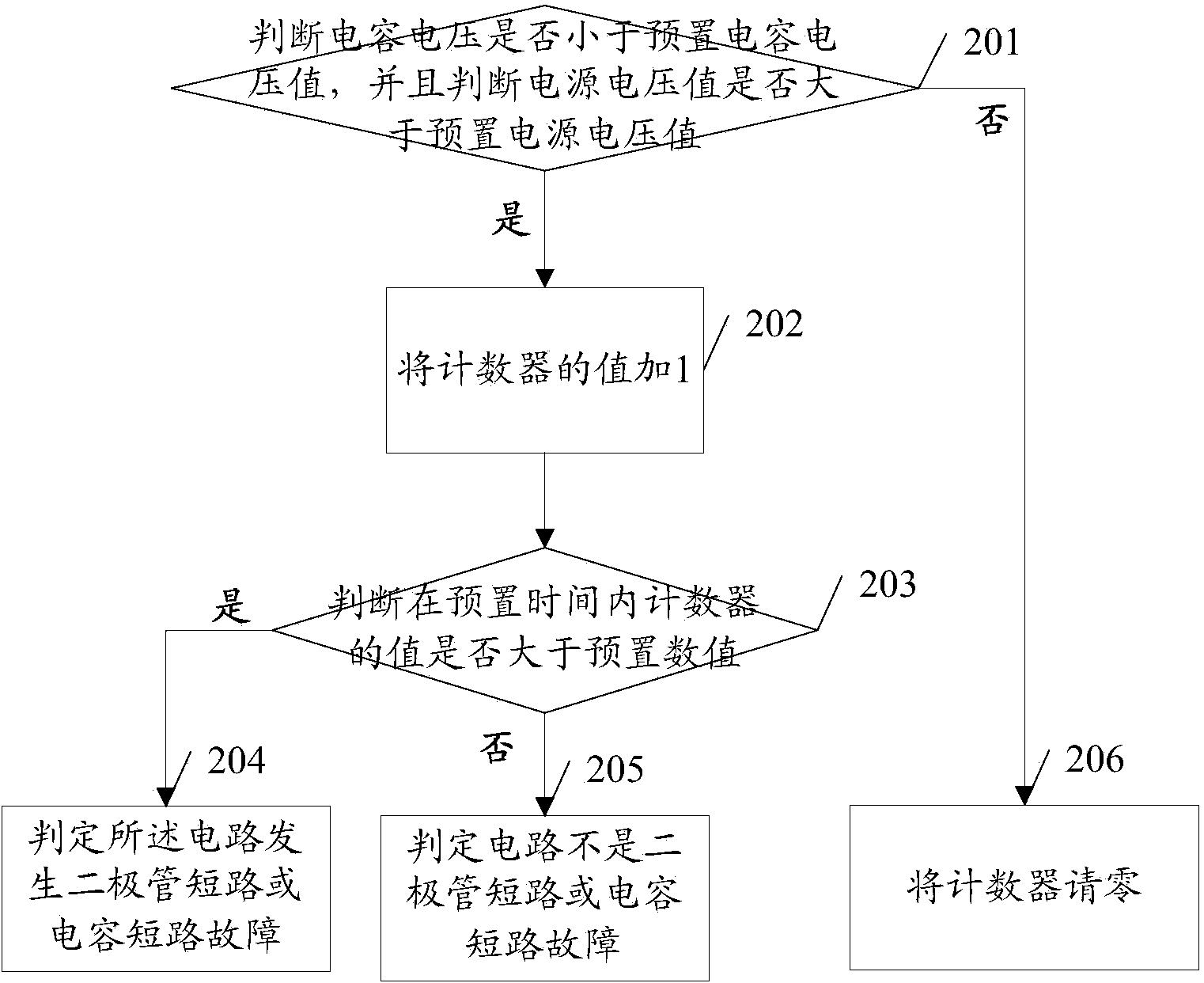

Circuit fault detection method, circuit fault detection system and controller

ActiveCN103713255AEffective protectionTimely protectionElectronic circuit testingEmergency protective circuit arrangementsCapacitanceFault coverage

The embodiment of the invention discloses a circuit fault detection method, a circuit fault detection system and a controller. According to the method disclosed by the embodiment of the invention, fault detection is carried out by making use of repeated and cyclic behavior characteristics of a charger after a free-wheeling diode or a capacitor is short-circuited when electronic equipment is in a soft start or operation mode, and fault detection is carried out by making use of the characteristics of capacitor voltage and battery voltage in the operation process of the electronic equipment. According to the embodiment of the invention, different detection schemes are adopted according to different characteristics of the electronic equipment before and after startup, effective detection can be carried out under various operation conditions without increasing the device cost, and false report or missing report does not occur; and over-current signal detection is adopted in the embodiment of the invention to timely perform a wave sealing action, a device can be timely protected during fault detection, the fault coverage is not enlarged, damage to other adjacent devices can be avoided, and the detection is quick and effective.

Owner:HUAWEI DIGITAL POWER TECH CO LTD

Compressing method for SOC testing data suitable for suitable for multi-scanning chain designing core

InactiveCN101042714AImprove compression efficiencyImprove fault coverageSpecial data processing applicationsFault coverageComputer architecture

This invention relates to one SOC test data compression method for multi-scanning linkage design in SOC test technique, which solves the problems of current method for large volume of data and non-module fault coverage rate with high cost and comprises the following steps: a, ranking the test set TD according to multiple links; b, using similar group to divide formula set; c, ranking each set of decreasing order; d, setting dictionary items number; e, zero plus index code, one plus test section to express each test section to get compressed test set TE.

Owner:HARBIN INST OF TECH

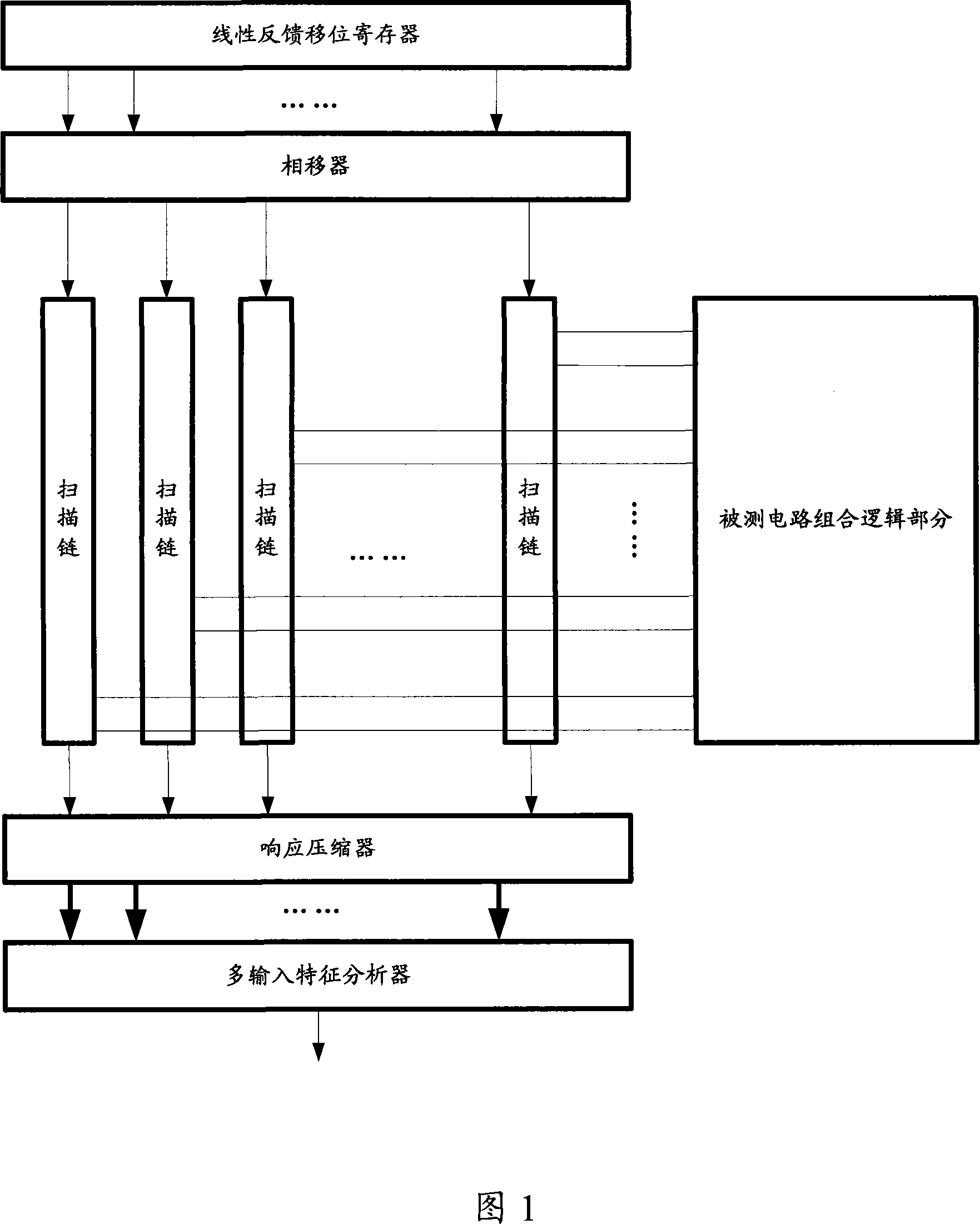

Device and method for determinacy self-testing test data compression

ActiveCN101226228ASave storage spaceCoverage with a high probability of failureElectrical testingLogic circuits using elementary logic circuit componentsFault coverageData memory

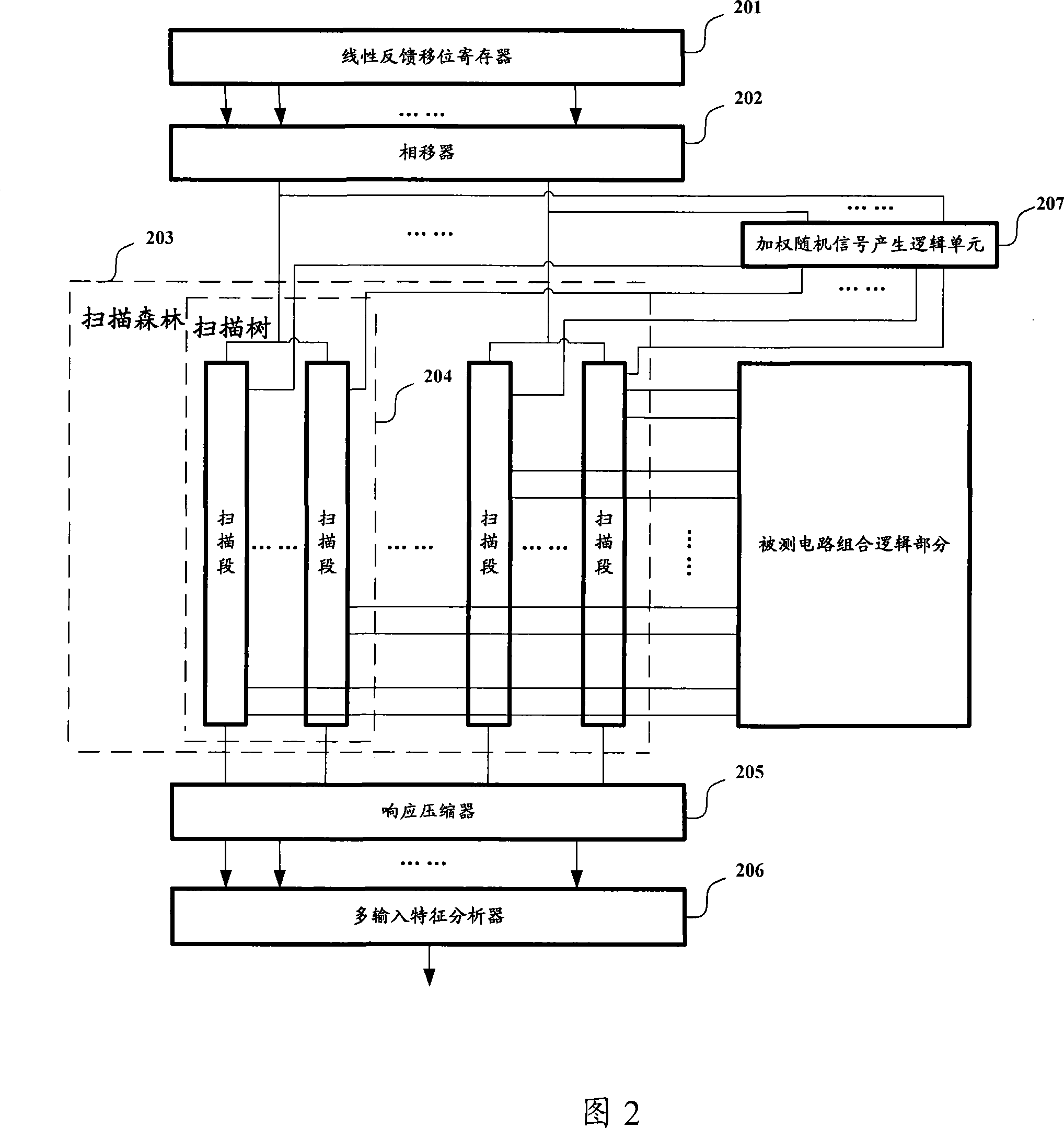

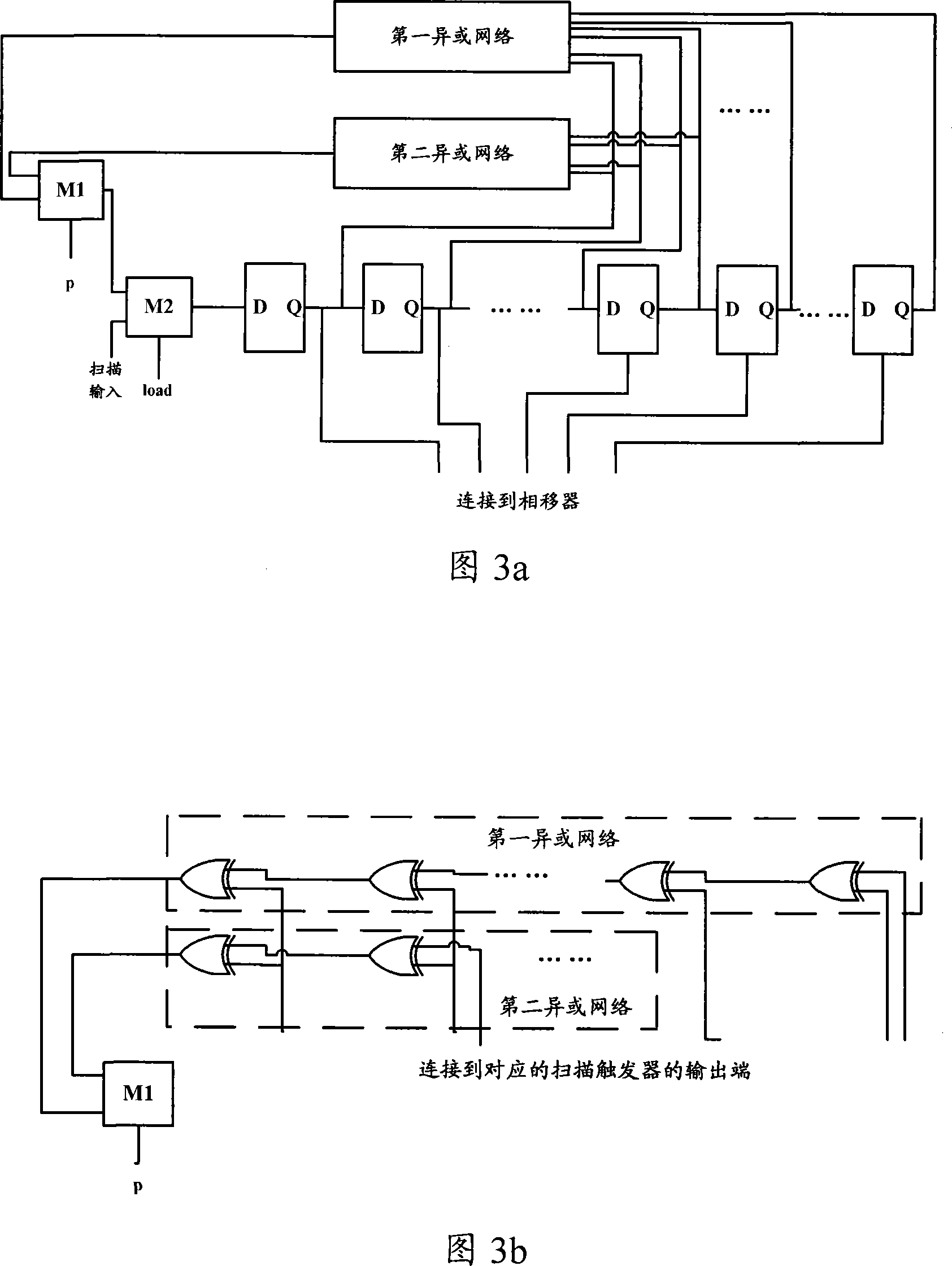

The invention relates to a method for compressing the test data of integrated circuit, belonging to integrated circuit technical field, in particular to a deterministic self-test test data compressor. The invention comprises a phase shifter, a response compressor, a linear feedback shift register with a first and a second xor network while the shift register is connected with the phase shift, a scanning tree and a weigh random signal generating logic unit while the scan forest is connected with the phase shift, the gating signal end of the scan forest is connected with the weight random signal generating logic unit, and the output of the scan forest is connected with the response compressor. The invention further provides a deterministic self-test test data compression method. The invention uses the weight random signal generating logic unit to control the frequency of special signal of the input signal of the scan forest, to improve the fault coverage rate into the false random self-test process, to reduce the test data memory space generated by deterministic test vector.

Owner:TSINGHUA UNIV

Integrated circuit with increased fault coverage

An electronic design automation (EDA) tool for increasing the fault coverage of an integrated circuit (IC) design includes a processor that inserts at least one XOR gate, an AND gate, an OR gate and a multiplexer between observation test points and an existing first scan flip-flop of the IC design. The XOR gate provides an observation test signal to the first scan flip-flop by way of the AND gate, the OR gate, and the multiplexer such that the observation test signal covers the presence of faults at the observation test points. The first scan flip-flop outputs a data input signal, a set of test patterns, and a first set of test signals based on the observation test signal to indicate whether the IC design is faulty or not. A testable IC that can be structurally tested is fabricated using the IC design.

Owner:NXP USA INC

Method for acquiring discrete state parameters of power transformer

The invention discloses a method for acquiring discrete state parameters of a power transformer, which solves problems of difficult power transformer state parameter recognition and difficult power transformer multi-source data mining. According to the invention, a discrete gas state parameter is acquired by adopting an improved equal width method according to the type and the content of dissolved gases in tested power transformer oil; a discrete partial discharge state parameter is acquired by adopting an information entropy decision tree method according to a discharge capacity statistical parameter, a discharge phase statistical parameter and a number of discharge statistical parameter; a discrete winding state parameter is acquired by adopting a binning method according to winding deformation and short-circuit current; and a discrete mechanical state parameter is acquired by adopting a chi-square test method according to the transformer temperature, vibration and noises. The method disclosed by the invention is applicable to the fields of power equipment detection and data mining, has the characteristics o f accurate data, high work efficiency, wide fault coverage, easy computer processing and the like, and has high economic values and broad market application prospects.

Owner:CHINA ELECTRIC POWER RES INST +3

Design method of scanning unit based on partial scanning of improved test vector set

InactiveCN102323538AReduce redundancyReduce hardware redundancyElectrical testingFault coverageOnline test

The invention discloses a design method of a scanning unit based on partial scanning of an improved test vector set, relating to the technical field of SOC (system-on-a-chip) test of digital integrated circuits, and solving the problems of delayed test, hardware redundancy and large required capacity of a memory in the conventional online test method. The method comprises the following steps of: firstly, obtaining an important equivalent output pin which is important to fault detection by stimulating a fault of an equivalent output pin in a combined part of a sequence circuit; secondly, obtaining the improved test vector set by stimulating a fault of an equivalent input pin in the combined part of the sequence circuit; and finally, according to the improved test vector set and an equivalent output pin which is unimportant to the fault detection, dividing triggers into fixed-input triggers and important triggers, and serially connecting the important triggers to form a partial scanningchain. By the method, the obtained scanning unit has a relatively high fault coverage rate and can reduce the hardware redundancy of a test circuit, the digit of bits of the test vector and the memory space.

Owner:HARBIN INST OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com