Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

107 results about "Design engineer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A design engineer is a person who may be involved in any of various engineering disciplines including civil, mechanical, electrical, chemical, textiles, aerospace, nuclear, manufacturing, systems, and structural /building/architectural. Design engineers tend to work on products and systems that involve adapting and using complex scientific and mathematical techniques. The emphasis tends to be on utilizing engineering physics and sciences to develop solutions for society.

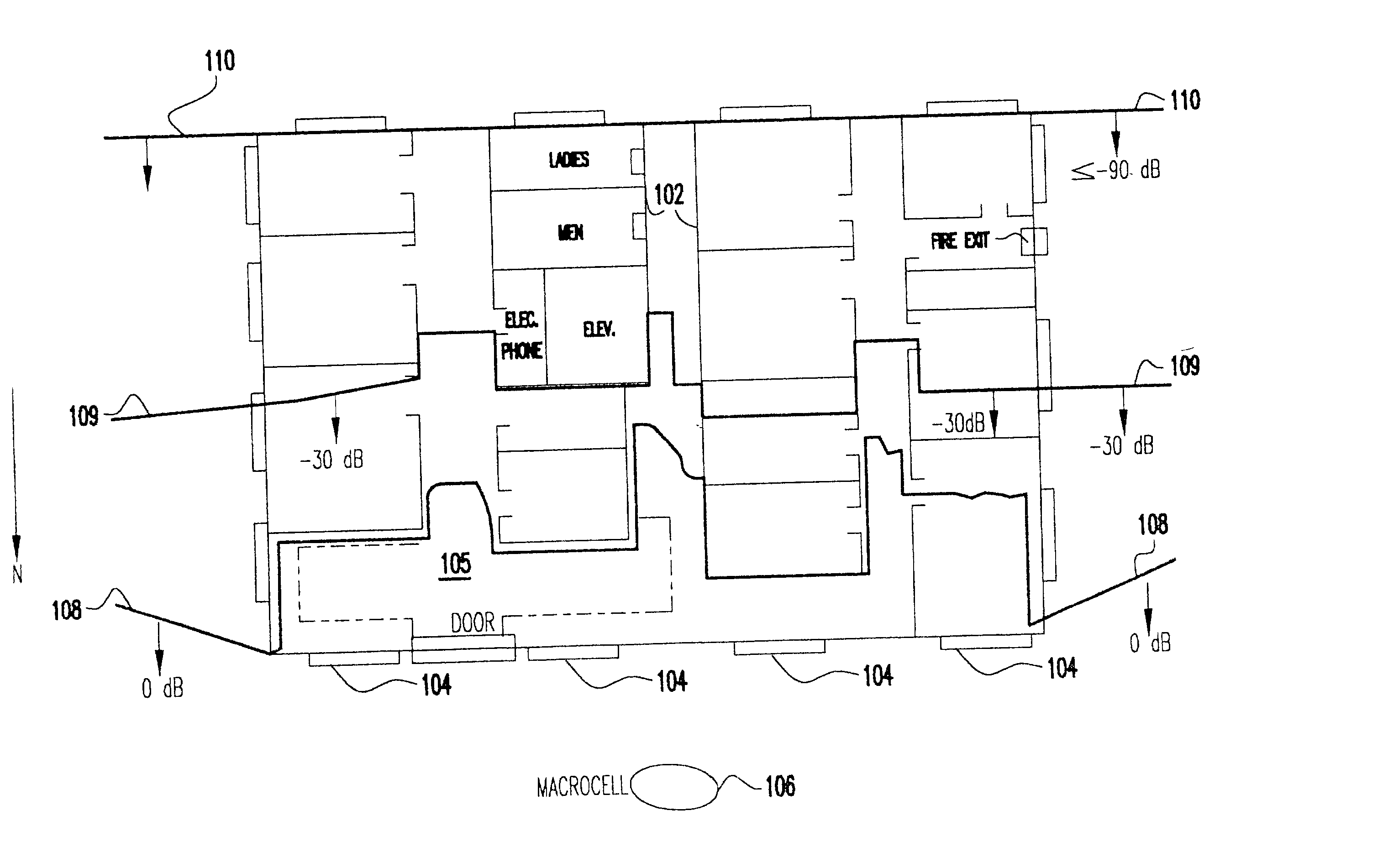

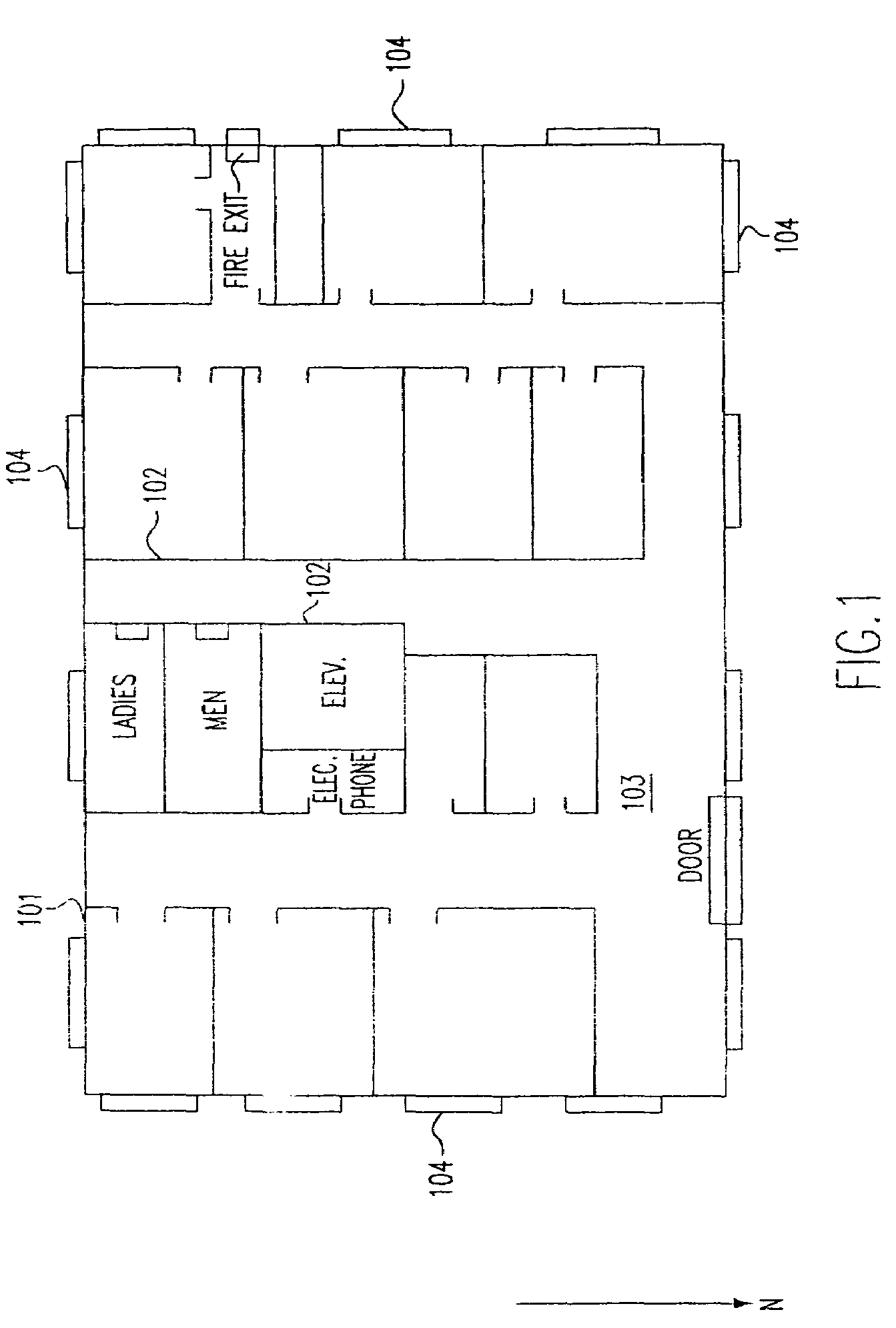

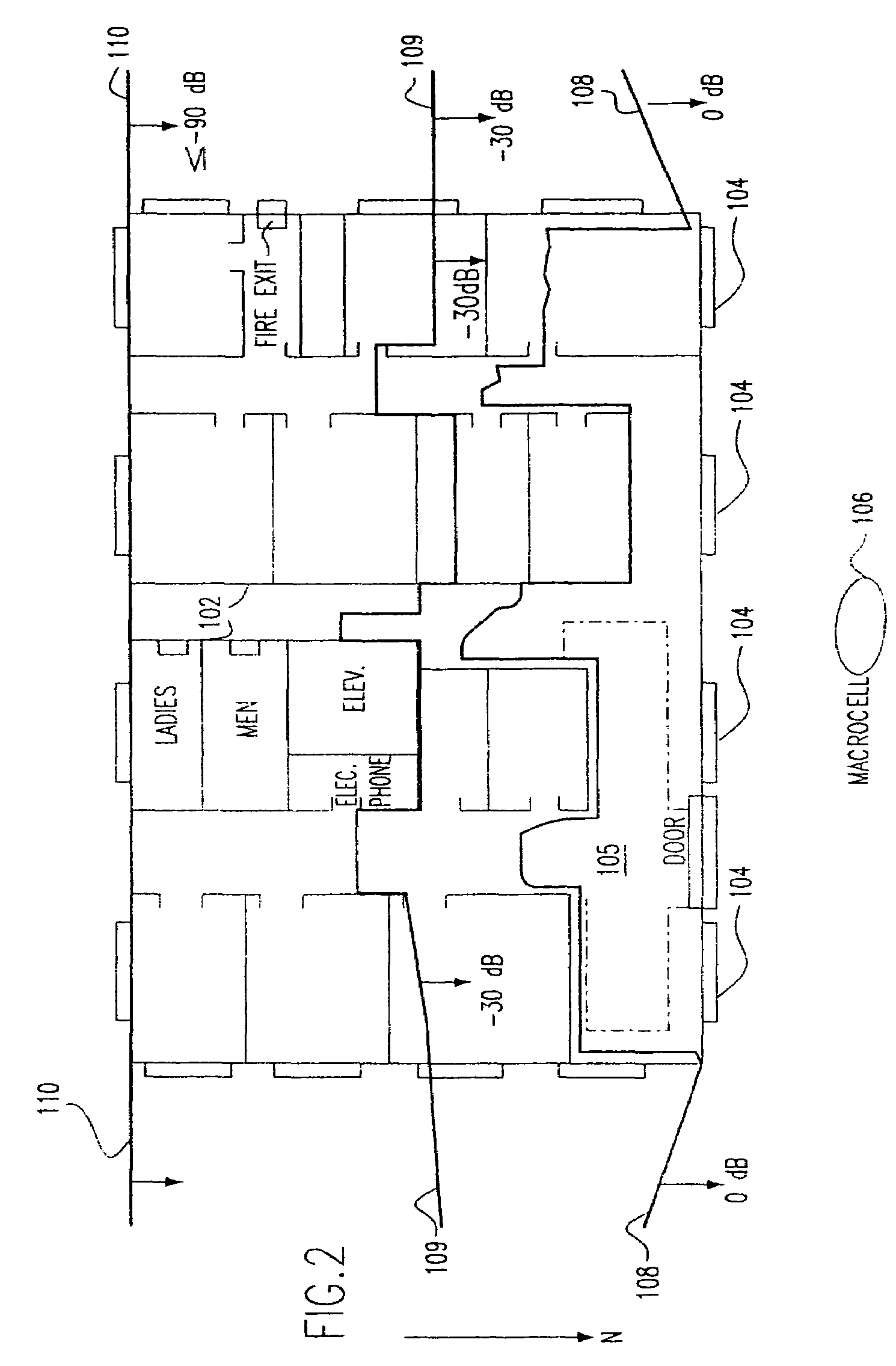

System and method for efficiently visualizing and comparing communication network system performance

InactiveUS7246045B1Easy to displayDrawing from basic elementsReceivers monitoringTerrainCommunications system

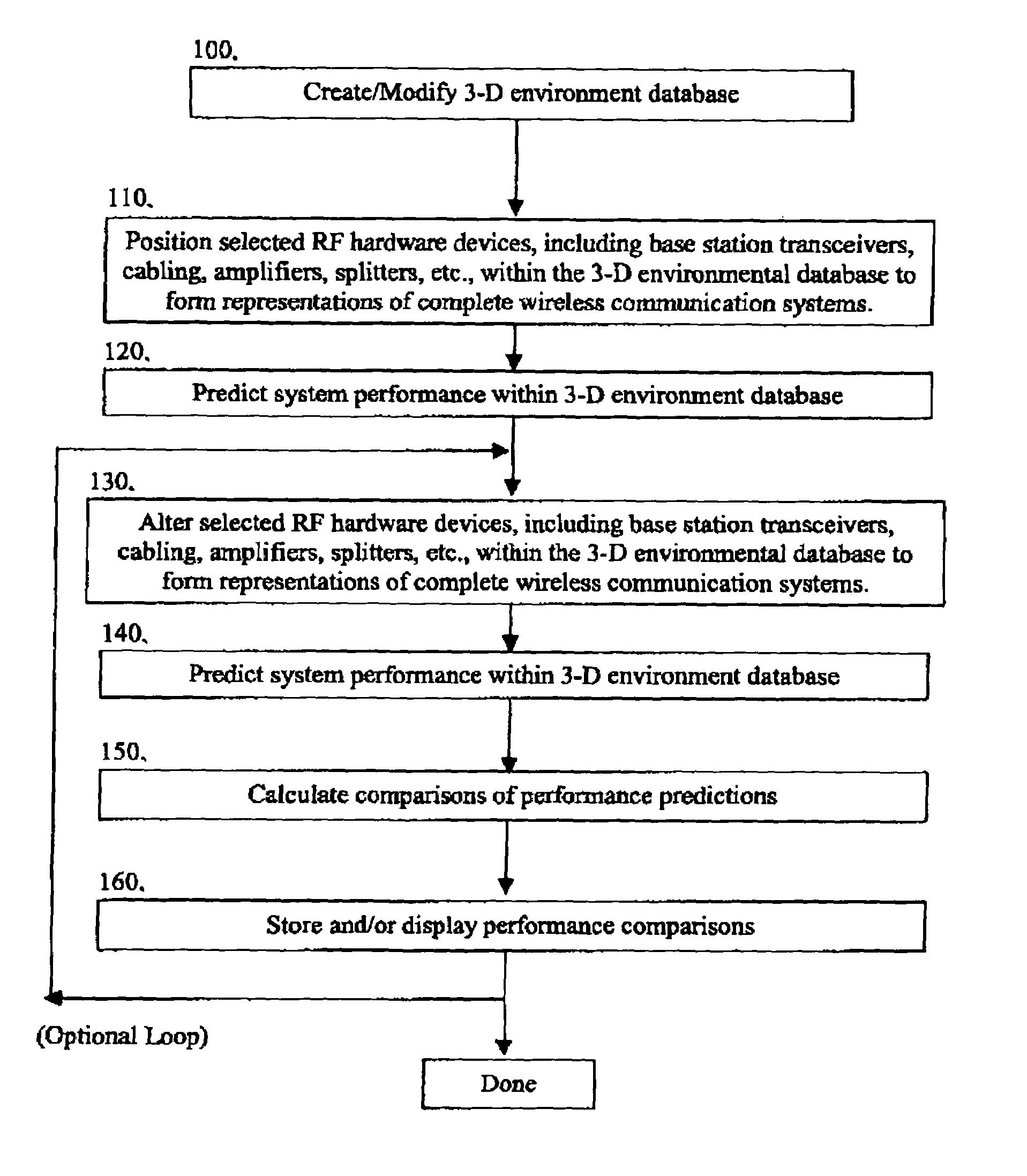

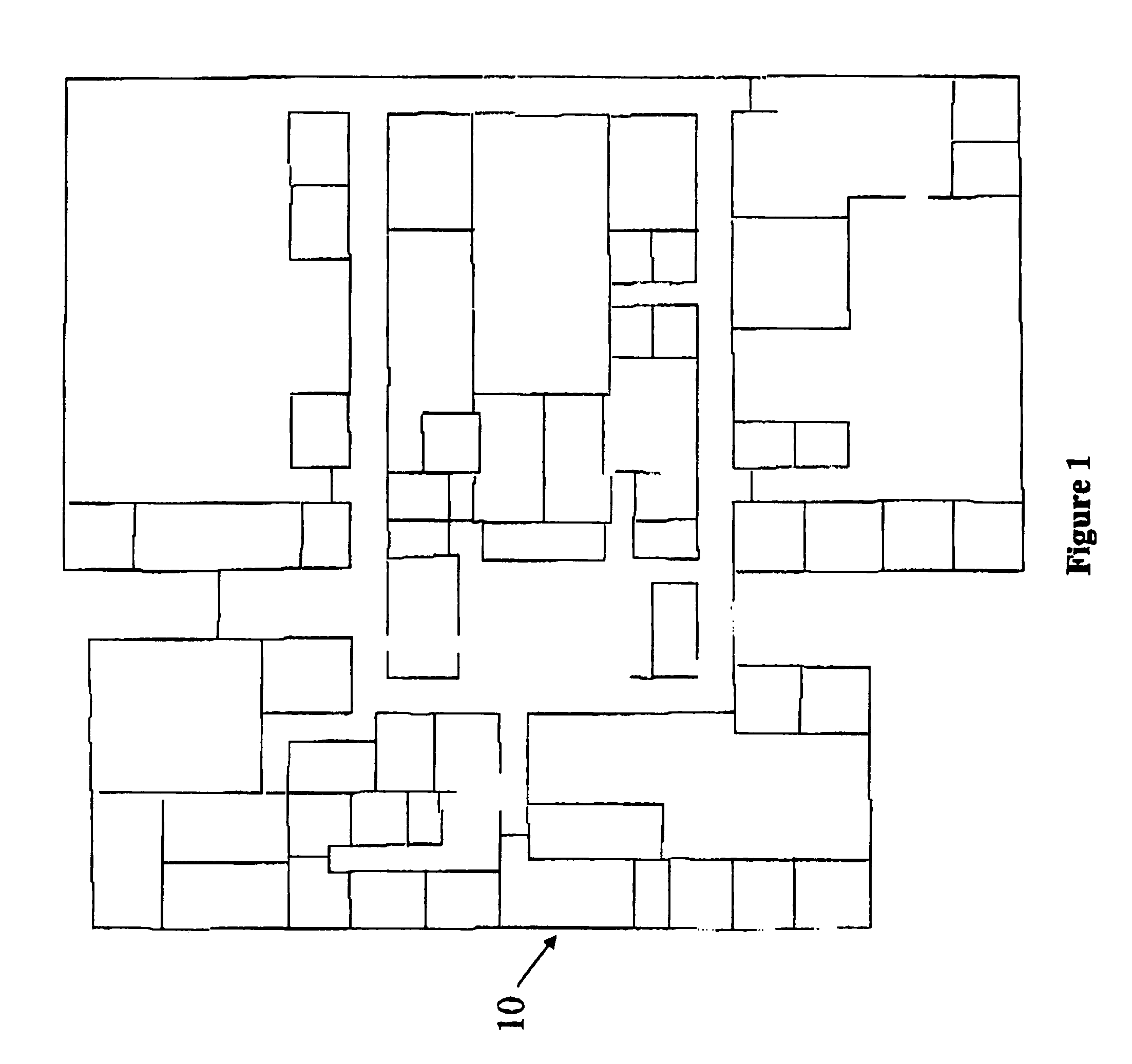

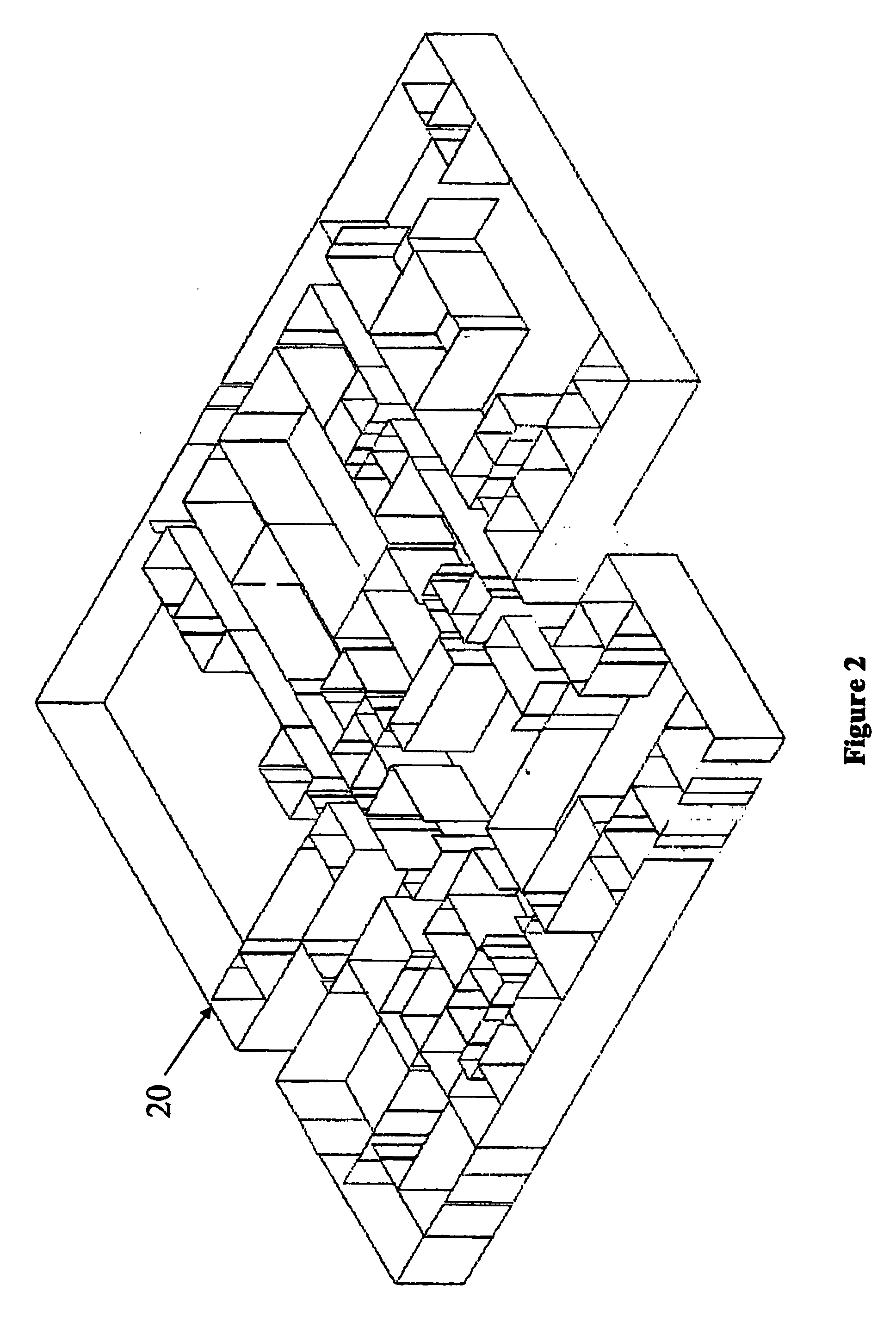

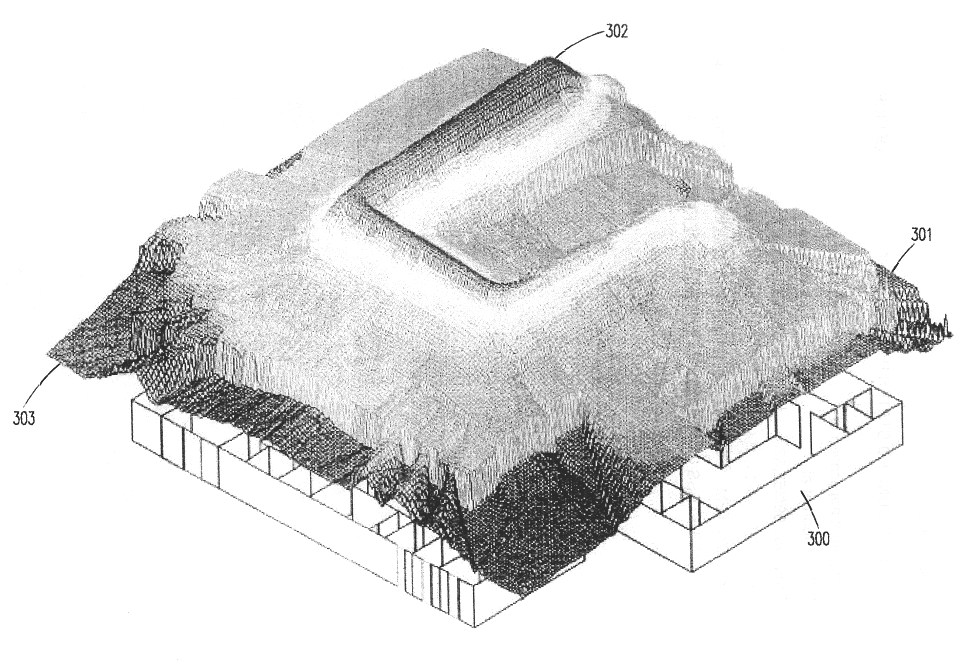

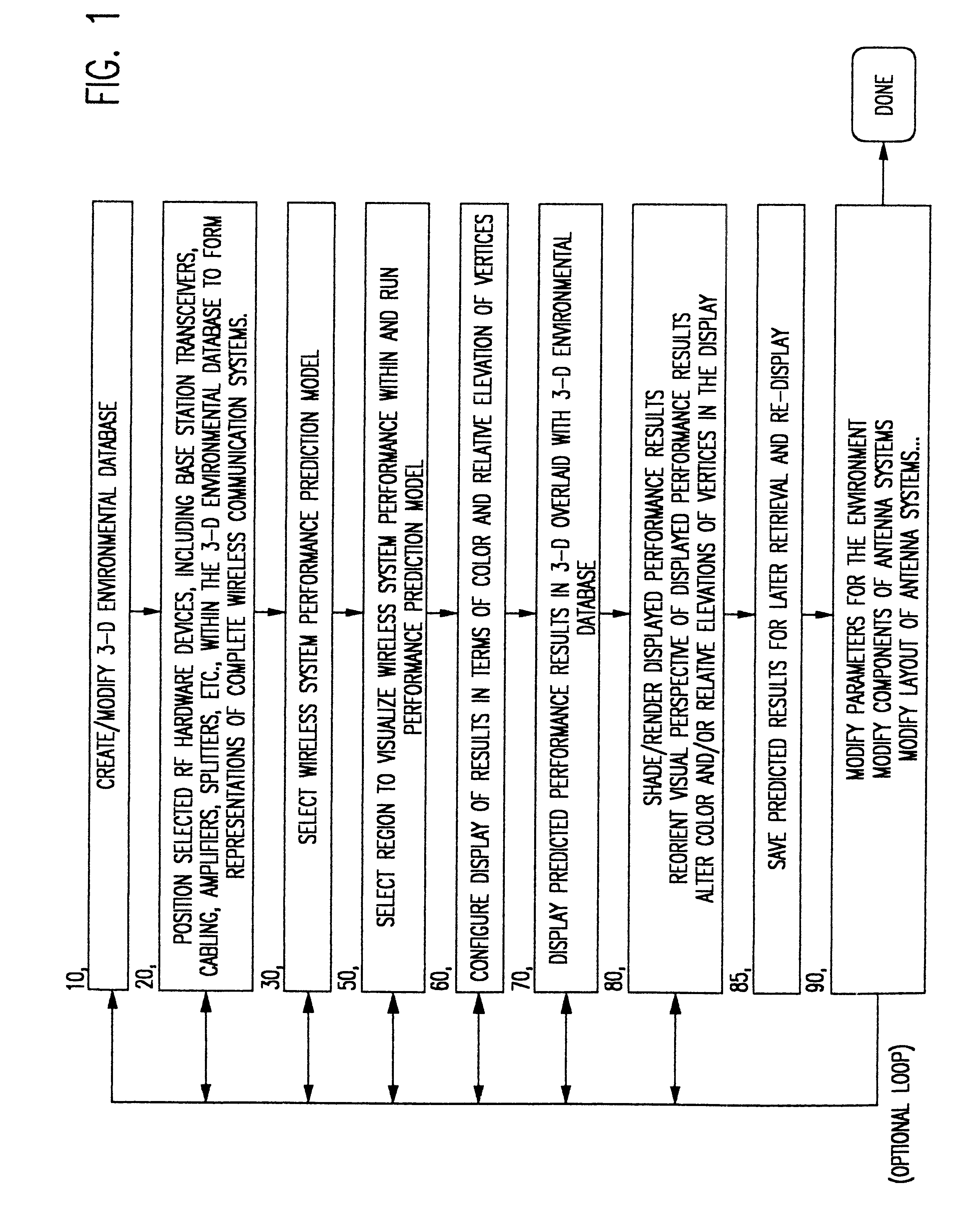

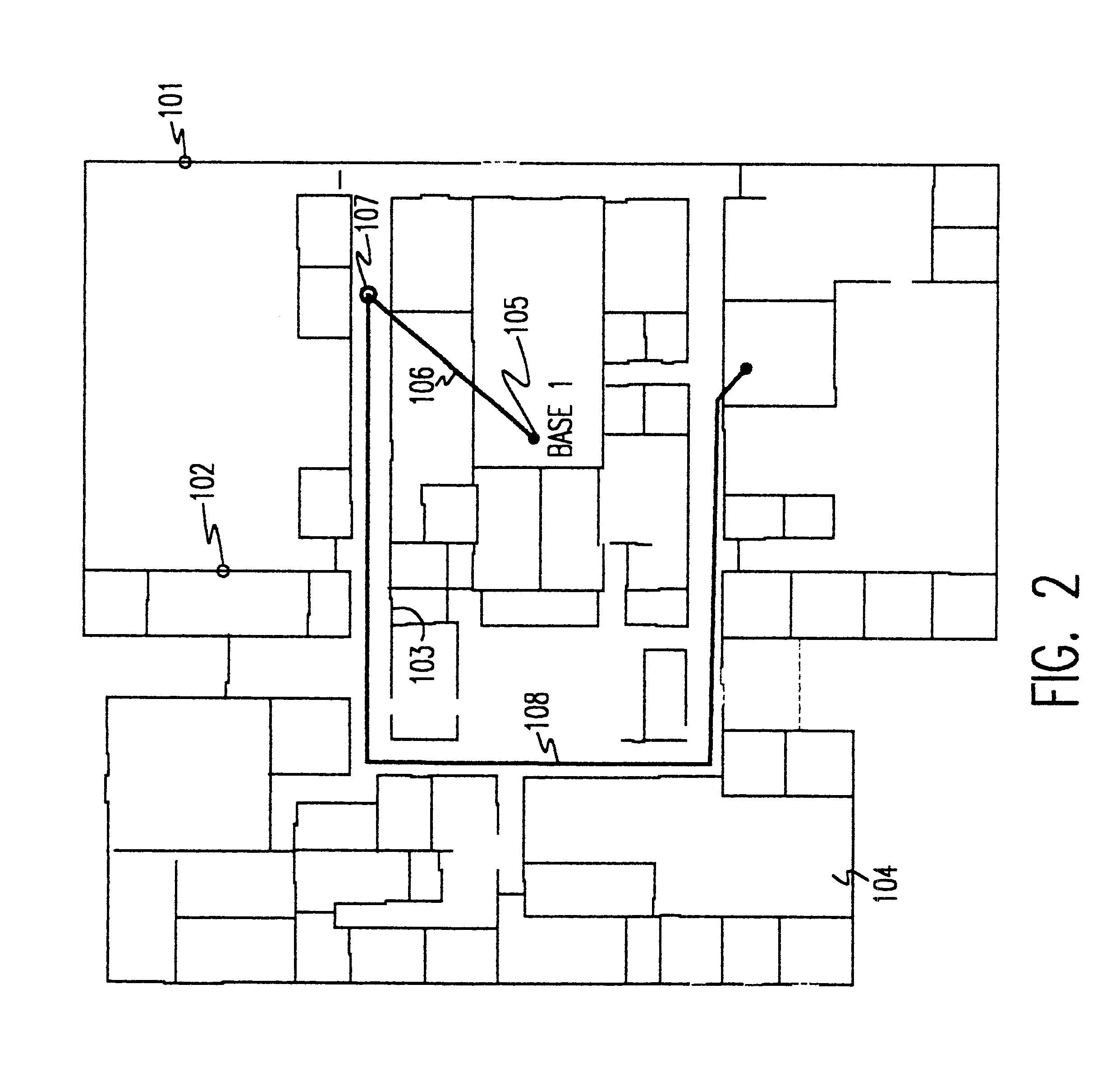

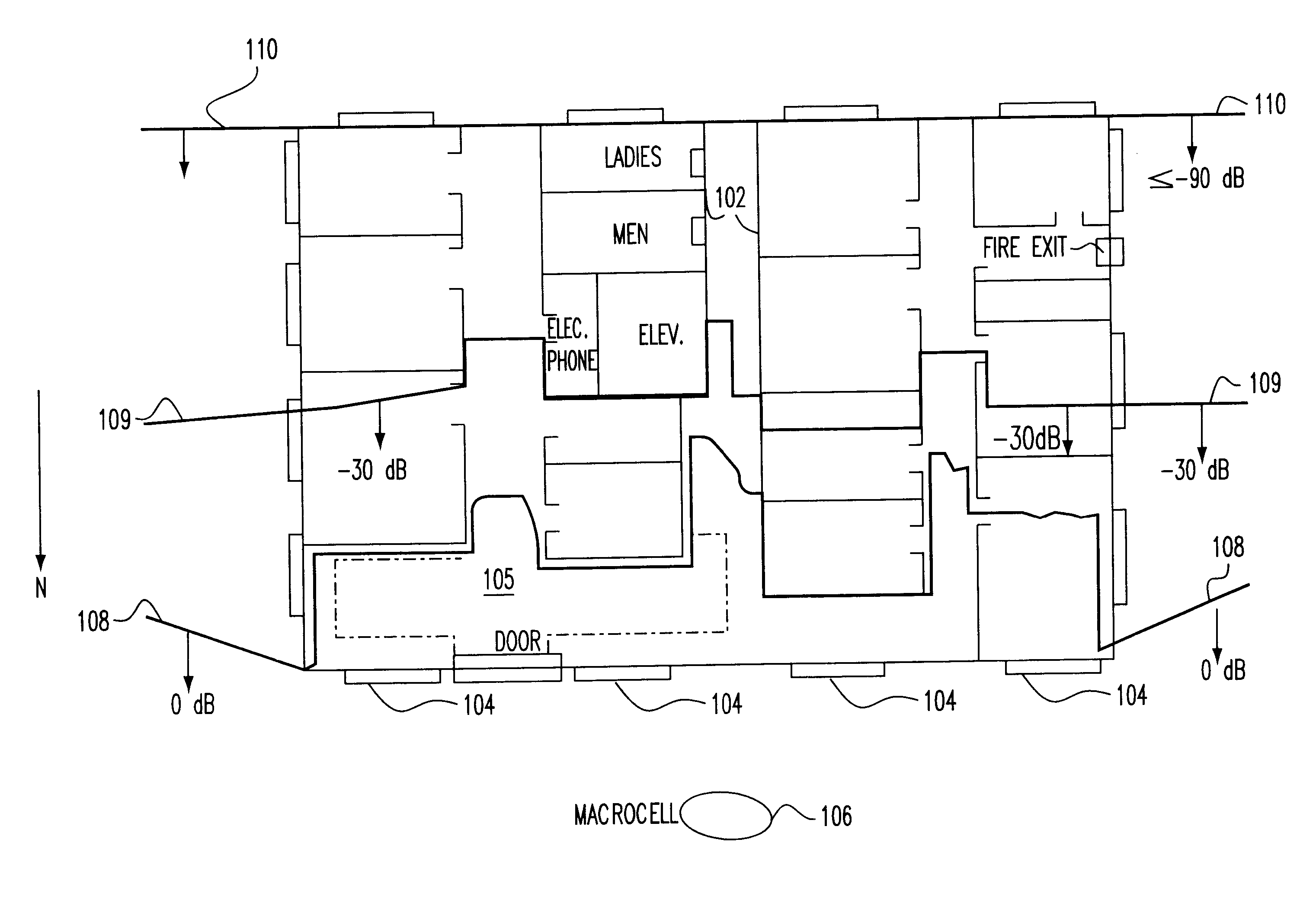

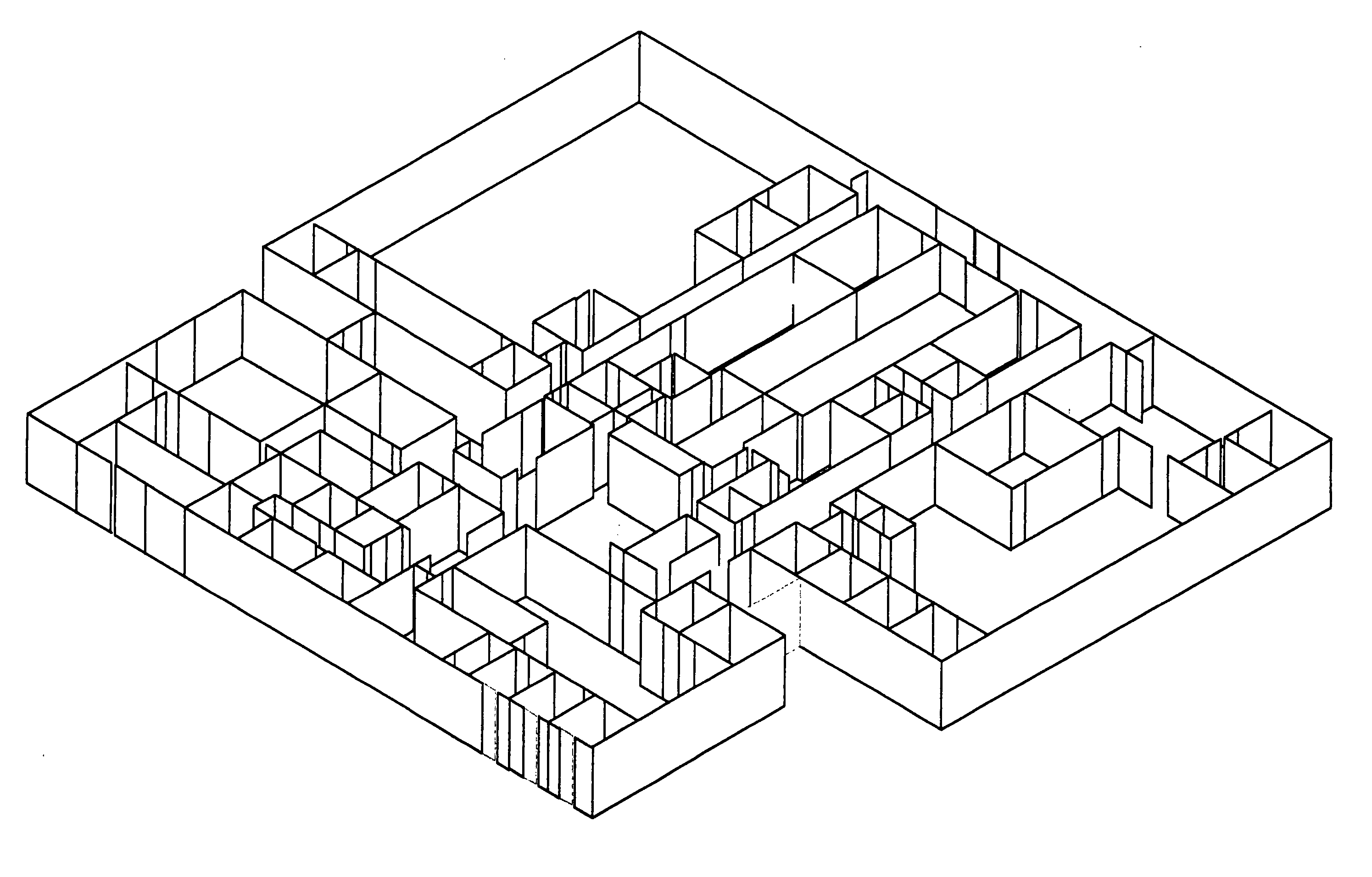

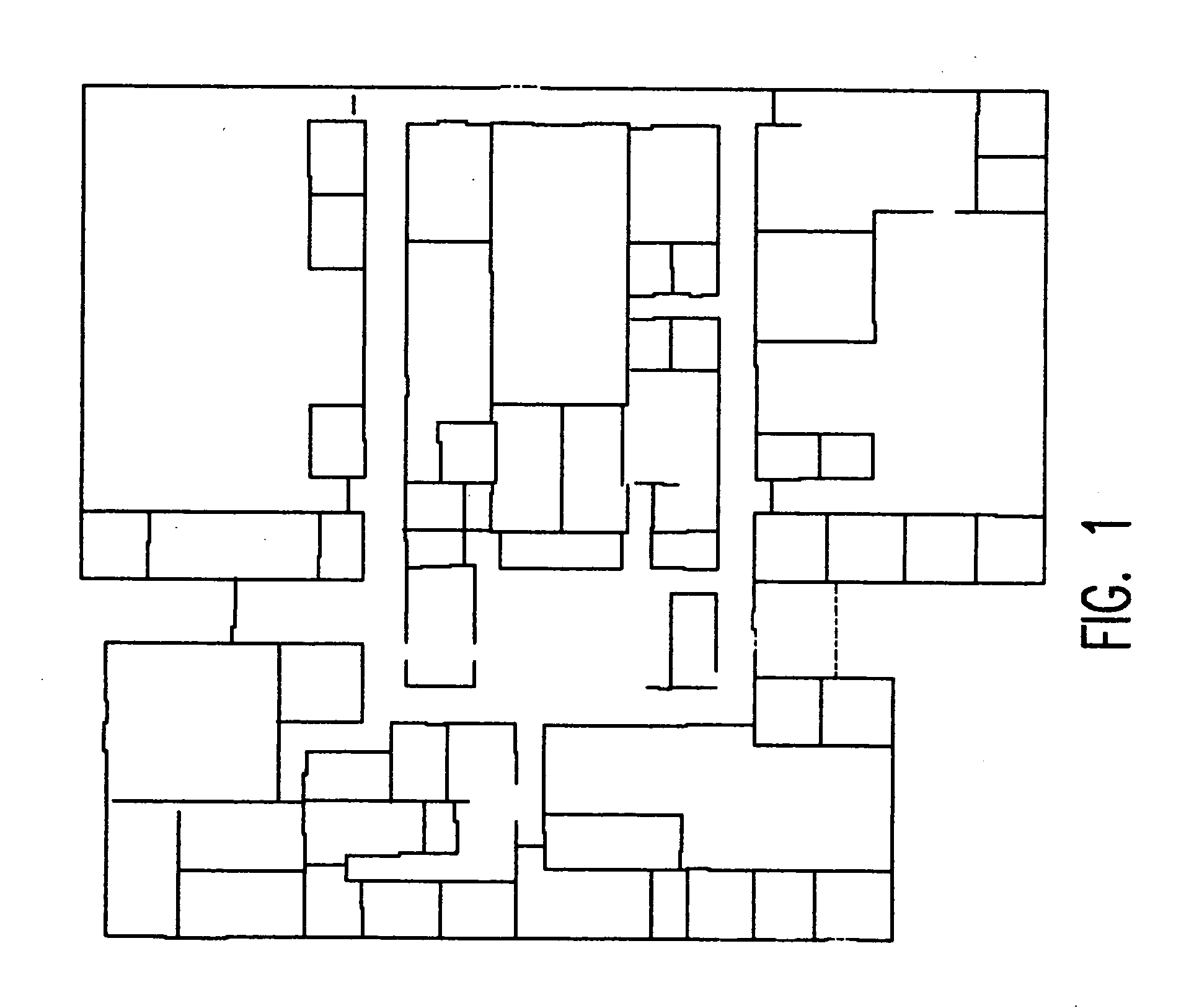

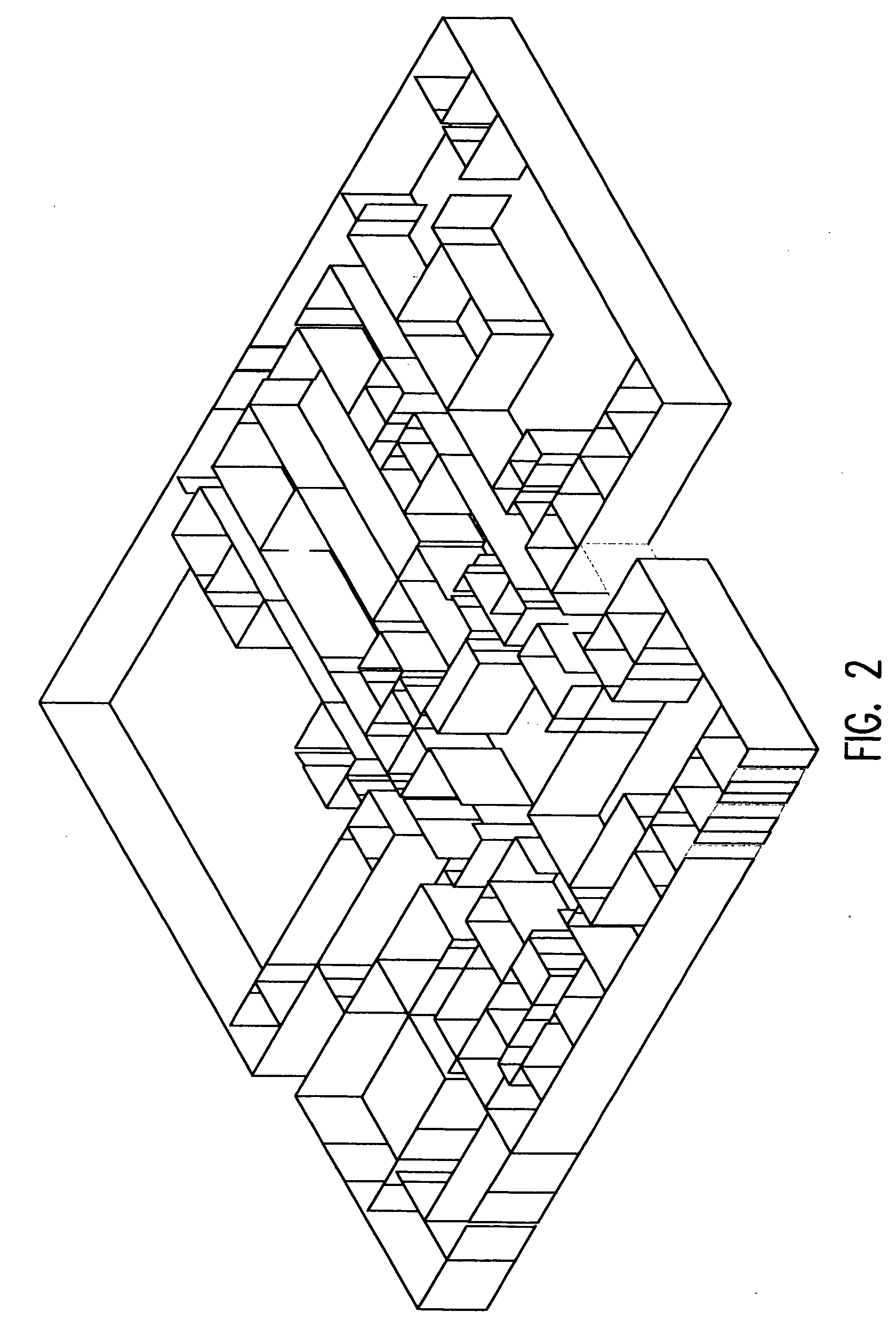

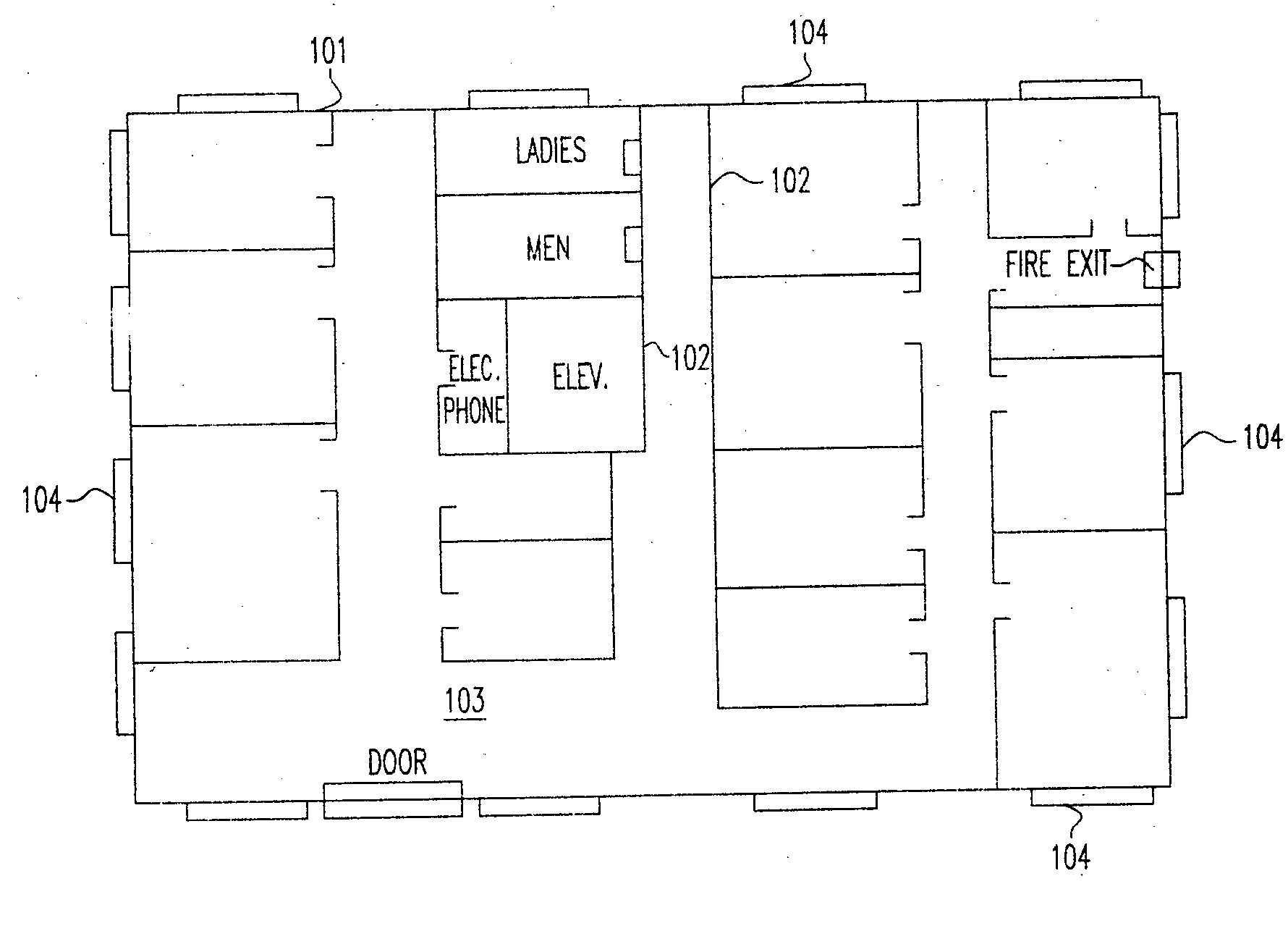

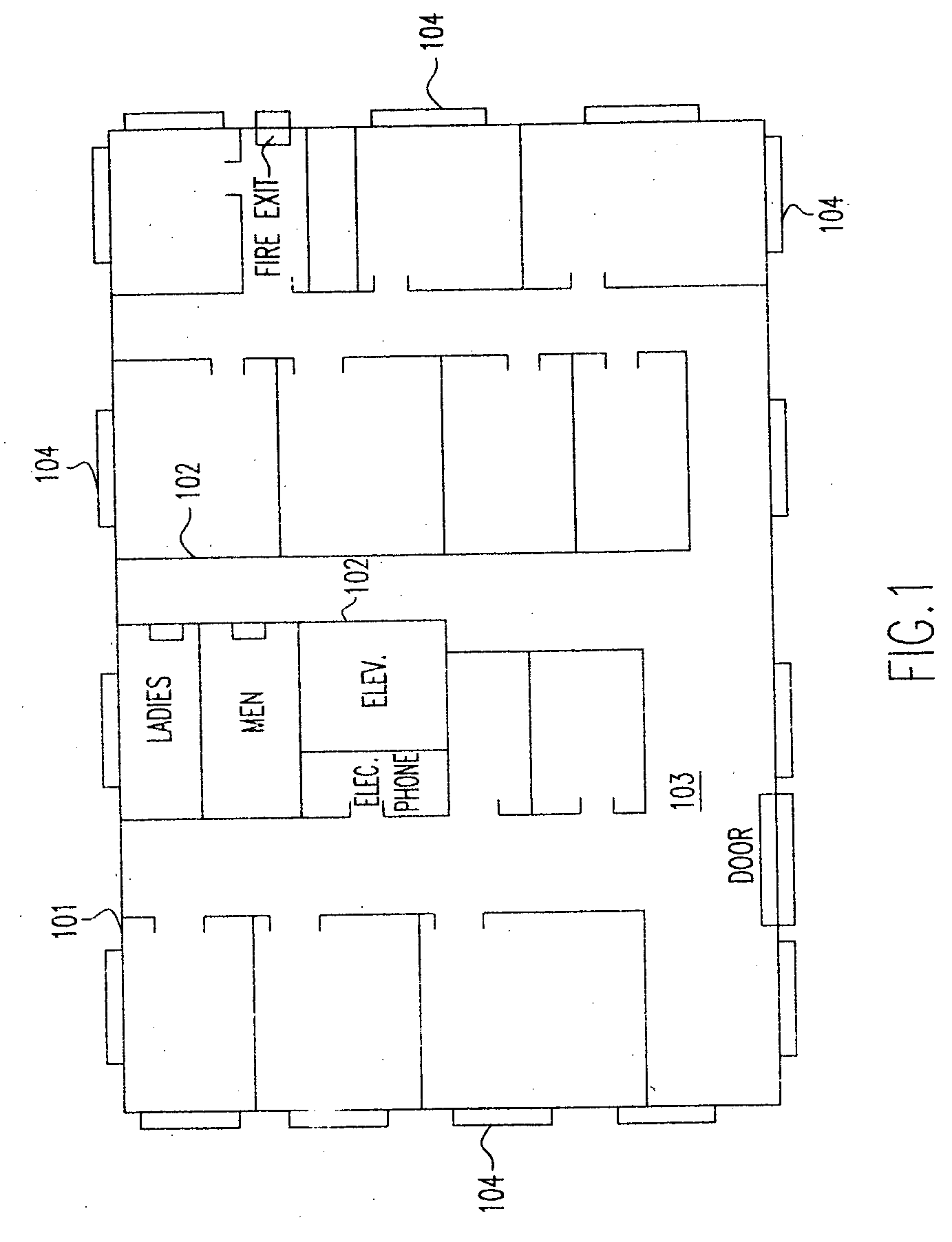

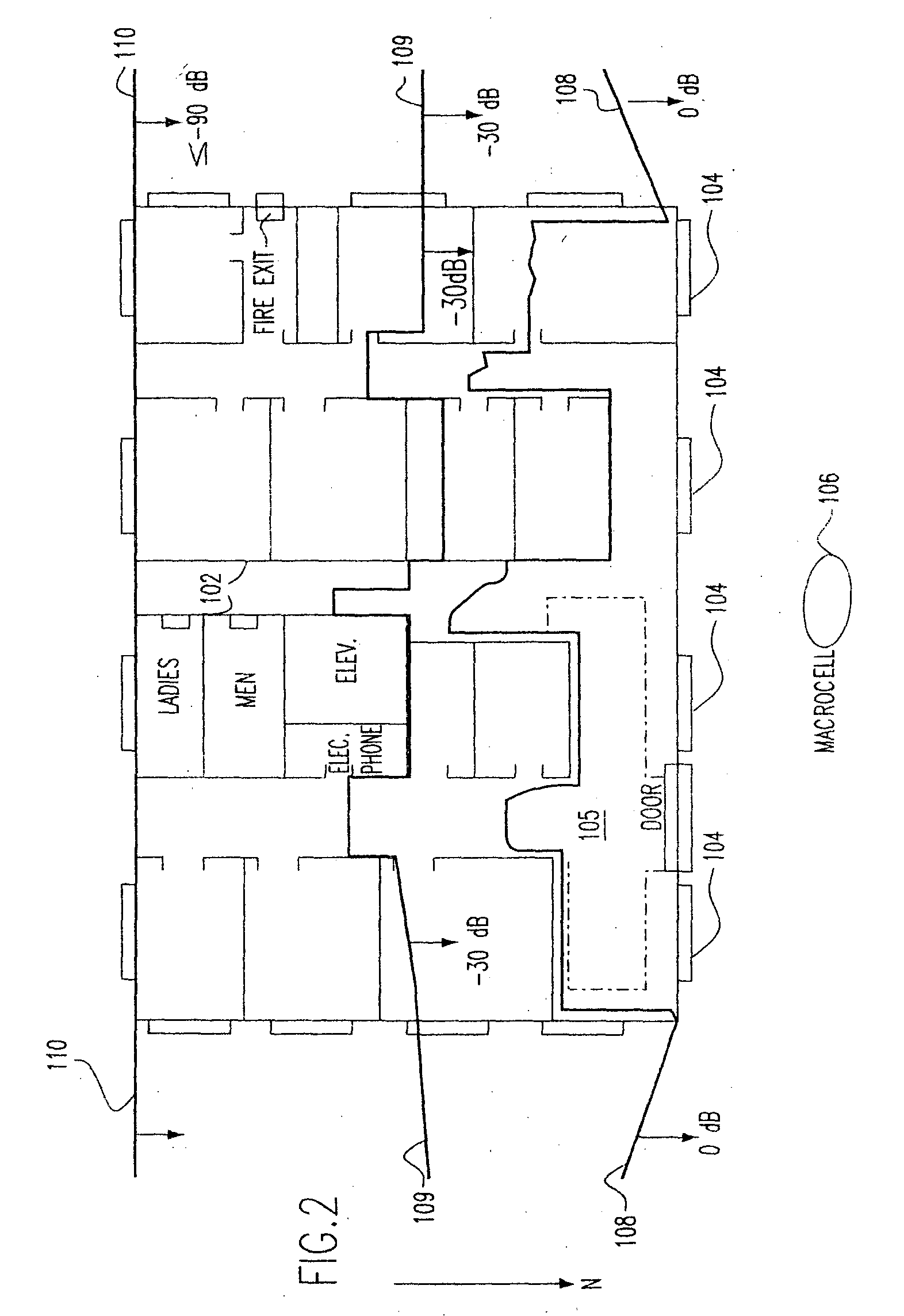

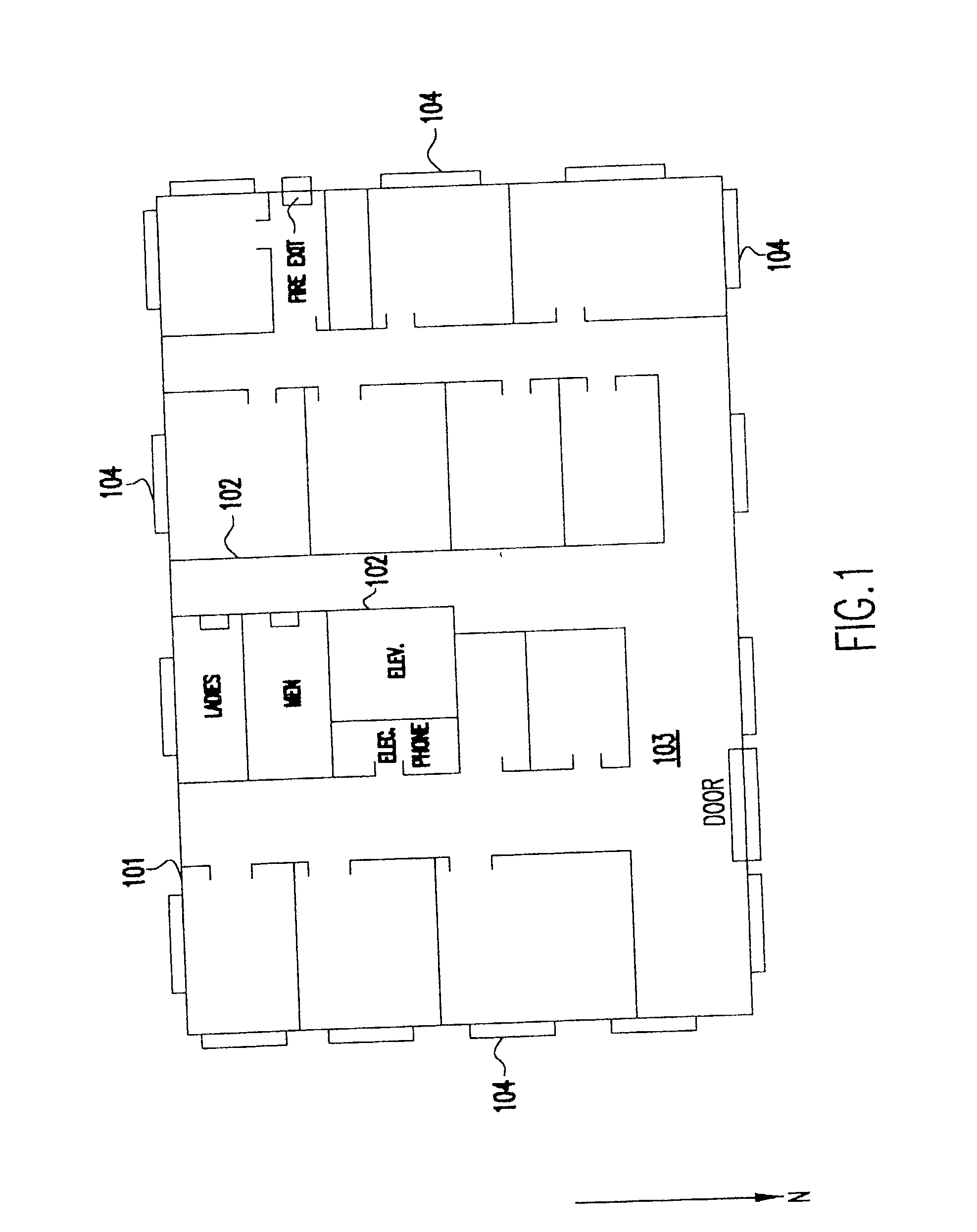

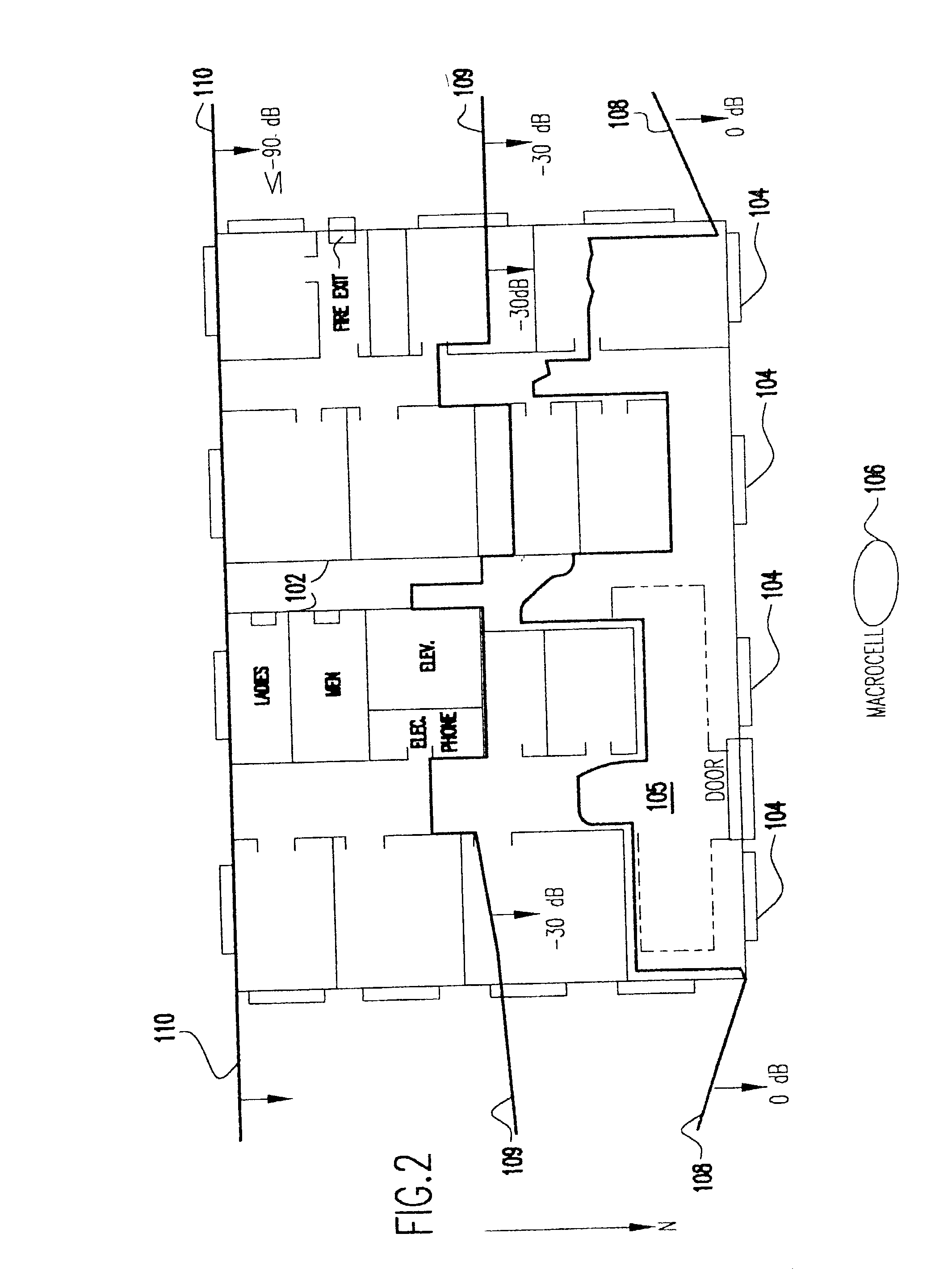

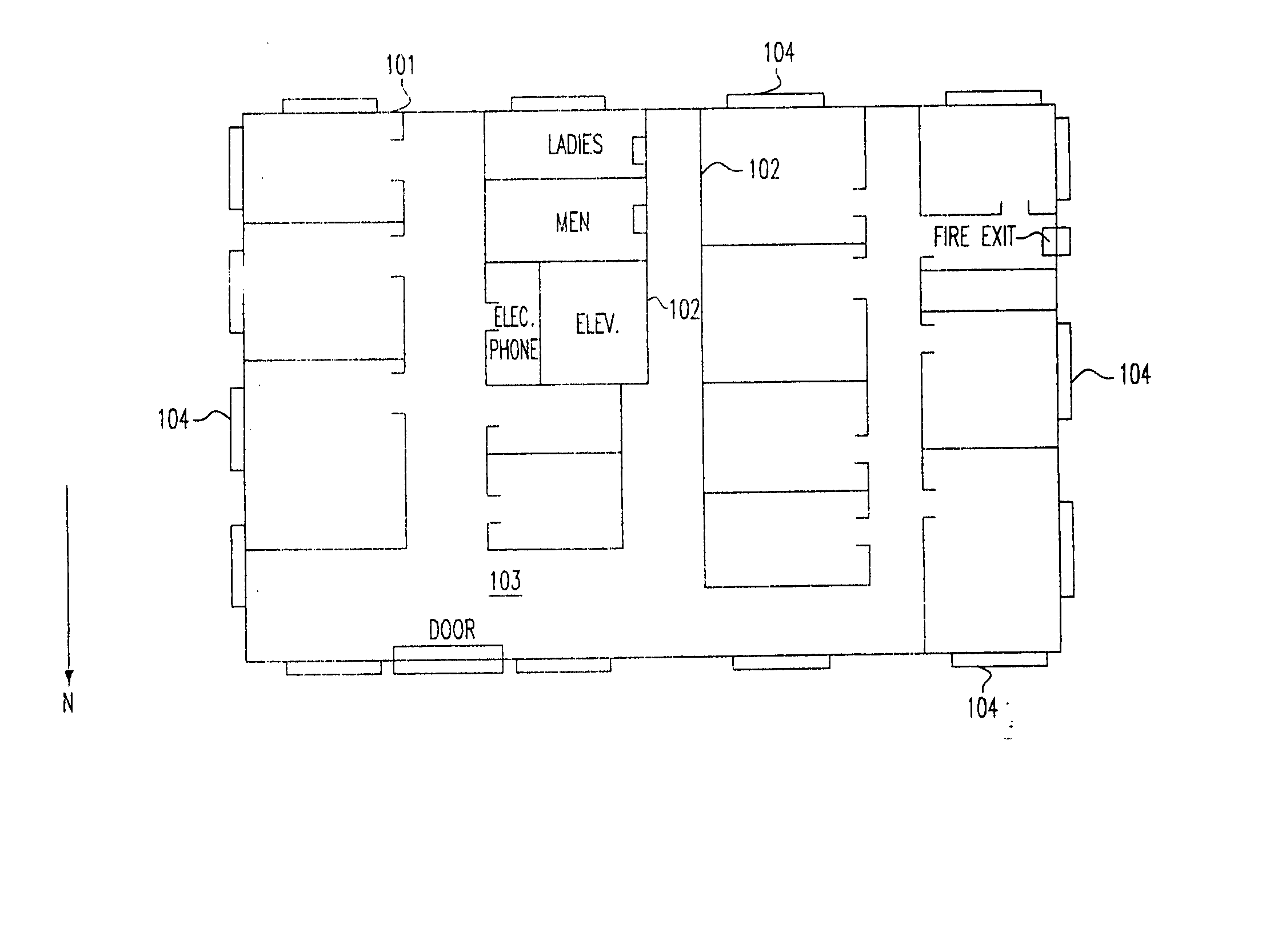

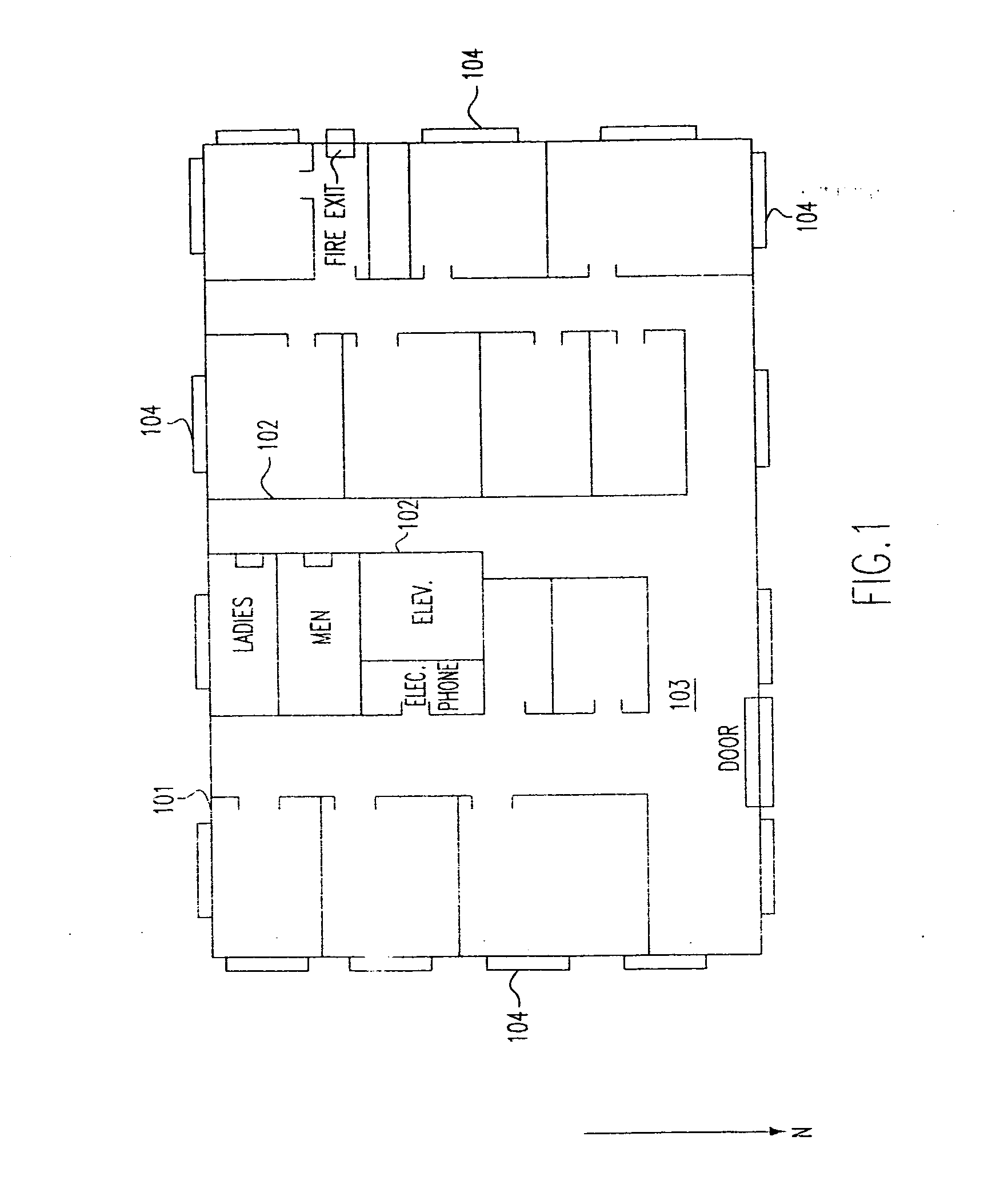

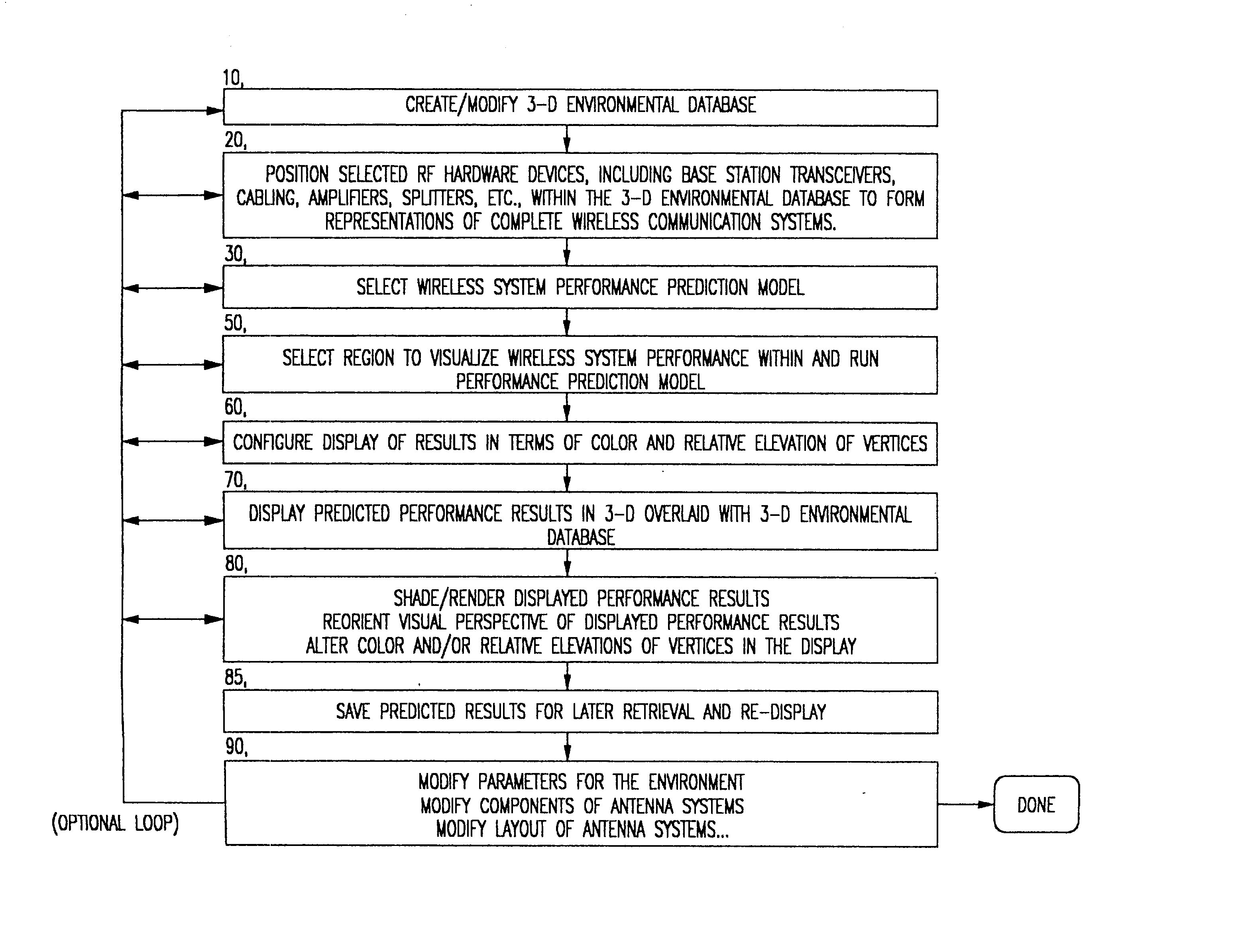

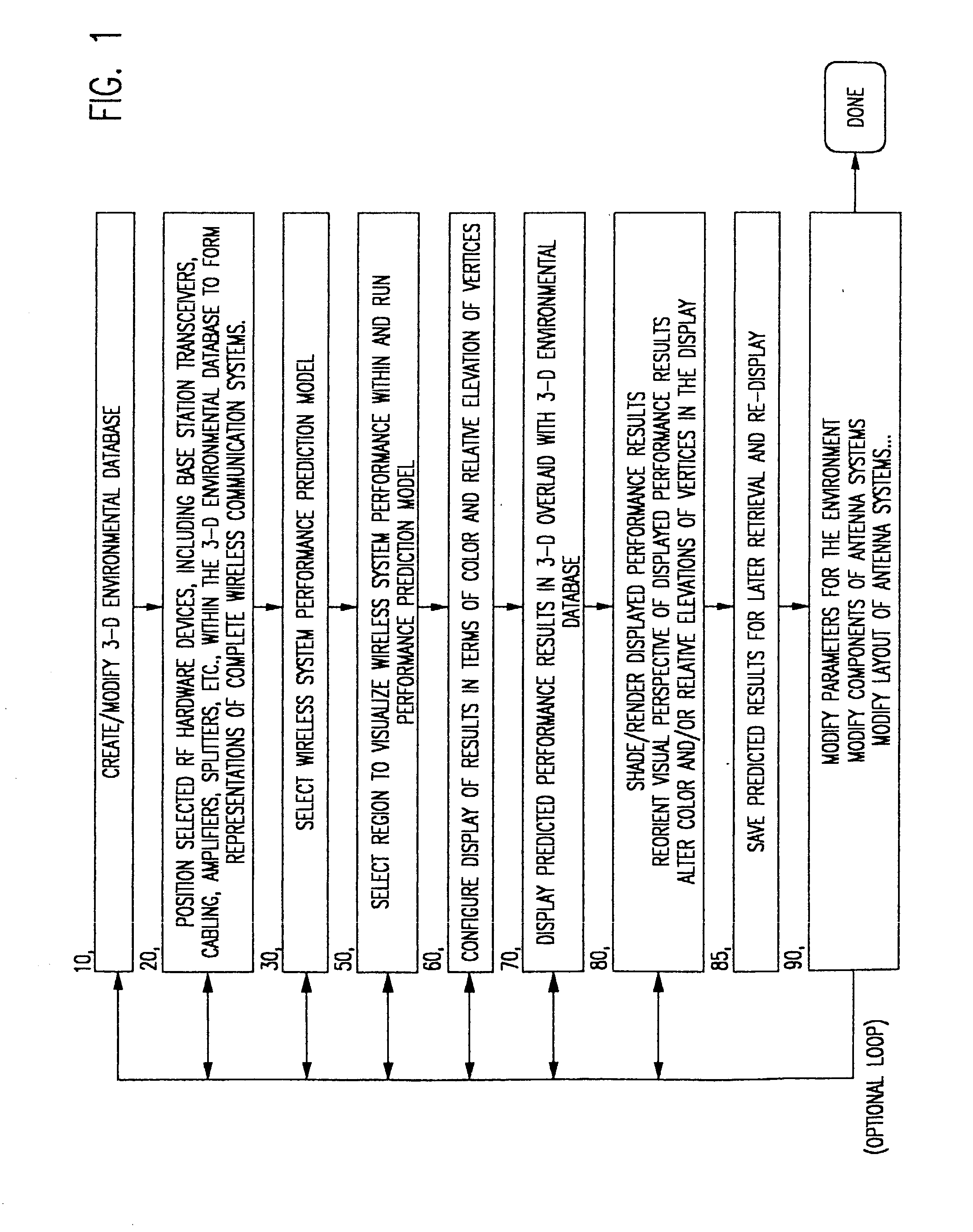

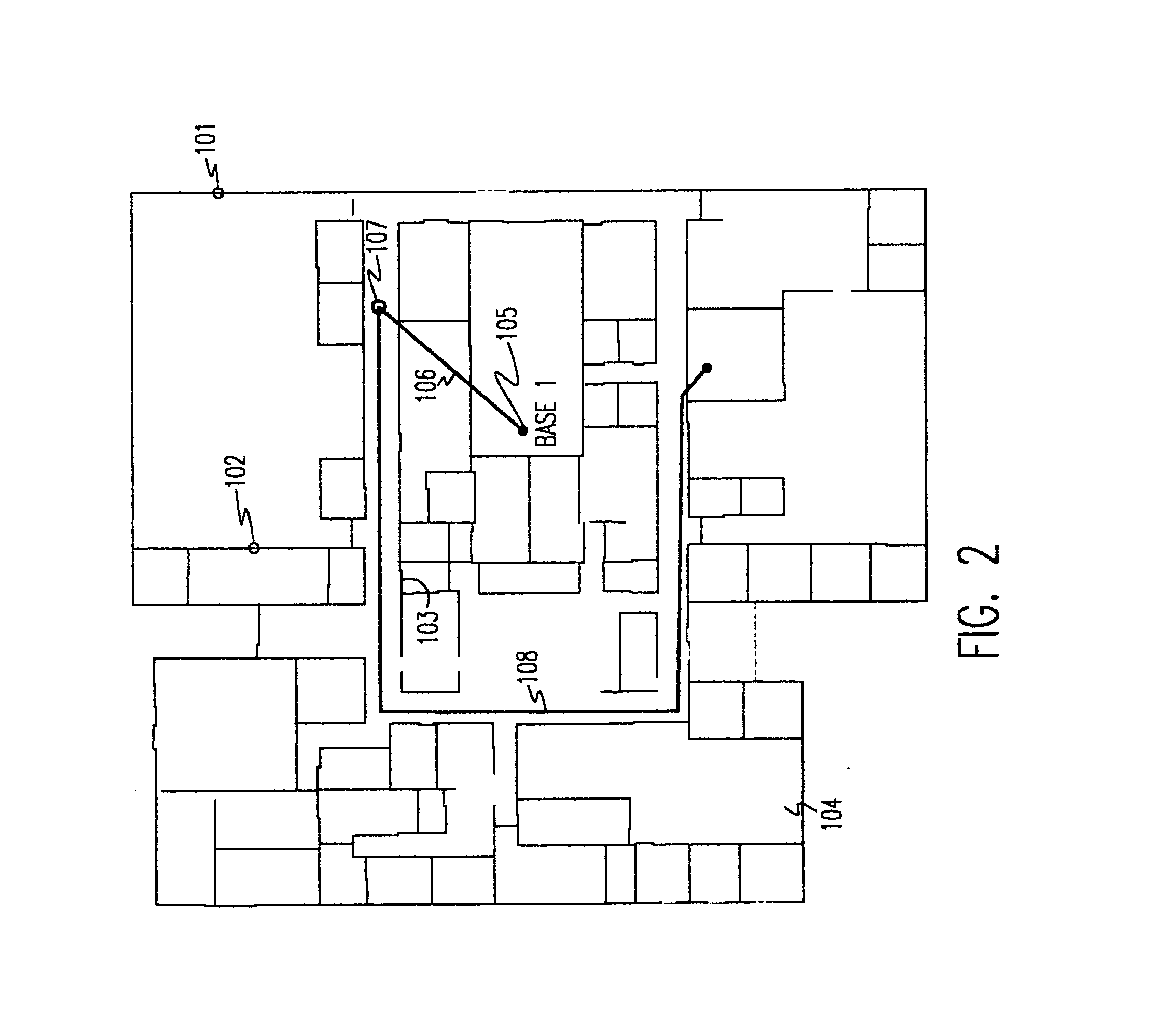

A method for visualizing and efficiently making comparisons of communication system performance utilizing predicted performance, measured performance, or other performance data sets is described. A system permits visualizing the comparisons of system performance data in three-dimensions using fluctuating elevation, shape, and / or color within a three-dimensional computer drawing database consisting of one or more multi-level buildings, terrain, flora, and additional static and dynamic obstacles (e.g., automobiles, people, filing cabinets, etc.). The method enables a design engineer to visually compare the performance of wireless communication systems as a three-dimensional region of fluctuating elevation, color, or other aesthetic characteristics with fully selectable display parameters, overlaid with the three-dimensional site-specific computer model for which the design was carried out.

Owner:EXTREME NETWORKS INC

System for the three-dimensional display of wireless communication system performance

InactiveUS6499006B1Receivers monitoringRadio/inductive link selection arrangementsTerrainCommunications system

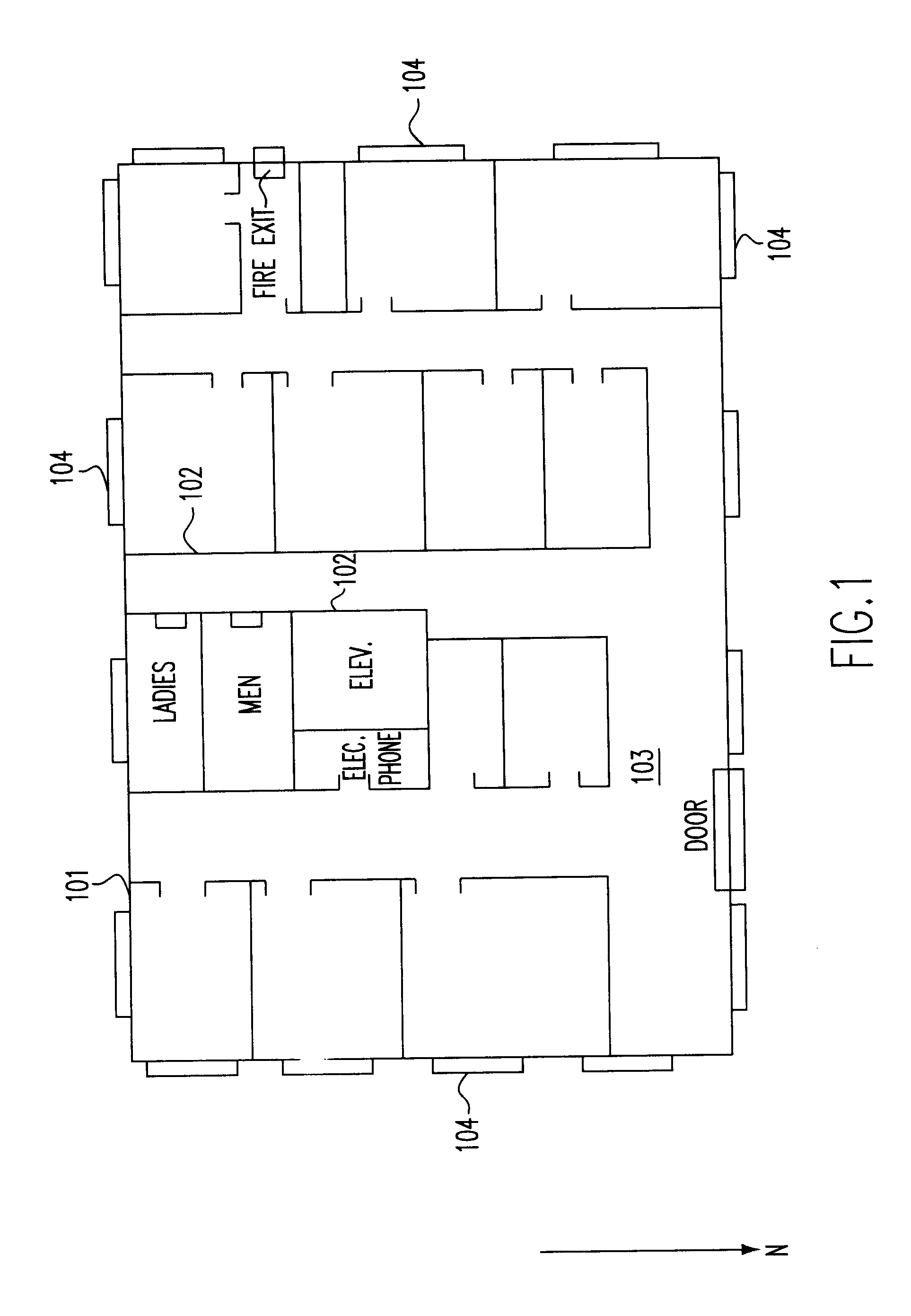

A method for displaying the results of predicted wireless communication system performance as a three-dimensional region of fluctuating elevation and / or color within a three-dimensional computer drawing database consisting of one or more multi-level buildings, terrain, flora, and additional static and dynamic obstacles (e.g., automobiles, people, filing cabinets, etc.). The method combines computerized organization, database fusion, and site-specific performance prediction models. The method enables a design engineer to visualize the performance of any wireless communication system as a three-dimensional region of fluctuating elevation, color, or other aesthetic characteristics with fully selectable display parameters, overlaid with the three-dimensional site-specific computer model for which the performance prediction was carried out.

Owner:EXTREME NETWORKS INC

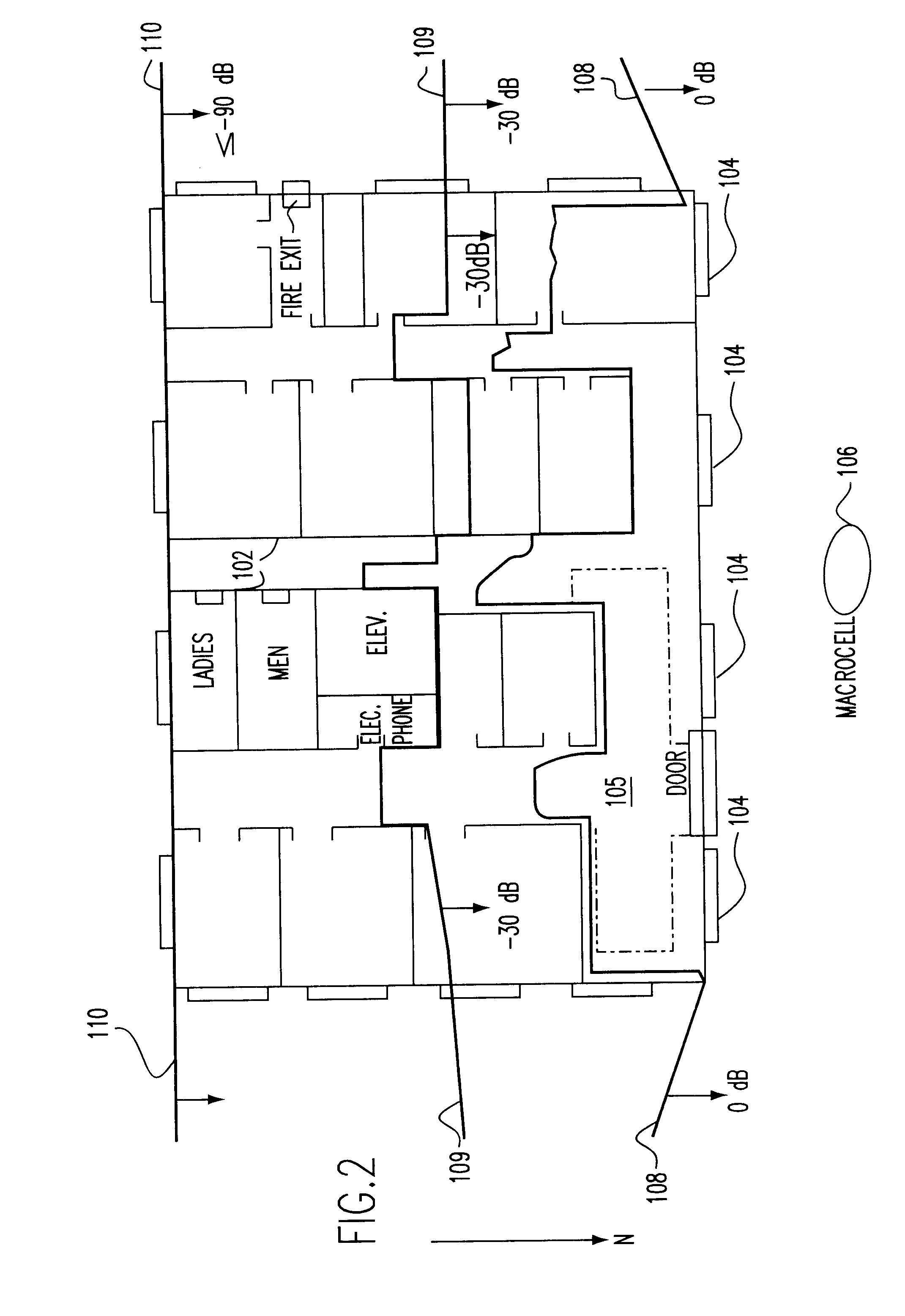

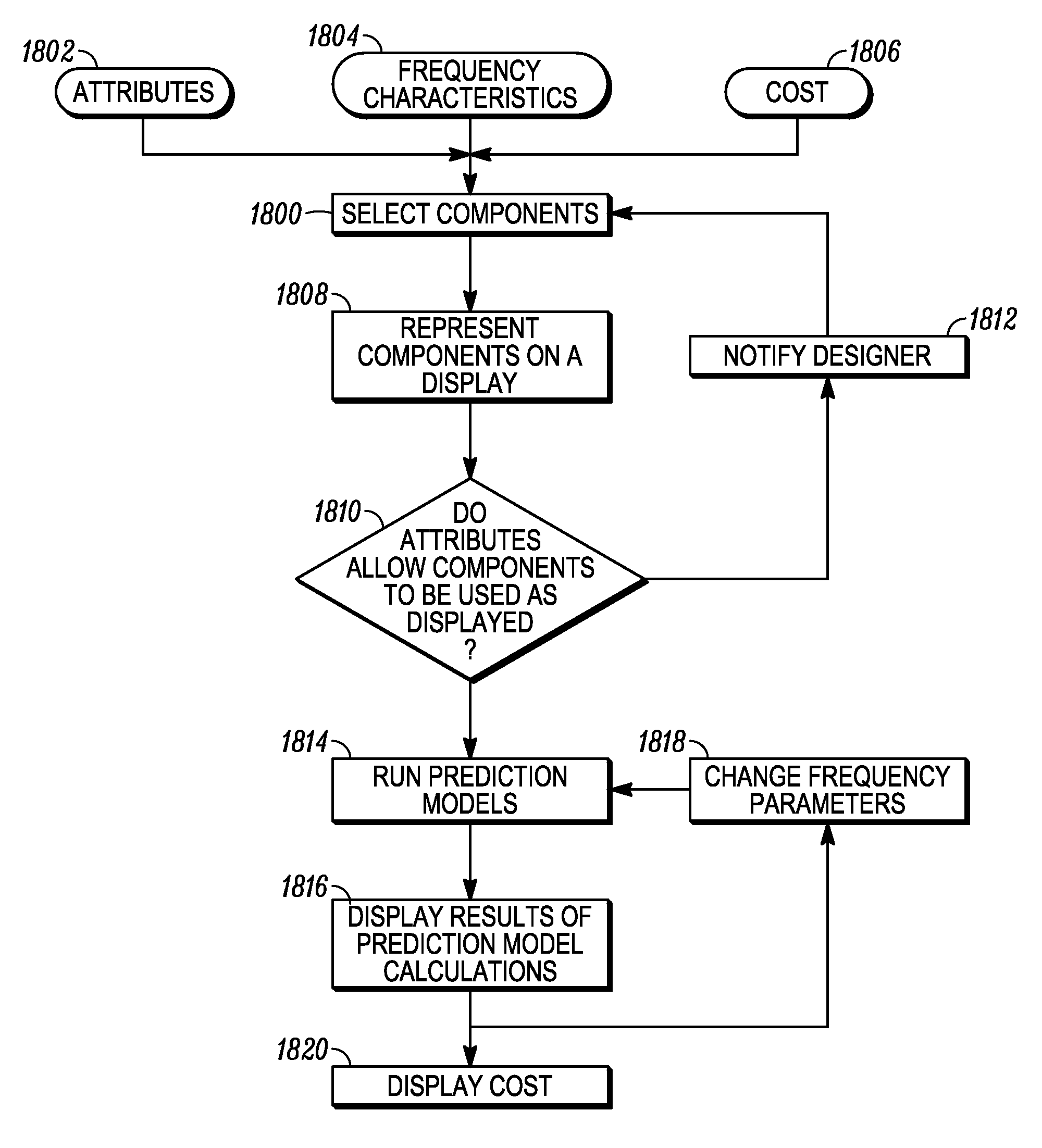

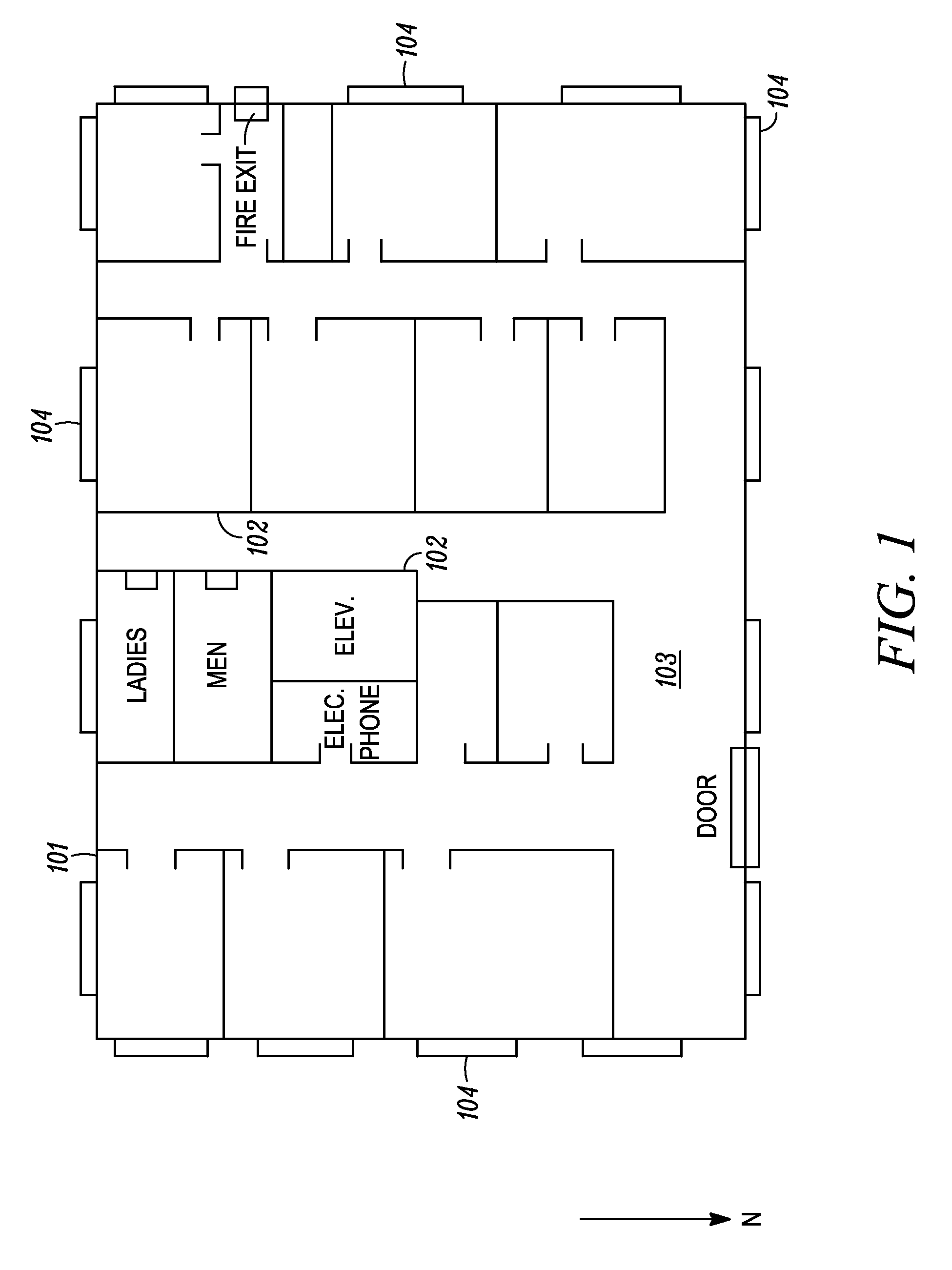

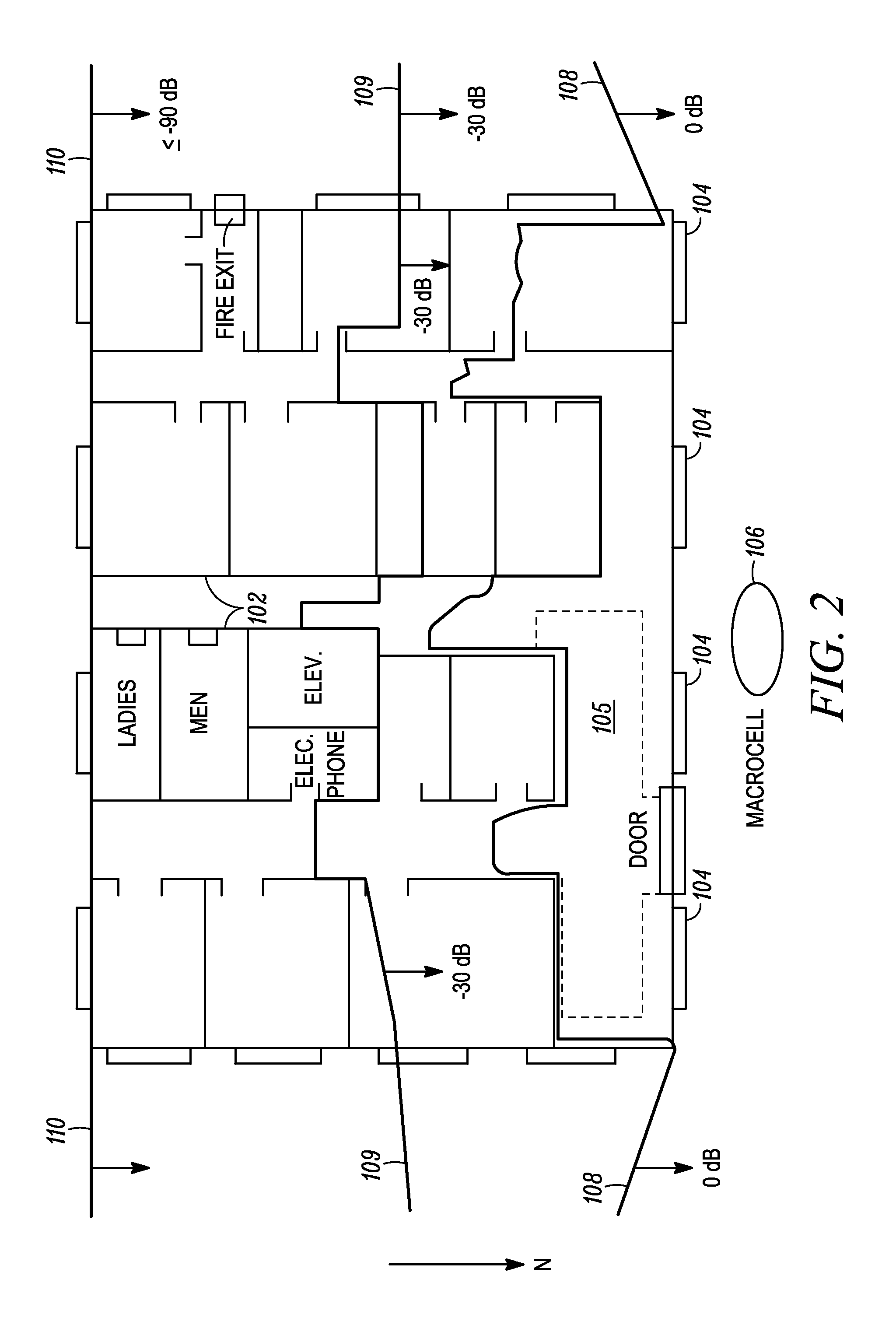

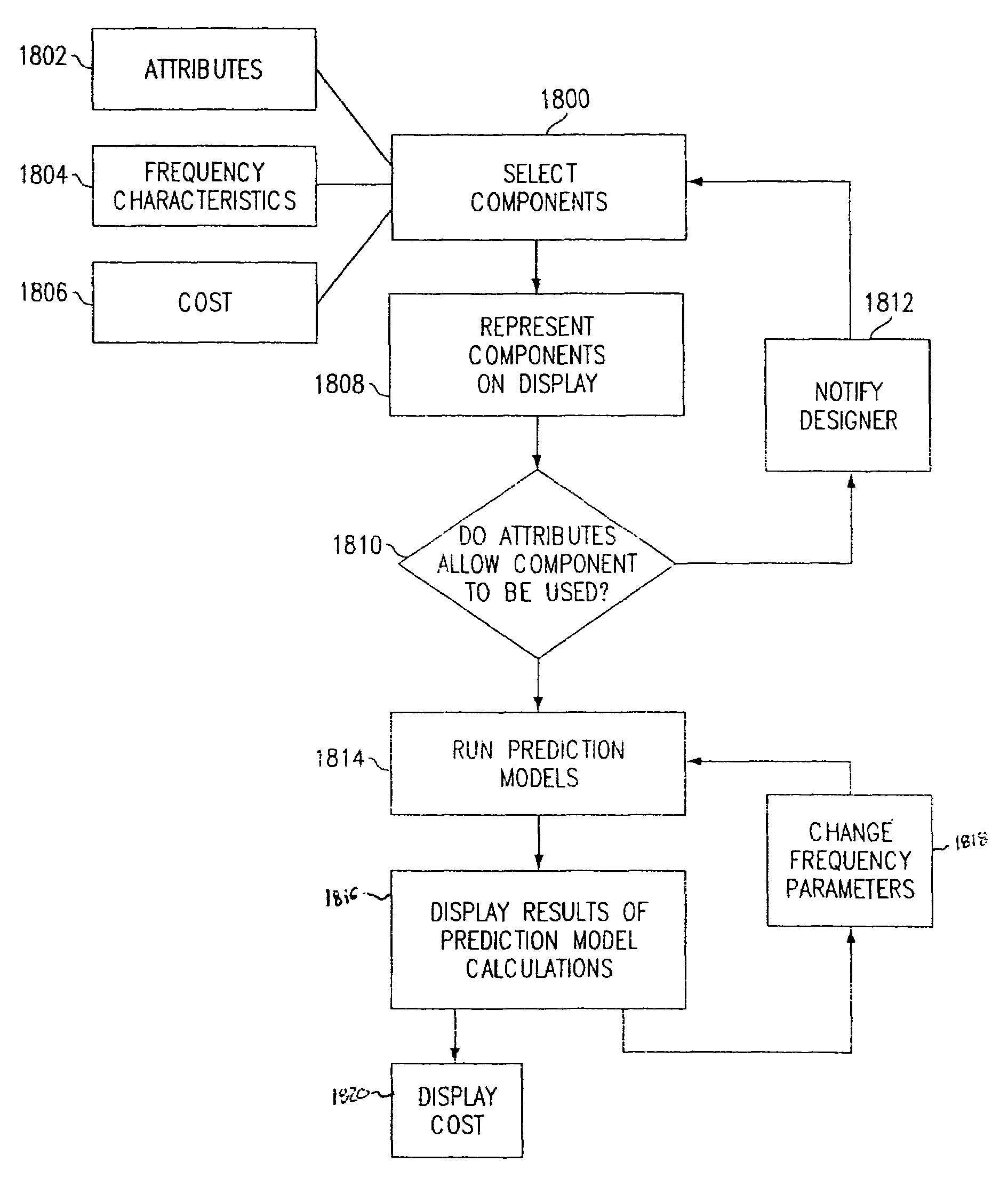

Method and system for designing or deploying a communications network which considers frequency dependent effects

InactiveUS6625454B1Simply and quickly prepareOptimize timingReceivers monitoringRadio/inductive link selection arrangementsBill of materialsDesign engineer

A computerized model provides a display of a physical environment in which a communications network is or will be installed. The communications network is comprised of several components, each of which are selected by the design engineer and which are represented in the display. Errors in the selection of certain selected components for the communications network are identified by their attributes or frequency characteristics as well as by their interconnection compatibility for a particular design. The effects of changes in frequency on component performance are modeled and the results are displayed to the design engineer. A bill of materials is automatically checked for faults and generated for the design system and provided to the design engineer. For ease of design, the design engineer can cluster several different preferred components into component kits, and then select these component kits for use in the design or deployment process.

Owner:EXTREME NETWORKS INC

Method and system for designing or deploying a communications network which considers component attributes

InactiveUS7085697B1Simply and quickly prepareOptimize timingAnalogue computers for electric apparatusRadio/inductive link selection arrangementsBill of materialsDisplay device

A computerized model provides a display of a physical environment in which a communications network is or will be installed. The communications network is comprised of several components, each of which are selected by the design engineer and which are represented in the display. Errors in the selection of certain selected components for the communications network are identified by their attributes or frequency characteristics as well as by their interconnection compatability for a particular design. The effects of changes in frequency on component performance are modeled and the results are displayed to the design engineer. A bill of materials is automatically checked for faults and generated for the design system and provided to the design engineer. For ease of design, the design engineer can cluster several different preferred components into component kits, and then select these component kits for use in the design or deployment process.

Owner:EXTREME NETWORKS INC

System and method for efficiently visualizing and comparing communication network system performance

A method for visualizing and efficiently making comparisons of communication system performance utilizing predicted performance, measured performance, or other performance data sets is described. A system permits visualizing the comparisons of system performance data in three-dimensions using fluctuating elevation, shape, and / or color within a three-dimensional computer drawing database consisting of one or more multi-level buildings, terrain, flora, and additional static and dynamic obstacles (e.g., automobiles, people, filing cabinets, etc.). The method enables a design engineer to visually compare the performance of wireless communication systems as a three-dimensional region of fluctuating elevation, color, or other aesthetic characteristics with fully selectable display parameters, overlaid with the three-dimensional site-specific computer model for which the design was carried out.

Owner:EXTREME NETWORKS INC

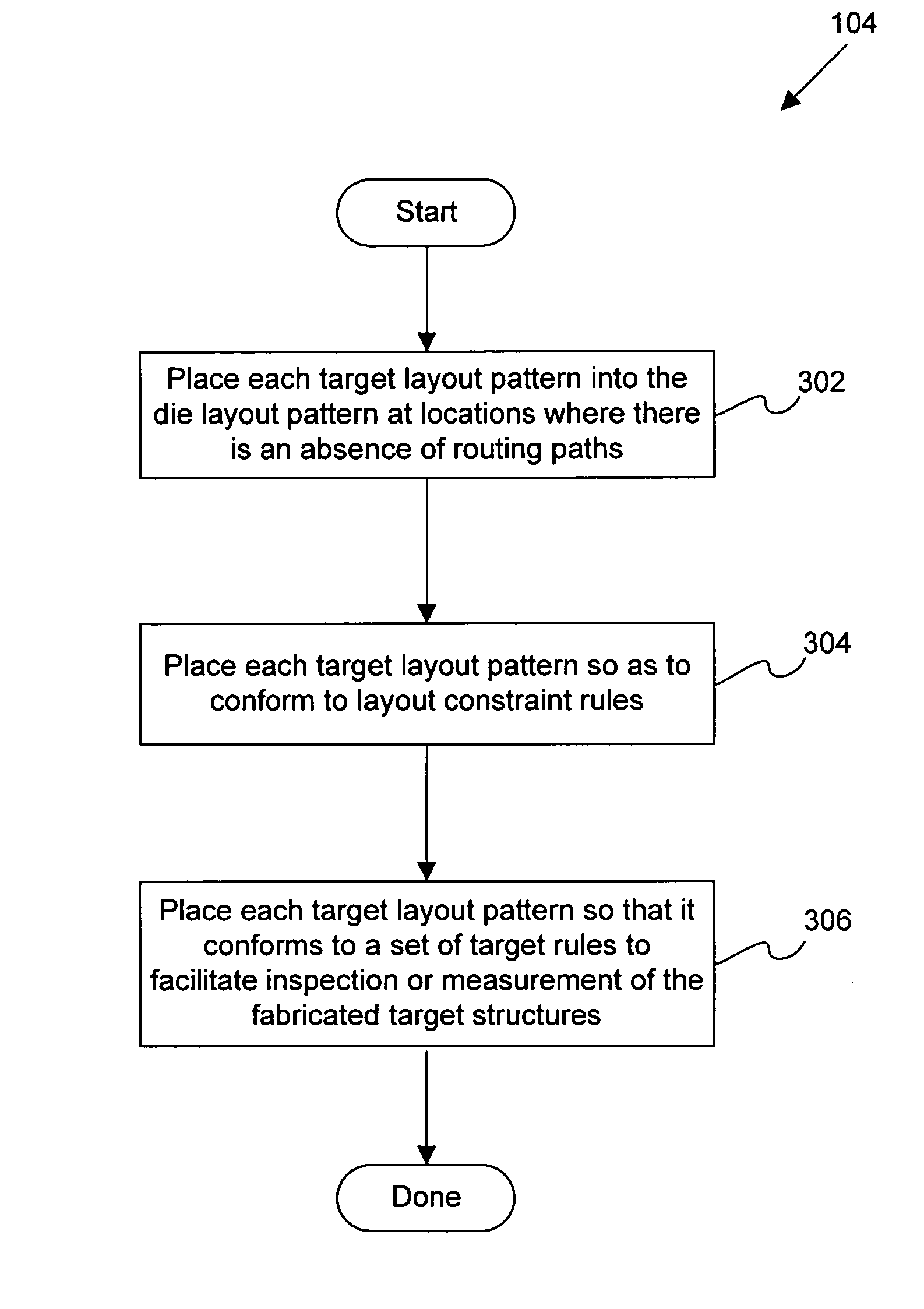

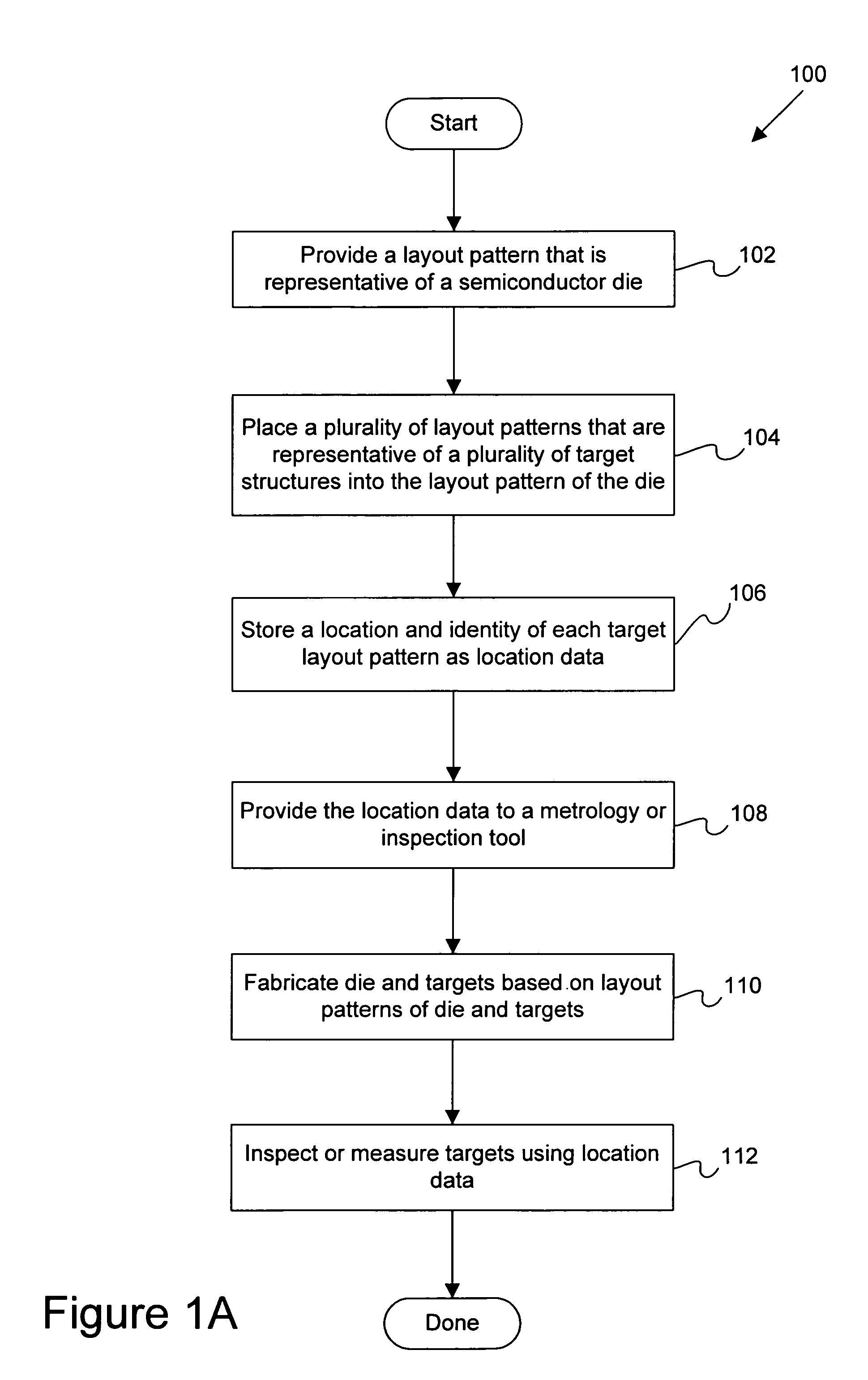

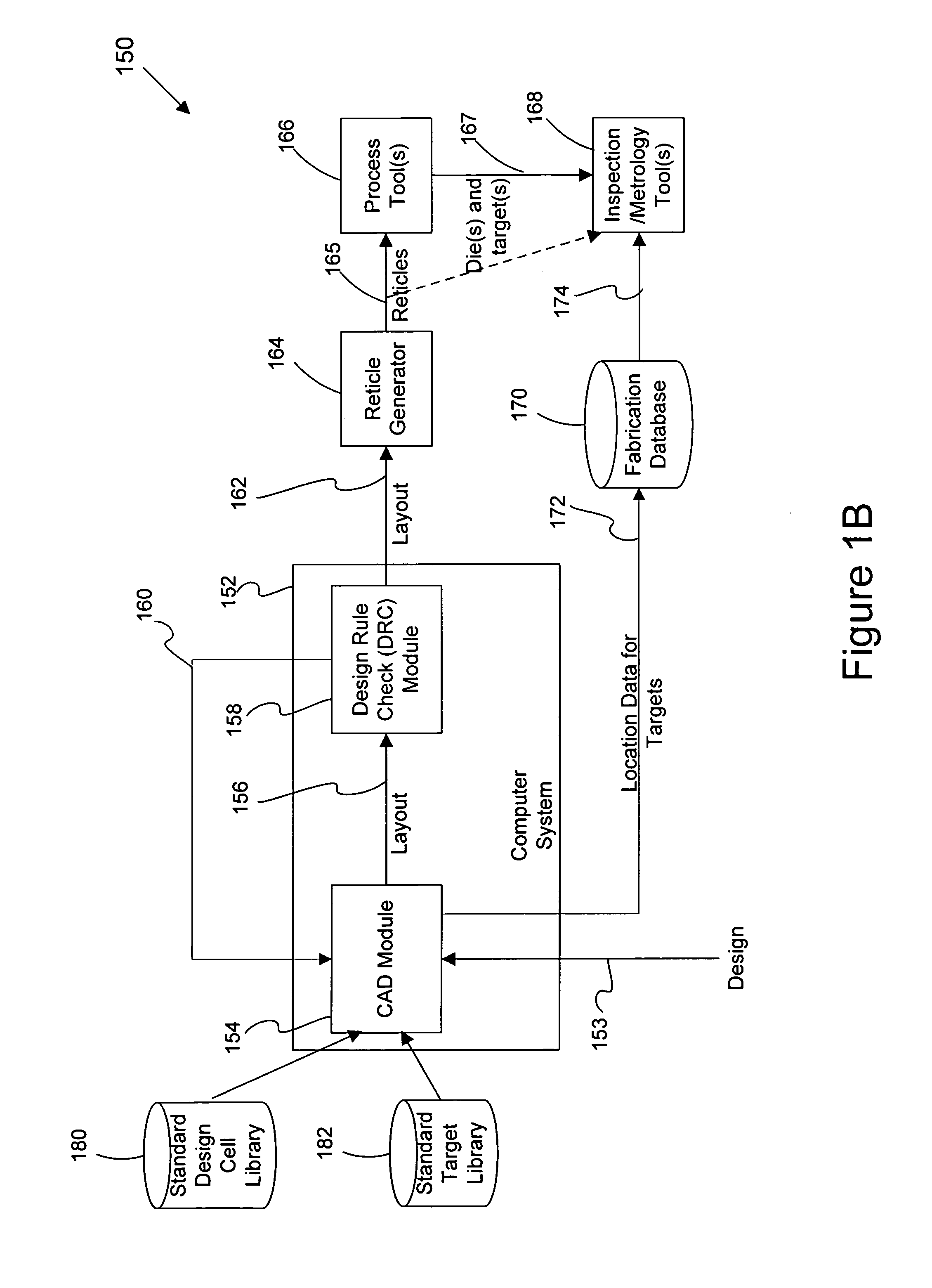

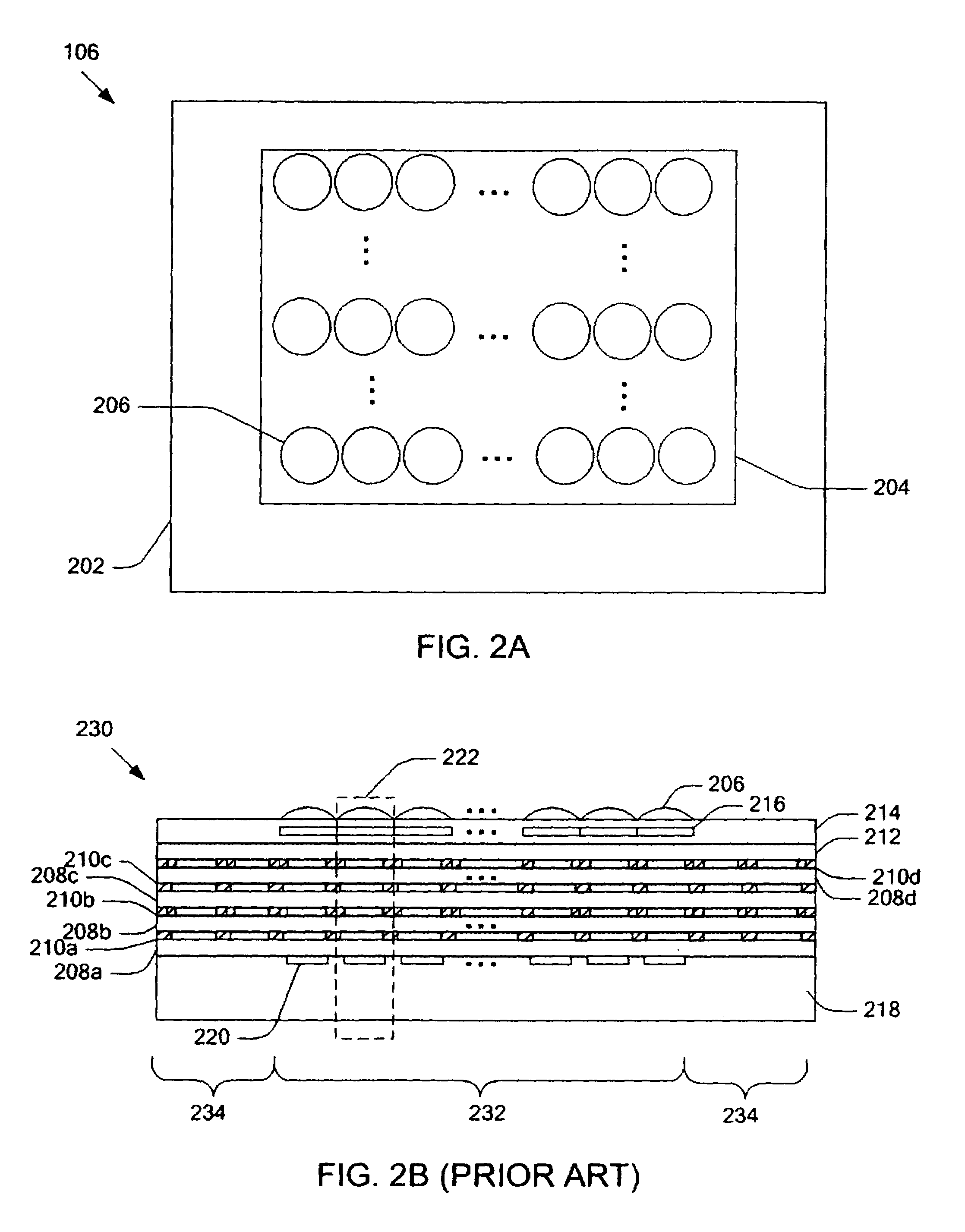

Apparatus and methods for providing in-chip microtargets for metrology or inspection

Disclosed are techniques and apparatus for providing metrology or inspection targets in-chip. That is, targets are integrated within the product device or die area. In general terms, the present invention provides techniques for enabling inspection or metrology on targets within the die or active area. Said in another way, target structures are inserted within the die or active area. In one embodiment, a set of rules are provided for integrating test structures within the die. For example, these rules may be implemented by one or more design engineers or by place-and-route tools which automatically generate the die layout pattern and thereafter insert the target structures into the die layout pattern based on these rules. Location data of each target is then retained during the layout generation and provided to one or more inspection or metrology tools and / or metrology engineers so that each target may be found and then inspected or measured.

Owner:KLA TENCOR TECH CORP

Method and system, with component kits for designing or deploying a communications network which considers frequency dependent effects

InactiveUS20040038683A1Simply and quickly prepareOptimize timingReceivers monitoringAnalogue computers for electric apparatusDesign engineerDisplay device

A computerized model provides a display of a physical environment in which a communications network is or will be installed. The communications network is comprised of several components, each of which are selected by the design engineer and which are represented in the display. Errors in the selection of certain selected components for the communications network are identified by their attributes or frequency characteristics as well as by their interconnection compatibility for a particular design. The effects of changes in frequency on component performance are modeled and the results are displayed to the design engineer. A bill of materials is automatically checked for faults and generated for the design system and provided to the design engineer. For ease of design, the design engineer can cluster several different preferred components into component kits, and then select these component kits for use in the design or deployment process.

Owner:EXTREME NETWORKS INC

Graphical user interface for testability operation

InactiveUS6341361B1Accurate analysisQuickly and efficiently and accurately testabilityElectronic circuit testingFunctional testingFault coverageGraphics

A graphical user interface (GUI) provides a design engineer the capability of automatically inserting scan logic and test logic into a design. The graphical user interface includes a scan insertion option for a design engineer to invoke a scan insertion tool to check the design for testability. The graphical user interface also permits the design engineer to invoke a test generation tool such as an automatic test pattern generator (ATPG) tool to check the design for fault coverage. The graphical user interface, which can serve as a front end for a design framework, enables a design engineer to efficiently increase testability while still in a design phase.

Owner:ADVANCED MICRO DEVICES INC

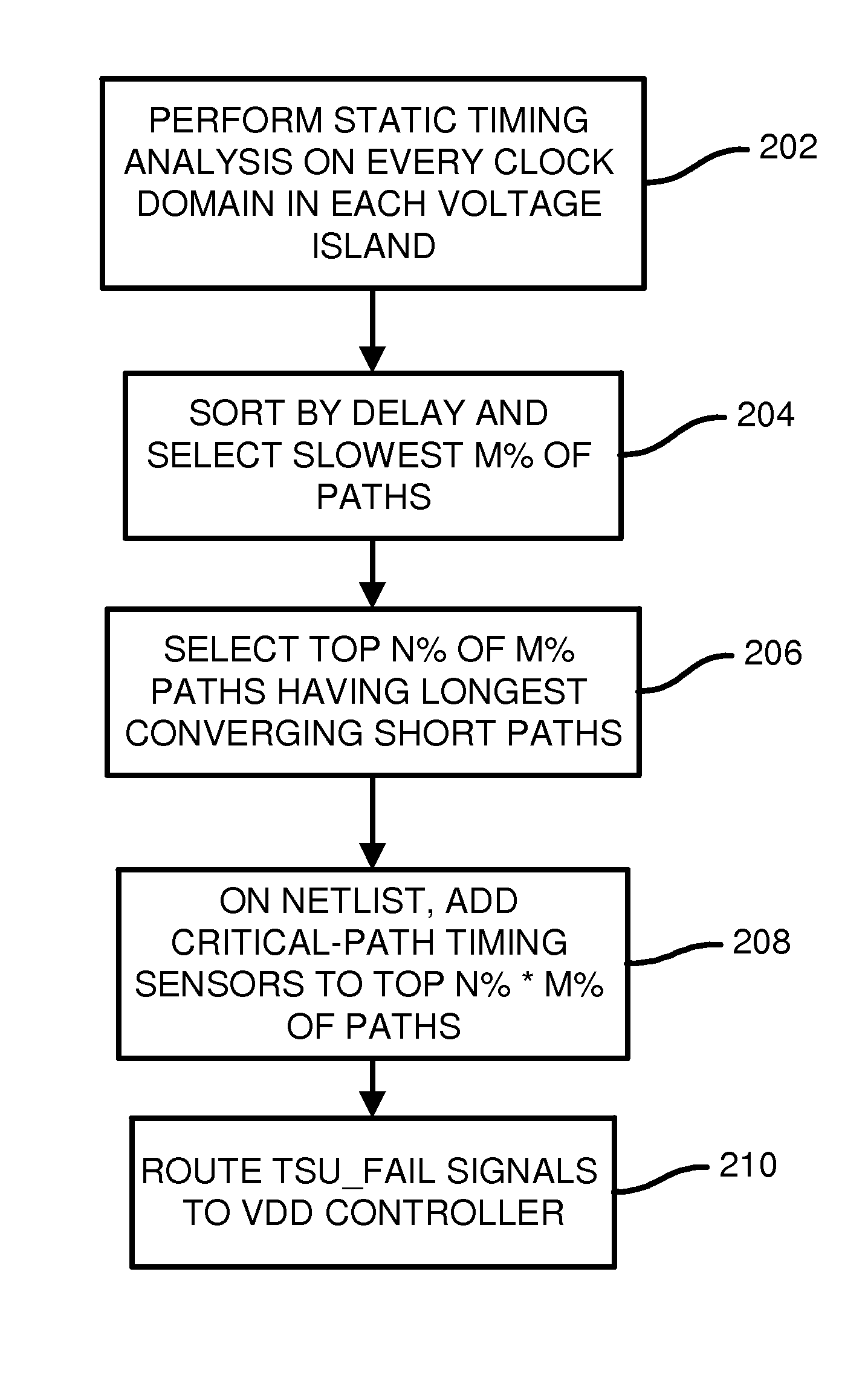

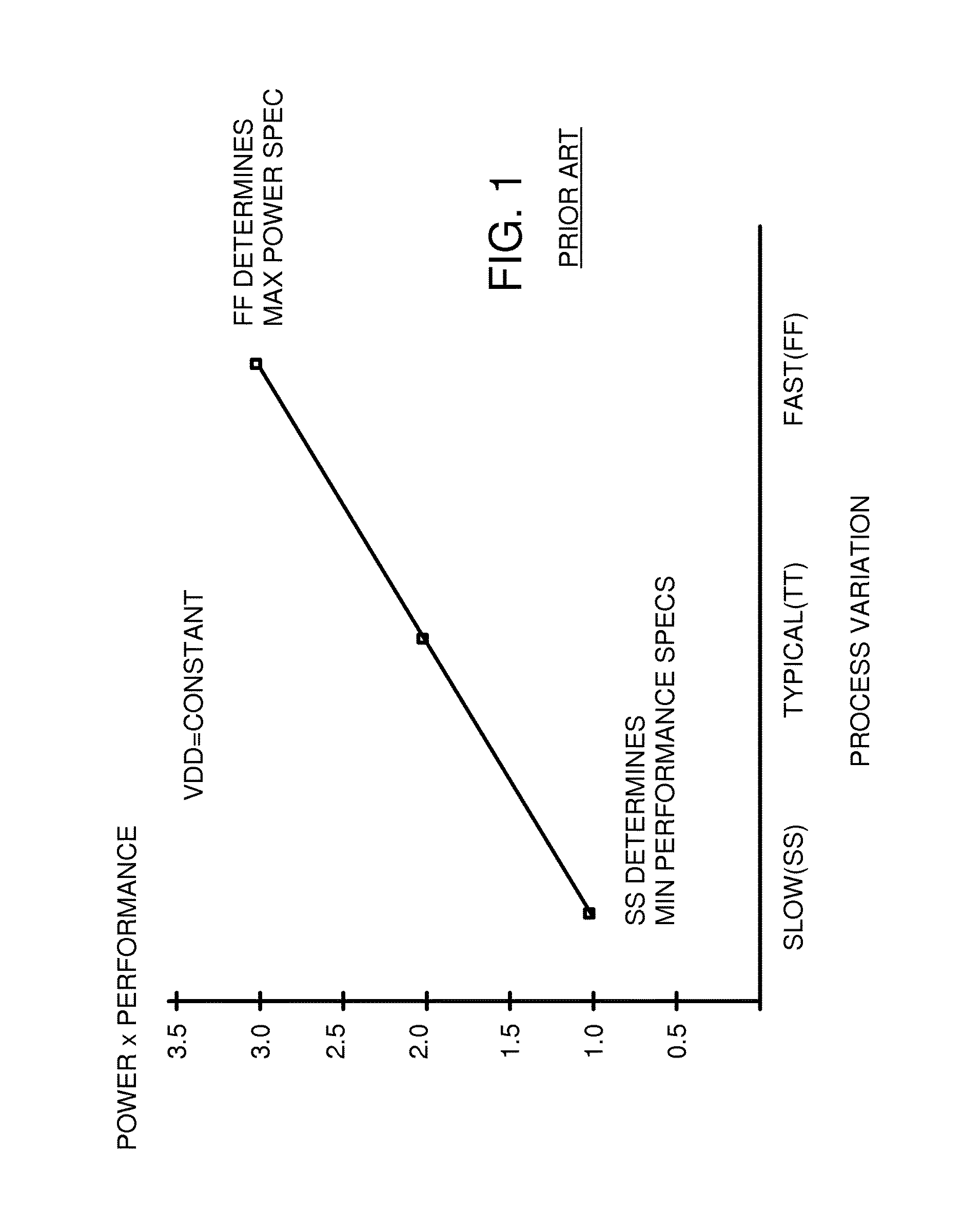

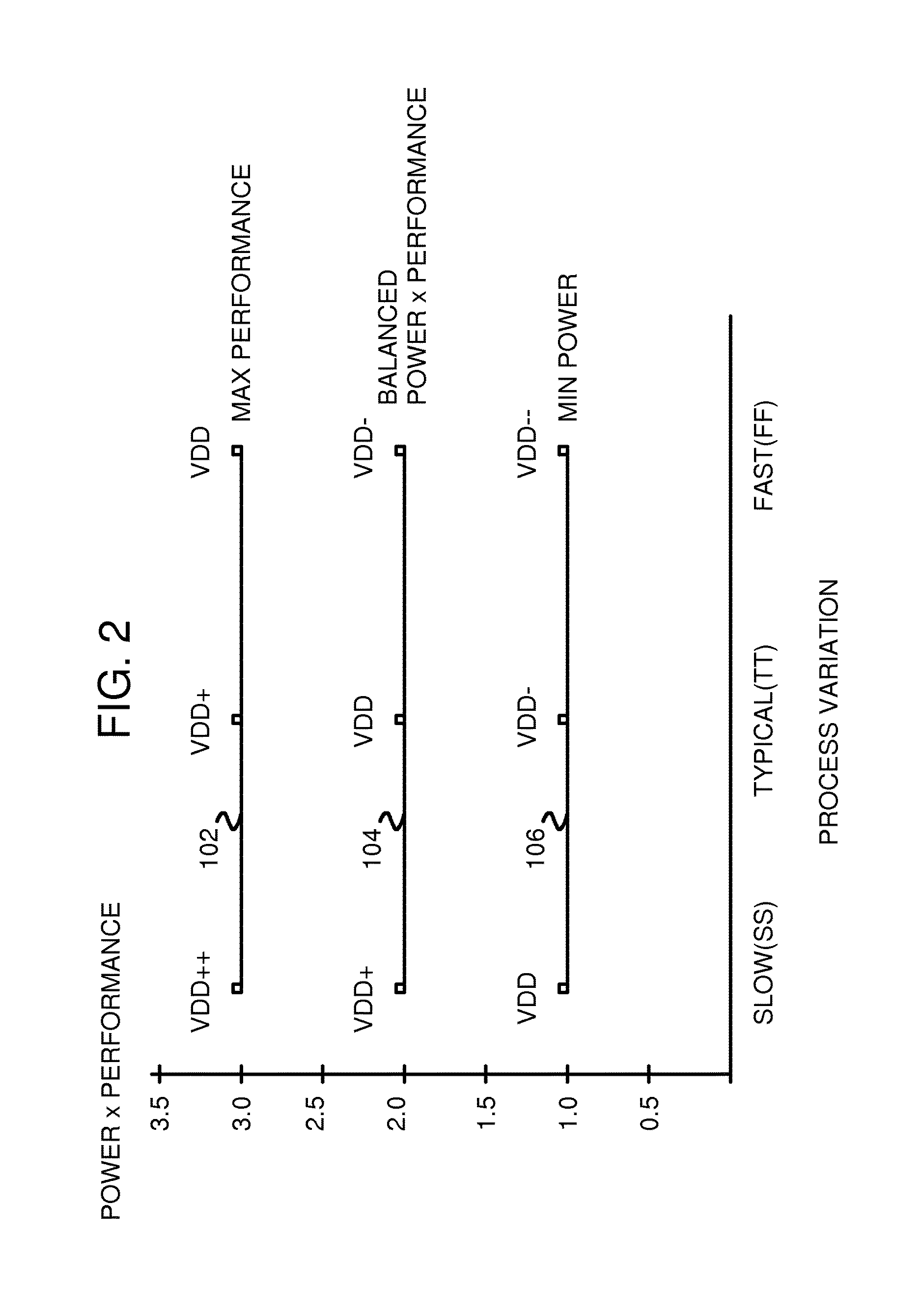

Method and algorithm for functional critical paths selection and critical path sensors and controller insertion

InactiveUS9536038B1CAD circuit designSpecial data processing applicationsDesign engineerCritical path method

CAD software examines delays of paths in a design from design engineers and first selects the longest paths. Then all paths that converge with these longest paths are examined for delays, and a fastest converging path is selected for each of the longest paths. The longest paths are again sorted by the fastest converging delay, and paths with slower converging paths are selected to be Functional Critical Paths (FCP's). Functional critical path timing sensors are added to each FCP to test setup time with an added margin delay. When the margined path delays fail to meet setup requirements, the functional critical path timing sensors signal a controller to increase VDD. When no failures occur over a period of time, the controller decreases VDD. The CAD software can replicate some of the FCP's and add toggle pattern generators and timing sensors and a margin controller to adjust the margin delay.

Owner:QUALCOMM INC

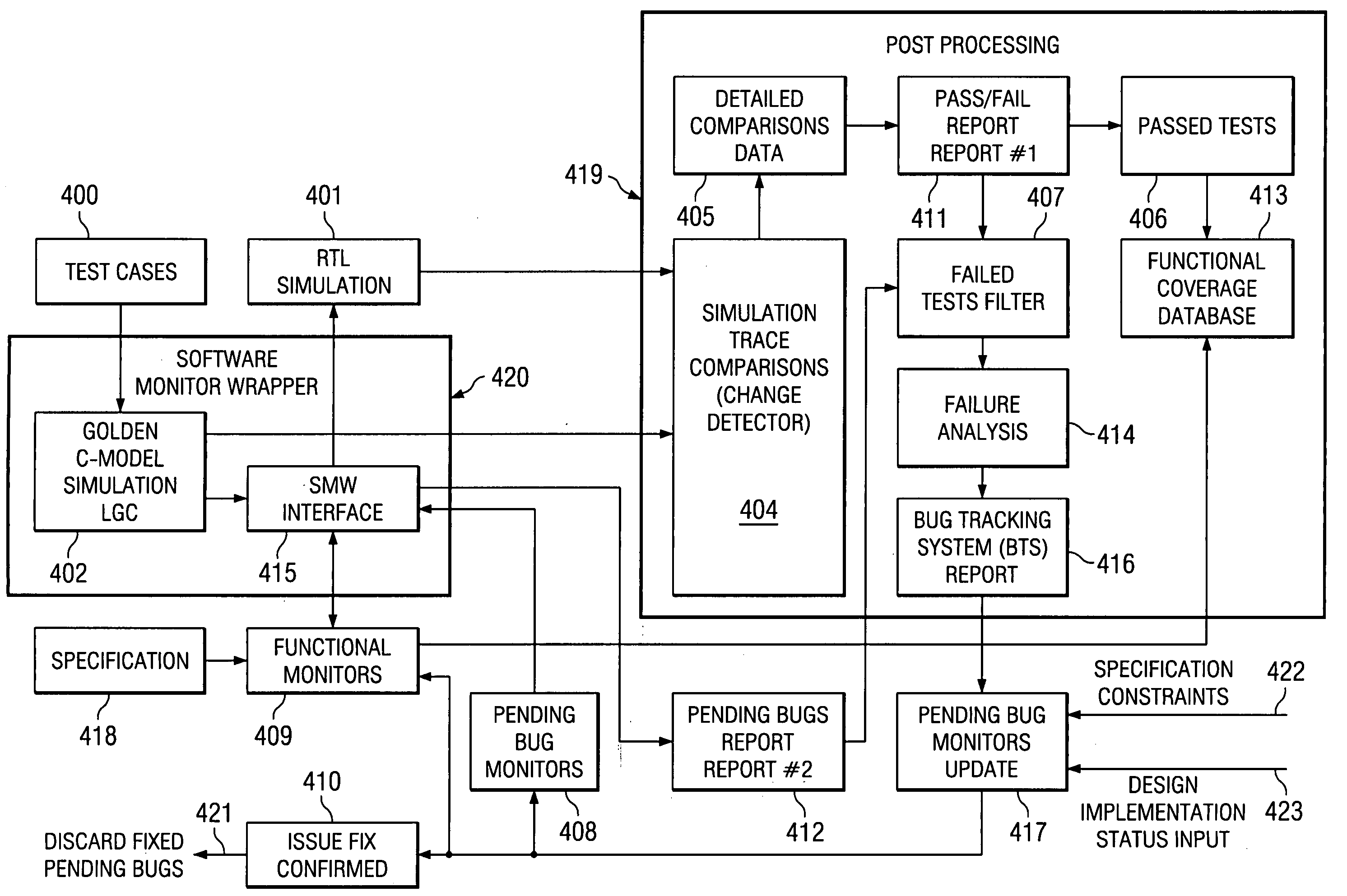

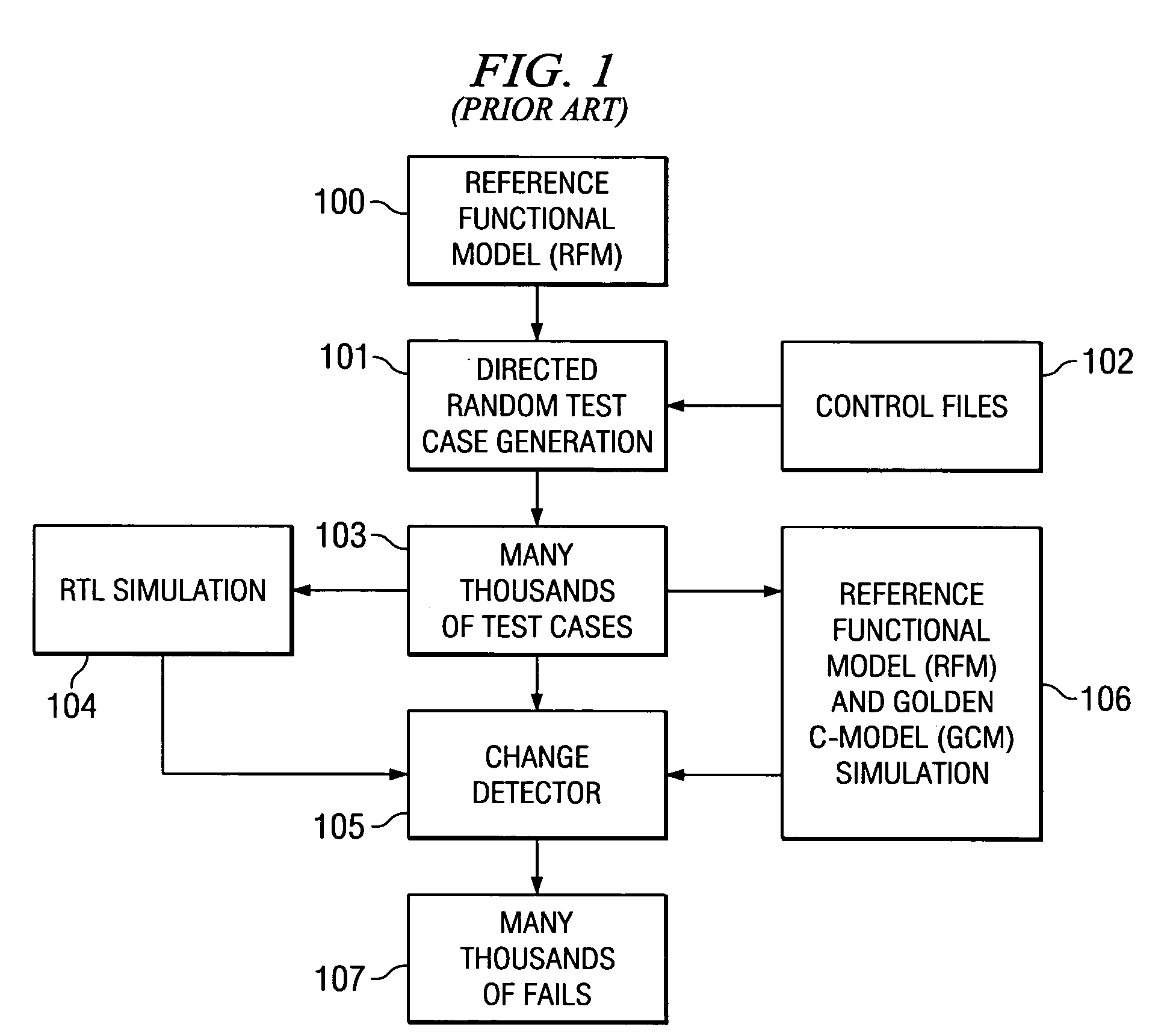

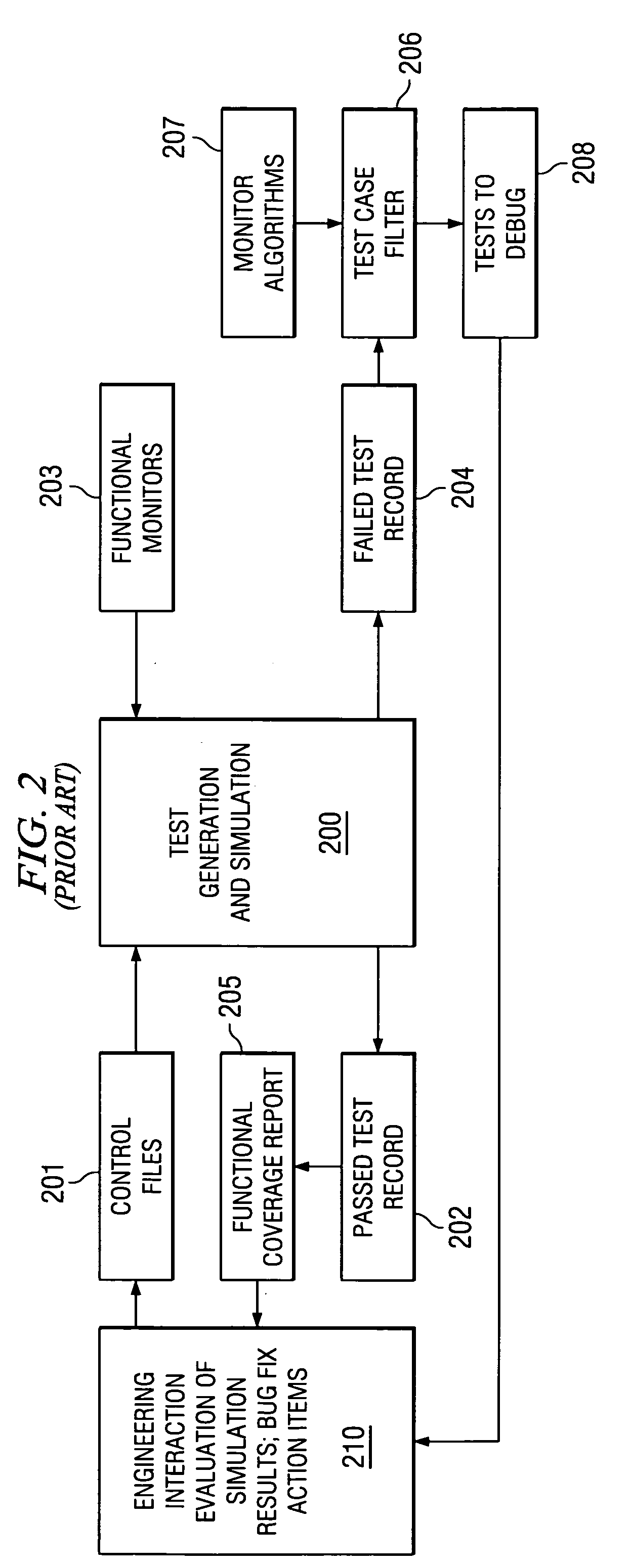

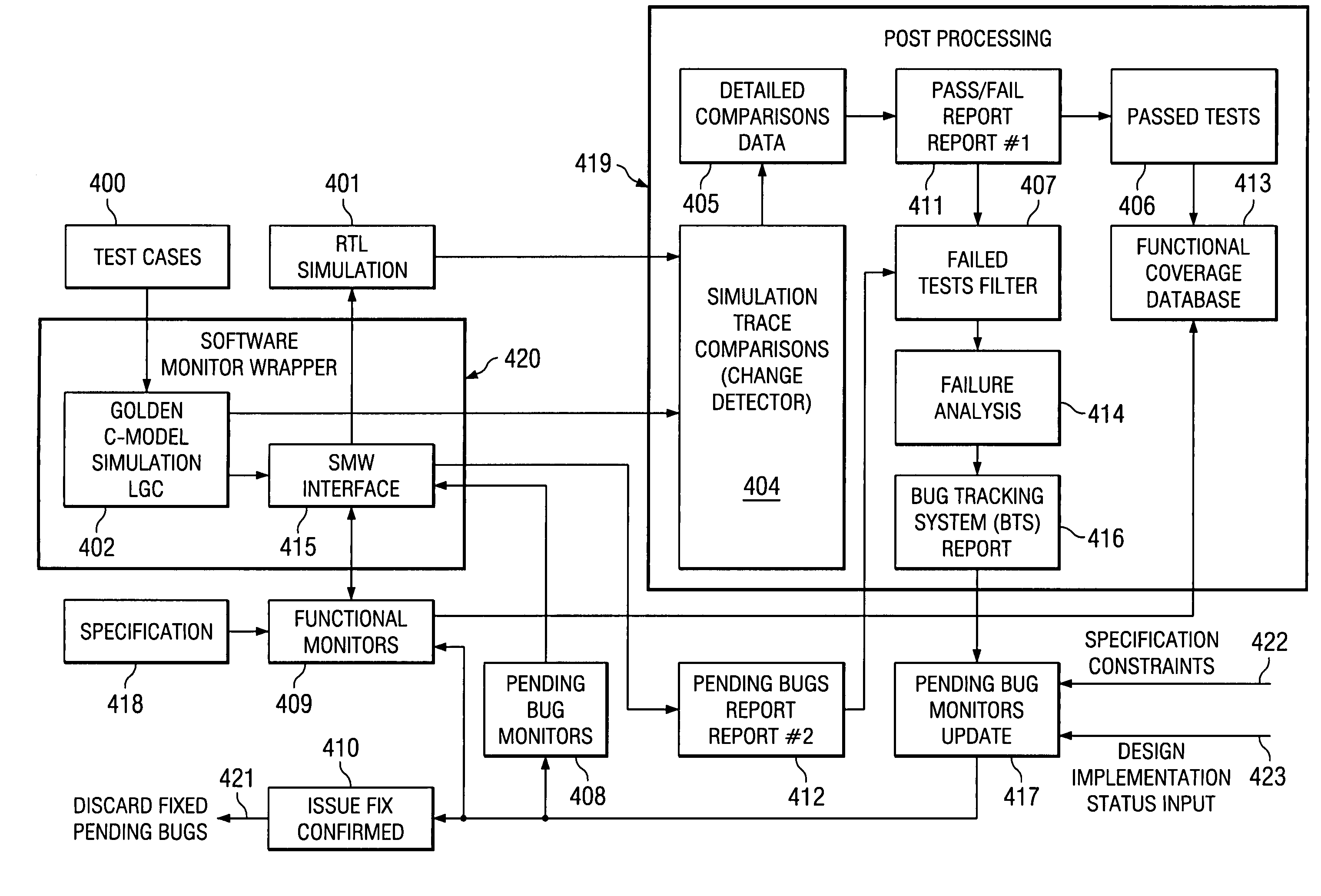

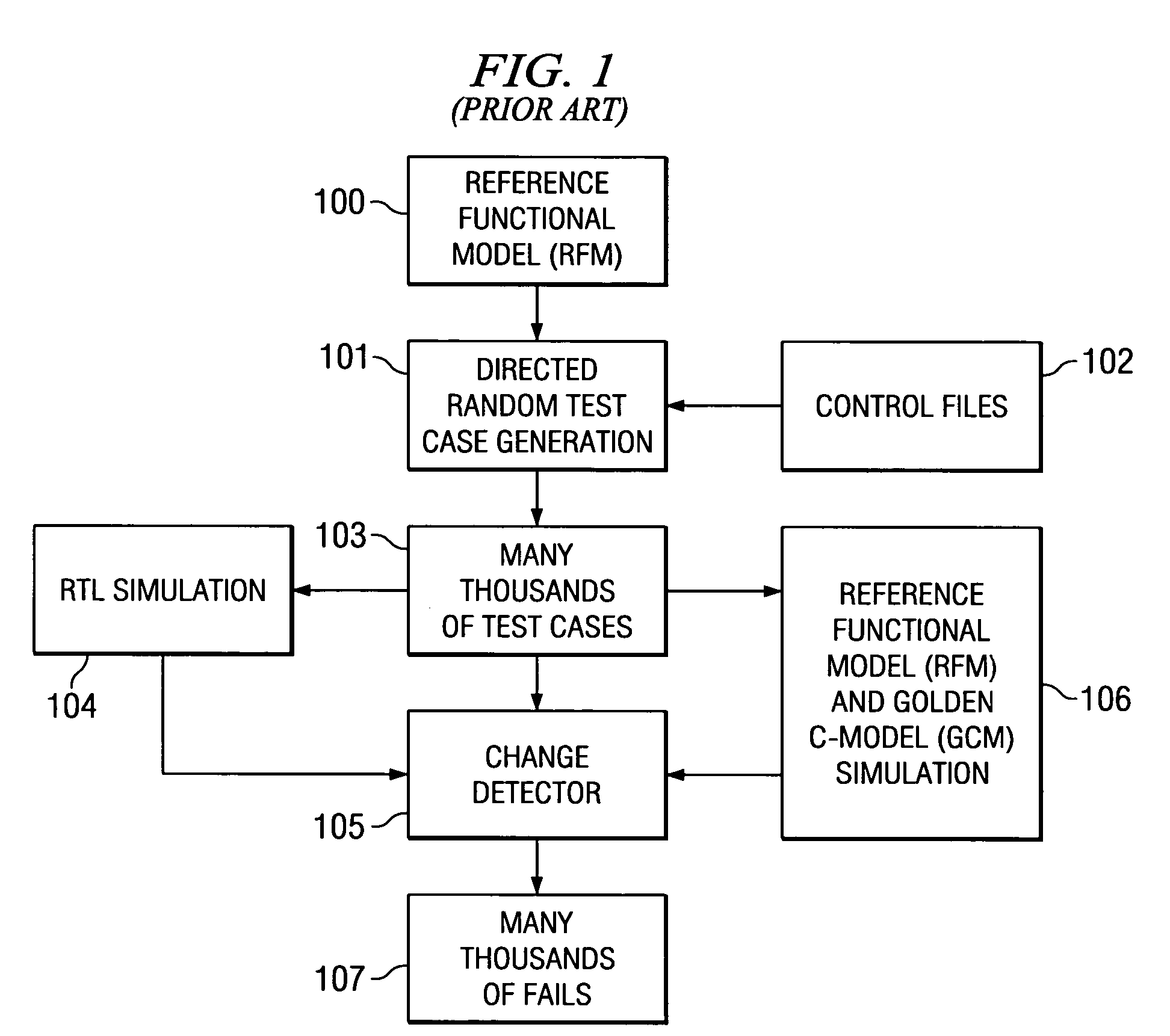

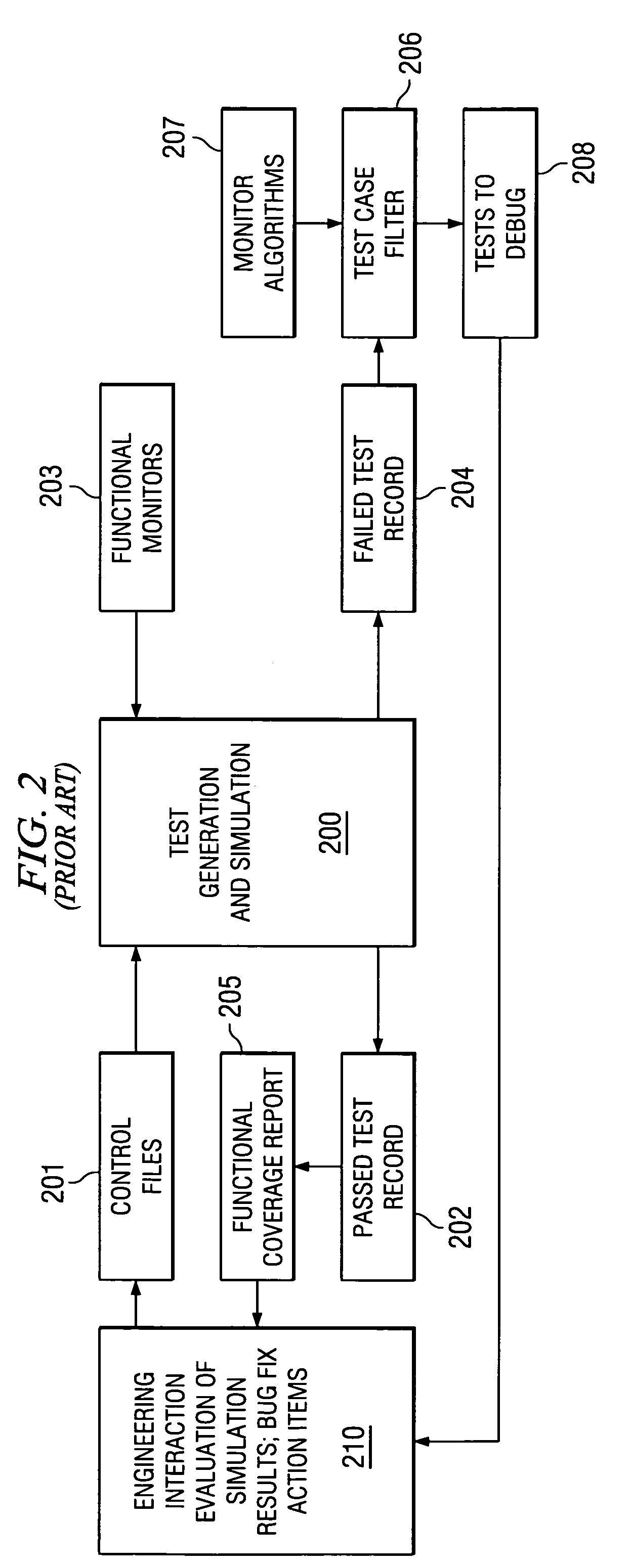

Pending bug monitors for efficient processor development and debug

ActiveUS20050149805A1Improve design and development efficiencyNew failureElectronic circuit testingError detection/correctionParallel computingDesign engineer

This invention addresses difficult issues encountered in simulations and design verification efforts on complex microprocessor / digital signal processor devices. The invention provides a means for monitoring and tracking pending bugs and automates the rejection of already known / pending bugs. This allows developers / debuggers to focus on finding and correcting new bugs. This improves design development efficiency many fold and lets design engineers and verification engineers focus on real, new and unique issues. This is especially true when test cases are generated in a random way and the test case contents are actually unknown.

Owner:TEXAS INSTR INC

Method and system for generating a real time bill of materials and evaluating network performance

InactiveUS20030050878A1Complete banking machinesAnimal feeding devicesSystems designBill of materials

An automated method for quickly generating a complete bill of materials and total cost information in real time. Components for a desired system are specified and / or replaced by substitute components, while continuously predicting the wireless system performance. A design engineer builds a model of the desired wireless communications system and specifies each component necessary to provide sufficient or optimal system performance. A parts list is maintained, in real time, that contains a definition of each system component and its associated performance and cost parameters. As the user changes wireless system designs through a series of "what-if" scenarios, components are replaced with substitute components, cable lengths are modified, antenna systems and base station parameters are re-designed and moved to alternate locations, etc. The bill of materials is automatically updated and component costs and total system costs are immediately available to the design engineer. The designer may choose to swap components for less expensive components or may investigate several alternate radio frequency distribution and antenna schemes, etc. The performance characteristics of the system are automatically updated as is the system cost as the designer to assesses the trade-offs between performance and cost at the same time.

Owner:EXTREME NETWORKS INC

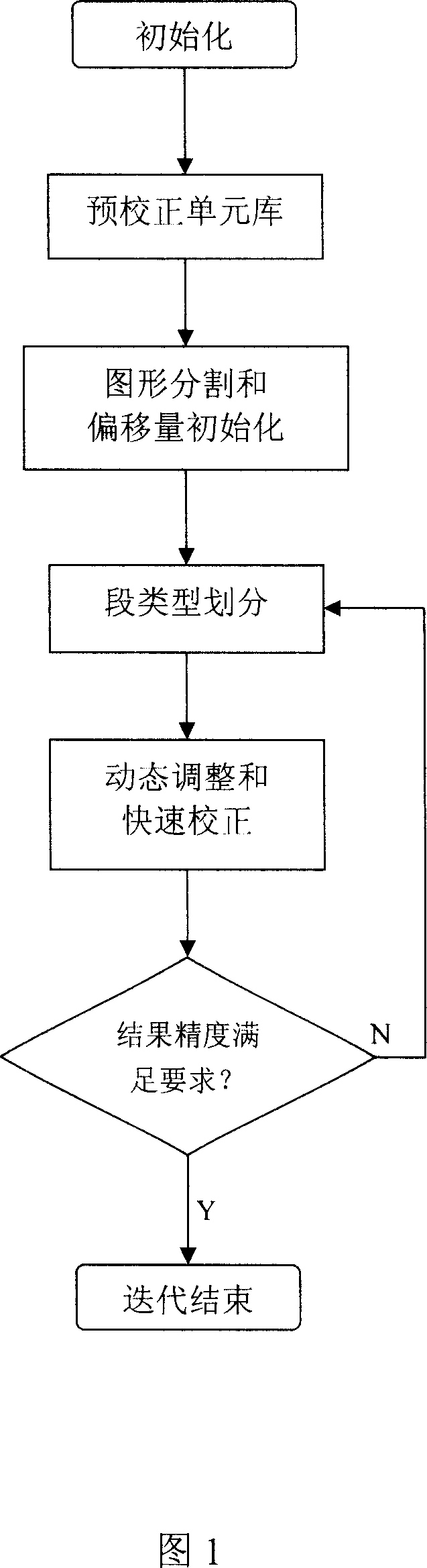

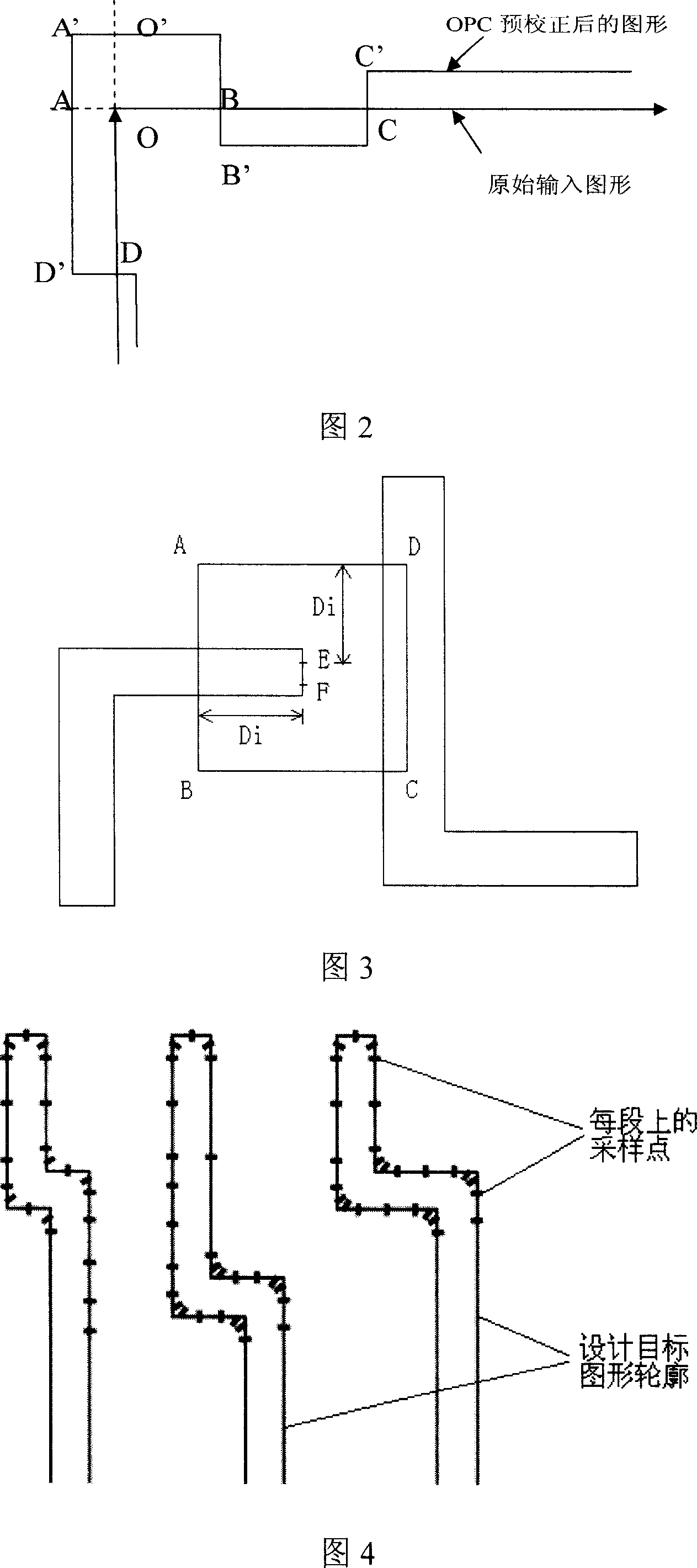

Method for correcting layering optical proximity effect

InactiveCN101013271AHigh speedImprove predictabilitySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusGraphicsDesign engineer

The invention discloses a hierarchical optical proximity effect correction method, including the preparation of the pre-correction module library, the initialization of the mask graphic offset and the step using dynamic adjustment algorithm for rapid computation, and it provides a method to make full use of the territory hierarchical structure in the optical proximity effect correction, and under the deep submicron conditions, the high precision mask process is considered as high costs for too big calculation quantities, and the computational complexity can be greatly reduced under the help of the new algorithm, and meanwhile, the new approach provides the module library with pre-correction results to IC design process, making the design engineer more flexible and effective to check the design. The method of the invention can be used for aided high-precision IC mask board, to increase the results predictability in IC design process, and OPC correction computational speed, lower costs, and increase IC production yield and reduce production cycle.

Owner:ZHEJIANG UNIV

Method and system, with component kits, for designing or deploying a communications network which considers frequency dependent effects

InactiveUS20040133415A1Simply and quickly prepareOptimize timingAnalogue computers for electric apparatusTelephonic communicationDesign engineerDisplay device

A computerized model provides a display of a physical environment in which a communications network is or will be installed. The communications network is comprised of several components, each of which are selected by the design engineer and which are represented in the display. Errors in the selection of certain selected components for the communications network are identified by their attributes or frequency characteristics as well as by their interconnection compatibility for a particular design. The effects of changes in frequency on component performance are modeled and the results are displayed to the design engineer. A bill of materials is automatically checked for faults and generated for the design system and provided to the design engineer. For ease of design, the design engineer can cluster several different preferred components into component kits, and then select these component kits for use in the design or deployment process.

Owner:EXTREME NETWORKS INC

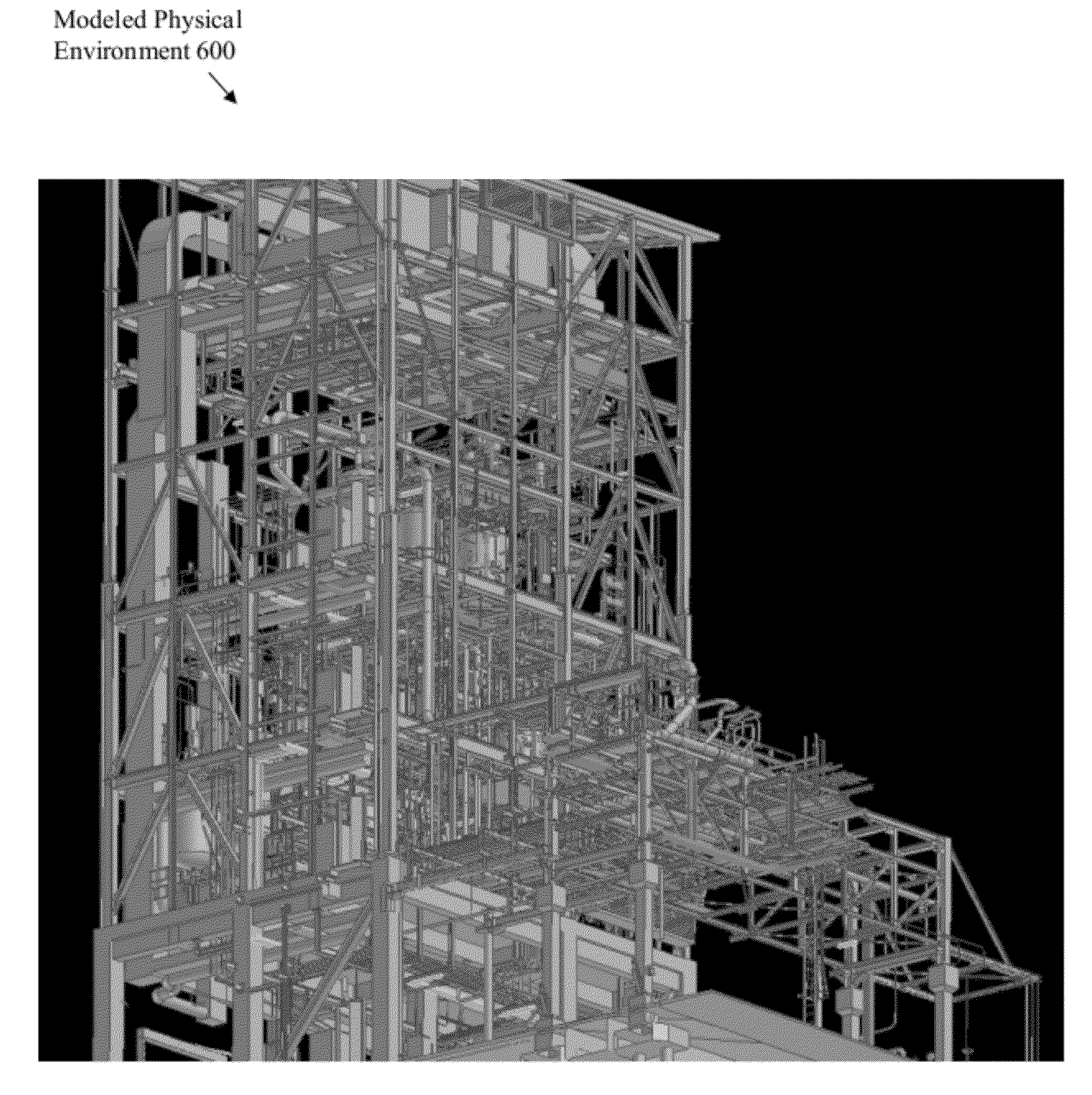

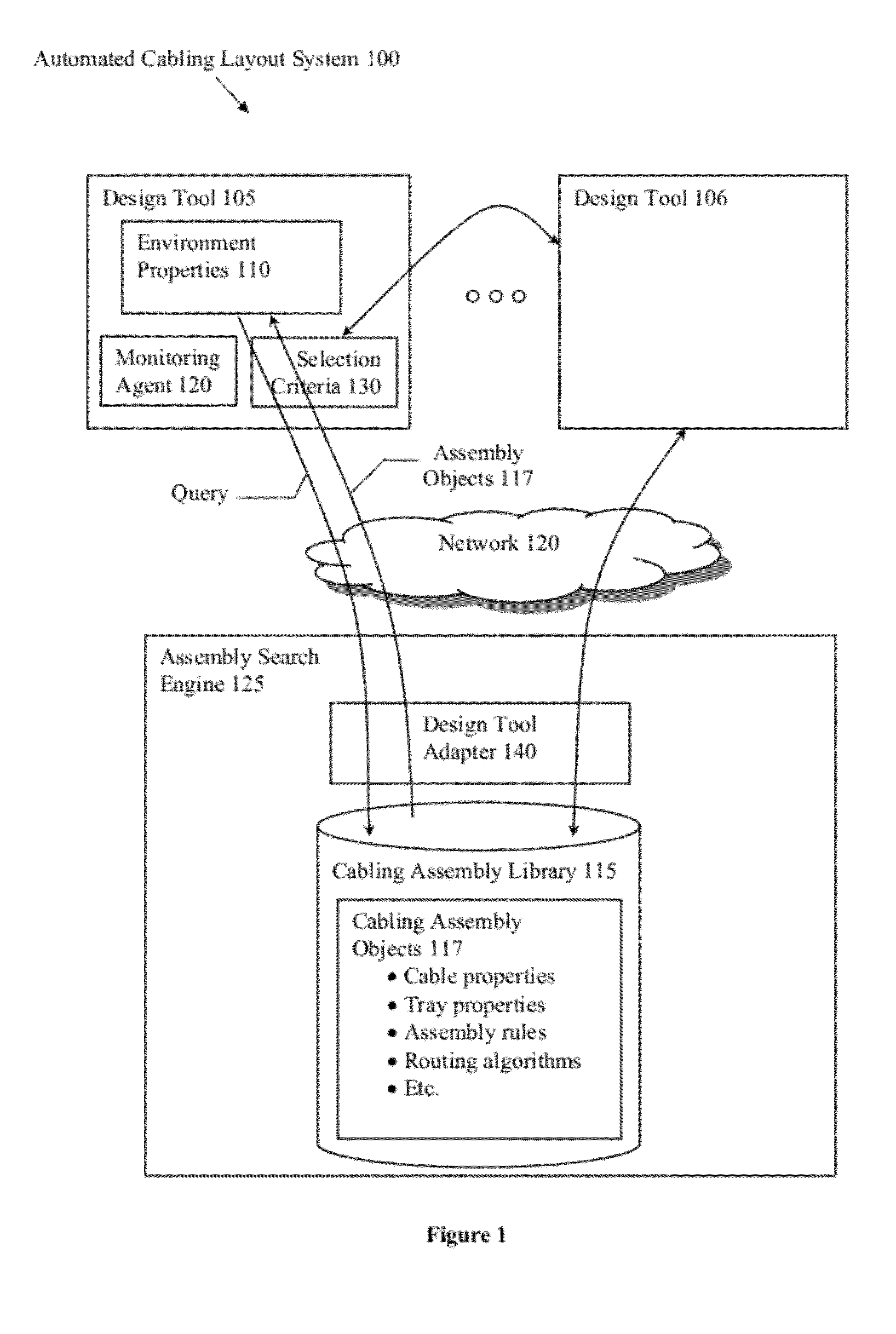

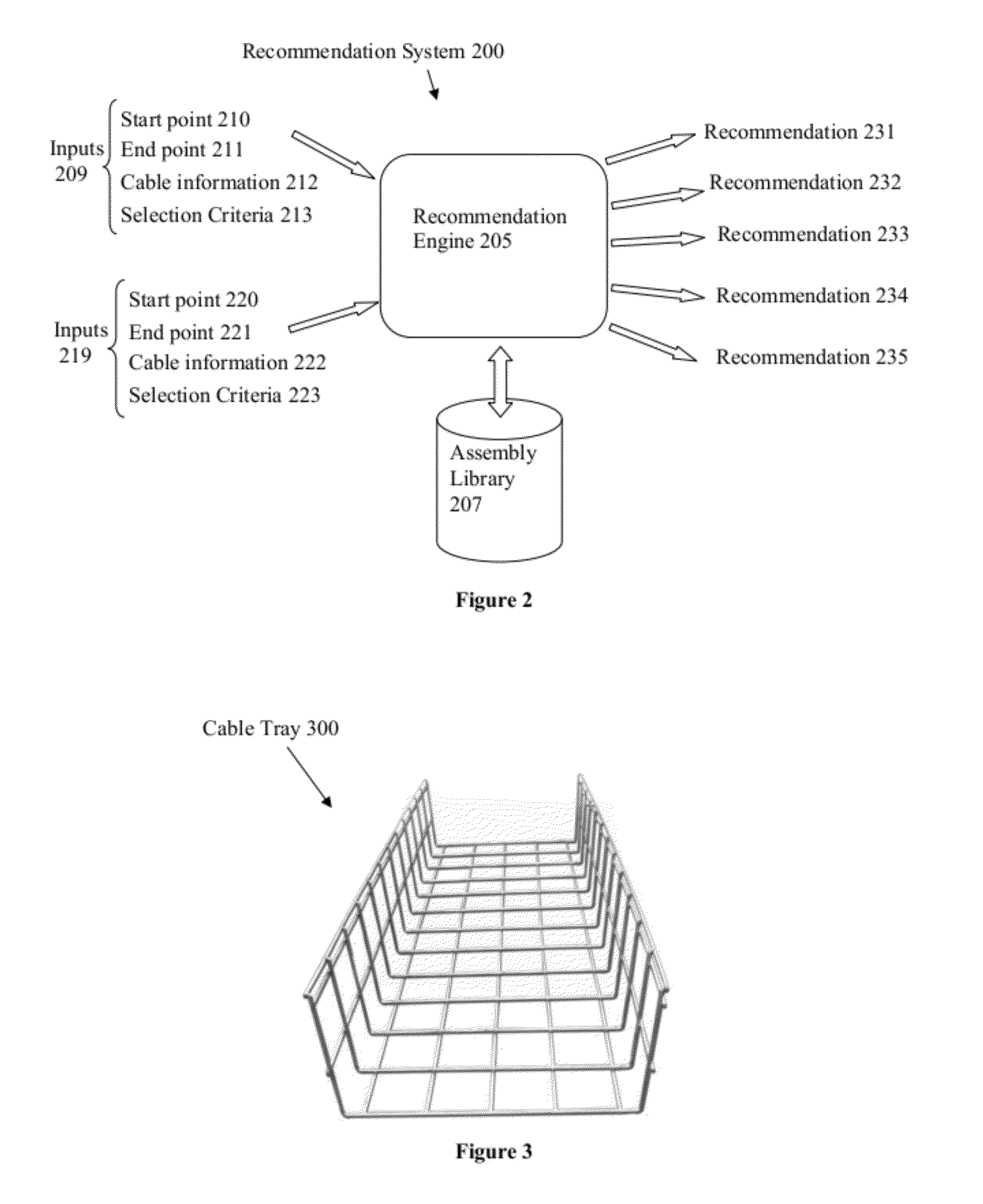

Automated cabling layout systems and methods

Automated cabling layout systems and methods are presented. A cabling assembly library stores multiple generic, design-tool agnostic cabling assembly objects representing cabling layout objects (e.g., cables, trays, mounts, conduits, etc.). The cabling assembly objects further include design rules governing the conditions of use of the cabling assembly object. Design engineers or designers can query the library to identify appropriate cabling assembly objects that would be appropriate for using within a modeled physical environment. One or more matching cabling assembly objects can be converted to an appropriate format for a design tool and instantiated into the modeled environment. The design tool can create modeled cabling layouts from the instantiated assemblies according to the design rules of the corresponding cabling assembly objects.

Owner:FLUOR TECH CORP

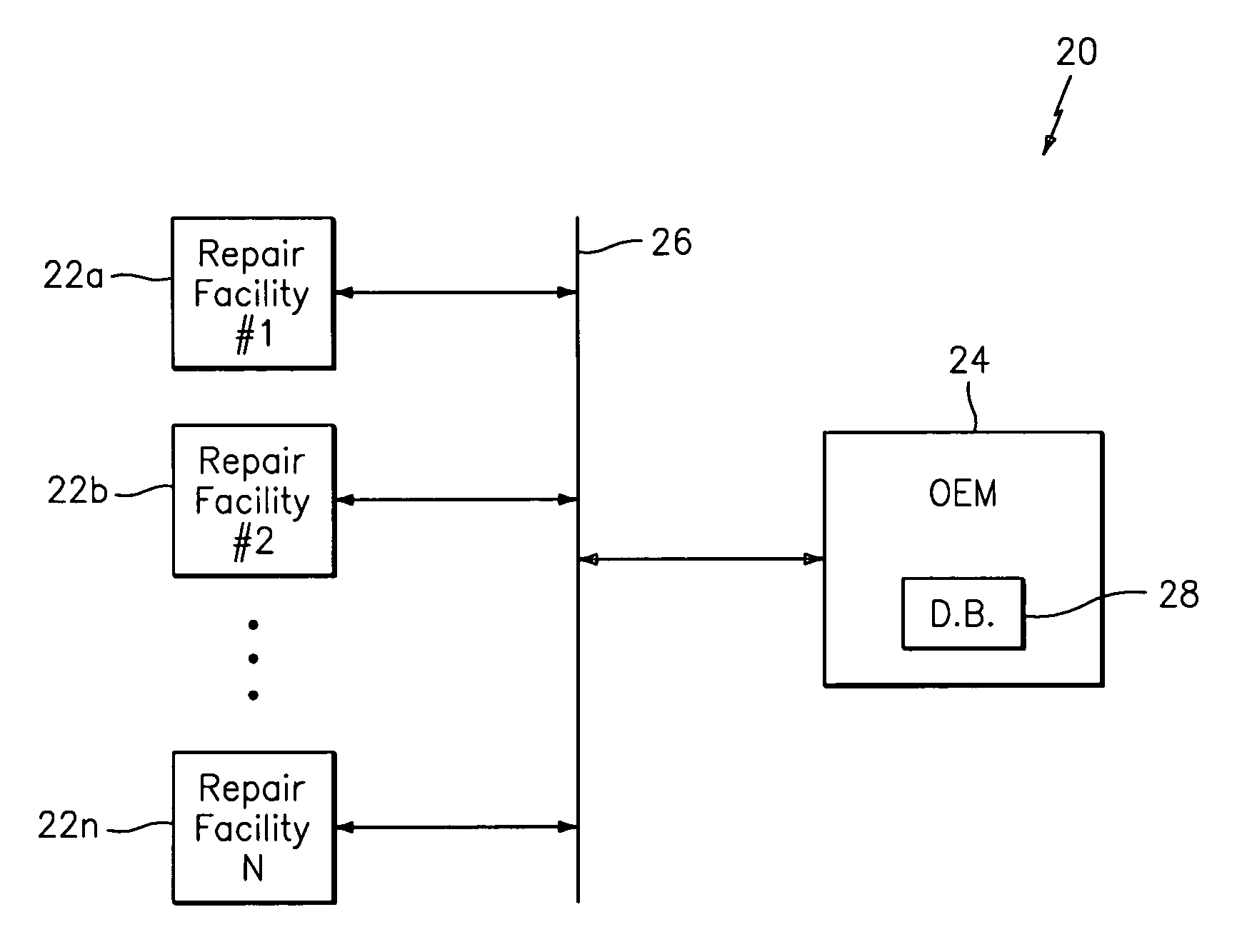

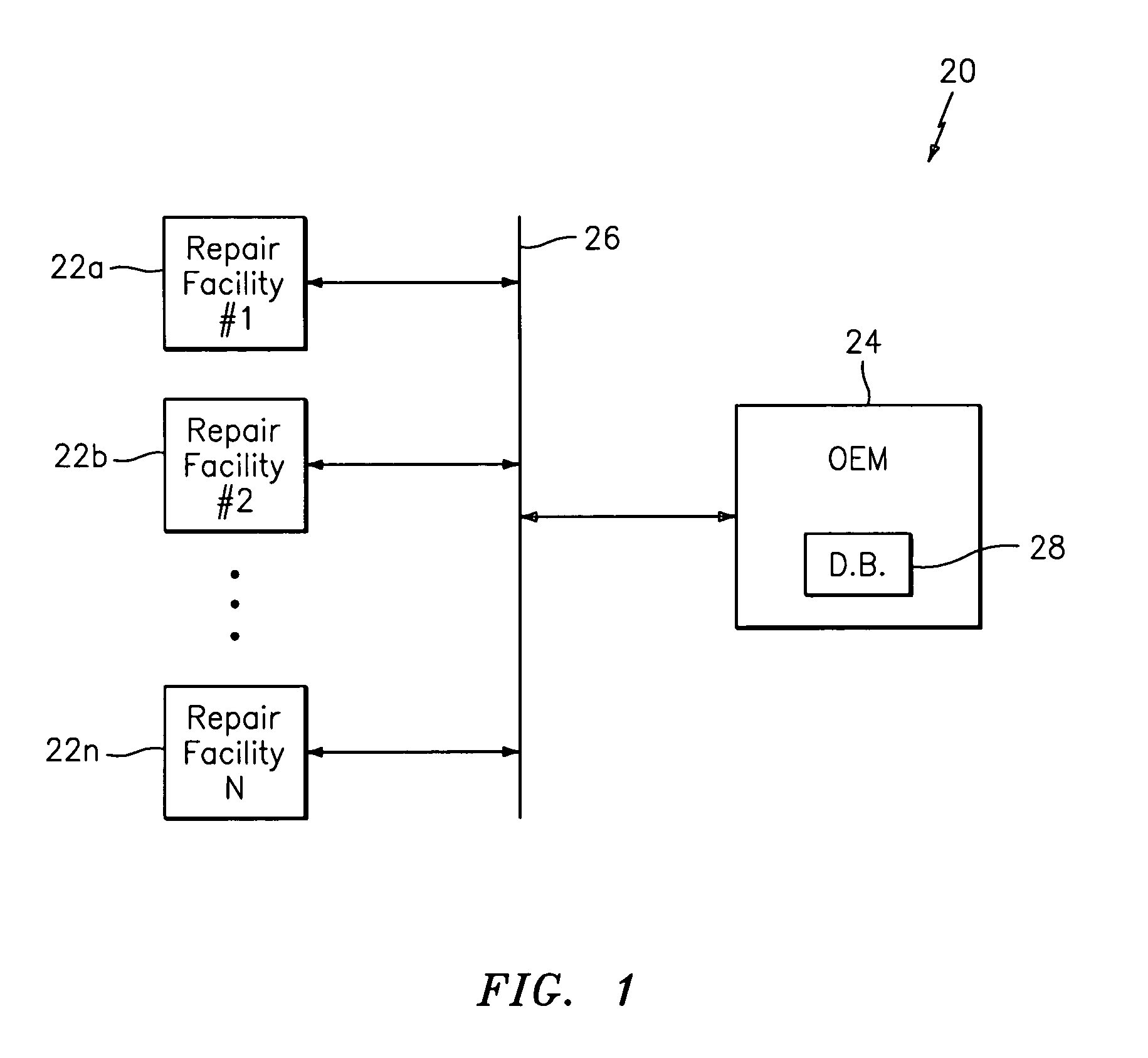

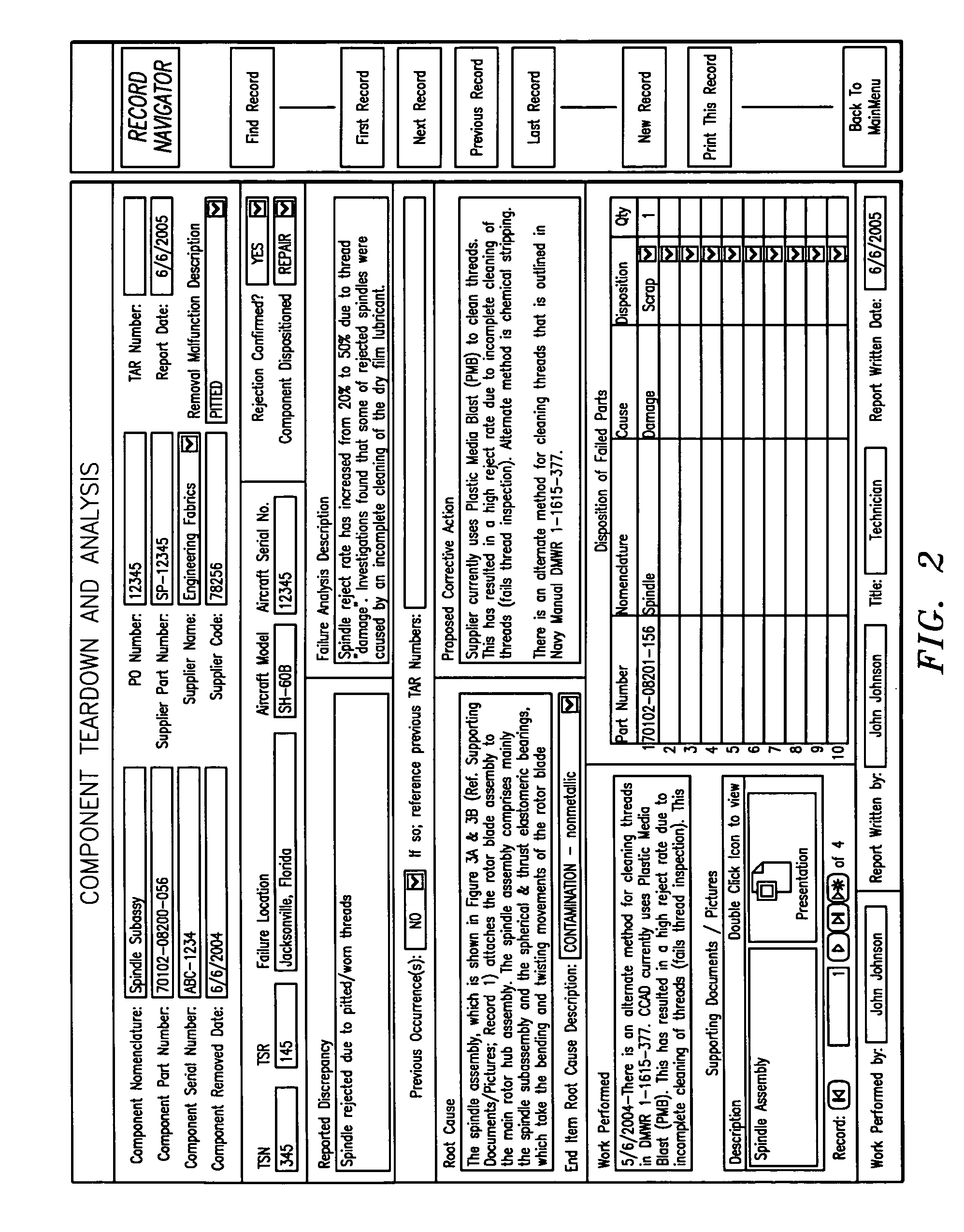

Supplier teardown & analysis reporting system

InactiveUS20070294052A1Facilitates design engineer understandingFailed analysisPlug gaugesAmplifier modifications to reduce noise influenceProgram planningAction plan

A Supplier Teardown and Analysis Reporting System (STARS) captures information pertaining to component removals or failures that caused an unscheduled maintenance action. The detailed data facilitates design engineers understanding of failure drivers and propose improvements and commence implementation of a Corrective Action Plan at the earliest practicable time.

Owner:SIKORSKY AIRCRAFT CORP

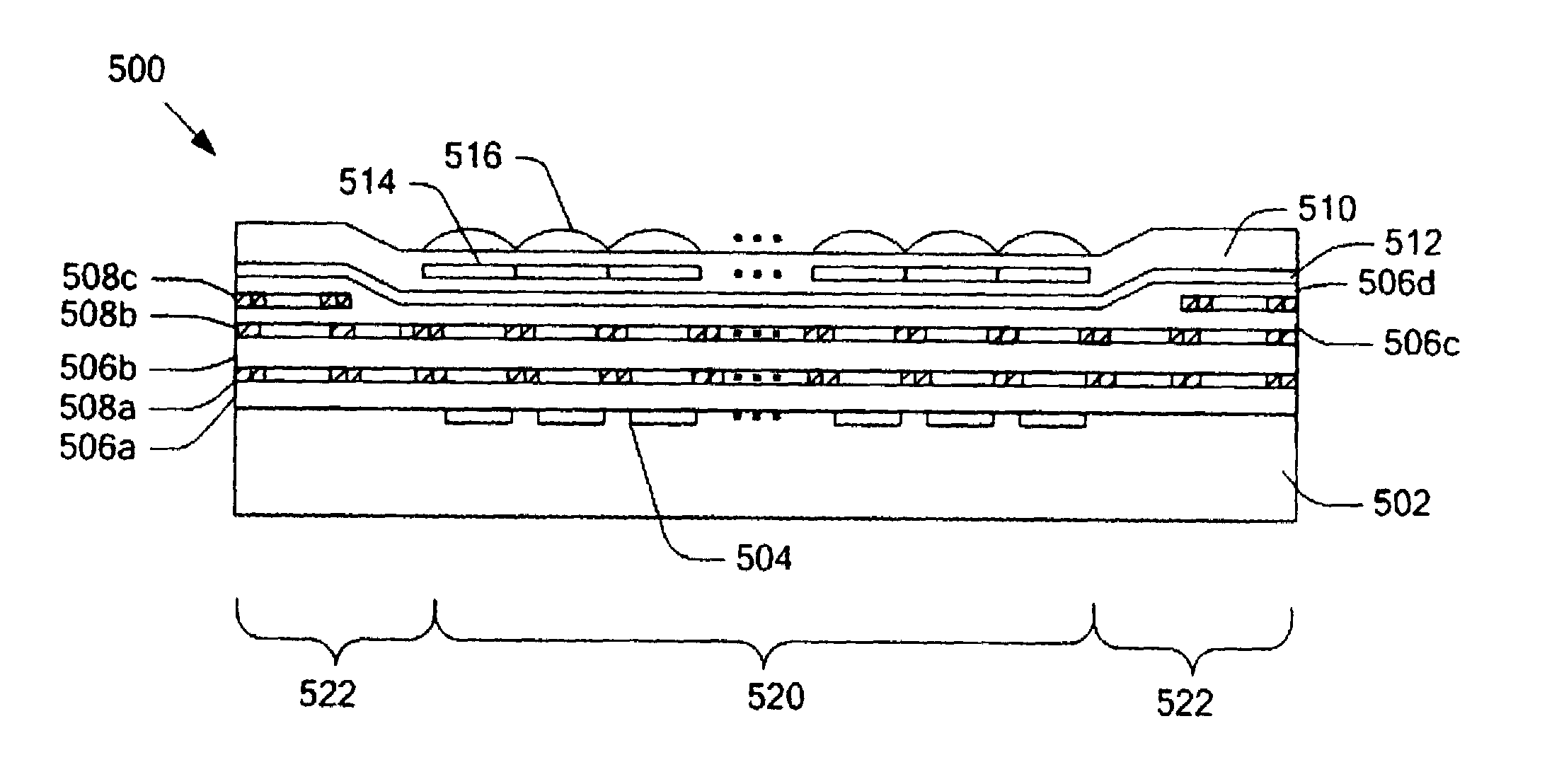

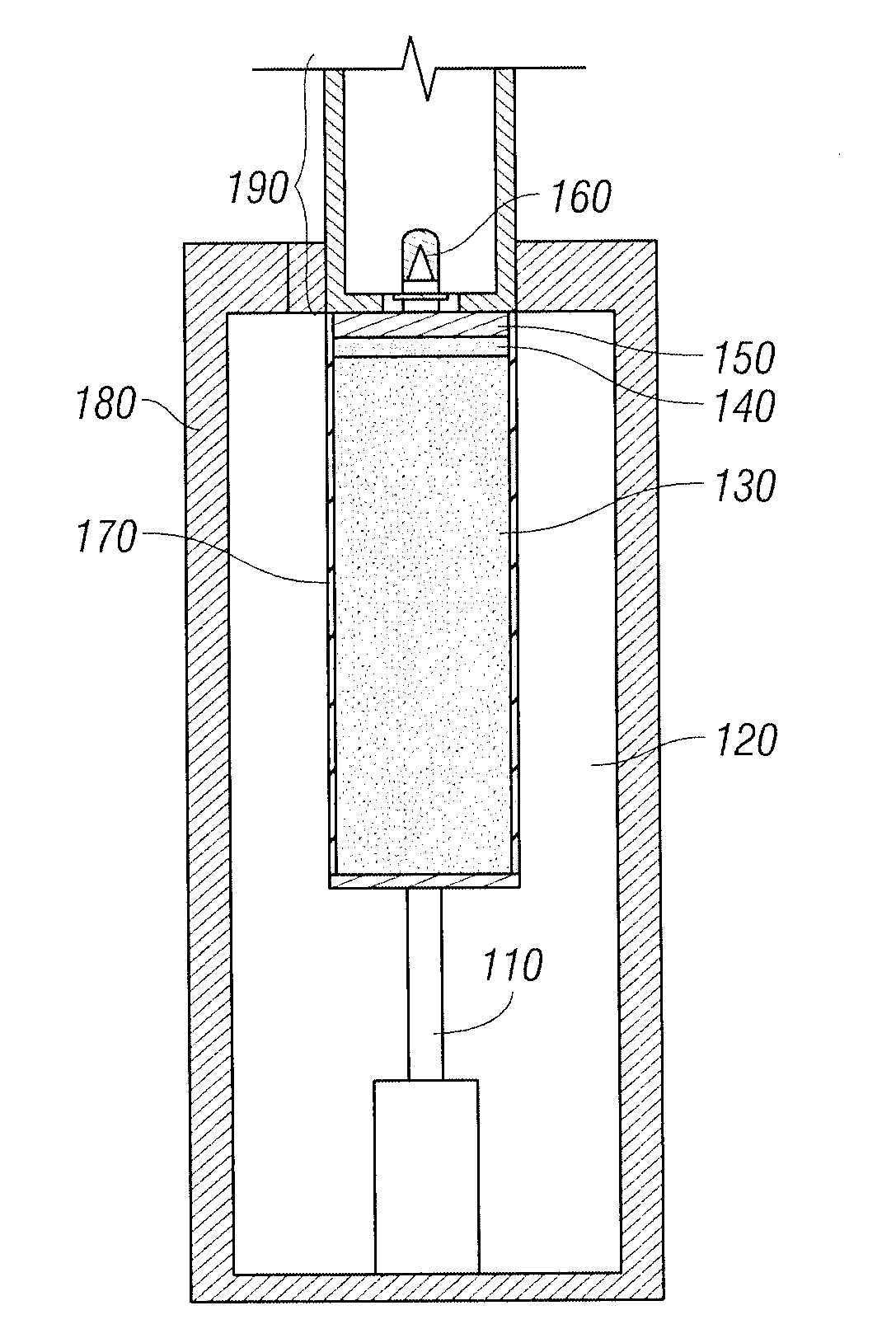

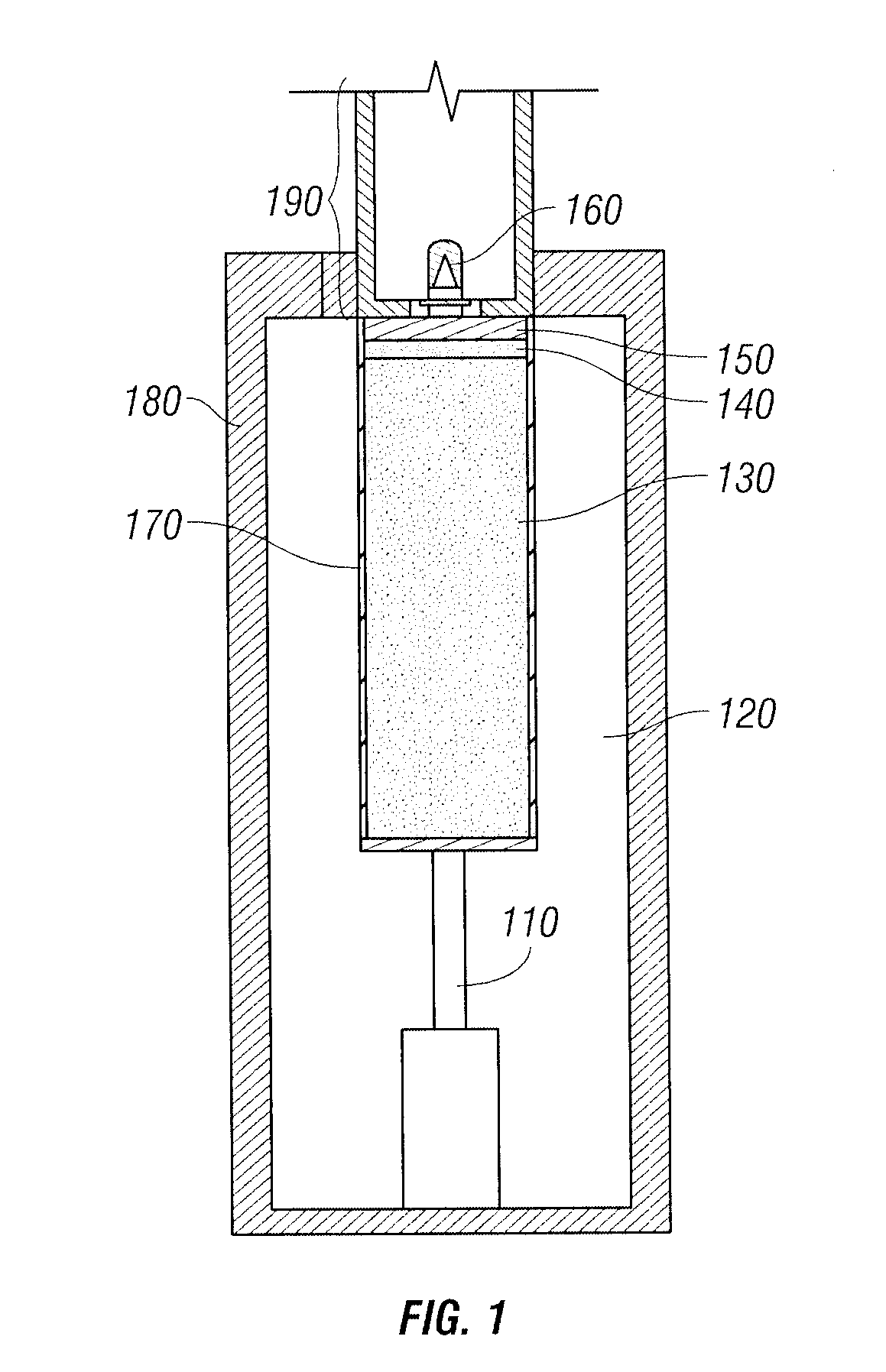

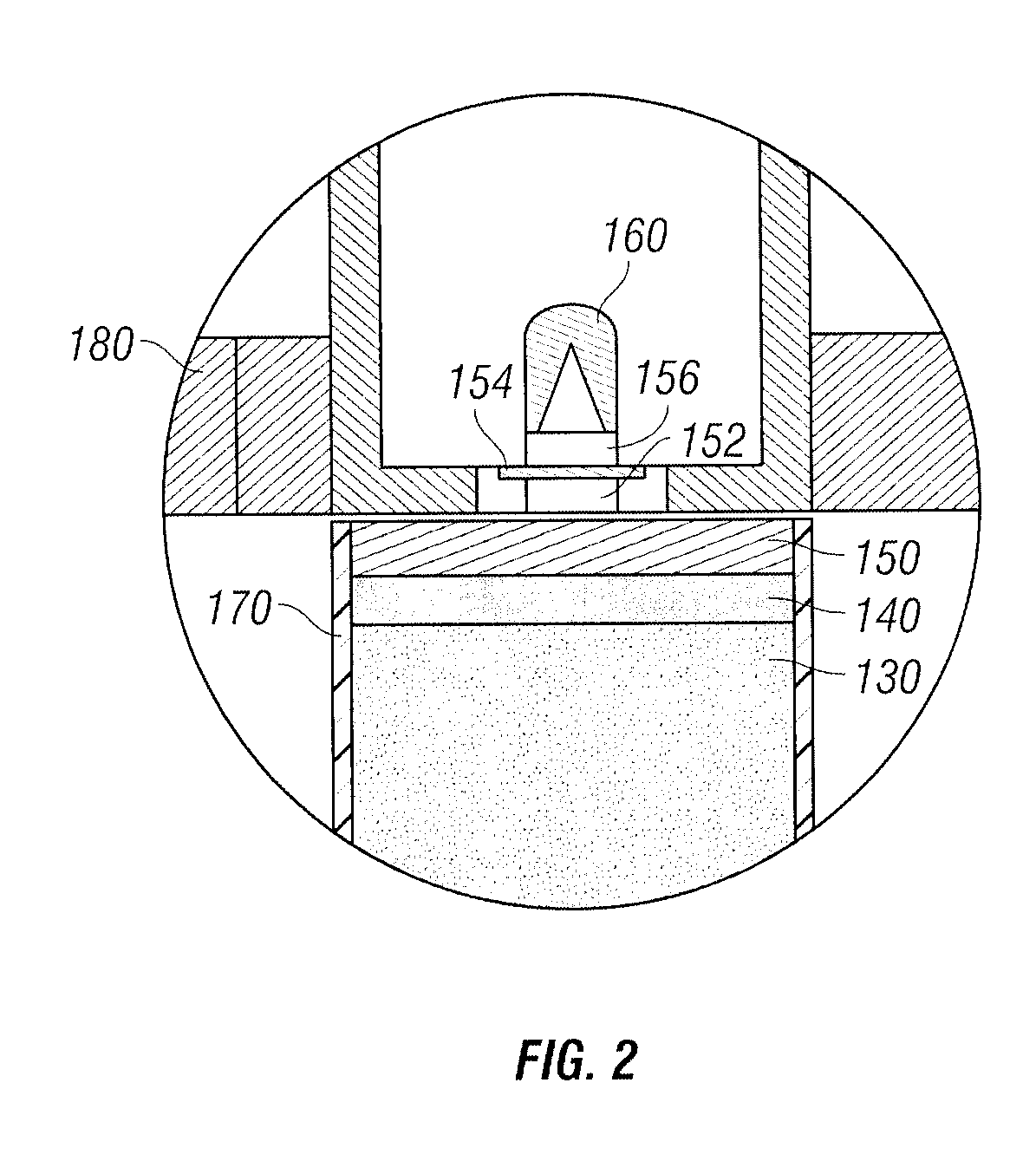

Optically improved CMOS imaging sensor structure to lower imaging lens requirements

ActiveUS7297916B1Lower lens requirementReduce thicknessTelevision system detailsSolid-state devicesVariable thicknessCamera lens

A sensor die that lowers the lens requirements by the use of a variable thickness distribution over the sensor die. The sensing portion of the sensor die has a different number of layers than the non-sensing portion of the sensor die. By reducing the thickness of each layer and / or eliminating one or more unnecessary layers in the sensing portion, the thickness of the sensing portion is reduced to lower the amount of stray light and allow an increase in chief ray angle as well as a decrease in the F-number of the imaging system coupled to the sensor die without compromising the image quality of the sensor die. Also, the thickness reduction provides the design engineers with extra allowance in handling the chief ray angle and F-number for a given lens requirements.

Owner:ASML NETHERLANDS BV +1

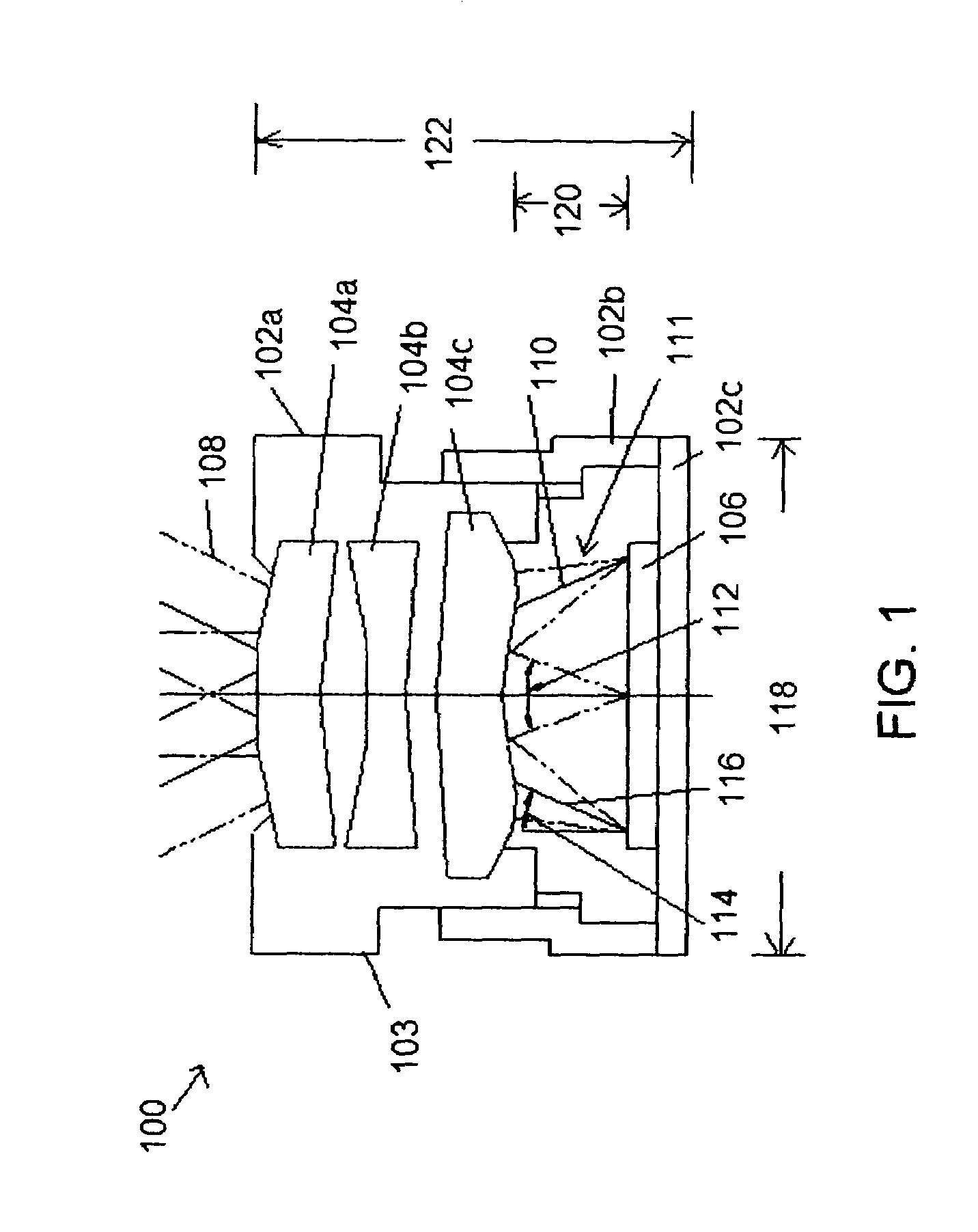

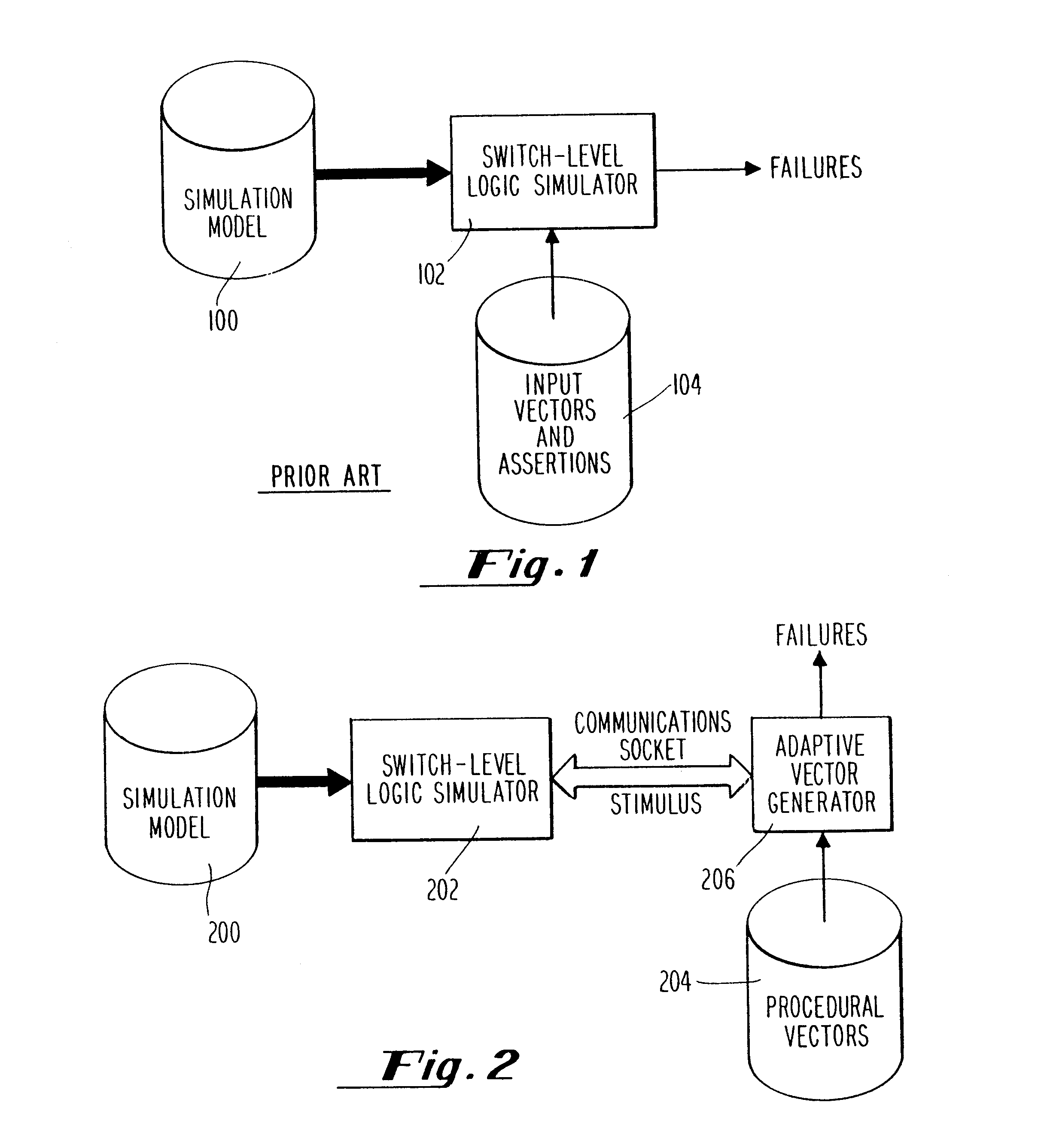

Bidirectional socket stimulus interface for a logic simulator

InactiveUS6421823B1Logical operation testingGeneral purpose stored program computerStimulus patternComputational logic

A communications socket between a logic simulator and a system for generating input stimuli based on the current state of the logic simulator is provided. Input stimuli to the logic simulator for use in implementing a particular circuit design simulation are calculated by interfacing an input program which models the function of the circuit being designed with the logic simulator. The lines in this input program are converted by an adaptive vector generator into communications signals which are understandable by the logic simulator so that the desired simulation may take place. The input program thus enables the adaptive vector generator to behaviorally model complex logical systems that the logic simulator model is only a part of and allows for more accurate and detailed simulation. The adaptive vector generator does this by determining the next input vector state in accordance with the present state of the logic simulator model as received from the communications socket. In other words, based on the state data received from the logic simulator, the adaptive vector generation automatically calculates the next stimulus pattern for the logic simulator model and provides this stimuli to the logic simulator through the communications socket. This technique removes the tediousness of the prior art techniques in that the design engineer no longer needs to specify every input step and to anticipate the output state of the circuit.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Method and system, with component kits, for designing or deploying a communications network which considers frequency dependent effects

InactiveUS7680644B2Method is fastGuaranteed continuous performanceAnalogue computers for electric apparatusTelephonic communicationBill of materialsDisplay device

A computerized model provides a display of a physical environment in which a communications network is or will be installed. The communications network is comprised of several components, each of which are selected by the design engineer and which are represented in the display. Errors in the selection of certain selected components for the communications network are identified by their attributes or frequency characteristics as well as by their interconnection compatibility for a particular design. The effects of changes in frequency on component performance are modeled and the results are displayed to the design engineer. A bill of materials is automatically checked for faults and generated for the design system and provided to the design engineer. For ease of design, the design engineer can cluster several different preferred components into component kits, and then select these component kits for use in the design or deployment process.

Owner:EXTREME NETWORKS INC

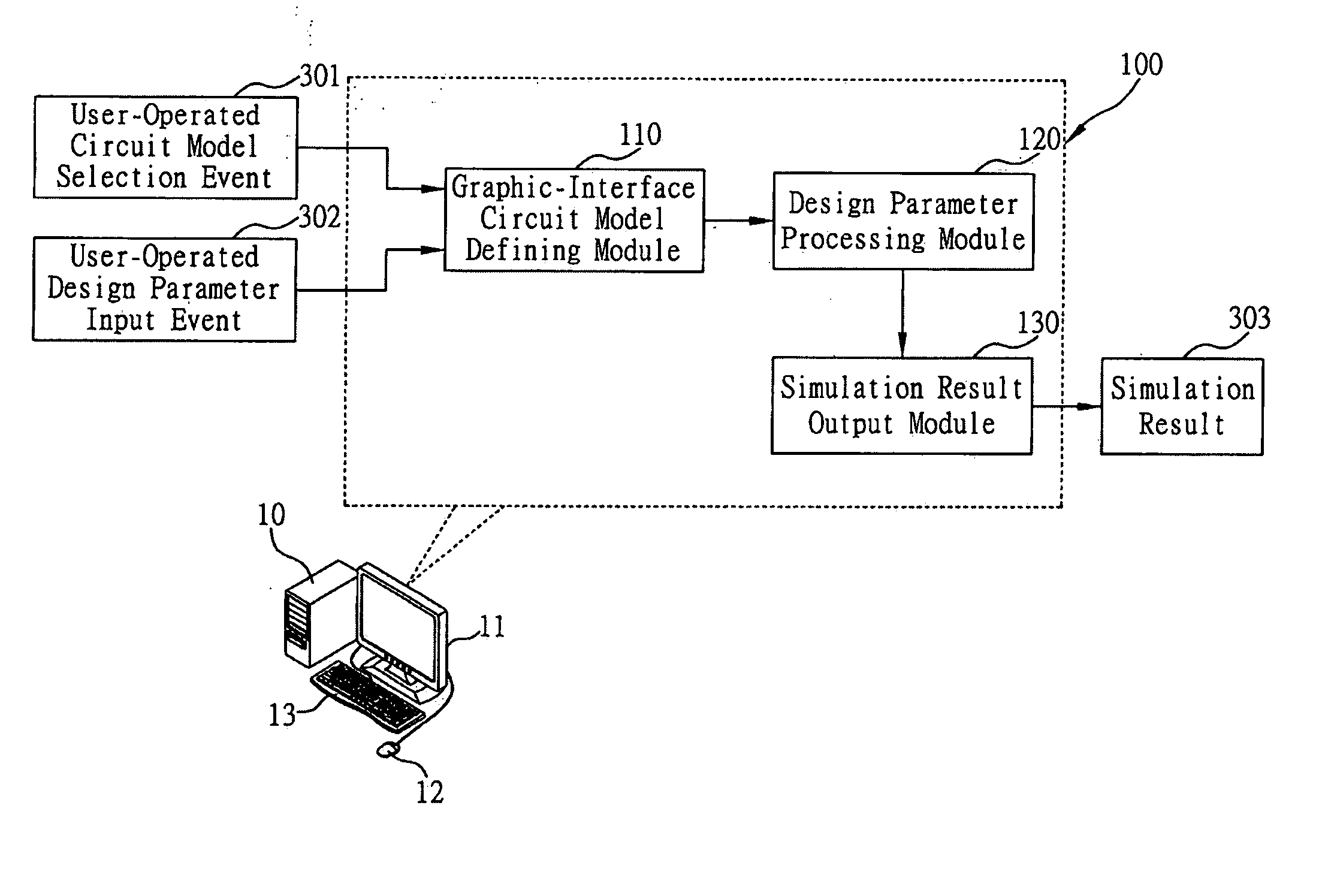

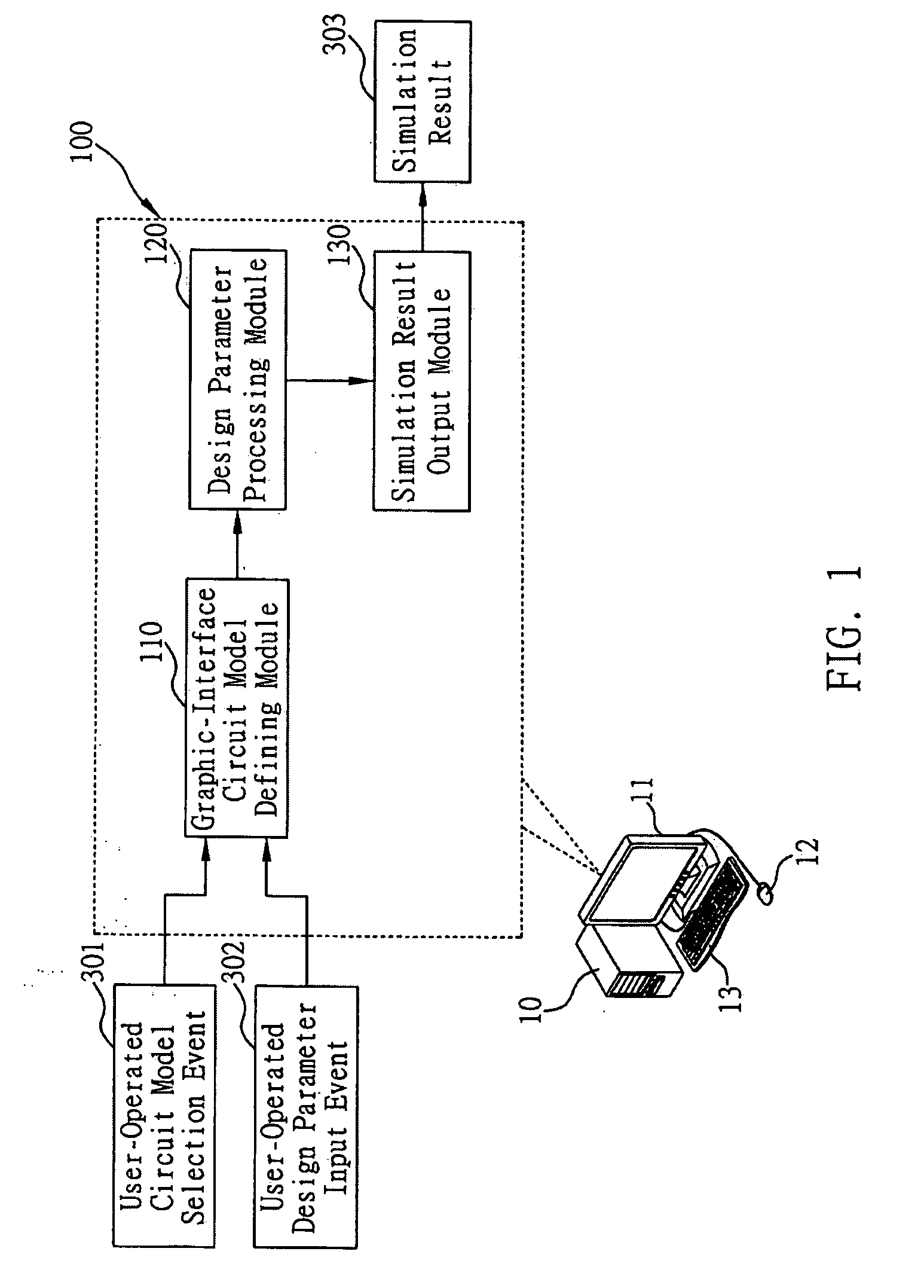

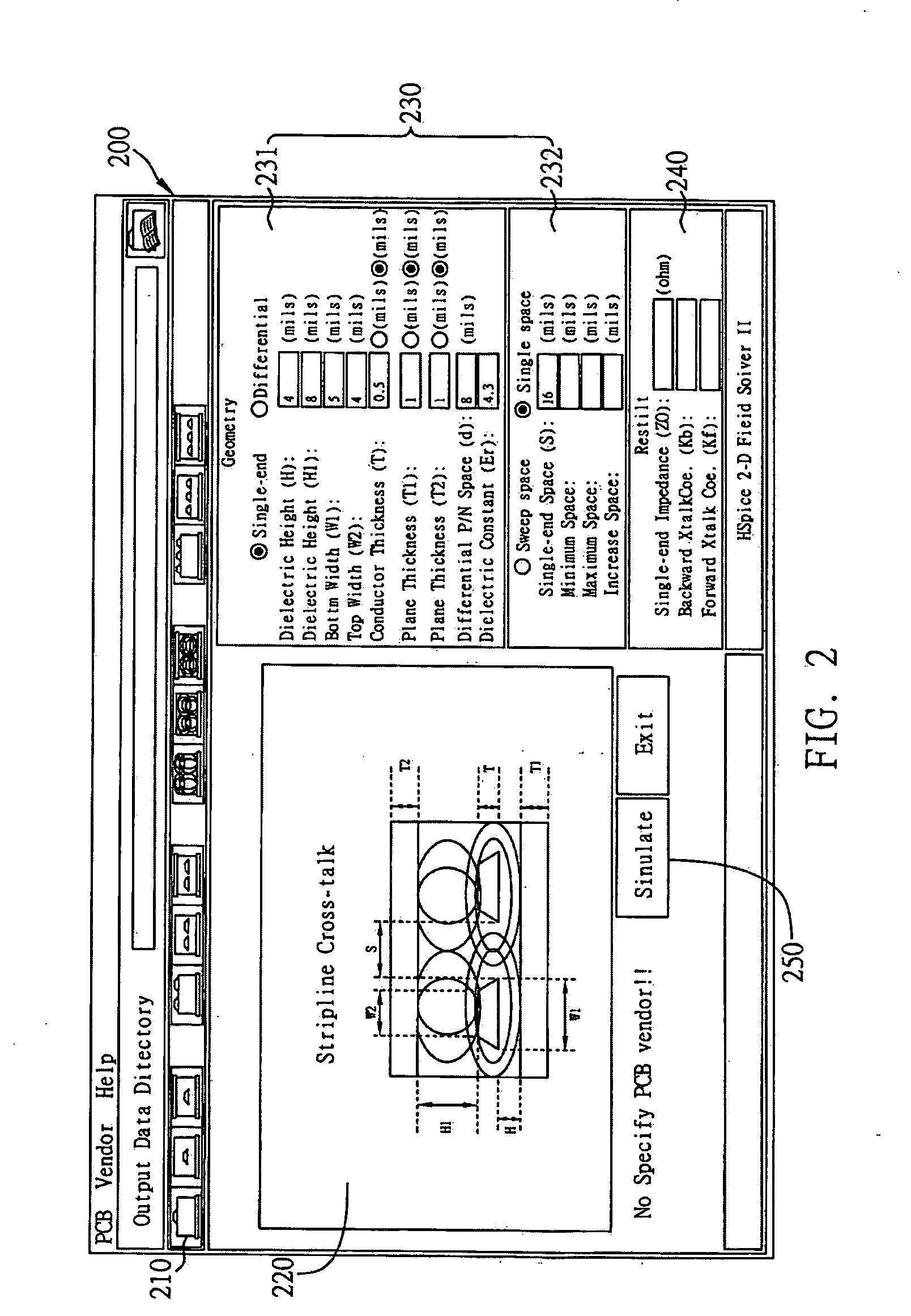

Computer-aided ultrahigh-frequency circuit model simulation method and system

InactiveUS20070233443A1Convenient and efficientSimulation of high-speed digital circuit models more convenient and efficientComputer aided designSpecial data processing applicationsComputer architectureComputer-aided

A computer-aided ultrahigh-frequency circuit model simulation method and system is proposed, which is designed for use in conjunction with a computer platform for providing a user-operated ultrahigh-frequency circuit model simulation function, which is characterized by the provision of a graphic interface that allows the user to select a desired circuit model and input a set of design parameters about the selected circuit model, and whereupon a set of operating characteristics data can be automatically determined through simulation. This feature allows the circuit design engineer unnecessary to write lengthy circuit model description files for the description of the intended circuit models, thereby making the simulation of high-speed digital circuit models more convenient and efficient.

Owner:INVENTEC CORP

Pending bug monitors for efficient processor development and debug

ActiveUS6993736B2Improve development efficiencyNew failureElectronic circuit testingError detection/correctionDesign engineerParallel computing

This invention addresses difficult issues encountered in simulations and design verification efforts on complex microprocessor / digital signal processor devices. The invention provides a means for monitoring and tracking pending bugs and automates the rejection of already known / pending bugs. This allows developers / debuggers to focus on finding and correcting new bugs. This improves design development efficiency many fold and lets design engineers and verification engineers focus on real, new and unique issues. This is especially true when test cases are generated in a random way and the test case contents are actually unknown.

Owner:TEXAS INSTR INC

Method for the development and quality control of flow-optimized shaped charges

ActiveUS20090217739A1Rapid turnaround testingQuick and efficient progressExplosive chargesAmmunition testingShaped chargeDesign engineer

An improved test setup facility, referred to as a “Quick Development Cell” (QDC), which allows for rapid turnaround testing with valuable feedback to a design engineer. Because the QDC allows for quick and efficient testing at a sufficient frequency, QDC tests are compatible with production quality control. In addition to fostering improvement of the API's Section 2 type tests using stressed natural rock for benchmark experiments, the QDC tests allow for progress to be made towards the development of a flow-optimized shape charge and superior well performance.

Owner:WELLS FARGO BANK NAT ASSOC +1

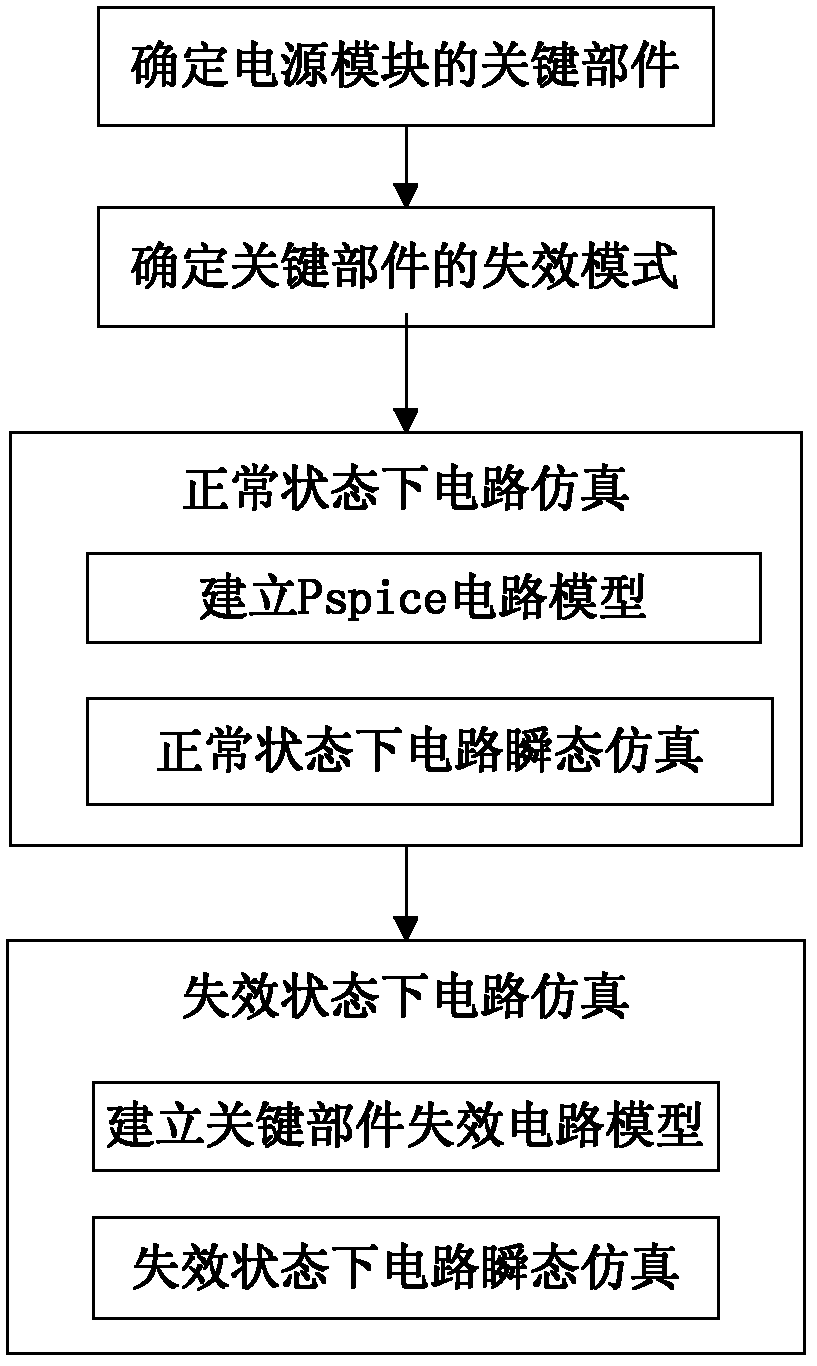

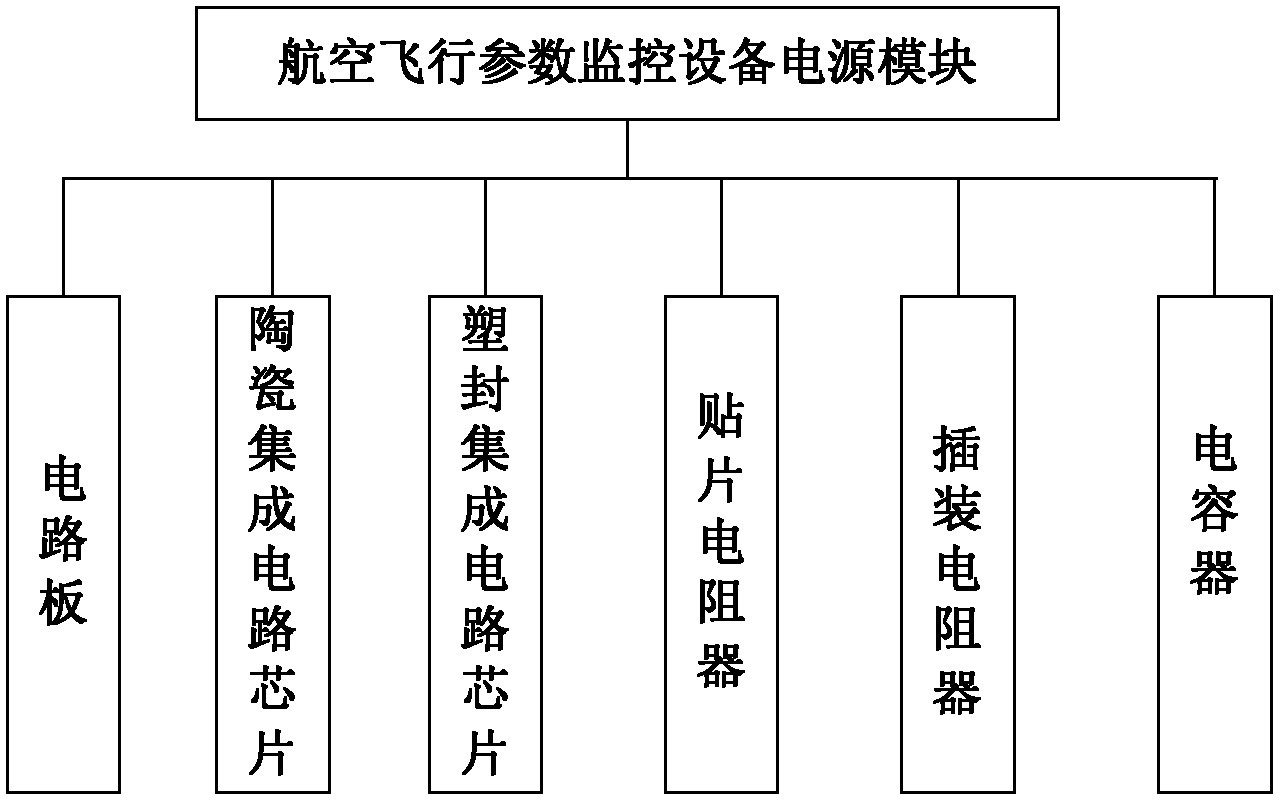

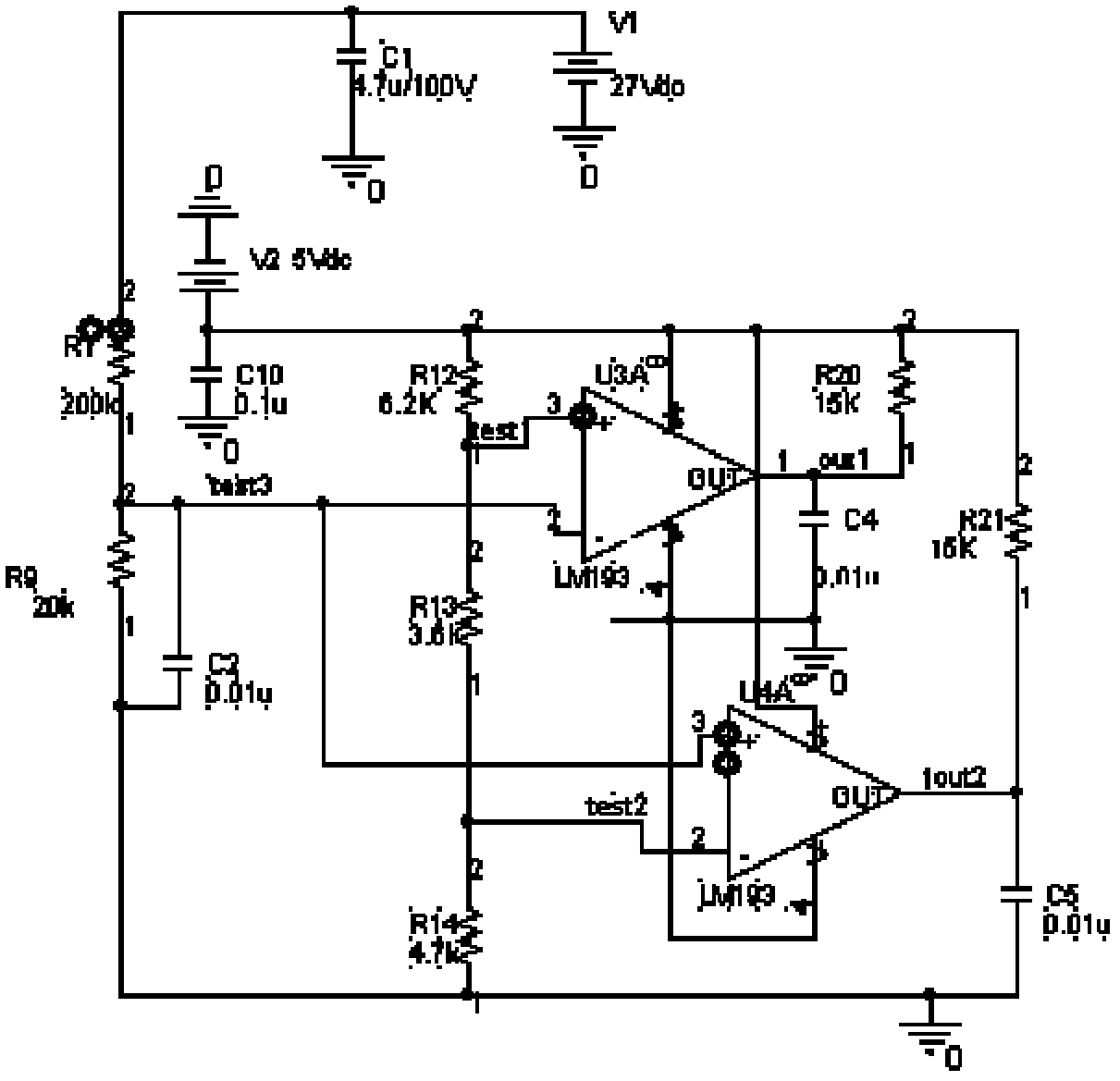

Failure modes and injection simulation (FMIS) method for power module of aerial parameter processing device

ActiveCN102592021AEase of evaluationAvoid failureDesign optimisation/simulationCAD circuit designAviationDesign improvement

Disclosed is an FMIS method for a power module of an aerial parameter processing device. The FMIS method includes steps of determining critical components of a power module of an aerial parameter processing device; determining failure modes of the critical components; performing transient circuit simulation of the power module under a normal condition; and performing transient circuit simulation of the power module under a failure condition. By means of the FMIS method for the power module of the aerial parameter processing device, the failure modes of the power module of the aerial parameterprocessing device are determined based on a stress simulation method and failure mode injection technology, circuit output is obtained quantitatively in the failure modes, evidence is provided for design engineers to evaluate the influence and determine the harmfulness of the failure modes, and simultaneously for the design improvement of the power module. The FMIS method for the power module of the aerial parameter processing device has good practical value and wide application prospect in the simulation technical field of product reliability.

Owner:BEIJING LANWEI TECH CO LTD

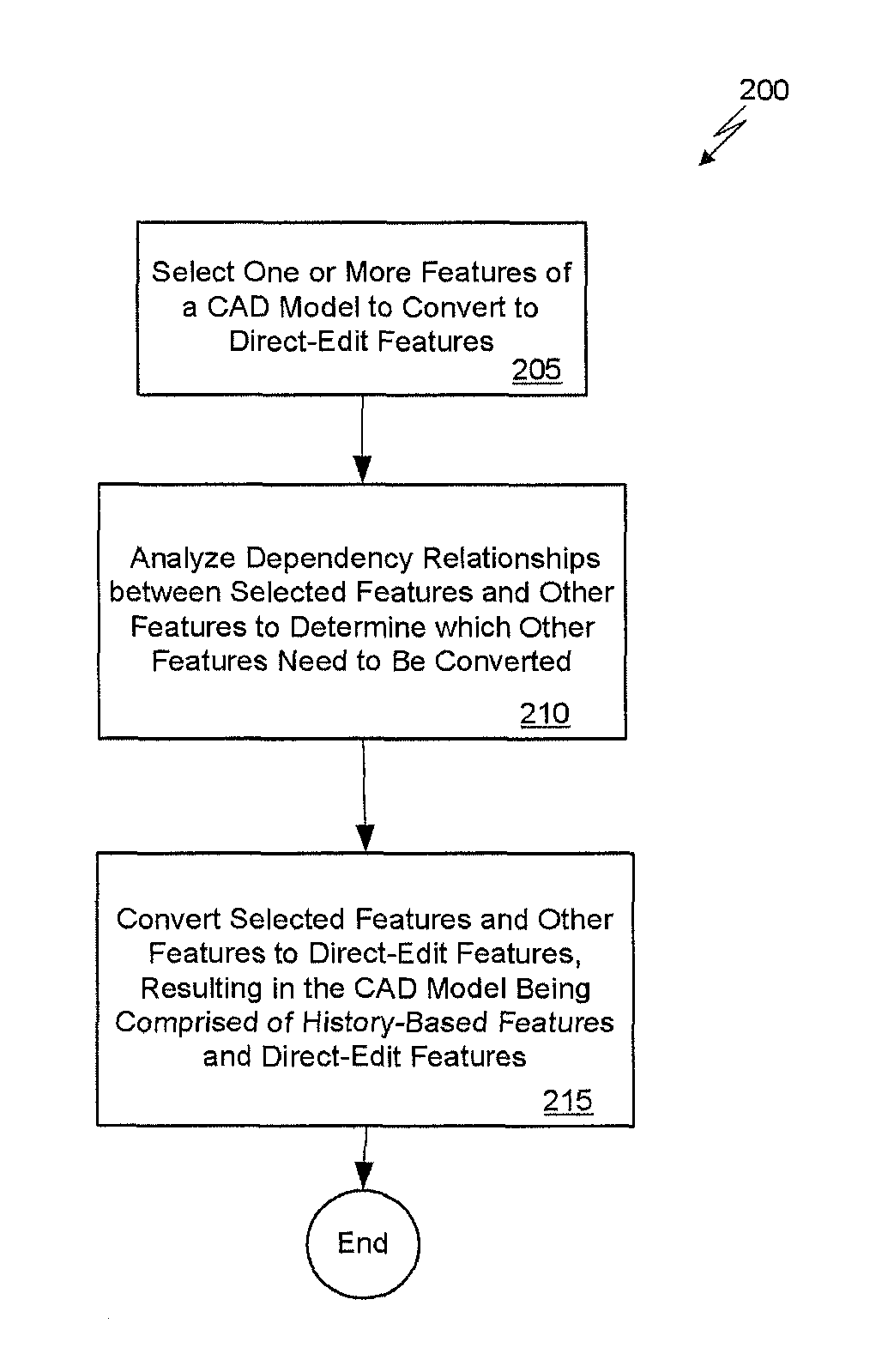

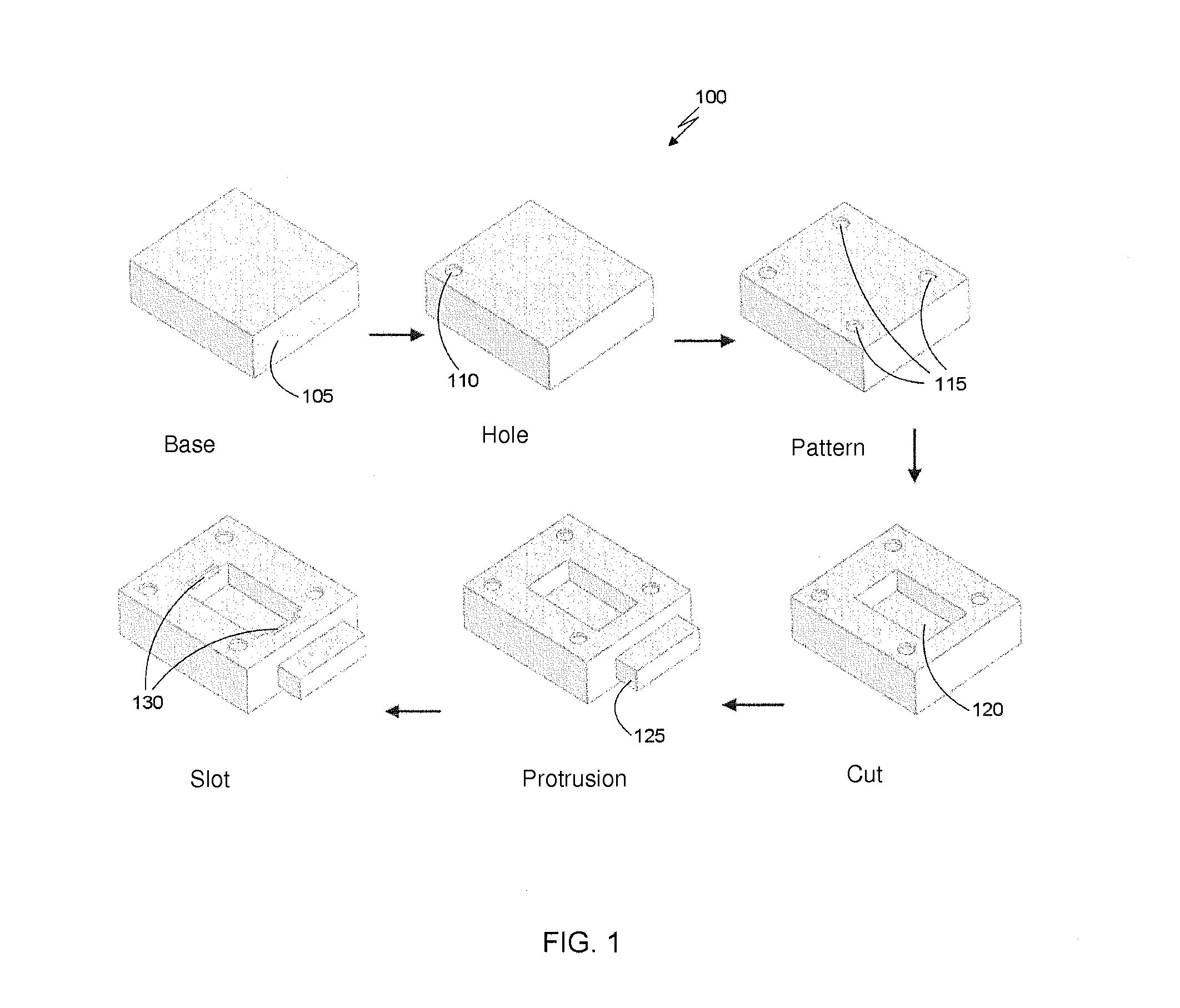

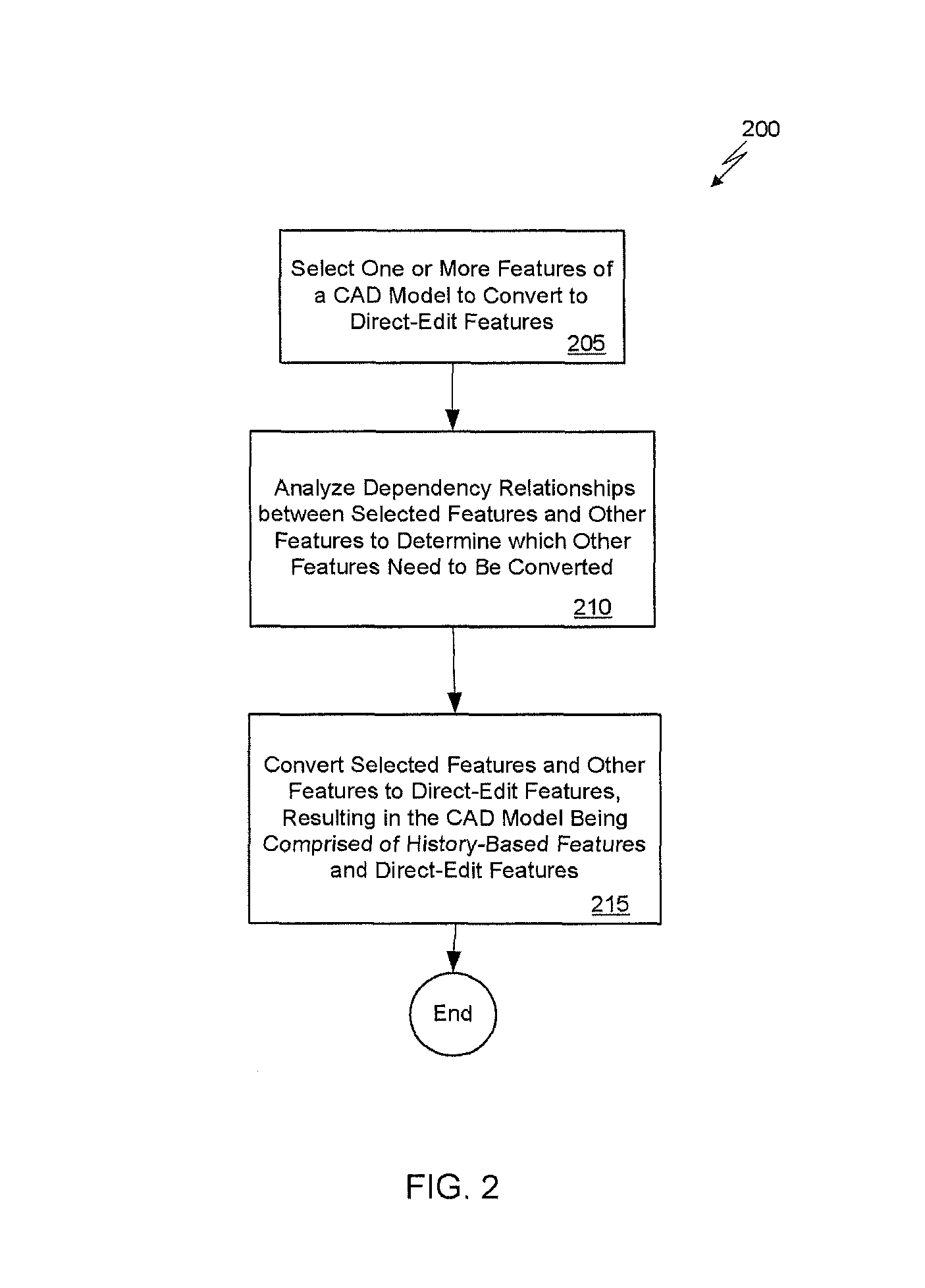

Methods and systems for converting select features of a computer-aided design (CAD) model to direct-edit features

Editing features of a history-based computer-aided design (CAD) model may be difficult and may require redesigning much of the CAD model modify features. The solutions described herein allow a design engineer to modify an existing history-based CAD model by automatically determining history-based features that need to be converted to direct-edit features, creating a body of direct-edit features from the determined features, and creating a model containing both the direct-edit feature body and remaining history-based features. Such a CAD model containing both kinds of features may be referred to as a hybrid model.

Owner:DASSAULT SYST SOLIDWORKS CORP

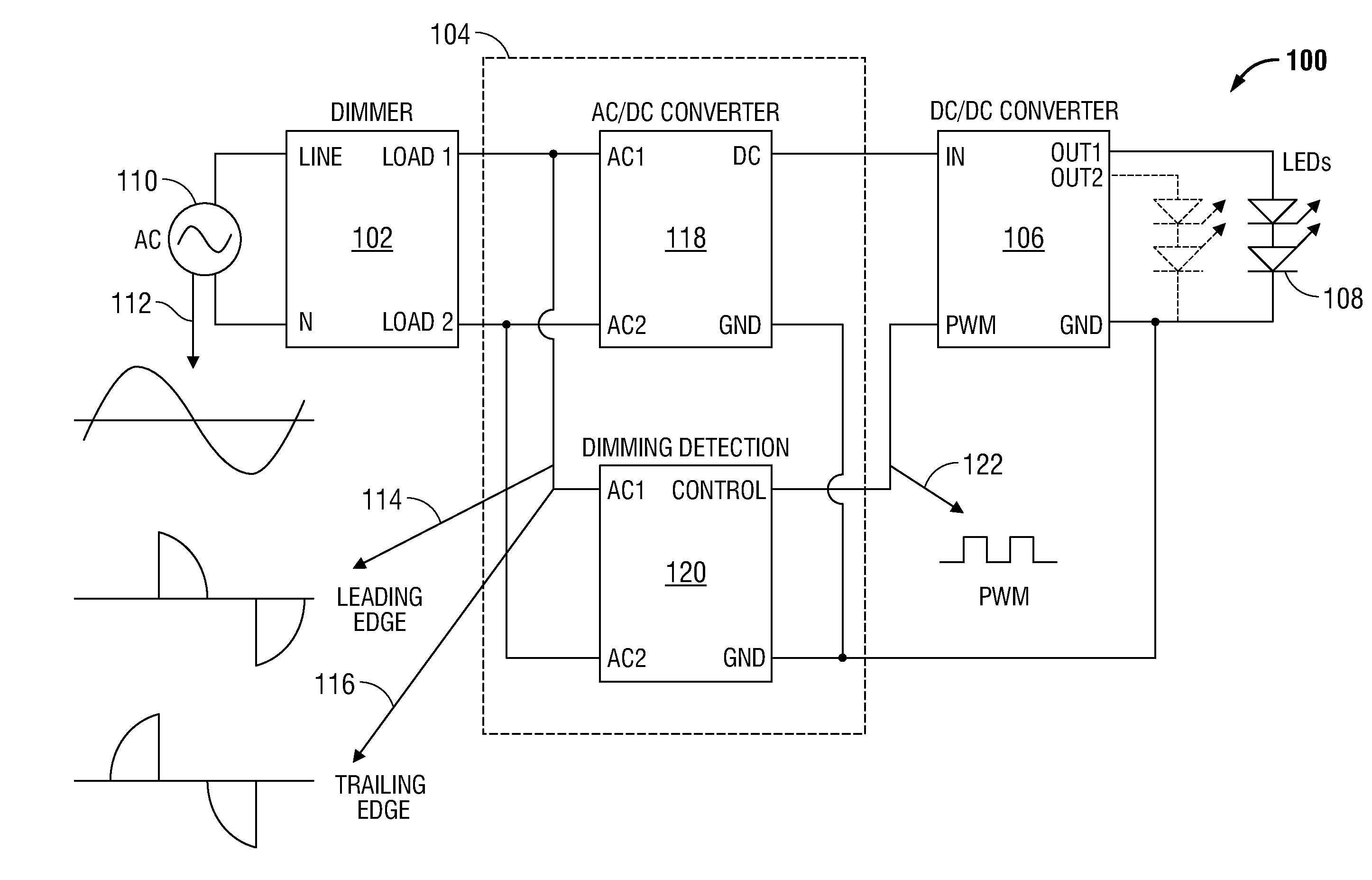

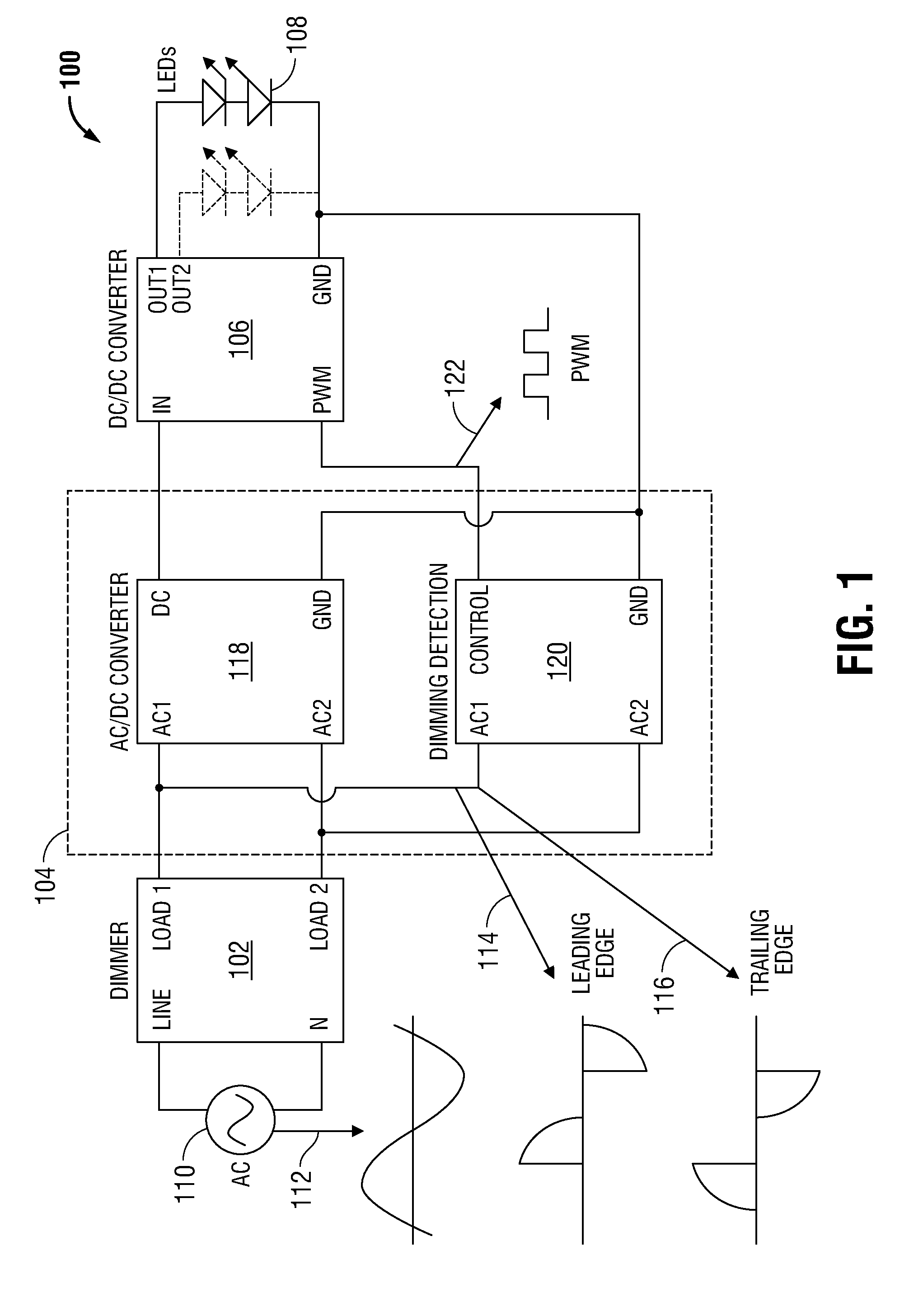

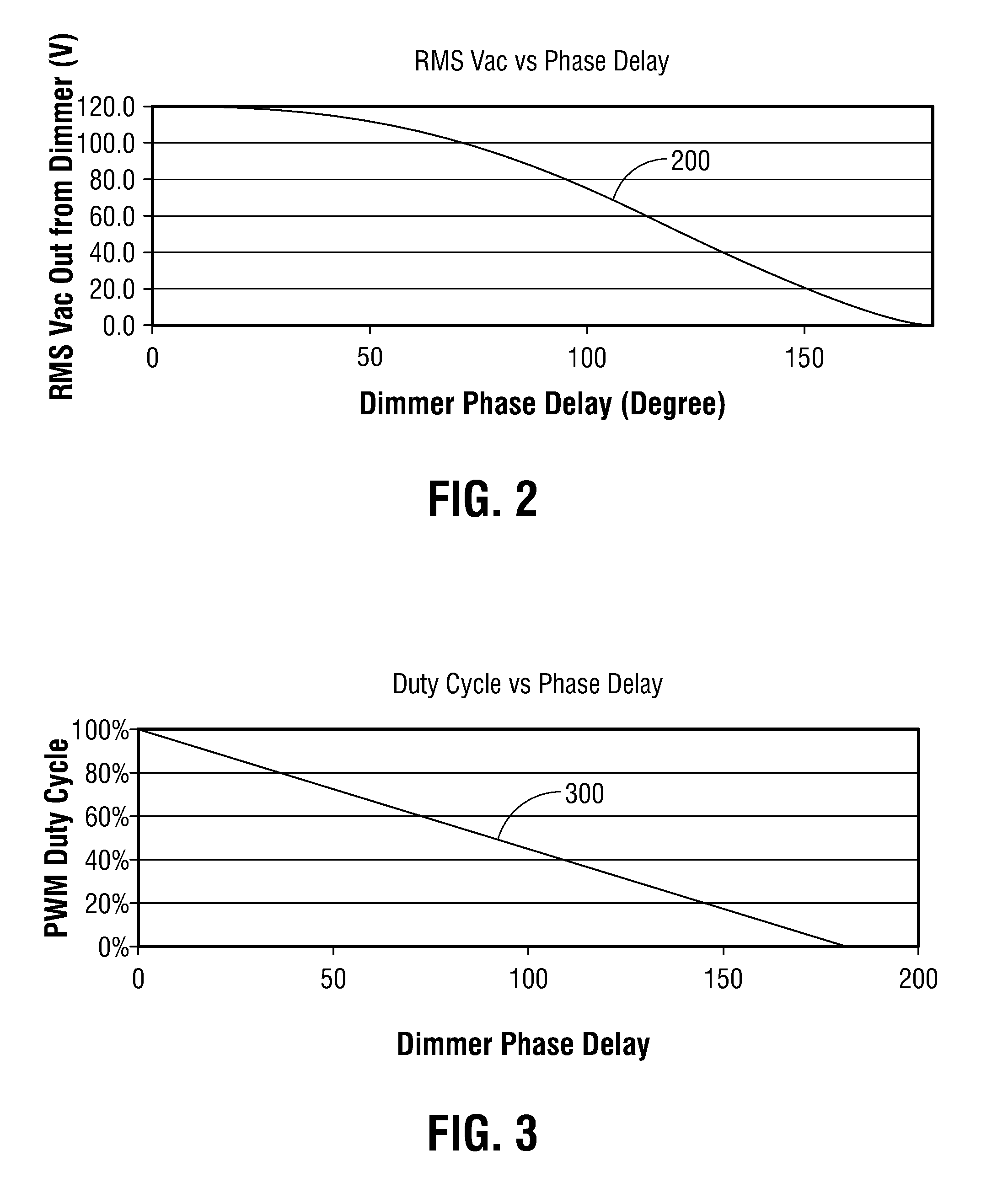

Controlling LED current from a constant voltage source

ActiveUS20150382421A1Optimizes current consumptionReduce the amount requiredElectrical apparatusElectroluminescent light sourcesDriver circuitControl signal

An LED driver circuit provides dimming control in LED lighting applications that can accommodate an AC / DC constant voltage converter. The driver circuit provides a dimming control signal that is used to directly control the DC output current of a downstream DC / DC converter driving an LED array. The dimming control signal tracks the AC or DC output from a dimming controller such that variations in the AC or DC voltage are reflected in the dimming control signal. This dimming control signal is then provided to the downstream DC / DC converter, bypassing the AC / DC constant voltage converter to directly control dimming of the LED array. Such an arrangement lets lighting design engineers deploy the familiar and well-understood constant voltage converter topology in LED lighting applications while retaining the ability to control dimming in the LED lighting applications.

Owner:ABL IP HLDG

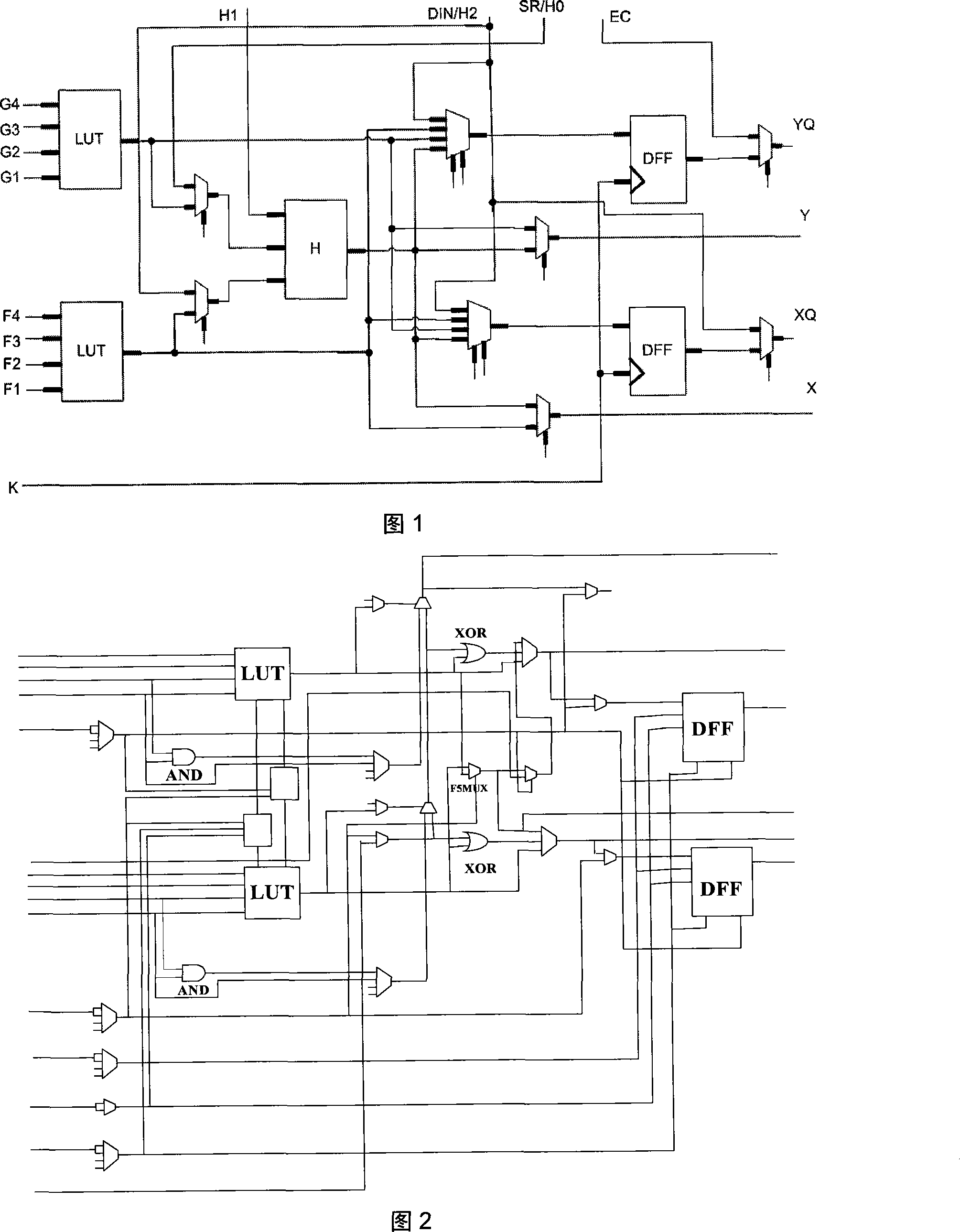

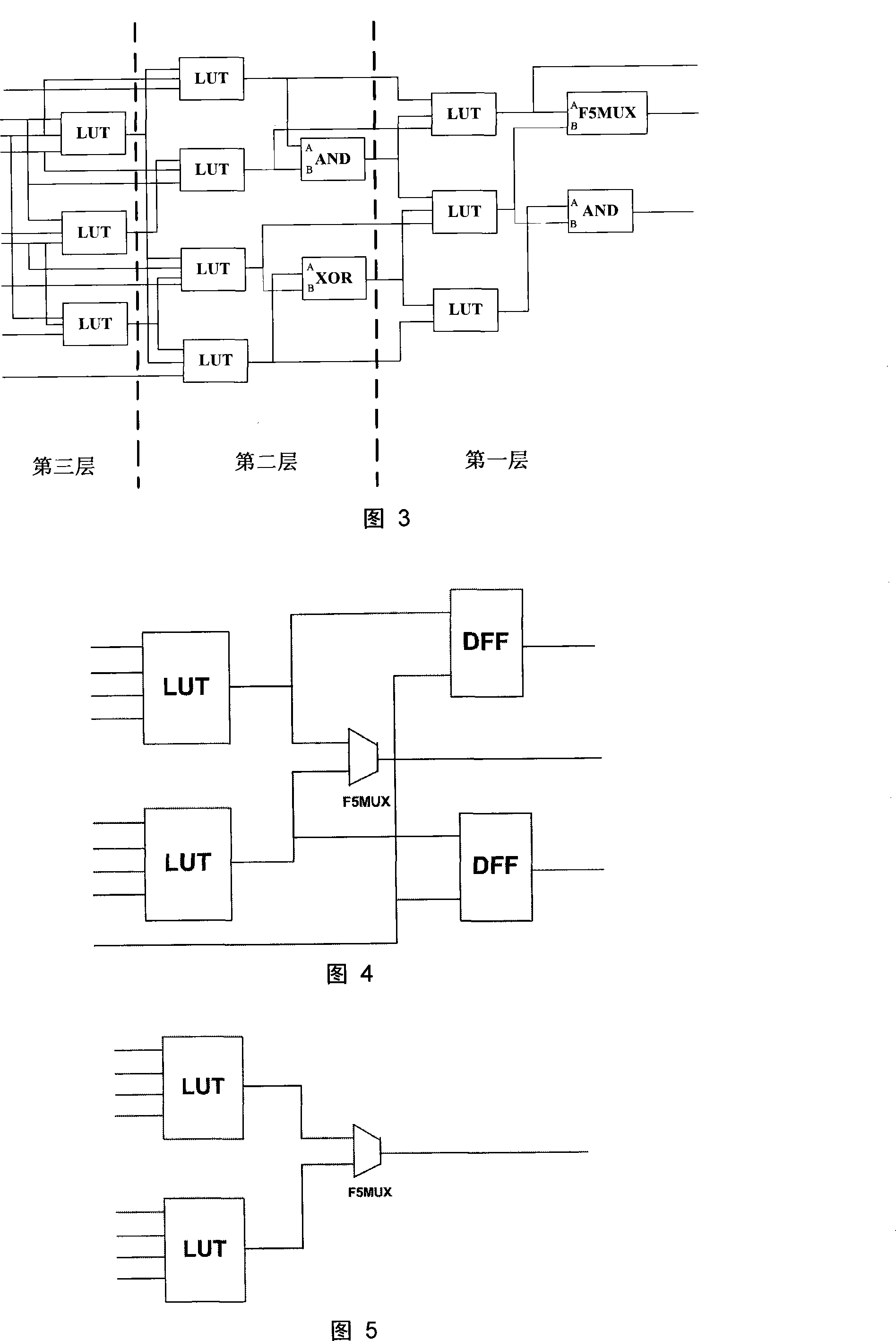

Programmable logic device fast logical block mapping method

InactiveCN101246511AReduce usageIncrease profitSpecial data processing applicationsHardware structureExtensibility

The invention relates to a rapid logic mapping method for FPGA, belonging to the electronic technique field. A demixing and classification mapping to a programmable logic unit is raised to reduce the complexity of algorithm, a match degree coefficient is introduced to enhance the performance of the algorithm, and then a high performance rapid logic mapping method for FPGA is obtained. Experimental data show that the performance of the invention is enhanced by 12.59 percent compared to the conventional figure matching with the structure mapping algorithm, the complexity of algorithm is decreased largely from O(m) down to O(m), the invention can be widely applied in logic unit structure mapping for artery FPGA in modern times, the extendibility of FPGA logic unit mapping module in the operating efficiency and algorithm of the entire FPGA CAD flow is enhanced largely. The high performance rapid FPGA logic unit mapping method can also conduct the design of the FPGA programmable logic unit hardware structure, so that the structure advantages and disadvantages of the programmable logic unit can be estimated by the hardware design engineer before making chips, the design period is shortened largely, the success rate of a new device is increased, the design cost is saved.

Owner:FUDAN UNIV

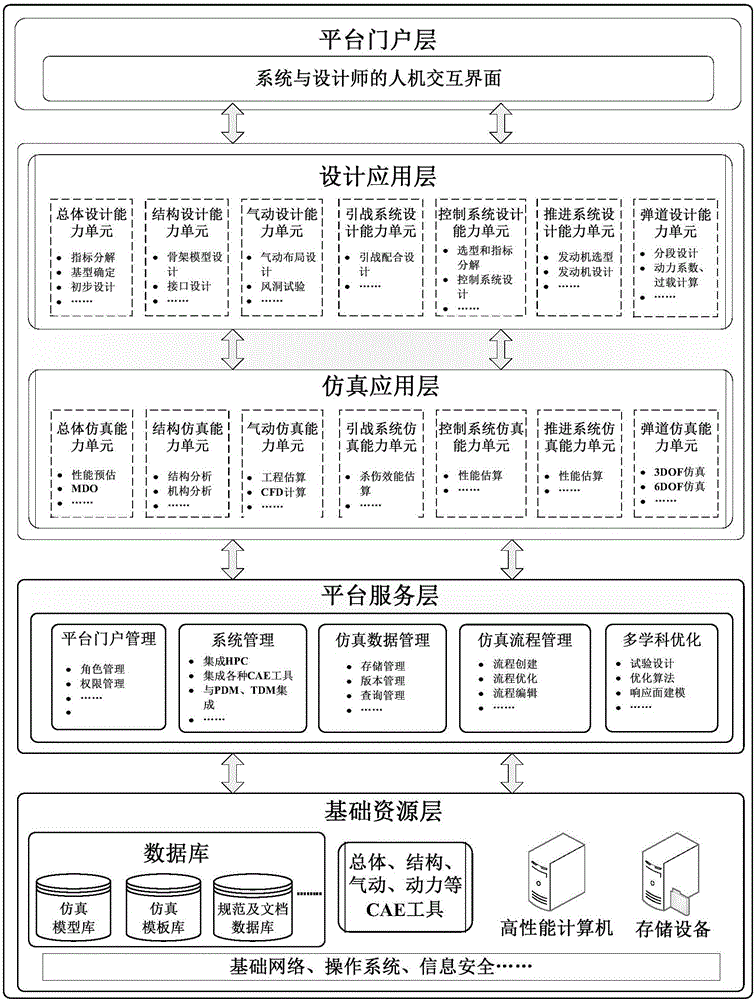

Missile design and simulation integrated platform

InactiveCN106570243ARealize unified managementEasy to operateSimulator controlCAD network environmentManagement toolGuidance control

The invention discloses a missile design and simulation integrated platform comprising a platform portal layer serving as a portal for united work of missile design engineers and missile simulation engineers of each specialty; a design application layer applied to rapid design of overall missile, guidance control system, structure and pneumatic specialties; a simulation application layer used for performing simulation analysis on the overall missile, guidance control system, structure and pneumatic specialties; a platform service layer used for performing effective configuration management on existing missile knowledge data, professional models, analysis processes, professional tools and IT tools of enterprises; and a basic resource layer used for performing effective share management on product design experiences, software analysis tools and hardware computation equipment formed by accumulating, summarizing and concluding during missile research and development processes. According to the platform provided by the invention, digital design simulation of an overall missile scheme and accumulation and reuse of design knowledge are achieved, and a professional design, simulation analysis and data management tool is provided for overall missile designers.

Owner:SHANGHAI INST OF ELECTROMECHANICAL ENG

System for the three-dimensional display of wireless communication system performance

InactiveUS20030014233A1Receivers monitoringAnalogue computers for electric apparatusTerrainCommunications system

A method for displaying the results of predicted wireless communication system performance as a three-dimensional region of fluctuating elevation and / or color within a three-dimensional computer drawing database consisting of one or more multi-level buildings, terrain, flora, and additional static and dynamic obstacles (e.g., automobiles, people, filing cabinets, etc.). The method combines computerized organization, database fusion, and site-specific performance prediction models. The method enables a design engineer to visualize the performance of any wireless communication system as a three-dimensional region of fluctuating elevation, color, or other aesthetic characteristics with fully selectable display parameters, overlaid with the three-dimensional site-specific computer model for which the performance prediction was carried out.

Owner:EXTREME NETWORKS INC

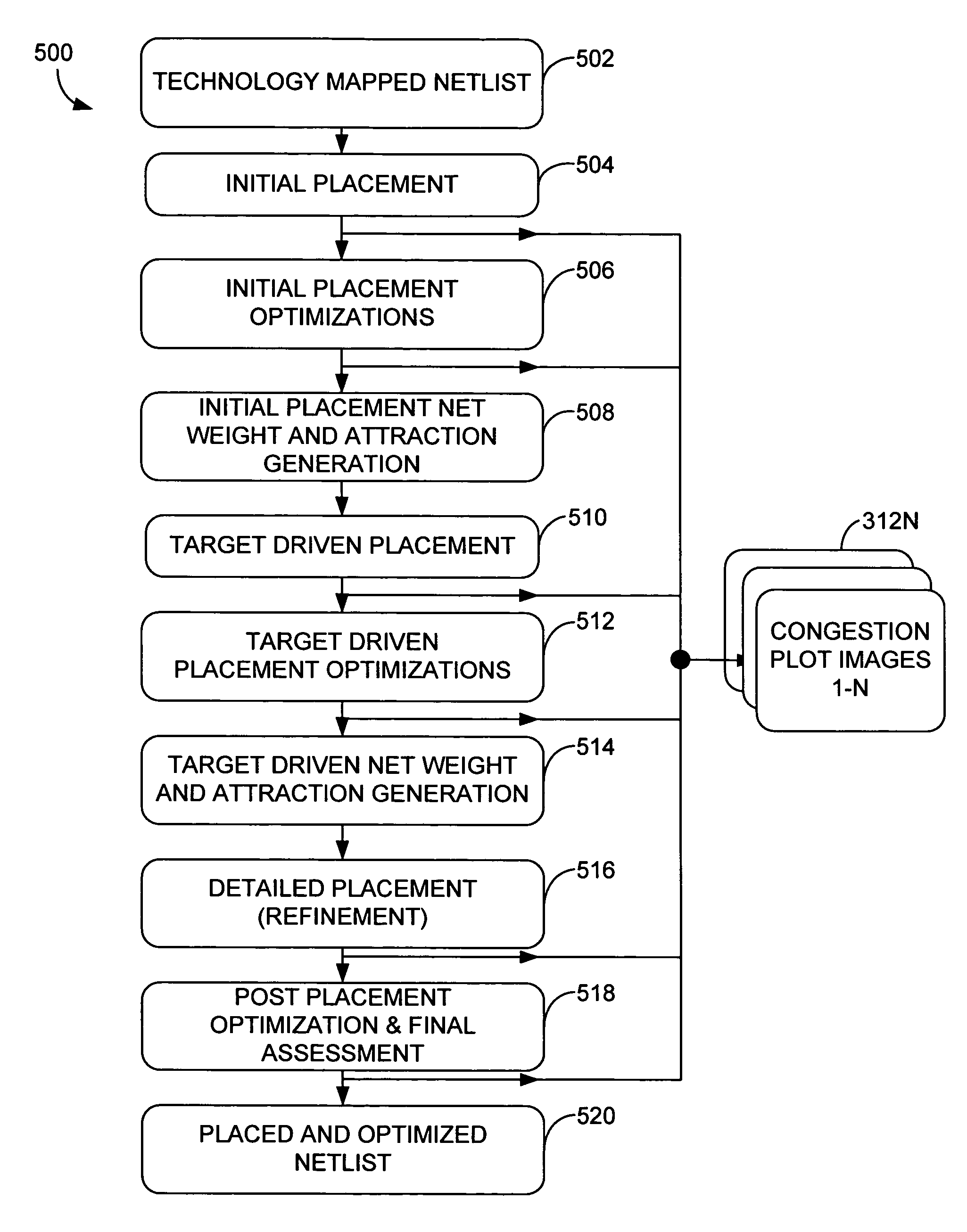

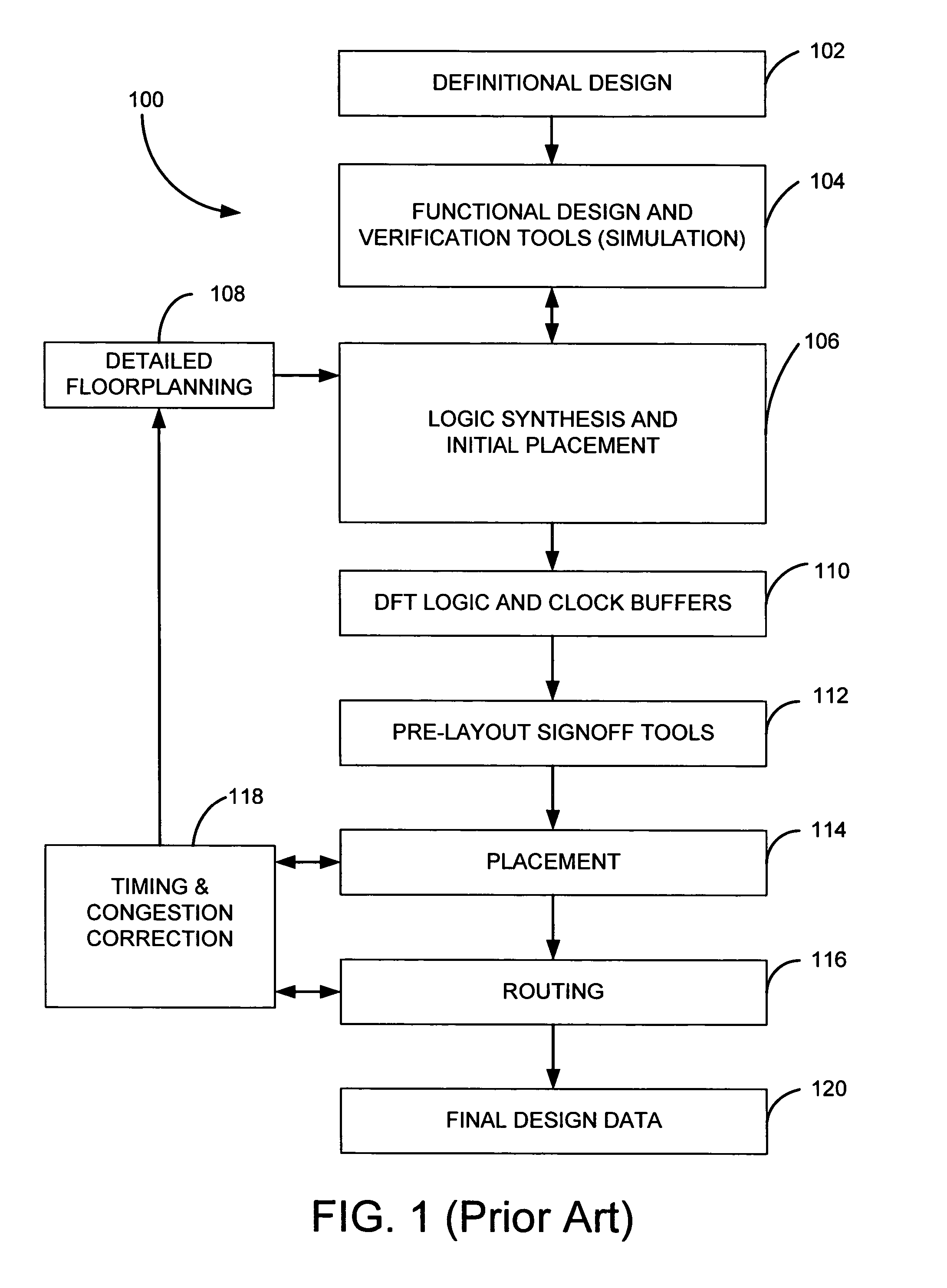

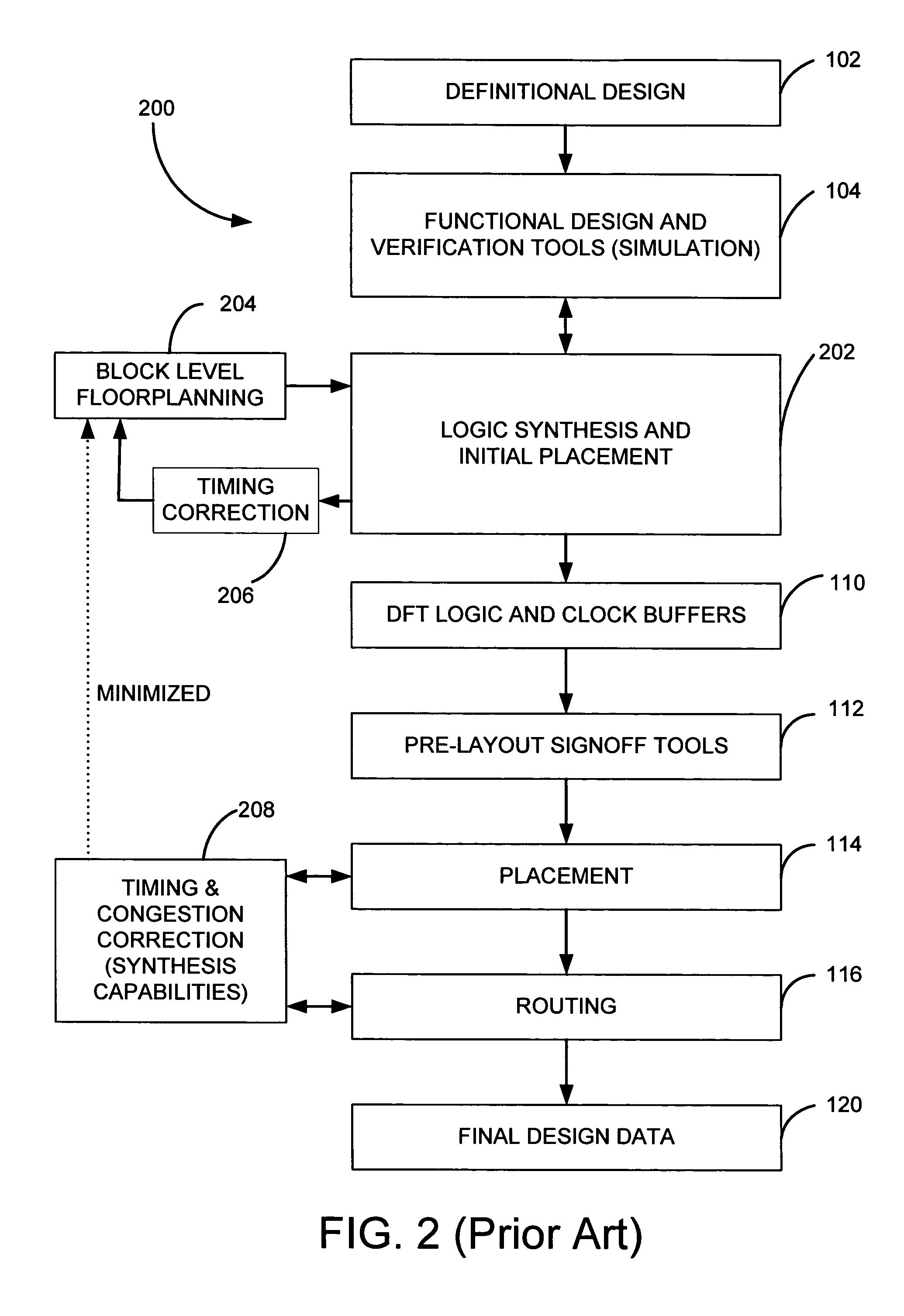

Generation of graphical congestion data during placement driven synthesis optimization

InactiveUS7100140B2Shorten the timeComputer programmed simultaneously with data introductionCAD circuit designGraphicsDesign engineer

The present invention provides a method and a computer-readable program for providing generation of graphical congestion images during placement driven synthesis optimization. These graphical congestion images enable a design engineer to make changes and / or improvements to subsequent processes in the design flow before the current placement driven synthesis step completes, thus saving time. This information also provides valuable debug information to PDS developers.

Owner:IBM CORP

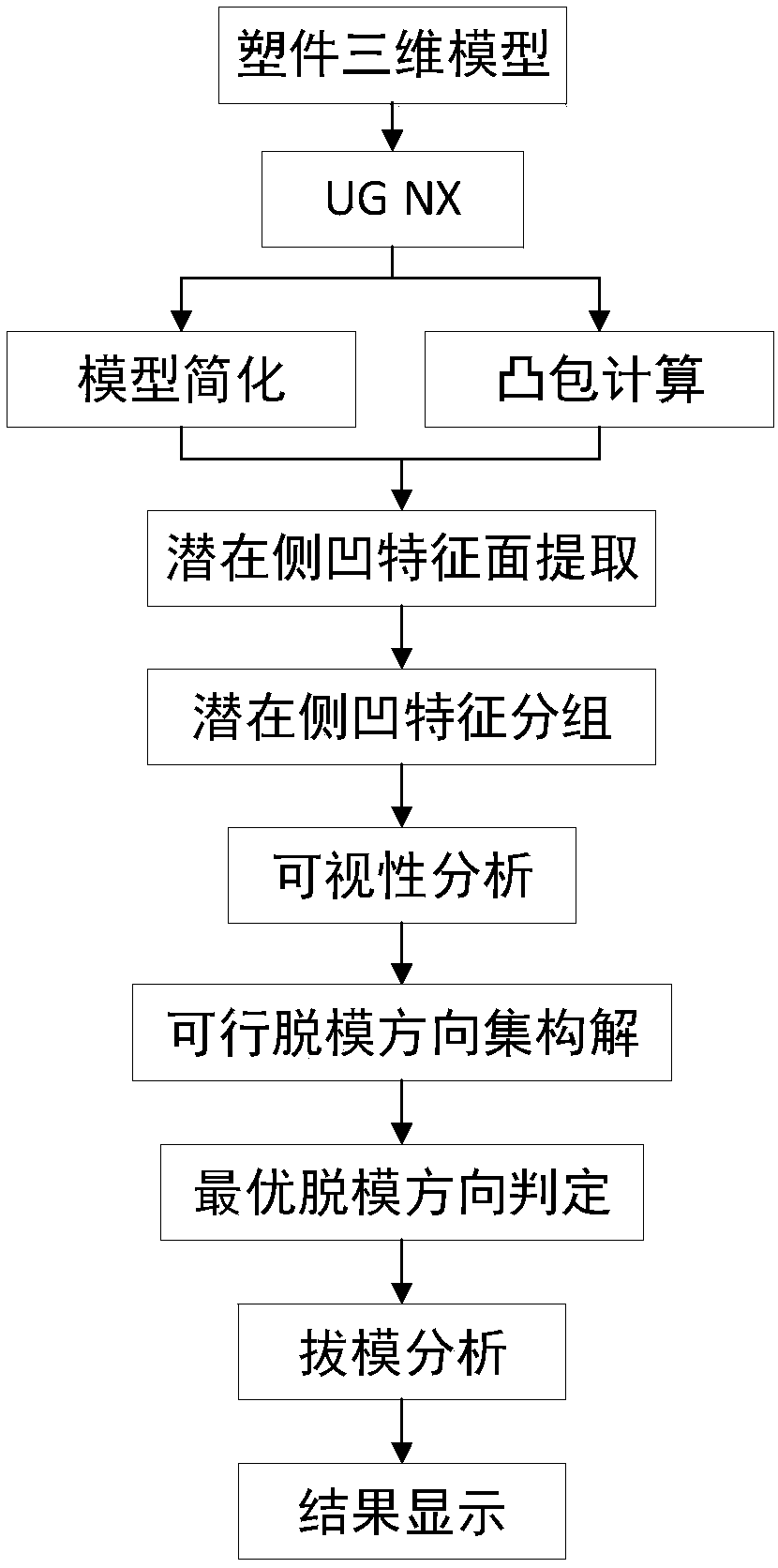

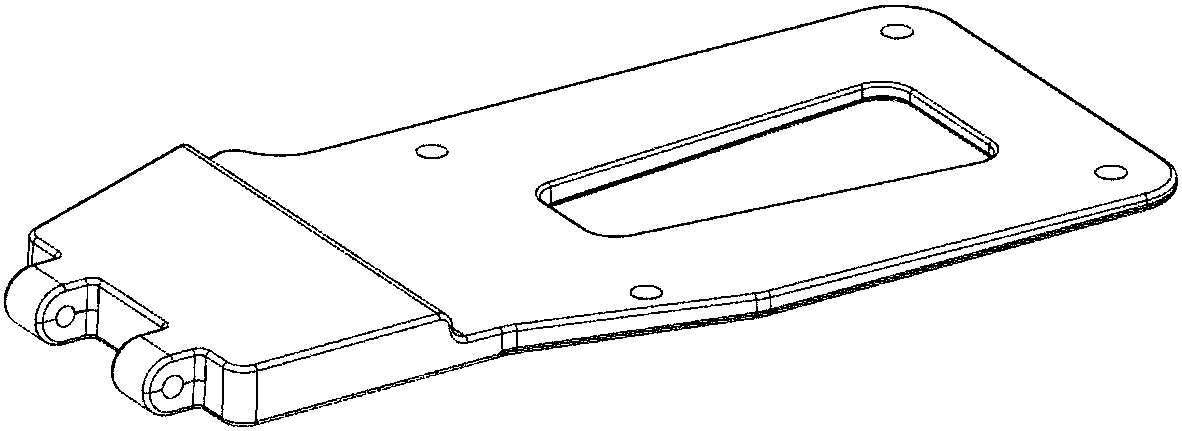

Geometric moldability analysis method of plastic parts based on UGNX system

ActiveCN108182318AFast dynamic adjustmentIncrease flexibilityDesign optimisation/simulationSpecial data processing applicationsDesign engineerEngineering

The invention belongs to the field of injection molds, and discloses a geometric moldability analysis method of plastic parts based on a UGNX system. The method includes the following steps that (a) simplification of a three-dimensional entity model is achieved to obtain a simplified model; (b) convex hulls of the model simplified through a wrap geometry method are adopted, and a plurality of potential undercut feature faces are obtained; (c) the potential undercut feature faces are divided into a plurality of potential undercut features according to the connection relationship, visual de-molding analysis is conducted on the potential undercut features so as to obtain the de-molding directions corresponding to the potential undercut features and undercut features, and therefore, the several de-molding directions and the undercut features corresponding to the de-molding directions are obtained; (d), the optimal de-molding direction is selected, and according to the de-molding direction,the draft angle of each face of the simplified model is determined. Through the method, a geometric moldability analysis system of the plastic parts is provided, and dependence on the design engineer's experience is reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

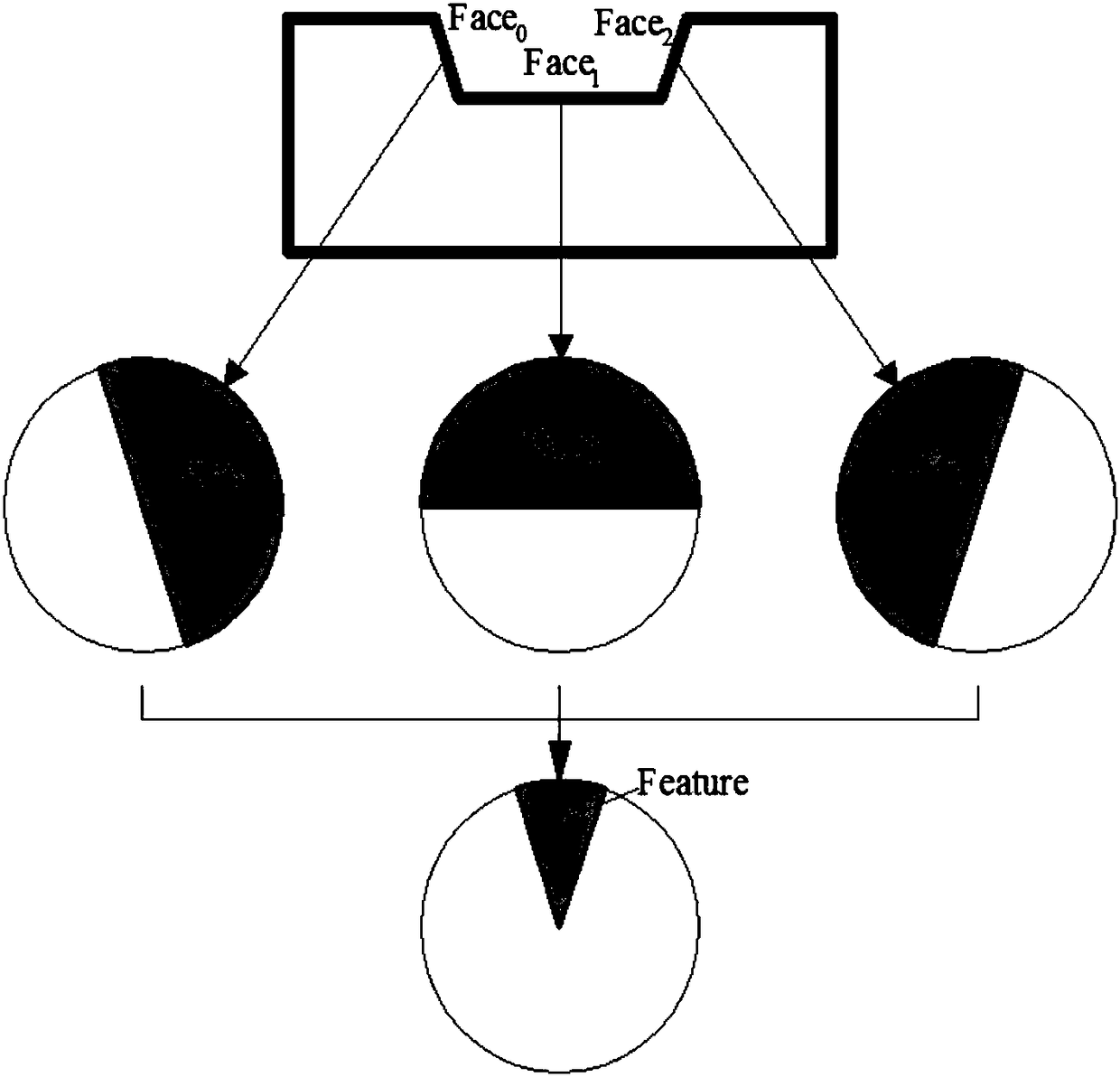

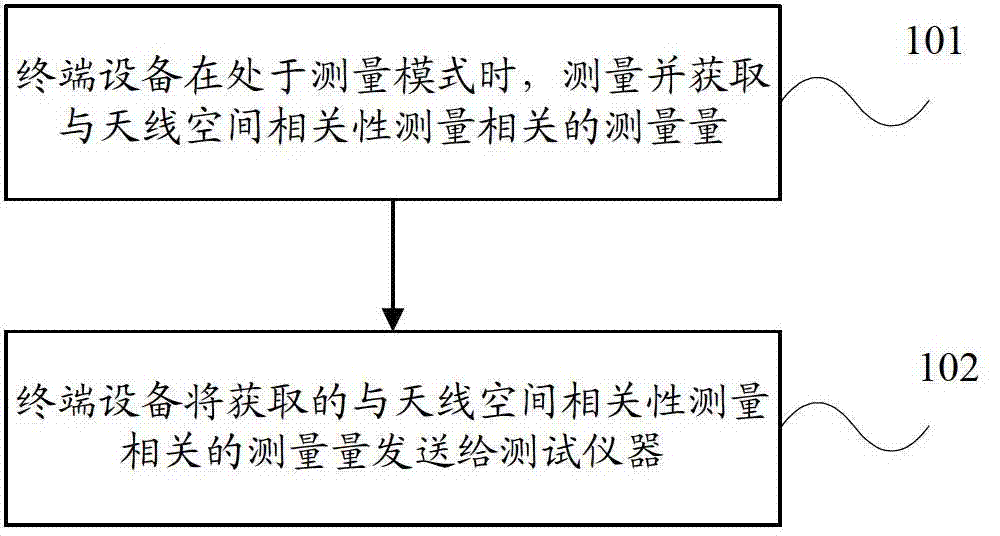

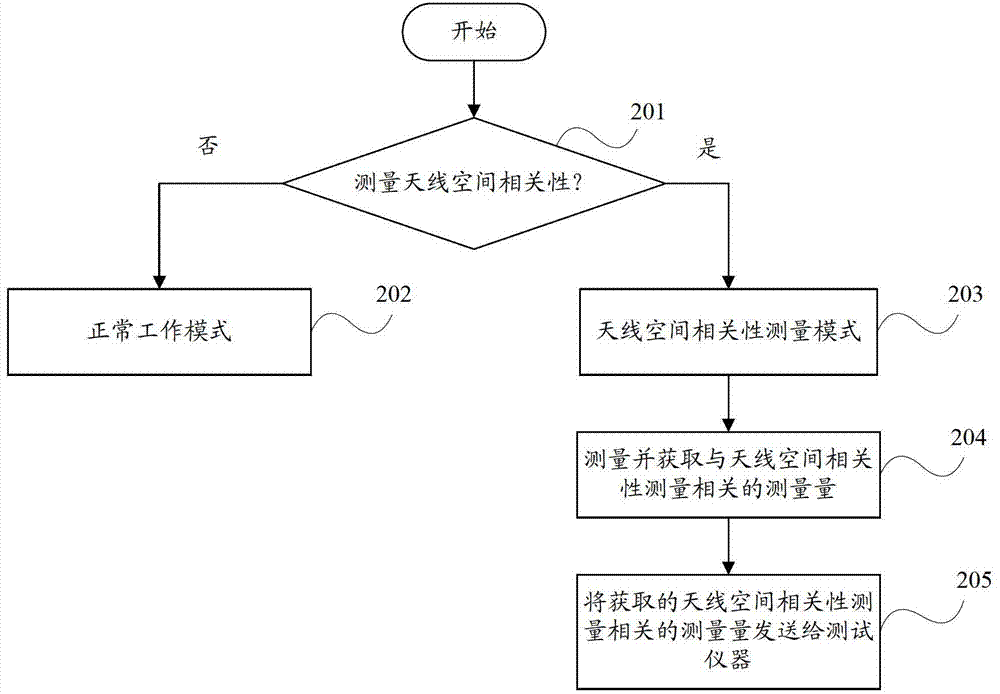

Antenna spatial correlation measuring method and device and terminal device

InactiveCN102833768AVerify designTransmitters monitoringReceivers monitoringAntenna designSpatial correlation

The embodiment of the invention provides an antenna spatial correlation measuring method and device and a terminal device. The method comprises the following steps: in a measurement mode, measuring and acquiring a measurement quantity related to antenna spatial correlation measurement, and sending the measurement quantity related to antenna spatial correlation measurement to a testing instrument. After entering into the measurement mode, the terminal device measures and calculates the measurement quantity required by antenna spatial correlation measurement and sends the measurement results to the testing instrument; and through antenna spatial correlation parameters displayed by the testing instrument, the result of terminal device antenna spatial correlation can be calculated, thereby providing a basis for optimizing the antenna design by an antenna engineer and a hardware design engineer.

Owner:HUAWEI DEVICE CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com