Programmable logic device fast logical block mapping method

A mapping method and programming logic technology, applied in the electronic field, can solve problems such as unacceptable running time, exponential increase in complexity, and incomparable performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

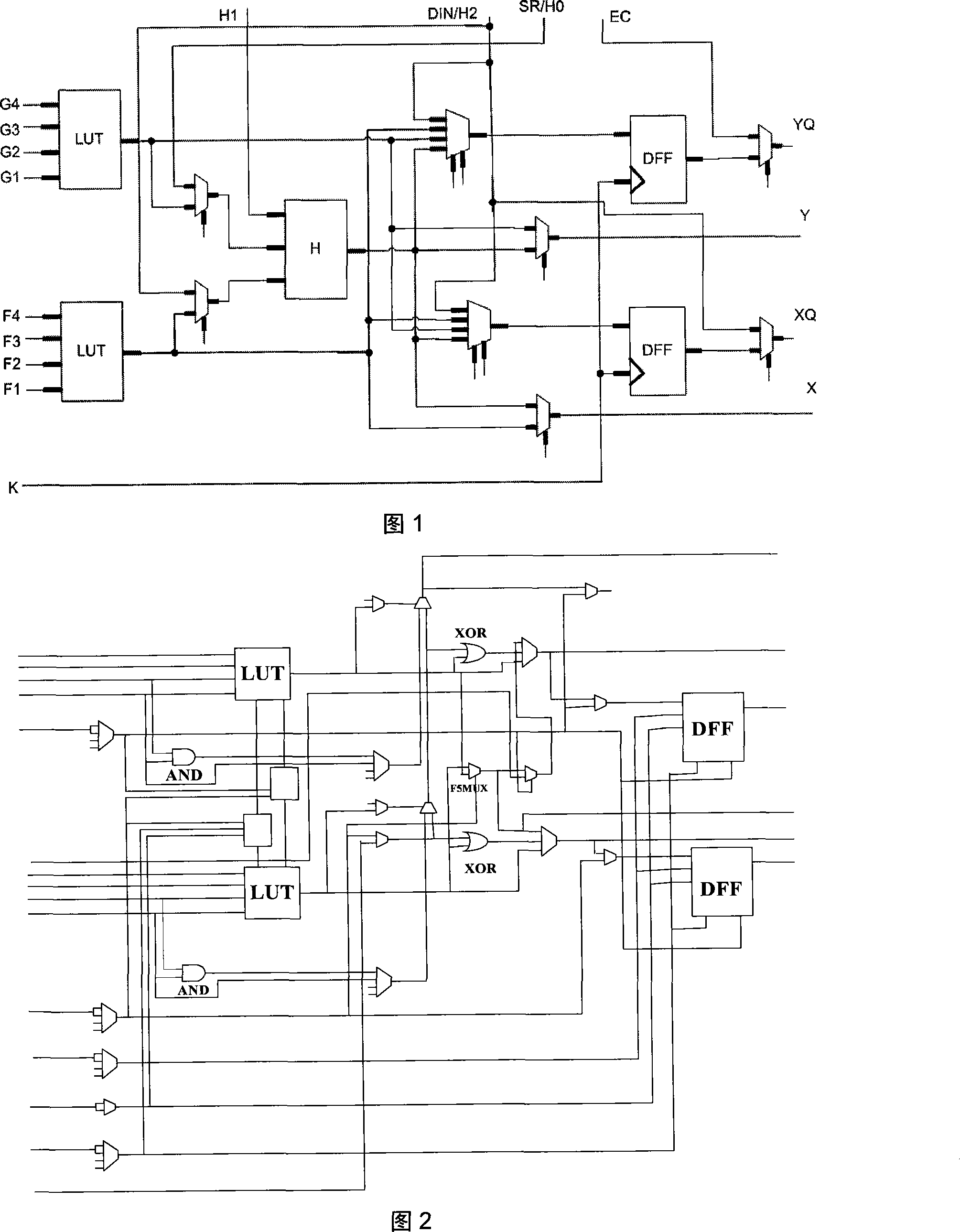

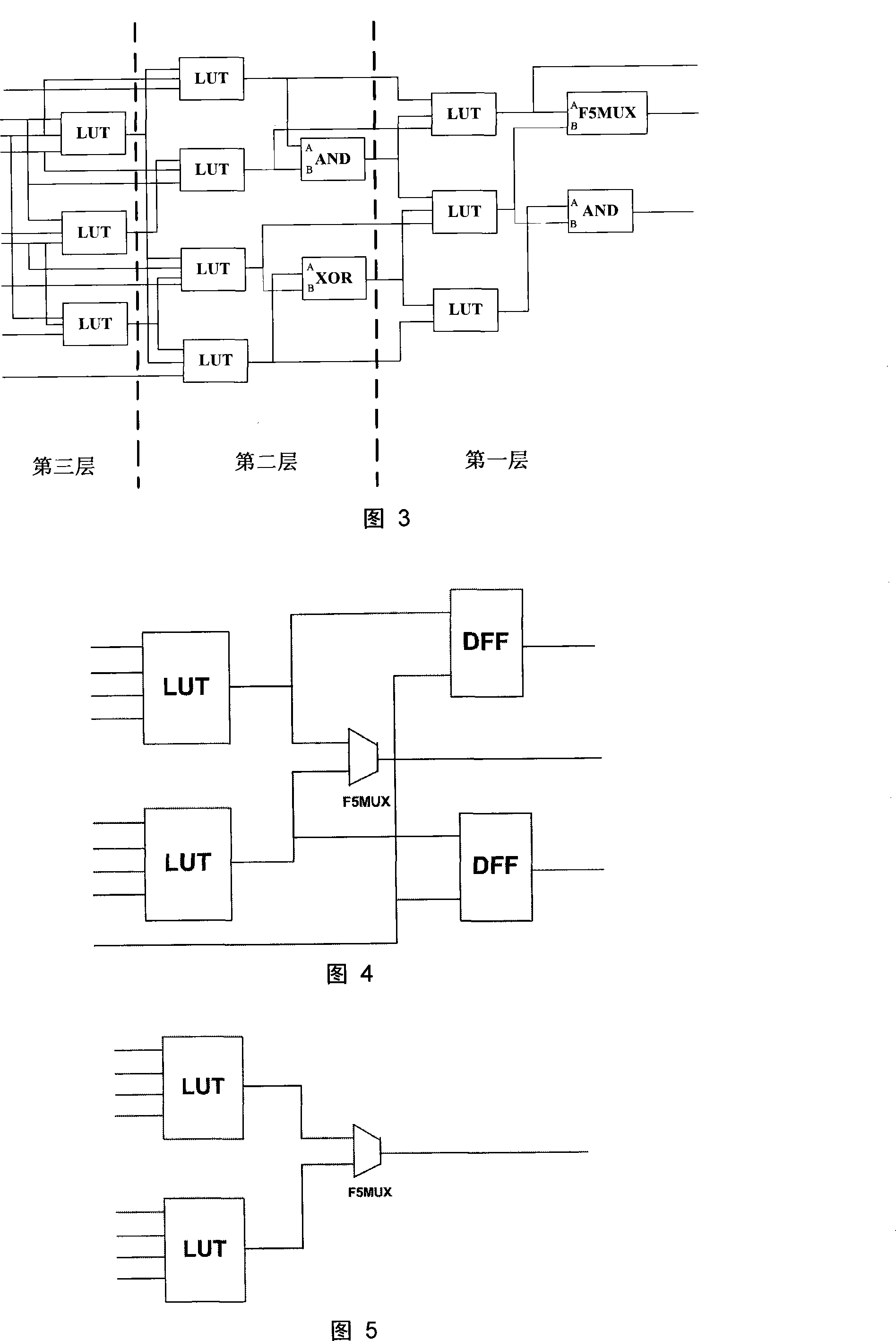

[0061] Figure 4 shows a simple use case of a user circuit. Here we take the chip structure of the SpartanII series as an example to introduce the entire matching mapping process.

[0062] Firstly, the sequential circuit part and the combined circuit part in the user circuit are separated, and the information of the sequential circuit part is stored. FIG. 5 is a schematic diagram showing the result after removing the sequential circuit part in the user circuit shown in FIG. 4 .

[0063] The next step is to map the remaining combinational and functional circuits in the user circuit.

[0064] Figure 5 is also a functional circuit of the SpartanII series chips, which can be known by comparing Figure 2 and Figure 5. Figure 6 shows another functional circuit of the SpartanII series chips.

[0065] In the process of matching, 1) we can implement the user circuit with one SpartanII logic block unit as shown in FIG. 5 , and 2) it can also implement it with two logic block units as sh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com