Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

135 results about "Logic mapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

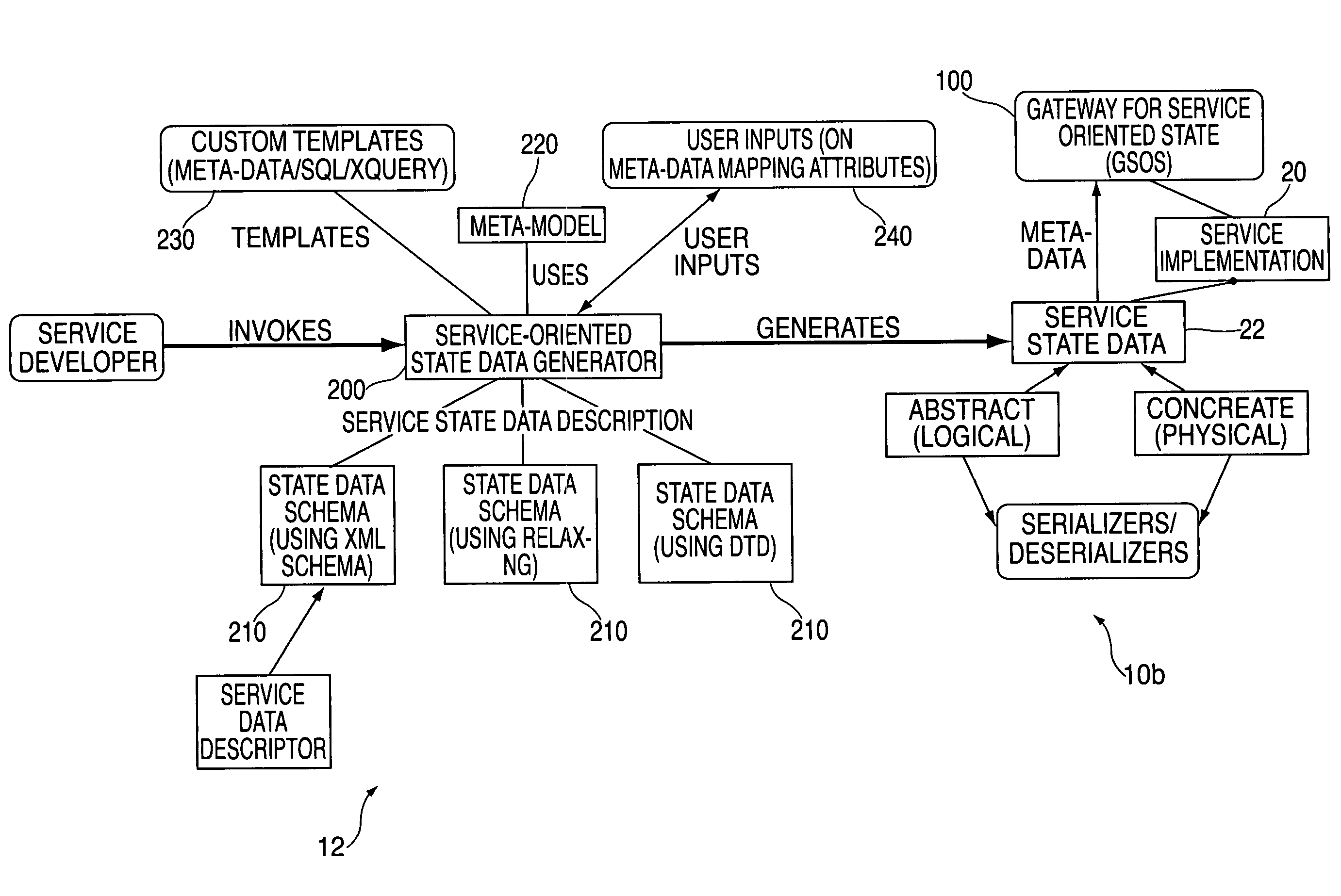

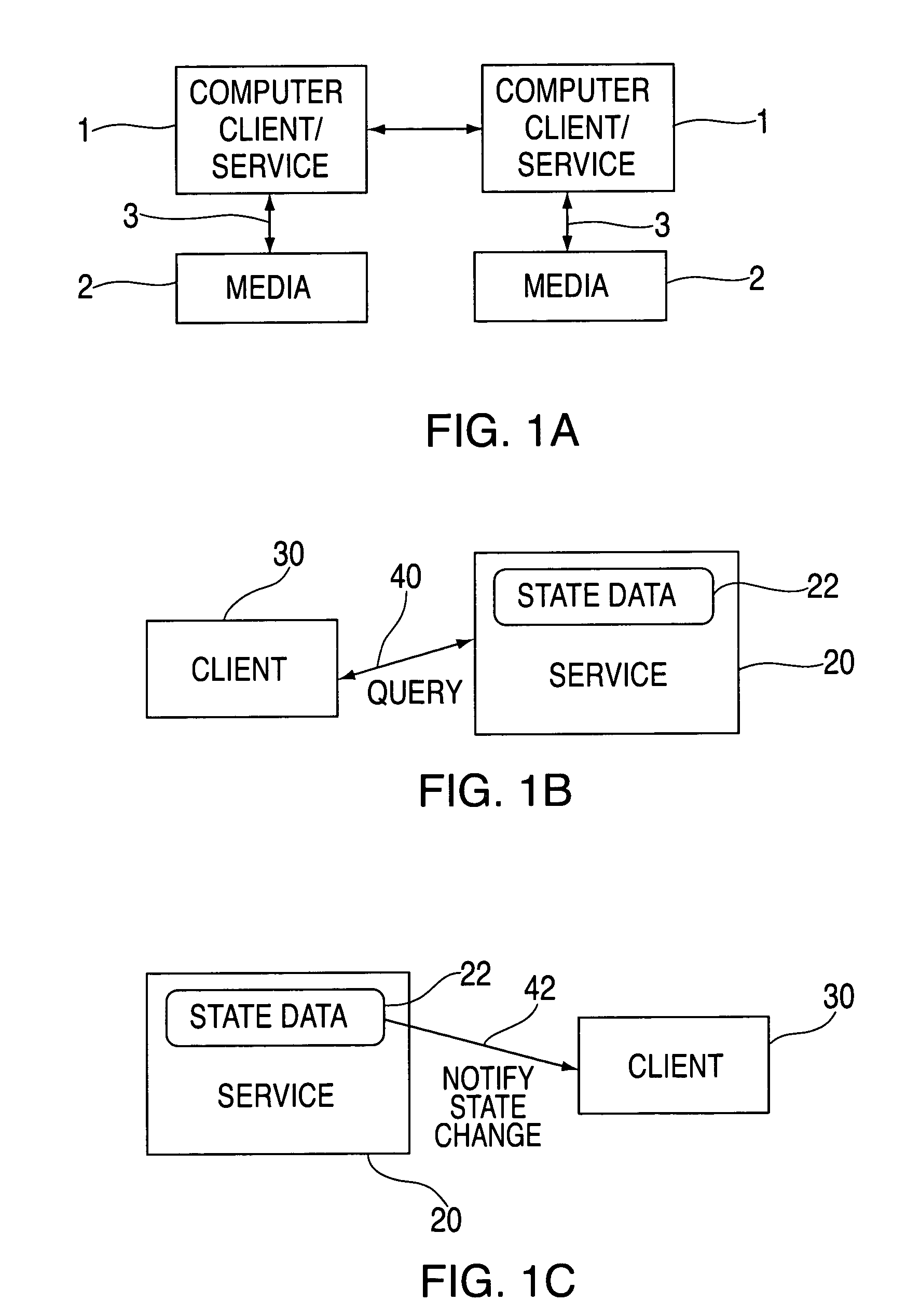

Method and apparatus for generating service oriented state data mapping between extensible meta-data model and state data including logical abstraction

InactiveUS7287037B2Data processing applicationsMultiple digital computer combinationsData descriptionData information

A method and apparatus for generating service state data and extensible meta-data information with a service oriented state data generator (SSDG) comprising: establishing a platform independent, extensible meta-data model for the meta-data information; obtaining state data schema based on a service state data description; defining an extensible set of meta-data attributes and templates corresponding to the meta data based on requirements of a service; and utilizing the meta-data model and based on the state data schema and the attributes, generating service state data based on the service state data schema; and The service state data including at least one of: state data, state data logical mapping, state data physical mapping, meta-data associated with the service state data and meta-data model correlations associated with the meta-data.

Owner:IBM CORP

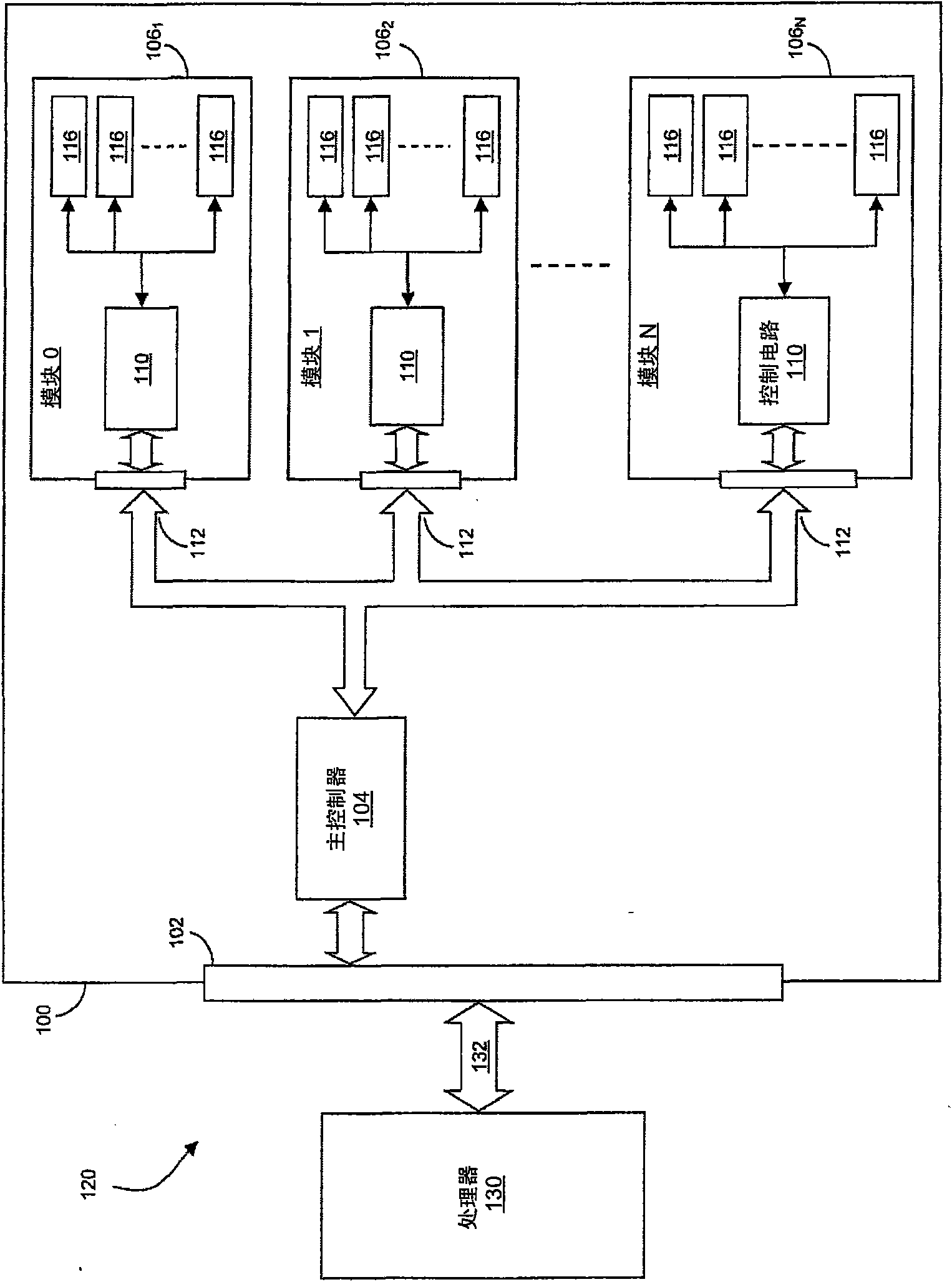

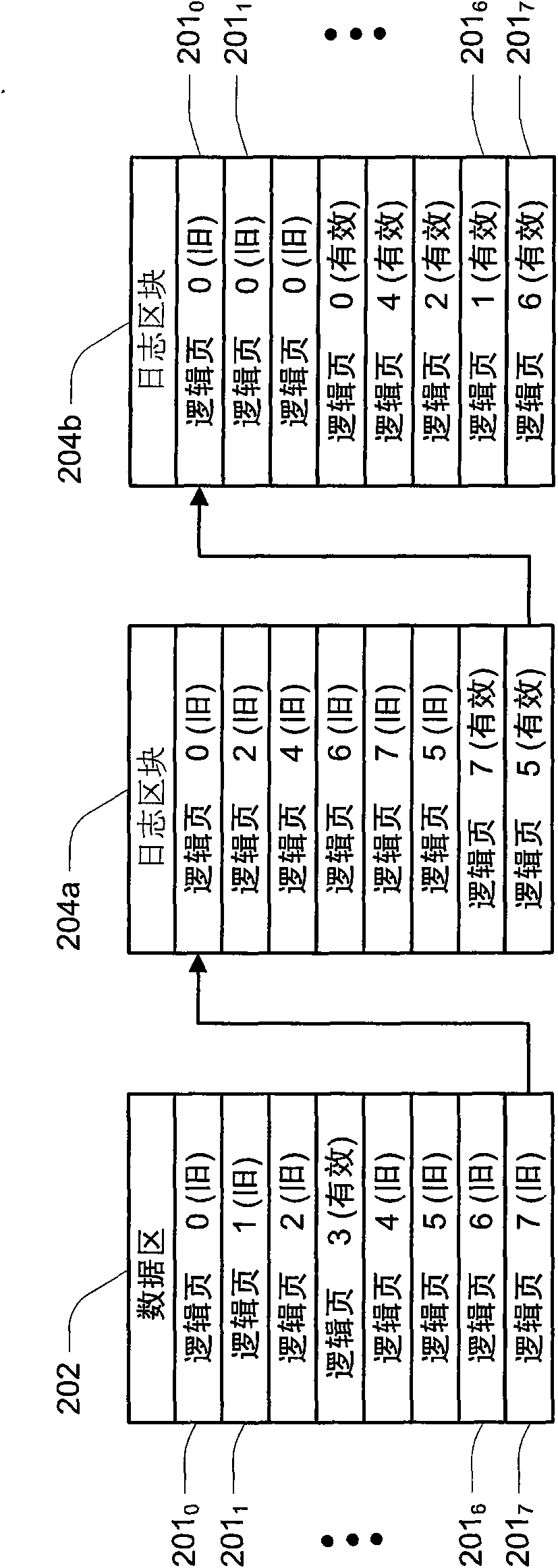

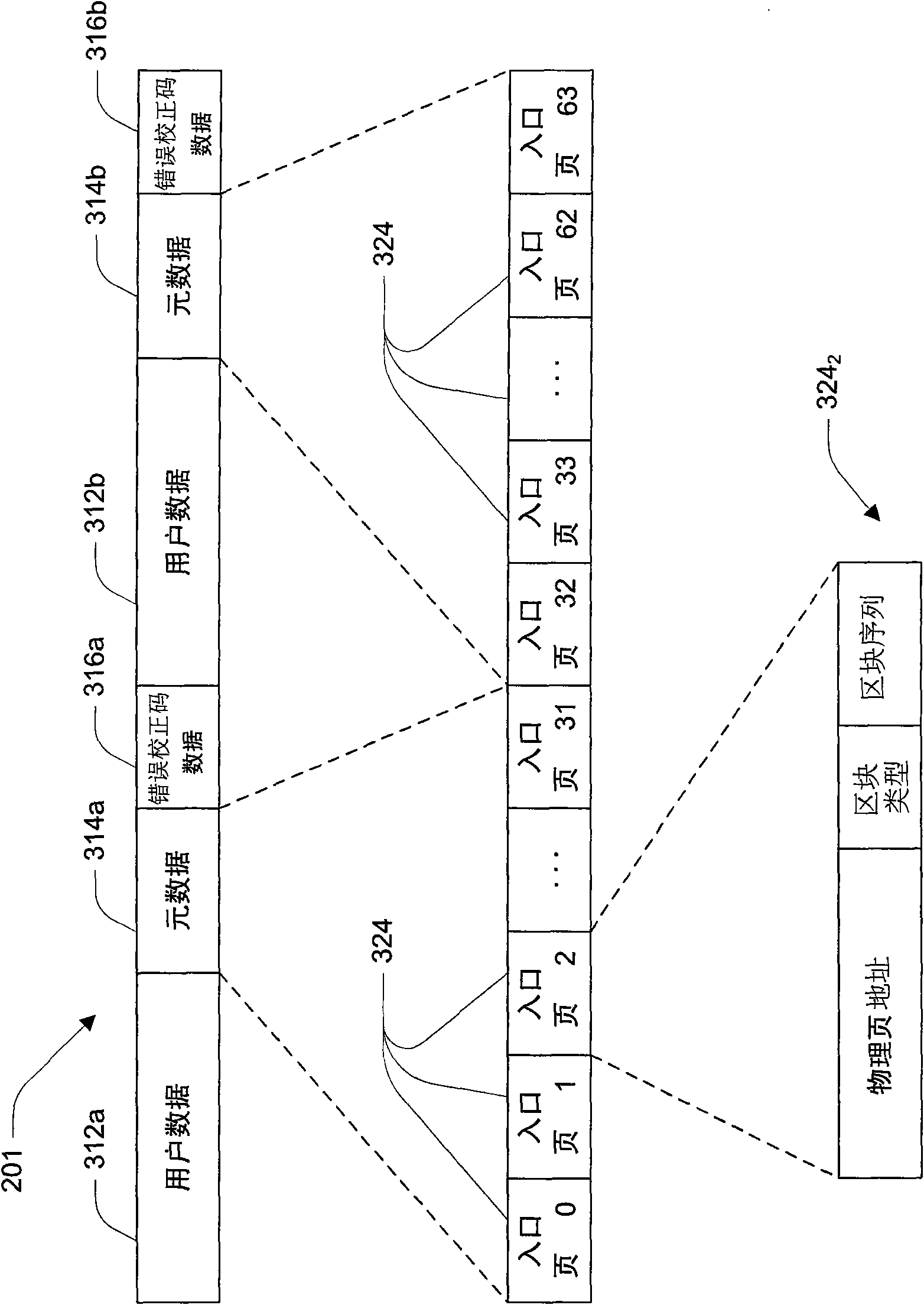

Built-in mapping message of memory device

ActiveCN101676882AMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer scienceMemory module

A storage module and a method for operating the memory module to build the mapping message into the block of a memory unit to which the mapping message belongs are disclosed. Specifically, when writing into a page according to a logic data block, the page comprises the snapshot of the current mapping message of the logic data block; with the method, the final effective physical page of the logic data block contains physical / logic mapping of the block. Thus, each effective page of the memory device is substituted and scanned for reconstructing the mapping message, and the memory module can only scan the final effective physical page of each logic data block. Once the final effective physical page of the logic data block is found, the latest mapping message of the logic data block can be read from the page.

Owner:MICRON TECH INC

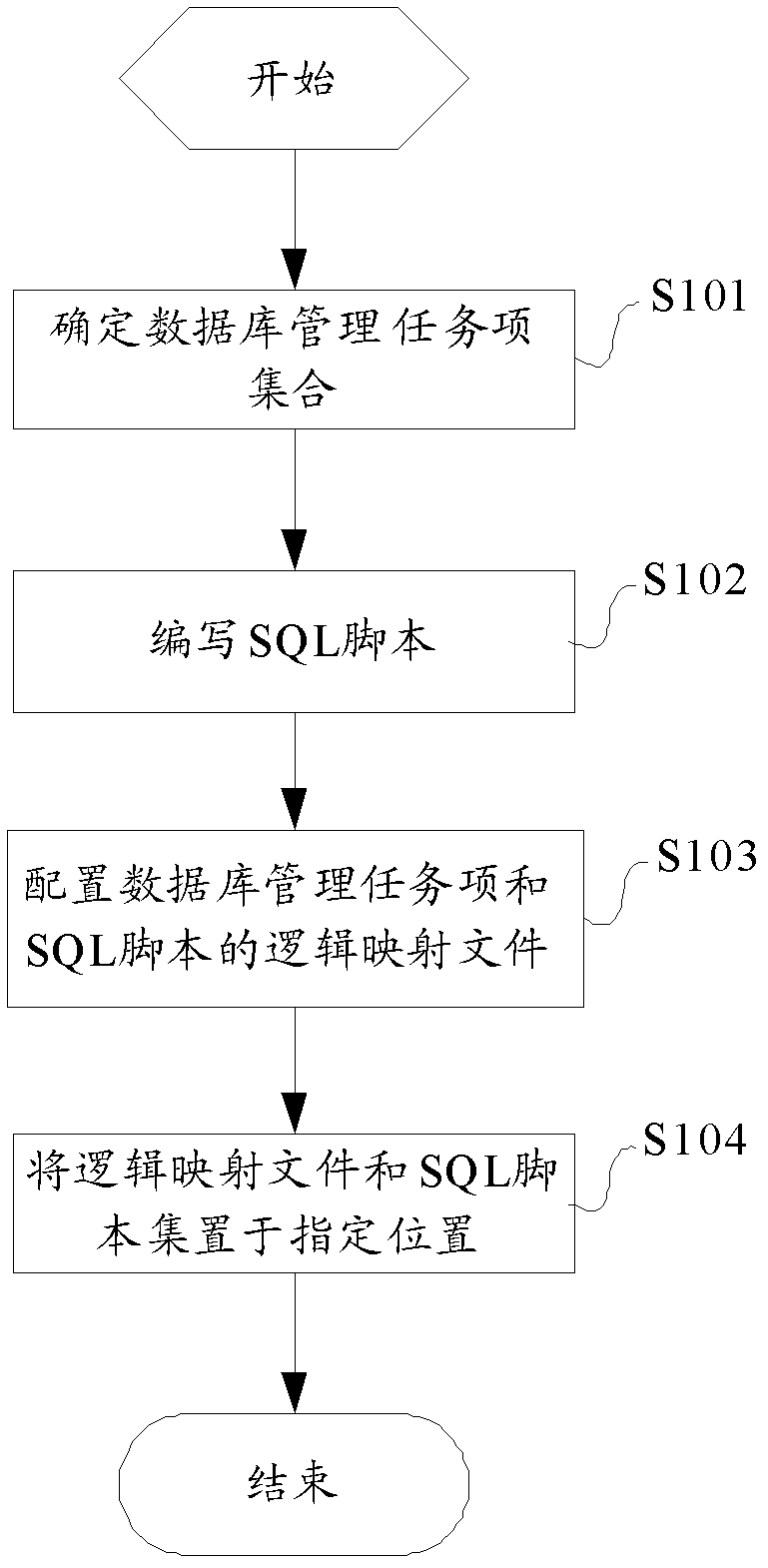

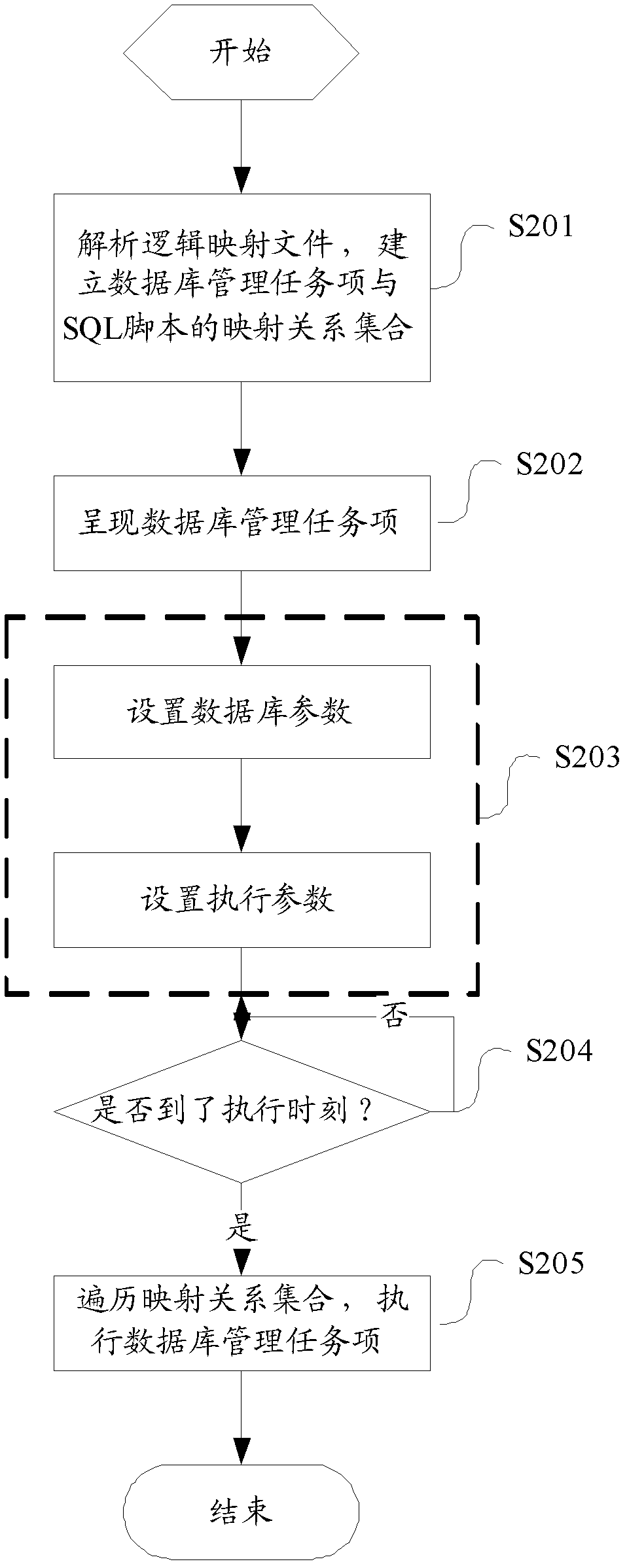

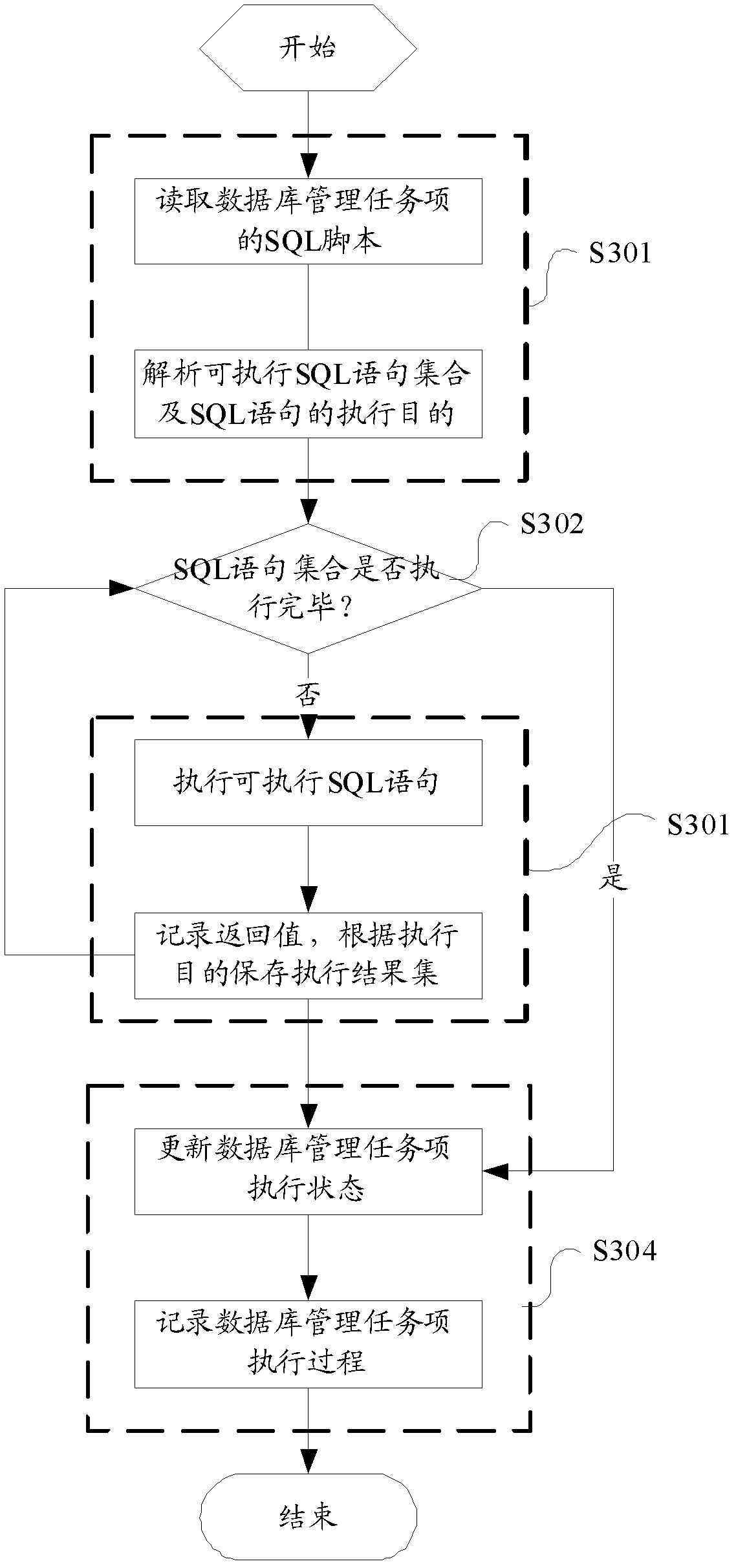

SQL (Structured Query Language)-based database management method and device

ActiveCN102323945AReduce manual interventionRealize automatic batch executionSpecial data processing applicationsManagement processClient-side

The invention discloses an SQL (Structured Query Language)-based database management method and device. The method comprises the steps of: compiling a corresponding SQL script by aiming at each database management task item to form an SQL script set; establishing a logic mapping file of each database management task item with a corresponding SQL script; and deploying the SQL script set and the logic mapping file at a position available for access of a database management client side. According to the invention, by configuring the mapping relation between the database management task items andthe corresponding SQL scripts, the automatic batch execution and the result analysis and storage of the database management task items can be realized, so that manual interventions in a database management process can be reduced, the execution efficiency can be increased and the maintenance cost can be reduced.

Owner:NANJING ZNV SOFTWARE CO LTD

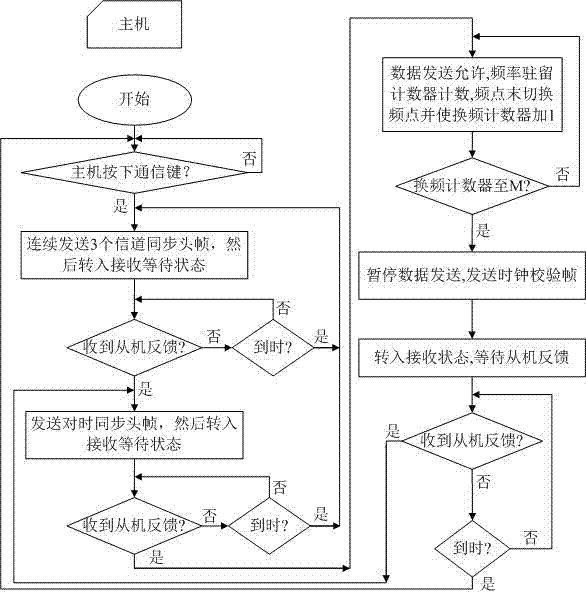

Realization method of fast frequency hopping communication

InactiveCN102651655AShort synchronization timeLow probability of out of syncTransmissionComputer scienceError correcting

The invention relates to a realization method of fast frequency hopping communication. The method is based on the frame synchronization technology, synchronization information is contained in protocol frames, the confirmation is carried for three times to ensure that the normal and stable synchronization is built between a host machine and a sub machine, and further, the synchronization information enters the fast frequency hopping communication process. Two kinds of frames: protocol frames and data frames are used in the communication process. In the synchronization building and frequency hopping communication processes, the protocol frames and the data frames are respectively subjected to interweaving coding with higher error correcting and checking capability and Reed-Solomon (RS) coding (Reed-Solomon is a code invented by IrvingStoyReed and GustaveSolomon who are American mathematicians and engineers), the transmission reliability is ensured, and the anti-interference capability is improved. During the frequency hopping communication, chaos sequences generated based on logistic mapping (a logic mapping provided by PierreFran oisVerhulst) are adopted as frequency hopping patterns, so the randomness of the frequency hopping frequency is enhanced, and the anti-interference performance and the detection resistance performance of a frequency hopping radio station are improved.

Owner:BEIJING UNIV OF CHEM TECH

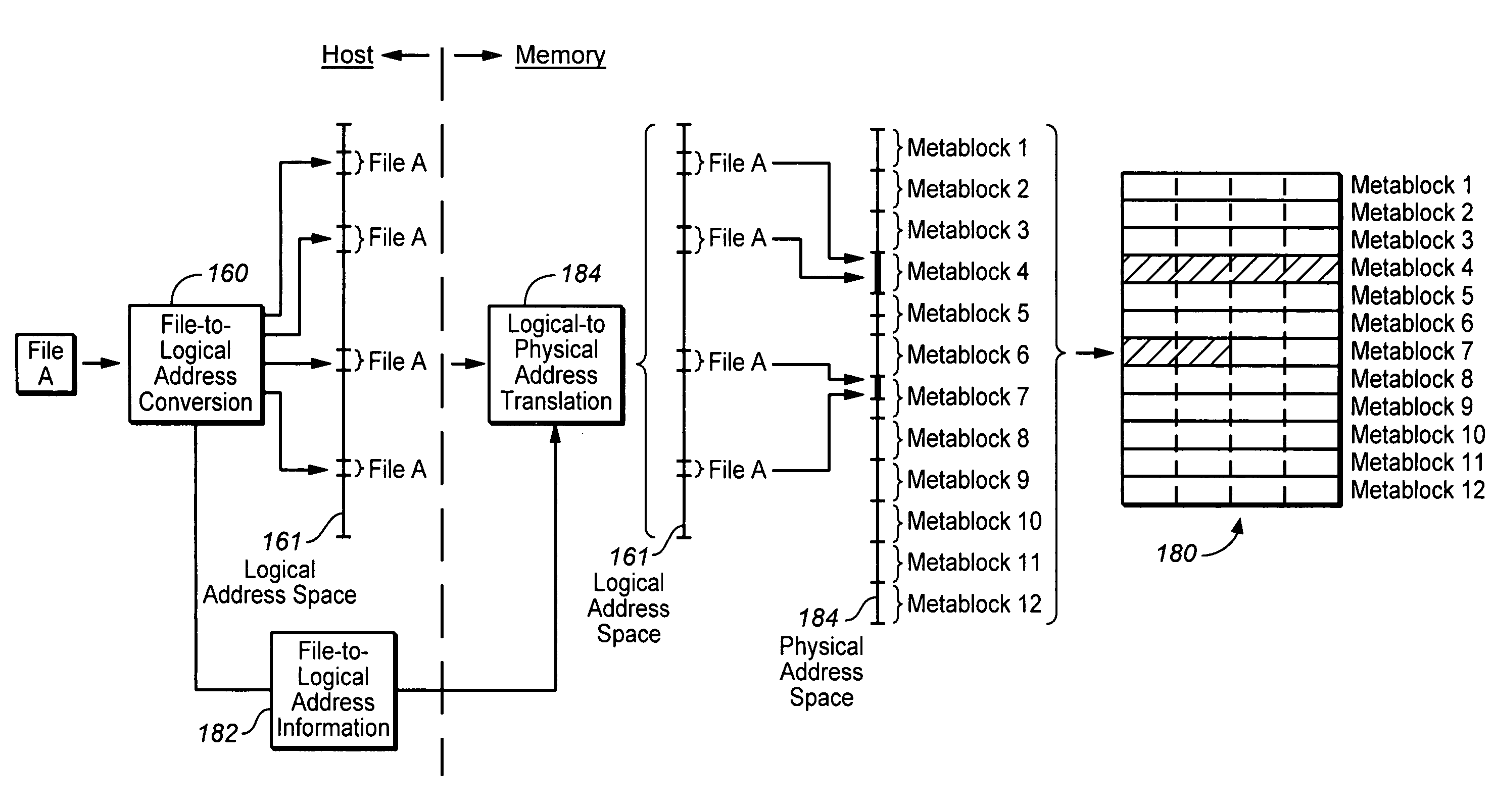

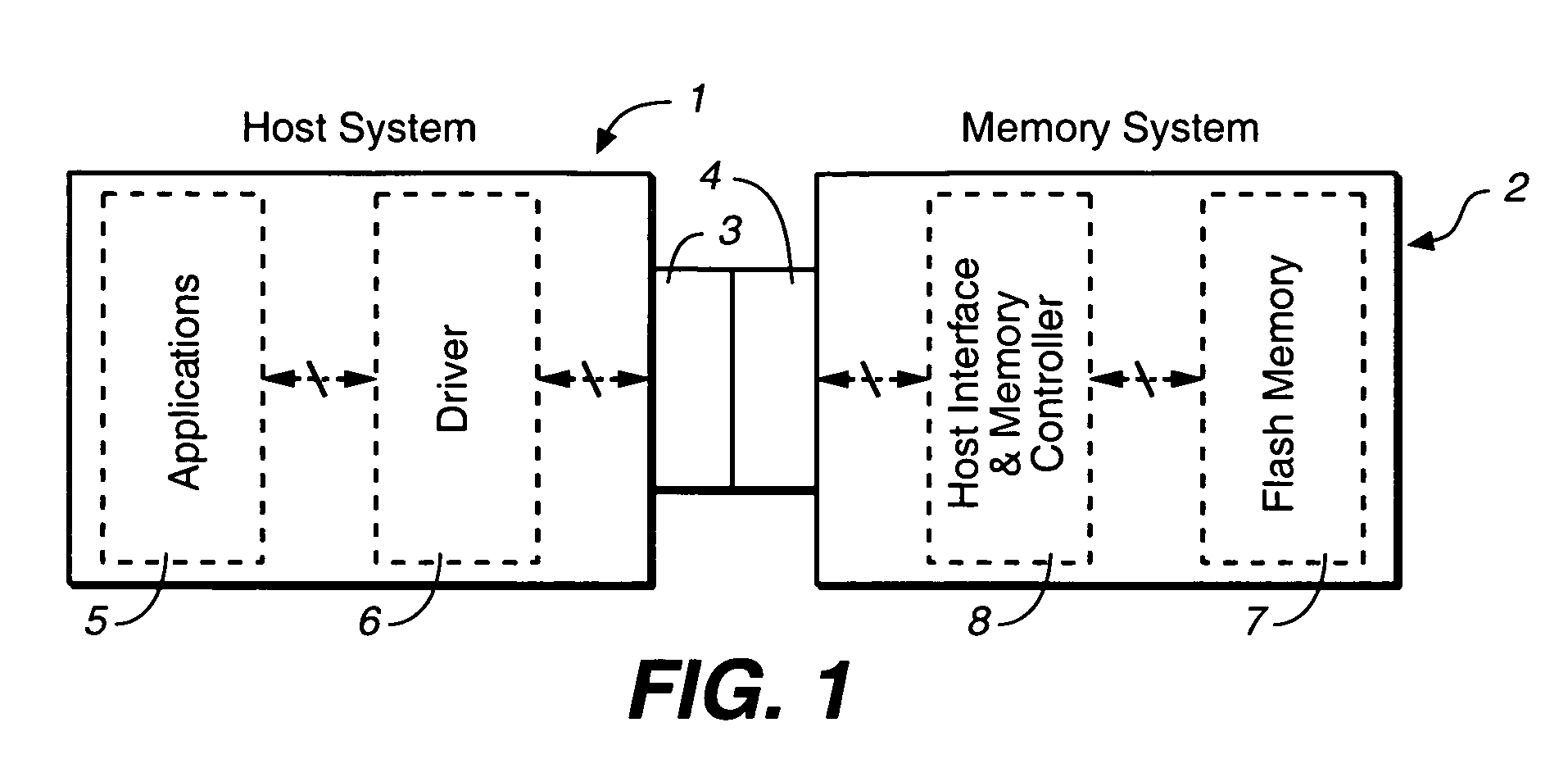

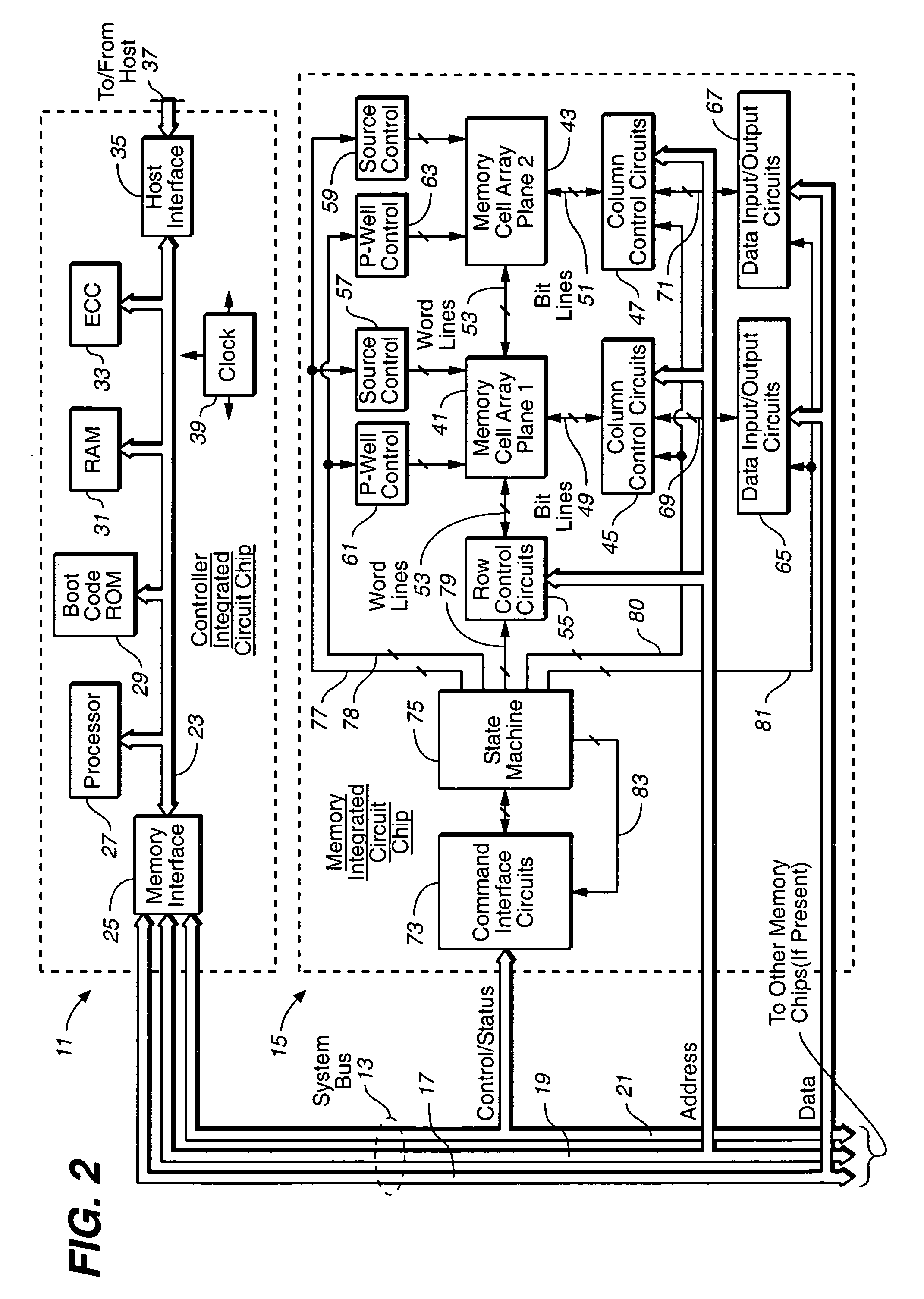

Logically-addressed file storage methods

ActiveUS7877540B2Efficient storagePromote recoveryMemory architecture accessing/allocationMemory systemsLogic mappingMemory systems

Files that are mapped to a logical address range by a host become logically fragmented prior to being sent to a memory system. Subsequently, the logically fragmented portions are reassembled when they are stored in blocks in the memory system. The host supplies information to the memory system regarding file-to-logical mapping of data prior to sending the data. The memory selects storage locations for the data based on the files to which the data belong.

Owner:SANDISK TECH LLC

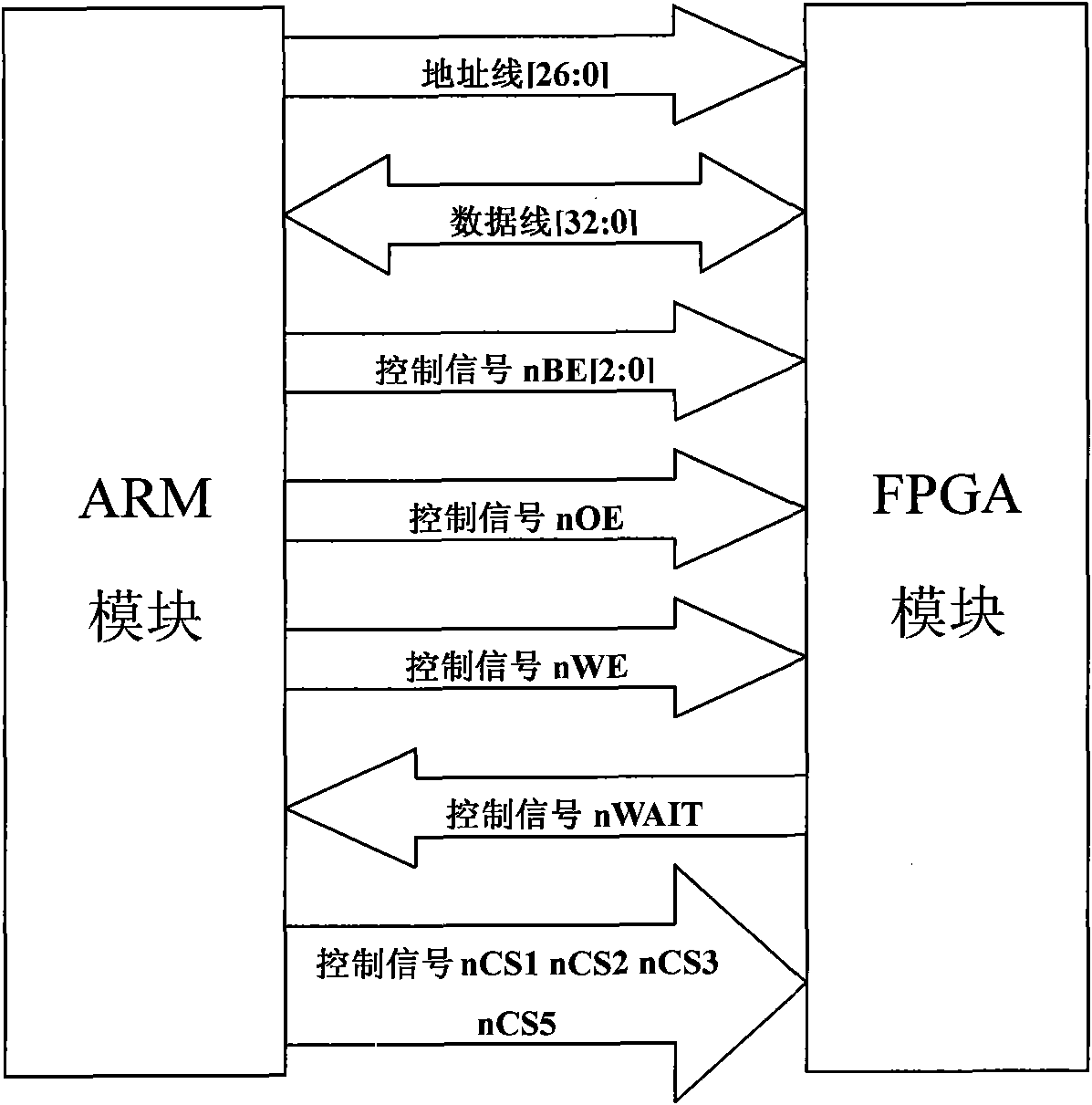

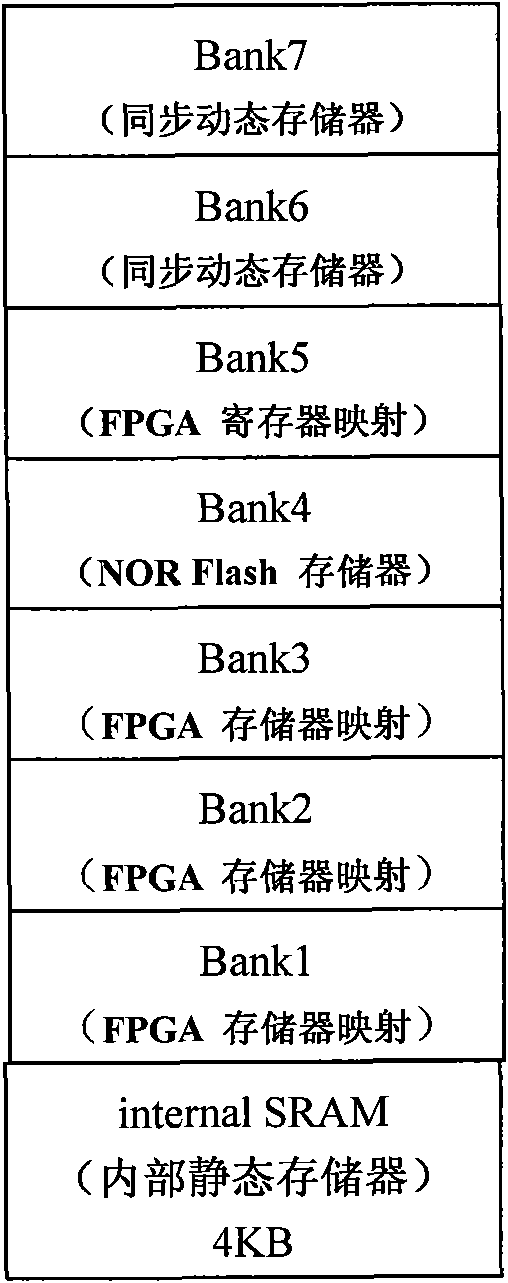

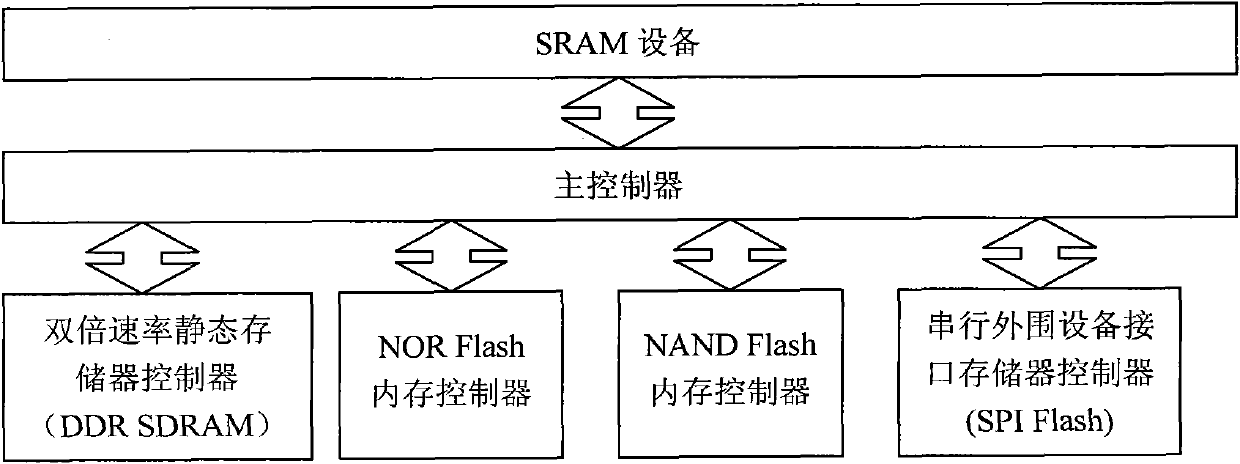

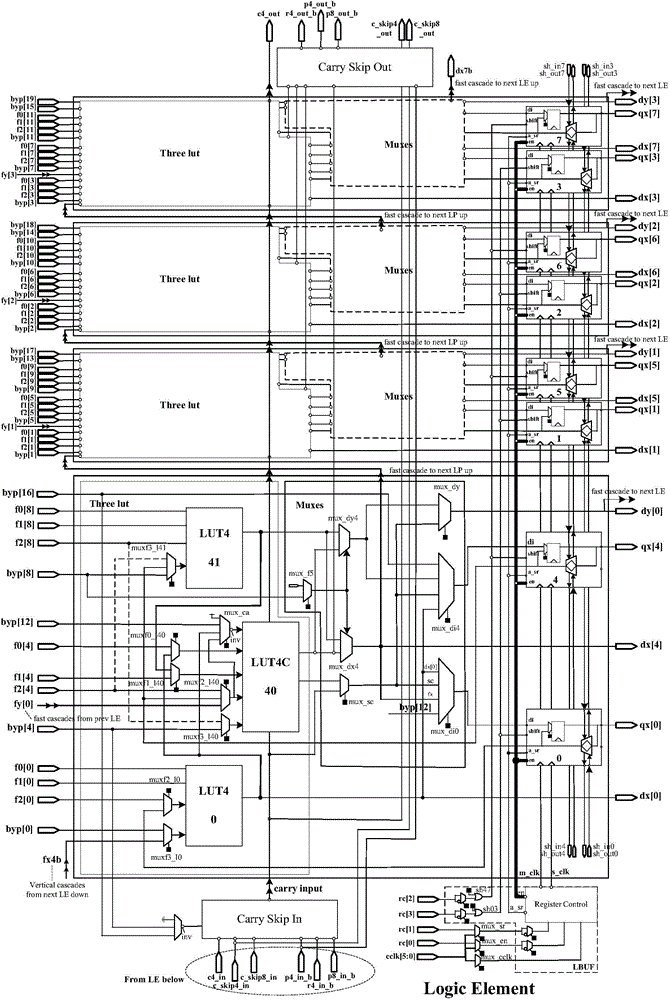

Multi-interface memory verification system based on FPGA

The invention discloses a multi-interface memory verification system based on an FPGA, which comprises an ARM module and an FPGA module, wherein the ARM module and the FPGA module are connected in a bus mode, a method of simulating an SRAM external memory through the FPGA end is adopted for logically mapping a controller in the FPGA into the ARM memory for providing data and a control visit interface, the system adopts an asynchronous bus communication mode, asynchronous control signals, asynchronous addresses, and data signals output by the ARM are synchronized to an internal clock region of the FPGA, and the system memory data and the control interface uniformly adopt the direct mapping method of the memory data, so a controller IP core of each memory is transplanted and integrated in the system, and the data visit interface is realized in an FIFO mode. The invention can flexibly support memories with the newest interface types, the newest memory chip can be tested and verified in the shortest time, at the same time, various kinds of chip test and demonstration can be carried out, and the actual use time period of the novel memory chip is greatly shortened.

Owner:EAST CHINA NORMAL UNIV

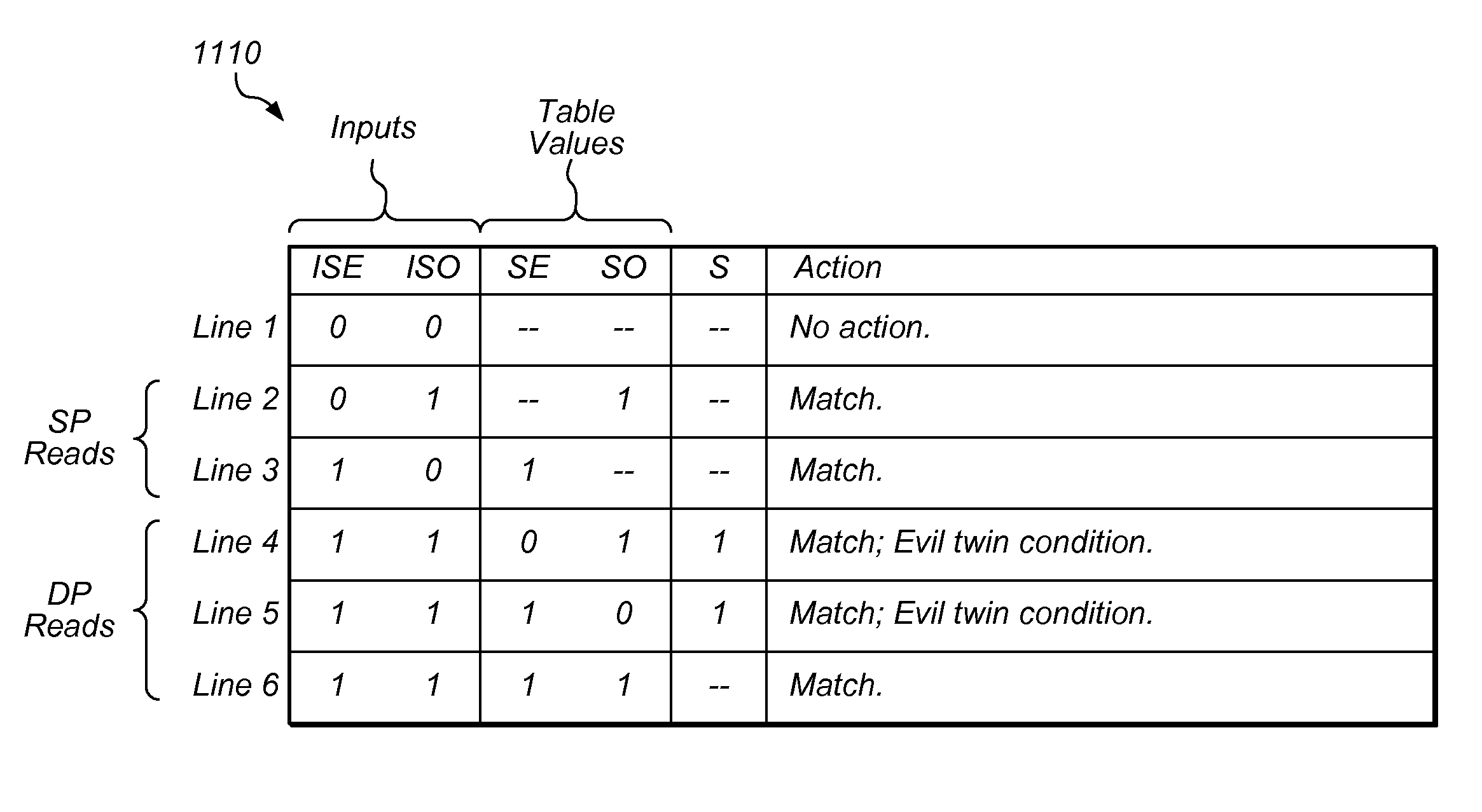

Logical map table for detecting dependency conditions

ActiveUS20100274993A1Detection can be executedDigital computer detailsSpecific program execution arrangementsContent-addressable storageProgramming language

Techniques and structures are described which allow the detection of certain dependency conditions, including evil twin conditions, during the execution of computer instructions. Information used to detect dependencies may be stored in a logical map table, which may include a content-addressable memory. The logical map table may maintain a logical register to physical register mapping, including entries dedicated to physical registers available as rename registers. In one embodiment, each entry in the logical map table includes a first value usable to indicate whether only a portion of the physical register is valid and whether the physical register includes the most recent update to the logical register being renamed. Use of this first value may allow precise detection of dependency conditions, including evil twin conditions, upon an instruction reading from at least two portions of a logical register having an entry in the logical map table whose first value is set.

Owner:ORACLE INT CORP

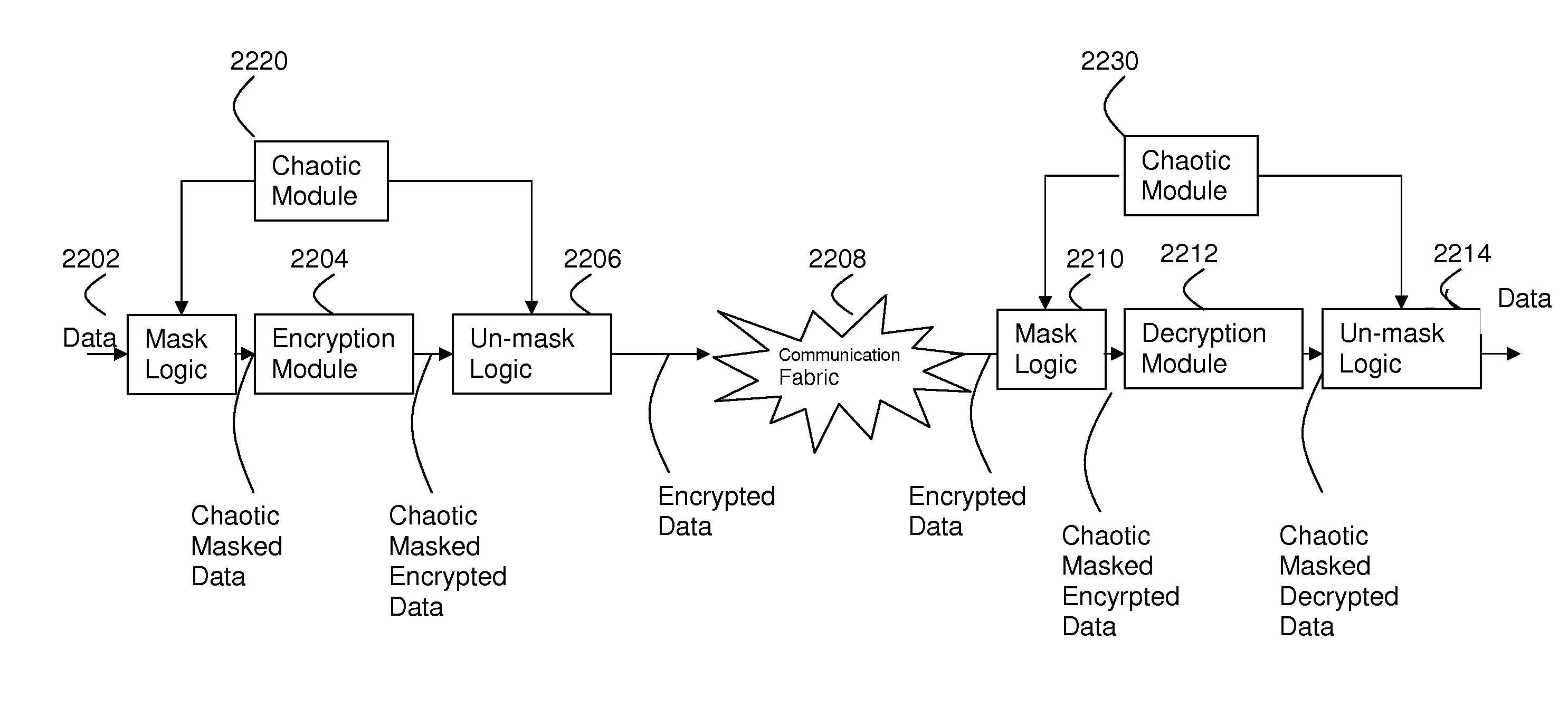

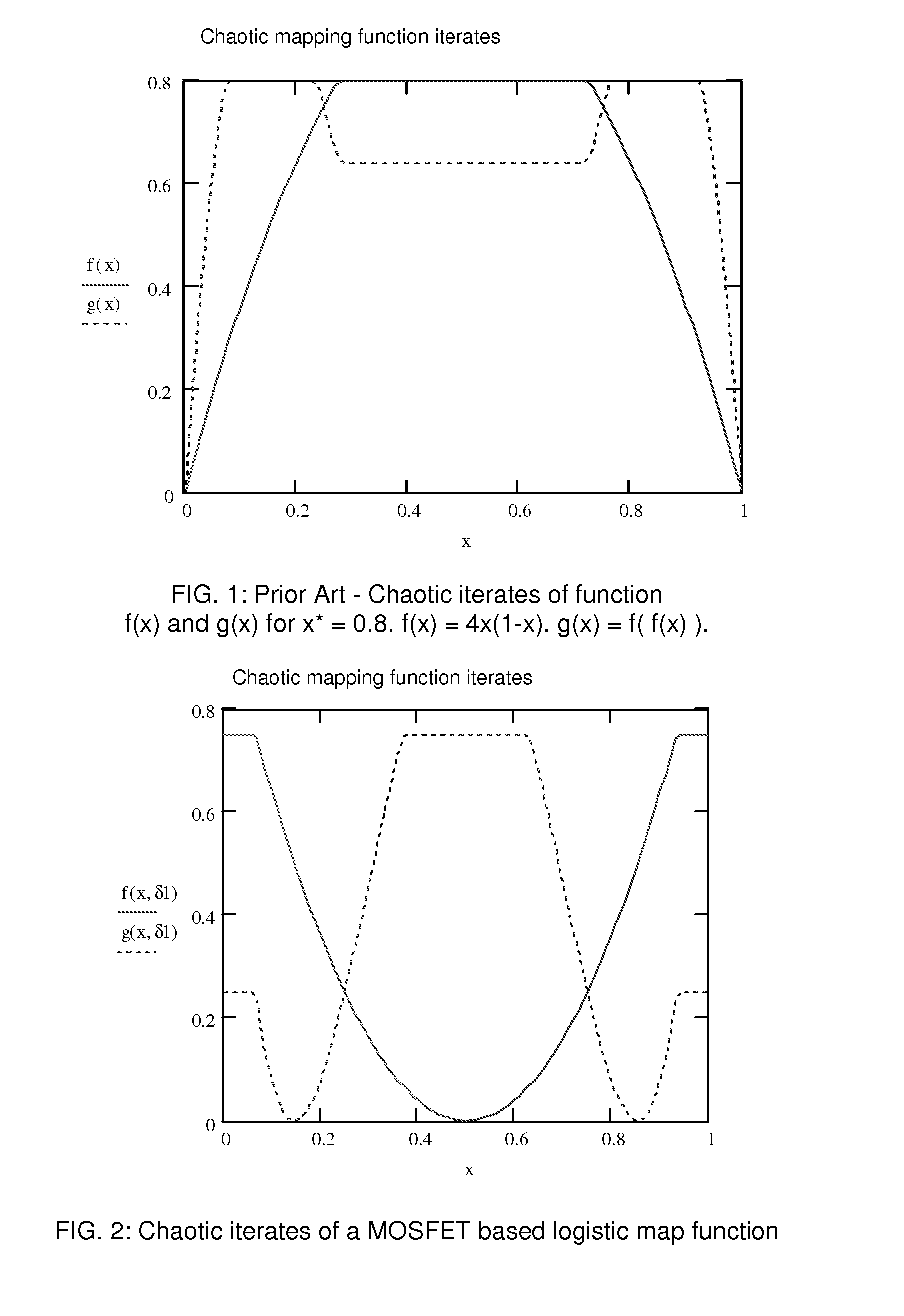

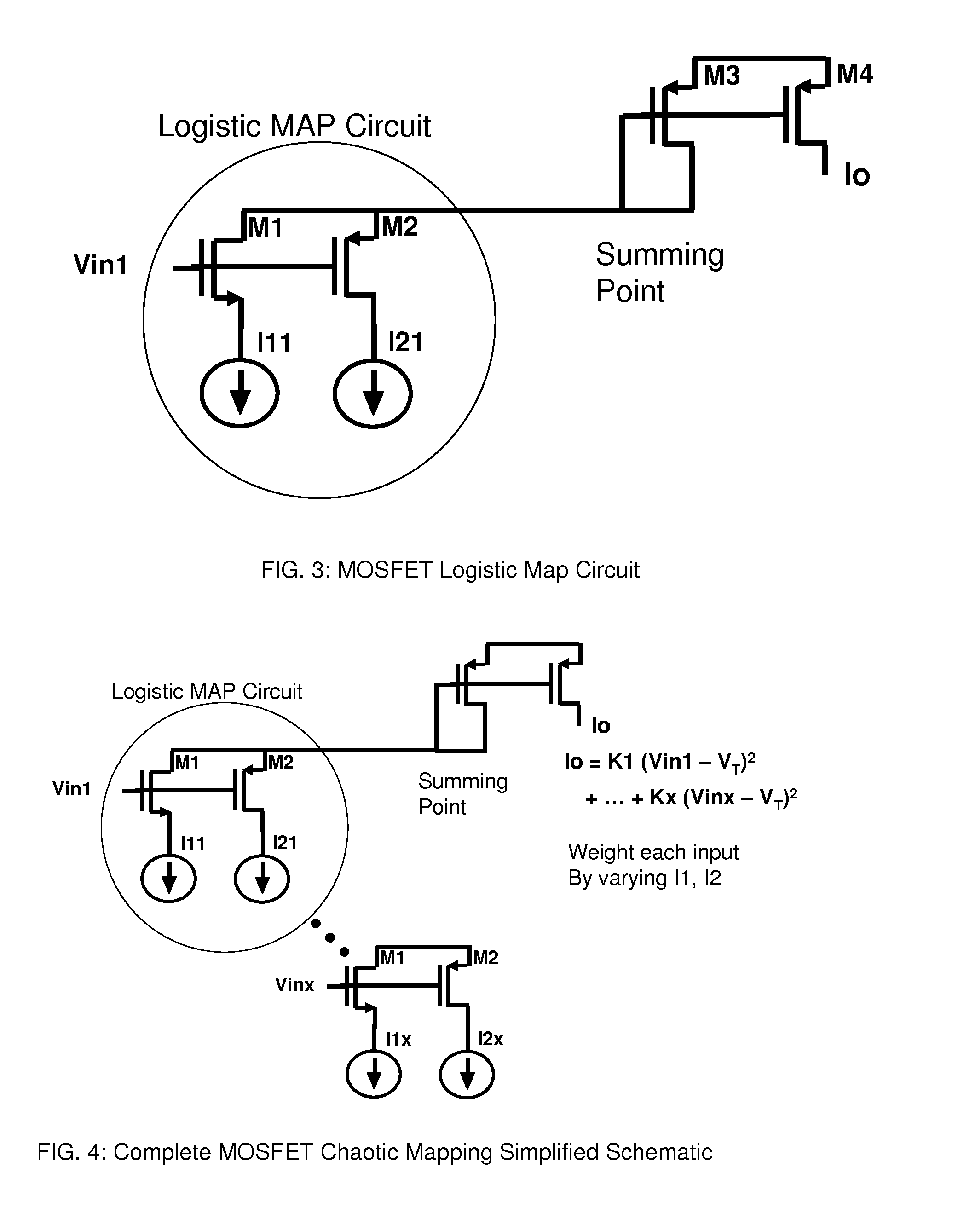

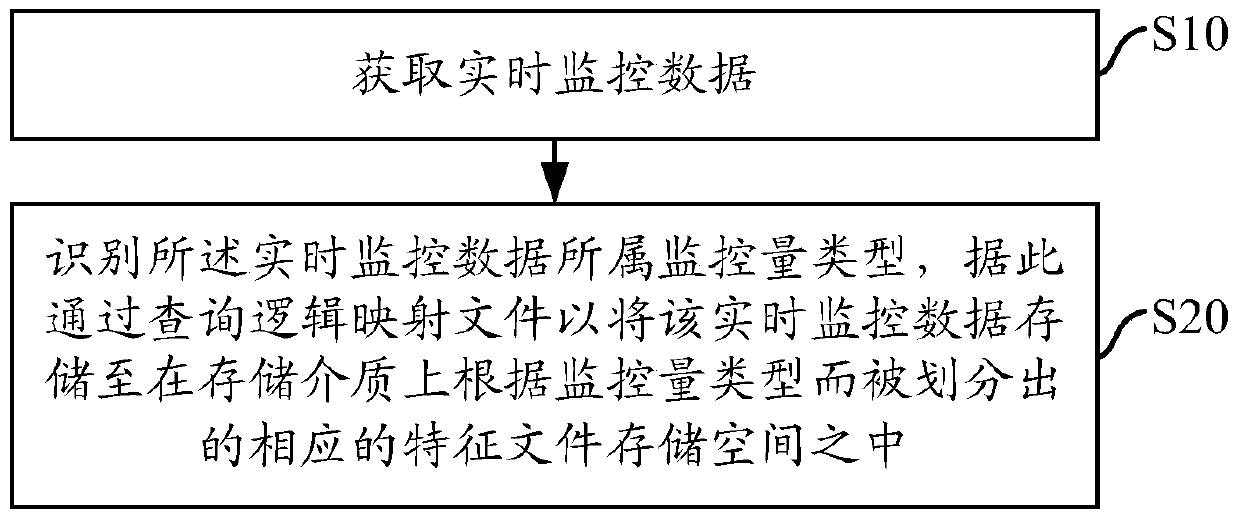

High utilization universal logic array with variable circuit topology and logistic map circuit to realize a variety of logic gates with constant power signatures

ActiveUS20110085662A1Avoid detectionPower reduction in field effect transistorsLogic circuits characterised by logic functionMulti inputConstant power

Disclosed is a novel circuit able to generate any logic combination possible as a function of the input logic signals. The circuit is described as a 2 input logistic map circuit but may be expanded to 3 or more inputs as required. Further disclosed is a universal logic array with variable circuit topology. A metallization layer and / or a via interconnection between cells in the array elements produce a circuit topology that implements a Boolean function and / or chaotic function and / or a logic function. The novel circuit provides a circuit topology for secure applications with no obvious physical correspondence between control signal values and input to output mapping. Further disclosed is a network which has a power signature independent of input signal state and output transition. This provides a very useful circuit to protect data from decryption from power signature analysis in secure applications.

Owner:CHAOLOGIX INC

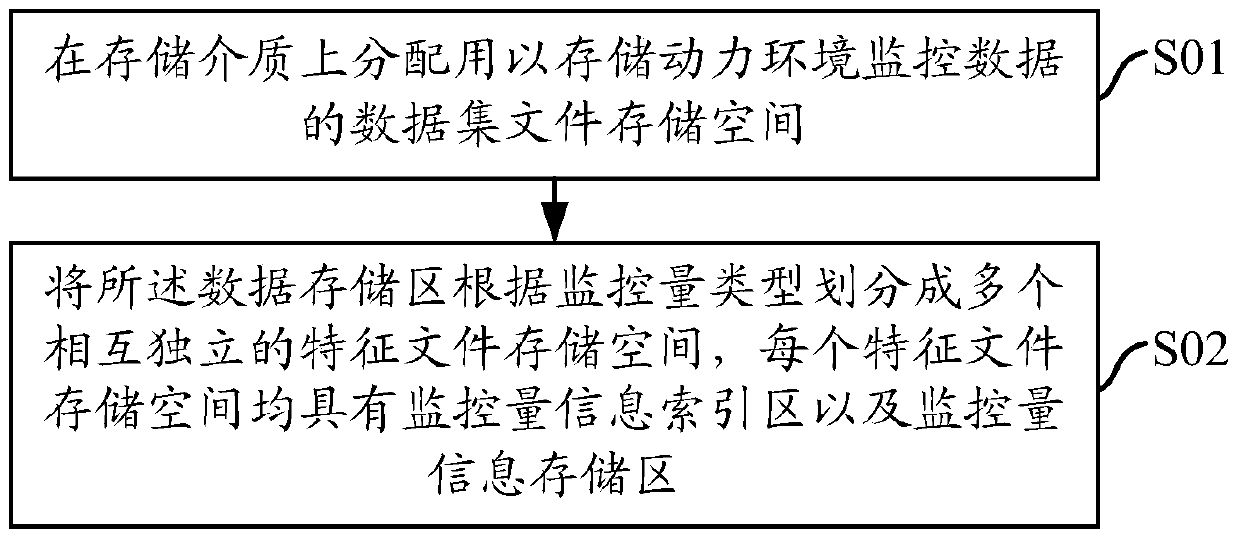

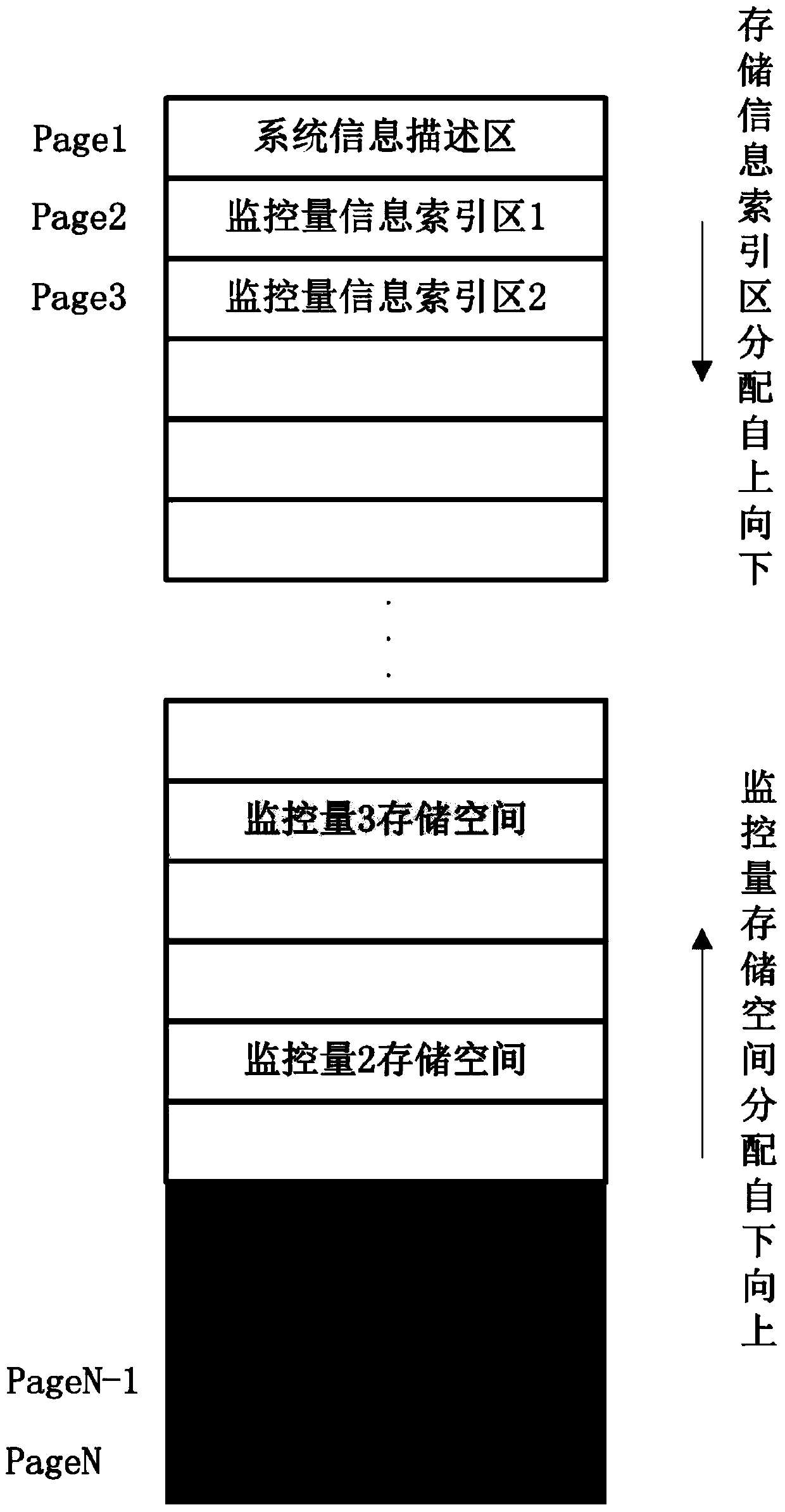

Storage method and device of dynamic environment real-time monitoring data

ActiveCN104978361ASize does not need to expandSimplified data storage structureSpecial data processing applicationsData accessQuery statement

The invention discloses a storage method and device of dynamic environment real-time monitoring data, and is applied to embedded intelligent acquisition equipment in a dynamic environment monitoring system. The method comprises the following steps: obtaining real-time monitoring data; and identifying a monitoring amount type to which the real-time monitoring data belongs, and inquiring a logic mapping file to store the real-time monitoring data into a corresponding feature file storage space divided according to the monitoring amount type on a storage medium in real time. A data storage implementation algorithm is simple, complex SQL (Structured Query Language) query statements and fussy data conversion are avoided, the method is easy in implementation, the operations of time and labor waste data deletion and database compression are avoided, a data access operation can be quickly realized, and CPU (Central Processing Unit) and memory resource consumption is low.

Owner:SHENZHEN ZTE NETVIEW TECH

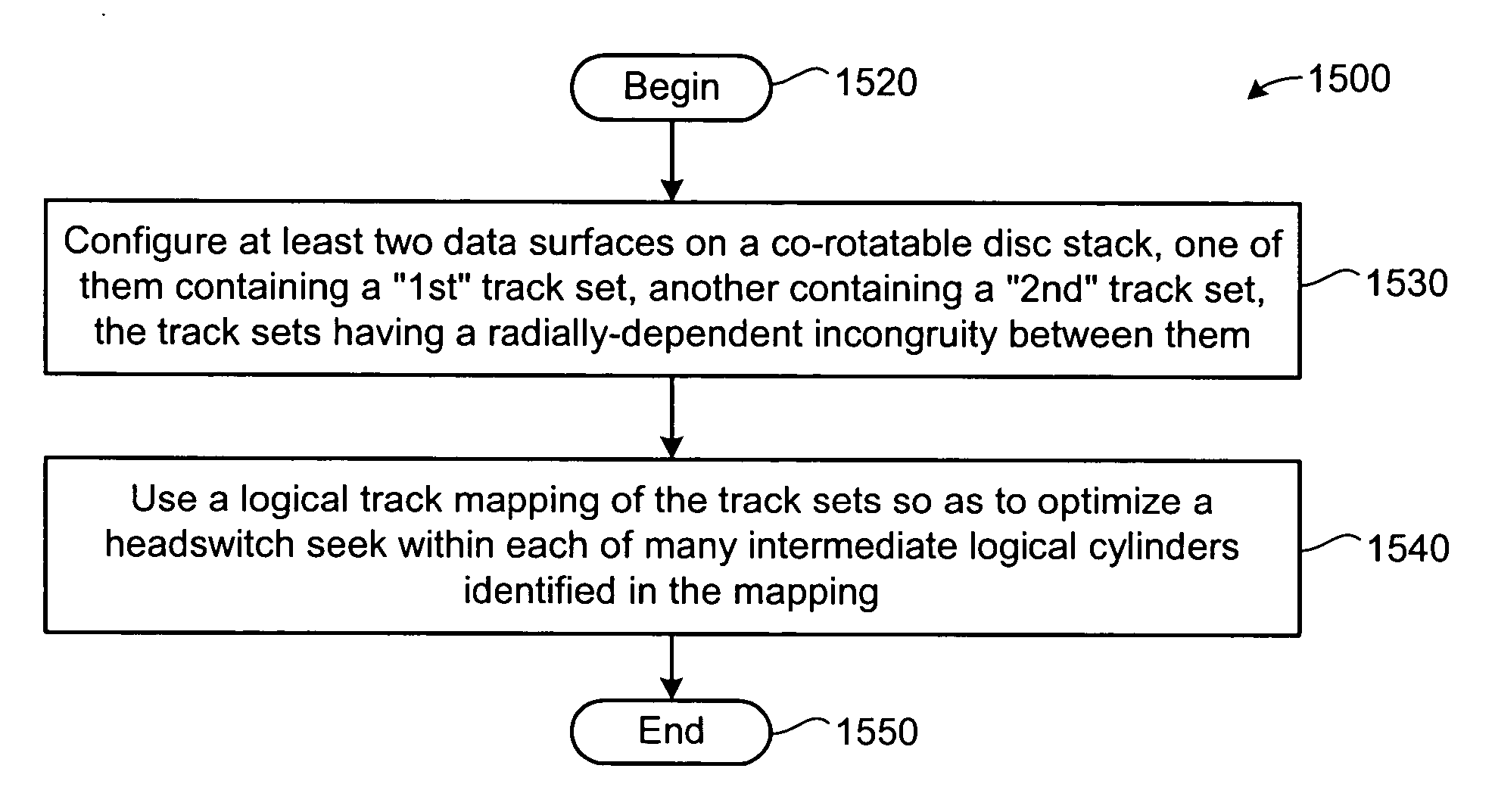

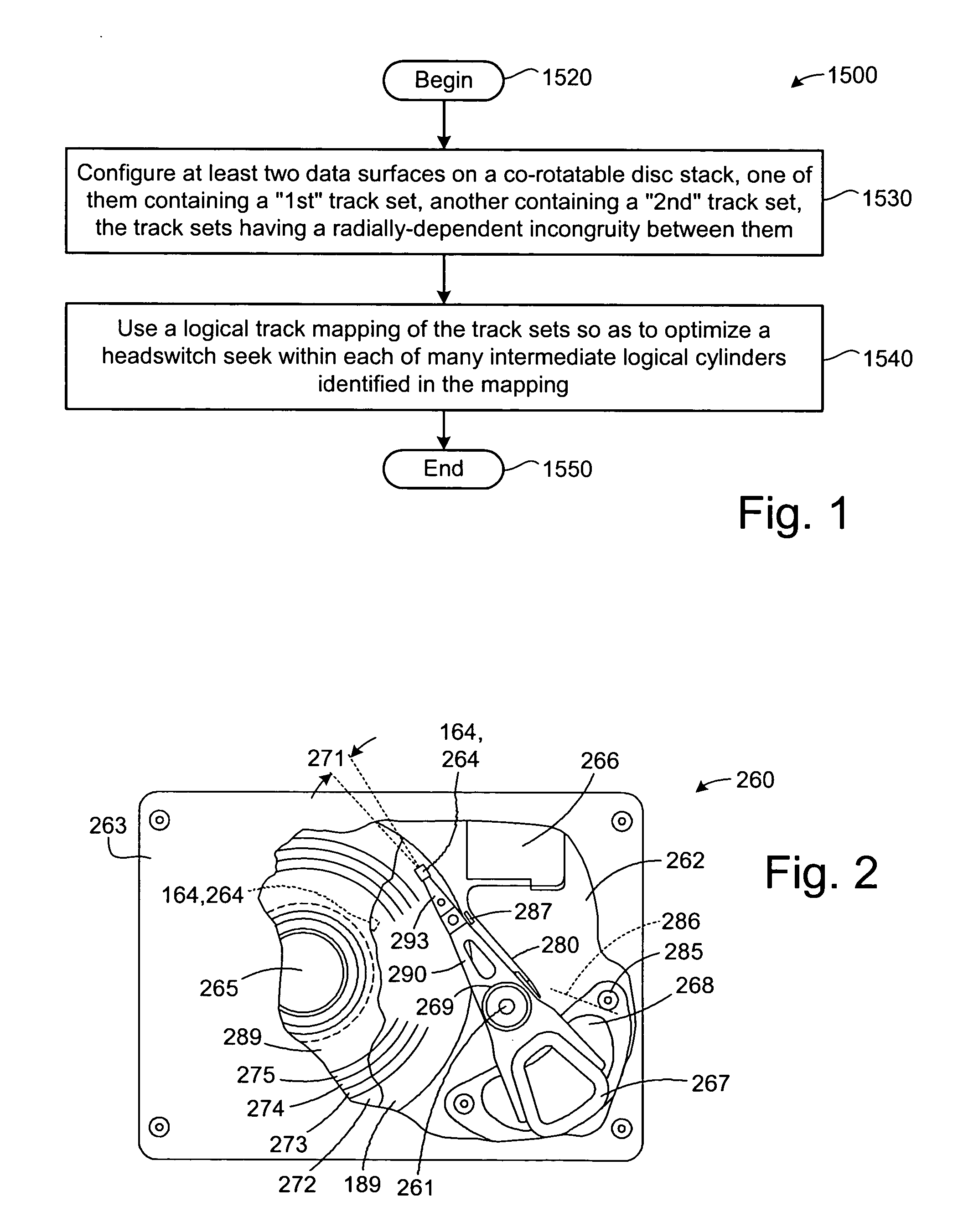

Logical mapping for improved head switching between corresponding tracks in a data handling device

InactiveUS20050078566A1Combination recordingDisposition/mounting of recording headsData processing systemTheoretical computer science

In a data handling system having a radially-dependent track incongruity between data surfaces, at least some tracks are logically mapped so that tracks on different data surfaces correspond with one another. The correspondence is defined by the mapping so as to shorten an average headswitch seek. For example, a logical track mapping of first and second non-coaxial track sets can be defined so as to optimize a headswitch seek within each of many intermediate logical cylinders identified in the mapping.

Owner:SEAGATE TECH LLC

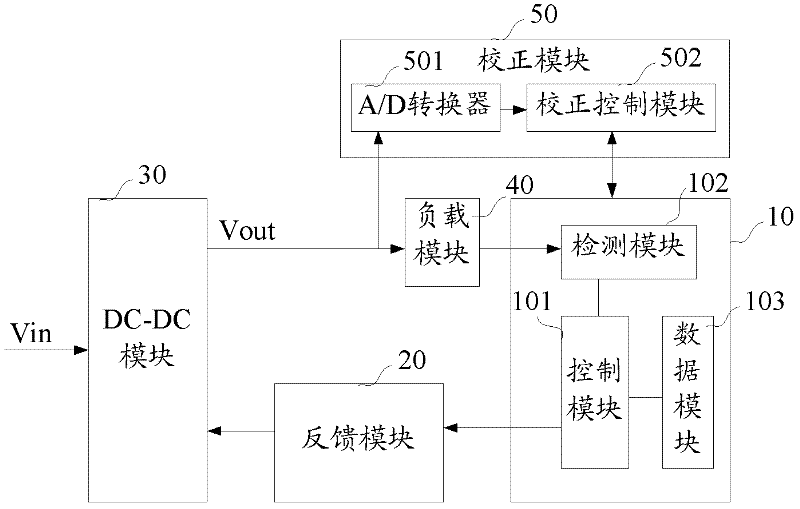

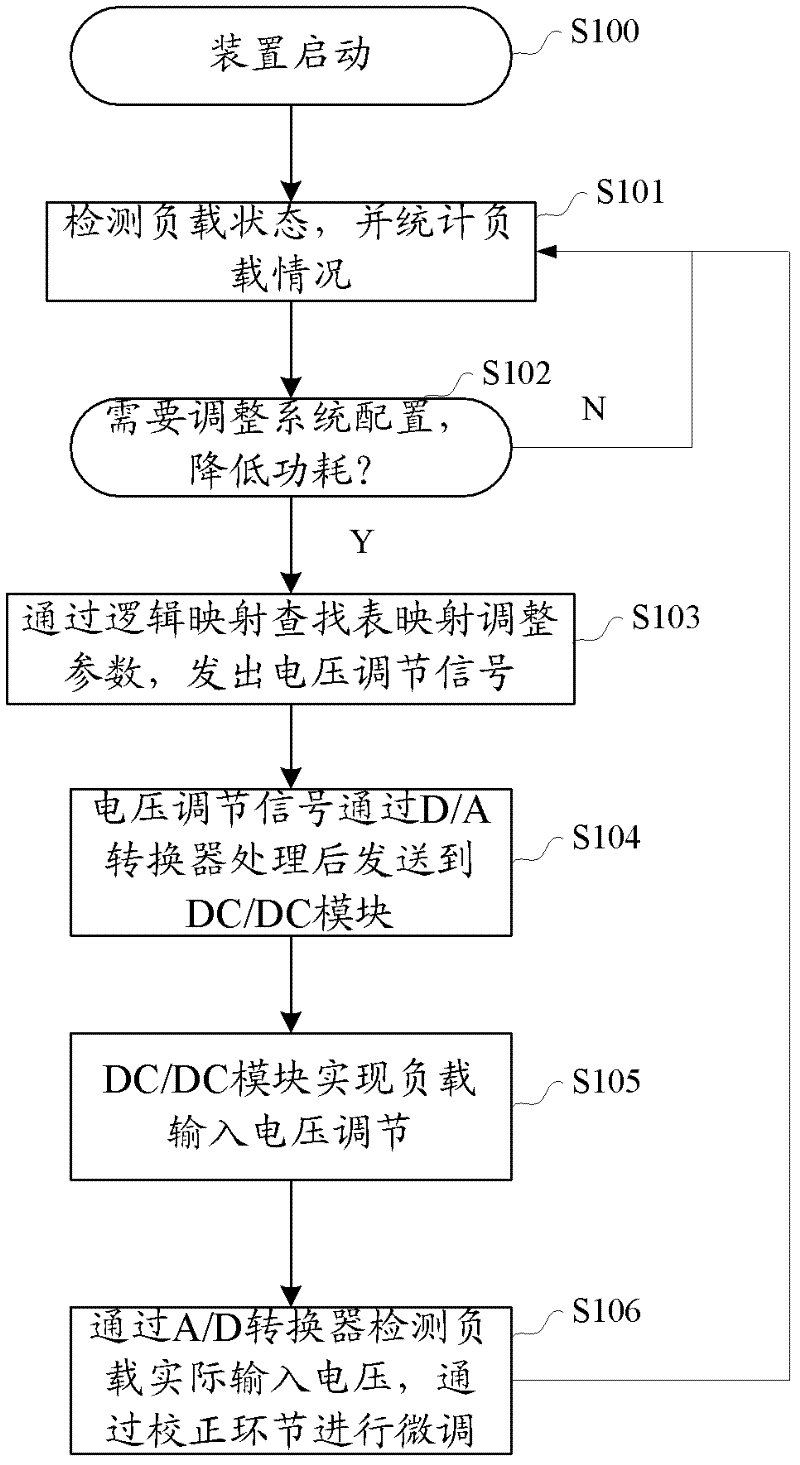

Device and method for reducing power consumption of electronic equipment

ActiveCN102346540AReduce power consumptionAutomatically adjust the input voltage sizePower supply for data processingVoltage regulationLow power dissipation

The invention discloses a device and method for reducing power consumption of electronic equipment. The method comprises the following steps: obtaining the load state information of a load module; obtaining a voltage regulation signal according to the load state information and a pre-stored logic mapping query table; and regulating the magnitude of the input voltage of the input end of the load module according to the voltage regulation signal. In the invention, the mechanism of logic mapping query table is introduced; and when the load state changes, the magnitude of the input voltage of the load module can be automatically adjusted so as to save energy of the electronic equipment and achieve the purpose of reducing the power consumption.

Owner:ZTE CORP

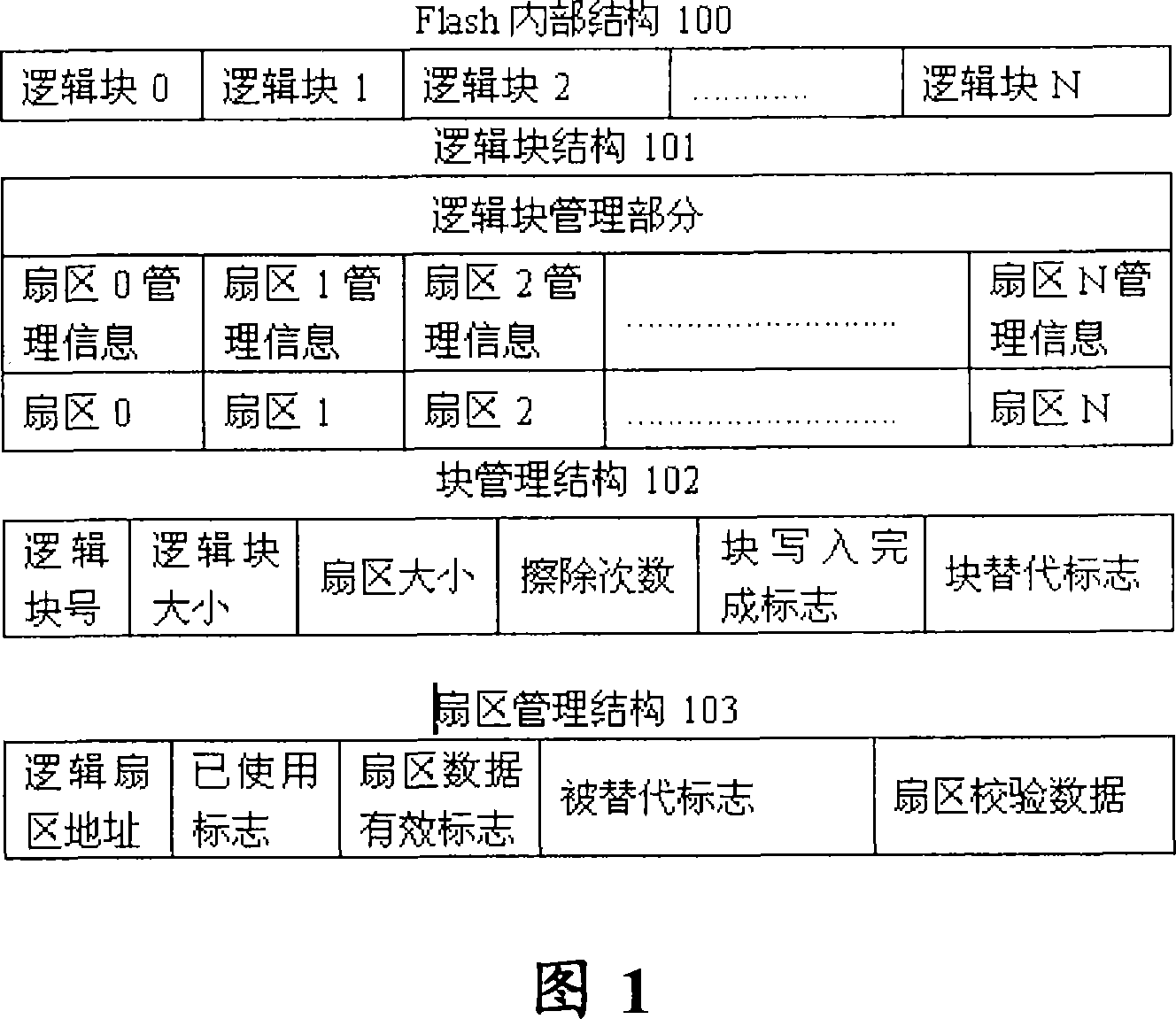

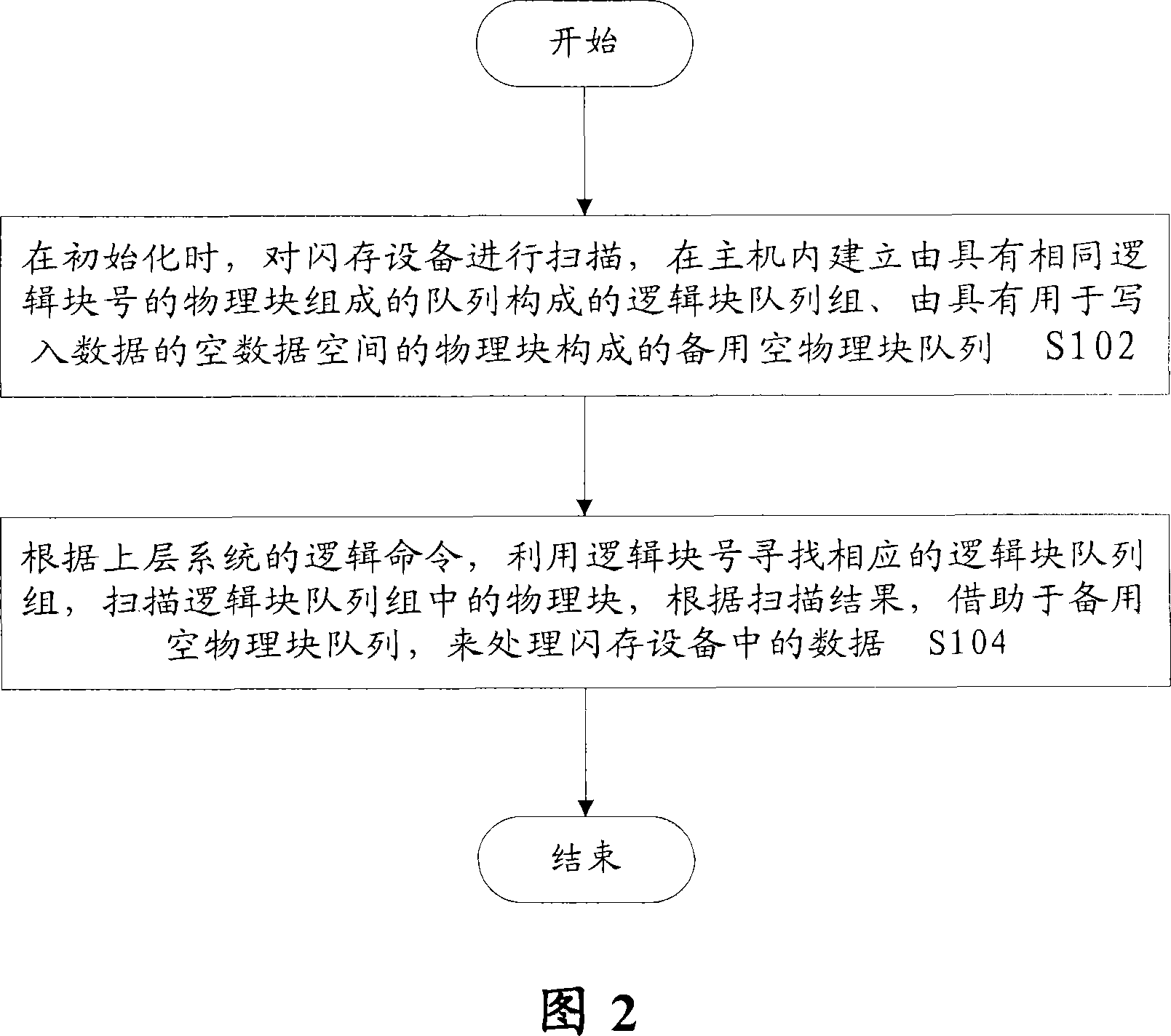

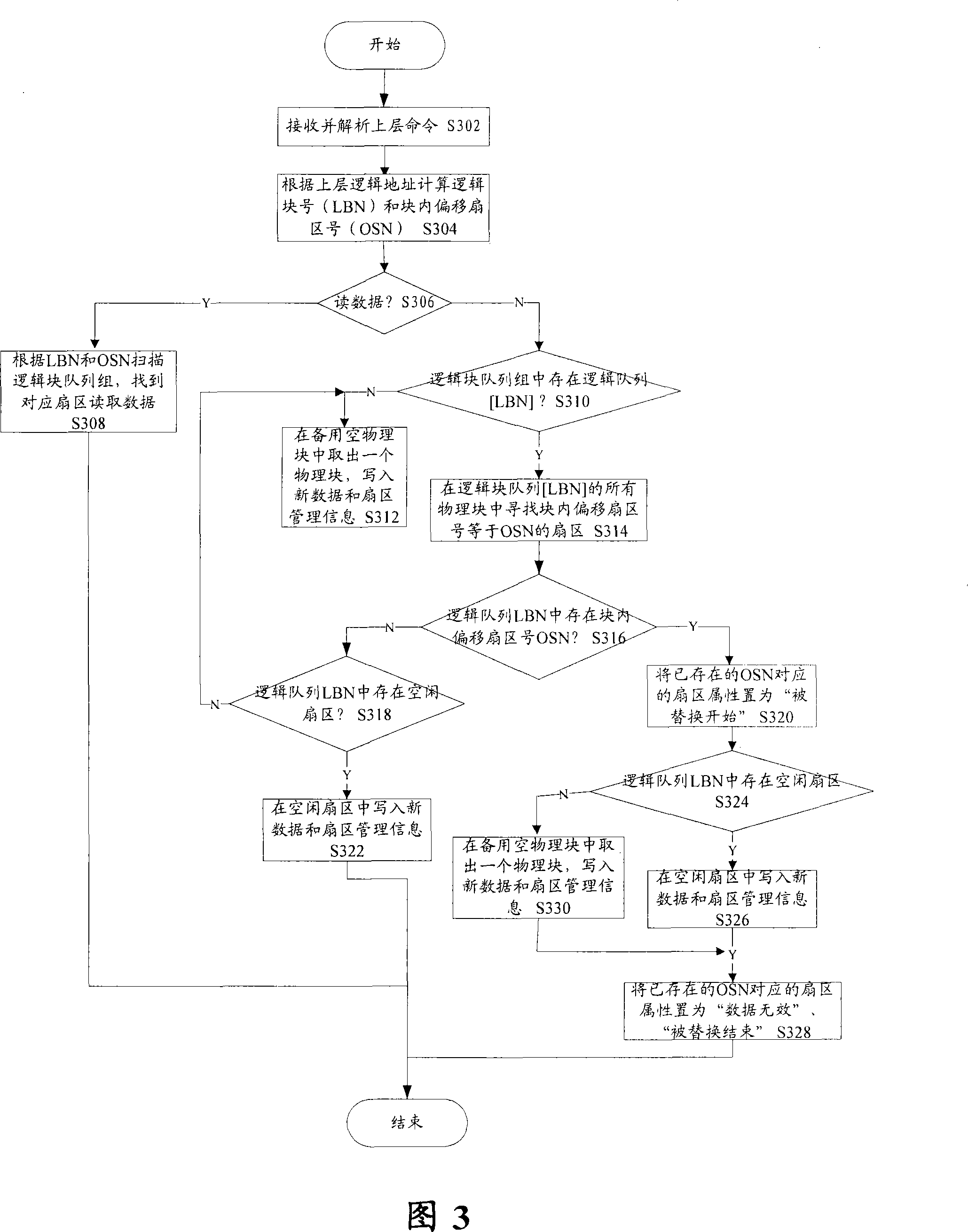

Method for processing data of flash memory equipment

InactiveCN101231617ASimplify the logical address mapping relationshipExtended service lifeMemory adressing/allocation/relocationRead-only memoriesData stabilityLogic mapping

The invention provides a data processing method for a flash memory device. The method comprises the following steps that: step S102, the flash memory device is scanned during the initialization, a logical block queue group and a spare empty physical block queue are established in a host computer, the logical block queue group is formed by queues composed of physical blocks with the same logical block number, and the spare empty physical block queue is composed of physical blocks with empty data spaces, in which data can be written; step S 104, the corresponding logical block queue group is searched by utilizing the logical block number according to the logical order of an upper-level system, the physical blocks in the logical block queue group are scanned, and the data in the flash memorydevice is processed by dint of the spare empty physical block queue according to the scanning result. Through the technical proposal of the invention, the logical mapping relation is simplified, the efficiency is improved, the data stability is ensured, and the service life of the flash memory is prolonged.

Owner:ZTE CORP

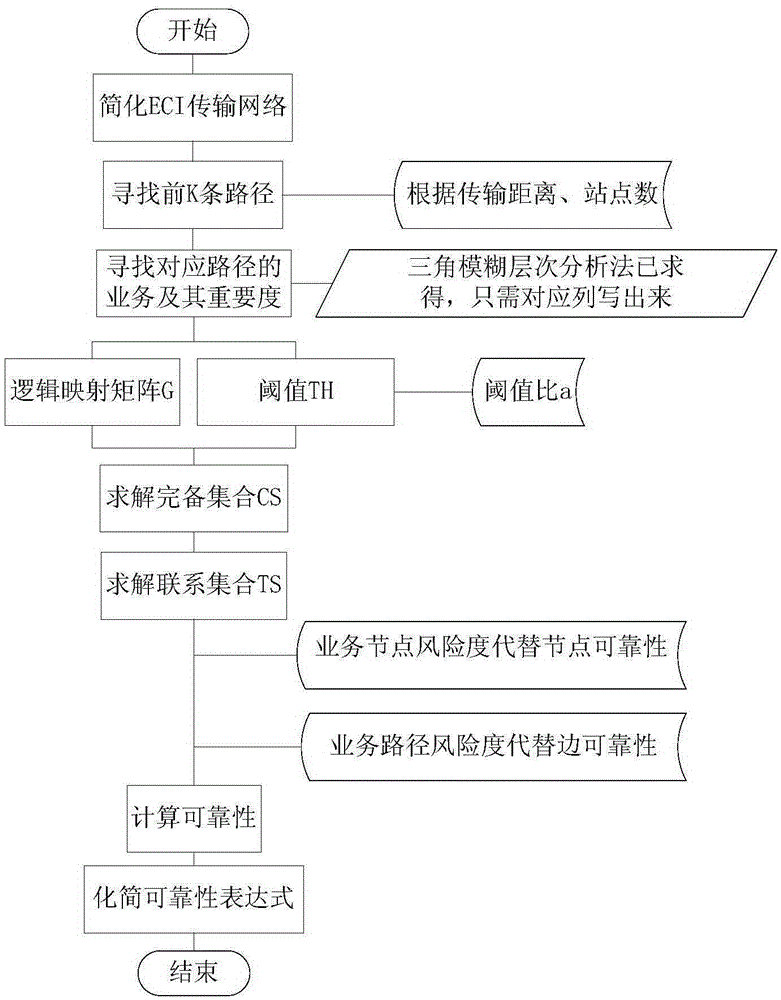

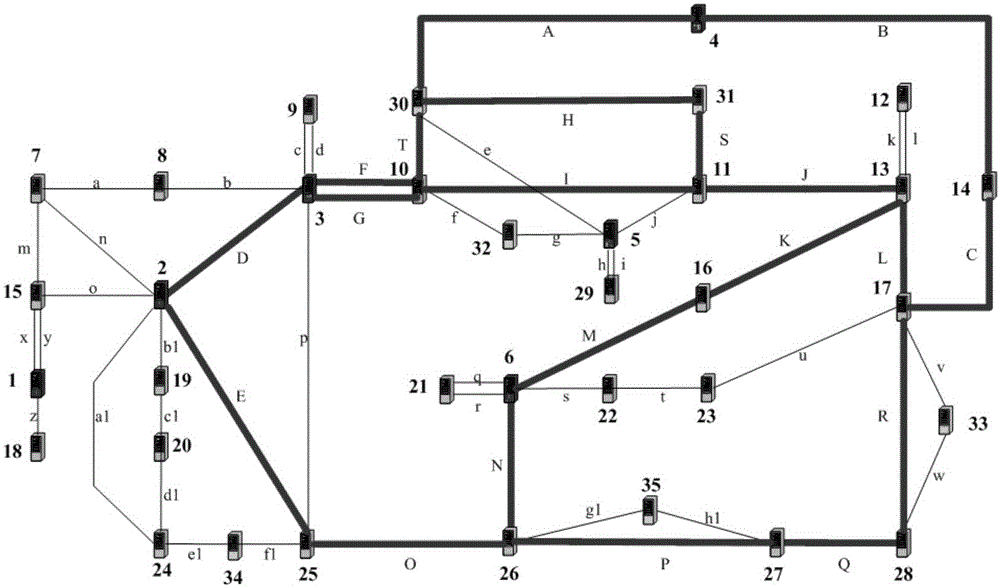

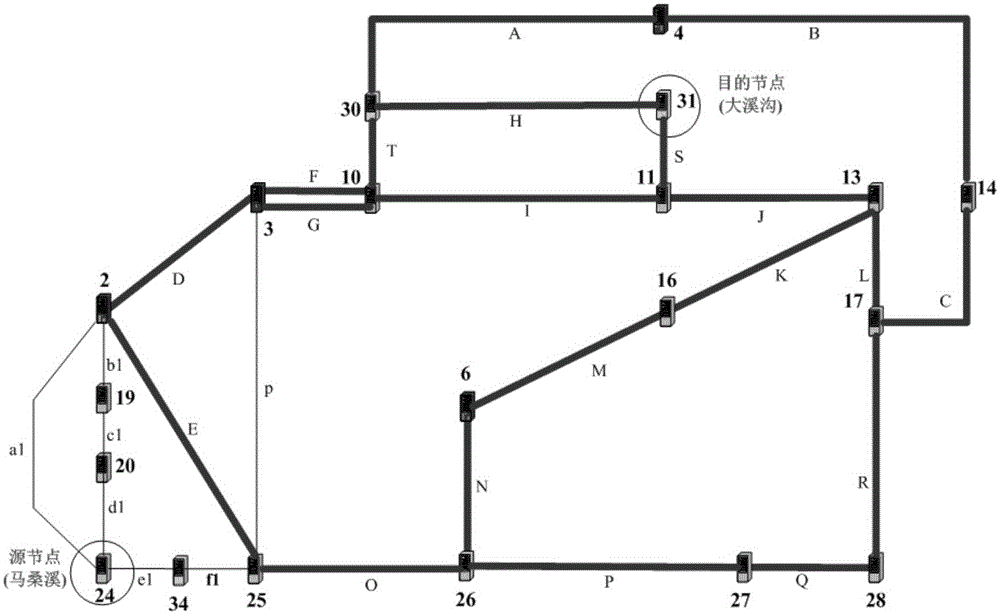

Electric power communication service routing assignment method based on service importance

ActiveCN105306364AMeet reliability requirementsData switching networksElectric powerDistributed computing

The invention discloses an electric power communication service routing assignment method based on service importance. The method comprises the following steps of: S1, performing network simplification for an electric power communication routing network, setting a source node and a target node, seeking K paths according to different circuit transmission paths, and setting corresponding importance for each path, wherein K is not less than 1; S2, obtaining a logic mapping matrix G and a threshold value TH according to an electric power communication routing network reliability analysis model; S3, seeking a complete set CS and a touch set TS according to the logic mapping matrix G and the threshold value TH; S4, substituting node reliability with service node risk degree, meanwhile, substituting edge reliability with service path risk degree, finally, calculating a numerical value of reliability, and thereby obtaining an optimal path of the electric power communication routing network.

Owner:STATE GRID CORP OF CHINA +2

Hybrid nanotube/CMOS dynamically reconfigurable architecture and an integrated design optimization method and system therefor

InactiveUS8117436B2EfficiencyLong latencySolid-state devicesDigital computer detailsLinear temporal logicEngineering

A hybrid nanotube, high-performance, dynamically reconfigurable architecture, NATURE, is provided, and a design optimization flow method and system, NanoMap. A run-time reconfigurable architecture is provided by associating a non-volatile universal memory to each logic element to enable cycle-by-cycle reconfiguration and logic folding, while remaining CMOS compatible. Through logic folding, significant logic density improvement and flexibility in performing area-delay tradeoffs are possible. NanoMap incorporates temporal logic folding during the logic mapping, temporal clustering and placement steps. NanoMap provides for automatic selection of a best folding level, and uses force-direct scheduling to balance resources across folding stages. Mapping can thereby target various optimization objectives and user constraints. A high-density, high-speed carbon nanotube RAM can be implemented as the universal memory, allowing on-chip multi-context configuration storage, enabling fine-grain temporal logic folding, and providing a significant increase in relative logic density.

Owner:QUEENS UNIV OF KINGSTON +1

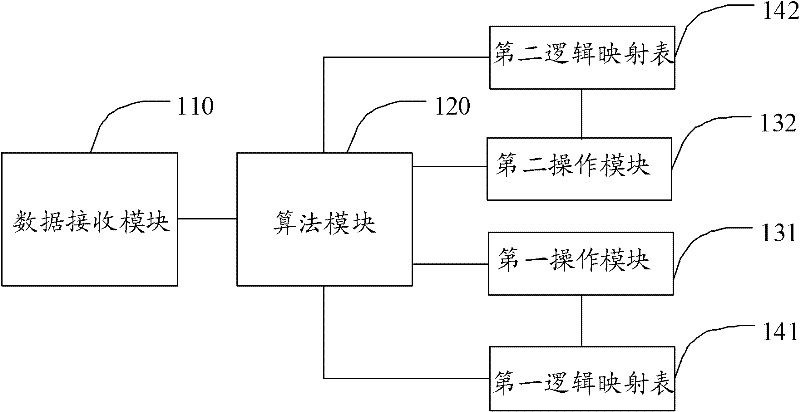

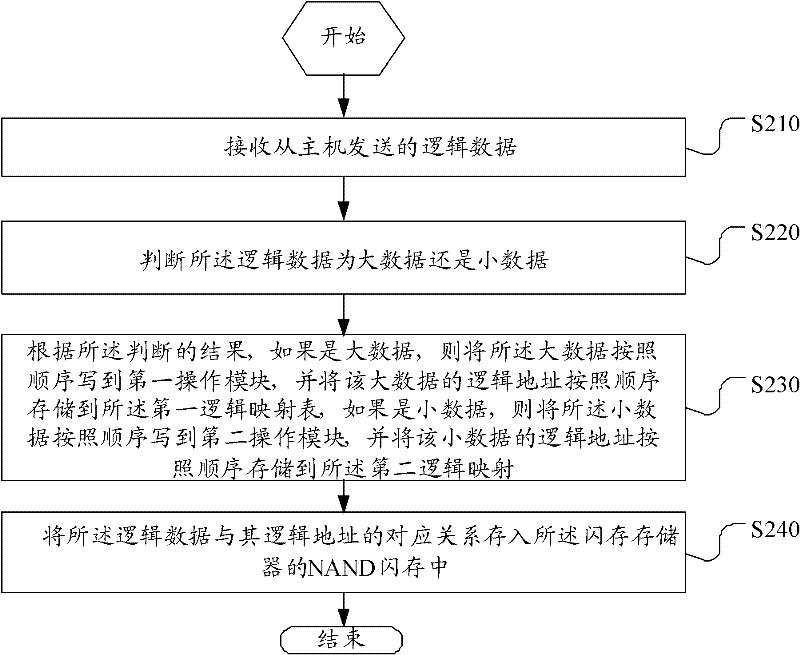

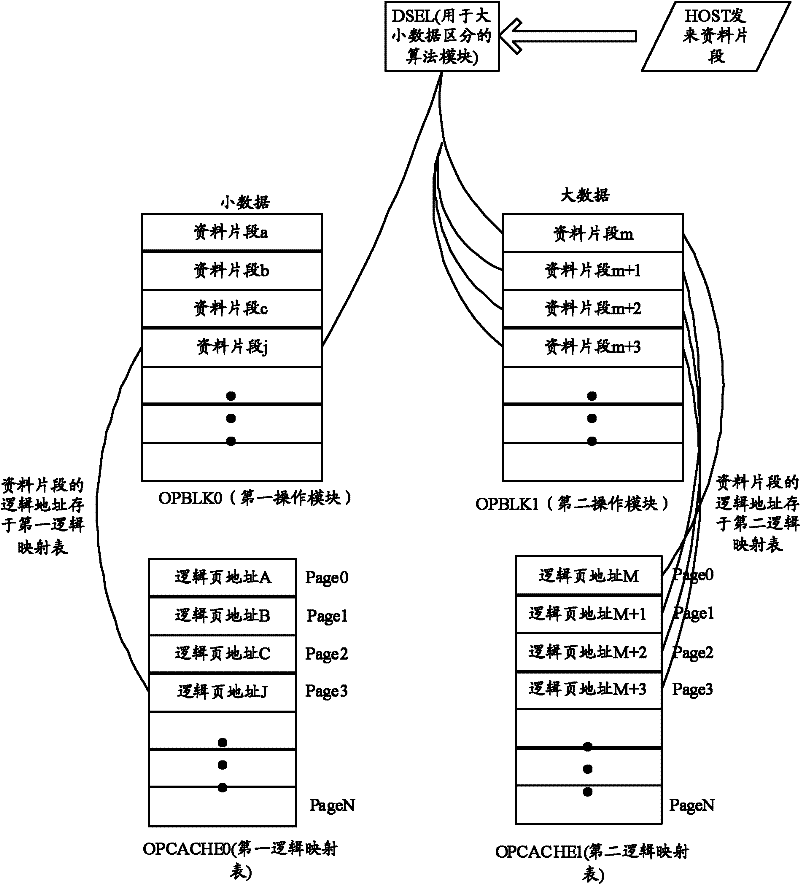

Flash memory and data receiving method thereof

ActiveCN102541755AImprove the efficiency of storing discontinuous logical dataImprove efficiencyMemory adressing/allocation/relocationRandom access memorySmall data

The invention relates to a flash memory and a data receiving method thereof. The flash memory is provided a first operation module and a second operation module; and the random-access memory (RAM) of the flash memory is provided with a first logic mapping table and a second logic mapping table. The method comprises: receiving logic data sent by master and slave computers; judging whether the logic data are big data or small data; and if the logic data are big data, writing the big data into the first operation module according to a sequence and storing the logic address of the big data into the first logic mapping table according to a sequence, or if the logic data are small data, writing the small data to a second operation module according to a sequence, storing the logic address of the small data into the second logic mapping table according to a sequence, and storing the corresponding relationship between the physical address of the logic data and the logic address of the logic data into the not and (NAND) flash of the flash memory. The flash memory and the data receiving method avoid preparing and transferring the logic data and improve the efficiency of the storage of discontinuous logic data.

Owner:SLICONGO MICROELECTRONICS INC

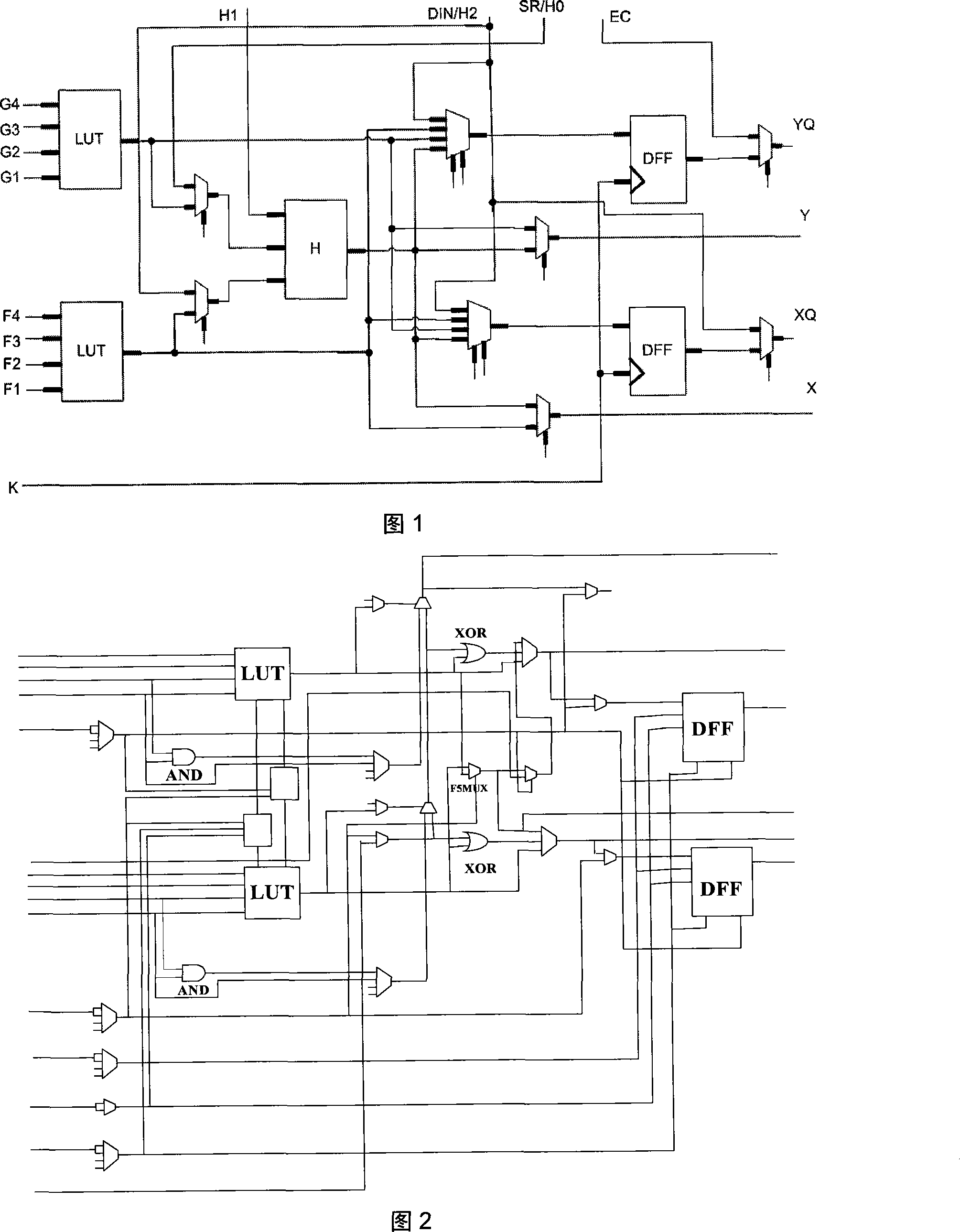

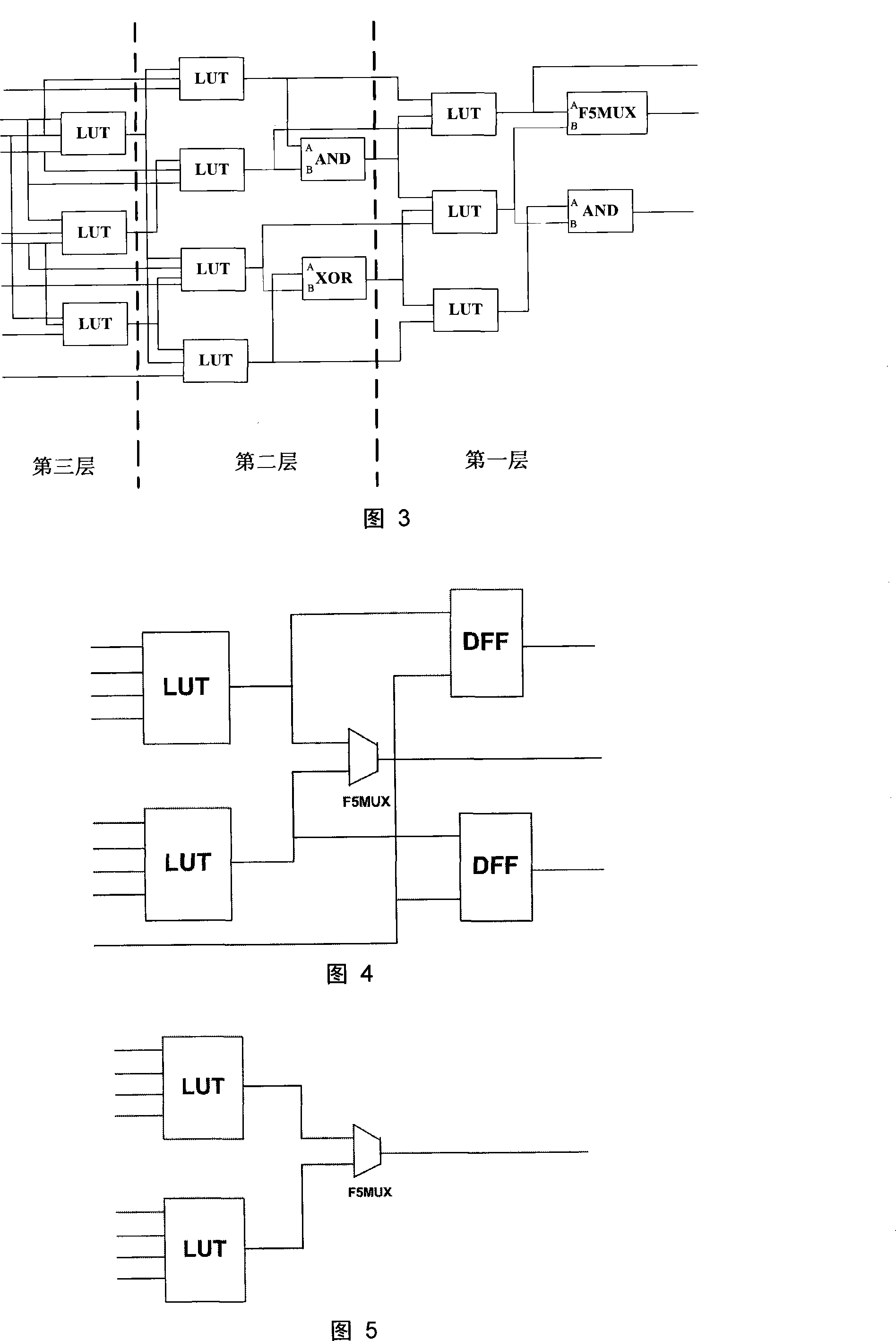

Programmable logic device fast logical block mapping method

InactiveCN101246511AReduce usageIncrease profitSpecial data processing applicationsHardware structureExtensibility

The invention relates to a rapid logic mapping method for FPGA, belonging to the electronic technique field. A demixing and classification mapping to a programmable logic unit is raised to reduce the complexity of algorithm, a match degree coefficient is introduced to enhance the performance of the algorithm, and then a high performance rapid logic mapping method for FPGA is obtained. Experimental data show that the performance of the invention is enhanced by 12.59 percent compared to the conventional figure matching with the structure mapping algorithm, the complexity of algorithm is decreased largely from O(m) down to O(m), the invention can be widely applied in logic unit structure mapping for artery FPGA in modern times, the extendibility of FPGA logic unit mapping module in the operating efficiency and algorithm of the entire FPGA CAD flow is enhanced largely. The high performance rapid FPGA logic unit mapping method can also conduct the design of the FPGA programmable logic unit hardware structure, so that the structure advantages and disadvantages of the programmable logic unit can be estimated by the hardware design engineer before making chips, the design period is shortened largely, the success rate of a new device is increased, the design cost is saved.

Owner:FUDAN UNIV

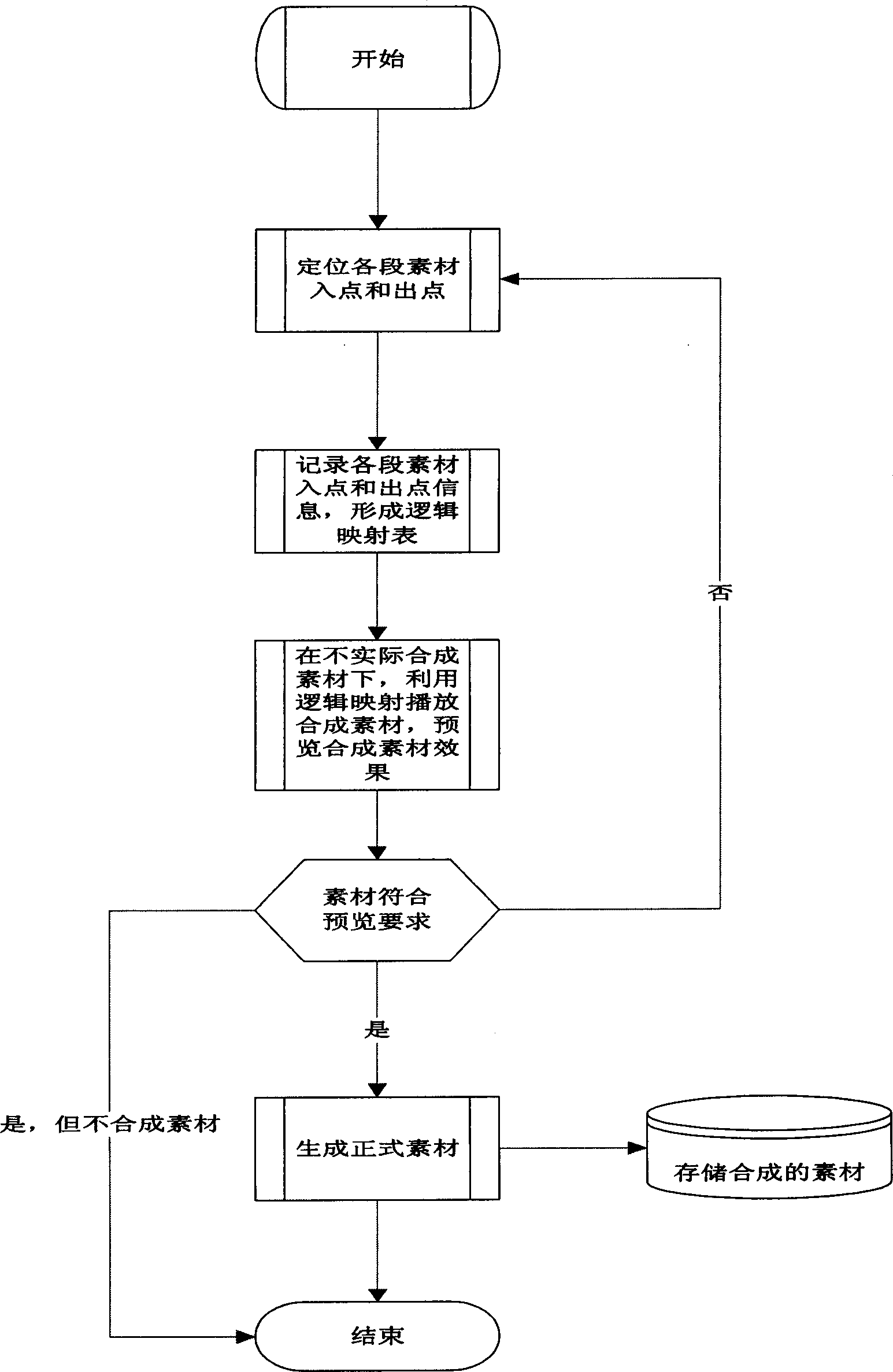

Video frequency source material synthesizing method

ActiveCN1812550AHigh synthesis efficiencyEasy to modifyTelevision system detailsCarrier editingMagnetic tapeSource material

A method for synthesizing video material includes utilizing control property of video server to record entrance point and exit point of material positioning and to map them to be logic mapping table for realizing logic synthesized effect, only modifying entrance point and exit point information on logic mapping table when material is required to be modified.

Owner:BEIJING FOUNDER ELECTRONICS CO LTD +1

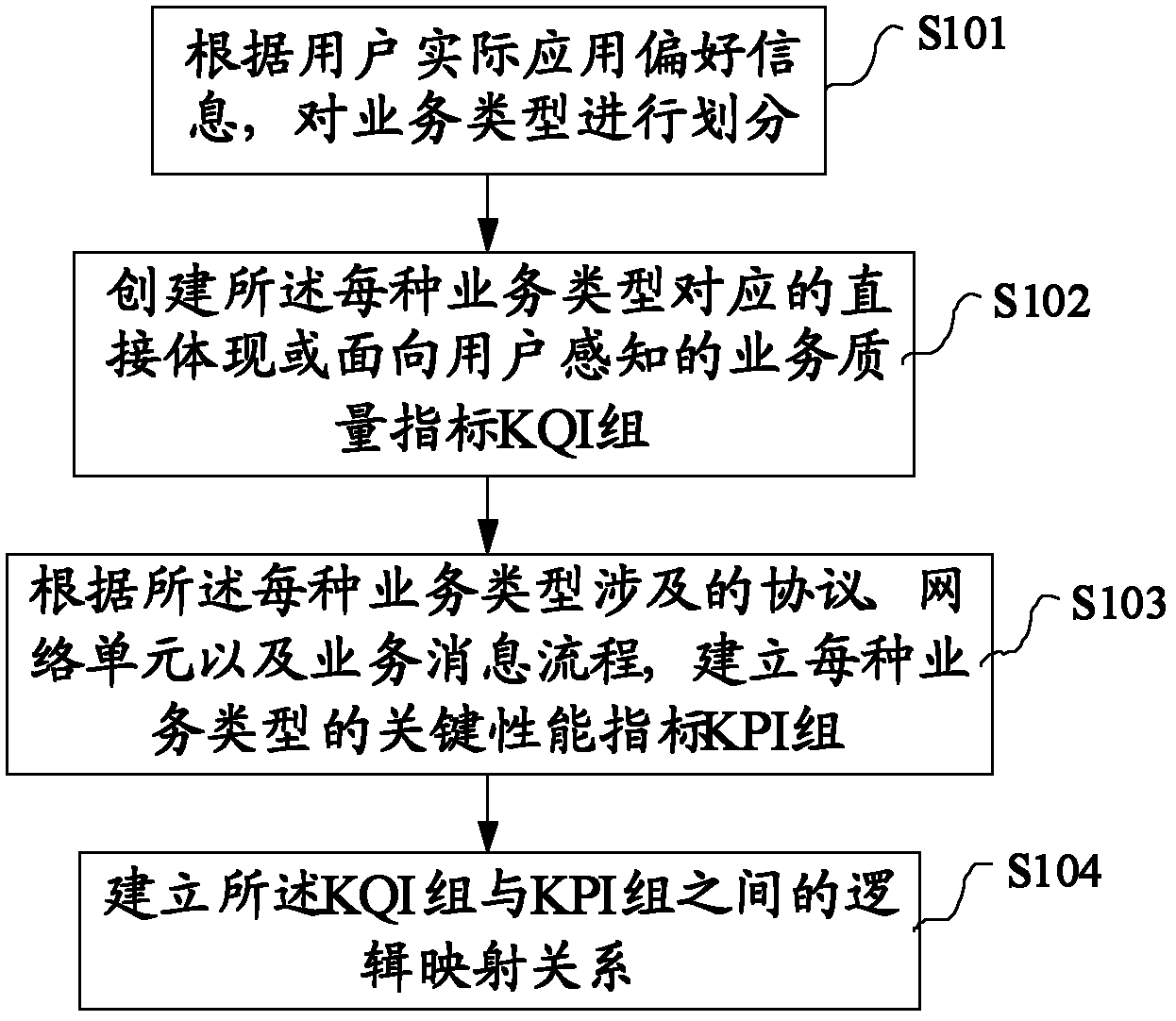

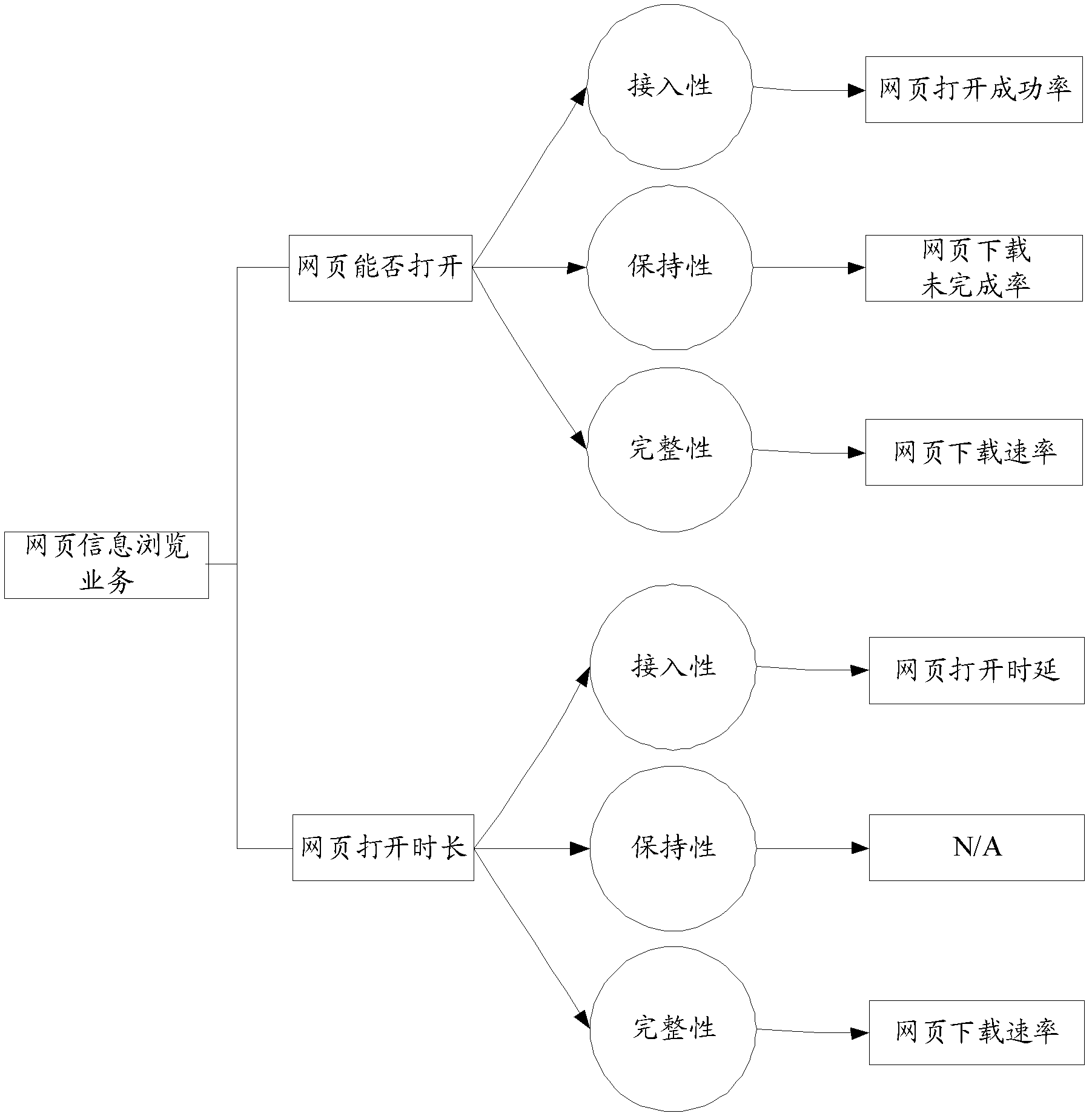

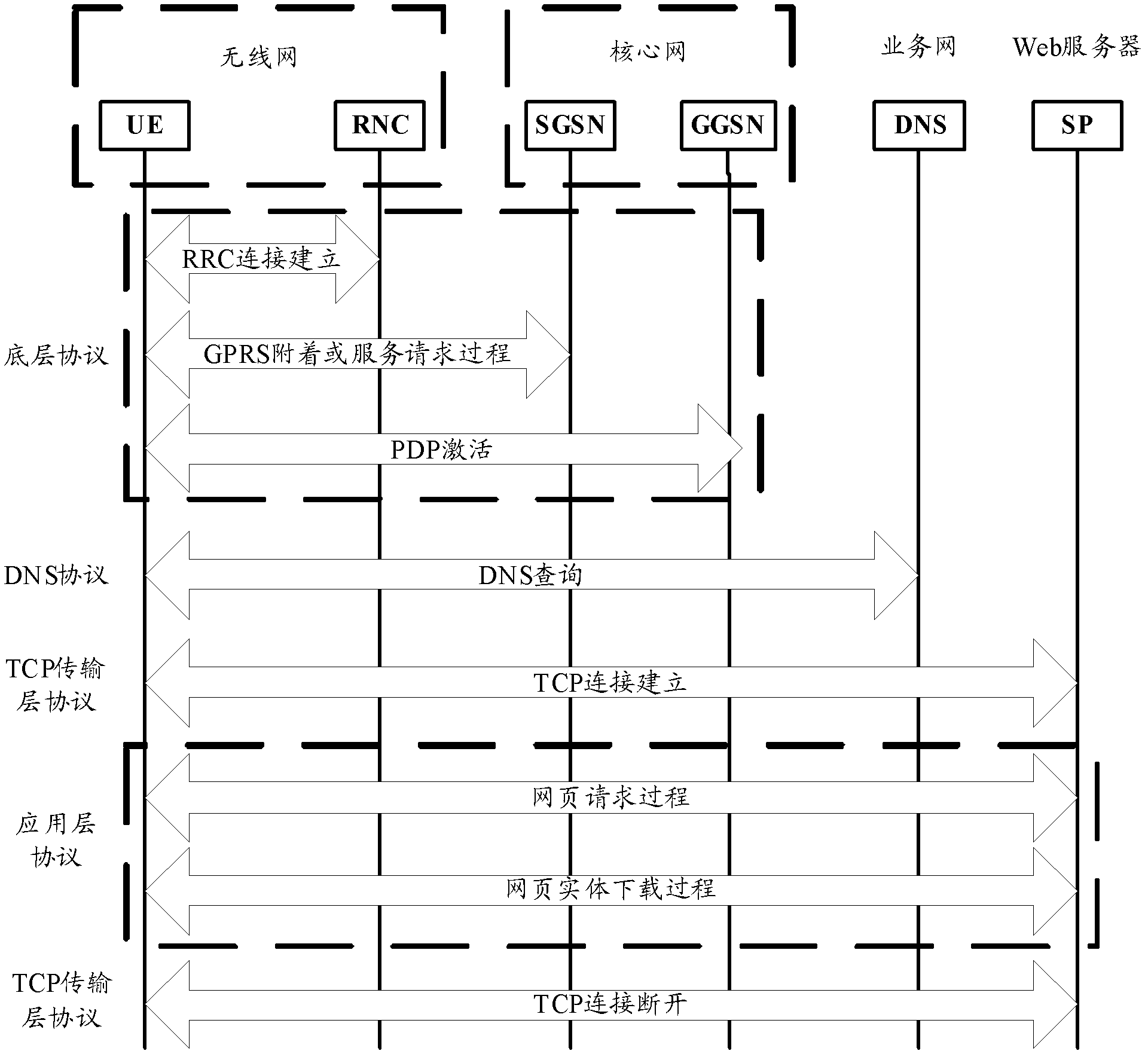

Method and system for constructing communication service quality evaluation system

ActiveCN103024793AEffectively reflect perceptionPerformance reflectionWireless communicationMessage flowUser perception

The invention discloses a method and a system for constructing a communication service quality evaluation system, wherein the method comprises the steps of: according to practical application preference information of users, dividing service types; establishing a KQI (Key Quality Indicator) group (directly showing or facing user perception) corresponding to each service type; according to a protocol, a network unit and service message flow related to each service type, establishing the KPI (Key Performance Indicator) group of each service type; and establishing a logic mapping relation between the KQI group and the KPI group. The service quality evaluation system constructed by the method not only can effectively reflect the user perception, but also can well reflect performances of a whole network and construction units of the whole network.

Owner:ZTE CORP

Method and device for avoiding repeated storage of content in distributed cache cooperation

ActiveCN104901996AReduce traffic between domainsReduce trafficTransmissionTraffic capacityDistributed cache

The invention discloses a method for avoiding repeated storage of content in distributed cache cooperation. The method comprises the steps as follows: using a binary identifying method to perform binary identification on content data blocks; establishing two-level logic mapping tables based on the binary identification of the content data blocks to organize caching content, and performing cache cooperation on the caching content based on distributed Hash operation; receiving a request for a certain content data block from the external by an edge content router, forwarding the request to an internal node which is in charge of storing the content via two-stage routing, transmitting the data block with the node which is in charge of the corresponding content data block to the edge content router, and updating cache replacement control state information of corresponding items of the two-level mapping tables; and receiving a certain data block from the external by the edge content router, forwarding the data block to an internal node which is in charge of storing the content through two-stage routing, and establishing corresponding two-level mapping relationships in the routing forwarding process.. The method of the invention could avoid repeated storage of the content, thereby reducing network flow and improving user experience.

Owner:NANJING NORMAL UNIVERSITY

Data reconstruction method and system, and memory control circuit unit

The invention provides a data reconstruction method and system, and a memory control circuit unit. The method comprises the steps of reading entity-logic mapping information in a rewritable nonvolatile memory module and time information corresponding to the entity-logic mapping information; sorting the entity-logic mapping information according to the time information corresponding to the entity-logic mapping information; and reconstructing a logic-entity mapping table according to the sorted entity-logic mapping information, and restoring the reconstructed logic-entity mapping table in a buffer memory. When the logic-entity mapping table is disrupted due to damage of the rewritable nonvolatile memory module, the logic-entity mapping table can be reconstructed according to the existing entity-logic mapping information, so that data stored in the rewritable nonvolatile memory module is identified.

Owner:PHISON ELECTRONICS

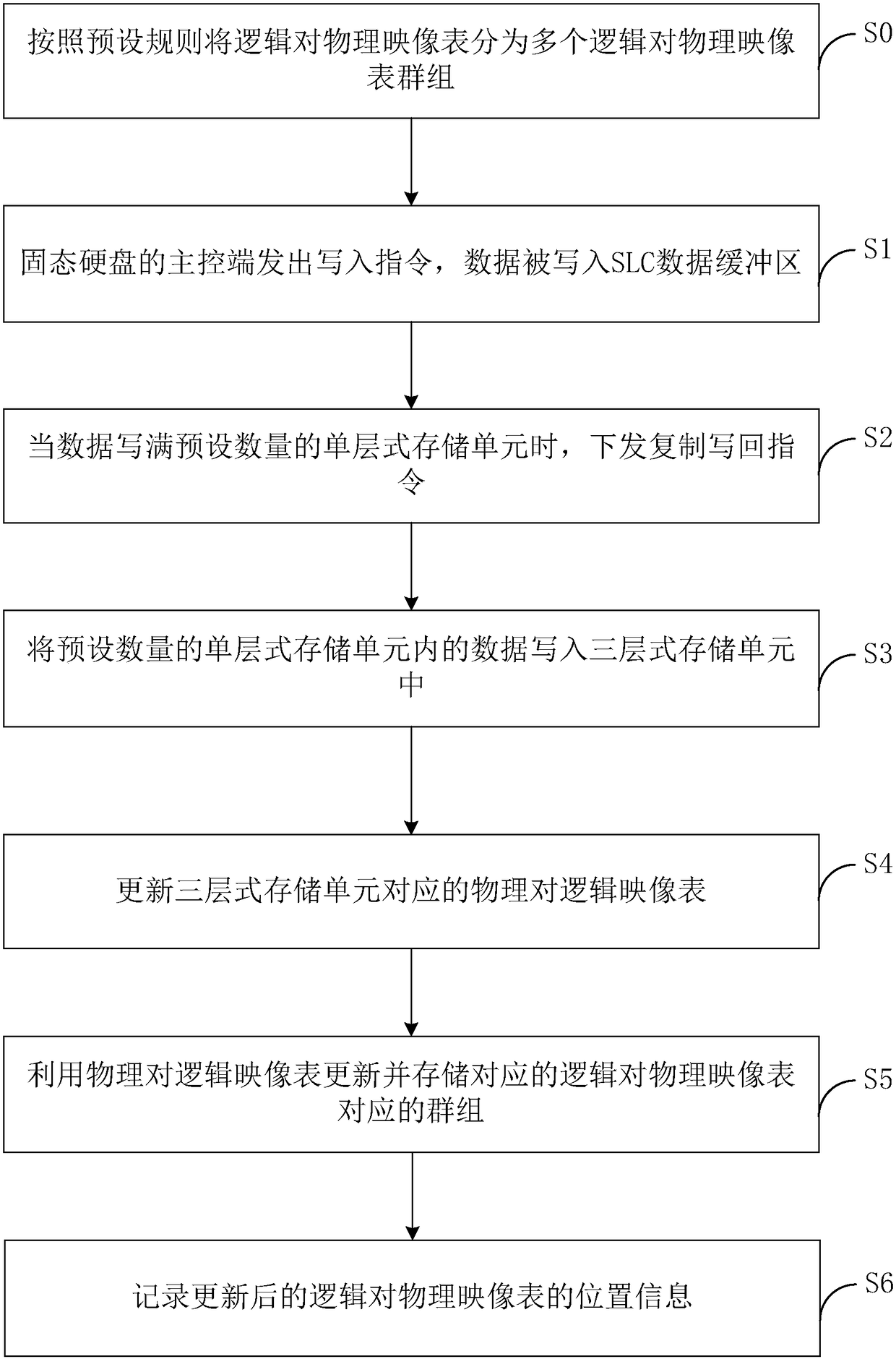

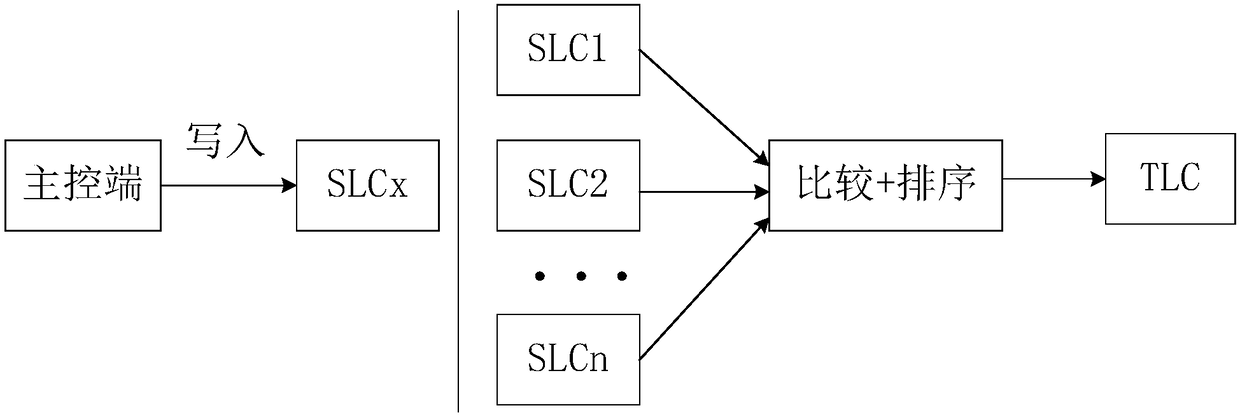

Writing method of TLC NAND FLASH solid-state disk

InactiveCN108733318AImprove access performanceIncrease write speedInput/output to record carriersWaste collectionSolid-state drive

The invention relates to a writing method of a TLC NAND FLASH solid-state disk. The solid-state disk comprises single-layer storage units and a three-layer storage unit. The method comprises the following steps of: S1, giving a writing instruction by a main control end of the solid-state disk and writing data into an SLC data buffer area; S2, when a preset quantity of single-layer storage units isfully written with the data, distributing a copy and write-back instruction; S3, writing the data in the preset quantity of single-layer storage units into the three-layer storage unit; and S4, updating a physical pair logic mapping tale corresponding to the three-layer storage unit. Through implementing the method, the data writing speed of the main control end can be improved, the reading timecan be shortened, the waste collection frequency of the solid-state disk can be decreased and then the access efficacy of the solid-state disk can be improved.

Owner:YEESTOR MICROELECTRONICS CO LTD

Logical map table for detecting dependency conditions between instructions having varying width operand values

Owner:ORACLE INT CORP

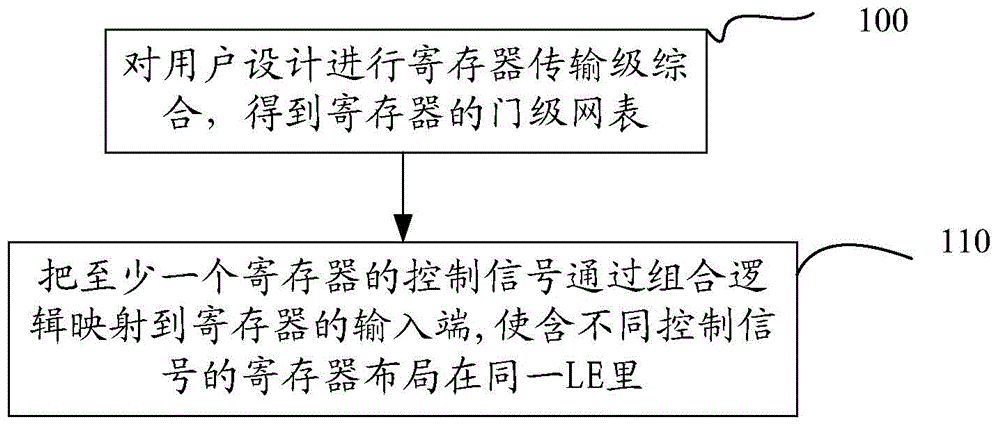

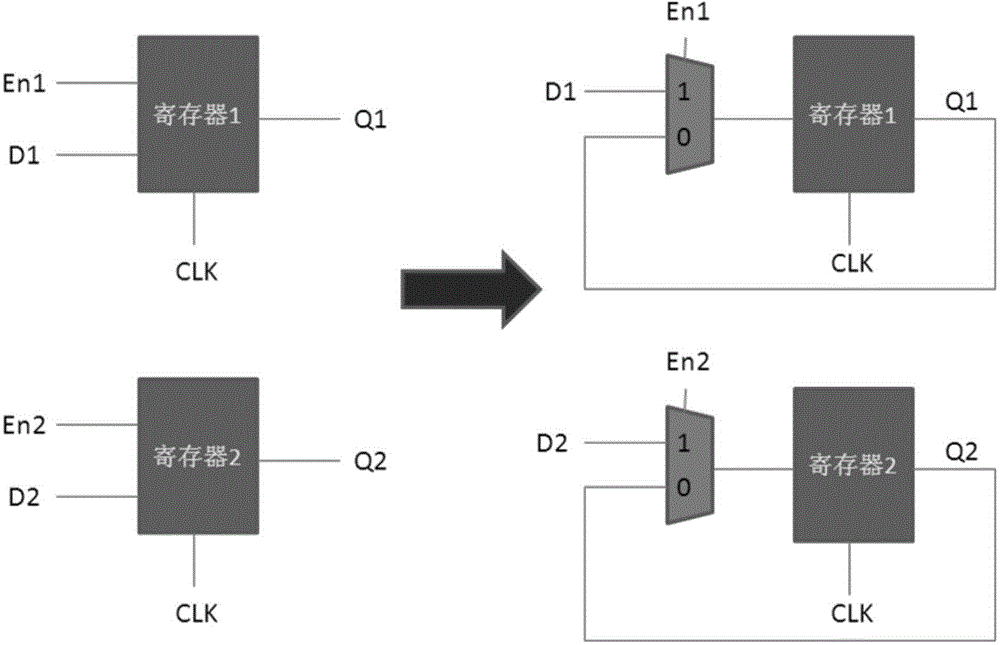

Technological mapping method and integrated circuit for optimizing register control signal

ActiveCN104424367ASolve the resultSolve complexitySpecial data processing applicationsLogic circuitsComputer architectureControl signal

The invention relates to a technological mapping method and an integrated circuit for optimizing a register control signal. The method comprises the following steps of: performing register transport level integration on a user design to obtain a gate level net list of a register; mapping a control signal of at least one register to an input end of the register by virtue of combined logic mapping, so that the register with different control signals is arranged in the same LE. The technological mapping method can be used for enabling the register with multiple independent control signals to arrange in the same PLB, so that the quantity of the independent control signals is lowered, and the wiring success rate is increased.

Owner:CAPITAL MICROELECTRONICS

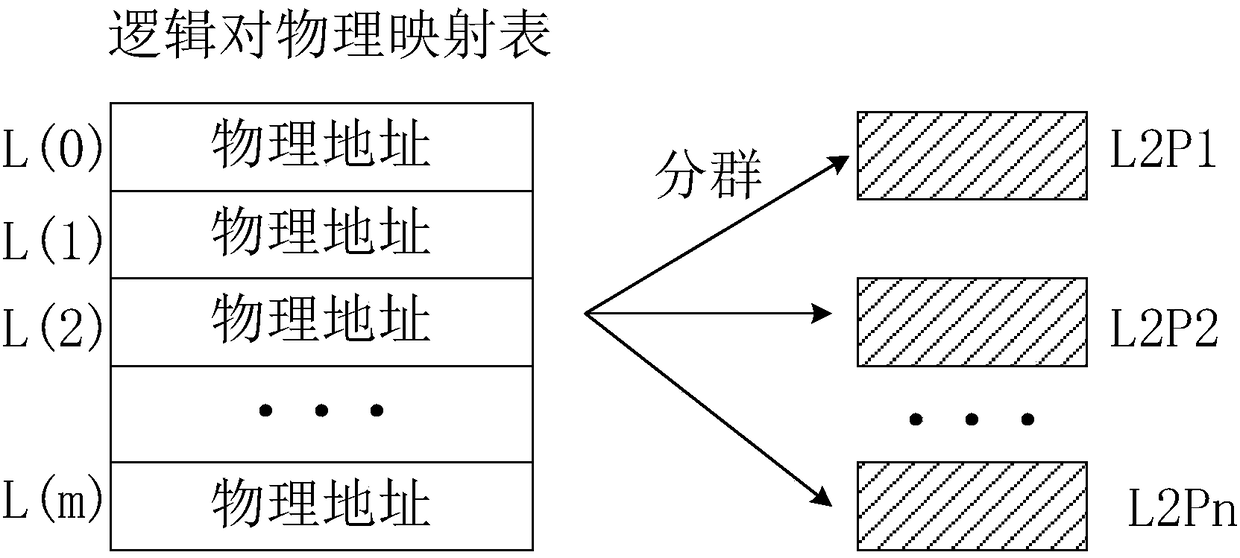

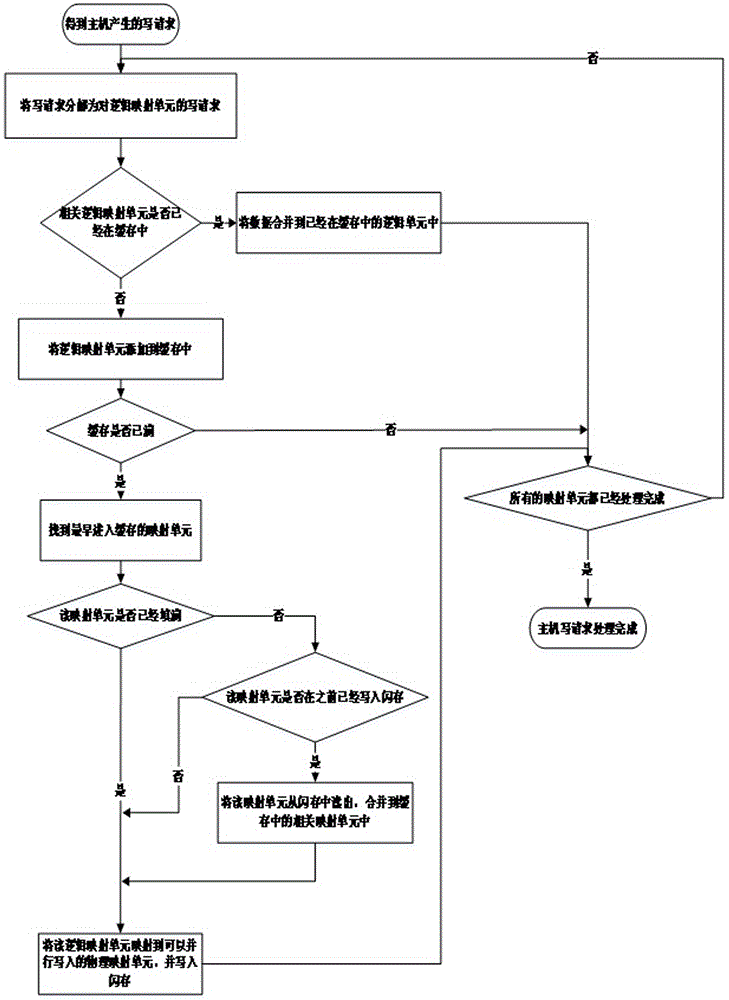

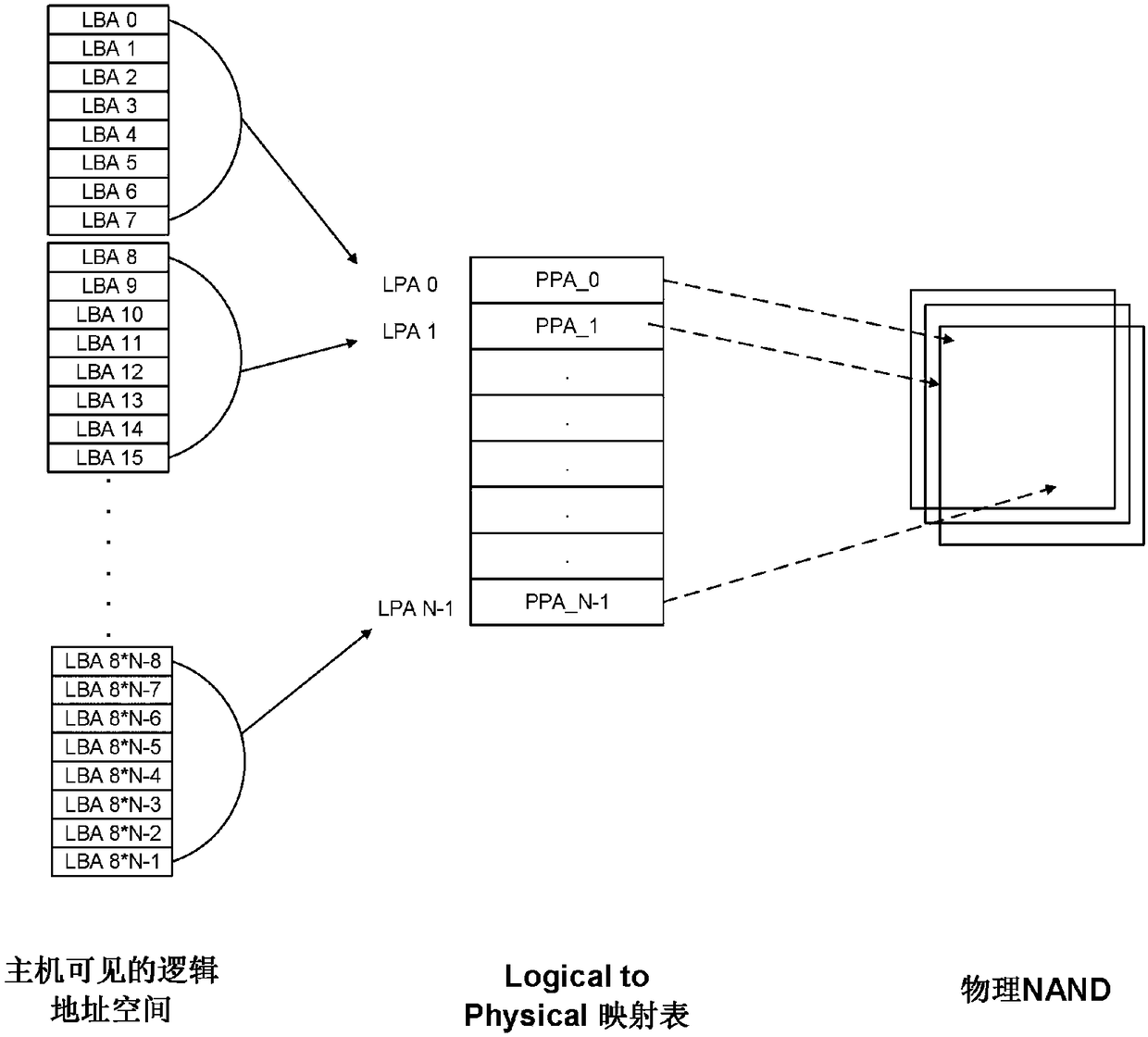

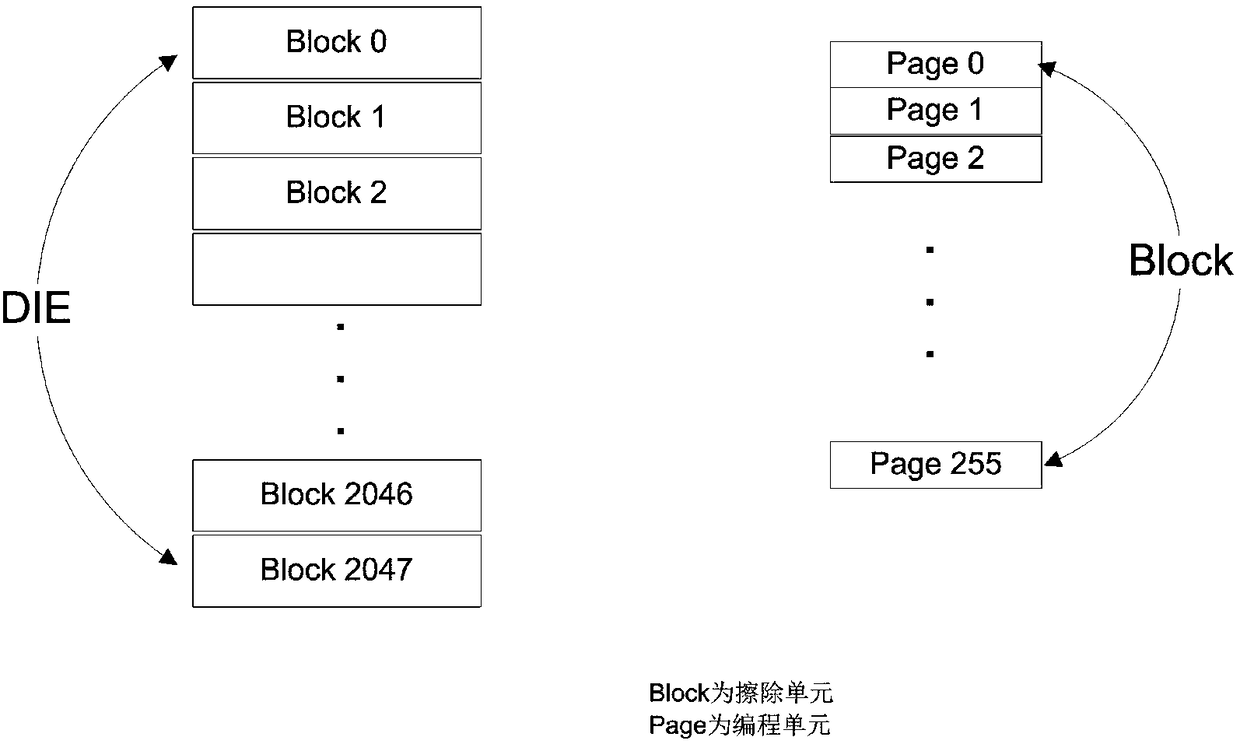

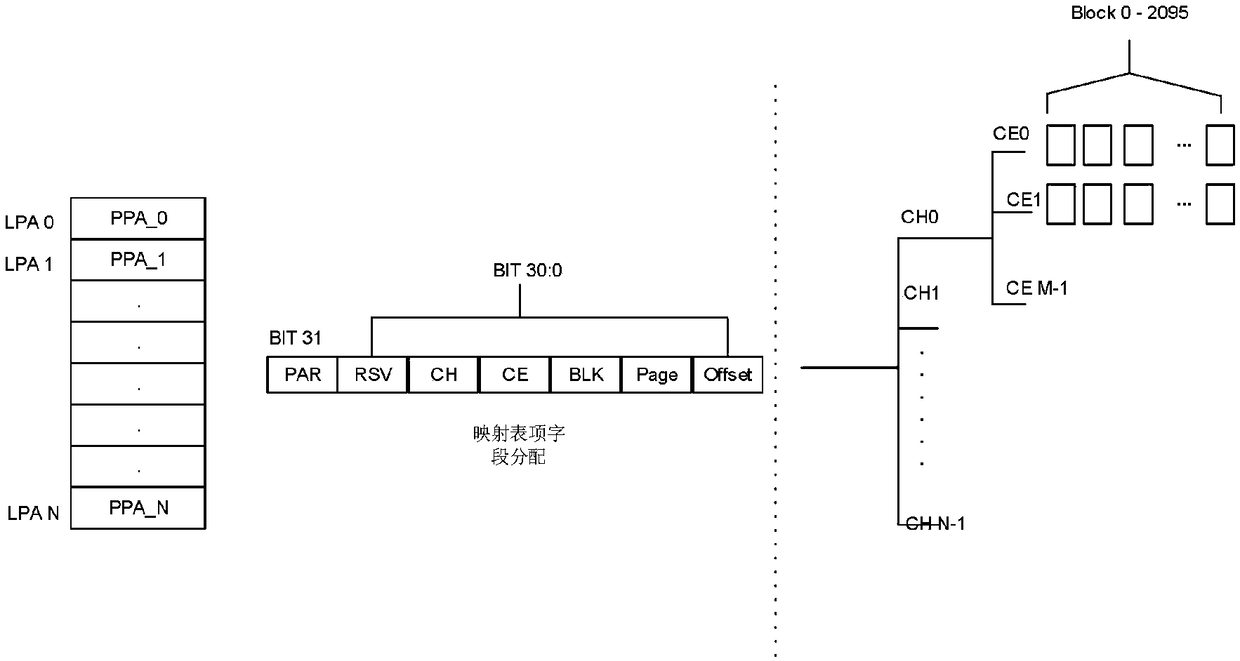

Logical block address-to-physical block address mapping method for high-capacity solid-state disk

ActiveCN106021159AReduce sizeElectric digital data processingComputer architectureLogical block addressing

The invention discloses a logical block address-to-physical block address mapping method for a high-capacity solid-state disk. The method comprises the steps of defining that a logical mapping unit is composed of a plurality of logic blocks; decomposing a write request of a host into a write request for the logical mapping unit; judging whether the logical mapping unit is in a cache or not, adding the logical mapping unit to the cache, and judging whether the cache is full or not; judging whether the logical mapping unit entering the cache at the earliest is written in the cache or not if the cache is full; mapping the logical mapping unit entering the cache at the earliest to a physical mapping unit capable of realizing parallel write, writing the logical mapping unit into a flash memory if the logical mapping unit is not written into the cache; reading the mapping unit from the flash memory if the mapping unit is written into the flash memory previously, combining the mapping unit with the data in the cache, mapping the combined logical mapping unit to the physical mapping unit capable of realizing parallel write, and writing the logical mapping unit into the flash memory. The size of a mapping table is controlled.

Owner:BEIJING KUANGEN NETWORK TECH

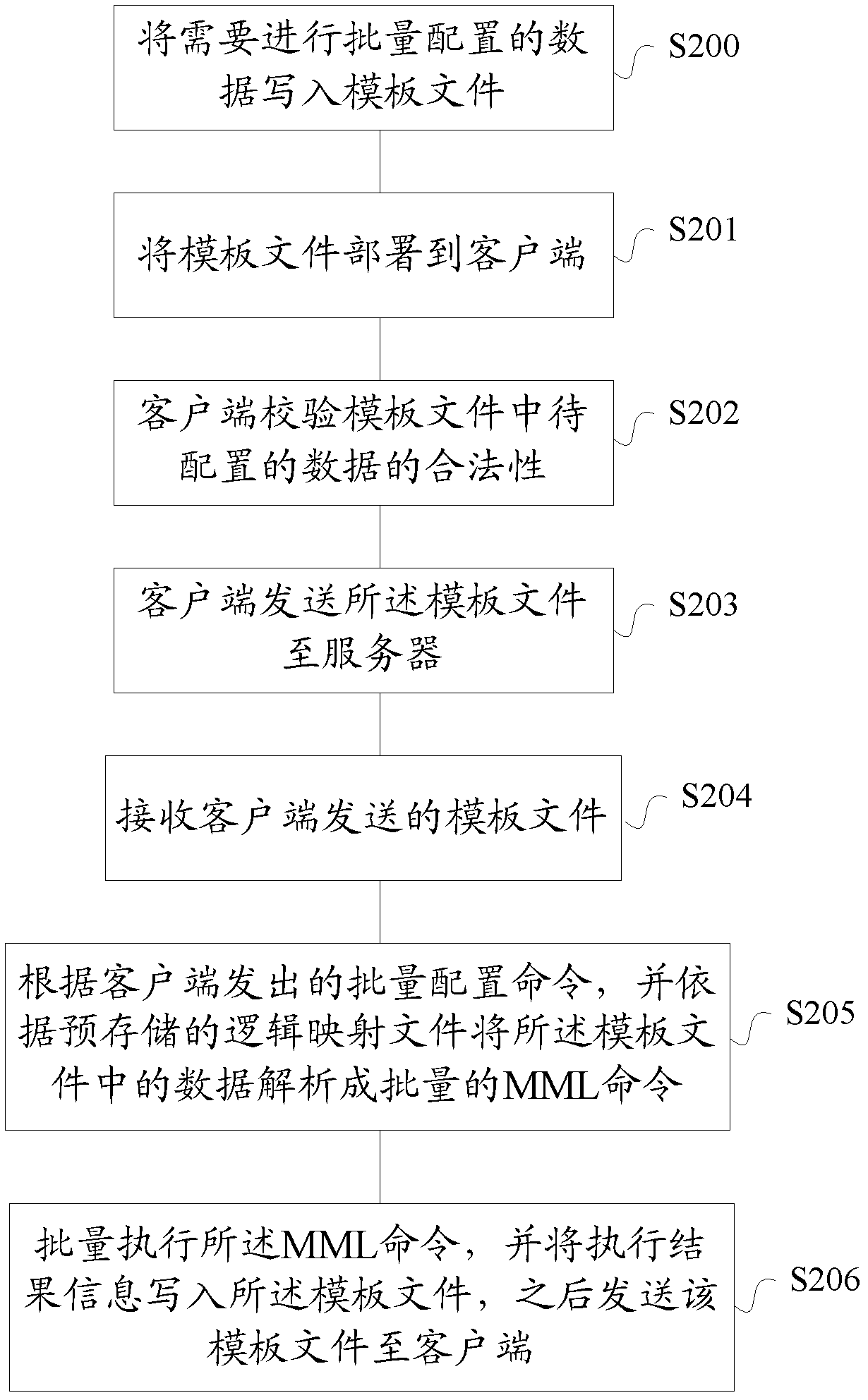

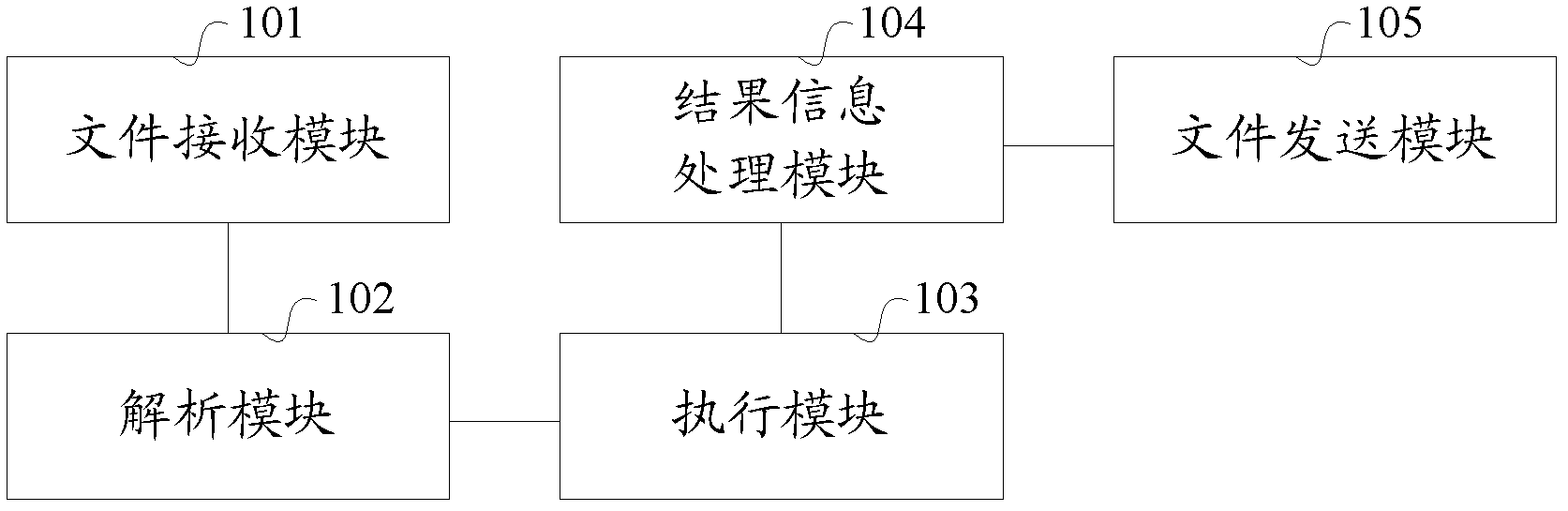

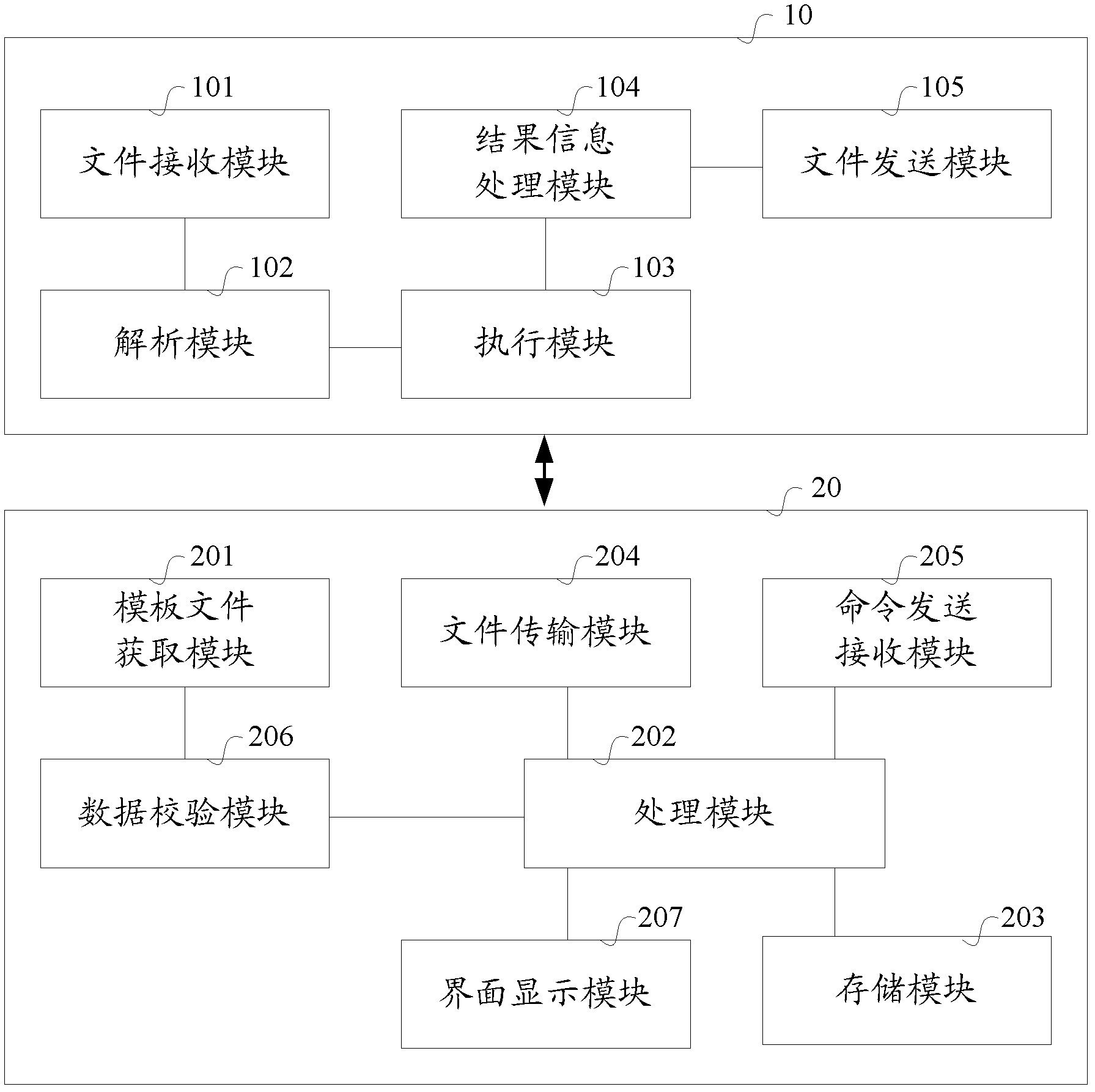

MML-based (man-machine-language-based) method, server and system for configuring large volume data

ActiveCN103001786AFully reuseImprove development efficiencyData switching networksMan machinePaper document

The invention discloses an MML-based (man-machine-language-based) method, server and system for configuring large volume data. The method includes: receiving template document transmitted by a client; analyzing data in the template document into batch MML commands according to a batch configuration command given by the client and prestored logic mapping document; executing the MML commands in batch, writing execution result information into the template document, and transmitting the template document to the client. The template document with written to-be-configured data is analyzed into MML commands for execution according to the prestored logic mapping document, original codes can be fully utilized, development efficiency is improved, and complexity is reduced.

Owner:ZTE CORP

Large-capacity solid state disk mapping method

InactiveCN108255742AImprove access efficiencyAddressing Increased DRAM DemandMemory systemsPhysical spaceTheoretical computer science

The invention discloses a large-capacity solid state disk mapping method. The method is characterized by comprising the steps of dividing a logic address space accessed by a host into N sub logic address spaces same in size; correspondingly dividing a physical space of a solid state disk into N sub physical spaces same in size, which correspond to the sub logic address spaces, wherein N is 2n; separately maintaining a sub logic mapping table for each sub physical space and each sub logic address space; and searching for or updating the corresponding sub logic mapping table according to the sublogic address space which a logic address of the host belongs to during access of the host. By adding a partition mechanism, the mapping table is established for each partition, so that the problem of DRAM demand increment caused by 32bit deficiency of mapping table items is solved, the cost is reduced and the mapping table access efficiency is improved.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

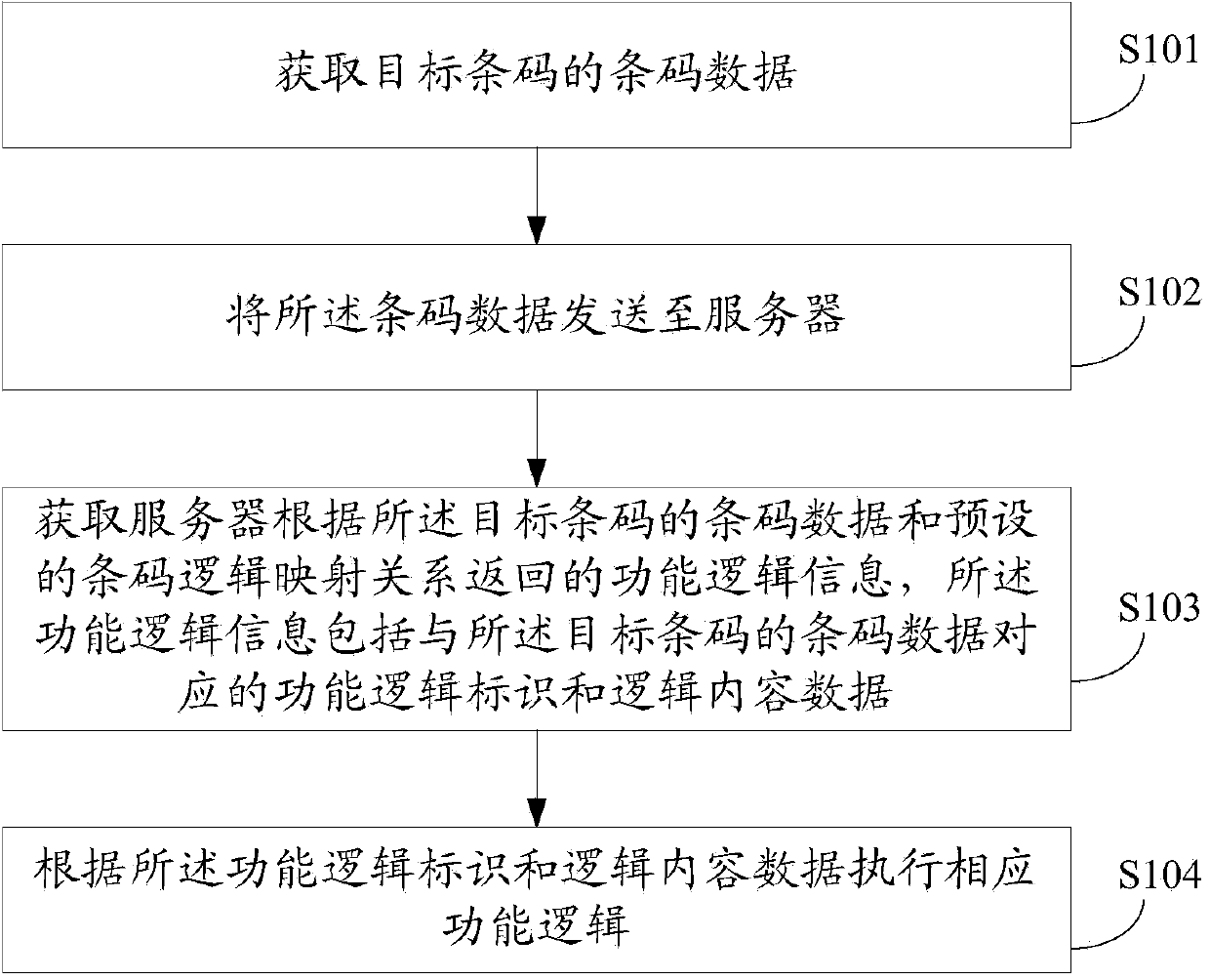

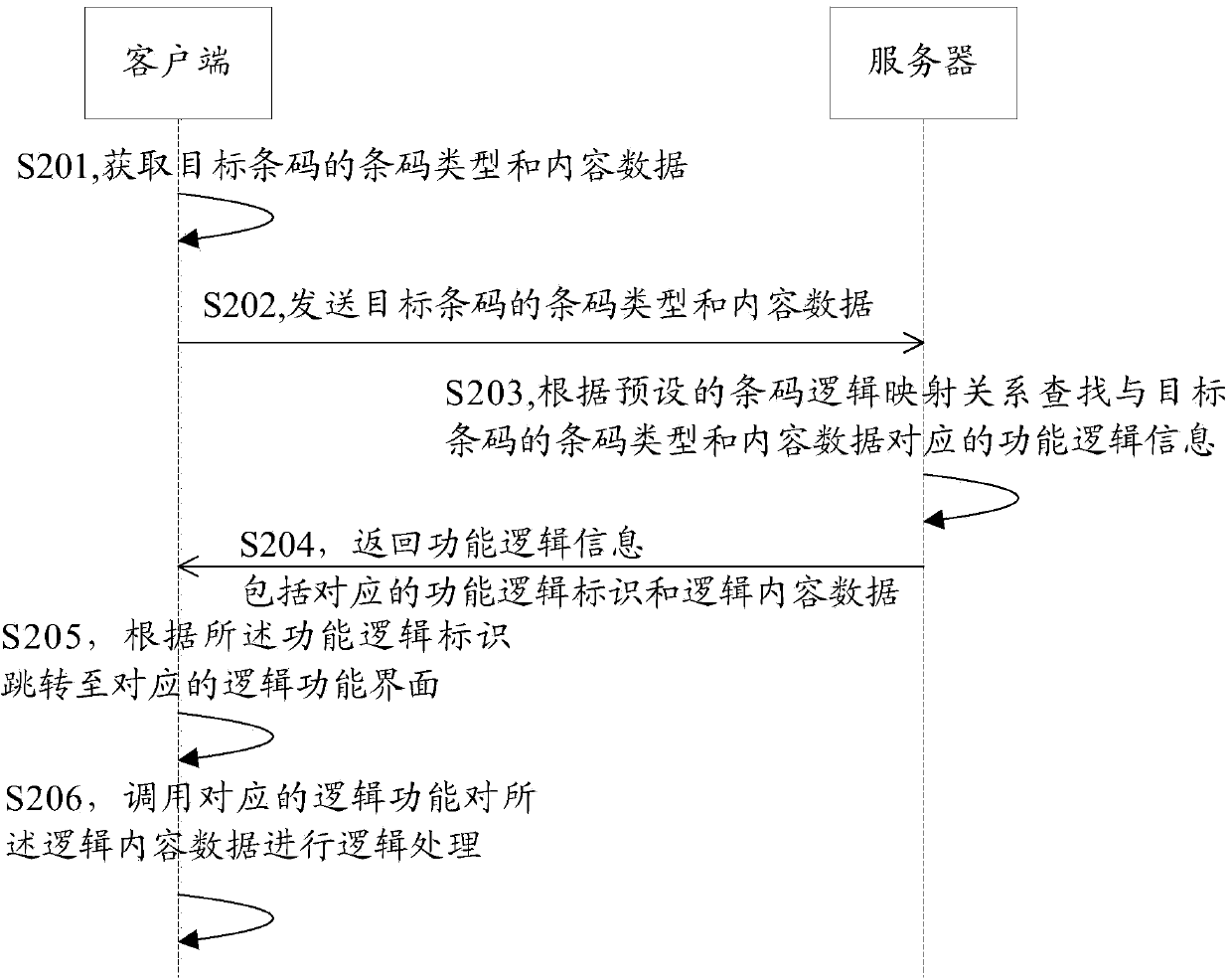

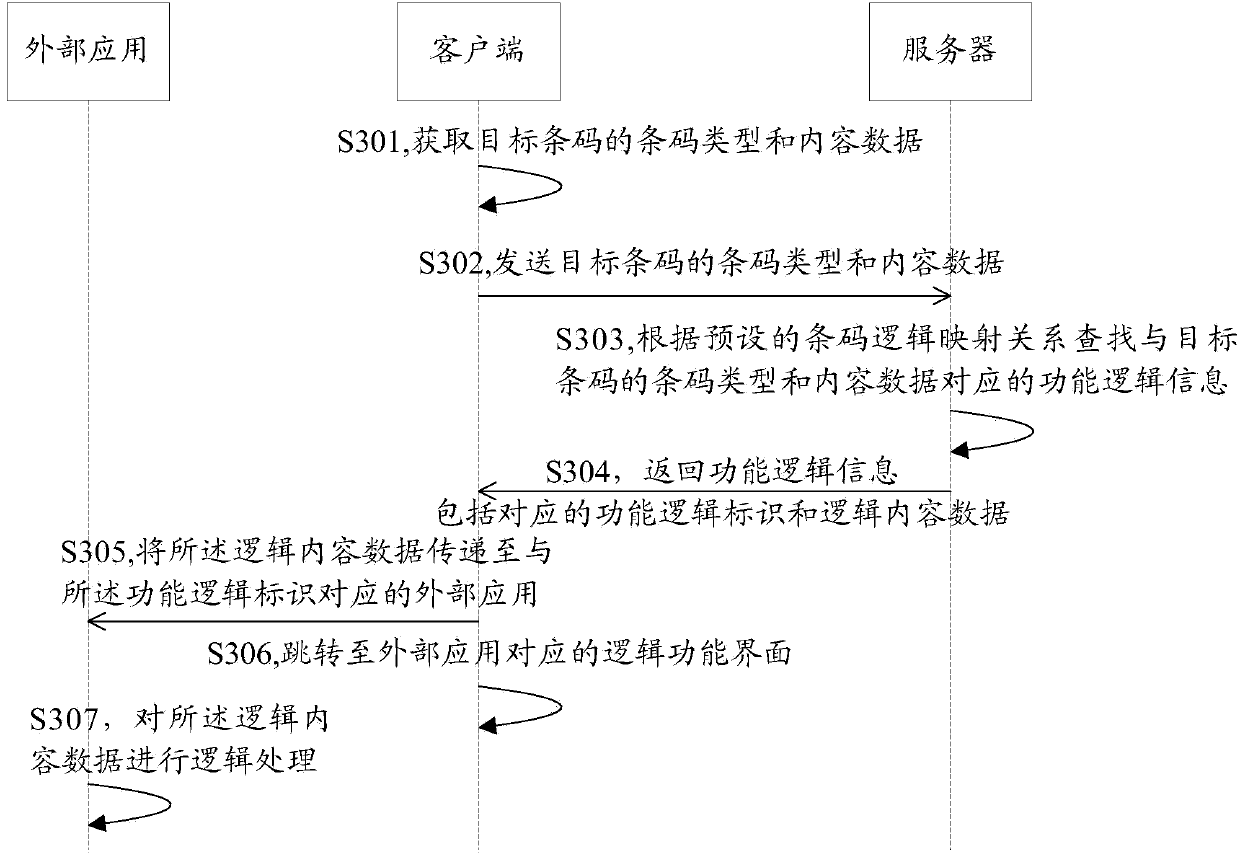

Bar code data-based functional logic jumping method, client and system

ActiveCN104200252AEnhance jump abilityTransmissionRecord carriers used with machinesProgramming languageLogic mapping

The invention discloses a bar code data-based functional logic jumping method, client and system. The bar code data-based functional logic jumping method includes that a client acquires the bar code data of a target bar code, the bar code data of the target bar code comprises the bar code type and content data of the target bar code, and the bar code type comprises one-dimensional code or two-dimensional code; the client sends the bar code data to a server; the client acquires functional logic information returned from the server according to the bar code data of the target bar code and a preset bar code logic mapping relationship, wherein the functional logic information comprises a functional logic mark and logic content data corresponding to the bar code data of the target bar code; the client performs the corresponding functional logic according to the functional logic mark and logic content data. The bar code data-based functional logic jumping method, client and system are capable of reinforcing the bar code jumping ability and effectively widening the bar code application scene and use range.

Owner:TENCENT TECH (SHENZHEN) CO LTD

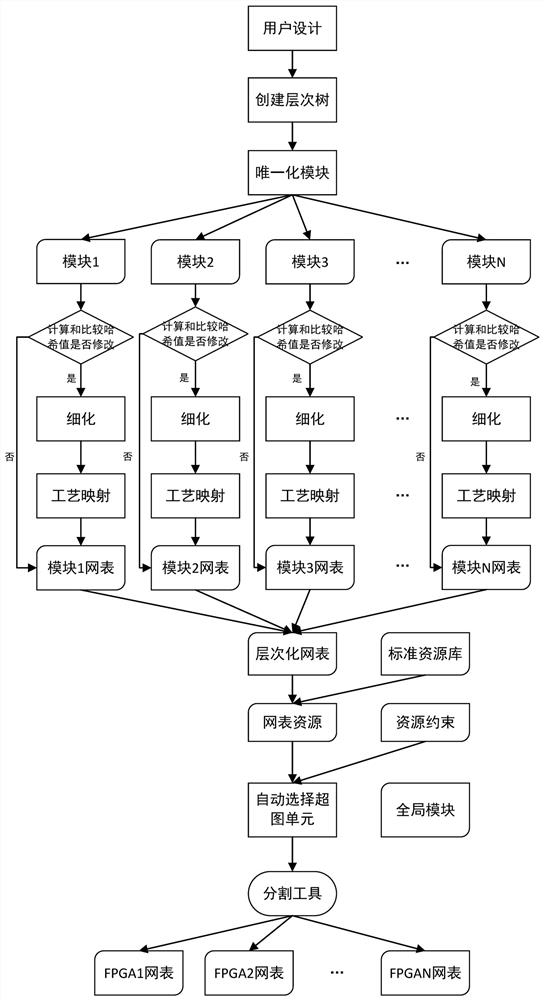

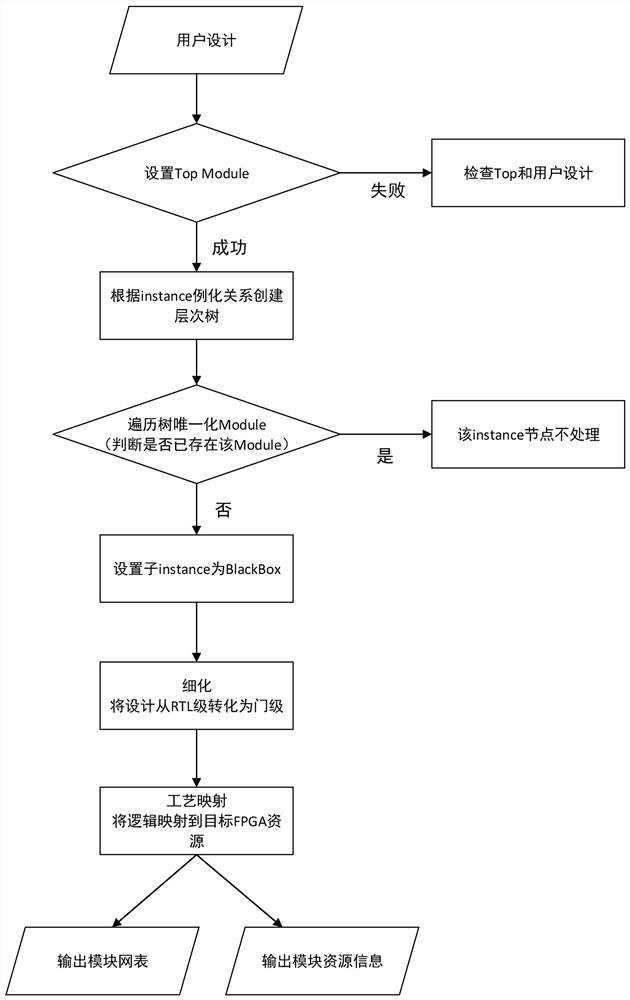

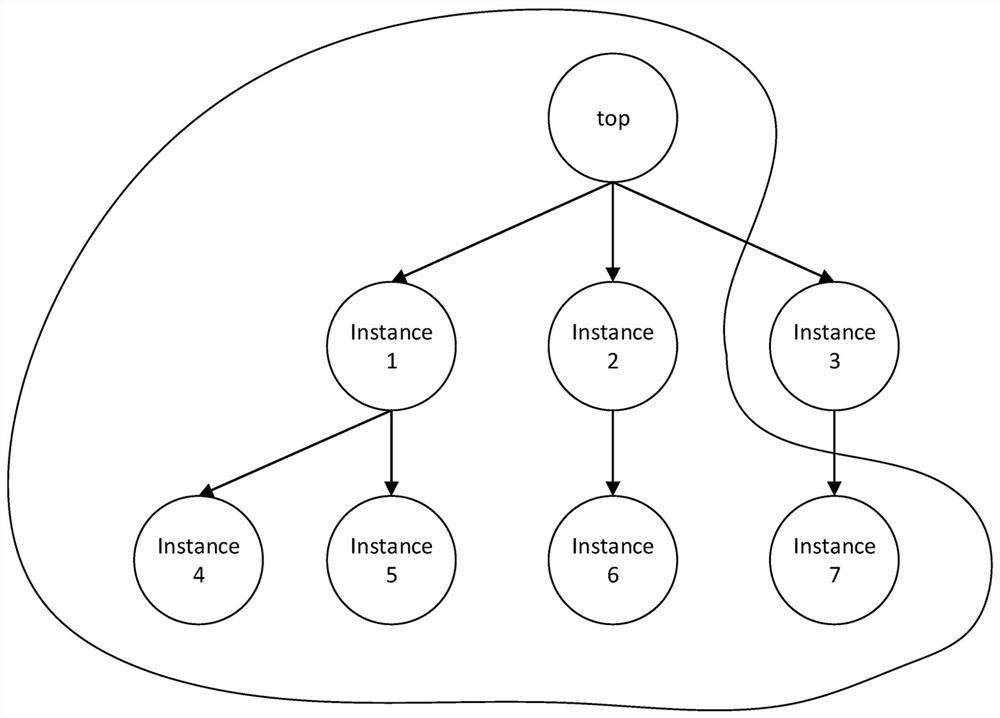

Parallel RTL synthesis method based on multi-FPGA system and storage medium

PendingCN114330174AReduce volumePrecise compilationComputer aided designSpecial data processing applicationsTest designComputer architecture

The invention discloses a parallel RTL synthesis method based on a multi-FPGA system and a storage medium. The parallel RTL synthesis method based on the multi-FPGA system comprises the following steps: traversing each instance of a tested design according to a top node to create a hierarchical tree; traversing the hierarchical tree in parallel to uniquely process each module, and recording a hash value of the module after uniquely processing; taking modules as units, performing parallel refinement and logic mapping on each module, and converting a tested design corresponding to each module into a gate-level circuit from an RTL (Register Transfer Language); combining the gate-level circuits corresponding to the modules into a whole to form a hierarchical netlist; counting resources consumed by the hierarchical netlist, and automatically selecting a hypergraph unit according to resource constraints; and performing segmentation by adopting a segmentation tool to form a netlist corresponding to each FPGA. According to the method, parallel comprehensive processing of the RTL is realized, a large-scale integrated circuit can be dealt with, and meanwhile, the simulation verification efficiency can be improved.

Owner:深圳国微晶锐技术有限公司

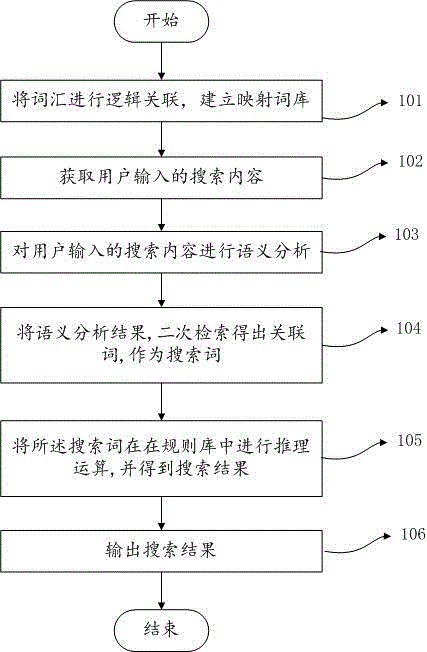

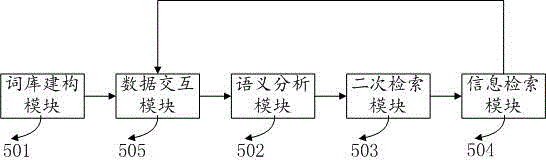

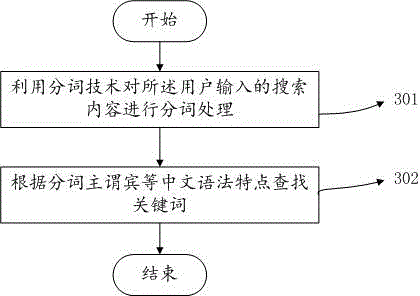

O2B intelligent searching method and system

InactiveCN104679784AExcavate accuratelyMeet the requirementsSpecial data processing applicationsSearch wordsUser input

The invention discloses an O2B intelligent searching method and system and belongs to the technical field of computer. The O2B intelligent searching method includes that carrying out logic association on words, and building a mapping lexicon; acquiring search content input by a user; carrying out semantic analysis on the search content input by the user; carrying out quadratic search on the semantic analysis result to obtain associated words, and using the associated words as search words; reasoning the search words in a rule base, and obtaining the search result; outputting the research result. The O2B intelligent searching method and system have beneficial effects that the improved O2B intelligent searching method is provided for overcoming the disadvantage that an existing search engine cannot meet the real demand of a user, through semantic analysis and logic mapping, the complicated and changing language is simplified, and the real demand of the user is translated precisely to provide precise search service.

Owner:上海博科资讯股份有限公司

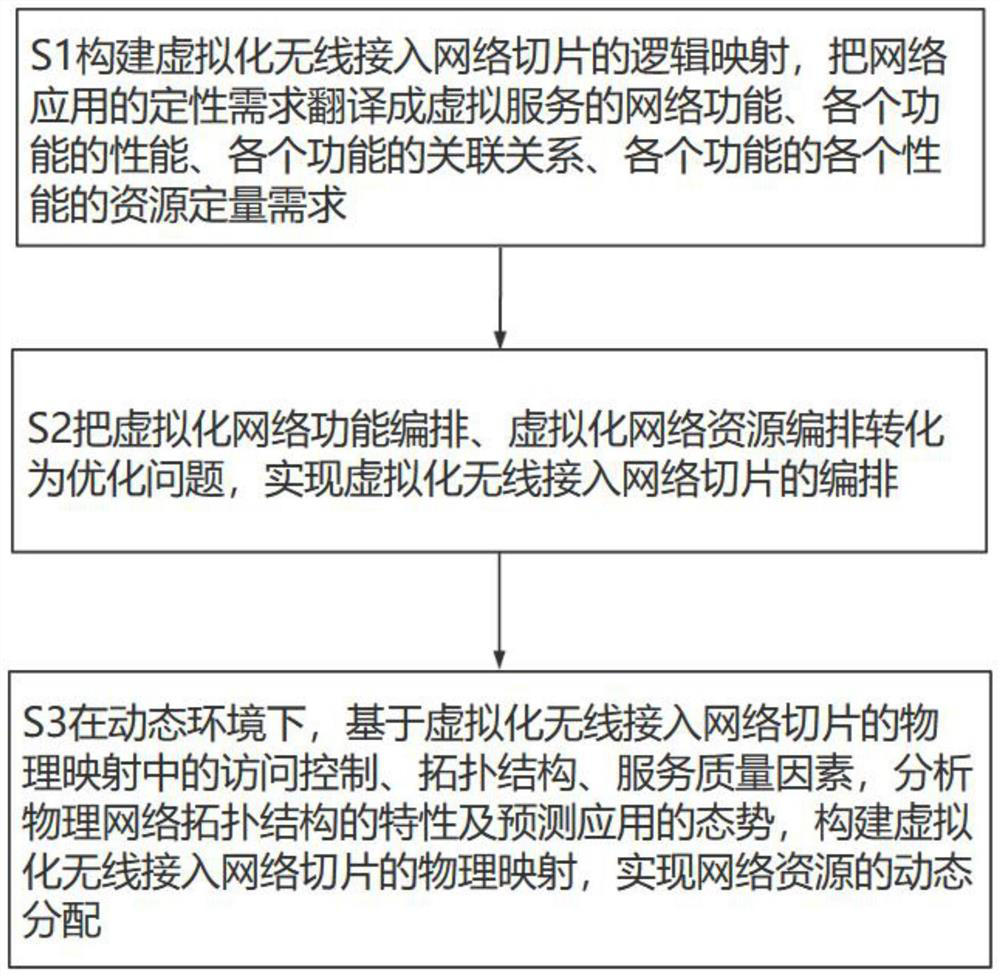

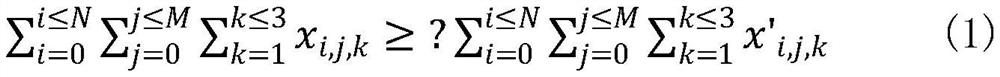

Method for generating web application slices in virtualized wireless access edge cloud

ActiveCN112887142ARealize resource migrationAchieve migrationData switching networksAccess networkVirtualization

The invention provides a method for generating web application slices in virtualized wireless access edge cloud, which comprises the following steps: S1, constructing logic mapping of virtualized wireless access network slices, translating the qualitative demand of the network application into the network function of the virtual service, the performance of each function, the association relationship of each function and the resource quantitative demand of each performance of each function; S2, converting virtualized network function arrangement and virtualized network resource arrangement into optimization problems, and realizing arrangement of virtualized wireless access network slices; and S3, constructing physical mapping of virtualized wireless access network slices, and realizing dynamic distribution of network resources. The heterogeneous multi-base-station joint mapping virtualized network resource migration is realized, the cell boundary limitation is broken, and the link quality between the virtual cell and the terminal is always better.

Owner:GUIZHOU UNIV +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com