Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5149 results about "Memory systems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In addition to these homologous features of memory systems in both plants and animals, plants have also been observed to encode, store and retrieve basic short-term memories. One of the most well-studied plants to show rudimentary memory is the Venus flytrap.

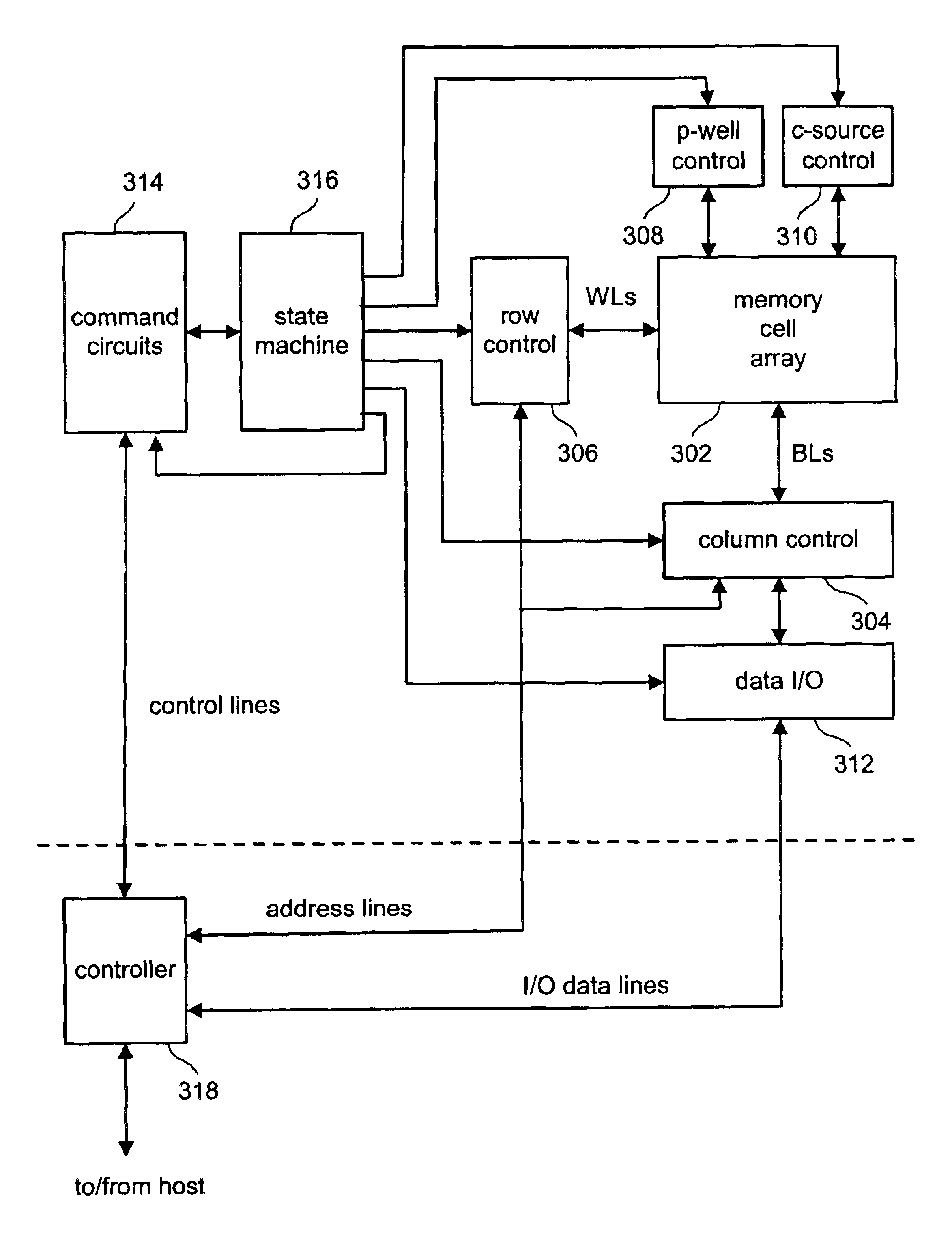

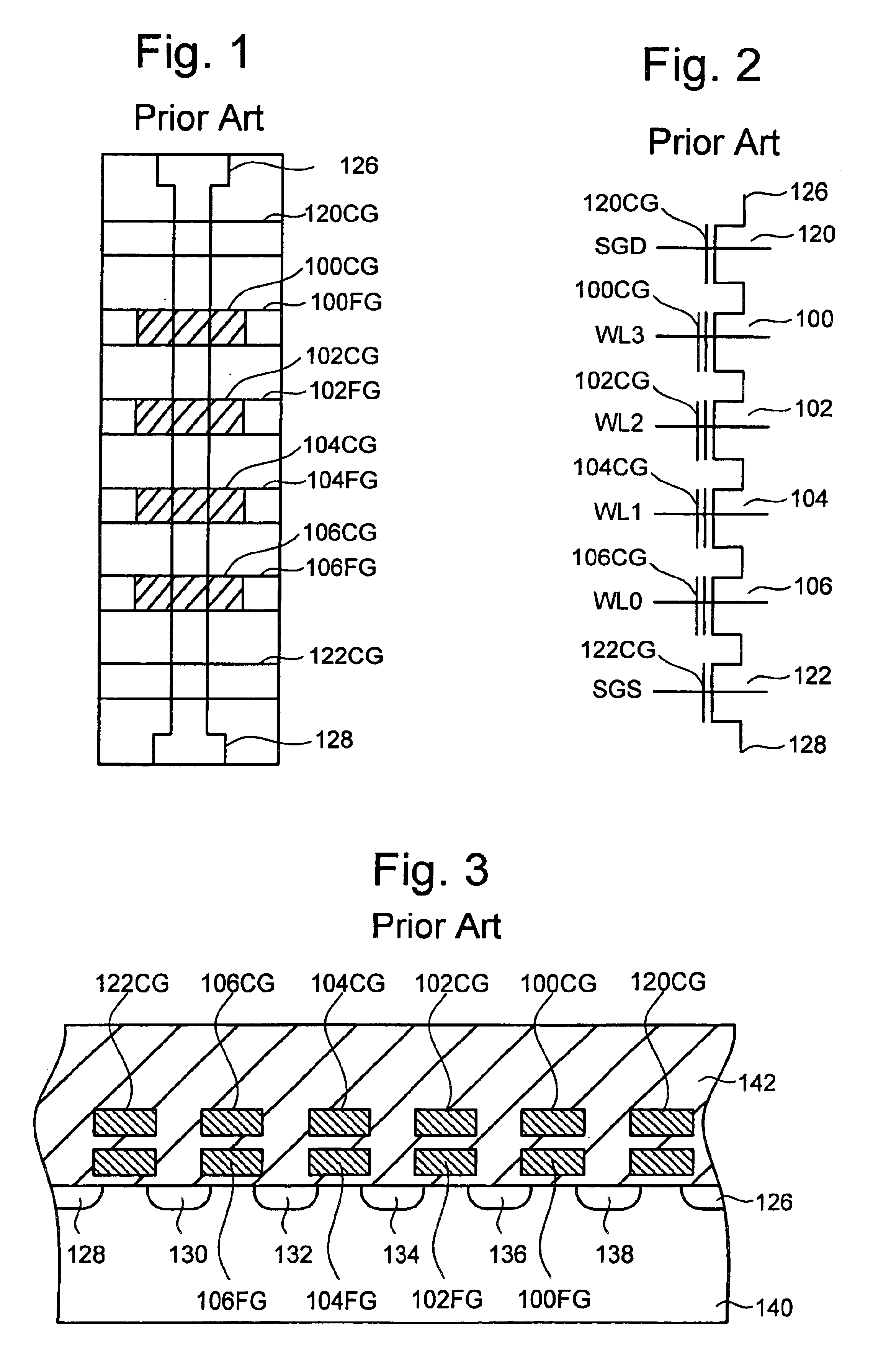

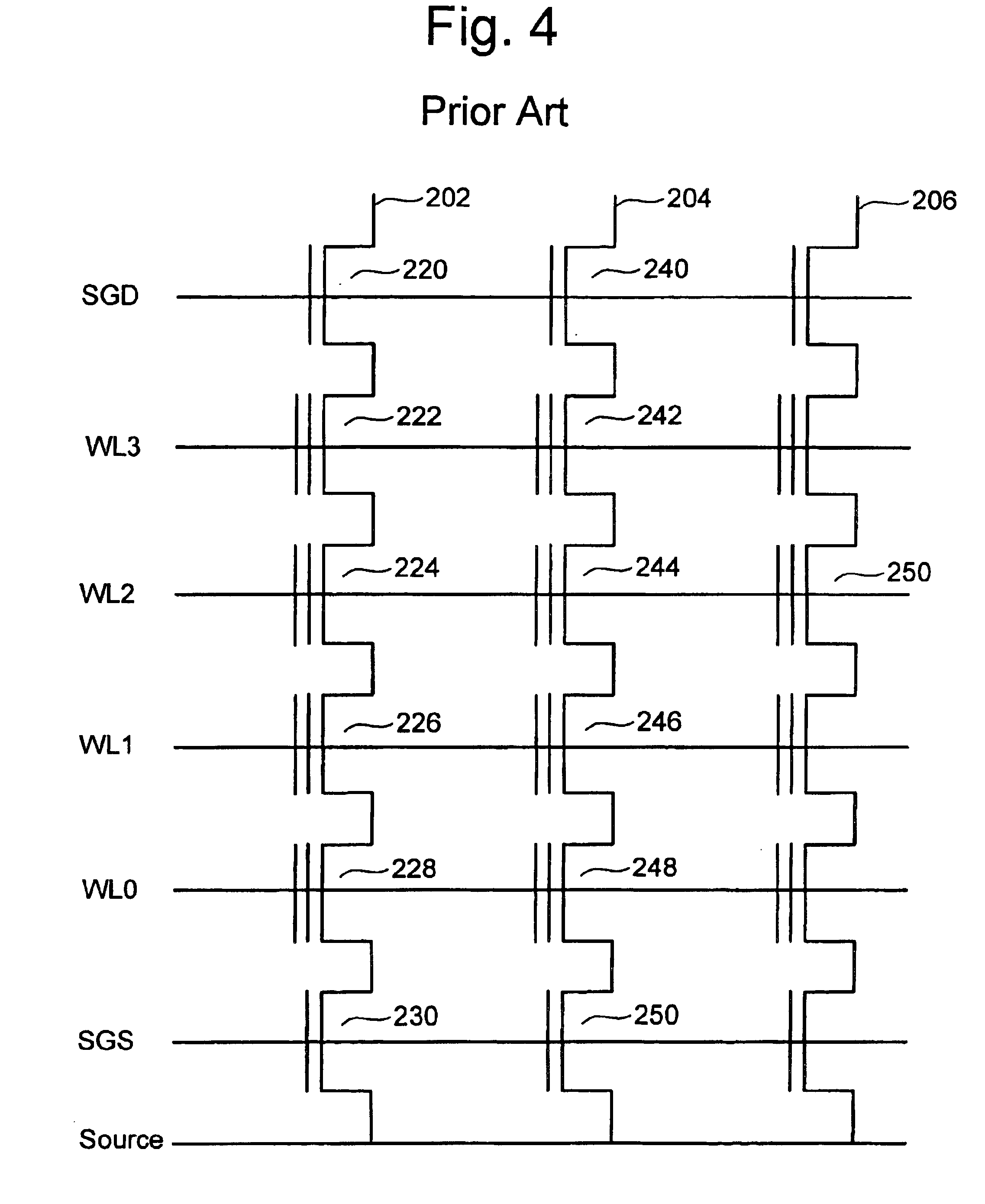

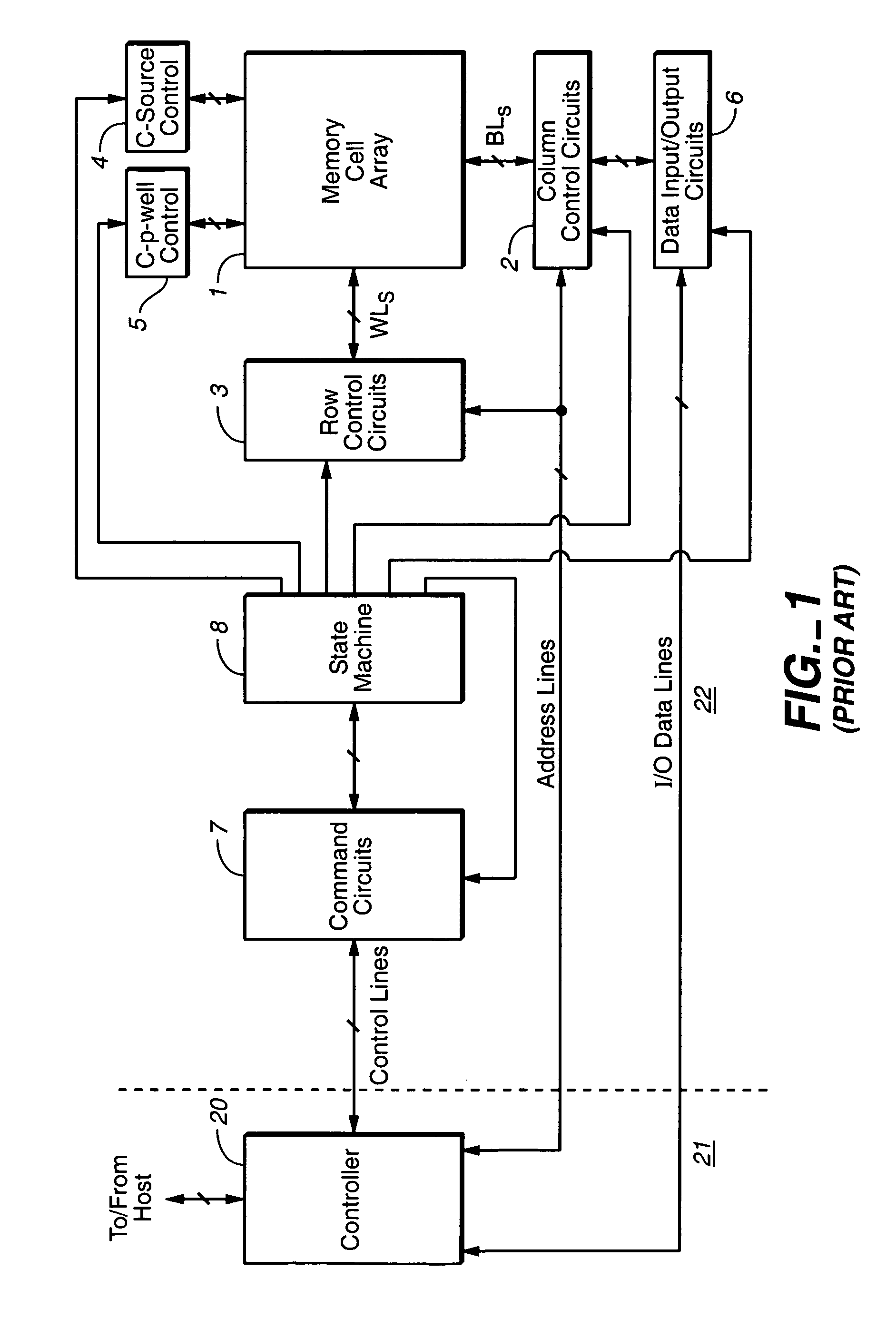

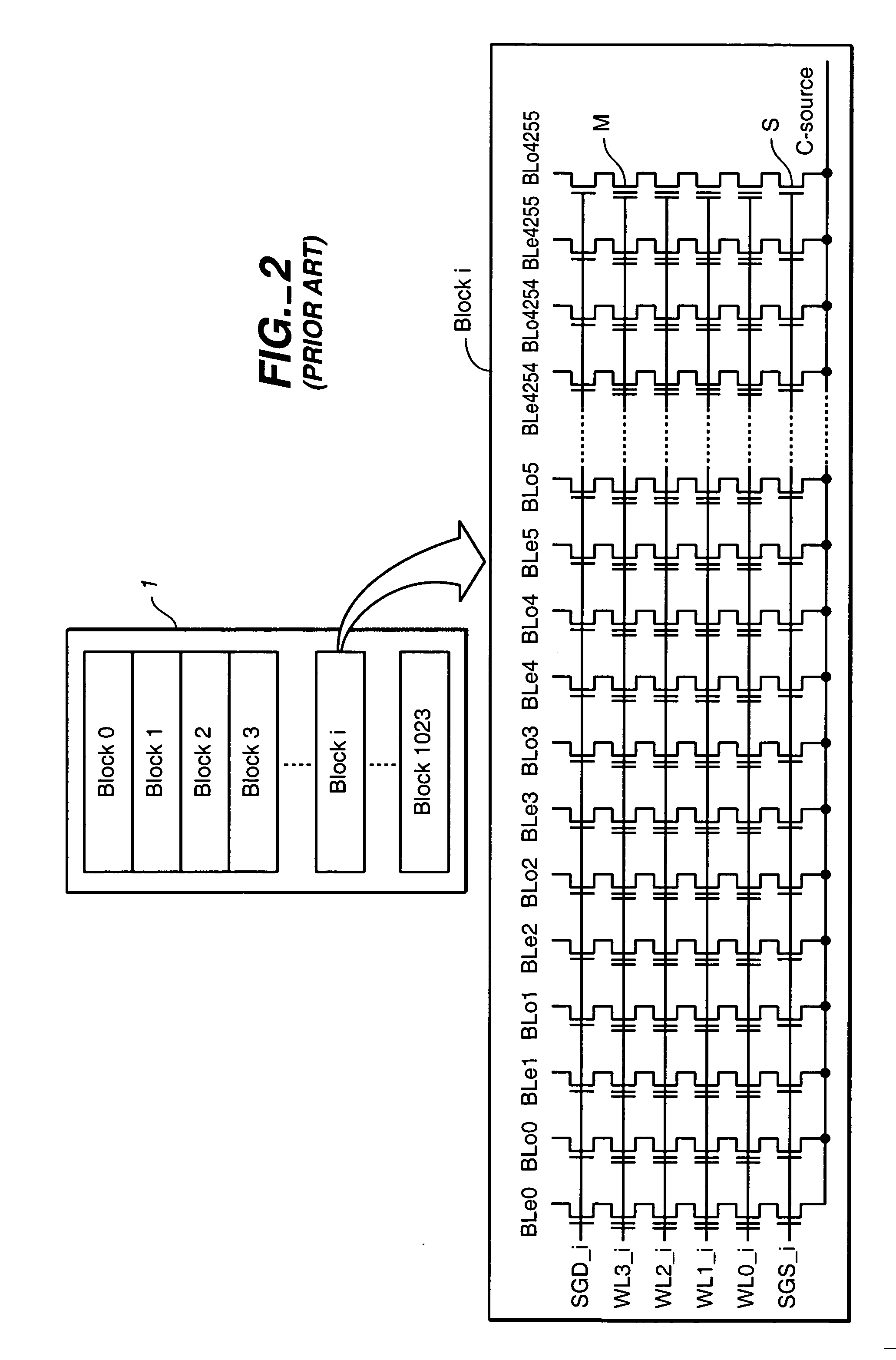

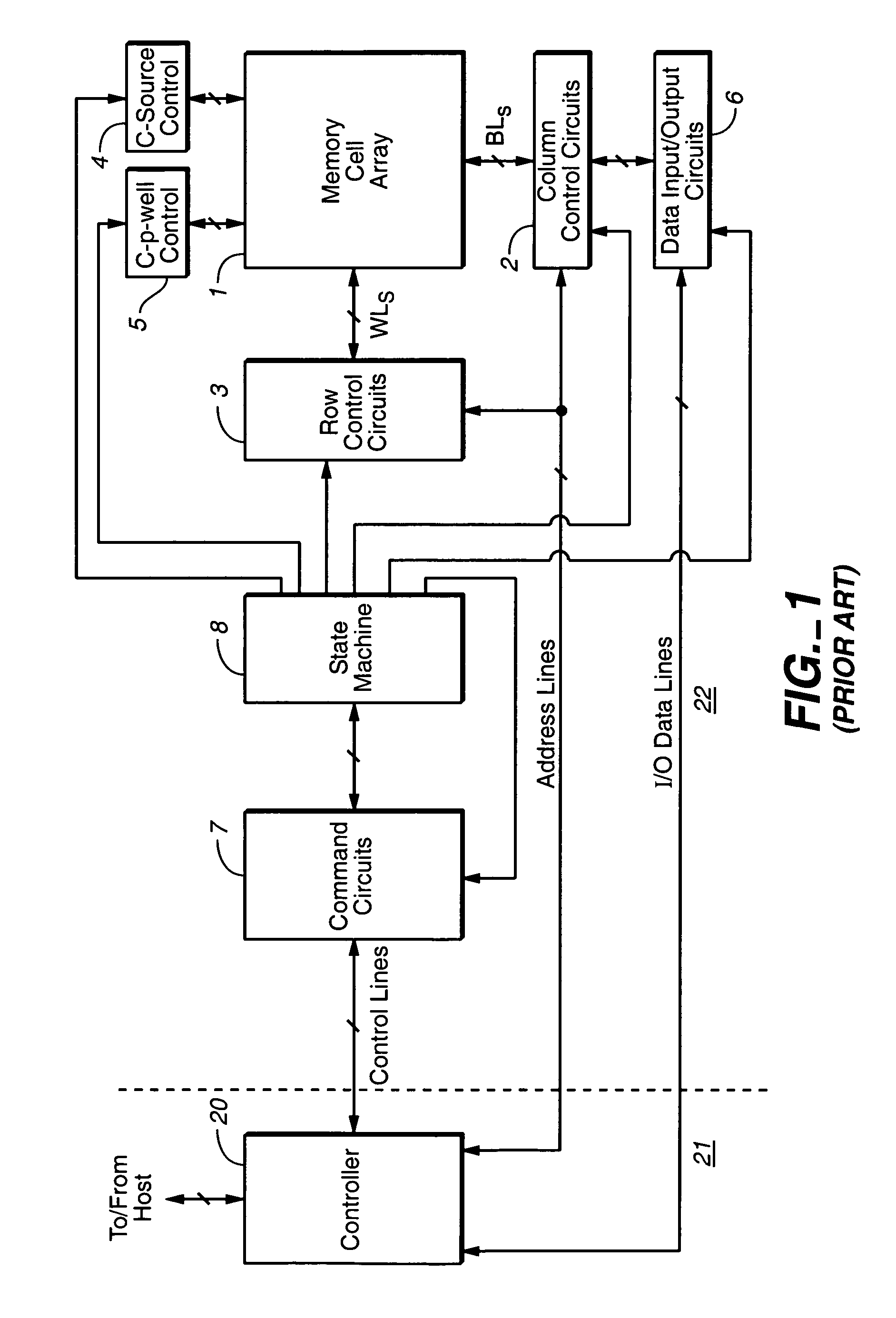

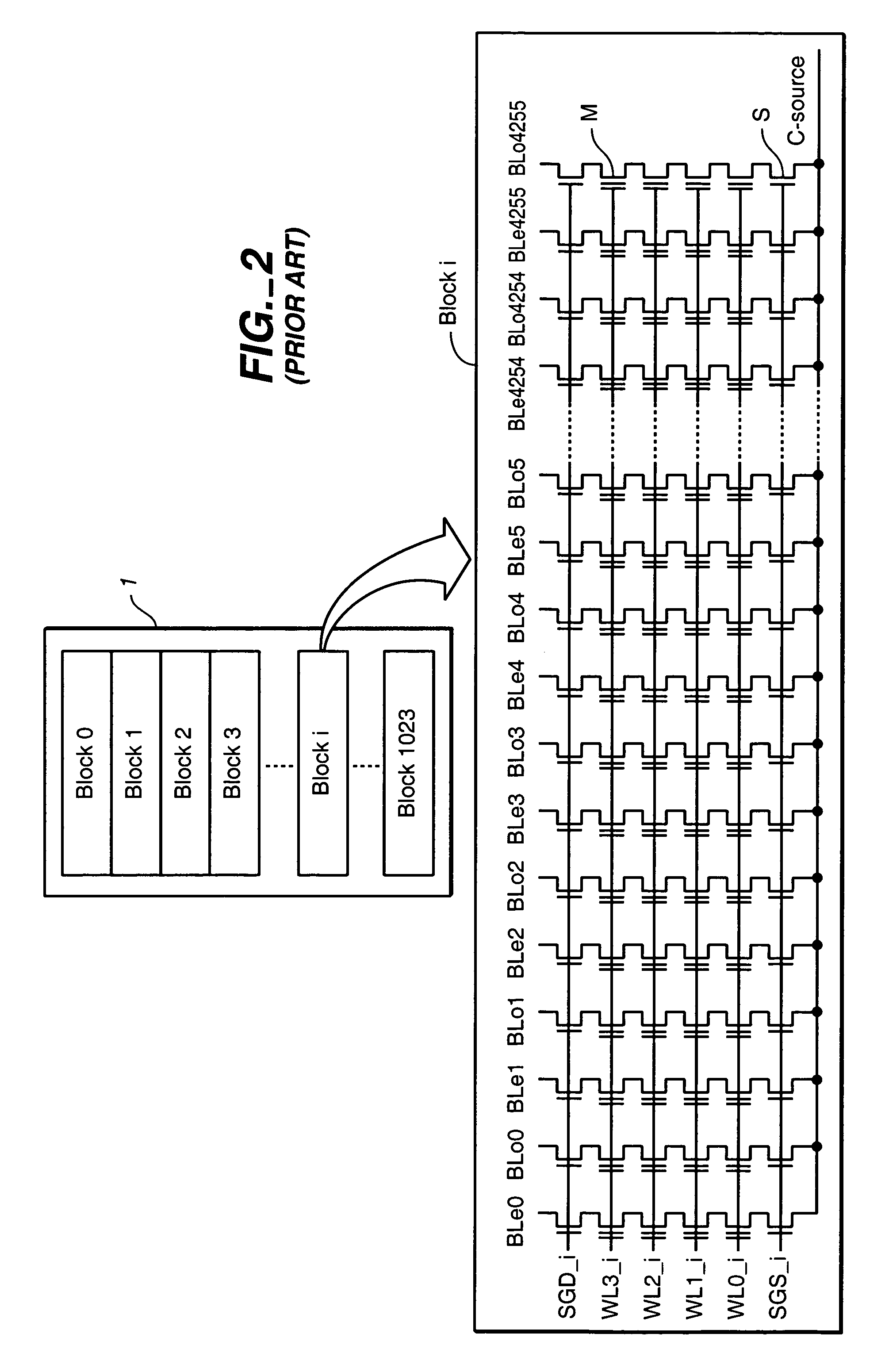

Source side self boosting technique for non-volatile memory

InactiveUS6859397B2Improve performanceMinimize program disturbRead-only memoriesDigital storagePre-chargeProgramming process

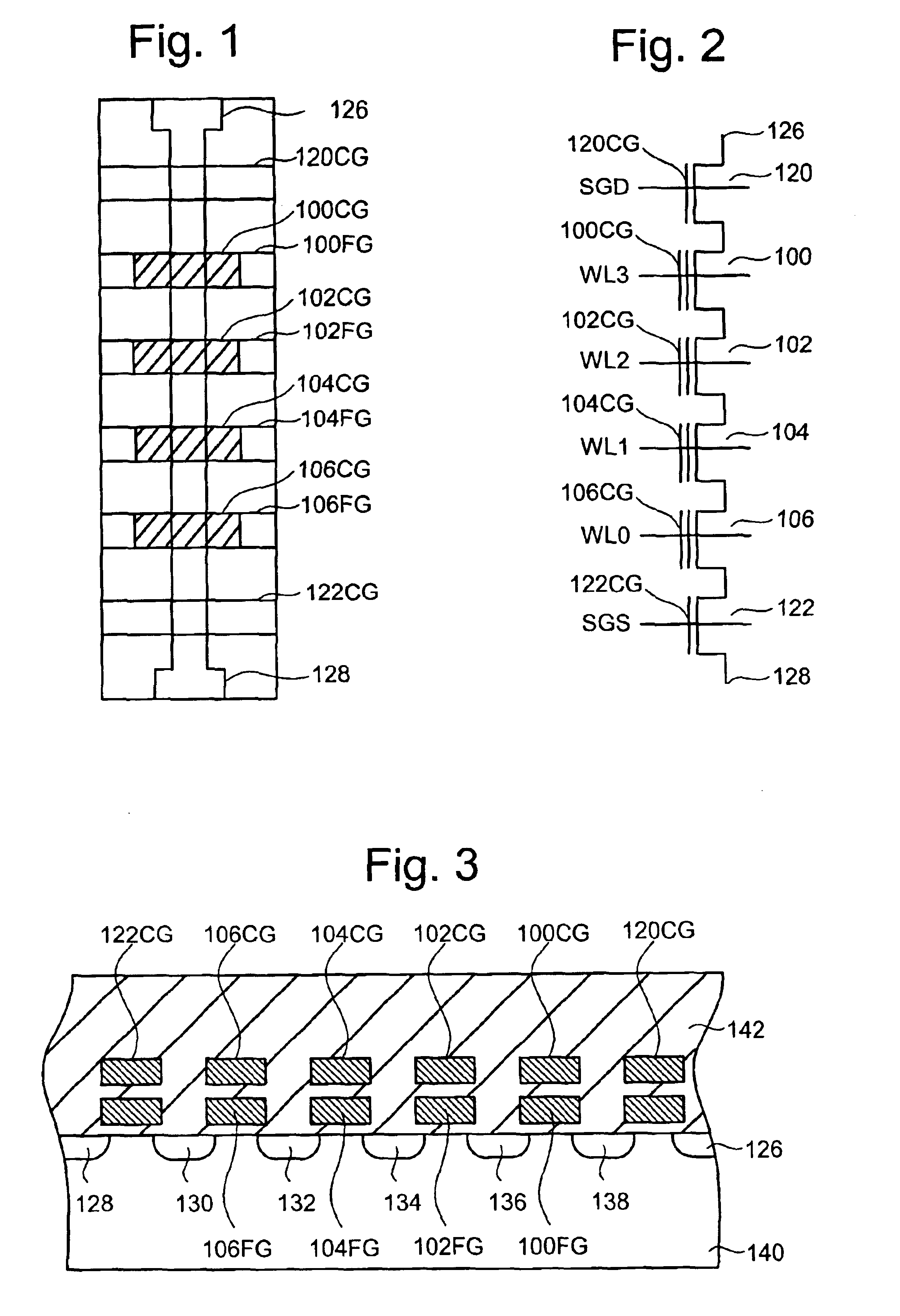

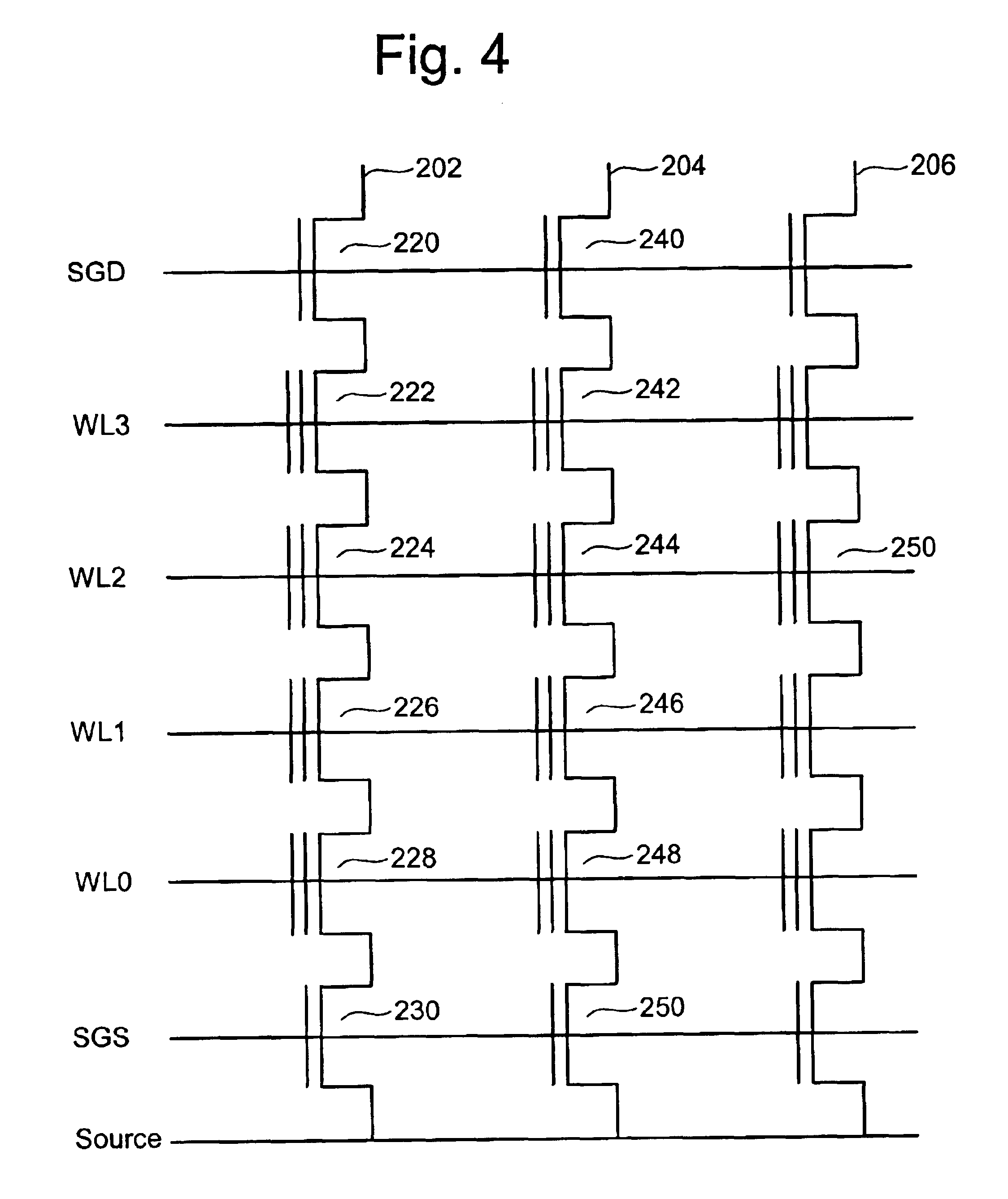

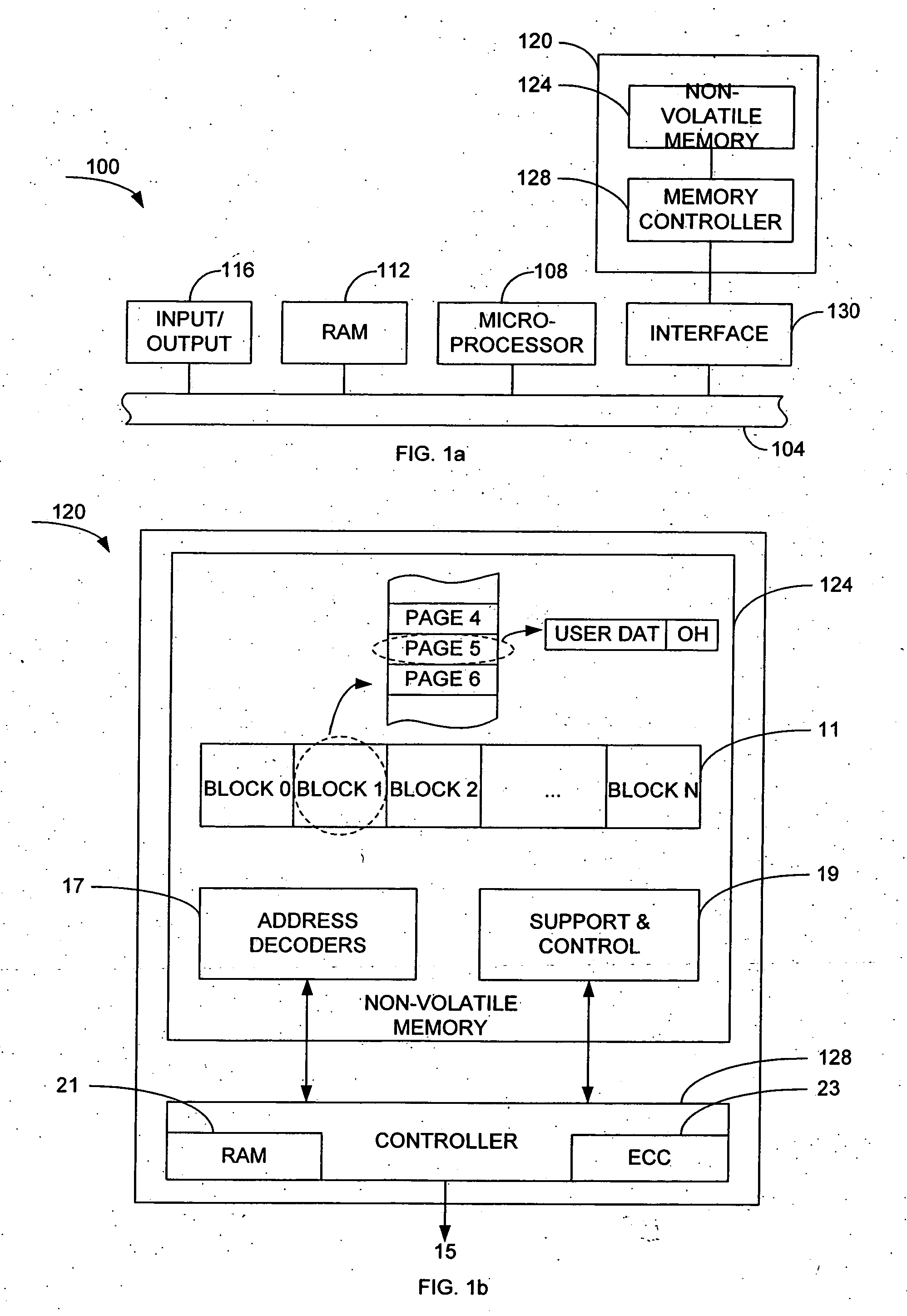

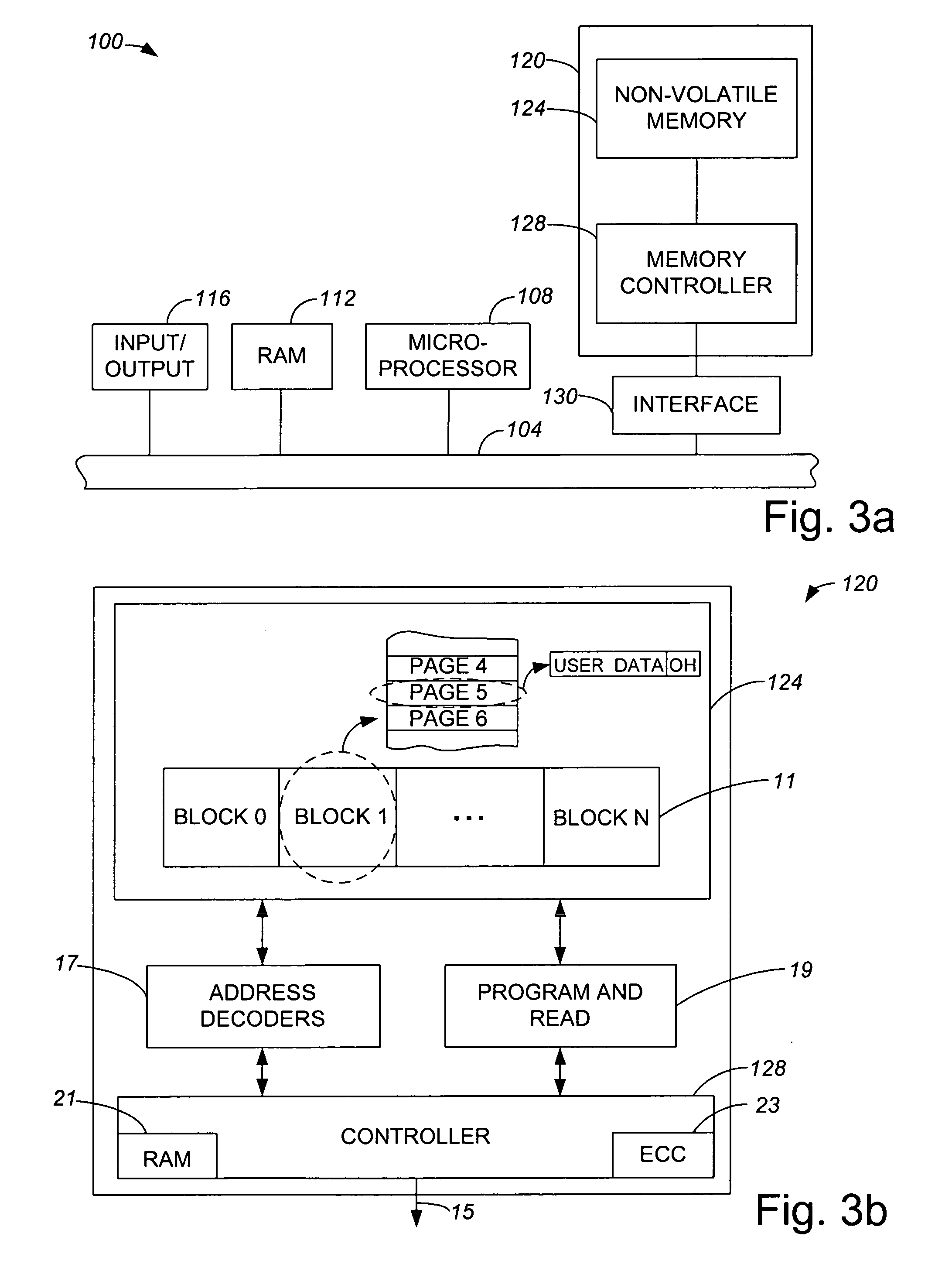

A non-volatile semiconductor memory system (or other type of memory system) is programmed in a manner that avoids program disturb. In one embodiment that includes a flash memory system using a NAND architecture, program disturb is avoided by increasing the channel potential of the source side of the NAND string during the programming process. One exemplar implementation includes applying a voltage (e.g. Vdd) to the source contact and turning on the source side select transistor for the NAND sting corresponding to the cell being inhibited. Another implementation includes applying a pre-charging voltage to the unselected word lines of the NAND string corresponding to the cell being inhibited prior to applying the program voltage.

Owner:SANDISK TECH LLC

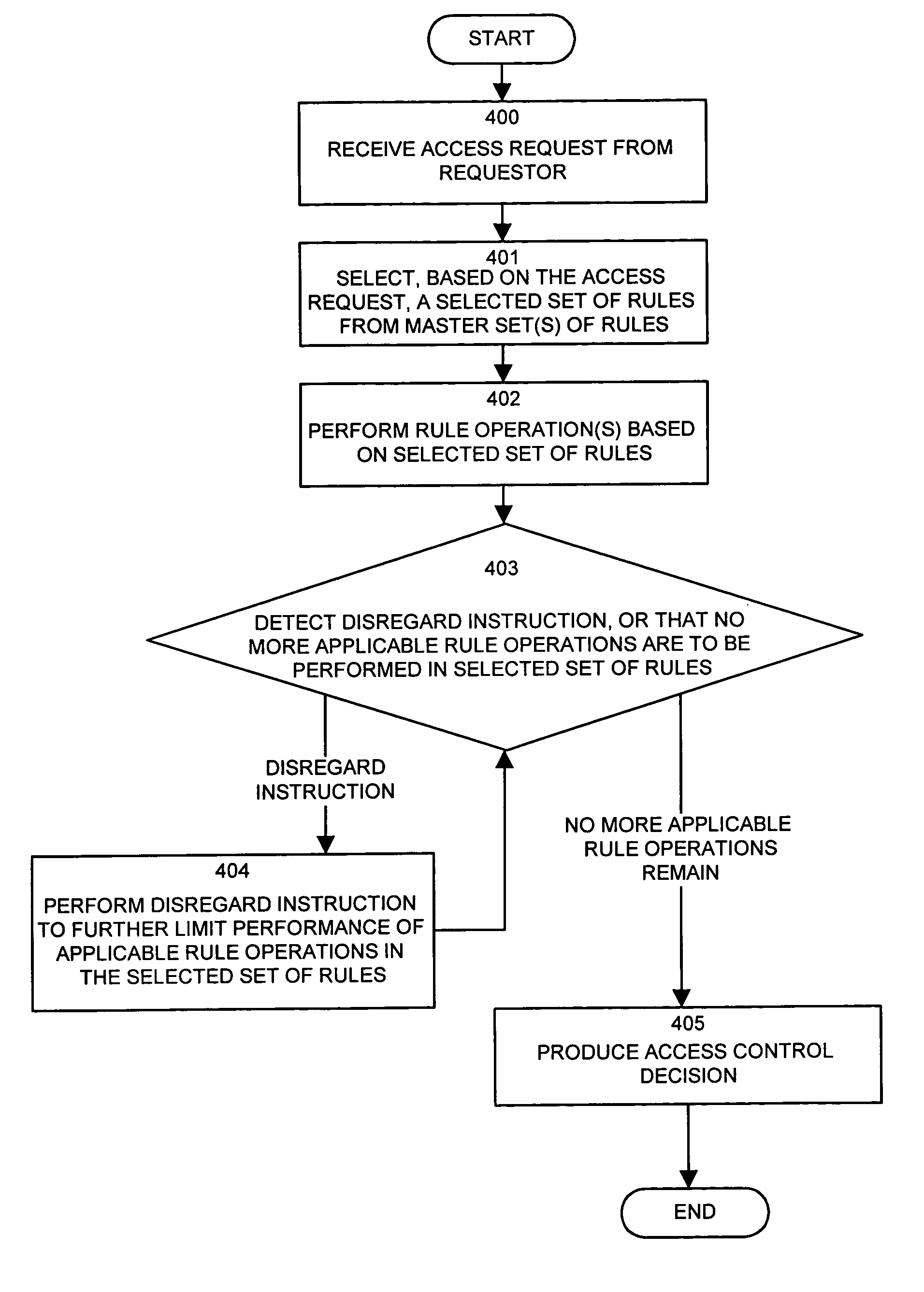

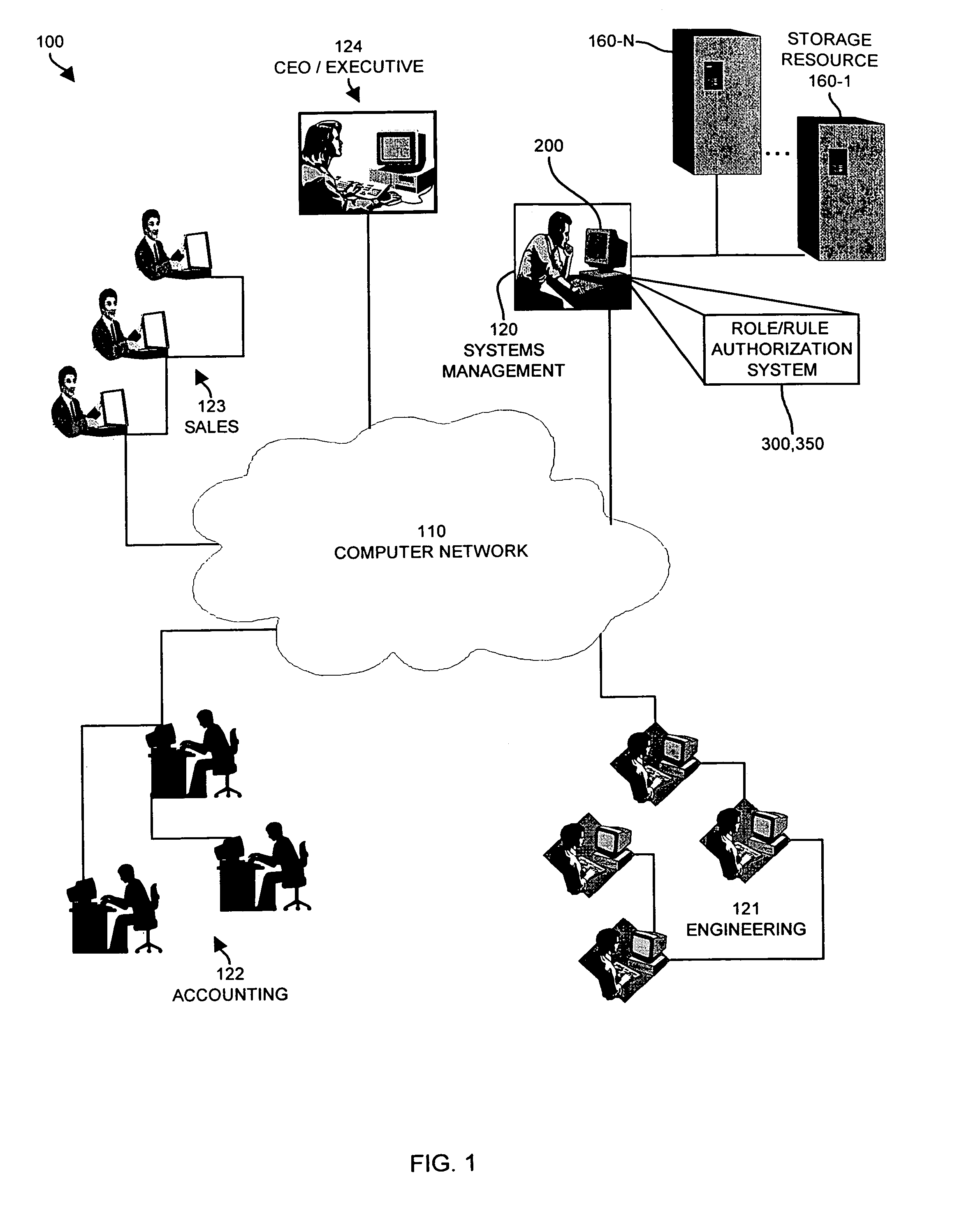

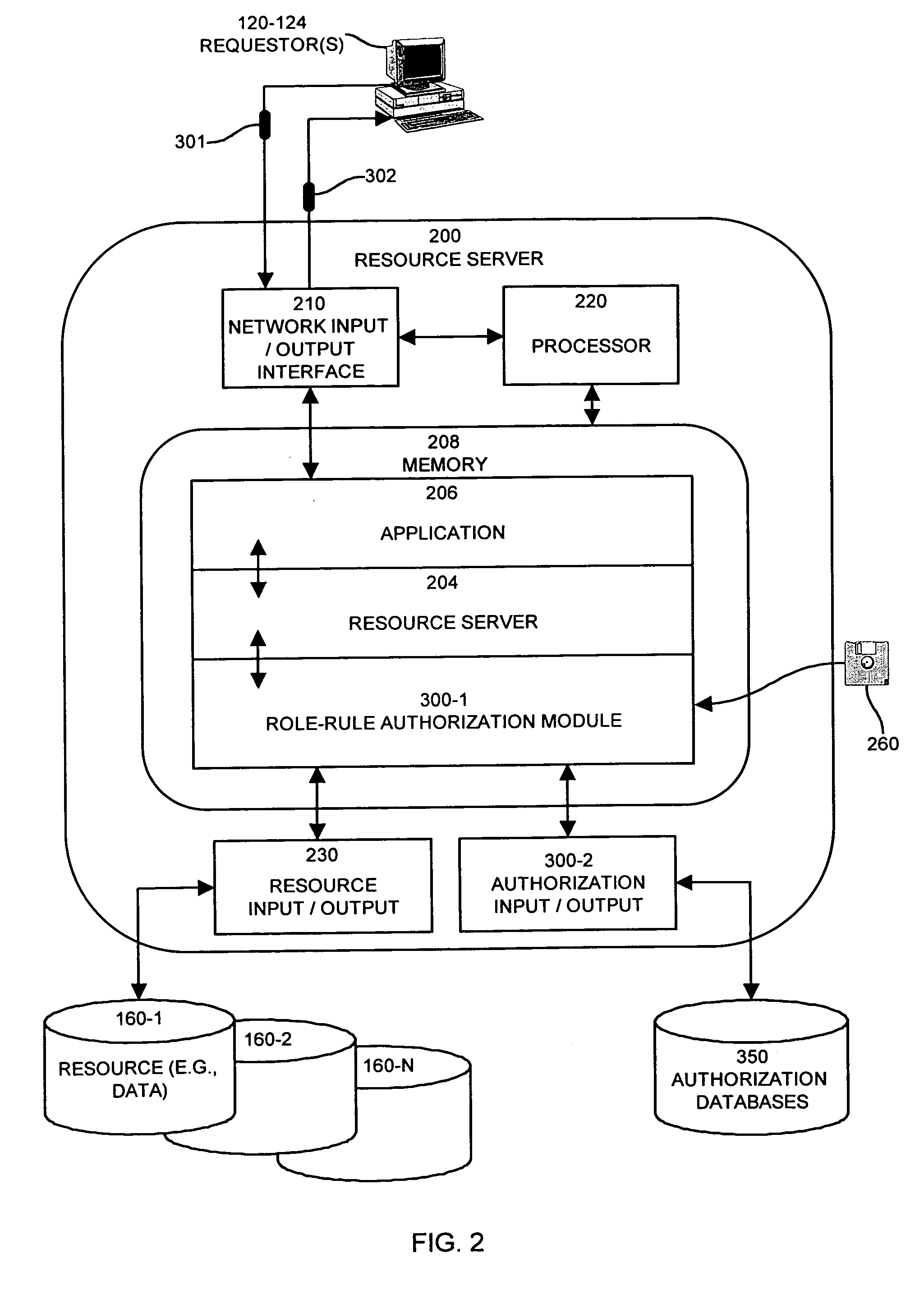

Methods and apparatus for controlling access to a resource

InactiveUS7185192B1Limit staff employee accessVerification of the security policy more straightforwardData processing applicationsDigital data processing detailsProgramming languageDecision taking

An input / output interface receives an access request from a requester. A processor associated with the input / output interface applies a filter operation to select a subset of rules from a master set of rules maintained within an authorization database. Rules can be selected in this manner using filter operations so that all rules in the rule set need not be processed. A rule may include a disregard instruction. The processor further performs at least one rule operation based on the subset of rules to produce an access control decision in the memory system until either a rule operation including a disregard instruction is performed to limit performance of rule operations in the selected set of rules or until all rule operations in the selected set of rules that are applicable to the access control decision are performed.

Owner:EMC IP HLDG CO LLC

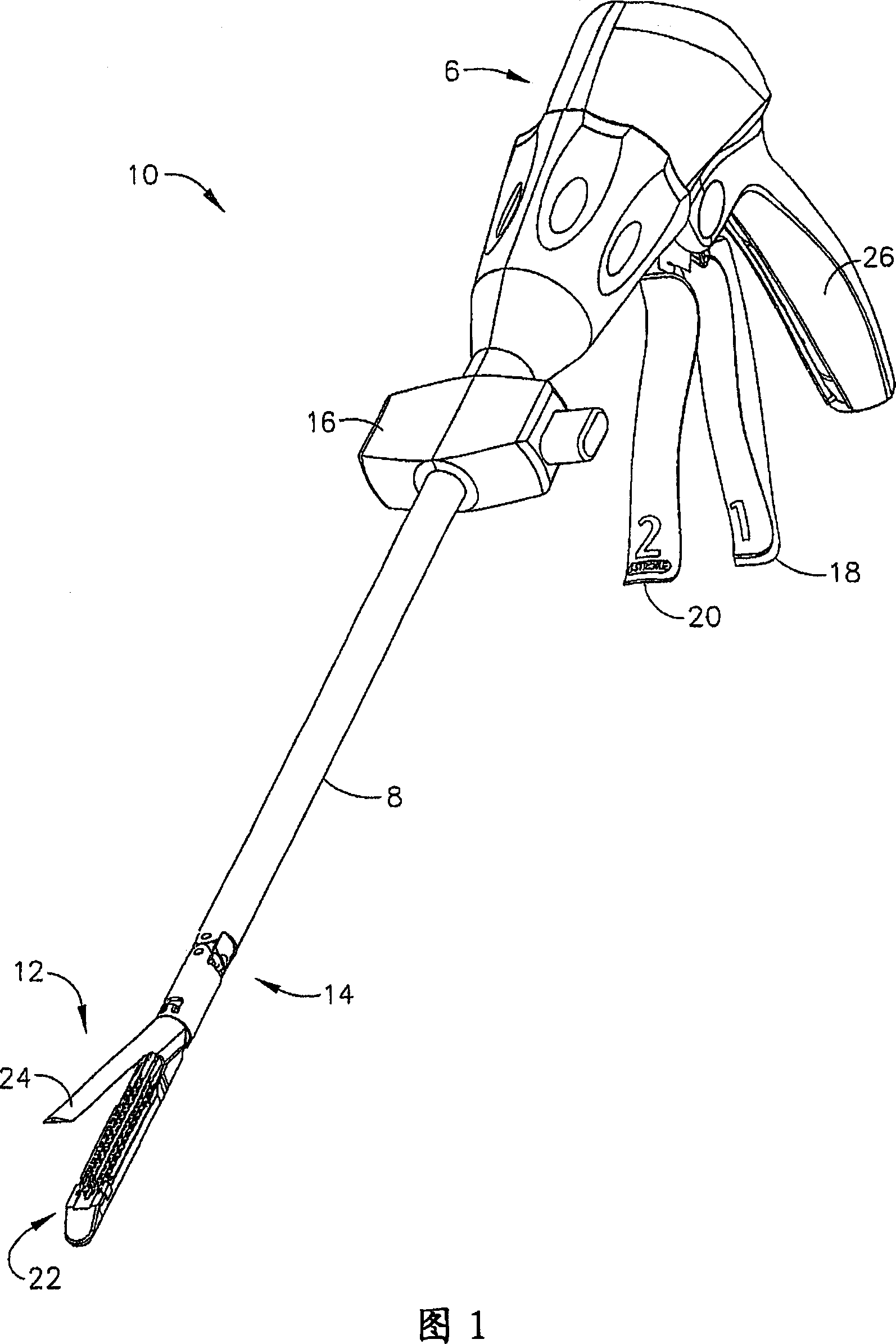

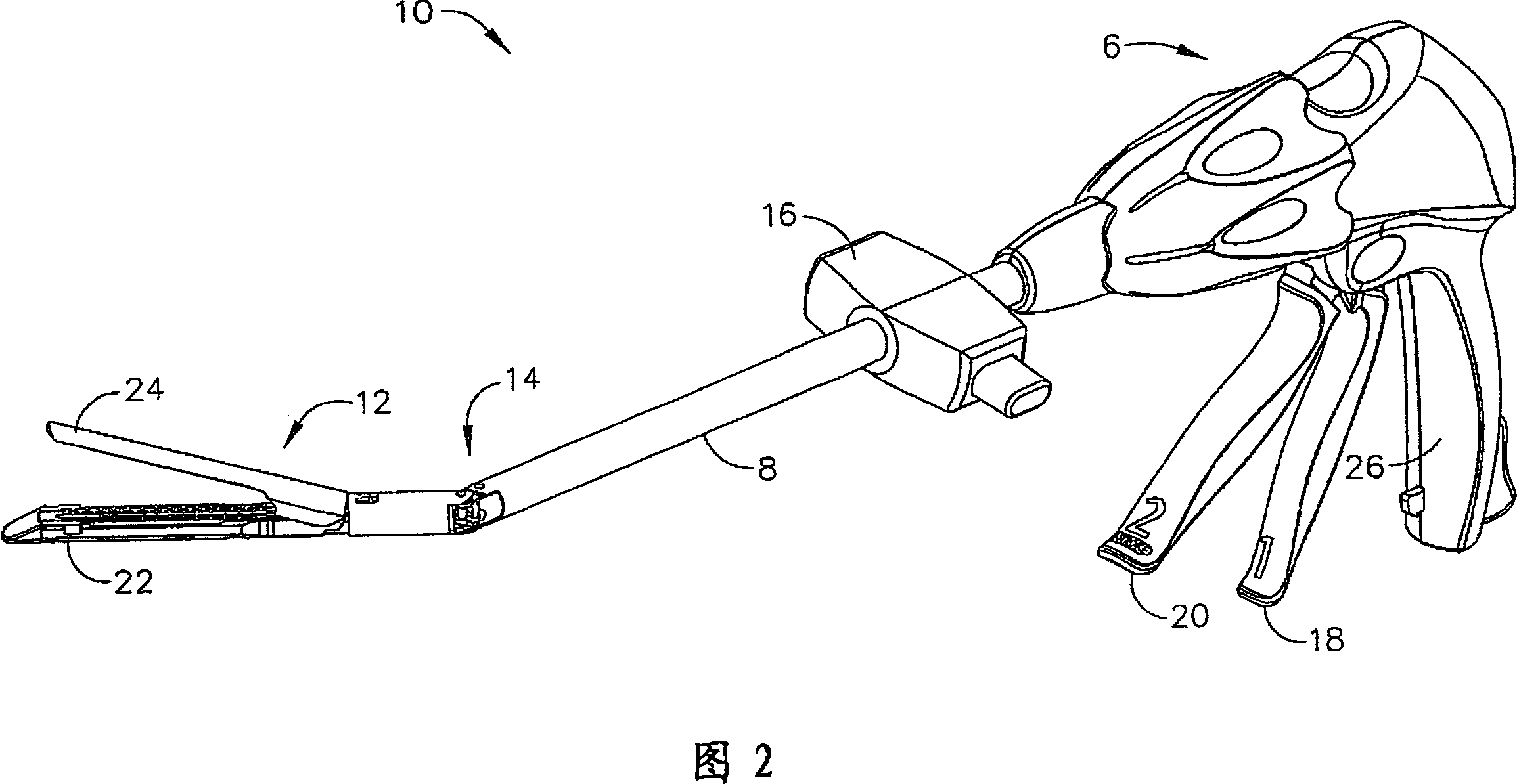

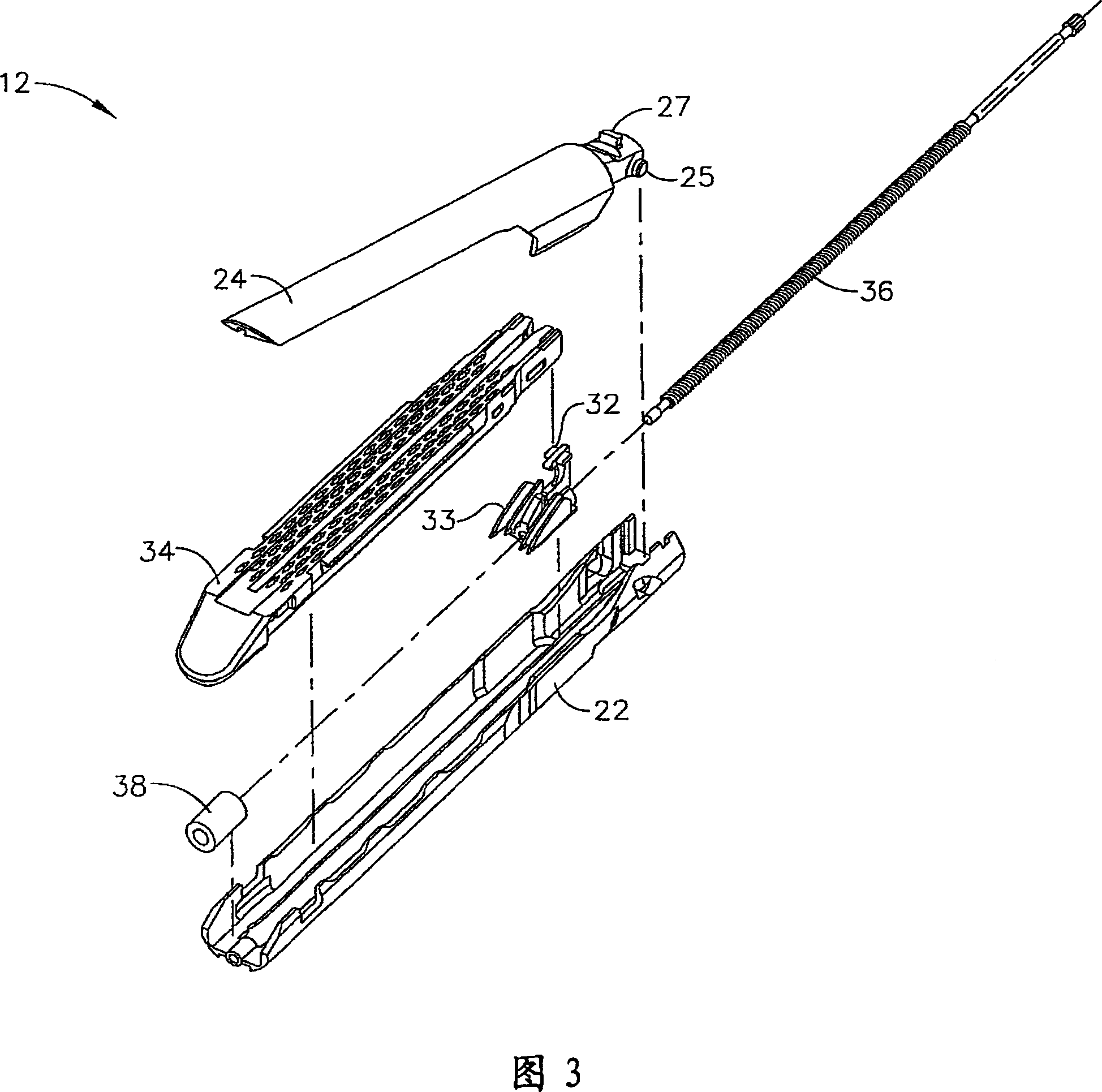

Surgical instrument having recording capabilities

A surgical instrument is disclosed. The surgical instrument has an end effector and a trigger in communication with the end effector. The surgical instrument also has a built-in memory system for recording the instrument condition during a use process. The recording system comprises: a first sensor located on or inside the instrument and an externally accessible built-in memory device in communication with the first sensor. The first sensor has an output that represents a first condition of either the trigger or the end effector. The memory device is configured to record the output of the first sensor. In various embodiments, memory device may include an output port and / or a removable storage medium.

Owner:ETHICON ENDO SURGERY INC

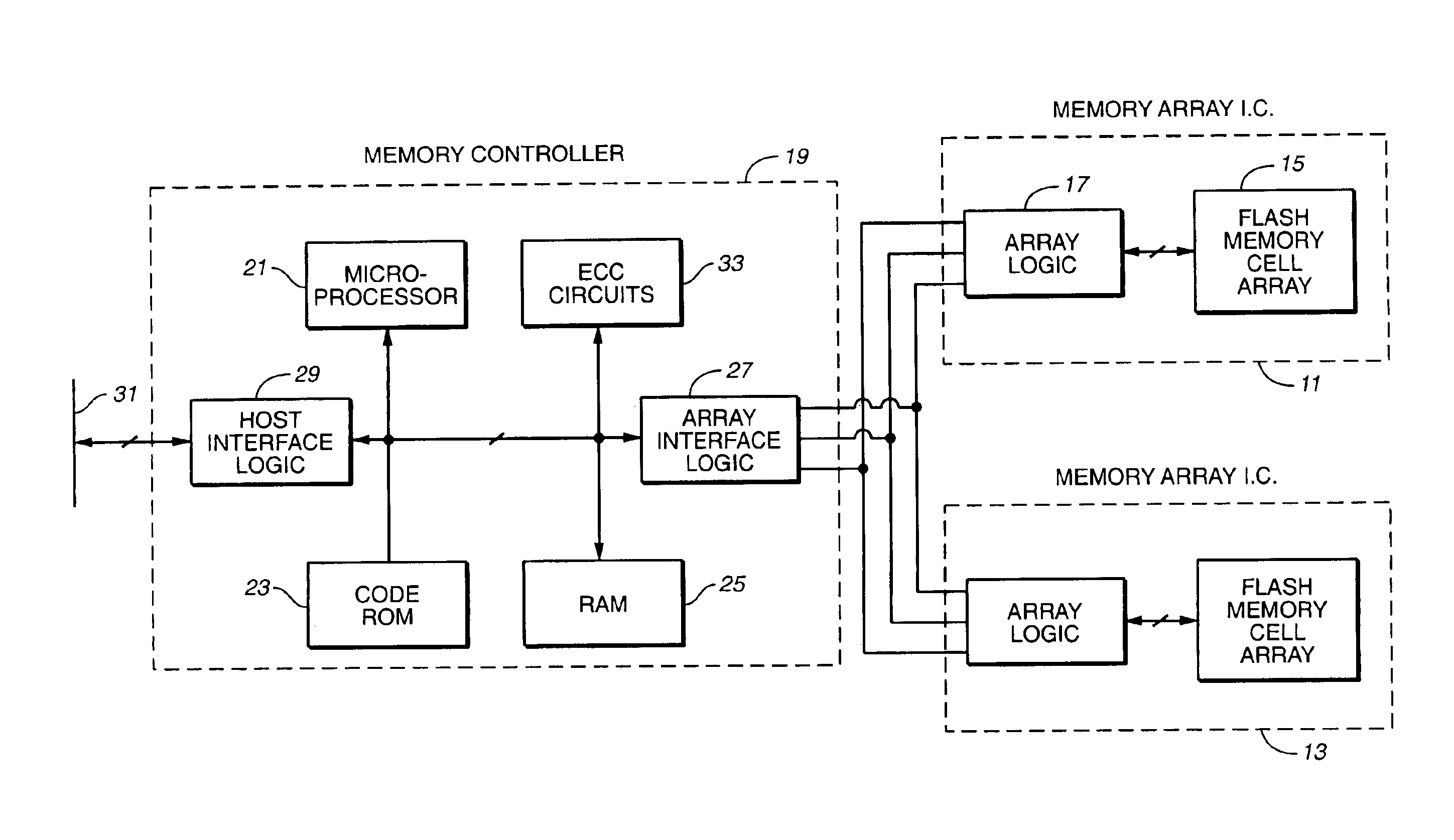

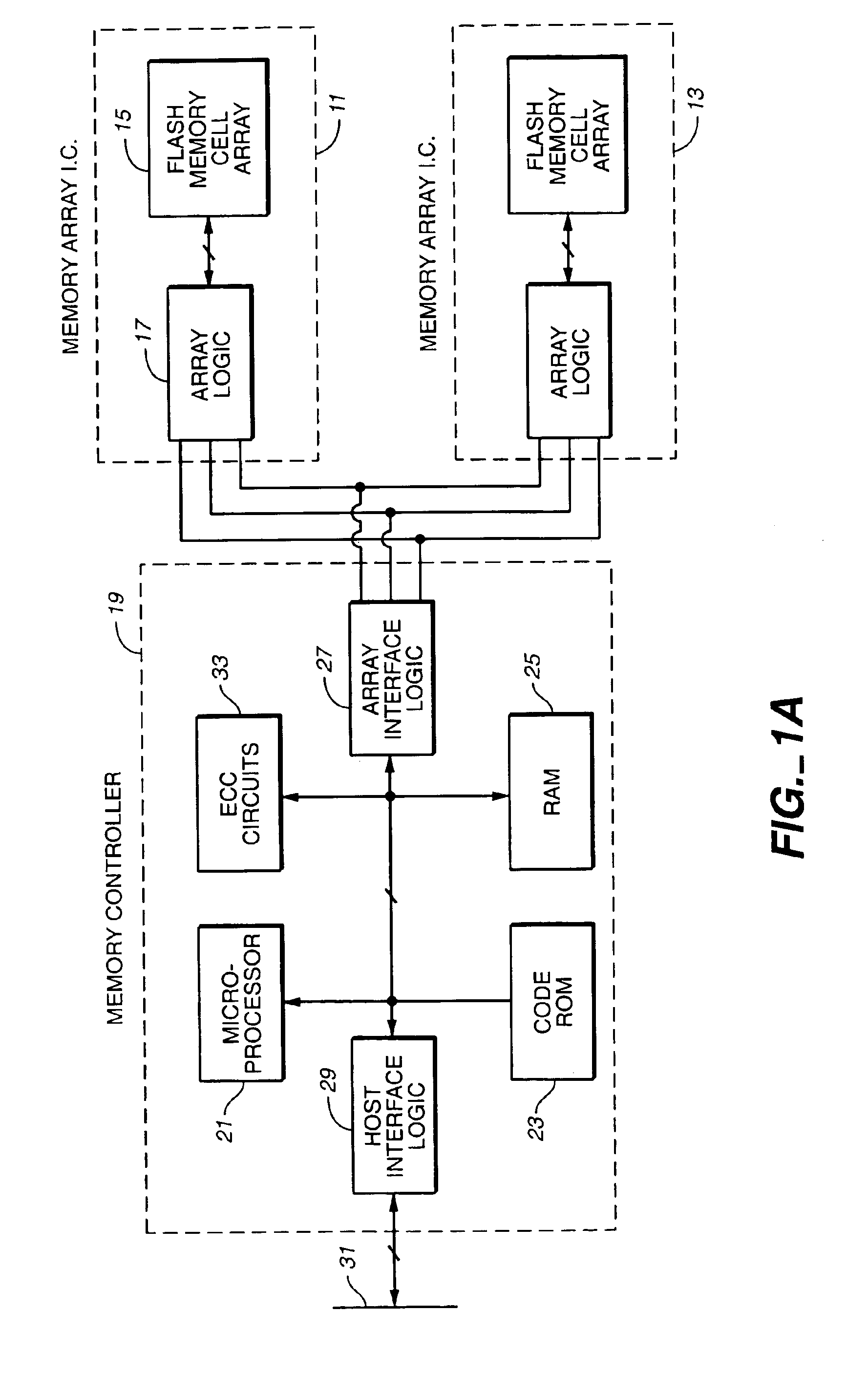

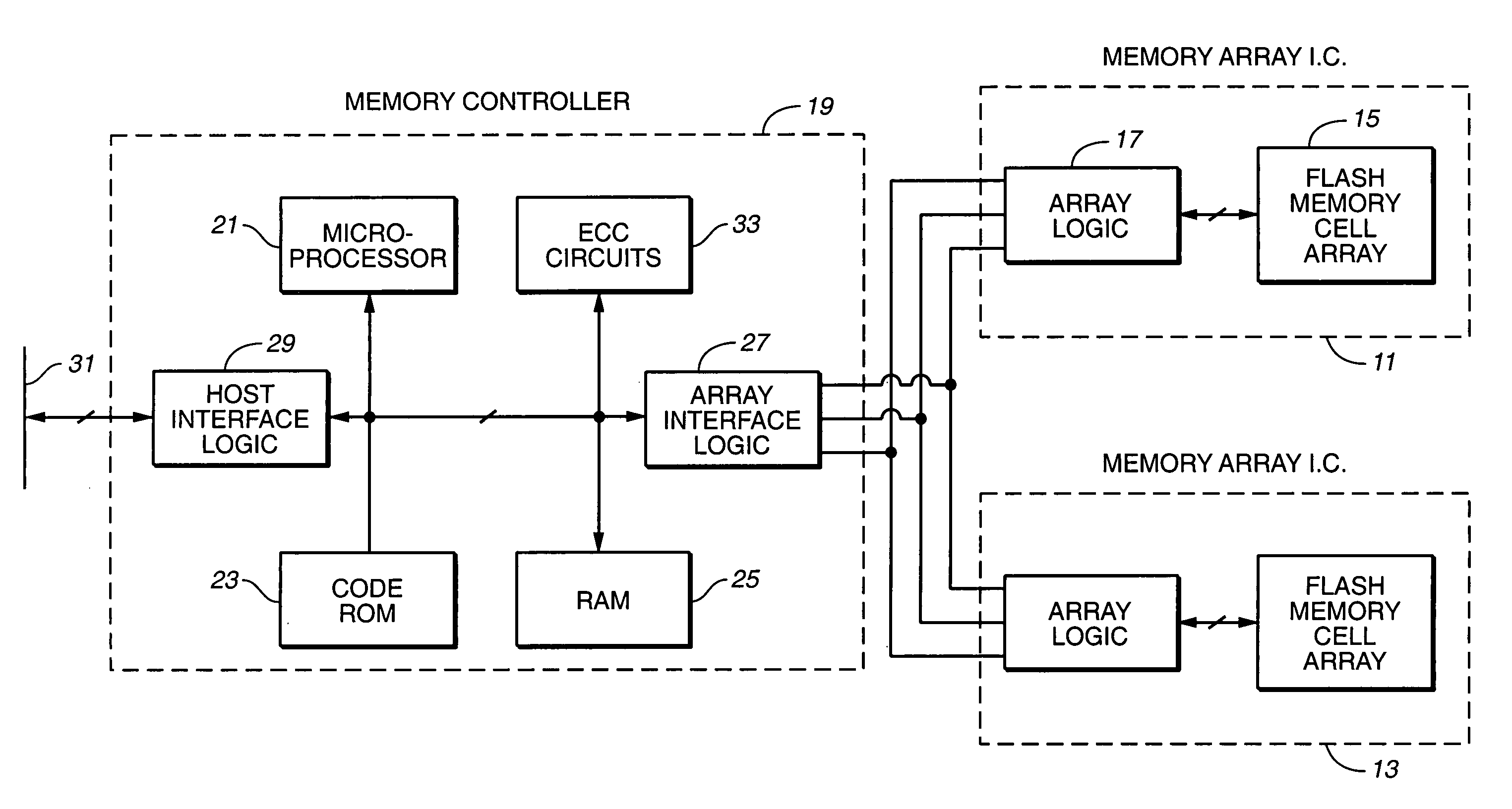

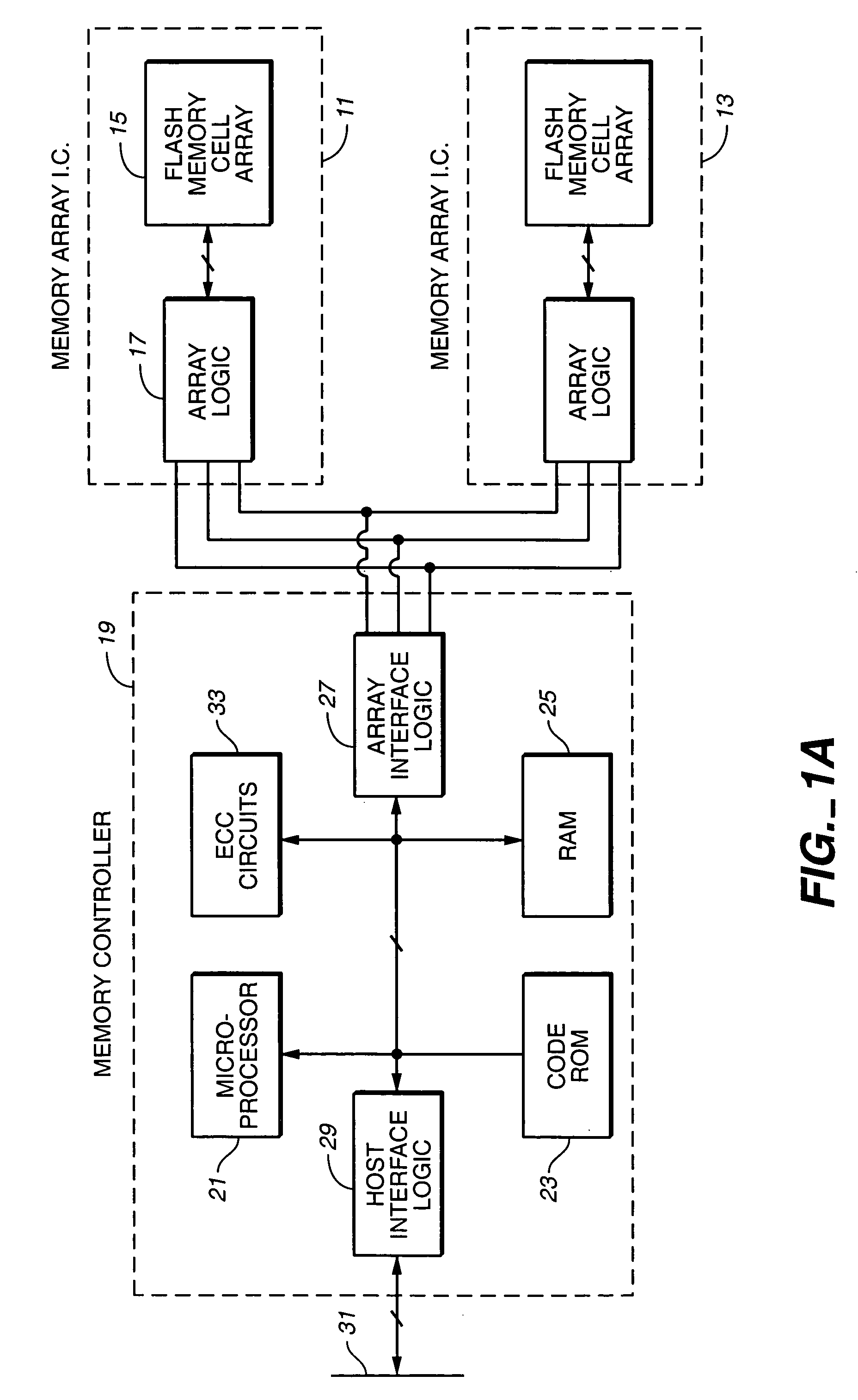

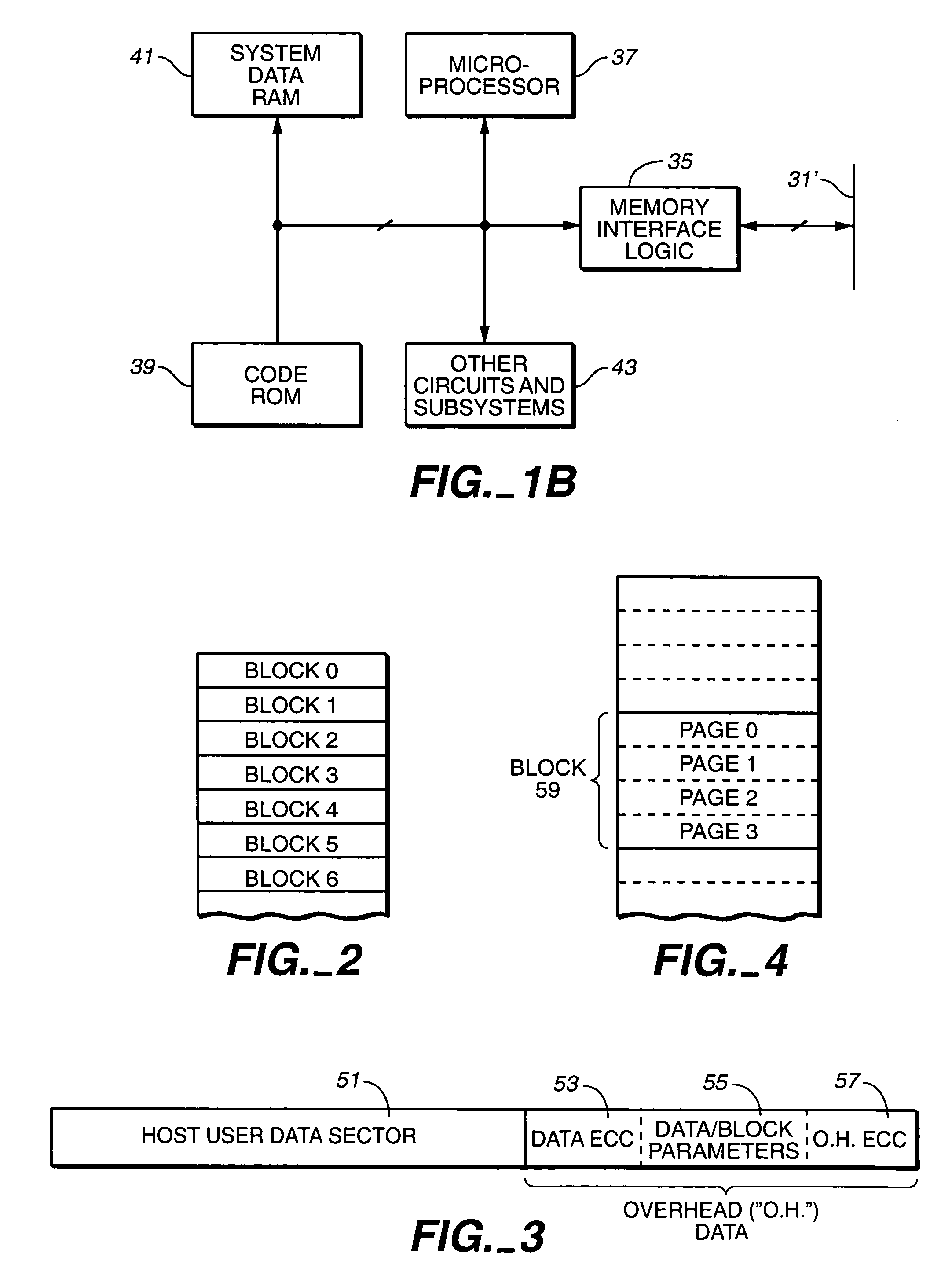

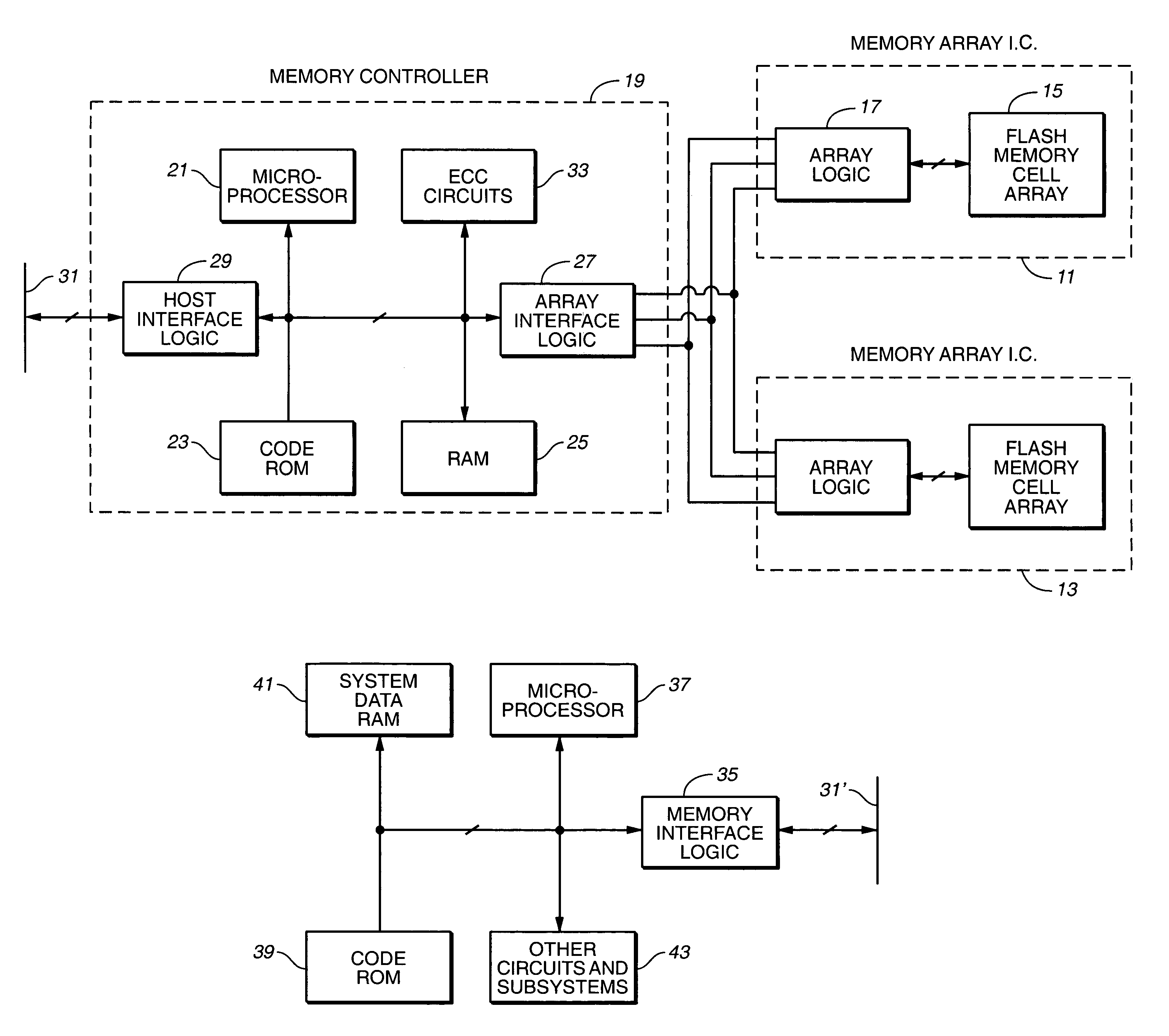

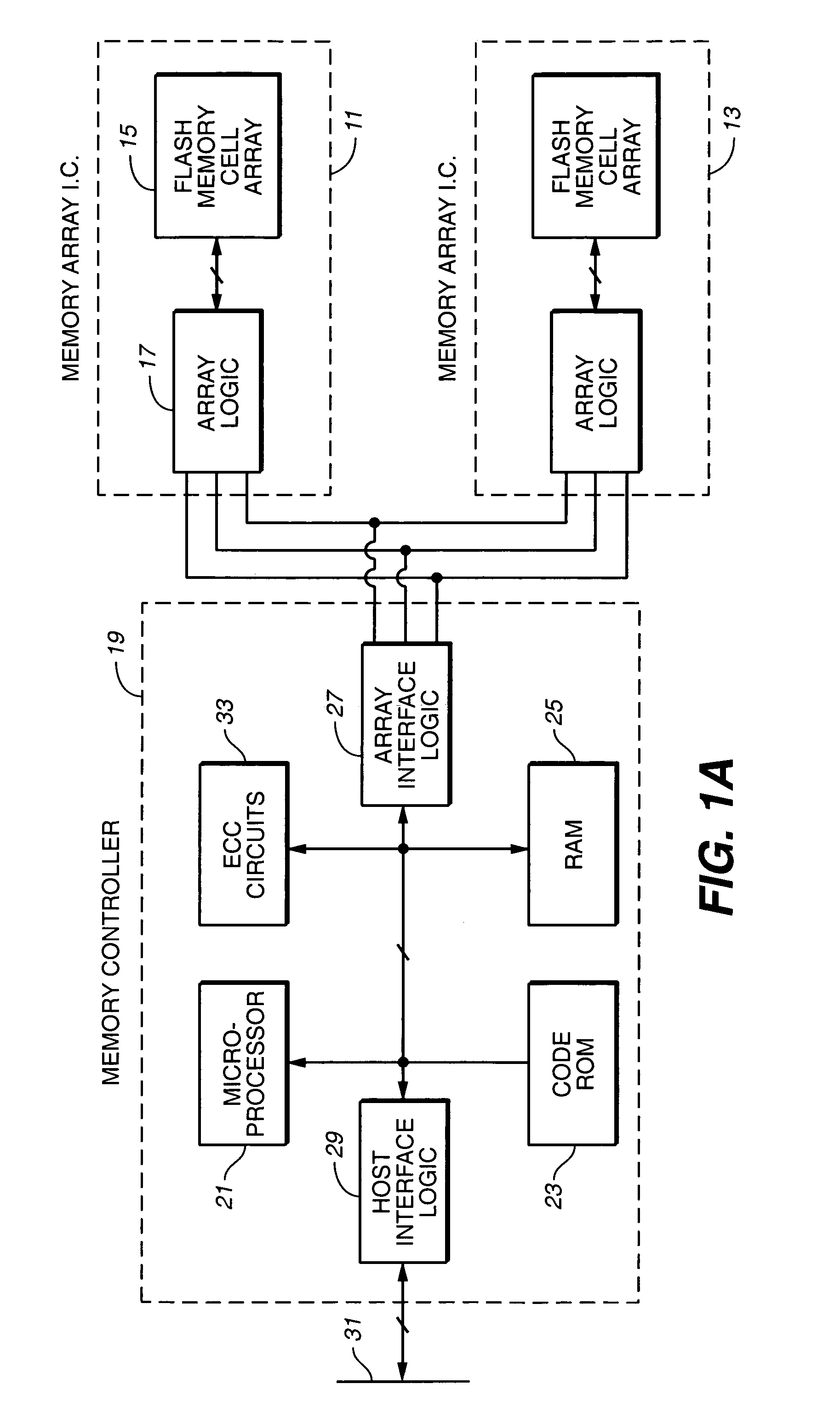

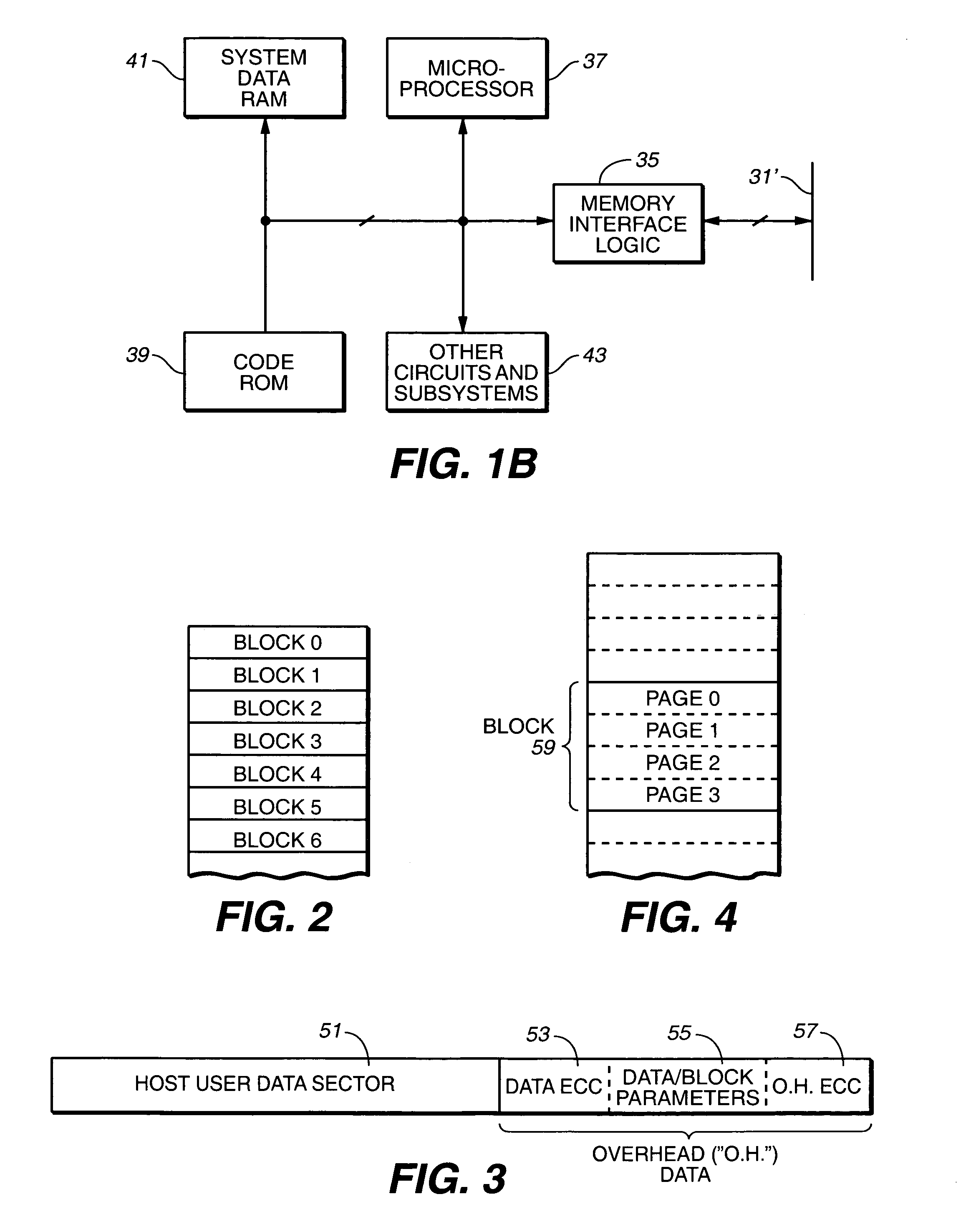

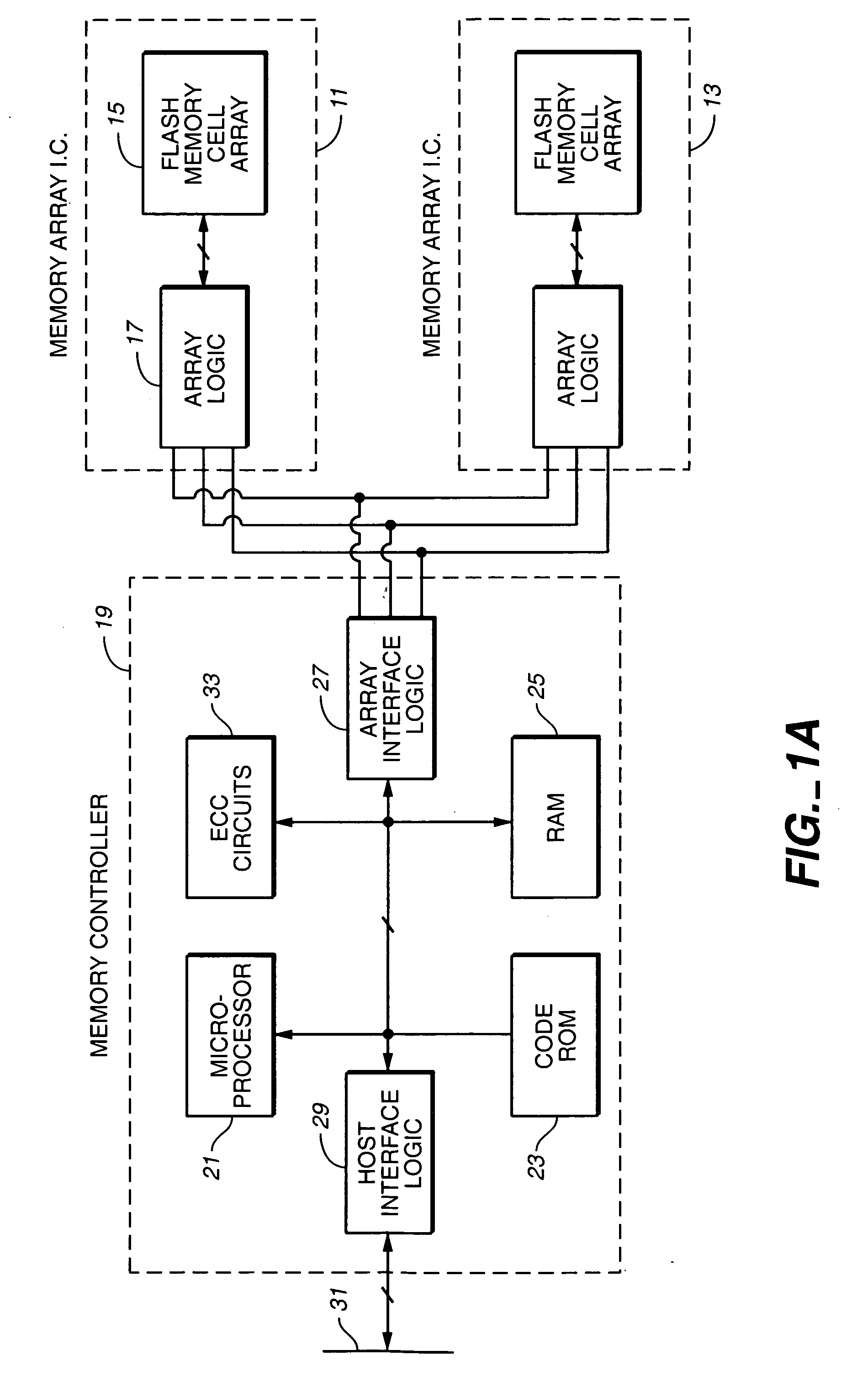

Flash memory data correction and scrub techniques

ActiveUS7012835B2Data disturbanceReduce storage dataMemory loss protectionRead-only memoriesData integrityData storing

In order to maintain the integrity of data stored in a flash memory that are susceptible to being disturbed by operations in adjacent regions of the memory, disturb events cause the data to be read, corrected and re-written before becoming so corrupted that valid data cannot be recovered. The sometimes conflicting needs to maintain data integrity and system performance are balanced by deferring execution of some of the corrective action when the memory system has other high priority operations to perform. In a memory system utilizing very large units of erase, the corrective process is executed in a manner that is consistent with efficiently rewriting an amount of data much less than the capacity of a unit of erase.

Owner:SANDISK TECH LLC

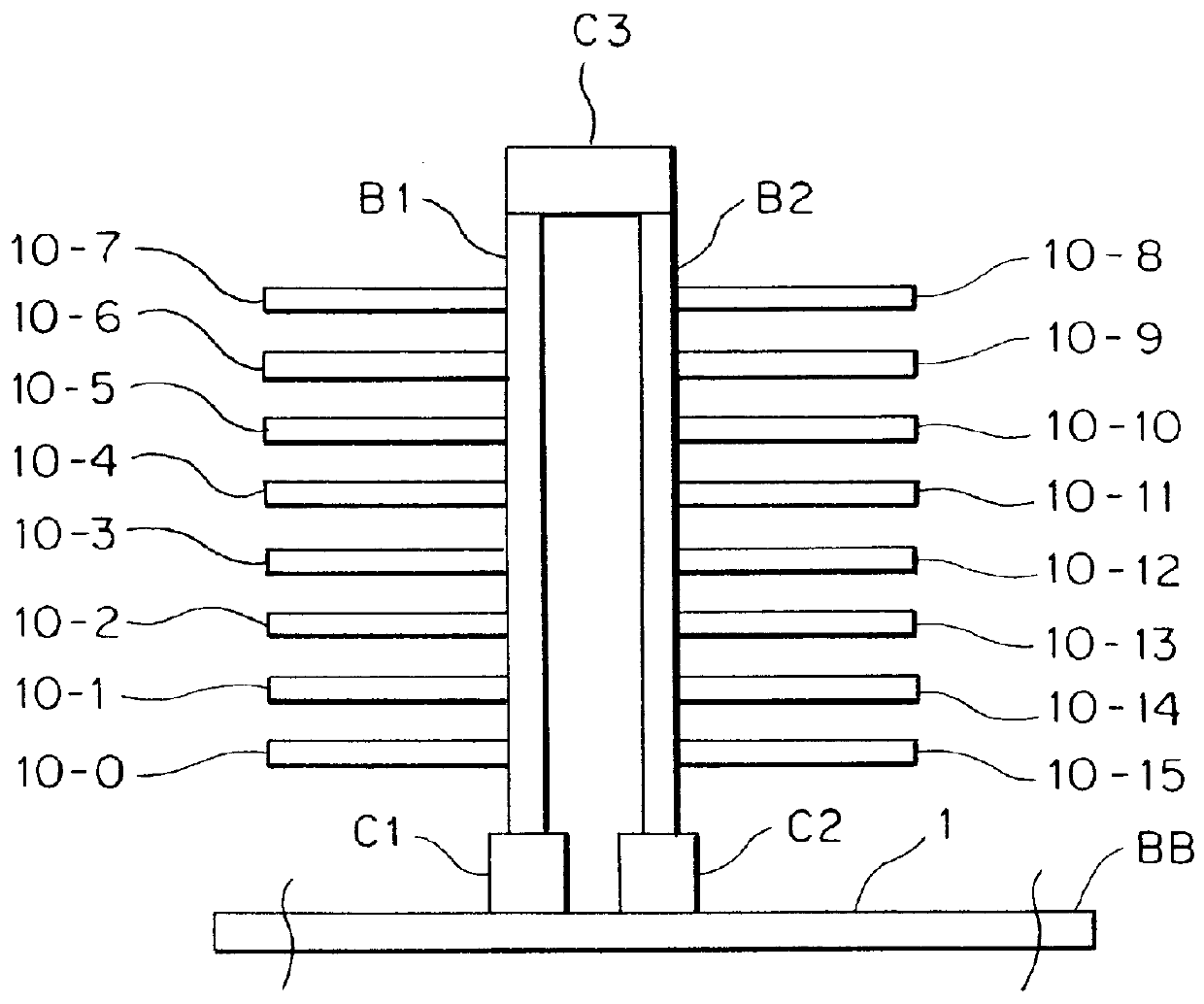

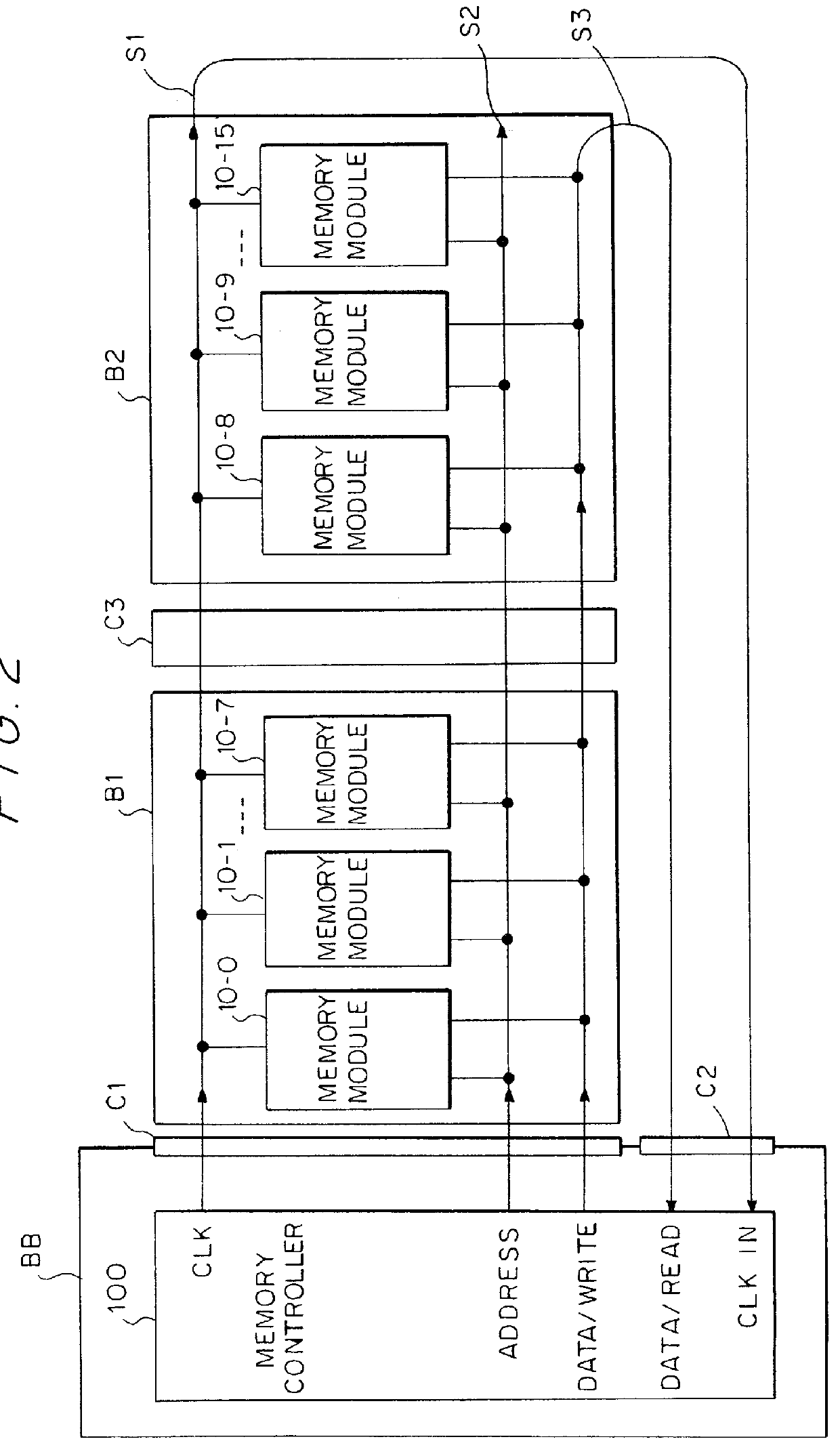

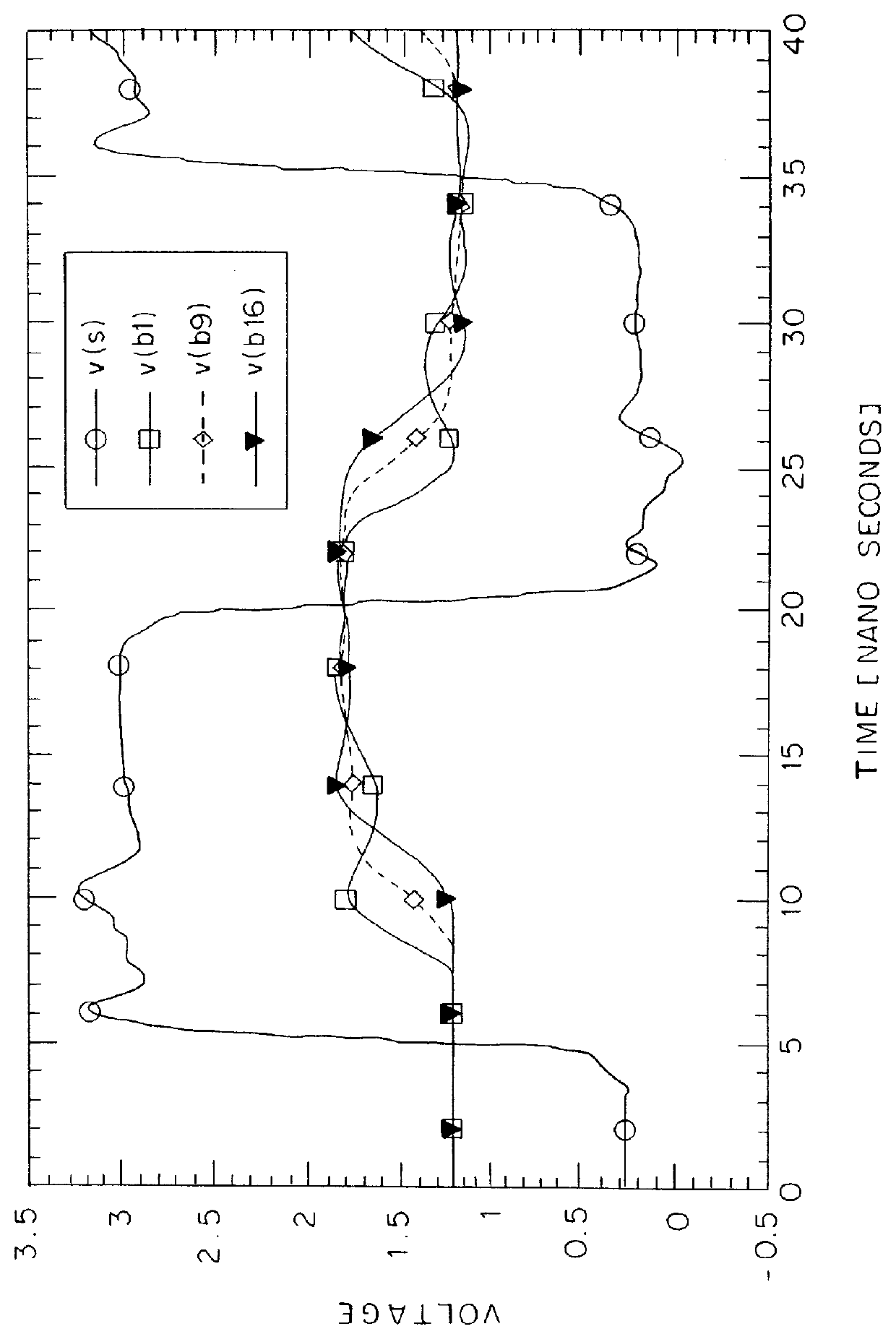

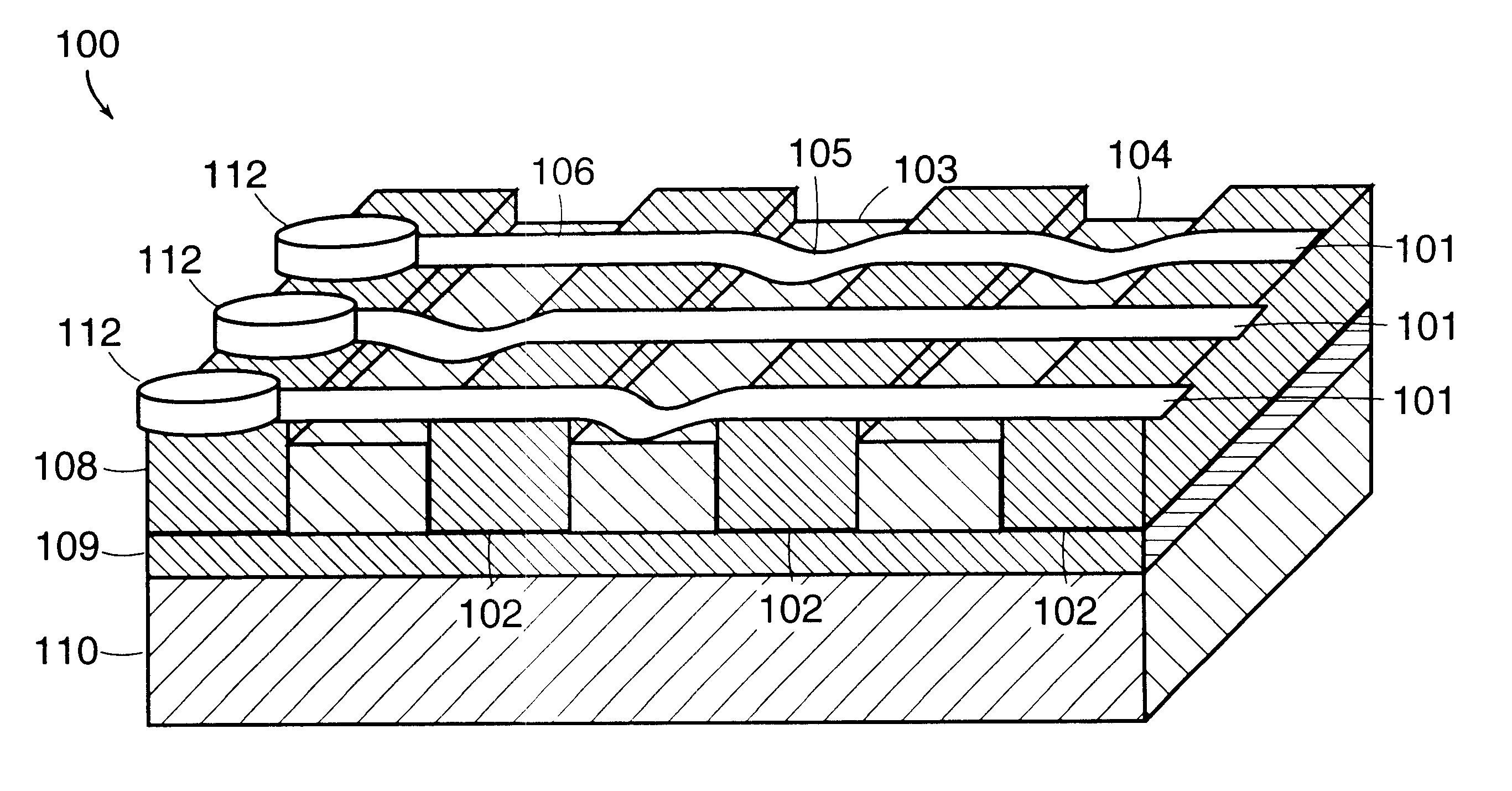

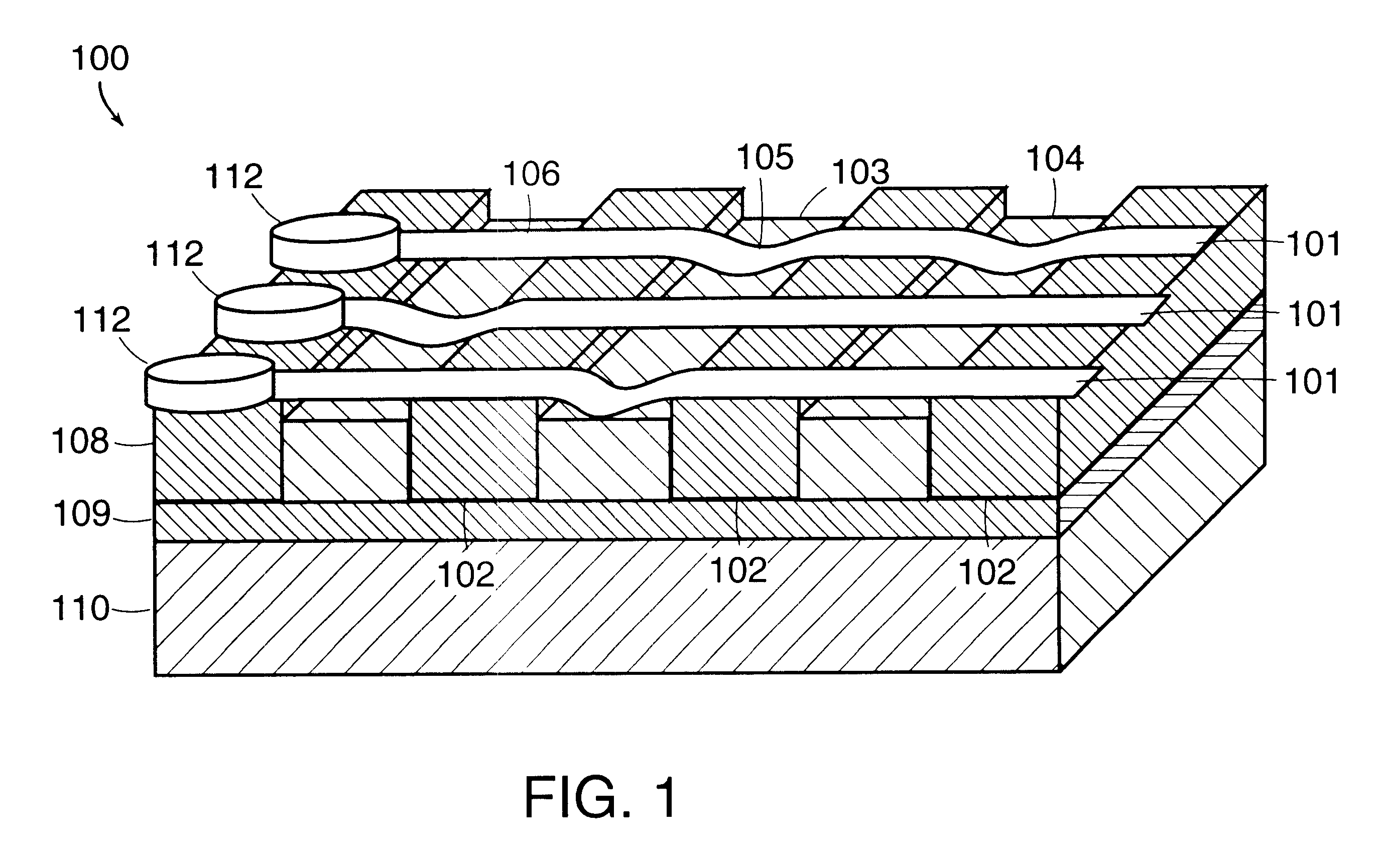

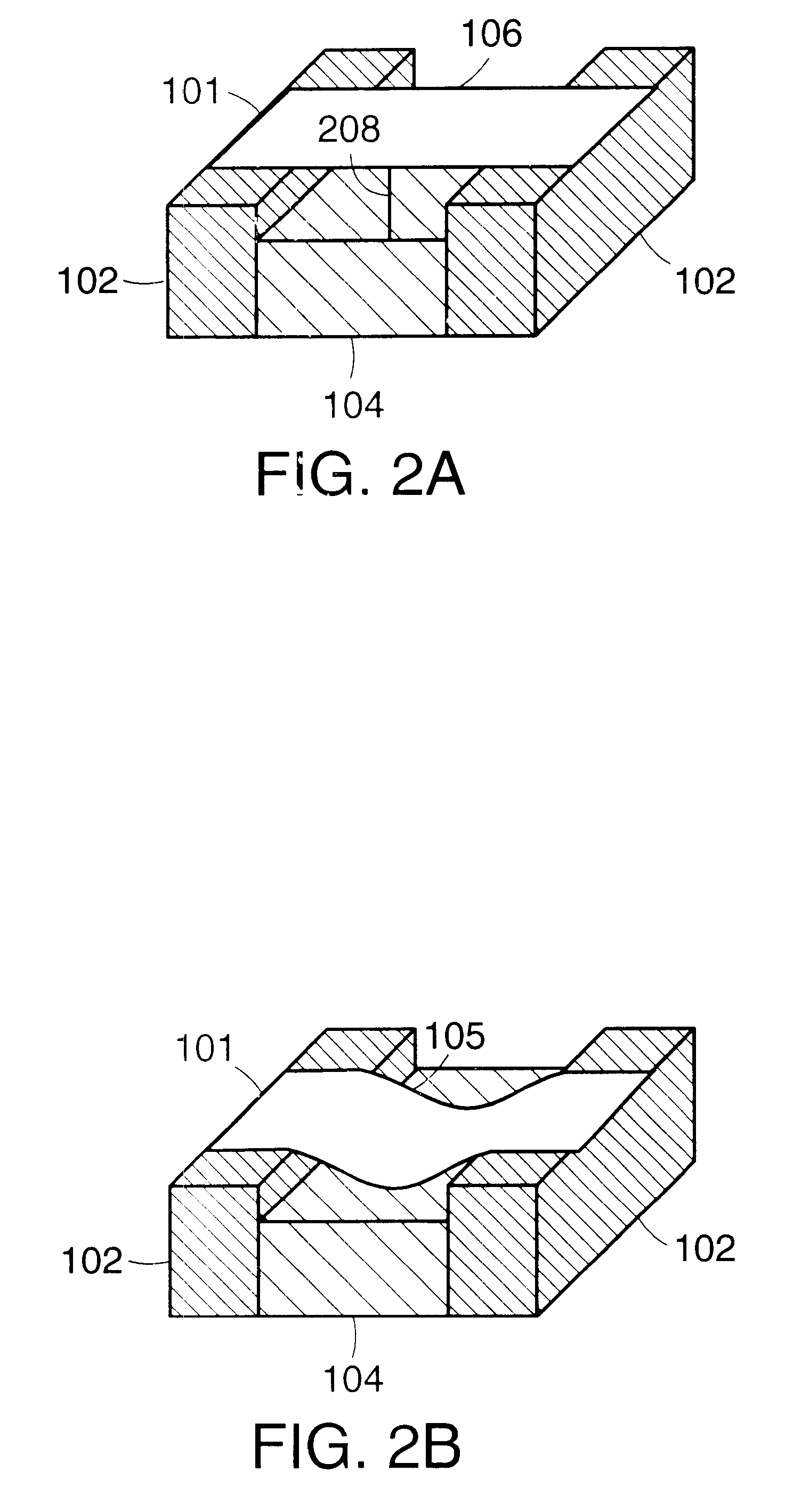

Source-clock-synchronized memory system and memory unit

InactiveUS6034878ALarge data storage capacity per memoryImprove installation densityMemory adressing/allocation/relocationDigital storageMemory bankComputer module

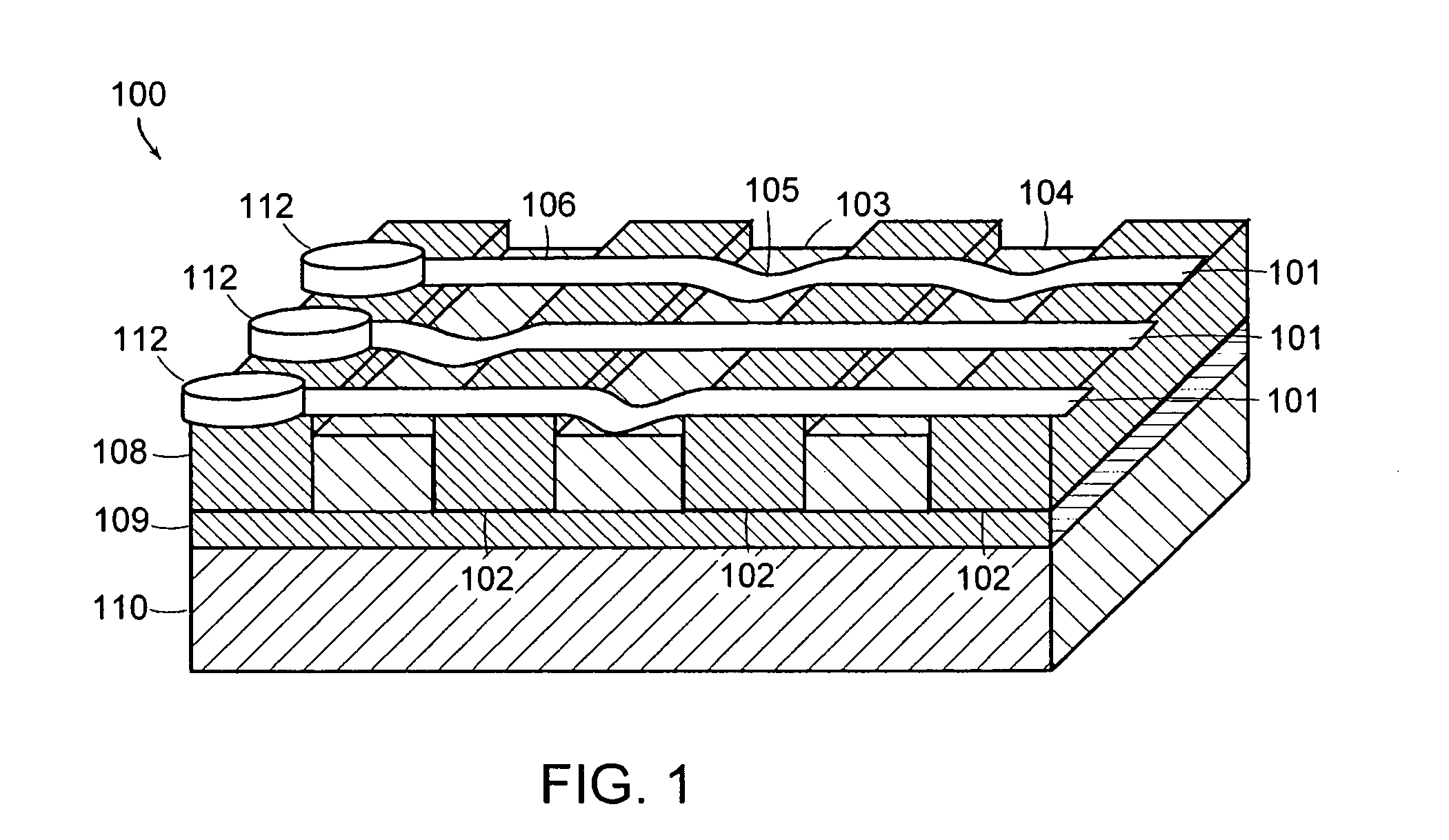

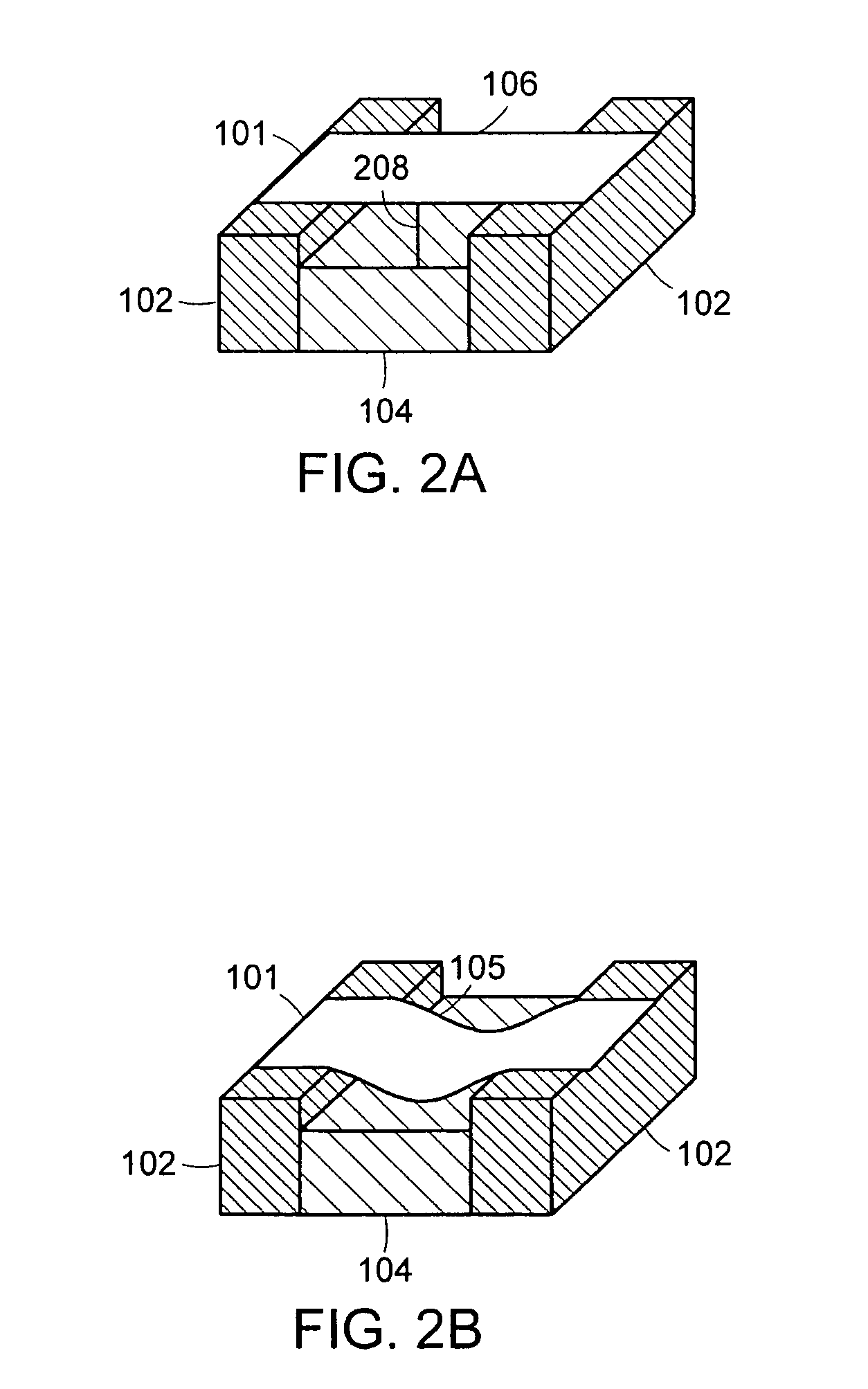

A source-clock-synchronized memory system having a large data storage capacity per memory bank and a high mounting density. The invention includes a memory unit having a first memory riser board B1 mounted on a base board through a first connector C1 and a second memory riser board B2 mounted on the base board BB through a second connector C2. The first memory riser board has a plurality of first memory modules mounted on the front surface thereof and the second memory riser board has a plurality of second memory modules mounted on the front surface thereof. The first and second memory riser boards are arranged in such a way that the back surface of the first memory riser board faces the back surface of the second memory riser board. The invention further includes a board linking connector for connecting signal lines on the first memory riser board to corresponding signal lines on the second memory riser board.

Owner:DELTA KOGYO CO LTD +1

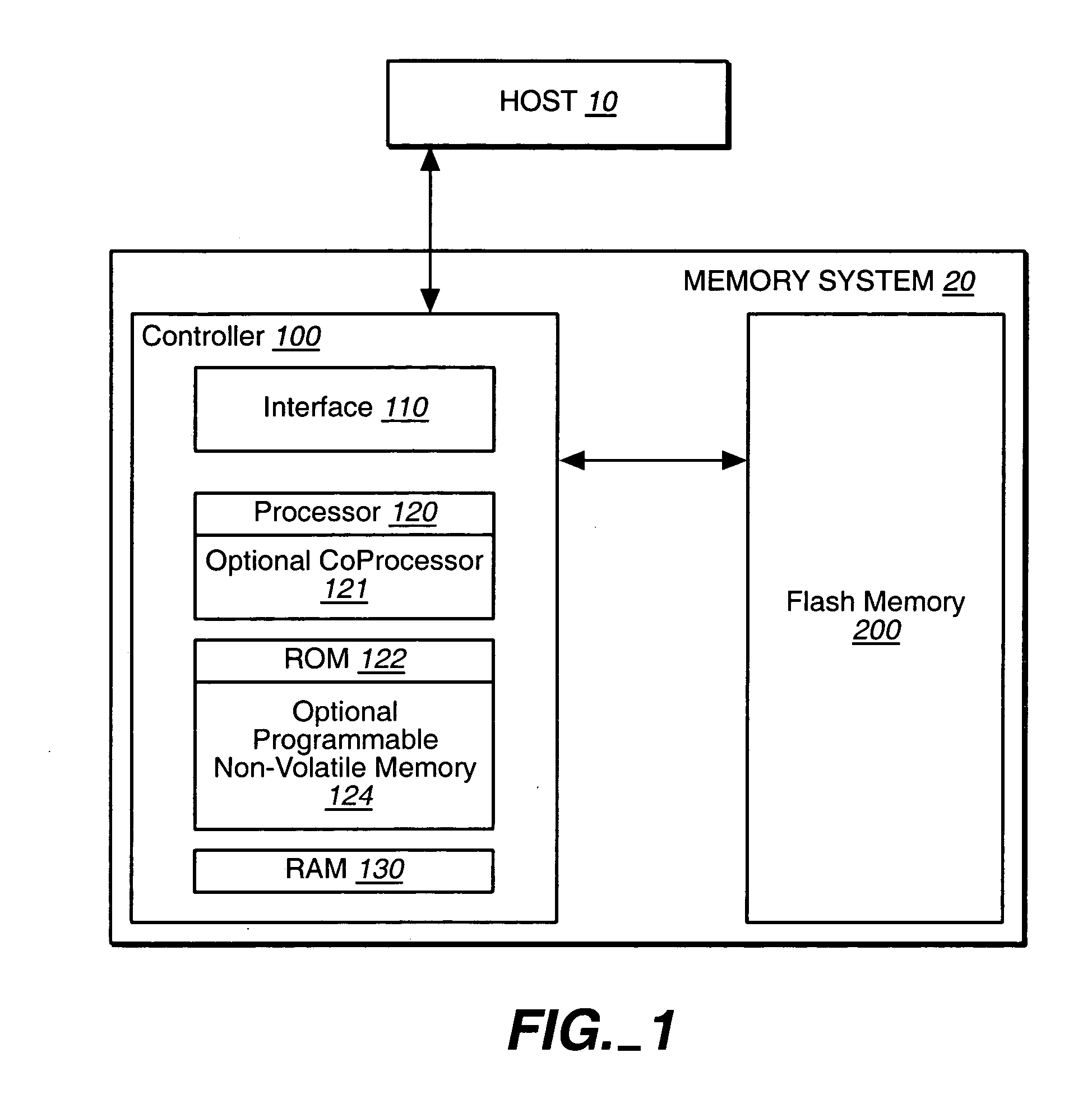

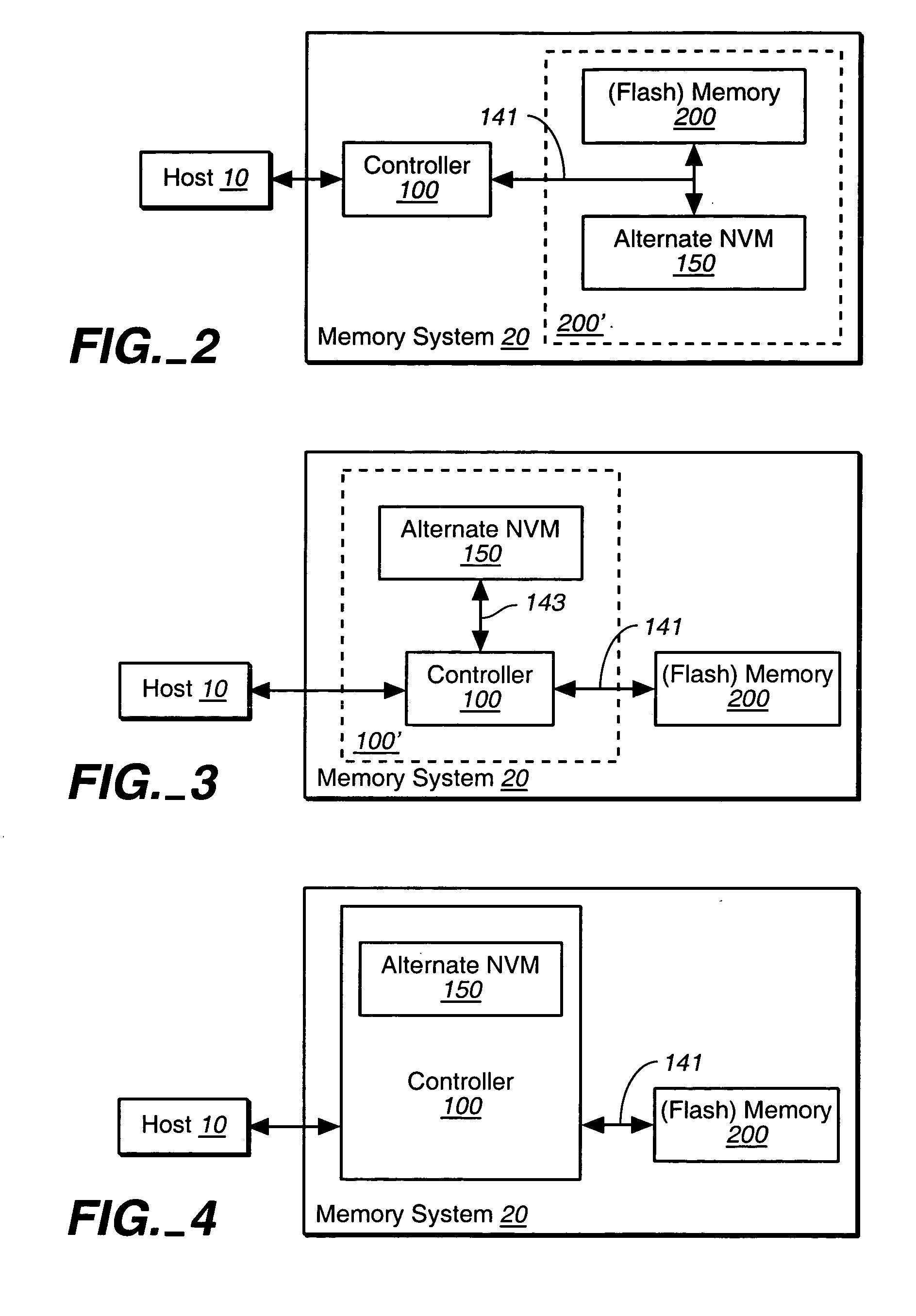

Hybrid non-volatile memory system

InactiveUS20050251617A1Easy accessMemory architecture accessing/allocationInput/output to record carriersData controlControl data

The present invention presents a hybrid non-volatile system that uses non-volatile memories based on two or more different non-volatile memory technologies in order to exploit the relative advantages of each these technology with respect to the others. In an exemplary embodiment, the memory system includes a controller and a flash memory, where the controller has a non-volatile RAM based on an alternate technology such as FeRAM. The flash memory is used for the storage of user data and the non-volatile RAM in the controller is used for system control data used by the control to manage the storage of host data in the flash memory. The use of an alternate non-volatile memory technology in the controller allows for a non-volatile copy of the most recent control data to be accessed more quickly as it can be updated on a bit by bit basis. In another exemplary embodiment, the alternate non-volatile memory is used as a cache where data can safely be staged prior to its being written to the to the memory or read back to the host.

Owner:SANDISK TECH LLC

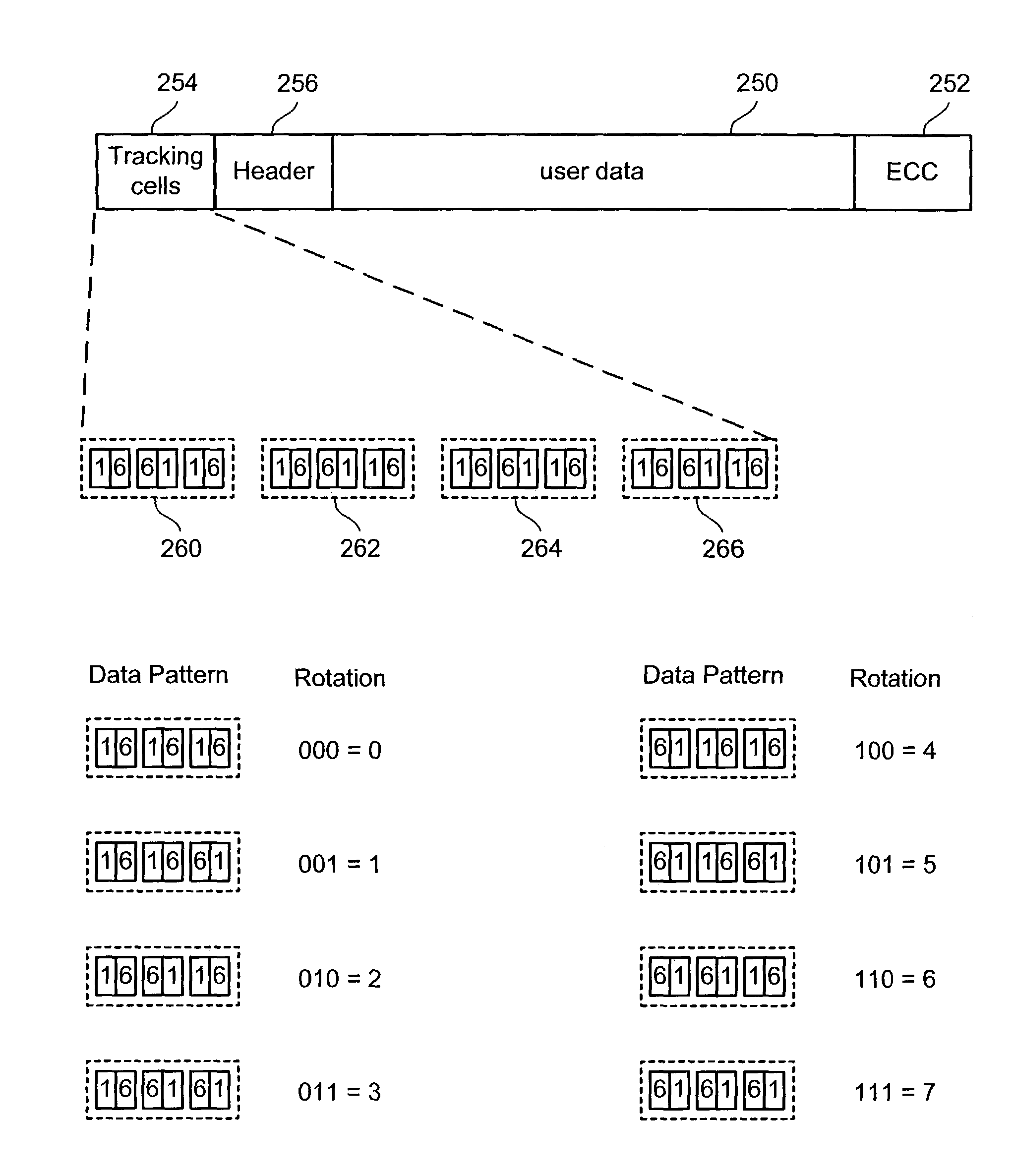

Tracking cells for a memory system

Tracking cells are used in a memory system to improve the read process. The tracking cells can provide an indication of the quality of the data and can be used as part of a data recovery operation if there is an error. The tracking cells provide a means to adjust the read parameters to optimum levels in order to reflect the current conditions of the memory system. Additionally, some memory systems that use multi-state memory cells will apply rotation data schemes to minimize wear. The rotation scheme can be encoded in the tracking cells based on the states of multiple tracking cells, which is decoded upon reading.

Owner:SANDISK TECH LLC

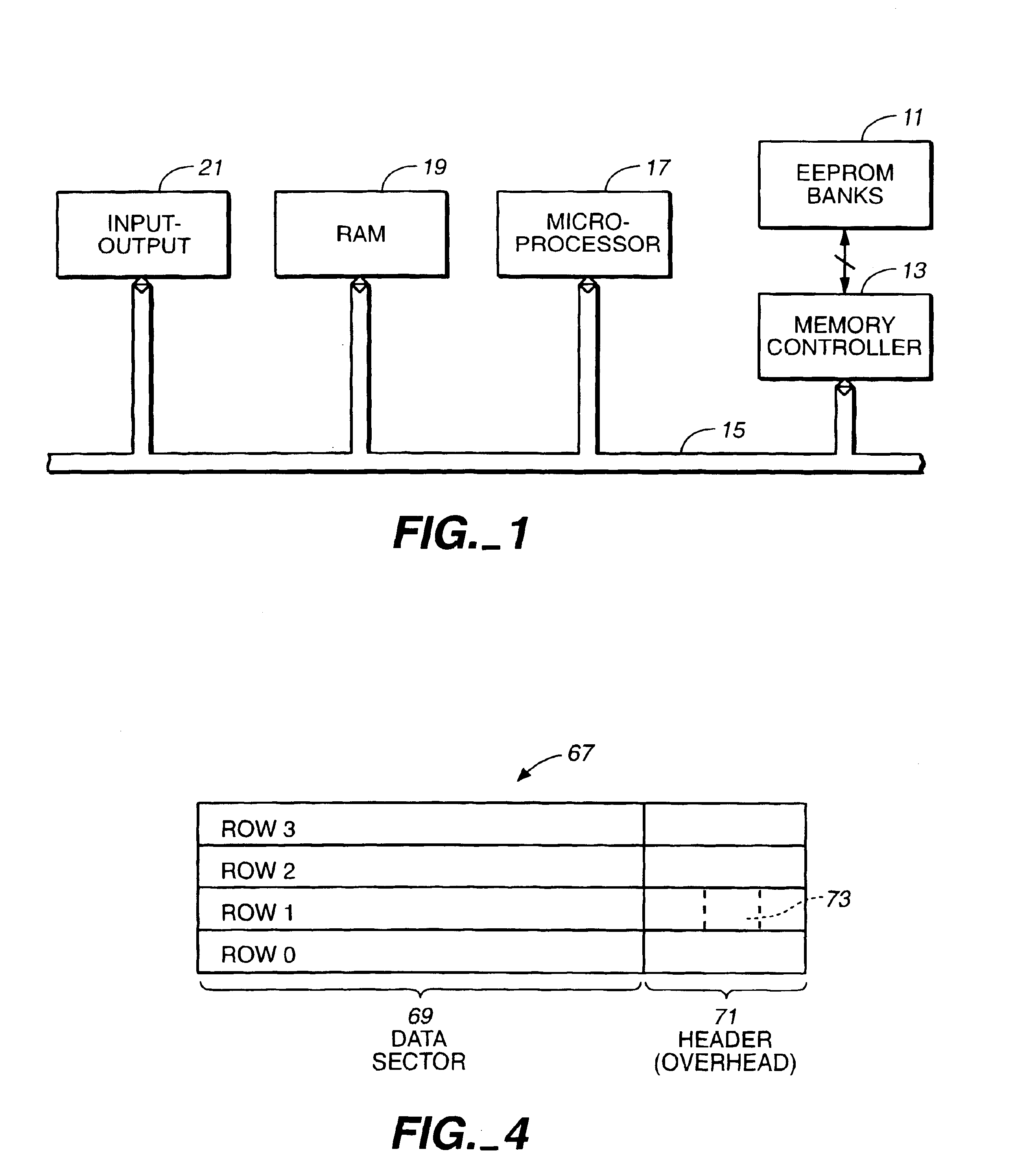

Wear leveling techniques for flash EEPROM systems

InactiveUS6850443B2Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

Hybrid circuit having nanotube electromechanical memory

A hybrid memory system having electromechanical memory cells is disclosed. A memory cell core circuit has an array of electromechanical memory cells, in which each cell is a crossbar junction at least one element of which is a nanotube or a nanotube ribbon. An access circuit provides array addresses to the memory cell core circuit to select at least one corresponding cell. The access circuit is constructed of semiconductor circuit elements.

Owner:NANTERO

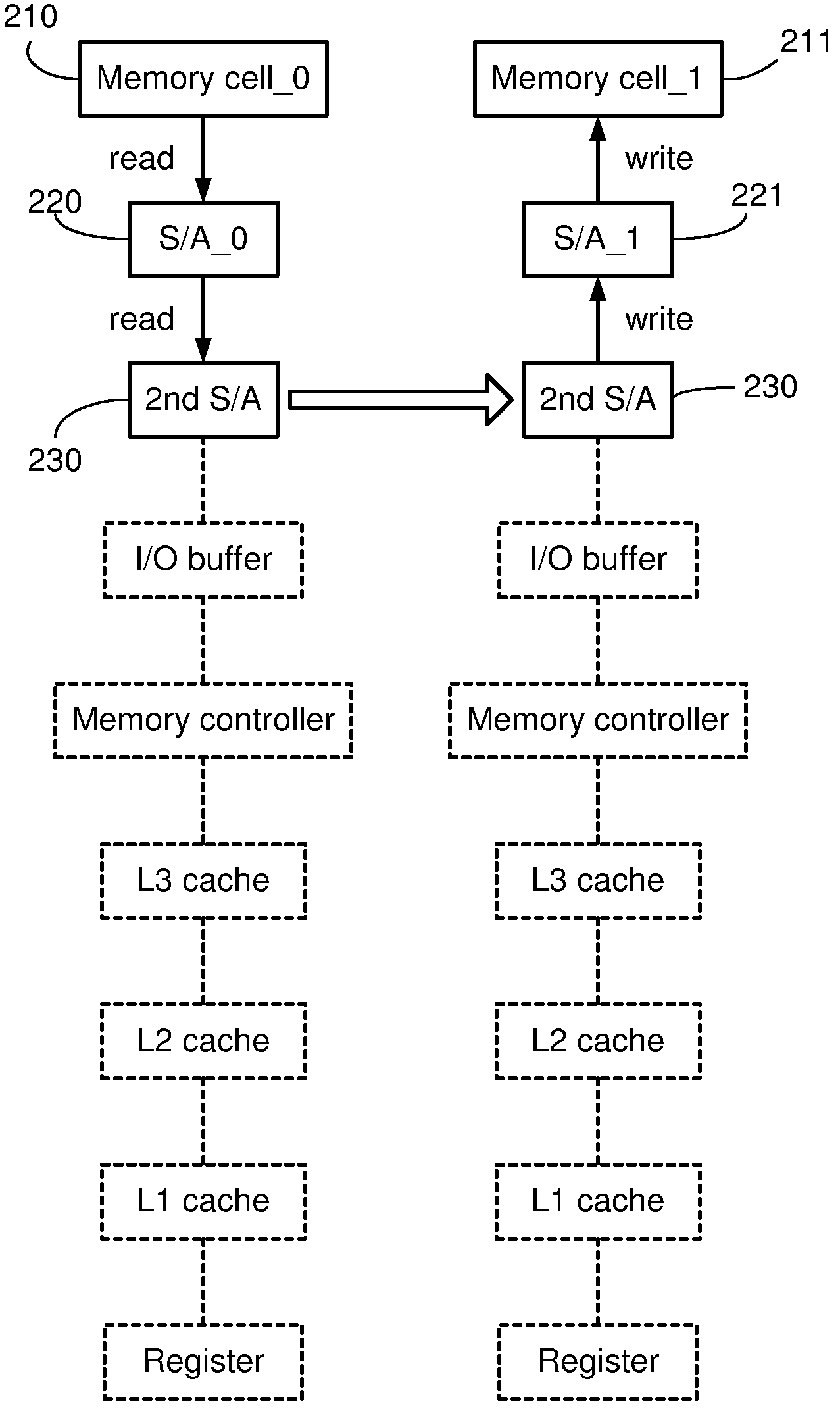

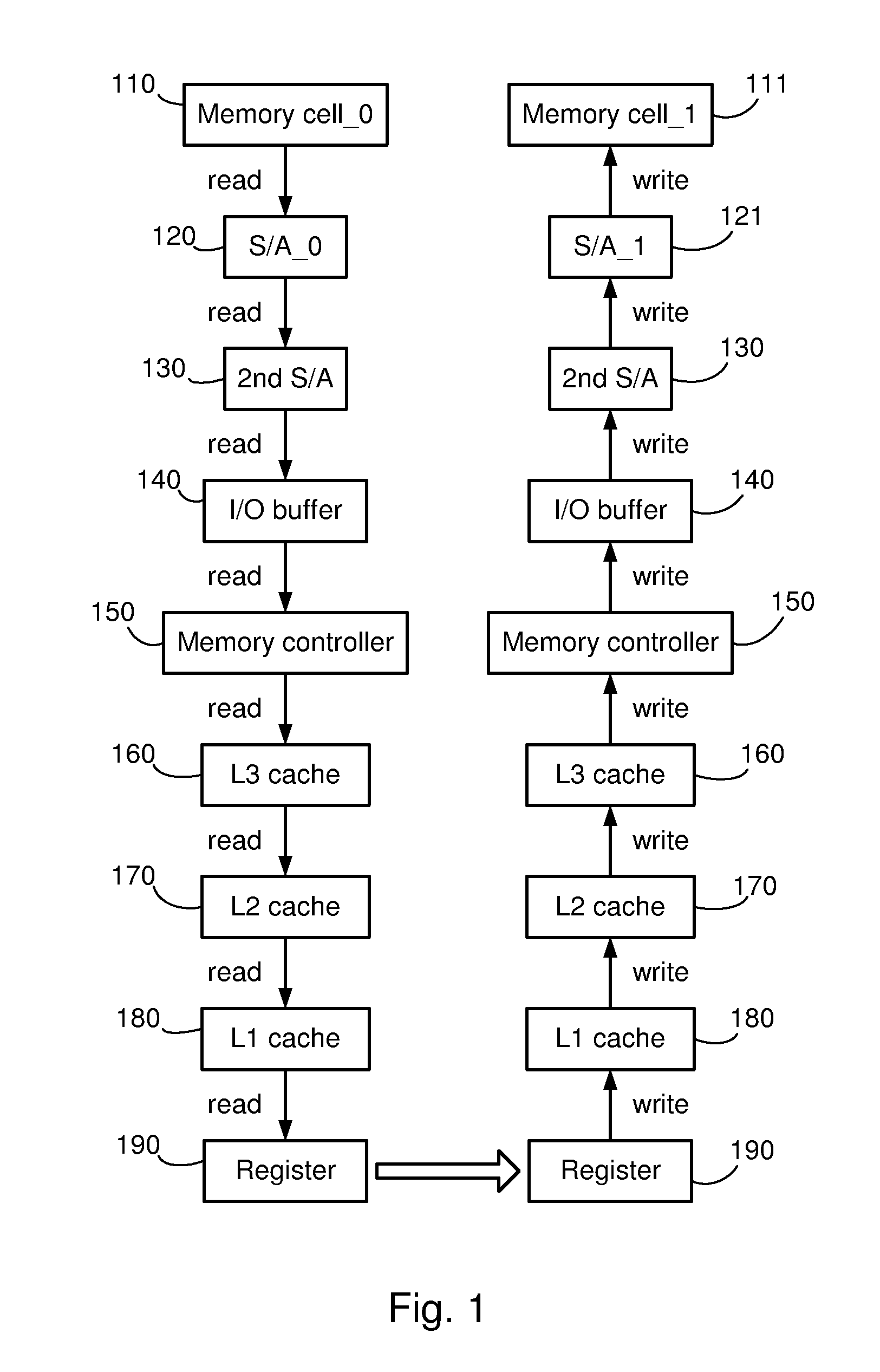

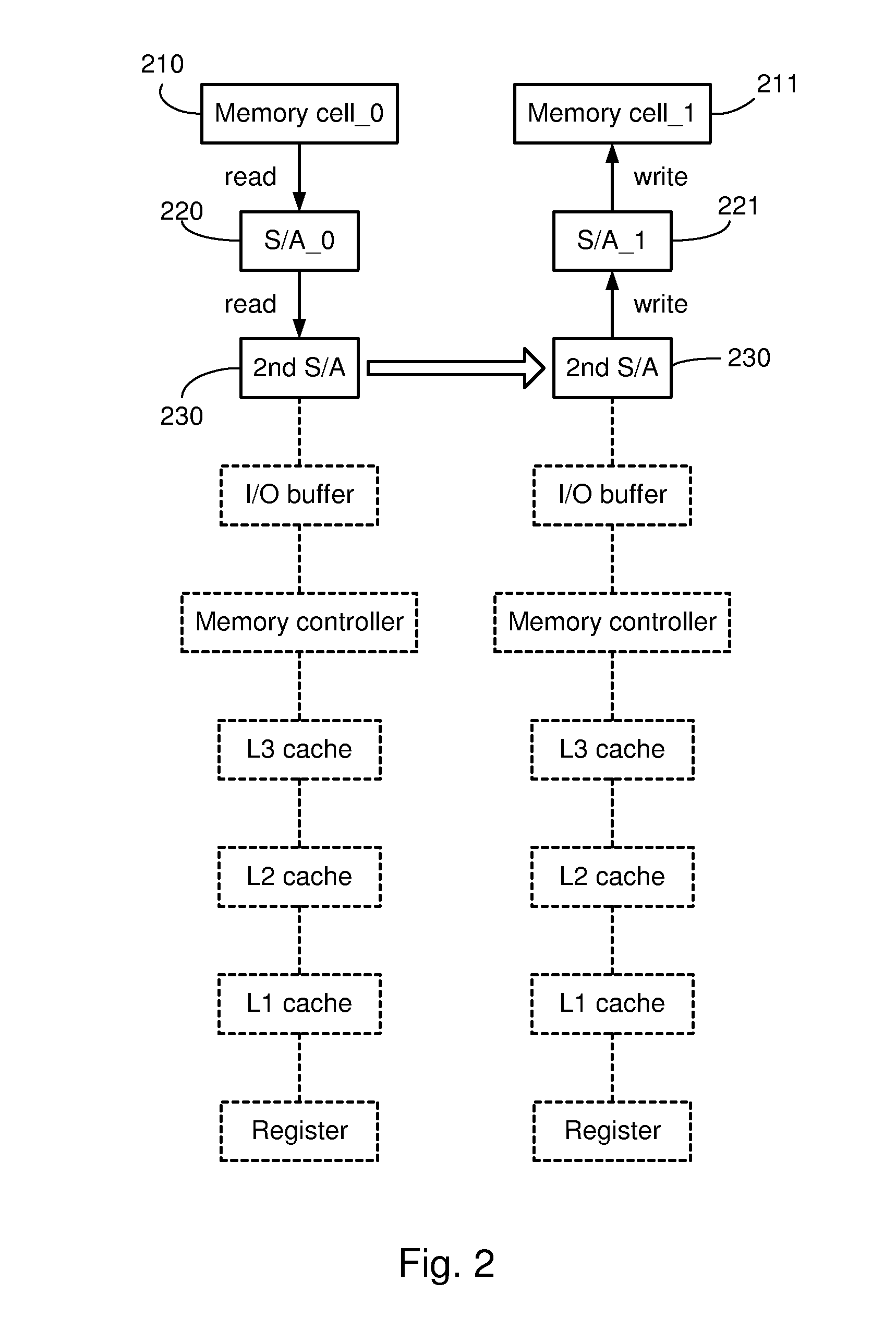

Systems and methods for data transfers between memory cells

Systems and methods for reducing the latency of data transfers between memory cells by enabling data to be transferred directly between sense amplifiers in the memory system. In one embodiment, a memory system uses a conventional DRAM memory structure having a pair of first-level sense amplifiers, a second-level sense amplifier and control logic for the sense amplifiers. Each of the sense amplifiers is configured to be selectively coupled to a data line. In a direct data transfer mode, the control logic generates control signals that cause the sense amplifiers to transfer data from a first one of the first-level sense amplifiers (a source sense amplifier) to the second-level sense amplifier, and from there to a second one of the first-level sense amplifiers (a destination sense amplifier.) The structure of these sense amplifiers is conventional, and the operation of the system is enabled by modified control logic.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

Tracking cells for a memory system

Tracking cells are used in a memory system to improve the read process. The tracking cells can provide an indication of the quality of the data and can be used as part of a data recovery operation if there is an error. The tracking cells provide a means to adjust the read parameters to optimum levels in order to reflect the current conditions of the memory system. Additionally, some memory systems that use multi-state memory cells will apply rotation data schemes to minimize wear. The rotation scheme can be encoded in the tracking cells based on the states of multiple tracking cells, which is decoded upon reading.

Owner:SANDISK TECH LLC

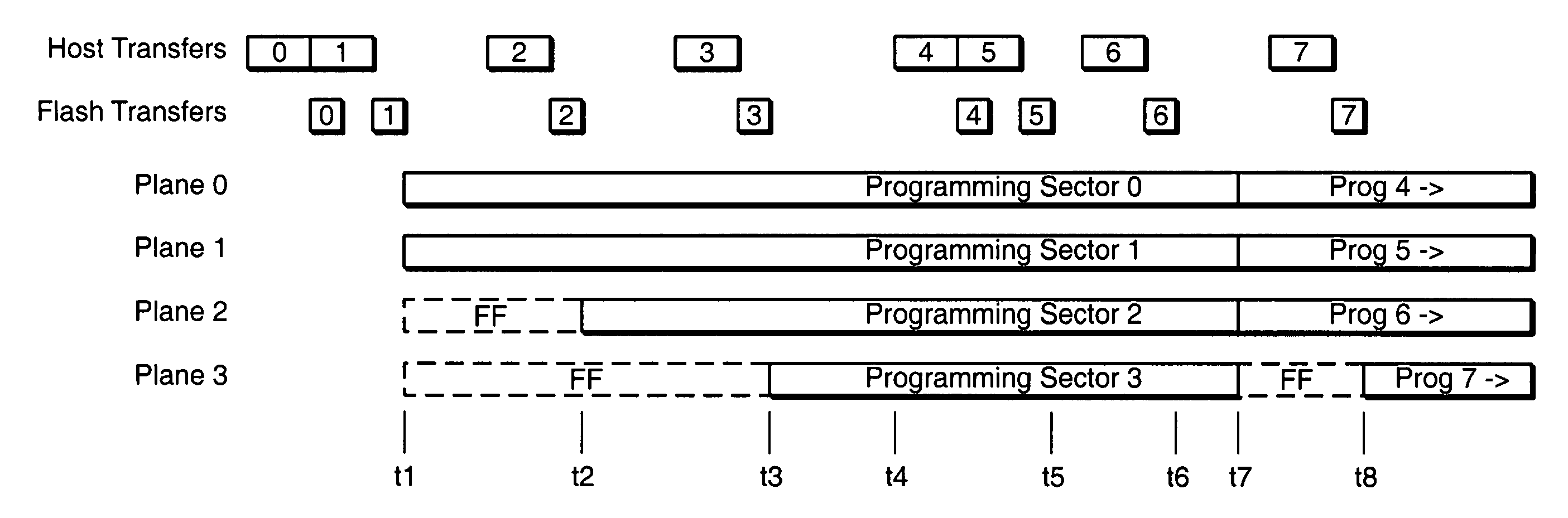

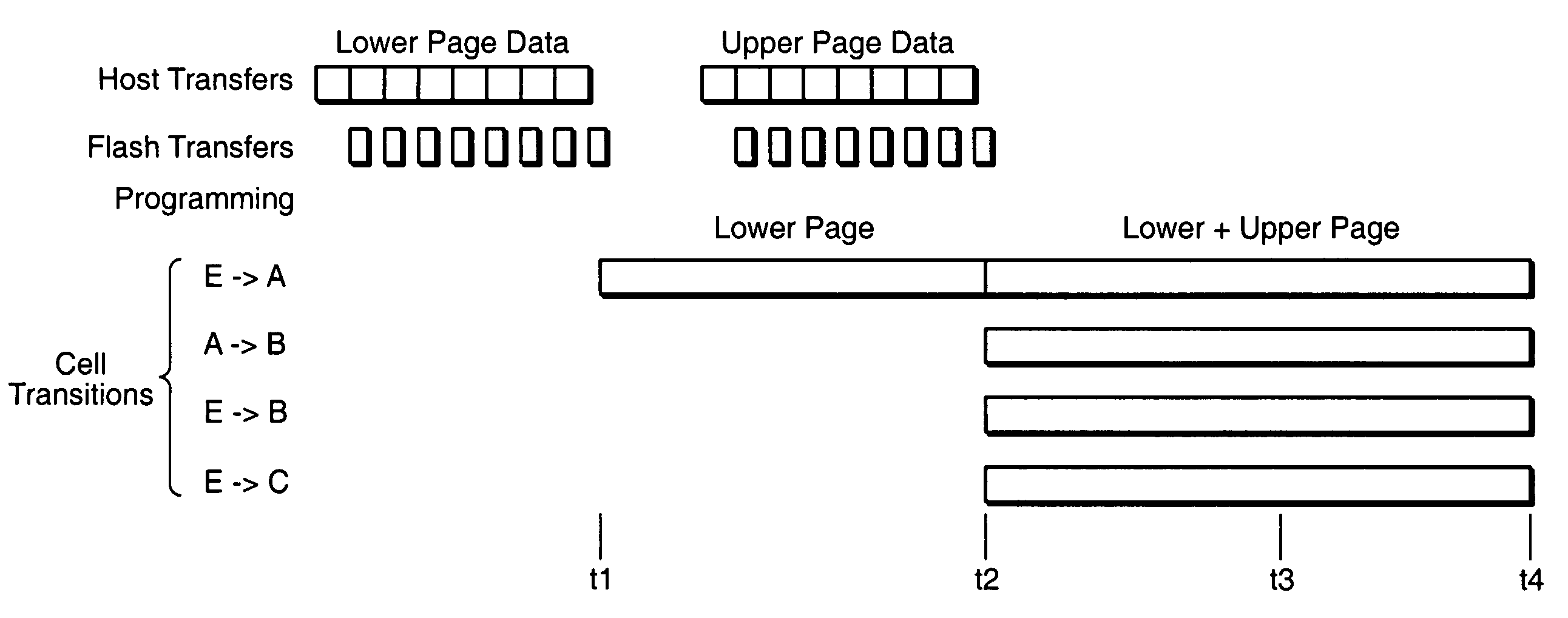

Pipelined programming of non-volatile memories using early data

ActiveUS20060126390A1Improve performanceRead-only memoriesDigital storageFull dataProgramming process

The present invention presents techniques whereby a memory system interrupts a programming process and restarts it including additional data. More specifically, when a memory system programs data into a group of cells together as programming unit, programming can begin with less than the full data content which the group can hold. In one embodiment, the present invention allows overlapped programming of upper and lower data pages, where once the memory begins programming the lower logical data page, if data is received for the upper page assigned to the same physical page, programming is interrupted and recommenced with the concurrent programming of both the upper and the loser pages. In a complimentary embodiment, when a page contains multiple sectors of data, programming of the physical page can begin when one or more, but less than all, of the sectors forming the corresponding logical page have been received, stopped and restarted to include additional sectors of the page.

Owner:SANDISK TECH LLC

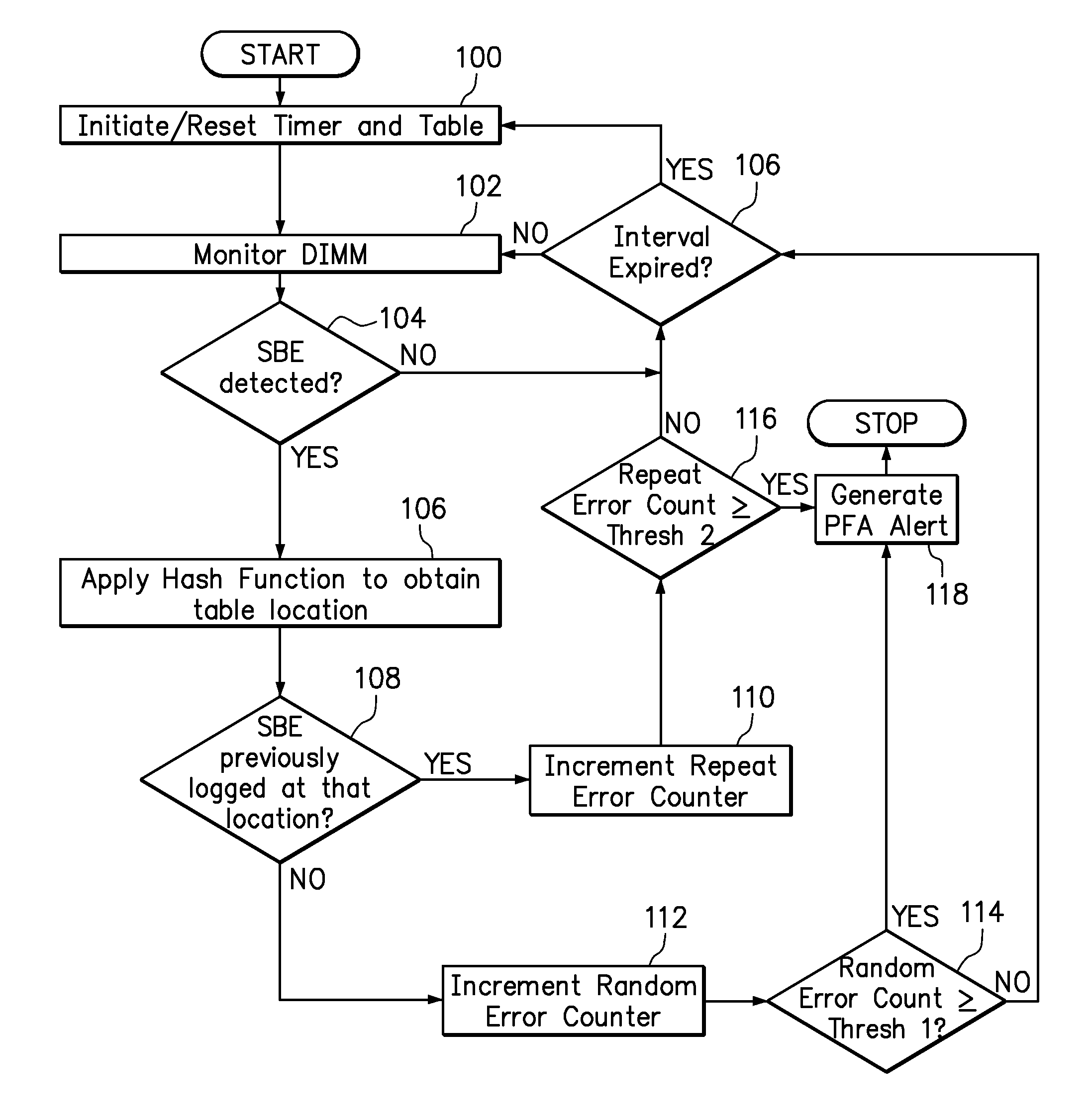

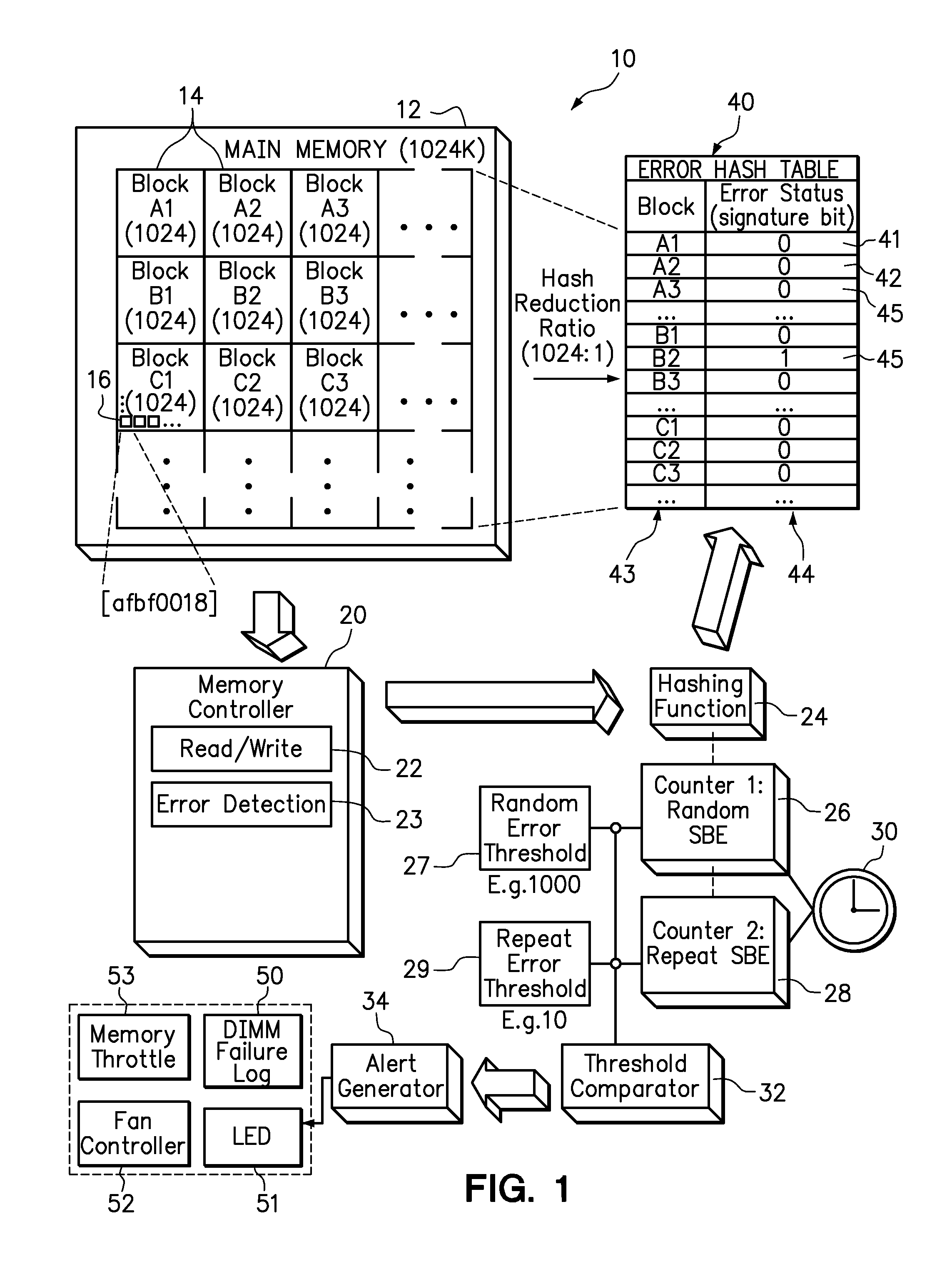

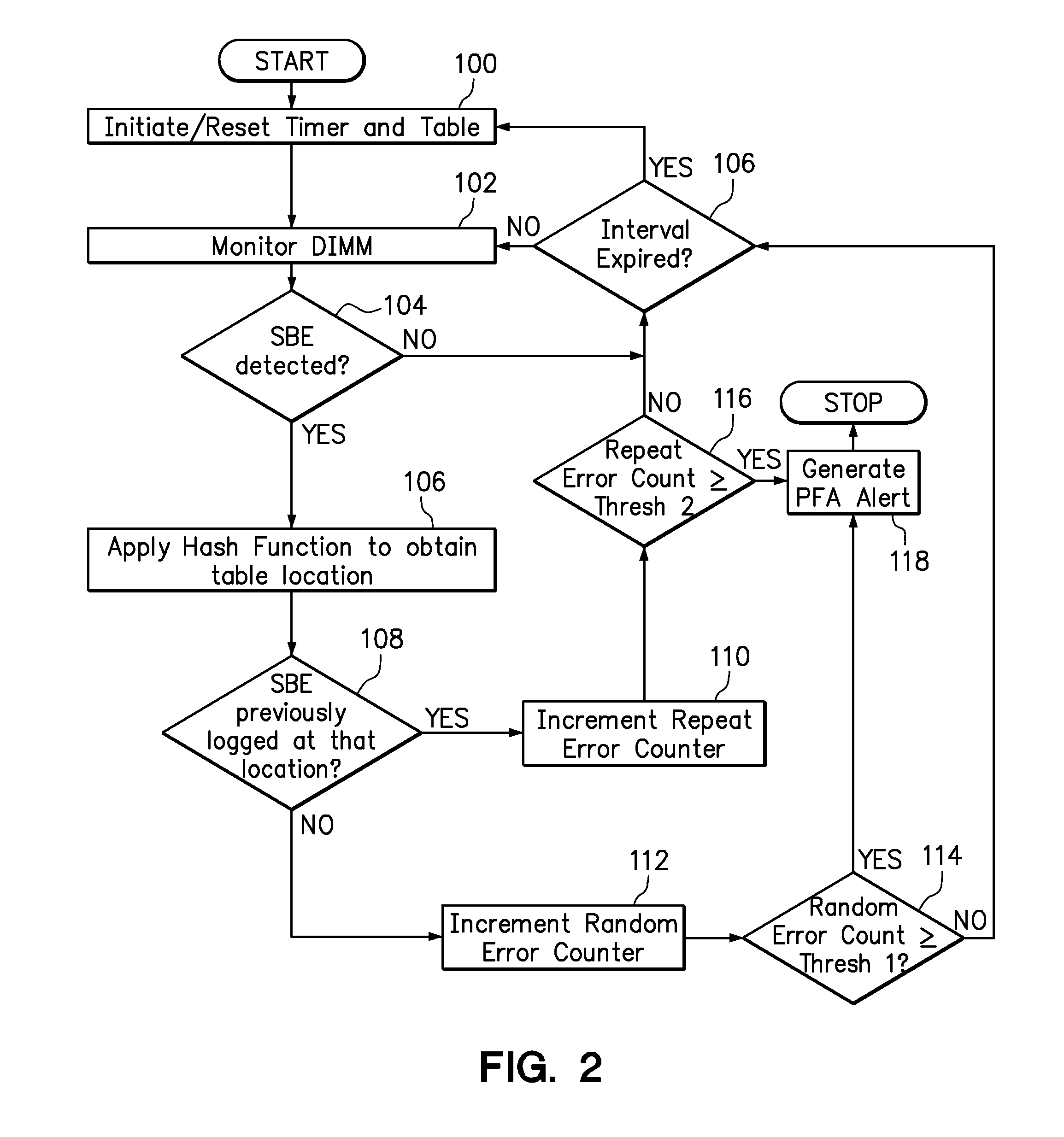

Use of hashing function to distinguish random and repeat errors in a memory system

One embodiment provides an error detection method wherein single-bit errors in a memory module are detected and identified as being a random error or a repeat error. Each identified random error and each identified repeat error occurring in a time interval is counted. An alert is generated in response to a number of identified random errors reaching a random-error threshold or a number of identified repeat errors reaching a repeat-error threshold during the predefined interval. The repeat-error threshold is set lower than the random-error threshold. A hashing process may be applied to the memory address of each detected error to map the location of the error in the memory system to a corresponding location in an electronic table.

Owner:LENOVO GLOBAL TECH INT LTD

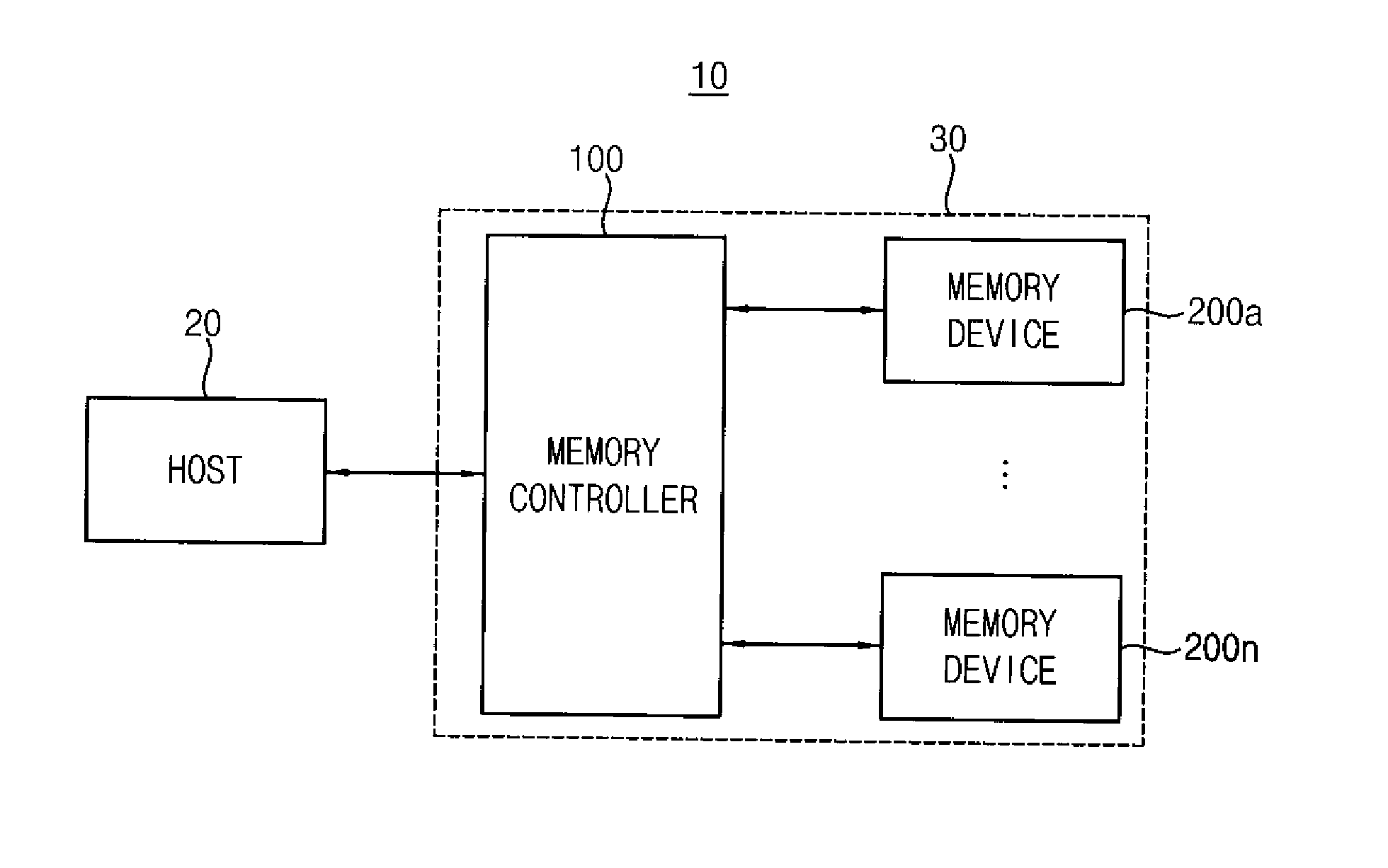

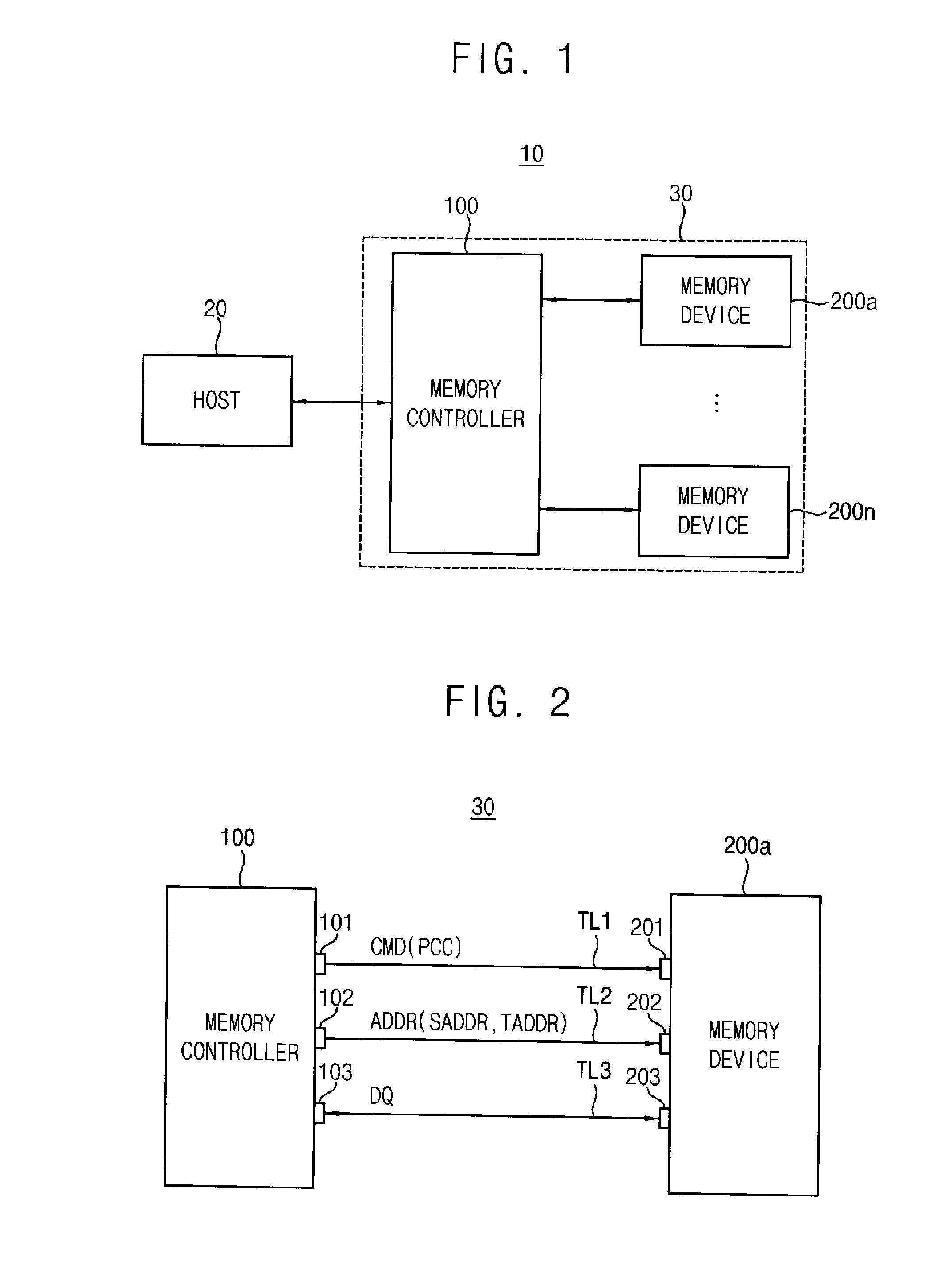

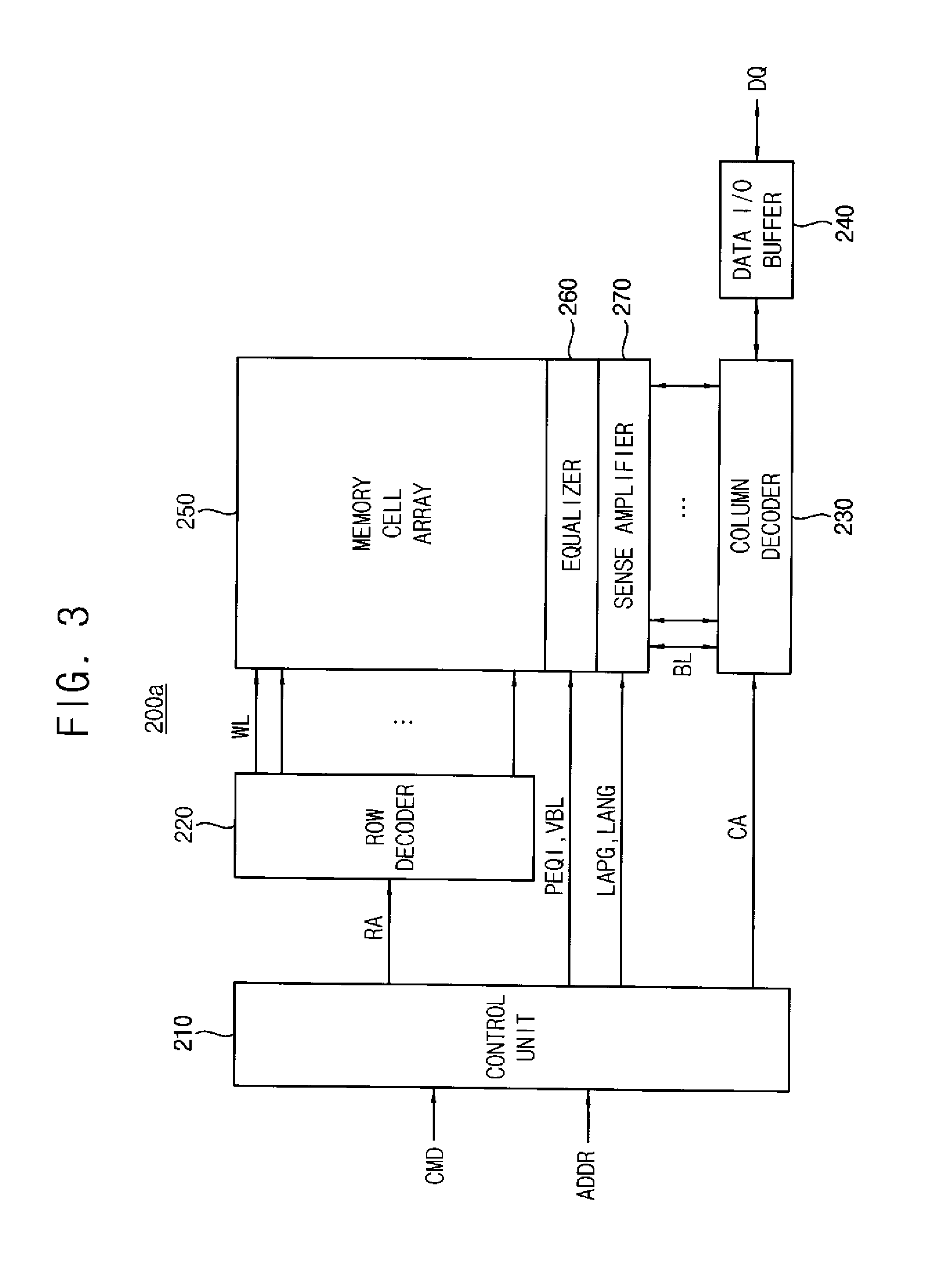

Methods of copying a page in a memory device and methods of managing pages in a memory system

A method of copying a page in a memory device having a plurality of memory blocks and a plurality of sets of bit lines is disclosed, wherein each of the plurality of memory blocks includes a plurality of pages, and each set of bit lines corresponds to a respective memory block, wherein first bit lines of a source memory block that includes a source page are respectively coupled to second bit lines of a target memory block that includes a target page. The method includes disconnecting between the first bit lines of thea source memory block including a source page and from the second bit lines of a the target memory block including a target page; transferring data stored in the source page to the first bit lines of the source memory block; transferring the data from the first bit lines of the source memory block to the second bit lines of the target memory block; and writing the data transferred to the second bit lines of the target memory block into the target page.

Owner:SAMSUNG ELECTRONICS CO LTD

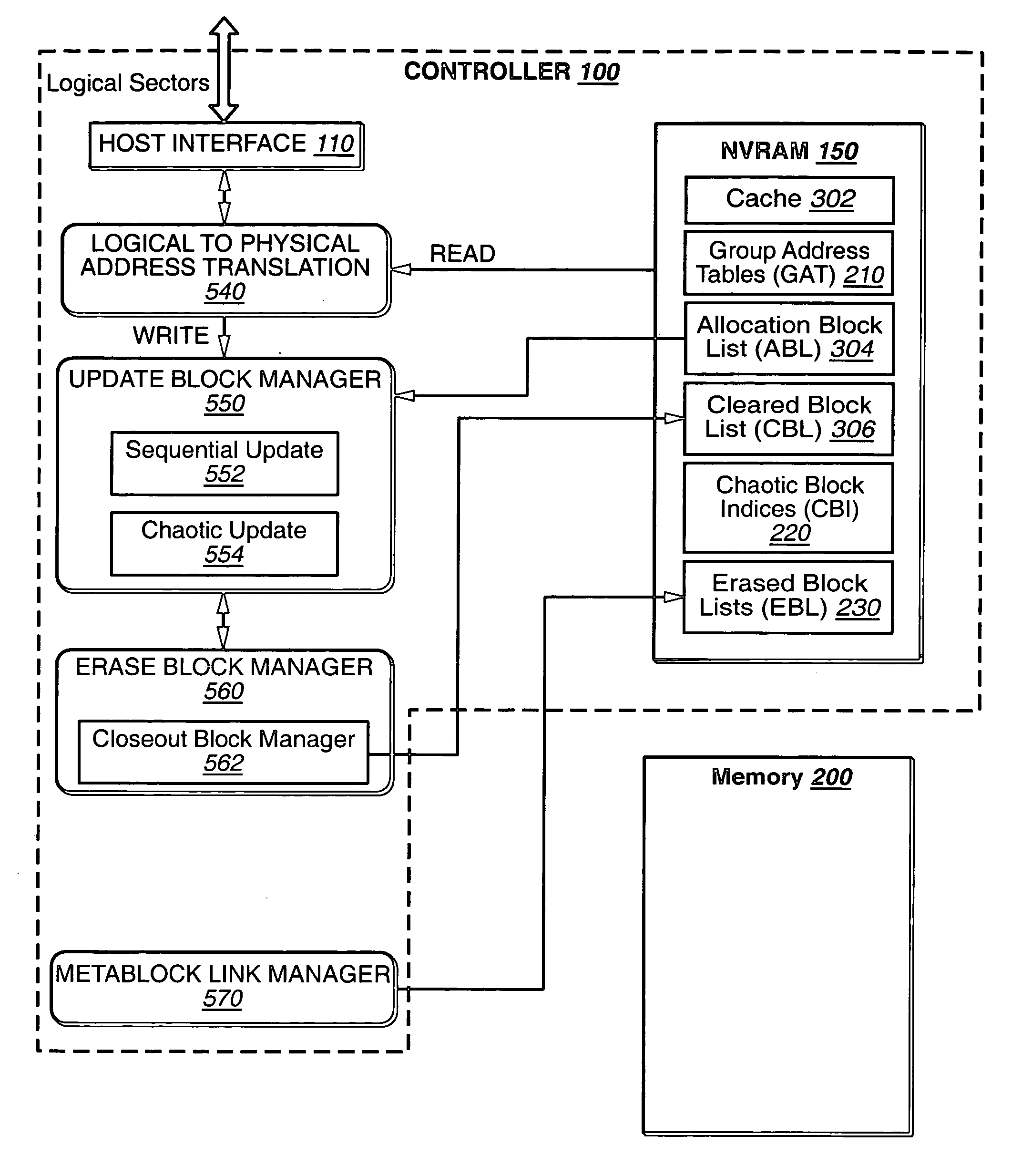

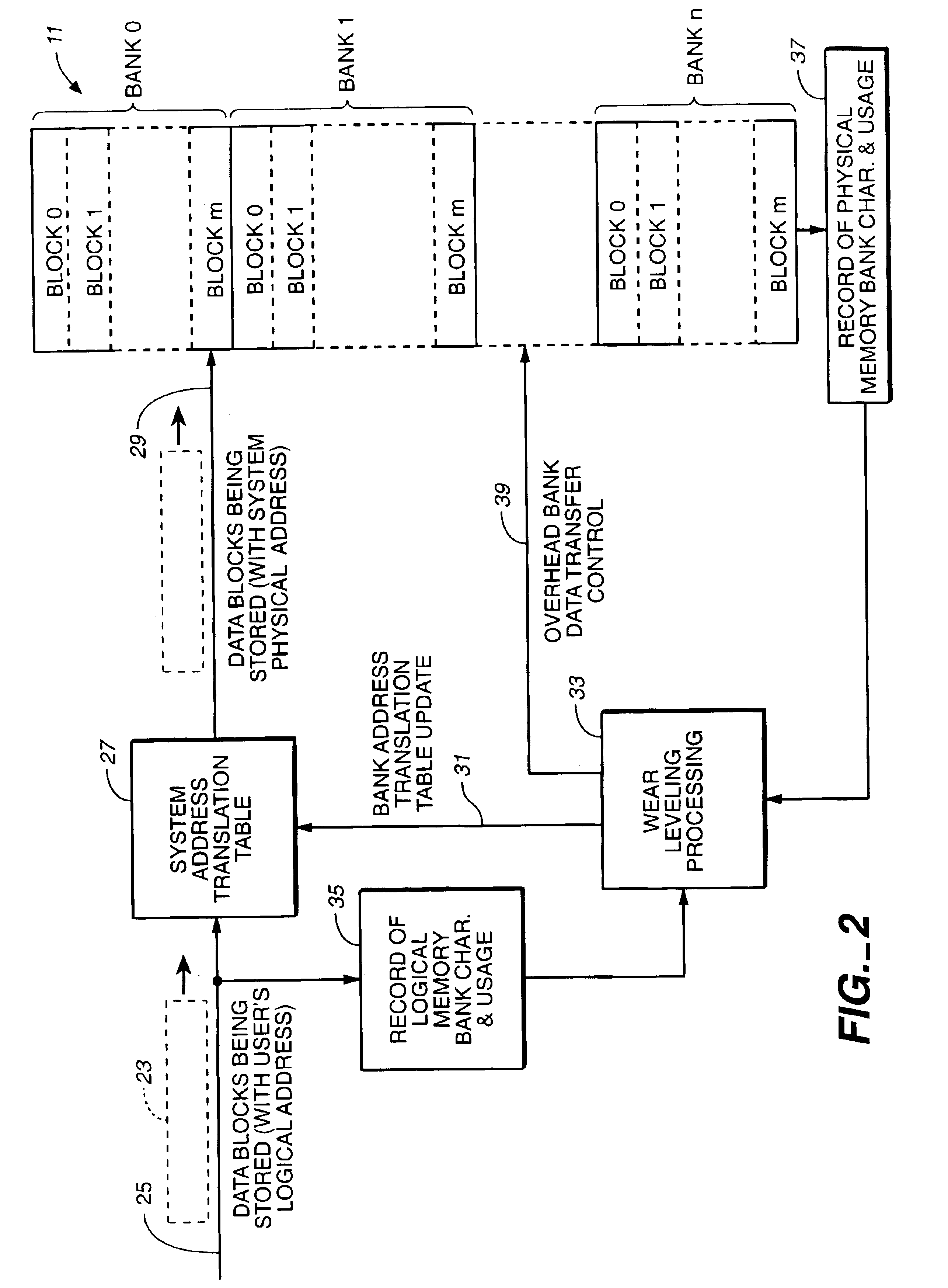

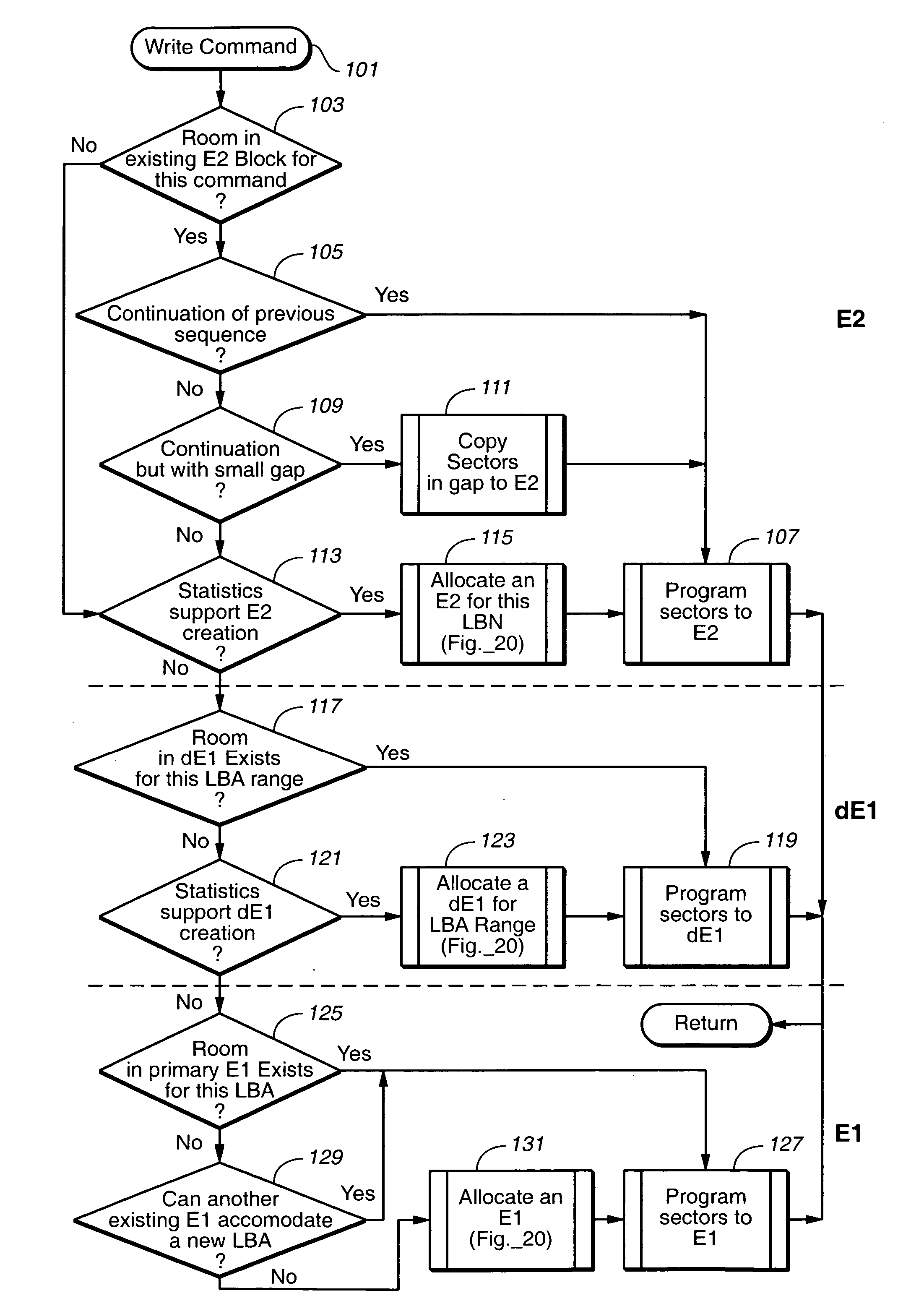

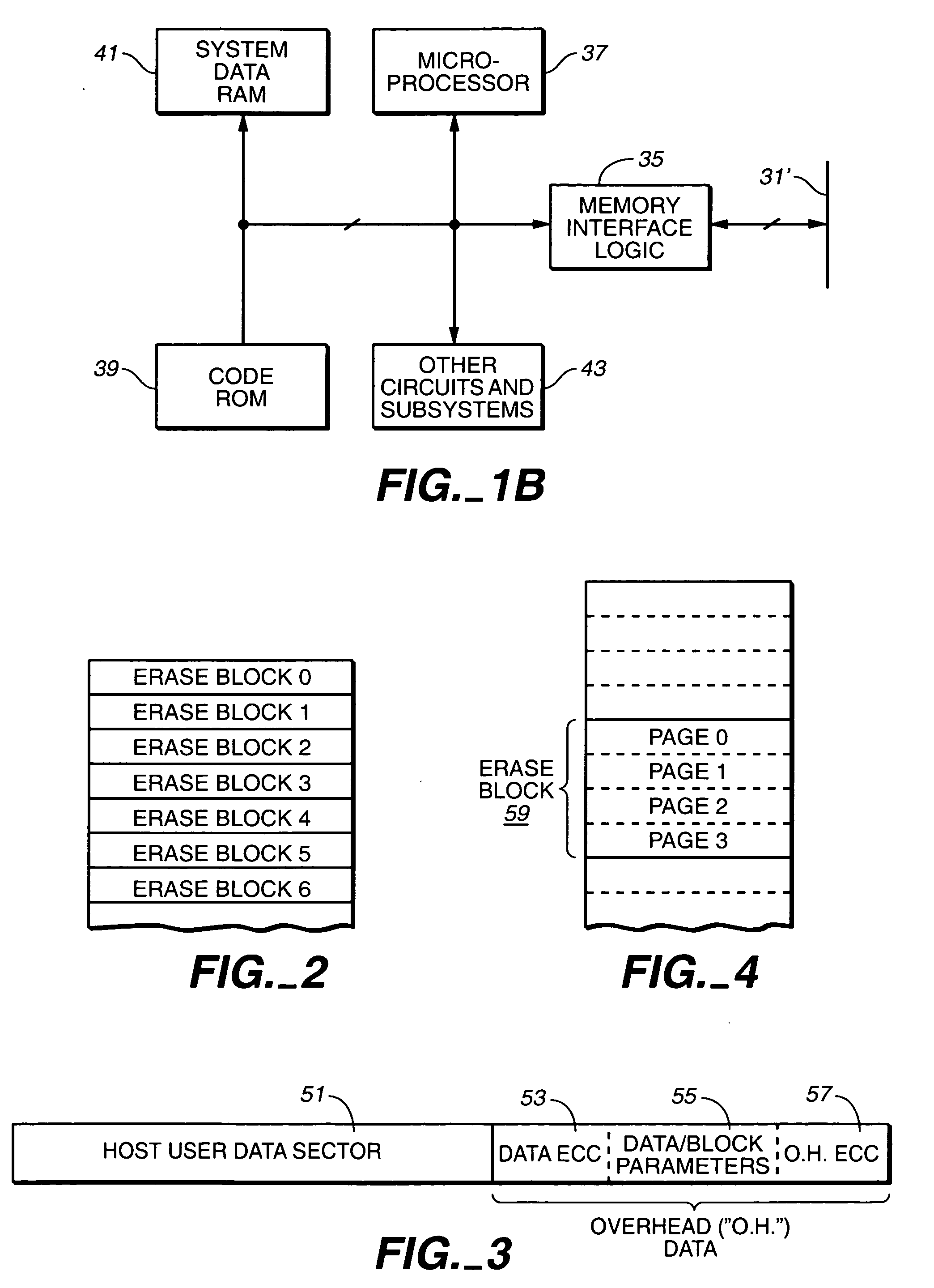

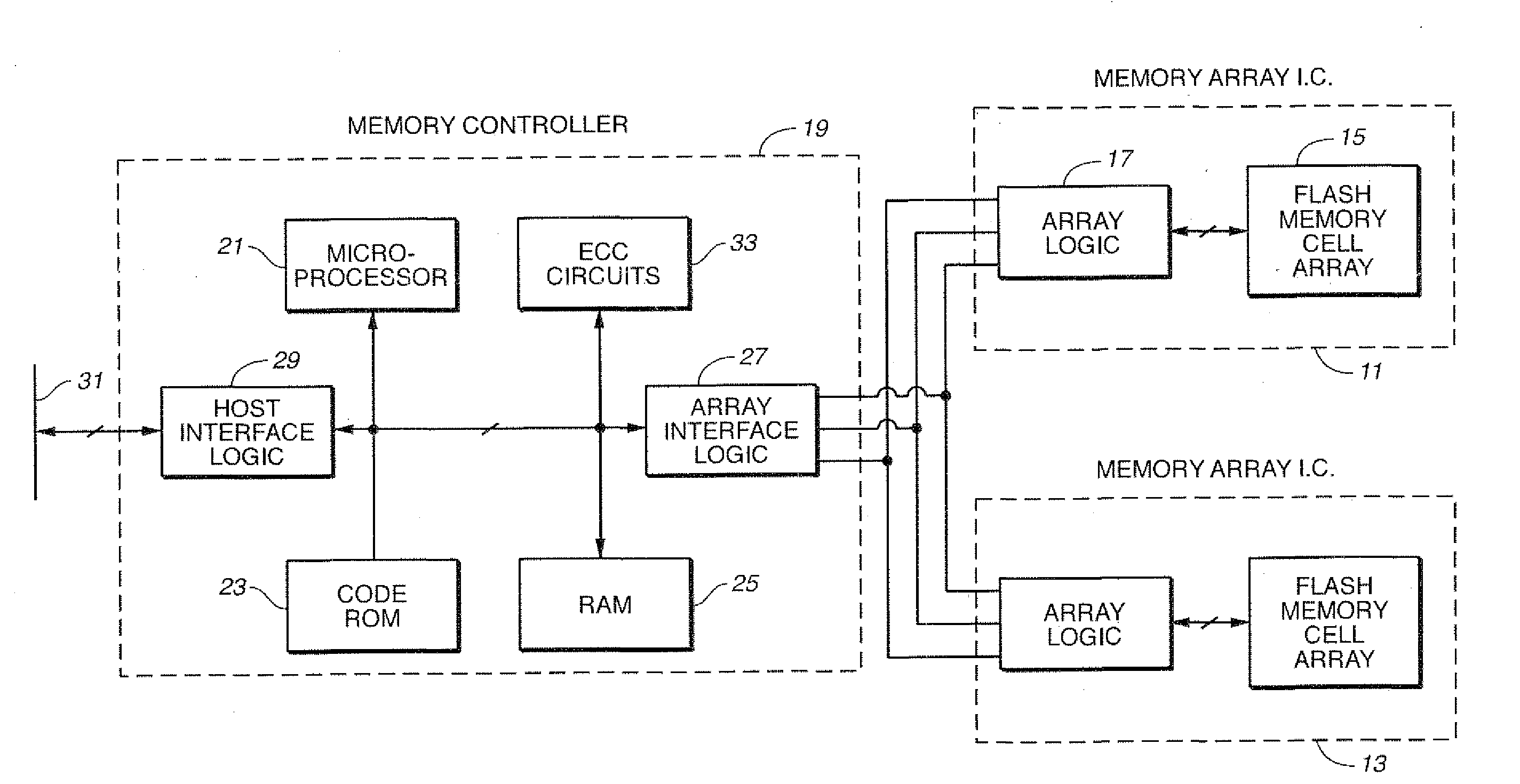

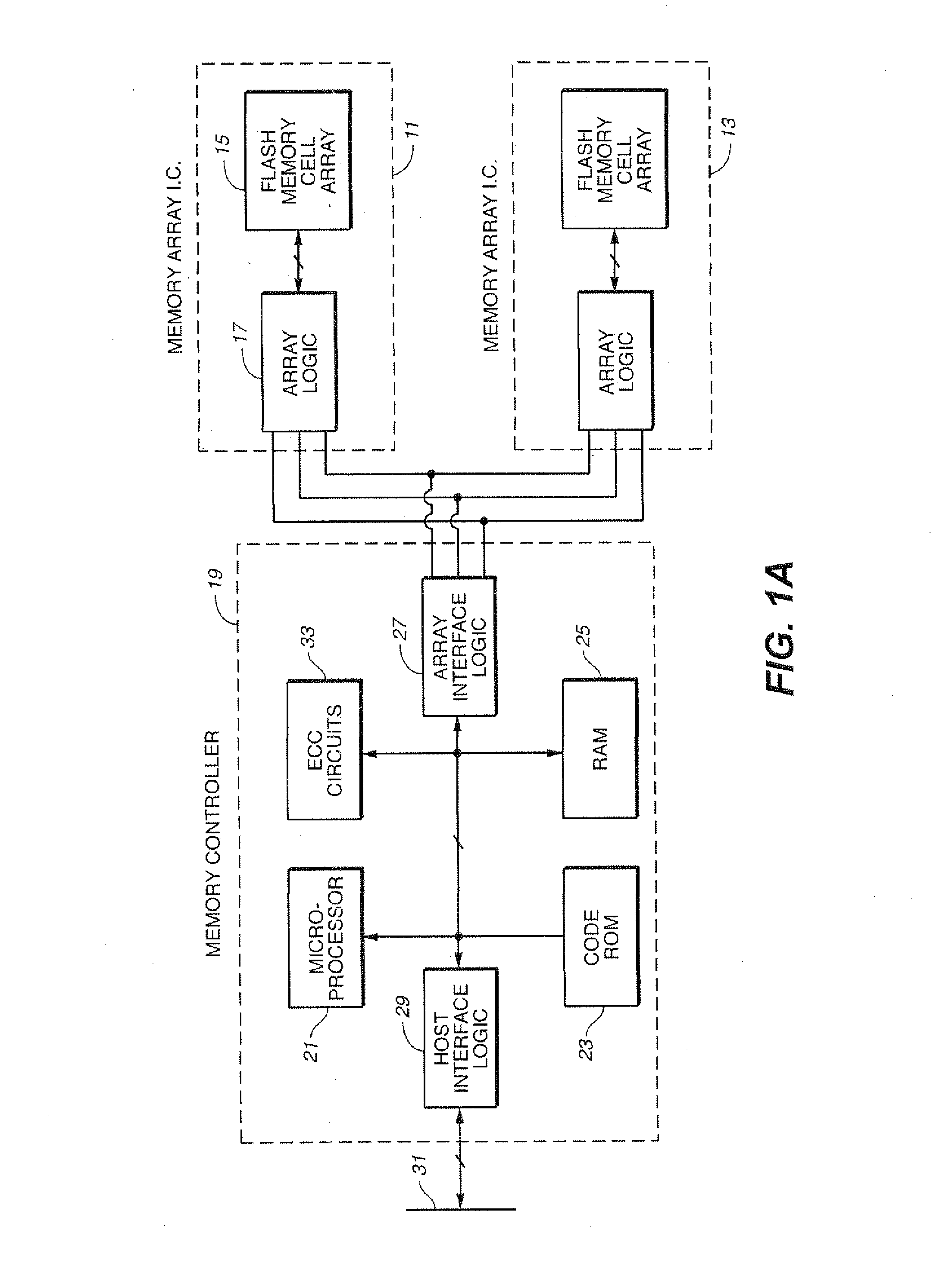

Management of non-volatile memory systems having large erase blocks

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

Flash memory data correction and scrub techniques

ActiveUS20050073884A1Data disturbanceReduce storage dataMemory loss protectionRead-only memoriesData integrityData storing

In order to maintain the integrity of data stored in a flash memory that are susceptible to being disturbed by operations in adjacent regions of the memory, disturb events cause the data to be read, corrected and re-written before becoming so corrupted that valid data cannot be recovered. The sometimes conflicting needs to maintain data integrity and system performance are balanced by deferring execution of some of the corrective action when the memory system has other high priority operations to perform. In a memory system utilizing very large units of erase, the corrective process is executed in a manner that is consistent with efficiently rewriting an amount of data much less than the capacity of a unit of erase.

Owner:SANDISK TECH LLC

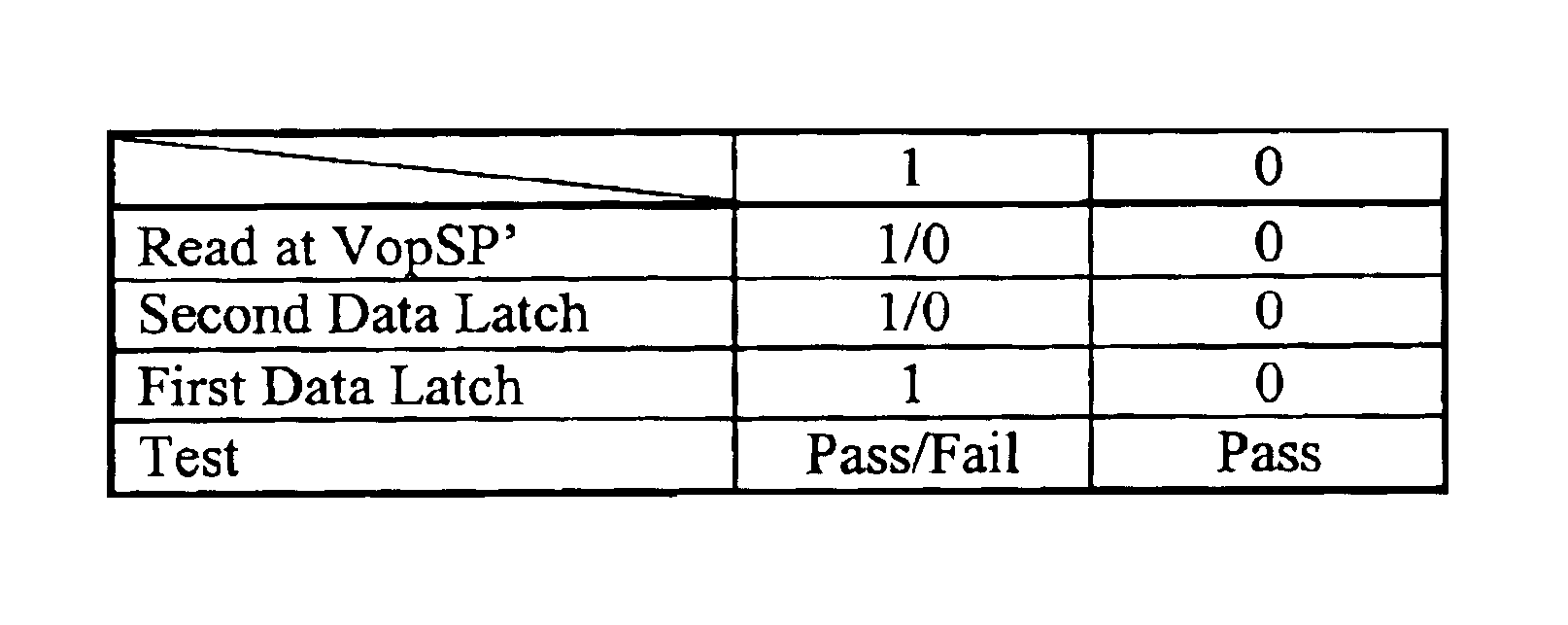

Detecting over programmed memory

ActiveUS6917542B2Lower requirementRead-only memoriesDigital storageComputer architectureThreshold voltage

Owner:SANDISK TECH LLC

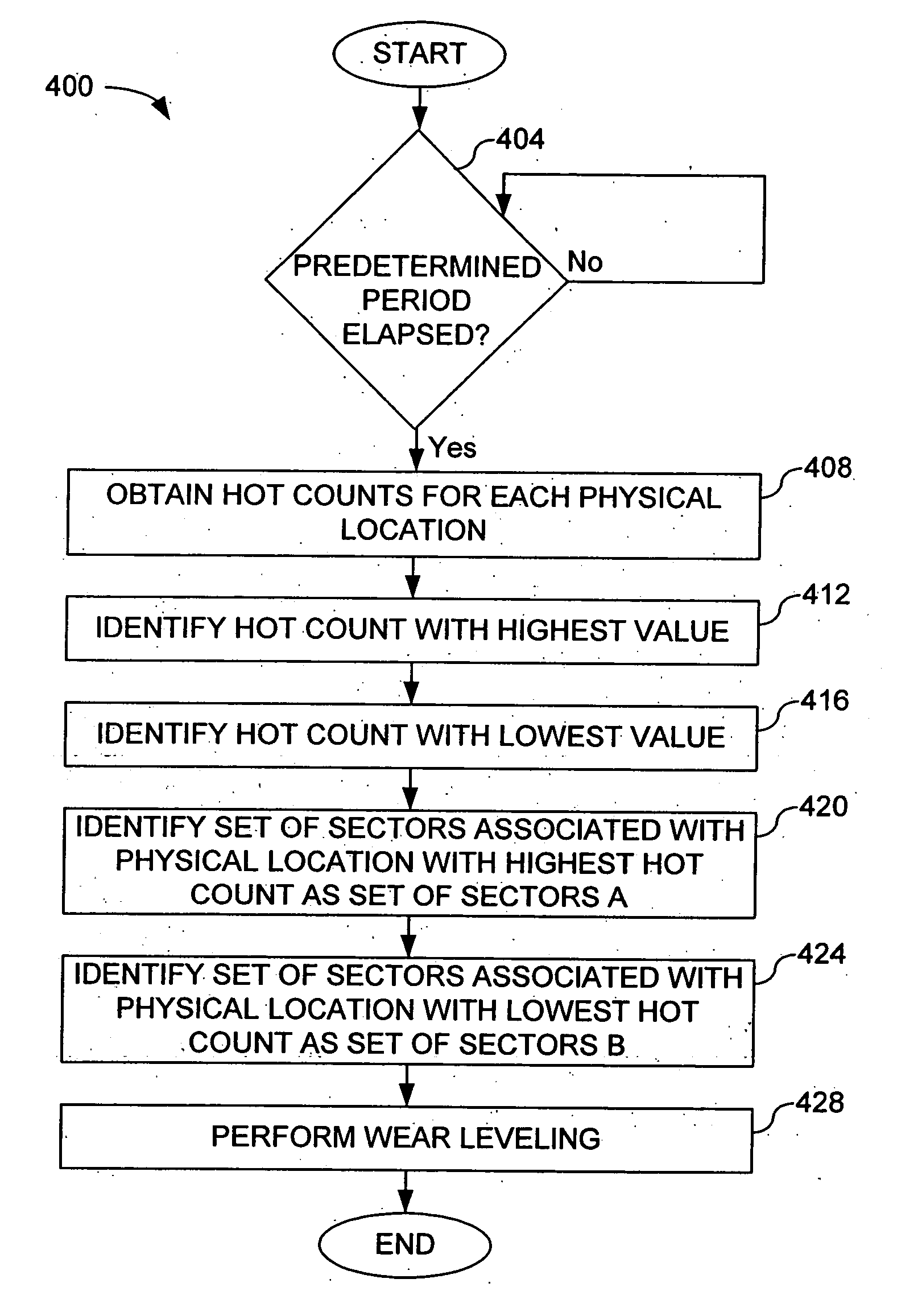

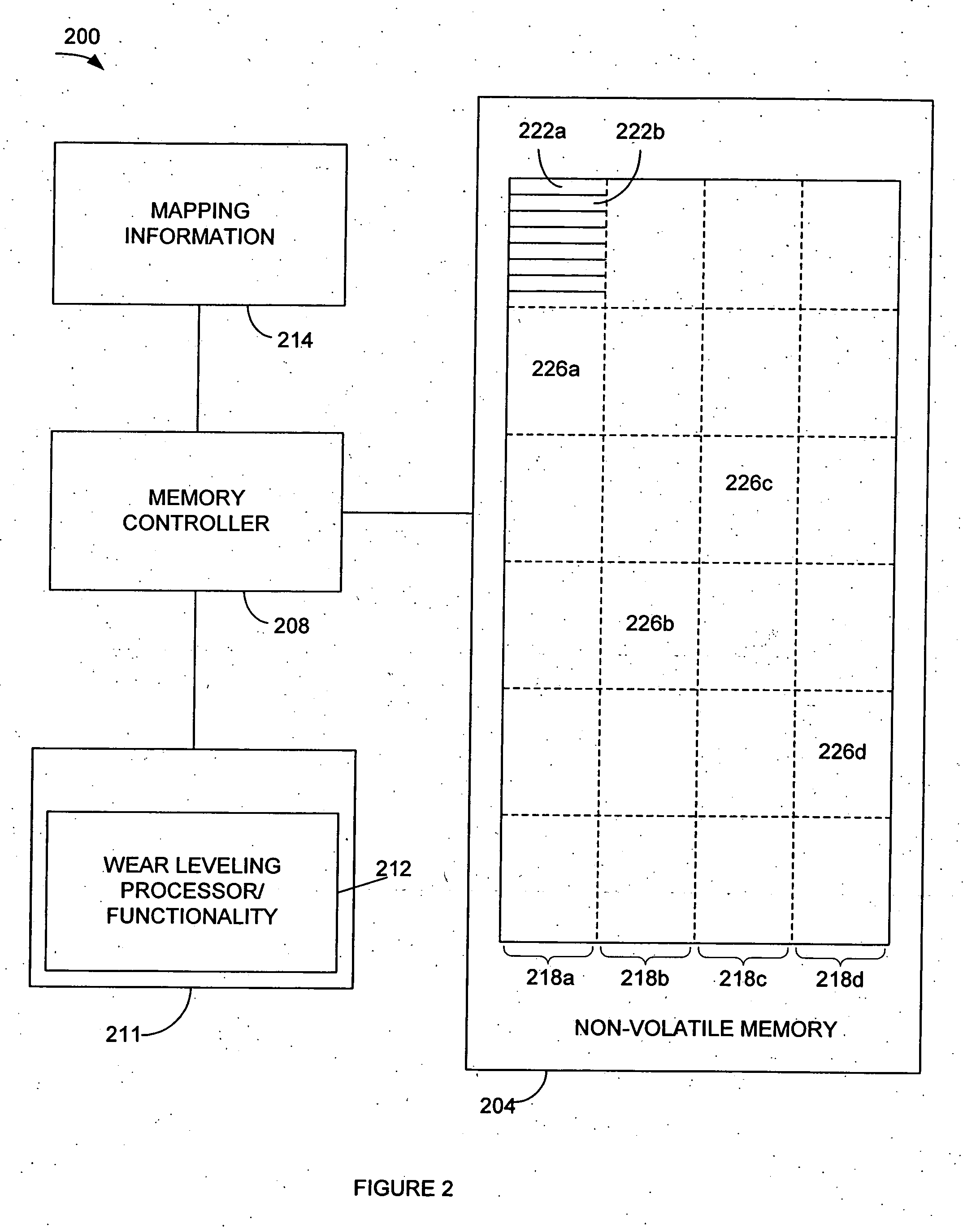

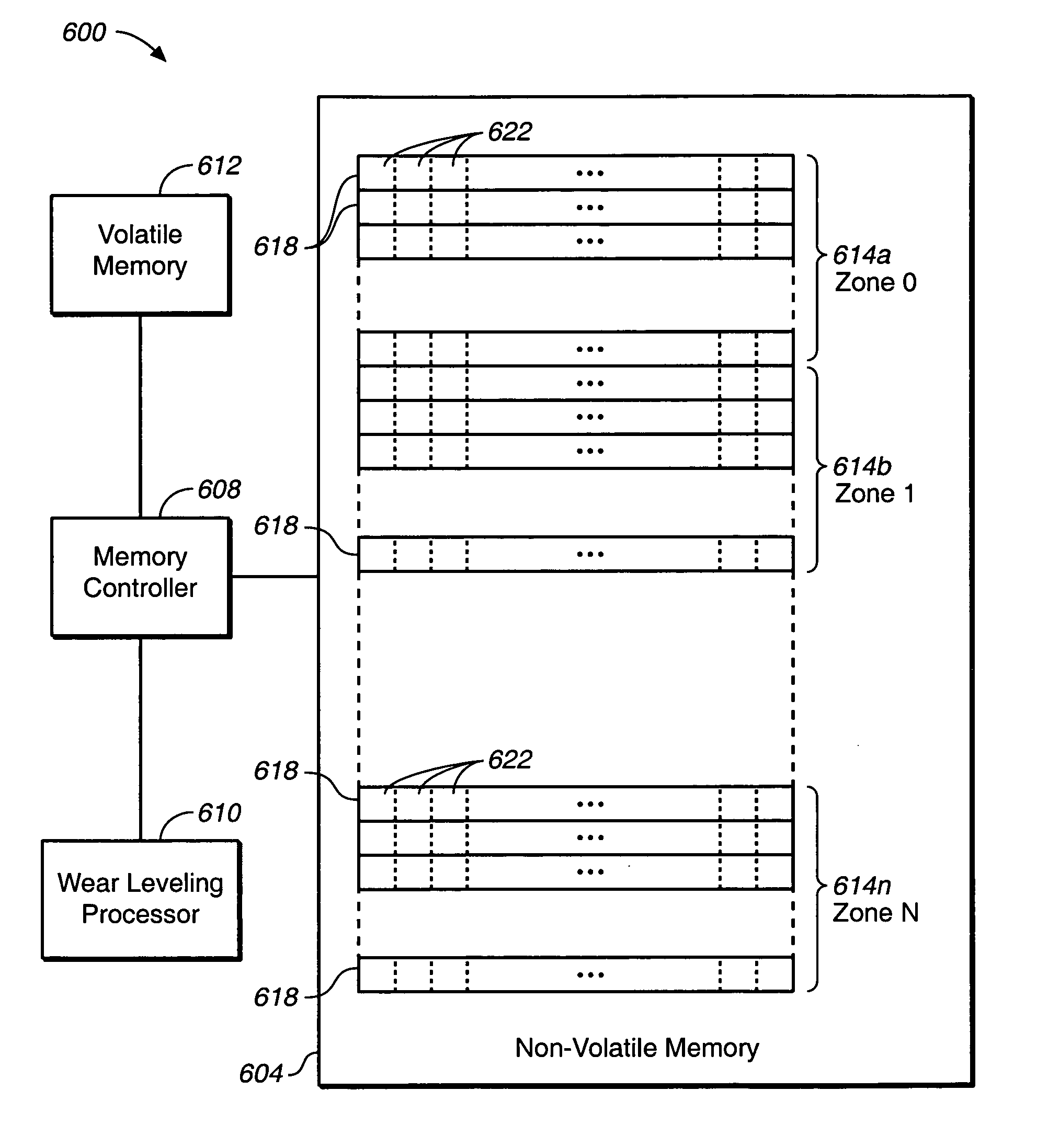

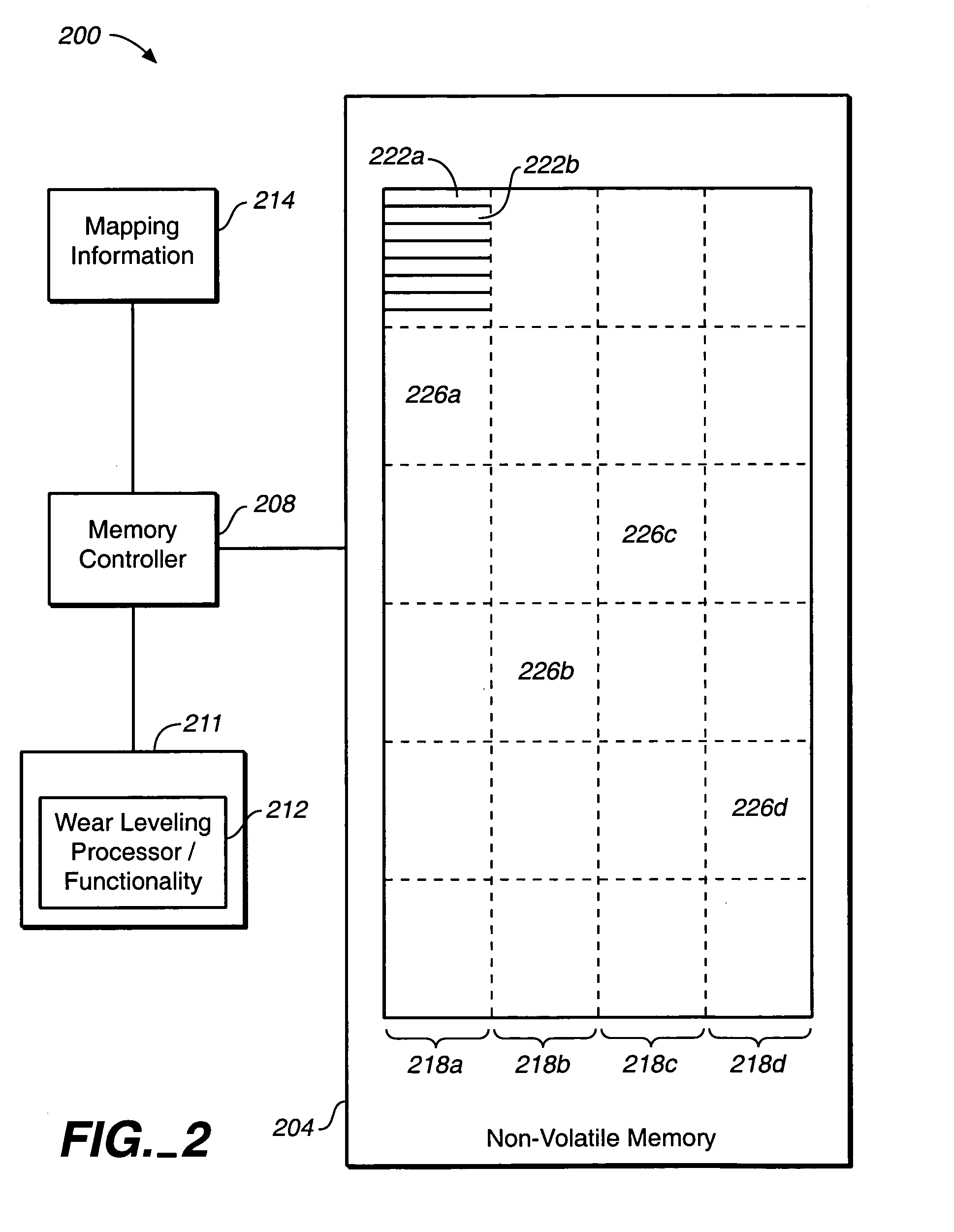

Automated wear leveling in non-volatile storage systems

ActiveUS20040083335A1Precise positioningMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingNon-volatile memory

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. Included is a method for performing wear leveling in a memory system that includes a first zone, which has a first memory element that includes contents, and a second zone includes identifying the first memory element and associating the contents of the first memory element with the second zone while disassociating the contents of the first memory element from the first zone. In one embodiment, associating the contents of the first memory element with the second involves moving contents of a second memory element into a third memory element, then copying the contents of the first memory element into the second memory element.

Owner:SANDISK TECH LLC

Corrected data storage and handling methods

InactiveUS7173852B2Data disturbanceReduce storage dataRead-only memoriesDigital storageData integrityTime limit

In order to maintain the integrity of data stored in a flash memory that are susceptible to being disturbed by operations in adjacent regions of the memory, disturb events cause the data to be read, corrected and re-written before becoming so corrupted that valid data cannot be recovered. The sometimes conflicting needs to maintain data integrity and system performance are balanced by deferring execution of some of the corrective action when the memory system has other high priority operations to perform. In a memory system utilizing very large units of erase, the corrective process is executed in a manner that is consistent with efficiently rewriting an amount of data much less than the capacity of a unit of erase. Data is rewritten when severe errors are found during read operations. Portions of data are corrected and copied within the time limit for read operation. Corrected portions are written to dedicated blocks.

Owner:SANDISK TECH LLC

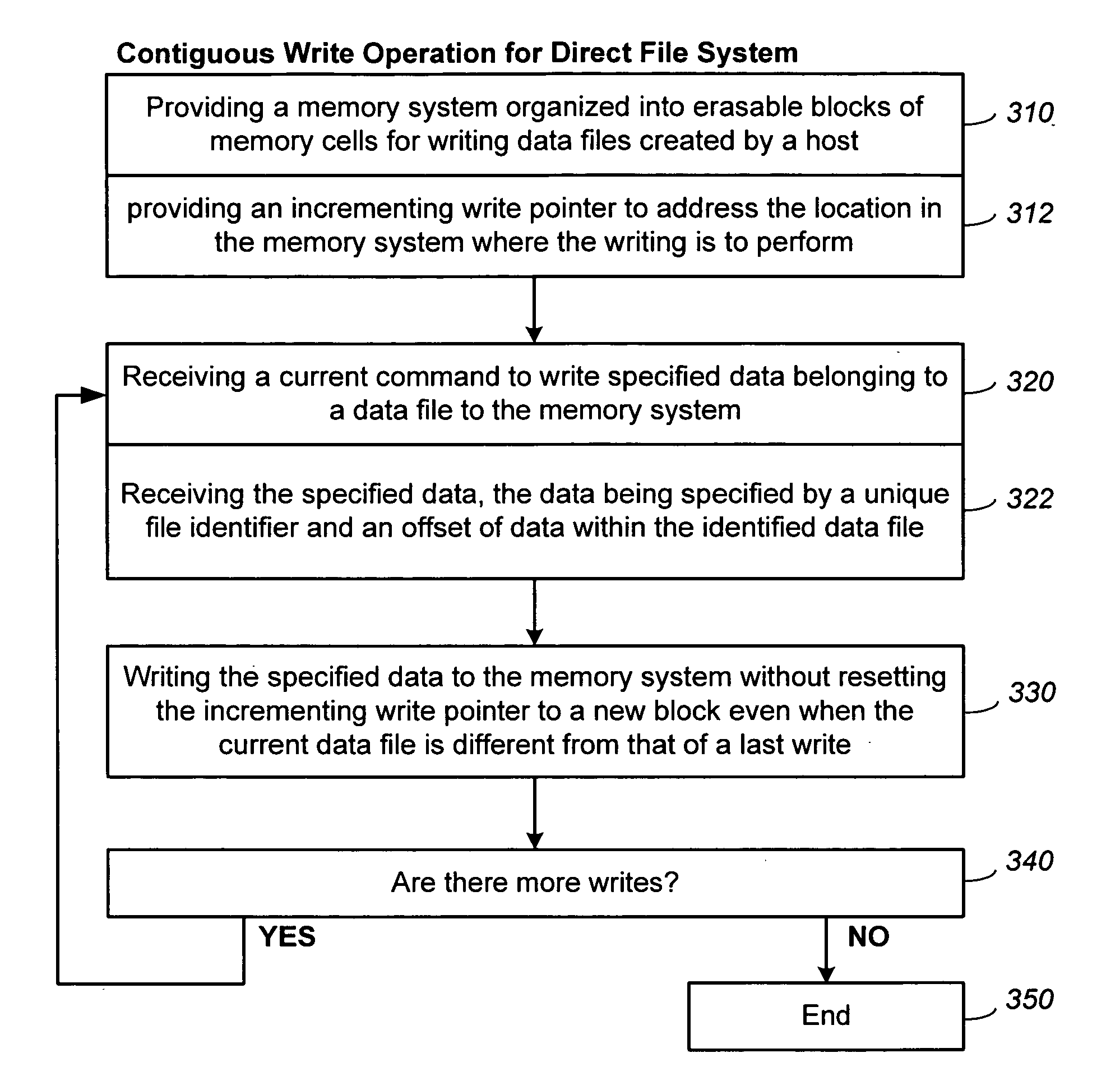

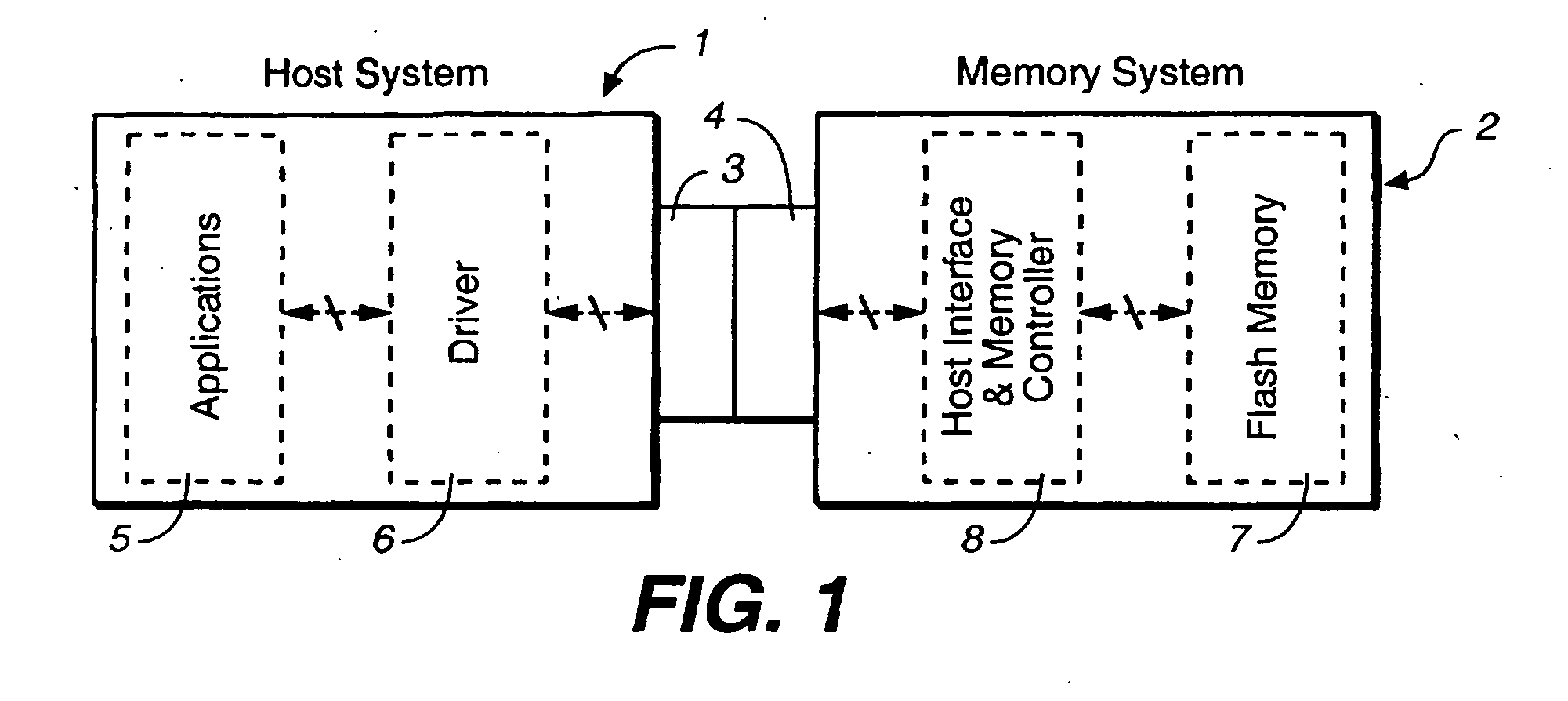

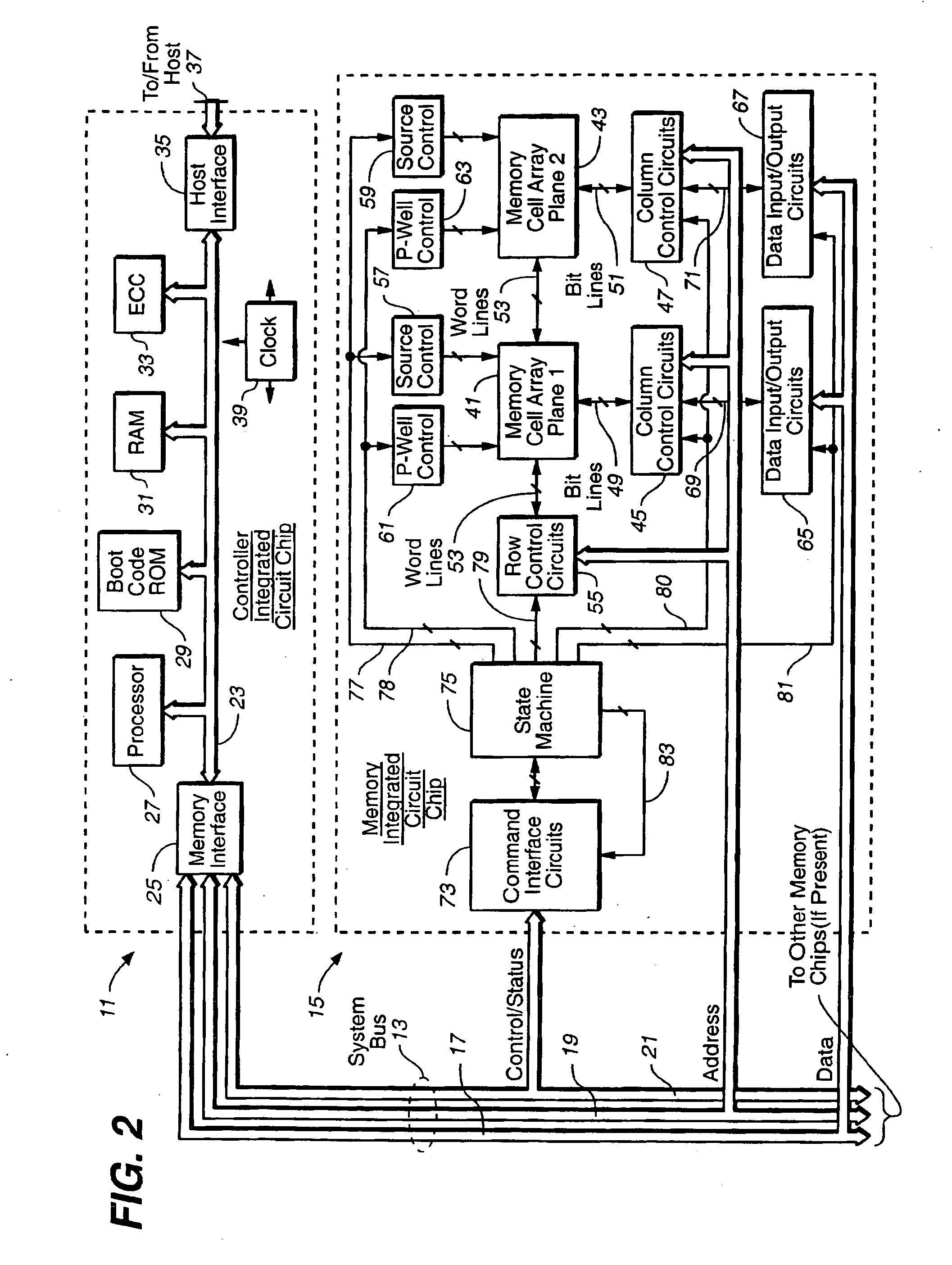

Methods for memory allocation in non-volatile memories with a directly mapped file storage system

InactiveUS20070156998A1Improve performanceEfficient packagingMemory architecture accessing/allocationMemory systemsData compressionWrite pointer

In a memory system with a file storage system, a scheme for allocating memory locations for a write operation is to write the files substantially contiguously in a memory block one after another rather than to start a new file in a new block. In this way, they are more efficiently packed into the blocks by being written contiguously one after another. In a preferred embodiment, an incrementing write pointer points to the write location in memory for the next data for a file, which is independent of the offset address of the data within the file. When a current write block becomes filled with file data, an erased block is allocated, and the write pointer is moved to this block. Similarly a relocation pointer is used for data relocation during garbage collection or data compaction operations.

Owner:SANDISK TECH LLC

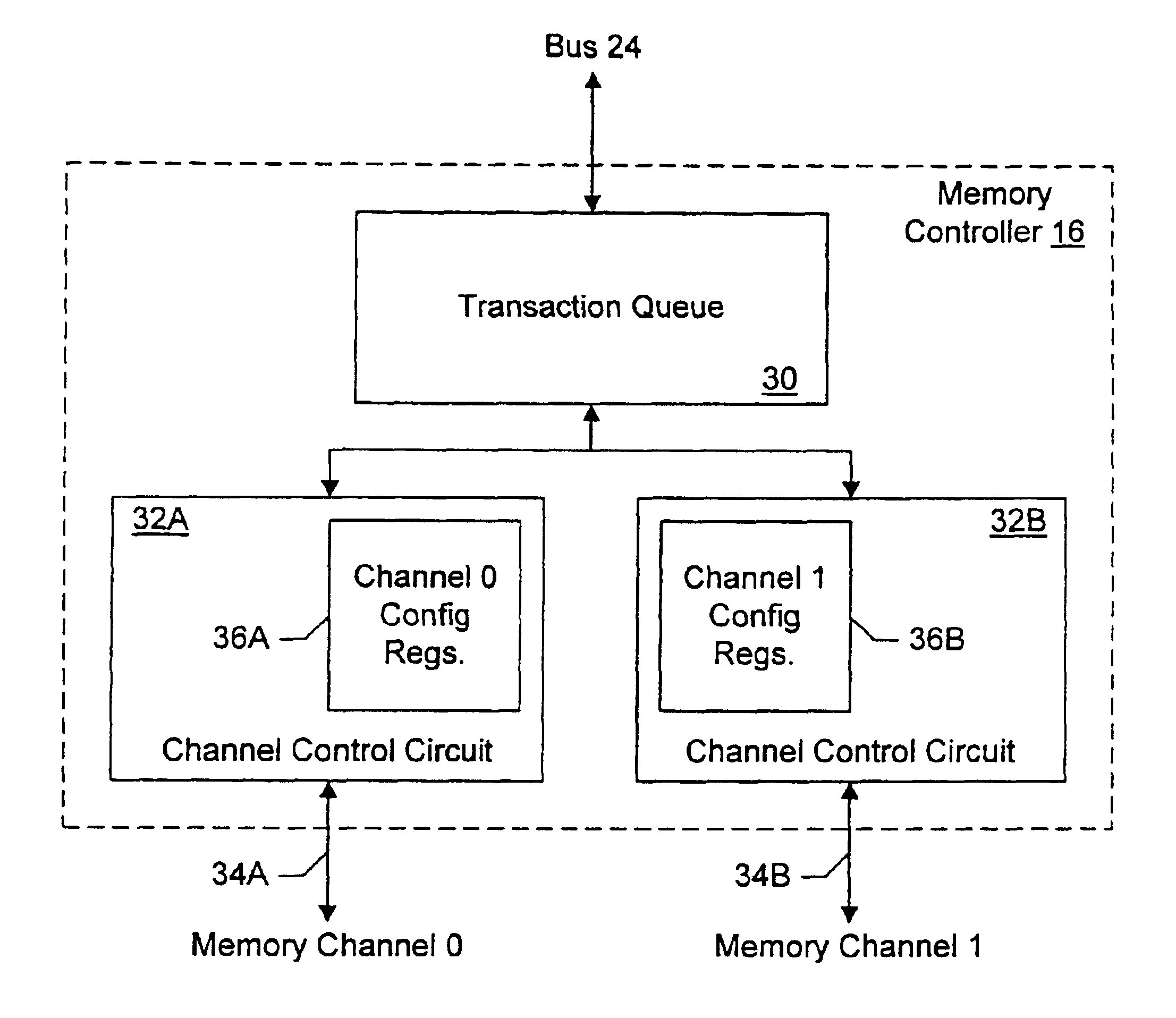

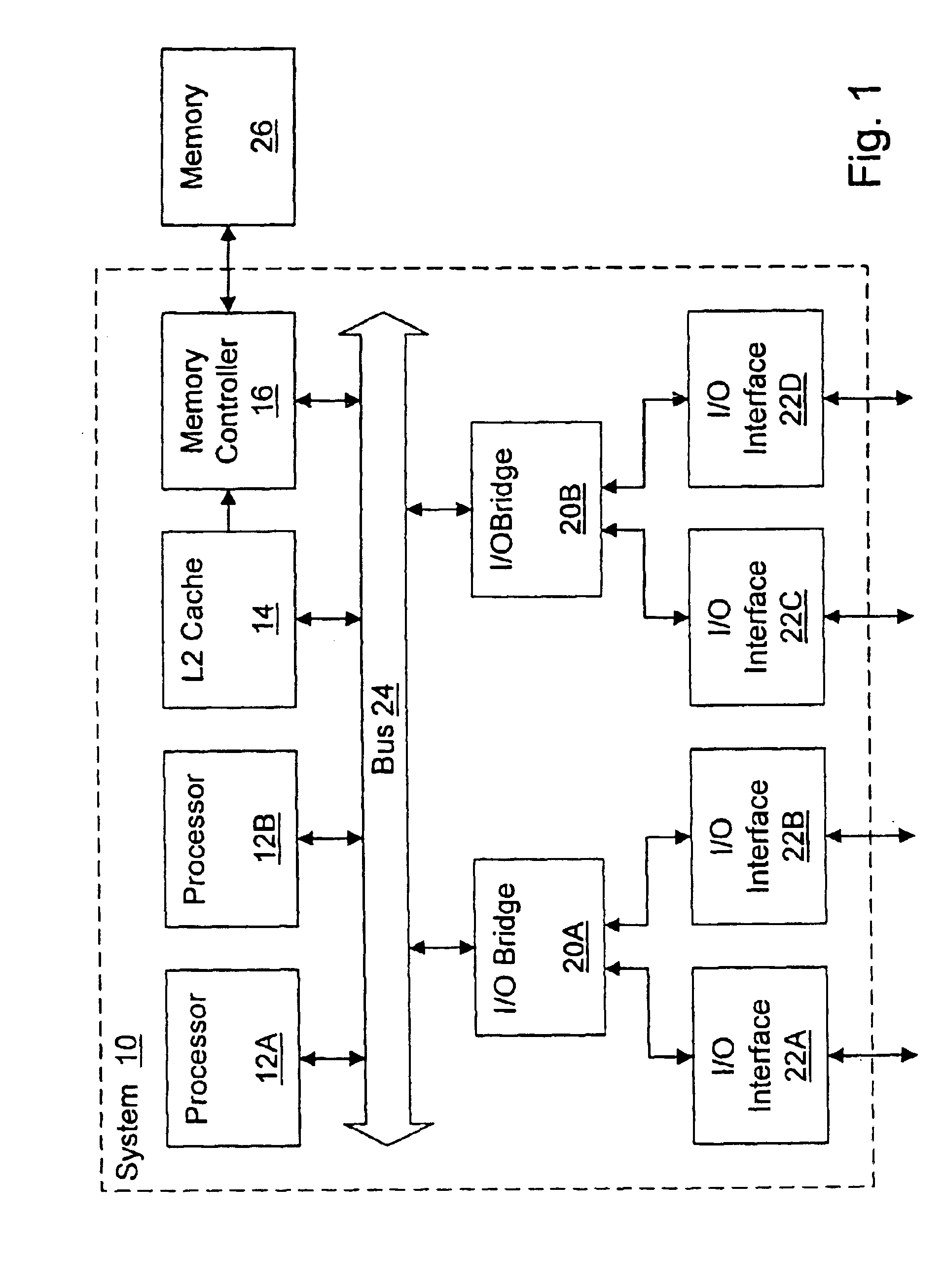

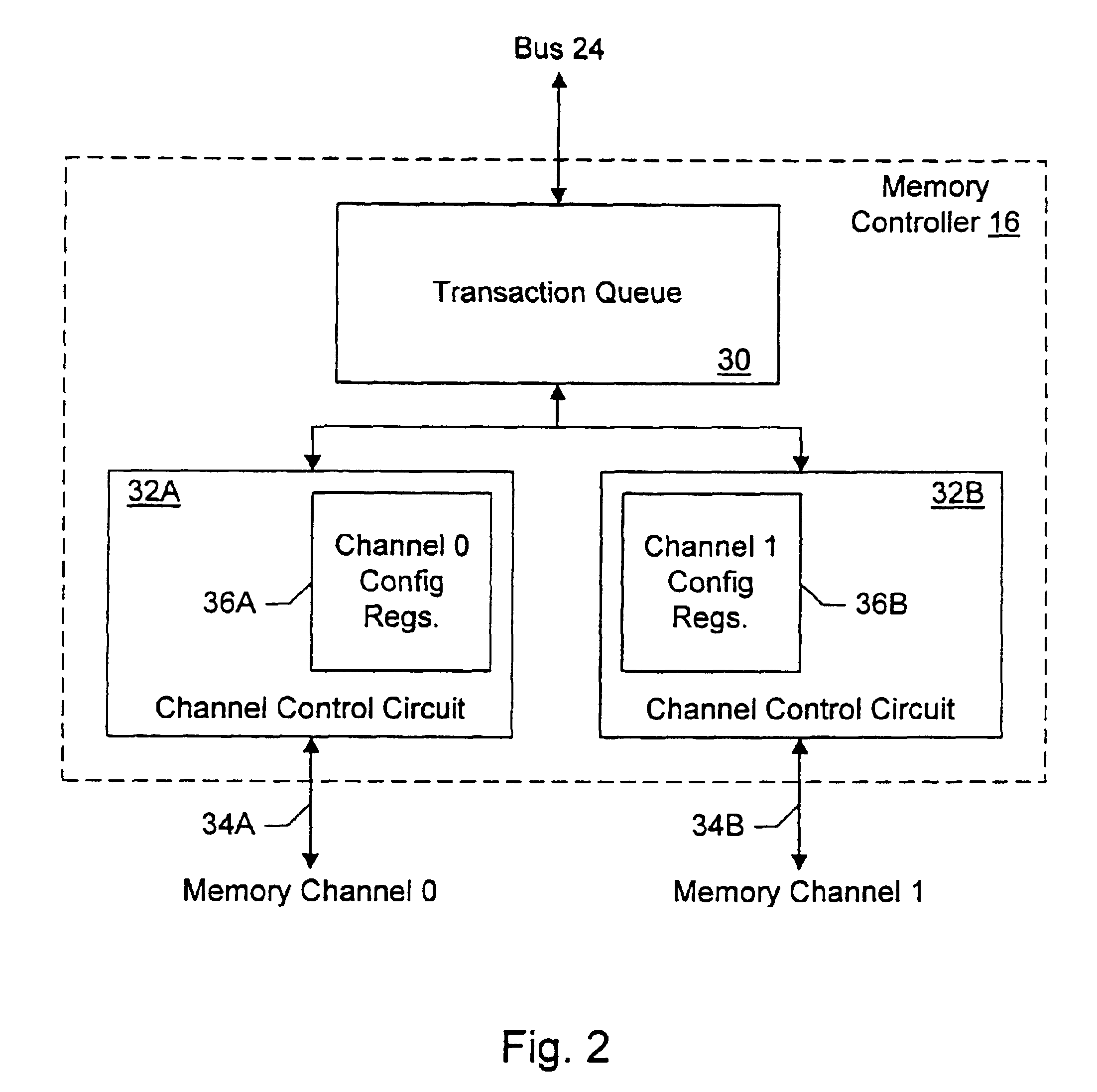

Memory controller with programmable configuration

InactiveUS6877076B1Flexible configurationOpen in timeMemory adressing/allocation/relocationMicro-instruction address formationProcessor registerParallel computing

Owner:AVAGO TECH INT SALES PTE LTD

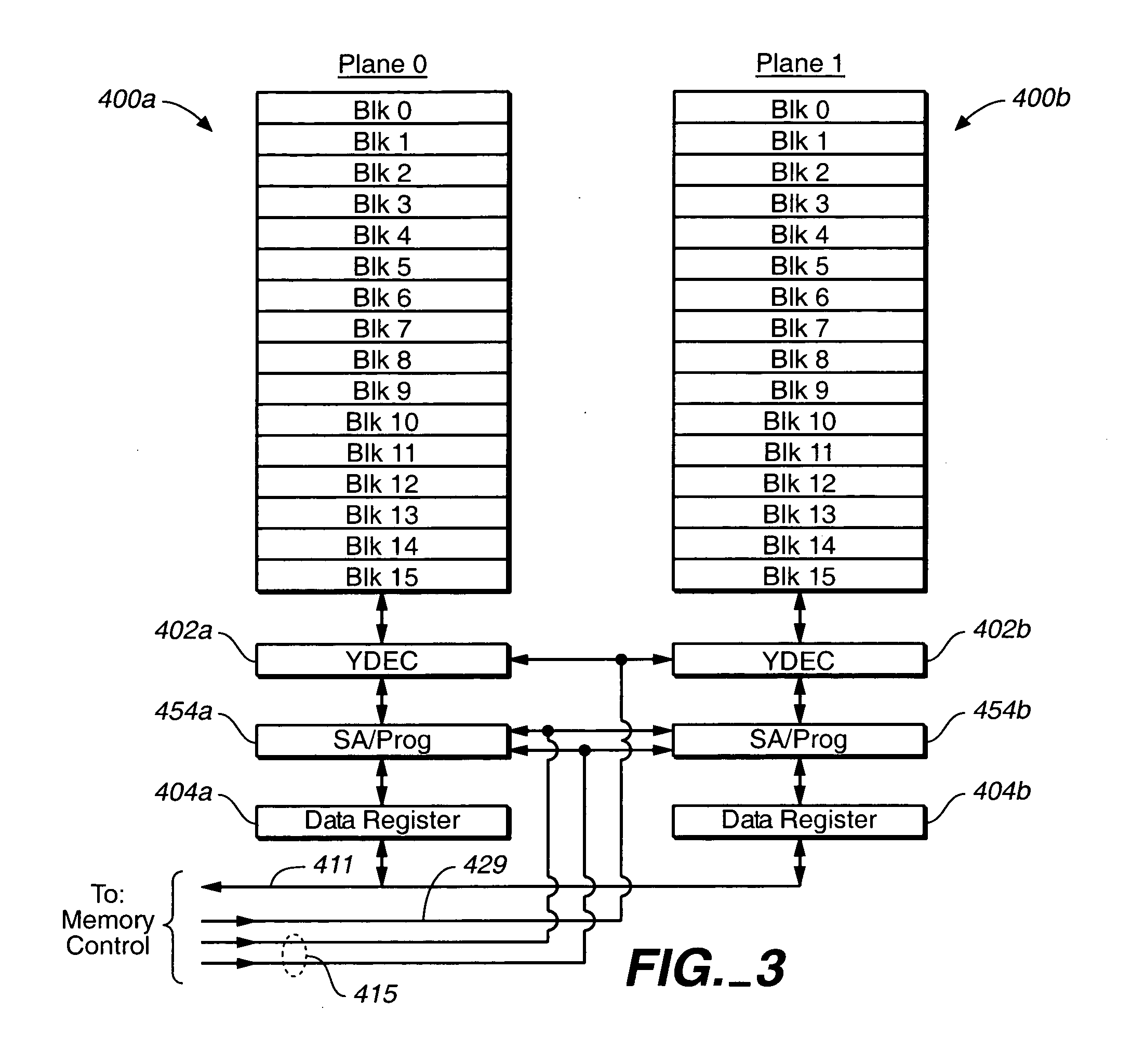

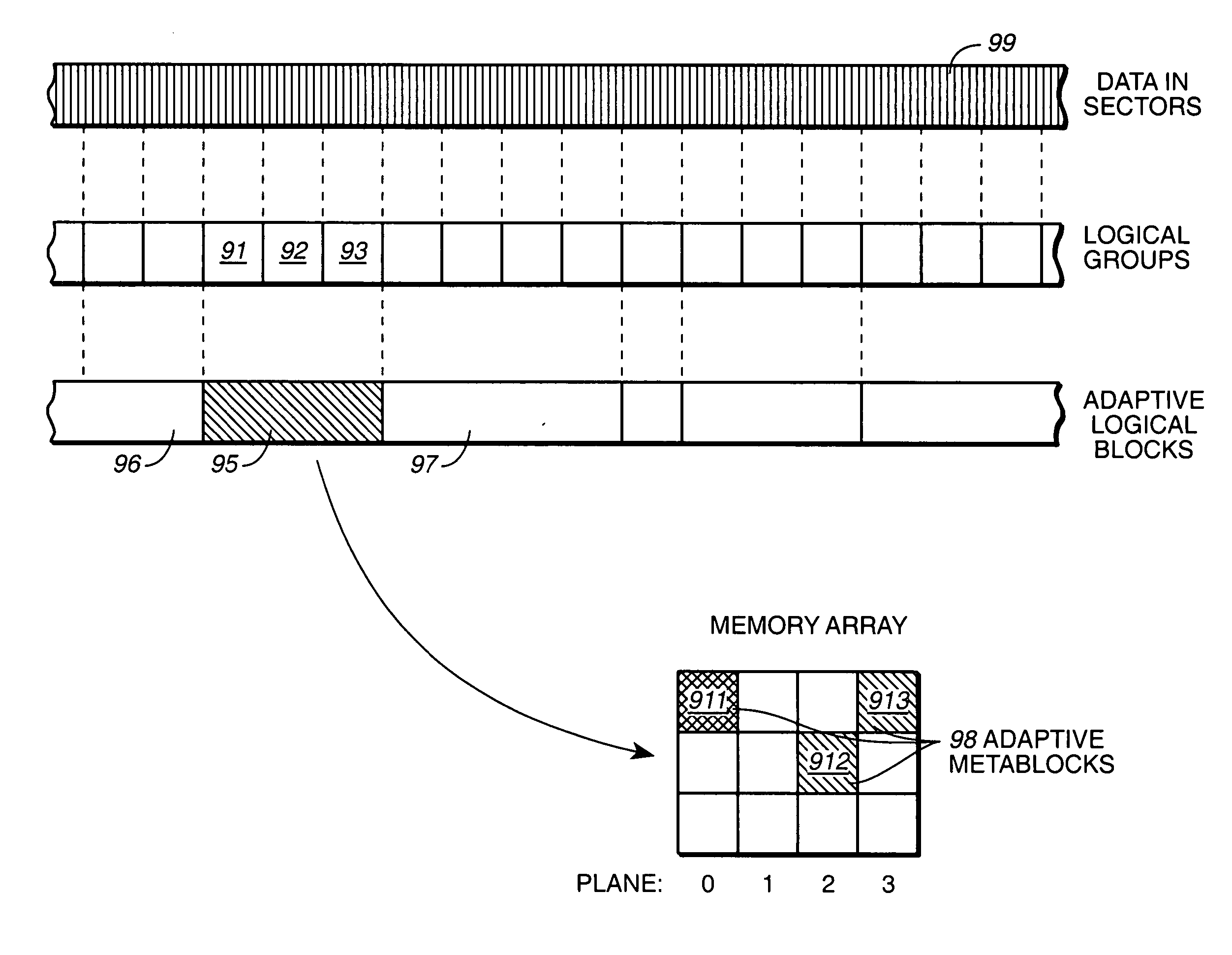

Adaptive metablocks

ActiveUS20050144357A1Reduce the impactEfficient updateMemory architecture accessing/allocationMemory adressing/allocation/relocationData selectionTheoretical computer science

In a memory system having multiple erase blocks in multiple planes, a selected number of erase blocks are programmed together as an adaptive metablock. The number of erase blocks in an adaptive metablock is chosen according to the data to be programmed. Logical address space is divided into logical groups, a logical group having the same size as one erase block. Adaptive logical blocks are formed from logical groups. One adaptive logical block is stored in one adaptive metablock.

Owner:SANDISK TECH LLC

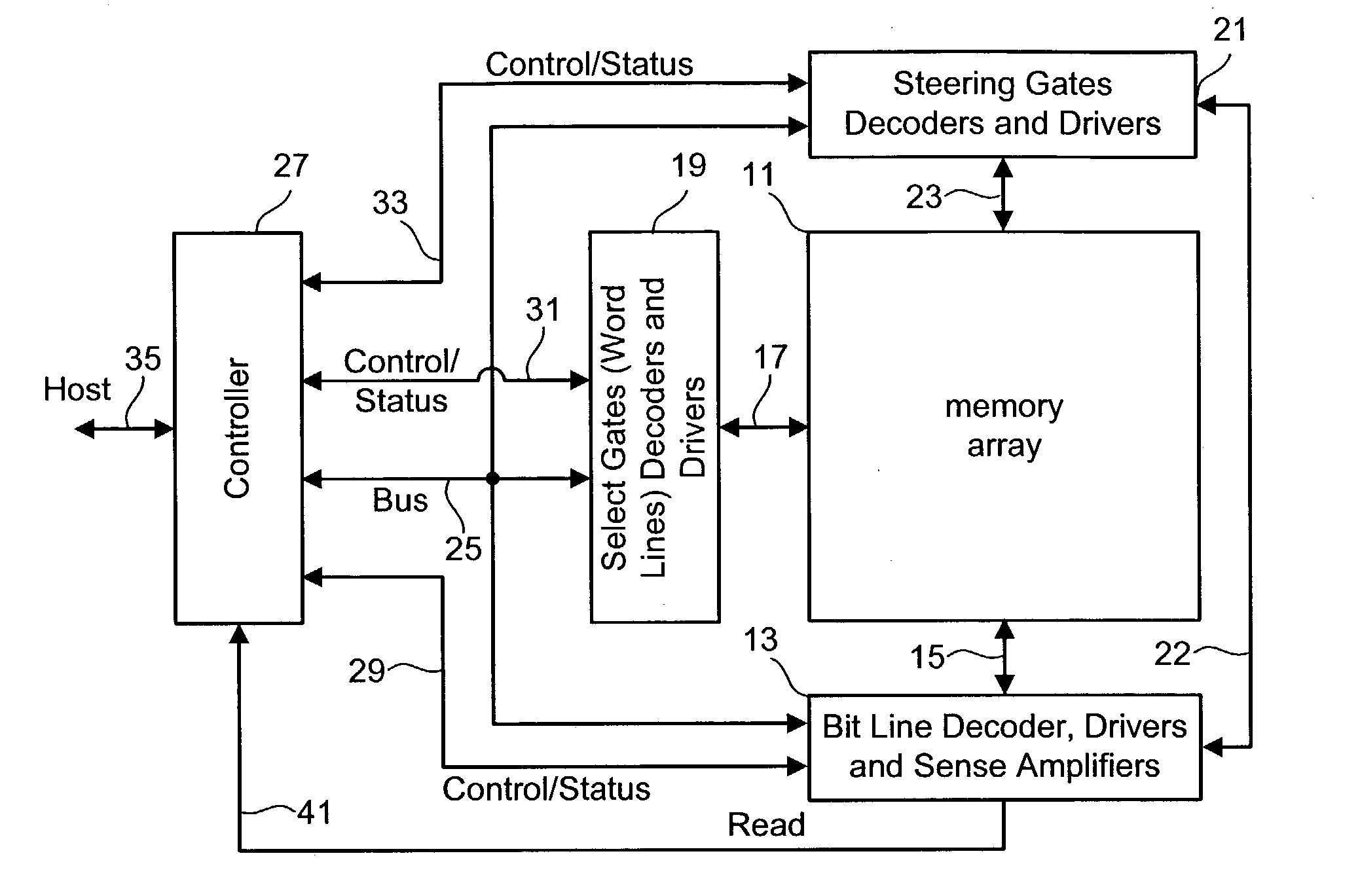

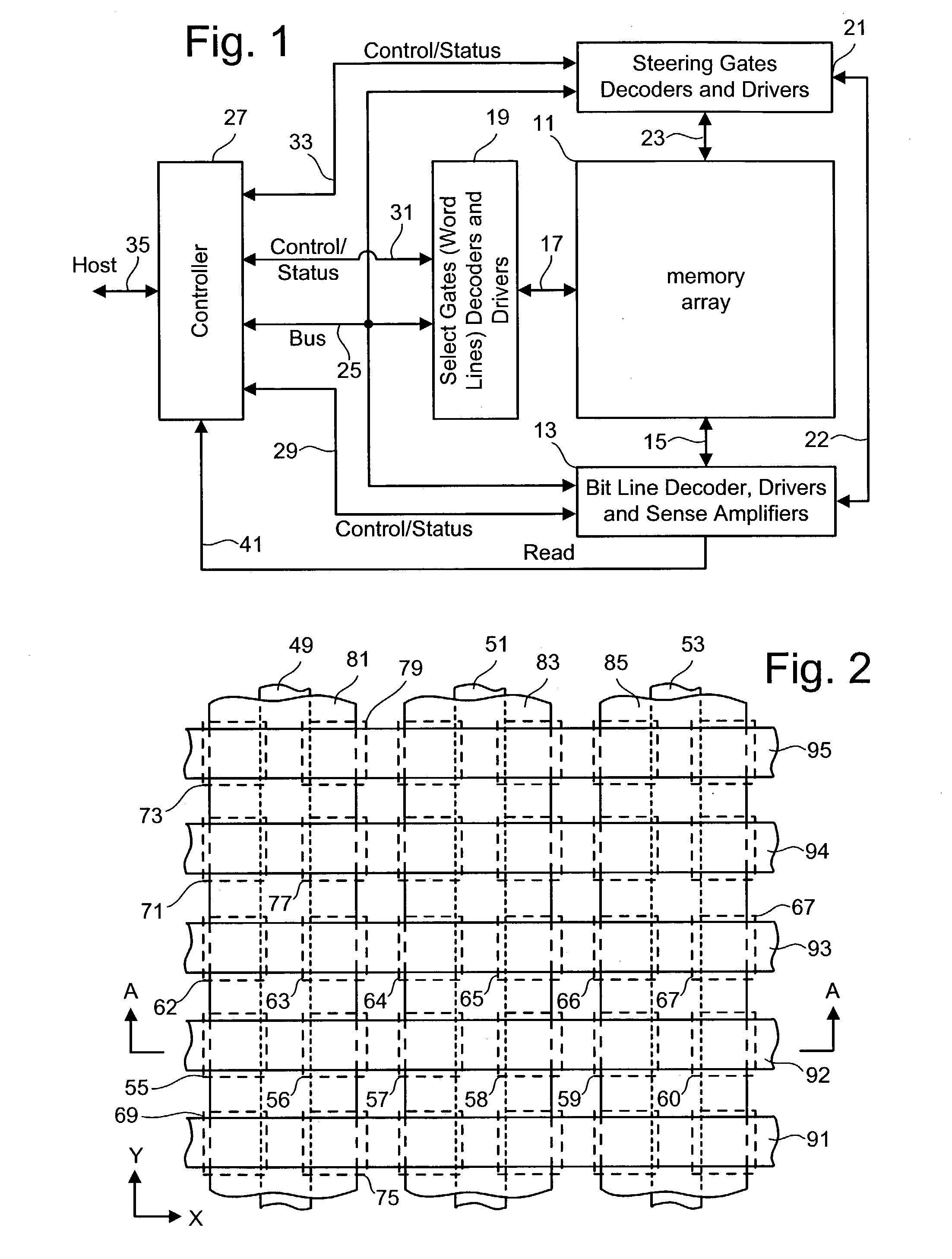

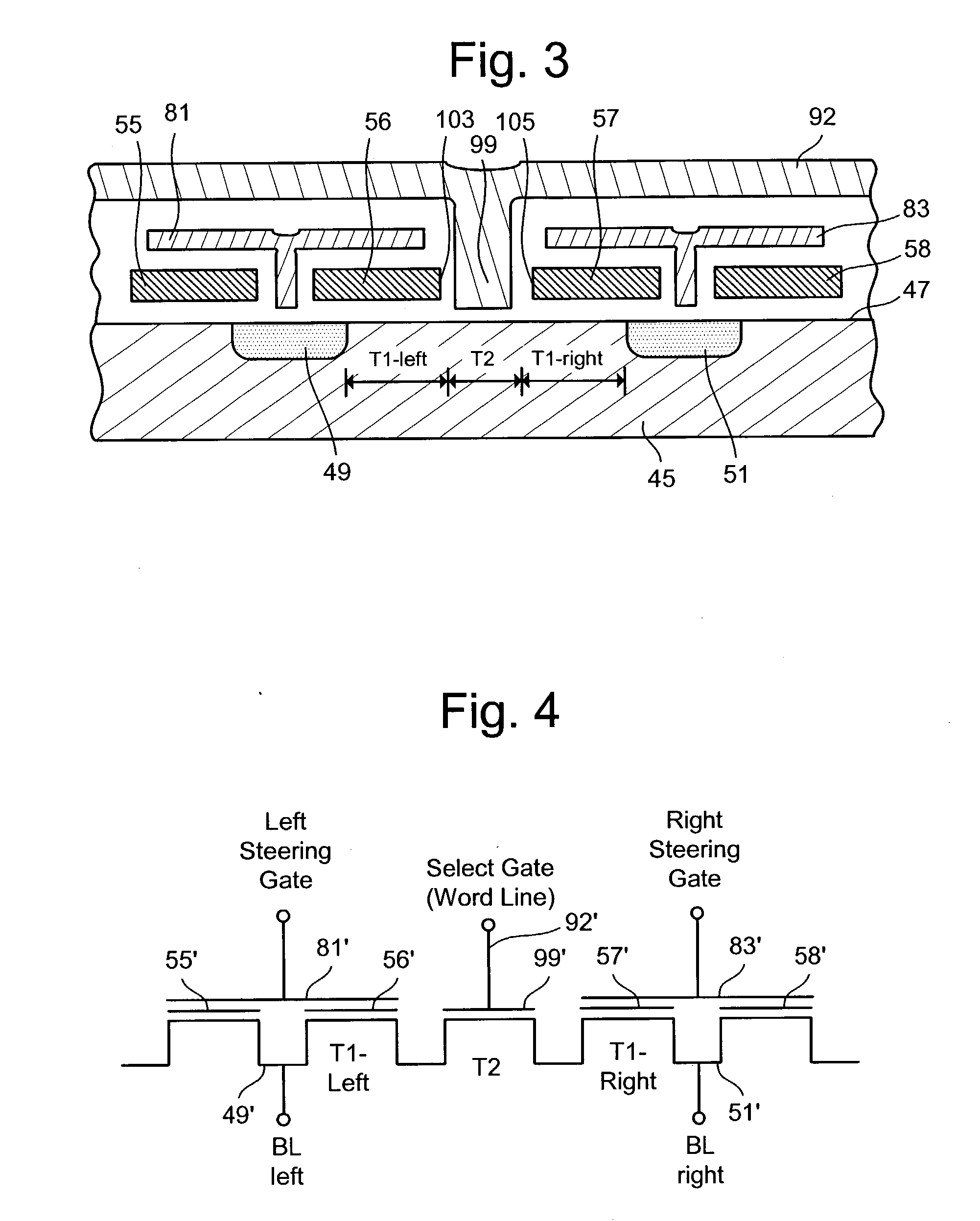

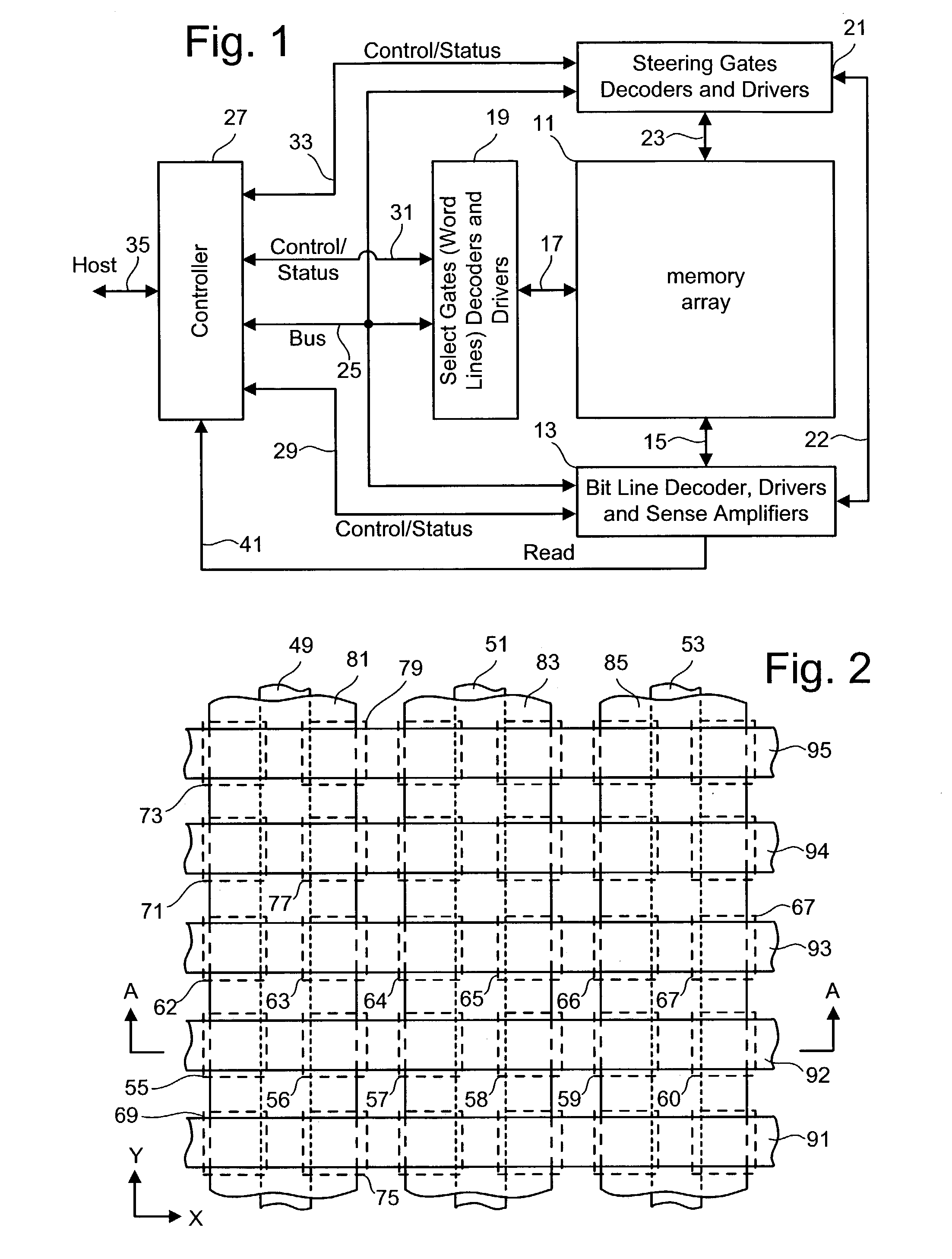

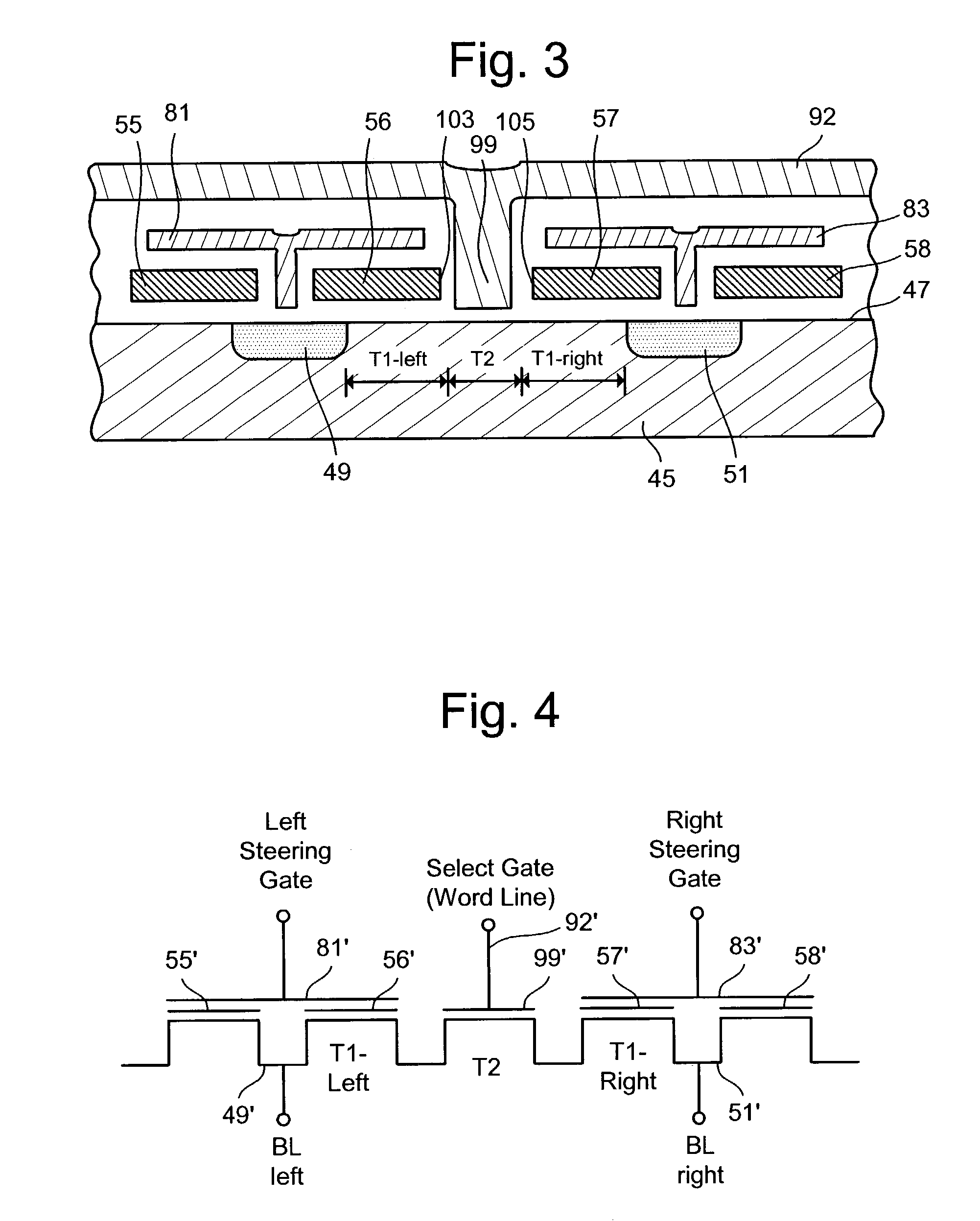

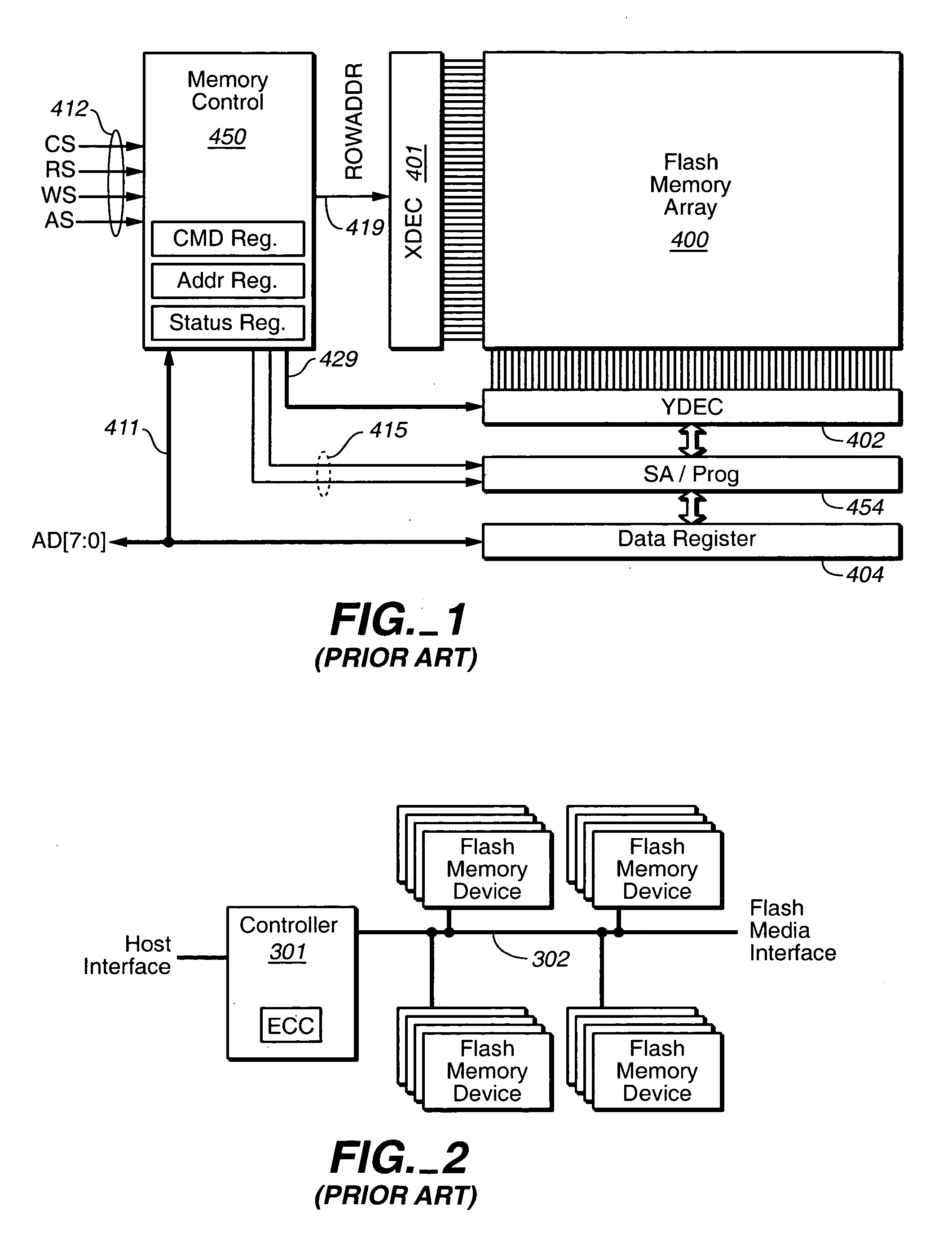

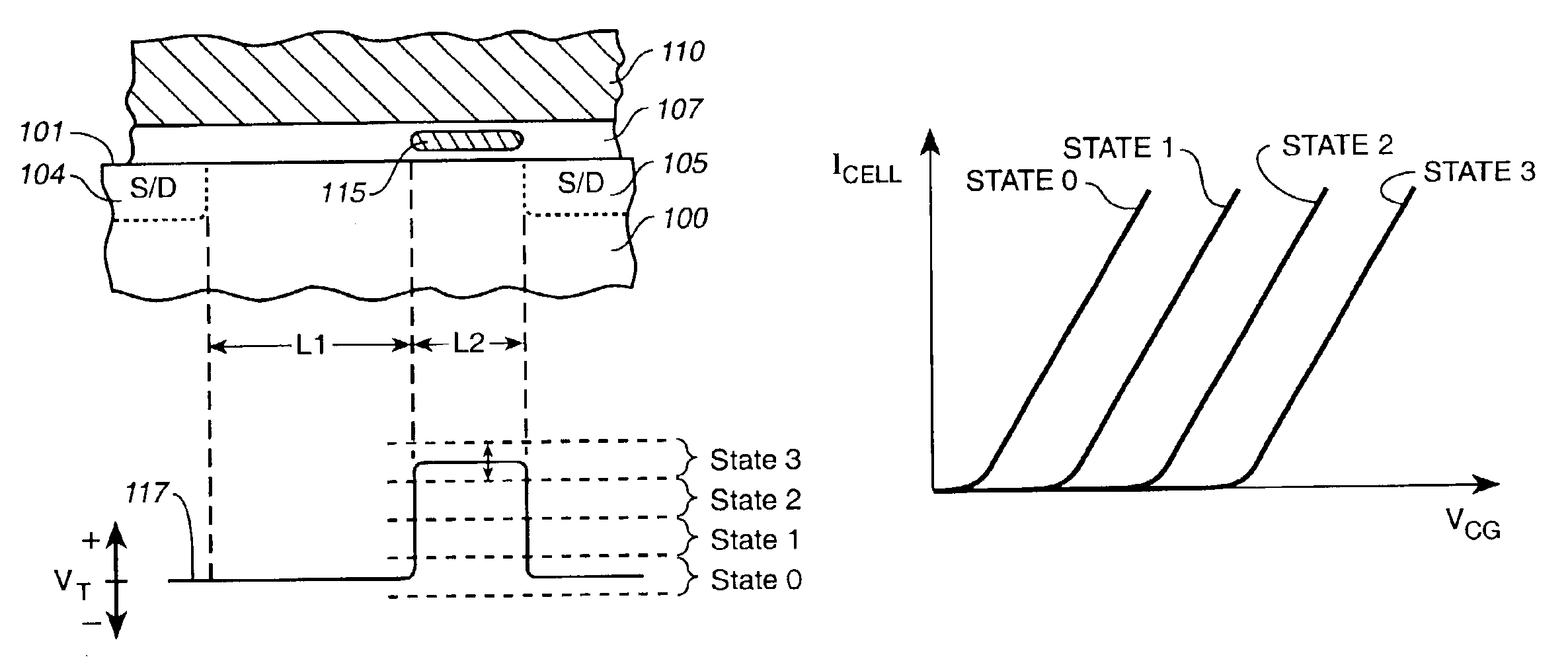

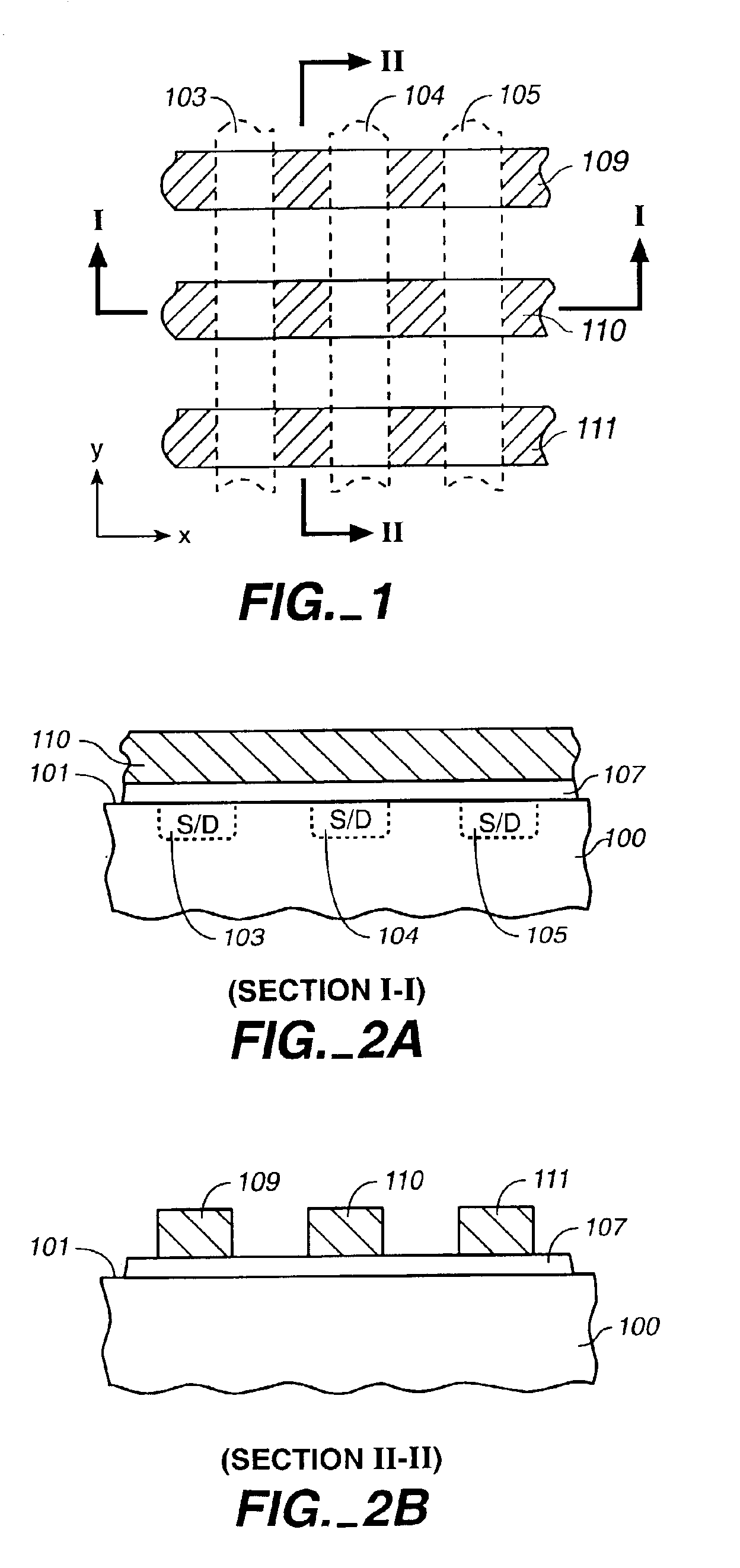

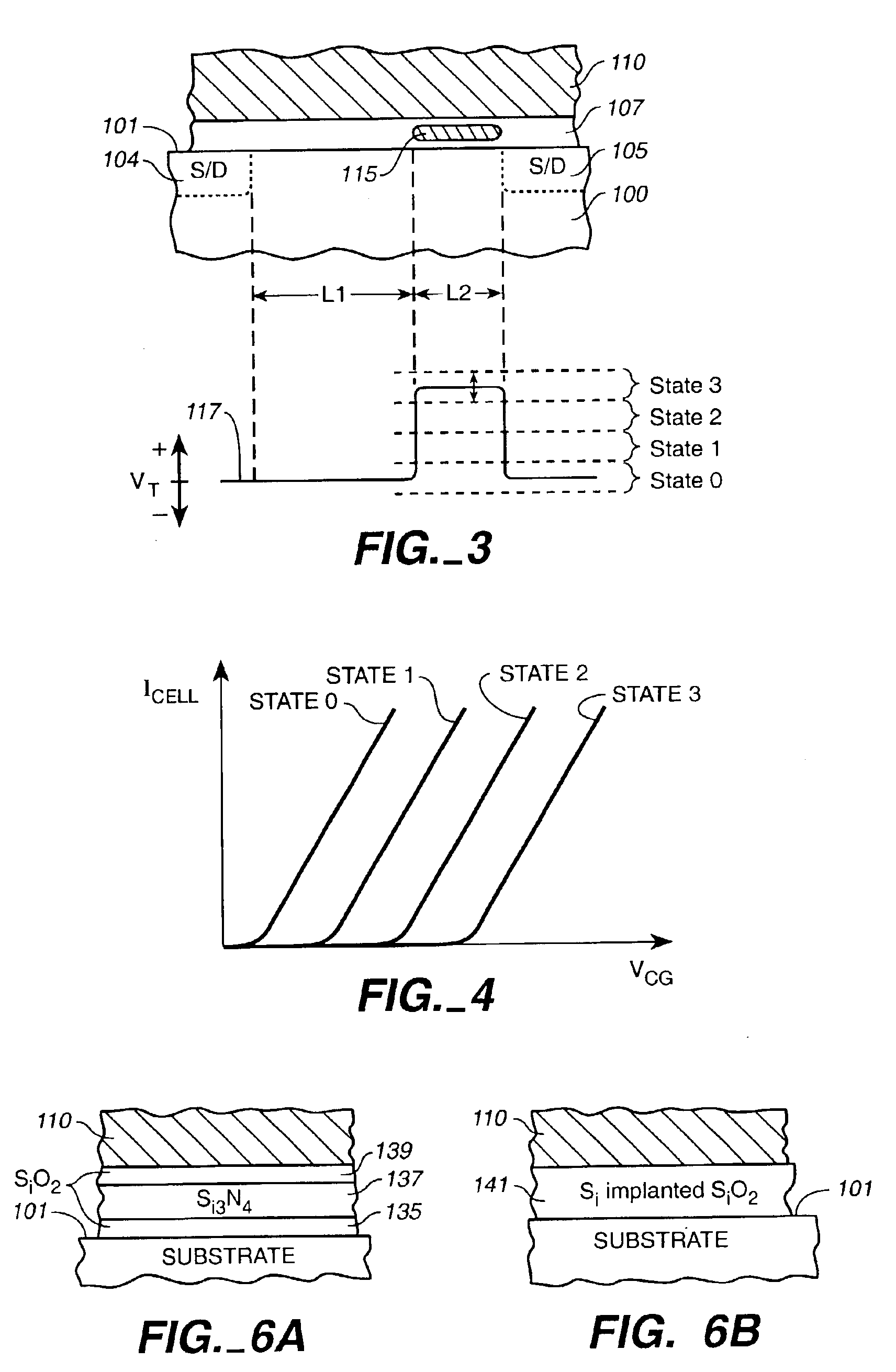

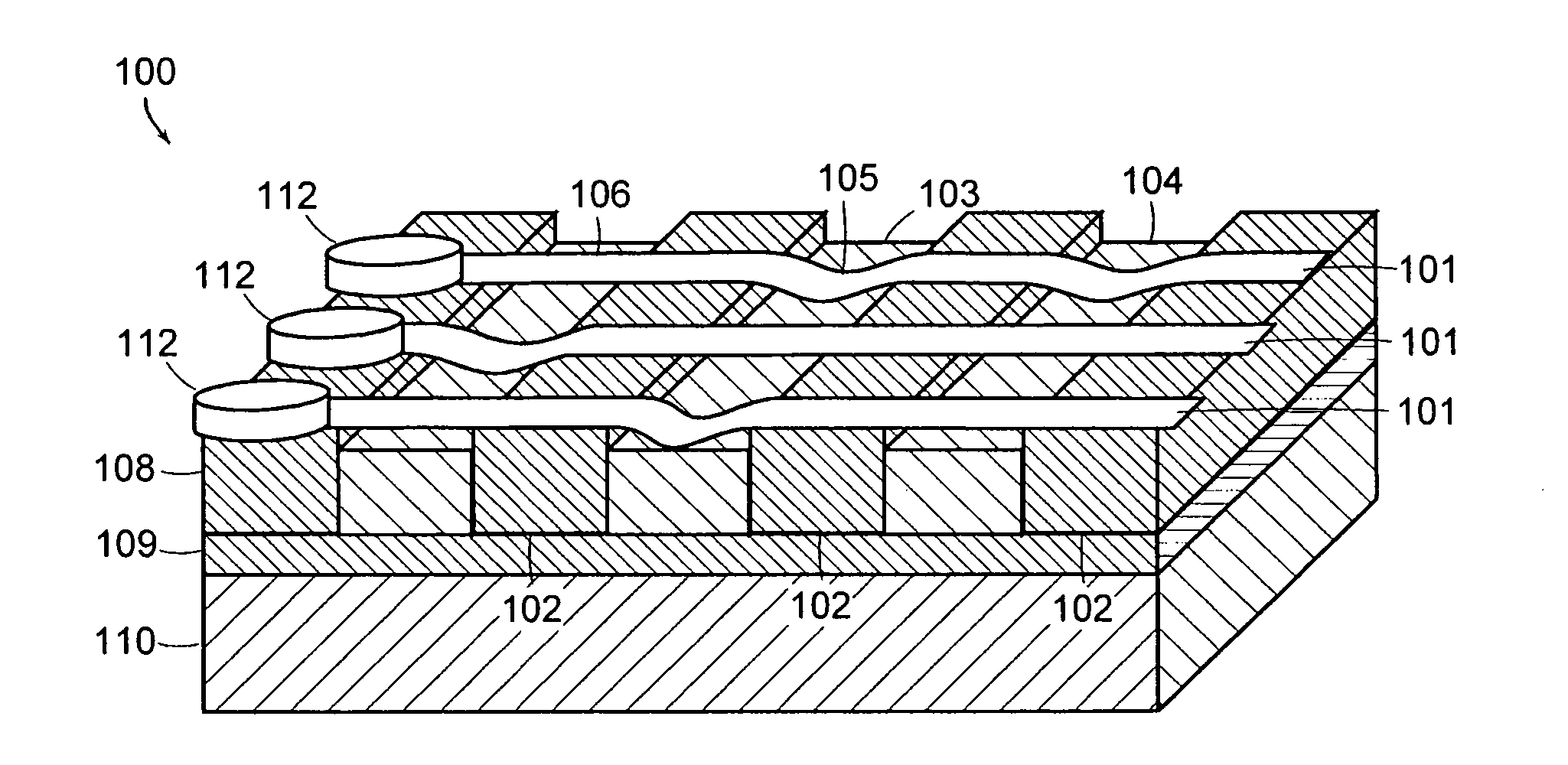

Multi-state non-volatile integrated circuit memory systems that employ dielectric storage elements

InactiveUS6925007B2Increase the number ofExtend effective lifeTransistorNanoinformaticsEngineeringDielectric layer

Non-volatile memory cells store a level of charge corresponding to the data being stored in a dielectric material storage element that is sandwiched between a control gate and the semiconductor substrate surface over channel regions of the memory cells. More than two memory states are provided by one of more than two levels of charge being stored in a common region of the dielectric material. More than one such common region may be included in each cell. In one form, two such regions are provided adjacent source and drain diffusions in a cell that also includes a select transistor positioned between them. In another form, NAND arrays of strings of memory cells store charge in regions of a dielectric layer sandwiched between word lines and the semiconductor substrate.

Owner:SANDISK TECH LLC

Pipelined programming of non-volatile memories using early data

Owner:SANDISK TECH LLC

Device selection circuitry constructed with nanotube technology

A memory system having electromechanical memory cells and decoders is disclosed. A decoder circuit selects at least one of the memory cells of an array of such cells. Each cell in the array is a crossbar junction at least one element of which is a nanotube or a nanotube ribbon. The decoder circuit is constructed of crossbar junctions at least one element of each junction being a nanotube or a nanotube ribbon.

Owner:NANTERO

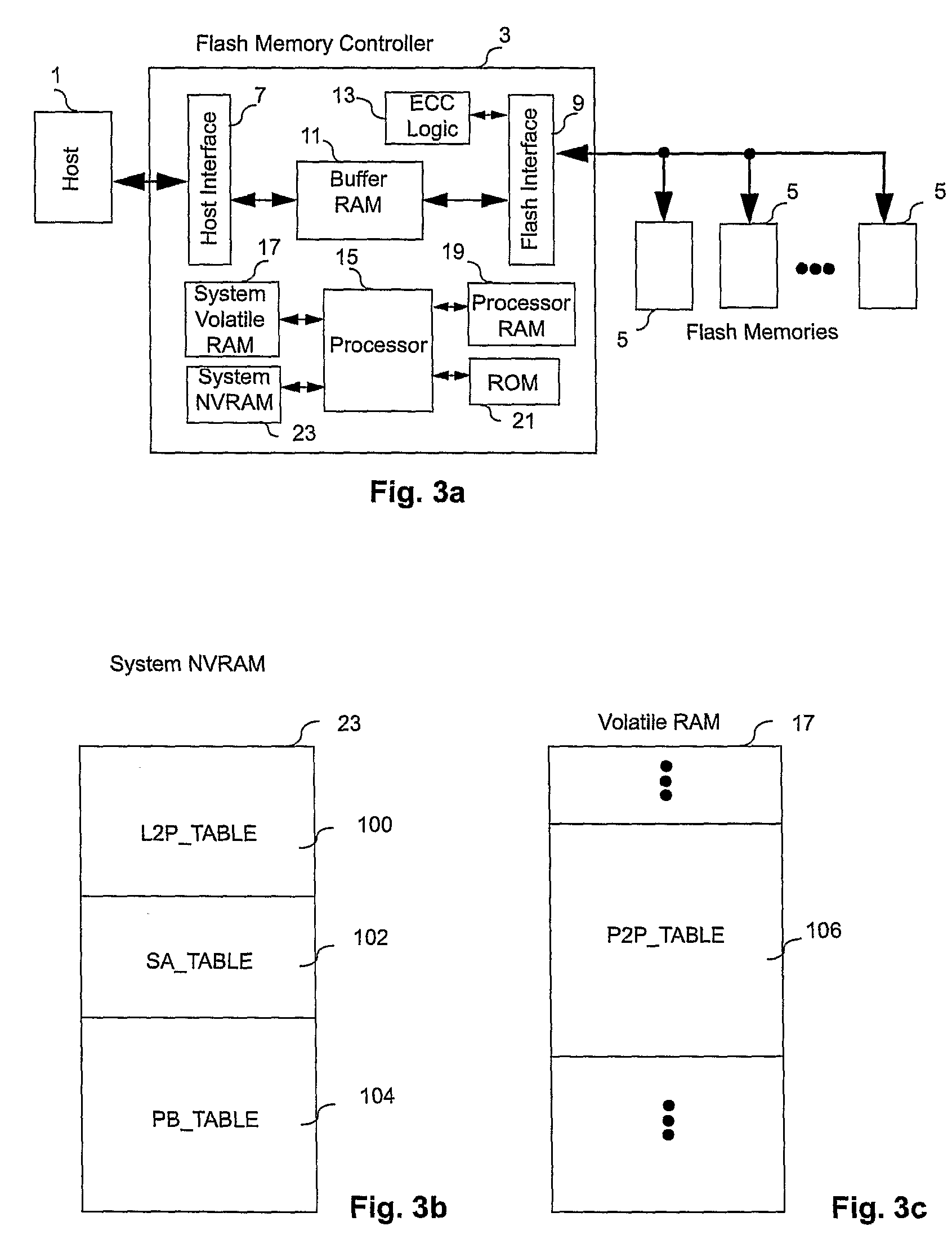

Controller for Non-Volatile Memories and Methods of Operating the Memory Controller

ActiveUS20080270680A1Improve system performanceReduce stepsMemory adressing/allocation/relocationRead-only memoriesMemory controllerByte

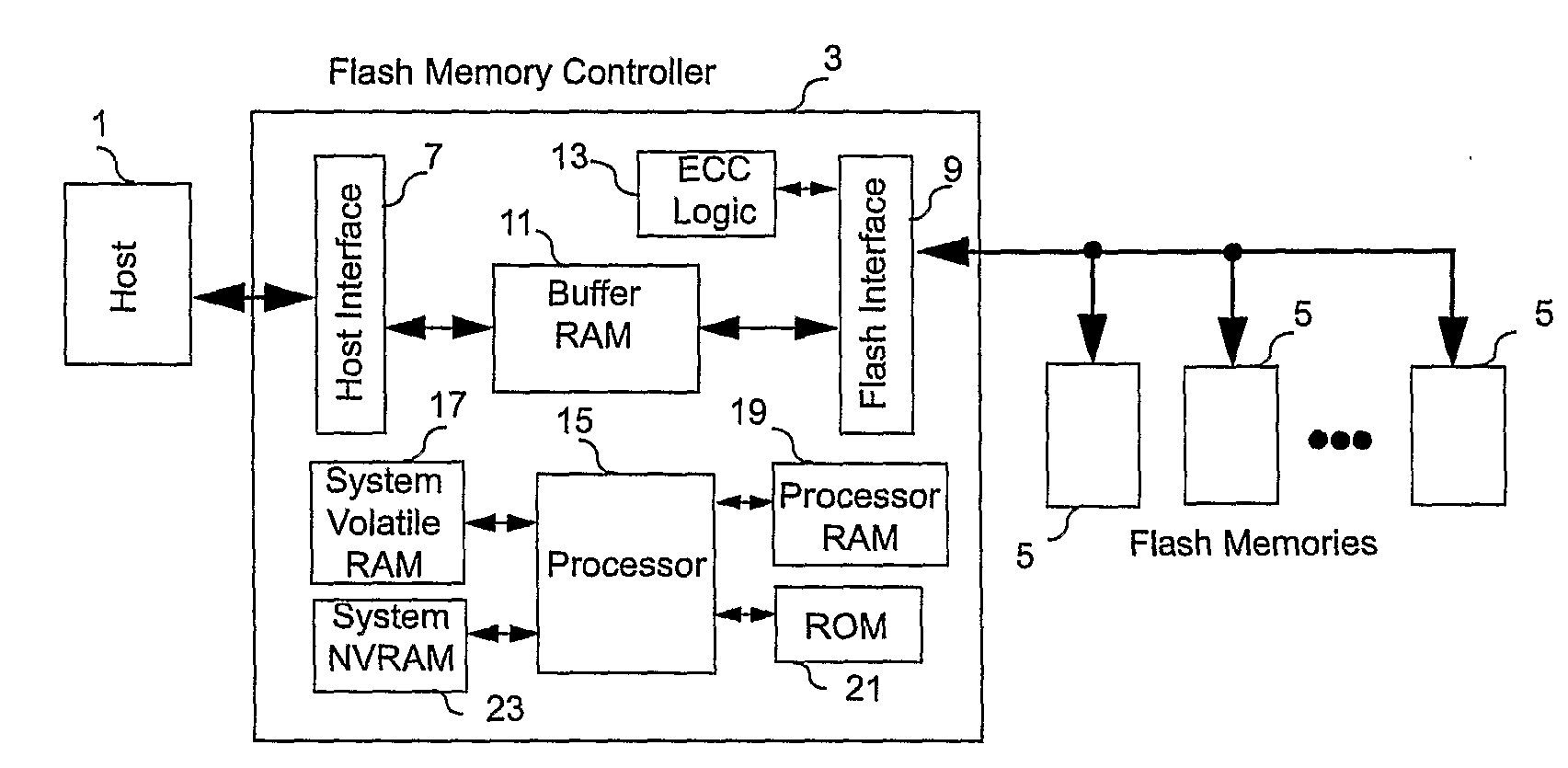

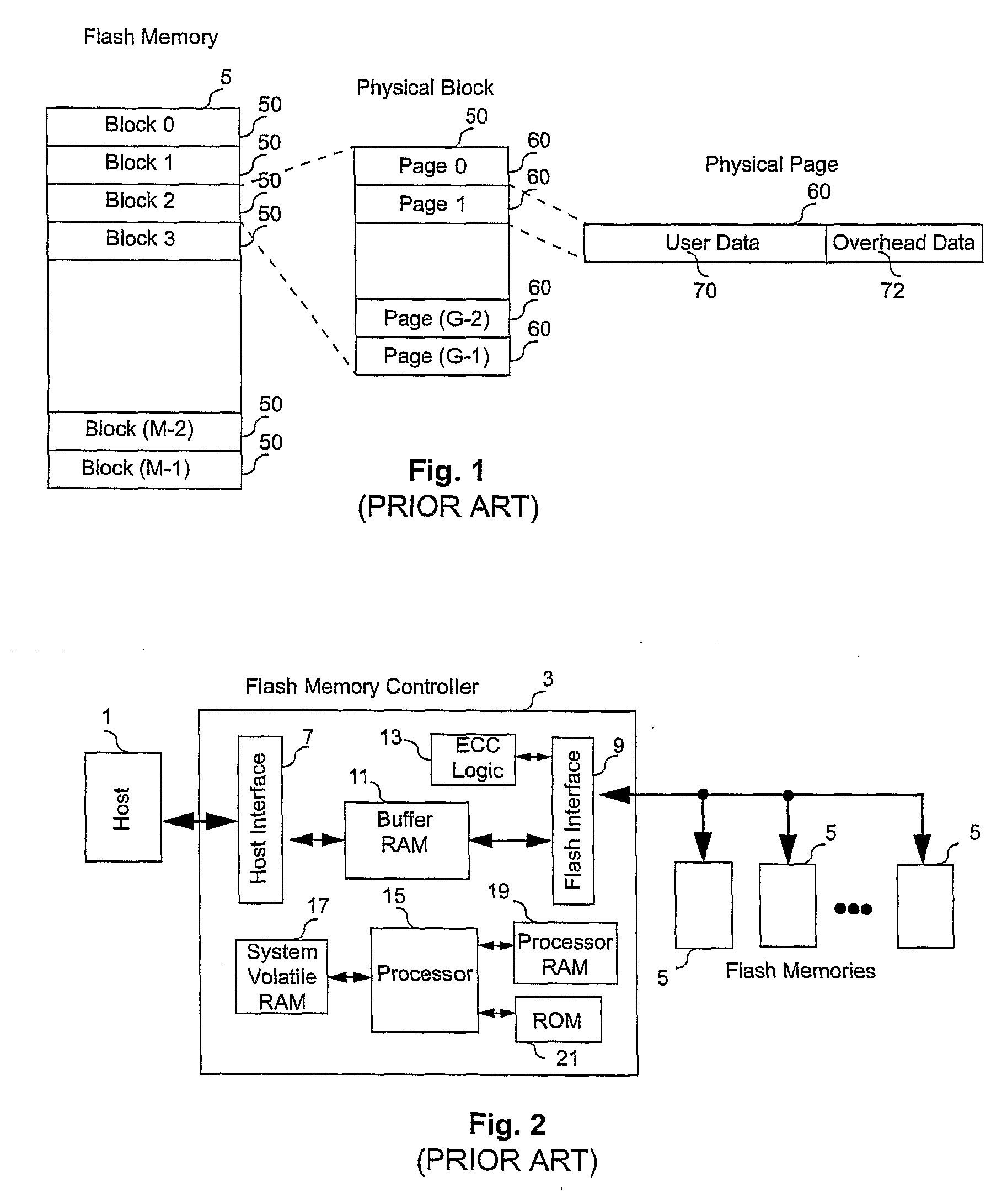

A non-volatile memory system (3) is proposed consisting of a first non-volatile flash memory (5) having a plurality of blocks, each block having a plurality of pages, each block being erasable and each page being programmable, and a second non-volatile random access memory (23) having a plurality of randomly accessible bytes. The second non-volatile memory (23) stores data for mapping logical blocks to physical blocks and status information of logical blocks. Each logical block has an associated physical page pointer stored in the second non-volatile memory (23) that identifies the next free physical page of the mapped physical block to be written. The page pointer is incremented after every page write to the physical block, allowing all physical pages to be fully utilized for page writes. Furthermore, a method of writing and reading data is disclosed whereby the most recently written physical page associated with a logical address is identifiable by the memory system without programming flags into superseded pages, or recording time stamp values in any physical page or block of the first non-volatile memory (5). Furthermore, a method is provided for a logical block to be mapped to two physical blocks instead of one to provide additional space for page writes, resulting in reduction in page copy operations, thereby increasing the performance of the system.

Owner:CHANG CHEE KENG

Scrub Techniques for Use with Dynamic Read

The decision on whether to refresh or retire a memory block is based on the set of dynamic read values being used. In a memory system using a table of dynamic read values, the table is configured to include how to handle read error (retire, refresh) in addition to the read parameters for the different dynamic read cases. In a refinement, the read case number can used to prioritize blocks selected for refresh or retire. In cases where the read scrub is to be made more precise, multiple dynamic read cases can be applied. Further, which cases are applied can be intelligently selected.

Owner:SANDISK TECH LLC

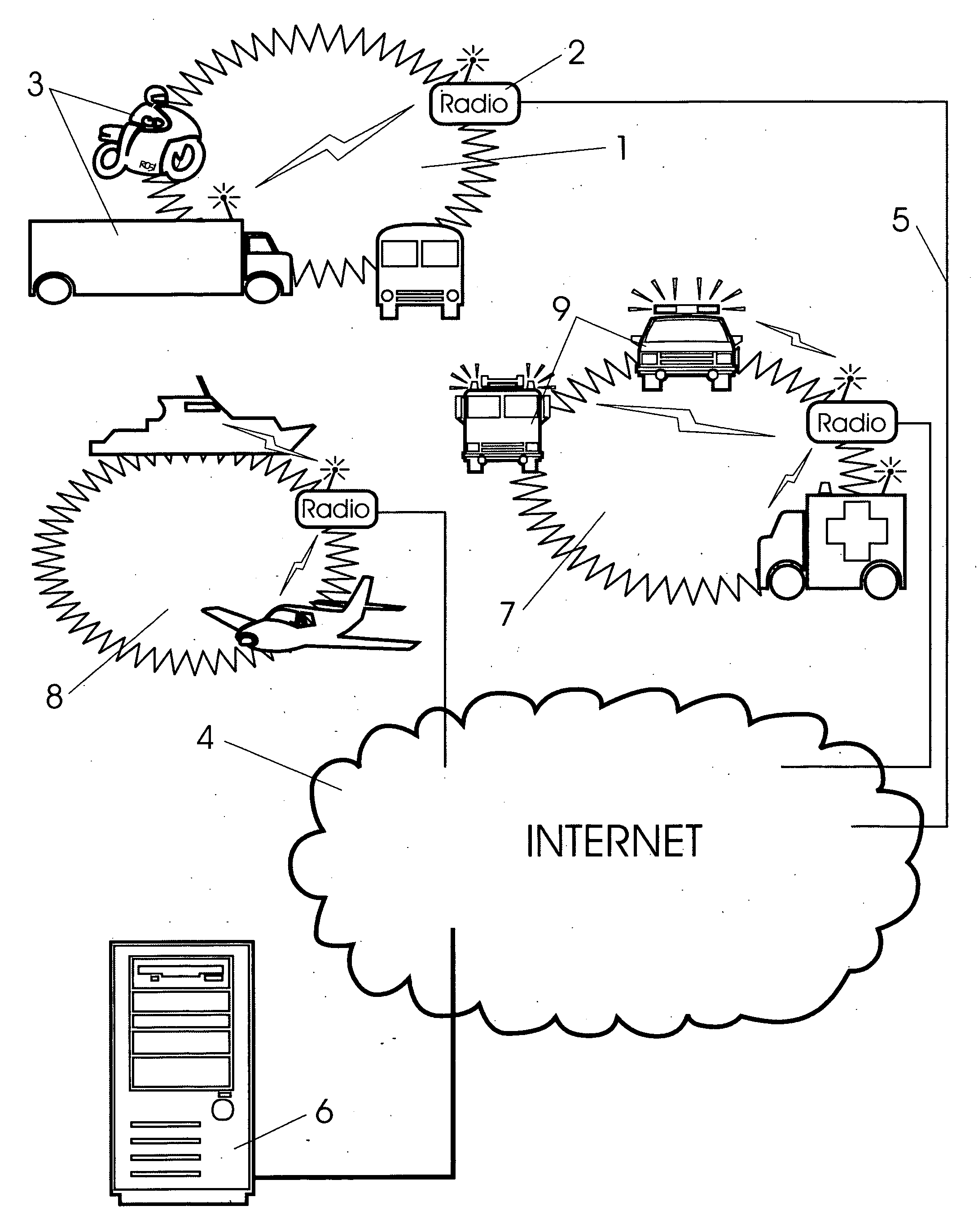

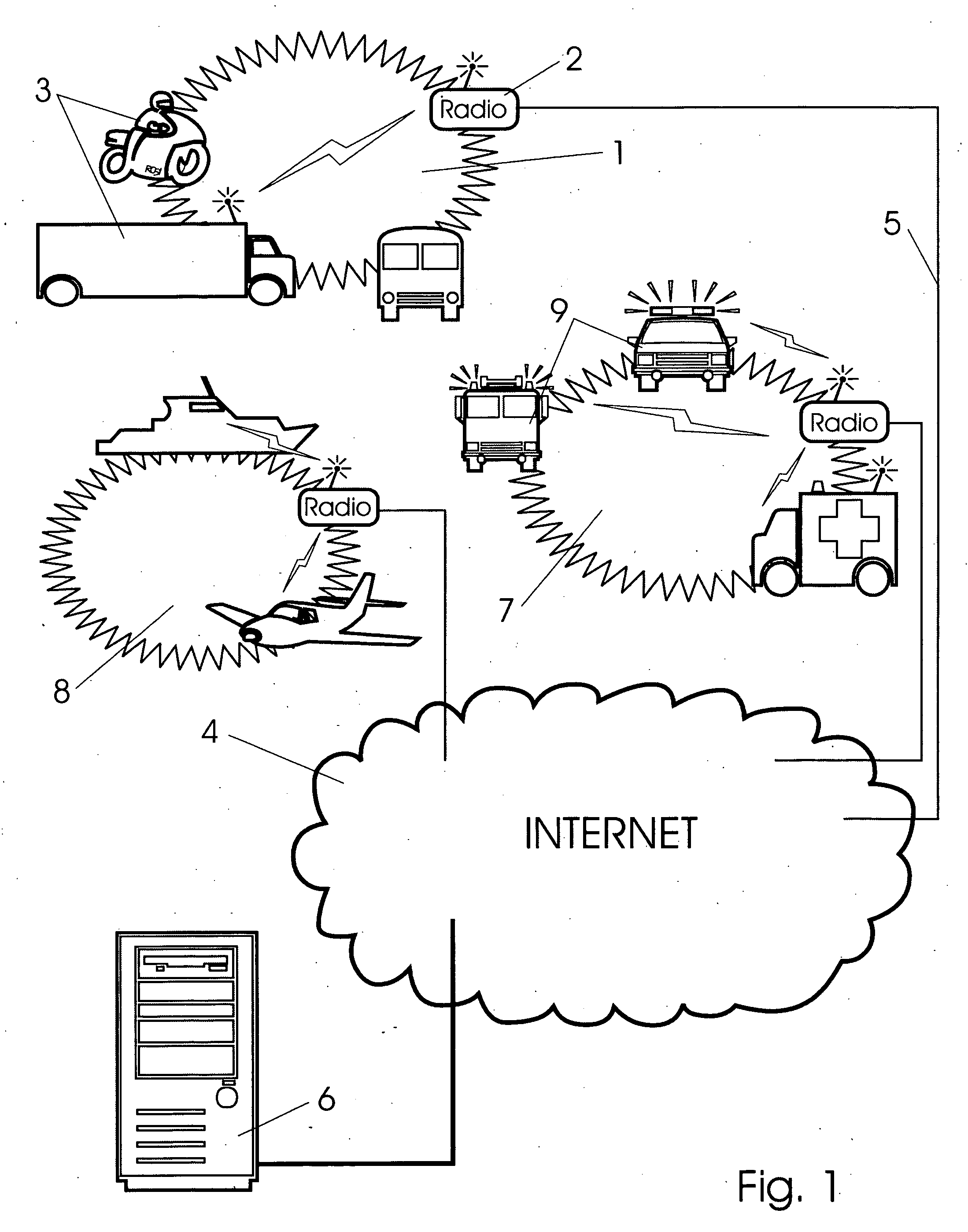

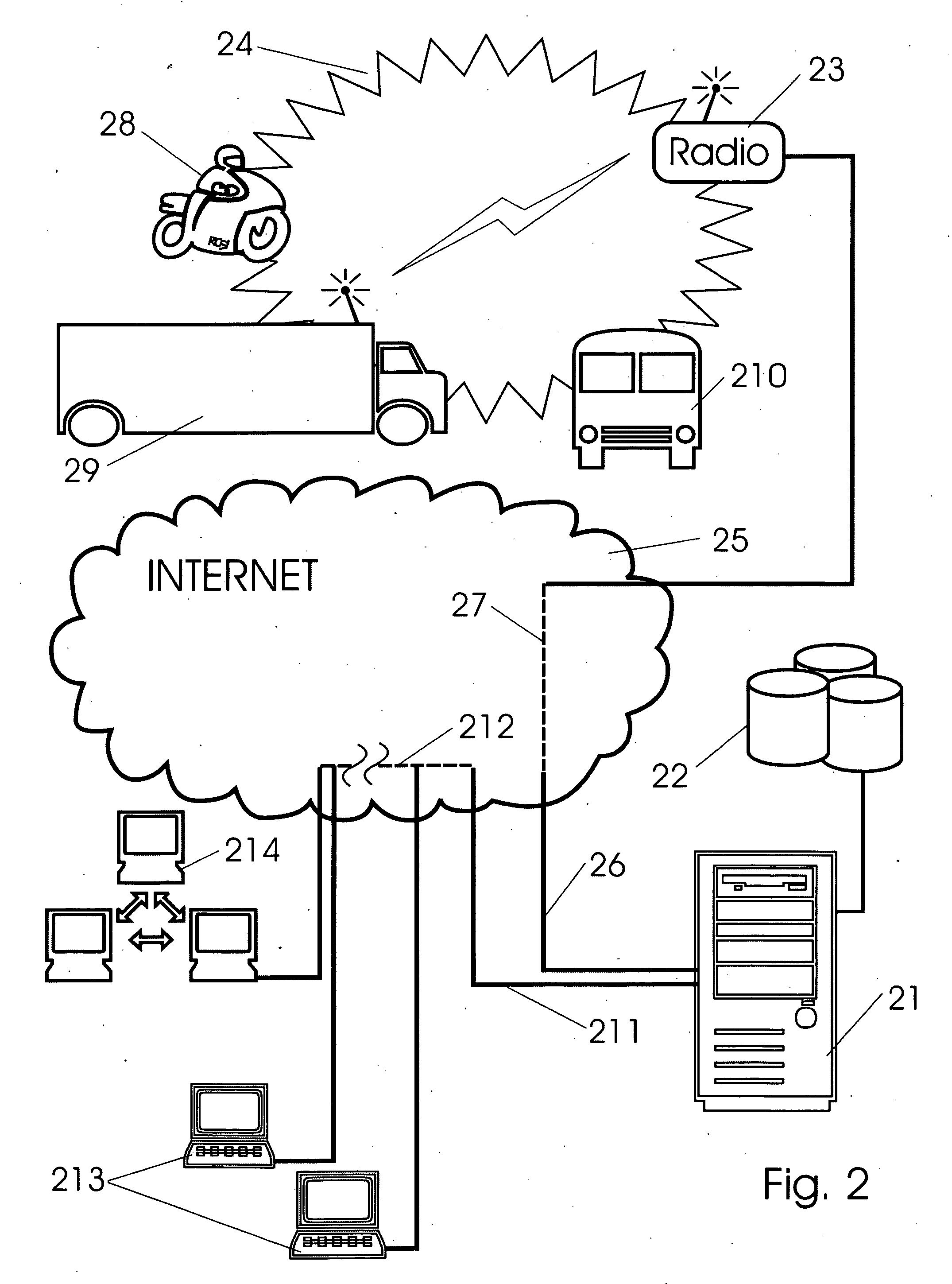

Vehicle event recorder systems

Vehicle recorder systems are arranged in configured with a video camera, light-weight memory systems, and radio communications facility suitable for use in conjunction with an automobile. An automobile equipped with these video recorder systems used normally throughout the service today, provides a video record of unusual events which may occur from time-to-time. Events such as accidents, near-miss incidents, driving of use, among others, trigger a system to preserve video images collected before and after the moment of the event. Replay of these images yield information regarding cause and true nature of the event. These systems are particularly arranged about, and in support of fleet use of vehicles. That is, groups of vehicles are arranged and coupled together whereby a plurality of such vehicles may communicate with a common system providing a fleet manager advanced fleet management tools.

Owner:SMARTDRIVE SYSTEMS

Automated wear leveling in non-volatile storage systems

ActiveUS7120729B2Lower Level RequirementsAvoid uneven wearMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingMemory systems

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. Included is a method for performing wear leveling in a memory system that includes a first zone, which has a first memory element that includes contents, and a second zone includes identifying the first memory element and associating the contents of the first memory element with the second zone while disassociating the contents of the first memory element from the first zone. In one embodiment, associating the contents of the first memory element with the second involves moving contents of a second memory element into a third memory element, then copying the contents of the first memory element into the second memory element.

Owner:SANDISK TECH LLC

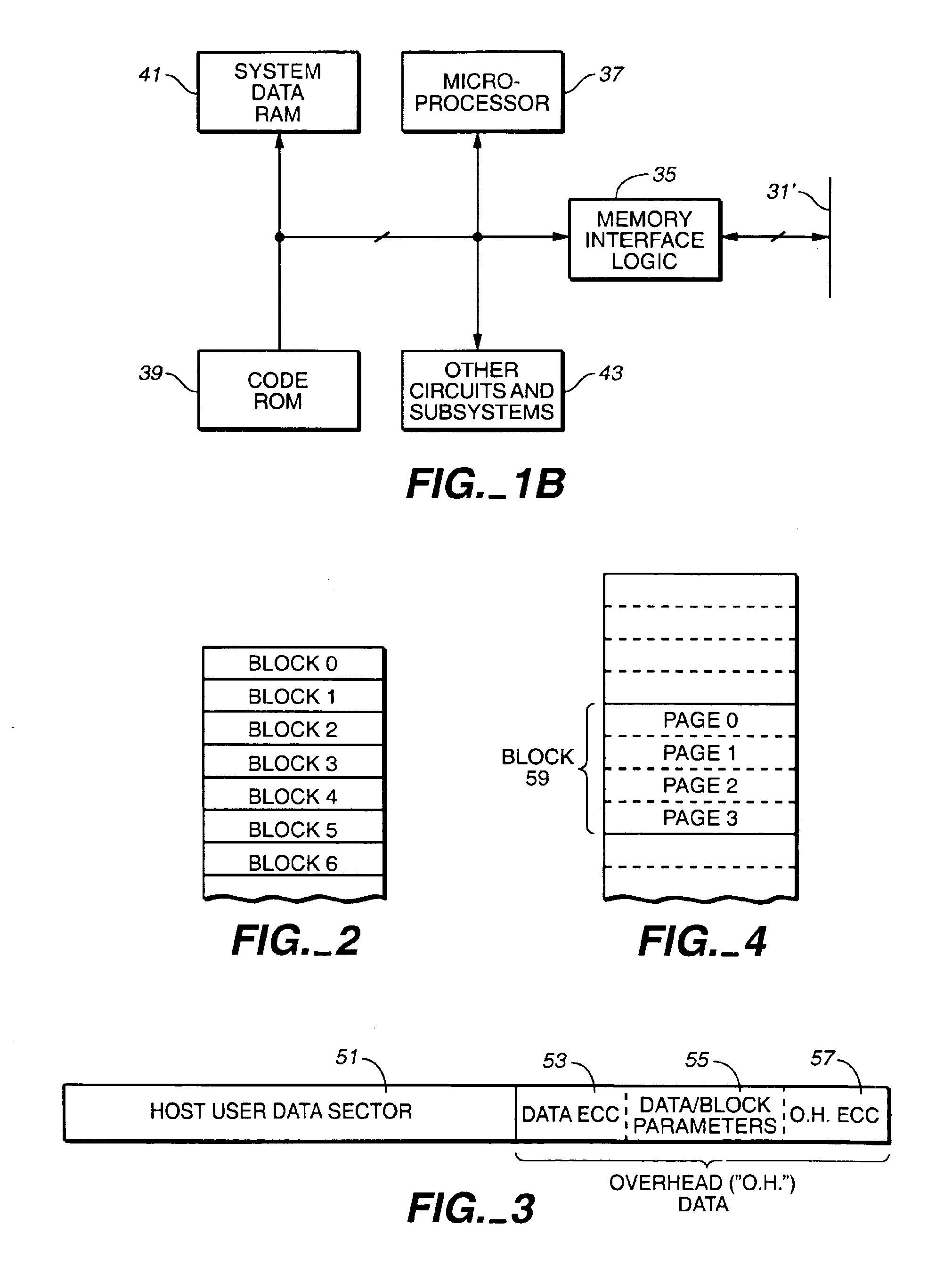

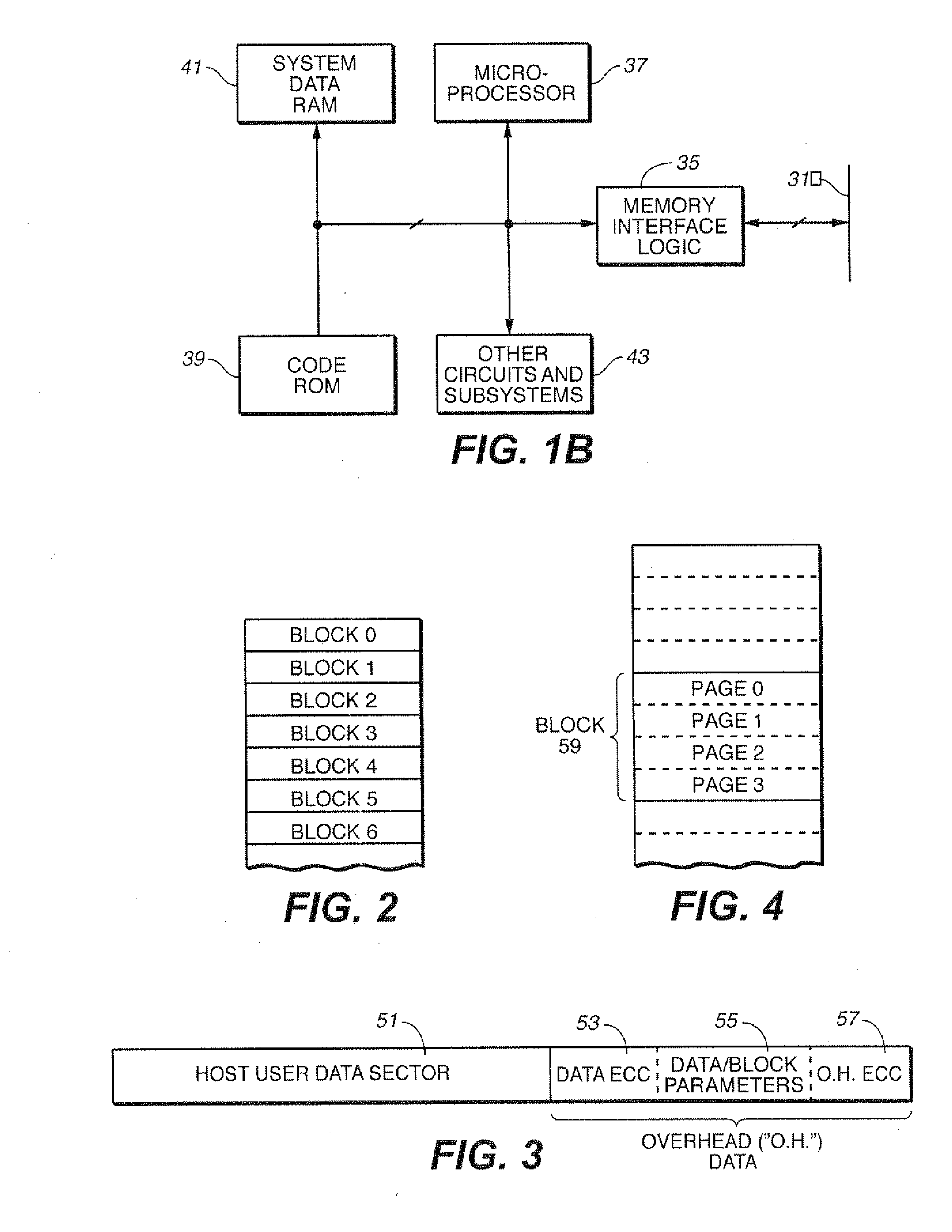

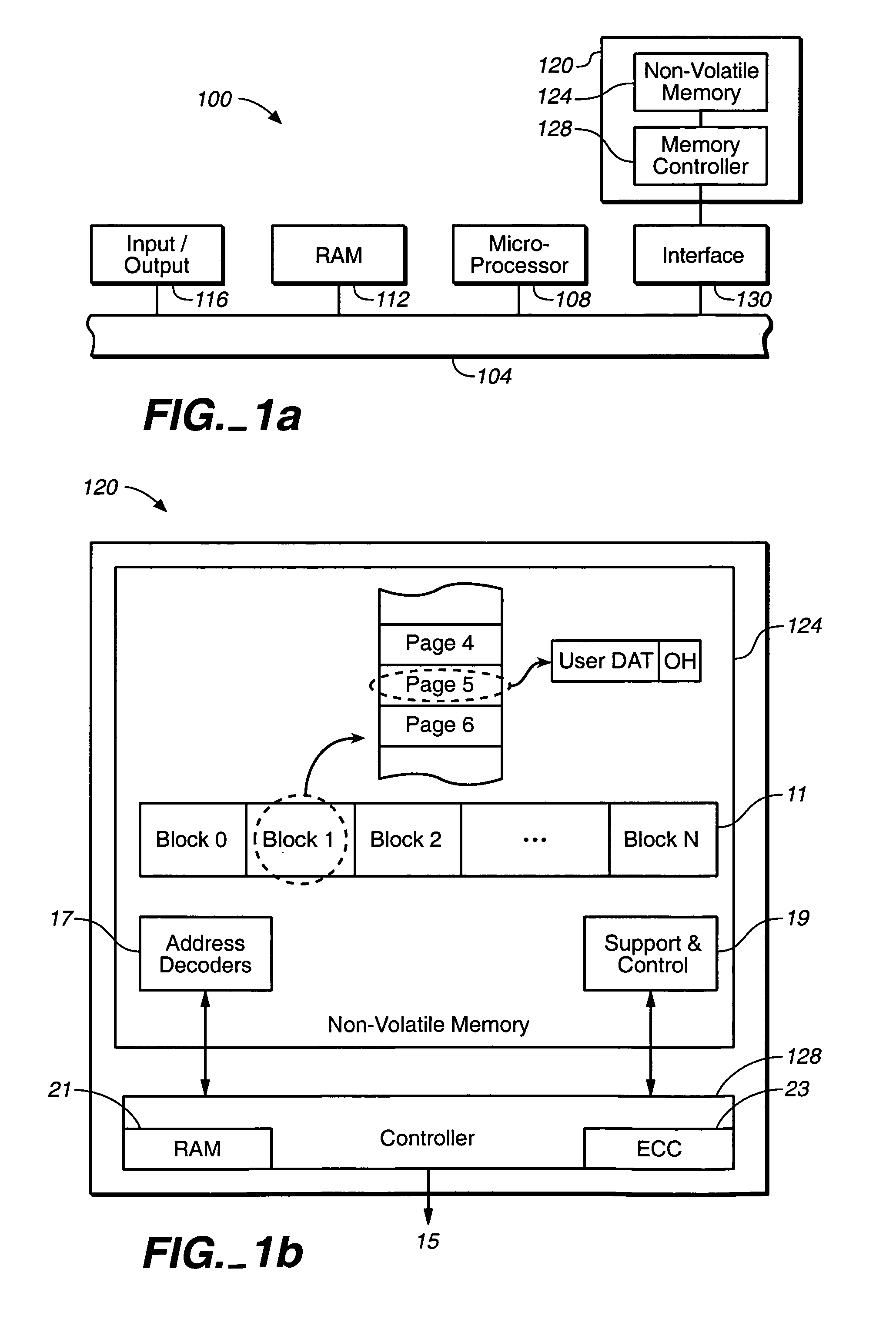

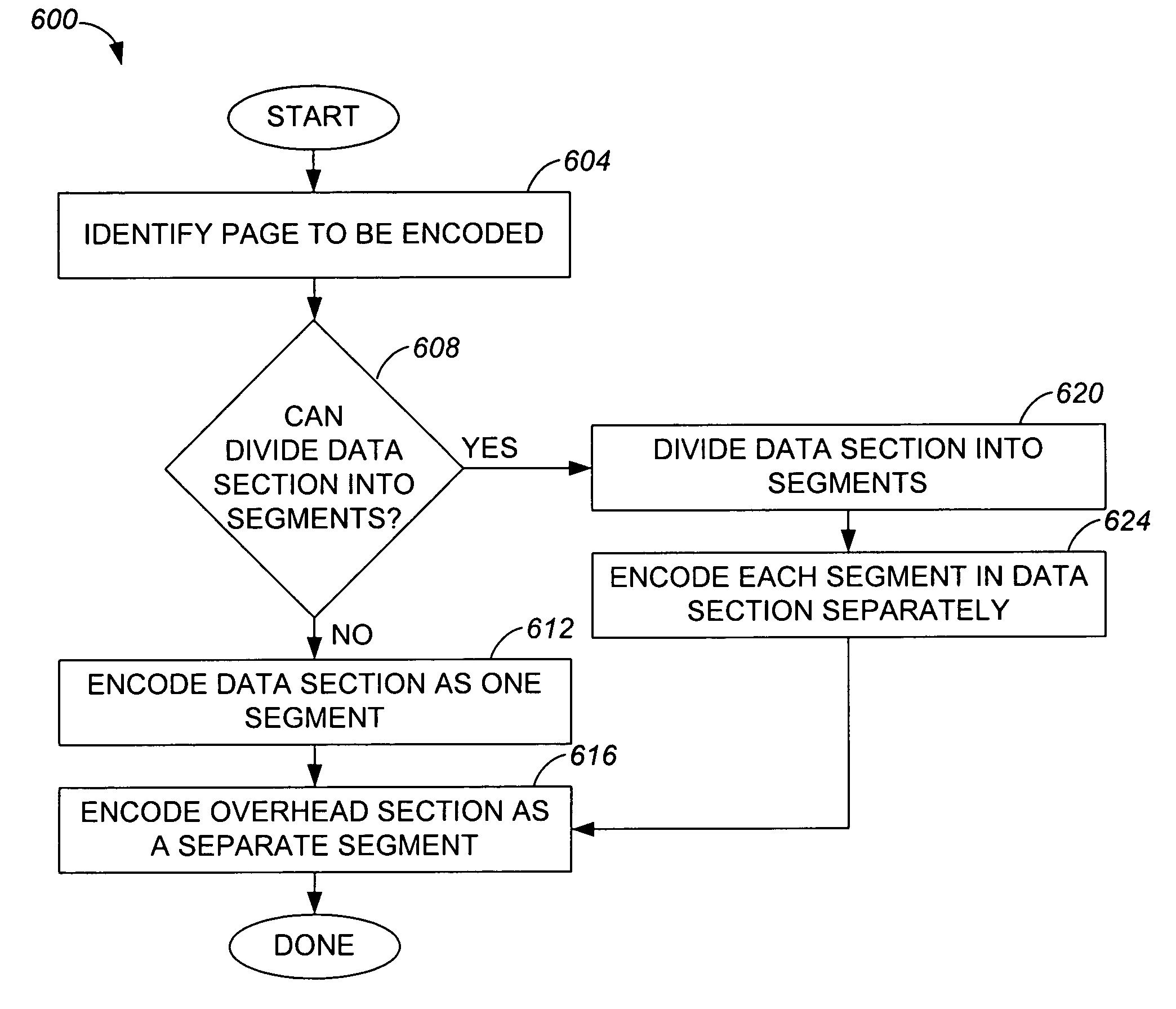

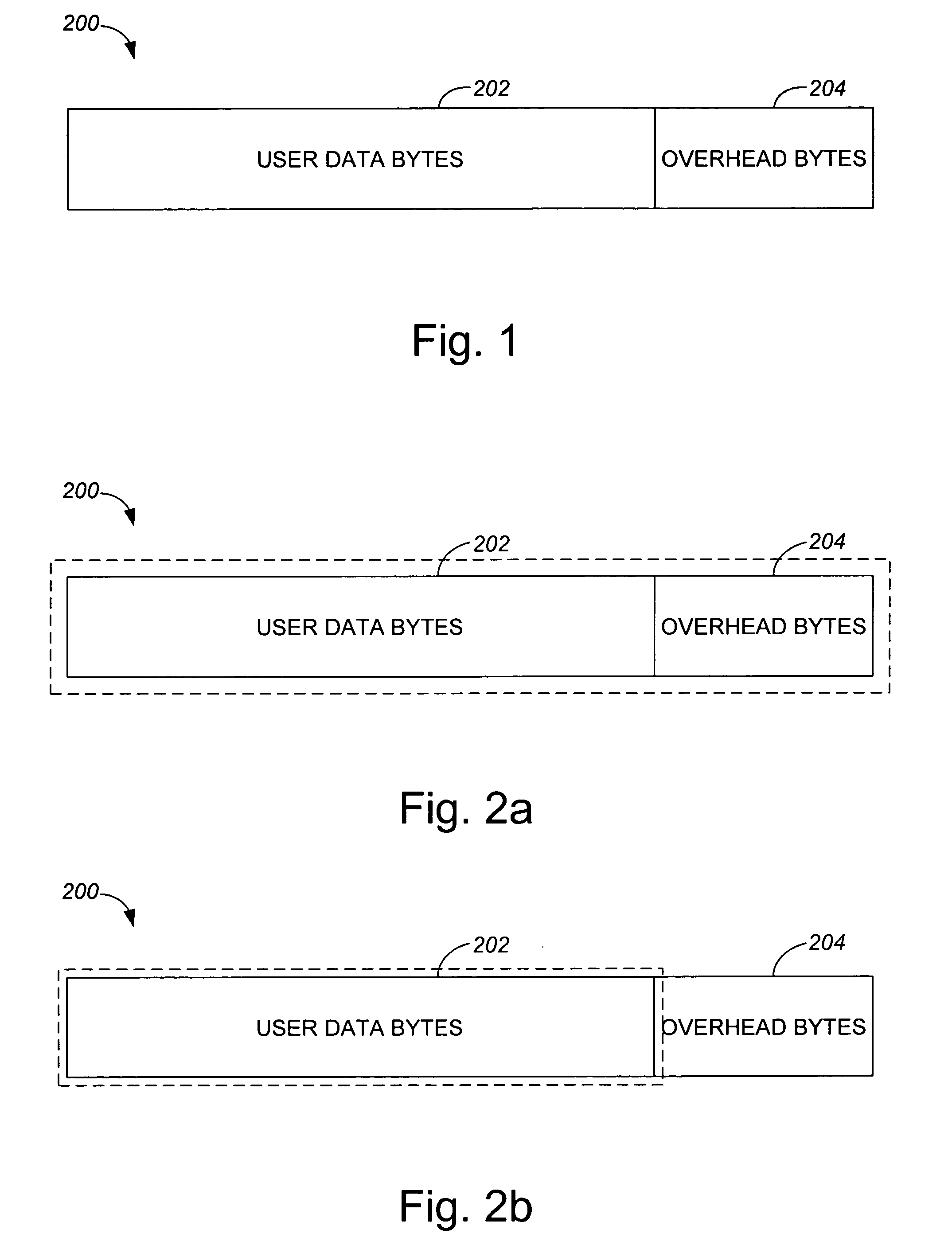

Method and apparatus for managing the integrity of data in non-volatile memory system

Methods and apparatus for encoding data associated with a page by dividing the page into segments and separately encoding the segments using extended error correction code (ECC) calculations are disclosed. According to one aspect of the present invention, a method for encoding data associated with a page which has a data area and an overhead area within a non-volatile memory of a memory system includes dividing at least a part of the page into at least two segments of the data, the at least two segments of the data including a first segment and a second segment, and performing ECC calculations on the first segment to encode the first segment. The method also includes performing the ECC calculations on the second segment to encode the second segment substantially separately from the first segment.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com