Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Failed analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

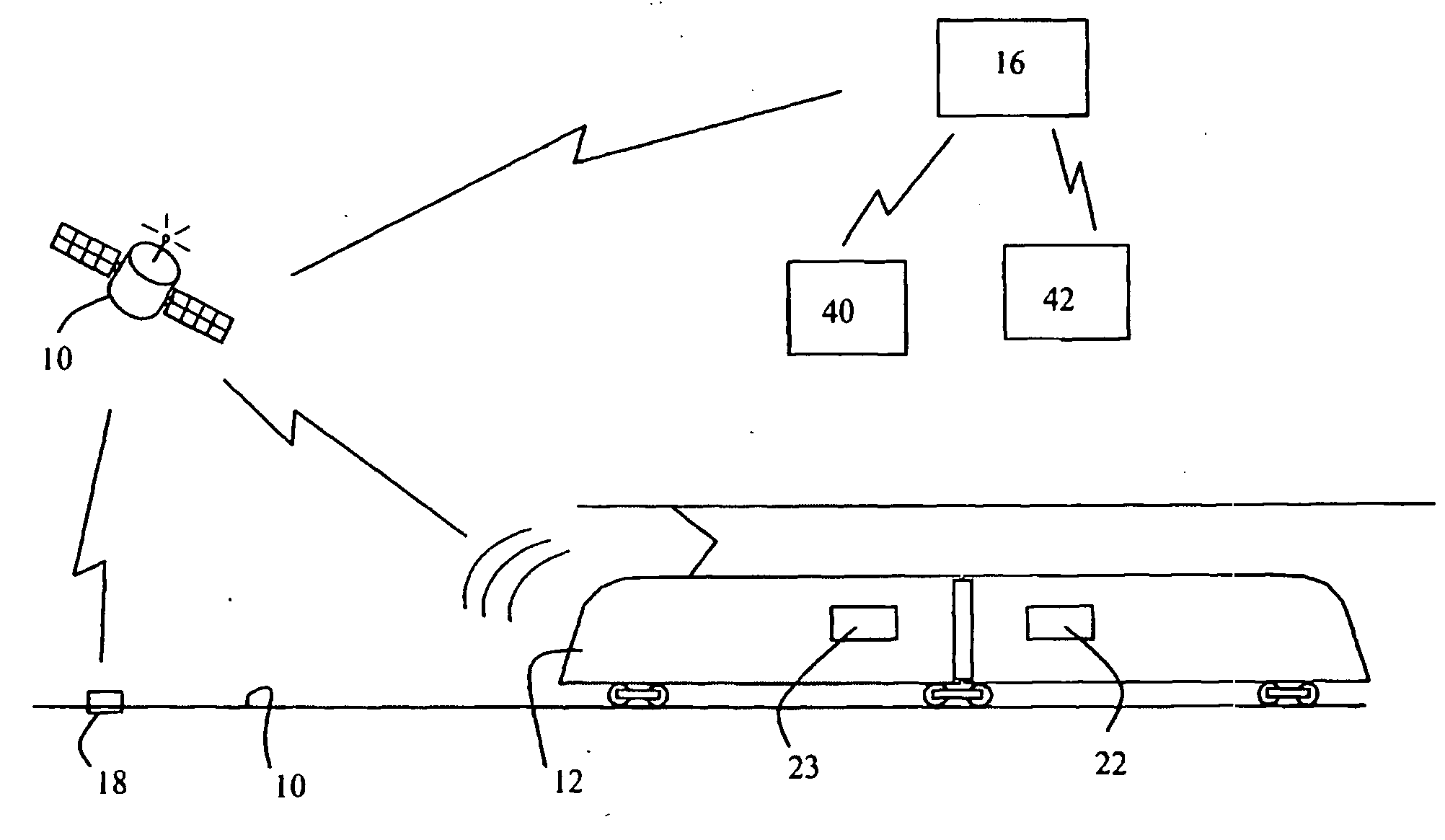

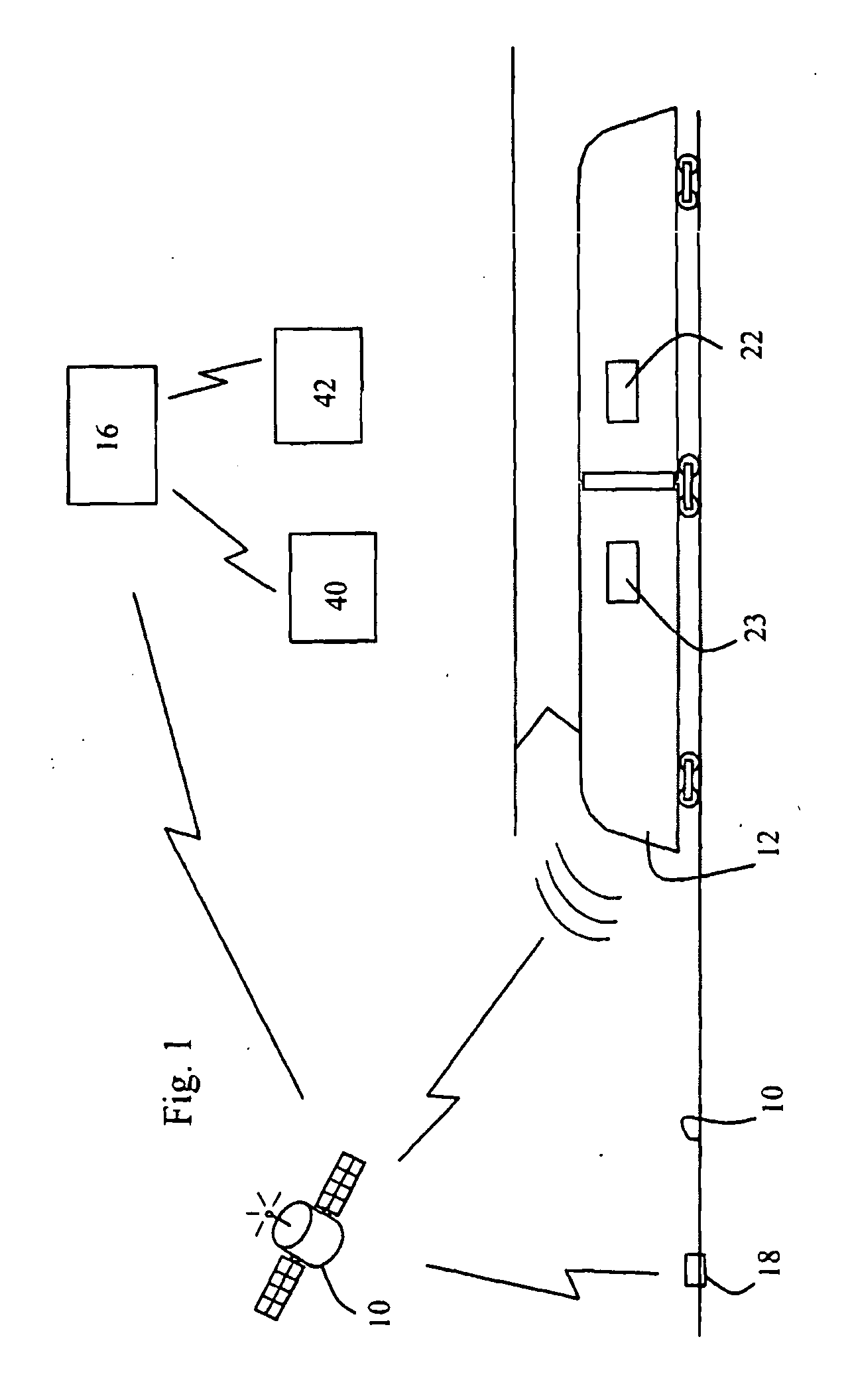

Diagnostic system and method for monitoring a rail system

InactiveUS20100204857A1Failed analysisVehicle testingRegistering/indicating working of vehiclesOn boardEvent data

The vehicles (12) of at least one fleet of rail vehicles are provided with on-board sensors (22) and rail vehicle positioning means (23). The rail infrastructure on which the rail vehicles circulate is provided with fixed rail infrastructure sensors (18). The rail infrastructure-related sensor data is merged with the rail vehicle-related sensor data, with location data representative of the location of the rail infrastructure-related sensors and with the rail vehicle position data for generating series of categorized event data representative of the occurrence of categorized events at a given location on the rail infrastructure over time and / or on a given rail vehicle of the fleet over time. The series of categorized events data representative of at least one category of events can be compared over any predetermined period of time to identify any location of the rail infrastructure and / or any rail vehicle which exhibits a series of events data that is significantly different from the other locations of the rail infrastructure and / or rail vehicles of the fleet over said predetermined period of time.

Owner:BOMBARDIER TRANSPORTATION GMBH

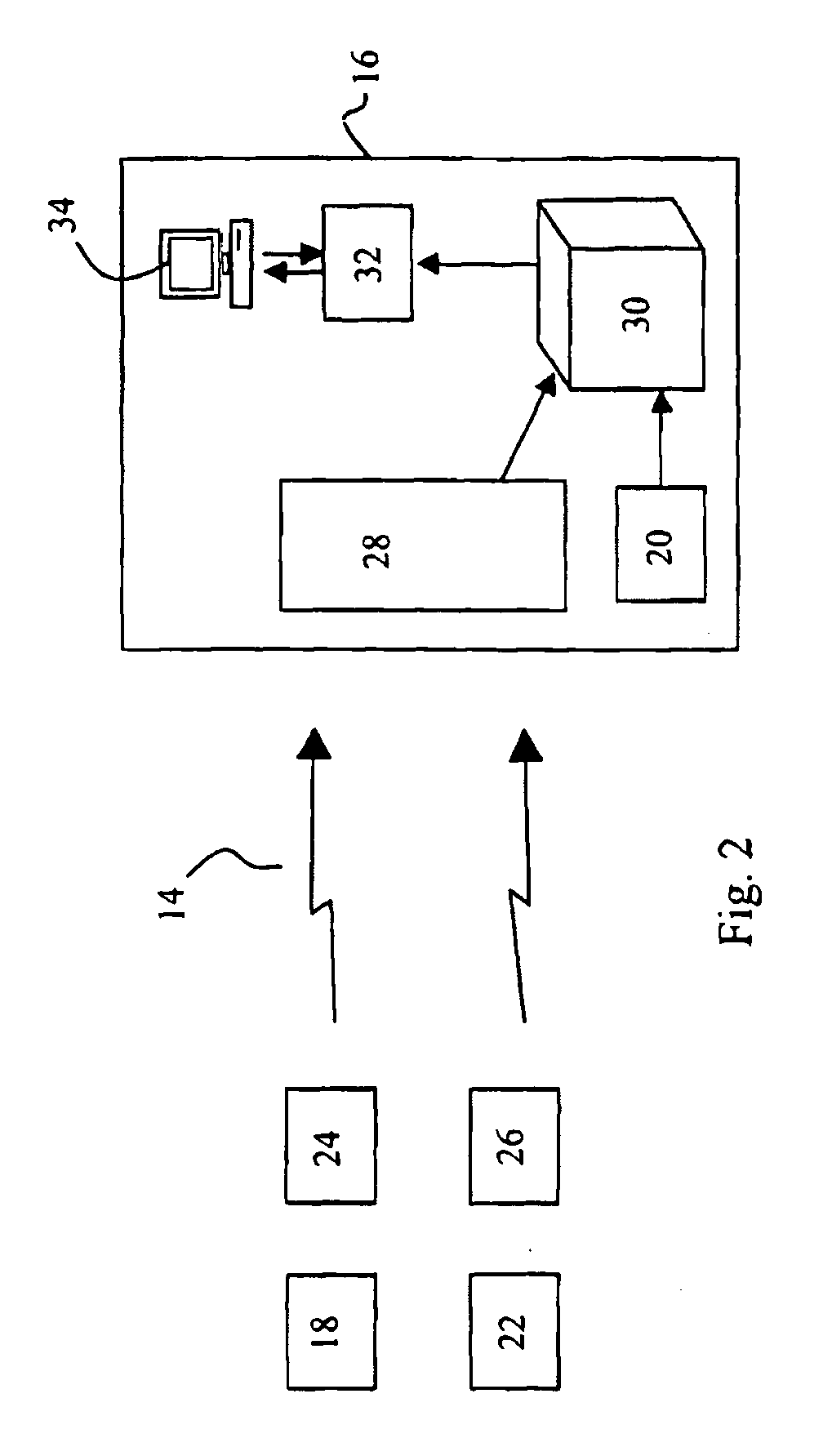

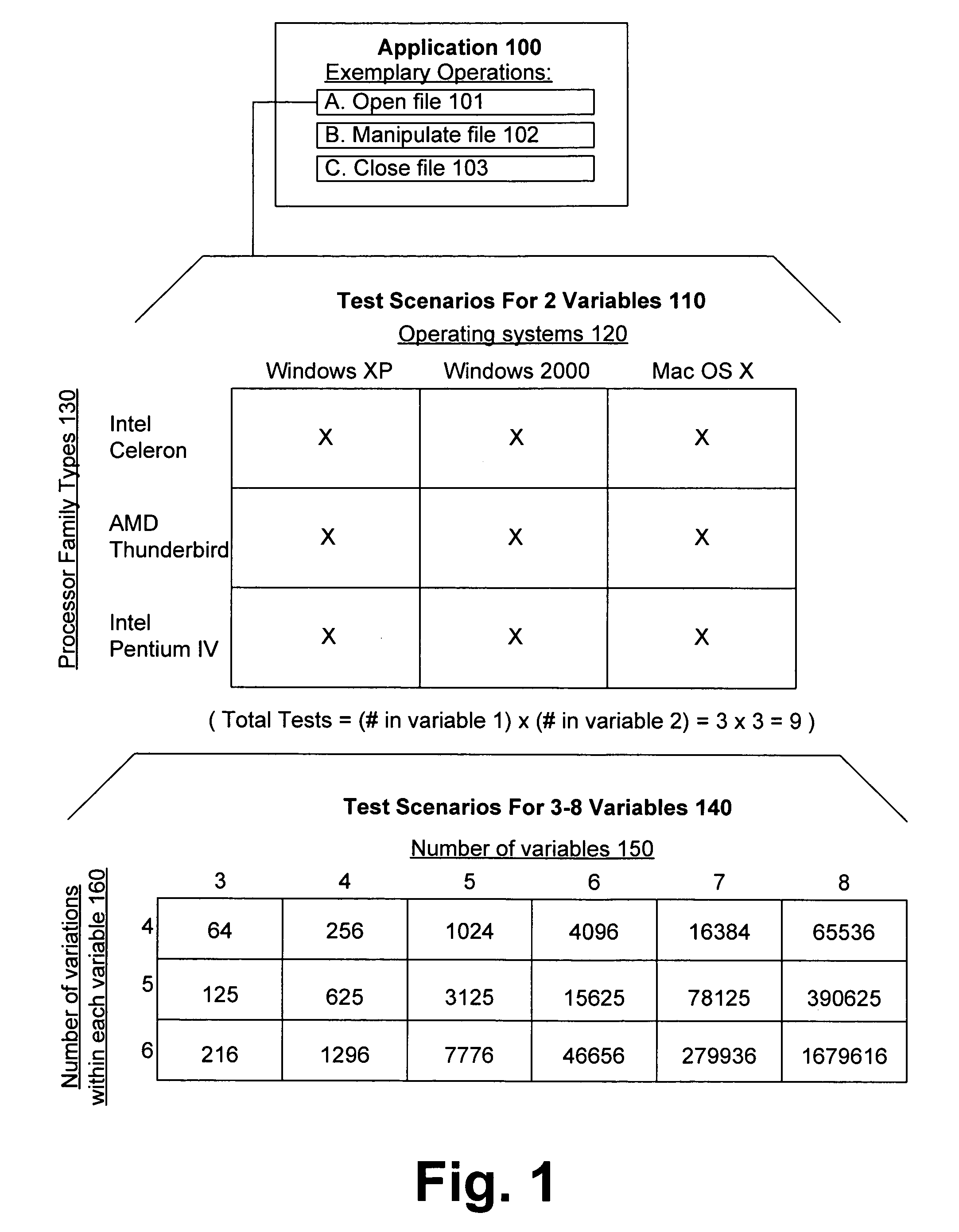

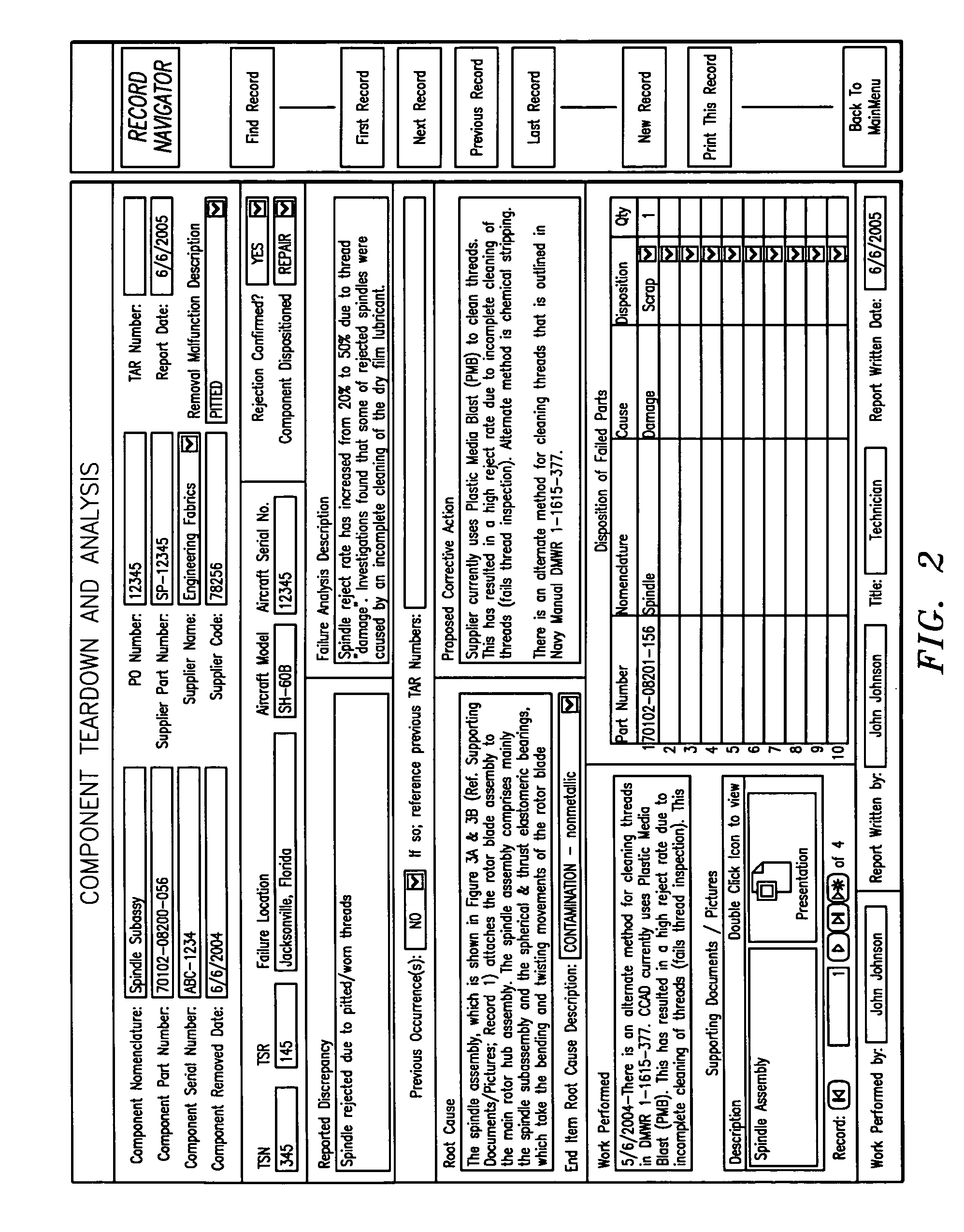

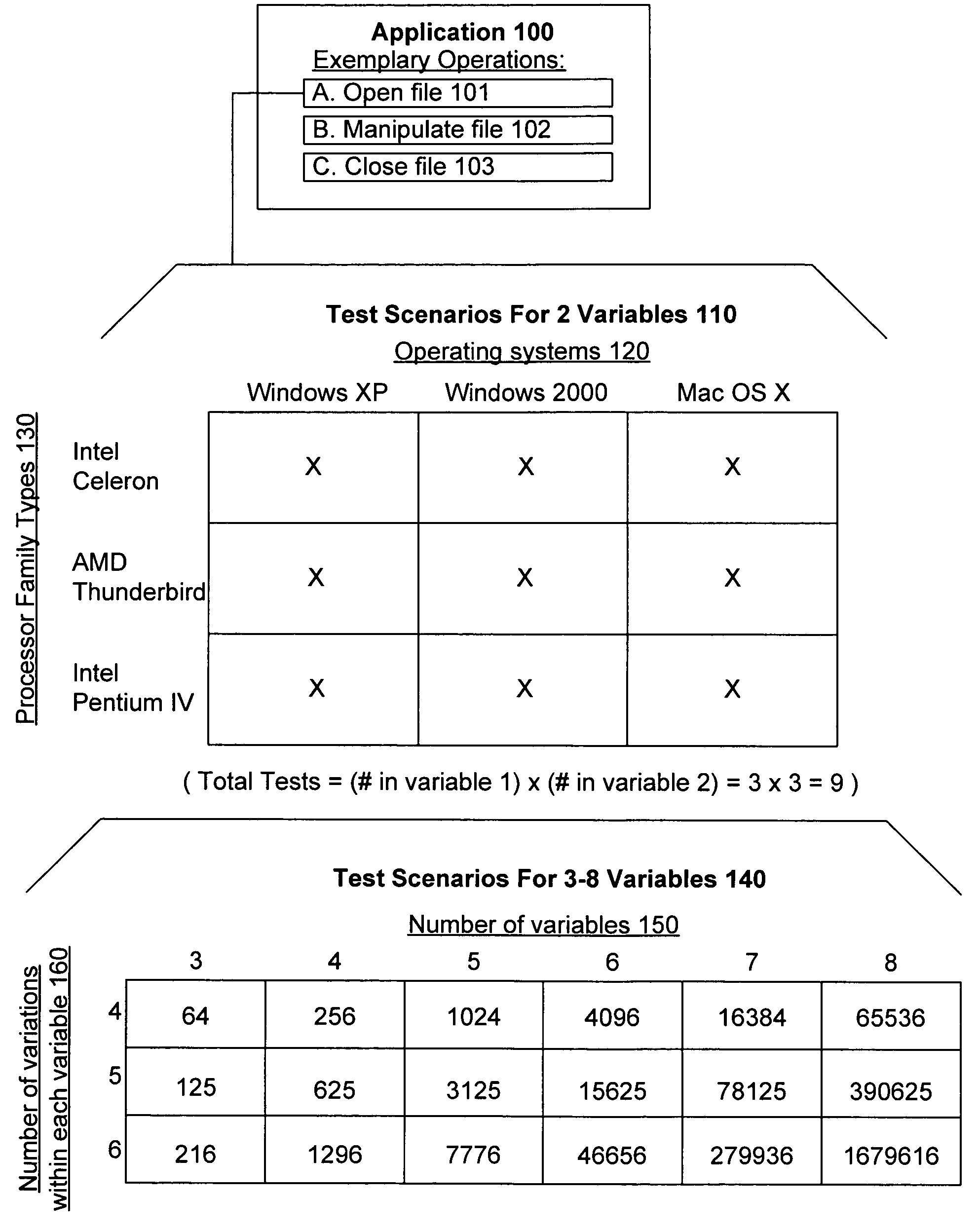

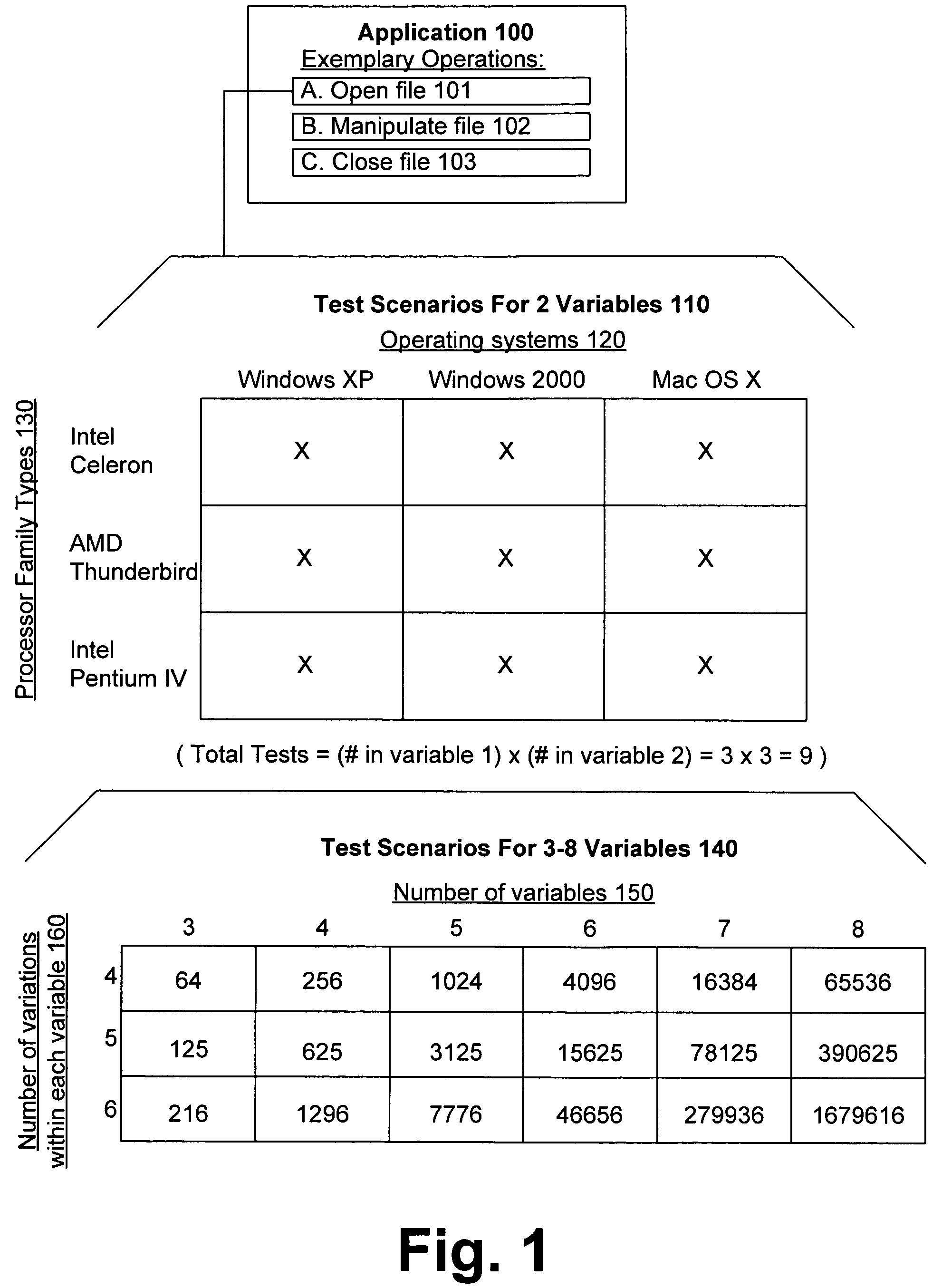

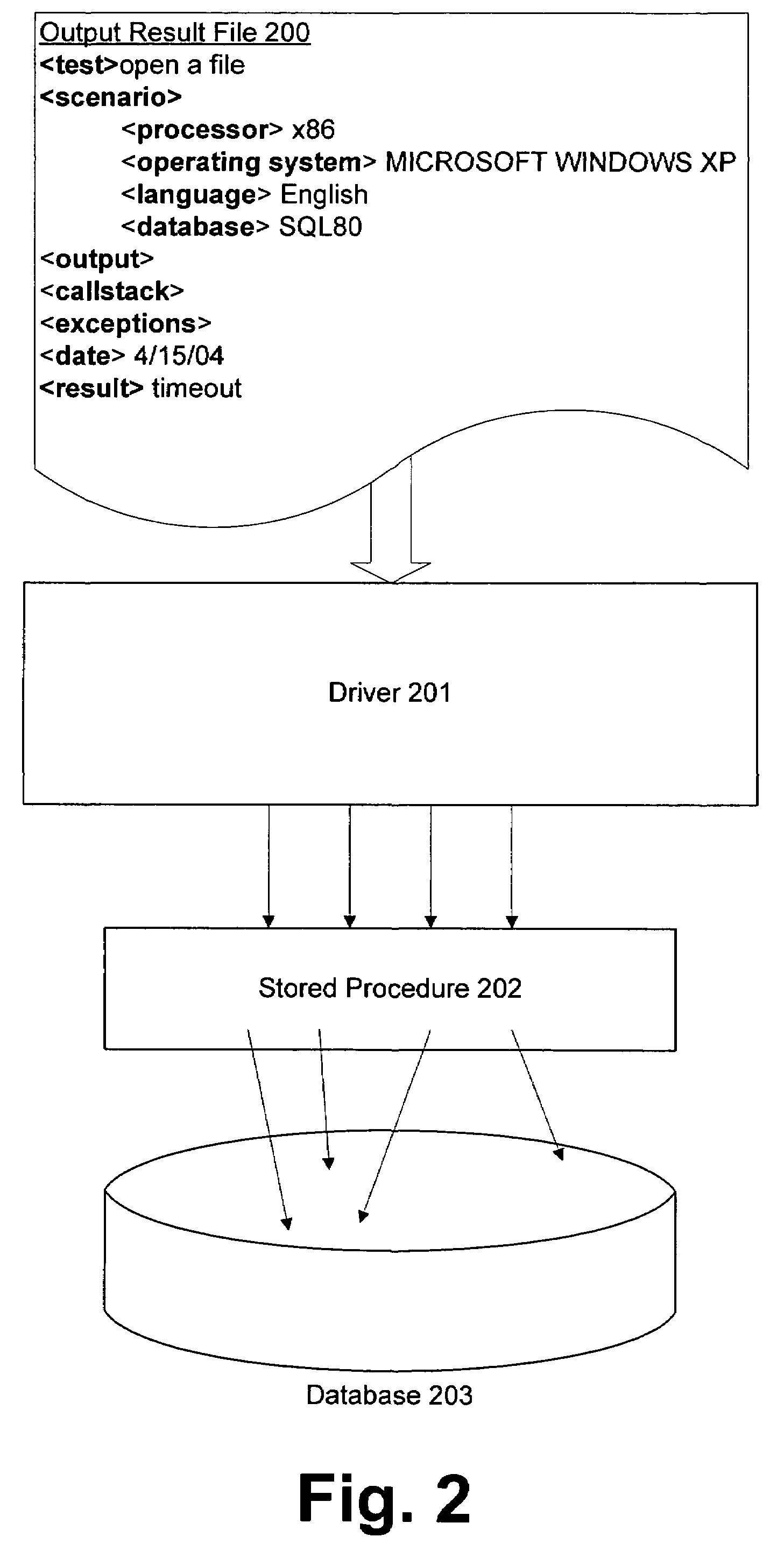

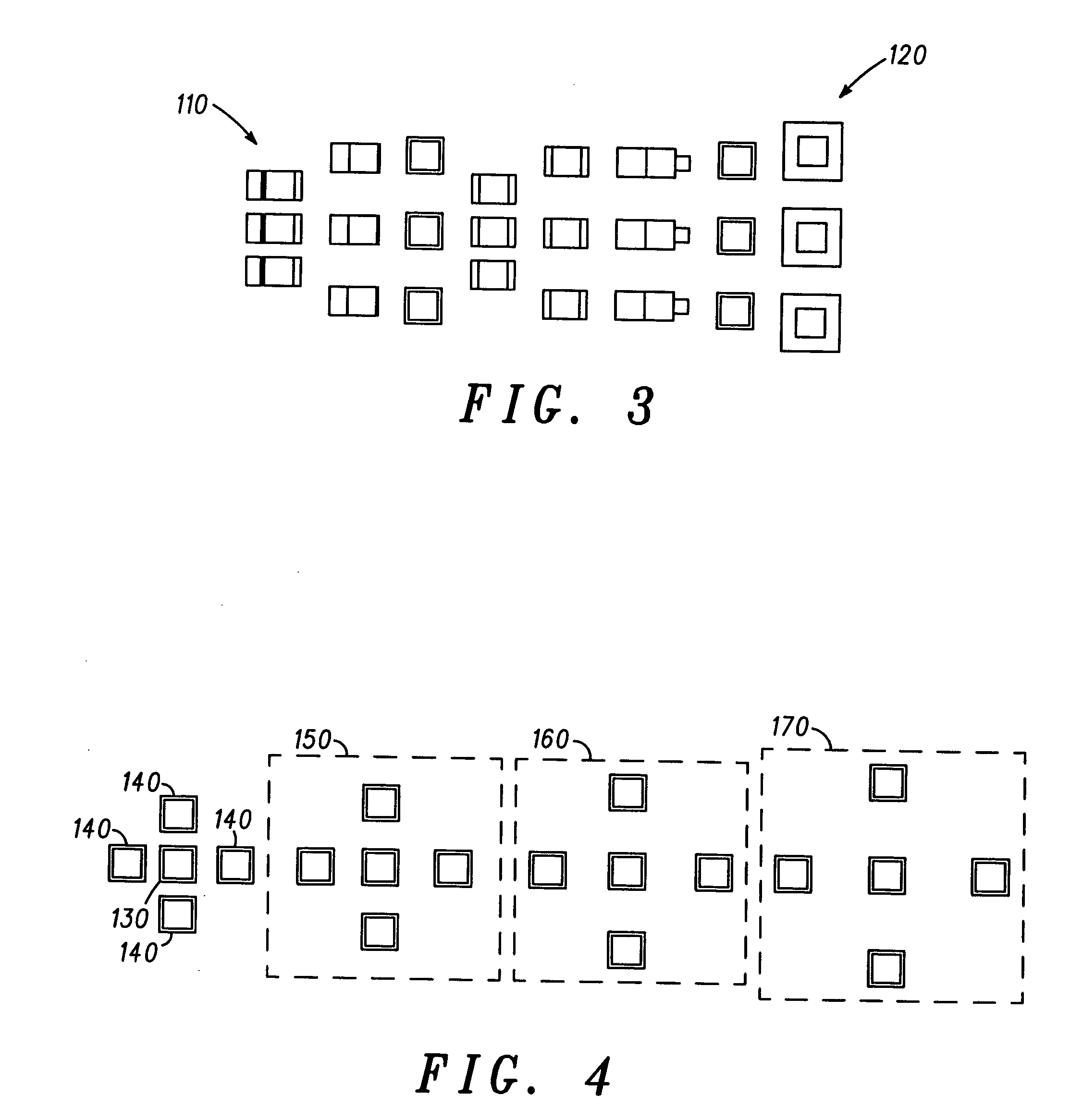

Systems and methods for automated classification and analysis of large volumes of test result data

ActiveUS20050257086A1Facilitate failure analysisFailed analysisError detection/correctionGraphicsGraphical user interface

Test result data can be classified across multiple tests, test scenarios, and lab runs. Test result files can be parsed by extracting information from them. Extracted information can be compared to failure information in a database. If a match is found, the extracted information can be linked to the failure, creating a history for each failure. New failures can be identified when no match is found. Failure data can be cross-referenced to further aid in results analysis. For each failure, lists of useful information can be accessed. Analysis information can be associated with failures, for example whether the failure is new, occurred previously, is for a different reason than expected, or has been added to a baseline of expected failures. A Graphic User Interface (“GUI”) is also provided to expose the analyzed results to the result analyzers.

Owner:MICROSOFT TECH LICENSING LLC

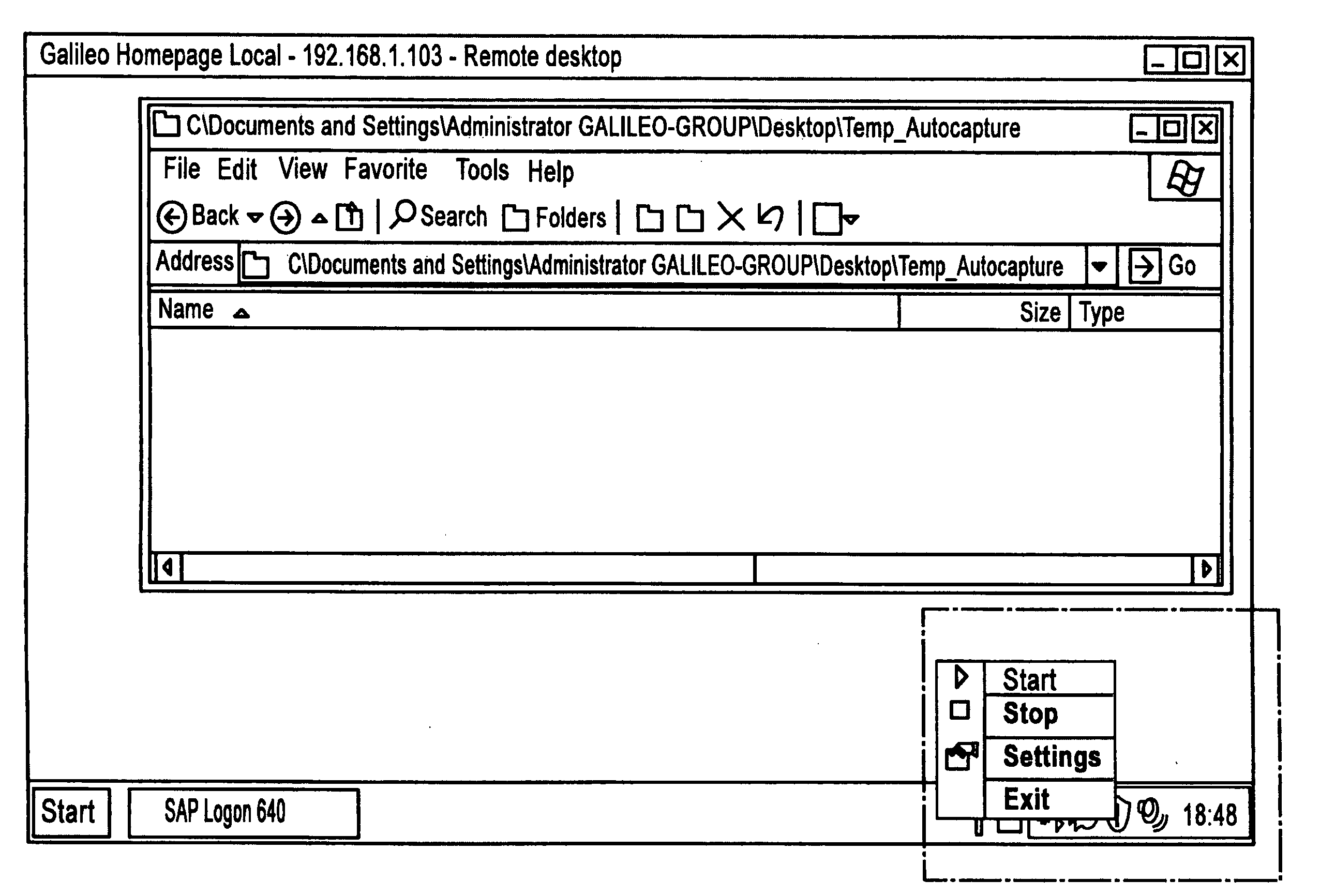

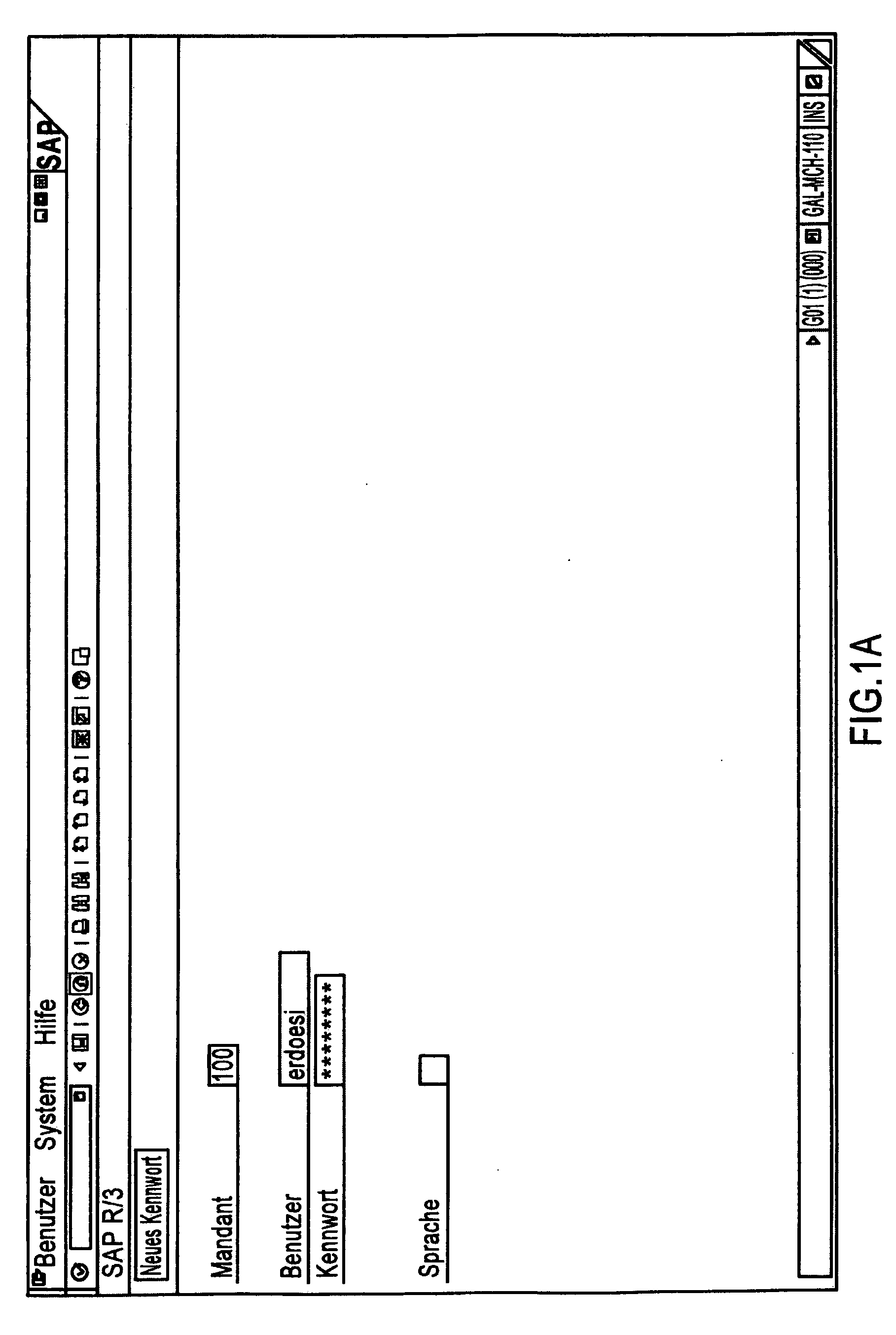

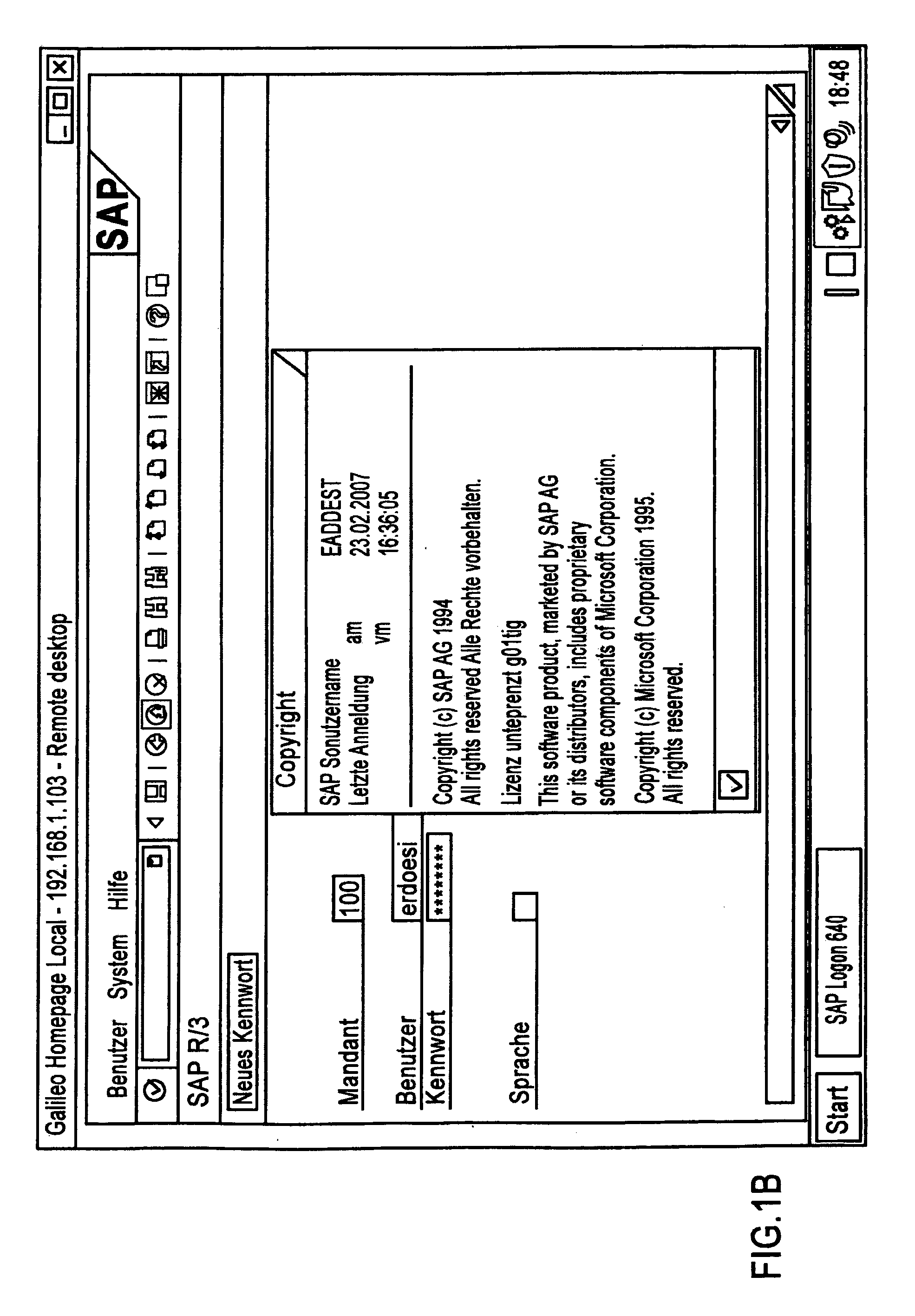

Software event recording and analysis system and method of use thereof

InactiveUS20080256399A1Low costFailed analysisError detection/correctionOperational systemApplication software

A software service running in the background of an operating system and used by a user to record metadata and screen shots of the user interface screens in an operating system whenever errors occur in the operating system or in any application running on the operating system. The software service also manages the recorded data to ensure resources are used efficiently to minimize the use of storage space in the recording location or buffer. The software running in the background monitors, filters and logs programs and user actions, and if a problem occurs within the monitored software, a problem report can be created for a support team to analyze and include corresponding recorded data. The suggested selection of recorded data can be displayed and edited by the user.

Owner:GALILEO TOOLS

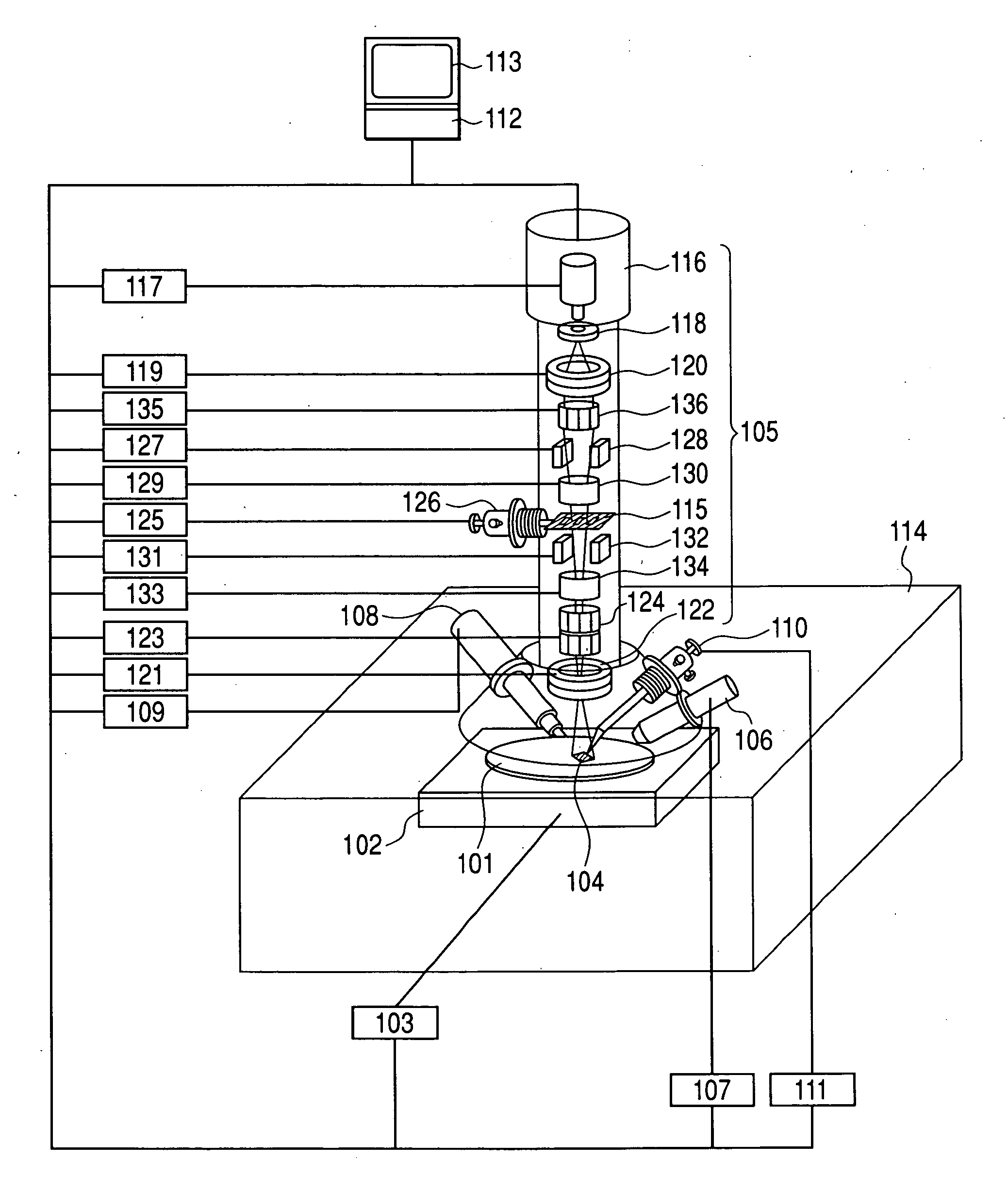

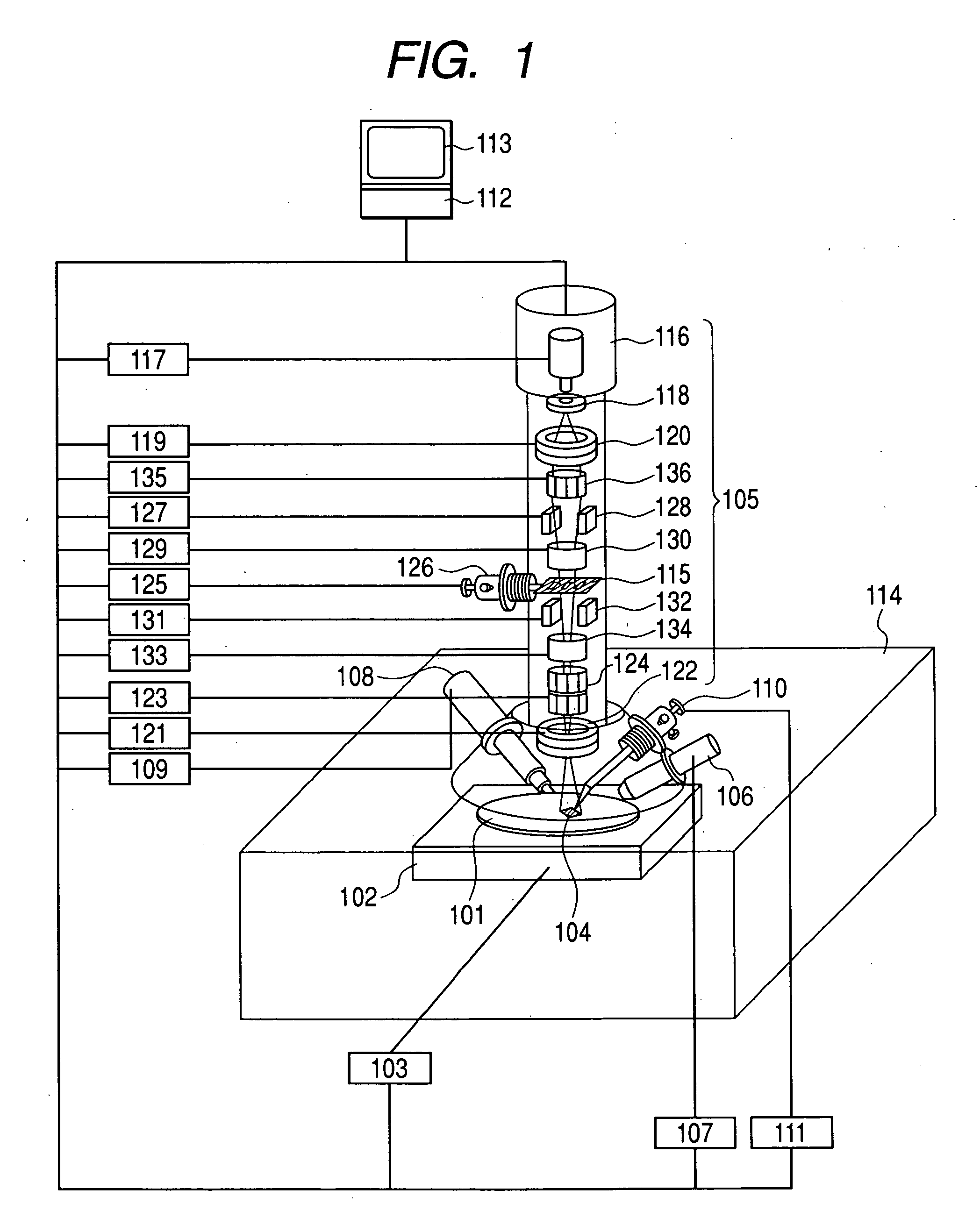

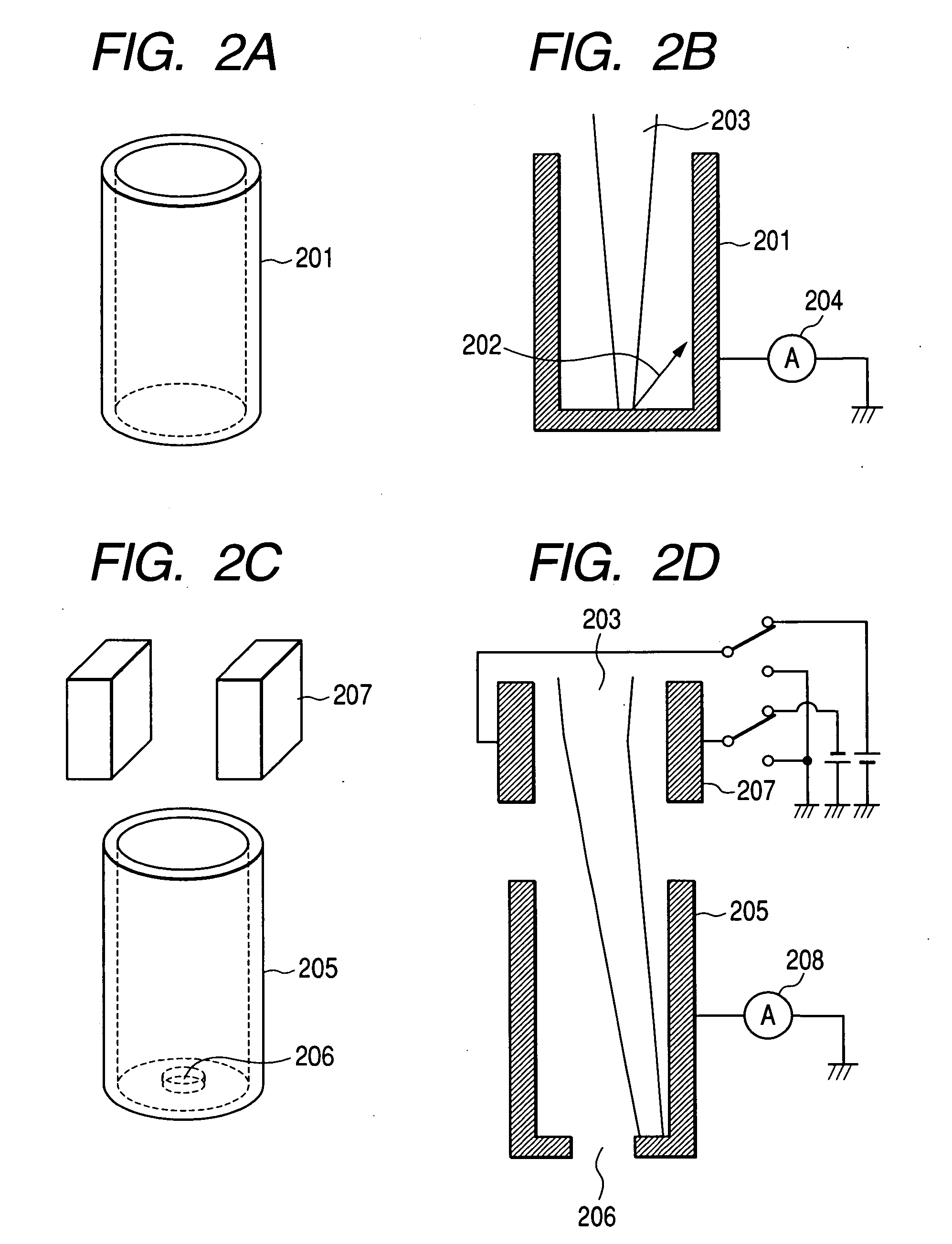

Apparatus for ion beam fabrication

ActiveUS20080283778A1Stable operation of apparatusIncrease productionMaterial analysis using wave/particle radiationElectric discharge tubesAtomic physicsFaraday cup

The apparatus for ion beam fabrication, which has been able to detect any anomalous condition of ion beams only by means of the current irradiated on the specimen, could not compensate the failure by investigating the cause and could not realize stable processing. To solve the problem described above, the present invention includes the first and second blankers and Faraday cups switches ON and OFF the first and second blankers and monitors beam current at two positions above and below the projection mask. By adopting this configuration, it will be possible to acquire the information on failure in ion beam, sort out the cause of the failure and to compensate the failure while limiting damages to the projection mask. As a result, it will be possible to realize stable processing by means of ion beam, and to use the ion beam fabricating device on a stable basis.

Owner:HITACHI HIGH-TECH CORP

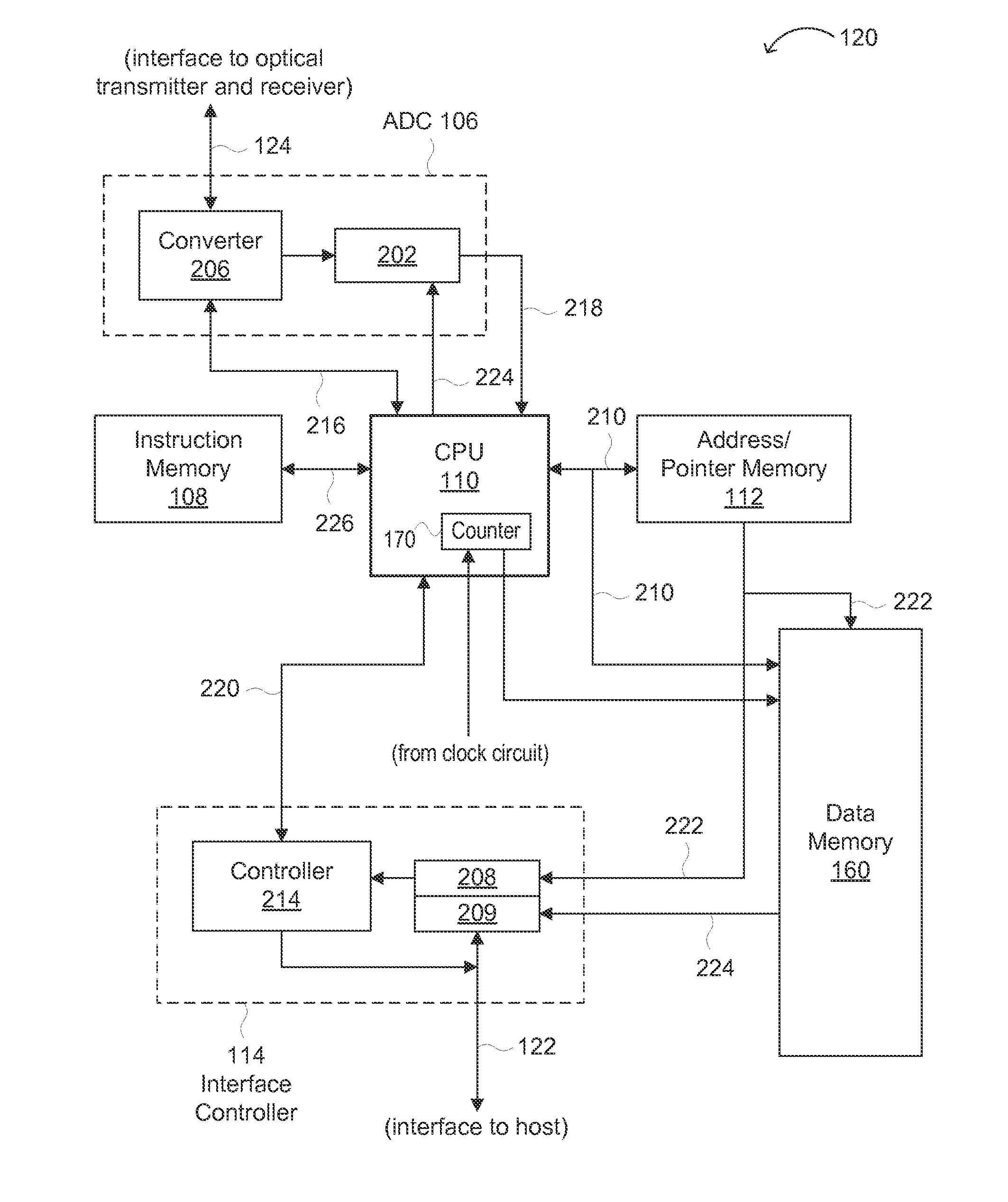

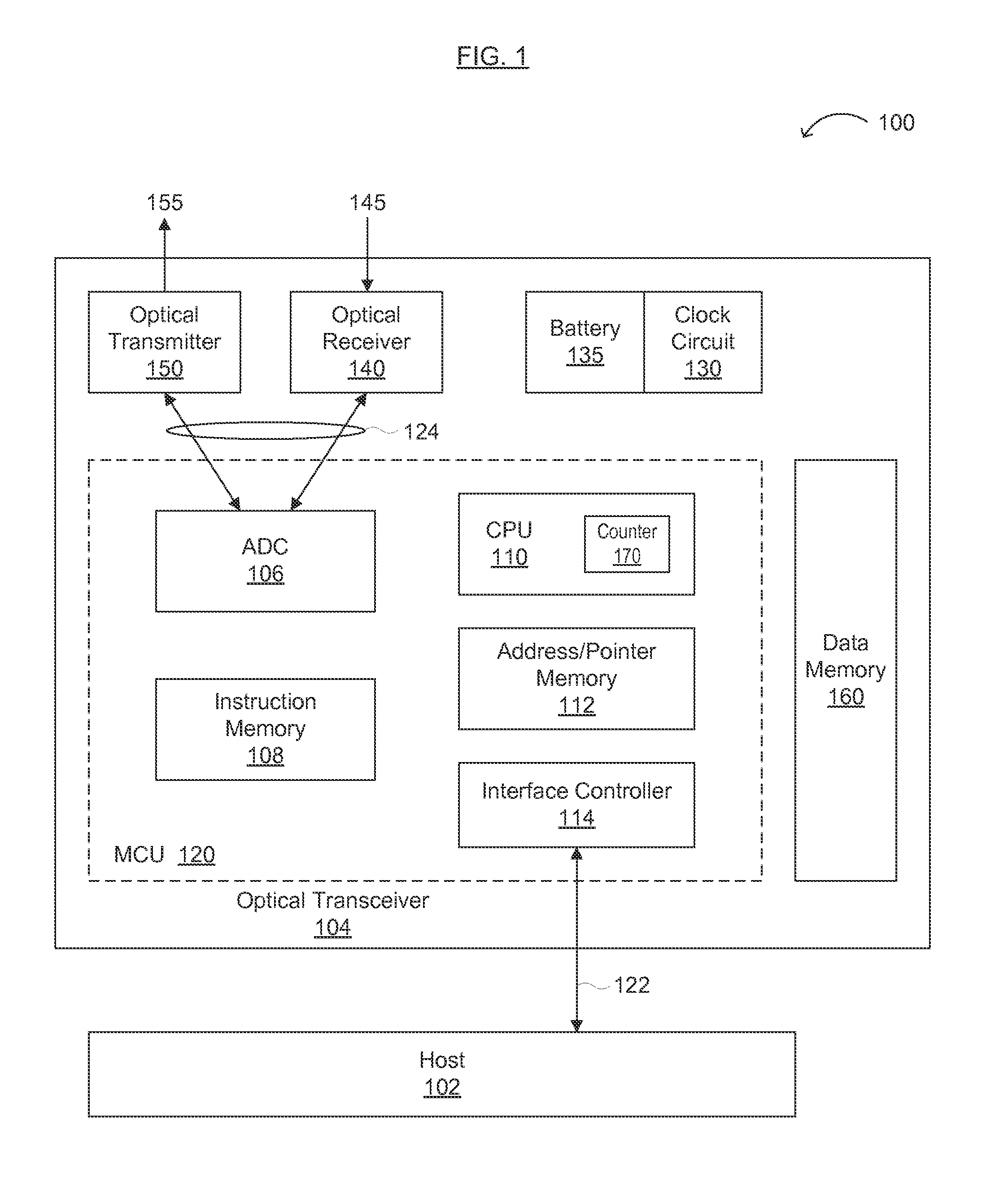

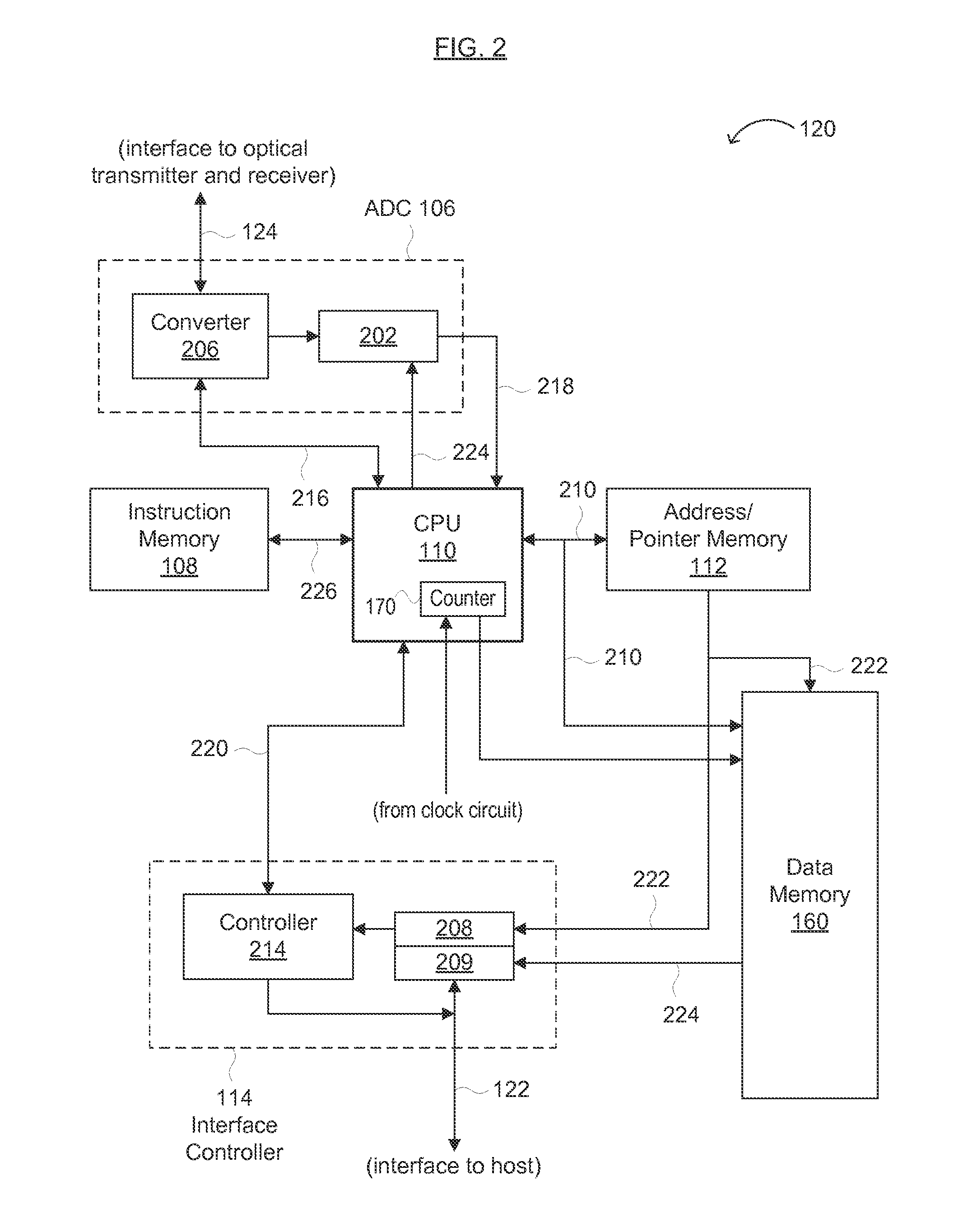

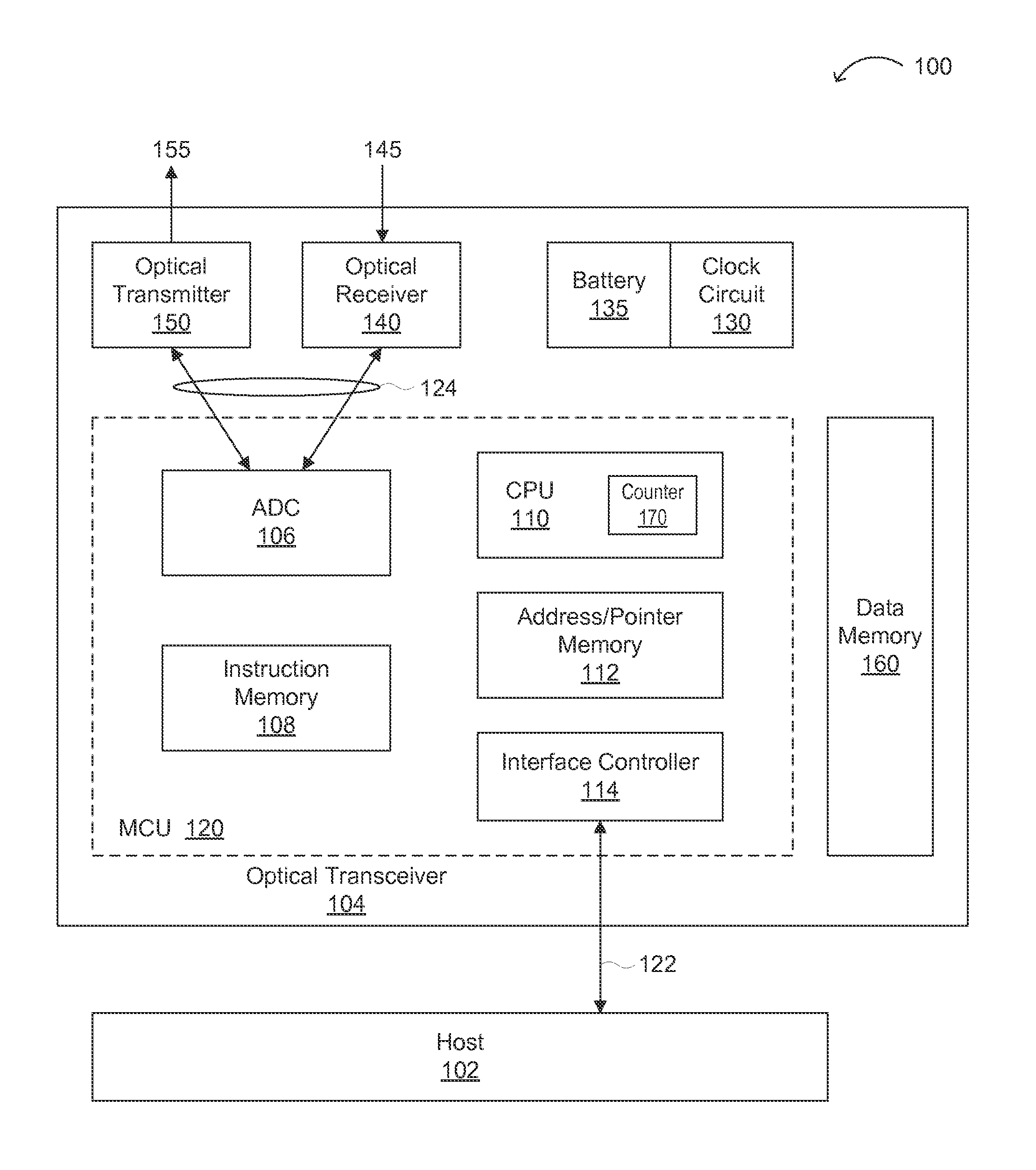

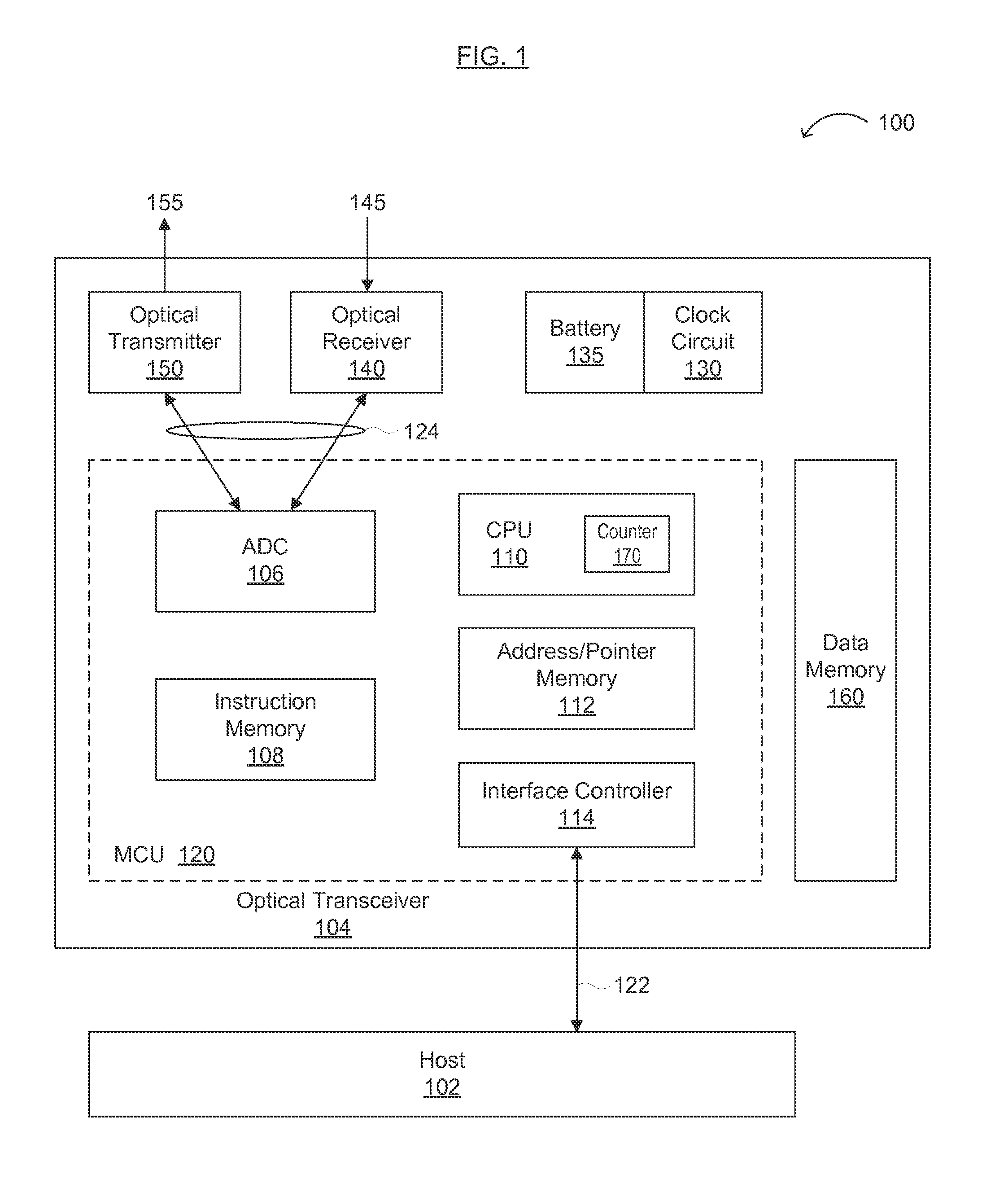

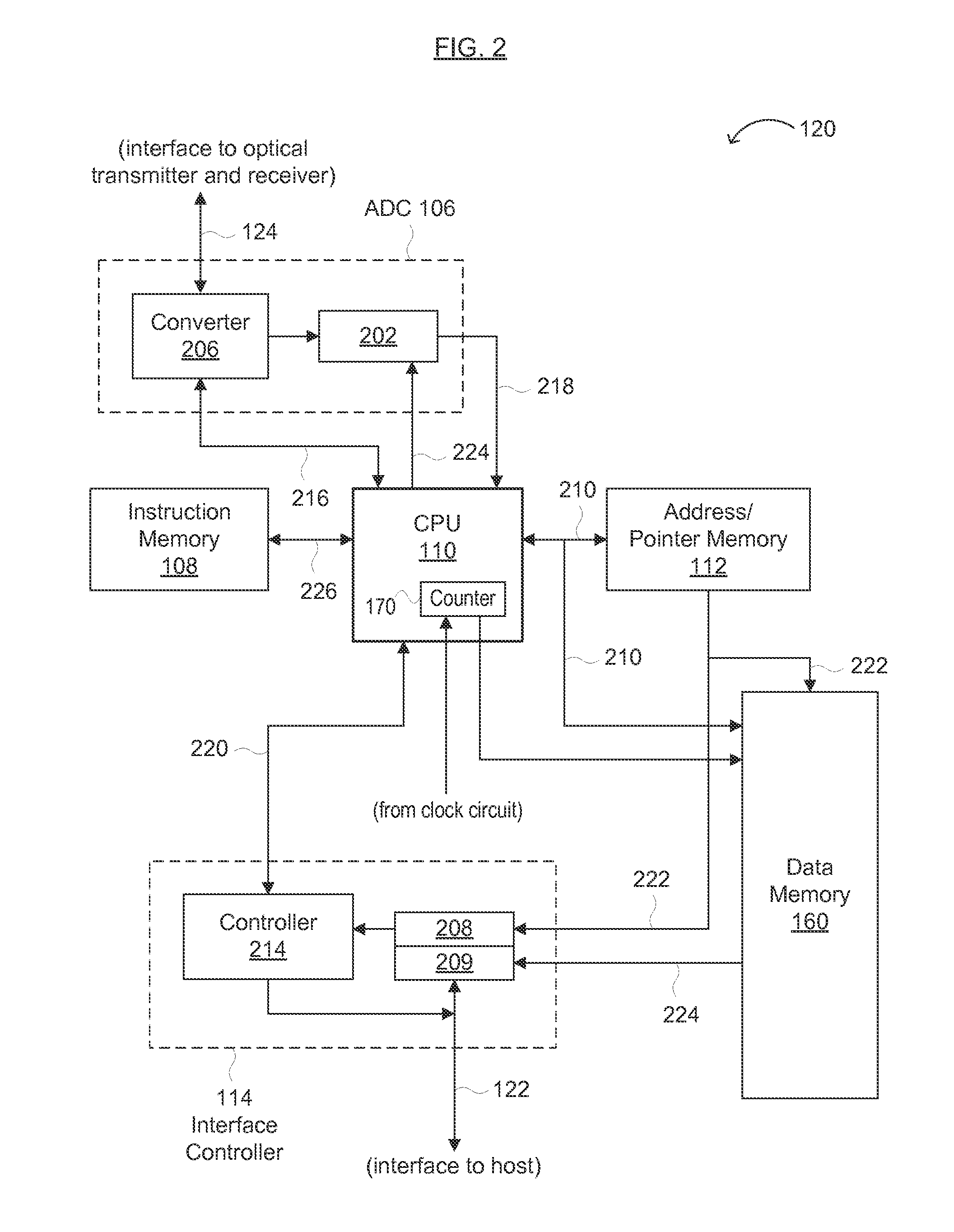

Enhanced Status Monitoring, Storage and Reporting for Optical Transceivers

ActiveUS20130251361A1Accurate informationEnhance failure analysisTransmission monitoringTransmission monitoring/testing/fault-measurement systemsTransceiverEngineering

An optical transceiver and methods for using the same are disclosed. The optical transceiver and methods may be useful for providing more accurate information regarding trends in operation of the optical transceiver, predicting an impending failure of the optical transceiver, and providing details of the optical transceiver prior to failure. The optical transceiver generally includes (1) at least one of (i) a receiver configured to receive optical information and (ii) a transmitter configured to transmit optical information, (2) circuitry configured to sample data for one or more operational parameters of the receiver and / or transmitter, (3) logic configured to perform one or more statistical calculations on the sampled data to generate statistical information, and (iv) one or more memories configured to store the sampled data and the statistical information.

Owner:SOURCE PHOTONICS

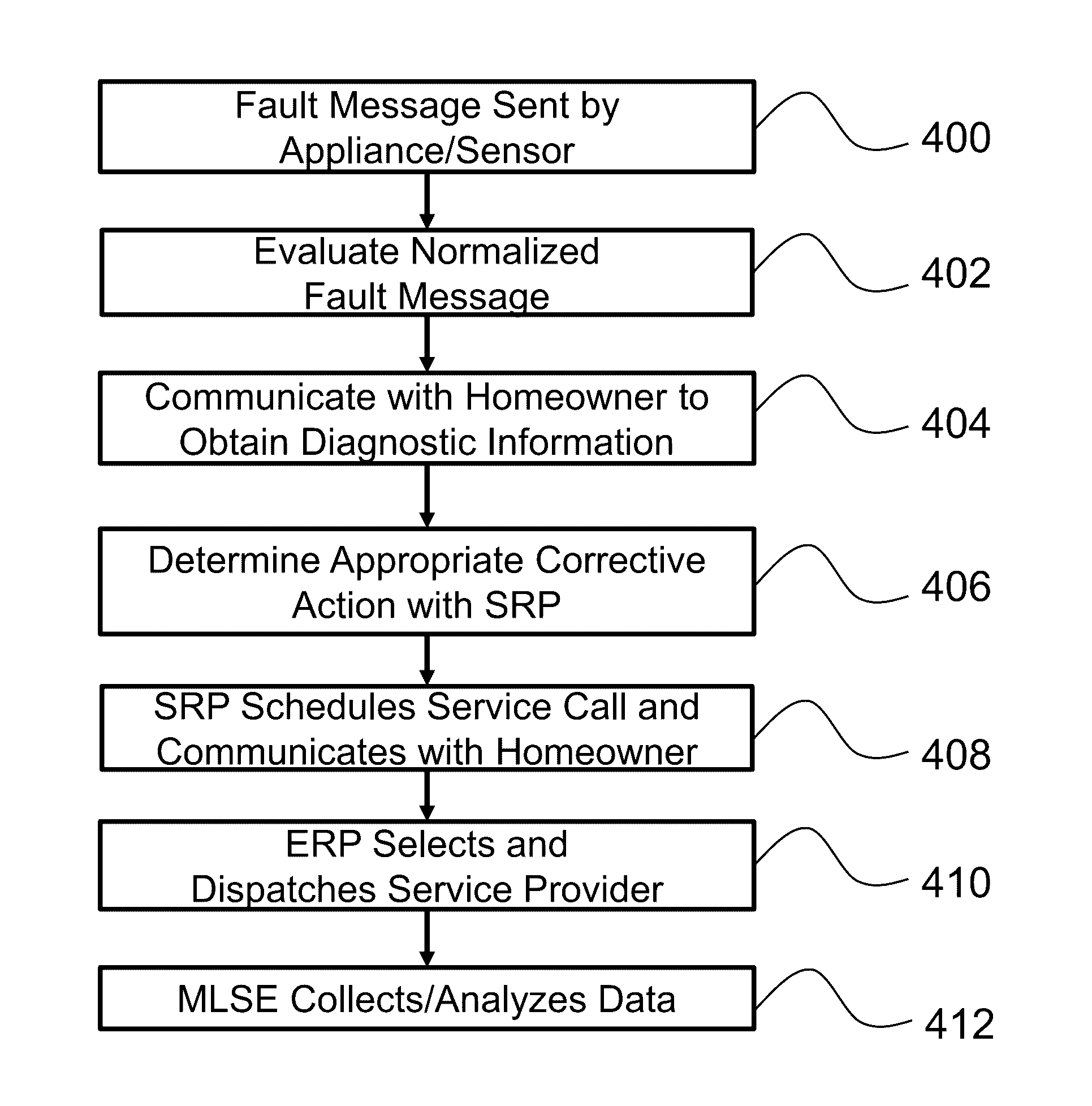

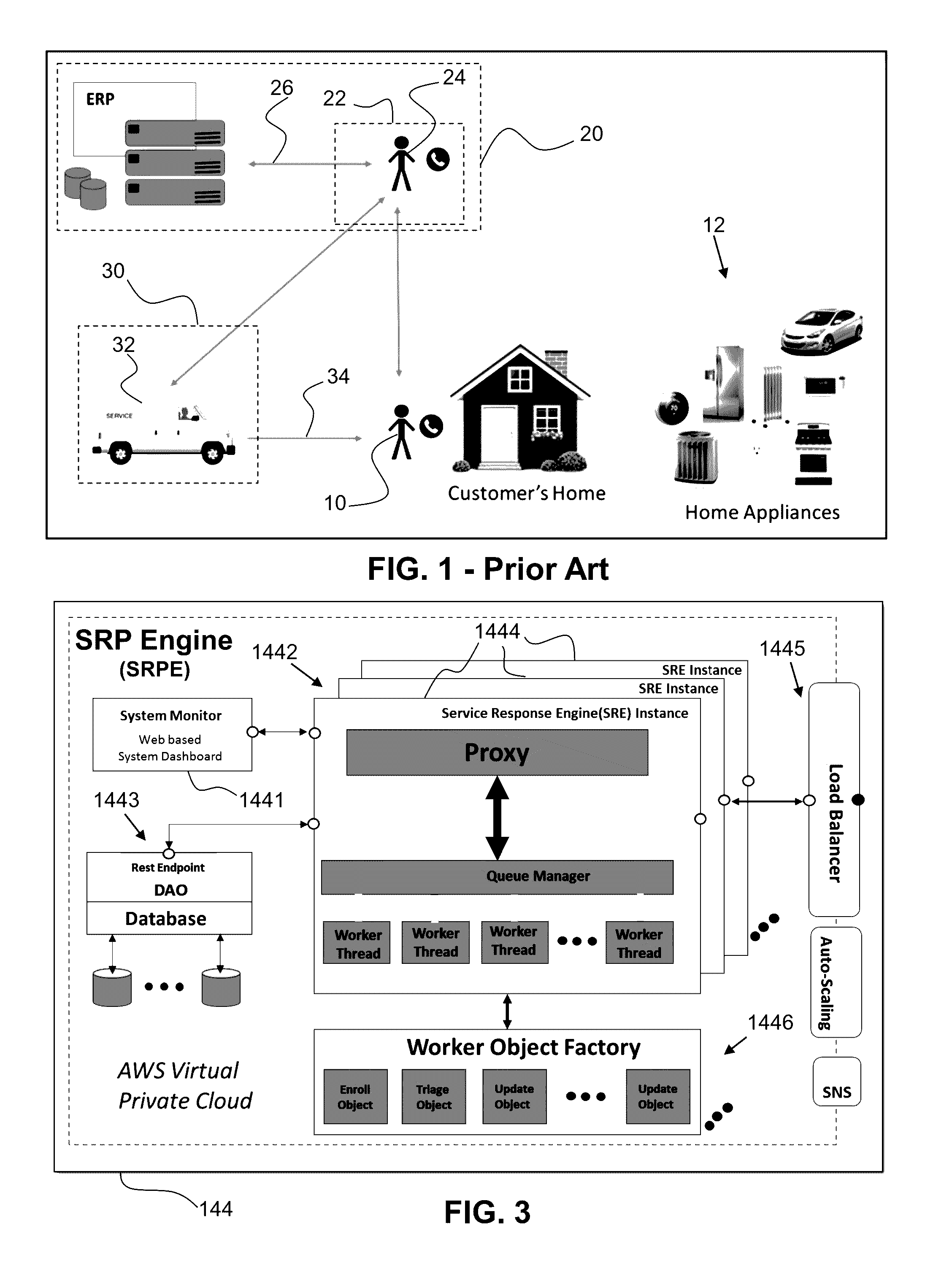

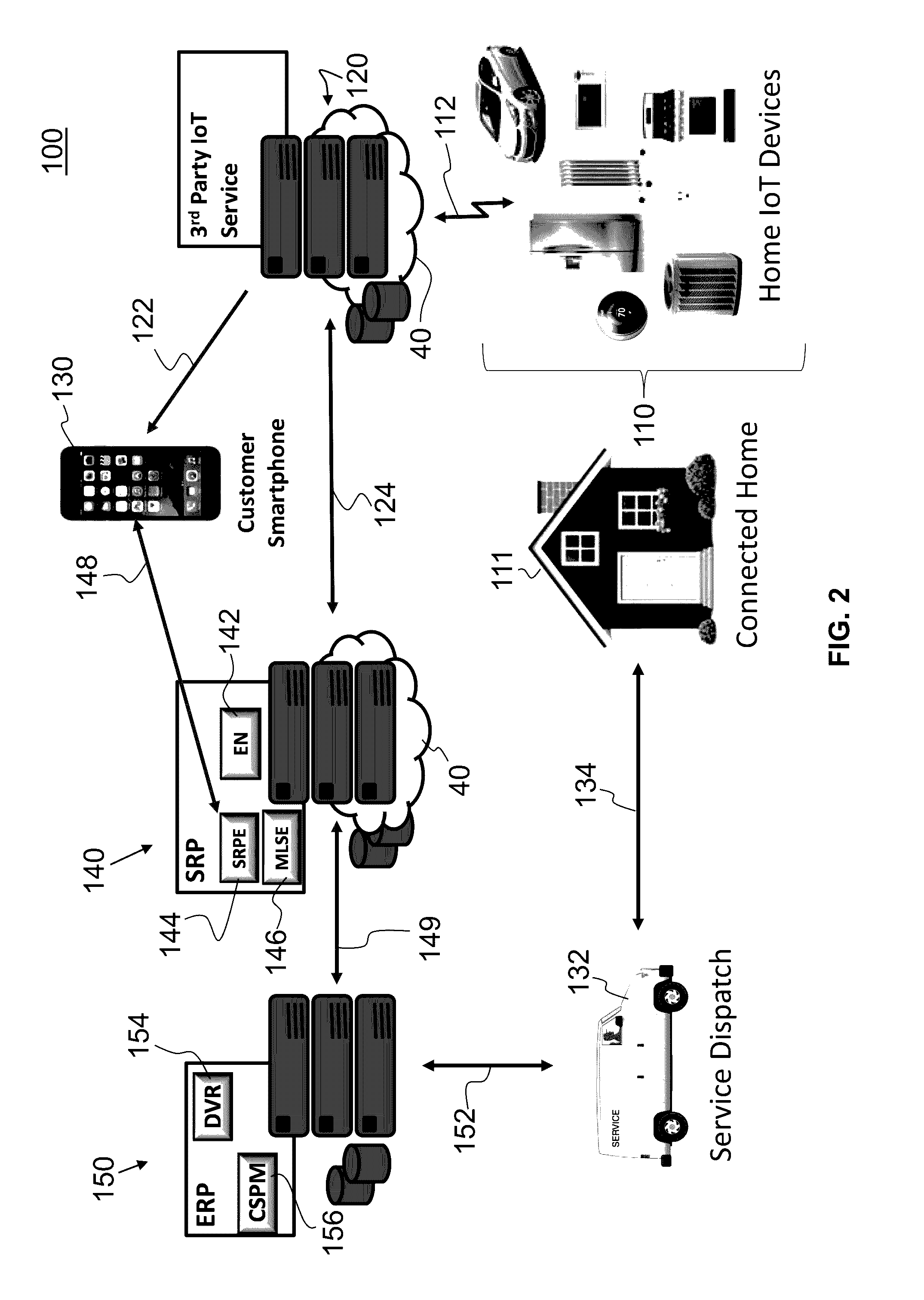

Systems and methods for efficiently handling appliance warranty service events

InactiveUS20170004508A1Easy to handleFast and accurate processingData switching by path configurationHybrid transportTriageManagement system

An automated event management system for smart appliances residing at locations of owners and communicatively connected to respective smart-appliance event-reporting platforms includes a service response platform and an enterprise resource platform. The service response platform receives appliance event messages from respective ones of the smart appliances and normalizes them into outbound service call requests having a standardized format and determines an appropriate responsive action to the outbound service call request by accessing data including past information and performing a triage to determine root failures. Based upon the determination a trade and replacement parts are selected. After repair information is gathered to diagnose that repair and improve the data for future use. The enterprise resource platform manages the service providers by scheduling service calls directly in calendars, by dispatching the providers, by selecting replacement parts and communicating with the owners regarding the service call, and by transmitting the service call data.

Owner:CROSS COUNTRY HOME SERVICES

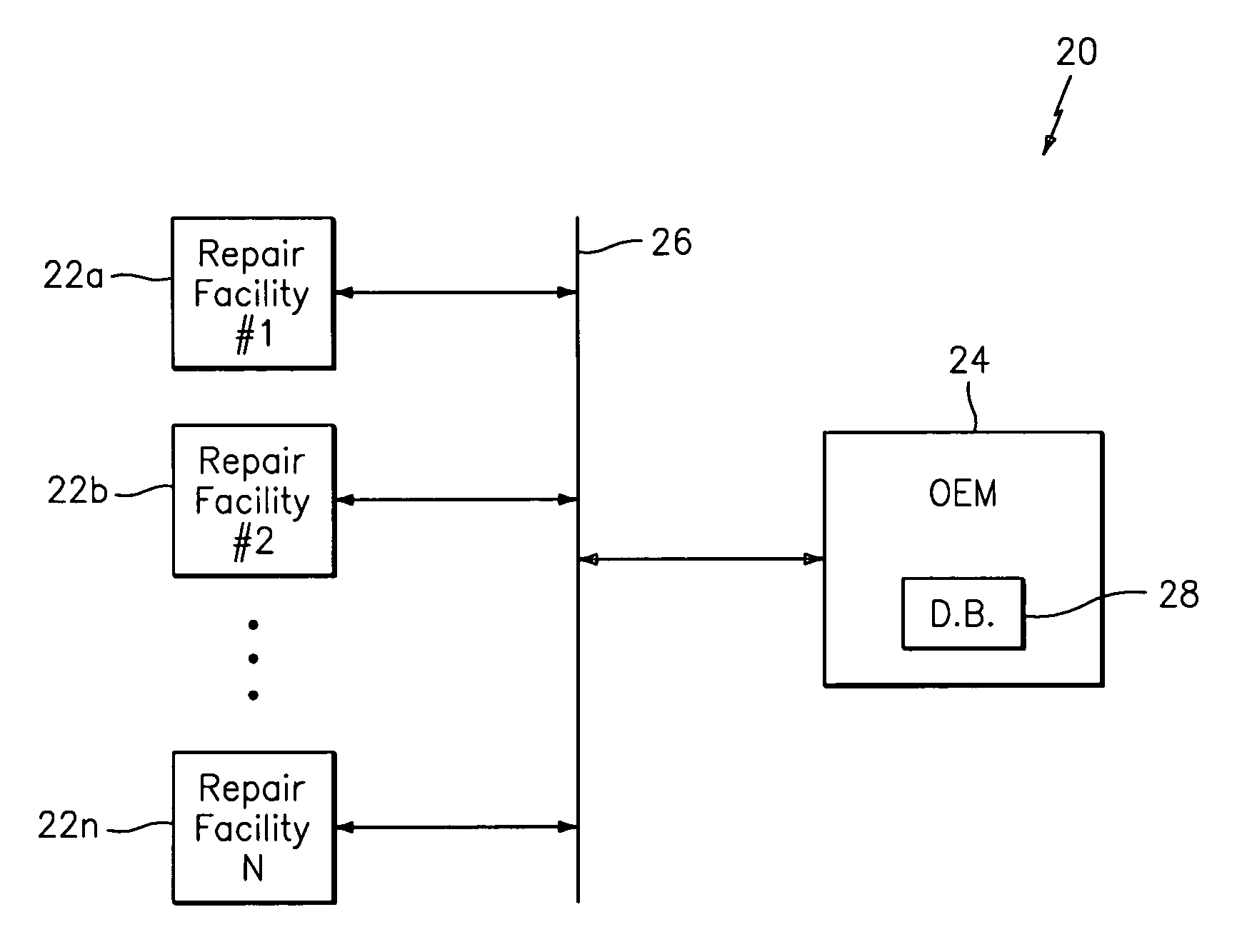

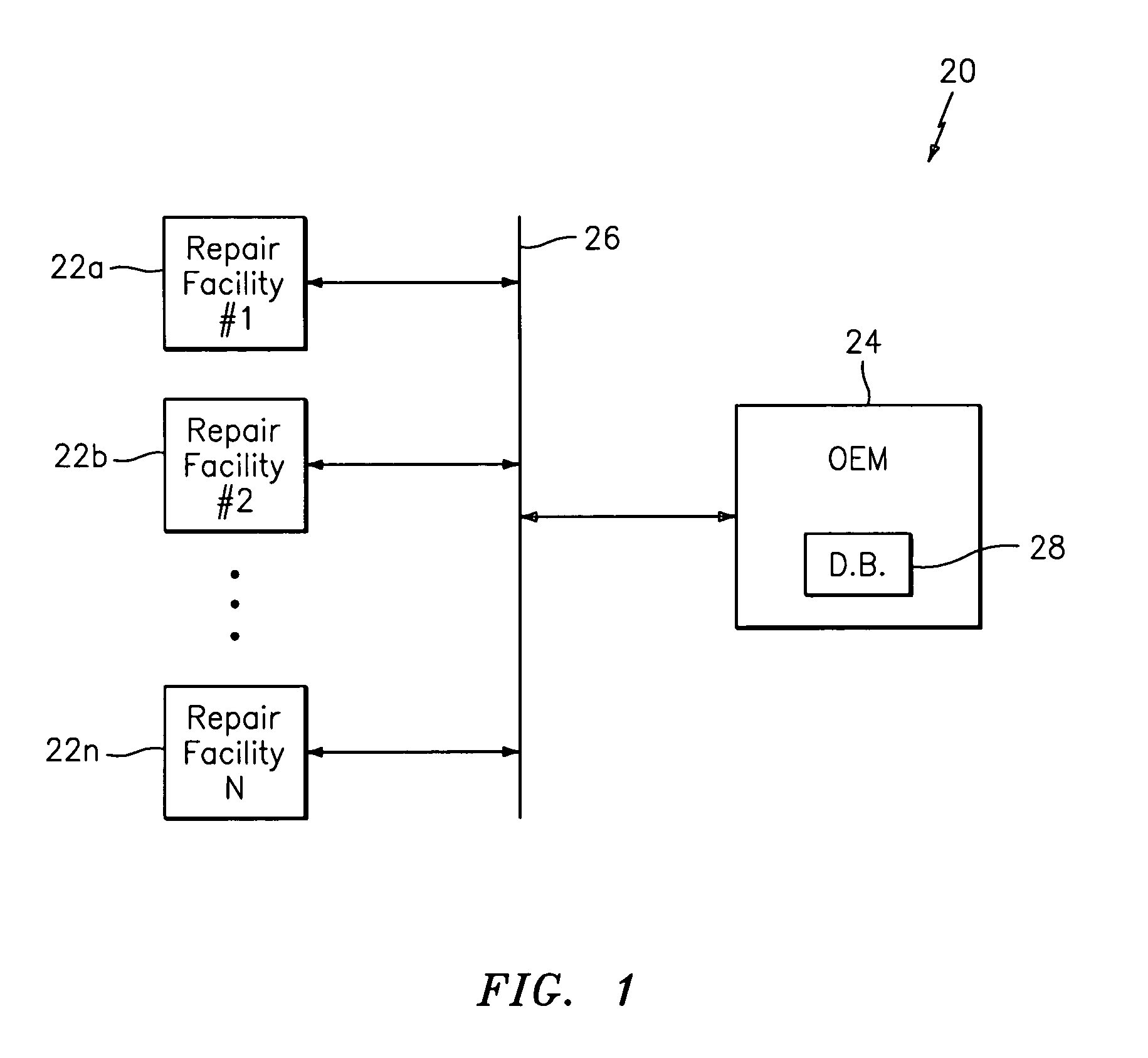

Supplier teardown & analysis reporting system

InactiveUS20070294052A1Facilitates design engineer understandingFailed analysisPlug gaugesAmplifier modifications to reduce noise influenceProgram planningAction plan

A Supplier Teardown and Analysis Reporting System (STARS) captures information pertaining to component removals or failures that caused an unscheduled maintenance action. The detailed data facilitates design engineers understanding of failure drivers and propose improvements and commence implementation of a Corrective Action Plan at the earliest practicable time.

Owner:SIKORSKY AIRCRAFT CORP

Systems and methods for automated classification and analysis of large volumes of test result data

Test result data can be classified across multiple tests, test scenarios, and lab runs. Test result files can be parsed by extracting information from them. Extracted information can be compared to failure information in a database. If a match is found, the extracted information can be linked to the failure, creating a history for each failure. New failures can be identified when no match is found. Failure data can be cross-referenced to further aid in results analysis. For each failure, lists of useful information can be accessed. Analysis information can be associated with failures, for example whether the failure is new, occurred previously, is for a different reason than expected, or has been added to a baseline of expected failures. A Graphic User Interface (“GUI”) is also provided to expose the analyzed results to the result analyzers.

Owner:MICROSOFT TECH LICENSING LLC

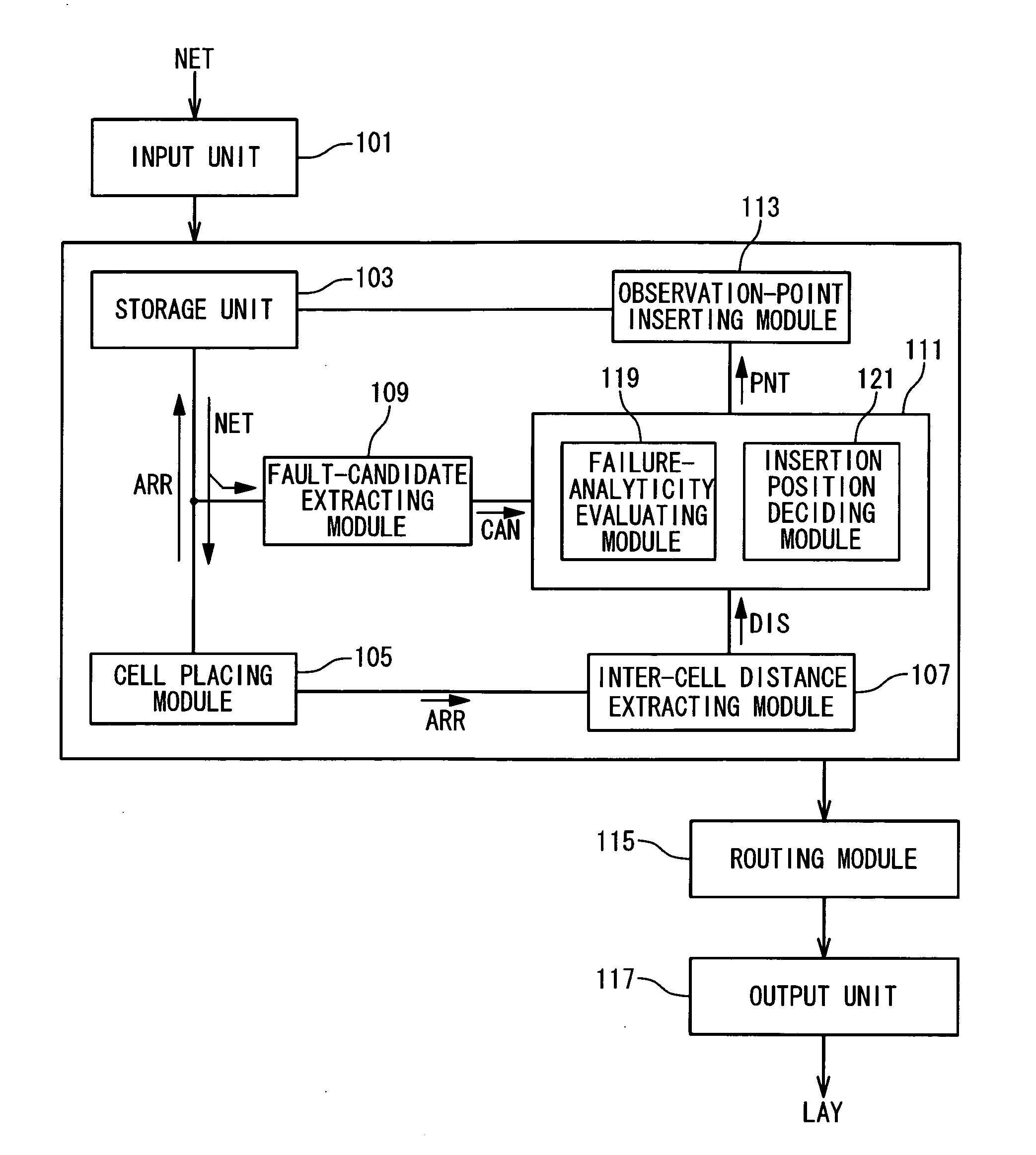

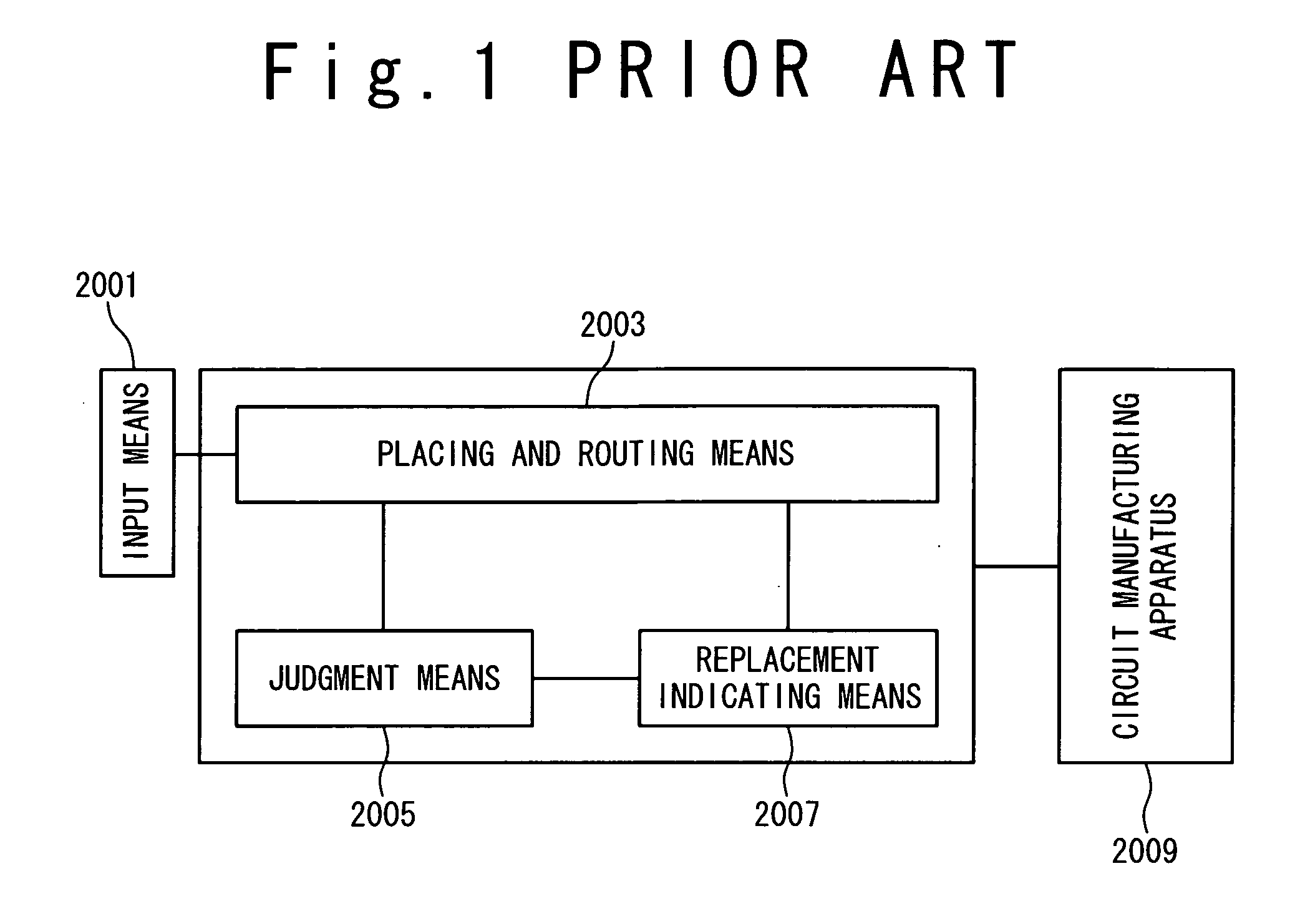

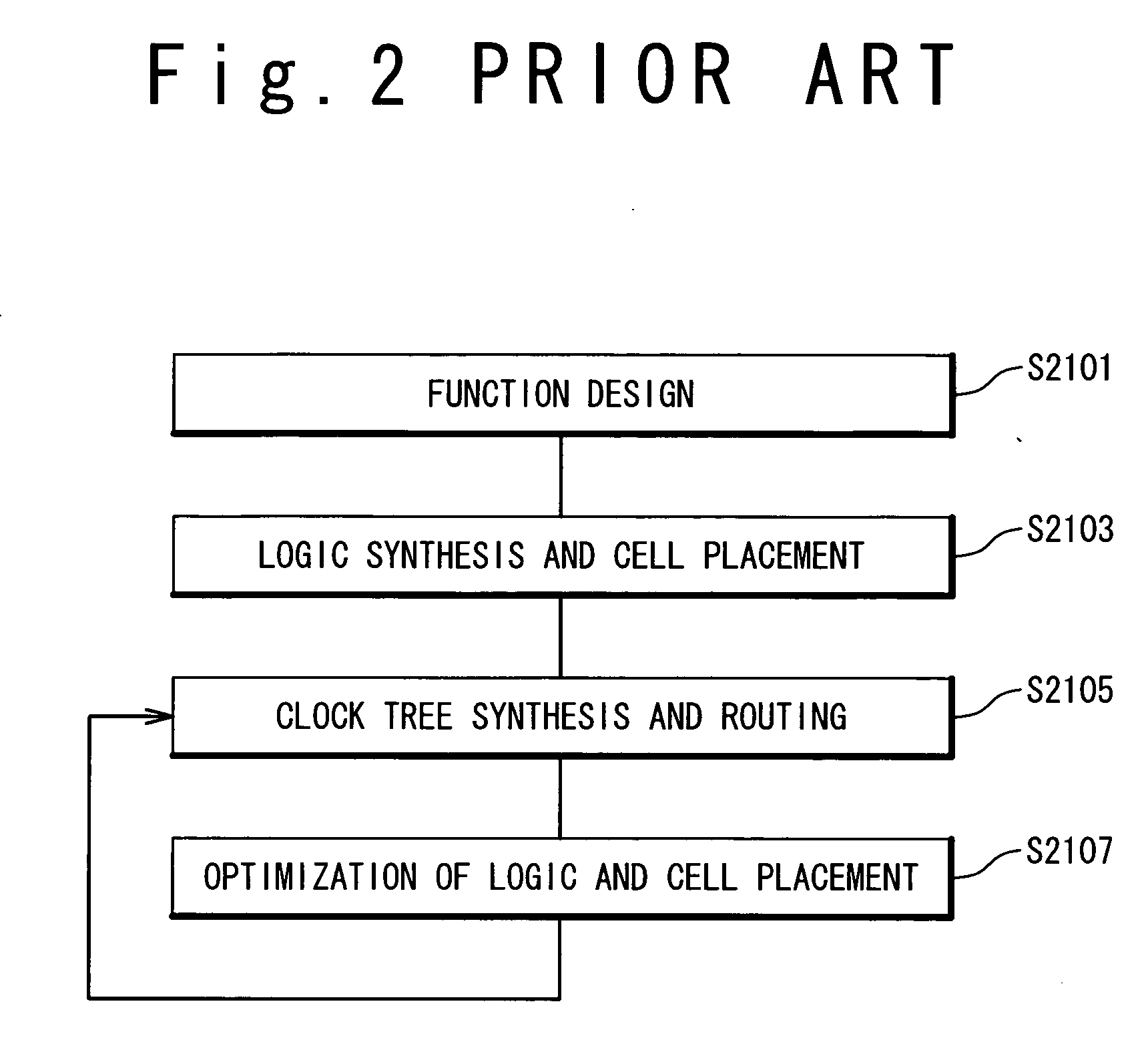

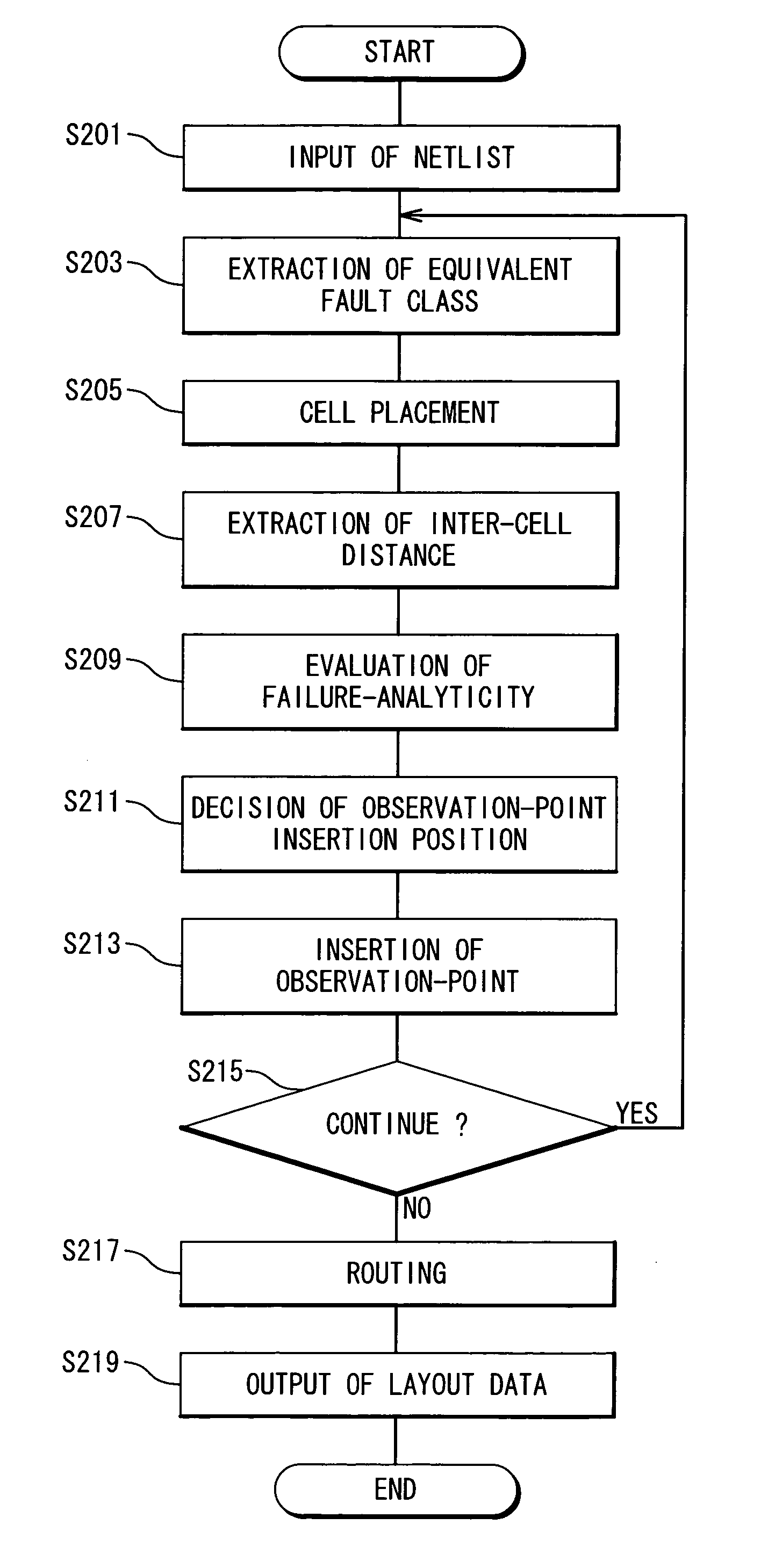

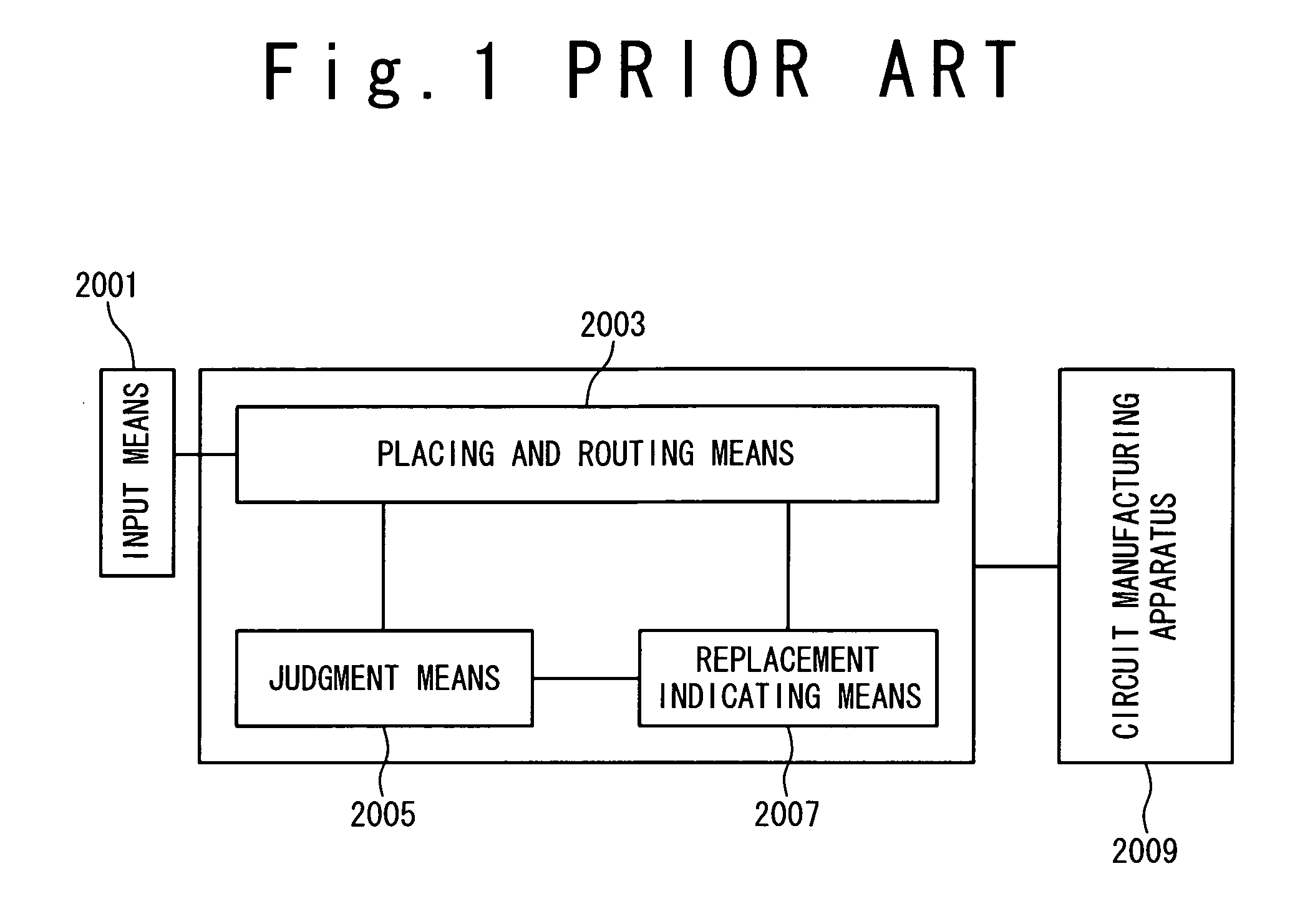

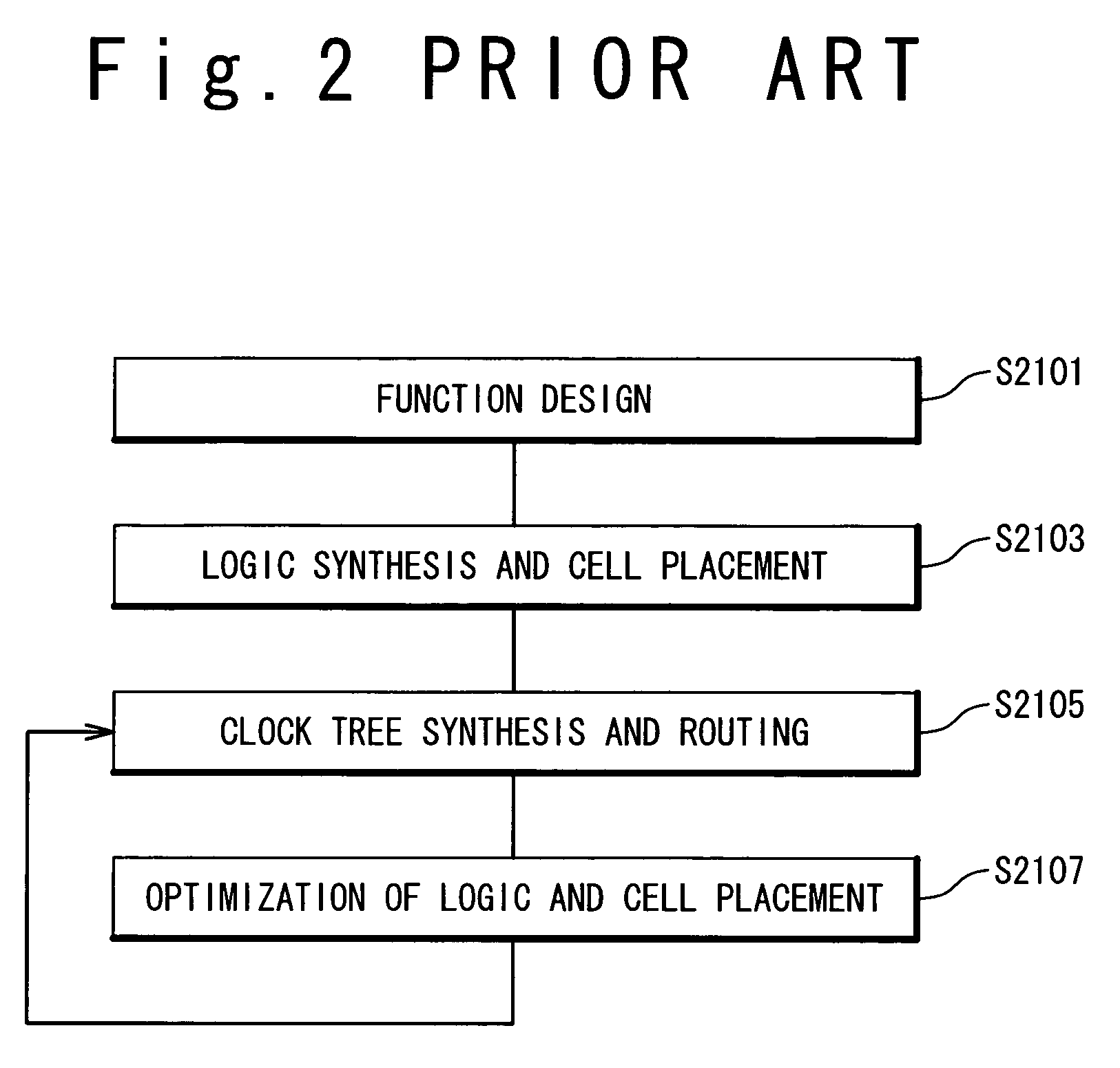

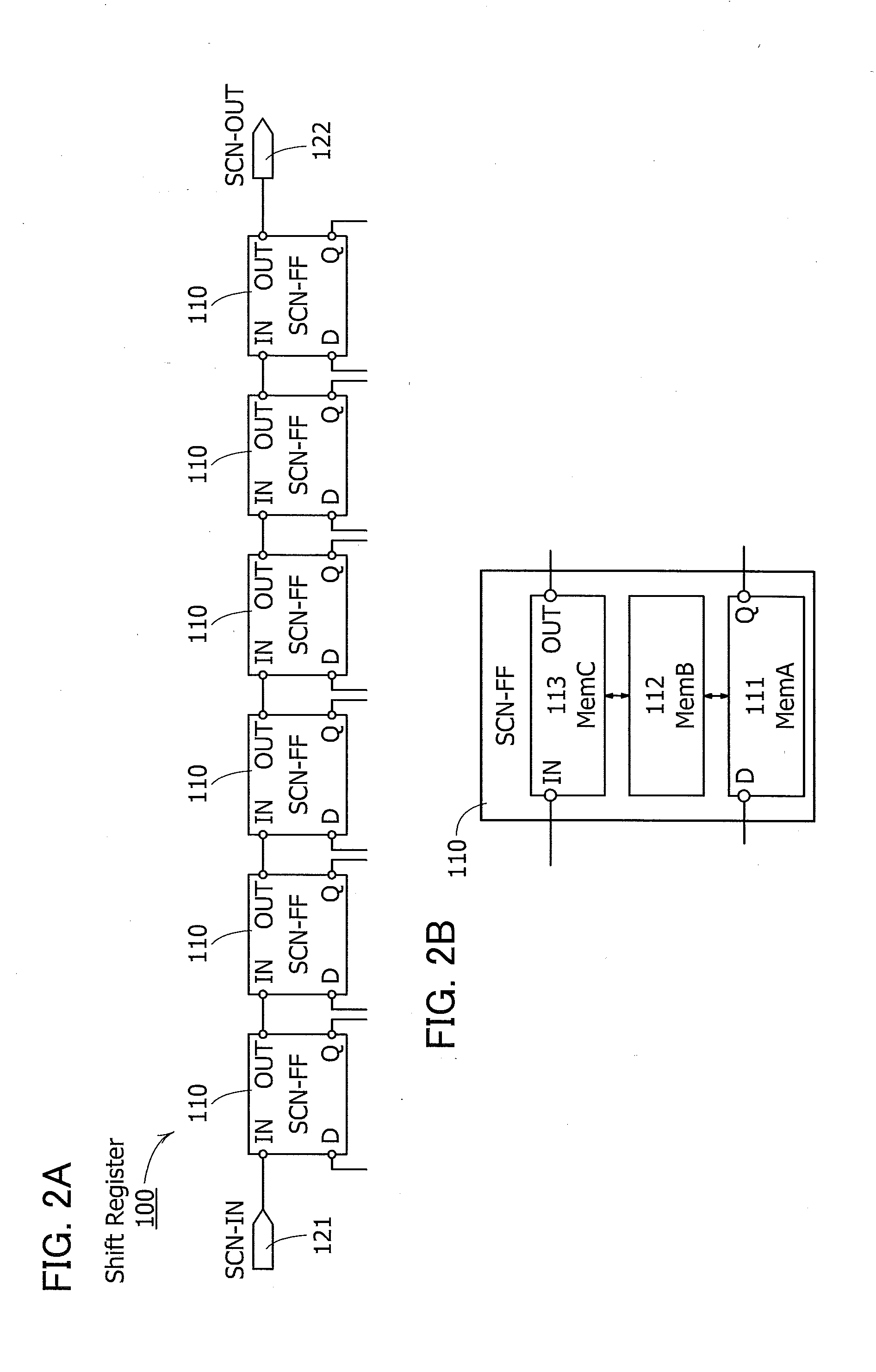

Circuit design system and circuit design program

ActiveUS20070113127A1Reduce in quantityImprove failure-analyticityElectronic circuit testingDetecting faulty computer hardwareComputer architectureObservation point

A circuit design system has: a storage unit in which a netlist is stored; a fault-candidate extracting module configured to extract equivalent fault class Gi from the netlist; a judgment module configured to select a target node out of a plurality of nodes Ni1 to Niji included in the equivalent fault class Gi, wherein Ji is a number of nodes included in the equivalent fault class Gi; and an observation-point inserting module configured to update the netlist by inserting at least one observation point into the target node. The judgment module decides the target node based on the number Ji.

Owner:RENESAS ELECTRONICS CORP

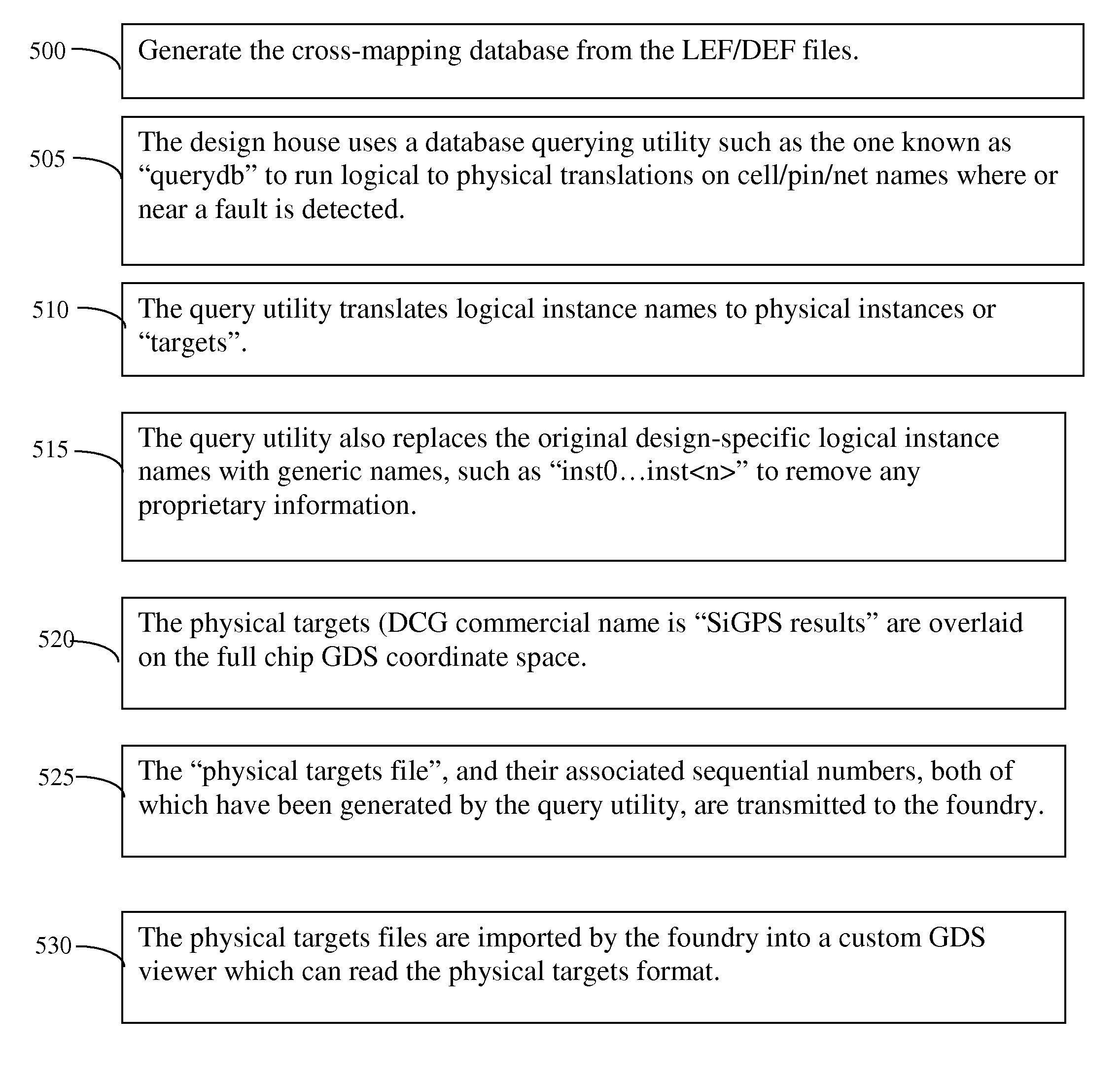

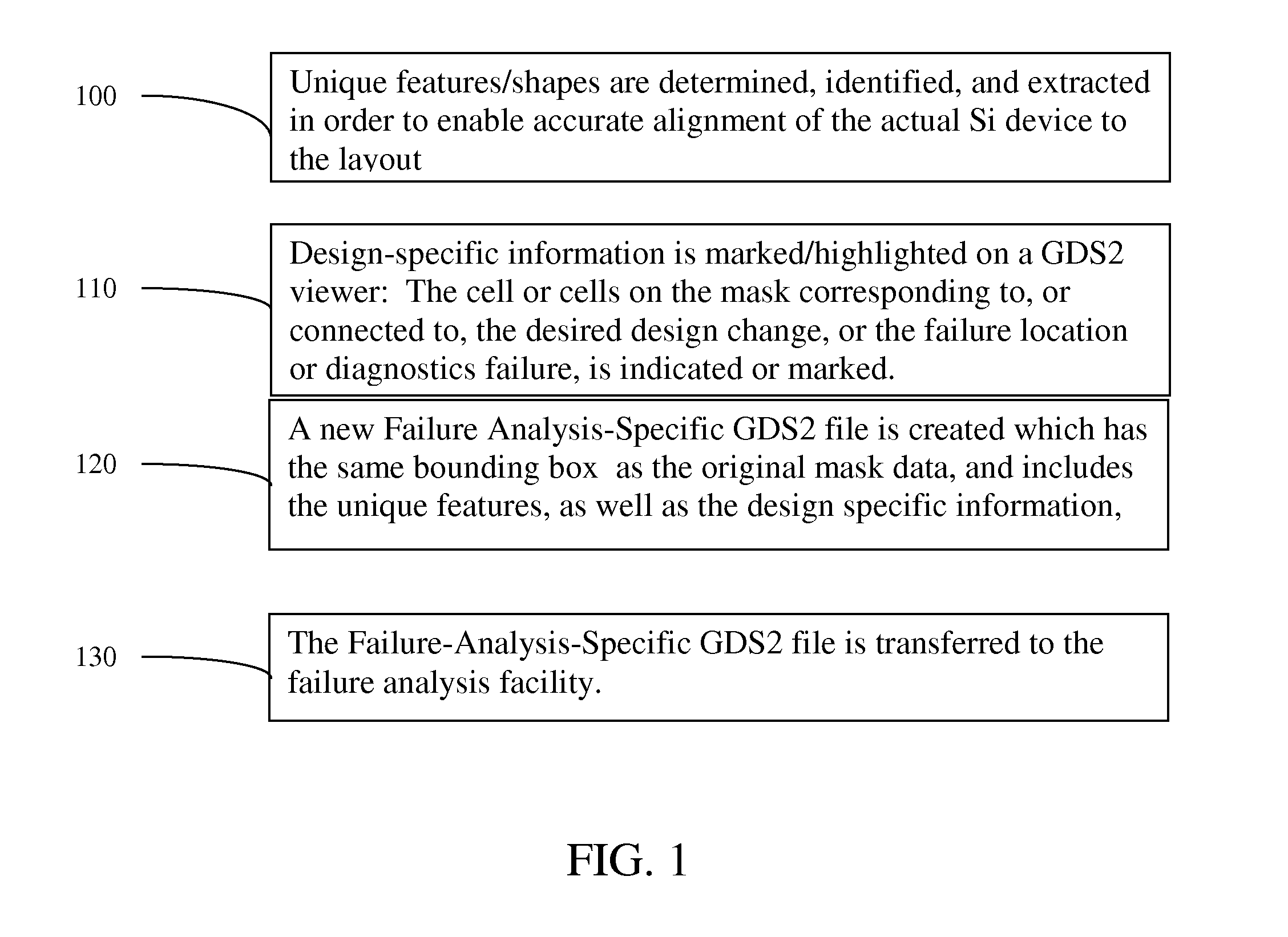

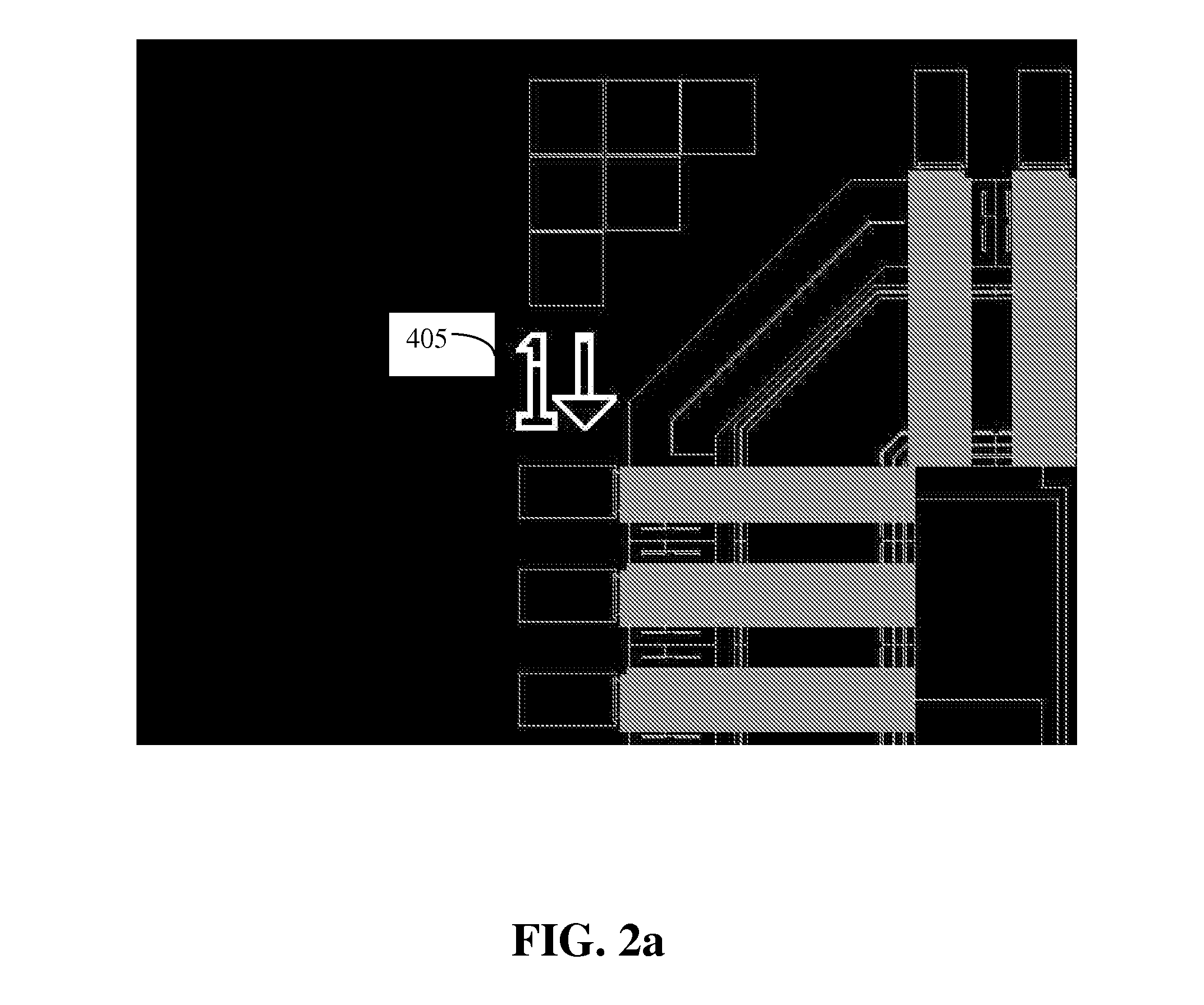

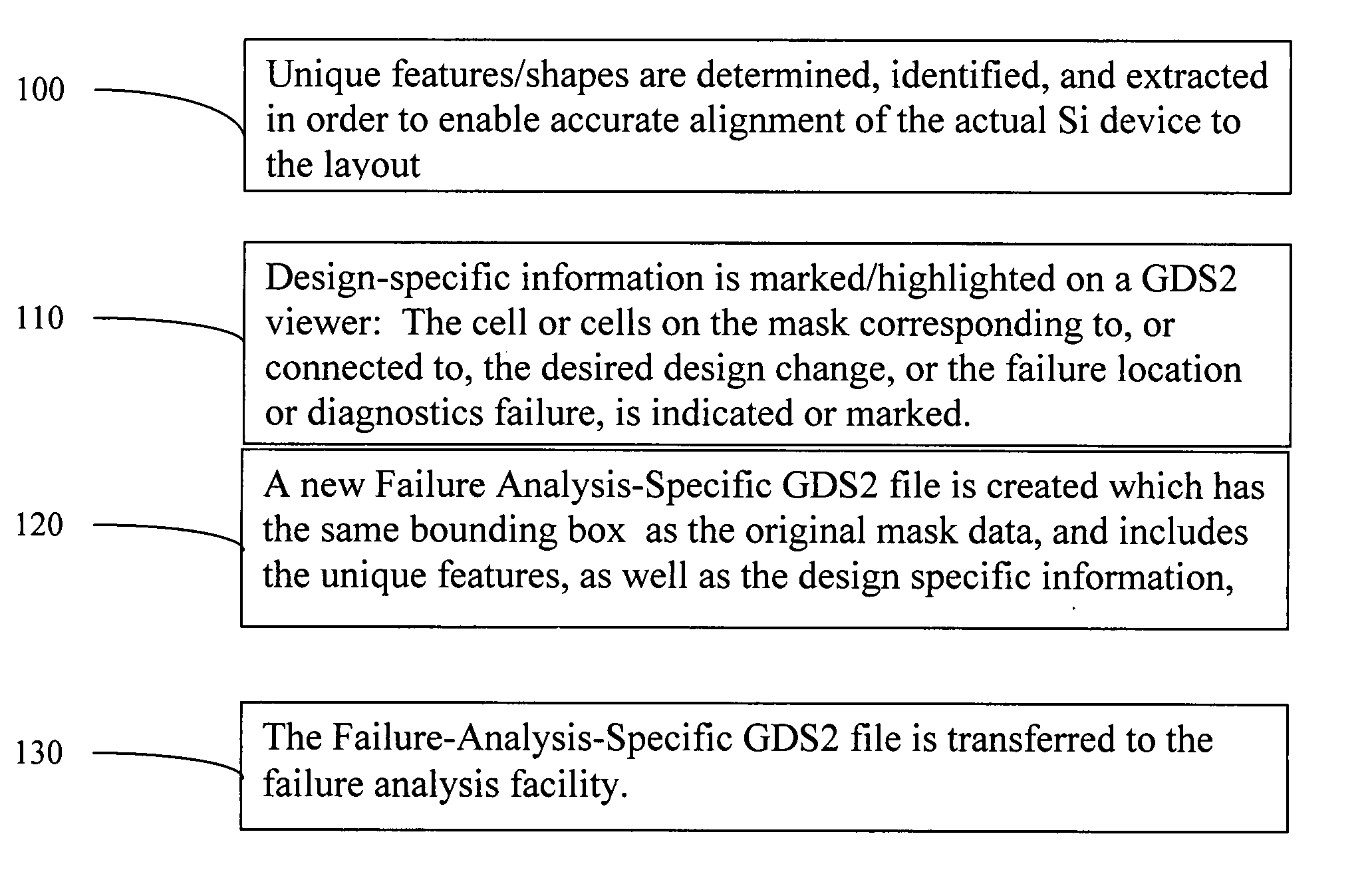

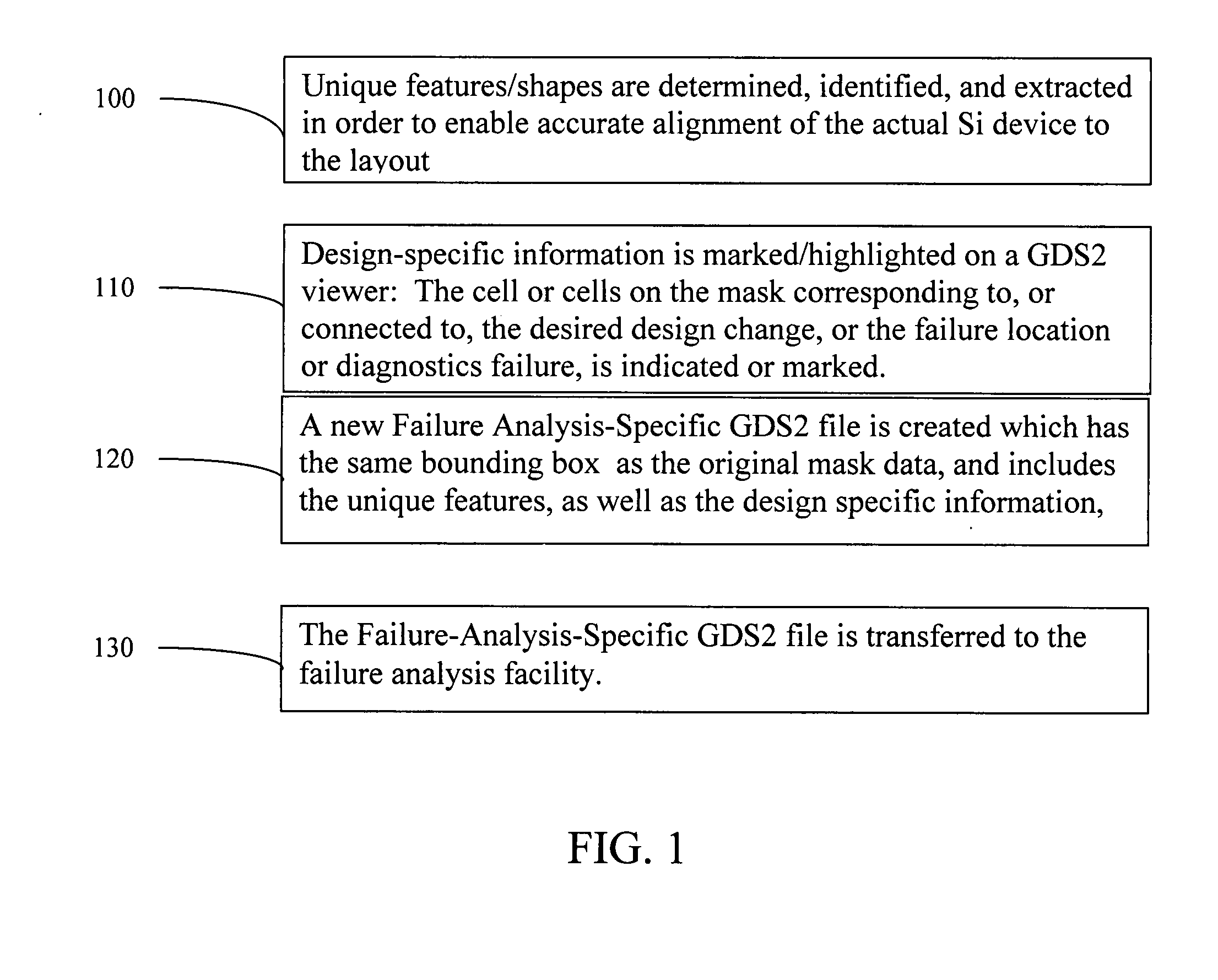

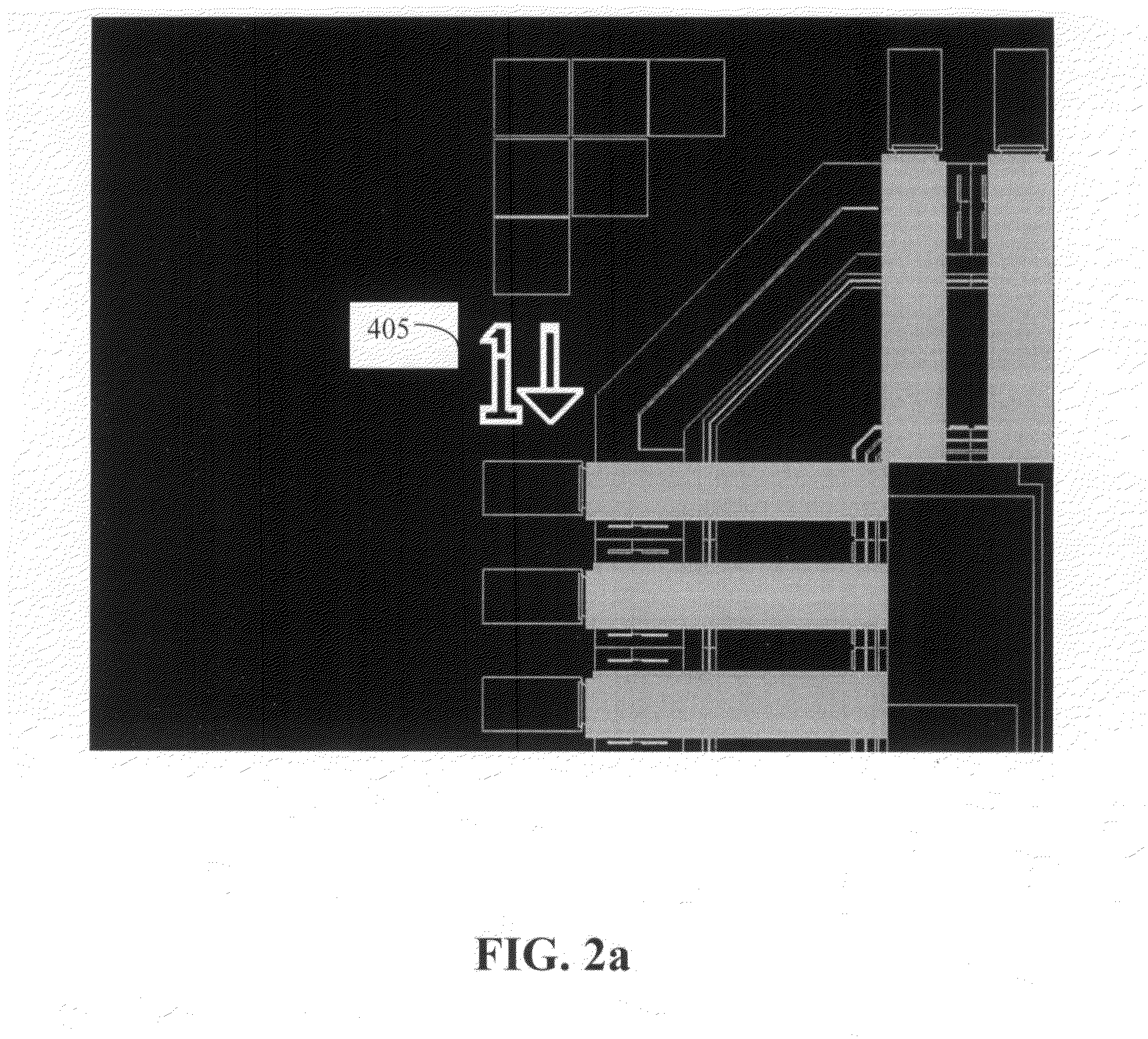

Method to transfer failure analysis-specific data between design houses and fab's/FA labs

InactiveUS8645896B1Effective failure analysisFailed analysisDetecting faulty computer hardwareComputer aided designFailure analysis

A method and system for an IC design house to transfer design and layout information to a fabrication or failure analysis facility on a need-to-know basis to enable effective failure analysis while not providing unnecessary or extraneous information.

Owner:DCG SYST

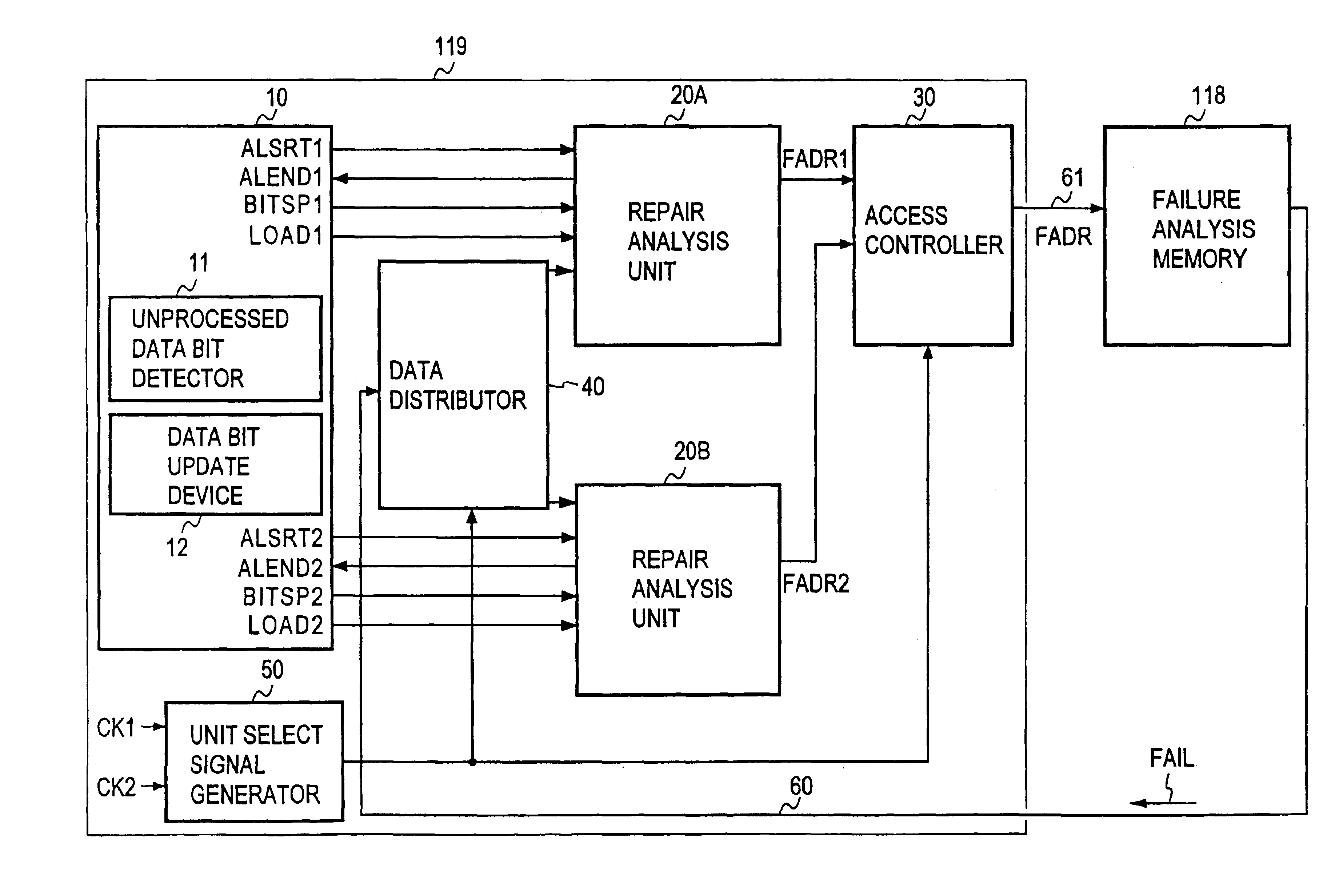

Memory defect redress analysis treating method, and memory testing apparatus performing the method

InactiveUS6907385B2Increase speedFailed analysisDigital computer detailsNuclear monitoringFailure analysisMemory testing

There are provided a failure repair analyzing and processing method and a memory testing apparatus provided with a failure repair analyzing and processing apparatus using this method, that are capable of reducing a time duration required to perform the failure repair analysis and processing for a multi-bit memory having redundancy structure. A plurality of repair analysis units as well as a common failure analysis memory are provided, and these repair analysis units are concurrently operated in parallel with each other, thereby to carry out respective repair analyses and processings for failure memory cells of plural data bits read out from the failure analysis memory in the plural repair analysis units concurrently and in parallel with each other. As a result, a time duration required to execute the failure repair analysis and processing is shortened.

Owner:ADVANTEST CORP

Enhanced status monitoring, storage and reporting for optical transceivers

ActiveUS8886033B2Accurate informationFailed analysisTransmission monitoringTransmission monitoring/testing/fault-measurement systemsTransceiverEngineering

An optical transceiver and methods for using the same are disclosed. The optical transceiver and methods may be useful for providing more accurate information regarding trends in operation of the optical transceiver, predicting an impending failure of the optical transceiver, and providing details of the optical transceiver prior to failure. The optical transceiver generally includes (1) at least one of (i) a receiver configured to receive optical information and (ii) a transmitter configured to transmit optical information, (2) circuitry configured to sample data for one or more operational parameters of the receiver and / or transmitter, (3) logic configured to perform one or more statistical calculations on the sampled data to generate statistical information, and (iv) one or more memories configured to store the sampled data and the statistical information.

Owner:SOURCE PHOTONICS

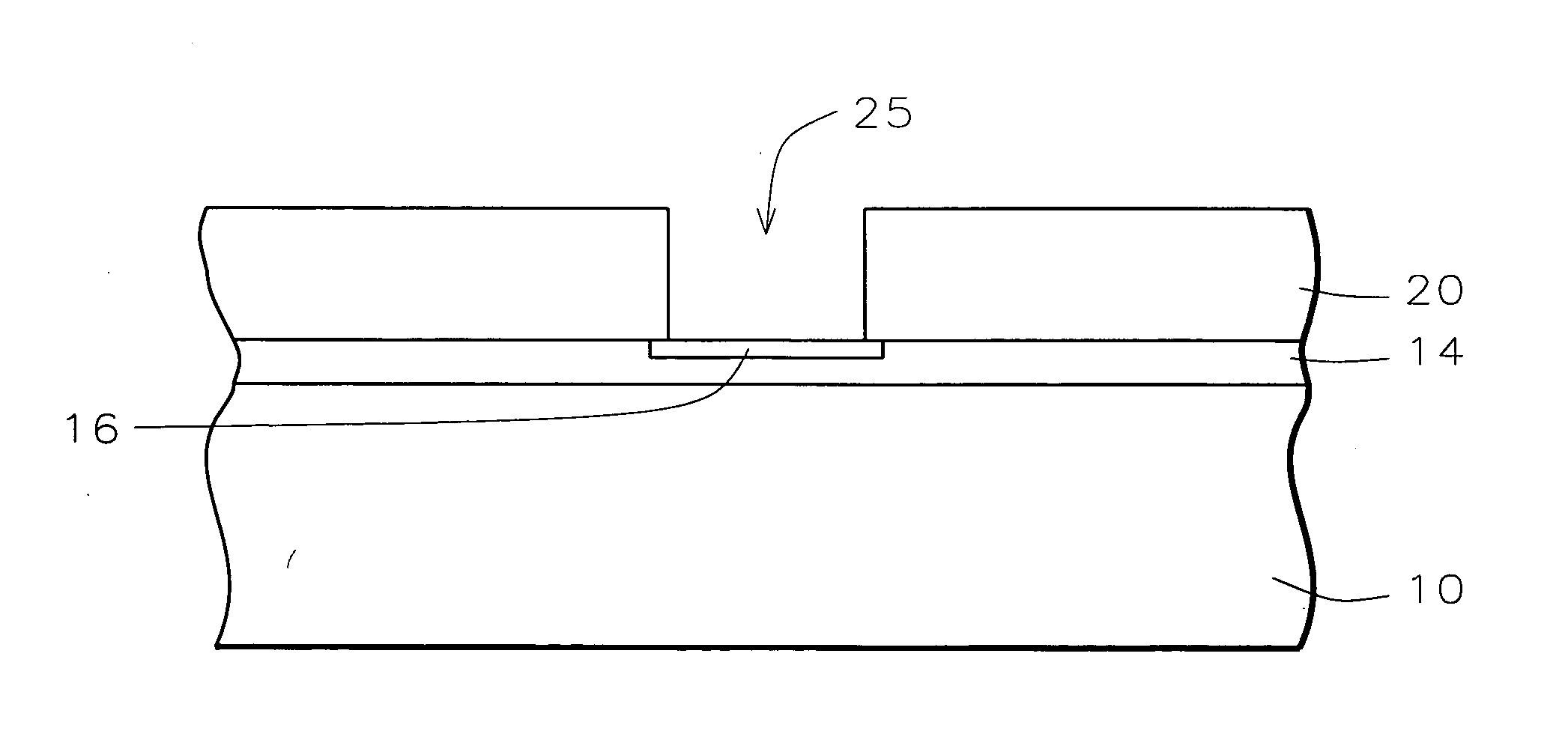

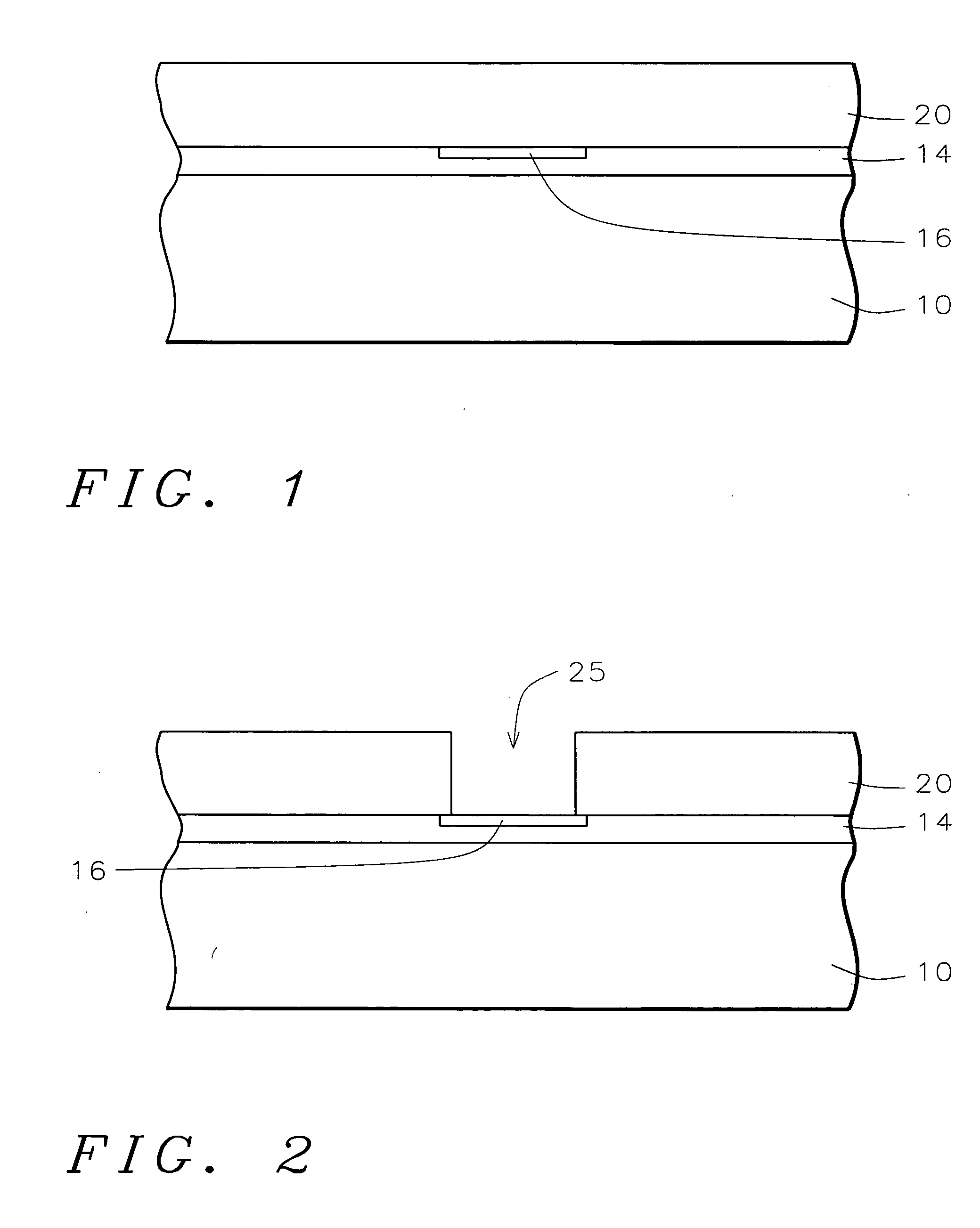

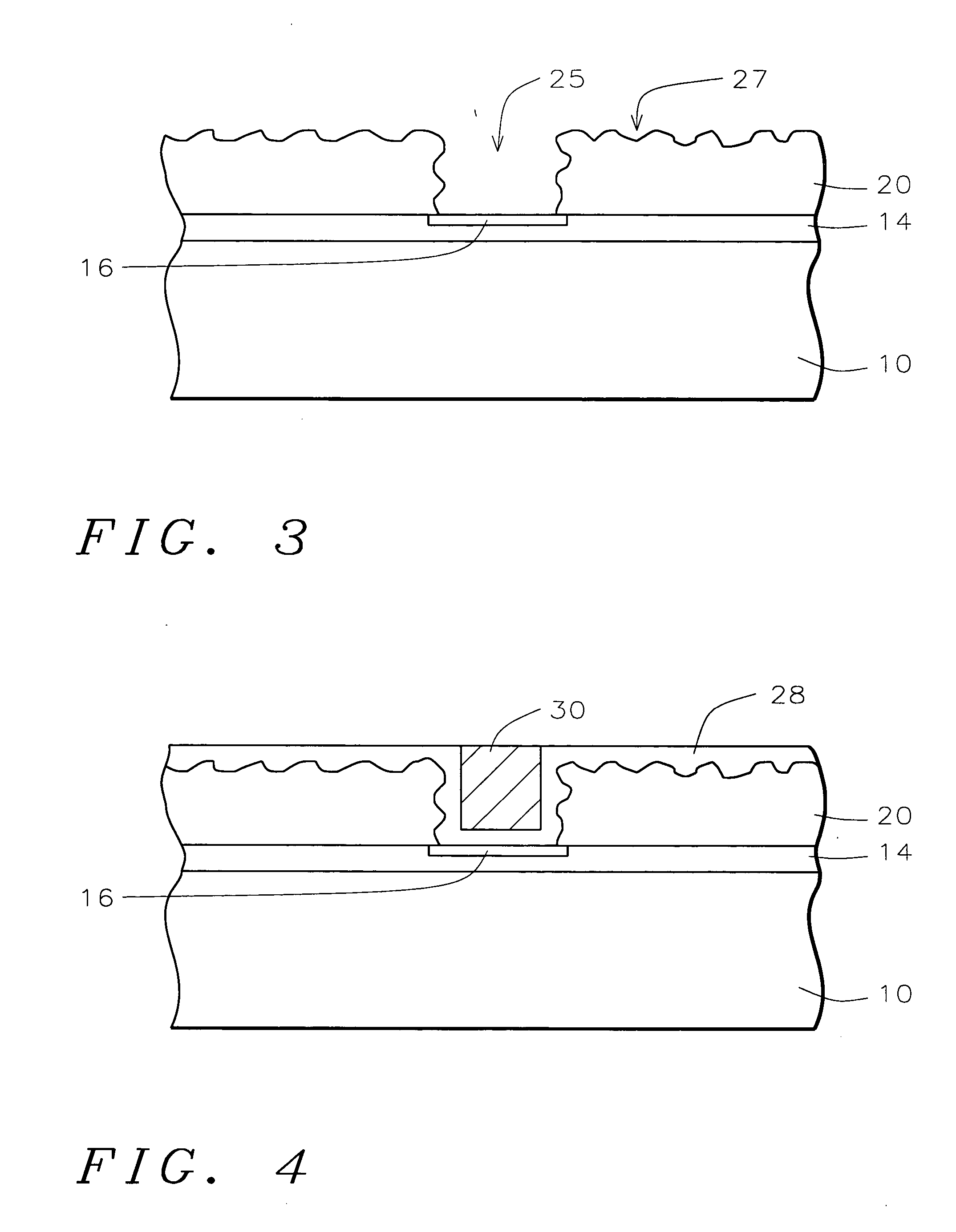

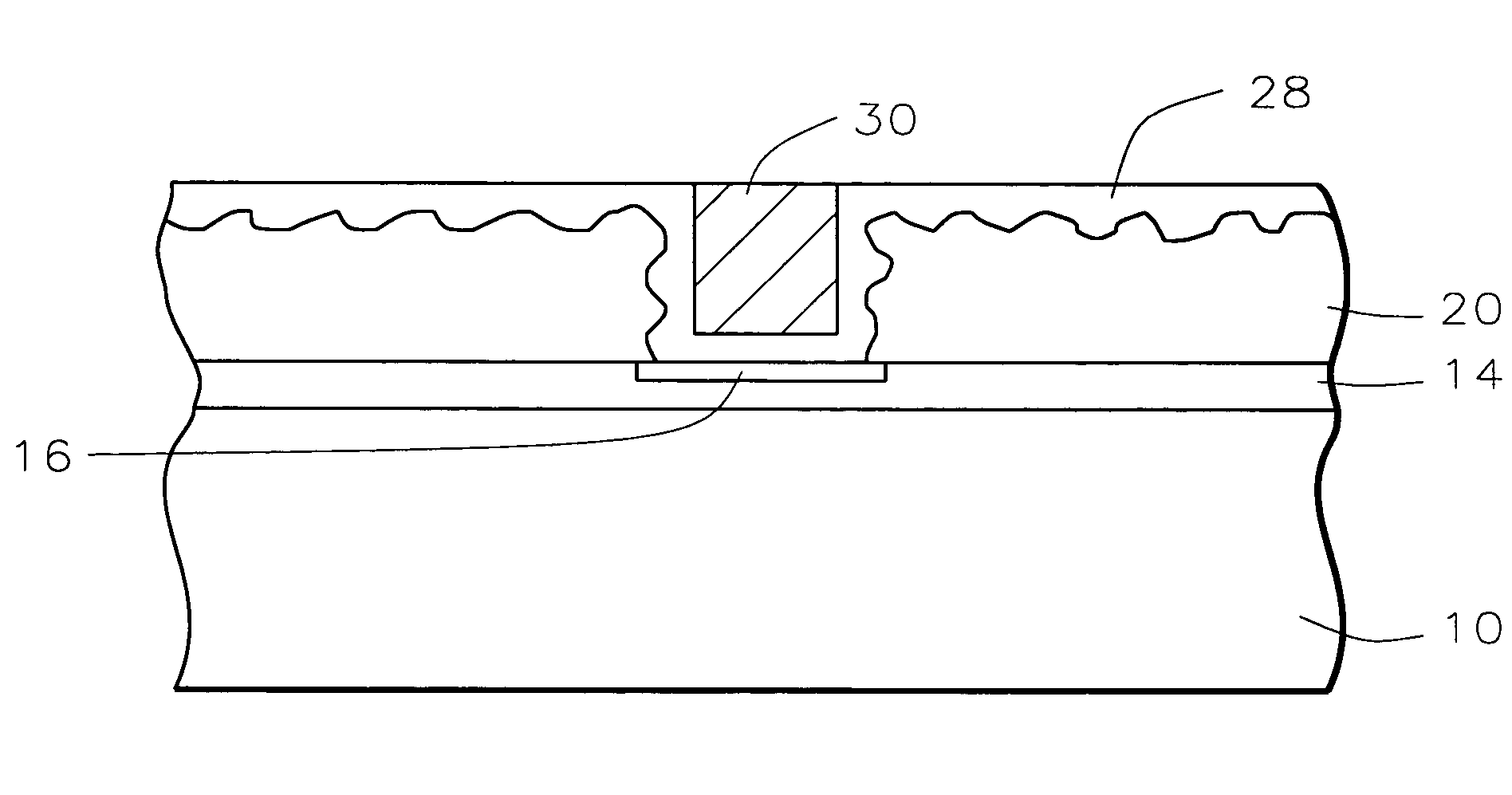

Novel device structure having enhanced surface adhesion and failure mode analysis

InactiveUS20050272260A1Failed analysisEasy to disassembleSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDevice material

A substrate is provided having semiconductor device structures formed in and on the substrate. The semiconductor device structures comprise conductor layers embedded in openings in dielectric layers having a dielectric constant of less than 4.5. The dielectric layer has a roughness between the dielectric and the conductor wherein the roughness of the dielectric layer divided by the thickness of a barrier layer underlying the conductor layer is 0 to 1. The integrated circuit structure is prepared for failure analysis by removing the low dielectric constant dielectric layers and exposing the conductor layers for further failure analysis by optical examination or scanning electron microscope (SEM).

Owner:TAIWAN SEMICON MFG CO LTD

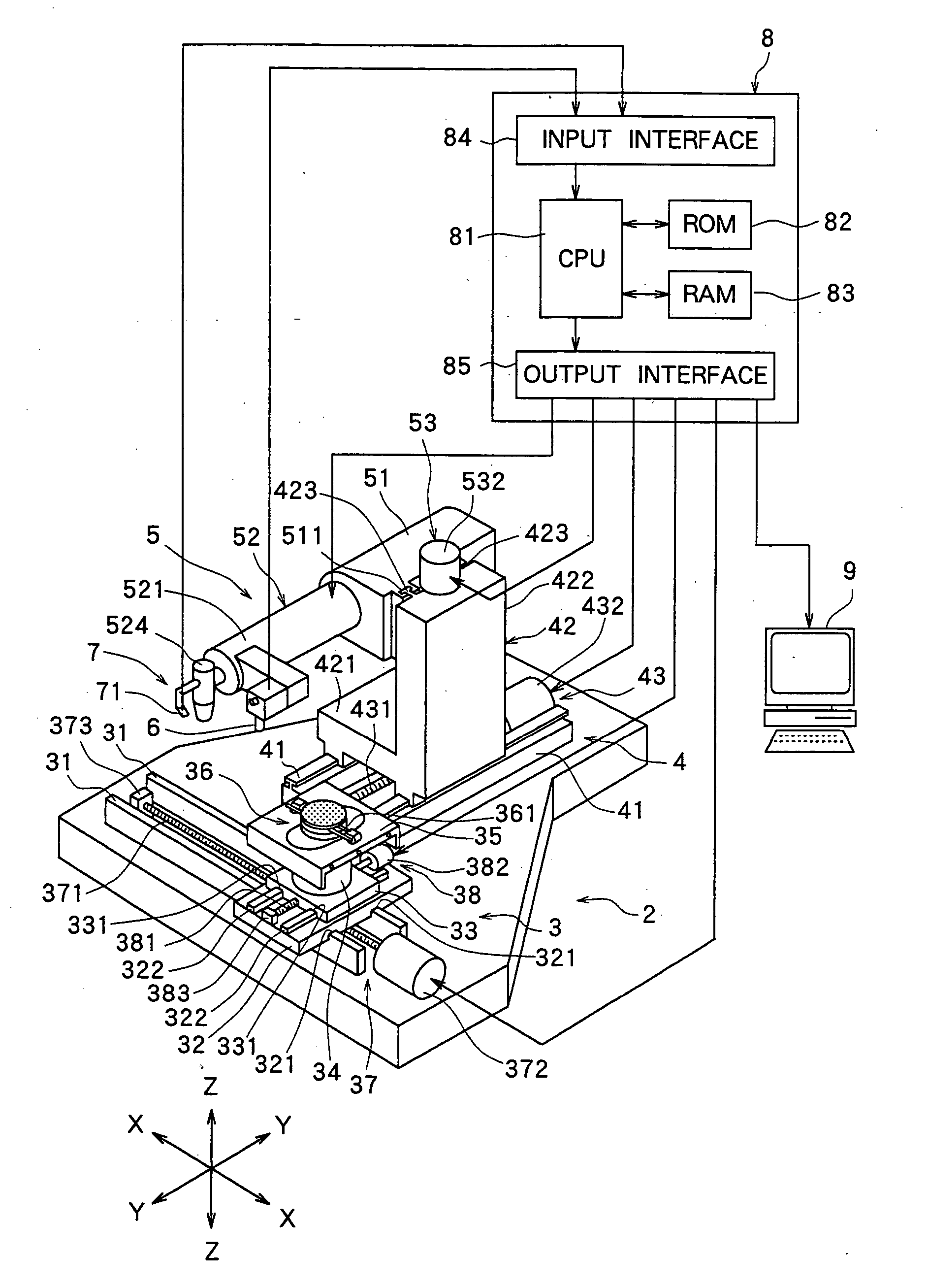

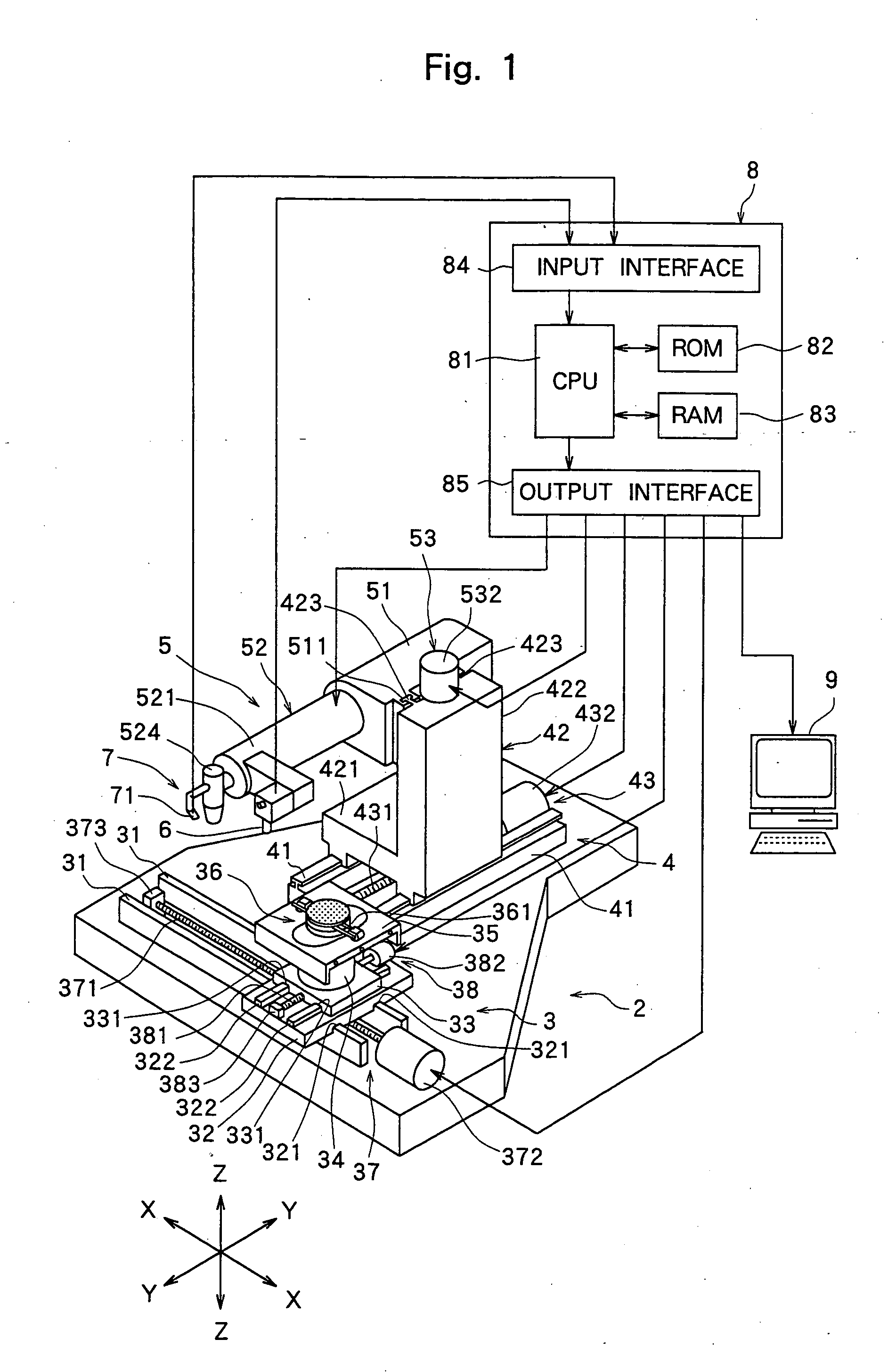

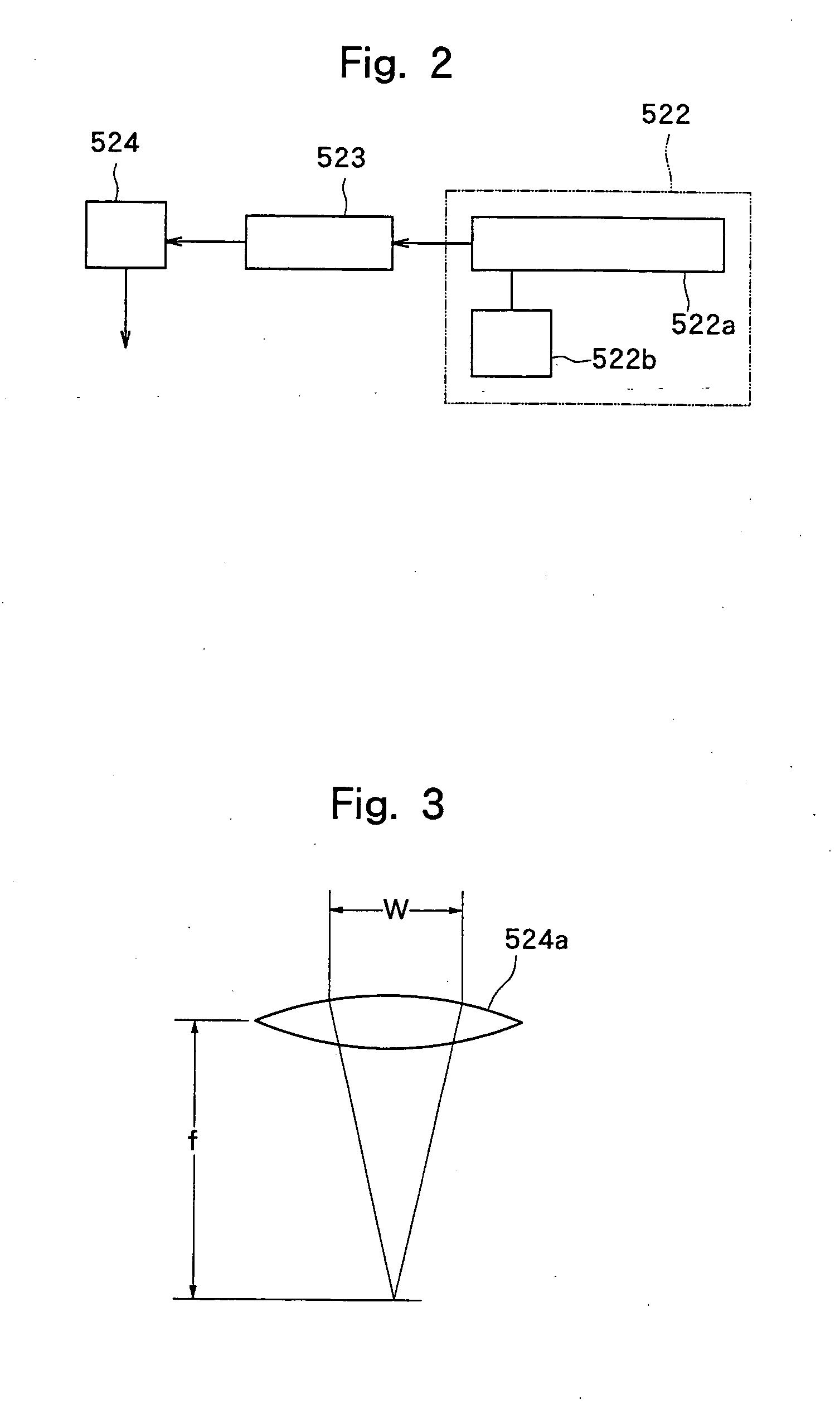

Laser beam machine

InactiveUS20050082264A1Failed analysisSemiconductor/solid-state device manufacturingMetal working apparatusOptoelectronicsLaser beams

A laser beam machine comprising a chuck table for holding a workpiece and a laser beam application means for applying a laser beam to the workpiece held on the chuck table, wherein the machine further comprises a light detection means for detecting light of a processing portion of the workpiece to which a laser beam is applied from the laser beam application means and a control means for judging whether the output value of the light detection means falls within a predetermined permissible range.

Owner:DISCO CORP

Circuit design system and circuit design program

ActiveUS7600203B2Reduce in quantityImprove failure-analyticityElectronic circuit testingDetecting faulty computer hardwareComputer architectureObservation point

A circuit design system has: a storage unit in which a netlist is stored; a fault-candidate extracting module configured to extract equivalent fault class Gi from the netlist; a judgment module configured to select a target node out of a plurality of nodes Ni1 to Niji included in the equivalent fault class Gi, wherein Ji is a number of nodes included in the equivalent fault class Gi; and an observation-point inserting module configured to update the netlist by inserting at least one observation point into the target node. The judgment module decides the target node based on the number Ji.

Owner:RENESAS ELECTRONICS CORP

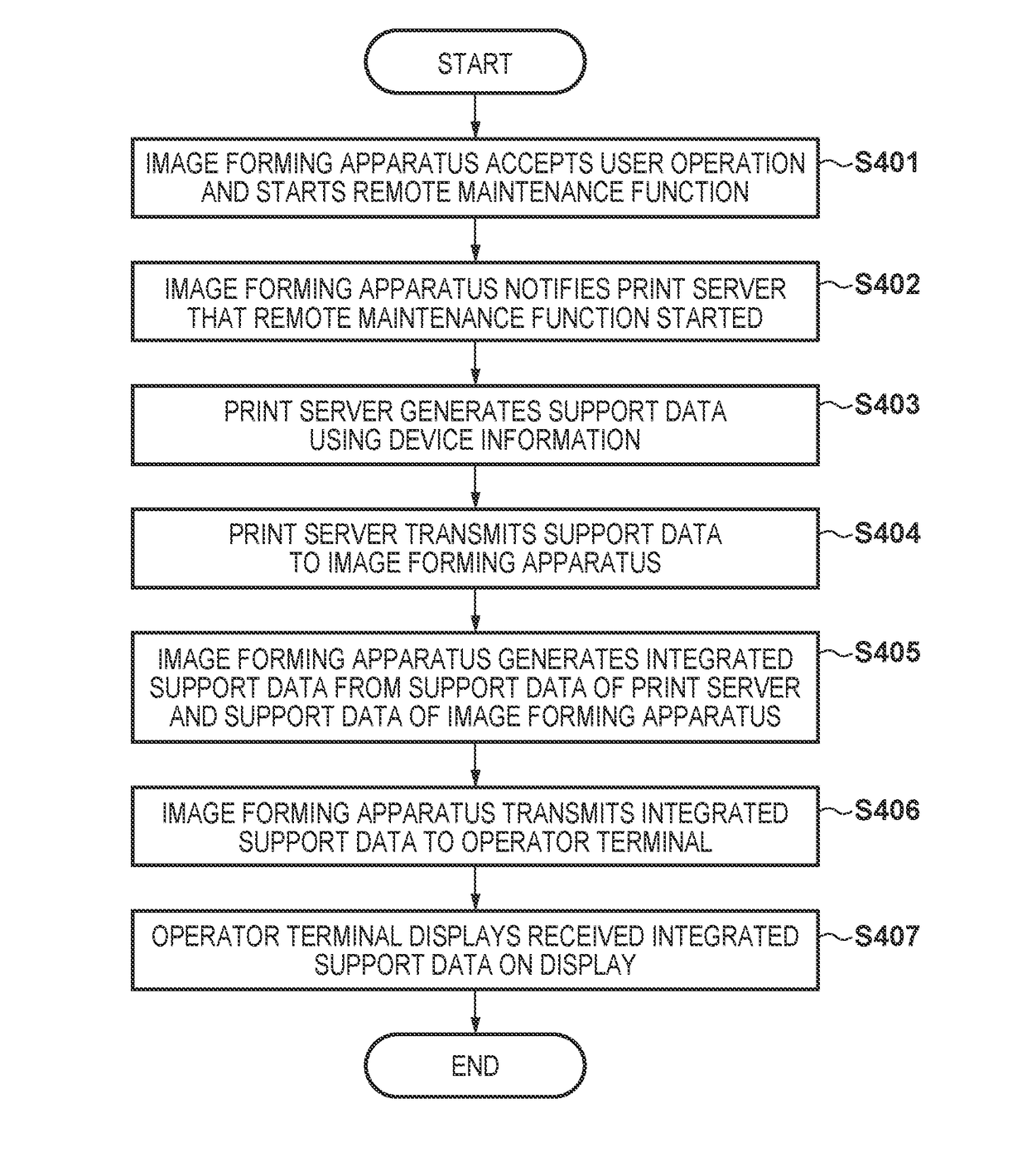

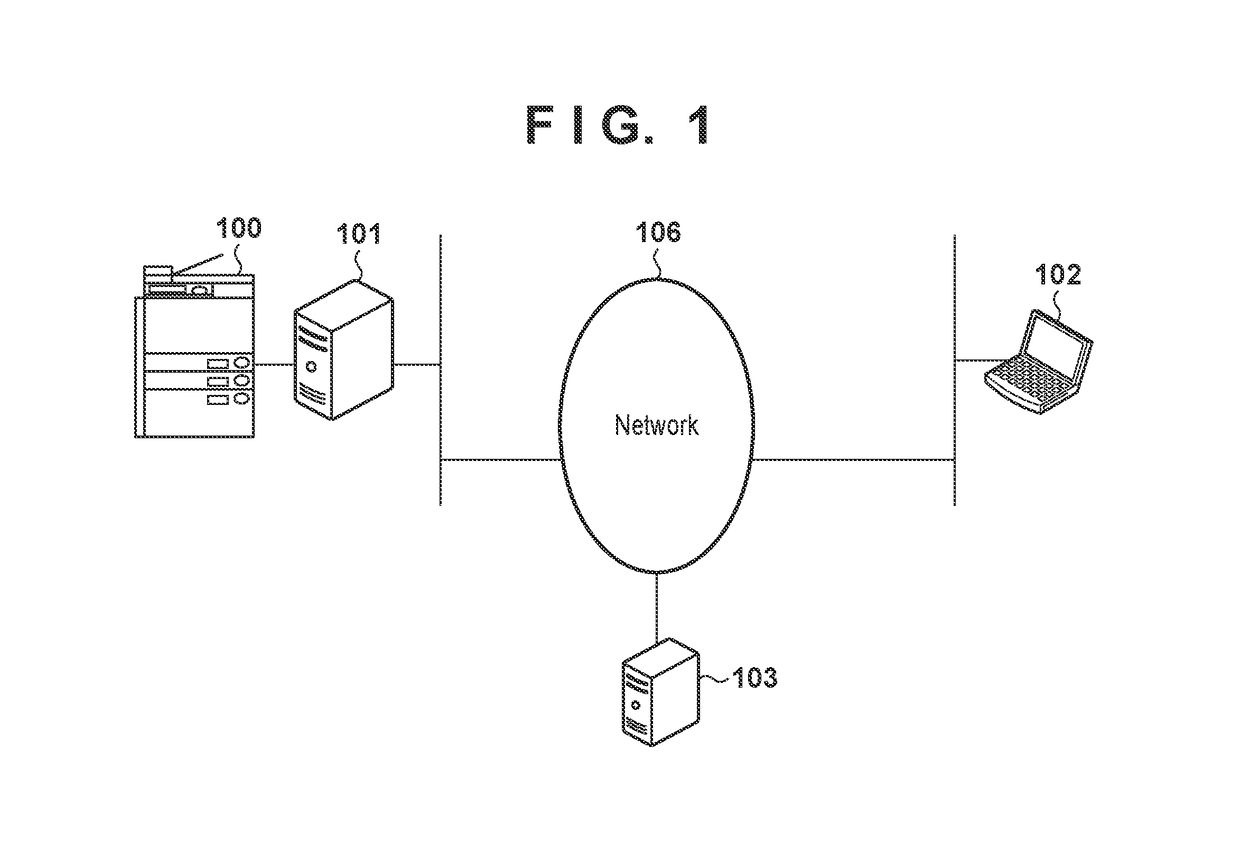

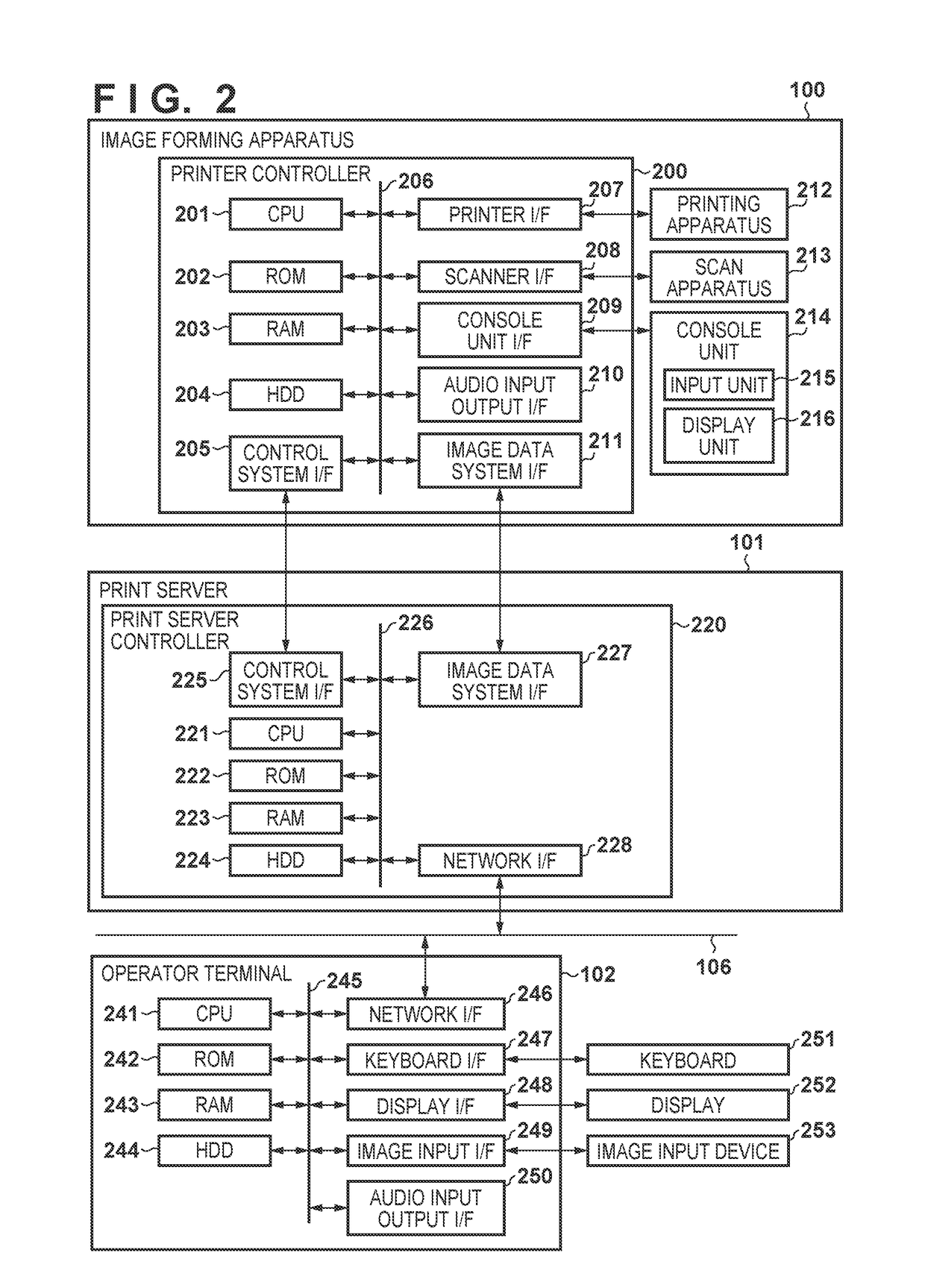

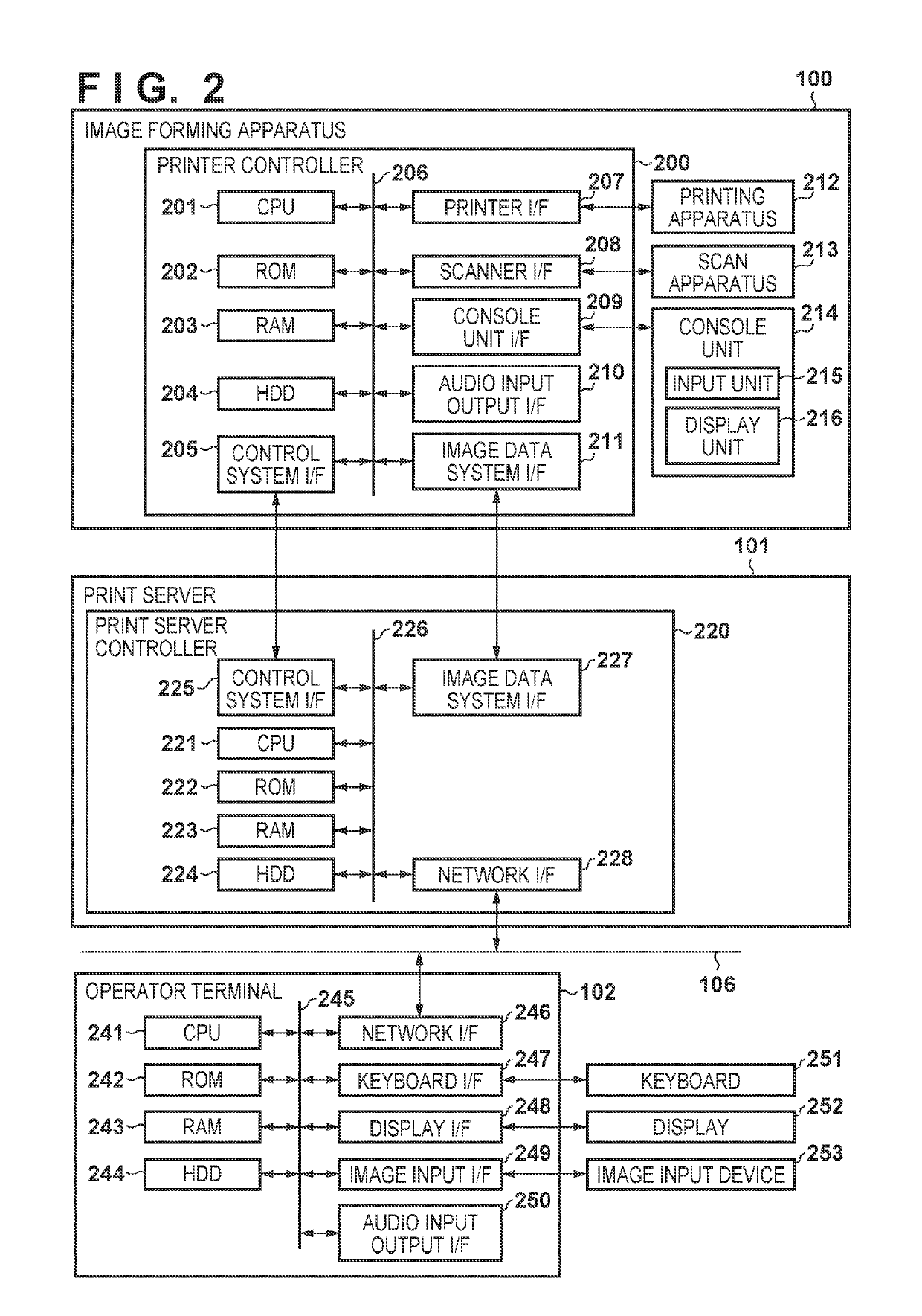

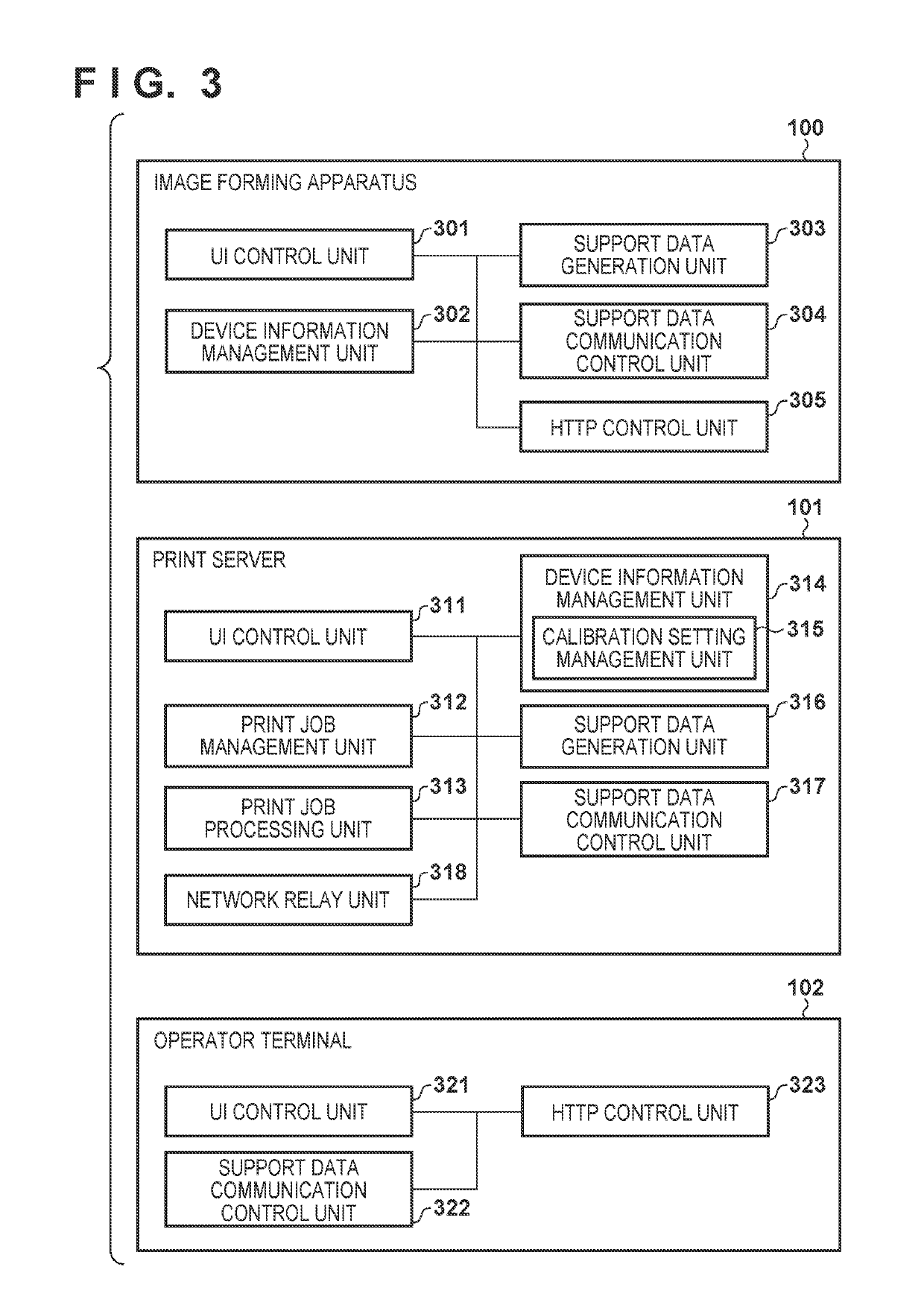

Remote maintenance system, image forming apparatus, external terminal, methods of controlling these, and storage mediums

ActiveUS20170208184A1Reduce downtimeOptimization of failure analysisPictoral communicationImage formationComputer science

An image forming apparatus accepts a start of the remote maintenance function for resolving a failure of the image forming apparatus in accordance with instructions of an operator using an external terminal, generates support data including information of at least one of device information of the print server and device information of the image forming apparatus, which is that is information necessary when the operator analyzes the failure of the image forming apparatus, and transmits it to the external terminal.

Owner:CANON KK

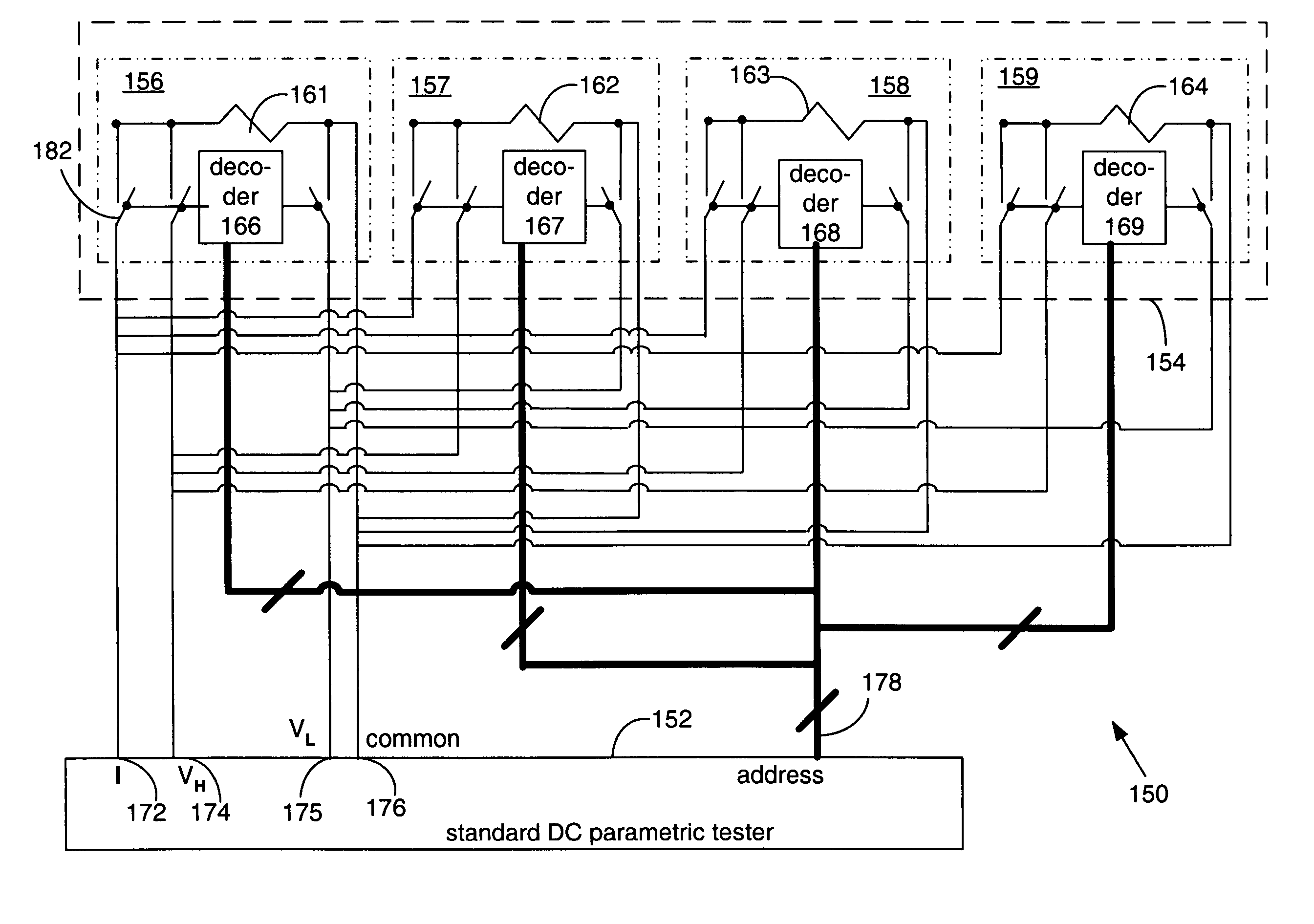

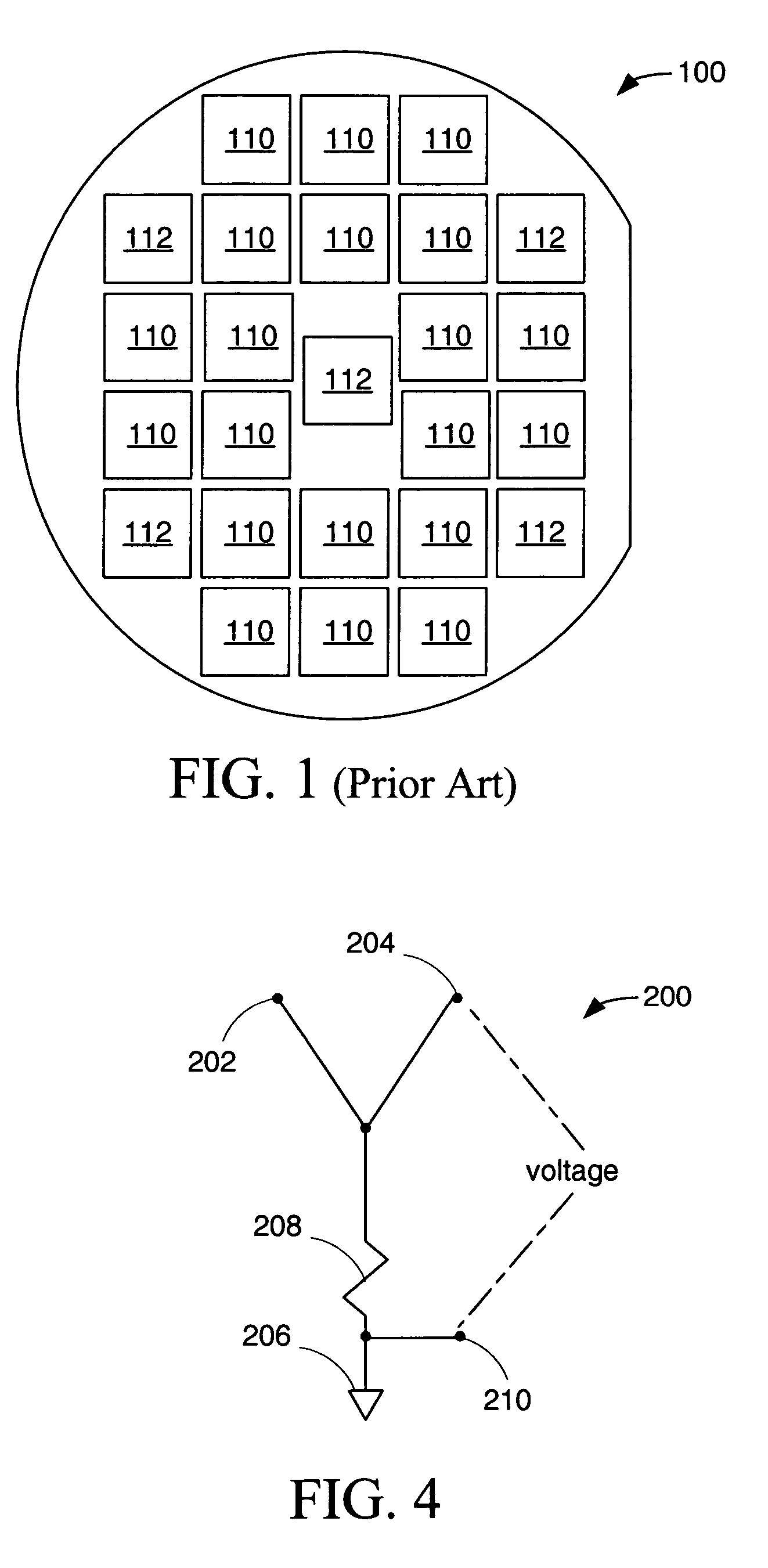

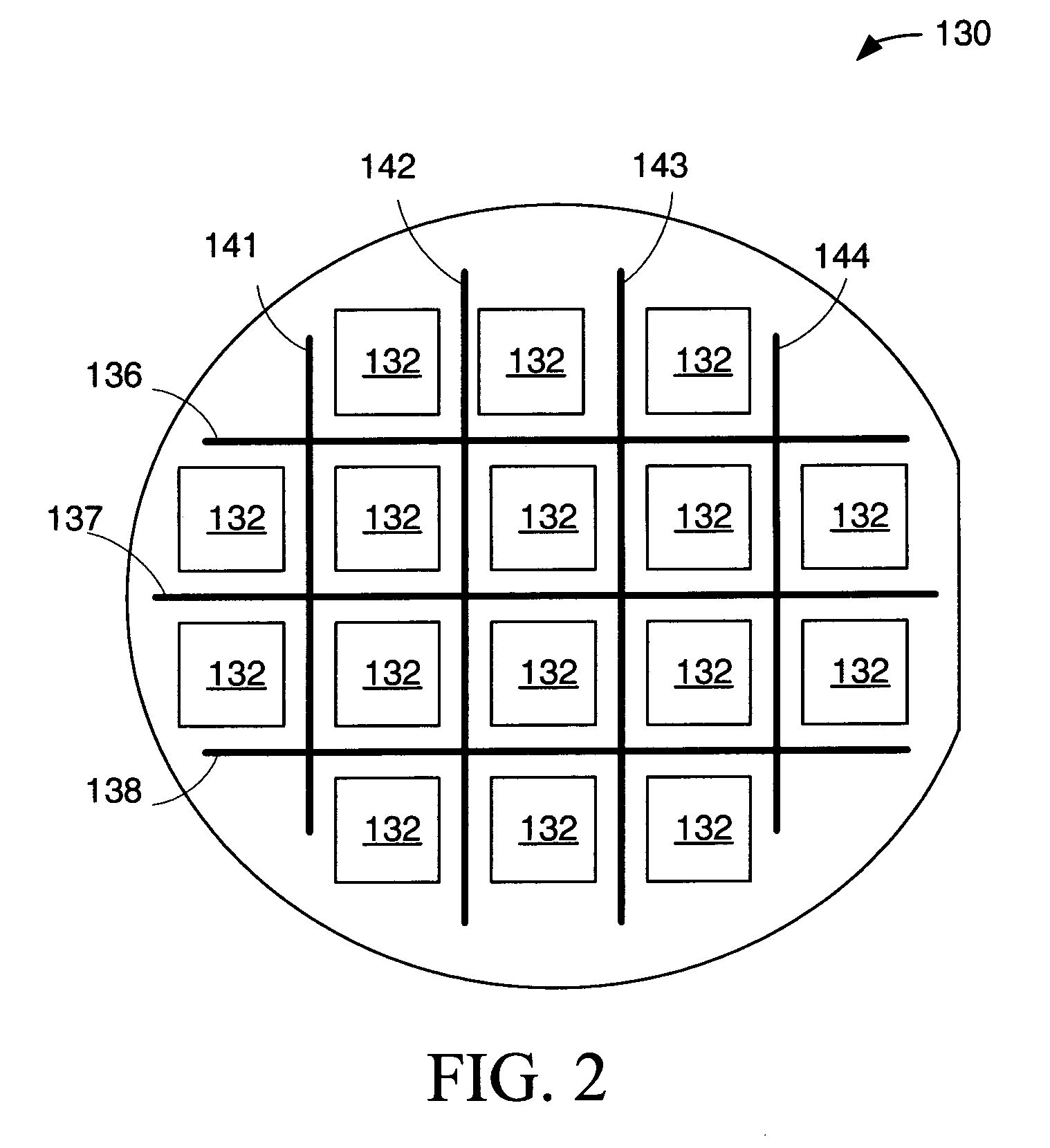

Testing vias and contracts in integrated circuit

InactiveUS7046026B2Failed analysisSemiconductor/solid-state device testing/measurementElectronic circuit testingHigh resistanceElectrical resistance and conductance

A test arrangement is designed to test whether one in a chain of vias or contacts has abnormally high resistance. The arrangement contains a plurality of via or contact chains and a plurality of decoders. The chains are switchably connected to a resistance measurement device. Each decoder has a unique address such that it will generate a control signal when a predetermined address is address thereon. The control signal is used to close a switch, which connect one of the chains to the resistance measurement device. By sequentially applying different addresses to the decoders, the resistance of the chains can be individually measured.

Owner:XILINX INC

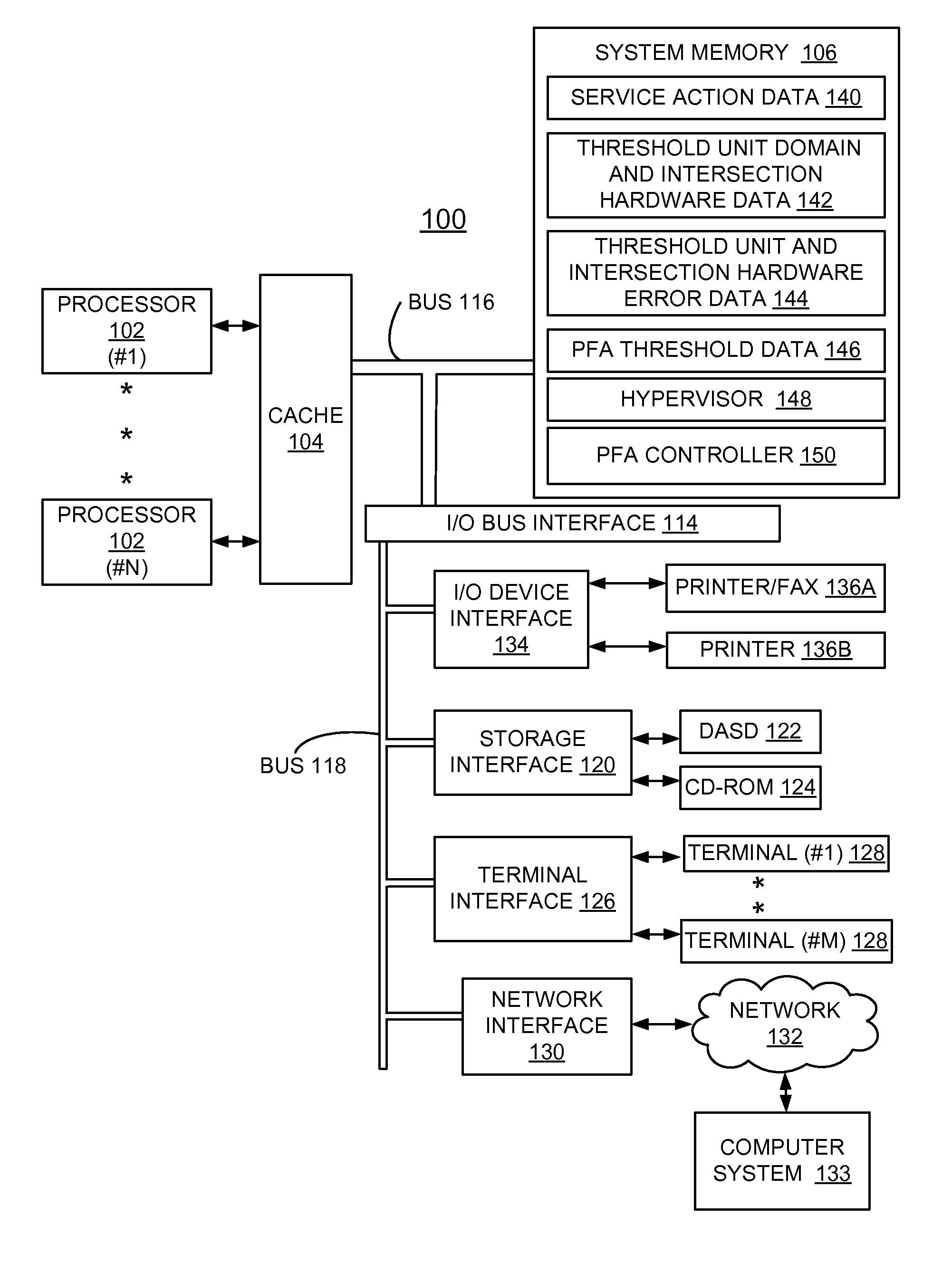

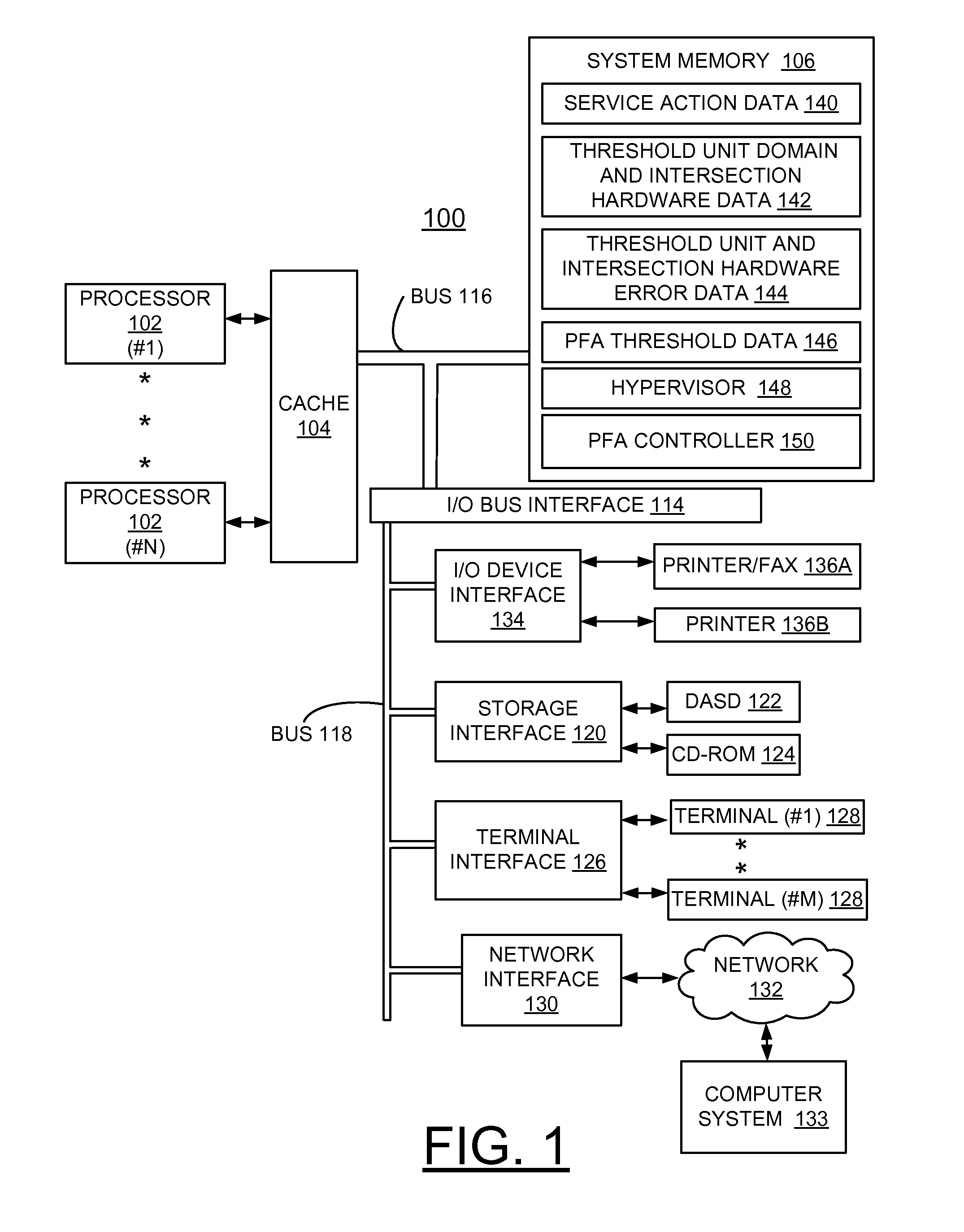

Implementing tiered predictive failure analysis at domain intersections

InactiveUS20150286514A1Failed analysisNegative effectNon-redundant fault processingPredictive failure analysisComputerized system

A method and apparatus are provided for implementing enhanced tiered Predictive Failure Analysis (PFA) at domain intersections in a computer system. When recoverable errors trigger PFA calculations on an individual threshold unit, PFA calculations are performed on the individual threshold unit. A threshold domain of all intersection hardware with the individual threshold unit is established. PFA calculations are performed on all intersection hardware in the threshold domain. A repair action is triggered based upon comparing the PFA calculations for the individual threshold unit and comparing the PFA calculations for each intersection hardware.

Owner:IBM CORP

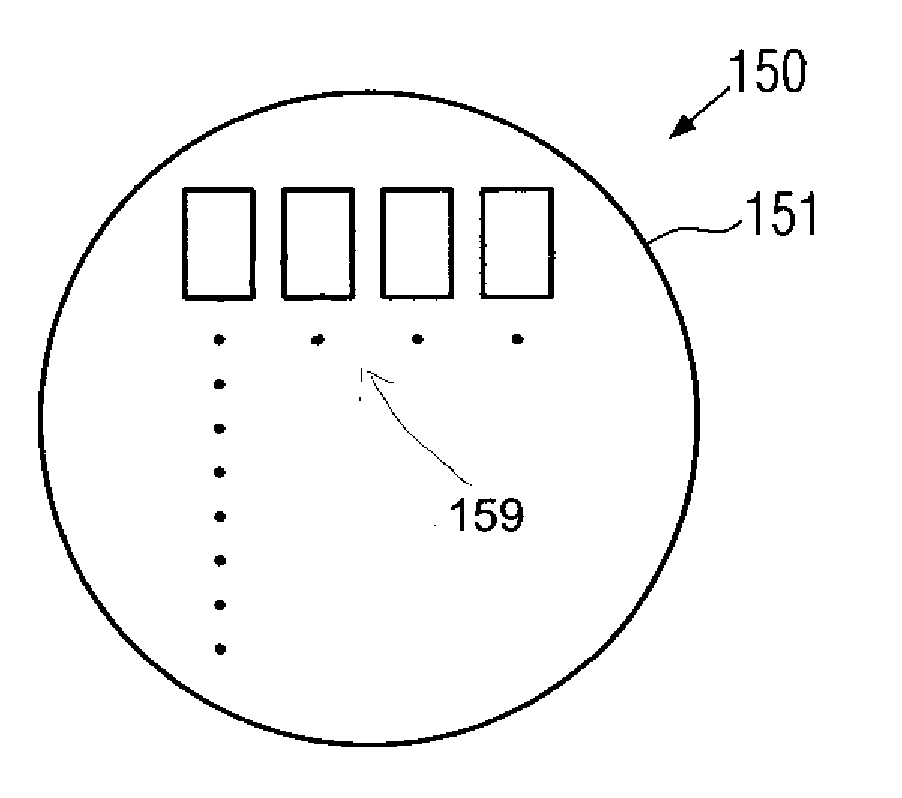

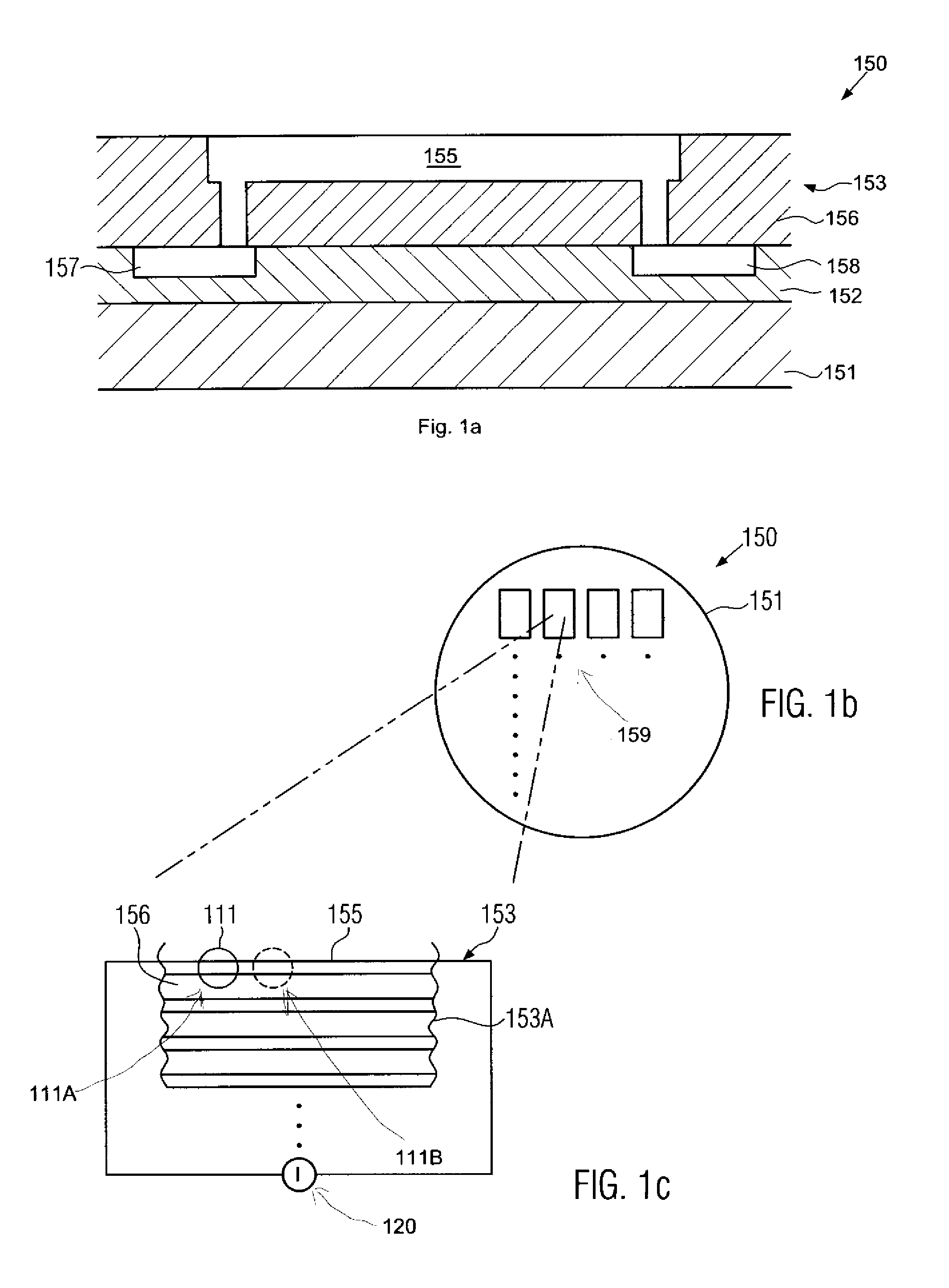

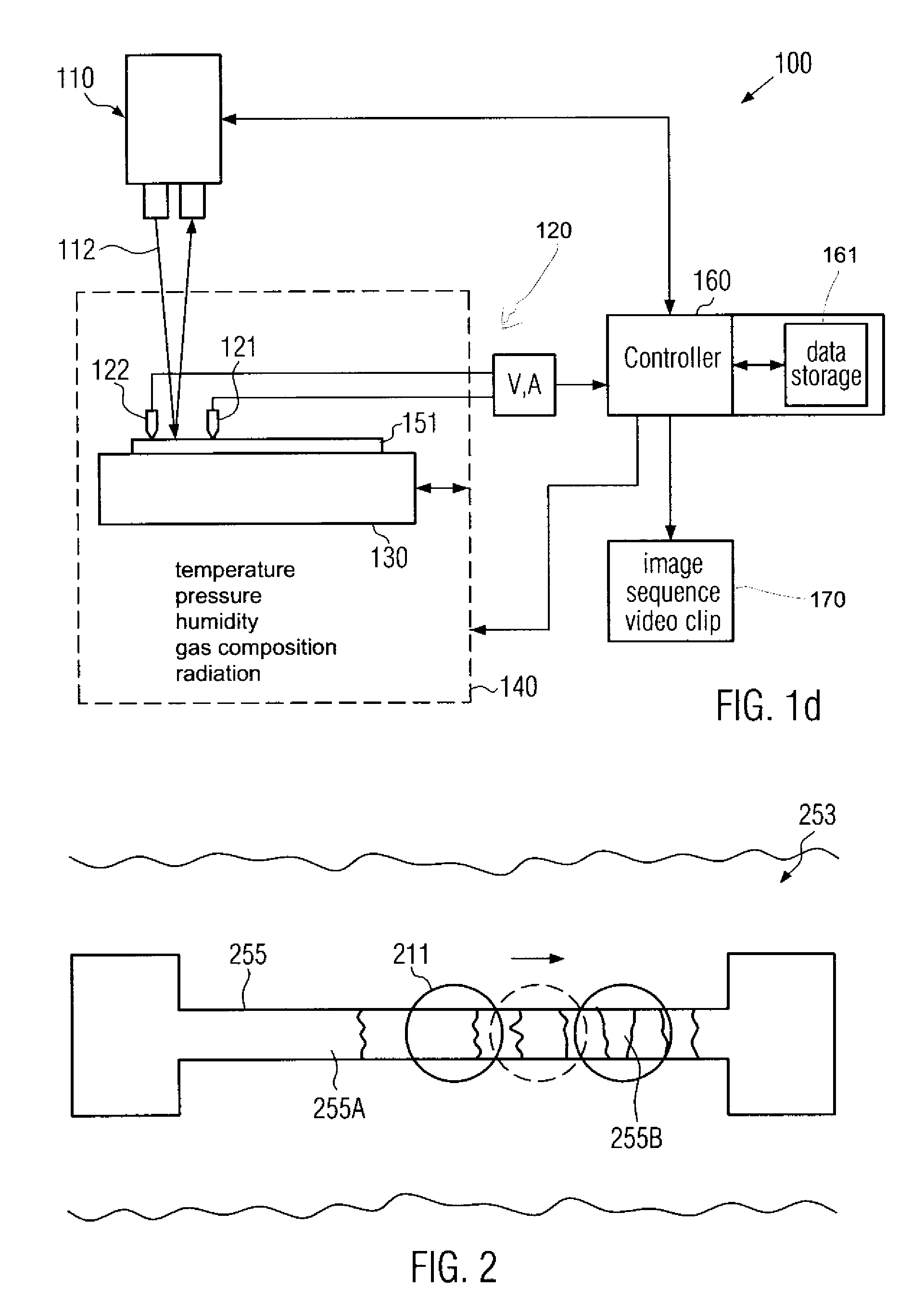

Technique for monitoring dynamic processes in metal lines of microstructures

ActiveUS20070044710A1Improve efficiencyFailed analysisFrom gel statePolycrystalline material growthDielectricDevice material

By locally heating specific scan positions within a region of interest and automatically obtaining respective measurement data in a time-resolved and spatially-resolved fashion, dynamic processes within a metallization layer of semiconductor devices may be efficiently monitored and / or modified. For instance, OBIRCH and SEI techniques may be used in combination with the automated data recording and manipulation, thereby providing an efficient means for in situ failure analysis, defect identification, for any dynamic degradation processes in interconnects and interlayer dielectrics.

Owner:ADVANCED MICRO DEVICES INC

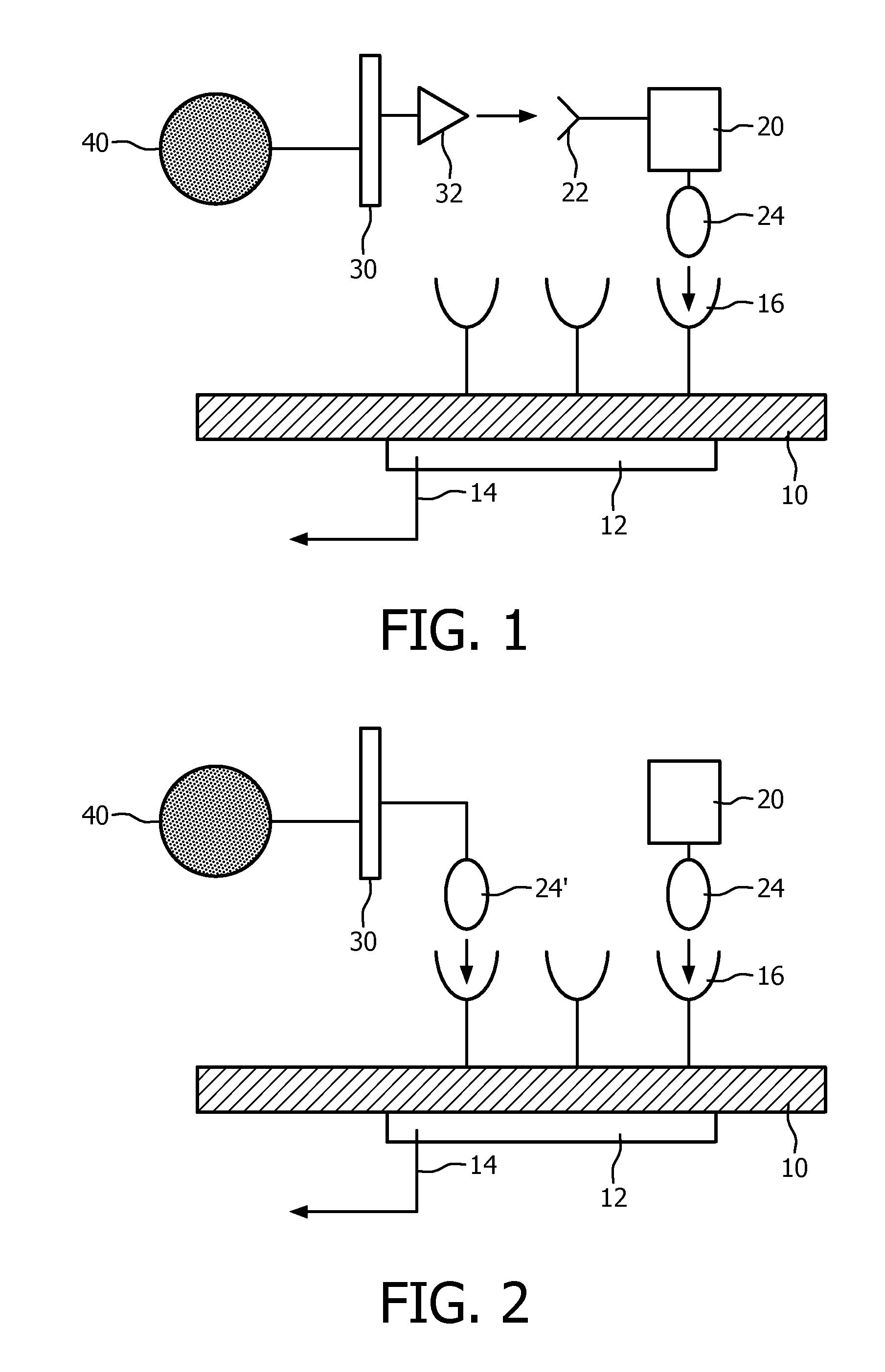

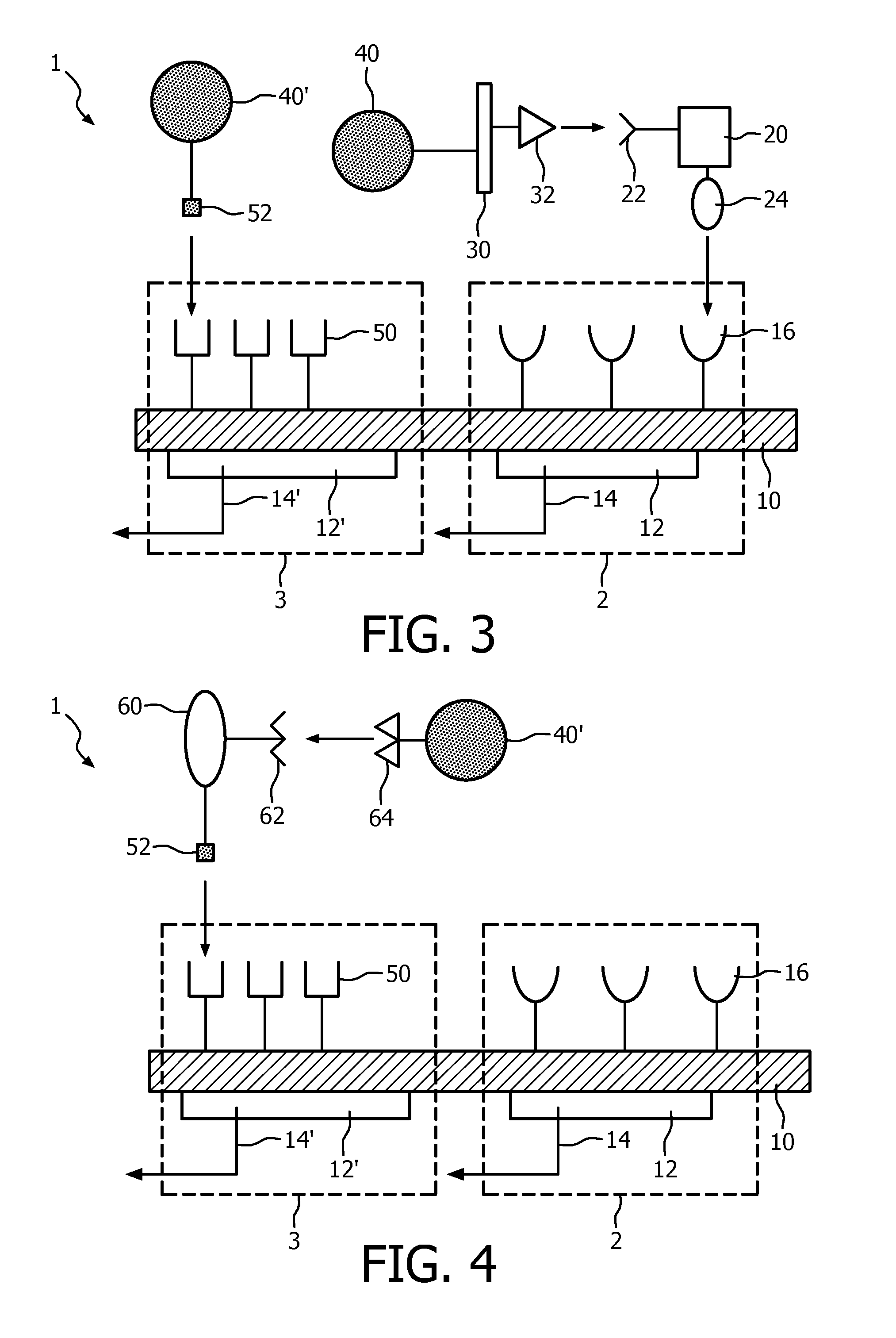

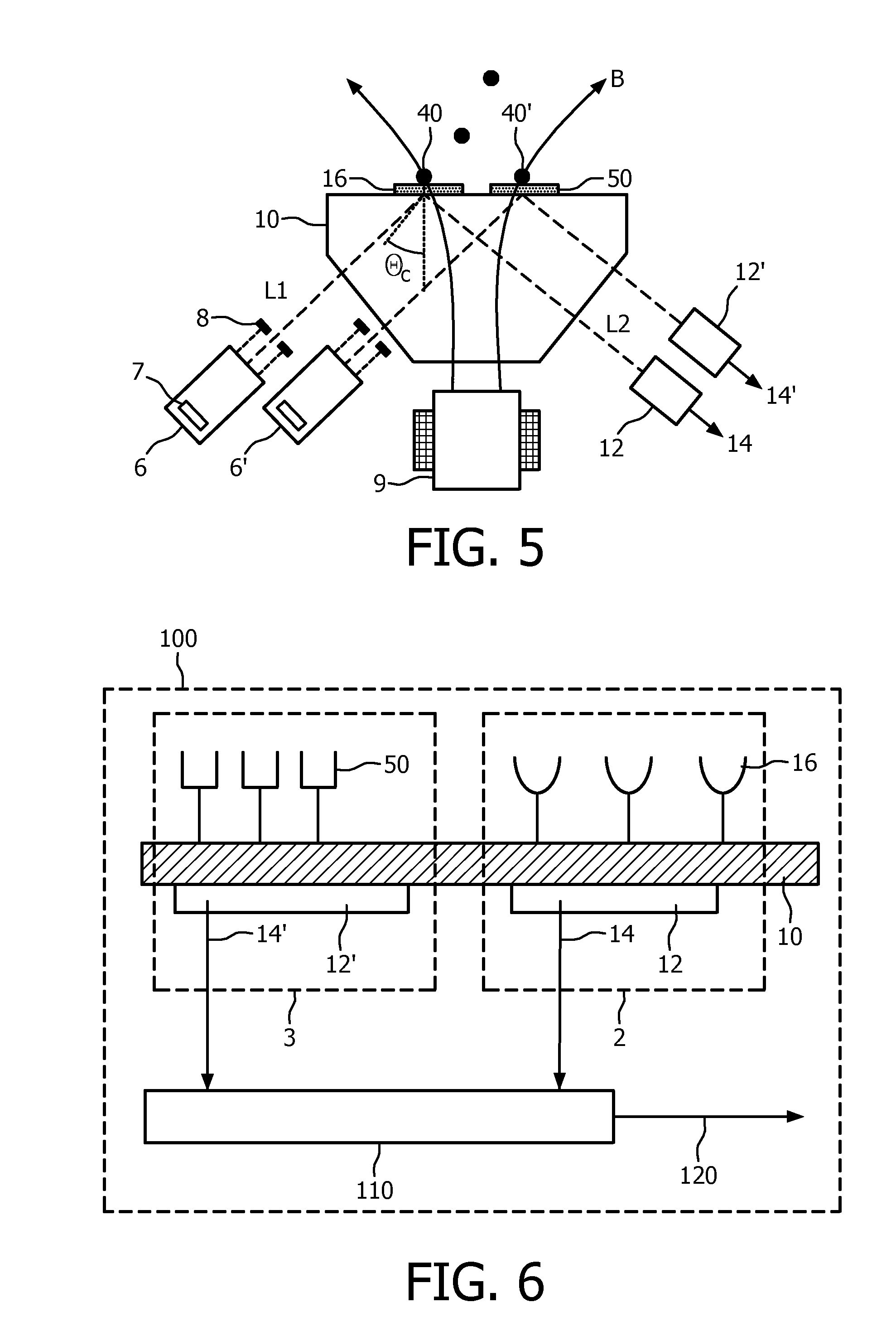

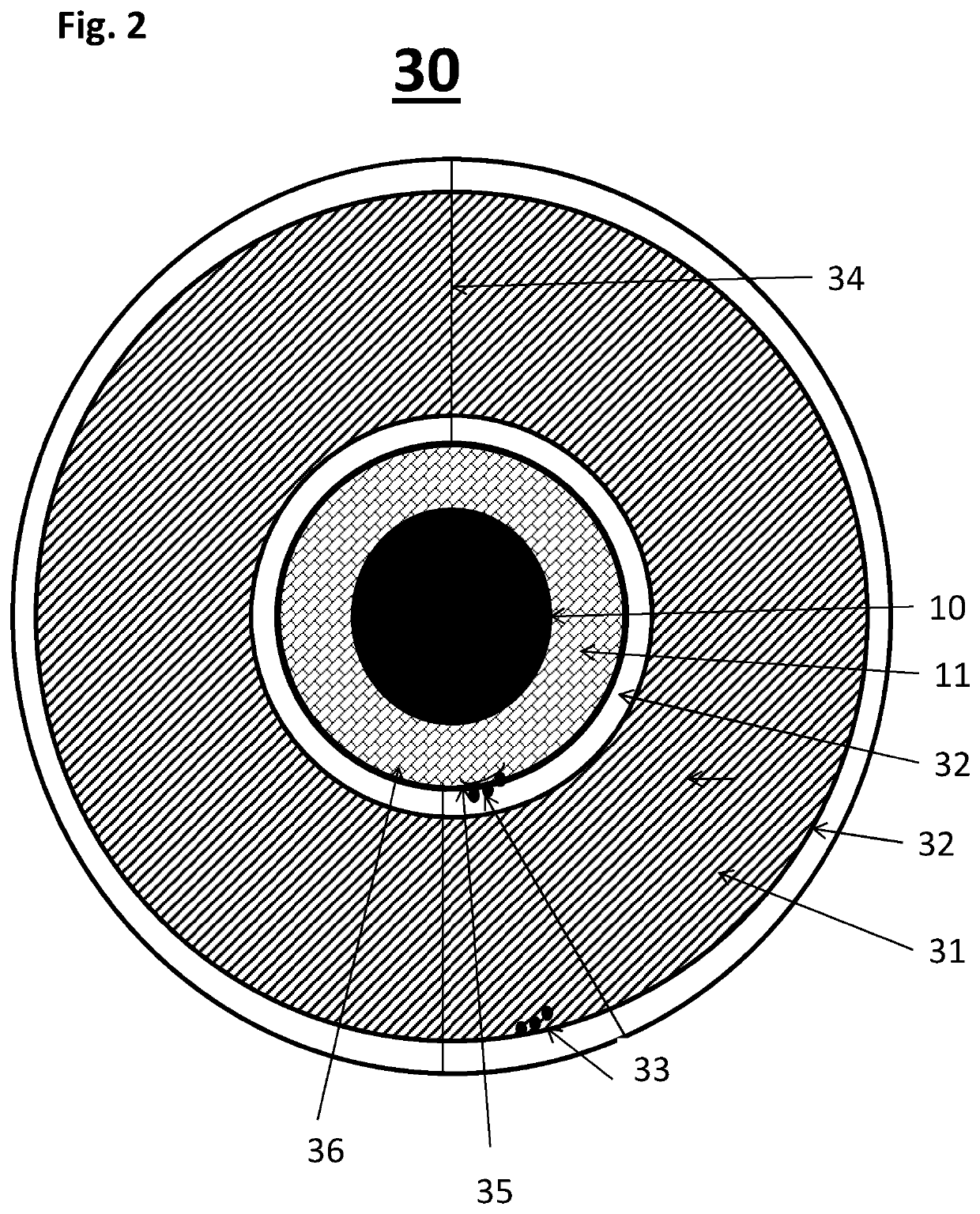

Magnetic sensor device, method of operating such a device and sample

ActiveUS20120107961A1Easy to detectFailed analysisComponent separationMaterial analysis by electric/magnetic meansEngineeringReference sensor

A sensor device (1) for detecting the presence of a target molecule (20) in a sample, is disclosed. The sensor device comprises a measurement sensor (2) comprising a first moiety (16) for forming a binding couple with a first further moiety comprising the target molecule (20) and a detectable label (40) and a reference sensor (3) comprising a second moiety (50) for forming a further binding couple with a second further moiety comprising a further detectable label (40′). The sensor device is adapted to generate a first detection signal (14) from the detection of the detectable label (40) in the first further moiety bound to the first moiety (16) and to generate a second detection signal (14′) from the detection of the further detectable label (40′) in the second further moiety bound to the second moiety (50), wherein at least during operation of the sensor device the second further moiety is expected to be present in a predefined amount such that the value of the second detection signal (14′) falls within an expected signal value window when the binding reaction of the second further moiety to the second moiety takes place as expected. An apparatus comprising such a sensor device, methods of operating the sensor device and apparatus and a sample for use with the sensor device are also disclosed.

Owner:SIEMENS HEALTHINEERS NEDERLAND BV

Method for measuring an impedance of an electric cable, a coupler arrangement and uses thereof

ActiveUS20190369152A1High measurement sensitivityFailed analysisInstrument screening arrangementsElectrical testingElectricityMeasurement point

The invention relates to a method for cable condition monitoring of an electric cable. The method comprises inducing a test current in the electric cable, measuring a resulting current in a measurement point of the electric cable by measuring a magnetic nearfield of the electric cable, measuring a resulting voltage in the measurement point of the electric cable by measuring an electric nearfield of the cable, calculating an impedance of the electric cable based on the resulting current and the resulting voltage by a line resonance analysis system, and analysing the impedance by the line resonance analysis system establishing a condition of the electric cable. A coupler arrangement providing a non-galvanic connection to the cable is also disclosed.

Owner:WIRESCAN

Method to transfer failure analysis-specific data between data between design houses and fab's/FA labs

InactiveUS20090007033A1Failed analysisDetecting faulty computer hardwareComputer aided designFailure analysis

A method and system for an IC design house to transfer design and layout information to a fabrication or failure analysis facility on a need-to-know basis to enable effective failure analysis while not providing unnecessary or extraneous information.

Owner:CREDENCE SYSTEMS +1

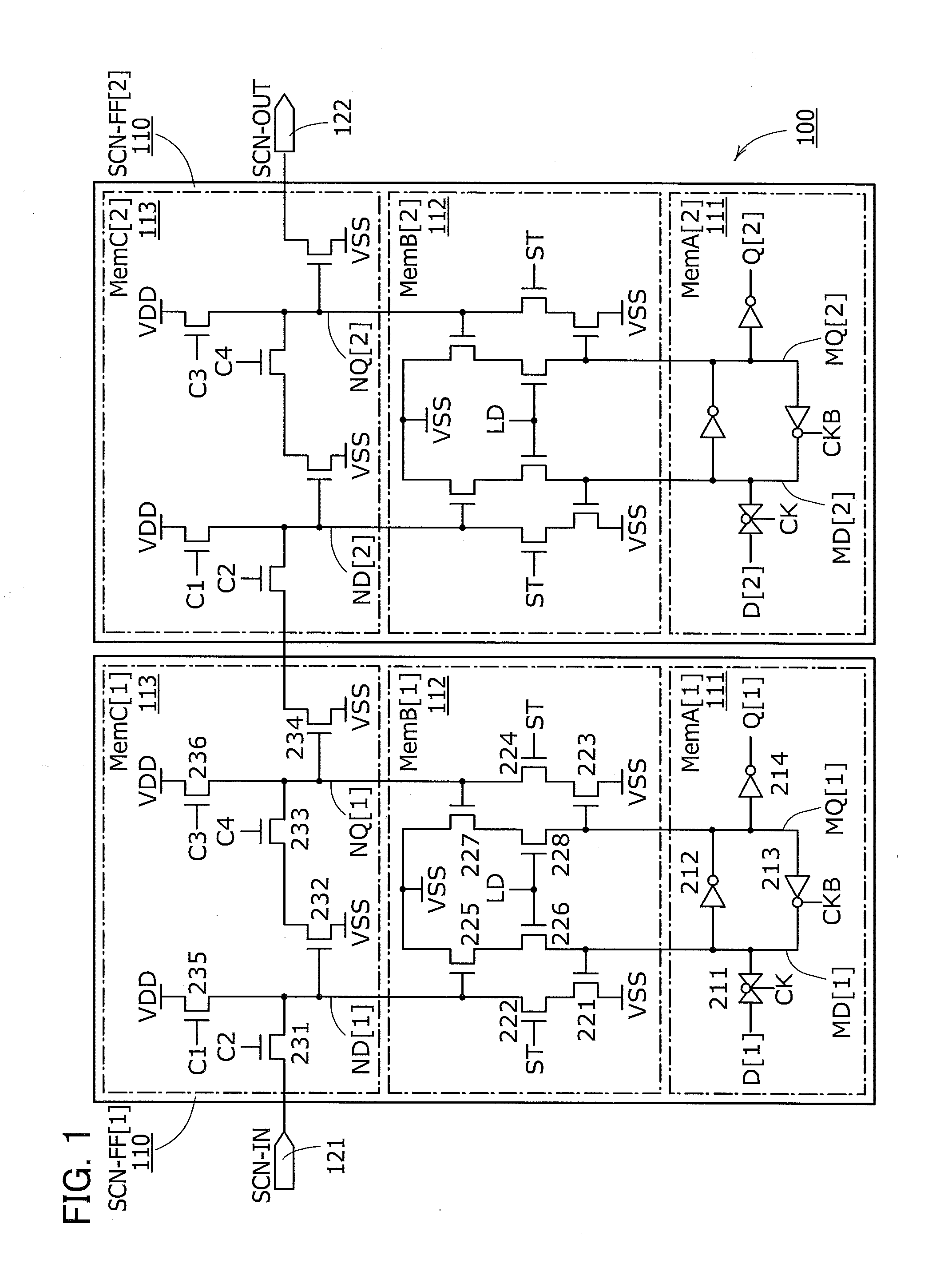

Semiconductor Device

ActiveUS20140226781A1Reduce power consumptionImprove reliabilityDigital storageComputer hardwarePower semiconductor device

A register for a scan test has a data saving function. A scan flipflop includes first to third memory circuits. The first memory circuit is a memory circuit functioning as a register of a combination circuit in normal operation. The second memory circuit is a memory circuit for backup of the first memory circuit. The third memory circuit has a function of transferring data to a flipflop in a next stage. Further, the second memory circuit has a function of writing data of the first memory circuit to the third memory circuit and a function of writing data of the third memory circuit to the first memory circuit. At a given time, data of the first memory circuit can be extracted from an external device and data can be stored in the first memory circuit from an external device.

Owner:SEMICON ENERGY LAB CO LTD

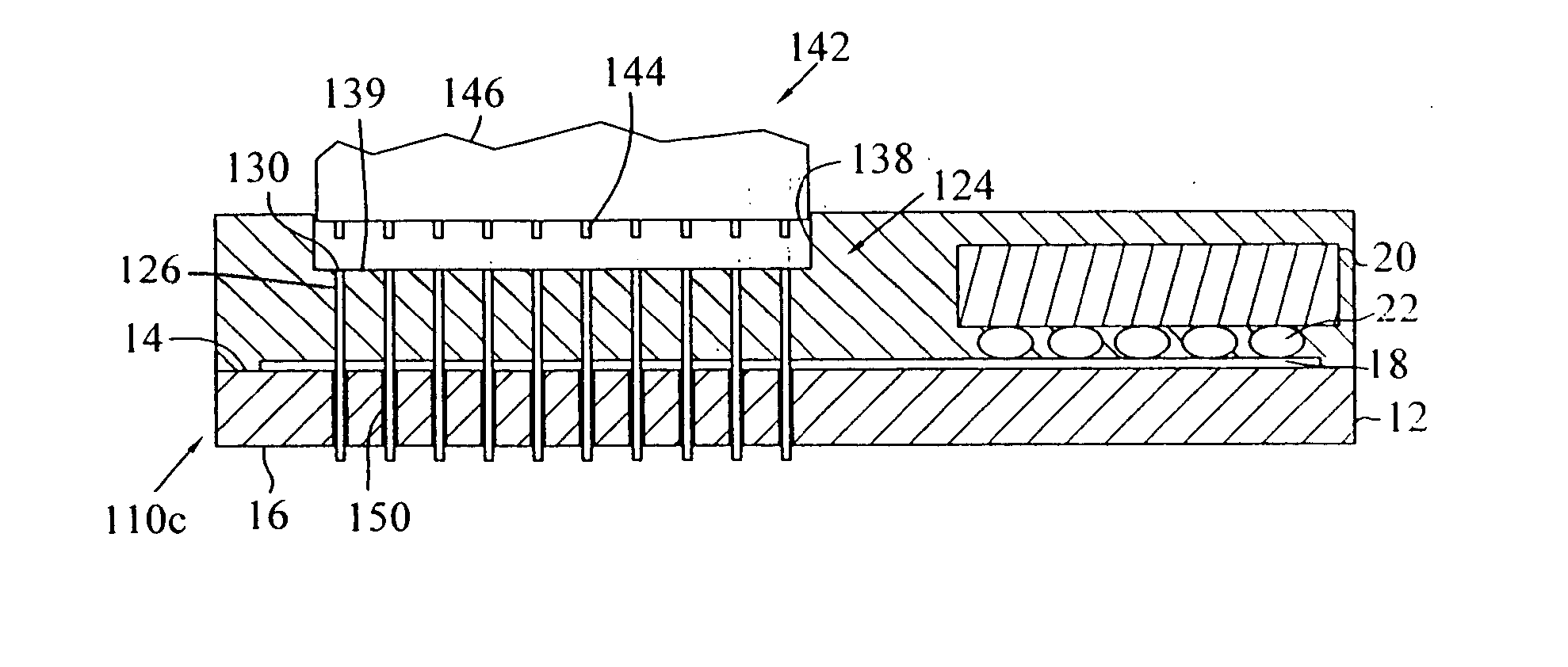

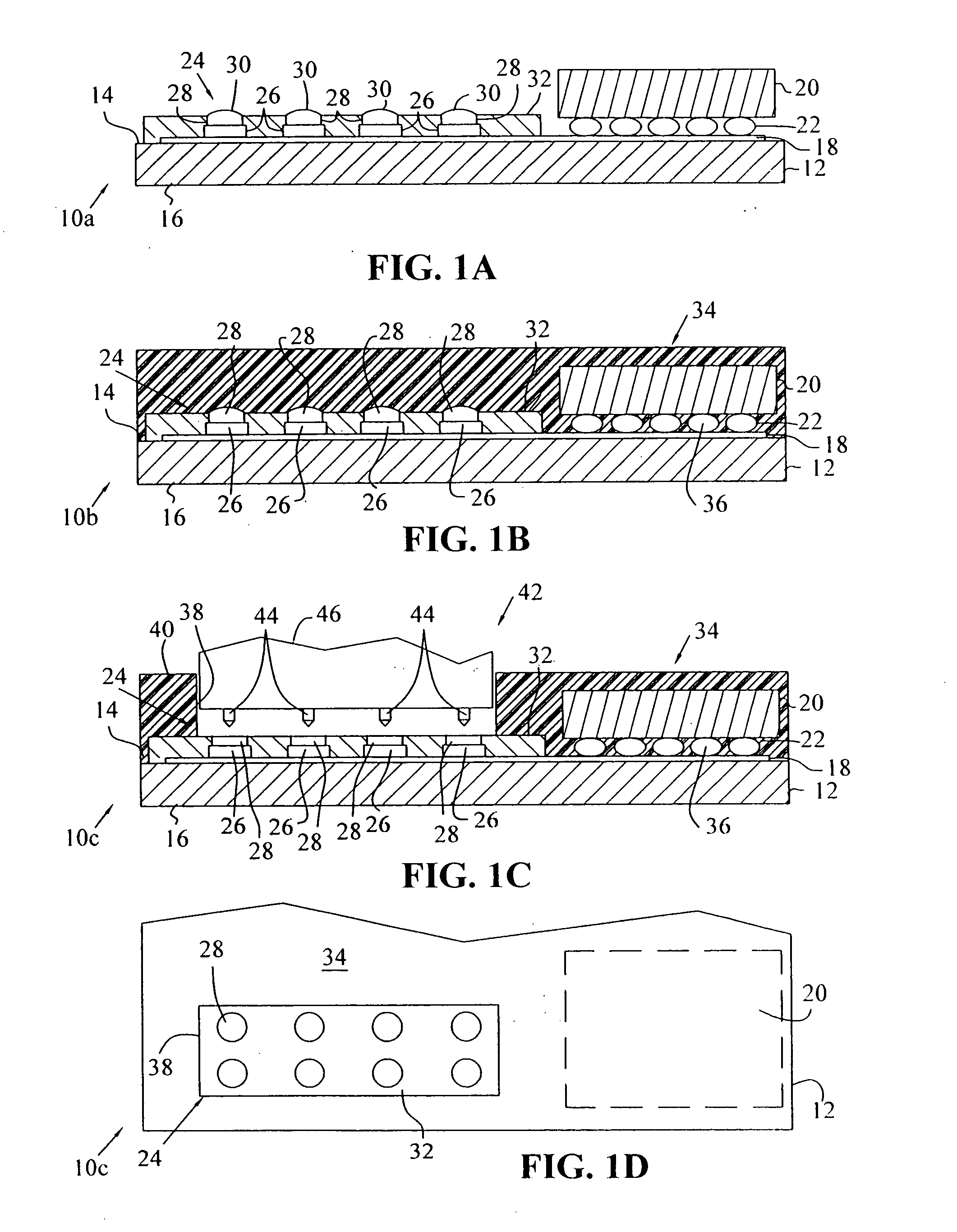

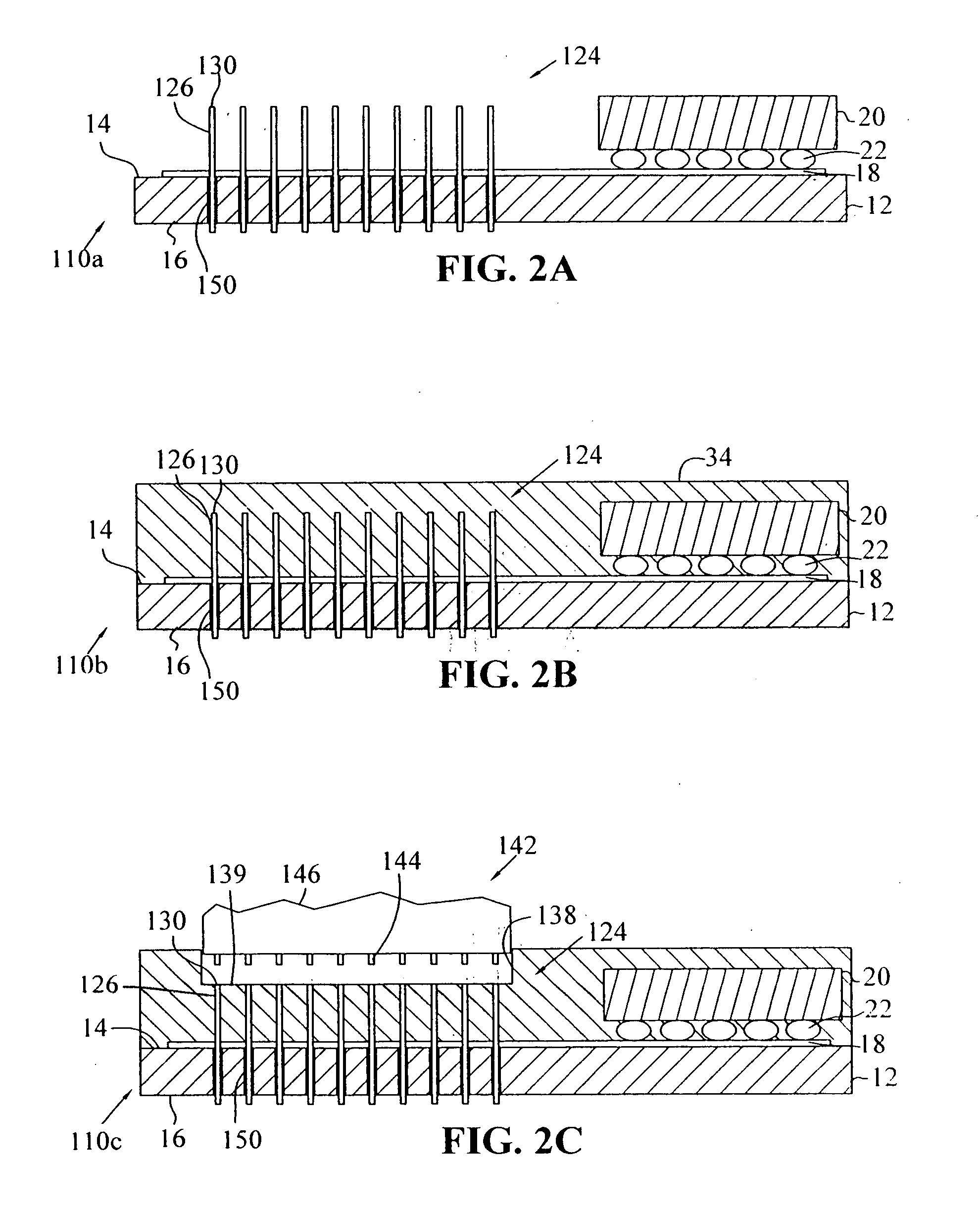

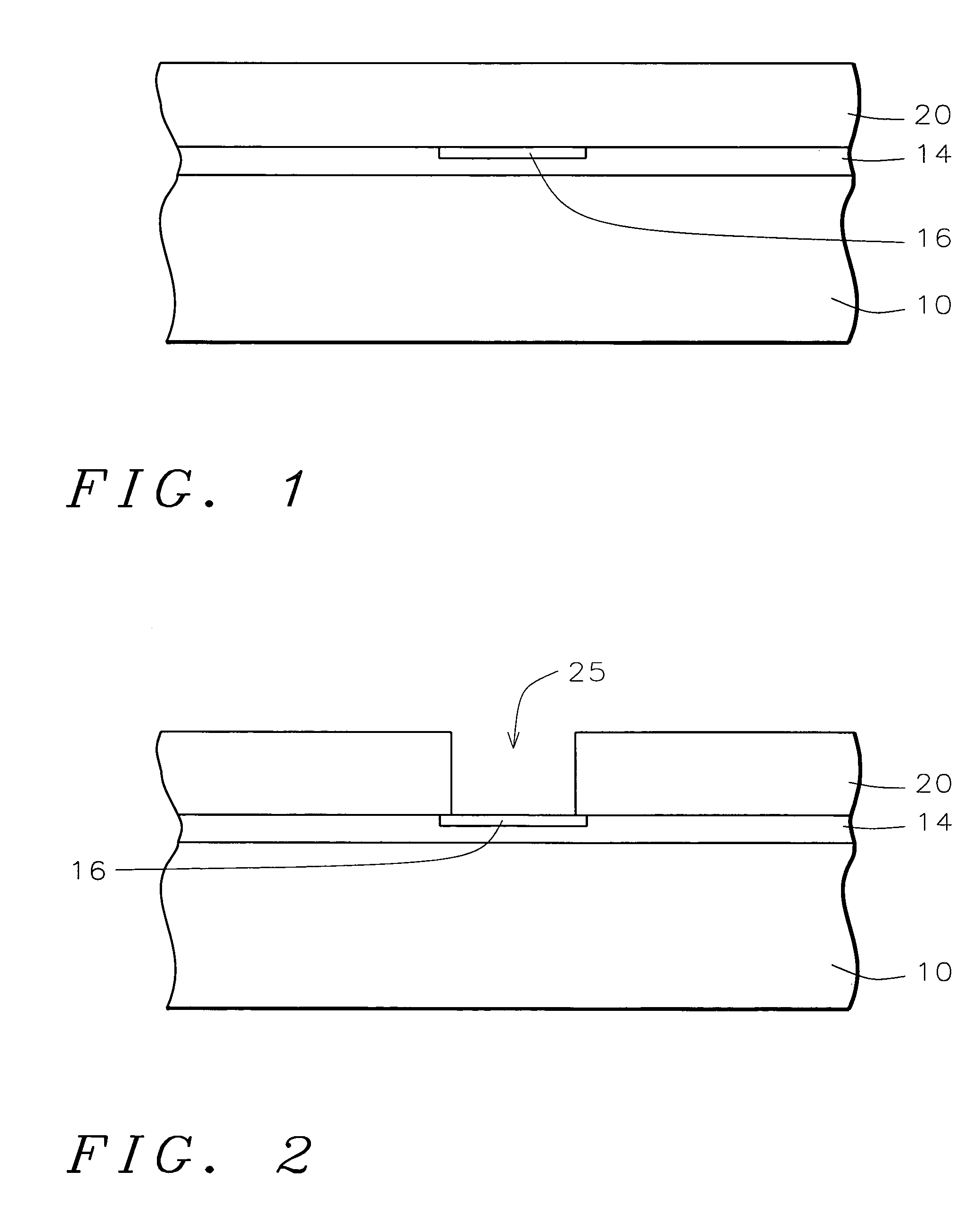

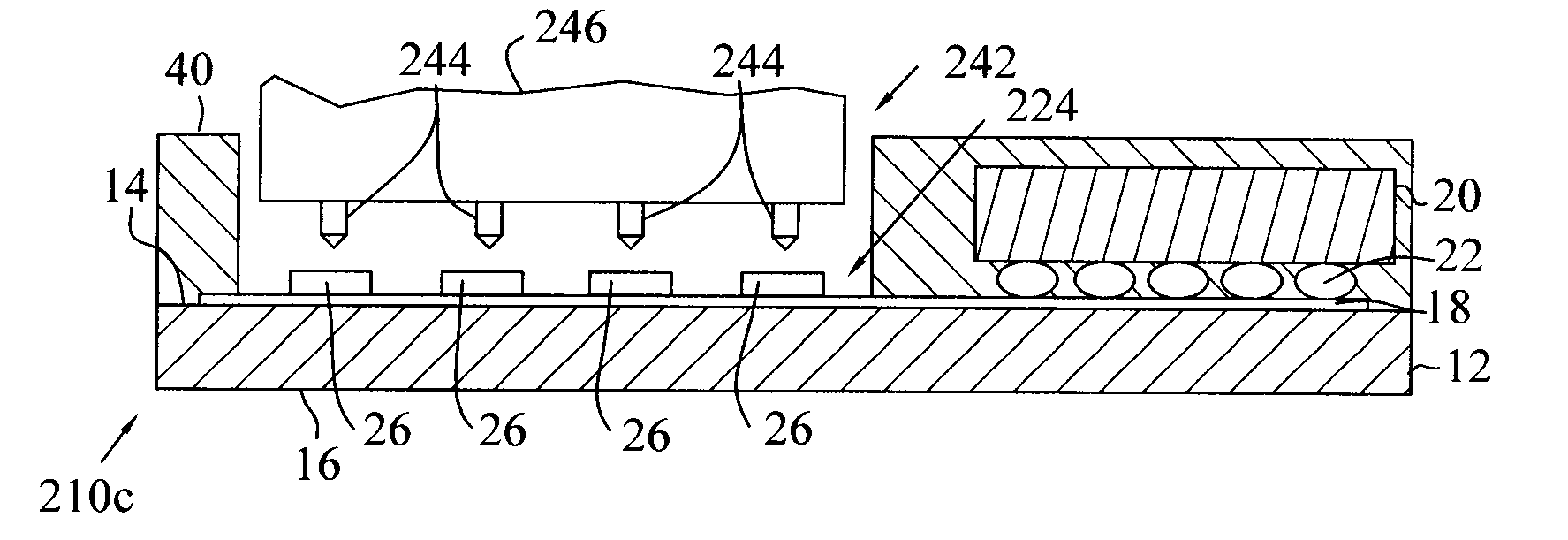

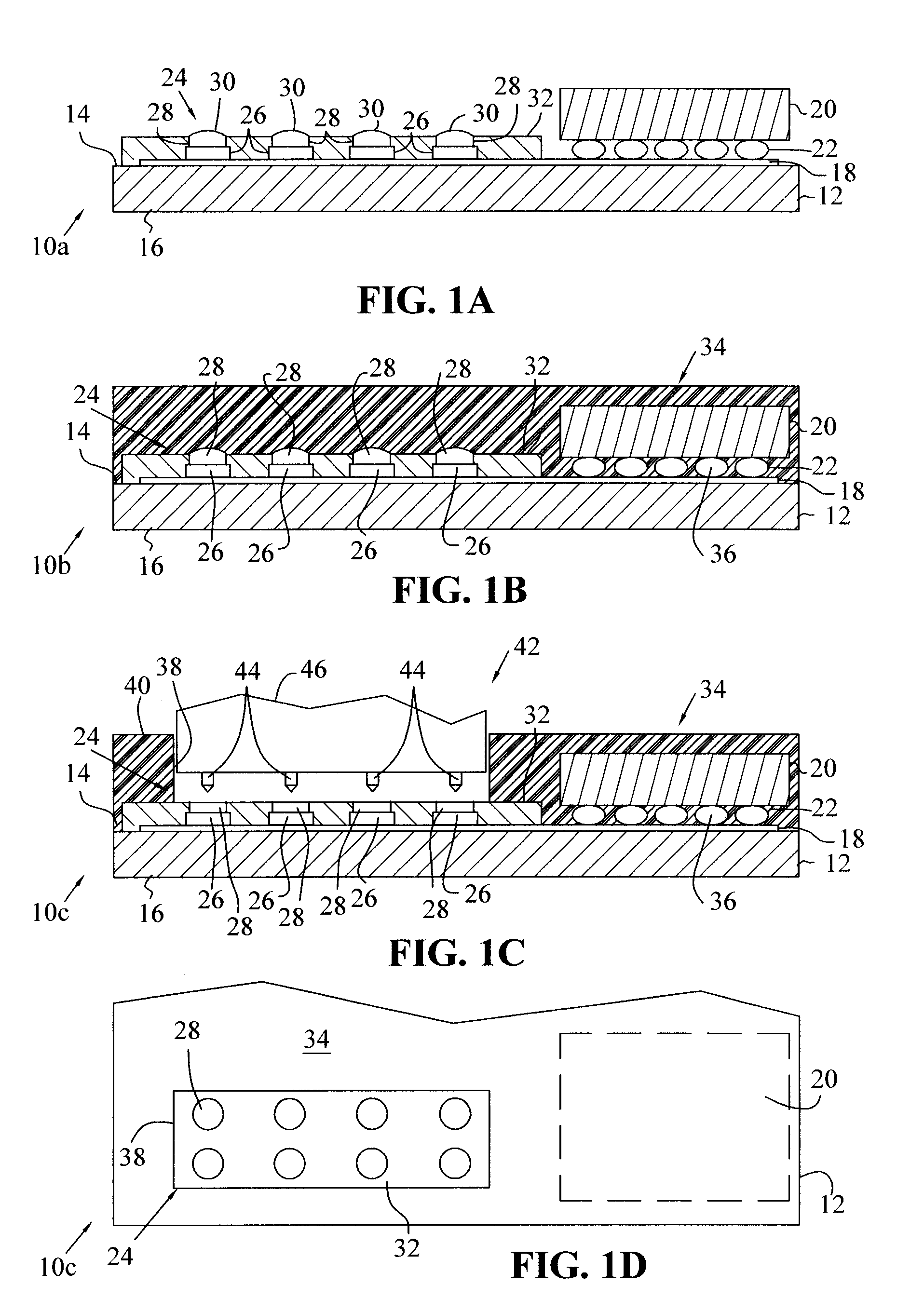

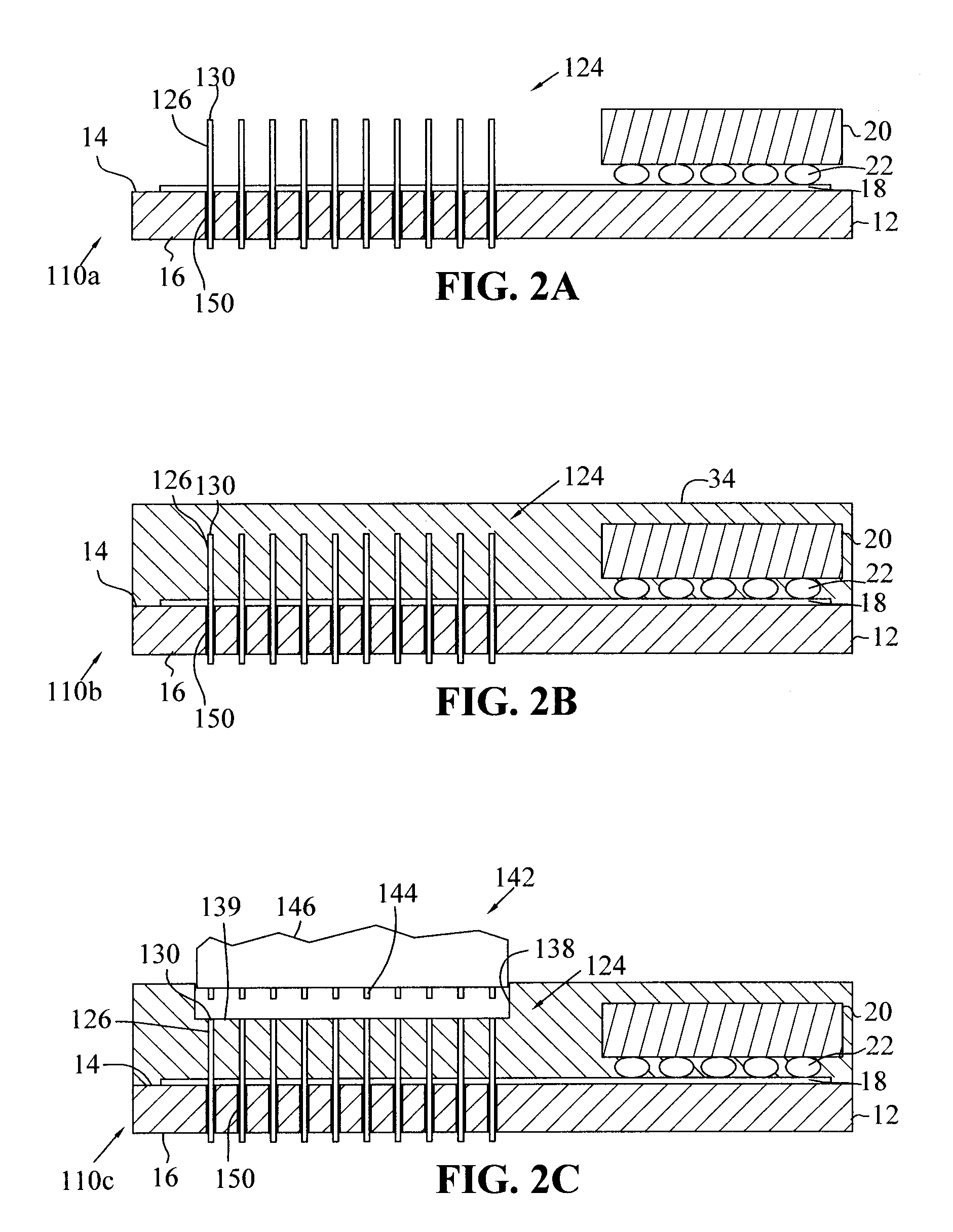

Methods to provide and expose a diagnostic connector on overmolded electronic packages

ActiveUS20060027394A1Reduce riskInexpensive and efficient methodSemiconductor/solid-state device testing/measurementSolid-state devicesEpoxyElectrical conductor

An overmolded electronic assembly is provided having a circuit board with electronic devices and a diagnostic connection. The diagnostic connection includes electrical conductors having a distal end projecting above a first side of the circuit board, for example, circuit pads having solder thereon or conductive pins oriented substantially perpendicular to the circuit board. The electrical conductors are overmolded with sealing material along with the other electronic devices and circuit board area. The sealing material is a dielectric, for example, a thermoset polymer base such as epoxy that may include another material such as a fill material. In order to provide a diagnostic connection to the circuit and electronic devices, the encapsulation or sealing material overlying the electrical conductors is removed from the outside surface down to at least the distal end of the electrical conductors. The arrangement of the electrical conductors and the method of removal of the sealing material prevents damage to the circuit and electronic devices and provides instrumentation used during product development and facilitates failure analysis. The sealing material may be removed, for example, by mechanical cutting, laser cutting, or high pressure jet erosion, for example, by a high pressure water or liquid nitrogen stream.

Owner:DELPHI TECH IP LTD

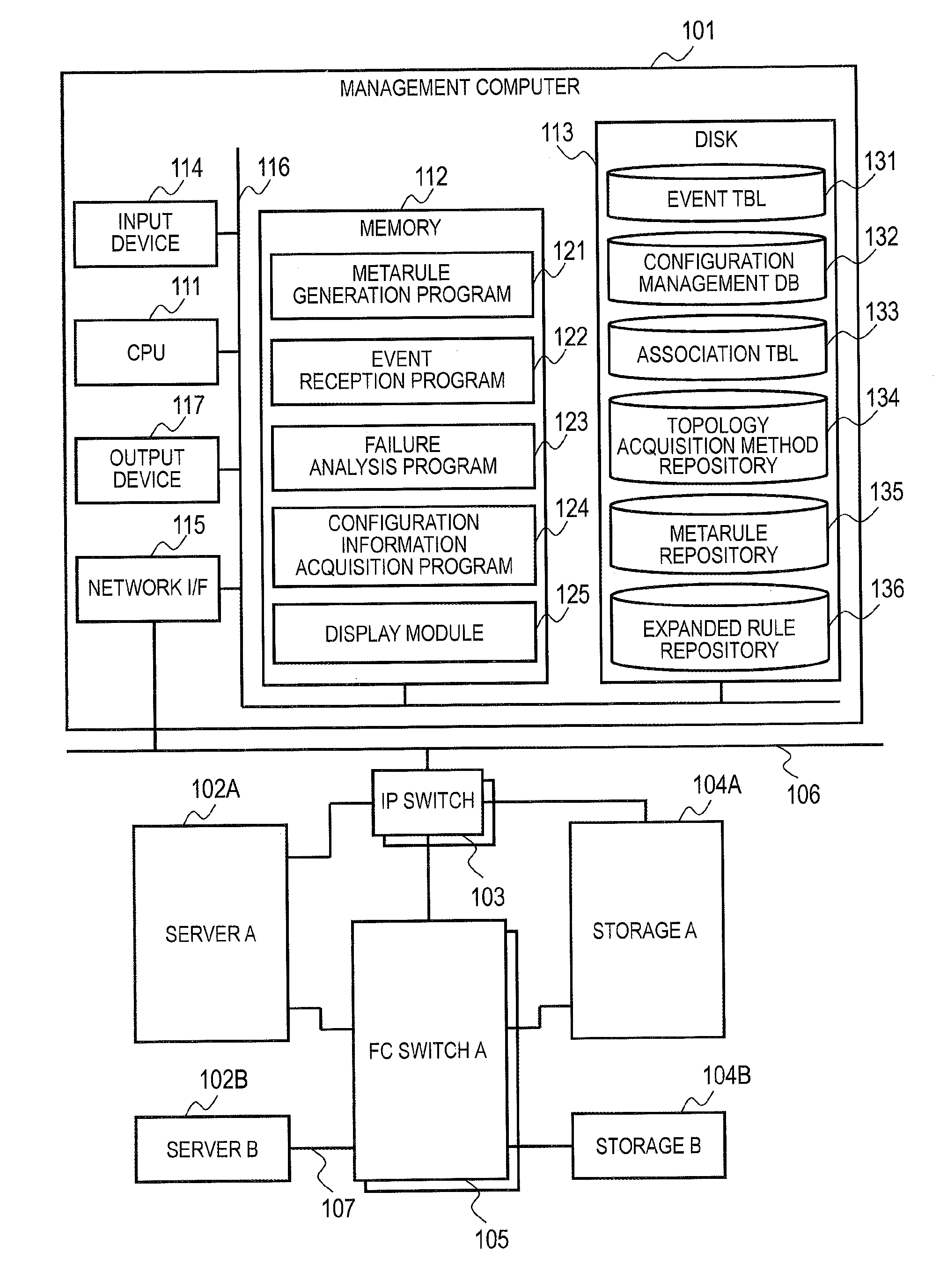

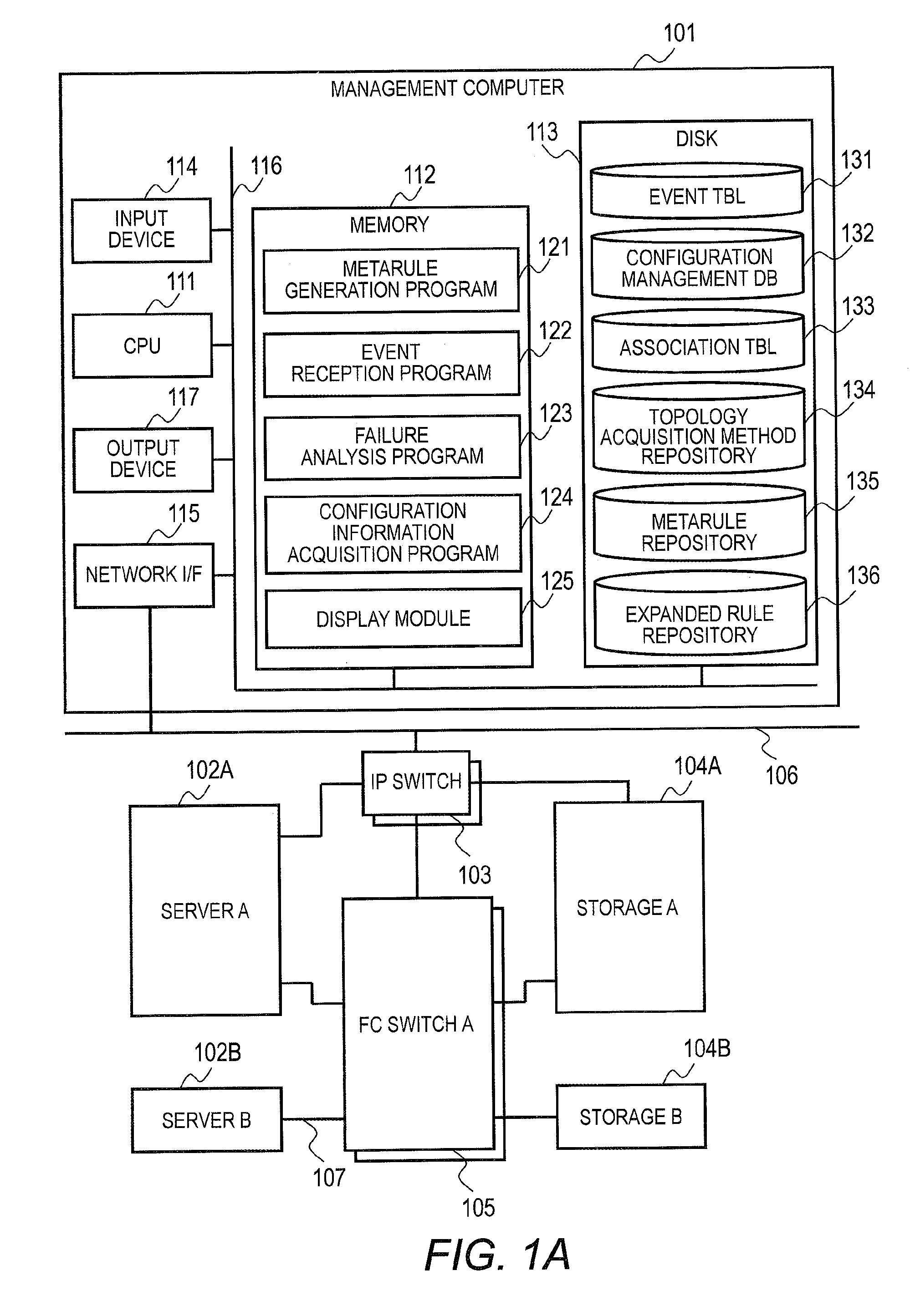

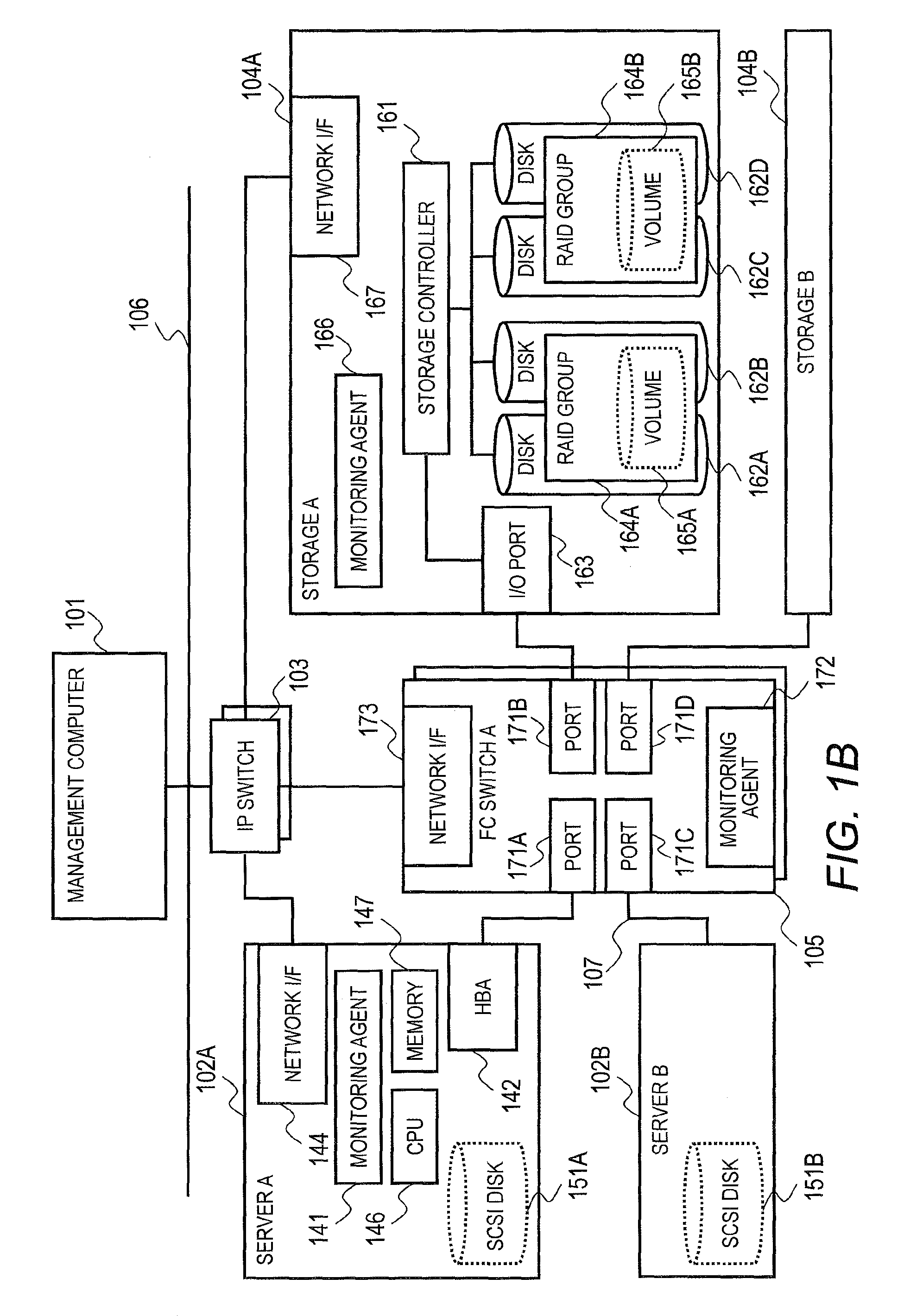

Management computer and rule generation method

InactiveUS20150242416A1Failed analysisWeb data indexingDigital data processing detailsManagement objectCondition part

There is provided a management computer comprising a processor and a storage resource. The processor acquires information on a type of the first management object and the second management object; traces association from the type of the second management object to the type of the first management object; generates a metarule including a condition part and a conclusion part; generates a method of acquiring information on a topology constructed by the association from the type of the second management object to the type of the first management object based on a method of the trace from the type of the second management object to the type of the first management object; acquires the information on the topology based on the generated method; generates an expanded rule from the generated metarule and the acquired information on the topology; and analyzes a detected new failure based on the generated expanded rule.

Owner:HITACHI LTD

Remote maintenance system, image forming apparatus, external terminal, methods of controlling these, and storage mediums

ActiveUS10341503B2Reduce downtimeFailed analysisPictoral communicationDigital output to print unitsImage formationComputer terminal

An image forming apparatus accepts a start of the remote maintenance function for resolving a failure of the image forming apparatus in accordance with instructions of an operator using an external terminal, generates support data including information of at least one of device information of the print server and device information of the image forming apparatus, which is that is information necessary when the operator analyzes the failure of the image forming apparatus, and transmits it to the external terminal.

Owner:CANON KK

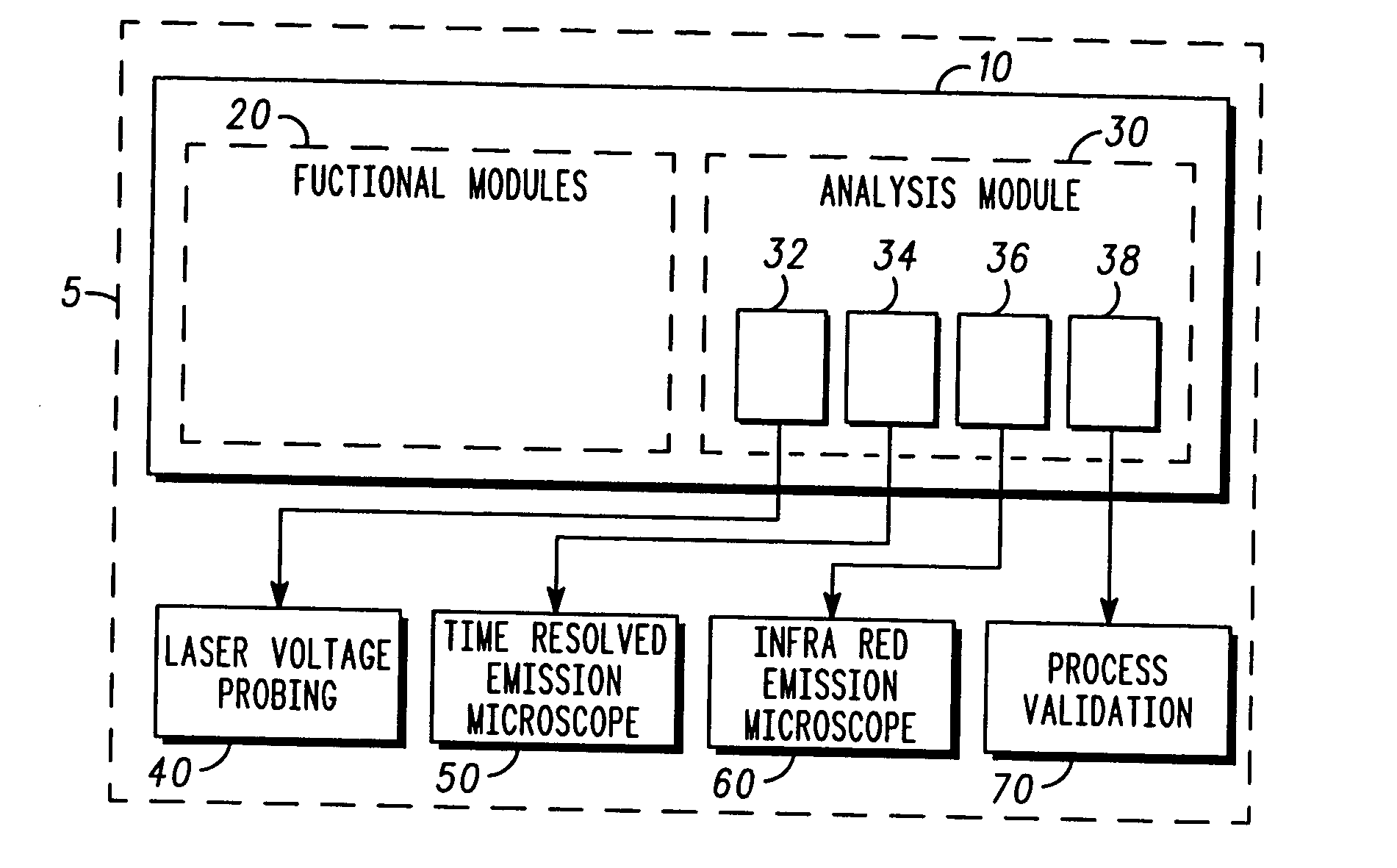

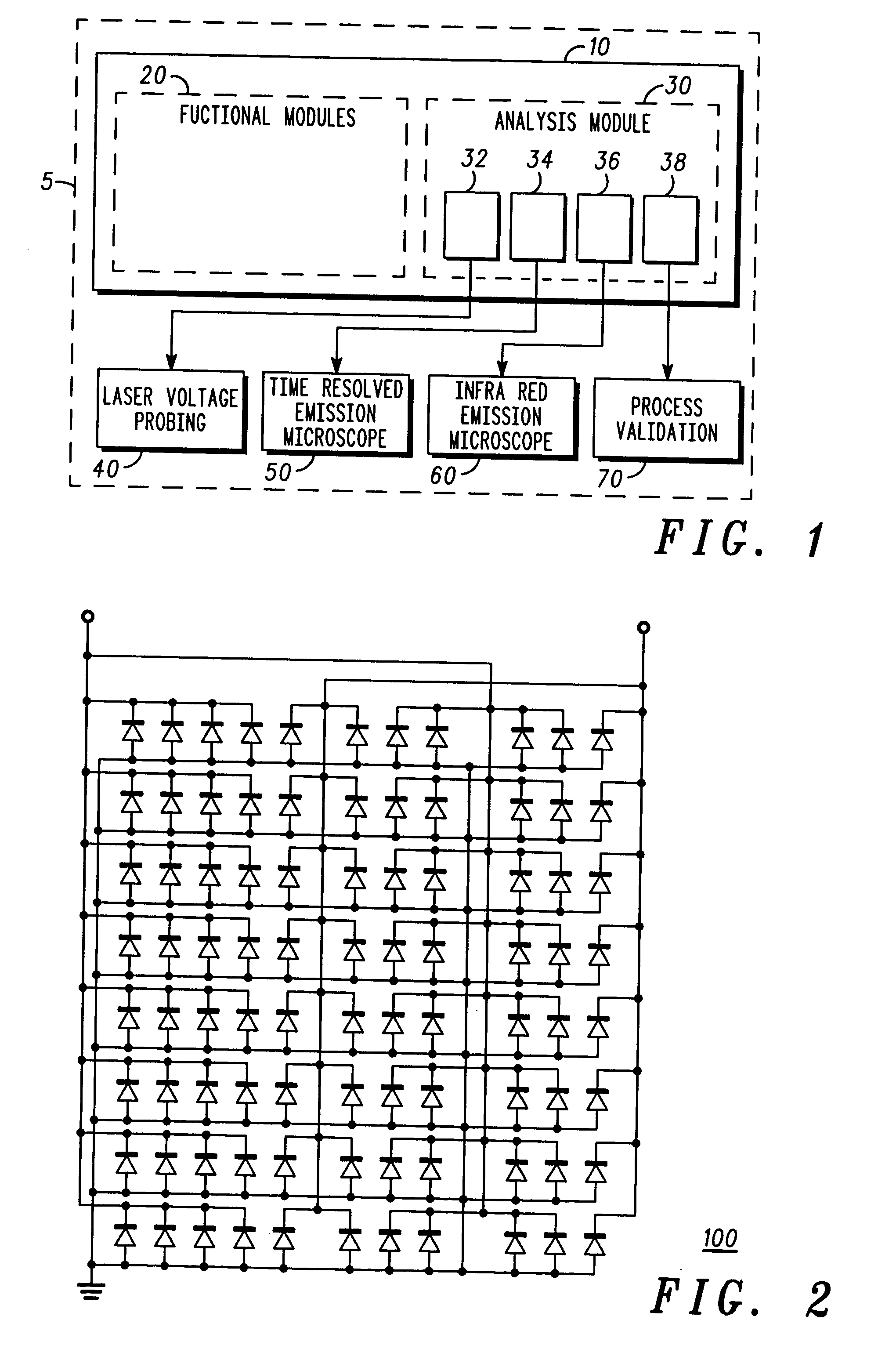

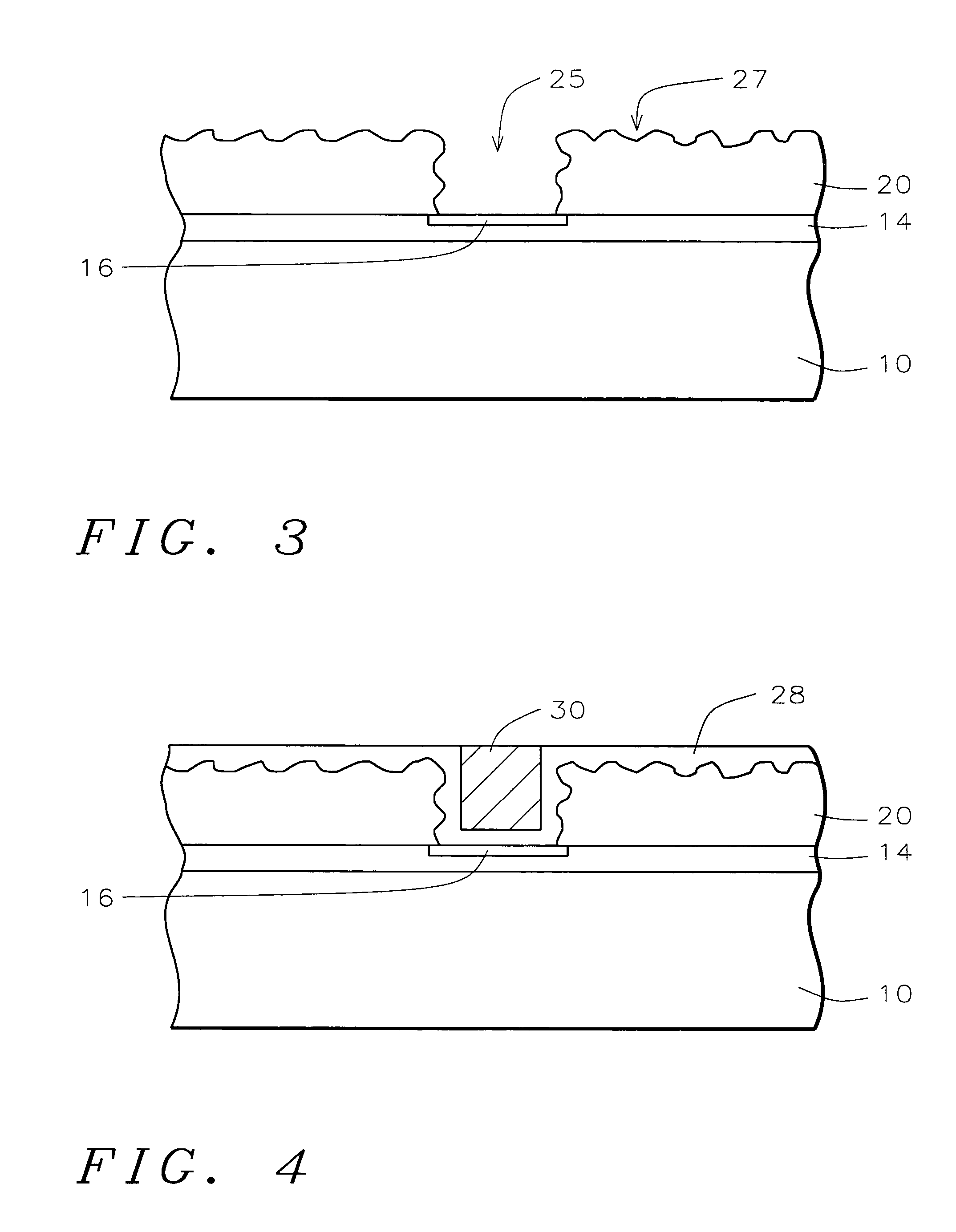

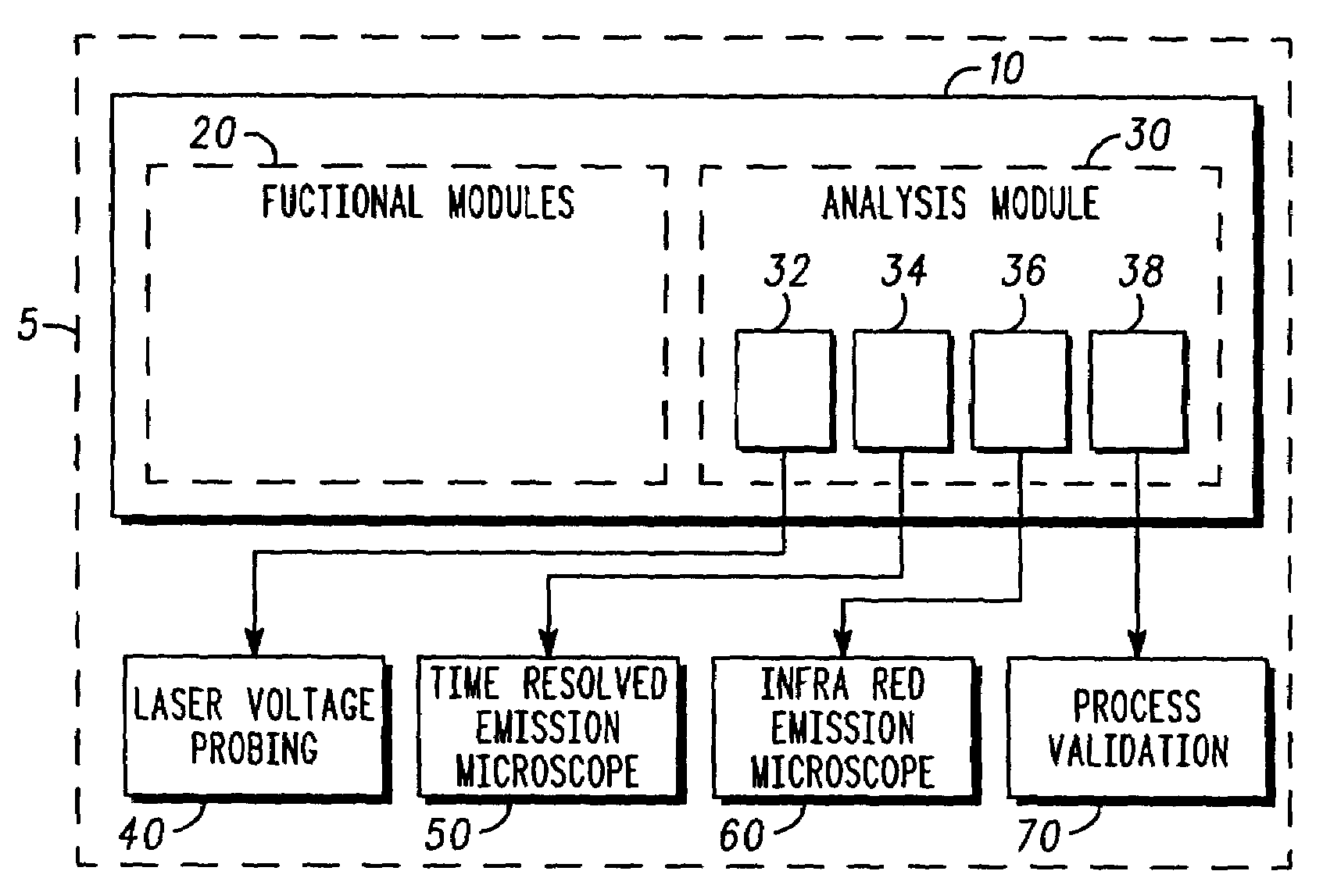

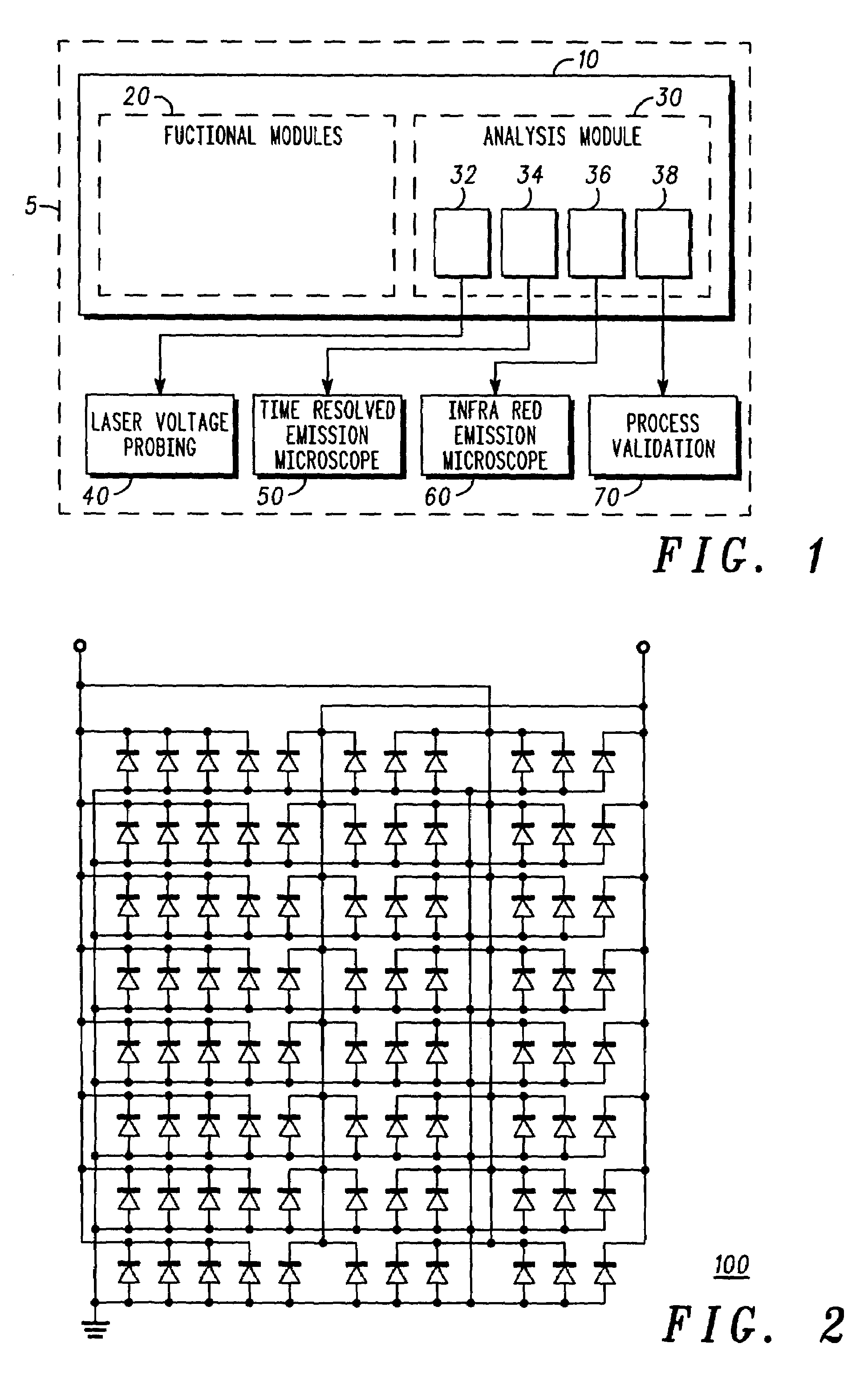

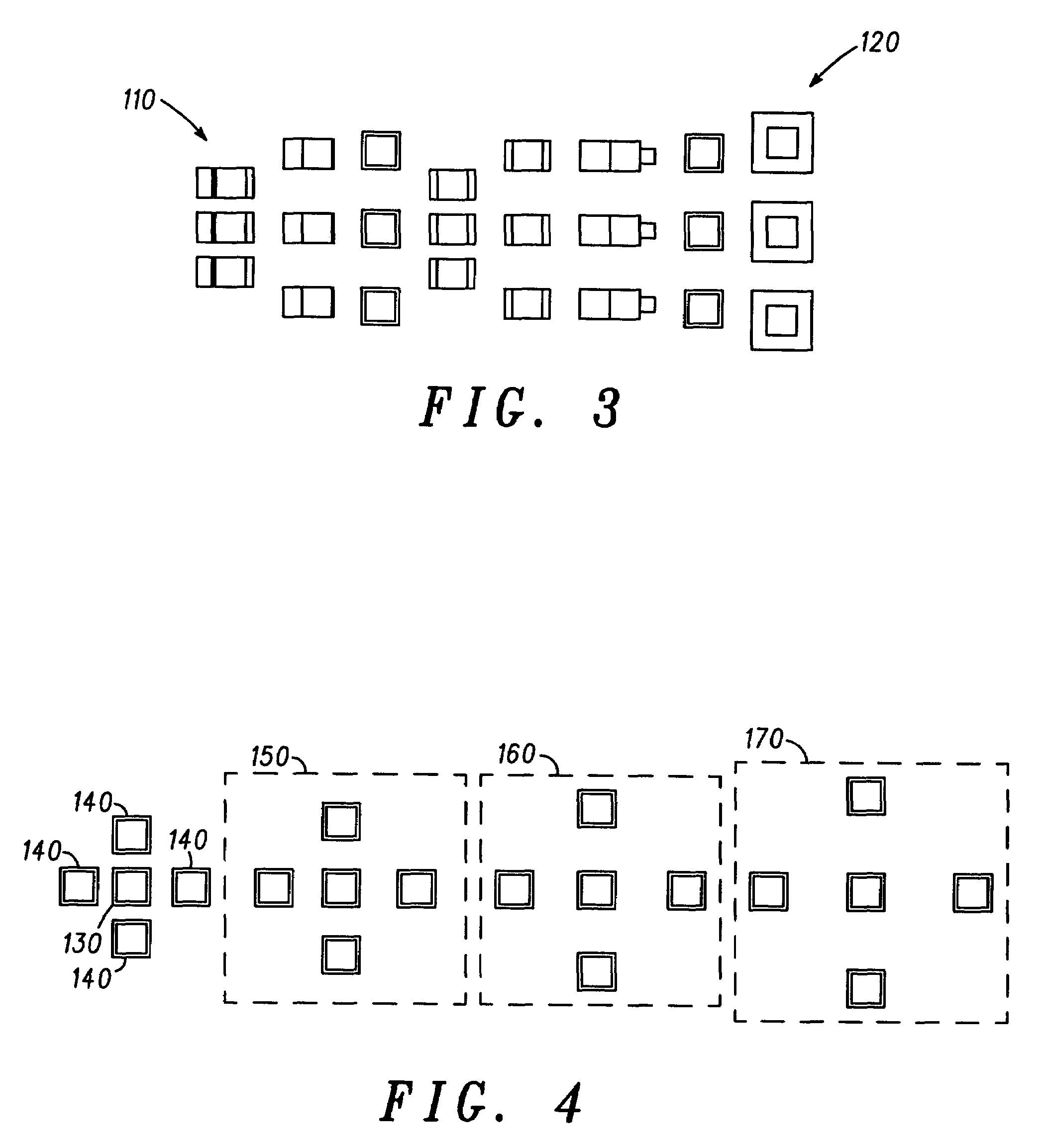

Analysis module, integrated circuit, system and method for testing an integrated circuit

ActiveUS20040064772A1Failed analysisSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceTest structureFunctional module

A system (5) for testing and failure analysis of an integrated circuit (10) is provided using failure analysis tools (40, 50, 60). An analysis module (30) having a number of submodule test structures is incorporated into the integrated circuit design. The test structures are chosen in dependence upon the failure analysis tools (40, 50, 60) to be used. The rest of the integrated circuit contains function modules (20) arranged to provide normal operating functions. By analysing the submodule test structures of the analysis module (30) using the failure analysis tools (40, 50, 60), physical parameters of the integrated circuit (10) are obtained and used in subsequent testing of the function modules (20) by the failure analysis tools (40, 50, 60), thus simplifying the testing of the integrated circuit (10) and reducing the time taken to perform a failure analysis procedure.

Owner:NXP USA INC

Device structure having enhanced surface adhesion and failure mode analysis

InactiveUS7157367B2Failed analysisEasy to disassembleSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDevice material

A substrate is provided having semiconductor device structures formed in and on the substrate. The semiconductor device structures comprise conductor layers embedded in openings in dielectric layers having a dielectric constant of less than 4.5. The dielectric layer has a roughness between the dielectric and the conductor wherein the roughness of the dielectric layer divided by the thickness of a barrier layer underlying the conductor layer is 0 to 1. The integrated circuit structure is prepared for failure analysis by removing the low dielectric constant dielectric layers and exposing the conductor layers for further failure analysis by optical examination or scanning electron microscope (SEM).

Owner:TAIWAN SEMICON MFG CO LTD

Methods to provide and expose a diagnostic connector on overmolded electronic packages

ActiveUS7553680B2Failed analysisAvoid damageSemiconductor/solid-state device testing/measurementSolid-state devicesElectrical conductorLaser cutting

An overmolded electronic assembly is provided having a circuit board with electronic devices and a diagnostic connection. The diagnostic connection includes electrical conductors having a distal end projecting above a first side of the circuit board, for example, circuit pads having solder thereon or conductive pins oriented substantially perpendicular to the circuit board. The electrical conductors are overmolded with sealing material along with the other electronic devices and circuit board area. The encapsulation or sealing material overlying the electrical conductors is removed from the outside surface down to at least the distal end of the electrical conductors. The sealing material may be removed, for example, by mechanical cutting, laser cutting, or high pressure jet erosion, for example, by a high pressure water or liquid nitrogen stream.

Owner:DELPHI TECH IP LTD

Analysis module, integrated circuit, system and method for testing an integrated circuit

ActiveUS7151387B2Failed analysisSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceFailure analysisCircuit design

A system (5) for testing and failure analysis of an integrated circuit (10) is provided using failure analysis tools (40, 50, 60). An analysis module (30) having a number of submodule test structures is incorporated into the integrated circuit design. The test structures are chosen in dependence upon the failure analysis tools (40, 50, 60) to be used. The rest of the integrated circuit contains function modules (20) arranged to provide normal operating functions. By analysing the submodule test structures of the analysis module (30) using the failure analysis tools (40, 50, 60), physical parameters of the integrated circuit (10) are obtained and used in subsequent testing of the function modules (20) by the failure analysis tools (40, 50, 60), thus simplifying the testing of the integrated circuit (10) and reducing the time taken to perform a failure analysis procedure.

Owner:NXP USA INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com